Technical University of Denmark

## An Adaptive Middleware for Improved Computational Performance

Bonnichsen, Lars Frydendal; Probst, Christian W.; Karlsson, Sven

Publication date: 2016

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

*Citation (APA):* Bonnichsen, L. F., Probst, C. W., & Karlsson, S. (2016). An Adaptive Middleware for Improved Computational Performance. Kgs. Lyngby: Technical University of Denmark (DTU). (DTU Compute PHD-2015; No. 390).

## DTU Library Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

## An Adaptive Middleware for Improved Computational Performance

Lars Frydendal Bonnichsen

Kongens Lyngby 2015

Technical University of Denmark Department of Applied Mathematics and Computer Science Richard Petersens Plads, building 324, 2800 Kongens Lyngby, Denmark Phone +45 4525 3031 compute@compute.dtu.dk www.compute.dtu.dk

# Summary (English)

The performance improvements in computer systems over the past 60 years have been fueled by an exponential increase in energy efficiency. In recent years, the phenomenon known as the end of Dennard's scaling has slowed energy efficiency improvements — but improving computer energy efficiency is more important now than ever. Traditionally, most improvements in computer energy efficiency have come from improvements in lithography — the ability to produce smaller transistors — and computer architecture - the ability to apply those transistors efficiently. Since the end of scaling, we have seen diminishing returns from developments in lithography and modern computer architectures are so complicated requiring significant programming effort to exploit efficiently — software developers undertaking such a task will need all the help they can get, in order to keep the programming effort down.

In this thesis we champion using software to improve energy efficiency — in particular we develop guidelines for reasoning and evaluating software performance on modern computers, and a middleware that has been designed for modern computers, improving computational performance both in terms of energy and execution time. Our middleware consists of a new power manager, synchronization libraries using hardware transactional memory (for locks, barriers, and task synchronization), and two concurrent map data structures, which can be deployed in computer systems with little to no effort. At a fundamental level, we are improving computational performance by exploiting modern hardware features, such as dynamic voltage-frequency scaling and transactional memory. Adapting software is an iterative process, requiring that we continually revisit it to meet new requirements or realities; a time consuming process which we hope to simplify by analyzing the realities of modern computers, and providing guidelines explaining how to get the most performance out of them. <u>ii</u>\_\_\_\_\_

# Summary (Danish)

De sidste 60 år er computere blevet drastisk hurtigere, takket være eksponentielle forbedringer i deres energi effektivitet. Energi forbedringerne har sænket farten de sidste år, pga. et fænomenet *the end of Dennard's scaling*, på trods af at det i dag er ekstremt økonomisk attraktivt at lave energi effektivitet. Traditionelt set har de største forbedringer i beregningsmæssig energi effektivitet kommet fra litografi, som har leveret mindre transistorer, og computer arkitektur, som har anvendt det stigende antal transistorer effektivt. Desværre giver mindre transistorer aftagende afkast, og forbedringerne i computer arkitektur har gjort computere så komplekse at det ofte kræver en ekstrem programmerings indsats at anvende dem effektivt. Hvis moderne software udviklere skal kunne udnytte moderne computer arkitekturer effektivt, så behøver de al den hjælp de kan få.

I denne afhandling bruger vi software til at forbedre energi effektivitet, ved (1) at udvikle retningslinjer til at optimere og evaluere software ydelse, baseret op analyser af moderne computere, og (2) at optimere middleware mod moderne computeres features, såsom dynamisk skift af spænding og frekvens og transaktionel hukommelse. Vores middleware består af en ny strømstyring, synkroniserings biblioteker som bruger hardware transaktionel hukommelse (til låse, barriere, og tasks), og to parallelle data strukturer (maps). Alle delene af middlewaren kan genanvendes med relativt lille arbejdsindsats. At tilpasse software er i sig selv en iterativ proces, som kræver at vi genovervejer vores fremgangsmåder, så vi kan optimere mod nye krav og nye realiteter. Det er en tidskrævende proces, som vi håber på at forenkle igennem retningslinjer, som forklarer hvordan vi bedst udnytter moderne computere. iv

# Preface

This thesis was prepared at the Department of Applied Mathematics and Computer Science, in the Technical University of Denmark in partial fulfillment of the requirements for acquiring the Ph.D. degree in engineering.

The Ph.D. study was carried out under supervision of Professor Christian W. Probst and Professor Sven Karlsson in the period from October 2012 to September 2015.

The Ph.D. project was funded by the European collaborative project PaPP (Portable and Predictable Performance on Heterogeneous Embedded Manycores) funded jointly by the ARTEMIS Joint Undertaking and national governments under the Call 2011 Project Nr. 295440.

> Kongens Lyngby, September 2015 Lars Frydendal Bonnichsen

# Acknowledgements

First I would like to thank my supervisors, Christian and Sven. Their support and direction during the development of this thesis helped me better understand and express the problems the problems I have faced. I would especially like to thank them for fostering an environment that encourages diverse approaches, where no solution is off the table.

I am grateful to my defense committee, Alberto Lluch Lafuente, Uwe Assmann, and Rene Rydhof Hansen, for their interest, inquiries, and pleasant demeanor.

I would like to thank Alessandro, Artur, Andreas, Laust, Marieta, Nicklas, and my supervisors, for assisting in proofreading various drafts of this thesis. Their help was instrumental for providing some semblance of a readable manuscript. They cannot be blamed for any remaining faults or poorly constructed phrases — those are entirely my doing.

I am deeply appreciative of Vladimir Vlassov, and the group at the School of Information and Communication Technology at KTH, for hosting me on an external stay. I am especially thankful for the warm welcome that I received from Ahsan, Ananya, Artur, and Georgios during the stay, and the many productive, enlightening, and memorable discussions we have had.

I am forever indebted to the Winamp team, especially Justin Frankel, for creating the Advanced Visualization Studio — a creative and friendly development environment — which was my first real entry into programming.

I would like to thank all my friends at DTU and all my friends outside work,

especially Martin and Kavan, for all the memorable moments, and for providing a mostly stress free environment where I could regain my sanity, without worrying about the state of computer science.

Finally, I would like to thank my family, and especially my parents, for supporting me throughout my life, and in particular throughout the past three years. If you are reading this, please know that I love all of you, and cannot thank you enough for all you have done for me.

ix

## Contents

| Summary (English) i |      |                                            |              |  |  |

|---------------------|------|--------------------------------------------|--------------|--|--|

| Su                  | mm   | ary (Danish)                               | iii          |  |  |

| Pr                  | efac | 9                                          | $\mathbf{v}$ |  |  |

| Ac                  | knov | wledgements                                | vii          |  |  |

| 1                   | Intr | oduction                                   | 1            |  |  |

|                     | 1.1  | Contributions                              | 4            |  |  |

|                     | 1.2  | Synopsis                                   | 5            |  |  |

| 2                   | Bac  | kground                                    | 7            |  |  |

|                     | 2.1  | Power consumption                          | 7            |  |  |

|                     | 2.2  | Performant computers                       | 10           |  |  |

|                     | 2.3  | Optimizing software performance            | 19           |  |  |

| 3                   | Wo   | rkload Aware Energy Management             | <b>27</b>    |  |  |

|                     | 3.1  | CPU frequencies and workloads              | 28           |  |  |

|                     | 3.2  | Evaluation                                 | 36           |  |  |

|                     | 3.3  | Related work                               | 42           |  |  |

|                     | 3.4  | Future work                                | 47           |  |  |

|                     | 3.5  | Concluding remarks                         | 50           |  |  |

| 4                   | Min  | imizing Blocking with Transactional Memory | 53           |  |  |

|                     | 4.1  | Avoiding Blocking in OpenMP                | 54           |  |  |

|                     | 4.2  | Evaluation                                 | 59           |  |  |

|                     | 4.3  | Limitations and Related Work               | 64           |  |  |

|                     | 4.4  | Concluding remarks                         | 66           |  |  |

| 5              | Opt                                     | imizing for Lock-Elision                    | 67  |  |  |

|----------------|-----------------------------------------|---------------------------------------------|-----|--|--|

|                | 5.1                                     | Designing for HTM                           | 68  |  |  |

|                | 5.2                                     | BT-trees                                    | 69  |  |  |

|                | 5.3                                     | Evaluation of BT-trees                      | 78  |  |  |

|                | 5.4                                     | ELB-trees                                   | 88  |  |  |

|                | 5.5                                     | Evaluation of ELB-trees                     | 96  |  |  |

|                | 5.6                                     | Related work                                | 101 |  |  |

|                | 5.7                                     | Concluding remarks                          | 104 |  |  |

| 6              | Con                                     | clusion                                     | 105 |  |  |

|                | 6.1                                     | Contributions                               | 105 |  |  |

|                | 6.2                                     | Future directions and limitations           | 108 |  |  |

| Α              | Pro                                     | of of ELB-tree semantics                    | 111 |  |  |

|                | A.1                                     | Definitions                                 | 112 |  |  |

|                | A.2                                     | Search tree proof                           | 113 |  |  |

|                | A.3                                     | Correctness                                 | 116 |  |  |

|                | A.4                                     | Lock-freedom                                | 118 |  |  |

|                | A.5                                     | Conclusion                                  | 119 |  |  |

| в              | TSX Support in Broadwell Processors 121 |                                             |     |  |  |

|                | B.1                                     | Desktop Broadwell TSX coverage by branding  | 121 |  |  |

|                | B.2                                     | Server Broadwell TSX coverage by branding   |     |  |  |

|                | B.3                                     | Mobile Broadwell TSX coverage by branding   |     |  |  |

|                | B.4                                     | Embedded Broadwell TSX coverage by branding |     |  |  |

| Bibliography 1 |                                         |                                             |     |  |  |

## CHAPTER 1

# Introduction

It seems to be popular opinion that writing efficient programs will be increasingly difficult and expensive in the coming years, as programmers have to come up with increasingly contrived ways of exploiting available hardware. With this thesis I will show that it is possible to improve computational performance — both in terms of *energy* and *execution time* efficiency — by adapting systems' middleware layer to current workloads and hardware trends.

Improving energy efficiency is one of the main challenges for modern computer systems. In 2012 computers were one of the main electricity consumers, representing an estimated 4.6 % of the world's electricity consumption [VHLL+14] — a ratio which seems to be ever increasing [Koo08, LVHV+12, Mil13]. Reducing computer energy consumption will not only reduce the economical and environmental costs associated with computing,  $b_2^1$ ut also allow for faster computers, since most modern computers are designed to fit within a fixed power budgets. Technologies which improve computational speed can also be applied to improve computational energy efficiency, so from our perspective, both.

At a hardware level, computational speed is usually limited by feasible power consumption. Increasing power consumption reduces battery life and generates more heat. The heat generated in modern data centers results in expensive cooling requirements, which typically consume as much energy as the computers themselves. In short, improving energy efficiency makes computation cheaper, faster, less harmful to the environment, and easier to power by batteries.

Traditionally, computers have become exponentially more energy efficient, largely thanks to improvements in computer architecture and lithography [KBSW11]. The improvements in lithography directly resulted in smaller and more energy efficient transistors. The improvements in computer architecture have found ways to apply the increasing number of transistors efficiently. Unfortunately the improvements from both computer architecture and lithography have decreased over recent years, in a phenomenon known as *the end of Dennard's scaling*, which is characterized by slower performance improvements from the technology for developing and producing smaller transistors (lithography), and the technology for applying an increasing number of transistors (computer architecture).

Developments in lithography have grown increasingly complicated and expensive  $[M^+11, HH08]$ . This trend is not new, but the developments have slowed down in recent years, as the size of transistors' gate oxide approximates the size of atoms, making them more susceptible to quantum mechanical effects. The lower limit viable transistor size has been adjusted several times with unexpected technological breakthroughs [BMSMMA12], but at this moment even Intel expects transistor size reductions to be slower in the foreseeable future [Alp15]. Meanwhile, the energy efficiency benefits from smaller transistors have lessened, because the power consumption of smaller transistors is more affected by leakage power [Boh07].

Computer architectures have had difficulties in efficiently using the increasing number of transistors available on computer chips. Since the 1980's most computer architecture improvements have come from exploiting parallel computations. Some computations can be performed in parallel implicitly, while other computations must explicitly be made parallel by programmers. Implicit parallelism is more attractive, because it does not require more programming effort, but it has also yielded diminishing returns.

The end of scaling means that it has become increasingly difficult and expensive to improve computational performance in terms of execution time and energy efficiency, increasing the value of alternative approaches. From a software standpoint, we can improve computation performance through (1) improved power management, and (2) faster algorithms, particularly algorithms which expose parallelism efficiently. All energy efficiency improvements in software require some effort to apply, but reusable software components, or middleware, can improve the energy efficiency of a wide range of applications relatively cheaply. My main hypothesis is:

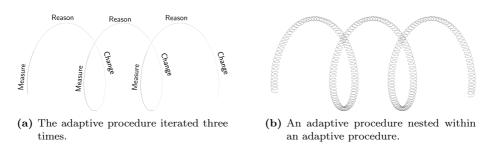

Figure 1.1: The adaptive procedure.

Middleware adapted to current needs can improve computational performance without being prohibitively expensive to deploy.

- Measuring their execution time, memory allocations, and general behavior.

- Reasoning about the programs bottlenecks, and how we can remove them.

- Changing the programs to remove the bottlenecks.

It is an iterative process, which can be repeated several times. The adaptive process can also be automated, such that the computer dynamically measures, detects bottlenecks, and changes its own behavior accordingly. Both automatic and manual adaptivity can coexist in the same system, as illustrated by Figure 1.1b. For instance, we can manually adapt an algorithm in a program which is running on a computer which automatically adapts to its workloads. Having such nested adaptive processes will affect how they change and reason about their bottlenecks, hopefully complementing each other. Manually adapting systems in the adaptive process mirrors the scientific model — stating a hypothesis (reasoning), testing the hypothesis (measuring), and accepting or rejecting the hypothesis (changing). Automatically adapting systems in the adaptive process mirrors the general structure of control systems — consisting of sensors, which measure the environment, actuators which change the environment, and control logic which decides which changes to make (reasoning).

## 1.1 Contributions

Through the adaptive approach — measuring, reasoning, and changing — we have developed a series of new middleware which can significantly improve performance:

- 1. A power management scheme pappeadapt, which reduces energy consumption by adapting the processors voltage and frequency settings to accommodate the current workload.

- On four benchmark suites, <code>pappeadapt</code> reduced energy consumption by  $41.5\,\%$  (geometric mean), without requiring any changes to the benchmarks.

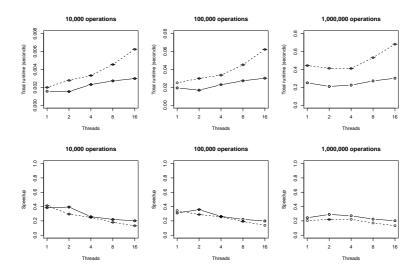

- 2. New implementations of lock and barriers which minimize the amount of time threads spend waiting for each other (blocking), by applying modern computers support for Hardware Transactional Memory (HTM).

- The lock and barrier implementations enable applications to benefit further from explicit parallelism, without requiring any changes except that the applications link against our OpenMP library (TurboBŁYSK).

- 3. BT-trees, a new efficient implementation of map data structures, providing high sequential and parallel performance on modern computers with HTM support.

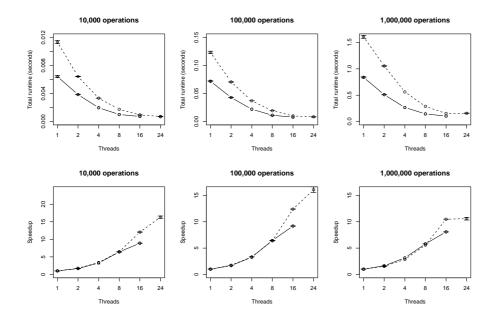

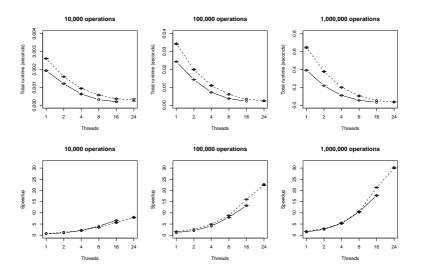

- operations on BT-trees are up to 5.3 times faster than traditional maps using HTM, and up to 3.9 times faster than state of the art concurrent ordered maps.

- 4. ELB-trees, a new implementation of relaxed map data structures, providing high parallel performance in workloads which support its relaxed semantics without requiring HTM support.

Our findings have contributed to deliverables in the PaPP project, as well as the following publications:

• Lars Bonnichsen, Sven Karlsson, Christian Probst: "ELB-trees an efficient and lock-free B-tree derivative" in the International Workshop on Multi-/Many-code Computing Systems (*MuCoCoS*) 2013, IEEE [BKP13]. This paper introduces and evaluates ELB-trees.

- Lars Bonnichsen, Christian Probst, Sven Karlsson: "Hardware Transactional Memory Optimization Guidelines, Applied to Ordered Maps" in the International Symposium on Parallel and Distributed Processing with Applications (*ISPA*) 2015, IEEE [BPK15]. This paper derives a set of guidelines for using HTM efficiently, applies the guidelines to develop the concurrent map BT-trees, and evaluates BT-trees.

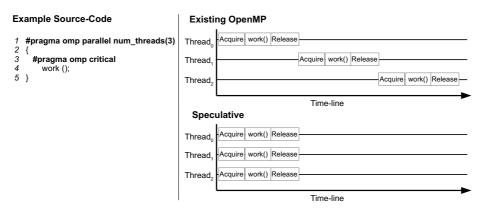

- Lars Bonnichsen, Artur Podobas: "Using Transactional Memory to Avoid Blocking in OpenMP Synchronization Directives — Don't Wait, Speculate!" in the International Workshop on OpenMP (*IWOMP*) 2015, Springer [BP15]. This paper illustrates our lock and barrier implementations, and evaluates them through an OpenMP library, on a set of benchmarks and microbenchmarks.

## 1.2 Synopsis

The rest of this dissertation is organized into the following 6 chapters:

- **Chapter 2** reviews the theory and practice of modern computers power consumption and capabilities, and relates it to our adaptive framework for software development.

- Chapter 3 presents a new power governor, pappeadapt, which improves energy efficiency by trading processor speed for lower power consumption on workloads where the processor speed is not a performance bottleneck. pappeadapt uses a variation of Amdahl's law to predict the optimal trade-off between speed and power consumption. The predictions are based on performance counter measurements from online experimentation.

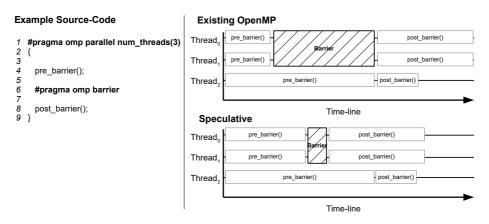

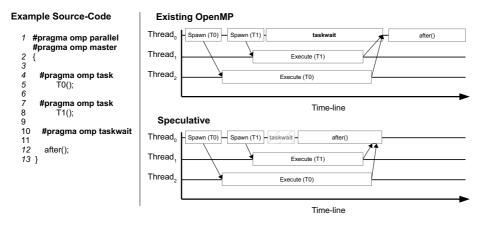

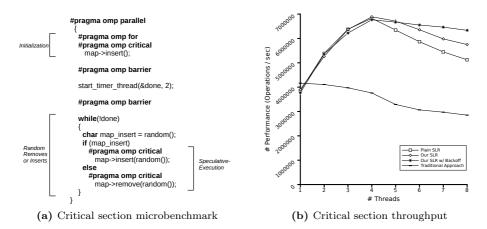

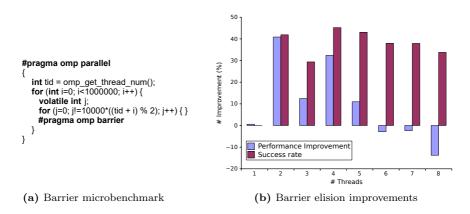

- Chapter 4 presents speculative techniques which exploit HTM allowing for further parallelism. The techniques can reduce execution time and energy consumption significantly, but may increase power consumption. We implement the speculative techniques in BLYSK, an OpenMP runtime, replacing its traditional blocking synchronization, with speculative synchronization. Speculation is not always beneficial, so we include mechanisms which minimize the drawbacks of speculation, such as the lemming effect [DLM<sup>+</sup>09]. The content of this chapter is based on a published paper [BP15].

- **Chapter 5** explores how to further reduce execution time by designing and manually rewriting code for HTM. We present five guidelines for optimizing code for speculative execution, and illustrate them on a new concurrent

ordered map, BT-trees. BT-trees benefit significantly more from speculation than traditional ordered maps — achieving high time and energy efficiency, but they are still quite straightforward, unlike traditional concurrent ordered maps. Using the the lessons learned from BT-trees, we present to a lock-free map design, ELB-trees, which can be used on computers without HTM support. The lock-free design appears to scale as well as the transactional design, but it is not as general or efficient, because it does not have the strong ordering guarantees provided by TM. The content of this chapter is based on two published papers [BPK15, BKP13].

Chapter 6 concludes the thesis by summarizing our findings, discussing their implications, and outlining possibilities for future work.

## Chapter 2

# Background

In this chapter we first introduce the terminology for expressing computational performance in Section 2.1, and before the background for reasoning about computational performance in Section 2.2. Finally we describe how we adaptively improve computational performance in Section 2.3.1

## 2.1 Power consumption

We consume energy for most activities: transportation (burning gasoline), physical activity (burning glucose), and computation (consuming electrical charge). The consumed energy does not disappear, it is transformed into other forms of energy, mainly heat: Consuming a lot of energy, typically produces a lot of heat. We generally want computations to consume less energy, so we produce less heat, reduce the computation's electrical cost, improve the computer's battery life, and potentially allow the computation to finish faster.

The energy required for an activity can be calculated from its power consumption (P) and its execution time (D, short for delay):

E = PD

We can evaluate computational performance both in terms of execution time (D)and energy consumption (E). Energy is a larger concern today due to stricter requirements on battery life, heat emissions, and electricity bills in modern systems such as mobile devices, low noise personal computers, and large scale data centers. Simply measuring either energy consumption or execution time is fine as longs the other does not change. Traditionally software developers have preferred evaluating performance with execution time, because it is easy measure and most computers we use have a fixed upper bound on power consumption, making D a good approximation of E. However, given modern hardware trends, we cannot generally assume that our power consumption is fixed, rather we should whenever possible measure both energy consumption and execution time when evaluating computational performance.

We can evaluate the combined energy and execution time cost with ED,  $ED^2$ , or another similar function. The cost ED puts equal emphasis on energy consumption and execution time, valuating 10% execution time reduction, as equally valuable as a 10% energy reduction. The cost  $ED^2$  puts additional emphasis on execution time, valuating a 10% execution time reduction, as equally valuable as a  $1 - (1 - 0.1)^2 = 19\%$  energy reduction. The cost functions can be generalized to  $ED^N$ , allowing us express the relative worth of time and energy savings.

Unlike software development, hardware development has always been very energy aware: Consuming too much power heats up the hardware, increasing its failure rate making high power consumption prohibitive. A processors power consumption depends on its CPU frequency, or more accurately on its transistors' switching frequency (f). Transistor switching frequencies and voltages are normally scaled together, traditionally satisfying the formula:

$$P \propto f^3$$

(A)

Many hardware developers traditionally used  $ED^2$  as their performance metric, because it is independent of the transistor frequency when (1) Formula (A) holds and (2) the transistor frequency is inversely proportional to execution time  $(D \propto f^{-1})$  [MNP02]. Formula (A) is a good rule of thumb for the majority of CMOS transistors deployed from 1980 to 2004. Formula (A) does not hold for entire computer systems, due to the power consumed by other components, such as monitors and storage. Formula (A) does not hold for newer transistors, due to static power consumption being a more dominant factor in their power consumption [HSN04]. The static power consumption is caused by electric charged leaked by the transistors, at a rate which is independent of the frequency, but dependent on the voltage. Dynamic power consumption and CMOS short circuiting represent the other components of transistor power consumption, components which do depend on the frequency  $(P(f) = P_{short(f)} + P_{dynamic(f)} + P_{static})$ .

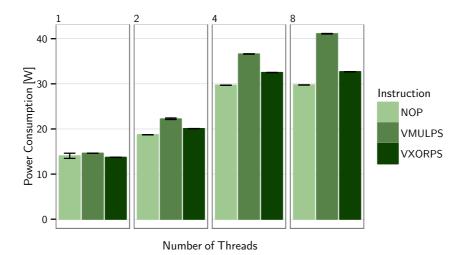

Figure 2.1: Mean processor power consumption as a function of instructions and number of threads. The error bars indicate 95% confidence intervals computed through bootstrapping.

In other words, the conditions do not hold, so we cannot assume that  $ED^2$  is independent of the frequency.

A processors power consumption is not just a function of its processor voltage and frequency, but also the code it is running and especially the amount of parallelism. For instance, Figure 2.1 shows the processor power consumption of the machine listed in Table 2.1 operating at 3.6 GHz while executing NOP instructions — doing nothing — vectorized XOR instructions — repeatedly inverting 256 bits — and vectorized multiplications. We would expect NOP instructions to be cheaper than vectorized multiplications and bit flips, an expectation which is especially true at high levels of parallelism. In the single threaded case, the

| Xeon E3-1276 v3<br>Hz, TurboBoost to 3.6 GHz |

|----------------------------------------------|

| es, 8 threads                                |

| B L1D, 8 MiB L3                              |

| 5.2.0                                        |

| tu Server 14.04.1 LTS                        |

| x 3.17.0-031700-generic                      |

| e 2.19                                       |

|                                              |

Table 2.1: Experimental machine

power consumption is fairly similar for all the instructions, while there is a larger difference in the 8 threaded case. The difference is larger in the parallel case for two reasons: (1) the higher CPU activity leads to a higher fraction of dynamic power consumption and (2) the multiplications yield higher power consumption at 8 threads than 4 due to underutilized ports at 4 threads (See 2.2.2.3), while the NOP and XOR fully utilize their ports at 4 threads.

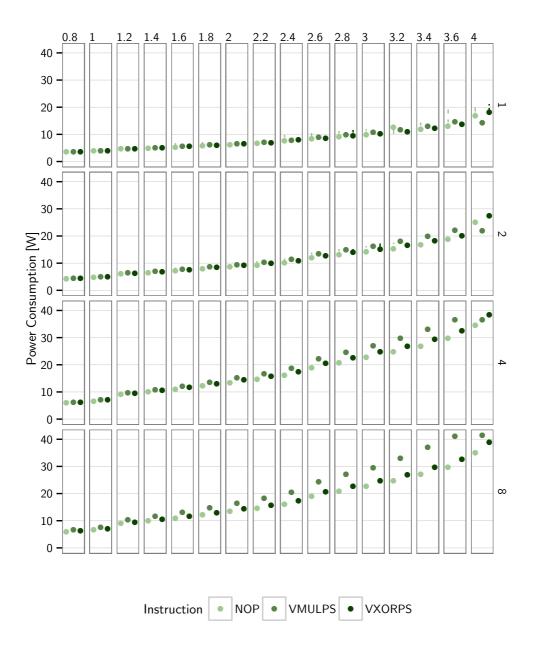

Modern Intel processors have a feature called TurboBoost, which allows the processor to automatically — at a hardware level — increase the CPU frequency and voltage when the power consumption is below safe thresholds. Modern AMD processors have a similar feature called Turbo Core. These "Turbo" features only increase the CPU frequency, when the processor power consumption is significantly lower than their Thermal Design Power (TDP) — i.e. when the processor can safely increase its power consumption [GBCH01]. Dynamically increasing the CPU frequency has varying effects based on the computers workload and number of instructions executed, as illustrated by Figure 2.2. Enabling TurboBoost, as indicated by going from 3.6 to 4 GHz, does not increase the processors frequency or clock frequency when executing instructions with high power consumption, such as the vectorized multiplication. The NOP and XOR instructions yield higher power consumption than the vectorized multiplications in the single and two threaded cases, because the TurboBoost feature operates at the highest frequency, while the effective CPU frequency is lower in the four and eight threaded cases.

Computer hardware optimizes for power consumption adaptively — based on what it is computing. To reason about software performance and power consumption – and to adaptively optimize software performance – we need an understanding of how the hardware behaves.

## 2.2 Performant computers

Modern computers apply a lot of hardware cleverness to improve their performance, both in terms of energy and execution time. This section aims to build an intuition about computational performance by briefly reviewing (1) what programs are from a low level perspective, (2) how a modern processor operates, and (3) how to quantify a processor's performance.

Figure 2.2: Median processor power consumption as a function of instructions (color), number of threads (y-axis), and CPU frequency (x-axis). The small dots indicate individual observations.

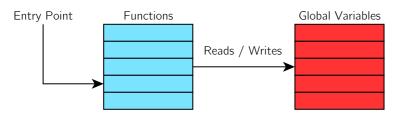

Figure 2.3: From a low level perspective programs consist of functions, global variables, and an entry point.

### 2.2.1 Instructions: The smallest program fragments

This section provides a brief introduction to what computer instructions are, such that we can discuss program behaviors at a detailed level.

Processors execute programs. Programs consist of three things, as illustrated by Figure 2.3: (1) a set of functions, (2) a set of global variables, and (3) an entry point into the program, indicating where the program starts. The global variables are essentially preallocated storage, while the functions describe what the program can do. The functions are built from instructions, which are the smallest unit of code available. Each instruction represents a small calculation or operation, such as "add A and B", "copy the value of A to B", "divide A and B", "AND the bits in A and B" (bitwise and), "count the number of set bits in A" (population count)", etc.

Instructions are seemingly executed sequentially, one at a time. Processors can change the flow of executed instructions with *jumps* and *branches*: Jumps, as in "jump to A", ensure that the instruction executed next is "A", and branches, as in "if A > B jump to C", conditionally changes the instruction executed next. Jumps and branches can be used to express conditional expressions, loops, and recursion.

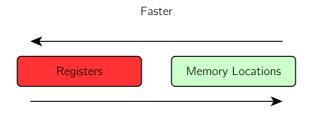

Instructions can operate on constants (immediates) and two kinds of variables (1) directly accessed *registers* and (2) indirectly accessed *memory locations*. Figure 2.4 outlines the main differences between registers and memory locations. Memory locations can be addressed as arrays in instructions, for instance A[B], or A[(B << C) + D], allowing memory locations to indirectly refer to different variables depending on the values the other variables. Registers are faster to access than memory locations, but also more limited: they cannot be addressed as an array, and are in short supply, with most processors having 14, 31, or 63 generally usable registers, while memory locations are far more abundant — most processors having memory address spaces of  $2^{32}$  or  $2^{64}$  bytes.

More general and abundant

Each processor supports a fixed set of instructions, called its Instruction Set Architecture (ISA). The ISA does not only dictate which operations are directly supported as instructions, but also how memory locations can be addressed, and which combinations of memory locations and registers can be used for instructions. The limited set of instructions and the limited number of registers available, make it difficult and time consuming to write larger programs directly with instructions.

High level languages reduce the work required by programmers with compilers which transform high level code into instructions; compilers which automatically allocate registers for intermediate computations, and select instructions and addressing modes which match the computation and the ISA.

Knowing how to read and write functions with instructions is useful to get a mental model of what a computer does, as well as a means for understanding compiler output. From a processor's ISA you can estimate how many instructions and memory accesses a computation should take; If the compiler output uses more instructions than you expected, then you can either solve the problem by writing the instructions manually, or giving the compiler more information (See Section 2.3 step 3).

### 2.2.2 Processor cleverness

This section gives a brief overview of some of the ways that modern computer architectures accelerate execution of instructions, providing a background for reasoning about program performance.

Inspecting the instructions of a computation only vaguely hints at the computations execution time, because modern computers use a wealth of tricks to

Figure 2.5: A typical cache hierarchy with 3 layers.

speed up common computations. Processors can execute instructions out of order and in parallel, as long as the instructions are sufficiently independent that the changed ordering does not change the outcome of the computation. In the following paragraphs we will describe five such techniques: caching, prefetching, pipelining. register renaming, and superscalar processing.

#### 2.2.2.1 Caches

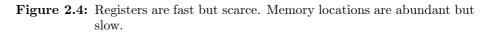

Caches provide quick — several orders of magnitude faster — access to cached memory locations. Memory accesses which are in a cache (*cache hits*) have lower latency, while memory accesses which are not in a cache (*cache misses*) suffer the full memory latency. Currently most processors provide 2-3 layers of caches, as illustrated by Figure 2.5, which dramatically reduce the average memory access latency, and allow memory operations to proceed in parallel.

The cache layers range from small and fast, to large and slow, for instance the Intel Haswell i7-4770 has an L1 cache latency of 4-5 cycles, L2 cache latency of 12 cycles, L3 cache latency of 36 cycles, and a typical RAM latency of 200 cycles [7-c]. In most applications the majority of memory accesses are to locations cached in in the L1 cache, which significantly speeds up the average memory latency.

Each cache layer tracks a fixed number of cache lines, which are typically 32, 64, or 128 continuous bytes. The cache lines are automatically added to the cache whenever they are used. Because caches have fixed sizes, adding a new cache line also evicts an old cache line, but in typical use the most recently accessed

data will be cached. Memory access through caches typically speed up access to recently accessed data (*temporal locality*) — because that memory most still in the cache, i.e. not evicted yet — and data adjacent to recently accessed data (*spatial locality*) — because adjacent data is likely in the same cache line.

Caches are separate components in the processor, responsible for accessing memory. All of the cache layers can also keep multiple memory access in flight at any time, providing a high memory bandwidth in spite of the memory latency. The lowest layer of the caches are usually duplicated, providing a private L1 cache for each processor core, while higher cache layers are shared between cores, in order to use the caches efficiently, as illustrated in Figure 2.5.

The highest layer of the cache, or the Last Level Cache (LLC) as it is normally called, is responsible for fetching memory from RAM. LLC's typically fetch multiple cache lines at a time, for instance two consecutive cache lines, because the program is likely to need the memory — and fetching two consecutive cache lines from RAM concurrently takes significantly less time than fetching two cache, one at a time — further strengthening the benefit of spatial locality.

Most modern processors also include *prefetchers*, which further exploit spatial locality, by predicting which memory locations are likely to be used next, and fetching the memory before any CPU requests it. Prefetchers can dramatically reduce memory access latency when there is a delay between each consecutive memory access, and the spatial distance between consecutive memory accesses is predictable. For instance, a program which processes consecutive cache lines at a rate of one line per 1000 clock cycle will likely to benefit from a prefetcher, because the prefetcher is likely to predict the memory access pattern, and fetch the memory before it is used for the first time.

#### 2.2.2.2 Pipelines

The processor can execute a series of instructions in parallel by executing separate stages of the instructions in a pipeline. Pipelining splits instruction execution into several shorter stages, which allows the processor to operate at a lower voltage — or a higher frequency. Instruction execution is often separated into several stages — for instance stages for fetching instructions, decoding instructions, performing calculations, etc.— with typical modern processors having10-20 pipeline stages. Pipelining works really well as long as the processor knows which instruction is executed next, but it has a harder time handling branches and indirect jumps.

A traditional pipelined processor has one instruction in flight for every pipeline

stage. When a pipelined processor encounters a branch, it has to guess whether the branch will be taken or not, because the instructions which determine the outcome of branch may be in flight. The pipeline continues operating as usual if the processor guesses correctly, but if the processor mispredicts the branch, it has to stop the instructions currently in the pipeline, waiting for them to finish. Mispredicting a branch means that the pipeline has to be flushed, i.e. a typical cost of 10-20 cycles. Modern processors have branch prediction hardware, which track the recent history of the most frequently encountered branches, to reduce branch misprediction rates. Branch prediction hardware tend to be accurate when the branches are easy to predict — for instance if they are mostly taken, or taken every other time they are executed — and inaccurate when the branches are seemingly random.

#### 2.2.2.3 Out of order processing

Out of order processors apply register renaming and superscalar execution, to exploit implicit parallelism and minimize latencies.

With register renaming, the processor does not immediately write to registers, but to a temporarily allocated buffer. This scheme allows the processor to execute instructions in parallel with instructions that use the old register value, as well as instructions which use the new value. Register renaming allows the processor to separate the start of an instructions execution (instruction issue), from the end of an instructions execution (instruction retire), allowing instructions to be underway (in flight) for a long time. Having multiple instructions in flight can hide the latency of memory accesses or slow instructions, by executing other instructions concurrently, as well as permitting further parallelism such as superscalar execution.

With superscalar execution, the processor has multiple functional units, also known as ports, each of which can execute an in flight instruction. For instance, Intel Haswell processors have 8 ports per core, each of which can execute a subset the instructions in the ISA. The ports are rarely fully utilized, so modern processors use simultaneous multi processing (SMT, or hyperthreading), letting multiple CPUs operate on a single set of ports [TEL95]. Having multiple CPUs allows the processor to execute multiple threads of the program in parallel, but the CPUs which share ports will individually execute slower if the ports become contended.

Modern out of order processors can issue several instructions per cycle — as long as the instructions are aligned properly — and retire several instructions per cycle, exposing a great deal of parallelism implicitly. Unfortunately, CPUs occasionally have to stop issuing new instructions — an action known as a frontend stall — due to two limitations in register renaming: (1) you can only have a limited number of instructions in flight — due to the limited number of temporarily allocated buffers — and (2) you can only issue a limited number of instructions after the oldest in flight instruction — because you need to track dependencies between instructions.

#### 2.2.2.4 Alternate processor designs

When combined, caches, pipelines, branch prediction, register renaming, and superscalar execution enable implicitly parallelizing instruction and memory access. The hardware required all of the cleverness takes requires a lot of transistors. Alternative processor designs, such as graphics processors (GPUs), deemphasize these forms of implicit parallelism, allowing them to fit more cores and wider vector units in the same space and power budget. Alternative processor designs tend to favor the energy efficiency through parallelism in applications which have very regular memory access patterns. As a consequence, most systems use GPUs as a way to complement regular processors, rather than replace regular processors: When GPUs can execute programs efficiently — when the program is embarrassingly parallel and has a regular memory access patters — GPUs are often significantly more efficient than regular processors, but graphics processors are not always able to execute programs efficiently. Despite the potential savings from applying GPUs, we believe the architecture of regular processors will continue to be viable for the foreseeable future.

### 2.2.3 Performance counters

Modern processors include *performance counters* which count specific events in the processor, such as:

- Executed instructions (retired instructions), which can be further classified as branches, loads from memory, stores to memory, and computations.

- Mispredicted branches and CPU frontend stalls.

- Cache misses and cache hits at the various layers of the cache.

These performance counters can guide optimization efforts:

Figure 2.6: Precise measurements have low variation. Accurate measurements have little bias.

- If the workload causes many cache misses, then try to minimize them, by reordering the data or the order of the memory accesses.

- If the workload executes many instructions, then look for a more efficient algorithm or implementation, which will execute fewer instructions.

- If the workload causes many branches, or branch mispredictions, then try to replace the branches with arithmetic, or make the branches easier to predict.

The operating system Linux has a profiling tool perf, which uses the Linux system call perf\_event\_open to access performance counters. perf can sample the performance counters while applications are running to determine which parts of the application causes most of the events. The performance counters are managed by the operating system because they are a fixed hardware resource, which applications must share. Most modern operating systems have similar tools and system calls to Linux's perf and perf\_event\_open.

Linux also provides APIs (sysfs) for reading the power controllers on modern computers, such as those on Xilinx Zynq boards [Sri15] and Intel processors (Intel RAPL) [Int15a]. The measurement facilities for performance counters and power consumption are not perfectly accurate due to hardware and software limitations, but they are representative enough to identify and classify bottlenecks, making it easy to direct optimization efforts.

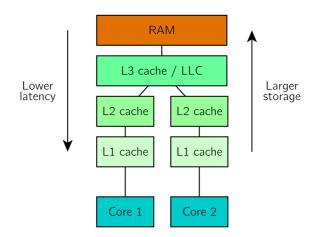

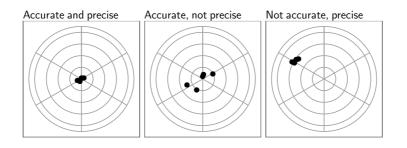

The fundamental difference between intrusive and non-intrusive profilers is that intrusive profilers are precise, while non-intrusive profilers are accurate, as illustrated by Figure 2.6. Intrusive profilers change the application under test, to precisely detect whether there is anything wrong with the application. Intrusive profiler output is precise — repeating the experiments will yield the same results — but it is not accurate — the intrusive profilers change the application, so it can be misrepresentative. Non-intrusive profilers accurately detect how well the implementation performs: Their output is accurate because the profiler does not change the function under test, but it is not precise because of measurement errors. Measurement errors are caused by inaccurate performance counters and external events, such as the room temperature, background processes running on the computer, iterrupts, randomized memory layout, and the operating systems state [WM<sup>+</sup>08, WTM13]. We can usually compensate for poor measurement precision by repeating experiments, so we can look at the distribution and median of the results, but we cannot compensate for poor measurement accuracy.

## 2.3 Optimizing software performance

In this thesis, we adapt systems to improve performance by either: (1) lowering the voltage and frequency level, increasing execution time, but lowering power consumption, or (2) running more efficiently, reducing execution time. We take the first approach in Chapter 3, and the second approach — exposing further parallelism — in Chapter 4 and 5. Section 2.3.1 describes our adaptive procedure for improving software performance, without exposing further parallelism.

### 2.3.1 Adapting software for performance

We optimize functions through an adaptive process — alternating between measuring, reasoning and changing the function — in order to gain confidence in the implementations correctness, ensure that it is efficiently compiled, and meassure its performance. The procedure typically involves iterating over 5 steps:

- 1. Write an implementation of the function.

- 2. Test the implementation using:

- (a) Static analysis tools (Frama-C, lint, etc.) and compiler options (See Listing 2.1) to detect likely bugs.

- (b) Tests that give random and valid input to function, while checking that the function output is correct. Such tests follow a Hoare Logic precondition / postcondition style, and are known as stress tests, fuzzing, and quick checking.

- (c) Intrusive profilers (such as valgrind, gprof, and pin) to detect memory leaks and incorrect use of APIs.

- 3. Sanity check the implementation with an intrusive profiler, to ensure that code is compiled efficiently.

- 4. Use a non-intrusive profiler (such as **perf** and oprofile) to detect and minimize bottlenecks.

- 5. Go to step 1 if the implementation is not fast or energy efficient enough, otherwise accept the implementation.

The following paragraphs illustrate step 2 to 4, showing the tools and methods we use in each step.

#### Step 2.a: Testing with static analysis tools

Static analysis tools and compilers with additional warnings enabled can help detect programming errors. These tools are especially useful in languages such as C and C++ which operate under the motto "the programmer is always right" letting programmers do strange things such as type casting, using unitialized variables, and omitting return values in functions. Allowing the programmer to do strange things often leads to errors; errors which compilers and static analysis tools can detect.

Modern compilers, such as GCC, LLVM, and ICC, support a wealth of *warning* options for detecting likely bugs, disallowing language features, and suggesting improvements for the code. These compilers generally do not enable all of their warning options by default, or even when using options such as -Wall, is often understood to mean "enable all warnings", but actually means "enable all warnings that most people care about": We are not "most people", in fact very few people have the exact needs of "most people", and could benefit from more aggressive warnings from compilers and static analysis tools. To illustrate, we generally use the warning issues such ranging from excessive stack usage, and dangerous type casts, to memory accesses outsde array bounds. In our opinion, using static analysis and compiler options to detecting likely bugs, and dangerous language constructs is important for all code, not just performance critical code may further benefit from compiler based suggestions for optimizations.

#### Step 2.b: Testing with fuzzing

Fuzz tests are small programs which generate valid input for functions, call the

```

_{1} gcc -c file.c -o file.o -O2 \setminus

_2 -W -Wpedantic -Wextra -Wall -Wno-unused-function -Wabi \setminus

-Wstrict-aliasing=2 -Wstrict-overflow=1 -Wabi -Wcast-align \

3

-Wstack-usage=32768 -Wframe-larger-than=32768 -Wcast-qual \

4

-Wsync-nand -Wtrampolines -Wsign-compare -Wformat-signedness \

\mathbf{5}

-Werror=float-equal -Werror=missing-braces -Werror=init-self

6

-Werror=logical-op -Werror=write-strings -Werror=nonnull \

\overline{7}

-Werror=array-bounds -Werror=char-subscripts -Werror=address \

8

-Werror=enum-compare -Werror=implicit-int -Werror=main \

9

-Werror=aggressive-loop-optimizations -Werror=sequence-point \

10

-Werror=parentheses -Werror=pointer-sign -Werror=return-type \

11

-Werror=uninitialized -Wno-error=maybe-uninitialized \

12

-Werror=volatile-register-var -Werror=ignored-qualifiers \

13

-Werror=missing-parameter-type -Werror=old-style-declaration \

14

-Wsuggest-final-types -Wsuggest-final-methods \

15

-Wsuggest-attribute=format -Wsuggest-attribute=pure \

16

-Wsuggest-attribute=const -Wsuggest-attribute=noreturn \

17

-Wsuggest-override

18

```

Listing 2.1: How we typically use the GCC compiler to detect likely errors (bright highlights), forbid certain errors (medium highlights), and suggest function annotations (dark highlights).

functions with the input, and check that the functions produce valid outputs. We usually check the output by comparing it to the output of known good functions, or by checking the function satisfies its postconditions.

Listing 2.2 illustrates fuzz testing for a logarithm base 10 function over the integers from 1 to 99. The fuzz test (Line 13) tests the our function (Line 3) on randomly generated inputs from 1 to 100 (Line 16) by comparing with the output from a known good implementation (Line 19). Because the function is defined over a small domain of inputs, we can use a simple implementation consisting of two branches, where we expect most inputs only execute one branch, since most values are presumably greater than 10. Having a simple implementation often leads to faster code which the compiler can optimize more efficiently. In other words, being aware of a functions input domain or preconditions is often important for implementing functions efficiently.

Fuzz tests are trivial to write when you know the functions preconditions and postconditions. In our example, we have a very strict precondition – the input must be in the range [1;99] small input domain, so we could also test the implementation exhaustively — over all valid inputs — but exhaustive tests are not always feasible. Randomized tests can also be used to evaluate a function implementations performance, later in the adaptive development procedure. We can usually generate representative random input much faster than the functions being tested execute, by using state of the art pseudo random number genera-

```

1 /** A log10 function over the 11 /** Compare log10New's output

domain 0-99. */

12 with log10 over random input */

3 int log10New(int val) {

2

13 void log10Test() {

4 if (val > 10)

14 int i = 1000000;

5

return 2:

15

while(--i) {

if(val > 1)

int in = random(1, 99);

6

16

int r1 = log10New(in);

7

return 1;

17

int r2 = log10(in);

return 0;

8

18

9}

assert(r1 == r2);

19

20 }

10

21 }

```

Listing 2.2: Fuzz testing a logarith base 10 function

tors, such as Mersenne Twister [MN98] or lfib4 [Mar99]. Since fuzz testing can improve our confidence in a function implementations correctness and performance, we recommend fuzz testing any safety or performance critical functions — fuzz testing may be overkill for trivial and non-critical code.

#### Step 2.c: Testing with intrusive profilers

We test whether uses APIs correctly with intrusive profilers, such as valgrind. valgrind can count the number of times functions are called — indicating whether they are used correctly — detect misaligned data access — indicating invalid type casts, and memory leaks. These tests are useful both for safety and performance critical code, because mistakes such as memory leaks often harm both correctness and performance. The following command shows how to use valgrind to detect misuses of APIs, in the program linear\_search:

```

valgrind -v --fair-sched=yes --track-origins=yes \

--leak-check=full --show-leak-kinds=all "./linear_search"

```

#### Step 3: Sanity checking with intrusive profilers

After checking the correctness of the function implementation, we can use intrusive profilers to detect whether the implementation was compiled efficiently. We need to check the quality of compiled performance critical functions, because the compiler will sometimes produce inefficient code. Inefficiently compiled code is usually caused by abstractions made in the program, abstractions which we assume the compiler can optize. There are limits to how much a compiler can optimize our programs automatically, because compilers are tools; not magic wands. We can check the quality of compiled code with with intrusive profilers, such as valgrind and pin, by asking them to count the number of instructions executed or memory references. Poorly compiled code will often execute far more instructions and memory references than neccessary, making them easy to

```

1 // Running valgrind from a shell

2 valgrind --fair-sched=yes --tool=cachegrind --cache-sim=yes \

"./linear\_search"

3

4 cg\_annotate --show='Dw' \$(ls -t cachegrind.out.* | head -n 1) \

--auto=yes --threshold=2

5

6 \text{ cg}_annotate --show='Ir' \ (ls -t cachegrind.out.* | head -n 1) \

--auto=yes --threshold=2

7

8

9 // Valgrind output showing the problem

Dw

10

. void linearSearch(int*i, int*array, int value, int n) {

11

12 33,000,000

for(*i = 0; *i < n; *i += 1)

if(array[*i] == value)

13

0

return:

14

.

. }

15

```

```

Listing 2.3: Using valgrind to detect code paths which contribute to more than 2% of the total number of memory writes and instructions executed in the program linear_search.

```

detect.

Listing 2.3 illustrates how to use valgrind to look for poorly compiled code in linear\_search, an exaple program performing 1,000,000 linear searches over an array of length 32. After running the code (Line 2) we ask valgrind to show us the code which causes most writes (Line 4), and we are informed that the linear search performs 33,000,000 writes (Line 12), whereas we would expect it to perform 1,000,000 writes — one write per call to the function. The compiler generated code which writes to memory whenever the code increments the index i, because the compiler did not know whether i overlaps with the array — a problem known as pointer aliasing, because it occurs when two pointers point to the same data. Since the function linear\_search does not indicate whether the pointer alias the compiler has to assume that they can alias, generating code which writes to memory whenever i is updated, rather than just at the end of the function call. Pointer aliasing is a common problem, and in this case we could solve the problem in three ways: (1) tell the compiler that **array** and **i** do not overlap, by annotating them with the type qualifier restrict, (2) move the function linearSearch to a header file, so it can be inlined from its call sites and the compiler can determine if the array and i alias, or (3) ask the compiler to perform whole program optimization or link time optimization, so the compiler can determine if the **array** and **i** alias.

Intrusive profilers can also reveal problems such as redundant branches, which were not optimized out because the compiler did not know the valid range of variables. Such problems can be fixed by restricting the valid range of variables, for instance: if (A < 1) \_\_builtin\_unreachable(); will inform compilers such as GCC and LLVM that A cannot be smaller than 1.

Using intrusive profiler output often requires that we reason about performance critical code using a mental model of what the code's instructions should be. The output makes it easy to filter away non performance critical code, saving a lot of developer effort compared to manually inspecting the code's instructions, but it is still time consuming and it only makes sense for applications which are performance critical.

#### Step 4: Detecting bottlenecks with non-intrusive profilers

After whether the function implementation is correct and properly compiled, we can use non-intrusive profilers such as **perf** to measure the performance of the function, and to detect its bottlenecks. To illustrate, we can use **perf** to measure the performance of a program, such as **linear\_search**, with the shell command:

```

perf stat -e L1-dcache-load-misses -e L1-dcache-store-misses \

-e cache-misses -e cycles -e instructions -e cpu-clock \

-e task-clock -e page-faults -e minor-faults "./linear_search"

```

The measurement can be used to compare the performance metrics of different implementations, allowing us to shed some light on how they perform. We usually supplement the performance metrics with measurements of energy consumption through APIs like Intel RAPL.

perf to detect bottlenecks in programs — in this case linear\_search — using commands like:

perf record --call-graph dwarf -F 39 -e task-clock "./linear\\_search"

perf report

The bottlenecks indicate where the program spends its time, allowing us to direct further optimization efforts.

#### Discussion

Executing an iteration of the adaptive procedure, from step 1 to 4, gives us confidence that the function implementation is correct, efficiently compiled, and tells us how well it performs. The adaptive procedure contains nested adaptive behavior; we repeatedly adapt the implementation in step 2.a, 2.b, 2.c, 3, and 4. We change the function implementation and measure its behavior until it

satisfies the requirements that we expect from our reasoning. The process is time consuming, but we have found it worthwhile, because it gives us a framework for supporting development of performance and safety critical code.

The format that we have described only operates on a single function. The adaptive process is normally nested in an adaptive process for optimizing all performance critical functions in the whole program. To minimize the effort required for implementing functions, we normally only use the development procedure for performance and safety critical code. While the process requires a good deal of effort, we have also outlined cases where the different steps can be skipped, and we believe that it is the minimum required effort to be reasonably confident that our implementations are efficient and correct.

We have used the development procedure while developing the middleware described in the remainder of this thesis. In some cases, we use the adaptive procedure was mostly to ensure correctness of the code, in other cases we use the procedure to optimize the code. We have generally found that the the effort required for the adaptive development procedure is lower than normal, unstructured, and ad-hoc program development. The main benefit from the procedure came in the form of improved implementations, and understanding of errors in early forms of the middleware, but in some places we also improved our designs by repeatedly changing, measuring, and reasoning about it.

## Chapter 3

# Workload Aware Energy Management

In Chapter 2 we showed that setting CPU frequencies is a delicate tradeoff between execution time and power consumption. Reducing a processor's frequency and voltage trades a reduced its power consumption, for an increased execution time: Reducing the processors dynamic power consumption is not always a viable method for reducing the systems energy consumption due to the static power consumption (current leakage) and the power consumption from other components, such as memories and screens.

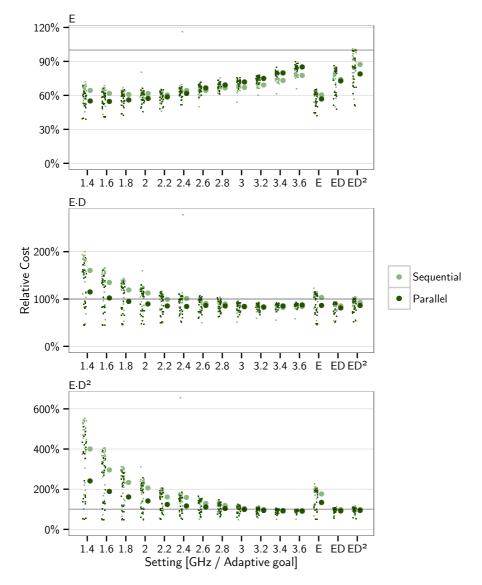

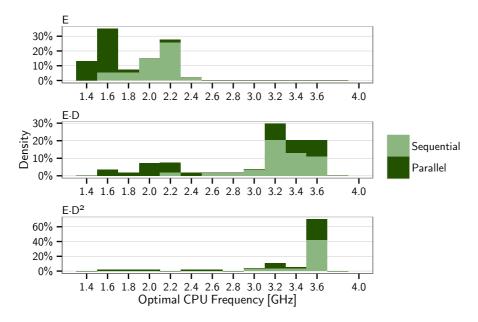

In this chapter we introduce pappeadapt (pronounced papp-e-adapt), a power governor which automatically reduces the CPU frequency when reducing the frequency does not significantly increase the execution time. pappeadapt reduces the processors geometric mean energy consumption by 41.5%, ED by 16.4%, and  $ED^2$  by 4.7%, on the benchmark suites NPB 3.3.1 [BBB+91], SPEC2006 [Hen06], PARSEC 3.0 [Bie11], SPLASH-2x [WOT+95].

pappeadapt uses a combination of online experimentation and prediction to adapt the CPU frequency. The predictions are based on Amdahl's law, cheap to calculate, and very precise.

This chapter introduces:

- Two microbenchmarks which exemplify compute-bound and memory-bound workloads.

- The compute-bound microbenchmark can be used to identify good fixed CPU frequencies which provide good energy costs  $(ED^N)$ .

- The proposal and evaluation of a model, based on Amdahl's law, for predicting the execution time of memory-bound workloads.

- An adaptive method for optimizing CPU frequencies to the systems current workload.

This chapter is structured as follows: Section 3.1 illustrates why, when, and how we can save energy by reducing CPU frequencies. Section 3.2 evaluates the effects of statically or adaptive reducing CPU frequencies. Section 3.3 relates our work to prior work, Section 3.4 suggests improvements to pappeadapt based the evaluation and the related work, and finally Section 3.5 summarizes our findings.

### 3.1 CPU frequencies and workloads

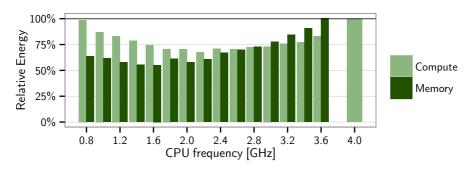

We can reduce energy costs  $(E, ED, \text{ and } ED^2)$  by selecting the right CPU frequency. The optimal CPU frequency is not necessarily the highest or lowest supported CPU frequency, and the optimal frequency also depends on the system's workload. To illustrate this point Figure 3.1 shows the processor energy consumption as a function of the CPU frequency in a memory-bound and a compute-bound microbenchmark, on an Intel Xeon based server server dubbed **xeon** (see Table 3.1.

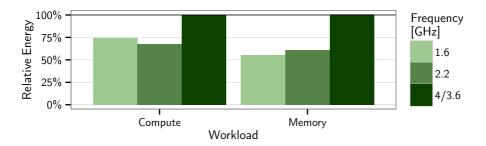

The most energy efficient CPU frequencies on **xeon** are  $f_{hi} = 2.2 \text{ GHz}$  and  $f_{lo} = 1.6 \text{ GHz}$  in the compute and memory-bound workloads respectively. Figure 3.2 shows the relative energy consumption at  $f_{lo} f_{hi}$  and the baseline (4 GHz and 3.6 GHz). On **xeon**, restricting the CPU frequency to  $f_{hi}$  saves 32% to 39% energy, and restricting the CPU frequency to  $f_{lo}$  saves 25% to 45%. Simply restricting the CPU frequency to  $f_{hi}$  or  $f_{lo}$  can improve energy efficiency significantly.

We have made similar observations on a small Intel NUC dubbed **snuc** (see Table 3.1), and when optimizing for energy delay products (ED), or energy delay squared products  $(ED^2)$ : The optimal CPU frequency depends on the workload, it is lower for memory-bound workloads  $(f_{lo})$  and higher for compute-bound workloads  $(f_{lo})$ . Optimizing for ED yields higher optimal CPU frequencies than optimizing for E, and optimizing for  $ED^2$  yields the highest optimal CPU

Figure 3.1: xeon's processor relative energy consumption in two workloads. Section 3.1.2 describes the workloads. Lower is better.

Figure 3.2: Energy consumption at 1.6 GHz, 2.2 GHz, and the baseline. Lower is better.

frequencies. The highest possible CPU frequency (the baseline) frequently yields the optimal (lowest)  $ED^2$  in compute-bound workloads. Restricting the CPU frequency to  $f_{lo}$  in the compute-bound workload increases ED by 41% and  $ED^2$  by 181% on **xeon**. Simply restricting the CPU frequency to  $f_{hi}$  may slightly improve ED and  $ED^2$ , while restricting the CPU frequency to  $f_{lo}$  may dramatically harm ED and  $ED^2$ .

#### Relationship between throughput and Frequency

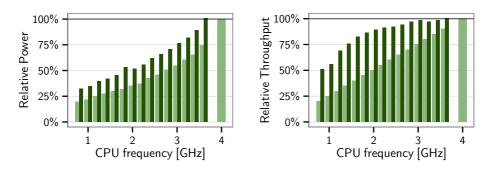

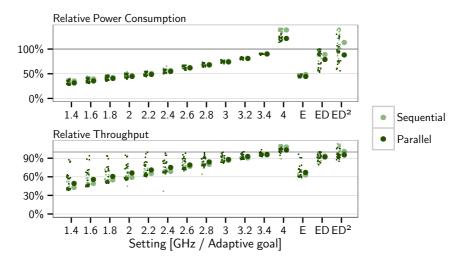

Figure 3.3 explains why the optimal CPU frequency is workload dependent: Throughput is workload dependent, growing linearly when compute-bound, and sublinearly when memory-bound, while power consumption grows with the frequency regardless of the workload. Compute-bound workloads maximize their energy efficiency at higher CPU frequencies than memory-bound workloads, because compute-bound workloads' throughput benefit more from high CPU frequencies.

Figure 3.3: xeon's processor power consumption and throughput in two workloads. Lower is better.

Memory-bound workloads spend the majority of their execution time off-chip fetching memory from RAM, while most execution time in compute-bound workloads is spent on-chip, crunching numbers, branching, or fetching memory from caches. On-chip activities speed up linearly with the CPU frequency, while off-chip activities are independent of the CPU frequency, allowing us to model execution time from the time spent on on-chip activities ( $C_{on}$ ) measured in clock cycles, and the time spent on off-chip activities, measured in seconds:

$$D = D_{off} + \frac{C_{on}}{f},\tag{1}$$

The model can be derived from Amdahl's law  $\left(D(n) = D(1)\left(s + \frac{1-s}{n}\right)\right)$  by substituting the speedup factor (n) with f, and the unimproved fraction (s) by  $\frac{D_{off}}{D_{off}+C_{onf}-1}$ . The model assumes that on-chip and off-chip activities do not overlap, simplifying the model, but it can still accurately predict relative execution time.

| Name                                                                                | xeon                                                                                                                | snuc                                                                          |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Processor                                                                           | Intel Xeon E3-1276 v3                                                                                               | Intel Celeron N2820                                                           |

| CPU Frequency                                                                       | $3.6\mathrm{GHz}$ , boost to $4\mathrm{GHz}$                                                                        | $2.13\mathrm{GHz}$ , boost to $2.4\mathrm{GHz}$                               |

| Processor cores                                                                     | 4 cores, 8 threads                                                                                                  | 2  cores, 2  threads                                                          |

| Processor caches                                                                    | 32 KiB L1D, 8 MiB L3                                                                                                | ??? L1D, 1 MiB L2                                                             |

| C/C++ Compiler                                                                      | GCC 5.2.0                                                                                                           | GCC 5.2.0                                                                     |

| Operating system                                                                    | Ubuntu Server 14.04.1 LTS                                                                                           | Fedora LXDE 21                                                                |

| Kernel                                                                              | Linux 3.17.0-031700-generic                                                                                         | ???                                                                           |

| C library                                                                           | eglibc 2.19                                                                                                         | glibc ???                                                                     |

| Processor cores<br>Processor caches<br>C/C++ Compiler<br>Operating system<br>Kernel | 4 cores, 8 threads<br>32 KiB L1D, 8 MiB L3<br>GCC 5.2.0<br>Ubuntu Server 14.04.1 LTS<br>Linux 3.17.0-031700-generic | 2 cores, 2 threads<br>??? L1D, 1 MiB L2<br>GCC 5.2.0<br>Fedora LXDE 21<br>??? |

Table 3.1: Experimental machines

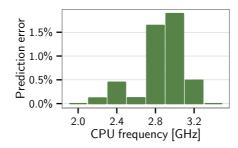

Figure 3.4: Difference between measured and predicted execution time from formulae (2) and (3). Lower is better.

#### Predicting execution time

Based on two performance measurements at different CPU frequencies, we can predict the performance at any CPU frequency, with the following relation, derived from Equation (1):

$$D \propto m + f^{-1},\tag{2}$$

where *m* represents how memory-bound the workload is. Given  $D_1$ , the execution time at CPU frequency  $f_1$ , and  $D_2$ , the execution time at CPU frequency  $f_2$  (with  $f_1 \neq f_2$ ) we have:

$$\frac{D_1}{D_2} = \frac{m + f_1^{-1}}{m + f_2^{-1}} \Leftrightarrow \underline{m} = \frac{D_2 f_2 - D_1 f_1}{f_1 f_2 (D_1 - D_2)}$$

(3)

We can predict the relative execution time at any CPU frequency with Formula (2) once we know m. Figure 3.4 shows the difference between the predicted and measured execution time in the memory-bound workload, where the predictions are based on the execution times at the CPU frequencies 2.0 GHz and 3.4 GHz. The predictions deviate at most 1.9% from the measurements, indicating that the predictions are more than accurate enough. We can predict which CPU frequency is most energy efficient from the estimated execution times and power consumption at every CPU frequency.

#### 3.1.1 The power manager

Our power manager pappeadapt optimizes energy costs  $(ED^N)$  by adapting the CPU frequency to the current workload. We implemented pappeadapt as a seperate program, which monitors all applications on the system as they are running (online). pappeadapt experimentally uses the CPU frequencies  $f_{lo}$  the lowest potentially optimal CPU frequency — and  $f_{hi}$  — the highest potentially optimal CPU frequency — to identify how memory-bound the workload using equation (3). Based on the estimate pappeadapt predicts which frequency is optimal with formula (2). pappeadapt adapts to changing workloads by repeating the experiment and prediction approximately once per second. In order to make the online adaptivity, pappeadapt requires a brief training step.

#### Ahead of time training

pappeadapt requires a training session before use: run the compute and memorybound microbenchmarks at each possible CPU frequency, while measuring the systems power consumption, cache misses, and execution time. From the training data, we can determine:

- $f_{lo}$  The most efficient CPU frequency for the memory-bound workload.

- $f_{hi}\,$  The most efficient CPU frequency for the compute-bound workload.

- $\vec{P}$  The relative power consumption at every CPU frequency. We measure this for the compute-bound workload, and assume that proportional power consumption is independent of the workload.

- $cm_{lo}$  10% of the cache miss rate of the memory-bound workload. We assume workloads with fewer cache misses are compute-bound.

The training step takes less than 2 minutes on **xeon**. We conduct cache measurements with Linux **perf** and power measurements using Intel RAPL, which measures the energy consumed by the entire processor package (cores, caches, integrated GPUs, etc.).

#### **Online adaptivity**

pappeadapt adapts the systems CPU frequency in real time with the 4 step procedure in Listing 3.1:

1. Measure the performance of the frequency  $f_{hi}$  for 0.1 seconds (see Line 3). Repeat this step as long as the cache miss rate (cm) is very low (Line 4).

```

1 while(true) {

do { // 1. Experiment with fHi

2

hi = measure(fHi, 0.1);

3

} while(hi.cm <= cmLo);</pre>

4

// 2. Experiment with fLo

\mathbf{5}

lo = measure(fLo, 0.1);

6

// 3. Predict the best frequency

7

if (lo.ir >= hi.ir) {

8

best = F[0];

9

} else {

10

11

m = (fHi*lo.ir-fLo*hi.ir) /

(fHi*fLo*(hi.ir-lo.ir));

12

bestCost = P[0] *

13

pow(m + 1/F[0], N + 1);

14

best = F[0];

15

16

for (i = 1..nF-1) {

17

newCost = P[i] *

18

pow(m + 1/F[i], N + 1);

19

if(newCost < bestCost) {</pre>

20

bestCost = newCost;

21

best = F[i];

22

}

23

}

24

}

25

// 4. Use the best frequency

26

for(i=1..8) {

27

tmp = measure(best, 0.1);

28

if(tmp.cm<cmLo && best!=fHi)</pre>

29

break:

30

}

31

32 }

```

Listing 3.1: The pappeadapt's energy saving procedure.

- 2. Measure the performance of the frequency  $f_{lo}$  for 0.1 seconds (Line 6).

- 3. Predict the best CPU frequency, in two steps:

- (a) Use the measurements to estimate how memory-bound the workload is with Equation (3) (Line 11 12).

- (b) Use the estimate to predict the cost of the different CPU frequencies with Formula (2). Select the frequency with the lowest cost (Line 17 – 24).

- 4. Use the predicted best CPU frequency for 0.8 seconds (Line 27). Restart the procedure early, if the system exhibits very few cache misses (Line 29).

The procedure uses the function measure(frequency, time), which sets the CPU frequency to frequency, measures all applications on the computer for

```

1 char array[256 << 20];</pre>

2 memset(array, 1, 256 << 20);</pre>

3 for(int j = 0; j < 16; j++) {</pre>

for(int i = 0; i < 256 << 20; ) {

1 volatile int a = 0:

_2 while (a < 512 << 20)

char inc = array[i];

5

a++:

array[i] = inc * inc;

3

6

i = i + inc * 256;

7

(a) Compute-bound micro-

}

8

benchmark

9 }

(b) Memory-bound microbenchmark

```

Listing 3.2: The microbenchmarks

time seconds, and returns the cache misses per second (cm) and instructions retired per second (ir). We estimate the workloads performance with the instruction retire rate (ir) — the number of instructions executed — implicitly assuming that the instruction retire rate would be constant if we did not change the CPU frequency. Generally we cannot assume that the instruction retire rate will be constant — the workload can change while we were measuring, and it can enter a different phase of computation — but because we are measuring in short durations the workloads behavior is likely unchanged [SEH11]. As such, our predictions are based on Equation (3), by substituting  $D = \frac{1}{ir}$ .

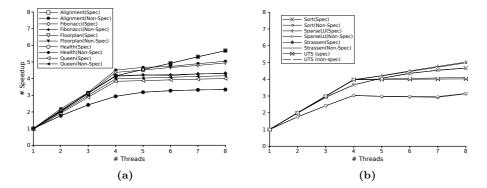

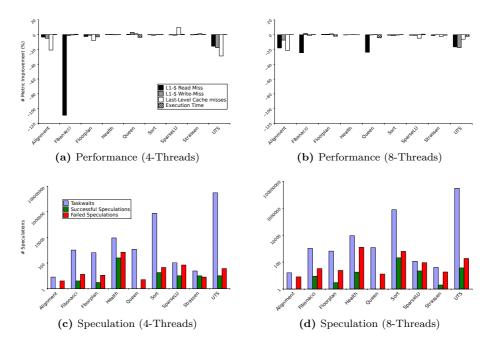

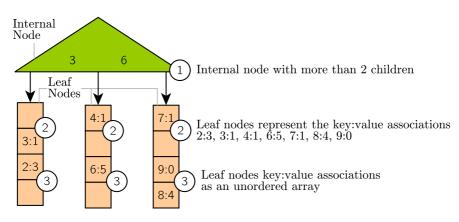

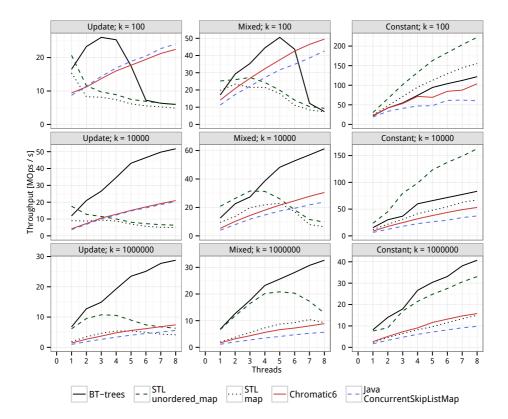

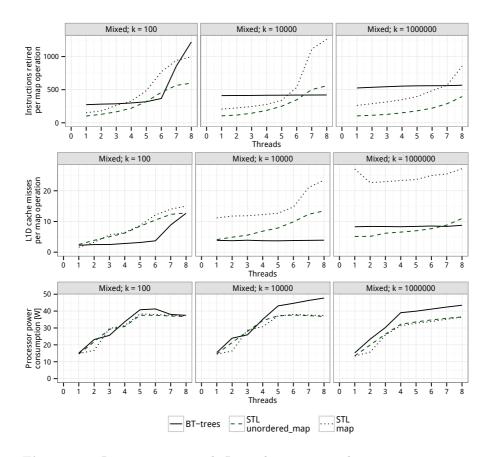

#### 3.1.2 The microbenchmarks