#### Technical University of Denmark

#### An Asynchronous Time-Division-Multiplexed Network-on-Chip for Real-Time Systems

Kasapaki, Evangelia; Sparsø, Jens; Schoeberl, Martin

Publication date: 2015

Document Version

Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA)

Kasapaki, E., Sparsø, J., & Schoeberl, M. (2015). An Asynchronous Time-Division-Multiplexed Network-on-Chip for Real-Time Systems. Kgs. Lyngby: Technical University of Denmark (DTU). (DTU Compute PHD-2015; No. 361).

#### DTU Library

Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# An Asynchronous Time-Division-Multiplexed Network-on-Chip for Real-Time Systems

Evangelia Kasapaki

Kongens Lyngby 2015 PhD-2015-361

Technical University of Denmark

Department of Applied Mathematics and Computer Science

Matematiktorvet, building 303B,

2800 Kongens Lyngby, Denmark

Phone +45 4525 3351

compute@compute.dtu.dk

www.compute.dtu.dk PhD-2015-361

#### **Summary (English)**

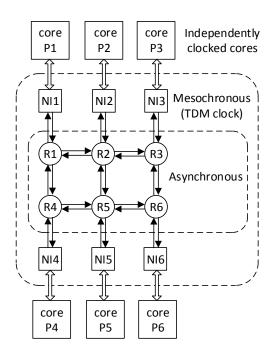

Multi-processor architectures using networks-on-chip (NOCs) for communication are becoming the standard approach in the development of embedded systems and general purpose platforms. Typically, multi-processor platforms follow a globally asynchronous locally synchronous (GALS) timing organization. This thesis focuses on the design of Argo, a NOC targeted at hard real-time multi-processor platforms with a GALS timing organization.

To support real-time communication, NOCs establish end-to-end connections and provide latency and throughput guarantees for these connections. Argo uses time division multiplexing (TDM) in combination with a static schedule to implement virtual end-to-end circuits. TDM is a straightforward way to provide guarantees and to share the resources efficiently, and it has an efficient hardware implementation. Argo supports a GALS system organization, and additionally it explores more flexible timing within its structure, to address signal distribution issues, using a network of asynchronous routers.

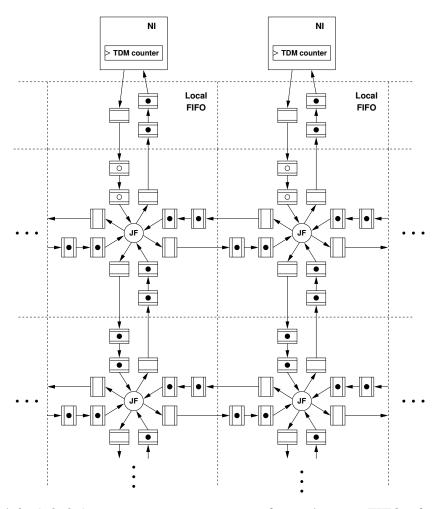

NOCs consist of a switching structure of routers connected by links, with network interfaces (NIs) that connect the processors to the switching structure. Argo uses a novel NI design that supports time-predictability, and asynchronous routers that form a time-elastic network. The NI design integrates the DMA functionality and the TDM schedule, and uses dual-ported local memories. The routers combine the router functionality and asynchronous elastic behavior. They also use a gating mechanism to reduce the energy consumption. The combination of the NI design and the router design supports the formation of end-to-end paths in the NOC, from the local memory of a sending core to the local memory of a receiving core. These end-to-end paths do not require any dynamic arbitration, buffering, flow control, or clock synchronization, in the routers or the NIs.

This thesis explores the implementation of the individual components of Argo, as well as several complete instances of the Argo NOC. The implementations target both FPGA technology and 65 nm CMOS technology. It is shown that (i) the NI design is scalable and four to five times smaller than previously published NIs for similar NOCs, (ii) the router design is power efficient and two to three times smaller than equivalent router designs, and (iii) the overall Argo NOC is around four times smaller than other TDM NOCs. Argo is an important part of the T-CREST paltform and used in a number of configurations.

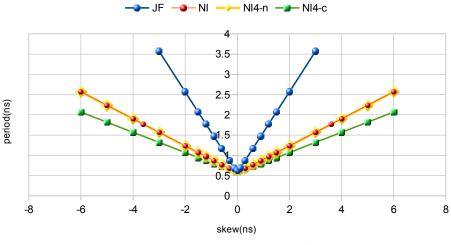

The flexible timing organization of Argo combines asynchronous routers with mesochronous NIs, which are connected to individually clocked cores, supporting a GALS system organization. The mesochronous NIs operate at the same frequency, possibly with some skew, while the network of asynchronous routers absorbs this skew within certain limits. The elasticity of the asynchronous network is explored, answering the question of how much skew the Argo NOC can absorb. A qualitative analysis studies the parameters affecting the elasticity and its limits. A quantitative analysis models the Argo behavior using timed-graph models and worst-case timing separation of events analysis to evaluate the elasticity of Argo. The results show that the skew absorbed by the network of routers can be two or more cycles, depending on the frequency applied at its endpoints, the NIs.

Overall this thesis presents the design and implementation of Argo, and the analysis of its elastic behavior. It shows that Argo provides hard real-time guarantees in a straightforward way, it has an efficient implementation and it is time-elastic.

#### Resumé (Dansk)

Multi-processor arkitekture der bruger intra-chip netværk (eng: NOCs) til kommunikation er ved at blive en standard tilgangen i udviklingen af indlejrede systemer og generelle platforme. Typisk er tidssynkroniseringen i en multi-processor platform organiseret i et globalt asynkron lokalt synkron (GALS) domæne. Denne afhandling fokusere på designet af Argo, der er et NOC målrettet til multi-processor platforme til hårde realtids systemer med en GALS organisering af tidssynkroniseringen.

For at supportere realtids kommunikation, etablere NOCs end-to-end forbindelser og tilvejebringer latens og gennemløbs garantier for disse forbindelser. Argo bruger tidsmultiplexing (eng: TDM) i kombination med en statisk tidsplan til at implementere virtuelle end-to-end kredsløb. TDM er en ligefrem måde hvorpå garantier og effektiv deling af ressourcer kan tilvejebringes med en effektiv hardware implementering. Argo supportere systemer organiseret ved hjælp af GALS og derudover kan Argo bruges til at udforske en struktur med en mere fleksibel tidssynkronisering, der adressere signal distributions problemer med et netværk af asynkrone routere.

NOCs består af en kommunikations struktur af routere forbundet af links, med et netværks interface (NI), der forbinder processorne til kommunikations strukturen. Argo bruger et nyt NI design der supportere tidsforudsigelighed og asynkrone routere der udgøre et tidselastisk netværk. NI designet integrer DMA funktionaliteten og TDM tidsplanen, og bruger to-ported lokale hukommelser. Routerne kombinere routingsfunktionalitet og den asynkrone elastisk opførsel. Routerne bruger også en gating mekanisme til at reducere energi forbruget. Kombinationen af NI designet og router designet supportere kommunikations kannaler gennem NOC'et, fra den lokale hukommelse hos en sendende kerne til den lokale hukommelse hos en modtagende kerne. Disse kommunikations kannaler kræver ingen dynamisk arbitrering, buffering, flow kontrol eller klok synkronisering i hverken routere eller NI'er.

Denne afhandling udforsker implementationer af de individueller komponenter i Argo, såvel som en række af komplette instanser af Argo NOC'en. Implementationerne henvender sig både til FPGA teknologi og 65 nm CMOS teknologi. Det bliver vist at (i) NI designet er skalerbart og fire til fem gange mindre end tidligere publiceret NI designe af lignende NOC'er, (ii) router designet er energi effektivt og to til tre gange mindre end lignende router design, og (iii) i alt

er Argo NOC'et cirka fire gange mindre end andre TDM NOC'er. Argo er en vigtig del af T-CREST platformen og brugt i et antal af konfigurationer.

Argos fleksible tidssynkroniseret organisation kombinere asynkrone routere med mesokrone NI'er, som er forbundet til individuelt klokkede kerner, der supportere GALS system organisation. De mesokrone NI'er operere ved den samme frekvens, muligvis med tidsforskydelse af klokken, men netværket af asynkrone routere kan absorbere denne tidsforskydning op til en vis grænse. Elasticiteten af det asynkrone netværk bliver udforsket for at svare på spørgsmålet, hvor meget tidsforskydning af klokken kan Argo NOC absorbere. En kvalitativ analyse studere hvordan parametre påvirker elasticiteten og dens grænser. En kvantitativ analyse modellere Argos opførsel ved hjælp af timed-graph modeller og en analyse af værste tilfælde af tidsseparation mellem begivenheder for at evaluere elasticiteten af Argo. Resultatet viser at den tidsforskydelsen af klokken som netværket af routere kan absorbere er to eller flere klok cykler, afhængigt af den frekvens der påvirker NI'erne.

Samlet set præsentere denne afhandling design og implementation af Argo og analysen af dennes elastiske opførsel. Afhandlingen viser at Argo levere hårde realtids garantier på en ligefrem måde, samt har en effektiv implementation og en elastisk tidsopførsel.

#### **Preface**

The work of this thesis was conducted at the Department of Applied Mathematics and Computer Science at the Technical University of Denmark in fulfillment of the requirements of the Ph.D. program. The work of this thesis was partially funded by the European Union's 7th Framework Programme project Time-predictable Multi-Core Architecture for Embedded Systems (T-CREST) under grant agreement no. 288008. The work of this thesis comprises work package 3 of the T-CREST project. The result of this thesis is part of the T-CREST platform and is avaliable under the BSD open source licence.

This work was supervised by Professor Jens Sparsø and Associate Professor Martin Schoeberl. Some of the results presented in this thesis were obtained in collaboration with Rasmus Bo Sørensen, Christoph Müller, and Ioannis Kotleas. The text of the thesis indicates whenever results of such a collaboration are presented. The integration of the T-CREST platform was a collective effort of the whole T-CREST project group. In addition, Joachim Rodrigues and Oskar Andersson from the Department of Electrical and Information Technology of Lund University provided help with the EDA tools.

The thesis describes the design and implementation of the Argo NOC and an analysis of its elastic timing. The thesis consists of ten chapters organized in four parts. The first part introduces the subject and presents the state of the art. The second part presents the design and implementation of the Argo NOC. The third part presents the analysis of its elasticity. The fourth part concludes the thesis.

The thesis does not contain any material that has been accepted for the award of any other degree or diploma in my name, in any university or other institution and, to the best of my knowledge does not contain any material previously published by another person, except where due reference is made in the text of the thesis.

Lyngby 27 March 2015

Evangelia Kasapaki

# Publications and Technical Reports

#### **Journal Publications**

- M. Schoeberl and S. Abbaspour and B. Akesson and N. Audsley and R. Capasso and J. Garside and K. Goossens and S. Goossens and S. Hansen and R. Heckmann and S. Hepp and B. Huber and A. Jordan and E. Kasapaki and J. Knoop and Y. Li and D. Prokesch and W. Puffitsch and P. Puschner and A. Rocha and C. Silva and J. Sparsø and A. Tocchi. T-CREST: Time-predictable Multi-Core Architecture for Embedded Systems. In Journal of Systems Architecture, 2015. published online, to appear in print.

- 2. E. Kasapaki and M. Schoeberl and R. B. Sørensen and C. T. Müller and K. Goossens and J. Sparsø. Argo: A real-time network-on-chip architecture with an efficient GALS implementation. In IEEE Transactions on VLSI Systems, 2015, to appear.

#### Conference Publications

- 1. E. Kasapaki, and J. Sparsø. The Argo NOC: Combining TDM and GALS. In *ECCTD*, 2015, Aug 2015.

- 2. C. Müller, E. Kasapaki, R. Sørensen, and J. Sparsø. Synthesis and layout of an asynchronous network-on-chip using standard EDA tools. In *NORCHIP*, 2014, pages 1–6, Oct 2014.

- 3. I. Kotleas, D. Humphreys, R. Sørensen, E. Kasapaki, F. Brandner, and J. Sparsø. A loosely synchronizing asynchronous router for TDM-scheduled NOCs. In *Networks-on-Chip (NoCS)*, 2014 Eighth IEEE/ACM International Symposium on, pages 151–158. IEEE, Sept 2014.

- 4. E. Kasapaki and J. Sparsø. Argo: A time-elastic time-division-multiplexed NOC using asynchronous routers. In *Proc. IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC)*, pages 45–52. IEEE Computer Society Press, May 2014.

- 5. E. Kasapaki, J. Sparsø, R. Sørensen, and K. Goossens. Router designs for an asynchronous time-division-multiplexed network-on-chip. In *Proc. of Euromicro Conference on Digital System Design (DSD)*, pages 319–326, Sept. 2013.

- 6. J. Sparsø, E. Kasapaki, and M. Schoeberl. An area-efficient network interface for a TDM-based network-on-chip. In *Proc. Design Automation and Test in Europe (DATE)*, pages 1044–1047, Mar. 2013.

- 7. M. Schoeberl, F. Brandner, J. Sparsø, and E. Kasapaki. A statically scheduled time-division-multiplexed network-on-chip for real-time systems. In *Proc. IEEE/ACM International Symposium on Networks-on-Chip (NOCS)*, pages 152–160, May 2012.

#### **Technical Reports**

- 1. E. Kasapaki and R. B. Sørensen. Argo programming guide.

- 2. T-CREST Project. D3.1 Survey of time-predictable and asynchronous NOCs, and their WCET analysis. http://www.t-crest.org/page/results, 2014.

- 3. T-CREST Project. D3.2 Simulation model of the self-timed NOC. http://www.t-crest.org/page/results, 2014.

- 4. T-CREST Project. D3.3 Hardware implementation of the self-timed NOC. http://www.t-crest.org/page/results, 2014.

- 5. T-CREST Project. D3.4 Report documenting the hardware implementation of the self-timed NOC. http://www.t-crest.org/page/results, 2014.

- 6. T-CREST Project. D3.5 Report on impact of asynchronicity on predictability of the NOC. http://www.t-crest.org/page/results, 2014.

- 7. T-CREST Project. D3.6 FPGA implementation of self-timed NOC. http://www.t-crest.org/page/results, 2014.

- 8. T-CREST Project. D3.7 Analysis report on FPGA implementation of self-timed NOC. http://www.t-crest.org/page/results, 2014.

- 9. T-CREST Project. D3.8 Integration report of the full system implemented in an FPGA. http://www.t-crest.org/page/results, 2014.

#### **Acknowledgements**

First of all I would like to thank my supervisor Jens Sparsø for his invaluable help and support, for sharing his experience and ideas and for the inspiring discussions. I would also like to thank my co-supervisor Martin Schoeberl for his feedback and his encouragement in reaching for the best. I am grateful to both of them for their time and for the opportunities they have given me.

I also appreciate the brainstorming and the interesting discussions with my colleagues Rasmus, Christoph, Luca, Ioannis, Florian, Alexander, and Sahar.

I am always grateful to my parents for their love and support in my every pursuit.

I would also like to thank Wolfgang for his constant help and support in every aspect of this path.

I would also like to thank my friends Aliki and Maria for being close even from far.

Furthermore, I would like to thank the fellow PhD students and friends Domi, Laura, Alessio, Fontas, Stavros for walking the same path and showing me the way. I enjoyed all the fun moments and new experiences we shared together.

Moreover I would like to thank Nikos for always being there for a good discussion or a chat, Søren for helping me find my way in Denmark, Nils for all the dances and for his friendship, Aris and Spyridoula for being there for a break and whenever needed. And finally thanks to all the dance people that shared a dance with me and made Denmark a warmer place.

This thesis was funded by the European Union's 7th Framework Programme project Time-predictable Multi-Core Architecture for Embedded Systems (T-CREST) under grant agreement no. 288008. I would like to thank the partners of the project for the interesting discussions during this work.

#### **Contents**

| Su | ımma         | ry (English)                                   | İ   |  |  |  |  |

|----|--------------|------------------------------------------------|-----|--|--|--|--|

| Re | sumé         | e (Dansk)                                      | iii |  |  |  |  |

| Pr | eface        |                                                | v   |  |  |  |  |

| Pu | blicat       | tions and Technical Reports                    | vii |  |  |  |  |

| Ac | know         | ledgements                                     | ix  |  |  |  |  |

| I. | Int          | roduction and State of the Art                 | 1   |  |  |  |  |

| 1. | Introduction |                                                |     |  |  |  |  |

|    | 1.1.         | Real-Time Systems                              | 4   |  |  |  |  |

|    | 1.2.         | MPSoC and NOCs                                 | 4   |  |  |  |  |

|    | 1.3.         |                                                | 5   |  |  |  |  |

|    | 1.4.         |                                                | 5   |  |  |  |  |

|    | 1.5.         | Contributions                                  | 6   |  |  |  |  |

|    | 1.6.         | Thesis Organization                            | 7   |  |  |  |  |

| 2. | Bacl         | kground                                        | 9   |  |  |  |  |

|    | 2.1.         | Real-Time Systems                              | 9   |  |  |  |  |

|    | 2.2.         | Multi-Processor Systems-on-Chip                | 11  |  |  |  |  |

|    |              | 2.2.1. On-chip Communication: Networks-on-Chip | 12  |  |  |  |  |

|    |              | 2.2.2. Timing Organization and GALS            | 13  |  |  |  |  |

|    | 2.3.         | The T-CREST Platform                           | 13  |  |  |  |  |

|    | 2.4.         | NOCs in More Depth                             | 14  |  |  |  |  |

|    |              | 2.4.1. Basic Concepts                          | 14  |  |  |  |  |

|    |              | 2.4.2 Architecture                             | 18  |  |  |  |  |

xii Contents

|     | 2.5. | 2.4.3. Core-to-Core Communication          | 19<br>21 |

|-----|------|--------------------------------------------|----------|

|     | 2.3. | Real-Time NOCs and WCET                    |          |

|     |      | 2.5.1. WCET Analysis                       | 21       |

|     | 2.6  | 2.5.2. Impact of NOC on the WCET           | 22       |

|     | 2.6. | Asynchronous Design Perspective            | 24       |

|     |      | 2.6.1. Why Asynchronous?                   | 24       |

|     |      | 2.6.2. Challenges in Asynchronous Design   |          |

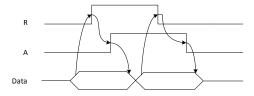

|     |      | 2.6.3. Handshake Protocols                 | 26       |

|     |      | 2.6.4. Data encodings                      | 27       |

|     |      | 2.6.5. Muller C-element                    | 29       |

|     |      | 2.6.6. Timed-Graph Models                  | 29       |

| 3.  |      | ted Work                                   | 31       |

|     | 3.1. | Real-time Platforms and Projects           | 31       |

|     | 3.2. | Real-Time NOC Approaches                   | 32       |

|     | 3.3. | Timing Organization in NOCs                | 34       |

|     | 3.4. | Real-Time NOC Designs                      | 34       |

|     |      | 3.4.1. SoCBUS                              | 34       |

|     |      | 3.4.2. 4S project Network                  | 36       |

|     |      | 3.4.3. Nostrum                             | 37       |

|     |      | 3.4.4. Æthereal/Aelite                     | 39       |

|     |      | 3.4.5. MANGO                               | 40       |

|     |      | 3.4.6. Kalray NOC                          | 42       |

|     |      | 3.4.7. Summary                             | 43       |

|     | 3.5. | •                                          | 44       |

| II. | De   | sign and Implementation                    | 45       |

| 4.  |      | NOC Architecture                           | 47       |

|     | 4.1. | Fundamental Architecture Decisions         | 47       |

|     | 4.2. | Overall Argo NOC Architecture              | 48       |

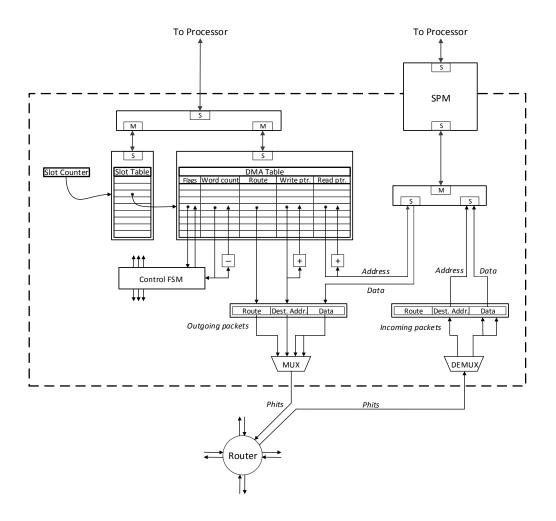

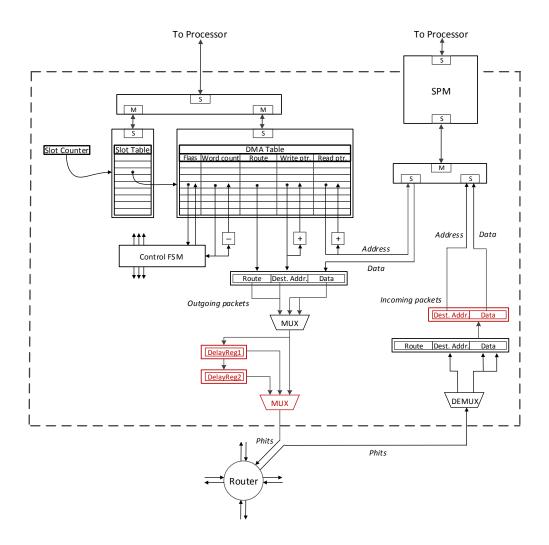

|     |      | 4.2.1. NIs with TDM-driven DMA Controllers | 50       |

|     |      | 4.2.2. Asynchronous Network of Routers     | 51       |

|     | 4.3. | Packet Format                              | 52       |

|     | 4.4. | Timing Organization                        | 53       |

|     | 4.5. | Interfaces                                 | 55       |

|     | 4.6. | Initialization Process                     | 56       |

|     | 4.7. | TDM Scheduling                             | 57       |

|     | 4.8. | WCET Analysis                              | 58       |

|     | 4.9. | Discussion                                 | 59       |

| 5.  | Netv | vork Interface                             | 61       |

|     | 5.1. | Network Interface Design                   | 61       |

|     |      |                                            |          |

Contents

|      |       | 5.1.2. Core-to-Core Communication             | 3 |

|------|-------|-----------------------------------------------|---|

|      |       | 5.1.3. Micro-Architecture and Functionality 6 | 5 |

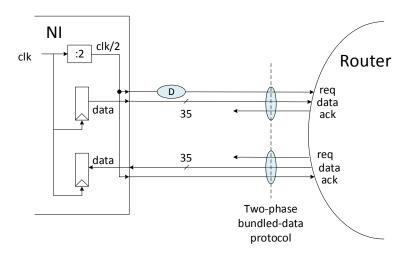

|      |       | 5.1.4. NI for Asynchronous Network 6          | 6 |

|      | 5.2.  | Implementation Results                        | 8 |

|      |       | 5.2.1. FPGA Implementation                    | 8 |

|      |       | 5.2.2. ASIC Implementation                    | 9 |

|      | 5.3.  | Discussion                                    | 0 |

| 6.   | Rout  | er Architecture 7                             | 1 |

| 0.   |       | Basic Router pipeline                         |   |

|      | 6.2.  | Asynchronous Argo Router                      |   |

|      | 0.2.  | 6.2.1. Architecture and Functionality         |   |

|      |       | 6.2.2. Initialization and Performance         | _ |

|      | 6.2   |                                               |   |

|      | 6.3.  | •                                             |   |

|      |       | 6.3.1. 4ph-bd                                 |   |

|      |       | 6.3.2. 2ph-bd                                 |   |

|      |       | 6.3.3. 2ph-bd-g                               | - |

|      |       | 6.3.4. 2ph-bd/LEDR-g                          | - |

|      | 6.4.  | Mesochronous Router                           |   |

|      | 6.5.  | Implementation                                |   |

|      |       | Results                                       |   |

|      | 6.7.  | Discussion                                    | 4 |

| 7.   | Imple | ementation Results 8                          | 7 |

|      | 7.1.  | Platform Timing Organizations                 | 8 |

|      | 7.2.  | Argo NOC Implementation                       | 8 |

|      | 7.3.  | Argo Simulation                               | 0 |

|      | 7.4.  | Implementation Scenarios                      | 0 |

|      | 7.5.  | Argo ASIC Implementation                      | 1 |

|      |       | 7.5.1. Synthesis                              | 1 |

|      |       | 7.5.2. Layout                                 |   |

|      | 7.6.  | Argo FPGA Implementation                      |   |

|      | 7.7.  | Open-Source Platform with the Synchronous NOC |   |

|      | 7.8.  | T-CREST Platform with the Synchronous NOC     |   |

|      | 7.9.  | Use of Argo NOC                               |   |

|      |       | Discussion                                    |   |

|      | 7.10. | Discussion                                    | U |

|      |       |                                               | _ |

| III. | Ela   | sticity Analysis 9                            | 9 |

| 8.   | Theo  | oretical Analysis 10                          | 1 |

|      | 8.1.  | Argo Timing Organization                      | 1 |

|      |       | Oli A C. CEIDO                                | 2 |

|      |       | 8.1.1. Argo as a Structure of FIFOs           | J |

|      | 8.2.  | Qualitative Analysis                          |   |

xiv Contents

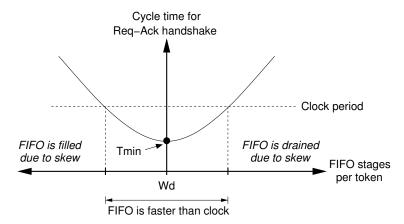

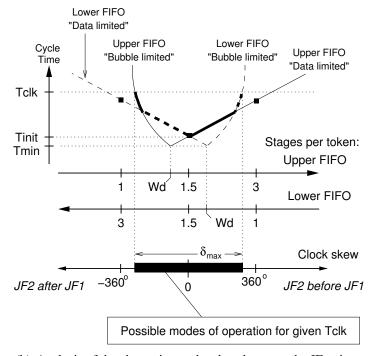

|     |        | 8.2.2.      | Performance and Elasticity of Asynchronous FIFO Rings |       |

|-----|--------|-------------|-------------------------------------------------------|-------|

|     |        | 8.2.3.      | Skew Limits                                           |       |

|     | 8.3.   | Discus      | ssion                                                 | . 108 |

| 9.  | Mod    | el-base     | ed Analysis                                           | 111   |

|     | 9.1.   | Elastic     | city Analysis Approach                                | . 111 |

|     |        | 9.1.1.      | TSE Algorithm                                         | . 112 |

|     | 9.2.   | STG M       | Model Analysis of Argo                                | . 113 |

|     |        | 9.2.1.      | STG Specification                                     | . 113 |

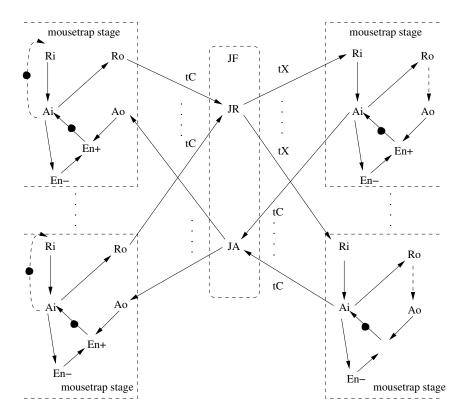

|     |        | 9.2.2.      | Argo STG Model                                        | . 114 |

|     |        | 9.2.3.      | TSE Analysis Results                                  |       |

|     | 9.3.   | <b>FBCN</b> | Model Analysis of Argo                                |       |

|     |        | 9.3.1.      | FBCN Specification                                    |       |

|     |        | 9.3.2.      | Argo FBCN model                                       | . 119 |

|     |        | 9.3.3.      | Performance Analysis                                  |       |

|     |        | 9.3.4.      | Oscillating behavior                                  | . 123 |

|     |        | 9.3.5.      | TSE Analysis Results                                  |       |

|     | 9.4.   | Discus      | ssion                                                 |       |

|     |        |             |                                                       |       |

| IV. | Co     | nclusi      | ions                                                  | 129   |

| 10  | . Con  | clusions    | s                                                     | 131   |

|     | 10.1   | . Overvi    | iew                                                   | . 131 |

|     |        |             | butions                                               |       |

|     |        |             | ssion                                                 |       |

|     |        |             | Work                                                  |       |

|     |        |             | usion                                                 |       |

| Bil | bliogr | aphy        |                                                       | 137   |

# Part I. Introduction and State of the Art

## 1

#### Introduction

Digital systems are an integral part of everyday life; they exist as embedded systems in commonly used devices. Consumer electronics, household appliances, telecommunication systems and industrial, transportation, and medical applications are some of the areas that use embedded computational systems. The functionality of these systems is often critical for the safety of people, as in transportation and medical applications. In addition, the timing of these systems is important, as in transportation. Thus, besides the requirements for efficiency, these systems also have real-time requirements for their operation.

*Real-Time systems* are systems with real-time requirements from their environment. They are built to guarantee the response of each operation within strict timing constraints. Efficiency is not the primary goal. To provide timing guarantees, it must be possible to analyze them and to provide worst-case guarantees of their operation and timing.

According to Moore's Law, increasing computational needs drive demands for higher performance systems. The high performance processors built nowadays do not satisfy these computational needs. The current approach to providing higher performance systems is to integrate a number of processors in a single system on a chip. *Multi-processor Systems-on-Chip (MP-SoC)* facilitate the construction of larger systems in a composable way, the reuse of individual components, the reduction of design-time, and high performance. Such systems require a communication medium that satisfies the communication requirements, which increase as the system gets larger. Networks-on-chip is the most promising approach to deal with the increasing communication requirements.

Furthermore, advances in silicon technology and manufacturing processes lead to integration of larger systems in smaller areas. The effects of long wires and signal distribution in large systems cause critical problems for the functionality of these systems. An important problem is the clock distribution over the entire system. Problems of clock skew and jitter demand complex solutions for correct operation.

4 Introduction

The focus of this thesis is the implementation of a Network-on-Chip for a MPSoC platform that is suitable for real-time systems. This implies that it must be analyzable and able to offer real-time guarantees. In addition, as determined by technology advances, it must be efficient, matching the current computational needs, and it must be able to handle signal distribution issues over the chip area.

#### 1.1. Real-Time Systems

Embedded systems commonly have real-time requirements.

*Real-time systems* are those systems in which the correctness of the system depends not only on the logical results of computation but also on the time at which the results are produced [155].

While *general purpose* systems focus on performance improvement, *real-time* systems focus on the time-predictability and analyzability of the system. The goal is to provide guarantees on the worst-case behavior, rather than optimized performance. A special subcategory is *hard real-time* systems. In such systems the consequences of failing to meet a deadline are severe [155]. Hard real-time systems are the context of this thesis.

Real-time requirements refer to both hardware and software. The development of such systems puts emphasis on the analyzability of the entire system. The standard approach for computational systems emphasizes optimizing the average-case performance. However techniques aiming at performance optimization often make the system difficult to analyze or have a negative effect on the worst-case execution. Real-time systems should be developed in a way that they are easy to analyze and are time-predictable, and consequently they are able to provide worst-case execution-time (WCET) guarantees. A metric for optimization is to optimize the worst-case performance instead of the average-case.

Approaches that satisfy the WCET guarantees focus on controlling the execution of tasks over time. This may include analysis of task data flows, or time scheduling of tasks.

#### 1.2. MPSoC and NOCs

The increasing computational needs and Moore's Law have led to exploration of architectures that take advantage of modularity and reuse. According to International Roadmap of Semiconductors [161] the silicon process leading to higher transistor density, the demands for higher performance, and the demands for decreasing time-to-market, drive the development of integrated systems with many processing cores on a single chip, i.e., *Multi-processor systems-on-Chip (MPSoCs)*. MPSoC systems allow modularity and reuse, thereby reducing the time-to-market and increasing productivity. In addition, they offer higher computational power compared to single high-cost and high-performance processors.

MPSoCs aim at increasing the performance of systems. They provide architectures that take advantage of reuse and modularity and provide better performance. While they meet their goal in terms of design productivity and computational needs, limitations arise with regard to the on-chip communication. As systems become larger with more processing cores to satisfy the

computational needs, the communication becomes a bottleneck. Additionally, the evolution of silicon technology with regard to transistor sizes, i.e., deep submicron technologies and nanotechnologies, leads to high-density integration and allows bigger systems to be placed on a chip, further increasing the on-chip communication. The challenges in deep sub-micron and nanotechologies, including increased leakage power, temperature susceptibility, signal integrity, and parameter variability, make it even more important to find an efficient and reliable way of implementing the communication. The above factors indicate the need for efficient communication.

Traditionally, buses have been used to facilitate on-chip communication. However, they do not meet the current demands for performance and scalability. In large systems, with many processing cores demanding access to a shared bus, the bus becomes a bottleneck. *Networks-on-Chip (NOCs)* satisfy the needs for communication performance, scalability and flexibility.

#### 1.3. Timing Organization

The increasing size of systems integrated on a single high-density chip raises signal distribution issues. Signals such as clock and reset that need to be distributed over the entire chip area pose a big challenge for most systems. Traditional globally synchronous systems fail to maintain the performance scaling improvements. Approaches to meeting the clock distribution challenge include extensive clock-tree synthesis to achieve maximally simulteneous arrival of the clock to every part of the chip and more flexible timing organizations of the system, such as mesochronous or asynchronous timing. These flexible timing organizations offer timing elasticity, such that they tolerate clock variations or entirely eliminate the clock. When applied to an entire system, all these techniques carry an overhead. The most widely used approach, especially in MPSoCs, is the *Globally-Asynchronous Locally-Synchronous (GALS)* organization. GALS systems consist of a number of synchronous islands that communicate with asynchronous protocols. This organization is ideal for the modular construction of MP-SoCs. However, the problem of signal distribution is still apparent for NOCs, which span the entire chip area. Therefore, the clock distribution within the NOC is still a challenge, requiring a more flexible solution for the NOC itself.

#### 1.4. Goals and Challenges

The focus of this thesis is a NOC suitable for real-time systems and for GALS system organization. The goal is to design and implement a NOC that is: (i) time-predictable, such that it provides guarantees for real-time requirements, (ii) time-elastic, such that it is tolerant to signal distribution and synchronization issues, and (iii) has an efficient implementation.

A particular challenge with this goal is to combine time-predictability and time-elasticity, two intuitively contradicting features, in one design. Traditional approaches offer solutions that achieve one or the other feature, and combinations include the elements of both solutions with an increased cost for integration. Our approach deals with both features in one solution, while also facing the challenge of finding an efficient implementation. It acieves that by rethinking

6 Introduction

the design and applying each feature in different levels of the design as it will be explained in detail in 4.

#### 1.5. Contributions

This thesis contributes the design, the implementation, and the elasticity analysis of an asynchronous time-predictable NOC, named Argo. The contributions of this thesis fall within two domains: Firstly the design and implementation of the Argo NOC, and secondly the analysis of its elastic behavior.

#### **Design and Implementation:**

The first domain to which this thesis contributes is the design and implementation of Argo. The contributions include the design of the NOC's building blocks, i.e., router and network interface (NI), the integration of them in the Argo NOC, the novel timing organization, and the implementation of Argo.

- Router: A contribution of this thesis is a novel NI design. This supports the time-predictability of the NOC by applying a TDM communication scheme. The NI is implemented in ASIC and FPGA technologies, and evaluated in terms of area and scalability. The implementation results show that the NI is very efficient compared to alternative NI designs in the literature.

- NI: A second contribution is the design and implementation of an asynchronous router, using the time-division multiplexing (TDM) scheme. The contribution involves exploration of several designs, their implementation in ASIC and FPGA technologies, and evaluation. The ASIC implementation includes both synthesis and layout of the designs. The final asynchronous Argo router is area-efficient, time-elastic, power-efficient on idle traffic, and with comparable speed to the equivalent synchronous designs.

- NOC: The integration of the above components into the entire Argo NOC involves a number of design decisions. The combination of the design decisions both in the router and NI lead to an efficient Argo NOC design. This novel design creates direct paths from the local memory of a processing core to the local memory of a remote processing core, thereby allowing the data to traverse the NOC without the need for any arbitration, buffering, end-to-end flow control, or synchronization. The contibution of this thesis includes implementation of the integrated Argo NOC in ASIC and FPGA technologies. The ASIC implementation includes synthesis and layout. The FPGA technology offers the possibility to prototype. Argo is shown to be very area-efficient, while being time-predictable.

- **Timing Organization:** Another contribution of the design refers to the timing organization of the NOC. Argo supports GALS system organization. The novel contribution of this thesis refers to the combination of time-predictable NIs with a time-elastic asynchronous network of routers. This timing organization is a novel approach that allows

the NIs to operate mesochronously while the elastic asynchronous network absorbs skew in signal distributions. This organization offers time-predictable communication that is highly tolerant to signal distribution issues.

#### **Elasticity Analysis:**

The second domain to which this thesis contributes is an analysis of the elastic timing behavior of the Argo NOC. The contribution includes an elasticity analysis of the network of asynchronous routers and its safe encapsulation in a time-predictable environment of mesochronous NIs.

- Qualitative Analysis: A contribution of this thesis is the understanding of the principles of the elastic network of asynchronous routers. This thesis contributes by providing insight into the elastic behavior and exploring its limits. A qualitative analysis contributes a relation of elasticity to performance. The exploration of the limits of the elasticity sets the elasticity bounds for safe operation.

- Quantitative Analysis: The last contribution of this thesis is a model analysis of the Argo NOC structure. This thesis contributes in describing the elastic behavior of Argo in timed-graph models, and analyzing them with an algorithmic/mathematical tool. The results of this analysis are supported by the implementation of an Argo instance. The quantitative analysis shows the wide limits of Argo elasticity.

#### 1.6. Thesis Organization

The thesis is organized in four parts. Part I sets the scene for the thesis. Chapter 1 introduces the topic and the main aspects that are dealt with in the thesis. Chapter 2 presents the background and context of the thesis. The chapter includes background on real-time systems, multi-processor systems-on-chip, networks-on-chip, networks-on-chip from the real-time aspect, and asynchronous design. In addition Chapter 2 presents the T-CREST multi-core platform, which is the context for the network-on-chip developed in this thesis. Chapter 3 reviews the state-of-the-art in real-time projects, the approaches in real-time NOCs and in timing organization of NOCs. Furthermore, it analyzes in more detail some representative NOC designs in the area of real-time NOCs.

Part II of this thesis presents the design and implementation of the Argo NOC. Chapter 4 presents the basic principles of Argo. It deals with the overall NOC architecture and the overall timing organization. This includes the initialization process, the scheduling of the communication, and the real-time properties of the NOC obtained through a WCET analysis. Chapter 5 presents the Argo NI design and its implementation. This includes the basic ideas that lead to an efficient design, its architecture and functionality, and its interaction with the asynchronous network of routers. The chapter also presents the results of the NI implementation. Chapter 6 presents the asynchronous Argo router design and its implementation. The chapter also presents the alternative router designs that were explored in this work. Finally, implementation results of all the design are presented and compared. Chapter 7 presents the Argo NOC

8 Introduction

implementation. This includes simulation, and implementation of various instances in various technologies, the challenges, and the results from this implementation. Additionally, this chapter presents the implementation of the entire T-CREST platform and ways to use the Argo NOC at the application level. As the Argo NOC code is open-source, the chapter provides information on how to access the code.

Part III of this thesis presents the elasticity analysis of Argo. Chapter 8 presents the elastic timing behavior of Argo and the qualitative analysis of the elasticity of Argo. Chapter 9 presents the quantitative analysis of the elasticity in Argo. This includes the description of the Argo NOC in two different timed-graph models and a analysis through the timing separation of events approach.

Finally, part IV gives an overview of the work done in this thesis and the insights gained. Chapter 10 presents the conclusions of this work. This includes a review of the contributions, assessment of the results, potential open issues and overall conclusions.

## 2 Background

This chapter provides the background knowledge which this thesis builds on. It describes the basis concepts of real-time systems and the various parameters related to them, and presents MPSoCs and the challenges they involve in more detail, as they were briefly touched upon in Chapter 1. It also presents the T-CREST project, as the MPSoC platform that is the context for the Argo NOC, and provides a more in-depth presentation of NOCs, explaining terminology and the basic concepts. After presenting the background on real-time systems and NOCs, this chapter focuses on real-time NOCs and their timing properties. Finally, this chapter provides some background material on asynchronous design, required for the understanding of the principles and concepts used in the development of the asynchronous Argo NOC.

#### 2.1. Real-Time Systems

As mentioned in Chapter 1,

*real-time systems* are those systems in which the correctness of the system depends not only on the logical results of computation but also on the time at which the results are produced [155].

A common basis for all real-time systems is the *predictability* of the system. A system is predictable if it can guarantee that an operation can be completed within its requirements [154]. For a system to be *time-predictable*, it should provide a way to analyze whether the operations executed on the system meet their deadlines. To do so, the operations of the system are organized in *tasks* with specific deadline requirements and known *worst-case execution times* (*WCETs*).

Many classifications of real-time systems, based on different parameters affecting them, have been presented in the literature. Stankovic et al. [154] define five dimensions, according to which they classify real-time systems. These dimensions are: (i) the granularity of the

Background Background

deadline and the laxity of the tasks, (ii) the strictness of the deadline, (iii) the reliability requirements, (iv) the size and coordination of components, and (v) the environment. Kopetz [77] makes the following distinctions: (i) hard and soft real-time systems, (ii) fail-safe and fail-operational, (iii) guaranteed response and best effort, (iv) resource-adequate and resource-inadequate, (v) event-triggered and time-triggered.

Some of the parameters affecting a real-time system and the corresponding classifications are explained below:

- With respect to the strictness of the deadline of an operation or task, real-time systems are divided into *soft* and *hard* real-time [154, 77]. Hard real-time systems require their tasks to be completed within strict deadlines. In soft real-time systems, tasks may complete, even after the required deadline. A system may also execute a combination of hard and soft real-time tasks.

- With respect to the reliability and the effect of failure, some operations are defined as critical [154] or safety-critical. Missing a deadline of a critical task has severe consequences. Resources are therefore often dedicated to critical tasks, even if they are not used for the remaining operation. A system may solely execute critical tasks or have tasks of different criticality levels. To avoid the severe consequences after a failure, some real-time systems detect and identify the failure, such that they make a transition to a safe state or operational state with minimal consequences, gracefully degrading. The former type of system is called fail-safe and the latter fail-operational [77].

- With respect to the guarantees given, a real-time system can be classified as *guaranteed* response or best effort [77]. A guaranteed response system can provide analytic guarantees, based on load and fault worst-case assumptions. A best effort system provides the best achievable response in its current condition.

- With respect to the provision of resources a real-time system can be classified as *resource-adequate* or *resource-inadequate* [77]. Resource-adequate systems offer sufficient resources for every possible scenario. As this may result in a waste of resources, some real-time systems are resource-inadequate but rely on probabilistic analysis and dynamic allocation of resources. However, safety-critical systems need to be resource-adequate.

- With respect to the size of the system, the coordination of components may cause complications [154]. Tasks or components of a system need to operate in coordination. The completion of one task may depend on the completion of others. *Isolating* the execution of tasks simplifies the predictability analysis, but as the size of a system increases the interactions become more complex.

- With respect to the way in which operations are executed in a system, real-time systems are classified as *event-triggered* or *time-triggered* [77]. In event-triggered systems, operations are initiated by given events. In time-triggered systems the operations are initiated at specified points in time.

- With respect to the environment and the interaction of the system with it, real-time systems are classified as *static* or *dynamic* [154]. The environment of a system can be

deterministic and well-defined but in many cases the environment is dynamic. Systems that operate in deterministic environments can be static. To interact with a dynamically changing environment, a system needs to adapt to the changes of the environment. Such a system is dynamic.

A system is composed of a number of components at the hardware and software level. The hardware platform, the operating system, the compiler, and the application tasks comprise different layers of the system. Stankovic et al. [154] refers to two approaches to achieve predictability. In the *layer-by-layer* approach, every layer of the system is required to be predictable. In such a system, all components need to provide WCET guarantees, e.g. for the use of hardware resources, or for the execution of application tasks. This method requires careful planning and scheduling of all operations involved, as well as their interactions, such that everything is guaranteed. In the *top-layer* approach, an effort is made to ensure that the top layer is time-predictable and that the rest of the layers support the necessary actions, so that predictability is achieved at the top level.

The operation of real-time systems often relies on scheduling and careful planning of the sequences of the tasks. The scheduling is done statically or dynamically. Static scheduling evaluates the requirements of the tasks executed on the system and generates a static schedule of the tasks. It considers all tasks and their requirements to be known. This type of scheduling is good for systems in static environments, or in systems with static behavior. Dynamic scheduling considers the current condition of the system and evaluates a schedule based on this. Scheduling can be done off-line or on-line. Schedulability analysis can also be applied to analyze whether a system running a set of tasks is able to meet its requirements [156]. Liu et al. [82] deal with scheduling algorithms for multiple tasks on a single processor for hard-real-time systems. Ramamritham et al. [134] explore the scheduling and operating system support for real-time systems, and also scheduling algorithms for real-time multiprocessor systems [133].

The Argo NOC presented in this thesis was developed in the context of a hard real-time system. The approach to predictability followed in the system is the layer-to-layer approach. It uses isolation of operations and provides guaranteed responses in the operations executed in the NOC. Argo follows off-line static scheduling of communication. This also includes analysis for the adequecy of resources, as the requirements are analyzed to generate the schedule. The operations executed in the system are time-triggered.

#### 2.2. Multi-Processor Systems-on-Chip

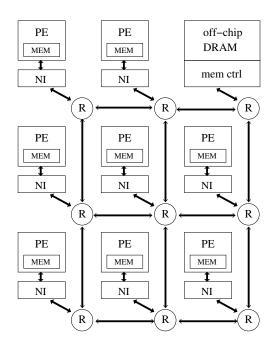

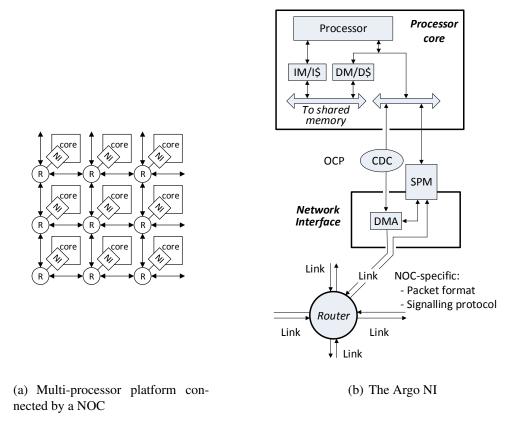

To meet the increasing computational needs and to exploit modularity and reuse, the dominant design approach in embedded systems is to use multi-processor systems. A typical multi-processor architecture is illustrated in Figure 2.1. It consists of several *processing elements* (*PEs*) or *processing cores*, organized in grids or clusters. The architecture includes a memory system. This can be a single off-chip shared main memory (DRAM), or multiple on-chip memory units, owned privately by the cores, or shared among clusters of cores. The memory is organized in a hierarchy that consists of the main memory, caches in the cores, and possibly local private memories. In addition, the cores typically contain DMA controllers, implementing data transfers separately from the core operation. In this way, computation is separated from

Background Background

Figure 2.1.: Example multi-processor system.

communication. The cores and the shared memory are connected with an interconnection medium. This medium may be a shared bus or a network. The network, as shown in Figure 2.1, is typically a structure of routers (R) connected through network interfaces (NI) with the cores. Challenges in the development of such systems include optimization of communication, memory access, real-time guarantees, and software development for parallelization [68].

#### 2.2.1. On-chip Communication: Networks-on-Chip

The focus of this thesis lies on the challenges of on-chip communication. Traditionally, buses have been used for this purpose, but they do not meet current demands on performance and scalability. In large systems with many processing cores demanding access to a shared bus, the bus becomes a bottleneck. Benini in [19] suggests that the interconnection technology will be the limiting factor in future SOCs. Interconnection networks, and in particular *Networks-on-Chip (NOCs)* offer a better and more flexible solution for meeting the communication requirements. NOCs satisfy the needs for scalability and flexible sharing of the communication network [57], [19]. They offer reliable and efficient communication, in terms of power and clock synchronization [18]. They are scalable, modular, testable, and reliable [147]. Arteris presents a comparison between a traditional bus example design and a NOC architecture [8]. NOCs are also supported as a better solution over direct wiring connections, for their advantages in structure, performance, modularity and reliability [36] [176]. NOCs and their fundamentals will be presented in more detail in Section 2.4.

#### 2.2.2. Timing Organization and GALS

The increasing performance demands and the evolution of silicon technology has led to integration of larger systems with multiple components on a single chip. Therefore, the distribution of a single clock signal to the entire, dense chip area is becoming an increasingly challenging process due to parameter uncertainty and variability [161]. Different synchronization options are presented by Messerschmitt [94].

Globally synchronous systems require the concurrent arrival of the clock to every part of the system. In large multi-processor systems, with long wires, skew and jitter effects make this an impossible task. Techniques to deal with these effects include building buffer networks to balance the clock delays in different parts of the chip [136].

Another approach to dealing with clock distribution and synchronization is *mesochronous* timing organization. The global clock arrives with some phase difference, i.e., *skew*, to various areas of the chip. Thus, one global frequency is maintained throughout the chip, but with different phase differences in different areas. With mesochronous timing organization, the various parts of the system operate on the same frequency but with a bounded phase difference. Parts with clock skew are synchronized using mesochronous synchronizers [105], [93].

Entirely *asynchronous* timing organization is also possible. However, the implementation of an entire multi-processor system asynchronously is a challenging task. As the asynchronous design process is not well-supported by EDA tools, the development and testing of a large system is a practical challenge.

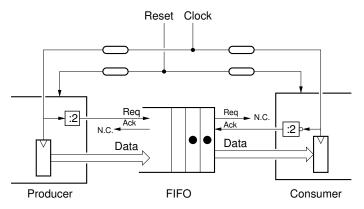

A different approach, widely used in recent years, to timing organization is the *Globally-Asynchronous Locally-Synchronous (GALS)* organization [78]. The design consist of a number of parts operating in independent clock domains, and therefore locally synchronous. The individual clock domains communicate asynchronously, so the system is globally asynchronous. A NOC-based MPSoC platform naturally supports a GALS timing organization where the components of the system operate within different clock domains [78]. The most common way to resolve synchronization among the different clock domains is with FIFO based synchronizers. Some solutions are presented in [30], [29], [17].

#### 2.3. The T-CREST Platform

This thesis was conducted within the FP-7 project T-CREST. The T-CREST project aims at the development of a real-time multi-core platform. The goal is to redesign each of the components of the architecture with a focus on analyzability and time-predictability. The typical design approach for general purpose systems is to optimize the average case, possibly leading to a poor worst-case performance. The design strategy of the T-CREST project is to optimize the WCET instead of average-case execution time and to achieve a low WCET bound. The project deals with the design of the hardware platform, the compiler, the WCET analysis tools, and the development of industrial test cases to evaluate the platform.

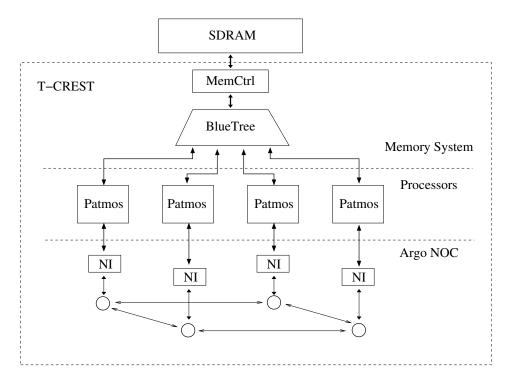

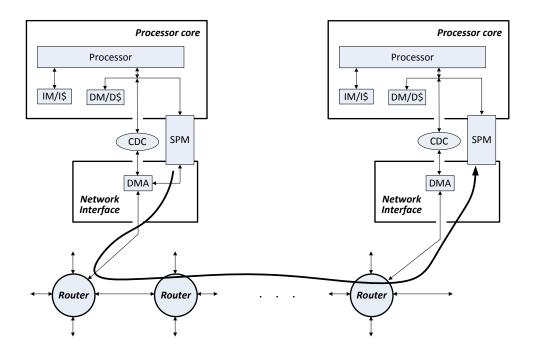

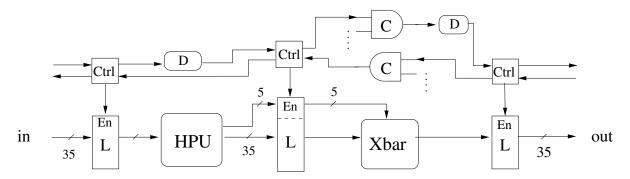

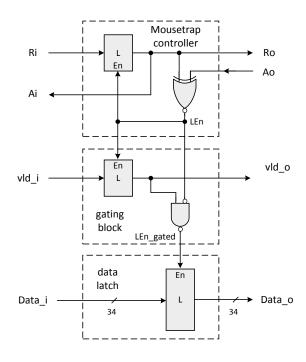

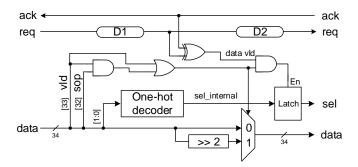

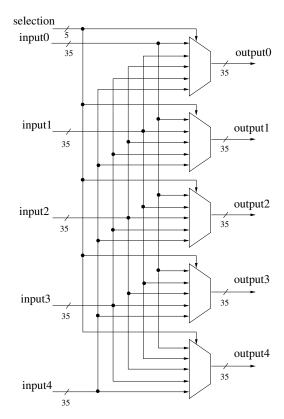

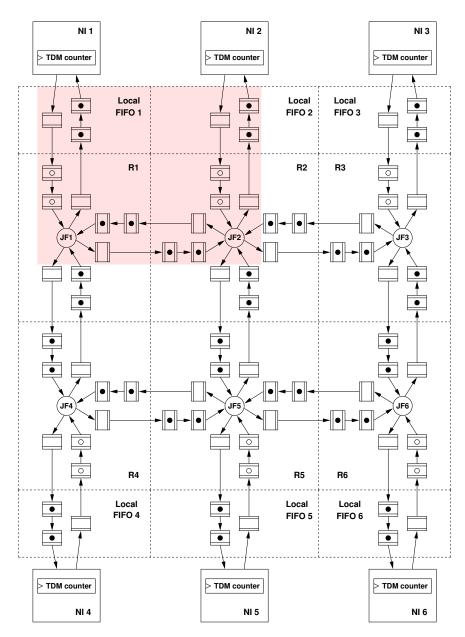

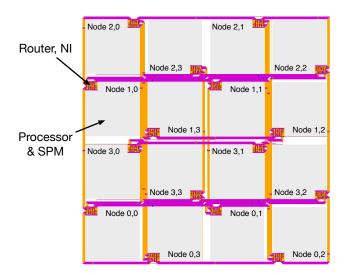

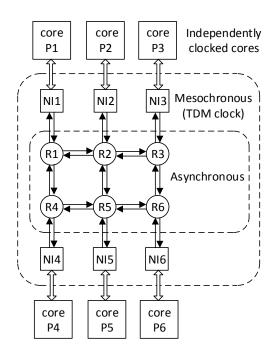

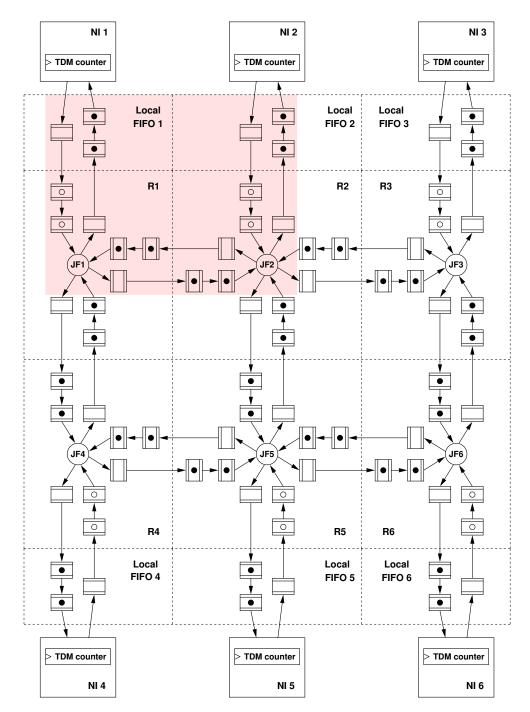

The T-CREST platform consists of a number of Patmos processors connected by the Argo NOC, and a shared memory, accessed through a second NOC. The architecture of T-CREST platform is shown in Figure 2.2. Patmos [143] is a RISC-style, time-predictable processor. It includes caches designed with an emphasis on the WCET analysis (method cache [42], data

14 Background

Figure 2.2.: T-CREST platform architecture.

cache, stack cache [2]), each optimized for the specific sets of data which it holds. For each processor there exists a local, private *scratch-pad memory (SPM)*. The Argo NOC connects the Patmos processors, implementing message-passing between them, and is the focus of this thesis. Argo offers end-to-end channels for DMA-controlled transfers of data from an SPM to a remote SPM. A second NOC, the BlueTree [50], a tree-based NOC, provides access to the shared off-chip main memory. Access to the memory is controlled by a memory controller [5], [79], [52].

#### 2.4. NOCs in More Depth

As requirements for high performance lead to multi-core architectures integrated on a single chip (MPSoC), the requirements for on-chip communication increase as well. As presented in Section 2.2.1, a bus is not a suitable medium for large scale communication. NOCs aim at dealing with this communication challenge. As shown in many publications (e.g. [36], [44], [135]), NOCs are the most promising solution for the current communication needs. They offer flexible communication, scalability and favor reuse and composable architectures [36], [57], [19]. This section focuses on NOCs, discussing their basic concepts and architecture.

#### 2.4.1. Basic Concepts

A NOC is a shared medium that provides the infrastructure to implement communication paths among cores connected to this infrastructure. It consists of switching nodes and links connecting the nodes. These comprise the shared resources that are shared among a number of

communication channels. From an architectural point of view, the basic building blocks of a NOC are: (i) the switching nodes or *routers*, (ii) the *links*, and (iii) the *network interfaces* (NI) or *network adapters* that connect the processing cores to the network of routers and links, as shown in Figure 2.1. Routers and links comprise the switching network and NIs bridge the processing cores and the switching network of routers. From a conceptual point of view, the basic concepts of NOCs are their topology, the ways data are transferred throughout the network (routing scheme, flow control), and the quality of service which they offer.

#### **Protocol Stack**

A relationship between the NOC design and the OSI protocol stack is often proposed ([19], [135], [22]). This section does not provide a precise OSI mapping but aims at building an understanding of the functionality and the services which a NOC offers. Benini et al. [19] propose a micronetwork stack adaptation of the OSI protocol stack to the services that MPSoCs connected by a NOC implement. According to the micronetwork stack, the architecture and the control of the NOC relate mainly to the *data link layer*, the *network layer*, and the *transport layer*. The *physical layer* of the stack corresponds to the physical wiring in the NOC.

The data link layer relates to services implemented by the routers and the links, concerning the propagation of data from router to router through a link. As the physical layer relates to the physical wires of the link, ways to ensure reliable use of the link are required. These include flow control over the link, and error detection or synchronization functionality implemented in the routers or links. The network layer relates to the network formed by the routers and links. It considers the way the nodes are connected, i.e. topology, the way the data is transferred within the network structure, i.e. routing scheme, etc. The transport layer relates to functionality offered at the endpoints of the network to the processing cores. These services are implemented typically in the NIs and include end-to-end flow control and reliable transfer of entire messages, without knowledge of the internal structure of the routers.

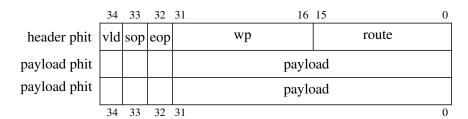

#### **Data Organization**

Data is organized in units and the different layers in the above layer abstraction operate on different granularity units. Cores at the end of the NOC consider *transactions* or *messages* as the basic communication data units. At the NIs, *messages* are organized into *packets*. A *Packet* is the basic data unit for an end-to-end transmission. Packets consist of a number of *flits* (*flow-control digits*). A *flit* is the smallest data unit to which flow-control and routing are applied, as explained further in this section. Flits can be further divided into *phits* (*physical digits*). A *phit* is the data unit that propagates through a physical pipeline stage in one clock cycle. The transport layer is responsible for translating messages to packets. Services of the network layer are applied at the granularity of *packets* or *flits*. Services of the data link layer are applied at the granularity of *phits*. Services of the physical layer operate at the granularity of *phits*.

#### **Topology**

The *topology* of a NOC refers to the arrangement of routers in the network structure and the way they are connected. The topology can be ring, tree (binary or fat), mesh, torus or bi-

Background Background

torus, star, and many hybrid and custom structures [38]. The mesh and torus structures can be two-dimensional (2D) or N-dimensional for arbitrary N, and they are the most common [137]. Routers in mesh structures are connected in four dimensions with other routers. The example network shown in Figure 2.1 follows the mesh topology. Tori follow the same principle, with wrap-around at the endpoints of the mesh. Bi-tori use bi-directional links. Æthereal [54] and aelite [59] are examples of mesh topologies while Nostrum [96] follows a bi-torus topology. Proteo [146], Octagon NOC [69], and the time-triggered NOC [140] follow a ring topology. SPIN [57] and Butterfly FT [118] follow a fat-tree topology. Pande et al. [119] compare a number of topologies.

#### **Routing scheme**

The *routing scheme* refers to the way in which the path which a packet follows from source to destination, over a number of nodes (hops) of the switching structure, is chosen. There are several routing algorithms based on the requirements and focus of an NOC. Routing decisions may be made at the source node, (*source routing*), or in the switching nodes, (*distributed routing*). In source routing the routing information of the packet is attached to the packet at the source and travels along with the packet thoughout the route. In distributed routing the decision is made and executed in the switching nodes. There are *minimal* and *non-minimal* algorithms, in terms of whether the chosen route is the shortest or not. Based on the outcome of the routing algorithm, the algorithm may be *deterministic* or *adaptive*. Deterministic routing algorithms always result in the same route for the same source-destination pair. The adaptive algorithms consider the state of the network while making the route selection dynamically [44]. These algorithms reduce congestion in the network, but are more complex to implement, thus they introduce a high implementation cost. Static routing is also possible, by analyzing the behavior of the NOC and providing static connections.

An example of an algorithm that is deterministic and minimal is the dimension-order routing. According to this, packets are routed in every dimension in strict order. XY-routing is often used in 2D mesh or tori. In XY-routing, packets are routed first in the X and then in the Y dimension. Hu et al. [64] and Siebenborn et al. [145] analyze the communication to provide static routing decisions. Neeb et al. [110] compare deterministic and adaptive routing algorithms. Hu et al. [63] and Ascia et al. [9] further explore routing techniques.

#### Flow control

Another characteristic of a NOC is the *flow control* or *switching technique*. Flow control refers to the way data is forwarded through the network [44], [135]. It can be viewed as a resource allocation problem or a contention resolution problem [38]. The resources involved can be bandwidth, buffering or control. Flow control is applied on the level of routers, i.e. from one router to the next, or at the level of NIs, i.e. end-to-end flow control.

There are two main switching techniques that control the propagation of data from router to router; *circuit-switching* and *packet-switching*. In *circuit-switching*, connections are set before transmitting the data, such that end-to-end paths, i.e., circuits, are established and the data travels unblocked from source to destination. Consequently, circuit-switching requires no buffering. In contrast to this, *packet-switching* allocates bandwidth and buffering to data units,

i.e., packets or flits. Flow control in packet-switching is applied at the granularity of *packets* or *flits* and it requires corresponding buffering resources in the routers.

In more detail, depending on the granularity of the packet-switching mechanism, we can distinguish between mechanisms applied when using packet granularity and flit granularity. Store-and-forward and (virtual) cut through are packet-switching flow-control mechanisms applied with packet granularity. Wormhole switching or wormhole routing is applied at the granularity of flits. In store-and-forward, a router stores a packet and waits until the entire packet arrives before forwarding it to the next node. In virtual cut-through, the router forwards the data as soon as the header arrives. Both techniques forward the packets as long as there is enough space for an entire packet in the next router. In wormhole routing a flit is forwarded upon arrival if the next router has available buffering space for a flit. Thereby, a packet transmission is pipelined through the network and a router needs to store only one flit. Most NOCs are packet-switching NOCs with wormhole routing and varying buffering configurations, e.g. [4], DSPIN [99], QNOC [27], XPIPES [21], Hermes [103], etc. Bufferless packet-switching NOCs are also possible; these drop the packets that cannot be forwarded to the next hop. Such NOCs include techniques for detecting and resending the packet if it is dropped. A way to control the availability of buffering space over the next hops is by using *credit-based* schemes as in QNOC [27] and MANGO [25]. Virtual-channels (VCs) are used to multiplex the use of physical links. MANGO [25] is a example of a NOC using VCs. Mello et al. [92] evaluate the use of VCs in Hermes [103].

An alternative approach for flow-control is *virtual circuit-switching*. Virtual circuit-switching multiplexes the allocation of resources to data units. *Time-division multiplexing (TDM)* allocates resources to virtual circuits over fixed-duration time-slots, such that end-to-end circuits are formed in specific time-intervals. Nostrum [96], Æthereal [54], and Aelite [59] are based on TDM schemes. *Spatial division multiplexing* is another way of multiplexing multiple virtual circuits over a link. Leroy et al. [81] propose a NOC that statically allocates subset of links to virtual circuits.

A different aspect of flow-control, concerned with the allocation of resources at the end-points, i.e. in the NIs, is *end-to-end* flow-control. A widely used type of end-to-end flow control is *credit-based* flow control. According to this scheme, credits related to the available buffering space at the end-points are exchanged between source and destination. Data transmission at the source is initiated when sufficient credits are received from the destination. Since this is an end-point functionality, it is commonly implemented in the NIs [131].

#### **Quality-of-Service**

Another feature of a NOC is the *Quality-of-service* (*QoS*) which it offers. Aspects of the QoS can be throughput, latency, and data integrity. Two main categories appear with respect to the guarantees they offer to the connections which they implement: Best-effort NOCs (BE) and Guaranteed Service NOCs (GS) [135]. BE NOCs provide no guarantees. They are optimized for the average-case scenario and aim at providing easy, efficient and fair sharing of the network resources. Their main focus is to minimize the latency of a packet transmission under the given conditions, without any guarantee. GS NOCs provide guarantees on throughput and latency. They are optimized for worst-case scenarios and aim at providing guarantees to connections by reserving resources. Most NOCs in the literature aim at providing BE services. However,

18 Background

some NOCs support the combination of the two services in one NOC [135]. Æthereal NOC [54] implements both services. BE NOCs using priorities aim at providing "softer" guarantees. Examples of such NOCs are the QNOC [27], and the NOC proposed by Felicijan [47]. NOCs based on circuit-switching or virtual circuit-switching, i.e. TDM, provide "hard" GS. Examples are aelite [59], MANGO [25], and Nostrum [96].

#### 2.4.2. Architecture

As mentioned at the beginning of this section the basic building blocks of a NOC are: (i) the *routers* or switching nodes, (ii) the *links*, and (iii) the *network interfaces (NIs)*.

#### **Routers**

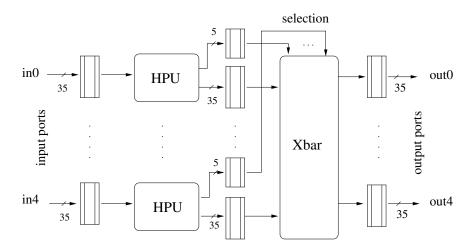

A typical router provides storage space and control functionality. The functionality it offers ranges from simple switching input to output ports to complex routing and arbitration. The router functionality depends on the specific features which the NOC implements, e.g. the routing scheme, the flow control, the quality of services, etc. A typical packet-switching router supports buffering, routing, allocation of resources, arbitration, and switching. The latency of a packet or flit to propagate through the router depends on the pipeline stages of the router, i.e. the functionality it implements. Various router designs have been published in the literature and their stages range from single to multiple. The typical pipeline stages of a wormhole router include buffering, at the input or output ports, switching of inputs to output ports, and arbitration of output ports. In addition, in the case of distributed routing, the router pipeline implements the routing algorithm. Furthermore, if multiple VCs share a link, a VC allocator allocates VC resources. Peh et al. [122] present the micro-architecture of a typical wormhole router in more detail and a delay model for the router. In bufferless flow control schemes, such as circuit-switching, buffers are eliminated.

The area of a router depends mainly on its buffering capabilities, and additionally on the functionality it implements. As mentioned by Salminen et al. [137], and as shown in many NOC examples (e.g. [75], [146]), the buffers occupy 50-90% of the router area. The buffer area depends on the topology, the flow control scheme, and the flit width. The topology determines the number of ports. The buffers are placed at input ports, output ports, or both. Multiple VCs sharing a link may be associated with separate buffers. The depth of the buffers is also a design decision for the NOC, as well as the flit width. However, the router is highly dependent on the specific features of the NOC which it is a part of, and therefore the router architecture, area and latency vary, depending on the details of the NOC.

#### Links

Links connect routers to form the network structure. They may be uni-directional or bidirectional, may be shared among several channels, and may be simple physical wires or implement more complex functionality. In the basic case they are simple wires. Alternatively, they address issues of synchronization, link level flow-control, reliability, additional buffering, pipelining and encoding. For example, links in the Aelite [59] and in Spidergon STNoC [33] implement mesochronous synchronization.

#### **Network Interface**

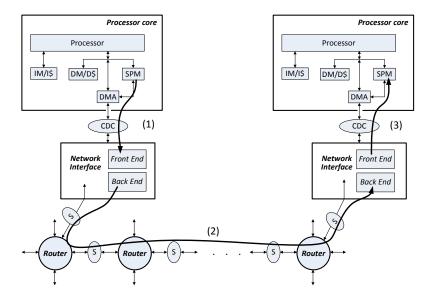

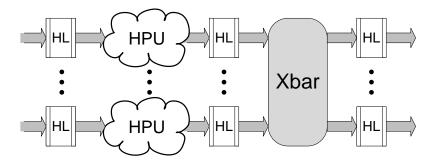

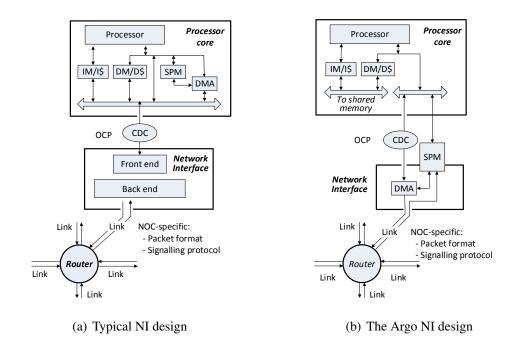

The network interface (NI) bridges the processing cores with the network of routers. The NIs translate the processor transactions to the network-specific stream of packets. They implement functionality of the transport layer [19], [33], [22], and they decouple computation from communication [135]. NIs consist of a *front end* and a *back end* (alternatively *shell* and *kernel* [33]), as illustrated in Figure 2.3. The front end implements the interface to the cores. This is a bus-style read-write transaction interface, based on some standard protocol such as AMBA AXI [7] or OCP [3]. The front end transforms the processor transactions into a form of connection-oriented packet-streaming interface, and encapsulates the services provided by the network. The back end implements the interface to the network of routers. This is a packet-stream interface and is specific to the NOC. It implements functions that are related to the NOC functionality, like splitting and re-assembling of packets, routing, buffering and end-to-end flow control.

The NI design architecture is related to the OSI stack model. It follows a layered design approach to separately implement services intended for the different stack layers. The back end corresponds to the services of the network and the front end to services of the transport and session layer.

There are few papers in the literature addressing the design of NIs, and reporting implementation results. Saponara et al. [138], Radulescu et al. [131], Hansson et al. [59], and Copola et al. [33] are a few exceptions reporting implementation results of NIs. Radulescu et al. [131] present the implementation of an NI for the Æthereal NOC. Hansson et al. [59] present the NI implementation of the aelite NOC. Copola et al. [33] addresses the design of a NI for the Spidergon NOC developed by ST Microelectronics, and Saponara et al. [138] reports details of the NI for the same NOC. Saponara et al. [138] compares against a number of other NI designs, including an NI for the Æthereal NOC [131]. The area measures that Saponara et al. [138] report for typical NIs range from 7 to 50 kgates, where a kgate is 1000 minimum size two-input NANDs. Common to all the designs is that the NI back end includes a large amount of buffering, which is the reason for their large area.

#### 2.4.3. Core-to-Core Communication

In most multi-processor platforms, processing cores contain some cache memory and some local scratchpad memory (SPM). Figure 2.3 shows a typical processing core and NI architecture. The processing cores contain instruction and data caches, and a local SPM. The SPM of a processing core contains the message to be transfered to the local SPM of another processing core. Typically, DMA controllers implement background DMA-driven block transfers from core to core. They are typically placed in the processing cores as shown in Figure 2.3 and their role is to offload the core from the data-transfer operations across the network. In this way they isolate the program execution from the network-related operations, making WCET analysis easier. The functionality of a DMA controller includes the transfer of the message data from the local SPM of the core to the local NI. The NI is responsible for organizing the data into packets and inject them to the network of routers.

For a message transfer in a multi-processor platform with a typical NI architecture and a mesochronous network of routers, data crosses several layers of functionality, and several clock

20 Background

Figure 2.3.: Typical NI architecture and end-to-end communication datapath.

domains from the sending SPM, through the network of routers, and into the receiving SPM. The transfer is illustrated in Figure 2.3 and the following steps describe the process:

- 1. At the source end, the DMA controllers transfer the data from the local SPM to the front end of the NI, across a clock-domain. A clock-domain crossing (CDC) is required in the interface between the core and the NI. The NIs buffer the data as a number of connection-oriented channels, and organize them into packets for the different channels.

- 2. Several channels request access to the network of routers and arbitration among them is required. The back end of the NI performs arbitration and injects the packets into the network of routers. The packets travel across the network of routers to the receiving NI, through synchronizers placed on every link. The synchronization along the path and the limited buffering capabilities in the NIs call for end-to-end flow control among the NIs.

- 3. At the receiving end, the NIs restructure the messages from the packet streams, and the DMA controllers transfer the data from the front end of the NI to the local SPM, across another clock-domain (CDC).

The above steps of the data transfer show that an amount of buffering is required in the NIs. In addition, arbitration and end-to-end control among NIs is required. Clock-domain-crossings at the source and receiving ends, and mesochronous synchronizers along the router paths, add to the complexity of the architecture. Even with TDM that achieves low complexity in the routers, the overhead from arbitration, end-to-end flow control, buffering, and synchronization is large. The Argo architecture entirely eliminates this overhead by a number of design decisions.

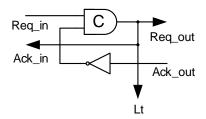

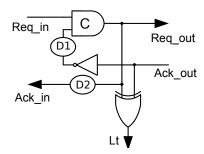

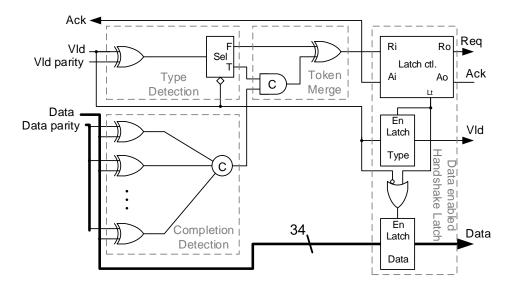

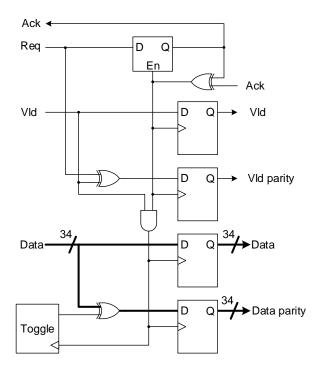

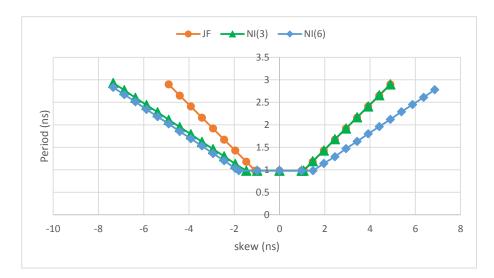

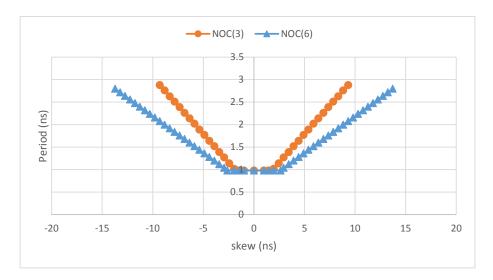

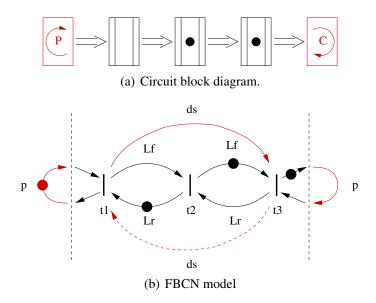

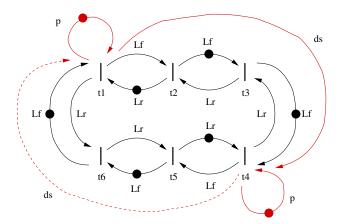

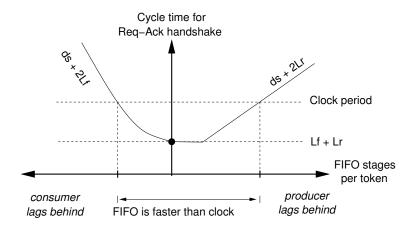

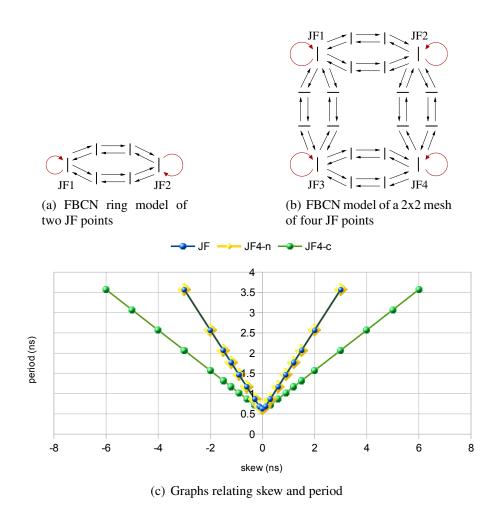

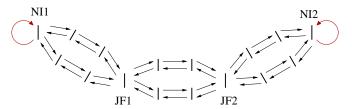

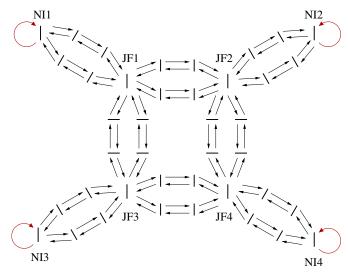

### 2.5. Real-Time NOCs and WCET