#### Technical University of Denmark

#### Forward Error Correcting Codes for 100 Gbit/s Optical Communication Systems

Li, Bomin; Larsen, Knud J.; Forchhammer, Søren; Tafur Monroy, Idelfonso

Publication date: 2014

Document Version Peer reviewed version

Link back to DTU Orbit

Citation (APA):

Li, B., Larsen, K. J., Forchhammer, S., & Tafur Monroy, I. (2014). Forward Error Correcting Codes for 100 Gbit/s Optical Communication Systems. Technical University of Denmark (DTU).

#### DTU Library

Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

### Forward Error Correcting Codes for 100 Gbit/s Optical Communication Systems

**Bomin Li**

Supervisors: Professor Knud J. Larsen Professor Idelfonso Tafur Monroy Professor Søren Forchhammer

Delivery date: June 10, 2014

Department of Photonics Engineering Technical University of Denmark Ørsteds Plads 343 2800 Kgs. Lyngby Denmark

DTU Fotonik Department of Photonics Engineering

### Abstract

This PhD thesis addresses the design and application of forward error correction (FEC) in high speed optical communications at the speed of 100 Gb/s and beyond. With the ever growing internet traffic, FEC has been considered as a strong and cost-effective way to improve the quality of transmission (QoT) to meet the increasing demand on the quality of service (QoS). The scientific content presented in this thesis tackles three major research problems. Firstly, the study of FEC codes becomes essential to get a high coding gain (CG) suited for 100 Gb/s optical fiber links. Secondly, low-complexity low-power-consumption FEC hardware implementation plays an important role in the next generation energy efficient networks. Thirdly, a joint research is required for FEC integrated applications as the error distribution in channels relies on many factors such as non-linearity in long distance optical fiber links, cross-talks in wavelength division multiplexing (WDM) setups and so on.

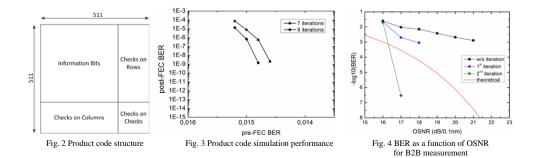

FEC with a product code structure has been investigated theoretically and experimentally. The iterative decoding method applied to FEC codes in a product code structure can effectively reduce the bit error rate (BER). Proposals on beyond bound decoding (BBD) and adaptive FEC algorithms are also presented. BBD is an add-on in some cases to help with the further reduction of the BER.

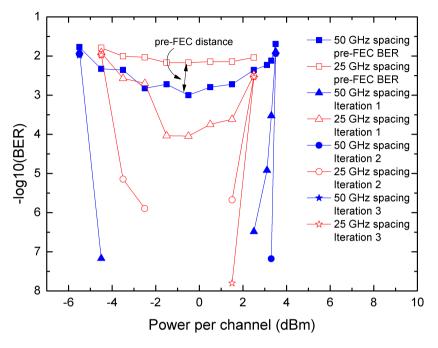

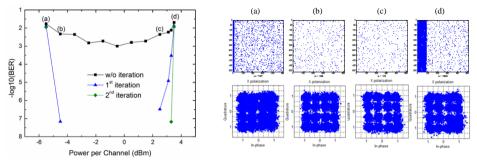

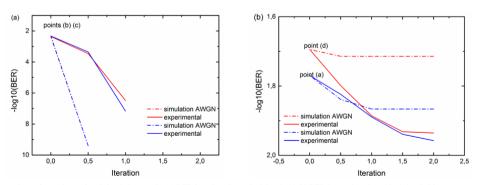

FEC aided transmission in a short distance data center link is presented. With the help of FEC and a low cost vertical-cavity surfaceemitting laser (VCSEL), 100 Gb/s raw data rate is achieved, which demonstrates the possibility of building a high speed short-range link with cheap elements. FEC integration in a WDM metropolitan transmission link is also presented. The experimental performance of FEC in both linear and nonlinear regimes is demonstrated in a dual polarization (DP) 16-ary quadrature amplitude modulation (16QAM) and coherent detection based WDM transmission over 741 km at a raw data rate of 88.8 Gb/s. FEC can compensate in both regimes, but the channel analysis does not show an additive white Gaussian noise (AWGN) channel. Besides, a denser WDM grid changes the shape of the BER curve based on the analysis of the experimental results, which requires a stronger FEC code.

Furthermore, a proof-of-the-concept hardware implementation is presented. The tradeoff between the code length, the CG and the complexity requires more consideration in the FEC code choice in a certain application. The presented adaptive FEC is one of the few published research results to enable the efficient bandwidth usage as the transmission channels can be affected by many factors.

In conclusion, the results presented in this thesis consist of proposals on FEC codes and their associated experimental demonstration and hardware implementation. The demonstrated high CG, flexibility, robustness and scalability reveal the important role of FEC techniques in the next generation high-speed, high-capacity, high performance and energy-efficient fiber-optic data transmission networks.

## Resumé

Denne PhD afhandling omhandler design og anvendelse af fejlkorrigerende koder (Forward Error Correction - FEC) i optisk højhastighedskommunikation med transmissionshastigheder på 100 Gb/s og derover. Med den konstant voksende internettrafik er FEC blevet betragtet som en vigtig og cost-effektiv metode til forbedring af transmissionskvaliteten (quality of transmission - QoT) med henblik på at imødekomme de voksende krav til "quality of service" (QoS). De videnskabelige resultater der præsenteres i denne afhandling tackler tre grundlægende problemer. For det første er det nødvendigt at studere fejlkorrigerende koder for at opnå det høje "coding gain (CG)" der er brug for med en 100 Gb/s optisk forbindelse. For det andet spiller hardwareløsninger med lav kompleksitet og lavt energiforbrug en vigtig rolle i næste genrations energi-effektive netværk. For det tredje kræves en samlet undersøgelse af kommunikationssystemer med FEC da fordelingen af transmissionsfejl afgøres af mange forskellige faktorer som fx ulineariteter i langdistance fiberoptiske forbindelser, krydstale i WDM systemer og så videre.

Fejlkorrektion med produktkoder er undersøgt såvel teoretisk som eksperimentelt. Den iterativ dekodningsmetode der er anvendt til fejlkorrigerende koder i en produktkode struktur kan effektivt reducere bitfejlsandsynligheden (Bit Error Rate - BER). Forslag til dekodning ud over de teoretiske grænser (Beyond Bound Decoding - BBD) og adaptive dekodningsalgoritmer bliver præsenteret. BBD er en udvidelse der kan anvendes i visse tilfælde for yderligere at reducere BER.

Transmission med FEC for kort datacenter links præsenteres. Ved hjælp af FEC og billige Vertical-cavity surface-emitting laser (VCSEL) kan man opnå rå datahastigheder på 100 Gb/s, hvilket demonstrerer mulighederne for at konstruere et hæjhastigheds kortrækkænde link med billige elementer. Integration af FEC i WDM link for metronetværk bliver også præsenteret. Den eksperimentelle ydeevne af FEC både i det lineære og det ulineære områder demonstreres med dual polarisation 16QAM og transmission over 741 km med WDM baseret på kohærent detektion og en rå datahastighed på 88,8 Gb/s. FEC kan kompensere i begge områder, men analyse af transmissionskanalen viser støj der ikke er additiv hvid Gaussisk. Desuden ændrer et tættere grid i WDM kurveformerne for de eksperimentelle resultater så der kræves en kraftigere fejlkorrigerende kode.

Endelig præsenteres en "proof-of-the-concept" hardware implementering. Trade-off mellem kodelængde, CG og kompleksitet kræver yderligere overvejelse af FEC system for visse anvendelser. Det adaptive kodningssystem der præsenteres er et af de få publicerede forskningsresultater der muliggør effektiv brug af båndbredde når transmissionskanalen påvirkes af mange forskellige faktorer.

Som konklusion indeholder denne afhandling forslag til fejlkorrigerende koder med eksperimentelle resultater og hardwareimplementering. Det påviste høje coding gain, fleksibilitet, robusthed og mulighed for skalering understreger den vigtige rolle for FEC tekniker i næste generations højhastighed, stor kapacitet, hæj ydeevne og energieffektive fiber-optiske data transmissions netværk.

## Acknowledgements

I would like to acknowledge my supervisors, Professor Knud J. Larsen, Professor Idelfonso Tafur Monroy and Professor Søren Forchhammer, for their guidance in my professional development. I would also like to thank associate Professor Darko Zibar for his support in helping me to carry out my PhD study cross two groups: Coding and Visual Communication group and Metro-Access and Short Range Systems group.

Thanks to all my colleagues in both groups, Valeria, Robert, Neil, Antonio, Fotini, Kamau, Roberto, Thang, Maisara, Xiaodan, Silvia, Molly, Anna, Miguel, Xema, Martí, Jesper, JJ, Mario, Edson, Lucas, Christoph, Xu, Alexander, Claire, Xin, Huynh, Jari, Ann, Marco, Nino, Metodi, Ehsan, Jacob, Jokab, Matteo, and all other researchers, guest PhD students, visiting professors, bachelor students, master students and the administration, for the wonderful work time, lab time, travel time and coffee time we spent together. Thanks to the partners in the department and outside DTU for the great collaborations.

Thanks to my boys, Hans and Kevin, for those unforgettable laughing and crying moments in this challenging adventure. Thanks to my husband, Yanghui, and my parents, Shouzhen and Jinfa, for your love and support all the time.

Finally, thanks to all my friends, mentioned or not mentioned above, for always being there when you are in need.

## **Summary of original work**

# Original publications included in this PhD thesis

- [A] Bomin Li, D. Zibar, Knud J. Larsen, and I. Tafur Monroy, "Over 10 dB Net Coding Gain Based on 20% Overhead Hard Decision Forward Error Correction in 100G Optical Communication Systems," in 37th European Conference on Optical Communication (ECOC 2013), paper Tu.6.A.3, 2011.

- [B] Bomin Li, Knud J. Larsen, J. J. Vegas Olmos, D. Zibar, and I. Tafur Monroy, "Application of Beyond Bound Decoding for High Speed Optical Communications," in Asia Communications and Photonics Conference 2013 (ACP 2013), paper AF4C.6, 2013.

- [C] Cristian Prodaniuc, Bomin Li, and Knud J. Larsen, "Adaptive Forward Error Correction in High Speed Optical Communications," *Global Journal on Technology*, vol. 3, 2013.

- [D] Bomin Li, Knud J. Larsen, Darko Zibar and I. Tafur Monroy, "Forward Error Correction for 400 Gbps High Speed Optical Fiber Links," submitted to *IEEE Communications Letters*.

- [E] Roberto Rodes, Michael Müeller, Bomin Li, Jose Estaran, Jesper Bevensee Jensen, Tobias Gruendl, Markus Ortsiefer, Christian Neumeyr, Juergen Rosskopf, Knud J. Larsen, M.-C. Amann, and I. Tafur Monroy, "High-Speed 1550 nm VCSEL Data Transmission Link Employing 25 GBd 4-PAM Modulation and Hard Decision Forward Error Correction," Journal of Lightwave Technology, vol. 31, no. 4, pp. 689–695, 2013.

- [F] Bomin Li, Robert Borkowski, Jose Estaran, Molly Piels, Darko

- Zibar, Knud J. Larsen, and I. Tafur Monroy, "Experimental Performance of FEC for Linear and Nonlinear Optical Fiber Transmissions," submitted to *IEEE Photonics Technology Letters*.

#### **Contributions closely related to this PhD thesis**

[e] R. Rodes, J. Estaran, B. Li, M. Muller, J. B. Jensen, T. Gruendl, M. Ortsiefer, C. Neumeyr, J. Rosskopf, K. J. Larsen, M.-C. Amannn and I. Tafur Monroy, "100 Gb/s single VCSEL data transmission link," in 2012 Optical Fiber Communication Conference (OFC 2012), paper PDP5D.10, 2012.

# Remaining scientific contributions published during this PhD

- [1] J. J. Vagas Olmos, Lau Frejstrup Suhr, Bomin Li, and I. Tafur Monroy, "Five-level polybinary signaling for 10 Gbps data transmission systems," *Optics Express*, vol. 21, no. 17, pp. 20417–20422, August. 2013.

- [2] J.J. Vegas Olmos, L.F. Suhr, Bomin Li, and I. Tafur Monroy, "10 Gbps Five Levels Polibinary Signaling for Short Range and Access Networks," in Asia Communications and Photonics Conference 2013 (ACP 2013), paper AW4G.3, 2013.

## Contents

| Ab                                                   | ostra                         | ct           |                                |   |   | i        |  |  |  |

|------------------------------------------------------|-------------------------------|--------------|--------------------------------|---|---|----------|--|--|--|

| Re                                                   | Resumé i                      |              |                                |   |   |          |  |  |  |

| Ac                                                   | kno                           | wledgeme     | nts                            |   |   | v        |  |  |  |

| Su                                                   |                               | ary of orig  |                                |   |   | vii      |  |  |  |

|                                                      | Orig                          | inal publica | ations                         | • | • | vii      |  |  |  |

|                                                      | Closely related contributions |              |                                |   |   |          |  |  |  |

|                                                      | Remaining contributions       |              |                                |   |   |          |  |  |  |

| 1                                                    | Introduction                  |              |                                |   |   |          |  |  |  |

|                                                      | 1.1                           | Outline of   | the thesis                     | • |   | 1        |  |  |  |

|                                                      | 1.2                           | Motivation   |                                | • |   | <b>2</b> |  |  |  |

| 1.3 Advanced techniques in high speed optical commun |                               |              |                                |   |   | 3        |  |  |  |

|                                                      |                               |              | h order modulation format      |   |   | 4        |  |  |  |

|                                                      |                               |              | erent detection                |   |   | 5        |  |  |  |

|                                                      |                               |              | velength devision multiplexing |   |   | 6        |  |  |  |

|                                                      | 1.4 Forward error correction  |              |                                |   |   | 8        |  |  |  |

|                                                      |                               |              | ics                            |   |   | 8        |  |  |  |

|                                                      |                               | 1.4.2 Cod    | e overview                     | • |   | 10       |  |  |  |

|                                                      |                               |              | ptive algorithm                |   |   | 11       |  |  |  |

|                                                      |                               | 1.4.4 Har    | dware implementation           | • |   | 12       |  |  |  |

|                                                      |                               |              | lications                      |   |   | 14       |  |  |  |

| 2                                                    | State of the art              |              |                                |   |   | 15       |  |  |  |

| -                                                    | 2.1                           |              | codes                          |   |   | 15       |  |  |  |

|                                                      | 2.2 Adaptive FEC              |              |                                |   |   | 18       |  |  |  |

|                                                      | 2.3                           |              | implementation                 |   |   | 19       |  |  |  |

|                                                      | 2.4 FEC application           |              |                                |   |   | 23       |  |  |  |

| 3                                                                                    | Description of papers                                                                    |                         |                                                                                                                 |    |  |  |  |  |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

|                                                                                      | 3.1                                                                                      | Produc                  | ct code                                                                                                         | 27 |  |  |  |  |

|                                                                                      | 3.2                                                                                      |                         |                                                                                                                 |    |  |  |  |  |

|                                                                                      | 3.3                                                                                      | Hardw                   | vare implementation                                                                                             | 29 |  |  |  |  |

|                                                                                      | 3.4                                                                                      | FEC a                   | pplication                                                                                                      | 30 |  |  |  |  |

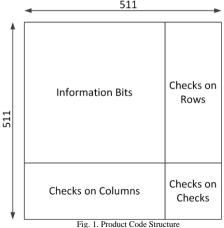

| 4                                                                                    | Product codes and their decoding                                                         |                         |                                                                                                                 |    |  |  |  |  |

|                                                                                      | 4.1                                                                                      | Basics of product codes |                                                                                                                 |    |  |  |  |  |

|                                                                                      |                                                                                          | 4.1.1                   | Code construction                                                                                               | 33 |  |  |  |  |

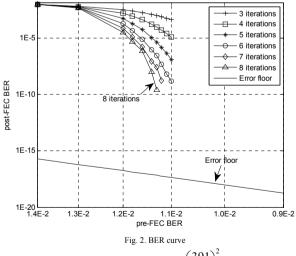

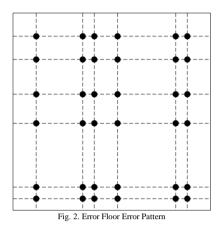

|                                                                                      |                                                                                          | 4.1.2                   | Iterative decoding and error floor                                                                              | 34 |  |  |  |  |

|                                                                                      |                                                                                          | 4.1.3                   | Code performance                                                                                                | 36 |  |  |  |  |

|                                                                                      | 4.2                                                                                      | Latest achievements     |                                                                                                                 |    |  |  |  |  |

|                                                                                      |                                                                                          | 4.2.1                   | Single chip FPGA implementation                                                                                 | 37 |  |  |  |  |

|                                                                                      |                                                                                          | 4.2.2                   | FEC performance affected by channel wavelength                                                                  |    |  |  |  |  |

|                                                                                      |                                                                                          |                         | spacing in WDM systems                                                                                          | 40 |  |  |  |  |

| 5                                                                                    | Summary                                                                                  |                         |                                                                                                                 |    |  |  |  |  |

|                                                                                      | 5.1                                                                                      | •                       | isions                                                                                                          | 45 |  |  |  |  |

|                                                                                      |                                                                                          | 5.1.1                   | Product code systems                                                                                            | 45 |  |  |  |  |

|                                                                                      |                                                                                          | 5.1.2                   | Adaptive algorithm                                                                                              | 46 |  |  |  |  |

|                                                                                      |                                                                                          | 5.1.3                   | Hardware implementation                                                                                         | 46 |  |  |  |  |

|                                                                                      |                                                                                          | 5.1.4                   | FEC application                                                                                                 | 46 |  |  |  |  |

|                                                                                      | 5.2                                                                                      | Future                  | e work                                                                                                          | 47 |  |  |  |  |

| Bi                                                                                   | bliog                                                                                    | graphy                  |                                                                                                                 | 61 |  |  |  |  |

|                                                                                      |                                                                                          |                         |                                                                                                                 |    |  |  |  |  |

| Li                                                                                   | st of                                                                                    | acrony                  | yms                                                                                                             | 63 |  |  |  |  |

| Pa                                                                                   | Har                                                                                      | d Decis                 | ver 10 dB Net Coding Gain Based on 20% Overhead<br>ion Forward Error Correction in 100G Optical Com-<br>Systems | 67 |  |  |  |  |

| Pa                                                                                   | Paper [B]: Application of Beyond Bound Decoding for High Speed<br>Optical Communications |                         |                                                                                                                 |    |  |  |  |  |

| Pa                                                                                   | Paper [C]: Adaptive Forward Error Correction in High Speed Op-<br>tical Communications   |                         |                                                                                                                 |    |  |  |  |  |

| Paper [D]: Forward Error Correction for 400 Gbps High Speed Op-<br>tical Fiber Links |                                                                                          |                         |                                                                                                                 |    |  |  |  |  |

- Paper [E]: High-Speed 1550 nm VCSEL Data Transmission LinkEmploying 25 GBd 4-PAM Modulation and Hard Decision Forward Error Correction85

- Paper [F]: Experimental Performance of FEC for Linear and Non-<br/>linear Optical Fiber Transmissions93

### Chapter 1

### Introduction

#### **1.1 Outline of the thesis**

This thesis is a summary of my PhD study performed at the department of photonics engineering, technical university of Denmark, Chapter 1 is an introduction to the motivation, the advanced techniques as well as FEC in high speed optical communications. Section 1.1 is the outline of the thesis, followed by the motivation in section 1.2. Section 1.3 covers the basics of high order modulation format, coherent detection and WDM that build the system framework for FEC application with proposed codes in this thesis. Section 1.4 is an overview of the concept, basics, algorithms, implementations and applications of FEC. Chapter 2 reports on the current state of the art in the key areas as below: the code development in section 2.1, the adaptive algorithm in section 2.2, the hardware implementation in section 2.3 and the applications in section 2.4. Chapter 3 describes the novelty behind each of the papers included in this thesis. The individual author contribution is included as well. Chapter 4 covers the basics of a FEC code with a product code structure. Latest achievements are included as well. The thesis is concluded by chapter 5. Section 5.1 summarizes the main achievements of the presented work. An outlook on future research options is presented in section 5.2.

#### **1.2 Motivation**

In its flagship regulatory report 2013 [1], International Telecommunication Union (ITU) confirms continued rapid expansion of tech markets worldwide. It points out that rapid growth of broadband has seen global IP traffic skyrocket from around one petabyte 20 years ago to an estimated 44,000 petabytes (44 exabytes) at end 2012. As an indicator of the sheer volume this represents, that amount of data would take 1,100 years to download over a 10 Mb/s broadband link, or more than 200,000 years over a dial-up connection. Looking forward in the coming years, Cisco Visual Networking Index forecasts that by the end of 2015, annual global IP traffic will exceed one zettabyte (capacity equivalent to one billion modern hard disks 1 terabyte each) and will reach 1.4 zettabyte per annum by 2017 [2]. Global Internet Protocol (IP) traffic has increased fourfold over the past 5 years, and will increase threefold over the next 5 years. Overall, IP traffic will grow at a compound annual growth rate (CAGR) of 23 percent from 2012 to 2017. Metro traffic will surpass long-haul traffic in 2014, and will account for 58 percent of total IP traffic by 2017.

Rich-bandwidth services such as video on demand, high definition TV and cloud computing are pushing the needs for improvements in optical transport network (OTN). This fast growing capacity consequently results in a need of higher speed or more spectrum-efficient transmission systems. High-order modulation format and coherent detection techniques are reappearing as an area of interest due to their capability to provide the capacity towards 400 Gb/s and beyond [3]. These techniques enable a high spectrum efficiency with the cost of increased complexity, which eventually leads to a higher implementation cost. WDM techniques are also intensively investigated. By multiplexing multiple optical carriers onto a single fiber with different wavelength lasers, the capacity is multiple times folded.

Yet, in the meanwhile higher loss should be expected. Losses due to for example chromatic dispersion (CD), polarization mode dispersion (PMD), nonlinear loss (NL), inter-channel interference (ICI) and intrachannel interference decrease the system performance. FEC, among many innovative methods to compensate losses, plays an important role as a cost effective solution to obtain the preferred transmission quality by using error correcting codes (ECC) [4]. It introduces redundancy in the transmission sequence to protect the valid information

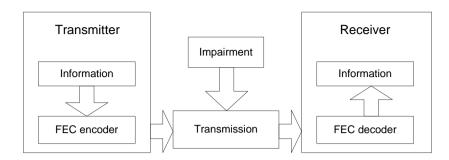

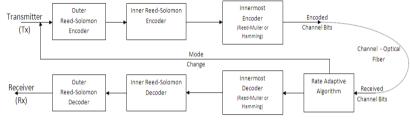

Figure 1.1: FEC integration in a transmission setup.

from being corrupted. Fig. 1.1 shows the framework of the FEC integration in a transmission setup. At the transmitter end, the information bits are encoded by adding a certain number of redundant bits based on an error-correcting mechanism. At the receiver end, within its error correcting capability, the decoder is able to recover the original information sequence by correcting errors introduced in the transmission. In today's and next generation coherent optical communication systems, powerful FEC codes will be necessary to achieve high net coding gain (NCG) larger than 10 dB at a reference BER of  $10^{-15}$ .

FEC technology has been intensively employed in optical communication systems. By FEC integration, the system performance is improved with the cost of reduced bandwidth usage and added FEC encoder and decoder implementation expenses. Therefore, to find a balance, the candidate FEC codes have to be evaluated by but not limited to the parameters as below:

- Coding gain;

- Error floor;

- Redundancy;

- Implementation complexity;

- Encoding and decoding delay.

Details of FEC are included in section 1.4.

# 1.3 Advanced techniques in high speed optical communications

This chapter covers some key technologies that enable optical communications beyond 100 Gb/s. High order modulation format, coherent

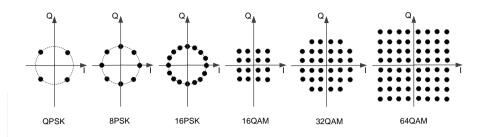

Figure 1.2: Constellation diagrams of selected higher-order modulation formats.

detection and WDM are explained in section 1.3.1, section 1.3.2 and section 1.3.3, respectively. However, there are many other techniques that are not covered by this thesis.

#### 1.3.1 High order modulation format

High order modulation format is a modulation format that maps m bits to a symbol, where *m* is usually 4 or more. In the early nineties of last century, proposals of different modulation formats based on the modulation of both quadratures did not attract much attention, due to the unavailability of complex high speed electronics. Besides, the emergence of Erbium doped fiber amplifier (EDFA) offers immediate modulation/direct detection (IM/DD) systems to scale to a higher capacity. In the late nineties, driven by the interest in the transmission of longer distance and higher robustness, differential binary phase shift keying (DBPSK) became attractive because of its property of robustness against non-linearity affect [5]. High order modulation format started to play an important role when fiber optics systems evolved to 100 Gb/s. By mapping several bits to a symbol, higher spectrum efficiency and lower symbol rate can be achieved. This overcame the barrier of system upgrade limited by relatively low speed electronics. Fig. 1.2 shows some constellation diagrams of selected high-order modulation formats of phase shift-keying (PSK) and QAM. From left to right these modulation formats are quadrature phase shift keying (QPSK), 8-ary PSK (8PSK), 16-ary PSK (16PSK), 16-ary QAM (16QAM), 32-ary QAM (32QAM) and 64-ary QAM (64QAM).

QPSK was the first high order modulation format being investigated. It can provide good performance over long distance optical link and it doubles the spectrum utilization. This modulation format in combination with digital equalization was demonstrated to have high tolerance to CD and PMD [6]. Polarization division multiplexing (PDM) QPSK was treated as a spectrally efficient solution to 100 Gb/s and beyond [7].

Commercial PDM-QPSK coherent systems at 40 Gb/s and 100 Gb/s have been reported [8]. The ASIC implemented DSP performs allelectronic CD and PMD compensation, frequency and phase locking, and polarization de-multiplexing. Experiments have shown that coherent systems with advanced modulation format return an increase in capacity of around 1 dB per year [9]. The use of high spectrally efficient phase modulation to increase both per-channel interface rates and aggregate WDM capacities is the next evolutionary step [11]. Enabled by digital coherent receivers, 16QAM, 64QAM [12] and 256QAM [13] can be employed to meet the increasing capacity demand. A transmission of a 1.1 Tb/s super channel in 100 GHz optical bandwidth based on PDM-256QAM and spatially coupled FEC is presented in [10]. The accompanied issue of reduced Euclidean distances between constellation points is expected to be compensated by FEC and coded modulation [14, 15].

#### 1.3.2 Coherent detection

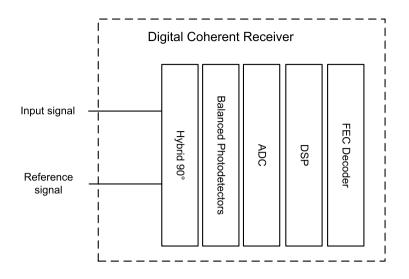

Coherent detection is a signal detecting technique of phase locking to the carrier wavelength. As shown in Fig. 1.3, the polarization controlled input and reference signals are fed into 90° hybrid, where the reference signal is commonly generated by local oscillator (LO). The signals detected by balanced photo-detectors are sampled by high speed analog-to-digital-converters (ADCs) and processed by digital signal processing (DSP), where channel equalization, carrier and phase recovery, frame demodulation can all be done in the electrical domain. Linear and non-linear digital equalizers have been proven to be helpful in dispersion compensation, which relaxes the requirements for FEC code selection [16, 17]. Furthermore, as coherent detection conveys any information (amplitude, phase, and polarization) from the optical domain to the electrical domain, the compensation on linear impairment such as CD and PMD, can be performed straightforward. Nonlinearity can also be compensated with the cost of complicated algorithms, for example digital backpropagation (DBP) [18]. Enabled by this ability, high order modulation formats like QAM uses the complex plane more effi-

Figure 1.3: Coherent receiver.

ciently than the IM/DD format that is limited to the use of intensities. The coherent detection technique, together with high order modulation format, releases the demand of very high speed analog-to-digital converter (ADC) in 100 Gb/s transmission systems. FEC decoder is an option to further reduce the BER. The error correcting capability provided by the integrated FEC can reduce the pre-FEC BER from around  $1.4 \cdot 10^{-2}$  and  $4.3 \cdot 10^{-3}$  to  $10^{-15}$ , respectively based on 20% and 7% overhead hard decision (HD) codes. Besides, the provided information by coherent detection enables soft decision (SD) FEC codes to achieve a higher coding gain compared to the same HD FEC codes, usually around 1.5 dB more.

#### 1.3.3 Wavelength devision multiplexing

WDM technology multiplexes a number of optical carriers onto a single fiber by using different wavelengths of laser light. With this method, the capacity in a single fiber channel is tens of times larger compared to using only one optical carrier in the single fiber channel. Early WDM was expensive and complicated to run. Coarse WDM (CWDM) systems provide up to 8 channels in the C-band of silica fiber around 1550 nm. The channel spacing grid for CWDM was standardized in ITU-T G.694.2 [21]. Dense WDM (DWDM) is also running in C-band, with a

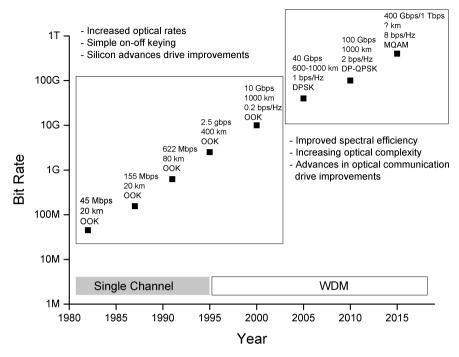

Figure 1.4: WDM development Overview [19].

higher number of channels. The fixed channel spacings ranging from 12.5 GHz to 100 GHz are defined in [22]. A typical system uses 40 channels with 100 GHz spacing, or 80 channels with 50 GHz spacing, or 160 channels with 25 GHz spacing. DWDM setups help to increase the capacity without the employment of high speed electronics (e.g. >40 Gb/s) and keep the compatibility with 10 Gb/s synchronous optical network-ing/synchronous digital hierarchy (SONET/SDH) equipment. Since the wavelengths are put close to each other, how to mitigate the crosstalk and inter-channel interference becomes an interesting topic.

Fig. 1.4 shows the development history of WDM technology in high speed optic-fiber transmissions. This figure is reproduced from the figure in [19]. Until the late 1990s, most optical networks were singlechannel systems operating at a data rate of 10 Gb/s and below. Signals were modulated with the IM/DD format, also known as On-Off Keying (OOK). In late 1990s, WDM systems enabled capacity upgrade by transmitting multiple wavelengths in a single fiber. In 20th century, research on advanced modulation format and denser WDM transmission has managed to increase the capacity to 100 Gb/s. Even higher capacity in future will be driven by the improvements in optical modulation, optical components, coherent detection, DSP, FEC and the arising topic on photonic integrated circuits (PICs) [23].

#### **1.4 Forward error correction**

FEC is considered as a cost effective method in high speed optical communications to achieve desired system performance. Today almost all applications have FEC considered as a part of the system in order to reach a certain BER with a low cost. This chapter provides an overview of various FEC aspects. Section 1.4.1 explains the basic concepts of FEC codes. Section 1.4.2 is an overview of different candidate codes. Section 1.4.3 discusses the concept of adaptive FEC. Section 1.4.4 covers the topic of hardware implementation. Section 1.4.5 shows examples of FEC applications.

#### 1.4.1 Basics

A couple of important concepts that are often used in FEC are explained in this section.

#### Overhead

When FEC is integrated in a system, an ECC is applied to the original information sequence by adding redundancy. An information sequence of k bits or symbols is encoded to a longer sequence of n bits or symbols, while the original information sequence and the encoded sequence meet the requirement of one-to-one mapping. The code rate R is the ratio of bit rate without FEC to bit rate with FEC:

$$R = \frac{k}{n} \tag{1.1}$$

The overhead is the relationship of the redundancy and the information length:

$$oh = \frac{n-k}{k} = \frac{1}{R} - 1$$

(1.2)

When the overhead increases, the net data rate, on the contrary, reduces if the line rate is fixed.

Figure 1.5: Coding gain.

#### Net coding gain

The definitions of CG and NCG can be found in ITU-T G.975.1 [20]. CG means the improvement of received optical sensitivity by using FEC, without considering penalty by bit rate increasing. NCG has bit rate increasing penalty considered in addition to the CG. As the code rate R is less than 1, a NCG is always smaller than the corresponding CG. NCG is characterized by both the code rate R, and the maximum allowable BER ( $B_{in}$ ) of the input signal to the FEC decoder that can be reduced to a reference output BER ( $B_{out} = B_{ref}$ ) by applying the FEC algorithm. Notice that NCG should refer to a binary symmetric channel with AWGN:

$$NCG = 20log10 \left( erfc^{-1} \left( 2B_{ref} \right) \right) - 20log10 \left( erfc^{-1} \left( 2B_{in} \right) \right) + 10log10 \left( R \right)$$

(1.3)

with  $erfc^{-1}$  the inverse of the complementary error function :

$$erfc(x) = 1 - erf(x) \tag{1.4}$$

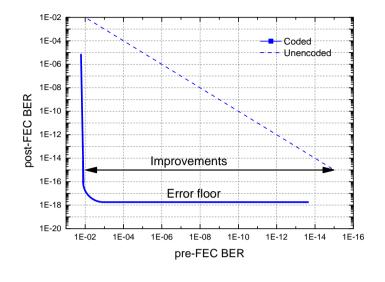

Fig. 1.5 shows an improvement on the pre-FEC BER axis between coded data and unencoded data. This improvement is translated into NCG when the corresponding pre-FEC BERs at two curves are plugged into the equation 1.3. Notice that the improvement is measured at a post-FEC BER of  $10^{-15}$ , where the pre-FEC BER of unencoded data is also  $10^{-15}$ . In principle, the more NCG is, the better error correcting capability the code provides. Yet, the bit rate penalty is of great importance in real systems.

#### Error floor

Error floor is that the output BER of a FEC code based on a certain decoding algorithm is bounded by a threshold. The example shown in Fig. 1.5 is that the post-FEC BER is bounded by a value between  $10^{-17}$  and  $10^{-18}$ . It means that despite the effort of the decoder, this value is the best post-FEC BER this decoding algorithm can achieve for the code.

Besides the importance of NCG, a candidate code desires for an error floor below the reference post-FEC BER. The recommended post-FEC BER from Optical Internetworking Forum (OIF) is currently  $10^{-15}$  [24]. A candidate code will not be regarded as suitable if it suffers from a high value error floor, for example  $10^{-10}$ .

#### 1.4.2 Code overview

In this section we will go through the candidate codes that are categorized into three generations. The first generation FEC uses classical HD codewords, mainly represented by Reed-Solomon (RS) code. This HD code with 6.7% overhead is a linear block code. RS(255, 239) is the most commonly used first generation FEC code, where 239 is the length of information symbols and 255 is the encoded length with redundancy. The error correcting theory shows that the minimum distance is 17 and it can correct up to 8 error symbols. It provides around 6 dB NCG for a post-FEC BER of  $10^{-15}$ . RS (255, 239) is recommended for long-haul transmission as defined in ITU-T G.709 [25].

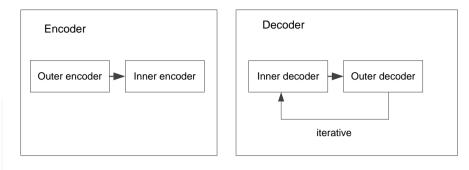

The second generation FEC uses also HD codes to provide a higher NCG, but with a more complicated algorithm. Fig. 1.6 shows an example of concatenated codes. At the transmitter side the information is first encoded by outer encoder and then by inner encoder. At the receiver side the decoding is done in an opposite way. Iterative decoding can be applied to concatenated codes. ITU-T G.975.1 lists some candidate codes for the second generation FEC. These HD codes have an overhead ranging from 6.7% to 25%, providing a NCG of around 8 to 10

Figure 1.6: Concatenated Code.

dB. A systematic binary LDPC code with a NCG of 8.02 dB at a reference BER of  $10^{-15}$  is also included as a candidate code in ITU-T G.975.1. It is a linear block that has the property of a few 1s in the parity check matrix with the rest a large amount of 0s. It was first introduced by Gallager in his PhD thesis in 1960s [26]. But it did not attract much attention until about fifteen years ago when the implementation of LDPC encoders and decoders becomes reasonably efficient due to the development of manufacturing process.

The third generation FEC usually uses SD method to obtain even higher NCG of over 10 dB. LDPC codes continue to be popular. Variants of LDPC codes are studied to provide NCGs close to the Shannon limit with the help of the decoding methods like sum-product [27], message passing [28] and belief propagation [29]. The variants are also studied to overcome the well-known error floor issue [30].

The proposals on new candidate codes never stop as the standardization of FEC is unclear for the next generation high speed optics-fiber communications. The fast capacity evolvement puts stricter requirements on FEC in no time. There are many other proposals besides the above mentioned ones, among which the FEC codes with a product code structure are what we study in this thesis. Details are in chapter 4.

#### 1.4.3 Adaptive algorithm

The drastically increased transmission speed in optical communications towards 400 Gbps and beyond makes the channel impairments become more and more severe. WDM technique will be the key enabler of the next generation high capacity optic-fiber networks. As discussed before, the reduction of spacing to a smaller grid makes the impairment and noise compensation more challenging. Increased nonlinear loss due to the increased power for increased number of channels will be costly to be compensated for each individual channel. Besides, the properties of all channels are not similar. Different lightwave paths experience different penalties. Furthermore, unpredictable burst errors, for example due to temperature drifting, degrade the system performance and limit the data transmission distance. Therefore, the adaptive FEC scheme would be essential to provide robustness, flexibility and high throughput for the next generation optical networks. By offering a flexible error protection capability, compared to a fixed rate FEC algorithm, an adaptive FEC algorithm usually provides:

- The capability to correct various types of errors;

- Less encoding and decoding delay in less noisy channel;

- Improved performance in noisy channel;

- Higher gain by average;

- Lower power by average.

#### 1.4.4 Hardware implementation

Application specific integrated circuit (ASIC) is an integrated circuit designed for a specific application, not for the general purpose use. It can be any specific application and the running speed is fast and guaranteed. The improved complementary metal-oxide-semiconductor (CMOS) technology, lowered from above 100 nm in 2000 [31] to today's 16 nm FinFET [32], enables ASIC designs with smaller area, reduced power consumption, faster speed and more complicated functionality. Today some building blocks such as micro-processers can be integrated in an ASIC as well. This kind of ASIC is called system on chip (SoC) [33] and provides a strong processing ability to support more sophisticated customer's requirements. Hardware description languages (HDLs) such as very high speed integrated circuit HDL (VHDL) [34], Verilog HDL [35] and systemVerilog [36] are used to describe the inparallel functionalities.

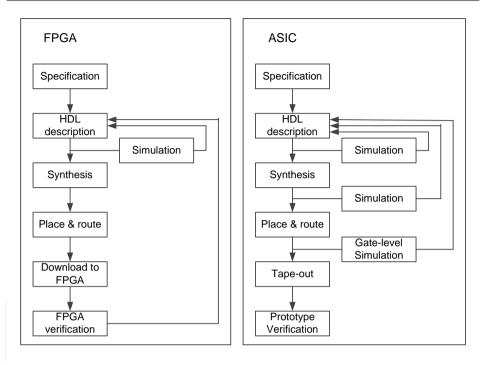

Field programmable gate arrays (FPGA) is an integrated circuit to be programmed after its manufacturing. It has programmable logic cells and programmable interconnects. The same HDLs are used in functional descriptions for FPGA applications. The compiled netlist can be downloaded into FPGA and verified on the test board. If bugs

Figure 1.7: Design flows of FPGA and ASIC.

are found in the verification, the modification can be made in the functional description and the compiled netlist can be downloaded again into FPGA. The modifications can be made as many as desired, without a demand for a thorough test of the functional description. ASIC designs, on the contrary, have a strict requirement in covering the functional test as much as possible before it goes to the actual tape-out stage.

The comparison of FPGA and ASIC design flows is shown in Fig. 1.7. Though ASIC and FPGA both use HDLs to describe the functionality from the start, there are some differences between these two techniques:

- FPGA is faster in development FPGA is a pre-factorized integrated circuit (IC);

- FPGA is more flexible The changes can be made and verified in FPGA as much as preferred;

- FPGA is reusable When an application is verified, an FPGA chip can be reused for other application purposes;

- ASIC is more compact It is user defined specific application;

• Cost is dependent on the application - FPGA is more costly for large production volumes, but cheaper in the case of small amount of productions.

#### 1.4.5 Applications

FEC is intensively considered in various applications. In WDM systems [37] that seem to be the dominant technology for high-capacity spectrum-efficient transmissions, FEC can help in applications such as the integration of low cost elements in next generation data centers [38], the deployment of advanced systems, for example RoF (radio-overfiber) [39], in metro/access network and the extension of the transmission distance in long haul transmission systems [40, 41, 42, 43].

In recent years FEC limit has been used as a reference in experimental demonstrations to evaluate the system performance. A successful sequence recovery at  $10^{-3}$  or even  $10^{-2}$  would be declared error free, assuming the use of FEC codes. This is not enough as there are many limitations to prevent FEC from performing in the expected way, i.e. as for the AWGN channel. Cycle slip, non-linearity, interference, etc. will all affect the behavior of FEC in an unexpected way. Therefore it is important to have FEC integrated in any given system to illustrate the actual improvements yielded by FEC.

### **Chapter 2**

### State of the art

The study of FEC is always a branch in the study of optical communications. To fulfil the ever increasing demand in different application scenarios, the adoption of FEC has to consider many aspects, for example the properties of candidate codes, the complexity of hardware implementation and the simplicity to be plugged into a system. In this chapter we will have an overview of the development of FEC from different perspectives. Section 2.1 is the overview of proposals on candidate codes. Section 2.2 shows the research work carried out for adaptive FEC. Hardware implementation and application scenarios are presented in section 2.3 and section 2.4 respectively.

#### 2.1 Candidate codes

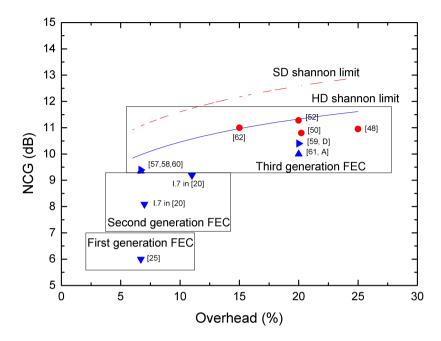

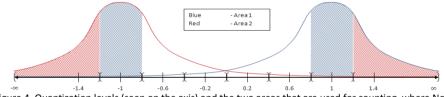

This section is an overview of the three generations of FEC codes with some highlights in Fig. 2.1. The blue solid curve represents for the HD Shannon limit while the red dashed curve represents for the SD Shannon limit. The red circle spots are SD-FEC codes and the blue triangle spots are HD-FEC codes.

The first integration of RS code into a 565 Mb/s optical signal opened a door of using FEC to push margins in different aspects for optical communications [44]. RS code is a non-binary cyclic ECC invented by Irving S. Reed and Gustave Solomon. It is specified in the ITU-T recommendation G.709 how an information sequence is encoded into a RS(255, 239) code on OTN interfaces [25]. With 6.7% overhead, it provides around 6 dB NCG at a reference BER of  $10^{-15}$ . Together

Figure 2.1: Overview of FEC codes.

with other simple linear codes such as Bose-Chaudhuri-Hocquenghem (BCH) code [45], RS code represents the first generation FEC.

LDPC codes started to attract attention for long haul optical communication in 2002 [46]. Simulations show that for a reference BER of  $10^{-6}$  it provides 1.2 dB NCG over RS(255, 239). LDPC codes, together with some concatenated code, are specified in the ITU-T recommendation G.975.1 as candidate FEC codes for high bit-rate DWDM submarine systems [20]. However, these codes can be applied to other high bit-rate optical systems as well. These codes with a varying overhead 6.7% to 25% are called second generation FEC codes, providing NCGs from 8 dB to 10 dB.

Many other codes have been proposed ever since. They are in general called the third generation FEC. The study of the third generation FEC consists of both HD-FEC and SD-FEC. A common property of the third generation FEC codes is to provide higher NCG than the second generation FEC codes provide, usually over 10 dB, at the cost of a higher overhead than 6.7%. There are also some reports on 6.7% overhead HD-FEC codes with NCGs of around 9.4 dB.

Among the various proposals for the third generation FEC codes, LDPC codes have been a very popular candidate due to its strong decoding capability at a relatively high input BER. Besides the binary LDPC codes, the non-binary LDPC codes for optical communication systems are proposed in [47], reporting a coding gain of 9.9 dB at a reference BER of 10<sup>-10</sup>, based on simulations for a 12.59% overhead LDPC code. Another example of SD-LDPC code is LDPC(24015, 19212) code of rate 0.8 with a NCG of 10.95 dB at a reference BER of  $10^{-12}$  [48]. Long irregular SD-LDPC coded orthogonal frequency division multiplexing (OFDM) is reported in [49]. To overcome the well-known error floor issue, the concatenations of LDPC codes with other codes are studied. The concatenations of SD-LDPC and 7% overhead HD-FEC codes for application in systems beyond 40 Gb/s are presented in [50, 51]. The simulation shows a NCG of 10.8 dB for a code with around 20.5% overhead. A SD-LDPC(18353, 15296) code with a NCG of 11.28 dB at 20% redundancy is mentioned in [52].

Concatenated codes from the concatenation of RS codes and other simple linear codes are still ongoing. A serial block turbo code (BTC) that is a concatenation of RS code and Reed-Muller (RM) code is reported in [53]. The simulation is done for a binary phase shift keying (BPSK) signal over an AWGN channel. The simulation result shows that this code outperforms RS(255, 239) with around 2 dB. Concatenated codes of BCH codes are reported in [54, 55, 56]. They have similar performance compared to the second generation FEC specified in ITU-T G.975.1. But the short length of some codes may be beneficial in the hardware implementation.

Other codes than LDPC codes and concatenated codes are reported as well. A so called Swizzle code is proposed in [57]. This code has a NCG of 9.45 dB at a cost of 6.7% overhead for a reference BER of  $10^{-15}$ . Staircase code is presented in [58, 59]. With 6.7% overhead and 20% overhead, this code can provide NCGs of around 9.4 dB and 10.4 dB. The error floor is way below  $10^{-15}$ . The study of a continuously interleaved BCH (CI-BCH) code is reported by Vitesse [60]. This 6.7% overhead HD-FEC code yields 9.35 dB NCG at the error floor of less than  $10^{-15}$ . The product VSC9804 is a 20% overhead version CI-BCH and its key features state a NCG of more than 10 dB [61]. A SD turbo block code (TBC) with around 15% overhead is demonstrated to be able to provide over 11 dB NCG [62]. We have also proposed FEC codes with 20% overhead that yield NCGs of from 10 to 10.4 dB at a reference BER of 10<sup>-15</sup> [**A**, **B**, **D**].

#### 2.2 Adaptive FEC

The study of adaptive FEC is not mature and expands in multiple subareas.

In 2005, a SDH based adaptive error correction scheme for WDM networks was proposed [63]. It suggests to take the advantage of multichannel systems and to use a dedicated channel for the redundancy transmission. This scheme provides a better performance than using fixed codes as in ITU-T G.707 and ITU-T G.709 that limit the correction capability and efficiency for different patterns. The redundant bits of payloads for all other channels are transmitted based on time division multiplexing (TDM) at a fixed rate to enable synchronization at the receiver end.

In 2007, an adaptive FEC method for high speed optical Ethernet was proposed [64]. It points out that high speed optical Ethernet has to consider the problem of physical channel errors. The probability of correctly transporting Ethernet data packets whose lengths are greater than 1280 bytes will be near to 0 when BER of the physical channel is greater than  $5 \cdot 10^{-4}$ . In the test FEC was considered at packet level and the redundancies from 2 bits to 32 bits were used. Packets under test were from 16 bytes to 1518 bytes. The test results show less than 1% packet loss at the channel BER of  $10^{-3}$ .

In 2009, a rate adaptive LDPC-coded multilevel modulation with coherent detection for high speed optical transmission was presented [65]. It chooses quasi-LDPC code in the adaptive scheme. Each channel is encoded with a configurable quasi-LDPC code based on its channel condition. The simulation shows that at a target BER of  $10^{-9}$  the NCG ranges from 9.16 dB to 10.09 dB.

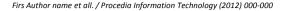

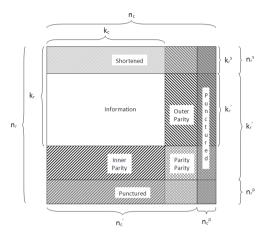

In 2011, a rate-adaptive coding method for optical fiber transmission systems was presented in [66]. This rate-adaptive transmission scheme for long-haul systems uses a fixed modulation format (PDM-QPSK) at a fixed symbol rate, with the deployment of variable rate HD serially concatenated RS over a wide range. Shortening and puncturing are used for the code rate variation. Simulation results show a transmission distance of 2000 km at 100 Gbit/s with single carrier DP-QPSK modulation and coherent detection. In 2012, we proposed a rate-adaptive coding scheme using twolayered variable rate FEC for optical fiber transmission systems, also with the fixed signal constellation and symbol rate [**C**]. The first level uses serially concatenated HD-RS codes to provide a CG of up to 12.25 dB. For lower signal-to-noise ratio (SNR) transmissions, a second layer of coding is employed. By using 3-bit quantization SD extended Hamming(8, 4, 4) code or RM(1, 4) code, the CGs can be extended to 15.75 dB and 18 dB respectively.

In 2013, a study of rate adaptive FEC in optical transport unit (OTU) framing was presented [67]. It proposes to segment OTU4V into tributary slots to realize the variation of parity length without varying the frame length. Combining the conventional attached parity region with the parity transmitted in ODTUs, a NCG improvement of 1.5 dB is expected.

In 2013, an adaptive FEC for energy efficient OTN was reported in [68]. This paper describes from the traffic point of view how an adaptive FEC scheme can help with energy efficient OTNs. It proposes a modification in OTN frame format to confine with variable FEC coding methods in order to reduce the power consumption during periods of low traffic.

The most recently published study on an adaptive FEC scheme is on the spectrum-efficiency of transparent OTN design with variable rate FEC codes [69]. This paper addresses from the network planning standpoint the tradeoff between transmission rate and optical reach. It employs the algorithm described in [66] to illustrate the idea. The case study shows the increase of spectrum efficiency supports total traffic around three times higher than that with mixed line rate.

#### 2.3 Hardware implementation

Thanks to the more advanced CMOS technology, the hardware implementation of FEC has been pushed from a throughput of 3.2 Gb/s to a throughput of 100 Gb/s and is still moving forward. An overview of reported research results can be found in the tables 2.1 to 2.5. The table 2.1 shows two implementations at a low throughput of less than 5 Gb/s, a SD-RS code and a HD-RS code. The implementation for SD-RS with the more advanced CMOS technology shows a reduced voltage supply as well. The table 2.2 shows again one SD-FEC implementation and one HD-FEC implementation. They both have a throughput

| Code                      | SD-RS [70]        | HD-RS [71] |

|---------------------------|-------------------|------------|

| Throughput (Gb/s)         | 2.56              | 3.2        |

| Overhead (%)              | 6.7               | 6.7        |

| NCG (dB @a reference BER) | -                 | -          |

| CMOS technology           | 90 nm             | 0.18 µm    |

| Number of gates           | $45.3~\mathrm{K}$ | 21 K       |

| Memory (bits)             | -                 | -          |

| Delay                     | -                 | -          |

| Voltage supply            | 0.98 V            | 1.8 V      |

| Power consumption         | 19.6 mW           | -          |

Table 2.1: Overview of hardware implementation - part 1

Table 2.2: Overview of hardware implementation - part 2

| Code                      | SD-BTC [72]        | HD-RS [73]                        |

|---------------------------|--------------------|-----------------------------------|

| Throughput (Gb/s)         | 12.4               | 10                                |

| Overhead (%)              | 23.6               | 6.7                               |

| NCG (dB @a reference BER) | $10.1 \ @10^{-13}$ | $5.5 \ \mathbf{@}10^{\text{-}12}$ |

| CMOS technology           | 0.13 µm            | 0.16 µm                           |

| Number of gates           | 16 M               | 1.8 M                             |

| Memory (bits)             | 4 M                | -                                 |

| Delay                     | -                  | $5.73~\mu s$                      |

| Voltage supply            | -                  | -                                 |

| Power consumption         | -                  | 343 mW                            |

around 10 Gb/s. With a higher overhead and a more complicated decoding algorithm, the SD-FEC provides almost a double NCG than the HD-FEC can. The tables 2.3 and 2.4 are examples of hardware implementations of the second generation FEC codes, while the table 2.5 includes two implementations of the third generation FEC codes that provide higher NCGs compared to the second generation FEC. It is pointed out in [73] that the power consumption of the decoder core is a small part of the power consumption of an entire chip. Two thirds of the power consumption of an entire chip is due to I/O power. Therefore the power consumption for the second implementation in the table 2.5 is suspected to be the chip power consumption while the other mentioned power consumption values are for the decoder cores.

Besides the listed ASIC decoders, some interesting FPGA implementations are listed below. A 10 Gb/s orthogonally concatenated BCH

| HD-RS [73]                        | HD-RS [74]                                                            |

|-----------------------------------|-----------------------------------------------------------------------|

| 40                                | 115                                                                   |

| 6.7                               | 6.7                                                                   |

| $5.5 \ \mathbf{@}10^{\text{-}12}$ | -                                                                     |

| 0.16 µm                           | 0.13 µm                                                               |

| 400 K                             | 378 K                                                                 |

| -                                 | -                                                                     |

| 1.5 µs                            | 800 ns                                                                |

| -                                 | $1.2~\mathrm{V}$                                                      |

| 361  mW                           | -                                                                     |

|                                   | 6.7<br>5.5 @10 <sup>-12</sup><br>0.16 μm<br>400 K<br>-<br>1.5 μs<br>- |

Table 2.3: Overview of hardware implementation - part 3

**Table 2.4:** Overview of hardware implementation - part 4

| Code                      | Concatenated       | Concatenated        |  |

|---------------------------|--------------------|---------------------|--|

|                           | BCH [56]           | BCH [75]            |  |

| Throughput (Gb/s)         | 102.4              | 110.1               |  |

| Overhead (%)              | 6.7                | 6.7                 |  |

| NCG (dB @a reference BER) | $7.98 \ @10^{-12}$ | $9.19$ @ $10^{-15}$ |  |

| CMOS technology           | 90 nm              | 90 nm               |  |

| Number of gates           | 1.4 M              | 3.732 M             |  |

| Memory (bits)             | -                  | 4.114 M             |  |

| Delay                     | 13.8 µs            | 38 µs               |  |

| Voltage supply            | 1.1 V              | 1.1 V               |  |

| Power consumption         | -                  | -                   |  |

Table 2.5: Overview of hardware implementation - part 5

| Code                      | i-BCH [76]                  | SD-TPC [62]         |

|---------------------------|-----------------------------|---------------------|

| Throughput (Gb/s)         | 110.1                       | 100                 |

| Overhead (%)              | 6.7                         | 15                  |

| NCG (dB @a reference BER) | $9.34 \ \mathbf{@}10^{-15}$ | $11 @ 10^{-15}$     |

| CMOS technology           | 90 nm                       | 40 nm               |

|                           |                             | 640 K flip-flops    |

| Number of gates           | 3.087 M                     | 6.3 M               |

|                           |                             | combinatorial gates |

| Memory (bits)             | $5.705 \ \mathrm{M}$        | 9 M                 |

| Delay                     | 66 µs                       |                     |

| Voltage supply            | -                           | -                   |

| Power consumption         | -                           | 7 W (chip)          |

encoder is presented in [77]. The design was realized in FPGA and the simulations show a data rate of 10 Gb/s with clock frequency of 156 Hz. To eliminate the well-known LDPC error floor issue, the design of a LDPC code and its hardware architecture are jointly investigated [78]. With an FPGA-based study of the dominant error events, the parity check matrix is optimized to lower the error floor to  $10^{-13}$ . A SD-LDPC code of 24576 bits with 20% overhead was implemented in an FPGA chip. The NCG is 10.7 dB at a reference BER of  $10^{-13}$ . Another try on an FPGA chip is a triple-concatenated SD-FEC using LDPC(4608, 4080) [79]. This 20.5% overhead code was implemented in a FPGA chip with a clock frequency of 556 KHz and a throughput of 100 Gb/s. A NCG of 10.8 dB is expected at a post-FEC BER of  $10^{-15}$  with the concatenation of a second generation code.

Besides, a real time 120 Gb/s coherent PDM-QPSK transceiver implemented as a 40 nm CMOS ASIC is reported in [80, 81]. It contains 63 GSamples/s ADCs, DSP and SD-FEC. The chosen turbo product code (TPC) yields a NCG of 11.1 dB at a post-FEC BER of  $10^{-15}$ . The test of ASIC design was carried out in a WDM environment with multi-path interference considered.

Table 2.6 includes some highlights of the hardware implementations from the industry. 100G FEC product releases include VSC9804 [61] and Viasat ECC66100 series [82]. HD-FEC and SD-FEC respectively. VSC9804 is a 20% overhead HD CI-BCH code with a NCG of over 10 dB. The ECC66100 series consists of SD-TPC with an overhead of 15% or 20% and NCGs of 11 and 11.3 dB, respectively. Viasat also releases the ECC66200 series for 200G applications [83], based on 7% and 20% overhead SD-TPC codes with NCGs of 10.2 and 11.3 dB respectively. Without revealing details, Huawei [84] and ZTE [85] have announced their in-house self-developed FEC algorithms for 100G or higher bit rate optical transmissions. Huawei's block interleaved convolutional code (BICC) is an LDPC-based SD-FEC scheme. With 20% or larger overhead, it provides over 11.5 dB NCG. The FPGA demonstration is reported in [86]. Huawei points out that this SD-FEC, together with spectrum compression at the transmitter, reduces the transmission penalty caused by rate increases at the transmitter and ensures the desired CG for high overhead SD-FEC. ZTE 's 100G SD-TPC has 15% overhead and allows an input BER threshold of between  $1.8 \cdot 10^{-2}$  and  $2 \cdot 10^{-2}$  that translates to around 11 dB NCG. ZTE declares that this SD-FEC scheme with 15% overhead offers higher transmis-

| Code   | Company | Throughput (Gb/s) | Overhead (%) | NCG (dB)  |

|--------|---------|-------------------|--------------|-----------|

| CI-BCH | Vitesse | 100               | 20           | > 10      |

| SD-TPC | Viasat  | 100               | 15           | 11        |

| SD-TPC | Viasat  | 100               | 20           | 11.3      |

| SD-TPC | Viasat  | 200               | 7            | 10.2      |

| SD-TPC | Viasat  | 200               | 20           | 11.3      |

| BICC   | Huawei  | 100               | 20           | > 11.5    |

| TPC    | ZTE     | 100               | 15           | $\sim 11$ |

Table 2.6: 100 Gb/s FEC highlights from the industry

sion efficiency and better wave filtering performance than a 20% overhead FEC scheme. Other companies, for example Altera [88], also have proposals for 100G FEC solutions.

Reduced circuit complexity is a very important issue for 100 Gb/s and above FEC implementation. Viasat's ECC6100 series in 40 nm CMOS technology has more than 20 M equivalent gates. Coriant points out in [87] that close to half of the power dissipation of a 100 Gb/s DSP-ASIC digital logic core in a line card application is from SD-FEC. Therefore, the more mature and cheaper CMOS process is essential to simplify the implementation and reduce the cost in future.

#### 2.4 FEC application

FEC can compensate all kinds of impairments, but the achievable improvements vary from one application to another as the error distributions are different. This section lists some applications with novelties.

A study of using 160-km repeater spans and advanced FEC is reported in [89]. It is attractive to use long repeater spans as it can substantially save capital and operational expenditure. The novelty of this paper includes the use of a span longer than 150 km and a transmission link of 480 km over three 160-km spans as well as the integration of FEC. The experiment was done in a 160 Gb/s RZ-DPSK data transmission link excluding the FEC overhead. The analysis shows the promise of a transmission over 1000 km at 160 Gb/s with a repeater spacing of 160 km.

Employing concatenated FEC to mitigate polarization-sensitivity in all-optical wavelength conversion is reported in [90]. All-optical wavelength-conversion can be efficiently performed by means of semiconductor optical amplifier (SOA) with the shortcoming of being sensitive to the relative polarization of optical signals. A FEC mechanism was introduced and demonstrated in a 10 Gb/s lightwave channel that the conversion may be made insensitive to random fluctuations of the polarization. No error was observed after FEC decoding without the control of the polarization before the converter.

A FEC aided demonstration of silicon based wavelength conversion is reported in [91]. The experiment consisted of two cascaded nonlinear optical signal processes, i.e. 160 Gbit/s all optical wavelength conversion based on cross-phase modulation (XPM) in a silicon nanowire and subsequent 160 Gbit/s-to-10 Gbit/s de-multiplexing using a highly nonlinear fiber (HNLF). With the integration of 6.6% overhead FEC, the transmitted sequence was recovered without observing any error.

A paper on the impact of error control with FEC on energy-efficient reliable data transfers over optical networks is presented in [92]. In this paper, two schemes are studied for energy efficient reliable delivery of large files (hundreds of GBs) over core optical networks: automatic repeat request (ARQ), and hybrid ARQ that combines ARQ with FEC. A new model is proposed in hybrid ARQ to estimate the energy consumption for performing encoding and decoding operations by incorporating different block sizes and FEC error correcting capability. The analysis shows that when the pre-FEC channel BER is in excess of  $10^{-5}$ , hybrid ARQ offers better performance than ARQ in terms of energy efficiency. When BER is lower than  $10^{-5}$ , hybrid ARQ behaves similarly to ARQ. Therefore hybrid ARQ seems to fit better in the design of energy efficient network in future.

A study of ECC for pulse amplitude modulation (PAM) signals in data center applications can be found in [93]. This paper experimentally demonstrates PAM modulation with FEC integration for a 25 Gb/s per channel data center, which is a cheaper solution than using QAM modulation format or polarization multiplexing as explained in [94]. The demonstration was done in a transmission distance of over 500 m as specified in [95] and some selected FEC codes failed to provide the minimum CG requirement [96] of 5.8 dB at a BER of  $10^{-15}$  while others succeeded.

A field trial of 112 Gb/s dual-carrier differential quaternary phaseshift keying (DQPSK) channel upgrade in an installed 516-km fiber link and reconfigurable optical add-drop multiplexer (ROADM) is reported in [97]. This demonstration for 100 Gb/s metro area network requires neither high-end ADC/DSP nor fast optical polarization tracking. No error was observed in the transmission of a 100GE signal over 106 hours with OTU4 framer and FEC.

SD-FEC in a non-AWGN channel is studied in [98]. A conditionally bivariate Gaussian noise model (CBGN) is used to analyze the impact of correlations among the signal's two quadrature components and LDPC codes are evaluated in this channel. It shows that the shape of the noise clouds significantly affects the detection performance for SD decoding. Conventional DSP algorithms may unintentionally shape the noise clouds into AWGN-like clouds, which destroy useful information for SD-FEC.

The hybrid SD/HD FEC scheme under extreme XPM conditions is evaluated in [99]. If TPC code is used and there is no interleaving, the presence of NLs alters the input-output BER relationship. When TPC is replaced by a long LDPC code, input-output BER relationship remains essentially unaffected due to the deeper interleaving innate in the long LDPC code. By interleaving 4 TPC codewords, it also shows the unaffected input-output BER relationship. Interleaving FEC codes helps PMD mitigation as well [100]. With polarization scramblers (PSs), the interleaving LDPC codes are tolerant to a large PMD.

A study of SD faster than Nyquist (FTN) technologies in PDM-QPSK transmission is shown in [101]. FTN signaling can transmit up to twice the bits as ordinary modulation at the same bit energy, spectrum, and error rate. The method is directly applicable to OFDM and QAM signaling [102]. In a 20-channel 224 Gbps (56Gbaud) PDM-QPSK experiment in 50 GHz grid over 3040-km G.652 fiber and EDFA-only link, with 7% overhead SD-FEC, 4 bit/s/Hz net spectral efficiency was achieved. It indicates that SD-FTN algorithm enables 400G long haul transmissions.

In the next generation network solutions, the selection of FEC codes has to jointly consider many factors to balance the tradeoff among performance, energy efficiency and FEC overhead [103, 104, 105].

# **Chapter 3**

# **Description of papers**

This thesis is based on a number of articles already published or submitted to peer-reviewed journals and conference proceedings. This chapter states the main contribution of the thesis, including the description of the novelty, the individual author contribution and comment to the papers.

The included papers are categorized into four aspects, the same as in chapter 2. The papers  $[\mathbf{A}, \mathbf{B}]$  present the results of proposed code algorithms in section 3.1. The paper  $[\mathbf{C}]$  presents the result on adaptive FEC in section 3.2. In section 3.3 the paper  $[\mathbf{D}]$  presents a code proposal together with its implementation for 400 Gb/s optical transmissions. In the final section 3.4 the experimental results are presented in the papers  $[\mathbf{E}, \mathbf{F}]$ .

### 3.1 Product code

**Paper [A]:** Over 10 dB Net Coding Gain Based on 20% Overhead Hard Decision Forward Error Correction in 100G Optical Communication Systems

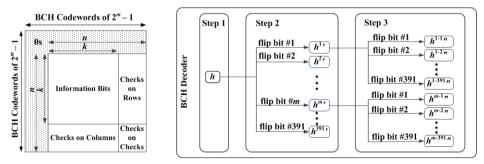

This paper, presented at 37<sup>th</sup> European Conference on Optical Communication (ECOC 2011), proposes a new encoding and decoding FEC algorithm for 100 Gb/s optical communications. As the research for optical communications moved from 40 Gbps to 100 Gbps based on DP-QPSK modulation and coherent detection, the increased optical signalto-noise ratio (OSNR) requirement has pushed the study of FEC to evolve from the second generation to the third generation for a NCG of 10 dB or even higher. The overhead requirement is relaxed in the meanwhile, based on the suggestion from OIF [24]. The proposed code in this paper is one of the first several reported research achievements on 20% overhead FEC with over 10 dB NCG. The error floor turns out to meet today's requirement of  $10^{-15}$ . The hardware implementation is also investigated in the paper and it shows the possibility for an implementation in several state-of-the-art FPGA chips.

*Comment:* In section 2 where the code construction is explained, the length of leading zeroes is 980, which is a typo. The correct length should be 1656.

The individual author contribution: contributed to the introduction and motivation of the paper; performed the simulation and analysis of the proposed code; prepared and revised the manuscript.

# **Paper [B]:** Application of Beyond Bound Decoding for High Speed Optical Communications

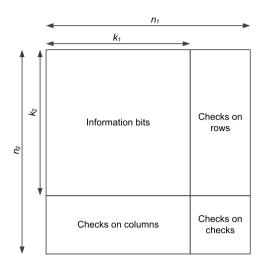

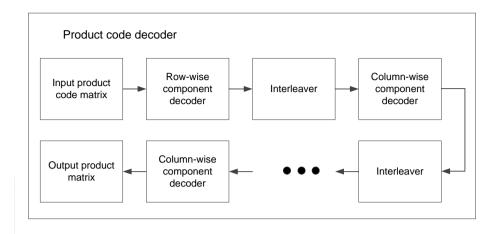

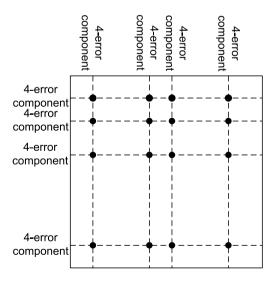

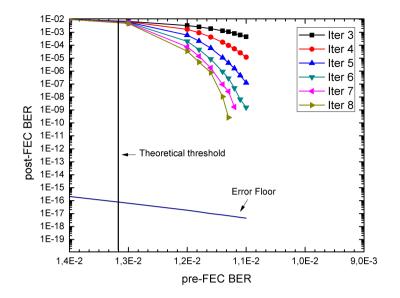

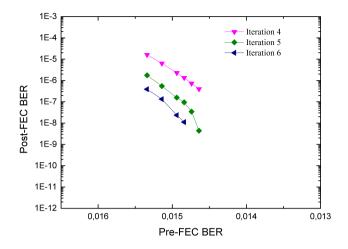

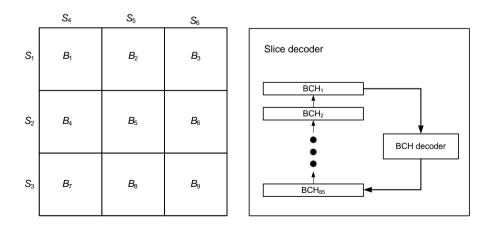

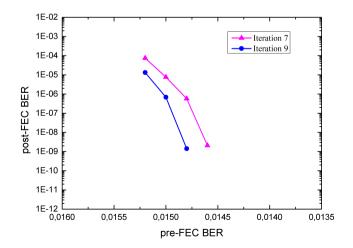

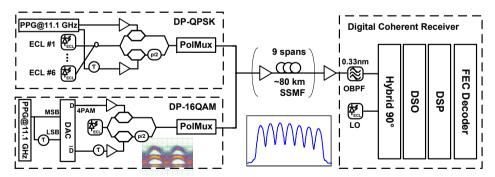

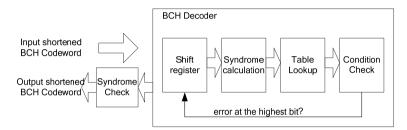

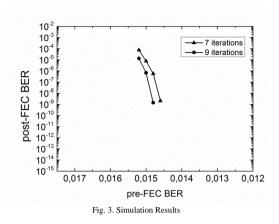

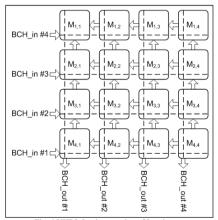

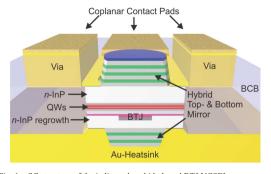

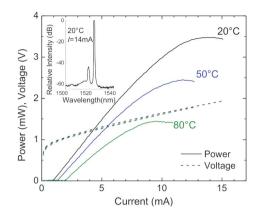

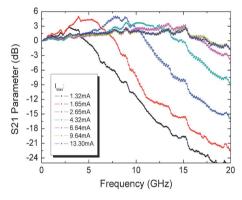

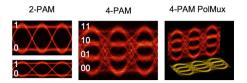

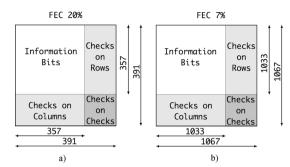

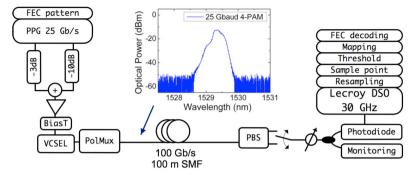

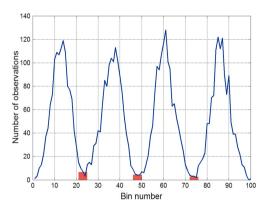

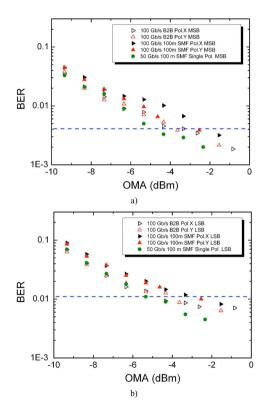

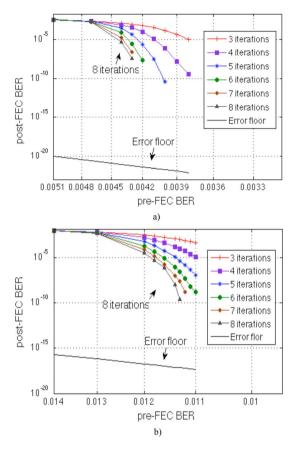

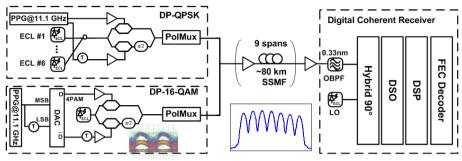

This paper, presented at Asia Communications and Photonics Conference 2013 (ACP 2013), proposes a new decoding FEC algorithm for 100 Gb/s optical communications. In the paper [**A**], the proposed code takes the advantage of reduced decoding error probability. This paper studies how to improve the decoding capability further, having this advantage considered. The component code in [**A**] can correct up to 3 errors and detect 4 errors based on minimum distance decoding (MDD) method. In this paper, the decoding success probability when there are 4 errors. Notice that no decoding error exists if a component has 4 errors in it. When there are more than 4 errors in a component, the decoding error probability is small. The method can be applied to any code with BCH components or similar, not limited to a product code structure.