# CAPACITOR-LESS VAR COMPENSATOR BASED ON A MATRIX CONVERTER

A Thesis

by

# DIVYA RATHNA BALAKRISHNAN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

December 2010

Major Subject: Electrical Engineering

Capacitor-Less VAR Compensator

Based on a Matrix Converter

Copyright 2010 Divya Rathna Balakrishnan

# CAPACITOR-LESS VAR COMPENSATOR BASED ON A MATRIX CONVERTER

### A Thesis

by

### DIVYA RATHNA BALAKRISHNAN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE

Approved by:

Chair of Committee, Robert S. Balog Committee Members, Hamid Toliyat

Shankar Bhattacharyya

Won-jong Kim

Head of Department, Costas Georghiades

December 2010

Major Subject: Electrical Engineering

#### **ABSTRACT**

#### Capacitor-Less VAR Compensator

Based on a Matrix Converter. (December 2010)

Divya Rathna Balakrishnan, B.Tech., National Institute of Technology, Karnataka, India

Chair of Advisory Committee: Dr. Robert S. Balog

Reactive power, denoted as volt-ampere reactive (VARs), is fundamental to ac power systems and is due to the complex impedance of the loads and transmission lines. It has several undesirable consequences which include increased transmission loss, reduction of power transfer capability, and the potential for the onset of system-wide voltage instability, if not properly compensated and controlled. Reactive power compensation is a technique used to manage and control reactive power in the ac network by supplying or consuming VARs from points near the loads or along the transmission lines. Load compensation is aimed at applying power factor correction techniques directly at the loads by locally supplying VARs. Typical loads such as motors and other inductive devices operate with lagging power factor and consume VARs; compensation techniques have traditionally employed capacitor banks to supply the required VARs. However, capacitors are known to have reliability problems with both catastrophic failure modes and wear-out mechanisms. Thus, they require constant monitoring and periodic replacement, which greatly increases the cost of traditional load compensation techniques.

This thesis proposes a reactive power load compensator that uses inductors (chokes) instead of capacitors to supply reactive power to support the load. Chokes are regarded as robust and rugged elements; but, they operate with lagging power factor and thus consume VARs instead of generating VARs like capacitors. A matrix converter interfaces the chokes to the ac network. The matrix converter is controlled using the Venturini modulation method which can enable the converter to exhibit a current phase reversal property. So, although the inductors draw lagging currents from the output of the converter, the converter actually draws leading currents from the ac network. Thus, with the proposed compensation technique, lagging power factor loads can be compensated without using capacitor banks.

The detailed operation of the matrix converter and the Venturini modulation method are examined in the thesis. The application of the converter to the proposed load compensation technique is analyzed. Simulations of the system in the MATLAB and PSIM environments are presented that support the analysis. A digital implementation of control signals for the converter is developed which demonstrates the practical feasibility of the proposed technique. The simulation and hardware results have shown the proposed compensator to be a promising and effective solution to the reliability issues of capacitor-based load-side VAR compensation techniques.

To my family

#### **ACKNOWLEDGEMENTS**

I would like to express my deep sense of gratitude and regard to my advisor and mentor, Dr. Robert Balog. His invaluable guidance and unstinted support have made this work possible. I would like to thank him for being so encouraging, understanding and patient at all times. I am happy to have had the opportunity to pursue research under his guidance and am grateful to him for the many things I have learnt during the course of my work.

My sincere thanks are due to Dr. Hamid Toliyat, Dr. Shankar Bhattacharyya and Dr. Won-jong Kim for sparing their valuable time to serve on my defense committee. I would also like to thank Dr. Prasad Enjeti for his initial guidance on my research.

I am grateful to the entire staff of the Electrical Engineering Department for supporting me during my academic program at Texas A&M University. I am thankful to my research group for making my laboratory experience so wonderful. I would like to specially thank Mehran, Daniel and Somu for their assistance with my research work.

I am deeply indebted to my parents, sister and brother-in-law whose unconditional love, support and encouragement have greatly contributed to the completion of this work. I owe my gratitude to them for always believing in me and helping me through my academic pursuit.

#### **NOMENCLATURE**

VAR Volt-ampere reactive MC 3-phase ac-to-3-phase ac matrix converter Line-neutral ac network voltage (phase 1)  $v_{1,LN}$ Line-neutral ac network voltage (phase 2)  $v_{2,LN}$ Line-neutral ac network voltage (phase 3)  $v_{3,LN}$ Line-neutral matrix converter input voltage (phase 1)  $v_{i1,LN}$ Line-neutral matrix converter input voltage (phase 2)  $v_{i2.LN}$ Line-neutral matrix converter input voltage (phase 3)  $v_{i3,LN}$ Line-neutral matrix converter output voltage (phase 1)  $v_{o1,LN}$ Line-neutral matrix converter output voltage (phase 2)  $v_{o2,LN}$ Line-neutral matrix converter output voltage (phase 3)  $v_{o3,LN}$ Ac network line current (phase 1)  $i_1$  $i_2$ Ac network line current (phase 2) Ac network line current (phase 3)  $i_3$ Load current drawn from ac network (phase 1)  $i_{Load1}$  $i_{Load2}$ Load current drawn from ac network (phase 2) Load current drawn from ac network (phase 3)  $i_{Load3}$ Matrix converter input current (phase 1)  $i_{i1}$  $i_{i2}$ Matrix converter input current (phase 2) Matrix converter input current (phase 3)  $i_{i3}$

$i_{o1}$  Matrix converter output current (phase 1)

$i_{o2}$  Matrix converter output current (phase 2)

$i_{o3}$  Matrix converter output current (phase 3)

$\Phi_i$  Initial phase of matrix converter input voltage (phase 1)

$\Phi_o$  Initial phase of matrix converter output voltage (phase 1)

$\omega_i$  Angular frequency of matrix converter input voltages

$\omega_o$  Angular frequency of matrix converter output voltages

$\omega$  Angular frequency of ac network voltages

$V_{LN,rms}$  RMS value of ac network voltages

$L_{MC}$  3-phase choke at output of matrix converter

H Modulation matrix of matrix converter

S Switching matrix of matrix converter

$H_1H_2H_3$  Modulation functions of the Venturini method

$S_1 S_2 S_3$  Switching functions of the Venturini method

q Modulation index of the matrix converter

$f_{sw}$  Switching frequency of the matrix converter

# **TABLE OF CONTENTS**

|            |                                                                                                          | Page |

|------------|----------------------------------------------------------------------------------------------------------|------|

| ABSTRAC'   | Т                                                                                                        | iii  |

| DEDICATI   | ON                                                                                                       | V    |

| ACKNOWI    | LEDGEMENTS                                                                                               | vi   |

| NOMENCI    | _ATURE                                                                                                   | vii  |

| TABLE OF   | CONTENTS                                                                                                 | ix   |

| LIST OF FI | GURES                                                                                                    | xi   |

| LIST OF TA | ABLES                                                                                                    | xvi  |

| CHAPTER    |                                                                                                          |      |

| I          | INTRODUCTION                                                                                             | 1    |

|            | A. Classification of Compensation Techniques  B. Previous Work in Reactive Power Compensation            | 1 2  |

|            | C. Capacitors in Reactive Power Compensation                                                             | 9    |

|            | D. Proposed Compensation Technique                                                                       | 13   |

|            | E. Overview of Thesis                                                                                    | 14   |

| II         | MATRIX CONVERTER AND ITS OPERATION                                                                       | 16   |

|            | A. Introduction to the Matrix Converter  B. Application of the Venturini Modulation Method to the Matrix | 16   |

|            | Converter                                                                                                | 18   |

|            | C. Derivation of the Current Phase Reversal Property                                                     | 21   |

|            | D. Switch Realization of the Modulation Functions                                                        | 24   |

|            | E. Simulation Results                                                                                    | 28   |

| III        | THE PROPOSED VAR COMPENSATOR                                                                             | 48   |

|            | A. System Description and Analysis                                                                       | 49   |

|            | B. Simulation Results.                                                                                   | 52   |

| CHAPTER    |                                                                    | Page |

|------------|--------------------------------------------------------------------|------|

| IV         | DIGITAL IMPLEMENTATION OF CONTROL SIGNALS FOR THE MATRIX CONVERTER | 66   |

| V          | CONCLUSION                                                         | 80   |

| REFERENCES |                                                                    | 82   |

| APPENDIX A |                                                                    | 87   |

| APPENDIX B |                                                                    | 99   |

| APPENDIX C |                                                                    | 102  |

| VITA       |                                                                    |      |

# LIST OF FIGURES

| FIGURE |    |                                                                         |    |

|--------|----|-------------------------------------------------------------------------|----|

|        | 1  | Thyristor-switched capacitor                                            | 4  |

|        | 2  | Thyristor-controlled reactor                                            | 5  |

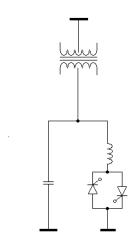

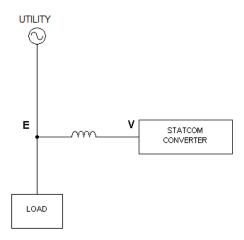

|        | 3  | VSI-based STATCOM                                                       | 6  |

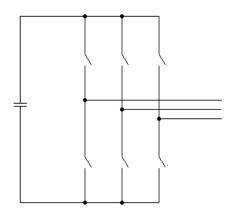

|        | 4  | CSI-based STATCOM                                                       | 6  |

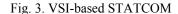

|        | 5  | Reactive power flow between ac network and STATCOM                      | 7  |

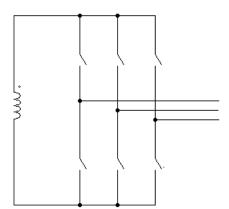

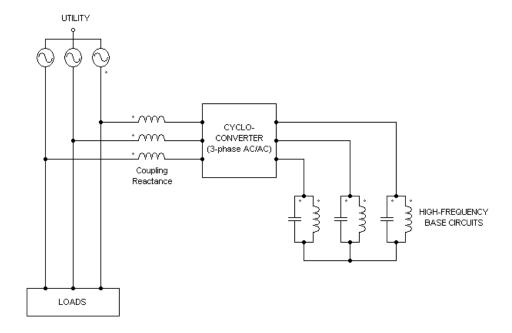

|        | 6  | STATCOM based on a cycloconverter                                       | 8  |

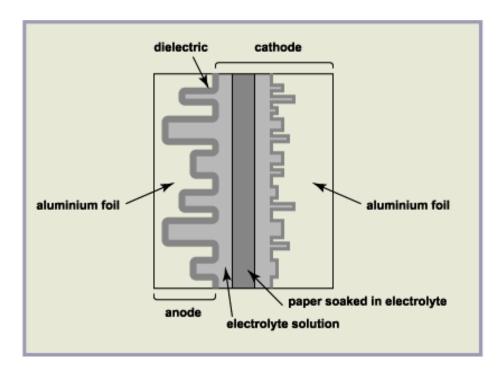

|        | 7  | Cross-section of an electrolytic capacitor – taken from [8]             | 10 |

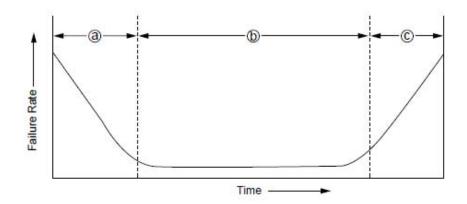

|        | 8  | Bathtub curve of capacitor failures – taken from [10]                   | 11 |

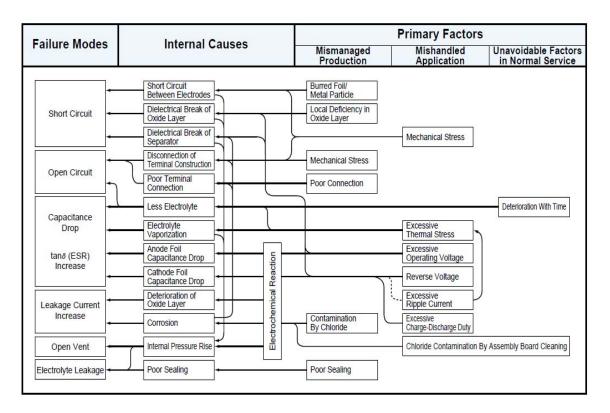

|        | 9  | Different failure mechanisms of capacitor failures – taken from [10]    | 12 |

|        | 10 | Equivalent circuit of a capacitor.                                      | 13 |

|        | 11 | Basic layout of a 3/3 MC                                                | 16 |

|        | 12 | Block diagram of MC showing voltages and currents                       | 19 |

|        | 13 | Modulation function and its discrete version                            | 26 |

|        | 14 | Switching function for a discrete interval $k$ , $0 \le k \le N-1$      | 27 |

|        | 15 | Different bi-directional switch realizations based on discrete switches | 27 |

|        | 16 | System simulated to study MC operation                                  | 28 |

|        | 17 | Modulation functions and switching functions                            | 30 |

|        | 18 | Switching sequence of the Venturini method                              | 31 |

|        | 19 | Line-neutral input voltages and output voltages of the MC               | 32 |

| FIGURE |                                                                     |    |

|--------|---------------------------------------------------------------------|----|

| 20     | Output currents and input currents of the MC                        | 33 |

| 21     | Accuracy of MC waveforms for switching frequency of 12kHz           | 34 |

| 22     | Comparison between modulation and switch-averaged functions for     |    |

|        | switching frequency of 12kHz                                        | 35 |

| 23     | Accuracy of MC waveforms for switching frequency of 1.2 kHz         | 36 |

| 24     | Comparison between modulation and switching functions for switching |    |

|        | frequency of 1.2 kHz                                                | 37 |

| 25     | Accuracy of MC waveforms for switching frequency of 120kHz          | 38 |

| 26     | Comparison between modulation and switch-averaged functions for     |    |

|        | switching frequency of 120kHz                                       | 38 |

| 27     | Schematic of system in PSIM                                         | 39 |

| 28     | PSIM simulation - line-neutral input and output voltages of the MC  | 40 |

| 29     | PSIM simulation - output and input currents of the MC               | 41 |

| 30     | Some input filter topologies                                        | 43 |

| 31     | Schematic of MC system with input line filters in PSIM              | 44 |

| 32     | PSIM simulation with input filters - source, MC input and MC output |    |

|        | voltages (phase 1)                                                  | 45 |

| 33     | PSIM simulation with input filters – MC output, MC input and source |    |

|        | currents (phase 1)                                                  | 46 |

| 34     | The proposed VAR compensator                                        | 49 |

| 35     | MATLAB simulation - Input and output voltages (phase 1) of the MC   | 53 |

| FIGURE |    |                                                                         | Page |

|--------|----|-------------------------------------------------------------------------|------|

|        | 36 | MATLAB simulation – Output and input currents (phase 1) of the MC       | 54   |

|        | 37 | MATLAB simulation - Phase relationships between voltages and            |      |

|        |    | currents of the MC                                                      | 54   |

|        | 38 | MATLAB simulation – Lagging load currents and UPF ac network            |      |

|        |    | currents showing the achieved reactive power compensation               | 55   |

|        | 39 | Variation of lagging reactive power compensated and real power drawn    |      |

|        |    | by the MC with modulation index 'q'                                     | 56   |

|        | 40 | PSIM schematic of ac network power system with a load and the           |      |

|        |    | proposed VAR compensator                                                | 57   |

|        | 41 | Bi-directional switch sub-circuit of the MC (common-collector           |      |

|        |    | configuration)                                                          | 58   |

|        | 42 | Example for four-step commutation                                       | 59   |

|        | 43 | Switching sequence for example four-step commutation                    | 59   |

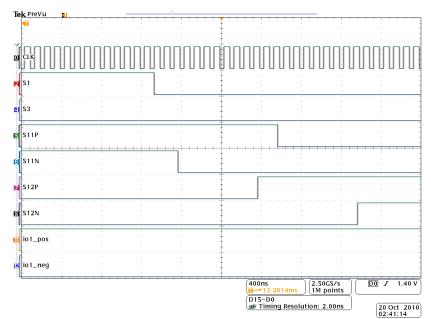

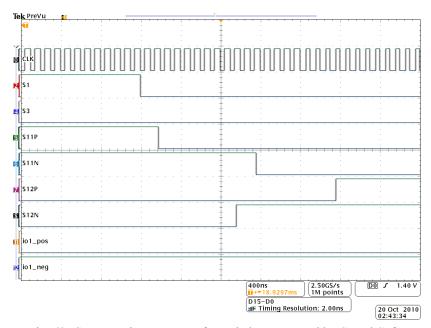

|        | 44 | Switching functions S1, S2 and S3                                       | 61   |

|        | 45 | Switching functions S1, S2 and S3 (zoomed in)                           | 61   |

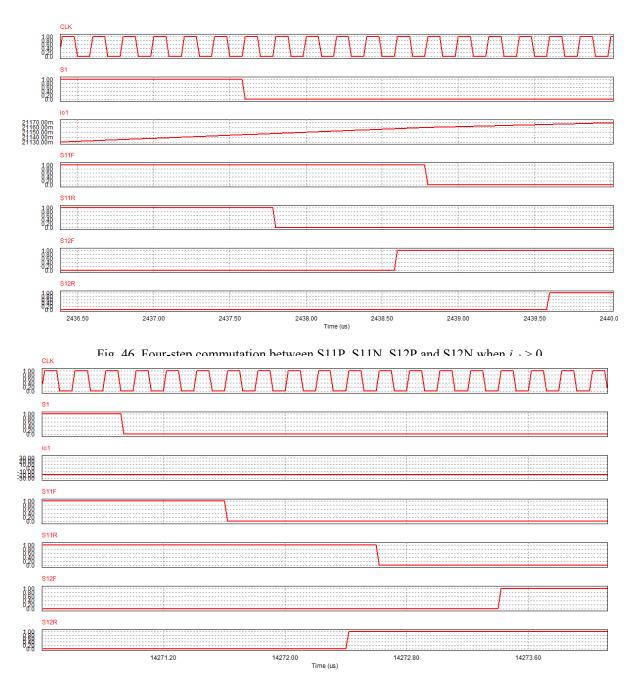

|        | 46 | Four-step commutation between S11P, S11N, S12P and S12N when <i>io1</i> |      |

|        |    | > 0                                                                     | 62   |

|        | 47 | Four-step commutation between S11P, S11N, S12P and S12N when <i>io1</i> |      |

|        |    | < 0                                                                     | 62   |

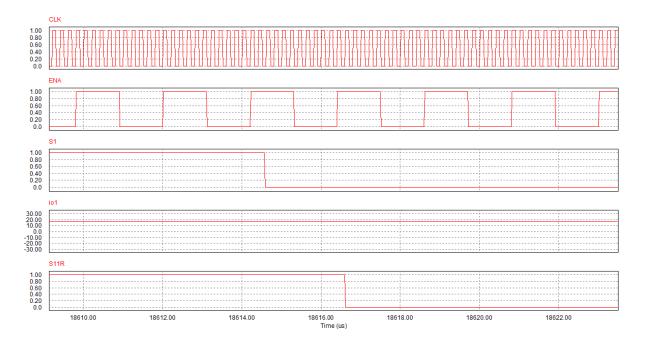

|        | 48 | Function of the ENA (enable) signal                                     | 63   |

| F | FIGUR | E                                                                      | Page |

|---|-------|------------------------------------------------------------------------|------|

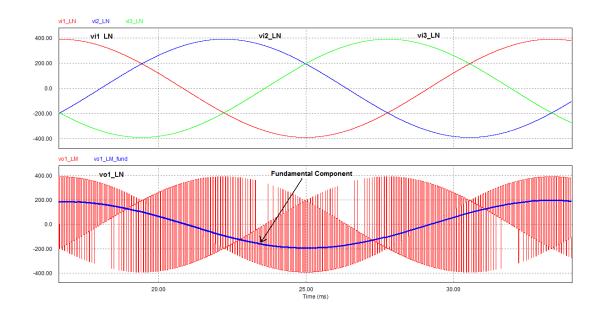

|   | 49    | The input and output voltages (phase 1) of the MC using four-step      |      |

|   |       | commutation with Venturini's modulation method                         | 64   |

|   | 50    | Ac network current (load + compensator currents) in relation to the ac |      |

|   |       | network voltage, showing that VAR compensation has taken place         | 64   |

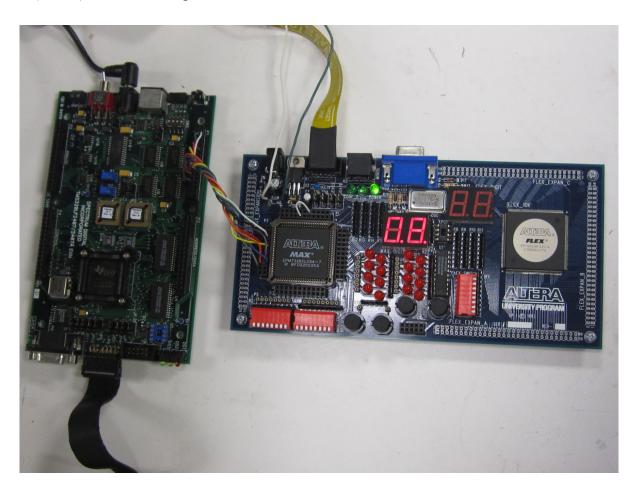

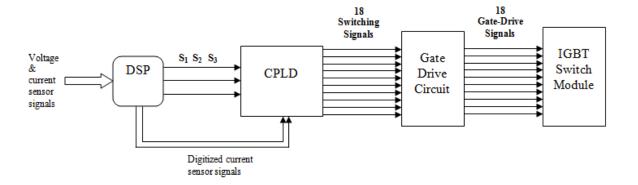

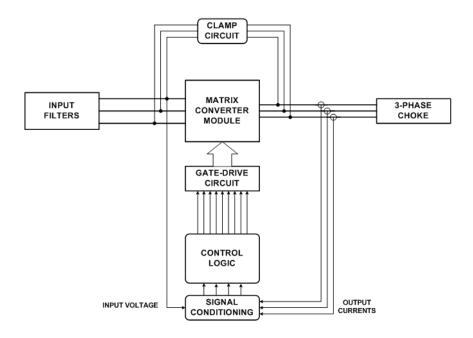

|   | 51    | Block diagram of hardware implementation of the VAR compensator        | 79   |

|   | 52    | Block diagram of the digital implementation of control signals for the |      |

|   |       | MC                                                                     | 67   |

|   | 53    | Schematic of CPLD logic in Quartus                                     | 69   |

|   | 54    | State machine representation of four-step commutation                  | 70   |

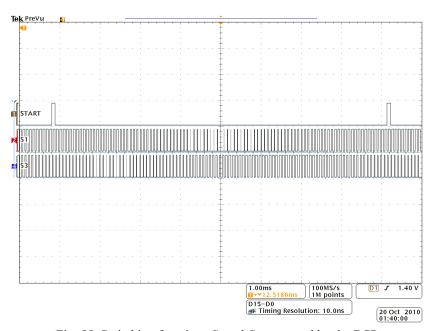

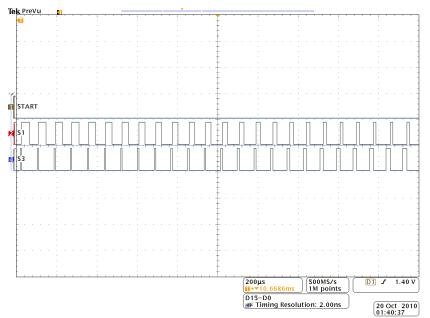

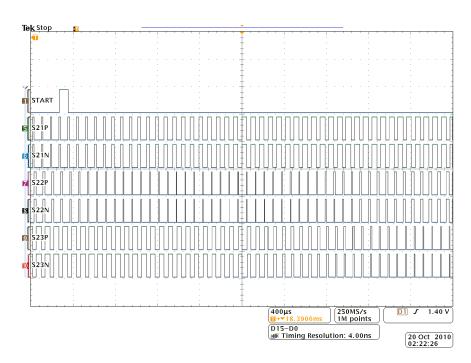

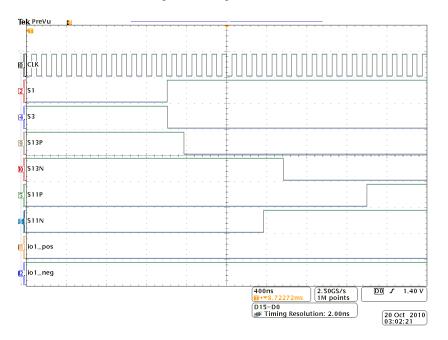

|   | 55    | Switching functions S1 and S3 generated by the DSP                     | 72   |

|   | 56    | Zoomed-in image of the switching functions                             | 72   |

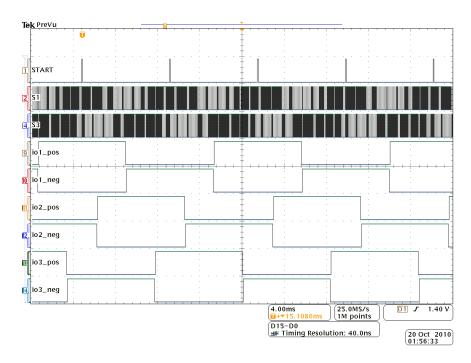

|   | 57    | Current directions generated by the DSP                                | 73   |

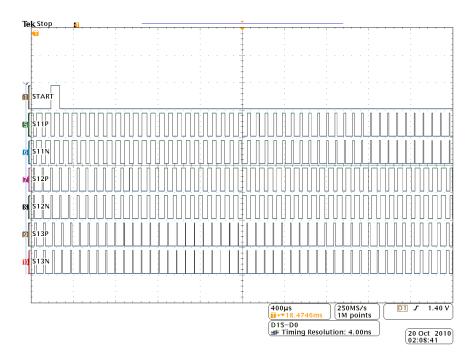

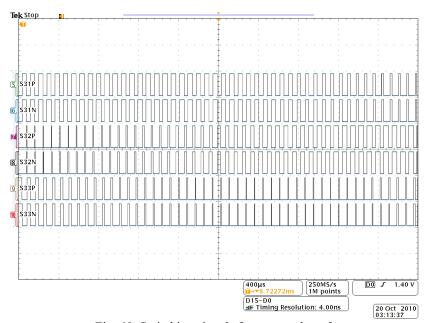

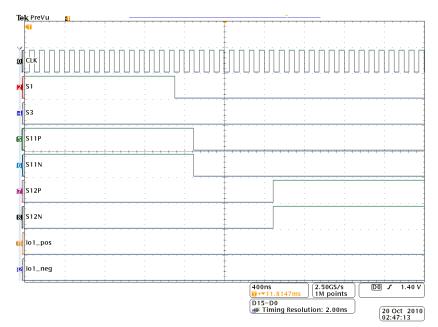

|   | 58    | Switching signals for output phase 1                                   | 74   |

|   | 59    | Switching signals for output phase 2                                   | 74   |

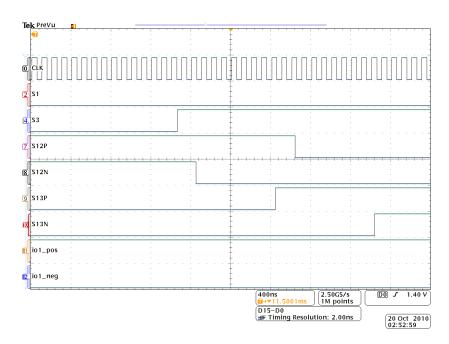

|   | 60    | Switching signals for output phase 3                                   | 75   |

|   | 61    | Commutation sequence for switches governed by S1 and S2 for positive   |      |

|   |       | output current                                                         | 75   |

|   | 62    | Commutation sequence for switches governed by S1 and S2 for negative   |      |

|   |       | output current                                                         | 76   |

|   | 63    | Commutation sequence for switches governed by S1 and S2 for zero       |      |

|   |       | output current                                                         | 76   |

| I | FIGURE |                                                                      |     |

|---|--------|----------------------------------------------------------------------|-----|

|   | 64     | Commutation sequence for switches governed by S2 and S3 for positive |     |

|   |        | output current                                                       | 77  |

|   | 65     | Commutation sequence for switches governed by S3 and S1 for negative |     |

|   |        | output current                                                       | 77  |

|   | 66     | Block diagram of hardware implementation of the VAR compensator      | 79  |

|   | 67     | PSIM C block used for generation of S1, S2 and S3                    | 99  |

|   | 68     | Generation of the basic three switching functions                    | 101 |

|   | 69     | Generation of delayed versions of the switching functions            | 101 |

|   | 70     | Generation of the switching signal                                   | 101 |

# LIST OF TABLES

| TABLE |                                                                    | Page |

|-------|--------------------------------------------------------------------|------|

| 1     | System parameters used for simulation                              | 29   |

| 2     | Comparison of expected and simulated output voltages of the MC     | 35   |

| 3     | Magnitudes and phase angles of fundamental components of MC        |      |

|       | waveforms                                                          | 42   |

| 4     | Input line filter parameters                                       | 43   |

| 5     | Magnitudes and phase angles of fundamental components of waveforms |      |

|       | for the MC system with input filters                               | 47   |

| 6     | System parameters used for simulation                              | 52   |

| 7     | State table showing switching signal outputs                       | 71   |

#### **CHAPTER I**

#### INTRODUCTION

Reactive power, known as volt-ampere reactive (VARs), is attributed to the complex impedance of typical ac power system loads and transmission lines. Even though its presence in the power system network is fundamental, it has several undesirable consequences including reduced stability limits (steady-state, dynamic and transient) and lowered power transfer capability. It also leads to increased transmission losses, inefficient performance of power system equipment and the potential for the onset of system-wide voltage instability (caused by variation in the reactive power demands of the loads), if not properly compensated and controlled [1]. *Reactive power compensation* is defined as the management and control of reactive power in the ac network, achieved by supplying or absorbing VARs from the system [2].

### A. Classification of Compensation Techniques

VAR compensation may be achieved by absorbing or injecting reactive power at either the transmission level, known as *transmission compensation*, or near the load, known as *load compensation* [1]. Transmission compensation is used to maintain the specified voltage at different buses by injecting variable amounts of reactive power into the transmission lines. As a result, the stability limits and the power transfer capability are improved and tighter system voltage control is achieved. Transmission compensation

This thesis follows the style of *IEEE Transactions on Power Electronics*.

is performed at the ac network level in the system and does not address the load-side source of VARs in the system - the reactive load. Load compensation, on the other hand, is aimed at applying power factor correction techniques directly at the load to locally supply VARs required by the loads. Consequently, the effective system load – the original intended load together with the compensator, appear as unity power factor loads that do not draw VARs from the source. So, transmission losses and required current carrying capacity of lines are minimized. Further, the power transfer capability and stability limits of the system are not deteriorated by the load and voltage instability is simplified. Large scale customers such as industries are often penalized for drawing excessive reactive power from the ac network; so they are motivated to employ load compensation techniques to locally supply VARs to their loads.

# B. Previous Work in Reactive Power Compensation

Several reactive power compensation solutions that are applicable to load compensation have been proposed in the past and are summarized below [2-5]. Load compensation employs shunt-connected techniques and so, series compensation methods have been omitted from the discussion.

# 1. Mechanically switched capacitors and reactors

Initially, mechanically switched capacitor and reactor banks were used to provide lagging and leading reactive power to support the power system. Depending on the VAR requirement, the banks are switched in and out of the system through mechanical relays

and circuit breakers. This approach is fundamentally discrete and the compensation solution does not offer continuously variable reactive power support. It also suffers from other drawbacks including slow speed of response, lifetime wear-out of the switch elements, switching transients and lack of flexible, continuously variable VAR compensation.

#### 2. Synchronous condensers

Synchronous condensers are essentially synchronous motors operated at no-load. By varying the excitation field, the rotating loads can be made to supply VARs (under-excited) or consume VARs (over-excited) from the ac system. The advantages of synchronous condensers include continuously variable reactive power support, high short-term overload capability and harmonic-free operation. However, they suffer from major disadvantages including high installation time and costs, maintenance costs, mechanical losses and slow response time. Further, they contribute to high system fault current and cannot be easily relocated due to their large size.

# 3. Static VAR Compensator (SVC)

With advances in semiconductor technology, the solutions listed above were subsequently replaced by the static VAR compensator (SVC) which consists of banks of capacitors and reactors that are switched on/off or phase-controlled using thyristors. The number of banks switched in at a time depends on the VAR requirement.

#### a. Thyristor-Switched Capacitor (TSC)

A thyristor-switched capacitor (TSC) consists of banks of capacitors switched in and out of the ac power system using a pair of anti-parallel thyristors as shown in Fig. 1. The switching in and switching out actions are carried out at instants when the capacitor voltage equals the positive or negative peak of the ac line voltage, to prevent switching transients. This introduces a maximum response delay of 1 cycle when switching in and ½-cycle when switching out the capacitor bank [2, 5]. A current-limiting series reactor is used to prevent any likelihood of switching transients. The reactor and capacitor form a notch filter to prevent resonance with the power system current harmonics. TSC banks may be connected in wye or delta configurations, though the latter is preferred when unbalanced VAR consumption is expected [5].

A TSC has good response time and low maintenance and installation costs as it has no moving parts. It also has negligible harmonics when switched appropriately. However, a TSC cannot provide continuous VAR control as it is essentially just a solid-

Fig. 1. Thyristor-switched capacitor

state version of the mechanically switched capacitor bank. As each TSC bank requires a pair of thyristors, it is uneconomical especially at high voltage levels due to the cost of high voltage thyristors and their gate drive circuits. The peak inverse voltage of each thyristor is twice the ac network voltage peak. Protective equipment must be installed to prevent thyristor failure due to line voltage transients and fault currents. Due to these disadvantages, a TSC is practically not an attractive compensation solution.

### b. Thyristor-Controlled Reactor (TCR)

A thyristor-controlled reactor (TCR) consists of shunt capacitors in parallel with reactors connected to the power network through a pair of anti-parallel thyristors as shown in Fig. 2. The effective reactance of the TCR and so, the reactive power drawn by it, are controlled by varying the firing angles of the thyristors. As the firing angle increases, the effective inductance of the TCR increases. A filter is used in parallel with the TCR as the gating action generates low-order odd harmonics. In three-phase

Fig. 2. Thyristor-controlled reactor

arrangements, the reactors of the TCR are connected in delta to remove unbalance, while the capacitors may be connected in delta or wye.

With fast response times, acceptable cost and the ability to balance loads, the TCR is considered to be a good compensation technique. However, though a continuous VAR control range can be achieved, it is discontinuous in time as firing angle adjustments can be made only once per ½-cycle. The other disadvantage of the TCR is that the reactor must be of a rating comparable to that of the capacitor to be able to provide leading VARs as well.

## 4. Static Synchronous Compensator (STATCOM)

A static synchronous compensator (STATCOM) is based on power electronic converters that behave as ideal ac sources such as the voltage-source and current-source inverters shown in Fig. 3 and Fig. 4, respectively. The converters are connected to the ac power system network through reactors as shown in Fig. 5. Depending on the relative

Fig. 4. CSI-based STATCOM

magnitudes of the ac network voltage E and the converter voltage V, variable amounts of reactive power are injected into the network. When |E| > |V|, the converter injects lagging VARs into the ac network and vice versa [2, 5].

The power electronic converters are made to operate at high switching frequencies using various pulse-width modulation (PWM) techniques. So, the STATCOM can provide smoothly variable reactive power as a continuous function of time. The high frequency switching harmonics generated can be easily filtered. More importantly, the STATCOM does not require large number of reactive elements, thus reducing the cost ad size of compensation techniques. Since the STATCOM is a force-commutated converter operating at high frequencies, it generally employs switches such as insulated-gate bipolar transistors (IGBTs) and integrated gate-commutated thyristors (IGCTs). However, these switches are not yet developed for high voltage ratings. To overcome this issue, multi-level converters are used [2]. The STATCOM is able to

Fig. 5. Reactive power flow between ac network and STATCOM

provide compensation characteristics almost identical to the synchronous condensers. However, it does not have the high overload capability of the rotating synchronous machine.

# 5. Compensation using Thyristor-Based Cycloconverters

Direct ac-ac cycloconverters, naturally-commutated and force-commutated, can be used for reactive power compensation [5] in a way similar to inverters, as shown in Fig. 6. As the converter is made to draw only reactive or harmonic power, it is sufficient to use passive tank circuits at the input of the converter. While naturally commutated cycloconverters can inject only leading VARs into the system, force-commutated

Fig. 6. STATCOM based on a cycloconverter

cycloconverters can be controlled to inject lagging VARs as well [5]. Another STATCOM based on the concept of "power doubling" was proposed by Gyugyi [5] and implemented in [6], wherein reactive power could be injected by the cyclo-converter through both its input and output terminals.

Though the cycloconverters seemed to be compact solutions to reactive power compensation, they did not gain much popularity as they required a very large number of thyristors (36 switches for three-phase converter) which needed to be switched at very high frequencies (approximately ten times the line frequency), which was not possible at that time.

### C. Capacitors in Reactive Power Compensation

Many typical loads such as motors and inductive loads operate with lagging power factor, which means that they consume VARs. So, load compensation techniques employ capacitor banks to locally supply the VARs needed by the load. However, capacitors are known for being highly unreliable components with both catastrophic and wear-out failure mechanisms. With the extensive use of power electronics in VAR compensation (as in the voltage source inverter-based STATCOM), aluminum electrolytic dc capacitors are widely used due to their advantages of high energy density, reasonable voltage ratings and low cost per unit energy. But, 60% of power electronic failures are attributed to them [7]. They have a short life-span (generally, less than 10,000 hours at rated conditions) and must be frequently replaced. The reliability issues of aluminum electrolytic capacitors are discussed below.

## 1. Construction of the Electrolytic Capacitor

A cross-section of the electrolytic capacitor is shown in Fig. 7. The anode of the capacitor is an aluminum foil that is coated with aluminum oxide, the dielectric which is formed through chemical reactions. The cathode consists of a paper strip impregnated with an electrolyte, which is in contact with another aluminum foil. Several layers of cathode and anode are wound in an alternating manner [8].

- Failure Types and Mechanisms of the Electrolytic Capacitor

Capacitor failure types can be listed as follows [9]:

- i. Early failures: They occur during the first year of energizing the capacitors. They are attributed to defects in the manufacturing, testing and installation procedures.

Fig. 7. Cross-section of an electrolytic capacitor – taken from [8]

- Random failures: These less probable failures occur due to operating conditions such as lightning surges.

- iii. Wear-out failures: These are attributed to wear-out and aging of the capacitor dielectric. They form a large percentage of capacitor failures and will be discussed in detail.

These failures are shown as a function of time in the bathtub curve of Fig. 8.

Capacitor failures occur through the several mechanisms/modes listed in Fig. 9. Early and random failures are attributed to catastrophic mechanisms including open-circuit, short-circuit, open vent, increased leakage current and electrolytic leakage [10]. Wear-out failures in electrolytic capacitors are primarily driven by a mechanism called 'partial discharge' which can be defined as the incomplete charge transfer (discharge) occurring across the space (such as gaps) between the electrode and the electrolyte [11]. Partial discharge leads to the decomposition of electrolyte, producing hydrogen gas

a – Early failure period b – Random failure period c – Wear-out failure period

Fig. 8. Bathtub curve of capacitor failures – taken from [10]

which decreases the corona inception voltage (breakdown voltage) below the voltage rating of the capacitor. Operation of such a capacitor results in high internal temperatures, arcing, bulging and its consequent failure. The factors contributing to the occurrence of partial discharge include higher operating temperatures, manufacturing defects and conditions such as over-voltages.

#### 3. Failure Detection Mechanisms

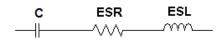

The equivalent model of a capacitor, shown in Fig. 10, includes an effective series resistance (ESR) and an effective series inductance (ESL) along with the capacitor [12]. Failure of capacitors is accompanied by a decrease in its capacitance and, more

Fig. 9. Different failure mechanisms of capacitor failures – taken from [10]

importantly, by an increase in the ESR. Several techniques have been developed to use the ESR as a means to monitor the health of electrolytic capacitors and accurately detect faults [7, 12, 13].

From the above discussion, it is clear that aluminum electrolytic dc capacitors, with their catastrophic failure modes and wear-out mechanisms, require constant monitoring and periodic replacement. Ac capacitors also suffer from similar reliability problems. Thus, capacitors greatly increase the maintenance and operational costs of the traditional load compensation techniques and are undesirable components.

# D. Proposed Compensation Technique

This thesis proposes a reactive power load compensator that uses inductors (chokes) instead of capacitors to supply reactive power to support the load. Inductors are regarded as robust and rugged elements and are not subject to service life-limiting failure mechanisms. However, it is also well known that they have lagging power factor and consume VARs, which is the opposite reactive power behavior of the capacitor. The proposed load compensator interfaces the inductive choke element to the ac network with a 3-phase ac-to-3-phase ac direct matrix converter (MC). The MC is controlled by the Venturini modulation technique which has the advantageous property that it can

Fig. 10. Equivalent circuit of a capacitor

enable the MC to invert the phase of the current from the input to the output [14]. So, although the inductive choke draws lagging currents from the output of the converter, through this current phase reversal property of the modulation technique, the converter draws leading currents from the ac network. Thus, with the proposed compensation technique, lagging power factor loads can be compensated without using capacitor banks. This thesis will examine the fundamental relationships of the matrix converter controlled by the Venturini modulation technique and apply them to a shunt-connected load-side VAR compensator.

#### E. Overview of Thesis

The matrix converter and its historical background are introduced in Chapter II.

Detailed operation of the converter using the Venturini modulation method is presented, and the derivation of the current phase reversal property is examined. Simulation results of the converter in MATLAB and PSIM environments are produced and discussed in detail.

The schematic of the proposed VAR load compensator is presented in Chapter III. The application of the current reversal property to the compensator is justified. The capacity of the compensator is given mathematically. MATLAB and PSIM simulations examining the performance of the compensator are also presented.

The digital implementation of the compensator in hardware is presented in Chapter IV. A possible solution to the hardware set-up of the entire system is explored.

Control signals of the system, generated using a DSP and a CPLD, are presented. The practical feasibility of the proposed compensator is thus shown.

Conclusion drawn from this thesis are presented in Chapter V. Future work is also discussed.

Portions of Chapters II, III and IV have been previously published in [15] at the IEEE 42nd North American Power Symposium (NAPS) 2010.

#### **CHAPTER II**

#### MATRIX CONVERTER AND ITS OPERATION

#### A. Introduction to the Matrix Converter

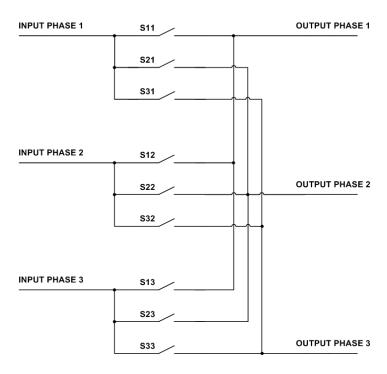

A *matrix converter* is a direct ac-to-ac force-commutated converter which has the ability to transform the magnitude, phase angle and frequency of the input voltage without using intermediate energy storage elements. An *m/n* matrix converter results in energy conversion between '*m*' output phases and '*n*' input phases. As 3-phase power is most widely used, the 3/3 matrix converter (MC) will be considered hereafter. The basic layout of the MC, shown in Fig. 11, illustrates that each of the output phases is connected to every input phase by a matrix of switches. There are no intermediate

Fig. 11. Basic layout of a 3/3 MC

energy storage elements and the switches are *bi-directional* (*bi-lateral*) – capable of handling positive as well as negative voltages and currents (four-quadrant operation).

The concept of direct ac-to-ac converters was introduced by Hazeltine in 1923 [16], but a detailed treatment was first carried out by Gyugyi and Pelly in [16], where they are referred to as *frequency changers* or *cycloconverters*. These converters were based on the semiconductor device thyristor and were broadly classified as naturally commutated (NCCs) and force-commutated (FCCs). Though cycloconverters offered a wide range of operational flexibility, their widespread usage was hindered by the large requirement of thyristors (36 switches for 3-phase applications) and the difficulty of switching these early technology thyristors at relatively high frequencies (approximately ten times the line frequency). With developments in power transistor technology, interest in cycloconverters was reestablished [17]. However, the earnest development of direct ac-ac converters was initiated by the Venturini and Alesina [14, 18] in which they introduced the concept of the matrix converter. They developed and analyzed the principle of the 'low-frequency modulation matrix', which views the converter as a single mathematical transfer function (direct modulation method). Following the work of Venturini and Alesina, several modulation methods were proposed as summarized in [17].

The Venturini modulation method is characterized by sinusoidal input and output waveforms. It has a maximum attainable voltage gain of 0.5, which could be increased to 0.866 by the addition of common-mode voltages to the output voltages [19]. But, this increase is obtained at the cost of greater switching frequencies and implementation

complexities. The indirect modulation methods, which model the MC as a two-stage transfer function, were analyzed in [20]. These methods were able to increase the voltage gain to 1.05 at the expense of low-frequency distortion in the input/output waveforms or both [17]. Space vector modulation methods were developed in [21-24] with the aim of achieving the superior performance of space vector based inverters in MCs as well. But, even these methods have a limited voltage gain of 0.866 and offer similar performance as the Venturini modulation method.

This thesis implements the Venturini modulation method because it can be operated such that it has the advantageous current phase reversal property, which is fundamental to the operation of the proposed reactive power load compensator. The maximum voltage gain of 0.5 is not viewed as a limitation in this application of a matrix converter as the output terminals of the MC are internal nodes of the VAR compensator and do not connect to any load such as a motor, where the output voltage is important. Thus, other modulation methods need not be explored with the aim of improving the voltage gain.

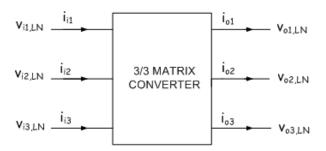

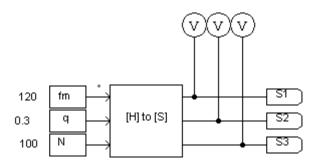

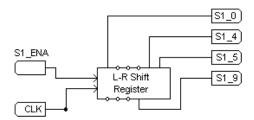

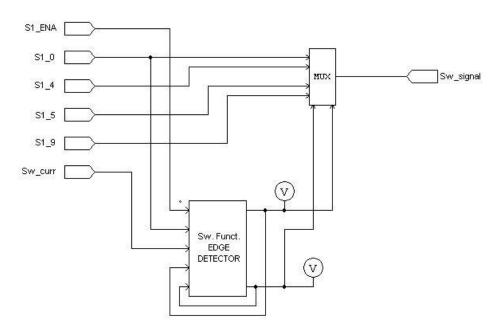

# B. Application of the Venturini Modulation Method to the Matrix Converter

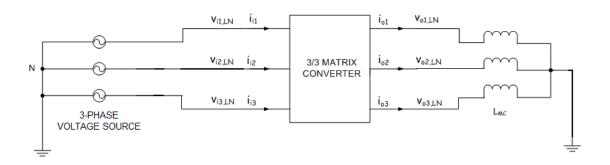

A block diagram of the MC indicating the input and output currents and voltages is shown in Fig. 12. The line-neutral input voltages of the MC are given by  $v_{i1,LN}$ ,  $v_{i2,LN}$  and  $v_{i3,LN}$ , while the line-neutral output voltages are denoted by  $v_{o1,LN}$ ,  $v_{o2,LN}$  and  $v_{o3,LN}$ . The input and output line currents of the MC are given by  $i_{i1}$ ,  $i_{i2}$ ,  $i_{i3}$  and  $i_{o1}$ ,  $i_{o2}$ ,  $i_{o3}$  respectively. While the amplitudes of the input and output voltages are denoted by  $V_i$

Fig. 12. Block diagram of MC showing voltages and currents

and  $V_o$  respectively, the phase angles are given by  $\Phi_i$  and  $\Phi_o$  respectively. The input and output side frequencies of the converter are denoted by  $\omega_i$  and  $\omega_o$ .

The MC can be modeled as a mathematical transfer function, the modulation matrix **H** which relates the input and output voltages.

$$\begin{bmatrix} v_{o1,LN} \\ v_{o2,LN} \\ v_{o3,LN} \end{bmatrix} = \mathbf{H} \times \begin{bmatrix} v_{i1,LN} \\ v_{i2,LN} \\ v_{i3,LN} \end{bmatrix}$$

(1)

where

$$\mathbf{H} = \begin{bmatrix} H_{11} & H_{12} & H_{13} \\ H_{21} & H_{22} & H_{23} \\ H_{31} & H_{32} & H_{33} \end{bmatrix}$$

(2)

The modulation matrix element  $H_{xy}$  is the transfer function between the  $x^{th}$  output phase and the  $y^{th}$  input phase. Since there are no energy storage elements in the MC and assuming that there is no power loss in the MC, the instantaneous three-phase powers are equal on the input and output sides. Consequently, the relationship between the input and output currents of the MC is given by (3).

$$\begin{bmatrix} i_{i1} \\ i_{i2} \\ i_{i3} \end{bmatrix} = \mathbf{H}^T \times \begin{bmatrix} i_{o1} \\ i_{o2} \\ i_{o3} \end{bmatrix}$$

(3)

where  $\mathbf{H}^T$  is the transpose of the modulation matrix  $\mathbf{H}$ .

According to the Venturini modulation method, the proposed generalized modulation matrix for the MC [14] is given by (4-6), the detailed mathematical treatment of which is presented in [18]. Depending on our requirements of output frequency, phase angle and amplitude in relation with the input voltage parameters, the corresponding **H** matrix is derived.

$$\mathbf{H} = \frac{1}{3}\alpha_{1}\begin{bmatrix} 1 + 2qCS(0) & 1 + 2qCS(-2\pi/3) & 1 + 2qCS(2\pi/3) \\ 1 + 2qCS(2\pi/3) & 1 + 2qCS(0) & 1 + 2qCS(-2\pi/3) \\ 1 + 2qCS(-2\pi/3) & 1 + 2qCS(2\pi/3) & 1 + 2qCS(0) \end{bmatrix} + \\ \frac{1}{3}\alpha_{2}\begin{bmatrix} 1 + 2qCA(0) & 1 + 2qCA(-2\pi/3) & 1 + 2qCA(2\pi/3) \\ 1 + 2qCA(-2\pi/3) & 1 + 2qCA(2\pi/3) & 1 + 2qCA(0) \\ 1 + 2qCA(2\pi/3) & 1 + 2qCA(0) & 1 + 2qCA(-2\pi/3) \end{bmatrix}$$

$$CS(x) = \cos(\omega_{m}t + x)$$

$$CA(x) = \cos[(-\omega_{m} + 2\omega_{i})t + x]$$

$$\omega_{m} = \omega_{o} - \omega_{i}$$

where

$$\alpha_{1} = \frac{1}{2}[1 + \tan(\phi_{i}) \cdot \cot(\phi_{o})]$$

$$\alpha_{2} = 1 - \alpha_{1}$$

$$q = \frac{V_{o}}{V}$$

(5)

The above equations are subjected to the constraints given by (6) to ensure that the matrix **H** is finite, positive, semi-definite and therefore, invertible.

$$\alpha_1 \ge 0$$

$$\alpha_2 \ge 0$$

$$0 \le q \le \frac{1}{2}$$

(6)

# C. Derivation of the Current Phase Reversal Property

Consider the following input voltages for the MC of Fig. 12 such that the input frequency  $\omega_i$  is set to  $\omega$  and the input phase angle  $\Phi_i$  is set to 0.

$$v_{i1,LN} = V_i \cos(\omega t)$$

$$v_{i2,LN} = V_i \cos(\omega t - 2\pi/3)$$

$$v_{i3,LN} = V_i \cos(\omega t + 2\pi/3)$$

(7)

Further, let the desired output voltages be in phase with the input voltages and have the same frequency, such that

$$\begin{aligned}

\omega_o &= \omega_i = \omega \\

\phi_o &= \phi_i = 0^\circ

\end{aligned} \tag{8}$$

Then, from (5), we have

$$CS(x) = \cos(x)$$

$$CA(x) = \cos(2\omega t + x)$$

$$\omega_m = 0$$

$$\alpha_1 = 0$$

$$\alpha_2 = 1$$

(9)

Substituting (9) into (4), we obtain the following modulation matrix

$$\mathbf{H} = \begin{bmatrix} H_1 & H_2 & H_3 \\ H_2 & H_3 & H_1 \\ H_3 & H_1 & H_2 \end{bmatrix} = \mathbf{H}^T$$

(10)

where

$$H_{1} = \frac{1}{3} (1 + 2q \cos(2\omega t))$$

$$H_{2} = \frac{1}{3} (1 + 2q \cos(2\omega t - 2\pi/3))$$

$$H_{3} = \frac{1}{3} (1 + 2q \cos(2\omega t + 2\pi/3))$$

(11)

It can be seen that the modulation functions  $H_1$ ,  $H_2$  and  $H_3$  have twice the frequency ' $2\omega$ ' as that of the input and output voltages. The term 'q', known as the modulation index, is the ratio between the output and input voltage amplitudes and is a control parameter of the modulation functions (5). The coefficient '1/3' is used to limit the duty cycle of the MC switches to 2/3, this maximum value being reached when one of the other modulation functions becomes zero. The coefficient '2' is used to ensure that the output phases are never left unconnected even when one of the modulation functions becomes zero. The 'unity' term asserts the same property when the required output voltages are zero and consequently, 'q' is made to be zero.

The modulation matrix of (10) and (11) must result in the MC operation as described in (7) and (8). As verification, (10)-(11) and (7) are substituted into (1). The resulting output voltages are obtained as in (12) and they are found to be in conformity with the desired output voltage parameters.

$$v_{o1,LN} = qV_i \cos(\omega t)$$

$$v_{o2,LN} = qV_i \cos(\omega t - 2\pi/3)$$

$$v_{o3,LN} = qV_i \cos(\omega t + 2\pi/3)$$

(12)

Let it now be assumed that the output currents have a phase angle  $\Phi$  with respect to the output voltages and are given by

$$i_{o1} = I_o \cos(\omega t + \phi)$$

$i_{o2} = I_o \cos(\omega t + \phi - 2\pi/3)$

$i_{o3} = I_o \cos(\omega t + \phi + 2\pi/3)$  (13)

Substituting (10) and (13) into (3), the following input currents are obtained

$$i_{i1} = qI_o \cos(\omega t - \phi)$$

$$i_{i2} = qI_o \cos(\omega t - \phi - 2\pi/3)$$

$$i_{i3} = qI_o \cos(\omega t - \phi + 2\pi/3)$$

(14)

The output current  $i_{ol}$  can be expressed as a phasor as follows

$$i_{o1} = \operatorname{Re}\left\{I_{o} \times e^{j(\omega t + \phi)}\right\} = \operatorname{Re}\left\{I_{o} e^{j\omega t} \times e^{j\phi}\right\}$$

$$\therefore \quad \widetilde{I}_{o1} = I_{o} \angle \phi \tag{15}$$

Similarly, the input current  $i_{ol}$  can be expressed as a phasor as

$$i_{i1} = \operatorname{Re} \left\{ q I_o \times e^{j(\omega t - \phi)} \right\} = \operatorname{Re} \left\{ q I_o e^{j\omega t} \times e^{-j\phi} \right\}$$

$$\therefore \quad \widetilde{I}_{i1} = q I_o \angle - \phi$$

(16)

Comparing (15) and (16), it is clearly seen that there is a reversal in the sign of the phase angles of the output and input currents – the *current phase reversal* property. Similarly, this property can be observed in all the phase currents by expressing them in the phasor notation. Comparing the voltage and current expressions, it can be observed that while the output currents lead the corresponding output voltages by  $\Phi$ , the input currents lag the corresponding input voltages by  $\Phi$ . This implies that the current phase reversal property evaluates to a power factor reversal between the input and output terminals as both the input and output voltages have phase angles of 0 degrees. Thus, the modulation

matrix **H** which operates the MC with the special current phase reversal property has been established.

### D. Switch Realization of the Modulation Functions

The mathematical model of the MC presented in the previous section will now be implemented in the switch matrix of Fig. 11. Switching functions which define the on/off states of the switches as a continuous function of time are to be derived from the modulation functions. The relationships between the input and output voltages and currents of the MC can be expressed in terms of these switching functions as

$$\begin{bmatrix} v_{o1,LN} \\ v_{o2,LN} \\ v_{o3,LN} \end{bmatrix} = \mathbf{S} \times \begin{bmatrix} v_{i1,LN} \\ v_{i2,LN} \\ v_{i3,LN} \end{bmatrix}$$

(17)

$$\begin{bmatrix} i_{i1} \\ i_{i2} \\ i_{i3} \end{bmatrix} = \mathbf{S}^T \times \begin{bmatrix} i_{o1} \\ i_{o2} \\ i_{o3} \end{bmatrix}$$

(18)

with

$$\mathbf{S} = \begin{bmatrix} S_{11} & S_{12} & S_{13} \\ S_{21} & S_{22} & S_{23} \\ S_{31} & S_{32} & S_{33} \end{bmatrix}$$

(19)

where the matrix element  $S_{xy}$  represents the switching function governing the switch connecting the  $x^{th}$  output phase and the  $y^{th}$  input phase.

Comparing (2) and (19), the modulation function associated with each switching function is easily inferred. As there are three basic functions  $H_1$ ,  $H_2$  and  $H_3$  in the chosen

Venturini modulation matrix (10)-(11), the **S** matrix is constituted by three corresponding switching functions

$$\mathbf{S} = \begin{bmatrix} S_1 & S_2 & S_3 \\ S_2 & S_3 & S_1 \\ S_3 & S_1 & S_2 \end{bmatrix}$$

(20)

It is assumed that the switches are operated at a frequency much higher than the input and output frequencies such that their average behavior, given by their duty cycles over each switching period, equals the modulation function values at each instant of time. Thus, while the **H** matrix is a 'low-frequency' description of the MC, the **S** matrix additionally includes a range of switching harmonics. To obtain the on-off times from the duty cycle values (modulation functions), a suitable switching period  $T_{disc}$  is obtained by dividing the time period of the modulation functions into 'N' time intervals given by

$$T_{disc} = \frac{2\pi/2\omega}{N} = \frac{\pi}{N\omega} \tag{21}$$

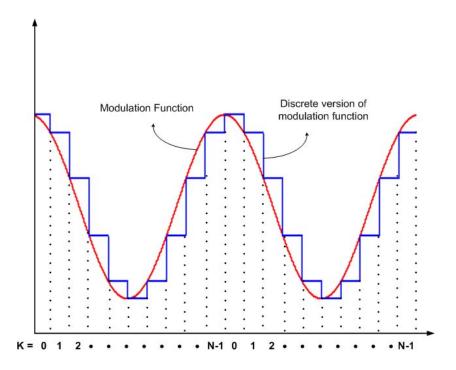

Discrete-time versions of the modulation functions (switch-averaged functions), developed by applying a zero-order hold of time period  $T_{disc}$  as shown in Fig. 13, determine the switch duty ratios over each of the 'N' intervals. The 'ON' times of the three switching functions are then derived as

$$t_{1}[k] = \frac{T_{disc}}{3} \times (1 + 2q \cos(2\omega T_{disc}k))$$

$$t_{2}[k] = \frac{T_{disc}}{3} \times (1 + 2q \cos(2\omega T_{disc}k - 2\pi/3))$$

$$t_{3}[k] = \frac{T_{disc}}{3} \times (1 + 2q \cos(2\omega T_{disc}k + 2\pi/3))$$

(22)

where  $0 \le k \le N-1$

Fig. 13. Modulation function and its discrete version

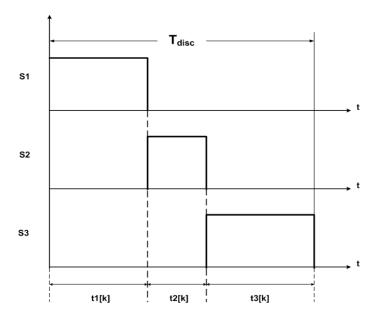

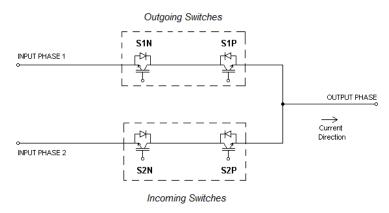

Within each  $k^{th}$  interval, the switches governed by  $S_1$  are turned on for time  $t_1$ , followed by the switches governed by  $S_2$  and  $S_3$  which are turned on for times  $t_2$  and  $t_3$ , respectively, as shown in Fig. 14. Based on this pattern, the on-off states of the switches can be obtained as a function of time, thus, completely defining the switching functions.

The effective switching frequency is

$$f_{sw} = \frac{1}{T_{disc}} \tag{23}$$

Fig. 13 implies that as the value of N is increased, the switching functions more accurately model the modulation functions.

Fig. 14. Switching function for a discrete interval k,  $0 \le k \le N-1$

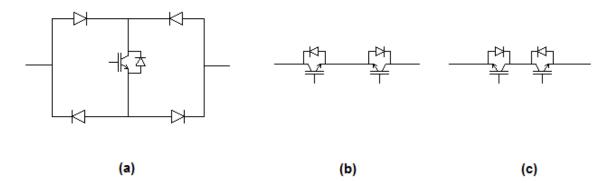

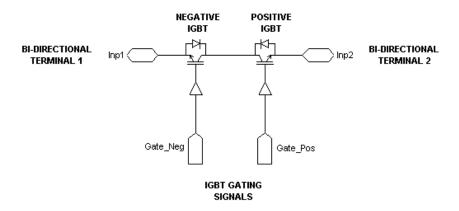

As mentioned before, the MC requires bi-directional switches; but, semiconductor switches with inherent bi-directional capability are not yet commercially available. So, bilateral functionality is constructed from one or more unidirectional

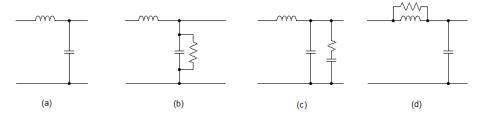

Fig. 15. Different bi-directional switch realizations based on discrete switches

switch elements. Three possible realizations are illustrated in Fig. 15 [17, 25]. The diode bridge type realization (Fig. 15(a)) requires only a single controlled switch but is generally not practical due to the diode losses. The common-emitter (Fig. 15(b)) and common-collector (Fig. 15(c)) configurations are more efficient realizations, but they require two gate-drive circuits and careful commutation techniques to prevent converter failures. The common-collector configuration is the more preferred switch arrangement as it requires lesser number of isolated gate-drive power supplies than the common-emitter configuration. For example, in the case of the MC, while the common-emitter configuration requires 9 isolated power supplies, the common-collector configuration requires only 6 supplies. This reduced number of supplies is also an advantage in view of the isolation distance between independent voltage potentials within the MC.

## E. Simulation Results

The system shown in Fig. 16 has been considered for simulation study. The MC is connected to a 3-phase wye-connected source of 480V (rms) line-line voltage and 60

Fig. 16. System simulated to study MC operation

TABLE 1. System parameters used for simulation

| Parameter                                                | Value       |

|----------------------------------------------------------|-------------|

| Line-to-line input voltage of the MC $V_{LL,rms}$        | 480 V       |

| Three-phase load at the MC output                        | 20mH        |

| Angular frequency of power grid voltage ω                | 2π*60 rad/s |

| Discrete intervals per period of modulation function $N$ | 100         |

Hz frequency. A 3-phase inductive load of 20 mH is considered at the output of the MC. The operating parameters of the MC are summarized in TABLE 1. From (21) and (23), it is seen that the resulting switching frequency is 12 kHz. Line filters must be used between the MC and the source to eliminate the high order harmonics in the input currents. They have been excluded from the initial study to obtain a better understanding of the MC operation. The effect of filters on the system will be considered later in this chapter.

### 1. Simulation in MATLAB

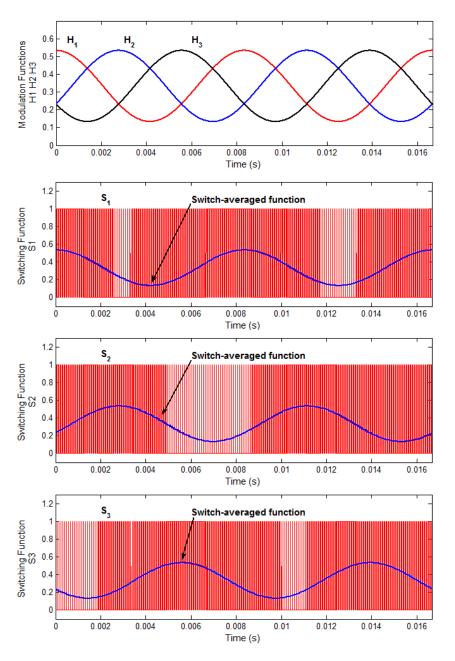

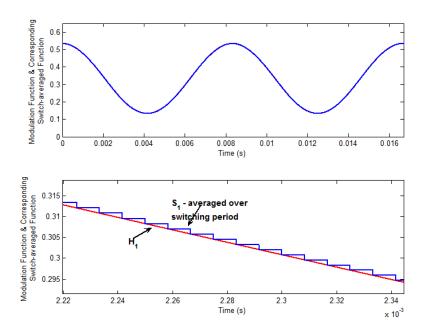

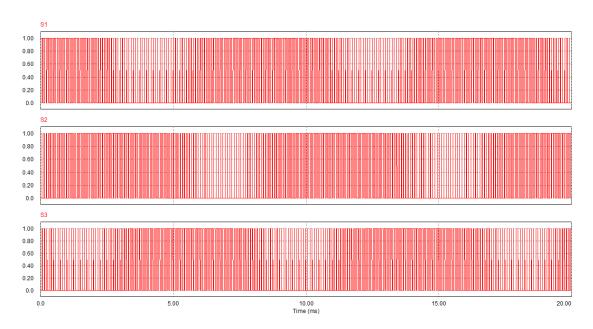

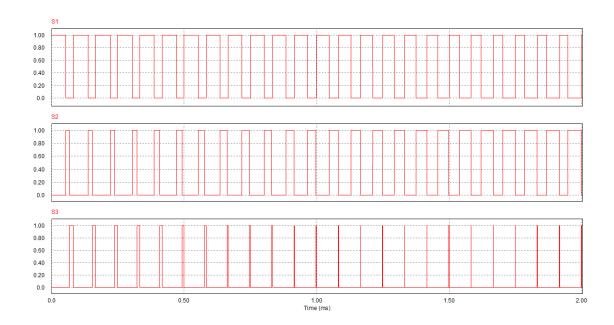

The 'ON' times of the switches are obtained using (22). The switching functions, which are vectors of 1's and 0's, are derived by expressing these 'ON' times in terms of a suitable time step. The simulated modulation and switching functions are shown in Fig. 17. The switch-averaged function, obtained by averaging the switching functions over every switching period  $T_{disc}$ , closely follows the corresponding modulation function. This indicates that the switching function models the modulation function as expected.

Fig. 17. Modulation functions and switching functions

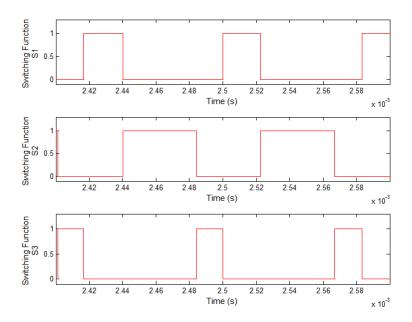

The switching sequence followed in the Venturini technique is shown in Fig. 18 and is in accordance with Fig. 14

Fig. 18. Switching sequence of the Venturini method

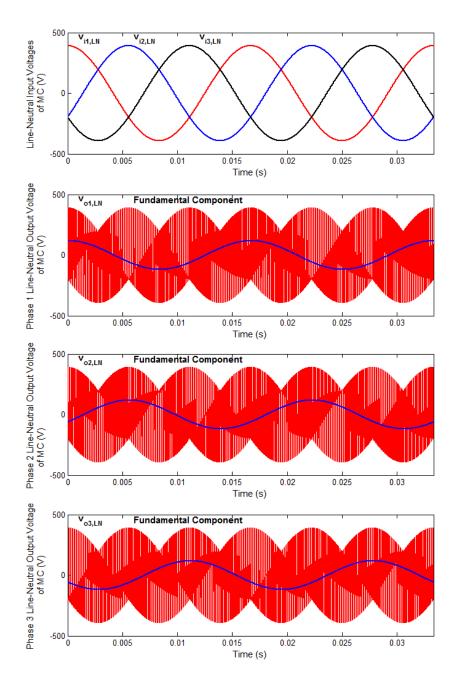

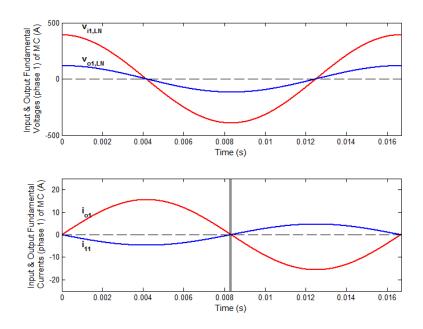

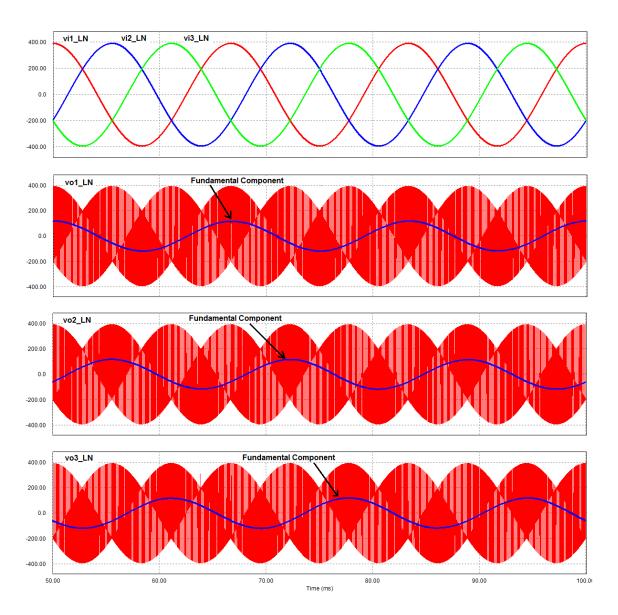

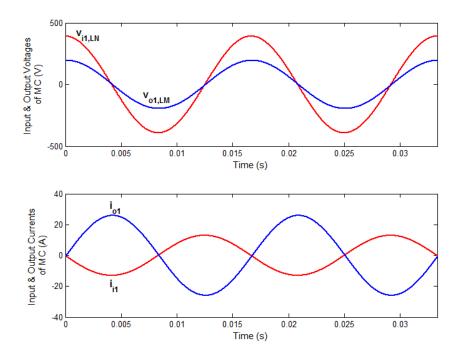

The line-neutral input and output voltages, obtained using (17) are shown in Fig. 19. The switching nature of the output voltages, which sequentially take the values of all three input voltages, is apparent from the figures. It can be seen that the fundamental components of the output voltages, obtained by using the Fast Fourier Transform (FFT), are stepped down from the inputs by a factor of q (0.3), and are in phase with the corresponding input voltage.

Fig. 19. Line-neutral input voltages and output voltages of the MC

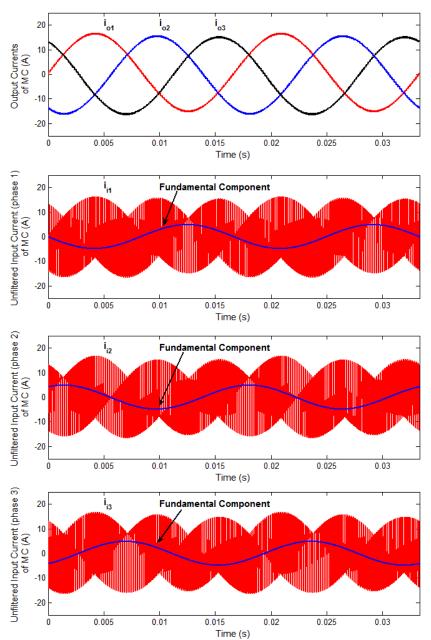

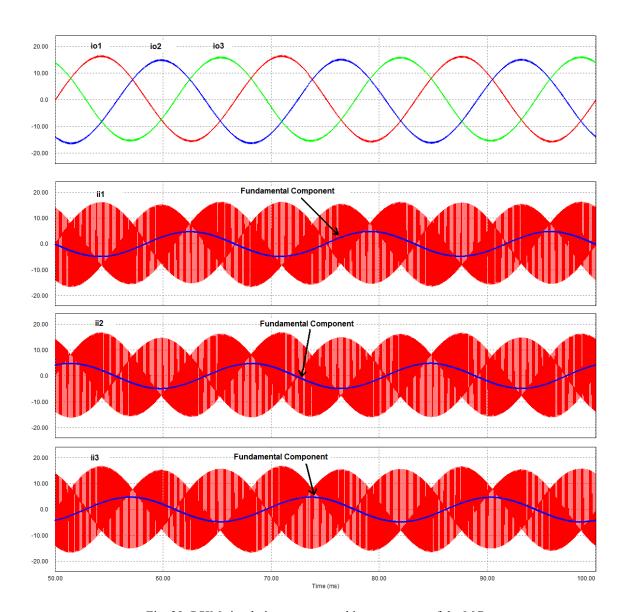

The currents of the MC are shown in Fig. 20. The input currents are seen to be switching between the output currents as indicated by (18). The fundamental components of the input currents are stepped down by a factor of 0.3 when compared to the output currents.

More importantly, each input current has exactly the opposite phase as the corresponding output current, as expected from (13) and (14). Thus, the Venturini modulation method is seen to assert the unique property of phase reversal between the input and output currents.

Fig. 20. Output currents and input currents of the MC

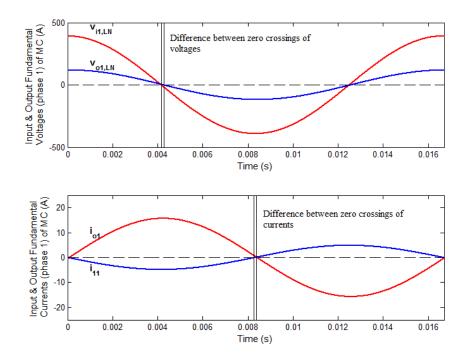

The fundamental components of the voltages and currents of one phase of the MC are shown in Fig. 21.

Fig. 21. Accuracy of MC waveforms for switching frequency of 12kHz

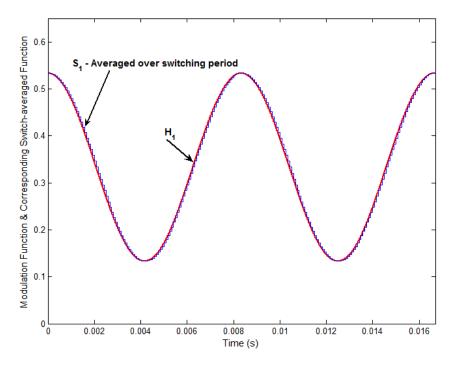

The magnitudes and phase angles of the fundamental components of the MC voltages are summarized in TABLE 2. Slight differences between the simulated and expected values can be noted from the table. Also, a closer observation of Fig. 21 shows that the input and output voltages are not exactly in phase, and the input and output currents are not exactly out of phase. This deviation has been found to be attributed to the modeling inaccuracy introduced by the Venturini method while deriving the switching functions from the discrete-time modulation functions (Fig. 13). The difference between the modulation function and its discrete version for a switching frequency of 12 kHz is shown in Fig. 22.

TABLE 2. Comparison of expected and simulated output voltages of the MC

|             | Magnitude      |                 | Phase          |                 |

|-------------|----------------|-----------------|----------------|-----------------|

|             | Expected value | Simulated value | Expected value | Simulated value |

| $v_{ol,LN}$ | 117.58 V       | 118.27 V        | 0°             | -1.80°          |

| $v_{o2,LN}$ | 117.58 V       | 118.27 V        | -120°          | -121.80°        |

| $V_{o3,LN}$ | 117.58 V       | 118.28 V        | 120°           | 118.20°         |

| $i_{oI}$    | 15.59 A        | 15.69 A         | -90°           | -91.81°         |

| $i_{o2}$    | 15.59 A        | 15.69 A         | 150°           | 148.20°         |

| $i_{o3}$    | 15.59 A        | 15.69 A         | 30°            | 28.20°          |

| $i_{il}$    | 4.68 A         | 4.85 A          | 90°            | 90.11°          |

| $i_{i2}$    | 4.68 A         | 4.85 A          | -30°           | -30.11°         |

| $i_{i3}$    | 4.68 A         | 4.84 A          | -150°          | -150.00°        |

Fig. 22. Comparison between modulation and switch-averaged functions for switching frequency of 12kHz

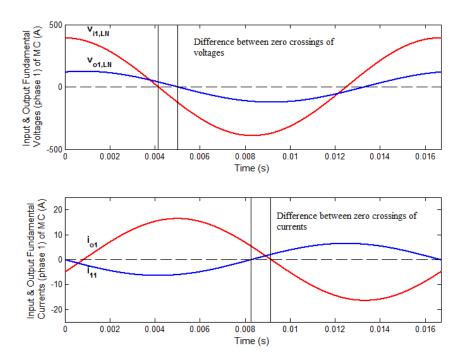

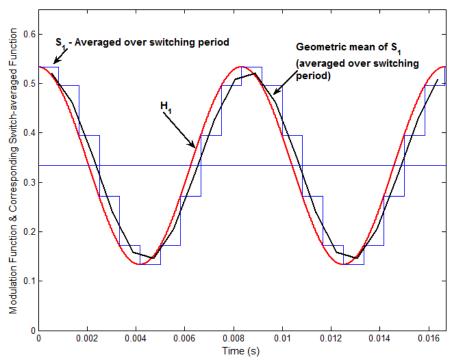

As mentioned earlier, the discrete versions follow the original modulation functions with greater accuracy as the zero-order hold period  $T_{disc}$  is decreased. In other words, as the switching frequency is increased by using larger values of 'N', the switching functions will more closely model the modulation functions. The modeling inaccuracy is depicted for a switching frequency of 1.2 kHz (N=10) in Fig. 23 and Fig. 24. In Fig. 24, the phase difference between the modulation function  $H_I$  and the geometric mean of the discrete version of  $H_I$  is approximately 0.26 radians. The phase difference in voltages of Fig. 23 is also approximately the same (0.32 radians). Thus, the correlation between the modeling error of the Venturini method and the inaccuracy in the MC waveforms is further ascertained.

Fig. 23. Accuracy of MC waveforms for switching frequency of 1.2 kHz

Fig. 24. Comparison between modulation and switching functions for switching frequency of 1.2 kHz

The voltage and current waveforms for a switching frequency of 120 kHz (N=1000), shown in Fig. 25, illustrate near-ideal behavior of the MC. Practically no difference exists between the modulation function and its discrete function as illustrated in Fig. 26.

Fig. 25. Accuracy of MC waveforms for switching frequency of 120kHz

Fig. 26. Comparison between modulation and switch-averaged functions for switching frequency of 120kHz

Fig. 27. Schematic of system in PSIM

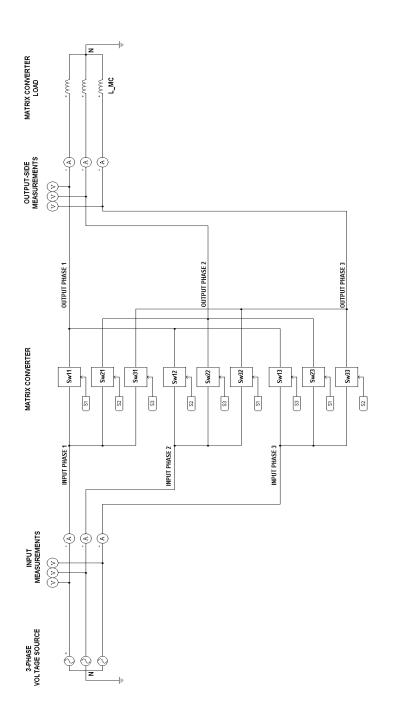

# 2. Simulation in PSIM

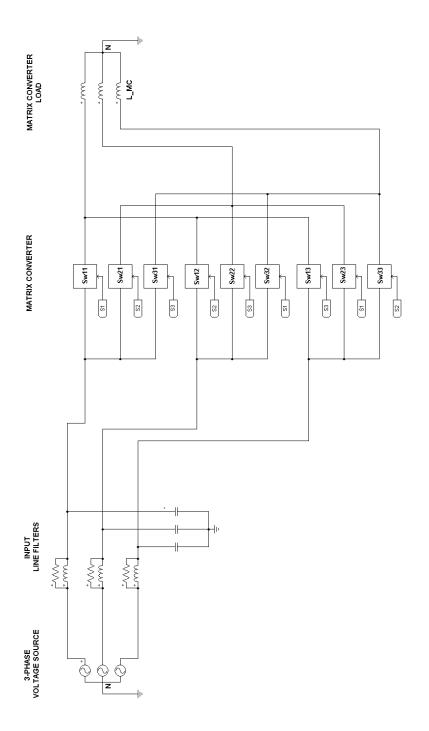

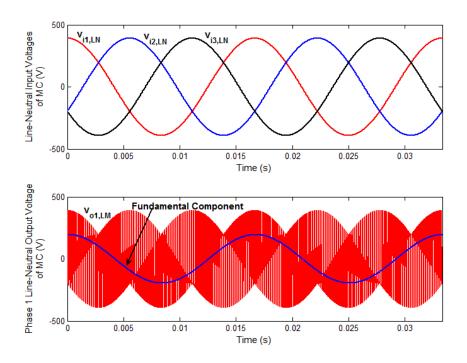

The system of Fig. 16 was implemented in PSIM as shown in Fig. 27. The control logic for switch signal generation is provided in Appendix B. The line-neutral input and output voltages are shown in Fig. 28.

Fig. 28. PSIM simulation - line-neutral input and output voltages of the MC

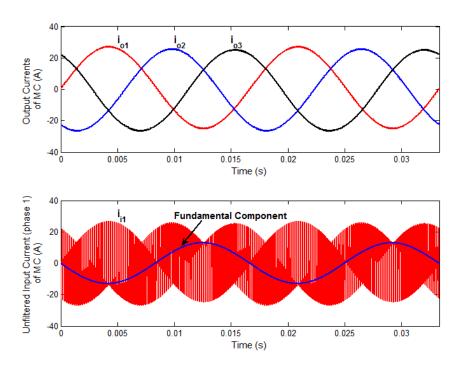

The input and output currents of the PSIM-simulated system are shown in Fig. 29.

Fig. 29. PSIM simulation - output and input currents of the MC

The fundamental components of the MC voltages and currents are given in TABLE 3. Comparing the values with those of TABLE 3, it can be seen that the PSIM simulations are in close agreement with the MATLAB simulation results (the magnitude values

differ by a maximum of  $\pm 3.6\%$ , while the phase angle values differ by a maximum of  $\pm 2.5\%$ ).

TABLE 3. Magnitudes and phase angles of fundamental components of MC waveforms

| PARAMETER                                         | MAGNITUDE | PHASE ANGLE |  |

|---------------------------------------------------|-----------|-------------|--|

| Line-neutral MC input voltage (phase 1) $v_{il}$  | 391.92 V  | -0.02°      |  |

| Line-neutral MC input voltage (phase 2) $v_{i2}$  | 391.92 V  | -120.02°    |  |

| Line-neutral MC input voltage (phase 3) $v_{i3}$  | 391.92 V  | -119.98°    |  |

| Line-neutral MC output voltage (phase 1) $v_{ol}$ | 114.48 V  | -1.76°      |  |

| Line-neutral MC output voltage (phase 2) $v_{o2}$ | 117.31 V  | -119.50°    |  |

| Line-neutral MC output voltage (phase 3) $v_{o3}$ | 119.85 V  | -118.21°    |  |

| MC input current (phase 1) $i_{il}$               | 4.93 A    | 91.12°      |  |

| MC input current (phase 2) $i_{i2}$               | 4.79 A    | -31.32°     |  |

| MC input current (phase 3) $i_{i3}$               | 4.68 A    | -148.65°    |  |

| MC output current (phase 1) $i_{ol}$              | 15.50 A   | -91.20°     |  |

| MC output current (phase 2) $i_{o2}$              | 15.79 A   | 148.76°     |  |

| MC output current (phase 3) $i_{o3}$              | 15.64 A   | 27.86°      |  |

# 3. Addition of Input Line Filters

Second-order filters are required between the voltage source and the MC to reduce harmonic content of the currents drawn from the source. Several filter topologies have been discussed in literature [26, 27] some of which are shown in Fig. 30. The filter topology of Fig. 30 (d) has been chosen due to its high damping factor and relatively

Fig. 30. Some input filter topologies

lower losses. The PSIM schematic of the system with input filters is shown in Fig. 31. Damping resistors connected in parallel with the inductors reduce ringing effects. The cut-off frequency  $\omega_{cut-off}$  of the filter is chosen as 1.2 kHz, which is  $1/10^{th}$  the switching frequency. The filter parameters are chosen according to (24). The damping resistor is chosen to result in a filter damping factor  $\zeta$  of 0.5. It is then adjusted during simulation to improve the system performance. The resulting filter parameters are given in TABLE 4.

$$\omega_{cut-off} = 1/\sqrt{L_{filter}C_{filter}}$$

$$\zeta = \frac{1}{2R_{damp}} \sqrt{\frac{L_{filter}}{C_{filter}}}$$

(24)

TABLE 4. Input line filter parameters

| PARAMETER                             | VALUE |

|---------------------------------------|-------|

| Per-phase inductance $L_{filter}$     | 1 mH  |

| Per-phase capacitance $C_{filter}$    | 20 μΗ |

| Per-phase damping resistor $R_{damp}$ | 10 Ω  |

Fig. 31. Schematic of MC system with input line filters in PSIM

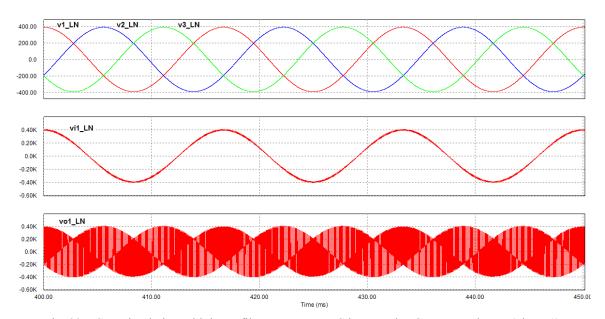

The line-neutral voltages of the system are given in Fig. 32. The upper row shows the source voltages, while the second row displays the MC input voltages (after the filter stage). The last row shows the resulting MC output voltage of phase 1. It is seen that the filter contributes to some ringing in the MC input voltages. As the damping resistor is increased, the ringing effect decreases; however, it deteriorates the filtering action of the input filter.

Fig. 32. PSIM simulation with input filters - source, MC input and MC output voltages (phase 1)

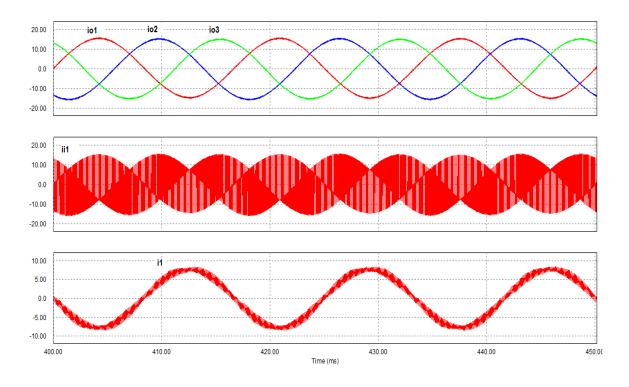

The currents of the system are shown in Fig. 33. The top-most row shows the three output currents of the MC. The MC input current of phase 1 is shown in the second row, while the filtered current drawn from the voltage source is given in the last row. The figure shows that appropriate filtering has taken place.

Fig. 33. PSIM simulation with input filters – MC output, MC input and source currents (phase 1)

The magnitudes and phase angles of the fundamental components of the MC waveforms are summarized in TABLE 5. It is seen that the filters have not altered the basic operation of the MC – the current phase reversal property. A comparison with TABLE 3 shows the unfiltered and filtered cases to be in close agreement (magnitudes and angles differ by a maximum of  $\pm 3.5\%$  and  $\pm 1\%$ , respectively).

TABLE 5. Magnitudes and phase angles of fundamental components of waveforms for the MC system with input filters

| PARAMETER                                         | MAGNITUDE | PHASE ANGLE |

|---------------------------------------------------|-----------|-------------|

| Line-neutral MC input voltage (phase 1) $v_{il}$  | 394.83 V  | -0.04°      |

| Line-neutral MC input voltage (phase 2) $v_{i2}$  | 394.78 V  | -120.04°    |

| Line-neutral MC input voltage (phase 3) $v_{i3}$  | 394.80 V  | -119.96°    |

| Line-neutral MC output voltage (phase 1) $v_{ol}$ | 110.81 V  | -1.36°      |

| Line-neutral MC output voltage (phase 2) $v_{o2}$ | 113.79 V  | -119.06°    |

| Line-neutral MC output voltage (phase 3) $v_{o3}$ | 116.22 V  | -118.53°    |

| MC input current (phase 1) $i_{il}$               | 4.77 A    | 90.88°      |

| MC input current (phase 2) $i_{i2}$               | 4.65 A    | -31.54°     |

| MC input current (phase 3) $i_{i3}$               | 4.54 A    | -148.96°    |

| MC output current (phase 1) $i_{ol}$              | 15.02 A   | -90.97°     |

| MC output current (phase 2) $i_{o2}$              | 15.33 A   | 149.09°     |

| MC output current (phase 3) $i_{o3}$              | 15.18 A   | 28.03°      |

In conclusion, it is seen that the simulation results support the mathematical analysis of the MC using the Venturini modulation method. The current phase reversal property has been presented and is applied to the problem of VAR compensation in the following chapter.

#### **CHAPTER III**

#### THE PROPOSED VAR COMPENSATOR

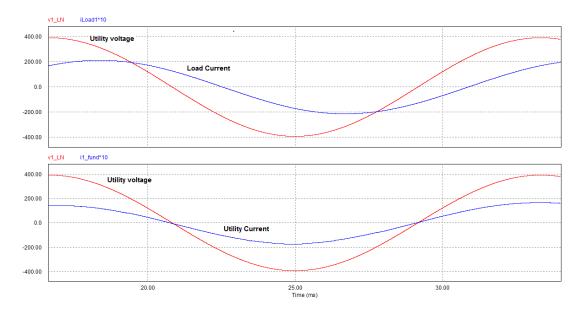

The Venturini modulation method for a MC was introduced in Chapter II and modulation functions  $H_1$ ,  $H_2$  and  $H_3$  were developed as in (10) and (11) which operate the converter such that the phase of currents are reversed between the input and the output. Simulation results of the MC system shown in Fig. 16 further illustrate this property by showing that while the output currents lag the output voltages due to the inductive element, the input currents actually lead the corresponding input voltages. Thus, the inductor on the MC output is made to appear as a capacitor at the MC input by the Venturini modulation method.

This current phase reversal property of the MC finds important application in reactive power load compensation, where capacitors are used extensively to locally provide lagging VARs to loads, despite their serious reliability issues. This thesis proposes a reactive power load compensator consisting of the MC with a 3-phase choke (inductive) element connected at its output terminals. By controlling the modulation index 'q', the MC can be operated to draw variable leading VARs from the source, while the choke draws lagging VARs from the MC output terminals.

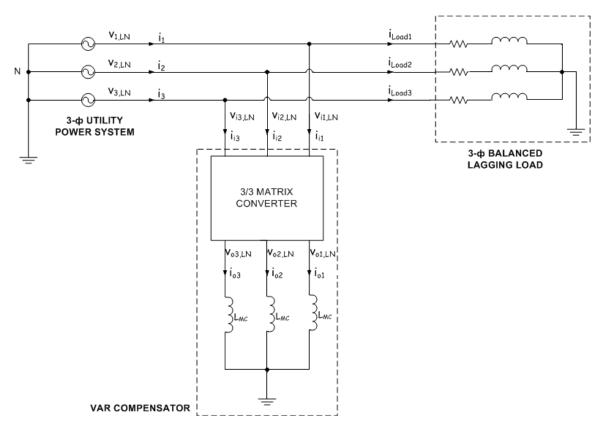

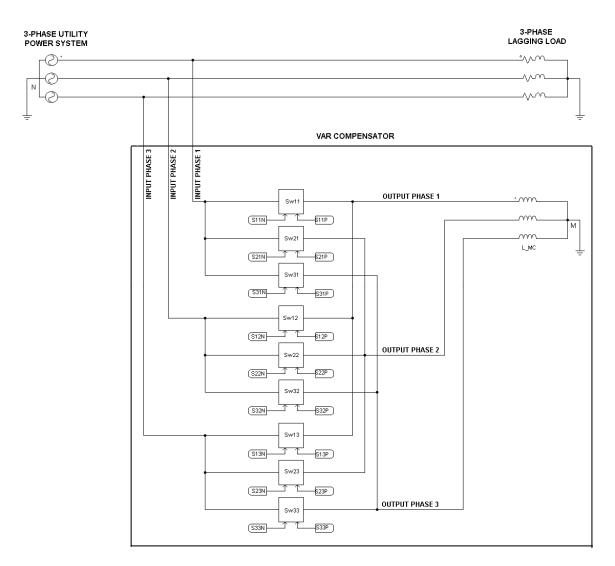

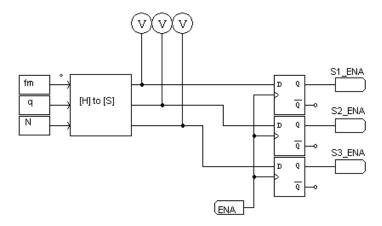

## A. System Description and Analysis

The layout of a test case ac power system with a lagging load that needs compensation is shown in Fig. 34. The proposed VAR compensator is shunt-connected to the system at a point near the load. Though the source is typically  $\Delta$ -connected, its wye equivalent has been used to facilitate understanding the phase relationship between phase currents and voltages. The line-neutral ac network voltages are denoted by  $v_{I,LN}$ ,  $v_{2,LN}$  and  $v_{3,LN}$  and are also equal to the MC input voltages  $v_{iI,LN}$ ,  $v_{i2,LN}$  and  $v_{i3,LN}$ , respectively. The magnitude and frequency of the voltages are denoted by  $V_{LN,rms}$  and  $\omega$  respectively. The line-neutral MC output voltages are given by  $v_{o1,LN}$ ,  $v_{o2,LN}$  and  $v_{o3,LN}$ .

Fig. 34. The proposed VAR compensator

The 3-phase choke element, denoted by  $L_{MC}$ , draws currents  $i_{o1}$ ,  $i_{o2}$  and  $i_{o3}$  from the output terminals of the MC. The currents drawn by the MC from the system are denoted by  $i_{i1}$ ,  $i_{i2}$  and  $i_{i3}$ , while the currents drawn by the load are given by  $i_{Load1}$ ,  $i_{Load2}$  and  $i_{Load3}$ . The total currents drawn by the effective load, the original lagging load in parallel with the compensator, are given by  $i_1$ ,  $i_2$  and  $i_3$ .

Let the ac network and MC input voltages be given by (25). Let it be assumed that in order to provide complete load compensation, the MC is operated with a modulation index ' $q_{comp}$ '. Then, from (12), we obtain the MC output voltages as in (26).

$$v_{1,LN} = v_{i1,LN} = \sqrt{2} \times V_{LN,rms} \cos(\omega t)$$

$$v_{2,LN} = v_{i2,LN} = \sqrt{2} \times V_{LN,rms} \cos(\omega t - 2\pi/3)$$

$$v_{3,LN} = v_{i3,LN} = \sqrt{2} \times V_{LN,rms} \cos(\omega t + 2\pi/3)$$

(25)

$$v_{o1,LN} = \sqrt{2} \times q_{comp} \times V_{LN,rms} \cos(\omega t)$$

$$v_{o2,LN} = \sqrt{2} \times q_{comp} \times V_{LN,rms} \cos(\omega t - 2\pi/3)$$

$$v_{o3,LN} = \sqrt{2} \times q_{comp} \times V_{LN,rms} \cos(\omega t + 2\pi/3)$$

(26)

The choke element draws currents that lag the MC output voltages by exactly 90° as given by (27). By virtue of the current reversal property of the Venturini modulation method (13)-(14), the input currents of the MC are then derived as in (28).

$$i_{o1} = \sqrt{2} \times q_{comp} \times \frac{V_{LN,rms}}{\omega L_{MC}} \times \cos(\omega t - \pi/2)$$

$$i_{o2} = \sqrt{2} \times q_{comp} \times \frac{V_{LN,rms}}{\omega L_{MC}} \times \cos(\omega t - \pi/2 - 2\pi/3)$$

$$i_{o3} = \sqrt{2} \times q_{comp} \times \frac{V_{LN,rms}}{\omega L_{MC}} \times \cos(\omega t - \pi/2 + 2\pi/3)$$

(27)

$$i_{i1} = \sqrt{2} \times q_{comp}^{2} \times \frac{V_{LN,rms}}{\omega L_{MC}} \times \cos(\omega t + \pi/2)$$

$$i_{i2} = \sqrt{2} \times q_{comp}^{2} \times \frac{V_{LN,rms}}{\omega L_{MC}} \times \cos(\omega t + \pi/2 - 2\pi/3)$$

$$i_{i3} = \sqrt{2} \times q_{comp}^{2} \times \frac{V_{LN,rms}}{\omega L_{MC}} \times \cos(\omega t + \pi/2 + 2\pi/3)$$

(28)

The instantaneous input power per-phase is obtained as a product of the input voltages and currents of the compensator

$$p(t)_{per phase} = \left(\sqrt{2} \times V_{LN,rms} \cos(\omega t)\right) \times \left(\sqrt{2} \times q_{comp}^{2} \times \frac{V_{LN,rms}}{\omega L_{MC}} \times \cos(\omega t + \pi/2)\right)$$

$$= 2 \times \frac{q_{comp}^{2} V_{LN,rms}^{2}}{\omega L_{MC}} \times \cos(\omega t) \times \cos(\omega t + \pi/2)$$

(29)

Using standard trigonometric identities, we have

$$p(t)_{per phase} = \frac{q_{comp}^{2} V_{LN,rms}^{2}}{\omega L_{MC}} \times \left[\cos(2\omega t + \pi/2) + \cos(-\pi/2)\right]$$

$$= \frac{q_{comp}^{2} V_{LN,rms}^{2}}{\omega L_{MC}} \times (-)\sin(2\omega t)$$

(30)

It is seen that the instantaneous power associated with the MC input has only a negative double frequency component. This indicates that while the MC does not consume any real power, it supplies reactive power to the ac network. The total three-phase reactive power supplied by the MC to the ac network is then given by

$$Q = 3 \times \frac{(q_{comp})^2 \times (V_{LN,rms})^2}{\omega L_{MC}}$$

(31)

So, in order to compensate a load requiring 'Q' lagging VARs, the MC must be operated at a modulation index ' $q_{comp}$ ' which satisfies (31). From this equation, it is seen that the

reactive power compensated by the MC increases with the modulation index. Further, lesser the choke inductance  $L_{MC}$ , greater is the compensation. The choke value is decided by considering the maximum required compensation at the modulation index limiting value which is 0.5.

# B. Simulation Results

The system shown in Fig. 34 was simulated in MATLAB and the parameters used are listed in TABLE 6. The line-to-line voltage (phase voltage) of the  $\Delta$ -configured ac power grid is chosen as 480 V which results in the line-to-neutral voltage of 277.13 V for the wye-model in Fig. 34. The maximum required reactive power compensation is given by

$$Q_{Load} = P_{Load} \times \tan(\cos^{-1}(p.f.))$$

(32)

TABLE 6. System parameters used for simulation

| PARAMETER                                                | VALUE       |

|----------------------------------------------------------|-------------|

| Line-to-neutral power grid voltage $V_{LN,rms}$          | 277.13 V    |

| Angular frequency of power grid voltage $\omega$         | 2π*60 rad/s |

| Per-phase resistance of load $R_{Load, per phase}$       | 14.75 Ω     |

| Per-phase inductance of load $L_{Load, per phase}$       | 29.34 mH    |

| Total rated real power of load $P_{Load}$                | 10 kW       |

| Power factor of load <i>p.f.</i>                         | 0.8         |

| Total maximum load reactive power requirement $Q_{load}$ | 7.5 kVAR    |

| VAR rating of compensator                                | 8.0 kVAR    |

| MC output-side inductance $L_{MC}$                       | 20 mH       |

| Discrete intervals per period of modulation function $N$ | 100         |

| Operating modulation index $q_{comp}$                    | 0.4954      |

The VAR rating of the compensator is chosen accordingly. The required  $L_{MC}$  is calculated using (31). The chosen 'N' gives a reasonable switching frequency of 12 kHz. Using the chosen MC parameter values, the modulation index is recalculated using (31).

## 1. Simulations in MATLAB

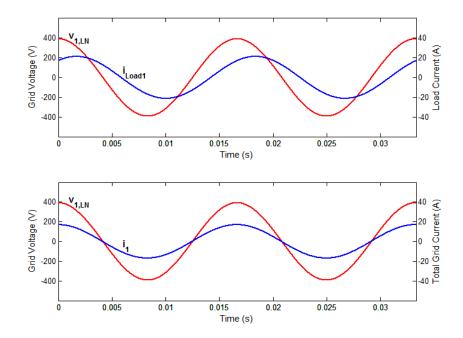

The system is simulated in MATLAB as mentioned in Chapter II. The input and output voltages of phase 1 of the MC are given in Fig. 35. The input and output currents of the MC phase 1 are shown in Fig. 36. The phase relationships between the fundamental components of the input and output voltages and currents are illustrated in Fig. 37.

Fig. 35. MATLAB simulation - Input and output voltages (phase 1) of the MC

Fig. 36. MATLAB simulation - Output and input currents (phase 1) of the MC

Fig. 37. MATLAB simulation - Phase relationships between voltages and currents of the MC  $\,$

The simulation result of Fig. 38 shows that reactive power compensation has been achieved. Though the load draws lagging current  $i_{LoadI}$ , the effective load (the compensator and the original load) draws unity power factor (UPF) current  $i_I$  that is in phase with the ac network voltage.

Fig. 38. MATLAB simulation – Lagging load currents and UPF ac network currents showing the achieved reactive power compensation

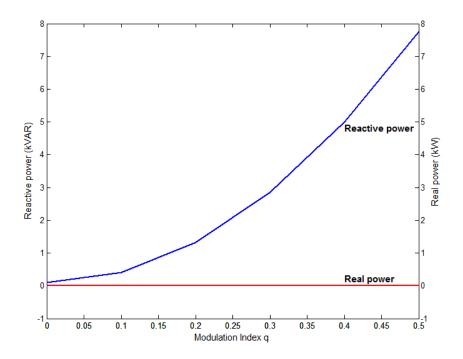

The variation of reactive power compensation with the modulation index 'q' for the given compensator parameters is shown in Fig. 39. As expected from (31), the VAR compensation increases with the square of the modulation index. Since there were no losses modeled in the converter, there is no real-power flow. Interestingly, the figure shows a small offset in the relationship between 'q' and the reactive power compensated. For example, when 'q' is zero, the reactive power compensated is non-zero (90 VAR).

Fig. 39. Variation of lagging reactive power compensated and real power drawn by the MC with modulation index 'q'

This error, which is the result of the switching functions not exactly implementing the modulation functions, decreases with an increase in the value of 'N', as explained in Chapter II. Another solution to the error that might be explored in future work is the introduction of a phase shift ' $\delta$ ' in the modulation functions as in

$$H_{1} = \frac{1}{3} (1 + 2q \cos(2\omega t + \delta))$$

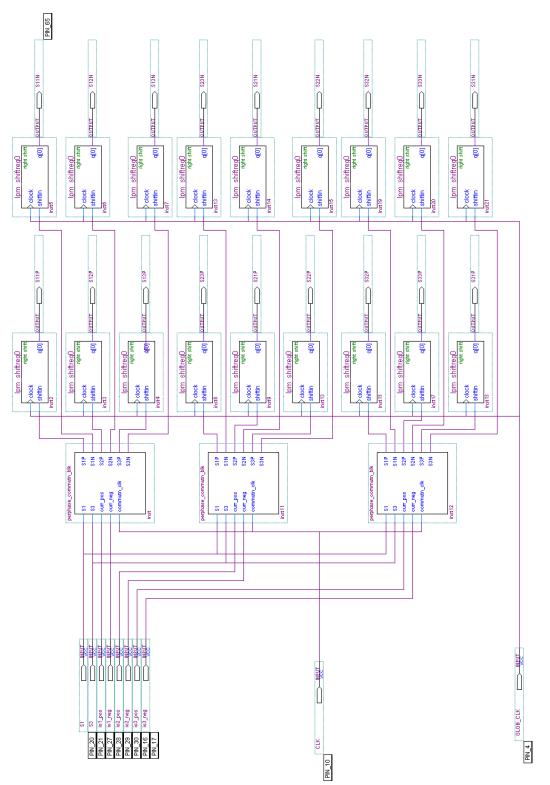

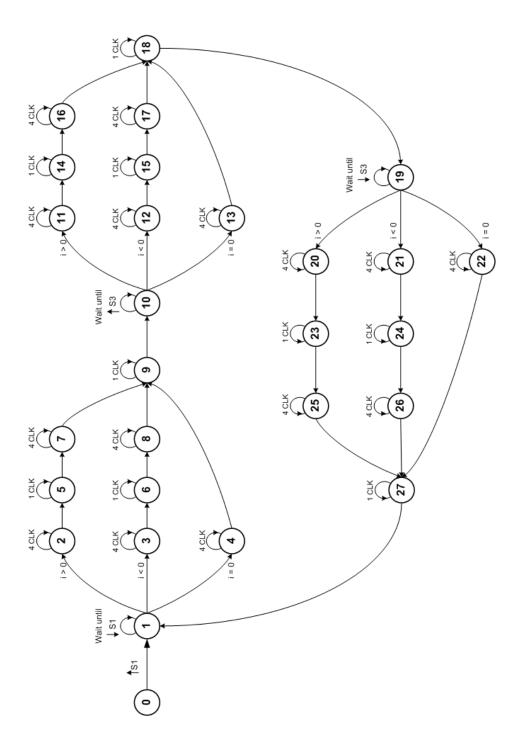

$$H_{2} = \frac{1}{3} (1 + 2q \cos(2\omega t - 2\pi/3 + \delta))$$