### HARDWARE ACCELERATOR FOR MIMO WIRELESS SYSTEMS

A Dissertation

by

### PANKAJ BHAGAWAT

### Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

December 2011

Major Subject: Computer Engineering

## HARDWARE ACCELERATOR FOR MIMO WIRELESS SYSTEMS

### A Dissertation

by

## PANKAJ BHAGAWAT

### Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

| Chair of Committee, | Gwan Choi          |

|---------------------|--------------------|

| Committee Members,  | Jiang Hu           |

|                     | Rabi Mahapatra     |

|                     | Jim Ji             |

| Head of Department, | Costas Georghiades |

December 2011

Major Subject: Computer Engineering

### ABSTRACT

Hardware Accelerator for MIMO Wireless Systems. (December 2011) Pankaj Bhagawat, B.S., National Insitute of Technology, Tiruchirapally, India; M.S., Texas A&M University

Chair of Advisory Committee: Dr. Gwan Choi

Ever increasing demand for higher data rates and better Quality of Service (QoS) for a growing number of users requires new transceiver algorithms and architectures to better exploit the available spectrum and to efficiently counter the impairments of the radio channel.

Multiple-Input Multiple-Output (MIMO) communication systems employ multiple antennas at both transmitter and at the receiver to meet the requirements of next-generation wireless systems. It is a promising technology to provide increased data rates while not involving an equivalent increase in the spectral requirements. However, practical implementation of MIMO detectors poses a significant challenge and has been consistently identified as the major bottleneck for realizing the full potential that multiple antenna systems promise. Furthermore, in order to make judicious use of the available bandwidth, the baseband units have to dynamically adapt to different modes (modulation schemes, code rates etc) of operations. Flexibility and high throughput requirements often place conflicting demands on the Very Large Scale Integration (VLSI) system designer. The major focus of this dissertation is to present efficient VLSI architectures for configurable MIMO detectors that can serve as accelerators to enable the realization of next generation wireless devices feasible. Both, hard output and soft output detector architectures are considered. To My Parents, Brother, Sister-in-Law, Sidharth and Anirudh

#### ACKNOWLEDGMENTS

My doctoral studies would not have been possible without the support and guidance of my advisor, Dr. Gwan Choi. He consistently helped me to grasp concepts of technical work and bigger things in life. I would like to thank all my committee members, Dr.Mahapatra, Dr.Hu, and Dr. Ji, for valuable inputs and advice. The students of the computer engineering and systems group were very equally helpful to me. I would especially like to express my gratitude to Rajballav Dash, Yoonseoke Yang, Kiran Gunnam, Rohit Singhal, Richeek Arya, Ehsan Rohani, and Euncheol Kim. I would like to thank all my friends in CollegeStation whose company I enjoyed fully.

My family always gave me unconditional love during the course of my stay here. My parents, brother, and sister-in-law were always solidly behind me. I will always cherish the experiences that I had with my two young nephews, Sidharth and Anirudh. Last but not the least, I am thankful to Mr. Roger Lorenzo, Dr. Jay Porter, Dr. Joseph Morgan for constantly helping me enhance my teaching skills.

# TABLE OF CONTENTS

## CHAPTER

| Ι   | INTRODUCTION                                                                                                                                                                                            | 1                                                                                                                                                                                              |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | <ul> <li>A. Approaches to Achieve High Data Rates and Better QoS</li> <li>B. Hardware Implementation Perspective</li> <li>C. Motivation and Contributions</li> <li>D. Organization of Thesis</li> </ul> | 2<br>5<br>8<br>11                                                                                                                                                                              |

| II  | BACKGROUND                                                                                                                                                                                              | 12                                                                                                                                                                                             |

|     | <ul> <li>A. MIMO Wireless Systems: An Overview</li></ul>                                                                                                                                                | 12<br>13<br>16<br>16<br>18<br>19<br>20                                                                                                                                                         |

| III | VLSI ARCHITECTURES FOR MIMO DETECTION:A COM-<br>PARATIVE ANALYSIS                                                                                                                                       | 22                                                                                                                                                                                             |

|     | <ul> <li>A. MIMO Detection</li></ul>                                                                                                                                                                    | <ol> <li>23</li> <li>23</li> <li>25</li> <li>26</li> <li>28</li> <li>29</li> <li>31</li> <li>31</li> <li>32</li> <li>33</li> <li>35</li> <li>36</li> <li>37</li> <li>39</li> <li>43</li> </ol> |

|         | <ol> <li>Building Blocks</li> <li>Detection in Multicore Setup:</li> </ol> | 44<br>45                                                                   |

|---------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|

| IV      | CONFIGURABLE HARD OUTPUT DETECTOR                                          | 52                                                                         |

|         | <ul> <li>A. Configurable Detector</li></ul>                                | 52<br>53                                                                   |

|         | Systems                                                                    | 57                                                                         |

|         | Design Case Study                                                          | 64<br>65<br>66<br>67<br>68<br>69                                           |

| V       | CONFIGURABLE SOFT OUTPUT DETECTOR                                          | 72                                                                         |

|         | <ul> <li>A. Soft Detection</li></ul>                                       | 73<br>75<br>77<br>78<br>80<br>83<br>84<br>85<br>86<br>87<br>89<br>92<br>94 |

| VI      | CONCLUSION                                                                 | 96                                                                         |

| REFEREN | NCES                                                                       | 98                                                                         |

| VITA    |                                                                            | 106                                                                        |

Page

# LIST OF TABLES

| TABLE | Ι                                 | Page |

|-------|-----------------------------------|------|

| 1     | Implementation Results (16-QAM)   | 50   |

| 2     | Implementation Results (64-QAM)   | 51   |

| 3     | Comparison with Existing Designs  | 55   |

| 4     | FPGA Implementation Details       | 57   |

| 5     | Comparison                        | 64   |

| 6     | ASIC Implementation Details       | 71   |

| 7     | Synthesis Results                 | 84   |

| 8     | Synthesis Results and Comparisons | 94   |

# LIST OF FIGURES

| FIGURI | E                                                         | Page |

|--------|-----------------------------------------------------------|------|

| 1      | Wireless Transceiver                                      | 2    |

| 2      | SM Based MIMO System                                      | 4    |

| 3      | Multi User Scenario in a Broadcast Channel                | 5    |

| 4      | Algorithmic Complexity Vs. Available Processing Power [7] | 6    |

| 5      | Architectural Flexibility Vs. Hardware Efficiency [8]     | 7    |

| 6      | Heterogeneous MultiProcessor System Approach              | 8    |

| 7      | Performance of Basic MIMO Techniques, [15], [9]           | 13   |

| 8      | Wideband MIMO (OFDM) System                               | 14   |

| 9      | Equivalent Narrowband MIMO System                         | 15   |

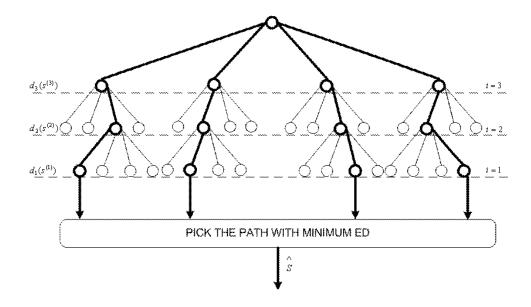

| 10     | Simplified Tree Structure for Detection                   | 29   |

| 11     | Dataflow for Architectures                                | 30   |

| 12     | High Level Architecture for Staggered Sphere Decoding     | 32   |

| 13     | Enumeration Scheme for 16-QAM                             | 33   |

| 14     | Architecture for MCU1                                     | 34   |

| 15     | Details of $MCU_4$                                        | 38   |

| 16     | Details of $PC_k$ k=1,2,3,4                               | 39   |

| 18     | Details of $MCU_k$ k=1,2,3,4                              | 39   |

| 17     | Details of the PDU                                        | 40   |

| 19     | Details of the Quantize Block                             | 40   |

| 20     | Details of the X-block                                    | 42   |

| 21 | BER for Suboptimal Norms and Finite Bit Precision                                           | 43 |

|----|---------------------------------------------------------------------------------------------|----|

| 22 | Compare Select Operation                                                                    | 45 |

| 23 | Multicore Detection for MIMO-OFDM Systems                                                   | 46 |

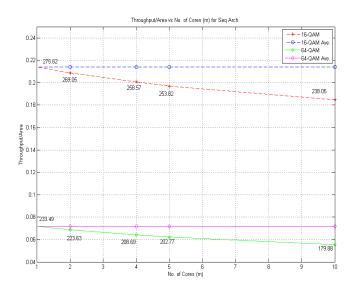

| 24 | Throughput/Area Efficiency for Sequential Arch                                              | 46 |

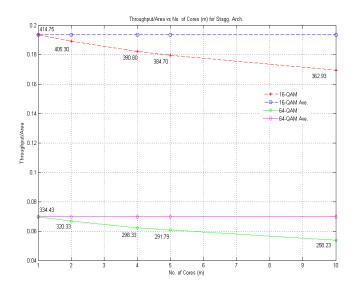

| 25 | Throughput/Area Efficiency for Staggered Arch                                               | 47 |

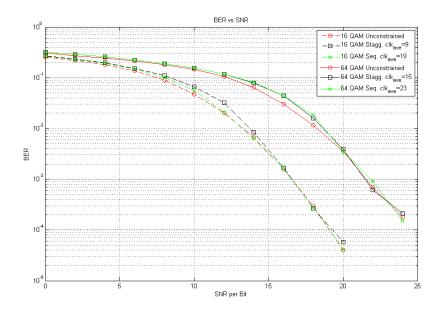

| 26 | BER Performance of the Sequential, and Staggered Architectures<br>Under Resource Constraint | 49 |

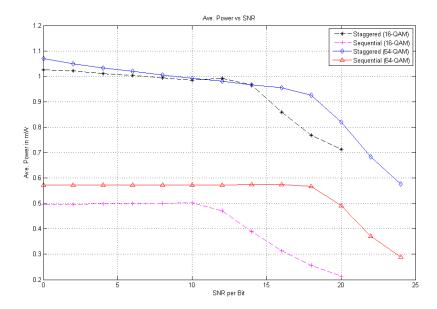

| 27 | Power Consumption Per Vector Symbol as a Function of Eb/No $.$ .                            | 50 |

| 28 | High level architecture                                                                     | 53 |

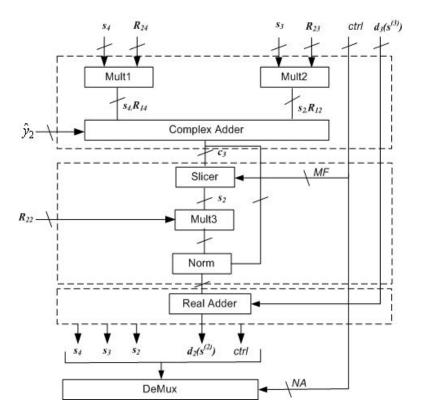

| 29 | Metric Computation Unit of Level 1                                                          | 54 |

| 30 | Slicer                                                                                      | 56 |

| 31 | Output and Control Waveforms                                                                | 58 |

| 32 | Tree Structure for FSD Algorithm and Systolic-Like Array Architecture                       | 59 |

| 33 | FMU                                                                                         | 60 |

| 34 | Node Details                                                                                | 61 |

| 35 | Micro-Architecture of MCU2                                                                  | 62 |

| 36 | MIMO-OFDM Detection Interface Timing                                                        | 65 |

| 37 | High Level Architecture for FSD Based MIMO Detection                                        | 66 |

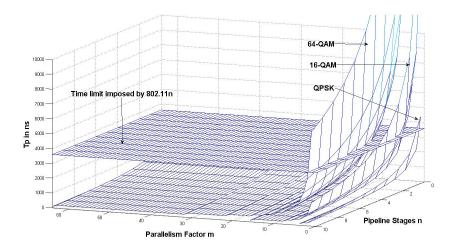

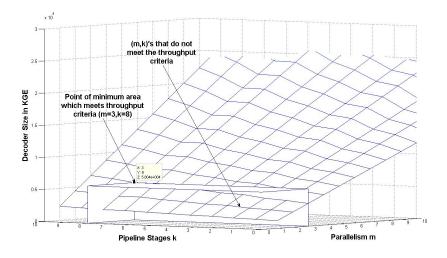

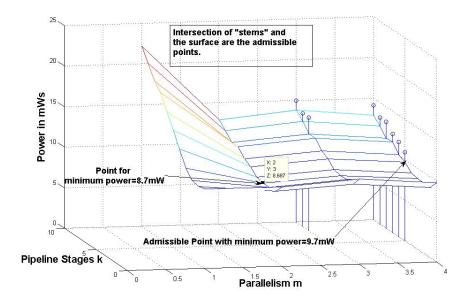

| 38 | Tp vs (m,k) and Constraint Due to 802.11n $\hdots$                                          | 68 |

| 39 | Area vs. Tp for 64-QAM                                                                      | 69 |

| 40 | Aggregate Power vs m,k                                                                      | 70 |

| 41 | The Algorithm Flow                                                                          | 75 |

Page

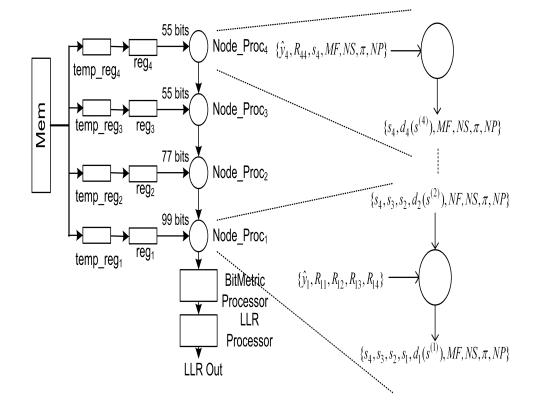

| 42 | High Level Architecture of the Detector                                                   | 77 |

|----|-------------------------------------------------------------------------------------------|----|

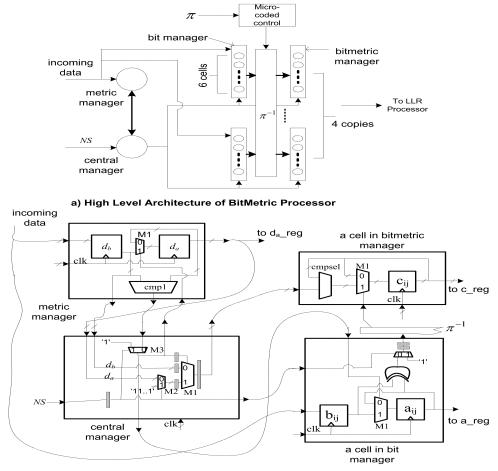

| 43 | BitMetric Processor                                                                       | 79 |

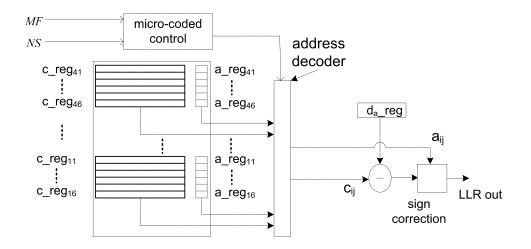

| 44 | LLR Processor                                                                             | 81 |

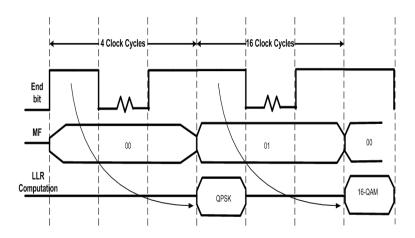

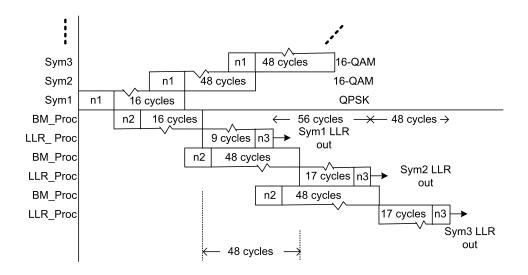

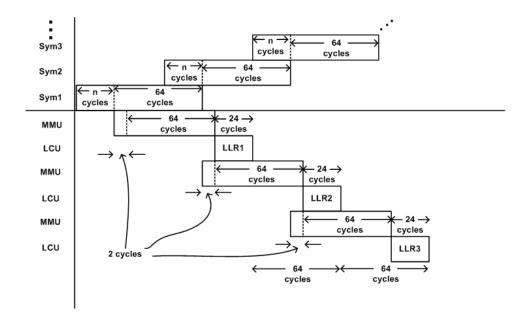

| 45 | Timing Diagram                                                                            | 82 |

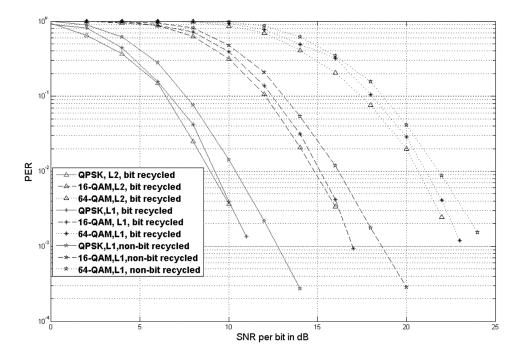

| 46 | PER Performance of LORD Algorithm                                                         | 84 |

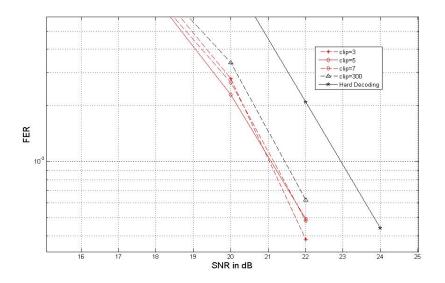

| 47 | FER vs SNR For Various Clipping Values                                                    | 86 |

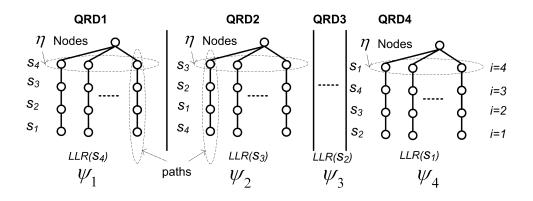

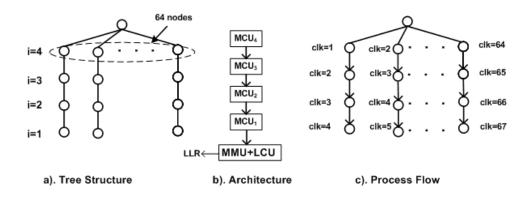

| 48 | Tree Structure and High Level Architecture/Process-Flow $\ . \ . \ .$ .                   | 87 |

| 49 | Timing Diagram                                                                            | 88 |

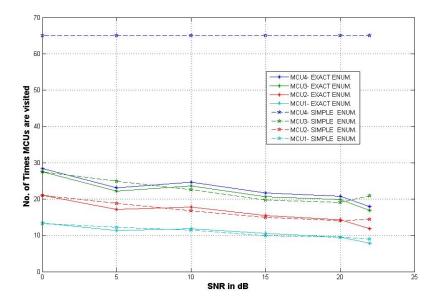

| 50 | Node Pruning Behavior for $l^2$ with SNR $\ldots \ldots \ldots \ldots \ldots \ldots$      | 89 |

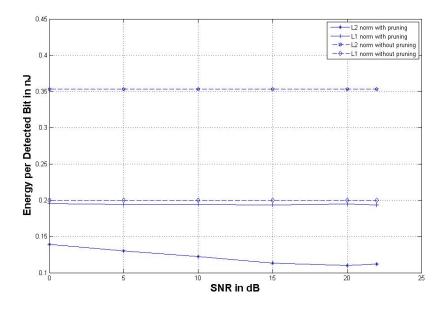

| 51 | Clock Gating Details                                                                      | 90 |

| 52 | Energy per Detected Bit vs SNR for $l^2$ , $l^1$ Norms With and With-<br>out Clock Gating | 92 |

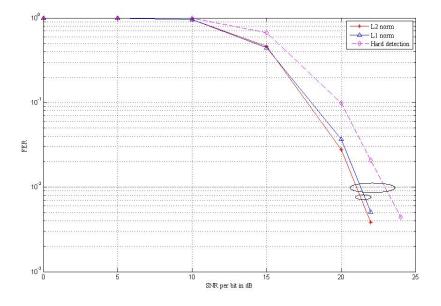

| 53 | FER Performance of Proposed Scheme                                                        | 93 |

Page

### CHAPTER I

#### INTRODUCTION

Wireless communication has become one of the most important technological achievements of humankind in recent years. Not surprisingly, it has led to huge commercial opportunities for a large number of entrepreneurs. The main reasons for this commercial success is the advent of low cost end-user equipments, worldwide standardization of the technology and affordable services. With the increasing usage of portable computers and mobile phones capable of supporting multimedia content, wireless services have attracted lot of attention.

Due to increasing popularity of multimedia applications the demand for high data rates and better Quality of Service (QoS) is also increasing rapidly. This has led to evolution of wireless standards that can support high data rates. In fact the demand for data rates have been almost doubling every 18 months [1]. Unfortunately, the data rates over a wireless communication channel are limited by the capacity of channel. Further exacerbating the situation is the fact that even this capacity is mostly unachievable owing to a variety of channel impairments. One way to increase the data rate is by increasing the bandwidth of the wireless channel. However, this approach is impractical because spectrum is scarce resource. Hence, meeting the demand for higher data rates and better QoS requires new technologies algorithms and techniques to make judicious use of the the available spectrum.

The journal model is IEEE Transactions on VLSI Systems.

A. Approaches to Achieve High Data Rates and Better QoS

Important signal processing techniques developed in recent history that has enabled us to achieve higher data rates with good QoS include:

- Multiple Antenna Systems.

- Transmitter Side Precoding.

- Strong Forward Error Control (FEC) Codes.

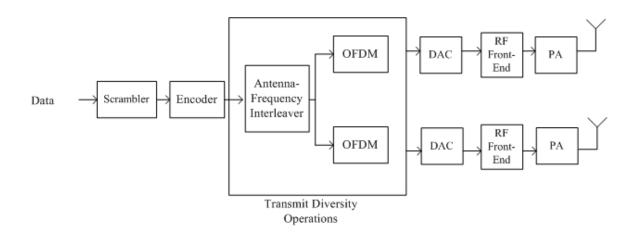

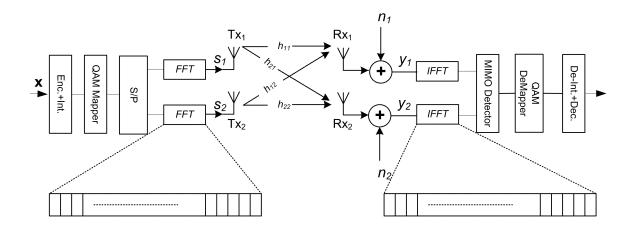

Multiple Antenna Systems: A Multiple-input multiple-output (MIMO) communication system [2] uses multiple antennas at the transmitter as well as at the receiver to support the high data rate requirements of next-generation wireless systems. MIMO technology is a promising approach for providing increased data rates without requiring an equivalent increase in the bandwidth requirements. Fig. 1 [3] shows block

Fig. 1. Wireless Transceiver

diagram of a wireless transceiver for MIMO system. The technique achieves better

data rates and QoS by using three types of gains, namely, array gain, diversity gain, and multiplexing gain[2].

- 1. Array gain basically means that the receiver side is able to pick up a larger part of the transmitted power. This leads to increased range of the communication system.

- 2. Diversity gain refers to the improved QoS due to the fact that the receiver gets multiple copies of the same data. This is an effective technique to counter fading.

- 3. Multiplexing gain is achieved because the transmitter sends independent data streams over the same channel at the same time. This leads to a linear increase in the data rates.

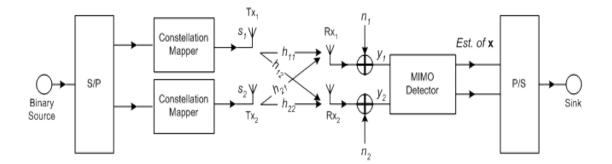

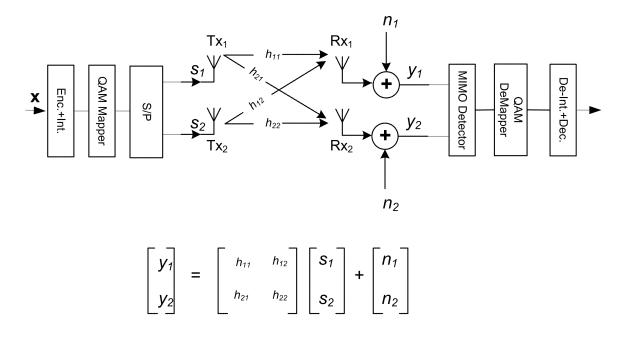

A trade off between these three gains is possible. For instance, space-time codes usually does well to achieve more diversity. Whereas, beamforming technique is good for exploiting array gain. On the other hand spatial multiplexing (SM) uses all available antennas to possibly achieve the highest data rates that can be supported by the channel. For this reason SM based MIMO systems have emerged as a very important scheme to improve the data rates. SM achieves higher data rate by sending independent data from each transmit antenna using same frequency band. For example, in Fig. 2 the system sends two data symbols  $s_1$  and  $s_2$  at the same time and on the same frequency band. The result is that the system can now support two data symbols instead of just one (unlike a Single Input Single Output(SISO) system). Hence, SM-MIMO boosts the data rate proportionately with the number of antennas. However, on the receiver side each antenna sees a weighted superposition (or interference) of all the transmitted symbols. For example  $Rx_1$  sees  $s_1h_{11} + s_2h_{21}$  and  $Rx_2$  sees

Fig. 2. SM Based MIMO System

$s_1h_{12} + s_2h_{22}$ , where the terms  $h_{11}$ ,  $h_{12}$  etc are the channel gains (assumed to be known by the receiver) that distort the transmitted symbols. This interference needs to be removed at the receiver to maintain the data fidelity.

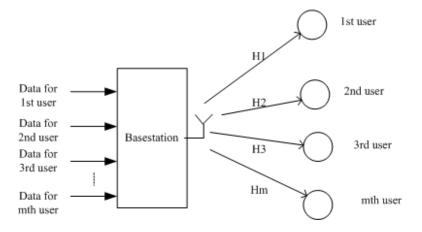

Transmitter Side Precoding: The removal or cancellation of the interference can be done at transmitter as well. This scenario can occur, for example, in a broadcast channel where a single base station intends to communicate with multiple users Fig. 3. Each user ends up receiving not only its own data, but also sees the data symbols intended for other users as unknown interference. This interference, if left as is can cause a significant degradation in the system capacity. However, this interference can be removed by precanceling it at the transmitter. One way to precancel the interference is by using Dirty Paper Precoding (DPC) scheme [4]. Besides broadcast channels, DPC finds applications in numerous other situations; inter-symbol interference (ISI) channels, cooperative networks, and digital watermarking to name a few.

Fig. 3. Multi User Scenario in a Broadcast Channel

Low Density Parity Check (LDPC) Codes: LDPC codes [5] are known to achieve information rates very close to the capacity of the channel when iteratively decoded. Other competing FEC codes such as Turbo codes [6] are also know to be performing close to the capacity. However, the decoders for LDPC codes have arithmetic computation requirements that are an order of magnitude less than Turbo decoders for similar bit-error rate (BER) performance. Algorithms for decoding LDPC codes also have the advantage of being inherently parallel. In principle, this permits the use of multiple parallel processing elements to increase the throughput of the decoder. For these reasons the LDPC codes are increasingly finding applications in upcoming wireless standards.

### B. Hardware Implementation Perspective

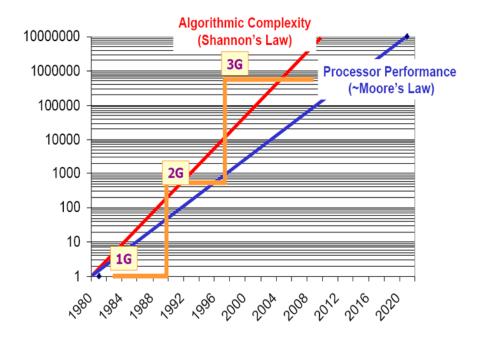

Fig. 4 depicts how the complexity of algorithms vs. processing power will likely evolve with newer generation of wireless standards. To further improve usage of the

Fig. 4. Algorithmic Complexity Vs. Available Processing Power [7]

spectrum the transmitter at the basestation the changes the transmission modes (e.g. modulation schemes, number of antennas, code rates) on the fly. This entails that the baseband hardware must be flexible enough to support runtime configuration.

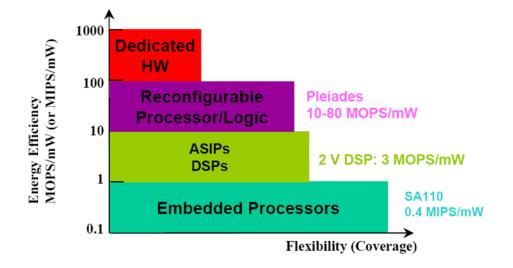

The general purpose processors allow the designers maximum flexibility with lowest efficiency (in terms of throughput/area and power consumption). Whereas the ASICs offer most efficient solutions but is not flexible. DSPs, Application Specific Instruction Processors (ASIP) and FPGA offer a mix of efficiency and flexibility Fig. 5.

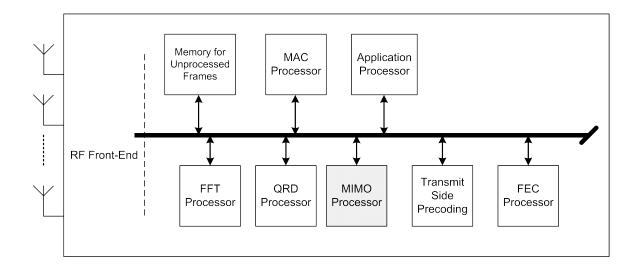

Because of increased availability of silicon area it is now economical to build a network of function specific processors that can work in unison on a same chip. Het-

Fig. 5. Architectural Flexibility Vs. Hardware Efficiency [8]

erogeneous MultiProcessor System on Chip (MPSoC), which have multiple function hardware accelerators governed by a central processor, is becoming popular approach for realizing future wireless systems. One possible MPSoC for baseband processing is depicted in Fig. 6. Because a wide range of functional units can be integrated on a single chip it is now possible to realize a highly flexible solution which is far more efficient than DSP or ASIPs. This approach also leads to improved productivity of engineers as the design process is more decentralized [9].

In a large system on chip power considerations are important not just because of battery life concerns but also due to concerns about the chip reliability. Smaller transistors leads to higher density and the circuit can be run at higher speeds. Although smaller transistors consume lesser power, the increased density and speed leads to higher thermal density which can cause the chip to fail. Another important design

Fig. 6. Heterogeneous MultiProcessor System Approach

criteria from a power perspective is the energy efficiency (J/bit) of the design. The energy efficiency is important for the battery life of devices, whereas, the thermal distribution of the chip is critical for faultless functioning of the chip.

### C. Motivation and Contributions

The implementation complexity of the detector for MIMO systems has been consistently identified as the major bottleneck for realizing the full potential that multiple antenna systems promise. For this reason this dissertation deals with VLSI architectures for MIMO detectors.

Implementation Challenges for MIMO Detectors: The practical implementation of MIMO systems is constrained by the high complexity of the detection algorithms at the receiver. This is primarily due to the need for complex arithmetic and the complicated data flow requirements of the underlying algorithms. The MIMO detectors can be broadly classified into two classes: 1) Linear detectors, and 2) Non-linear detectors. Linear detectors take a suboptimal approach in demapping the received symbols. They can be implemented in a systolic like manner with constant throughput and good scalability w.r.t. the antenna size and modulation scheme. The detection algorithms in this domain are highly suitable for practical implementation and will likely meet the exacting throughput requirements of next generation wireless systems. Linear detectors, however, suffer from poor BER performance which makes them unattractive from wireless system designer's point of view. On the other hand non-linear detectors have complicated data-flow, variable throughput, and unfavorable scalability. They, however, provide close to optimal BER performance and are hence more suitable from algorithmic point of view. The need for close to optimal BER performance and flexibility requirements of the future wireless standards makes the detector design even more challenging. This is because flexibility and throughput often place conflicting demands on the designer. The contributions of this dissertation are as follows:

Architectural evaluation of hard decision detector: We consider three different architectures for MIMO detectors. Three architectures considered are: 1) Sequential 2) Staggered and 3) Parallel. We present detailed hardware architectures and their ASIC implementation. We compare the architectural figures of merit of Sequential and Staggered architectures under two situations, first, when the detection process (carried out in multi-core setup) has variable runtime and second when a fixed runtime budget is enforced via scheduling. We show that enforcing/scheduling runtime budget per block of data causes deterioration in the efficiency of the architectures. The staggered architecture achieves significantly higher throughput than the sequential one, and half the throughput of the parallel approach (using an area of much less than half of the parallel implementation). Part of this work can be found in [10].

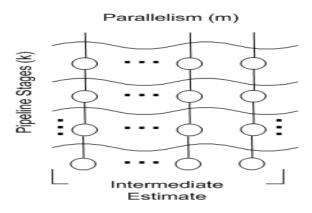

Runtime configurable hard detector: We developed a flexible architecture capable of configuring itself to process QPSK, 16-QAM, and 64-QAM modulation schemes. This architecture is further modified to support variable number of antennas, i.e., for 2x2, 3x3, and 4x4 MIMO systems. The architecture has a systolic like flow with excellent scalability. The degree of pipelining can be changed with little redesign effort. Another important feature of the architecture is that it does not incur any latency for configuring itself. Moreover, for a given operating mode its throughput is completely predictable. These qualities makes it much easier to integrate in a wireless MPSoC. Additionally, the detector provides close to optimal Maximum Likelihood(ML) solution leading to close to the best attainable BER [11].

We also present a constraint aware architecture space exploration for the 802.11n standard [12]. We carry out extensive architectural space exploration to address the issues of power consumption, area for the configurable detectors. Ultimately, we come up with two designs that target low area and low power respectively while meeting the demands of the baseband time constraints.

Runtime configurable soft decision detector: Soft decision basically means that the detector provides the FEC decoder(like LDPC) with the confidence of its decisions. This leads to significant improvement in the BER performance of the whole system. The process of getting soft decisions is even more complicated than getting hard decisions. We present a configurable detector architecture for in a high order(4x4) MIMO wireless system. It is a customized architecture that provides soft values with systolic-like data and control flow. The detector is able to switch between three different modulation schemes (QPSK, 16-QAM, and 64-QAM) without any configuration latency. Multiple detector cores can be stacked to achieve very high throughput. We also derive a lower complexity algorithm soft decision algorithm. We then present a systolic like for this algorithm. A Single detector core achieves constant throughput of 215Mbps (even for a 64QAM 4x4 MIMO system).

#### D. Organization of Thesis

The organization of the dissertation is as follows:

Chapter II provides background on the MIMO based wireless systems. We explain how various MIMO techniques achieve higher data rates and better QoS. We also describe basic algorithms used for detection in a MIMO system. We describe the system model that will used in this work. In Chapter III we present comparative study of three architectures and their ASIC implementation results. First half of the chapter provides description of the architectures and second half is devoted to their evaluation in practical scenarios. Chapter IV deals with the configurable MIMO detector with close to optimal error rate performance. We present the detailed architecture and its FPGA and ASIC implementation results. This chapter is concluded by considering a design case study for detectors in a 802.11n WLAN system that require on the fly configuration. Chapter V deals with systolic like architectures for soft output MIMO detection. We present a detector that can be configured to support three different modulation schemes. In this chapter we present a lower complexity algorithm and corresponding architecture for soft detection. Finally, Chapter VI concludes the dissertation.

### CHAPTER II

#### BACKGROUND

This chapter begins with providing a broad perspective of a MIMO wireless system. We explain various techniques available to extract better diversity and maintain QoS. We also explain the MIMO system model that is under consideration and introduces the notations that will be used. A brief description of the fundamental algorithmic choices for MIMO detection is also provided. System and hardware design considerations are discussed.

A. MIMO Wireless Systems: An Overview

The increased number of antennas in a MIMO wireless system leads to increased spatial diversity. Diversity basically means that independent versions of signals are transmitted so that the probability of all of them being corrupt is reduced. Spatial diversity means that these multiple copies of signals are transmitted from elements in space i.e. by using multiple antennas.

Techniques such as Maximum Ratio Combining [13] or Space-Time-Block-Coding [13] allows for using multiple antennas at either the transmit or the receive side. In the beginning the aforementioned techniques provided only receive or transmit diversity. These methods successfully achieved diversity gain by providing multiple copies of same data leading to improved BER. Diversity gain is quantified as a ratio of the SNR with diversity to SNR without diversity. This is reflected as the slope of the BER curve in a log-scale. It has been shown that the the maximum diversity gain is N, if N independent copies (using N antennas) of a given signal are transmitted [14]. These techniques basically use diversity to combat the effects of fading.

However, using multiple antennas at the receive and transmit allows us to ob-

tain spatial multiplexing gain . Spatial multiplexing gain means that if M transmit antennas and N receive antennas are used, recovery of  $\min(M,N)$  different signals is possible. Important implication of this is that higher data rates can be achieved without requiring additional bandwidth. A comparison of some schemes at the algorithmic level can be found in [15] and [9]. We reproduce it in Fig. 7.

| Code                               | Diversity Gain | Max Rate $[sym/s/Hz]$     |

|------------------------------------|----------------|---------------------------|

| Alamouti STBC                      | 2M             | 1                         |

| Orthogonal Designs                 | NM             | 1                         |

| Linear Dispersion                  | < NM           | $\approx \leq \min(M,N)$  |

| TR-STBC                            | NML            | <1                        |

| STBC + Frequency domain Processing | NML            | <1                        |

| Tarokh STTC                        | NM             | 1                         |

| V-BLAST                            | $\leq M$       | $\min(M,N)$               |

| H-BLAST                            | $\leq M$       | $\approx \leq \min(M,N)$  |

| D-BLAST                            | $\leq M$       | $\approx \leq \min(M, N)$ |

Fig. 7. Performance of Basic MIMO Techniques, [15], [9]

### B. MIMO System Model

In this section we start by explaining the MIMO-OFDM model. Orthogonal Frequency Division Multiplexing (OFDM) technique is used in wideband communication systems to combat the multipath (which leads to frequency selective channel) fading. Wideband MIMO systems Fig. 8 can be considered equivalent to a set of narrowband MIMO systems Fig. 9 if OFDM is also used. This equivalence simplifies the analysis of the system and make it easier to design receivers.

Fig. 8. Wideband MIMO (OFDM) System

Hence, we will consider a simple narrowband system model as the basis for the discussions in this work. In the system under consideration, as shown in Fig. 9, the term  $M_T$  and  $M_R$  denotes the number of transmit antennas and the number of receive antennas respectively. In this work we will assume  $M_R=M_T=4$  unless otherwise specified.

MIMO Channel: The equivalent baseband model of the MIMO wireless channel can be expressed as the following relation.

$$\mathbf{y} = \mathbf{H}\mathbf{s} + \mathbf{n} \tag{2.1}$$

where  $\mathbf{y} = [y_1, y_2, ..., y_{M_R}]^T$  is a  $M_R \times 1$  received vector,  $\mathbf{s} = [s_1, s_2, ..., s_{M_T}]^T$  is  $M_T \times 1$ transmitted vector and will be referred to as a MIMO symbol in the sequel,  $\mathbf{n}$  is  $M_R \times 1$ zero mean complex Gaussian noise vector, and  $\mathbf{H}$  is a  $M_R \times M_T$ -dimensional complex matrix. The  $(i, j)^{th}$  element,  $h_{ij}$ , of the matrix  $\mathbf{H}$  denotes the complex channel gain from the  $j^{th}$  transmit antenna to the  $i^{th}$  receive antenna. For the simulations in this

Fig. 9. Equivalent Narrowband MIMO System

work, an i.i.d. Rayleigh fading channel model is assumed. Hence, the entries of **H** are chosen independently as zero mean complex Gaussian random variables.

- Transmitter: Each entry  $s_i$   $(i = 1, 2, ...M_T)$  in the MIMO symbol **s**, is drawn from a set  $\Omega$  of cardinality  $\eta$ . In general the members of the set  $\Omega$  are complex numbers with their real and imaginary parts of the form  $\{-\sqrt{\eta} + (2k - 1)\}$ where  $k=1,2,...\sqrt{\eta}$ . This scheme is called as a  $\eta$ -ary Quadrature Amplitude Modulation (QAM) and  $s_i$  are called QAM symbols. The QAM symbols are generated by mapping(using look-up table, for instance) a group (of size  $\log_2 \eta$ ) of binary bits onto a symbol(a complex number) from  $\Omega$ .

- Receiver: The received signal vector  $\mathbf{y}$  is picked up by the  $M_R$  antennas at

the receiver. The objective of the MIMO detector is to estimate  $\hat{\mathbf{s}}$  of  $\mathbf{s}$  based on the the observation of  $\mathbf{y}$  along with the knowledge of  $\mathbf{H}$ . The knowledge of  $\mathbf{H}$  can be obtained by using some training (e.g. using pilot symbols).

### C. Important Available Algorithms

In this section important algorithms that are available for MIMO detection are described.

### 1. Linear Detection

Linear detectors attempt to find the solution by multiplying the inverted channel matrix **H** with the received vector **y**. More specifically, the estimate  $\hat{s}$  of the transmitted vector **s** is computed by:

$$\widehat{\mathbf{s}} = \mathbf{G}\mathbf{y}$$

(2.2)

where **G** is an equalization matrix. However, equation (2.2) provides the unconstrained estimate. This basically means that the result of equation (2.2) is a complex number and not a QAM symbol(QAM symbols are constrained to a limited set of constellation points). To get to the constrained solution the detector carries out a slicing operation. In slicing operation, the detector compares the real and imaginary parts of  $\hat{s}$  from equation (2.2) with the appropriate thresholds to find out the closest QAM symbol.

The complexity of this algorithm is dominated by computation of the equalization matrix. In packet based systems, where data is transmitted in packets (consisting of several MIMO symbols) that experience constant **H**. This means that the equalization matrix needs to be computed only once per packet. This not a big problem if packet size is large. However, if the packet size is small then the overall complexity will increase as the receiver has to invert the matrix more often. The detection of all the MIMO symbols in a packet can then use same estimation matrix and the detector only has to carry out the slicing operation (which relatively simple operation).

There are two important algorithms in this class of detection scheme: Zero Forcing (ZF), and Minimum Mean Squared Error (MMSE). Basically both these algorithms make use of channel matrix inversion and vector multiplication with the received vector  $\mathbf{y}$ . The ZF detector uses the pseudo-inverse of  $\mathbf{H}$  given by:

$$\mathbf{G} = (\mathbf{H}^H)^{-1} \mathbf{H}^H \tag{2.3}$$

where  $\mathbf{H}^{H}$ , is the hermitian of the matrix  $\mathbf{H}$ . The corresponding ZF estimate  $\hat{\mathbf{s}}_{ZF}$  of the transmitted vector  $\mathbf{s}$  is then given by:

$$\hat{\mathbf{s}}_{ZF} = (\mathbf{H}^H)^{-1} \mathbf{H}^H \mathbf{y} = \mathbf{s} + \tilde{\mathbf{n}}_{ZF}$$

(2.4)

The effective channel matrix  $\hat{\mathbf{H}}$  is now an identity matrix  $\mathbf{I}$ . This means that the interference from the other streams is completely eliminated as desired. However, the major disadvantage of this algorithm is that the term  $\tilde{\mathbf{n}}_{ZF}$  leads to noise enhancement.

In case of MMSE detection the estimator matrix **G** is mathematically expressed as:

$$\mathbf{G} = (\mathbf{H}^H + N_0 \mathbf{I})^{-1} \mathbf{H}^H \tag{2.5}$$

This algorithm essentially tries to minimize the error  $\mathbb{E} \|\mathbf{s}_{ZF} - \mathbf{s}\|^2$ . This algorithm tries to strike a balance between interference and noise enhancement. The problem with this algorithm is that accurate estimate of  $N_0$  is needed.

These detectors are low complexity and their VLSI architectures have highly regular data and control flow. This makes it very attractive in terms of meeting the throughput and power consumption requirements. However, both algorithms suffer from poor BER because of noise enhancements and remaining interference. Moreover, the process of channel inversion is prone to numerical errors. Therefore, the results from these detectors are found to be severely sub-optimal BER performance and is unable to exploit the full potential of a MIMO wireless system.

### 2. Successive Interference Cancellation

SIC is a recursive algorithm which provides a BER performance that is between the linear detectors and optimal detectors. The complexity of SIC detectors is also increased in comparison to linear detectors, but is far less than the brute force optimal detector. SIC detector proceeds in serial fashion by first detecting a symbol then subtracting an estimate of the detected symbol's contribution to the received vector. Thus once a symbol is detected it is considered as interference for other symbols and is canceled out.

For mathematical description of SIC, consider the model given by equation (2.1). The algorithm first initializes  $y^1 = y$  and defines  $H^i = [h_i, h_{i+1}, ..., h_{M_T}]$ , where elements  $h_i$  denotes the  $i^{th}$  column of the matrix **H**. The estimation matrix for  $H^i$ is denoted by  $G^{(i)}$ . Beginning with i = 1, SIC goes through following steps until  $i = M_T$ :

$$\hat{x}_i = \mathbf{G}_i^{(i)} y^{(i)} \tag{2.6}$$

$$\hat{s}_i = Q(\hat{x}_i) \tag{2.7}$$

$$\mathbf{y}^{(i+1)} = \mathbf{y}^{(i)} - \hat{s}_i \mathbf{h}_i \tag{2.8}$$

where Q(.) is the slicing function. The vectors  $\mathbf{G}_{i}^{(i)}$  are called nulling vectors and are simply the  $i_{th}$  row of the corresponding estimator matrix  $\mathbf{G}$ . The estimator matrix  $\mathbf{G}$  can be one of the two as described earlier. This leads to ZF-SIC or MMSE-SIC depending on which estimator matrix is chosen. SIC algorithms do not completely exploit the available diversity in the system. Moreover, they suffer from error propagation problems. This happens when an error is made in detecting the first symbol. Due to recursive nature of the algorithm, this error in decision is propagated to other symbols in the vector. Though better than the linear detectors, this algorithm is still sub-optimal with increased implementation complexity and increased power consumption.

#### 3. Maximum Likelihood Detection

It has been shown that the optimal maximum likelihood (ML) estimate  $\hat{\mathbf{s}}_{ml}$  of  $\mathbf{s}$  is given by equation (2.9):

$$\hat{\mathbf{s}}_{ml} = \arg \min_{\mathbf{s} \in \Omega^{M_T}} \|\mathbf{y} - \mathbf{Hs}\|^2$$

(2.9)

Basically the above equation means that the optimal estimate  $\hat{\mathbf{s}}$  of the transmitted vector  $\hat{\mathbf{s}}$  is the one that minimizes the euclidean distance between the received vector  $\mathbf{y}$  and the *transformed* transmitted vector  $\mathbf{Hs}$ . Straightforward way to solve (2.9) is by computing the distances for all possible combinations of  $\mathbf{Hs}$  and declaring the combination that gives minimum distance as the estimate  $\hat{\mathbf{s}}$ .

An important advantage of this algorithm is that there is no matrix inversion involved. The absence of matrix inversion greatly aids the hardware implementation of the algorithm. Major disadvantage of this algorithm is that the search space grows very quickly with the modulation scheme (i.e.  $\eta$ ), and the number of transmit antennas ( $M_T$ ). If  $\eta$ -ary modulation scheme is used in a  $M_T \times M_R$  MIMO system the total possible combinations for **s** is  $\eta^{M_T}$ . This search space quickly becomes too large to be processed in real-time in today's computing technologies.

### 4. Sphere Decoding

This is also algorithmically optimal detection method. It constraints the search space for transmitted symbol vector. This algorithm has shown promise at being able to handle strong algorithmic requirements (BER Performance) with reduced design complexity and power requirements. One way to efficiently search for  $\hat{\mathbf{s}}_{ml}$  is to evaluate only a small subset of all the possible vectors. This can be achieved by noting that  $\mathbf{H}$  can be triangularized using QR decomposition:  $\mathbf{H} = \mathbf{QR}$ , where,  $\mathbf{R}$  is an upper triangular matrix, and  $\mathbf{Q}^{H}$  is the Hermitian of a unitary matrix  $\mathbf{Q}$ . Hence, the cost function given by equation (2.9) can now be rewritten as [16],

$$\hat{\mathbf{s}} = \|\mathbf{y} - \mathbf{H}\mathbf{s}\|^2 = \|\hat{\mathbf{y}} - \mathbf{R}\mathbf{s}\|^2, and \ \hat{\mathbf{y}} = \mathbf{Q}^{\mathbf{H}}\mathbf{y}$$

(2.10)

Equation 5.3 can be further expanded as shown in equations (5.4), (5.5), and (5.6).

$$d_i(s^{(i)}) = d_{i+1}(s^{(i+1)}) + |e_i(s^{(i)})|^2$$

(2.11)

$$|e_i(s^{(i)})|^2 = |c_{i+1}(s^{(i+1)}) - R_{ii} \cdot s_i|^2$$

(2.12)

$$c_{i+1}(s^{(i+1)}) = \hat{y}_i - \sum_{j=i+1}^{M_T} R_{ij} \cdot s_j$$

(2.13)

The quantity  $|e_i(s^{(i)})|^2$  will be called the Incremental Euclidean Distance (IED), and the term  $d_i(s^{(i)})$  will be called Partial Euclidean Distance (PED) for i > 1, and Euclidean Distance (ED) for i = 1. The fact that **R** is upper-triangular ensures that each term on LHS of equations (5.4),(5.5),and (5.6) depends only on the current level i, and the history of the path to reach that level(note that in equations (5.6), the index j runs from i + 1 to  $M_T$ ). Because the PED's depend only on  $s^{(i+1)}$ , they can be associated with corresponding nodes in a  $\eta$ -ary tree with  $M_T$  levels. The computation of the terms  $d_1(s^{(1)})$  can then be interpreted as a traversal of the tree from the root( $i = M_T$ ) to the leaf (i = 1)corresponding to **s**. The estimate can now be obtained by searching the leaf with the smallest ED and returning the path from the top level to that leaf as  $\hat{\mathbf{s}}_{ml}$ . The complexity of this tree search can be greatly reduced by noting that IEDs are always positive, and hence if the PED of a node exceeds a predefined threshold (called radius) the subtree rooted at that node can be excluded from further search. This approach is commonly known as sphere decoding [16].

### CHAPTER III

# VLSI ARCHITECTURES FOR MIMO DETECTION:A COMPARATIVE ANALYSIS

In this chapter we present ASIC implementations of three different architectures for MIMO detectors. Three architectures considered are: 1) Sequential 2) Staggered and 3) Parallel. We also compare the architectural figures of merit of sequential and staggered architectures under two situations, first, when the detection process (carried out in multi-core setup) has variable runtime and second when a fixed runtime budget is enforced per block of data. We show that enforcing/scheduling runtime budget per block of data causes deterioration in the efficiency of the architectures. The parallel architecture provides the highest throughput, albeit at a much higher cost. The sequential architecture provides the lowest throughput at the lowest cost. The throughput and the cost of staggered design lies in between parallel and sequential architectures.

Although low complexity algorithms such as VBLAST [17] are suitable for hardware implementation they suffer from significant degradation in their error rate performance. A family of algorithms under active consideration relies on a tree based search that is more complex but provide excellent BER. Two of the most notable approaches in this family are the Sphere Decoding (SD) algorithm [18], which is a Depth First Search (DFS) based algorithm, and the K-best algorithm which is a Breadth First Search (BFS) based algorithm [19]. Authors in [20] provide two ASIC implementations of the SD algorithm. Implementation of K-best algorithm has been reported in [21]. The SD implementation in [20] takes a sequential approach, whereas in [19],[21] the authors take a highly parallel approach to MIMO detection. Both approaches have their merits and demerits. For instance, being serial in nature the implementation of the SD algorithm requires smaller silicon area than the K-best algorithm, but has highly variable throughput. Hence, it is difficult to integrate it into the overall communication system. On the other hand, the K-best algorithm provides a fixed throughput while utilizing a much higher silicon area due to extensive sorting operations [21]. In general, the tree based algorithms offer a good trade-off between performance and complexity [22]. A low complexity algorithm has been reported in [23]. This algorithm, called the Fixed-Throughput Sphere Decoder (FSD), relies on a special ordering of the columns of the channel matrix, which results in a significantly reduced search space. Further simplification is proposed in [24], that simplifies the complexity associated with the column ordering, this algorithm has been names Conditionally Ordered Successive Interference Cancellation (COSIC). The resulting implementation has a very simple data path and is able to achieve close to Maximum Likelihood (ML) solution. The authors in [23] have presented an implementation of fully parallel architecture (BFS based) to implement the algorithm, which provides very high and fixed throughput. However, a fully parallel approach consumes large area and incurs many redundant computations. A sequential architecture [24], in conjunction with radius reduction technique reduces redundant computations and consumes less silicon real estate, but has lower throughput than the parallel scheme. In [20], ASIC implementations of different architectures have been compared.

### A. MIMO Detection

#### 1. Model for Spatial Multiplexing

For convenience we will reproduce the information from chapter II. The baseband system model for a MIMO system with  $M_T$  transmit and  $M_R$  receive antennas can be given by equation (3.1) [25].

$$\mathbf{y} = \mathbf{H}\mathbf{s} + \mathbf{n} \tag{3.1}$$

where  $\mathbf{y} = [y_1, y_2, ..., y_{M_R}]^T$  is a  $M_R \times 1$  received vector,  $\mathbf{s} = [s_1, s_2, ..., s_{M_T}]^T$  is  $M_T \times 1$ transmitted vector (will be referred to as a MIMO symbol in the sequel),  $\mathbf{n}$  is  $M_R \times 1$ zero mean complex Gaussian noise vector, and  $\mathbf{H}$  is a  $M_R \times M_T$ -dimensional complex matrix. The  $(i, j)^{th}$  element,  $h_{ij}$ , of the matrix  $\mathbf{H}$  denotes the complex channel gain from the  $j^{th}$  transmit antenna to the  $i^{th}$  receive antenna.

Each entry  $s_i$   $(i = 1, 2, ...M_T)$  in the MIMO symbol **s**, is drawn from a set  $\Omega$  of cardinality  $\eta$ . In general the members of the set  $\Omega$  are complex numbers with their real and imaginary parts of the form  $\{-\sqrt{\eta} + (2k - 1)\}$  where  $k=1,2,...\sqrt{\eta}$ . This scheme is called as a  $\eta$ -ary Quadrature Amplitude Modulation (QAM) and  $s_i$  are called QAM symbols. The QAM symbols are generated by mapping a group (of size  $\log_2 \eta$ ) of binary bits onto a symbol(a complex number) from the set  $\Omega$ .

The objective of the MIMO detector is to estimate  $\hat{\mathbf{s}}$  of  $\mathbf{s}$  based on the the observation of  $\mathbf{y}$  along with the knowledge of  $\mathbf{H}$ . It has been shown that the optimal or the ML estimate  $\hat{\mathbf{s}}_{ml}$  of  $\mathbf{s}$  is given by equation (3.2) [25]:

$$\hat{\mathbf{s}}_{ml} = \arg \min_{\mathbf{s} \in \Omega^{M_T}} \|\mathbf{y} - \mathbf{Hs}\|^2$$

(3.2)

A straightforward way to compute  $\hat{\mathbf{s}}_{ml}$  is to evaluate equation (3.2) for all possible  $\mathbf{s}$  and pick the one that minimizes R.H.S of equation (3.2). This exhaustive search approach is impractical even for moderately sized MIMO systems. For a 4x4 16-QAM MIMO system this approach would require evaluating 16<sup>4</sup> combinations of  $\mathbf{s}$  before a decision on  $\hat{\mathbf{s}}_{ml}$  can be made.

### a. Sphere Decoding

One way to efficiently search for  $\hat{\mathbf{s}}_{ml}$  is to evaluate only a small subset of all the possible vectors. The sphere decoder achieves this by searching for the potential candidates for  $\hat{\mathbf{s}}_{ml}$  within a *sphere* of radius r. This can be mathematically expressed as:

$$\|\mathbf{y} - \mathbf{Hs}\|^2 \le r \tag{3.3}$$

The Sphere Decoding (SD) algorithm works by transforming the original problem as a tree search, wherein any branch of the tree with a path metric greater than a predefined threshold (or radius r) is pruned. This helps in reducing the search space greatly. The SD algorithm tends to have exponential complexity at low SNRs and polynomial complexity at higher SNRs [26], [27]. This algorithm, however, does provide the optimal (ML) estimate  $\hat{\mathbf{s}}$  of  $\mathbf{s}$ .

The hardware architecture and its implementation for SD has been studied extensively in [16]. One of the major problems with SD is that it takes highly variable amount of time to converge to a solution. This attribute is undesirable in practical situation, as it makes the integration of the detector hardware very difficult in an overall system. Several algorithms have been proposed to reduce (or completely get rid) of this variability. Popular among them include K-Best, FSD/COSIC. These algorithms, however, do not provide the exact ML solution. But as shown in aforementioned references, their BER performance is very close to the optimal. This makes them very attractive vis-a-vis hardware implementation.

### b. K-Best and FSD/COSIC Algorithms

K-Best differs from sphere decoder algorithm in that it retains a fixed number (K) of branches (or nodes) at each level of the tree. The path with least cumulative metric

at the leaf level is declared as the estimate  $\hat{\mathbf{s}}$ . This non-recursive nature of K-best has important implications for its hardware implementation. Major advantage of K-best is its constant throughput and ease of designing pipelined architecture (owing to its non-recursive nature). However, this algorithm tends hit error floor as SNR increases [28]. This loss can be partially recovered by increasing the value of K for higher SNRs. Also, K-best involves sorting requiring large amount of data flow which is generally very power hungry. Some sort free versions of K-best algorithms have been proposed recently [29],[30].

The FSD algorithm obviates the need for sorting. It is shown in [31] that this algorithm also achieves full diversity. Moreover, its Bit Error Rate (BER) performance is very close to the ML performance. The COSIC algorithm differs from FSD only in its preprocessing stage. Empirical studies suggest that COSIC algorithm also performs close to ML, and performs well in higher SNR regimes as well (unlike K-best algorithm). Moreover, FSD/COSIC both can provide fixed throughput depending on how the hardware architecture is designed. FSD/COSIC offers more avenues for pipelining and parallelism than SD or even K-best. Hence, we choose to use COSIC algorithm for our detector.

#### B. Hardware Architectures

In this section we begin by reviewing the mathematics of the MIMO detection problem. This is followed by a brief review of FSD/COSIC algorithm, and then we present the sequential, fully serial, and parallel architectures to implement it. Equation (3.2) can be simplified by triangularizing **H** using QR decomposition:  $\mathbf{H} = \mathbf{QR}$ , where, **R** is an upper triangular matrix, and  $\mathbf{Q}^{H}$  is the Hermitian of a unitary matrix **Q**. Hence, the cost function given by equation (3.2) can now be rewritten as shown in (3.4) [22],

$$\hat{\mathbf{s}} = \|\mathbf{y} - \mathbf{H}\mathbf{s}\|^2 = \|\hat{\mathbf{y}} - \mathbf{R}\mathbf{s}\|^2, and \ \hat{\mathbf{y}} = \mathbf{Q}^{\mathbf{H}}\mathbf{y}$$

(3.4)

Equation (3.4) can be further expanded as shown in (3.5)-(3.7).

$$d_i(s^{(i)}) = d_{i+1}(s^{(i+1)}) + |e_i(s^{(i)})|^2$$

(3.5)

$$|e_i(s^{(i)})|^2 = |c_{i+1}(s^{(i+1)}) - R_{ii} \cdot s_i|^2$$

(3.6)

$$c_{i+1}(s^{(i+1)}) = \hat{y}_i - \sum_{j=i+1}^{M_T} R_{ij} \cdot s_j$$

(3.7)

The quantity  $d_i(s^{(i)})$  is called the cumulative metric. The quantity  $|e_i(s^{(i)})|^2$  is called the incremental metric. The vector  $s^{(i)} = [s_i, s_{i+1}, ..., s_{M_T}]$  in equation (3.5)-(3.7) denotes a partial vector symbol candidate. Term  $d_i(s^{(i)})$  will be called Partial Euclidean Distance (PD) for i > 1, and Euclidean Distance (D) for i = 1. Because the PD's depend only on  $s^{(i+1)}$ , they can be associated with corresponding nodes in a  $\eta$ -ary tree with  $M_T$  levels. Alternatively, the computation of the terms  $d_i(s^{(i)})$  can be interpreted as a traversal of the tree from the root to the leaf corresponding to s, where (i = 1) corresponds to leaf nodes. The estimate can now be obtained by searching the leaf with smallest D and returning the path from the top level  $(i = M_T)$ to that leaf as s. The PD's and D's in equation (3.5) are equivalently referred to as the node's metric in the sequel. To reduce the search space aggressive pruning of the tree is needed. Sphere decoding does this by pruning a branch of the tree whenever the PD of a node on the branch exceeds a certain limit (radius r). Appropriately setting the radius r restricts the number of nodes visited in the search, since  $d_i(s^{(i)})$  in equation (3.5) is monotonically increasing. Hence any node that has a PD more than r need not be considered any further. This is called the Sphere Criterion or SC [20]. This effectively prunes the whole sub-tree rooted at that node, thus greatly reducing the search space. Fixing the value of r is in general difficult. If r is too small then we

may have to restart the decoder as no point may be found. Similarly if r is too large the decoder may visit a very large number of nodes leading to excessive latency. To counter this problem a scheme known as radius reduction [25] is used, wherein the initial value of r is set to infinity, and is updated whenever the D of a newly evaluated leaf is less than the current value of the radius. This scheme works best if the nodes are processed in an ascending order of their PD's (i.e. the most promising candidates are processed first). This scheme is called Schnorr-Euchner (SE) ordering [20].

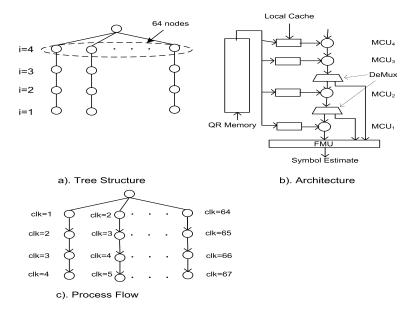

## 1. FSD/COSIC Algorithm

The FSD algorithm is essentially based on reordering the columns of the **H** matrix such that the tree search is simplified [22]. The idea is to evaluate all candidate QAM symbols for the stream with lowest SNR and only the best child of parents for subsequent levels. The reason for this is that the weakest stream has largest probability of error and because all candidates are considered this error probability does not influence the decision later. For subsequent levels, this algorithm follows strongest stream first philosophy to achieve best possible BER performance. On a tree this translates to computing PD's for all nodes at the top level, but only the best child (child with least PD/D) is considered for lower levels. For a 4x4 system with 16 QAM, this entails computing PD's/D's for a maximum of 16x4=64 nodes, significantly reducing the search space. Fig. 10 shows the tree structure for FSD (thick lines) for the case of 3x3 with 4 QAM modulation. Each circle represents a computation of the equations from equation (3.5)-(3.7). As mentioned, earlier all nodes at level i=3 are evaluated and only the best child is considered for levels i=2and i=1.

Here we use COSIC algorithm to demonstrate the performance of architectures.

Fig. 10. Simplified Tree Structure for Detection

## 2. Parallel, Sequential and Staggered Detector Architectures

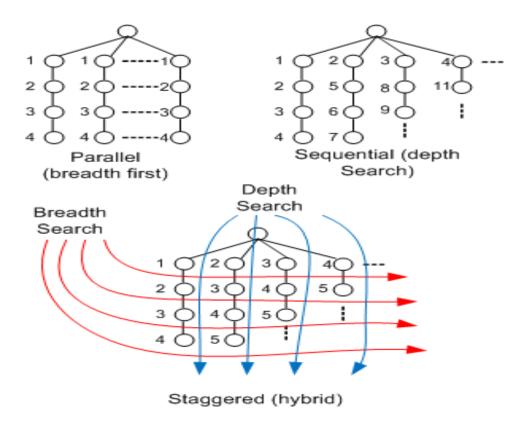

In this section we describe different architectures with that can be used to implement COSIC. In Fig. 11 we show the serial, sequential [24] and fully parallel [23] architectural dataflow. The numbers next to the nodes indicates the clock cycle in which that node was processed.

## a. Sequential Data Flow

The sequential architecture consists of two units. The first unit is capable of computing the top level (i = 4) PD's in ascending order and perform radius check (check for SC violation). The second unit concurrently computes PD's/D's for i = 1, 2, 3(second unit is idle for the first clock cycle) and performs radius check. PD's/D's are computed using a Metric Computation Unit(MCU). The sequential architecture makes use of the radius reduction scheme and node pruning. The nodes labeled 4,7,...can potentially update the radius value. Note that in sequential scheme the radius update may happen every 3 cycles (after first 4 cycles). The major drawback of this architecture is that it provides a highly variable throughput. The latency for detecting one vector symbol is dependent on the channel conditions and noise level.

Fig. 11. Dataflow for Architectures

#### b. Parallel Data Flow

In parallel architecture, all  $\eta$  nodes at every level are evaluated in parallel using  $\eta$  units. Each unit is capable of computing PD's/D's, but does not perform a radius check. After reaching level i = 1, a compare/select logic picks the path with least D, and declares it as  $\hat{s}$ . This scheme has a fixed throughput because it takes 4 cycles to compute the estimate  $\hat{s}$  irrespective of channel conditions and noise level. The parallel architecture does not do any node pruning, however, it incurs redundant computations leading to higher energy consumption.

#### c. Staggered Data Flow

The staggered architecture has a schedule that is staggered in time. One copy of MCU is deployed at each level. The staggered computation is explained as follows. In the first cycle a node is evaluated at level 4 (labeled 1 in the Fig. 11). In second cycle a node at level 4 and level 3 are evaluated (labeled 2 in the Fig. 11). From the 4th cycle onwards one node (subject to SC) from each level is evaluated (resulting in a potential radius update at every cycle). This approach is a hybrid between the fully serial and the fully parallel architecture, in that it initiates a new breadth and depth search every cycle (Fig. 11). It does not deliver a fixed throughput in contrast to the fully parallel implementation of the COSIC algorithm, but has variability which is much less than serial and sequential architecture due to per cycle radius update. Like sequential architecture, the staggered architecture too follows the radius reduction technique with pruning, thus reducing redundant computations in comparison to the parallel architecture. Also, after the first four cycles, potentially a new leaf node is reached which leads to faster radius reduction. This results in reduced variability of runtime.

#### 3. Architecture and Implementation Details

In this subsection, we describe the architecture and implementation of details for staggered architecture. Details for sequential and parallel architectures can be deduced easily from this.

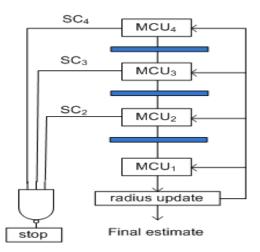

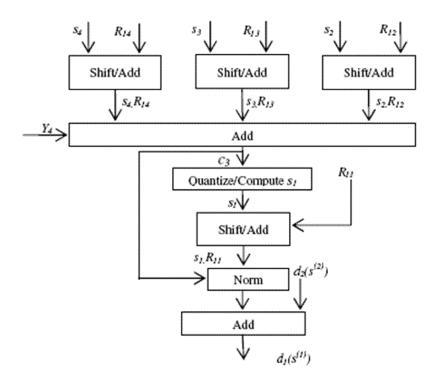

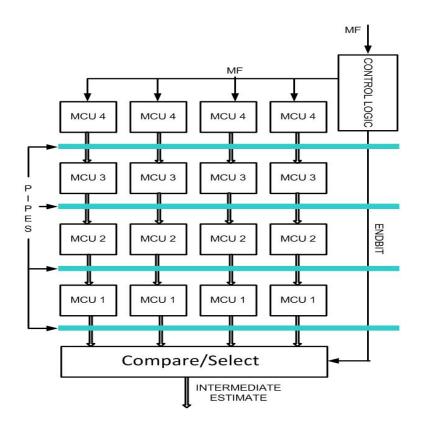

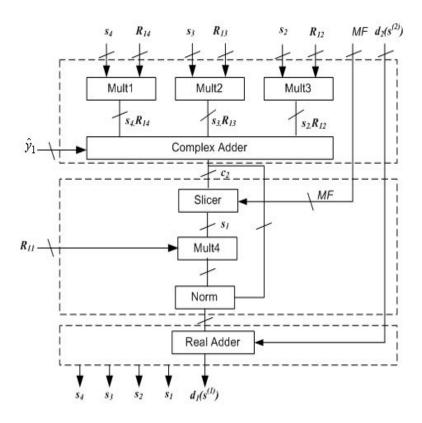

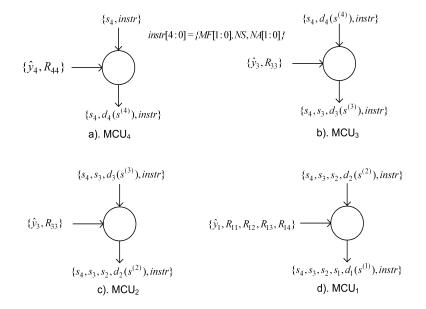

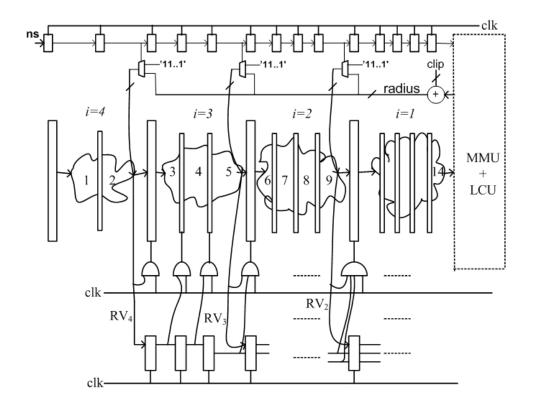

Fig. 12 shows high level architecture for the staggered decoding scheme. It has four units  $MCU_4$  through  $MCU_1$  operating in a pipeline. The task of  $MCU_4$  is to generate QAM symbols  $(s_4)$  and their metric in ascending order (using the enumeration scheme in Fig. 13) and to perform the radius check. The outputs of  $MCU_4$  are:  $SC_4$  (a '1' indicates an SC violation at i = 4),  $s_4$ , the QAM symbol currently under consideration, and  $d_4(s^{(4)})$ , the PD associated with  $s_4$ .

Fig. 12. High Level Architecture for Staggered Sphere Decoding

$MCU_3$ ,  $MCU_2$ , and  $MCU_1$  differ from  $MCU_4$  in that they do not enumerate the QAM symbols. Instead they find the best child of the input node, compute the associated PD (or D), and perform the radius check ( $MCU_1$  does not perform a radius check, since it is implicitly done in the "Radius update" block).

## 4. Metric Computation Unit

Each node in Fig. 12 represents a Metric Computation Unit (MCU) that computes metrics  $d_i(s^{(i)})$  using equations (3.5)-(3.7). For i = 4, 3, 2, 1, the equations equations (3.5)-(3.7) can be expanded as follows:

$$d_4(s^{(4)}) = |y_4 - R_{44}.s_4|^2 \tag{3.8}$$

$$d_3(s^{(3)}) = d_4(s^{(4)}) + |y_3 - R_{34}.s_4 - R_{33}.s_3|^2$$

(3.9)

$$d_2(s^{(2)}) = d_3(s^{(3)}) + |y_2 - R_{24}.s_4 - R_{23}.s_3 - R_{22}.s_2|^2$$

(3.10)

$$d_1(s^{(1)}) = d_2(s^{(2)}) + |y_1 - R_{14} \cdot s_4 - R_{13} \cdot s_3 - R_{12} \cdot s_2 - R_{11} \cdot s_1|^2$$

(3.11)

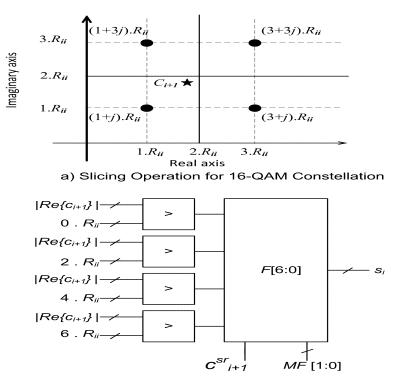

Fig. 13. Enumeration Scheme for 16-QAM

Notice that the number of computations required in equations (3.8)-(3.11) dependent on the level *i* of the tree. The largest number of computations are required at

i = 1 i.e. at the leaf nodes equation (3.11). Fig. 14 shows an MCU which can handle computations at i = 1. Note that for, the parallel, and sequential architectures the same MCU is used to compute metrics for different values of i. This can be achieved by adapting the MCU to perform the computations of equations (3.10),(3.9) and (3.8). For the sequential architecture, however, the MCU has to be adapt between levels i = 1, 2, 3 only, since at the i = 1 level we have a dedicated unit to compute PD's.

Fig. 14. Architecture for MCU1

It is clear from equations (3.8)-(3.11), that the adaptation can be carried out simply by input reassignment and by setting some of the operands to zero. In the sequel we will refer to MCU configured for a level *i* as  $MCU_i$ . Physically the MCU is the same; it is merely reconfigured to operate at different levels *i*. When the MCU is configured to evaluate nodes at level i > 1 many adders remain idle during the computation. The terms in equations (3.8)-(3.11) involving multiplications of the form  $R_{ij}.s_i$  can be computed using shift and add operation. This is possible because the real and imaginary parts of  $s_i$  can only take values for example {-3,-1, 1, 3} for 16-QAM.

#### 5. Enumeration

To process the children nodes of a node in ascending order of their PD's, the distances of  $c_{i+1}$  from the scaled (by  $R_{ii}$ ) QAM points need to be ordered. A straightforward way to do this is to directly compute all distances and sort them. However, this approach is not efficient as only one node from the top level is needed at a time.

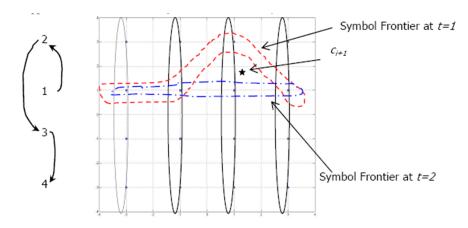

A more efficient way to achieve this is through direct enumeration of QAM symbols based on the location of  $c_{i+1}$  in the constellation. Many enumeration techniques exist in literature. In [25] the author proposes a method based on dividing the constellation into concentric circles [25]-[20]. Recently a new technique has been proposed in [24],[33]. The basic idea is to divide the constellation (Fig. 13) in a number of columns (four in case of 16-QAM). The order of points in these columns is already known given the location of  $c_{i+1}$ . For the example shown in the Fig. 13, the order is shown on the left hand side of the constellation diagram. This order is identical for every column. Also notice that only one element in SF and MF will change at a time. For instance, in the SF at time t = 1 is 2, 6, 10, 14. Since the minimum distance symbol is '10', the SF is updated at t = 2 to 2, 6, 9, 14. The set of best QAM symbols (or simply symbol) from every column will be called a Symbol Frontier or SF. The SF can at most have 4 elements in it. Using symbols in the SF their PD's can be

computed using equations (3.8)-(3.11). The set of PD's of the elements in the SF will be called Metric Frontier or MF. The best symbol (closest to  $c_{i+1}$ ) out of all 16 symbols can now be found by picking the symbol associated with the minimum element in the MF. Note that the SF and hence MF keep changing with time. Note that only the location of the imaginary part of  $c_{i+1}$  is required to compute the order of symbols in each column. Symmetry of the QAM constellation can be exploited to reduce the number of decisions we have to make in order to locate  $c_{i+1}$  in the constellation. For instance if  $c_{i+1}$  was in the third quadrant of the constellation, we can ignore the signs of its real and imaginary part to get  $c'_{i+1}$ . The SF can be computed for  $c'_{i+1}$ . To get back the SF associated with the original  $c_{i+1}$  we simply change the signs of real and imaginary parts of the SF elements. This way we only need to compare the imaginary part of  $c_{i+1}$  with  $R_{ii}$ , and  $2.R_{ii}$ . Also note that for i = 4,  $c_{i+1} = \hat{y}_4$ .

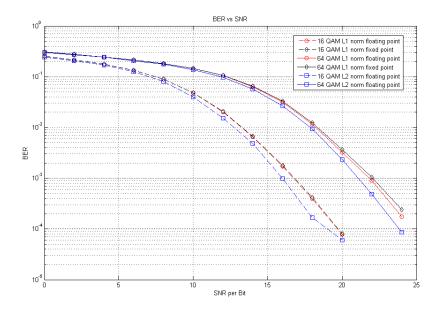

## 6. Simplified Norm Computation

The MCU as shown in Fig. 14 has a block labeled "Norm". The Euclidean norm or  $l^2$  norm involves a squaring operation which requires multipliers. Multipliers are in general expensive in terms of hardware cost. In [20] it has been shown that the use of simplified norms leads to significant reduction in hardware cost with some BER degradation. The Euclidean norm in equation (3.5) can be replaced with  $l^1$  or  $l^{\infty}$  norm to simplify the implementation of equations (3.5)-(3.7). The  $l^1$  norm approximation is given by:

$$d_i(s^{(i)}) = d_{i+1}(s^{(i+1)}) + |Re\{e_i(s^{(i)})\}| + |Im\{e_i(s^{(i)})\}|$$

(3.12)

and the  $l^{\infty}$  norm approximation is given by:

$$d_i(s^{(i)}) = max(d_{i+1}(s^{(i+1)}), |Re\{e_i(s^{(i)})\}|, |Im\{e_i(s^{(i)})\}|)$$

(3.13)

where Re and Im denotes real and imaginary parts. The use of  $l^1$  norm is of particular interest as it causes the BER to degrade only by about 0.4dB [20]. The use of  $l^{\infty}$  norm on the other hand causes about 1.4 dB loss [20]. Both these norms have almost the same hardware complexity [20]; however the algorithm takes much longer to converge when the  $l^1$  norm is used [20],[22]. In the rest of this chapter, we will use the  $l^1$  norm due to its better BER.

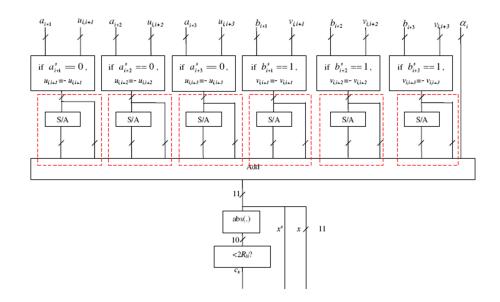

## 7. Architecture of $MCU_4$

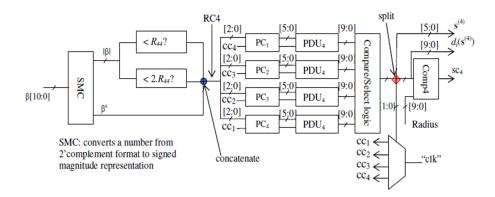

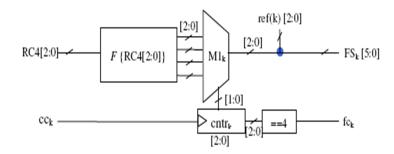

Fig. 15 shows the detailed structure of  $MCU_4$ . As mentioned earlier,  $MCU_4$  outputs symbols and associated PD's in their ascending order. To this end it follows the enumeration strategy outlined earlier. Recall that knowing the location of  $c_{i+1}$  in the constellation tells us the order of the QAM points in each column. Once the location of  $c_{i+1}$  is known, the SF is computed using a bank of  $PC_k$  blocks (k=1,2,3,4). A bank of Partial Distance Units (PDUs) operates on the SF to compute MF. A PDU block computes the distance of  $c_{i+1}$  from a scaled QAM symbol. The compare select logic picks the best symbol based on the minimum PD. Fig. 16 shows details of the  $PC_k$ block. It consists of a combinational logic block (F), which outputs the imaginary parts of the QAM symbols in signed magnitude format. It has four outputs of three bits each. These outputs correspond to the unique pattern of imaginary parts of the four symbols in a column depending on location of  $c_{i+1}$  in the constellation. These imaginary parts are finally concatenated with the real part (notice that in each column the symbols have identical real parts). The counter labeled  $cntr_k$ , is a 3 bit counter whose two LSBs select the best available symbol in column k. Note that we need a three bit counter in order to identify the exhaustion of a column. Since the column has only 4 symbols in it, a value of 4 (counter starts from value '000') indicates that all the symbols in that column have been exhausted. Hence,

Fig. 15. Details of  $MCU_4$

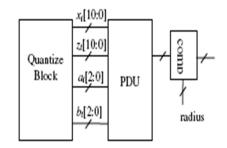

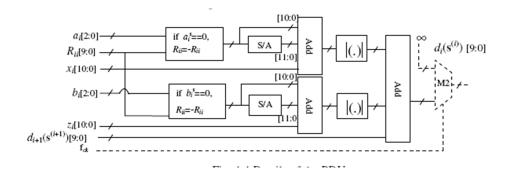

whenever counter value is 4 a signal  $f_{ck}$  is generated. This signal alerts the PDU to saturate its output. This essentially excludes symbols from that column from further consideration. The outputs of a  $PC_k$  block (a frontier symbol from  $k^{th}$  column  $FS_k$ and a control signal  $f_{ck}$ ,) are fed to a PDU. The PDU computes the associated PD of the  $FS_k$ . The compare/select logic block along with the demultiplexer identifies which frontier symbol needs to be replaced. Fig. 17 shows details of a PDU. The PDU at the top level differs with the one shown in Fig. 17 in that there is no  $d_{i+1}(s^{(i+1)})$ input, since  $d_5(s^{(5)}) = 0$ . Also, for PDUs at levels i < 4 there is no  $f_{ck}$  input, and no multiplexer M2. This difference is indicated in Fig. 17 by means of dotted lines.

Fig. 16. Details of  $PC_k$  k=1,2,3,4

Fig. 18. Details of  $MCU_k$  k=1,2,3,4

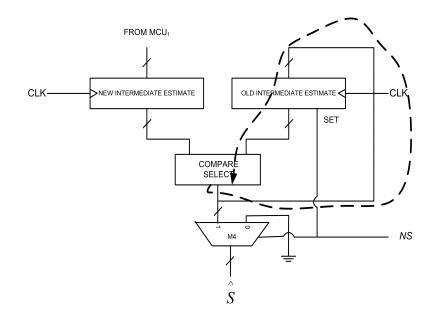

## 8. Architecture of $MCU_3, MCU_2, MCU_1$

The top level architecture of  $MCU_3$  through  $MCU_1$  is shown in Fig. 18.  $MCU_3$ through  $MCU_1$  differ from  $MCU_4$  in that they don't have to explicitly enumerate QAM symbols in sorted order; all that is needed to be done by  $MCU_3$ - $MCU_1$  is to find the best child. Finding best child essentially means "quantizing"  $c_{i+1}$  (Fig. 13)

Fig. 17. Details of the PDU

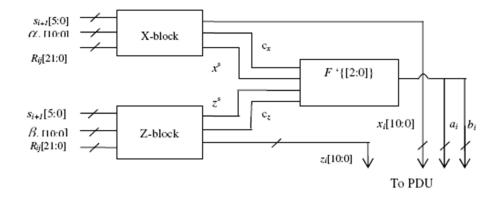

to the nearest QAM symbol. Fig. 19 shows the details of the "Quantize" block.

Fig. 19. Details of the Quantize Block

Let  $y_i = \alpha_i + j\beta_i$ ,  $s_i = a_i + jb_i$ ,  $R_{ij} = u_{ij} + jv_{ij}$ , and  $c_{i+1} = x_i + jz_i$ . Substituting these expressions in equation (3.8) and after some algebraic manipulations equation (3.8) can be written as (for i=1,2,3):

$$x_{i} = \alpha_{i} + \sum_{k=1}^{M_{T}-i} \left[ (-u_{i,i+k})(a_{i+k}) + (v_{i,i+k})(b_{i+k}) \right]$$

(3.14)

$$z_{i} = \beta_{i} + \sum_{k=1}^{M_{T}-i} [(-u_{i,i+k})(b_{i+k}) + (-v_{i,i+k})(a_{i+k})]$$

(3.15)

Note that for i = 4  $x_i = \alpha_i$ , and  $y_i = \beta_i$ . Since  $c_{i+1}$  is also a complex number we need to quantize it along both the real and imaginary dimensions. For this purpose we use the X-block (for the real part) and the Z-block (for the imaginary part). These blocks compute  $x_i$  and  $z_i$  using equations (3.14),(3.15). Note that here we have exploited the symmetry of the QAM constellation. First we find the magnitude of real and imaginary parts of  $c_{i+1}$ , so that the new  $c'_{i+1} = |x_i| + j \cdot |y_i|$  is now in the first quadrant. Using the sign bits  $x^s$  and  $z^s$  along with the location of the  $c'_{i+1}$  we can find the location of  $c_{i+1}$ . This function is carried out by F' block which is a very simple combinational block which directly outputs the QAM symbol (indicated by  $a_i$ and  $b_i$  in the Fig. 19 in signed magnitude format. Fig. 20 shows more details of the X block. The X-block carries out computations according to equation (3.14). Product terms in equation (3.14) are implemented using shift and add function (shown by the dotted boxes). The multi-operand additions are performed by an arithmetic Sum of Products (SOP) block [40]. The Z-block is structurally similar to the X-block with inputs reassigned, as can be seen from equation (3.15).

Sequential architecture implementation: Recall that this architecture has two MCU's. The first MCU computes the PD's of children of the root node in their ascending order. The second MCU serially evaluates nodes at levels i = 3, 2, 1. Both the units are capable of carrying out a radius check. The MCU at the top level stops evaluating nodes whenever the SC is violated. The second MCU continues

Fig. 20. Details of the X-block

until all the nodes evaluated by the first unit are processed. Notice that the top level MCU is exactly same as that in the staggered architecture. The second MCU has to be reconfigured according to the level of the node it is computing. Fully serial architecture implementation: In this architecture there is only one MCU that is shared between all the levels of the tree. Notice that the first four cycles are spent to compute the SF/MF. Hence, the first node at the top level is available for computation only at the 5<sup>th</sup> clock cycle. Notice that in this scheme the unit has to be reconfigured for i = 4, 3, 2, 1.

Fully parallel architecture implementation: In this architecture, there are 16 MCU's operating concurrently. These MCU's evaluate all 16 nodes at a given level in a single cycle. In this architecture the MCU's also have to be reconfigured for i = 4, 3, 2, 1. The difference between the MCU's in the parallel and the staggered

Fig. 21. BER for Suboptimal Norms and Finite Bit Precision

architectures is that in the parallel architecture, the enumeration is not carried out. The quantization operation (of  $c_{i+1}$ ), however, is still needed for levels i = 1, 2, 3 in the parallel architecture.

C. Discussion

In this section we present the implementation results and analyze the architectures in situations that occur in real-life baseband systems. We start by noting that both sequential and staggered architectures have variable throughputs, something which is undesirable in practical systems. On the other hand, parallel architecture provide constant throughput at a much higher cost per unit area. The implementation of the aforementioned architectures was done using a customized Compare/Select and Comparator blocks and standard cell based design in 100 nm technology [34]. The customized Compare/Select block was simulated in SPICE3 [35] to obtain its delay and power. The customized Comparator block is implemented as designed in [39]. Hence the area, delay and power of the comparator as reported in [39] (for a 100 nm technology) are used as such. For the standard cell based design, the delay was computed from a sensitizable timing analysis tool (Sense) [36] and the power was computed using a script written in the SIS [37] logic synthesis environment. This script computes the re-convergence adjusted signal probability, which in turn is used to compute the dynamic power consumption of the design. For both designs, the active area was computed and used to estimate the area of the architectures discussed above. We chose wordlengths of elements of coefficients as 11bits for 16-QAM and 12bits for 64-QAM. The fixed point vs floating point BER is compared in Fig. 21.

### 1. Building Blocks

Compare Select Circuit: The Compare/Select block uses the Longest Prefix Matching (LPM) circuit designed in [38]. The logic behind the Compare/Select block is illustrated in Fig. 22 with an example. Consider the problem of finding the maximum among three 4 bit operands as shown in part (a) of Fig. 22. The LPM looks each column of bits at a time (starting from the MSB) and eliminates the operand that has a '0' in that column, if anyone of the other bits is a '1'. Hence in part (b) of Fig. 22 operand '0101' is eliminated. Hence, only the first two operands contend. Since both these operands have the same bit in column 2 (part (a) of Fig. 22), the LPM looks for the next column. In column 3, the second operand has a '0' and hence gets eliminated. Thus the LPM declares the first operand as the largest value.

| <b>√</b> 1011 | <b>√</b> 1011 | <b>√</b> 1011 | <b>√</b> 1011 |

|---------------|---------------|---------------|---------------|

| <b>√</b> 1001 | ✓ 1001        | √ 1001        | ✓ 1001        |

| ✓ 0101        | <b>x</b> 0101 | × 0101        | × 0101        |

| (a)           | (b)           | (C)           | (d)           |

Fig. 22. Compare Select Operation

Sum-of-Product(SOP): The remainder of the design is standard cell based, implemented in 100 nm technology. The multi-operand addition is done using a Sumof-Product (SOP) design [40]. The SOP is better than a tree of adders, since it has a single carry chain. The SOP block consists of 3 steps - Partial Product generation, Partial Product reduction using half and full adders and a single final 2 operand binary adder. The final adder is implemented using a fast Kogge-Stone adder [41].

## 2. Detection in Multicore Setup:

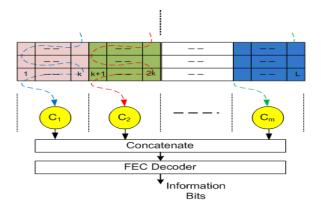

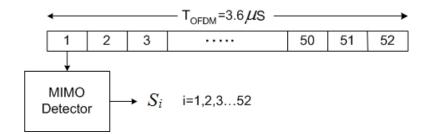

Due to the ever increasing throughput requirements placed on the baseband processor multiple detector cores will have to be used to support it. This arrangement is shown in (Fig. 23) where we employ m cores for detection. The aim is to analyze the area efficiency (throughput/area) as we increase m. The exact value of L changes with different standards, for example, 802.11n has 64 tones, LTE has 512 tones.

Fig. 23. Multicore Detection for MIMO-OFDM Systems

Fig. 24. Throughput/Area Efficiency for Sequential Arch