# LINEARIZATION AND EFFICIENCY ENHANCEMENT TECHNIQUES FOR RF AND BASEBAND ANALOG CIRCUITS

A Dissertation

by

MOHAMED SALAH MOHAMED MOBARAK

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

December 2010

Major Subject: Electrical Engineering

# LINEARIZATION AND EFFICIENCY ENHANCEMENT TECHNIQUES FOR RF AND BASEBAND ANALOG CIRCUITS

#### A Dissertation

by

## MOHAMED SALAH MOHAMED MOBARAK

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Edgar Sanchez-Sinencio Committee Members, Jose Silva-Martinez

Prasad Enjeti

Mahmoud El-Halwagi

Head of Department, Costas N. Georghiades

December 2010

Major Subject: Electrical Engineering

#### ABSTRACT

Linearization and Efficiency Enhancement Techniques for RF and Baseband Analog

Circuits. (December 2010)

Mohamed Salah Mohamed Mobarak, B.S., Cairo University, Egypt;

M.S., Cairo University, Egypt

Chair of Advisory Committee: Dr. Edgar Sanchez-Sinencio

High linearity transmitters and receivers should be used to efficiently utilize the available channel bandwidth. Power consumption is also a critical factor that determines the battery life of portable devices and wireless sensors. Three base-band and RF building blocks are designed with the focus of high linearity and low power consumption.

An architectural attenuation-predistortion linearization scheme for a wide range of operational transconductance amplifiers (OTAs) is proposed and demonstrated with a transconductance-capacitor (Gm-C) filter. The linearization technique utilizes two matched OTAs to cancel output harmonics, creating a robust architecture. Compensation for process variations and frequency-dependent distortion based on Volterra series analysis is achieved by employing a delay equalization scheme with on-chip programmable resistors. The distortion-cancellation technique enables an IM3 improvement of up to 22dB compared to a commensurate OTA without linearization. A

proof-of-concept lowpass filter with the linearized OTAs has a measured IM3 < -70dB and 54.5dB dynamic range over its 195MHz bandwidth.

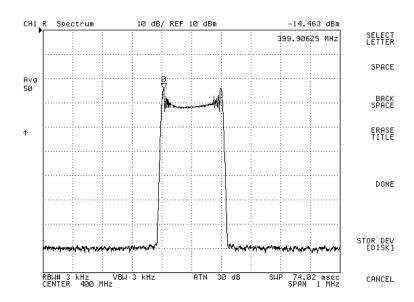

Design methodology for high efficiency class D power amplifier is presented. The high efficiency is achieved by using higher current harmonic to achieve zero voltage switching (ZVS) in class D power amplifier. The matching network is used as a part of the output filter to remove the high order harmonics. Optimum values for passive circuit elements and transistor sizes have been derived in order to achieve the highest possible efficiency. The proposed power amplifier achieves efficiency close to 60% at 400 MHz for -2dBm of output power.

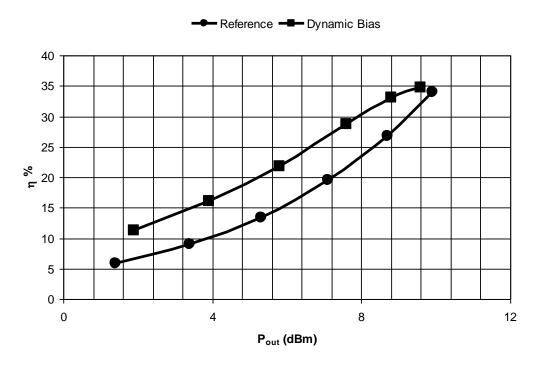

High efficiency class A power amplifier using dynamic biasing technique is presented. The power consumption of the power amplifier changes dynamically according to the output signal level. Effect of dynamic bias on class A power amplifier linearity is analyzed and the results were verified using simulations. The linearity of the dynamically biased amplifier is improved by adjusting the preamplifier gain to guarantee constant overall gain for different input signal levels.

# DEDICATION

To the memory of my mother

To my father

To my brothers and sisters

To my wife

For all their love and support

#### **ACKNOWLEDGEMENTS**

I would like to express my deep gratitude to my advisor, Dr. Edgar Sanchez-Sinencio, for his guidance and support throughout the course of my research. His valuable comments and encouragement made this research possible and I deeply appreciate his immediate help in solving many problems that I have faced during my studies.

I would like to thank Dr. Jose Silva-Martinez for being a member of my committee and for his valuable input, suggestions and comments especially on the Gm-C filter linearization project. I also would like to thank my committee members Dr. Prasad Enjeti and Dr. Mahmoud El-Halwagi for their time and valuable comments.

I am grateful to Marvin Onabajo for being a good friend and for his significant contribution to the Gm-C filter project. I also would like to express my appreciation to Erik Pankratz, Mohamed El-Nozahi, Heng Zhang, Jason Wardlaw, Mohamed Elsayed, and Mohammed Abdul-Latif for their valuable discussions.

I enjoyed the company and discussions with many friends including Faramarz Bahmani, Faisal Hussien, Marvin Onabajo, Mohamed Elsayed, Mohammed Abdul-Latif, Mohamed El-Nozahi, Ahmed Amer, Ehab Sobhy, Ahmed Helmy, Ramy Saad, Aymen Ameen, Ahmed Ragab, and Jason Wardlaw. Their help and encouragement was an essential factor for me during my study.

I am indebted for my family for their love, support, patience, and encouragement throughout my studies.

# TABLE OF CONTENTS

|            |                                                                                    | Page     |

|------------|------------------------------------------------------------------------------------|----------|

| ABSTRACT   | Γ                                                                                  | iii      |

| DEDICATION | ON                                                                                 | v        |

| ACKNOWI    | LEDGEMENTS                                                                         | vi       |

| TABLE OF   | CONTENTS                                                                           | vii      |

| LIST OF FI | GURES                                                                              | ix       |

| LIST OF TA | ABLES                                                                              | xiii     |

| CHAPTER    |                                                                                    |          |

| I          | INTRODUCTION                                                                       | 1        |

|            | 1.1 Motivation                                                                     | 1 2      |

| II         | ATTENUATION-PREDISTORTION LINEARIZATION OF CMOS OTAS FOR OTA-C FILTER APPLICATIONS | 4        |

|            | 2.1 Introduction                                                                   | 4        |

|            | 2.2 Attenuation-Predistortion Linearization Methodology                            | 7        |

|            | 2.2.1 Single-Ended Circuits                                                        | 9        |

|            | 2.2.2 Fully-Differential Circuits                                                  | 11       |

|            | 2.2.3 Scaling of Attenuation Ratios                                                | 14       |

|            | 2.3 Volterra Series Analysis                                                       | 16       |

|            | 2.4 Circuit Level Considerations                                                   | 21       |

|            | 2.4.1 Fully-Differential OTA with Floating-Gate FETs                               | 21       |

|            | 2.4.2 Common-Mode Feedback Design                                                  | 24<br>26 |

|            | 2.4.3 Proof-of-Concept Filter Realization                                          | 30       |

|            | 2.6 Measurement Results                                                            | 33       |

|            | 2.6.1 OTA                                                                          | 33       |

|            | 2.6.2 Second Order Low Pass Filter                                                 | 39       |

|            | 2.7 Excess Phase Compensation                                                      | 45       |

|            | 2.8 Linearization without Power Budget Increase                                    | 47       |

| CHAPTER  |                                                                    | Pag |

|----------|--------------------------------------------------------------------|-----|

| III      | HIGH EFFICIENCY CLASS D POWER AMPLIFIER FOR LOW POWER APPLICATIONS | 4   |

|          | FOWER AFFLICATIONS                                                 |     |

|          | 3.1 Introduction                                                   | ۷   |

|          | 3.2 High Efficiency Power Amplifier Architectures                  | 4   |

|          | 3.2.1 Class E PA                                                   | 4   |

|          | 3.2.2 Class D PA                                                   | 4   |

|          | 3.3 Zero Voltage Switching in Class D PA                           |     |

|          | 3.4 Circuit Level Implementation                                   | (   |

|          | 3.4.1 Class D PA Circuit                                           | 6   |

|          | 3.4.2 PA Driver Circuit                                            |     |

|          | 3.5 Measurement Results                                            | 6   |

| IV       | HIGH EFFICIENCY CLASS A POWER AMPLIFIER WITH                       |     |

|          | DYNAMIC BIAS CONTROL                                               | 7   |

|          | 4.1 Introduction                                                   | -   |

|          | 4.2 Dynamic Bias of Class A Power Amplifier                        | 8   |

|          | 4.2.1 Dynamic Bias Effect on Amplifier Linearity                   | 9   |

|          | 4.2.2 Efficiency Improvement Using Dynamic Bias                    | 9   |

|          | 4.3 Power Amplifier Circuit Implementation                         | 9   |

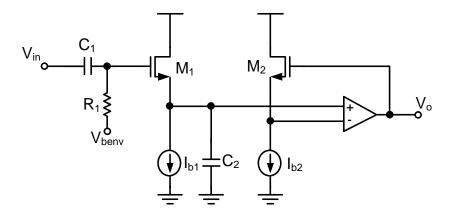

|          | 4.3.1 Envelope Detector Design                                     | (   |

|          | 4.3.2 Operational Amplifier Design                                 | (   |

|          | 4.4 Experimental Results                                           | 10  |

| V        | CONCLUSIONS                                                        | 10  |

| REFERENC | CES                                                                | 1   |

| VITA     |                                                                    | 1   |

# LIST OF FIGURES

| FIGURE |                                                                                                                                                                                                                                       |    |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1    | Block diagram of cross coupled amplifiers.                                                                                                                                                                                            | 6  |

| 2.2    | Block diagram of the proposed attenuation-predistortion technique                                                                                                                                                                     | 9  |

| 2.3    | Attenuation-predistortion linearization scheme for single-ended circuits.                                                                                                                                                             | 10 |

| 2.4    | Block diagram of the fully differential implantation of the attenuation-predistortion technique                                                                                                                                       | 12 |

| 2.5    | Attenuation-predistortion linearization for fully-differential circuits                                                                                                                                                               | 12 |

| 2.6    | Low-frequency model for the fully-differential attenuation-predistortion scheme.                                                                                                                                                      | 14 |

| 2.7    | Non-linear model for fully-differential attenuation-predistortion cancellation                                                                                                                                                        | 17 |

| 2.8    | Folded-cascode OTA (implements $G_m$ in the main and auxiliary paths)                                                                                                                                                                 | 21 |

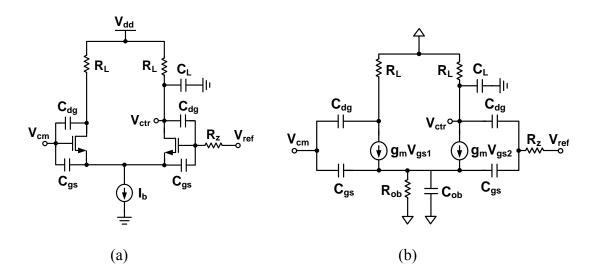

| 2.9    | (a) Error amplifier circuit in the CMFB loop and (b) small-signal equivalent circuit                                                                                                                                                  | 24 |

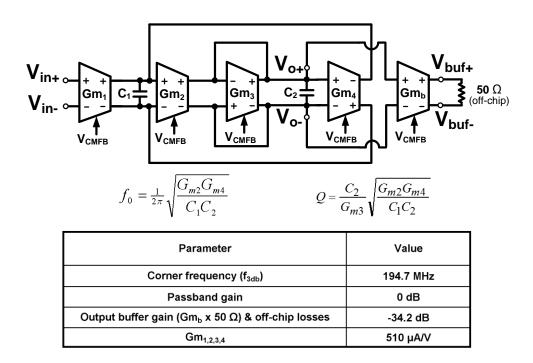

| 2.10   | Fully-differential 2 <sup>nd</sup> -order lowpass filter diagram and design parameters                                                                                                                                                | 27 |

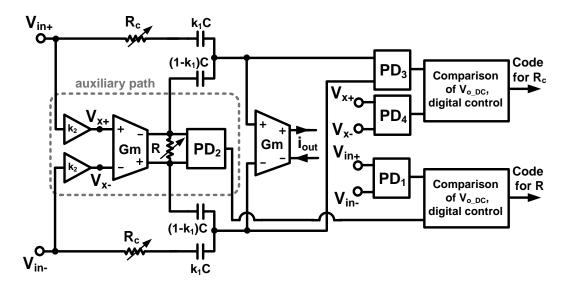

| 2.11   | Block diagram of the proposed automatic linearity tuning scheme                                                                                                                                                                       | 28 |

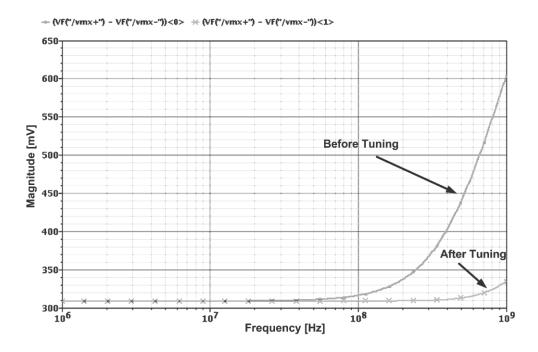

| 2.12   | Simulated AC amplitude at the input of the main OTA (PD <sub>3</sub> in Fig. 2.11) before and after adjustment of resistor $R_c$ to its optimum value. (The voltage at PD <sub>3</sub> is ideally equal to $V_x = k_2 \cdot V_{in}$ ) | 29 |

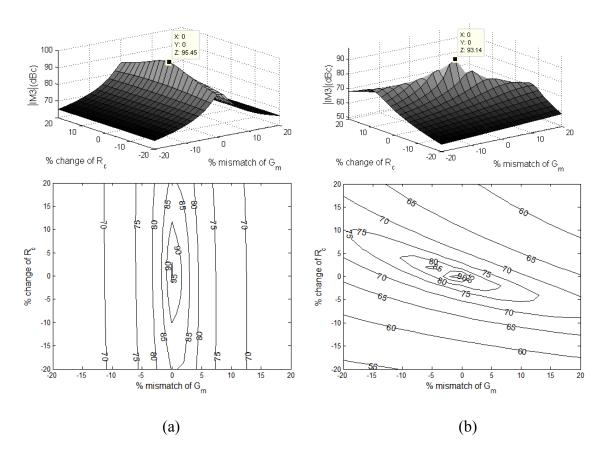

| 2.13   | Sensitivity of  IM3  (in dBc) to component mismatches calculated with equation (2.15): (a) 10MHz signal frequency, (b) 200MHz signal frequency                                                                                        | 31 |

| FIGURE | ,                                                                                                                                                                                                                                                            | Page    |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

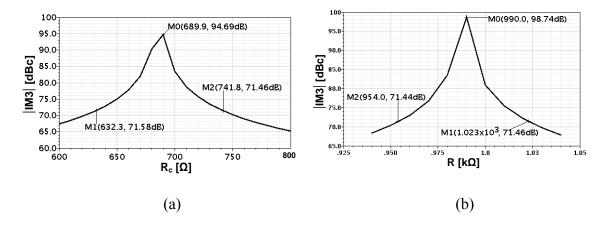

| 2.14   | Simulations showing sensitivity to variation and mismatch of critical components: (a) $ IM3 $ vs. change in $R_c$ (Fig. 2.5) at 350MHz, (b) $ IM3 $ vs. R (in Fig. 2.5) with 10% transconductance mismatch between main OTA and auxiliary OTA at 350MHz.     | 33      |

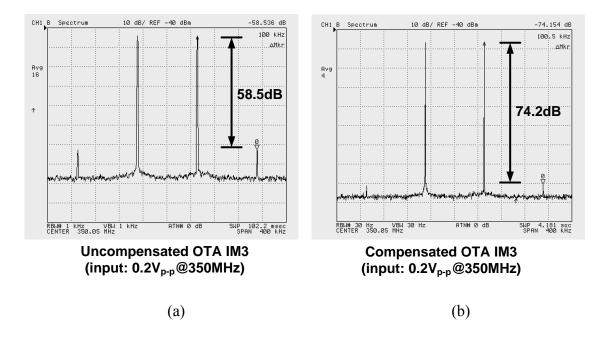

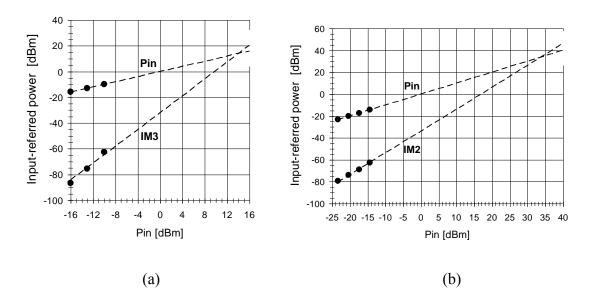

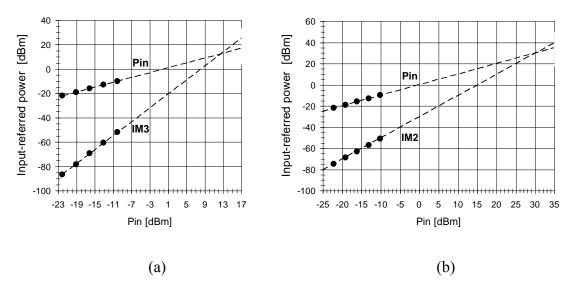

| 2.15   | Measured linearity with $0.2V_{p-p}$ input swing from two tones, each $0.1V_{p-p}$ (-16dBm) on-chip after accounting for off-chip losses at the input: (a) reference OTA, (b) compensated OTA                                                                | 34      |

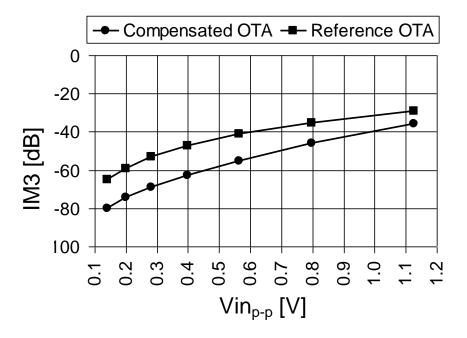

| 2.16   | Measured IM3 vs. input peak-peak voltage for reference OTA and compensated OTA obtained using two tones having 100kHz separation around 350MHz.                                                                                                              | 35      |

| 2.17   | Measured IM3 dependence of the compensated OTA on phase shift obtained with two test tones having 100kHz separation around 350MHz. (The least significant bit of the digital control code changes the value of phase shift resistor $R_c$ by $\sim\!3\%$ )   | 37      |

| 2.18   | Filter measurements: (a) transfer function with $\sim\!\!34dB$ total losses (input loss and output buffer attenuation). (b) IM3 with $0.2V_{p-p}$ input swing from two tones, each $0.1V_{p-p}$ (-16dBm) on-chip after accounting for off-chip input losses. | 39      |

| 2.19   | Measured filter IM3 vs. frequency with two test tones having 100kHz separation                                                                                                                                                                               | 40      |

| 2.20   | Measured IM3 vs. input peak-peak voltage for the linearized filter obtained with two test tones having 100kHz separation around 150MHz                                                                                                                       | l<br>41 |

| 2.21   | Measured in-band intercept point curves for the filter:<br>(a) IIP3 [two tones, $\Delta f = 100 \text{kHz}$ around 150MHz],<br>(b) IIP2 [two tones, $\Delta f = 100 \text{kHz}$ around 2MHz]                                                                 | 41      |

| 2.22   | Measured out-of-band intercept point curves for the filter: (a) IIP3 [ $f_1$ = 275MHz, $f_2$ = 375MHz, $f_{IM3}$ = 100MHz], (b) IIP2 [ $f_1$ = 375MHz, $f_2$ = 375.1MHz, $f_{IM2}$ = 100kHz]                                                                 | 42      |

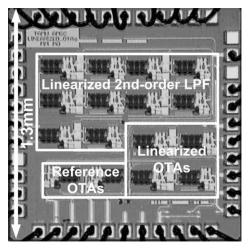

| 2.23   | Die micrograph of the OTAs and filter in 0.13μm CMOS technology. (Reference OTA area: 0.033mm², linearized OTA area: 0.090mm²)                                                                                                                               | 43      |

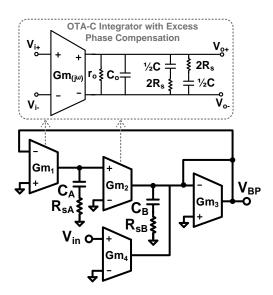

| 2.24   | Single-ended equivalent block diagram of a bandpass biquad                                                                                                                                                                                                   | 45      |

| FIGURE |                                                                                                                                                                                                  | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

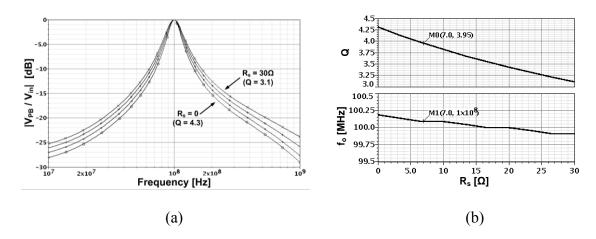

| 2.25   | BP filter simulations with different $R_s$ values for excess phase compensation: (a) frequency responses, (b) quality factor and center frequency; where $R_s = R_{sA} = R_{sB} \cdot (C_B/C_A)$ | 46   |

| 3.1    | Class E power amplifier                                                                                                                                                                          | 51   |

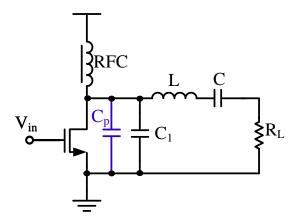

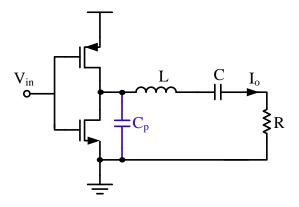

| 3.2    | Class D power amplifier                                                                                                                                                                          | 54   |

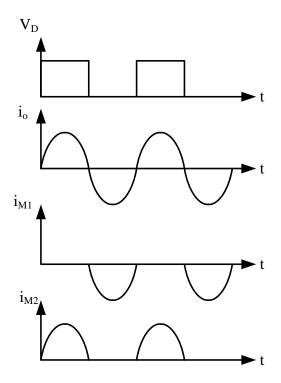

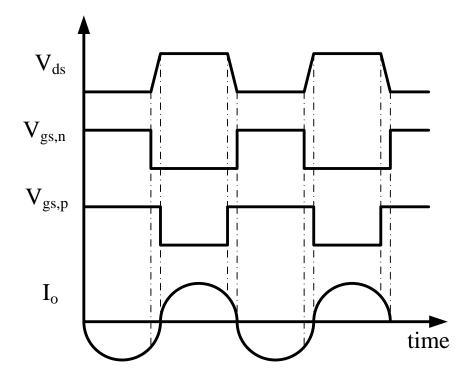

| 3.3    | Voltage and current waveforms of class D power amplifier                                                                                                                                         | 54   |

| 3.4    | Soft switching in class D power amplifier                                                                                                                                                        | 56   |

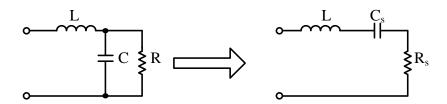

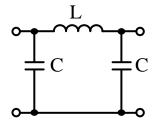

| 3.5    | Step down matching network                                                                                                                                                                       | 57   |

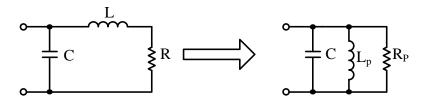

| 3.6    | Step up matching network                                                                                                                                                                         | 58   |

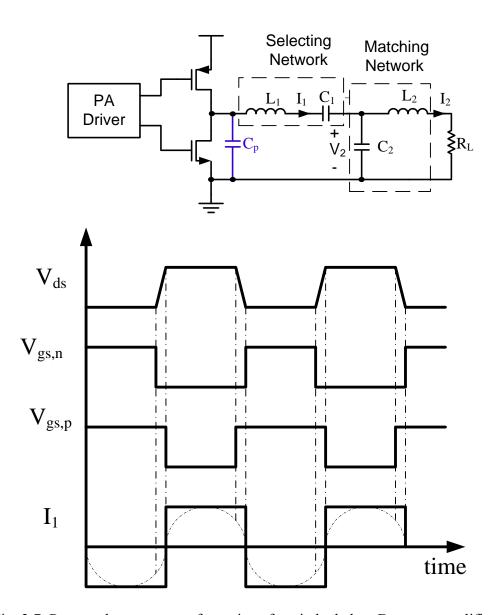

| 3.7    | Proposed current waveforms in soft switched class D power amplifier                                                                                                                              | 59   |

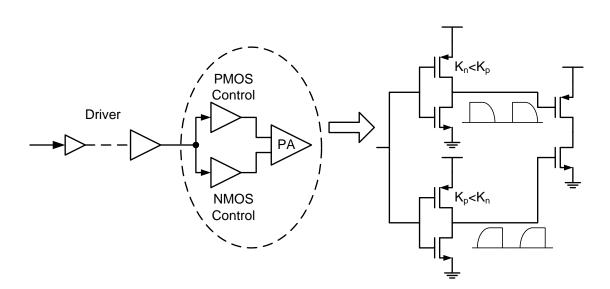

| 3.8    | Power amplifier driver circuit                                                                                                                                                                   | 67   |

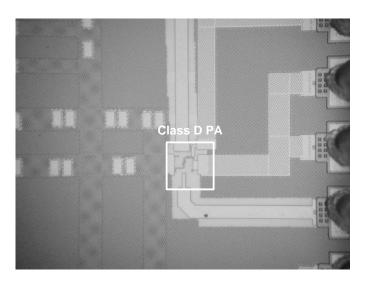

| 3.9    | Class D PA chip micrograph                                                                                                                                                                       | 68   |

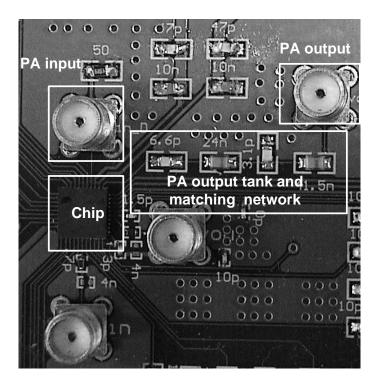

| 3.10   | PCB of class D power amplifier                                                                                                                                                                   | 69   |

| 3.11   | PCB trace model                                                                                                                                                                                  | 70   |

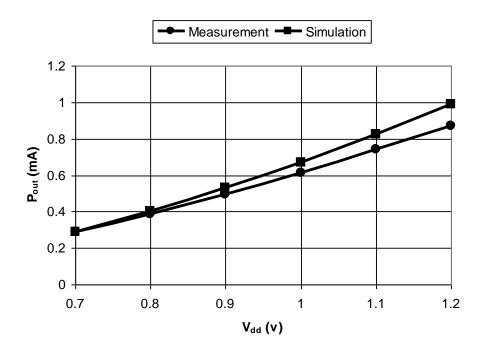

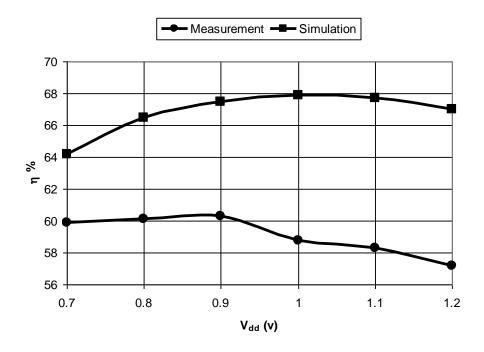

| 3.12   | Output power versus supply voltage                                                                                                                                                               | 71   |

| 3.13   | Power amplifier efficiency versus supply voltage                                                                                                                                                 | 71   |

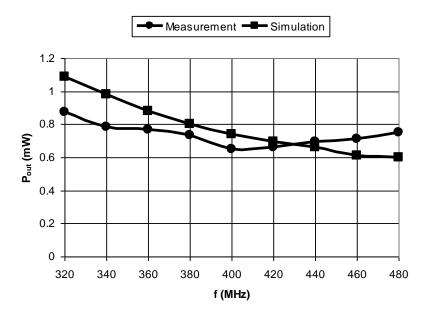

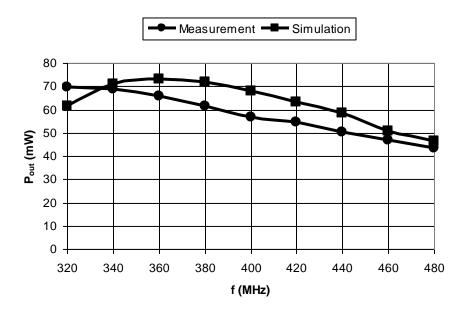

| 3.14   | Frequency response of power amplifier                                                                                                                                                            | 72   |

| 3.15   | Power amplifier efficiency at different frequencies                                                                                                                                              | 73   |

| 3.16   | Power amplifier output for FSK modulated signal                                                                                                                                                  | 73   |

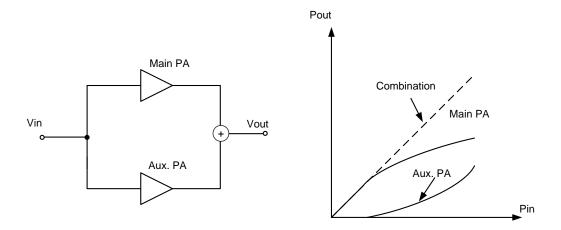

| 4.1    | Doherty amplifier concept.                                                                                                                                                                       | 76   |

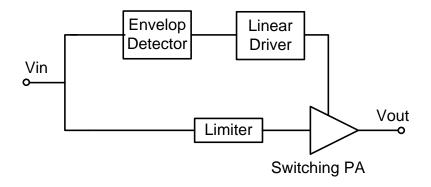

| 4.2    | Envelop elimination and restoration.                                                                                                                                                             | 77   |

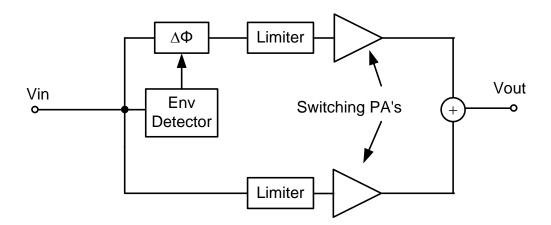

| 4.3    | Linear amplification using non linear amplifier (outphasing technique)                                                                                                                           | 77   |

| FIG | URE  |                                                                                                             | Page |

|-----|------|-------------------------------------------------------------------------------------------------------------|------|

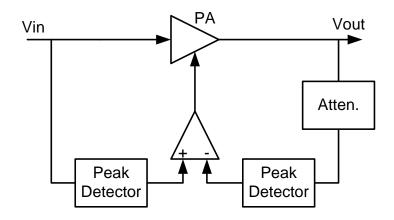

| ۷   | 1.4  | Envelope feedback.                                                                                          | 79   |

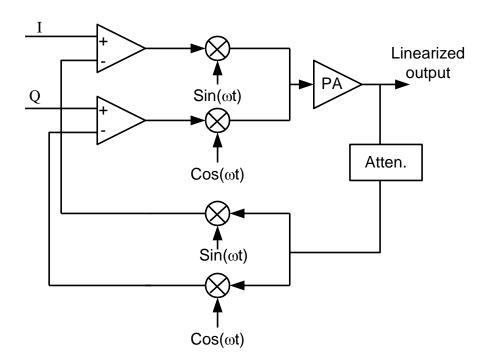

| ۷   | 1.5  | Cartesian feedback.                                                                                         | 79   |

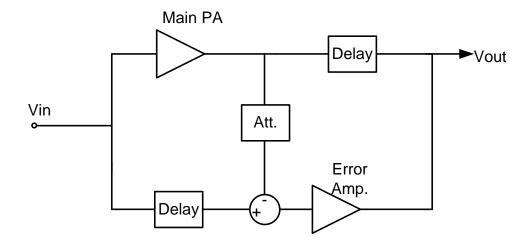

| ۷   | 1.6  | Feedforward linearization.                                                                                  | 80   |

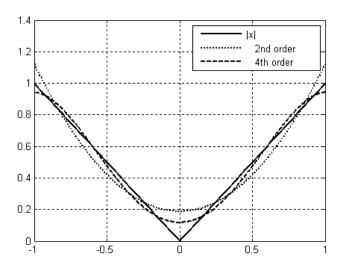

| ۷   | 1.7  | Second and fourth order approximations of the absolute value function                                       | 88   |

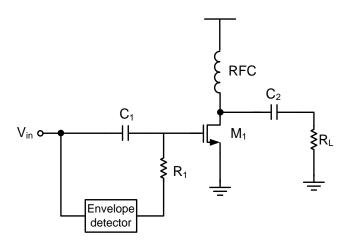

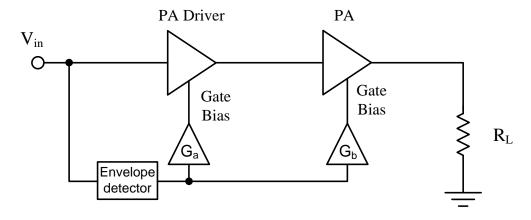

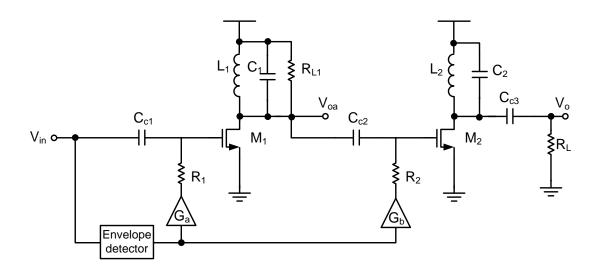

| ۷   | 1.8  | Power amplifier linearization using envelope signal.                                                        | 90   |

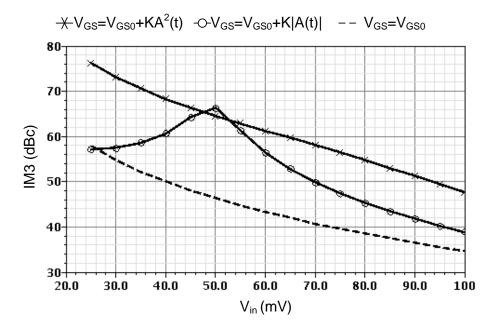

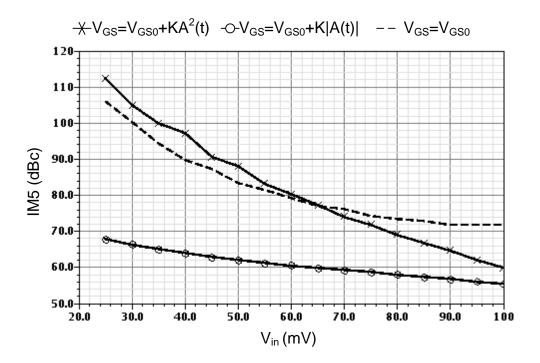

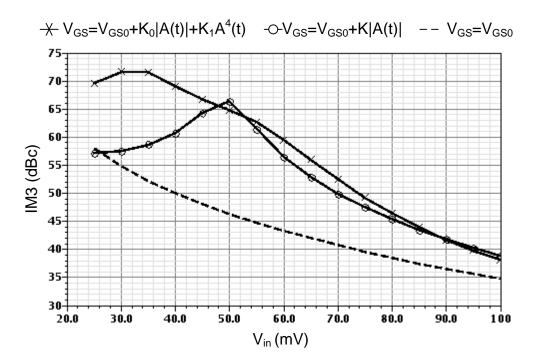

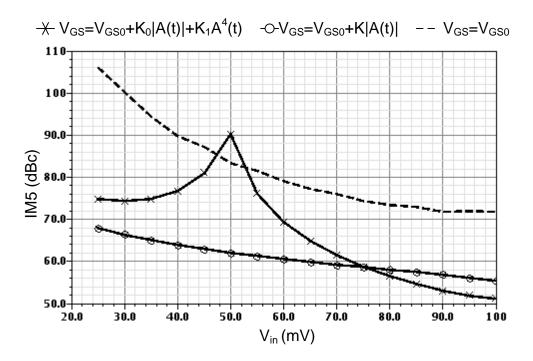

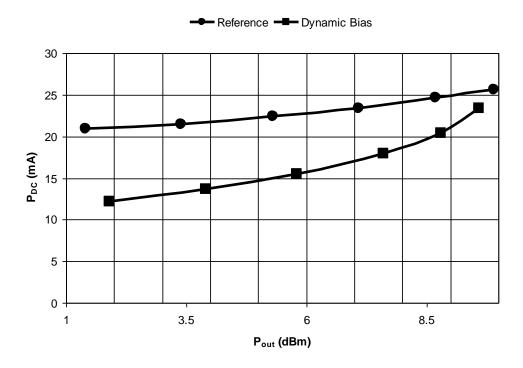

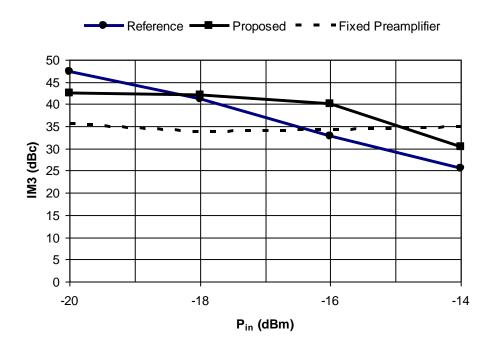

| 2   | 1.9  | Third order inter-modulation versus input amplitude for different control schemes                           | 90   |

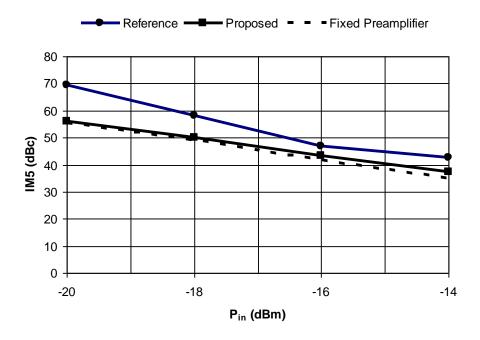

| 2   | 4.10 | Fifth order inter-modulation versus input amplitude for different control schemes                           | 91   |

| ۷   | 4.11 | Third order inter-modulation versus input amplitude with improved control scheme                            | 92   |

| ۷   | 1.12 | Fifth order inter-modulation versus input amplitude with improved control scheme.                           | 93   |

| ۷   | 1.13 | Efficiency enhancement through dynamic bias of the power amplifier                                          | 94   |

| ۷   | 1.14 | Power amplifier schematic                                                                                   | 97   |

| ۷   | 1.15 | Envelope detector schematic                                                                                 | 98   |

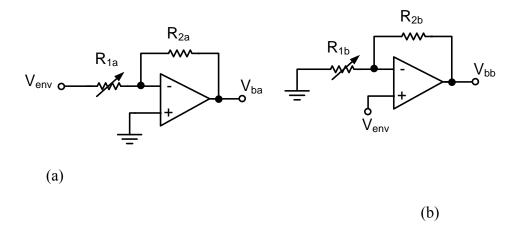

| ۷   | 4.16 | Dynamic bias amplifiers: (a) Gain stage of preamplifier $(G_a)$ , (b) Gain stage of power amplifier $(G_b)$ | 99   |

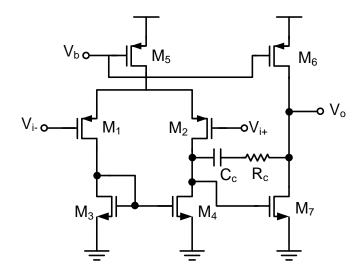

| ۷   | 1.17 | Two stage op-amp schematic                                                                                  | 100  |

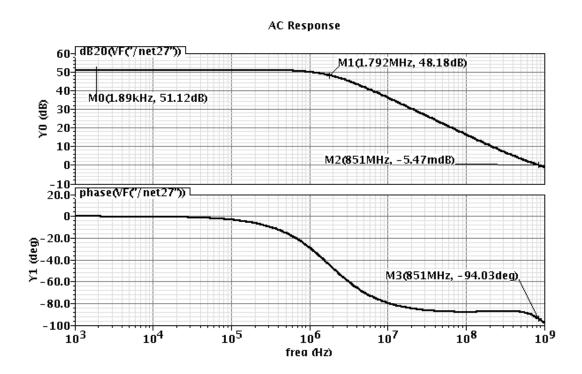

| ۷   | 1.18 | Frequency response of the operational amplifier                                                             | 100  |

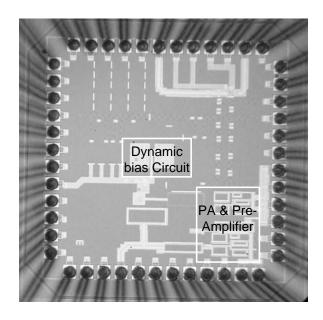

| ۷   | 1.19 | Power amplifier chip micrograph                                                                             | 101  |

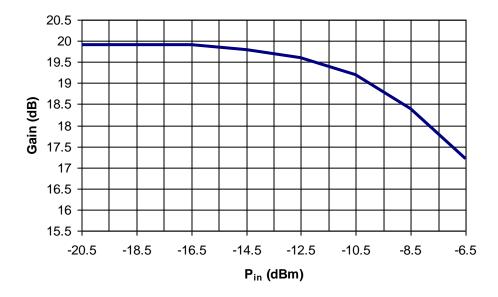

| ۷   | 1.20 | Gain of the reference power amplifier                                                                       | 102  |

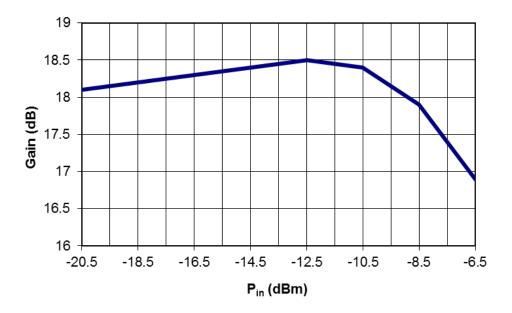

| ۷   | 1.21 | Gain of the power amplifier with dynamic bias only at the output stage                                      | 103  |

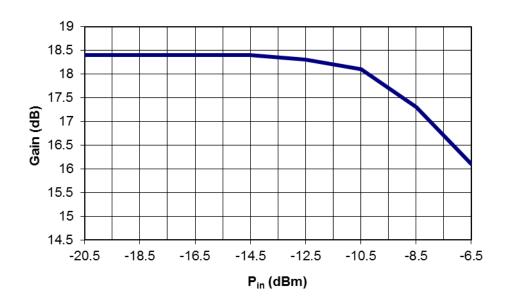

| ۷   | 1.22 | Gain of the proposed dynamically biased power amplifier                                                     | 103  |

| FIGURE                                                                                  | Page |

|-----------------------------------------------------------------------------------------|------|

| 4.23 Efficiency of the proposed dynamic bias amplifier and the amplifier                |      |

| 4.24 Power consumption of the proposed dynamic bias amplifi and the reference amplifier |      |

| 4.25 Third order inter-modulation of the proposed and the refer amplifiers              |      |

| 4.26 Fifth order inter-modulation of the proposed and the reference amplifiers          |      |

# LIST OF TABLES

| TABLE |                                                                            | Page |

|-------|----------------------------------------------------------------------------|------|

| 2.1   | Measured main parameters of the reference folded-cascode OTA               | 34   |

| 2.2   | Comparison of OTA linearity and noise measurements                         | 37   |

| 2.3   | OTA comparison with prior works                                            | 38   |

| 2.4   | Comparison of wideband G <sub>m</sub> -C lowpass filters                   | 44   |

| 2.5   | Simulated comparison: OTA linearization without power consumption increase | 48   |

| 3.1   | Transistor parameters                                                      | 66   |

| 3.2   | PA circuit component values.                                               | 67   |

#### CHAPTER I

#### INTRODUCTION

#### 1.1 Motivation

Internet, smart phones, and global positioning system (GPS) navigation have become an essential part of our daily lives. Advances in communication technologies enabled the integration of multiple features to a single device, for example mobile phones are used to transfer videos as well data over the internet and they can be used as GPS navigation devices beside their main use of transmitting voice signals. Moreover, many new applications that utilize wireless bandwidth have recently emerged such as satellite communications which is being used to provide important services to remote locations. These advances in wireless systems led to a very crowded wireless spectrum. The amount of data required to be transmitted over the wireless connections has increased significantly while the available bandwidth is very limited.

New techniques must be used in order to allow high data rate transmission over the available bandwidth and to extract the weak signal received in the presence of strong interference. Low noise receivers are necessary to distinguish the received signal from the noise level. On the other hand, high linearity receiver is required to minimize the effect of the interfering signals over the desired signal.

This dissertation follows the style of IEEE Journal of Solid-State Circuits.

Low power operation is also desired for mobile transceivers. In some applications, such as sensor networks or implantable medical sensors, power consumption is a crucial factor when designing the transceiver building blocks. The goal of this research is to develop new circuits and techniques to build high linearity receivers and high efficiency transmitters. While the noise contribution of the first block in wireless receiver is the most critical compared to the rest of the receiver, the non-linearity of base-band blocks in wireless receivers is the dominant source of non-linearity in the whole receiver. On the transmitter side, the power amplifier efficiency is one of the major factors that determine the whole transmitter power consumption. New circuit techniques has been proposed for the following base-band and RF blocks

- 1) High linearity base-band filter using attenuation-predistortion linearization technique for the use in wide-band receivers.

- 2) High efficiency class D power amplifier for low output power applications.

- 3) High efficiency class A power amplifiers with dynamic bias control for high linearity transmitters in applications that involve envelope modulated signal transmission.

## 1.2 Dissertation Organization

Chapter II discusses the development of new architectural technique for the linearization of operational transconductance amplifiers (OTA) that is used as a part of OTA-C filters. Since there is an increasing demand of higher data rate and consequently

wider channel bandwidth, the high frequency effects associated with the proposed techniques is analyzed and frequency compensation scheme is proposed. Tradeoff associated with the proposed techniques, effect of process-voltage-temperature (PVT) variations is also provided in details. Measurement result of a standalone operational transconductance amplifier is presented and compared to a reference transconductance amplifier fabricated on the same chip that doesn't utilize the proposed linearization technique. Results of second order low pass filter that is build using the proposed OTA is also given.

Design of high efficiency switching power amplifiers is addressed in Chapter III with a description of the advantages and the disadvantages of different power amplifier classes. Efficiency analysis of class D power amplifier is provided and optimization of class D efficiency for low power applications is given. The high efficiency operation is verified with the measurement results of a 400 MHz class D power amplifier.

Chapter IV presents a study of class A power amplifier dynamic biasing and its effect on the amplifier linearity. High efficiency and high linearity operation of class A power amplifier using dynamic biasing is proposed. Linearity enhancement using dynamic bias is analyzed and measurement results for dynamically biased class A amplifier is provided.

Conclusions are summarized in Chapter V and possible areas of future work are also presented.

#### CHAPTER II

# ATTENUATION-PREDISTORTION LINEARIZATION OF CMOS OTAS FOR OTA-C FILTER APPLICATIONS\*

#### 2.1 Introduction

Operational transconductance amplifiers (OTAs) are essential elements of transconductance-capacitor ( $G_m$ -C) filters [1]-[3],  $\Delta\Sigma$  modulators [4], gyrators, variable-gain amplifiers, and negative-resistance elements. Compared to their active-RC counterparts,  $G_m$ -C filters enable low-power operation and tuning of the filter characteristics at higher frequencies, but are less linear. Tunable active-RC filters are suitable for low-frequency applications (e.g. <20MHz in [5]); however, extending their use to higher frequencies would require significantly more power. On the other hand, OTA-based filters in wireless receivers and continuous-time (CT)  $\Delta\Sigma$  analog-to-digital converters (ADCs) increasingly mandate good linearity at higher frequencies. These applications typically require highly linear OTAs with third-order inter-modulation (IM3) distortion better than -60dB. Further advances in high-frequency  $G_m$ -C filters with SNDRs over 50dB are also desirable for channel selection/equalization in multi-Gbps portable data communication devices [3], and for possible application in next generation analog-to-information receivers with dynamic range > 90dB in 200MHz bandwidth [6].

<sup>\*© 2010</sup> IEEE. Chapter II is in part reprinted, with permission, from "Attenuation-predistortion linearization of CMOS OTAs with digital correction of process variations in OTA-C filter applications," M. Mobarak, M. Onabajo, J. Silva-Martinez, and E. Sánchez-Sinencio, *IEEE J. Solid-State Circuits*, vol. 45, no. 2, pp. 351-367, Feb. 2010.

For more information go to http://thesis.tamu.edu/forms/IEEE%20permission%20note.pdf/view.

Viable high-frequency G<sub>m</sub>-C filter solutions were presented in [1] and [7] with 3-dB frequencies at 275MHz and 184MHz, respectively. The topology reported in [1] has low noise, limited linearity, and a pseudo-differential realization prone to low power supply rejection ratio (PSRR). The filter in [7] achieves high linearity with relatively low power but higher noise. Trade-offs between linearity, noise, power, and operating frequency are common and have been incorporated into figures of merit (FOMs) such as in [8] and [9]. The filter cutoff frequency tuning range can also be incorporated into a FOM [10], which aids in the comparison of G<sub>m</sub>-C filters for applications in which reconfigurability is important; e.g. wide tuning capability such as the 25:1 range in [10] is beneficial in multi-standard receivers. Recent works also address alternative filter structures such as the source-follower-based approach [11] and performance improvement of typical OTA topologies [12].

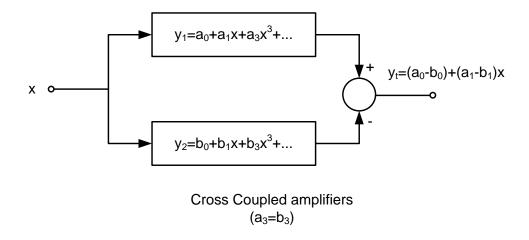

A popular linearization approach is to cross-couple two transconductors, theoretically cancelling certain harmonics at specific bias conditions over a limited frequency range. Non-linearity cancellation with two devices in parallel has been successfully extended to narrow-band RF transconductors in [13]. A typical cross-coupled OTA contains two paths; each having different transconductance and the same amount of harmonic distortion as illustrated by the block diagram in Fig. 2.1. When cross-coupled, the equal harmonics cancel under ideal conditions and the effective transconductance is the difference between the two paths. The frequency dependence of this approach has been analyzed with Volterra series in [14], in which the analytical expressions are correlated with measurement results. Process-voltage-temperature (PVT)

variations, high-frequency effects, and device modeling inaccuracies will create unforeseen mismatches between the two amplifiers. Therefore, precision tuning of bias currents/voltages is typically required. Signal attenuation can be also used to linearize the amplifier in the expense of gain reduction. Attenuation and cross-coupling has been combined for the low-noise amplifier in [15], in which distortion cancellation is restricted to third-order non-linearities with feedforward path and precise off-chip input attenuation. Accurate modeling of frequency-dependent distortion characteristics on the MOSFET device level is presented in [16].

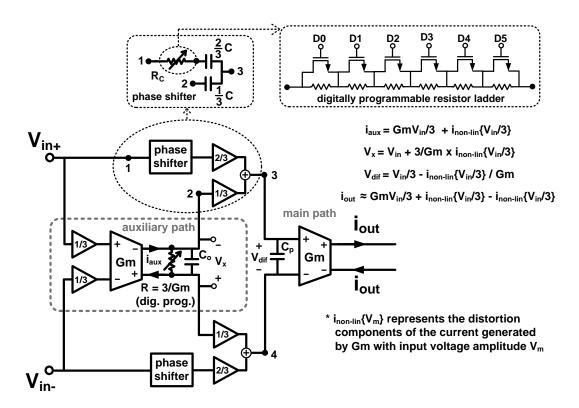

Fig. 2.1. Block diagram of cross coupled amplifiers.

For a source coupled differential pair biased by a current source  $I_{DC}$ , the differential output current is expressed in terms of the differential input voltage  $v_d$  as  $I_o = v_d \sqrt{\beta I_{DC} - \beta^2 v_d^2/4}$ , where  $\beta = \mu_0 C_{ox} W/L$ ,  $\mu_0$  is the electron mobility,  $C_{ox}$  is the gate oxide per unit area, W is the transistor width, and L is the transistor length. The bias

current of the differential pair can be adjusted dynamically in order to linearize the OTA [17]. If the bias current  $I_{DC}$  is adjusted such that  $I_{DC} = I_{DC0} + (\beta/4)v_d^2$ , then the output current is linearly proportional to the input differential voltage  $v_d$  and it is given by  $I_o = v_d \sqrt{\beta I_{DC0}}$ . However, in deep submicron technologies, other third order nonlinearities arise from short channel effects which were neglected in the previous analysis and thus finite third order nonlinearities will not be cancelled by this technique.

The proposed methodology is an architectural solution that achieves up to 22dB IM3 improvement over an identical non-linearized OTA design at frequencies as high as 350MHz. It can be generalized to fully-differential topologies which offer higher PSRR and common-mode rejection ratio (CMRR). Since the maximum frequency is mainly limited by process parasitics and OTA performance, the approach shows promise of exceeding 350MHz bandwidth in future nanoscale CMOS processes. Robust linearization over a wide frequency range demands a mechanism to correct for high-frequency effects and PVT variations, for which a digital programmability scheme is proposed.

#### 2.2 Attenuation-Predistortion Linearization Methodology

Signal attenuation at the OTA input [14] reduces the effective transconductance and decreases the SNR. Alternatively, distortion cancellation by means of cross-coupled differential pairs results in increased power consumption and noise proportional to the transistor parameters in the additional path. Since the extra differential pair normally has less transconductance than the main pair, the effective transconductance is reduced by

10-50%. However, both transistor pairs should have the same third-order non-linearity, which translates into different transistor sizes and bias currents for each pair. As a result, the cross-coupling technique is sensitive to PVT variations and restricted to narrow frequency ranges. Another common method to linearize a transistor having transconductance  $g_m$  is to add a degeneration resistor  $R_{sd}$  at the source [14], which makes the third-order harmonic distortion proportional to the factor  $1/(1+g_mR_{sd})^3$ . Nonetheless, large degeneration resistance results in higher input-referred noise, lower transconductance, and less voltage headroom. The effective transconductance ( $g_{msd}$ ) and the input-referred noise ( $v_{nsd}^2$ ) with resistive source degeneration are given by

$$g_{msd} = \frac{g_m}{1 + g_m R_{sd}}$$

,  $v_{nsd}^2 \approx \frac{4KT}{g_m} \left(\frac{2}{3} + g_m R_{sd}\right)$ , (2.1)

where the noise coefficient  $\gamma$  was approximated as 2/3. For example, using a degeneration factor  $g_m R_{sd} = 2$  will ideally result in IM3 improvement of approximately 29dB, an input-referred noise power increase by a factor of 4, and a decrease of the transconductance to one third of its original value. But based on simulations of the OTA from this work with  $g_m R_{sd} = 2$ , the expected IM3 improvement would be 25.2dB with an associated noise power increase of more than 9 times.

The proposed attenuation-predistortion [18] method is independent of OTA topology and involves cancellation of all distortion components except those from secondary effects at high frequencies. It can be used in conjunction with other circuit-level linearization techniques internal to the OTA, such as source degeneration or cross-coupling.

## 2.2.1 Single-Ended Circuits

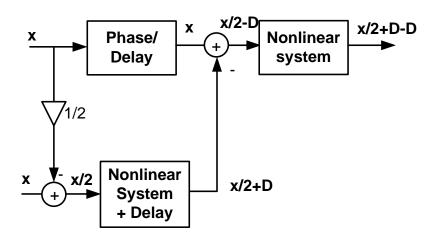

The proposed linearization scheme is illustrated in Fig. 2.2 where the non-linear system is linearized by subtracting the harmonics created in an identical system. Fig. 2.3 depicts the single-ended architecture that contains an auxiliary branch with an OTA having identical dimensions, DC bias, and AC common-mode conditions as in the main path to generate the distortion components required for cancellation.

Fig. 2.2. Block diagram of the proposed attenuation-predistortion technique.

An important advantage of identical paths is robustness to PVT variations because of optimal device matching obtainable from proper layout. In this scheme, it is avoided to base the distortion cancellation on branches with different transconductor device dimensions or bias conditions, which would degrade matching accuracy. But even with minimized mismatches, non-linearities are particularly frequency-dependent at high frequencies and remain sensitive to PVT variations as established in Section 2.5.

Hence, the proposed linearization method involves variable resistors to tune performance and counteract high-frequency degradation as well as PVT variations. Either a resistive or capacitive divider can form the attenuator at the input of the auxiliary path; however, resistors add more noise.

Fig. 2.3. Attenuation-predistortion linearization scheme for single-ended circuits.

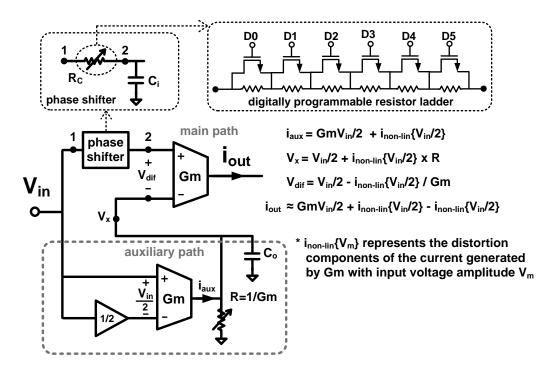

Distortion cancellation in the single-ended case requires  $G_m \times R = 1$ , which is ascertained by the following analysis. For a certain input voltage amplitude  $V_m$ , the output current can be divided into a linear part  $i_{lin}\{V_m\} = G_m \times V_m$  and a non-linear part  $i_{non-lin}\{V_m\} = g_{m2} \times V_m^2 + g_{m3} \times V_m^3 + ...$ , where  $g_{m2}, g_{m3},...$  are Taylor series coefficients of the transconductance. The differential input of the main OTA is:  $V_{dif} = V_{in} - [V_{in}/2 + i_{non-lin}\{V_{in}/2\}/G_m] = V_{in}/2 - i_{non-lin}\{V_{in}/2\}/G_m$ . Under ideal conditions, the distortion

generated in the auxiliary path,  $-i_{non-lin}\{V_{in}/2\}$ , cancels out the distortion in the main voltage-to-current conversion. In practice, distortion caused by non-linearities at the output of the auxiliary OTA and high-frequency effects introduces some finite uncancelled distortion. Capacitor  $C_0$  represents the lumped output capacitance of the auxiliary OTA, input capacitance of the main OTA, and layout parasities. Resistor  $R_c$  of the phase shifter and equivalent input capacitance  $C_i$  provide  $1^{st}$ -order frequency compensation, creating a pole to equalize the phase shift between the main and auxiliary paths. Compensation is necessary at high frequencies because parasitic capacitance  $C_0$  at the negative input terminal of the main OTA creates a pole with resistor R in the auxiliary path.

# 2.2.2 Fully-Differential Circuits

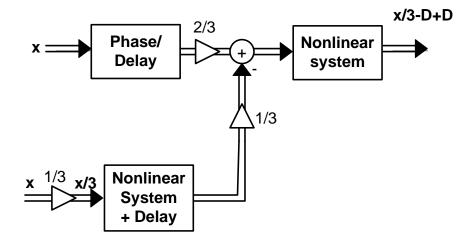

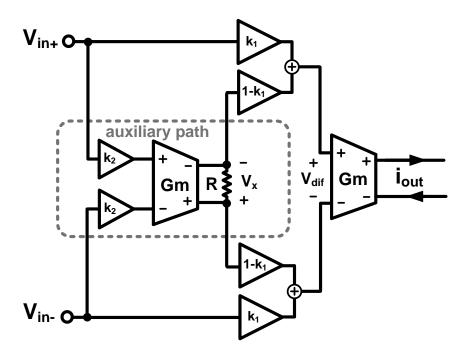

A conceptual diagram of the proposed linearization approach for a fully-differential transconductor (G<sub>m</sub>) and the corresponding circuit diagram are displayed in Fig. 2.4 and Fig. 2.5 respectively. In the fully-differential case, attenuation factors at the input of the transconductors are chosen such that it can be realized with floating-gate devices as described in Section 2.4.1.

As discussed in [14], [19] and [20], the inherent input attenuation with floating-gate stages enhances the OTA linearity. The distortion cancellation principle is the same as in the single-ended case, but different conditions must be satisfied for fully-differential implementation, which are explained in Sections 2.2.3 and 2.4.1 with regards to the attenuation ratios.

Fig. 2.4. Block diagram of the fully differential implantation of the attenuation-predistortion technique.

Fig. 2.5. Attenuation-predistortion linearization for fully-differential circuits.

By selecting an input attenuation ratio of 1/3 and voltage gain of 3 in the auxiliary branch ( $G_m \times R = 3$ ), the signal amplitude  $V_x$  is equal to  $V_{in}$  plus three times the distortion components caused by the non-linear current  $i_{non-lin}\{V_{in}/3\}$  from the transconductor with input amplitude of  $V_{in}/3$ . In the main path, the effective differential OTA input is:  $V_{dif} = 2V_{in}/3 - V_x/3 = 2V_{in}/3 - [V_{in} + 3\times i_{non-lin}\{V_{in}/3\}/G_m] / 3 = V_{in}/3 - i_{non-lin}\{V_{in}/3\}/G_m$ . Thus, the differential signal contains the attenuated input signal and the inverse of the distortion generated by the identical  $G_m$  in the auxiliary branch for distortion cancellation during the voltage-to-current conversion in the main path. Ideally, the distortion components are canceled by the equal and opposite terms from the predistortion of the differential input signal except for negligible higher-order components.  $C_0$  in Fig. 2.5 represents the equivalent differential capacitance of all parasitic capacitances at the output of the auxiliary OTA and  $C_p$  is the differential equivalent of the parasitic capacitances at the input of the main OTA. Expressions for optimum distortion cancellation at high frequencies are provided in Section 2.3.

Linear RC phase shifter networks are chosen for the frequency compensation implementation in order not to affect the cancellation scheme. Resistors R and  $R_c$  are tuned with 6-bit resolution to compensate for mismatches/PVT variations. The phase shifter block is utilized to equalize the delay from the input to summing nodes 3 and 4 in Fig. 2.5. Furthermore, the phase shifter enables optimization of the non-linearity cancellation based on high-frequency effects.

## 2.2.3 Scaling of Attenuation Ratios

Depending on application-specific requirements, the design parameters in the attenuation-predistortion linearization approach can be selected to adjust the voltage swings and the effective transconductance. Fig. 2.6 shows the fully-differential attenuation-predistortion linearization scheme, where frequency compensation and parasitic capacitors have been omitted for simplicity.

Fig. 2.6. Low-frequency model for the fully-differential attenuation-predistortion scheme.

The following analysis assumes floating-gates as a practical attenuator implementation choice under the constraint that factors  $k_1$  and  $(1-k_1)$  are related as elaborated upon in Section 2.4.1, but less restrictive types of attenuators could also be

used. As mentioned before, the output current  $i_o$  of an OTA due to an input voltage  $V_m$  can be modeled as having a linear and a non-linear part:  $i_o = G_m V_m + i_{non-lin} \{V_m\}$ . Ignoring high-frequency and secondary effects, the following relation can be written:

$$i_{out} \approx G_m (k_1 - (1 - k_1)k_2 G_m R) V_{in} - (1 - k_1) G_m R \cdot i_{non-lin} \{ k_2 V_{in} \} + i_{non-lin} \{ (k_1 - (1 - k_1)k_2 G_m R) V_{in} \}$$

(2.2)

where:  $i_{non-lin}\{k_2V_{in}\}\cdot R(1-k_1) \le (k_1-(1-k_1)k_2G_mR)V_{in}$  is assumed in the approximation. To cancel the distortion, the following conditions should hold:

- i) The auxiliary and main OTAs should have the same effective input voltage amplitudes such that an identical distortion is created at their respective outputs.

- ii) The gain in the auxiliary path must ensure that the distortion through this signal path reaches the output of the main OTA with a gain of -1.

- iii) The internal signal swings should be bounded, i.e.:

$$k_2 G_m R \le 1 \tag{2.3}$$

Applying conditions i) and ii), cancellation of the non-linear terms in (2.2) requires:

$$(1-k_1)G_mR = 1$$

,  $k_2 = k_1/2$  (2.4)

Consequentially, the effective transconductance with linearization is given by

$$G_{meff} = (k_1 - (1 - k_1)k_2G_mR)G_m = (k_1/2)G_m = k_2G_m$$

(2.5)

Condition iii) depends on the application and is not always necessary. Cancellation of distortion with the proposed technique requires weakly non-linear operation in the auxiliary branch, which is ensured by limiting the signal swing with this condition. The example that is presented in Fig. 2.5 was derived with  $k_2G_mR=1$ ,

ensuring that the signal swing at the output of the auxiliary OTA is the same as at its input. This choice was made to maintain the same maximum input voltage swing as the initial OTA without saturating the OTA in the linearization path. If the specified input signal is  $k_2G_mR$  times below the OTA saturation level, then  $k_2$  can be increased accordingly to obtain  $k_2G_mR > 1$  and higher effective transconductance based on (2.5). But, this choice is only permissible if a reduction of the maximum input swing by  $k_2G_mR$  can be tolerated, which would imply a reduction in the dynamic range. Typically, choosing  $k_2G_mR = 1$  is advantageous to maintain the same maximum input voltage swing as the original OTA after linearization. Selection of  $k_1 = 2/3$  and  $k_2 = 1/3$  results in the highest effective transconductance that can be achieved in (2.5) based on the above conditions while also satisfying the attenuation factor relationships in the floating-gate devices (Section 2.4.1) with identical signal swings at the input and output of the auxiliary OTA ( $k_2G_mR = 1$ ). Hence,  $G_mR = 3$  under the stated conditions.

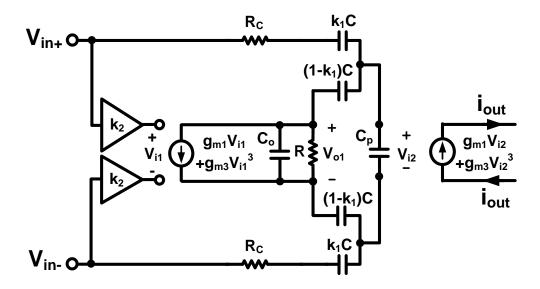

## 2.3 Volterra Series Analysis

The preceding expressions are valid at low frequencies and give insight into the conditions to cancel total distortion when secondary effects are negligible. Volterra series analysis [21] is used to find the optimum compensation resistor value for linearization at high frequencies. Employing a  $3^{rd}$ -order model of transconductor non-linearity, the simplified model of the proposed attenuation-predistortion linearization technique is shown in Fig. 2.7. In this analysis,  $g_{m1}$  represents the linear transconductance and  $g_{m3}$  the third-order component. Resistor ( $R_c$ ) compensates for

high-frequency linearity degradation by equalizing the delays in the main and auxiliary paths.

Fig. 2.7. Non-linear model for fully-differential attenuation-predistortion cancellation.

The differential voltage  $V_{i2}(t)$  at the input of the main OTA is given by

$$\begin{split} V_{i2}(t) &= - \Big( g_{m1} k_2 V_{in}(t) + g_{m3} [k_2 V_{in}(t)]^3 \Big) \cdot \frac{R \cdot (1 - k_1)}{1 + 2C_p / C} \cdot \frac{1 + j\omega C k_1 R_c}{1 + j\omega b - c\omega^2} \\ &+ V_{in}(t) \cdot \frac{k_1}{1 + 2C_p / C} \cdot \frac{1 + j\omega C (1 - k_1) R / 2 + j\omega C_o R}{1 + j\omega b - c\omega^2} \end{split} \tag{2.6}$$

where:

$$b = \frac{C(k_1/2)(1-k_1)(R+2R_c) + 2k_1C_pR_c + (1-k_1)C_pR}{1+2C_p/C} + C_oR$$

$$c = \frac{k_1(1-k_1)CC_pRR_c + CC_ok_1(1-k_1)RR_c + 2k_1C_pC_oR_cR}{1+2C_p/C}$$

Following the same analysis as in Section 2.2.3 but taking the parasitic capacitances  $C_p$  and  $C_o$  into account, the conditions for distortion cancellation at low frequencies are:

$$\frac{g_{m1} \cdot R \cdot (1 - k_1)}{1 + 2C_p / C} = 1 \quad , \quad k_2 = \frac{k_1 / 2}{1 + 2C_p / C}$$

(2.7)

With the above provisions, the output current of the main OTA after algebraic simplifications is:

$$i_{out}(t) = g_{m1}V_{i2}(t) + g_{m3}[V_{i2}(t)]^{3}$$

$$\approx g_{m1}V_{in}(t) \cdot \frac{(k_{1}/2)}{1 + 2C_{p}/C} \cdot \frac{1 + j\omega C((1 - k_{1})R - k_{1}R_{c}) + j2\omega C_{o}R}{1 + j\omega b - c\omega^{2}}$$

$$-g_{m3}\left(\frac{k_{1}V_{in}(t)/2}{1 + 2C_{p}/C}\right)^{3} \cdot \frac{1 + j\omega Ck_{1}R_{c}}{1 + j\omega b - c\omega^{2}}$$

$$+g_{m3}\left(\frac{k_{1}V_{in}(t)/2}{1 + 2C_{p}/C} \cdot \frac{1 + j\omega C((1 - k_{1})R - k_{1}R_{c}) + j2\omega C_{o}R}{1 + j\omega b - c\omega^{2}}\right)^{3}$$

$$(2.8)$$

Assuming weakly non-linear operation based on condition iii) in Section 2.2.3 and that the signal can be expressed as a sum of sinusoids with noncommensurate frequencies, the harmonic input method can be applied to calculate the Volterra series coefficients [21] and theoretically demonstrate the non-linearity cancellation with the proposed scheme. Taking a single input  $V_{in}(t) = e^{j\omega_i t}$  and substituting into (2.8) to express the linear transfer function  $H_1$ :

$$H_{1} = g_{m1} \cdot \frac{(k_{1}/2)}{1 + 2C_{p}/C} \cdot \frac{1 + j\omega C((1 - k_{1})R - k_{1}R_{c}) + 2j\omega C_{o}R}{1 + j\omega b - c\omega^{2}}$$

(2.9)

Selecting  $V_{in}(t) = e^{j\omega_1 t} + e^{j\omega_2 t} + e^{j\omega_3 t}$  and making the appropriate substitutions for calculation of the third-order transfer function (H<sub>3</sub>) yields the following equality after

expansion and omission of all terms that do not contain the  $\exp(j\omega_1 t + j\omega_2 t + j\omega_3 t)$  factor relevant to  $H_3$ :

$$H_{3}(\omega_{1}, \omega_{2}, \omega_{3}) = g_{m3}\left(\frac{k_{1}/2}{1+2C_{p}/C}\right)^{3}\left(\frac{1+j\omega_{1}C((1-k_{1})R-k_{1}R_{c})+2j\omega_{1}C_{o}R}{1+j\omega_{1}b-c\omega_{1}^{2}}\right) \cdot \left(\frac{1+j\omega_{2}C((1-k_{1})R-k_{1}R_{c})+2j\omega_{2}C_{o}R}{1+j\omega_{2}b-c\omega_{2}^{2}}\right)\left(\frac{1+j\omega_{3}C((1-k_{1})R-k_{1}R_{c})+2j\omega_{3}C_{o}R}{1+j\omega_{3}b-c\omega_{3}^{2}}\right) - g_{m3}\left(\frac{k_{1}/2}{1+2C_{p}/C}\right)^{3}\frac{1+j(\omega_{1}+\omega_{2}+\omega_{3})Ck_{1}R_{c}}{1+j(\omega_{1}+\omega_{2}+\omega_{3})b-c(\omega_{1}+\omega_{2}+\omega_{3})^{2}}$$

$$(2.10)$$

The amplitude of the third harmonic distortion (HD3) current due to a sinusoidal input signal  $V_{in}sin(\omega t)$  is given by

$$i_{o3} = \frac{1}{4} V_{in}^{3} H_{3}(\omega, \omega, \omega) =$$

$$\frac{1}{4} g_{m3} \left( \frac{V_{in} k_{1}/2}{1 + 2C_{p}/C} \right)^{3} \left( \frac{1 + j\omega C((1 - k_{1})R - k_{1}R_{c}) + 2j\omega C_{o}R}{1 + j\omega b - c\omega^{2}} \right)^{3}$$

$$-\frac{1}{4} g_{m3} \left( \frac{V_{in} k_{1}/2}{1 + 2C_{p}/C} \right)^{3} \frac{1 + j3\omega Ck_{1}R_{c}}{1 + j3\omega b - 9c\omega^{2}}$$

(2.11)

Elimination of HD3 requires that  $i_{o3} = 0$ , hence

$$\frac{1 + j\omega C((1 - k_1)R - k_1R_c) + 2j\omega C_o R}{1 + j\omega b - c\omega^2} = \sqrt[3]{\frac{1 + j3\omega Ck_1R_c}{1 + j3\omega b - 9c\omega^2}}$$

(2.12)

The cubic root in (2.12) can be approximated with  $\sqrt[3]{1+x} \approx 1+x/3$  for x << 1. Thus,

$$\frac{1+j\omega C((1-k_1)R-k_1R_c)+2j\omega C_oR}{1+j\omega b-c\omega^2} \approx \frac{1+j\omega Ck_1R_c}{1+j\omega b-3c\omega^2}$$

$$\Rightarrow R_c \approx \frac{(1-k_1)+2C_o/C}{2k_1}R \quad \text{to cancel HD3}$$

(2.13)

For a two-tone input signal of the form  $V_{in1}sin(\omega_1 t)+V_{in2}sin(\omega_2 t)$ , the IM3 current can be determined with Volterra series according to the following equation:

$$i_{IM3} = \frac{3}{4} V_{in1}^{2} V_{in2} H_{3}(\omega_{1}, \omega_{1}, -\omega_{2}) =$$

$$g_{m3} \left( \frac{k_{1}/2}{1 + 2C_{p}/C} \right)^{3} \left( 3V_{in1}^{2} V_{in2}/4 \right) \left( \frac{1 + j\omega_{1} C((1 - k_{1})R - k_{1}R_{c}) + 2j\omega_{1}C_{o}R}{1 + j\omega_{1}b - c\omega_{1}^{2}} \right)^{2}$$

$$\cdot \left( \frac{1 - j\omega_{2} C((1 - k_{1})R - k_{1}R_{c}) - 2j\omega_{2}C_{o}R}{1 - j\omega_{2}b - c\omega_{2}^{2}} \right)$$

$$- g_{m3} \left( \frac{k_{1}/2}{1 + 2C_{p}/C} \right)^{3} \left( 3V_{in1}^{2} V_{in2}/4 \right) \frac{1 + j(2\omega_{1} - \omega_{2})Ck_{1}R_{c}}{1 + j(2\omega_{1} - \omega_{2})b - c(2\omega_{1} - \omega_{2})^{2}}$$

$$(2.14)$$

Simplifying  $i_{\text{IM}3}$  for two intermodulation tones that are close together ( $\omega_1 \approx \omega_2 \approx 2\omega_1 - \omega_2$ ) yields:

$$i_{IM3} \approx \frac{3g_{m3}V_{in1}^{2}V_{in2}}{4} \left(\frac{k_{1}/2}{1+2C_{p}/C}\right)^{3} \left(\frac{1+j\omega_{1}C((1-k_{1})R-k_{1}R_{c})+2j\omega_{1}C_{o}R}{1+j\omega_{1}b-c\omega_{1}^{2}}\right)^{2} \cdot \left(\frac{1-j\omega_{1}C((1-k_{1})R-k_{1}R_{c})-2j\omega_{1}C_{o}R}{1-j\omega_{1}b-c\omega_{1}^{2}}\right) -g_{m3} \left(\frac{k_{1}/2}{1+2C_{p}/C}\right)^{3} \left(3V_{in1}^{2}V_{in2}/4\right) \frac{1+j\omega_{1}Ck_{1}R_{c}}{1+j\omega_{1}b-c\omega_{1}^{2}}$$

$$\Rightarrow R_{c} \approx \frac{(1-k_{1})+2C_{o}/C}{2k_{1}}R \qquad for \quad i_{IM3} \approx 0$$

(2.15)

In the discussed example case with  $k_1$ =2/3, the condition to cancel IM3 with the phase shifter block in Fig. 2.5 is  $R_c$ =(R/4)\*(1+6C<sub>o</sub>/C). To ensure high linearity with variations of parasitic capacitances, the programmable range of  $R_c$  is selected based on process corner simulations as described in Section 2.5.

# 2.4 Circuit-Level Considerations

# 2.4.1Fully-Differential OTA with Floating-Gate FETs

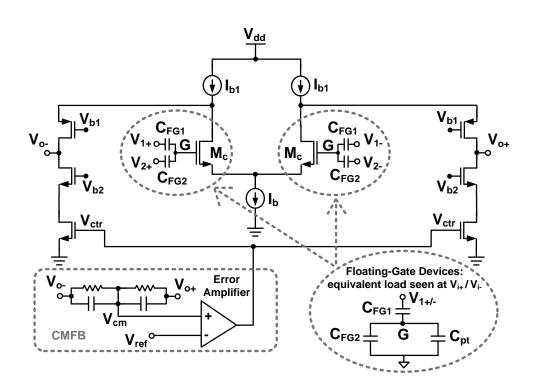

Fig. 2.8 displays the schematic of the OTAs implemented on the 0.13µm CMOS test chip with a 1.2V supply, and its common-mode feedback (CMFB) circuit.

Fig. 2.8. Folded-cascode OTA (implements G<sub>m</sub> in the main and auxiliary paths).

Attenuators  $k_1$ ,  $(1-k_1)$ , and  $k_2$  are realized with floating-gate devices for attenuation-predistortion linearization of this fully-differential topology. The gates (G) of the standard NMOS transistors in the OTA core are not resistively biased and are only connected to two conventional metal-insulator-metal (MIM) capacitors. Fig. 2.8 also

visualizes the equivalent capacitive load seen at the  $V_{1+}$  and  $V_{1-}$  inputs, where  $C_{pt}$  represents the effective gate-to-ground<sub>(AC)</sub> capacitance from transistor parasitic capacitances. With this configuration, the gate voltages are:  $V_{G+/-} = (C_{FG1}/C_{total})V_{1+/-} + (C_{FG2}/C_{total})V_{2+/-}$ , where  $C_{total} \approx C_{FG1} + C_{FG2}$  when  $C_{pt}$  is negligible. It follows that the attenuation factors in Fig. 2.6 are:  $C_{FG1}/C_{total} = k_1$  and  $C_{FG2}/C_{total} = (C_{total}-C_{FG1})/C_{total} = 1-k_1$ . The accuracy of the  $k_1$  and  $(1-k_1)$  factors predominantly depends on the matching of the MIM capacitors  $C_{FG1}$  and  $C_{FG2}$ , which can be achieved within 0.1-1% using proper layout techniques. As assessed in Section 2.5, such a matching accuracy is more than sufficient with the 3%-step programmability of resistor R for gain mismatch compensation in both paths.

In the layout, all nodes G at the floating gates in Fig. 2.8 are connected to the top metal layer using standard poly-metal contacts and metal-metal vias. During fabrication, this connection ensures that any charge stored on the floating gates flows to the substrate because all connections to the top metal are still joined prior to their separation during the last etching step. Thus, no charge is stored on the floating gates when the substrate contacts are also connected to the top metal layer [22], allowing gate discharge into the substrate before the last etching operation. After etching, the top metal extensions of the gates without trapped charge are floating, leaving only the connections to the two MIM capacitors. The floating-gate device design expressions for  $k_1$  and  $(1-k_1)$  above are assuming absence of excess charge on the floating gates, which is a satisfied condition without extra fabrication steps as a consequence of the gate and substrate connections to the top metal. A special programming technique for non-zero charge on the floating

gates was not utilized in this work, but a more sophisticated floating-gate device implementation as presented in [19] could be explored, which promises additional potential for compensation of inherent transistor threshold voltage offsets in the OTA's input differential pair.

The phase shifter in Fig. 2.5 creates an extra pole within the linearized architecture that the reference OTA does not have. This phase delay is roughly the same as the delay from the pole formed by R and  $C_0$  in the auxiliary path. In low-loss (high-Q) designs, the additional pole can affect the gain of integrators and the frequency response of biquad sections if  $1/(RC_0)$  is not significantly larger than the operating frequency. A load compensation scheme is discussed in Section 2.7 for such situations.

Identical standalone OTAs are included on the same die to obtain reference linearity measurements. The reference OTA also has a floating-gate input attenuation of 1/3 for fair performance comparison. In this way, the linearity benefit from the input attenuation is isolated from the architectural linearization proposed in Fig. 2.5, and both OTAs have the same effective transconductance (Gm/3 in this case), but the linearization results in doubled power consumption. Since attenuation and feedback linearization techniques have known linearity and effective transconductance trade-offs, the circuit-level comparison is focused on the predistortion linearization scheme relative to a commensurate OTA with equal input attenuation factor. This baseline OTA in Fig. 2.8 was biased with  $I_b = 0.95$ mA and  $I_{b1} = 0.85$ mA, having an effective transconductance of  $510\mu$ A/V. The linearization does not require any design changes in this core OTA, but redesign of the OTA is an option if it is required to meet the same power budget after

linearization, which is possible as long as OTA bandwidth reduction can be tolerated. Such a linearization under power constraint is disclosed in Section 2.8.

## 2.4.2 Common-Mode Feedback Design

Suppression of undesired common-mode signals and noise is vital for linearity at high frequencies. The CMFB circuit should have high gain to accurately control the common-mode output voltage while maintaining a large bandwidth to reject common-mode noise in the band of interest. The CMFB amplifier is shown in Fig. 2.9, where  $V_{ctr}$  is the control voltage applied to the OTA in Fig. 2.8.

Fig. 2.9. (a) Error amplifier circuit in the CMFB loop and (b) small-signal equivalent circuit.

Neglecting the effect of the output resistance  $R_{ob}$  and capacitance  $C_{ob}$  of the current source  $I_b$  in Fig. 2.9, the transfer function of the error amplifier is:

$$\frac{V_{ctr}}{V_{cm}} = \frac{g_m R_L}{2} \cdot \frac{1 + s R_z C_{dg} + s^2 R_z C_{dg} C_{gs} / g_m}{1 + 2s \zeta / \omega_n + s^2 / \omega_n^2}$$

(2.16)

where:

$$2\zeta/\omega_{n} = R_{z}(C_{dg} + C_{gs}/2 + (g_{m}R_{L}/2)C_{dg} + (R_{L}/R_{z}) \cdot (C_{dg} + C_{L}))$$

$$1/\omega_{n}^{2} = R_{z}R_{L}C_{dg}C_{gs}/2 + R_{z}R_{L}(C_{dg} + C_{gs}/2)C_{L}$$

The zeros of this transfer function are given by

$$\omega_{z1}, \omega_{z2} = -\frac{g_m}{2C_{gs}} \left( 1 \pm \sqrt{1 - \frac{4C_{gs}}{g_m R_z C_{dg}}} \right)$$

(2.17)

and the pole locations in the transfer function are approximately:

$$\omega_{p1} \approx -\frac{1}{R_z (C_{dg} + C_{gs}/2 + (g_m R_L/2)C_{dg} + (R_L/R_z) \cdot (C_{dg} + C_L))}$$

$$\omega_{p2} \approx -\frac{C_{dg} + C_{gs}/2 + (g_m R_L/2)C_{dg} + (R_L/R_z) \cdot (C_{dg} + C_L)}{R_L C_{dg} C_{gs}/2 + R_L (C_{dg} + C_{gs}/2)C_L}$$

(2.18)

The pole  $\omega_{p1}$  is inversely proportional to the compensation resistor  $R_z$ . Another pole in the CMFB loop is formed at the output of the OTA:  $\omega_{p3}\approx 1/(r_oC_o)^{-1}$ , where  $r_o$  is the output resistance of the OTA and  $C_o$  is the load capacitance. Assuming that the CMFB gain-bandwidth (GBW) is larger than the two dominant poles  $\omega_{p1}$  and  $\omega_{p3}$ , the CMFB gain-bandwidth product can approximated as

$$GBW \approx \sqrt{A_0 \cdot \omega_{p1} \cdot \omega_{p3}} \approx \sqrt{A_0 \cdot \omega_{p3} \cdot \frac{2}{R_z (C_{gs}/2 + (g_m R_L/2)C_{dg})}}$$

(2.19)

where  $A_0$  is the CMFB loop gain. The effect of the two zeros on the GBW was assumed to be negligible for simplicity; however their effect on the PM cannot be neglected and should be taken into account. A small  $R_z$  is desired to achieve high CMFB bandwidth.

However, the two zeros  $(\omega_{z1}, \, \omega_{z2})$  tend to go to infinity as  $R_z$  approaches zero, which will have an adverse effect on phase margin. If  $4C_{gs}/g_mR_zC_{dg} <<1$ , the two zeros can be approximated as

$$\omega_{z1} \approx -\frac{1}{R_z C_{dg}}$$

,  $\omega_{z2} \approx -\frac{g_m}{C_{gs}} \left( 1 - \frac{C_{gs}}{g_m R_z C_{dg}} \right)$  (2.20)

Hence, the phase margin can be estimated as follows:

$$PM \approx \tan^{-1} \left( \sqrt{A_0 \cdot \omega_{p3} \cdot \frac{2R_z C_{dg}^2}{(C_{gs}/2 + (g_m R_L/2)C_{dg})}} \right)$$

(2.21)

Thus, the addition of the compensation resistor  $R_z$  results in two zeros in the transfer function of the error amplifier, which helps to insure stability of the CMFB loop. The simulated AC response of the CMFB loop has a 51.9dB low-frequency gain and a 424.9MHz unity-gain frequency with 42.5 $^{\circ}$  phase margin.

# 2.4.3 Proof-of-Concept Filter Realization

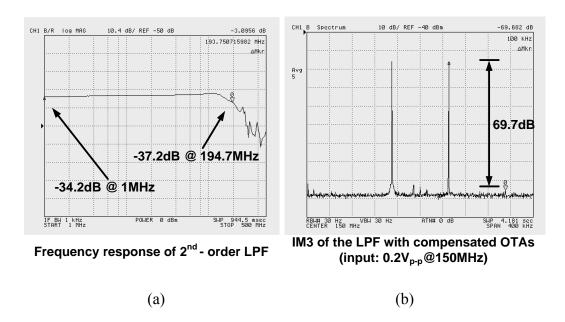

A  $2^{nd}$ -order  $G_m$ -C biquad filter was designed with attenuation-predistortion-linearized OTAs to verify that the proposed methodology is suitable for filters with  $G_m$ -C integrator loops. Fig. 2.10 shows the filter schematic and specifications. The lowpass output of the biquad was measured using another OTA as buffer to drive the  $50\Omega$  input impedance of the spectrum analyzer.

The primary motivation for digital correction (Section 2.5) to enhance linearity performance with severe process variation is compatibility with digitally-controlled receiver calibration approaches that involve the baseband filter.

Fig. 2.10. Fully-differential 2<sup>nd</sup> -order lowpass filter diagram and design parameters.

Practical implementation details for receivers with digital performance monitoring and calibration of analog blocks are described in [23]-[25]. They incorporate accurate digital monitoring and I/Q mismatch correction in the digital signal processor (DSP) as well as a few analog observables that give some insights into the operating conditions, such as outputs from received signal strength indicators or DC control voltages of blocks. The possibility exists to generate and apply test tones at the input of an analog block and extract performance indicators from the output spectrum in the DSP, which contains distortion components. Conversely, calibration could also be performed by monitoring the bit error rate (BER) in the DSP from processing a special test sequence or customary pilot symbols at the beginning of receptions. Since linearity degradation impacts the BER, such a calibration could be computationally more efficient

than calculating and analyzing the fast Fourier transform in the DSP. Regardless of the specific digital calibration algorithm, the digitally-controlled correction capability of the proposed linearization scheme can potentially enable filter linearity tuning in integrated receiver applications without the need for extra DACs.

An alternative automatic calibration that does not involve an on-chip DSP but dedicated analog and simpler digital logic circuitry is displayed in Fig. 2.11.

Fig. 2.11. Block diagram of the proposed automatic linearity tuning scheme.

From the conditions for optimum distortion cancellation described in Section 2.2.3, the gain of the auxiliary path must be equal to  $k_2G_mR$ , which is unity in the discussed design example. This can be ensured by measuring the signal level at the input and output of the auxiliary OTA with power or peak detectors (PD<sub>1</sub>, PD<sub>2</sub>), and controlling the digital code of resistor R until the gain is unity. The simplest control

algorithm would be to cycle through the codes that determine the value of R until the difference in the DC output voltages of  $PD_1$  and  $PD_2$  is minimized, which can be performed digitally by detecting the toggling instance at the output of a single comparator. At higher frequencies, the parasitic pole in the auxiliary path starts to affect the distortion cancellation, causing the signal level at the output of the auxiliary OTA to decrease with increasing frequency. Hence, the differential input signal to the main OTA at  $PD_3$  increases as a result, which is shown in Fig. 2.12.

Fig. 2.12. Simulated AC amplitude at the input of the main OTA (PD<sub>3</sub> in Fig. 2.11) before and after adjustment of resistor  $R_c$  to its optimum value. (The voltage at PD<sub>3</sub> is ideally equal to  $V_x = k_2 \cdot V_{in}$ ).

By measuring this signal that is ideally equal to  $k_2 \cdot V_{in}$  with PD<sub>3</sub>, the value of the phase shift resistor  $R_c$  can be adjusted until the outputs of PD<sub>3</sub> and PD<sub>4</sub> are equal. This comparison can be completed with the same logic as for PD<sub>1</sub>/PD<sub>2</sub>, but it has to be done with an input signal at the maximum frequency at which high linearity is desired. The automatic tuning has not been implemented on the circuit level, but simulations with different values of  $R_c$  showed that amplitude detection within 4.6% is required to detect  $R_c$  changes within 5% at 350MHz, which is sufficient for IM3 higher than 70dBc (Section 2.5). In differential gain measurements, PVT errors in the detectors are cancelled except for the errors from unavoidable mismatches between the two detectors. Errors from mismatches are less than 5% at 2.4GHz [26], and more accurate amplitude detection is achievable at lower frequencies. In [27] for example, differential on-chip amplitude measurements were conducted up to 2.4 GHz using detectors with a die area of 0.031mm<sup>2</sup> and negligible loading of the signal path ( $C_{in} < 15$ fF).

## 2.5 Compensation for PVT Variations and Frequency-Effects

Since the frequency compensation is based on equalization of phase shifts from RC time constants in the main and auxiliary paths, the optimum linearity point is subjected to PVT variations. Resistors R and  $R_c$  in Fig. 2.5 can be adjusted digitally to ensure high linearity. When implementing the attenuation ratios with matched capacitors, the variation of the resistors and transconductance mismatch between the auxiliary and main paths become the main sources of IM3 degradation. Fig. 2.13

illustrates the technique's sensitivity to 20% variation of  $R_c$  and  $G_m$  based on expression for IM3 in (2.15).

Fig. 2.13. Sensitivity of |IM3| (in dBc) to component mismatches calculated with equation (2.15): (a) 10MHz signal frequency, (b) 200MHz signal frequency.

In theory, the |IM3| (in dBc) without parameter variation is infinite. After introducing a numerical resolution constraint, the peak |IM3| is limited to around 95dBc. Fig. 2.13 (a) reveals that  $G_m$ -mismatch results in more degradation than  $R_c$  variation at low frequencies, but at high frequencies variation of  $R_c$  becomes equally significant as

evident from Fig. 2.13 (b). In general, less than  $\pm 10\%$  mismatch of  $G_m \times R$  and  $\pm 5\%$  variation of  $R_c$  are required for theoretical |IM3| higher than 70dBc. Under consideration of the trend towards increasing intra-die variability in modern CMOS processes, programmability of R and  $R_c$  is necessary to guarantee  $G_m \times R$  gain and  $R_c$  values within these limits. The determination of the appropriate incremental resistor step size is elaborated next.

To obtain a practical assessment of the distortion cancellation sensitivity, the compensation resistor value and transconductance mismatch in the two paths were varied in circuit simulations using Spectre. The resulting |IM3| is plotted vs. deviation from the nominal design parameters in Fig. 2.14, showing an |IM3| better than 71dBc for  $\pm 7.5\%$  R<sub>c</sub>-variation and |IM3| better than 71dBc for  $\pm 3.3\%$  R-variation in the presence of 10% G<sub>m</sub>-mismatch. The reference OTA has |IM3| of 51dBc. It is imperative for effective distortion cancellation to implement the resistor ladders with 3% steps, enabling digital correction of relatively small intra-die mismatches. To account for large absolute variations of parameters, the adequate resistor tuning range should be selected based on simulations under anticipated worst-case conditions.

In this work, simulations with process-corner models and temperatures ranging from -40°C to 100°C were conducted. Based on these simulation results, a conservative range from ~30 to  $2.2k\Omega$  (approximately 3% - 200% of the nominal value) and 6-bit resolution were chosen for the programmable resistors  $R_c$  and R (Fig. 2.5) in this prototype design.

Fig. 2.14. Simulations showing sensitivity to variation and mismatch of critical components: (a) |IM3| vs. change in  $R_c$  (Fig. 2.5) at 350MHz, (b) |IM3| vs. R (in Fig. 2.5) with 10% transconductance mismatch between main OTA and auxiliary OTA at 350MHz.

## 2.6 Measurement Results

## 2.6.1 OTA

Table 2.1 summarizes the characterization results for the OTA. Two  $0.1V_{p-p}$  (-16dBm) tones with 100kHz frequency separation and a combined voltage swing of  $0.2V_{p-p}$  were applied during IM3 measurements. The results in Fig. 2.15 demonstrate IM3 enhancement from -58.5dB to -74.2dB at 350MHz coupled with a rise in input-referred noise from  $13.3nV/\sqrt{Hz}$  to  $21.8nV/\sqrt{Hz}$  and twice the power dissipation, while other performance parameters are not affected significantly. The linearization decreased the SNR in 1MHz BW from 74.5dB to 70.2dB, but allowed to improve the IM3 by 15.7dB.

Table 2.1 Measured main parameters of the reference folded-cascode OTA.

| Parameter                          | Measurement       |  |  |

|------------------------------------|-------------------|--|--|

| Transconductance (G <sub>m</sub> ) | 510 μ <b>Α/</b> V |  |  |

| IM3 @ 50MHz<br>(Vin = 0.2 Vp-p)    | -55.3 dB          |  |  |

| Noise (input-referred)             | 13.3 nV/√Hz       |  |  |

| Power with CMFB                    | 2.6 mW            |  |  |

| PSRR @ 50MHz                       | 48.9 dB           |  |  |

| Supply voltage                     | 1.2 V             |  |  |

Fig. 2.15. Measured linearity with  $0.2V_{p-p}$  input swing from two tones, each  $0.1V_{p-p}$  (-16dBm) on-chip after accounting for off-chip losses at the input: (a) reference OTA, (b) compensated OTA.

Depending on the frequency and switch settings, IM3 enhancement up to 22dB was achieved with the compensation resistor ladders having 6-bit resolution. If more linearity improvement is required, the resolution of the resistor ladders (R and R<sub>c</sub>) in Fig. 2.5 can be increased by adding more control bits or using a MOS in triode region as one of the elements to obtain a series resistance that is closer to the optimum value for distortion cancellation.

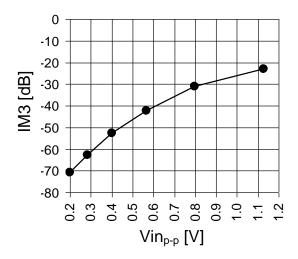

The IM3 from the two-tone tests of the reference and linearized OTAs around 350MHz is plotted versus input peak-to-peak voltage in Fig. 2.16. This comparison demonstrates that the IM3 enhancement from the linearization scheme requires weakly non-linear operation.

Fig. 2.16. Measured IM3 vs. input peak-peak voltage for reference OTA and compensated OTA obtained using two tones having 100kHz separation around 350MHz.

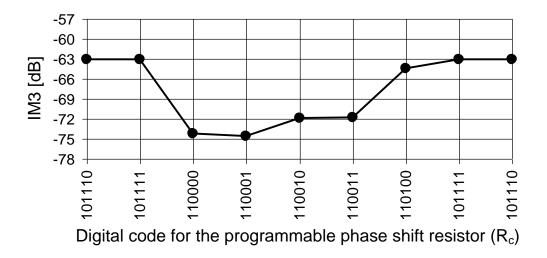

Even though the linearization effectiveness decreases with increasing input signal swing, the IM3 improvement is still 11dB with 0.8V<sub>p-p</sub> differential signal swing for this design with 1.2V supply. Since the distortion cancellation exhibits the highest sensitivity to phase shifts at high frequencies, the control code of the phase shift resistor R<sub>c</sub> in Fig. 2.5 has been changed from its optimum value. The resulting effect on the IM3 of the linearized OTA at 350MHz is plotted in Fig. 2.17, which validates that variable phase compensation is in fact required for optimum linearity performance. Two resistor ladder settings satisfy that the IM3 attenuation is more than 74dB, hence the selected 3% step for the least significant digital bit in this design was appropriate. Together with the plot obtained by sweeping resistor R<sub>c</sub> in simulations (Fig. 2.14a), the measurements indicate that the amount of IM3 improvement predominantly depends on the step size of the programmable resistor ladder, which promises even better distortion cancellation with finer resolution.

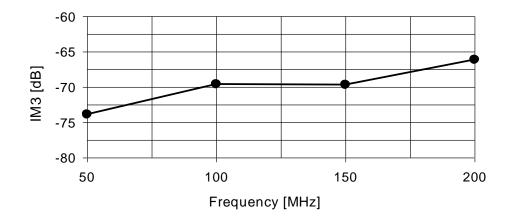

Table 2.2 includes noise and IM3 measurement results at various frequencies, demonstrating the effectiveness of the broadband linearization scheme with the associated input-referred noise. Performance trade-offs can be assessed with the figure of merit from [8]: FOM = NSNR +  $10\log(f/1MHz)$ , where NSNR =  $SNR_{(dB)}$  +  $10\log[(IM3_N / IM3)(BW / BW_N)(P_N / P_{dis})]$  from [9], the SNR is integrated over 1MHz BW, IM3 is normalized with  $IM3_N = 1\%$ , bandwidth is normalized with  $BW_N = 1Hz$ , and power consumption is normalized with  $P_N = 1mW$ .

Fig. 2.17. Measured IM3 dependence of the compensated OTA on phase shift obtained with two test tones having 100kHz separation around 350MHz. (The least significant bit of the digital control code changes the value of phase shift resistor  $R_c$  by  $\sim$ 3%).

Table 2.2 Comparison of OTA linearity and noise measurements.

| OTA type                                         | Input-<br>referre | Power           |          |             | V <sub>p-p</sub> ) | Normalize d  FOM * |

|--------------------------------------------------|-------------------|-----------------|----------|-------------|--------------------|--------------------|

|                                                  | d noise           | consumptio<br>n | 50 MHz   | 150<br>MHz  | 350<br>MHz         | (at 350<br>MHz)    |

| Reference<br>(input att. =<br>1/3)               | 13.3<br>nV/√Hz    | 2.6 mW          | -55.3 dB | -60.0<br>dB | -58.5<br>dB        | 56.7               |

| Linearized<br>(att. = 1/3 &<br>compensation<br>) | 21.8<br>nV/√Hz    | 5.2 mW          | -77.3 dB | -77.7<br>dB | -74.2<br>dB        | 64.3               |

<sup>\*</sup> See Table 2.3 for details.

Experimental results are compared with previously reported architectures in Table 2.3. The OTA linearized with input attenuation-predistortion shows a competitive performance with respect to the state of the art. High linearity at high frequencies is realized in this design example, showing the potential of the technique.

Table 2.3 OTA comparison with prior works.

|                        | [1]*       | [11]*                | [14]                 | [12]                    | [7]*                   | This work       |

|------------------------|------------|----------------------|----------------------|-------------------------|------------------------|-----------------|

| IM3                    | -          | -47 dB               | -70 dB               | -60 dB                  | -                      | -74.2 dB        |

| IIP3                   | -12.5 dBV  | -                    | -                    | -                       | - 7 dBV                |                 |

| f                      | 275 MHz    | 10 MHz               | 20 MHz               | 40 MHz                  | 40 MHz 184 MHz         |                 |

| Input voltage          | -          | 0.2 V <sub>p-p</sub> | 1.0 V <sub>p-p</sub> | 0.9 V <sub>p-p</sub>    | 0.9 V <sub>p-p</sub> - |                 |

| Power / transconductor | 4.5 mW     | 1.0 mW               | 4 mW                 | 9.5 mW                  | 1.26 mW                | 5.2 mW          |