# IMPROVING RELIABILITY AND PERFORMANCE OF NAND FLASH BASED STORAGE SYSTEM

by

## Jie Guo

B.S. in Electrical Engineering,

University of Electronic Science and Technology of China, China,

2005

M.S. in Electrical Engineering,

University of Electronic Science and Technology of China, China,

2008

Submitted to the Graduate Faculty of

the Swanson School of Engineering in partial fulfillment

of the requirements for the degree of

# Doctor of Philosophy

University of Pittsburgh

2016

# UNIVERSITY OF PITTSBURGH SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

Jie Guo

It was defended on

February 12th, 2016

and approved by

Yiran Chen, Ph.D., Associate Professor, Department of Electrical and Computer Engineering

Panos K. Chrysanthis, Ph.D., Professor, Department of Computer Science

Amro El-Jaroudi, Ph.D., Associate Professor, Department of Electrical and Computer Engineering

Hai Li, Ph.D., Associate Professor, Department of Electrical and Computer Engineering Kartik Mohanram, Ph.D., Associate Professor, Department of Computer Science

Dissertation Director: Yiran Chen, Ph.D., Associate Professor, Department of Electrical and Computer Engineering Copyright © by Jie Guo 2016

### IMPROVING RELIABILITY AND PERFORMANCE OF NAND FLASH BASED STORAGE SYSTEM

Jie Guo, PhD

University of Pittsburgh, 2016

High seek and rotation overhead of magnetic hard disk drive (HDD) motivates development of storage devices, which can offer good random performance. As an alternative technology, NAND flash memory demonstrates low power consumption, microsecond-order access latency and good scalability. Thanks to these advantages, NAND flash based solid state disks (SSD) show many promising applications in enterprise servers. With multi-level cell (MLC) technique, the per-bit fabrication cost is reduced and low production cost enables NAND flash memory to extend its application to the consumer electronics.

Despite these advantages, limited memory endurance, long data protection latency and write amplification continue to be the major challenges in the designs of NAND flash storage systems. The limited memory endurance and long data protection latency issue derive from memory bit errors. High bit error rate (BER) severely impairs data integrity and reduces memory durance. The limited endurance is a major obstacle to apply NAND flash memory to the application with high reliability requirement. To protect data integrity, hard-decision error correction codes (ECC) such as Bose-Chaudhuri-Hocquenghem (BCH) are employed. However, the hardware cost becomes prohibitively with the increase of BER when the BCH ECC is employed to extend system lifetime. To extend system lifespan without high hardware cost, we has proposed data pattern aware (DPA) error prevention system design. DPA realizes BER reduction by minimizing the occurrence of data patterns vulnerable to high BER with simple linear feedback shift register circuits. Experimental results show that DPA can increase the system lifetime by up to  $4 \times$  with marginal hardware cost.

With the technology node scaling down to 2Xnm, BER increases up to  $10^{-2}$ . Harddecision ECCs and DPA are no longer applicable to guarantee data integrity due to either prohibitively high hardware cost or high storage overhead. Soft-decision ECC, such as lowdensity parity-check (LDPC) code, has been introduced to provide more powerful error correction capability. However, LDPC code demands extra memory sensing operations, directly leading to long read latency. To reduce LDPC code induced read latency without adverse impact on system reliability, we has proposed FlexLevel NAND flash storage system design. The FlexLevel design reduces BER by broadening the noise margin via threshold voltage ( $V_{th}$ ) level reduction. Under relatively low BER, no extra sensing level is required and therefore read performance can be improved. To balance  $V_{th}$  level reduction induced capacity loss and the read speedup, the FlexLevel design identifies the data with high LDPC overhead and only performs  $V_{th}$  reduction to these data. Experimental results show that compared with the best existing works, the proposed design achieves up to 11% read speedup with negligible capacity loss.

Write amplification is a major cause to performance and endurance degradation of the NAND flash based storage system. In the object-based NAND flash device (ONFD), write amplification partially results from onode partial update and cascading update. Onode partial update only over-writes partial data of a NAND flash page and incurs unnecessary data migration of the un-updated data. Cascading update is update to object metadata in a cascading manner due to object data update or migration. Even through only several bytes in the object metadata are updated, one or more page has to be re-written, significantly degrading write performance. To minimize write operations incurred by onode partial update and cascading update, we has proposed a Data Migration Minimizing (DMM) device design. The DMM device incorporates 1) the multi-level garbage collection technique to minimize the unnecessary data migration of onode partial update and 2) the virtual B+ tree and diff cache to reduce the write operations incurred by cascading update. The experiment results demonstrate that the DMM device can offer up to 20% write reduction compared with the best state-of-art works.

### TABLE OF CONTENTS

| 1.0 | IN' | <b>TRODUCTION</b>                                  |

|-----|-----|----------------------------------------------------|

|     | 1.1 | MOTIVATION                                         |

|     |     | 1.1.1 Challenge 1: Limited Device Endurance        |

|     |     | 1.1.2 Challenge 2: High Data Protection Overhead   |

|     |     | 1.1.3 Challenge 3: Write Amplification             |

|     | 1.2 | Dissertation Contribution and Outline              |

| 2.0 | DP  | A: DATA PATTERN AWARE ERROR PREVENTION TECHNIQUE 9 |

|     | 2.1 | Preliminary                                        |

|     |     | 2.1.1 MLC NAND Flash Basics                        |

|     |     | 2.1.2 Program Disturb                              |

|     |     | 2.1.3 Read Disturb                                 |

|     |     | 2.1.4 Retention Time                               |

|     | 2.2 | Motivations                                        |

|     |     | 2.2.1 Lifetime Model                               |

|     | 2.3 | DPA Overview                                       |

|     | 2.4 | DPA-PPU: Pattern Probability Unbalance             |

|     | 2.5 | DPA-DRM: Data-Redundancy Management                |

|     | 2.6 | Experimental Results                               |

|     |     | 2.6.1 DPA Error Failure Rate                       |

|     |     | 2.6.2 Overheads of DPA                             |

|     | 2.7 | Chapter 2 summary                                  |

| <b>3.0</b> | FL            | FLEXLEVEL NAND FLASH STORAGE SYSTEM DESIGN TO RE-           |    |  |  |  |

|------------|---------------|-------------------------------------------------------------|----|--|--|--|

|            | DU            | CE LDPC LATENCY                                             | 33 |  |  |  |

|            | 3.1           | LDPC Code and Relative Works                                | 33 |  |  |  |

|            | 3.2           | Motivations                                                 | 34 |  |  |  |

|            | 3.3           | FlexLevel NAND Flash Storage System Overview                | 37 |  |  |  |

|            | 3.4           | LevelAdjust: $V_{th}$ Level Adjustment                      | 38 |  |  |  |

|            |               | 3.4.1 Basic LevelAdjust Technique                           | 38 |  |  |  |

|            |               | 3.4.2 NUNMA Technique: Non-uniform Noise Margin Adjustment  | 40 |  |  |  |

|            |               | 3.4.3 LevelAdjust Overhead Evaluation                       | 42 |  |  |  |

|            | 3.5           | AccessEval: Access Pattern Evaluation                       | 44 |  |  |  |

|            |               | 3.5.1 AccessEval Overview                                   | 44 |  |  |  |

|            |               | 3.5.2 IWFR Data Identification                              | 45 |  |  |  |

|            |               | 3.5.3 AccessEval Overhead Discussion                        | 48 |  |  |  |

|            | 3.6           | Experimental Results                                        | 49 |  |  |  |

|            |               | 3.6.1 LevelAdjust Efficiency                                | 49 |  |  |  |

|            |               | 3.6.2 AccessEval Performance Evaluation                     | 52 |  |  |  |

|            | 3.7           | Chapter 3 summary                                           | 55 |  |  |  |

| <b>4.0</b> | PE            | RFORMANCE OF OBJECT BASED NAND FLASH STORAGE                |    |  |  |  |

|            | $\mathbf{SY}$ | <b>STEM</b>                                                 | 57 |  |  |  |

|            | 4.1           | Background                                                  | 57 |  |  |  |

|            |               | 4.1.1 Basics of NAND Flash Memory                           | 57 |  |  |  |

|            |               | 4.1.2 Basics of Object-based NAND Flash Device              | 58 |  |  |  |

|            | 4.2           | Motivation                                                  | 59 |  |  |  |

|            | 4.3           | Related Works                                               | 61 |  |  |  |

|            | 4.4           | Optimization of Object-based NAND Flash Device              | 62 |  |  |  |

|            |               | 4.4.1 An Overview of Data Migration Minimizing (DMM) Device | 63 |  |  |  |

|            |               | 4.4.2 Multi-level Garbage Collection (MLGC)                 | 64 |  |  |  |

|            |               | 4.4.3 Virtual B+ Tree                                       | 66 |  |  |  |

|            |               | 4.4.3.1 Overview of Virtual B+ Tree                         | 67 |  |  |  |

|            |               | 4.4.3.2 Write overhead of virtual B+ tree                   | 68 |  |  |  |

|     |      |        | 4.4.3.3 Storage overhead of the virtual B+ tree                                   | 69  |

|-----|------|--------|-----------------------------------------------------------------------------------|-----|

|     |      | 4.4.4  | Diff Cache                                                                        | 70  |

|     |      | 4.4.5  | Power Failure Handling Approach                                                   | 73  |

|     |      |        | 4.4.5.1 Overview of DMM data recovery                                             | 73  |

|     |      |        | 4.4.5.2 Data recovery implementation                                              | 76  |

|     | 4.5  | ObjN   | andSim: ONFD Simulator                                                            | 76  |

|     |      | 4.5.1  | Simulation Platform                                                               | 76  |

|     |      | 4.5.2  | Overall Architecture of ObjNandSim                                                | 78  |

|     |      | 4.5.3  | Hardware Component                                                                | 80  |

|     |      | 4.5.4  | Software Component                                                                | 80  |

|     |      |        | 4.5.4.1 Software component function                                               | 80  |

|     |      |        | 4.5.4.2 I/O operation flow of the ObjNandSim $\ldots \ldots \ldots \ldots \ldots$ | 81  |

|     | 4.6  | Expe   | rimental Results                                                                  | 86  |

|     |      | 4.6.1  | Simulation Setup                                                                  | 86  |

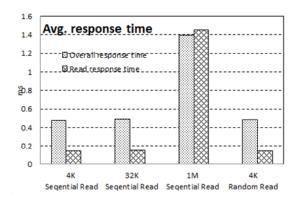

|     |      | 4.6.2  | ObjNandSim Evaluation                                                             | 88  |

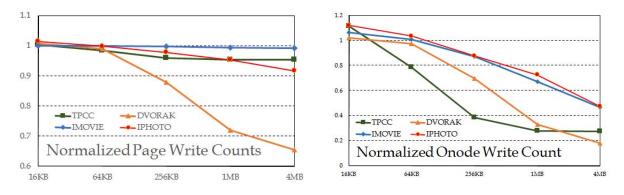

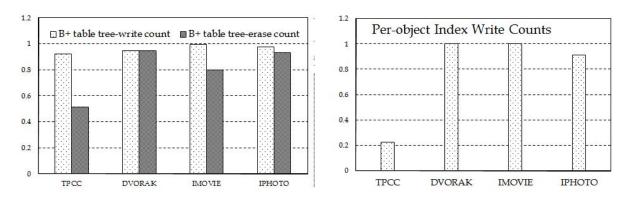

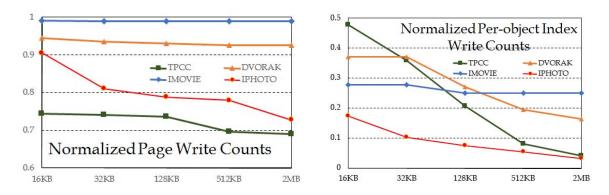

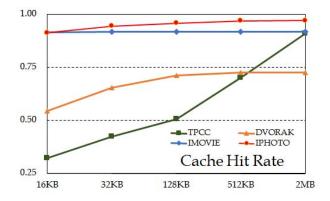

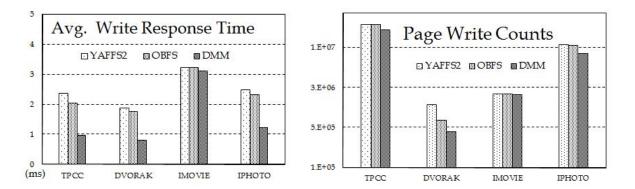

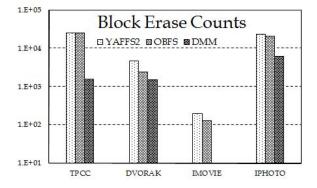

|     |      | 4.6.3  | Evaluation of DMM Device Efficiency                                               | 93  |

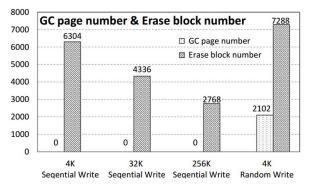

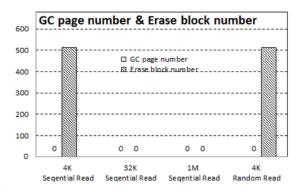

|     |      |        | 4.6.3.1 Evaluation of MLGC                                                        | 93  |

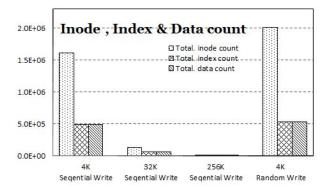

|     |      |        | 4.6.3.2 Evaluation of the virtual B+ tree                                         | 95  |

|     |      |        | 4.6.3.3 Evaluation of diff cache                                                  | 95  |

|     |      |        | 4.6.3.4 The overall performance improvement                                       | 97  |

|     | 4.7  | Sumn   | nary                                                                              | 98  |

| 5.0 | CO   | NCL    | USION AND FUTURE WORK                                                             | 99  |

|     | 5.1  | Disser | rtation Conclusion                                                                | 99  |

|     | 5.2  | Futur  | e Work                                                                            | 101 |

|     | 5.3  | Disser | rtation Summary                                                                   | 102 |

| BIE | BLIO | GRA    | PHY                                                                               | 104 |

### LIST OF TABLES

| 1  | File data characteristics                                                                    | 15 |

|----|----------------------------------------------------------------------------------------------|----|

| 2  | Workload characteristics.                                                                    | 22 |

| 3  | The parameters of MLC NAND flash                                                             | 22 |

| 4  | Sixty-four polynomials employed for scrambling                                               | 23 |

| 5  | The probability of each polynomial to reduce 1's number                                      | 25 |

| 6  | Required extra LDPC soft sensing levels                                                      | 36 |

| 7  | Bit value mapping under ReduceCode                                                           | 39 |

| 8  | $V_{th}$ transaction under 2-step programming operation $\ldots \ldots \ldots \ldots \ldots$ | 41 |

| 9  | Workloads access pattern characterization                                                    | 46 |

| 10 | Non-uniform LevelAdjust configuration                                                        | 49 |

| 11 | BER comparison under three NUNMA configurations                                              | 51 |

| 12 | MLC NAND flash specification                                                                 | 53 |

| 13 | Write Overhead of the Virtual B+ Tree                                                        | 68 |

| 14 | The definition of the variables of the restoration procedure                                 | 76 |

| 15 | The object operations implemented NandOsdSim                                                 | 81 |

| 16 | The default parameters of NAND flash memory                                                  | 87 |

| 17 | Workload characteristics                                                                     | 87 |

### LIST OF FIGURES

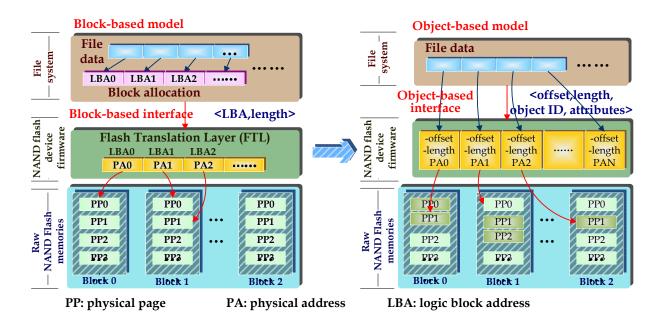

| 1  | The block-based storage v.s. the object-based storage    | 5  |

|----|----------------------------------------------------------|----|

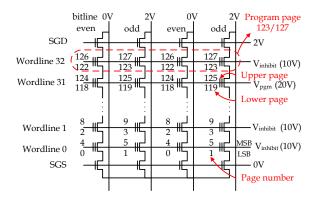

| 2  | MLC NAND flash memory circuit structure.                 | 10 |

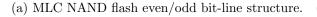

| 3  | The program method and RTN noise of NAND flash memory.   | 11 |

| 4  | The device noise in NAND flash memory.                   | 12 |

| 5  | The ECC failure rate of NAND flash based storage system  | 16 |

| 6  | DPA Architecture Overview                                | 17 |

| 7  | Architecture of DPA-PPU.                                 | 18 |

| 8  | Redundant pages & data pages                             | 20 |

| 9  | The ratio of 1's before and after de-correlation.        | 22 |

| 10 | The efficiency of DPA-PPU to reduce 0's ratio            | 28 |

| 11 | $V_{th}$ distribution after DPA-PPU.                     | 29 |

| 12 | The ECC failure rates under different device noise.      | 30 |

| 13 | Tradeoff between read count and P/E cycle count          | 30 |

| 14 | The performance overhead of DPA-DRM                      | 32 |

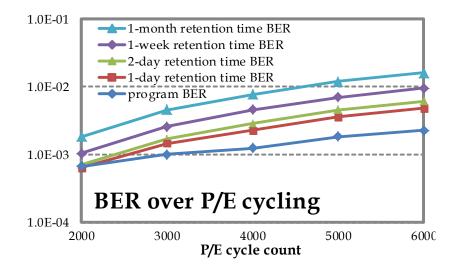

| 15 | NAND flash memory BER over P/E cycling                   | 36 |

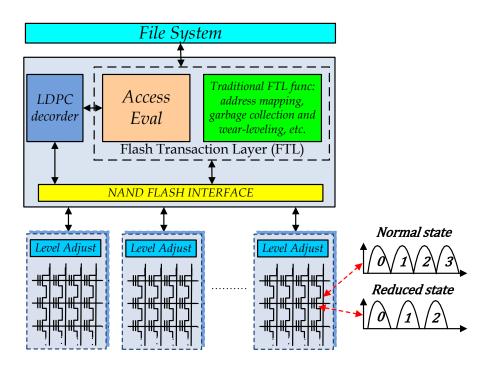

| 16 | FlexLevel NAND flash storage system overview             | 37 |

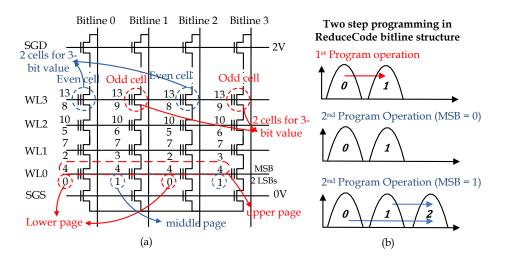

| 17 | ReduceCode bitline structure.                            | 40 |

| 18 | Bit error occurrence probability at four $V_{th}$ levels | 42 |

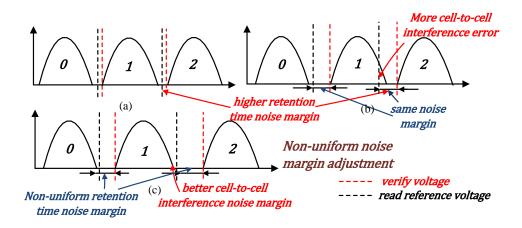

| 19 | NUNMA technique.                                         | 43 |

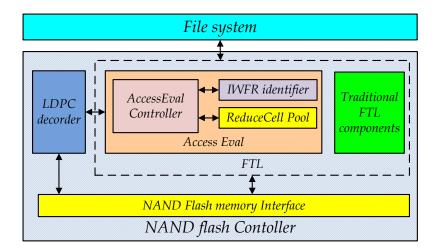

| 20 | AccessEval architecture                                  | 45 |

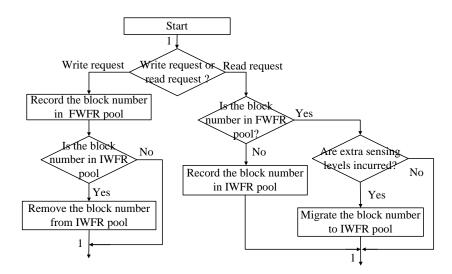

| 21 | IWFR identification flow.                                | 47 |

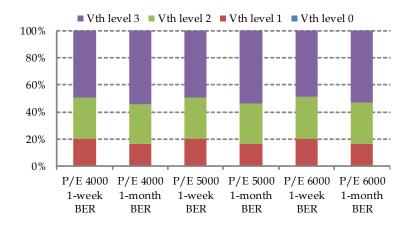

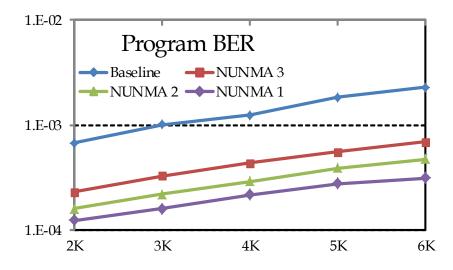

| 22 | Program BER in reduced state cells                       | 50 |

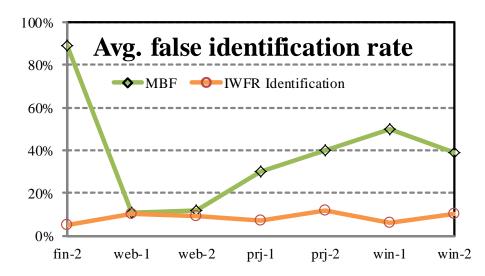

| 23 | Average false identification rate of IWFR identification technique     | 52  |

|----|------------------------------------------------------------------------|-----|

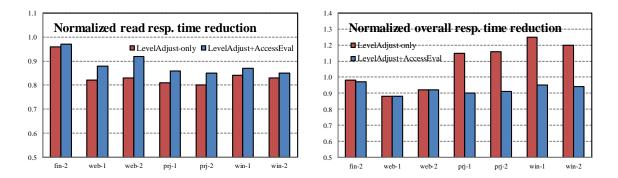

| 24 | The performance improvement of the Flex-level design.                  | 54  |

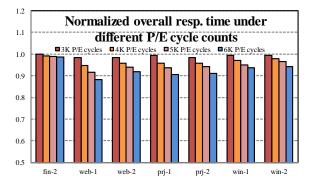

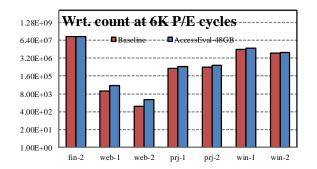

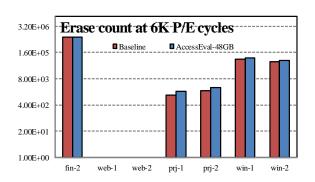

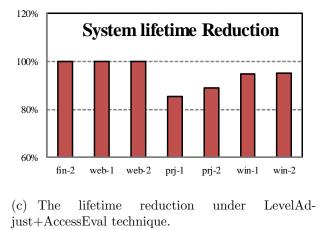

| 25 | The lifetime cost of LevelAdjust+AccessEval technique                  | 56  |

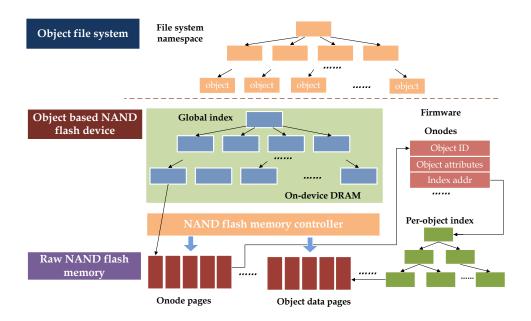

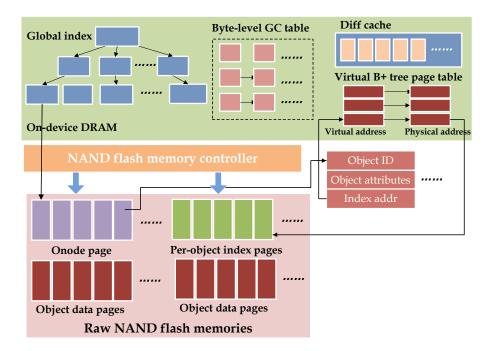

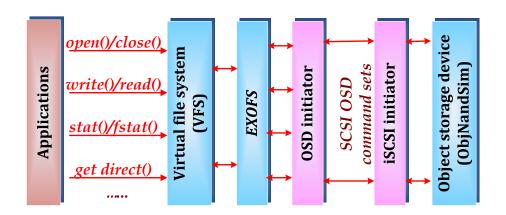

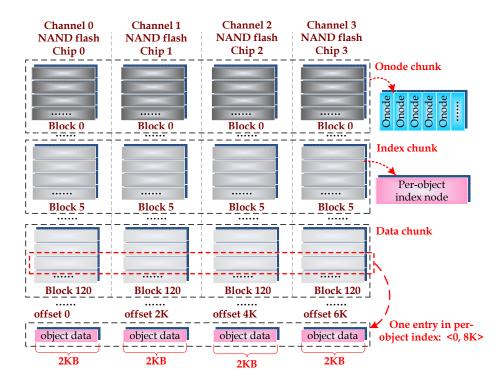

| 26 | The architecture of object-based storage system.                       | 58  |

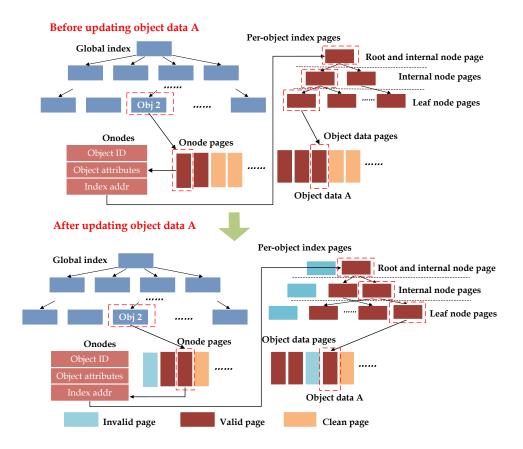

| 27 | An example of cascading update                                         | 60  |

| 28 | The overall architecture of the DMM device.                            | 63  |

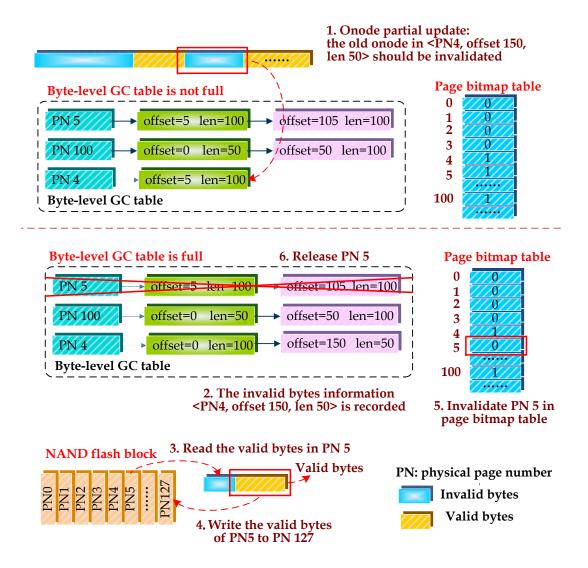

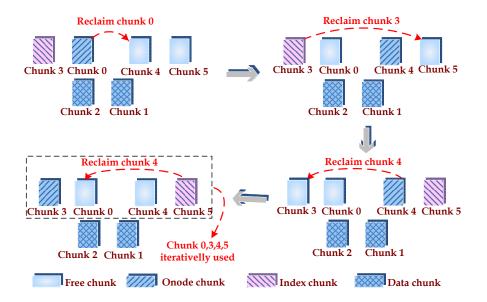

| 29 | Multi-level garbage collection.                                        | 66  |

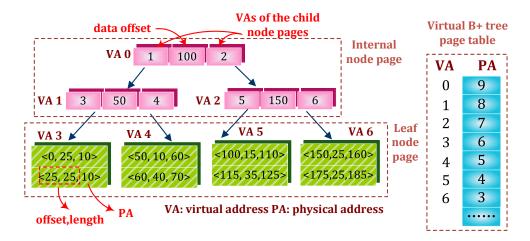

| 30 | The virtual B+ tree                                                    | 67  |

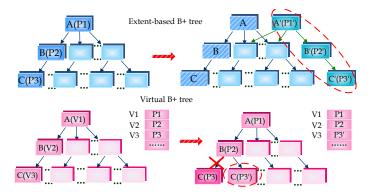

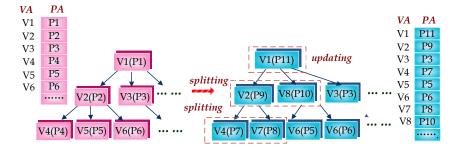

| 31 | Insertion operation of virtual B+ tree                                 | 69  |

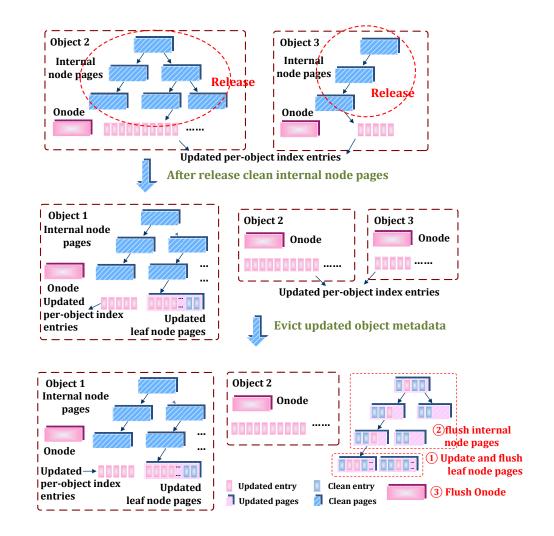

| 32 | An example of the diff cache.                                          | 72  |

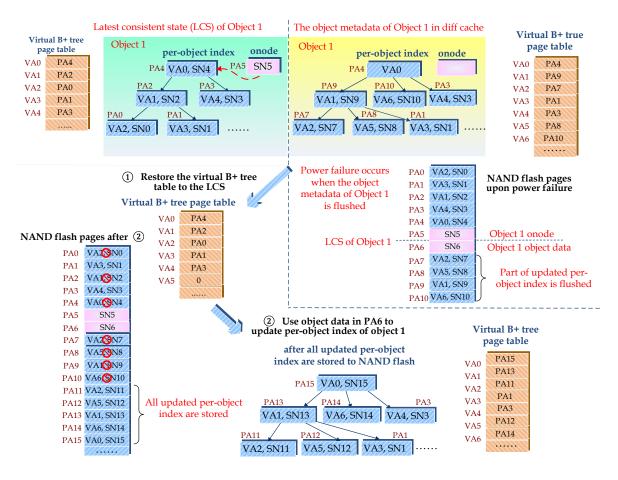

| 33 | An example of per-object index recovery.                               | 75  |

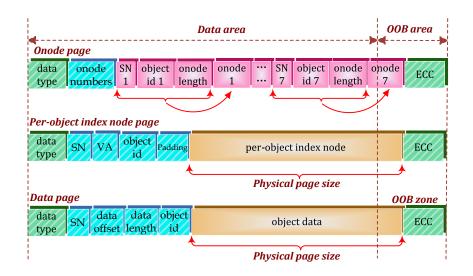

| 34 | The format of the page metadata.                                       | 75  |

| 35 | The architecture of simulation platform                                | 78  |

| 36 | The architecture of ObjNandSim.                                        | 79  |

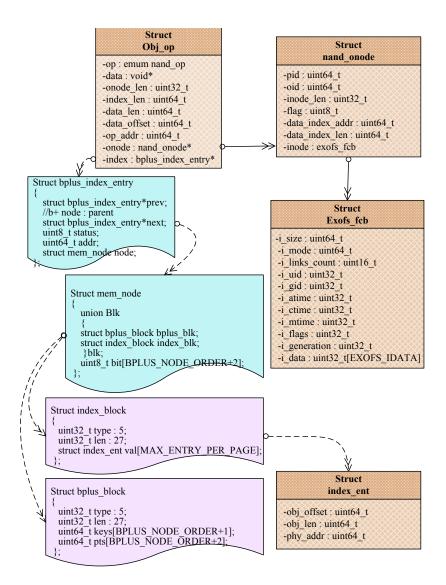

| 37 | The data type and dependency in the ObjNandSim                         | 82  |

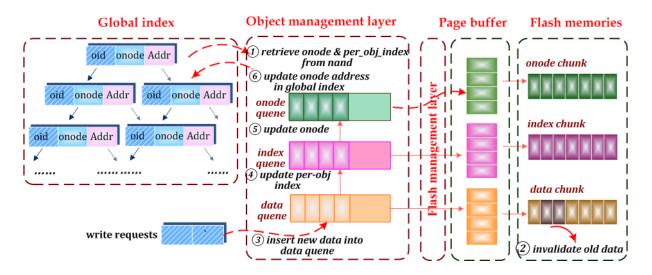

| 38 | The ObjNandSim write I/O flows.                                        | 83  |

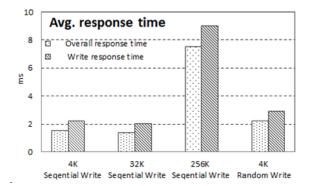

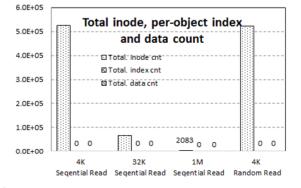

| 39 | The sequential and random average response time under DMMbench         | 88  |

| 40 | The sequential and random performance under DMMbench                   | 92  |

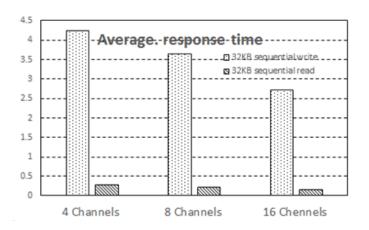

| 41 | The sequential write and read response time under 4, 8 and 16 channels | 92  |

| 42 | The performance of MLGC under different byte-level GC table sizes      | 93  |

| 43 | The efficiency of the virtual B+ tree                                  | 94  |

| 44 | The efficiency of the diff cache.                                      | 96  |

| 45 | The overall efficiency of the DMM device                               | 97  |

| 46 | The data layout of existing ONFD                                       | 102 |

| 47 | The biased chunk reclamation issue in ONFD.                            | 103 |

#### PREFACE

This dissertation is submitted in partial fulfillment of the requirements for Jie Guo's degree of Doctor of Philosophy in Electrical and Computer Engineering. It contains the works done from September 2011 to January 2016. My advisor is Yiran Chen, University of Pittsburgh, 2010 – present.

The work is original to the best of my knowledge, except where acknowledgement and reference are made to the previous work. There is no similar dissertation that has been submitted for any other degree at any other university.

Part of the work has been published in the following conferences:

1. **DAC2015**: **J. Guo**, W. Wen, J. Hu, D. Wang, H. Li and Y. Chen, "FlexLevel: a Novel NAND Flash Storage System Design for LDPC Latency Reduction," Design Automation Conference (DAC), Jun. 2015, pp. 1-6.

2. ASP-DAC2014: J. Guo, Z. Chen, D. Wang, Z. Shao and Y. Chen, "DPA: A Data Pattern Aware Error Prevention Technique for NAND Flash Lifetime Extension," 19th Asia and South Pacific Design Automation Conference (ASP-DAC), Jan. 2014, pp. 592 - 597.

3. **DATE2013**: **J. Guo**, J. Yang, Y. Zhang and Y. Chen, "Low Cost Power Failure Protection for MLC NAND Flash Storage Systems with PRAM/DRAM Hybrid Buffer," Design, Automation & Test in Europe (DATE), Mar. 2013, pp. 859 - 864.

DATE2013: J. Guo, W. Wen, S. Li, H. Li and Y. Chen, "DA-RAID-5: A Disturb Aware Data Protection Technique for NAND Flash Storage Systems," Design, Automation & Test in Europe (DATE), Mar. 2013, pp. 380-385. Part of the work has been submitted to the journals and conferences:

1. **TCAD2016**: **J. Guo**, W. Wen, J. Hu, D. Wang, H. Li and Y. Chen, "FlexLevel NAND Flash Storage System Design to Reduce LDPC Latency," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), submitted on Jan. 31st.

2. MSST2016: J. Guo, C. Min, T. Cai and Y. Chen, "A Design to Reduce Write Amplification in Object-based NAND Flash Devices," International Conference on Massive Storage Systems and Technology (MSST), submitted on Feb. 12th.

#### ACKNOWLEDGEMENTS

I would like to acknowledge the support of my advisor, Yiran Chen, whose support made this work possible, and to National Science Foundation Project (NSF CCF-1217947, NSF CNS-1116171, NSF CNS-1342566) for directly providing much of the financial support. I'd like to thank Professor Yiran Chen and Professor Hai (Helen) Li for their excellent guidance during the research. Professor Yiran Chen gives me guidance of NAND flash memory designs from device modeling, circuit implementation to architecture simulations and validations. Special thanks go to Professor Panos K. Chrysanthis, Professor Amro El-Jaroudi, Professor Hai (Helen) Li and Professor Kartik Mohanram for being my committee members. I also would like to thank Professor Jingtong Hu from Oklahoma State University and Professor Tao Cai from Jiangsu University, for their guidance and encouragement during my Ph.D. study.

In addition, I'd like to express my gratitude to the members from Evolutional Intelligent (EI) lab at Swanson School of Engineering, especially Wujie Wen and Chuhan Min, for their consistent supports during my research. Finally, I'd like to thank my husband, Zhigang Wang, an associate professor in University of Electronic Science and Technology of China (UESTC) and my parents in China for their great encouragement during the whole Ph.D. research.

#### 1.0 INTRODUCTION

#### 1.1 MOTIVATION

Magnetic hard disk drives (HDD) have been the dominant second storage medium for several decades. However, time-consuming seek and rotation process rooted in HDD operating mechanism has been a major performance bottleneck for the random-write intensive applications. This performance concern motivates many research efforts on NAND flash memory technology. NAND flash memory can offer fast access time, good scalability and low power consumption. Thanks to these advantages, NAND flash memory is applied to various storage systems ranging from low-power embedded systems to high-end servers.

A NAND flash cell is a floating gate transistor with programmable threshold voltage  $(V_{th})$ . The stored values are represented by different  $V_{th}$  levels. For example, in a single-level cell (SLC), one bit is stored, which is represented by two  $V_{th}$  levels. In a multi-level cell (MLC), four  $V_{th}$  levels are employed to represent two bits. To store the data into the NAND flash cell, electrons are injected to the floating gate by the program operation. Before the cell is re-programmed, an erase operation has to be performed to remove the electrons from the floating gate. The program and erase operations cause the major reliability and performance problems in NAND flash based storage system which are summarized as follows:

1. Limited device endurance. The program/erase (P/E) operations wear out the NAND flash cells and introduce bit error rate (BER). BER gradually increases with P/E cycling and eventually results in cell failure. Due to high BER, NAND flash memory has short endurance: 5000 P/E cycles under 3Xns technology node [1]. Such a limited endurance cannot meet the reliability requirement of enterprise application.

- 2. High data protection overhead. To prevent data corruption under high BER, error correction codes (ECCs) are usually employed in NAND flash based storage systems. Typically, low-density parity-check (LDPC) code is adopted to provide powerful error correction capacity. However, the LDPC code incurs high read overhead, which hinders its application in the read-critical applications.

- 3. Write amplification. The erase-before-write (i.e., *out-of-place update*) memory characteristic introduces more data migration or write operations than requested, which is called write amplification. Write amplification shortens system endurance and incurs write performance degradation.

These three reliability and performance issues are discussed below in Sections 1.1.1, 1.1.2 and 1.1.3, respectively.

#### 1.1.1 Challenge 1: Limited Device Endurance

The endurance issue of NAND flash memory is rooted from the intrinsic device noises. As mentioned above, the stored data is represented by different  $V_{th}$  levels. However, in reality,  $V_{th}$  levels are not clearly separated: Intrinsic device noise easily fluctuates  $V_{th}$ , resulting in overlapping of neighboring  $V_{th}$  levels. Previous works identify random telegraph noise (RTN), cell-to-cell interference and retention time limit as three major noise sources in NAND flash cells [2, 3, 4, 5]. RTN causes  $V_{th}$  fluctuation by electron capture and emission events at a charge trap site near interfaces. Cell-to-cell interference noise stems from capacitancecoupling. It results in  $V_{th}$  increase of one floating gate transistor when its neighboring cells are programmed. Retention time noise causes charges to leak away from the floating gate, leading to  $V_{th}$  decrease. Among these three type of noise, RTN and retention time noise rise up as P/E cycle increases, resulting in more severe  $V_{th}$  shift.

A direct result of the device noise is bit errors. Due to noise augmentation, these bit errors increase with P/E cycling. To prevent data corruption from bit errors, error correction code (ECC), such as Bose-Chaudhuri-Hocquenghem (BCH) code is usually deployed in NAND flash based storage system. The ECC controls the uncorrectable bit error rate (UBER) of the storage system under an acceptable level, e.g.,  $10^{-14}$ . The acceptable P/E

cycles of NAND flash memory, i.e., device endurance, is limited by maximum allowed UBER. Under 3Xnm technology node, the MLC NAND flash memory endurance is reduced to 5000 P/E cycles [1]. The limited endurance of MLC NAND flash memory is acceptable for consumer application but cannot meet the requirement of highly reliable enterprise application. Therefore, increasing device endurance is critical to expand the MLC NAND flash memory to the application with high reliability requirement. One way to extend device endurance is to increase the error correction capacity of BCH ECC. However, enhancement of BCH ECC error correction capacity incurs prohibitively high hardware cost [6].

#### 1.1.2 Challenge 2: High Data Protection Overhead

As mentioned in the previous section above, ECC is employed in the NAND flash based storage system to protect data integrity. The selection of ECC is based on error correction capability. The qualified ECC should guarantee that the UBER of the storage system is under an acceptable level. A widely applied ECC in the NAND flash based storage system is BCH ECC. BCH ECC is hard-decision in nature. It can fast correct bit errors by decoding binary information. However, as the technology node scales down to 2Xnm, BER can reach up to  $10^{-2}$  [7]. Under such a high BER, BCH ECC is no longer applicable since realization of stronger error correction capability requires prohibitively high hardware cost.

To offer more powerful error correction capacity, low-density parity-check (LDPC) code is adopted. LDPC code adopts a sparse  $M \times N$  parity-check matrix. The matrix is represented by a bipartite graph with N variable nodes and M check nodes. Error correction is realized by iteratively computing error messages, which are exchanged between variable nodes and check nodes [8]. Under low BER, LDPC can work in the similar manner as hard-decision ECC without introducing extra overhead. When BER is high, LDPC needs to work in a soft-decision fashion, which demands log-likelihood-ratio (LLR) information [9] to achieve better error correction capability. In NAND flash memories, the LLR information can only be acquired by extra fine-grain memory sensing operations. More memory sensing levels offer more accurate LLR information and therefore, provide more powerful error correction performance. However, more memory sensing levels cause longer read latency, which severely degraded the system read performance.

#### 1.1.3 Challenge 3: Write Amplification

Write amplification results from the out-of-place update of NAND flash memory [10][11]. With more data being written than requested, write amplification directly results in system endurance reduction and write performance degradation. As the technology node scales down, the memory performance and endurance are continuously degrading: The program latency under 2Xns technology node increases to 3ms [12]; under the sub-20ns technology node, rated memory endurance decreases to 3000 P/E cycles [13]. Hence, reducing write amplification become critical to improve system performance and reliability.

One way to minimize write amplification is to reduce data migration of garbage collection by optimizing the layout of hot and cold data [14][15]. Unfortunately, under the existing block-based storage model, hot and cold data cannot be accurately identified. As shown in Fig. 1, in the block-based model, the file system manages logical blocks and allocates them to the stored file data. The logical block address (LBA) is the only data identifier in the underlying NAND flash device. Unaware of block allocation policies at the file system layer, LBA cannot accurately identify data access patterns [16]. In addition, due to out-of-place update, an indirection table is needed in the NAND flash device to map LBAs to physical addresses, which significantly increases memory consumption [17].

To eliminate this architectural limitation, an object-based storage model is proposed [18]. In this model, the storage management layer is offloaded to the underlying object-based NAND flash device (ONFD) [18, 19]. The ONFD manages data by unit of object instead of by logical blocks. Understanding the object semantics, the ONFD can utilize the object attributes to improve accuracy of data pattern identification [19, 20]. In addition, the ONFD eliminates adoption of the indirection table, simplifying system design and reducing memory consumption.

With object semantics, two causes to write amplification in the ONFD have been identified. One cause is onode partial update. Onode is a data structure in the ONFD to store object attributes [19]. Due to small size, more than one onode is stored in a physical page to reduce internal fragmentation [19]. Update to an onode incurs partial update to a physical page, i.e., onode partial update. Due to the page-unit write in the ONFD [10], onode partial

Figure 1: The block-based storage v.s. the object-based storage.

update invokes unnecessary migration of the un-updated data. Another write amplification cause is cascading update. In the ONFD, the physical addresses of object data are main-tained in per-object indices; the address of the per-object index root node page is stored in the onode [19]. The per-object index is implemented with extent-based B+ tree [21]. When object data is updated, due to out-of-place update, the wandering tree issue causes the cascading update within a per-object index [22]. In addition, the cascading update changes the address of per-object index root node page. Hence, the corresponding onode are also updated. Despite several bytes update to the object metadata, one or more page have to migrate entirely, causing significant write amplification.

#### 1.2 DISSERTATION CONTRIBUTION AND OUTLINE

In this dissertation, we propose three technologies to handle the design challenges from limited endurance, high data protection overhead and write amplification. The proposed technologies are decoupled into three main research scopes: 1) A system-level solution to achieve system lifetime extension, 2) a novel hardware and software co-design to minimize LDPC incurred read overhead and 3) an architectural solution at the firmware level to reduce write amplification in ONFD.

For Research Scope 1, we propose a novel technique to extend lifetime of MLC NAND flash based storage system. Previous works reveal that BER heavily depends on  $V_{th}$  levels. For example, [2, 4] identify that most retention time errors occur in  $V_{th}$  level 2 and  $V_{th}$  level 3. [23] reveals that programming to  $V_{th}$  level 1 and level 3 incurs most cell-to-cell interference bit errors. If the vulnerable  $V_{th}$  levels can be avoided, BER can be effectively reduced and therefore the device endurance can be extended. Inspired by this idea, we propose Data Pattern Aware (DPA) error protection technique which utilizes a data pattern unbalancing technique combining the existing BCH ECC to protect data integrity [24]. Our contribution of this scope is summarized as follows:

- We propose Pattern Probability Unbalance (**DPA-PPU**) to reduce the probability of data patterns that are sensitive to bit errors. DPA-PPU identifies the data correlation and adopts de-correlation and scrambling accordingly to unbalance the number of 1's and 0's in the stored data. By increasing the ratios of 1's, fewer cells are placed on the vulnerable  $V_{th}$  levels and therefore the BER of NAND flash memories is effectively reduced.

- We propose Data-Redundancy Management (**DPA-DRM**) to mitigate DPA-PPU induced performance degradation and provide protection to the redundant bits. DPA-PPU with different unbalancing efficiencies is adopted at different P/E cycle counts to avoid unnecessary redundancy write. Due to random data patterns, we also provide stronger protection to the redundant bits.

The simulation result shows that DPA technique can increase NAND flash storage system lifetime by  $4\times$  with marginal hardware and power overhead, offering a complementing solution to other NAND flash lifetime enhancement techniques like wear-leveling.

For Research Scope 2, we propose a novel design FlexLevel to achieve read speed-up in the LDPC code applied NAND flash storage system [25]. The FlexLevel is motivated by the fact that LDPC read overhead heavily depends on BER and that BER is partially determined by the noise margin. Hence, LDPC read overhead reduction can be realized by noise margin increase. In FlexLevel, to diminish BER, we increase the noise margin of the NAND flash cell by  $V_{th}$  level reduction. Thereby, adoption of soft-decision LDPC can be avoided and read performance is improved. The contribution of this scope is summarized as follows:

- We propose LevelAdjust technique to reduce BER at the device level. It first decreases the number of  $V_{th}$  levels in the NAND flash cell to extend the noise margin of each  $V_{th}$ level. To further inhibit BER increase in the post cycling stage, we adopt NUNMA technique to increase retention time noise margin. By minimizing device BER, no extra memory sensing is needed for LDPC code and therefore read latency can be reduced.

- LevelAdjust technique enhances device reliability at the cost of memory capacity loss. To balance storage space reduction and performance improvement, we propose FlexLevel-AccessEval scheme (referred to AccessEval hereafter) at the system level. To maximize the efficiency of LevelAdjust technique, we only apply LevelAdjust techniques to the stored data with high soft-decision cost. Here, soft-decision cost denotes soft-decision LDPC induced performance degradation. By adopting AccessEval scheme, our FlexLevel design can achieve 11% read speedup with only 6.25% density loss.

For Research Scope 3, we propose a novel architectural design to reduce write amplification in ONFD. As mentioned in Section 1.1, two major causes to write amplification in ONFD are onode partial update and cascading update. To minimize onode partial update and cascading update induced data migration, the Data Migration Minimization (DMM) device design is proposed. Our contribution of this scope is summarized as follows:

• A multi-level garbage collection (MLGC) technique is proposed to reduce writes of onode partial update. MLGC adopts both page-level and byte-level garbage collection: When onode partial update occurs, instead of moving the un-updated bytes immediately, MLGC records the information of invalid bytes temporarily. By grouping invalid bytes incurred by multiple onode partial updates, the amount of moved data can be reduced.

- A virtual B+ tree is proposed to reduce cascading update within the per-object index. Each node page of the virtual B+ tree is assigned with a virtual address. The parent node page records the virtual addresses of the child node pages. A page table is used to map the virtual addresses to the physical addresses. Migration of the child node pages is only reflected in the page table without update to the parent node page. As such, cascading update induced data migration can be effectively reduced.

- The diff cache is proposed to further minimize cascading update. The diff cache leverages DRAM to reduce the writes to NAND flash memory. Due to the limited size, the diff cache selectively buffers data depending on the data type. To maximize the cache utilization, a diff cache replacement policy is proposed.

We evaluate the efficiency of the DMM device design under four workloads. The experimental results show that compared with the best art-of-state works, the DMM device can achieve up to 20% write reduction and extend the system lifetime by 76%. For future work directions, we will to explore the optimization space in the ONFD to improve wear-level efficiency.

The outline of this dissertation is summarized as follows: Chapter 1 presents the overall picture of this dissertation, including the research motivations, scopes and contributions; Chapter 2 introduces the proposed *data pattern aware* (DPA) data protection scheme and discusses its efficiency and overhead in detail; Chapter 3 analyzes NAND flash memory error patterns and describes the details of our proposed FlexLevel system design; Chapter 4 demonstrates the benefits of the proposed architectural solution – *data migration minimization* (DMM), in improving system performance and extending system lifetime of the ONFD. Chapter 5 finally summarizes the research work and presents the potential future research directions.

#### 2.0 DPA: DATA PATTERN AWARE ERROR PREVENTION TECHNIQUE

In this chapter, we will present our Data Pattern Aware (DPA) error prevention technique. The structure of this chapter is organized as the follows: Section 2.1 presents the preliminary knowledge of NAND flash memories; Section 2.2 quantitatively characterizes bit error rate and error patterns of NAND flash memories; Section 2.3, 2.4 and 2.5 present DPA architecture and discuss DPA-PPU and DPA-DRM details, respectively; Section 2.6 presents the experimental results; Section 2.7 summarizes this chapter.

#### 2.1 PRELIMINARY

#### 2.1.1 MLC NAND Flash Basics

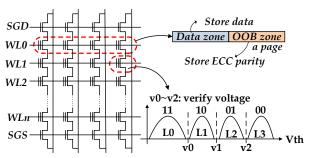

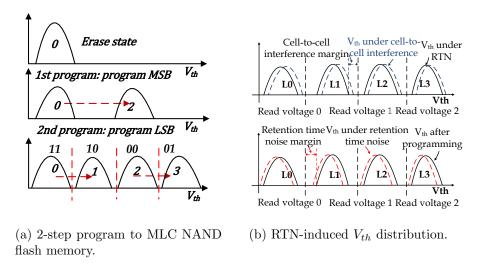

MLC NAND flash memory is composed of a number of blocks. A block is an array of NAND flash cells, or floating gate transistors, which can be sub-divided into a number of pages. Usually, a MLC NAND flash block has an even/odd bit-line structure, which is depicted in Fig. 2(a) [4]. Under the even/odd bit-line structure, a wordline stores two page groups, an even and an odd page group. Operations to each page group are realized by selecting the corresponding wordline and bitline. Each page group contains two pages: a lower page and an upper page. The most significant bit (MSB) and least significant bit (LSB) in the same cell belong to the lower page and the upper page in one page group, respectively. Each MLC NAND flash cell stores 2 bits by four  $V_{th}$  levels. L0 (the lowest level) ~ L3 (the highest level) represent 11,10,01,00, respectively as shown in Fig. 2(b). Each page consists a data area and a Out-Of-Band (OOB) zone for ECC parity redundancy.

(b) MLC NAND flash device structure and the  $V_{th}$  distribution.

Figure 2: MLC NAND flash memory circuit structure.

MLC NAND flash supports three operations: program, read and erase. Program operation realizes injection of pre-defined amount of electrons to configure  $V_{th}$ . A two-step program operation can be performed to each cell as shown in Fig. 3(a) [2, 26]. The first program operation stores data in MSB and the second program operation stores LSB data. Program is performed by unit of page and all the pages within a block should be programmed sequentially. The logic bits are read out by comparing cell's  $V_{th}$  with a series of read reference voltages [4]. Erase operation removes electrons from floating gate to reduce NAND flash to a ready state ( $V_{th}$  level 0) for incoming program operations. Unfortunately, these operations cannot achieve ideal  $V_{th}$  distribution due to intrinsic noises. These noises lead to high BER and severely impair data integrity. There are three major contributors to  $V_{th}$ distortion which are identified by previous work: program disturb, retention time limit and read disturb [3, 4, 2].

#### 2.1.2 Program Disturb

Program disturb stems from the combinative effect of random telegraph noise (RTN) and cell-to-cell interference. RTN develops from electrons capture and emission at charge trap sites. As shown in Fig. 3(b), RTN can either increase or reduce the  $V_{th}$  of the programmed

Figure 3: The program method and RTN noise of NAND flash memory.

cell and results in wider threshold voltage distribution. [3] reveals that the effect of RTN is aggregated over P/E cycling. Assume that  $\lambda$  is the mean value of  $V_{th}$  shift. RTN induced  $V_{th}$  shift  $\Delta V_{rtn}$  is modeled by [3]

$$p_{\Delta V_{rtn}} = \frac{1}{2\lambda} exp(-\frac{|\Delta V_{rtn}|}{\lambda}).$$

(2.1)

Programming one cell provokes the  $V_{th}$  shift of the neighboring cells via parasitic capacitancecoupling. This is cell-to-cell interference. The  $V_{th}$  shift of the victim cell  $\Delta V_{c2c}$  can be modeled by [3]

$$\Delta V_{c2c} = \sum_{k=0} \Delta V_p^{(k)} \times \gamma^{(k)}.$$

(2.2)

$\Delta V_p^{(k)}$  and  $\gamma^{(k)}$  denote the  $V_{th}$  shift of the interfering cell after programming and coupling ratio, respectively. In the even/odd bit structure, there exists coupling ratios on three directions:  $\gamma_y$ ,  $\gamma_x$  and  $\gamma_{xy}$  [27]. Cell-to-cell interference noise margin is shown in Fig. 4(a). Each  $V_{th}$  level is confined by lower and/or upper read reference voltages ( $V_{rd-ref}$ ). Since cellto-cell interference noise incurs  $V_{th}$  increase, cell-to-cell interference noise margin is defined as the voltage difference between  $V_{th}$  after RTN and the upper read reference voltage. [23] shows that the effect of cell-to-cell interference is  $V_{th}$  level dependent. The largest  $V_{th}$  transition of the victim cell occurs when the interfering cell is programmed to level L1 and L3.

(b) Description of read disturb. Both the read and unread cells are exposed to risk of read disturb.

Figure 4: The device noise in NAND flash memory.

#### 2.1.3 Read Disturb

Read disturb is originated from both Fowler-Nordheim tunneling mechanism and stress induced leakage current (SILC). The read operation is shown in Fig. 4(b). The verify voltage  $V_{READ}$  (0~4V) is applied to the wordline of the read page while  $V_{PASS}$  (6V) is applied to the unread pages in the same block. Both  $V_{PASS}$  and  $V_{READ}$  cause electrons to transmit to the floating gate, directly leading to  $V_{th}$  increase. The BER resulting from read disturb increases with P/E cycling and read count. The research of [28] shows the lowest level L0 is most susceptible to read disturb.

#### 2.1.4 Retention Time

Retention time limitation results from electron detrapping and SILC. Electrons are trapped in transistor tunnel oxide through P/E cycling [3]. These trapped electrons gradually leak away and assist charges stored on floating gates to escape, leading to  $V_{th}$  decrease (Fig. 4(b)). It is shown that retention time error dominates the post-cycling error [2]. According to [3],  $V_{th}$  shift distribution due to retention time limitation is modeled by  $N(\mu_d, \sigma_d^2)$ .  $\mu_d$  and  $\sigma_d^2$  can be expressed by

$$\begin{cases} \mu_d = K_s(x - x_0) K_d N^{0.3} ln(1 + t/t_0), \qquad (2.3) \end{cases}$$

$$\int \sigma_d^2 = K_s(x - x_0) K_m N^{0.4} ln(1 + t/t_0).$$

(2.4)

Here,  $K_s$ ,  $K_d$ ,  $K_m$  and  $t_0$  are constants. N is P/E cycle count.  $x_0$  is  $V_{th}$  of level 0. x is the initial  $V_{th}$  after programming and t is storage time. As shown in Fig. 4(a), retention time noise margin is defined as the voltage difference between the lower read reference voltage and the  $V_{th}$  after programming (under the effect of both RTN and cell-to-cell interference). Eq. 2.3 and 2.4 shows that higher initial  $V_{th}$  incurs larger threshold voltage shift.  $V_{th}$  level L3 is most vulnerable to retention time error.

#### 2.2 MOTIVATIONS

#### 2.2.1 Lifetime Model

BCH ECC code is prevalently employed in NAND flash based storage system to prevent data from bit error. A NAND flash block lifetime is defined as P/E cycle count when ECC failure rate reaches a threshold  $T_{uber}$ . ECC failure rate for a NAND flash block can be expressed by

$$F = max(f_{prog}, f_{rd}, f_{rt}).$$

$$(2.5)$$

$f_{prog}, f_{rd}$  and  $f_{rt}$  are error rate induced by program disturb, read disturb and retention time limitation, respectively. Assume n-bit BCH ECC (m,l,n) is performed to l-bit data block. m denotes the total codeword length. The yield  $Y_{ber}(n)$  can be expressed by

$$uber(k) = \frac{1 - \sum_{i=0}^{k} C_m^i p_c^i (1 - p_c)^{(m-i)}}{n}.$$

(2.6)

Here,  $p_c$  is BER of a single NAND flash cell. Assume the probability that each flash cell be programmed to threshold voltage  $(V_{th})$  level Li is  $p_i$  (i = 0, 1, 2, 3). The error rate of each level is represented by  $p_{li}$ .  $p_c$  can be calculated by

$$p_c = \sum_{i=0}^{3} p_{li} \times p_i.$$

(2.7)

$p_i$  is determined by the ratio of 1's and 0's in the data stored in flash cells. p(0) and p(1)denote the probability of 1's and 0's.  $p_0 \sim p_3$  can be represented by p(1)p(1), p(0)p(1), p(1)p(0) and p(0)p(0).

Based on Eq. 3.1,2.7, to estimate uber(k), we need to first calculate value of  $p_{li}$  as well as the probability of 1's and 0's p(0) and p(1). We employ reliability models in Section 2.1 to evaluate the error rate of each  $V_{th}$  level  $p_{li}$ . The flash model proposed in Eq. 2.1,2.2,2.3,2.4 is used to estimate the program disturb and retention time error rate. Based on the research of [29, 28, 30], we set  $V_{th}$  fluctuation led by read disturb as random variables with Gaussian distribution. The mean  $\mu_{rd}$  and variation  $\sigma_{rd}$  are expressed by

$$\begin{cases} \mu_{rd} = \frac{1}{\gamma} In[1 + \gamma\beta t_s e^{\gamma(V_{CG} - V_{T,0})} N^{0.3} K_r] \\ \sigma_{rd} = \sqrt{\alpha(1 - e^{\gamma\mu_{rd}})} \end{cases}$$

(2.8)

$$\sigma_{rd} = \sqrt{\alpha (1 - e^{\gamma \mu_{rd}})} \tag{2.9}$$

$\gamma, \beta, K_r$  and  $\alpha$  are coefficients.  $V_{CG}$  and  $V_{T,0}$  represent the voltage applied to the wordline and the voltage in floating gate.  $t_s$  and N denote read pulse duration and P/E cycle count, respectively.

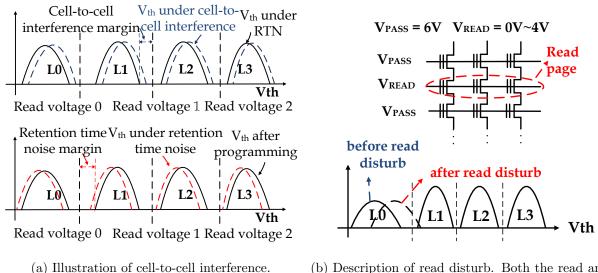

To evaluate probability of 1's and 0's, we investigate 1's and 0's distribution in seven types of data listed in Table 1. Fig. 5(a) shows that 1's ratio in system metadata files is around 45% while others are approximately 50%. Hence, it is safe to assume that p(0) =p(1) = 0.5. For the evaluation purpose, we perform 8-bit BCH ECC to a 512B data block and  $T_{uber}$  is set  $10^{-13}$  [2]. The L0  $V_{th}$  is modeled by Gaussian distribution N(1.1, 0.35). The ISPP verify voltages and the incremental program step voltage are 2.55, 3.15, 3.75 and 0.3, respectively [27].  $\lambda$  is set  $2.8 \times 10^{-4} N^{0.4}$  based on [31]. We adopt the emerging all-bit-line structure. The coupling ratios  $\gamma_y$  and  $\gamma_{xy}$  are set 0.08 and 0.0048 [27]. By fitting the data in [5],  $K_d$  and  $K_m$  are  $4 \times 10^{-5}$  and  $3 \times 10^{-6}$ . For the read disturb model,  $\gamma$ ,  $\beta$ , and  $t_s$  are set 1.1,  $8.8 \times 10^5$ ,  $8 \times 10^{-2}$  respectively. By fitting the data in [29, 28],  $\alpha$  and  $K_r$  are set

| file type               | number | file size      |

|-------------------------|--------|----------------|

| mp3 file                | 2      | 7.5MB, 6.3MB   |

| mp4 file                | 1      | 101MB          |

| compressed file(tar.gz) | 2      | 5.3MB,4.2MB    |

| pictures (.jpg)         | 2      | 1.42MB, 1.37MB |

| pdf file                | 2      | 8.6MB,4.2MB    |

| office files(.ppt)      | 2      | 797KB, 1.2MB   |

| system matadata file    | 6      | total 0.5MB    |

Table 1. File data characteristics

$5.3 \times 10^{-2}$  and 11.9. Read disturb is evaluated under 10K read count and retention time error rate is estimated with 1 year elapsed time. The ECC failure rate under different P/E cycle count is shown in Fig. 5(b). Data integrity cannot be guaranteed after 7.5K P/E cycling.

#### 2.3 DPA OVERVIEW

Our DPA error prevention scheme aims to minimize the error rate of a single cell. Our scheme is based on the following pattern-dependent bit error features:

- Program disturb bit error is prone to occur when the interfering cell is programmed to  $V_{th}$  L1 and L3.

- It is highest probability that retention time error occur at  $V_{th}$  level L3.

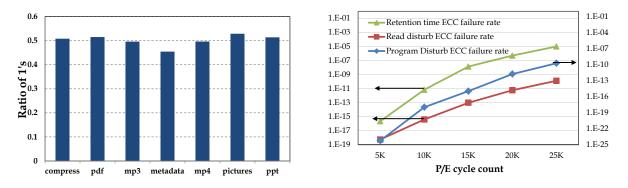

To minimize the effect of program disturb and retention time noise, DPA scheme increases the probability of  $V_{th}$  level L0 by maximizing the ratio of 1's in the stored data. The DPA

(a) The distribution of 1's number in 8-bytes data (b) The 8-bit ECC failure rate under different P/E cyblock. cling.

Figure 5: The ECC failure rate of NAND flash based storage system

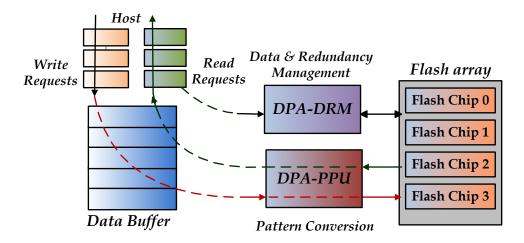

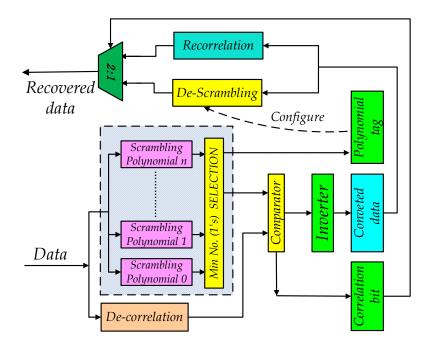

error prevention system is illustrated in Fig. 6. DPA incorporates DPA-PPU and DPA-DRM. DPA-PPU implements data pattern conversion and DPA-DRM performs data management to mitigate DPA-PPU induced performance overhead. In our system, we employs a data buffer with simple LRU replacement cache policy. A array of flash chips are deployed to increase the access throughout. The write data from the host is first stored in the data buffer and data pattern conversion is performed to the evicted data before it is flushed to flash memory. For the read requests, the data is read out from flash and is recovered by DPA-PPU and sent back to the host.

#### 2.4 DPA-PPU: PATTERN PROBABILITY UNBALANCE

To place more cell in  $V_{th}$  level L0, DPA-PPU performs data pattern conversion to increase the number of 1's. Since it is easier to decrease the number of 1's, we choose to reduce the number of 1's first and then inverts the whole data page. Our DPA-PPU investigates data correlation of the stored data. For the strong correlated data, de-correlator proposed in [32] is adopted to decrease the number of 1's. It performs simple XOR operation to neighboring data and reduction of 1's number can be realized by incurring negligible redundant overhead.

Figure 6: DPA Architecture Overview

Recently, many signal processing techniques are employed in the flash memory storage system [33, 34, 27, 35, 36]. In this work, we utilize a scheme based on scrambling coding to unbalance the number of 0's and 1's for the weakly correlated data. Basically, scrambling implements modulo 2 operation in Galois Field via cyclic XORing the data stream with a polynomial. If we can choose a appropriate polynomial whose pattern overlaps with the data to the maximum degree, 1-to-0 ratio can be effectively un-equalized. DPA-PPU performs data pattern conversion to increase the ratio of 1's in the stored data by performing de-correlation or scrambling, followed by bit inversion operation. If the data demonstrates a strong correlation, the de-correlation scheme in [32] can be adopted to decrease the number of 1's in the data by applying XOR operations between neighboring bytes. If the data is weakly correlated, we propose a scheme based on scrambling coding to skew the ratio of 1's and 0's. After the de-correlation or scrambling, all data bits are flipped to obtain the codeword of which the majority are 1's.

The architecture of DPA-PPU is presented in Fig. 7. A data page is divided into multiple data chunks. The data chunks are processed by de-correlation and scrambling circuits in parallel. Scrambling circuit performs modulo 2 division, i.e., cyclic XOR, on the data by using a polynomial as divider. If the pattern of the polynomial overlaps with the data much, the number of 1's can be effectively reduced. DPA-PPU implements n different scrambling

Figure 7: Architecture of DPA-PPU.

circuits which are differentiated by the polynomial tags from 0 to n-1. The data is scrambled by different polynomials and the result that has the fewest 1's will be selected as the output of scrambling circuit. Then the number of 1's in the output data from de-correlation and scrambling circuits are checked by a comparator. The one with the fewer 1's is selected and inverted before being flushed into the flash chips. If the de-correlated data is selected then the correlation bit is set to 1. Otherwise, the correlation bit is set to 0. The corresponding polynomial tag (if applicable) and the correlation bit must be also stored in the flash chip as they are required when re-correlation or descrambling is performed for data recovery at read operations.

The scrambling circuit efficiency is determined by the polynomial pattern, the data chunk size, the number of polynomials and the polynomial order. For example, the number of 1's can be effectively reduced by maximizing the overlapping bits between the data and the polynomial. In normal applications, the occurrence probabilities of 1's and 0's in the stored data are approximately equal [32]. Hence, the polynomials with a 1-to-0 ratio of 1:1 are generally

preferred. The increases of data chunk size diversifies the data pattern and thus potentially decreases the overlapping area between the data chunk and the polynomial. Hence, the scrambling efficiency degrades when the data chunk size rises. Similarly, increasing the number of polynomials may enhance the scrambling efficiency by maximizing pattern overlapping probability. Polynomial order itself does not directly affect the scrambling efficiency. However, the polynomial with a higher order can offer more available polynomials which may improve the pattern overlapping probability.

The scrambling-descrambling circuits can be implemented with simple linear feedback shift registers (LFSRs) with very marginal hardware cost. At 65nm technology node, the power of the scrambling-descrambling circuit is around 9mW, which is negligible compared to the large power consumption of the read and write operations of NAND flash based storage system (which is at  $\geq 5W$  for a 256GB system). Since only one correlation bit is required by one data page, the incurred hardware cost is negligible. Similarly, the hardware overhead of polynomial tags is also marginal: assume the data chunk size is 8B and total 64 16-order polynomials are included in the scrambling-descrambling circuits, the extra space required to store the polynomial tags in a 256GB NAND flash based storage system is only 16GB (6%) because one third of the tags can be stored in OOB zone.

#### 2.5 DPA-DRM: DATA-REDUNDANCY MANAGEMENT

DPA-PPU converts the data page into the pattern with more 1's to reduce the error rate resulting from retention time limitation and program disturb. To reduce DPA-PPU induced redundancy overhead, we employ a chunk-size-adaptive DPA-PPU scheme. The error rate resulting from retention time increases with P/E cycle count. Therefore, at the early post cycling stage, we adopt a large chunk to achieve a moderate un-equalization rate due to relatively low error rate. As the error rate increases with P/E cycling, a small chunk size is adopted to maximize the probability the flash cell be placed on level L0. However, smaller chunk size incurs more redundancy. There are two problems with the redundant bits: (1)

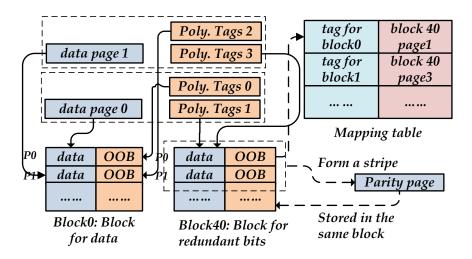

Figure 8: Redundant pages & data pages

They are characteristics of more random patterns than the converted data; (2)They introduce extra write operations and therefore accelerate the wear-out of flash memory and incur performance degradation.

Due to the random patterns, the redundant page is vulnerable to retention time error than the converted data. Therefore, we differentially deal with the converted data and the redundant bits. Each data page consists of multiple data chunks with multiple polynomial tags. We store a part of the polynomial tags in the OOB area of the data page and the rest is stored in a **redundant page**. Redundant pages and data pages are stored in different blocks. A mapping table is utilized to track the redundant pages. Since the redundant page is vulnerable to retention time error, we perform RAID-5 to the redundant pages. Instead of grouping the stripe by logic page number of conventional RAID-5 [37], we form the stripe by the physical page number and the parity page is stored in the same block to eliminate the necessity of extra mapping table. An example is shown in Fig. 8. Assume data page 0 have two polynomial tags: tag 0 and tag 1. OOB space can hold only one tag and ECC parity. The data page 0 and data page 1 store the tag 0 and tag 2 in the OOB space of the data page with the tag 1 and tag 3 in a redundant page. Redundant pages are stored in flash block 40 and 2 redundant pages form a stripe. A parity page is calculated and stored back to block 40. To minimize redundancy-induced performance degradation, we adopt a delay write similar to [37]. When a redundant page is ready, it stays in the data buffer and is flushed to NAND flash only due to system idle time. For the read operation, the redundant page are read out with the data page to configure the de-scrambling circuit for data recovery. Therefore, to reduce read response time, we store the redundant pages and the data page to two different chip so that data page and the redundant page can be accessed in parallel. The performance overhead of DPA-DRM is evaluated in Section 2.6. Our DPA-DRM introduces a mapping table. A block of data pages only consume one or two redundant pages and therefore, mapping table is small. For 256GB storage system, it only consumes several mega bytes. The mapping table resides in data buffer for fast access. DPA-PPU places more cells on  $V_{th}$  level L0 and exposes them to higher risk of read disturb. However, increase of the cell  $V_{th}$  level L0 also mitigates the cell-to-cell interference and provide larger noise margin to read disturb. The effect of DPA scheme on read disturb will be evaluated in Section 2.6.

#### 2.6 EXPERIMENTAL RESULTS

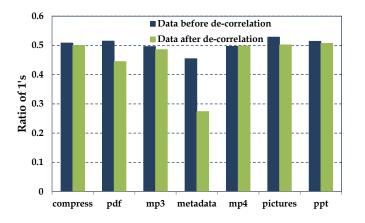

Flashsim [38] is adopted as our simulation platform. We modify the simulator by adding multi-chip access capability and incorporate our DPA error prevention scheme in it. The benchmarks representing five applications are selected to evaluating our scheme. The work-load characteristics are listed in Table 2. The specification of MLC NAND flash memory used for our experiment is summarized in Table 3. The storage system capacity is set 256GB. A 8-bit BCH ECC (4200,4096,104) is applied to every 512-byte data block. We first study the efficiency of the de-correlation and scrambling circuits on reducing the ratio of 1's in the data (or reducing the ratio of 0's in the data after the bit inversion in Fig. 7) for the seven data types listed in TABLE 1, Fig. 9 shows the ratio of 1's in the data before and after processed by de-correlation circuit. Among all data types, only *system metadata* exhibits good correlation where the ratio of 1's decreases from 0.45 to 0.27. Other data types, however, display a more random pattern and the reduction of the ratio of 1's is very small after the de-correlation.

| Disk trace      | Write ratio | Seq.wr. | Application                 |

|-----------------|-------------|---------|-----------------------------|

| WIN 7           | 42%         | 15.2%   | p2p, office and web serfing |

| RHEL            | 93%         | 2.3%    | Server access               |

| TPC-C           | 99%         | 0.9%    | OLTP application            |

| financial [39]  | 98%         | 1.9%    | OLTP application            |

| web search [39] | 0.02%       | 0       | Access to search engines    |

Table 2. Workload characteristics.

Table 3. The parameters of MLC NAND flash

| Canadity | Block Size      | Block Number | Page Size     |

|----------|-----------------|--------------|---------------|

| Capacity | 512KB           | 4096         | 4KB+218Bytes  |

|          | Program Latency | Read Latency | Erase Latency |

| Timing   | $900 \ \mu s$   | $50 \mu s$   | 3.5ms         |

Figure 9: The ratio of 1's before and after de-correlation.

In the evaluations of different scrambling schemes, the default values of data chunk size, polynomial number and polynomial order are set to 8B, 64 and 16, respectively. The 64 polynomials we use are listed in Table 4. We only change the value of one parameter each time to evaluate its impact on scrambling efficiency. We show the probability of each scrambling polynomials to reduce the number of 1's in Table 5. The scrambling is inefficient to reduce 1's number in the system metadata file: The total probability of the sixty-four polynomials to reduce 1's is only 10%. This is because the system metadata file has fewer 1's than 0's. Scrambling (or OXRing) these data with the polynomials with equal 1's and 0's generates more 1's. For other type of data, the scrambling demonstrates good efficiency: Each polynomial has approximately 50% probability to reduce 1's numbers.

| poly. no | polynomial                                                         | poly. no | polynomial                                                                           |

|----------|--------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------|

| 0        | $x^{16} + x^{15} + x^{14} + x^7 + x^5 + x^4 + 1$                   | 1        | $x^{16} + x^{12} + x^{11} + x^9 + x^2 + x^1 + 1$                                     |

| 2        | $x^{16} + x^{10} + x^8 + x^7 + x^6 + x^5 + x^3 + x^1 + 1$          | 3        | $x^{16} + x^{11} + x^7 + x^6 + x^4 + x^3 + x^2 + x^1 + 1$                            |

| 4        | $x^{16} + x^{12} + x^6 + x^5 + x^4 + x^3 + x^2 + x^1 + 1$          | 5        | $x^{16} + x^{12} + x^{10} + x^9 + x^7 + x^4 + x^3 + x^1 + 1$                         |

| 6        | $x^{16} + x^{12} + x^{10} + x^9 + x^8 + x^6 + x^2 + x^1 + 1$       | 7        | $x^{16} + x^{13} + x^{12} + x^9 + x^8 + x^7 + x^6 + x^4 + 1$                         |

| 8        | $x^{16} + x^{12} + x^{11} + x^8 + x^6 + x^5 + x^3 + x^1 + 1$       | 9        | $x^{16} + x^{15} + x^{14} + x^9 + x^8 + x^6 + x^5 + x^4 + 1$                         |

| 10       | $x^{16} + x^{13} + x^{12} + x^{11} + x^{10} + x^9 + x^8 + x^7 + 1$ | 11       | $x^{16} + x^{15} + x^{14} + x^{11} + x^{10} + x^9 + x^8 + x^5 + 1$                   |

| 12       | $x^{16} + x^{15} + x^{12} + x^{11} + x^{10} + x^9 + x^6 + x^5 + 1$ | 13       | $x^{16} + x^{15} + x^{13} + x^{12} + x^8 + x^7 + x^6 + x^5 + 1$                      |

| 14       | $x^{16} + x^{12} + x^8 + x^7 + x^6 + x^4 + x^3 + x^1 + 1$          | 15       | $\left  x^{16} + x^{15} + x^{14} + x^{12} + x^{11} + x^{10} + x^7 + x^4 + 1 \right $ |

| 16       | $x^{16} + x^{12} + x^{11} + x^{10} + x^7 + x^2 + 1$                | 17       | $x^{16} + x^{13} + x^{11} + x^6 + x^5 + x^4 + 1$                                     |

| 18       | $x^{16} + x^{13} + x^8 + x^7 + x^5 + x^4 + 1$                      | 19       | $x^{16} + x^{13} + x^9 + x^7 + x^5 + x^4 + 1$                                        |

| 20       | $x^{16} + x^8 + x^7 + x^5 + x^4 + x^3 + x^2 + x^1 + 1$             | 21       | $x^{16} + x^9 + x^8 + x^7 + x^6 + x^5 + x^4 + x^3 + 1$                               |

| 22       | $x^{16} + x^{14} + x^{11} + x^8 + x^5 + x^4 + 1$                   | 23       | $x^{16} + x^{15} + x^{11} + x^8 + x^5 + x^4 + 1$                                     |

| 24       | $x^{16} + x^{12} + x^{11} + x^8 + x^5 + x^1 + 1$                   | 25       | $x^{16} + x^{12} + x^{11} + x^7 + x^4 + x^1 + 1$                                     |

| 26       | $x^{16} + x^{12} + x^{11} + x^7 + x^3 + x^2 + 1$                   | 27       | $x^{16} + x^{15} + x^{10} + x^7 + x^6 + x^4 + 1$                                     |

| 28       | $x^{16} + x^{12} + x^{10} + x^9 + x^6 + x^1 + 1$                   | 29       | $x^{16} + x^{12} + x^{11} + x^7 + x^4 + x^1 + 1$                                     |

Table 4. Sixty-four polynomials employed for scrambling

| poly. no | polynomial                                       | poly. no | polynomial                                              |

|----------|--------------------------------------------------|----------|---------------------------------------------------------|

| 30       | $x^{16} + x^{15} + x^{10} + x^7 + x^6 + x^4 + 1$ | 31       | $x^{16} + x^{15} + x^{14} + x^8 + x^6 + x^4 + 1$        |

| 32       | $x^{16} + x^5 + x^3 + x^2 + 1$                   | 33       | $x^{16} + x^{14} + x^{13} + x^{11} + 1$                 |

| 34       | $x^{16} + x^5 + x^4 + x^3 + 1$                   | 35       | $x^{16} + x^{13} + x^{12} + x^{11} + 1$                 |

| 36       | $x^{16} + x^6 + x^4 + x^1 + 1$                   | 37       | $x^{16} + x^{15} + x^{12} + x^{10} + 1$                 |

| 38       | $x^{16} + x^8 + x^7 + x^5 + 1$                   | 39       | $x^{16} + x^{11} + x^9 + x^8 + 1$                       |

| 40       | $x^{16} + x^9 + x^4 + x^2 + 1$                   | 41       | $x^{16} + x^{14} + x^{12} + x^7 + 1$                    |

| 42       | $x^{16} + x^9 + x^4 + x^3 + 1$                   | 43       | $x^{16} + x^{13} + x^{12} + x^7 + 1$                    |

| 44       | $x^{16} + x^9 + x^5 + x^2 + 1$                   | 45       | $x^{16} + x^{14} + x^{11} + x^7 + 1$                    |

| 46       | $x^{16} + x^9 + x^7 + x^2 + 1$                   | 47       | $x^{16} + x^{14} + x^9 + x^7 + 1$                       |

| 48       | $x^{16} + x^{12} + x^{11} + x^{10} + x^8 +$      | 49       | $x^{16} + x^{15} + x^{14} + x^{13} + x^{12} + x^{11} +$ |

|          | $x^7 + x^6 + x^5 + x^4 + x^3 + x^2 + x^1 + 1$    |          | $x^{10} + x^9 + x^8 + x^6 + x^5 + x^4 + 1$              |

| 50       | $x^{16} + x^{12} + x^{11} + x^{10} + x^9 +$      | 51       | $x^{16} + x^{15} + x^{14} + x^{13} + x^{12} +$          |

|          | $x^8 + x^7 + x^5 + x^4 + x^3 + x^2 + x^1 + 1$    |          | $x^{11} + x^9 + x^8 + x^7 + x^6 + x^5 + x^4 + 1$        |

| 52       | $x^{16} + x^{13} + x^{11} + x^{10} + x^9 +$      | 53       | $x^{16} + x^{15} + x^{14} + x^{13} + x^{12} + x^{11} +$ |

|          | $x^7 + x^6 + x^5 + x^4 + x^3 + x^2 + x^1 + 1$    |          | $x^{10} + x^9 + x^7 + x^6 + x^5 + x^3 + 1$              |

| 54       | $x^{16} + x^{13} + x^{12} + x^{11} + x^8 +$      | 55       | $x^{16} + x^{15} + x^{14} + x^{13} + x^{12} + x^{11} +$ |

|          | $x^7 + x^6 + x^5 + x^4 + x^3 + x^2 + x^1 + 1$    |          | $x^{10} + x^9 + x^8 + x^5 + x^4 + x^3 + 1$              |

| 56       | $x^{16} + x^{13} + x^{12} + x^{11} + x^9 +$      | 57       | $x^{16} + x^{15} + x^{14} + x^{13} + x^{11} +$          |

|          | $x^8 + x^7 + x^6 + x^5 + x^3 + x^2 + x^1 + 1$    |          | $x^{10} + x^9 + x^8 + x^7 + x^5 + x^4 + x^3 + 1$        |

| 58       | $x^{16} + x^{13} + x^{12} + x^{11} + x^{10} +$   | 59       | $x^{16} + x^{15} + x^{14} + x^{13} + x^{12} + x^{10} +$ |

|          | $x^9 + x^7 + x^6 + x^4 + x^3 + x^2 + x^1 + 1$    |          | $x^9 + x^7 + x^6 + x^5 + x^4 + x^3 + 1$                 |

| 60       | $x^{16} + x^{13} + x^{12} + x^{11} + x^{10} +$   | 61       | $x^{16} + x^{15} + x^{13} + x^{12} + x^{11} + x^{10} +$ |

|          | $x^9 + x^7 + x^6 + x^5 + x^4 + x^3 + x^1 + 1$    |          | $x^9 + x^7 + x^6 + x^5 + x^4 + x^3 + 1$                 |

| 62       | $x^{16} + x^{14} + x^{11} + x^9 + x^8 +$         | 63       | $x^{16} + x^{15} + x^{14} + x^{13} + x^{12} + x^{11} +$ |

|          | $x^7 + x^6 + x^5 + x^4 + x^3 + x^2 + x^1 + 1$    |          | $x^{10} + x^9 + x^8 + x^7 + x^5 + x^2 + 1$              |

Table 4 (continued)

| poly. no | metadata | pdf      | compress | $\operatorname{ppt}$ | mp3      | mp4      | picture  |

|----------|----------|----------|----------|----------------------|----------|----------|----------|

| 0        | 0.000015 | 0.438711 | 0.471996 | 0.417557             | 0.440888 | 0.440549 | 0.534002 |

| 1        | 0        | 0.441995 | 0.472435 | 0.421484             | 0.448484 | 0.442699 | 0.541311 |

| 2        | 0        | 0.441939 | 0.475722 | 0.421859             | 0.447419 | 0.444703 | 0.542909 |

| 3        | 0.000021 | 0.440033 | 0.472821 | 0.419434             | 0.441828 | 0.441283 | 0.535894 |

| 4        | 0.000498 | 0.438511 | 0.471682 | 0.416916             | 0.439944 | 0.439712 | 0.530911 |

| 5        | 0.003138 | 0.443568 | 0.476516 | 0.423597             | 0.446503 | 0.445241 | 0.548343 |

| 6        | 0.00036  | 0.440135 | 0.474084 | 0.421106             | 0.445015 | 0.442773 | 0.546743 |

| 7        | 0.009584 | 0.439273 | 0.47067  | 0.419279             | 0.450382 | 0.441269 | 0.535987 |

| 8        | 0.000904 | 0.440829 | 0.475366 | 0.422825             | 0.44839  | 0.444916 | 0.54392  |

| 9        | 0.000072 | 0.440239 | 0.471414 | 0.420736             | 0.448248 | 0.441094 | 0.537634 |

| 10       | 0        | 0.433379 | 0.465882 | 0.415668             | 0.444976 | 0.438262 | 0.52978  |

| 11       | 0.000082 | 0.438736 | 0.469896 | 0.418377             | 0.448772 | 0.440774 | 0.53904  |

| 12       | 0.00396  | 0.438495 | 0.469067 | 0.420166             | 0.444459 | 0.440136 | 0.537302 |

| 13       | 0        | 0.439279 | 0.469607 | 0.418782             | 0.44554  | 0.440156 | 0.536442 |

| 14       | 0.020626 | 0.444134 | 0.476009 | 0.422674             | 0.443483 | 0.44471  | 0.544833 |

| 15       | 0        | 0.438562 | 0.471534 | 0.420231             | 0.452096 | 0.441536 | 0.534617 |

| 16       | 0.004699 | 0.440247 | 0.473177 | 0.420474             | 0.448235 | 0.442807 | 0.545585 |

| 17       | 0.02232  | 0.432267 | 0.460016 | 0.413064             | 0.440436 | 0.433806 | 0.51866  |

| 18       | 0.001125 | 0.442318 | 0.473832 | 0.422917             | 0.448515 | 0.443491 | 0.542439 |

| 19       | 0        | 0.435023 | 0.46326  | 0.41667              | 0.444034 | 0.436332 | 0.521316 |

| 20       | 0.000144 | 0.442425 | 0.476081 | 0.420478             | 0.444676 | 0.443124 | 0.539964 |

| 21       | 0.000005 | 0.436087 | 0.463277 | 0.413615             | 0.443698 | 0.436131 | 0.523366 |

| 22       | 0.00001  | 0.44069  | 0.473147 | 0.420055             | 0.442139 | 0.442136 | 0.542116 |

| 23       | 0        | 0.437115 | 0.464452 | 0.416242             | 0.446398 | 0.437421 | 0.525261 |

| 24       | 0        | 0.440651 | 0.473223 | 0.421484             | 0.448845 | 0.442935 | 0.54197  |

Table 5. The probability of each polynomial to reduce 1's number

Table 5 (continued)

| poly. no | metadata | pdf      | compress | $\operatorname{ppt}$ | mp3      | mp4      | picture  |

|----------|----------|----------|----------|----------------------|----------|----------|----------|

| 25       | 0        | 0.436435 | 0.465094 | 0.415462             | 0.44855  | 0.437481 | 0.525322 |

| 26       | 0.003343 | 0.440164 | 0.47173  | 0.419896             | 0.441298 | 0.441608 | 0.539524 |

| 27       | 0.000185 | 0.43668  | 0.465181 | 0.414801             | 0.447648 | 0.437535 | 0.526578 |

| 28       | 0.000005 | 0.442247 | 0.474702 | 0.42222              | 0.448543 | 0.443607 | 0.54371  |

| 29       | 0        | 0.43625  | 0.464912 | 0.416166             | 0.450187 | 0.43754  | 0.527631 |

| 30       | 0.000257 | 0.443861 | 0.477076 | 0.421856             | 0.444209 | 0.443435 | 0.541014 |

| 31       | 0        | 0.436375 | 0.463546 | 0.415226             | 0.443077 | 0.437117 | 0.526386 |

| 32       | 0.00169  | 0.44151  | 0.473586 | 0.41996              | 0.447599 | 0.442491 | 0.542267 |

| 33       | 0.020215 | 0.433343 | 0.460023 | 0.412842             | 0.442338 | 0.433617 | 0.517418 |

| 34       | 0.009106 | 0.440225 | 0.470997 | 0.419154             | 0.448194 | 0.441919 | 0.539684 |

| 35       | 0.014971 | 0.433186 | 0.459926 | 0.412919             | 0.441133 | 0.433608 | 0.519018 |

| 36       | 0.000955 | 0.444899 | 0.475905 | 0.42331              | 0.448923 | 0.445061 | 0.546133 |

| 37       | 0        | 0.433029 | 0.461257 | 0.415673             | 0.440956 | 0.435036 | 0.521418 |

| 38       | 0.000272 | 0.439374 | 0.47022  | 0.418455             | 0.447588 | 0.440331 | 0.537422 |

| 39       | 0        | 0.435306 | 0.46454  | 0.4144               | 0.44497  | 0.43723  | 0.528459 |

| 40       | 0.000575 | 0.439338 | 0.470926 | 0.418815             | 0.446566 | 0.441134 | 0.541256 |

| 41       | 0        | 0.436811 | 0.46576  | 0.415142             | 0.443259 | 0.438342 | 0.529789 |

| 42       | 0.000021 | 0.439517 | 0.471394 | 0.421001             | 0.447655 | 0.442378 | 0.54276  |

| 43       | 0        | 0.438367 | 0.466656 | 0.414496             | 0.447086 | 0.438388 | 0.528789 |

| 44       | 0.000026 | 0.443264 | 0.47431  | 0.421401             | 0.44757  | 0.443815 | 0.543008 |

| 45       | 0        | 0.435302 | 0.465885 | 0.415209             | 0.441262 | 0.438547 | 0.528529 |

| 46       | 0        | 0.443567 | 0.476831 | 0.424812             | 0.449777 | 0.445766 | 0.544746 |

| 47       | 0        | 0.434661 | 0.465893 | 0.417268             | 0.440229 | 0.438003 | 0.530022 |

| 48       | 0.007658 | 0.43774  | 0.470313 | 0.415336             | 0.436354 | 0.43882  | 0.52801  |

| 49       | 0.00037  | 0.438954 | 0.471142 | 0.419517             | 0.448708 | 0.441169 | 0.53715  |

| 50       | 0.004001 | 0.439752 | 0.472526 | 0.419452             | 0.441584 | 0.441125 | 0.535459 |

| 51       | 0        | 0.439336 | 0.470785 | 0.418509             | 0.44948  | 0.441376 | 0.537395 |

| 52       | 0.000026 | 0.436671 | 0.471413 | 0.417003             | 0.438932 | 0.439507 | 0.529943 |

| poly. no | metadata | $\mathbf{pdf}$ | compress | $\operatorname{ppt}$ | mp3      | mp4      | picture  |

|----------|----------|----------------|----------|----------------------|----------|----------|----------|

| 53       | 0.009676 | 0.440834       | 0.471516 | 0.419007             | 0.448926 | 0.442098 | 0.540658 |

| 54       | 0.000021 | 0.435268       | 0.47043  | 0.414848             | 0.435516 | 0.438059 | 0.527065 |

| 55       | 0.000437 | 0.439448       | 0.471522 | 0.419285             | 0.446475 | 0.442177 | 0.539935 |

| 56       | 0.004746 | 0.441804       | 0.472875 | 0.419781             | 0.443671 | 0.44236  | 0.542425 |

| 57       | 0.009835 | 0.44219        | 0.471141 | 0.421075             | 0.448039 | 0.442399 | 0.539407 |

| 58       | 0        | 0.442474       | 0.472383 | 0.419839             | 0.441966 | 0.441578 | 0.536879 |

| 59       | 0        | 0.442562       | 0.471749 | 0.421147             | 0.448386 | 0.442328 | 0.540393 |

| 60       | 0.001705 | 0.443609       | 0.476583 | 0.421987             | 0.448994 | 0.445104 | 0.547865 |

| 61       | 0.002624 | 0.440573       | 0.471773 | 0.420737             | 0.448184 | 0.442375 | 0.540288 |

| 62       | 0.000914 | 0.435672       | 0.46928  | 0.414176             | 0.433102 | 0.437578 | 0.527946 |

| 63       | 0.003765 | 0.443383       | 0.4741   | 0.421855             | 0.447927 | 0.444083 | 0.543792 |

Table 5 (continued)

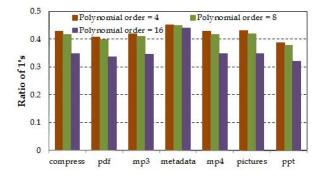

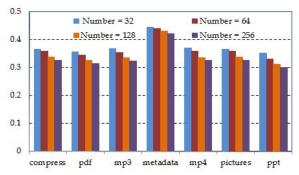

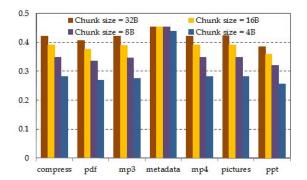

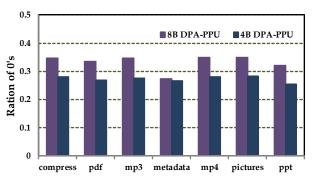

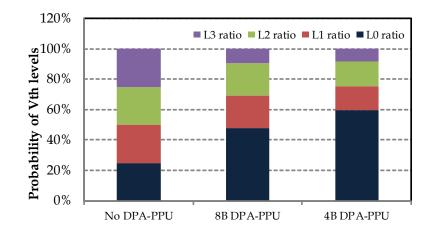

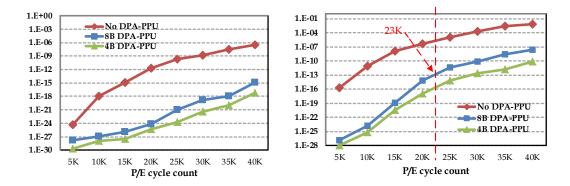

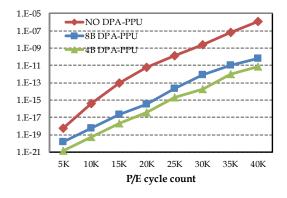

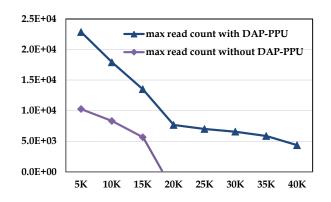

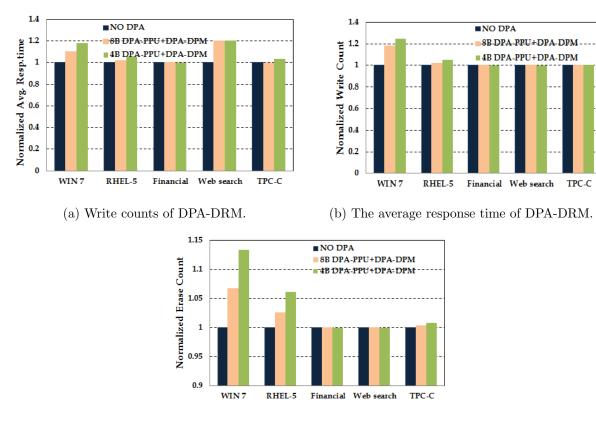

As shown in Fig. 10(a), the average ratio of 1's decreases from 0.42 to 0.34 in the scrambling scheme as the polynomial order rises from 4 to 16. Such improvement is due to increase of the available polynomials. Fig. 10(b) shows that the average ratio of 1's decreases by 11.5% as the polynomial number changes from 32 to 256. Fig. 10(c) shows that the ratio of 1's increases from 0.27 to 0.42 on average by increasing the chunk size from 4B to 32B due to the reduced overlap pattern between the data chunk and the polynomial.