# Modelling, Fabrication and Characterisation of the EEPROM

# Thesis submitted by Anthony James Chester for the degree of

Doctor of Philosophy

# Department of Electrical Engineering University of Edinburgh Scotland

August 1993

#### Abstract

The Electrically Erasable Programmable ROM (EEPROM) is used in applications such as microcontrollers and mass storage media. Each of these markets is rapidly expanding. However, EEPROMs are particularly susceptible to reliability problems, since they must survive severe voltage and current stressing. This has a knock on effect, since operating speed must be reduced, to increase reliability. Motorola's implementation of the EEPROM is the Floating Gate Electron Tunnelling MOS (FETMOS), which has been adopted for study in this thesis.

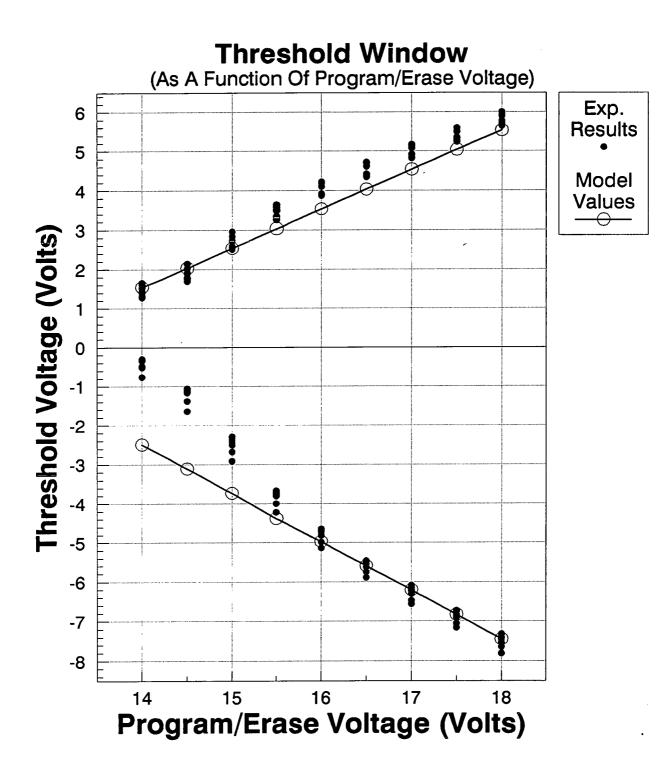

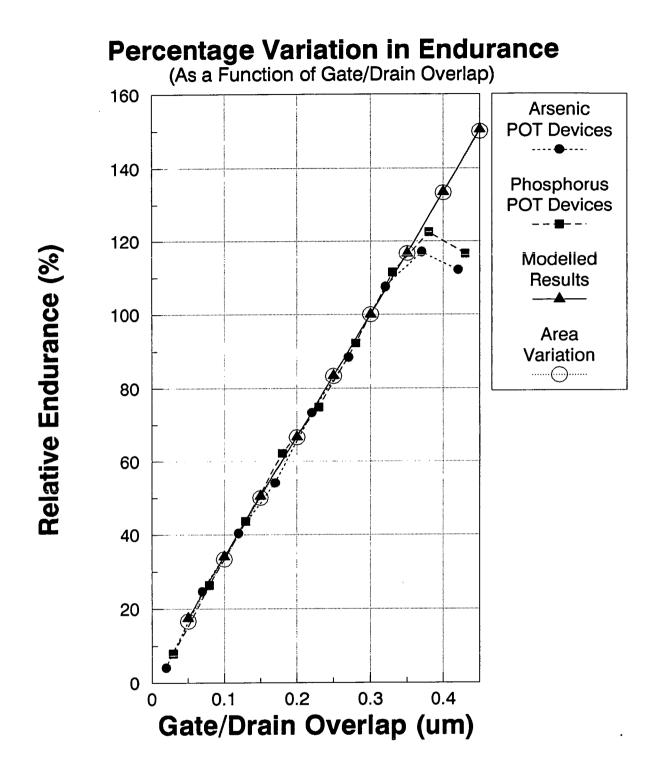

An analytic model has been developed for the FETMOS, which encompasses transient response, threshold window and reliability. A good correlation has been shown between modelled data and experimental results, testifying to the model's accuracy. The effect of basic design parameters upon threshold window has been characterised, thus indicating how processing variations may be used to tailor the EEPROM threshold window. Equally, the model may be used to predict the effect of sizing down a circuit - this is important as integration densities escalate. Program endurance is the most pressing reliability issue. Modelling has indicated that, large improvements may be made in this by increasing the floating gate/drain overlap, with little effect on threshold window.

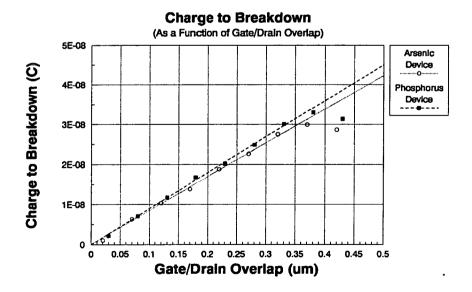

An novel experiment has then been devised to monitor the effect of floating gate/drain overlap and doping species, upon EEPROM reliability. For this, transistor arrays with a spectrum of well defined gate/drain offsets have been produced. The results of these are consistent with the model. It has also been found that the chemistry of the dopant has only a tangential effect upon reliability.

In conclusion, it is proposed that an increase in the tilt angle of the drain implant would be the most suitable method to increase the overlap, since no adjustment is then required in the thermal budget of the process. An increase in the drain doping density could also be used, to similar effect.

## Declaration

I declare that the research documented in this thesis is original and entirely of my own making, except where it has been indicated to the contrary.

.

.

Anthony James Chester

#### Acknowledgements

I wish to express my thanks to all those people who helped in any way towards this PhD. In particular, I would like to thank my academic supervisor, Dr. A.J.Walton, both for offering his expert help and guidance throughout this Ph.D. program, and for allowing me autonomy in all my final decisions.

I would also like to thank my industrial supervisor, Paul Tuohy, for his excellent technical discussions, particularly with respect to EEPROM modelling.

Many thanks to all staff and students of the Edinburgh Microfabrication Facility, past and present, whose support has been greatly appreciated.

I conclude with an acknowledgement to the Science and Engineering Research Council and from Motorola, who provided financial assistance under a CASE award scheme.

# **Table of Contents**

| 1. | Intr | oductio | on                                 | •   |     |     |   |   |     | 1  |

|----|------|---------|------------------------------------|-----|-----|-----|---|---|-----|----|

|    | 1.1  | Floatin | ng Gate Technologies               | ••  |     | ••  | • | • |     | 3  |

|    |      | 1.1.1   | The FETMOS Device                  |     | • • |     | • | • | ••• | 3  |

|    |      | 1.1.2   | The FLOTOX Device                  | ••  | ••  |     | • | • |     | 5  |

|    |      | 1.1.3   | The Flash EEPROM                   |     |     |     | • | • |     | 6  |

|    |      | 1.1.4   | Contrast Between FETMOS/FLOTOX and | Fla | lsh |     | • | • | • • | 8  |

|    | 1.2  | Utility | of the EEPROM                      |     |     |     | • | • |     | 9  |

|    |      | 1.2.1   | Program/Data Storage Media         |     |     |     | • | • |     | 9  |

|    |      | 1.2.2   | Embedded Systems                   | ••  |     |     | • | • |     | 10 |

|    |      | 1.2.3   | Embryonic Technologies             | ••• |     |     | • | • |     | 10 |

|    | 1.3  | Reliabi | ility                              | ••  |     |     | • | • |     | 11 |

|    |      | 1.3.1   | Shrinking Geometries               | • • | • • |     | • | • |     | 12 |

|    |      | 1.3.2   | Reliability In General             | ••• | • • |     | • | • |     | 13 |

|    |      | 1.3.3   | Reliability and the EEPROM         | ••  | ••• |     | • | • |     | 14 |

|    | 1.4  | Thesis  | Plan                               | ••  | ••• | • • | • | • |     | 14 |

| 2. | EEF  | PROM    | Physics and Reliability            |     |     |     |   |   |     | 18 |

|    | 2.1  | Fowler  | -Nordheim Tunnelling               |     | ••• |     |   | • | • • | 18 |

|    |      | 2.1.1   | Wave Particle Duality              |     |     |     |   | • |     | 18 |

|    |     | 2.1.2   | Fowler-Nordheim Tunnelling in MOS Structures        | 20 |

|----|-----|---------|-----------------------------------------------------|----|

|    |     | 2.1.3   | Factors Which Affect Fowler-Nordheim Tunnelling     | 22 |

|    |     | 2.1.4   | An Equation to Describe Fowler-Nordheim Tunnelling  | 25 |

|    | 2.2 | Reliab  | ility Issues                                        | 26 |

|    |     | 2.2.1   | Oxide Breakdown                                     | 26 |

|    |     | 2.2.2   | Analysis of Reliability Data                        | 31 |

|    |     | 2.2.3   | Accelerated Testing                                 | 33 |

|    |     | 2.2.4   | EEPROM Reliability Issues                           | 34 |

|    | 2.3 | Impro   | ving EEPROM Operation and Reliability               | 37 |

| 2  | Dom | ivation | n of a FETMOS Model                                 | 43 |

| э. | Der |         |                                                     |    |

|    | 3.1 | Overv   | iew                                                 | 43 |

|    | 3.2 | Distril | oution of Injected Charge in a Capacitor System     | 44 |

|    | 3.3 | Deriva  | ation of Equations to Describe the FETMOS Device    | 47 |

|    |     | 3.3.1   | Equivalent Capacitive Circuit for the FETMOS Device | 47 |

|    |     | 3.3.2   | Coupling Ratios                                     | 49 |

|    |     | 3.3.3   | The Electric Field as a Function of Time            | 50 |

|    |     | 3.3.4   | Threshold Voltage as a Function of Electric Field   | 56 |

|    |     | 3.3.5   | Initial Electric Field                              | 59 |

|    |     | 3.3.6   | Summary of Equations                                | 59 |

|    | 3.4 | Calcul  | ation of FETMOS Parameters                          | 61 |

|    |     | 3.4.1   | Overview                                            | 61 |

|    |     | 3.4.2   | Geometry of the FETMOS Device                       | 62 |

|    |     | 3.4.3   | Calculation of Capacitances                         | 63 |

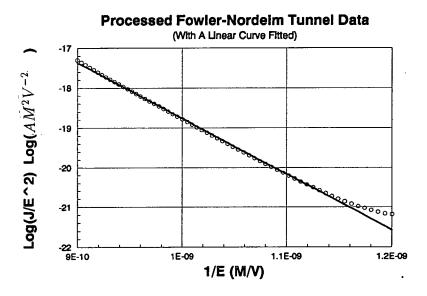

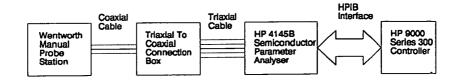

|    |     | 3.4.4   | Measurement of Fowler-Nordheim Coefficients         | 64 |

.

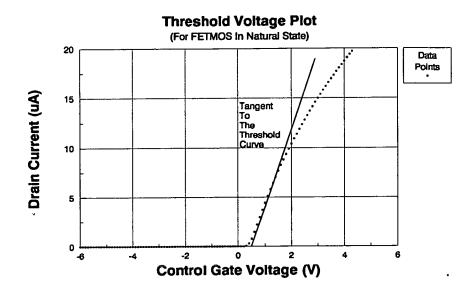

|    |     | 3.4.5    | Measurement of Threshold Voltage                                | 67  |

|----|-----|----------|-----------------------------------------------------------------|-----|

|    |     | 3.4.6    | Calculation of RC Time Constant, $	au$                          | 69  |

|    | 3.5 | Verific  | ation of the FETMOS Model Against Experimental Results .        | 70  |

|    |     | 3.5.1    | Overview                                                        | 70  |

|    |     | 3.5.2    | Comparison of Model Predictions and Experimental Results        | 71  |

|    | 3.6 | Conclu   | usion                                                           | 73  |

| 4. | Ana | alysis U | Jsing the FETMOS Model                                          | 76  |

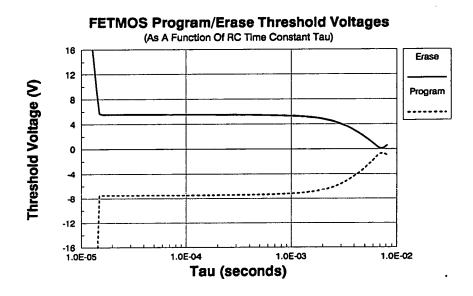

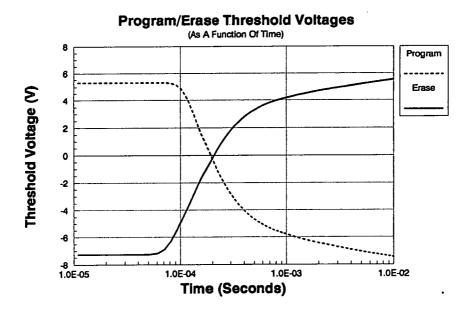

| •  | 4.1 | Transi   | ent Analysis of the FETMOS Device                               | 76  |

|    |     | 4.1.1    | Threshold Window as a Function of Time                          | 76  |

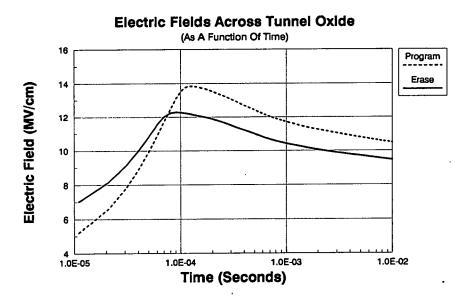

|    |     | 4.1.2    | Electric Fields as a Function of Time                           | 77  |

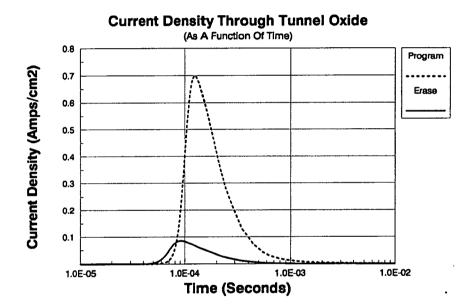

|    |     | 4.1.3    | Current Densities as a Function of Time                         | 78  |

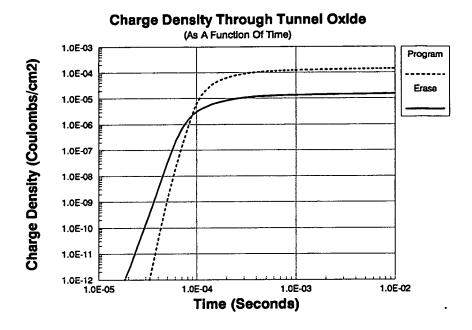

|    |     | 4.1.4    | Charge Densities as a Function of Time                          | 79  |

|    | 4.2 | A Met    | hodology for Modelling EEPROM Endurance                         | 80  |

|    | 4.3 | Analy    | sis of the Threshold Window and Endurance                       | 84  |

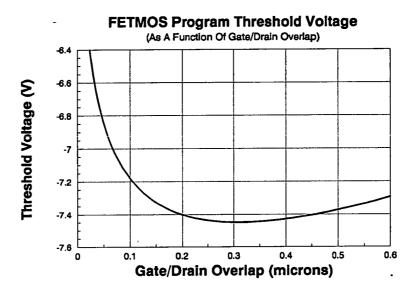

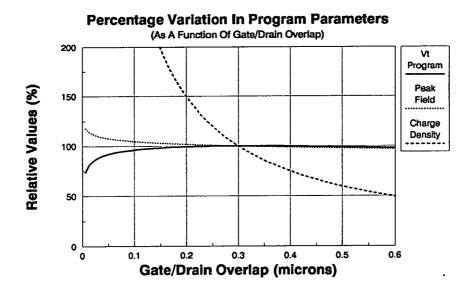

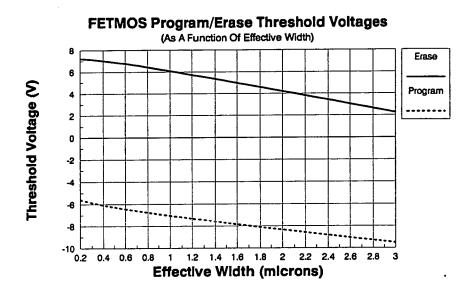

|    |     | 4.3.1    | Effect of Varying Floating Gate/Drain Overlap                   | 84  |

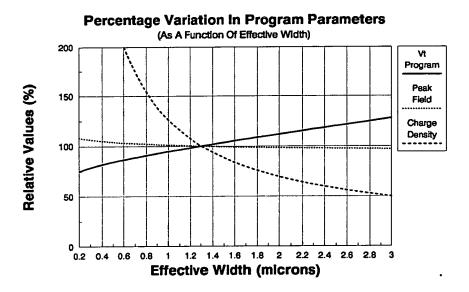

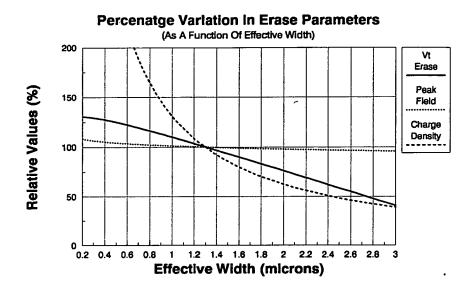

|    |     | 4.3.2    | Effect of Varying Effective Width                               | 87  |

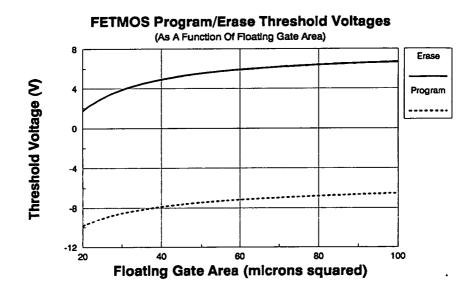

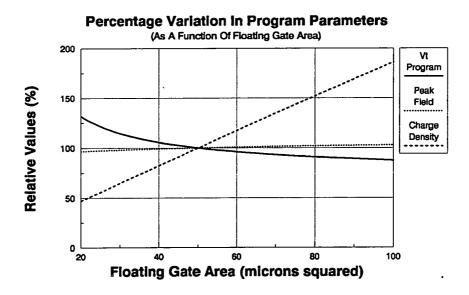

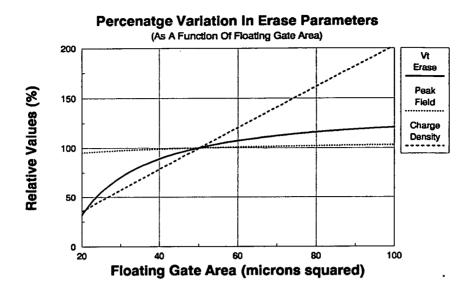

|    |     | 4.3.3    | Effect of Varying Floating Gate Area                            | 90  |

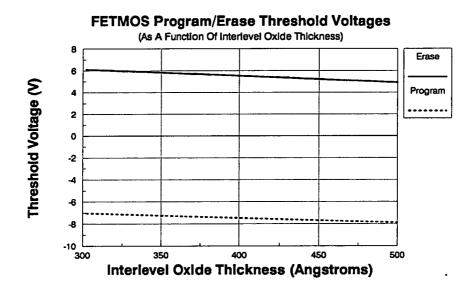

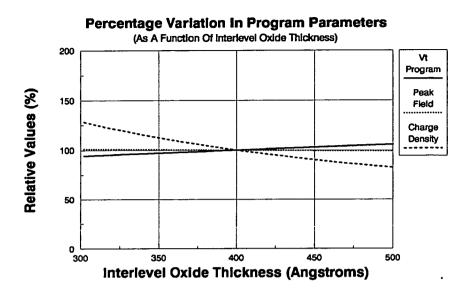

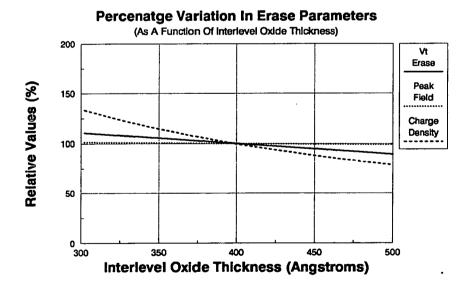

|    |     | 4.3.4    | Effect of Varying Interlevel Oxide Thickness                    | 93  |

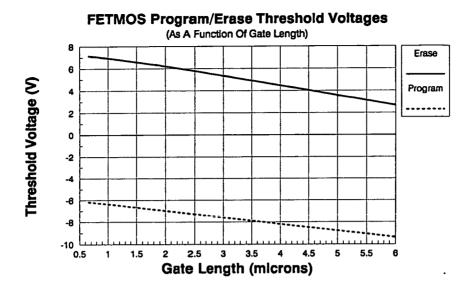

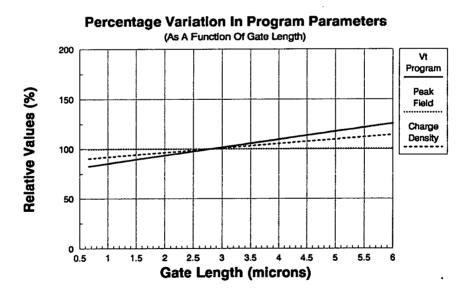

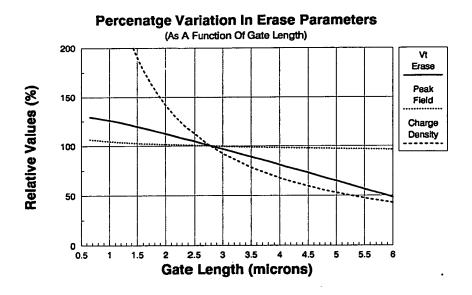

|    |     | 4.3.5    | Effect of Varying Floating Gate Length                          | 96  |

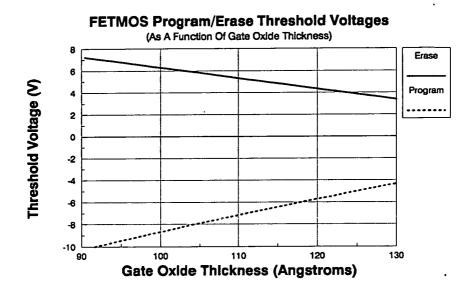

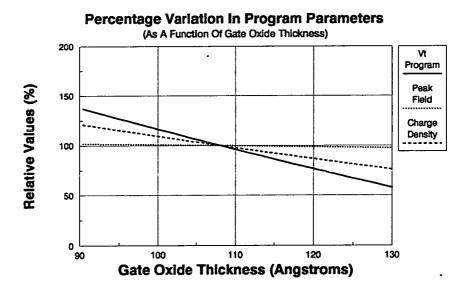

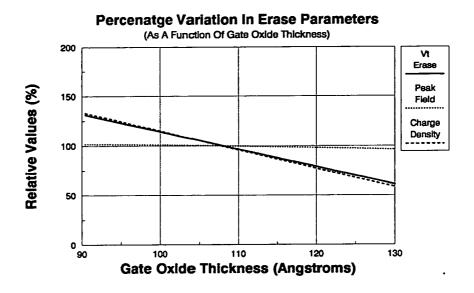

|    |     | 4.3.6    | Effect of Varying Gate Oxide Thickness                          | 99  |

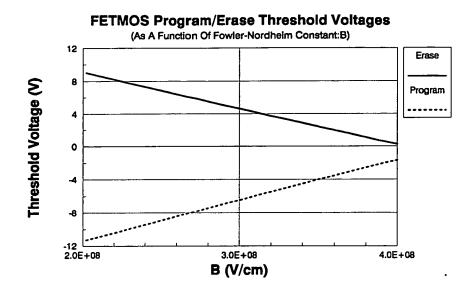

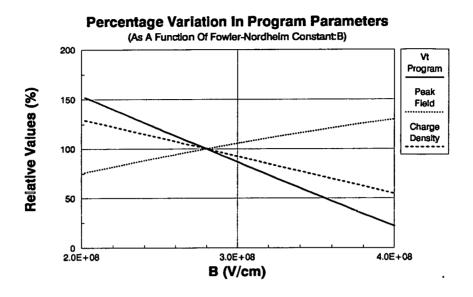

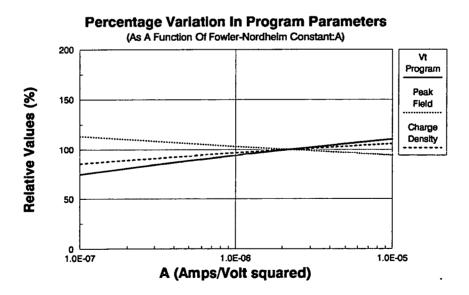

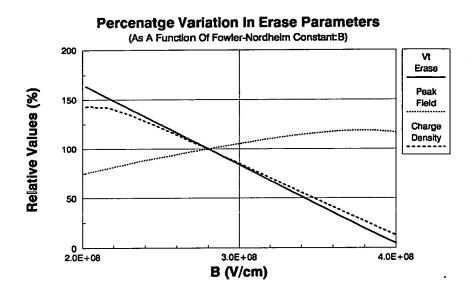

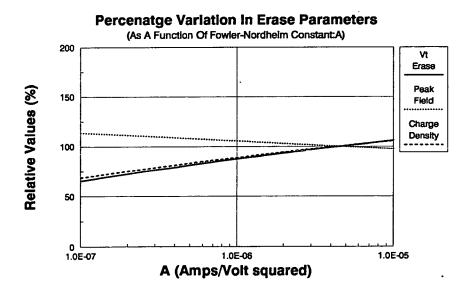

|    |     | 4.3.7    | Effect of Varying Fowler-Nordheim Coefficients, A and B $\ .$ . | 102 |

|    | 4.4 | Concl    | usion                                                           | 107 |

| 5. | Fabi | ricatio | n of EEPROM Structures                                 | 1   | 10  |

|----|------|---------|--------------------------------------------------------|-----|-----|

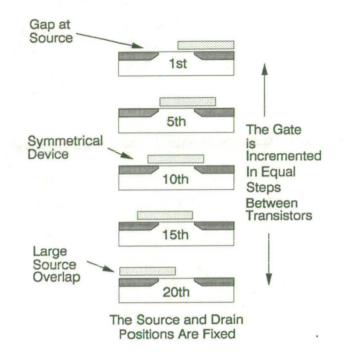

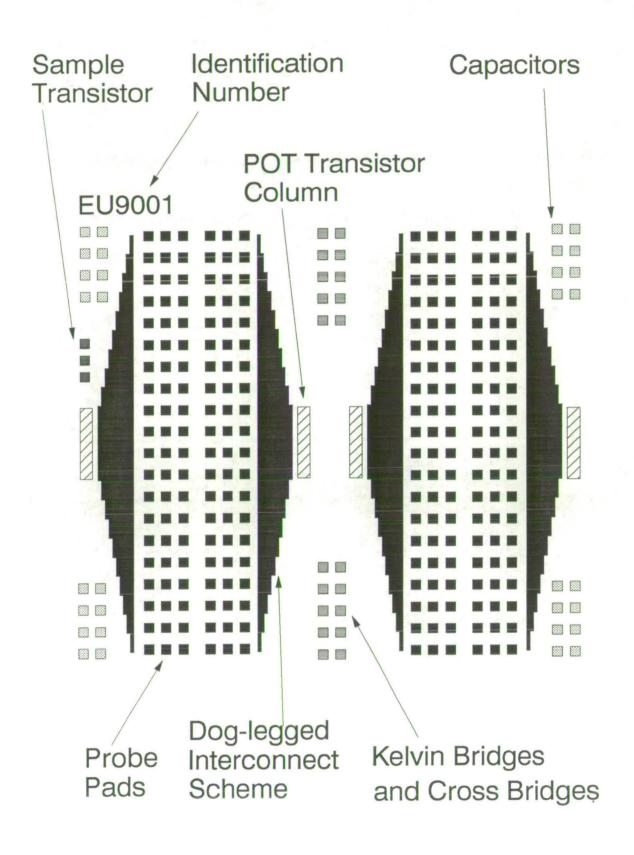

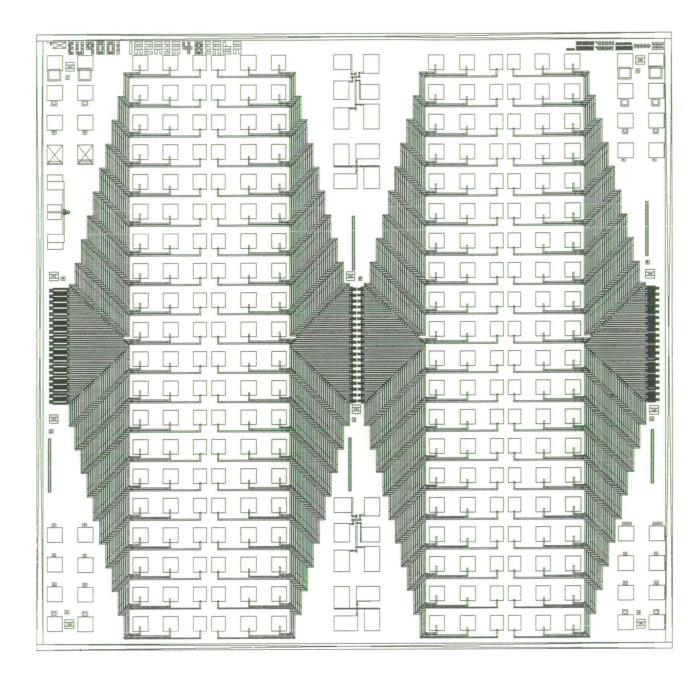

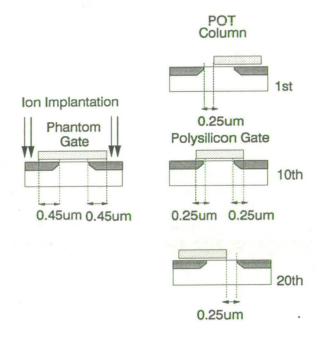

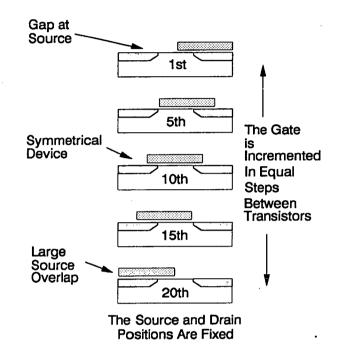

|    | 5.1  | The P   | rogressional Offset Technique                          | • • | 110 |

|    | 5.2  | Proces  | sing                                                   | ••  | 112 |

|    |      | 5.2.1   | Overview                                               | • • | 112 |

|    |      | 5.2.2   | The Bi-Poly Process                                    | ••• | 112 |

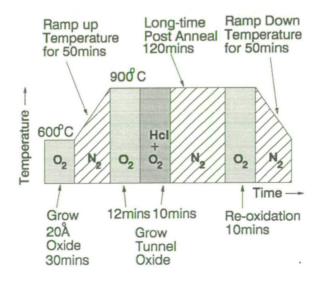

|    |      | 5.2.3   | Growth of High Integrity Thin Oxide Films              | • • | 115 |

|    |      | 5.2.4   | Complete Process Flow                                  | • • | 120 |

|    | 5.3  | Circui  | t Design                                               | ••• | 131 |

|    |      | 5.3.1   | Reticle Production                                     | ••  | 131 |

|    |      | 5.3.2   | Transistor Design                                      |     | 131 |

|    |      | 5.3.3   | Interconnection Scheme                                 | ••• | 135 |

|    |      | 5.3.4   | Test Structures                                        | ••• | 136 |

|    | 5.4  | Simula  | ation                                                  | ••• | 136 |

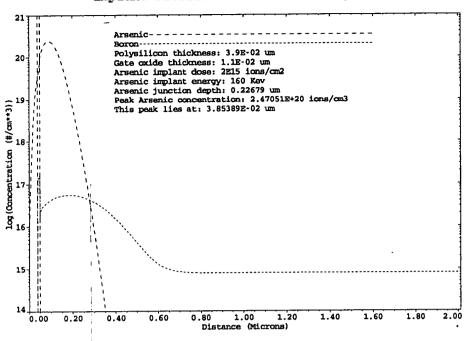

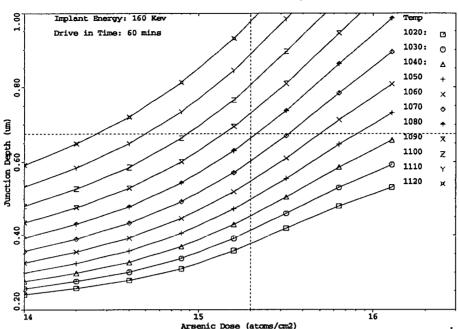

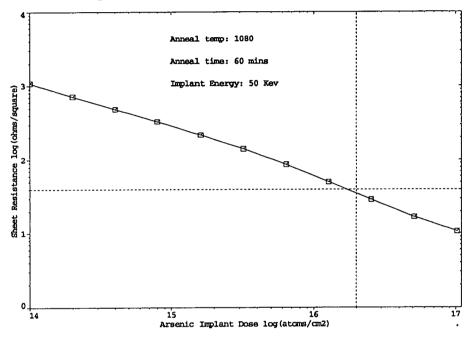

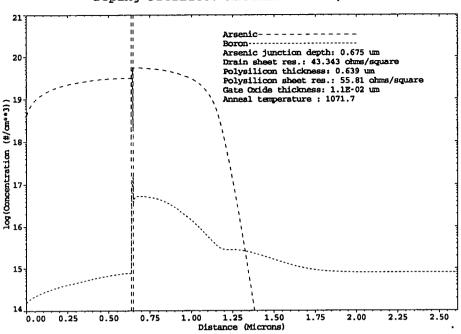

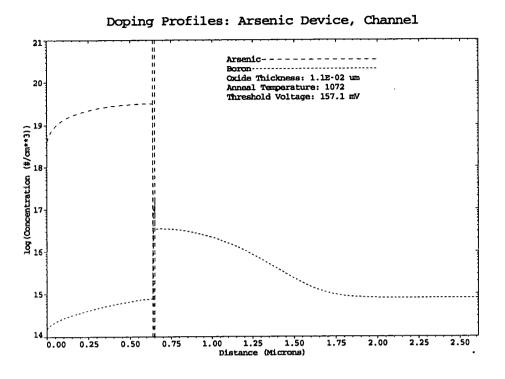

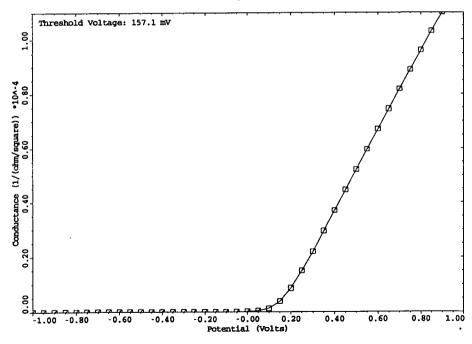

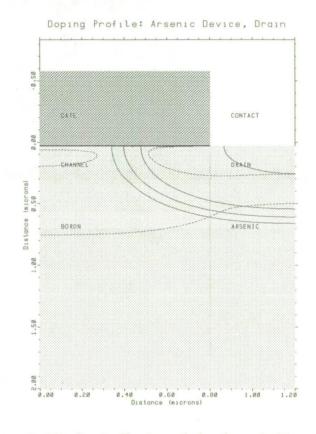

|    |      | 5.4.1   | 1 Dimensional Simulation of Arsenic Transistors        | ••• | 138 |

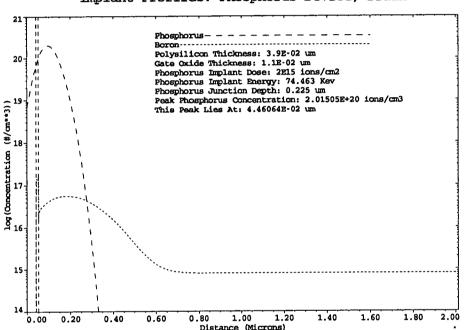

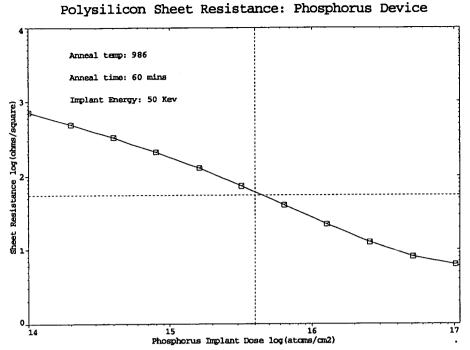

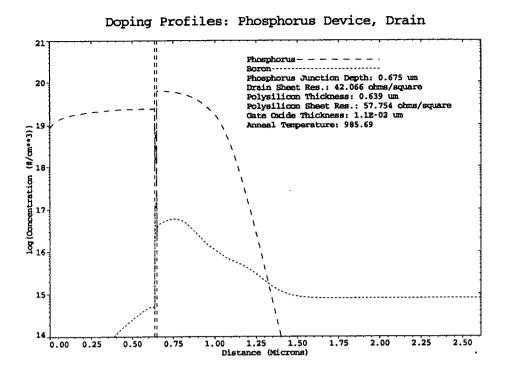

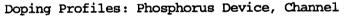

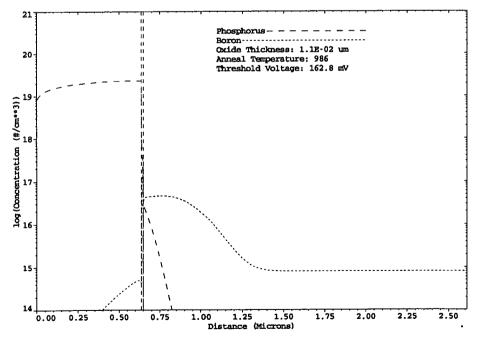

|    |      | 5.4.2   | 1 Dimensional Simulation of the Phosphorus Transistors | ••• | 143 |

|    |      | 5.4.3   | 2 Dimensional Simulation of Transistors                | ••• | 146 |

|    | 5.5  | Conclu  | usion                                                  | ••• | 148 |

| 6. | Ana  | dysis o | of EEPROM Structures                                   | 1   | 152 |

|    | 6.1  | Proces  | ss Quality                                             | ••  | 152 |

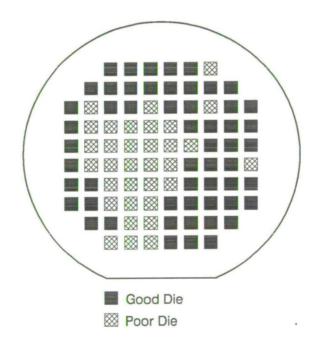

|    |      | 6.1.1   | Wafer Yield                                            |     | 153 |

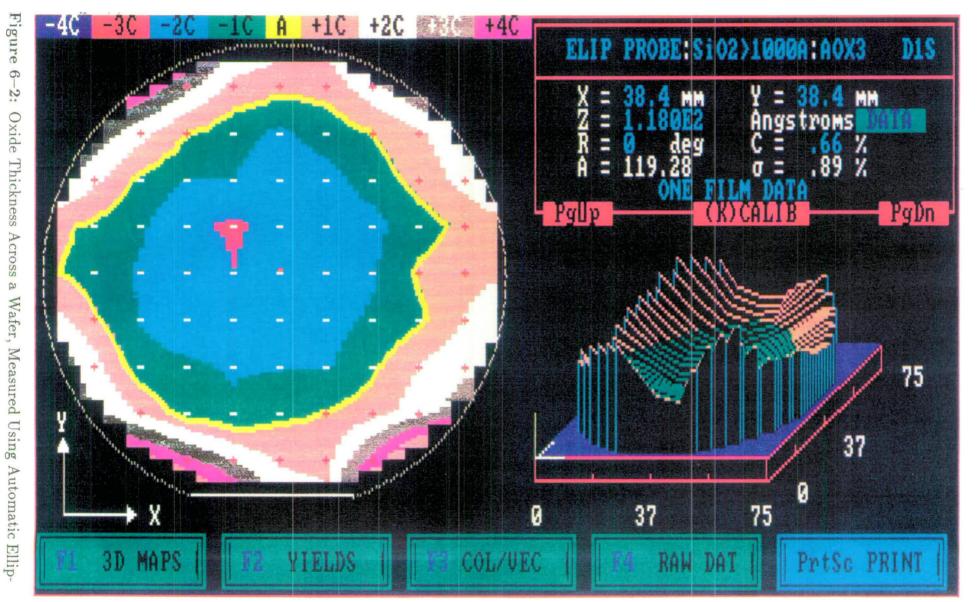

|    |      | 6.1.2   | Gate Oxide Thickness                                   |     | 154 |

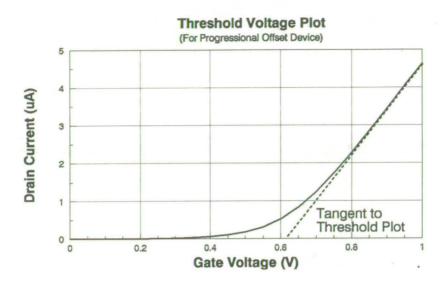

|    |      | 6.1.3   | Threshold Voltage                                      | ••• | 154 |

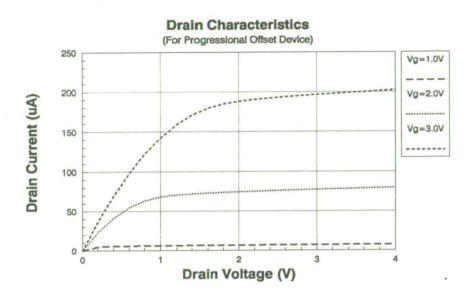

|    |      | 6.1.4   | Drain Characteristics                                  | • • | 156 |

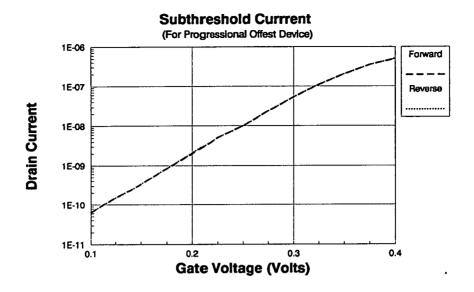

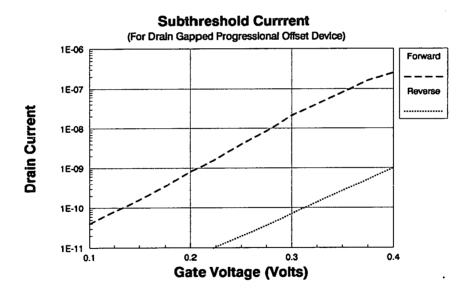

|    | 6.2  | Assess  | sment of POT Array Symmetry                            | • • | 156 |

|                  | 6.3  | Reliability Analysis                                              |  |  |  |  |

|------------------|------|-------------------------------------------------------------------|--|--|--|--|

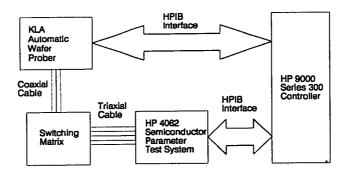

|                  |      | 6.3.1 Test Methodology                                            |  |  |  |  |

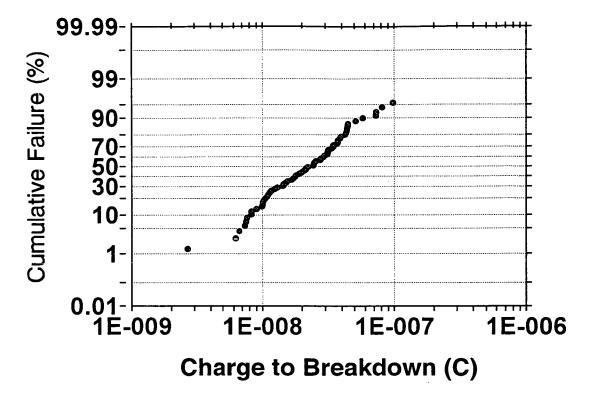

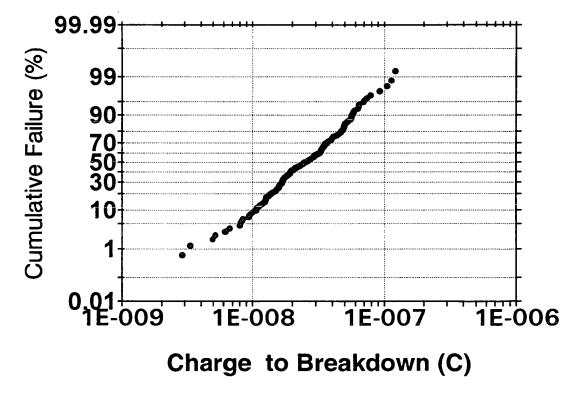

|                  |      | 6.3.2 Reliability of Progressional Offset Transistors             |  |  |  |  |

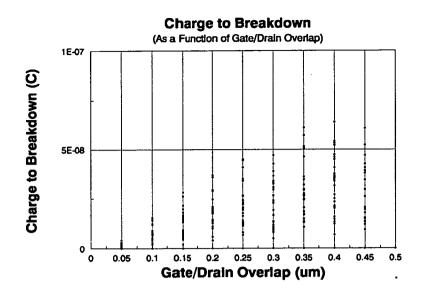

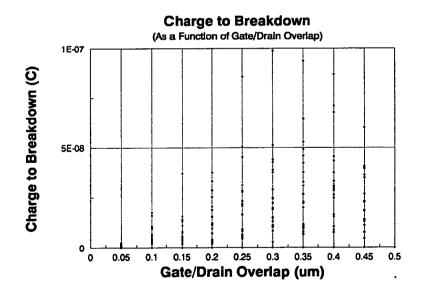

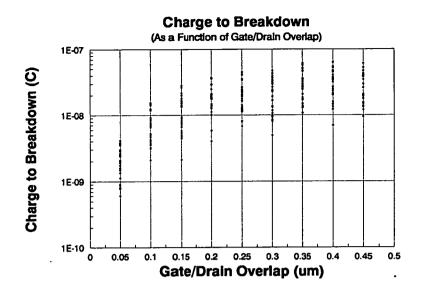

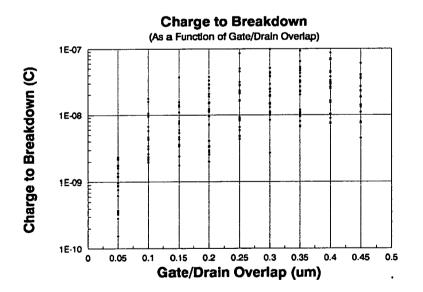

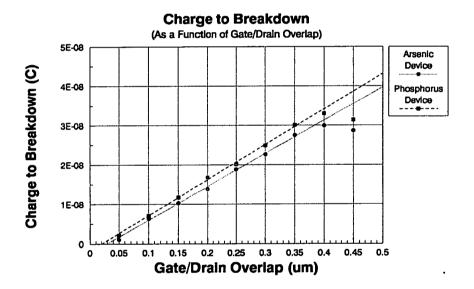

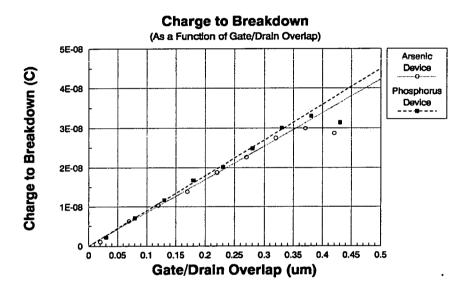

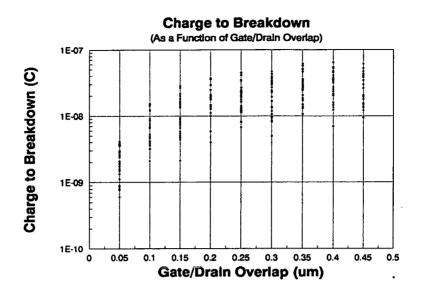

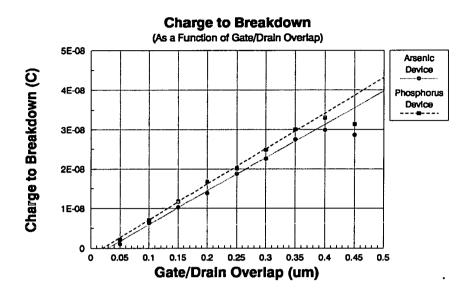

|                  |      | 6.3.3 Average Charge to Breakdown                                 |  |  |  |  |

|                  |      | 6.3.4 Calculation of Lateral Diffusion                            |  |  |  |  |

|                  |      | 6.3.5 Prediction of EEPROM Endurance from Experimental Results169 |  |  |  |  |

|                  | 6.4  | Conclusion                                                        |  |  |  |  |

| 7.               | Con  | clusion 175                                                       |  |  |  |  |

|                  | 7.1  | Modelling                                                         |  |  |  |  |

|                  |      | 7.1.1 Discussion of Results                                       |  |  |  |  |

|                  |      | 7.1.2 Areas for Further Modelling                                 |  |  |  |  |

|                  | 7.2  | Experimental                                                      |  |  |  |  |

|                  |      | 7.2.1 Discussion of Results                                       |  |  |  |  |

|                  |      | 7.2.2 Areas for Further Experimental Investigation                |  |  |  |  |

|                  | 7.3  | Concluding Remarks                                                |  |  |  |  |

| $\mathbf{A}_{]}$ | ppen | dices                                                             |  |  |  |  |

|                  | A.   | Summary of Paper i                                                |  |  |  |  |

|                  | B.   | Program in C to Model the EEPROM vii                              |  |  |  |  |

|                  | C.   | Program to Measure Threshold Voltage                              |  |  |  |  |

|                  | D.   | Process Simulation                                                |  |  |  |  |

|                  | E.   | Program to Analyse POT Devices                                    |  |  |  |  |

# Chapter 1

# Introduction

The microelectronics industry ebbs and flows on a tide of technical innovation, particularly so in today's climate of economic aggression. As silicon processing technology becomes more sophisticated, so transistor geometries have shrunk and integration densities increased. The Dynamic Random Access Memory (DRAM) rides the crest of this technological wave, with the highest transistor count per chip. The quest for ever shrinking device geometries is lead primarily by insatiable thirst of the microcomputer for more memory. However, the DRAM does have a draw back in terms of its volatility, ie. it looses data when the power is turned off. For this reason magnetic storage media are required, although these have slow read/write and access times. The paradigm would be a *nonvolatile* semiconductor memory, and this is indeed a description of the Electrically Erasable Programmable Read Only Memory (EEPROM). The EEPROM is one of the more sophisticated types of semiconductor memories available, and has been adopted for study in this thesis. To recap, it offers:

- 1. Non-volatility. In common with magnetic storage media, the EEPROM retains data when the power supply is switched off.

- 2. Electrical programmability and erasability. As for the ubiquitous DRAM, data is updated electrically.

A broad spectrum of technologies may be included under the EEPROM banner. Amongst these are: MNOS devices (metal-nitride-oxide-semiconductor) for space

1

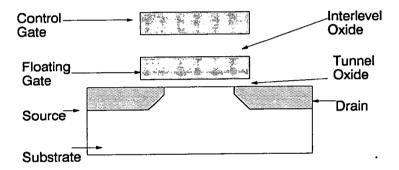

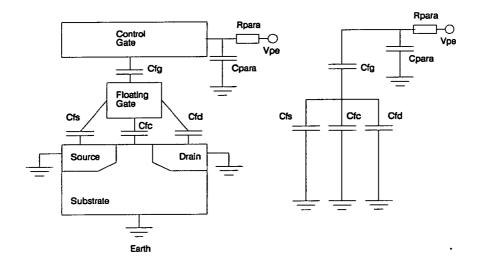

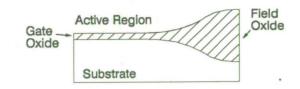

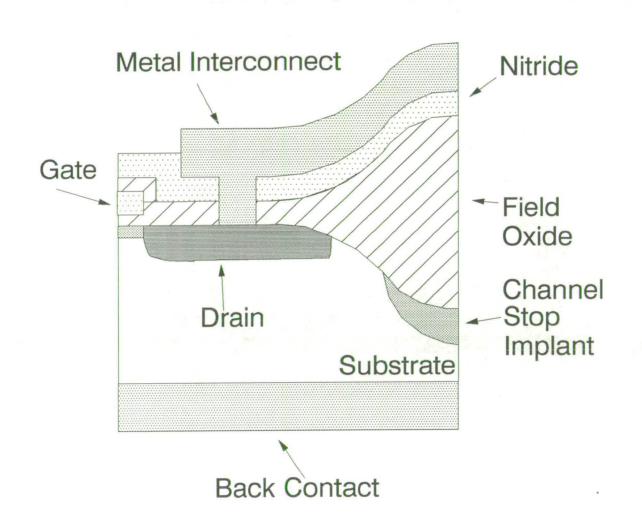

and military applications [1], devices using ferroelectric materials [2] [3], and novel micro-machined designs [4]. However, the most dominant technologies are the "Floating Gate" technologies, which are readily compatible with main stream MOS processes. This project will be limited solely to these devices. A generic floating gate EEPROM structure is illustrated in figure 1–1. This is similar to ordinary MOSFETs, but for the addition of a floating gate, which is electrically isolated. To program or erase the EEPROM charge is injected onto the floating gate, and (depending on its polarity) the underlying channel will go into either inversion or accumulation. Thus, by modulating the threshold voltage, a logic 1 or logic 0 is defined <sup>1</sup>. This is equivalent to the operation of EPROM. However, the EPROM must be illuminated in U.V. light for charge removal from the floating gate, whereas the EEPROM allows both program and erase electrically.

Figure 1-1: Cross Section Illustrating a Generic EEPROM Design.

<sup>&</sup>lt;sup>1</sup>A programmed EEPROM may be defined as one with either positive or negative charge on the floating gate. In literature no rule has been adopted. In this thesis "programmed" describes an EEPROM with positive charge on the floating gate, and "erased" indicates injected electrons. This is irrespective of the nomenclature used in a referenced paper.

# 1.1 Floating Gate Technologies

Many designs have been realised using the floating gate [1] [5]. From these, three have been singled out for discussion.

- 1. The Floating Gate Electron Tunnelling MOS (FETMOS). This is the EEP-ROM fabricated by Motorola for their microcontrollers, at East Kilbride, and features most strongly in this work.

- 2. The Floating gate Tunnel Oxide (FLOTOX). This device is the most popular of the mature technologies [6] [7].

- 3. The flash EEPROM. These devices have a very "bright" future [8] [9].

Both FLOTOX and flash EEPROMs share features of the FETMOS [10]. Each technology will be described below, and contrasts will be made.

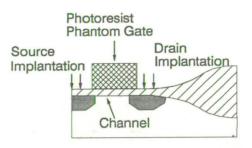

## 1.1.1 The FETMOS Device

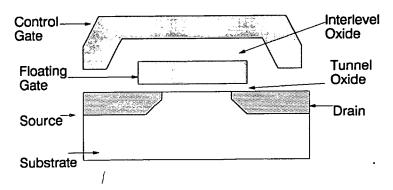

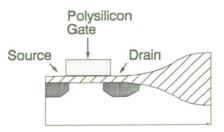

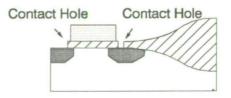

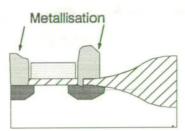

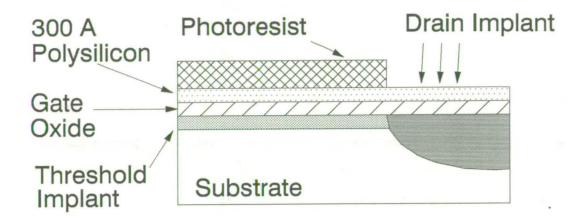

A cross section of the FETMOS transistor is given in in figure 1-2 [11], the simplicity of which is evident. Table 1-1 summarises the program, erase and read voltages. The high voltages are usually produced "on chip" with charge pumping techniques [12].

Figure 1-2: Cross Section of FETMOS Device. This is Realised in NMOS.

| FETMOS Operational Voltages |              |       |            |            |  |  |  |

|-----------------------------|--------------|-------|------------|------------|--|--|--|

|                             | Control Gate | Drain | Source     | Substrate  |  |  |  |

| Program                     | 0 <i>V</i>   | 18V   | Floating   | 0 <i>V</i> |  |  |  |

| Erase                       | 18V          | 0V    | 0 <i>V</i> | 0V         |  |  |  |

| Read                        | 0 <i>V</i>   | 1V    | 0 <i>V</i> | 0 <i>V</i> |  |  |  |

Table 1-1: FETMOS Operating Voltages.

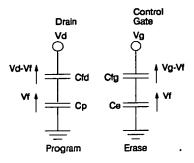

For programming a positive potential is applied to the drain. Through capacitively coupling, an electric field is generated across the tunnel oxide [13]. Providing the field is high enough, electrons may then cross the tunnel oxide, from the floating gate to the drain. Electron transport is by Fowler-Nordheim tunnelling [11], which is discussed in more detail in chapter 2. Thus positive charge is left on the floating gate, which shifts the FETMOS threshold voltage negatively, to  $\simeq -5V$ [14]. To ensure a large enough field  $\simeq 7MVcm^{-1}$ , a thin tunnel oxide of 110Å is used. Notice that a transistor with a negative threshold will be effectively switched on. Hence the source is allowed to float, avoiding the onset of a channel current, which would otherwise retard the programming operation. Once sufficient charge has collected on the floating gate, the voltage across the tunnel oxide falls, and tunnelling will stop. Thus the process is self limiting.

Erase is a similar operation, but the electric field now falls between the substrate and floating gate, and electrons flow onto the floating gate. This gives a positive shift in the FETMOS threshold voltage, to  $\simeq +5V$  [14]. Such a device is said to have a "Threshold Window" of  $\pm 5V$ .

To read stored data it is sufficient to apply 1V to the drain. Current flow (or absents) indicates the threshold voltage of the device, hence defining a logic 1 or 0. It would be possible to upset the threshold condition of the FETMOS during read, since the applied voltages could act as a "small program operation". This effect is called read disturb, and is minimised by limiting the read voltage to the lowest possible value [11]. One should also remember that, due to the thin gate

oxide, the drain voltage couples strongly to the floating gate. Thus the measured threshold voltage is sensitive to drain voltage.

In a complete memory cell, an enhancement select transistor is added in series with a FETMOS device. The select transistor provides cell isolation during read and allows program/erase of individual words of data.

## 1.1.2 The FLOTOX Device

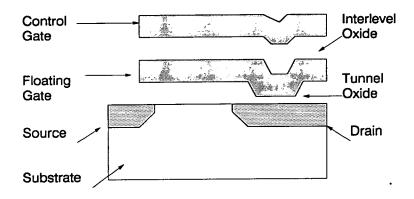

A cross section of the FLOTOX transistor is given in in figure 1-3 [15], and operating voltages in table 1-2 [16] [7]. This is similar to the FETMOS, but the tunnel oxide of  $\sim 110$ Å is located above the drain.

Figure 1-3: Cross Section of FLOTOX Device. This is Realised in NMOS.

| FLOTOX Operational Voltages |              |       |            |            |  |  |  |

|-----------------------------|--------------|-------|------------|------------|--|--|--|

|                             | Control Gate | Drain | Source     | Substrate  |  |  |  |

| Program                     | 0 <i>V</i>   | 18V   | Floating   | 0 <i>V</i> |  |  |  |

| Erase                       | 18V          | 0V    | 0V         | 0 <i>V</i> |  |  |  |

| Read                        | 0 <i>V</i>   | 1V    | 0 <i>V</i> | 0V         |  |  |  |

Table 1-2: FLOTOX Operational Voltages.

In programming, electrons pass from the floating gate to the drain by Fowler-Nordheim tunnelling, to give a negative threshold voltage shift of  $\simeq -4V$  [16] [7]. For erase the electric field again falls between the drain and floating gate. However, electrons flow onto the floating gate, to leave a positive threshold voltage of  $\simeq +8V$  [16].

A FLOTOX device is read in the same way as a FETMOS, and a select transistor is added to form a complete memory cell.

#### 1.1.3 The Flash EEPROM

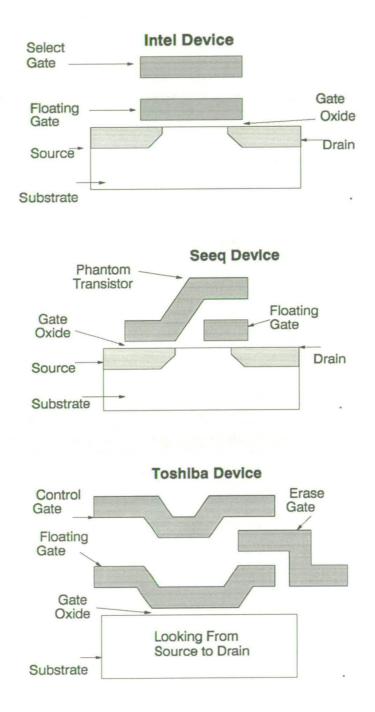

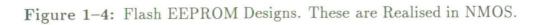

There are many suppliers of the flash EEPROM, and each has taken a slightly different approach to the device. The main suppliers are Intel, Seeq and Toshiba, all producing 1Mbit size arrays [9]. Figure 1–4 [10] illustrates the designs from these manufacturers. It is interesting to notice that the simplest device, by Intel, has the fastest access time, 120ns, and the best reliability,  $10^5$  program/erase cycles. This compares with access times for Seeq and Toshiba of 200ns and 170ns respectively, and reliabilities of  $10^3$  and  $10^2$  program/erase cycles, respectively.

Flash EEPROMs are programmed by Fowler-Nordheim tunnelling [10]<sup>2</sup>, in a similar manner to the FETMOS. However, memory cells are all programmed simultaneously, from which stems the name *flash*. In the SEEQ device for example, the drain is raised to  $\simeq +19V$ , while the control gate is grounded and the source is left floating [17]. Electrons pass from the floating gate to the drain, giving a negative threshold voltage shift.

Most flash EEPROMs are erased using a hot-electron injection technique [10]. An electrons is said to become hot when its drift velocity is comparable to its thermal velocity [18]. Thus, erasing requires a large voltage of  $\simeq +20V$  [17] on the drain and control gate, while the source and substrate are grounded [10]. Channel hot electrons are created in the high electric field near the drain junction. Since

<sup>&</sup>lt;sup>2</sup>For consistency within this thesis, program will describe the condition with stored positive charge on the floating gate. However, many flash EEPROM manufacturers consider program to denote stored electrons.

#### Chapter 1. Introduction

the oxide field favours injection, the electrons are then transported to the floating gate [1]. A positive threshold voltage shift results. Of course, channel hot electron injection can only bring electrons onto the floating gate.

The read operation resembles that of the FETMOS, where the threshold voltage defines either a logic 1 or 0.

# 1.1.4 Contrast Between FETMOS/FLOTOX and Flash

Memory technology in general is driven by cell size, and this will form the framework this discussion.

#### Flash EEPROM

To achieve a smaller cell in flash memories, the select transistor is omitted. Flash memories thus forgo the ability to be programmed in small sections, eg. in words. Instead they must be programmed in large blocks, this is known as bulk programming. From a practical view this is the main distinction between flash cells and FETMOS/FLOTOX cells.

#### FETMOS and FLOTOX

From the viewpoint of integration the FETMOS structure exhibits a number advantages over the FLOTOX [19]:

- A smaller cell area, which allows denser memory circuits to be produced.

- A simpler cell structure, which is compatible with easier scaling of dimensions [1].

- One less photomask layer is required during processing.

- The FLOTOX requires tighter lithographic control, for defining extremely small tunnel oxide dimensions.

A recognised drawback of the FETMOS is that it allows a higher substrate current during programming [20]. This is due to its low drain junction breakdown voltage [19]. Thus it draws more current than the FLOTOX during the program operation. Logic circuits including relatively small FETMOS arrays are generally unaffected by the higher current requirement [20]. However, for large arrays, special attention to charge pump design is needed. A number of other limitations have been cited for the FETMOS including:

- Threshold voltage shifts due to charge trapping in the tunnel oxide.

- Reduced endurance due to the inclusion of low integrity field oxide edges in the tunnel area.

However, the significance of these concerns remains a moot point [19].

# 1.2 Utility of the EEPROM

Let us now discuss the most popular uses for the EEPROM. There are two major driving forces in the development of EEPROM technology. One is for high density memories requiring low cell size and lowest cost per bit. The other requirement is in non-volatile low density memories, for micro-controllers and programmable logic type applications.

# 1.2.1 Program/Data Storage Media

EEPROM technologies of all kinds have been produced simply as memory chips [1] [11], as such they were intended mainly to displace the EPROM [1]. However, flash EEPROMs are now beginning to have a far reaching impact. With their high densities they are winning an increasing market share from magnetic tape and disc storage media.

Advantages of EEPROM over magnetic media include:

- Physical ruggedness.

- Light weight.

- Low power consumption.

Flash EEPROM replacements for the hard disc will be available very soon in the form of memory cards  $\simeq 20$  Mbyte [8]. The effect on portable computers is to increase battery life from  $\simeq 4$  hours to between 30 and 60 hours. Weight is also reduced, from  $\simeq 7$  pounds to between 1 and 2 pounds [8]. The optimism felt by the industry for this technology may be summed up in a quote from Intel's marketing manager (made in 1990) [9]: "We understood DRAMs to be the smallest and simplest memory device available but now flash is *that* and non-volatile too. The Intel 1Mbit flash EEPROM is *smaller* than the NEC 1Mbit DRAM"...

### 1.2.2 Embedded Systems

EEPROMs may be embedded into logic circuits, such as microcontrollers. These are close cousins of the microprocessor, but have added features such as A to D conversion and EEPROM memory. In a microcontroller the EEPROM is often used to store the configuration of a machine, before power down. FETMOS devices are produced by Motorola on there HC11 micro-controller, in a block of 512 Bytes [21]. This has a large share in the lucrative automotive market, for self-tuning engine systems, where the EEPROM stores the engine configuration when the journey is over.

# 1.2.3 Embryonic Technologies

EEPROMs offer advantages in many of tomorrow's technologies such as artificial intelligence, self adaptive systems [1]. The elegance of an EEPROM solution to a problem is epitomised in Neural Networks. Briefly, these are systems which mimic the brain. Information is transmitted between neurons as discrete nerve impulses, with information encoded as an analogue potential: an "impulse density" [22]. Neurons receive impulses at "synaptic sites" and an arriving impulse generates an analogue potential, which is scaled in proportion to a "synaptic weight". Arriving potentials are summed, and when the summed potential exceeds a given threshold, nerve impulses are generated and transmitted to other neurons. At face value such a system may not appear very powerful, and an individual neuron does only very simple tasks. The high computing power of neural systems arise from the collective behaviour of large, highly interconnected, fine grain networks [23]. The learning function of neural networks originates from their ability to change the synaptic weights. Responses of the system may then optimised to solve a particular problem, eg. pattern recognition. In VLSI neural network circuitry the synaptic weight is commonly stored in a shift register [22], which is costly in terms of chip area. Alternatively however, an EEPROM may be used to store the synaptic weight, as an analogue charge on the floating gate [24]. Thus the number of transistors required per neuron is reduced, and a finer network produced. Naturally there are problems in such an implementation: program/erase characteristics of EEPROMs tend to vary across a wafer; and reliable EEPROMs are required, for which the program/erase characteristics remain stable with use [24].  $^3$

# 1.3 Reliability

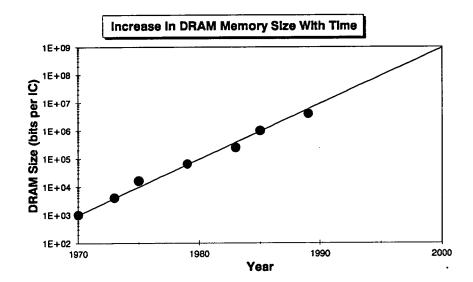

Since the first integrated circuits were made (around 1959) the maximum number of devices that can be successfully integrated into a single chip of silicon has risen steadily. This trend in increasing transistor counts was vocalised by Moore, who predicted in 1964 that the number of transistors would at least double every two years. The validity of this is born out in Figure 1-5 [25], which gives the transistor

<sup>&</sup>lt;sup>3</sup>A "feedback-based" programming method has been used to over come these problem, though its slowness limits the usefulness of the EEPROM in the system [24].

counts per die for the densest examples of memory circuits, the DRAM. With more transistors available, it has become possible to produce logic circuits such as microcontrollers, with ever greater functionality. Indeed, as the level of integration on logic circuitry swells, so more of the transistor budget may be allocated to memory structures [25].

Figure 1-5: Increase in Integration Levels Over a Period of Years.

## 1.3.1 Shrinking Geometries

While there are many technologies available, MOS devices are at the leading edge of VLSI in terms of packing density, and will receive sole attention here. Integration levels may be increased in a number of ways [26]:

- 1. Increasing Die Area. Unfortunately this also makes the circuits more prone to defects, so reducing yield.

- 2. Design Improvements. Use of more efficient circuit architectures, which requires less components.

- 3. Circuit Layout. Careful attention to the layout can give a reduction in the area needed by a circuit.

4. Scaling down device feature size. In its simplest form this simply means reducing all dimension by a factor  $\alpha$ .

Scaling makes the largest contribution to the increasing complexity of integrated circuits [26]. Although there must be a limit beyond which further integration becomes uneconomic. In the the early 1980s it was argued that pushing minimum geometries below  $0.5\mu m$  would yield only diminishing returns [27]. In the interim improvements in device design and fabrication technology have reduced this limit. Today's research have yielded silicon MOSFETS in the deep-sub-micron regime, with channel lengths of  $0.15\mu m$  [28]. Meanwhile, state of the art circuits in commercial production have critical dimensions of  $\sim 0.8\mu m$  [28]

#### 1.3.2 Reliability In General

As transistor density escalates so do reliability problems. Integrated circuits generally have very long life expectancies  $\sim$  decades. Never the less they do suffer from reliability problems. General reliability problems come in many guises, but two principal classes are:

- 1. Electromigration in metal interconnections [29]

- Transistor threshold shift and gate oxide rupture, due to hot electron effects

[30]. These can be minimised by careful engineering of the drain region.

In a logic circuit, the failure of only one device may cause the entire circuit to fail. Reliability may be measured in terms of FITs, where 1 FIT represents 1 failure in  $10^9$  device hours. (eg: if  $10^9$  transistors are tested for an hour, and one fails, we have 1 FIT). Currently acceptable failure rates are considered to be ~ 100 FITs [31]. Clearly however, as transistor counts grow, so FIT rates must fall. A daunting 0.1 FIT rate has been proposed as a reliability goal for the year 2001, by The Semiconductor Research Council [32]. Thus, methods of improving device reliability are a major concern to the semiconductor industry as a whole.

## 1.3.3 Reliability and the EEPROM

Due to the tunnelling of electrons through the gate oxide, EEPROMs are especially susceptible to reliability problems. FETMOS devices have a maximum life expectancy of only  $10^5$  program/erase cycles [11], while flash EEPROMs have a life expectancy of ~  $10^3$  cycles [10], depending on the manufacturer. In addition, EEPROMs are sensitive to fabrication conditions and may not display an acceptable threshold window, so lowering yield. Accurate control of the processing and reduction of impurities obviously help. Beyond this, two areas are of interest:

- It would be useful to know exactly how a change in processing effects the threshold window and reliability of an EEPROM. For instance, a smaller floating gate may give a higher threshold voltage, or improved reliability. With this knowledge, some degree of process optimisation may be possible.

- 2. It would also be beneficial to design a device with a higher innate reliability.

These then, form the joint objectives of this thesis.

# 1.4 Thesis Plan

Before tackling either of the above problems however, it will be necessary to more closely examine the mechanics of the EEPROM. This will be the subject for Chapter 2. In chapter 3 a model is derived for the FETMOS device, and in chapter 4 this is used to analyse FETMOS threshold window and reliability. In chapter 5 the fabrication of novel test structures is described, which are equivalent to a set of FETMOS devices. In chapter 6 these test structures are used to analyse FET-MOS reliability. Finally, in chapter 7 results are summarised, overall conclusions are drawn, and recommendations are made regarding improved FETMOS design.

# Bibliography

- H.E.Meas, J.Witters, and G.Groeseneken. Trends in non-volatile memory devices and technologies. In ESSDERC Bologna, pages 743-754, 1987.

- [2] D.Bondurant and F.Gnadinger. Ferroelectrics for nonvolatile RAMs. IEEE Spectrum, 26(7):30-33, 1989.

- [3] B.C.Cole. Finally, it's ferroelectric. *Electronics*, pages 88-89, August 1989.

- [4] B.Halg. On a micro-electro-mechanical nonvolatile memory cell. IEEE Transactions On Electron Devices, 37(10):2230-2236, October 1990.

- [5] H.Haznedar. Digital Microelectronics, pages 476-496. Benjamin Cummings, 1991.

- [6] R.Bez, D.Cantarelli, and P.Cappelletti. Experimental transient analysis of the tunnel current in EEPROMs. IEEE Transactions On Electron Devices, 37(4):1081-1086, 1990.

- [7] E.S.Yang. Microelectronic Devices, chapter Charge-Coupled And Nonvolatile Memory Devices. McGraw-Hill Book Company, 1988.

- [8] D.Manners. Intel chip ousts hard discs. Electronics Weekly, (1587):24, 1992.

- [9] S.Parry. Flash of memory to fill the gap. New Electronics (On Campus), 1(2):11, 1990.

- [10] R.D.Pashley and S.K.Lai. Flash memories: The best of two worlds. IEEE Spectrum, 26(12):30-33, December 1989.

- [11] C.Kuo, Y.R.Yeargain, and W.J.Downey. An 80ns 32K EEPROM using the FETMOS cell. IEEE J.Solid State Circuits, (5):821-827, October 1982.

- [12] J.F.Dickson. On-chip high voltage generation in MNOS integrated circuits using an improved voltage multiplier technique. IEEE Journal Of Solid State Circuits, (3):374-378, 1976.

- [13] J.Callder. Master's thesis, University Of Edinburgh, 1988.

- [14] J.R.Yeargain and C.Kuo. A high density floating-gate EEPROM cell. In IEEE IEDM, pages 24-27, 1981.

- [15] S.K.Lai, V.K.Dham, and D.Guterman. Comparison and trends in today's dominant EE technologies. In IEEE IEDM, pages 580-583, 1986.

- [16] P.I.Suciu, B.P.Cox, D.D.Rinerson, and S.F.Cagnina. Cell model for EEP-ROM floating gate memories. In IEEE IEDM, pages 737-740, 1982.

- [17] G.Samachisa, C-S.Su, and Y-K.Kao. A 128k flash EEPROM using double polysilicon technology. In IEEE International Solid State Circuits Conference, pages 76-77, 1987.

- [18] B.G.Streetman. Solid State Electronic Devices, chapter 3. Energy Bands And Charge Carriers In Semiconductors. Prentice/Hall International Editions, 1980.

- [19] C.Kuo, K.Fu, P.Kim, M.Chonko, and J.Jorvig. High FETMOS EEPROM cell using ONO inter-polysilicon dielectrics. pages 98-99.

- [20] K.Y.Chang, S.Cheng, and K-M.Chang. An advanced high voltage CMOS process for custom logic circuits with embedded EEPROM. In CICC, 1988.

- [21] HCMOS Single-Chip Microcomputer, chapter 1. Motorola Inc, 1985.

- [22] A.Masaki, Y.Hirai, and M.Yamada. Neural networks in CMOS: A case study. IEEE Circuits And Devices, 6(4):12-17, 1990.

- [23] H.P.Graf and L.D.Jackel. Analogue electronic neural network circuits. IEEE Circuits And Devices, 5(4):44-50, 1989.

- [24] C-K.Sin, A.Kramer, and V.Hu. EEPROM as an analog storage device, with particular application in neural networks. *IEEE Transactions On Electron Devices*, 39(6):1410-1419, 1992.

- [25] P.P.Gelsinger, P.A.Gargini, and G.H.Parker. Microprocessor circa 200. IEEE Spectrum, 26(10):43-47, October 1989.

- [26] D.Gorham, J.Wood, and D.Butts. Field Effect Devices And VISI, chapter 5 Steps Towards VLSI. The Open University Press, 1985.

- [27] R.T.Bates. Nanoelectronics. Solid State Technology, 32(11):101-107, November 1989.

- [28] R-H.Yan, K.F.Lee, and D.Y.Jeon. 89GHz ft room-temperature silicon MOS-FETs. IEEE Electron Device Letters, 13(5):256-257, May 1992.

- [29] E.A.Amerasekra and D.S.Campbell. Failure Mechanisms In Semiconductors, chapter 3. John Wiley And Sons, 1987.

- [30] J.J.Sanchez, K.K.Hsueh, and T.A.DeMassa. Drain-engineered hot-electronresistant device structures: A review. IEEE Transactions On Electron Devices, 36(6):1125-1132, June 1989.

- [31] D.L.Crook. Evolution of reliability engineering. In *IEEE/IRPS*, pages 2-7, 1990.

- [32] C.Hu. IC reliability simulation. IEEE Journal Of Solid State Circuits, 27(3):241-246, March 1992.

# Chapter 2

# EEPROM Physics and Reliability

# 2.1 Fowler-Nordheim Tunnelling

Fowler-Nordheim tunnelling describes a quantum mechanical effect, implicitly linked with theories produced by quantum physicists during the early twentieth century. Although Fowler-Nordheim (FN) tunnelling is often mentioned in literature, the underlying physics of the effect only ever receive a cursory consideration. In this thesis FN tunnelling is met both in the analysis of test structures and in the modelling of the EEPROM cell. As such, FN tunnelling is central to the fabric of the thesis and merits a closer examination. With a clear understanding of the FN tunnelling mechanism, the physical accuracy of any model for the EEPROM cell may be assessed with greater confidence. The relationship between the FN tunnel current and parameters within a test structure (eg. gate oxide thickness) may also be better understood. Quantum mechanics is a very broad subject and only the salient features relating to FN tunnelling will be examined.

#### 2.1.1 Wave Particle Duality

Following Einstein's theory (in 1905) that light may exhibit both a wave and a particle nature, de Broglie (in 1924) extended the idea of dualism, to suggest that particles may also exhibit a wave nature. This is to say particles such as electrons also behave as waves [1]. Their wavelength is given by:

$$\lambda = \frac{h}{mv}$$

Where:

- $\lambda = Wave length$

- $h = \text{Planck's constant} = 6.625 \times 10^{-34} Js$

- m = Mass of the particle (eg. rest mass of an electron =  $9.1091 \times 10^{-31} Kg$ )

- v = Velocity of the particle

Waves normally conjure up an image of a moving entity (eg. sea waves travelling towards the shore), and a *free* electron will fit such a description. However, an electron *bound* within a silicon atom will be stationary, and as such it can exist only as a standing wave. An analogy for this regime is that of a guitar string fixed at both ends, in which a stationary wave may also be produced.

All waves may be described by an appropriate set of equations (eg. Maxwell's equations for electromagnetic radiation). It was Schrödinger (in 1925) who developed an equation to describe the wave nature of particles [2]. Even though the mathematics is quite complex, it is interesting to include a version of Schrödinger's equation, if only to introduce the variable  $\Psi$ . Hence, the standing wave associated with an electron (for a one dimensional case) may be described by [2]:

$$-rac{\hbar^2}{2m}rac{d^2\Psi}{dx^2}+V\Psi=E\Psi$$

Where:

- $\Psi$  = The quantity which varies in the wave.

- $\hbar = \frac{h}{2\pi} = \text{Reduced Planck's constant} = 1.054 \times 10^{-34} Js$

- m = Mass of the electron

- x = Position

- $\left(-\frac{\hbar^2}{2m}\frac{d^2\Psi}{dx^2}\right)$  = Kinetic energy of the electron.

- V = Potential energy of the electron

- E = Total energy of the electron

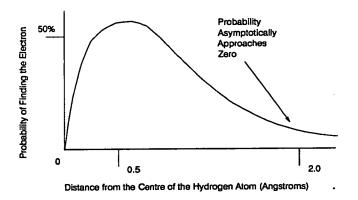

The concept of  $\Psi$  itself is an abstract one, but was given a tangible interpretation by Born, who proposed that  $|\Psi|^2 dx$  represents the probability of finding an electron between a distance x and x + dx from an origin. As an example, consider an electron bound within a single hydrogen atom. For the electron in its lowest energy level  $|\Psi|^2 dx$  is illustrated in Figure 2-1.

Figure 2-1: Probability of Finding an Electron at a Distance x From the Center of a Hydrogen Atom.

The salient feature to note is that at large radii,  $|\Psi|^2 dx$  decreases asymptotically, but never reaches zero. There is a possibility that the electron could be found any where, either inside or outside the atom. In fact, one can never be certain where an electron is at any time.

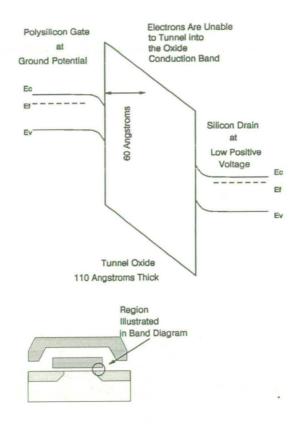

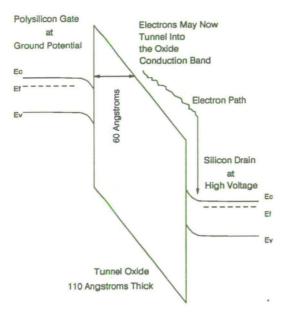

#### 2.1.2 Fowler-Nordheim Tunnelling in MOS Structures

The energy band diagram for a MOS structure is given in figure 2-2 [3] This is equivalent to the region in a FETMOS device where the floating gate and drain overlap. Electrons in the polysilicon conduction band meet a large energy barrier at the polysilicon/oxide interface, whose height is 3.1eV. Application of a small voltage to the drain,  $\sim 1V$ , will cause the energy bands to bend, with the majority of the voltage falling across the oxide. However, in the dark and at room temperature, few electrons have sufficient energy to surmount the barrier, and current flow will be negligible. Remembering the function  $|\Psi|^2$ , it can be said that

Figure 2-2: Energy Band Diagram for a MOS Structure, Under a Small Applied Bias. This is Equivalent to the Floating Gate/Drain Overlap Region of a FETMOS Device.

there is a possibility of the electrons leaving the polysilicon gate and reaching the drain. The probability of this increases for thinner tunnel oxides, and at  $60\text{\AA}$  the probability is sufficiently high for the current to become significant. This process is known as quantum mechanical tunnelling. It places a theoretical limit on the minimum oxide thickness suitable for a floating gate EEPROM. Oxides below  $60\text{\AA}$  would readily leak charge, giving data retention problems. However, for a  $110\text{\AA}$  tunnel oxide the current flow is negligible.

As the drain voltage is raised so band bending becomes more pronounced. This represents a lowering in the energy level of the oxide conduction band. Once

#### Chapter 2. EEPROM Physics and Reliability

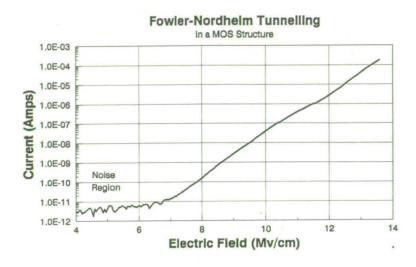

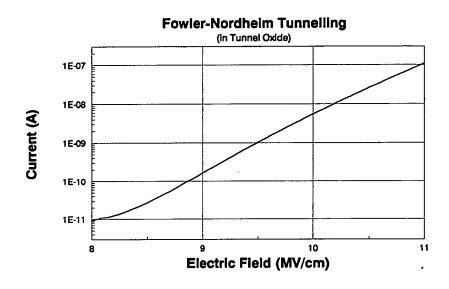

band bending has become sufficient, electrons can cross into the oxide conduction band. This is Fowler-Nordheim tunnelling, which becomes significant for an oxide electric field of  $\sim 7MV \, cm^{-1}$  or greater. Here, the polysilicon gate/oxide interface is referred to as the "injecting interface". Tunnelling electrons are then accelerated to the drain, and as they travel electrons loose energy in collisions with atoms in the oxide, this is illustrated in figure 2–3. Since the energy barrier between holes and the oxide valence band, 4.3eV [4], is larger than that between electrons and the oxide conduction band, 3.1eV, the hole current is negligible in comparison. The electrical characteristic for a MOS structure under a voltage ramp is given in figure 2–4.

Figure 2-3: Energy Band Diagram Illustrating Fowler-Nordheim Tunnelling in a MOS Structure.

### 2.1.3 Factors Which Affect Fowler-Nordheim Tunnelling

Fowler-Nordheim tunnelling is an electrode limited process, as opposed to a bulk limited process [5]. Thus, the tunnelling current will be varied by phenomena at the injecting interface. Some effects are negligible, such as image force barrier lowering, which tends to "round off" of top of the polysilicon/oxide energy barrier

Figure 2-4: Electrical Characteristic for a MOS Structure Under a Voltage Ramp. This measurement was made on a MOS capacitor of area  $2.5 \times 10^{-4} cm^2$

[6] [7]. This has little effect since electrons are mainly distributed at the base of the energy barrier, whereas rounding is confined to the top of the barrier. The energy of incident electrons may be increased by temperature or illumination, at higher energies these electrons have a shorter distance to tunnel. However, the majority of factors are process dependent, such as doping density of the polysilicon. This may be used to increase the number of electrons incident on the silicon surface, and hence the tunnel current. Indeed, the polysilicon/oxide interface itself is not well defined, rather there is a transition region of  $\simeq 10 \text{\AA}$  which consists of silicon rich oxide [8]. This region contains silicon "islands" at which the electric field is locally enhanced, increasing the tunnel current [9]. It has also been noticed, that the Fowler-Nordheim coefficients A and B increase as oxides become thicker, in the range 60Å to 140Å, but saturate towards thicker oxides [10]. While there is no good argument to explain this, it may be that the thin transition region at the  $S_i/S_iO_2$  interface becomes more influential for thinner oxides [10]. Defects of various descriptions will also effect tunnelling [11] [12], these are discussed further in chapter 5. However, two of the most significant influences on Fowler-Nordheim tunnelling are charge trapping, and field enhancement due to asperities.

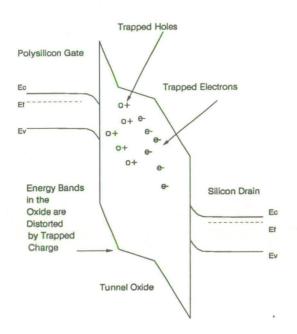

### Charge Generation and Trapping in the Oxide

A proportion of the electrons being accelerated towards the drain experience impact ionisation events in the oxide, which produce electron/hole pairs [13]. The holes are then accelerated towards the gate, and electrons continue towards the drain. A proportion of each charge species becomes trapped in the oxide, which affects the field at the injecting interface [14], as illustrated in figure 2–5. Hole trapping enhances the field at the injecting interface, whereas electron trapping reduces it.

Figure 2-5: Energy Band Diagram for a MOS Structure After Charge Trapping.

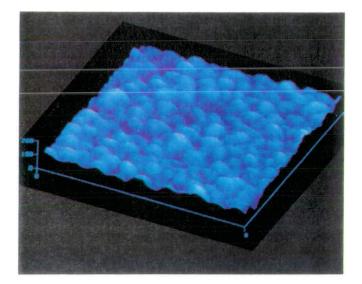

#### Asperities at the Injecting Interface

The crystals which make up polysilicon form a rough surface with many ridges, or "asperities" [14], as illustrated in figure 2–6 [15]. These bend the electric field lines which become crowded at the asperities, since electric field lines always lie normal to the surface of a conductor [7]. Thus, asperities at the injecting interface will locally enhance the electric field [14], usually by a factor of 3 to 5 times [16]. Therefore the tunnelling current becomes locally enhanced, as will the associated charge trapping. In some devices asperities are enhanced during processing, to give so called textured surfaces. These devices use much thicker tunnel oxides, of  $\simeq 600$ Å to 1000Å [16], while still providing the required tunnel currents. Although a thin tunnel oxide is no longer necessary, charge trapping becomes enhanced, which reduces any benefits [17].

Figure 2-6: Quantum Tunnelling Micrograph, Illustrating Asperities on a Polysilicon Surface.

# 2.1.4 An Equation to Describe Fowler-Nordheim Tunnelling

Fowler-Nordheim tunnelling is described by equation (2.1):

$$J = AE^2 exp^{\left(\frac{-B}{E}\right)} \tag{2.1}$$

Where:

- J =Current density flowing through the oxide.

- E = Electric field strength across the oxide.

• A and B = Fowler-Nordheim Coefficients.

The Fowler-Nordheim coefficients may calculated either experimentally [18], or theoretically [6] [5]. For theoretical calculations A and B are expressed in terms of fundamental parameters such as the height of the polysilicon/oxide energy barrier. To give greater accuracy modifying factors may also be added, to account for such effects as image barrier lowering [5]. Even so, no theoretical expression has been developed to include all factors which effect Fowler-Nordheim tunnelling, such as trapping of carriers in the oxide [13]. In addition, oxide processing has a significant effect on tunnelling characteristics. Accurate values for A and B should therefore be extracted from experimental data. This is considered in chapter 3.

# 2.2 Reliability Issues

#### 2.2.1 Oxide Breakdown

Since EEPROM failures result almost exclusively from tunnel oxide degradation, we shall first review tunnel oxide reliability. As with all VLSI processes, manufacturers take much trouble to produce good quality oxides, and over the small area of one EEPROM cell the oxide should be of uniformly good integrity. Therefore, we will be concerned largely with defect free oxides in our review.

The reliability of thin oxide films is of great importance to the MOS semiconductor industry, since oxide failures make up a large proportion of yield loss. For this reason, a wealth of material has been published on the subject. Never the less, the mechanism of oxide failure is not well understood, and there are a number of comp eting theories in existence. To give a feel for the processes associated with oxide degradation, the impact ionisation model has been chosen for consideration [13] [19] [20]. This is a well established model for which supporting evidence is still being produced today [21]. The hole trapping phenomenon this proposes, would explain why radiation hard processing techniques, as used in this work, produce oxides of superior quality.

#### Methods of Oxide Stressing

An oxide must be stressed to assess its reliability, and the stressing techniques may be subdivided into two categories [22]:

- 1. TZDB: Time Zero Dielectric Breakdown. This is essentially field dependent stress.

- 2. TDDB: Time Dependent Dielectric Breakdown. This is essentially time dependent stress.

TZDB: A ramped voltage is applied to the oxide causing it to rupture. The steep rise in current observed at breakdown then gives a convenient and unambiguous signal that rupture has occurred. The quality of the oxide will be indicated by the electric field required for breakdown, given in  $MVcm^{-1}$ . TZDB can be categorised into three modes [11] [23]:

- 1. A mode. This is attributed to pin holes in the gate oxide because of the nearly zero breakdown field of  $E_{BD} \leq 1 M V cm^{-1}$ .

- 2. B mode. This is caused by a defect, giving intermediate breakdown field of  $1MVcm^{-1} < E_{BD} \leq 8MVcm^{-1}$ . The upper limit of the B mode breakdown voltage is determined self-healing energy, which is necessary to explosively evaporate the gate polysilicon layer above the B mode defect. The lower limit for this breakdown is determined by thermal breakdown. Breakdown happens when the Joule heating due to conduction, for which power= $I^2R$ , exceeds the rate of energy dissipation.

- 3. C mode. This failure mode is due to intrinsic breakdown of the oxide, and typically occurs for  $E_{BD} \ge 8MV cm^{-1}$ .

The field at which intrinsic breakdown occurs defines the "dielectric strength" of the oxide sample. Note that for oxides thinner than  $\simeq 150$ Å, it becomes difficult to distinguish between B and C mode failures [23].

TDDB: A constant voltage, or constant current, is applied to the oxide until it ruptures. In essence, there is no qualitative difference between constant current or constant voltage stressing [13], and for this review constant voltage stressing will be considered, as this method of testing is used in this project. The applied voltage should be sufficient to produce a Fowler-Nordheim tunnel current in the oxide, while still remaining below the oxide's dielectric strength. Again, the steep rise in current observed at breakdown gives an unambiguous signal that rupture has occurred. In this case, however, oxide quality is indicated by the amount of charge which has passed through the oxide before breakdown. On a practical level, this will be the integral of current as a function of time, referred to as  $Q_{BD}$ .

Although one EEPROM program/erase operation is short lived (~ 10ms), over the life time of an EEPROM many such operations will take place, and the net length of time spent in programming/erasing will be up to  $10^5$  times as long [24]. Thus constant current or voltage stressing will roughly emulate conditions during programming/erasing of an EEPROM [13]. TDDB has therefore been chosen as the principle method of investigating the relative reliabilities of devices fabricated in this work.

#### The Impact Ionisation Model

The Impact Ionisation Model sets out principally to explain TDDB, although literature suggests that breakdown mechanisms for TDDB and TZDB are the same [25]. Conceptually TDDB can be thought of as a two stage process:

- 1. Build up.

- 2. Runaway.

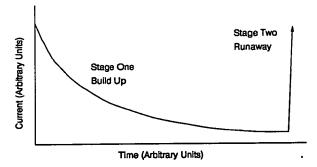

Figure 2-7 shows a graph of current against time (I/t), for a constant voltage TD-DB test. Since the runaway stage takes only fractions of a second to be completed, it is the build up stage which determines the life time of the oxide.

During the build up stage, electrons will pass into the oxide conduction band by Fowler-Nordheim tunnelling. The salient feature of this build up stage is a

Figure 2-7: Current Against Time for a Constant Voltage TDDB Test.

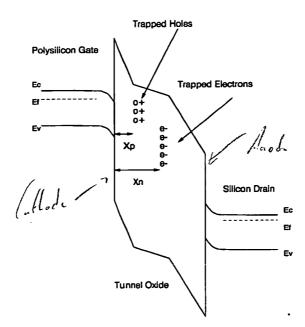

decrease in tunnel current with time, which is widely accepted to be a result of electron trapping in the oxide. Electrons will become trapped over a wide range of distances from the injecting interface, or cathode. However, trapped electrons may be modelled as a charge sheet, whose centroid lies at  $X_N$ , as illustrated in figure 2-8. The effect of trapped electrons is to reduce the field at the cathode, while increasing the anode field. This reduction in cathode field is responsible for the reduction in tunnel current. Notice also, that the slope of the TDDB curve never becomes level, indicating that electron trapping continues throughout the entire test, ie. the traps are never completely filled. This non-saturating behaviour is a general feature of TDDB testing, and is believed to be due to the generation of electron traps during the test, under the influence of the high field.

A proportion of the injected electrons gain sufficient energy to cause impact ionisation and generate electron/hole pairs [26]. Generated electrons then continue to the anode, while holes are swept back towards the cathode. A number of these holes become trapped in the oxide, also illustrated in figure 2-8. Again, hole trapping proceeds over a range of distances from the cathode. This may also be modelled as a charge sheet, whose centroid lies at  $X_P$ . By enhancing the cathode field trapped holes tend to raise the magnitude of tunnel current, and so have a contrary effect to trapped electrons. Thus the question is raised, why should the effect of electron trapping dominate? It has been proposed that the hole trapping proceeds only over a small area of the oxide, and experiment has indicated that

Figure 2-8: Energy Band Diagram to Illustrate Charge Trapping During Voltage Stressing of the Oxide.

hole trapping is localised to approximately 1 part in  $10^6$  of the total oxide area [13].

Even in a good quality oxide there will be a degree of inhomogeneity, hence we may subdivide areas into two categories, connected in parallel:

- 1. "Robust areas". These are relatively *un-susceptible* to hole trapping at the cathode.

- 2. "Weak areas". These are relatively *susceptible* to hole trapping at the cathode.

A positive feedback loop evolves in the weak areas, since the increased current produces a larger number holes through impact ionisation, which enhances the cathode field ..... and so on. Associated with this will be a localised increase in the rate of electron trapping, which locally raises the anode field. Given that the impact ionisation coefficient has a strong field dependence, this phenomenon will provide an added fillip to the positive feedback cycle. Once the localised current density obtains a "critical value" runaway will begin, this is stage two of the TDDB process. Current instability then leads to electrical and thermal runaway, associated with catastrophic failure.

Early breakdowns, resulting from defects, may also be described by the impact ionisation model [13]. Such defects are assumed to suffer from a combination of one or more of the following ailments:

- A high density of hole traps.

- A large hole capture cross section.

- A lower effective tunnelling barrier height.

### 2.2.2 Analysis of Reliability Data

Consider a batch of wafers, on which thin  $S_iO_2$  capacitors have been fabricated. The reliability of the batch as a whole, will be an aggregate of of the reliability of individual capacitors. Some capacitors will be more reliable than others, and this spread will have a random nature. Therefore, many capacitors should be tested to access the reliability of the batch, and statistical validity will improve as larger sample sizes are used.

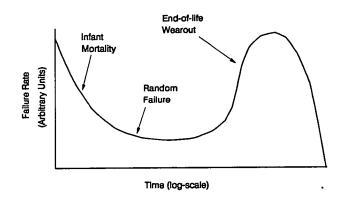

Historically, the microelectronics industry has used the "bathtub curve" when discussing reliability [27]. The results which could be expected from a TDDB test over a large sample of oxide capacitors is illustrated in figure 2–9. This curve is characterised by three regions [28]:

- 1. A high initial failure rate, the so called "infant mortality" period.

- 2. A low but nonzero midlife failure rate, attributed to random failures. This region represents the useful life of the capacitor.

- 3. An increasing failure rate at end-of-life, due to intrinsic wearout mechanisms.

Figure 2-9: "Bathtub Curve".

The overall shape of the bathtub curve will vary, depending on the processing conditions of the oxide. The entire curve may be characterised using a Weibull distribution [29] [30], and equation (2.2) gives a simple form of this:

$$F(t) = 1 - e^{\left(-\frac{1}{\alpha}t^{\beta}\right)}$$

(2.2)

where:

- F =Cumulative probability of failure.

- t = Time to breakdown.

- $\alpha = \text{Constant}$

- For β < 1 the failure rate decreases with time.</li>

For β = 1 the failure rate is constant.

For β > 1 the failure rate increases with time.

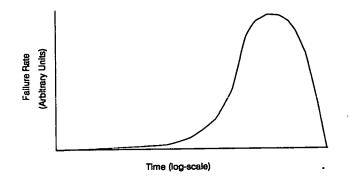

Of course, low infant mortality and midlife failure rates are preferable. However, for this project intrinsic reliability problems are of chief interest, associated with end-of-life failure. For previous researchers the intrinsic breakdown of  $S_iO_2$ has been shown to have a log-normal distribution [20]. This gives it the bell shaped Gaussian curve, observed when a logarithmic x-axis is used, as in figure 2-10. This distribution is characterised by two parameters:

- 1. The median time to failure. This is the time taken for half of the sample to fail.

- 2. The shape factor  $\sigma$ . A low value of  $\sigma$  indicates a failure distribution which is tightly grouped in time.

Figure 2-10: A Gaussian Distribution.

The validity of this model for the failure distribution can be checked by plotting the results on a log-normal graph. The graph can then be scrutinised, to ensure all points lie on a straight line. Significant nonlinearity may indicate that more than one failure mechanism is at play [29]. The shape factor  $\sigma$  will be the slope of this line.

# 2.2.3 Accelerated Testing

Clearly, the bathtub curve is produced by testing capacitors to destruction. However, if normal operating conditions were used for stressing, tests would take an inordinate length of time. A method for accelerating wearout is obviously required, and for this the semiconductor industry commonly uses increased temperature, voltage, current density or humidity [29]. The reliability under normal operation can then be calculated from the accelerated test, using an acceleration factor. The great majority of accelerated life tests for semiconductors use temperature acceleration. However, high temperature acceleration is not always the most appropriate stress, since "threshold triggered" mechanisms may be encountered [30]. These are failure mechanisms which are only encountered above a certain threshold temperature. It is possible to detect the onset of a threshold triggered mechanism, by testing reliability at sequentially raised temperatures. This methodology is called "step-stress". It should also be remembered that while high stressing conditions will be suited to detecting wearout mechanisms with high activation energies, there is a risk that a low activation energy mechanism may be concealed. Here again step-stress methodology can be used to detect low activation energy mechanisms. Now, Fowler-Nordheim tunnelling is primarily driven by an increase in electric field, while the integrity of an oxide is judged by its charge to breakdown. Therefore, voltage acceleration has been chosen for use in this project.

## 2.2.4 EEPROM Reliability Issues

#### Long Term Charge Retention

For good long term reliability of the EEPROM it is essential that less than 10% of the stored charge leaks away in 10 years [31]. The key to avoiding leakage is the strong dependence of tunnel current on voltage across the oxide, as characterised by the Fowler-Nordheim tunnelling curve. The current rises by an order of magnitude for every 0.8V increase in applied voltage. Simple arithmetic can be used to prove the long term retention of any EEPROM, as follows [31]:

- Programming voltage = 18V.

- Average programming current  $\simeq 1 \times 10^{-10} A$  [32].

- Average charge stored on floating gate  $\simeq 8 \times 10^{-14} C$  [31].

- Read voltage = 1V.

- Ratio of read disturb current to programming current =  $\frac{(18V-1V)}{0.8} \simeq 20$  orders of magnitude.

- Read disturb current =  $\frac{1 \times 10^{-10}}{1 \times 10^{20}} = 1 \times 10^{-30} A.$

- Now imagine the EEPROM is read for 10 years  $(3 \times 10^8 \text{ seconds})$ . The charge lost will be =  $3 \times 10^8 \times 1 \times 10^{-30} = 3 \times 10^{-22}C$ .

- As a percentage, only  $\frac{3\times10^{-22}}{8\times10^{-14}} \times 100 = 3.7 \times 10^{-7}\%$  of the charge is lost.

Evidently then, charge leakage is negligible.

#### Endurance

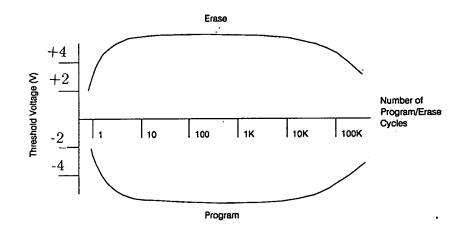

During a life time of being continually programmed and erased, the threshold voltages of an EEPROM will vary. The program/erase endurance characteristics of a typical FETMOS device is given in figure 2–11, this shows program/erase threshold against the number of program/erase cycles [24].

Figure 2-11: Typical Endurance Characteristic for a FETMOS Device.

The endurance characteristic can be divided into 4 regions:

- 1. Initially the width of the threshold window increases as positive charge is trapped during program/erase operations [24], this regime lasts for  $\simeq 10$  cycles.

- 2. The width remains constant for  $\simeq 1 \times 10^3$  cycles.

- 3. After  $\simeq 1 \times 10^3$  cycles the effect of electron trapping during program/erase operations becomes evident. This trapped negative charge reduces the Fowler-Nordheim tunnel current and closes the threshold window, this process is called "trap-up".

- 4. After  $\simeq 1 \times 10^5$  cycles the effect of electron trap-up has closed the threshold window to such an extent, that programmed and erased devices may no longer be distinguished. The EEPROM has now failed.

One should notice that an EEPROM failure occurs even before the tunnel oxide has ruptured. Programming is more susceptible to trap-up than erasing, since the program current is localised, whereas the erase current is distributed over the entire channel region [33].

#### **Firm Errors**

Ionising radiation incident on an EEPROM, may excite the stored electrons. Thus, providing them with sufficient energy to leave the floating-gate. Conversely, electrons may be provided with sufficient energy to pass into a floating gate where positive charge is stored. Over an extended period of time many such ionising events would cause the data to be lost. Outside space or military applications, the most common source for this radiation is actually the integrated circuit package [4].

#### Soft Errors

Ionising radiation may also upset the sense circuitry, which reads the EEPROM cells. A single ionising event is enough to cause a soft error, but the error can be corrected by simply re-reading the data [4].

#### Logic Circuits with Embedded EEPROM

In a system containing embedded EEPROM, high voltage transistors are required for the programming/erasing circuitry. In order to reduce the number of masking steps and make the process economic, high voltage transistors and logic transistors use the same gate oxide [34]. Clearly there is a trade off, since logic transistor require thin oxide  $\sim 200$ Å for speed and density, whereas high voltage transistors require thick gate oxide 400Å for reliability. Thus the inclusion of EEPROM has an effect on the whole circuit.

# 2.3 Improving EEPROM Operation and Reliability

Two avenues lie open for investigation of the EEPROM, either computer simulation or the fabrication of a set of test devices. Once set up, a simulations allows a large amount of data to be produced relatively quickly. Thus, the effect of varying all parameters in an EEPROM can be assessed, and the most significant identified. Once an important parameter has been isolated, eg. gate/drain overlap, a set of test structures may be fabricated to assess model predictions.

Therefore, it has been decided to produce a model for the FETMOS, in terms of its basic design parameters, such as oxide thickness and gate/drain overlap. The effect of these parameters on FETMOS operation and reliability can then be assessed. No model for the FETMOS currently exists, nor does a suitable methodology for modelling reliability. The development of a new model is discussed in chapters 3 and 4.

Already it has been observed at Motorola that FETMOS devices fabricated with phosphorus drains, are more reliable than those fabricated with arsenic. Phosphorus has a greater mobility in silicon, than does arsenic, and produces a larger gate/drain overlap. Although one may conjecture that improved reliability is due to increased tunnel area, there is nothing to prove that chemistry does not account for improved reliability. Conjecture is an insubstantial foundation on which to base costly commercial semiconductor technologies. This is especially true in today's climate of economic aggression [35]. It would be interesting to clarify the reason for this reliability improvement scientifically. To this authors knowledge, the relationship between doping or gate/drain overlap, and device reliability has not been investigated in previous research. The fabrication of devices to test this will be the subject of chapters 5 and 6.

# **Bibliography**

- M.N.Rudden and J.Wilson. Elements Of Solid State Physics. John Wiley and Sons, 1984.

- [2] A.P.French and E.F.Taylor. An Introduction To Quantum Physics. Van Nostrand Reinhold (UK) Co. Ltd., 1979.

- [3] S.M.Sze. Physics of semiconductor devices, chapter 7, MIS diode and charge coupled devices. John wiley and sons, 1981.

- [4] H.Haznedar. Digital Microelectronics, pages 476-496. Benjamin Cummings, 1991.

- [5] M.Lenzlinger and E.H.Snow. Fowler-Nordheim tunneling into thermally grown SiO<sub>2</sub>. J.Appl.Phys, 40(1):278-283, January 1969.

- [6] Z.A.Weinberg. On tunneling in metal-oxide-silicon structures. J.Appl.Phys, 53(7):5052-5056, July 1982.

- [7] M.A.Plonus. Applied Electromagnetics, chapter 2, Conductors and charges. McGraw-hill book company, 1978.

- [8] S.S.Cohen. Electrical properties of post-annealed thin SiO<sub>2</sub> films. J.Electrochem.soc Solid State Science And Technology, 130(4):929-932, April 1983.

- [9] D.J.Dimaria, T.N.Theis, and J.R.Kirtley. Electron heating in silicon dioxide and off-stoichiometric silicon dioxide films. *IEEE Transactions On Electron Devices*, 57(4):1214-1238, February 1985.

- [10] C.Chang, R.W.Brodersen, and C.Hu. Direct and Fowler-Nordheim tunneling in thin gate oxide MOS strucure. In *Insulating Films On Semiconductors*, pages 176-179. Elsevier Science Publishers B.V (North-Holland), 1983.

- [11] H.Shirai, K.Kanya, and A.Yamaguchi. Effect of oxide-induced stacking faults on dielectric breakdown characteristics of thermal silicon dioxide. J. Appl. Phys., 66(11):5651-5653, December 1989.

- [12] C.Hashimoto, S.Muramoto, N.Shiono, and O.Nakajima. A method of forming thin and highly reliable gate oxides. *Journal Of The Electrochemical Society*, 127(1):129–135, 1980.

- [13] Ih-C.Chen, S.E.Holland, and C.Hu. Electrical breakdown in thin gate and tunneling oxides. *IEEE Transactions On Electron Devices*, 32(2):413-422, February 1985.

- [14] C-Y.Wu and C-F.Chen. Transport properties of thermal oxide films grown on polycrystalline silicon - modeling and experiments. *IEEE Transactions On Electron Devices*, 34(7):1590-1601, July 1987.

- [15] I.Smith and R.Howland. Applications of scanning probe microscopy in the semiconductor industry. Solid state technology, 33(12):53-56, December 1990.

- [16] S.K.Lai, V.K.Dham, and D.Guterman. Comparison and trends in today's dominant EE technologies. In IEEE IEDM, pages 580-583, 1986.

- [17] H.E.Meas, J.Witters, and G.Groeseneken. Trends in non-volatile memory devices and technologies. In ESSDERC Bologna, pages 743-754, 1987.

- [18] A.Kolodny, S.T.K.Nieh, B.Eitan, and J.Shappir. Analysis and modelling of floating-gate EEPROM cells. *IEEE Transactions On Electron Devices*, 33(6):835-844, 1986.

- [19] C-F.Chen, C-Y.Wu, and M-K.Lee. The dielectric reliability of intrinsic thin  $SiO_2$  films thermally grown on a heavily doped si substrate- characterization

and modeling. IEEE Transactions On Electron Devices, 34(7):1540-1552, 1987.

- [20] Y.Hokari, T.Baba, and N.Kawamura. Reliability of 6-10nm thermal SiO<sub>2</sub> films showing intrinsic dielectric integrity. IEEE Transactions On Electron Devices, 32(11):2485-2491, November 1985.

- [21] E.Rosenbaum, R.Rofan, and C.Hu. Effect of hot-carrier injection on n- and p-MOSFET gate oxide. *IEEE Electron Device Letters*, 12(11):599-601, November 1991.

- [22] B.Root and M.Davis. Reliability Testing Seminar 10-14 June 1991. Masic Europe - Sienna Technologies.

- [23] K.Yamabe and K.Taniguchi. Time dependent dielectric breakdown of thin thermally grown SiO<sub>2</sub> films. IEEE Transactions On Electron Devices, 32(2):423-428, February 1985.

- [24] C.Kuo, Y.R.Yeargain, and W.J.Downey. An 80ns 32K EEPROM using the FETMOS cell. IEEE J.Solid State Circuits, (5):821-827, October 1982.

- [25] S.K.Haywood, M.M.Heyns, and R.F.DeKeersmaeker. The statistics of dielectric breakdown in mos capacitors under static and dynamic voltage stress. In Applied Surface Science, Insulating Films On semiconductors, volume 30, pages 325-331, 1987.

- [26] S.D.Brorson, D.J.DiMaria, and M.V.Fischetti. Direct measurement of the energy distrigution of hot electrons in silicon dioxide. J.Appl.Phys, 58(3):1302– 1313, August 1985.

- [27] E.A.Amerasekera and D.S.Campbell. Failure Mechanisms In Semiconductor Devices. J.Wiley and Sons, 1987.

- [28] R.J.Allen and W.J.Roesch. Reliability prediction: The applicability of high temperature testing. Solid State Technology, 33(9):103-108, 1990.

- [29] S.M.Sze, editor. VLSI Technology, chapter 14. McGraw-Hill International Editions, 1988.

- [30] S.K.Haywood, M.M.Heyns, and R.F.DeKeersmaecker. The statistics of dielectric breakdown in MOS capacitors under static and dynamic voltage stress. In Applied Surface Science, pages 325-331, May 1987.

- [31] W.S.Johnson, G.L.Kuhn, A.L.Renninger, and G.Perlegos. 16-K EE-PROM relies on tunneling for Byte-erasable program storage. *Electronics*, pages 113– 117, February 1980.

- [32] P.I.Suciu, B.P.Cox, D.D.Rinerson, and S.F.Cagnina. Cell model for EEP-ROM floating gate memories. In IEEE IEDM, pages 737-740, 1982.

- [33] J.S.Witters, G.Groesenken, and H.E.Maes. Degradation phenomena of tunnel oxide floating gate EEPROM devices. In IMEC, pages 167-170, 1987.

- [34] K.Y.Chang, S.Cheng, and K-M.Chang. An advanced high voltage CMOS process for custom logic circuits with embedded EEPROM. In CICC, 1988.

- [35] G.Kaplan. Europower 92, how a united Europe plans to exploit technology to improve its trading posture. *IEEE Spectrum*, page 20, 1990.

# Chapter 3

# Derivation of a FETMOS Model

# 3.1 Overview

In the words of Einstein "A model should be as simple as possible, but no simpler". In adopting this approach to modelling, it is hoped to place interesting effects in the lime-light, without clouding results with more subtle (but unimportant) phenomena. Reliability is a key area [1], and it is proposed to model this, in terms of fundamental physical parameters, such as gate oxide thickness and gate length. It will then be possible to vary each parameter, and find the most influential. In this way a means to enhance FETMOS endurance can be found. The dependence of the threshold window upon fundamental parameters is also of interest. Even in a well established process the threshold window varies <sup>1</sup>, and may stray outside limits required by accompanying circuitry. It is therefore desirable that the model can predict parameter variations, which can be used to restore the threshold window, to its original value. Finally, the model should also provide the capability to probe internal currents and fields, during program and erase operations.

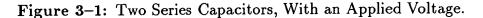

Endurance is a key reliability issue for the EEPROM. However, no suitable methodology currently exists to access this. No model exists for the FETMOS either, although models have been developed for a variety of other EEPROM devices. Hence, a new methodology for calculating reliability and a new model for the FETMOS are required. Previously, models have been produced for both

<sup>&</sup>lt;sup>1</sup>As noted in discussion with Motorola.

avalanche type electron injection devices [2], and Fowler-Nordheim type injection devices [3,4,5,6,7]. These models are all based on the capacitive equivalent circuit for the cell. However, only two of the models, [6] and [7], account for parasitic resistances and the ramped nature of the program/erase voltage. Inclusion of these parasitic values allows an accurate transient analysis to be made. This will be important in deriving a methodology to calculate reliability. Suciu's model for the FLOTOX [7] was deemed to be the best of these, since it includes parasitic factors most elegantly into the model equations. The FETMOS can be described by a capacitor network, which is equivalent to the FLOTOX. Therefore, Suciu's FLOTOX model may be used as the basis for the FETMOS model.

However, before deriving the model it will be useful to consider a simple capacitor network containing injected charge. Thus, assumptions made during the derivation will be have a solid foundation.

# 3.2 Distribution of Injected Charge in a Capacitor System

The FETMOS device is to be studied in terms of a lumped capacitor network, containing injected charge. Thus, information is required regarding the charge distribution. How much injected charge resides on each capacitor? Furthermore, will an applied voltage cause the injected charge to re-distribute itself? These questions can be answered by considering the simple case of two series capacitors.

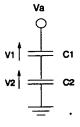

Figure 3-1 shows two series capacitors *without* any injected charge. An applied voltage induces an equal charge on each capacitor. We have:

$$Q_{1} = Q_{1o}$$

$$Q_{2} = Q_{2o}$$

$$V_{a} = V_{1} + V_{2}$$

$$V_{a} = \frac{Q_{1o}}{C_{1}} + \frac{Q_{2o}}{C_{2}}$$

(3.1)

$$V_a - \frac{Q_{1o}}{C_1} - \frac{Q_{2o}}{C_2} = 0 \tag{3.2}$$

Where:

- $Q_1$  = Net charge on  $C_1$ .

- $Q_2 =$ Net Charge on  $C_2$ .

- $Q_{1o} =$  Induced charge on  $C_1$ .

- $Q_{2o} =$  Induced charge on  $C_2$ .

- $V_a =$  Applied voltage.

- $V_1 = \text{Voltage across } C_1.$

- $V_2 =$ Voltage across  $C_2$ .