# Design and simulation of an MIMD shared memory multiprocessor with interleaved instruction streams

Thomas R. Stiemerling

Ph.D.

University of Edinburgh

1991

#### **Abstract**

The design of the Eppl'MIMD shared memory multiprocessor is described, and its performance evaluated by simulation. The Epp1 has a dancehall architecture with p instruction interleaved RISC processors connected to p shared memories by a packet switched, combining, indirect binary n-cube multistage network composed of  $\frac{p}{2}\log_2 p \ 2 \times 2$  crossbar switches. There is no processor cache or local memory, and no paged virtual memory. Memory addresses are low order interleaved across the memories. The fetch-and-add instruction is used for inter-process synchronisation, and the switches support the combining of load and fetch-and-add memory requests. Simulation results of a single Epp1 processor with varying interleaving level and instruction mix are presented, and of an isolated network with varying queue size and network load. A distributed time-driven, instruction level simulator of the Epp1 design has been implemented in Occam, and runs on a transputer based, distributed memory multiprocessor. Three parallel benchmark programs: matrix multiply, bitonic merge sort and Moore shortest path, have been written in the processor assembly language, and are used as workloads in the simulations. The programs use the fetch-and-add instruction to implement process control primitives. A number of simulation experiments have been carried out using the Eppl simulator which investigate the effect on performance of increasing the system size (speed-up), varying the switch queue and wait-buffer size, increasing the combining level, increasing the interleaving level, and varying the network and memory speed relative to the processor. These experiments are repeated for each benchmark program, and detailed execution statistics are presented for each simulation. A dynamic execution profile for each benchmark program is also presented.

Dedicated to Trish and Benjamin, and in memory of my grandfather Apa.

# Acknowledgements

I would like to thank my supervisors Nigel Topham and Roland Ibbett for getting me started and helping me along, and Peter Osmon for enabling me to finish. Many people have provided moral and technical support during the past few years, so thanks also to: Tim Lees, Pawel Paczkowski and Richard Eyre-Todd for putting up with me in the office; Mikeee Norman, Greg Wilson, Lyndon Clarke, Steve Booth and Mike Brown for help with the ECS; Angus Duggan for PostScript and Latex hackery; and Steve Renals for being my buddy and flatmate. The final thanks go to STC Research Ltd. and Dad for their financial support.

#### Declaration

I declare that this thesis was written by myself, and that the work described herein is my own.

#### Quotations

"A general purpose multiprocessor should be scalable, *i.e.*, show higher performance when more hardware resources are added to the machine. Architects of such multiprocessors must address the loss in processor efficiency due to two fundamental issues: long memory latencies and waits due to synchronisation events." [1]

"It seems that enough research has already been done in evaluating interconnection networks in isolation. We strongly feel that more work is needed at the system level that includes the interconnection network as a major component." [2]

"An extant microprocessor was chosen as the PME processor. We feel that this was an appropriate design decision in that we were able to concentrate on other design issues instead of designing yet another microprocessor." [3]

"Fully-fledged, cycle-by-cycle simulation of the multiprocessor is very tedious, especially if the goal of the analysis is to understand the performance of the multiprocessor for very large configurations and very large problem sizes." [4]

"Precise estimates of the interaction between components of such a system can only be obtained by simulation at or below the memory reference level, requiring excessive computing resources. Results of detailed simulation will depend strongly on the specific algorithm being simulated, providing results that are not easily generalised." [5]

# Contents

| 1 | Inti | roduct | ion                                               | 1  |

|---|------|--------|---------------------------------------------------|----|

|   | 1.1  | Origin | nal work                                          | 3  |

|   | 1.2  | Chapt  | ter overview                                      | 4  |

| 2 | Bac  | kgrou  | nd                                                | 7  |

|   | 2.1  | Instru | ction interleaving                                | 7  |

|   |      | 2.1.1  | Single instruction stream pipelines               | 8  |

|   |      | 2.1.2  | Multiple instruction stream pipelines             | ξ  |

|   |      | 2.1.3  | Performance of instruction interleaved pipelines  | 11 |

|   |      | 2.1.4  | Example instruction interleaved processor designs | 11 |

|   | 2.2  | Packe  | t-switched multistage networks                    | 14 |

| ٠ |      | 2.2.1  | Network topology                                  | 14 |

|   |      | 2.2.2  | Packet routing                                    | 16 |

|   |      | 2.2.3  | Routing conflicts                                 | 17 |

|   |      | 2.2.4  | Hot-spot contention                               | 17 |

|   |      | 2.2.5  | Combining                                         | 19 |

|   | 2.3  | Synch  | ronisation with fetch-and-add                     | 20 |

|   |      | 2.3.1  | Semaphores                                        |    |

|   |      | 2.3.2  | Barrier synchronisation                           | 22 |

|   |      | 2.3.3  | Test-modify-retest functions                      |    |

|   |      | 2.3.4  | Parallel queue algorithm                          |    |

|   | 2.4  |        | mance evaluation of multiprocessors               | 26 |

CONTENTS

|   |     | 2.4.1  | Analytical models                               | 26 |

|---|-----|--------|-------------------------------------------------|----|

|   |     | 2.4.2  | Simulation models                               | 27 |

|   |     | 2.4.3  | Parallel simulation                             | 29 |

|   | 2.5 | Exam   | ple shared memory multiprocessors               | 30 |

|   |     | 2.5.1  | Heterogeneous element processor (HEP)           | 30 |

|   |     | 2.5.2  | Circulating context multiprocessor (CCMP)       | 31 |

|   |     | 2.5.3  | Columbia homogeneous parallel processor (CHoPP) | 31 |

|   |     | 2.5.4  | BBN Monarch                                     | 32 |

|   |     | 2.5.5  | NYU Ultracomputer                               | 33 |

|   |     | 2.5.6  | IBM Research parallel processor prototype (RP3) | 33 |

|   | 2.6 | Comm   | nents                                           | 34 |

| 3 | Epp | 1 mul  | tiprocessor design                              | 35 |

|   | 3.1 | The p  | rocessor                                        | 35 |

|   |     | 3.1.1  | Process context                                 | 38 |

|   |     | 3.1.2  | Merging queues                                  | 41 |

|   |     | 3.1.3  | Memory interface                                | 41 |

|   |     | 3.1.4  | Instruction execution                           | 42 |

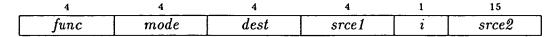

|   |     | 3.1.5  | Instruction format                              | 44 |

|   |     | 3.1.6  | Instruction set                                 | 44 |

|   |     | 3.1.7  | Single processor simulation                     | 47 |

|   | 3.2 | The ne | etwork                                          | 54 |

|   |     | 3.2.1  | Ports                                           | 56 |

|   |     | 3.2.2  | Packet format                                   | 56 |

|   |     | 3.2.3  | Routing                                         | 57 |

|   |     | 3.2.4  | Combining                                       | 57 |

|   |     | 3.2.5  | Decombining                                     | 58 |

|   |     | 3.2.6  | Isolated network simulation                     | 60 |

|   | 3.3 | The m  | nemory                                          | 64 |

|   |     | 3.3.1  | Operation                                       | 65 |

|   | • |

|---|---|

| v | 1 |

| • | 4 |

## CONTENTS

|   | 3.4 | Comme   | ents                            | 66 |  |  |  |

|---|-----|---------|---------------------------------|----|--|--|--|

| 4 | Epp | 1 simul | ator                            | 67 |  |  |  |

|   | 4.1 | Occam   | and transputers                 | 67 |  |  |  |

|   | 4.2 | Simulat | ion engine                      | 69 |  |  |  |

|   | 4.3 | Simulat | tor structure                   | 71 |  |  |  |

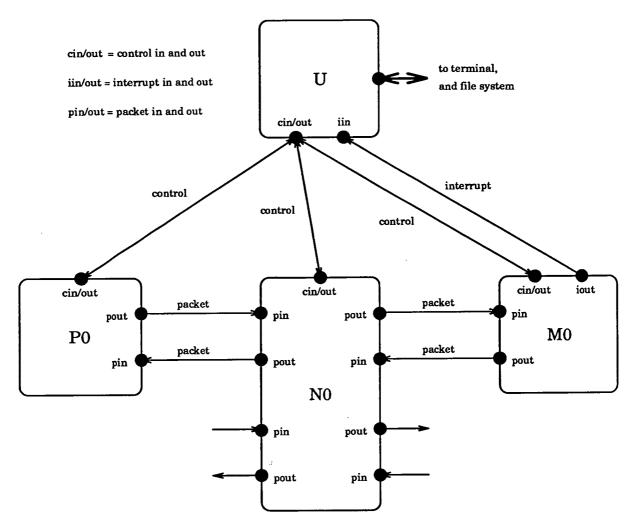

|   |     | 4.3.1   | Domain topology                 | 71 |  |  |  |

|   |     | 4.3.2   | Module distribution             | 72 |  |  |  |

|   |     | 4.3.3   | Communications harness          | 73 |  |  |  |

|   | 4.4 | The use | er-interface                    | 75 |  |  |  |

|   |     | 4.4.1   | System reset and initialisation | 76 |  |  |  |

|   |     |         | Loading a program               |    |  |  |  |

|   |     | 4.4.3   | Program execution               | 77 |  |  |  |

|   |     | 4.4.4   | Displaying state and statistics | 78 |  |  |  |

|   | 4.5 | The mo  | odules                          | 79 |  |  |  |

|   |     | 4.5.1   | Clocking                        | 81 |  |  |  |

|   |     |         | Interrupts                      |    |  |  |  |

|   |     | 4.5.3   | Clock factor                    | 83 |  |  |  |

|   | 4.6 | Simula  | tor performance                 | 83 |  |  |  |

|   | 4.7 |         | ents                            |    |  |  |  |

| 5 | Ber | ıchmarl | k programs                      | 86 |  |  |  |

|   | 5.1 | Choice  | of algorithms                   | 87 |  |  |  |

|   | 5.2 |         |                                 |    |  |  |  |

|   | 5.3 |         | multiply                        |    |  |  |  |

|   |     | 5.3.1   | Parallel algorithm              | 90 |  |  |  |

|   |     | 5.3.2   | Implementation                  | 90 |  |  |  |

|   | 5.4 | Bitonic | c merge sort                    | 91 |  |  |  |

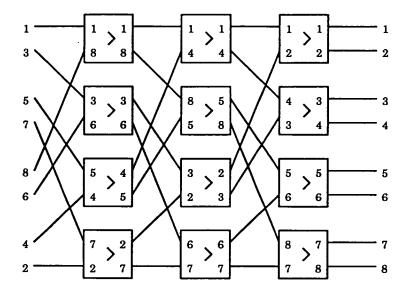

|   |     | 5.4.1   | Parallel algorithm              | 93 |  |  |  |

|   |     | 5.4.2   | Implementation                  |    |  |  |  |

|   | 5.5 | Moore   | shortest path                             |

|---|-----|---------|-------------------------------------------|

|   |     | 5.5.1   | Parallel algorithm                        |

|   |     | 5.5.2   | Implementation                            |

|   | 5.6 | Comm    | nents                                     |

| 6 | Per | formar  | nce evaluation 103                        |

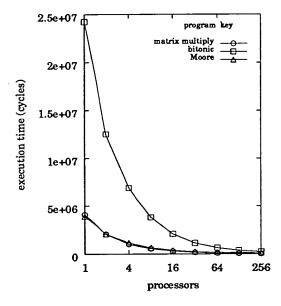

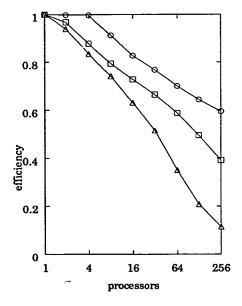

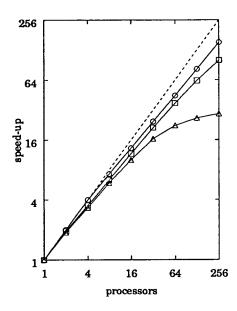

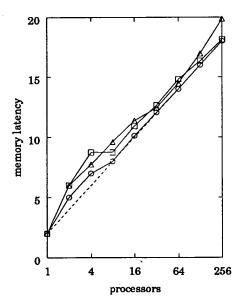

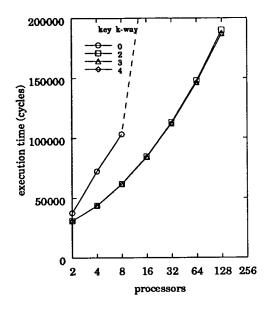

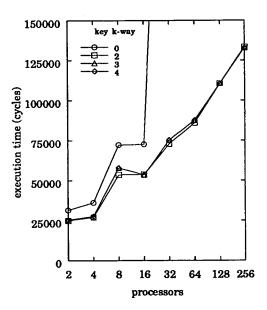

|   | 6.1 | Progra  | nm speed-up                               |

|   |     | 6.1.1   | Simulation details                        |

|   |     | 6.1.2   | Description of results                    |

|   |     | 6.1.3   | Summary                                   |

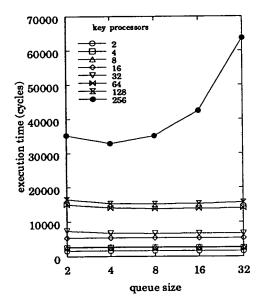

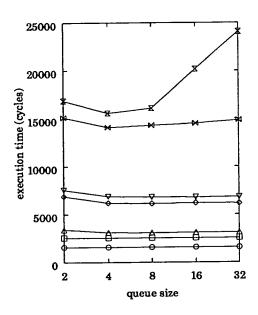

|   | 6.2 | Queue   | e and wait-buffer size                    |

|   |     | 6.2.1   | Simulation details                        |

|   |     | 6.2.2   | Description of results                    |

|   |     | 6.2.3   | Summary                                   |

|   | 6.3 | Comb    | ining level                               |

|   |     | 6.3.1   | Simulation details                        |

|   |     | 6.3.2   | Description of results                    |

|   |     | 6.3.3   | Summary                                   |

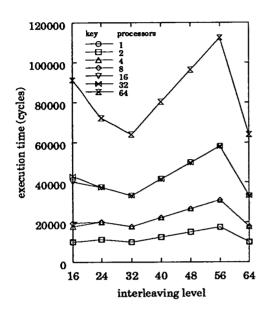

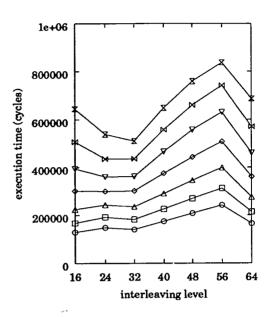

|   | 6.4 | Interle | eaving level                              |

|   |     | 6.4.1   | Simulation details                        |

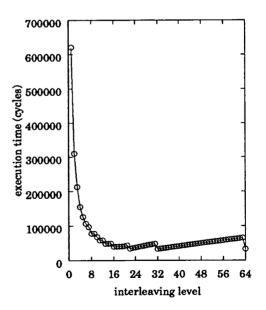

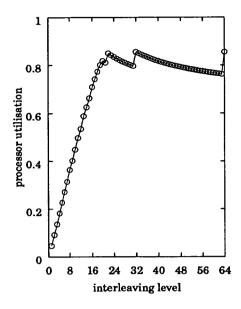

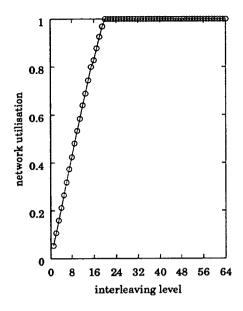

|   |     | 6.4.2   | Description of results                    |

|   |     | 6.4.3   | Summary                                   |

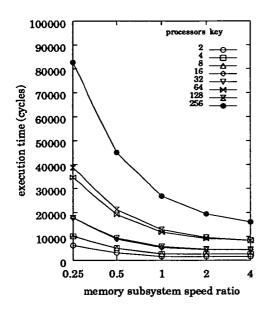

|   | 6.5 | Relati  | ve module speed                           |

|   |     | 6.5.1   | Simulation details                        |

|   |     | 6.5.2   | Description of results                    |

|   |     | 6.5.3   | Summary                                   |

|   | 6.6 | Progra  | am execution profiles                     |

|   |     | 6.6.1   | Simulation details                        |

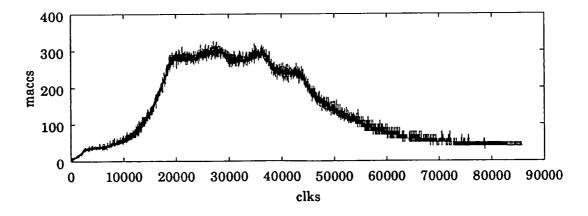

|   |     | 6.6.2   | Description of matrix multiply profile    |

|   |     | 6.6.3   | Description of bitonic merge sort profile |

|   |               | 6.6.4 Description of Moore shortest path profile |  | . 134 |

|---|---------------|--------------------------------------------------|--|-------|

|   | 6.7           | Comments                                         |  | . 138 |

| 7 | Con           | nclusion                                         |  | 139   |

|   | 7.1           | Summary of results                               |  | . 140 |

|   |               | 7.1.1 Instruction interleaving                   |  | . 140 |

|   |               | 7.1.2 Combining and fetch-and-add                |  | . 142 |

|   |               | 7.1.3 Time-driven simulation                     |  | . 144 |

|   | 7.2           | Future work                                      |  | . 144 |

|   |               | 7.2.1 Immediate improvements                     |  | . 145 |

|   |               | 7.2.2 Further research                           |  | . 146 |

| A | Assembly code |                                                  |  | 162   |

|   | A.1           | 1 mmult.asm                                      |  |       |

|   | A.2           | 2 bitonic.asm                                    |  |       |

|   | A.3           | 3 moore.asm                                      |  |       |

# Chapter 1

# Introduction

An MIMD shared memory multiprocessor consists of a number of processors connected by a network to a number of memories. Each processor can access all the memories, and executes one or more independent processes. The processes communicate and synchronise using variables in the shared memory. Such multiprocessors are attractive for a number of reasons: similar programming and operating system techniques to those found in multiprogrammed uniprocessors can be used, the homogeneity of the processors allows load balancing to be easily achieved using self-scheduling [6], the low inter-process communication cost allows the execution of fine-grain processes, and message-passing interprocess communication can be implemented on top of the shared memory. To be scalable, i.e., to maintain performance with increasing size, shared memory systems must be able to overcome the increasing cost of memory access and inter-process communication as the system size increases. The interconnection requirements of small shared memory systems, with a maximum of 16 processors say, can be satisfied by the combination of a fast shared bus and "snoopy"-caching [7]. For larger systems it is necessary to use a higher performance, more scalable network such as a multistage network [8].

This thesis describes the design and simulation of an MIMD shared mem-

ory multiprocessor system which is named the Edinburgh parallel processor One (Epp1). The Epp1 multiprocessor has a conventional "dancehall" architecture with processors on one side of a multistage network connected to an equal number of memories on the other side. The processors have a reduced instruction set (RISC) architecture, and support the concurrent execution of multiple processes (the terms "process", "context" and "instruction stream" are used rather inter-changeably in this thesis) by replicating register files and other resources in each processor. An atomic fetch-and-add instruction is provided for inter-process synchronisation. The network is packet switched, and consists of  $2 \times 2$  switches connected in an indirect binary n-cube topology. The switches support the combining of load and fetch-and-add memory requests directed at the same memory location. There is no processor cache, local memory, or paged virtual memory, and all memory requests traverse the network to one of the shared memories.

The Epp1 design exists on paper and as a simulation program only, and is used as a didactic tool for investigating the components of the design and their interaction in the whole system. No implementation of the design is intended. The main features of the design are the interleaving of processes on each processor, the combining of memory requests in the multistage network, and the use of the fetch-and-add instruction as the synchronisation primitive. These features have been separately included into other MIMD shared memory multiprocessor designs (Section 2.5), but they have not previously been included together in the same system.

The performance of the Epp1 design is evaluated by detailed simulation of the complete design at the instruction level. The availability of a powerful computing resource, the Edinburgh Concurrent Supercomputer (ECS), allows the simulation of large Epp1 configurations (up to 256 processors) within reasonable time scales. The ECS is a distributed memory multiprocessor constructed from transputers, and the Epp1 simulator is written in Occam to execute in parallel on the ECS. The simulated Epp1 processors execute instructions from programs

that are loaded into the simulated memories. The programs are written in the Epp1 assembly language and assembled into Epp1 machine code. Benchmark programs are used to provide workloads for the simulation experiments, these are assembly language implementations of three well known parallel algorithms: matrix multiply, bitonic merge sort and Moore shortest path. The matrix multiply program multiplies two integer matrices, the bitonic merge sort program sorts a sequence of integers, and the Moore shortest path program finds the shortest path from a source node to every other node in a weighted directed graph. All process control and synchronisation in the programs is implemented using the fetch-and-add instruction.

The simulation experiments are performed by executing the benchmark programs with various values of the Epp1 system parameters. The simulator records the program execution time and the system execution statistics, and any changes in these can then be related to changes in the system parameters. The simulation experiments described here investigate the effect on performance of: increasing the system size while keeping the program size constant (relative speed-up), varying the switch queue and wait-buffer size, increasing the combining level, increasing the interleaving level, and varying the network and memory speed relative to the processor. A dynamic execution profile of each benchmark program is also presented which shows how the execution statistics vary during the execution of the program.

## 1.1 Original work

The following original work has been carried out as part of the research leading to this thesis:

• The context-flow processor design of Topham (Section 2.1.4) was extended to a 32-bit instruction set including the fetch-and-add instruction.

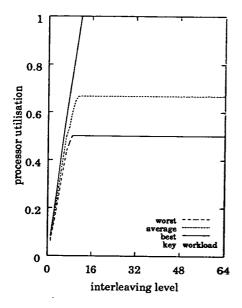

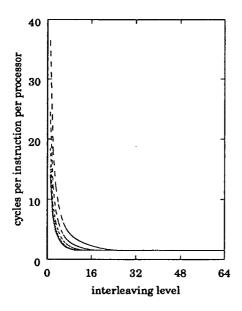

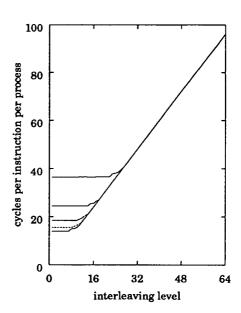

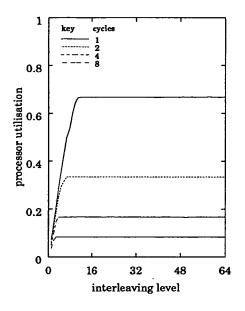

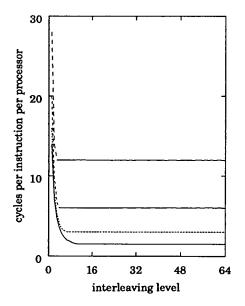

- Simulations of a single Epp1 processor were carried out to find the performance bounds of the processor, executing synthetic instruction mixes, with increasing interleaving level and memory latency.

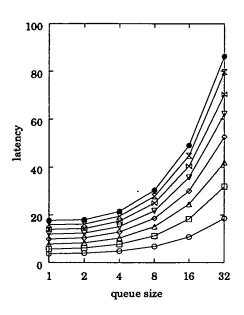

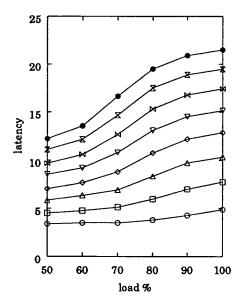

- Simulations of the isolated Epp1 network were carried out to find the performance bounds of the network, using randomised addresses, with varying switch queue sizes, network loads and hot-spot percentages.

- A parallel simulator of the complete Epp1 design was implemented in Occam on a transputer based distributed memory multiprocessor, allowing the simulation of a 256 processor Epp1 system on 128 transputers.

- An assembler of the Epp1 instruction set was written to produce machine code executable by the simulator.

- Three benchmark programs were written in Epp1 assembly code to implement parallel matrix multiply, bitonic merge sort and Moore shortest path algorithms. Existing fetch-and-add based process control and synchronisation mechanisms were used in the programs.

- Simulations of the complete Epp1 design executing the benchmark programs were carried out to observe the effect of various system parameters on performance, and to collect dynamic execution traces of the programs.

# 1.2 Chapter overview

The chapters in the thesis are ordered so that the Epp1 design, the Epp1 simulator, and the benchmark programs are described before the main results, gathered from the simulations of the complete Epp1 design, are presented.

Chapter 2 describes the relevant background and previous research. First, instruction interleaved processor design is introduced, and examples of previous

single processor instruction interleaved designs are described. Second, multistage networks are introduced, and aspects of their design including topology and combining are described. Third, synchronisation using fetch-and-add is introduced, and example algorithms for implementing semaphores, barriers, and parallel queues are described. Fourth, performance evaluation of multiprocessor systems is reviewed, and parallel time-driven simulation methodology is introduced. Finally, a number of example MIMD shared memory systems are described.

Chapter 3 describes the Epp1 design in three sections on the processor, network switch and memory. The processor section includes a detailed description of the structure and function of the processor pipeline, a description of the instruction set, and simulation results showing performance characteristics of a single processor. The network section includes a description of the network switch functions, such as routing and combining, and simulation results of an isolated network with randomised addressing.

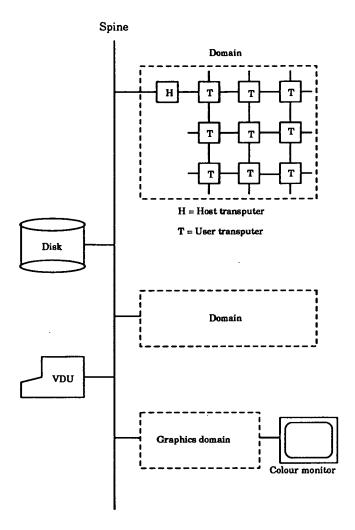

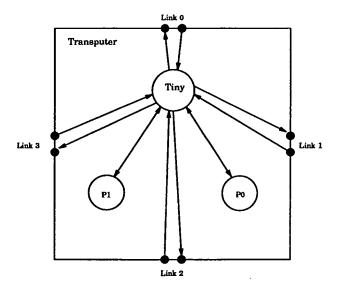

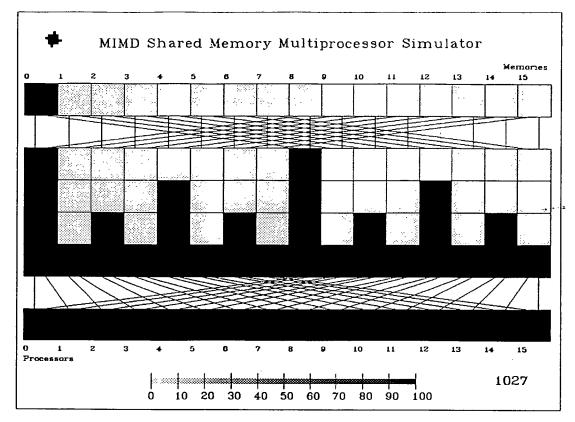

Chapter 4 describes the Epp1 simulator. First, the Occam language and the transputer are reviewed briefly. Second, the Edinburgh Concurrent Supercomputer is introduced, and the structure of its transputer domains described. Third, the operation and function of the simulator is described, including how the simulation is parallelised and how the parallel modules communicate. Fourth, the user-interface and commands available are described. Fifth, the clocking of the modules is described. Finally, performance results of the simulator itself are presented.

Chapter 5 describes the three benchmark programs. First, the choice of algorithms is discussed. Second, the process control mechanisms are described. Each program is then described in turn, showing how it was implemented in the assembly language of the Epp1 processor.

Chapter 6 describes and presents results from the simulation experiments which investigate the effect on system performance of system size, queue and

wait-buffer size, combining level, interleaving level and relative processor speed.

A dynamic execution profile for each program is also presented.

Chapter 7 summarises the research and results described in the thesis. Improvements to the design and simulator, and further research topics, are suggested.

Appendix A contains Epp1 assembly code listings for the benchmark programs which are described in Chapter 5.

Appendix B contains the detailed execution statistics from the simulation experiments which are described in Chapter 6.

# Chapter 2

# Background

This chapter provides the relevant background information for the chapters which follow. The first section introduces instruction interleaving, and gives examples of processor designs that implement instruction interleaving. The second section introduces packet-switched multistage interconnection networks, and discusses the topology, routing of packets, and contention in such networks. The third section introduces synchronisation using the fetch-and-add instruction, and describes some synchronisation algorithms implemented with fetch-and-add. The fourth section discusses performance evaluation of multiprocessor designs, and describes parallel time-driven simulation. The final section briefly describes some example MIMD shared memory multiprocessor designs.

## 2.1 Instruction interleaving

Pipelining increases processor throughput, defined as the number of instructions executed in unit time, by reducing the machine cycle time and allowing concurrent execution of a number of instructions. Generally processor pipelining is divided into two levels: instruction pipelining, and function or arithmetic pipelining [9, 10, 11]. Instruction pipelining divides the normal instruction execution sequence

into a number of stages, typically: instruction fetch, instruction decode, operand fetch, instruction execution, and result store. Current microprocessors are usually pipelined at this level. To achieve maximum performance particular function blocks, such as a floating point arithmetic unit, are further pipelined. Function pipelining is found in vector supercomputers for example.

#### 2.1.1 Single instruction stream pipelines

In a conventional instruction pipeline, which is executing a single instruction stream, each stage of the pipeline contains an instruction from that stream (or is empty). To utilise the pipeline efficiently there must be a sufficiently long sequence of instructions to fill the pipeline. Due to discontinuities in the instruction stream only pipelines with a small number of stages can be utilised efficiently. Three possible causes of discontinuities are: branch dependence, data dependence and memory latency.

When a branch instruction occurs and the branch is taken, assuming that instructions are not prefetched from the branch address, then instructions in the pipeline after the branch have to be flushed from the pipeline and new instructions fetched from the branch address. To reduce the loss of performance caused by branch dependence a number of methods such as branch prediction, branch target buffers and delayed branching are used [9, 12, 13, 11].

Sequential instructions in an instruction stream are likely to have data dependencies between them. These can lead to reduced utilisation because reading of operands may have to be delayed to satisfy the dependency. Such data dependence conflicts occur particularly in processors with a long pipeline, or with multiple pipelines of differing lengths in which the order of instruction completion must be maintained. To ensure that the dependencies are satisfied methods such as register scoreboarding, internal forwarding and compiler data dependence analysis are used [9, 11, 14].

Pipeline throughput is limited by memory latency, as the pipeline can only

execute as fast as the instructions are supplied. In a single processor system the memory latency is usually equal to the memory access time. In multiprocessor systems memory requests generally have to traverse an interconnection network, so the memory latency is higher due to network delay and contention. Methods of reducing memory latency include the use of caches, local memory, separate data and instruction busses (Harvard architecture), and decoupling memory access from instruction execution [15, 16].

One way of side-stepping these dependency and latency problems, and increasing the utilisation of the pipeline, is to implement a multiple instruction stream pipeline.

#### 2.1.2 Multiple instruction stream pipelines

In an instruction interleaved pipeline instructions from more than one instruction stream are executed concurrently. If only one instruction from each instruction stream is allowed to be executed at any one time, then each stage of the pipeline contains an instruction from a different instruction stream (or is empty). Effectively the pipeline switches context to a different instruction stream every cycle. Instruction interleaving is also variously known as: micro-multiprogramming [17], virtual-processing [18], context-flow [19], circulating-contexts [20], state multiplexing [21], and multi-threading [1].

The main aim of instruction interleaving is greater pipeline utilisation. If each instruction stream is restricted to executing a single instruction at a time, then the dependency problems described above do not occur. Because each stage of the pipeline contains an instruction from a different instruction stream, there are no branch dependencies and thus no branch penalty. Also, because each instruction in an instruction stream is completed before the next one is issued, there are no data dependencies. So two possible causes of discontinuities in the pipeline have been removed, and as long as sufficient instruction streams are provided the pipeline can operate at maximum throughput. The multiple functional units

may also be better utilised if the instruction streams execute different instruction types.

Although instruction interleaving does nothing to reduce memory latency, it does allow the pipeline to tolerate higher memory latency. This is because memory access and execution can be overlapped, since while some instruction streams wait for memory accesses to complete others can be executed. Memory access and instruction execution are thus de-coupled. If the memory system is also pipelined, for instance in shared memory multiprocessor systems that have pipelined multistage networks, then this effectively extends the length of the execution pipeline and more instruction streams must be executed to achieve maximum pipeline utilisation.

To implement instruction interleaving starting with a conventional single instruction stream processor requires the addition of extra hardware (registers and other function blocks) to the pipeline. Each instruction stream requires extra state information, such as a process number in addition to the usual registers and flags, and all the state information must be replicated for each instruction stream. Extra logic is required to control the multiple instruction streams, but conversely none of the logic to handle branch and data dependency is required. To maintain a high pipeline utilisation the processor must support a sufficient number of instructions streams to fill the pipeline, and the operating system and applications programs must be sufficiently parallel to keep all the instruction streams busy.

Data-flow systems [22] have similarities to instruction interleaved systems, and also use the arguments for greater processor utilisation given above [23, 1]. A process (instruction stream) in a data-flow machine is typically a single instruction, and processes are not associated with any one processor. An advantage of data-flow systems over the instruction interleaved systems described here is that they also provide implicit synchronisation between processes. The hardware implementation and programming of data-flow systems is not straightforward though [24].

#### 2.1.3 Performance of instruction interleaved pipelines

Assuming a simple linear pipeline with P stages executing p instruction streams  $(p \le P)$ , then (ignoring start-up time):

pipeline throughput = p/P instructions per cycle instruction stream throughput = 1/P instructions per cycle

The pipeline throughput is the number of instructions executed per cycle, and the instruction stream throughput is the number of instructions executed per stream per cycle. The maximum pipeline throughput is achieved when p = P. If the number of streams is greater than the number of stages (p > P), then the throughput per stream will be reduced as there will be contention for the pipeline.

The performance of the HEP processor (Section 2.5.1), which supports multiple instruction streams, has been characterised using the  $r_{\infty}$  (maximum throughput) and  $n_{1/2}$  (half-performance vector length) parameters that have previously been applied only to vector and array processors [25]. The half-performance vector length in an instruction interleaved system is the number of instruction streams required to achieve half the maximum throughput. Topham [26] also describes a simple analytical model of a context-flow processor. These models provide 'similar results to the actual performance results of a single HEP processor [27], which show that pipeline throughput increases linearly as more instruction streams are added, up to the maximum defined by the pipeline length. Generally, the effective pipeline length is greater than the actual pipeline length because of memory access latency.

A number of single processor designs which support instruction interleaving are summarised below.

#### 2.1.4 Example instruction interleaved processor designs

In the shared resource processor design [18], up to 32 concurrently executing instruction streams share 7 pipelined functional units and a memory interface.

Each instruction stream has its own instruction decoder, register set and instruction and data caches. Contention for the functional units is minimised by allocating time-slices during which each instruction decoder can issue an instruction. The instruction set includes a spawn instruction for starting a new instruction stream and fetch-and-add instructions for synchronisation. Simulations of the design indicate that a high processor throughput and functional unit utilisation can be achieved.

The P\* or multiple stream registerless shared resource processor design [28], consists of fetch, decode and execute pipeline stages combined with special associative queues which buffer and merge instruction streams. Each instruction stream state consists of a program counter, instruction register and status bits. Instructions are memory to memory and there are no explicitly addressable registers. There are five memory ports which can all make concurrent requests, so multiport memory is required. The design provides high utilisation of individual processor components, decouples processor throughput from memory access time, and the additional hardware cost per instruction stream scales well.

The virtual multiprocessor design [29], is a pipelined processor supporting multiple instruction streams. Various pipeline layouts and control strategies were compared for this design. A straight through pipeline gives the best cost/performance ratio for varying degrees of multiprocessing. A single chip implementation of the virtual multiprocessor was also considered [30]. The use of a central register file was compared to incorporating the registers into the pipeline stages. The latter allows the use of dynamic logic and minimises interconnections, but the cost of the processor will depend heavily on the size of the register set, since it is replicated in each pipeline stage. Instruction traces were used to find an optimum register set size for a central register file, and adding registers was shown to be substantially less effective in improving performance than increasing the level of multiprocessing.

The cyclic pipeline computer design [31], is a pipelined processor support-

ing multiple instruction streams which is to be implemented in Josephson-junction technology. Because Josephson-junction gates are self-latching there is no need for latches between pipeline stages, and this allows the pipeline to be clocked using only a single-phase clock. The memory is also to be implemented using Josephson-junction devices, and has a four stage pipeline. A silicon version of the processor (FLATS-2) is being implemented.

The VMP or virtual multiprocessor design [32], is based on the IBM370 CPU and uses multiprogramming at the instruction level. Each virtual CPU (instruction stream) has a separate register set, but shares all other processor resources. The optimum number of virtual CPU's in the design is dependent on the average instruction completion time.

The Context-flow processor design [19, 26, 33], is a VLSI pipelined RISC processor supporting multiple instruction streams. A proposed implementation [34] is based around an off-the-shelf pipelined floating-point ALU, with a multiport register file, three merging queues, and some custom VLSI implementing the control unit. Up to 64 concurrently executing instruction streams can be spawned on demand. The original context-flow proposal also included a message-passing interprocess communication mechanism in which processes communicate through special channels in memory. The Epp1 processor described in Chapter 3 is based on the context-flow processor design.

Because instruction interleaved processors can execute efficiently even with high memory latencies they are obvious candidates for multiprocessor systems. Two shared memory multiprocessor designs that support instruction interleaving, the HEP and CCMP, are described in Section 2.5. There are other multiprocessor designs which although not strictly instruction interleaved do support fast context-switching of processes within the processor [35, 36]. There are also a number of hybrid multiprocessor designs which combine features of message-passing and data-flow systems [37, 38, 39], and have similarities to instruction interleaved systems.

This concludes the background section on instruction interleaving; the next section introduces multistage networks.

## 2.2 Packet-switched multistage networks

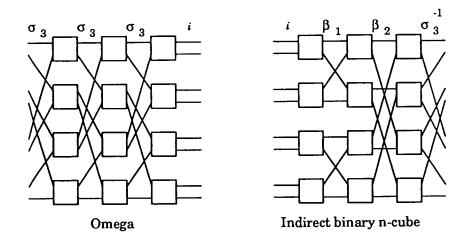

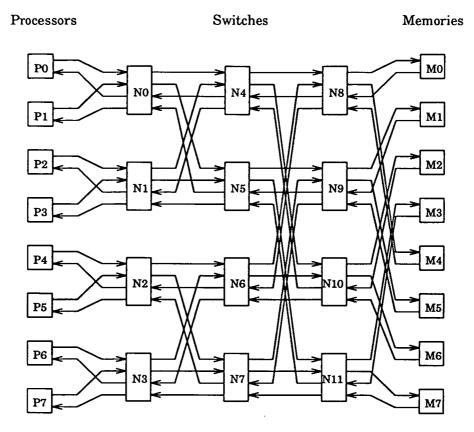

A multistage network consists of a number of stages of small crossbar switches in which the outputs of one stage are connected to the inputs of the next stage according to some permutation. There are many flavours of multistage network [8], and only rectangular, two-sided, uni-directional, packet-switched, blocking networks are considered here. Such a network with n inputs and  $k \times k$  switches has  $\log_k n$  stages with n/k switches in each stage, the same number of outputs as inputs (rectangular), the outputs are on the opposite side of the network to the inputs (two-sided), messages are transmitted across the network in packets using store-and-forward routing (packet-switched), and there is only one path between each input and each output in the network (blocking). The indirect binary n-cube [40] and the omega [41] networks, shown in Figure 2.1, are examples of this type of network. A number MIMD shared memory multiprocessor systems use this kind of multistage network to connect the processors to the memories, for example the RP3, HEP, CHoPP and Monarch (see Section 2.5), and also the Epp1 design described in the next chapter.

To restrict the discussion further only relevant aspects of multistage network design and performance are discussed here. In particular, VLSI implementation [42, 43], and fault-tolerance/error-correction [44, 45] are not reviewed.

## 2.2.1 Network topology

There are many different classifications of multistage networks. Some of these describe classes of networks such as SW-banyan [46], delta [47] and cube [44]; and some describe a particular network topology such as the indirect binary n-cube, omega, baseline [48] and flip [49]. A number of these network topologies

Figure 2.1: Omega and indirect binary n-cube multistage network topologies

have been shown to be isomorphic [48].

The topology of a multistage network can be defined by the degree of the switches in the network, and how the switches are connected. These connections can be conveniently described using permutation functions [14], some of which are defined below. The argument to each function is the binary representation of a network port input number x.

$$x = \{b_n, b_{n-1}, \dots, b_{k+1}, b_k, b_{k-1}, \dots, b_2, b_1\}$$

The identity permutation is i, where:

$$i(x) = x$$

The shuffle permutation  $\sigma_k$  is defined as the cyclic left shift of the k least significant bits of x.

$$\sigma_k(x) = \{b_n, \dots, b_{k+1}, b_{k-1}, \dots, b_1, b_k\}$$

The inverse shuffle permutation  $\sigma_k^{-1}$  is defined as the cyclic right shift of the k least significant bits of x.

$$\sigma_k^{-1}(x) = \{b_n, \dots, b_1, b_k, \dots, b_2\}$$

The butterfly permutation  $\beta_k$  exchanges the first and  $k^{th}$  bits of x.

$$\beta_k(x) = \{b_n, \dots, b_1, b_{k-1}, \dots, b_k\}$$

As shown in Figure 2.1, the stages of the omega network are connected by repeated shuffle permutations (where  $k = \log n$ ), and a final identity permutation. The stages of the indirect binary n-cube are connected by butterfly permutations (where k varies with the stage), and a final inverse perfect shuffle.

In a shared memory multiprocessor system with a dancehall configuration, two of the multistage networks described above are required: one (the request network) to route the request packets from the processors to the memories, and one (the acknowledge network) to route the acknowledge packets back from the memories to the processors.

#### 2.2.2 Packet routing

Packet switching allows packets to be pipelined through the network, and the network cycle time is only limited by the time it takes to transmit a packet from one stage to the next (routing and wire delay). A packet typically consists of a number of fields including: a type field, a source address field, a destination address field and a data field. In a memory request packet the type field defines the type of memory access, the source address field contains the number of the requesting processor, and the destination field contains a memory number and an offset within that memory. In a memory acknowledge packet the destination field contains the processor number to which the acknowledge packet should be routed back.

Routing is controlled at each switch by a number of bits from the destination address [50]. If the network has  $k \times k$  switches, then  $\log_2 k$  bits are required in each switch to specify where the packet is routed. Therefore  $\log_2 k \times \log_k n$  bits are required to route a packet through an n input network. To maintain the same

numerical ordering of inputs and outputs, the routing bits must be interpreted from the most significant end of the destination address in an omega network, and from the least significant end in an indirect binary n-cube network. After the packet has been routed in the switch, the destination address can simply be shifted  $\log_2 k$  places to discard the used bits. The return address can be included in the request packet before it is transmitted, or more conveniently, it can be generated as the packet moves through the network [51].

#### 2.2.3 Routing conflicts

If two packets in a switch are addressed to the same output, then some conflict resolution strategy is required. Possible options are to block, re-route or discard one of the conflicting packets. Blocking is discussed below. Re-routing was proposed for the Burroughs FMP network [52, 53], and implemented in the HEP network. The choice of which packet proceeds depends on the priority algorithm used, for example: random, round-robin, or adaptive priority [54].

Packets that have been blocked must be queued in the switch until they can be routed onwards. Incorporating queues in a switch improves network performance because it allows packets from a preceding switch to progress even when a packet in the current switch is blocked. The queues can be positioned either at the inputs or outputs of the switch, or incorporated into the crossbar [55]. The network throughput increases as the queue size is increased, but the network latency increases as well, and therefore small queues of length 4 to 8 packets are optimal [56, 57].

#### 2.2.4 Hot-spot contention

Apart from the existence of routing conflicts, network performance can be further reduced by contention for the memories which occurs when a number of memory requests are addressed to the same memory bank. So that sequential memory

requests are not directed at the same memory, logical memory addresses can be interleaved or hashed to produce the physical address. The RP3 and Monarch designs both use hashing, which has the effect of randomising the memory access pattern. This method does not reduce contention when the memory requests are addressed to the same location however.

Memory locations which have a statistically significant higher percentage of requests directed at them than other locations are termed hot-spots. As the number of requests addressed to the hot memory location increase eventually a point is reached where more packets arrive than the memory can service per cycle, and the requests are queued. Ultimately an effect called tree saturation [58] occurs, in which the switch queues from the hot memory back to the network inputs are all full. Then, not only the traffic directed at the hot-spot is blocked, but all other traffic which must pass through those switches. A hot-spot can arise from access to shared variables [58, 59, 60], or from block transfers [61]. Simulations show that network performance degrades soon after a hot-spot becomes active, and that the effects of the hot-spot remain for some time after it is no longer active [62].

A number of ways to reduce hot-spot contention have been proposed. A method of combining memory requests to the same location is described in the following section. Other methods include moving the location of the hot-spot between memories [63]. Such a roving memory location (RML) is implemented as a special packet which moves from memory to memory, satisfying any requests for the hot-spot which have been queued in the memory. Instead of implementing hardware combining, accesses to shared variables could be implemented in software [64]. Each shared variable is then replaced by a tree of variables which are evenly distributed among the memories. A different network architecture could also be used, for instance the circuit-switched multistage network of the BBN Butterfly [65, 66]. This network is non-blocking, and therefore no situation analogous to tree saturation occurs, although there is still contention for access

to the network.

#### 2.2.5 Combining

The Ultracomputer, RP3, Monarch and CHoPP multiprocessor designs all include some form of combining. Only a brief description of the combining mechanism is given here as the details depend on the particular switch design [67, 68, 69, 70]. Also the combining mechanism used in the Epp1 design is similar to that used in the Ultracomputer and RP3, and is described in detail in Chapter 3.

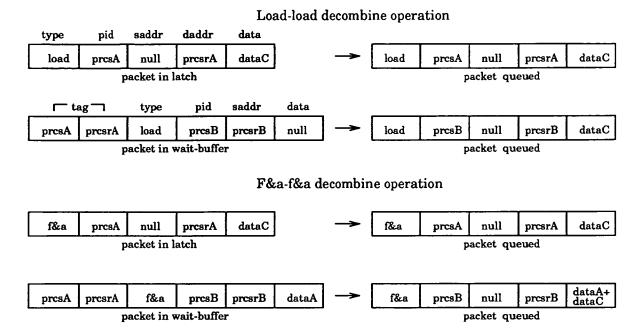

Combining [71, 72] occurs in the network switches. If two request packets addressed to the same memory location meet in a switch they can be combined. The combining operation involves updating the packets' data fields, depending on the memory request type, and then one of the packets is forwarded and the other packet is stored in the switch. When the returning acknowledge packet passes back through the switch from memory, the stored packet is decombined. Again, the specific decombining operation depends on the request type.

A request packet may be combined more than once on its way to memory. The number of times a packet can combine in each switch is given by the combining level [73], and depends on the switch implementation. With a combining level k, or k-way combining, a packet can combine k-1 times in each switch. For example with 2-way combining, also called pairwise combining, a packet can only combine once per switch. An initial performance analysis of pairwise combining [58] showed that combining improves network performance, and that tree-saturation can be prevented. Subsequent research [73, 74] suggests that, for large networks and heavy loads, pairwise combining is not enough to reduce tree saturation effectively, and 3-way combining must be used.

Combining is particularly effective when used in conjunction with the fetchand-add operation described in the following section, and was originally proposed in the Ultracomputer design to allow simultaneous fetch-and-add memory accesses to be carried out efficiently [51].

## 2.3 Synchronisation with fetch-and-add

In a shared memory multiprocessor interprocess communication and synchronisation occurs using shared variable's. Synchronisation primitives, such as mutual exclusion and condition synchronisation [75], are implemented using atomic read-modify-write operations such as fetch-and-add or test-and-set.

The fetch-and-add instruction has been used in single processor machines such as the IBM370, and in shared memory multiprocessor designs such as the Ultracomputer, RP3, Monarch and CHoPP. The instruction f&a(v,x) adds the given value x to the variable v, and returns the variables previous value. Fetch-and-add has efficiency advantages over the simpler test-and-set instruction, for example it can be used directly to update a shared variable, so removing the need for locking. A number of synchronisation and other algorithms using fetch-and-add have been developed in conjunction with the Ultracomputer and RP3 designs [76, 77]. Versions of some of these algorithms implementing semaphores, barrier synchronisation, test-modify-retest functions, and a parallel queue are described below. These algorithms are used subsequently in the Epp1 benchmark programs described in Chapter 5.

#### 2.3.1 Semaphores

Implementations of the p() and v() semaphore operations [75], are shown in Figure 2.2 using a pseudo-C syntax. The function f&a(s,x) behaves as defined above. The address of the semaphore is passed in argument s.

The p() function first waits for the semaphore's value to be greater than zero. The semaphore is then decremented using f&a, and if the returned value is greater than zero the function returns. Otherwise the semaphore is incremented using f&a, and the function loops back to the beginning. This implementation of the p() function is blocking, since the process calling the function will busy-wait until the function succeeds. The v() function increments the semaphore using

```

int p(s)

int *s;{

int t;

while(1){

while(*s<=0);

if((t=f&a(s,-1))>0)

return(t);

else

f&a(s,1);}}

int v(s)

int *s;{

return(f&a(s,1));}

```

Figure 2.2: P and V semaphore functions

f&a, and returns.

The test of the semaphore's value at the start of the p() function, before the first f&a, is necessary to avoid the possibility of livelock. Assume a p() function without this initial test. If a large number of processes all executed p() on a semaphore in parallel, then the semaphore would have a large negative value after the f&a. If another process executed v() at the same time, the semaphore would still have a negative value. Therefore all the processes executing p() would be locked out, perhaps indefinitely.

The main application of these semaphore functions is to implement mutual exclusion, for instance to lock a shared variable during an update. If the shared variable has an associated semaphore s, which is initialised to 1, then a process calls p(s) to lock and v(s) to release the variable. If the update is simply an addition, then it may be possible to use f&a directly on the shared variable without explicitly using a lock.

```

void join(count,maximum)

int *count,maximum;{

f&a(count,1);

while(*count<maximum);}</pre>

```

Figure 2.3: A join function

```

void barrier(count,maximum)

int *count,maximum;{

int t;

t=(*count<maximum);

if(f&a(count,1)==(2*maximum-1)) *count=0;

while((*count<maximum)!=t);}</pre>

```

Figure 2.4: A barrier function

#### 2.3.2 Barrier synchronisation

A barrier synchronisation is used to ensure all parallel parts of a computation have completed before the next is scheduled [75, 78]. If the barrier is used only once then a simple join (which is counterpart to a fork) can be used, such as the function shown in Figure 2.3. The count variable is initialised to zero. Processes calling join() increment the count, and are blocked until the count equals the maximum.

If the barrier is to be re-used, for instance if it separates iterations of a loop, then care must be taken that there is no possibility of processes from different iterations overtaking each other and thus causing deadlock. The barrier algorithm shown in Figure 2.4 is a re-usable implementation [79], allowing the same counting variable to be used in subsequent barriers. The count variable is initialised to zero. As processes call barrier() they are blocked until the count equals the maximum, and then maximum processes are allowed to pass. When the processes reach the barrier again in the next iteration, they are blocked until the count equals 2\*maximum-1. Then maximum processes are again allowed to pass, and the

```

int tir(semaphore,increment,maximum)

int *semaphore,increment,maximum;{

int t;

while(1){

while(*semaphore>=maximum);

if((t=f&a(semaphore,increment))<maximum)

return(t);

else

f&a(semaphore,-increment);}}</pre>

```

Figure 2.5: Test-increment-retest function

```

int tdr(semaphore,decrement)

int *semaphore,decrement;{

int t;

while(1){

while(*semaphore<=0);

if((t=f&a(semaphore,-decrement))>0)

return(t);

else

f&a(semaphore,decrement);}}

```

Figure 2.6: Test-decrement-retest function

count is reset.

#### 2.3.3 Test-modify-retest functions

The test-increment-retest (TIR) and test-decrement-retest (TDR) functions are used frequently in fetch-and-add based algorithms [76, 71]. Blocking implementations of these functions are described here, and are used in the parallel queue algorithm described below.

The tir() function shown in Figure 2.5 has three arguments: the semaphore, the value of the increment, and the maximum the semaphore can reach. The function first tests the value of the semaphore to prevent livelock (as explained

above), and then increments the semaphore. If the returned value is below the maximum then the function succeeds. TIR can be used to spawn a number of processes, giving each one a unique index number (the value returned by the function). This index number can then be used for accessing parts of a shared data structure such as an array.

The tdr() function shown in Figure 2.6 has two arguments: the semaphore and a decrement. If the value of the semaphore is greater than zero, the semaphore is decremented and the function returns, otherwise it is blocked. TDR is similar to the p() function defined above, except that the decrement is passed as an argument.

#### 2.3.4 Parallel queue algorithm

Blocking implementations of parallel insert and delete functions for a parallel FIFO queue [76] are presented here. The queue is implemented using a circular buffer, and consists of a header and an array of entries as defined below:

```

struct{

int insert, delete, entry;} entrystruct

struct{

int size, upper, lower, insert, delete; /* header */

struct entrystruct entries[];} queuestruct

```

The queue header contains five fields: the queue size, an upper bound, a lower bound, an insert pointer and a delete pointer. The upper bound contains the number of items in the queue plus the number of active insertions. The lower bound contains the number of items in the queue minus the number of active deletions. The insert pointer points to the tail of the queue. The delete pointer points to the head of the queue. Each queue entry has three fields: an insert semaphore, a delete semaphore and a data value. The insert semaphore indicates whether the data field is empty and available for insertion. The delete semaphore indicates whether the data field is full and available for deletion. These semaphores are

```

void insert(queue,value)

struct queuestruct *queue;

int value;{

int t;

tir((queue->upper),1,(queue->size));

t=f&a((queue->insert),1)%(queue->size);

p(queue->entries[t]->insert);

queue->entries[t]->entry=value;

v(queue->entries[t]->delete);

f&a((queue->lower),1);}

```

Figure 2.7: Insert function

```

void delete(queue,value)

struct queuestruct *queue;

int *value;{

int t;

tdr((queue->lower),1);

t=f&a((queue->delete),1)%(queue->size);

p(queue->entries[t]->delete);

*value=queue->entries[t]->entry;

v(queue->entries[t]->insert);

f&a((queue->upper),-1);}

```

Figure 2.8: Delete function

necessary to ensure correct synchronisation when there is a concurrent insertion and deletion of the same entry, or when there are two concurrent insertions of the same entry.

The insert() function appends the given data value to the tail of the queue. The tir() function is first called on the upper bound, and blocks until there is room in the queue for insertion. Then the insert pointer is incremented, and the offset of the entry in the queue calculated. Next p() is called on the entry's insert semaphore. When this succeeds the data value is written, v() is called on the delete semaphore, and the lower bound is incremented.

The delete() function removes the entry at the head of the queue. First the tdr() function is called on the lower bound, which blocks until an item is available to delete. Then the delete pointer in incremented, and the offset of the entry in the queue calculated. Next p() is called on the entry's delete semaphore. When this succeeds the data value is read, v() is called on the insert semaphore, and the upper bound is decremented.

The queue can be used as a parallel data structure or to schedule processes for example. For process scheduling each queue entry can point to a process control block, and processes are removed from the queue when a processor becomes free (self-scheduling). Only individual processes can be scheduled this way, which is not efficient for scheduling a large number of identical processes. To do this efficiently a multi-queue algorithm can be used, in which each queue entry also contains a multiplicity count [76]. Unfortunately the parallelism of the multi-queue has to be restricted, compared to the above algorithm, to ensure correctness.

## 2.4 Performance evaluation of multiprocessors

To evaluate the performance of multiprocessor designs the same techniques used for uniprocessor designs are applied [80], but can be complicated by the size, parallelism and synchronisation inherent in the design to be evaluated. Performance evaluation methodologies are divided into analytical and simulation based techniques. The application of parallelism to increase simulation speed has required the development of new simulation algorithms.

#### 2.4.1 Analytical models

Analytical models try to capture the behaviour of a system in a set of equations, and are frequently based on a stochastic analysis of the system's changes of state (for instance using queueing network theory) [80, 81]. Because such models are

quite general they have a wide applicability, and may be used to evaluate similar systems without much change. Assuming closed-form equations can be derived for the model, then it can be solved efficiently and will not require excessive computing resources, although many iterations may be needed before the model settles down and produces reliable results. The size of parallel systems complicate the solution of queueing network models due to the combinatorial explosion in the number of possible states, and the correct modelling of synchronisation is difficult because of the loose-coupling assumed in some of the models. Because of their formulation, analytical models can generally only provide information about the average steady-state behaviour, or performance bounds, of the system being modelled. To validate an analytical model also usually requires comparing the model to a more detailed simulation of the same system.

Various stochastic models including queueing networks have been used to model multiprocessor network performance [47, 57, 2]. These models assume that memory addresses are uniformly distributed and that all addresses are independent, and provide results for best-case network throughout and delay under these conditions. To evaluate the effect of a memory hot-spot the models have been extended to account for a fraction of the memory requests, the hot-spot percentage, being directed at the hot-memory [58, 73, 74]. Stochastic Petri nets have been used to model bus-based multiprocessor systems [81]. The RP3 project developed a spreadsheet program which used queueing analysis to show network performance for various configurations [5].

#### 2.4.2 Simulation models

Simulation models try to capture the behaviour of a system in the code of the simulator program. A simulation model is more specific to the system being evaluated, and is also more computationally intensive than an analytical model. There is no restriction on what can be modelled, allowing dynamic effects to be investigated, and simulation models can also be used for functional verification

as well as performance evaluation.

Simulation models are generally divided into instruction, register-transfer and gate level models. As the model becomes more detailed the amount of structural information in the model increases. General simulator systems allow the modelled design to be specified using a hardware description language, which may be a high level description such as ISP [82] and VHDL [83], or in terms of function blocks and registers, or logic gates, depending on the level of the simulation. Custom simulators are usually implemented using a high-level language in the form of a behavioural description. Specific language features may guide the choice of language, for example using Occam to explicitly describe the parallelism in a system [84, 85].

The input to instruction level simulators consists of either synthetic test data, which may be stochastically generated, or actual program code, or traces of instructions or memory accesses taken from existing machines. The latter is traditionally referred to as trace-driven simulation. To use a trace-driven simulator the appropriate traces must first be available, which may not be the case if the system to be simulated uses novel instructions for example. A number of systems to produce multiprocessor traces have been developed [80, 4, 86, 87]. An example is PSIMUL which is a simulation tool developed in conjunction with the RP3 project [87]. PSIMUL simulates the execution of a shared memory machine using instruction traces collected from the execution of parallel applications on a uniprocessor. The memory reference traces generated by PSIMUL have been used to analyse memory reference behaviour [88], to drive multiprocessor and network simulations [89], and to analyse multiprocessor cache performance [90].

A number of projects involving the design of a multiprocessor system have developed simulators for performance evaluation. For example the NYU Ultracomputer was first simulated using the Washcloth simulator [91] which ran on a CDC6600. Rather than simulating a processor, the CDC processor itself was used, and programs could be compiled from a high level language and executed

directly. Special instructions were added to implement fetch-and-add. A number of different machine models were simulated, including the paracomputer model, and a model with a multistage network. An extension to the simulator included tag-bits in each memory word, to compare the efficiency of tag-bits to fetch-and-add synchronisation.

#### 2.4.3 Parallel simulation

To increase simulation speed, and allow larger systems to be simulated, parallel simulators have been developed to run on multiprocessor machines. Peacock et al [92] have defined a taxonomy of distributed simulation (which could also be applied to shared memory simulation), in which simulators are divided depending on how simulation time is treated. In an event-driven simulation the simulated system changes state at varying, unpredictable simulation time intervals, whereas in a time-driven simulation the state changes occur at constant time intervals. The simulation is further defined as being tight if each component of the simulation has exactly the same value of simulation time at any instant, or loose if the components may have differing values.

In an event-driven simulation the simulated system changes state in response to events. Because these events can arrive out of order they must first be ordered into the correct sequence. There has been much research on algorithms for improving the efficiency of distributed event-driven simulators [92, 93, 94, 95, 96]. The generality of event-driven simulation systems allows them to be used in simulating a variety of different systems. Parallel logic gate simulators have been implemented using distributed event-driven simulation on transputer networks [97, 98].

Algorithms for time-driven simulation have not received an equivalent amount of attention to those for event-driven simulation. This may be because time-driven simulation is less general, and has been used mostly for bespoke simulations. A shared memory time-driven simulation has been used to simulate a

multistage interconnection network on a shared memory multiprocessor [99, 100]. After each network cycle the processes simulating the network switches are synchronised using a barrier. In a distributed time-driven simulation the simulator modules synchronise using message-passing. This allows more parallelism than a shared memory time-driven simulation using barrier synchronisation, because connected modules synchronise directly by the exchange of packets. The Epp1 simulator described in Chapter 4 uses a loose distributed time-driven simulation methodology.

# 2.5 Example shared memory multiprocessors

A number of MIMD shared memory multiprocessor designs have been referred to and are now described briefly below. These designs are relevant because they include either combining multistage networks and/or instruction interleaved processors. The descriptions are brief and only include gross architectural features such as processor and network configuration, and synchronisation mechanisms.

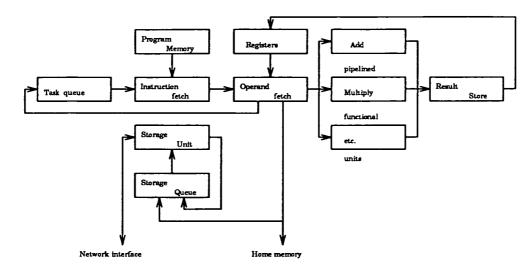

# 2.5.1 Heterogeneous element processor (HEP)

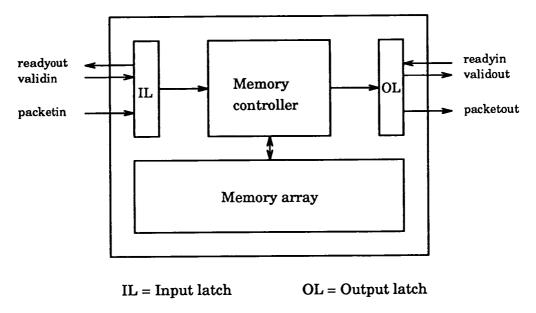

The HEP [101] is a shared memory MIMD multiprocessor machine consisting of up to 16 instruction interleaved processors connected to memories by a packet-switched multistage network. Each processor, shown in Figure 2.9, can support up to 1024 instruction streams, and contains 8 pipelined functional units, 2048 general-purpose registers, 4096 constant registers and 4 Mbytes of local instruction memory. The network is constructed from bi-directional three port switches, and can re-route blocked packets. Each processor also has a direct connection to one of the memories (called its home memory). Synchronisation is through full/empty bits in the memory and processor registers, using blocking load and store instructions.

Figure 2.9: Block diagram of HEP processor

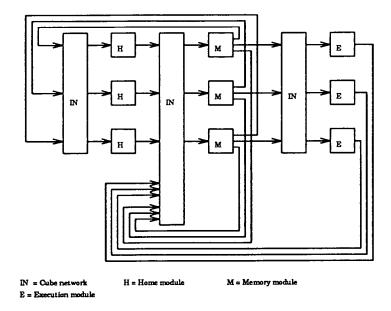

## 2.5.2 Circulating context multiprocessor (CCMP)

The CCMP [20, 102, 63] is an MIMD shared memory multiprocessor design supporting extensive pipelining and multiple instruction streams (processes). The CCMP design shown in Figure 2.10 is split up into home modules, memory modules and execution modules which are connected by buffered singlestage cube networks. The instruction counter and other context of each process is stored in the process's home module. The execution modules contain an instruction decoder and an execution pipeline, and can execute instructions from any process, allowing automatic dynamic load balancing. Instruction execution starts with a process fetching an instruction from memory and then the operands specified in the instruction, then the process is routed to one of the execution modules and the instruction is executed with the result being stored in memory or a register in the process's home module. Synchronisation is based on an atomic swap operation.

# 2.5.3 Columbia homogeneous parallel processor (CHoPP)

The CHoPP-1 [36] is an MIMD shared memory multiprocessor machine which consists of up to 16 processors connected to a "conflict free" memory. The

Figure 2.10: Overview of a closely coupled CCMP configuration

CHoPP-1 design is more closely related to the GEM architecture of Cohn [103], rather than the original CHoPP proposal [104]. The processors have a very long instruction word (VLIW) architecture, with each instruction being 256 bits long. Each processor can store the context of up to 64 processes, and a context switch within the processor takes three cycles. The execution units are not instruction interleaved however. Synchronisation is achieved using 2-bit memory tags and special load and store instructions. Processor registers are also tagged, allowing asynchronous memory accesses. There is also a compare-and-swap instruction and a fetch-and-add instruction, with fetch-and-adds being combined in the network.

#### 2.5.4 BBN Monarch

The Monarch [105] is an MIMD shared memory multiprocessor design consisting of up to 65K processors connected to memories by a synchronous hybrid multistage network. The processors are 64-bit with a RISC architecture, have an instruction cache, and overlap memory access with instruction execution to mask memory latency. The network is non-rectangular (more processors than memory

modules), with multiple paths between each source and destination, and uses a hybrid switching strategy. Memory requests are submitted synchronously by the processors, allowing efficient implementation of read combining. Memory words and processor registers have an 8-bit tag, which is used to implement garbage collection algorithms and interprocess synchronisation.

### 2.5.5 NYU Ultracomputer

The Ultracomputer [106] is an MIMD shared memory multiprocessor design consisting of up to 4K processors connected to memories by a combining omega multistage network. The major contribution has been the development of the fetchand-add synchronisation primitive and network combining mechanisms. Other areas of investigation include synchronisation algorithms using fetch-and-add, operating system issues such as process scheduling and memory management, and application code development. A number of bus-based prototypes of the Ultracomputer have been constructed using off-the-shelf processors, and are used for software development, particularly a parallel UNIX<sup>1</sup> implementation. The VLSI design of combining switches is also in progress. Much of the design has been realised in the RP3 described below.

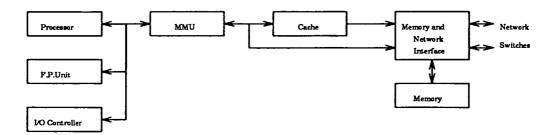

# 2.5.6 IBM Research parallel processor prototype (RP3)

The RP3 [107] is a shared memory MIMD multiprocessor machine consisting of up to 512 processor-memory elements (PME's), connected by two multistage networks. Each PME, shown in Figure 2.11, contains a 32-bit RISC microprocessor, a 32 Kbyte cache and 4 Mbytes of memory. Memory stores are executed asynchronously allowing overlap of memory access and execution. Two networks are provided, one is a high-bandwidth bipolar non-combining banyan network with 128 inputs, and the other a low bandwidth CMOS combining omega network with

<sup>&</sup>lt;sup>1</sup>UNIX is a trademark of AT&T Bell Labs.

Figure 2.11: Block diagram of RP3 processor-memory element

64 inputs. The latter is used exclusively for transmitting fetch-and-add requests. The PME memory has a soft division into local and shared memory, and shared memory addresses are hashed to reduce contention. A number of fetch-and-op functions are provided for interprocess synchronisation.

#### 2.6 Comments

The areas of processor instruction interleaving, packet-switched combining multistage networks, and fetch-and-add synchronisation have all been introduced in this chapter. Existing shared memory multiprocessor designs which include one or more of these features were briefly described. The Epp1 multiprocessor design described in the next chapter combines all these features in a single design.

# Chapter 3

# Epp1 multiprocessor design

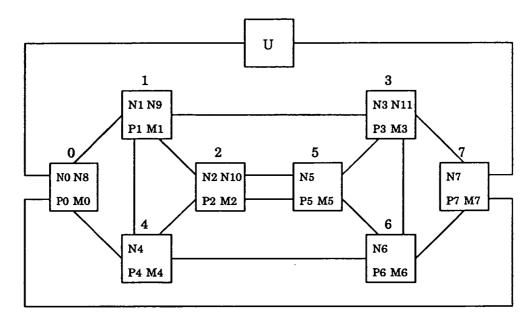

The Epp1 MIMD shared memory multiprocessor design consists of p instruction interleaved RISC processors connected to p memories by a packet-switched combining indirect binary n-cube multistage network constructed from  $\frac{p}{2}\log_2 p$  switches. The processors have no local memory or caches, and there is no virtual memory support. Figure 3.1 shows an 8 processor Epp1 system with 12 network switches and 8 memories.

1

The following sections describe in detail the design of the Epp1 processor, network switch and memory. The processor section includes a description of the processor pipeline, the instruction set, and the results from the simulation of a single processor. The network section includes a description of the combining mechanism, and the results from the simulation of an isolated network.

# 3.1 The processor

The Epp1 processor supports the concurrent execution of a number of interleaved instruction streams (or processes), and should be implementable as a single-chip VLSI pipelined RISC microprocessor (although implementation issues are not discussed here). This design is an extension of Topham's context-flow processor

Figure 3.1: Components of an 8 processor Epp1 system

(Section 2.1.4), and has been deliberately kept simple and idealised. Some of the features required in a real processor implementation, but not necessary for the simulations, have been left out to simplify the processor design. For example floating-point support, supervisor mode and exception/interrupt handling. Some of these issues are discussed in [19, 26]. This section effectively describes the Epp1 processor as it is simulated in the Epp1 simulator.

The processor has a general purpose instruction set with a single 32-bit instruction format. Instruction decoding is hard-wired, and there is no microcode. All instructions complete in one instruction cycle, but require a number of clock cycles. Most instructions have a three address register-to-register format (two sources, one destination), and load/store instructions are used for memory access.

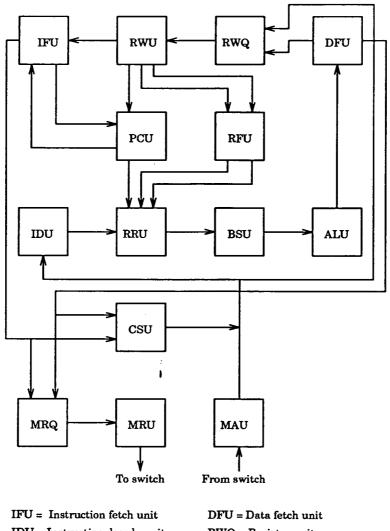

Figure 3.2 shows a block diagram of the processor which consists of an 8

IDU = Instruction decode unit

RRU = Register read unit

BSU = Barrel shift unit

ALU = Arithmetic logic unit

CSU = Context store unit

MRQ = Memory request queue

RWQ = Register write queue

RWU = Register write unit

PCU = Program counter unit

RFU = Register file unit

MRU = Memory request unit

MAU = Memory acknowledge unit

Figure 3.2: Block diagram showing pipeline units of Epp1 processor

stage circular execution pipeline, three register files, two merging queues, and a memory interface. The pipeline stages all have a 1 clock cycle latency and are clocked continuously and simultaneously by the same clock signal. The number of processes that are executed concurrently by the processor depends on the implementation, and on reset all the processes start executing together. In the processor simulations described in this chapter up to 64 processes are executed per processor. Each process has only a single instruction in execution at any one time, and each instruction requires one pass around the execution pipeline to complete. Each stage of the pipeline contains either an instruction from one of the executing processes or is empty (contains a null process).

#### 3.1.1 Process context

Each process has a context in the processor (apart from any other context in main memory associated with the program being executed). This context is shown in Table 3.1 and consists of: a process identification number (pid), a register set, some condition flags, and various operands and control signals used in instruction execution. These are described further below.

Some of the context of a process will move around the pipeline with the process and is called dynamic context, while the rest will be grouped together and only accessed at certain stages, and is called static context [33, 108]. Examples of dynamic context are the *pid*, condition flags, operands and control signals, which move with the process from one pipeline stage to the next. The registers are examples of static context, they are accessed only at certain pipeline stages and it is more area efficient to group them together. Some of the dynamic context, such as the operands and control signals, may exist only for a few pipeline stages. When an instruction is decoded by the instruction decode unit (IDU) a number of control signals are generated, which move from stage to stage with the process. This is called data-stationary control [109, 110] because the control signals move with the data.

| context       | size (bits) | description                   |  |

|---------------|-------------|-------------------------------|--|

| r0-r13        | 32          | general purpose registers     |  |

| pc (r14)      | 32          | program counter               |  |

| sr (r15)      | 32          | status register               |  |

| valid         | 1           | valid process bit             |  |

| pid           | 6           | process number                |  |

| carry         | 1           | carry flag                    |  |

| minus         | 1           | minus flag                    |  |

| overflow      | 1           | overflow flag                 |  |

| zero          | 1           | zero flag                     |  |

| instruction   | 32          | instruction code              |  |

| immediate     | 32          | immediate operand             |  |

| opbsel        | 1           | operand B select              |  |

| read1enable   | 1           | enable register read port 1   |  |

| read1address  | 4           | read port 1 register address  |  |

| read2enable   | 1           | enable register read port 2   |  |

| read2address  | 4           | read port 2 register address  |  |

| write1enable  | , 1         | enable register write port 1  |  |

| write1address | 4           | write port 1 register address |  |

| write2enable  | 1           | enable register write port 2  |  |

| write2address | 4           | write port 2 register address |  |

| opa           | 32          | operand A                     |  |

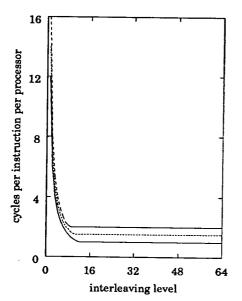

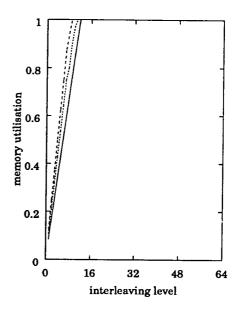

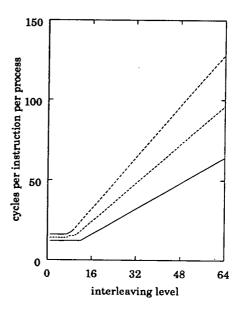

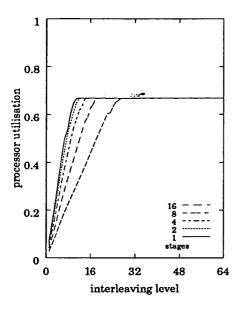

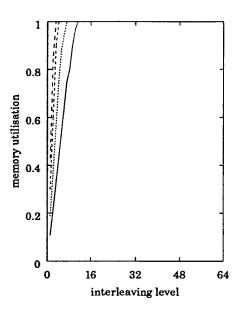

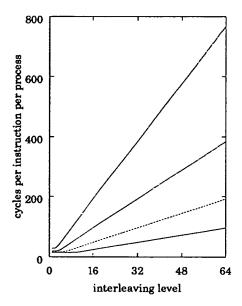

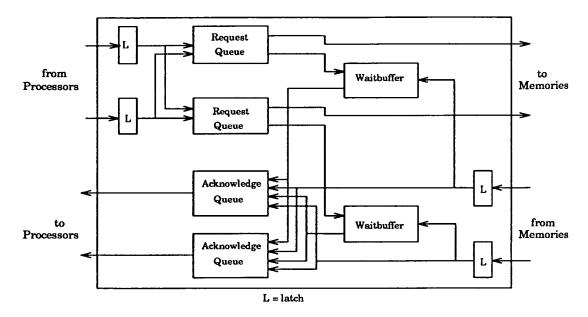

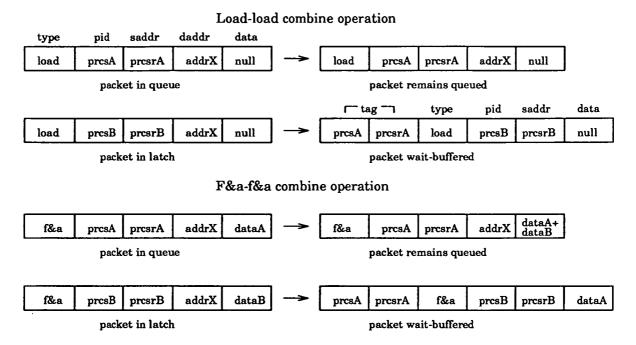

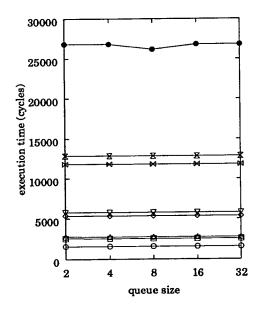

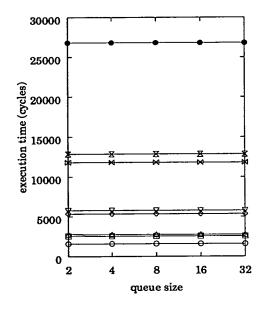

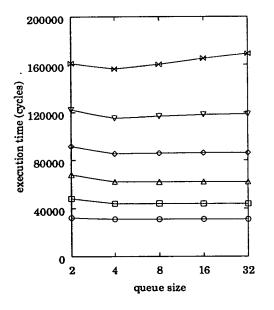

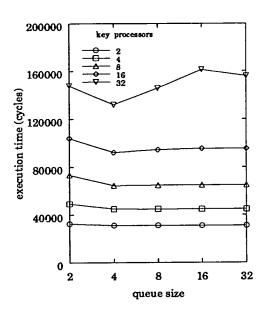

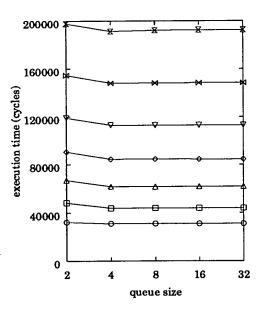

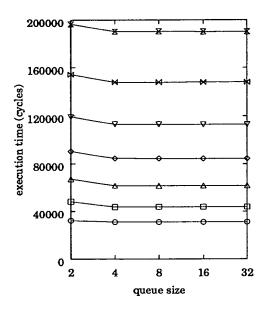

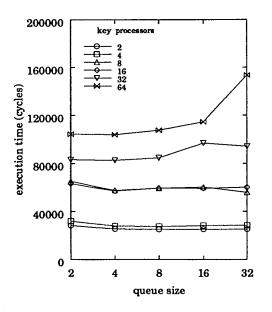

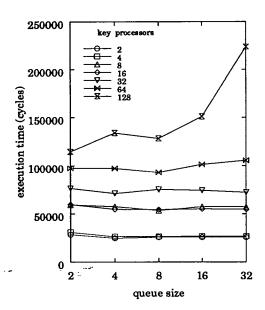

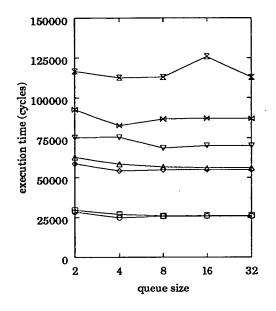

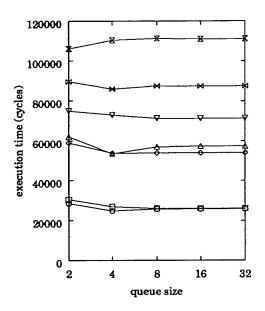

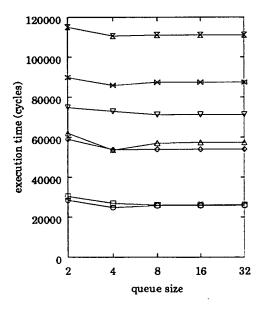

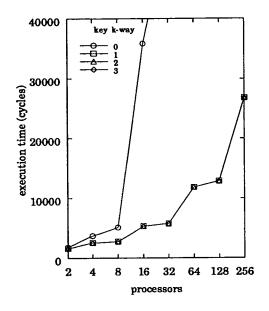

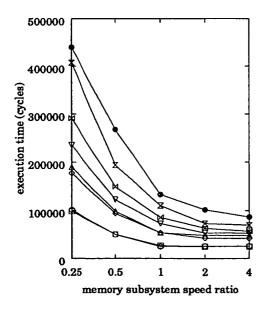

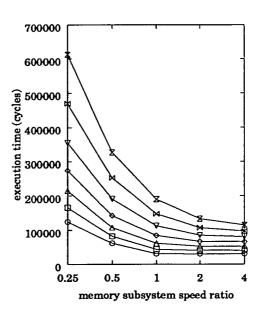

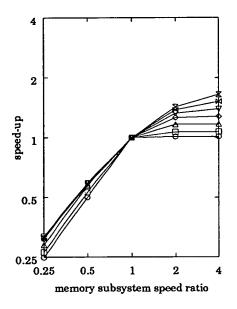

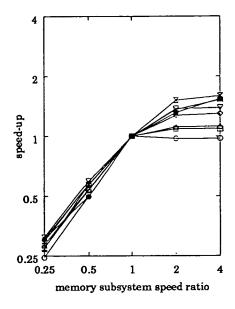

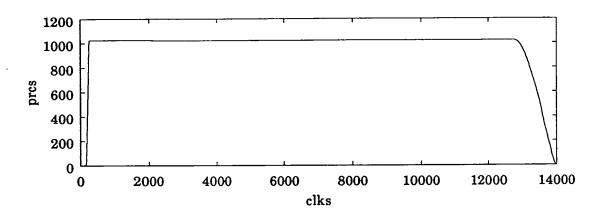

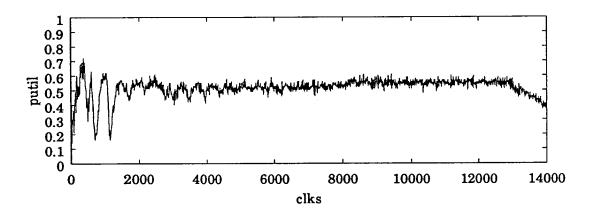

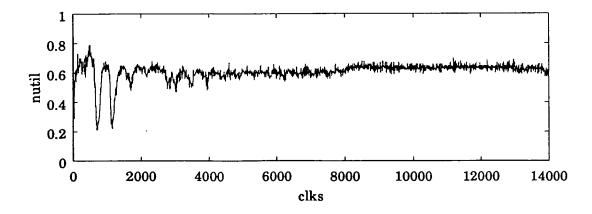

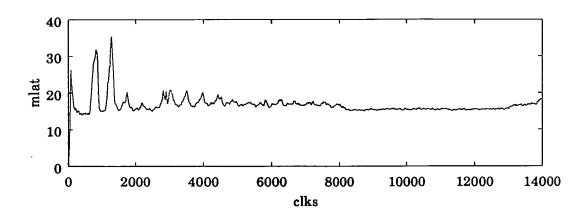

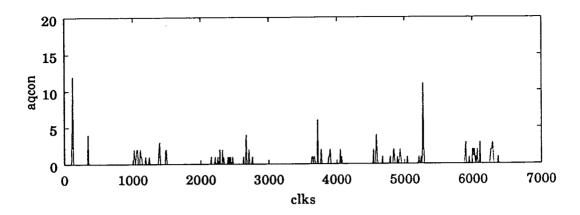

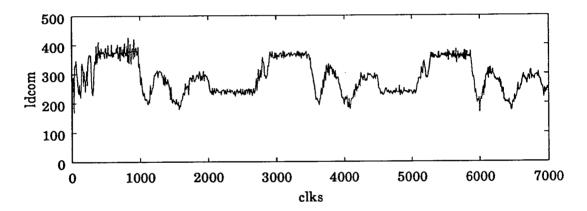

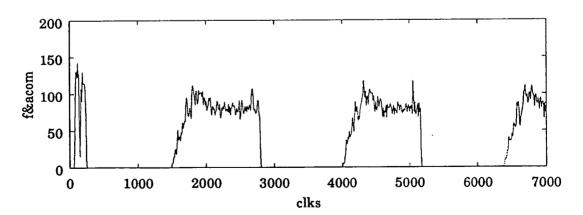

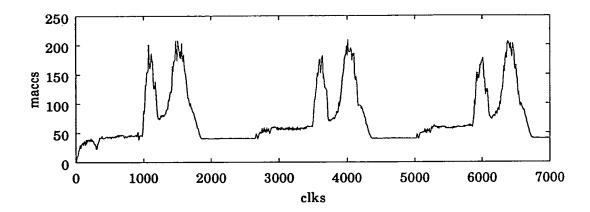

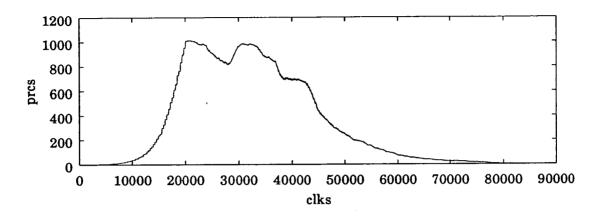

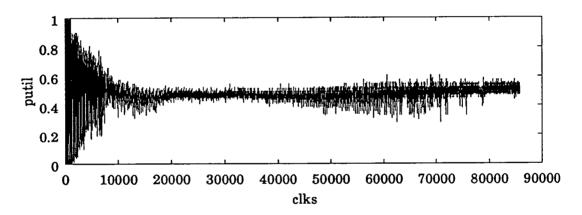

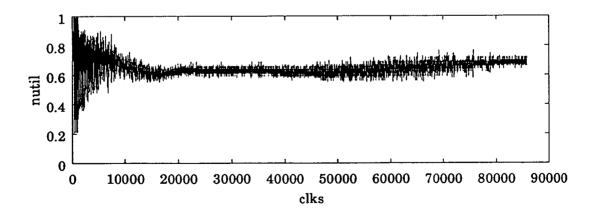

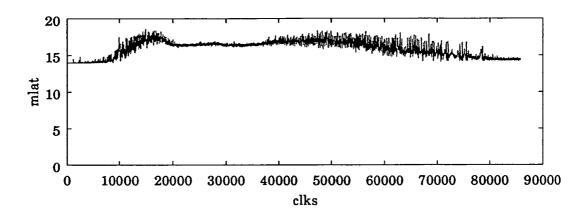

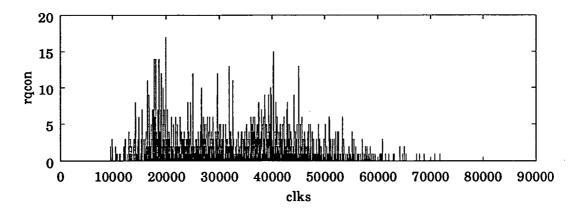

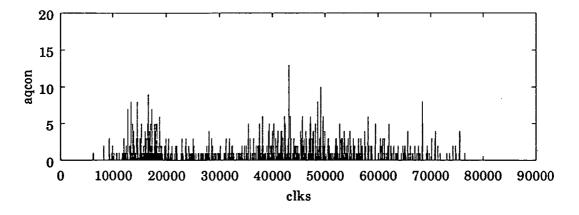

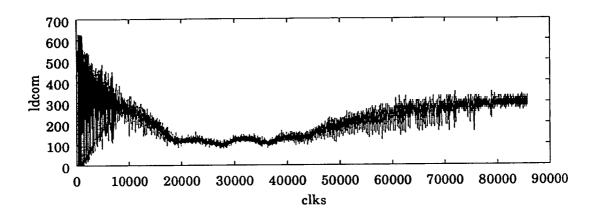

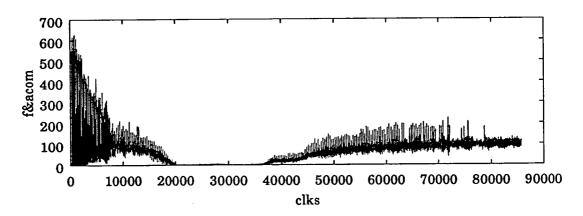

| opb           | 32          | operand B                     |  |