# Developing CMOS compatible ElectroWetting-on-Dielectric (EWOD) microfluidic technology

Yifan Li

A thesis submitted for the degree of Doctor of Philosophy.

The University of Edinburgh.

Oct 2007

#### Abstract

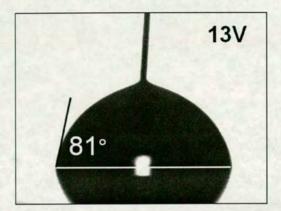

The work presented in this thesis is associated with the development of electrowetting on dielectric (EWOD) technology. One of the main issues of concern was robustly driving droplet movement using low voltage without device malfunction caused by poor dielectric quality. In this work, anodic  $Ta_2O_5$  dielectric, an alternative insulator with a high  $\kappa$  (8 to 25) was used to fabricate low voltage EWOD systems. The uniform and pinhole-free layer has a surface roughness of a few angstroms, enabling an ultra thin Amorphous Fluoropolymer (aFP) layer to be employed to reduce the EWOD driving voltage to 13V. The result shows that, when the  $\kappa$  reaches a certain level, a smooth insulating surface and a thin layer of aFP is more important than a higher value of the dielectric constant in achieving low voltage EWOD droplet maniulation.

Further achievements of this work is the integration of an active EWOD device with CMOS technology. One of the motivations behind this approach is based upon the desire to increase the number of control electrodes, requiring the implementation of on-chip microelectronic line-column drivers. Increasing the number of electrodes is attractive as it provides the opportunity to finely adjust droplet size, and also increases the number of droplets that can be moved simultaneously. Moreover, the integration can provide on chip sensing, which is disirable in Lab-on-a-chip applications. The tradeoffs associated with minimising the drive voltage while keeping the postprocess simple and low cost are assessed. Taking issues into account, the first active EWOD device was successfully fabricated and used to demonstrate droplet manipulation.

This thesis also reports two applications related to lab-on-a-chip and microrobotics developed using the above technologies. The capability to expand the system by using low voltage and active EWOD technology is highlighted in discussing future work.

### Acknowledgements

First of all, I would like to thank my supervisors Dr. Les Haworth and Prof. Anthony Walton for their continuous support and encouragement during my Ph.D. study.

I would also like to thank my colleagues who have been working with me in the our group, Cami, Andy, Kin, Ran, Andreas, Alan R., Tom, Rebecca, Petros, Peter E., Hugh, Gerry, Ewan, Kevin, Jon, Stewart, Can, Gerard, Isaac, Enrico, Richard, Alec, Alan G., Peter L., Valerie, Byron, Claire, Ingrid, Ian, Tony S. and all the others I meet everyday in the SMC. And those who left the group, Stefan, Natalie, Martin, Liudi, Louise, Andrew, Jennifer, Madeleine, Jo, all the people here that shared the same coffee room with me.

Also thanks to Dr. Mita Yoshio, Dr. William Parkes, Bruce Rae and Dr. Robert Henderson for their collaborating on the project. Adam Collin, Adam Stokes, Keith Muir, Neil Hutcheon, Peng Li and Alexander Kazantzis for working with and assisting me when doing their undergraduate and master degree projects. Dr. Huamao Lin and Mrs. Huihong Li for bearing me during the two years of flat sharing. Dr. Cheng Zhan for sharing a fruitful life here in Edinburgh. Special thanks to Dr. Yijia Fan for sharing a meatful life with me, the lamb you cooked is the best I have ever tasted. My thanks are also given to Xiaoyan Hou, Yi Jiang, Jieqiong Yang, Yuanyuan Fei, Bing Xia and Shushan Liu for their warmhearted encouragement during my thesis writing.

Last but not least, I would like to thank my family, especially my parents for their 26 years of support.

# Contents

|   |       | Declaration of originality iii                             |

|---|-------|------------------------------------------------------------|

|   |       | Acknowledgements iv                                        |

|   |       | Contents                                                   |

|   |       | List of figures                                            |

|   |       | List of tables                                             |

|   |       | Acronyms and abbreviations xv                              |

|   |       |                                                            |

| 1 | Intro | duction 1                                                  |

|   | 1.1   | Introduction                                               |

|   | 1.2   | MEMS, microfluidics and CMOS                               |

|   | 1.3   | Motivation                                                 |

|   | 1.4   | Project objectives                                         |

|   | 1.5   | Thesis content summary and layout                          |

|   |       | roWetting-On-Dielectrics - Theory and Application 6        |

| 2 |       | to retend on Dielectrics Incorp and Pr                     |

|   | 2.1   | Mampatating riquid in dropret form                         |

|   |       | 2.1.1 Dielectrophoresis (DEP)                              |

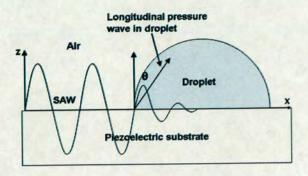

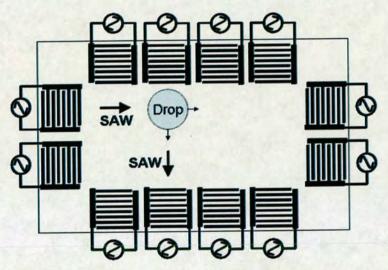

|   |       | 2.1.2 Surface reconsite wave (Sixty)                       |

|   | 2.2   | Electro-Wetting on Dielectrics (EWOD)                      |

|   |       | 2.2.1 Surface tension and system scaling                   |

|   |       | 2.2.2 Contact angle and surface tension                    |

|   |       | 2.2.3 Young-Lippmann equation                              |

|   |       | 2.2.4 Electro-Wetting on Dielectrics (EWOD)                |

|   |       | 2.2.5 Droplet movement by changing contact angle           |

|   |       | 2.2.6 Critical voltage and dielectrics                     |

|   |       | 2.2.7 Contact angle saturation                             |

|   |       | 2.2.8 Other droplet manipulations                          |

|   | 2.3   | EWOD developments and applications                         |

|   |       | 2.3.1 Developments                                         |

|   |       | 2.3.2 Applications                                         |

|   | 2.4   | Conclusion                                                 |

| • |       | ication and Characterisation of Passive EWOD Electrodes 25 |

| 3 | 2     | reation and characterisation of Lassive 2000 22000 2000    |

|   | 3.1   | indoduction 1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.         |

|   | 3.2   |                                                            |

|   |       | 3.2.1 Contact Angle Measurement System                     |

|   |       | 5.2.2 Sjotom for dropret manipulation                      |

|   | 3.3   | Material evaluation for EWOD fabrication                   |

|   |       | 3.3.1 Aluminium electrode EWOD devices                     |

|   |       | 3.3.2 Dielectrics and contact angle measurements           |

|   | 3.4   | Passive single metal layer EWOD device                     |

|   |       | 3.4.1 Device layout                                        |

| 3.4.2 Device fabrication and packaging 3.4.3 Electrode array design 3.5.1 EWOD control system 3.5.5 EWOD control system 3.5.1 Manual control unit 3.5.2 Program control unit 3.5.2 Program control unit 3.6 Summary 4.2 Low Voltage EWOD using Anodic Tantalum Pentoxide 4.1 Introduction 4.2 Low voltage EWOD development 4.3 Low voltage EWOD development 4.3 Ultra thin aFP layer on high- k dielectric 4.3 Ultra thin aFP layer on high- k dielectrics 4.3.1 aFP thicknesses and critical voltages 4.3.2 Insulating dielectric for ultra thin aFP 4.4 Sample fabrication for material evaluation 4.4.1 Ultra thin aFP sin coating 4.5 Measurements 4.6.1 Dynamic contact angle with applied voltage 4.6.2 Contact angle saturation 4.6.3 Droplet manipulation demonstration 5.4 4.6.1 Electric field induced Early Contact Angle Saturation 5.7 4.7 Electric field induced Early Contact Angle Saturation 5.8 4.7.1 Electric fields in Ultra-thin aFP layers 5.2 Auth-level metallisation EWOD array 5.3 Tantalum-aluminium structures for low voltage EWOD-CMOS systems 5.3.1 Structure design and fabrication 5.3.2 Experiment and results 5.4 Conclusions and future work 6.5 Integration of CMOS and EWOD Technologies 6.1 Active EWOD arrays 6.2 Comparative study of active EWOD fabrication processes 6.2.1 Compatibility with CMOS technology 6.2.2 Critical driving voltage concerns 6.2.3 Process flow suggestions 6.2.4 Post-process on an EWOD CMOS backplane chip 6.3.1 Backplane chip design 6.3.2 Post processes 6.3.3 Droplet manipulation test 6.4 Conclusions and future Work 6.5 Conclusions and future Work 6.6 Conclusions and future Work 6.7 Conclusions and future Work 6.6 Conclusions and future Work 6.7 Conclusions and future Work 6.7 Conclusions and future Work 6.8 Conclusions and future Work 6.9 Conclusions and future Work 6.1 Conclusions 7 Conclusions 7 Conclusions 7 Conclusions |   |      |                                                        |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|--------------------------------------------------------|---|

| 3.5 EWOD control system 39 3.5.1 Manual control unit 39 3.5.2 Program control unit 39 3.5.2 Program control unit 39 3.6 Summary 42  4 Low Voltage EWOD using Anodic Tantalum Pentoxide 43 4.1 Introduction 43 4.2 Low voltage EWOD development 43 4.2.1 Anodic Ta <sub>2</sub> O <sub>5</sub> as an insulating dielectric 44 4.3 Ultra thin aFP layer on high- k dielectrics 45 4.3.1 aFP thicknesses and critical voltages 45 4.3.2 Insulating dielectric for ultra thin aFP 47 4.4 Sample fabrication for material evaluation 48 4.4.1 Ultra thin aFP spin coating 49 4.5 Measurements 52 4.6 Results and discussion 53 4.6.1 Dynamic contact angle with applied voltage 53 4.6.2 Contact angle saturation 54 4.6.3 Droplet manipulation demonstration 57 4.7 Electric field induced Early Contact Angle Saturation 58 4.7.1 Electric fields in Ultra-thin aFP layers 58 4.7.2 Early Contact Angle Saturation 59 4.8 Conclusion and discussion 61 5 EWOD Electrode Array 62 5.1 Large EWOD array 62 5.2 Multi-level metallisation EWOD array 63 5.3 Tantalum-aluminium structures for low voltage EWOD-CMOS systems 66 5.3.1 Structure design and fabrication 67 5.3.2 Experiment and results 68 5.4 Conclusions and future work 69 6 Integration of CMOS and EWOD Technologies 71 6.2 Comparative study of active EWOD fabrication processes 72 6.2.1 Compatibility with CMOS technology 73 6.2.2 Critical driving voltage concerns 74 6.2.3 Process flow suggestions 74 6.3 Post-process on an EWOD CMOS backplane chip 75 6.3.1 Backplane chip design 75 6.3.2 Post processes 63.3 Droplet manipulation test 79 6.4 Conclusions and future Work 79                                                                                                                                                                                                                                                                                                                                                                                                       |   |      | 5.4.2 Device faorication and packaging                 |   |

| 3.5.1 Manual control unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |      | 5.4.5 Electrode array design                           |   |

| 3.5.2 Program control unit 39 3.6 Summary 42  4 Low Voltage EWOD using Anodic Tantalum Pentoxide 4.1 Introduction 43 4.2 Low voltage EWOD development 43 4.2.1 Anodic Ta <sub>2</sub> O <sub>5</sub> as an insulating dielectric 44 4.3 Ultra thin aFP layer on high-κ dielectrics 45 4.3.1 aFP thicknesses and critical voltages 45 4.3.2 Insulating dielectric for ultra thin aFP 47 4.4 Sample fabrication for material evaluation 48 4.4.1 Ultra thin aFP spin coating 49 4.5 Measurements 52 4.6 Results and discussion 53 4.6.1 Dynamic contact angle with applied voltage 53 4.6.2 Contact angle saturation 54 4.7 Electric field induced Early Contact Angle Saturation 57 4.7 Electric fields in Ultra-thin aFP layers 58 4.7.2 Early Contact Angle Saturation 59 4.8 Conclusion and discussion 61  5 EWOD Electrode Array 62 5.1 Large EWOD arrays 62 5.2 Multi-level metallisation EWOD array 63 5.3 Tantalum-aluminium structures for low voltage EWOD-CMOS systems 66 5.3.1 Structure design and fabrication 67 5.3.2 Experiment and results 68 5.4 Conclusions and future work 69  6 Integration of CMOS and EWOD Technologies 71 6.1 Active EWOD arrays 72 6.2 Comparative study of active EWOD fabrication processes 72 6.2.1 Compatibility with CMOS technology 73 6.2.2 Critical driving voltage concerns 74 6.2.3 Process flow suggestions 74 6.2.4 Post-process complexity 75 6.3 Post-process complexity 75 6.3 Post-processes 76 6.3.1 Backplane chip design 75 6.3.2 Post processes 76 6.3.3 Droplet manipulation test 79 6.4 Conclusions and future Work 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 3.5  | EWOD control system                                    |   |

| 3.6       Summary       42         4       Low Voltage EWOD using Anodic Tantalum Pentoxide       43         4.1       Introduction       43         4.2       Low voltage EWOD development       43         4.2.1       Anodic Ta <sub>2</sub> O <sub>2</sub> as an insulating dielectric       44         4.3       Ultra thin aFP layer on high-κ dielectrics       45         4.3.1       afFP thicknesses and critical voltages       45         4.3.2       Insulating dielectric for ultra thin aFP       47         4.4       Sample fabrication for material evaluation       48         4.4.1       Ultra thin aFP spin coating       49         4.5       Measurements       52         4.6       Results and discussion       53         4.6.1       Dynamic contact angle with applied voltage       53         4.6.2       Contact angle saturation       54         4.6.3       Droplet manipulation demonstration       57         4.7       Electric fields in Ultra-thin aFP layers       58         4.7.1       Electric fields in Ultra-thin aFP layers       58         4.7.2       Early Contact Angle Saturation       59         4.8       Conclusion and discussion       61         5       EWOD Electrode Ar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |      | 5.5.1 Wandar Control unit                              |   |

| 4 Low Voltage EWOD using Anodic Tantalum Pentoxide 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |      | 5.5.2 Hogiam control and                               |   |

| 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 3.6  | Summary                                                | 2 |

| 4.1 Introduction       43         4.2 Low voltage EWOD development       43         4.2.1 Anodic Ta <sub>2</sub> O <sub>5</sub> as an insulating dielectric       44         4.3 Ultra thin aFP layer on high-k dielectrics       45         4.3.1 aFP thicknesses and critical voltages       45         4.3.2 Insulating dielectric for ultra thin aFP       47         4.4 Sample fabrication for material evaluation       48         4.4.1 Ultra thin aFP spin coating       49         4.5 Measurements       52         4.6 Results and discussion       53         4.6.1 Dynamic contact angle with applied voltage       53         4.6.2 Contact angle saturation       54         4.6.3 Droplet manipulation demonstration       57         4.7 Electric field induced Early Contact Angle Saturation       58         4.7.1 Electric fields in Ultra-thin aFP layers       58         4.7.2 Early Contact Angle Saturation       59         4.8 Conclusion and discussion       61         5 EWOD Electrode Array       62         5.1 Large EWOD arrays       62         5.2 Multi-level metallisation EWOD array       63         5.3.1 Structure design and fabrication       67         5.3.2 Experiment and results       68         5.4 Conclusions and future work       69     <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4 | Low  | Voltage EWOD using Anodic Tantalum Pentoxide 43        | 3 |

| 4.2. Low voltage EWOD development       43         4.2.1 Anodic Ta <sub>2</sub> O <sub>5</sub> as an insulating dielectric       44         4.3 Ultra thin aFP layer on high-κ dielectrics       45         4.3.1 aFP thicknesses and critical voltages       45         4.3.2 Insulating dielectric for ultra thin aFP       47         4.4 Sample fabrication for material evaluation       48         4.4.1 Ultra thin aFP spin coating       49         4.5 Measurements       52         4.6. Results and discussion       53         4.6.1 Dynamic contact angle with applied voltage       53         4.6.2 Contact angle saturation       54         4.6.3 Droplet manipulation demonstration       57         4.7 Electric field induced Early Contact Angle Saturation       58         4.7.1 Electric fields in Ultra-thin aFP layers       58         4.7.2 Early Contact Angle Saturation       59         4.8 Conclusion and discussion       61         5 EWOD Electrode Array       62         5.1 Large EWOD arrays       62         5.2 Multi-level metallisation EWOD array       63         5.3.1 Structure design and fabrication       67         5.3.2 Experiment and results       68         5.4 Conclusions and future work       69         6 Integration of CMOS and EWOD Technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7 |      |                                                        | 3 |

| 4.2.1 Anodic Ta <sub>2</sub> O <sub>5</sub> as an insulating dielectric       44         4.3 Ultra thin aFP layer on high-κ dielectrics       45         4.3.1 aFP thicknesses and critical voltages       45         4.3.2 Insulating dielectric for ultra thin aFP       47         4.4 Sample fabrication for material evaluation       48         4.4.1 Ultra thin aFP spin coating       49         4.5 Measurements       52         4.6 Results and discussion       53         4.6.1 Dynamic contact angle with applied voltage       53         4.6.2 Contact angle saturation       54         4.6.3 Droplet manipulation demonstration       57         4.7 Electric field induced Early Contact Angle Saturation       58         4.7.1 Electric fields in Ultra-thin aFP layers       58         4.7.2 Early Contact Angle Saturation       59         4.8 Conclusion and discussion       61         5 EWOD Electrode Array       62         5.1 Large EWOD arrays       62         5.2 Multi-level metallisation EWOD array       63         5.3.1 Structure design and fabrication       67         5.3.2 Experiment and results       68         5.4 Conclusions and future work       69         6 Integration of CMOS and EWOD Technologies       71         6.1 Active EWOD arrays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |      |                                                        | 3 |

| 4.3       Ultra thin aFP layer on high-κ dielectrics       45         4.3.1       aFP thicknesses and critical voltages       45         4.3.2       Insulating dielectric for ultra thin aFP       47         4.4       Sample fabrication for material evaluation       48         4.4.1       Ultra thin aFP spin coating       49         4.5       Measurements       52         4.6       Results and discussion       53         4.6.1       Dynamic contact angle with applied voltage       53         4.6.2       Contact angle saturation       54         4.6.3       Droplet manipulation demonstration       57         4.7       Electric field induced Early Contact Angle Saturation       58         4.7.1       Electric fields in Ultra-thin aFP layers       58         4.7.2       Early Contact Angle Saturation       59         4.8       Conclusion and discussion       61         5       EWOD Electrode Array       62         5.1       Large EWOD arrays       62         5.2       Multi-level metallisation EWOD array       63         5.3.1       Structure design and fabrication       67         5.3.2       Experiment and results       68         5.4       Conclusions a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |      |                                                        | 1 |

| 4.3.1 aFP thicknesses and critical voltages       45         4.3.2 Insulating dielectric for ultra thin aFP       47         4.4 Sample fabrication for material evaluation       48         4.4.1 Ultra thin aFP spin coating       49         4.5 Measurements       52         4.6 Results and discussion       53         4.6.1 Dynamic contact angle with applied voltage       53         4.6.2 Contact angle saturation       54         4.6.3 Droplet manipulation demonstration       57         4.7 Electric field induced Early Contact Angle Saturation       58         4.7.1 Electric fields in Ultra-thin aFP layers       58         4.7.2 Early Contact Angle Saturation       59         4.8 Conclusion and discussion       61         5 EWOD Electrode Array       62         5.1 Large EWOD arrays       62         5.2 Multi-level metallisation EWOD array       63         5.3 Tantalum-aluminium structures for low voltage EWOD-CMOS systems       66         5.3.1 Structure design and fabrication       67         5.3.2 Experiment and results       68         5.4 Conclusions and future work       69         6 Integration of CMOS and EWOD Technologies       71         6.1 Active EWOD arrays       71         6.2 Comparative study of active EWOD fabr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 4.3  |                                                        | 5 |

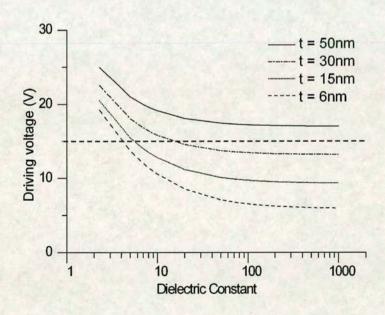

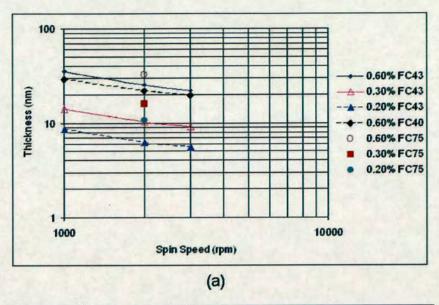

| 4.4 Sample fabrication for material evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      | 4.3.1 aFP thicknesses and critical voltages            |   |

| 4.4       Sample fabrication for material evaluation       48         4.4.1       Ultra thin aFP spin coating       49         4.5       Measurements       52         4.6       Results and discussion       53         4.6.1       Dynamic contact angle with applied voltage       53         4.6.2       Contact angle saturation       54         4.6.3       Droplet manipulation demonstration       57         4.7       Electric field induced Early Contact Angle Saturation       58         4.7.1       Electric fields in Ultra-thin aFP layers       58         4.7.2       Early Contact Angle Saturation       59         4.8       Conclusion and discussion       61         5       EWOD Electrode Array       62         5.1       Large EWOD arrays       62         5.2       Multi-level metallisation EWOD array       63         5.3.1       Structure design and fabrication       67         5.3.2       Experiment and results       68         5.4       Conclusions and future work       69         6       Integration of CMOS and EWOD Technologies       71         6.1       Active EWOD arrays       72         6.2.1       Comparative study of active EWOD fabrication proce                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |      |                                                        | 7 |

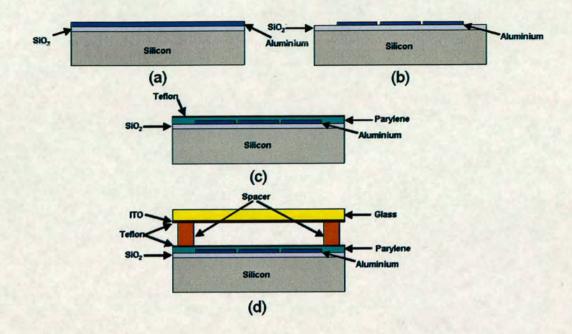

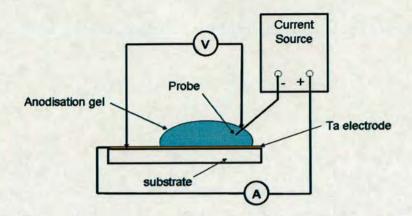

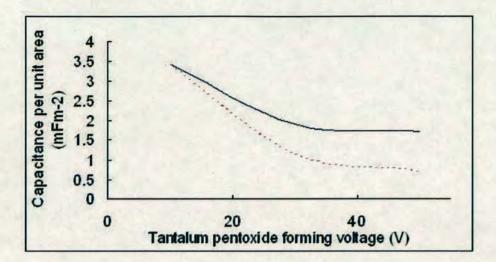

| 4.5 Measurements       52         4.6 Results and discussion       53         4.6.1 Dynamic contact angle with applied voltage       53         4.6.2 Contact angle saturation       54         4.6.3 Droplet manipulation demonstration       57         4.7 Electric field induced Early Contact Angle Saturation       58         4.7.1 Electric fields in Ultra-thin aFP layers       58         4.7.2 Early Contact Angle Saturation       59         4.8 Conclusion and discussion       61         5 EWOD Electrode Array       62         5.1 Large EWOD arrays       62         5.2 Multi-level metallisation EWOD array       63         5.3 Tantalum-aluminium structures for low voltage EWOD-CMOS systems       66         5.3.1 Structure design and fabrication       67         5.3.2 Experiment and results       68         5.4 Conclusions and future work       69         6 Integration of CMOS and EWOD Technologies       71         6.1 Active EWOD arrays       71         6.2.2 Critical driving voltage concerns       72         6.2.1 Compatibility with CMOS technology       73         6.2.2 Critical driving voltage concerns       74         6.2.3 Process flow suggestions       74         6.2.4 Post-process complexity       75 <td></td> <td>4.4</td> <td>Sample fabrication for material evaluation</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 4.4  | Sample fabrication for material evaluation             |   |

| 4.6       Results and discussion       53         4.6.1       Dynamic contact angle with applied voltage       53         4.6.2       Contact angle saturation       54         4.6.3       Droplet manipulation demonstration       57         4.7       Electric field induced Early Contact Angle Saturation       58         4.7.1       Electric fields in Ultra-thin aFP layers       58         4.7.2       Early Contact Angle Saturation       59         4.8       Conclusion and discussion       61         5       EWOD Electrode Array       62         5.1       Large EWOD arrays       62         5.2       Multi-level metallisation EWOD array       63         5.3       Tantalum-aluminium structures for low voltage EWOD-CMOS systems       66         5.3.1       Structure design and fabrication       67         5.3.2       Experiment and results       68         5.4       Conclusions and future work       69         6       Integration of CMOS and EWOD Technologies       71         6.1       Active EWOD arrays       71         6.2       Comparative study of active EWOD fabrication processes       72         6.2.1       Comparative study of active EWOD fabrication processes       72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |      | 4.4.1 Olda dilli al 1 Spili codding                    |   |

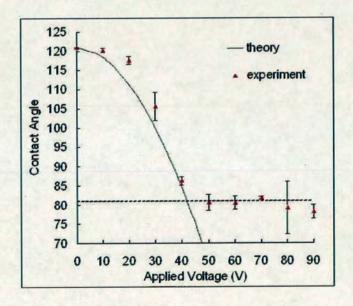

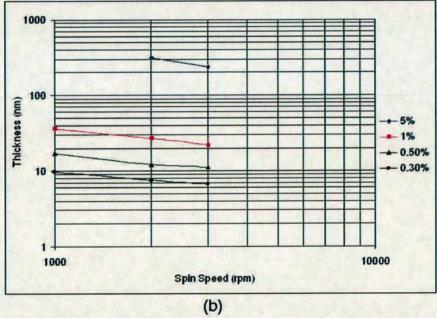

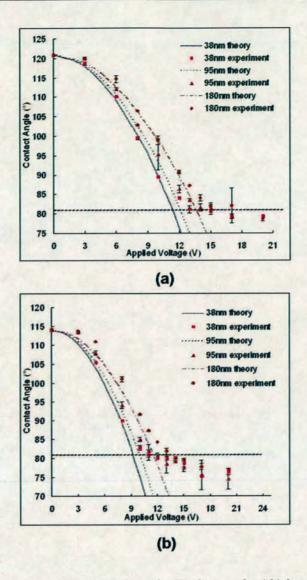

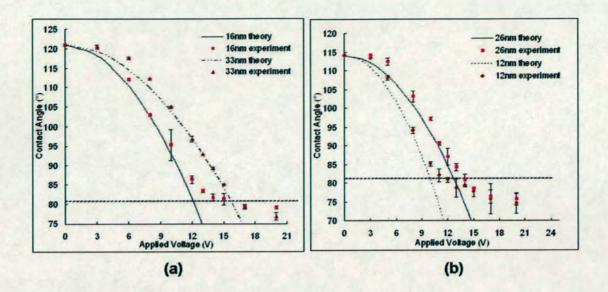

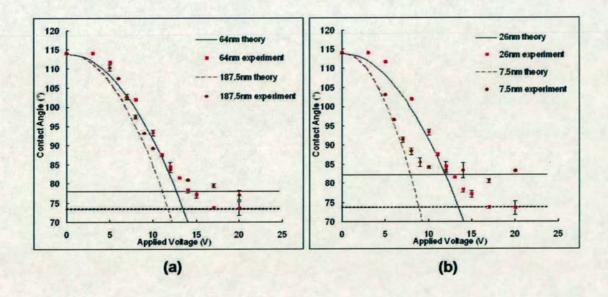

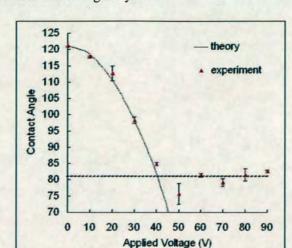

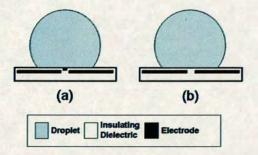

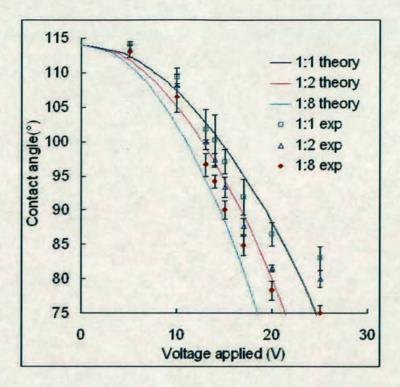

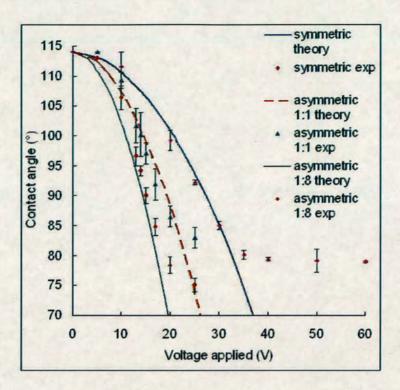

| 4.6.1 Dynamic contact angle with applied voltage       53         4.6.2 Contact angle saturation       54         4.6.3 Droplet manipulation demonstration       57         4.7 Electric field induced Early Contact Angle Saturation       58         4.7.1 Electric fields in Ultra-thin aFP layers       58         4.7.2 Early Contact Angle Saturation       59         4.8 Conclusion and discussion       61         5 EWOD Electrode Array       62         5.1 Large EWOD arrays       62         5.2 Multi-level metallisation EWOD array       63         5.3 Tantalum-aluminium structures for low voltage EWOD-CMOS systems       66         5.3.1 Structure design and fabrication       67         5.3.2 Experiment and results       68         5.4 Conclusions and future work       69         6 Integration of CMOS and EWOD Technologies       71         6.1 Active EWOD arrays       71         6.2 Comparative study of active EWOD fabrication processes       72         6.2.1 Compatibility with CMOS technology       73         6.2.2 Critical driving voltage concerns       74         6.2.3 Process flow suggestions       74         6.2.4 Post-process complexity       75         6.3.1 Backplane chip design       75         6.3.2 Post processes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 4.5  | Wicasurements                                          |   |

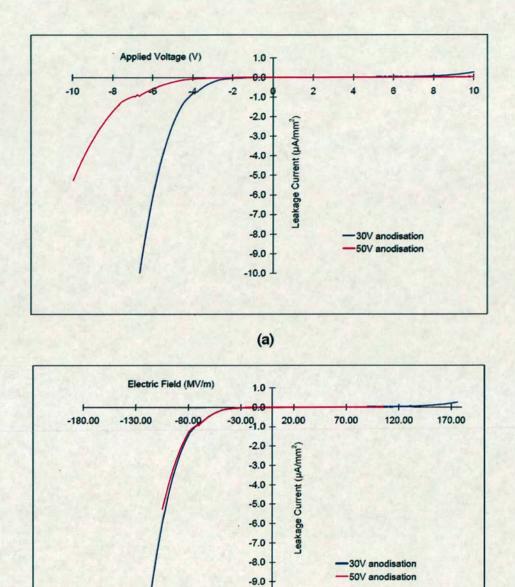

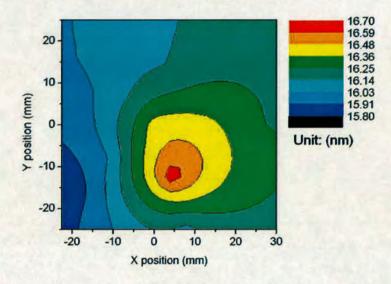

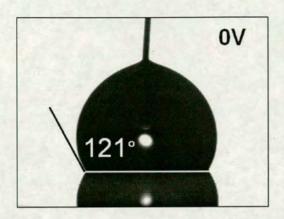

| 4.6.2 Contact angle saturation 54 4.6.3 Droplet manipulation demonstration 57 4.7 Electric field induced Early Contact Angle Saturation 58 4.7.1 Electric fields in Ultra-thin aFP layers 58 4.7.2 Early Contact Angle Saturation 59 4.8 Conclusion and discussion 61  5 EWOD Electrode Array 62 5.1 Large EWOD arrays 62 5.2 Multi-level metallisation EWOD array 63 5.3 Tantalum-aluminium structures for low voltage EWOD-CMOS systems 66 5.3.1 Structure design and fabrication 67 5.3.2 Experiment and results 68 5.4 Conclusions and future work 69  6 Integration of CMOS and EWOD Technologies 71 6.1 Active EWOD arrays 71 6.2 Comparative study of active EWOD fabrication processes 72 6.2.1 Compatibility with CMOS technology 73 6.2.2 Critical driving voltage concerns 74 6.2.3 Process flow suggestions 74 6.2.4 Post-process complexity 75 6.3 Post-process on an EWOD CMOS backplane chip 75 6.3.1 Backplane chip design 75 6.3.2 Post processes 76 6.3.3 Droplet manipulation test 78 6.4 Conclusions and future Work 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 4.6  | Results and discussion                                 |   |

| 4.6.3 Droplet manipulation demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      | 4.0.1 Dynamic contact ungle with applied total         |   |

| 4.7 Electric field induced Early Contact Angle Saturation       58         4.7.1 Electric fields in Ultra-thin aFP layers       58         4.7.2 Early Contact Angle Saturation       59         4.8 Conclusion and discussion       61         5 EWOD Electrode Array       62         5.1 Large EWOD arrays       62         5.2 Multi-level metallisation EWOD array       63         5.3 Tantalum-aluminium structures for low voltage EWOD-CMOS systems       66         5.3.1 Structure design and fabrication       67         5.3.2 Experiment and results       68         5.4 Conclusions and future work       69         6 Integration of CMOS and EWOD Technologies       71         6.1 Active EWOD arrays       71         6.2 Comparative study of active EWOD fabrication processes       72         6.2.1 Compatibility with CMOS technology       73         6.2.2 Critical driving voltage concerns       74         6.2.3 Process flow suggestions       74         6.2.4 Post-process complexity       75         6.3 Post-process on an EWOD CMOS backplane chip       75         6.3.1 Backplane chip design       75         6.3.2 Post processes       76         6.3.3 Droplet manipulation test       78         6.4 Conclusions and future Work       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      | 4.0.2 Contact angle saturation                         |   |

| 4.7.1 Electric fields in Ultra-thin aFP layers       58         4.7.2 Early Contact Angle Saturation       59         4.8 Conclusion and discussion       61         5 EWOD Electrode Array       62         5.1 Large EWOD arrays       62         5.2 Multi-level metallisation EWOD array       63         5.3 Tantalum-aluminium structures for low voltage EWOD-CMOS systems       66         5.3.1 Structure design and fabrication       67         5.3.2 Experiment and results       68         5.4 Conclusions and future work       69         6 Integration of CMOS and EWOD Technologies       71         6.1 Active EWOD arrays       71         6.2 Comparative study of active EWOD fabrication processes       72         6.2.1 Compatibility with CMOS technology       73         6.2.2 Critical driving voltage concerns       74         6.2.3 Process flow suggestions       74         6.2.4 Post-process complexity       75         6.3 Post-process on an EWOD CMOS backplane chip       75         6.3.1 Backplane chip design       75         6.3.2 Post processes       76         6.3.3 Droplet manipulation test       78         6.4 Conclusions and future Work       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      | 4.0.5 Diopict mampatation demonstration 1.1.1.         |   |

| 4.7.2 Early Contact Angle Saturation       59         4.8 Conclusion and discussion       61         5 EWOD Electrode Array       62         5.1 Large EWOD arrays       62         5.2 Multi-level metallisation EWOD array       63         5.3 Tantalum-aluminium structures for low voltage EWOD-CMOS systems       66         5.3.1 Structure design and fabrication       67         5.3.2 Experiment and results       68         5.4 Conclusions and future work       69         6 Integration of CMOS and EWOD Technologies       71         6.1 Active EWOD arrays       71         6.2 Comparative study of active EWOD fabrication processes       72         6.2.1 Compatibility with CMOS technology       73         6.2.2 Critical driving voltage concerns       74         6.2.3 Process flow suggestions       74         6.2.4 Post-process complexity       75         6.3 Post-process on an EWOD CMOS backplane chip       75         6.3.1 Backplane chip design       75         6.3.2 Post processes       76         6.3.3 Droplet manipulation test       78         6.4 Conclusions and future Work       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 4.7  | Electric field induced Early Contact i ingle Saturday  |   |

| 4.8 Conclusion and discussion       61         5 EWOD Electrode Array       62         5.1 Large EWOD arrays       62         5.2 Multi-level metallisation EWOD array       63         5.3 Tantalum-aluminium structures for low voltage EWOD-CMOS systems       66         5.3.1 Structure design and fabrication       67         5.3.2 Experiment and results       68         5.4 Conclusions and future work       69         6 Integration of CMOS and EWOD Technologies       71         6.1 Active EWOD arrays       71         6.2 Comparative study of active EWOD fabrication processes       72         6.2.1 Compatibility with CMOS technology       73         6.2.2 Critical driving voltage concerns       74         6.2.3 Process flow suggestions       74         6.2.4 Post-process complexity       75         6.3 Post-process on an EWOD CMOS backplane chip       75         6.3.1 Backplane chip design       75         6.3.2 Post processes       76         6.3.3 Droplet manipulation test       78         6.4 Conclusions and future Work       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      | T./.1 Electric fields in Citita tilli al 2 lajors      |   |

| 5         EWOD Electrode Array         62           5.1         Large EWOD arrays         62           5.2         Multi-level metallisation EWOD array         63           5.3         Tantalum-aluminium structures for low voltage EWOD-CMOS systems         66           5.3.1         Structure design and fabrication         67           5.3.2         Experiment and results         68           5.4         Conclusions and future work         69           6         Integration of CMOS and EWOD Technologies         71           6.1         Active EWOD arrays         71           6.2         Comparative study of active EWOD fabrication processes         72           6.2.1         Compatibility with CMOS technology         73           6.2.2         Critical driving voltage concerns         74           6.2.3         Process flow suggestions         74           6.2.4         Post-process complexity         75           6.3.1         Backplane chip design         75           6.3.2         Post processes         76           6.3.3         Droplet manipulation test         78           6.4         Conclusions and future Work         79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      | 4.7.2 Early Contact ringle Saturation                  |   |

| 5.1 Large EWOD arrays       62         5.2 Multi-level metallisation EWOD array       63         5.3 Tantalum-aluminium structures for low voltage EWOD-CMOS systems       66         5.3.1 Structure design and fabrication       67         5.3.2 Experiment and results       68         5.4 Conclusions and future work       69         6 Integration of CMOS and EWOD Technologies       71         6.1 Active EWOD arrays       71         6.2 Comparative study of active EWOD fabrication processes       72         6.2.1 Compatibility with CMOS technology       73         6.2.2 Critical driving voltage concerns       74         6.2.3 Process flow suggestions       74         6.2.4 Post-process complexity       75         6.3 Post-process on an EWOD CMOS backplane chip       75         6.3.1 Backplane chip design       75         6.3.2 Post processes       76         6.3.3 Droplet manipulation test       78         6.4 Conclusions and future Work       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 4.8  | Conclusion and discussion                              | 1 |

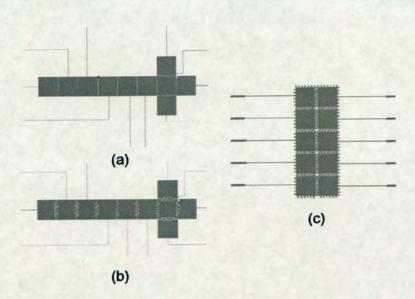

| 5.1       Large EWOD arrays       62         5.2       Multi-level metallisation EWOD array       63         5.3       Tantalum-aluminium structures for low voltage EWOD-CMOS systems       66         5.3.1       Structure design and fabrication       67         5.3.2       Experiment and results       68         5.4       Conclusions and future work       69         6       Integration of CMOS and EWOD Technologies       71         6.1       Active EWOD arrays       71         6.2       Comparative study of active EWOD fabrication processes       72         6.2.1       Compatibility with CMOS technology       73         6.2.2       Critical driving voltage concerns       74         6.2.3       Process flow suggestions       74         6.2.4       Post-process complexity       75         6.3       Post-process on an EWOD CMOS backplane chip       75         6.3.1       Backplane chip design       75         6.3.2       Post processes       76         6.3.3       Droplet manipulation test       78         6.4       Conclusions and future Work       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5 | EW   | OD Electione Array                                     | 2 |

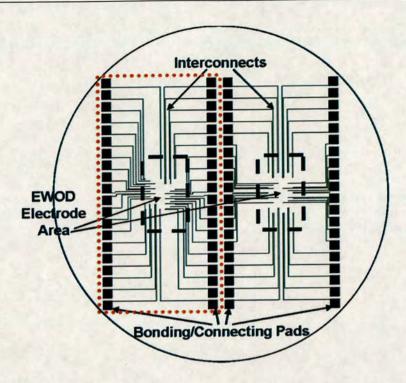

| 5.2       Multi-level metallisation EWOD array       63         5.3       Tantalum-aluminium structures for low voltage EWOD-CMOS systems       66         5.3.1       Structure design and fabrication       67         5.3.2       Experiment and results       68         5.4       Conclusions and future work       69         6       Integration of CMOS and EWOD Technologies       71         6.1       Active EWOD arrays       71         6.2       Comparative study of active EWOD fabrication processes       72         6.2.1       Compatibility with CMOS technology       73         6.2.2       Critical driving voltage concerns       74         6.2.3       Process flow suggestions       74         6.2.4       Post-process complexity       75         6.3       Post-processes on an EWOD CMOS backplane chip       75         6.3.1       Backplane chip design       75         6.3.2       Post processes       76         6.3.3       Droplet manipulation test       78         6.4       Conclusions and future Work       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 5.1  | Large EWOD arrays                                      |   |

| 5.3.1 Structure design and fabrication       67         5.3.2 Experiment and results       68         5.4 Conclusions and future work       69         6 Integration of CMOS and EWOD Technologies       71         6.1 Active EWOD arrays       71         6.2 Comparative study of active EWOD fabrication processes       72         6.2.1 Compatibility with CMOS technology       73         6.2.2 Critical driving voltage concerns       74         6.2.3 Process flow suggestions       74         6.2.4 Post-process complexity       75         6.3 Post-process on an EWOD CMOS backplane chip       75         6.3.1 Backplane chip design       75         6.3.2 Post processes       76         6.3.3 Droplet manipulation test       78         6.4 Conclusions and future Work       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 5.2  | Willi-level inclaims at long Birds                     |   |

| 5.3.2 Experiment and results  5.4 Conclusions and future work  68  69  6 Integration of CMOS and EWOD Technologies  6.1 Active EWOD arrays  6.2 Comparative study of active EWOD fabrication processes  6.2.1 Compatibility with CMOS technology  6.2.2 Critical driving voltage concerns  6.2.3 Process flow suggestions  6.2.4 Post-process complexity  6.3 Post-process on an EWOD CMOS backplane chip  6.3.1 Backplane chip design  6.3.2 Post processes  6.3.3 Droplet manipulation test  6.4 Conclusions and future Work  6.5  6.6  6.7  6.7  6.7  6.7  6.8  6.9  6.9  6.9  6.9  6.9  6.9  6.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | 5.3  | Tantalum-aluminum structures for for voltage 2 of      |   |

| 5.4 Conclusions and future work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      | 5.5.1 Structure design and fastication                 |   |

| 6 Integration of CMOS and EWOD Technologies         71           6.1 Active EWOD arrays         71           6.2 Comparative study of active EWOD fabrication processes         72           6.2.1 Compatibility with CMOS technology         73           6.2.2 Critical driving voltage concerns         74           6.2.3 Process flow suggestions         74           6.2.4 Post-process complexity         75           6.3 Post-process on an EWOD CMOS backplane chip         75           6.3.1 Backplane chip design         75           6.3.2 Post processes         76           6.3.3 Droplet manipulation test         78           6.4 Conclusions and future Work         79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      | 5.5.2 Experiment and results                           |   |

| 6.1 Active EWOD arrays       71         6.2 Comparative study of active EWOD fabrication processes       72         6.2.1 Compatibility with CMOS technology       73         6.2.2 Critical driving voltage concerns       74         6.2.3 Process flow suggestions       74         6.2.4 Post-process complexity       75         6.3 Post-process on an EWOD CMOS backplane chip       75         6.3.1 Backplane chip design       75         6.3.2 Post processes       76         6.3.3 Droplet manipulation test       78         6.4 Conclusions and future Work       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 5.4  | Conclusions and future work                            | 9 |

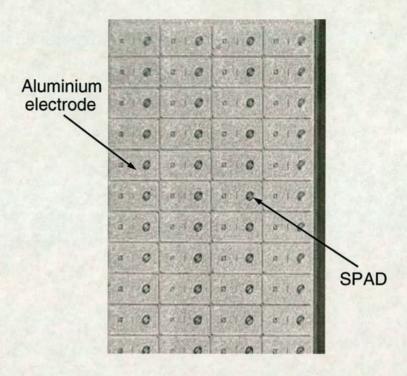

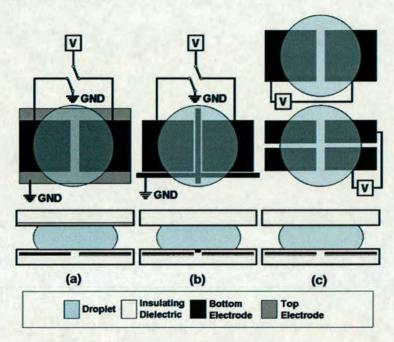

| 6.1 Active EWOD arrays       71         6.2 Comparative study of active EWOD fabrication processes       72         6.2.1 Compatibility with CMOS technology       73         6.2.2 Critical driving voltage concerns       74         6.2.3 Process flow suggestions       74         6.2.4 Post-process complexity       75         6.3 Post-process on an EWOD CMOS backplane chip       75         6.3.1 Backplane chip design       75         6.3.2 Post processes       76         6.3.3 Droplet manipulation test       78         6.4 Conclusions and future Work       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6 | Inte | gration of CMOS and EWOD Technologies 7                | 1 |

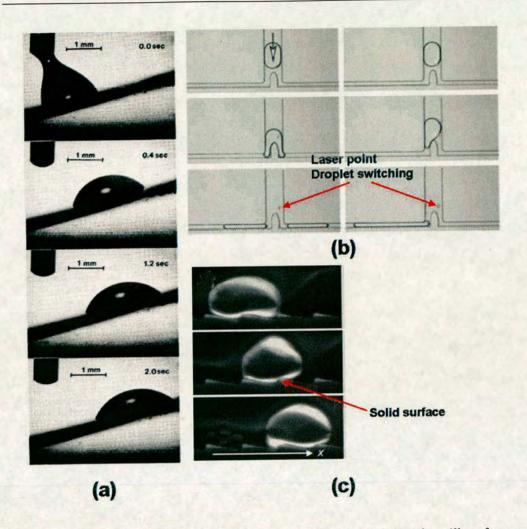

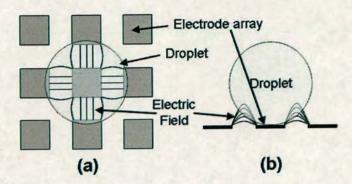

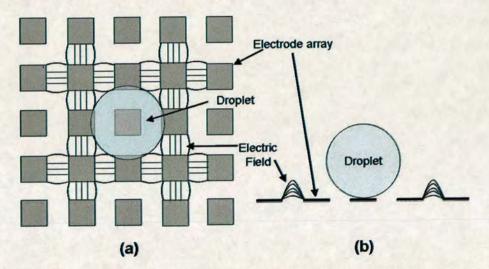

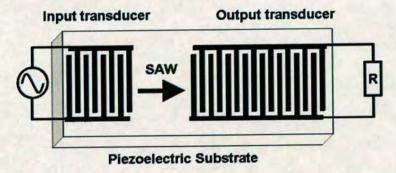

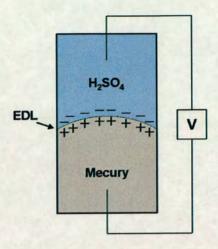

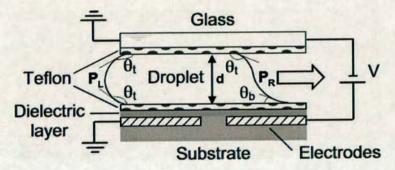

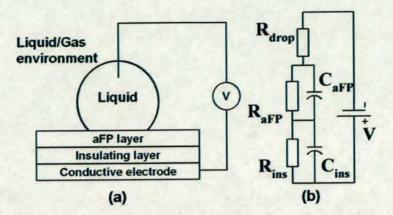

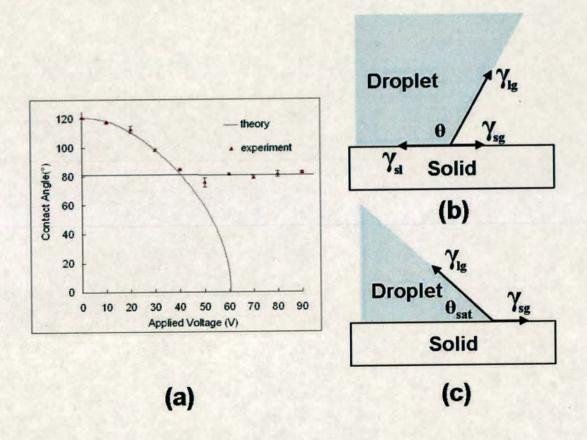

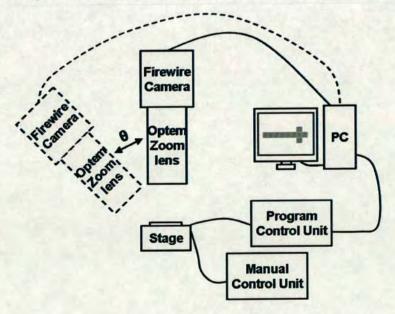

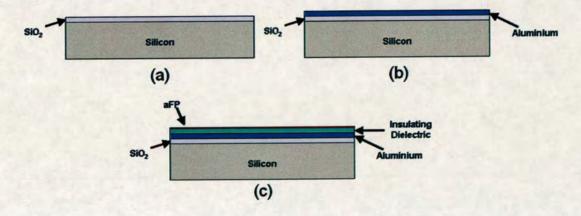

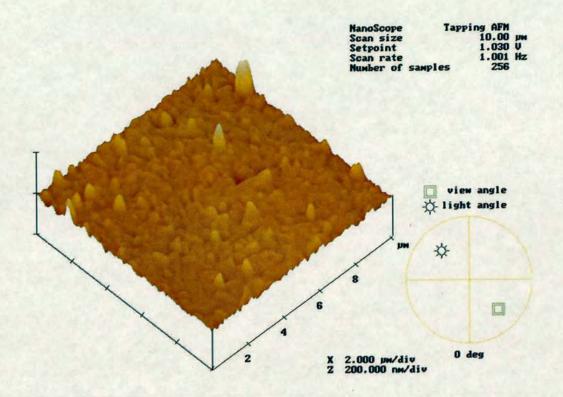

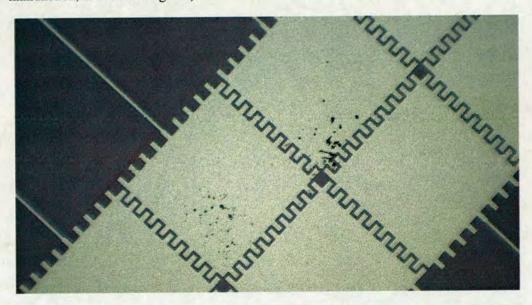

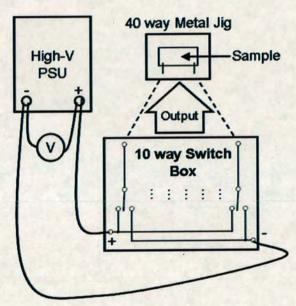

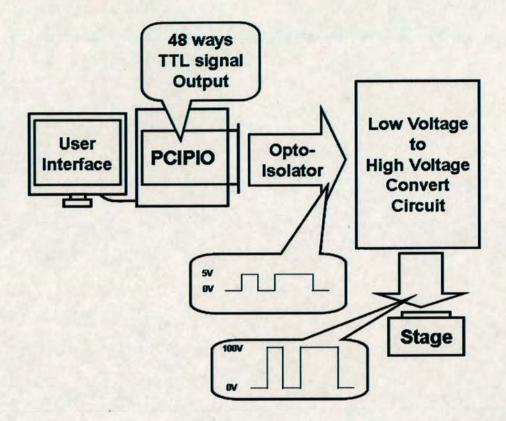

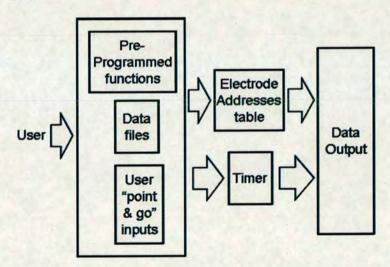

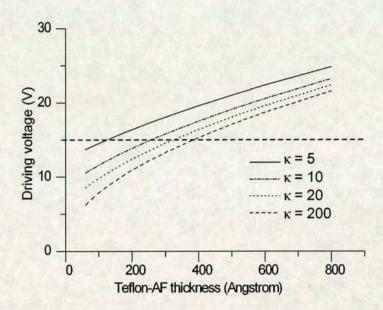

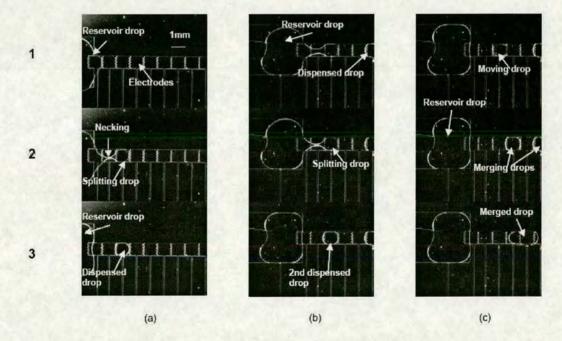

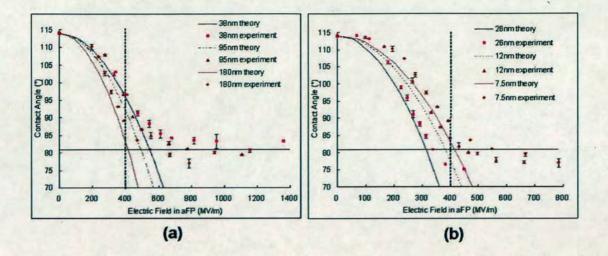

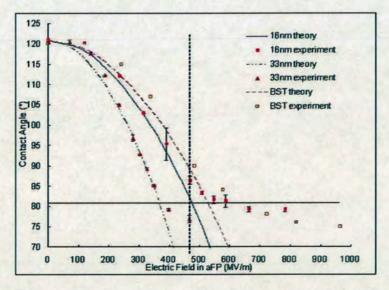

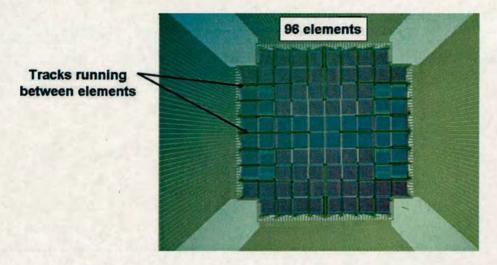

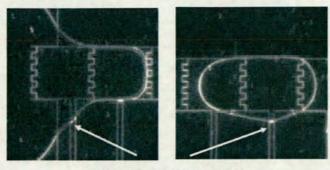

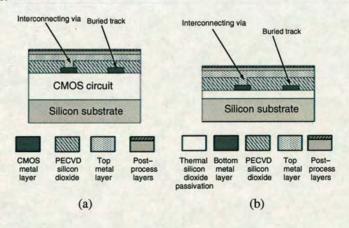

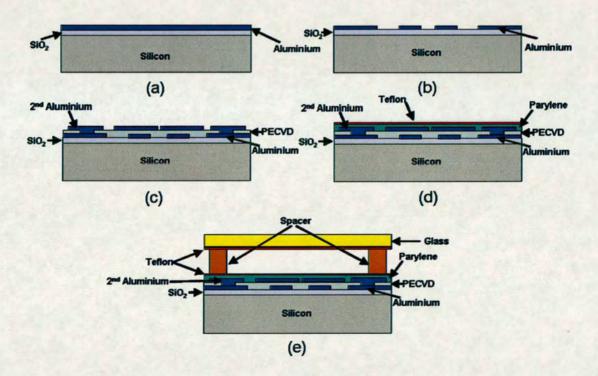

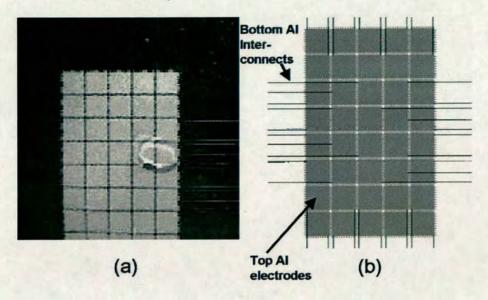

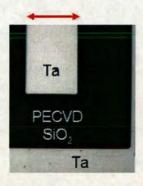

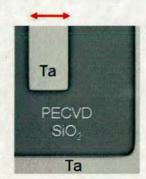

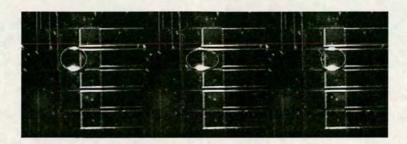

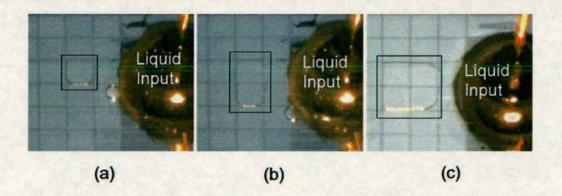

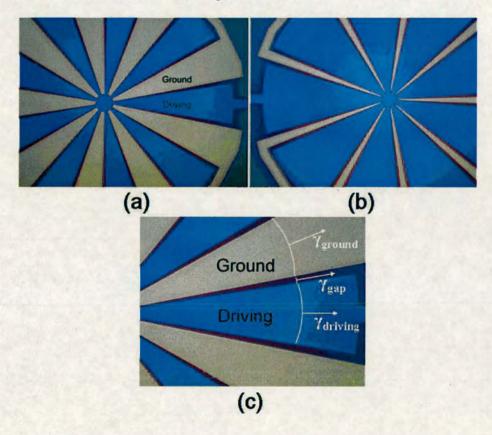

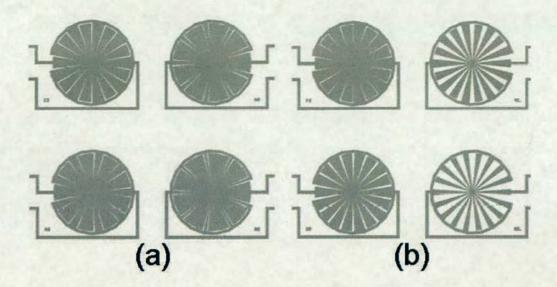

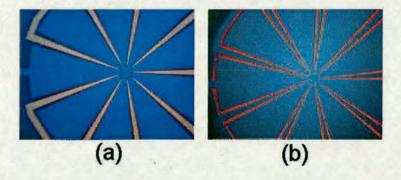

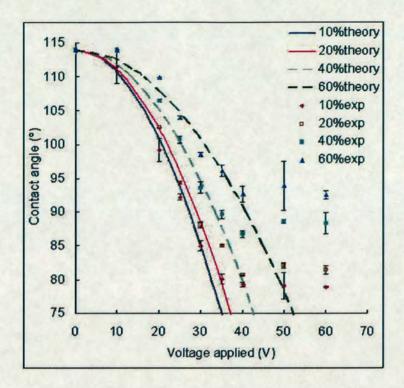

| 6.2 Comparative study of active EWOD fabrication processes       72         6.2.1 Compatibility with CMOS technology       73         6.2.2 Critical driving voltage concerns       74         6.2.3 Process flow suggestions       74         6.2.4 Post-process complexity       75         6.3 Post-process on an EWOD CMOS backplane chip       75         6.3.1 Backplane chip design       75         6.3.2 Post processes       76         6.3.3 Droplet manipulation test       78         6.4 Conclusions and future Work       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |      | Active EWOD arrays                                     | 1 |