## Self-Timed Field Programmable Gate Array Architectures

Robert Payne

Doctor of Philosophy University of Edinburgh 1997

## **Abstract**

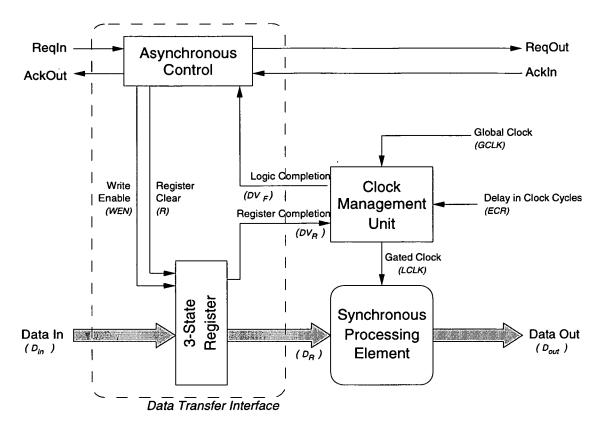

Dynamic hardware systems exploit the in-system reconfigurability of Field Programmable Gate Arrays (FPGAs), but are currently limited by the delay properties of synchronous FPGA architectures. Synchronous circuits are difficult to manipulate dynamically, since this alters their internal delays. The speed-independent properties of self-timed circuits overcome this problem, thus allowing the full benefits of dynamic reconfiguration to be exploited. The general properties of self-timed systems, such as modularity, low power and data dependent delays also provide benefits to less dynamic FPGA systems as well.

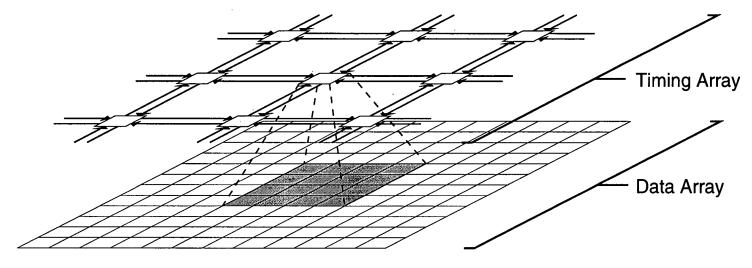

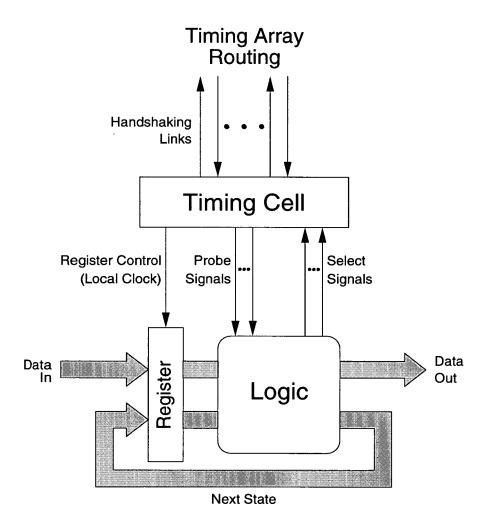

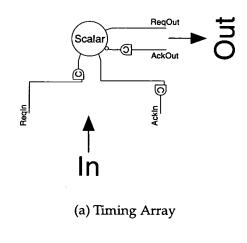

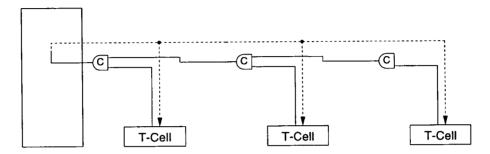

This thesis introduces a model for self-timed FPGA architectures called STACC (Self-Timed Array of Configurable Cells). STACC architectures replace the global clock of an FPGA with an array of timing cells that provide local self-timed control to a region of logic blocks. STACC differs from previous self-timed FPGA architectures in that it does not disrupt the structure of the logic blocks.

The STACC model is used to produced a self-timed version of the Xilinx XC6200 FPGA. Example circuits for the self-timed XC6200 demonstrate the benefits of self-timing for implementing dynamic hardware systems. Evaluation of the architecture shows that the implementation overhead of the timing array is reasonable, and that the self-timed XC6200 has the potential to out-perform the synchronous XC6200 through use of data dependent delays.

## Acknowledgements

I would like to thank Gordon Brebner for his advice, relaxed style of supervision and his patient hyphen-eradication in the drafts. Also, Iain Lindsay for feedback on the electronic engineering aspects of the work. Vinod Rebello and Robert Mullins provided various tips and advice concerning asynchronous circuit design. Thanks to Anne for proof-reading.

Finally, thanks to the various players of badminton and flingers of frisbees, residers in Liberton and brewers of coffee, bakers of cakes and office-mates who kept me as a reasonably well balanced and adjusted person during the course of writing this thesis.

### Declaration

I declare that this thesis was composed by me and that the work contained therein is my own, except where stated otherwise in the text. Parts of the work have previously been presented in the following:

- [i] R.E.Payne. Self-Timed FPGA Systems. In *Proceedings of the 5th International Workshop on Field Programmable Logic and Applications*, LNCS 975, September 1995.

- [ii] R.E.Payne. Asynchronous FPGA Architectures. In *IEE Proceedings on Computers and Digital Techniques, Special Issue on Asynchronous Processors*, September 1996.

- [iii] R.E.Payne. Self-Timed Reconfigurable Elements. In *Proceedings* of the First U.K. Asynchronous Forum, December 1996.

- [iv] R.E.Payne. Run-time Parameterised Circuits for the Xilinx XC6200. To be published in *Proceedings of the 7th International Workshop on Field Programmable Logic and Applications*, September 1997.

## **Table of Contents**

| Chapte | r 1 Introduction                                   | 4  |

|--------|----------------------------------------------------|----|

| 1.1    | Reconfigurability and Self-Timing                  | 4  |

| 1.2    | Thesis Structure                                   | 5  |

| 1.3    | Contributions                                      | 8  |

| Chapte | r 2 Field Programmable Gate Arrays                 | 9  |

| 2.1    | Background                                         | 9  |

| 2.2    | Elements of an FPGA Architecture                   | 10 |

| 2.3    | Function Blocks                                    | 11 |

| 2.4    | Reconfigurable Interconnect                        | 15 |

| 2.5    | Configuration Memory                               | 19 |

| 2.6    | Repetition, Hierarchy and Symmetry                 | 21 |

| 2.7    | Dynamic Hardware Systems                           | 22 |

| 2.8    | Summary                                            | 27 |

| Chapte | er 3 Self-Timed Systems                            | 28 |

| 3.1    | Background                                         | 28 |

| 3.2    | Synchrony, Asynchrony and Self-Timing              | 28 |

| 3.3    | A Comparison of Self-Timed and Synchronous Systems | 30 |

| 3.4    | Self-Timed Communication Protocols                 | 34 |

| 3.5    | Self-Timed Circuit Implementation                  | 38 |

| 3.6    | Current Research                                   | 44 |

| 3.7    | Summary                                            | 46 |

| Chapte | er 4 Self-Timed FPGAs                              | 47 |

| 4.1    | Introduction                                       | 47 |

| 4.2    | Motivation for Self-Timed FPGA Systems             | 47 |

| 4.3    | Self-Timed Dynamic Hardware Systems                | 49 |

| 4.4    | Self-Timed Systems on Current FPGAs                | 52 |

| 45     | Current Asynchronous EPCA Architectures            | 54 |

| 4.6    | Summary                             | 64  |

|--------|-------------------------------------|-----|

| Chapte | r 5 STACC                           | 65  |

| 5.1    | Introduction                        | 65  |

| 5.2    | STACC Design Decisions              | 65  |

| 5.3    | The STACC Model                     | 68  |

| 5.4    | Example Timing Array Configurations | 72  |

| 5.5    | Summary                             | 77  |

| Chapte | r 6 Reconfigurable Elements         | 78  |

| 6.1    | Introduction                        | 78  |

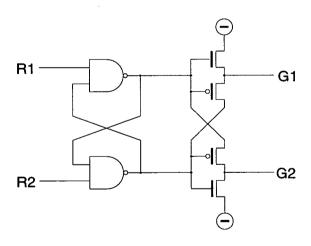

| 6.2    | Reconfigurable C-Muller Gates       | 78  |

| 6.3    | Branch and Merge Elements           | 83  |

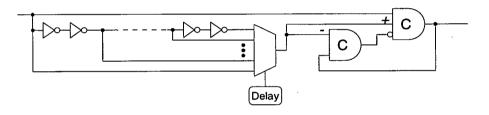

| 6.4    | Delay Elements                      | 88  |

| 6.5    | Summary                             | 93  |

| Chapte | er 7 Timing Cells                   | 94  |

| 7.1    | Introduction                        | 94  |

| 7.2    | Timing Cell Design Decisions        | 95  |

| 7.3    | Two-Phase Timing Cells              | 98  |

| 7.4    | Four-Phase Timing Cells             | 106 |

| 7.5    | Selective Communication Timing Cell | 112 |

| 7.6    | Arbitrating Timing Cell             | 115 |

| 7.7    | Summary                             | 118 |

| Chapte | er 8 Timing Array Routing           | 119 |

| 8.1    | Introduction                        | 119 |

| 8.2    | Transparent Routing Structures      | 120 |

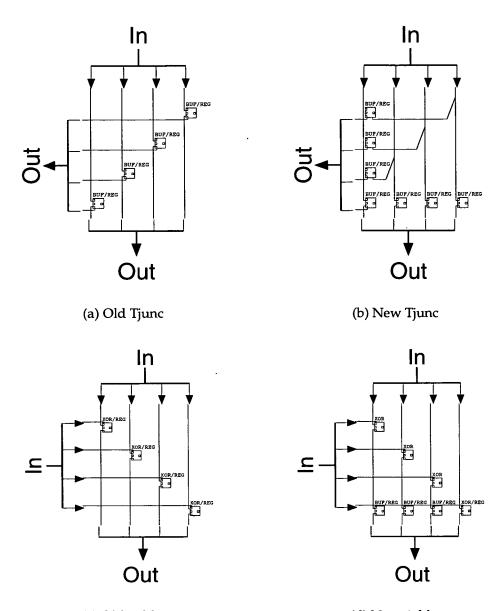

| 8.3    | Routing Handshaking Signals         | 123 |

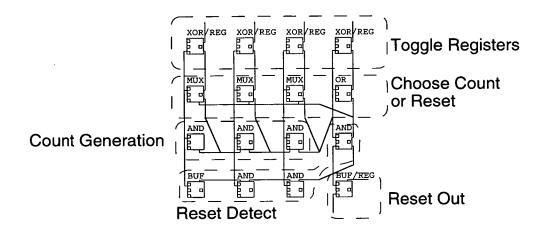

| 8.4    | Distributed C-Muller Gate Routing   | 131 |

| 8.5    | Summary                             | 138 |

| Chapte | er 9 Self-Timing the Xilinx XC6200  | 140 |

| 9.1    | Introduction                        | 140 |

| 9.2    | XC6200 Architecture                 | 141 |

| 9.3    | STACC Architecture Design Process   | 149 |

| 9.4    | Self-Timing the XC6200              | 153 |

| 9.5    | Summary                             | 160 |

| Chapter 10 Circuit Design for the Self-Timed XC6200 |     |  |

|-----------------------------------------------------|-----|--|

| 10.1 Introduction                                   | 162 |  |

| 10.2 Design Tools and Simulation                    | 162 |  |

| 10.3 Example Circuits                               | 165 |  |

| 10.4 Design Techniques and Experience               | 192 |  |

| 10.5 Summary                                        | 200 |  |

| Chapter 11 Self-Timed XC6200 Evaluation             | 202 |  |

| 11.1 Introduction                                   | 202 |  |

| 11.2 Implementation Overhead                        | 202 |  |

| 11.3 Flow Control without the Timing Array          | 206 |  |

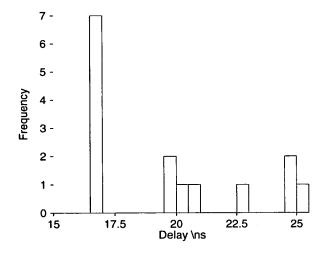

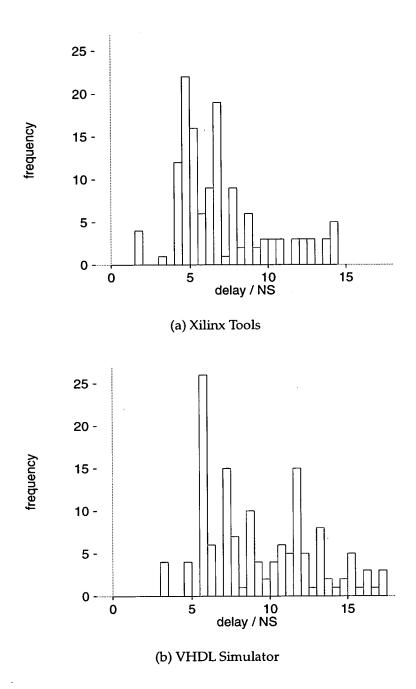

| 11.4 Delay Performance                              | 210 |  |

| 11.5 Extensions to the Architecture                 | 223 |  |

| 11.6 Summary                                        | 232 |  |

| Chapter 12 Conclusions                              |     |  |

| 12.1 Overview                                       | 234 |  |

| 12.2 Conclusions                                    | 234 |  |

| 12.3 Self-Timed FPGA Architectures                  | 237 |  |

| 12.4 Future Work                                    | 239 |  |

| 12.5 Summary                                        | 242 |  |

| Appendix A Finite Fields                            |     |  |

| A.1 Introduction                                    | 243 |  |

| A.2 Finite Fields                                   | 243 |  |

| A.3 Error Detection and Correction Applications     | 246 |  |

| Appendix B Self-timed XC6200 Evaluation Data        |     |  |

| Bibliography                                        |     |  |

## Chapter 1

## Introduction

## 1.1 Reconfigurability and Self-Timing

Field Programmable Gate Arrays (FPGAs) are a form of programmable logic; they are devices designed to implement a wide range of different logic circuits. The key property of programmable logics that differentiates them from custom hardware is their reconfigurability. Such devices cannot compete with a custom hardware implementation in terms of density or speed, but their reconfigurability allows hardware designs to be created and changed rapidly, thus reducing time-to-market and costs over custom hardware.

Traditionally, programmable logics have been configured in special programmers that are external to the host system. However, many current FPGAs have SRAM configuration memories, which can be programmed in-system. Thus, a configuration can be loaded into the FPGA and run, just like a software program, but with performance closer to that of dedicated hardware. Dynamic hardware systems attempt to exploit the software-like reconfigurability of SRAM FPGAs. For example, such systems can be used to implement circuits larger than the size of the FPGA, by swapping parts of the circuitry to and from the FPGA; or circuits can be customised for a particular problem on the fly.

However, the exploitation of reconfigurability in dynamic hardware systems is limited by the delay properties of the FPGA architecture. Changing the environment or shape of a circuit alters the delay properties of the circuit, which means it can fail to meet the global clock in synchronous systems. The starting point for this thesis is the proposal to utilise the speed-independence of self-timed circuits to allow the rapid manipulation of circuits in dynamic hardware systems. Such an approach promises to allow the full dynamic reconfigurability of FPGAs to be exploited.

Current synchronous-oriented FPGA architectures pose problems for the implementation of self-timed circuits. The assumptions made in self-timed communication protocols are often not maintained by synchronous FPGA architectures. The approach taken in this thesis is to develop self-timed FPGA architectures to overcome the problems with current FPGAs.

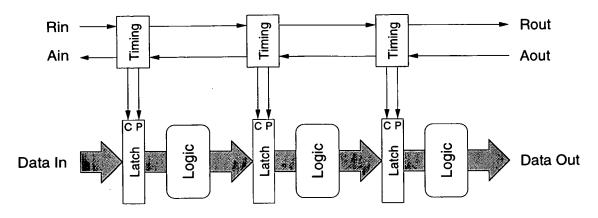

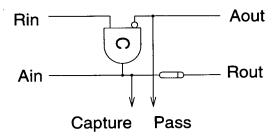

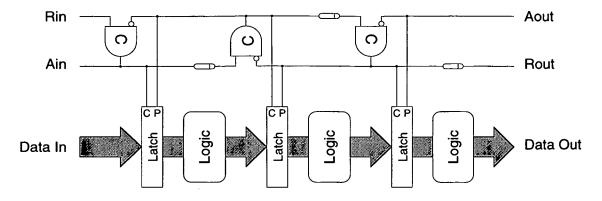

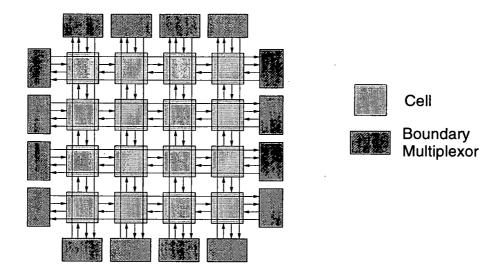

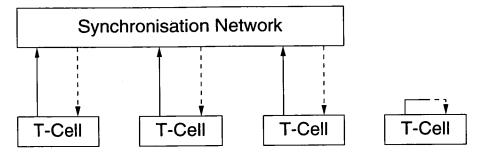

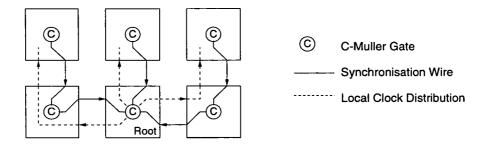

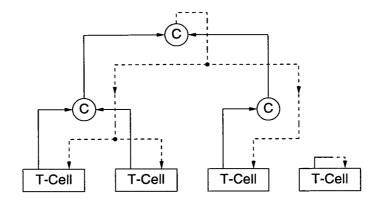

The thesis introduces a new model for self-timed FPGA architectures called STACC (Self-Timed Array of Configurable Cells). In STACC, the global clock of a synchronous FPGA architecture is replaced with an array of timing cells. These timing cells provide local timing control to regions of logic blocks, which are left unaltered from the original synchronous FPGA architecture. The clear split between timing cells and data cells (logic blocks) in STACC reflects the split in self-timed bundled-data protocols between control path and data path.

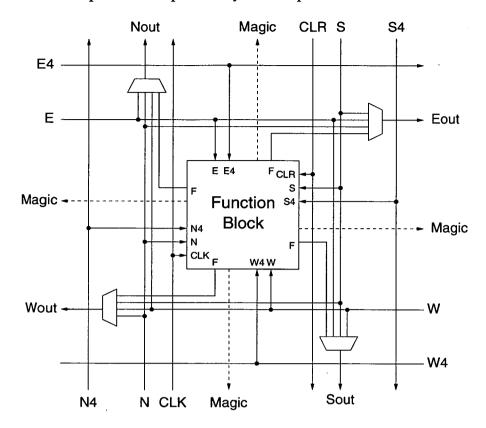

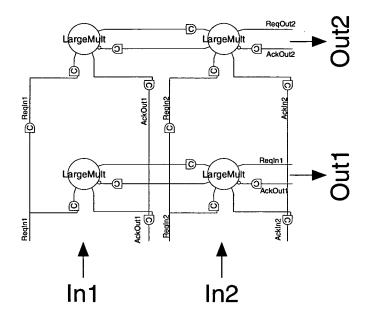

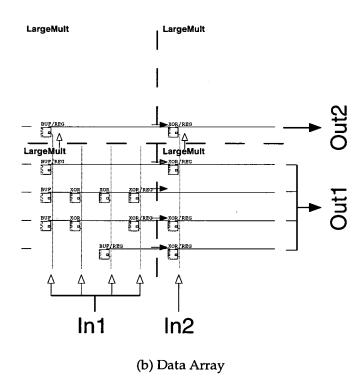

To demonstrate the viability of STACC, the STACC model is applied to the Xilinx XC6200 FPGA architecture. The Xilinx XC6200 was chosen since it is a recent architecture (first silicon in 1995), and that it includes features for the use of dynamic hardware. The self-timed XC6200 architecture is used to construct circuits parameterised at run-time, which demonstrate the benefits of self-timing for dynamic hardware systems.

#### 1.2 Thesis Structure

The thesis consists of four main parts. The introductory chapters present background material on FPGAs and self-timed systems, and outline the potential benefits of self-timed FPGA systems. The second part of the thesis introduces the STACC model for self-timed FPGA architectures, and develops the circuit elements required for the construction of STACC architectures. The third part of the thesis concerns the application of the STACC model to the Xilinx XC6200 FPGA architecture. Finally, the thesis concludes with a summary of the main results and a discussion of possible future work.

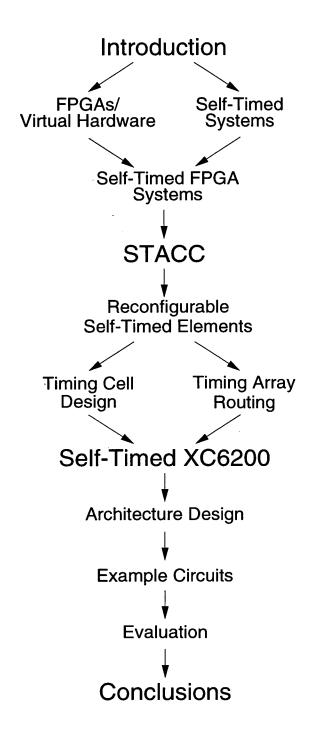

Figure 1.1 summaries the structure of the thesis and shows the relationship between the chapters. Below, a chapter by chapter summary for each part of the thesis is given.

#### 1.2.1 Introduction

Chapter 2 covers background material on FPGAs. A key part of this chapter is the discussion of dynamic hardware systems, virtual hardware, and run-time

Figure 1.1: Thesis Structure

parameterised circuits. **Chapter 3** introduces self-timed systems and includes a detailed discussion of bundled-data systems.

Chapter 4 is central to the rest of the thesis. It considers the potential benefits and drawbacks of self-timing for FPGA systems in general, and dynamic hardware in particular. The chapter also reviews the current research on self-timed circuits using synchronous FPGAs and proposed self-timed FPGA architectures.

#### **1.2.2 STACC**

Chapter 5 introduces a model for self-timed FPGA architectures: STACC (Self-Timed Array of Configurable Cells). The STACC model involves replacing the global clock in a synchronous FPGA with an array of timing cells that provide local clock signals.

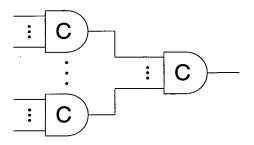

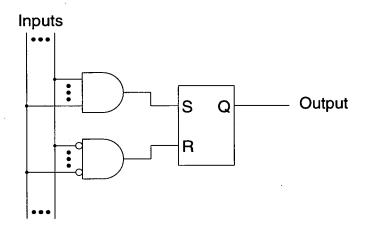

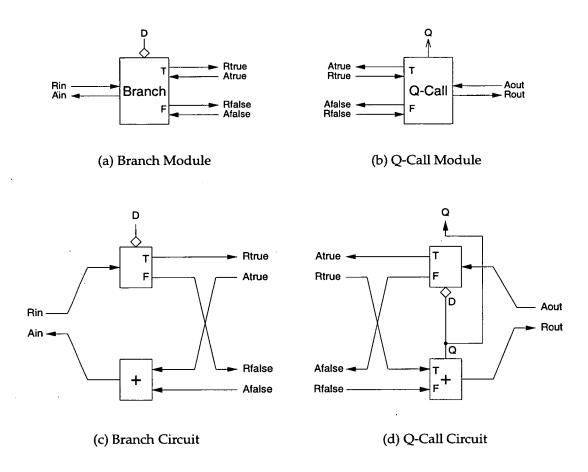

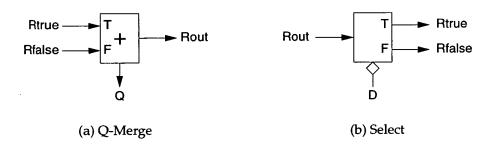

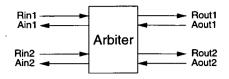

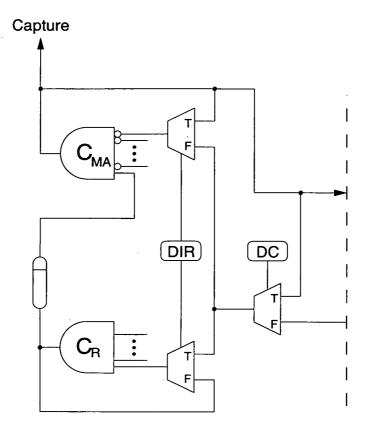

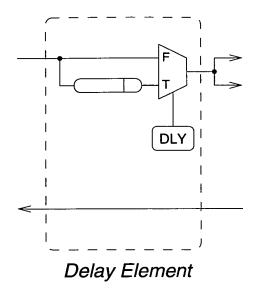

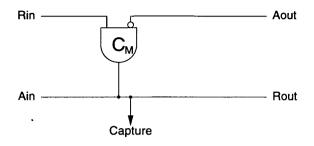

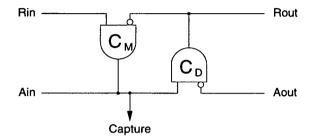

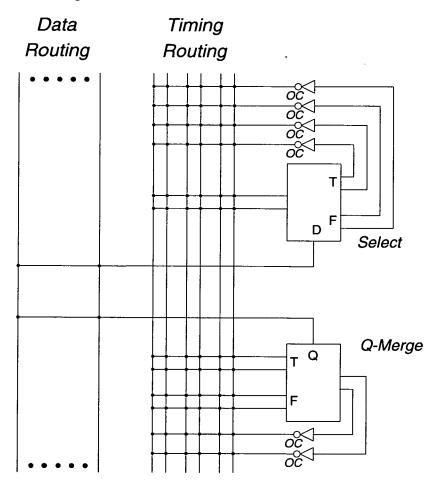

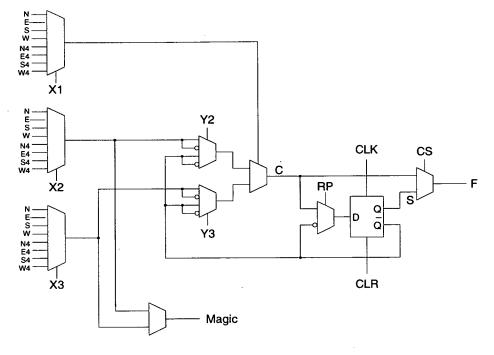

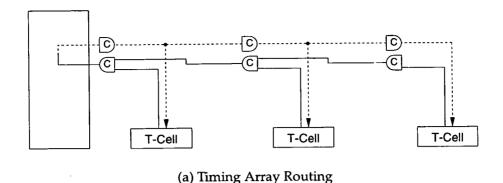

The next three chapters focus on the implementation of the timing array in STACC architectures. Chapter 6 introduces several new self-timed elements, such as the Q-Merge/Select pair and the reconfigurable C-Muller gate, which are used as building blocks for the timing array. Chapter 7 describes in detail the design of timing cells for STACC. The timing cell is developed from a basic reconfigurable C-Muller gate into a timing cell capable of selective communication and arbitration. Chapter 8 concerns routing structures for handshaking signals in the STACC timing array. These structures are based on another development of the reconfigurable C-Muller gate: the handshaking crossbar.

#### 1.2.3 A Self-Timed XC6200

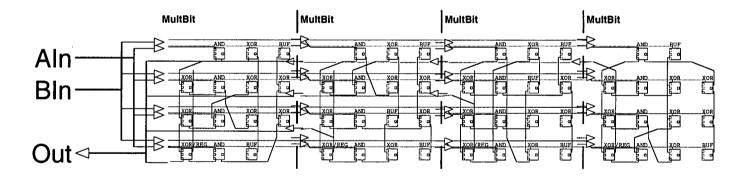

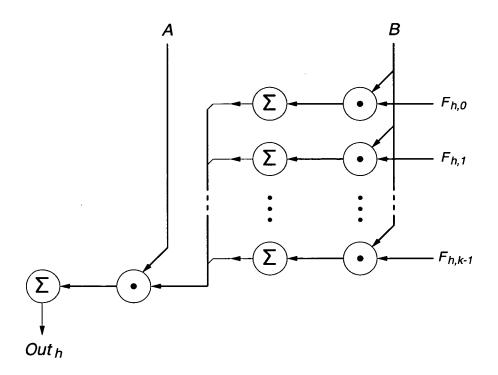

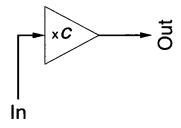

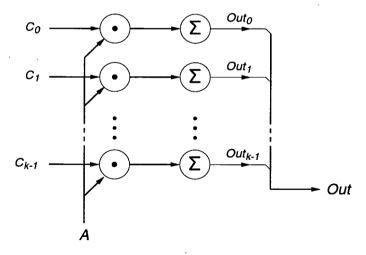

Chapters 9 to 11 concern the application of the STACC model to a contemporary FPGA architecture: the Xilinx XC6200. **Chapter 9** introduces the current XC6200 architecture, concentrating on the features useful for dynamic hardware, and then presents the design of a self-timed XC6200 using the STACC model. **Chapter 10** contains a case study of the use of the self-timed XC6200 for implementing dynamic hardware systems. The example circuits are runtime parameterised circuits for finite field operations with application to Reed-Solomon error correction. Finally, **Chapter 11** compares the self-timed XC6200 relative to the synchronous XC6200, considering its delay performance and the implementation overhead of the timing array.

#### 1.2.4 Conclusions

**Chapter 12** summarises the main results of the work. The chapter ends with a discussion of possible directions for future research.

#### 1.3 Contributions

This thesis makes original contributions in a number of areas. The main contributions are listed below. These points are expanded upon in Chapter 12, which summarises the conclusions of the thesis.

- **Self-timed Dynamic Hardware:** A key contribution of the thesis is the identification of the benefits of self-timed circuits for implementing dynamic hardware systems. Previous work on self-timed circuits for FPGAs have concentrated only on the prototyping of self-timed systems.

- STACC: is a new model for creating self-timed reconfigurable architectures. Unlike previous self-timed FPGA architectures (MONTAGE, PGA-STC), STACC-based architectures do not alter the structure of the logic blocks for self-timing.

- Self-timed Reconfigurable Elements: The thesis introduces a number of new self-timed elements, potentially of wider use in self-timed design: the Q-Merge/Select Pair, the reconfigurable C-Muller gate, the STACC timing cell and handshaking crossbars.

- **Self-timed XC6200:** Using the STACC model, this thesis presents the design, simulation and evaluation of a new self-timed FPGA architecture based on the Xilinx XC6200.

- Run-Time Parameterised Circuits: The circuits developed for run-time parameterisation on the self-timed XC6200 are of note, due to the hierarchy of parameterisation, and the benefits arising from self-timing. Some of the design techniques developed, such as the abstract block size, are applicable to XC6200 designs in general.

- Current Sensing Completion Detection (CSCD): The thesis provides insight into the potential benefits of the CSCD delay scheme and proposes the use of CSCD for meta-stability resolution.

## **Chapter 2**

## Field Programmable Gate Arrays

## 2.1 Background

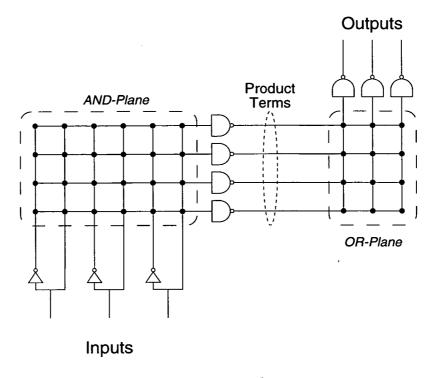

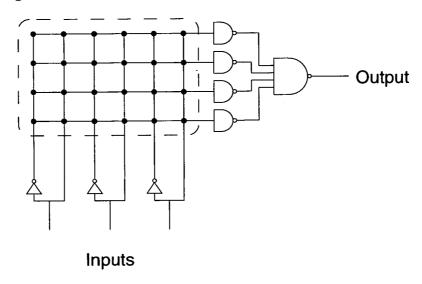

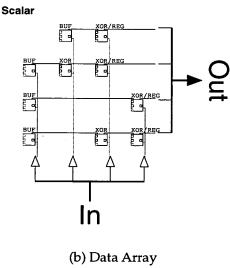

FPGAs are the successors to earlier forms of programmable logic such as PLAs and PALs. The initial need for programmable logics has been to integrate a number of SSI (Small Scale Integration) or MSI (Medium Scale Integration) parts on a single chip, without the expense or time of building a custom part. A key difference of FPGAs from these previous forms of programmable logic is the size of circuit that can be implemented on one device. Whilst earlier programmable logic devices could replace a small number of SSI or MSI parts, FPGAs can implement VLSI parts (over 10,000 gate equivalents) within a single programmable device. The implementation of larger circuits within FPGAs has necessitated a change in architecture. Earlier programmable logic devices, such as PLAs (see Figure 2.1), implemented circuits as a two-level logic function, i.e., a boolean sum of products. Such devices had two planes of logic: an AND plane that produced the product terms from the inputs and an OR-plane that summed the products to produce the outputs.

However, the use of two-level logic functions becomes cumbersome for larger circuits, since the size of each plane increases more rapidly than the complexity of the circuit. A solution is to factorise the two-level logic functions and implement the circuits using multi-level logic functions. To implement multi-level logic functions, FPGA architects have drawn on the design of Mask Programmable Gate Arrays (MPGAs). MPGAs are a semi-custom implementation style for ASICs (Application Specific Integrated Circuits). MPGAs save cost on expensive custom masks, by having a fixed set of masks defining a collection of basic building block gates (such as NAND gates), and then use a few custom masks to define the routing between them. The key difference between MPGAs and FPGAs is the method of configuration. In MPGAs, the config-

Figure 2.1: PLA Architecture

uration is defined by the routing masks whilst, in FPGAs, it is defined by a configuration memory. MPGAs and FPGAs are sufficiently related that FPGA designs can be migrated directly to MPGAs with similar architectures. For example, CLA is an MPGA version of the Algotronix CAL architecture [65], and the Xilinx HARDWIRE architecture is an MPGA version of the XC4000 FPGA [124].

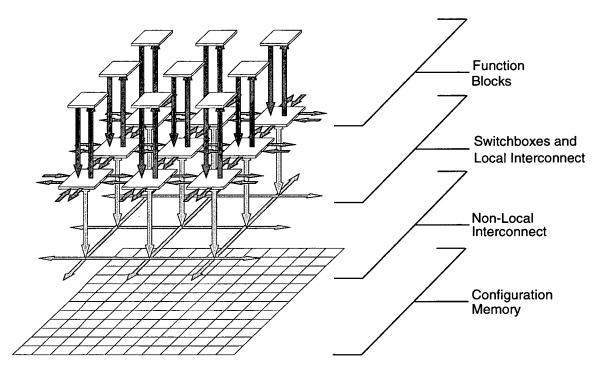

### 2.2 Elements of an FPGA Architecture

Figure 2.2 shows an idealised FPGA architecture. The architecture consists of an array of function blocks. Each function block can be configured to implement a variety of basic gates and a basic memory element, such as a D-type flip-flop. The function blocks are wired together to form a circuit using reconfigurable interconnect. Switchboxes connect a function block's inputs and outputs to the interconnect. Typically, architectures provide separate interconnect for routing local and non-local signals. At the edge of the array, special input/output switchboxes are provided to connect to external signals. The circuit implemented by the FPGA is determined by values stored in the FPGA's configuration memory. The configuration memory determines the functions implemented by the function blocks and the routing implemented

Figure 2.2: Elements of an FPGA Architecture

by the switchboxes.

Currently, a large number of FPGA architectures are available commercially, with little agreement on a common design. The following sections examine the decisions made in current FPGA architectures. They discuss the design of the function blocks (Section 2.3), reconfigurable interconnect (Section 2.4) and configuration memory (Section 2.5). Some desirable properties of how these elements are assembled to create an FPGA architecture are discussed in Section 2.6. The use of FPGAs in dynamic hardware applications is discussed in Section 2.7.

### 2.3 Function Blocks

Current architectures use a wide variety of function blocks. A basic requirement of the function blocks is that any logic function can be constructed given a sufficient supply of them. Two-input NAND or NOR gates are sufficient for this purpose, however most FPGA architectures choose to use function blocks that can implement any boolean function of between 2-5 boolean variables.

Current FPGA architectures use five basic styles of function block: primitive gates, LUTs (Look-Up Tables), multiplexors, PALs (Programmable Array Logic) and CAMs (Content Addressable Memories). These styles are described below. In addition, most architectures embellish the basic choice of function

block with additional features to improve the implementation of certain functions, such as dedicated carry logic for adders and counters.

#### **Primitive Gate Function Blocks**

The simplest function block possible for an FPGA is to supply a primitive gate such as two-input NAND or NOR gate. All other logic functions can be built given a sufficient supply of these gates. This approach has been adopted successfully in 'sea of gates' MPGAs. The advantage of using primitive gates is that the function block is easy to design and small, so can be replicated in large numbers. The main drawback of using such basic elements for FPGAs is that it requires a large amount of slow reconfigurable interconnect. Most FPGA architectures use more complex cells, with mostly fixed internal, routing for speed. At the time of writing, the only FPGA architecture to use a primitive gate function block has been the GEC-Plessey ERA architecture [33, 45].

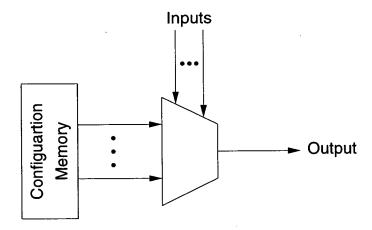

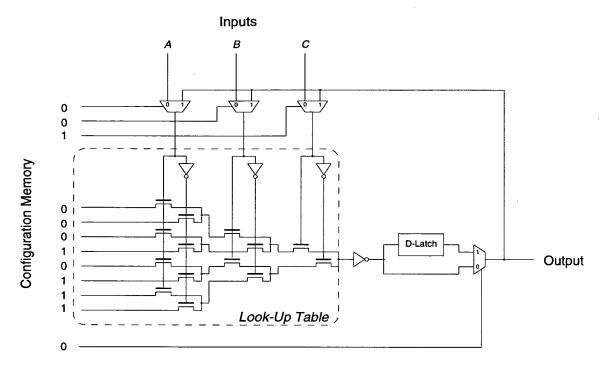

#### **Look-Up Table Function Blocks**

Figure 2.3 shows the design of a Look-Up Table (LUT) function block. The multiplexor is used to select an output value from a configuration memory. Essentially, each function block acts as a small ROM (Read Only Memory), whose output is selected by the input signals. To provide one boolean function of N input variables requires  $2^N$  configuration bits. Architectures such as the Xilinx XC4000 [124] and AT&T ORCA [9] allow the LUT to be split into sub-LUTs to provide more functions, but of fewer variables. For example, the Xilinx XC4000 [124] architecture allows a function block to provide two boolean functions of four variables each or one boolean function of five variables.

Figure 2.3: Look-Up Table Function Block

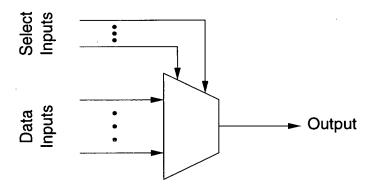

#### **Multiplexor Based Function Blocks**

Figure 2.4 shows the function block of a multiplexor based FPGA. A multiplexor with N select inputs is capable of implementing all boolean functions of N+1 input variables. In contrast to a LUT based function block, a multiplexor based function block is not directly configured by a configuration memory. Instead, the function is determined by configuring routing to the select and data inputs of the multiplexor. Configuring this routing becomes costly for large multiplexors, so typically FPGA architectures, such as the Algotronix CAL1024 [3] and Actel Act1000 [2] use small multiplexors with only one or two select inputs.

Many FPGA architectures add additional logic to the multiplexor. The Act1000 FPGA [2] includes a two input NOR gate on one of the select inputs of the multiplexor. The Cypress pASIC380 [24] includes a number of wide input AND gates that can be tapped separately as outputs. Architectures like the Atmel AT6000 [10] add so much additional logic to the multiplexor that they can be regarded as being a separate type of 'complex gate' function block.

Figure 2.4: Multiplexor Function Block

#### **PAL Based Function Blocks**

PAL based architectures can be considered as an evolutionary step from older two-level programmable logics to current FPGA architectures. FPGAs like the Altera MAX series [4], can be considered as 'Mega-PALs' where a small number of traditional PALs are placed on the same chip with limited reconfigurable interconnect to join them.

Figure 2.5 shows a PAL (Programmable Array Logic) based function block. Each output is implemented as a boolean sum of products. Product terms are generated by wide input AND gates and then summed together using a fixed OR gate; in Figure 2.5, De Morgan's rule allows NAND gates to be used in

place of AND and OR gates. The functions implementable by a PAL based function block are limited by the number of available product terms. Certain functions, in particular XOR like functions, use a large number of product terms, so map poorly to PAL based function blocks. However, most logic functions need considerably less product terms than the worst case. Furthermore, PAL based designs lead to very dense implementation when used with fuse based configuration memories (see Section 2.5).

Figure 2.5: PAL Function Block

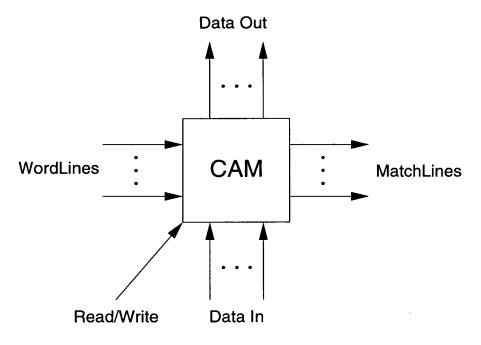

#### **Content Addressable Memory Function Block**

Figure 2.6 shows a novel Content Addressable Memory (CAM) function block that has been designed by Oxford Parallel [110]. The CAM based function block can act in two modes. In the first mode, the cell can act as a Random Access Memory (RAM). A word of the RAM is selected with the word select lines. Data can be read or written using the data out and data in signals in conjunction with a read/write signal. When reading in this mode, the CAM cell acts in a similar way to a LUT based function block. In the second mode, the cell compares the contents of the data input with the RAM contents. If the data matches, then the appropriate match line goes high. In this mode, the CAM cell acts in a similar way to the product terms in a PAL based function unit, which only go high when they match a particular data input pattern. The advantage of the CAM based design over the other function blocks is the variety of structures it can implement. As well as being able to implement LUT and PAL structures, it can easily implement dense RAM and CAMs in the FPGA.

Figure 2.6: CAM based Function Block

#### 2.3.1 Memory Elements

Most FPGA architectures provide a dedicated memory element as part of the function block. Exceptions are the Actel Act1000 [2], and GEC-Plessey ERA [33, 45] architectures, which require the memory elements to be implemented from the basic function block. Typically, architectures have D-type registers or latches as the basic memory elements. In architectures with more than one output from the function block, usually only some of the outputs are connected to memory elements. In all architectures, the configuration can choose to bypass the memory element if the output of the logic block is not registered.

Most FPGAs are poor at implementing dense memory structures such as RAM. The Xilinx XC4000 [124] architecture overcomes this by allowing the configuration memory of the LUT to be used alternatively as a block of SRAM. The Oxford Parallel FPGA [110] also allows dense memory structures to be implemented using its CAM based function blocks.

## 2.4 Reconfigurable Interconnect

Current FPGAs use a wide range of interconnect architectures. The architectures can be classified according to the type of basic interconnection resource provided and how the basic interconnect elements are joined together to form the routing network. Most architectures also provide special routing resources

for signals, such as reset and clock signals.

#### 2.4.1 Interconnect Elements

FPGAs use a number of basic elements to interconnect their routing resources. These are described below.

#### **Bidirectional Interconnect**

In FPGAs using fuse based configuration (see Section 2.5), two wire segments can be joined simply by blowing a fuse. The connections are bidirectional, since signals can flow in either direction through the fuse. Crossbar switches can be constructed from a grid of overlap wires with fuses at the intersections. In FPGAs using SRAM configuration memories, bidirectional connections require pass transistors controlled by configuration bits. These interconnect elements require more silicon area than in fuse based architectures. Also, pass transistors have a higher electrical resistance than fuses, so bidirectional buffering is required. The direction of buffering must be determined by additional configuration bits, as in the Xilinx XC3000 and XC4000 architectures [124].

#### **Unidirectional Interconnect**

To avoid implementing bidirectional buffers, many FPGAs with SRAM configuration memories, such as the Algotronix CAL [3], constrain wires to having one fixed driver. This constrains the direction of signal flow along wires within the architecture to be unidirectional. Unidirectional signalling leads to less flexibility in the use of the routing resources, but single direction drivers avoid the possibility of driver conflicts where multiple drivers drive signals to opposing values.

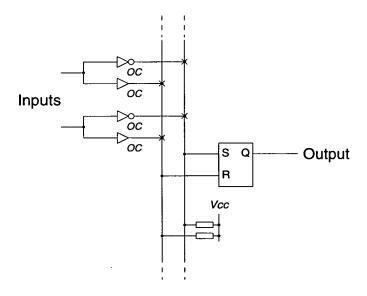

#### **Open Collector and Tristate Interconnect**

Architectures, such as the XC4000 [124] and Oxford Parallel [110], include interconnect with open collector drivers. The advantage of open collector drivers is that wide input OR and AND gates can be constructed using wired logic. Indeed, older two-level programmable logics used wired logic to implement the bulk of their circuitry. The Xilinx XC3000 and XC4000 [124] architectures include tristate drivers, to allow bus-like structures to be built on the FPGA. When using tristate drivers, the designer has the responsibility of avoiding

driver conflicts, arising from more than one tristate driver driving the signal at any one time.

#### 2.4.2 Routing Networks

Current FPGA architectures provide two basic styles of interconnection network based on separate routing channels or integrated routing and function blocks. The choice of interconnect network is strongly influenced by whether signals are unidirectional or bidirectional. Unidirectional architectures favour the point to point links used in integrated architectures, whilst bidirectional architectures favour the use of separate routing channels.

#### **Separate Routing Channels**

FPGAs that use a channel based interconnect network (such as Actel [2], Altera [4] and Xilinx [124]), emulate the style of routing in many MPGAs. In channel based routing topologies, routing channels run horizontally and vertically through the architecture. At the intersection of the channels, switchboxes allow signals to move from horizontal to vertical channels. Other switchboxes allow the function blocks to connect to the routing channels. Channel based routers usually supply a variety of different lengths of wire segments in the routing channel for local and non-local routing. Typically, many short segments are provided for local interconnect, with fewer medium length and full length wire segments for non-local routing.

#### **Integrated Routing and Logic**

Architectures such as the Algotronix CAL [3] have integrated routing and logic blocks. There is no clear differentiation between function block and routing as there is with channel based routing. Typically, routing in these architectures is based on a nearest neighbour mesh. A problem with nearest neighbour meshes is the lack of non-local routing. Earlier architectures, such as the CAL1024 [3], chose not to supply any at all. Later architectures such as the Xilinx XC6200 [123] architecture include a hierarchy of non-local routing structures.

#### **Hybrid Routing Schemes**

The TRIPTYCH [55] and Atmel AT6000 [10] architectures combine aspects of both channel and integrated routing schemes. In TRIPTYCH, most connections use local point-to-point links along a nearest diagonal neighbour mesh.

Additionally, function blocks are connected to vertical routing channels for non-local signals. In the AT6000 architecture, vertical and horizontal buses are provided in addition to the nearest neighbour mesh.

### 2.4.3 Clock Routing

Currently, all commercial FPGA architectures are geared towards the design of synchronous systems. Most architectures have dedicated clock routing to allow the distribution of a global clock signal with minimum skew across the FPGA. Typically, a choice of several global clock signals is given to allow two and four phase synchronous clocking schemes to be implemented. Most architectures also allow clocks to be driven from the local routing, but this option is rarely used, as it lacks the low skew characteristics of the dedicated clock routing. Furthermore, a number of different clocks operating asynchronously to each other creates interfacing problems.

The alternative to implementing synchronous circuits on FPGAs is to use self-timed or asynchronous circuits, which do not require a global clock signal. Implementing self-timed circuits on current FPGAs is discussed in Chapter 4, and the design of dedicated FPGA architectures for implementing self-timed circuits is the subject of the rest of the thesis.

## 2.4.4 Input/Output Interface

At the edge of an FPGA, special blocks are needed to allow the input and output of signals to and from the FPGA. Most commercial FPGA architectures try to limit the number of input and output pins to save on packaging costs. Several schemes are used to minimise the number of pins.

The simplest is only to provide some of the inputs/outputs from the array as pins. Another alternative is to share input/output pins with the configuration interface, since in most FPGA architectures, once the FPGA is programmed these pins are not used. However, this requires additional circuitry to implement the switching from configuration mode to input/output mode. An approach adopted in the Algotronix CAL1024 [3] architecture is to use ternary signalling. Ternary signalling uses special circuitry to share an input and an output on the same pin. The illegal state when the output is being driven to a different value from the input is detected by special circuitry, and the value being received can be reconstructed from knowledge of the signal being driven on the line. FPGAs using addressable SRAM as configuration memory, such as

CAL [3], provide another option for input/output. Data can be read and written into the array using the SRAM interface. Potentially, using this interface could alleviate the need for other input/output pins altogether, but currently no FPGAs have adopted this approach.

A conflicting objective to minimising the number of pins is to allow the array to be naturally extended, which requires all input and outputs to be provided as pins. This is extremely costly; of all the FPGAs discussed, only CAL [3] manages this, and this is through its use of ternary signalling. Even providing all the necessary extensions, an array of FPGAs cannot be treated as a uniform array due to the magnitude of off-chip delays.

One method of providing a large array of FPGA chips, which is as close as possible to one uniform array of function blocks is WSI (Wafer Scale Integration). An example of this approach is the Teramac [108] system built by HP Laboratories, which integrates several FPGAs on one MCM (Multi-Chip Module). Also Isshiki et al [64] have built a MCM with 12 Xilinx XC3042 chips and an Aptix FPID (Field Programmable Interconnect Device) as additional interconnect.

## 2.5 Configuration Memory

Current FPGAs use two basic types of configuration memories: fuse based and SRAM based. The key difference between these two types of configuration memory is that SRAM based designs have the the potential to be reconfigured in-system, whilst fuse based designs need to be programmed externally to the system in a special programmer. However, fuses can be implemented more compactly, which leads to a different style of architecture from SRAM based ones, where the configuration memory is relatively expensive to implement. These two types of configuration memory are discussed below.

## 2.5.1 Fuse based Configuration Memory

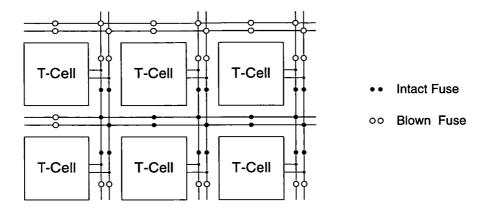

Fuse based FPGAs use the same configuration method as the older two-level forms of programmable logic, such as PALs. In fuse based FPGAs, the configuration is determined by the pattern of blown and unblown fuses. The principal advantage of fuse based configuration over SRAM, is that fuses are efficient to implement on silicon. At the silicon level, a fuse can be created at the crossing point of two wires. Special processing steps are used to make a thin layer of semi-conductor between the two wires that can be made non-

conducting (blown) by the application of high voltages. Many manufacturers [24, 4] use anti-fuses instead. An anti-fuse is the opposite of a fuse: it is non-conducting until a high voltage is applied to it. Other types of fuses allow the configuration to be erased electrically or using ultra-violet light. Compact arrays of fuses can be created using a grid of wires as in PLA-type architectures.

The configuration of fuse based FPGAs requires a special programmer to generate the high voltages required to blow the fuses. The configuration interface of fuse based FPGA allows the programmer to apply these voltages to each fuse individually in the architecture by having each fuse at the crossing point of a row and column to which the appropriate voltage can be applied.

### 2.5.2 Static RAM Configuration Memory

A major development of some FPGA architectures from older programmable logics is the use of SRAM for the configuration memory. The benefit of SRAM is that the configuration of the FPGA can be altered in-system, rather than needing the device to be removed from the system to a special programmer. A drawback of using SRAM is that it requires more silicon area since a SRAM cell implementation requires several transistors and associated wiring, whilst a fuse can be created simply at the crossing point of two wires. Another drawback is that the configuration is volatile, so needs to be reloaded every time the system is powered up.

Two methods are used for configuring SRAM FPGAs. One option is to configure the SRAM serially, as in the Xilinx XC4000 architecture [124] by providing all the configuration data to configure the FPGA in sequence. In serial access SRAM FPGAs, the configuration memory of the FPGA is implemented as a very long shift register. The use of the term SRAM (Static Random Access Memory) by such FPGA manufacturers in this case is a misnomer, since clearly the access is not random. The advantage of a serial interface is that there is no need to supply address signals to the FPGA, to indicate which part of the SRAM is to be programmed. This leads to a saving in silicon area and pins required for the configuration interface.

The alternative to serial access is a normal addressable SRAM interface as used in the Algotronix [3] and Atmel [10] FPGA architectures. The advantage of a true random access interface is that parts of the chip can be selectively reconfigured. In addition, the interface can be used to read back results from the array. The Xilinx XC6200 architecture [23] extends the basic SRAM access by allowing the use of 'wild cards' in the address given to the SRAM, so that arrays

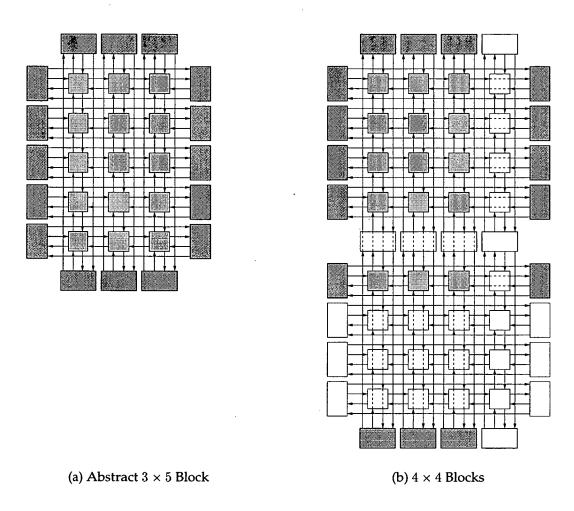

## 2.6 Repetition, Hierarchy and Symmetry

The previous sections have concentrated on the basic elements and structures used in FPGA architectures. This section focusses on some desirable higher level properties of an FPGA architecture, which arise from the way elements are put together. These features are particularly important to FPGA design tools which are used to generate the configuration of the FPGA.

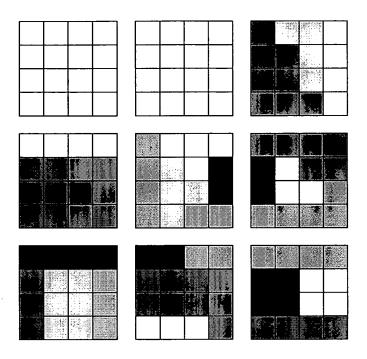

A fundamental requirement of an FPGA architecture is that the basic cell of the architecture can be replicated to form a regular array. A result of this repetition is that a design placed at one point in the array can generally be transposed to another position without change. All current FPGAs are based on a rectangular repeat pattern, but other shapes that give a regular covering of the silicon could be used, such as hexagons or equilateral triangles. Some FPGAs build the architecture as a hierarchy of elements, rather than using a simple repeating structure. The top level of the hierarchy is repeated across the silicon. For instance the Altera Flex 8000 [4] architecture consists of Logic Element Blocks grouped together into Logic Array Blocks.

Another desirable property of an FPGA architecture is symmetry, which allows designs to be rotated and flipped. This property is desirable for placement and routing software, since it allows more options for placement and routing of designs. Many architectures display reflective symmetry in one direction (such as the Cypress [24]) and some in two directions (such as TRIPTYCH [55]). Some also have rotational symmetry, for example, the Oxford Parallel [110] architecture has rotational symmetry of order two, whilst the AT6000 [10] has rotational symmetry of order four. Another useful property, related to symmetry, is for the architecture to provide function blocks with interchangeable inputs. For example, LUT based function blocks allow any permutation of inputs to be used. This flexibility allows routing software more options in how to route signals to a function block.

Many architectures add irregular features to their function blocks to improve the implementation of certain functions. For example Xilinx [124] and Altera [4] provide special carry generators to improve implementation of counters and adders. With the emergence of the PREP [1] benchmarks as an industrial standard, such features may increase with manufacturers striving to improve their benchmark performance. However, less regular features are more

difficult for synthesis tools to use. For example the XC4000 [124] carry logic can only be used by a special XBLOX generator program rather than the standard placement and routing software. This is a similar observation to that made by RISC processor designers: complex features are difficult for compilers to use effectively.

## 2.7 Dynamic Hardware Systems

A key difference of many FPGA architectures over older forms of programmable logic is the use of SRAM for the configuration memory. Rather than needing a special programmer to be reconfigured, such devices can be reconfigured in-system. The reconfigurability of SRAM FPGAs is more akin to software than hardware: a configuration file can be loaded into the FPGA's configuration memory and then run in a similar way to software. In other words, SRAM FPGAs can act as 'soft-hardware'. Systems that exploit the reconfigurability of SRAM FPGAs are often referred to as *dynamic hardware systems*.

Current dynamic hardware systems can be classified into two groups dependent on the system architecture. The first class of dynamic hardware system consists of an FPGA and microprocessor with the FPGA being used as a co-processor. The second class of dynamic hardware system consists of a large array of FPGAs connected by a routing network, similar in structure to current parallel computers.

### 2.7.1 Co-processor Dynamic Hardware Systems

Co-processor dynamic hardware systems consist of a closely coupled system of FPGA and microprocessor. Computation is shared between the microprocessor and the FPGA. In such systems, the FPGA is configured with a set of instructions adapted to the application problem. Good candidates for migration from software to the FPGA are inner loops of program code. Work at UMIST [85] is examining the automatic and user guided migration of target code from software to hardware.

For co-processor systems to show significant performance gains, the performance gain of the FPGA must outweigh the additional communication cost of going to the co-processor. Hence, it is preferable in co-processor dynamic hardware systems to place the microprocessor and FPGA on the same local bus, as in the HARP board [93] and EVC [21]. Both Page [94] and DeHon [28] argue that the natural progression is for FPGA co-processors to be integrated

on the same piece of silicon, very much as floating point units have migrated from being co-processors to being an integrated part of microprocessors.

#### 2.7.2 Large Array Dynamic Hardware Systems

Large array dynamic hardware systems resemble parallel systems in many ways, and in particular massively parallel systems, such as the Connection Machine [58] or DAP [59]. Both consist of a large array of processing elements joined by a routing network, and are loosely coupled to a host computer that deals with input/output and reconfiguration. The main difference between massively parallel computers and large array dynamic hardware systems is that the dynamic hardware systems do not have a global instruction issue. Instead, in dynamic hardware systems, the program is hardwired by the configuration. Another difference is that large array dynamic hardware systems have a more flexible interconnect architecture, but again it is fixed by the configuration.

Both massively parallel computers and large array dynamic hardware systems have been targeted at similar application domains. Large array dynamic hardware systems have demonstrated superior performance on several problems compared to far more expensive parallel systems. The Splash and Splash2 systems [6] have shown considerable speed-up on the searching of genetic databases [98] and the travelling salesman problem [49]. The PAM architecture [12] has recorded the fastest implementation of the RSA cryptography algorithm [79]. The SPACE machine [89] has been used for road traffic simulations. Cellular automata applications have been implemented by a number of researchers [90, 65, 63]. However, the lack of dedicated floating point units in large array dynamic hardware systems make them a poor match for many high performance computing applications.

### 2.7.3 Models of Dynamic Hardware Systems

In the previous section, current dynamic hardware systems were classified broadly into two groups based on the system architecture. Some machines do not fit well into either group. For example, systems such as ArMen [99] and CM2X [101] combine aspects of the co-processor and parallel system approaches. Both these machines are parallel computers where the processors have FPGA co-processors attached.

Boloski et al [13] and Guccione [53] have suggested alternative methods of

classifying dynamic hardware systems, to the one adopted here. Both authors introduce a broad definition of reconfigurability. For example, an ALU in a normal processor can be regarded as a reconfigurable unit, with a small number of reconfiguration bits that define which arithmetic function that it performs.

Boloski et al [13] use this idea to compare SIMD (Single Instruction Multiple Data) parallel computers and FPGAs. They consider FPGAs as a class of ELIW (Extremely Long Instruction Word) architecture. Since the instruction is so long, systems either load the instruction infrequently, as in FPGAs, or shorten the instruction by sending the same instructions to all parts of the array, as in SIMD parallel computers. Boloski et al argue for a hybrid architecture, which consists of a local configuration as in a FPGA, along with a global instruction issue as in a SIMD array.

Guccione [53] uses the concept of reconfigurable units to propose a classification scheme similar in spirit to Flynn's classification of parallel systems. He chooses to classify dynamic hardware systems by whether they have large or small reconfigurable units, and whether they include on-board memory. However, the difference between what constitutes a large or small reconfigurable unit is unclear, and does not lead to a clear classification scheme.

#### 2.7.4 Virtual Hardware

Dynamic hardware systems introduce a new resource into computing architectures, namely reconfigurable hardware. Like other resources within a computer, reconfigurable hardware is limited and often the need for more reconfigurable hardware than is available will arise. *Virtual hardware systems* attempt to give the illusion of more reconfigurable hardware than is actually available. Conceptually, virtual hardware is analogous to virtual memory. Virtual memory emulates a much larger memory space by swapping pages of memory between a much smaller physical memory space and a backing store. In virtual hardware, a much larger area of reconfigurable hardware is emulated by swapping configuration data between reconfigurable hardware and a backing store.

The term 'virtual hardware' is used by many authors to refer to any system composed of reconfigurable FPGAs. In this thesis, virtual hardware is used to refer to the class of system which involves swapping parts of a circuits to and from the FPGA during the operation of the circuit. The term dynamic hardware system is used to refer to the more general class of system that utilises the reconfigurability of SRAM based FPGAs.

A key consideration in the design of virtual hardware systems is the time taken to reconfigure the array. If the reconfiguration takes longer than the time to perform the operations in software then there is no performance gain. Several researchers, such as Ling [72] and DeHon [28], have suggested minimising configuration times by having FPGA architectures with more than one configuration memory, so that one configuration can be changed whilst another configuration is in use. The benefits of such an approach are debatable, since configuration memory represents a large proportion of the silicon real estate of an FPGA architecture. It may be as effective to provide more reconfigurable logic, rather than provide extra configuration memories with additional circuitry to switch between different configuration memories.

#### 2.7.5 Current Virtual Hardware Systems

Most implementations of virtual hardware to date have been limited to a fixed pattern of swapping circuits to and from known locations on the reconfigurable hardware. The advantage of such systems is that, as the pattern of swapping is fixed and the location of the circuits known, then each configuration of the reconfigurable hardware can be simulated to check for correct operation. However, this approach requires algorithms that have clear boundaries between different stages.

Several such applications have been in the domain of neural networks. The RRANN system [32, 31] divided the circuit between the different phases of the neural network, so different circuits were loaded for the back propagation and forward propagation stages of the algorithm. Lysaght et al [76, 75] adopt a different approach to implementing neural networks by swapping in different circuits for each layer of the neural network.

More general virtual hardware systems have been built where the pattern of swapping and location of circuits within the virtual hardware is less limited. French et al [34] proposed a co-processor dynamic hardware system where the FPGA is used as instruction cache: instructions not already in the FPGA are loaded in when required. Writhlin and Hutchings [122] have implemented such a scheme called DISC (Dynamic Instruction Set Computer). Instructions may be dynamically loaded at any position in a one-dimensional space on the FPGA. An interesting feature of this system is that the microprocessor has been removed from the system and instead a small processor is configured on the FPGA itself. A dynamic paging system has been developed by Brebner and Gray [18] for a fax decoding circuit. In this system, pages of the fax decoding

circuit are loaded on demand when the circuit indicates a page fault. Work by Brebner [16, 17] has also examined virtual hardware operating systems.

Simulation work by Ling [72] has investigated the idea of performing the whole of a computation using virtual hardware. This complicates the architecture as circuits can communicate between pages of the virtual hardware. A mechanism must be provided for transferring results between two hardware pages, when potentially one of the hardware pages is not loaded into the reconfigurable hardware.

#### 2.7.6 Run-Time Parameterised Circuits

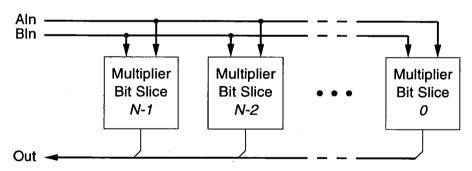

Parameterisation of circuits is now a common part of many FPGA design tools. For instance, many graphical design tools allow the definition of a bit sliced component of arbitrary width, such as a *N*-bit wide adder. More comprehensive parameterisation can often be achieved through use of a Hardware Design Language, for example, VHDL [62] or Ruby [74].

However, the parameterisation of these designs is fixed at compile time. Often, it would be useful for an application to specify the parameterisation of a hardware accelerator at run time rather than compile time. For example, a constant multiplier circuit is quicker and more compact than a general multiplier circuit. If a large number of data values are to be multiplied by a constant value, then it is beneficial to configure an instance of a parameterised circuit at run time, rather than using a general purpose multiplier circuit.

Similar concepts are being explored in the context of partial evaluation in functional programming languages by Singh et al [107]. An important property of run-time parameterised circuits is that they have the potential to outperform a dedicated hardware implementation. This arises since the dedicated hardware is optimised for solving a class of problems, whilst a run-time parameterised circuit is optimised to solve a particular instance of a problem.

Run-time parameterised circuits share many of the same problems with virtual hardware systems. The central issue is that the generation of the configuration must be done quickly, otherwise the speed-up of using virtual hardware is lost in the time taken to generate the configuration and then reconfigure the FPGA. The central challenge to designers of these systems is ensuring that the configuration works as expected without having time to use complex place and route algorithms and delay analysis algorithms that are used in design tools.

## 2.8 Summary

This chapter has discussed the basic elements of an FPGA architecture, and described the wide variety of architectures currently available. The latter part of the chapter described how the in-system reconfigurability of FPGAs with SRAM configuration memories is being used in dynamic hardware systems. Virtual hardware systems and run-time parameterised circuits were identified as classes of dynamic hardware system which present particularly challenging problems to researchers, since the FPGA configuration is often determined on the fly.

## **Chapter 3**

## **Self-Timed Systems**

## 3.1 Background

Today, most digital systems are built synchronously. The synchronous approach has not always been dominant. Machines such as ORDVAC (1951) and MU5 (1969) were built asynchronously [35]. The synchronous design style has come to dominate for a variety of reasons, principally to do with ease of design and ease of testing. In the meantime, asynchronous design has been relegated to a niche academic discipline. However, the problems of clock distribution and power dissipation as clock frequencies increase are bringing the future dominance of synchronous systems into doubt. These problems coupled with improved asynchronous design styles, have led to a resurgence of interest in asynchronous design from academia over the last few years. Industry is now taking an interest in asynchronous design with Phillips [116], Intel [120] and Sun [109] funding research.

## 3.2 Synchrony, Asynchrony and Self-Timing

The terms synchronous and asynchronous are used in a variety of different ways and different contexts in both hardware and software communities. In this section, the definitions used in this thesis are introduced. At the systems level, a *synchronous system* is one where all the communication actions are synchronised, typically by a global clock signal. In contrast, each communication within an *asynchronous system* is independent of any other; there is no global synchronisation of the whole system. However, within an asynchronous system, individual communications may be synchronised locally depending on the form of communication protocol used.

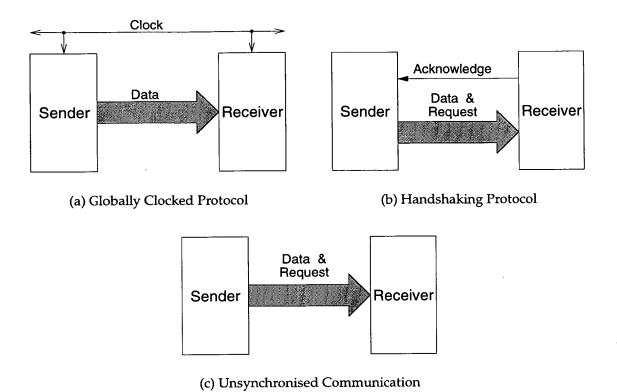

Figure 3.1(a) illustrates the communication protocol used in synchronous

Figure 3.1: Communication Protocols

systems. Data is transferred from sender to receiver on the tick of a global clock signal. Every communication in the system is synchronised by the global clock.

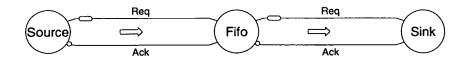

Figure 3.1(b) shows another form of synchronised communication: a *hand-shaking* protocol. The sender transmits data to the receiver together with an implicit or explicit request signal. Having received the request signal and the data, the receiver indicates receipt using the acknowledge signal. This *request/acknowledge handshake* synchronises the communication; the sender cannot send more data until it has received an acknowledge from the receiver. Though the communication is synchronised, a system built using handshaking protocols is asynchronous, since each communication is independent.

An unsynchronised communication protocol is shown in Figure 3.1(c). The only difference from the handshaking protocol is the lack of acknowledge signal, but as a result the communication is not synchronised: the sender sends data when it wants, without waiting for the receiver.

These communication protocols make a variety of different assumptions about the delays in the communication channel between sender and receiver. The globally clocked communication protocol assumes the data from the sender will be valid at the receiver before the next clock tick. This requirement

places a rigid limit on the delay of all modules in the system; every module's delay must always be less than the clock period. For the asynchronous communication protocol of Figure 3.1(c), the assumption is that the receiver must always be able to process communications as fast as the sender can produce them, since there is no way for the receiver to regulate the incoming data flow. Thus, in the globally clocked protocol, the speed of the module is determined by the clock, and in the unsynchronised protocol, the speed of a module is determined by the rate of communications from the sender.

In contrast to the other two protocols, the handshaking protocol of Figure 3.1(b) is *speed-independent*: the protocol places constraints on the ordering of signals, but not on the time taken to produce or consume the communications by a module. Systems composed using handshaking protocols are known as *self-timed*; each part of the system proceeds at its own pace, rather than having its pace determined externally by a clock signal or by the arrival of data. Most modern asynchronous systems are self-timed and the terms are often used synonymously in the literature.

Though self-timed protocols make no assumptions about the time taken to produce or consume communications, different protocols do make different assumptions concerning the delays within the communication channel. *Delaysensitive* protocols make an assumption of similar wiring delays, so that an ordering in time of signals at the sender will arrive in the same order at the receiver. Seitz [104] refers to a region within a system where this assumption can be made as an *equi-potential region*. No such assumption is made by *delayinsensitive* protocols: such protocols assume that any signal can be arbitrarily delayed, so an ordering in time of signals at the sender may arrive in a different order at the receiver.

# 3.3 A Comparison of Self-Timed and Synchronous Systems

The differences in the communication protocols described above lead to a wide range of differences in the systems composed using them. Below the benefits and drawbacks of self-timed systems relative to synchronous systems are considered. In the comparison, systems that use unsynchronised communication (i.e. asynchronous but not self-timed) are excluded. Such systems have properties of both self-timed and synchronous systems, but do not possess some of the key advantages of self-timed systems such as robustness and modularity.

Asynchronous communication comes into its own when communicating over a distance, so that waiting for the acknowledge signal to return, or distributing a clock incurs a significant performance penalty. Asynchronous communication protocols are considered in [113].

## 3.3.1 Advantages of Self-Timed Systems

#### **Modularity**

Self-timed modules may easily be composed into a working system. For delayinsensitive modules, the modules can simply be joined together and the composition will work. For delay-sensitive modules, the modules must be connected using similar wiring, so that signals are not re-ordered. The modularity of self-timed systems allows incremental change; a module can be replaced by one with similar functionality, but different performance and the composition will still work. In contrast, synchronous systems are less modular, since the designer is always concerned with whether each module and the wiring will meet the global clock constraint.

#### **Robustness**

Synchronous systems are generally dependent on an external clock source for timing. Localised effects, such as temperature and operating voltage, that affect the delays within the system do not affect the external clock source. Hence, a synchronous system may fail at higher temperatures, or at low voltages when the internal delays exceed the clock period.

Self-timed systems are more robust since they rely on internal sources of timing for their operation, so all the delays in the system are scaled by the environmental effects. As a result, self-timed systems have the potential for increased performance over synchronous systems where the worst case environmental conditions have to be assumed.

Delay-insensitive self-timed systems are particularly robust with respect to environmental effects, since there are no assumptions made about signal delays except for isochronic forks (see Section 3.4.3). Such systems are robust to large changes in temperature and voltage [83]. Also, delay-insensitive circuits can easily be migrated to different implementation technologies (such as Gallium Arsenide [112]).

#### No Global Clock

In synchronous systems, much effort has to be spent in ensuring that the global clock signal goes reliably to all parts of the circuit. Avoiding clock skew becomes very costly in terms of power, and clock routing area as a synchronous system becomes larger and the clock frequency becomes higher. It is reported that the DEC 21064 Alpha [30] uses six levels of clock buffering in distributing the clock signal, and has a 30W power requirement. In self-timed circuits, the timing information only has to be consistent locally rather than globally, which is much simpler to ensure.

#### Average Case Performance

Self-timed modules generate their own timing signals, so can pass on results at their own speed, instead of having to wait for the next global clock change. This allows self-timed circuits to utilise the average case performance of the circuit rather than being limited by the worse case performance as synchronous systems are.

This fact also allows the use of area efficient implementations, which are impractical in synchronous systems because the worse case delay is so much larger than the average case delay. For example, with an N-bit adder, a circuit where the carry ripples up the circuit can be used, as the worst case will only occur on average once in  $2^N$  additions (see [44] for a more detailed analysis of self-timed adders).

#### Low Power

In CMOS circuits, the static power consumption is almost zero. However, the constant changing of a global clock signal in a synchronous system causes transitions to be continually passing through the system, resulting in dynamic power consumption even when no valid data is passing through. In self-timed systems, transitions are only produced when data is passing through the system; there is no dynamic power consumption when the system is idle.

#### Meta-stability

All synchronous systems have the potential for failure when interfacing with their external environment. The problem arises when sampling an external signal that is not synchronised to the global clock. The signal may be changing when sampled, which can lead to the sampling flip-flop entering a *meta-stable*

state: a state where it is unable to decide whether the sample was a logic one or zero. This meta-stable state will eventually resolve to logic one or logic zero, but takes an arbitrary amount of time to do so.

Circuits can be built that detect the end of a meta-stable state, but the signal that indicates the end of meta-stable state is itself not synchronised to the clock, so the problem repeats itself. However, in a self-timed system, there is no clock to synchronise to, so the self-timed system can wait for the resolution of the meta-stable state before continuing. Seitz [104] discusses meta-stability in more detail.

#### **Flow Control**

Many systems need to regulate the flow of data between different parts of the system, for example, to prevent a buffer over filling or to share a resource between different processes. Within synchronous systems, flow control has to be implemented using additional circuitry which mimics the handshaking protocols of self-timed systems. In self-timed systems, flow control comes for free as part of the communication protocol.

# 3.3.2 Disadvantages of Self-Timed Systems

# **Extra Circuitry**

Self-timed circuitry is generally larger than equivalent synchronous circuitry as they must generate their own timing signals. The degree of overhead depends on the communication protocol used. Bundled-data protocols (see Section 3.4.2) only require two extra signals, a request and an acknowledge, so are efficient to implement if the data bundle is relatively large. Simple delayinsensitive protocols (see Section 3.4.3) use two wires to transmit one data bit so have greater area overheads.

# Testing

Testing self-timed systems for defects is harder than in the synchronous case. In a synchronous system there is a clear transition from one global state to another on the tick of the global clock. The clock can be used to single step the system so that there is time to ascertain the current system state. Additionally, if a manufacturing defect results in increased internal delays within a synchronous system, then the system can simply be run at a slower clock

speed. In a delay-sensitive self-timed system, the part may be useless, unless some method for altering the internal timing delays is provided.

### Difficult to Design

Asynchronous circuits have a reputation for being difficult to design. Partly this is because they lack the clean change of global state that occurs in synchronous circuits, and partly it is due to the possibility of race and hazard conditions. This is one of the most frequently quoted reasons why most circuits are built in a synchronous fashion.

The actual difficulty of asynchronous design depends on the style chosen. Many early asynchronous design styles [114,71] used unsynchronised communication protocols rather than self-timed protocols. Such circuits were dependent on the fact that the feedback loop to establish the new state of the circuit was faster than the time taken for a new input to arrive (known as *fundamental* and *input/output mode* circuits). Such design styles needed careful design to avoid races and hazards.

Most modern asynchronous circuits use self-timed protocols. Bundled-data systems (see Section 3.4.2) are similar to synchronous systems in that the same data path is used. Once the different timing style has been understood, they are no more difficult to design then synchronous systems. Delay-insensitive protocols are more difficult to design because the designer must still be conscious of possible races and hazards. However, synthesis tools (such as [82, 119]) have been developed that automate this translation process, eliminating race and hazard conditions from designs. On a larger scale, self-timed circuits become easier to design due to other properties such as modularity and robustness.

# 3.4 Self-Timed Communication Protocols

So far, only the general nature of self-timed communication protocols has been discussed. This section examines in detail the wide range of self-timed communication protocols that are used. The protocols can be classified at several levels. At the lowest level, protocols have to attach significance to the transitions of individual signals within the protocol. Once the significance of individual transitions is determined, the protocols need to encode the data and request signals. The encoding of the data and request signals determine whether the protocol is delay-sensitive or delay-insensitive. Finally, the protocols need to determine the conventions for the ordering of the handshaking signals.

nals. These issues are discussed below. Hauck [54] gives further background on self-timed communication protocols.

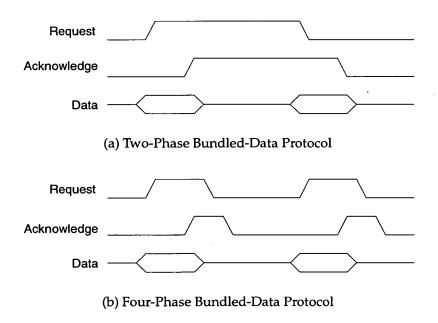

# 3.4.1 Signalling Conventions

In self-timed protocols, transitions on wires are often more important than the actual level. Most self-timed communication protocols come in several varieties that differ in which transitions are significant within the protocol. Protocols where all transitions on wires are significant are termed *two-phase*, *transition*, *event* or *non-return-to-zero* (*NRZ*) protocols. The term two-phase protocols refers to the two transitions used in the request/acknowledge handshake. Protocols where transitions in one direction only (logic zero to one or logic one to zero) are significant are termed *return-to-zero* (*RZ*) or *four-phase* protocols. Four-phase signalling requires an additional redundant return-to-zero or *recovery* transition before the next significant transition, thus four transitions are involved in the request/acknowledge handshake. In four-phase signalling, the choice of which transition is significant can be different for different wires within a system.

Both two-phase and four-phase signalling have advantages. Two-phase signalling involves fewer transitions on a wire so can be faster and use less power than four-phase signalling, which requires two redundant transitions. However, the redundant transitions in four-phase protocols can be overlapped with the computation phase within a module. Hence, two-phase signalling is only significantly faster when communication time for the handshake is longer than computation within the module. An advantage of four-phase signalling is that the circuitry is often much simpler as the signals are in the same state at the end of the handshake, which can lead to performance advantages merely because of smaller circuit size [95]. Another option is to use the redundant transitions in a four-phase protocol to indicate another sequential event, for example, acknowledge and release signals in four-phase arbiters can be combined.

An alternative to two-phase and four-phase signalling is *single-track hand-shaking* [115]. Single-track handshake circuits use the same wire for request and acknowledge signals. The sender pulls the wire high to indicate a request and the receiver pulls it back low to indicate an acknowledge. A benefit of this approach is that it only uses a single wire with two phases and returns the signal to its initial state. However, complex driving and detection circuits are required for the single-track approach.

#### 3.4.2 Bundled-Data Protocols

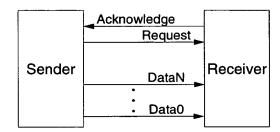

In *bundled-data* protocols (Figure 3.2), a data bundle is passed to the receiver together with a separate request signal. A transition on the request signal signifies valid data on the data bundle. Hence the request must only be asserted after the data is valid; this is known as the *bundling constraint*. Bundled-data protocols are delay-sensitive, since even though the request wire is asserted after the data at the sender, arbitrary delays in wires could result in this ordering not holding at the receiver.

Figure 3.2: Bundled-Data Protocol

Figure 3.3: Bundled-Data Protocol Timing

Figure 3.3 illustrates the timing of two-phase and four-phase bundled-data protocols. In both protocols, a transition on the request signal signifies that the data is valid. When the receiver has captured the data, it asserts the acknowledge signal to signify to the sender that it can change the values on its data lines. In the two-phase protocol of Figure 3.3(a), this completes the handshake,

and the protocol is repeated for transitions on the handshaking signals in opposite directions. In contrast, the four-phase bundled-data protocol (Figure 3.3(b)) has an additional recovery phase during which the request followed by the acknowledge signals are reset to their original states.

# 3.4.3 Delay-insensitive Protocols

Delay-insensitive protocols make the assumption that arbitrary delays can be introduced on any signal. Hence an ordering in time of signals at the sender is not necessarily preserved at the receiver.

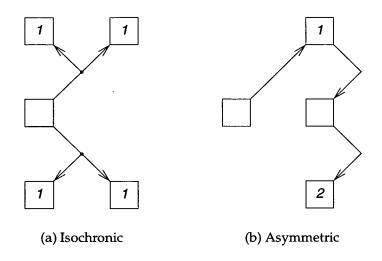

Martin [81] shows that only a very restricted class of circuit can be made delay-insensitive at the transistor level. He argues that the best compromise to delay-insensitivity that can be made is the use of *isochronic forks*. An isochronic fork places a one-sided bound on certain delay paths of transitions from a forking (fanning out) signal. By using isochronic forks at the transistor level, gates with delay-insensitive interfaces can be built, so at higher levels of abstraction, delay-insensitive systems can be built.

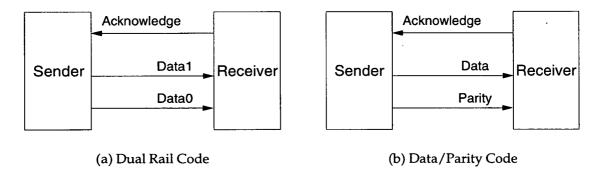

Due to the arbitrary signal delay, a single request signal that indicates the validity of the data cannot be used, since the request signal may be re-ordered, so it arrives before the data signals. Instead, delay-insensitive protocols combine the data and request signals into a codeword. The codewords are arranged such that any subset of the transitions composing a codeword are not codewords themselves. Hence, when a receiver receives a codeword, it knows that it has received all the transitions from the sender, and can safely return an acknowledge signal. Verhoeff [117] discusses the mathematics of delay-insensitive codes in more detail.

Figure 3.4: Delay-Insensitive Communication of One Bit

The simplest delay-insensitive protocols transmit one bit of data, and hence require two codewords. The most common one-bit code is the *dual-rail code*

(Figure 3.4(a)). In the dual rail-code a transition on one wire indicates the value one and a transition on the other indicates the value zero. An alternative is to use a *data/parity* code (Figure 3.4(b)). The data/parity code uses a data signal that signals a change in the data value, and a parity wire that signals when there is no change in the data value. An advantage of this code as a two-phase encoding scheme (as used by McAuley [84]) is that the data value is always available on the data line. Such codes where the data is available without the need for encoding/decoding, are known as *systematic codes*.

A variety of codes exist to transmit more than one bit of data. The simplest technique is simply to encode each bit using the one-bit protocols discussed previously. However, this requires two wires for each data bit, which is costly. Delay-insensitive codes that use less than two wires per bit require more complex encoding/decoding. An example are k-out-of-n protocols. Each codeword involves k transitions from n wires, thus k-out-of-n protocols allow n choose k values to be communicated.

Sperner codes, a class of k-out-of-n code, are the optimal delay-insensitive code, in the sense that they maximise the number of codewords for a given number of wires, but are difficult to encode/decode. *Knuth codes* are a subset of Sperner codes which are easier to encode/decode. A disadvantage of both Sperner and Knuth codes are that they are non-systematic. An alternative systematic encoding that uses less than two wires per bit are *Berger codes*. In a Berger code the data is transmitted along with a binary number (known as the parity) indicating the number of zeros in the data.

# 3.4.4 Handshaking Conventions

Several options exist within handshaking protocols, concerning whether the sender or receiver initiates the handshake. Protocols initiated by the sender are known as *push* handshaking protocols (the sender 'pushes' the data to the receiver). Receiver initiated handshaking protocols are known as *pull* protocols (the receiver 'pulls' the data from the sender). Another option within the handshaking protocol is to implement a *two-way* data transfer. Data is transfered on both the request and acknowledge phases of the handshake.

# 3.5 Self-Timed Circuit Implementation

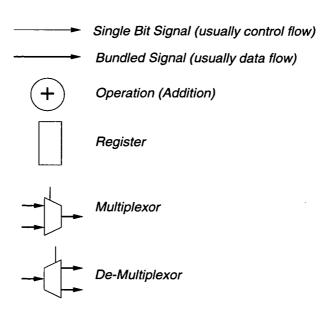

The preceding discussion focussed on the protocols themselves rather than on their implementation. This section examines some basic circuit elements used in the implementation of self-timed circuits, which will be used in later chapters.

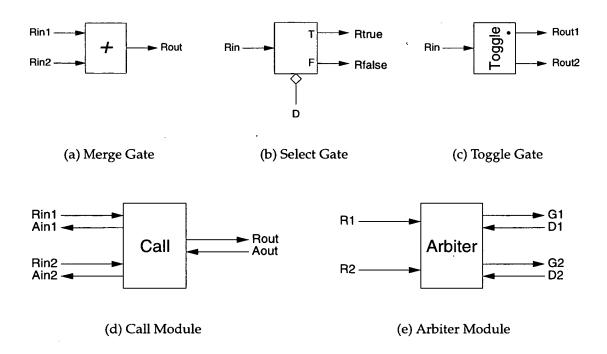

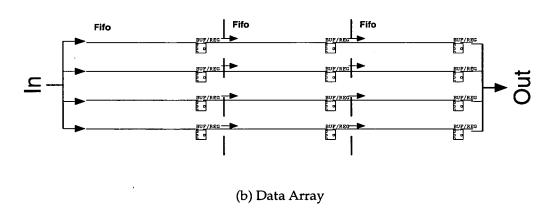

In particular, the C-Muller gate is described, which forms the basic synchronisation element in a large number of self-timed implementation styles. Building on the C-Muller gate, self-timed pipelines are discussed using the example of Sutherland's Micropipelines [111]. Also, Sutherland's choice of control blocks is examined, since these are typical of the control blocks used in a variety of self-timed circuit design styles.

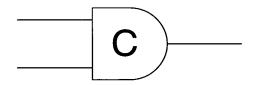

### 3.5.1 The C-Muller Gate

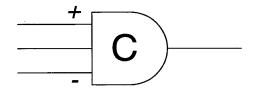

The *C-Muller gate* or *Rendezvous element* (see Figure 3.5) forms the basic synchronisation element in many self-timed circuits. In event-based (two-phase) signalling, the C-Muller gate can be thought of as acting as an AND gate for events: the C-Muller gate will not generate an output event until events have occured on all of its inputs.

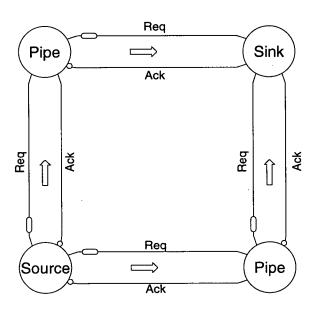

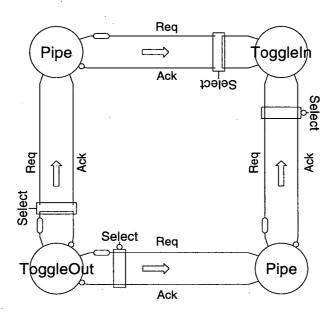

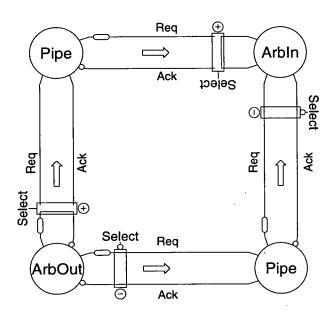

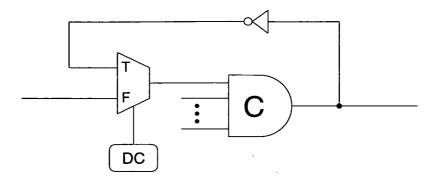

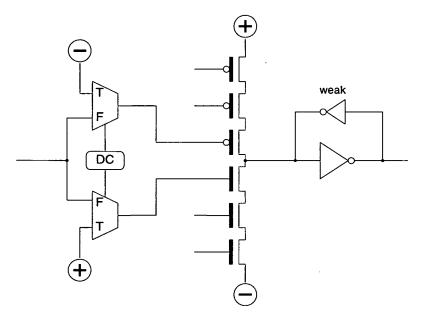

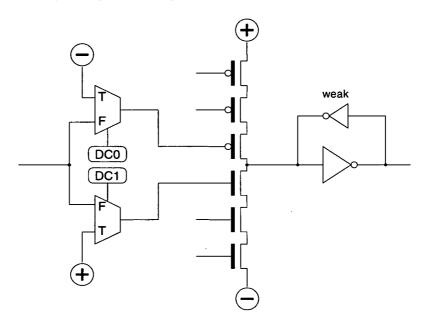

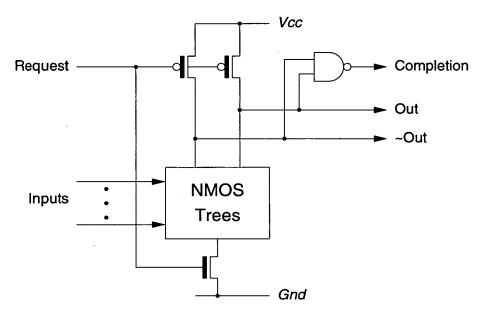

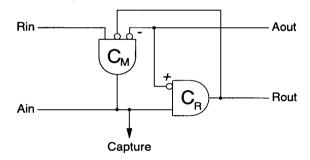

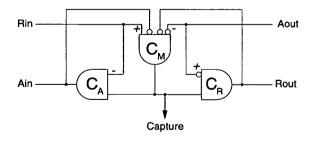

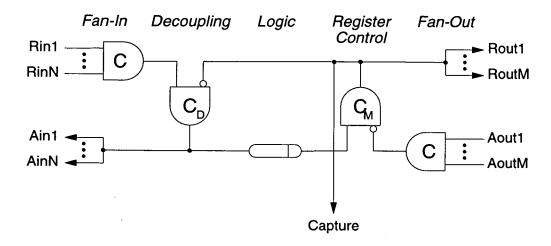

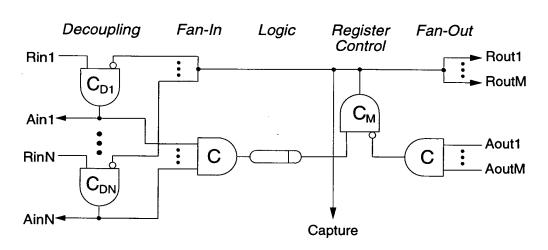

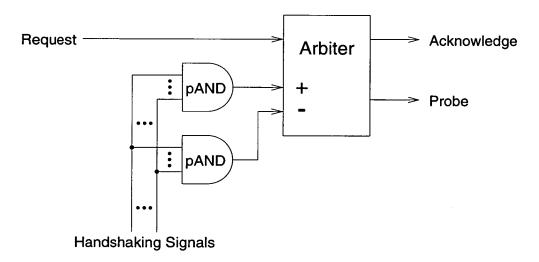

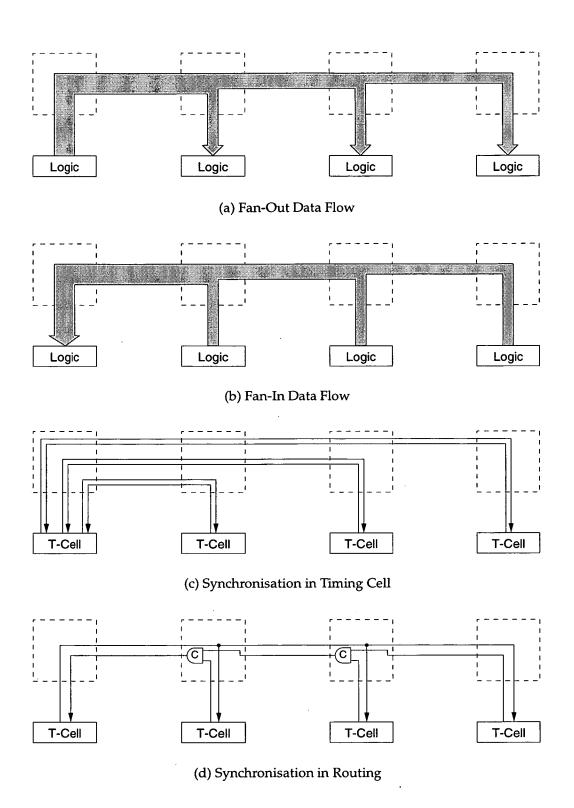

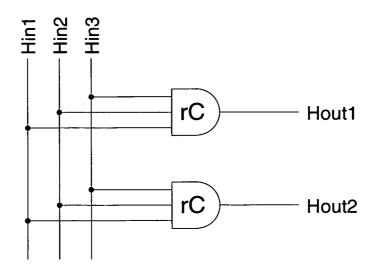

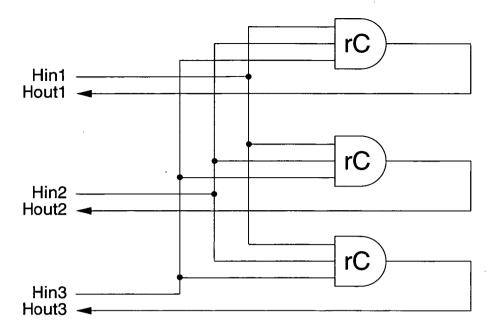

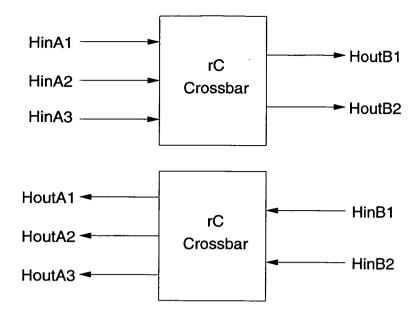

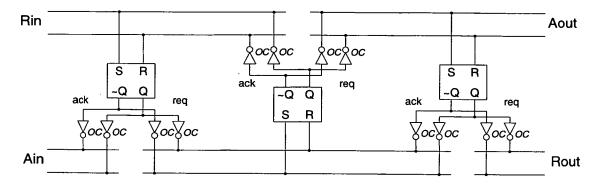

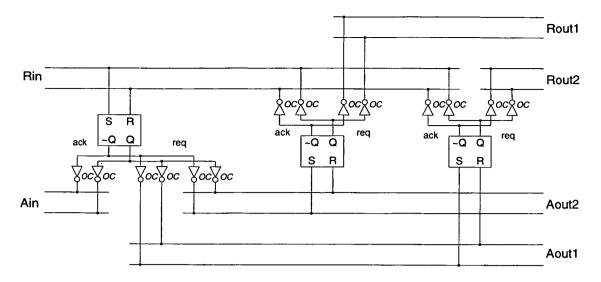

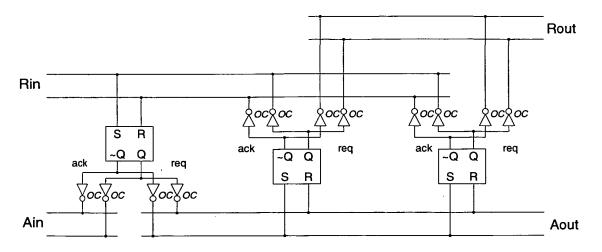

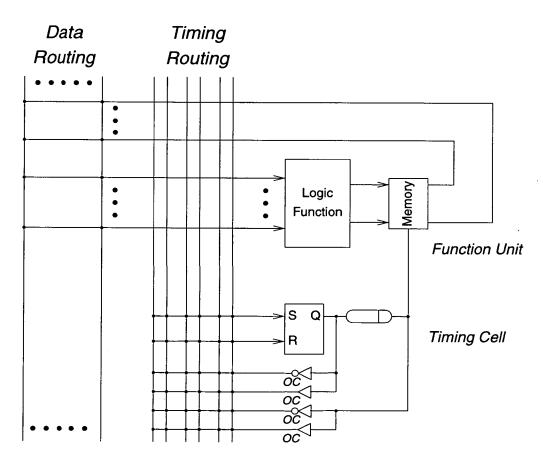

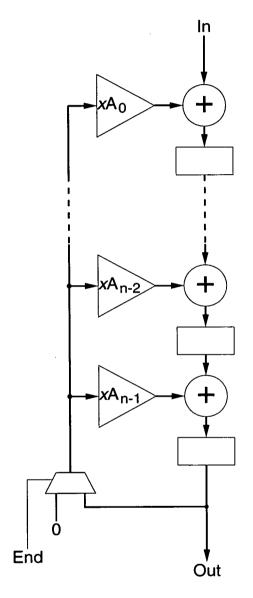

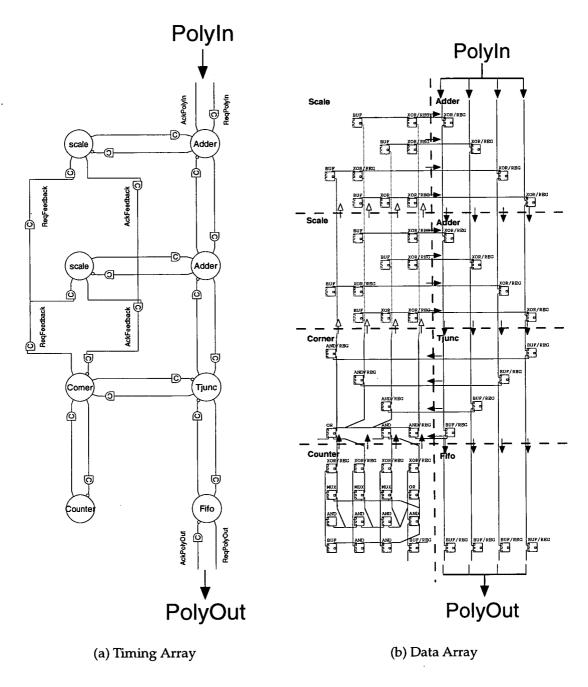

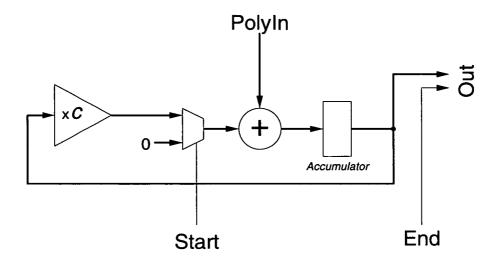

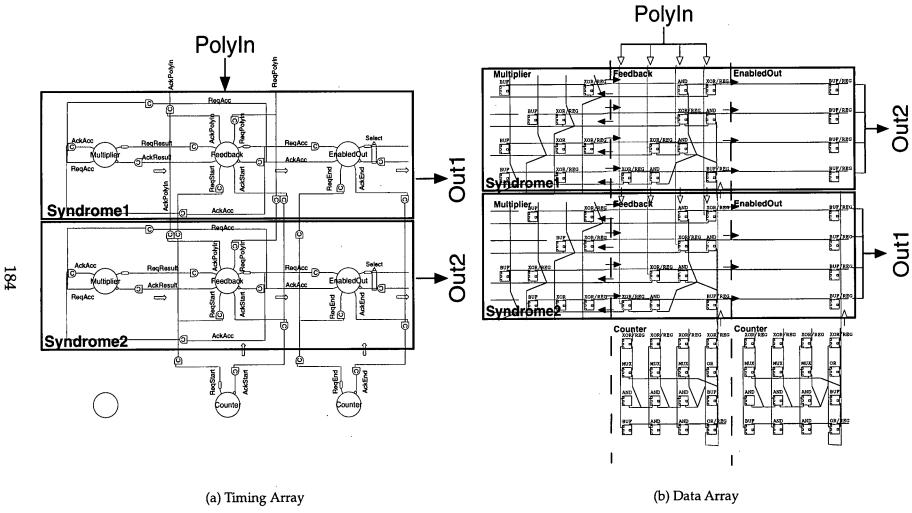

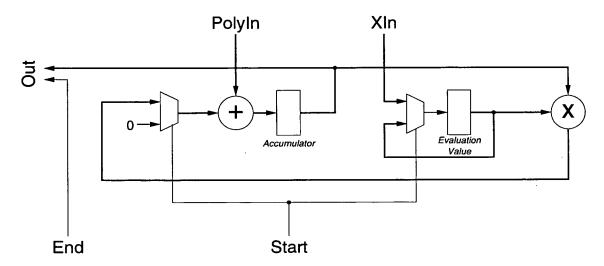

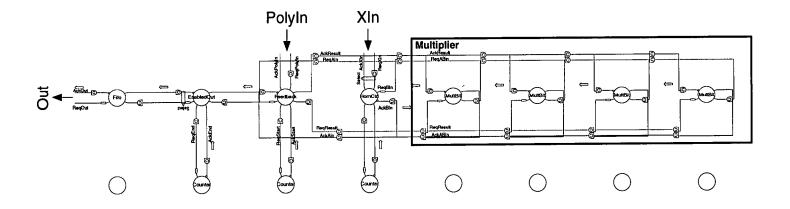

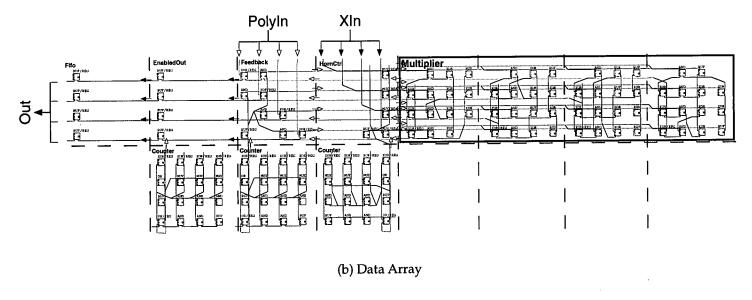

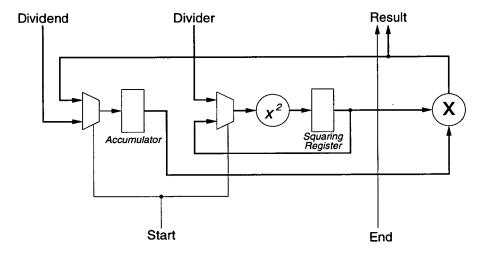

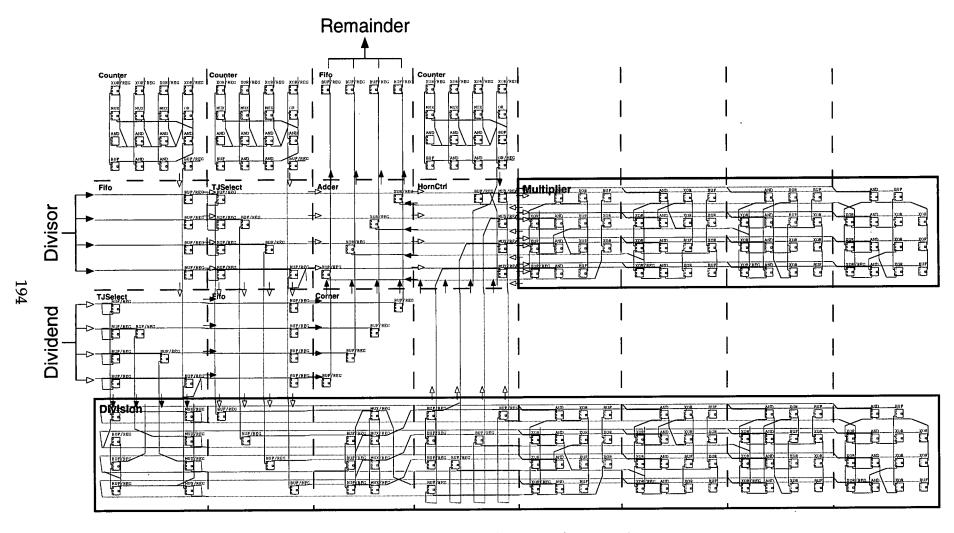

Figure 3.5: Two-Input C-Muller Gate