# An OS-Based Alternative to Full Hardware Coherence on Tiled Chip-Multiprocessors

Christian Fensch

Doctor of Philosophy Institute of Computing Systems Architecture School of Informatics University of Edinburgh 2008

## Abstract

The interconnect mechanisms (shared bus or crossbar) used in current chip-multiprocessors (CMPs) are expected to become a bottleneck that prevents these architectures from scaling to a larger number of cores. Tiled CMPs offer better scalability by integrating relatively simple cores with a lightweight point-to-point interconnect. However, such interconnects make snooping impractical and, thus, require alternative solutions to cache coherence.

This thesis proposes a novel, cost-effective hardware mechanism to support shared-memory parallel applications that forgoes hardware maintained cache coherence. The proposed mechanism is based on the key ideas that mapping of lines to physical caches is done at the page level with OS support and that hardware supports remote cache accesses. It allows only some *controlled* migration and replication of data and provides a sufficient degree of flexibility in the mapping through an extra level of indirection between virtual pages and physical tiles.

The proposed tiled CMP architecture is evaluated on the SPLASH-2 scientific benchmarks and ALPBench multimedia benchmarks against one with private caches and a distributed directory cache coherence mechanism. Experimental results show that the performance degradation is as little as 0%, and 16% on average, compared to the cache coherent architecture across all benchmarks for 16 and 32 processors. Abstract

# Declaration

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified.

(Christian Fensch)

Declaration

# **Related Publications**

Parts of this thesis have been published in the proceedings of the 14th IEEE International Symposium on High-Performance Computer Architecture (HPCA), pages 355–366, February 2008.

**Related** Publications

## Acknowledgements

This thesis is the product of a journey that to some extend started in 2001. The accomplishment of this journey would not have been possible without the continuing support of the many friends and colleagues that I met or made on the way. As such, I feel that part of this success is due to their effort in providing me with much needed support throughout all this time.

I would like to express my thanks to my colleagues at the University of California at Irvine Niall Dalton, Fermin Reig, Jeffrey von Ronne, Christian Stork, Lei Wang, Ning Wang and Efe Yardımcı. In particular, I am grateful to Dr. Wolfram Amme and Prof. Michael Franz who convinced me to pursue postgraduate studies outside Germany.

I would like to thank my dear friends Carla Delgado-Battenfeld, Sytze Dijkstra, Christophe Dubach, Rosa Mendoza and Gaya Nadarajan in Edinburgh for their morale support and friendship. In particular, I am grateful that Ingo Battenfeld, Asuka Ishikawa and John Thomson not only shared the office with me but also provided support and encouragement at critical times.

Finally, I am greatly indebted to my supervisor Dr. Marcelo Cintra for his continuing support into my work and for his advice to always aim to publish at a top conference. After many failed attempts, I understand the insight in this and I am grateful that he was so insisting on this issue. A cknowledgements

# Contents

| Abstract |                          |                                                     |                |  |  |  |  |  |  |

|----------|--------------------------|-----------------------------------------------------|----------------|--|--|--|--|--|--|

| De       | Declaration              |                                                     |                |  |  |  |  |  |  |

| Re       | Related Publications vii |                                                     |                |  |  |  |  |  |  |

| Ac       | Acknowledgements         |                                                     |                |  |  |  |  |  |  |

| 1.       | Intro                    | oduction                                            | 1              |  |  |  |  |  |  |

|          | 1.1.                     |                                                     | 1              |  |  |  |  |  |  |

|          | 1.2.                     | Contribution of this Thesis                         | 3              |  |  |  |  |  |  |

|          | 1.3.                     |                                                     | 3              |  |  |  |  |  |  |

|          | 1.4.                     | Structure of this Thesis                            | 4              |  |  |  |  |  |  |

| ١.       | Ba                       | ckground                                            | 5              |  |  |  |  |  |  |

| 2.       | Parallel Programming     |                                                     |                |  |  |  |  |  |  |

|          | 2.1.                     | Message Passing                                     | $\overline{7}$ |  |  |  |  |  |  |

|          | 2.2.                     | Shared Memory                                       | 8              |  |  |  |  |  |  |

|          |                          | 2.2.1. Sequential Consistency                       | 9              |  |  |  |  |  |  |

|          |                          | 2.2.2. Weak Consistency                             | 9              |  |  |  |  |  |  |

|          |                          | 2.2.3. Release Consistency                          | 10             |  |  |  |  |  |  |

|          |                          | 2.2.4. Processor Consistency                        | 11             |  |  |  |  |  |  |

|          | 2.3.                     | Distributed Shared Memory                           | 11             |  |  |  |  |  |  |

| 3.       | Cache Coherence 13       |                                                     |                |  |  |  |  |  |  |

|          | 3.1.                     | ~                                                   | 14             |  |  |  |  |  |  |

|          | 3.2.                     | Directory Based                                     | 15             |  |  |  |  |  |  |

|          | 3.3.                     | Scalability of Buses and Crossbars                  | 15             |  |  |  |  |  |  |

|          |                          | 3.3.1. Shared Busses                                | 15             |  |  |  |  |  |  |

|          |                          | 3.3.2. Crossbars                                    | 16             |  |  |  |  |  |  |

|          | 3.4.                     | Distributed Directory Cache Coherence               | 17             |  |  |  |  |  |  |

|          | 3.5.                     | Complexity of Distributed Directory Cache Coherence | 19             |  |  |  |  |  |  |

| 4.       | Tiled Architectures21    |                                                     |                |  |  |  |  |  |  |

|          | 4.1.                     |                                                     | 22             |  |  |  |  |  |  |

|          |                          |                                                     | 22             |  |  |  |  |  |  |

|          |                          | 4.1.2. On-Chip Networks                             | 23             |  |  |  |  |  |  |

|          |                          | 4.1.3. RAW cluster                                  | 23             |  |  |  |  |  |  |

|                |                                                                                                                                          | 4.1.4. RAW Compiler: Maps                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23                                                                                                                                                                                 |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |                                                                                                                                          | 4.1.5. RAW Compiler: StreamIt                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24                                                                                                                                                                                 |

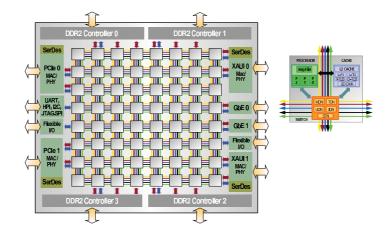

|                |                                                                                                                                          | 4.1.6. Tilera TILE64                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24                                                                                                                                                                                 |

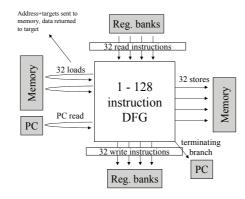

|                | 4.2.                                                                                                                                     | Trips                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25                                                                                                                                                                                 |

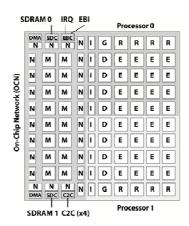

|                | 4.3.                                                                                                                                     | Cyclops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28                                                                                                                                                                                 |

|                |                                                                                                                                          | WaveScalar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                                                                                                                                                 |

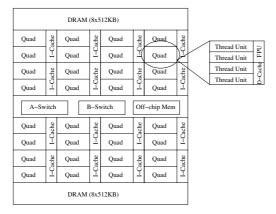

|                | 4.5.                                                                                                                                     | Vector Threads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 30                                                                                                                                                                                 |

|                | 4.6.                                                                                                                                     | Intel's Tera-scale Computing Prototype Polaris                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 31                                                                                                                                                                                 |

|                |                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                    |

| 5.             | Soft                                                                                                                                     | ware Distributed Shared Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33                                                                                                                                                                                 |

|                |                                                                                                                                          | IVY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34                                                                                                                                                                                 |

|                |                                                                                                                                          | Language based SW DSMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35                                                                                                                                                                                 |

|                |                                                                                                                                          | 5.2.1. Munin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 36                                                                                                                                                                                 |

|                |                                                                                                                                          | 5.2.2. C Region Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 36                                                                                                                                                                                 |

|                |                                                                                                                                          | 5.2.3. Orca                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36                                                                                                                                                                                 |

|                | 5.3.                                                                                                                                     | TreadMarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36                                                                                                                                                                                 |

|                | 5.4.                                                                                                                                     | Additional SW DSM systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 37                                                                                                                                                                                 |

|                | 5.5.                                                                                                                                     | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38                                                                                                                                                                                 |

|                | 5.6.                                                                                                                                     | Relation to Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                    |

|                |                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                    |

|                |                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 41<br>43                                                                                                                                                                           |

| 6.             | Base                                                                                                                                     | eline Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                    |

| 6.             | Base<br>A Se                                                                                                                             | eline Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43                                                                                                                                                                                 |

| 6.             | Base<br>A Se<br>7.1.                                                                                                                     | eline Architecture<br>cheme to Avoid Cache-Incoherence                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>43</b><br><b>45</b><br>45                                                                                                                                                       |

| 6.             | Base<br>A Se<br>7.1.                                                                                                                     | eline Architecture cheme to Avoid Cache-Incoherence Overview Detailed Description                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>43</b><br><b>45</b><br>45<br>45                                                                                                                                                 |

| 6.             | Base<br>A Se<br>7.1.<br>7.2.<br>7.3.                                                                                                     | eline Architecture cheme to Avoid Cache-Incoherence Overview Detailed Description                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>43</li> <li>45</li> <li>45</li> <li>45</li> <li>49</li> </ul>                                                                                                             |

| 6.             | Base<br>A Se<br>7.1.<br>7.2.<br>7.3.<br>7.4.                                                                                             | eline Architecture cheme to Avoid Cache-Incoherence Overview Detailed Description Migration Extension                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>43</li> <li>45</li> <li>45</li> <li>45</li> <li>49</li> <li>52</li> </ul>                                                                                                 |

| 6.             | Base<br>A Se<br>7.1.<br>7.2.<br>7.3.<br>7.4.                                                                                             | eline Architecture cheme to Avoid Cache-Incoherence Overview Detailed Description Migration Extension Read-Only Sharing Extension                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>43</li> <li>45</li> <li>45</li> <li>45</li> <li>49</li> <li>52</li> <li>56</li> </ul>                                                                                     |

| 6.             | <b>Base</b><br>7.1.<br>7.2.<br>7.3.<br>7.4.<br>7.5.<br>7.6.                                                                              | eline Architecture cheme to Avoid Cache-Incoherence Overview Detailed Description Migration Extension Read-Only Sharing Extension Hardware Complexity                                                                                                                                                                                                                                                                                                                                             | <ul> <li>43</li> <li>45</li> <li>45</li> <li>45</li> <li>49</li> <li>52</li> <li>56</li> </ul>                                                                                     |

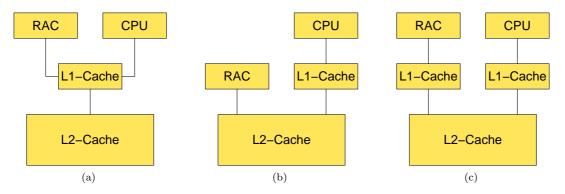

| 6.<br>7.       | <b>Base</b><br>7.1.<br>7.2.<br>7.3.<br>7.4.<br>7.5.<br>7.6.<br>7.7.                                                                      | eline Architecture cheme to Avoid Cache-Incoherence Overview Detailed Description Migration Extension Read-Only Sharing Extension Hardware Complexity 2-Level Cache Hierarchy Performance Issues                                                                                                                                                                                                                                                                                                  | <ul> <li>43</li> <li>45</li> <li>45</li> <li>45</li> <li>49</li> <li>52</li> <li>56</li> <li>57</li> </ul>                                                                         |

| 6.<br>7.       | <b>Base</b><br>7.1.<br>7.2.<br>7.3.<br>7.4.<br>7.5.<br>7.6.<br>7.7.<br><b>Syne</b>                                                       | eline Architecture cheme to Avoid Cache-Incoherence Overview Detailed Description Migration Extension Read-Only Sharing Extension Hardware Complexity 2-Level Cache Hierarchy Performance Issues                                                                                                                                                                                                                                                                                                  | <ul> <li>43</li> <li>45</li> <li>45</li> <li>45</li> <li>49</li> <li>52</li> <li>56</li> <li>57</li> <li>58</li> </ul>                                                             |

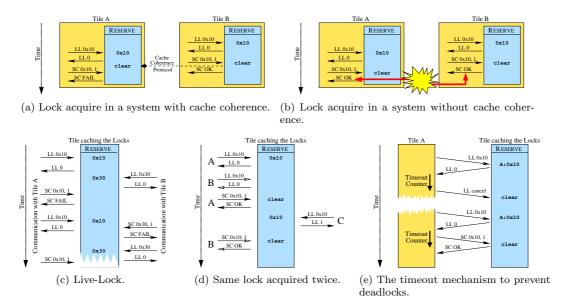

| 6.<br>7.       | Base<br>7.1.<br>7.2.<br>7.3.<br>7.4.<br>7.5.<br>7.6.<br>7.7.<br>Sync<br>8.1.                                                             | eline Architecture cheme to Avoid Cache-Incoherence Overview Detailed Description Migration Extension Read-Only Sharing Extension Hardware Complexity 2-Level Cache Hierarchy Performance Issues chronisation                                                                                                                                                                                                                                                                                     | <ul> <li>43</li> <li>45</li> <li>45</li> <li>45</li> <li>49</li> <li>52</li> <li>56</li> <li>57</li> <li>58</li> <li>61</li> </ul>                                                 |

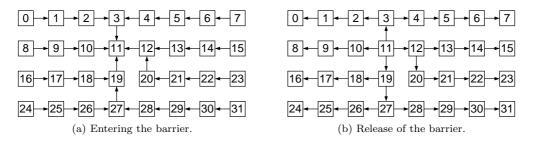

| 6.<br>7.       | Base<br>7.1.<br>7.2.<br>7.3.<br>7.4.<br>7.5.<br>7.6.<br>7.7.<br><b>Sync</b><br>8.1.<br>8.2.                                              | eline Architecture cheme to Avoid Cache-Incoherence Overview Detailed Description Migration Extension Read-Only Sharing Extension Hardware Complexity 2-Level Cache Hierarchy Performance Issues Locks Locks                                                                                                                                                                                                                                                                                      | <ul> <li>43</li> <li>45</li> <li>45</li> <li>45</li> <li>45</li> <li>52</li> <li>56</li> <li>57</li> <li>58</li> <li>61</li> <li>61</li> </ul>                                     |

| 6.<br>7.<br>8. | Base<br>A Se<br>7.1.<br>7.2.<br>7.3.<br>7.4.<br>7.5.<br>7.6.<br>7.7.<br>Syne<br>8.1.<br>8.2.<br>8.3.                                     | eline Architecture         cheme to Avoid Cache-Incoherence         Overview         Detailed Description         Migration Extension         Read-Only Sharing Extension         Hardware Complexity         2-Level Cache Hierarchy         Performance Issues         Chronisation         Locks         Barriers         Enforcing Proper Order of Memory Operations at Synchronisation Events                                                                                                | <ul> <li>43</li> <li>45</li> <li>45</li> <li>45</li> <li>49</li> <li>52</li> <li>56</li> <li>57</li> <li>58</li> <li>61</li> <li>63</li> </ul>                                     |

| 6.<br>7.<br>8. | Base<br>7.1.<br>7.2.<br>7.3.<br>7.4.<br>7.5.<br>7.6.<br>7.7.<br>Sync<br>8.1.<br>8.2.<br>8.3.<br>Ada                                      | eline Architecture         cheme to Avoid Cache-Incoherence         Overview         Detailed Description         Migration Extension         Read-Only Sharing Extension         Hardware Complexity         2-Level Cache Hierarchy         Performance Issues         Chronisation         Locks         Barriers         Enforcing Proper Order of Memory Operations at Synchronisation Events                                                                                                | <ul> <li>43</li> <li>45</li> <li>45</li> <li>45</li> <li>49</li> <li>52</li> <li>56</li> <li>57</li> <li>58</li> <li>61</li> <li>63</li> <li>65</li> </ul>                         |

| 6.<br>7.<br>8. | Base<br>7.1.<br>7.2.<br>7.3.<br>7.4.<br>7.5.<br>7.6.<br>7.7.<br>Syne<br>8.1.<br>8.2.<br>8.3.<br>Ada<br>9.1.                              | eline Architecture         cheme to Avoid Cache-Incoherence         Overview         Detailed Description         Migration Extension         Migration Extension         Read-Only Sharing Extension         Hardware Complexity         2-Level Cache Hierarchy         Performance Issues         Chronisation         Locks         Barriers         Enforcing Proper Order of Memory Operations at Synchronisation Events         pting PARMACS for the Proposed Architecture                | <ul> <li>43</li> <li>45</li> <li>45</li> <li>45</li> <li>49</li> <li>52</li> <li>56</li> <li>57</li> <li>58</li> <li>61</li> <li>63</li> <li>65</li> <li>67</li> </ul>             |

| 6.<br>7.<br>8. | <b>Base</b><br>7.1.<br>7.2.<br>7.3.<br>7.4.<br>7.5.<br>7.6.<br>7.7.<br><b>Sync</b><br>8.1.<br>8.2.<br>8.3.<br><b>Ada</b><br>9.1.<br>9.2. | eline Architecture         cheme to Avoid Cache-Incoherence         Overview         Detailed Description         Migration Extension         Migration Extension         Read-Only Sharing Extension         Hardware Complexity         2-Level Cache Hierarchy         Performance Issues         Chronisation         Locks         Barriers         Enforcing Proper Order of Memory Operations at Synchronisation Events         pting PARMACS for the Proposed Architecture         CREATE | <ul> <li>43</li> <li>45</li> <li>45</li> <li>45</li> <li>49</li> <li>52</li> <li>56</li> <li>57</li> <li>58</li> <li>61</li> <li>63</li> <li>65</li> <li>67</li> <li>67</li> </ul> |

| 6.<br>7.<br>8. | Base<br>7.1.<br>7.2.<br>7.3.<br>7.4.<br>7.5.<br>7.6.<br>7.7.<br>8.1.<br>8.2.<br>8.3.<br>Ada<br>9.1.<br>9.2.<br>9.3.                      | eline Architecture  cheme to Avoid Cache-Incoherence  Overview Detailed Description Migration Extension Read-Only Sharing Extension Hardware Complexity 2-Level Cache Hierarchy Performance Issues Chronisation Locks Barriers Enforcing Proper Order of Memory Operations at Synchronisation Events Enforcing Proper Order of Memory Operations at Synchronisation Events CREATE WAIT_FOR_END                                                                                                    | <ul> <li>43</li> <li>45</li> <li>45</li> <li>45</li> <li>49</li> <li>52</li> <li>56</li> <li>57</li> <li>58</li> <li>61</li> <li>63</li> <li>65</li> <li>67</li> <li>68</li> </ul> |

| III. Setup, Results and Related Work72                                        |

|-------------------------------------------------------------------------------|

| 10. Fictional Models 73                                                       |

| 10.1. Mystery Cache                                                           |

| 10.2. Directory Cache                                                         |

| 10.3. Software Distributed Shared Memory                                      |

| 10.4. Big Cache                                                               |

| 10.5. Fast Network                                                            |

| 10.6. Fast Synchronisation                                                    |

| 11. Benchmarks 79                                                             |

| 11.1. The SPLASH-2 Benchmarks                                                 |

| 11.2. The ALPBench Benchmark                                                  |

| 12. Simulation Setup 8                                                        |

| 12.1. Simulator                                                               |

| 12.2. System Parameters                                                       |

| 12.3. Systems Evaluated                                                       |

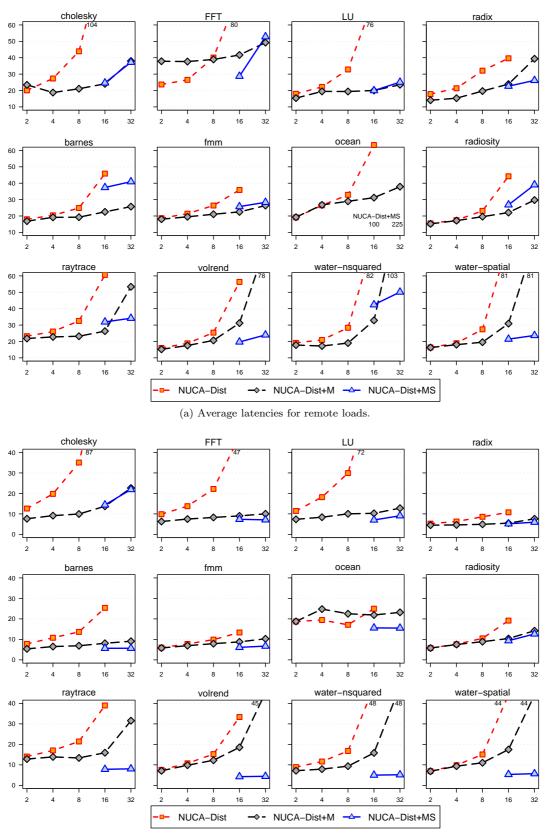

| 13. Performance Results 8                                                     |

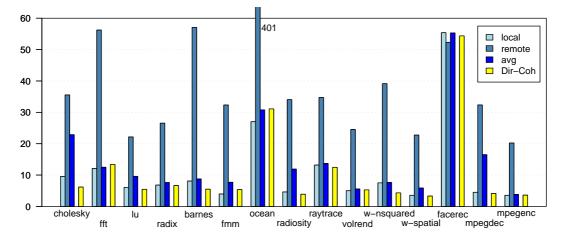

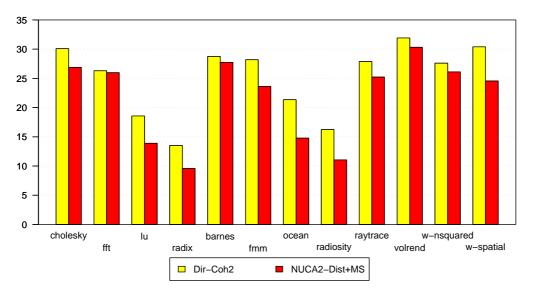

| 13.1. Overall Performance                                                     |

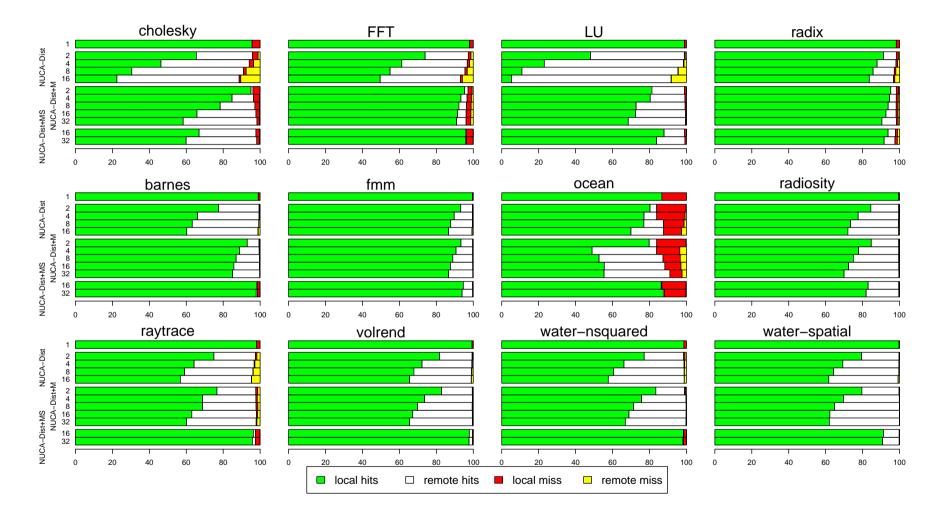

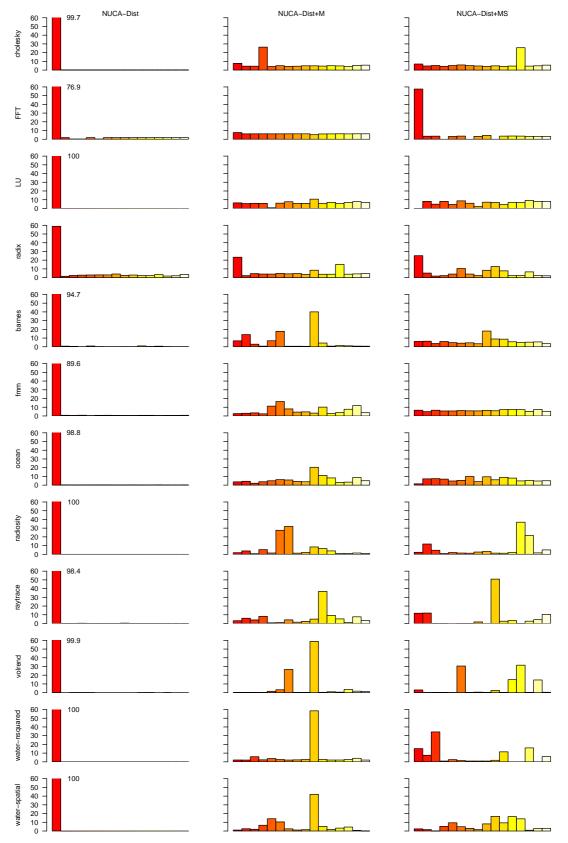

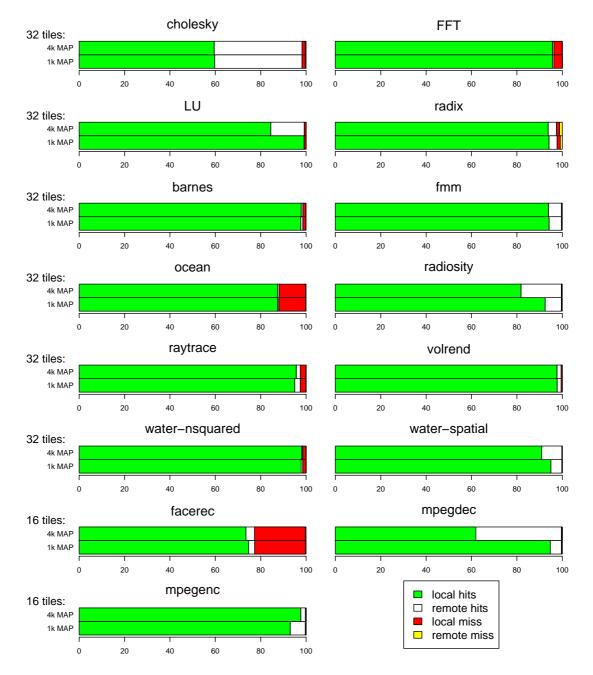

| 13.2. Memory Access Breakdown                                                 |

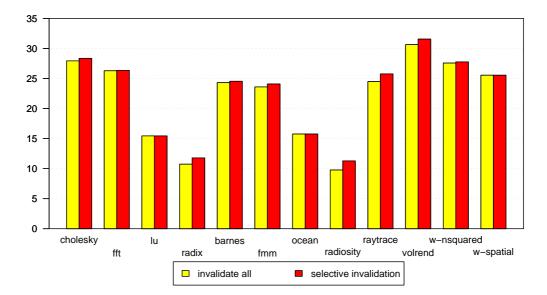

| 13.3. Latency of Lock Acquire Operations                                      |

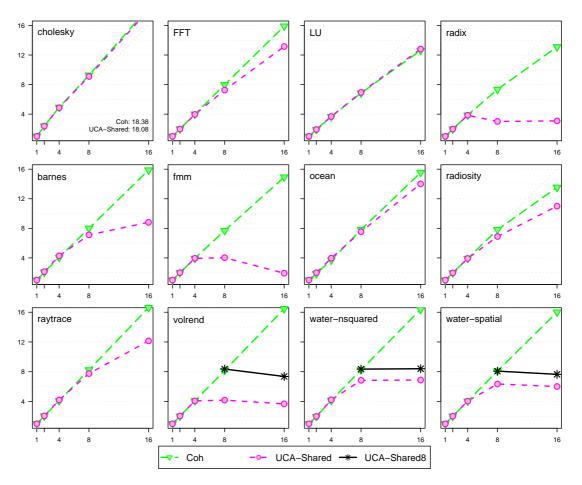

| 13.4. Software DSM Results                                                    |

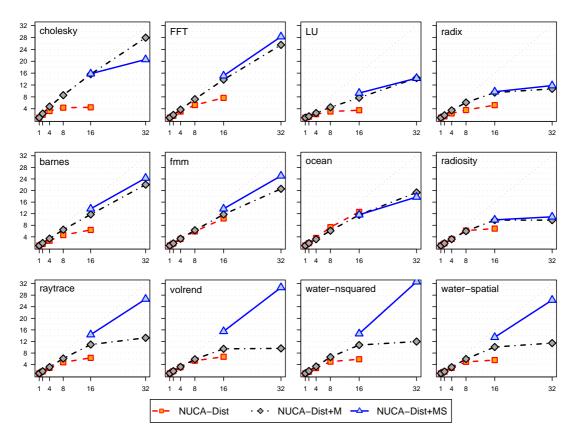

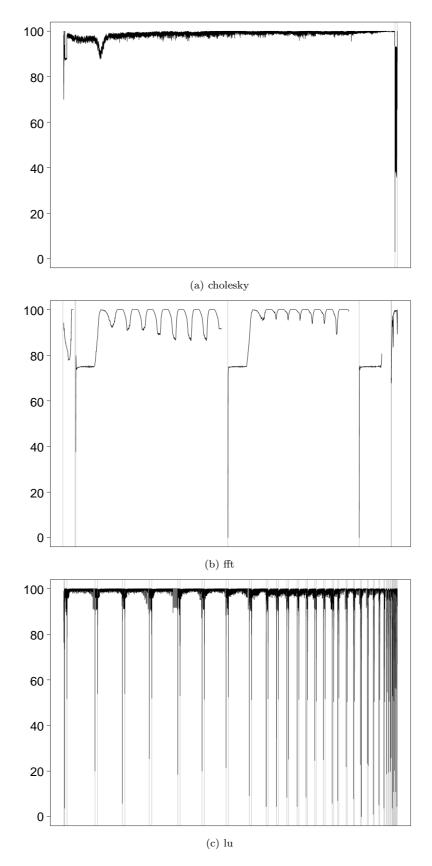

| 13.5. Impact of the Migration, Read-Only Sharing and Selective Invalidation 9 |

| 13.6. General Notes on Individual Overhead Analysis                           |

| 13.7. Analysis of Introduced Overheads by Migration and Read-Only Sharing 10  |

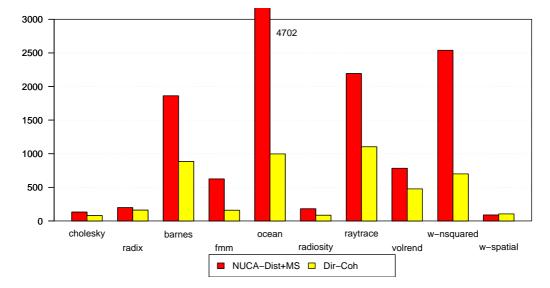

| 13.8. Network Traffic Analysis                                                |

| 13.9. Network Latencies Analysis                                              |

| 13.102-Level Cache Hierarchy                                                  |

| 13.11MAP Table Granularity                                                    |

| 13.12Effects of Sharing and Replication of Data                               |

| 14. Related Work 12                                                           |

| 14.1. Distributed Caches                                                      |

| 14.2. OS Controlled Migration                                                 |

| 14.3. Alternative Hardware Cache Coherence Schemes                            |

| 14.4. Hybrid Cache Coherence Schemes                                          |

| 14.5. Remote Access Mechanisms                                                |

| 14.6. Fast Synchronisation Mechanisms                                         |

| 15. Conclusions and Future Work 12                                            |

| 15.1. Summary of Contributions                                                |

| 15.2. Future Work                                                             |

| Bibliography 13                                                               |

| Appendix 141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|--|

| A. Liberty Simulation Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                       |  |  |  |  |  |

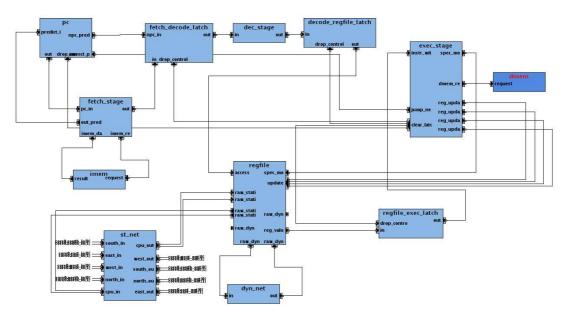

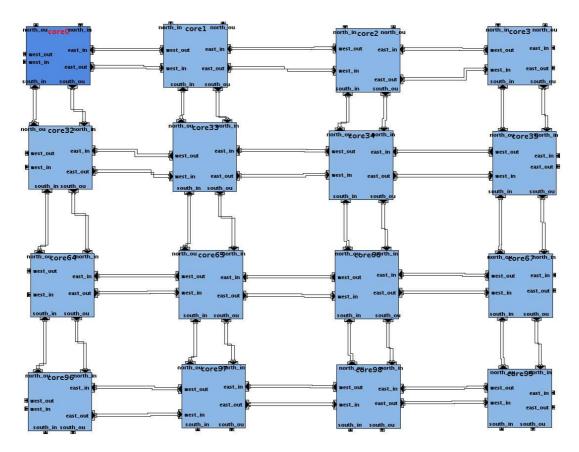

| B. The RAWplus Simulator         B.1. The Main CPU         B.1.1. Fetch Stage         B.1.2. Decode Stage         B.1.3. Register File         B.1.4. Execution and Write-Back Stage         B.2. Memory System         B.2.1. The Remote Cache Access Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |  |  |  |  |  |

| <ul> <li>B.2.2. The Cache-Coherence Module</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |  |  |  |  |  |

| C. Sample Listings C.1. Thread Creation C.2. Locks C.3. Barriers C.4. Contemportation C.5. Co | 153                                                   |  |  |  |  |  |

# 1. Introduction

## 1.1. Chip-Multiprocessors and the Cache Coherence Problem

Chip-multiprocessors (CMP) have now replaced very wide-issue out-of-order super scalar processors as they provide higher aggregate computational power, multiple clock domains, better power efficiency, and simpler design through replicated building blocks.

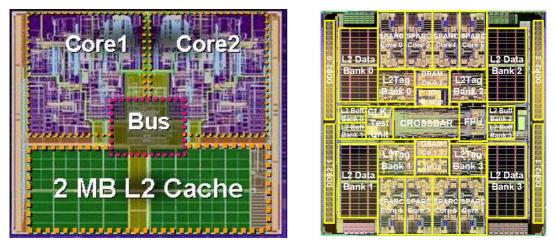

Current chip-multiprocessors are at the moment commonly built around a relatively small number of cores (2 to 8), each with its own L1, and possibly L2, cache, and are connected through an on-chip interconnect to a lower level shared cache. So far, the choice of on-chip interconnect has followed those of multi-chip symmetric multiprocessor (SMP) systems: shared bus fabrics and crossbars. Supporting shared-memory parallel applications requires cache coherence, which is greatly facilitated by the use of buses and crossbars in current CMPs. Such interconnects allow for straightforward hardware cache coherence mechanisms based on snooping [MMG<sup>+</sup>06, MB05] and directories [KST04, KAO05].

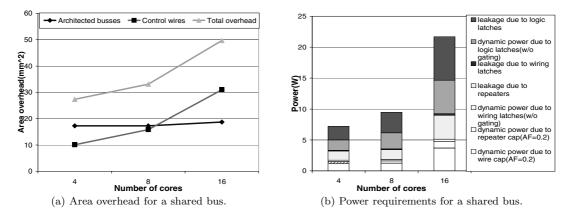

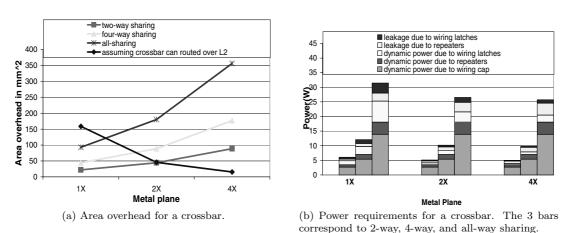

Unfortunately, as pointed out in [KZT05], future technology scaling will lead to on-chip interconnects having different sets of tradeoffs and design issues than traditional off-chip interconnects. In particular, global wires do not scale down at the same rate as other features shrink, which means that either the delay or the area overheads, or both, of buses and crossbars increase (likely exponentially for the delay and polynomially for the area) as process scales. In fact, the detailed study in [KZT05] clearly shows that the area and delay overheads of buses and crossbars will become prohibitively high in CMPs with more than 8 or 16 cores in 65nmand smaller processes. In order to scale the number of cores in a CMP above this barrier a different approach will be necessary. In particular it will be necessary to resort to a scalable interconnect type.

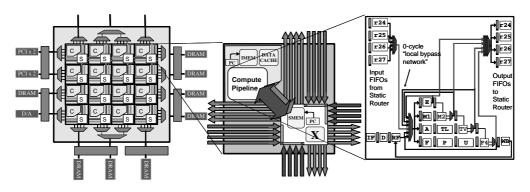

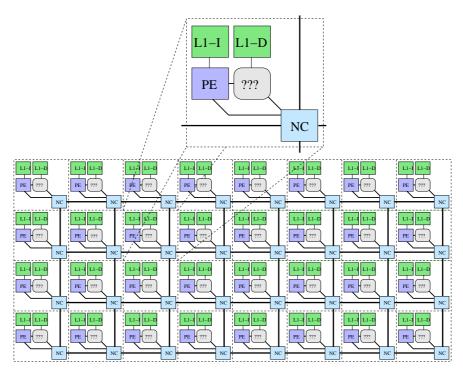

Tiled CMPs [BKM<sup>+</sup>04, CCC<sup>+</sup>02, KBH<sup>+</sup>04, SMSO03, TLM<sup>+</sup>04] (also known as cellular multiprocessors and grid processors) have been investigated with the goal of how to build a larger processor by combining multiple small "cores" together. These systems were designed with different goals in mind: Some designs tried to provide an alternative to ever more complicated super scalar processors by finding new ways of exploiting ILP in sequential applications. Other designs focused on stream processing, where the data is passed from processing element to processing element and each processing element performs a part of the total computation. Tiled CMPs are built from a relatively large number ( $\geq 32$ ) of relatively simpler cores plus a tightly integrated and lightweight point-to-point interconnect. Such interconnects are suitable not only because their peak bandwidth naturally scales with the number of cores, but also because, due to the short-length wires and low radix, their area overhead is a fixed, independent, fraction of the number of cores (unlike buses and crossbars where this overhead usually increases polynomially). Unfortunately, while these interconnects are very scalable, they do not lend themselves well to the implementation of snooping cache coherence protocols<sup>1</sup>. The alternative to continue enforcing cache coherence in such systems is to employ distributed directory schemes, which have been used in multi-chip multiprocessors in the past (e.g., [LLG<sup>+</sup>90, ASL03, LL97]). These have proven fairly scalable, reaching up to hundreds of processors. Snooping protocols are already somewhat difficult to completely debug and verify due to subtle corner cases and state transitions [Hag07]<sup>2</sup>, and distributed directories, with even more states, races, and corner cases, are notoriously even harder to debug and verify (e.g., [ASL03]).

Most of this complexity stems from the fact that requests cannot always be resolved at the home directory, but must in some cases generate further requests (such as forwarding and invalidation requests), which lead to complex protocols with subtle race conditions and several pending states. Moreover, distributed directory schemes are more involved in a CMP environment than they are in multi-chip systems. One reason for this is that in multi-chip systems the home node always has a directory entry for each and every memory line assigned to it as well as a placeholder for the data, while on a CMP each tile has only entries for the few memory lines that fit in its cache. Because caches are small and replacements are frequent, the situation where the directory information is not available on chip can occur more frequently, leading to longer pending state periods and further race conditions. Obviously, keeping more entries in each directory is possible (e.g., [BW04, CPV05, KBK02, ZA05]), at the expense of more directory storage per tile, but it still does not solve the problem of possibly frequent spills of directory state off-chip. All this complexity is of serious concern, as it is not clear how much design re-use is possible with respect to protocols and directory coherence controllers. If little design re-use is possible, and considering previous experiences with the design of such protocols, then designing and verifying the directory coherence protocol for each new generation of the CMP architecture will likely become an expensive bottleneck.

An alternative to enforce coherence in a distributed memory system is to use the OS' virtual memory (VM) system to handle the copies of virtual pages, as was done on software DSM systems (e.g., [CBZ91, KHS<sup>+</sup>97, Li88, RLW94]). In this scheme, all caches are private and it is the responsibility of software to maintain coherence. As with distributed directories, such schemes have only been tested on multi-chip systems and must be adapted to operate on a CMP. A major drawback of directly porting software DSM schemes to the CMP environment is that such schemes require moving, comparing ("diff"), and copying data in physical memory pages to enforce coherence. This is because creating multiple physical copies of the same virtual page is the only way to cope with false sharing and the inability of the hardware to identify which parts of a cache line have been modified. In this way, at communication points, such as lock transfers and barriers, the individual copies must be compared against the previous stable copy of the page and the modifications must be merged into a single new stable copy of the page. These operations are likely to be extremely costly in a CMP, will consume precious offchip memory bandwidth, and generate much pollution in the relatively small on-chip caches. In fact, previous work on software DSM systems showed that the costs of managing the multiple copies of pages, generating diffs, and updating pages, correspond to a significant fraction of the costs in these systems [ISL96].

<sup>&</sup>lt;sup>1</sup>Promising recent research has attempted to implement snooping-like protocols on top of scalable interconnects [MHW03, MH06], but their tradeoffs are still open to investigation.

<sup>&</sup>lt;sup>2</sup>Further suggestion to the difficulty of complete verification is the recent Core 2 Duo Errata AI39: "Cache Data Access Request from One Core Hitting a Modified Line in the L1 Data Cache of the Other Core May Cause Unpredictable System Behavior" [Int07]. While it is not officially stated as so, this clearly suggests some nagging bug in the coherence protocol implementation, which was only identified after product shipping.

Overall, the potentially complex hardware solution of distributed directories and the potentially high-overhead software-only solution of a VM-based scheme are two extremes in the spectrum of solutions for the cache coherence problem in tile CMPs.

## 1.2. Contribution of this Thesis

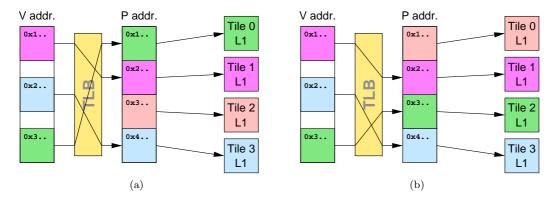

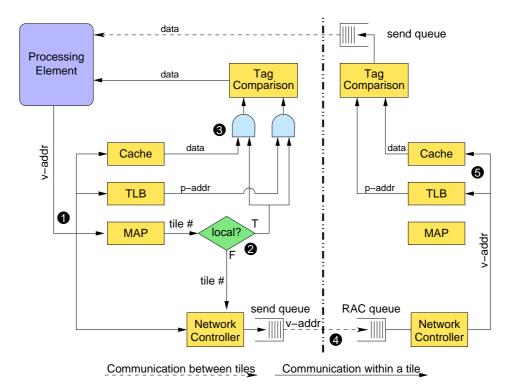

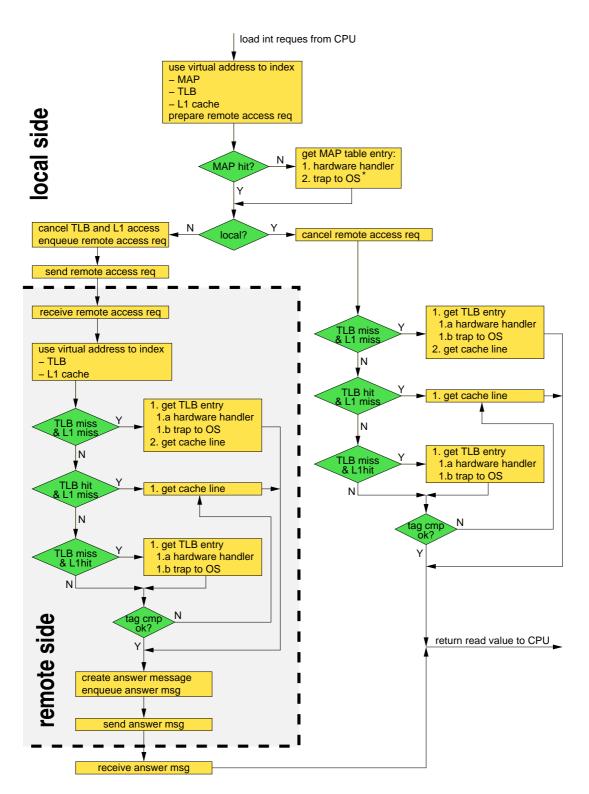

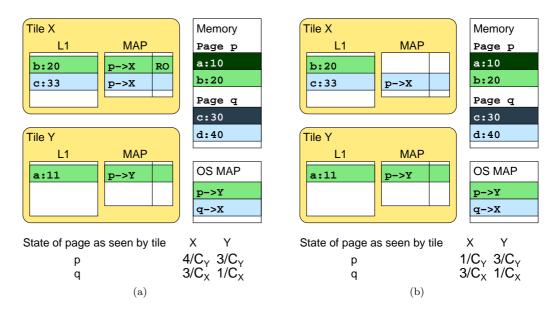

This thesis proposes an alternative cost-effective software/hardware mechanism to support shared-memory parallel applications that forgoes hardware maintained cache coherence. The proposed mechanism is based on the key ideas that mapping of lines to physical caches is done at the page level with OS support and that the hardware efficiently supports remote cache accesses. An extension of the basic scheme only allows some *controlled* migration and replication of data. Data is migrated by refreshing the page mappings at barriers. Read-only sharing is done with the help of the existing write-protection mechanisms in the TLB/OS. Overall, the mechanisms allow a sufficient degree of flexibility in the mapping and sharing. This thesis also addresses in depth some issues that arise from the implementation of the technique, such as the implementation of memory locks.

By moving the key coherence handling and decision making to software (in our case the OS), the proposed scheme, like software-managed coherence mechanisms [CH04, KOH<sup>+</sup>94], benefits from the possibility to modify the protocol after hardware shipping, which may allow for customising the protocol to application behaviour and for more easily fixing bugs. Like other recent attempts to divide coherence labour between OS/software and hardware [ZH07, ZRKH06], the mechanism is likely to be more cost-effective and easier to verify and validate than distributed directory schemes. Unlike such previous trap-based schemes, however, the small hardware extensions to support an extra level of indirection between virtual pages and tiles as well as to support remote cache accesses minimise the need for OS and trap handler activity. In the proposed scheme, only the processor's first load or store to data in a page requires trap handler intervention and only the system's first load or store to data in a page requires full OS intervention. Also, unlike recent hardware-only schemes for co-operative distributed caching [BW04, CPV05, KBK02, ZA05] the proposed scheme does not rely on broadcasts, centralised tag stores, or large redundant tag stores in order to map, locate, and access data cached remotely.

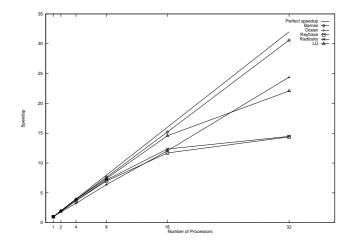

The proposed tiled CMP architecture is evaluated on benchmarks from two very different domains – the SPLASH-2 scientific benchmarks and the ALPBench multimedia benchmarks. The system is compared against one with a distributed directory cache coherence mechanism. Experimental results show that the proposed scheme performs very close to this system with a performance gap as close as 0% (no gap) and 16% on average, across all benchmarks for 16 and 32 processors.

## 1.3. Summary of Work

The basic idea of this thesis is that instead of keeping the distributed caches coherent, they are prevented from becoming incoherent by simply disallowing data to be stored in more than one cache. However, unlike previous work, this work does not move the data to another cache in order to enforce the invariant. Instead, other processors are allowed to access the cache, which stores the data, remotely. The allocation of which data is stored in which cache is done at page granularity. This information is stored in an OS managed table that is similar to the page table (used to translate virtual to physical addresses). This basic scheme is then extended to allow some form of migration and read-only sharing.

## 1.4. Structure of this Thesis

The remaining of this thesis is structured as follows: Chapter 2 to 4 discuss the motivation for this work and present important background information. Chapter 5 discusses software DSM systems, which are somewhat between related work and background information and as such deserve a separate chapter, apart from the other related work presented later in chapter 14. Chapter 6 to 9 present the baseline architecture and in detail the proposed architecture extensions. They also discuss support for synchronisation operations and how these operations are implemented in the proposed architecture. Fictional models, which are used to evaluate the performance of the proposed architecture, are presented in chapter 10. Chapter 11 presents the applications used to evaluate the proposed architecture. Chapter 12 explains the simulation setup, while chapter 13 discusses the performance of the proposed system in detail. Finally, chapter 15 concludes this thesis, and shows future research directions. Part I.

Background

# 2. Parallel Programming

Parallel programming assumes that a problem can be split into several independent parts that can be executed in parallel. These parts are then run as independent execution threads (the term thread is used here in a broader sense and should not be confused with "thread" as it is used in the context of operating systems). Although there are cases where these threads are completely independent and do not communicate with each other, in most cases some form of communication is necessary. In general there are two different approaches to how this communication is performed. One approach assumes that a shared address space exists that can be used for communication; the other approach assumes a distributed address space. Having a shared address space makes developing parallel applications more similar to developing traditional sequential applications. All programming constructs from sequential programming are still present. In particular the usage of pointers is still possible. For example, one thread might pass a pointer to another thread as part of the communication between them. Similarly a thread might just follow pointers within a linked data structure. However in the distributed memory approach things are not that simple. The destination of a pointer might be different for a different thread. For example a pointer to 0x10000000 might point for one thread to the beginning of a linked list element, while on another one it points to the middle of the data structure. Due to this problem, threads cannot use pointers when communicating with each other. Instead, the whole element has to be sent as a message from one thread to the other. This restriction makes it more complicated to pass information that is stored in pointer based data structures from one thread to another.

On the actual hardware side, these two approaches have been matched with machines that lend themselves particularly well to one of the approaches. Shared memory machines are a good match for the approach that assumes a shared address space, while machines with distributed memory are more suited for the approach that does not assume this shared address space. However, it should be noted that either machine is able to also support the other approach. A shared memory machine can communicate by messages through the shared address space without using pointers. And a distributed memory machine can use an additional software layer that provides the illusion of a shared address space. The following sections describe these programming schemes in more detail and highlight their respective advantages and disadvantages.

## 2.1. Message Passing

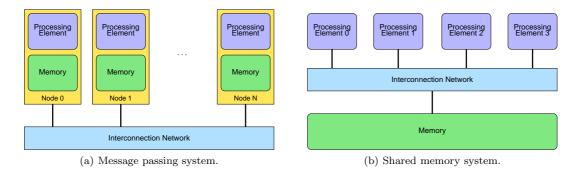

Message passing systems have been developed as a solution to combine the computational power of several smaller systems in order to process larger programs. Usually each system is a self contained computer with its own processor and memory. These nodes are then connected using some kind of interconnect. The basic structure is shown in figure 2.1a. The whole computation is now broken into smaller parts that are assigned to individual nodes. Each node performs a

#### 2. Parallel Programming

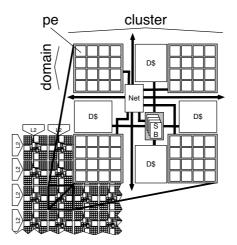

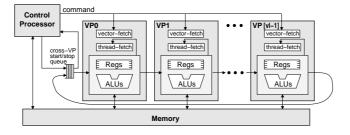

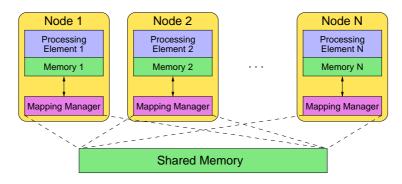

Figure 2.1: Overview of basic parallel systems.

part of the computation and then sends the intermediate results to other nodes that depend on these results.

One advantage of message passing systems is that they scale to thousands of nodes (for example the largest Blue Gene/L installation features 106,496 nodes). Furthermore, since it exposes communication directly to the programmer, he or she can optimise the algorithms to the communication pattern. However, this exposed communication is also the obstacle for the widespread use of message passing systems. Programmers have to handle data placement (including replication) and migration themselves. These tasks are non-trivial and sometimes as demanding as the development of the program itself. Still, it seems that there is today no alternative programming model to write applications for systems with thousands of nodes other than message passing.

## 2.2. Shared Memory

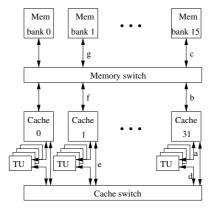

The Shared Memory model has first been used in early multi chip multiprocessors that connect several CPUs via a shared bus to a memory system (shown in figure 2.1b). This model simplifies it for programmers to write multi processor programs, since it removes the burden of distributing data across different nodes and accessing data that is stored on a remote node. Since CPUs in these early systems did not have local caches or out-of-order execution, the shared bus could act as serialisation point for all memory requests. All write accesses become immediately visible to all processing elements.

One problem has been created with the introduction of hardware caches: processing elements keep local copies of data for fast access under hardware control. This data might no longer be identical to the data stored in main memory: writes by other processors to shared memory might not be reflected in the local cache. Similarly writes to the local cache might not be written back to shared memory that is visible to all.

Another problem is caused by out-of-order execution, since it allows processing elements to reorder instructions differently from the original order specified in the program. While a processing element ensures that by doing so the semantic is not changed with respect to single processor execution, the situation becomes more complicated once out-of-order processing elements are used in a multi processor system. Imagine a program that spins on a memory variable before it reads some other value from memory. An out-of-order processor might not detect a dependency for the second load and issue it before the spinning load. These problems have prompted research into consistency models, their relations with each other and programming implications. These models will be briefly discussed in sections 2.2.1 to 2.2.3.

In terms of scalability, the largest shared memory system built so far consists of 512 nodes (SGI Altix 3000). While Cray X1E allows up to 1024 nodes with 4 processors each, no such system has been installed so far.

#### 2.2.1. Sequential Consistency

Sequential Consistency (SC) is probably the oldest and most intuitive consistency model that exists [Lam79]. The model makes two requirements: firstly, all memory requests issued by an individual processor appear in the order specified by the program. Secondly, all memory requests from all processors appear to be serviced from a single FIFO queue.

While these requirements make programming fairly straight forward, they limit hardware scalability, instruction level parallelism, etc. For example, a single FIFO queue would soon become a bottleneck. Based on these observations two research areas have started: Ways to support more sophisticated hardware while still maintaining Sequential Consistency and research into other consistency models. The first area includes techniques such as cache coherence protocols (discussed in more detail in chapter 3), memory barriers to prevent reordering of memory instruction across the barrier and speculation based approaches that require a rollback once a modification to an address with an out-of-order load is detected [GFV99, Yea96].

Also, since enforcing Sequential Consistency in hardware can be very costly, research started into other consistency models that are less restrictive than Sequential Consistency and either still allow an intuitive way of programming or implement Sequential Consistency using library functions. Providing a full list of other consistency models is outside the scope of this thesis. Adve and Gharachorloo have compiled a list of several consistency models, their implementation and programming implications [AG96]. Steinke and Nutt have compiled a similar list, but also investigate the relation between different consistency models [SN04]. The next sections present some important consistency models that will be referred to in later parts of this thesis.

#### 2.2.2. Weak Consistency

Even though Sequential Consistency is a very intuitive model, its main problem is the additional cost required to maintain the illusion of serialised accesses to memory. It has been noted that requiring this for every memory operation is mostly unnecessary. Thus, models were developed that do not enforce the requirement of sequential access for all memory accesses, but still offer a sufficient intuitive behaviour to be useful to programmers. Dubois et al. [DSB86] noticed that it was enough to ensure Sequential Consistency for access to synchronisation variables and make a few further restrictions on other memory accesses. The model they proposed was called Weak Consistency and requires that:

- Access to shared synchronisation variables is sequentially consistent.

- No access to a shared synchronisation variable is performed before all previous memory requests to shared data have been completed.

- No access to normal shared data is performed before all access to shared synchronisation variables have been completed.

#### 2. Parallel Programming

These conditions ensure that a normal access to shared data will either be before or after a synchronisation operation. All processing nodes must see these normal accesses occur in this order with respect to the synchronisation operation. These simple restrictions match the requirements for locks and barriers very well and as such allow an easy implementation of these synchronisation constructs.

#### 2.2.3. Release Consistency

The above restrictions might be sometimes too strict, since they just assume one kind of synchronisation operation. Instead synchronisation operations are usually used for different purposes: some instructions are used to import updated information (such as the acquire of a lock); other instructions are used to export information (such as the release of a lock). Gharachorloo et al. [GLL+90] used this observation to define a more relaxed consistency model called "Release Consistency" (RC). The model requires that:

- Before a normal load or store operation is allowed to perform<sup>1</sup> with respect to any other processor, all previous acquire accesses must be performed.

- Before a release access is allowed to perform with respect to any other processor, all previous normal load and store operation must be performed.

- Special accesses (such as acquire and release) are sequentially consistent with respect to one another.

An acquire operation guarantees that the process is provided with all required updates. There are two different flavours of release consistency:

- **Eager Release Consistency** requires that all updates be performed when an acquire operation happens.

- Lazy Release Consistency tries to delay all updates as much as possible [KCZ92]. The idea is to only make memory updates visible if these are really needed. For example, the arrays a, b and c were modified and thread x is acquiring a lock. Eager Release Consistency would now require that all modifications are made visible to thread x. However, this might be unnecessary, if thread x only accesses array b. Thus, with Lazy Release Consistency thread x is only informed that a, b and c are modified. Once an actual access to one of these arrays in performed, then the modifications to that array are made visible to thread x.

Making modifications visible usually involves communication between different threads. By reducing the number of modifications that are made visible, Lazy Release Consistency is able to reduce the amount of communication that is required.

Release consistency is the consistency model that is used by a wide range of languages, such as Java [GJSB05], OpenMP [Ope05] and Unified Parallel C [UPC05].

<sup>&</sup>lt;sup>1</sup>The expression "to perform" refers to accessing the memory and either reading or storing a value to/from a register. An access is considered "performed" once its outcome can no longer be affected by another access.

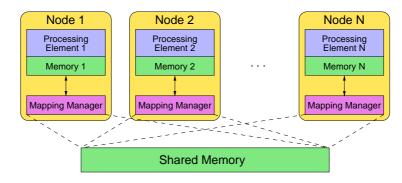

Figure 2.2: Overview of a distributed shared memory.

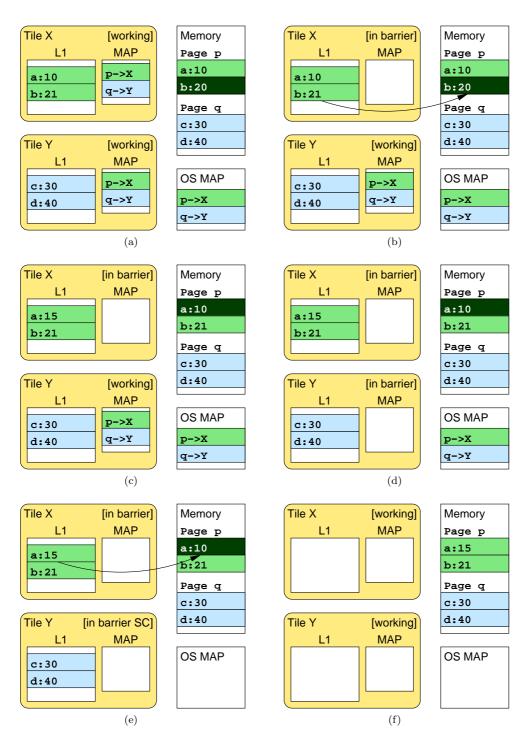

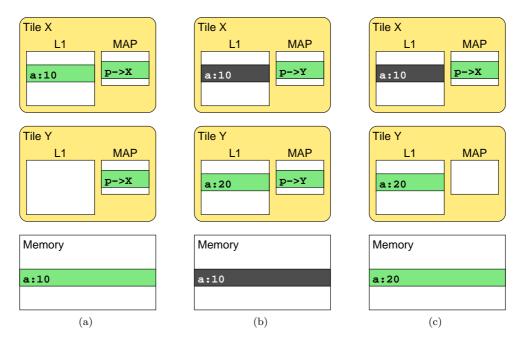

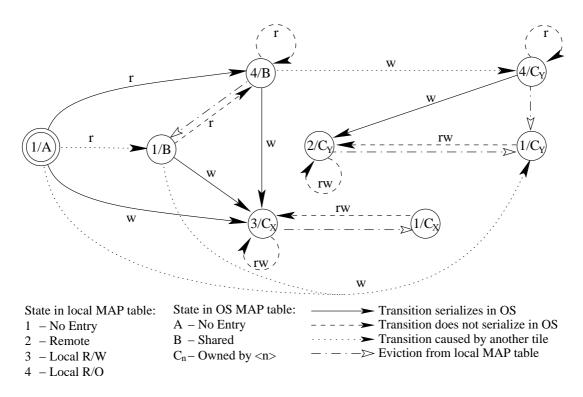

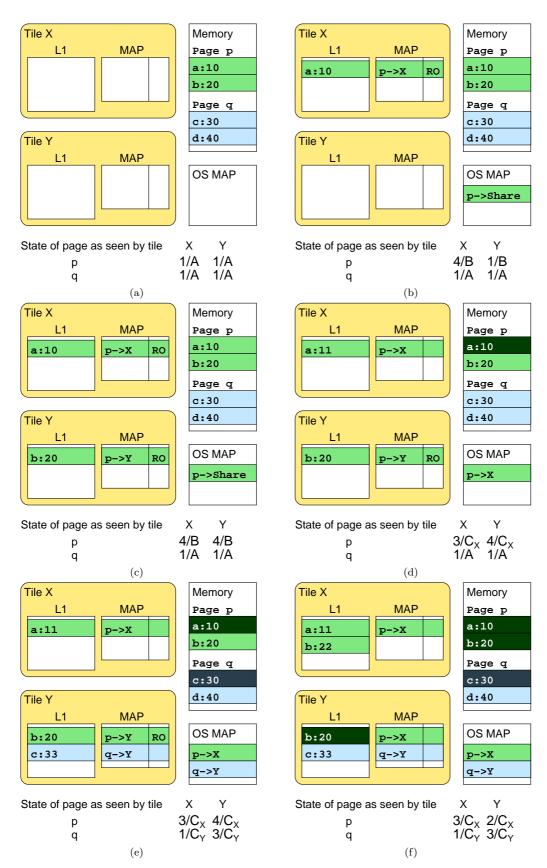

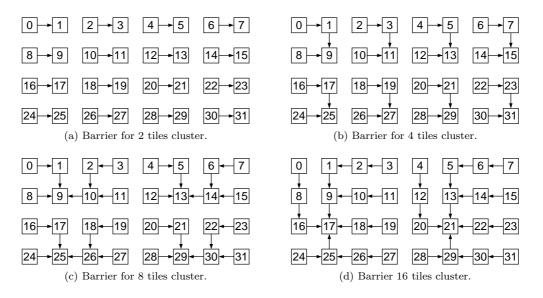

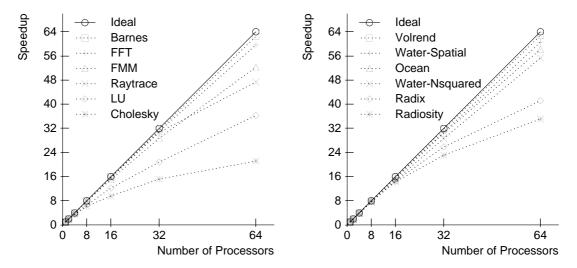

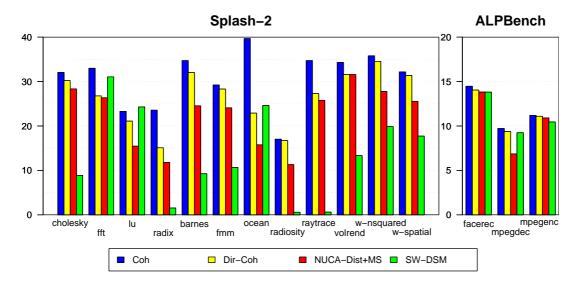

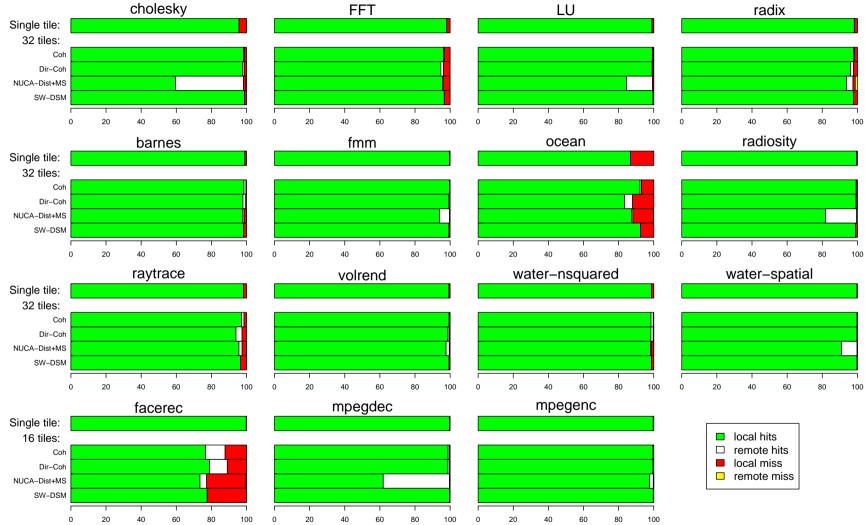

#### 2.2.4. Processor Consistency