# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# **Efficient Cross-architecture Hardware Virtualisation**

Tom Spink

Doctor of Philosophy

Institute for Computing Systems Architecture

School of Informatics

University of Edinburgh

2016

#### **Abstract**

Hardware virtualisation is the provision of an isolated virtual environment that represents real physical hardware. It enables operating systems, or other system-level software (the *guest*), to run unmodified in a "container" (the *virtual machine*) that is isolated from the real machine (the *host*).

There are many use-cases for hardware virtualisation that span a wide-range of end-users. For example, home-users wanting to run multiple operating systems side-by-side (such as running a Windows® operating system inside an OS X environment) will use virtualisation to accomplish this. In research and development environments, developers building experimental software and hardware want to prototype their designs quickly, and so will virtualise the platform they are targeting to isolate it from their development workstation. Large-scale computing environments employ virtualisation to consolidate hardware, enforce application isolation, migrate existing servers or provision new servers. However, the majority of these use-cases call for *same*-architecture virtualisation, where the architecture of the guest and the host machines match—a situation that can be accelerated by the hardware-assisted virtualisation extensions present on modern processors. But, there is significant interest in virtualising the hardware of different architectures on a host machine, especially in the architectural research and development worlds.

Typically, the instruction set architecture of a guest platform will be different to the host machine, e.g. an ARM guest on an x86 host will use an ARM instruction set, whereas the host will be using the x86 instruction set. Therefore, to enable this cross-architecture virtualisation, each guest instruction must be emulated by the host CPU—a potentially costly operation. This thesis presents a range of techniques for accelerating this instruction emulation, improving over a state-of-the art instruction set simulator by  $2.64\times$ . But, emulation of the guest platform's instruction set is not enough for full hardware virtualisation. In fact, this is just one challenge in a range of issues that must be considered. Specifically, another challenge is efficiently handling the way external interrupts are managed by the virtualisation system. This thesis shows that when employing efficient instruction emulation techniques, it is not feasible to arbitrarily divert control-flow without consideration being given to the state of the emulated processor. Furthermore, it is shown that it is possible for the virtualisation

environment to behave incorrectly if particular care is not given to the point at which control-flow is allowed to diverge. To solve this, a technique is developed that maintains efficient instruction emulation, and correctly handles external interrupt sources.

Finally, modern processors have built-in support for hardware virtualisation in the form of instruction set extensions that enable the creation of an abstract computing environment, indistinguishable from real hardware. These extensions enable guest operating systems to run directly on the physical processor, with minimal supervision from a hypervisor. However, these extensions are geared towards same-architecture virtualisation, and as such are not immediately well-suited for cross-architecture virtualisation. This thesis presents a technique for exploiting these existing extensions, and using them in a cross-architecture virtualisation setting, improving the performance of a novel cross-architecture virtualisation hypervisor over state-of-the-art by  $2.5\times$ .

## Lay Summary

Processors are at the centre of any computer system, and they can be found in surprising places. Laptops, smart phones, fridges, toasters, televisions and ovens are all examples of where computer processors can be found in the modern world. A significant problem is that these processors all need to be designed and tested by someone, but how can you test the design for a processor that has not been created yet? The answer to this is to simulate the processor, and realistically, the simulator should be fast.

The easiest way to simulate a new processor is to make a computer program that pretends to be this new processor, and runs it step-by-step. But, this kind of approach to simulation is not very fast, so the underlying goal of this thesis is to speed it up. A standard technique to improve this is to convert a whole sequence of individual steps into one larger (but more efficient) step. However, this technique can be implemented in a number of ways, and the first key idea is to look at the connections between the steps in more detail, to make jumping between them more efficient.

If you want to simulate an entire computer system, however, this approach is still not good enough, because there are a lot more things to consider. For example, when you use a keyboard, it tells the processor to stop what it is doing, and look at the key that was pressed. This kind of behaviour also slows down simulators, so another idea presented is a fast means of handling this.

Finally, the key idea presented at the end of this thesis is that instead of writing a program that pretends to be a processor, you can take the similarities between a real processor and the simulated processor, and use this to speed up the simulation.

## Acknowledgements

There are a range of people that I would like to acknowledge for their support during my time as a PhD student, and I would like to begin by thanking the residents of office 1.34, who made my time at the University of Edinburgh thoroughly enjoyable, and were an excellent forum for ideas. Specifically, I would like to extend my thanks to Oscar Almer, Matthew Bielby, Bruno Bodin, Tobias Edler von Koch, Stephen Kyle and Volker Seeker for their excellent company and support. Deserving a special mention is my friend Harry Wagstaff, whom I have collaborated with over the past few years.

I would also like to extend my deepest thanks and gratitude to Björn Franke, who has been a fantastic supervisor—his guidance has been invaluable and his support and encouragement has made this research a thoroughly enjoyable experience.

And finally, I would like to thank my family, and especially my wife Jennifer, for the encouragement, the support and the patience they have continually shown me throughout this escapade.

# **Declaration**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified.

(Tom Spink)

### **Publications**

The following publications have been made during the course of this PhD, some of which are used as the basis for chapters:

- Tom Spink, Harry Wagstaff and Björn Franke

"Hardware Accelerated Cross-Architecture Full-System Virtualization"

In ACM Transactions on Architecture and Code Optimization (TACO) 13, 4,

Article 36, October 2016

- This publication forms the basis of Chapter 6

- Tom Spink, Harry Wagstaff and Björn Franke

"Efficient Asynchronous Interrupt Handling in a Full-system Instruction Set Simulator"

In Proceedings of the 2016 SIGPLAN/SIGBED conference on Languages, compilers and tools for embedded systems (LCTES'16), Santa Barbara, CA, USA, June 2016.

- This publication forms the basis of Chapter 5

- Tom Spink, Harry Wagstaff, Björn Franke and Nigel Topham

"Efficient Dual-ISA Support in a Retargetable, Asynchronous Dynamic Binary Translator"

In Proceedings of the 2015 International Conference on Embedded Computer

In Proceedings of the 2015 International Conference on Embedded Computer Systems, Architectures, Modeling and Simulation (SAMOS'15), Samos Island, Greece, July 2015.

- Tom Spink, Harry Wagstaff, Björn Franke and Nigel Topham "Efficient code generation in a region-based dynamic binary translator." In Proceedings of the 2014 SIGPLAN/SIGBED conference on Languages, compilers and tools for embedded systems (LCTES'14), Edinburgh, UK, June 2014.

- This publication forms the basis of Chapter 4

- Harry Wagstaff, Tom Spink and Björn Franke

"Automated ISA branch coverage analysis and test case generation for retargetable instruction set simulators"

In Proceedings of the 2014 International Conference on Compilers, Architecture and Synthesis for Embedded Systems (CASES'14), New Delhi, June 2014.

# **Table of Contents**

| 1 | Intr | oductio | on                                              | 1  |

|---|------|---------|-------------------------------------------------|----|

|   | 1.1  | Backg   | round                                           | 3  |

|   | 1.2  |         | ation                                           | 5  |

|   | 1.3  |         | iew & Contributions                             | 7  |

| 2 | Bacl | kgroun  | d & Related Work                                | 9  |

|   | 2.1  | Termi   | nology                                          | 9  |

|   |      | 2.1.1   | Overview                                        | 9  |

|   |      | 2.1.2   | Definitions                                     | 10 |

|   | 2.2  | Instru  | ction Emulation                                 | 12 |

|   |      | 2.2.1   | Interpretation                                  | 12 |

|   |      | 2.2.2   | Dynamic Binary Translation                      | 14 |

|   |      | 2.2.3   | Translation Granularity                         | 15 |

|   |      | 2.2.4   | Region-based DBT Systems                        | 16 |

|   |      | 2.2.5   | Code Generation and Optimisation in DBT Systems | 16 |

|   |      | 2.2.6   | DBT Systems using LLVM for JIT Compilation      | 18 |

|   | 2.3  | Interru | upt Handling                                    | 18 |

|   |      | 2.3.1   | Virtual Machines                                | 21 |

|   | 2.4  | MMU     | Virtualisation                                  | 21 |

|   | 2.5  | User-n  | node Simulation                                 | 22 |

|   | 2.6  | Hardw   | vare Virtualisation                             | 25 |

|   |      | 2.6.1   | Same-architecture Virtualisation                | 25 |

|   |      | 2.6.2   | Cross-architecture Virtualisation               | 28 |

|   | 2.7  | Summ    | arv                                             | 31 |

| 3 | Infr  | astruct  | ure                                       | 33 |

|---|-------|----------|-------------------------------------------|----|

|   | 3.1   | GENSI    | M                                         | 33 |

|   |       | 3.1.1    | High-level Architecture Description       | 35 |

|   |       | 3.1.2    | Output Components                         | 37 |

|   |       | 3.1.3    | Automated Model Testing                   | 38 |

|   | 3.2   | ARCSI    | M                                         | 38 |

|   |       | 3.2.1    | LIVM Compiler Infrastructure              | 40 |

|   | 3.3   | CAPTIV   | VE                                        | 40 |

|   |       | 3.3.1    | KVM                                       | 41 |

|   |       | 3.3.2    | Intel VT                                  | 42 |

|   | 3.4   | QEMU     | Г                                         | 43 |

|   | 3.5   | Evalua   | ntion                                     | 43 |

|   |       | 3.5.1    | Guest Architecture and Platform           | 44 |

|   |       | 3.5.2    | SPEC-CPU2006 Benchmark Suite              | 45 |

|   |       | 3.5.3    | EEMBC Benchmark Suite                     | 46 |

|   |       | 3.5.4    | Choice of Benchmarks                      | 46 |

| 4 | Effic | cient Dy | ynamic Binary Translation                 | 47 |

|   | 4.1   | Introd   | uction                                    | 48 |

|   |       | 4.1.1    | Key Ideas                                 | 48 |

|   |       | 4.1.2    | Motivating Example                        | 49 |

|   |       | 4.1.3    | Contributions                             | 53 |

|   |       | 4.1.4    | Overview                                  | 53 |

|   | 4.2   | Backg    | round                                     | 54 |

|   |       | 4.2.1    | Region Compilation                        | 54 |

|   |       | 4.2.2    | Region Selection                          | 55 |

|   | 4.3   | Metho    | dology                                    | 56 |

|   |       | 4.3.1    | Region Entry Optimisation                 | 56 |

|   |       | 4.3.2    | Translation Lookup Cache                  | 57 |

|   |       | 4.3.3    | Branching                                 | 57 |

|   |       | 4.3.4    | Region Chaining                           | 60 |

|   |       | 4.3.5    | Region Registration in Translation Caches | 61 |

|   |       | 4.3.6    | Continuous Profiling and Recompilation    | 61 |

|   |       | 4.3.7    | Host Machine Code Generation              | 62 |

|   | 4.4   | Experi   | mental Evaluation                         | 65 |

|   |       | 4.4.1    | Experimental Methodology 65                                    |  |

|---|-------|----------|----------------------------------------------------------------|--|

|   |       | 4.4.2    | Experimental Results for SPEC-CPU2006 66                       |  |

|   |       | 4.4.3    | Impact of Optimisations 67                                     |  |

|   |       | 4.4.4    | JIT Compilation Performance 69                                 |  |

|   | 4.5   | Summ     | ary & Conclusions                                              |  |

| 5 | Effic | cient In | iterrupt Virtualisation 71                                     |  |

|   | 5.1   | Introd   | uction                                                         |  |

|   |       | 5.1.1    | Key Idea                                                       |  |

|   |       | 5.1.2    | Motivating Example                                             |  |

|   |       | 5.1.3    | Contributions                                                  |  |

|   |       | 5.1.4    | Overview                                                       |  |

|   | 5.2   | DBT G    | Granularity and the Problem of Inserting Interrupt Checks . 79 |  |

|   | 5.3   | Region   | n-based Interrupt Checking                                     |  |

|   |       | 5.3.1    | Avoiding Interrupt Edge Bloat 81                               |  |

|   |       | 5.3.2    | Interrupt Check Placement Schemes 82                           |  |

|   |       | 5.3.3    | Servicing an Interrupt                                         |  |

|   | 5.4   | Experi   | imental Evaluation                                             |  |

|   |       | 5.4.1    | Experimental Methodology                                       |  |

|   |       | 5.4.2    | Experimental Setup                                             |  |

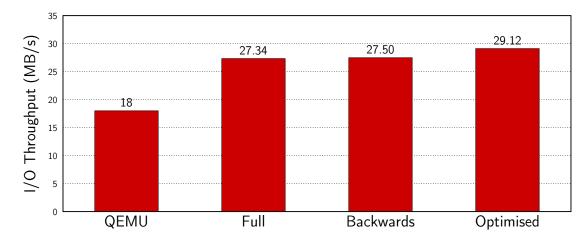

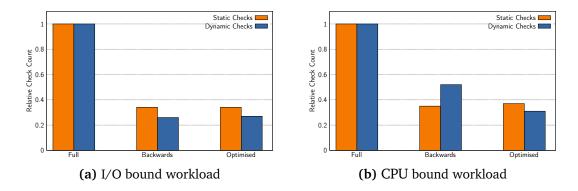

|   |       | 5.4.3    | Key Results for I/O-bound Workloads 88                         |  |

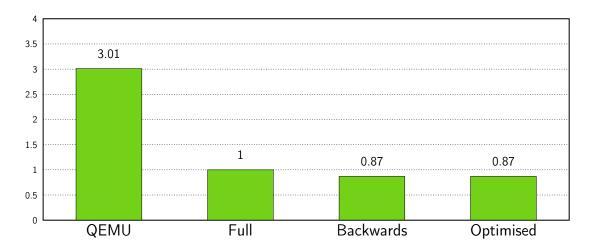

|   |       | 5.4.4    | Key Results for CPU-bound Workloads 88                         |  |

|   |       | 5.4.5    | Further Analysis                                               |  |

|   | 5.5   | Summ     | nary & Conclusions                                             |  |

| 6 | Har   | dware .  | Accelerated Cross-architecture Virtualisation 95               |  |

|   | 6.1   | Introd   | uction                                                         |  |

|   |       | 6.1.1    | Key Idea                                                       |  |

|   |       | 6.1.2    | Motivating Example                                             |  |

|   |       | 6.1.3    | Contributions                                                  |  |

|   |       | 6.1.4    | Overview                                                       |  |

|   | 6.2   | Backg    | round                                                          |  |

|   |       | 6.2.1    | KVM                                                            |  |

|   |       | 6.2.2    | Intel VT                                                       |  |

|   | 6.3   | Virtua   | lisation Infrastructure                                        |  |

|   |       | 6.3.1    | System Components                                              |  |

|    |       | 6.3.2   | Overview                                                                                        | 106 |

|----|-------|---------|-------------------------------------------------------------------------------------------------|-----|

|    |       | 6.3.3   | CPU Virtualisation                                                                              |     |

|    |       | 6.3.4   | MMU Virtualisation                                                                              |     |

|    |       | 6.3.5   | Device Virtualisation                                                                           |     |

|    |       | 6.3.6   | IRQ Virtualisation                                                                              |     |

|    | 6.4   | Experi  | mental Evaluation                                                                               |     |

|    |       | 6.4.1   | Experimental Setup                                                                              |     |

|    |       | 6.4.2   | Key Results                                                                                     |     |

|    |       | 6.4.3   | Comparison to Existing Techniques                                                               |     |

|    |       | 6.4.4   | I/O Performance                                                                                 |     |

|    |       | 6.4.5   | Additional Hardware Support for MMU Virtualisation                                              | 134 |

|    |       | 6.4.6   | Slow-down over Native Execution on High-End Hardware                                            |     |

|    | 6.5   | Summ    | ary & Conclusions                                                                               | 136 |

|    |       |         |                                                                                                 |     |

| 7  | Con   | clusion | s                                                                                               | 137 |

|    | 7.1   | Contri  | butions                                                                                         | 138 |

|    |       | 7.1.1   | Efficient Dynamic Binary Translation                                                            | 138 |

|    |       | 7.1.2   | Efficient Interrupt Virtualisation                                                              | 138 |

|    |       | 7.1.3   | $\label{prop:continuous} \mbox{Hardware Accelerated Cross-architecture Virtualisation} \ . \ .$ | 139 |

|    | 7.2   | Critica | l Analysis                                                                                      | 140 |

|    |       | 7.2.1   | GENSIM Limitations                                                                              | 140 |

|    |       | 7.2.2   | Significantly Different Memory Management Units                                                 | 140 |

|    |       | 7.2.3   | Assumptions                                                                                     | 141 |

|    | 7.3   | Future  | . Work                                                                                          | 141 |

|    |       | 7.3.1   | Efficient Interrupt Virtualisation                                                              | 142 |

|    |       | 7.3.2   | Hardware Accelerated Cross-architecture Virtualisation                                          | 143 |

|    | 7.4   | Summ    | ary and Final Remarks                                                                           | 146 |

| Bi | bliog | raphy   |                                                                                                 | 147 |

|    | . 0   |         |                                                                                                 |     |

# List of Figures

| 1.1 | Real hardware vs. virtual hardware                                    | 2   |

|-----|-----------------------------------------------------------------------|-----|

| 1.2 | Types of hypervisors                                                  | 4   |

| 1.4 | Types of Hypervisors                                                  | 4   |

| 2.1 | A typical <i>fetch</i> , <i>decode</i> , <i>execute</i> sequence      | 12  |

| 2.2 | Example loop-based and threaded interpreter implementations           | 13  |

| 2.3 | Example synchronous and hybrid dynamic binary translator im-          |     |

|     | plementations                                                         | 14  |

| 2.4 | An illustration of how interrupt checking might work in an interprete | er- |

|     | based system                                                          | 19  |

|     |                                                                       |     |

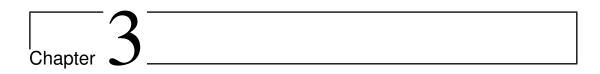

| 3.1 | A high-level overview of the GENSIM generation tool                   |     |

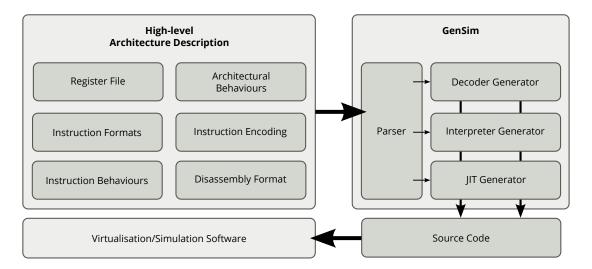

| 3.2 | Main execution loop of ArcSim                                         | 39  |

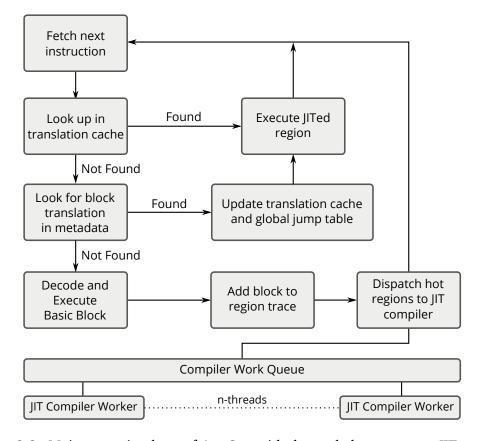

| 3.3 | High-level overview of CAPTIVE                                        | 41  |

| 4.1 | Two methods of instruction emulation: an interpreter, and a dy-       |     |

|     | namic binary translator                                               | 47  |

| 4.2 | An example ARM function that calculates the factorial of a number.    | 50  |

| 4.3 | Sub-optimal and optimal host machine code generated by two            |     |

|     | different code generation strategies                                  | 52  |

| 4.4 | Example control-flow graphs                                           | 54  |

| 4.5 | Interaction between regions via the global jump table and the         |     |

|     | internal interactions between basic blocks, either directly or via    |     |

|     | the local jump table                                                  | 57  |

| 4.6 | Sub-optimal code resulting from incomplete alias analysis             | 64  |

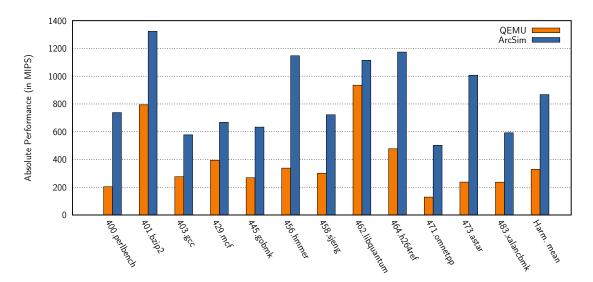

| 4.7 | Absolute performance figures in MIPS for the long-running SPEC-       |     |

|     | CPU2006 integer benchmarks                                            | 66  |

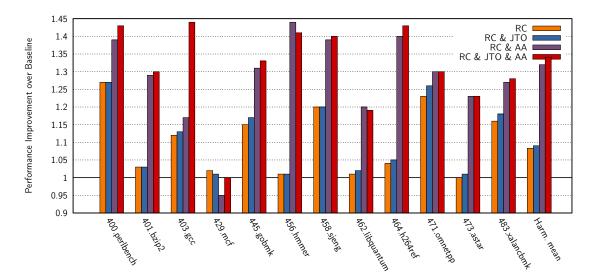

| 4.8  | A breakdown of the performance impact of different optimisations.    | 67  |

|------|----------------------------------------------------------------------|-----|

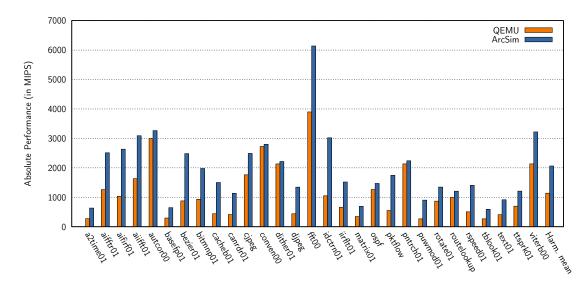

| 4.9  | Absolute performance figures in MIPS for the shorter-running         |     |

|      | EEMBC benchmarks                                                     | 68  |

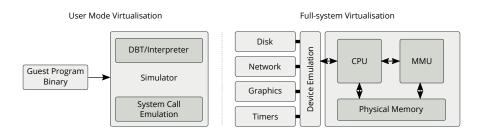

| 5.1  | Differences between user-mode simulation and hardware virtu-         |     |

|      | alisation                                                            | 71  |

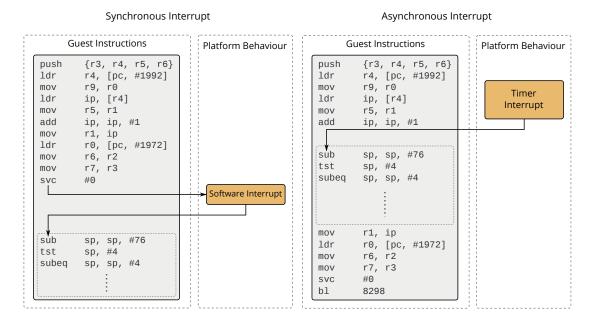

| 5.2  | A comparison between synchronous and asynchronous interrupts.        | 72  |

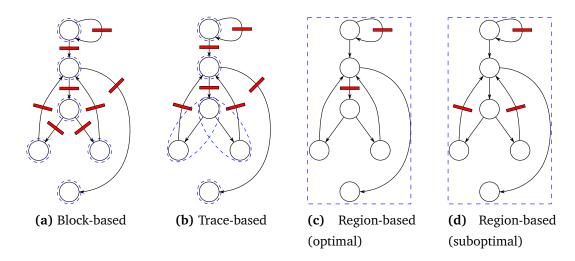

| 5.3  | Interrupt checks inserted by various interrupt check placement       |     |

|      | schemes                                                              | 75  |

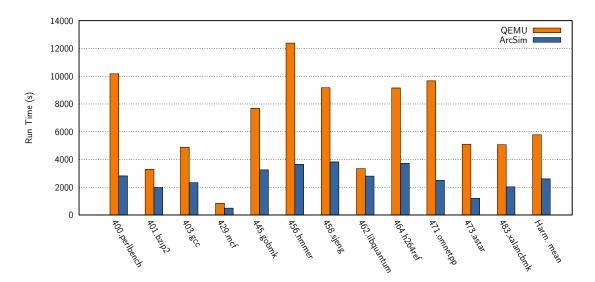

| 5.4  | Comparison of user-mode simulation performance between ARC-          |     |

|      | SIM and QEMU                                                         | 76  |

| 5.5  | Example code that depends on interrupt checking                      | 77  |

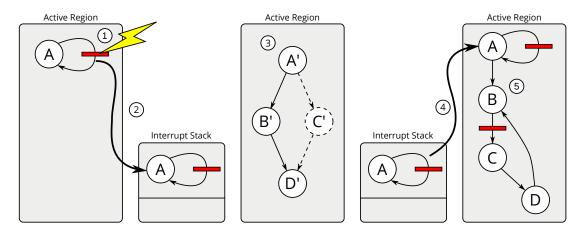

| 5.6  | Flow of region forming when an interrupt occurs                      | 82  |

| 5.7  | Optimised interrupt check placement algorithm for arbitrary code     |     |

|      | regions                                                              | 84  |

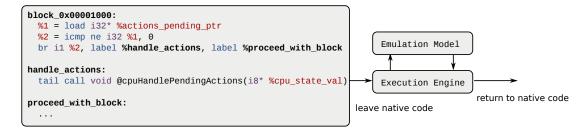

| 5.8  | LIVM IR emitted for interrupt checking at the head of a basic block. | 85  |

| 5.9  | Absolute I/O throughput in MB/s, measured with the hdparm            |     |

|      | benchmark                                                            | 87  |

| 5.10 | Relative reduction in wall-clock run-time of the SPEC-CPU2006        |     |

|      | integer benchmark                                                    | 88  |

| 5.11 | Reduction in static and dynamic interrupt checks for I/O and         |     |

|      | CPU bound workloads                                                  | 90  |

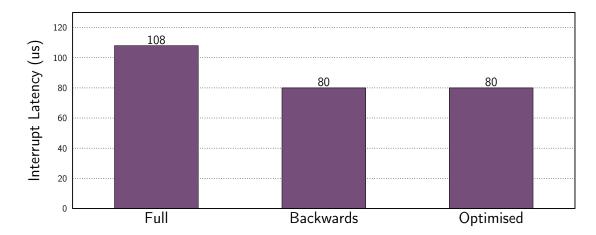

| 5.12 | Absolute interrupt latency in $\mu s$                                | 91  |

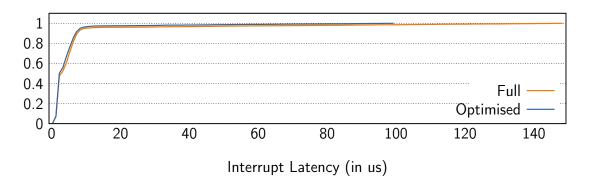

| 5.13 | Cumulative distribution of interrupt latencies for the optimised     |     |

|      | placement scheme                                                     | 91  |

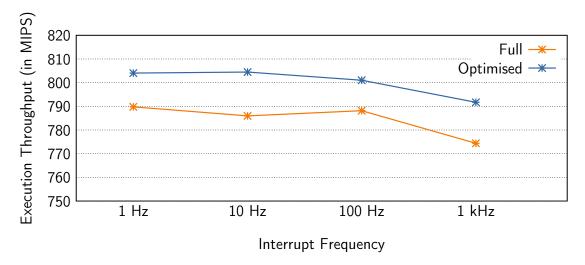

| 5.14 | Comparison of the full placement scheme versus the optimised         |     |

|      | placement scheme using a range of interrupt frequencies              | 92  |

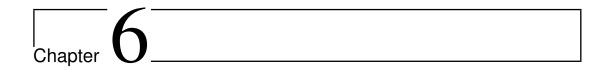

| 6.1  | Hardware-assisted cross-architecture hardware virtualisation         | 96  |

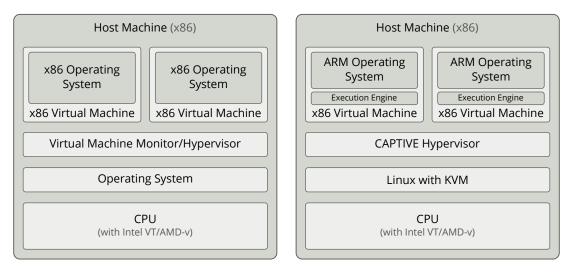

| 6.2  | Distribution of operations in the SPEC-CPU2006 integer bench-        |     |

|      | marks                                                                | 98  |

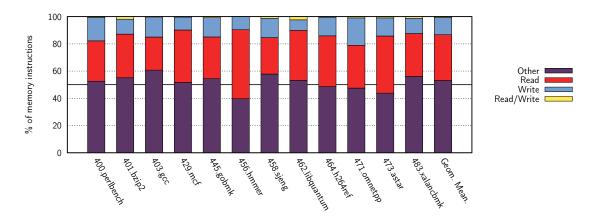

| 6.3  | The operation of an ARMv7-A MMU                                      | 99  |

| 6.4  | The operation of an x86 MMU                                          | 100 |

| 6.5  | Arcsim is a software-based hardware virtualisation system, and       |     |

|      | Captive is hardware-accelerated                                      | 103 |

| 66   | A high-level overview of CAPTIVE's infrastructure                    | 104 |

| 6.7  | Example inputs and outputs during the JIT compilation phase of                 |

|------|--------------------------------------------------------------------------------|

|      | CPU virtualisation                                                             |

| 6.8  | An overview of the operation of the Captive JIT                                |

| 6.9  | An example of guest system mode tracking for two different sce-                |

|      | narios                                                                         |

| 6.10 | Operation when virtualising memory accesses                                    |

| 6.11 | An example mapping of an ARM L2 descriptor to an x86 page                      |

|      | table entry                                                                    |

| 6.12 | Address-space identifier tracking implementation                               |

| 6.13 | Native VM physical and virtual memory organisation                             |

| 6.14 | An example of a PC-relative load instruction being translated by               |

|      | Captive and Qemu                                                               |

| 6.15 | An illustration of the fast device access operation                            |

| 6.16 | An illustration of the injection of an IRQ into the native virtual             |

|      | machine                                                                        |

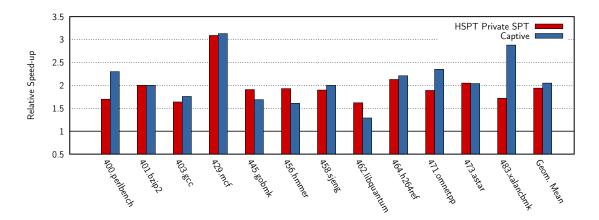

| 6.17 | Key results, showing relative speed-up and absolute run time. $$ . $$ . $$ 131 |

| 6.18 | Relative performance improvement of SPEC benchmarks by HSPT                    |

|      | and Captive, over the Android Emulator baseline                                |

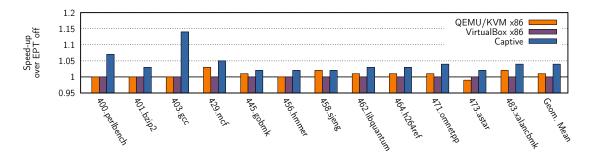

| 6.19 | Relative performance improvement gained by turning on Intel's                  |

|      | extended page tables                                                           |

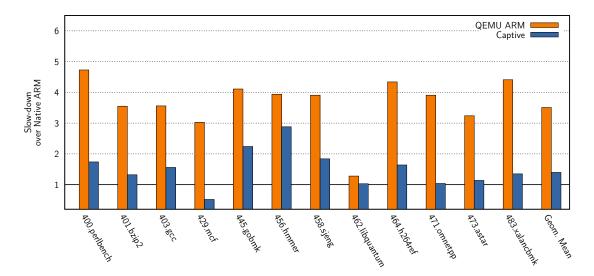

| 6.20 | Relative slow-down of QEMU and CAPTIVE over native execution                   |

|      | on a physical ARM platform                                                     |

# List of Tables

| 2.1 | Comparison of user-mode simulators                          | 23  |

|-----|-------------------------------------------------------------|-----|

| 2.2 | Comparison of same-architecture hardware virtualisers       | 26  |

| 2.3 | Comparison of hardware virtualisers                         | 28  |

| 3.1 | A list of the integer benchmarks in the SPEC-CPU2006 bench- |     |

|     | mark suite                                                  | 45  |

| 3.2 | Benchmark categories included in the EEMBC v1.1 benchmark   |     |

|     | suite                                                       | 46  |

| 4.1 | Host configuration                                          | 65  |

| 4.2 | ArcSim configuration                                        | 65  |

| 5.1 | Host configuration                                          | 86  |

| 5.2 | ArcSim configuration                                        | 86  |

| 6.1 | Host configuration                                          | 130 |

| 6.2 | Absolute I/O throughput for various execution environments  | 133 |

Chapter 1

# Introduction

There are many uses for hardware virtualisation in today's modern computing environments. Data centres wanting to lower their hardware costs and increase resource utilisation will look to virtualisation as a way to consolidate servers [119], users wanting the convenience of running multiple operating systems on their computers without the inconvenience of rebooting will often use virtualisation to run two (or more) operating systems side-by-side [47] and hardware and software developers wanting to prototype, debug and benchmark their designs will use virtualisation to create an isolated test environment [64, 112] that represents the target platform.

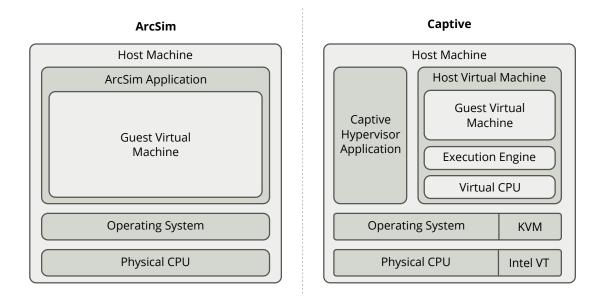

Hardware virtualisation is the process of creating a virtual representation of a particular hardware platform, providing an environment that appears to be a separate physical machine. Virtualising an entire platform can be quite straightforward when the *guest* machine is of the same architecture as the *host* machine—modern processor vendors provide hardware support [65, 4] out-of-the-box for this, allowing unmodified guest operating systems to run in virtual machines at near-native speeds [117]. But, when the need arises for *cross*-architecture virtualisation, there is no longer a one-to-one mapping of architectural components from the guest to the host, and these mismatched components need to be emulated in software.

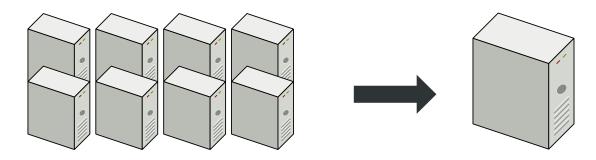

**Figure 1.1:** Instead of debugging applications on real hardware, virtualisation enables creating a virtual version of the hardware on which application development and testing can occur.

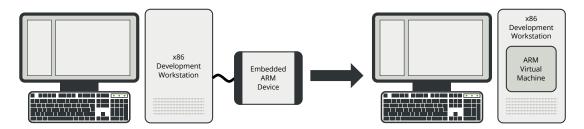

There is quite a large market for cross-architecture hardware virtualisation. It is used extensively during hardware development for rapidly prototyping platforms that may not yet exist, or to make modifications to an existing platform to observe how it may affect applications. Imperas [64] produce a suite of tools for developers that enable unmodified guest operating systems to run in a so-called *virtual platform*. This allows developers to boot an entire operating system compiled for a different architecture, in a virtual machine on their development workstation.

Software engineers use cross-architecture virtualisation to obtain a virtual representation of the platform their applications are targeting, allowing them to rapidly test and debug applications on their development workstation, without having to deploy it to a real device. Synopsys® produce tools under their *Virtual Prototyping* [112] offering that enables simulation of hardware platforms still under development, so that developers can begin producing applications for a platform that has not yet been materialised. Similarly, ARM® produce a configurable simulation tool called *Fast Models* [12] that enables developers to construct a virtual platform out of multiple architectural building blocks.

One of the most widely used [8] cross-architecture virtualisation systems is the Android<sup>®</sup> Emulator, which enables software developers to test their applications in the context of an unmodified ARM<sup>®</sup> Android<sup>®</sup> environment (Figure 1.1). This is important when developing native applications designed to run directly on ARM<sup>®</sup> processors, as it is time consuming and costly to continuously deploy to a real device for testing.

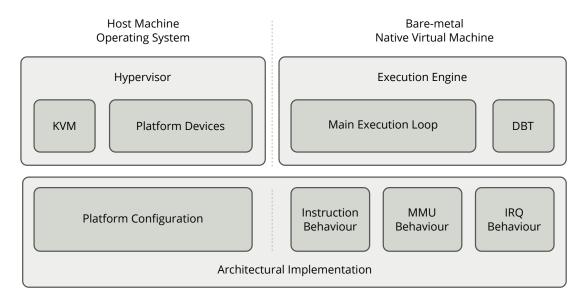

In order to support cross-architecture hardware virtualisation, it is necessary to emulate the behaviour of the hardware of the target platform on the host. This involves providing faithful emulation of guest instructions, and software implementations of architectural components (such as the *memory management unit* (MMU) and interrupt controller). It also involves emulating platform devices, such as disk or network devices. If an unmodified guest operating system is to be booted in this *virtual* environment, these components must all behave exactly as they would in a *physical* environment.

Virtualisation requires support from a *virtual machine monitor* (VMM) or *hypervisor*, which allocates and manages physical resources for the virtual guest. There are many open-source and commercial hypervisors available for *same*-architecture virtualisation, and the wide availability of hardware-accelerated extensions for virtualisation makes it a viable technology for production use. However, the majority of hypervisors that support *cross*-architecture virtualisation are for research purposes or detailed simulation—the most notable exception being QEMU [21].

### 1.1 Background

Support for hardware virtualisation appeared in systems as early as 1972 (on the IBM System/370 mainframe), and was used as a method of partitioning the physical machine into multiple virtual machines that appeared to users as their own private system. But, towards the end of the 1970s, virtualisation lost traction due to a significant increase in computing power on commodity processors (coupled with more modern forms of process isolation) effectively negating the need for it at that time. Thus, virtualisation became a software problem, and in fact software solutions for virtualisation of x86 processors outperformed the initial hardware support provided by Intel® and AMD® in the early 2000s. A resurgence of interest in the virtualisation space has led to improvements in hardware support, and now modern processor vendors provide *instruction set extensions* (ISEs) that can be used to present an abstract computing platform, allowing unmodified guest operating systems of the same architecture to run virtualised at near-native speeds—an important property for businesses wanting to deploy virtualised systems.

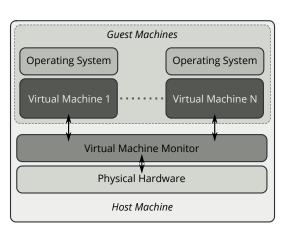

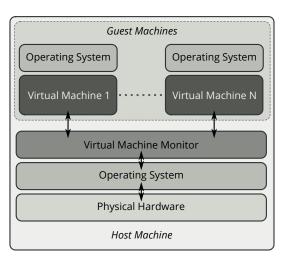

The requirements for hardware virtualisation were formalised in 1974 by Popek and Goldberg [101], who identified two types of hypervisor (shown in Figure 1.2) and made three key insights about the operation of virtual machines:

Type 1: Native VMM

Type 2: Hosted VMM

**Figure 1.2:** Popek and Goldberg identified two different types of *virtual machine monitor*. A **type 1** or **native** VMM runs directly on the host hardware, whereas a **type 2** or **hosted** VMM runs within the confines of an operating system.

- 1. A virtual machine must not exhibit a difference in behaviour to the physical machine it is modelling.

- 2. A virtual machine must be fast and efficient.

- 3. The *virtual machine monitor* (VMM) or *hypervisor* must remain in control of the physical machine's resources.

Whilst the authors applied these characteristics to virtual machines in general (without specifically targeting the same-architecture or cross-architecture usecase), the consequence of (2) is that software-based emulators and simulators were excluded from being classified as VMMs, since at the time of publication they could not satisfy the "efficiency" requirement. Unfortunately, this is a problem for cross-architecture virtualisation, as a software-based *instruction set simulator* (ISS) is *necessary* for performing the emulation of guest instructions. This is because the guest platform has a different *instruction set architecture* (ISA) to the host, and therefore guest instructions cannot execute natively on the host's physical processor. However, this observation assumed a slow interpreter-based ISS was used to emulate guest instructions, and so software emulation was discounted as a viable VMM for this reason.

However, more recent improvements to *dynamic binary translation* (DBT) have made software-based virtualisation systems more competitive with—and

1.2. Motivation 5

in some cases more efficient than—hardware-assisted virtualisation. This means that a suitably engineered software-based virtualisation system can meet the requirements for hardware virtualisation, and hence cross-architecture virtualisation can be considered a viable form of virtualisation.

There are four major challenges that need to be addressed when developing a cross-architecture hardware virtualisation hypervisor, each with their own impact on the performance and correctness of such a system:

- 1. **Instruction emulation:** The faithful and efficient execution of guest machine instructions.

- 2. **Interrupt handling:** The timely, and correct, handling of external interrupts, by altering control-flow (e.g. to interrupt handlers) as required.

- 3. **Memory management unit virtualisation:** Performing efficient memory address translation for guest architectures with an MMU, or access permission checking for those with an MPU.

- 4. **Device emulation:** Providing implementations of devices that may exist on the platform.

Each of these virtualisation challenges shall be visited over the course of this thesis, and techniques to improve the efficiency of their implementation shall be presented.

#### 1.2 Motivation

It is clear to see that cross-architecture virtualisation is a desirable technology across a range of disciplines, and it follows that due to the necessity of emulating architectural components in software, there is an unavoidable performance penalty. As mentioned previously, in the same-architecture case, modern processors from a range of vendors (Intel®, AMD®, ARM®, MIPS®, PowerPC®) provide hardware accelerated support for virtualisation, enabling unmodified guest operating systems to run natively on the host machine with very little supervision. This is because architectural behaviour is the same between guest and host, and platform devices can (if desired) be passed straight through to the guest. But, when the architecture of the guest is different to the host, there is no longer the possibility of mapping guest platform behaviour directly to host

platform behaviour, and the mismatched components of the guest system must be emulated.

Consider the use of the Android Emulator in a development environment. Developers want to debug and test their applications locally without having to deploy to real devices constantly. Deploying an application to a device can be time consuming, but so can using a slow emulator. In fact, Intel have recognised this particular issue and developed their own technique for improving the performance of the Android Emulator [109]. Whilst their technique uses hardware acceleration for virtualisation, it relies on an x86 version of Android, and so is not a cross-architecture solution. Therefore, this does not solve the problem of efficiently developing and debugging native ARM applications in an emulator. Furthermore, this is application specific, and does not solve the general problem of efficiently virtualising platforms that may not even exist yet.

Many architecture design companies that provide tools (such as compilers) for their architectures supply simulators as a basic tool. For example, ARM provide a development suite called DS-5 Development Studio that is available with a technology called *Fast Models*. This tool can be user-configured to virtualise an ARM platform, and can reach speeds that are close to native platform speeds. However, when additional components are enabled, the system quickly loses traction as its implementation is based on an event-driven framework. Synopsys provide a virtualisation tool called *Virtual Prototyping*, used to aid development on their own platforms.

QEMU [21] is a popular open-source full-system virtualisation hypervisor that supports a wide range of guest machine architectures, and is used throughout academia and the software/hardware development industry. In fact, it forms the basis of the Android Emulator as supplied as part of the Android software development kit (SDK). Out-of-the-box, QEMU supports many different guest architectures, but the software itself is not easily retargetable. Porting QEMU to another architecture requires manually coding an instruction decoder and building a translation routine that uses the internal *tiny code generator* (TCG) DBT to translate decoded instructions into QEMU's own intermediate representation.

#### Goal

The goal of this thesis is to develop techniques that can be used by hypervisors for fast and efficient cross-architecture hardware virtualisation, with an additional focus on ease of use and retargetability.

#### 1.3 Overview & Contributions

Chapter 2 shall introduce terminology associated with the virtualisation of computer systems, along with existing techniques for both same-architecture and cross-architecture virtualisation. These techniques shall be accompanied by related work in the area, relevant to the challenges that are being tackled in later chapters.

Following this, in Chapter 3, an introduction to the software tools developed and extended as part of this research shall be presented, along with descriptions of the frameworks used and the general methodology employed for performance evaluation.

Chapter 4 will tackle the initial challenge of efficient guest instruction emulation, by seeking to introduce techniques to increase the performance of a software-based *instruction set simulator* (ISS). This introduces fundamental and significant improvements to *dynamic binary translation* (DBT), which are necessary for efficient emulation of guest instructions.

In Chapter 5, the challenges associated with extending this ISS to support hardware virtualisation will be investigated, by focussing on asynchronous interrupts that are necessary for emulating a guest platform, and cause performance regressions in DBT-based virtualisation systems.

Chapter 6 exploits hardware-assisted virtualisation technology that is present on modern processors to develop a novel hypervisor for fast and efficient cross-architecture virtualisation. The four major factors for cross-architecture virtualisation are considered and novel techniques for accelerating each of these are presented.

Finally, Chapter 7 will summarise, conclude and present future work in the field of efficient hardware virtualisation.

# Background & Related Work

This chapter shall first define terminology that will be used throughout the remainder of this thesis, followed by a brief introduction to some important concepts involved in cross-architecture hardware virtualisation. These concepts shall be supplemented with related work in the area of hypervisor performance and implementation strategies.

## 2.1 Terminology

There is a range of terminology in use when discussing virtualisation of computer systems, and this section shall define and describe the terms that will be used throughout the remainder of this thesis. The majority of these terms are widely used in literature, but due to the complex, multi-layered and potentially confusing nature of hardware virtualisation systems, it is important to define at this point how the particular term is intended to be perceived.

#### 2.1.1 Overview

The three main terms that are used throughout this area of research are:

- **Virtualisation:** The provision of a *virtual* version of an existing *physical* component.

- Emulation: The imitation of the behaviour of a particular component.

- **Simulation:** The emulation of a particular component, but coupled with the ability to instrument and inspect the behaviour of that component.

This thesis is primarily concerned with *virtualisation*, but *emulation* of some form is a necessity for cross-architecture virtualisation. *Simulation* is an overlapping area, and is an important technique for debugging and monitoring purposes, however this thesis is not concerned with precise simulation, but shall introduce it as future work in Section 7.3.

#### 2.1.2 Definitions

**Definition 1** (Architecture). The architecture of a computer system describes how the system functions, and how it is organised. Typically it also defines the instruction set architecture (ISA), which describes what instructions are available, how they are encoded, and how they behave.

**Definition 2** (Platform). The platform is how a particular computer system is configured, i.e. which architecture it is built upon, what features are employed from that architecture, what type of processor(s) are in use, what devices are available and generally how the system "fits together".

**Definition 3** (Virtual Machine). A virtual machine (VM) is an isolated, virtual representation of a computer system.

**Definition 4** (Host Machine). *The host machine is the physical computer, on which a virtual machine is intended to be created.*

**Definition 5** (Guest Machine). *The guest machine is the particular computer system that is being virtualised and being represented by a virtual machine.*

**Definition 6** (User-mode Simulation). *User-mode simulation, as shall be described in Section 2.5, is the act of simulating a computer program that is designed to be run on a particular architecture, on a different architecture (although the architectures could be the same). This kind of simulation is limited to single programs running inside an operating system, and requires the simulator to emulate the behaviour of the original guest operating system.*

**Definition 7** (Full-system Simulation). Full-system simulation is the act of simulating an entire computer system. This term can be synonymous with hardware virtualisation but as mentioned previously, simulation implies that some form of instrumentation or inspection is involved to gain insight into the behaviour of the system.

**Definition 8** (Hardware Virtualisation). As described in Section 2.6, and as will be presented throughout the remainder of this thesis, hardware virtualisation is the act of providing a virtual machine that represents a real physical machine—including all of the architectural behaviour and hardware devices present on the platform being virtualised.

**Definition 9** (Same-architecture Virtualisation). *Virtualisation when the guest machine and the host machine are of the same* architecture.

**Definition 10** (Cross-architecture Virtualisation). *Virtualisation when the guest machine and the host machine are of different architectures.*

**Definition 11** (Hardware-assisted Virtualisation). Not to be confused with hardware virtualisation, hardware-assisted virtualisation is when the host machine architecture provides additional support for performing hardware virtualisation, e.g. Intel VT [65] or AMD-V [4].

**Definition 12** (Hypervisor). Sometimes termed a virtual machine monitor, a hypervisor is a piece of software that is responsible for managing the lifecycle of a virtual machine. Normally, the hypervisor creates and starts the VM, along with allocating and managing host machine resources (such as memory) that will be virtualised.

Furthermore, there are two types of hypervisor that are relevant to hardware virtualisation:

**Type 1 (native):** A hypervisor that runs directly on the host machine hardware.

**Type 2 (hosted):** A hypervisor that runs inside a normal operating system.

**Definition 13** (Instruction Emulation). *Instruction emulation is the act of executing a guest machine instruction, on the host machine, causing the state of the virtual machine to change as it would if the instruction was executed on a real guest machine.*

**Definition 14** (Device Emulation). *Device emulation is generally a software implementation of a real hardware device that emulates the behaviour of that device when the virtual machine accesses it.*

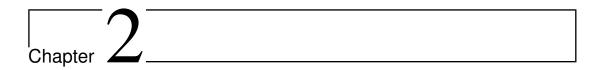

Figure 2.1: A typical fetch, decode, execute sequence.

#### 2.2 Instruction Emulation

Any form of cross-architecture simulation or virtualisation requires the emulation of guest machine instructions, as these instructions cannot directly execute on the host machine. Typically, a guest machine will be in a particular *state*, and executing an instruction causes that state to change. The *behaviour* of a particular instruction is defined by the *instruction set architecture* (ISA).

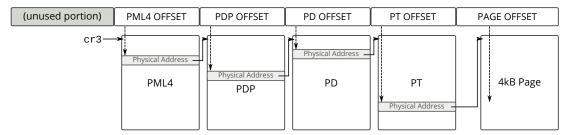

From a functional perspective, processors execute instructions by **fetching** an instruction from memory (pointed to by the *program counter* (PC) register), **decoding** it into its constituent fields, and then **executing** the associated behaviour. This is shown in Figure 2.1. In reality, the situation is much more complex, with e.g. superscalar processors, pipelines, out-of-order execution, speculation, branch prediction and etc. all contributing to a highly complex execution model. However, this high-level sequence is typically the basis for the variety of execution models available to cross-architecture virtualisation systems.

There are various approaches to implementing the execution model in a virtualisation system, each with their own benefits and drawbacks. The two most common approaches are *interpretation* and *dynamic binary translation*, and these have further possible implementation choices. An overview of each of these approaches shall be given in the following sections, along with associated related work in the area.

#### 2.2.1 Interpretation

An interpreter is effectively the implementation of the fetch-decode-execute cycle described above. It has the benefit of being a very straightforward approach to instruction emulation, but suffers from performance limitations.

Listing 2.1 shows a typical loop-based interpreter, where each instruction

**Listing 2.1:** Interpreter Loop

#### Listing 2.2: Threaded Interpreter

```

jump_table = [&OPCODE_ADD, &OPCODE_SUB];

do {

insn = FETCH();

2

opcode = DECODE();

insn = FETCH();

3

opcode = DECODE();

switch (opcode) {

goto & jump_table[opcode];

case OPCODE_ADD:

6

<behaviour>

OPCODE ADD:

break;

<behaviour>

case OPCODE_SUB:

insn = FETCH();

9

10

<behaviour>

10

opcode = DECODE();

11

break:

11

goto & jump_table[opcode];

12

12

} while (true)

13

OPCODE SUB:

<behaviour>

14

15

insn = FETCH();

opcode = DECODE();

16

goto &jump_table[opcode];

```

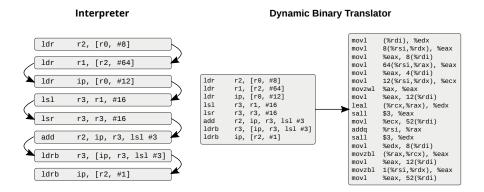

**Figure 2.2:** A typical interpreter-based virtualisation system. Listing 2.1 shows a loop-based interpreter, and Listing 2.2 shows a more efficient *threaded* implementation.

is fetched from the guest machine's memory, decoded, then a branch is made to the behaviour for that instruction. After the behaviour completes, the interpreter loops around and starts again. Even if the individual instruction behaviours are optimised aggressively, the rate at which instructions execute is effectively fixed.

A more efficient approach is to dispatch to the behaviour for the next instruction, immediately after the current instruction has finished executing, instead of looping around. This type of implementation is called a *threaded* interpreter, and is shown in Listing 2.2. Instead of executing in a loop, control-flow threads from one instruction behaviour to the next, by dispatching to instruction behaviour via a *jump table*.

A further optimisation that can be made is to introduce a decode cache, eliminating the cost of decoding guest instructions, if the instruction has been recently seen. This is important for looping control-flow in the guest, where the same instructions will be executed many times in quick succession.

Even if control-flow is improved, and decode caches are used, an interpreter will always reach a performance ceiling. This is because this method of execution considers each instruction individually, and invokes a distinct emulation for each instruction type.

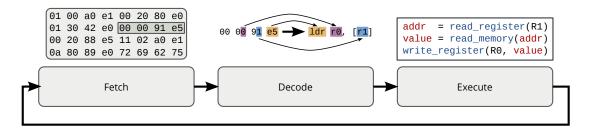

**Figure 2.3:** Two examples of possible dynamic binary translation implementations. (a) shows a synchronous DBT that translates guest basic blocks on demand. (b) shows a DBT that initially executes guest basic blocks in an interpreter, until they become hot. At this point, the basic block is translated.

#### 2.2.2 Dynamic Binary Translation

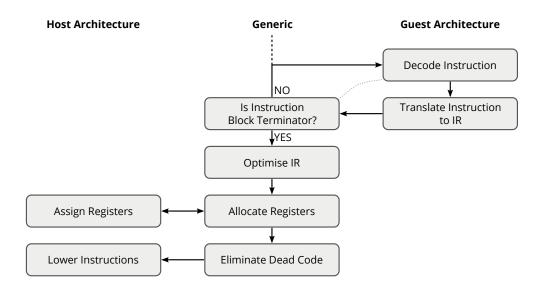

Dynamic binary translation is an execution model that translates guest machine instructions into corresponding host machine instructions as the virtual machine is running. This technique opens up the scope for executing many guest instructions as a unit, because (unlike an interpreter) it is no longer constrained to operating on an instruction-by-instruction basis.

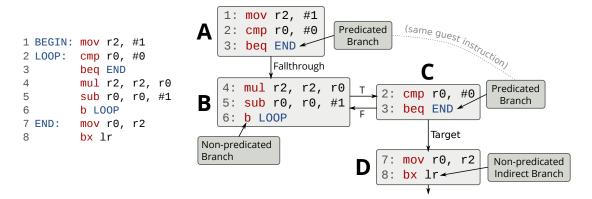

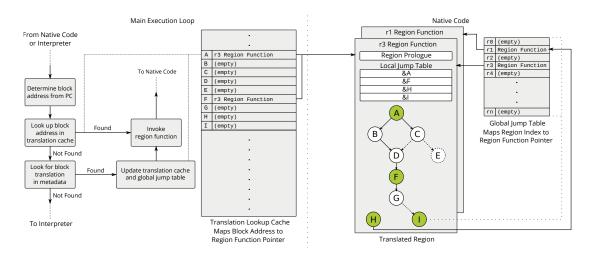

For example, a typical unit of translation in a DBT system is a basic block, where a basic block is a *straight-line*, *single-entry*, *single-exit* region of instructions. A DBT will decode each instruction in a guest basic block, and produce host machine code that represents the behaviour of that entire instruction sequence. There is not necessarily a one-to-one mapping between guest basic blocks and host basic blocks, as some instructions may raise exceptions (that require early exiting from the block) or the guest architecture may support *predicated* instructions (that only execute if certain flags are set).

Figure 2.3 shows two examples of possible DBT implementations. Figure 2.3a shows a synchronous block-based DBT, where the DBT will translate guest basic blocks on-demand, i.e. when a translation does not exist. Figure 2.3b shows a DBT/interpreter hybrid, where execution will initially proceed through an interpreter, until a block becomes "hot". At this point, the block will be translated, and execution will transition to native code, until a translation does not exist.

A modification may be made to the hybrid approach, by turning the translation of hot blocks into an *asynchronous* operation [24], meaning that execution

of the guest system can progress (in the interpreter) whilst translations are being performed in the background, hiding the compilation latency.

#### 2.2.3 Translation Granularity

An important detail to consider when developing a DBT system is the *granularity* of the translation, or what comprises a translation unit. For example, is the translation performed instruction-by-instruction, or are entire basic blocks translated?

Typically, the more guest instructions that are considered in a translation unit, the more efficient the translated code will be. This is because optimisations can be applied across the translation unit as a whole, leading to highly efficient host machine code. The trade-off, however, is between translated code quality and compilation latency. Spending more time translating code (or simply translating more instructions at-a-time) results in a longer compilation time, impacting on the overall throughput of the system. However, the performance gains of DBT greatly outweigh the added latency of a translation phase, when compared to an interpreter-based system.

Translation granularity can be broadly classified into four different schemes:

- **Instruction:** A single guest instruction is translated into one or (usually) more host instructions. This is no better than an interpreter, however, and would in fact perform much worse due to the added translation penalty.

- Basic Block: A straight-line, *single-entry, single-exit* region of guest instructions are translated into multiple host instructions.

- **Linear Trace:** A sequence of guest basic blocks that only jump forward (i.e. there are no loops) are translated.

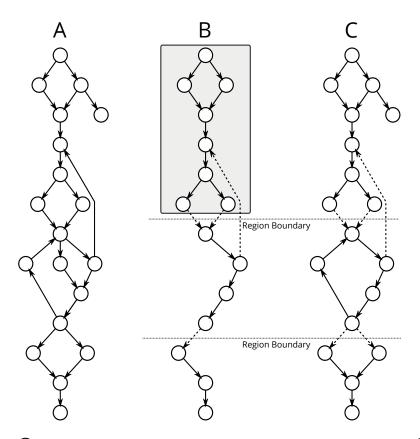

- Region: A multi-entry, multi-exit region of guest instructions, possibly comprising cyclic control flow, is translated to corresponding host machine code.

A region-based DBT offers the most scope for generating high-quality native code, but it requires dynamic profiling during the application's run in order to *form* regions and determine which discovered basic blocks are worth translating. Region forming is the process of determining which basic blocks should be

logically considered part of a particular region, and various schemes have been proposed for this purpose [26, 55, 57, 62]. An asynchronous form of this style of DBT will be discussed further in Chapter 4.

#### 2.2.4 Region-based DBT Systems

Region-based JIT compilation has been used for some time in Java virtual machines, e.g. Suganuma et al. [110, 111], but has only been considered more recently for DBT systems [69, 24, 72]. The reason for this late adoption of region based policies has been presumably the increased latency for compilation and optimisation of larger regions, which has only been addressed recently with the introduction of decoupled, latency-hiding JIT compilation task farms [24]. The bulk of the work in this field has focussed on region selection though, and less on code generation and optimisation for dynamically discovered regions. In Jones and Topham [69] large translations units (i.e. regions) are introduced for dynamic binary translation, and region selection policies based on strongly connected components, control flow graph fragments and OS pages are compared. A refined page based region selection scheme is developed in Böhm et al. [24] and combined with a parallel JIT compilation task farm. Specific optimisations for a DBT system, which compiles guest- to host code via *Java Virtual Machine* (JVM) bytecode, are considered in Kaufmann and Spallek [72].

#### 2.2.5 Code Generation and Optimisation in DBT Systems

Most DBT systems appear to have adopted a code generation strategy operating on individual basic blocks or linear traces of basic blocks. For example, QEMU [21] implements such an approach using its own *tiny code generator* (TCG) and additional block chaining, translation caching and lazy condition evaluation.

Dynamo [17] is a dynamic optimisation system, i.e. the input is a native instruction stream. Dynamo uses an interpreter for initial execution until a "hot" instruction sequence is identified. At that point, Dynamo generates an optimised version of the trace into a software code cache. Dynamo treats backward branches as trace delimiters, i.e. traces are by definition linear. After translation it emits an optimised single-entry, multi-exit, contiguous sequence of instructions for each trace. Trace optimisation in Dynamo considers branch types,

but is generally less aggressive than what can be achieved when considering a region that contains cyclic control-flow.

DynamoRio [27] is a successor of Dynamo. DynamoRio operates on two kinds of code sequences: basic blocks and traces. Both have linear control flow, with a single entrance and potentially multiple exits, but no internal join points. Optimisations are restricted to the linear control flow present in traces. The single-entry multiple-exit format simplifies analysis algorithms, but limits the scope of optimisations that can be applied.

Strata [56] is a retargetable DBT system offering additional uses for dynamic instrumentation and optimisation. Different fragment selection policies [57] have been evaluated for Strata, but all of these policies are based on linear traces, possibly spanning branch or function call boundaries. Strata uses chaining of traces to avoid overheads associated with returning to the main execution loop after every native trace. An ARM port of Strata considers architecture-specific optimisations, e.g. relating to the exposed PC [92].

The optimisations performed by UQDBT – a machine-adaptable dynamic binary translator – are discussed in Cifuentes and Emmerik [35], Ung and Cifuentes [116]. This tool uses an algorithm for finding hot paths using edge weight profiles, and optimises code in a machine-independent way, based on hot path information. Whilst units of translation in UQDBT are basic blocks, for its hot path (re)optimisation it groups hot basic blocks and their connecting control flow edges into regions. The paper focuses primarily on newly discovered hot paths and locality transformations, but does not provide a complete code generation strategy. A particular aspect of code generation in DBT systems, namely recovery of jump table case statements, is discussed in Cifuentes and Emmerik [34].

Rosetta [2] is a DBT that translates PowerPC G3, G4 and AltiVec instructions to x86 instructions. It is based on QuickTransit by Transitive [1], and was released by Apple in 2006, after the ISA of their Macintosh platform was changed from PowerPC to x86. Rosetta is a user-mode DBT, as its primary purpose was to allow legacy PowerPC-based Macintosh applications to run on modern Intel-based Macintosh computers.

Liu et al. [82] introduce a translation system based on "hybrid binary translation", which involves an offline *static* binary translation phase and falling back to a run-time *dynamic* binary translation system to handle untranslated code.

### 2.2.6 DBT Systems using LLVM for JIT Compilation

LLVM [77] is a popular open-source compilation framework, that can be employed as a JIT compiler for DBT. It contains a wide range of high-quality optimisation passes that lead to the production of highly efficient machine code.

A parallel and concurrent JIT compilation task farm for use in DBT systems is presented by Böhm et al. [24]. The JIT compiler is based on the LIVM framework, which is used for translation of paged regions of target instructions to host instructions. The paper discusses a particular region selection scheme and parallel JIT compilation, but provides no details of the actual code generation approach used.

LnQ [61] extends QEMU with an LLVM-based JIT compiler, but does not consider code regions for translation, instead it uses linear traces.

HQEMU [59] is a multi-threaded dynamic binary translator, which extends QEMU with multiple instances of the LLVM compiler for JIT compilation. HQEMU builds on top of LLVM, but it only operates on linear traces and does not support region-based compilation.

Guo et al. [50] look at a particular DBT challenge, which is mapping the behaviour of guest machine vector instructions onto host machine vector instructions. Specifically, they look at optimising the dynamic translation of ARM Neon and *vector floating point* (VFP) into corresponding host machine instructions. Their approach is to generate LLVM bytecode that closely models the vector-specific behaviour of the guest instruction, which is highly amenable to lowering into host machine vector instructions.

# 2.3 Interrupt Handling

Virtualising an entire computer system means honouring the multitude of architectural behaviours that exist on the target platform. A particular challenge for virtualisation is the efficient handling of *asynchronous* interrupts, i.e. those interrupts that are raised by external signals (such as devices), and not related to the directly executing instruction.

In order to maintain consistency, virtualisation systems can only handle interrupts at well-defined points during execution, which at a minimum is an instruction boundary. Diverting control-flow during the execution of an instruc-

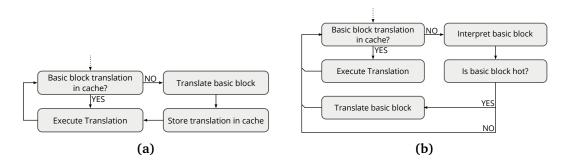

**Figure 2.4:** An illustration of how interrupt checking might work in an interpreter-based system. In this example, a pending interrupt is checked for after the interpreter has executed one basic block of guest instructions.

tion would lead to corruption of guest machine state, as guest instructions must appear to execute atomically.

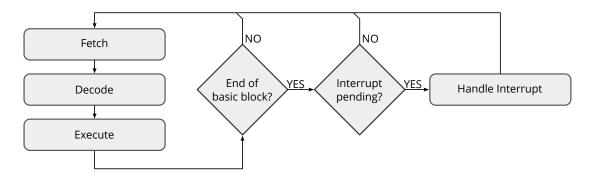

As shown in Figure 2.4, in an interpreter based system, interrupt checking is very straightforward—a check can be made after each instruction, or after a certain number of instructions (which in the example is a basic block). However, for DBT-based systems, diverting control-flow to an interrupt handler, as specified by the architectural behaviour, requires adding interrupt checks to the translated code, ensuring any pending interrupts are handled. As shall be described in Chapter 5, it is not possible to arbitrarily place these interrupt checks without considering the effect they have on the behaviour and performance of the virtual machine.

The optimal placement of interrupt checks can be compared to the optimal insertion of profiling counters. However, updating profiling counters does not introduce additional control-flow—since the majority of cases are simple counter updates. Whilst reducing the number of counter updates can lead to performance improvements by reducing the amount of memory accesses, the problem for DBT is slightly different in that extra control-flow must be added to perform interrupt checks, thus causing additional latency in the optimiser, and resulting in less optimal code being generated. The technique described by Ball and Larus [18] addresses the optimal placing problem, but does not address the issues that are encountered with additional exit points being introduced.

Whilst there are a number of full-system simulators available, either open-source (e.g. QEMU [21], ARM-Iss [84] or MARSSx86 [97]) or under a commercial license (e.g. Simics [87]), only a few papers on interrupt handling in DBT

systems have been published [25].

Older versions of QEMU utilised a zero-overhead interrupt checking scheme, which suffered from serious race-conditions. However, later versions have addressed these issues by inserting checks at the head of every basic block.

ARM-Iss [84] is an instruction set simulator for the ARM architecture. It is based on an interpretive execution model with additional instruction caching. ARM-Iss checks for pending interrupts after each instruction. Whilst accurate, this further exacerbates the performance penalty of a DBT-based system.

MARSSx86 [97] is a full-system simulator for x86 CPUs. Under the hood, MARSSx86 uses QEMU for functional simulation and PTLsim for cycle-accurate modelling, using decomposition of x86 instructions into RISC-like  $\mu$ -ops and using basic block buffers to form traces of x86  $\mu$ -ops. MARSSx86 delays the interrupt issued to the CPU until the CPU comes into the stable state, defined at opcode commit boundaries. Once the interrupts are issued to the CPU MARSSx86 switches from detailed simulation to functional emulation for correctly decoding the interrupt. The emulator mode sets up the correct CPU context to handle the interrupt but it does not start executing the interrupt handler. After the correct CPU context is set up, MARSSx86 switches back to the detailed simulation and starts simulating the interrupt handler code in kernel mode. Due to its cycle-accurate approach interrupt handling in MARSSx86 is precise, but it only operates at a throughput of about 200 kilo instruction commits per second (KIPS).

An improved mechanism for the precise simulation of interrupts in cycle-accurate simulators has been presented by Brandner [25]. The simulator speculatively executes instructions of the emulated processor assuming that no interrupts will occur. At restore-points this assumption is verified and the processor state reverted to an earlier restore-point if an interrupt did actually occur. Whilst effective at speeding up cycle-accurate simulation this is still too costly for high-speed functional ISS.

A software simulator based on COTSon [7] that faithfully simulates x86 hardware at a speed in the tens of MIPS range has been described by Ryckbosch et al. [104]. Details on interrupt handling are not provided, though. Similarly, the strategies for interrupt checking are not further specified for Giano [45], SimFlex [52] or Graphite [91]. Gem5 [22] performs per-instruction interrupt checking due to its ambition to support cycle-accurate simulation.

#### 2.3.1 Virtual Machines

Somewhat related to interrupt checking in an ISS is exception handling in a Java VM. Java exceptions are *synchronous*, though, i.e. they are related to the currently executing instruction and not triggered externally. Two techniques for dealing with Java exceptions during JIT compilation, namely *on-demand translation* of exception handlers and *exception handler prediction* are presented by Lee et al. [78].

A notable exception are *yield points* in the JikesRVM [68] Java VM, where interrupt checks are inserted in method prologues and epilogues, and on backedges. These checks are inserted to facilitate user-space scheduling of Java threads, but have been deprecated (as of version 3.1.0) in favour of native threading. JikesRVM inserts a yield point in a method prologue and epilogue, and on a control-transfer instruction (such as an if) when the target is backwards.

### 2.4 MMU Virtualisation

Virtualisation of the guest system's memory management unit (MMU) is arguably one of the most challenging parts of cross-architecture virtualisation. Memory accesses in a target program occur frequently, and so an inefficient implementation of the MMU will lead to severe performance penalties. MMU virtualisation involves translating the address of every memory access from a virtual address into a physical address, along with checking the permissions of the translation to see if the currently executing code is permitted to perform the particular operation.

On real hardware, these translations are defined by *page tables*, which map *pages* of virtual memory onto *pages* of physical memory and define flags that specify access permissions. Generally, an operating system will create a *virtual memory area* (VMA) for each process, and apply the necessary protection flags, for example, to ensure user code cannot interfere with kernel data structures.

For same-architecture virtualisation, modern processor vendors have recognised the performance penalty that emulating an MMU introduces, and have designed hardware support for accelerating virtualised MMUs. This hardware support is termed *second-level address translation* (SLAT), and examples of this

are Intel's Extended Page Tables (EPT) and AMD's Rapid Virtualization Indexing (RVI).

However, for cross-architecture virtualisation, all of the approaches to MMU virtualisation are software-based, employing techniques such as caching, exploitation of host memory protection features and shadow page tables in an attempt to accelerate costly memory address translations. Most of the work on accelerating virtualised MMUs is based on QEMU and aims to improve over its default software MMU implementation and caching strategy.

Early work in the context of Simics [86] introduced a software caching mechanism, which improved the performance of interpreted memory operations by reducing the number of calls to complex memory simulation code [85].

More recently, Chang et al. [31], Wang et al. [125], Hong et al. [60] have presented novel schemes for speeding up address translation in full-system simulators, by utilising shadow page tables and co-ercing the host operating system into maintaining a virtual memory mapping with mmap-based shared memory.

In Chang et al. [31], a shadow page table – called embedded shadow page table (ESPT) – is embedded into the address space of a cross-ISA dynamic binary translation (DBT) system. ESPT uses the hardware memory management unit in the CPU to translate memory addresses, instead of software translation.

However, the original ESPT approach has a few drawbacks. For example, its implementation relies on a loadable kernel module (LKM) to manage the shadow page table. Using LKMs is less desirable for system virtual machines due to portability, security and maintainability concerns. Hence, a different implementation – called HSPT – adopts a shared memory mapping scheme to maintain the shadow page table using only mmap system calls [125].

Dynamic resizing of a software TLB is proposed in [60]. Using per-pagetable utilisation information, the size of the software TLB is adjusted for each process separately.

# 2.5 User-mode Simulation

Most instruction set simulators, either academic or commercial, are user mode simulators, which do not provide support for privileged instructions, interrupt handling, devices or a memory management unit. As such they are not capable of hosting an operating system, but only a single process which interacts with

| Simulator    | Engine       | Multi-core | Detailed | Target ISA            |

|--------------|--------------|------------|----------|-----------------------|

| CMP\$im      | Bin. Instr.  | Yes        | Cache    | Intel x86             |

| FastSim      | Direct Exec. | No         | Yes      | SPARC v9              |

| Graphite     | Direct Exec. | Yes        | Yes      | Intel x86             |

| HORNET       | Interpreter  | Yes        | Yes      | MIPS                  |

| Shade        | DBT          | No         | No       | SPARC v8/9, MIPS 1    |

| SimpleScalar | Interpreter  | Yes        | Yes      | Alpha, PISA, ARM, x86 |

| SlackSim     | Interpreter  | Yes        | Yes      | SimpleScalar/PISA     |

| Sniper       | Direct Exec. | Yes        | Yes      | Intel x86             |

| QEMU         | DBT          | Yes        | No       | Multiple available    |

| WWT II       | Direct Exec. | Yes        | Yes      | SPARC v9              |

| ZSim         | Direct Exec. | Yes        | Yes      | Intel x86             |

**Table 2.1:** Comparison of user-mode simulators: techniques and capabilities.

the simulator though emulated system calls. This form of simulation is not applicable to hardware virtualisation, but it is related to the instruction emulation requirement for cross-architecture virtualisation.

A number of user mode simulators are listed in Table 2.1 and are briefly discussed in the following paragraphs.

CMP\$im [66] uses binary instrumentation as an alternative to executiondriven and trace-driven simulation methodologies. Using the binary instrumentation tool Pin [83], CMP\$im is used to characterise cache performance and data sharing behaviour of multi-threaded workloads at speeds of 4-10 MIPS.

FastSim [107] is a cycle-accurate, direct-execution simulator of an out-of-order uni-processor. It models a SPARC v8 instruction set running on a MIPS R10000-like microarchitecture and simulates a single processor. FastSim's processor model supports out-of-order instruction execution, speculative execution, and an aggressive non-blocking cache.

Graphite [91] is an open-source distributed parallel multi-core simulator infrastructure. Graphite combines several techniques including: direct execution, seamless multi-core and multi-machine distribution, and lax synchronisation. Graphite is capable of accelerating simulations by distributing them across multiple commodity Linux machines. When using multiple machines, it provides the illusion of a single process with a single, shared address space, allowing it to run off-the-shelf pthread applications with no source code modification.

HORNET [80] is a configurable, cycle-level multi-core simulator with sup-

port for a variety of memory hierarchies, interconnect routing and *virtual chan-nel* (VC) allocation algorithms, as well as accurate power and thermal modelling. Its multi-threaded simulation engine divides the work equally among available host processor cores, and permits either cycle-accurate precision or increased performance, at the cost of some accuracy, via periodic synchronisation. HORNET can be driven in network-only mode by synthetic patterns or application traces, or in full multi-core mode using a built-in MIPS core simulator.

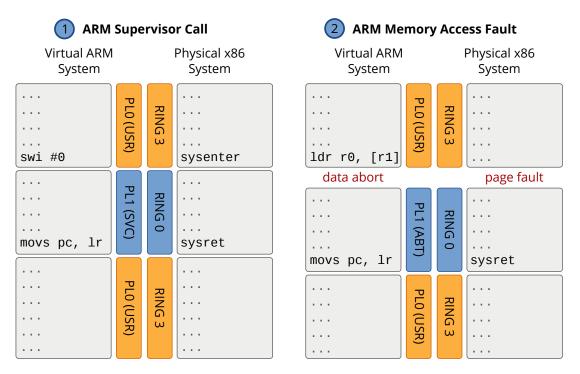

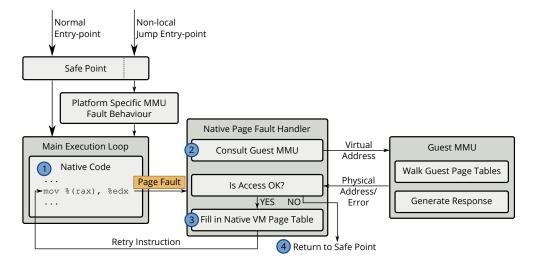

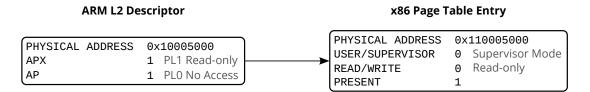

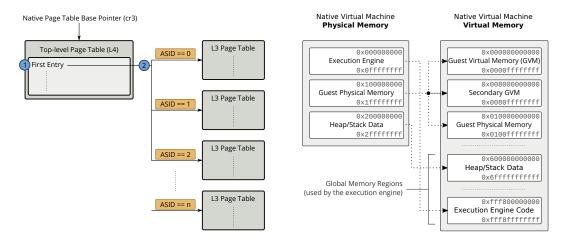

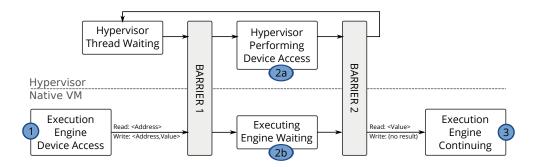

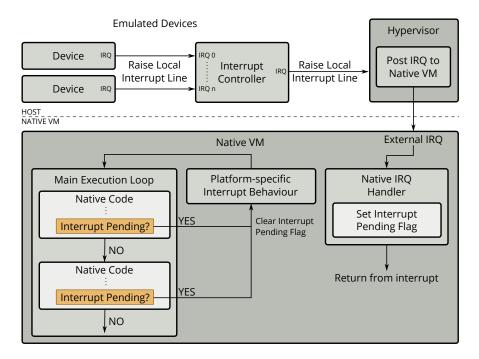

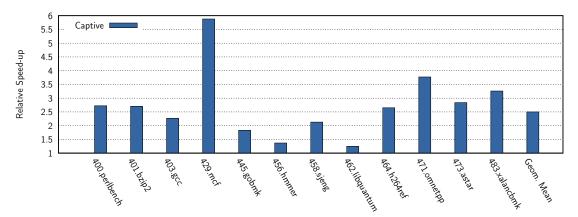

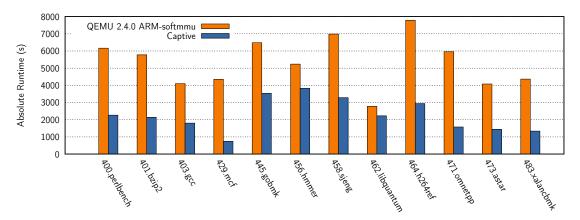

Shade [36] is an instruction-set simulator and custom trace generator. Application programs are executed and traced under the control of a user-supplied trace analyser. To reduce communication costs, Shade and the analyser are run in the same address space. To further improve performance, code which simulates and traces the application is dynamically generated and cached for reuse. It runs on SPARC systems and, to varying degrees, simulates the SPARC (Versions 8 and 9) and MIPS I instruction sets.