# Yield Improvement of VLSI Layout Using Local Design Rules

Thesis submitted by

Gerard A. Allan

for the degree of

Doctor of Philosophy

Edinburgh Microfabrication Facility,

Department of Electrical Engineering,

University of Edinburgh,

Scotland.

1992

#### Abstract

The demand for larger more complex systems on a single IC has shown a steady increase and to date has been met by improvements in fabrication technology. In the future it may not be possible to satisfy this demand in the same way, as it will become increasingly expensive to obtain the required process improvements. It seems likely that the demand for even larger single chip systems will continue and that the commercial success of these devices will become more heavily dependent on their yield. At the same time there is also a continuing trend towards more automate layout generation and these layouts are usually less dense than those produced using traditional hand-crafted designs.

This thesis addresses the problem of maximising the yield of circuit layouts and introduces a yield improvement concept of Local Design Rules. These are integrated circuit layout rules that are used to increase a circuits yield by making more efficient use of the circuit area. The rules define a more optimum feature size and spacing of components in relation to the surrounding layout geometry. This enables the "unused" silicon to be reclaimed and used to enhance the circuit yield without violating the layout design rules.

The type of circuit and nature of circuit layout to which local design rules can be applied to give useful yield improvement are discussed highlighting the problems in a fabrication process that can be improved by this type of layout manipulation. The impact of layout changes on the circuit performance that have been made on the suggestion of local design rules is addressed.

Algorithms for the automatic application of track displacement, track width increase and contact increase local design rules are presented along with a spatial data structure suitable for efficient design rule checking of the suggested layout changes. These algorithms have been implemented and used to apply local design rules to integrated circuit layouts. Finally, several examples are presented with results from Monte Carlo yield simulations.

## Declaration

I declare that this thesis has been completed by myself and that all the work included in this thesis is entirely my own except where otherwise indicated.

Gerard A. Allan.

### Acknowledgements

I would like to thank my supervisor Dr Anthony Walton, who has provided invaluable help and advice during all the stages of this work. My thanks also go to the EMF staff who have answered all my questions, even the stupid ones, and provided both assistance and on the spot tutorials.

I would also like to thank my fellow PhD students, who have over the years proved an endless source of help and humour, without whom I could have finished this work 6 months earlier.

Finally, and most importantly, I would like to thank my parents, family and friends without whose support this thesis could not have been achieved.

This work was funded by the SERC.

# Table of Contents

| 1. | Intr | oducti | on                                              | 1  |

|----|------|--------|-------------------------------------------------|----|

|    | 1.1  | Defect | Sensitivity                                     | 2  |

|    | 1.2  | Object | ives :                                          | 3  |

|    | 1.3  | Overvi | ew                                              | 6  |

|    |      | 1.3.1  | Using LocDes                                    | 6  |

|    |      | 1.3.2  | Outline                                         | 7  |

| 2. | Bac  | kgrour | ıd                                              | 10 |

|    | 2.1  | Introd | uction                                          | 10 |

|    | 2.2  | Types  | of Yield Loss                                   | 12 |

|    |      | 2.2.1  | Gross Yield                                     | 12 |

|    |      | 2.2.2  | Random defects                                  | 13 |

|    |      |        | Extra and Missing Material Defects              | 14 |

|    | ,    |        | Oxide Pinholes                                  | 14 |

|    |      |        | Junction Leakage                                | 15 |

|    |      | 2.2.3  | Fault Clustering.                               | 16 |

|    |      |        | The Influence of Clusters on LDRs Effectiveness | 17 |

|    | 2.3  | Yield  | and Chip Area                                   | 17 |

|      | 2.3.1   | Poisson Statistics,                                          | 17 |

|------|---------|--------------------------------------------------------------|----|

|      | 2.3.2   | Window Method                                                | 18 |

|      | 2.3.3   | Boltzmann Statistics                                         | 19 |

|      | 2.3.4   | Bose-Einstein Statistics                                     | 20 |

|      | 2.3.5   | Experimental Methods                                         | 20 |

|      | 2.3.6   | Chip Area and Wafer Size                                     | 21 |

| 2.4  | Defect  | Density and Size distribution                                | 22 |

| 2.5  | Experi  | mental Determination of Defect Density and Size Distribution | 25 |

|      | 2.5.1   | Defect Density                                               | 29 |

|      | 2.5.2   | Defect Size distribution                                     | 32 |

| 2.6  | Detern  | nination of Optimal Layout Rules                             | 33 |

|      | 2.6.1   | Test Structures                                              | 34 |

|      |         | Improvements in Test Device Design                           | 35 |

|      | 2.6.2   | Test Structures for Defect Clusters                          | 36 |

| 2.7  | Statist | ical Determination of Layout Rules                           | 38 |

|      | 2.7.1   | STRUDEL                                                      | 38 |

| 2.8  | Yield I | Prediction from the Circuit Layout.                          | 39 |

|      | 2.8.1   | VLASIC                                                       | 39 |

|      |         | Relevance to LDRs                                            | 40 |

|      | 2.8.2   | Virtual Layout                                               | 40 |

|      | 2.8.3   | RYE                                                          | 41 |

|      | 2.8.4   | McYield                                                      | 42 |

| 2.9  | Fault 1 | Colerant Techniques                                          | 43 |

| 2 10 | Conclu  | sions                                                        | 16 |

80

4.6

| 5. | Loca | al Design Rules.                        | 81  |

|----|------|-----------------------------------------|-----|

|    | 5.1  | Local Design Rules                      | 81  |

|    | 5.2  | Defining the Local Design Rules         | 83  |

|    | 5.3  | Potential Layout Changes                | 84  |

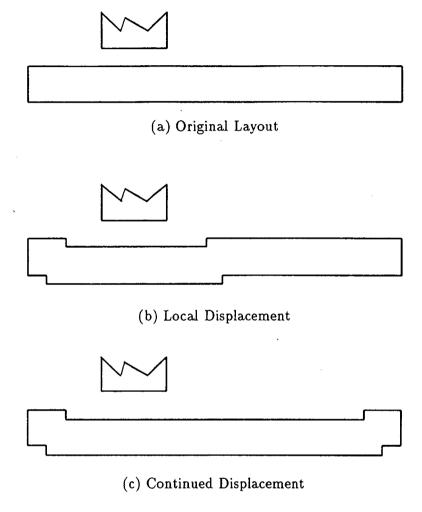

|    |      | 5.3.1 Track Displacement                | 85  |

|    |      | 5.3.2 Change in Fault Size Distribution | 87  |

|    |      | 5.3.3 Displacement Strategies           | 91  |

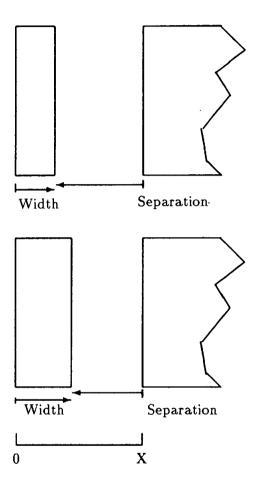

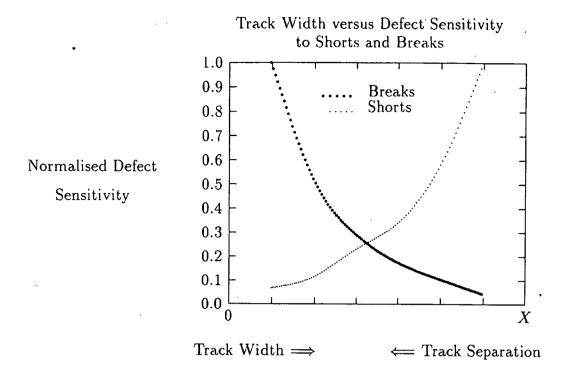

|    |      | 5.3.4 Increase Track Width              | 93  |

|    |      | 5.3.5 Increased Contact Size            | 95  |

|    | 5.4  | Performance                             | 99  |

|    |      | 5.4.1 Increased Contact Size            | 99  |

|    |      | 5.4.2 Track Displacement                | 100 |

|    |      | 5.4.3 Increased Track Width             | 102 |

|    | 5.5  | Reliability                             | 104 |

|    | 5.6  | Suitable Fabrication Processes.         | 104 |

|    |      | 5.6.1 Volume Production                 | 105 |

|    | 5.7  | Suitable Circuits for LDRs              | 106 |

|    | 5.8  | Applying Local Design Rules             | 109 |

|    | 5.9  | Conclusions                             | 109 |

| 6. | The  | e LocDes Program.                       | 10  |

|    | 6.1  | The LocDes Program                      | 110 |

|    |      | 6.1.1 Local Design Rules                | 110 |

|    | •    | 6.1.2 Design Rule Checking              | 111 |

|    |     |         | implementation                      |              |

|----|-----|---------|-------------------------------------|--------------|

|    | 6.2 | Opera   | ating Modes                         | 11           |

|    |     | 6.2.1   | X Window User Interface             | 114          |

|    |     | 6.2.2   | Batch Processing                    | 116          |

|    |     |         | Order of LDR Application            | 116          |

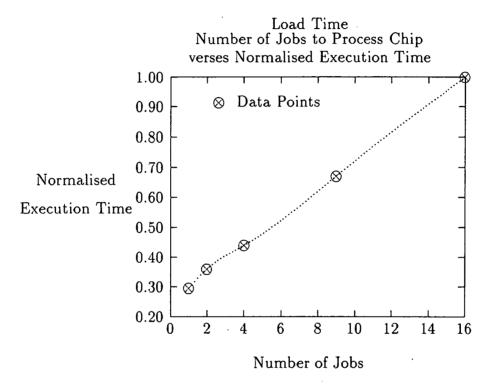

|    |     |         | Execution Time                      | 118          |

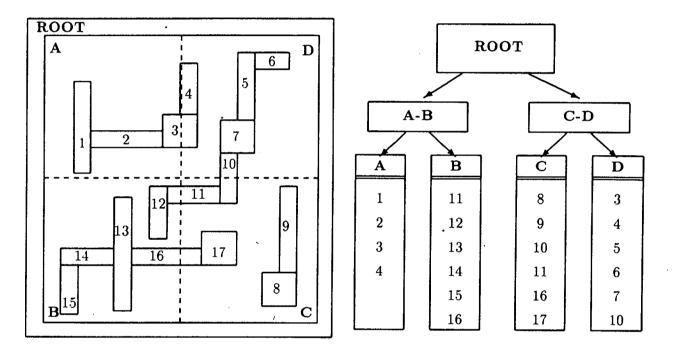

|    | 6.3 | Loss o  | of Hierarchy                        | 119          |

|    | 6.4 | Initial | lisation                            | 121          |

|    | 6.5 | Apply   | ring Local Design Rules             | 1 <b>2</b> 4 |

|    |     | 6.5.1   | Increase Track Width                | 124          |

|    |     | 6.5.2   | Increase Contact Size               | 126          |

|    |     | 6.5.3   | Track Displacement                  | 126          |

|    |     |         | Displacement of Track at Crossovers | 131          |

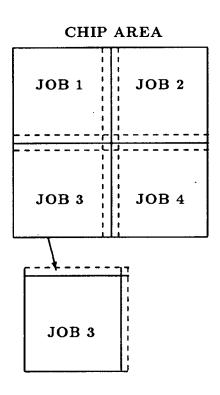

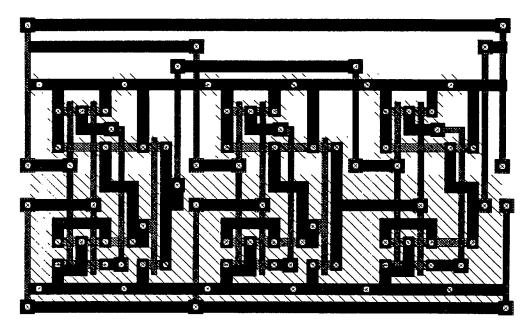

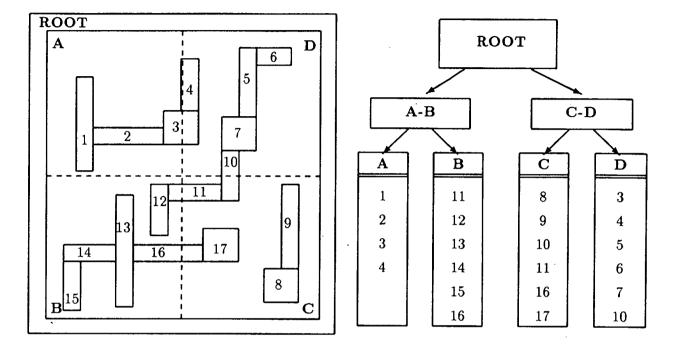

|    | 6.6 | Large   | Circuit Layouts                     | 1 <b>3</b> 2 |

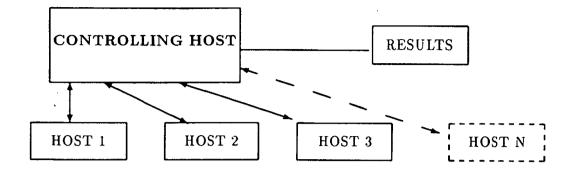

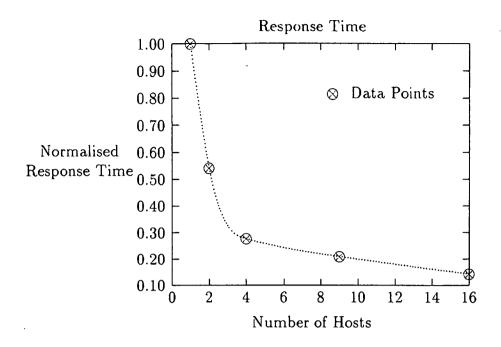

|    |     | 6.6.1   | Distributed Processing              | 136          |

|    |     |         | Interprocess Communication          | 138          |

|    | 6.7 | Conclu  | usions                              | 140          |

| 7. | Des | ign Ru  | ıle Checking.                       | 41           |

|    | 7.1 | Introd  | uction                              | 41           |

|    | 7.2 |         | Width LDRs                          |              |

|    | 7.3 |         | ct and Contact Overlap LDRs         |              |

|    | 7.4 |         | cement Extensions.                  |              |

|    | 7.5 |         | l Data Structure                    |              |

|    |     |         |                                     | -            |

|    |     | 7.5.1  | Common Spatial Data Structures            | 1  |

|----|-----|--------|-------------------------------------------|----|

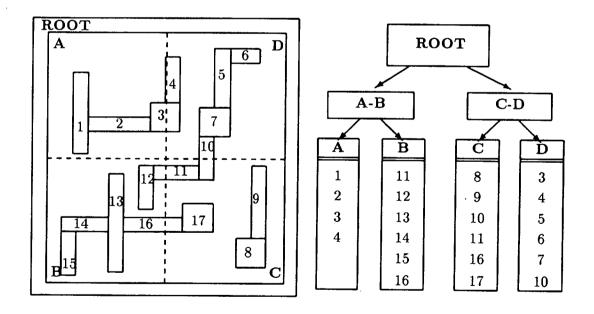

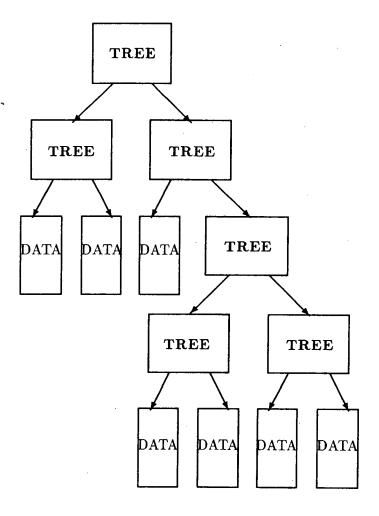

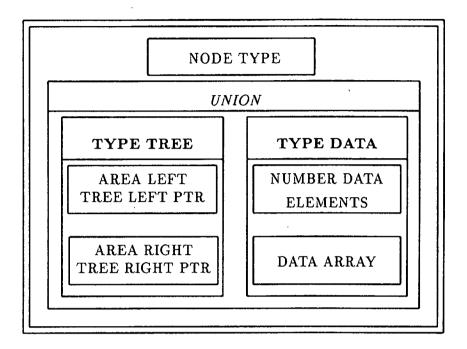

|    |     | 7.5.2  | The Adaptive Multiple Storage Binary Tree | 1  |

|    |     |        | Binary Tree Elements                      | 4  |

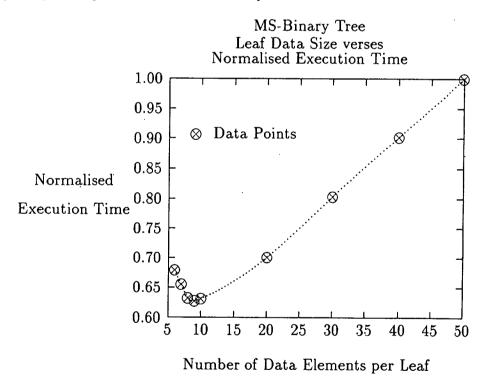

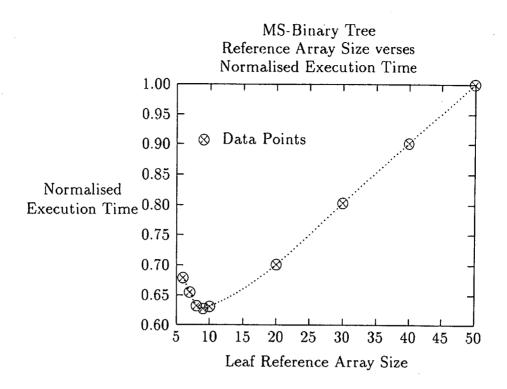

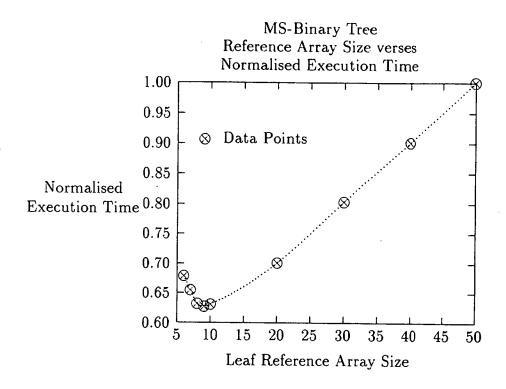

|    |     |        | Optimum Size of Index Array               | 5  |

|    | 7.6 | Geome  | etry Search Algorithm                     | 6  |

| •  | 7.7 | Conclu | usions                                    | 7  |

| 8. | Res | ults   | 15                                        | 8  |

|    | 8.1 | Applic | cation of LDRs to Routing                 | 8  |

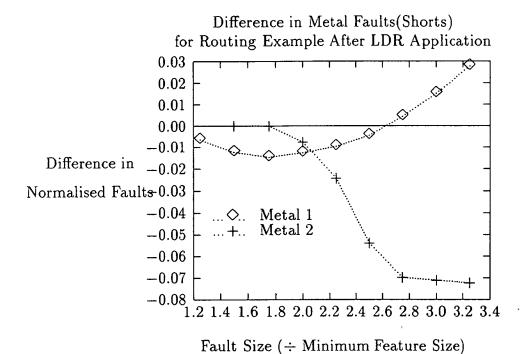

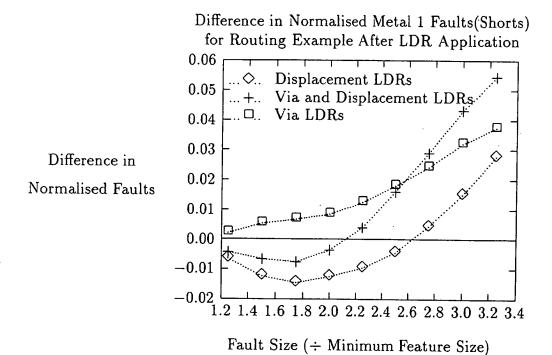

|    |     | 8.1.1  | Track Displacement LDR                    | ,9 |

|    |     |        | Effects on Metal 1                        | 9  |

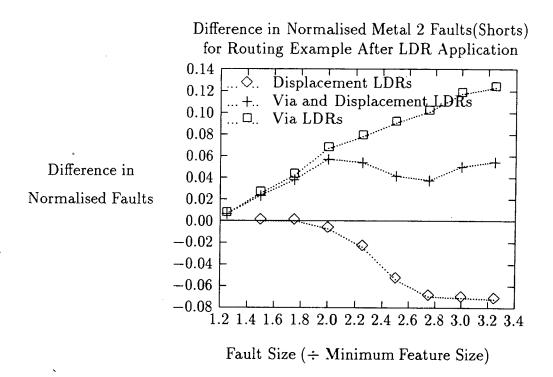

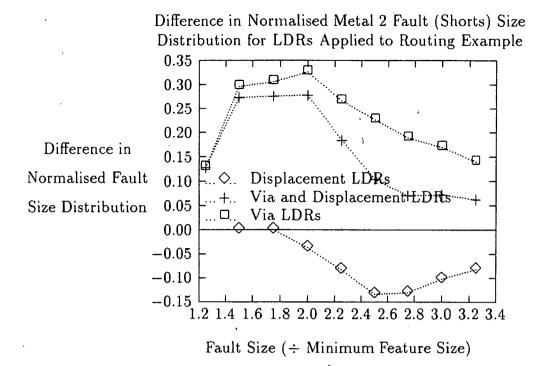

|    |     |        | Effects on Metal 2                        | 1  |

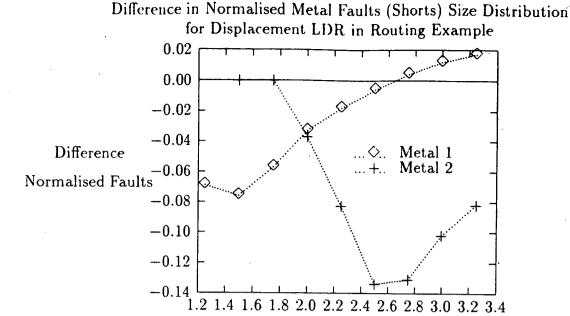

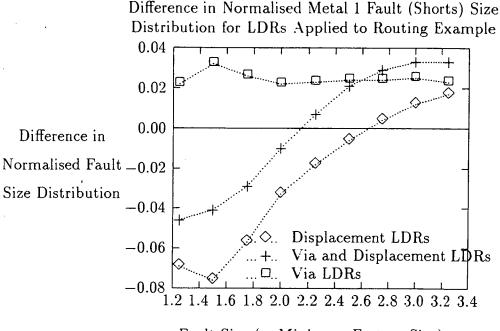

|    |     |        | Difference in Fault Size Distribution     | 1  |

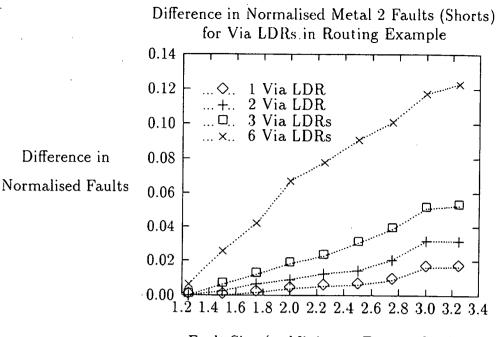

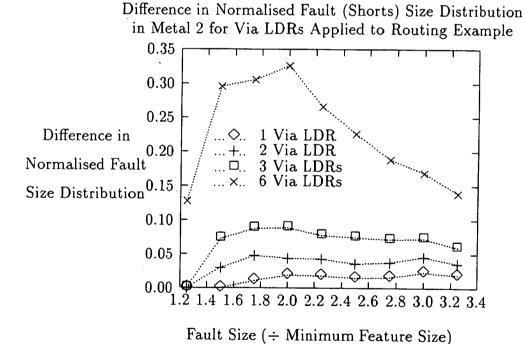

|    |     | 8.1.2  | Contact/Via Increase LDR                  | 1  |

|    |     |        | Effects on Metal 1                        | 2  |

|    |     |        | Effects on Metal 2                        | 4  |

|    |     |        | Effects on Via Layer                      | 8  |

|    |     |        | Percentage Change in Faults               | 8  |

|    | 8.2 | Applie | cation of LDRs to Layout Cells            | 0  |

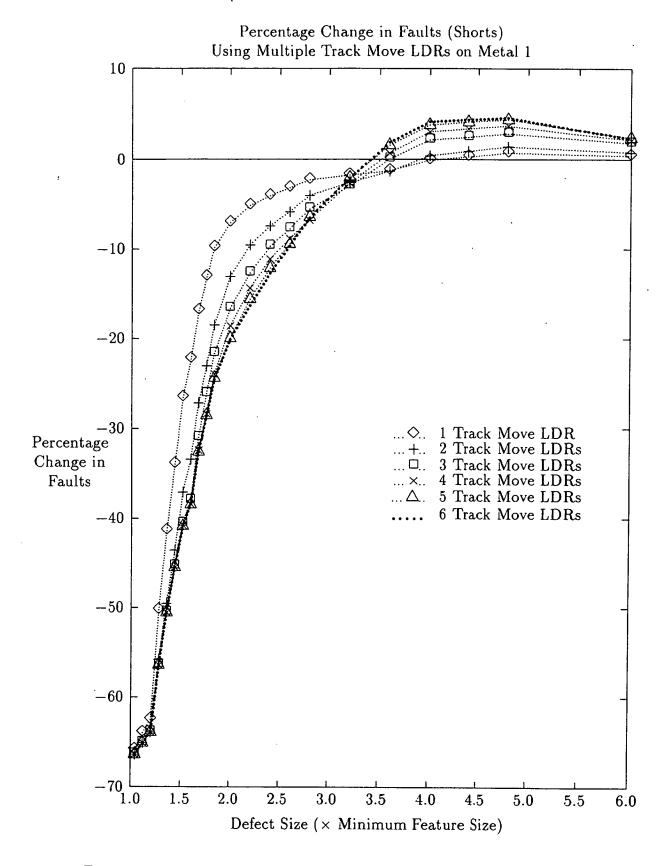

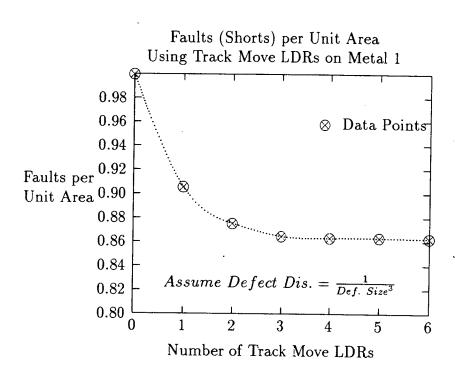

|    |     | 8.2.1  | Track Displacement LDR                    | 2  |

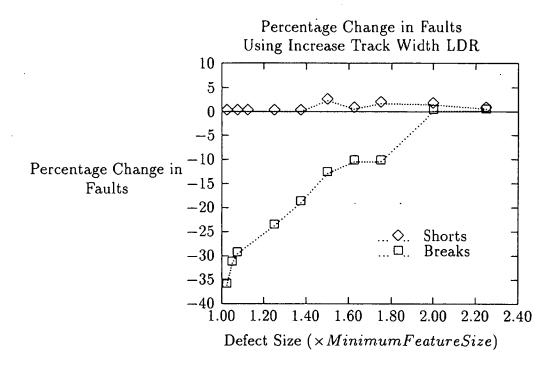

|    |     | 8.2.2  | Change in Track Width                     | 3  |

|    | 8.3 | Using  | LDRs                                      | 8  |

|    | 0 1 | Canal  | vaiona 17                                 | .0 |

| €. | Dis  | cussion | n and Conclusions                      | 180 |

|----|------|---------|----------------------------------------|-----|

|    | 9.1  | Introd  | luction                                | 180 |

|    | 9.2  | Local   | Design Rules                           | 18  |

|    |      | 9.2.1   | Performance                            | 181 |

|    |      | 9.2.2   | Reliability                            | 182 |

|    | 9.3  | LDRs    | and the Fabrication Process            | 183 |

|    | 9.4  | Suitab  | ole Circuits                           | 183 |

|    | 9.5  | The L   | ocDes Program                          | 184 |

|    |      | 9.5.1   | Using LocDes                           | 186 |

|    |      | 9.5.2   | Who Will Use LocDes?                   | 187 |

|    |      | 9.5.3   | Introducing Yield to Circuit Designers | 188 |

|    | 9.6  | Future  | e Improvements to LocDes               | 189 |

|    |      | 9.6.1   | Great Flexibility                      | 189 |

|    |      | 9.6.2   | More Effective Layout Adjustment       | 189 |

|    |      | 9.6.3   | CIF File Size                          | 190 |

|    | •    | 9.6.4   | Making LocDes More Usable              | 191 |

|    | 9.7  | Yield ! | Simulation                             | 193 |

|    | 9.8  | Result  | s                                      | 194 |

|    |      | 9.8.1   | Track Displacement                     | 194 |

|    |      | 9.8.2   | Track Width                            | 194 |

|    |      | 9.8.3   | Contact Increase                       | 195 |

|    | 9.9  | Yield l | Improvement from LDRs                  | 195 |

|    | 9.10 | Future  | Work                                   | 196 |

|    |      | 9.10.1  | Sources of Yield Improvement           | 197 |

| Table of Contents  |      | viii |

|--------------------|------|------|

| ·                  |      |      |

| 9.11 Conclusions . | <br> | 200  |

# List of Figures

| 2-1  | Fixed Area of Oxide                                               | 15 |

|------|-------------------------------------------------------------------|----|

| 2-2  | Displacement to Reduce Critical Oxide Area                        | 15 |

| 2-3  | Normalised Defect Distribution                                    | 23 |

| 2-4  | Serpentine and Comb Test Structure                                | 26 |

| 2-5  | Wafer Map of Serpentine Test Structures:Linear Scale              | 27 |

| 2-6  | Wafer Map of Comb Test Structures:Linear Scale                    | 27 |

| 2-7  | Wafer Map of Serpentine Test Structures:Log Scale                 | 28 |

| 2-8  | Wafer Map of Comb Test Structures:Log Scale                       | 28 |

| 2-9  | Defect Size Distribution Generated from Comb Test Structure       | 32 |

| 2-10 | Defect Size Distribution Generated from Serpentine Test Structure | 33 |

| 3-1  | Missing and Extra Material Defects                                | 48 |

| 3-2  | Extra Material Defects on Layout                                  | 49 |

| 3-3  | Yield Simulator Initialisation Algorithm                          | 52 |

| 3–4  | Transistor Source and Drain Generation from Layout                | 53 |

| 3–5  | Defect Generation Algorithm                                       | 54 |

| 3–6  | Circular Defect Approximation                                     | 55 |

| 3–7  | Extra Material Defect Fault Detection Algorithm                   | 56 |

| 3-8  | Missing Material Defect Fault Detection Algorithm                 | 58 |

| 3-9  | Missing Material Defects on Layout                                | 58 |

|------|-------------------------------------------------------------------|----|

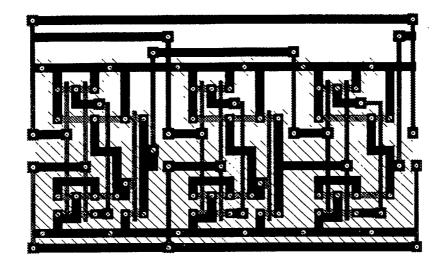

| 3-10 | CMOS cell used in Yield Simulation                                | 60 |

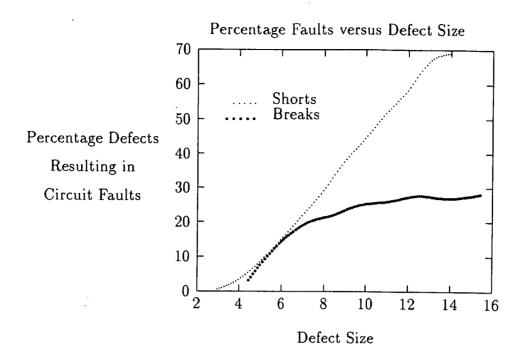

| 3-11 | Graph of Faults(%) versus Defect Size on CMOS layout              | 62 |

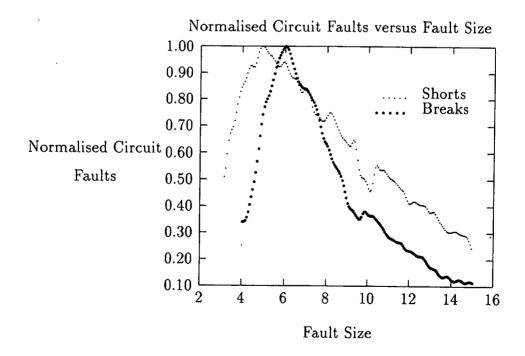

| 3-12 | Graph of Normalised Faults versus Fault Size                      | 62 |

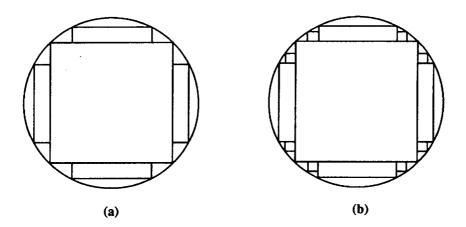

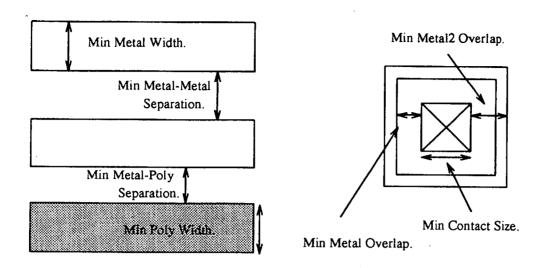

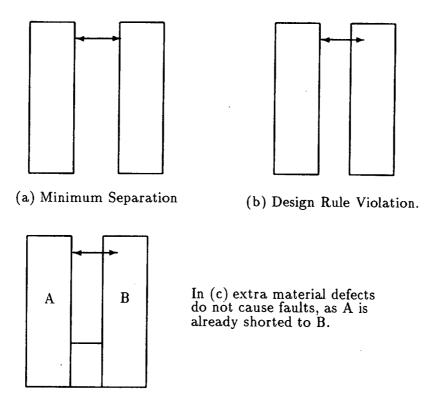

| A_1  | Examples of Global Design Rules                                   | 65 |

|      |                                                                   |    |

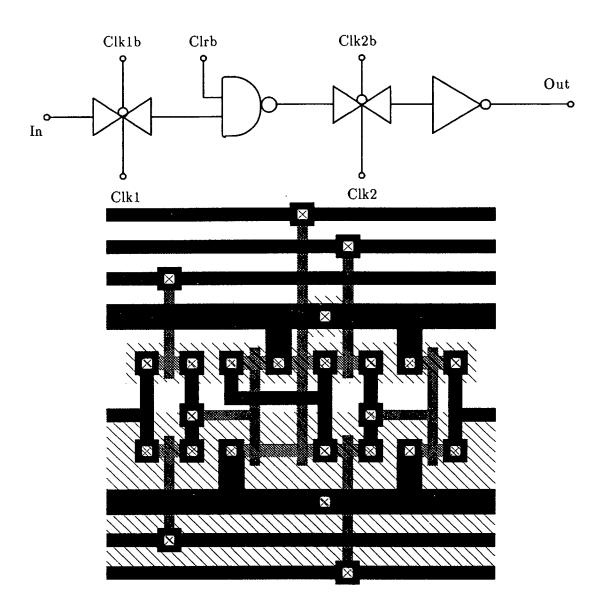

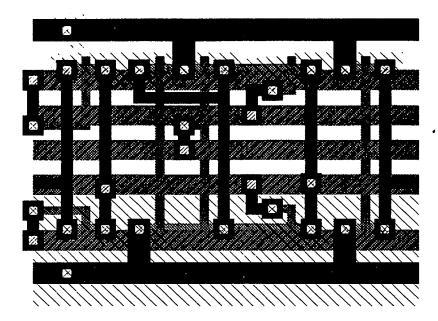

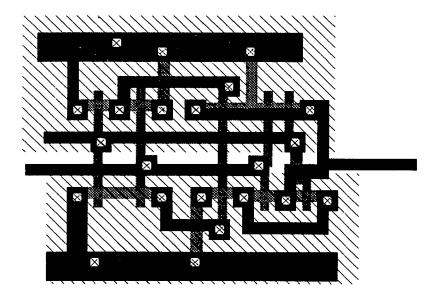

| 4-2  | Dynamic Shift Register Cell                                       | 68 |

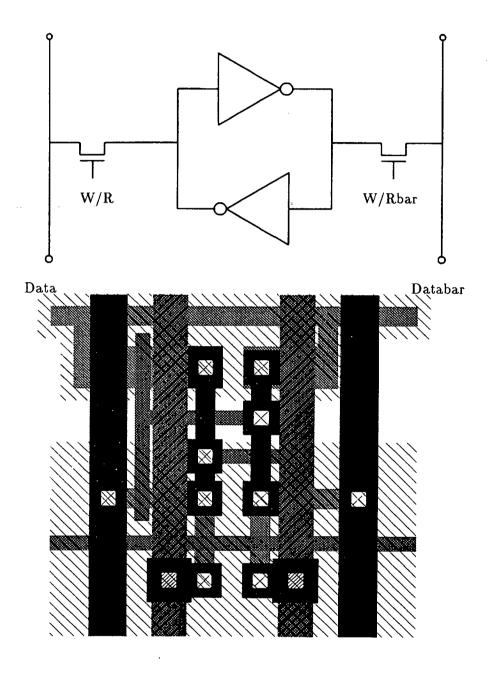

| 4-3  | 6 Transistor RAM Cell                                             | 69 |

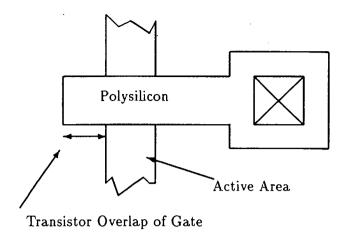

| 4-4  | Transistor Overlap of Gate                                        | 70 |

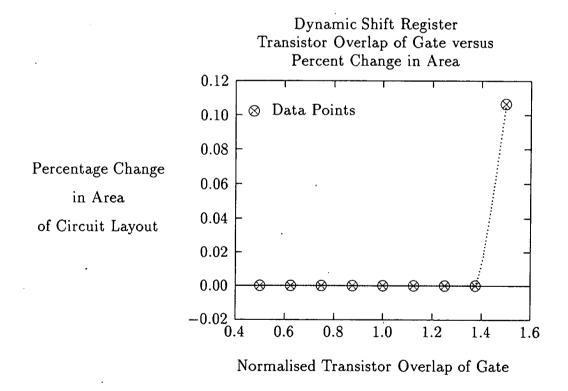

| 4-5  | Results from Changing Transistor Overlap of Gate:Shift Register . | 70 |

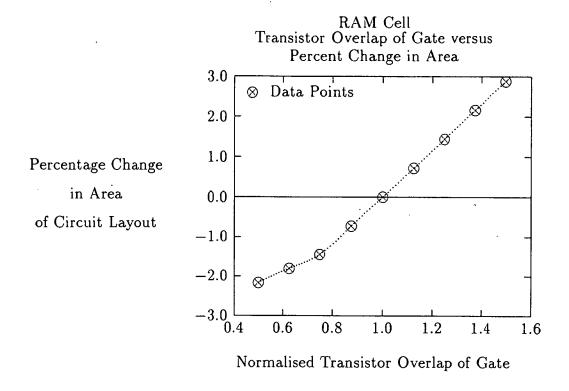

| 4-6  | Results from Changing Transistor Overlap of Gate:RAM Cell         | 71 |

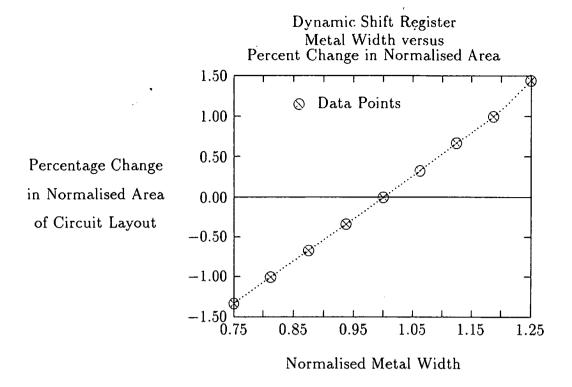

| 4-7  | Results from Changing Metal 1:Shift Register Cell                 | 72 |

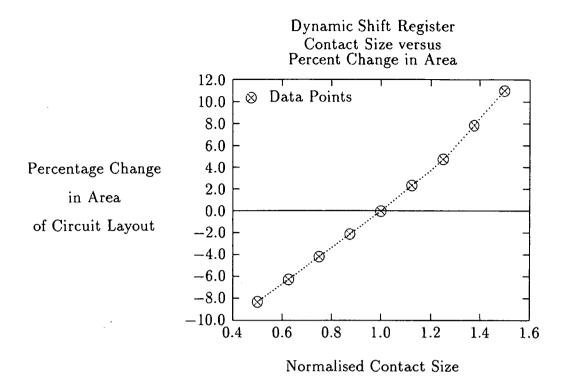

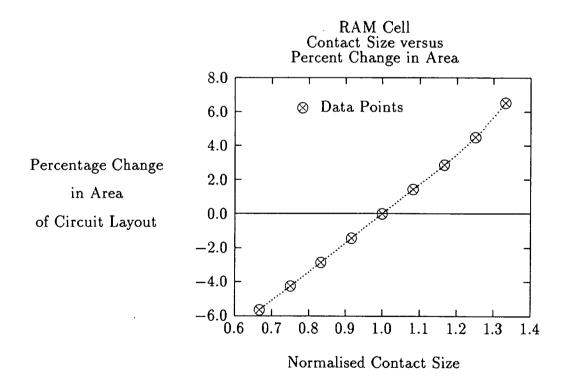

| 4-8  | Results from Changing Contact Size:Shift Register Cell            | 73 |

| 4-9  | Results from Changing Contact Size:RAM Cell                       | 73 |

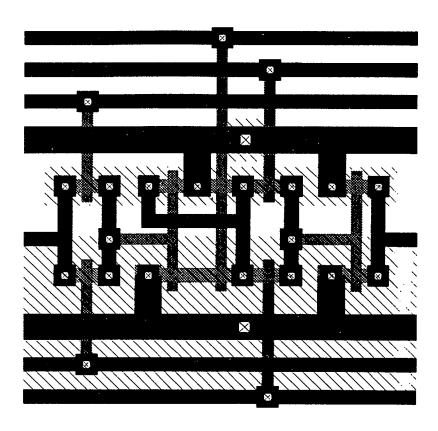

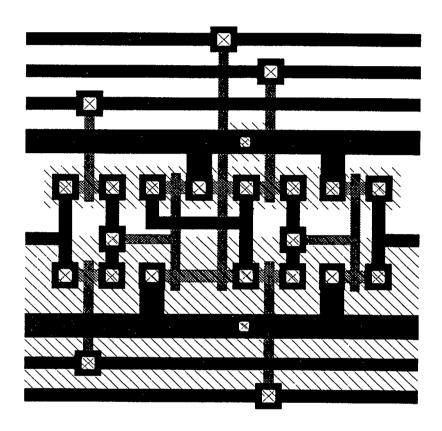

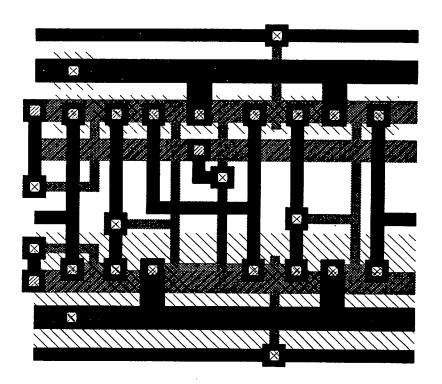

| 4-10 | Shift Register with Contact 75% of Original Size                  | 74 |

| 4-11 | Shift Register with Contact 125% of Original Size                 | 75 |

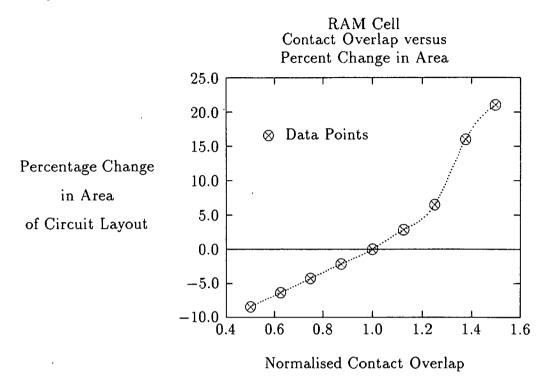

| 4-12 | Results from Changing Contact Overlap:RAM Cell                    | 76 |

| 4-13 | Results from Changing Contact Overlap:Shift Register Cell         | 77 |

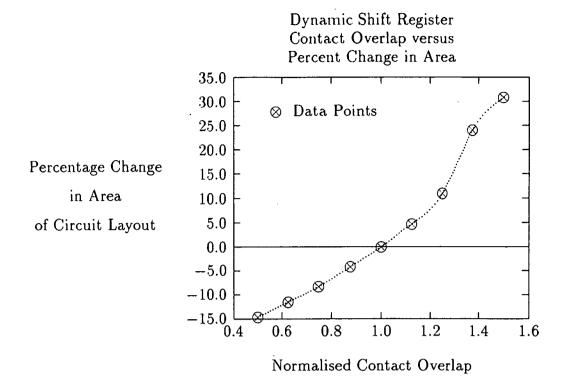

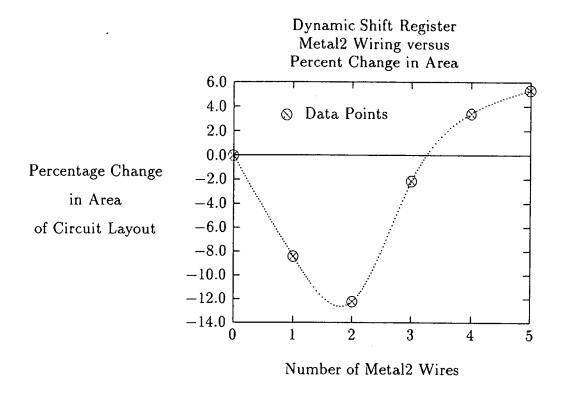

| 4-14 | Use of Metal 2 in Shift Register Cell                             | 78 |

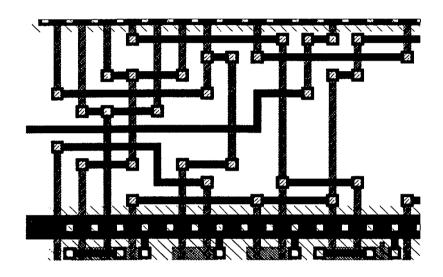

| 4-15 | Three Metal 2 Wire Layout of Shift Register Cell                  | 78 |

| 4-16 | Five Metal 2 Wire Layout of Shift Register Cell                   | 79 |

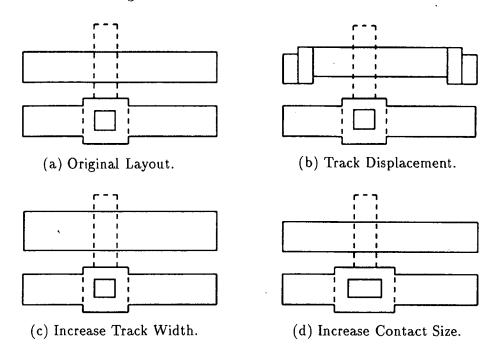

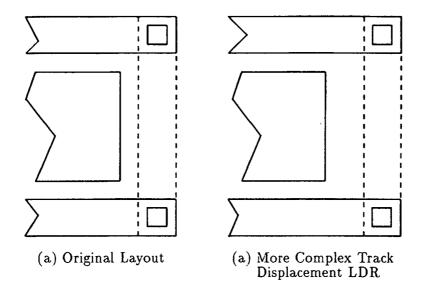

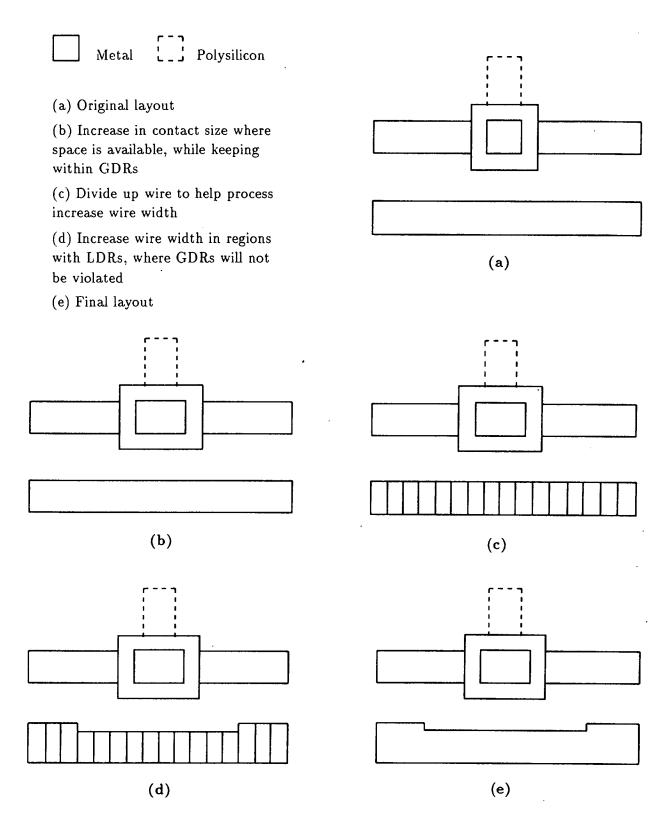

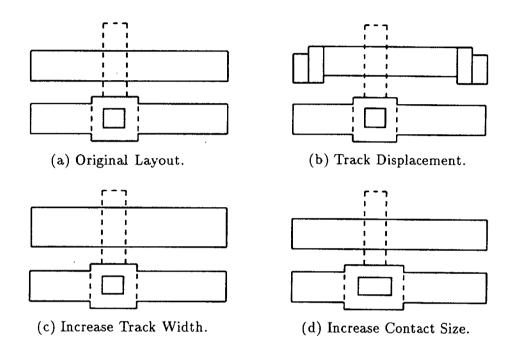

| 5-1  | Potential Layout Changes to Enhance Yield                         | 85 |

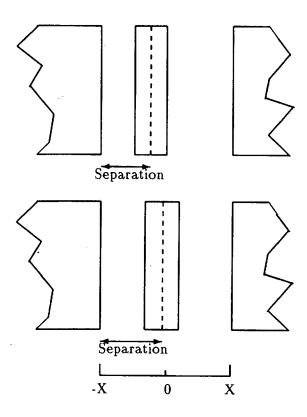

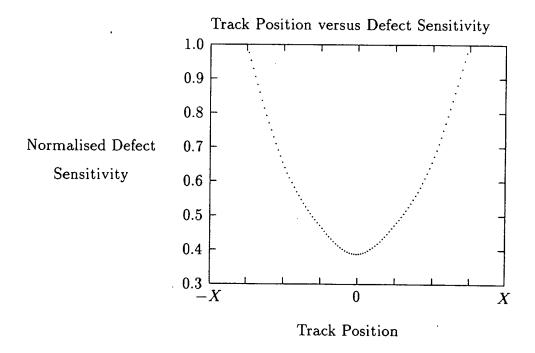

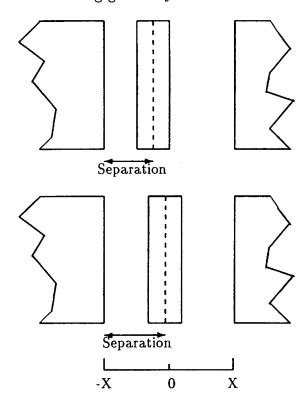

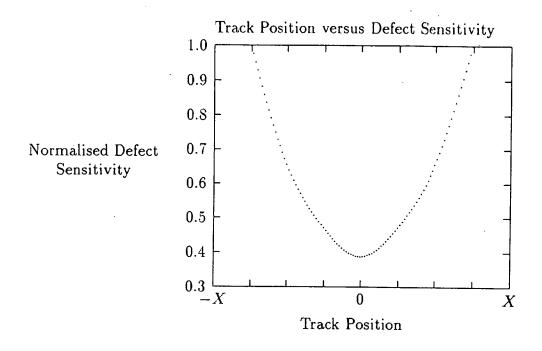

| 5-2  | Test for Optimum Separation of Geometry                           | 86 |

| 5–3  | Optimum Geometry Separation Results                               | 86 |

| ıs | St OL I | igures .                                                                                        | Xı  |

|----|---------|-------------------------------------------------------------------------------------------------|-----|

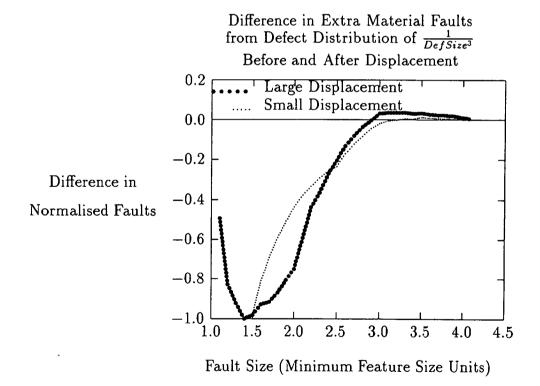

|    | 5-4     | Effect of Displacement on Fault Size Distribution                                               | 88  |

|    | 55      | Distribution of Faults Sizes Before and After Displacement                                      | 89  |

|    | 5-6     | Difference Between Distribution of Faults Sizes Before and After Displacement                   | 89  |

|    | 5-7     | Standard Change in Fault Distribution from Track Displacement LDR Application to Circuit Layout | 90  |

|    | 5-8     | Difference in Fault Size Distribution After Displacement of Track.                              | 90  |

|    | 5-9     | Possible Displacement Strategies                                                                | 92  |

|    | 5-10    | Test for Optimum Width/Separation of Geometry                                                   | 94  |

|    | 5-11    | Optimum Width/Separation Results                                                                | 95  |

|    | 5-12    | Combined Results of Extra and Missing Material Defects for Increased Geometry Width/Separation  | 96  |

|    | 5-13    | Increased Contact Size with Polysilicon Interaction                                             | 97  |

|    | 5-14    | Increased Contact Size without Polysilicon Interaction                                          | 98  |

|    | 5-15    | Resistance and Contact Size in a Metal-Polysilicon Contact                                      | 101 |

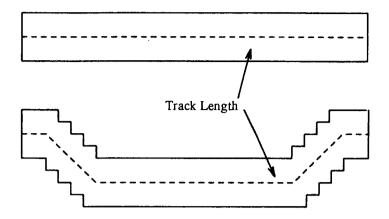

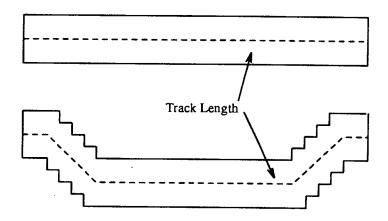

|    | 5-16    | Increased Track Length with Displacement                                                        | 102 |

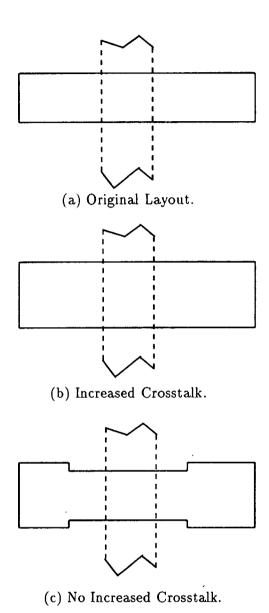

|    | 5-17    | Track Width Increase and Cross Talk                                                             | 103 |

|    | 5-18    | RAM Cell with Little Scope for LDRs                                                             | 107 |

|    | 5–19    | 2 Input XNOR Gate with Scope for LDRs                                                           | 107 |

|    | 5-20    | Example of Interconnect with Scope for LDRs                                                     | 108 |

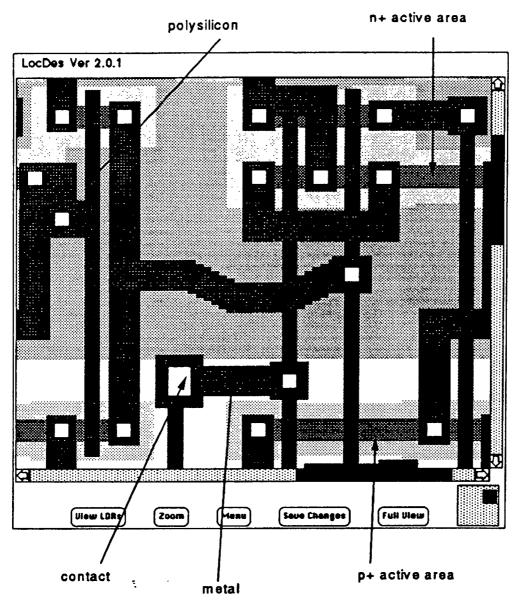

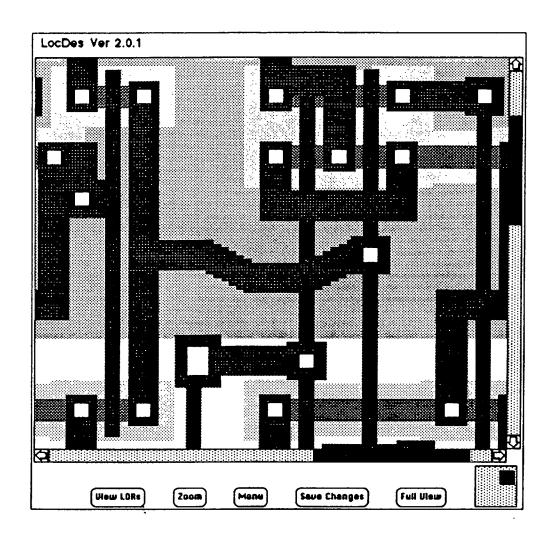

|    | 6–1     | LocDes X Window User Interface                                                                  | 115 |

|    | 6-2     | Application of LDRs Algorithm                                                                   | 117 |

|    | 6-3     | Initialisation of Data and Rules for LocDes Program                                             | 122 |

|    | 6-4     | Design Rules for Same Node Geometry                                                             | 123 |

| r ·             | • |   |

|-----------------|---|---|

| List of Figures |   | X |

| not of figures  |   |   |

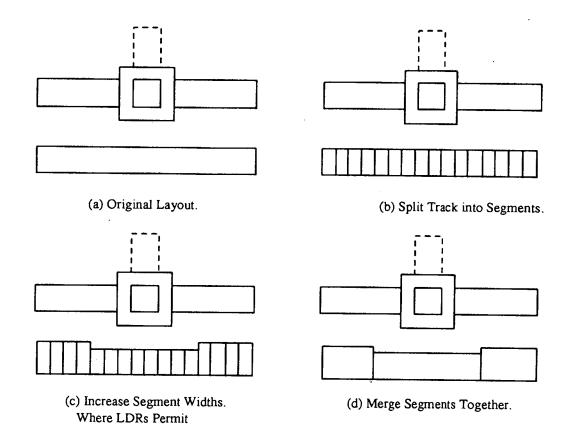

| 6-5 Track Width LDR Algorithm                                              | 25 |

|----------------------------------------------------------------------------|----|

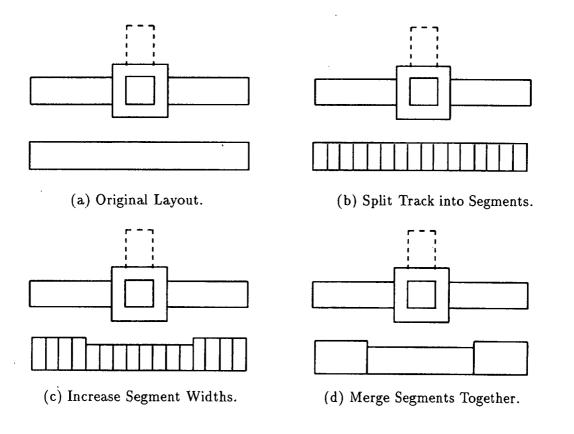

| 6-6 Application of Track Width LDR                                         | 25 |

| 6-7 Contact LDR Algorithm                                                  | 27 |

| 6-8 Application of Contact LDR                                             | 28 |

| 6-9 Track Displacement LDR Algorithm                                       | 29 |

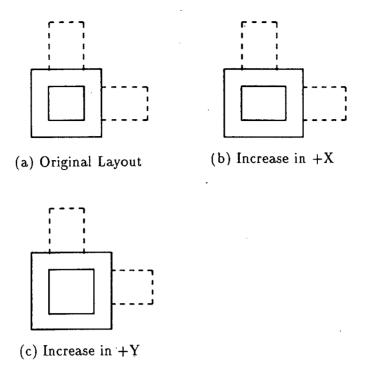

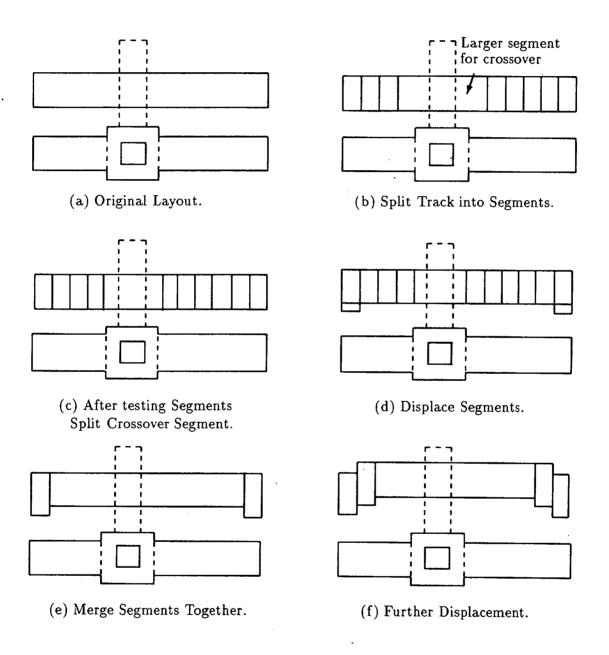

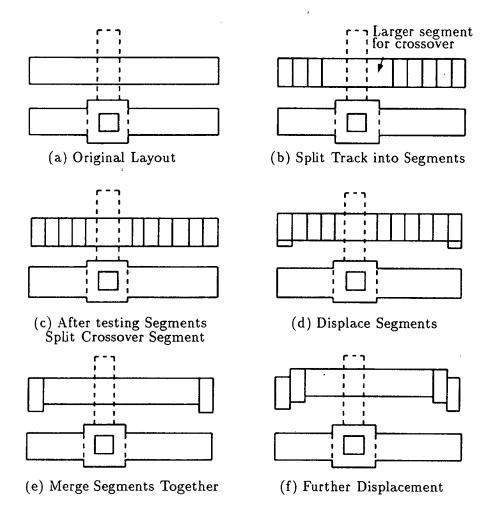

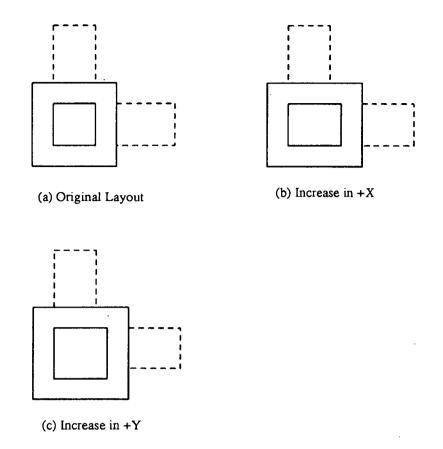

| 6-10 Application of Track Displacement LDR                                 | 30 |

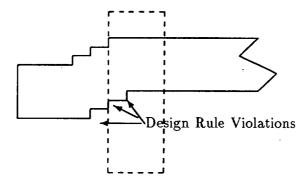

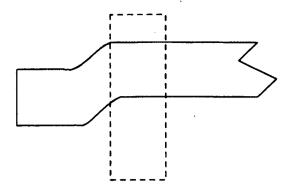

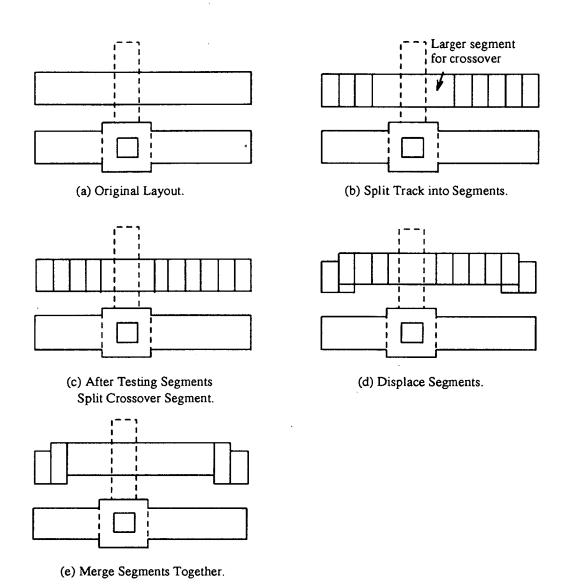

| 6-11 Crossover with Track Displacement Resulting in Design Rule Violations | 31 |

| 6-12 Resulting Physical Layout from Track Displacement at Crossover.       | 32 |

| 6-13 Segment Generation from Large Circuit Layouts                         | 33 |

| 6-14 Graph of LocDes Load Time                                             | 34 |

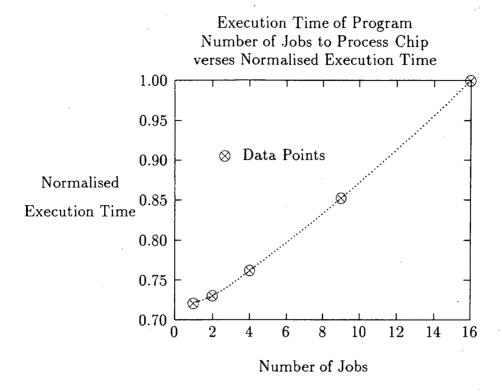

| 6-15 Graph of LocDes Execution Time                                        | 35 |

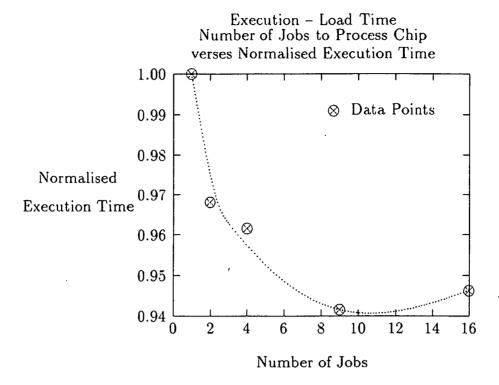

| 6-16 Graph of Execution Time minus Load Time                               | 36 |

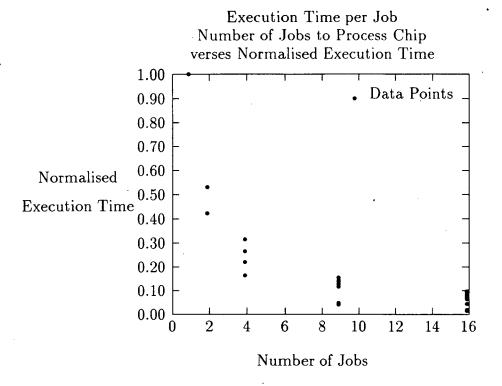

| 6-17 Graph of Execution Time Per Job in LocDes                             | 37 |

| 6-18 Data Flow in Parallel operation of LocDes                             | 38 |

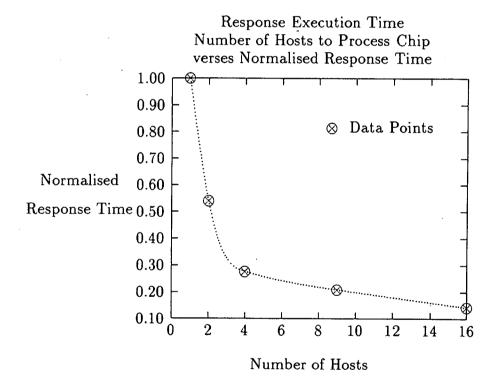

| 6-19 Response Time of Parallel LocDes                                      | 38 |

| 7-1 Design Rule Checking Algorithm for Track Width LDRs 14                 | 42 |

| 7-2 Design Rule Checking in Track Width LDR                                | 44 |

| 7-3 Design Rule Checking Algorithm for Contact Overlap 14                  | 45 |

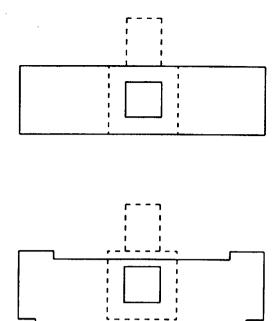

| 7-4 Contact Overlap Violation by Displacement                              | 47 |

| 7-5 Fixed Layer Generation Algorithm                                       | 47 |

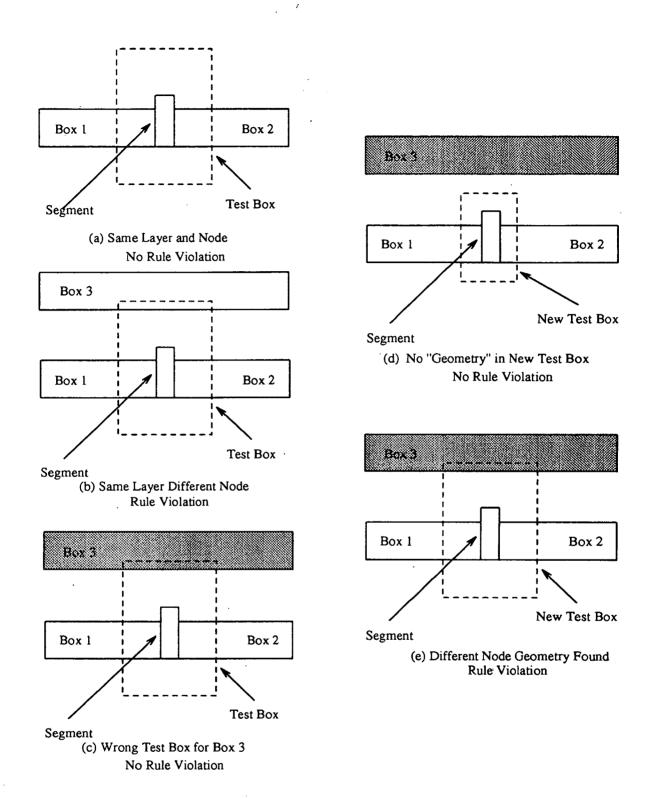

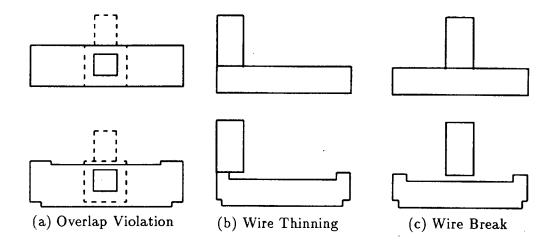

| 7-6 Potential Errors from Track Displacement                               | 48 |

| 7-7 Extra Design Rule Checking for Segment Displacement Algorithm. 14      | 49 |

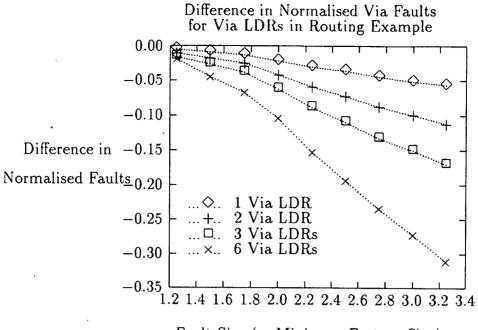

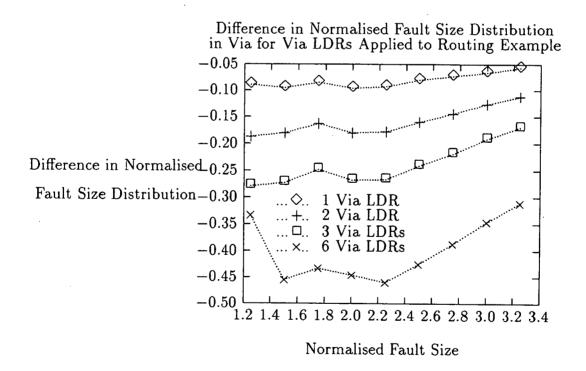

| 8-14 | Routing Example Results: Fault Size Distribution for Via Faults  |     |

|------|------------------------------------------------------------------|-----|

|      | After Via LDR Application                                        | 169 |

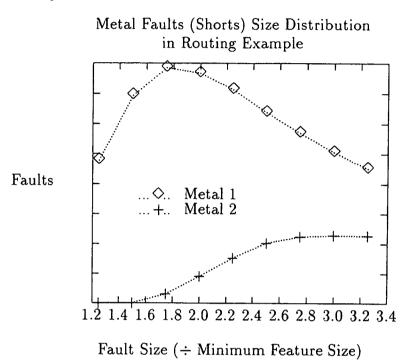

| 8-15 | Routing Example Results: Fault Size Distribution of Metal Layers | 170 |

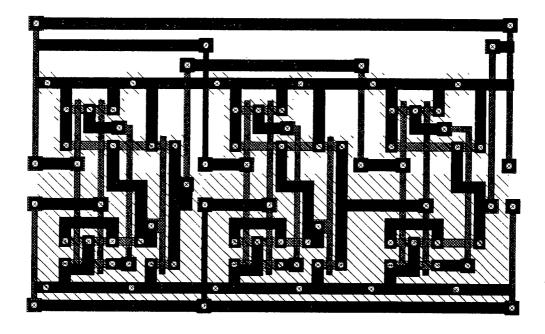

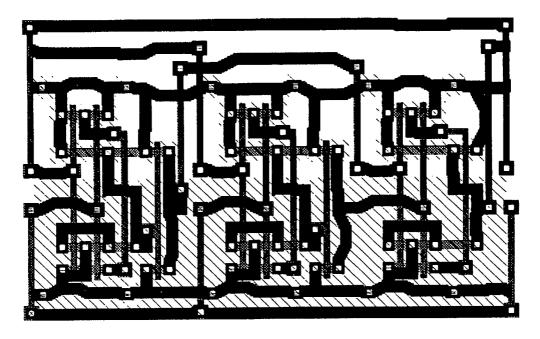

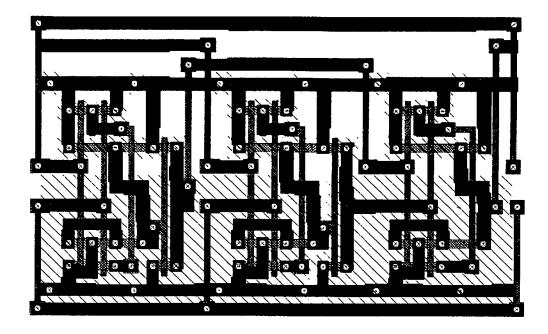

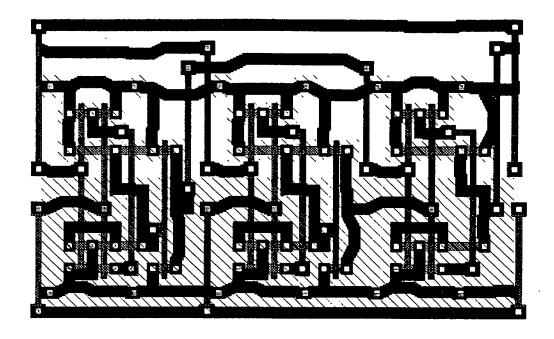

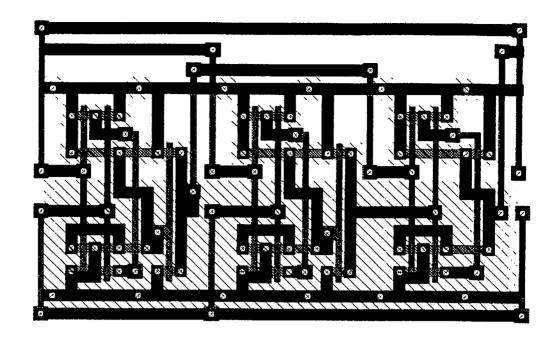

| 8-16 | Random Logic Cell                                                | 172 |

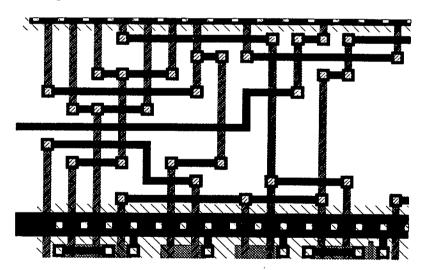

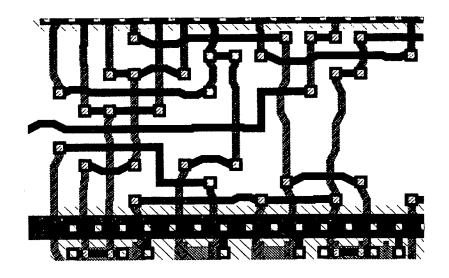

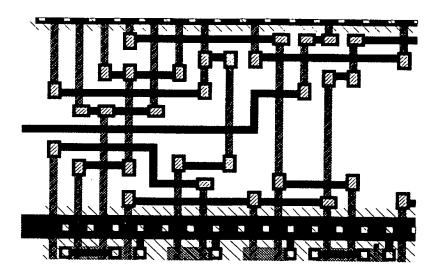

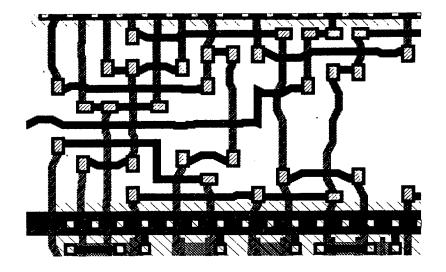

| 8-17 | Random Logic Cell After 6 Track Displacement LDR Iterations .    | 173 |

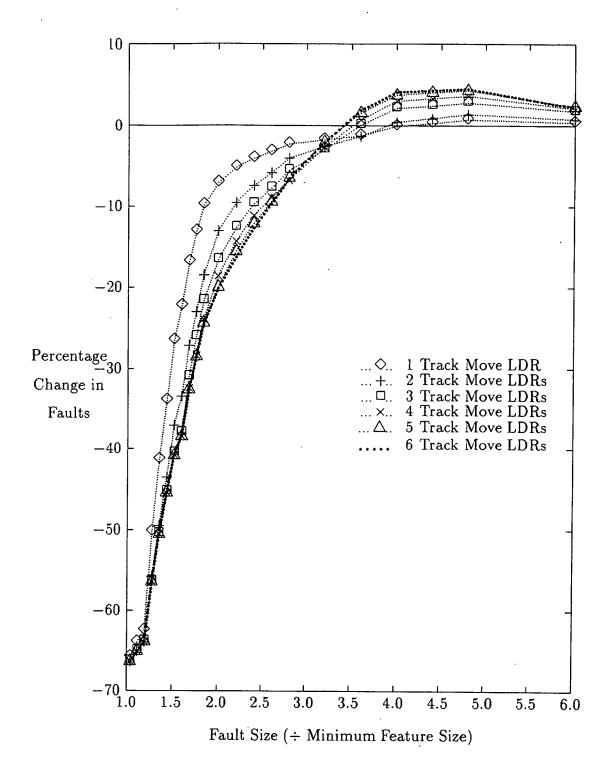

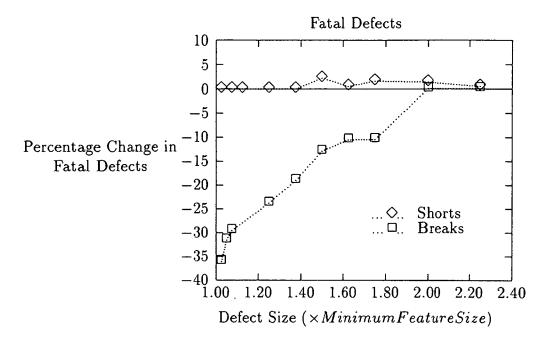

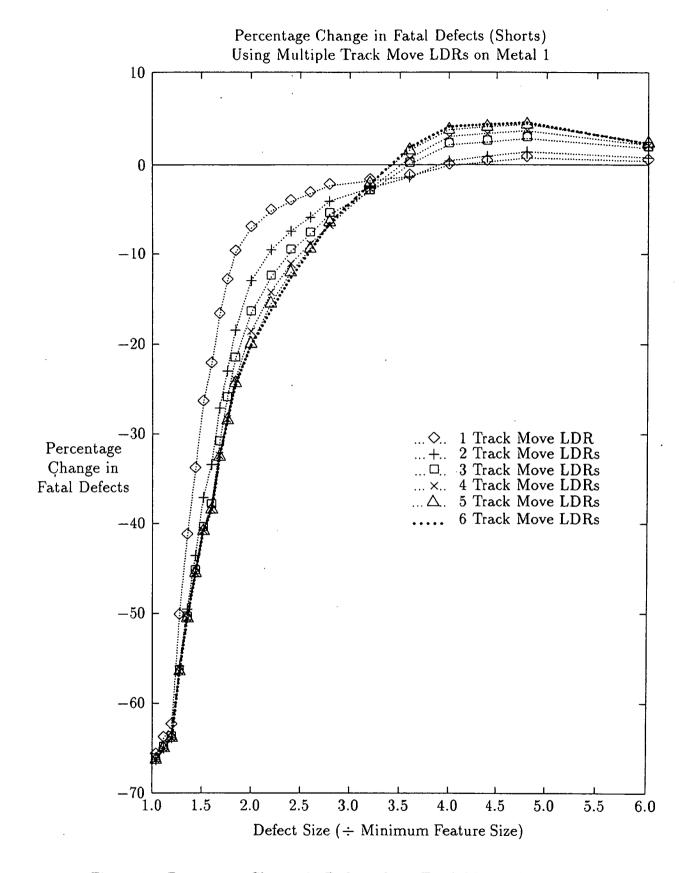

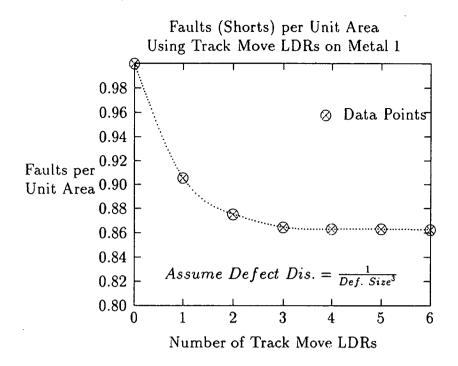

| 8-18 | Percentage Change in Defects from Track Move LDRs                | 174 |

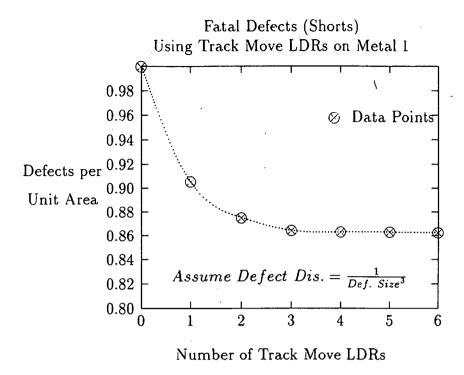

| 8-19 | All Short Fatal Defects Using Track Displacement LDRs            | 175 |

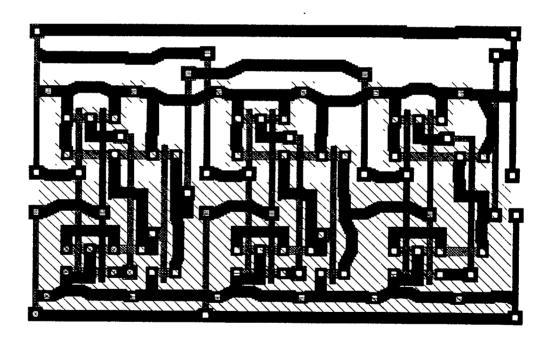

| 8-20 | Random Logic Cell After Track Width Increase LDR                 | 176 |

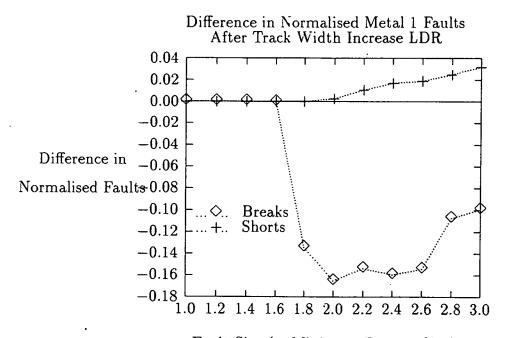

| 8-21 | Random Logic: Difference in Normalised Faults After Track Width  |     |

|      | Increase LDR                                                     | 176 |

| 8-22 | Random Logic: Difference in Normalised Fault Size Distribution   | •   |

|      | After Track Width Increase LDR                                   | 177 |

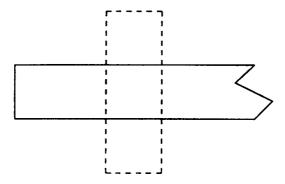

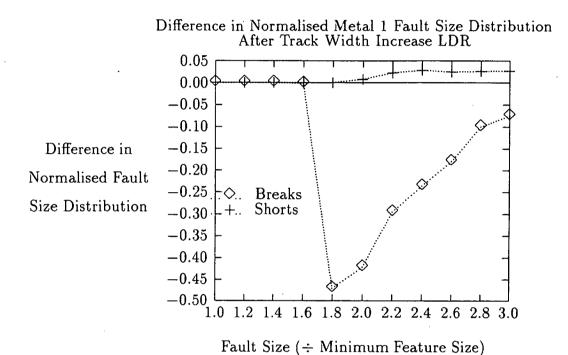

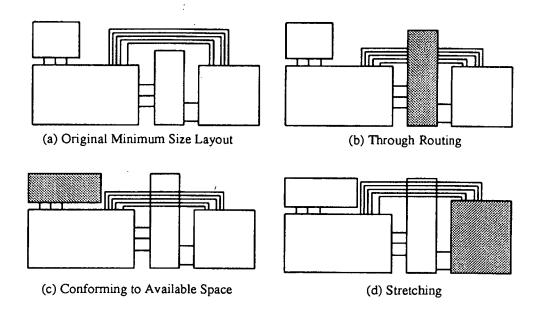

| 9-1  | More Complex Track Displacement LDR                              | 190 |

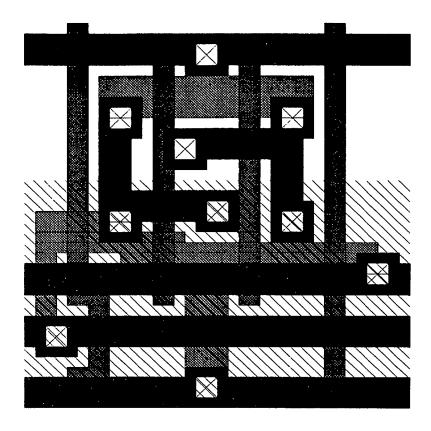

| 9-2  | Application of Yield Improvement Techniques to an IC             | 199 |

# List of Tables

| 2-1 | Measurements of Defect Densities from Comb Test Structure                 | 30  |

|-----|---------------------------------------------------------------------------|-----|

| 2–2 | Measurements of Defect Densities from Serpentine Test Structure           | 31  |

| 3-1 | Results of Extra and Missing Material Defect Simulation on a C-MOS layout | 61  |

| 8-1 | Routing Example: Percentage Change in Faults from LDR Application         | 171 |

# Chapter 1

# Introduction

The fabrication of integrated circuits is a complex process that can have many hundreds of process steps. Developments in fabrication technology have resulted in a continual reduction in the feature size of integrated circuit components. Feature sizes as small as  $0.6\mu$ m are now being introduced into commercial plants[1]. Not only are feature sizes being reduced but the actual area of ICs has shown a tendency to increase, as more functionality is demanded. This means that the manufacturing complexity of integrated circuits is being driven from two directions; smaller feature sizes and larger chip area. This places a heavy burden on process engineers, requiring continual improvements in the fabrication process in order to produce ICs with an acceptable yield. Materials used in the fabrication of these devices must be ultra-pure and the environment in which the devices are processed must be free of contaminants.

The cost of process improvements and tooling up for the next generation of semiconductors is prohibitively expensive. There are only a few companies that are able to commit the required investment and even then it is often only with the help of national governments[2]. Other IC manufacturers must attempt to stretch their existing processes to meet the demand for greater functionality and better performance demanded by their customers. Since the required investment is so great even a small increase in return can amount to a substantial sum. The return on investment from a fabrication plant is dependent to a large extend on

the yield of the product (integrated circuits) that the plant produces. This implies that any improvement in yield is of considerable commercial interest.

## 1.1 Defect Sensitivity

It has long been recognised[3, 4] that the yield of an integrated circuit is dependent on the "active area" of the circuit. This area is not the physical dimensions of the chip, but a calculated value that is based on the defect sensitivity. Defect sensitivity is often defined in terms of the critical area[5]. The critical area, and therefore the defect density, is determined by the circuit geometry, in particular, the size and proximity of the circuit components that define the circuit.

RAM cell designers appear to be most aware of the importance of layout to the final yield of the circuit. RAM cell design in a commercial environment[6] typically involves tuning both the layout and the fabrication process to minimise the critical area and so optimise the yield.

While RAM cell designers have been intimately concerned with the yield obtained from a given circuit layout, designers of general purpose digital circuits have neglected the possibility of fine tuning a layout to achieve increases in yield. Great care is taken to reduce the physical area that an integrated circuit design will occupy but, so long as the layout does not violate any of the design rules, no further modification would normally be made. Little or no effort is expended to maximise the yield of the layout inside the area already defined by the circuit.

There are many reasons why circuit designers do not attempt minor modifications that would improve circuit yield:

- no tools may be available to measure the yield of the layout

- IC manufacturers do not usually inform designers of the defect levels in the manufacturing process. This makes it difficult to determine the yield or relative yield of different layout options

• designer have traditionally not been responsible for the yield of their circuit, since that is seen as the domain of the process engineer.

Whatever the reasons for the lack of interest in the past, in the future commercial pressures may force circuit designers to take some of the responsibility for the yield of the circuits they design. If that is the case then tools to aid the designer will be required.

## 1.2 Objectives

This thesis addresses the issue of layout modification to improve the defect sensitivity and hence the yield of circuit layout. Layout modifications can only improve the yield of integrated circuits when they affect, for the better, process steps that are ordinarily the source of yield losses. Ideally such a process step should be modified to reduce to zero the number of defects that it introduces. Where this cannot be achieved, because of either the high cost of modifying the process or the inability of current technology to solve the problem, it makes sense to reduce the sensitivity of the layout to those defects that will be introduced.

The main objective of this work was to develop a method to increase the yield of integrated circuits by modifying the circuit layout to decrease the sensitivity of the circuit to defects. Defects are inevitably present in the manufacturing process, therefore, reducing the defect sensitivity of a circuit will in general increase the circuit's yield.

While yield improvement was the overall aim there were a number of objectives and goals which are required to fulfill this.

#### • Examine Layout and Layout Rules

Layout generated by a number of sources particularly layout that had been automatically generated, was examined in order to determine the effect of layout rules on circuit area. If changes in layout rules do not greatly affect the circuit area and give increased defect sensitivity then the design rules should be modified.

#### • Suitable Layout Modifications

If, in order to decrease the defect sensitivity, the layout is to be modified, these modifications will have to be simple in order that they can be easily accomplished, either by hand or automatically. Modifications that require the re-working of large areas of a circuit, in order to accommodate a layout change, are unacceptable, even where yield improvements can be achieved.

It is necessary to determine a set of simple layout changes that can be made, which do not impact greatly on neighbouring layout and yet reduce the defect sensitivity.

#### • Measure Change in Defect Sensitivity

The effect any layout modifications has on the defect sensitivity of the circuit layout must be modelled or measured in some way, in order to determine if the objective of decreasing the defect sensitivity has been achieved.

#### • Automate the Process of Layout Modification

The process of layout modification is time consuming and therefore not suitable to be done by hand. If the process is to be used in a commercial environment, it must be automated to allow layout modifications to be made with as little intervention from the circuit designer as possible.

#### • Description of Layout Modifications

In order to automate the layout modifications they must be described in a form that can be easily interpreted by a computer program. That is a simple set of rules or tests must be developed that indicate whether an individual piece of circuit layout can be usefully modified within the constraints imposed by its immediate environment.

#### • Efficient Algorithms

The automation process will be required to operate on large circuit layouts.

In order for these modifications to be made in a reasonable time, algorithms that are time efficient must be researched and tailored to suit the particular requirements of the automation software.

#### • Selective Control of Automation Process

It was considered desirable that a circuit designer should have the option of applying the layout changes selectively. This would be done by indicating those pieces of layout that are to be changed. This implies some sort of interactive control of the layout modification process must be made available.

#### • Parallel Execution

Equally desirable is a fast response time, so that very large designs can be processed quickly. Even with efficient algorithms very large designs are likely to take too long for commercial use. To speed up this response time the automation process should be capable of processing a layout in parallel. This requirement may affect the design of the layout modification algorithms.

#### • Direct Future Research

The objectives of this work were limited to simple layout modifications. Another aim was to gain enough experience with these simple layout modifications to develop an understanding of what could be achieved by more detailed modifications. This experience will be used to determine how practical it would be to design a system to automatically apply much more sophisticated layout manipulations to increase circuit yield.

#### 1.3 Overview

This work describes a method for decreasing the defect sensitivity of IC layout. This method uses what have been termed Local Design Rules (LDR). These are rules that can be used by a designer, but more usefully by a computer program, to test whether a particular piece of circuit layout, from an existing completed IC design, can be modified to increase the circuit yield. The LDRs do not increase the circuit area, but instead use any redundant space that is available between the existing circuit layout geometry. That is LDRs suggest layout modifications that make more effective use of the original circuit area.

Whether LDRs can be usefully applied to a given circuit design is highly dependent on both the type of layout and the fabrication process to be used to manufacture the IC. Since LDRs make use of redundant space, it follows that layout generated by automatic layout tools is more suited to this process than an equivalent hand crafted layout, since hand crafted designs are nearly always more dense than automated designs.

The implementation of a computer program called LocDes that is used to apply LDRs to circuit layout is described. The algorithms that are used by LocDes to perform the layout modifications and the associated design rule checking are presented.

### 1.3.1 Using LocDes

The LocDes program is a post-processor of integrated circuit layout. Only when the design of an integrated circuit or cell has been completed would LocDes normally be used. The program searches the layout for instances of circuit geometry that it considers non-optimal. That is a piece of layout for which there is a LDR that describes conditions that match those of the particular piece of layout. The LDR will then prescribe a layout modification that can be used to reduce the

defect sensitivity of the layout. The modification is only applied if none of the layout design rules are violated.

Because modifications would usually be made to completed integrated circuit designs, those designs whose simulated performance is close to the performance specifications may not be suitable for LDR modifications. This is due to the fact that some layout changes may adversely affect the performance of a circuit (this is discussed in greater detail in chapter 5). Where performance is critical and the expected performance of a device is so close to its specifications limits that indiscriminate layout modifications cannot be contemplated, the circuit designer can use an interactive version of the program. This allows the designer to select which layout is to have LDRs applied, ensuring that critical areas of the circuit remain unaffected. An alternative is to apply LDRs earlier in the layout process. By applying LDRs to individual circuit cells before simulation of their electrical characteristics, the designer can build the circuit from these blocks. The designer will then be able to determine the performance of the circuit in the usual way and make any modification to the already "enhanced" cell in the normal way.

#### 1.3.2 Outline

#### Chapter 2: Background

This chapter gives some background material necessary to the understanding of the work in the later chapters. The definition of yield as used in this thesis is given along with some discussion on the causes of yield loss. Yield prediction is explored both in terms of chip area and the defect sensitivity of the circuit layout. A number of layout based yield prediction methods are discussed.

Layout based yield prediction is to a large extend dependent on the defect density and size distribution. Results are presented for an experimental determination of defect density size distribution based on metal serpentine and comb test structures.

#### Chapter 3: Yield Simulation

As there was no suitable yield simulator available, when this work was undertaken, a method of analysing the results obtain from the application of LDRs to circuit layout was required. This chapter describes the implementation of a yield simulator that uses the Monte Carlo method to estimate yield. This simulator was designed to predict the yield of tracks (metal1, metal2, polysilicon shorts and breaks), to enable the effectiveness of LDRs to be established, by comparison of the enhanced layout with the original version. Details of defect placement and fault analysis used by the simulator are presented and discussed.

#### Chapter 4: Design Rules

This chapter introduces integrated circuit layout design rules. These rules determine the minimum size and spacing of circuit components. The influence of these rules on circuit area, for different circuit layouts, is investigated using a circuit compactor. The results of these investigations and their implications for yield improvement strategies are discussed. The importance of defect sensitivity and the possibility of decreasing it for non-optimal layouts is highlighted,

#### Chapter 5: Local Design Rules

This chapter introduces Local Design Rules (LDR). These rules are used to describe the conditions under which a specific layout modification can be made. LDRs to increase track width, displace tracks and increase contact/via size are presented. The conditions under which these LDRs can be used and the effect the layout modifications have on the defect sensitivity, performance and reliability of circuits is explored. Layout modifications to increase yield are not recommended for all circuit types and fabrication conditions, and an explanation is given of those circuit types and fabrication processes that may prove suitable.

#### Chapter 6: The LocDes Program

The LocDes program is presented. This program has been designed to automatically apply LDRs to integrated circuit layout. The program can operate with either the X windows user interface, allowing selected layout to be modified, or in a batch mode, where all of the layout is adjusted where possible. The algorithm-

s used by the program to implement, track width changes, track displacement and contact/via adjustments are given. The parallel operation of the program is discussed. This allows very large circuit layouts to be processed in a reasonable time.

#### Chapter 7: Design Rule Checking

The execution speed of the LocDes program is largely dependent on the design rule checking that is required to ensure that all the layout changes performed by the program do not violate the design rules. This chapter presents and explains the design rule checking algorithms used for each of the LDRs that can be applied by the LocDes program. The speed of these algorithms is in turn highly dependent on the speed of the geometry searches. The adaptive multiple storage binary tree data structure used to achieve fast region searches is explained.

#### Chapter 8: Results

This chapter presents results from the application of LDRs to circuit layouts made by the LocDes program. These results, in the form of the differences in defect sensitivity, were obtained using the Monte Carlo yield simulator presented in chapter 2. Results for LDRs applied to a routing network and a random logic layout are presented and discussed. The difficulty of determining the effect of LDRs on the defect sensitivity of the circuit layout is highlighted, since LDRs can simultaneously affect a number of different fault mechanisms.

#### Chapter 9: Discussion and Conclusions

This chapter summarises the work presented in this thesis. The future role of LDRs and LocDes within the IC design process are discussed. Possible improvements to LocDes to make it more usable in a design environment are discussed, as are possible improvements to the type and range of LDRs. A more efficient method of yield simulation using analytical techniques based on polygon manipulation is highlighted. The lessons learned during the work involved in this thesis have been used to develop a plan for an automatic layout system capable of producing IC layout with a yield comparable to hand-crafted designs.

# Chapter 2

# Background

This chapter provides some background to yield and yield prediction. The importance of defect size distribution and density is explored. Some experimental results for defect size distribution are presented that are in agreement with other reported results.

### 2.1 Introduction

The manufacture of integrated circuits is a complex and exacting task. At present it is not possible to control the material quality or process parameters to the extent that a 100% defect free product can be produced. It is not likely that such a state of perfection will be reached in the foreseeable future. Once it is accepted that defects will occur, the task of process engineers and designers of integrated circuits is to achieve the highest value of yield and predict accurately what that yield will be.

There are two types of yield loss - structural and performance. Shorts and opens are examples of structural faults. Performance faults add resistance and capacitance; the circuit may still work but not at the desired specification. The fraction of chips that pass a number of electrical tests of dc connectivity and performance is known as the yield. There are a number of mechanisms that

cause yield loss and points in the production line at which yield can be measured. We will consider the yield to be the number of circuits working when tested before the wafer is scribed and individual chips are wire bonded and packaged.

To date the most important way of improving both the performance of MOS chips and their density has been the use of scaling. Scaling has physical and process limits. The physical limits are absolute. The process limitations are the result of the lithographic process. The dominant limiting factor has been shown to be drain area breakdown – merging of the source and drain [7]. Sub-micron geometries have already been achieved commercially by many fabricators and the trend is now to 0.5 micron levels and lower. These scaled down devices are more process sensitive, relying on thinner and better oxides. Major improvements in the quality of the materials used in the manufacture and the cleanliness of the environment in which the circuits are manufactured must be achieved if such circuits are to be manufactured at a profitable level of yield.

While the major increases in yield in ICs are the result of improved fabrication techniques, the yield at any point in time is also determined by the layout rules employed by the designer. The dimensions of circuit features determine the yield of the circuit and the overall circuit size. To maximise profits it is necessary to find the optimum layout rules that give the maximum number of working chips from a given wafer area[8, 9]. As the fabrication process becomes more complex, with an increasing number of layers and process steps, the interaction of these layers makes it increasingly important to optimise the layout rules to obtain high yields and compact circuits.

The circuit designer can affect yield by making the right choice in the size and position of circuit features. It is also possible to design circuits that are tolerant to faults and so make it possible for a circuit to perform its function even though it is less than perfect. The size of the circuit is also very important since larger circuits tend to have a lower yield than small circuits. A choice must be made between fitting a system on a single chip or a dividing it into a number of different chips. An understanding of this relationship with area is important for a designer

working on a large system so that an informed decision of the optimum chip size can be made[10].

An important factor to consider in development of a new process is the learning curve, whereby the yield improves by approximately 20% [11] every time the number of batches that have been processed doubles. In the early stages of production this can lead to very significant improvements in yield.

## 2.2 Types of Yield Loss

Yield loss can arise from many different causes. IC fabrication is a complex process which requires very strict control of many process parameters such as temperature, humidity, concentration of doping agents, and purity of all materials used. Because of the complexity of the process it is not altogether surprising that some circuits do not function correctly. The total yield loss of a functionally correct design is often divided up into gross yield losses and faults from random defects.

#### 2.2.1 Gross Yield.

Gross yield losses are usually caused by manufacturing errors affecting the whole or a large part of the wafer [11]. Excessive variation in processes parameters such as process time, temperature, doping concentrations and lithographic faults, are usually the cause of this form of yield loss. Gross yield losses can often be found by visual inspection of wafers or measurements made during the process from test structures formed in the kerf[12]. Wafers with gross yield loss can removed from the production line before the processing is completed. The test structures are used to ensure that circuit elements, transistors, vias, contacts etc. are within the process window (i.e., within the range of parameters that will ensure working devices). The distribution of device parameters within the process window is of special interest to manufacturers who sort their product by performance.

While LDRs could in some circumstances be used to decrease the sensitivity to some types of global defects (for example, increasing contact overlap to reduce sensitivity to mis-alignment) the effectiveness of such LDRs will be limited. In general a global defect results in a large area of unusable wafer. Unless layout modifications can be applied to all the susceptible components in this area (e.g. all contact overlaps) and give a significant degree of protection, it is likely that there will still be some defects that will result in circuit faults. Consequently it is not recommended the LDRs be used to solve gross yield loss problems.

#### 2.2.2 Random defects.

Random defects are spot or small area defects. Spot defects are found randomly their concentration normally varies over the wafer surface as a function of radius. Typically the concentration of defects is greater towards the edge of the wafer [13, 14]. Stapper[11] suggests that more than 80% of yield loss is due to random rather than gross defects, while a figure of 60% is suggested by Mangir[15, 16].

These random defects are the result of local process fluctuation that only affect a very small area of a device. If a circuit is made more tolerant to these types of defect, an increased production yield will result.

In mature MOS fabrication processes a few small area defect types dominate the total yield loss. These are extra and missing material defects, oxide pinholes and junction leakage[17-19]. These are discussed in greater detail below.

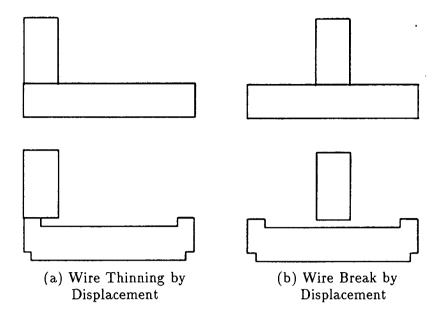

Some other defects that cause localised circuit faults are hillocks, which cause shorts between conducting layers and step coverage breaks where thinning at crossovers causes tracks to break. However these defects are due to global rather than local process disturbances[20]. They are best resolved by adjusting the process itself, rather than using LDRs to reduce the sensitivity to a global error.

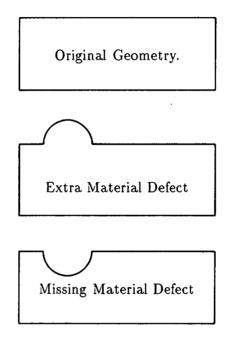

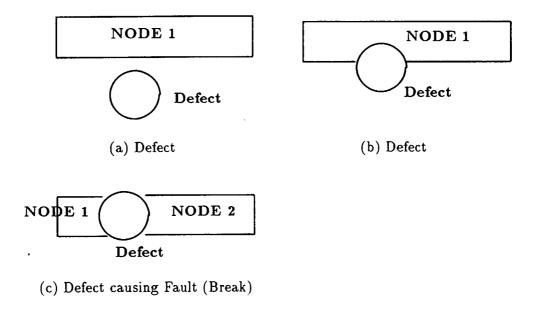

#### Extra and Missing Material Defects

These defects are caused by dust particles on masks/reticles, the wafer surface and chemicals used in the fabrication process. The dust particles lead to unexposed resist, which when developed results in an unwanted "pinhole". This pinhole will result in a missing material defect if the next stage is an etch or an extra material defect will be formed, if the following stage is a deposition.

Because of the close association of extra and missing material defects to the lithographic process these defects are often called photo or lithographic defects[18].

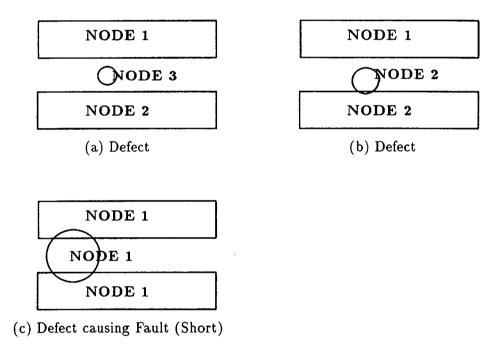

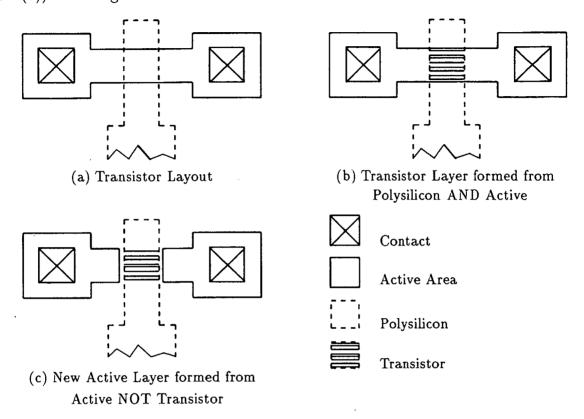

Missing material defects are responsible for metal/polysilicon track breaks while extra material defects cause track shorts as well as missing contacts/vias (the contact cut is not etched away).

The sensitivity of a circuit to metal and polysilicon extra/missing defects can be reduced by LDRs. In particular width increase LDRs reduce the sensitivity to missing material defects and track displacement LDRs reduce the sensitivity to extra material defects. Yield loss from missing contacts can also be attacked by using LDRs to increase the contact size, so that a larger defect is required to totally close the contact.

#### Oxide Pinholes

Oxide pinholes are primarily caused by a deficiency of oxygen at the Si-SiO<sub>2</sub> interface, tensile stress, surface imperfections and contamination[21-23]. The yield of oxide layers is a function of the area of oxide.

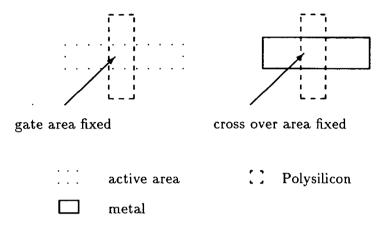

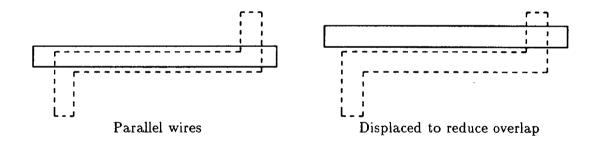

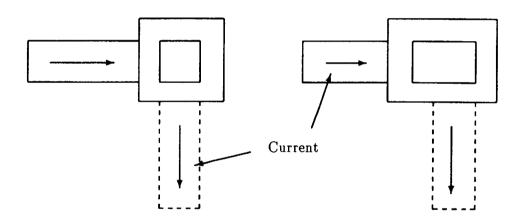

In general it is not possible to reduce the area of critical oxide, since gate area and the overlap area of conductor are fixed (figure 2-1). This makes it difficult to design LDRs to decrease the sensitivity to this type of defect. However, where separate layers form tracks running on top and parallel (figure 2-1) to each other it may be possible to displace one or both of the tracks to reduce the area

of overlap and therefore the probability of a fault from an oxide pinhole. For example, this situation can occur between polysilicon and metal 1 as shown in figure 2-2. An LDR to perform this layout modification is feasible, but has not been implemented. The occurence of such parallel wires is low in most layout styles (metal and poly are often run perpendicular to each other) so that it is unlikely that this adjustment would be required very often.

Figure 2-1: Fixed Area of Oxide

Figure 2-2: Displacement to Reduce Critical Oxide Area

#### Junction Leakage

Junction leakage occurs where crystal defects or contamination are present at a junction [24]. The high electric fields at these points cause large current leaks across the junction, resulting in poor performance or a failed device. Junction leakage defects can be a substantial source of yield loss in RAMs[17-19, 24]. This is not such a problem in general purpose digital circuits as the density of active

devices is usually much lower. The yield loss is a function of diffusion area and periphery.

There is little that could be done to affect the sensitivity of circuits to these defects since diffusion areas are usually at the minimum required to form the active devices and connect to other conducting layers. Consequently, the number of layout changes that could be made is small.

#### 2.2.3 Fault Clustering.

The distribution of spot defects is random though in a complex manner. It has been observed that the defects on a wafer have a tendency to form clusters[25]. It is thought that this occurs as a result of clouds of particles in the materials used in the fabrication process. This implies that if there is a defect present the probability that another defect is present on an adjacent site increases. If there are a number of related defects then the probability of there being a large cluster of defects increases. This has important consequences for the yield and reliability of redundant circuits (section 2.9).

There is some dispute as to the definition of what constitutes a defect cluster [26]. This is a result of practical difficulties in measuring clusters. For instance, what appears to be a cluster of defects may in fact be unrelated random defects that have the same position on the wafer map but have been caused by different process steps. It is often difficult to determine the cluster size. Even if it can be shown that the defects were all caused by the same process step it is not clear whether a particular defect, near what is considered the cluster edge, is in fact a random defect close to a cluster or indeed part of another adjacent cluster. Attempts to define mathematical models that overcome these difficulties have been hindered by the lack of relevant data[27]. There is an understandable reluctance by IC manufacturers to release the raw wafer map data that can be used to verify existing models and aid in the proposition of new models

#### The Influence of Clusters on LDRs Effectiveness

How much defect clusters will affect the usefulness of layout modifications in reducing defect sensitivity is dependent on the ratio of the faults that are caused by single defects and those caused by defect clusters. If a large percentage of all circuit faults are due to single defects then layout modifications will affect the final yield by reducing the number of single defect faults. However, if defect clusters are the major source of circuit faults, then the density of clusters will determine whether layout modifications can improve the yield.

If layout modifications give x% reduction in single defect sensitivity then the corresponding reduction for defect clusters is  $100 \times (\frac{x}{100})^n\%$ , where n is the number of defects per circuit area or cluster density. For example, if a 10% reduction in defect sensitivity is obtained for a single defect the equivalent reduction in defect sensitivity for a defect cluster of density 2 defects/circuit area is only 1%.

There is no reliable data concerning either the defect density of clusters or the ratio of faults caused by single defects and defect clusters. Consequently, it is not possible to draw any conclusions on the impact of the defect clustering phenomena on the effectiveness of layout modification in reducing defect sensitivity. Also, since each process has unique defect statistics it is likely that some processes will be more suitable than others.

### 2.3 Yield and Chip Area.

#### 2.3.1 Poisson Statistics.

There is a large volume of work on the statistics of yield which relates yield to the defect density and chip size. One of the earlier papers is by Murphy[3]. Murphy noted that an exact calculation of yield could only be made by examining each circuit on its individual merits. Considering this to be too difficult a task an

attempt to relate the yield of a chip to its area is given. Assuming the defects to be randomly distributed, Poisson statistics are used to generate an equation for yield

$$Y = \exp(-DA) \tag{2.1}$$

Y = yield

D = Defect density (defects/area)

A = Area

This equation states that the logarithm of yield decreases linearly with the area of chip. This equation is not in agreement with results found in practice, giving an overly pessimistic estimate for large chips. Equation 2.1 assumes random defects while in practice it is found that the defects are distributed non-randomly. This disagreement can be overcome by regarding the problem as a sum of sub areas each with a different defect density.

$$Y = \int_0^\infty \exp(-DA) f(D) dD$$

(2.2)

f(D) = probability of defects

The defect probability function (f(D)) must be found experimentally. Equation 2.2 assumes that there is only one defect type or one major defect type. This unrealistic assumption can be overcome by calculating the yield for every defect type so that the yield of a process with n defect types can be expressed by equation 2.3.

$$Y_{total} = Y_n Y_{(n-1)} Y_{(n-2)} \dots Y_2 Y_1$$

(2.3)

### 2.3.2 Window Method.

Experimental results have shown that the Poisson method of yield calculation consistently gives lower predicted yield than those observed in large chips. This is due to the assumption that defects are randomly distributed. Evidence that

defects are not randomly distributed can be seen graphically by use of the "window method" originally described by Seeds[28]. In this method a wafer map of defective and working chips is divided into areas of integral numbers of chips. An estimate of the number of working larger chips obtainable can be found by counting the number of larger areas that have only working chips in them. However great care has to be taken when using this method as the sensitive area of a chip may differ from its actual area and the ability of a circuit to operate with a performance fault is liable to vary from one chip design to another. This method can only be considered accurate where the larger chip is equivalent to the sum of the smaller chips. This does not occur often. The "window method" does however suggests that the Poisson statistics are not an accurate prediction of yield for larger chips.

### 2.3.3 Boltzmann Statistics

It can be shown [29] that the Poisson model is false since it is based on Boltzmann statistics in which all spot defects are considered distinguishable. Boltzmann statistics give,

$$Y = (1 - \frac{1}{N})^{NAD} (2.4)$$

$$\lim_{N \to \infty} Y = \exp(-DA) \tag{2.5}$$

N = Number of cells

A = Active area of cell

D = Average Defect Density of Randomly distributed defects.

However defects can be considered to be caused by a number of distinct mechanisms producing a number of indistinguishable defects.

### 2.3.4 Bose-Einstein Statistics

Using Bose-Einstein statistics in which all defects are considered indistinguishable [29]. The equation for yield becomes

$$Y = \frac{1 - 1/N}{1 + AD - 1/N} \tag{2.6}$$

$$\lim_{N \to \infty} Y = \frac{1}{1 + AD} \tag{2.7}$$

For a more general case with n different defect types the yield then becomes

$$Y = \frac{1}{1 + AD_1} \times \frac{1}{1 + AD_2} \times \dots \times \frac{1}{1 + AD_n}$$

(2.8)

Each of the terms in the yield equation represents a defect mechanism with defect density D(n). This statistical representation tends to over-estimate the yield obtained from large chips.

### 2.3.5 Experimental Methods

The defect density has been found experimentally to be distributed according to the gamma function[19]. If this function is used as the model for defect densities the resulting equation for yield is a negative binomial distribution. The resulting yield equation is empirical, not based on any physical model or mathematical theory. This gamma function produces a yield function that is not linear with the logarithm of yield and actually over-estimates the yield of larger chips but gives a good fit within the range of chip sizes in the data base.

$$Y = \frac{1}{(AD/n + 1)^n} \tag{2.9}$$

Where n = (mean/standard deviation)<sup>2</sup> of defect density

measurements taken from different wafers within a batch

and a number of different sites on the wafers.

The yield of a process cannot be well modelled by a simple mathematical or physical model. There are a number of parameters involved and they do not obey any simple relationship. Often the best approach is to empirically form an equation for yield. This has the benefit of at least being accurate within the data, base provided which for most purposes is all that is required. One method is to use the relationship derived by Murphy with a gamma function of defect density using an experimentally determined mean and standard deviation of faults in test devices[30].

Data from commercial fabrication lines has shown that there are difficulties in fitting yield data to yield models. Stapper suggested that this was because the defect sensitivity of circuits is not directly proportional to area. Stapper[19] demonstrated that yield data for ROS <sup>1</sup> circuits can be more easily interpreted by comparing the yield of the chip versus the number of data bits (sub-circuits) rather than the area. This suggests that yield is not so much a function of circuit area as defect sensitivity and where defect sensitivity is not proportional to area the standard yield models will not hold. Some methods of yield prediction using defect sensitivity are given in section 2.8.

### 2.3.6 Chip Area and Wafer Size.

Yield can also be affected by the size of the chip relative to wafer size. The optimum chip size for maximum silicon usage is dependent on the relative size of chip to wafer. Gupta[10] gives the results of a computer program to give the optimum placement of square chips on a wafer. An empirical formula is generated from the computer program output.

$$N = \frac{W}{Z^2 - \frac{3.54}{Z/R} + 0.94} \tag{2.10}$$

N = number of chips

<sup>&</sup>lt;sup>1</sup>ROS read only store, memory chips that are fabricated with a fixed set of information

Z = chip size (length of side)

R = effective radius

W = slice area (usable area of wafer)

An effective wafer radius is used since the edges of the chip are not suitable for chip production. This is due to defects introduced by handling and optical distortion at the edges of the wafer[13, 14]. The size of this effective radius will depend on the process used but can commonly be expected to be of the order of 10mm less than the actual wafer radius. The formula can be used to find the amount of wafer actually used as chip area and therefore the wastage. The results show that for chip sizes greater than 0.3 of the effective radius the empirical formula becomes inaccurate. At this size careful choice of the chip size can lead to significantly less wastage of wafer area.

# 2.4 Defect Density and Size distribution.

The shortage of published data on defect densities in the literature can be attributed to the variation between processes and the commercial sensitivity of such information. However the state of the art is approximately 1 defect/cm<sup>2</sup>[31]. There is a shortage of data on the clustering of defects and more clustering information would be useful to the designer of fault tolerant circuits.

It has been observed that smaller defects are more common than large defects, this is true of both air-borne and chemical defects[9]. It has further been observed that below some diameter defect densities fall to zero since they are no longer resolved.

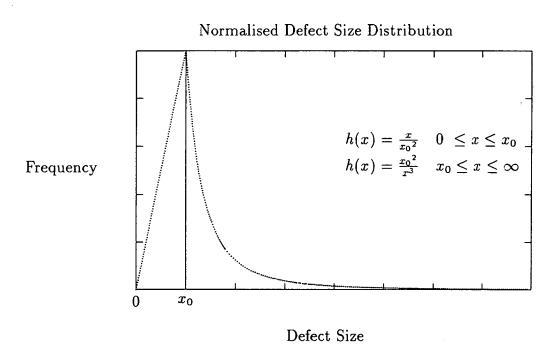

Stapper observed on memory devices that defect size fell off as  $\frac{1}{x^n}$ , where x is the defect diameter. Small defect sizes could not be observed and were assumed to rise to a peak then fall of linearly as shown graphically in figure 2-3. The

normalised distribution function is,

$$h(x) = \frac{2(n-1)x}{(n+1)x_0^2} \quad 0 \le x \le x_0 \tag{2.11}$$

$$h(x) = \frac{2(n-1)x}{(n+1)x_0^2} \quad 0 \le x \le x_0$$

$$h(x) = \frac{2(n-1)x_0^{n-1}}{(n+1)x^n} \quad x_0 \le x \le \infty$$

(2.11)

Where the value of n is chosen to fit the experimental data

Stapper fitted equations 2.11 and 2.12 to process data with a best fit of 3.02. This value agrees well with other reported values for n. Stapper[4] reports another fabrication process gave n=3.1 for extra material defects and n=2.9 for missing material defects. For n=3 the equations 2.11 and 2.12 become,

$$h(x) = \frac{x}{x_0^2} \quad 0 \le x \le x_0 \tag{2.13}$$

$$h(x) = \frac{x_0^2}{x^3} \quad x_0 \le x \le \infty$$

(2.14)

Figure 2-3: Normalised Defect Distribution

The most important part of the curve is the section for defects greater than  $x_0$ . The  $x_0$  point is the minimum size defect that can be resolved by the lithographic process. Since circuit geometry must always have greater width and separation than the minimum resolvable size it follows that defects smaller than this size will not cause circuit faults. The defect size distribution has shown itself to be remarkably constant with ever decreasing values of  $x_0$ . It is believed[32] that the distribution will remain proportional to the cube of the defect size for the foreseeable future.

Alternative distributions have been proposed notably by Ferris-Prabhu[33] and Maly[34]. Ferris-Prabhu presented a more general distribution than that given above, which for suitable terms becomes equivalent to equations 2.13 and 2.14.

Maly suggested that the defect size was determined by mask defect diameter combined with the line width distortion that occurs when the mask pattern is applied to the IC. He also suggested that there is more than one source of defects. Measurements showed that there were two sources of defects, dust particles and the mechanical contact of the mask and wafers<sup>2</sup>. The probability density function for a single defect source was modelled by a Rayleigh distribution of,

$$f_r(x,\alpha) = \frac{x}{\alpha^2} \exp(-\frac{x}{2\alpha^2}) \quad x > 0$$

(2.15)

$$f_r(x,\alpha) = 0 x = 0 (2.16)$$

where  $\alpha$  is the distribution parameter.

The combination of air-borne and mechanical contact defects were modelled as,

$$f(R) = [\beta_1 f_r(R - m_1, \alpha_1) + (1 - \beta_1) f_r(R - m_2, \alpha_2)] \beta_2 + (1 - \beta_2) f_r(R - m_3, \alpha_3)$$

(2.17)

$\beta_1$  and  $\beta_2$  are weights for dust and mechanical defects

$m_1, m_2, \alpha_1$  and  $\alpha_2$  characterise dust defects

$m_3$  and  $\alpha_3$  characterise defects caused by mechanical contact

<sup>&</sup>lt;sup>2</sup>This source of defects has been eliminated in modern processes that no longer use contact printing.

In a modern process with no contact printing  $\beta_2 = 1$  so that equation 2.17 becomes

$$f(R) = \beta_1 f_r(R - m_1, \alpha_1) + (1 - \beta_1) f_r(R - m_2, \alpha_2)$$

(2.18)

# 2.5 Experimental Determination of Defect Density and Size Distribution

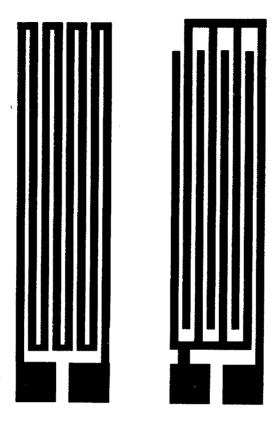

A series of metal 1 comb and serpentine structures similar to those shown in figure 2-4 were fabricated using the EMF  $6\mu m$  CMOS process.

- A serpentine structure can be used to detect missing material defects. Defects that break the track connecting the probe pads will register as a high resistance (open circuit) between the pads.

- A comb structure can be used to detect extra material defects. Where such

a defect connects the interdigitated tracks the resistance between the two

probe pads will be reduced in comparison to the high open circuit resistance

when no defect has been detected.

A series of these structures were fabricated with dimensions of 1.5, 2.0, 2.5 ... 9.0, 9.5 $\mu$ m. These dimensions refer to track width in the serpentine structures and track separation in the comb structure. To ensure the mode of failure would be shorts in the comb and breaks in the serpentine structure all track widths in the combs and all track separations in the serpentines were  $10\mu$ m.

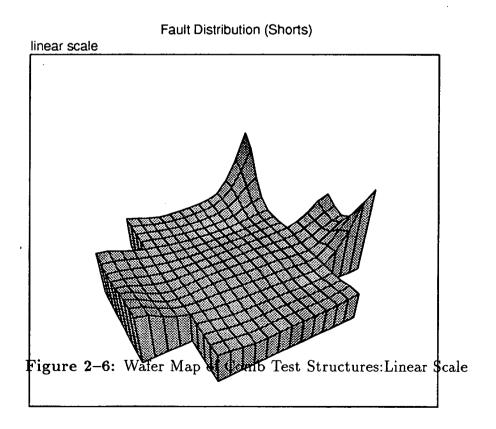

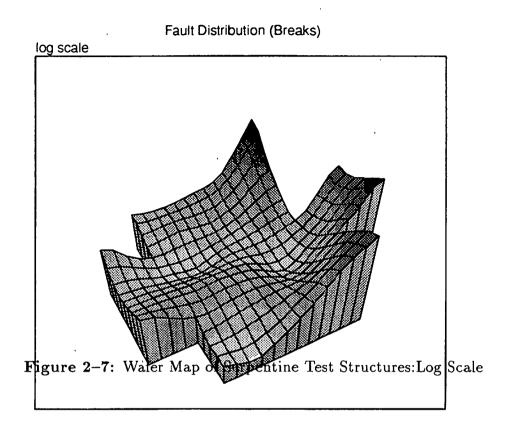

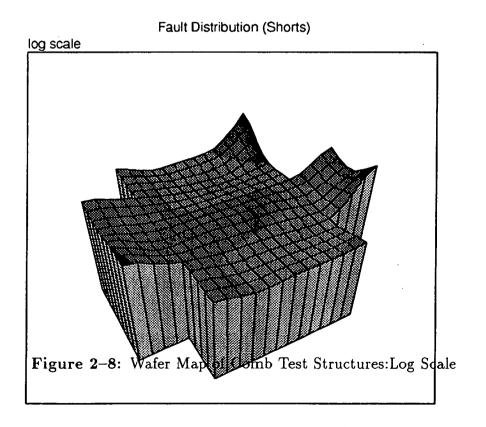

The experimental run consisted of 11 wafers with 37 measurable test sites giving a sample size of 407 for each of the structures. The combined results from all 11 wafers are given as wafer maps in figure 2–5 showing all the serpentine results and figure 2–6 the comb results. It can be seen from both of these figures that the number of defects tends to be greater towards the edge of the wafer and that the incidence of shorts (comb structure) is greater than breaks (serpentine

structure). This can be seen more clearly by taking the log of the defects found as shown in figures 2-7 and 2-8.

Figure 2-4: Serpentine and Comb Test Structure

# Fault Distribution (Breaks) linear scale Figure 2–5: Wafer Map of Verportine Test Structures:Linear Scale

### 2.5.1 Defect Density

The defect density of the process can be calculated from the number of defects detected by the test structures and the "active" test area. In the  $1.5\mu m$  serpentine test structure the active area is equal to 1.5 times the total conductor length between the two probe pads. Which in this case was 4mm (the test structure length) times 10 (the number of wire lengths) giving an active area of  $60,000\mu m^2$ . The active area of a comb structure is similarly calculated from the length and width of the conductor separation.

The defect density is found from,

$$Defect \ Density = \frac{D}{A \times N_{wafer} N_{sites}}$$

(2.19)

D = Total Number of defects

A = Active area

$N_{wafer}$  = Number of wafers

$N_{sites}$  = Number of test sites per wafer

The accuracy of the defect density can be found by calculating the confidence interval for D, the total number of defects. Using this confidence interval for D in equation 2.19, the confidence interval for the defect density can be found. The  $100(1-\mu)$  percent confidence interval for D is given by,

$$y - \frac{\sqrt{y(n-y)}}{\sqrt{n-1}} t_{\mu/2;n-1} \le D \le y + \frac{\sqrt{y(n-y)}}{\sqrt{n-1}} t_{\mu/2;n-1}$$

(2.20)

y = Total Number of defects measured

$n = N_{wafer} \times N_{sites}$

$t_{\mu/2;n-1}$ = 1.96 for  $\mu$ m = 0.05 n > 120

The defect density and 95% confidence interval for the comb and serpentine structures are given in tables 2-1 and 2-2.

| Comb Structure Experimental Results (Shorts) |                  |      |       |        |           |  |  |  |

|----------------------------------------------|------------------|------|-------|--------|-----------|--|--|--|

| Structure Size                               | Defect Density   | 95%  | Conf. | Inter. | Rel Error |  |  |  |

| (μ)                                          | $(defects/cm^2)$ |      |       |        | (%)       |  |  |  |

| 1.5                                          | 9.87             | 9.06 | to    | 10.68  | 16.5      |  |  |  |

| 2.0                                          | 4.32             | 3.73 | to    | 4.90   | 27.0      |  |  |  |

| 2.5                                          | 2.30             | 1.89 | to    | 2.71   | 35.8      |  |  |  |

| 3.0                                          | 1.47             | 1.16 | to    | 1.78   | 42.1      |  |  |  |

| 3.5                                          | 1.11             | 0.85 | to    | 1.36   | 45.6      |  |  |  |

| 4.0                                          | 1.07             | 0.84 | to    | 1.30   | 43.0      |  |  |  |

| 4.5                                          | 0.87             | 0.68 | to    | 1.07   | 45.1      |  |  |  |

| 5.0                                          | 0.60             | 0.44 | to    | 0.76   | 52.7      |  |  |  |

| 5.5                                          | 0.58             | 0.43 | to    | 0.72   | 51.2      |  |  |  |

| 6.0                                          | 0.55             | 0.41 | to    | 0.68   | 50.1      |  |  |  |

| 6.5                                          | 0.52             | 0.39 | to    | 0.64   | 49.6      |  |  |  |

| 7.0                                          | 0.36             | 0.26 | to    | 0.46   | 58.2      |  |  |  |

| 7.5                                          | 0.32             | 0.22 | to    | 0.41   | 59.8      |  |  |  |

| 8.0                                          | 0.26             | 0.18 | to    | 0.35   | 64.5      |  |  |  |

| 8.5                                          | 0.18             | 0.11 | to    | 0.25   | 76.1      |  |  |  |

| 9.0                                          | 0.19             | 0.13 | to    | 0.26   | 71.0      |  |  |  |

| 9.5                                          | 0.22             | 0.15 | to    | 0.29   | 64.0      |  |  |  |

Table 2-1: Measurements of Defect Densities from Comb Test Structure

| Serpentine Structure Experimental Results (Breaks) |                  |      |       |        |           |  |  |

|----------------------------------------------------|------------------|------|-------|--------|-----------|--|--|

| Structure Size                                     | Defect Density   | 95%  | Conf. | Inter. | Rel Error |  |  |

| (μ)                                                | $(defects/cm^2)$ |      |       |        | (%)       |  |  |

| 1.5                                                | 4.01             | 3.32 | to    | 4.71   | 34.7      |  |  |

| 2.0                                                | 2.01             | 1.56 | to    | 2.46   | 44.5      |  |  |

| 2.5                                                | 1.08             | 0.78 | to    | 1.38   | 56.0      |  |  |

| 3.0                                                | 0.70             | 0.47 | to    | 0.92   | 64.5      |  |  |

| 3.5                                                | 0.47             | 0.30 | to    | 0.65   | 73.1      |  |  |

| 4.0                                                | 0.34             | 0.20 | to    | 0.48   | 81.4      |  |  |

| 4.5                                                | 0.29             | 0.17 | to    | 0.41   | 83.5      |  |  |

| 5.0                                                | 0.23             | 0.13 | to    | 0.34   | 88.0      |  |  |

| 5.5                                                | 0.20             | 0.11 | to    | 0.29   | 91.8      |  |  |

| 6.0                                                | 0.18             | 0.10 | to    | 0.27   | 90.5      |  |  |

| 6.5                                                | 0.16             | 0.08 | to    | 0.23   | 94.7      |  |  |

| 7.0                                                | 0.16             | 0.09 | to    | 0.23   | 89.2      |  |  |

| 7.5                                                | 0.16             | 0.09 | to    | 0.23   | 86.8      |  |  |

| 8.0                                                | 0.15             | 0.08 | to    | 0.21   | 88.0      |  |  |

| 8.5                                                | 0.15             | 0.09 | to    | 0.22   | 83.5      |  |  |

| 9.0                                                | 0.12             | 0.06 | to    | 0.17   | 91.8      |  |  |

| 9.5                                                | 0.11             | 0.06 | to    | 0.16   | 93.2      |  |  |

Table 2-2: Measurements of Defect Densities from Serpentine Test Structure

### 2.5.2 Defect Size distribution

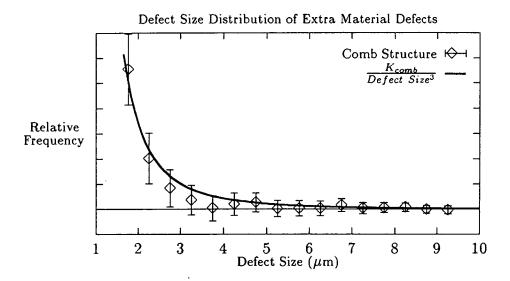

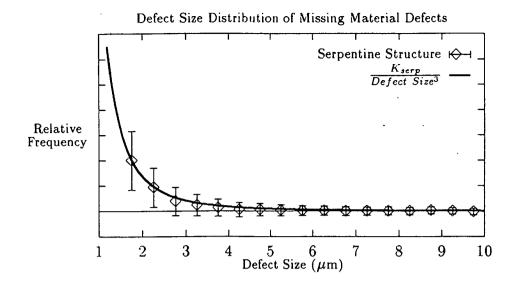

The defect size distribution can be found from the change in defect density as a result of increased track width and separation in the serpentine and comb structures. Subtracting the defect density of a  $2\mu$ m structure for that of the  $1.5\mu$ m structure gives the contribution to the defect density due to defects less then  $2\mu$ m and greater then  $1.5\mu$ m. The defect size distribution of extra material defects (shorts) found from the comb structure defect densities is given in figure 2–9. A similar distribution for missing material defects calculated from the serpentine defect densities is given in figure 2–10. Curves of the form  $\frac{K}{Defect\ Size^3}$  can be found to fit the data within the error bars, derived from the 95% confidence interval of the defect densities. This suggests that the defect size distribution is proportional to  $\frac{1}{Defect\ Size^3}$  in agreement with reported defect size distributions of other fabrication processes.

Figure 2-9: Defect Size Distribution Generated from Comb Test Structure

Figure 2-10: Defect Size Distribution Generated from Serpentine Test Structure

# 2.6 Determination of Optimal Layout Rules.

In order to optimise the yield from a process the optimal layout rules must be determined. These rules should give the IC designer a complete list of the acceptable line widths and spacings for all of the layout geometry. They should also indicate the spacing and line widths required between different layers to avoid undesired interaction between these layers e.g. metal width over polysilicon for good step coverage. Layout rules should, where possible, be kept as simple as possible to enable a designer to work with them competently and efficiently. The rules should where necessary take account of the type of circuit being designed. The design of very regular structures like memories requires very detailed design rules if high yielding circuits are to be fabricated. Logic circuits may not require the same detail. In-house designs allow for the use of a more detailed design rule set, where the designer works through many designs and where it is therefore worth the investment of time to learn and use a more complex rule base giving a better representation of the optimal layout rules. Where the fabricator is trying

to sell the process to designers in other companies it may be better to have very simple design rules to reduce the investment in retraining designers required by companies when changing between processes.

### 2.6.1 Test Structures.

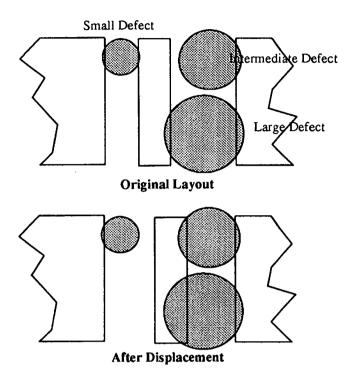

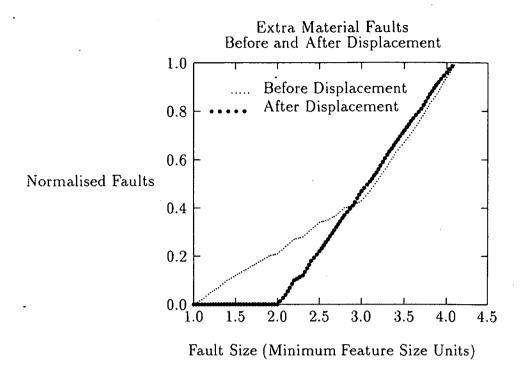

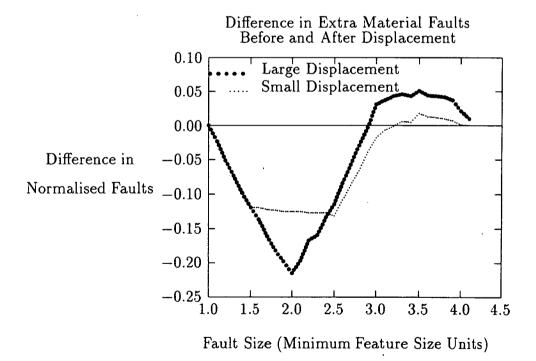

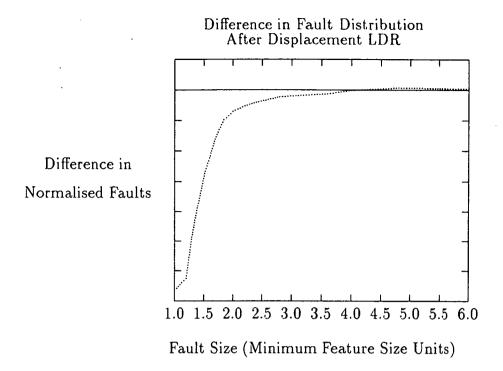

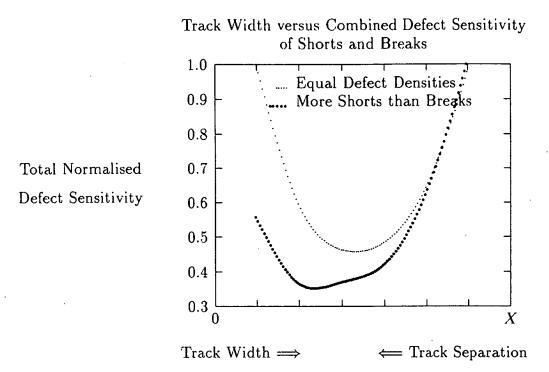

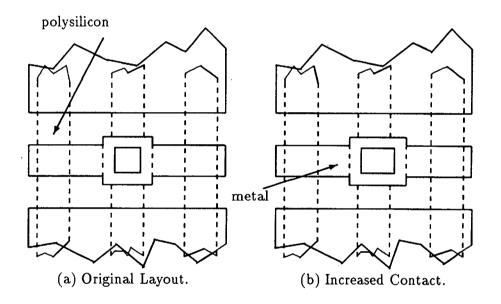

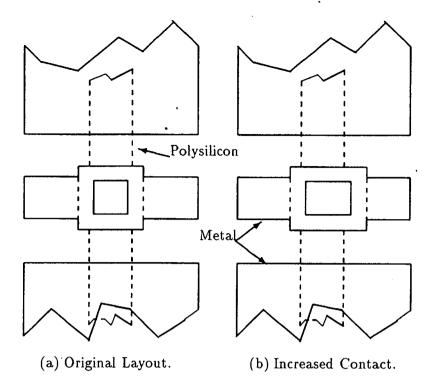

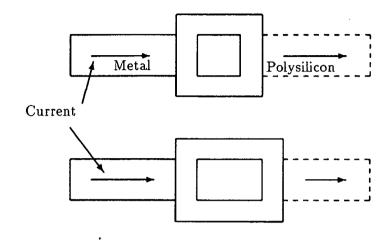

The design/layout rules are normally determined experimentally using test structures. Test structures for layout rules must be simple, to allow easy interpretation of the results and should be worst case layouts, sensitive to misalignment and dimensional tolerances.