## CMOS PROCESS SIMULATION

Thesis submitted by

# ALISTAIR GEORGE BUTTAR

for the degree of

## DOCTOR OF PHILOSOPHY

## Edinburgh Microfabrication Facility Department of Electrical Engineering University of Edinburgh

1986

## DECLARATION

I declare that all the work done in this Thesis is entirely my own except where otherwise indicated.

This Thesis is the result of a CASE project with Motorola Ltd., East Kilbride.

# CONTENTS

÷

--

.

.

.

| CHAPTER UNE : INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| CHAPTER TWO : REVIEW OF CMOS TECHNOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | y                                                              |

| CHAPTER THREE : REVIEW OF PROCESS SIMULATION ACTIVITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 33                                                             |

| CHAPTER FOUR : 1-D PROCESS SIMULATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40                                                             |

| <ul> <li>4.1 Ion Implantation</li> <li>4.2 Thermal Uxidation</li> <li>4.3 Diffusion <ul> <li>4.3.1 General Discussion of Diffusion</li> <li>4.3.2 Low Concentration Diffusion in an Inert Ambient</li> <li>4.3.3 Uxidation Ennanced Diffusion</li> <li>4.3.4 Segregation</li> <li>4.3.5 Measurement of Doping Profiles by the Deep Depletion C-V Method</li> <li>4.3.6 High Concentration Diffusion</li> <li>4.3.7 Diffusion in Polysilicon</li> </ul> </li> <li>4.4 Material Deposition and Etcning</li> <li>4.5 1-D SUPREM Simulation of a P-well CMUS Process</li> </ul> | 40<br>53<br>57<br>60<br>64<br>68<br>71<br>78<br>94<br>95<br>96 |

| CHAPTER FIVE : MUS CAPACITANCE-VOLTAGE CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 105                                                            |

| <ul> <li>5.1 Uses and Types of C-V Measurements</li> <li>5.2 Uniform Doping Profiles</li> <li>5.3 Non-Uniform Doping Profiles</li> <li>5.4 EPCAP Simulation Results and Determination<br/>of Flatband Voltage</li> </ul>                                                                                                                                                                                                                                                                                                                                                    | 105<br>108<br>110<br>121                                       |

| CHAPTER SIX : ANALYTICAL PROCESS MODELS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 128                                                            |

| <ul> <li>6.1 The Redistribution of Impurities Near Mask Edges</li> <li>6.1.1 Review of 2-D Analytical Process Models</li> <li>6.1.2 Ion Implantation at a Non-Vertical Mask Edge</li> <li>6.1.3 Diffusion Under a Non-Vertical Mask Edge</li> <li>6.1.4 2-D Nature of a Diffused P-well</li> <li>6.2 Temperature Modelling for Transient Annealing</li> <li>6.2.1 Uses of Transient Annealing in MUS Processing</li> <li>6.2.2 Review of Temperature Models for Electron-Beam Annealing</li> <li>6.2.3 Temperature Model for a Scanning Electron-Beam</li> </ul>            | 128<br>128<br>131<br>143<br>152<br>156<br>156<br>156           |

| 6.2.4 Application to Determine Scan Pitch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 161                                                            |

.

| CHAPTER                                                                                      | SEVEN      |                                                  | 2-D   | SIMULA  | TION   | UF    | HIGH    | CONCENT       | RATION   | PROFILES | 168 |

|----------------------------------------------------------------------------------------------|------------|--------------------------------------------------|-------|---------|--------|-------|---------|---------------|----------|----------|-----|

|                                                                                              | 7.1<br>7.2 | Current Status of 2-D High Concentration Profile |       |         |        |       |         |               |          |          | 168 |

|                                                                                              |            |                                                  | ellin |         |        |       | -       |               |          |          | 170 |

| -                                                                                            | 7.3        | 2-D                                              | Ion   | Implan  | tatio  | n Usi | ng the  | e Pearso      | n IV     |          |     |

|                                                                                              |            | Distribution                                     |       |         |        |       |         |               |          | 172      |     |

| 7.4 Numerical models for 2-D Diffusion                                                       |            |                                                  |       |         |        |       |         |               |          | 174      |     |

| 7.4.1 Diffusion of Threshold Adjust Implants                                                 |            |                                                  |       |         |        |       |         |               |          | 174      |     |

|                                                                                              | 7.4.       |                                                  |       |         |        |       |         | n Region      |          |          | 179 |

| 7.5 Simulation Results for a P-well CMOS Process 7.6 Measurement of Effective Channel Length |            |                                                  |       |         |        |       |         |               | 184      |          |     |

| ,                                                                                            | 7.6        | Meas                                             | suren | ent of  | Effe   | ctive | e Chanr | nel Leny      | th       |          | 205 |

| СНАРТЕК                                                                                      | EIGHT      | :                                                |       |         |        | υF    | SIMULT  | <b>ANEOUS</b> | DIFFUS   | ION      |     |

|                                                                                              |            |                                                  | AND   | UX1DA   | TION   |       |         |               |          |          | 212 |

| 8                                                                                            | 8.1        | Uffs                                             | sets  | Wnicn   | Influe | ence  | Effect  | ive Cha       | nnel wic | itn      | 212 |

| 8                                                                                            | 3.2        | Curr                                             | rent  | Status  | of 2   | -D Si | multar  | ieous Di      | ffusion  |          |     |

|                                                                                              |            |                                                  |       | ation ( |        |       |         |               |          |          | 214 |

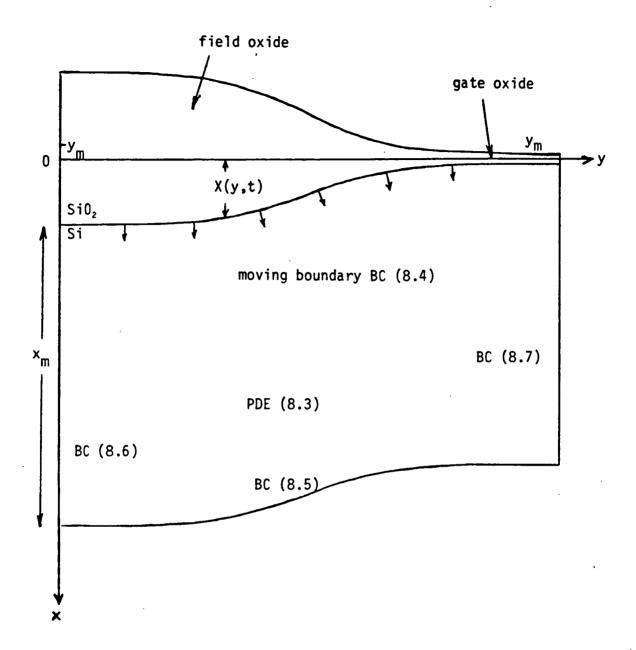

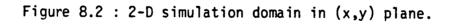

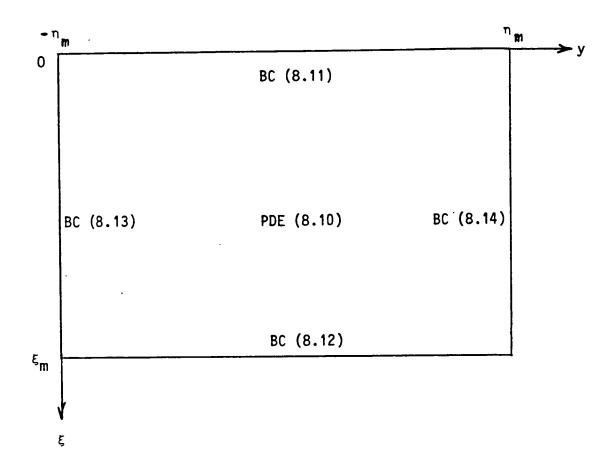

|                                                                                              |            |                                                  |       |         |        |       |         | ny Uxid       |          |          | 217 |

|                                                                                              |            |                                                  |       |         |        |       |         |               | Process  |          | 234 |

| 8                                                                                            | 3.5        | Meas                                             | urem  | ent of  | Effe   | ctive | Chann   | el Widt       | h        |          | 258 |

| CHAPTER                                                                                      | NINE       | : (                                              | ONCL  | USIONS  |        |       |         |               |          |          | 272 |

|                                                                                              |            |                                                  |       |         |        |       |         |               |          |          | 272 |

| APPENDI                                                                                      | (A:        | EPI                                              | C PR  | UGRAM : | STRUC  | TURE  |         |               |          |          | 276 |

| REFERENC                                                                                     | CES        |                                                  |       |         |        |       |         |               |          |          | 282 |

|                                                                                              |            |                                                  |       |         |        |       |         |               |          |          |     |

.

.

#### Abstract

1

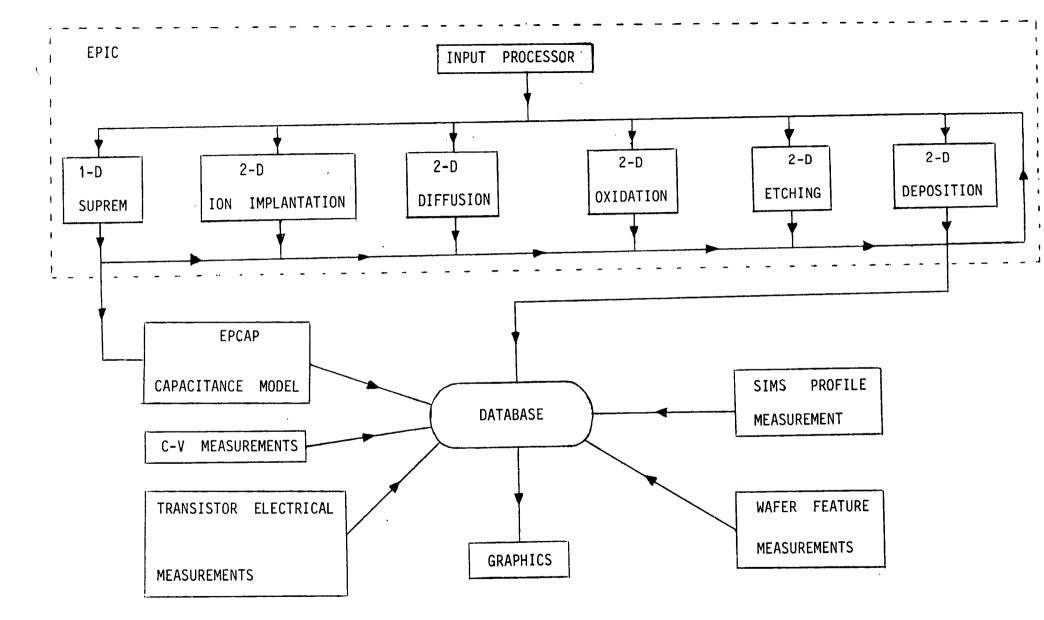

The fabrication of CMUS integrated circuits nave now reached so nigh a level of complexity as to require, not only 1-D, but also 2-D computer simulation of process design, scaling and optimisation. A new 2-D simulator called EPIC (Edinburgh Program for Impurity Concentrations) has been developed to model complete fabrication processes in CMUS technology. The philosophy behind EPIC lies in a unique synergism of the well-established 1-D simulator SUPREM with new 2-D analytical and 2-D numerical process models.

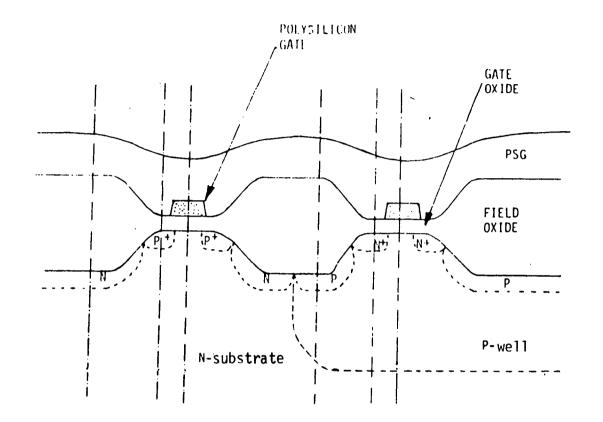

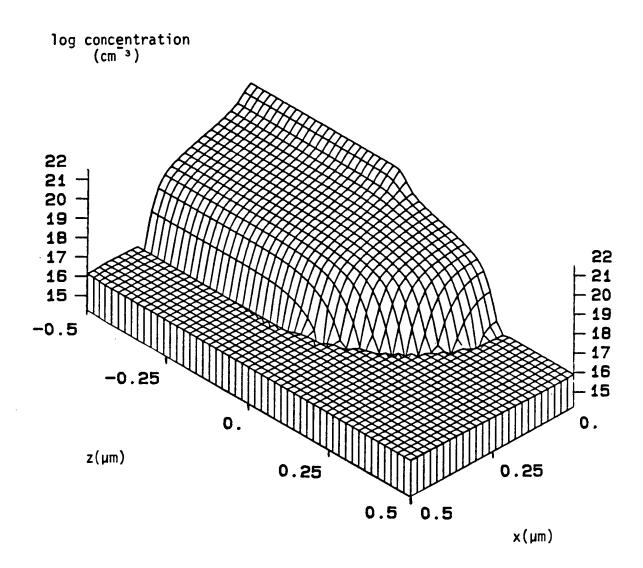

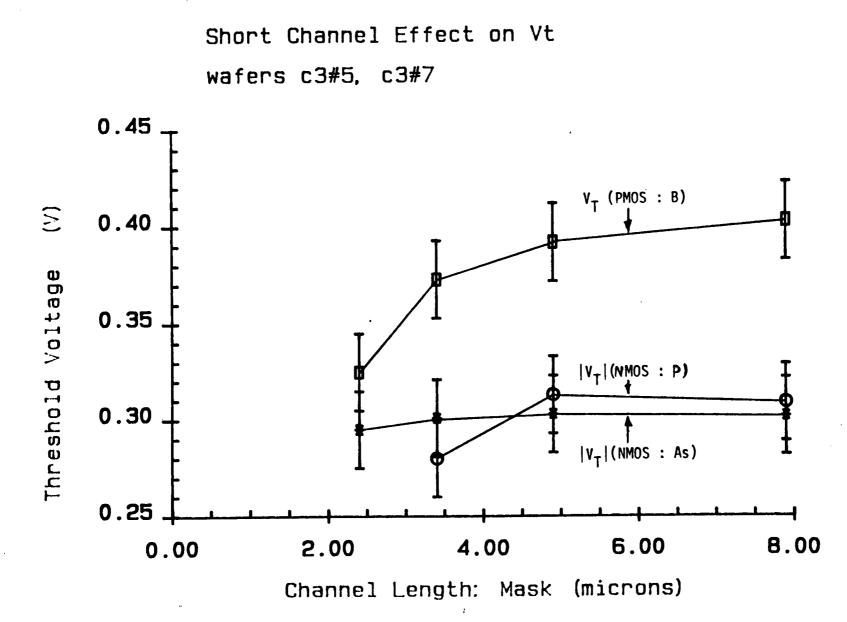

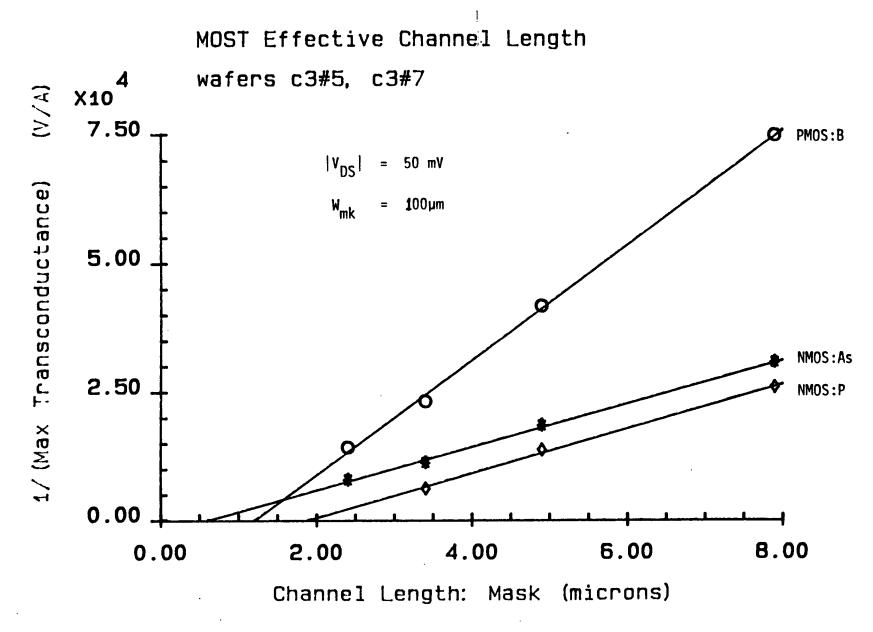

The first simulation of both vertical and lateral effects in a p-well CMOS process is presented. The formation of source/drain regions in both NMOS and PMOS field-effect transistors is modelled in 2-D to allow prediction of effective channel length. EPIC is also used to examine narrow width transistors by simulating impurity redistribution during formation of the bird's beak region between the field and yate oxides. In addition, the first algorithm capable of modelling the capacitance of CMOS structures with non-uniform doping profiles is presented. Publications by the author relevant to this work include:

A.G. Buttar and J.M. Robertson, "Computer Simulation - The Key to Flexibility in CMOS Technology", Proc of Technical Programme, Semiconductor '83 International, Birmingham, England, 27 - 29 Sept 1983.

A.G. Buttar, M.N. Kozicki and J.M. Robertson, "Temperature Modelling for Transient Annealing", in Proc. 8th Symposium on Solid State Device Technology, Canterbury, Kent, 13-16 Sept 1983, The Inst. of Phys. Studies.

A.G. Buttar and J.M. Robertson, "Control of Width Effects in Small Geometry CMOS Devices", in Proc. Simulation of Semiconductor Devices and Processes Conf. (ed. K. Board and D.R.J. Owen), Swansea, 9-12 July 1984, Pineridge Press, p 547.

#### ACKNOWLEDGEMENTS

I would like to take this opportunity to thank Dr J.M. Robertson for setting up this CASE PhD project in the first place, and also for supervision during this research programme. Continual support in computer programming and graphics was provided by Dr A.J. Walton and thanks are due to all other members of the Edinburgh Microfabrication Facility.

I am grateful to the SERC for providing financial assistance.

I would like to acknowledge the support of Motorola Semiconductors in this project, and in particular Mr J. Burnie for education and supervision in all aspects of wafer fabrication. His arrangements for the processing of test wafer batches and continued enthusiasm for the project have been much appreciated. Dr G. Bennett must be thanked for allowing the fabrication of non-standard wafers in the production environment at Motorola in East Kilbride.

Implementation of the transient temperature model for electron beam annealing of silicon wafers would not have been possible without the help of Dr M.N. Kozicki.

Last, but not least, I would like to thank Mrs E. Paterson for the high quality of typing in this Thesis, and for showing no impatience with the large equations.

### CHAPTER ONE : INTRODUCTION

It is the aim of this introduction to outline the importance and uses of modelling and simulation in Complementary Metal-Oxide-Semiconductor (CMOS) Integrated Circuit (IC) technology. The recent surge of interest in the general topic of simulation /1/ has been stimulated by rapid advances in computer technology which have allowed complex physical systems such as those encountered in fields of science and engineering, meteorology, geophysics, etc, to be considered without over-simplification of the model in order to make the solution procedure tractable. Although accurate physical models are important, the sophistication of mathematical analysis used to solve a problem is usually dictated by the level of computational ability available. Consequently, it is generally true that the more comprehensive the computer model is, the more computing power is required. It is interesting to note that integrated circuit simulation is in a unique position since this very activity aids 'in the development of faster computers which, in turn, offer a more comprehensive simulation capability.

While computer systems have been used to solve problems in academic subjects and fundamental research for several decades, it is only recently that the capabilities of such tools have been realised in both light and heavy manufacturing industries. The computer is now frequently used as a large 'database' in which to store vast amounts of information in a readily retrievable way. Data can be collected from the outside world, subsequently processed, and

- 1 -

then, either presented in tabular or graphical form, or transmitted to another system via a communications network. In particular, Computer-Aided-Manufacture (CAM) is now widely used in the IC manufacturing industry to alleviate administrative and inventorial tasks, and also increase production efficiency. Equally important is the role of computer simulation in the engineering of semiconductor products /2,3,4/, and none more so than in the case of CMOS technology which has now advanced to such a level of complexity as to require Computer-Aided-Design (CAD) of both circuit layout and fabrication process. A review of techniques used to fabricate integrated circuits which make use of complementary n-channel and pchannel transistors is given in Chapter 2. Most manufacturers are either converting existing NMOS designs to CMOS, or designing in CMOS from the beginning, in order to take advantage of recent advances in CMOS technology. This progress in itself has provided the incentive to further enhance circuit design methodology. Simulation provides an aid in the design of a cost-effective CMOS process to satisfy an IC market which is continually asking for larger and faster chips. While NMOS will remain a mainstream technology, process simulation is a useful tool in the design of a modular process architecture in which NMOS wafers are manufactured as a subset of the CMOS process /5/.

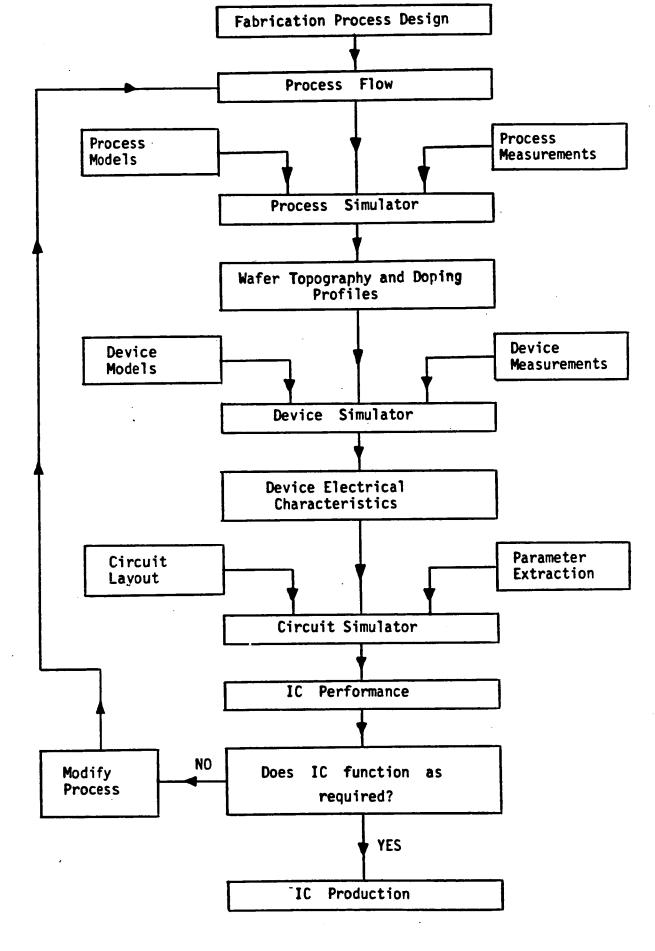

The modelling and simulation of a semiconductor IC is summarised by the flowchart of figure 1.1. The simulation task is generally split into a hierarchy of three levels, which are applied sequentially in the research and development of an IC product. The

- 2 -

Figure 1.1 : IC Simulation Flowchart

individual roles of process, single device and circuit simulations are now clarified.

The simulation chain begins with a specification of the details of the fabrication process. Usually an existing process is modified, but, less frequently, a novel process must be designed. The process flow comprises a sequential list of all stages in the fabrication procedure. A process model is formulated for each type of process step, eg ion implantation. The process flow and relevant process measurements are passed as input to a process simulator. In general the output from a process simulation program consists of the dopant distributions in the silicon, and details of any other material layer present, for example, silicon dioxide, polysilicon, etc. This information is then fed to a device simulation program which has the capability of modelling the electrical response of basic circuit elements such as resistors, capacitors and MOS Often, additional parameters for the program are transistors. determined from electrical measurements of test structures which constitute part of a process control chip. While models for resistors and capacitors are straightforward, accurate MUS transistor models are relatively sophisticated /6,7/. Results of such simulations are simplified to semi-empirical forms suitable for incorporation in a CAD circuit simulation program /8/. It is important that an automated method exists for extracting parameters for use in such circuit simulations /9/.

In addition to modelling the devices which are designed ex-

- 4 -

plicitly as part of an IC layout, the magnitude of parasitic effects must be determined. Examples of unwanted effects include parasitic MOS transistor action between adjacent diffusion tracks, short and narrow channel effects at small geometries, interlayer capacitance, latch-up in CMOS circuits, threshold voltage shifts, etc. Such phenomena are sensitive functions of the impurity concentration profiles in the silicon. Simulations are required to investigate the operation of circuit designs both at a functional level, assuming a given time for each logic transition, and also at the transistor level, to ensure that 'rise' and 'fall' times of nodes are sufficiently fast for reliable circuit operation. From this general discussion of simulation, it is clear that accurate process modelling is essential for adequate circuit simulation.

While the present work is concerned with the application of computer simulation to CMOS processing technology, the drive to develop process simulators originally came from the requirement in bipolar technology to fabricate narrow transistor base regions reproducibly /10/. Demand for simulations of MOS processes grew in the 1970's, and the first general purpose simulator to be offered to both academic and commercial semiconductor houses was SUPREM (Stanford University Process Engineering Models) /11/. This program allows modelling of one-dimensional (1-D) impurity distributions in silicon and silicon-dioxide, and remains the most widely used process simulator in the semiconductor industry at the present time. Chapter 4 demonstrates how SUPREM (Version II) can be used to simulate a typical CMOS fabrication process.

- 5 -

The main limitation with SUPREM is that it can only simulate profiles in 1-dimension, and therefore it cannot realistically describe small geometry MUS structures. 2 or 3-dimensional programs have been written, but they are very slow and of limited accuracy. A more economical approach is therefore necessary. This has lead to EPIC (Edinburgh Program for Impurity Concentrations), and it is the major result of this research project. Its structure and capabilities are described in Appendix A and in the following chapters.

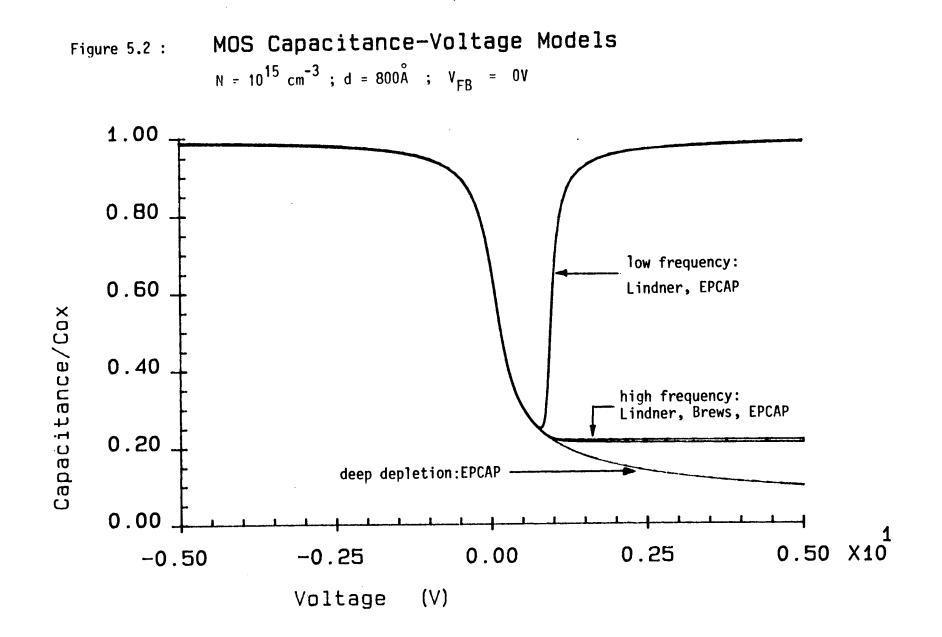

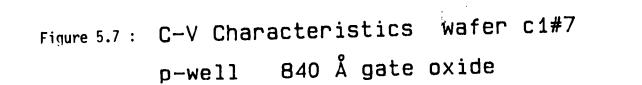

In a semiconductor factory, process monitoring is vitally important for maximisation of wafer yield and isolation of production problems. Capacitance-voltage (C-V) measurements of MOS capacitors on test wafers are routinely carried out to test for contamination Mobile metal ions alter the of high temperature furnace tubes. capacitance and therefore threshold voltage of MOS flat-band transistors /13/ and are potentially disastrous to MOS processes. Knowledge of the theoretical C-V curve is required to determine flat-band capacitance, defined by the shift between ideal and measured characteristics. A theory for C-V characteristics of nonuniform doping profiles in NMOS technology /14/ is generalised to accommodate CMOS structures in Chapter 5. A comparison of theoretical and measured results provide a check on the accuracy of the 1-U process model, and examples of the calculation of flat-band capacitance are presented.

Process modelling is undoubtedly the weakest link in the

- 6 -

simulation chain of figure 1.1, and lags behind current IC processes in production. Most simulation activity in the past has been concerned with only a few sequential process steps, for example, one ion implantation followed by one subsequent anneal step. The goal of process simulation must be to offer a predictive capability to However, with the advent of model complete fabrication processes. Very-Large-Scalefollowed by Large-Scale-Integration (LSI) Integration (VLSI), the routine fabrication in production of devices with dimensions approaching one micron has given rise to a need for two-dimensional (2-D) and three-dimensional (3-D) process simula-The lateral effects which could previously be ignored now tors. have a dominating effect on device characteristics. The MOS transistor is intrinsically at least a two-dimensional (2-D) device, since a vertical electric field is used to control current flow in a Accurate transistor models, therefore require lateral direction. doping concentration profiles in more than one-dimension. 2-D analytical models for ion implantation and impurity redistribution due to diffusion are considered in Chapter 6.

Transient annealing of silicon using electron beam heating as a promising technique for VLSI technologies. A 3-D model for temperature distribution in a silicon wafer due to a scanning electron beam is presented in the same chapter since the diffusion of heat energy and the diffusion of impurity species at low concentration are described by the same differential equation i.e. Fick's law.

While analytical techniques are suitable for modelling the

- 7 -

diffusion of low concentration impurity profiles in non-oxidizing furnace ambients, a more sophisticated model is required to simulate the high concentration profiles in diffused source/drain regions of the wafer. Chapter 7 describes how such a model can be used to predict the effective channel length of both n-channel and p-channel MOS transistors.

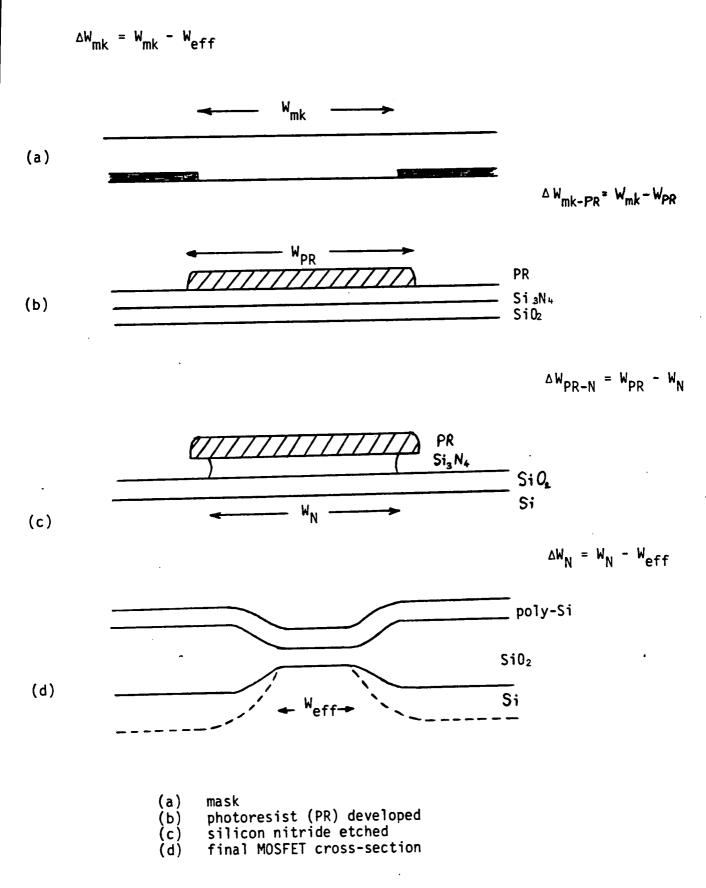

A model for simultaneous diffusion and local oxidation of silicon (LOCOS) has been developed to simulate narrow channel effects in the MOS transistor. This complex moving boundary diffusion problem is dealt with in Chapter 8. A precise estimate of effective channel width is only possible through a combined use of 2-D process and device simulators. A non-planar device analysis is beyond the scope of this thesis, however it is shown that simulation results are consistent with MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) electrical data.

This brief thesis outline demonstrates many of the problems which are inherent in any description of process simulation: individual problems are difficult and must be treated in some depth, but there is also a complex interaction between process steps. Any successful software package must therefore be able to describe individual process steps, and also their aggregation into a complete process. The approach which has been used in this thesis is to describe the individual topics in the following chapters, and to give an overview of the program architecture of EPIC in Appendix A.

- 8 -

# CHAPTER TWO : REVIEW OF CMOS TECHNOLOGY

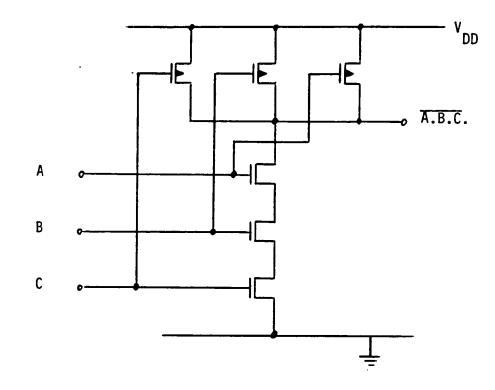

Complementary Metal-Oxide-Semiconductor (CMOS) technology was first proposed by Sah and Wanlass /12/ in 1963 for circuit applications which require very low static power consumption. Figure 2.1 shows a static three-input NAND gate in which a p-channel MOS transistor complements each n-channel MOS transistor. A logic '1' is required at all three inputs to give an output of '0'. Because no dc path exists to ground, current is only consumed during switching.

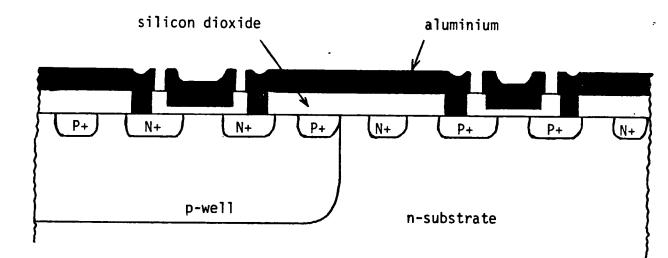

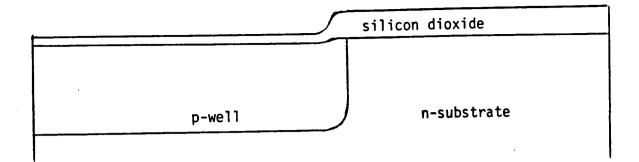

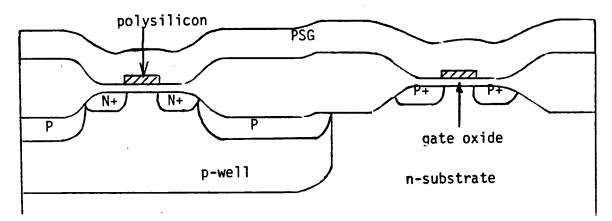

CMUS circuits can be fabricated using either p-wells, n-wells or both n-wells and p-wells, i.e. twin wells. Early CMOS used a pwell as shown by figure 2.2 because boron was the only element available that would form deep but lightly doped tubs. Use of an n-type starting wafer was compatible with PMUS, the mainstream integrated MOS technology of that time. In this approach n-channel transistors are fabricated in the p-well and p-channel transistors in the n-substrate. A metal gate electrode is deposited and patterned after the source and drain regions have been diffused into the wafer. To allow for misregistration, which always occurs to some extent, a large safety margin is used to ensure that the metal overlaps with the diffusion regions. Only then can a complete channel form when the gate is appropriately biased. Metal gate CMUS parts are therefore slow due to a large 'Miller' feedback capacitance between the gate and source/drain regions.

- 9 -

Figure 2.1 : .Three-input CMOS NAND gate

Figure 2.2. : P-well metal gate CMOS cross-section.

Throughout the 1960's and early 1970's, static CMUS circuit designs were wasteful of die area and consequently lagged behind PMUS and bipolar technologies. However, the advantage of very low power dissipation allowed CMOS to be used in specialised products such as calculators, wristwatches and other portable products. Renewed interest in CMUS was stimulated by more inspired design practices through the use of clocked circuitry /242/.

Subsequently, faster circuits were fabricated using a polycrystalline silicon or 'polysilicon' gate electrode which allows the diffused source and drain regions to be formed after polysilicon deposition and self-aligned to the gate edge as shall be shown in the description of a silicon-gate CMUS process to follow. RCA developed closed CUS/MUS logic or ' $C^2L$  CMUS' where the gate of the MUSFET completely surrounds the drain. This technology was used in a 1K static random access memory (RAM) /243/ and an 8-bit microprocessor /244/.

By the end of the 1970's, large NMOS circuits were dissipating up to 1 watt of power, which is dangerously close to the limit for normal plastic packaging. High temperatures lead to aluminium electromigration and other reliability problems. However, CMOS circuits were not subject to this problem and, in addition the p-channel transistor found uses as an active pull-up device in dynamic circuitry. The use of twin-wells allowed optimisation of each transistor type independently /246, 295/, and the flexibility of CMOS allowed other types of devices to be fabricated on the same wafer. Hitachi

- 11 -

for example used a buried-junction FET of JFET as part of a static RAM cell and the intrinsic n-p-n bipolar transistor of the p-well process to boost the current of output buffers /245/. Motorola announced a high speed CMOS logic family as a low power alternative to LSTTL /247/. Matsushita /128/ developed an n-well CMOS process which replaced all furnace doping steps by ion implantation technology. The speed, layout density and power dissipation of circuits could be optimised by designing some sections in NMOS and others in CMOS on the same die /248, 249/.

Since logic levels swing all the way between the supply rails, noise immunity is high and CMOS circuits find applications in harsh environments such as down drilling wells or inside engines /250/. A high demand for CMOS circuits and advancing fabrication equipment technology has helped to increase process yields and lower costs so that CMOS is now often preferred to NMOS /251-254/.

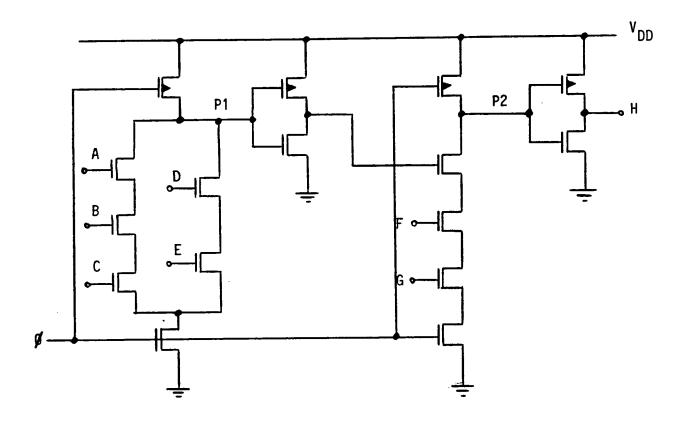

Latest circuits optimise speed and layout density by the use of CMOS domino logic /255/ which is demonstrated in figure 2.3. This dynamic technique requires only a single clock signal, and is particularly effective when the logic gates are complex. When the clock  $\not$  is low, nodes P1 and P2 are pre-charged to V<sub>DU</sub>. The inputs are then applied, and when  $\not$  goes high,P1 and then P2 are conditionally discharged in a ripple or 'domino' fashion. Domino CMUS has been successfully used in the Arithmetic Logic Unit (ALU) of a single chip 32-bit microprocessor /256/ at AT & T Bell Laboratories. Care must be taken in pipe-lined data paths to avoid 'race condi-

- 12 -

Figure 2.3 : CMOS Domino Logic

(A-G are inputs, H is the output and  $\not \! B$  is the clock)

tions' whereby false outputs appear momentarily before a valid logic level is attained. Instead of using n-channel devices for all logic blocks, p-logic and n-logic stages can be alternated to give racefree operation. Although discharge times are longer in the p-logic blocks, this arrangement offers a higher degree of logic flexibility and has been termed 'no race' or NORA CMOS /257/.

CMUS is also pervading the semiconductor memory market, and access times of static RAM circuits are reported to be as fast as NMUS versions /258/ and even bipolar ECL designs /259/, but with greatly reduced power consumption. N-well CMOS has been used in preference to p-well for both a dynamic RAM /26U/ and a read-only memory (ROM) /261/. NMUS dynamic RAM's require a negative back bias or 'charge-pump' to sweep up injected carriers, however, this is not necessary in CMOS, and the use of ground potential in a psubstrate is more effective /283/.

Analogue or linear design in NMUS technology has been made difficult by the assymetric electrical characteristics of enhancement and depletion transistors. The complementary enhancement transistors of CMOS are much more suited to such applications and many analogue CMUS circuits bear a close resemblance to their bipolar equivalents /262/. Efficient CMOS operational amplifiers have been presented /263, 264/. Switched capacitor filters implemented in CMOS technology are finding applications in high frequency communication systems /265/ and in speech synthesis techniques /266/. The use of standard cells greatly reduces the time required to com-

- 14 -

plete a circuit design. Both analogue and digital functions can be designed as blocks and then inserted into a library for use in different systems /267/. Automatic routers are currently being developed to interconnect library cells by optimisation of data paths which are represented by vectors.

The gate array or uncommitted logic array (ULA) comprises a collection of functional blocks which are not linked by interconnects until the metallisation stage /298/. Although a high degree of redundancy is inherent in such semiconductor products, a fast turn-around time is possible and arrays of 20K gates have been reported /268/. In such temporarily uncommitted designs, the number of input and output signals ('fan-ins' and 'fan-outs') is not usually known. The difficulties encountered in designing ratioed NMUS circuits to deal with uncertainties in loading between stages are not nearly so critical in CMUS.

Since a high percentage of die area is occupied by interconnects, a much more dense circuit is possible with the use of multilevel interconnects /276/. One of the major problems currently being encountered by the semiconductor industry in the development of VLSI processes is the fabrication of reliable parts using doublelevel aluminium /269, 276, 289/. In the future CMOS wafer topography will move further away from the traditional isoplanar structure and progressively more three-dimensional, hence requiring a more sophisticated hierarchical design methodology /270/.

- 15 -

Process simulation is currently struggling to keep pace with rapidly advancing processing technology. The following 'industry standard' p-well CMUS process is chosen as the subject for the present modelling activity.

## 2.2 A TYPICAL CMOS PROCESS FLUW

Virtually all silicon for integrated circuit fabrication is prepared by the Czochralski growing technique /271/. This method allows simultaneous doping of the silicon, but as the silicon crystal grows, the melt becomes progressively enriched with impurities due to segregation effects between the liquid and solid phase. As a result of this, the dopant concentration in the crystal is nonuniform and when the material is sawn into slices, a variation in doping level is found not only from wafer to wafer, but also radially across each wafer. Since all starting wafers show a large tolerance in electrical resistivity, implantation of ions into high resistivity starting material is used to dope the silicon surface to a high degree of precision.

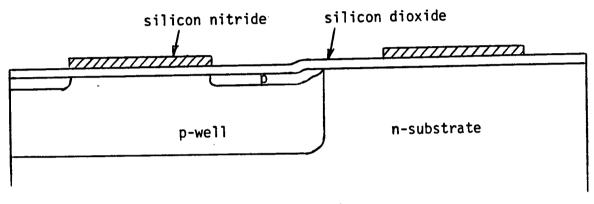

Figures 2.4(a-e) show several key stayes in the fabrication of a silicon-gate p-well CMUS wafer. In the description to follow, details of photolithography /273/ are omitted for simplicity. Dopant concentration is fixed in the n-substrate by ion implantation of phosphorus ions  $(^{31}P^+)$  followed by a high temperature drive-in cycle in an oxidising ambient. After photoresist is deposited and patterned, the unprotected regions of oxide are etched in buffered hy-

- 16 -

(a) p-well formation

(b) definition of active transistor regions

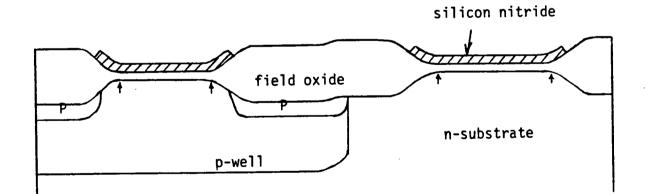

(c) field oxidation (arrows indicate position of silicon nitride formation).

Figure 2.4 : Key stages in a typical CMOS process.

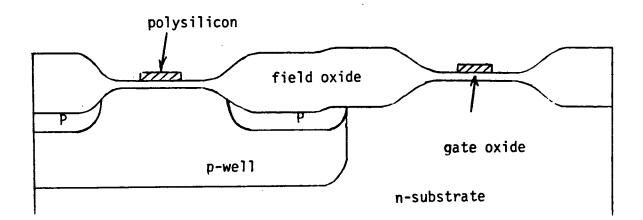

(d) definition of polysilicon gates

(e) cross-section of finished wafer

Figure 2.4 (continued) : Key stages in a typical CMOS process

:

drofluoric (HF) acid to define the p-well regions. Boron  $\binom{11}{B^+}$  is then implanted and diffused into the wafer at high temperature to form net p-type tubs as shown by figure 2.4(a). An oxide step is necessary at this stage in the process in order that subsequent layer masks can be aligned to visible p-well boundaries. For this reason, photoresist alone cannot be used as a mask against p-well implantation. This oxide step is often omitted in cross-sectional views.

Next the oxide layer is stripped, and a fresh 'pad' oxide is grown on which to deposit a layer of silicon nitride  $(Si_3N_4)$  at low pressure using chemical vapour deposition LPCVD /197/. Photoresist is patterned to leave the active device regions covered. The nitride in the field regions is then etched in a plasma /272/ as shown in figure 2.4(b). The lateral extent of the etch is important because it influences the final effective channel width of the MUSFET.

With the n-substrate region covered with the photoresist, boron is implanted into the field regions while the n-channel active device regions are masked by the nitride layer as in figure 2.4(b). After a neutral ambient drive-in, the thick field oxide is grown using local oxidation of silicon (LOCOS) /274, 275/ in burnt hydrogen, with the addition of HCl gas to suppress the occurrence of oxidation-induced stacking faults and to getter sodium ion contamination /41, 42, 111, 116, 118/. Figure 2.4(c) shows the wafer topography after field oxidation, and the situation of the channel stop (CS) region of boron which suppresses parasitic n-channel MOSFET ac-

- 19 -

tion in the p-well field region.

An n-type field implant in the n-substrate region is not usually required since, contrary to the behaviour of boron, phosphorus tends to pile up at the surface of the silicon.

The stress induced during local oxidation causes the edges of the nitride layer to bend upwards like a 'bird's beak'. Next the oxynitride, nitride and pad oxide layers are removed and a dry oxidising ambient is used to grow the gate oxide. During field oxidation, silicon nitride forms at the Si -  $SiO_2$  interface under the edge of the nitride mask /277/ as shown by the arrows in figure 2.4(c). At this place, growth of the gate oxide is impeded and inspection of the wafer through a high power optical microscope reveals a 'white ribbon' around the active regions. Such oxides exhibit low breakdown voltages and also give rise to poor subthreshold device characteristics. This problem is remedied by the use of a sacrificial gate oxide which is grown and then etched back before a second and final gate oxide layer is formed /278/.

No threshold adjust implant is required if the source/drain implant is used to dope the polysilicon. In this approach, the polysilicon is heavily doped n-type (N+) in the p-well regions and heavily p-type (P+) in the n-substrate regions /246/. Judicious choice of doping level in each region allows NMOS and PMOS threshold voltages in the ranges 0.6V to 1.0V and -0.6V to -1.0V respectively. However, polysilicon tracks which cross well boundaries must be

- 20 -

'boot-strapped' with metal to prevent the formation of rectifying p-n junctions.

Modern CMUS processes use LPCVD of polysilicon /280/ which is then blanket doped with phosphorus by either a high temperature furnace treatment or ion implantation to compensate the part of the boron source/drain implant which remains in the polysilicon. While the n-channel MOSFET remains unaltered, the work function in the pchannel transistor changes such that an extra surface implant is required to achieve a useful value of threshold voltage. If the concentration of phosphorus in the n-substrate region is reduced, the threshold voltage of the parasitic field MUS transistor becomes unacceptably low. Hence the n-substrate region is implanted with boron and the dose of this implant is typically high enough to invert the surface of the silicon to p-type. When this occurs, the p-channel MUSFET operates as a buried channel device /279/. To avoid the use of an extra masking stage, a non-selective threshold implant can be used provided the p-well concentration levels are reduced to compensate for the addition of more boron later in the process flow.

The polysilicon is patterned to define MOS transistor gates and interconnecting tracks as indicated in figure 2.4(d). A high degree of control in the lateral extent of the etch is necessary to ensure a low tolerance in the effective channel length of transistors /281/.

- 21 -

A further masking stage is required for each of the N+ and P+ source/drain implants. If P+ polysilicon is retained in the process, a thin layer of oxide is grown on the polysilicon to prevent counter doping of the gate electrode by the heavily phosphorus-doped phosphosilicate glass (PSG) which is deposited to isolate the polysilicon and aluminium layers.

A high temperature treatment follows to repair lattice damage and decrease sheet resistance in the source/drain regions and also to flow the PSG layer over the surface of the wafer. Contact cuts are etched through the oxide in preparation for aluminium deposition by electron-beam evaporation or sputtering /282/. A layer of silicon dioxide or silicon nitride is used to passivate and protect the finished wafer. Unly the bonding pad areas remain open at the surface to allow connection of the integrated circuit to a suitable package. Figure 2.4(e) shows the final CMUS wafer cross-section, where contact cuts and metallisation have been omitted for simplicity.

Although MOS technologies have been traditionally referred to as 'iso-planar', the wafer topography and doping profiles are clearly 3-D in nature. Adequate representation of cross-sections such as that depicted in figure 2.4(e) necessitates multi-dimensional process modelling. Simulation of lateral effects in wafers is particularly attractive as an engineering tool since no method exists of experimentally profiling silicon in more than 1-D.

- 22 -

A variety of fabrication options are currently being investigated to extend CMOS technology through VLSI (Very Large Scale Integration) and into ULSI (Ultra Large Scale Integration) levels of complexity. Some form of simulation is necessary to aid in the development of these processes and so a short review of the current status of advanced CMOS is now presented in order to set a perspective for simulation effort in the future.

## 2.3 ADVANCED CMUS TECHNULOGY

It is generally believed in the semiconductor industry that CMOS will be the dominant VLSI/ULSI technology /322/. However, as device geometries are shrunk to one micron and below, a variety of parasitic effects influence device operation.

It has been observed that  $\alpha$ -particles from the atmosphere or the packaging material of the integrated circuit can corrupt data in dynamic RAM circuits /284/. A single  $\alpha$ -particle incident on the silicon wafer generates several hundred thousand electron-hole pairs. If enough minority carriers (electrons in p-type silicon) diffuse into the depletion region of a storage capacitor then a logic '1' can be switched to a logic '0' which then constitutes an erroneous bit of information. If the memory cells are placed in a pwell, the electrons generated in the n-substrate are repelled by the built - in potential of the well-substrate p-n junction, and the occurrence of a soft error is less likely /285/.

- 23 -

Despite this advantage, the use of n-wells is now preferred for several reasons. N-well CMOS uses p-type starting material and so is compatible with NMOS. Carrier mobility is degraded by the presence of dopants of either type and is a function of the total (not net) impurity concentration. Current CMOS circuit designs often rely on the faster n-channel transistors to conditionally discharge output nodes, and such devices in a p-substrate offer a higher gain than those in a p-well.

1

Une of the biggest problems to be overcome in the development of a VLSI GMOS process is the parasitic bipolar mechanism known as 'latch-up' /65-68/. With reference to figure 2.4(e), the vertical n-p-n and lateral p-n-p structures in the p-well CMOS process together make up a thyristor (p-n-p-n device) which, when appropriately biased by a noise spike, gives rise to a sustained current between the positive and negative terminals of the power supply. The latch-up current can only be terminated when the power is switched off, by which time the circuit is likely to be permanently damaged. Because the mobility of holes is less than that of electrons, the gain of the vertical p-n-p in an n-well process is less than the gain of the vertical n-p-n in a p-well process, and hence the n-well process is less susceptible to the occurrence of latchup.

An increase in the well and substrate concentration levels reduces the risk of latch-up by decreasing the minority carrier lifetime in the parasitic bipolar transistor base regions. Howev-

- 24 -

er, a larger back-gate bias effect /13/ is induced in the active MUS transistors.

Other attempts to eliminate latch-up have included the diffusion of gold atoms into the wafer /286/ or the use of internal gettering /287/ to reduce minority carrier lifetime. The use of Schottky barriers in a CMOS process is also reported to solve latch-up problems /288/.

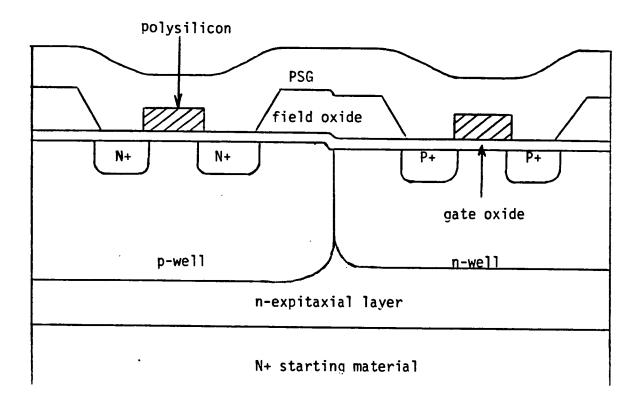

One of the most effective methods of decreasing the lateral resistance of the well is to use a heavily doped substrate on which a near-intrinsic epitaxial layer is grown. From then on, a normal process flow can be adopted. Both N+ substrates /290, 291, 294/ and P+ substrates /283, 292/ have been utilised, but fabrication costs are high and defect density is increased /296/. Figure 2.5 shows a twin-well CMOS process using N+ starting material. The transition region between the substrate and the epitaxial layer contains point defects which help to getter unwanted impurity atoms from the surface of the wafer.

While these processing techniques reduce the possibility of latch-up occurring, it is still necessary to take precautions at the design level. Input and output buffers for example should be completely surrounded by 'guard-rings' which are hardwired to the power supply to collect any minority carriers in the substrate /258/.

One technology which eliminates latch-up problems is silicon-

- 25 -

Figure 2.5 : Twin-well CMOS

. .

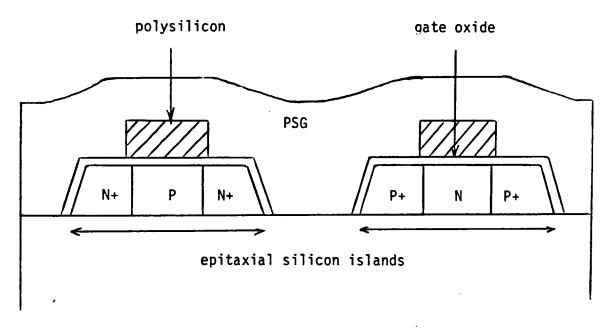

Figure 2.6 : Silicon-on-Sapphire (SOS) CMOS

on-sapphire (SOS) by using an insulating substrate material /297, 298/. An epitaxial layer of silicon is grown on the sapphire, and then selectively etched to form islands in which to form n-channel and p-channel MOSFET's as shown in figure 2.6. Field oxide is not required and the spacing between transistors is only determined by how well the epitaxial islands can be defined. Also no separation is necessary between the diffused N+ and P+ regions on the output node of an inverter hence allowing a high packing density of SOS circuits boast a low susceptibility to radiation transistors. and because the substrate is non-conducting, parasitic capacitances Using similar design rules, SUS is about twice as fast as are low. bulk CMOS in VLSI /300/. High performance applications justify the added processing cost and Toshiba manufacture a 16-bit microprocessor using SOS technology /301/.

Since the fabrication of CMUS/SUS wafers is made difficult by the difference in thermal expansion between sapphire ( $\propto - Al_2 o_3$ ) and silicon, there is great interest in obtaining an insulating substrate by other techniques. High dose oxygen implantation into silicon wafers followed by an anneal treatment gives a buried silicon dioxide layer with silicon at the surface /302/. Nitrogen can be implanted to form a silicon nitride layer in a similar fashion /303/. Alternatively, a one-micron thick layer of oxide can be grown on the surface of the wafer, and then a layer of polysilicon is deposited using LPCVD. The grained silicon structure is melted and grown into a single crystal by thermal radiation from halogen lamps /304/. Such silicon-on-insulator (SOI) techniques remain

- 27 -

research topics currently and are not yet feasible for the production environment.

As device geometries are shrunk to dimensions below 2 micron for VLSI, a variety of parasitic effects become important for device performance /306,309/, and these are collectively known as 'short and narrow channel effects'. The 2-D nature of device structures can no longer be ignored, and threshold voltage becomes a function of device size /305/.

While the transistors themselves exhibit higher switching speeds, the maximum operating frequency of VLSI circuits is limited by the resistance of diffused regions and polysilicon interconnects which contribute to large RC time delays. Refractory metal silicides can be fabricated on the surface of these doped areas in order to increase their conductivity /253/. Smaller contact openings and more shallow source/drain junction depths also increase the series resistance to transistors /306/. The transconductance of devices with gate oxide thicknesses below 100Å degrades since this dimension is comparable with the thickness of the inversion layer and a large portion of the applied gate-source voltage appears across the channel hence decreasing the effective gate capacitance /306/.

Use of the traditional 5V TTL-compatible power supply causes problems for VLSI MOS devices. As the transistor channel length is reduced, the drain depletion region extends to the source giving rise to unrestricted current flow despite a gate voltage correspond-

- 28 -

ing to the 'off' condition /7, 311/. N-channel devices already require a surface implant of boron to allow the use of an N+ polysilicon gate electrode. To suppress punch-through, an additional deep implant of boron is required to raise the p-type dopant concentration in the bulk while not contributing appreciably to the threshold voltage. A high lateral electric field gives rise to 'hot' carriers which are sufficiently energetic to create free electrons and holes /306/. Substrate currents can initiate parasitic bipolar mechanisms like latch-up. Another is 'snap-back' /299/ which is characterised by a state of negative differential resistance in the  $I_{DS} - V_{DS}$  relationship. Since the p-channel MOSFET operates as a buried-channel device, careful process design is necessary to ensure good sub-threshold characteristics /310/.

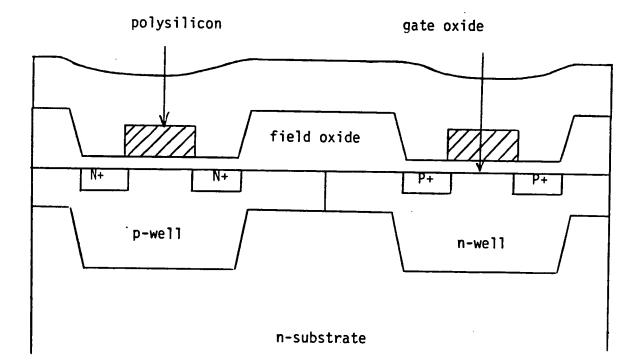

Despite the above-mentioned complications to basic transistor operation, a process which holds promise for advanced VLSI and ULSI levels of circuit complexity is retrograde well CMUS. Compared to conventional bulk CMOS, the main difference of this approach is that the p-well implant is performed after the active device regions have been formed. A high energy, typically 400 - 600 keV, is used to accelerate boron ions through the field oxide into the underlying silicon /293, 296/. Only a brief anneal is necessary instead of the customary long p-well drive-in step. A channel-stop (CS) region is formed in the p-well field area and boron suck-out due to oxidation is minimised. The net p-type doping concentration reaches its maximum value in the bulk of the transistor active region and suppresses drain-source punchthrough. This process has been ex-

- 29 -

tended to twin retrograde wells /294/, as shown in figure 2.7. Since the tubs form four distinct regions in the silicon, this technology is consequently referred to as 'quadruple well CMUS'.

Because changes in processing technology tend to be evolutionary rather than revolutionary due to the immense cost of introducing changes into a wafer production line, quadruple well CMOS has the potential to be the dominant VLSI/ULSI circuit technology. However, the advancement of this technique to a feasible production process is hampered by the lack of a commercially available ion implanter which is reliable and capable of the high acceleration voltages necessary to implant ions through the thick field oxide.

Even more dense circuit layouts are possible by increasing the level of integration in the vertical direction of the wafer. The use of triple-level polysilicon permits fabrication of very small dynamic RAM cells /312/. A further step towards three-dimensional (3-D) integration is taken by stacked CMUS (ST-CMUS) /313/. In this sophisticated process flow, p-channel transistors are created in a laser-recrystallised polysilicon layer and are placed directly above the n-channel devices.

Since the bird's beak transition region of conventional MUS technologies is wasteful of die area, several new isolation techniques have been proposed for advanced processes /50, 51, 314-317/. The most promising is 'deep-trench' isolation /318/ which has been used to reduce the separation between n-channel and p-channel

- 30 -

Figure 2.7 : Quadruple-well CMOS

transistors and also increase latch-up immunity. The deep trenches are created using reactive ion etching (RIE). The sidewalls are oxidised and then the pits are filled with polysilicon. The surface of the wafer must be planarised to avoid step coverage problems when the aluminium layer is deposited.

Powerful single-chip silicon systems can be realised by combining bipolar and MOS elements on the same die in a 'BIMOS' process. The feasibility of this approach has already been demonstrated in a dynamic RAM design /319/. Fairchild have developed a complex process which combines bipolar, CMOS and high voltage DMOS transistors /320/. Most of the large semiconductor manufacturers are engaged in research to fabricate BIMOS circuits, but since process details are proprietary, little published material has yet emerged.

It is clear from this review and discussion of CMUS technology that processing techniques are becoming more complex and consequently increased use of computer aids is now required. When used in conjunction with test chip data /321/, computer simulation provides an aid to understanding phenomena, and offers a valuable tool for CMOS process development in VLSI/ULSI.

- 32 -

## CHAPTER THREE : REVIEW OF PROCESS SIMULATION ACTIVITY

A large amount of research work on individual process steps, such as ion implantation, diffusion, oxidation, etc., has been reported in the literature. The power of process simulation lies in the combination of models for each fabrication step to allow simulation of complete processes from beginning to end. Several man years of effort is involved in the development of such a simulation package. The realisation of such a project calls on a variety of disciplines including semiconductor physics, processing knowledge, computer programming and applied numerical analysis.

As well as being important for process development and understanding, simulation provides a convenient means of carrying out a process sensitivity analysis to determine those parameters which have a critical effect on device characteristics and thus require a high degree of control on the production line. A process variation analysis has been undertaken by Aoki et al /241/ with the program CASTAM. Herr et al /240/ have reported a statistical modelling approach to determine best and worst case device parameters for circuit design.

While simulation of impurity concentration profiles only is discussed in this thesis, modelling of wafer topography /233/ is becoming increasingly important for VLSI. The most advanced general purpose simulator for dealing with the process steps of lithography, deposition and etching is SAMPLE /231, 232/.

- 33 -

The 2-D models of this program have been applied to the projection printing of positive photoresist /234/ and negative photoresist /235/, and also to the electron-beam exposure of resist /236/. Plasma etching of material layers is a critical process step in MOS technologies. The width of a silicon nitride track defines the effective channel width of the MOS transistor, and the width of a polysilicon track defines the effective channel length, assuming all other offsets are fixed. A high degree of control in etching characteristics is necessary since any variations in nitride or polysilicon linewidths appear as a tolerance on the electrical characteristics of devices. Optimisation of etched profiles is possible using both vertical and lateral etch rate components /237/. Deposition models for electron-beam evaporation or sputtering of aluminium aid in the reduction of step coverage problems /238/.

Several process simulators which model impurity distributions in silicon have been reported in the literature and these are summarised in table 3.1. For comparison, the EPIC program produced in this project has also been included, although it is described more fully later. A 1-D process simulator allows modelling of the impurity profile in the vertical direction in the wafer, but if lateral effects are also important, for example in the length and width cross-sections of a small geometry MUS transistor, then a 2-D simulator is required.

The complexity of mathematical process models means analytical methods can only be applied to certain aspects of the process, and in general, accurate results are only possible by using a numerical method.

- 34 -

| Process<br>Simulator | D | References | Place of Origin           | Num. <sup>*</sup><br>Method | N <b>on-</b> Un.<br>Mesh | High<br>Conc.<br>Diff. | Niff.<br>and<br>Oxid. | Applications     |

|----------------------|---|------------|---------------------------|-----------------------------|--------------------------|------------------------|-----------------------|------------------|

| SUPREM II            | 1 | 11,97      | Stanford Univ,            | FD                          | 1                        | √                      | 1                     | used extensively |

| SUPREM III           | 1 | 181, 229   | Stanford Univ.            | FD                          | 1                        | 1                      | √                     | N-well CMOS      |

| ICECREM              | 1 | 81, 188    | Munich Univ."             | FD                          |                          | 1                      | 1                     | used extensively |

| SUPRA                | 2 | 16, 202    | Stanford Univ.            | FD                          | √                        | √                      |                       | NMOS             |

| FEDSS                | 2 | 17, 230    | IBM                       | FE                          | 1                        | √                      |                       | N-well CMOS      |

| ROMANS II            | 2 | 20-22      | Rockwell                  | SD                          |                          | 1                      | 1                     | N-well CMOS      |

| BICEPS               | 2 | 27-29      | AT & T Bell Labs          | FD                          | !                        | 1                      | √                     | NMOS             |

| LADIS                | 2 | 25,26, 180 | Siemens                   | FD                          |                          | 1                      | 1                     | NMOS, DIMOS      |

| Taniguchi et al      | 2 | 19         | Toshiba                   | FD                          |                          | 1                      | 1                     | NMOS             |

| RECIPE               | 2 | 198        | Rensselaer<br>Poly. Inst. | ?                           |                          |                        |                       | NMOS             |

| EPIC                 | 2 | 31         | Edinburgh Univ.           | FD                          | 1                        | 1                      | 1                     | P-well CMOS      |

•

\* FD = Finite Difference; FE = Finite Element; SD = Semi-Discretisation

Table 3.1 : <u>Review of 1-D and 2-D process simulators</u>

٠

method. Such numerical analyses fall into three categories: the finite difference (FD) method, the finite element (FE) method and the semi-discretisation (SD) method or method of lines.

Advantages are to be gained in the use of a non-uniform mesh where a fine grid is used to accommodate rapidly varying impurity profiles due to ion implantation or thermal oxidation at the surface of the wafer, and a coarse mesh in the bulk where impurity concentration gradients are not large. It is essential to adopt such an approach in the simulation of a bulk CMOS process which makes use of an n-well, p-well or both types of well, in order to reduce computation times.

High concentration ion implantation and diffusion models are required to model source/drain regions in MOS processes. The concentration dependence of the diffusivity gives rise to non-linear diffusion, which cannot be modelled analytically. The 1-D programs SUPREM II /11,97/, SUPREM III /181,229/ and ICECREM /81, 188/ solve for impurity diffusion in inert and oxidising furnace ambients. However, the diffusion coefficient of species in the oxide is very low, and during a non-oxidising (inert) anneal step in the fabrication process, the Si - SiO<sub>2</sub> interface can be approximated by a reflecting boundary. This approach is used by all the 2-D process simulators reviewed. All these programs use a well established numerical method, except in the case of RECIPE /198/ which uses an 'incremental solution method'. The mathematical basis of this work is suspect, and the authors do indeed confess that diffusion results

- 36 -

could be inaccurate by a factor of 2.

The simulation of impurity diffusion during thermal oxidation of the silicon wafer is a complex moving boundary problem. The 1-D programs of table 3.1 model simultaneous diffusion and oxidation without the use of any simplifying assumptions. Simulation of the transition region between the active and field regions commonly known as the 'bird's beak' requires a 2-D model. All attempts to solve this problem so far have been forced to neglect impurity diffusion in the oxide and to model segregation effects purely as an interfacial flux in the form of a boundary condition. In practical situations this is a good approximation, as shall be demonstrated in chapter 8. Instead of a 2-D numerical model, SUPRA /16, 202/ uses a semi-empirical model which can generate only approximate results in general situations, and therefore cannot be credited as a realistic diffusion/oxidation simulator. The model of Taniguchi et al /19/ assumes a bird's beak angle of precisely 45° which rarely occurs in FEDSS /17, 230/ models non-rectangular practical MOS processes. structures but completely neglects impurity segregation effects. An accurate and mathematically valid numerical treatment, however, is used by the programs ROMANS II /20-22/, BICEPS /27-29/ and LADIS /25, 26, 180/.

The 1-D programs SUPREM II and ICECREM are available to anyone from the authors for merely handling costs, and are consequently used extensively in the semiconductor industry. SUPREM III is capable of modelling multilayered structures, for example, polysilicon

- 37 -

and gate oxide in the cross-section through the active device region of the MOS transistor, and results have been presented for an n-well CMUS process /229/.

A 1-D process simulator called PROSIM II has recently been reported by Fair et al /239/. Although the program has been used to predict source/drain junction depths in CMUS, details of the process models have not yet been presented.

In the field of 2-D process simulation, SUPRA, BICEPS and the program of Taniguchi et al have been applied to NMOS technology, and in addition, LADIS allows simulation of DIMOS transistors /13/.

N-well CMOS processes have been simulated by FEDSS and ROMANS II and although no simulation results have yet been presented, RU-MANS II is the only 2-D process simulator capable of modelling impurity profiles in silicon-on-sapphire (SUS) CMOS /22/.

From table 3.1, the most popular solution technique is the finite difference method. The alternative finite element method has attractions in that it can use a mesh structure which conforms to the physical boundaries of the device. However, the resultant matrix structure is less amenable to iterative solution. Finite difference methods have been much more widely used both for device and process simulation. It was therefore decided to use finite difference analyses for all the models developed in the course of this project.

The programs reviewed in table 3.1 provide a good starting

- 38 -

point but none of the 2-dimensional packages are yet sufficiently comprehensive to be generally usable. The main features which were considered in the definition of EPIC were:

- \* 2-D representation

- \* Use of analytical solutions where possible

- \* Numerical solution by finite difference methods

- \* Executable on a small VAX computer

- \* Modules to describe single process steps

- \* Linked modules for whole fabrication processes

The program architecture is described in Appendix A, and the single process step modules in the following chapters. By using this approach, it has been possible to devise a program which is unique in its scope of application, but which remains economical to use. This thesis and the previous work by Buttar et al /31/ comprise the first 1-D and 2-D simulation of of a complete p-well CMUS process, and the program may also be applied to n-well or twin-well CMOS structures.

Two features have contributed to the detailed efficiency of EPIC:

- (i) use of SUPREM 1-D profiles to define initial mesh conditions for 2-D simulations.

- (ii) use of a non-uniform mesh to give an economical representation of deep non-uniform dopant profiles.

Electron-beam annealing is a promising technique which holds promise for VLSI MUS technologies. A simple annealing model for use in the development of scanning electron-beam systems is presented in chapter 6.

# CHAPTER FOUR : 1-D PROCESS SIMULATION

# 4.1 ION IMPLANTATION

Ion implantation is now the principal doping technique used in the fabrication of integrated circuits because it offers several advantages over furnace doping methods. A high degree of uniformity and reproducibility is possible by monitoring the ion beam Since the MOSFET is a surface-effect device, the silicon current. surface must be free of contaminants in order to ensure reliable device operation. Ion implantation can be performed through a passivating layer of silicon dioxide on the wafer surface. In addition, photoresist, silicon dioxide and silicon nitride can be used to mask regions of the silicon from the impinging beam. Implantation is carried out at low temperatures and so no impurity diffusion takes place. This is important in MOS technologies because VLSI devices require highly doped but shallow impurity profiles in source/drain regions to minimise short channel effects /69-71/. In addition source/drain regions can be self-aligned to polysilicon gates hence reducing parasitic gate/source and gate/drain capaci-Short channel (<2µm) MOS transistors require a gate adjust tances. implant to fix the threshold voltage and also a deeper implant to suppress drain-source punch-through /83.99/.

The theoretical background for ion implantation is due to

- 40 -

Lindhard, Scharff and Shiott /79/ and this work is known as the LSS theory. An amorphous target is assumed to provide both electronic and nuclear stopping of incident ions and the predicted profile takes the form of a symmetrical Gaussian distribution given by

$$N(x) = \frac{Q}{\sqrt{\frac{\pi}{2}} \Delta R_{p} \{1 + erf(\frac{R_{p}}{\sqrt{2} \Delta R_{p}})\}} exp \{-\frac{(x - R_{p})^{2}}{2\Delta R_{p}^{2}}\} (4.1)$$

where x is distance into the silicon, Q is the implant dose,  $R_p$  is the projected range of the ion in silicon and  $\Delta R_p$  the projected standard deviation or range straggle. The so-called error function is defined by x

$$erf(x) = \frac{2}{\sqrt{\pi}} \int exp(-\gamma^2)d\gamma \qquad (4.2)$$

The LSS range statistics for  $R_p$  and  $\Delta R_p$  have been computed as a function of implant energy by Gibbons et al /80/. While LSS theory considers amorphous targets, silicon wafers are single crystals, and a certain amount of ion channeling always occurs along major crystallographic directions /85/. Ions which find themselves channeled between adjacent lattice planes penetrate deeper into the silicon and give rise to a 'tail' on the Gaussian distribution. The effects of channeling can be reduced, but not eliminated, by both rotating and tilting the wafer prior to implantation, and also by using a passivating silicon dioxide layer to randomise the ion directions before they reach the silicon /92/.

If the assymetric nature of the distribution- is not too

- 41 -

severe then a good fit to the experimental results is obtained by using the third moment ratio estimate or 'skewness' Y which characterises the degree of tilt of the profile. In this formulation two half-Gaussian profiles with different range straggles are joined at a common range /80,100/.

The best fit to experimental profiles is obtained by considering, in addition to the skewness Y, the kurtosis  $\beta$  which indicates flatness at the top of the profile. The four parameters  $R_p, \Delta R_p, \gamma$  and  $\beta$  are incorporated into a Pearson distribution of type IV defined by /81,82,103/

$$f_p(x) = k_p [b_2(x-R_p)^2 + b_1(x-R_p) + b_0]^{\frac{1}{2b_2}}$$

exp {

$$-\frac{b_1}{b_2} + 2a}{\sqrt{4b_0b_2 - b_1^2}}$$

} arctan {  $\frac{2b_2(x - R_p) + b_1}{\sqrt{4b_0b_2 - b_1^2}}$  } (4.3)

where

$$b_1 = a = -\frac{\Delta R_p \gamma(\beta + 3)}{A}$$

(4.4)

$$b_0 = - \frac{\Delta R_p^2 (4\beta - 3\gamma^2)}{A}$$

(4.5)

$$b_2 = - \frac{(2B - 3\gamma - 6)}{A}$$

(4.6)

$$A = 10\beta - 12\gamma^2 - 18$$

(4.7)

The constant  $k_p$  is determined from the normalisation integral  $\int_{0}^{\infty} f_p(x) dx = 1$ (4.8)

and the complete ion distribution is given by

$$N(x) = Q f_{p}(x)$$

(4.9)

For a Pearson type IV distribution B must satisfy

$$\beta \ge \beta_{\min} = \frac{48 + 39\gamma^2 + 6(\gamma^2 + 4)^{3/2}}{32 - \gamma^2}$$

(4.10)

Boron profiles in particular are well modelled using this distribution /81,82,92/.

The remainder of this section considers how ion implantation theory may be implemented in process simulation models.

- 43 -

SUPREM II uses joined half-Gaussian distributions for phosphorus and arsenic, and Pearson IV distributions for boron. EPIC uses Pearson IV distributions for all three elements. The values of kurtosis ß are taken from ICECREM /81/ and are

$$\beta = \begin{cases} 1.5 \beta_{\min} ; B, P \\ \beta_{\min} ; As \end{cases}$$

(4.11)

Implantation of ions is rarely performed into bare silicon in MUS processes, but usually through a passivating layer such as silicon dioxide. The basic LSS theory cannot be applied to multilayered structures and only two general theories have been developed to model the range of ions and lattice damage in arbitrary solid targets.

The first method is to solve the Boltzmann Transport Equation /87/ to obtain the implanted profile in 1-D. No generalisation to more than one-dimension has yet been reported, so the method has only limited use in a VLSI process simulation program.

The second method relies on a Monte Carlo technique /88-90, 101,102/, which involves the modelling of each scattering event as a projectile collides with target atoms. Because each ion path must be simulated, the procedure must be repeated very many times in order to build up a statistically valid distribution, and so execution times of Monte Carlo programs are long.

- 44 -

Alternative methods, which are simpler to implement, replace masking layers by equivalent thicknesses of silicon to allow the use of LSS data. Sakurai et al /91/, Furukawa and Ishiwara /93/, and Ryssel and Hoffman /92/ use a density transformation based on the projected standard deviation. If the thickness of passivating layer is  $d_1$  and the range straggle of the incident ion in this material is  $\Delta R_{p1}$ , then the effective thickness of silicon  $d^*$  is given by

$$d^{\star} = \frac{\Delta R_{p}}{\Delta R_{p_{1}}} d_{1}$$

(4.12)

EPIC.uses a transformation based on the projected range, as used by Antoniadis and Dutton in SUPREM II /11, 97/ and Tielert /94/. If the projected range of the incident ion in the masking layer is R<sub>D1</sub> then the equivalent thickness of silicon is given by

$$d^{\star} = \frac{R_{p}}{R_{p_{1}}} d_{1}$$

(4.13)

The implantation of ions through multilayered structures gives rise to recoil or knock-on implantation of ions /95/. If the mass of the implanted ions is similar to the mass of the atoms comprising the masking layer, a large fraction of the energy of the primary projectiles can be transferred to the atoms of the masking layer which are themselves implanted into the silicon. Knock-on implantation of silicon and oxygen atoms has been observed to occur during high dose arsenic implantation through oxide into the source/drain regions of MOS devices. However, experimental results

- 45 -

show that the free-carrier mobility is not degraded in those regions /86/.

Sputtering of target atoms occurs for very high implant doses  $(>10^{17} \text{ ions cm}^{-2})$  and low energies (<10 keV) /92/, but this effect is negligible in all practical situations in current MOS processes.

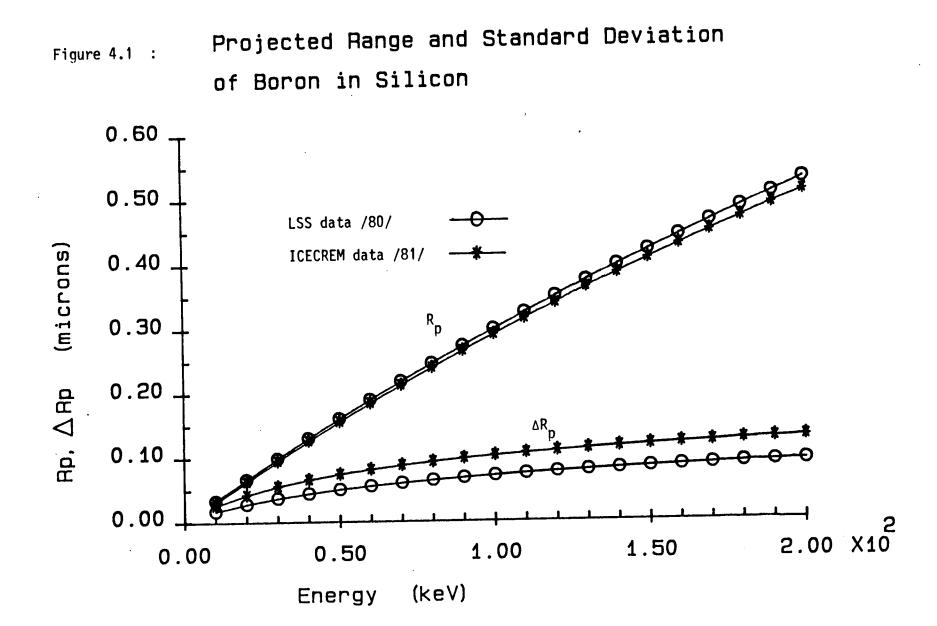

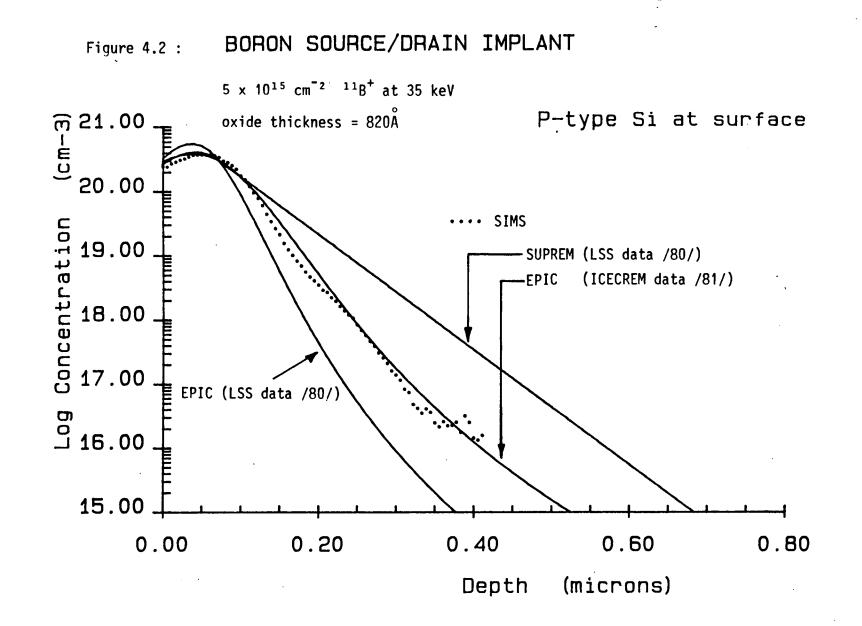

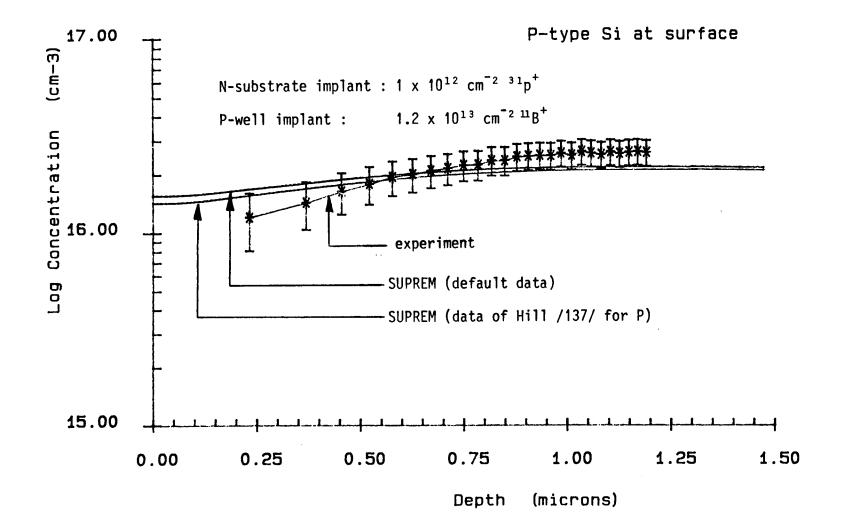

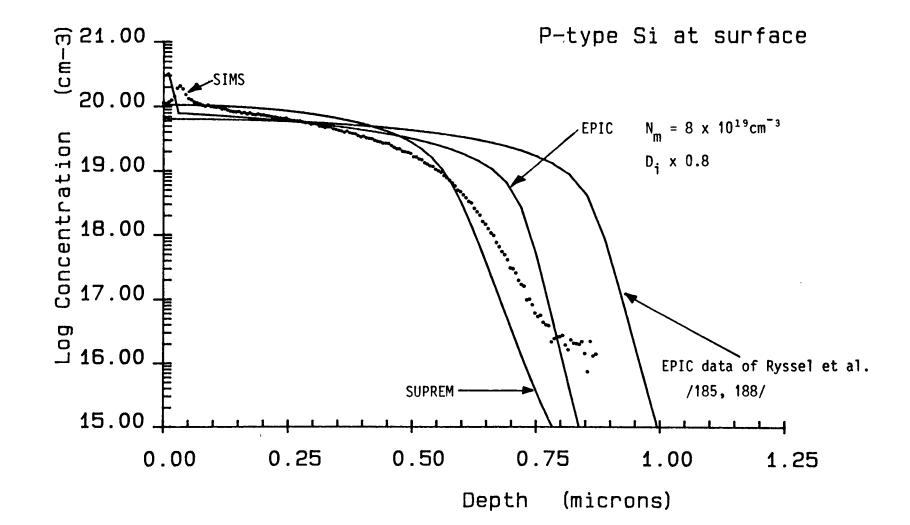

In order to test the accuracy of EPIC in one-dimension, simulation results are compared with Secondary Ion Mass Spectrometry (SIMS) data /96, 104/ for typical source/drain implants of CMOS technologies. In the present study, SIMS analysis was obtained commercially through Loughborough Consultants Ltd. EPIC uses the LSS statistics of Gibbons et al /80/ in all cases except for the data of range  $R_p$  and standard deviation  $\Delta R_p$  for boron in silicon where the values used are those appearing in the program ICECREM /81/. Figure 4.1 shows a comparison of LSS data and empirically obtained ICECREM data for  $R_p$  and  $\Delta R_p$  for a range of implant energies between 10 keV and 200 keV. Figure 4.2 shows SIMS experimental data for a high dose boron implant through an oxide of thickness 820Å.

Dopant concentration is plotted as a function of depth from the silicon surface, and the concentration of dopant in the oxide layer is not considered.

SUPREM II fits an exponential tail to the Pearson IV distri-

- 47 -

•

- 48 -

bution which overestimates the extent of ion channeling. Also shown are the simulation results of EPIC using both LSS data and ICECREM data, of which the latter clearly gives the best agreement with the SIMS data. The ICECREM data for boron is therefore also used in the 2-D implantation models in EPIC.

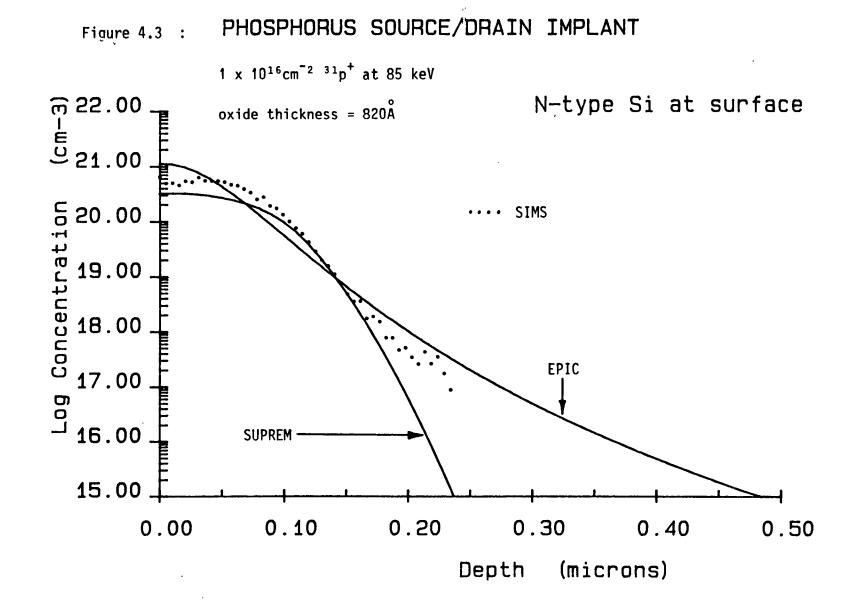

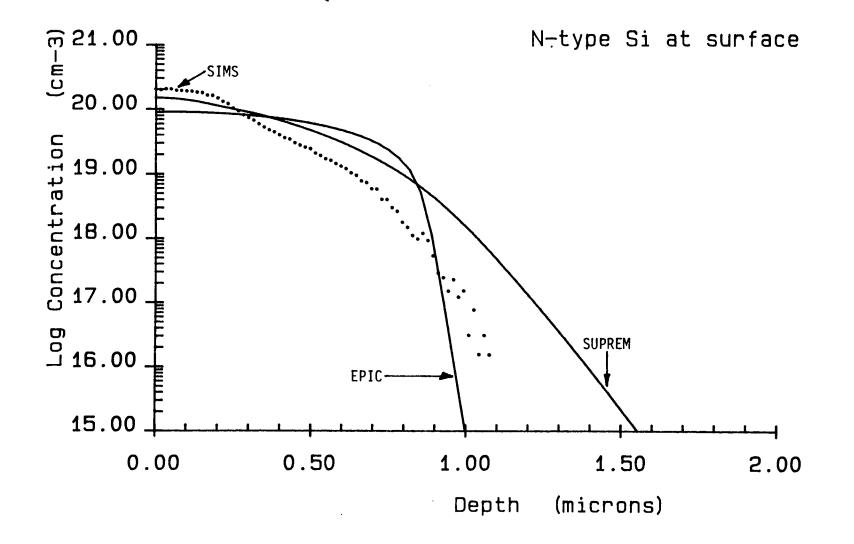

The SIMS results for a phosphorus implant are shown in figure 4.3. The use of joined half-Gaussian profiles in SUPREM underestimates both the surface concentration of phosphorus, and the extent of the distribution tail. EPIC, in contrast, overestimates the surface concentration and slightly overestimates the distribution The top of the experimentally measured profile is much tail. flatter than is expected from LSS statistics, and this discrepancy is attributable to the masking layer of oxide. Both SUPREM and EPIC assume that masking layers have no effect on the range straggle, however Monte Carlo calculations of phosphorus implanted at 150 keV through a 1500Å thick layer of SiU, predict a flatter peak region compared with LSS distributions /98/.

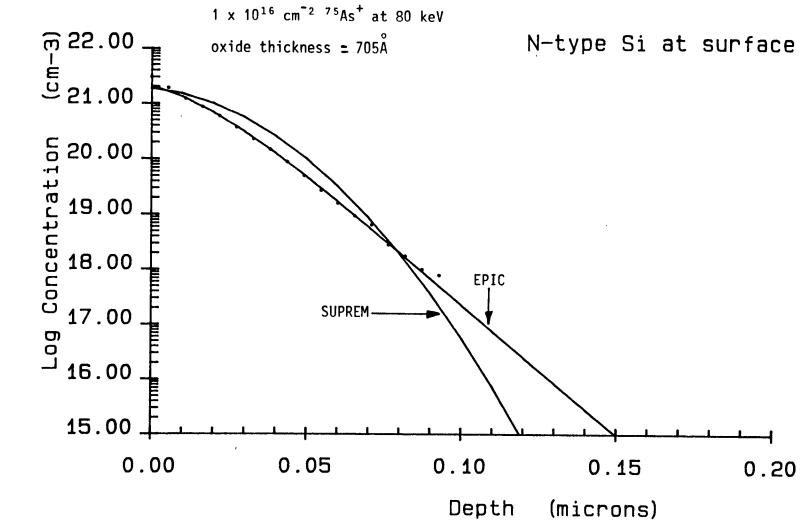

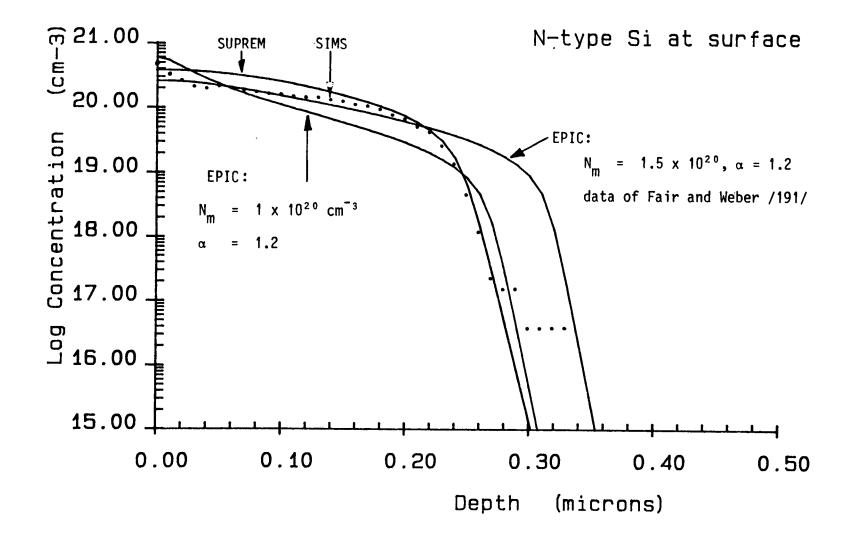

Figure 4.4 shows a comparison of SIMS results for an arsenic implant with the joined half-Gaussian profiles of SUPREM and the Pearson IV distribution of EPIC. Conversion of the masking oxide layer to an equivalent thickness of silicon using the LSS data of projected standard deviation in (4.12), or range in (4.13), does not adequately model the stopping power of SiU<sub>2</sub> for As implantation. In the present work, LSS statistics for an energy of 80 keV predict a

E.

- 49 -

- 50 -

Figure 4.4 : ARSENIC SOURCE/DRAIN IMPLANT

51 -

I.

greater stopping power than is experimentally observed. The same effect is evident in the work of Hirao et al /86/ who present SIMS results for 180 keV As implants, but do not consider any model for the stopping of As in  $SiO_2$ . Table 4.1 summarises the results using equations (4.12) and (4.13) for both energies.

| As implant<br>energy (keV) | d <sub>1</sub> (Å) | d (Å)<br>eq.(4.12) | d (Å)<br>eq.(4.13) | d <sup>*</sup> (Å)<br>exper-<br>imental |

|----------------------------|--------------------|--------------------|--------------------|-----------------------------------------|

| 80                         | 705                | 970                | 869                | 530                                     |

| 180                        | 970                | 1318               | 1185               | 955                                     |

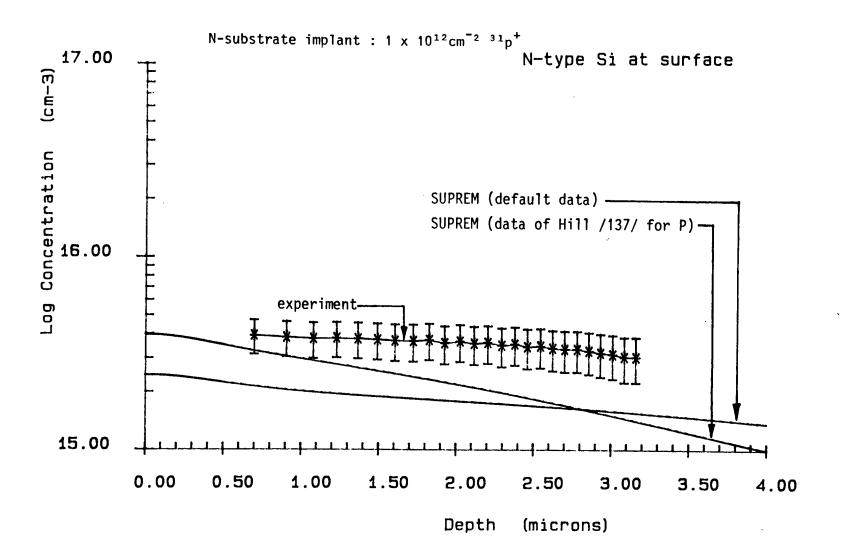

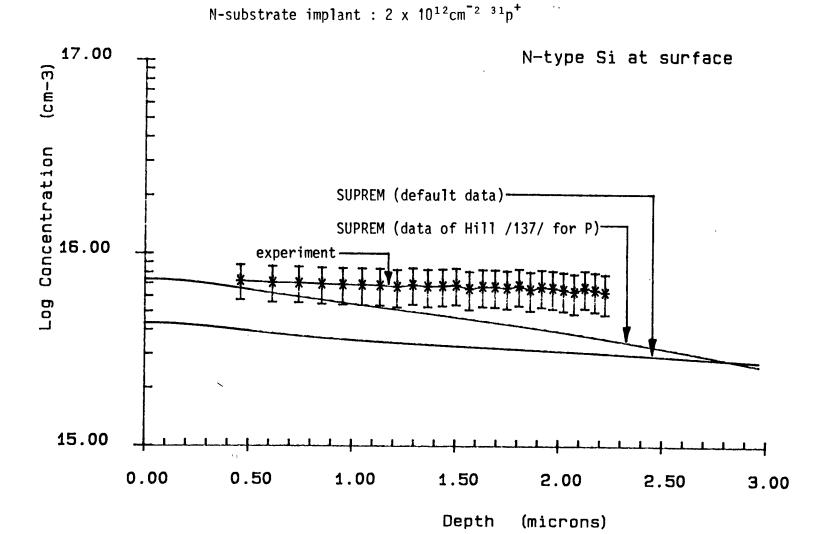

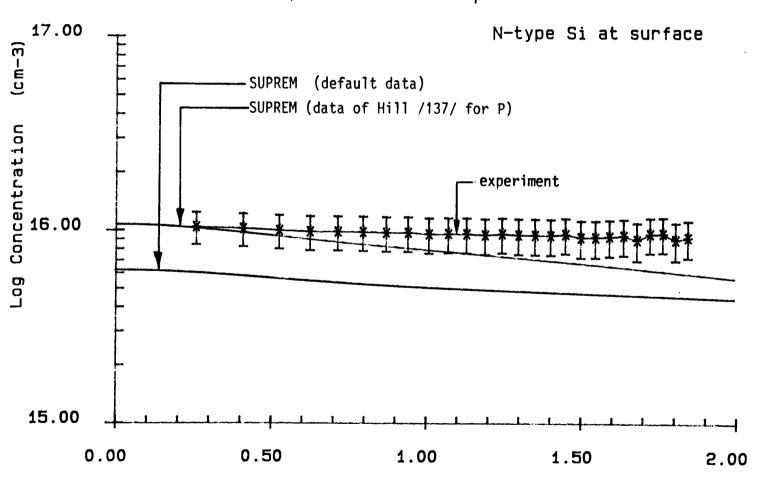

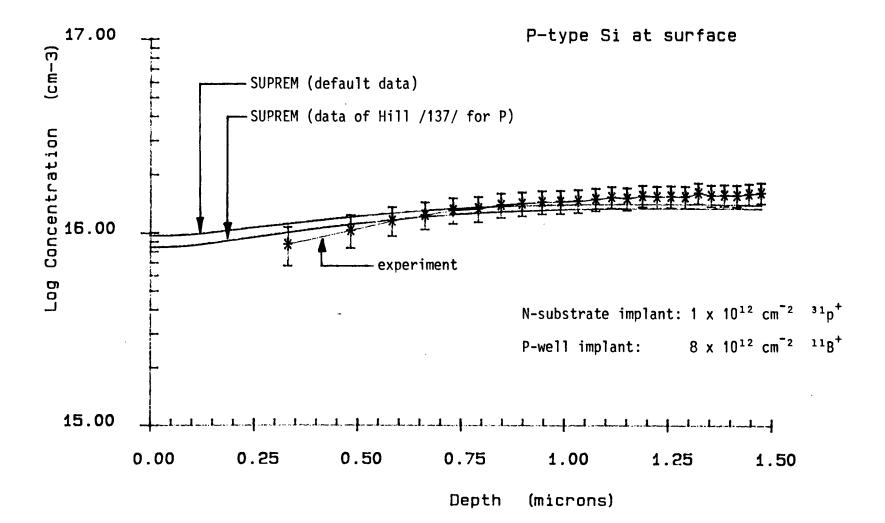

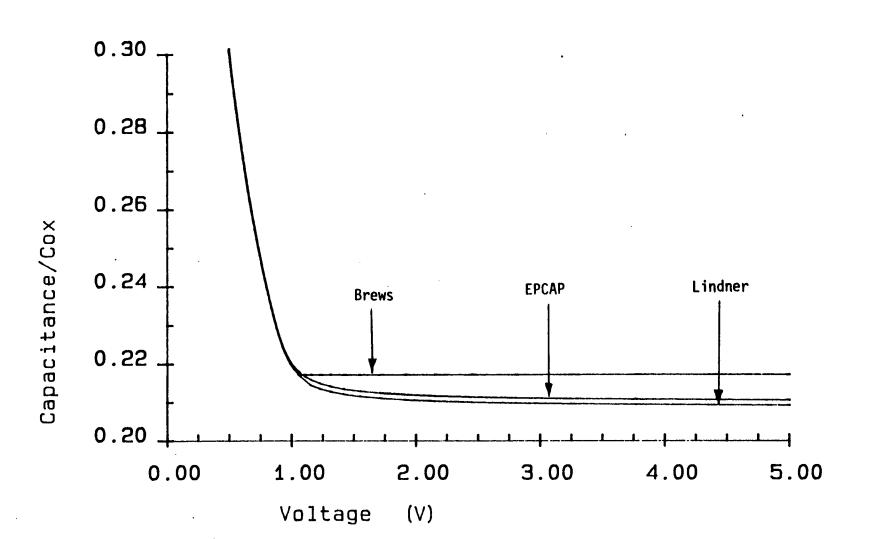

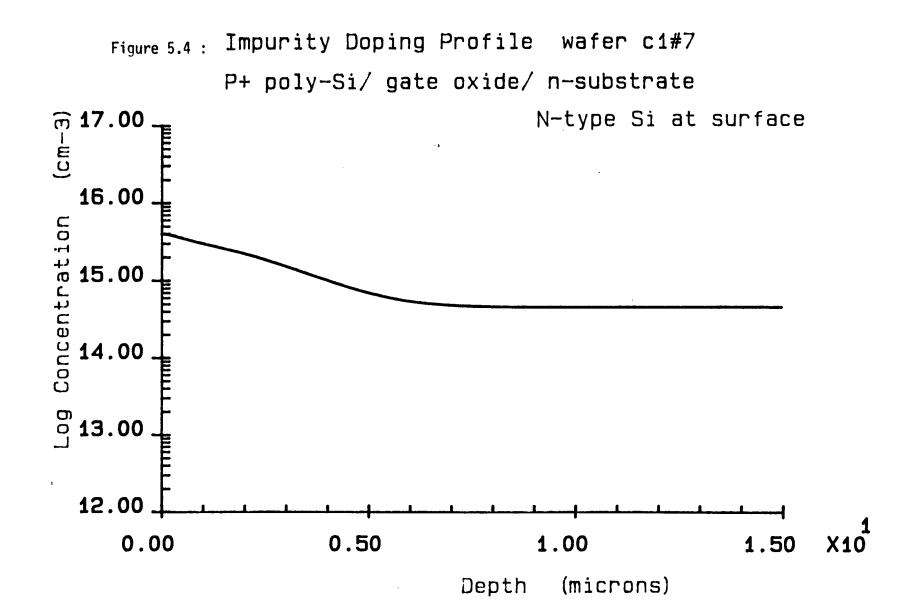

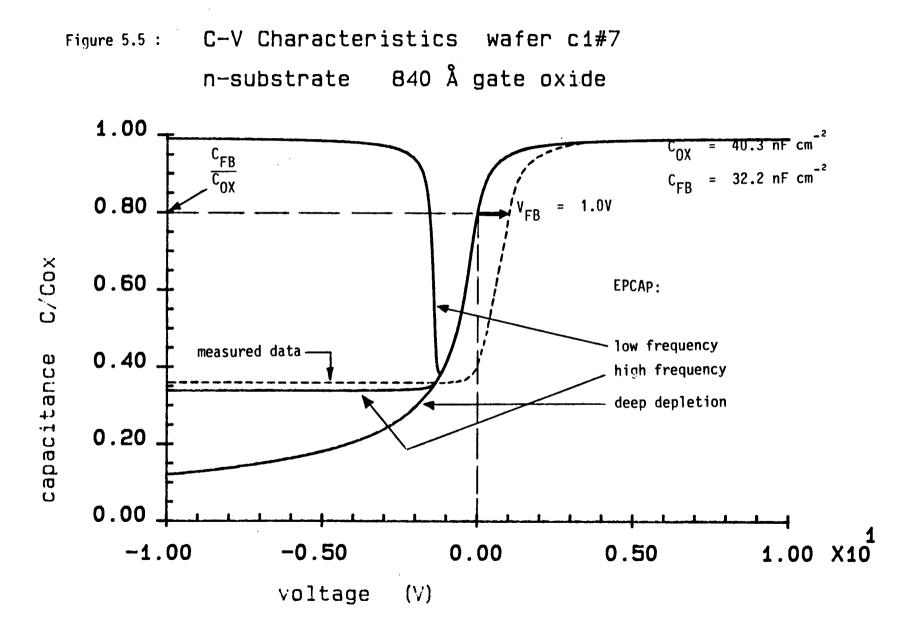

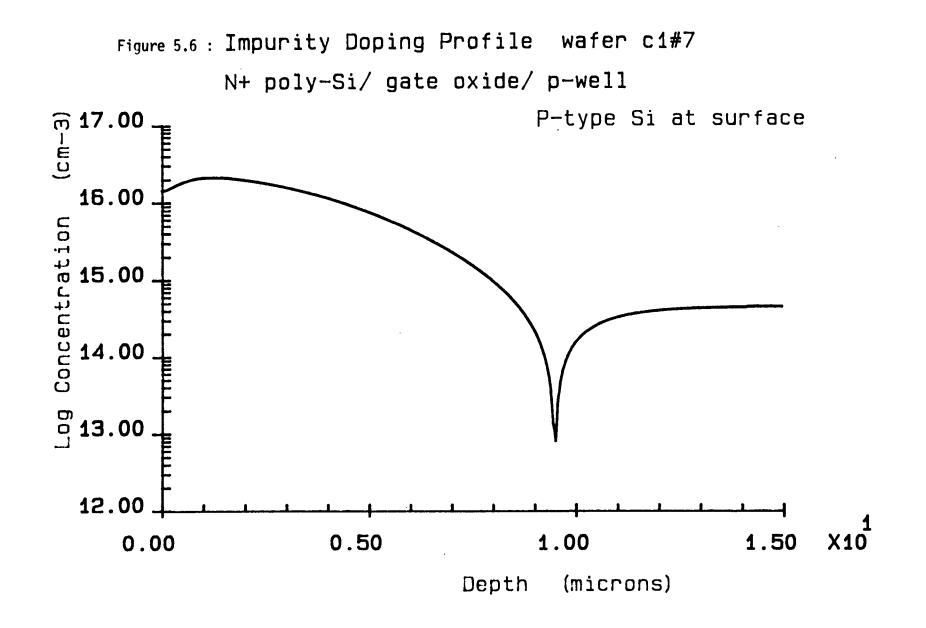

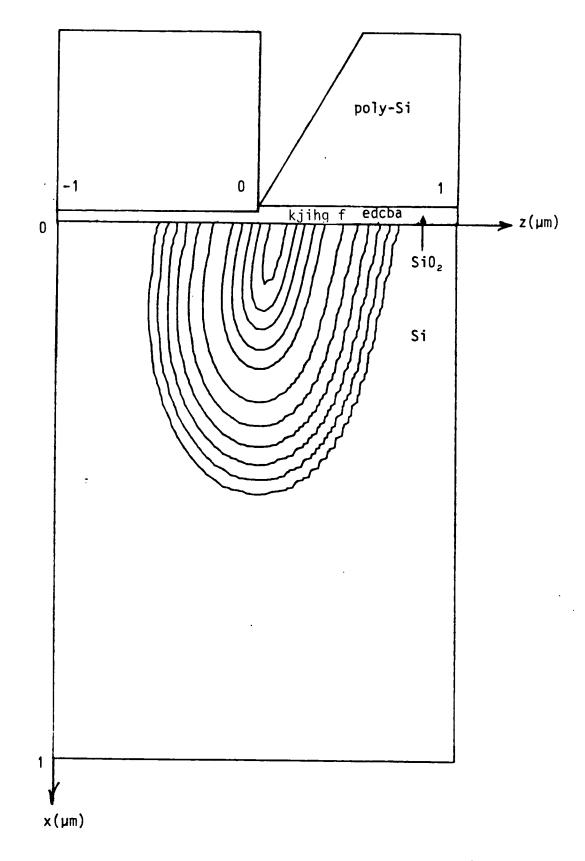

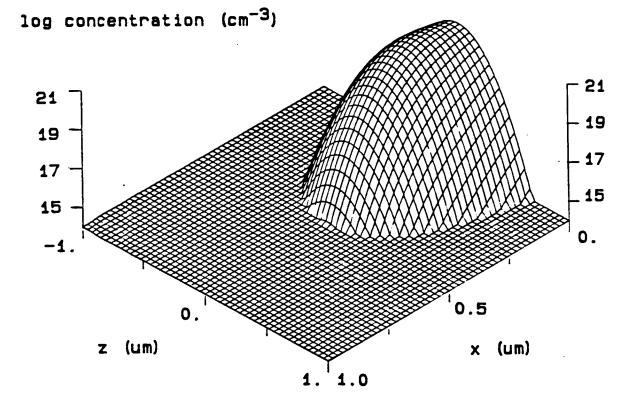

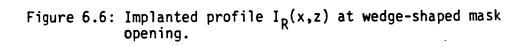

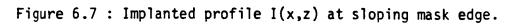

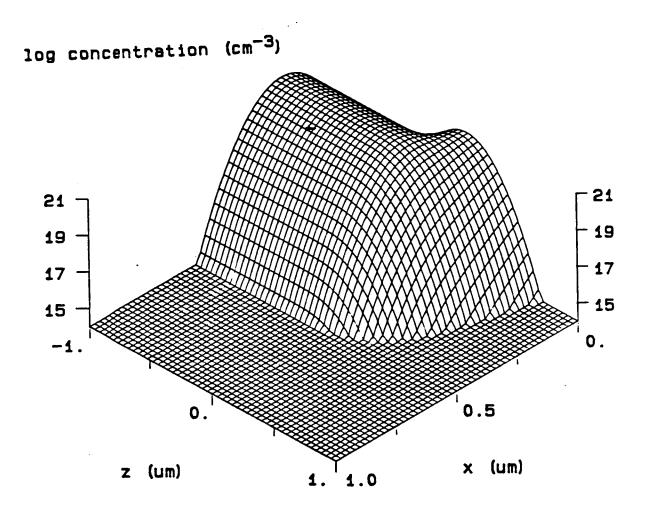

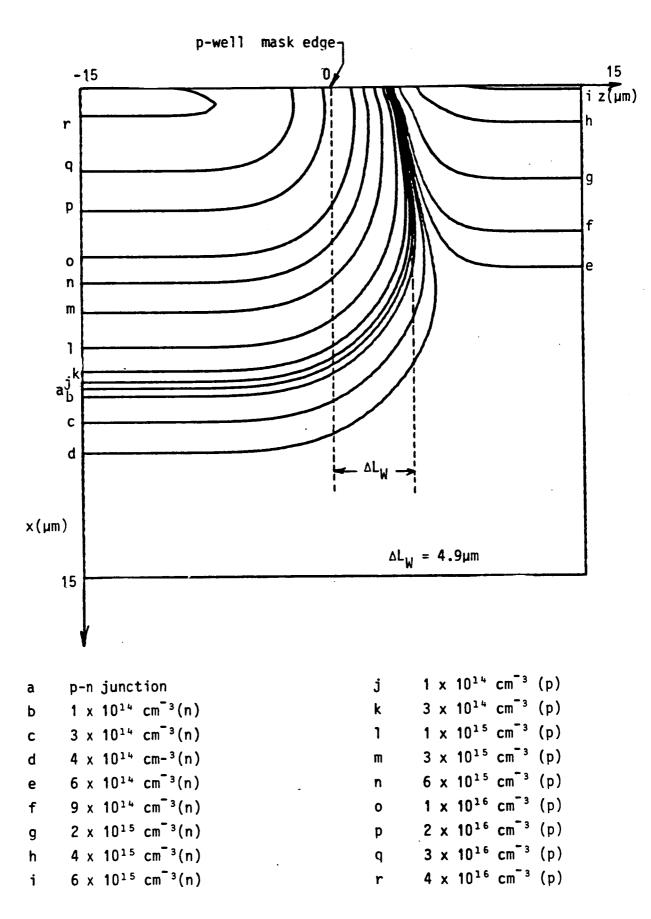

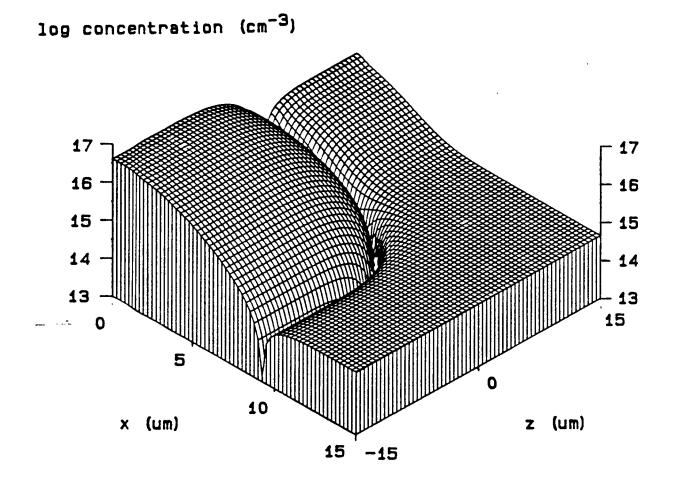

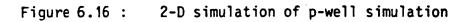

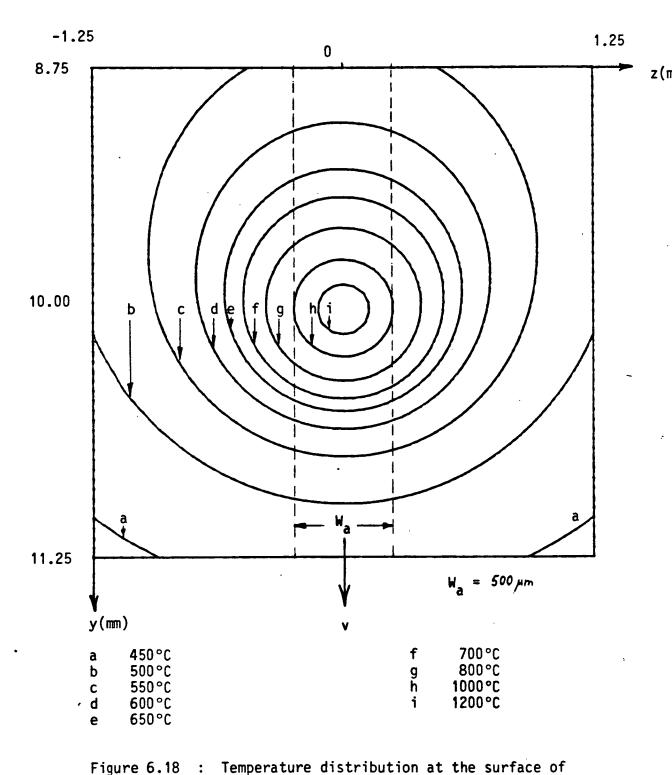

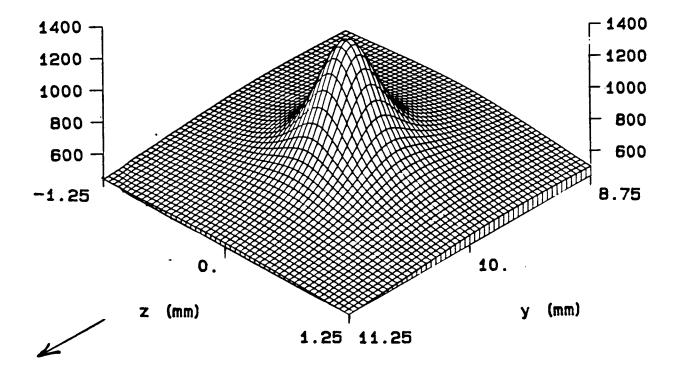

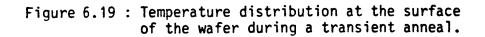

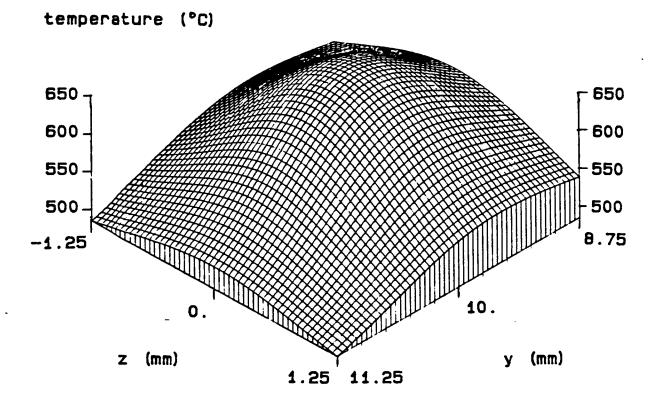

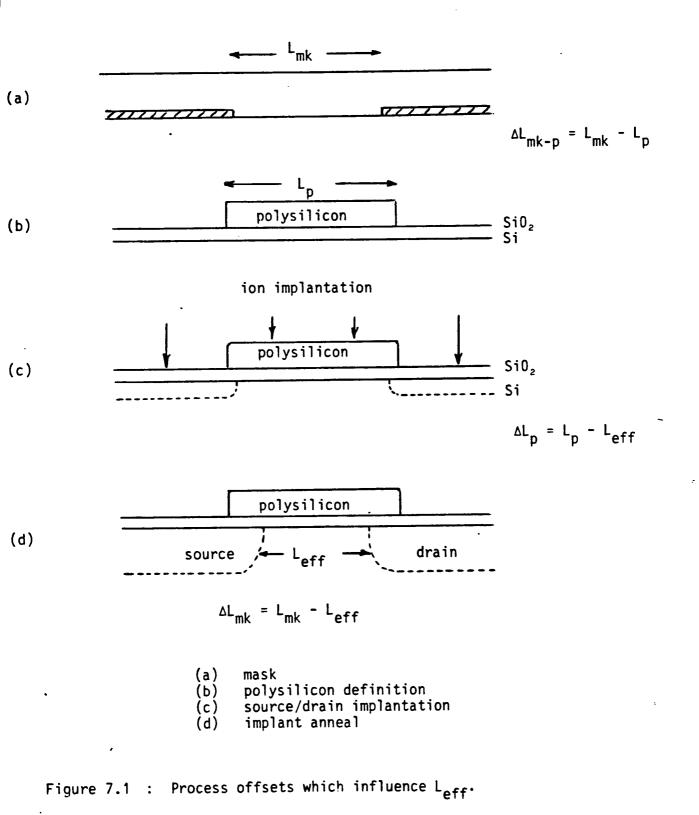

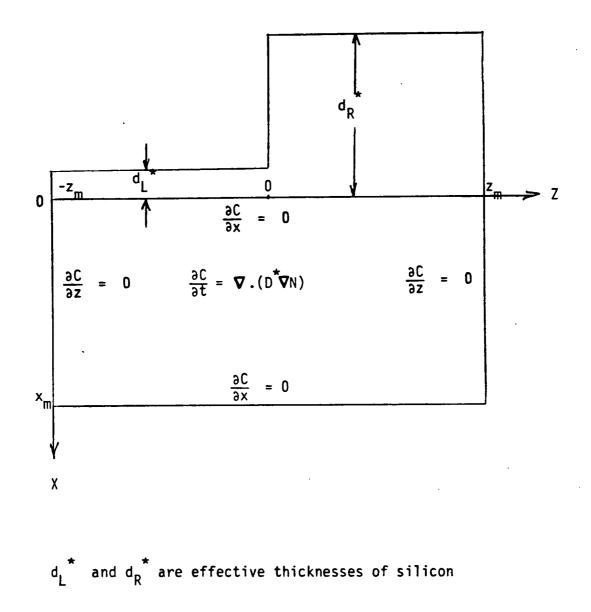

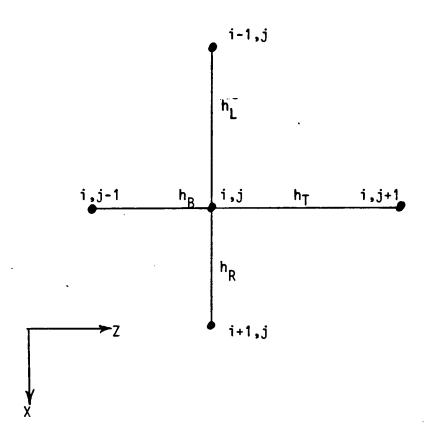

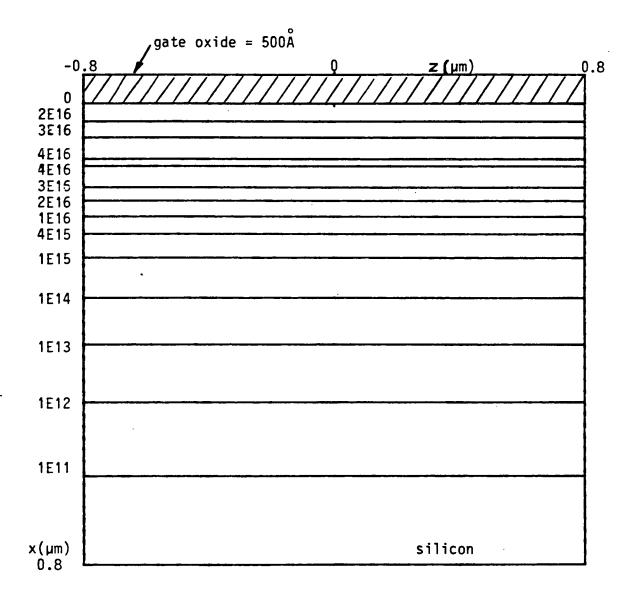

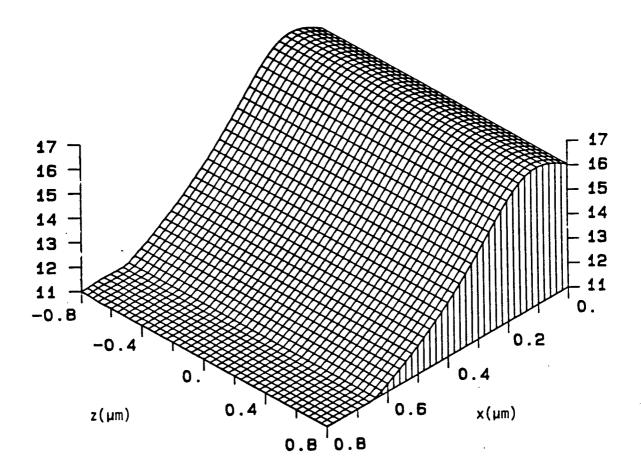

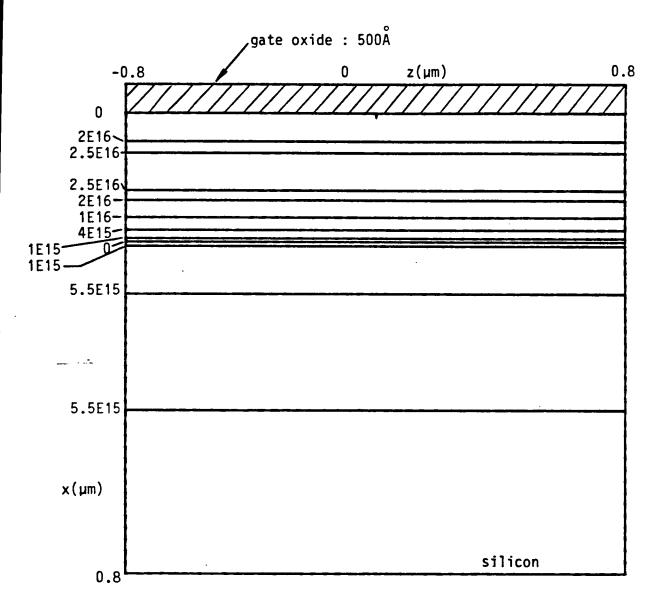

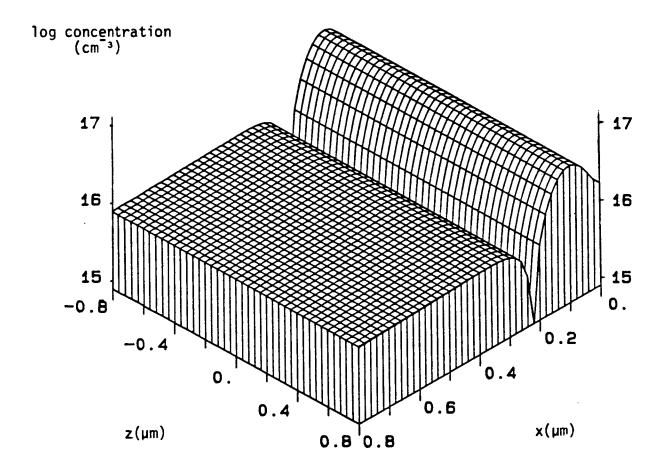

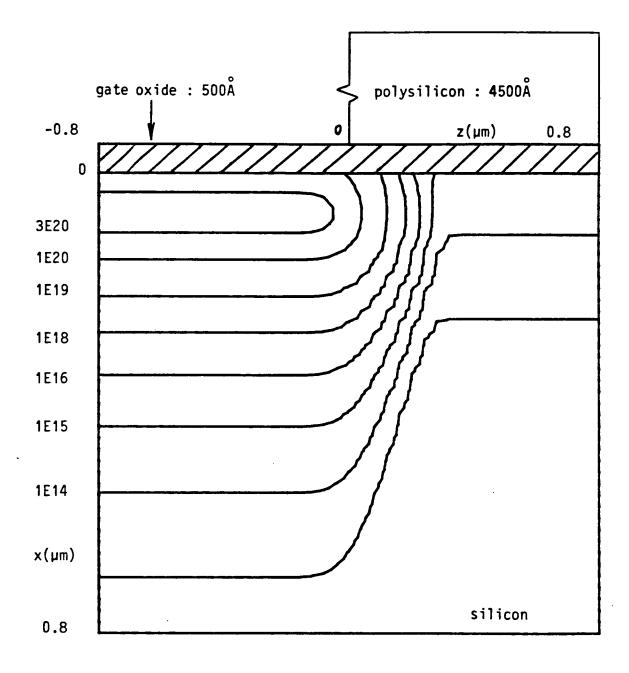

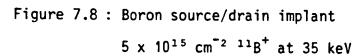

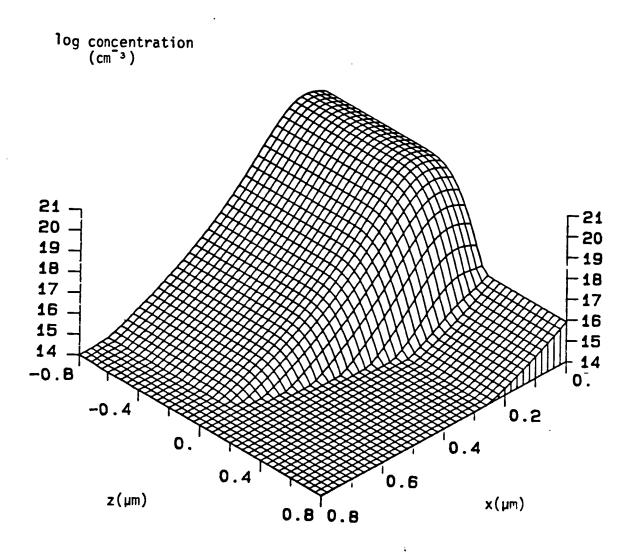

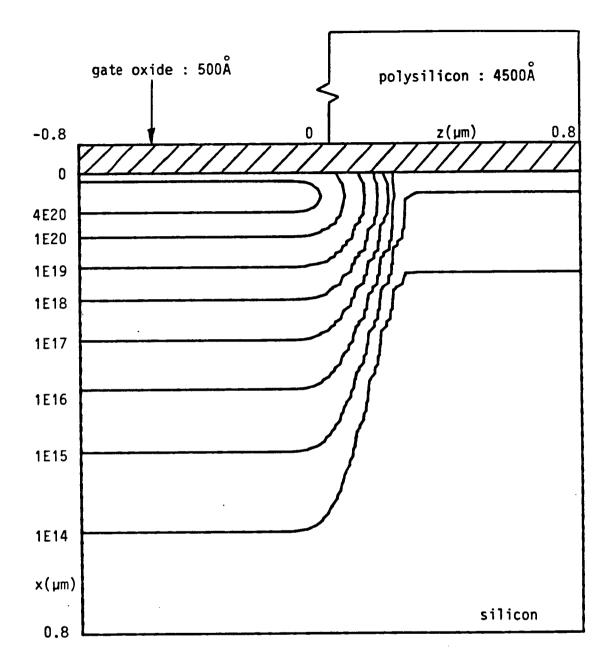

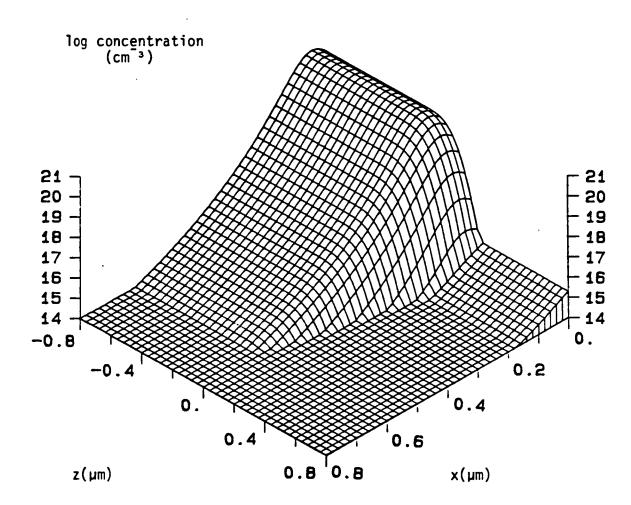

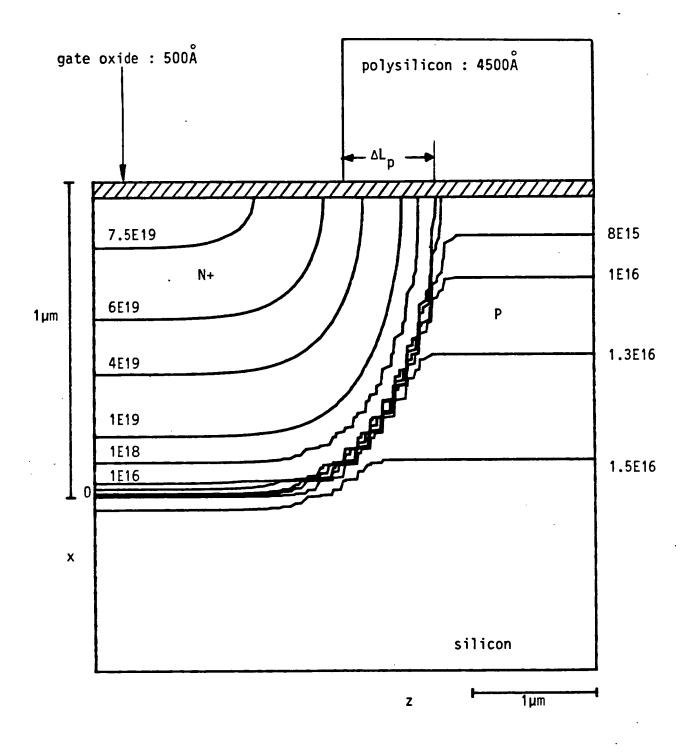

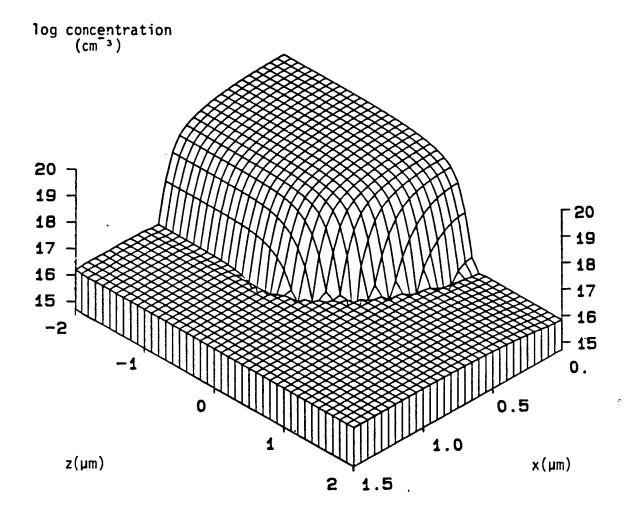

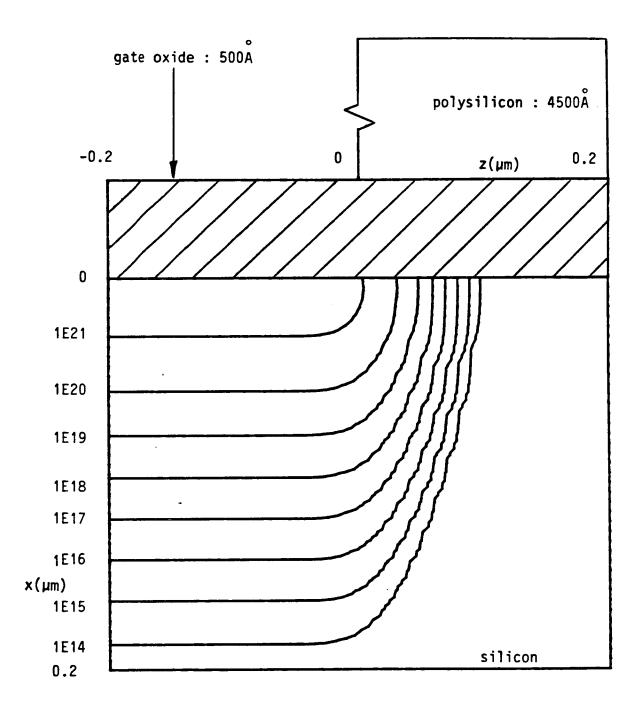

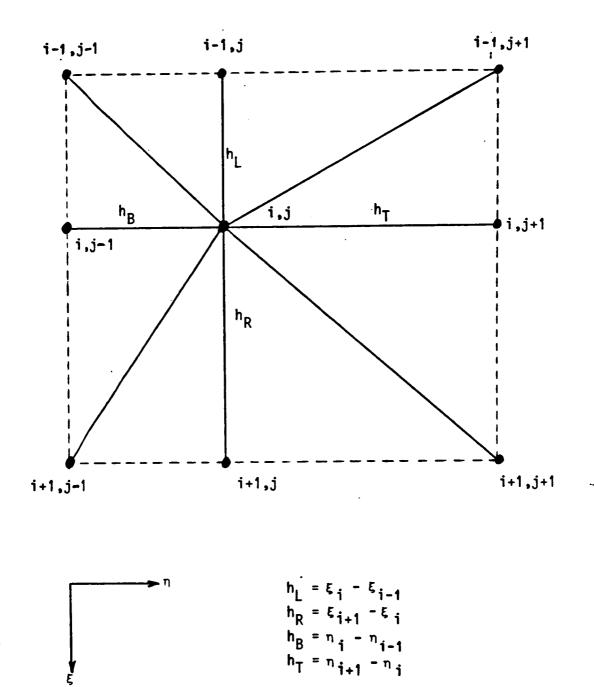

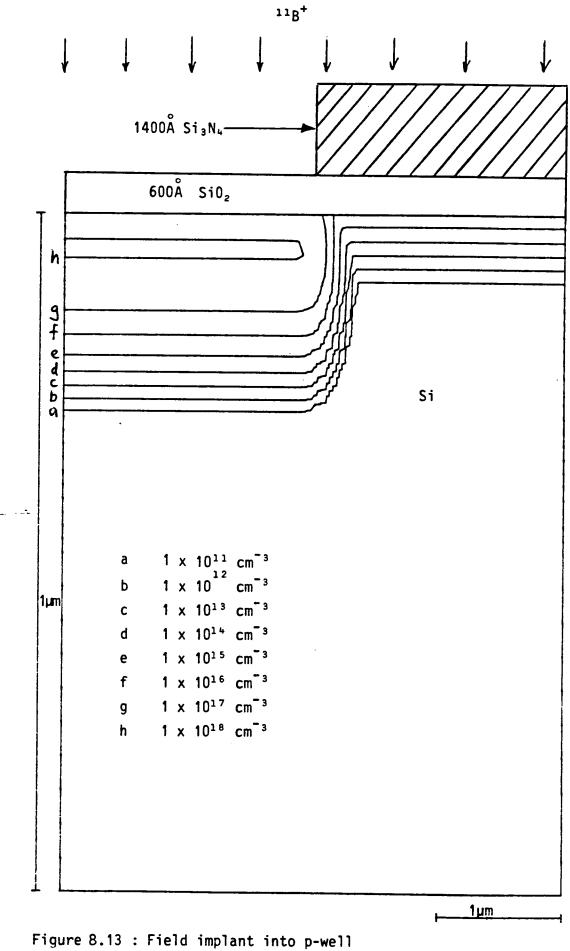

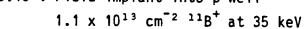

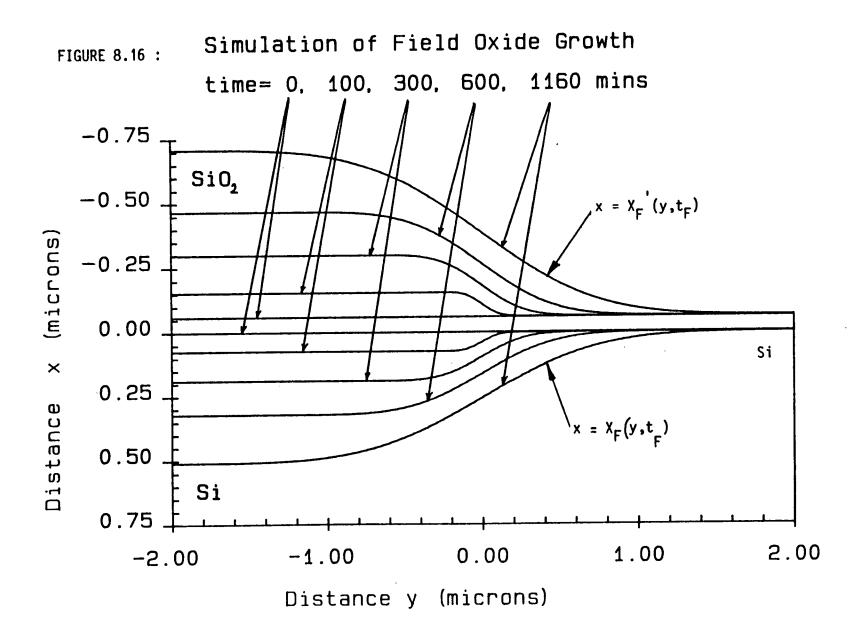

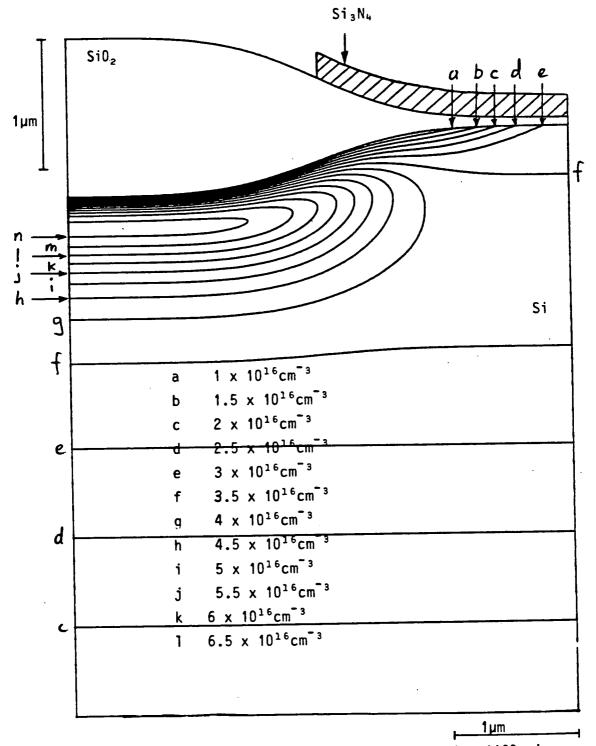

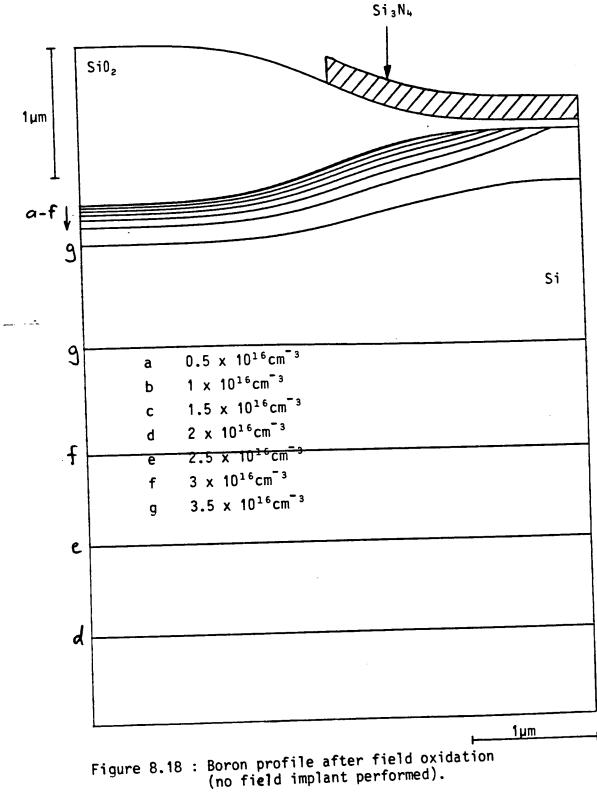

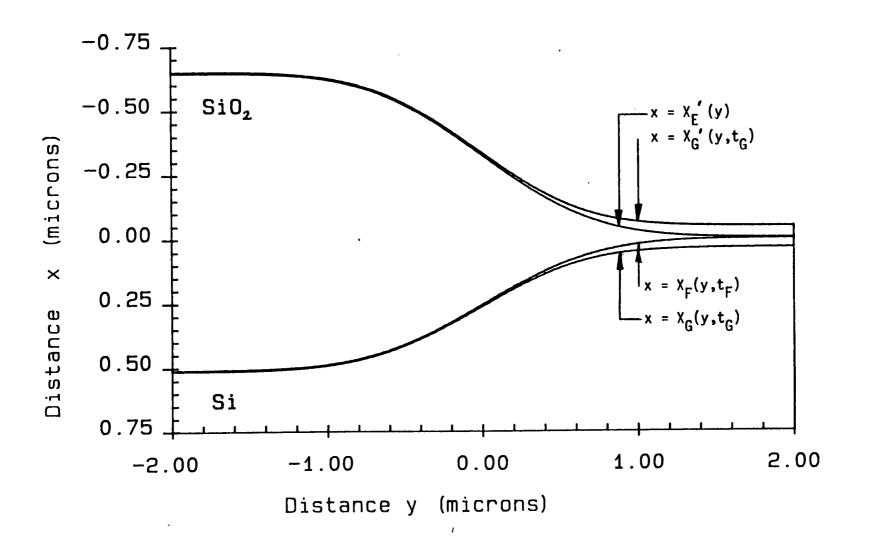

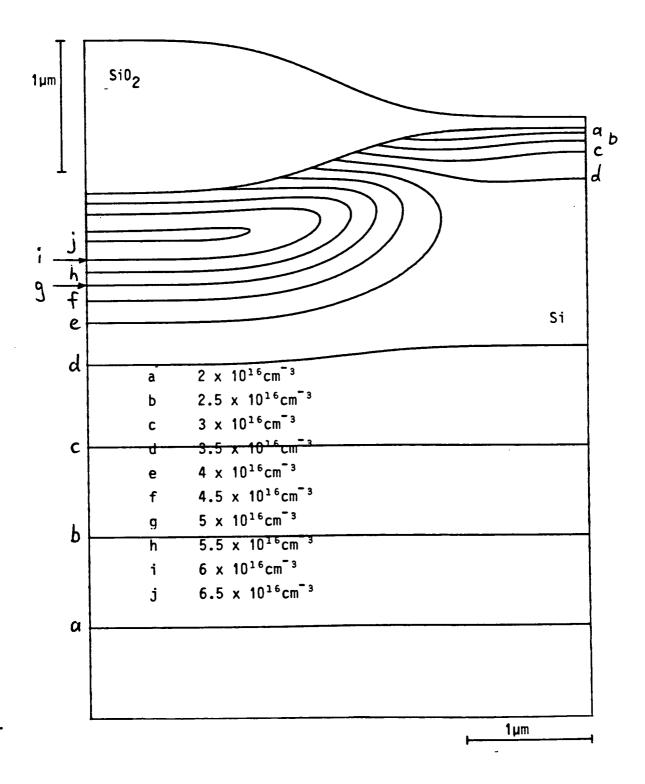

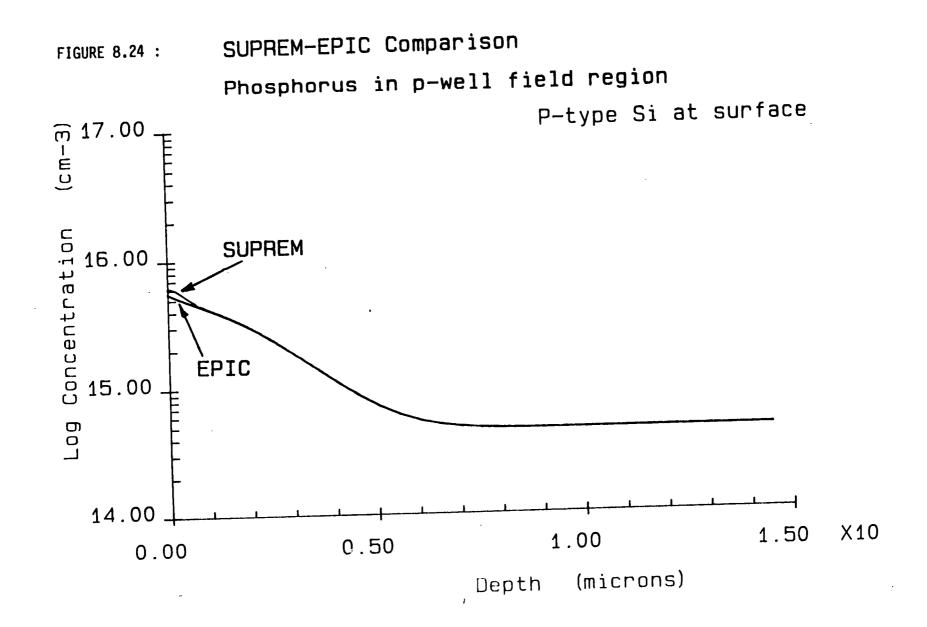

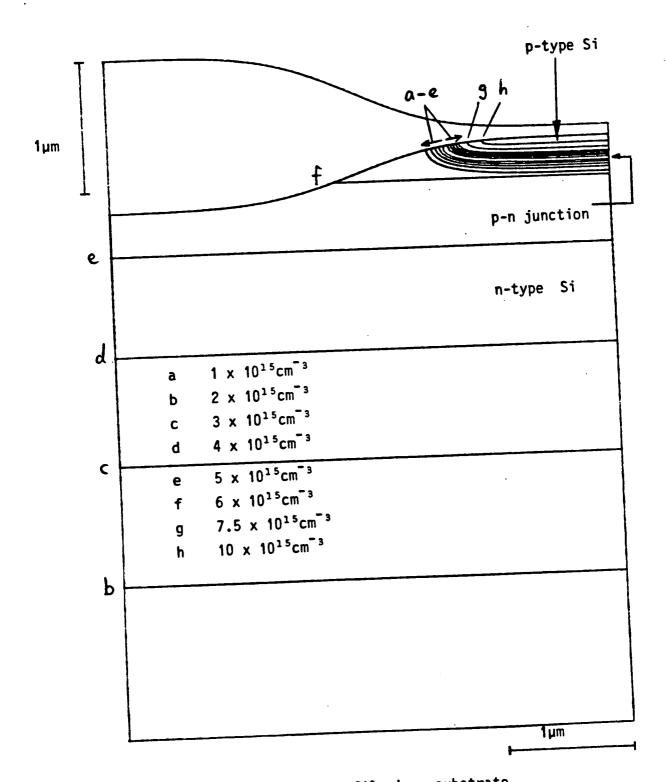

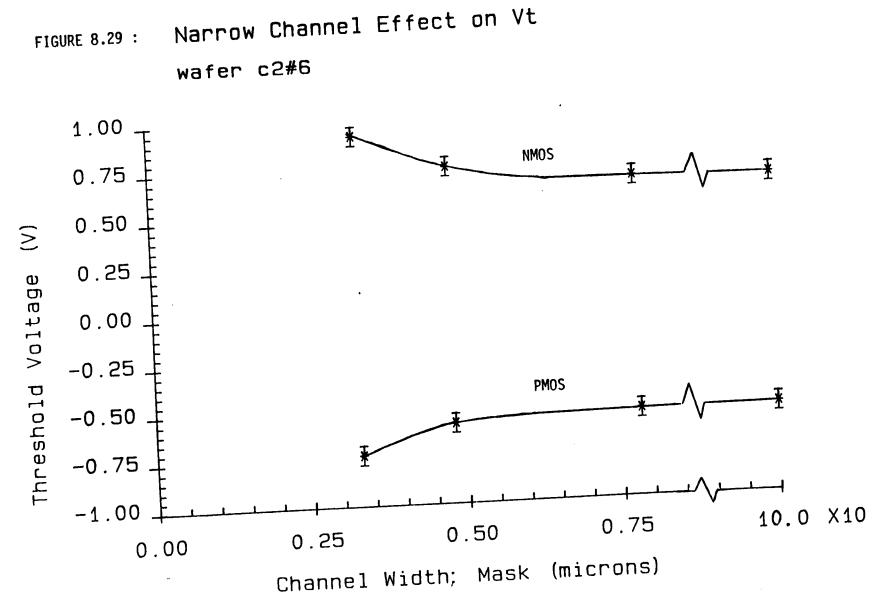

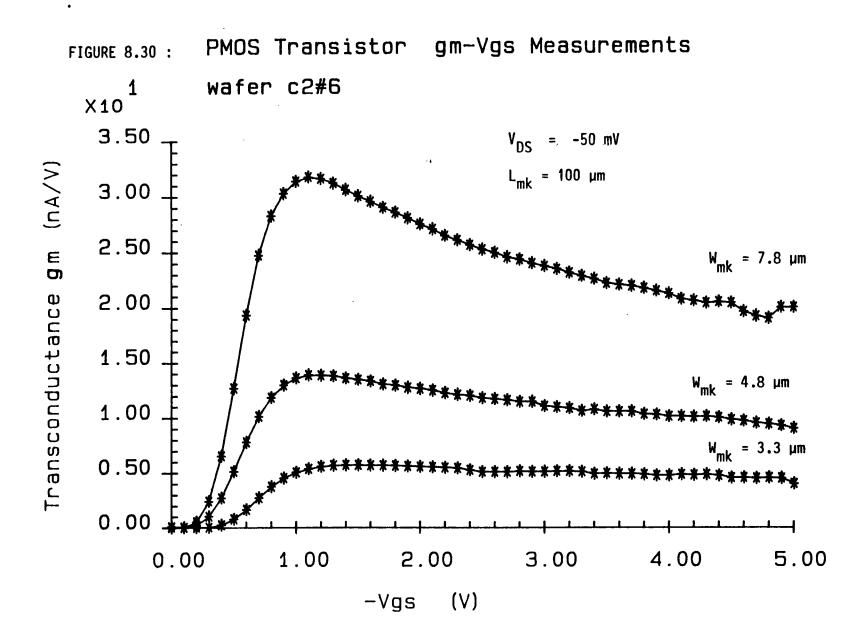

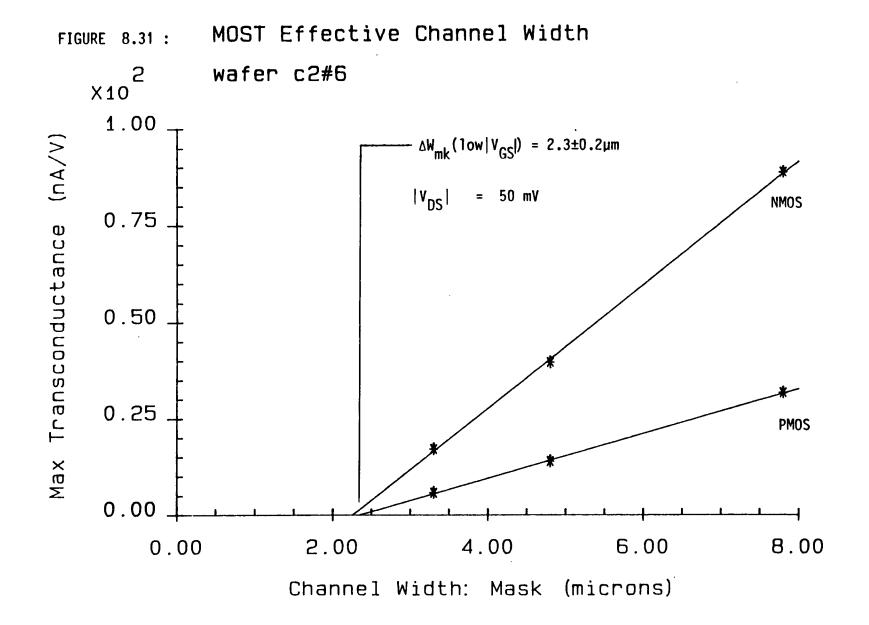

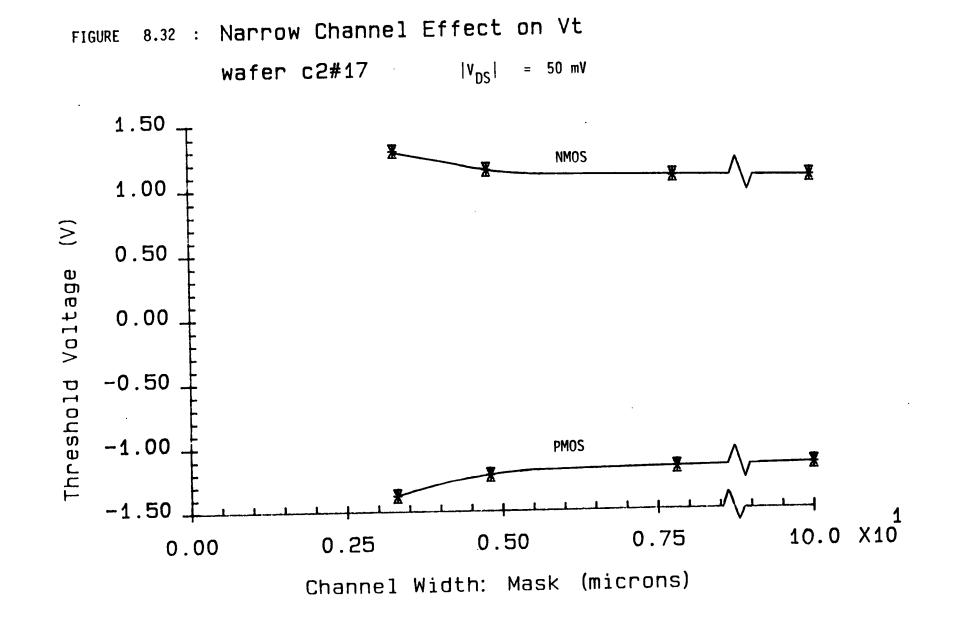

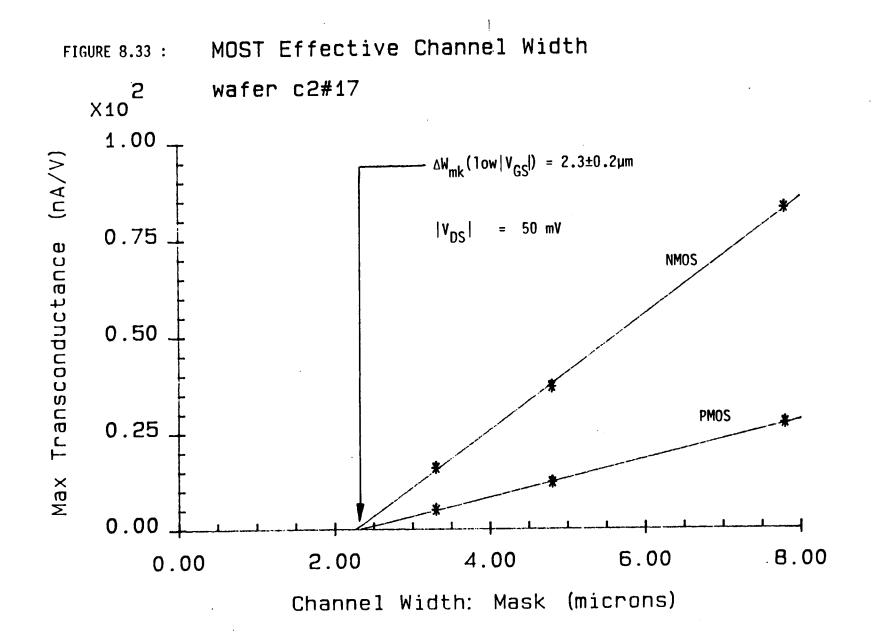

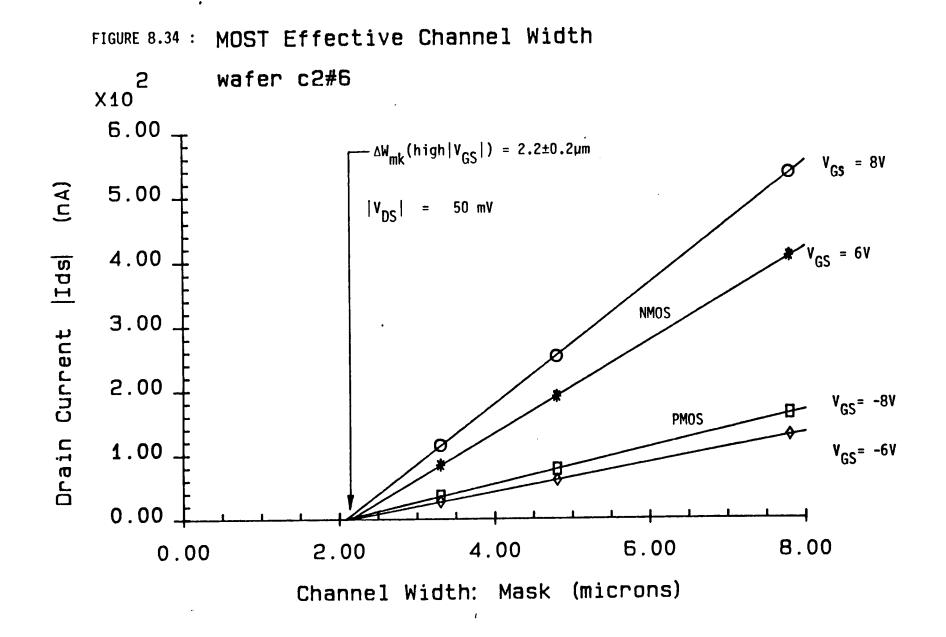

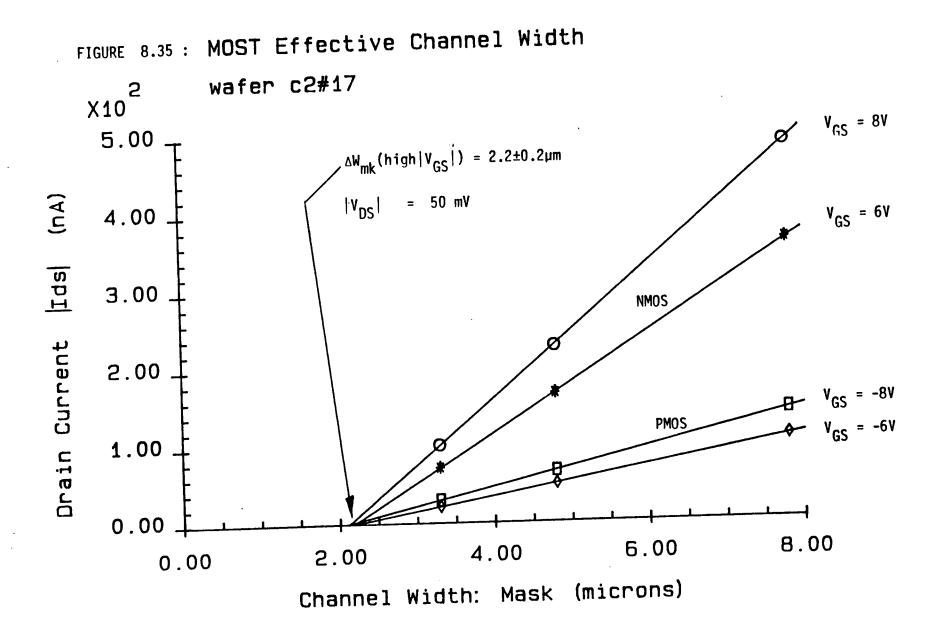

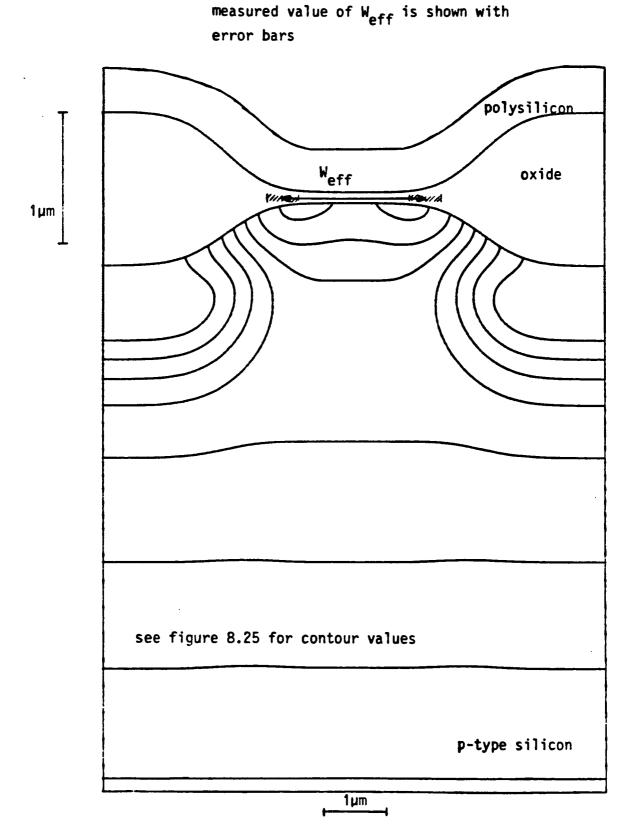

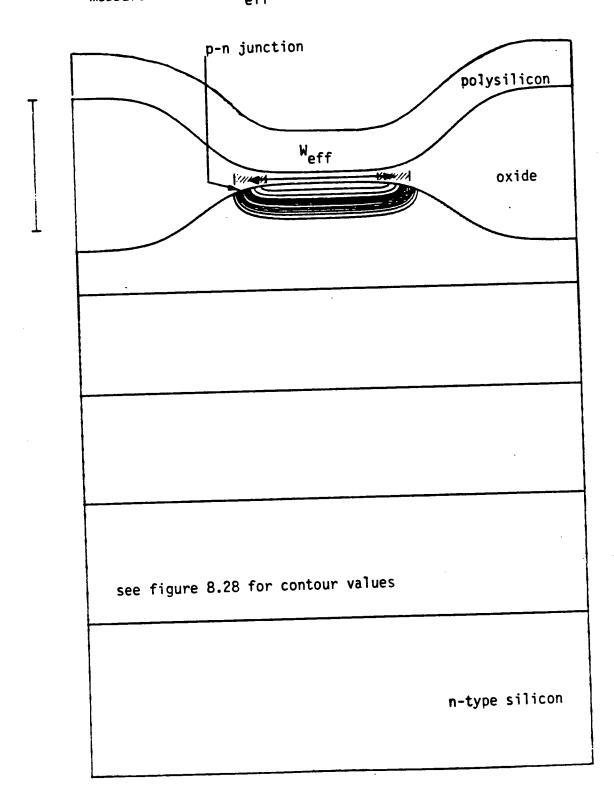

Table 4.1 : <u>Comparison of modelled and experimental equivalent thicknesses</u> of Si for As implanted at two different energies