## Achieving Parallel Performance in Scientific Computations

Lyndon J. Clarke

Submitted for the degree of Doctor of Philosophy

University of Edinburgh September 1990

## Declaration

This thesis has been composed entirely by myself.

The work reported in Section 2.4 (Deadlock Avoidance) was performed in collaboration with Michael G. Norman and with some assistance from Dominic M.N. Prior. All other work reported herein is my own, except where otherwise stated.

#### Lyndon J. Clarke

#### Acknowledgements

I should like to express my gratitude to Professor D. J. Wallace, Professor R. A. Cowley, Doctor R. D. Kenway and Doctor Alastair D. Bruce for academic and practical guidance given during my postgraduate study. Thanks are also due to all of my colleagues, past and present, in the University for helpful discussions, assistance in the use of various computer systems and advice freely given in the preparation of this thesis.

I should like to acknowledge the award of a Science and Engineering Research Council grant and the financial support of the Edinburgh Parallel Computing Centre, formerly the Edinburgh Concurrent Supercomputer Project.

Finally I am indebted to my parents and grandmother for financial assistance, and to Rachael for patience and moral support.

#### Abstract

The exploitation of high performance computing will be a major factor in the future advancement of science as computational methods are increasingly becoming a third discipline alongside theory and experiment. Despite advances which are being made in VLSI technology, enabling the *construction* of faster uniprocessor machines, it is now widely recognised that the future of high performance computing will be dominated by parallel architectures. It is of prime importance that the scientific community is able to effectively program such machines.

In the case of distributed memory MIMD architectures support is required for arbitrary communications between processing entities located at different processors, and operating on data stored in different memory units. If a message routing facility is not available in hardware it is necessary to provide a software implementation. Where this facility is available in hardware then a layer of software is required which presents the programmer with an interface to this hardware.

This thesis discusses a number of issues which arise in the implementation of message routing systems and the application interface. We have constructed such a system for use on arrays of INMOS transputers, called TINY, and the methods used in the implementation of this software are described. The system shares processor time with the application and we demonstrate that the processor bandwidth required by TINY is very small.

We have selected a concrete, but simple, application which utilises the services provided by this system. The implementation of this application was considerably simplified by the use of TINY and we show that the overheads induced by this software layer are insignificant. The application selected performs rendering of space filling molecular models, reflecting the growing importance of visualisation in science.

## Contents

1 Prologue

| 2 | Des | ign    |                      | 14 |

|---|-----|--------|----------------------|----|

|   | 2.1 | Introd | luction              | 14 |

|   | 2.2 | Syster | m Overview           | 16 |

|   |     | 2.2.1  | Communication Models | 17 |

|   |     | 2.2.2  | Transport Interface  | 18 |

|   |     | 2.2.3  | Network Interface    | 28 |

|   | 2.3 | Transı | port Layer           | 30 |

|   |     | 2.3.1  | Asynchronous Models  | 31 |

|   |     | 2.3.2  | Synchronous Models   | 32 |

|   | 2.4 | Netwo  | rk Layer             | 34 |

|   |     | 2.4.1  | Switching Techniques | 34 |

|   |     | 2.4.2  | Routing Functions    | 40 |

|   |     | 2.4.3 Deadlock Avoidance | 4 |

|---|-----|--------------------------|---|

|   |     | 2.4.4 Acyclic Routing    | 9 |

|   | 2.5 | Summary                  | 5 |

| 3 | Imp | olementation 6           | 7 |

|   | 3.1 | Introduction             | 7 |

|   | 3.2 | Overview                 | 8 |

|   | 3.3 | Topology Exploration     | 4 |

|   | 3.4 | Routing Function         | 1 |

|   |     | 3.4.1 Cyclic Routing     | 3 |

|   |     | 3.4.2 Acyclic Routing    | 4 |

|   |     | 3.4.3 Simulations        | 7 |

|   | 3.5 | Message Passing          | 0 |

| ` |     | 3.5.1 Simple Prototype   | 0 |

|   |     | 3.5.2 Improved Prototype | 0 |

|   |     | 3.5.3 Performance        | 2 |

|   | 3.6 | Summary                  | 3 |

| 4 | Арр | Dication 120             | ) |

|   | 4.1 | Introduction             | ) |

| 4.2 | Sequential Algorithm | 122 |

|-----|----------------------|-----|

| 4.3 | Parallel Adaption    | 126 |

| 4.4 | Summary              | 137 |

## 5 Epilogue

140

. •

# List of Figures

| 2.1  | A three layer model                              | 16 |

|------|--------------------------------------------------|----|

| 2.2  | Routing in a binary tree                         | 45 |

| 2.3  | Routing in a 2 dimensional grid                  | 46 |

| 2.4  | Routing in a Ring                                | 47 |

| 2.5  | Processors, Links and Connects                   | 51 |

| 2.6  | Valid Colouring of the Tetrahedron               | 56 |

| 2.7  | Satisfied Connects of the Tetrahedron            | 58 |

| 2.8  | Algorithm for Trivial Solution of Colouring      | 60 |

| 2.9  | Non-trivial Colouring of a Grid                  | 60 |

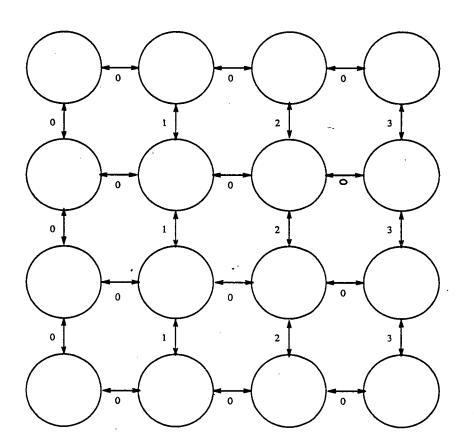

| 2.10 | Trivial Colouring of a Grid                      | 62 |

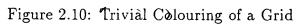

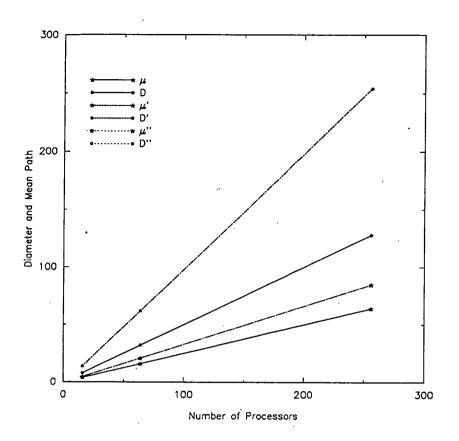

| 2.11 | Evaluation of Trivial Colouring of Rings         | 63 |

| 2.12 | Evaluation of Trivial Colouring of Tori          | 64 |

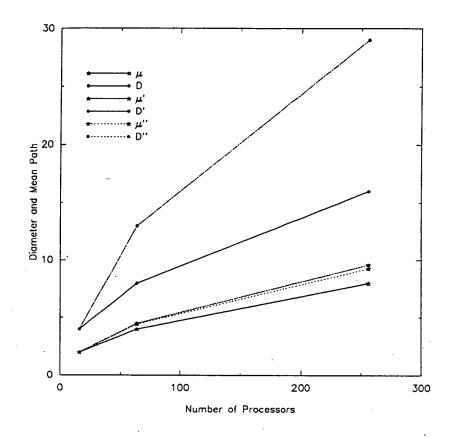

| 2.13 | Evaluation of Trivial Colouring of Random Graphs | 65 |

^

| 3.1  | A Simple Transport Layer Interface | 73  |

|------|------------------------------------|-----|

| 3.2  | Worm Algorithm                     | 75  |

| 3.3  | Probee Algorithm 7                 | 76  |

| 3.4  | Prober Algorithm                   | 77  |

| 3.5  | Buffer Process                     | 79  |

| 3.6  | Control Process                    | 80  |

| 3.7  | Flood Termination Condition        | 81  |

| 3.8  | Tree Labelling Algorithm           | 85  |

| 3.9  | Simple Router: Output process      | 92  |

| 3.10 | Simple Router: Sink process        | 93  |

| 3.11 | Simple Router: Input process       | 94  |

| 3.12 | Simple Router: Source process      | 95  |

| 3.13 | Simple Router: Directed routing    | 96  |

| 3.14 | Simple Router: Broadcast routing   | 97  |

| 3.15 | Improved Router: Data Structures   | 102 |

| 3.16 | Improved Router: Output Process    | 106 |

| 3.17 | Improved Router: Sink Process      | 107 |

| 3.18 | Improved Router: Input Process     | 108 |

| 3.19 | Improved Router: Source Process    | 109 |

| 3.20 | Improved Router: Queue Handling      | 110 |

|------|--------------------------------------|-----|

| 3.21 | Improved Router: Directed Routing    | 111 |

| 3.22 | Improved Router: Broadcast Routing   | 112 |

| 3.23 | Improved Router: Exceptional Routing | 113 |

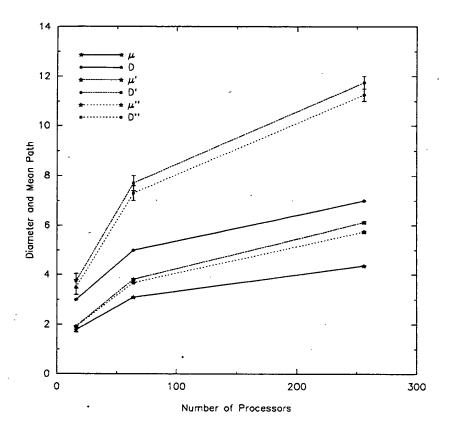

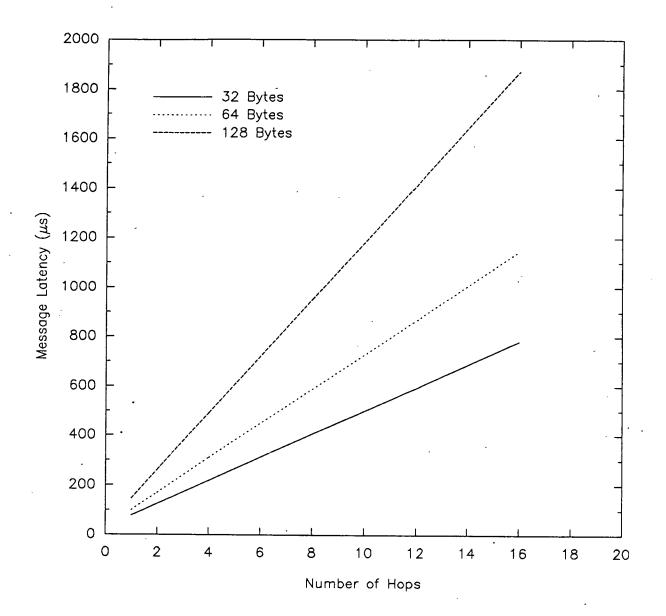

| 3.24 | Quiet Network Message Latency        | 115 |

| 4.1  | Calculation of Impingement           | 125 |

| 4.2  | Schema of Algorithm                  | 127 |

| 4.3  | Regular Domain Decomposition         | 130 |

| 4.4  | Schema of Parallel Algorithm         | 136 |

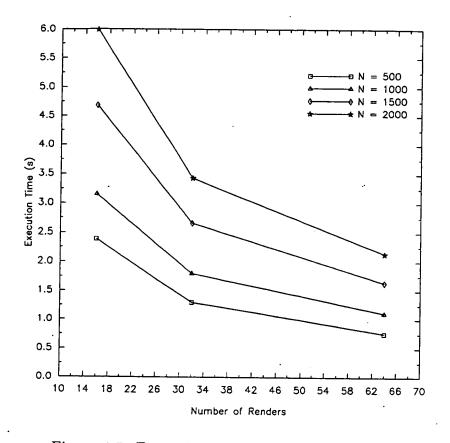

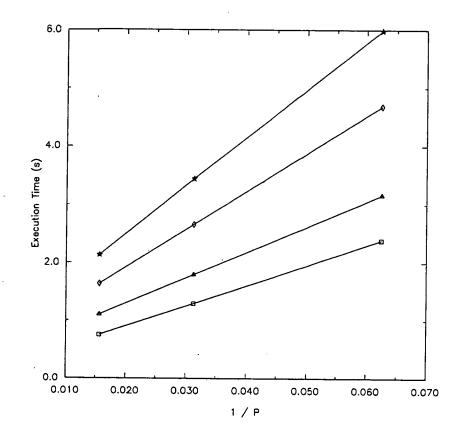

| 4.5  | Execution Time of Parallel Program   | 137 |

| 4.6  | Scaling Behaviour of Execution Time  | 138 |

## List of Tables

| 2.1 | Feature Identification in Connectionless Switching         | 39 |

|-----|------------------------------------------------------------|----|

| 3.1 | Evaluation of Acyclic Routing in Double Rings              | 89 |

| 3.2 | Evaluation of Acyclic Routing in Square Tori               | 89 |

| 3.3 | Evaluation of Acyclic Routing in Random Hamiltonian Graphs | 90 |

| 3.4 | Quiet Network Latency in TINY 1                            | 15 |

| 3.5 | Quiet Network Latency in the iPSC/2 1                      | 16 |

| 3.6 | Comparision of Neighbour Message Latencies                 | 17 |

| 3.7 | Parameters of Through Routing CPU Impact                   | 18 |

| 4.1 | Characterisation of Sequential Components                  | 28 |

| 4.2 |                                                            |    |

## Chapter 1

## Prologue

Parallel computers have now been in use by the scientific computing community in Edinburgh University for approximately a decade. During the past five years I have personally undertaken a number of applications in both SIMD (represented by the ICL-DAP) and distributed memory MIMD (represented by the MEIKO Computing Surface) architectures. The motivation for use of such machines is, of course, the possibility of solving physical problems which were previously intractable due to excessive execution times on conventional sequential machines, by exploiting parallel performance.

Calculations performed using the ICL-DAP have mainly featured the investigation of phase transition behaviour in simple spin models. In two specific calculations non-universal critical behaviour over a line of continuous transitions in the spin- $\frac{1}{2}$  Ising model [LB85] with first and second neighbour interactions, and tricritical behaviour in the spin-1 model with a quadratic spin self energy term [LS86], were studied extensively. The object of these studies was to utilise calculations of the free energy surface in coupling space in order to extract information about the relevant and marginal scaling fields. The computational core of these calculations is the Monte Carlo update of spin values for which the DAP is exceptionally well suited due to the large array of bit serial processors. In each case it proved very difficult to obtain data of sufficient statistical quality for the analysis proposed.

The MEIKO Computing Surface was used to investigate the behaviour of the two di-

mension Hubbard model which was thought to be relevant to the existence of high temperature superconductivity in ceramic oxides. The simulation technique employed was the Hybrid Monte Carlo algorithm [DKPR87]. The computational core of this method is the inversion of a large sparse matrix which we choose to perform using the conjugate gradients method; a suitable preconditioning matrix for this calculation is known. It was found to be very difficult to develop a program which executed rapidly enough to be of use in production calculations. Each conjugate gradient iteration requires (at least) two global summations to be performed and the associated matrix vector multiplication requires a relatively straightforward nearest neighbour exchange of edge data in the regular domain decomposition. The performance barrier was the fact that the communication overheads and corresponding performance degradation associated with these operations, particularly the global summation, precluded the use of large processor arrays.

It is uniformly observed that the effective programming of parallel computers has been considerably more difficult than conventional sequential programming. This has been especially true in the MIMD case where there is far greater freedom in machine architecture and programming methodology, and generally poorer support for the application programmer.

These machines have almost exclusively been programmed in the so-called "explicit message passing" paradigm, in which the programmer is responsible for coding data transfer between concurrently executing processing entities. The implementation of communication has often been the most difficult problem experienced by scientific programmers faced with an algorithm and such a computer.

Where the communication structure of the algorithm requires communication between entities which cannot be located on the same or neighbouring processors then it has been necessary to write message routing code for each application. Such software is notoriously difficult to code correctly, worse to debug, and was often very inefficient. This is unfortunate since the communication overheads associated with the parallel adaption of algorithms play a large part in controlling the parallel performance which may be achieved [Fox89].

I was convinced that this scenario was unnecessary since general purpose message

routing software could be written. Such an approach has the added advantage that time can be taken to ensure that the general purpose software is both correct and efficient. The bulk of this thesis describes work I have performed in expediting this approach.

In Chapter 2 issues arising in the design of a general purpose communication system are discussed. The chapter divides the problem into two major components; the application interface and message through routing. The division is facilitated by decomposing the system into two logical layers by analogy with the treatment of communication systems in computer networks.

This work has lead to the construction of a communication system for multiprocessors composed of INMOS T800 transputers. The implementation of this system, which uses ideas discussed in the previous chapter, is described in Chapter 3. This system shares CPU with the application program and it is therefore of particular importance that the processing bandwidth consumed should be minimal. The techniques developed to meet this requirement are discussed in detail.

The communication system has been incorporated into a large number of applications. In Chapter 4 one of these applications, implemented by myself, in the field of molecular graphics is described. The effect of communication overheads on the parallel adaption of the algorithm are analysed, and based on data obtained in the previous chapter they are found to be negligible. The system also provides a platform on which software presenting the programmer with a higher level model of parallel programming can be implemented. Examples of such models are LINDA [Gel85] and FORTNET [AH89].

## Chapter 2

## Design

## 2.1 Introduction

The construction of computer networks has generated a great deal of expertise in communication systems [Tan89] which the multicomputer community could well hope to benefit from. Indeed there is superficially a close similarity between the requirements of the communication system in a computer network and a multicomputer; each must provide end-to-end connections between several users on many machines in a fashion independent of the hardware in use. There is, however, a fundamental difference between computer networks and multicomputers; in a computer network the users are human beings who typically run independent programs and communicate with one another rather infrequently whereas in a multicomputer the "users" are elements of a single program which probably communicate with one another very frequently.

This difference between a computer network and a multicomputer has a number of consequences for the behaviour and requirements of the users, and for the hardware involved, for example:

• The users of a computer network require access to mail facilities, text editors, sophisticated document preparation systems; the users of a multicomputer require access to a high performance processor.

- The users of a computer network will tolerate failure in parts of the network, they go for lunch; the users of a multicomputer cannot tolerate failure in parts of the computer, the program fails.

- The number, and location, of users in a computer network changes frequently; the placement of application processes in a multicomputer is, almost invariably, static.

- The hardware of a computer network can be found in different buildings, cities and even countries; the hardware of a computer is usually found in a small number of boxes, often just one, in the same room.

- The topology of a computer network is variable; multicomputers often have fixed topology, and where the machine is reconfigurable this is (almost) never performed during program execution.

- The interprocessor communication links of a computer network are inherently noisy; the links inside a multicomputer are generally error free.

These observations naturally lead to different requirements for the properties and interfaces to the two types of communication systems. We would in principle like the multicomputer to be able to access facilities of the network, and users of the network should have access to the facilities of the multicomputer. It is clear that there should be a well-defined boundary and interface between the two systems.

The following assumptions about the requirements of the user and the underlying hardware are usually made:

- 1. Application processes generally require the illusion of complete connectivity.

- 2. The mapping of application processes onto processors is arbitrary but static.

- 3. The intercommunication links are completely error free and allow bidirectional traffic.

- 4. The interconnection topology of the processor array is arbitrary but static.

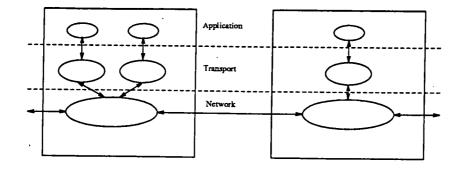

Figure 2.1: A three layer model.

It is convenient to divide a communication system into a number of *layers* each of which address separate issues arising in the design and implementation of these systems. For example the problem of efficient and correct routing of messages between processors is distinct from the problem of providing a suitable interface to the programmer.

In Section 2.2 we present an overview of the system decomposition we consider and the interfaces between the component layers. Sections 2.3 and 2.4 discuss the design of system components in detail.

## 2.2 System Overview

We consider a conceptual three layer structure as depicted in Fig 2.1. The components, *network*, *transport* and *application*, are named after layers of the OSI model [DZ83]; they perform approximately similar functions.

- Application This layer contains all user processes. Application entities enjoy the illusion of reliable communications between all pairs. This layer approximately corresponds to layer 7 of the OSI model. Each application entity uses the services of a single transport entity.

- **Transport** This layer is the interface between application and network. Transport is responsible for maintaining the security of communications between application entities. This layer approximately corresponds to layers 4 to 6 of the

OSI model. Each transport entity provides services to a single application entity and uses the services of a single network entity.

Network This layer is the actual message carrier. Network is responsible for passing message data between transport entities. It should avoid internal deadlock states without discarding messages. This layer approximately corresponds to layers 1 to 3 of the OSI model. Each network entity provides services to one or more transport identities.

The boundary between transport and application is very real. This is also the boundary between the communication system and the user and as such defines the user model of communication. This interface is discussed at length. The boundary between network and transport may be somewhat artificial and the interface is dealt with rather briefly.

## 2.2.1 Communication Models

The manner in which messages are communicated, the *communication model*, plays an important role in the implementation of all programs. We consider two models of communication that could be implemented and used, and indeed have been, *asynchronous* and *synchronous* communication.

In the asynchronous models messages appear to be sent from one process to another via an intervening medium which has a bounded capacity to store messages and is shared by all processes. The source process can send a message, for some destination, only when the medium is able to accept a message and may not wait for the destination to receive the message. The destination process can receive a message only when the medium contains a message for it, which the medium is able to deliver. The medium may be unable to deliver messages accepted from some sources because some destinations have not accepted messages which are deliverable. The medium may or may not guacantee that when a destination D receives a message from a source S there are no earlier messages for D from S within the medium. If such a guarantee is made then the medium is ordered, we say it preserves message sequentiality, else it is unordered. Since the medium has a bounded storage capacity the communication of arbitrarily large messages must be effectively synchronous and therefore also sequential whether or not the medium is ordered.

In the synchronous model messages appear to be sent directly from one process to another without being stored by an intervening medium. The source process can send a message, for some destination, only when the destination waits to receive the message; there is always a point at which the two processes are both waiting for transfer of the message to terminate although they may not resume simultaneously as measured in an external frame of reference. Message sequentiality is implicit. The synchronous model is implemented within an underlying asynchronous model by the use of a synchronisation protocol.

The question of which model to provide is not trivial. The asynchronous model necessarily offers more communication bandwidth and lower message latency than the synchronous model since no protocol messages are required. The synchronous model offers a precise definition of communication and its implementation can ensure that messages will always be delivered.

#### 2.2.2 Transport Interface

The transport interface defines the services provided to **a**pplication. It should be intuitive enough for general purpose users and at the same time powerful enough for sophisticated utility packages to be written. We discuss the issues of process identification, message addressing and selection, communication models, and present an example procedural interface.

#### **Process Identification**

In order to use a multicomputer there must be a *partition* of the processing and data of a program into a number of processes, which have distinct address spaces and exchange information by communication of messages, and a *placement* of pro-

cesses onto physical processors, in which at least one process is mapped onto each processor. The partitioning problem is determined mostly by details of the program whereas the placement problem is determined mostly by details of the multicomputer. In order that the partition can be defined without reference to the, perhaps as yet undetermined, placement we require that the identification of these *internal* processes should be defined by the partition. It is intuitive to identify such processes by a sequence of natural numbers, for example when there are N internal processes one might label them by integers in the interval (0, N].

Every program must have a means of collecting input and reporting output, typically via the utilities of an interactive terminal, file system, graphical device ... Whether a device exists internally within the multicomputer or externally within the computer network there must be a process within the multicomputer which interfaces between the user and the device providing a defined utility. Such interface processes are not considered to be part of the program but rather part of the environment within which the program executes and they are properly accessed by a procedural interface provided by the environment; the identification of these external processes should be defined by the environment. It is intuitive to identify such utilities by a textual string, for example one might label the terminal by the name "tty". The environment can provide a mapping of such names into integers, outwith (0, N], which identify the external process. Were all utilities localised, in the sense that they are provided by a single process, as the examples given above tend to be, then this method would be quite adequate. However we cannot discount the possibility of utilities which are distributed, in the sense that they are provided by many (communicating) processes, examples of which could be concurrent file systems, linear algebra packages, graphical rendering packages ...

There is a sense in which each utility, whether distributed or localised, is a program which co-operates with the user program and as such the partition of each program defines a set of labels for the processes it contains. The case of such a collection of programs can be homogeneously handled by introducing the concept of a *group*, a set of processes performing some named function. One such group is the user program, others are the utilities which the environment of the user program provides. In this method each group is identified by a textual string, its name, and the

. -

environment provides a mapping of group names into unique integer group labels. The processes internal to a group are defined by the group and can be labelled by a set of natural numbers as we previously labelled the processes internal to the user program; the system wide unique identifier of a process becomes a (group, process) label pair. The group mechanism need only be visible to programmers implementing utilities on the part of whom we can assume some sophistication; of course this does not prevent the mechanism being available to general purpose users.

We have frequently referred to the idea of a process as a processing entity with a private address space. In general we would like to avoid the constraint that such entities are purely sequential and allow them to be composed of a number of concurrent *threads* which share a common address space. This allows programmers to write programs which overlap communication with calculation within a process, which may in turn lead to a more effective overlap of calculation with calculation over a set of processes, and thereby enhance the performance of the program running on the multicomputer; as physical scientists we do, after all, have only one reason for using such a machine.

#### Addressing, Selection and Models

Processes exchange information by communication of messages. It seems then that a fundamental property of a message, aside from the data it may contain, is the pair of identifiers defining the source and destination processes; it is natural to think that processes send and receive messages. When the source wishes to send a message it specifies the identifier of the destination process, or perhaps the identifiers of permissible destination processes; an act of *addressing*. When the destination wishes to receive a message it specifies the identifier of the source process, or perhaps the identifiers of permissible source processes; an act of *selection*. Another property we could assign to a message is a *type* which in some way represents the meaning of the message; either or both of addressing and selection can be expressed in terms of, or in combination with, types. It is convenient to specify a type label as an integer in the interval (0, T] where T is a statically bounded number of message types.

Selection Above we hinted at the possibility of conditional output, in addressing, and conditional input, in selection. It is not necessary to provide both of these, however it is necessary to provide one and a system which offers conditional input as opposed to conditional output will be more intuitive to use. Another reason for choosing to provide conditional input lies in the fact that we can completely and sensibly define a conditional input without reference to the communication model whereas this is not true of conditional output. The question of how conditional input is presented is important. It is generally sufficient to allow a process to specify a number of (group, process) labels as alternatives however the time taken to determine which alternatives can be satisfied and which should be chosen necessarily increases as the number of alternatives specified; this is a real performance problem. A less formal method, which can be implemented reasonably efficiently and which experience suggests will nevertheless be very powerful, is to allow selection to be specified as a (group, process, type) label triplet, in which either process or group is allowed to be a wildcard indicating all, from which the goal is determined by the following scheme.

|         | · · ·                                                   |

|---------|---------------------------------------------------------|

| if      | group label is wildcard                                 |

|         | any message with given type                             |

| else if | process label is wildcard                               |

|         | any message from given group with given type            |

| else    | ŕ                                                       |

|         | any message from given (group, process) with given type |

Addressing We have discussed only point-to-point messages, in which there is exactly one source and one destination, thus far. In practice it is frequently necessary to send the same message to a significant number, i.e. close to N, of destinations. Of course this can always be achieved by sending the message to each in turn but it is often possible for the communication subsytem to perform the operation more efficiently when it provides for broadcast message routing. We take advantage of the structure implicit in the group mechanism to define a broadcast as a message sent to all members of a group and a global broadcast as a message sent to all members of all groups, both subject to the exception that the message is not delivered to its source. We could allow addressing to be specified as a (group, process, type) label pair triplet, similar to the specification of selection, from which the action is determined by the following scheme.

ifgroup label is wildcard<br/>global broadcast with given typeelse ifprocess label is wildcard<br/>broadcast to given group with given typeelsesend to given (group, process) with given type

Models We would like transport to provide for both synchronous and asynchronous models of communication. A message is labelled by a (source, destination, type) triple, where source and destination are process identifiers; it makes no sense for messages with the same label to be communicated within different models at different times. The communication model of each message should be statically determined by its label. It is convenient to allow this to be determined by the source process group label alone. We anticipate that a group will statically specify the types and associated models for internal communication, and will similarly specify the types and models of external messages which will be used to provide the services offered by the group. The user group does not provide services, it only uses those of other groups, and need only specify the types and models for its internal communication since any external communication is determined by the specifications given by other groups.

#### **Procedural Interface**

Just as utilities provided by the environment are properly accessed by a procedural interface the services offered by the communication subsystem should also be accessed by a procedural interface. This readily allows such services to be accessible from any number of languages and on any number of multicomputers provided that the necessary procedures can be written.

We give an example functional interface, in ANSI C, which exploits the ideas discussed above. Groups, processes and types will be labelled by integers. Message selection and addressing will be performed with a (group, process, type) label triplet as discussed and provision for hiding the group mechanism from general purpose users is explicitly made.

Symbolic Constants The following symbolic constants are declared:

WildLabel The wildcard label.

BadGroup Indicates a bad group parameter.

BadProcess Indicates a bad process parameter.

BadType Indicates a bad type parameter.

They have distinct negative values.

Names, Labels and Sizes Functions are provided for mapping a group name into a group label, and vice versa, determining the size of a group with a given label and determining the process label and enclosing group label of the calling process.

int groupLabelFromName(char \*groupName)

Determine a mapping of group name to group label.

Return the label of the group with name groupName, else BadGroup if there is no group with the given name.

char \*groupNameFromLabel(int groupLabel)

Determine a mapping of group label to group name.

Return a reference to the name of the group with label groupLabel, else a null reference if there is no group with the given label.

#### int groupSizeFromLabel(int groupLabel)

Determine the size of a group.

Return the size of the group with label groupLabel, else BadGroup if there is no group with the given label.

int getGroupLabel()

Return the label of the group containing the calling process.

int getGroupSize()

Return the size of the group containing the calling process.

24

#### int getProcessLabel()

Return the process label of the calling process.

Group Internal Messages Two functions provide for sending and receiving messages between processes within the same group and do not require a group label parameter.

int isend(int \*process, int type, void \*data, int size)

Send the message in the buffer referenced by data of length size bytes and of type given by type. The message is a broadcast to the group if the integer referenced by process has the value WildLabel, else a single send to the given process.

Return a non-negative integer, whose value is undefined, if the send was successful, else return one of:

BadProcess The process label was invalid,

BadType The type label was invalid.

Note:

1. The function blocks until the message can be sent.

25

int irecv(int \*process, int type, void \*data, int size)

Receive a message into the buffer referenced by data of length size bytes and of type given by type. The message will be received from any process in the group if the integer referenced by process has the value WildLabel, else from the given process.

Return a non-negative integer, whose value is the message size, if the receive was successful, else return one of:

BadProcess The process label was invalid,

BadType The type label was invalid.

Note:

- 1. If the message was longer than size then only the first size bytes are received and the remainder are lost. This is strictly an error and may be detected because the return value is greater than size.

- 2. The process label from which the message was received is stored in the integer referenced by process; this only affects that value if it was previously WildLabel.

. . . . . . . . . . . . . . . . . .

3. The function blocks until a suitable message can be received.

Group External Messages Two functions provide for sending and receiving messages between processes in different, or the same, groups and take a group label parameter.

26

. . . . . . . . . . . . . . . .

int esend(int \*group, \*process, int type, void \*data, int size)

Send the message in the buffer referenced by data of length size bytes and of type given by type. The message is a global broadcast if the integer referenced by group has the value WildLabel, else a broadcast to the given group if the integer referenced by process has the value WildLabel, else a single send to the given process in the given group.

Return a non-negative integer, whose value is undefined, if the send was successful, else return one of:

BadGroup The group label was invalid,

BadProcess The process label was invalid,

BadType The type label was invalid.

Note:

1. The function blocks until the message can be sent.

int erecv(int \*group, \*process, int type, void \*data, int size)

Receive a message into the buffer referenced by data of length size bytes and of type given by type. The message will be received from any process in any group if the integer referenced by group has the value WildLabel, else any process in the given group if the integer referenced by process has the value WildLabel, else from the given process in the given group.

Return a non-negative integer, whose value is the message size, if the receive was successful, else return one of:

BadGroup The group label was invalid,

BadProcess The process label was invalid,

BadType The type label was invalid.

Note:

- 1. If the message was longer than size then only the first size bytes are received and the remainder are lost. This is strictly an error and may be detected because the return value is greater than size.

- 2. The group label from which the message was received is stored in the integer referenced by group; this only affects that value if it was previously WildLabel.

- 3. The process label from which the message was received is stored in the integer referenced by process; this only affects that value if it was previously WildLabel.

- 4. The function blocks until a suitable message can be received.

#### 2.2.3 Network Interface

The network interface defines the services provided to transport. If transport implements synchronous communication between application entities then there is little point in network providing a synchronous model between transport entities. It makes most sense for network to provide an asynchronous model leaving flow control and synchronisation to the higher layers.

Each network entity has a number of conceptual ports, one connected to each transport entity, over which the network and transport entities communicate. Transport entities are addressed by a (processor, port) number pair, which can be packed into an integer; the abstraction from such placement details enjoyed by application can be provided entirely by transport which maps application process indentifiers into transport addresses.

We could conceive of the service being provided by a set of functions, which provide for directed asynchronous messages which are either ordered, in the sense that an ordered message will not arrive at its destination before an earlier ordered message, or unordered, and for asynchronous broadcast messages.

. . . . . . . . . .

#### void unordered(int transport, void \*data, int size)

Send an unordered message of length size bytes buffer referenced by data to the transport entity identified by transport.

void ordered(int transport, void \*data, int size)

Send an ordered message of length size bytes buffer referenced by data to the transport entity identified by transport.

• • • • • • • • • • • •

void broadcast(void \*data, int size)

Broadcast message of length size bytes in the buffer referenced by data to all other transport entities.

#### void receive(void \*data, int \*size)

Receive a message into the buffer referenced by data returning the size in size.

• • • • • • • • • • •

Of course, in practice transport would like to avoid taking a copy of data which must later be copied again to application, if this is possible, and these functions may not be realistic. In fact such a set of functions will probably not even exist; when network and transport share the same CPU and memory then the boundary between them should be artificial and when network comprises specialised routing hardware then the interface would probably be interrupt driven.

## 2.3 Transport Layer

In this section we discuss issues involved in the design of the transport layer. This layer provides service to the application layer using the service provided to it by network.

Our major requirements of transport are:

- 1. Transport supports the illusion of full connectivity and abstraction from process placement.

- 2. Transport fairly and efficiently implements the addressing and selection methods of the user model.

- 3. Transport maintains the reliability of communications between application entities, provided that no application entity indefinitely refuses to accept any deliverable asynchronous message.

Requirements 1 and 2 are self explanatory. The last point implies that in the synchronous model transport maintains the reliability of all communications whereas in an asychronous, or mixed, model application is responsible for implementing flow control in asynchronous messages.

### 2.3.1 Asynchronous Models

Experience in using the asynchronous model has shown that it is often possible for relatively inexperienced users to write programs with very simple communication patterns, and that sophisticated users can succesfully create programs with rather complicated communication patterns.

The absence of imposed flow control affords greater performance but can lead to a deadlock situation where cyclical dependencies in the communication of user processes fatally interact with the uncontrolled sharing of network storage resources, a problem for which we have borrowed the term *hangup* since the network itself is not in a deadlock state. Some simple examples of hangup are:

- A number of application entities attempt to send messages to one another and will only attempt to receive messages after completion of sending. The storage capacity of the system is used up and it cannot accept further messages until application accepts messages from it; application waits forever to send messages to it. Although this is a simple problem to solve it may be difficult for the less sophisticated programmer to diagnose.

- An application entity is waiting for a message of a particular type which it never receives despite the fact that it has been accepted by the system. The storage capacity of the system which would be required to deliver the message is taken up by messages for this entity but of a different type and thus the entity must accept some of these before the system can deliver the required message; application waits forever to receive a particular message. This problem may be more difficult to solve and diagnose.

Hangup may be avoided when the amount of message data which can be outstanding for any destination which might indefinitely refuse to receive said data, because

<u>,</u> ...

it is waiting to receive other data or to send data, can be bounded either due to the structure of communications natural to the application or by explicit flow control. If this bound is not zero then the destination is assuming it may use the storage capacity of network; the destination must reverse this assumption by installing sufficient buffering threads to reduce the bound to zero. The fact that a large number of programs have now been written within the asynchronous model is testimony to the fact that these bounds are often readily calculable.

#### 2.3.2 Synchronous Models

In order to implement the synchronous model a protocol is required between transport ent it es; this protocol determines when the source and destination application processes can be resumed, and when message data is transferred. The implementation need not suffer from the hangup problem since transport can trivially be arranged to behave as a sink.

Consider a very simple protocol, which requires a constant amount of memory at each transport. When a process wishes to source a message it sends the data immediately and waits for an acknowledge; when a process wishes to sink a message it waits to receive the message and then sends an acknowledge to the source. This achieves synchronisation between the source and sink but fails to avoid hangup, because messages are being stored in network. This problem can be removed by defining a retry message which transport sends back to the source whenever a message arrived but was discarded because the destination user process was not ready to receive the message; the source sends the message again whenever the retry message is received rather than the acknowledge. This busy wait technique is clearly capable of consuming enormous amounts of communication bandwidth.

We describe three further protocols, each of which require memory proportional to the number of processes, which use the communications bandwidth rather more efficiently.

Request-Transfer (RT) The source waits for a request for transfer message before sending the data transfer message. The destination sends the request message and waits for the transfer message. Transport requires a bit, or more realistically a word, at every source for every destination which may wish to receive from that source, with which to record the arrival of requests. This protocol has the disadvantage that it forces the destination to specify which source it wishes to receive from; conditional input is not possible.

**Transfer-Acknowledge (TA)** The source sends the data transfer message and waits for an *acknowledgement of transfer* message. The destination receives the data transfer then sends the acknowledgement. Transport requires a buffer at every destination for every source which may wish to send to that destination, with which to store the arriving data transfers. This protocol has the disadvantage that unless message buffers are very small an inordinate amount of memory may be required; it has the advantage of offering functionality well aligned to the requirements of applications.

**Request-Acknowledge-Transfer (RAT)** The source sends a request to transfer message and waits for an acknowledgement message before sending the transfer message. The destination chooses any request, sends the acknowledgement and waits for the transfer. Transport requires a bit, or more realistically a word, at every destination for every source which may wish to send to that destination, with which to record the arrival of requests. This protocol has the advantages of providing the right functionality and requiring relatively little memory; it has the disadvantage of being more expensive in communication of protocol. The time ordering of the request and acknowledge can be relaxed when the destination is performing an unconditional input if message sources also record the arrival of these "acknowledgement" messages.

## 2.4 Network Layer

In this section we discuss issues involved in design of the network layer. This layer provides services to the transport layer using the communication hardware of the multicomputer.

Our requirements of network are:

- 1. Network is capable of passing a message from any transport entity to any other transport entity, and from any transport entity to all other transport entities.

- 2. Network will not corrupt or discard messages, and any deliverable message which waits to be received by a transport entity will hold network resources indefinitely if required.

- 3. Network will not indefinitely fail to accept a message from any transport entity or indefinitely fail to deliver any accepted message, provided that no transport entity indefinitely fails to accept any deliverable message.

We demand 1 so that transport can always support the illusion of full connectivity and the abstraction from placement to application, and efficiently implement broadcast messages. In order for transport to securely implement synchronous messages 2 is essential. Deadlock and starvation in network are eliminated by 3 which we must ask in order to implement any reliable communications.

#### 2.4.1 Switching Techniques

Two important, and very different, switching techniques used in communication systems are circuit and packet switching. Two more recent techniques are virtual cut-through and wormhole switching.

#### **Circuit Switching**

The circuit switching technique is easily understood by analogy with the telephone system. When one subscriber dials the number of another the telephone system attempts to find a line between the two; a line is a sequence of available *wires* from the caller to the receiver. If the receiver is engaged or a line could not be found then the call fails and any wires used are retrieved. If, on the other hand, the receiver was available then the line is held until the two parties have finished their conversations and replaced their handsets, or until the caller becomes bored of waiting for the receiver to pick up the phone! Key features of circuit switching are:

- The initial establishment of the end-to-end connection.

- The use of a dedicated set of wires during the connection.

These features have a number of immediate consequences for the point-to-point and aggregate bandwidth of the system.

After call connection the point-to-point bandwidth is very high since there is a private set of wires; there is no need to store the message at an intermediate node while it waits for the outgoing wire to become available. The transfer time depends only on the message length.

The time taken to establish a connection can be very large, as our experiences with the telephone system will confirm. The number of wires waited for increases as the path length. The probability of a wire being free decreases as the network loading increases. The waiting time increases with the length of message waited for. A cross over occurs from a set up time depending only on the path length to one depending on both the path length and average message length.

Since a connection which is waiting for a free wire is itself holding wires the achieved aggregate bandwidth falls off heavily with loading and is rather smaller than the maximum available.

Circuit switching has been applied to multicomputers, in hardware, in the Direct Connect Module of the Intel iPSC/2 [Nug88].

#### **Packet Switching**

If circuit switching is compared to the telephone system then packet switching should be compared to the postal system. When one correspondent wishes to communicate with another they write down the contents of the message, package them up in an envelope, put the address of the recipient on the envelope, post it and never hear of it again unless the recipient chooses to reply explicitly. The mail will only handle letters below a certain weight; assume there is no parcel post service, so a really large message will have to be sent as several separately addressed letters. During transit each letter shares resources with a number of other letters; there are no dedicated lines. Key features of packet switching are:

- Messages may be fragmented into one or more separate packets, each of which is separately addressed.

- Packets do not reserve private lines, each packet is completely received before being forwarded.

The performance properties of a packet switched system are quite the inverse of a circuit switched system.

When a message packet arrives at an intermediate node the output link it will require may, in general, be busy. Whether or not this is the case the packet is completely received into a buffer before any of it is forwarded; these are commonly known as *store-and-forward* systems. It follows that the transfer time depends on both the path length and message length. This is unimportant for sufficiently small messages but the latency will probably be unacceptable for large messages.

It is easy to see that, as in the analysis of circuit switching, one finds that the effect of network loading is to add a term dependent on both the path length and average message length.

The achievable aggregate bandwidth of packet switched systems is generally better than that of circuit switched systems since, given some number of buffers at each communication link, a message waiting to propagate to the next node does not prevent use of the link which is used to arrive at the current node.

Packet switching has been applied to multicomputers, in software, in the Cosmic Cube [Sei85], the Intel iPSC/1 [Int86], and a number of routing systems for transputer arrays.

#### Virtual Cut-through

The virtual cut-through technique is a direct hybridisation of the circuit switching and packet switching methods and is based on the observation that in a packet switching system it is not necessary to store the whole message at an intermediate node if the outgoing link is not busy. This requires hardware which allows direct link to link and link to memory copies.

Key features of virtual cut-through are:

- Messages may be fragmented into one or more separate packets, each of which is separately addressed.

- Packets are stored in intermediate nodes only when the chosen output link is busy.

The performance properties of virtual cut-through systems are similar to circuit switched systems, without the requirement of initial path set up, in very lightly loaded networks; they are optimal for point-to-point bandwidth. In heavily loaded networks the probability of the next link being free is very small and there is a cross over to the properties of packet switched system.

Virtual cut-through has been applied to an experimental transputer communication system [Mcn] but is not used in any commercially available systems for multicomputers.

#### Wormhole

This technique splits a message into a number of, typically rather small, units known as *flits* of which only the first few contain addressing. An intermediate node accepting the message completely receives the first flit, and maybe a small number of following flits, before forwarding these flits in a manner similar to storeand-forward systems. Remaining flits are not received until the first flit has been forwarded and are always forwarded in the same way, if the message must wait for a blocked output channel then all channels behind the head are also temporarily blocked. Key features of wormhole switching are:

- Messages are fragmented into a number of small flits, only the first few of which contain addressing.

- All flits of a message follow the same path and only a small number are received before forwarding the message.

The performance properties of wormhole switching are also optimal for point-topoint bandwidth in lightly loaded networks. The achievable aggregate bandwidth suffers in a similar manner to circuit switched systems.

Wormhole switching has been applied to multicomputers, in hardware, in [DS88] and in the C104 routing chip [Pou90].

#### **Connectionless Switching**

We define a switching model, *connectionless* switching, which embraces the storeand-forward, virtual cut-through and wormhole techniques. The name is intended to imply that there is no dedicated connection set up before message transfer takes place, unlike circuit switching which can be described as *connection-oriented*.

The network consists of *network elements*, or simply *elements*, which are network processes controlling the use of some network resource. A message consists of a

| Feature | Store-and-forward | Virtual Cut-through | Wormhole |

|---------|-------------------|---------------------|----------|

| Element | Buffer set        | Buffer set          | Channel  |

| Unit    | Buffer            | Buffer              | Flit     |

| u .     | = 0               | > 0                 | = 0      |

| v       | > 0               | > 0                 | > 0      |

| w(m)    | = 0               | $\leq u$            | > 0      |

Table 2.1: Feature Identification in Connectionless Switching

finite number of *message units*, or simply *units*. A unit is the largest piece of message data that may be forwarded to or by message elements. Elements have a finite capacity for storage of units. The first unit, or first few units, alone carry addressing information for the complete message.

- 1. An element Q accepts the first v units of a message m, from an element or transport P, which establishes the portion of the message path leaving P.

- 2. The v units accepted by Q contain all addressing information and the routing function is applied to this information. These units may be modified to produce a set of  $v' \leq v$  units which allows for removal of redundant addressing etc.

- 3. The v' resulting units are forwarded to an element or transport R which establishes the portion of the message path leaving Q.

- 4. There may be a finite number,  $w(m) \ge 0$ , of remaining units which Q accepts from P and forwards to R.

- 5. Q has the capacity to store at most  $u \ge 0$  of the remaining units and uses this storage capability to concurrently accept units whilst waiting to establish R in 3 or for which R is not ready in 4.

This model is a description of the three switching techniques when the feature identifications of Table 2.1 are made.

## 2.4.2 Routing Functions

Routing functions deal with the business of moving messages between processors which are not directly connected. We consider functions which perform *directed* routing, from one processor to another, and *broadcast* routing, from one processor to all others. These kinds of functions can be further divided into *static* functions which always use the same routes and *adaptive* functions which vary the routes, in an attempt to alleviate the effects of localised congestion. We consider static and adaptive directed functions, and static broadcast functions.

#### **Directed Functions**

When a message at some processor must be delivered to some other processor there are generally a number of routes it could take; we need some criteria of goodness to determine which route to use. A simple and often used criteria is the *shortest path*, i.e. one that crosses the minimum number of links. A slightly more general criteria associates a cost with transfer over each link and we choose a route which minimises this cost; the shortest path approach associates equal cost with all links. Whenever the processor graph contains cycles we are liable to find that a number of routes have equal cost and the static routing function chooses a single one of these possibilities for all directed messages. We will also, and more frequently, refer to this routing function as *sequential*.

In order to effectively utilise network bandwidth under heavy load it is necessary to attempt to avoid highly localised areas of congestion by either routing messages around these areas or preventing the occurence of such areas. The problem is to decide which communication link should be used to forward a given message so that it will reach its destination in the minimum time. Of course this problem cannot be solved without quite considerable knowledge of the network current and future states; a good guess is the best that can realistically be hoped for and congestion control algorithms are concerned with making these guesses.

When the network shares CPU with the application we require that it be purely

reactive which implies that a local, or isolated [Tan89], algorithm is employed; each node makes a routing decision based on information it has gleaned about the network without specific exchange of information between nodes. A simple example of such an algorithm is the *hot potato* method; each node simply forwards the message on whichever link it thinks will first becomes ready without regard as to whether the chosen link actually takes the message any closer to its destination. Another is the *diffusive* method in which each node forwards the message on any randomly chosen link.

These approaches can be combined with a static knowledge of which links are on minimal cost paths and the decision is then which of these links to use. A number of possible methods for choosing the next link in the route are now described. In the absence of realistic and well understood models of a network under heavy load it is not possible to compare quantitatively the performance of these methods; a qualitative discussion is given.

- Least Used: The message is queued to the link which has been used the least. This method requires a counter for each link which is updated whenever the link is used. It is not able to adapt to local congestion and simply tries to use the links as evenly as possible.

- Random Link: The message is queued to a randomly chosen link. This method is easy to implement, requiring only the added complexity of using a random number generator. It is not able to adapt to local congestion; the hope is that by partially randomising message paths the probability of localised areas of congestion is decreased.

- Quiet Link: The message is queued to the link which has not been queued to for the longest period of time. This method requires the time of the last queueing event for each link to be recorded and the time for each suitable link to be inspected. The decision is based on the history of events which may not be a good guide to future events.

- Short Queue: The message is queued to the link which has the shortest queue of pending messages. This method requires the queue of waiting messages for

each suitable link to be inspected. The decision is based on the current state of the node which is a good guide to future events if areas of congestion are sparse.

First Ready: The message is queued to the link which will first become ready. This method directly addresses the question of future events, and is certainly the best of the algorithms we describe here. It can be implemented, for example, by placing the message in all suitable queues; the first queue to become ready removes the message from other queues so that it is forwarded only once as required. Unfortunately this requires twice as many queueing events as, for example, the short queue method and more complicated queueing structures which will consume additional CPU.

Notice that the last of these methods differs fundamentally from the others in that the message is not committed to being forwarded by an unready link if another possible link is ready. The method can be useful in designing deadlock free routing functions, as we shall later see, where the set of output links are not necessarily on a minimal cost path. Whether this is the case or not we shall use the term *quasiadaptive* to describe all of these methods since they contain a definite static component.

The quasiadaptive and static functions are easy to implement in general topologies when we introduce a routing table at each processor which typically maps the destination processor, and perhaps the arrival link, into a set of possible output links. In this way every message contains the number of the destination node and a table look-up determines the set of output links; the static function uses the first of the alternatives whereas the quasiadpative function chooses between them. In geometrically regular topologies the routing table can often be dispensed with since a simple rule determines the set of output links.

#### **Broadcast Functions**

We could always effect a broadcast routing function by generating a directed copy of the message to every other processor, and we could do this in such a way that every copy followed a minimal cost path. Observe that the same message, although a different copy, will pass over certain links a large number of times; clearly we can broadcast a message much more efficiently by avoiding this. We would ideally like a broadcast function to have the property that every broadcast message arrives at each processor, excluding the source, exactly once and preferably along minimal cost paths.

We can readily construct a static broadcast function which has these properties but we know of no adaptive broadcast functions which have both of these properties. We therefore limit ourselves to considering static broadcast functions.

When a minimal cost path from A to C passes through B then the portion of this path from B to C is necessarily a minimal cost path from B to C. We can exploit this trivial fact to build a directed tree with A at its root which contains every node and in which the path from A to any node is one of minimal cost. Consider the simple case where unit cost is associated with every link, shortest path routing. All processors neighbouring A become the children of A and A becomes their parent. These processors then, in turn, examine their neighbours and only when a neighbour has no parent they take that neighbour as a child. This process is repeated until all processors have parents or equivalently it is not possible for any processor to take a child. Because our multicomputer is conjoint and its links are undirected we can perform this calculation for every processor.

The (static) broadcast function is also easy to implement in general topologies when we introduce a routing table at every processor which maps the source processor into a set of output links. Every broadcast message contains the number of the source processor and a table look-up determines the set of output links; the message is replicated (it need not be copied) and forwarded by each of these links, simultaneously if they are ready. In geometrically regular topologies it is again often possible to replace the table with a simple rule.

### 2.4.3 Deadlock Avoidance

Deadlock arises within network when there exists a set of network elements each waiting to transfer a message unit to another element within the set, such that none can proceed before any other. Deadlock can also occur involving transport elements, in which the resources of network are overloaded and it is the responsibility of transport to avoid overloading network.

Elegant solutions to the network deadlock problem in a small number of topologies are known and it is useful to introduce these methods before discussing the general problem. We then present a method for avoidance of deadlock in arbitrary toplogies based on these ideas.

#### Trees

It has long been known how deadlock may be avoided in a network with a tree shaped topology [MS80]; a message originating in processor s destined to processor d is simply forwarded along the unique shortest path through the tree, exploiting the fact that the tree is an undirected acyclic graph.

One associates a single network element with each directed link. Each network element will accept units from any adjacent element or a source. The routing function may forward a message to an element at any adjacent link, or a sink.

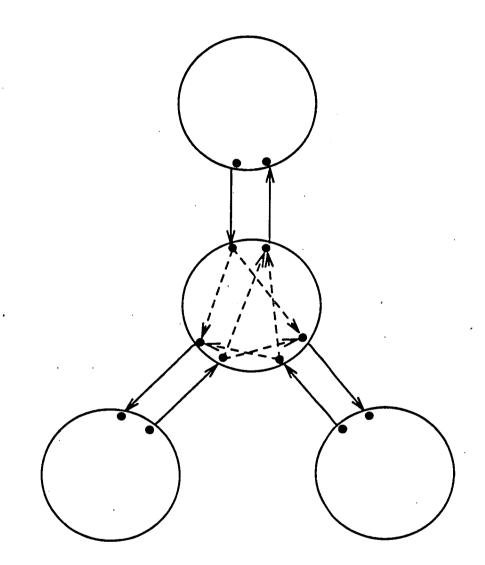

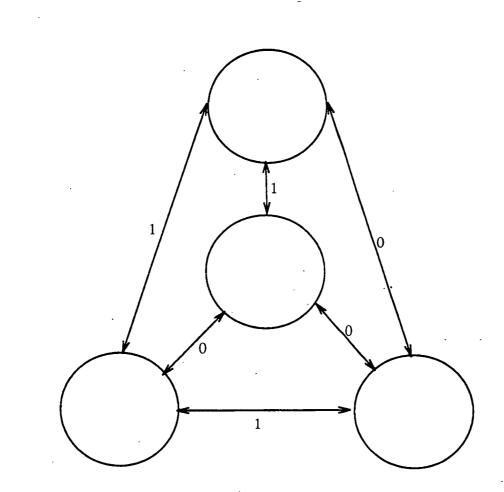

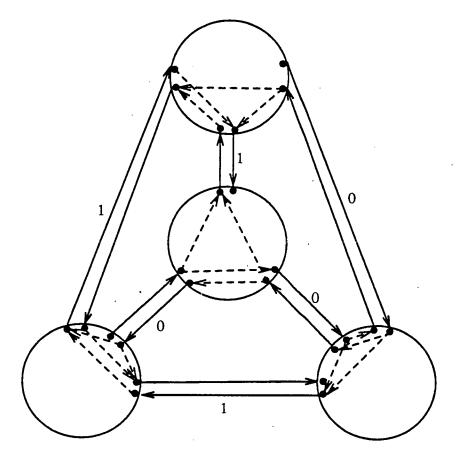

The dependency of network elements resolves into a directed acyclic graph, as depicted in Figure 2.2, and it is therefore not possible for a cycle of waiting network elements to exist.

#### Grids

The e-cube routing algorithm [DS88] solves the deadlock problem for multidimensional grids in such a way that all messages are delivered along shortest paths; in

Figure 2.2: Routing in a binary tree.

Figure 2.3: Routing in a 2 dimensional grid.

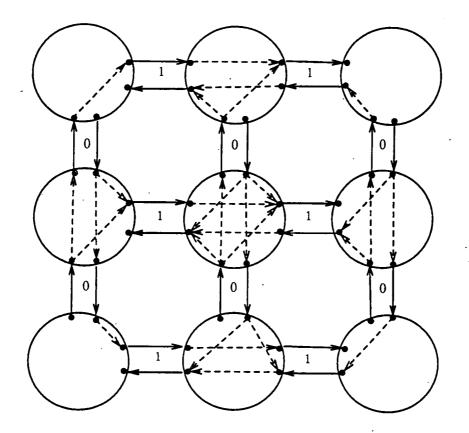

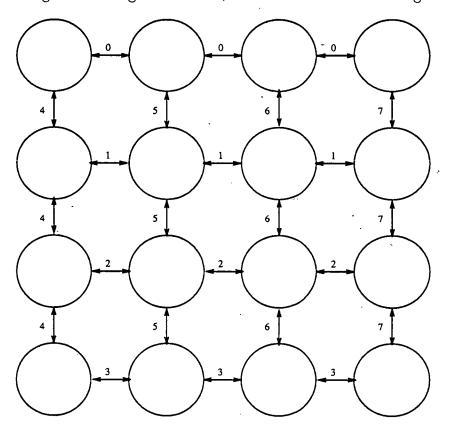

hypercubic grids the number of messages using any link is the same for all links. This algorithm exploits the fact that there are many shortest paths between nodes in these graphs and restricts the paths actually taken such that the graph of element, or link, dependencies is acyclic, as in the case of the tree graph.

One associates a single network element with each directed link. In a d dimensional grid one numbers the dimensions by natural numbers in (0, d] and labels each link by the number of its dimension. Each network element will accept units from any sink and any adjacent element. The routing function may forward a message to an element with an equal or larger label, or a sink.

The graph of element dependencies again resolves into a directed acyclic graph, as depicted in Figure 2.3, and there is a path from every node to every other node. We shall refer to this technique as *acyclic* routing.

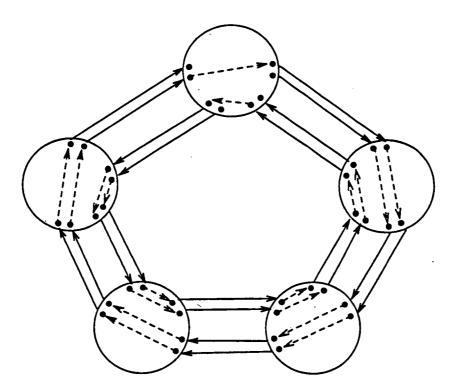

Figure 2.4: Routing in a Ring.

#### Rings

It is not possible to construct a routing function which leads to an acyclic dependency of network elements, as in the grid above, and preserves shortest message paths for all node pairs in rings of order greater than four.

The deadlock problem can be solved by use of acyclic routing when *multilinks*, an undirected link which is arranged to appear as a number of independent links, are introduced. A network element is associated with each directed component of the link. In the case of a ring we create two virtual links at each physical link, it is then possible to thread a chain through the graph which utilises all of the virtual links. Messages can be routed through this graph, shown in Figure 2.4, in a manner similar to the tree graphs above.

This is the loop free buffer graph technique of [MS80]  $(w(\alpha) \leq u)$ , and the virtual channel technique of [DS88]  $(w(\alpha) > u)$ .

In the regime  $w(\alpha) \leq u$ , there is another class of solutions in which one avoids

deadlock by ensuring that there is always a free buffer in each directed ring [Ros87]. This can be achieved in practice in a number of ways; for example a network element could simply not accept a packet from a transport element unless one of the buffer set associated with the network element is free. We shall refer to these methods as *circuit* routing.

#### General

We have discussed two routing techniques for avoidance of deadlock in network applied to specific topologies; we now describe how these methods can be applied to general topologies.

Acyclic Routing The method can be generalised to arbitrary topologies when one solves the problem of constructing an acyclic element dependency graph which nevertheless affords routes between all pairs of nodes.

One could trivially achieve this by exploiting the fact that any conjoint undirected graph contains a spanning tree; this would be a poor solution since very few of the links are utilised. We present below a method for calculation of link dependency which permits utilisation of all links. It is not generally possible to utilise shortest paths for all messages in this approach, consider for a moment the ring topology, however the method yields shortest paths in the tree and grid geometries as we should expect.

In the case of a multilink approach we can either analyse the multigraph directly or alternatively analyse the underlying physical graph and impose a linear ordering on components of multilinks. We take the latter approach in applying the results of our link dependency calculation to multigraphs for sake of simplicity in the algebra of the dependency calculation.

In the regime  $w(\alpha) \leq u$ , it is always possible for a message to utilise any outgoing link which is ready since this cannot cause a cycle of waiting elements. This has been exploited in the *resource ordering* approach of [Gun81] and is included in our directed routing function.

**Circuit Routing** The circuit routing technique described above for a ring can be utilised in arbitrary topologies when one observes that because the links are bidirectional we can construct a single directed ring that utilises all of the directed links, and route around this ring [Ros87]. Alternatively one can exploit the fact that in even valency graphs one can construct an Eulerian cycle [NLW88] and route this cycle as the ring.

These approaches lead t o message path lengths which increase linearly with order of the graph. We do not pursue this approach.

Again it is possible to route a message to any ready output link and this has been exploited in [Sur90]. This is capable of yielding short routes in lightly loaded networks since necessary short cuts will almost always be free. The probability of the short cut being free decreases with increasing network loading; message path lengths are extended which in turn exacerbates loading.

### 2.4.4 Acyclic Routing

#### Definitions

The description of the interconnection network will frequently refer to properties of graphs; it is useful to define the terms used at this early point. In this context a graph is a directed graph, i.e. there is a direction associated with edge, and we treat undirected graphs by constructing two opposing directed edges from each undirected edge.

A graph (V, E) is strictly undirected if for every edge  $E_{ij}$  there is an opposing edge  $E_{ji}$ , i.e.

$$E_{ij} \Rightarrow E_{ji} \forall i, j.$$

A graph (V, E) is strictly directed if for every edge  $E_{ij}$  there is no opposing edge  $E_{ji}$ , i.e.

$$E_{ij} \Rightarrow \neg E_{ji} \forall i, j.$$

A path within a graph (V, E) is subset of E leading continuously from one of V to another. The predicate  $\mathcal{P}_{i \to j}^{(E,V)}$  is true iff there is a path in E from  $V_i$  to  $V_j$ , i.e.

$$\mathcal{P}_{i \to j}^{(V,E)} \Rightarrow E_{ij} \lor (E_{ik} \land \mathcal{P}_{k \to j}^{(V,E)}).$$

A graph (V, E) is *conjoint* iff there is path in E from every vertex to every other vertex, i.e.

$$V_i \wedge V_j \wedge i \neq j \Rightarrow \mathcal{P}_{i \to j}^{(V,E)} \forall i, j.$$

A graph (V, E) is *acyclic* iff it contains no paths from any vertex back to itself,

$$V_i \Rightarrow \neg \mathcal{P}_{i \to i}^{(V,E)} \forall i$$

A graph (V, E) is *loosely acyclic* iff every strictly directed subgraph (V', E') of (V, E) is acyclic.

#### Components

Familiar features of the interconnection network are the processors and communication links. We denote the set of processors by P and refer to an individual processor with label i as  $P_i$ . We denote the directed communication links by L, each element of L is a processor pair ij,  $i \neq j$ , indicating that processor  $P_i$  is physically connected to processors  $P_j$ .

We demand that the physical links are bidirectional so that the graph (P, L) is strictly undirected; each physical link is a pair of directed communication links  $L_{ij}$ ,  $L_{ji}$ . We also demand that self links, i.e. a physical link which connects a processor to itself, be absent. Multiplet links, i.e. a set of more than one physical links connecting the same pair of processors, are formally merged into a single physical link.

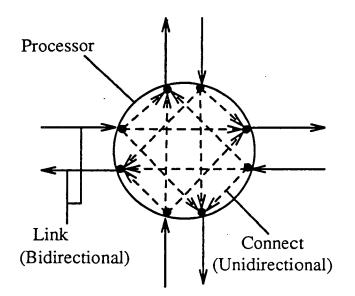

Figure 2.5: Processors, Links and Connects.

We express communication link dependency by the connect matrix, denoted by C. Each element of C is a processor triple  $C_{ijk}$ ,  $i \neq j \neq k$ , which determines the way in which  $L_{ij}$  may, or may not, forward data to  $L_{jk}$ . Note that the graph (L, C), in which  $C_{ijk}$  is shorthand for  $C_{ijjk}$ , is strictly directed. The relationship of processors, links and connects is depicted in Figure 2.5. We represent an interconnection network by (P, L, C), the combination of these three elements.

We define some useful quantities with which to describe an interconnection network.

A route within an interconnection network (P, L, C) is a subgraph of (L, C)which leads continuously from one processor to another. The predicate  $\mathcal{R}_{i \to l}^{(P,L,C)}$ is true iff there is a route in (L, C) from  $P_i$  to  $P_l$ , i.e.

$$\mathcal{R}_{i \to l}^{(P,L,C)} \Rightarrow L_{il} \lor \neg (\neg (L_{ij} \land \mathcal{P}_{ij \to kl}^{(L,C)} \land L_{kl}) \forall j, k).$$

An interconnection network (P, L, C) is fully connected iff there is a route from every processor to every other processor, i.e.

$$P_i \wedge P_j \wedge i \neq j \Rightarrow \mathcal{R}_{i \to j}^{(P,L,C)} \forall i, j.$$

An interconnection network (P, L, C) is cycle free iff (L, C) acyclic, i.e.

$$L_{ij} \Rightarrow \neg \mathcal{P}_{ij \to ij}^{(L,C)} \forall i, j.$$

#### Simple Graphs

**Routing** We associate a network element with each link  $L_{jk}$ . Each element will accept the first unit of a message from an element at any adjacent link  $L_{ij}$  and any source at  $P_j$  by performing a conditional input from all such elements and sources.

An element at link  $L_{ij}$  will establish the next link for a message  $\alpha$ , destined for a sink at processor  $d(\alpha) \neq j$ , by performing a conditional output of the first unit of  $\alpha$  to all links  $L_{jk}$  satisfying

$$\left(\neg (\neg \mathcal{P}_{jk \to k'd(\alpha)}^{(L,C)} \forall k') \land (C_{ijk} \lor w(\alpha) \leq u\right).$$

A source at processor  $P_j$  will similarly establish the first step of a message by conditional output to all elements  $L_{jk}$  satisfying

$$eg(\neg \mathcal{P}^{(L,C)}_{jk \to k'd(\alpha)} \,\forall \, k')$$

Note that these rules do not prevent messages  $w(\alpha) \leq u$  from *looping*; i.e. repeatedly following the same path. It is therefore necessary to restrict the links which may be used in through routing in order to avoid this phenomenon and any restriction which contains at least one of the links for which  $C_{ijk}$  is true will be permissible.

#### Multigraphs

We extend the notation for an interconnection network to explicitly handle multilinks. An extended network is constructed from an underlying cycle free and fully connected physical network, without multilinks, by imposing a linear order on the components of multilinks.

**Extended Interconnection Network** Let each communication link  $L_{ij}$  be composed of  $M_{ij}$  multilinks. Denote components of the multilink by  $L'_{inj}$ ,  $n \in (0, M_{ij}]$  with unique labels n.

Denote connects between multilink elements by  $C'_{imjnk}$ ,  $m \in (0, M_{ij}]$ ,  $n \in (0, M_{jk}]$ . Construct the connect matrix by applying:

$$C'_{imjnk} \Rightarrow L'_{imj} \land L'_{jnk} \land i \neq j \land j \neq k \land k \neq i \land ((n > m) \lor (n = m \land C_{ijk}))$$

Cycle Free There are no *n*-cycles for n = 1, 2 by virtue of

$$C'_{imjnk} \Rightarrow i \neq j \land j \neq k \land k \neq i$$

Expanding an *n*-cycle, n > 2, in (L', C') one readily obtains

$$\mathcal{P}_{i_0m_0i_1 \to i_0m_0i_1}^{(L',C')} \Rightarrow (L_{i_0i_1} \land \ldots \land L_{i_ni_0}) \land (\mathcal{P}_{i_0i_1 \to i_0i_1}^{(L,C)} \lor (m_0 < m_1 \land \ldots m_n < m_0))$$

which cannot be true because (L, C) is acyclic.

Fully Connected The construction of  $C_{imjnk}$  yields

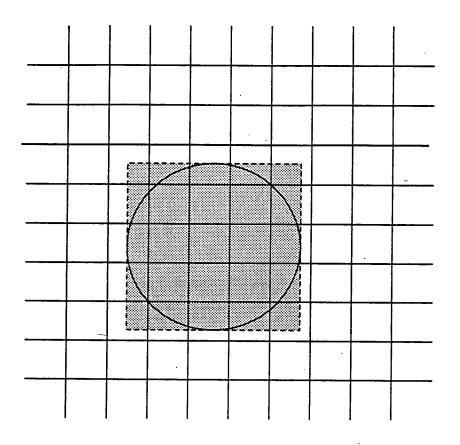

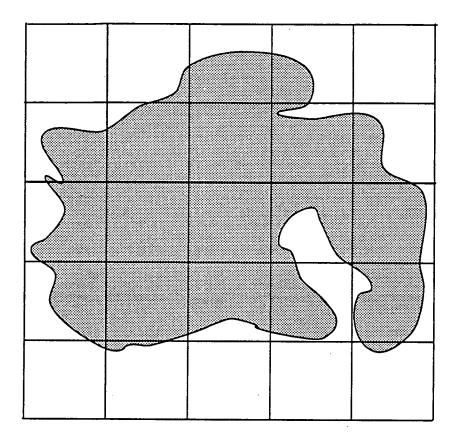

$$C_{ijk} \Rightarrow C_{imjnk} \forall i, j, k, m, n$$