# IDIOMATIC INTEGRATED CIRCUIT DESIGN

Neil Bergmann

Ph.D.

University of Edinburgh

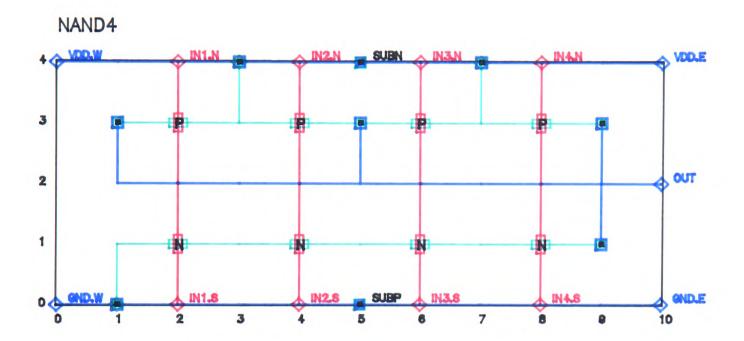

### ABSTRACT

An examination is made of the capture, storage and instantiation of well-known, generalised structures used in the design of MOS integrated circuits. These structures are called "idioms".

The capture of an idiom for translating from a high level language specification to a complete digital signal processing system, called the FIRST silicon compiler, is examined.

A system is presented which allows and encourages the capture of a large number of idioms at the cell level of IC design. This system is based on a purely textual language, VIRGIL, which captures circuits and idioms at the sticks level, in terms of a set of structural components laid out on a so-called virtual grid. The language supports parameterisation, selection and repetition as textual operations, and also allows idioms to be composed from a set of leaf cells which are joined by simple abutment.

An algorithm is presented for the conversion of virtual grid circuits into mask level representations, and in so doing the notion of a quasi-virtual grid is introduced.

A new style of CMOS design, called "generalised CMOS", is introduced, which allows the design of circuits which could be fabricated in a wide range of CMOS technologies. An idea for a method of converting existing mask level circuits into other technologies, called "sticks extraction", is presented.

A prototype implementation of a system to support the capture of idioms using the VIRGIL language, and their subsequent instantiation including conversion to mask geometry is discussed, and examples of idioms which have been captured by this system are presented.

### **ACKNOWLEDGEMENTS**

I would like to thank my supervisor, David Rees, for his guidance, support and encouragement throughout the period of my study for this thesis. Thanks must also go to the many people within the University of Edinburgh who assisted me during this time, most especially John Gray, Irene Buchanan, Gordon Hughes, Hamish Dewar, Peter Denyer and David Renshaw.

I am grateful to the University of Edinburgh for providing the facilities to conduct this research, and to the Association of Commonwealth Universities for their fianancial support under the Commonwealth Scholarship scheme.

### DECLARATION

I hereby declare that this thesis has been composed by myself and that the work described in this thesis is my own.

24.5.84

# CONTENTS

| 1: Intr | oduction9                                  |

|---------|--------------------------------------------|

| 1.1:    | The Need for Research into CAD for VLSI9   |

| 1.2:    | CAD in VLSI Design Capture10               |

| 1.3:    | Current CAD Tools for Design Capture       |

| 1.4:    | The Notion of Design "Idioms"19            |

| 1.5:    | The Scope of this Thesis                   |

|         |                                            |

| 2: The  | Current State of the Art25                 |

| 2.1:    | Structured VLSI Design                     |

| 2.2:    | VLSI Design Languages and                  |

|         | Programming Languages                      |

| 2.3:    | Design Languages and Verification28        |

| 2.4:    | VLSI Design Languages &                    |

|         | the Control of Complexity31                |

| 2.5:    | Composition of VLSI Designs33              |

| 2.6:    | Methods of Circuit Description37           |

| 2.7:    | Sticks Compaction41                        |

| 2.8:    | Technology Independent Design43            |

| 2.9:    | Cell Libraries45                           |

| 2.10    | : Silicon Compilers46                      |

|         |                                            |

| 3: The  | F.I.R.S.T. Silicon Compiler48              |

| 3.1:    | Background to the FIRST Silicon Compiler48 |

| 3.2:    | An Innovative Architecture49               |

| 3.3:    | Software Support for an                    |

|         | Integrated Design Environment              |

|    | 3.3.1: La    | nguage C | ompiler     | • • • • • • •                           | • • • • • • •   | 52   |

|----|--------------|----------|-------------|-----------------------------------------|-----------------|------|

|    | 3.3.2: Sin   | nulation |             |                                         | • • • • • • •   | 58   |

|    | 3.3.3: Ph    | ysical L | ayout       | • • • • • • • •                         | • • • • • • •   | 6 1  |

|    | 3.4: An Exam | mple Sys | tem         | • • • • • • •                           | • • • • • • •   | 65   |

|    | 3.5: Conclus | sions    | • • • • • • |                                         | • • • • • • •   | 7 0  |

|    |              |          |             |                                         |                 |      |

| 4: | : An Idiom D | escripti | on Lang     | uage                                    | • • • • • • •   | 72   |

|    | 4.1 The Vir  | tual Gri | .d          |                                         |                 | 7 2  |

|    | 4.2 Idioms   | and Inst | antiati     | ons                                     |                 | 7 7  |

|    | 4.3: VG - A  | Virtual  | Grid C      | ircuit                                  |                 |      |

|    | Descri       | ption La | nguage.     |                                         |                 | 78   |

|    | 4.3.1 Not    | es About | the La      | nguage D                                | escriptio       | on80 |

|    | 4.3.2 Alp    | habet    | • • • • • • |                                         |                 | 81   |

|    | 4.3.3 Ide    | ntifiers | 3           |                                         | • • • • • • •   |      |

|    | 4.3.4 Res    | erved Wo | ords        |                                         |                 |      |

|    | 4.3.5: Nu    | merals a | and Expr    | essions.                                | • • • • • • • • | 32   |

|    | 4.3.6: St    | atements | 3           |                                         |                 | 8 4  |

|    | 4.4: VG Lea  | f Cells. |             |                                         | • • • • • • • • | 8 4  |

|    | 4.4.1 Lea    | f Cell H | leader a    | nd Termi                                | nator           | 84   |

|    | 4.4.2: Le    | af Cell  | Compone     | nt Speci                                | fication.       | 8 5  |

|    | 4.4.3 An     | Example  | Leaf Ce     | ll Descr                                | iption          | 96   |

|    | 4.5: VG Com  | position | n Cells.    | • • • • • • • • • • • • • • • • • • • • | • • • • • • • • | 96   |

|    | 4.5.1: He    | ader and | l Termin    | ator Sta                                | tements.        | 9 9  |

|    | 4.5.2: Ba    | sic Comp | osition     | Operato                                 | ors             | 9 9  |

|    | 4.5.3: Ro    | tation a | ind Refl    | ection                                  | •••••           | 105  |

|    | 4.5.4: Po    | rt Hidin | ng & Ren    | aming                                   | • • • • • • • • | 1 08 |

|    | 4.6: VIRGIL  | - An Id  | liom Des    | cription                                | Language        | e113 |

|    | 4.6.1: Pa    | rameteri | sation      |                                         |                 | 114  |

|     |     | 4.    | 6.  | 2:  | Se  | e16   | ect          | io           | n.  |     | • • |     |       | • •          | • •          |       | • •   |     |              |     |     | •  | • • | • ( | •   | • • | . 1 | 17             |

|-----|-----|-------|-----|-----|-----|-------|--------------|--------------|-----|-----|-----|-----|-------|--------------|--------------|-------|-------|-----|--------------|-----|-----|----|-----|-----|-----|-----|-----|----------------|

|     |     | 4.    | 6.  | 3   | Rej | pet   | tit          | io           | n.  |     |     |     |       |              |              |       |       |     |              | • • |     | •  |     | • • |     | • • | . 1 | 18             |

|     |     | 4.    | 6.  | 4:  | Qı  | ua]   | Lif          | 'ie          | rs  |     |     |     | • •   |              |              | • •   |       |     |              |     |     | •  | • • | • • |     | • • | . 1 | 20             |

|     | 4.  | 7:    | С   | ir  | cu: | it    | Co           | nn           | еc  | ti  | o n | 8   | an    | đ            | th           | ei    | r     | ۷a  | 11           | di  | ty  |    |     | • • |     | • • | . 1 | 21             |

|     | 4.  | 8:    | A   | n : | Exa | a m j | ple          | : I          | di  | om  |     |     |       |              | • •          | • •   |       |     |              |     |     | •  |     | • ( |     |     | . 1 | 33             |

|     | 4.  | 9:    | S   | um  | ma  | ry.   | • • •        | • •          |     |     |     |     |       |              |              |       |       |     |              |     |     | •  |     | • • |     | • • | . 1 | 43             |

|     |     |       |     |     |     |       |              |              |     |     |     |     |       |              |              |       |       |     |              |     |     |    |     |     |     |     |     |                |

| 5 : | : s | ti    | c k | s   | Coi | npa   | act          | io           | n   | of  | t   | h e | · V   | 'i r         | • <b>t</b> ı | ıal   | . G   | ri  | .d.          |     |     | •  |     | • • |     | • ( | . 1 | 45             |

|     | 5.  | 1:    | В   | ac  | k g | roi   | ınd          | i.,          |     |     |     |     |       |              |              | · • • |       |     |              |     |     |    |     | • • |     | • • | . 1 | 45             |

|     | 5.  | 2     | Ma  | sk  | L   | eve   | el           | Re           | pr  | es  | e n | ta  | ti    | . o r        | n c          | n     | a     |     |              |     |     |    |     |     |     |     |     |                |

|     |     |       | Qu  | a s | i-  | Vi    | rti          | ıal          | G   | ri  | d.  |     |       |              |              |       |       |     |              |     |     |    |     | • • |     | • • | . 1 | <del>4</del> 8 |

|     | 5.  | 3:    | T   | ra  | ns  | la    | tic          | n            | to  | a   | Q   | )ua | si    | . <b>–</b> 1 | Jir          | rtu   | al    | . G | ri           | d.  |     | •  |     | •   |     | • , | . ; | 55             |

|     | 5.  | 4:    | D   | ev  | ic  | e '   | Ten          | ıpl          | at  | e s |     |     |       |              |              | · • • |       |     |              |     |     | •  |     | • • |     | • . | . 1 | 59             |

|     | 5.  | 5     | Со  | or  | di  | na    | te           | Ma           | pр  | in  | gs  | · • |       | • •          |              |       | • •   |     |              |     |     |    |     | •   |     | •   | . 1 | 57             |

|     | 5.  | 6:    | T   | 'ra | ns  | la    | tio          | o n          | of  | С   | MO  | S   | Ci    | r            | ui           | its   | s t   | . 0 | Ma           | sk  | : L | .e | v e | 1   |     |     | . 1 | 73             |

|     | 5.  | 7:    | S   | ti  | ck  | S     | Ext          | tra          | ct  | io  | n.  |     |       |              | • • •        |       | • • • |     |              |     |     |    |     |     |     | •   |     | 83             |

|     | 5.  | . 8 : | : 5 | um  | ma  | rу    |              |              |     |     |     |     |       |              |              |       |       |     |              |     |     |    |     | •   | • • | •   | . 1 | 96             |

|     |     |       |     |     |     |       |              |              |     |     |     |     |       |              |              |       |       |     |              |     |     |    |     |     |     |     |     |                |

| 6   | : A | l P   | ro  | to  | tу  | рe    | Ir           | npl          | em  | en  | ta  | ıti | . o r | ı (          | of           |       |       |     |              |     |     |    |     |     |     |     |     |                |

|     | t   | :he   | · V | IR  | GΙ  | L     | Sys          | 3 <b>t</b> e | m.  |     |     | • • |       |              | • • •        |       |       |     | • •          |     |     |    |     | •   |     | •   | . 1 | 98             |

|     | 6.  | 1:    | S   | уs  | te: | m     | 0 <b>v</b> e | erv          | 'ie | w.  |     | • • | • •   |              | • • •        |       |       |     |              |     |     |    |     |     |     |     | . 1 | 98             |

|     | 6.  | 2:    | A   | C   | el  | 1     | Lil          | ora          | ri  | a n |     |     |       |              |              |       |       |     |              |     |     | •  |     | •   |     | •   | . 1 | 98             |

|     | 6.  | 3:    | T   | еx  | t   | An    | aly          | ysi          | s.  |     |     |     |       |              | • •          | • • • |       | • • |              |     | •   |    |     |     |     |     | . 2 | 00             |

|     | 6.  | 4:    | I   | nt  | er  | naj   | 1 I          | Rep          | re  | se  | nt  | at  | ic    | n            | 01           | î a   | a V   | /ir | • <b>t</b> ı | ıal | . ( | ir | id  | . • |     |     | . 2 | 0 1            |

|     |     |       |     |     |     |       | ng           |              |     |     |     |     |       |              |              |       |       |     |              |     |     |    |     |     |     |     |     |                |

|     |     |       |     |     |     |       | ng           |              |     |     |     |     |       |              |              |       |       |     |              |     |     |    |     |     |     |     |     |                |

|     |     |       |     |     |     |       | ing          |              |     |     |     |     |       |              |              |       |       |     |              |     |     |    |     |     |     |     |     |                |

|     |     |       |     |     |     |       | ior          |              |     |     |     |     |       |              |              |       |       |     |              |     |     |    |     |     |     |     |     |                |

| <b>6.9: User Interface</b> 205                   |

|--------------------------------------------------|

| 6.10: Some Implementation Issues                 |

|                                                  |

| 7: Example Idioms210                             |

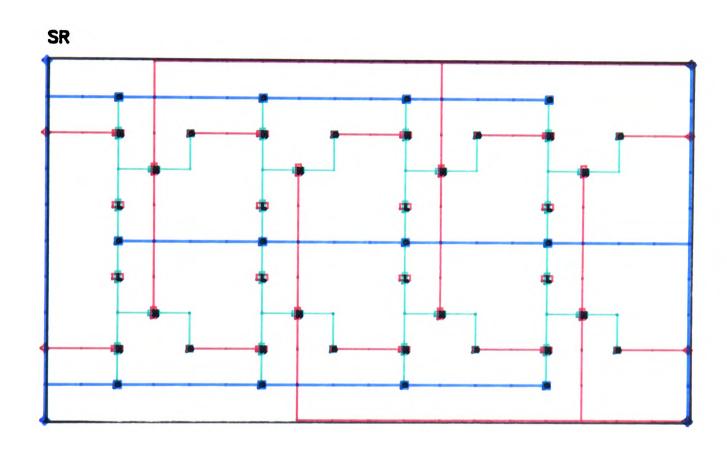

| 7.1: Shift Register210                           |

| 7.2: Programmable Logic Array210                 |

| 7.2.1 Introduction                               |

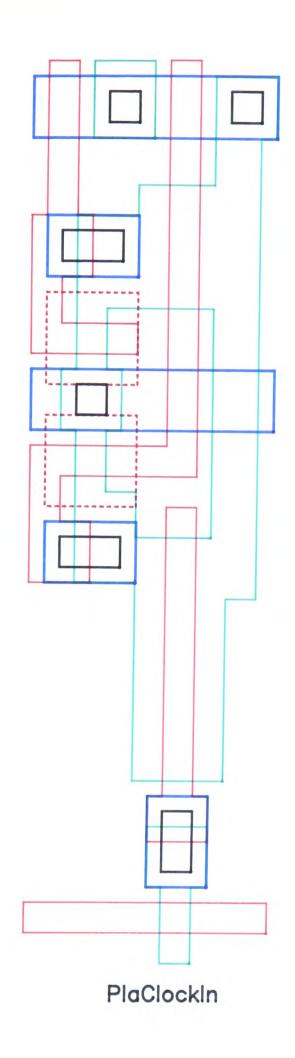

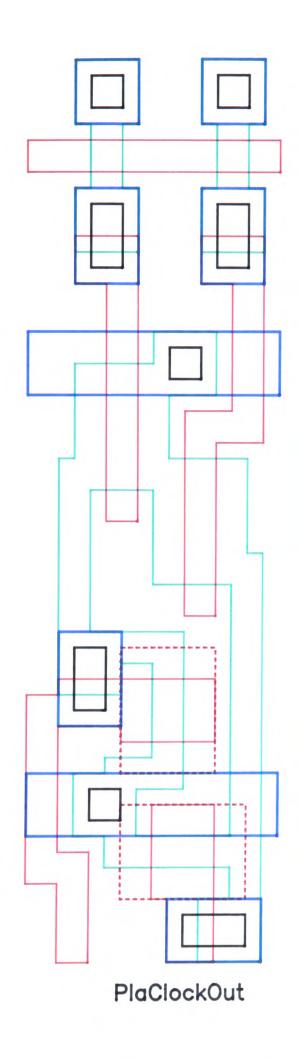

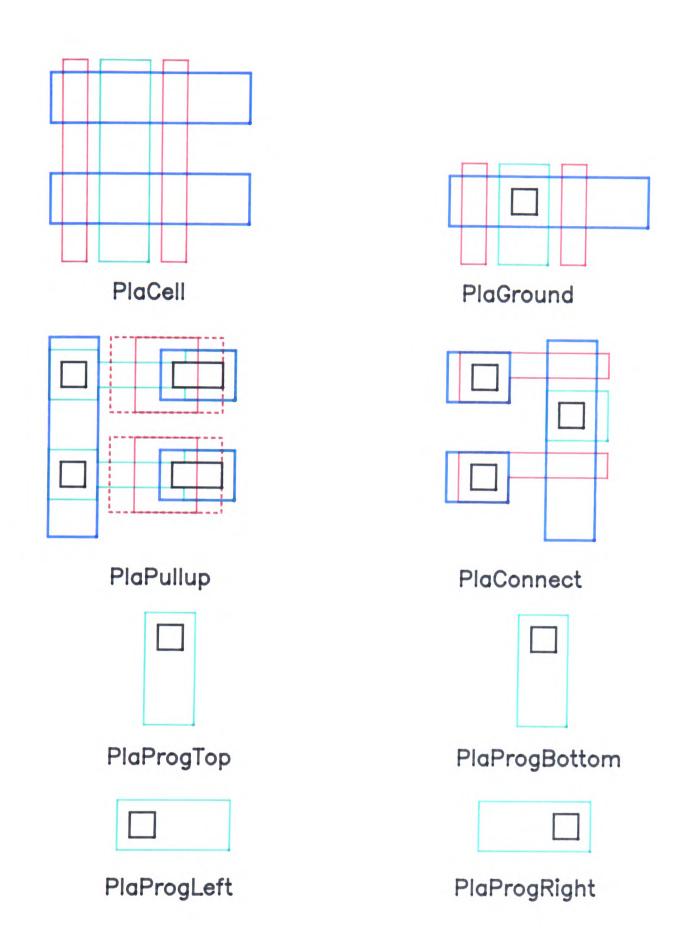

| 7.2.2: Capture at the Mask Level213              |

| 7.2.3: Capture Using VIRGIL215                   |

| 7.2.4: Comparison and Discussion221              |

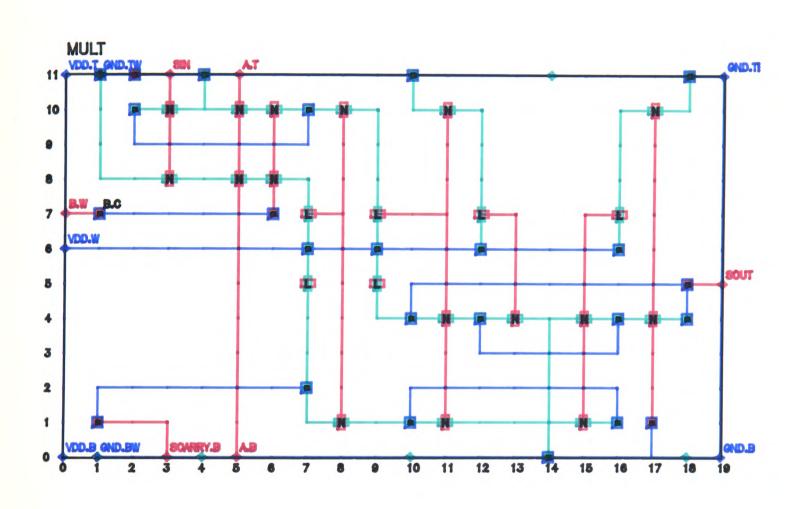

| 7.3: Parallel Multiplier223                      |

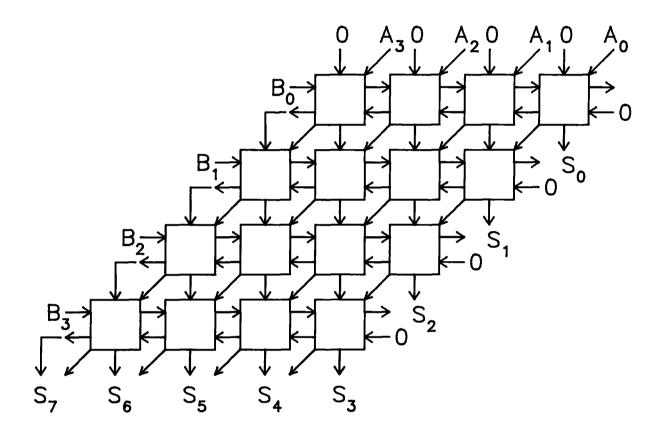

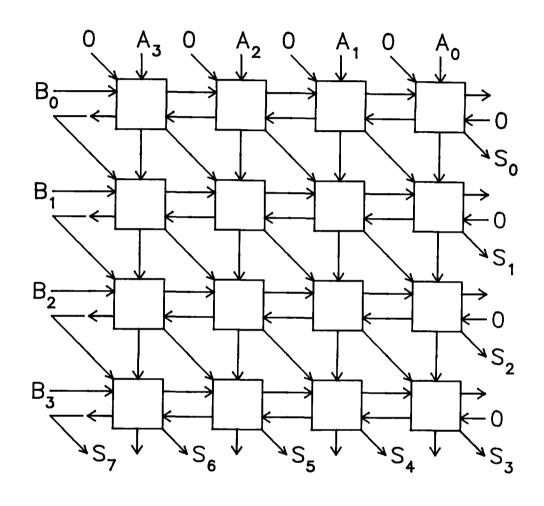

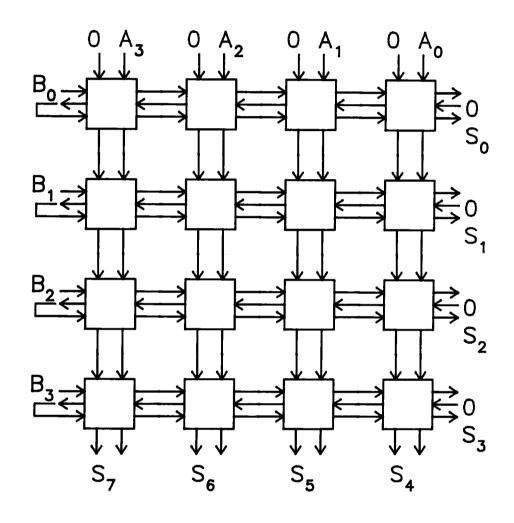

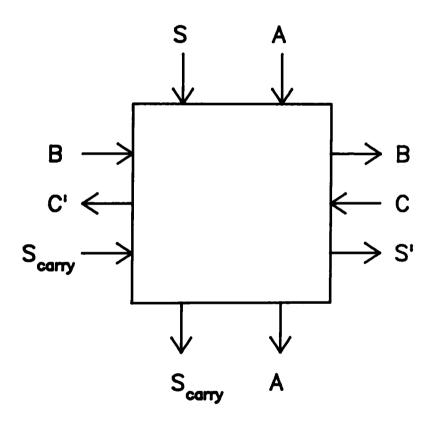

| 7.3.1 A Hardware Algorithm223                    |

| 7.3.2: A Multiplier Circuit229                   |

| 7.3.3: A Multiplier Chip232                      |

| 7.3.4: Discussion234                             |

|                                                  |

| 8: Conclusions and Limitations235                |

| 8.1: Conclusions235                              |

| 8.2: Limitations & Areas for Further Research238 |

|                                                  |

| Appendix A: VIRGIL "include" File                |

| Appendix B: PLA Mask Level Leaf Cells251         |

| Appendix C: PLA VIRGIL Cell Definitions257       |

| Appendix D: Mutiplier Cell Definitions275        |

|                                                  |

| Pefenences                                       |

#### 1: INTRODUCTION

### 1.1: The Need for Research into CAD for VLSI

A revolution is now underway which is comparable in scale and importance to the industrial revolution. This new revolution is based on the emerging field of Information Technology. One of the cornerstones of Information Technology is the provision of cheap, readily accessible computing power. It is only through the extensive use of Very Large Scale Integrated (VLSI) circuits that this power can be realised. The design of integrated circuits is then an area of immense interest, and will remain so for the forseeable future.

VLSI circuits are among the most complex systems designed by man. Mead [Mead 81] compares the design of an integrated circuit using the technology available by the end of this decade with the task of designing an urban density road network the size of an entire continent. Even with current leading edge technologies, managing the mere complexity of a VLSI circuit is the most pressing problem facing design engineers. Research into methods of handling this complexity is one of the most important tasks facing the academic and industrial communities. The provision of sophisticated Computer Aided Design (CAD) systems does and will continue to play a major role in the management of VLSI designs.

# 1.2: CAD in VLSI Design Capture

There are several rather distinct steps which can be identified in the design of VLSI circuits. These steps cannot be treated in complete isolation, rather each step should be considered in relation to the others.

Firstly, there is the specification of the intended function of the system to be designed. Next is the translation of this specification into a description of a physical realisation of that system. Next is the verification that the intended realisation performs the specified function. Finally there is device fabrication. The area of interest in this thesis is the translation of some specification into a description of a physical realisation, here called the design capture phase.

An integrated circuit is fabricated using a set of masks to define the patterns which will appear on the different physical layers of the circuit. The masks are in turn fabricated from some machine readable description of the geometric patterns which comprise them. Within the research and academic communities, a standard language for describing such patterns, CIF 2.0 [Mead 80], has now been established. The design capture phase may then be considered as the production of a CIF description of an IC from some initial specification.

The production of a set of mask descriptions is not a straightforward task, but rather it is a complicated and error prone process of multiple translations, each into a finer level of detail. A typical set of such translations might be as follows.

- (1) Translation of a general product specification, which may be a rather imprecise natural language description, into a formal behavioural specification, such as a set of input / output relations.

- (2) Design of an algorithm to implement the behavioural specification.

- (3) Choice of a hardware architecture to support the algorithm, and thence production of a system block diagram.

- (4) Mapping of the block diagram into a two-dimensional floorplan of a chip.

- (5) Production of logic diagrams to implement each hardware block.

- (6) Translation of logic circuits into a topological arrangement of transistors and their interconnections.

(7) Translation of this topological arrangement into final mask geometries.

Although such a description of the design process is perhaps oversimplified, it does serve to illustrate the number of different levels at which descriptions of a design exist, and the number of translations, each into a finer level of detail, which must be done to produce the final mask geometries. Such translations can be performed manually, or with the aid of CAD tools. Since the final design description exists as a machine readable CIF description, the designer's intent must at some stage be captured by a suitable CAD system. Once captured, the CAD system may then perform one or more of the above translations to yield the final mask level description.

Ideally, it might seem that this design capture should occur at as high a level as possible, so as to reduce the number of error-prone translations which must be performed manually. However, none of the translations are by any means straightforward. While it is probably true that CAD tools exist to perform all of the translations in some form or other, none of these tools are yet able to match the flexibility and ultimate area efficiency of good manual design. At present, the major advantages of automatic translations are that they are far quicker and less likely to contain design errors, so reducing both the length and number of design iterations

necessary. They are therefore most used in low and medium volume applications, where design cost is the major portion of overall device cost.

The tradeoffs which exist between automated and manual design are sufficiently varied for different applications that CAD tools which capture designs at many different levels are still used. As long as CAD tools do not perform as well as manual designers, such tradeoffs will continue to exist. One motivation for this thesis is to examine aspects of manual design and incorporate these into automated design systems, to make the latter more competitive.

#### 1.3: Current CAD Tools for Design Capture

A great variety of CAD tools for design capture already exist, and it is useful to examine some of these tools to place the work of this thesis in its correct perspective.

The most basic method of converting VLSI designs into machine readable form is by digitizing hard copy representations of mask geometries. Such a process is very error-prone, and is not viable for designs of VLSI complexity.

A more direct method of capturing designs at the mask level is by the use of a graphics workstation. Here the designer is able to create and manipulate shapes representing the actual mask geometries using some form of graphics editor. Such workstations allow the definition of individual cells, and also the composition of these cells to produce complete chips.

Design capture by graphics workstations is now quite a mature field, with many commercial manufacturers offering such systems for sale [Werner 83]. Design at the mask level gives the designer maximum flexibility to decide on the final circuit geometries. However, the designs produced at this level are not constrained to represent valid circuit constructs, and the detection and correction of errors in the mask definitions is a time-consuming task. Often such errors are not detected until prototype devices are fabricated.

Design directly at the mask level also suffers from another major disadvantage. The individual cells which make up a design are described absolutely in terms of their mask geometries. Such cells are considered to be "hard", in the sense that their structure is fixed. A change in one cell will often require changes to be made in many adjoining cells.

A solution to this problem is to design cells to be "soft", i.e. to be able to adapt automatically to their surroundings. The simplest method of achieving this is to describe cells, and indeed the whole chip, not as a set of mask geometries, but rather as a computer program which produces those geometries. If cells are carefully described in terms of their relationships with neighbouring cells, then when a change is made to one cell, and the program run again to produce a new design, all dependent cells will also have changed to match. Design by program also allows inherently programmable structures, such as PLA's to be easily described.

This type of IC design language can be produced by adding a set of routines to draw mask shapes onto an existing programming language. Such a language is called an embedded IC design language. This approach allows the full data and control structures of the original language to be used. Useful features can be added incrementally to the library of available routines to continually enrich and improve the language. An excellent example of such an approach is the language ILAP [Hughes 83], developed at Edinburgh University, and embedded in the programming language IMP [Robertson 83].

The amount of parameterisation which can be introduced into a design description using an embedded language is virtually unlimited, even to the extent of producing a

silicon compiler [Bergmann 83]. However, the design is still being specified in terms of the final mask patterns, and the responsibility still rests with the designer to ensure that these patterns represent valid circuits.

An alternative to embedded IC design languages is the use of a special purpose design language. In this case special syntactic structures are used to specify mask features. Such descriptions tend to be clearer and more concise than embedded language descriptions, however special purpose languages are usually not as rich in control and data structures. In addition, they require special compilers to be written for them. Examples of such languages are SILT [Davis 82], and SCALE [Marshall 84].

Some special purpose languages attempt to constrain the designer in the mask descriptions which can be described, in an attempt to reduce the possibility of design errors. Such languages are also able to provide special syntactic structures to aid in the composition of designs. SCALE [Marshall 84] is an example of such a language.

Many of the problems of mask level design can be attributed to the fact that a circuit is not constructed from arbitrary mask shapes, but rather from a set of

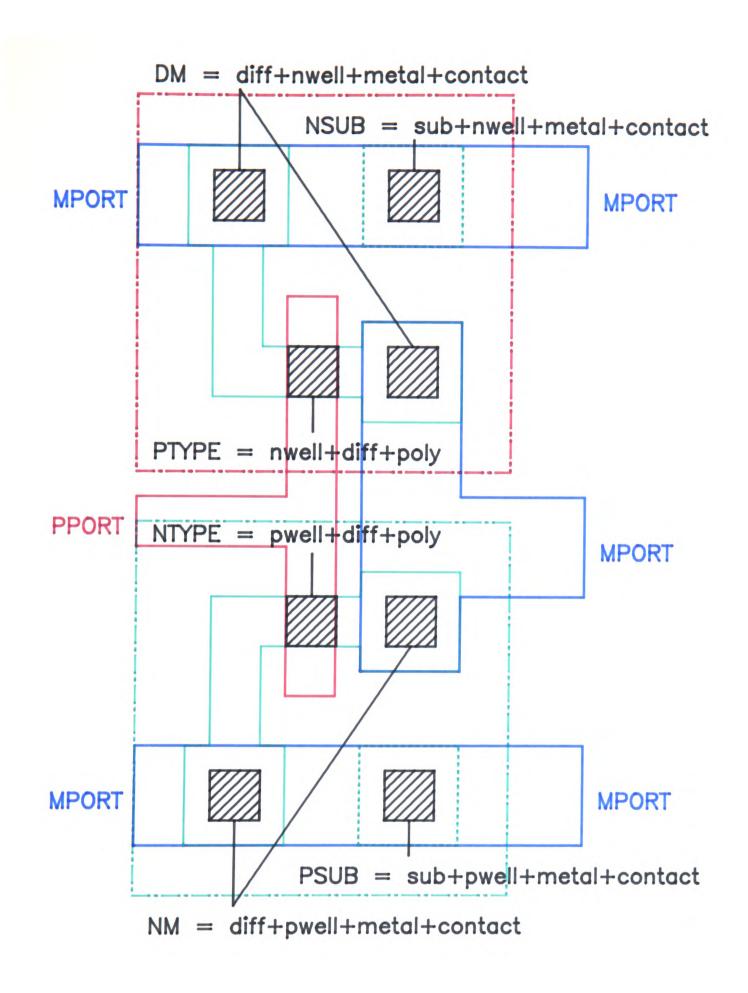

items with real circuit significance, notably transistors, wires, contacts and bonding pads. It is therefore sensible to allow a designer to design in terms of these structural components [Buchanan 80], rather than the mask shapes which comprise them. Also it is usually not the absolute position of such items which is important, but rather their topological arrangement with respect to each other. Design at the level of a topological arrangement of structural components is popularly referred to as "sticks" design [Williams 77], or alternatively as symbolic design.

Since sticks designs are concerned primarily with the relative placement of components, and not their absolute positions, sticks cells are inherently "soft" cells.

Thus the speed and convenience of graphical entry can be used without the disadvantages of "hard" cell descriptions. An example of a primarily graphics based sticks system is MULGA [Weste 81b]. Sticks descriptions can also be language based. ABCD [Rosenberg 82] is an example of a sticks language.

Since sticks descriptions do not specify the exact positions of structural items, the design is no longer tied to a single fabrication process, with its accompanying design rules. Rather, the conversion from sticks to mask geometries can incorporate these design rules, and so allow a single description to be fabricated

using several different technologies.

At levels of abstraction above sticks level, the designer is removed from many of the topological details of the final design. The design system itself determines these details. This can be done in two ways - either the system restricts the designs to a limited class of topological arrangements which are built into the system, or the system deduces a suitable arrangement from scratch, using sophisticated algorithms to do so. The fundamental principles by which such arbitrary arrangements should be determined are not well understood, and in general systems to produce arbitrary layouts do not perform particularly well.

Design at the logic level, in terms of boolean logic function primitives, is at present mostly restricted to standard cell systems. Here the designer is presented with a library of cells to perform various logic functions, which can then be connected together to produce complete chips. DUMBO [Wolf 83a], is an example of a system which can lay out arbitrary logic functions.

At the highest level are systems which take behavioural descriptions of complete systems, and produce complete chips which implement the specified behaviour. At present, all such systems - called silicon compilers - produce chips only within a limited architectural

framework. Often such systems are also restricted in the class of behavioural descriptions they can translate. Examples of such systems are Bristle Blocks [Johannsen 79], FIRST [Bergmann 83], Model [Gray 82], MacPitts [Siskind 82] and UNIT [Deas 83].

# 1.4: The Notion of Design "Idioms"

It has been shown that design capture can occur at any one of a large number of levels of abstraction. However all design capture mechanisms share a common feature - capture is achieved by the use of a fixed set of design primitives. These primitives vary from complete functional units in the case of a silicon compiler down to simple geometric shapes in the case of mask level design. Nonetheless, the design process remains one of composing elements from a set of available primitives together to give a system which exhibits the required behaviour.

One of the principle arguments in this thesis is that the composition of primitives to give solutions to specific problems relies heavily on the use of known constructs. These known constructs are called idioms, and the aspect of design concerned with their use is called idiomatic design. Idioms are in some sense the embodiment of a designer's experience.

Examples of idioms abound in IC design. At the mask level, structural primitives such as transistors and contacts could be considered as idioms constructed by overlaying particular shapes on particular layers. These idioms are so important that almost all mask level design systems include them in their set of design primitives.

It has already been explained that IC design involves translations into finer and finer levels of detail.

Idioms can be seen as known ways of making these translations. The Gate Array can be considered an idiom which maps a structural description in terms of interconnected transistors, onto a regular form of mask geometry. The PLA is an example of an idiom which maps from a set of boolean equations into mask geometries.

Idioms are equally valid whether the translations they represent are done manually or by CAD tools. In both cases, the larger the repertoire of idioms, the better the final design is likely to be. The aim of this thesis is then not just to investigate means of capturing designs but rather to investigate means of capturing idioms, so that these are available for use in many different designs.

## 1.5: The Scope of this Thesis

As described earlier, idioms exist at many different levels in the IC design process. For the purposes of this thesis, two areas of particular interest have been chosen.

The first of these is the investigation of idioms for the automatic production of complete integrated circuits - in other words, silicon compilers.

The second area of particular interest is in that of so-called "cell design". At this level, the designer produces the mask level layouts to implement individual logic functions. The division of a complete system into such cells is the final step in a top-down decomposition of a specification, and the design of these cells represents the first stage in a bottom-up implementation of that specification.

The study of idiomatic design at both these levels draws much from the ideas and principles developed in related fields of VLSI research. In chapter 2, the current state of research in these related areas will be examined, and some of the ways in which idiomatic design furthers many of these ideas will be noted.

Idioms at the two levels of particular interest in this thesis - cell idioms and silicon compiler idioms - differ not only in the level of the design hierarchy at which they exist, but also in the manner in which such idioms may be captured.

A silicon compiler represents the capture of a single, quite complex idiom. In chapter 3, a suite of software, written by the author, to capture a single idiom for the production of signal processing chips will be examined. It will be shown that by the production of an integrated software environment to specifically support this one idiom, a quick and economical method for designing one class of systems can be developed.

At the leaf cell level, it is possible not just to capture single idioms, but to design a system for the capture and instantiation of a large number of useful idioms by the production of an appropriate idiomatic design system. The design and investigation of such a system forms the basis for much of the remainder of this thesis. Such an investigation is valuable for several reasons.

Firstly, this area of design already makes heavy use of idioms based on designer experience. There is therefore a need for a system which can formalise the collection and retrieval of such idioms.

Secondly, the structure of idioms at this level is relatively straightforward. The idioms are in some sense recipes for producing mask level circuits to implement particular functions. Methods of describing mask level descriptions are well understood. Indeed, the design of mask level descriptions of IC cells is one of the most intensively investigated areas of IC design. This has the twin advantages that the investigation of idiom capture at this level can benefit from principles used in more traditional design systems, and also that any new ideas investigated for use in idiomatic design are likely to have application in the wider field of custom cell design.

Because of this possibility of the wider applicability of idiom capture techniques, it has been decided that, where possible, new and novel methods of design description will be investigated. In this way the work of this thesis can contribute not only to the novel field of idiomatic design, but can also explore ideas with applicability to more traditional design styles.

The most fundamental decision to be made in the production of the idiomatic design system is the way in which idioms are to be described. It is argued that design capture at the "sticks" level (i.e. joint structural and topological level) has overwhelming advantages over other levels of design description, such

as mask level. Furthermore, it will be shown that a so-called "virtual grid" [Weste 81a] provides an attractive and elegant method of sticks level circuit description. To these ends, a novel sticks level circuit description language has been devised, and this is described in detail in chapter 4.

Since the ultimate output from the idiomatic design system is mask level descriptions, a translator from sticks to mask level is needed. Such "sticks compactors" are presently a topic of keen research interest. A sticks compactor which combines some well established ideas about compaction with some novel and original ideas is presented in chapter 5.

A prototype implementation of an idiomatic design system has been developed, and this is described in chapter 6, along with a discussion of some of the software engineering issues raised in the production of such a suite of software.

Several specific examples of cell idioms which have been entered into the idiomatic design system are described in chapter 7. Some conclusions about the work of the thesis, plus some possible areas of further research are presented in chapter 8.

## 2: THE CURRENT STATE OF THE ART

The work of this thesis draws from many fields of VLSI design, most of which remain areas of active research interest. In this chapter, it is intended to review the current state of research in these areas, and where possible relate them to the work of this thesis.

#### 2.1: Structured VLSI Design

VLSI circuits differ from other methods of digital system implementation in several important ways.

The most fundamental feature of VLSI circuits is their overwhelming complexity [Mead 81]. Circuits containing over 200,000 transistors are now being designed and fabricated, and the number of devices which can be accommodated in a single integrated circuit is expected to continue to increase exponentially for the foreseeable future [Noyce 77]. The prospect of designing circuits of such complexity is even more daunting when it is remembered that even one single design error may render an entire circuit useless.

Another fundamental feature of VLSI circuits is that interconnections often have an equal or greater influence on circuit size and performance than do functional elements such as transistors [Sutherland 77]. There is

an inherent wiring "cost" associated with communication within an integrated circuit which must be taken account of during design. It is therefore important to plan the way individual sections of the circuit will be composed together early in the design process. This includes both the relative positions of the various parts of a circuit ("floorplanning") and the way in which connections will be made between these parts.

About 1970, the need for a more methodical approach to writing computer software became apparent as computer programs became increasingly complex. This need resulted in the development of "structured programming" techniques [Wirth 71b] [Dijkstra 72] [Knuth 74] [NATO 76] [Alagic 78] [Yourdan 78], which subsequently lead to the development of languages designed to support these techniques, such as Pascal [Wirth 71a] [Jensen 74], Modula [Wirth 77a] and ADA [DoD 78] [ADA 79].

The rapidly increasing complexity of VLSI circuits has resulted in the development of a similar, structured approach to VLSI design. The publication, in 1980, of a book by Mead and Conway [Mead 80], which presented a simple, structured approach to VLSI design, was an important force in bringing about the widespread acceptance of this new methodology.

# 2.2: VLSI Design Languages and Programming Languages

The structured design approach to VLSI is often thought of as a "computer science" approach, since it borrows heavily from many ideas inherent in structured programming. Just as structured programming lead to the development of new programming languages, so structured VLSI design has lead to a great deal of research into new VLSI design languages.

However, although new programming languages were quickly developed and widely accepted as a result of the development of structured programming, the development of VLSI design languages to support structured VLSI design are still mostly in the research stage, and no single language has yet to gain any wide acceptance outside the institutions where it was developed.

This can largely be attributed to some fundamental differences between the nature of computer programs and VLSI circuits. The most important of these is that in computers, memory is arranged as a one dimensional set of locations, all of which are more or less equally accessible. This corresponds well to the one dimensional nature of computer program text.

On the other hand, an IC is a two dimensional structure, where only physically adjacent points are accessible from any position in the circuit. The placement of the elements in an integrated circuit can have a major effect on circuit size and performance, since interconnecting elements must be physically joined by a wire which consumes space and has an inherent propagation delay.

The best way to represent the two dimensional aspects of a VLSI circuit in an essentially one dimensional textual language is by no means certain, and some of the diversity of VLSI design languages can be attributed to this uncertainty. It is argued that the development of VLSI design languages is fundamentally a more difficult problem than the development of programming languages, and in the following sections some of the features which affect the design of such languages are discussed.

# 2.3: Design Languages and Verification

Since the fabrication of a silicon chip is a lengthy and expensive process, and since chips cannot, in general, be modified after fabrication, it is essential that every effort be made to ensure that a design is correct before fabrication begins. This is called verification, and the ease with which design verification can be done is dependent on the design language used.

At the highest level, design languages for use with silicon compilers provide a functional description of a circuit. This functional specification can be simulated directly to determine the performance of the complete system at a functional level. Examples of such languages are the input language for FIRST, described in chapter 3, and also the language MODEL [Gray 82], which has its own special simulator called EXERT.

Design languages at the mask level have traditionally tended to describe only the physical geometry of circuits. In order to simulate a circuit it is necessary to know the structure of a circuit. This can be done by either extracting the electrical circuit from the circuit layout using computationally expensive CAD software, or alternatively, producing a separate structural description of the circuit by hand. The latter alternative is particularly unattractive since there can be undetected inconsistencies between the two circuit descriptions.

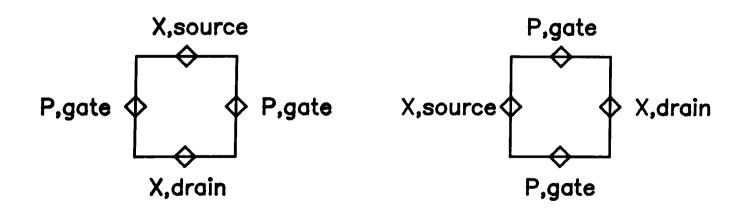

Buchanan [Buchanan 80] developed a language, ICSYS, which allows joint structural and physical descriptions of a circuit. A consistent design representation is thus ensured without the need for an expensive circuit extraction from the physical geometry. The idiom description language VIRGIL, which has been developed as part of this thesis and which is described in chapter 4,

includes both structural and physical information by describing circuits in terms of structural primitives which are implicitly interconnected according to their relative positions.

At present, the only method readily available to show that a circuit meets some behavioural specification is by simulation. Using a joint structural and physical design description can help to ensure that the simulation adequately reflects the performance of the physical circuit, however simulation can only ever show that a circuit performs correctly for those combinations of input values which have been exercised.

If both the circuit and the desired behaviour can be described using some formal calculus then it may be possible to formally prove that a circuit meets its specification. Milne [Milne 83a] has designed such a language, called CIRCAL, and Gordon [Gordon 81] has investigated similar ideas.

Furthermore, if a silicon compiler could be designed which accepted the behavioural specification of a circuit as its input language, then if the same formal proof methods were used to prove that the transformation (between specification and circuit) that is implemented by the silicon compiler is correct, then all circuits designed using the compiler could be guaranteed to meet

their specification [Milne 83b]. Such a breakthrough would eliminate the need for circuit simulation.

This formal approach is similar to that of formally proving computer programs correct, and the difficulties which have been encountered in the widespread application of program proving techniques indicates that the widespread application of similar techniques to VLSI circuit design may still be a long way in the future.

## 2.4: VLSI Design Languages & the Control of Complexity

One principle of structured VLSI design is to introduce sufficient hierarchy into a design that the amount of information which must be handled at any one time is not too great. It is obviously easier to adopt such a hierarchical design style if this methodology is specifically supported and encouraged by the design language being used.

Even simple geometric design languages such as CIF 2.0 [Mead 80] are capable of describing a design hierarchically by the definition of symbols, which may in turn be composed from previously defined symbols. Such symbols are very much like procedure calls in a high level programming language, except that no parameterisation of symbols is allowed.

More sophisticated languages such as SCALE [Buchanan 82] not only support a design hierarchy, but also allow the parameterisable definition of cells. Languages which can describe designs parameterisably can describe not only circuits but also idioms. The language VIRGIL is specifically for the description of idioms and as such has special support for both a hierarchical design style and parameterisation.

It is argued that textual design languages, such as VIRGIL, provide a powerful tool, not only for controlling design complexity, but also for providing additional design information which can help ensure the correct composition of designs.

Graphical design systems usually only support the simple repetition of fixed cells as an aid to building large regular structures. Textual languages, since they can easily accommodate selection, repetition and parameterisation, can describe far more general structures. Designing structures sufficiently generally that they can be used many times in one or more designs can be a valuable aid in reducing design complexity, and thus design time and design cost.

Graphical systems may facilitate the rapid entry of the physical aspects of a circuit design, but it has already been mentioned that it is also desirable to capture structural design information, rather than to attempt to infer structural details from the physical design.

Specifically, one often wants to name certain items in a design, such as ports for connection to other parts of the circuit, so that during design composition only like named ports are connected together. One might also like to include other useful information, such as whether outputs from one part of the circuit are restored or non-restored logic levels, and similarly whether inputs are designed to accept restored or non-restored levels. Textual languages allow the simple and natural specification and manipulation of such structural design information as well as the physical design details.

### 2.5: Composition of VLSI Designs

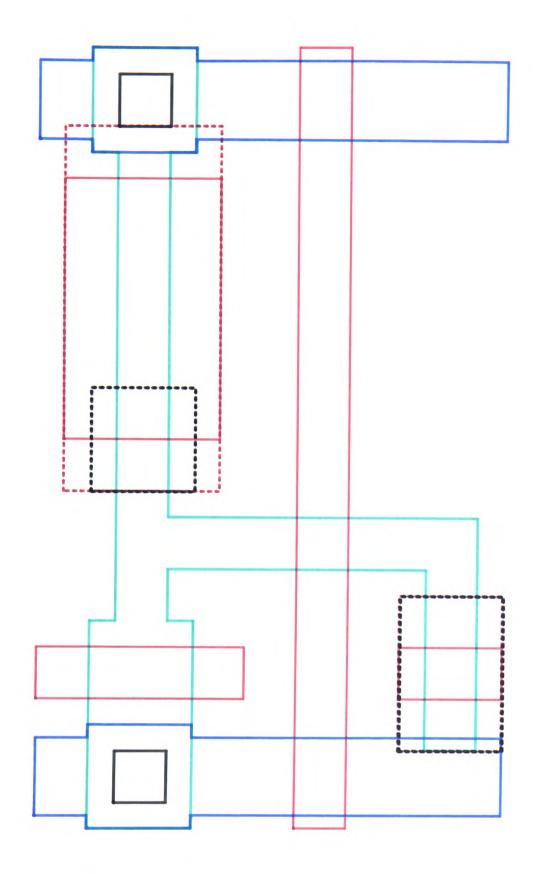

An essential feature in controlling design complexity is the use of hierarchy [Rowson 80]. Like SCALE, VIRGIL separates the design hierarchy into cells which contain only structural primitives, called leaf cells, and cells which contain only instances of other cells, called composition cells. This distinction helps to highlight what, in the author's opinion, is a fundamental difference between the tasks of designing leaf cells and of composing them together to give a complete circuit.

This composition of cells to give larger cells is a fundamental and frequently performed operation in a hierarchically designed system. Researchers with close contacts with industry already report that the composition phase of design now takes far longer than leaf cell design [Smith 83]. As circuits become more and more complex, so the proportion of time spent composing cells together will tend to become increasingly greater. The design process is again greatly eased if the design language being used specifically supports composition as a fundamental operation.

As mentioned earlier, there are two main factors which influence a composition operation - the relative position of cells and the interconnections between them. In some cases, it is possible that the definition of one of these also defines the other. In CIF, for example, composition is achieved by placing instances of cells at specified physical positions, relative to a common origin. If, in placing the cells, geometry from one cell touches or overlaps geometry from another cell then connection is made between the cells.

In the case of CIF, there is no guarantee that placing cells so that they touch or overlap produces correct connections between them. Rather, the resulting layout must be examined either manually or automatically to determine if connections have been made correctly. Often

incorrect connections can go undetected until circuits have been fabricated.

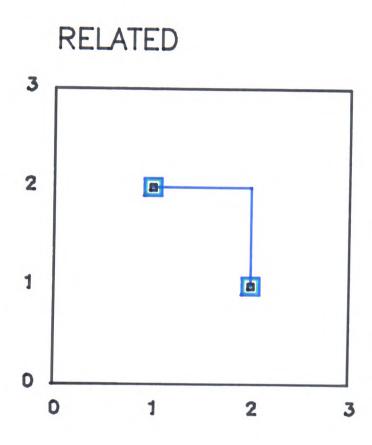

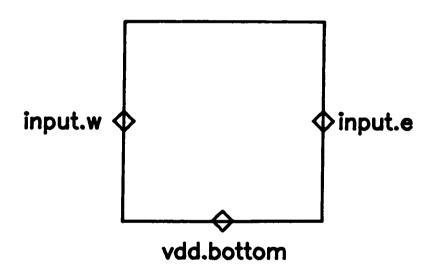

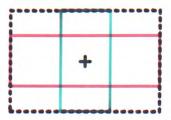

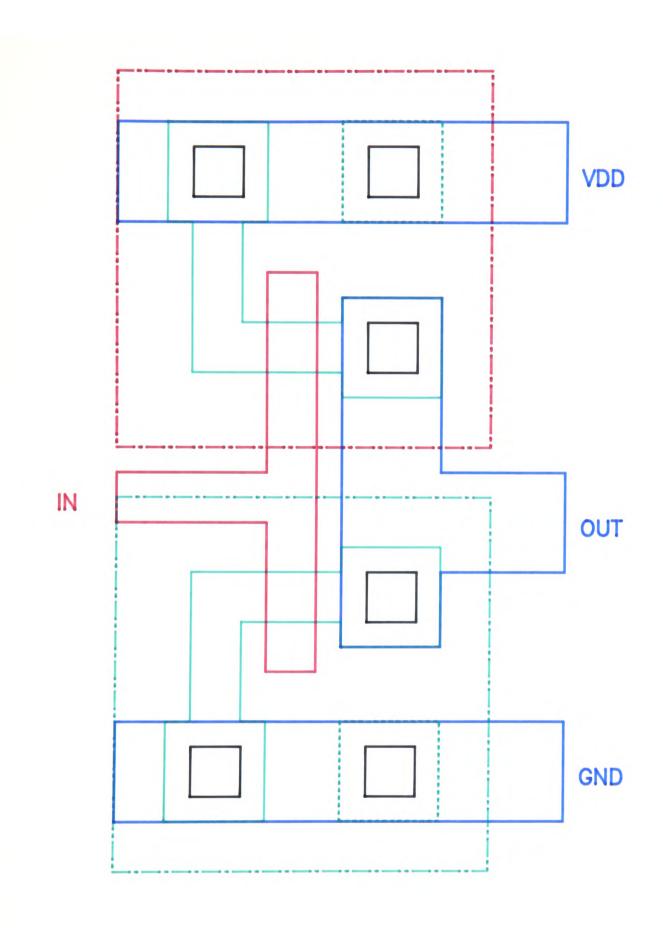

A better approach is to ensure that connections are only made as intended by the designer by explicitly checking connections as cells are being composed. To do this, the points where connections may be made to a cell must be identified. These are variously called "ports" or "pins". Such information is specifically included in languages, such as VIRGIL, which support joint structural and physical design descriptions.

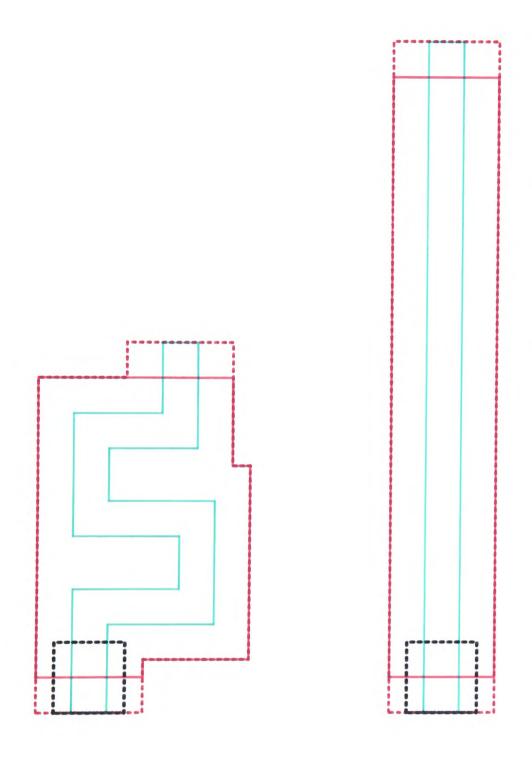

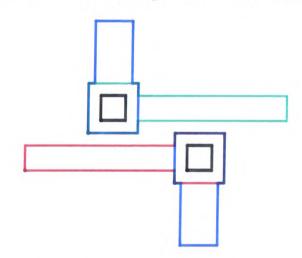

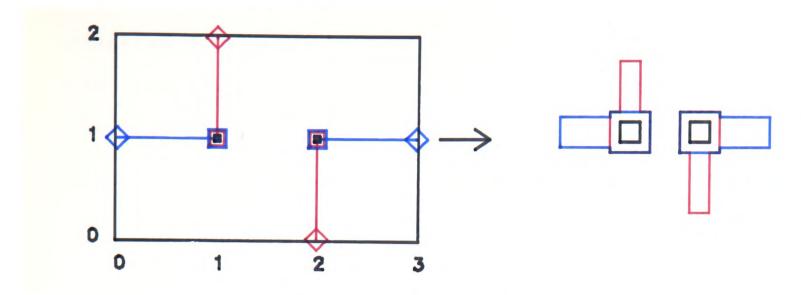

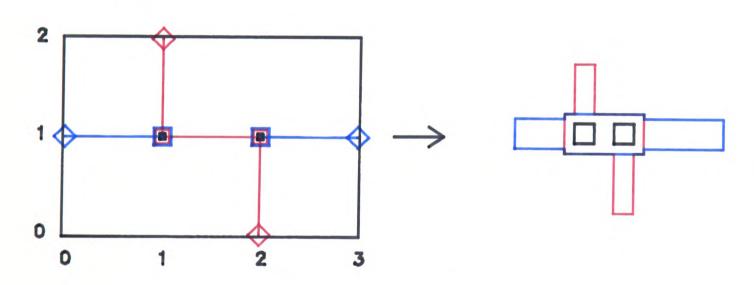

Next, the interconnections between ports of various cells must be specified. One method of doing this is by explicitly naming pairs of ports which are to be joined - this approach is used in SCALE, for example.

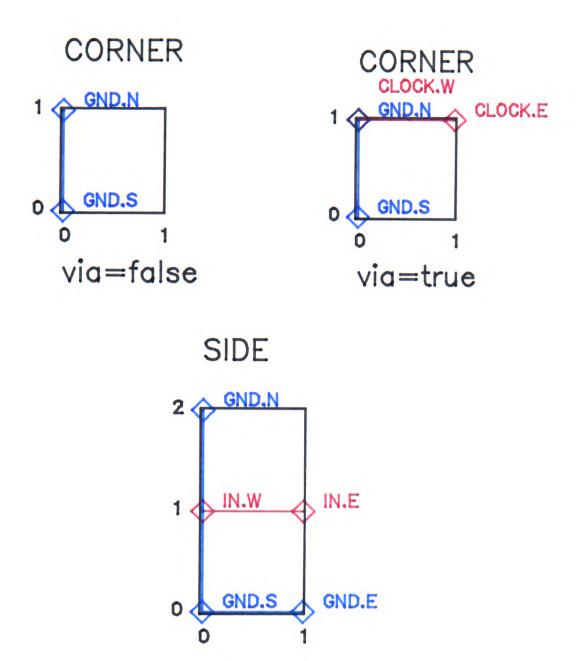

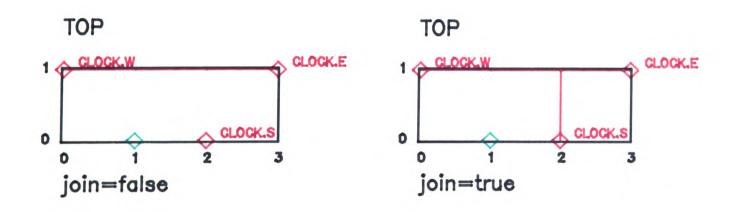

An alternative approach is to implicitly connect all pairs of ports along edges of cells which are placed next to each other (i.e. "abutted"). This is the approach used in VIRGIL. To avoid the problems of incorrect connections, pairs of ports are checked before connection to ensure that they match both in type (such as polysilicon, metal or diffusion) and in name. If ports do not match, then the composition of the cells containing them fails. The only concession made to this rule is that cells may be "stretched" so that matching ports align.

Other languages support more complex operations to assist in correctly joining ports together. In the proposed language SILVER [Rees 83], such operations are referred to as coercions. Examples of coercions would be the automatic inclusion of contacts between ports on different layers, and also the automatic insertion of routing networks between cells where ports cannot be joined by simply abutting the cells.

Other researchers [Lengauer 84] have also developed systems which apply such coercions to automatically aid the completion of cell composition operations.

Such sophisticated coercions are not included in VIRGIL, since it is argued that as VIRGIL is being used primarily to describe well known idioms, the nature of interconnections are already known and can be described precisely in the circuit description.

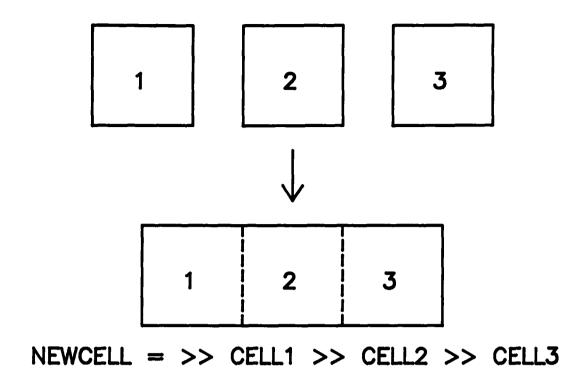

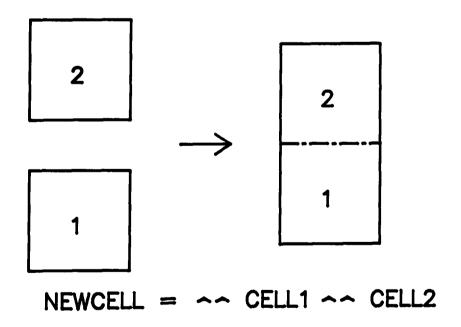

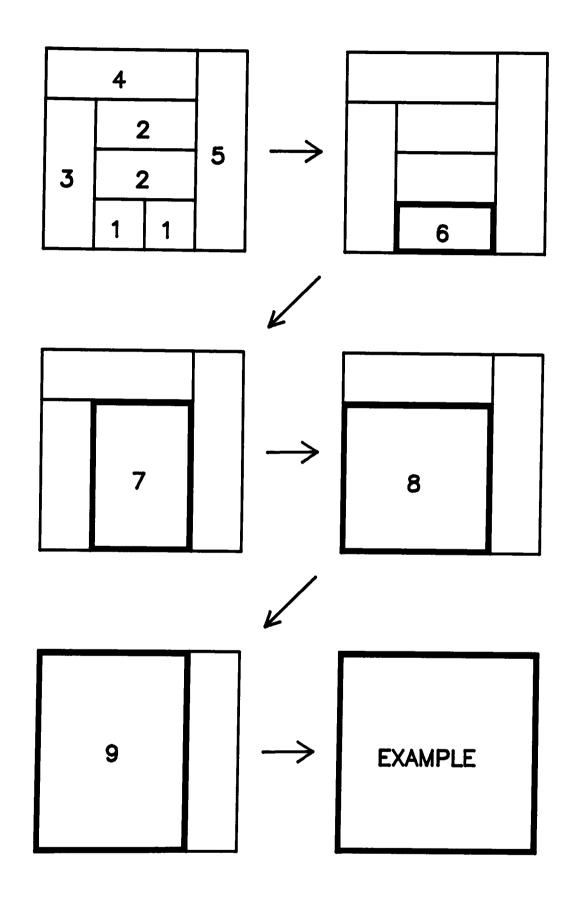

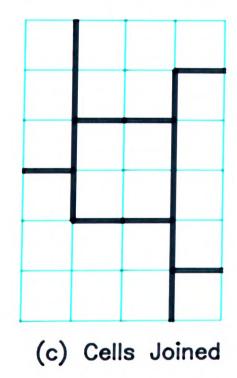

The only composition operation in VIRGIL is the abutting of cells together to produce larger cells. Relative placement of cells is achieved by specifying the way the cells are to be abutted. This contrasts with some other languages, such as ABCD [Rosenberg 82] where placement is done by instancing cells at specified positions. Part of the work of this thesis is to evaluate a system where all composition is in terms of simple abutment.

# 2.6: Methods of Circuit Description

Circuit description methods can be categorised both by the manner in which circuits are described (graphically or textually), and by the level at which they are described (mask level, sticks level, gate level etc.).

Some discussion of the various types of circuit description methods has already been presented in chapter 1. Tools for design at the mask level are now reasonably mature and well understood. However, design styles at higher levels of abstraction are still an area of active research interest.

The major area of interest in this thesis is the capture of idioms at the cell level. It is desired, not only to capture the functional aspects of these idioms, but also the topological aspects of their layout. For this reason, design styles which do not allow topology to be captured, such as gate level descriptions, are not considered further here.

At mask level, the designer is free to create an arbitrary collection of shapes on the various layers.

The object of most recently developed design styles is to somehow constrain this freedom so that the designer is less likely to introduce design errors, and also that the

amount of information needed to specify a design is reduced.

An early excursion into this field was the development of coarse-grid layout systems [Gibson 76] [Clary 80]. Here the designer could choose from a selection of rectangular "tiles" containing fragments of geometry, and by arranging these in a rectangular array, a complete design could be built up. Tiles would typically be about the size of the worst case tolerances in a given technology - say two or three lambda, in Mead-Conway terms. A major advantage of such systems is that tiles can be represented by different ASCII characters, allowing graphical design on normal alphanumeric terminals. Coarse grid systems, however, do not really provide any structural information about a circuit - they merely ease the task of describing its physical geometry.

A similar, alphanumeric based approach is the Bell Laboratories "gate matrix" design style [Lopez 80]. This imposes a structured design style on the user, which also allows the mapping of the alphanumeric grid of the circuit description onto a reasonably dense, variable pitch physical grid. Layouts exhibiting "hand-packed" densities are claimed, but this is most probably due to the structured design style rather than the design system which implements it.

Languages such as SCALE [Buchanan 82] and ICSYS

[Buchanan 80] allow the specification of joint structural and physical design descriptions at the mask level.

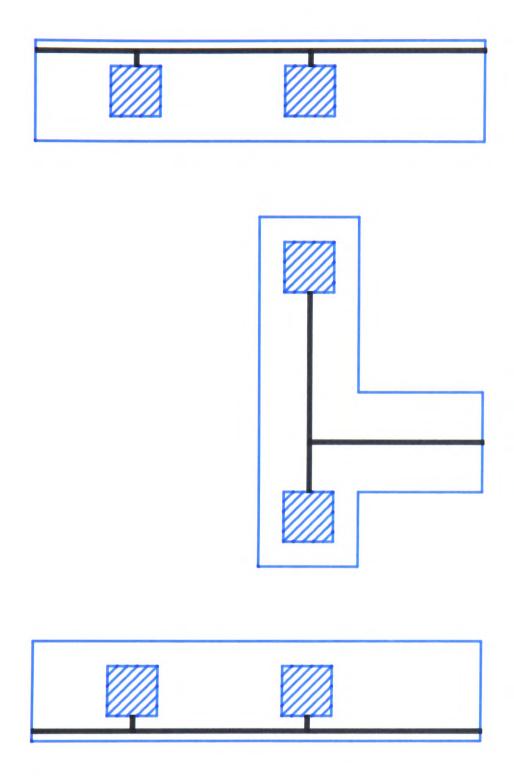

In a sticks based system, the designer is removed from the physical details about widths and separations, and designs in terms of structural primitives such as transistors, wires and contacts. Sticks based systems are thus not only design rule free but they also implicitly provide a joint structural and physical design description.

There are two methods by which sticks level design can be described. One method is by so called gridless design systems [Williams 78] [Dunlop 80] [Lengauer 84]. Here the designer specifies the relative positions of components, and their interconnections. This information constitutes a set of "constraints" which any mask level equivalent of the sticks description must meet. Within these constraints, components may be moved around so as to achieve a compact layout.

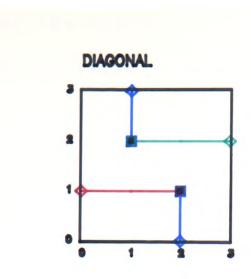

The other method is to arrange components using a so-called "virtual grid" [Weste 81a] [Rosenberg 82]. Structural components are laid out on a two dimensional grid, but unlike coarse grid systems, the grid lines have no implicit correspondence to physical positions. Rather, it is only the relative positions of components

which are implied by their positions on the grid which is strictly important. Thus, relative positions can be easily expressed without the need to reduce a circuit to a set of positional inequalities which must be both determinate and consistent, as is the case in most gridless sticks systems.

It is argued that the virtual grid provides a very neat and elegant method of representing sticks level designs which captures joint structural and physical design information. For this reason a virtual grid based sticks level design language has been chosen for the description of idioms.

Some other sticks based systems are either extensions of existing languages such as Pascal [Lengauer 84] or Lisp [Pettengill 83], or else they can be accessed via a procedural interface from such a language [Weste 81b]. Thus, such languages are capable of describing idioms as well as circuits. The VIRGIL language is not an extension of any other language, rather it is a special purpose language for the description of idioms. It is felt that the use of a special purpose language allows idioms to be described more naturally and more concisely than is possible with embedded languages. The manner in which parameterisable features have been added to VIRGIL is novel, and allows very general selection and repetition operations to be performed.

# 2.7: Sticks Compaction

Once a sticks description has been entered into a design system, it must at some stage be converted into mask geometries - a process called "sticks compaction".

Ideally, one would like the final mask arrangement to be optimally compact, but the determination of such a layout has been shown to be NP-complete with respect to the number of components being arranged [Schlag 83]. In most cases this is computationally too expensive, and so sub-optimal compactors are usually used.

The simplest method of compaction is so called 1-dimensional compaction, used in several design systems [Williams 78], [Dunlop 80]. In this method, components are placed as closely together as possible in the x-direction, and then as closely together as possible in the y-direction.

For gridless sticks systems, such compactors have been shown to exhibit complexity  $O(N^{**}1.5)$ , where N is the number of circuit components [Zinszner 83]. Weste [Weste 81b] describes a very simple algorithm which performs 1-dimensional compaction on a virtual grid with complexity O(N). An algorithm based on this approach has been implemented in this thesis.

The sticks compactor developed in this thesis combines this algorithm with some novel ideas about methods of specifying process-specific design rules. Some interesting results about the way in which interconnections between components at mask level can be realised are also presented. Perhaps the most important results produced during the work on compaction are those to do with the technology independence of CMOS circuits, which is discussed more fully in section 2.8.

Sticks compaction is an area of quite active research interest, and investigation of especially efficient or clever sticks compactors is outside the scope of this thesis. Some of these developments are nonetheless worthy of mention, since they could be applied to the VIRGIL system if it were to be developed beyond the research stage.

Improvements to the basic algorithm which has been used for virtual grid compaction can provide a constant factor speed up to the computation time needed for compaction [Boyer 83]. A similar approach can be employed to allow for hierarchical sticks compaction, which could give very considerable improvements in computation time, especially for very regular structures [Rosenberg 84]. Both these improvements are primarily to do with the time required for computing the compaction, and not with improving the density of the final mask

level description.

Such density improvements are the goal of so-called 2-dimensional compaction algorithms. Sometimes, in order to place components closer to each other in one dimension, it is necessary to move them apart in the other dimension. 1-dimensional compactors cannot detect this. An algorithm for detecting these situations and dealing with them has been presented by Wolf et al [Wolf 83b]. Similar optimisations can be made manually in the VIRGIL system, by the designer identifying and modifying critical areas of the circuit.

The compactor developed for this thesis is described in detail in chapter 5.

# 2.8: Technology Independent Design

One of the principles upon which the work of Mead and Conway [Mead 80] is founded is the production of a simple set of conservative geometric design rules for NMOS technologies, based on a single scalable constant, lambda. Designs based on these rules can be scaled simply by changing the value of lambda. It is estimated that these rules are sufficient to allow design down to about 1 micron feature sizes. Sequin [Sequin 82] has proposed a similar set of lambda based rules for CMOS processes.

By their very nature, sticks designs are design rule free, and so are even more applicable to producing designs which will remain valid as critical dimensions shrink. Sticks designs can also accommodate variations between design rules for processes which do not conform to lambda based rules.

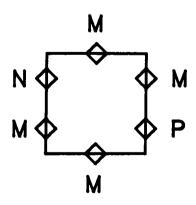

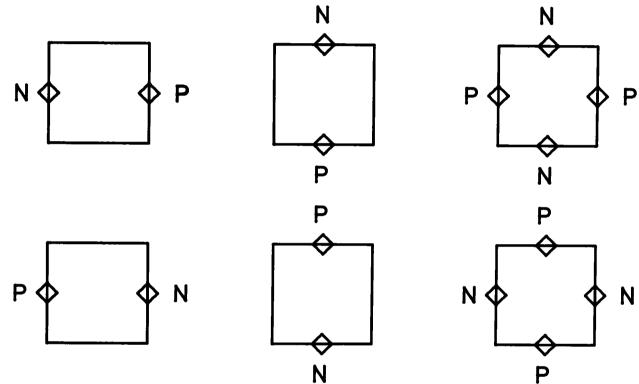

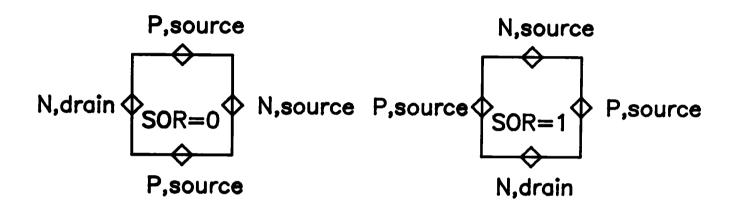

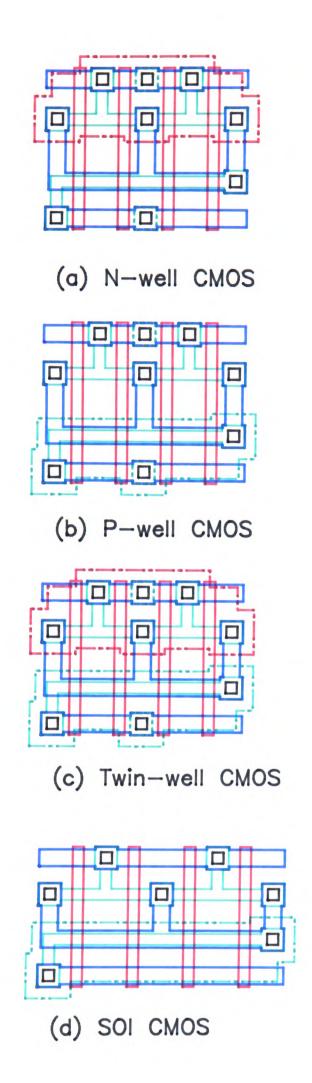

Design styles which allow a circuit to be implemented in several different processes within a general class of fabrication technology - say one layer metal, one layer polysilicon NMOS with buried contacts - are here called "process independent". Often such styles are called "technology independent", but here that term is reserved for design styles which can describe designs that are valid in several different general classes of fabrication technologies. Specifically, in section 5.6 of this thesis, a design style called "generalised CMOS" is introduced which allows circuit descriptions which can be implemented in four different classes of CMOS technologies, viz. n-well, p-well, twin-well and SOI (silicon-on-insulator).

At sticks level, the only significant difference between the four CMOS technologies mentioned above is the location of substrate wells (or in SOI, island dopings). There are several structures which are specific to certain technologies, such as island-island contacts in SOI, but these can be avoided.

To design technology independent CMOS circuits, it would be best if wells were not included at all in the design description, but rather included automatically if they are needed in a particular technology. An alternative is to include both p-wells and n-wells, and them remove one or other if they are not needed in the particular technology. The former seems a better solution, since the designer is freed from the need to describe wells at all.

The ways in which wells are handled in various sticks systems are not often described in detail or even mentioned. Zinszner et al [Zinszner 83] describe a sticks system which can specifically handle wells, but it seems that one must must explicitly include the specific well structure of the class of CMOS circuit being implemented - i.e. the design descriptions are process independent, not technology independent.

In chapter 5.6 of this thesis, an algorithm for automatically generating the specific well structure needed for a particular technology is presented.

### 2.9: Cell Libraries

At present, almost all integrated circuits are still custom designed. In some cases, a library of useful cells is maintained, but these are almost invariably

stored as mask geometries.

Recently, a library of such cells has been published [Newkirk 83]. Many of the cells described are part of larger parameterisable structures. Although the cells themselves are described in a standard language (CIF), the way in which they are composed to form these larger structures is described somewhat informally in the documentation. This is undoubtedly due to the lack of any standard procedural description language.

With the exception of a few very important and regular structures, such as counters, PLA's, ROM's and RAM's, design systems tend not to have a large repertoire of well known idioms available for instantiation. Partly, this is because with conventional, embedded mask level design languages, the capture and debugging of such idioms is a reasonably time consuming task.

The system presented in this thesis specifically supports and facilitates the concise description of idioms, and so will hopefully encourage the capture of a large number of useful structures.

#### 2.10: Silicon Compilers

Apart from the work on the capture of cell idioms, some work has been done in this thesis on the capture of

an idiom at the silicon compiler level.

Unlike cell design, silicon compilation is only a very new field, and there is little published work in this area. Mostly, this presents the results of compilers which have been developed to meet specific needs of particular projects.

The first silicon compiler was "Bristle Blocks"

[Johannsen 79], used to produce datapath chips.

MacPitts [Siskind 82] implements digital systems as a datapath plus controller, and includes specific support for concurrent datapath operations where possible.

Model [Gray 82] is a silicon compiler which allows arbitrary logic descriptions to be implemented as gate arrays.

The FIRST silicon compiler, described in chapter 3, is a compiler for bit-serial digital signal processing systems, and is a typical example of the first generation of silicon compilers.

### 3: THE F.I.R.S.T. SILICON COMPILER

In this chapter, a specific idiom for the production of complete VLSI systems from high level specifications is examined. More especially, the software to support this "silicon compiler" is discussed.

The FIRST silicon compiler idiom was devised by Dr. Peter Denyer, while the library of primitive functional cells was produced by David Renshaw. The author was responsible for writing the software to support the silicon compiler, i.e. the software which captures the idiom.

The work in this chapter was presented, in a slightly different form, at the 3rd Caltech Conference on VLSI in March, 1983 [Bergmann 83].

### 3.1: Background to the FIRST Silicon Compiler

The FIRST silicon compiler (Fast Implementation of Real-time Signal Transforms) has been developed as a cooperative project between the departments of Electrical Engineering and Computer Science at the University of Edinburgh, in order to allow the rapid investigation and implementation of VLSI digital signal processing systems.

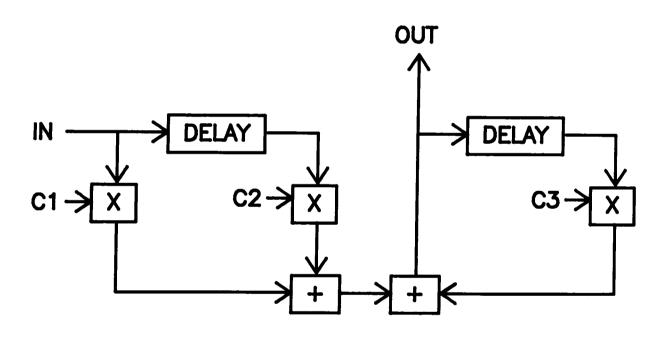

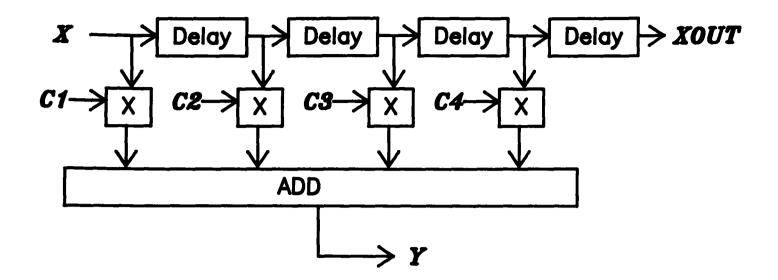

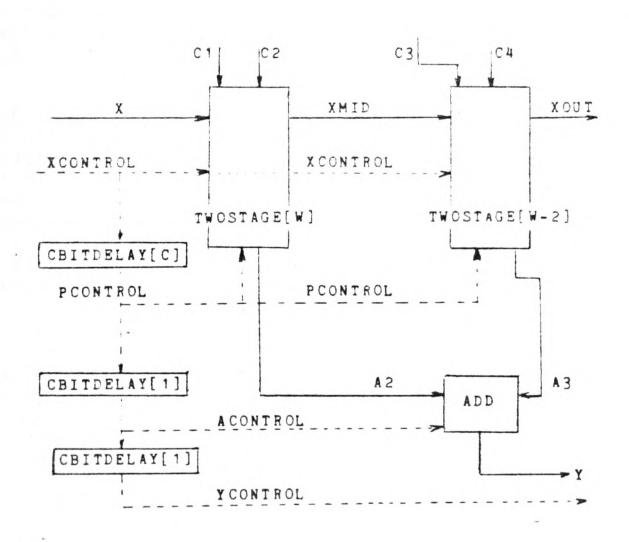

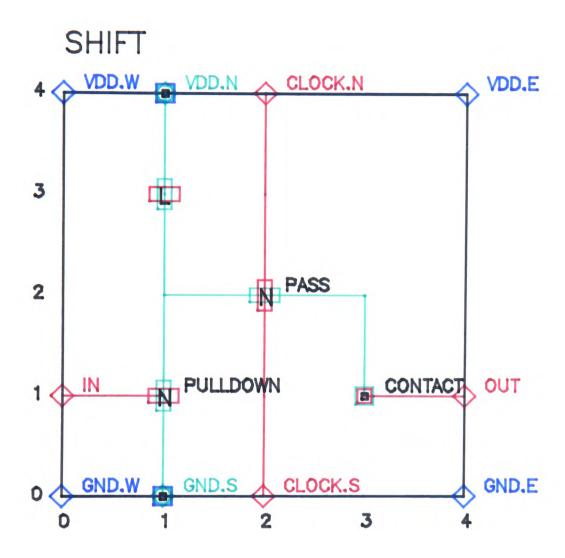

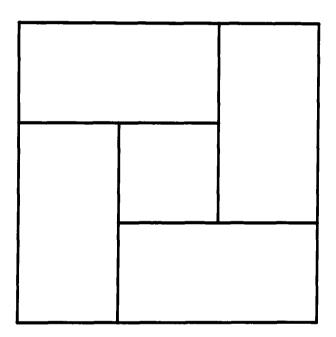

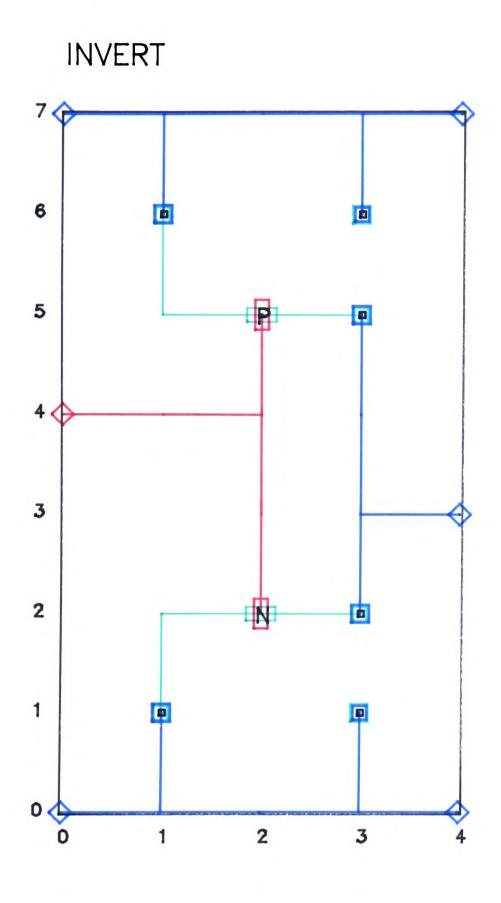

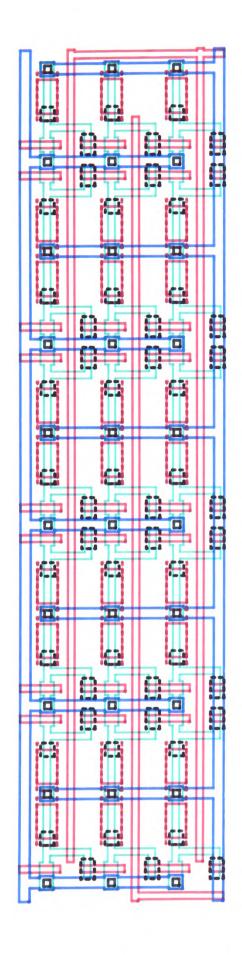

The FIRST system is built around an underlying bit-serial signal representation as proposed by Lyon [Lyon 81], and systems are implemented as hard-wired networks of pipelined bit-serial operators. A typical flow diagram for a system suitable for implementation by the FIRST compiler is shown in figure 3-1.

### 3.2: An Innovative Architecture

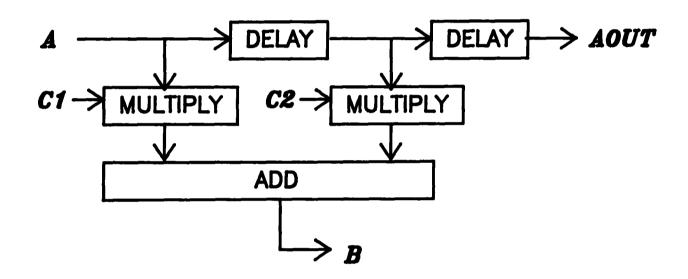

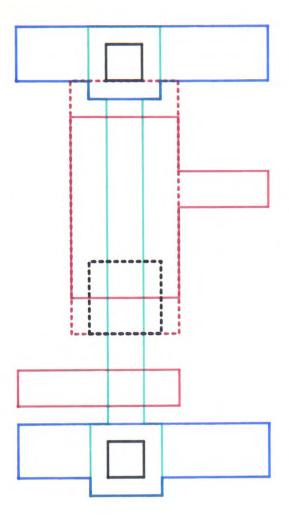

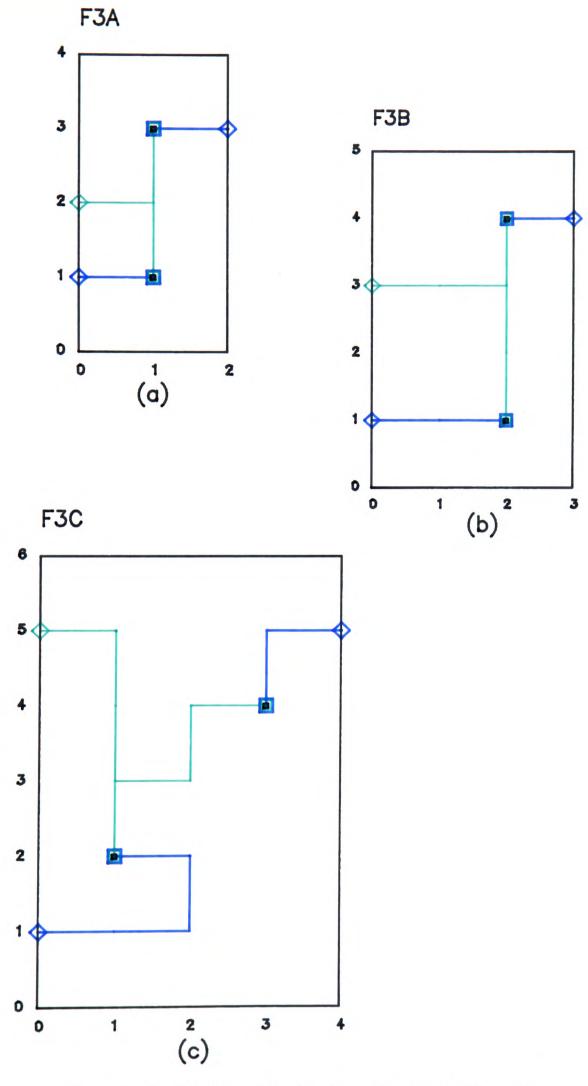

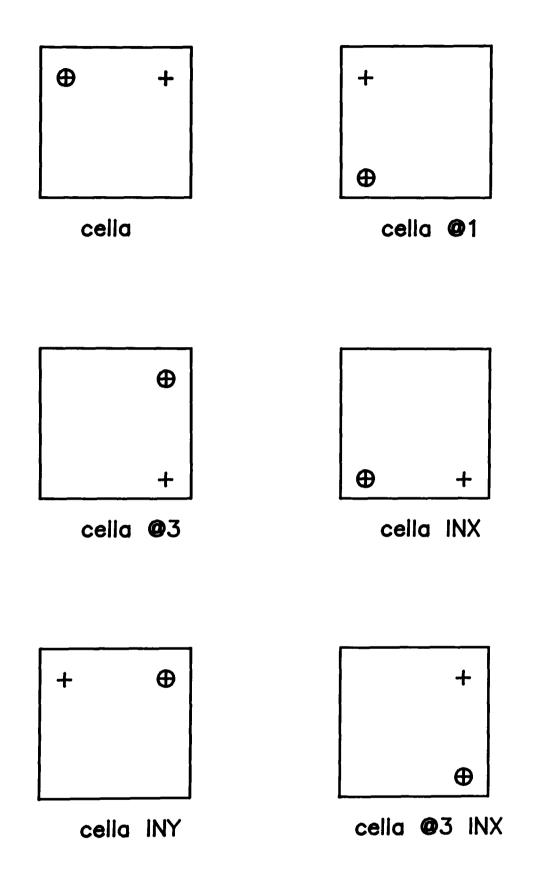

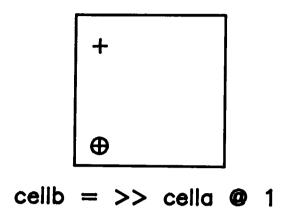

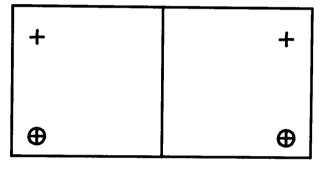

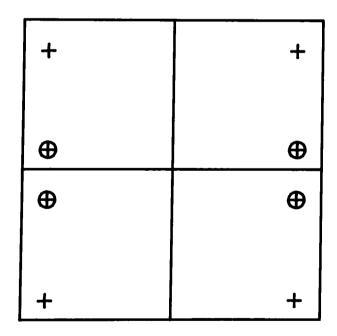

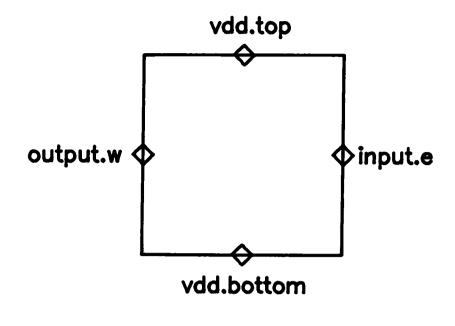

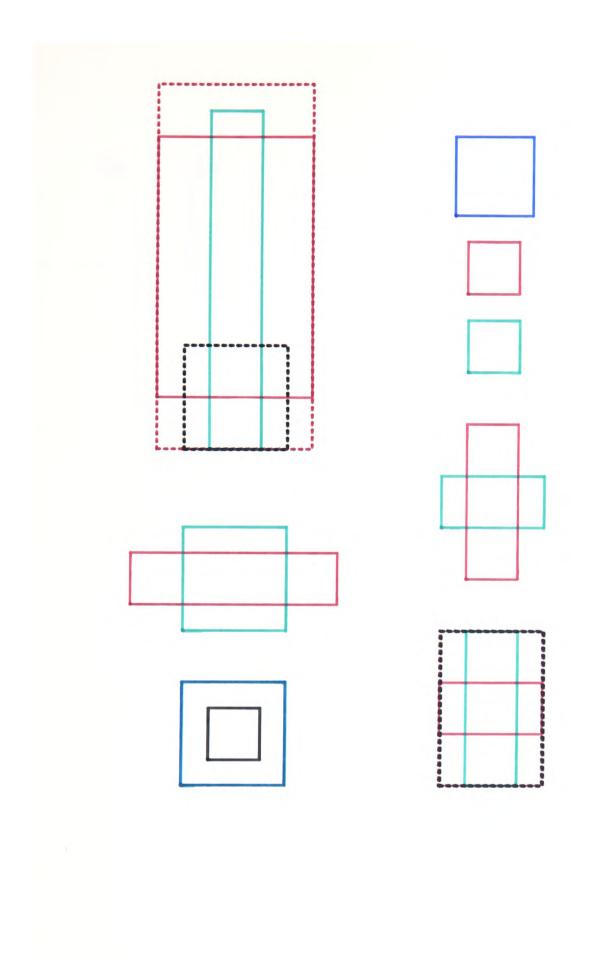

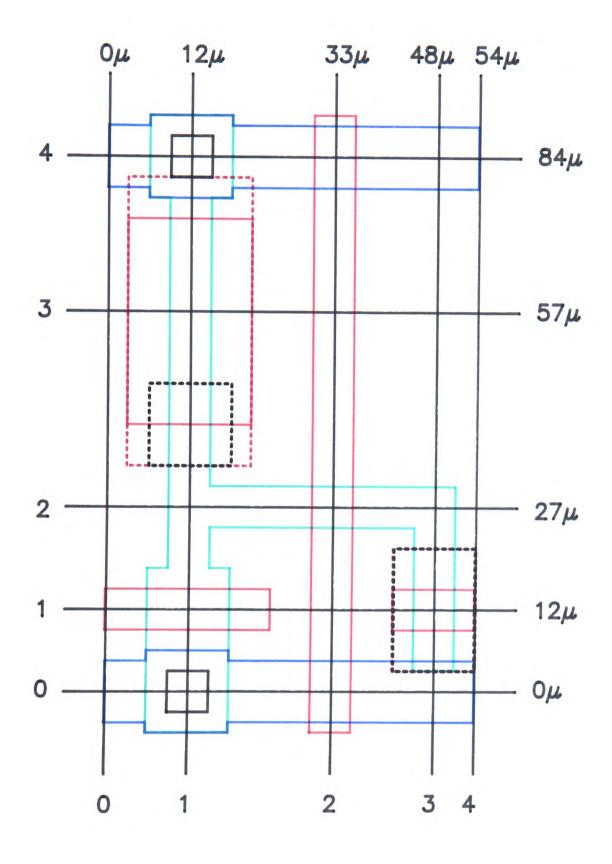

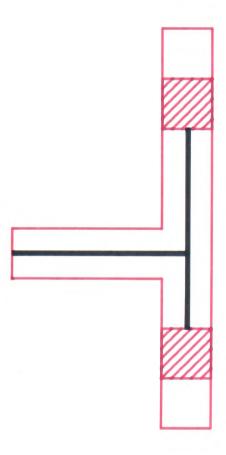

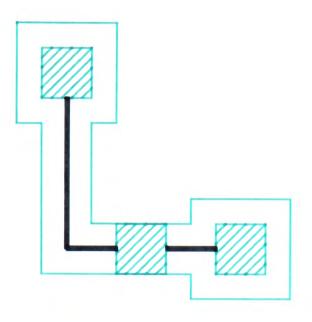

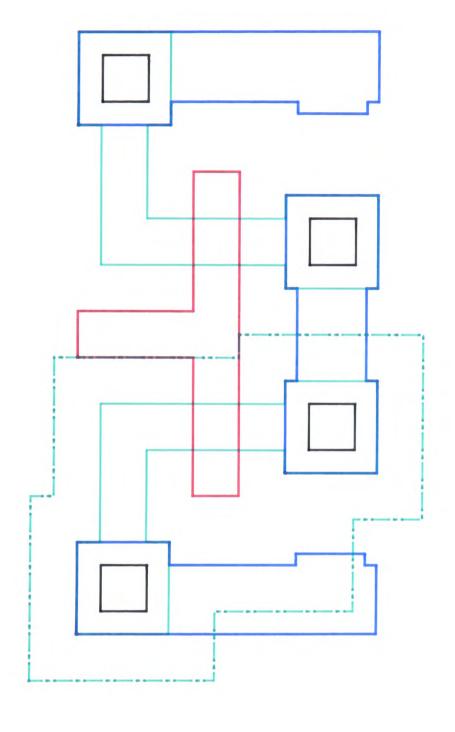

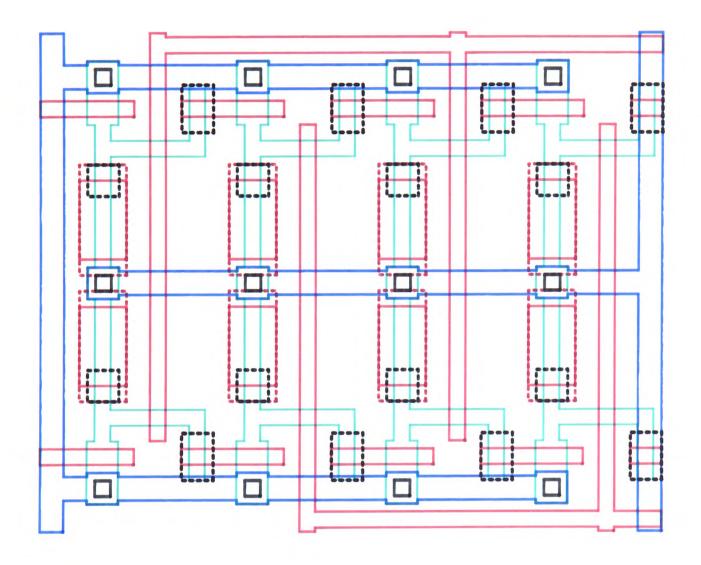

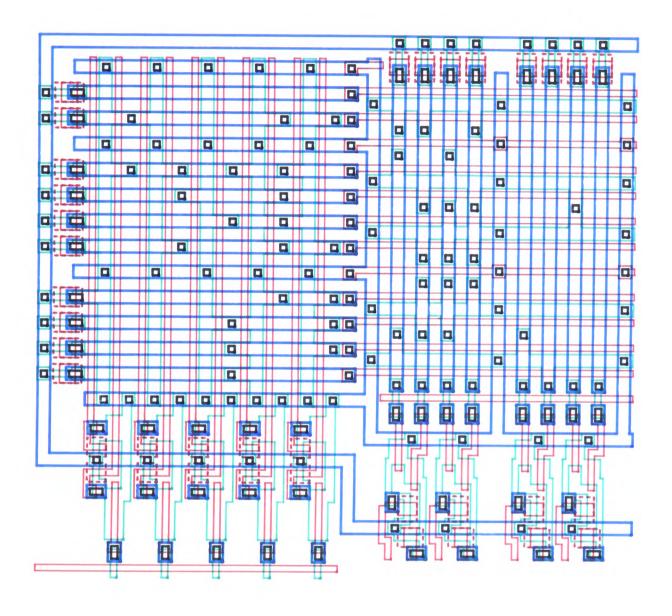

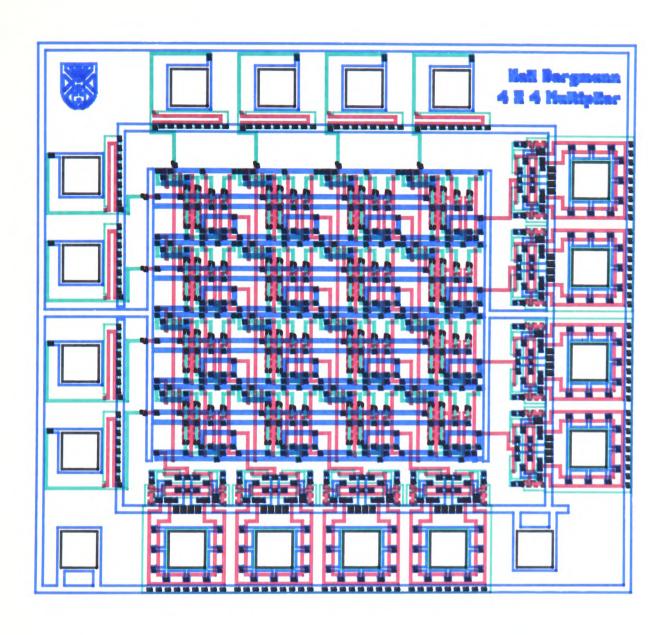

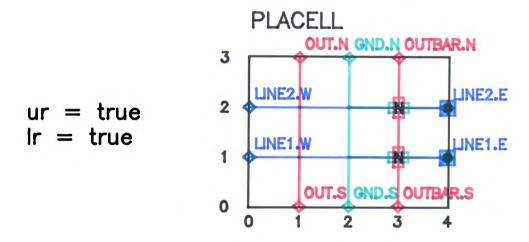

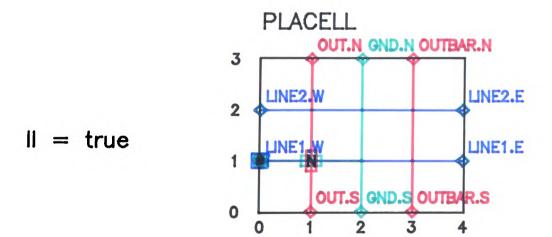

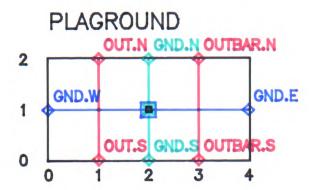

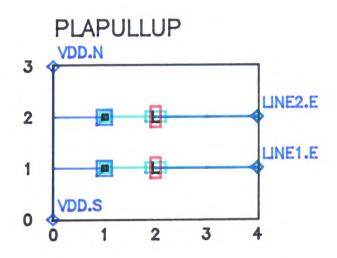

The hardware implementation of a FIRST circuit consists of a network of interconnected bit-serial operators, laid out according to a relatively fixed floorplan. Each bit-serial operator is implemented as a separate function block, which is, in turn, assembled from a library of hand-designed leaf cells. A typical leaf cell might comprise, say, a single bit-slice of a given function, and the complete operator would then be arranged, both logically and physically, as a linear systolic array of these individual bit-slices. In this way, the logical size and exact function of each function block can be easily varied by selecting different numbers and types of leaf cells. For example, figure 3-2 shows two possible configurations for a bit serial multiplier one which uses an 8-bit coefficient and rounds the least significant product bit, and the other which uses a 12-bit coefficient and truncates. (Note: the multiplier design uses 2-bit systolic array elements).

Figure 3—1: A Signal Processing System

Suitable for FIRST Implementation

| Top Cell                |                            |

|-------------------------|----------------------------|

| 2-bit<br>Slice          | 2-bit<br>Slice             |

| First<br>2-bit<br>Slice | Rounding<br>2-bit<br>Slice |

| Input Buffers           | Output Buffers             |

|                         |                            |

(a)

| Top Cell      |                |

|---------------|----------------|

| 2-bit         | 2-bit          |

| Slice         | Slice          |

| 2-bit         | 2-bit          |

| Slice         | Slice          |

| First         | Truncating     |

| 2—bit         | 2-bit          |

| Slice         | Slice          |

| Input Buffers | Output Buffers |

(b)

Figure 3—2: Two Possible Multiplier Configurations

(a) 8 bit coefficient, product is rounded

(b) 12 bit coefficient, product is truncated

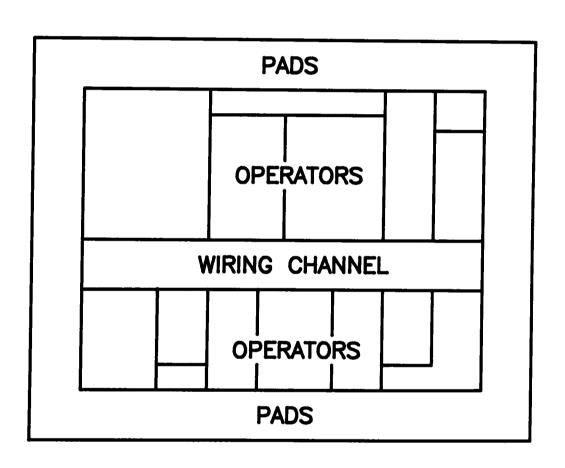

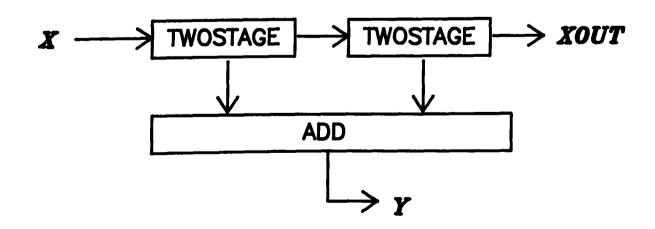

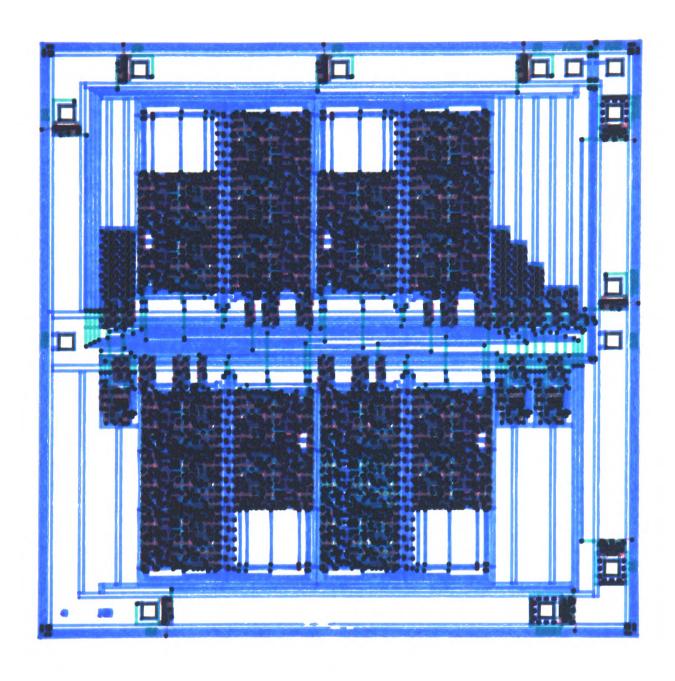

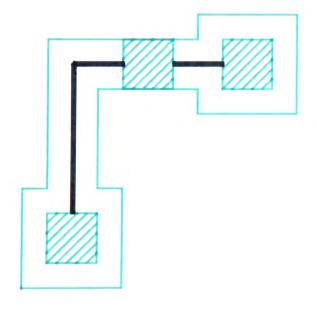

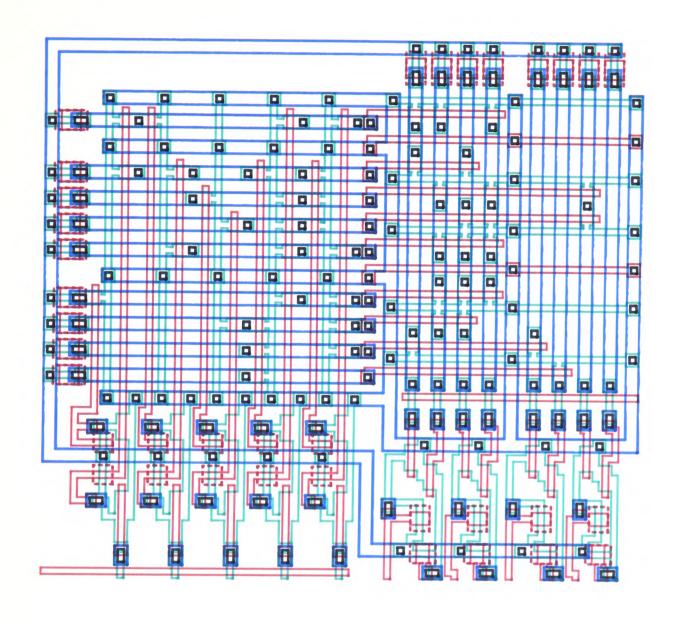

The function blocks on a chip are arranged in two rows along either side of a single, central communications channel. Interconnections between function blocks and connections to bonding pads are all made within this channel. A typical floorplan is shown in figure 3-3. Some silicon area is wasted by this approach, since function blocks may differ in height. Typically, this area is about 20% of the total chip area, which, since it is not active area, has only a linear effect on good die/wafer yield.

Bonding pads are arranged more or less evenly around the chip periphery. After some thought it was decided to allow the pad order to be user controlled, in order to improve PCB level wiring management.

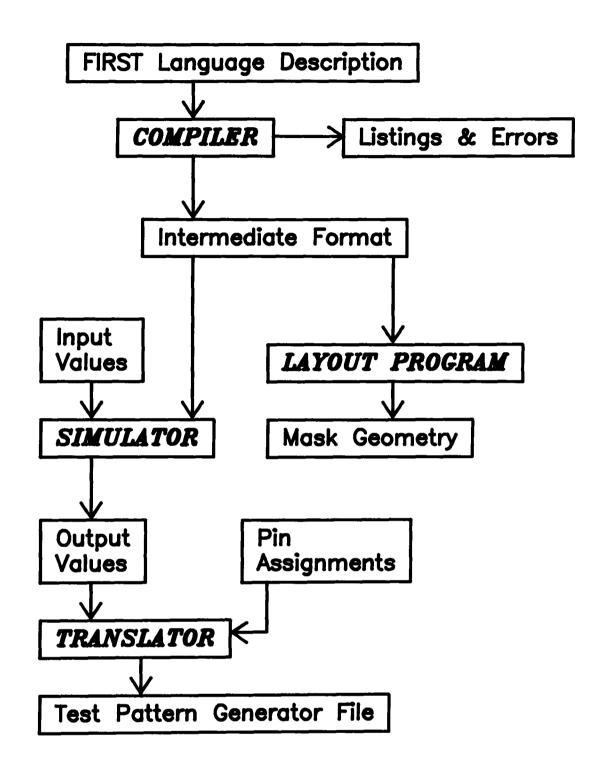

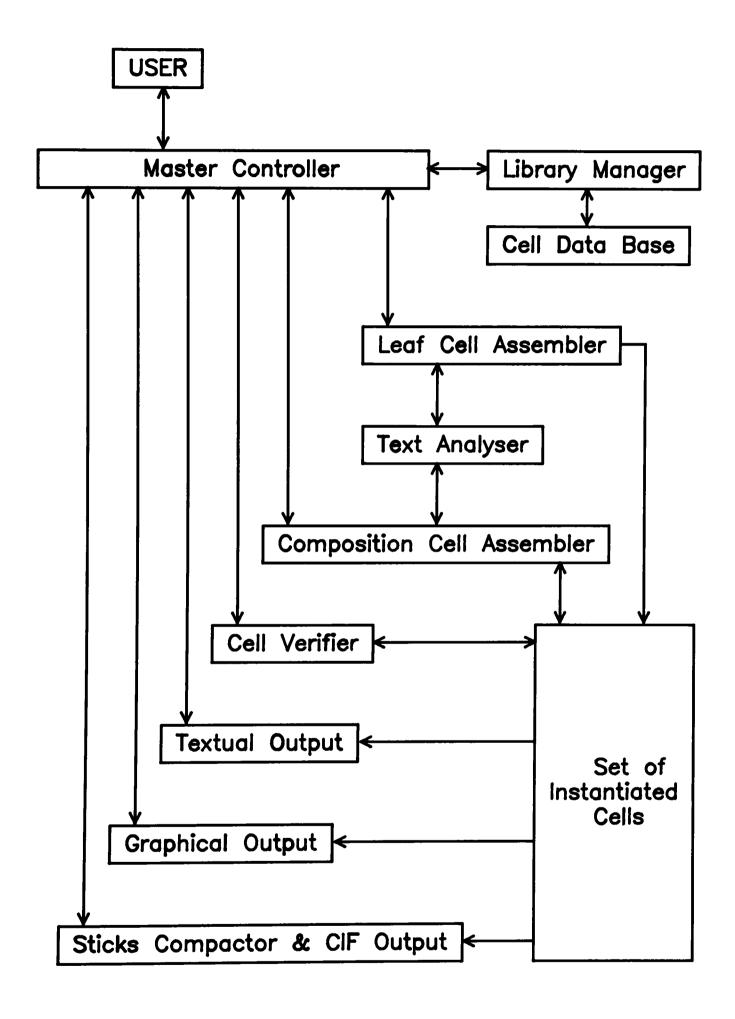

# 3.3: Software Support for an Integrated Design Environment

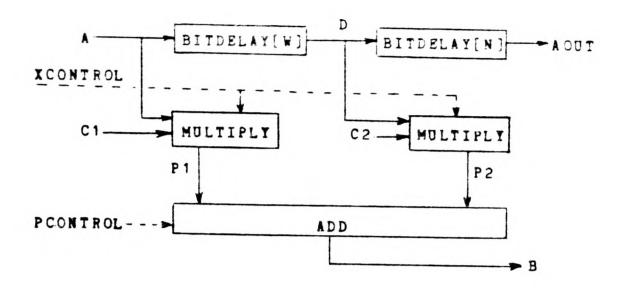

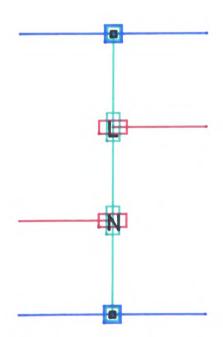

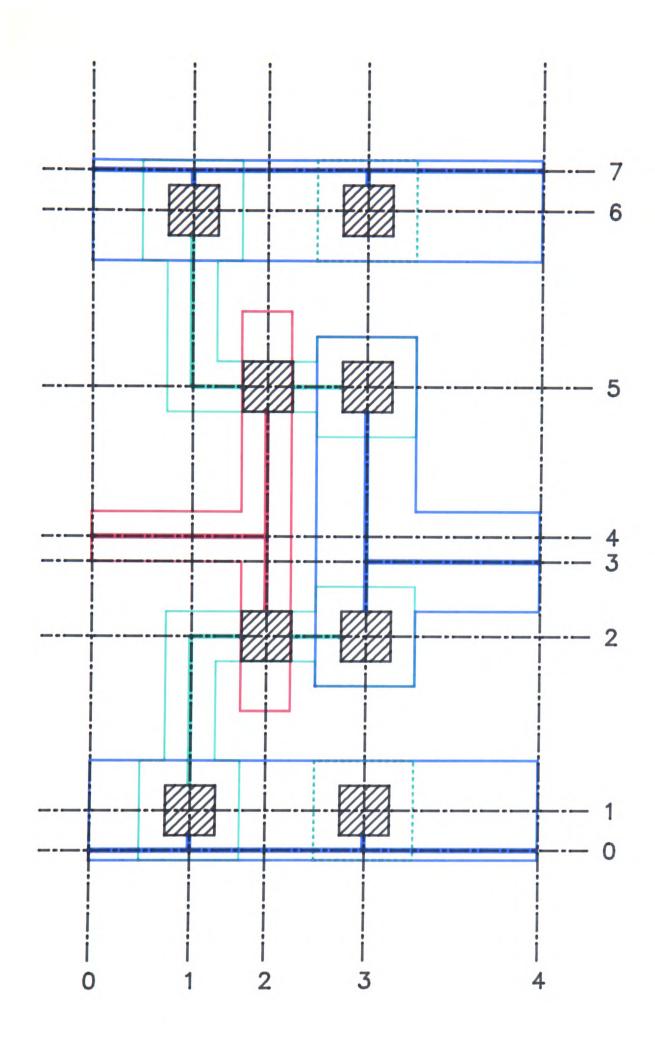

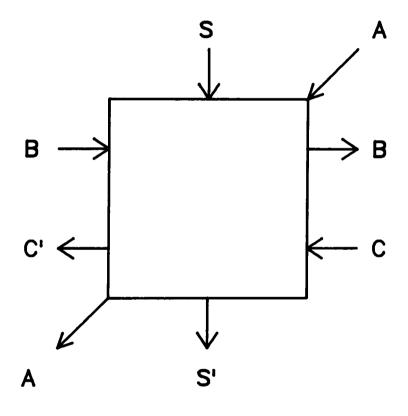

The software support for the FIRST system consists of a small suite of programs which are able to provide the designer with a complete, specialised design environment. The structure of this environment is shown in figure 3-4, and each of the major components is described below.

# 3.3.1: Language Compiler

The only design input available to the FIRST user is the FIRST high level language. This language provides a

Figure 3-3: Typical Floorplan

Figure 3-4: The Software Environment

structural description of the circuit under consideration, in that it describes the function blocks (i.e. bit-serial operators) which are present in a circuit, and their interconnections. In addition, because the structural design primitives have been chosen to correspond to functional design primitives, it also serves as a de facto functional description of a circuit. The language is able to capture the designer's intent in a form which closely matches the designer's logical conception of a system. This is a major advantage over designing with proprietary parts, where the designer must translate from his or her logical conception of a system into a quite different structural realisation, often in terms of ill-matched and inconvenient functional units.

The FIRST language identifies four distinct data types needed to build a circuit description:

- (1) OPERATORS, corresponding to arithmetic and logical functions.

- (2) CONSTANTS, which are integer expressions corresponding to the values of parameterisable operator attributes.

- (3) SIGNALS, corresponding to network nodes which carry sampled-signal data.

(4) CONTROLS, corresponding to network nodes which carry timing information such as 'START OF WORD' and 'START OF FRAME'.

A circuit is a collection of parameterised operators, each with a set of input and output ports which are connected to control or signal nodes. Interconnections between different operator ports are made implicitly by connecting several ports to the same node. Each operator invocation, corresponding to a line of the FIRST language description, contains the following information:

- the operator name.

- the values of any parameterisable attributes.

- ordered lists of the names of the nodes to which input/output ports are connected.

These different data types are syntactically separated in an operator invocation, which is in essence a mathematical expression in prefix notation. The general form is:

NAME [params] (ctls in -> ctls out) sigs in -> sigs out

e.g.

ADD [DELAY+2,0,0] (LSBTIME) A,B,CARRYIN -> SUM,CARRYCTT

The FIRST language also allows the definition of common, parameterisable sub-circuits as user-defined operators. These operators may then be invoked any number of times in exactly the same manner as primitive operators. Operator calls are grouped into CHIP definitions, corresponding to physical integrated circuits. These CHIP definitions may then be grouped into SUBSYSTEM definitions, and finally into a single SYSTEM definition. Thus the design language spans the whole hierarchy from structural primitives, to complete multi-chip signal processing systems.

The language compiler reduces this hierarchy into a list of primitive operator invocations, with node names replaced by unique node numbers. The resultant description is called the FIRST intermediate format, and it is this description which is used by later phases of the design software.

A high level language design interface allows considerable error checking to be performed, e.g. type checking, undefined names, incorrect number of operator port connections etc. The relatively constricted syntax of the language helps to avoid many of these errors in the first place.

The form of the language has been derived from the structural design language for the MODEL gate-array

design system [Gray 82]. The language compiler was built using the lexical and syntax analysis phases of an existing teaching compiler, SKIMP [Rees 80], with a custom "code generation" section added. The result is a very simple single pass, recursive descent compiler.

Since FIRST circuit descriptions are typically only about one page in length, the simplicity and ease with which the compiler can be altered have far outweighed any considerations about run-time efficiency.

### 3.3.2: Simulation

Two different simulators have been produced in the development of the FIRST system. The earlier simulator was clock driven. On each clock cycle, every operator in the system would be simulated in turn, using the present binary values on its input nodes along with any stored internal state to produce new values on its output nodes at the next clock cycle. Once all operators had been so invoked, the clock would advance by one cycle, and the process repeated. External inputs to the simulator were entered via an external data file. Similarly the values on any nodes could be output to another data file for subsequent inspection.

The operation of this simulator was a direct algorithmic interpretation of the physical circuit - so much so in fact that the functional definitions of

operators could often be written such that each logic equation in the functional description would have a direct hardware counterpart in the physical realisation. This proved useful in determining if a proposed hardware realisation of an operator did, in fact, implement the desired function, and also gave a great deal of confidence that the simulator provided an accurate model of operator behaviour.

However, because this simulator was using a sequential, word oriented machine (i.e. the computer) to directly simulate the operation of a highly concurrent, bit-oriented architecture, the computational effort required for a thorough simulation of a large system was unacceptable.

For this reason, another simulator has been designed which simulates a system at a higher level of abstraction. This simulator is event driven, and simulates the operation of individual operators on a word by word basis. The values on nodes, which in reality consist of serial bit streams, are modelled as discrete words of data occuring at discrete time intervals. When a new word of data reaches a node, an event is said to have occurred. Events are described in terms of the node to which they refer, the new value of that node as a result of the event, and the time at which the event occurs.

The scheduling of events is handled by keeping all pending events on an event queue. All events due to occur at a given time are removed from the queue, and the values of the associated nodes are updated to reflect their new values. All operators which have any of these nodes as their inputs are activated. The new values which have arrived at their inputs will generate new values at their outputs. These new values are modelled as further events scheduled to occur at some later time, as determined by the latency of the particular operator.

In general, new values should arrive at all inputs of a particular operator at the same time. If not, this usually implies that the designer has made an error in matching the latency of the various signal paths leading to this operator. When such mismatching occurs, the simulator issues a warning, and continues the simulation. The operation of the simulator in such cases will not truly echo that of the physical system, which is itself unlikely to be a valid circuit. Once all such timing "bugs" have been eliminated (and this simulator provides a powerful tool for such debugging) the designer can have a high degree of confidence in the simulation results.

Inputs and outputs to the system are again via external data files. These data files are essentially lists of events relevant to the system input or output nodes. Since the system is being modelled at a higher

level than in the clock driven simulator, the computing effort required for a given simulation has been reduced by about an order of magnitude.

A program also exists within the FIRST suite to convert the simulator's output into a form suitable for use with an automatic test pattern generation system.

## 3.3.3: Physical Layout

The task of the FIRST layout program is to produce a physical realisation of the system implied by a FIRST language description. This process proceeds in distinct phases, according to a strict layout strategy.

For every invocation of a predefined operator in a FIRST language description of a system, a corresponding function block appears in the physical layout. Each function block is assembled from the appropriate leaf cells as described above. Once constructed, operator blocks are placed along "waterfronts" at the top and bottom edges of a central wiring channel. The layout program uses the criteria of minimum chip area to decide on a suitable arrangement of the blocks. The size of operator bounding boxes typically covers quite a range of sizes. The overall size of the chip, however, depends on four main factors:-

- the height of the tallest block on the top row

- the height of the tallest block on the bottom row

- the width of the wider of the two rows

- the size of the wiring channel

The first three factors depend only on which blocks are placed on the top row, and which are placed on the bottom, and the placement algorithm first decides on this subdivision. Without rigorously attempting to explain the algorithm, the basic idea is to place all the tall blocks on the top row, and the short blocks on the bottom row, where the division between tall and short is chosen so that the total area is minimized. Perturbations are then made to this arrangement to reduce the area further by making the rows more equal in width. The size of the wiring channel is considered constant during these calculations.

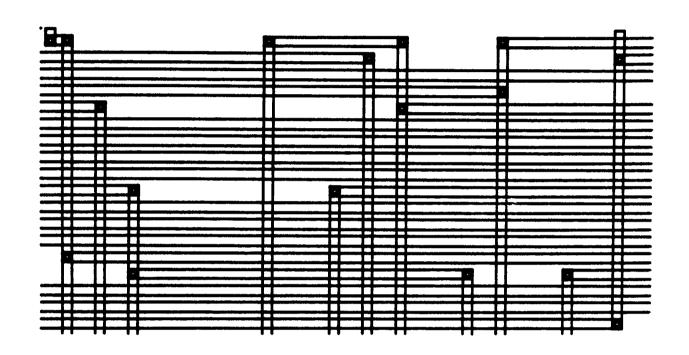

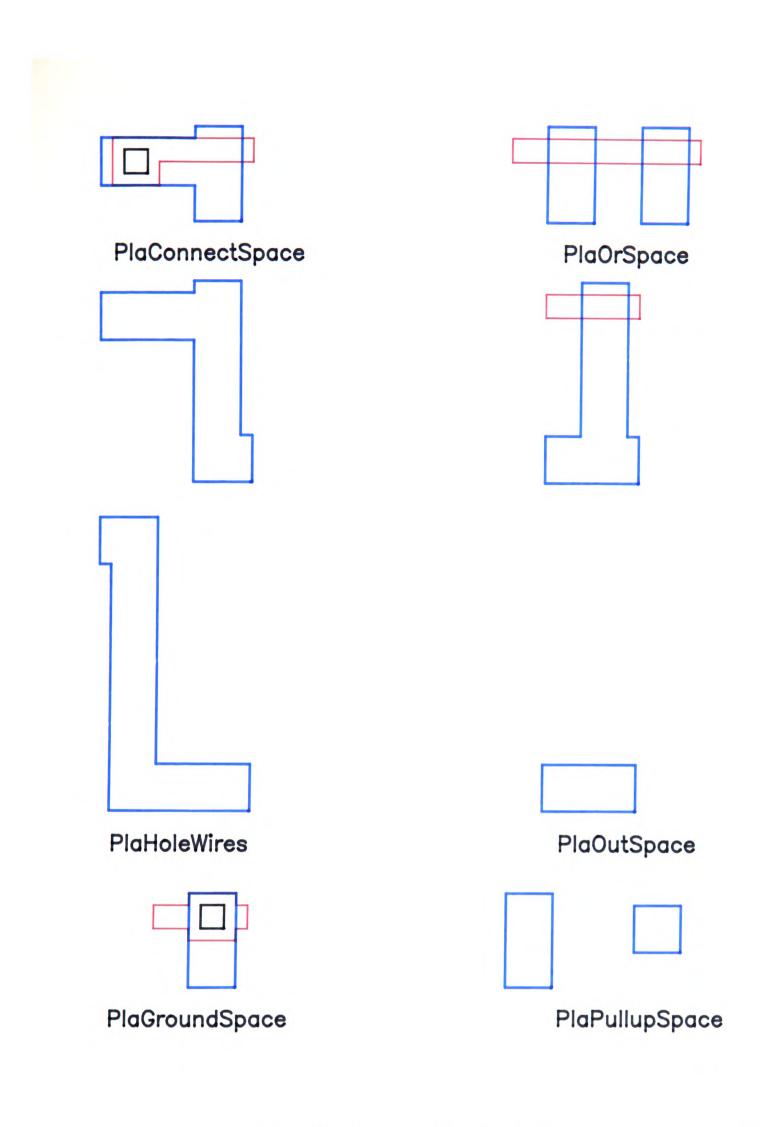

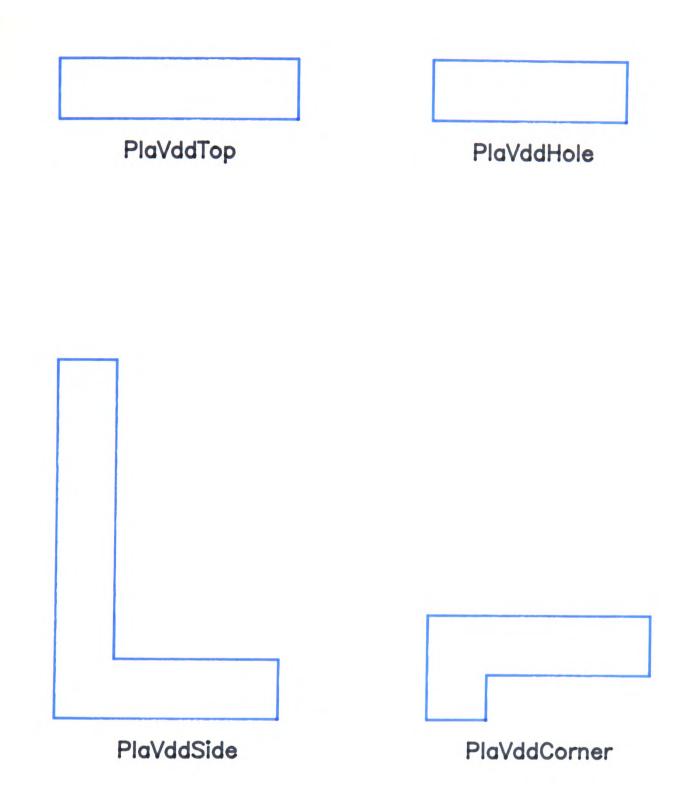

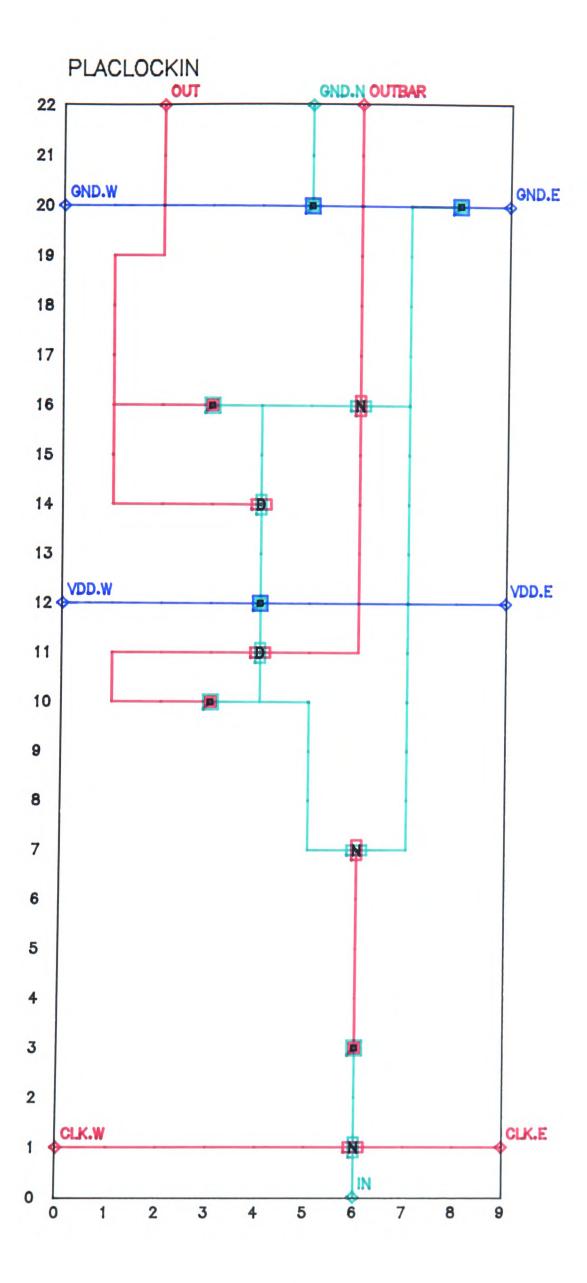

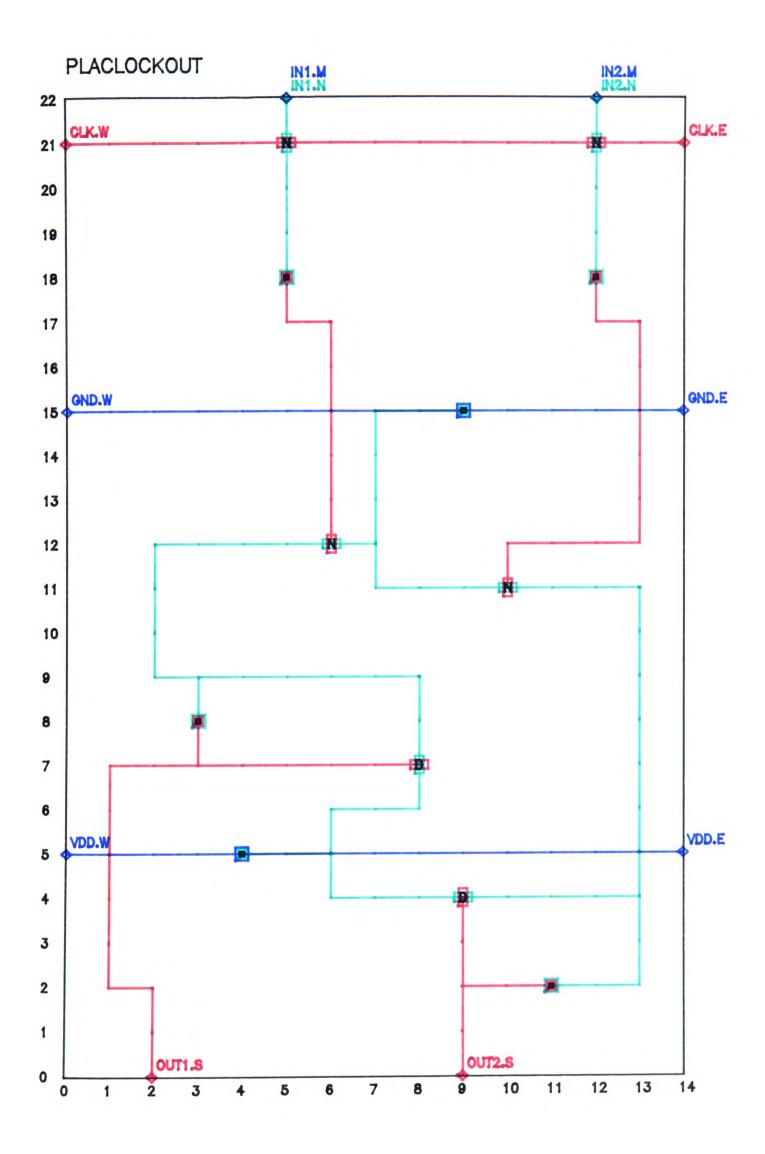

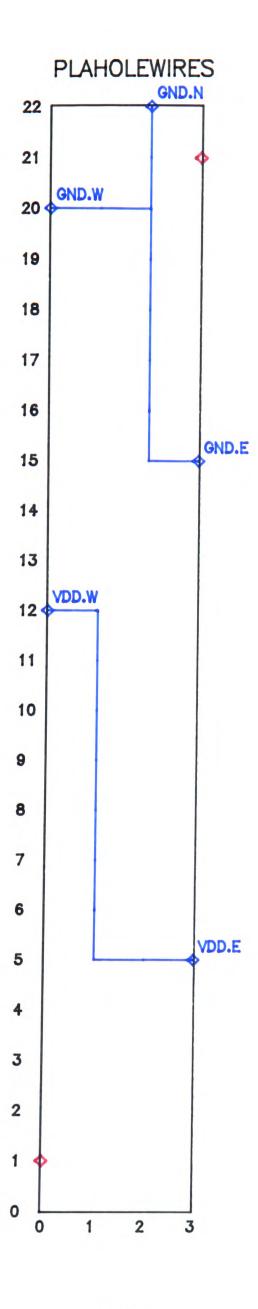

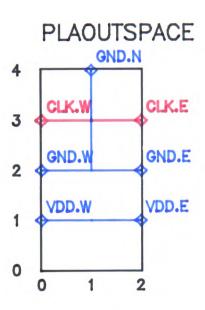

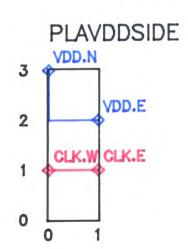

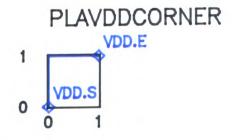

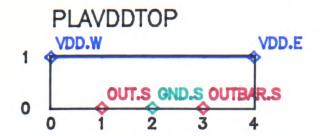

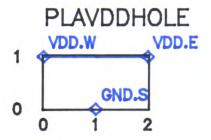

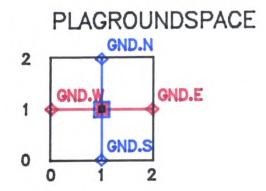

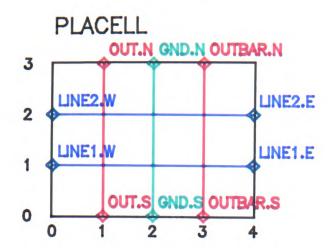

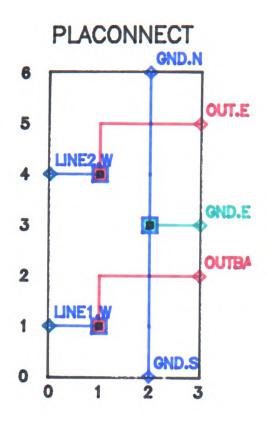

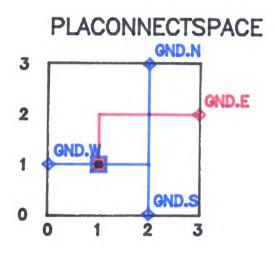

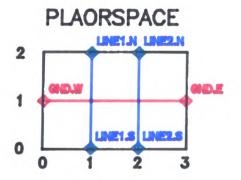

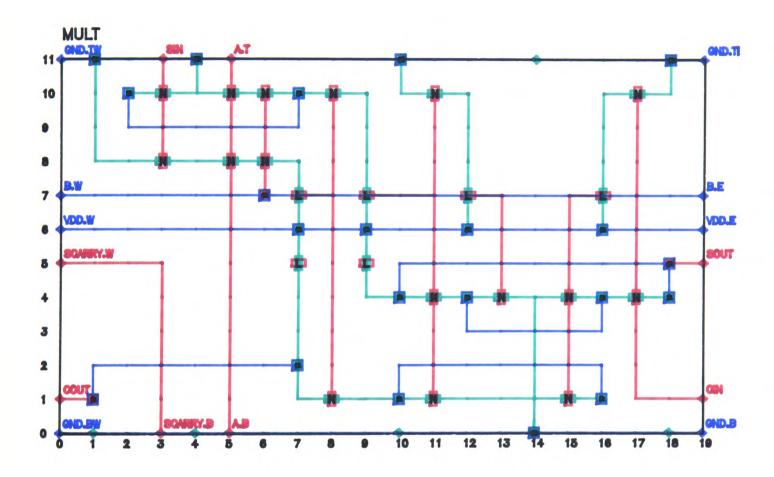

Next, the arrangement of the blocks within each row is decided. The width of the wiring channel, and hence total chip area will differ with different arrangements. Rather than use an algorithmic method for determining a good arrangement, the blocks are placed left to right within each row in the same relative order that they were invoked in the FIRST language description of the system. Since a designer may be expected to write this description such that the general flow of information is from one operator to the next down the page, such a