# **ADDRESS GENERATOR SYNTHESIS**

by

### **Douglas M. Grant**

A thesis submitted to the Faculty of Science, University of Edinburgh, for the degree of Doctor of Philosophy

Department of Electrical Engineering, 1991

# **Abstract of Thesis**

Increasing complexity of Application Specific Integrated Circuits (ASICs) has demanded a corresponding increase in the power of Computer Aided Design (CAD) tools, so that contemporary design tools can now synthesise an entire silicon architecture, given only a description of its functionality. Specialised automated synthesis techniques have now been applied to almost all parts of the architecture, but one area which remains unresolved is that of memory address generators.

Previously combined with other logic synthesis techniques, less than optimal solutions were often found for generating memory address sequences, and this thesis examines address generator synthesis as an individual step in the design process, as part of an investigation into high level synthesis. The synthesis techniques developed for address generators in the AG1 and AG2 tools presented, target specific architectural forms including counters, incrementors and ROM look-up tables, and the details of these are gathered within a comprehensive data structure which allows optimisation through hardware sharing to occur.

At a slightly higher level, the specification of address sequences as a stage in memory synthesis is also investigated and a behavioural to register-transfer level silicon compiler,  $MC^2$  is presented. The data path and memory architectures constructed by this tool are used to produce realistic address generation requirements whose implementations are also presented, synthesised by AG2.

It is shown that both array and non-array memory can benefit from more specialised address generator synthesis over the existing, mainly logic synthesis approach.

## **Declaration of Originality**

The material contained herein was researched and composed entirely by myself in the Department of Electrical Engineering at the University of Edinburgh, between October 1988 and October 1991.

## Acknowledgements

I would firstly like to thank my supervisors, Peter Denyer and Peter Grant for all their help and advice throughout my time at Edinburgh, all the guys from the SARI project, BAe for their sponsorship, Fiona from the TTC and Joan Burton for their help with all things complicated, Iain Finlay, Paul Neil, Jonathan Puddicombe and Hamish Fallside for putting up with my ranting in the office, and most of all thanks to Tracy my wife-tobe for all her support during those late night brainstorms.

# Contents

| Abstract                                                  | Ι   |

|-----------------------------------------------------------|-----|

| Declaration of Originality                                | П   |

| Acknowledgements                                          | П   |

| Contents                                                  | Ш   |

| Preamble                                                  | 1   |

| Chapter 1: Introduction to address generation             | 2   |

| Address Generation in Digital Systems                     | 2   |

| What is address generation?                               | 5   |

| The scope of address generation                           | 5   |

| Overview of address generation techniques                 | 6   |

| For control                                               | 6   |

| For memory access                                         | 6   |

| Overview of address generator synthesis techniques        | 7   |

| For control                                               | . 7 |

| For memory access                                         | 7   |

| Other related approaches                                  | 8   |

| The case for address generators based on counters         | 8   |

| Comments                                                  | 10  |

| Chapter 2: Introduction to address generator architecture | 11  |

| The memories                                              | 11  |

| The binary counter                                        | 12  |

| The ripple counter                                        | 12  |

| The serial carry counter                                  | 12  |

| The parallel synchronous counter                          | 13  |

| The serial/parallel synchronous counter                   | 13  |

| The pseudo-parallel synchronous counter                   | 14  |

| The modulus m counter                                     | 14  |

| Other address generator elements                          | 16  |

| Address ROMs                                              | 16  |

| Exclusive OR gates                                        | 18  |

| Clocked-bits                                              | 19  |

| Incrementors                                              | 19  |

| Logic                                                     | 20  |

| Cost breakdown of address generator elements              | 21  |

| Area-costs                                                | 21  |

|                                                           |     |

| Speed-costs                                                         | 22                   |

|---------------------------------------------------------------------|----------------------|

| Comments                                                            | 22                   |

| Chapter 3: Requirements for an address generator                    | 23                   |

| Data-dependant addressing                                           | 23<br>23             |

| Scheduled memory addressing                                         |                      |

|                                                                     | 24                   |

| Array access                                                        | 24                   |

| Control                                                             | 26                   |

| Comments                                                            | 26                   |

| Chapter 4: Address generation based on binary counters              | 27                   |

| Some traditional problems                                           | 27                   |

| Some manually designed address generators                           | 31                   |

| AG1 - Address generator synthesis based on binary counters          | 33                   |

| Data entry types                                                    | 34                   |

| Method                                                              | 34                   |

| Logic synthesis                                                     | <sup>-</sup> 37      |

| Output format                                                       | 40                   |

| Address generators designed using AG1                               | <b>4</b> 1           |

| Comparisons                                                         | 41                   |

| Use of the 'C' programming language                                 | 44                   |

| Comments                                                            | 44                   |

| Chapter 5: Introduction to behavioural synthesis                    | 46                   |

| What is behavioural synthesis?                                      | 46                   |

| Key steps in the high level synthesis process                       | 47                   |

| Capture of behaviour                                                | 48                   |

| Scheduling                                                          | 49                   |

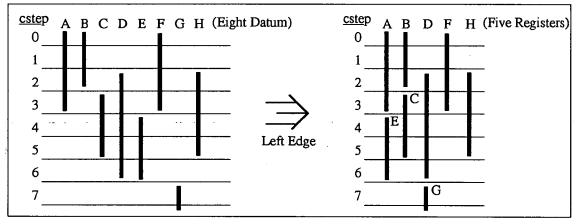

| Resource Allocation                                                 | <del>4</del> 9<br>51 |

| Data path synthesis                                                 | 51                   |

| Controller synthesis                                                | 55                   |

| Resulting design format                                             |                      |

| Impact on address generation                                        | 55                   |

| Comments                                                            | 56                   |

|                                                                     | 57                   |

| Chapter 6: A heuristic approach to memory, communication and contro | I                    |

| synthesis for scheduled algorithms                                  | 58                   |

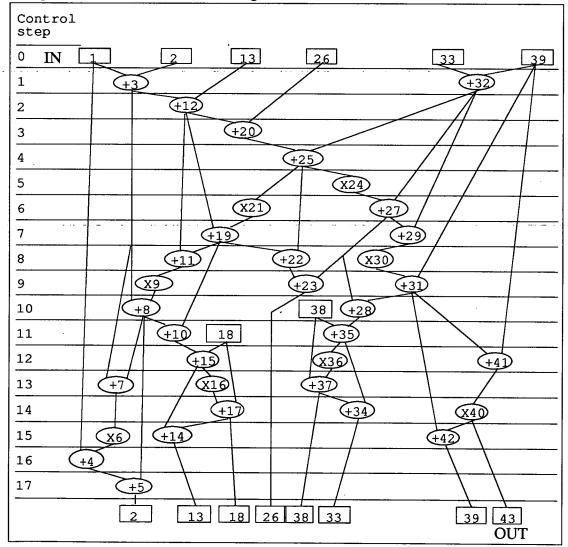

| The joy of synthesis!                                               | 58                   |

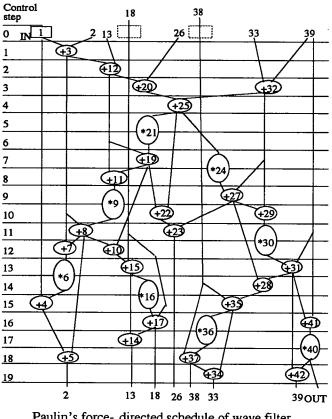

| Schedules and their scheduling method                               | 58                   |

| Constraints on this approach                                        | 62                   |

| MC <sup>2</sup> - Memory, Communications and Control synthesis      | 62                   |

|         | Schedule data-base                                              | 62         |

|---------|-----------------------------------------------------------------|------------|

|         | Pre-assignment or not?                                          | 65         |

|         | The Three Steps to heaven                                       | 65         |

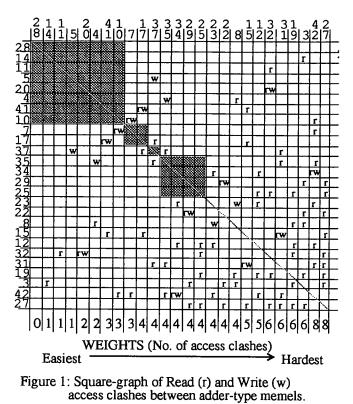

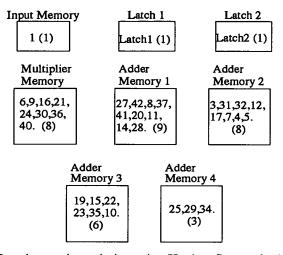

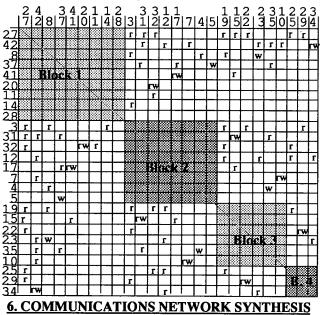

|         | Memory and communications synthesis                             | 65         |

|         | Address and control requirement analysis                        | 78         |

|         | Address and control sequence synthesis                          | 83         |

|         | Output format                                                   | 86         |

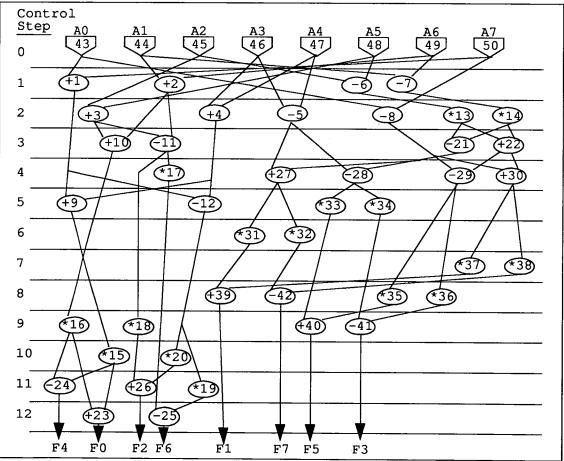

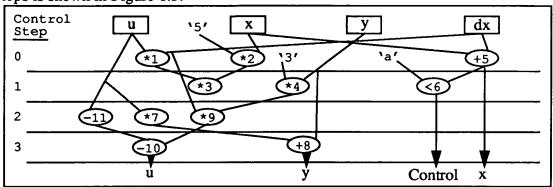

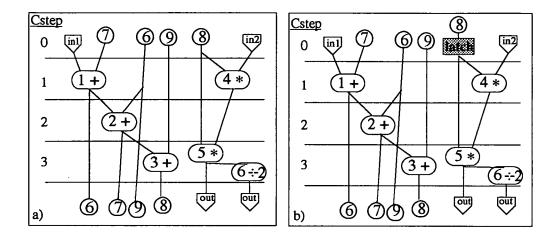

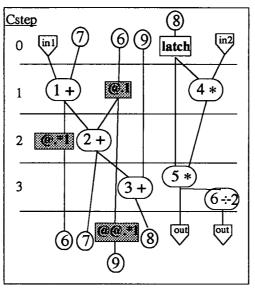

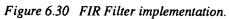

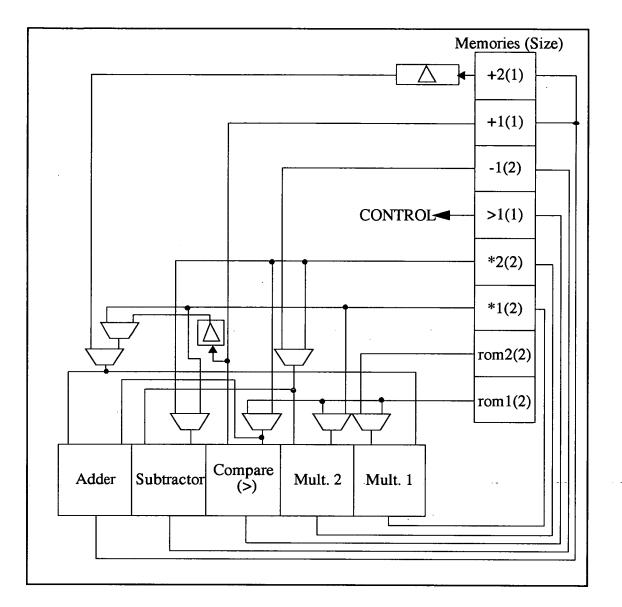

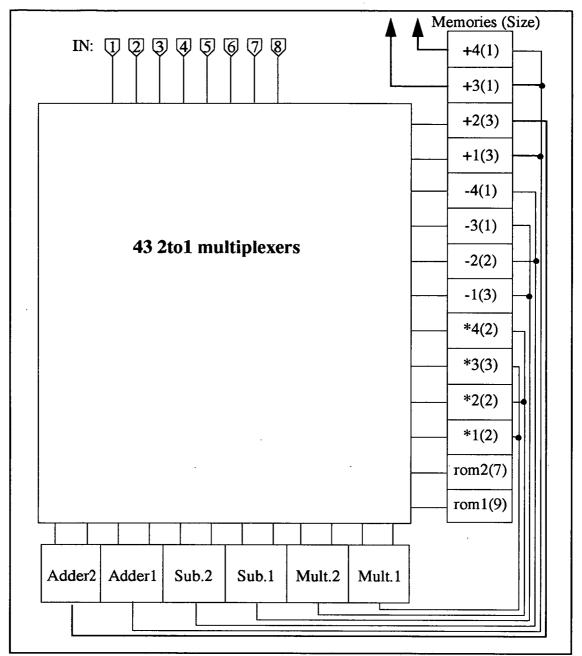

| So      | me synthesised data-path architectures                          | 88         |

| Co      | mparisons with related results                                  | 91         |

| AS      | Standard for behavioural synthesis results presentation         | 95         |

|         | blog for fast development                                       | 96         |

| Co      | mments                                                          | 96         |

| Chanter | 7: A general approach to address generator synthesis            | 00         |

|         | e need for generalisation                                       | 99<br>99   |

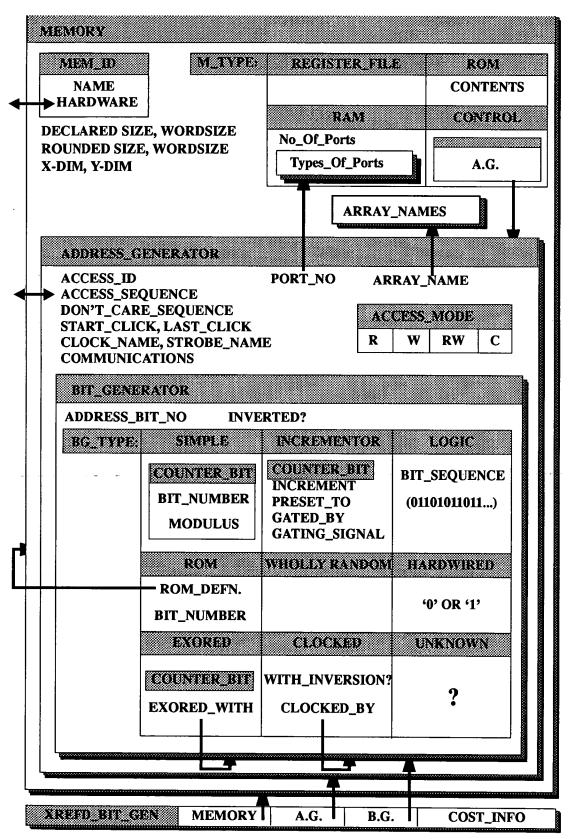

|         | e inevitable data model                                         | 99<br>99   |

|         | quirements of an address generator synthesis tool               |            |

|         | 32 - A general address generator synthesis tool                 | 102<br>102 |

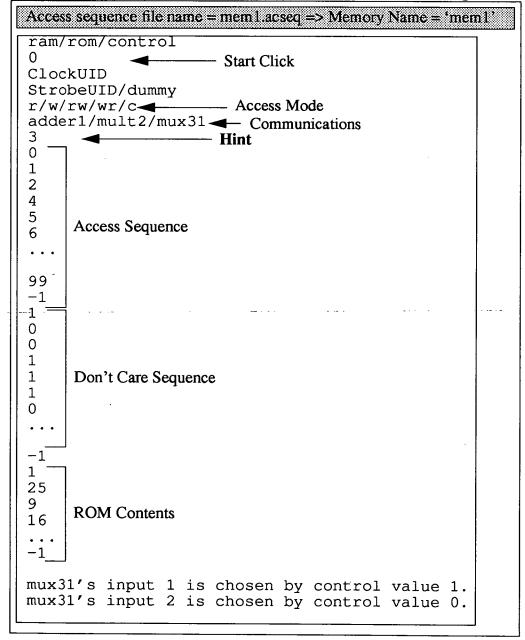

| AC      | Input format                                                    |            |

|         | Basic Method                                                    | 102        |

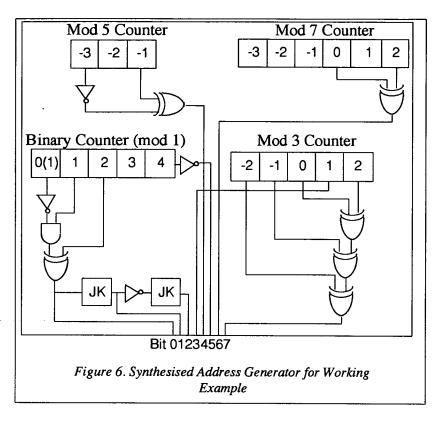

|         | A working example                                               | 105        |

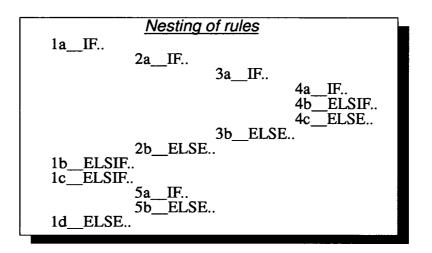

|         | Method                                                          | 106<br>108 |

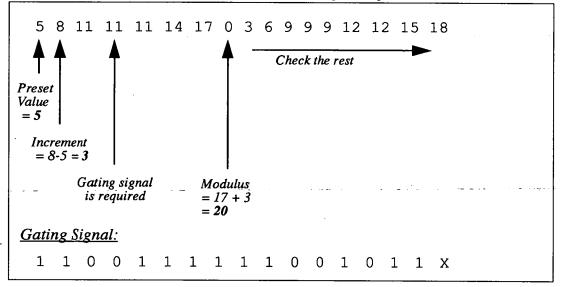

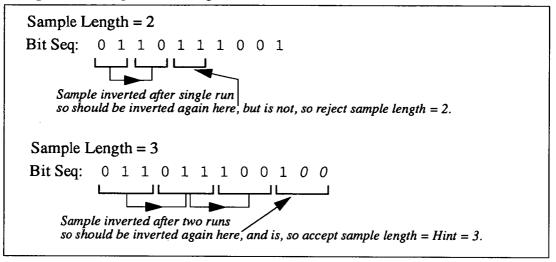

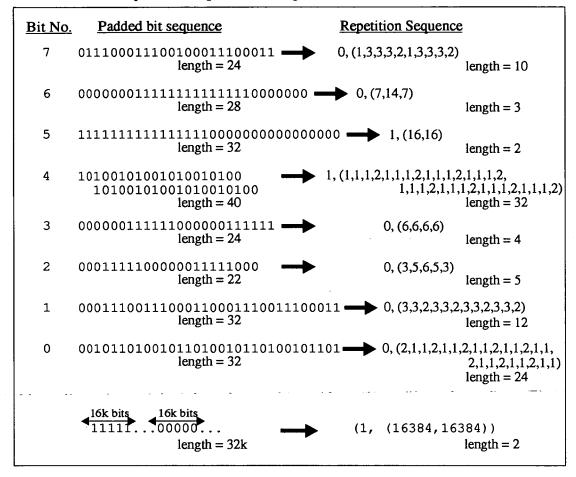

|         | Finding an Incremental Sequence                                 | 108        |

|         | Padding a Bit Sequence                                          | 108        |

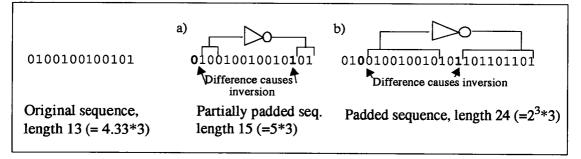

|         | Transformation to Repetition Sequence                           | 110        |

|         | Reducing the Repetition Sequence                                | 110        |

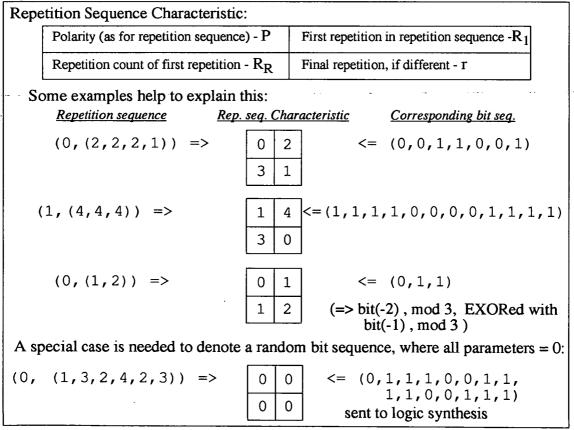

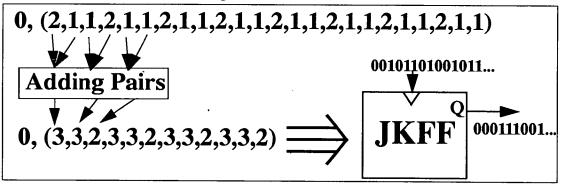

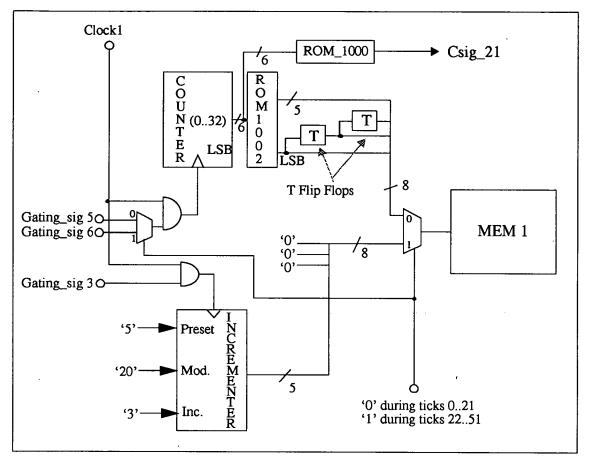

|         | The Repetition Sequence Characteristic                          |            |

|         |                                                                 | 113        |

|         | Matching the Charateristic to a Bit Sequence Generator          | 114        |

|         | Finding Clocked-type Bit Sequence Generators                    | 115        |

|         | Multiple Access Sequences                                       | 116        |

|         | Optimization                                                    | 116        |

| Oth     | Output format                                                   | 119        |

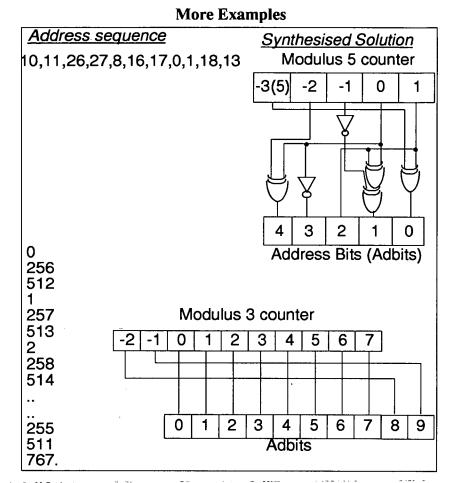

|         | her worked examples and results                                 | 120        |

|         | DA - A big step                                                 | 131        |

| Col     | mments                                                          | 131        |

| Chapter | 8: Address generator synthesis as part of a general behavioural |            |

|         | thesis toolset                                                  | 133        |

| Intr    | oduction to SAGE - Concepts and Reality                         | 133        |

|         | dress generation within SAGE                                    | 136        |

|         |                                                                 |            |

.

| Scheduled memory                                             | 136 |

|--------------------------------------------------------------|-----|

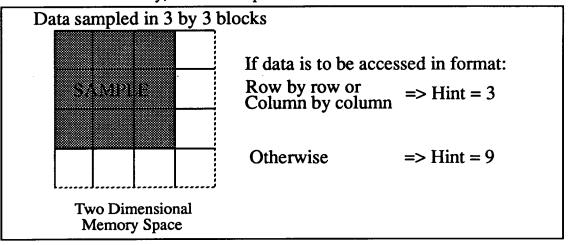

| Array memory                                                 | 137 |

| Macro-generation of counters                                 | 138 |

| Future plans                                                 | 139 |

| Comments                                                     | 139 |

| Chapter 9: Conclusions and new directions                    | 140 |

| References                                                   | 144 |

| Appendix A - Author's publications                           | 160 |

| Appendix B - Example output from AG2                         | 194 |

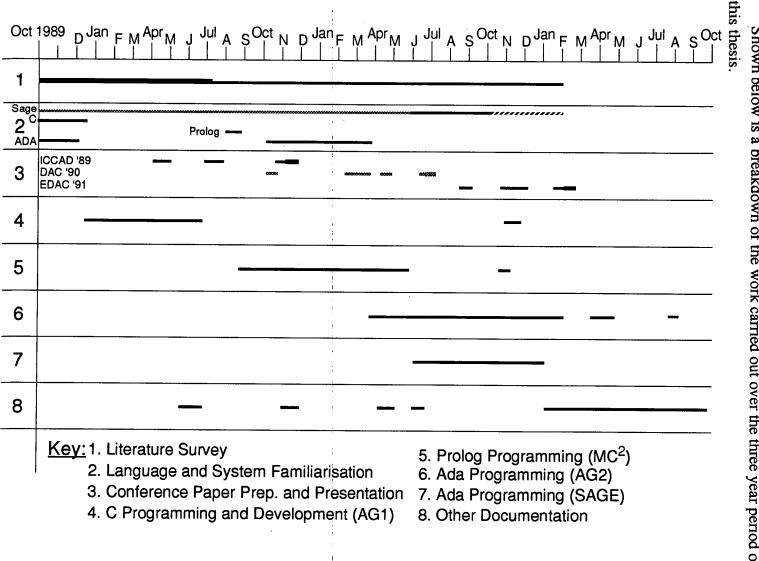

| Appendix C - Workplan                                        | 213 |

| Appendix D - User Guides                                     | 214 |

| Appendix E - Address generators for MC <sup>2</sup> examples |     |

| Also included: 1 disk containing all code.                   |     |

. . . . . . .

.

.

## Preamble

This thesis examines high level synthesis of data path architectures and in particular, address generation hardware. This is based upon the recognition of certain characteristics of binary sequences which relate directly to certain generation methods. The first chapter introduces the concept of address generation, and gives an overview of related work in this area, and then the motivation for this work is stated. Chapter 2 introduces the hardware involved in address generation, including counters, single logic gates and ROMs, and the next chapter illustrates the possible requirements for an address generator, before Chapter 4 looks at a simple address generator synthesis tool - AG1.

Next, in Chapter 5, the many and varied approaches to contemporary behavioural synthesis are documented, and then Chapter 6 presents a heuristic approach to memory, communication and control synthesis for scheduled algorithms -  $MC^2$ , which has been coded in Prolog. This step was necessary in order to produce some realistic address sequences for otherwise well-known examples.

Chapter 7 returns to address generator synthesis with a more complex address generator synthesis tool - AG2, and in Chapter 8 its application within a general behavioural synthesis tool is investigated. Finally, Chapter 9 presents conclusions and directions for future work.

Appendix A contains the author's publications and then Appendix B presents some annotated output from the tool described in Chapter 7. Appendix C gives account of how time was spent on this project, and Appendix D holds the user guides to the tools presented in this thesis. Also included with this thesis is a disc which holds all the code described in the text.

## Chapter 1 Introduction to Address Generation

#### **1.1 Address Generation in Digital Systems**

Since the first digital systems were constructed in the mid-1930s [200], great advances have been made in both their design and physical implementation. From the earliest vacuum tube transistors used by Newman and Pinkerton [201, 202], evolved solid-state logic [203], and with that came the first great improvement in the size, power consumption and reliability of digital circuit components.

As the properties of silicon as a substrate for both transistors and interconnect were developed in the early 1950's, a second step was taken in circuit performance, so that we now have highly complex micro-computers and data-processing hardware, integrated on a single chip (IC), less than three square centimetres in area.

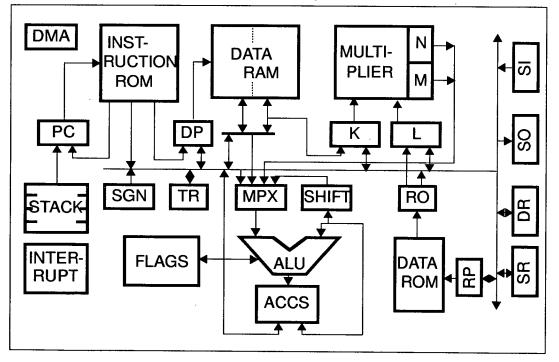

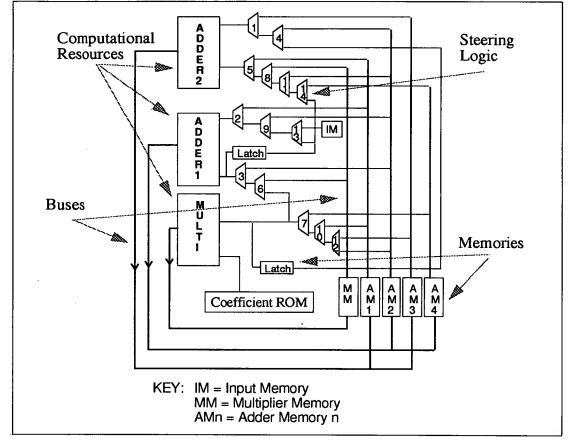

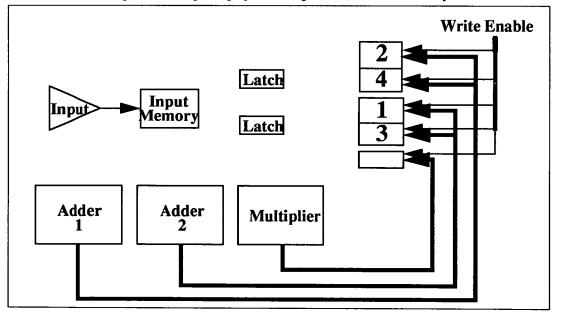

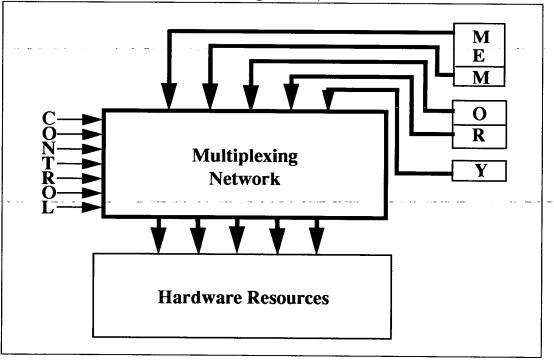

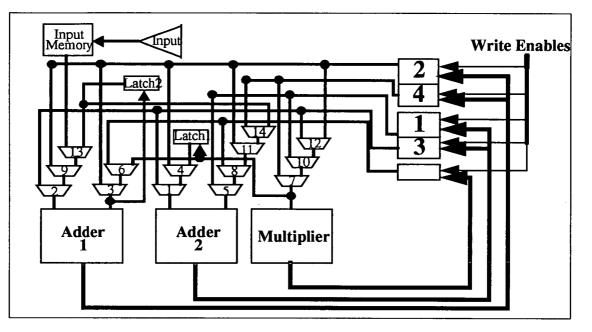

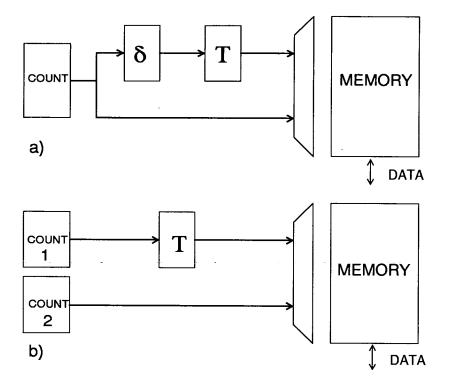

Figure 1.1 shows a typical Von Neumann data-processing architecture [204], in which data is guided between computational hardware and memory of some sort, under the direction of a process controller and ancillary hardware.

Figure 1.1 A typical data-processor architecture (NEC7720).

Computational hardware performs any *calculations* required on the data, for instance adding and multiplying, and this may be done by hardware dedicated to that

specific calculation - adders or multipliers - or by multi-function Arithmetic Logic Units (ALUs). The memory hardware implements storage for either long-term data, for fast, on-chip access, or for data being transferred between computational hardware elements.

Memories may be Read Only Memories (ROMs), Random Access Memories (RAMs), registers (latches) or register-files, shift registers, stacks, or any other data storage device, and in the case of ROMs, RAMs and register-files, these memories will need an address to be generated before data may be accessed.

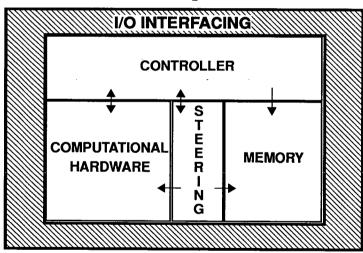

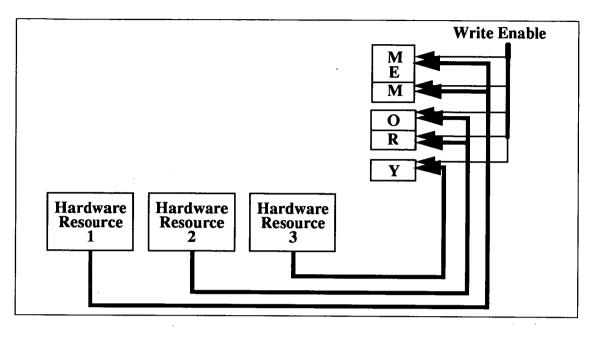

The steering logic, including multiplexers and demultiplexers, guides the data between all this circuitry, and is controlled by signals generated by a controller, which may be micro-programmed [84, 85], or have some simpler implementation [193, 194]. This controller may receive feedback from computational hardware, for decisionmaking, as well as interpreting externally applied information, and generating any clocking signals required by synchronous circuitry. Its other main task is to generate the control necessary for the memory hardware, consisting of Read/Write enable signals, the memory addresses, and any other Shift/Load/Push/Pull control signals. A simplified description of the architecture is shown in Figure 1.2.

Figure 1.2 Simplified data-processing architecture.

The huge rise in integrated circuit complexity, through Large Scale Integration (LSI), to Very Large Scale Integration (VLSI), soon overwhelmed the wholly manual approach to digital system design, but *also* provided a solution, in the form of Computer Aided Design<sup>\*</sup>. As more complex and powerful computers were designed, they were used to aid the design of even higher-performance systems (The DEC MicroVax

<sup>\*</sup> The IEEE Transactions on Computer Aided Design was created in 1982 to handle the increasing activity in this area.

prototype was designed using Genesil<sup>TM</sup>). At first the drafting of the physical layout of the circuits was the only design stage to benefit from these advances [95, 96], but more and more of a digital system designer's "toolkit" of methodologies have since been automated. These provide support in areas, from the geometry-level view of the chip, right up to the design of an entire IC, almost at the press of a button. Placement and routing, design-rule checking, combinatorial logic synthesis [62..68], and increasingly important, test [88..92], have and will continue to benefit from the increase in the power of the computers used to automate them.

Having automated what used to be the repetitive and error-prone tasks of a VLSI designer, more time could be devoted to the investigation of the design space, to perhaps find more efficient implementations of existing processors, or to develop wholly new architectures. Schematic capture of designs was developed to aid this investigation [127, 128], and it naturally followed that high-level synthesis of complete data-processing architectures was targeted next for automation [31,108].

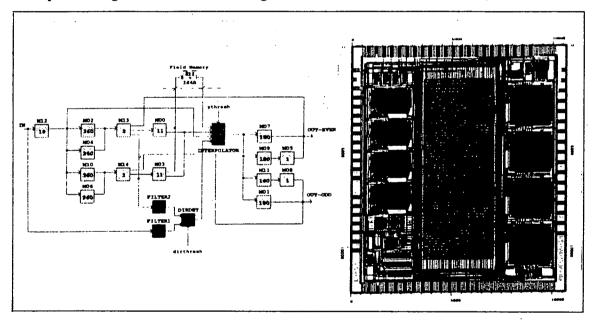

Figure 1.3 Architecture and chip layout by PHIDEO [61].

Contemporary high-level synthesis systems may be based on procedural, Hardware Description Languages (HDLs) [153..156], or on the more complete, VHSIC (Very High Speed IC) Hardware Description Language (VHDL) [157, 158] (now standardised - IEEE 1076), or Behavioural Description Languages [24,34] (usually inhouse), and can be used to produce gate-array [102], standard-cell [14], and other semicustom design method implementations of Application Specific ICs (ASICs), in the latest VLSI technologies [99, 100, 46, 36, 30].

One area of high-level synthesis which has been under-developed, is that of synthesis of application-specific address generators, as separate entities to the general controller on an IC. The hardware required for address generation can make up a large percentage of the total chip area (up to 50%), so there should be at least as much work done on its synthesis as there is for the computational part of the design. Some contemporary systems treat address generation as just another computation and design the hardware as a data path, but in [141] sequence generation is identified as a distinct basic block in a functional block environment, and it is the field of sequence generator synthesis which is targeted by this thesis.

#### 1.2 What is address generation?

To generalise as far as possible, address generation is the production of some sequence of binary words, of some width.

Since the primary use of these words is by memories, as addresses, the generation of them is known as address generation.

An address generator is therefore the hardware which actually produces these data, and may produce several addresses as part of its data word.

#### **1.3** The scope of address generation

As stated above, an address generator does of course generate addresses for memories, but can have other uses:

- i) To generate control bit sequences for steering logic (such as multiplexers).

- ii) To generate control bit sequences for selection of function in ALUs, and for other selection requirements.

- iii) To generate test patterns for a processor, on the same IC.

In order to place some limits on the scope of this thesis however, address generation is defined as being the production of a *predetermined* sequence of binary words of some width.

This precludes applications for which a sequence is dependent on internal variables or data, for instance the output from an adder during successive uses.

#### **1.4** Overview of address generation techniques

There follows an account of related techniques in sequence generation, both for control purposes and for memory access.

#### 1.4.1 For control

To date there are very few ASIC design systems which deal with the memory addressing problem as separate entity from the more general and possibly nondeterministic control problem. So control generation has dominated address generation techniques with most address generators eventually embedded in the controller.

Conventional approaches to control generation are, like most tried and tested means, too general in their methods to produce the most optimal architectures. They will produce passable results all the time but are not ideally suited to ASIC design.

The problem is usually one of mapping state numbers to actual control signals as fast as possible, using the least area of silicon. If there are just a few simple mappings then full combinatorial logic would be used, but as the number of inputs and outputs increases, a ROM look-up table may be used in conjunction with a (state) counter to produce any deterministic sequences, or as part of a FSM. However, as the number of inputs increases further, the ROM becomes outsized and a PLA is more likely. ROMs are also used as look-up tables as the basis for micro-programmed logic. A PLA may be used in conjunction with a binary counter to implement any combinatorial logic functions which map the linear state count to the control outputs, and this is certainly the most common form of controller architecture both for deterministic and non-deterministic sequences. The area of a PLA may be reduced by folding parts of the logic array, and their ease of programmability makes them very popular, but testing them as they stand is very difficult. By adding special structures to allow selection of each crosspoint on the PLA however, some PLAs may be used to test themselves [140].

Various other sequence generators and detectors are discussed in [152].

#### 1.4.2 For memory access

Several different address generation schemes have been reported, especially for array processing, based on adders [144], and on ALUs [145] which can use three types of address arithmetic to produce eleven different addressing modes in the Motorola DSP56000 chip. Address Calculation Units are also used in the Tektronix M275 programmable array processor [146] along with pointer registers. Counters have been

used in many cases, especially where the address sequence is to be used for array access, in a regular pattern [205].

#### 1.5 Overview of address generator synthesis techniques

Now we examine the diverse techniques for automatically synthesising sequence generators, for general control, and as a separate entity for memory access.

#### 1.5.1 For control

Devadas et al.'s MUSTANG system attempts to synthesise FSMs [64] using state assignment techniques to optimise a multi -level logic (multiple PLA) implementation [62], while Amman et al.'s SUCIM tool [66] aims at both optimal state assignment and state sequences. Here too, multiple PLA/ROM-structured FSMs are targeted for use with binary counters [65].

Micro-programmed controller synthesis has been around a relatively long time, with Grass and Lipp's LOGE system being a fair example[84, 85], and the Cathedral II system [81] synthesises micro-programmed control also.

The principals of combinatorial logic synthesis are described in [63] and the optimisation or minimisation of such logic is a popular subject [67, 68].

The Yorktown Silicon Compiler [73, 74] is one of the earlier systems for controller synthesis, and others include CPC [72] for use in the SYCO compiler, the SILC compiler [75], and work reported in [76, 77, 79, 80, 82].

#### 1.5.2 For memory access

A schematic capture method is reported in [142] which can be extended to the capture of address generation hardware, and in [143] address sequences for scheduled memory are produced automatically for multi-port memory allocations, but the problem of virtual to real address conversion is ignored, and no real synthesis is attempted.

In the Cathedral II system [162], background memory is synthesised in the form of Pointer Addressed Memories (PAMs), which only require an incremental address sequence, thus avoiding the construction of complex Address Calculation Units. For high speed circuits, the PHIDEO system [61] allows exploration of the address generation costs/ memory costs domain, and can synthesise address generators based on relative addressing using pointers, for a minimal sized memory structure, or based on counters for a possibly redundant memory, or based on otherwise minimised memory structures, which can lead to rather complex generators.

The author's own address generator synthesis systems, AG1 [149] and AG2 [148, 151], use decompositon of address sequences in trying to find a better hardware implementation than would normally be found using logic synthesis.

#### **1.6 Other related approaches**

There are other applications for sequence generators. BIST (Built-In Self Test) for PLA's [138], and more general use [135, 139], as well as other design techniques [136, 137] can utilise the same sort of architecture as address generators.

#### **1.7** The case for address generators based on counters

Counters are reliable, reuseable, testable and efficient, which makes such adaptable circuitry invaluable in chip design.

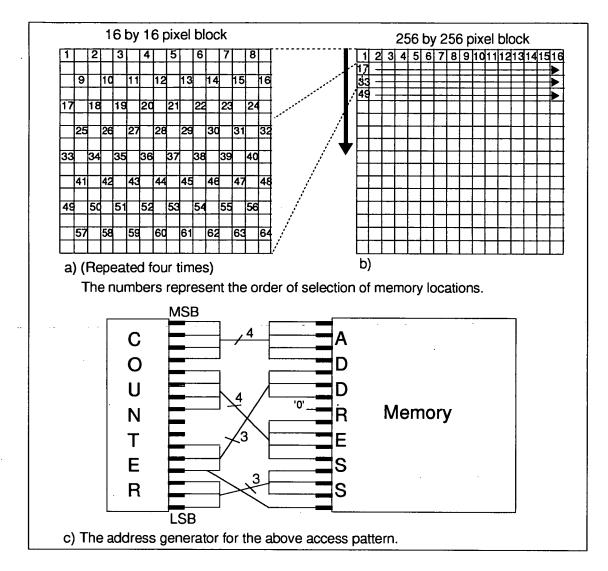

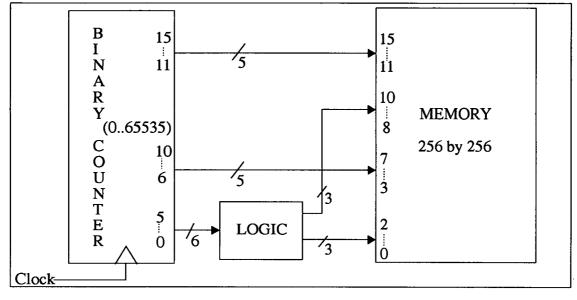

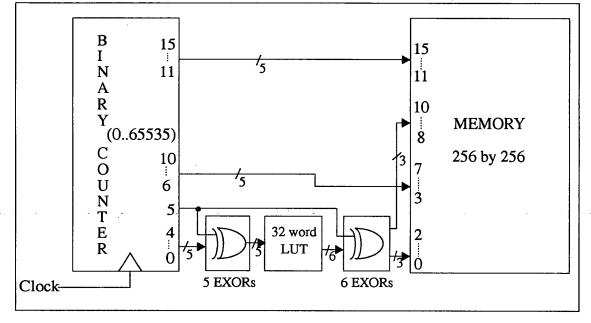

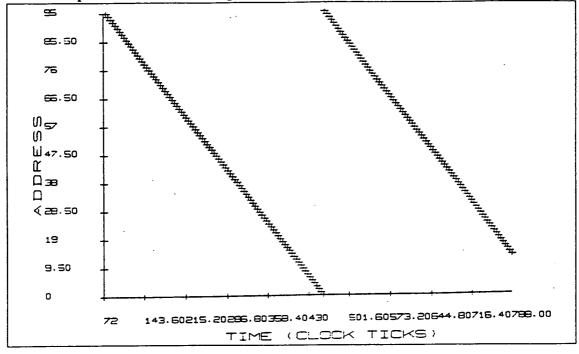

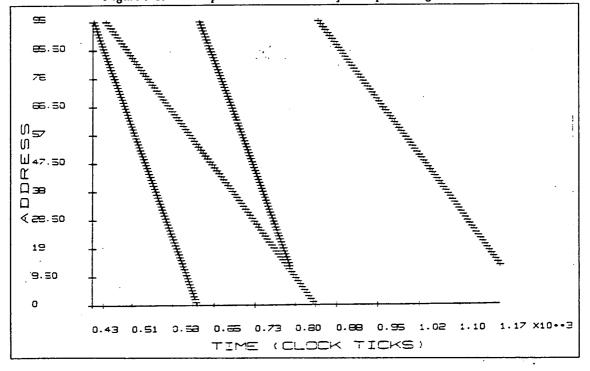

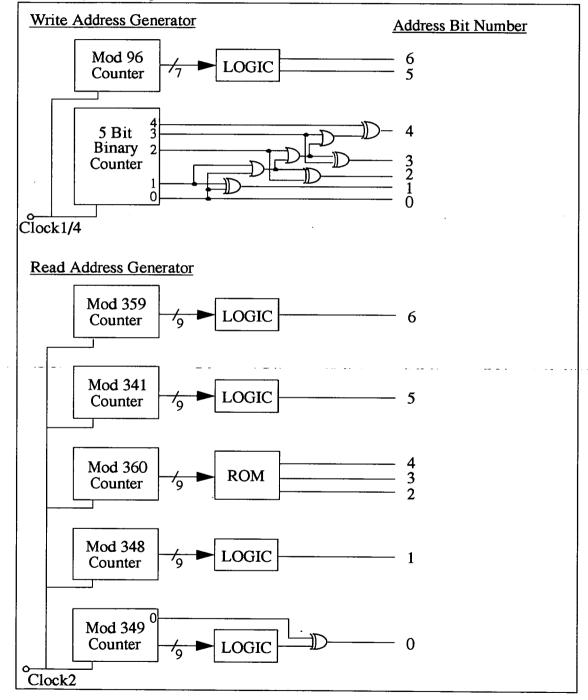

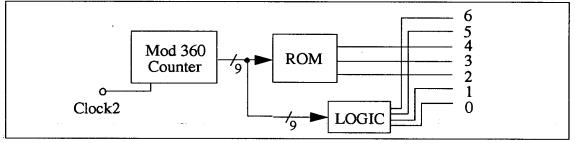

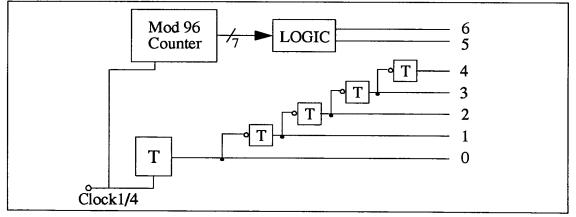

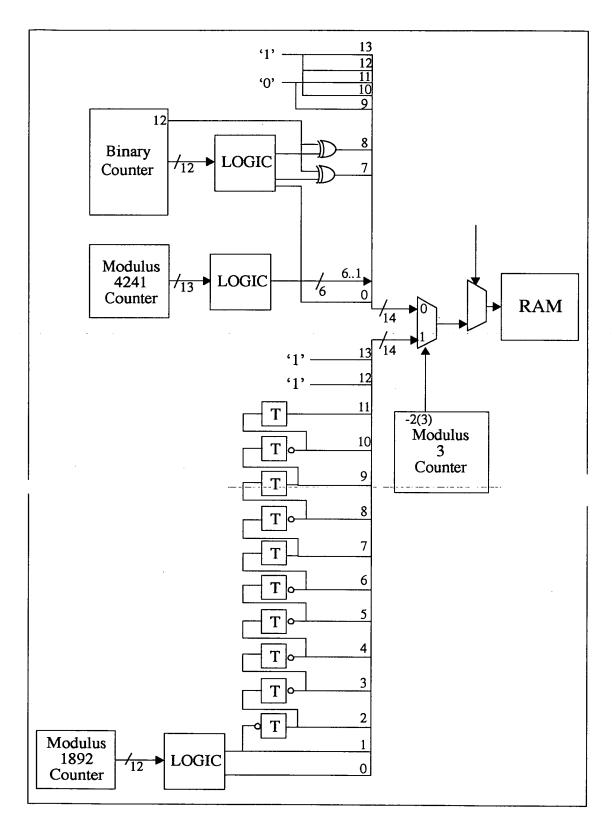

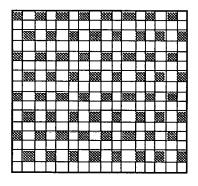

The use of counters in address generators is not a new concept [65], and in fact the subject matter for this thesis was originally inspired by some address generation hardware, manually designed for an image-processing application [205]. One such address generator is illustrated in Figure 1.4, along with a graphical description of the memory access sequence it produces. The gate array chip layout which includes this architecture can be seen in Figure 1.5.

Once this, and other solutions had also been produced automatically, it became apparent that counters could form a part of much more general-purpose address generators, if only the techniques for recognising their possible use could be developed.

6

Figure 1.4 Example of a counter in an address generator.

Figure 1.5 Chip layout of which about 50% of active area is address generation circuitry.

#### **1.8 Comments**

The DTI and the SERC have recently specified a new jointly funded collaborative programme - VLSI Design Automation for Information Technology Systems - whose workplan includes a sub-section on memory architectures which calls for "Novel configurations of memory and address generation, leading to reduced hardware requirements, involving automatic generation from system requirements" [206].

The design of address generators is at present an expert's task. The intuitive decisions made in their conception are based on a collection of experience of this and similar problems, from many different angles. It is only by utilising this experience that the human designer may hope to overcome the size and complexity of some of the design problems, to realise a working solution. But then a careful and often lengthy check must be made, perhaps using simulation, to ensure that no errors have occurred during the design. The size of the problem, however, will often make exhaustive simulation prohibitively expensive, so often the expert must be recalled to intuitively check the solutions by hand.

We believe that an address generator synthesis tool should not only guarantee correct solutions, which will also be testable, but should also do so with a vast improvement in design time. We will report later on such a tool which has mirrored manual designs with an increase of between one and three orders of magnitude in performance.

# 2 Introduction to address generator architecture

In Chapter 1, an address generator was defined as producing a predetermined sequence of binary words, of some width. To complicate proceedings a little we may add constraints of timing on both the address sequence as a whole, and on the speed of production of the data words. Area considerations may force re-use of all or some part of the address generator, so some outside control may be necessary, as well as the associated logic to implement that control. Power consumption may also figure in deciding on a specific address generator architecture.

Commencing with a description of the types of memories for which addresses may be generated, this chapter defines the constituent parts of successively more complex and generic address generators, starting with some different implementations of the most basic element - the binary counter. This is then generalised to a modulus m counter, before other pieces of the architectural jigsaw are examined. Finally, a breakdown of the costs of these address generator elements is presented.

#### 2.1 The memories

Before defining possible address generator architecture, we first examine the memories which can require addressing.

On the physical level, a RAM cell (bit) may be reduced to just five transistors for a slower, static approach [176], or to a single transistor in the faster, dynamic mode [178] which has refresh overheads. A ROM cell may also be reduced to a single transistor due to its simplicity [179]. Other novel approaches include magnetic bubble memories [180].

Memories may be Content-Addressable [172, 173, 177], or Content-Associative for faster access [171], or have other added features [174], and may be designed using many different styles [175] including Standard Cell, Super Integration and Structured Array to develop RAMs and Cache memory.

A highly parallel memory structure may be defined for parallel processor applications [170], and multi-phase clocking schemes may introduce other possibilities [181, 182..184]. A RAM may have one or possibly several pairs of address and data ports.

#### 2.2 The binary counter

Being such a well-known piece of hardware, the binary counter can take one of several proven forms, and more specialized architectures are possible with differing IC technologies [195, 196, 198]. The basis for all counters in this thesis is a series of JK master-slave flip-flops, whose values toggle at certain times.

#### 2.2.1 The ripple counter

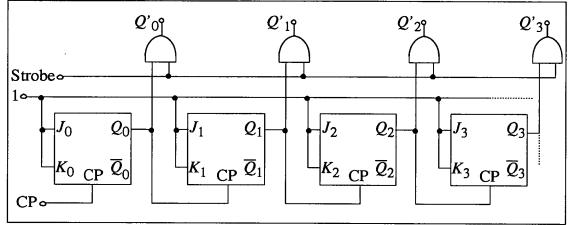

Simplest to construct is a ripple counter, which has all of its flip-flops, or bits, set to toggle at any time, by tying both J and K inputs to logic '1'. The first flip-flop, Bit 0, is clocked by an external clock, and its Q(time t) output is then used to clock the second flip-flop, Bit 1. The Q(t) output from this is used to clock Bit 2, and so on until a counter of the correct size (number of bits) is produced. The Q(t) outputs form the count word at time t - an output from the counter module - which may need to be strobed by a control signal to synchronise the signals.

Figure 2.1 The ripple counter with strobe.

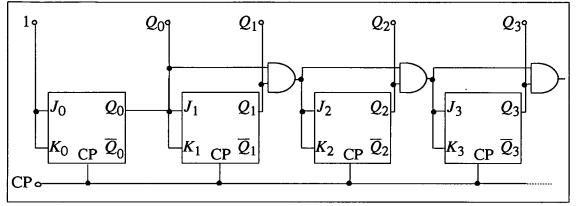

#### 2.2.2 The serial carry counter

To avoid the problem of synchronisation, and so the need for a strobe, the serial carry counter is constructed a little differently to the ripple counter. The first bit of the counter is set to toggle at any time as before, but instead of using its output to clock the next bit, this is done by the external clock itself. The second bit will only toggle if the Q(t-1) output of the first bit is in the high state. All other bits of this counter are also clocked by the same clock, and the value on their J and K inputs is set by the result of

ANDing the next lower bit's Q(t-1) output with its J (and K) input. In this way, the delay between the first and last bits of the counter settling is kept quite low.

Figure 2.2 The serial carry counter.

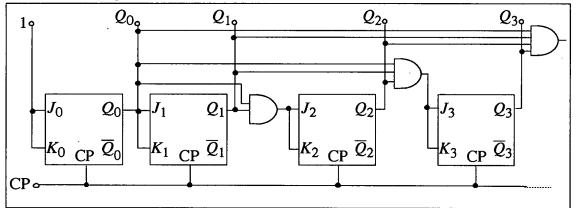

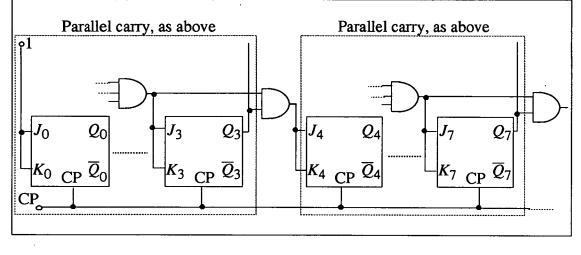

#### 2.2.3 The parallel synchronous counter

To increase the speed of the counter further, one must take a more parallel approach in its construction. Here, the first three bits work in the same way as for a serial carry counter, but any further bits will have their J and K inputs set by a logical AND of *all* lower Q(t-1) outputs.

Figure 2.3 The parallel synchronous counter.

#### 2.2.4 The serial/parallel synchronous counter

Since the parallel counter described above requires an (n-1) input AND gate to implement an n-bit counter, then as the number of bits increases so does the likelihood of AND gate fan-in rules being broken. This problem may be partially solved, at the expense of some speed, by placing an upper limit on the number of counter bits connected in this way. If this limit is reached during the construction of the counter, then a serial carry is taken to the next bit, and parallel carrying is commenced from there.

Figure 2.4 The serial/parallel synchronous counter.

#### 2.2.5 The pseudo-parallel synchronous counter

Another possible conglomeration of basic counter architectures is shown in Figure 2.5, where a large (Say > 4 bits) ripple counter is divided into equal slices, and each of these slices is clocked by a parallel carry from the previous slice, but remains, internally, a ripple counter.

Figure 2.5 The pseudo-parallel synchronous counter.

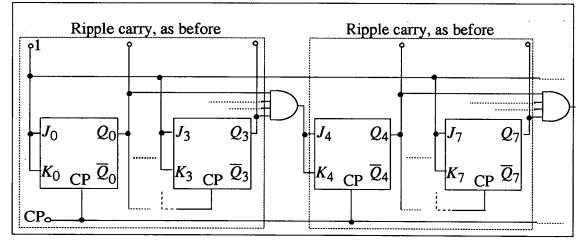

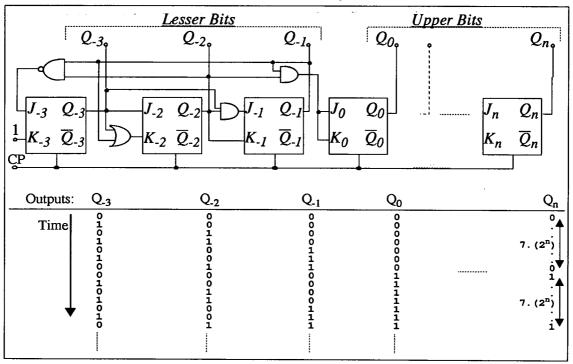

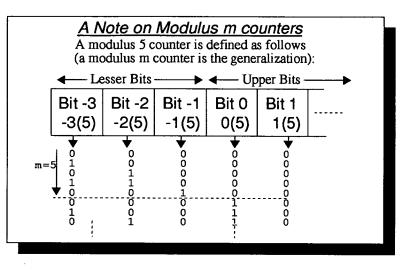

#### 2.3 The modulus m counter

A useful generalisation of the binary counter is the so-called modulus m (or modulo m [197]) counter. Instead of each counter bit producing streams of bit values which change value after some power-of-two of bits, *the modulus m counter produces*

streams of bit values which change after  $m \cdot 2^n$  bits, where n is the bit number on the counter  $(n \ge 0)$ . Thus a binary counter is in fact a modulus 1 counter.

A modulus m counter is basically two binary counters connected in series, with the first counter having the logic necessary to reset it after m clock ticks (or rather, when its count value would otherwise have reached m).

The bits of this first counter make up the *lesser* bits of the modulus m counter, as illustrated in Figure 2.6, which shows the architecture of a modulus 7 counter. The reset logic shown on the outputs of the lesser bits will henceforth be omitted for simplicity, and because the cost of this logic is minimal.

The second counter, clocked by the MSB of the first counter (or a combination of bits, if a more parallel carry counter is used), implements the *upper* bits of the modulus m counter, whose bit sequences follow the  $m.2^n$  repetition rule as defined above.

Figure 2.6 A modulus 7 counter.

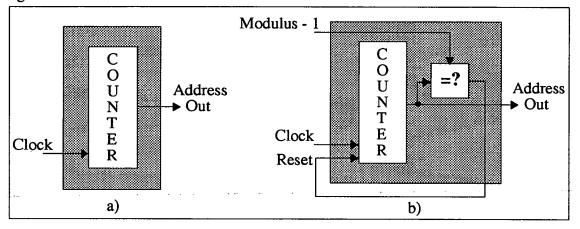

By using modulus m counters prudently, it is possible to realise very cheap and simple address generation schemes which implement complicated, non-binary access patterns, for array access. It is also possible to produce some very efficient schemes for scheduled memory address generation and even general control, usually the final element of a processor to be examined, can benefit from the use of modulus m counters. There are two, very basic address generation architectures which use a modulus m counter (Figure 2.7). The simplest is the preset-modulus counter, which has reset logic built directly onto the counter, as for the modulus 7 example above. The second address generator contains a parametrizable-modulus counter, which has an input dedicated to receiving the modulus parameter. It also contains a comparator, to generate the reset signal when needed.

Figure 2.7 Two basic address generators: a) Simplest counter; b) Parametrizable-modulus counter.

#### 2.4 Other address generator elements

Other address generator elements include: ROMs, dedicated to storing a sequence of addresses; incrementors (simplified adders); exclusive OR gates, and random logic.

#### 2.4.1 Address ROMs

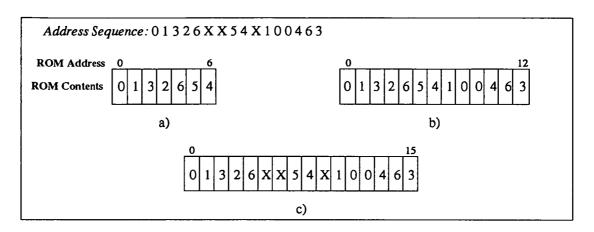

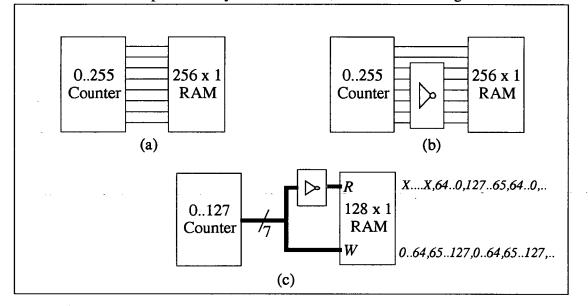

Address ROMs, and their own address generation schemes, have three distinct architectures, as illustrated in Figure 2.8:

- 1) A minimum-sized ROM, which contains only one copy of any address required.

- 2) A medium-sized ROM, which contains multiple copies of addresses needed more often.

- A maximum-sized ROM, which contains an address, required or not, for every control step of a process.

Figure 2.8 The three address ROM architectures: a) Minimum-sized; b) Medium-sized; c) Maximum-sized.

Often the choice of address ROM will be forced, by factors inherent in the overall address generation requirement. For example, in array access, one element of that array can be accessed in each control step, implying a maximum-sized ROM. But in the case of scheduled memory access, any form of address ROM is possible.

A maximum-sized ROM is created for scheduled memory, by filling any "Don't care" times in the original access sequence, with real addresses. This may seem strange, but it allows us the simplest of *ROM-address* generation schemes - A simple, binary counter. The very action of filling the "Don't care" times is a complicated one, and this should be done on a bitwise, rather than wordwise basis. This may even allow a cheaper address generation scheme than a ROM-based one. This problem is dealt with in Section 6.4.3.3.

A medium-sized address ROM can be created simply by storing in it only those addresses actually required, in that order, and allowing multiple copies of addresses. This slightly complicates matters for the *ROM-address* generator, in that the counter's clock must be gated by a control signal, which must be generated elsewhere, and which allows the counter to be clocked only once the current address in the ROM has been read out. With some care, it is possible that the gating control sequence for the ROMaddress counter could be given regularity by utilising any "Don't care" times available, and perhaps clocking the counter a little earlier than necessary.

A minimum-sized ROM is created if only one copy of any address required is stored within it. This can save a lot of ROM area, but *unless* the addresses are only ever needed once, or they are required often, but in a regular order, the address generation for the ROM access can result in yet another ROM-based address generator! This is obviously pointless, if we consider the example below.

Figure 2.9 Examples of a): good and b): bad uses of Minimum-sized ROMs.

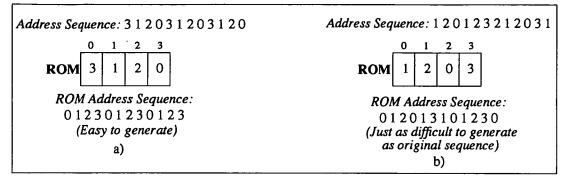

#### 2.4.2 Exclusive OR gates

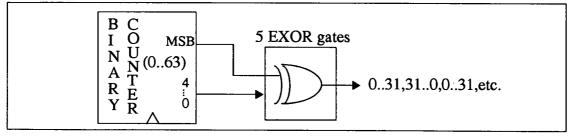

Exclusive OR (EXOR) gates are often essential to a good address generation solution, especially when used in conjunction with counters. An exclusive OR gate can be used to invert the polarity of some bit sequence, after some number of bits, as shown in Figure 2.10. The original bit sequence is input at A, and the second sequence, which controls the inversion of polarity, is applied at B. When the value at B is logic '0', the polarity of C follows that at A, and otherwise is the inversion of A. The bit sequence produced at C is then exclusive ORed with yet another bit sequence, and the same rules apply to that combination.

Usually the sequences fed in at B and D will be generated by a counter, causing a regular inversion of polarity, and often the sequence at A is produced by one or more bits from the same counter. In Figure 2.10, all bit sequences applied to the EXOR network are generated by a 4-bit, modulus 3 counter.

Figure 2.10 The effect of an EXOR network.

The sequence produced at E bears only a little resemblance to those used to generate it, and it is here that many problems arise, in recognising possible bit sequence generators.

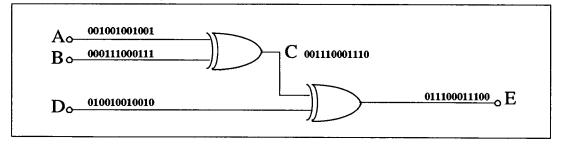

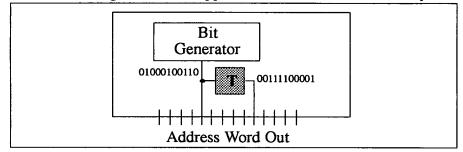

#### 2.4.3 Clocked-bits

It is often the case that one bit sequence within an address sequence may be generated by using another of its constituent bit sequences to clock a T-type flip-flop. This is illustrated in Figure 2.11. A ripple counter is formed in this way.

Figure 2.11 Example of Clocked-type bit sequence generator.

#### 2.4.4 Incrementors

Another commonly occurring element of address generators is the adder. This is perhaps most useful when the 'sum' output is fed back to one of the adder inputs, and the other input is hardwired or set externally to a constant binary value, thus creating an Incrementor. The adder can of course take one of several hardware implementations, including lookahead-carry in bit-parallel adders [185..189], and various bit-serial approaches [198].We will concentrate on the bit-parallel adders in this thesis, since the feedback is much simpler.

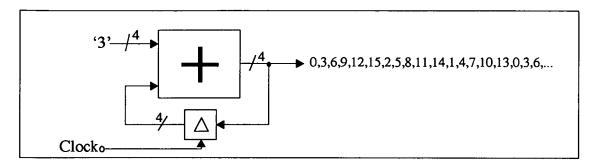

A simple incrementor is shown in Figure 2.12, where the increment is 3, and since this contains no reset circuitry, the address sequence produced does not repeat until after the third cycle, as shown.

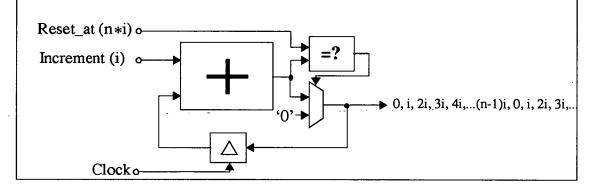

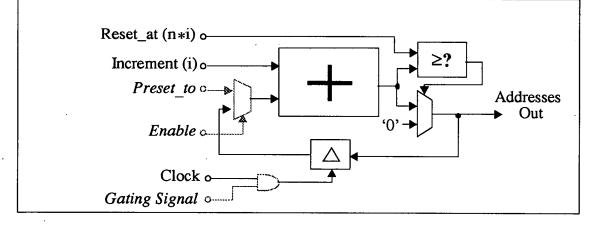

Figure 2.13 shows a more commonly used incrementor, which has circuitry to cause a reset of the incrementor at a value which will produce a shorter cyclic address sequence. Finally Figure 2.14 illustrates a general purpose incrementor, whose increment may be set externally, along with the value at/above which to reset, and also an optional preset value. Also included is an optional gating circuit, and corresponding gating signal, which enable the incrementor to remain at the same value for several control steps.

Figure 2.12 A simple incrementor.

Figure 2.13 Incrementor with reset.

Figure 2.14 A general purpose incrementor.

#### 2.4.5 Logic

The vague classification "logic", represents here either a Boolean network of any size, which is fed by some counter bits to produce address bit sequences, or that combinatorial logic required for any very local control (eg: Reset logic for counters).

- 20 -

#### 2.5 Cost breakdown of address generator elements

The area and speed of the hardware described are both technology-dependent, making costing a rather localised matter. For our purposes, ES2's Solo-1400 1.2 micron parts library [102] was suitable as the source of costs, where a "stage" is two transistors, or half a gate.

#### 2.5.1 Area-costs

Table 2.1 below shows the approximate areas of each address generator element in terms of the number of "stages" of logic which they will require.

| Component                         | Area c<br>Actual | ost in stages<br>Relative |

|-----------------------------------|------------------|---------------------------|

| Counters: Ripple (per bit)        | 27.4             | 1.00                      |

| Serial                            | 47.5             | 1.73                      |

| Parallel                          | 49               | 1.78                      |

| Serial/Parallel                   | 48               | 1.75                      |

| Pseudo-Parallel                   | 48               | 1.75                      |

| ROM (per bit, not incl. overhead) | 1                | NA                        |

| EXOR Gate                         | 7                | NA                        |

| JK Flip-Flop                      | 30               | 1.10                      |

| Incrementors: Simple              | 49               | 1.78                      |

| General Purpose                   | 58               | 2.11                      |

| Logic (per two-input gate)        | 2                | NA                        |

Table 2.1 Comparative area of address generator components.

The area of a ROM-based address generator can only be defined once the size of the ROM has been decided upon, since the ROM will have a certain overhead-cost for creation (address decode, etc.) which will be shared between all bit sequences contained in the ROM, as will the cost of the address generator for the ROM itself.

The ripple counter, although quite small, is unlikely to be used because of the problems its asynchronous output signals introduce, and because of the slow speed when used with strobing circuitry.

#### 2.5.2 Speed-costs

| Component |                    | Delay                    |                          |  |

|-----------|--------------------|--------------------------|--------------------------|--|

|           |                    | Actual                   | Relative                 |  |

| Counters  | : Ripple           | n                        | 10n                      |  |

| (n bits)  | Serial             | 2                        | 20                       |  |

|           | Parallel           | 1                        | 10                       |  |

|           | Serial/Parallel    | n/4                      | 2.5n                     |  |

|           | Pseudo-Parallel(4) | 4                        | 40                       |  |

| ROM       |                    | 3                        | 30                       |  |

| EXOR G    |                    | 0.1                      | 1                        |  |

| JK Flip-I | Flop               | 1                        | 10                       |  |

| Incremen  | ntors: Simple      | 1 (fast lookahead carry) | 10                       |  |

|           | General Purpose    | 3                        | 30                       |  |

| Logic     |                    | <1→∞                     | $<10 \rightarrow \infty$ |  |

The approximate delay of each component, in terms of the delay through a single JK flip-flop, are given in Table 2.2.

Table 2.2 Comparative speeds of components.

#### 2.6 Comments

An address generator is composed of a set of bit sequence generators, which may take any of the forms mentioned in this chapter. The next chapter will describe the different possible requirements for an address generator, for different memory architectures and for control purposes.

## 3 Requirements for an address generator

This chapter investigates the possible causes of requirements for an address generator.

#### 3.1 Data-dependent addressing

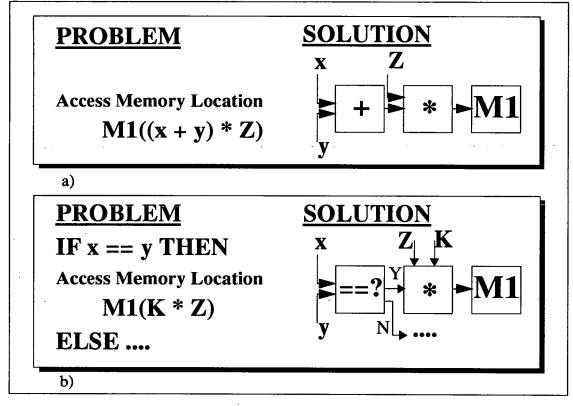

Data-dependent addressing requires an address generator to produce an address from variable data, either directly, as in case (a) below, or indirectly, as in case (b):

Figure 3.1 Data-dependent addressing schemes.

Neither of the cases above are applicable to the automatic address generator synthesis techniques targeted by this thesis, but in each case there is a definite direction to take for automation. In the case of direct transformation of available data, this can be recognised at a behavioural level, from the corresponding High-level description language, and address generation hardware constructed as part of the computational base [163]. Indeed, it is this approach which is taken in SAGE (See Chapter 8), a behavioural synthesis tool developed at the University of Edinburgh[150].

In the second case of data-dependent addressing - That of indirectly using available data to specify a wholly different address, or sequence of addresses (if a branch runs for

several control steps, or perhaps branches further) - no such scheme is possible. The simplest approach seems to be to use the branch conditions to select from a variety of ROM's which hold the possible address sequences, or to embed the address generator in the chip controller.

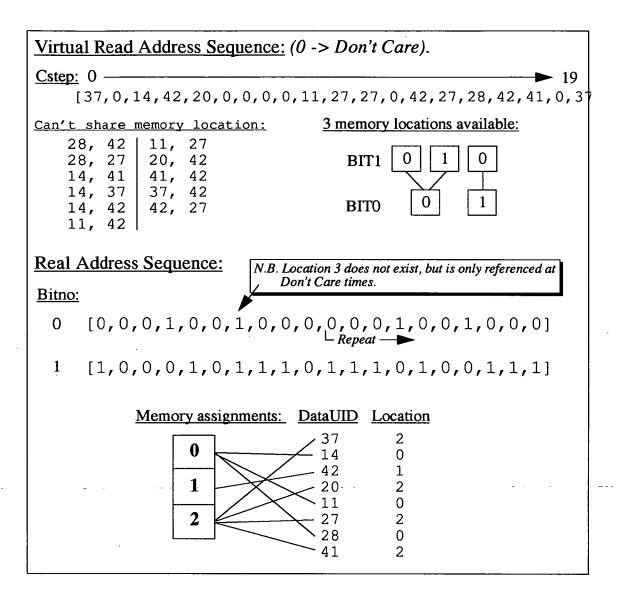

#### 3.2 Scheduled memory addressing

In a design with many operations and few resources, the data produced by operations may need to be stored over more than one clock tick, perhaps accessed several times during the lifetime of that data. Instead of assigning a single register to store each group of temporally disjoint data, a RAM or register file may be used which can hold much more data but which will require an address sequence to control access. Very often there will be times when no address is actually required, so that the address produced at that time may be any of those possible, and choosing one may have a significant effect on the cost of producing the address sequence. This is a problem which must be tackled before the address generator synthesis stage-proper, as part of the memory synthesis task (See Section 6.4.3.3).

#### 3.3 Array access

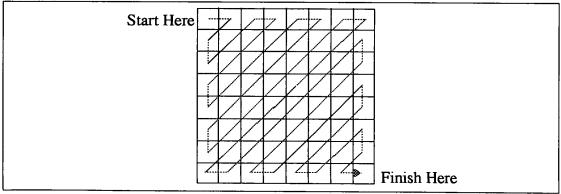

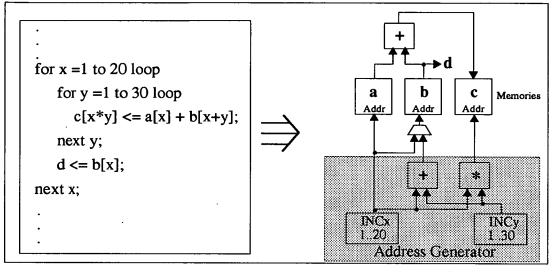

The final, and perhaps the most promising situation as far as synthesis is concerned, is that of array access. Here, one, two or more dimensional data arrays are written to and read from usually large memories. Commonly the access sequence will be predefined at synthesis time, most usually as a set of (nested) loops. It is a simple matter to deduce the access sequence thus required and to use decomposition methods to recognise the use of counters in its generation.

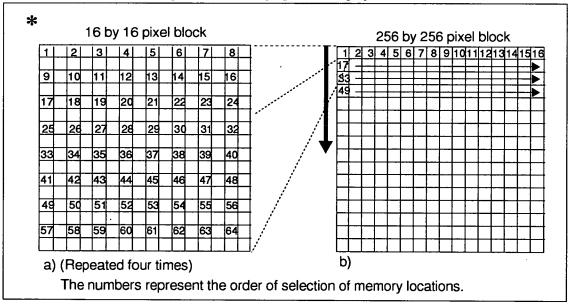

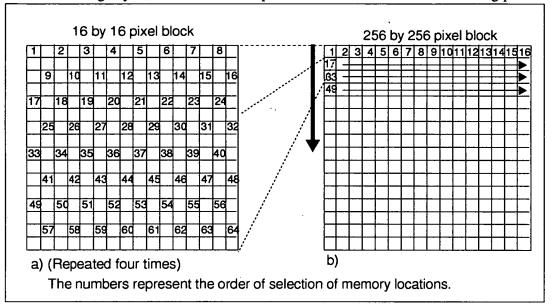

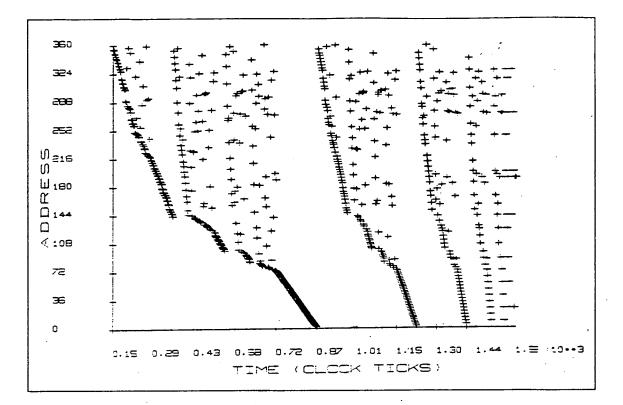

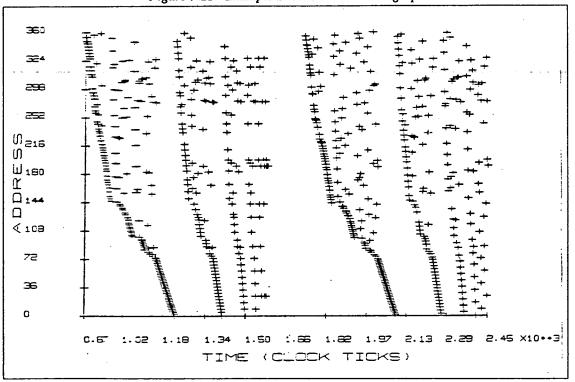

It is also possible that the synthesis stage could recognise oversized memories or redundant accesses and optimise them accordingly [166]. Figure 3.2 shows an example, where data is to be written to a memory in locations a[0] to a[255], and then read out again in four separate passes.

```

for i = 0 to 255 loop

get x;

store x in a[i];

next i;

for j = 0 to 3 loop

for i = (((j+1) * 64) -1) downto j*64 loop

read a[i];

next i;

next i;

I.E.: i = 63,62,...0,127,...64,195,...128,255,...196.

```

Figure 3.2 Example of array access specification.

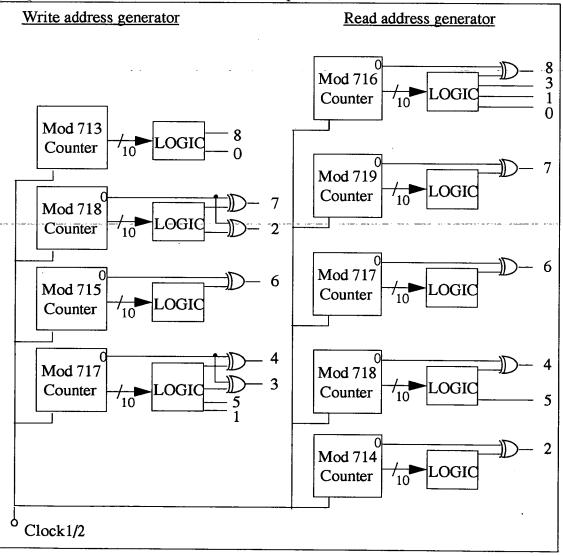

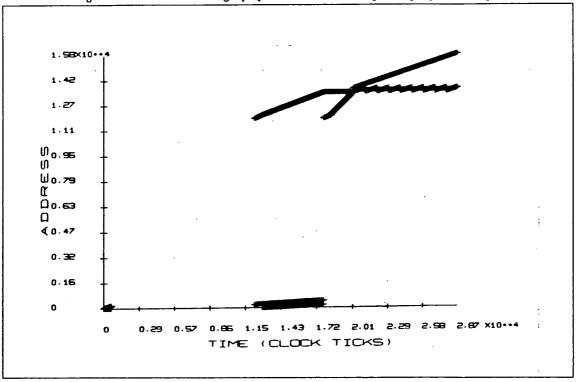

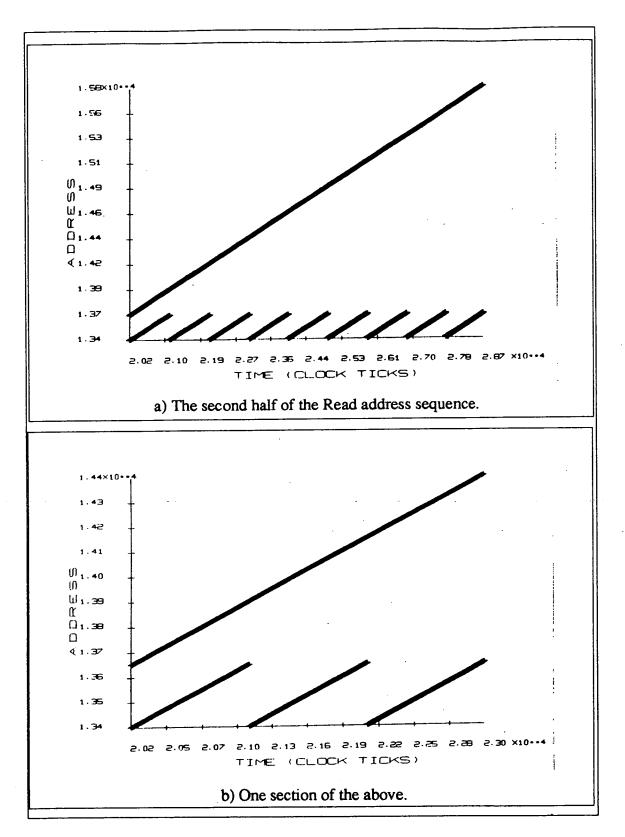

This obviously implies a 256-word RAM, with a simple counter to generate the write address sequence, and something a little more complex for the read address sequence, detailed in Figure 3.3a&b. Since the two most significant bits in each addressing scheme are produced by the corresponding bits from the (shared) counter, it is possible to reduce the memory size by half, and if the RAM may have two ports then the read and write sequences may be interleaved, as illustrated in Figure 3.3c.

Figure 3.3 Synthesis and optimisation of array access example.

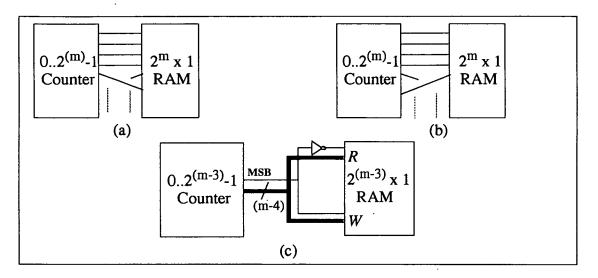

This generalises to the rule: "If the top n bits of the address word may be generated by the same counter bits for two access sequences, then as long as circumstances allow, the top (n-1) bits may be discarded, the memory shrunk by a factor of  $2^{(n-1)}$ , and the new most significant address bit inverted for one sequence. This is pictured in Figure 3.4.

Figure 3.4 Generalisation of memory optimising transformation.

#### 3.4 Control

Wherever a control bit sequence can be predefined, we can use the address generator synthesis techniques to try to find a cheap hardware implementation to produce it. As for scheduled memory address sequences, the binding of Don't Care values to actual values can be critical if such a solution is to be found. Requirements targeted here are multiplexer control, write enable signals for memories and ALU function-selection, amongst others.

#### 3.5 Comments

It becomes obvious that almost any deterministic sequence of binary words has the potential to be produced more cheaply than by the usual combinatorial logic methods. Not mentioned here are sequences to be produced by built-in self-test (BIST) circuitry, whose manual solutions bear a striking resemblance to those produced automatically for other sequence requirements. The next chapter will detail some of those solutions obtained using AG1 - a first attempt at an address generator synthesis tool.

## 4 Address generation based on binary counters

#### 4.1 Some traditional problems

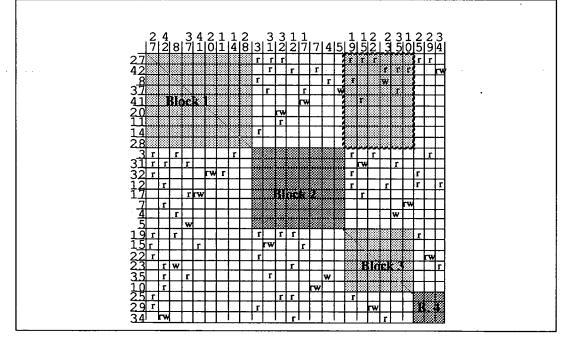

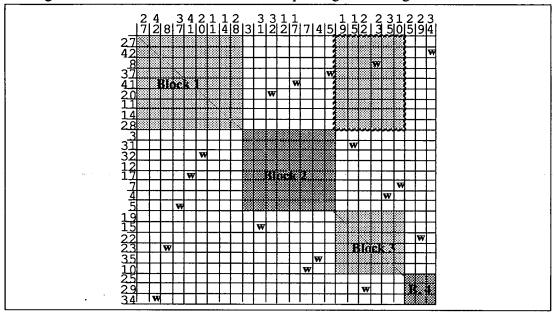

Many of today's sophisticated digital signal processors, be they bit-serial, bitparallel or distributed [36], have one thing in common: *Arrays* of data are processed. And it is today's chip designer who has to provide the knowledge to obtain an efficient memory-array access scheme. Very often, array data will be written to the memory in serial fashion, from the start of memory to the end, and the best way to generate the memory address sequence is with a simple binary counter, whose output is used directly as the address word. It is in reading the data back from memory, however, that address generation problems arise. The read-address sequence is rarely a simple count, and is more likely to be a steadily increasing sequence of addresses, but not necessarily of adjacent memory elements.

These memory elements (memels) can be likened to pixels (picture elements) of a digital image, and the two-dimensional memory "image" is simple to understand and useful also, as we will explain. In fact, digital image processing is one field which places great demands on the designer of array access hardware, and the examples given below could, or do, form part of an image processing system<sup>\*</sup>.

Figure 4.1 Threshold-determination filter access pattern.

\* Examples marked with a \* are real examples. Others are contrived, but still useful.

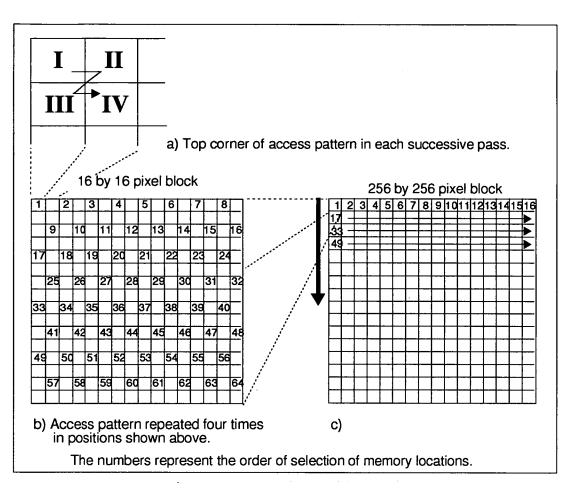

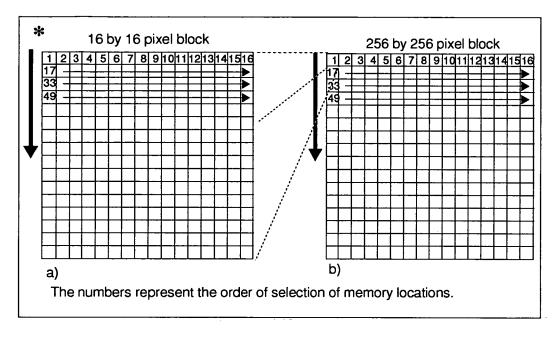

The first example is that of a thresholding filter, which must sample the image data in the pattern described in Figure 4.1, in order to find the correct quantisation level for each block of data. The address sequence for this access pattern is 64kwords long, as is the sequence for a second example, shown in Figure 4.2. Here, the access pattern has been skewed slightly from the first example, but remains a valid thresholding pattern.

Figure 4.2 Alternative thresholding access pattern.

A final thresholding pattern is shown in Figure 4.3. This also requires 64k accesses, in which the pattern from the first example is shifted one pixel between each of the four passes, in order to cover the *whole* area of memory.

Figure 4.3 Further alternative thresholding access pattern.

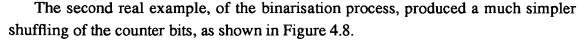

Following the determination of a local threshold for each block of data, the image will pass through a binarisation stage, producing the binary - black and white - image, and this too can have a non-linear address sequence. One such sequence is described below, and is much simpler than the thresholding patterns given before.

Figure 4.4 Binarisation stage access pattern.

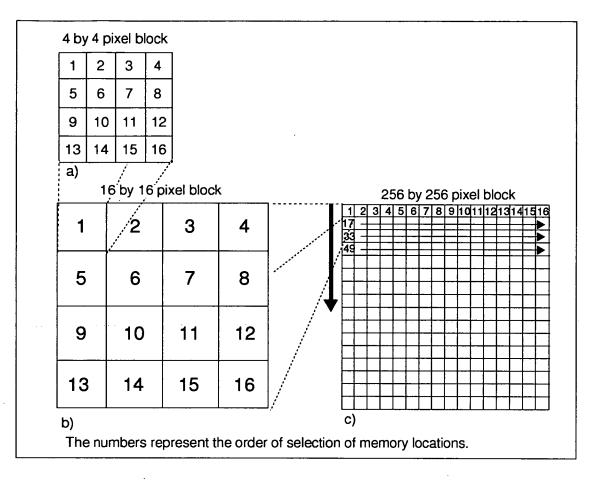

If the image processing application is one of image recognition, then the binary image will probably be passed through a correlator, which gives a measure of how well segments of the image match the same segments of a previously stored image. This could have the access pattern shown in Figure 4.5, which samples the data in four pixel by four pixel blocks.

Figure 4.5 Possible correlation filter access pattern.

# 4.2 Some manually designed address generators

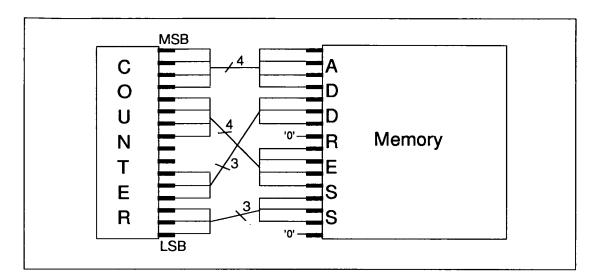

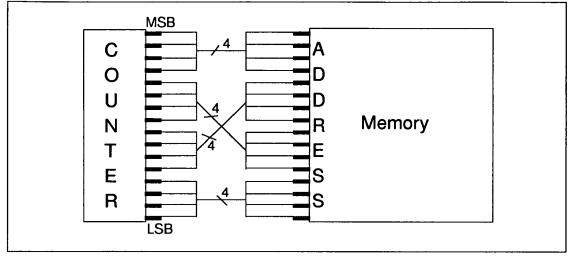

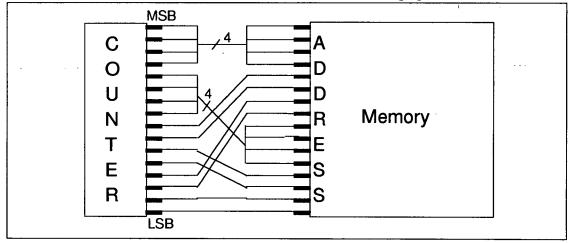

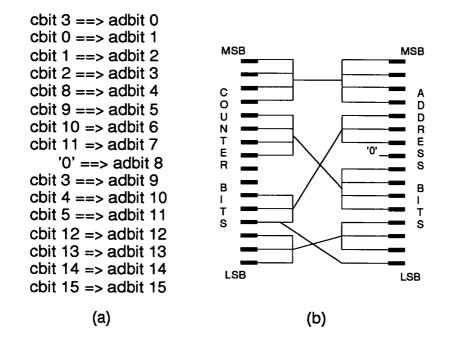

Shown below are the address generation solutions found manually for some of the examples given in Section 4.1. It should be said that these designs originally took a matter of man-days to produce, and considerably longer to verify by simulation (Indeed, exhaustive simulation of all 64k steps was never attempted). The address generator for the original thresholding filter consists of a 16-bit binary counter, whose output bits are "shuffled" by wiring only, before being connected to the 16-bit address port of the memory.

Figure 4.6 Original thresholding filter address generator.

The other two thresholding filter patterns produced the following address generators respectively.

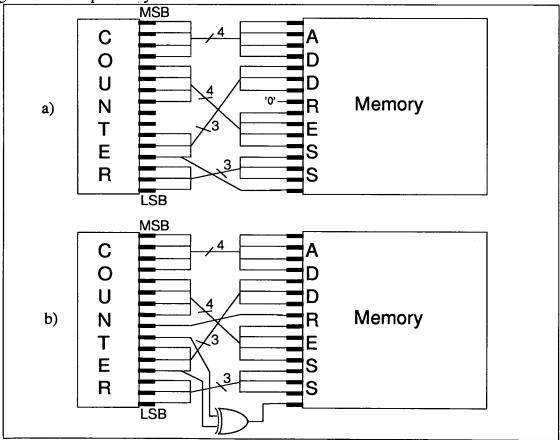

Figure 4.7 Other thresholding filter address generators.

Figure 4.8 Binarisation process address generator.

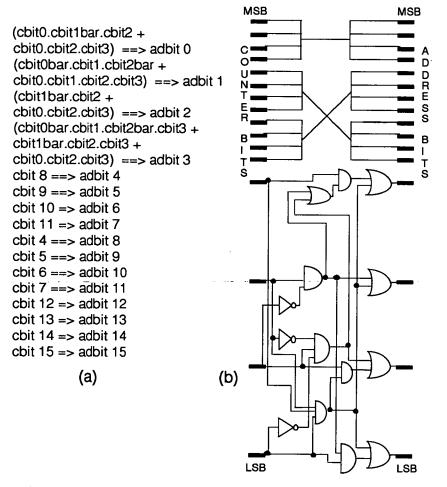

From the third contrived example of a possible correlation filter access sequence, was obtained a more complex transformation of the address bus, and this demonstrates some of the rules which *could* be used to automate this design process.

Figure 4.9 Address generator for possible correlation filter.

# 4.3 AG1 - Address generator synthesis based on binary counters

There follows a description of a tool developed to automatically design (describe) address generators of the type described above, based on the specification of the address sequence to be generated. A brief outline of modes of data entry is followed by the method behind the synthesis algorithms. A short description of how combinatorial logic

synthesis proceeds is then given, and finally the output format from the tool is explained.

For a more detailed description of the tool's functionality, and the source code itself, refer to Appendix D, and the diskette enclosed.

#### 4.3.1 Data Entry types

Four different methods exist to introduce the access sequence into AG1. The first allows generation of the sequence by software, possibly as a set of nested loops, as shown in Figure 4.10. The second data-entry method uses a built-in graphical entry tool to lay out the access pattern on a two-dimensional representation of the memory space. Like the first method, this is very amenable to the non-expert designer.

| for Y = 0 to 65535 step 4096,            | (block height = 16 rows)   |

|------------------------------------------|----------------------------|

| for $X = 0$ to 255 step 16,              | (block width = 16 columns) |

| for $i = 1$ to 4,                        | (do 4 times)               |

| for $y = 0$ to 4095 step 512,            | (every 2nd line)           |

| for $x = (y / 512) \mod 2$ to 15 step 2, | (every 2nd pixel, skewed)  |

| $address_{(time t)} = x + y + X + Y,$    |                            |

| next x,                                  |                            |

| next y,                                  |                            |

| next i,                                  |                            |

| next X,                                  |                            |

| next Y                                   |                            |

|                                          |                            |

Figure 4.10 Sequence specification by software.

The final two data-entry options deal with loading predefined bit sequences from file: Primarily sequences which follow no specific pattern, or which are not of length  $2^n$  bits. These sequences should, however, have 'padding' bits added to make the total length a power of two, since the main pre-requisite of all input sequences is that they have length  $2^n$ .

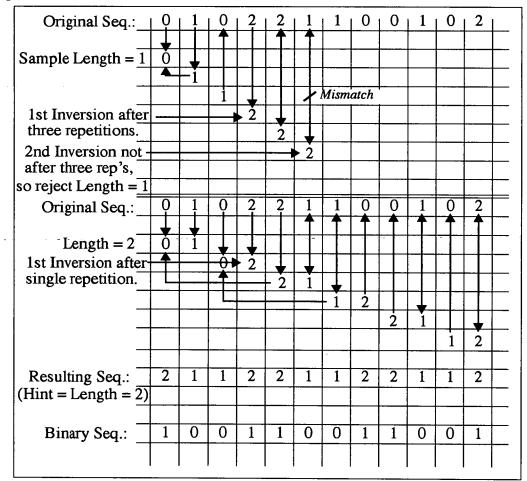

#### 4.3.2 Method

The basis for the synthesis method involves iteratively bisecting each bit sequence in the address sequence from the LSB to the MSB, recognising the presence of various binary counter bits in their generation. The length of the first and subsequent halves of the sequence, which should be length  $2^n$ , give indication as to the binary counter bit(s) involved, as described by the rules listed below.

1) Split sequence of bits, list[1..2n], into two halves, list[1..n] and list[n+1..2n].

For example the list:

becomes:

[0,0,0,0,1,1,1,1] and [0,0,0,0,1,1,1,1]

and the list:

[1,0,0,1,0,1,1,0,0,1,1,0,1,0,0,1]

becomes:

[1,0,0,1,0,1,1,0] and [0,1,1,0,1,0,0,1]

(These lists are much longer in practice).

2) If the list has a single entry (n = 1), then force the current address bit to '0' or '1', according to that entry, and then go on to examine the next most significant bit of the addresses.

This only happens if all the entries in the original list for the bit were identical.

3) If the two halves of the list are identical then halve the list by discarding the second half, and return to (1).

This controls the use of Rule 1 by allowing the first half of the list to be split further, only if both original halves are identical. For the first example given above, after the first split the two halves are identical, and so we can take the first half and split that:

#### [0,0,0,0,1,1,1,1]

becomes:

#### [0,0,0,0] and [1,1,1,1].

4) If the two halves are not identical, nor the logical inverse of each other, then we cannot use any counter bits directly connected to this address bit, and we go on to use the logic synthesis tool.

A list of bits must be symmetrical about the midpoint for things to procede further.

5) Rule 5 checks that the list has a length of  $2^m$  (which should always happen) and stores the fact that the (m+1)th counter bit,  $cbit_m$ , can be used to generate this list.

Rule 5 is invoked with the knowledge that the two halves of the list are not identical (otherwise it would have been split again) but that they are the logical inverse of each other (otherwise Rule 4 would have been invoked). Several possibilities arise at this point, with the list having many different possible forms:

[0,0,0,0] and [1,1,1,1],

[0,0,1,1,0,0,1,1] and [1,1,0,0,1,1,0,0],

[1,0,0,1] and [0,1,1,0],

[0,1,0,0,1,1,0,0] and [1,0,1,1,0,0,1,1], etc.

6a) If all bits in the first half, list[1..n], are equal, then the list has been reduced as far as possible, and Rule 7 is called.

Thus lists which conform perfectly with sequences produced by a binary counter bit are identified. For example, the sequence:

[0,0,0,0,1,1,1,1,0,0,0,0,0,1,1,1,1]

may be generated using Bit 2 of a binary counter.

6b) If not all bits in list[1..n] are identical, then use the (m + 1)th counter bit (from Rule (5)) XORed with whatever bit is chosen by halving the list again and returning to (2).

Rule 6b deals with the other possibilities from Rule 5. Any list which has the two halves non-identical, but logically inverse, and not all entries in one half the same, is the XOR function of the (m+1)th counter bit, with whatever is produced by halving the list again and returning to Rule 2. The XOR gate will allow the first half of the sequence to be inverted after a constant number of bits.

7) If the first bit in the list is a '1', then negate whatever counter bit, or combination of bits, has been chosen.

This implies that all bit sequences produced by counters begin with a '0', which is quite natural.

8) Print out the connections from counter bit(s) to address bit, and start at (1) with the next most significant address bit.

Once this process has been completed for all address bits, we have a list of connections from counter bits to address bits - the mapping, or transform - which will produce the correct sequence of addresses with the minimum of logic.

#### 4.3.3 Logic synthesis

Logic synthesis is done in two distinct steps in AG1. The first step is carried out on a bitwise basis across the address sequence, for any bit sequence which fails at Rule 4 above. The second step is one of global optimisation.

Firstly, the *minterm value* is determined as the binary value which appears *least* in the bit sequence. Then an algorithm iterates down the bit sequence and for every minterm a new logic function is produced in terms of a product of binary counter bits. Figure 4.11 shows the relationship between the binary counter which will be used to feed the logic, and the bit sequence to be produced.

| Counter Bits:   | 3<br>2<br>1<br>0 | 0<br>0<br>0<br>0 | 0<br>0<br>0<br>1 | 0<br>0<br>1<br>0 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>0 | 0<br>1<br>0<br>1 | 0<br>1<br>1<br>0 | 0<br>1<br>1<br>1 | 1<br>0<br>0<br>0 | 1<br>0<br>0<br>1 | 1<br>0<br>1<br>0 | 1<br>0<br>1<br>1 | 1<br>1<br>0<br>0 | 1<br>1<br>0<br>1 | 1<br>1<br>1<br>0 | $1 \rightarrow 1 \rightarrow$ | Logic |

|-----------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Target Sequence | :                | 0                | 1                | 1                | 1                | 0                | 1                | 0                | 0                | 0                | 1                | 0                | 1                | 0                | 0                | 0                | 0                                                                                                                                             |       |

Figure 4.11 Counter output against target bit sequence.

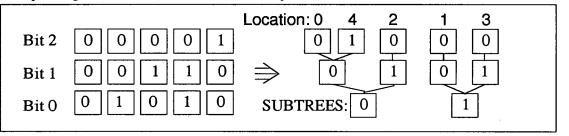

In order to get the minimum number of counter bits required to generate each minterm, an increasing number of bits of the counter are examined, and all possible combinations of each set of bits are tried, until the selected counter bits' values only ever correspond to a minterm. This is illustrated in Figure 4.12 where a *mask* is created to select the counter bits and the bit *pattern* seen through the mask appears at several locations in the count sequence. Only if all locations correspond to minterms is the combination of, and values of unmasked counter bits accepted, and the next minterm examined. Masked counter bits are stored in the pattern as '0's.

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 2 1 0 0 0 0 1 1 1 0 0 0 0 1 1 1 1 1 Counter Bits: 0 0 1 1 0 0 1 1 1 1 00 1 1 0 0 0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 A B 1 1 **Target Sequence:** 0 at A gives  $\overline{Bit1}$ . Bit0 which corresponds to minterms at D and E but Mask: not at X, so reject this mask (0011). at A gives Bit2.Bit0 which corresponds to minterms at C, E and F Mask: and to no maxterms, so the mask (0101) and pattern at A (0001) define the logic required for A. (The same would be found for C,E,F)

Figure 4.12 Masks and patterns for minterms.

Once each minterm has been defined in terms of a mask and pattern, in each random bit sequence of the same length, and attempt must be made to match all or part of each corresponding logic function to other minterms' logic, to get an optimised multi-level, multiple-output logic implementation of the sequence generator. A heuristic weighting system is employed to reduce the run-times of what is a complex problem, with the weights calculated as follows. Given that minterms A and B have masks  $m_A$  and  $m_B$  and counter bit patterns  $p_A$  and  $p_B$ , the weighting between A and B is taken as the number of '1' bits in

$(m_A \bigoplus m_B) \ (p_A \bigoplus p_B).$

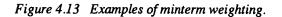

In other words, we give a high weighting between two minterms whose logic functions are identical, and a low weighting between those which are not at all alike. Figure 4.13 shows some examples of this.

| m <sub>A</sub> =0101                                          | m <sub>B</sub> = 1111 | m <sub>C</sub> = 0101        | m <sub>D</sub> = 0101 |  |  |  |  |

|---------------------------------------------------------------|-----------------------|------------------------------|-----------------------|--|--|--|--|

| $p_{A} = 0001$                                                | $p_{\rm B} = 0010$    | <b>p</b> <sub>C</sub> = 0001 | $p_{D} = 0101$        |  |  |  |  |

| Weightings: $w(A,B) = 1$ , $w(A,C) = 4$ , $w(A,D) = 3$ , etc. |                       |                              |                       |  |  |  |  |

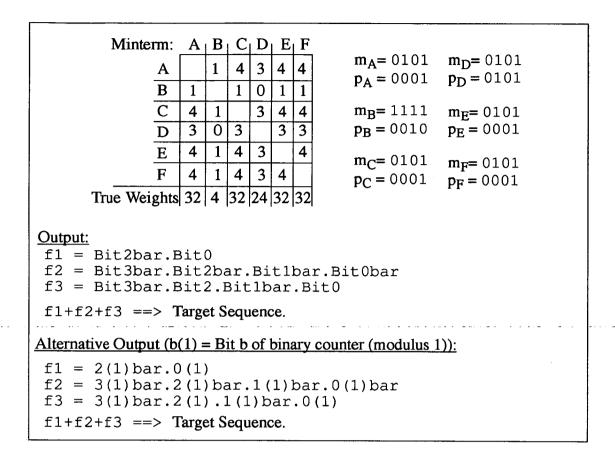

Once all minterms have been compared and weighted against all other minterms and the weights stored in an adjacency matrix (Figure 4.14), the total of all weights for each minterm in turn is calculated. If the number of '1' bits in the corresponding mask (Number Of Bits In Mask -: NOBIM) is greater than one (i.e.: More than one counter bit is involved in its generation) then this total is normalised by multiplying it by (Maximum\_possible\_NOBIM / NOBIM), and the result is stored in another, one dimensional table, as the true weight for that minterm. If only a single counter bit is involved (NOBIM = 1) then the true weight should be zero, since we will use the logic for the minterm with the highest weight to help generate other minterms, and the single counter bits are already available. Figure 4.14 gives the weightings for the sequence in Figure 4.12.

Choosing the minterm with the highest true weight (A), we then give it a unique function number, and then search through the original weight table for any similar logic functions. If the weight between two minterms is equal to the Maximum\_possible\_NOBIM, then they are given the same logic function number (C, E and F), but if the weight is smaller, but still > 0, and

$$(m_A \cdot m_B) \cdot (p_A \oplus p_B) == m_A,$$

then the current function number is stored alongside the other minterm as part of a sum of products. The weights against any completely specified minterms are zeroed in the original weight table, and a new set of true weights constructed, until no weights > 0 remain. Then any remaining minterms not so far given a function number have this added, and finally the logic functions are extracted from the mask and pattern information and printed out. Figure 4.14 shows the logic generated for the example.

Figure 4.14 Weights and true weights for example sequence.

#### 4.3.4 Output format

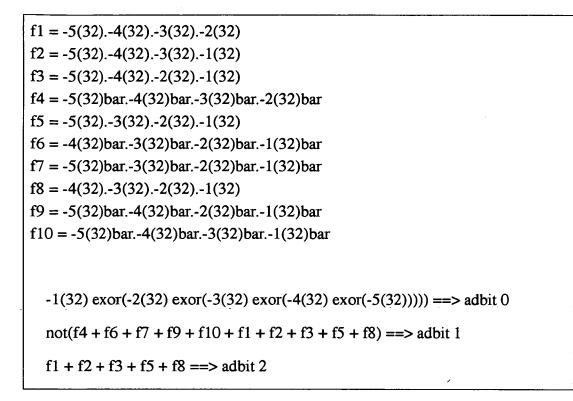

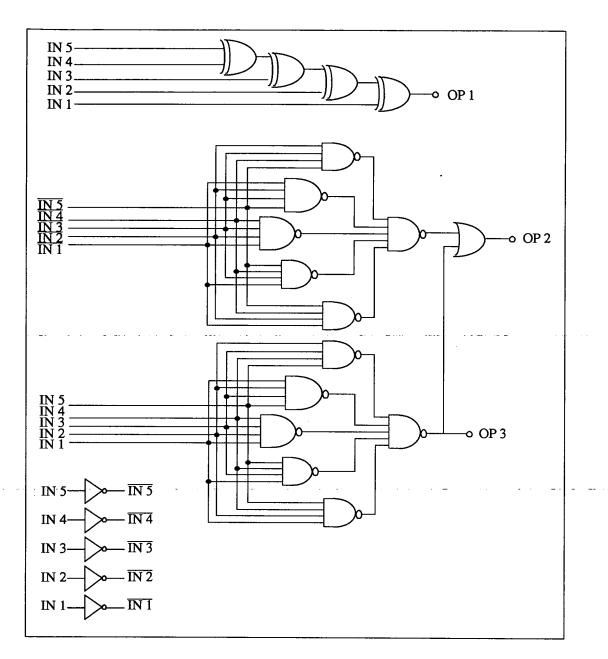

The output produced by AG1 is very simple to understand. Each bit of the address word is described in sum-of-products form, which can vary from involving a single binary counter bit to a multi-level logic description using several counter bits. The use of inversion and EXOR gates is also made perfectly clear. Figure 4.15 contains the description of a benchmark circuit, WGT(5) [69], which must produce a binary count of the number of '1' bits in a five-bit input word. Note that the modulus 32 counter is equivalent to a 5-bit binary counter.

Figure 4.15 Example of output from AG1 - Description of WGT(5).

#### 4.4 Address generators designed using AG1

All the address generators described in Section 4.2 were mirrored by AG1, and it is pleasing to note that the synthesised designs are identical to those produced manually. Examining the address generators in Figure 4.6 and Figure 4.8, a useful fact becomes apparent - we do not need such a large (64kword) memory. As long as the original data is available somewhere (if the image has not changed), then we need only store one sixteenth of the whole image at one time, and we can discard the top three bits of the address as unnecessary, inverting the fourth and so reducing the memory size drastically. This conclusion can be reached from the fact that all four top bits have no shuffle applied.

### 4.5 Comparisons

The logic synthesis tool, which was coded in a matter of weeks, nevertheless stands up to comparison with other logic synthesisers.

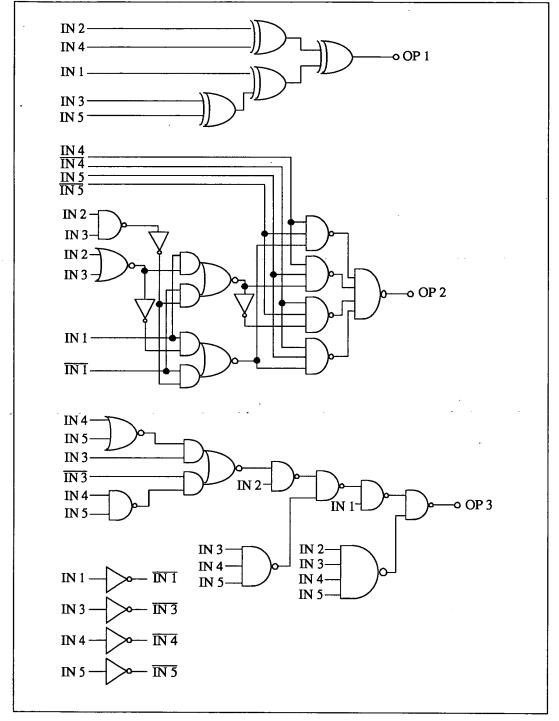

One benchmark example used was WGT(5), which must output the number of logic '1's in its 5-bit binary input. Its logic circuit as synthesised by Gatemap [71] is shown

in Figure 4.16, and the equivalent logic as defined by AG1 appears in Figure 4.17. The chain of exclusive OR gates was created by the core algorithm of AG1, while the other logic was synthesised by the logic synthesis part -: A joint effort.

Figure 4.16 Logic Synthesis results for WGT(5) benchmark by Gatemap, which requires 96 transistor pairs in CMOS (8 per EXOR gate).

Figure 4.17 Logic synthesis result for WGT(5) by AG1, which requires 89 transistor pairs.

The address generators described in Section 4.4 matched exactly those designed manually, and those which were not originally designed manually were carefully checked. Producing the same results as a human designer is no small victory for AG1, and coupled with the marked reduction in design time, as described in Table 4.1, AG1 is, for all its limitations, a very useful tool.

| Example       | Manual           | Gatemap   | AG1                                     |

|---------------|------------------|-----------|-----------------------------------------|

| WGT(5)        | 10 mins (approx) | 3.2 mins. | < 1 sec.                                |

| Image Filters | 10 hrs (approx)  | N.A.      | <10 mins.<br>(incl. recomp-<br>ilation) |

Table 4.1 Design-time comparisons.

# 4.6 Use of the 'C' programming language

The 'C' programming language was chosen for AG1, simply because it was the language best known to us at the time of coding. Despite this, 'C' was found to be almost perfect for the job, with its built-in array pointers and useful bitwise functions, and although strong typing and therefore code security is not encouraged, the language was found to be quite amenable to algorithm development.

#### 4.7 Comments

Obviously, despite all its complexity, AG1 is not a generally useful tool, in that the sequences fed to it must have length  $2^n$ , and any "good" solutions found, owe this entirely to the binary characteristics of the original access patterns. For instance, the correlation filter memory access pattern described in Section 4.1 differed from that defined for a real correlation filter [203], in that the real filter required data in three-by-three pixel blocks, instead of four-by-four. The manual design for the real filter's address generator included two long line delays, to obtain the three vertically adjacent pixels needed. This seemed a rather crude method, and prompted an investigation into address generation using non-binary counters, which is described in Chapter 7. The logic synthesis part of AG1 has proved to be useful on many occasions, and is re-used as part of the aforementioned investigation, and consequent synthesis tool.

The worst-case complexity of the various parts of AG1 are given below:

Sequence length =  $l_s = 2^n$ , Sequence width (bits) =  $w_s$ .

Loading sequence =  $O(l_s)$ .

Matching sequence to solution  $\approx O(w_s * l_s)$ .

Logic synthesis (m minterms):

Minterm detection  $\approx O(l_s + \frac{3l_s^3}{2}).$ Minterm factorisation  $\approx O(\frac{19m^2 + 2m^3}{5}).$

From these figures we can deduce that the logic synthesis tool will be slowed considerably for random bit sequences greater than length  $\approx 100$  bits, while the main part of AG1 will run in linear time.

# 5 Introduction to behavioural synthesis

# 5.1 What is behavioural synthesis?

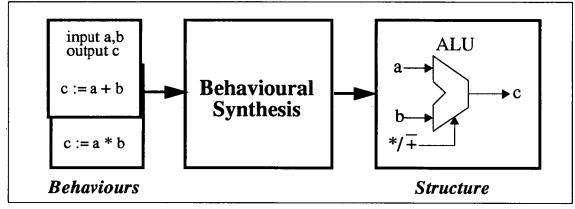

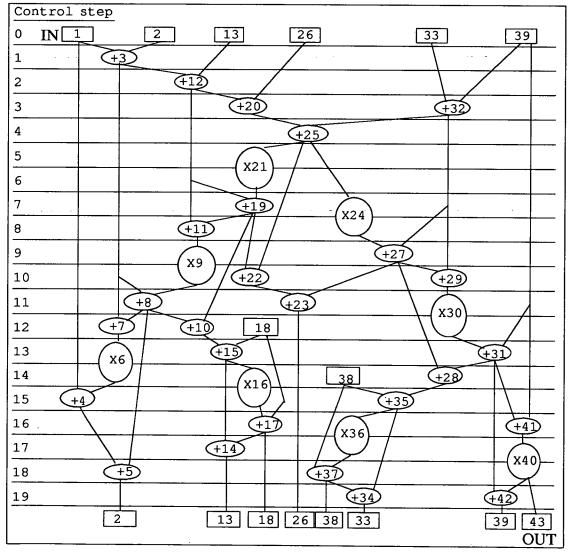

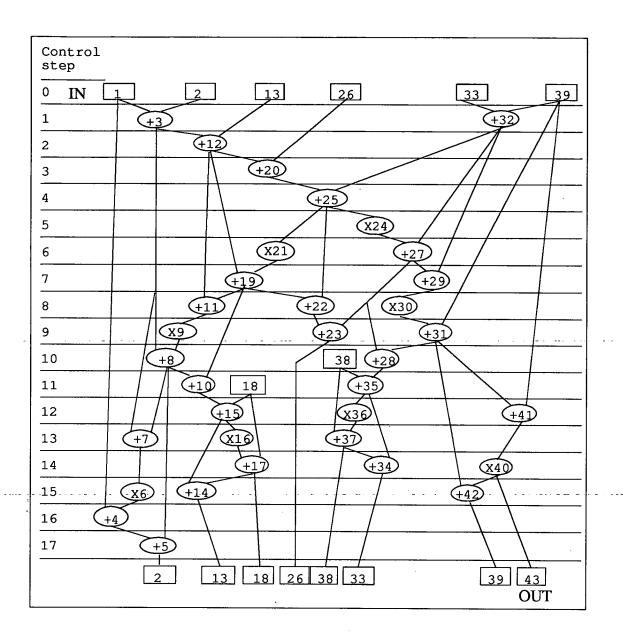

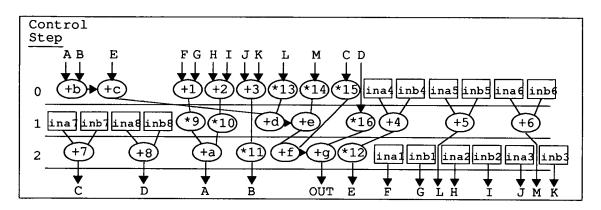

A behavioural synthesis tool will accept a description of what a processor is expected to do - its *behaviour*(s) - and generate a netlist of hardware components which will exhibit that behaviour, in a design anywhere from chip-level to system-level. Note that a processor may exhibit more than one behaviour, probably under external control. For instance, an Arithmetic Logic Unit (ALU), may add two numbers, multiply them, or utilise any other built-in functionality and so has a set of behaviours describing each function in turn.

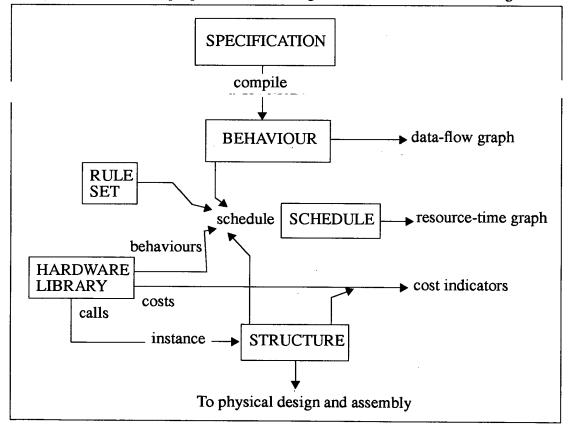

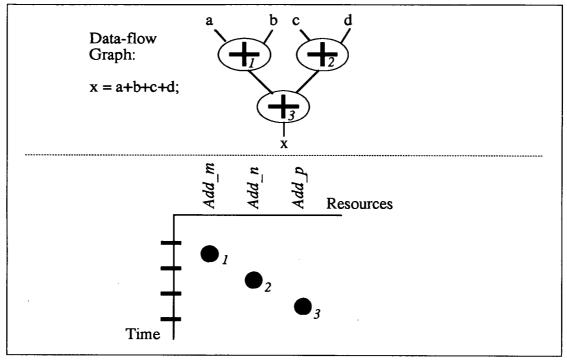

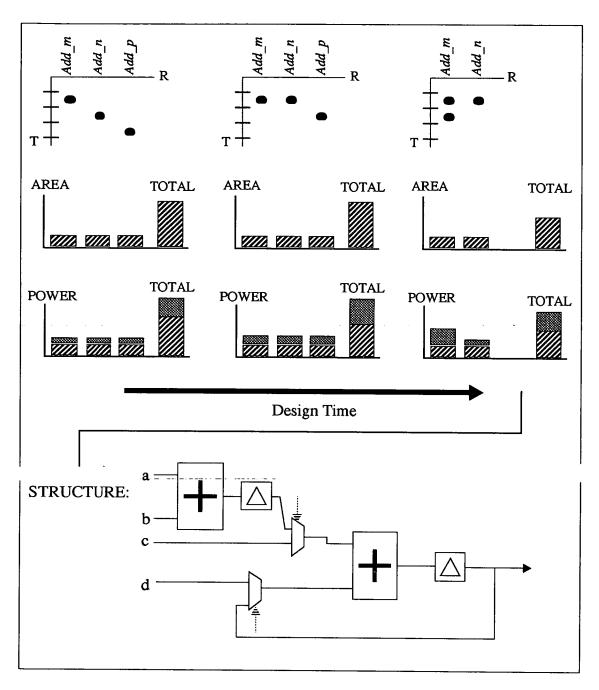

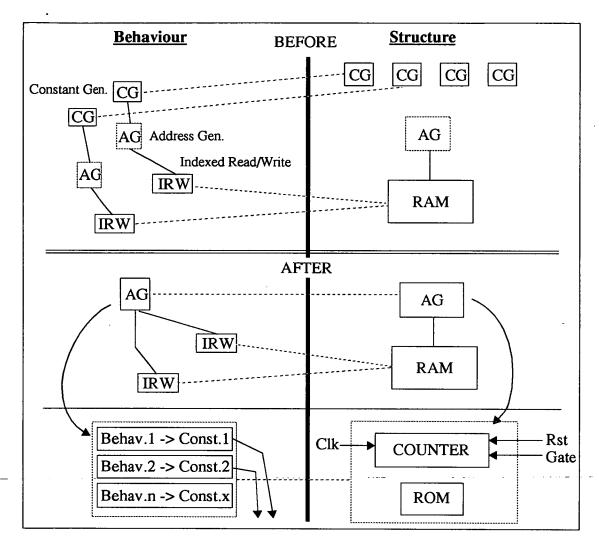

The netlist of hardware components forms the *structure* of the design and there can be only one structure for a given component, perhaps implementing several behaviours. The hardware components themselves may have behaviours and structure, and in order to generate correct and efficient hardware solutions, the simplest components should be chosen from a library on the merit of their ability to exhibit the required behaviour(s), as well as a number of other factors. The design process is summed up in Figure 5.1.

Figure 5.1 The Behavioural Synthesis Approach.

A major requirement of a behavioural synthesis system, is an ability to handle a hierarchical definition of a process [87, 93]. This allows the process to be broken down into ever-simpler processes, as in a typical manual design, and hopefully these simpler processes' behaviours will match those of some library components, which can then be used to implement those functions, as part of the overall processor architecture. A problem arises though, that decisions made at the simplified level may have major ramifications on the overall design, and the outcome of these decisions must be propagated back up through the design hierarchy - A computationally complex, and time consuming task. However, it is only with behavioural synthesis that we may

explore the design space so thoroughly, in such an efficient manner, and perhaps with parallel-processing [94], point tools [86] or some other recent development, it is possible that design time, from behavioural specification to netlist generation, could be reduced to a negligible span, by today's standards.

To get from the behavioural description to a register transfer level description, before logic and layout synthesis complete the design, is the task of high level synthesis. It is this area which will be explored in the following sections.

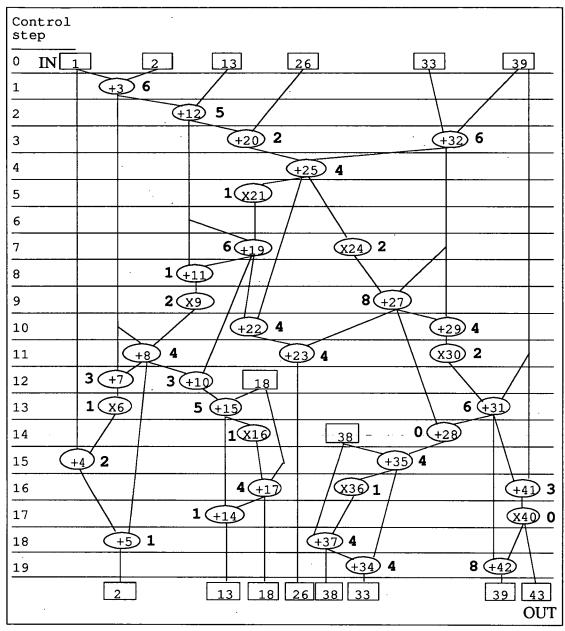

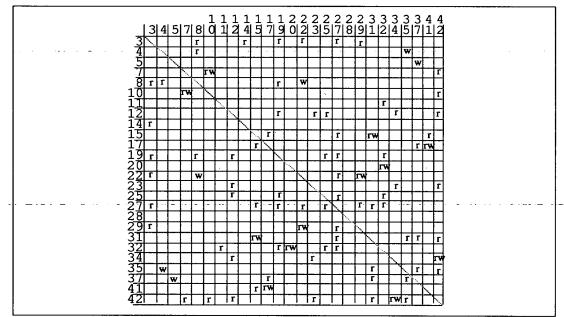

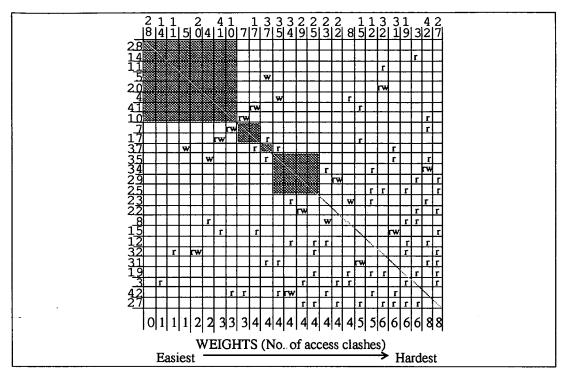

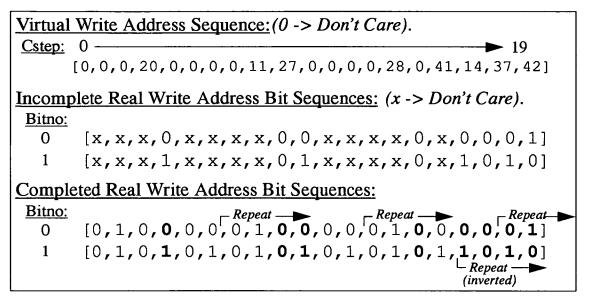

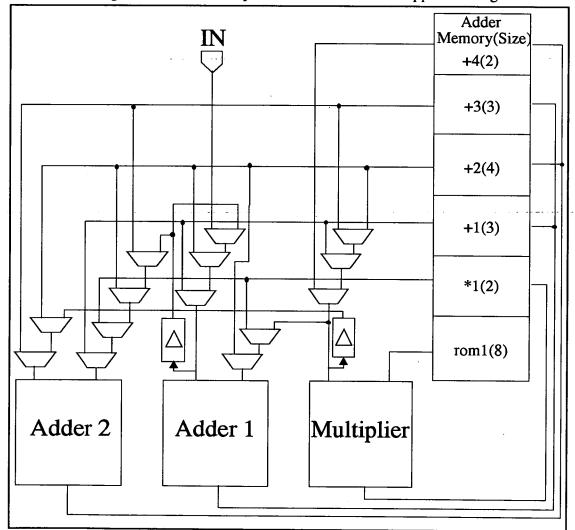

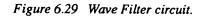

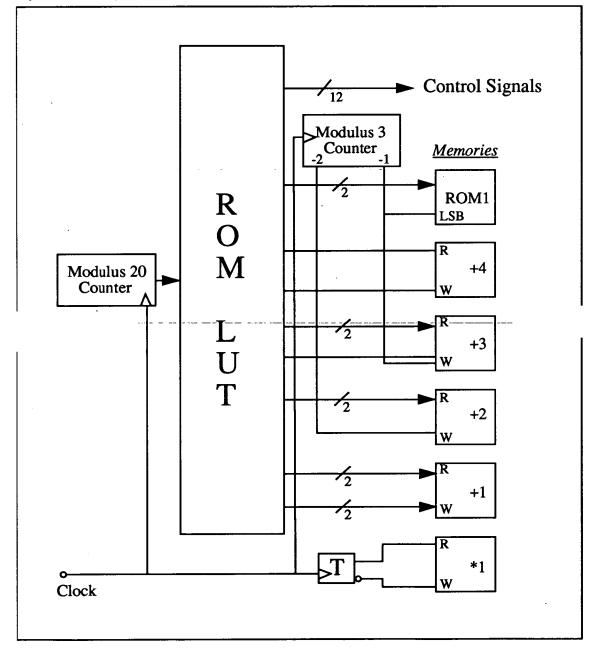

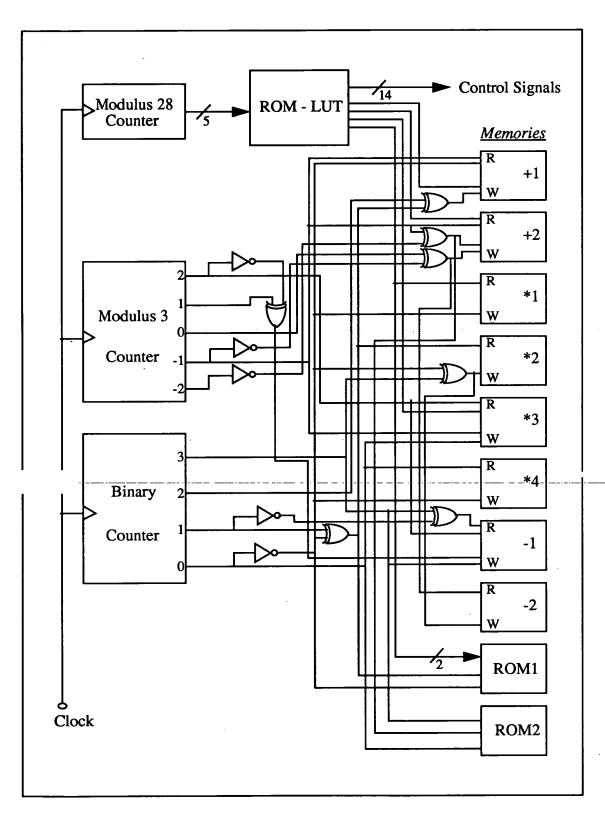

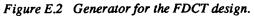

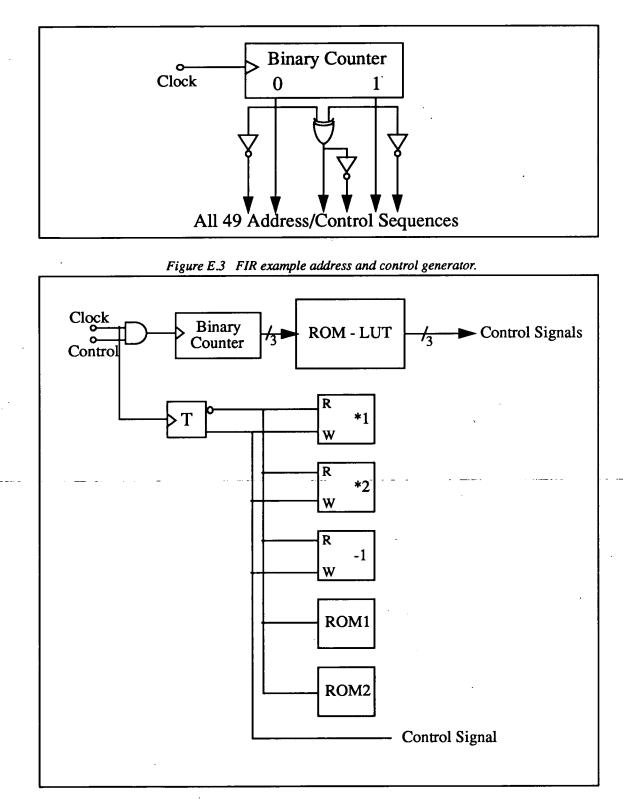

# 5.2 Key steps in the high level synthesis process