# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# Ensuring Performance and Correctness for Legacy Parallel Programs

Andrew J. McPherson

Doctor of Philosophy Institute for Computing Systems Architecture School of Informatics University of Edinburgh 2015

## Abstract

Modern computers are based on manycore architectures, with multiple processors on a single silicon chip. In this environment programmers are required to make use of parallelism to fully exploit the available cores. This can either be within a single chip, normally using shared-memory programming or at a larger scale on a cluster of chips, normally using message-passing.

Legacy programs written using either paradigm face issues when run on modern manycore architectures. In message-passing the problem is performance related, with clusters based on manycores introducing necessarily tiered topologies that unaware programs may not fully exploit. In shared-memory it is a correctness problem, with modern systems employing more relaxed memory consistency models, on which legacy programs were not designed to operate. Solutions to this correctness problem exist, but introduce a performance problem as they are necessarily conservative. This thesis focuses on addressing these problems, largely through compile-time analysis and transformation.

The first technique proposed is a method for statically determining the communication graph of an MPI program. This is then used to optimise process placement in a cluster of CMPs. Using the 64-process versions of the NAS parallel benchmarks, we see an average of 28% (7%) improvement in communication localisation over *byrank* scheduling for 8-core (12-core) CMP-based clusters, representing the maximum possible improvement.

Secondly, we move into the shared-memory paradigm, identifying and proving necessary conditions for a read to be an acquire. This can be used to improve solutions in several application areas, two of which we then explore.

We apply our acquire signatures to the problem of fence placement for legacy wellsynchronised programs. We find that applying our signatures, we can reduce the number of fences placed by an average of 62%, leading to a speedup of up to 2.64x over an existing practical technique.

Finally, we develop a dynamic synchronisation detection tool known as *SyncDetect*. This proof of concept tool leverages our acquire signatures to more accurately detect ad hoc synchronisations in running programs and provides the programmer with a report of their locations in the source code. The tool aims to assist programmers with the notoriously difficult problem of parallel debugging and in manually porting legacy programs to more modern (relaxed) memory consistency models.

# Lay Summary of Thesis

To perform computations that would be infeasible on a single processor, programmers turned to parallelism, where multiple processors cooperate to perform larger computations. There is a therefore a large body of legacy programs written for parallel computers. However, on modern systems these programs may not achieve their full potential performance, or even operate correctly.

Technological advances have lead to the development of Chip Multiprocessors (CMPs) where multiple processors are placed on a single silicon chip. This change has lead to parallel computers that are constructed using different configurations to older machines. Additionally these new CMPs have different (more relaxed) rules about how each processor interacts with the other processors. This is largely due to performance reasons. These changes mean that legacy parallel programs will face performance and correctness issues when run on modern systems.

Our focus is on addressing these issues, largely through (semi-) automatic methods. Such methods are attractive as they reduce the required effort and knowledge of the programmer bringing the legacy program to the modern system. We implement most of our techniques in the compiler, a tool that transforms the high level program written by the programmer into low level code that the computer can execute.

In this thesis we propose novel techniques that analyse or transform programs to ensure correctness and performance on modern systems. Our results comprise analyses with improved coverage and techniques that achieve correctness with less performance degradation than existing techniques.

# Acknowledgements

I am indebted to Dr. Vijay Nagarajan for his constant guidance while serving as my supervisor throughout this process. I would also like to thank my other supervisor Prof. Marcelo Cintra and also Dr. Susmit Sarkar, with whom I had the pleasure of collaborating. During my time in IF-1.05 (aka New Texas), I had the great fortune to enjoy the company of many fun and industrious people. Their friendship, advice, and patience proved crucial to my success.

George Stefanakis, Luís Fabrício Wanderley Góes, Karthik Thucanakkenpalayam Sundararajan, Vasileios Porpodas, Nikolas Ioannou, Lito Kriara, and Kiran Chandramohan understood the struggle and kept me on track throughout our time together. From my research group, Cheng-Chieh Huang, Bharghava Rajaram, Arpit Joshi, and Marco Elver offered innumerable fruitful discussions and were always willing to challenge my ideas. Their unique perspectives and insights significantly improved my understanding and the quality of my work. I also had the pleasure of sharing New Texas with a plethora of other great people during my studies, including Murali Emani, Stanislav Manilov, Ursula Challita, Praveen Tammana, and Rui Li amongst many.

While pursuing the PhD I had the opportunity to enjoy industrial internships with Intel Labs in Braunschweig, Germany and IBM Research in Haifa, Israel. These experiences were formative and greatly influenced my research and future career path. Therefore I would also like to thank Dr. Matthias Gries and Sergey Novikov with whom I collaborated at the respective institutions.

I must also thank my parents Cath and Mike. They have always been supportive of my efforts and I would not have reached this point without their commitment to my education from my earliest years.

Finally, I would like to thank Dr. Björn Franke (Edinburgh) and Dr. Alastair Donaldson (Imperial) for serving as my viva committee and offering such constructive feedback. I have left for pastures new, but despite all the challenges faced, I will always look fondly on the years I spent in New Texas. With hindsight I can say that it was worth it in the end.

# Declaration

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified. Some of the material in this thesis has been published in the following papers:

- Fence Placement for Legacy Data-Race-Free Programs via Synchronization Read Detection. Andrew J. McPherson, Vijay Nagarajan, Susmit Sarkar, Marcelo Cintra. Principles and Practices of Parallel Programming (PPoPP'15), San Francisco, California, February 2015. (*Extended Abstract*)

- Static Approximation of MPI Communication Graphs for Optimised Process Placement. Andrew J. McPherson, Vijay Nagarajan, and Marcelo Cintra. Languages and Compilers for Parallel Computing (LCPC'14), Hillsboro, Oregon, September, 2014.

(Andrew J. McPherson)

# Contents

| 1 | Intr | oductio | n                                                    | 1  |

|---|------|---------|------------------------------------------------------|----|

|   | 1.1  | Contex  | xt                                                   | 1  |

|   | 1.2  | Proble  | ems                                                  | 4  |

|   | 1.3  | Appro   | ach                                                  | 5  |

|   | 1.4  | Contri  | butions                                              | 5  |

|   |      | 1.4.1   | Static Approximation of MPI Communication Graphs     | 6  |

|   |      | 1.4.2   | Acquire Detection and Fence Placement for Legacy DRF |    |

|   |      |         | Programs                                             | 6  |

|   |      | 1.4.3   | Signature-based Dynamic Detection of Ad Hoc          |    |

|   |      |         | Synchronisation                                      | 7  |

| 2 | Bac  | kground | d                                                    | 9  |

|   | 2.1  | Archit  | ectures                                              | 9  |

|   |      | 2.1.1   | Practical Need for Parallel Architectures            | 9  |

|   |      | 2.1.2   | Early Multiprocessors                                | 9  |

|   |      | 2.1.3   | Current Manycores                                    | 10 |

|   | 2.2  | Progra  | mming models                                         | 11 |

|   |      | 2.2.1   | Message-passing                                      | 11 |

|   |      | 2.2.2   | Shared-memory                                        | 13 |

|   | 2.3  |         | ry Consistency Models                                | 14 |

|   |      | 2.3.1   | Foundations                                          | 14 |

|   |      | 2.3.2   | Sequential Consistency                               | 15 |

|   |      | 2.3.3   | Total Store Order                                    | 17 |

|   |      | 2.3.4   | Fully Relaxed                                        | 17 |

|   | 2.4  |         | ecture Examples                                      | 18 |

|   | ∠.⊤  | 2.4.1   | HPC Architecture                                     | 18 |

|   |      | 2.4.1   |                                                      | 10 |

|   |      | ∠.4.∠   | Workstation Architecture                             | 19 |

| 3 | Stat              | ic Appr                                                                                                               | oximation of MPI Communication Graphs               | 21                                                                               |

|---|-------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|

|   | 3.1               | Introdu                                                                                                               | uction                                              | 21                                                                               |

|   | 3.2               | Our A                                                                                                                 | pproach                                             | 24                                                                               |

|   |                   | 3.2.1                                                                                                                 | General Principles                                  | 25                                                                               |

|   |                   | 3.2.2                                                                                                                 | Context, Flow, and Process Sensitivity              | 27                                                                               |

|   |                   | 3.2.3                                                                                                                 | On-demand Evaluation                                | 28                                                                               |

|   |                   | 3.2.4                                                                                                                 | Special Cases                                       | 30                                                                               |

|   |                   | 3.2.5                                                                                                                 | Overall Algorithm                                   | 31                                                                               |

|   |                   | 3.2.6                                                                                                                 | Scalability                                         | 35                                                                               |

|   |                   | 3.2.7                                                                                                                 | Limitations                                         | 37                                                                               |

|   | 3.3               | Graph                                                                                                                 | Partitioning                                        | 38                                                                               |

|   | 3.4               | Result                                                                                                                | s                                                   | 38                                                                               |

|   |                   | 3.4.1                                                                                                                 | Coverage Results                                    | 39                                                                               |

|   |                   | 3.4.2                                                                                                                 | Communication Localisation                          | 40                                                                               |

|   |                   | 3.4.3                                                                                                                 | Performance Results                                 | 42                                                                               |

|   |                   | 3.4.4                                                                                                                 | Scalability Results                                 | 44                                                                               |

|   | 3.5               | Conclu                                                                                                                | isions                                              | 45                                                                               |

| 4 |                   |                                                                                                                       |                                                     |                                                                                  |

|   |                   | nire De                                                                                                               | tection and Fence Placement for Legacy DRF Programs | 47                                                                               |

| 7 | -                 |                                                                                                                       | tection and Fence Placement for Legacy DRF Programs | <b>47</b><br>47                                                                  |

| - | <b>Acq</b><br>4.1 | Introd                                                                                                                | uction                                              | 47                                                                               |

| • | -                 | Introdu<br>4.1.1                                                                                                      | uction                                              | 47<br>47                                                                         |

| • | -                 | Introdu<br>4.1.1<br>4.1.2                                                                                             | uction                                              | 47<br>47<br>48                                                                   |

| - | 4.1               | Introdu<br>4.1.1<br>4.1.2<br>4.1.3                                                                                    | uction                                              | 47<br>47<br>48<br>50                                                             |

| - | -                 | Introdu<br>4.1.1<br>4.1.2<br>4.1.3<br>Our A                                                                           | uction                                              | 47<br>47<br>48<br>50<br>52                                                       |

| • | 4.1               | Introdu<br>4.1.1<br>4.1.2<br>4.1.3<br>Our A<br>4.2.1                                                                  | uction                                              | 47<br>47<br>48<br>50<br>52<br>52                                                 |

| - | 4.1               | Introdu<br>4.1.1<br>4.1.2<br>4.1.3<br>Our A<br>4.2.1<br>4.2.2                                                         | uction                                              | 47<br>47<br>48<br>50<br>52<br>52<br>53                                           |

| - | 4.1               | Introdu<br>4.1.1<br>4.1.2<br>4.1.3<br>Our A<br>4.2.1<br>4.2.2<br>4.2.3                                                | uction                                              | 47<br>47<br>48<br>50<br>52<br>52<br>53<br>53                                     |

| - | 4.1               | Introdu<br>4.1.1<br>4.1.2<br>4.1.3<br>Our A<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                                       | uction                                              | 47<br>47<br>48<br>50<br>52<br>52<br>53<br>53<br>53                               |

| - | 4.1               | Introdu<br>4.1.1<br>4.1.2<br>4.1.3<br>Our A<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Correct                            | uction                                              | 47<br>47<br>48<br>50<br>52<br>52<br>53<br>53<br>54<br>56                         |

| - | 4.1               | Introdu<br>4.1.1<br>4.1.2<br>4.1.3<br>Our A<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Correct<br>4.3.1                   | uction                                              | 47<br>47<br>48<br>50<br>52<br>52<br>53<br>53<br>53<br>54<br>56<br>56             |

| - | 4.1               | Introdu<br>4.1.1<br>4.1.2<br>4.1.3<br>Our A<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Correct<br>4.3.1<br>4.3.2          | uction                                              | 47<br>47<br>48<br>50<br>52<br>52<br>53<br>53<br>53<br>54<br>56<br>56<br>57       |

| - | 4.1               | Introdu<br>4.1.1<br>4.1.2<br>4.1.3<br>Our A<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Correct<br>4.3.1<br>4.3.2<br>4.3.3 | uction                                              | 47<br>47<br>48<br>50<br>52<br>52<br>53<br>53<br>53<br>54<br>56<br>56<br>57<br>57 |

| - | 4.1               | Introdu<br>4.1.1<br>4.1.2<br>4.1.3<br>Our A<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Correct<br>4.3.1<br>4.3.2          | uction                                              | 47<br>47<br>48<br>50<br>52<br>52<br>53<br>53<br>53<br>54<br>56<br>56<br>57       |

|   |      | 4.3.7   | Informal explanation                              | 59 |

|---|------|---------|---------------------------------------------------|----|

|   |      | 4.3.8   | Formal proofs                                     | 61 |

|   | 4.4  | Impler  | nentation                                         | 63 |

|   |      | 4.4.1   | Identifying Control Acquires                      | 65 |

|   |      | 4.4.2   | Identifying Both Control and Address Acquires     | 66 |

|   |      | 4.4.3   | Generating Pruned Orderings                       | 66 |

|   |      | 4.4.4   | Fence Minimisation                                | 68 |

|   | 4.5  | Result  | s                                                 | 69 |

|   |      | 4.5.1   | Synchronisation Read Detection                    | 70 |

|   |      | 4.5.2   | Ordering Pruning                                  | 71 |

|   |      | 4.5.3   | Fence Placement                                   | 72 |

|   |      | 4.5.4   | Performance Improvements                          | 73 |

|   | 4.6  | Conclu  | asions                                            | 75 |

| 5 | Sign | ature-b | pased Dynamic Detection of Ad Hoc Synchronisation | 77 |

|   | 5.1  | Introdu | uction                                            | 77 |

|   | 5.2  | Our A   | pproach                                           | 79 |

|   |      | 5.2.1   | General Principles                                | 79 |

|   |      | 5.2.2   | Shared Access Detection                           | 80 |

|   |      | 5.2.3   | Last Writer Tracking                              | 80 |

|   |      | 5.2.4   | Acquire Detection                                 | 81 |

|   |      | 5.2.5   | Detecting Synchronisations                        | 83 |

|   |      | 5.2.6   | Distance Limit                                    | 86 |

|   | 5.3  | Limita  | tions                                             | 86 |

|   |      | 5.3.1   | Uncontested Synchronisation                       | 87 |

|   |      | 5.3.2   | Non-determinism                                   | 87 |

|   |      | 5.3.3   | Benign Data Races                                 | 88 |

|   |      | 5.3.4   | Taint Tracking                                    | 88 |

|   | 5.4  | Result  | 8                                                 | 88 |

|   |      | 5.4.1   | Blocking Synchronisation                          | 89 |

|   |      | 5.4.2   | Non-blocking Synchronisation                      | 89 |

|   |      | 5.4.3   | Synchronisation Kernels                           | 90 |

|   |      | 5.4.4   | FFT                                               | 92 |

|   | 5.5  | Conclu  | usions                                            | 95 |

| 6  | Rela   | ted Wo  | rk                                               | 97  |

|----|--------|---------|--------------------------------------------------|-----|

|    | 6.1    | Analys  | sis of Message-Passing Programs                  | 97  |

|    |        | 6.1.1   | Static Analysis of MPI Programs                  | 97  |

|    |        | 6.1.2   | Profiling and Dynamic Analysis of MPI Programs   | 98  |

|    |        | 6.1.3   | Process Placement                                | 99  |

|    | 6.2    | Shared  | l-Memory Correctness                             | 100 |

|    |        | 6.2.1   | Programmer-centric memory models                 | 100 |

|    |        | 6.2.2   | Delay-set analysis                               | 100 |

|    |        | 6.2.3   | Fence minimisation                               | 100 |

|    |        | 6.2.4   | Synchronisation detection                        | 101 |

|    |        | 6.2.5   | Hardware based memory ordering                   | 101 |

|    |        | 6.2.6   | SC-preserving compilers                          | 101 |

|    |        | 6.2.7   | Dynamic Scheduling                               | 102 |

|    |        | 6.2.8   | Dynamic Race Detectors                           | 102 |

| 7  | Con    | clusion | s and Future Work                                | 105 |

|    | 7.1    | Summ    | ary of Contributions                             | 105 |

|    | 7.2    | Future  | Work                                             | 106 |

|    |        | 7.2.1   | Static Approximation of MPI Communication Graphs | 106 |

|    |        | 7.2.2   | Shared-memory Correctness and Performance        | 107 |

| Bi | bliogi | raphy   |                                                  | 109 |

# **List of Figures**

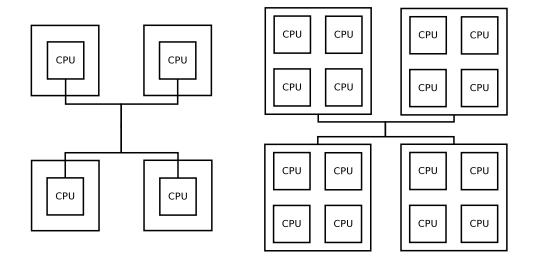

| 1.1 | Examples of an historical multiprocessing computer (left) and a mod-<br>ern manycore based cluster (right). Note that the use of CMPs in the<br>manycore system (right) necessarily creates a tiered topology, even<br>with a flat interconnect.                                                                                                                                                                                           | 3  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Simple example of the importance of memory consistency models in shared-memory programming. Initially, flag1 and flag2 are set to 0. Under SC, this code will ensure that only one or neither thread will enter the critical section. Crucially, under SC the threads cannot both enter the critical section. If the $w \rightarrow r$ ordering is relaxed, then this guarantee is lost.                                                   | 4  |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| 2.1 | Overview of different memory consistency models, by the orderings<br>of accesses to different memory locations that are enforced. Ticks in-<br>dicate that an ordering is enforced by that model                                                                                                                                                                                                                                           | 15 |

| 2.2 | Peterson's Algorithm [Pet81]. This provides mutual exclusion under SC. Under more relaxed consistency models, fence(s) are required to prevent incorrect behaviour and the violation of mutual exclusion. In particular, under a model like TSO where $w \rightarrow r$ orderings are not enforced, a fence is required in each thread at Point A. Fences at Points B prevent accesses in the critical section from being executed outside |    |

|     | the critical section.                                                                                                                                                                                                                                                                                                                                                                                                                      | 16 |

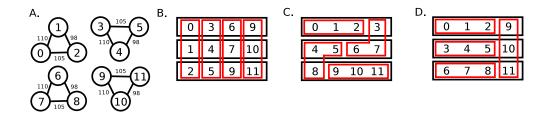

| 3.1 | A simplified communication graph for a 12 process program (A), where<br>triples of processes communicate heavily (see edge weights). Also<br>shown are three possible spatial schedules; Round Robin (B), by-rank<br>(C), and intelligent placement (D). Note that Round Robin scheduling<br>leads to all significant communication taking place between CMPs,<br>with intelligent placement localising communication from all but one<br>of the triples on a 4 core per node system. Additionally the other de-<br>fault schedule, by-rank similarly splits 2 of the triples across multiple<br>nodes. Assuming a cost model of intra-CMP communication being |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | cheaper than inter-CMP communication, Intelligent Placement is the best solution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 23 |

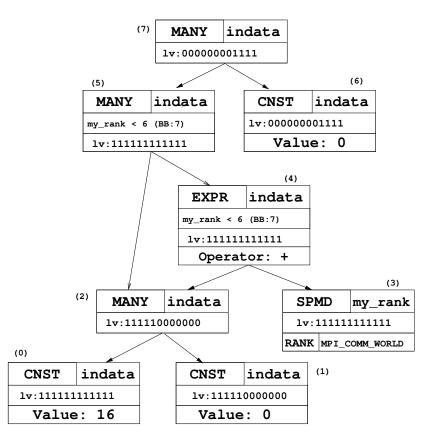

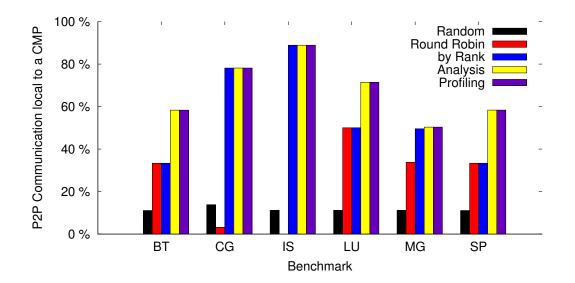

| 3.2 | The representation of <i>indata</i> at line 16 in Listing 3.1. In this figure <b>lv</b> represents live vector. We can see that after being redefined several times multiple nodes have been created and organised such that <i>indata</i> resolves to different values depending on the rank of the process                                                                                                                                                                                                                                                                                                                                                   | 30 |

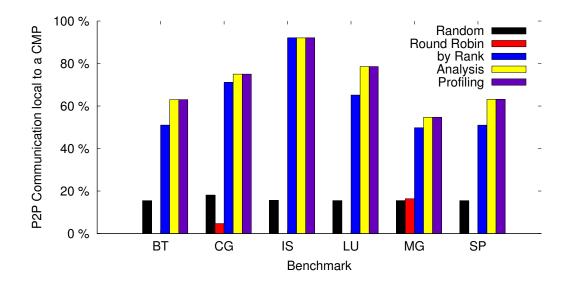

| 3.3 | Percentage of point-to-point communication localised to an 8-core per node CMP. We can see that in all cases we match the localisation provided by profiling. In 4 out of the 6 benchmarks we see an improvement over <i>by-rank</i> , on average an improvement of 28%                                                                                                                                                                                                                                                                                                                                                                                        | 41 |

| 3.4 | Percentage of point-to-point communication localised to a 12-code per node CMP. We can see that in all cases we match the localisation provided by profiling. In 5 out of the 6 benchmarks we see an improvement over <i>by-rank</i> , on average an improvement of 7%                                                                                                                                                                                                                                                                                                                                                                                         | 42 |

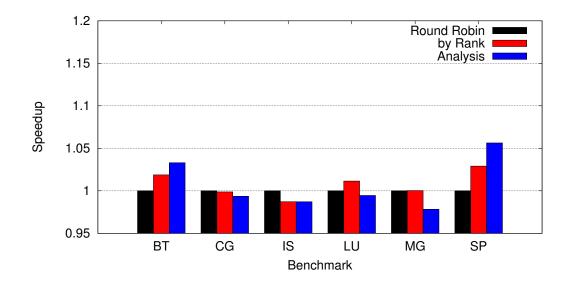

| 3.5 | Normalised speedup for 8-core per node machines for <i>round robin</i> , <i>by-rank</i> and <i>analysis</i> . The best result at this scale is SP, achieving a speedup of 1.03x (1.06x) over <i>by-rank</i> ( <i>round-robin</i> ). On average there is no speedup over <i>by-rank</i> , and only 1.01x over <i>round-robin</i>                                                                                                                                                                                                                                                                                                                                | 43 |

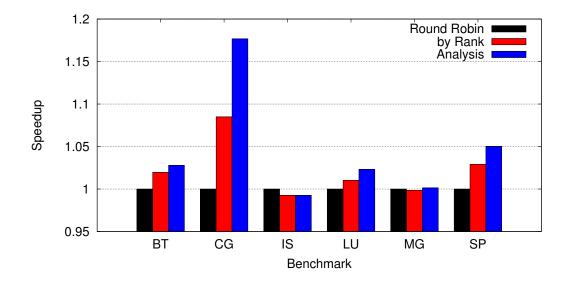

| 3.6 | Normalised speedup for 12-core per node machines for <i>round robin</i> , <i>by-rank</i> and <i>analysis</i> . The best result at this scale is CG, achieving a speedup of 1.08x (1.18x) over <i>by-rank</i> ( <i>round-robin</i> ). On average the speedup is 1.02x over <i>by-rank</i> and 1.04x over <i>round-robin</i>                                                                                                                                                                                                                                                                                                                                     | 44 |

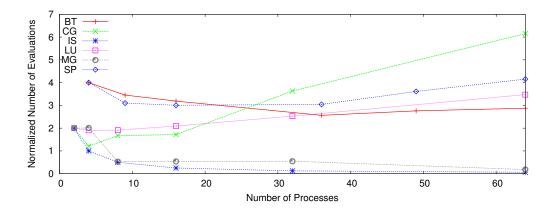

| 3.7 | Normalised total number of evaluations at each usable number of processes. BT and SP are normalised to 4 processes as they only support square numbers. Note that we achieve significantly better than the $O(n)$ worst case. In IS and MG we can also see the impact of reduced work per process as the number of processes is scaled. | 45 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1 | Examples of well-synchronised (a), and not well-synchronised (b) pro-<br>grams. Note that in example (a) SC semantics are required to ensure<br>correct operation on a relaxed architecture. In example (b) no such<br>semantics are required as the code is unsynchronised by design                                                   | 49 |

| 4.2 | An Example of (full) fence placement on legacy DRF code for Delay-<br>set and pruned orderings. By identifying that $a_2$ , $b_2$ , and $b_5$ are not ac-<br>quires we are able to avoid placing $F1$ , $F3$ and $F5$ as shown in Pruned<br>Orderings Fence Placement.                                                                  | 55 |

| 4.3 | The programming language for proofs. This tiny language is sufficient to deliver all the needed results.                                                                                                                                                                                                                                | 57 |

| 4.4 | The MP example. A classic producer-consumer synchronisation where the data access of $x$ is guarded by a control-dependency                                                                                                                                                                                                             | 60 |

| 4.5 | The MP example with pointer arithmetic.                                                                                                                                                                                                                                                                                                 | 60 |

| 4.6 | The Dekker Example                                                                                                                                                                                                                                                                                                                      | 61 |

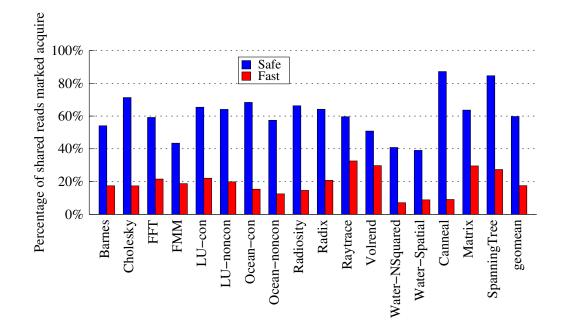

| 4.7 | Static percentage of potentially thread-escaping reads that our analysis marks as an acquire. The Fast form of our analysis marks on average only 18% of the shared reads as acquires. The Safe form of our analysis marks on average only 60% of acquires.                                                                             | 71 |

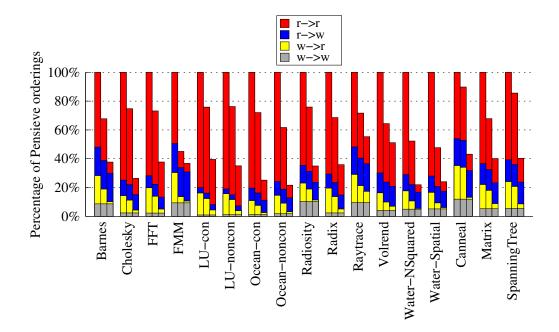

| 4.8 | A breakdown of orderings by type for Pensieve (left), Safe (centre),<br>and Fast (right). We see how our signatures have pruned $w \rightarrow r$ and<br>$r \rightarrow r$ orderings. With the Fast approach only 34% of orderings remain.<br>With the Safe approach 68% of the orderings remain.                                       | 72 |

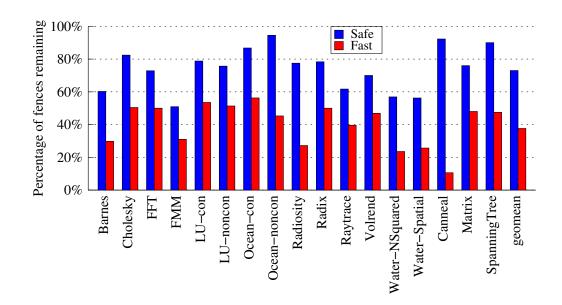

| 4.9 | Static percentage of full fences that remain on x86-TSO after using pruned orderings. We see that by using the Fast approach only 38% of Pensieve's fences are required. With the Safe approach 73% of the                                                                                                                              |    |

|     | fences placed for Pensieve remain.                                                                                                                                                                                                                                                                                                      | 73 |

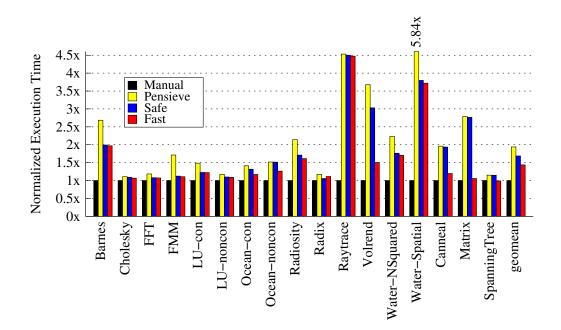

| 4.10 | Execution time with fences placed using Pensieve, Safe, and Fast, nor-     |    |  |  |  |

|------|----------------------------------------------------------------------------|----|--|--|--|

|      | malised against manual fence placement. On average our Fast ap-            |    |  |  |  |

|      | proach results in a 30% speedup over Pensieve. The Safe approach           |    |  |  |  |

|      | results in a 14% speedup on average                                        | 74 |  |  |  |

| 5.1  |                                                                            | 78 |  |  |  |

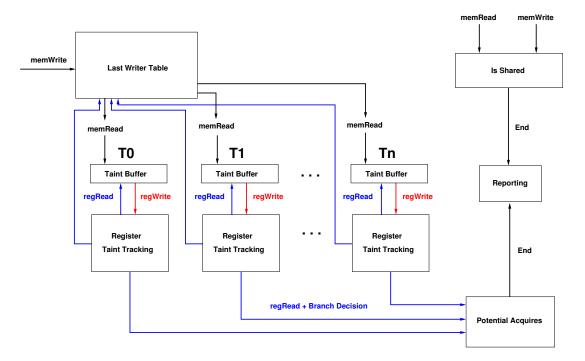

| 5.2  | A high level overview of the operations of SyncDetect                      | 85 |  |  |  |

| 5.3  | Simple blocking synchronisation between two threads                        | 89 |  |  |  |

| 5.4  | Simple non-blocking synchronisation between two threads. A call to         |    |  |  |  |

|      | sleep in thread 1 is used to ensure that we see the synchronisation occur  |    |  |  |  |

|      | in our experiment                                                          | 90 |  |  |  |

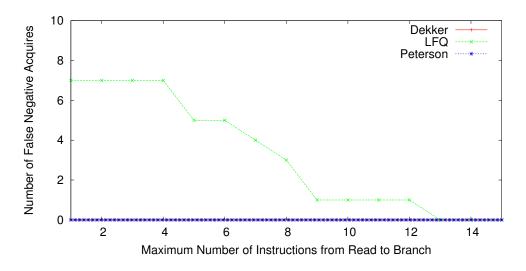

| 5.5  | The decrease in false negative acquires seen in the synchronisation ker-   |    |  |  |  |

|      | nels as the distance threshold is increased. Note that we see no false     |    |  |  |  |

|      | negatives reported for Dekker or Peterson at any positive threshold value. | 91 |  |  |  |

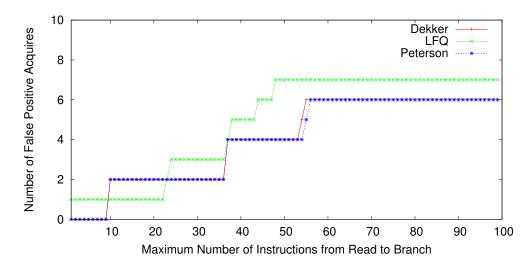

| 5.6  | The increase in false positive acquires seen in the synchronisation ker-   |    |  |  |  |

|      | nels as the distance threshold is increased.                               | 92 |  |  |  |

| 5.7  | Source and assembly level instructions from LFQ. Note that there are       |    |  |  |  |

|      | multiple instructions before the branch decision.                          | 93 |  |  |  |

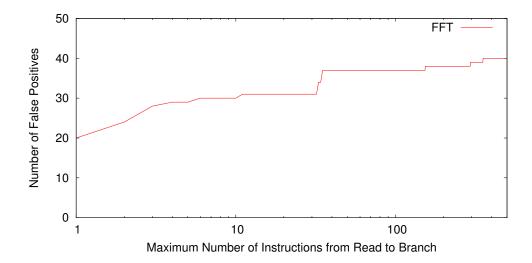

| 5.8  | A visualisation of the effectiveness of the distance heuristic on FFT.     |    |  |  |  |

|      | Shown are the number of false positive acquires reported at each po-       |    |  |  |  |

|      | tential threshold. There are no false negatives found in our investiga-    |    |  |  |  |

|      | tion of FFT, so no true positives are missed at any point shown. Note      |    |  |  |  |

|      | the log scale on the x axis.                                               | 94 |  |  |  |

|      |                                                                            |    |  |  |  |

# **List of Tables**

| 2.1 | The component configuration of a single node on the Eddie cluster                                                                                                                                                                                              | 18       |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.2 | A potential component configuration details of an HP Z840 Workstation.                                                                                                                                                                                         | 19       |

| 3.1 | Descriptions of node types used in our representations of partially eval-<br>uated variables. Each node in the representation is exactly one of these<br>types.                                                                                                | 29       |

| 3.2 | Coverage results and comparison with profiling for NAS Class A benchmarks using 64 MPI processes. As we can see, with the exception of MG, each <i>MPI_(I)Send</i> call site is being automatically and correctly evaluated in all contexts for all processes. | 39       |

| 4.1 | Sufficient orderings for correctness in a DRF program. Given a well-<br>synchronised program without data races, if these orderings are en-<br>forced then this is sufficient to ensure intended behaviour.                                                    | 53       |

| 4.2 | Breakdown of the types of acquires found in common synchronisation<br>kernels. Notably, no acquires are found to only meet the address sig-<br>nature. That is all acquires found to meet the address signature also                                           | 64       |

| 4.3 | meet the control signature                                                                                                                                                                                                                                     | 64<br>70 |

| 5.1 | A representation of the main data structure, mapping memory addresses<br>to the thread number and instruction pointer of the last writing instruc-<br>tion.                                                                                                    | 81       |

| 5.2 | A breakdown of the results of acquire detection and release inference<br>from applying our SyncDetect tool to three programs with ad hoc syn-<br>chronisation. Note that the numbers reported are based on lines in the                                        |          |

|     | source programs.                                                                                                                                                                                                                                               | 91       |

- 5.3 A breakdown of the acquire detection results on FFT from the SPLASH-2 suite. Note that numbers reported are lines in the source code. . . . 93

- 5.4 A breakdown of the inferred release results on FFT from the SPLASH2 suite. Note that numbers reported are lines in the source code. The two false negative releases are writes never read from and therefore could not be inferred from an acquire.

94

# **Chapter 1**

# Introduction

### 1.1 Context

Modern computers are based on manycore architectures to take advantage of the large number of transistors now available on each microchip and the limitations of uniprocessor performance, due to power and heat. In this environment, programmers are required to make use of parallelism to fully exploit the available cores. This can either be inside a single Chip Multiprocessor (CMP), or for larger scale programs requiring more cores than are available on a single CMP, multiple CMPs can be used in clusters of various topologies and design.

There are two major paradigms used to write parallel programs, shared-memory and message-passing. Shared-memory programming is traditionally used at a small scale, e.g. a single node, where executing elements (in this case threads) all have relatively efficient access to a common local memory (RAM) and share an address space. This common address space enables efficient communication as only pointers need to be passed between threads. Shared-memory programming can however be susceptible to error as threads can potentially interfere with one another if poorly programmed.

The other major paradigm is message-passing. This has been traditionally used at larger scales, e.g. multiple interconnected nodes. Here the executing elements (generally processes) can be completely independent and indeed may be running on entirely independent systems with private memory and storage. In this paradigm communication occurs through explicit calls to a message-passing library which facilitates the transfer of the specified data. The de facto standard for this paradigm is Message Passing Interface (MPI), which provides a wide range of communication and synchronisation primitives. With the advent of the ubiquitous manycore CMP, even a handheld computer (e.g. a mobile phone) can have a single CMP with 8 or more cores. In this environment, both paradigms (with the support of the underlying hardware and system software) must now operate efficiently and correctly on manycore based systems. There are a number of opportunities created by this move to CMPs, that these paradigms can exploit. For example, message-passing systems can use threads rather than processes when a shared-memory environment (e.g. the communicating processes are in a single CMP) is available. This can enable more efficient communication. However manycore CMPs can also present performance challenges for legacy or topology agnostic programs that were not written with modern CMPs in mind.

**Tiered Topology** – To better convey the organisation of a modern parallel computer, we must look at the historical context. Historically, parallel computers were multiprocessors where discrete Central Processing Units (CPUs) would be connected together in various configurations. Now that CMPs are ubiquitous, these instead are used to construct parallel computers. Despite the large (and growing) number of cores per CMP there is always a desire to handle larger (and growing) computational problems, larger than a single CMP can support. Therefore, as with CPUs in multiprocessors before them, CMPs are used collectively, connected together in various configurations. Figure 1.1 shows example configurations of both an historical multiprocessing parallel computer and a modern manycore based parallel computer to better illustrate the differences. It is worth noting that even with a flat interconnect (as in our examples), the use of CMPs necessarily creates a tiered topology where not all cores are equidistant, with those on the same CMP taking advantage of internal interconnects. This inherent complexity means that legacy parallel programs written without knowledge of this topology can face performance degradation if they unnecessarily make use of higher latency or lower bandwidth channels within the system. This also presents an opportunity for tools that improve the spatial scheduling of existing programs by better mapping them to these new topologies.

**Memory Consistency Model –** One critical factor in the design of a shared-memory parallel architecture like a CMP is the memory consistency model. A memory consistency model precisely defines how accesses to memory (reads and writes) executed in different cores by different threads interact. Programmers generally write programs expecting Sequential Consistency (SC) [CTMT07, Hil98, LP01, SNM<sup>+</sup>12]. SC is where the operations of each core (thread) are exposed to other cores (threads) in the order that they exist in the source program (program order). For preserving the appearance

Figure 1.1: Examples of an historical multiprocessing computer (left) and a modern manycore based cluster (right). Note that the use of CMPs in the manycore system (right) necessarily creates a tiered topology, even with a flat interconnect.

of SC we need only be concerned about memory accesses, as other operations are not exposed.

However, while programmers have written assuming SC as it is convenient and simple to reason about, the trend in architectures is towards increasingly relaxed memory consistency models. Some early multiprocessors (e.g. MIPS) did support SC [Yea96] but more modern architectures do not [Int09, SSA<sup>+</sup>11]. These architectures have hardware memory models where some (or all) the orderings of reads ands writes are not enforced by the hardware. This relaxation is largely for performance reasons as more and more cores are added to each chip. This relaxation already exists to varying degrees in commercial architectures, with x86 chips not enforcing write to read orderings [Int09], and POWER being even more relaxed [SSA<sup>+</sup>11].

This mismatch between programs written assuming SC and architectures supporting more relaxed models requires specific intervention to prevent unintended behaviour. To better illustrate this unintended behaviour we introduce a simple synchronisation example as Figure 1.2. In this example both shared variables flag1 and flag2 are initialised as 0. Under SC this code ensures that either one or neither thread can enter the critical section. On a more relaxed modern architecture however, the ordering of reads to be after writes (to different addresses in program order) is not enforced. Therefore the at most one thread guarantee is lost and both threads may enter the critical section, potentially simultaneously. If the reads are executed before the writes, both threads will enter the critical section, thus violating mutual exclusion.

T1T2flag2 = 1;

$$w$$

flag1 = 1; $w$  $\downarrow$  $\downarrow$  $\downarrow$ if (flag1 == 0) $r$ if (flag2 == 0) $r$  $\{$  $\{$  $\{$ // Critical Section// Critical Section $\}$

Figure 1.2: Simple example of the importance of memory consistency models in shared-memory programming. Initially, flag1 and flag2 are set to 0. Under SC, this code will ensure that only one or neither thread will enter the critical section. Crucially, under SC the threads cannot both enter the critical section. If the  $w \rightarrow r$  ordering is relaxed, then this guarantee is lost.

To correctly run a program like that in our example on a more relaxed architecture, fences must be introduced to prevent the compiler and hardware from reordering the memory accesses. This can either be done manually by an expert programmer or automatically by the compiler [LP01]. The issue with automatic intervention is that it is necessarily conservative and precision is difficult without a detailed understanding of the programmers intention. Conversely such automatic solutions are attractive in that they do not require an expert programmer and avoid the potential for such a programmer to introduce additional errors.

## 1.2 Problems

While both the paradigms outlined (message-passing and shared-memory) enable parallel computing, the differences inherent in their design are significant. Accordingly, while both have problems in communication and synchronisation for existing (legacy) programs on modern systems, the nature of the problems and the remedies available are paradigm specific.

In MPI, where all communication is performed through library calls, the correctness issue is one for library developers. However, a performance issue exists where programs written, unaware of the topology of the cluster of CMPs used, may have heavily communicating processes forced to use higher latency or lower bandwidth channels within the cluster. This negative impact on communication can significantly increase the start-to-end runtime of the program.

In a shared-memory environment, the problem is ensuring correctness without needlessly sacrificing performance. The relaxed memory models used in modern architectures (as outlined above) create a correctness issue for (legacy) code that was written assuming SC. An ad hoc synchronisation, that is one written using a sequence of reads and writes, that assumes SC, will not have expected behaviour on a more relaxed architecture unless the required orderings are explicitly enforced. Explicitly enforcing every ordering would solve this correctness issue, but have a seriously detrimental performance impact and remove the benefits of hardware implementing a relaxed memory model. Therefore there is a need to determine the minimal number of orderings that need enforcement, to solve the correctness issue with minimal loss of performance.

## 1.3 Approach

To address the problems present for existing code in both paradigms on modern architectures, we present static (compile-time) solutions. Static solutions have significant advantages, as compared to dynamic or profile-guided approaches. In particular, profile-guided analysis requires additional work on the part of the programmer and the use of potentially scarce or unavailable resources. Additionally, where correctness is a concern, the results of even multiple executions may not reveal all potential behaviours. Dynamic (runtime) transformation approaches can also introduce additional overhead, which must be overcome before providing an improvement over the baseline.

Static analyses do have limitations, in regard to reliance on alias analysis and the unavailability of program input. Program input can be particularly useful in applications such as debugging. Therefore we also present a proof of concept dynamic approach to the shared-memory correctness issue outlined above. This dynamic approach aims to identify and report ad hoc synchronisations to the programmer, to assist in debugging and porting legacy code to a relaxed architecture.

### 1.4 Contributions

In this thesis we make the following contributions. Firstly, a method for statically approximating the MPI communication graph, then used to optimise process placement in a CMP-based cluster. We then move into the shared-memory paradigm, identify-

ing and proving necessary conditions for a read to be an acquire. An application of these conditions is then developed, optimising fence placement through an improved approximation of delay-set analysis. Finally we present a tool for dynamic detection and reporting of ad hoc synchronisation leveraging the necessary conditions earlier identified. Before moving on to a background discussion, we first outline the novelty of each of the techniques proposed in this thesis.

#### 1.4.1 Static Approximation of MPI Communication Graphs

Inefficient communication can be a significant bottleneck in parallel programs. When an MPI program is run on a cluster of CMPs not all pairs of processes can communicate with equal bandwidth and latency. Programs written without knowledge of the topology of the cluster and the number of cores per CMP may not make efficient use of the system. Our aim is to colocate heavily communicating processes to the same CMP, though our work is applicable to other cost models or objective functions. Previous work has shown that MPI communication is generally statically determined by the programmer, implicit information that is currently ignored by the compiler. This static determination by the programmer allows compile-time analysis to effectively attempt to determine the communication graph and take action to intelligently place processes.

In Chapter 3 we present a purely static approach to determining the point-to-point communication graph of an MPI program. We propose a fully context and flow sensitive, interprocedural analysis framework for analysing MPI programs. This framework leverages a new data structure for maintaining partially evaluated variable representations for on-demand process sensitive evaluation. We use this framework to determine optimised process placement on a CMP-based cluster. Our analysis is the first to statically resolve and characterise the full point-to-point communication graph. In all but one case this only requires specifying of the number of processes.

## 1.4.2 Acquire Detection and Fence Placement for Legacy DRF Programs

In shared-memory parallel programming, being able to identify ad hoc synchronisations has a number of applications. These range from debugging (notoriously hard for parallel programs) to (as we will show) improving fence placement. In a data race free (DRF) program, synchronisation is annotated to allow the system to ensure no data races are introduced during compilation or execution. Recently programming mod-

#### 1.4. Contributions

els have been moving towards such DRF variants (e.g. C11 [BOS<sup>+</sup>11, BA08] and Java [MPA05]). However, there exists a large body of legacy code which has no annotations. These legacy programs would be DRF if only the annotations were added. As described earlier, ensuring correct operation of a program written assuming SC on a relaxed architecture requires explicitly enforcing orderings with fences. Where there are no annotations, the techniques used require program analysis. The seminal work in this area is delay-set analysis [SS88] which detects critical cycles between threads and the writes that would conflict. Our realisation is that programmers are not seeking to achieve SC, but data race freedom. For well-synchronised programs this only requires providing SC behaviour for synchronisation accesses.

In Chapter 4 we examine the nature of ad hoc synchronisation in a shared-memory environment. From this we determine the conditions a read must meet to be an acquire in a data race free (DRF) program. We then, for the first time, prove these are the necessary conditions. This is a significant contribution as it allows us to improve upon existing solutions in a number of application areas.

To demonstrate an application of this work we take the conditions determined and use them to improve delay-set analysis for well-synchronised (legacy DRF) programs. This improvement, is through using our signatures (conditions) to prune the number of required orderings determined by delay-set analysis (or its conservative approximation). This enables fence minimisation algorithms to place fewer fences, leading to improved performance.

# 1.4.3 Signature-based Dynamic Detection of Ad Hoc Synchronisation

Relatively precise identification of otherwise unmarked acquires and releases has two other important applications. The first is in the assistance of debugging of parallel programs, a notoriously difficult task. The second relates to the development of new language memory consistency models, e.g. C11, that require synchronisation to be explicitly marked. There exists a large body of legacy code that lacks such annotations. Tools that assist in identifying synchronisation can significantly aid the programmer in migrating programs to these new models.

In Chapter 5 we introduce SyncDetect, a proof of concept tool for dynamically detecting and reporting ad hoc synchronisations. Built on Intel's Pin framework, it is generally applicable and requires no program modification. It leverages the signatures

proven in Chapter 4 to identify reads that may be acquires and offers detection of (the more common) control acquires. We are also able to leverage the precision provided by dynamic analysis to additionally report the associated releases.

# **Chapter 2**

# Background

## 2.1 Architectures

### 2.1.1 Practical Need for Parallel Architectures

A significant class of computational problems (the majority of practical tasks) can to a greater or lesser extent be parallelised, that is they are not inherently sequential. Additionally, there is always a desire to attack larger and larger computational problems that are always infeasible for all practical purposes (in terms of running time), on a single CPU. These two factors create a climate in which using multiple CPUs in concert, to produce better absolute performance than a single CPU can offer, is a common use case.

Historically, one can define two major types of parallel computer. First is the cluster (multicomputer), constructed of multiple computers loosely connected over a network. Absent any additional abstraction, such a machine would use message-passing to operate in parallel. Second is the multiprocessor, where multiple CPUs are connected on a single bus using the same address space and therefore sharing memory.

### 2.1.2 Early Multiprocessors

Early multiprocessors were constructed by interconnecting discrete processors on a shared bus with a shared address space. Shared-memory programming is the natural paradigm here, although both major programming paradigms, the other being message-passing, are possible in this environment [LM92].

While many topologies and interconnect network designs are possible, ranging from a single shared bus to a full crossbar interconnect [BYA89], the distribution of

memory is arguably a more significant discriminant. These machines can be categorised into Uniform Memory Access (aka Symmetric Multiprocessing (SMP)), and Non Uniform Memory Access (NUMA) [HP11]. In an SMP machine the sharedmemory is centrally located, with all processors having essentially equal access to it. In a NUMA machine, the shared-memory is partitioned. In most cases, each partition is co-located with one of the processors creating a notion of local and remote memory, which can be exploited for performance reasons.

Significant historical examples include the Stanford Dash [LLG<sup>+</sup>92], which was the first to have a scalable cache coherency protocol. This allows shared-memory programs to make full use of the caches, rather than face the time penalty of communicating with memory on every access to shared data.

#### 2.1.3 Current Manycores

Current manycore systems are Chip Multiprocessors (CMPs), that is several interconnected CPUs co-located on a single silicon microchip. These manycore systems are now ubiquitous, present at all scales of general computing from the embedded (mobile phones) to supercomputers. This means that now even the most basic computer, outside of specialist embedded domains, supports parallelism. Current commercial architectures, such as Intel's Haswell processors [Int14] and those based on ARM's architectures [ARM14], support shared-memory programming. Whether it will be possible to maintain efficient cache coherent shared-memory as more and more cores are added to a CMP, is not yet known but seems unlikely. Therefore, future manycores may need to rely on Network on Chip (NoC) communication, where relatively distant cores on a CMP use message-passing to communicate. In such a future, sharedmemory programming may be possible for regions of the CMP but not as a whole. One such example of a possible future architecture is Intel's Single-chip Cloud Computer (SCC) [HDH<sup>+</sup>10]. This can be operated as a cluster on chip with each core running its own operating system, with communication through on chip message-passing.

As discussed above, the demand for computational power has always outstripped the supply provided by a single CPU. As with previous multiprocessors and clusters, the way to achieve increased performance is to construct machines connecting multiple units of the basic component. In the modern world this means connecting CMPs. At a small scale this could be a shared-memory machine where two or more CMPs share memory and an address space. At a larger scale this is as a cluster with many CMPs connected by a network and able to use message passing.

Before moving on to discuss programming models, it is worth noting that in recent years significant work has been done towards using Graphics Processing Units (GPUs) for general purpose computing. These architectures have proved effective at large scale computing [CBM<sup>+</sup>08], but are largely beyond the scope of this thesis and are therefore not discussed further.

### 2.2 Programming models

#### 2.2.1 Message-passing

Message-passing is a parallel programming paradigm in which communication takes place through explicit means. The de facto standard in this paradigm is Message Passing Interface (MPI) [mF]. Message-passing is prevalent as it allows for the writing of portable code, where the program is not tied to specific features of the architecture. Indeed a message-passing program can be supported on both shared-memory and more distributed machines. To run, the program only requires that some implementation of the message-passing library is provided for the target system.

To understand the organisation of MPI programs, it is first necessary to introduce two central concepts, the *communicator* and the *rank*. The *communicator* represents a set of processes that can communicate with each other. An MPI program normally starts by using MPI\_COMM\_WORLD, a communicator that encapsulates all the processes. Programmers can then however create communicators for subsets of those processes. The communicator is important as it enables simple use of global communication operations, e.g. reductions and broadcasts. In MPI these operations are run within a specific communicator, with all processes in that communicator involved.

To identify individual processes for communication, particularly on a non-global basis, MPI assigns each process a *rank* for each communicator of which it is a part. This is analogous to a thread ID that a shared-memory programmer might use to determine behaviour and organise communication. However, in MPI, these assignments are made by the library providing the MPI implementation. A process requests its rank through a library call. For example *MPI\_Comm\_rank*(MPI\_COMM\_WORLD, *&my\_rank*);, would store the processes rank for the MPI\_COMM\_WORLD communicator in the *my\_rank* variable.

MPI programs are traditionally written in a Single Program Multiple Data (SPMD)

style, where each process executes the same program, with process specific behaviours engendered through control statements. This, combined with the fact that communication takes place through explicit library calls, is significant as it determines how the programs can be analysed. The explicit nature of the communication means that (in contrast to shared-memory programming), identification of communication statements is, absent function pointers, trivial. Understanding the nature of the communication however, with regard to which processes are involved and the volume of data transferred, is not necessarily so simple.

One significant advantage MPI (or another message-passing implementation) offers is the separation between the programmer intention and the implementation of communication and synchronisation. This allows the programmer to use MPI library calls to communicate and synchronise, without considering the underlying implementation. This also means library developers can develop the most efficient implementations of communication primitives for their target systems. The outcome of this is portable code that (in theory) can make use of the most efficient communication algorithms available on any of the target systems on which it is run.

The portability of MPI programs, while an extremely valuable feature, with a program able to (without alteration) be compiled and run correctly on any system for which an MPI library has been implemented, does also introduce some issues. In particular, because the organisation of the program is decoupled from the organisation of the system, a legacy or system agnostic program may not achieve its optimal performance. Assuming a relatively homogenous system, in terms of computing resources, the key aspect in terms of relative performance is how the communication graph of the program maps onto the system. We define the communication graph as one where processes are represented as vertices, with undirected weighted edges representing the total volume of communication (in bytes) between processes.

If the mapping of this graph onto the system is poor, as without deliberate intervention it may be, the start-to-end runtime can be negatively affected. In more detail, if heavily communicating processes are required to make use of higher latency or lower bandwidth channels of communication within the system, the start-to-end runtime of the program may not be the minimum possible on the system. This is caused by processes being forced to wait for the communication to occur (blocking communication). In fact, even in nonblocking communication waits may be introduced if the receiving process reaches an *MPI\_Wait* call, where future statements are dependent on the receipt of data. In this thesis we seek to address the spatial scheduling issue in message-passing programs created by the running of legacy or system agnostic message-passing programs on modern manycore clusters. We exploit the SPMD and explicit communication nature of MPI programs to statically determine the communication graph. This work is presented as Chapter 3.

### 2.2.2 Shared-memory

Shared-memory programming is a parallel programming paradigm that allows threads to access memory using a common address space. Given the requirement of a system providing such an address space, shared-memory programming is normally and historically used at a smaller scale, a single multiprocessor, in modern terms within a Single CMP. While shared-memory programming does require a system that supports the paradigm, on such a system it does provide more flexibility than message-passing. Specifically, the programmer is not limited to the primitives provided by the message-passing library (e.g. MPI) and is free to construct their own synchronisations. This flexibility can however be the source of errors, either through poor programming, or as we will discuss further, a mismatch between the programmed for memory consistency model and that provided by the system.

Significantly, communication in shared-memory programming can merely be the passing of pointers between threads, rather than (as in message-passing) transmitting the entire data required by the receiving process. There are other costs associated with cache coherence (or manual flushing if the caches are not coherent), but these are minor considering that the passing of a potentially unbounded volume of data is possible via a single pointer.

This ability to work on a single set of data not copied or fragmented is advantageous but requires correct synchronisation to avoid potentially silent errors. In sharedmemory programming, correctness (with regard to program behaviour versus programmer expectation) depends on a correct understanding of the memory consistency model. Exclusively using library synchronisations does to some extent absolve the programmer of this responsibility but also removes much of the flexibility of sharedmemory programming. In more detail, when using library synchronisations, the programmer can assume that the library developer has correctly met the requirements of the memory model, by placing appropriate fences. When the programmer implements their own synchronisations, they cannot rely on that assumption. As we will see in Section 2.3, when the programmer makes use of ad hoc synchronisations, if the assumed memory consistency does not match that of the target system, errors may occur.

Recognising that shared-memory systems no longer support SC, development in languages that support shared-memory programming is trending towards data-race-free (DRF) based models. In these models, such as C11 [BOS<sup>+</sup>11, BA08] and the Java Memory Model [MPA05], the programmer is required to explicitly annotate synchronisation. This means that the programmer's expectations are explicitly defined and therefore the compiler is able to place the fences necessary to effectively strengthen the target system's memory consistency model for the annotated accesses. As these language models are relatively recent there exists a large body of legacy code that is well-synchronised and would meet these models, but lacks the annotations [XPZ<sup>+</sup>10]. We refer to such programs as Legacy DRF and target these in much of our shared-memory work as presented in this thesis.

In this thesis we seek to address the correctness issues introduced by running wellsynchronised shared-memory programs written with the expectation of SC on more relaxed architectures, while minimising the performance issues introduced by current solutions.

To identify acquires, we identify and prove two signatures. At least one of these signatures must be fulfilled for a read to be an acquire. We then use these signatures to improve existing fence placement techniques by reducing the set of accesses that must be considered synchronisations. Finally we use these signatures to power a dynamic synchronisation detection tool, where they serve to minimise false positives.

## 2.3 Memory Consistency Models

### 2.3.1 Foundations

The memory consistency model is a crucial element in the design of a shared-memory multiprocessor. It defines how the operations of one CPU will appear to another CPU. This is critical, as performance reasons dictate that operations are not actually executed in the (program) order specified by the programmer. This is also true of a uniprocessor, where the programmers instructions are reordered by the compiler and the hardware as well. This is done to make the best use of the resources and minimise stalls, where elements of the processor are forced to wait. In a uniprocessor, as long as control and data dependencies are respected, this reordering is safe.

|                        | $w \rightarrow w$ | $w \rightarrow r$ | $r \rightarrow w$ | $r \rightarrow r$ |

|------------------------|-------------------|-------------------|-------------------|-------------------|

| Sequential Consistency | 1                 | 1                 | 1                 | 1                 |

| Total Store Order      | 1                 | ×                 | 1                 | 1                 |

| Fully Relaxed          | ×                 | ×                 | ×                 | ×                 |

Figure 2.1: Overview of different memory consistency models, by the orderings of accesses to different memory locations that are enforced. Ticks indicate that an ordering is enforced by that model.

Where these reorderings, and (logically) simultaneous accesses by multiple CPUs to the same location, become problematic is in a shared-memory multiprocessor. Here, without a well-defined consistency model, adhered to by the programmer and the system, a read may return a stale value. In short, memory can be inconsistent.

Strict consistency, as provided by most uniprocessors, where any read to a location is guaranteed to return the result of the last write and a global order exists, is all but impossible to provide on a multiprocessor as memory accesses are not instantaneous. Therefore real world multiprocessors implement some weaker form of consistency, either the still relatively strong Sequential Consistency or a relaxed consistency model. We will now outline the details of common consistency models, beginning with Sequential Consistency. We will compare consistency models based on the memory orderings that they enforce. There are other details in specific implementations such as early access to data but considering the orderings enforced is sufficient for our purposes. Before going into the various models, we first present an overview of the orderings that each model enforces as Figure 2.1.

#### 2.3.2 Sequential Consistency

Sequential Consistency (SC) as introduced by Lamport [Lam79] is the strictest form of memory consistency that is practical on a shared-memory multiprocessor. However, modern machines do not provide it as enforcing SC carries a severe performance penalty. Some earlier multiprocessors (e.g. the SGI Origin2000 [LL97] based on the MIPS R10000 [Yea96]) did provide SC, but these are no longer current.

SC is defined by the fact that the operations of a CPU must appear to other CPUs to have been executed in program order and that all executions are equivalent to all the operations having been performed in some linear sequence. It entails that all memory accesses (reads and writes) must appear to have been executed in program order, but

| T1                                    | T2                               |

|---------------------------------------|----------------------------------|

| flag[0] = true;                       | flag[1] = true;                  |

| turn = 1;                             | turn = 0;                        |

| // Point A                            | // Point A                       |

| while $(flag[1] \&\& turn == 1) \{\}$ | while $(flag[0] \&\& turn == 0)$ |

| // Critical Section                   | // Critical Section              |

| // Point B                            | // Point B                       |

| flag[0] = false;                      | flag[1] = false;                 |

Figure 2.2: Peterson's Algorithm [Pet81]. This provides mutual exclusion under SC. Under more relaxed consistency models, fence(s) are required to prevent incorrect behaviour and the violation of mutual exclusion. In particular, under a model like TSO where  $w \rightarrow r$  orderings are not enforced, a fence is required in each thread at Point A. Fences at Points B prevent accesses in the critical section from being executed outside the critical section.

operations that are local to a CPU and therefore not exposed to other CPUs may still be reordered.