# Parallel Algorithms and Architectures for

VLSI Pattern Generation

Roderick David Wolfe Widdowson

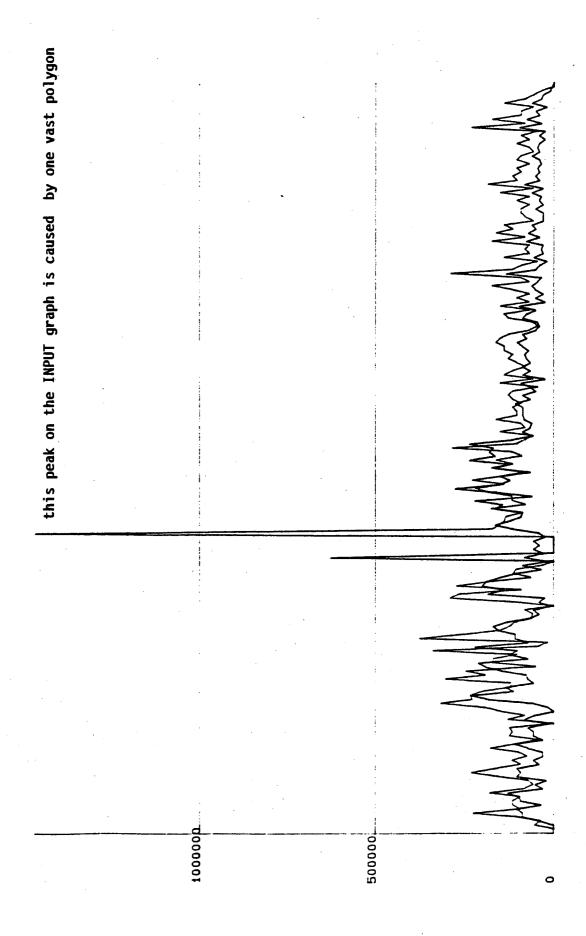

Ph D University of Edinburgh 1987

#### Abstract

The process of data preparation for pattern generation consists of the performing of various geometric operations upon a user's design. This is the final manipulation of the design prior to the making of the masks and can be exceptionally time consuming, especially when a very large user designs are being processed.

This thesis addresses one way of speeding up the processing - by the use of (relatively) small numbers of loosely coupled processors as a multiprocessing unit. The starting point of the work was commercial pattern generation system. This incorporated programs programs or modules to perform parsing and flattening, overlap removal (merging) and partitioning. The major results are a series of performance measurements obtained by emulating parallel processors with an appropriate interconnection pattern. These give a valuable indication of the degree of performance enhancement which this approach to parallelism may be expected to bring. Confirmation of these expectations via practical implementations on two varieties of workstation clusters is reported.

The three major parts of a Pattern Generation system, the merge stage whose most important aspect is overlap removal and sizing, and the decomposition and sort (termed fracture) for the two major types of lithographical equipment (electron-beam and photo-mechanical) are examined separately. Particular emphasis is placed on the merge stage, which is the most time critical part of the whole process. The method used to partition the merge task among processors is area subdivision.

The practical work carried out consisted of devising practical algorithms for the area subdivision and recombination, and in the setting up of test harnesses multiprocessor emulations.

## Acknowledgements

I should like to acknowledge the assistance of all the members of the Computer Science department but my particular thanks must go to David Rees who supervised this thesis.

Lattice Logic helped financially and the members of staff, both past and present, have been most supportive. In particular I thank John Gray for his constant encouragement. All the members of the ShapeSmith group, and in particular Neil Menzies and Gordon Hughes have helped me immensely to formulate and develop the ideas presented here.

This work was funded under the Cooperative Awards in Science and Engineering scheme by the United Kingdom Science and Engineering Research Council and Lattice Logic Ltd.

Finally I must thank my parents for their support over the years.

## Declaration

I hereby declare that this thesis has been composed by myself, and that the work it describes is my own.

Roderick David Wolfe Widdowson September 7, 1987

# Table of Contents

| 1. | Intr | oduct  | ion                                             | 10         |

|----|------|--------|-------------------------------------------------|------------|

|    | 1.1  | Makir  | ng Programs Run Faster                          | 11         |

|    |      | 1.1.1  | Algorithmic improvement                         | 11         |

|    |      | 1.1.2  | Improving the Software Implementation           | 12         |

|    |      | 1.1.3  | Improving the Hardware Implementation           | 13         |

|    |      | 1.1.4  | Assessing the performance improvement           | 13         |

|    | 1.2  | Parall | elism                                           | 15         |

|    |      | 1.2.1  | Algorithmic parallelism                         | 15         |

|    |      | 1.2.2  | Implementing parallelism                        | 16         |

| ı  |      | 1.2.3  | The pitfalls of parallelism                     | 22         |

|    | 1.3  | Patter | en Generation                                   | 23         |

|    |      | 1.3.1  | The motivation for faster pattern generation    | 25         |

|    |      | 1.3.2  | A method of speeding up pattern generation      | 25         |

|    |      | 1.3.3  | Restrictions upon pattern generation processing | 26         |

|    |      | 1.3.4  | The Overall techniques used                     | 28         |

|    | 1.4  | This I | Chesis                                          | <b>3</b> 0 |

|    |      | 1.4.1  | Description of the rest of the thesis           | 31         |

| Table of Contents |  |

|-------------------|--|

|                   |  |

| 2. | Dat | a Prep  | aration for Pattern Generation      | 33 |

|----|-----|---------|-------------------------------------|----|

|    | 2.1 | Mask I  | Making                              | 33 |

|    |     | 2.1.1   | Photo-mechanical mask makers        | 34 |

|    |     | 2.1.2   | Electron Beam mask-makers           | 37 |

|    |     | 2.1.3   | Other Pattern Generation Equipment  | 40 |

|    | 2.2 | The Fu  | ınction of Data Preparation for P.G | 42 |

|    | 2.3 | A P.G.  | . Data Preparation System           | 46 |

| 3. | The | Polyg   | on Merge Stage                      | 48 |

|    | 3.1 | Algorit | thms for Merging                    | 48 |

|    |     | 3.1.1   | Theoretical Preamble                | 49 |

|    |     | 3.1.2   | Area Based Algorithms               | 50 |

|    |     | 3.1.3   | Edge Based Algorithms               | 54 |

|    |     | 3.1.4   | Scan Line Algorithms                | 57 |

|    | 3.2 | Paralle | elising the Merge Stage             | 59 |

|    |     | 3.2.1   | The chosen algorithm                | 59 |

|    |     | 3.2.2   | Integrated Circuit Geometry         | 61 |

|    |     | 3.2.3   | Parallel Merge - How                | 63 |

|    |     | 3.2.4   | The system architecture             | 65 |

|    |     | 3.2.5   | Implementation                      | 67 |

|    | 3.3 | Results | s, Modifications and Limitations    | 70 |

|    |     | 3.3.1   | Accuracy                            | 71 |

|    |     | 3.3.2   | Speed - Overall                     | 73 |

|    |     | 3.3.3   | Load Balancing                      | 74 |

|    |     | 3.3.4   | Emulated Speed 78                              |

|----|-----|---------|------------------------------------------------|

|    |     | 3.3.5   | Communication costs                            |

|    |     | 3.3.6   | Processor Memory                               |

|    |     | 3.3.7   | Processor numbers                              |

|    | 3.4 | Conclu  | ısions                                         |

|    |     | 3.4.1   | Possible Improvements                          |

|    |     | 3.4.2   | Sequential Program Enhancement                 |

|    | 3.5 | Graph   | s                                              |

| 4. | The | Electi  | con Beam Fracture Stage 102                    |

|    | 4.1 | Algori  | thms for Ebeam Fracture                        |

|    |     | 4.1.1   | Theoretical Consideration of Decomposition 102 |

|    |     | 4.1.2   | Scan Line Algorithms                           |

|    |     | 4.1.3   | Sorting                                        |

|    | 4.2 | Paralle | elising Ebeam Fracture                         |

|    |     | 4.2.1   | Parallel Ebeam Fracture                        |

|    |     | 4.2.2   | The system architecture                        |

|    |     | 4.2.3   | Implementation                                 |

|    | 4.3 | Result  | s and Modifications                            |

|    |     | 4.3.1   | Accuracy and Flash Count                       |

|    | •   | 4.3.2   | Memory Cost                                    |

|    |     | 4.3.3   | Load Balance                                   |

|    |     | 4.3.4   | Processor Numbers                              |

|    |     | 4.3.5   | Emulated Speed                                 |

| Table ( | of | Contents |

|---------|----|----------|

|---------|----|----------|

|     | 4   | 4.3.6   | Communication Costs                         | 117          |

|-----|-----|---------|---------------------------------------------|--------------|

|     | 4.4 | Conclu  | asions                                      | 120          |

|     | 4.5 | Graph   | s                                           | 122          |

| 5.  | The | Optic   | al Fracture Stage                           | 27           |

|     | 5.1 | Algorit | thms for Ebeam Fracture                     | 127          |

|     |     | 5.1.1   | Theoretical Considerations in Decomposition | 127          |

|     |     | 5.1.2   | Algorithms for Polygon Decomposition        | 128          |

|     |     | 5.1.3   | Sorting                                     | 130          |

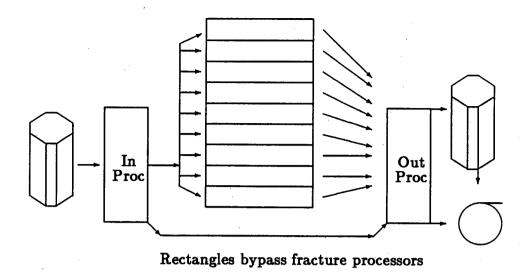

|     | 5.2 | Paralle | elising Optical Fracture                    | 131          |

|     |     | 5.2.1   | Parallel Optical Fracture                   | 131          |

|     |     | 5.2.2   | System architecture                         | 132          |

|     |     | 5.2.3   | Implementation                              | 132          |

|     | 5.3 | Result  | s and Modifications                         | 133          |

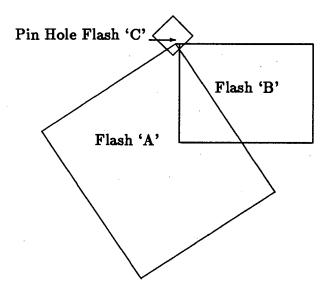

|     |     | 5.3.1   | Accuracy                                    | 133          |

|     |     | 5.3.2   | Memory Cost                                 | 135          |

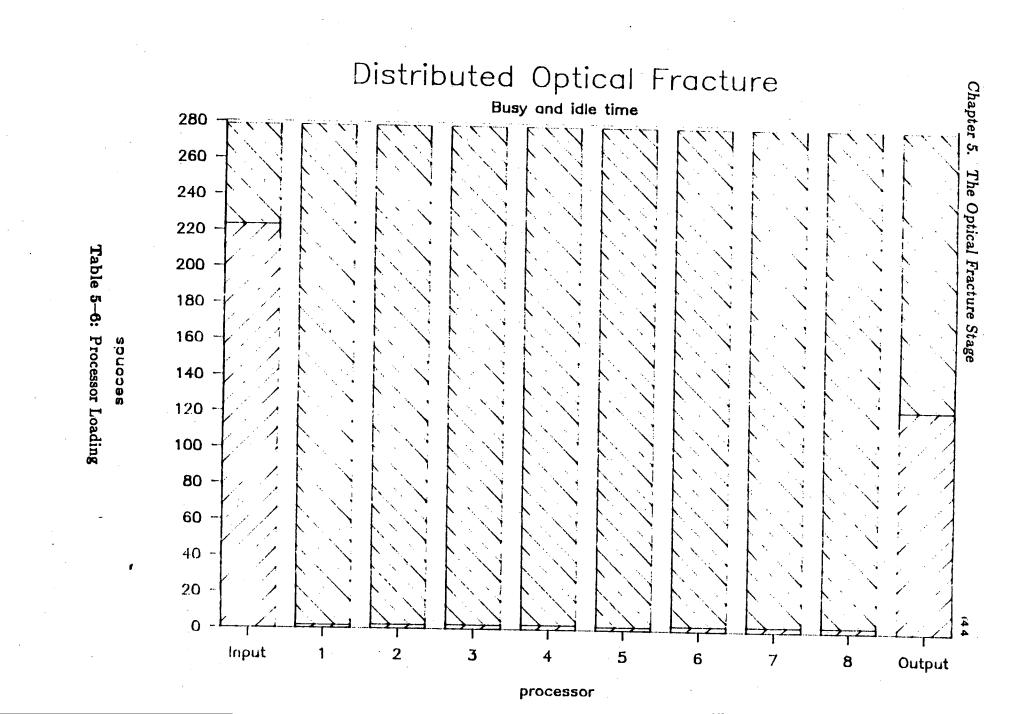

|     |     | 5.3.3   | Load Balance                                | 135          |

|     |     | 5.3.4   | Processor Numbers                           | 135          |

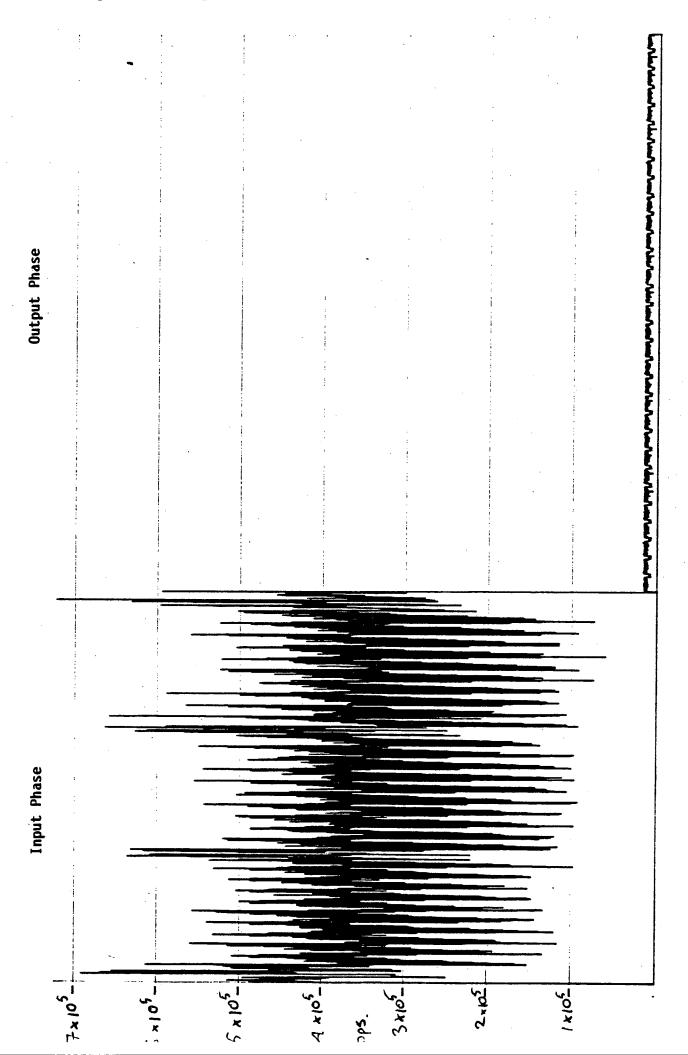

|     |     | 5.3.5   | Emulated Speed                              | 138          |

|     |     | 5.3.6   | Communication Costs                         | 141          |

|     | 5.4 | Conclu  | usions                                      | 142          |

| 6.  | Con | clusion | 18                                          | . <b>4</b> 6 |

| - • |     |         | ag the Bottleneck                           |              |

|     | 6.1 |         |                                             |              |

|     | 6.2 | Archite | ectures                                     | L <b>4</b> 8 |

|     | 6.3 | Furthe  | r Work                                      | 149          |

| Table of Contents |  | 5 |

|-------------------|--|---|

| A. An       | outline of changes made to the Merge code | 151 |

|-------------|-------------------------------------------|-----|

| <b>A.</b> 1 | The Original Code                         | 151 |

| <b>A.2</b>  | New Modules                               | 155 |

|             | A.2.1 The SPLIT Module                    | 155 |

|             | A.2.2 The STITCH Module                   | 157 |

|             | A.2.3 The OUTPUT Module                   | 159 |

| B. Tak      | te Three. Parallel Merge on Real Hardware | 161 |

| B.1         | Implementation                            | 162 |

|             | B.1.1 Background                          | 162 |

|             | B.1.2 Division and Recombination          | 162 |

|             | B.1.3 The Parallel Implementation         | 164 |

| <b>B.2</b>  | Results                                   | 168 |

|             | B.2.1 Vax Cluster                         | 168 |

|             | B.2.2 Diskless Sun Workstations           | 169 |

| ٠           | B.2.3 Final Points                        | 170 |

| Bil         | bliography                                | 172 |

# List of Figures

| 2–1  | Optical P.G. Data                                          | 35 |

|------|------------------------------------------------------------|----|

| 2–2  | Acute angle approximation for optical P.G                  | 36 |

| 2–3  | Flaring                                                    | 37 |

| 2–4  | Raster and Vector Scan Lithography                         | 38 |

| 2–5  | EBeam P.G. Data                                            | 40 |

| 2–6  | Bloating and overlap removal                               | 43 |

| 2-7  | Shrinking and overlap removal                              | 45 |

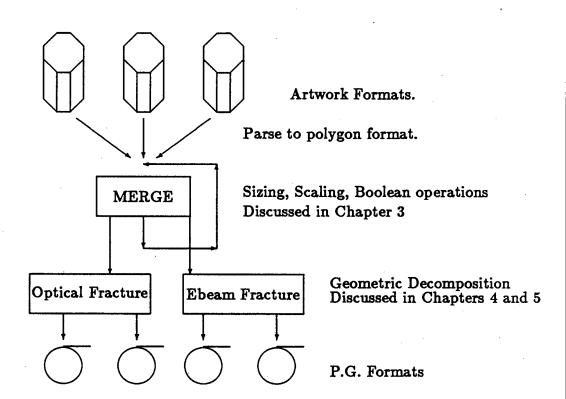

| 2–8  | Overall Architecture of a P.G. System                      | 47 |

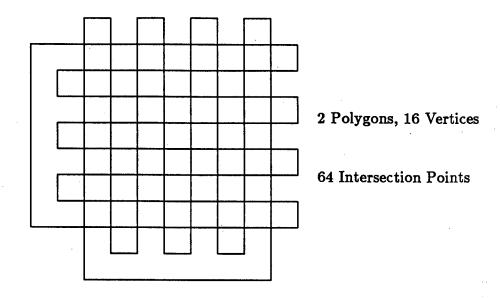

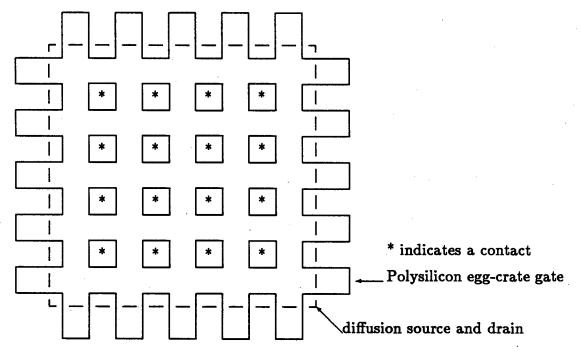

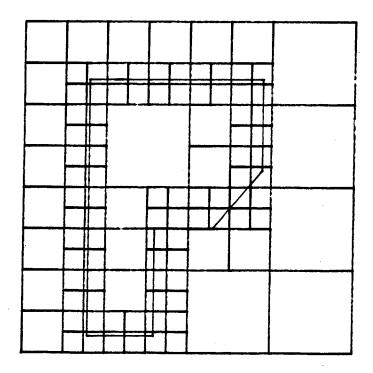

| 3–1  | Egg crates                                                 | 50 |

| 3–2  | Egg crates in Large Gated transistors                      | 51 |

| 3–3  | Quad Tree representation                                   | 53 |

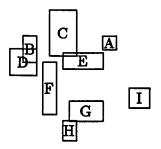

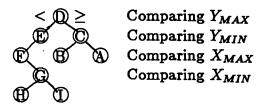

| 3–4  | Four dimensional binary search trees                       | 55 |

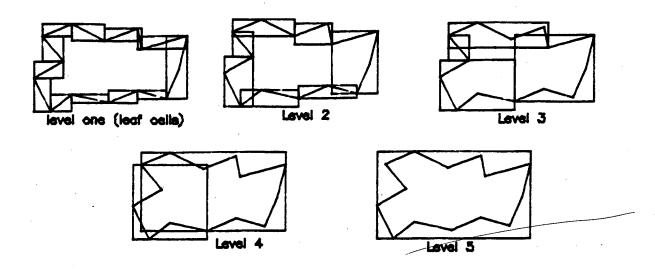

| 3–5  | Hierarchical bounding box representation of a line segment | 56 |

| 3–6  | Dividing two convex polygons into Slabs                    | 57 |

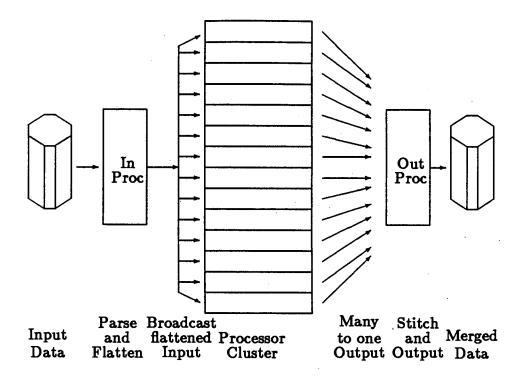

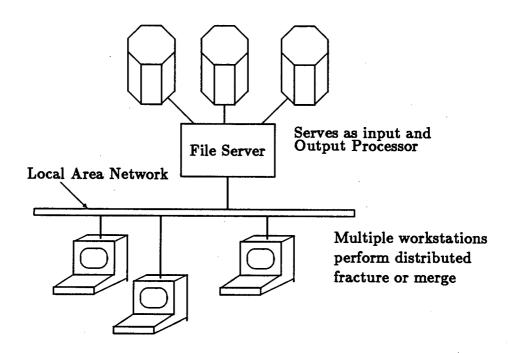

| 3–7  | The Overall System Architecture                            | 66 |

| 3–8  | Pictorial representation of the harness                    | 68 |

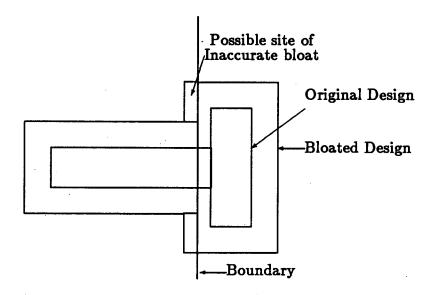

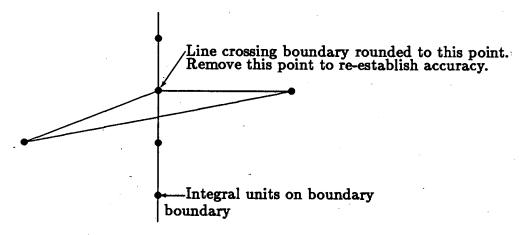

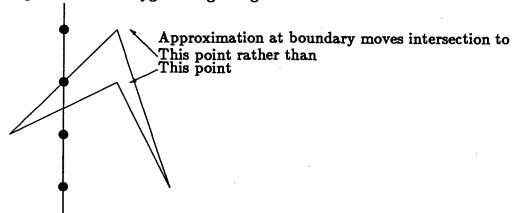

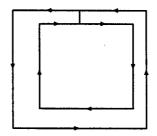

| 3-9  | Incorrect sizing at Boundaries                             | 70 |

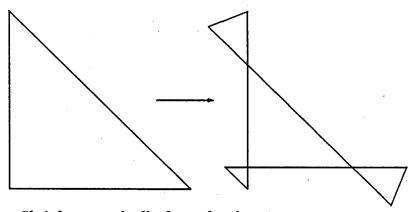

| 3–10 | Triangular differences                                     | 72 |

| List of Figures |   |   | 7 |

|-----------------|---|---|---|

| Tibe of Lighter | · | 4 |   |

|                 |   |   |   |

| 3–11        | Pentagonal differences                                 |

|-------------|--------------------------------------------------------|

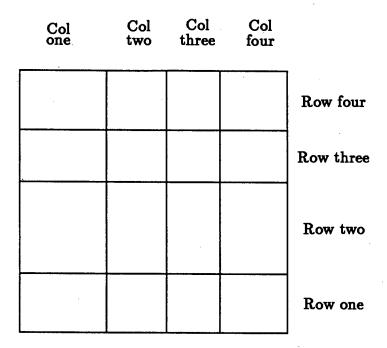

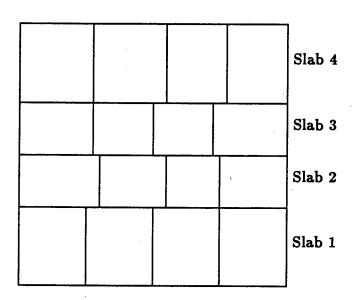

| 3–12        | Division into Y and X                                  |

| 3–13        | Division into Y and then X                             |

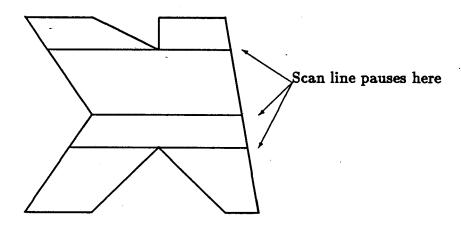

| 4-1         | Outputting trapezia from a Scan Line Algorithm 104     |

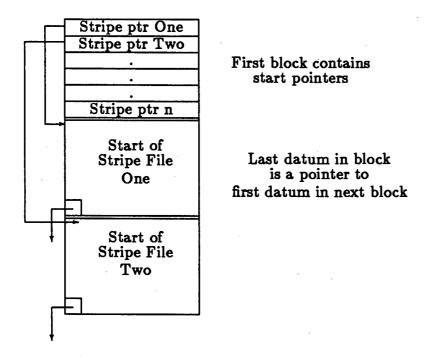

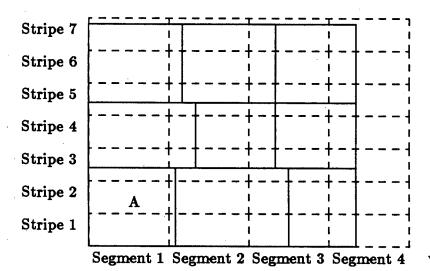

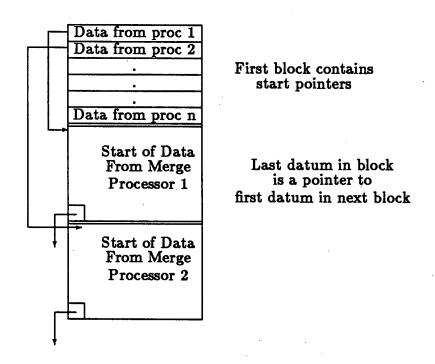

| 4–2         | Logical construction of the EFF files                  |

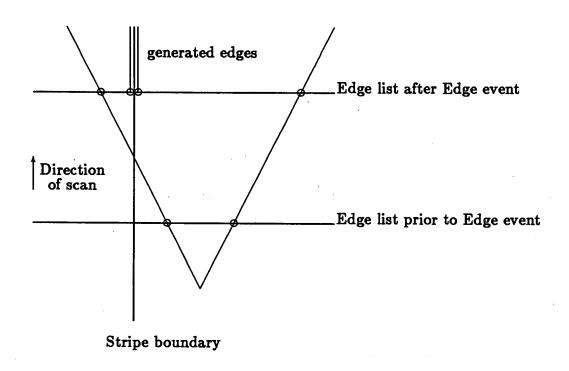

| 4-3         | Edge Event                                             |

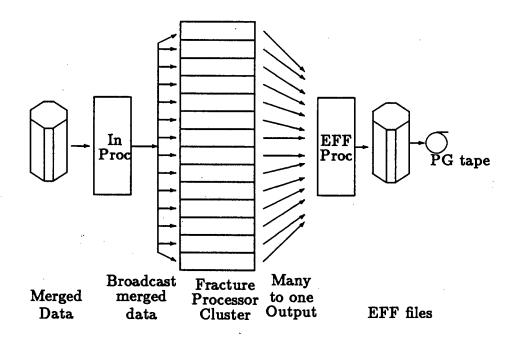

| 4–4         | System architecture of the Parallel Ebeam fracture 109 |

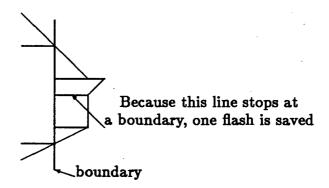

| 4-5         | Amended Algorithm: The reduced trapezia count          |

| 4–6         | Recovering Ullage in EFF Files                         |

| 5–1         | A complicated Polygon                                  |

| 5–2         | A Possible Covering with 265 Flashes                   |

| 5–3         | A Better Covering with 444 Flashes                     |

| 5-4         | System architecture for Parallel Optical Fracture      |

| 55          | The pinhole accuracy problem                           |

| 6–1         | Workstation based Architecture                         |

| <b>A-1</b>  | Self Touching Polygons                                 |

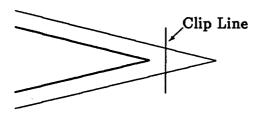

| A-2         | Clipping Acute Angles                                  |

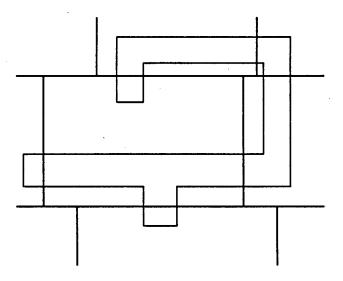

| A-3         | Nasty cases when clipping                              |

| A-4         | Nasty cases when Stitching                             |

| <b>A</b> –5 | Ordered Concurrent Output                              |

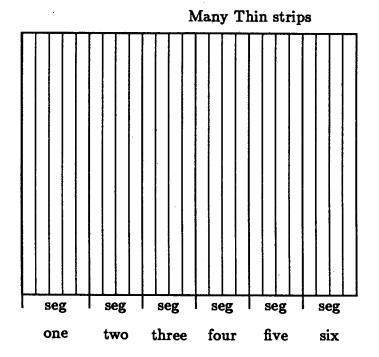

| B-1         | Using thin strips to determine segment width           |

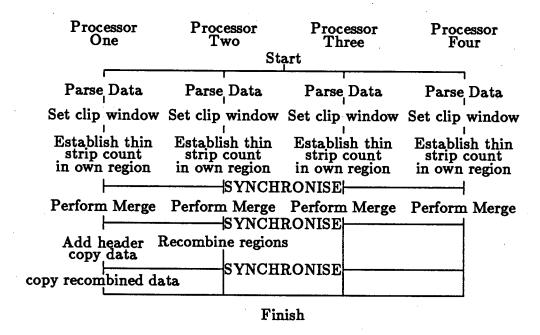

| B-2         | Schematic of Parallel Merge                            |

## List of Tables

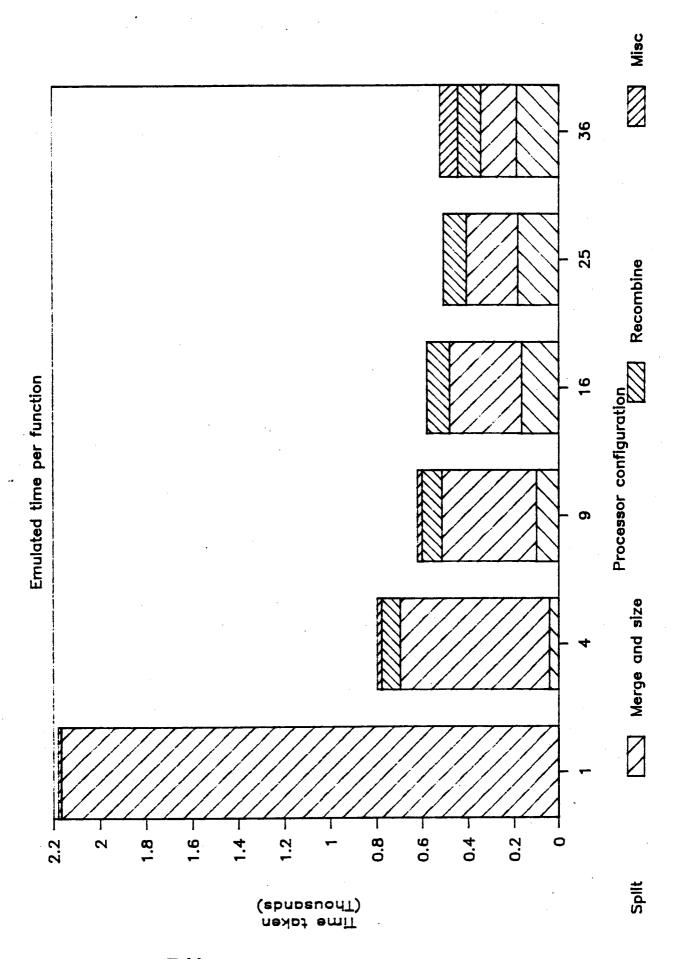

| 3–1  | Emulated Time                                       |

|------|-----------------------------------------------------|

| 3–2  | Emulated Processor Speedup                          |

| 3–3  | Communication Overhead                              |

| 3–4  | Average Bandwidth requirement 83                    |

| 3–5  | Peak Output Bandwidth requirement                   |

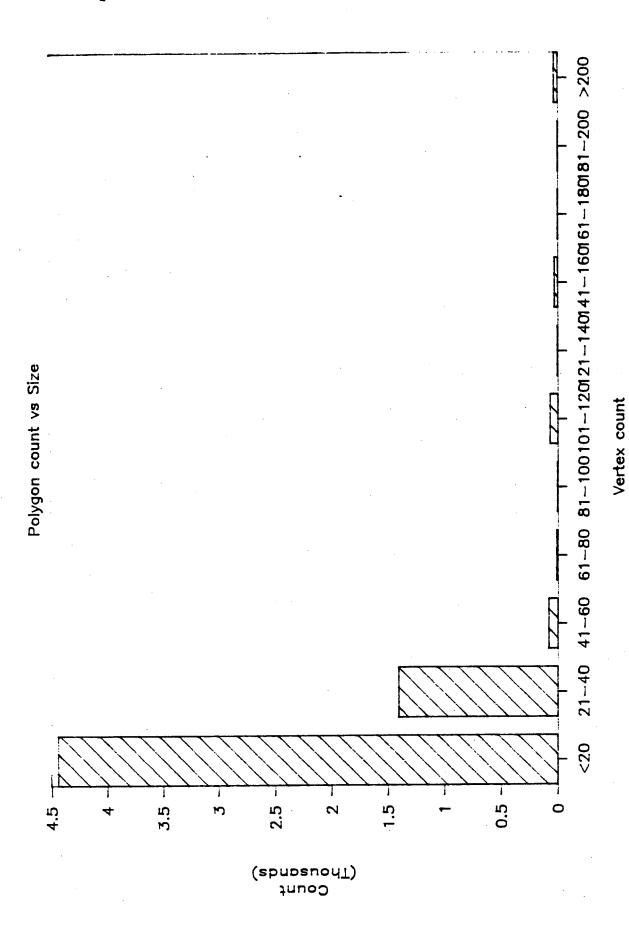

| 3–6  | Distribution of vertex count in merge data          |

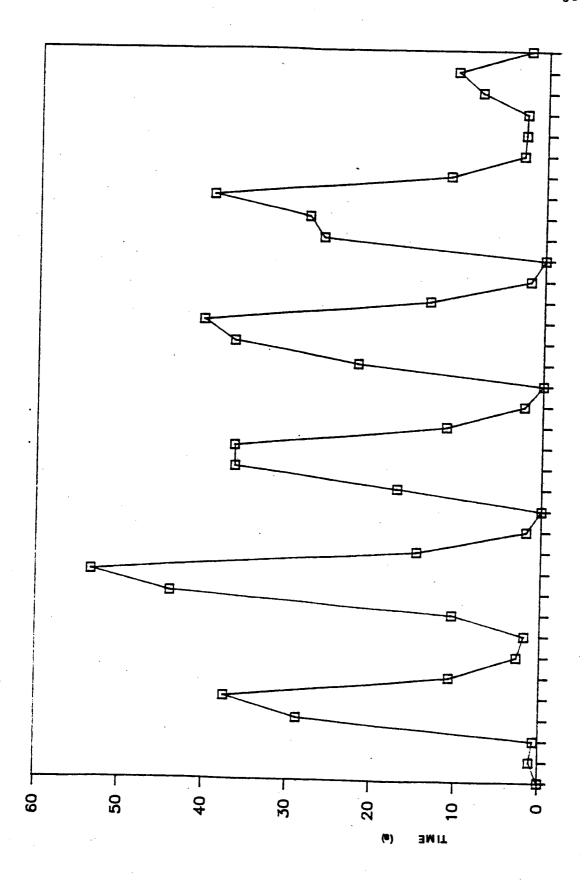

| 3–7  | Timing trend for pure merge, bloat and shrink 93    |

| 3–8  | Function versus Time 94                             |

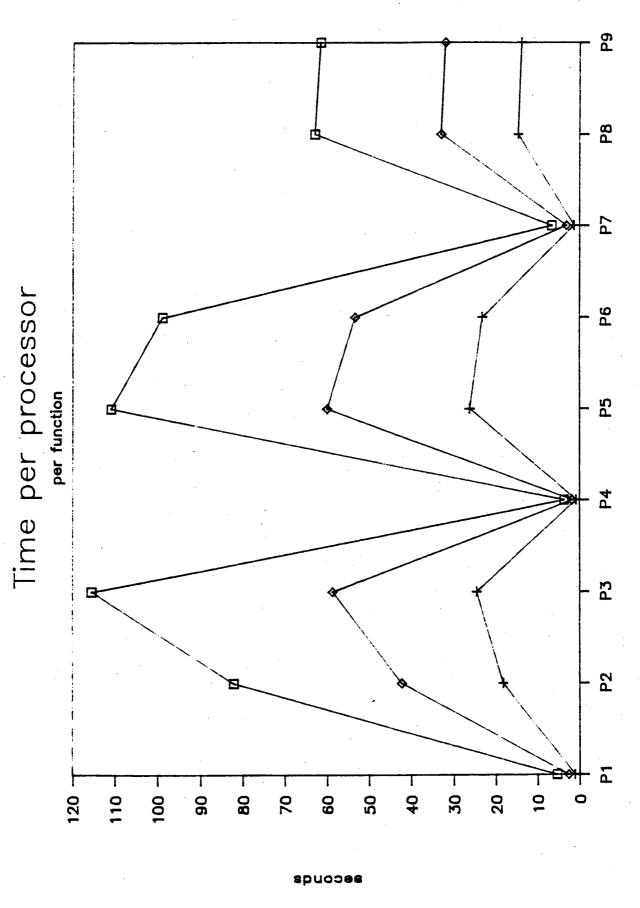

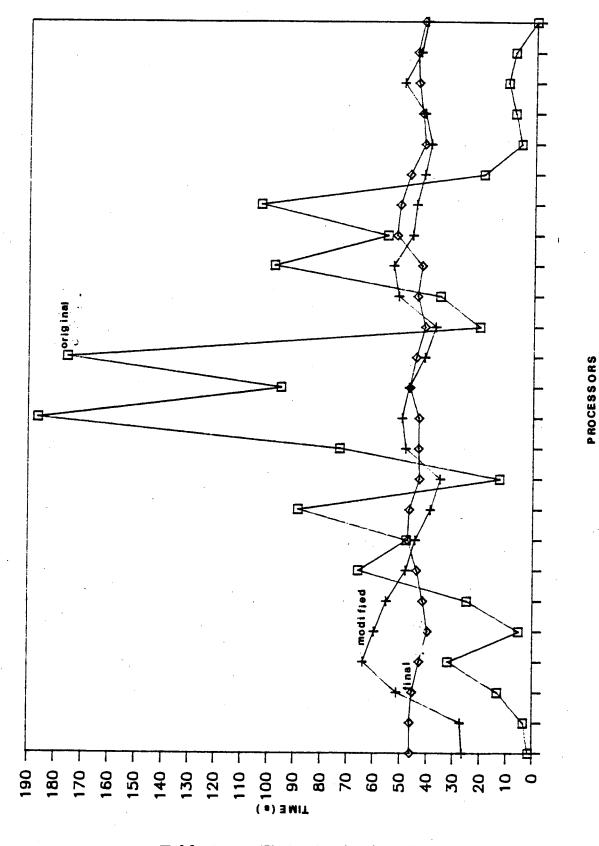

| 3–9  | Time Taken per Processor Merge stage only           |

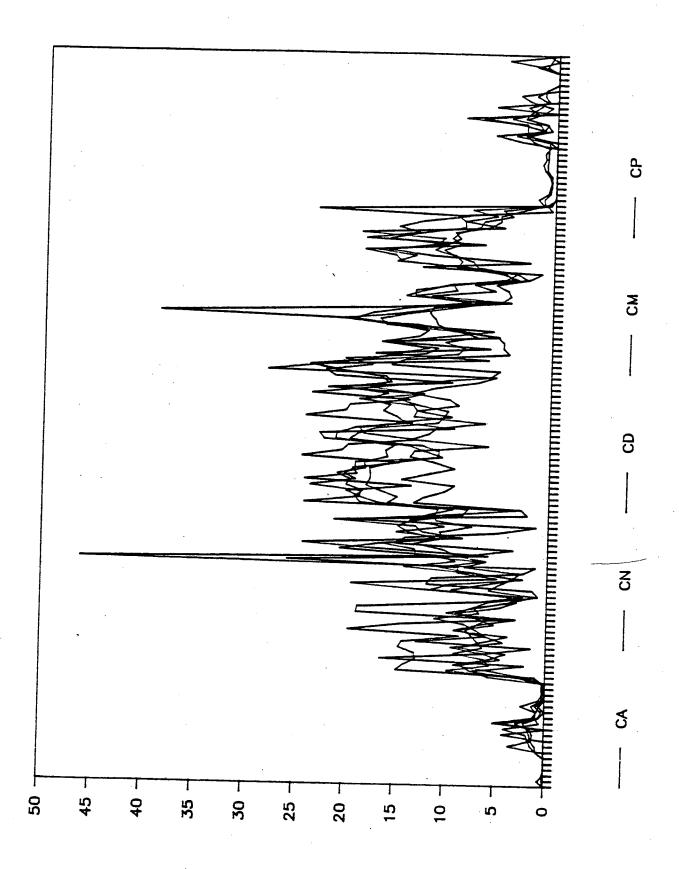

| 3–10 | Vertex Distribution in the X direction              |

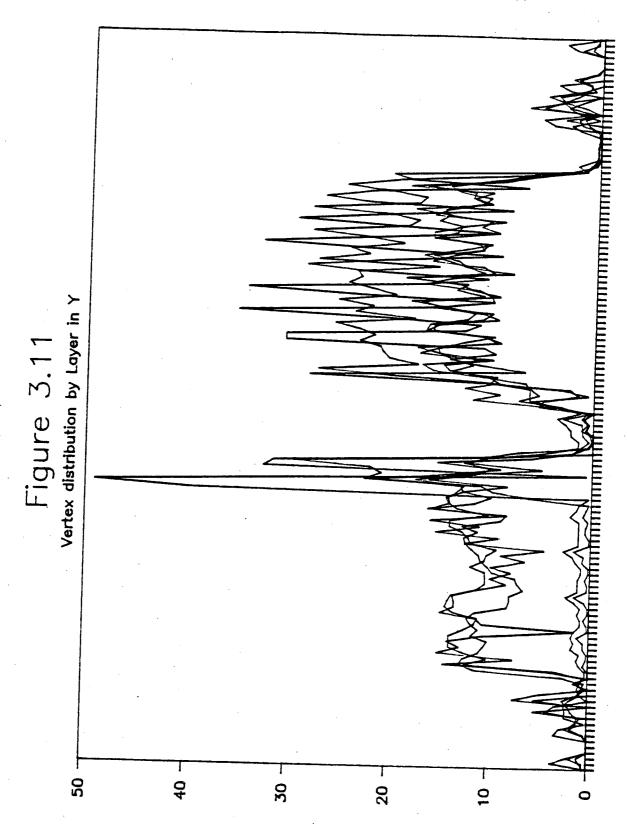

| 3–11 | Vertex Distribution in the Y direction              |

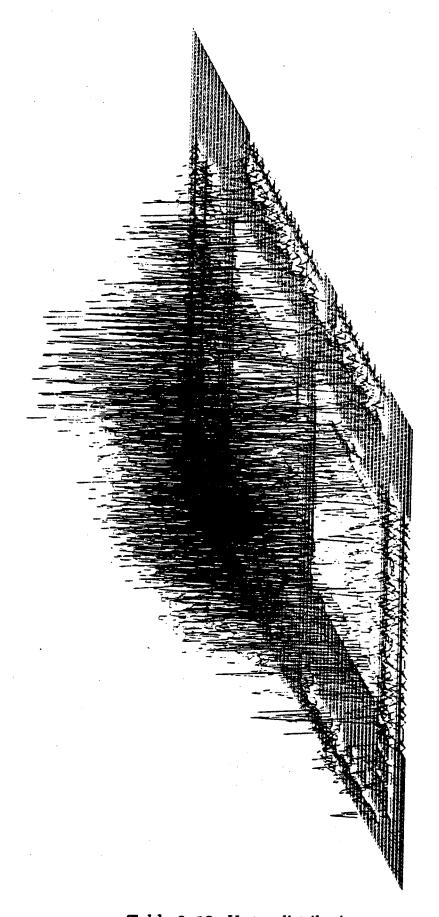

| 3–12 | Vertex distribution over area                       |

| 3–13 | Timing by the three division methods                |

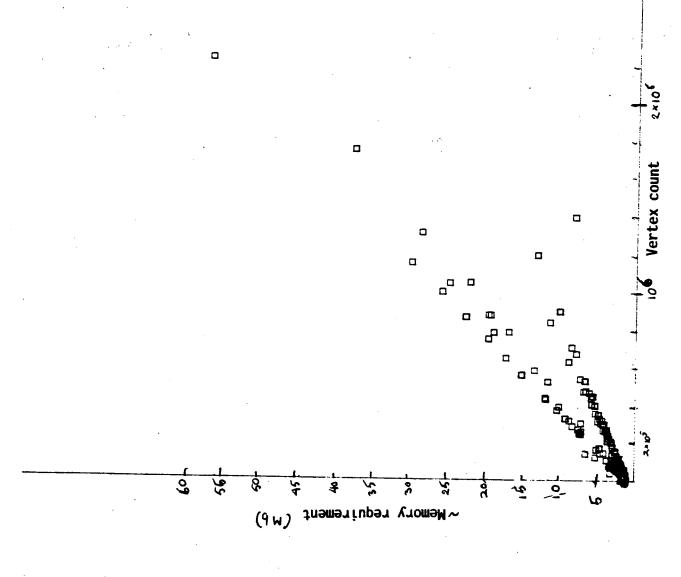

| 3–14 | Memory Requirement vs vertex count                  |

| 3–15 | Communication Costs for merging multiple Layers 101 |

| 4–1  | Time taken by Output processor                      |

| 4–2  | Breakdown of fracture timings for one layer         |

| 4–3  | Ebeam Fracture - Times and speedup                  |

List of Tables

| 4–4 | Ebeam fracture. Average and peak bandwidth                          |

|-----|---------------------------------------------------------------------|

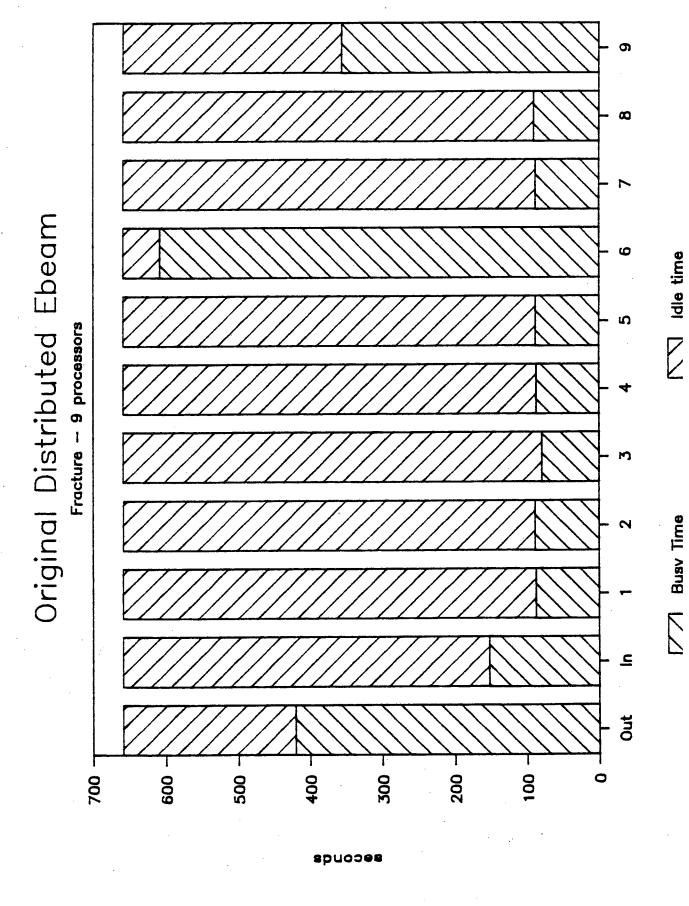

| 4–5 | Original distributed Fracture for 9 processors                      |

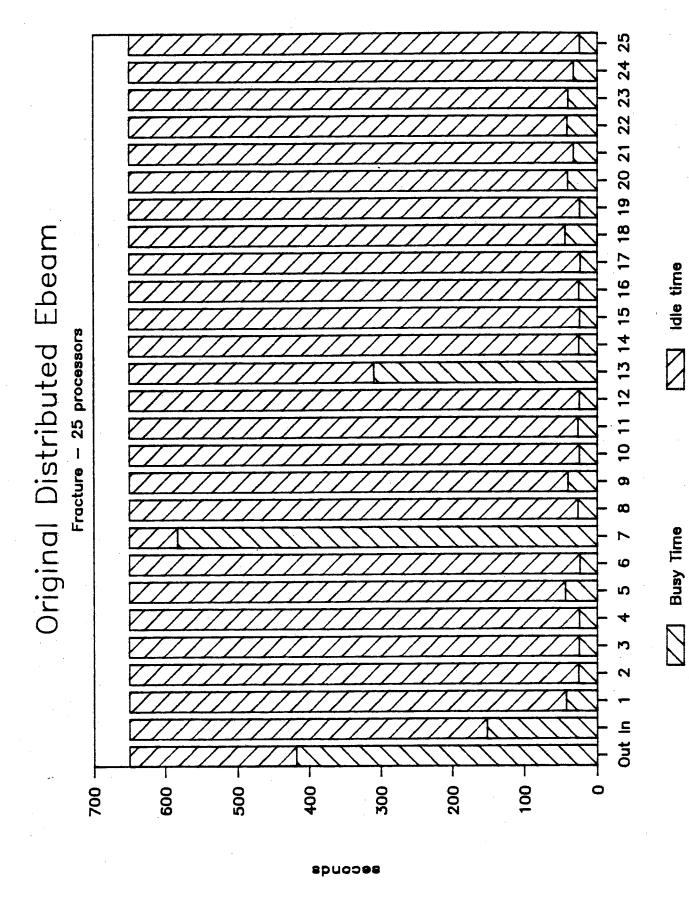

| 4–6 | Original distributed Fracture for 25 processors 123                 |

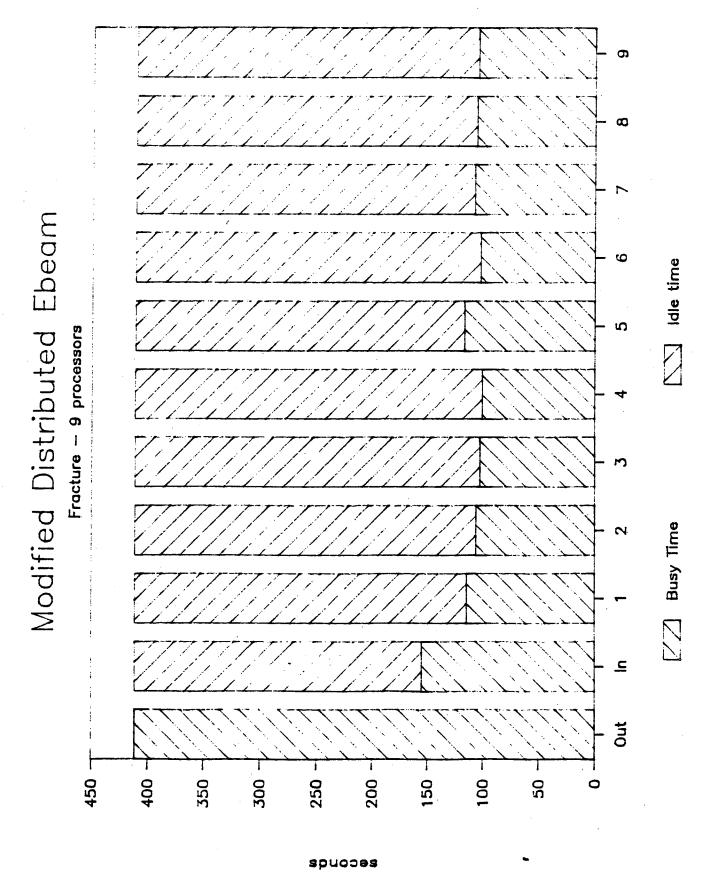

| 4–7 | Amended distributed Fracture for 9 processors 124                   |

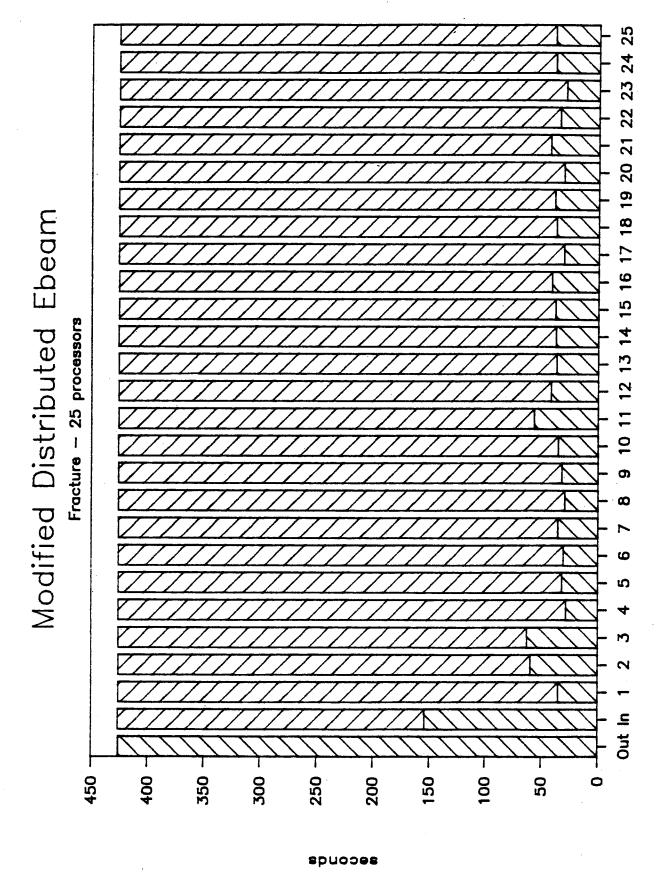

| 4–8 | Amended distributed Fracture for 25 processors                      |

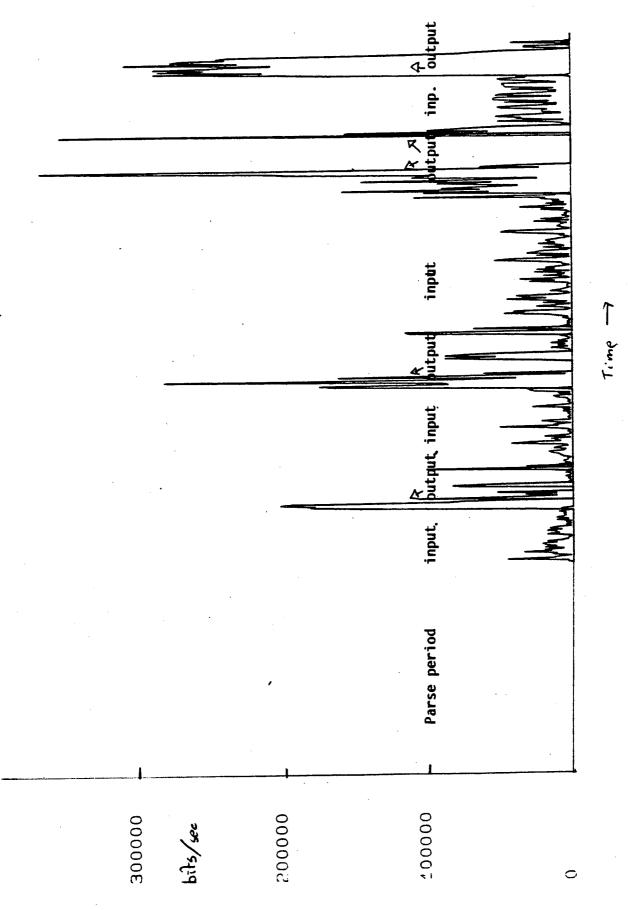

| 4-9 | Ebeam fracture. Data rate over time                                 |

| E 1 | Ontirel fracture. Cost baselous man formation.                      |

| 9-1 | Optical fracture. Cost breakup per function                         |

| 5–2 | Modified Optical fracture. Costs per function                       |

| 5–3 | Emulated time and fractional speed-up                               |

| 5–4 | Emulated time and fractional speed-up. 'Weak' synchronisation . 141 |

| 5–5 | Bandwidth requirements for optical fracture                         |

| 5–6 | Processor Loading                                                   |

| 5–7 | Bandwidth requirement over time                                     |

| B-1 | Actual time taken to process a design on a LAVC 169                 |

| B-2 | Actual time taken to process a design on a cluster of SUNS 170      |

## Chapter 1

### Introduction

As the packing density, size and consequently the shape count of integrated circuits becomes greater, the time taken to do all the data processing associated with generating the designs is increasing. One particular process which is rapidly becoming a bottleneck is the data preparation prior to pattern generation.

Simultaneously the demand for high speed turnaround of IC designs is increasing. Technological improvements have reduced turnaround to the extent that IC design could now be described as an interactive rather than batch process, by analogy to the technological improvements to operating systems which allowed the same transition to happen to programming.

This thesis addresses the problems of improving the performance of pattern generation data preparation through the exploitation of parallelism and discusses the software engineering issues involved in parallelising pattern generation algorithms.

#### 1.1 Making Programs Run Faster

As soon as the earliest computers had been built and demonstrated to work, the race to develop faster machines started. Improvements have been made by speeding parts from the complete range of the system hierarchy of the system, from the lowest level of hardware to the highest level of theoretical algorithmic design. For the purposes of further explanation it is useful to divide this hierarchy into three broad categories. The choice of three categories is arbitrary since the hierarchy of a computer system is continuous and so the actual boundaries between categories are somewhat fluid. The categories are: the basic algorithm, its software implementation and its hardware implementation; each of these is amenable to improvement,

#### 1.1.1 Algorithmic improvement

The algorithmic theorist, when looking for ways to improve systems, develops better algorithms in terms of asymptotic performance - that is the rate at which the algorithm gets slower as the input gets larger. Algorithms are independent of the technology of their implementation and of the computers upon which they run.

Algorithmic improvements are more important than technological ones. Consider for instance a system which requires an unordered set of data to be sorted according to some key. There are many sorting algorithms, but consider just two - insertion sort and merge sort. The time complexities of these are  $O(n^2)$  and  $O(n \log n)$  respectively. The former is a somewhat simpler algorithm and for small input data sizes might be faster. However there is a value for n for which the latter will be faster. This is always the case no matter what the implementation is - there will always be a value for n at which a mergesort running on the slowest hardware with an inefficient implementation in software is faster than an insertion sort on the fastest possible hardware with a 'perfect'

software implementation. Algorithmic development is therefore a vital first step in the speeding up of processing.

In some problems the output of a program may be correct (in some way) but are not the theoretical best or minimum. For instance a program may generate solutions to the travelling salesman problem which are feasible (and effectively usable), but may not guarantee to generate the *minimal* solution. Very often problems whose minimal solution is *NP* complete can be approximated to by use of polynomial algorithms.

#### 1.1.2 Improving the Software Implementation

The software engineer looks for ways to improve system performance by investigating techniques which improve the implementation of the algorithm in software. This ensures that the algorithm and the rest of the software supports for the system are expressed in the best possible form for the subsequent interpretation by the hardware. Software engineering covers that range of the system hierarchy which relates to the expression and interpretation of an algorithm.

At the highest level of implementation the job of the software engineer is somewhat similar to that of the algorithmic theorist; however, the aims may be somewhat different and this is discussed further below. For instance the engineer might seek to improve the implementation by running 'profiling' on the implementation and, having noticed those parts which were exercised most often, making sure that their implementation is as good as possible. These changes could be as simple as the reordering of the evaluation of conditions, or might entail unwinding commonly used procedures 'in line'.

Situated in the hierarchy somewhat below the the engineer interested in individual implementations are those investigating improvements to the means of implementation (and thus many implementations). For instance the compiler engineer might be interested in improving the quality of object code which the compiler generates.

At the lowest level the software engineer might develop the microcode which is the interface between hardware and software.

#### 1.1.3 Improving the Hardware Implementation

The hardware engineer may attempt to speed up a computing system by developing techniques which improve the basic hardware upon which the system is based. Again there is a broad range of options which are open to the hardware engineer. At the highest level there is no real boundary between the work of the software and the hardware engineer. At the lowest level the hardware engineer must be involved with the physics which govern electronics.

The majority of techniques used to speed up hardware use parallelism, these are detailed later, but the following points illustrate some of the options open to the hardware engineer over the hierarchy of hardware.

- increasing the basic clock speed of the hardware. If this is possible it immediately makes the complete system faster.

- Related to the above technique is speeding up the other parts of the system, for instance the mass storage system.

- The majority of programs show some sort of locality of reference. Introduction of cache memories exploits this locality both in the data and the instructions.

#### 1.1.4 Assessing the performance improvement

All the techniques for performance improvements are independent of each other. Thus for instance any improvement achieved by a software engineer is totally orthogonal both to improvements made to any basic algorithm (in as much as this would not affect the software implementation), or other improvements made to the implementation by hardware or software engineers.

In all three cases, algorithmic, software, and hardware improvement, what is being attempted is a reduction of a cost function. The precise cost function differs between algorithmic theorists and those performing the actual implementation. Indeed it may be different between engineers working at separate parts of the design hierarchy. Specifically, in order to be able to argue rigorously, algorithmic theorists deal only in orders of growth, and fixed bounds to these orders of growth. This make is possible to classify the algorithm's behaviour as the input becomes larger and thus look for ways to reduce the asymptotic performance.

In implementation the cost function is both considerably different and rather more general. In speeding up implementation, techniques are normally aimed at making a system run faster for a given size of input, thus improving the absolute performance. Other points which need to be taken into account when examining techniques to improve implementation and hence form part of the total cost function are pragmatic issues such as cost, reliability and supportability.

Thus a theorist may develop an algorithm which is better, since it exhibits a lower order of growth. The software engineer may choose not to implement this algorithm since according to the cost function which the software engineer uses the algorithm is worse. This might be due to the intricacy of the algorithm which makes the absolute performance for small input unacceptable, or perhaps the algorithm is so complex that any implementation would be unmaintainable. Finally since a theoretically minimal solution to a problem may be infeasible computationally a software engineer will trade off 'goodness' of solution against computation time.

#### 1.2 Parallelism

There are many techniques which may be applied at many places across the system design hierarchy. For instance many of the techniques developed to control the complexity of software design are equally applicable to controlling the complexity of Very Large Scale Integrated circuits.

One of the most useful techniques which can be used to increase the performance of computer systems is the harnessing of parallelism. It can be applied across the complete spectrum of the design hierarchy. Actual implementations have met with varying degrees of success. Parallelism may be studied by algorithmic theorists, software engineers and hardware engineers.

#### 1.2.1 Algorithmic parallelism

The computational complexity of parallel systems has been studied in great depth and many very interesting algorithms and architectures have resulted.

When implementing these algorithms there is a fundamental problem, which springs from the fact that the cost functions used to analyse concurrent algorithms differ considerably from those used by engineers. Typically theoretic measurements of complexity are based on a measure not only of asymptotic time performance, but also hardware complexity. Time is open ended - thus it is reasonable to talk of asymptotic time performance. Hardware, however, is not and so any algorithm which assumes an open ended amount of hardware must have a limit on its size of input.

Thus although Batcher's bitonic sorting algorithm [BDHM84] has time complexity  $O(\log^2 n)$ , the fact that its processor complexity (the rate of growth of the number of processors) is O(n) makes implementation difficult. Assume that a sorting engine was built to use bitonic sorting with k processors. Since the hardware size is fixed, once the input exceeds the limit of k processors the sorting engine ceases to function according to the algorithms and becomes purely a

faster machine and as such can only affect the absolute performance; for small inputs only a fraction of the available processing power is used.

This does not in any way decry the work done on algorithmic parallelism, it merely points out the problems of generally applying something which may appear to be good only within a limited cost function. The insights gained by theoretical analysis are of very great use. However, one of the limitations assumed in this thesis is that hardware is not unlimited. This thesis does not address algorithmic parallelism, it describes some algorithms which run on parallel architectures and achieve an absolute performance increase.

#### 1.2.2 Implementing parallelism

Given the possibility of concurrent hardware, the software and hardware engineer would seek to find methods to improve the absolute performance. The resulting system would have no upper limit on the input size. All data, regardless of size, would be processed faster. The ideal engineering solution is to improve the absolute speed of a parallel system by a factor close to the increase in hardware complexity.

Concurrency has been implemented right across the design hierarchy. The earliest techniques developed for its implementation were aimed at the lowest levels of the design hierarchy. With a few remarkable exceptions, development has been of techniques which are a progression up the design hierarchy, through the hardware hierarchy to the lower levels of the software hierarchy where most research is currently taking place. The reason that the highest level of hierarchy (the theory of algorithms) has already a substantial amount of results is that the cost functions used allow mathematically rigorous argument about parallel systems.

In his stimulating article [Den86] Denning notes the progression up the design hierarchy and divides the development of the implementation of parallelism into four stages. It should be mentioned that, as with all form of artificially im-

posed division, there are some developments which defy classification. However for the most part this classification remains as being very useful.

Stage One is the explicit addition of parallelism to the hardware. This is done in such a way as not to require changes to be made to the users' code.

At the lowest level of the hardware hierarchy, what is being made concurrent is the action of individual gates and transistors. An obvious move is from bit serial to bit parallel processing. This change is more effective than the next 'obvious' move to word parallel processing since the unit of operation in most algorithms is the word, not groups of words.

That bit parallel processing is not used throughout all hardware design is an interesting example of the effect of cost-functions. In many cases, especially when extreme packing density of circuits is desired, the simplicity of bit serial processing makes them favoured over the complexities (and greater size) of bit parallel implementations.

An interesting development of such ideas is the bit serial SIMD machine such as the DAP [HJ81, section 3.3]. Instead of processing words serially and bits in parallel these machines function by processing bits serially and words in parallel. An earlier and somewhat more complex example is the orthogonal computer [Sho70] which allowed dual modes of operation - bit serial word parallel and vice versa. Both these machines are somewhat out of the progression being examined here since programming them requires explicit knowledge of the architecture and their specialised op-codes thus disqualifying them from pure classification under stage one or stage two. This indicates the weakness of the classification.

Another popular technique for enhancing the absolute processing throughput of a computing system is to incorporate various *pipelines* into it. Use of pipelines stems from the observation that very often access to memory is sequential in nature, allowing prediction of where the next access will be. This is especially true for the instruction streams which make up programs. Pipelined instruction execution units work by dividing the handling of instructions into

separate parts, each of which may be dealt with by a separate piece of hardware. Once the instruction has been processed by one piece of hardware, it moves along to the next site in the pipeline and the next instruction can then be processed. Thus several instructions are processed in parallel, although the fixed order of processing is maintained. Parallelism has allowed more processing power to be introduced without making changes to the users' original programs. Most modern CPUs have some level of instruction pipelining.

In a similar manner, pipelining can be applied to the data stream [HJ81, chapter 2], thus introducing parallelism. In practice, the number of applications which can easily and invisibly utilise data pipelined architectures is limited.

The best example of a data-pipelined architecture are the current 'supercomputers' for instance the Cray series machines. Programming these machines need not require explicit and detailed knowledge of the architecture. Vectorising compilers and special purpose run time libraries make use of the vector instructions which utilise the pipelines.

At the highest level of hierarchy which still remains within the bounds of stage one development are the loosely coupled multiprocessors such as the DEC Vax-Cluster[KLS86]. These usually operate in conjunction with a multitasking operating system. Each process is assigned to one processor, either for its 'life' or, rather more flexibly, for one time-slice. The available concurrency is used, not to speed up the execution of one task, but to allow processing of more than one task in parallel. Thus no single task is performed fast, but more processes can be performed in parallel without performance degradation. Again no change needs to be made to the users' code. Such hardware is often the only way, and is currently the most cost-effective way, of increasing processing power of multiuser installations. A useful side effect of this sort of hardware is the added reliability, caused by the inherent redundancy.

Stage Two. In this stage, the parallelism is explicitly introduced into the system at the software level. In terms of the design hierarchy, development

here is at the highest levels of hardware and the lower levels of software, comprising as it does of both software and hardware architecture. The software engineer explicitly divides the system into *processes* which are then assigned to processors. Any inter-processor communication needs to be explicitly handled.

It is in order to ease the handling of such concepts as multiprocessing and interprocessor communication that special purpose languages such as OCCAM have been developed. Although their use is not obligatory, as witnessed by this thesis, they will considerably ease the process of implementation. The drawback with using such languages at present is that they are exceptionally difficult to debug. With traditional languages it is normally very easy to detect when a program has failed. However, as well as the normal methods of failure, parallel languages can also fail due to deadlock whose detection is not trivial. Fairness (equal resource allocation) is another problem which these languages need to address. The further development of such languages will greatly ease further research during this stage.

Another highly significant recent development are the public domain Remote Procedure Call systems. Any (inherently parallel) program written using these to control the parallelism is guaranteed at least a certain amount of portability (being amongst those parallel systems upon which the RPC has been mounted). The wider availability of these systems and their general acceptance will lead the way to 'portable parallelism' just as the development of high level languages paved the way for portable programs.

Currently most target hardware for this stage is relatively coarse grain MIMD [Fly72] with a maximum of a few hundred processing units. Given the restrictions of Amdahl's law (see section 1.2.3) it is difficult to see how any larger system could be effectively programmed, except in a few very special purpose situations. The processing units are all interconnected. A common interconnection is the n-dimensional cubes (as used by the INTEL iPSC, a derivative of the Caltech Cosmic cube [Sei85] and NCUBE/ten [HMS\*86]) although grids and shuffle exchange graphs are possible.

In as much as they may be placed in the classification, SIMD machines such as the aforementioned DAP may be placed in stage two by virtue of their explicit reference to parallelism. However they have not yet proved popular for implementation of stage two developments; this is probably due to the difficulty in envisaging algorithms for them. Most SIMD machines can be classified as belonging either to stage one although there are certain indications that they will play a role in stage three.

The work described in this thesis can be unequivocally placed into the second stage. The concurrency is explicitly described; this is done within the IMP language [Rob86], the parallelism being specified by a technique similar to remote procedure calls. The precise mechanism is described later.

Stage Three. From being explicitly described by the engineer, the parallelism becomes implicit in the language, the compiler and associated software extracts the concurrency from the language. The languages are likely to be non-imperative.

Whereas the second stage is currently the centre of investigation for the low to medium level software engineer, the third stage is currently the outpost of research at the highest levels of software engineering. No particular trend for target architectures for this stage of development has appeared yet; developments include dataflow machines [TBH82] and Logic In Memory machines such as the DAP and the Connection Machine.

Denning [Den86] infers that this stage will supercede stage two. This seems unlikely since it is more probable that each stage will develop techniques which will be, as all other techniques developed across the design hierarchy, orthogonal to each other. Thus any improvement made during stage two will be independent of changes made during stage three - just as the improved hardware developed during stage one can, and is, used as the base-level implementation for machine used in stage two.

Stage Four. Beyond saying that this will consist of

"...very high-level user interfaces capable of interacting with scientists (and engineers) at the same level of abstraction as scientists do with each other ..."

Denning gives no details of how this rather sweeping aim may or will be achieved and it is safe to assume that research in this field is some way off.

#### Current Research into Parallelism

The great boost which research in concurrency has recently received is due to several factors. These have affected the cost functions which in turn have meant that concurrency has become a viable (and indeed a vital) method of developing faster hardware.

- The cost of hardware has reduced significantly while the reliability has

increased markedly. This is in contradistinction to software which is currently the major cost factor in a system while also representing the greatest

source of unreliability.

- Many other implementation levels are approaching their cost-effective limits eg basic device speed. In order to win further performance increases different methods need to be developed to improve system performance.

- The mathematical background which has been developed by the theorists (both semantic and algorithmic) allow better formal reasoning about parallel hardware.

The ILLIAC IV computer of the University of Illinois [Slo67] was well before its time especially in the first two of these factors. The hardware was too expensive for a complete configuration ever to be built and even that which was constructed suffered from unreliability. At the same time faster computers could be built by improving other parts of the system.

There is no doubt that these factors have eased to the extent of allowing huge developments in the field of parallel hardware and it seems likely that the next few years will see the development of even more concurrent architectures.

#### 1.2.3 The pitfalls of parallelism

The pitfalls of parallelism are really just the limitations which parallel implementations have. However they are so fundamental that it is always worthwhile to point them out.

Shore. Having designed the Associative Processor [Sho73], an early logic-inmemory processor, Shore concluded that it was inappropriate for its design use (signal processing) because the processing ratio - the ratio of devices used as memory to those used for processing logic - was too high. He concludes that for systems with a high processing ratio, the chief aim of the software must be to keep the proportion of devices which are meaningfully active as high as possible.

In the light of current developments in VLSI it is dubious whether his conclusion is still valid. It can, however, be extended to apply to parallel systems where the equivalent aim is to keep as many processors as possible active. If, for instance, at any stage in the computation all the processors are waiting for one processor to complete its current task, the processing slows down to the speed of this one processor bottleneck.

Amdahl's Law This states [Amd67] that there is a proportion of processing which is inherently sequential. Amdahl terms this data management housekeeping and states that this takes up about 40% of the time, allowing that it could be reduced to 20%.

Assume that the housekeeping overhead is 20% and that this may be performed on a totally separate processor. Further assume that enough technological development has taken place to speed up the processing of the house-keeping

by a multiple of two. If the rest of the processing is totally parallelised to take effectively zero time, the total improvement can only be by factor of 10. This is obviously a useful speed-up, but is less than might have been expected.

It is only fair to point out that since these two papers were published many limitations which were then apparent have become less restrictive. In the former case, cost of the basic devices which VLSI has brought weakens the argument. In the latter case, many of the slow computations which these systems are designed to speed up have a small proportion of data management housekeeping and so are more amenable to improvement through the introduction of concurrency.

In both cases the restrictions have not been removed, they remain and have only been 'moved back'. The upshot is that these pitfalls remain and are just as deep. Although the immediate possibility of falling into them has been removed, they still remain to trap the over-ambitious and under-wary. For instance Amdahl's law must still hold (see for instance [DLS86, page 48] and several places in the following chapter). Indeed it is still the most critical software engineering issue in program parallelism. Fortunately several of those problems which are targets for being speeded up by parallelism are compute bound to the extent that the data management housekeeping may take up only a very small (say 1% or 2%) of the processing load. These problems are still subject to Amdahl's law and thus a basic speed up of the order of 50 to 100 times might be expected.

#### 1.3 Pattern Generation

Chapter two describes what is involved in performing pattern generation, together with an explanation and justification of each of the stages. What follows is a description of where and when pattern generation occurs in the process of designing VLSI integrated circuits. Once aware of this, it should be possible to define the limitations imposed upon the processing and so infer which level or levels of the implementation can be utilised to improve the performance.

Pattern generation is the final step of data processing which occurs before the physical processing associated with fabrication starts. The output of any integrated circuit design system, be it silicon compiler, gate-array personalisation system or full custom engineers work-station is a representation of the geometry which will exist on the final product (the chip). <sup>1</sup>

The first physical representation of this geometry is the *mask* which is used much as a photographic negative is, to project an image of the geometry onto the chip. *Mask making machines* convert geometric data presented in in the form of a *pattern tape* into physical masks. Their precise method of functioning is described in the next chapter.

For reasons which are fully explained in the next chapter, a considerable amount of processing needs to take place to convert the artwork representation into the pattern tape. This processing is termed pattern generation.

Data preparation for pattern generation is not dissimilar to compilation in that the (normally binary) output must be equivalent to the (often textual) input. Both input and output must be in a fixed form. Pattern generation suffers in a similar manner to compilation in that it incorporates functions which, although difficult to perform, appear easy to humans. In contrast to compilation, in pattern generation most of the high level structures of the input are not directly translatable to any structure in the input. Furthermore it is the norm for pattern generation input to be massive and pattern generation has no techniques which correspond to separate compilation.

<sup>&</sup>lt;sup>1</sup>In fact pattern generation is not limited to integrated circuit pre-processing. A good pattern generation system should be able to handle *any* sort of pattern data - be it for electronic systems (when the product is integrated circuits), optical systems (diffraction gratings) or acoustic systems (surface acoustic wave guides).

#### 1.3.1 The motivation for faster pattern generation

At first inspection, pattern generation is not an obvious candidate for speed enhancement. In sharp distinction to simulation and design rule checking, the traditionally time-consuming parts of the design process, pattern generation should only occur once. In fact it is not unknown for a design to go through many iterations even after the design has been sent to the mask shop.

The major motivation in speeding up pattern generation is not unrelated to Amdahl's argument. Considerable efforts have been and currently are being expended to speed up the design of integrated circuits. Leading the development are the fast prototyping services which will use the direct write devices mentioned in the next chapter. Once one bottleneck is removed it is bound to be replaced by another in a different part. Similarly once various parts of a design process have been speeded up the pattern generation stage will become the bottle-neck. Currently a large design may take several days to process prior to its manufacture as a mask. This is less than the turnaround offered by fast prototyping services. It is obviously essential to reduce the PG processing time so that it ceases to dominate the fabrication and preparation time.

#### 1.3.2 A method of speeding up pattern generation

Pattern generation, then, is a part of the VLSI design process which requires speeding up. In many other parts of VLSI design systems great speedups can be made by taking advantage of the hierarchical nature of the input data (for instance [Whi81]). This has paid great bonuses in very many cases, as well a serving as a good way to control the complexity of the system during its design. Although it may prove possible to make very limited use of hierarchy in future pattern generation systems, dependency upon hierarchy in order to speed up processing is inappropriate for two main reasons:

1. Pattern generation systems need to be able to deal with totally 'flat' input, that is data which has had all the hierarchy removed. Quite often this is the result of a previous attempt at pattern generation, the original data no longer being available.

2. Even were input restricted to hierarchical data, the concept of hierarchy is as varied as design styles. Because of this only the most general assumptions about the form of hierarchy present could be made. This in turn makes the processing considerably more difficult than it needs to be [BOW83].

Thus the chosen pattern generation system needs to be able to work upon totally flat data. It seems expedient to develop special purpose hardware to perform the process of pattern generation. In view of the amount of research currently being carried out in the field, a 'stage two' approach was decided upon. There are of course many alternative methods of speed improvement including the design of a special purpose piece of hardware. This would involve a higher cost than parallel machines (as well as being outwith the training of the author). In addition a parallel machine might prove useful in other regions of the design system. Given the plethora of different machines available it seemed pointless to develop a system targeted at any one hardware system. Rather it was decided to try to develop techniques which would allow pattern generation systems to run fast on a range of parallel MIMD hardware platforms. It was hoped that the applicability of such techniques might prove to be wider than just pattern generation processing.

Thus, in default of a single target architecture, the research and implementation were carried out in terms of broad restrictions which should encompass the greatest possible number of target architectures.

#### 1.3.3 Restrictions upon pattern generation processing

The first stage in doing any development of any techniques must be finding the limitations and factors which control development of pattern generation systems. Having found them the overall implementation techniques could be broadly formulated.

A fundamental restraint upon PG systems is the possible size of input data. This is where pattern generation sharply diverges from the closely related field of graphical image processing. In image processing it is possible to consider both pixel parallel (shape serial) and shape parallel (pixel serial) processing [Kil85] since the resultant image is considerably smaller than that involved in image generation - A graphical image is unlikely to be larger than 4k by 4k pixels or have no more than a few thousand objects to be shown. The equivalent representations of a state of the art design would be > 40k pixels and have millions of objects. Of course a graphical image needs to be processed considerably more quickly than an integrated circuit.

Accuracy is critical to pattern generation systems in that the output should be as precise an image of the input as possible. All rounding (which needs to be done since mask making machines have fixed accuracy which is often much less than the input accuracy) should be performed with the greatest possible care so as to minimise inaccuracy. Internal rounding (rounding which occurs as a result of fixed internal resolution) should be avoided wherever possible.

After accuracy, speed is the most important factor, hence the decision to conduct this research into speeding up the pattern generation process. As previously noted the major constraint on the work in this thesis was that any developed software should be able to run on a wide range of all the existing parallel hardware. This in turn meant that unbounded parallelism could not be assumed since it might not be present in every case, although it is desirable that such parallelism which is present be used fully. Having specified that the amount of available parallelism is limited, it is important to ensure that all individual processors are kept busy.

Given that final choice of machine has been circumvented, it would be precipitate to assume a high communication bandwidth. Furthermore no particular topology for interconnect could be assumed and so any assumed topology must be easily and cheaply implementable. This in turn means that communication must be considered as a restriction.

Finally, the processing units of most concurrent machines do not have unlimited or virtual memory. Any algorithms which run on concurrent hardware should not consume large amounts of memory or at worst they should have controllable memory requirement. Since memory is a cheap resource and (within limits) moderately easy to expand, the actual amount of memory available per processor can be considered to be large (but fixed). Of course, this limitation is not a restriction solely of multiprocessors since several uni-processors have a upper limit of 16 megabytes of user addressable memory.

To summarise, the five major restrictions are that any resulting system should be: accurate as described above, fast, making the best possible use of the available processing power, not overloading any communication system while only requiring a fixed amount of memory in each processing unit.

#### 1.3.4 The Overall techniques used

The general technique used throughout the the generation of the parallel system was to take, where appropriate, an existing sequential system and modify it, substantially in some cases, less so in others, to run on parallel hardware. Since there was possibility of limited amounts of concurrency, fairly course grain parallelism was used throughout. The individual techniques are discussed in the relevant chapters. In each chapter mention is made of the guidance which each limitation gave towards the further development - the solution which serves to meet one limitation goes a long way towards meeting several others.

Speed It is the central supposition of this thesis that any resulting system will be faster than any existing system. By making the best possible use of available processors, the best possible speed up should be achievable. How much performance improvement might be expected for a given increase in hardware size is discussed below.

Accuracy The basic system which served as the foundation for the research is acceptably accurate. It remains to ensure that the additions to the system do not introduce further errors. The fact that the resulting system was a direct derivation of an existing one means that any changes made to the original system in order to enhance accuracy could immediately be incorporated into the parallel system. This of course goes for all the limitations which are no per se limits introduced by parallelism (for instance memory requirement limitation).

Communication As noted above communication is a source of bottle-necks, the importance of the bottle-neck increasing as both the amount of concurrency and the speed of the basic processing units is increased. A good general rule to observe throughout is to reduce to a minimum, and if possible remove, any interprocessor communication. This leaves the sole communication being the distribution of the input data to the processing units and the transmission of the physical output data onto the necessary output media. Furthermore it was decided that whenever there was a choice in pay-off between memory, speed and causing extra communication the first two would be favoured over the latter.

Load balancing This requires that each of the processing units is given the same workload and so will complete at approximately the same time. This in turn requires that some relationship between some measure, applied to the input data, and processing time is established. Having found this measure and the associated relationship, some method must be found to divide up the processing effort equally. The measurement of the input data, the corresponding processing load analysis and data division should be easy to perform or the process of balancing the load will become so time consuming as to be self defeating.

Controlling memory use takes on two forms. Firstly it requires establishing whether the data which is memory resident *needs* to be resident for each processor or whether a different processing philosophy could allow the data to be processed in such a manner that no processor will ever exceed its memory

capability. If this cannot be done an assessment of memory requirement, preferably using the same input measure as used to gauge processing time, can then ensure that no processor ever 'runs out' of memory.

If the method of division and the ways of measurement are kept cheap, in terms of required processing, it is not unreasonable to assume that the speed up achieved is of the same order of magnitude as the increase in complexity of the hardware.

#### 1.4 This Thesis

Having chosen a system in need of temporal performance enhancement, defined the limitations and developed the ground rules for implementing the parallelism, the actual business of speeding up the individual programs could commence. In doing this, the techniques themselves could be developed.

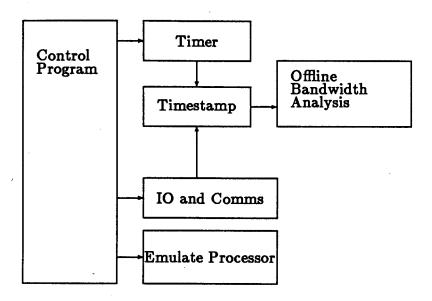

During the development of the parallel system, analysis needed to be carried out to ensure that the actual system would be faster. Other characteristics of the system which needed to be measured were the memory requirements and the communication bandwidth.

In each case the analysis and measurement of the developed system was by an emulation of the parallel system. Given such compiler technology and operating system support for communication as is needed, it would not be hard to make the system run on any real parallel processor.

The precise form which each emulation took is described in the relevant chapter. In general the concurrency was emulated by careful use of timing procedures placed around an iterative loop which simulated each processor in turn. Timing information was taken by associating a 'clock' with each process being emulated. This clock was started and stopped as processing was performed on behalf of each process. Support routines provided such extra information as finding out which processor became free first. Bandwidth was measured by gen-

erating a time-stamp log which could be analysed later. Memory requirements were measured by using calls to functions inherent in the operating system of the emulation computer. Great care had to be taken when communication was emulated, especially when bandwidth measurements were also being taken.

It must be borne in mind that the resulting emulation is of a system with processors which have the same power as the processor which performed the emulation. The bandwidth measurements would of course differ if the processing units were of a different power. This is not seen as a difficulty since what is being presented is a method of achieving speed up by using parallelism not a single parallel system.

In this way a good measure of the performance of the parallel system could be achieved in that if the system was not well behaved according to any of the constraints then the results would show this. However if the system was well behaved, the results could be assumed to be a reflection of a reasonably well performed implementation upon real parallel architecture. For instance although communication was fast in the emulation, a similar rate could be achieved in an implementation by utilising such techniques as double buffering and asynchrony - the results of the bandwidth measurement being low enough to ensure this; any remaining overhead would be mirrored in the emulation as time taken to write the trace file.

#### 1.4.1 Description of the rest of the thesis

The rest of this thesis falls into three parts. Chapter two describes the complete process or pattern generation (both the mask making and associated data preparation) in greater detail and gives some details of how one particular pattern generation system works. This is unfortunately required to motivate and support the next three chapters. Chapters three, four and five describe the actual work which was carried out. They are all of roughly the same form. Where it is appropriate a description of the range of algorithms possible and the chosen 'sequential' algorithm is given. There then follows a description of

the resultant, parallel algorithm, with justification for why it was chosen. Results, both the expected and (in a few cases) the unexpected are then given, and conclusions drawn. For each chapter important results are the maximum number of processors allowed for any stage in the system, this being governed by the input or output bottle-neck and secondly the data bandwidth which this number of processors require. Finally for each chapter there are several loose ends, most of which are the result of hindsight and are indications of the ways in which further research should take place.

The final chapter ties together the preceding chapters and draws some conclusions. There is a description of possible further developments incorporating other facets of implementation improvement. The implications of the developed techniques for applications other than pattern generation are discussed. The implications for architectures are also discussed.

## Chapter 2

# Data Preparation for Pattern Generation

#### 2.1 Mask Making

The function of a mask making machine is to convert a digital representation of the design, the pattern tape, into a physical representation, the mask set. The masks, which are normally copies of a master set, are used during the actual fabrication of the integrated circuit wafer.

Integrated circuit fabrication is a multi-stage operation. At the start of each stage a two dimensional pattern needs to be made upon the wafer surface. This pattern will control whether or not parts of the wafer are exposed to various processes - for instance ion implantation, ion diffusion, or metal or polysilicon deposition. The patterning is achieved by covering the entire wafer with a layer of photo-resist. The mask is brought up to the wafer surface and a light source (visible or u.v.) exposes the wafer. The light affects the resist, either breaking it down to make it soluble, or making it insoluble. In either case the excess resist is removed leaving the desired pattern upon the wafer surface to allow further processing. Integrated circuit design is the function of designing the precise geometry which is desired upon the surface of the wafer and thus the completed chips. It is the job of the mask making machine to generate the mask sets from a suitable representation of this data.

The earliest mask making systems were purely manual. Each layer was check-plotted at a large magnification. The precise image of the design was

hand cut and peeled into rubylith. The rubylith was photo-reduced to generate a reticle (normally a ten times copy) which was further reduced and duplicated in a step and repeat machine to the size required for the master mask.

The hand cutting and peeling of rubylith was very tedious, error prone and time consuming even at small scales of integration. Thus methods of automating the mask making process were introduced. The earliest development was the automation of the cutting process. The rubylith was cut by a device similar (and occasionally identical) to a flatbed plotter. The peeling stage continued to be performed manually - this was still time consuming and even more tedious than before. The way was therefore laid for the development of mask making machines which required very little operator intervention.

Modern mask making machines can be divided into two major types. The earlier, but still popular, photomechanical machines [Hen77], and the more recent electron beam machines. Photomechanical mask makers tend to be less accurate (in the sense of working to lesser tolerances) than electron beam machines; however the additional accuracy of electron beam machines is offset by the reduced cost, both capital and working, of photomechanically generated masks as well as the lessened problems attendant when working with a mature technology. Thus photomechanical mask making machines, although decreasing in popularity are still in the majority [Tra85]. Indeed current developments indicate that photomask making machines will exhibit a longevity which even its proponents would not have originally envisaged.

### 2.1.1 Photo-mechanical mask makers

Photo-mechanical (or optical) mask makers are those which are usually described in text books on VLSI design [MC80, section 4.2] [HS80]. A transparent plate (made usually of glass or quartz) is coated with a photographic emulsion. This plate is mounted onto a table which in turn is sighted below a movable light projection system with a rectangular aperture whose size may be varied. The plate can be moved relative to the light source along the X, Y and rota-

Figure 2-1: Optical P.G. Data

tional axes. In addition both the length and the width of the aperture can be adjusted. These are the five main parameters to the mask making machine; there are others, but these have no impact upon the related data preparation.

The pattern tape for the generation of masks for an optical machine consists of a series of quintuples, controlling the five major parameters. The mask maker functions by reading a tuple, adjusting its settings and then flashing an exposure. Figure 2-1 illustrates typical optical pattern generation data. Once the complete tape has been read, the plate is removed and developed in a similar manner to a photographic negative.

Typically the precision of optical mask makers is less than that required for the final mask<sup>1</sup>. Therefore the plate is often exposed at a ten time scale generating a 10× reticle which needs to be step and repeated to generate the master mask. When generating masks from reticles it is occasionally possible to combine two reticles thus allowing two patterns on the final mask. A combination

<sup>&</sup>lt;sup>1</sup>Typical parameters are: smallest box size (length and width)  $4\mu$ , box size increment  $0.5\mu$ , positional increment  $0.1\mu$ . These figures are those which are accepted by the machine. It is unclear whether they relate to the accuracy or the tolerance of the machine.

of more than two reticles is usually inadvisable due to realignment accuracy problems with the step and repeat machine. As the tolerance and accuracy of newer generations of optical mask makers get better, a trend is developing to generate 1× Reticles which require no photoreduction.

#### Side effects of optical mask-making

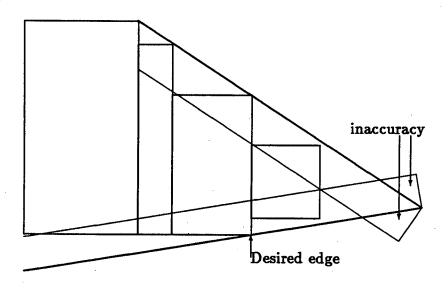

Figure 2-2: Acute angle approximation for optical P.G.

Because optical mask makers can only generate geometry which is made up of rectangles, not every input shape can be generated. In particular geometry containing acute angles cannot be represented and an element of approximation needs to be introduced - see Figure 2-2.

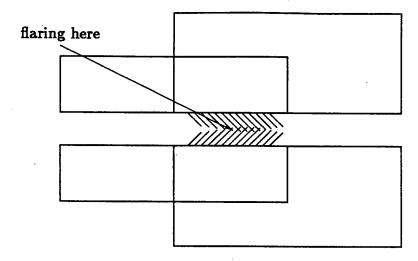

More problematic are *flaring* and *fogging*. It can be assumed that the first time an area of emulsion is exposed a rectangle corresponding to the input parameters is generated on the plate. Subsequent (over)exposures of the same area cause sideways scatter and thus exposure of areas *not* below the flash. The resulting inaccuracy manifests itself into two ways - flaring and fogging.

Figure 2-3: Flaring

Flaring When an edge of (for instance) a wire is flashed multiply, the sideways scatter causes flaring - see Figure 2-3. It is easy to see that this could cause design rule violations and subsequent reduction in yield in the final chips.

Fogging If an area is multiply overexposed scatter into neighbouring non-exposed areas can cause the fogging (partial exposure) of these regions - even if there has been no overlap along any edge. The amount of over-exposure has to be large (the order of tens of flashes not ones). There are cases where overlap can be beneficial since it can reduce flash count.

The speed which an optical mask maker takes to expose a plate is obviously a function of the input size. However the time taken to alter parameters also contributes sizeably. Well ordered data can be flashed at an average rate of 150 flashes per second. Flashing badly ordered data can be as slow as 2 flashes per second.

#### 2.1.2 Electron Beam mask-makers

In electron beam (or *Ebeam*) mask making the plate is exposed by a beam of electrons which may be deflected across the plate. As for graphics displays

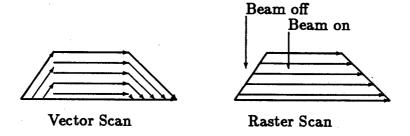

Figure 2-4: Raster and Vector Scan Lithography

which are, to an extent, based upon a similar technology, Ebeam machines may be divided up into up into vector scan and raster scan devices.

Raster Scan Devices are the more numerous type of device. As the pattern tape is read the pattern to be exposed upon the plate is written into a bit-map memory. This is scanned a line at a time; at the same time the electron beam scans across the surface of the design. The pattern in the bit-map controls whether the electron beam is turned on or not and thus where the emulsion is exposed.

Vector Scan Devices do not use a bit-map memory. As each shape is read from the pattern tape it is converted into a series of rasters which the electron beam then describes upon the surface of the plate. The earliest machines were of this type and the very latest machines have this capability. As well as the traditional problems for pattern generation outlined below, vector scan Ebeam machines present the pattern generation systems with the additional problems of dosage calculation due to proximity effect [Cha75] (an effect not dissimilar but unrelated from flaring). The calculations involved are somewhat complex and are not addressed in this thesis.

Figure 2-4 shows how the two types of Ebeam machine would generate a simple shape. Despite the difference in operation, the input formats, both in terms of overall organisation of the data and in terms of the individual data items, for the two types of machine are surprisingly similar. Neither vector scan

nor raster scan machines can expose a complete plate in one operation; rather the area of the plate is divided up into regions termed *stripes* or *tiles* which have to be processed in a fixed order. In raster scan machines the stripes, which are normally wide but short<sup>2</sup> have to be processed starting at the bottom left in increasing y value to form a *segment*. The segments are processed from left to right. In vector scan machines the regions are square<sup>3</sup> and processed in boustrophedonic (serpentine) order.

The pattern tape for Ebeam machines consists of a series of subfiles, one for each stripe. The subfiles have to be organised on the tape in the order in which the stripes will be processed. Each subfile consists of a series of descriptions of trapezia (quadrilaterals with two parallel sides) with the parallel sides being horizontal. Squares and triangles are special cases of trapezia. Figure 2-5 illustrates a typical Ebeam output. Trapezia are chosen since:

- All shapes may be represented as collections of trapezia.

- Trapezia may be easily vectorised.

- They are easily converted into bitmap format (rasterised)

#### Side effects of electron beam mask makers

The methods of functioning both of raster and vector scan machines is such that all data may be represented (to the level of accuracy of the machine) without the need for approximation which was required for optical machines. Although the data is still rounded to the nearest address unit, the levels of

<sup>&</sup>lt;sup>2</sup>Typically 32768 by 512 or 1024 address units. The address unit (a.u.) is the resolution of machine. Typically it is a few tenths of a micron

<sup>&</sup>lt;sup>3</sup>Typically 32768 a.u each side

Figure 2-5: EBeam P.G. Data

representational accuracy achievable by Ebeam machines are still much greater than those offered by optical systems.

Since raster scan machines represent the pattern in a bitmap there is no side effect of overlapping. However vector scan machines still suffer with sideways scatter with the attendant problems of fogging and flaring when an area is multiply exposed.

# 2.1.3 Other Pattern Generation Equipment

Although mask making equipment accounts for the vast majority of pattern generation systems there are other types of equipment which fall within the bounds of pattern generation and should, for the sake of completeness, be mentioned.

#### Direct Write and related devices

Machines of this class circumvent the requirement for masks by actually working on the wafer surface. The vast majority of devices in this class are still at the prototype stage. The motivation behind the development of these systems is to enhance the speed of processing of designs. It seems feasible to assume that direct write on wafer machines will be able to process ten layers in one hour.

This obviously increases the need for faster data preparation. There are two main classes, direct write systems and deposition systems.

Direct Write on Wafer Devices are used in the patterning for any layer during processing. Direct write devices function by using an electron beam to remove resist without the intermediate stages of mask making, exposure and development.

Laser and Plasma Deposition systems obviate the need for resist completely by depositing the upper (metal) layers of a semicustom design directly. In addition some systems can etch away layers (for instance for vias).

Formats and side effects. Systems of both these types are so new that their input formats are not known. However it seems likely that they will be similar to those for Ebeam machines (input based on simple shapes, covering discrete regions). Similarly the restrictions and side effects of these systems are unknown although avoidance of multiple exposure is vital for deposition and direct write systems.

#### Mask Checking Machines

The purpose of a mask checker is to ensure that there has been no error in the mask making process and that the masks reflect the input data. Early mask checkers functioned optically, more recent systems work electronically. As far as data preparation is concerned these are very similar to Ebeam machines, indeed in some cases the same data will drive both the mask maker and the mask checker.

#### Laser Driven Optical Equipment

Another recent development is the raster scan, laser driven optical mask maker [SR87]. This functions in a similar manner to a raster scan Ebeam machine,

but uses light (in the form of a laser) rather than electrons to expose the mask. The similarity of function is mirrored by the fact that these machines take as input format the 'industry standard' formats which are used to drive the Ebeam machines. Thus as far as data preparation is concerned these may be viewed as equivalent to Ebeam machines.

# 2.2 The Function of Data Preparation for P.G.

The ultimate purpose of pattern generation data preparation is to generate a pattern tape. The input is usually data expressed in an artwork format although P.G. format input is not unknown. P.G. data is that which forms the input to a mask maker<sup>4</sup>. Artwork data is the result of a design system. P.G. formats are rather more restricted than artwork formats in the following ways:

- As discussed earlier the shapes representable by a mask maker, and thus by a P.G. format, are limited. Artwork formats normally allow general polygons, boxes and wires (the last two being special cases of polygons).

- Artwork formats allow hierarchy. P.G. formats are completely flat.

- In P.G. formats the layers which will make up the individual masks need to be specified in order in their entirety. Artwork formats allow shapes to be specified on any layer at any time.

- Data which is an artefact of the design system and which will not cause geometry to appear on the masks. Examples include nodes, stretch points and text.

<sup>&</sup>lt;sup>4</sup>The term 'P.G. data' is often taken to mean data for optical machines only. In this thesis it refers to data for all types of pattern generation equipment discussed above.

To summarise, artwork formats reflect the ways that design systems and designers think and work, P.G. formats reflect the way in which mask makers function.

Pattern generation data preparation must perform the conversion from an artwork format to a P.G. format. In doing so it must take into account the side effects of the mask maker. In addition it may need to perform other operations which are the result of side effects of both the design style and the fabrication process. Functions which it should fulfil over and above the conversion include:

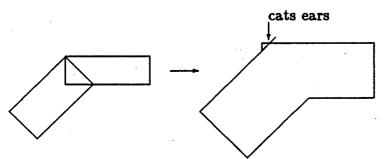

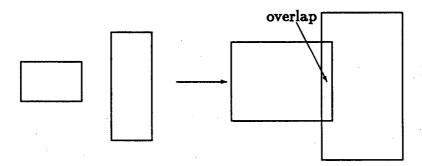

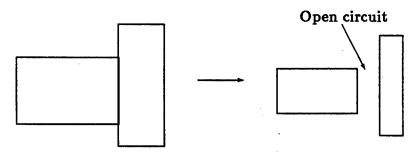

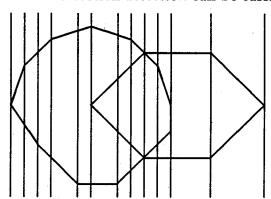

Overlap Removal. This ensures that there is no fogging or flaring during the mask making process. If the overlap removal is achieved by joining together all overlapping and abutting shapes into polygons it makes the sizing considerably simpler.

Pre-bloat overlap removal avoids cats ears

Overlap removal needed after bloating

Figure 2-6: Bloating and overlap removal

Sizing. Very often the fabrication techniques are such that the pattern made upon the plate should be larger or smaller than specified by the designer. This sizing is achieved by moving each edge by an absolute value in a normal direction. Thus the pattern (or field) becomes larger (respectively smaller) in that it covers a greater (respectively lesser) proportion of the area of the design. Performing of sizing is the most important function of P.G. data preparation systems. Both positive sizing (bloating) and negative sizing (shrinking) need to be carried out in conjunction with overlap removal. In fact as Figures 2-6 and 2-7 show, overlap removal needs to be performed both before and after sizing. When sizing angles, the apex will move by more than the amount of sizing. It is often useful to clip angles to reduce this effect. See for instance [BB80] or [Kil82].