# A Novel Test Structure to Monitor Electromigration

M.RAVINDRA

Ph.D. Thesis

Edinburgh Microfabrication Facility Department of Electrical Engineering University of Edinburgh Edinburgh 1992

#### Abstract

Electromigration continues to be one of the important failure mechanisms limiting the attainment of higher levels of reliability in sub-micron geometry VLSI circuits. Successful management of electromigration in future requires adoption of effective statistical process control techniques, in addition to the traditional quality control tests and inspections. The aim of this project was to develop a test structure and test methodology to monitor electromigration for metallisation process control.

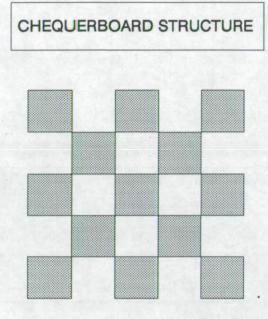

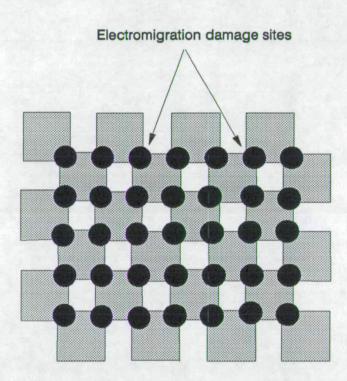

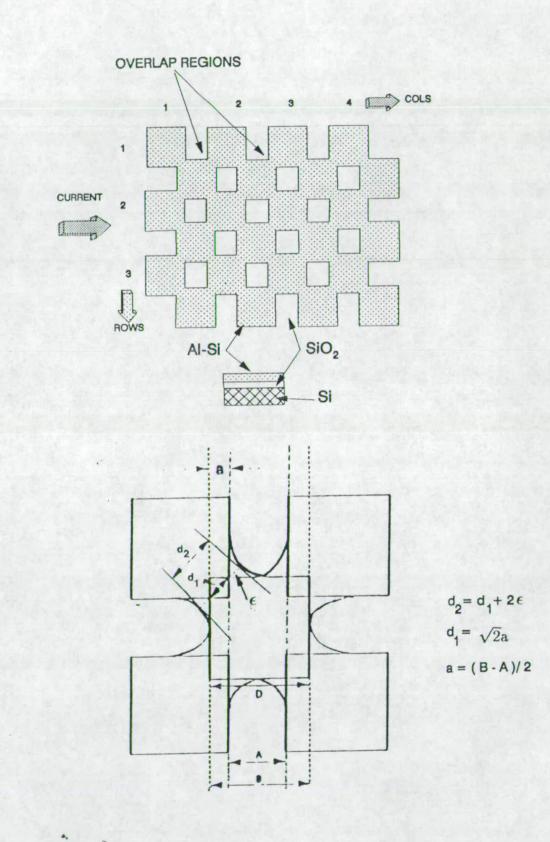

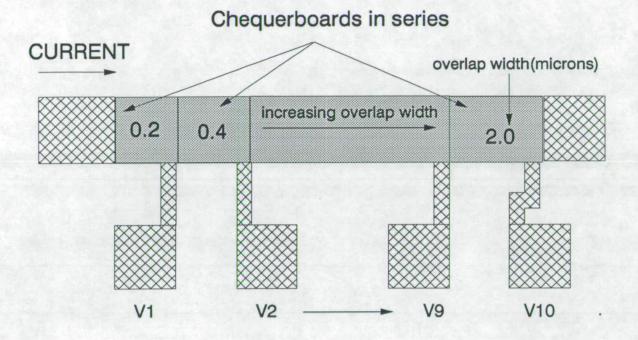

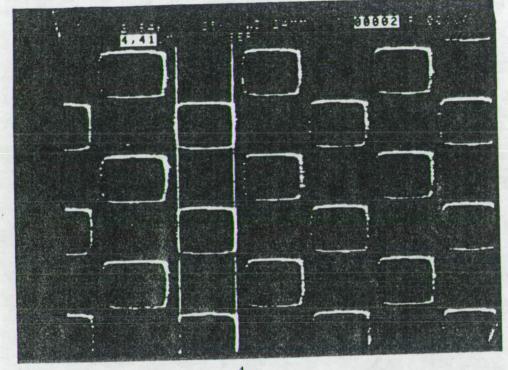

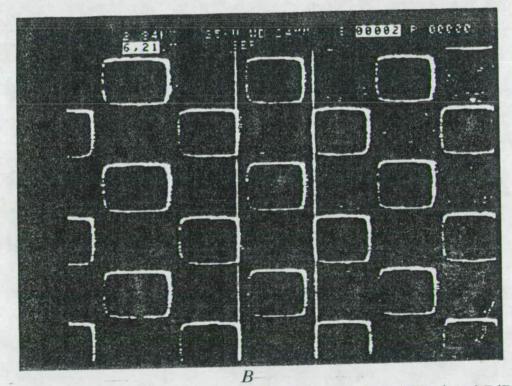

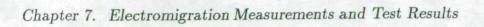

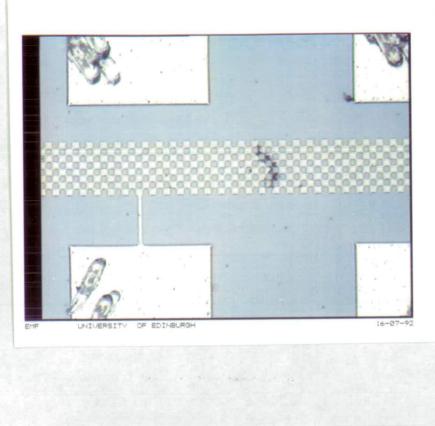

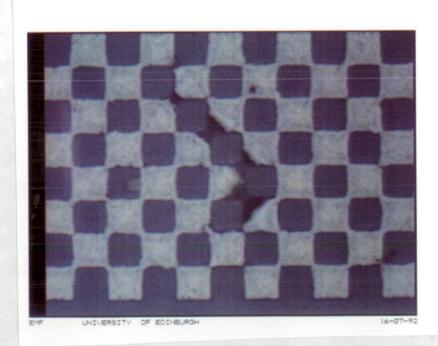

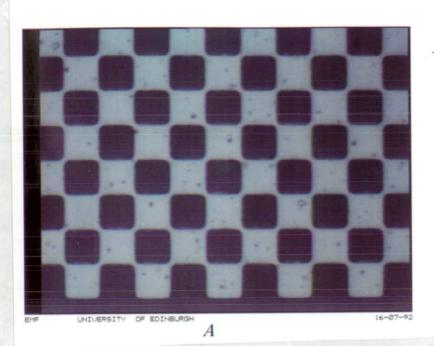

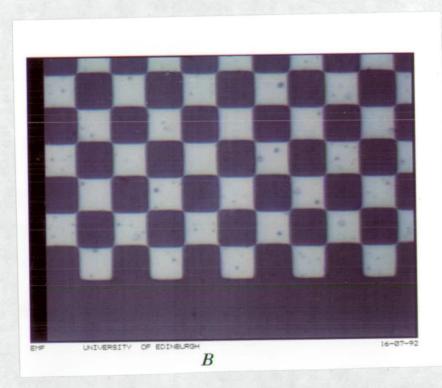

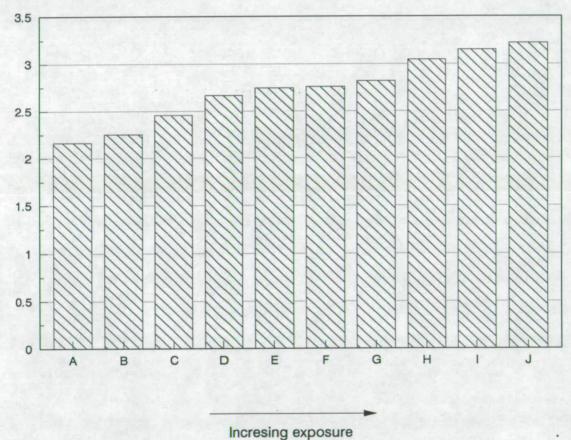

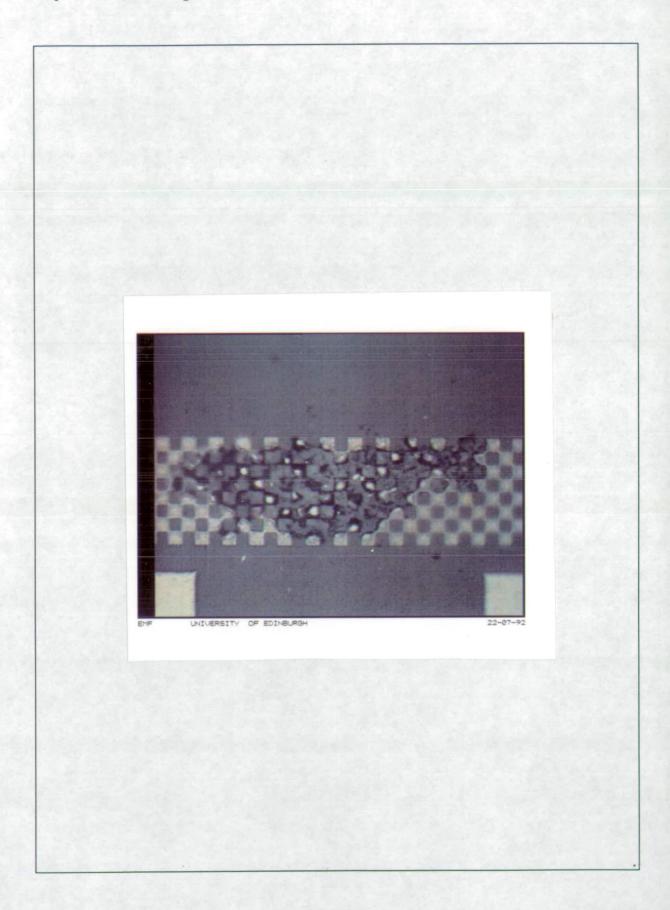

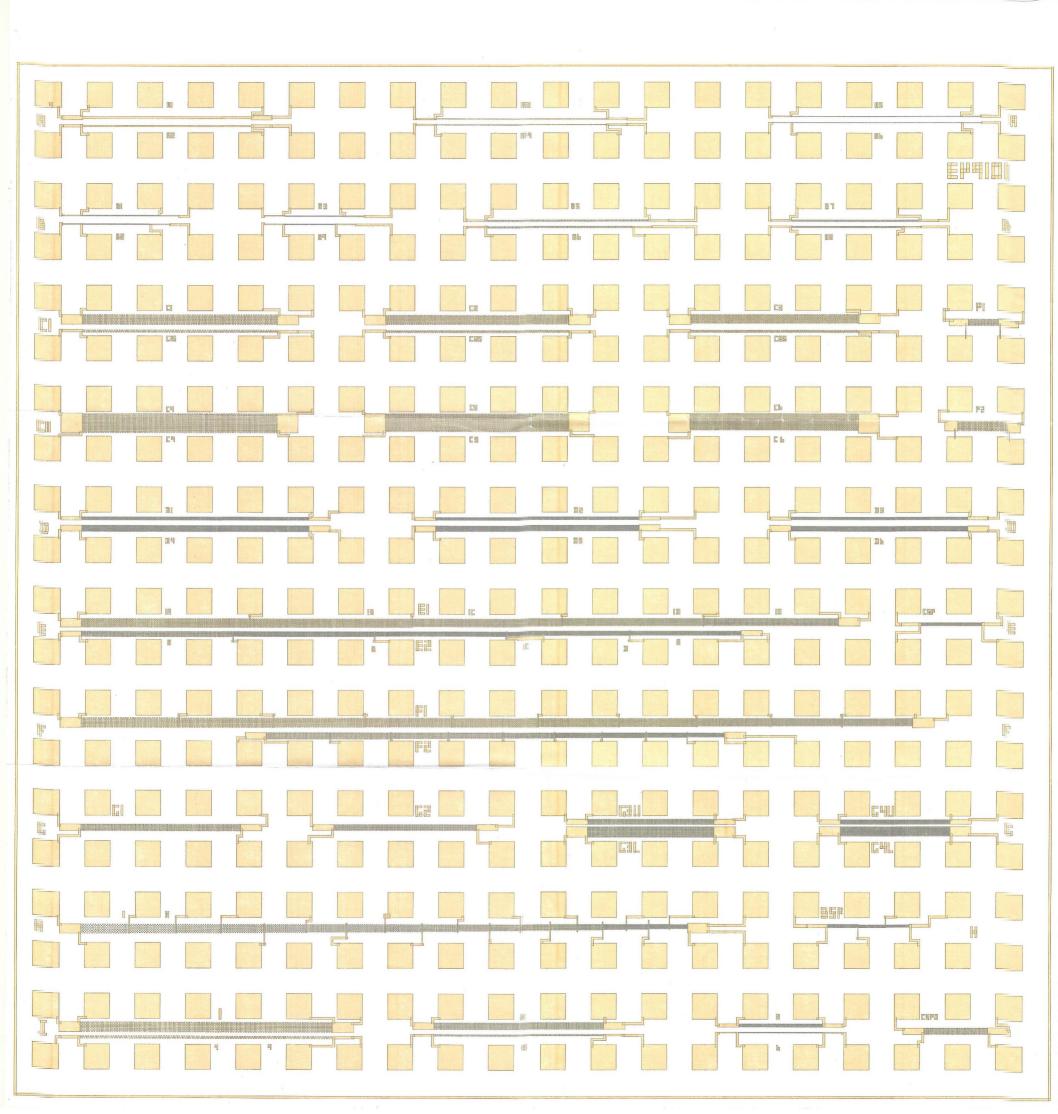

Based on analysis and some preliminary measurements on chequerboards, a new test structure and methodology was proposed to monitor electromigration. 'Chequerboards' are dense patterns of clear and opaque squares of metal film over silicon.

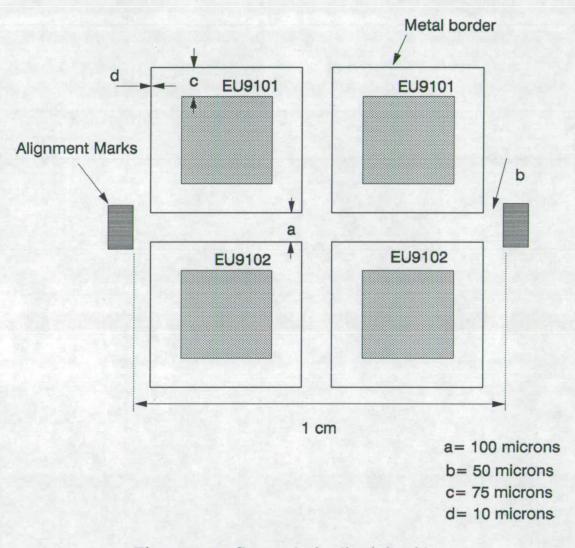

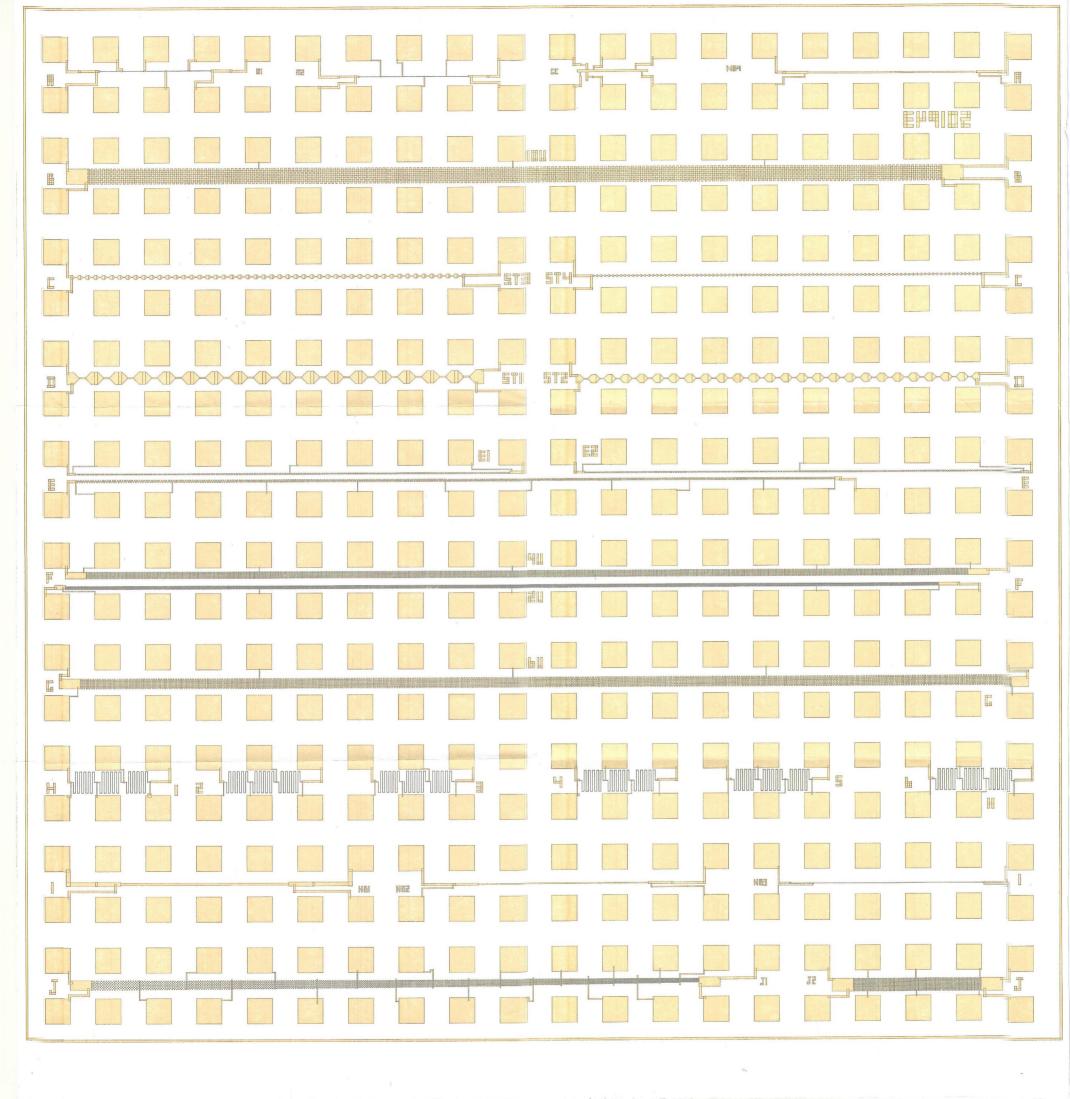

As part of this study, an electromigration test chip was designed. It consists of two designs: The design EU9101 mainly contains chequerboards while EU9102 contains conventional and other electromigration test structures for comparative assessment. The chip design, fabrication and measurement details including the instrumentation aspects are also given in the thesis.

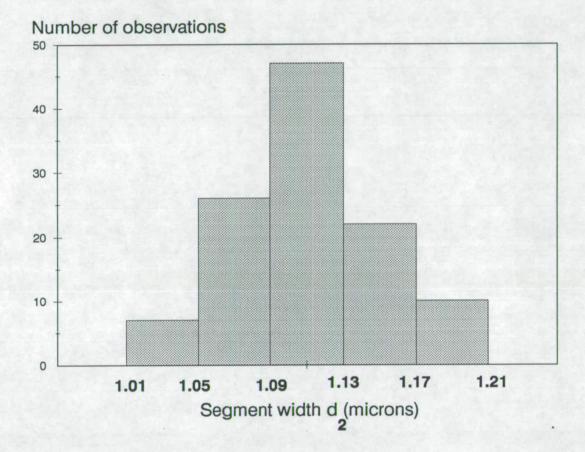

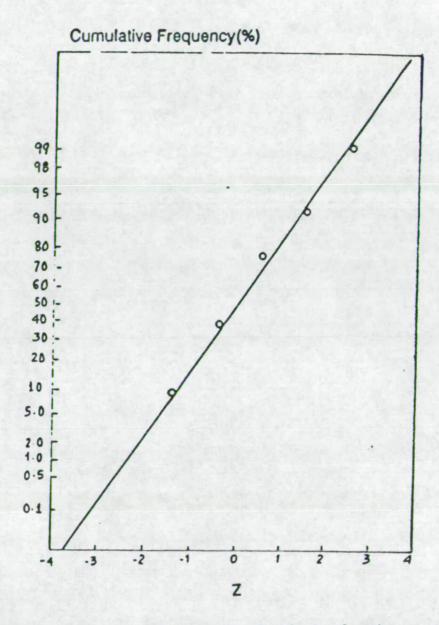

One of the key process parameters, namely, linewidth is chosen to demonstrate the sensitivity of the proposed methodology to monitor electromigration. Possible applications of the new structure in electromigration measurements, other than process monitoring are also discussed. The thesis also contains a review of the electromigration measurement techniques, some measurements using the conventional test structure and a detailed discussion on the limits of conventional tests.

### DECLARATION

I declare that the thesis has been composed by myself and that, except where stated otherwise, the work presented is my own.

M.RAVINDRA

TO MY PARENTS.

### Acknowledgements

I am very grateful to my supervisor, Professor John M.Robertson, for his very valuable guidance throughout the research work, his help and advice during my stay in Scotland and above all for providing a very good training in scientific analysis and reporting.

I thank my second supervisor, Dr.Les Haworth for his useful comments on the many reports written during the initial stages of the project and also for his help and advice. I would like to express my deep gratitude to Dr. Robert J.Holwill for critically reviewing the thesis and offering many useful suggestions. I am also grateful to Mr.Alan M.Gundlach for the advice on fabrication matters and, to Messers Alec Ruthven, Mike Fairgrieve, Brian Neilson, Dave Hope and J.D.M. Fraser for their technical and general help. I would like to thank Dr.A.J.Walton, Mr.W.Gammie, Mr.Z.Chen and all the EMF staff for their assistance and also I thank my friends Raymond Bienek, Anthony Chester, Nicos Porfiris, Robin Smith, Godfrey Gaston, John Thom, Robbie Hannah and Stewart Robertson for their cooperation and support.

I am very grateful to my parent organisation, the Indian Space Research Organisation for sanctioning the necessary leave and to the commonwealth commission in the U.K. for awarding the scholarship. Finally, I would like to thank all my family members for the continued encouragement throughout my research work. I thank my wife for typing the thesis and providing the necessary moral support.

| 1. | Inti | oduction 1                                                 |

|----|------|------------------------------------------------------------|

|    | 1.1  | Technology Trends                                          |

|    |      | 1.1.1 Level of Integration                                 |

|    |      | 1.1.2 Minimum Linewidth                                    |

|    |      | 1.1.3 Reliability Levels                                   |

|    |      | 1.1.4 Reliability Improvement Approaches                   |

|    | 1.2  | Scaling Trends and Wear-out Problems with VLSI circuits 10 |

|    | 1.3  | Electromigration Monitoring Requirements                   |

|    | 1.4  | Aim of the Project                                         |

|    |      | Bibliography 16                                            |

| 2. | Elec | tromigration and Metallisation Reliability 18              |

|    | 2.1  | Background                                                 |

|    |      |                                                            |

|    | 2.2  | Theory of Electromigration                                 |

|    |      | 2.2.1 Bulk Metals                                          |

|    |      | 2.2.2 Thin Films 21                                        |

|    | 2.3  | Factors Affecting Electromigration in Thin films           |

|    |      | 2.3.1 Composition of Metal                                 |

|    |      | 2.3.2 Linewidth                                            |

|    |      | 2.3.3 Linelength                                           |

|    |      | 2.3.4 Microstructure                                       |

|    |      | 2.3.5 Under and Over Layers                                |

|    |      | 2.3.6 Other Factors                                        |

|    | 2.4  | Failure Models                                             |

|    |      | 2.4.1 Black's Equation for MTF 30                          |

|    | 2.5 | VLSI circuit reliability simulation models                  | 35 |

|----|-----|-------------------------------------------------------------|----|

|    |     | 2.5.1 Motivation for Reliability Simulation                 | 35 |

|    |     | 2.5.2 Reliability Simulators for Electromigration           | 36 |

|    |     | Bibliography                                                | 38 |

|    |     |                                                             |    |

| 3. | Rev | view of Measurement Techniques                              | 42 |

|    | 3.1 | Introduction                                                | 42 |

|    | 3.2 | Accelerated Testing                                         | 43 |

|    | 3.3 | MTF Measurement                                             | 44 |

|    |     | 3.3.1 MTF Measurements on EMF Metallisation                 | 44 |

|    |     | 3.3.2 Test Results and Discussion                           | 47 |

|    | 3.4 | Resistometry                                                | 52 |

|    |     | 3.4.1 Resistometry Types                                    | 53 |

|    |     | 3.4.2 Problems with Resistometry                            | 55 |

|    | 3.5 | Fast Tests                                                  | 57 |

|    | 3.6 | Mass Transport Measurement                                  | 59 |

|    |     | Bibliography                                                | 60 |

|    | 1   |                                                             |    |

| 4. | Lim | its of Conventional Tests                                   | 64 |

|    | 4.1 | Introduction                                                | 64 |

|    | 4.2 | Process Capability                                          | 65 |

|    | 4.3 | Linewidth Control                                           | 65 |

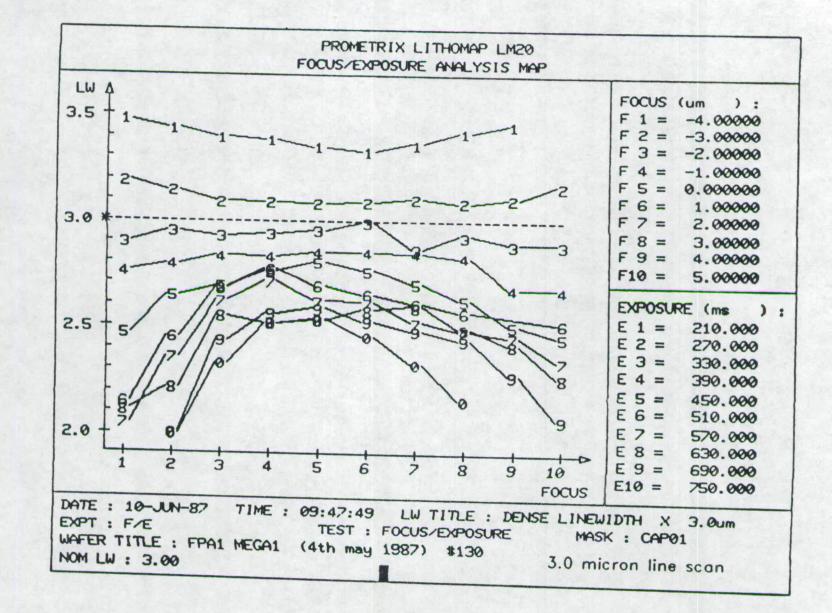

|    |     | 4.3.1 Factors Affecting Linewidth Control                   | 65 |

|    |     | 4.3.2 Linewidth Measurements                                | 68 |

|    | 4.4 | Conventional MTF tests and metallisation process monitoring | 72 |

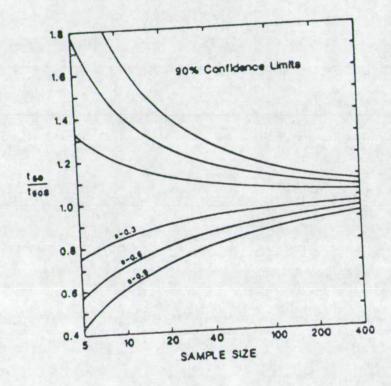

|    |     | 4.4.1 Sample Size                                        | 72  |

|----|-----|----------------------------------------------------------|-----|

|    |     | 4.4.2 MTF and Process Capability                         | 73  |

|    | 4.5 | Chapter Conclusions                                      | 75  |

|    |     | Bibliography                                             | 76  |

| 5. | Son | ne Studies on Chequerboards                              | 78  |

|    | 5.1 | Background                                               | 78  |

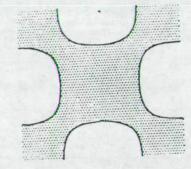

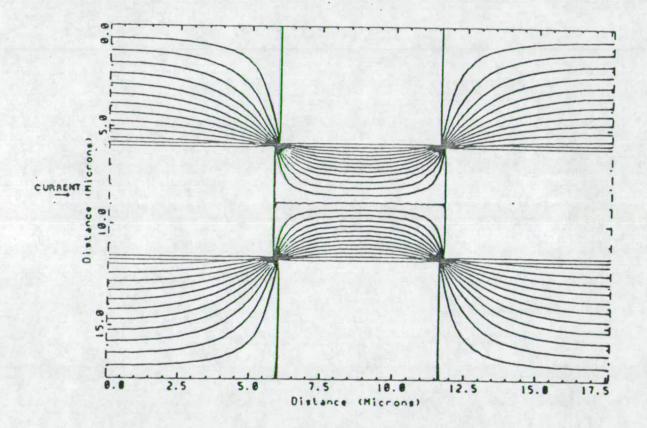

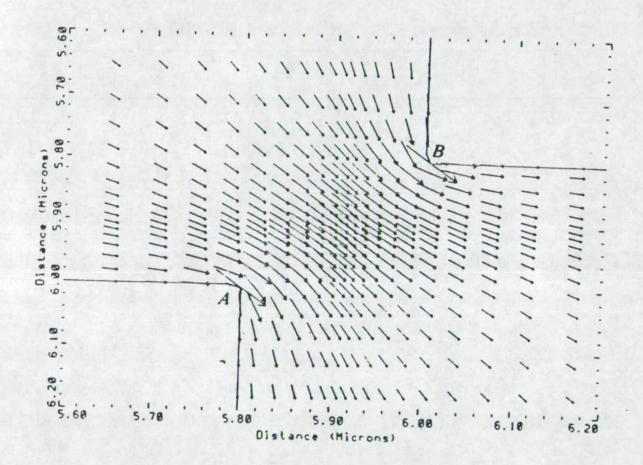

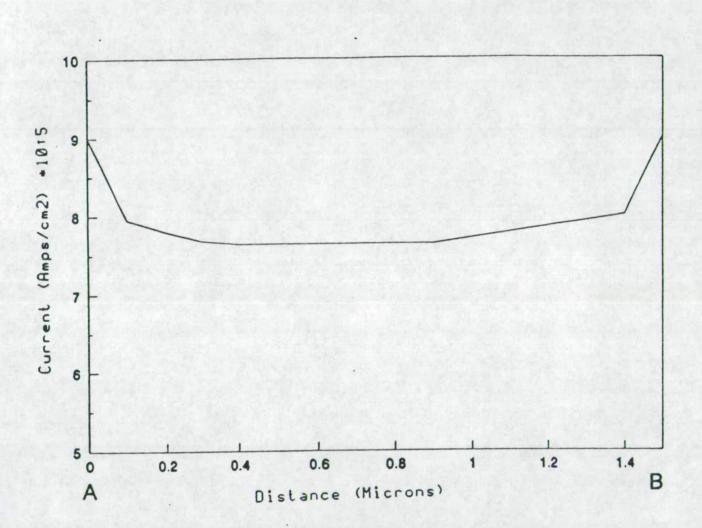

|    | 5.2 | Current-density Simulations of Chequerboard Structures   | 82  |

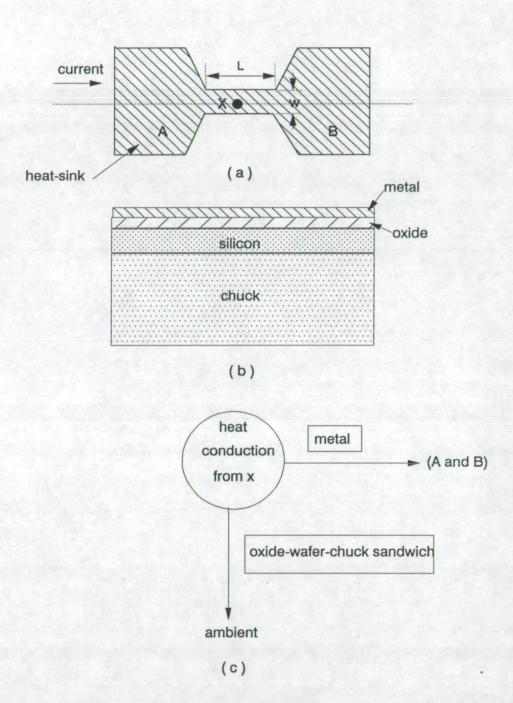

|    | 5.3 | Heat Dissipation in Chequerboards                        | 82  |

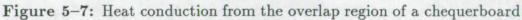

|    | 5.4 | Thermal Measurements                                     | 88  |

|    |     | 5.4.1 Temperature Coefficient of Resistance Measurements | 89  |

|    |     | 5.4.2 Integrity Tests                                    | 90  |

|    | 5.5 | Electromigration Model for Chequerboard Structures       | 92  |

|    | 5.6 | RRF Model and Chequerboard Structures                    | 97  |

|    |     | 5.6.1 Extraction of Parameters m and n                   | 97  |

|    | 5.7 | Chapter Conclusions                                      | 98  |

|    |     | Bibliography                                             | 100 |

| 6. | Chi | p Layout and Fabrication                                 | 102 |

|    | 6.1 | Introduction                                             | 102 |

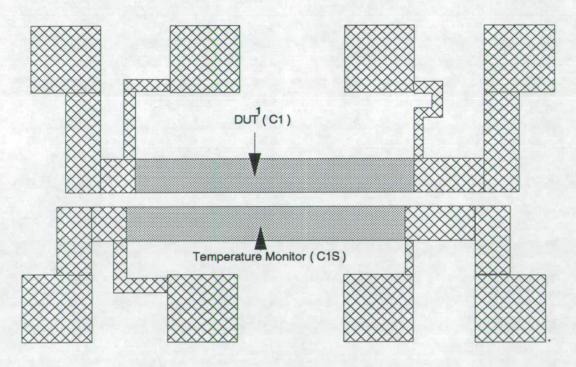

|    | 6.2 | Chip Layout                                              | 103 |

|    |     | 6.2.1 Chip Design                                        | 103 |

|    |     | 6.2.2 Test Structure Types and Their Purpose             | 105 |

|    | 6.3 | Fabrication                                              | 114 |

|    |     | 6.3.1 Starting Material                                  | 114 |

|   |      | 6.3.2   | Oxidation                                   |

|---|------|---------|---------------------------------------------|

|   |      | 6.3.3   | Aluminium Sputtering                        |

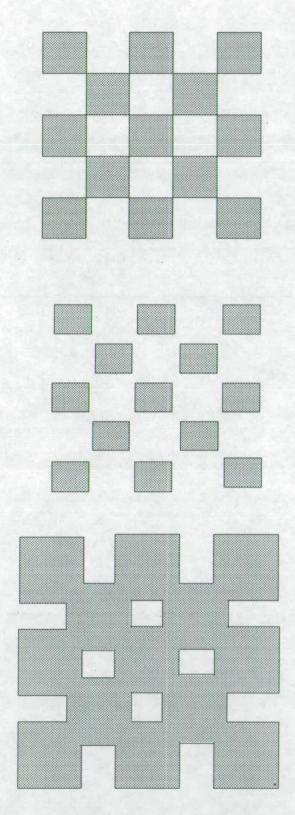

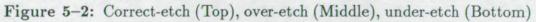

|   |      | 6.3.4   | Photolithography                            |

|   |      | 6.3.5   | Reactive Ion Etching (RIE) and Anneal       |

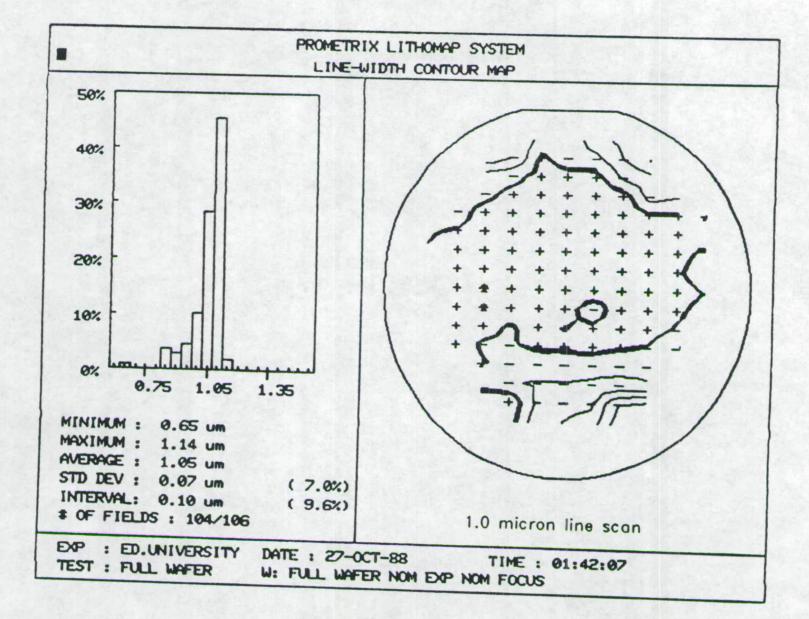

|   | 6.4  | Dimen   | nsional Measurements                        |

|   |      | 6.4.1   | Pattern Dimension Measurements on the Mask  |

|   |      | 6.4.2   | Oxide Thickness                             |

|   |      | 6.4.3   | Pattern Dimension Measurements on the Wafer |

|   |      | 6.4.4   | Metallisation Thickness                     |

|   |      |         | Bibliography                                |

| 7 | Elec | rtromi  | gration Measurements and Test Results 128   |

|   | Lice | 1.0     |                                             |

|   | 7.1  | Introd  | uction                                      |

|   | 7.2  | Instru  | mentation                                   |

|   | 7.3  | Measu   | rements                                     |

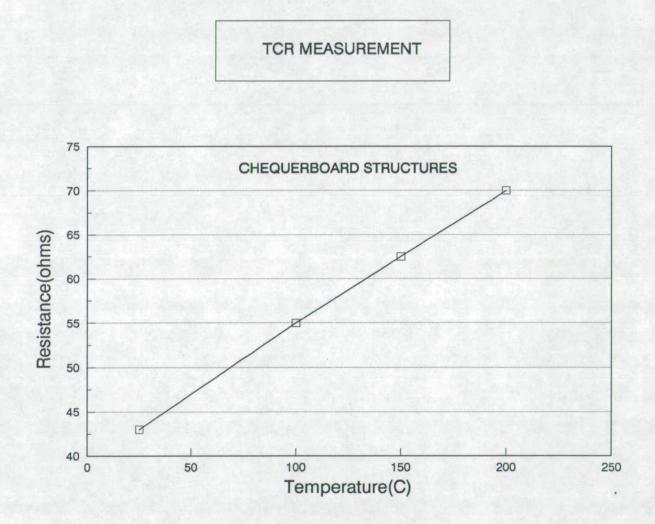

|   |      | 7.3.1   | Resistance Measurements                     |

|   |      | 7.3.2   | TCR Measurements                            |

|   |      | 7.3.3   | Thermal Measurements                        |

|   | 7.4  | Monite  | oring Resistance-Spikes                     |

|   | 7.5  | Resiste | ometry Measurements                         |

|   |      | 7.5.1   | Resistometry with Self-Heating              |

|   |      | 7.5.2   | Resistometry with External Heating          |

|   | 7.6  | Fast T  | ests                                        |

|   | 7.7  | Analys  | sis of Test Results                         |

|   |      | 7.7.1   | Determination of Activation Energy          |

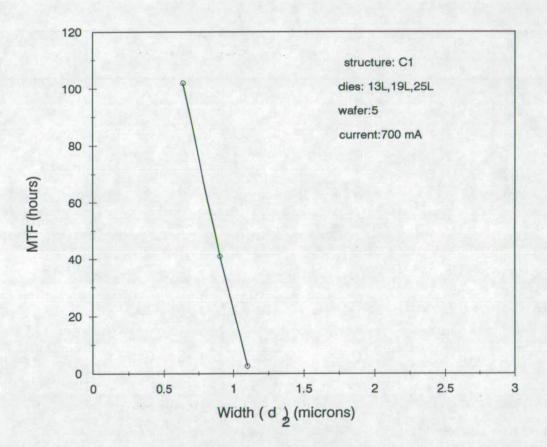

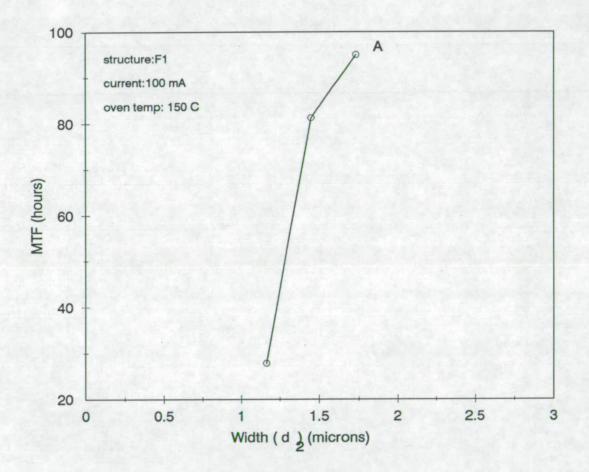

| 7.7.2 MTF Variations with Width                                    | 163 |

|--------------------------------------------------------------------|-----|

| 7.7.3 MTF of a Single Segment                                      | 165 |

| Bibliography                                                       | 169 |

| 8. Conclusions                                                     | 171 |

| 8.1 General Remarks                                                | 171 |

| 8.2 Suggestions for Further Work                                   | 175 |

| Bibliography                                                       | 178 |

| Appendices                                                         |     |

| A. Process Run-Sheet                                               | 179 |

| B. HP-BASIC Program Listing                                        | 183 |

| C. Mathematics of Failure Distributions                            | 190 |

| D. Electromigration MTF Estimations for Series-Parallel Elements 2 | 203 |

| E. Thermal Time Constants                                          | 206 |

| Bibliography                                                       | 212 |

| F. Chip Layout                                                     | 213 |

# Chapter 1

# Introduction

The quality and reliability requirements of present day integrated circuits(ICs) is increasing inexorably. The demand for higher speed, low power consumption and lower cost per gate has been the driving force to go for higher and higher levels of integration, development of new materials and processes and innovative designs. So far the tremendous advance in IC manufacturing techniques has not only offered improved performance and low cost, but improved reliability as well [1]. This improvement in reliability has not often been achieved easily. New technologies and processes have presented new challenges and failure mechanisms. So, new solutions have to be evolved to combat these problems [2]. The same trend is expected for future generation VLSI circuits.

## 1.1 Technology Trends

### 1.1.1 Level of Integration

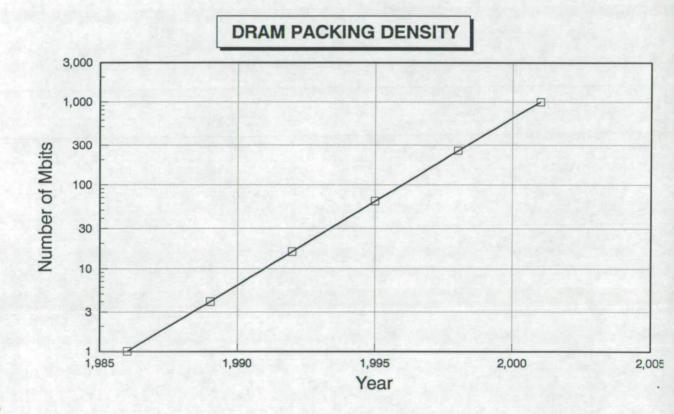

Since 1965, IC complexity has advanced from Small-Scale Integration (SSI) through Medium-Scale Integration (MSI) and Large-Scale Integration (LSI) and to Very-Large Scale Integration (VLSI) which has 10<sup>5</sup> or more components per chip. Figure 1–1 shows the remarkable growth achieved in DRAM (Dynamic Random Access Memory) packing density over the past few years and the expected trend [3]. The

#### Chapter 1. Introduction

packing density roughly quadruples every 3 years ("Moore's law"), and at this rate 1024 MDRAM (M for megabits) should be available by the year 2001. Of course no exponential growth can continue indefinitely. Limits may be imposed by physics, manufacturability, cost, performance and reliability. One objective of this thesis is to analyse one aspect of reliability measurement and specification.

Figure 1-1: Trends in level of integration

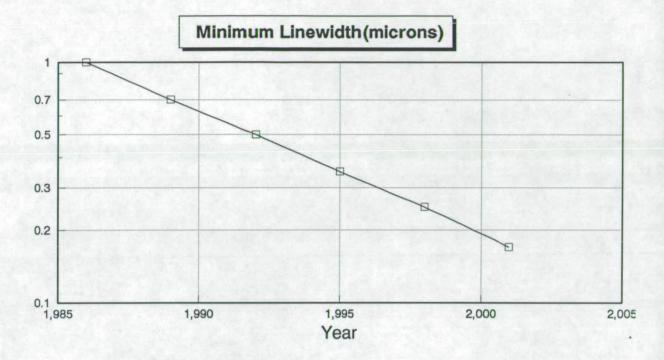

## 1.1.2 Minimum Linewidth

The most important factor in achieving very high component density is the continued reduction of the minimum linewidth as shown in Figure 1-2 [4]. At this rate, the minimum linewidth is planned to shrink to about 0.2  $\mu$ m in the year 2000.

2

Figure 1-2: Trends in minimum linewidth

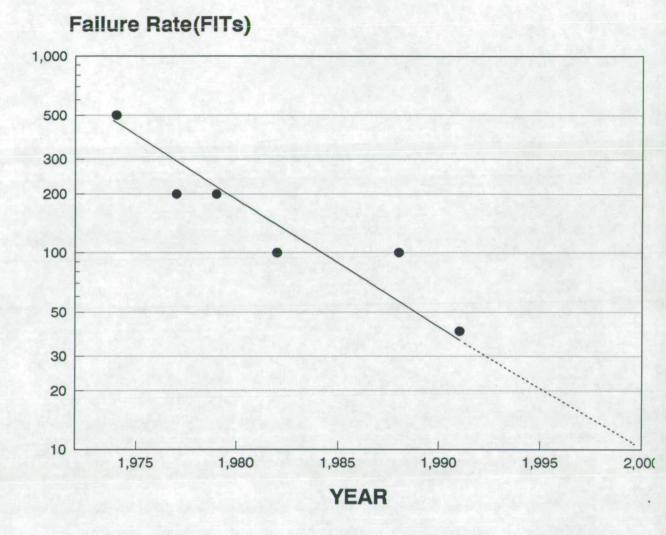

### 1.1.3 Reliability Levels

In spite of the ever-increasing complexity, the reliability of ICs is continually increasing. This is reflected in the decreasing failure -rate<sup>1</sup> goal of a manufacturer achieved over the years, as shown in Figure 1-3 [5]. 1 FIT corresponds to 1 failure in  $10^9$  device-hours of operation. The failure rate indicated here is that in the 'working life' period. This ('working life' period) is defined in the next section.

Although manufacturers may all have slightly different failure rate goals, customers will have a tendency to drive all the manufacturers to match the failure rate goals of the few most aggressive manufacturers. Therefore, all failure rate goals should tend to converge, but continue to decrease. Like Moore's Law for chip

<sup>4</sup>ratio of number of ICs failing per unit time to number surviving at any instant of time

Figure 1-3: Failure rate goal of a manufacturer versus time

densities, it appears that these market forces have also established an empirical law that govern the reliability performance.

Based on the projection in Figure 1-3, VLSI circuits failure rate goals at the turn of the century should be approximately 10 FITs.

### Chapter 1. Introduction

### 1.1.4 Reliability Improvement Approaches

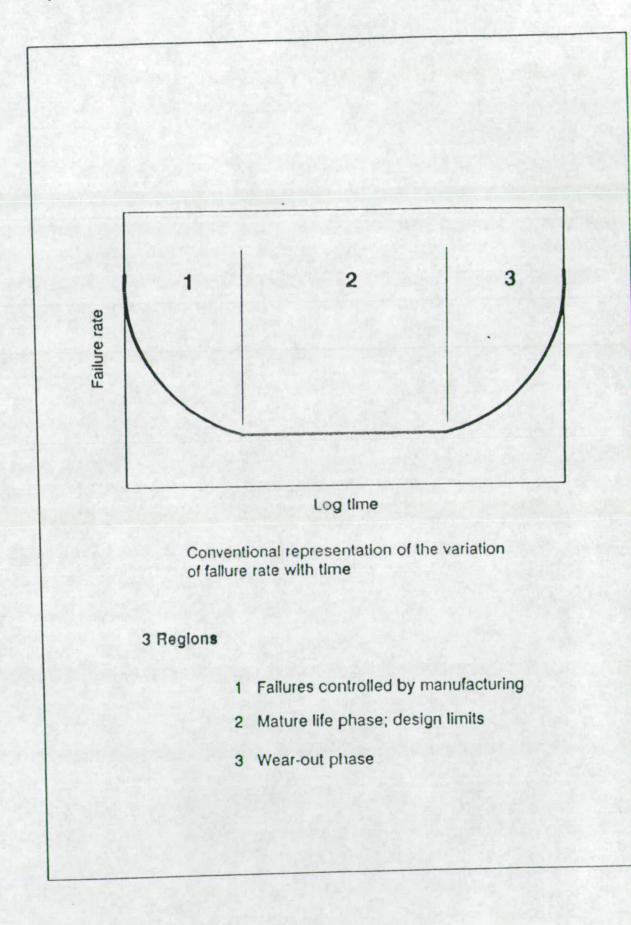

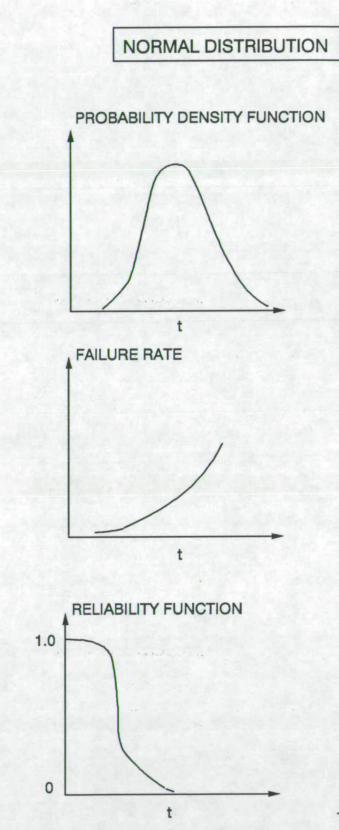

### The 'bathtub' curve

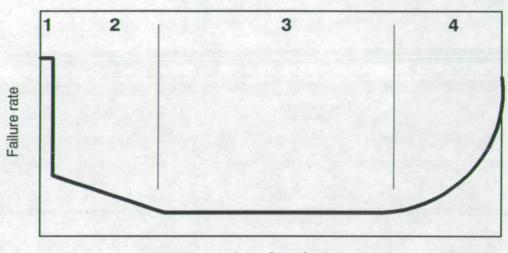

The conventional representation of the variation of failure rate of mechanical components with time is shown in Figure 1–4. This is commonly known as the 'bathtub' curve. However, for IC performance failure can be more realistically represented by 4 regions as shown in Figure 1–5 [6] :

### Region 1:

The failures in this region are caused by quality-related defects ("killer defects"), workmanship problems etc. Examples of such defects are oxide pinholes, photoresist or etching defects resulting in near-opens or shorts, weak die bonds, weak wire bonds, partially cracked packages. These defects cause yield losses that occur during the initial device testing period.

#### Region 2:

The failures in this region are caused by parametric degradations. Components which marginally meet the upper and lower parameter specifications (for example, threshold voltage) may fail during this period. For semiconductor components 'screening' tests are carried out to weed out such 'weak' devices. Examples of such generally used screening tests are, high temperature storage, 'burn-in', thermal cycling, centrifugal spinning, package leakage tests (hermeticity). Ideally the test time and temperature should be selected based on the specific failure mechanisms for a given technology and process and the corresponding activation energy. In practice, the general test conditions specified in military standards are used [7] since they represent a general catch - all standard. For example a typical high temperature storage test at 150°C for 24 hours; 'burn-in' for 168 hours etc.

Figure 1-4: The 'bathtub' curve

Log time

- 1 Yield due to killer defects

- 2 Early life parametric failures

- 3 User-induced failure

- 4 Wear-out mechanisms

Figure 1-5: The 'IC bathtub' curve

Chapter 1. Introduction

Region 3:

This is the region in which failure rate remains roughly constant. This is also known as the 'useful-life' or 'working-life' period. Failures in this region are caused by 'screening-escapes'.

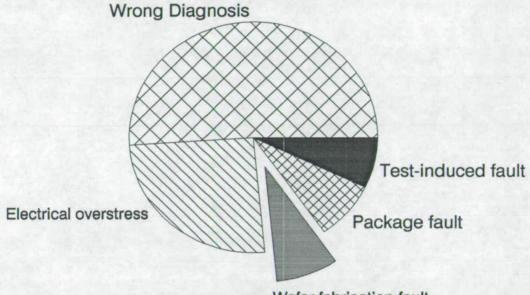

One typical distribution of failures in this region is given in Figure 1-6.

Wafer fabrication fault

Figure 1-6: Distribution of in-service failures

These data are from a manufacturer's product reliability report [8]. From this figure it is clear that a large percentage of failures are due to wrong diagnostics or misuse of the device and a very small percentage of failures can be attributed to intrinsic degradation processes. This implies that the inherent reliability of the present generation of ICs is quite high, in spite of the ever-increasing complexity. However, this does not mean that the future generation VLSI circuits can easily meet the projected reliability specifications shown in Figure 1-3.

Region 4:

This is the region in which failure rate increases with time. This is also known as the 'wear-out' region. Electromigration - the subject of this thesis - is a good

#### Chapter 1. Introduction

example for a failure mechanism in this region. The failure rate due to 'wearout' is expected to be very low during the 'useful-life' period of a component. However, improper design, materials, process and/or test conditions can cause wear-out failures during the typical 'useful-life' period.

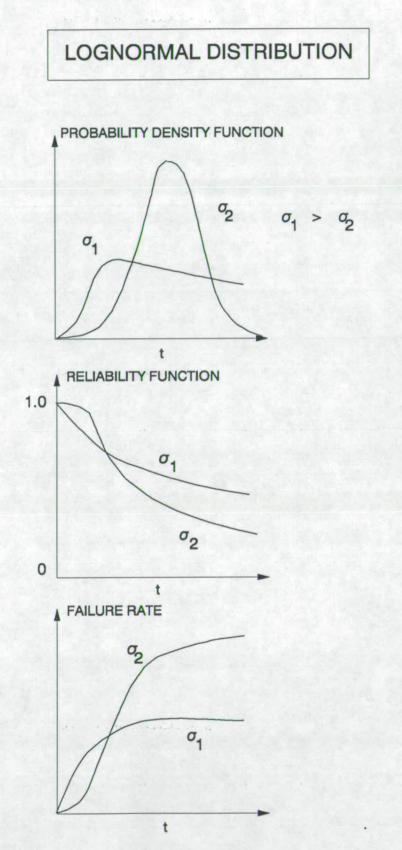

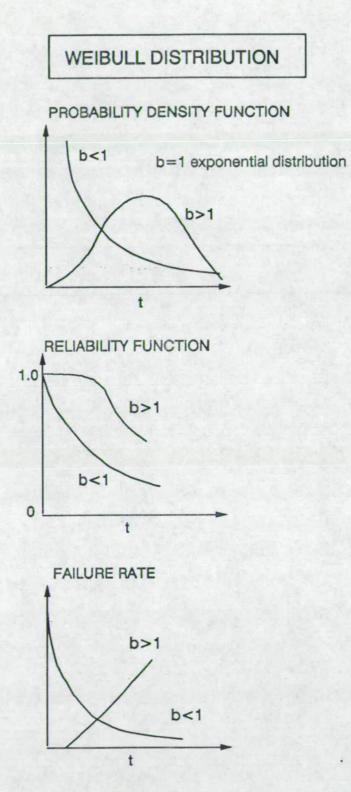

The mathematical details of the common distribution functions (Log-normal, Weibull etc.) used to represent these regions are given in Appendix C.

#### Traditional versus present trends

Traditionally, screening tests have been used to improve the reliability levels of ICs. For example, consider the general reliability level classification used by US military standards such as class S (high reliability components for critical space applications) or class B (for less critical airborne or ground applications). These are mainly specified in terms of the screening test specifications. For example, 168 hours burn-in for class B, 240 hours burn-in for class S etc. However, failures caused by manufacturing variations and occurring during actual field use can not always be eliminated by screening. Such failures are noticed even after highreliability screening tests. The whole methodology of end- of-line screening to achieve high reliability is now being questioned.

The trend now is to 'design-in' and 'build-in' reliability and to depend less and less on screening tests. Designing-in and building-in reliability includes use of conservative design rules, quality assurance of the materials, and statistical process control. Efforts are underway control to modernise the procedure for qualification of military high reliability microcircuits based on inline process monitoring of every wafer [9].

| Device or circuit parameters | Constant electric field scaling | Constant voltage scaling |  |

|------------------------------|---------------------------------|--------------------------|--|

| Device dimensions            | 1/lpha                          | $1/\alpha$               |  |

| Gate density                 | $\alpha^2$                      | $\alpha^2$               |  |

| Supply voltage               | 1/lpha                          | 1                        |  |

| Current                      | 1/lpha                          | α                        |  |

| Power/gate                   | $1/\alpha^2$                    | α                        |  |

| Power density                | 1                               | $\alpha^3$               |  |

| Current density              | α                               | $\alpha^3$               |  |

| Electric field               | 1                               | α                        |  |

Table 1-1: The effects of scaling on electic field and current density

# 1.2 Scaling Trends and Wear-out Problems with VLSI circuits

The shrinking in device geometries to achieve high packing densities is based on the so-called 'scaling rules' devised to preserve the operating characteristics. The scaling procedures and effects of these on electric field and current density in MOS devices are summarised in Table 1-1.

From Table 1-1 it is clear that current density increases by a factor of  $\alpha$  for constant field scaling and as  $\alpha^3$  for constant voltage scaling. There is an increase in electric field by a factor of  $\alpha$  for constant voltage scaling and no increase in electric field for constant field scaling (apparent from the name). This implies that the electric field dependent wear-out mechanisms such as time-dependent dielectric breakdown (TDDB) and hot-electron effects and current density dependent wearout mechanism- electromigration- are likely to be the most important wear-out failure mechanisms in the future complex VLSI circuits [10,11].

If the power supply voltage is scaled down as indicated in Table 1-1 for constant field scaling, then TDDB and the hot-electron effects should not worsen with scaling. However the trend is to scale down power supply voltage more slowly than device dimensions at some expense of power dissipation. The main reasons for this compromise are:

- 1. Non-standard supply voltages impose serious end-use compatibility problems

- 2. Reduced supply voltages imply reduced threshold voltages and therefore even tighter control over implant conditions.

Additionally the reduction in supply voltage is limited by built-in junction voltages which can not be scaled. Hence TDDB and hot-electron effects may still continue as dielectric wear-out problems of future complex VLSI circuits.

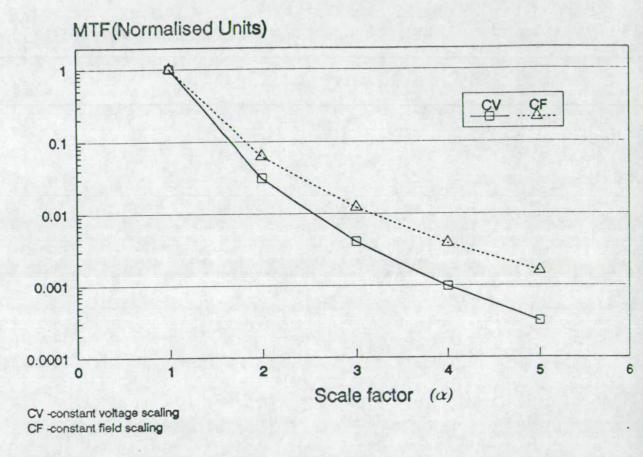

Both constant field scaling and constant voltage scaling result in increased susceptibility to electromigration. This is because of the increased current density in the case of constant field scaling and the drastic increase by a factor  $\alpha^3$  in current density and power density, in the case of constant voltage scaling. Power density leads to temperature rise in the chip and hence more rapid electromigration failure.

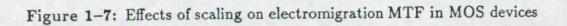

Gardner [12] has worked out the impact of the above 'scaling-rules' on median time to failure (this is denoted by MTF and represents the time for 50% failures to occur) due to electromigration in MOS devices using the well known Black's equation. The results of his analysis are shown in Figure 1–7. It is clear from this figure that as geometries shrink (i.e, scale factor increases) electromigration poses a serious threat to IC reliability. The problem is much more severe because, in addition to the obvious current density increase due to scaling, current crowding effects at steps and vias cause further reduction in the median time to failure.

The technological solutions offered to increase the MTF are to use multilayered structures where aluminium-alloy films are alternated with refractory-metal/alloy films such as titanium, tungsten etc. However the microstructural, metallurgical and chemical interactions between the layers is quite complex. Firstly, the exact mechanism responsible for MTF increase is not yet clear. For example, in the case

# ELECTROMIGRATION IN MOS ICs

### Chapter 1. Introduction

of titanium and aluminium multilayers the MTF increase may be due to the formation of the chemical compound TiAl<sub>3</sub> and/or microstructural changes following the heat treatment of the layers [13]. Secondly, some new problems (for example, increased whisker growth with TiW and TiN films) arise with these layers. Therefore, new solutions have to be found. Hence single layer aluminium-alloy films are not obsolete. Even though aluminium-copper films are more resistant to electromigration, these have dry etch, corrosion and Schottky contact problems [14]. In summary, aluminium-silicon alloys are likely to continue as the interconnect material for some time to come [15].

### **1.3 Electromigration Monitoring Requirements**

Electromigration has traditionally been measured through MTF tests and post mortem failure analysis, but these will be of limited use in future. This is mainly because such techniques can not be used to ensure the required electromigration resistance of the metallisation on every wafer in a lot and also because of cost and time considerations since typical test times may range from weeks to months.

A more fundamental approach to improved reliability would be by monitoring the quality of the materials and strictly controlling the process variables to target specifications. Although this sounds attractive and is very much in line with the best manufacturing practice for improved quality and reliability, it is not yet feasible because electromigration is affected by a large number of material and process parameters and the interactions between these is not always obvious. Figure 1–8 is a ' fishbone-diagram' showing the major material and process parameters affecting electromigration performance. Each of these may depend on a number of other parameters. For example, effective width on exposure control, photoresist thickness, and photoresist thickness on spin rate etc. It should be borne in mind that this is a simplified representation of the various factors affecting electromigration; the interdependence of many factors is not shown and in many cases it is not completely understood. For example, "presence of refractory metal layer over aluminium may modify the grain structure during heat treatment, in addition to other mechanisms in increasing the MTF.

Figure 1-8: Material and process parameters affecting electromigration

### 1.4 Aim of the Project

There is a strong need to develop a reliable process control test structure and test methodology to monitor electromigration for the reasons given in the previous section.

The main aim of the project was to develop a test structure and technique keeping in mind the following requirements: it should meet the compatibility requirements of a process monitor chip, sensitive to various factors that affect electromigration lifetime and should be usable to characterize 'sub-micron' metallisation geometries of the future complex VLSI circuits. By compatibility requirements it is meant that it should be possible to produce the new test structures with other test devices and to obtain test results quickly, preferably without using a hot chuck.

An additional objective of the project was to use the new test structure to develop statistical techniques to estimate the MTF of small segments of conductor in which current crowding effects are significant. The future VLSI circuits are most likely to contain a large number of such small segments such as bends, vias etc. and hence it is very likely that the circuits will be analysed for any loss of reliability inherent in the design.

# Bibliography

- F.Fantini. Reliability problems with VLSI. Microelectronics and Reliability, 24(2):275-296, 1984.

- [2] P.Brambilla et al. CMOS reliability: a useful case history to revise extrapolation effectiveness, length and slope of the learning curve. *Microelectronics* and *Reliability*, 21(2):191-201, 1981.

- [3] J.M.Robertson. Private communications.

- [4] S.Asai. Reliability and yield in MOS VLSI. IMEC(Belgium) summer course, 1989.

- [5] D.L.Crook. Evolution of reliability engineering. Reliability Physics, IEEE Annual Proceedings, pages 2-7, 1990.

- [6] J.Moltoft. Behind the 'bathtub' curve a new model and its consequences. Microelectronics and Reliability, 23:489-500, 1983.

- [7] Military standard: Test methods and procedures for microelectronics: MIL-STD-883D. US Department of Defense, Washington, 1988.

- [8] SIGNETICS INC. Product reliability report: R363, 1975.

- [9] E.B.Hakim. Advancement in complex microcircuit qualification. Solid State Technology, (5):98-100, 1989.

- [10] M.Davis and F.Hass. Inline wafer-level reliability monitors. Solid State Technology, (5):107-110, 1989.

- [11] P.Weiss. Study, design and test of semiconductor test structures for reliability evaluation of ICs. ESTEC Report, 1986.

- [12] Donald .S.Gardner, James D.Meindl, and Krishna C .Saraswat. Interconnect and electromigration scaling theory. *IEEE Transactions on Electron Devices*, ED-34(3):633-643, 1987.

- [13] Hoang H. Hoang. Effects of annealing temperature on electromigration performance of multilayer metallisation system. *Reliability Physics, IEEE Annual Proceedings*, pages 173–178, 1988.

- [14] N. P. Armstrong et al. Electromigration alternatives to aluminium-copper. IEEE VLSI Multilevel Interconnection Conference, pages 460-468, June 1988.

- [15] Dipankar Pramanik and Arjun N. Saxena. Aluminum metallisation for ULSI. Solid State Technology, (3):73-79, 1990.

# Chapter 2

# Electromigration and Metallisation Reliability

### 2.1 Background

Reliability studies on microeletronic circuits sponsored by US Air Force in the mid-1960s led to the identification of electromigration in thin metal films as one of the primary failure mechanisms limiting the reliability of film interconnections used in microelectronic devices [1]. This discovery fostered a period of intense activity in the study of electromigration phenomena in thin films which continues to this day [2,3,4]. While the majority of the work on bulk materials was concentrated on the electron-ion interactions and interaction of mobile defects and charge carriers [5], most of the studies on thin films were aimed at the rather practical aspect of conductor line failures in ICs. These studies were carried out on thin films prepared by evaporating metal layers onto insulating substrates and at moderate temperatures of about half the melting point of the metal.

With the rapid advancement in microelectronic materials and processing, new technological solutions were found to improve the electromigration resistance. These include microstructure modifications by various processing techniques (for example, increasing the grain size by using higher substrate temperatures[6]), alloying with other elements like copper [6] and formation of multilayer metallisation systems [7]. These new solutions brought new problems as well; for example, the excess copper forms a compound  $CuA1_2$  which is responsible for galvanic corrosion and degradation of Schottky contacts. It also causes dry etch problems. Thus,

### Chapter 2. Electromigration and Metallisation Reliability

addition of copper even though it improves the MTF of the conductor, brings new problems. Similarly multilayered sandwiches of aluminium-alloys with refractory metals/alloys, are prone to new problems because of the complex metallurgical, chemical and microstructural interactions between the layers [8]. For example, the mechanism causing whisker growth with titanium and tungsten multilayer structures is not yet fully understood. Hence aluminium-silicon alloy continues to be used as the most common inteconnect material and will probably continue for some time to come [9]. This means that electromigration continues to be an important wear-out problem.

Historically, the theory of electromigration was developed for bulk metals. However, the same approach can be used for thin films provided some appropriate modifications are made, for example, replacing the lattice diffusion coefficient by grain boundary diffusion coefficient. Hence the theory of electromigration in bulk metals is given first.

### 2.2 Theory of Electromigration

### 2.2.1 Bulk Metals

Electromigration is the term applied to the transport of mass in metals when stressed at high current densities. In other words it is the phenomenon of 'current induced atom flux'. The development of electromigration theory has evolved around two components of the driving force causing momentum transfer to the ions of the crystal : electrostatic and 'electron wind'. Early developments of the theory includes the semi-classical model by Fiks [10] in 1959, and by Huntington and Grone [11] in 1961, and the quantum mechanical model by Basvieaux and Friedel [12] in 1962. However the model proposed by Huntington and Grone is still commonly used and hence the salient features of this model are given.

Huntington and Grone [11] made light transverse scratches on the surface of gold wires and then used them as markers to observe motion of gold atoms when

#### Chapter 2. Electromigration and Metallisation Reliability

the current density was about  $10^4$  A/cm<sup>2</sup>. The experiments were carried out at high temperatures, (850°C-1000°C) for periods of several days. They developed a theory to explain the observed current-induced mass transport and its dependence on current density and temperature.

The following expression for the net atomic flux J in a lattice due to current density j was obtained :

$$\mathbf{J} = \left(\frac{\mathrm{ND}}{\mathrm{kT}}\right) \mathbf{Z}^* \mathbf{e} \rho \mathbf{j} \tag{2.1}$$

where,

N = density of ions

$D = D_o exp(-E_a/kT) =$  self-diffusion coefficient

$E_a = \text{activation energy}$

k = Boltzmann constant

$\rho = \text{resistivity}$

T = absolute temperature

$Z^*e =$  effective charge on the migrating ion

In the above equation 2.1 the effective charge  $Z^*e$  is defined and given by:

$$\mathbf{F} \equiv \mathbf{Z}^* \mathbf{e} \mathbf{E} \tag{2.2}$$

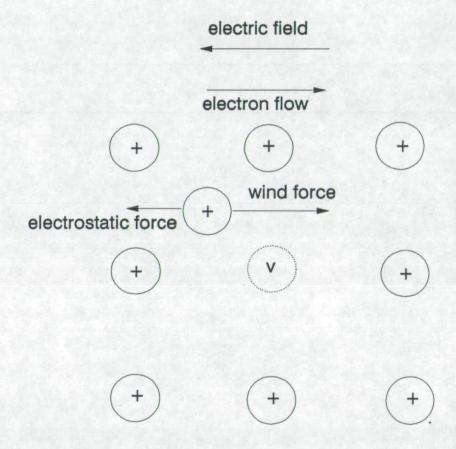

where E is the electric field and F is the total force acting on the migrating ion. The total force F consists of two components: electrostatic force ZeE (Z is the valency) and the 'wind force'. The direction of these two forces are opposite to each other. For example, for a positively charged ion, electrostatic force acts in the direction of the electric field, while 'wind force' acts in the direction of electron flow. The magnitude and sign of  $Z^*$  indicate the relative strength of the two forces. For instance, in gold the measured value of  $Z^*$  is about -7 [13] and since the the valency is 1 this implies that the wind force is about 8 times larger than the electrostatic force.

### 2.2.2 Thin Films

Electromigration studies in thin films are usually carried out at moderately low temperatures compared to the melting point of the metal, for example, less than 250°C for aluminium and the mass transport is mainly controlled by grain boundary diffusion; mass transport by lattice diffusion is negligibly small. A detailed theoretical discussion of electromigration in thin films is not yet attempted by researchers because of the complexity arising due to the grain boundaries [14].

In the absence of a rigorous theory, the atomic flux expression derived for bulk metals is modified to [15]:

$$J_{\rm b} = \left(\frac{\delta}{S}\right) \left(\frac{N_{\rm b} D_{\rm b}}{kT}\right) Z_{\rm b}^* e \rho j$$

(2.3)

where,  $J_b$  is the atomic flux along grain boundaries,  $N_b$  is the local density of ions in the grain boundaries,  $\delta$  is the effective width of the boundaries, S is the average grain size,  $D_b$  is grain boundary diffusion coefficient and  $Z_b^*e$  is the effective charge. It may be noted that  $Z_b^*$  and  $N_b$  may not be the same as these parameters in the lattice. Also, migrating impurity atoms often segregate to the boundaries which may modify the value of  $N_b$  and  $Z_b^*$ .

Expression 2.3 is based on the assumption that in all the grain boundaries mass transport proceeds with the same characteristics. However, in a film all grain boundaries are not alike. Typically the grain distribution is lognormal and the grain boundaries are oriented at random. Hence, the grain boundary parameters in equation 2.3 are always considered as suitable averages. These limitations should be borne in mind while using the above expression.

Electromigration causes mass transport along a thin film conductor, but such a displacement alone can not create a discontinuity in the film. For a discontinuity to occur there must be an imbalance in the electromigration flux at some point along the conductor path which is usually referred to as 'flux divergence'. Flux divergence will occur whenever there are changes in  $Z_b^*$  and  $D_b$ .

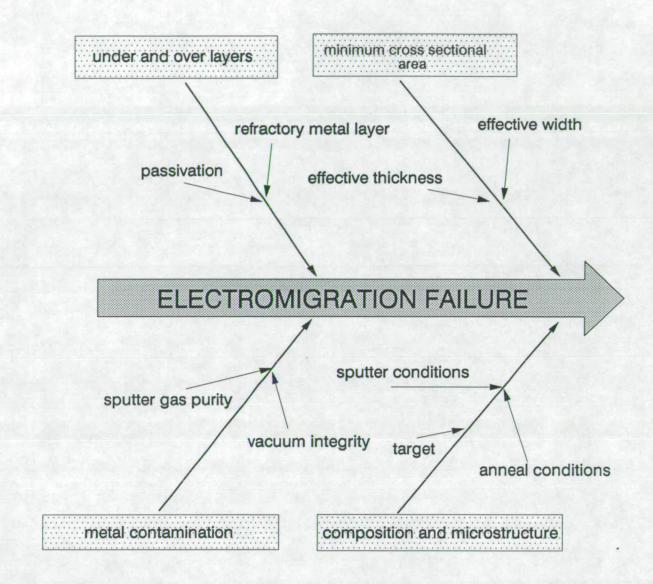

Figure 2-1: Mass transport at a triple point

A typical site in a thin film at which flux divergence occurs is schematically shown in Figure 2-1. This is known as a 'grain boundary triple point'— the junction of three grains. Here the electromigration-induced mass flux along the boundaries 1, 2, 3 represented as  $J_b^1$ ,  $J_b^2$ ,  $J_b^3$  respectively are such that,

$$J_{\rm b}^2+J_{\rm b}^3>J_{\rm b}^1$$

Under these circumstances, mass depletion will occur at the triple point and hence void formation. These voids grow in size and coalesce to form larger voids. A crack may then develop that eventually leads to discontinuity in the conductor path i.e. an open circuit.

# 2.3 Factors Affecting Electromigration in Thin films

Several material and process related factors have been reported to affect electromigration resistance. For instance, composition of the metal, anneal procedures, film deposition conditions, metal line geometry, contamination, passivation layer thickness, grain structure etc. [16,17,18,19,20]. This was shown in Figure 1-7 in the form of a simplified 'fishbone-diagram'.

These are now discussed further with reference to the commonly used aluminiumalloy metallisation.

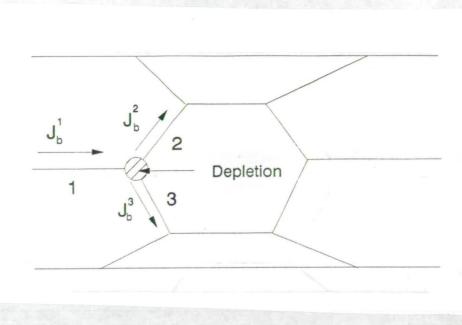

### 2.3.1 Composition of Metal

Significant improvements in MTF can be achieved by the addition of small quantities of metals like copper, silicon, titanium etc [16,17]. Addition of copper (up to 4% copper in Al-Si metallisation) increases the MTF by a factor of 70 to 100 [18]. The exact mechanism is not yet well established. Two reasons have been given; one is a reduction in grain boundary diffusivity (copper atoms segregate at the grain boundaries and so retard the electromigration-induced aluminium ion flux, the other is grain structure modification when the added copper helps to form 'bamboo' structures as shown in Figure 2-2 which may also be an important factor contributing to improvement in lifetime. Dry etch and other problems with copper, whisker growth with titanium, etc. have to be considered if these alloys are used instead of the common aluminium-silicon [8].

### 2.3.2 Linewidth

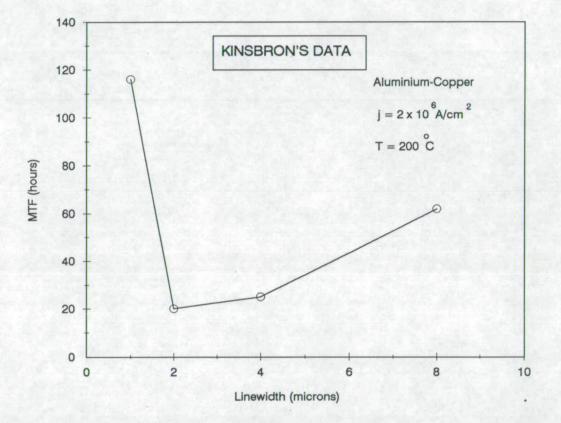

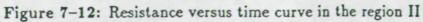

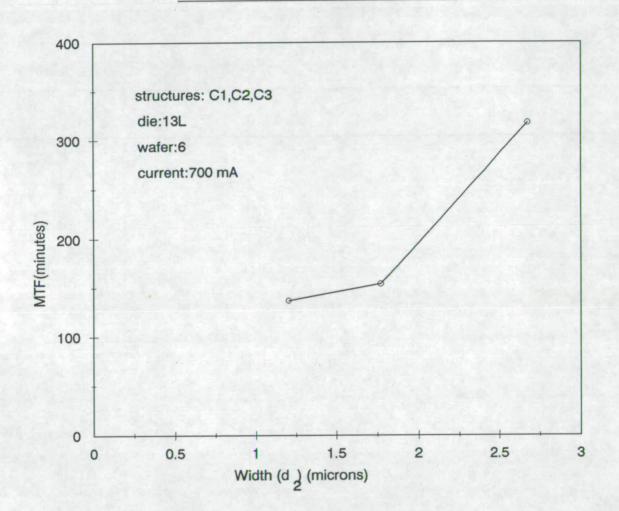

A number of experimental studies on the linewidth dependence of electromigration lifetime have been reported [21,22,19]. Figure 2–3 shows one typical example [22].

### Chapter 2. Electromigration and Metallisation Reliability

In general it has been noticed that MTF decreases with linewidth up to a 'critical width' below which the lifetime either levels off or increases.

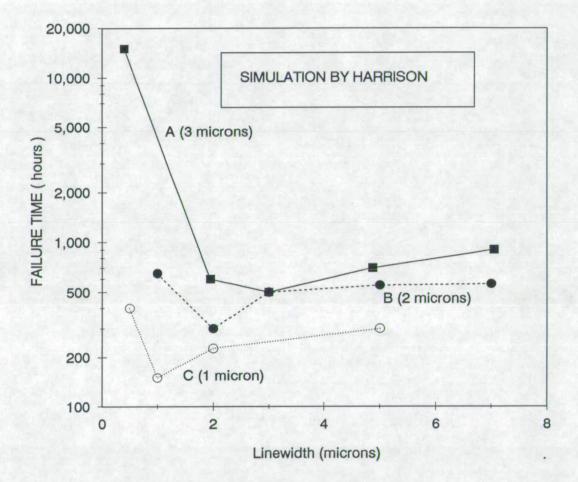

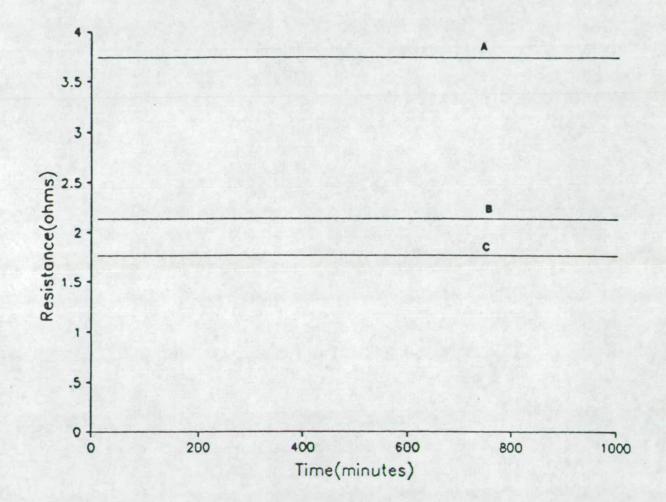

The improvement of MTF for linewidths smaller than the median grain size is usually explained in terms of the 'bamboo' grain structure in such fine lines [19]. These are further confirmed by computer simulations, taking microstructural aspects into consideration. For example, simulations by Harrison [23] on aluminium-copper metallisation is shown in Figure 2–4. The three curves correspond to median grain sizes of 3  $\mu$ m (curve A), 2  $\mu$ m (curve B) and 1  $\mu$ m (curve C). The standard deviation of the failure distribution also shows a similar behaviour. It follows from these simulations and the experimentally observed results that 'critical width' is a sensitive function of the metallisation process parameters such as, substrate temperature during deposition, anneal conditions etc. because these are the factors that affect grain size in the films [20].

Even though MTF may increase below the critical width, electromigration still continues as a major problem in sub-micron geometry ICs. This is because,

- 1. Current density increases with scaling and this will decrease MTF (it may be noted that Figure 2-3 is for a given current density).

- 2. Metallisation process parameters such as linewidth, sputter parametrs etc. may have to be monitored and controlled to take advantage of the increased MTF below the critical width. In general, statistical process control measures are becoming necessary to preserve process uniformity over a wafer and from wafer to wafer in a batch which is discussed in chapter 4.

Figure 2-2: Sketches of the normal grain structure and 'bamboo' structure

Figure 2-3: Experimentally measured MTF versus linewidth

Figure 2-4: Simulated MTF versus linewidth

## 2.3.3 Linelength

The MTF has been reported to first decrease and then become independent of the length for all practical purposes [24]. This is thought to be due to the higher probability of finding more defects in a longer metal line. However, if we are considering electromigration-induced failures caused by grain boundary defects then there should be no linelength dependence of electromigration lifetime. This is because there is an abundance of these defects in lines of any length.

## 2.3.4 Microstructure

Detailed investigations of electromigration in fine line aluminium by Vaidya and others [19] has shown that there is a strong correlation between microstructure and electromigration lifetime. MTF is shown to be proportional to an empirical microstructural quantity  $\eta$ , given by [19]

$$\eta = \frac{S}{\sigma^2} \log(I_{111}/I_{200})^3 \tag{2.4}$$

where S is the grain size,  $\sigma$  is the standard deviation in grain size distribution and  $I_{111}$  and  $I_{200}$  represent the intensity of X-ray diffraction peaks for (111) and (200) respectively.

A large number of process and material-related factors could cause variations in the microstructural parameter:

- Sputter deposition bias

- Deposition temperature

- Post-deposition annealing

- Addition of alloying elements

- Cleanliness of the vacuum during deposition

#### Chapter 2. Electromigration and Metallisation Reliability

Thus metal lines having identical geometry and metal composition may have different lifetimes depending on the deposition and anneal conditions.

## 2.3.5 Under and Over Layers

### Passivation

The technique of covering thin film conductors with an insulating dielectric layer has been found to be beneficial with respect to electromigration failure times. In the earliest implementation, aluminium conductors were covered with a layer of fused glass [25]. Subsequently, improvements in electromigration by orders of magnitude were reported for aluminium films covered with a layer of aluminium oxide obtained by anodisation [26]. The mechanism for the improvement is not well understood. It is believed that the passivation layer inhibits the hillock growth and defers the void formation. [18].

#### **Refractory metal layers**

Multilayer sandwiches of aluminium-alloys with refractory metals/alloys, have also been reported to significantly increase the MTF. However, the complex metallurgical, chemical and microstructural interactions between the layers responsible for this improvement is not yet fully understood [8]. For example, in the case of aluminium and titanium films the improvement in MTF has been observed only in the films where the intermetallic compound  $TiAl_3$  is formed. The presence of this compound which represents an electrically continuous layer is believed to block the propagation of the voids across the film. Additionally, new problems arise with these structures. For example, whisker growth with titanium and tungsten etc. However, research efforts are expected to continue to combat these deficiencies.

## 2.3.6 Other Factors

Many other factors have been reported to affect the electromigration resistance of thin films. These include, mechanical stress arising due to the difference in ther-

### Chapter 2. Electromigration and Metallisation Reliability

mal expansion coefficient between the metal and the insulator, reverse mass transport ('back flow') due to concentration and pressure gradients because of hillock formation [27] and the presence of hydrogen and other gaseous ambients during thin film deposition and anneal [28]. However, in general it is quite difficult to estimate the relative contribution to mass transport due to these factors and special experimental techniques have had to be developed to separate out the contribution to mass transport from these factors. For example, drift velocity measurements using aluminium-silicon segments over titanium-nitride films to study reverse mass transport [27].

## 2.4 Failure Models

The industrial requirement is to predict the electromigration-induced failure time when operating at the specified maximum current density and chip temperature for a given material, deposition process and track layout.

A satisfactory and complete model for failure should be able to predict the observed relations between the lifetimes of thin film conductors and such parameters as material, current density, test temperature, linewidth etc. For example, lifetime

increases as the linewidth increases (when the linewidth is significantly larger than the grain size) and it is inversely proportional to the square of the current density when j is about  $1 \times 10^6 A/cm^2$ .

Many failure models have been proposed [29,30]. However, the semi-empirical model proposed in 1969 by J.R.Black [25] has been very widely used in estimating the MTF of conductor lines so it is now discussed in detail.

## 2.4.1 Black's Equation for MTF

A metal ion which has been thermally activated and is at a saddle point (lifted out of its potential well and essentially free of the metal lattice) is acted on by two forces as shown in Figure 2-5:

Figure 2-5: Forces acting on an ion at its saddle point

- 1. The electric field applied to the conductor— this will exert a force on the activated positive ion in a direction opposite to electron flow.

- The rate of momentum exchange between the conducting electrons colliding with activated metal ions—this will exert a force on the metal ion in the direction of electron flow.

Because of shielding electrons, the force on the ion due to the electric field is quite small. The predominating force is due to the 'electron wind'. As a result, the thermally activated metal ions travel towards the positive side of the conductor. This can also be viewed as vacancies moving towards the negative side. The vacancies condense to form voids while the ions condense to form hillocks.

After being accelerated and colliding with ions elastically, the electrons impart all of their momentum to the ions. The rate of mass transport by momentum transfer between electrons and thermally activated ions is directly proportional to:

- Electron momentum

- The number of electrons/second/cm<sup>2</sup> available for striking the activated ions

- Effective target cross section

- Activated ion density

### **Electron Momentum**

The additional momentum picked up by an electron in an electric field E, in a distance of its mean free path  $\Lambda$  is given by

$$P = eE\tau = e\rho j\tau = e\rho j(\frac{\Lambda}{v})$$

(2.5)

where v is the average velocity,  $\tau$  is the mean free time between collisions, e is the charge on the electron,  $\rho$  is the volume resistivity and j the current density. The average velocity v is determined mainly by thermal velocity  $v_T$  and is perturbed only slightly by the drift velocity  $v_d$

### Number of electrons.

The number of electrons per second per unit cross sectional area, N, is related to current density (j) by

$$N = j/e \tag{2.6}$$

### Activated Ion Density $(\Theta)$ .

One may consider the number of activated ions per cubic centimeter in the metal to follow the Arrhenius equation as a function of temperature. Hence we get:

$$\Theta = F_1 \exp\left(-\frac{E_a}{kT}\right) \tag{2.7}$$

Where  $E_a$  is the activation energy in electron volts, F1 is a constant, and other symbols as defined earlier.

The MTF is considered to be inversely proportional to the rate of mass transport, and directly proportional to the film cross sectional area. That is,

$$MTF = \frac{F_2 wt}{R}$$

(2.8)

where  $F_2$  is a constant and R is the rate of mass transport given by

$$\mathbf{R} = (\mathbf{e}\rho\mathbf{j}) \left(\frac{\Lambda}{\mathbf{v}}\right) \left(\frac{\mathbf{j}}{\mathbf{e}}\right) \left(\mathbf{F}_{1} \exp\left(-\frac{\mathbf{E}_{\mathbf{a}}}{\mathbf{k}\mathbf{T}}\right)\right)$$

(2.9)

This gives

$$MTF = \frac{A}{j^2} \exp(\frac{E_a}{kT})$$

(2.10)

where the constant A depends on: film geometry (w and t), the electron mean free  $path(\Lambda)$ , average velocity (v),  $\cdots$  the volume resistivity of the metal and  $F_2/F_1$ .

### Chapter 2. Electromigration and Metallisation Reliability

Using this model and the experimental results on aluminium films, Black obtained an activation energy in the range 0.48 eV to 1.2 eV. He attributed this wide difference to the different mass transport processes, namely, grain boundary diffusion and lattice diffusion having different activation energies.

The drawback of Black's equation is that it does not satisfactorily explain the observed variation in MTF with grain boundary parameters such as median grain size, grain orientation etc. In addition, the finer details of mass transport in terms of grain structure of thin films are not dealt with in the model. Also, the linewidth dependence as in equation 2.8 (MTF  $\propto$  wt) is valid for wide metallisation lines for which the linewidth is larger than the median grain size. The increase in MTF at widths smaller than critical width (discussed in section 2.3.2) is not explainable using Black's equation.

Subsequent to Black's model a number of failure models have been proposed, mainly based on computer simulations of microstructure of thin films. These include the earlier attempts by Attardo et al (1971) [31] and more recent models by Huntington et al (1991) [32] continue to account for a large number of empirical results collected over the years. These simulations have some success in explaining the microstructural dependence of electromigration, but use complex models. For example, in the model used by Huntington et al [32] a grain boundary network is first established by laying down a random array of points in two dimensions and then constructing the perpendicular bisectors of lines joining nearby points. The planes so constructed form the grain boundaries. Having generated the above network many details have to be carefully worked out. This includes, the determination of the orientation of the individual grains, optimisation of the network to meet the minimum surface energy requirements etc. However, a simple failure model incorporating microstructural and temperature factors is not yet available. Hence, despite its drawbacks, Black's equation is very widely used in IC metallisation failure time predictions.

However, based on subsequent studies, Black's equation is usually modified to:

$$MTF = \frac{f(w) tA'}{j^{x}} exp(\frac{E_{a}}{kT})$$

(2.11)

where,

| x=1 | for $j \leq 1 \times 10^5 A/cm^2$     |

|-----|---------------------------------------|

| x=2 | for $j \geq 1 \times 10^{6} A/cm^{2}$ |

f(w) = w for wide lines with  $w \gg$  grain size and the functional relation is to be empirically obtained for widhs near critical width.

## 2.5 VLSI circuit Reliability Simulation Models

## 2.5.1 Motivation for Reliability Simulation

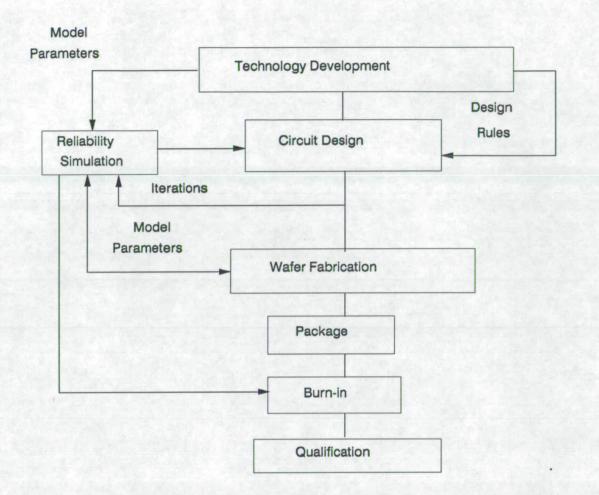

In designing a complex circuit, designers make a large number of circuit simulations, design changes and optimisations and can predict the circuit's performance reasonably accurately before committing it to silicon. It would be unthinkable to bypass the circuit simulation and optimisation and rely entirely on the testing of finished ICs to discover errors or to find out if the performance of the circuit meets specifications. Yet, this is basically the way IC reliability is treated today [33].

At the present time, reliability assurance relies mainly on failure detection, which occurs only at the end of a lengthy product development and qualification process. This practice poses serious problems for future complex VLSI circuits. Reliability failure, if detected during testing, or worse during field application, will be prohibitively costly both from time and cost points of view to fix the problem by process or design changes.

It is highly desirable to predict the circuit reliability at the circuit design stage. A schematic diagram of this methodology is shown in Figure 2-6 [33]. Several reliability simulators analogous to process simulators which contain separate models for diffusion, implantation, oxidation etc. have been reported in the literature to model electromigration, hot-electron degradation etc. [34,35]. In these simulators, a set of parameters relevant to circuit reliability is identified for each failure

### Chapter 2. Electromigration and Metallisation Reliability

Figure 2-6: A methodology of reliability assurance

mechanism. Computer programs are developed to predict circuit failure rate from these parameters .

The above methodology is still in its early stages and not well established. Development of simple methods of extracting these parameters for a given process or technology involving accelerated stress tests on test structures is one of the important research areas.

## 2.5.2 Reliability Simulators for Electromigration

Many of the VLSI circuit electromigration reliability simulators use the series model to express the failure [36,37]. That is, the failure rate of any one of the

segments (bends, vias etc.) in the IC causes IC failure and that the total failure rate is the sum of the individual failure rates:

$$\lambda = n_l \lambda_l + n_b \lambda_b + n_v \lambda_v + \dots$$

(2.12)

Where  $\lambda$  is the failure rate of the IC,

- $n_l =$  number of linear segments

- $\lambda_l =$ failure rate of linear segment

- $n_b =$ number of bends

- $\lambda_b =$ failure rate of bend

$n_v =$ number of vias

$\lambda_v =$ failure rate of via

It should be noted that in the absence of any technique to directly obtain the failure rate  $\lambda_l$  of a small linear segment, (generally of median grain size), it is a general practice to use the MTF of a lengthy line and estimate  $\lambda_l$  by applying statistical techniques [38]. Estimations of  $\lambda_b$  and  $\lambda_v$  are complicated because of current crowding effects. If we use the usual current density dependence (MTF  $\propto 1/j^2$ ) and inceased current density values due to current crowding, the calculated failure rate of VLSI circuits may come down to unrealistic values; on the other hand ignoring these effects overestimates the reliability. Quite often the latter approach is adopted [38] and  $\lambda_b$  and  $\lambda_v$  are usually estimated based on the expected changes in cross sectional area at a via or a bend. This is one important area where further research is needed.

A statistical methodology has been suggested in this thesis to estimate the MTF of small segments using the new test structures.

# Bibliography

- A.Blech and H.Sello. Rome Air Development Center, New York, Technical Report : TR-66-31, 1965.

- [2] J. R. Black. Electromigration a brief survey and some recent results. IEEE Transactions on Electron Devices, ED-16(4):338-347, 1969.

- [3] M. J. Attardo and R. Rosenberg. Electromigration damage in aluminium film conductors. J. Applied Physics, 41(6):2381-2386, 1970.

- [4] A. Bobbio and O. Saracco. Electromigration failure in aluminium thin films under constant and reversed DC powering. *IEEE Transactions on Reliability* (USA), <u>R23</u>:194-202, January 1974.

- [5] R.S.Sorbello. Electro and Thermo-Transport in Metals and alloys, chapter 1. AIME, New York, 1977.

- [6] S. S. Iyer and C. Y. Wong. Grain growth study in aluminium films and electromigration implications. J.Applied Physics, 57(10):4594-4598, 1985.

- Hoang H.Hoang and J.Michael .McDavid. Electromigration in multilayer metallisation systems. Solid State Technology, (10):121-126, 1987.

- [8] N. P. Armstrong et al. Electromigration alternatives to aluminium-copper. IEEE VLSI Multilevel Interconnect Conference, pages 460-468, 1988.

- [9] Dipankar Pramanik and Arjun N. Saxena. Aluminum metallisation for ULSI. Solid State Technology, (3):73-79, 1990.

- [10] V.B.Fiks. On the mechanism of the mobility of ions in metals. Soviet Physics

Solid State, (1):14, 1959.

- [11] H. B. Huntington and A. R. Grone. Current-induced marker motion in gold wires. J.Phys.Chem.Solids, 20 (1 and 2):76-87, 1961.

- [12] C.Bosvieux and J.Friedel. J.Phys. Chem. Solids, (23):123, 1962.

- [13] C.Herzig and D.Cardis. Matter transport in pure gold, induced by high direct current densities. Applied Physics, (5):317, 1975.

- [14] T.Kwok and P.S.Ho. Diffusion Phenomena in Thin Films and Microelectronic Materials, chapter 7, page 424. Noyes Publications, USA, 1988.

- [15] F.M.d'Heurle and P.S.Ho. Electromigration in thin films. In Thin Films: Interdiffusion and Reactions, chapter 8. Wiley-Interscience, New York, 1978.

- [16] K. V. Reddy, F. Beniere, and D. Kostopoulos. Electromigration and diffusion of copper in aluminium thin films. J.Applied Physics, <u>50(4)</u>:2782-2786, 1979.

- [17] P. B. Ghate. Electromigration induced failures in VLSI interconnects. Reliability Physics, IEEE Annual Proceedings, pages 292-299, 1982.

- [18] F.Fantini. Metallisation and electromigration. Interuniversity Microelectronics Centre (Belgium), summer course, 1989.

- [19] S. Vaidya, D. B. Fraser, and A. K. Sinha. Electromigration resistance of fine line aluminium for VLSI applications. *Reliability Physics, IEEE Annual Proceedings*, pages 165–170, 1980.

- [20] Dr.Hendel. Electromigration resistance improved through sputtering control. Microelectronic Manufacturing and Testing, pages 25-26, November 1990.

- [21] P.J.Dulnaik. Effect of integrated metallisation linewidth on the distribution of electromigration lifetime. Applied Physics Letters, 54(13):1229-1231, 1989.

- [22] E. Kinsbron. A model for the width dependence of electromigration lifetimes in aluminium thin-film stripes. Applied Physics Letters, <u>36(12)</u>:968-970, 1980.

- [23] J.W.Harrison. A simulation model for electromigration in fine-line metallisation of integrated circuits due to repetitive pulsed currents. *IEEE Transactions on Electron Devices*, 35(12):2170-2179, 1988.

- [24] B.N.Agarwala, M.J.Attardo, and A.P.Ingraham. Dependence of electromigration-induced failure time on length and width of aluminium thin film conductors. J.Applied Physics, 41(10):3954-3960, 1970.

- [25] J. R. Black. Electromigration failure modes in aluminium metallisation for semiconductor devices. Proceedings of the IEEE (USA), <u>57(9)</u>:1587-1594, 1969.

- [26] A.J.Learn. Effect of structure and processing on electromigration -induced failure in anodized aluminium. J.Applied Physics, <u>44</u>:1254, 1973.

- [27] I. A. Blech and C. Herring. Stress generation by electromigration. Applied Physics Lettesrs, 29(3):131-133, 1976.

- [28] R.W.Pasco, L.E.Felton, and J.A.Scwarz. The effects of hydrogen ambients on electromigration in aluminium-2% copper thin film conductors. *Solid State Electronics*, 26(11):1053-1063, 1983.

- [29] R.A.Sigsbee. Failure model for electromigration. Reliability Physics, IEEE Annual Proceedings, page 301, 1973.

- [30] J. M. Schoen. Monte Carlo calculations of structure\_induced electromigration failure. J. Applied Physics, 51(1):513-521, 1980.

- [31] M. J. Attardo, R.Rutledge, and R.C.Jack. Statistical metallurgical model for electromigration failure in aluminium thin-film conductors. J. Applied Physics, 42(11):4343-4349, 1971.

- [32] H.B.Huntington. A computer simulation of stripe deterioration through electromigration. J. Applied Physics, 70(3):1359-1368, 1991.

- [33] Chenming Hu. IC reliability simulation. IEEE J.Solid State Circuits, 27(3):241-246, 1992.

- [34] F.Najm et al. Probabilistic simulation for reliability analysis of CMOS VL-SI circuits. IEEE Transactions on Computer-Aided Design, <u>9(4)</u>:439-450, 1990.

- [35] B.J.Sheu et al. An integrated circuit simulator-RELY. IEEE J.Solid-State circuits, <u>24</u>:473-477, April 1990.

- [36] P.M.Lee et al. BERT-Circuit Aging Simulator. Electronics Research Laboratory of University of California report, January 1990.

- [37] D.F.Frost, K.F.Poole, and D.A.Haeussler. RELIANT: a reliability analysis tool for VLSI interconnects. *IEEE custom integrated circuits conference*, pages 27.8.1-27.8.4, 1988.

- [38] D. F. Frost and K. F. Poole. A method for predicting VLSI device reliability using series models for failure mechanisms. *IEEE Transactions on Reliability*, R-36(2):234-242, 1987.

# Chapter 3

# **Review of Measurement Techniques**

# 3.1 Introduction

Electromigration in thin films has many interesting features both from theoretical and technological points of view. The former include the nature of the 'wind force' at the grain boundaries, while the latter concerns mainly the more practical aspect of failure time predictions of IC metallisation. Accordingly the following two types of measurement techniques have evolved to meet these requirements:

1.Electron microprobe techniques, drift velocity measurements and mass transport measurements to measure the electromigration parameters of fundamental interest such as the effective charge  $(Z_b^*)$  and diffusion coefficient  $(D_b)$  at the grain boundary. Details of these measurement techniques can be found in a review article [1].

2. Conductor lifetime measurements (usually referred to as MTF measurements or lifetests), resistometry, fast tests, mass transport measurements and noise tests [2].

We are interested in type 2 measurements because these give parameters useful in assessing the IC metallisation reliability. Therefore these are discussed here. However, the noise measurements are not discussed here because the theory and analysis of these tests are yet to be developed and also the instrumentation requirements are quite complicated.

In the initial stages of this project some measurements were carried out using some of these techniques, in order to derive the constants in Black's equation for the EMF process and the results are also included here. In all of these measurements, accelerated testing are used to cut down the test times. Hence the various aspects of accelerated testing and acceleration factors are discussed first.

# 3.2 Accelerated Testing

Accelerated testing techniques involve stressing a part in an environment more severe than standard operation conditions. The stress conditions are selected under the assumption that factors controlling the degradation are the same failure mechanisms as those that predominate in typical operating conditions for the part. The observed behaviour of the part under these conditions is then related to its performance at actual operating conditions using a degradation model.

The major reason for using accelerated testing is to cut down the test times involved. The failure rate expected of the present day VLSI circuits under normal operating conditions is very low- of the order of 100 FITs. This corresponds to stressing 100 parts for approximately 11 years or equivalently 10,000 parts for approximately 1000 hours to observe one failure. In future the situation will be much more demanding; to monitor 100 parts for one failure in 114 years of operation under normal operating conditions. Obviously the test times and the number of test parts required make it extremely difficult to carry out reliability testing of a design in a time scale short enough that the design has not become obsolete before being produced. Also the usage of ASICs in military/aerospace applications means the number of samples actually needed may be far below that required for reliability testing. Using higher current densities and temperatures, one could shorten test times, for example: the MTF of 20 years at an operating temperature of 25° C and current density of  $1 \times 10^5 \,\text{A/cm}^2$  will be reduced to almost a few days at  $1 \times 10^{6} \text{A/cm}^{2}$  at 150°C for Al-1%Si metallisation [3]. However, one should be cautious in using high temperatures. At temperatures  $\geq 250^{\circ}$ C lattice diffusion may become predominant and it will be inappropriate to extrapolate these failure

rates to normal operating conditions where grain boundary diffusion dominates [4].

# 3.3 MTF Measurement [5-9]

This measurement records the time at which 50% of a large number of nominally identical specimens fail when subjected to constant current density at a given temperature. This is the most commonly used method for evaluating electromigration resistance [1]. The advantages of this method are its simplicity and well defined failure mode("open"). We have a good empirical database and experience and also the availability of standard test procedures and methods for reliability estimations [10-12]. Hence MTF measurement has been described as a ' a corner stone of metallisation reliability testing' [13] and MTF values are the most sought-after electromigration parameters.

However, the main practical disadvantage is ( ) the fact that it requires a large number of samples to be tested at elevated temperatures usually in a burnin chamber for test times that may range from weeks to months. There are some fundamental limitations of MTF measurements and these are discussed in detail in chapter 4.

## 3.3.1 MTF Measurements on EMF Metallisation

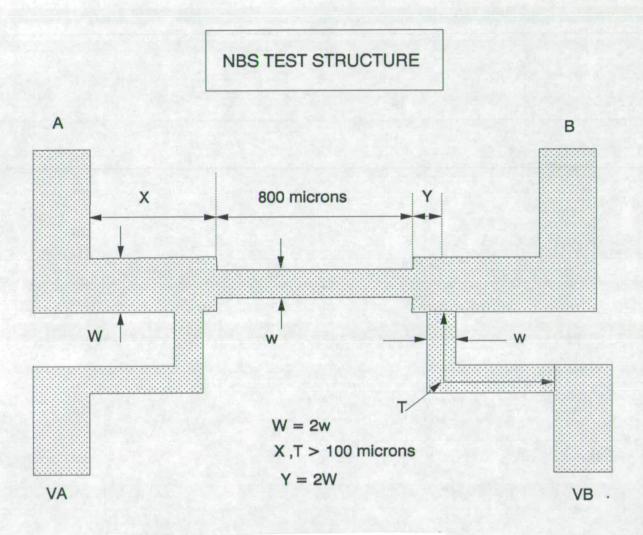

These measurements were done to derive the constants in Black's equation. The standard NBS [14] test structure commonly used for MTF tests was used which is shown in Figure 3–1. The process and other details are summarised in Table 3–1, the dimensions shown are the measured values (averages).

Ideally the number of samples used for electromigration MTF measurements should be as large as possible. However, test setup, cost and time factors forbid the use of a large number of samples and some compromises have to be made. A literature survey indicated that majority of experiments have been carried out with a sample size between 10 and 20. So the minimum acceptable sample size of 10

Figure 3-1: Test structure used for MTF measurements

| Wafer         | P-type, 3 inch dia.,     |               |

|---------------|--------------------------|---------------|

| Insulator     | Material                 | $SiO_2$       |

|               | Process                  | wet oxidation |

|               | Thickness                | 5600Å         |

| Metallisation | Material                 | Al-1%Si       |

|               |                          |               |

|               | Deposition               | sputtering    |

|               | Thickness                | $1.0 \mu m$   |

| Anneal        | 435°C, 10 min. $N_2/H_2$ |               |

Etch

Dry

Structure dimensions Width

$6.20 \mu m$

Length

$800 \mu m$

Table 3-1: Test structure and process details

was chosen. The samples were mounted in DIP packages and powered individually (current density of  $1 \times 10^6 A/cm^2$ ) and a HP computer was used to monitor the failure times. For stress experiments conducted at 150°C, printed circuit boards made from epoxy glass were used. But to conduct stress experiments at 175°C, these PCBs were not suitable and special jigs were fabricated using holes drilled in metal boards and high temperature IC sockets, turrets, solder and wires were used.

All the test samples were visually inspected for any defects using optical microscopes. Only defect free samples were used. The resistances of all the samples were measured at various temperatures inside the oven and the temperature coefficient of resistance was obtained. Using this, the temperature rise in all the samples when subjected to a current density stress of  $1 \times 10^6 \text{A/cm}^2$  was obtained. This was found to be approximately 3°C.

### 3.3.2 Test Results and Discussion

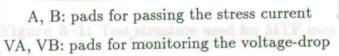

The time to failure data obtained is shown in Figure 3–2.

The activation energy is obtained using Black's equation as follows:

$$\begin{split} \mathrm{MTF}_{1} &= \frac{\mathrm{A}}{\mathrm{j}^{2}} \mathrm{exp}(\frac{\mathrm{E}_{\mathbf{a}}}{\mathrm{k}\mathrm{T}_{1}}) \\ \mathrm{MTF}_{2} &= \frac{\mathrm{A}}{\mathrm{j}^{2}} \mathrm{exp}(\frac{\mathrm{E}_{\mathbf{a}}}{\mathrm{k}\mathrm{T}_{2}}) \\ \frac{\mathrm{MTF}_{1}}{\mathrm{MTF}_{2}} &= \mathrm{exp}\frac{\mathrm{E}_{\mathbf{a}}}{\mathrm{k}} \left(\frac{1}{\mathrm{T}_{1}} - \frac{1}{\mathrm{T}_{2}}\right) \\ \mathrm{E}_{\mathbf{a}} &= \mathrm{k} \ln \left(\frac{\mathrm{MTF}_{1}}{\mathrm{MTF}_{2}}\right) / \left(\frac{1}{\mathrm{T}_{1}} - \frac{1}{\mathrm{T}_{2}}\right) \end{split}$$

where

- $T_1 = 150 + 3 + 273 = 426K \tag{3.1}$

- $T_2 = 175 + 3 + 273 = 451K \tag{3.2}$

- $MTF_1 = 30.5hours$  (3.3)

- $MTF_2 = 9hours$  (3.4)

Figure 3-2: failure time distribution

substituting the above values in the expression above, we get

$$E_a \simeq 0.8 eV$$

(3.5)

$$A \simeq 10.4 \times 10^3 [hours] [amperes/cm^2]^2$$

(3.6)

Most values of  $E_a$  for aluminium films lie in the range of  $0.6 \pm 0.2$  eV [12]. This spread is due to the fact that in addition to the mass transport due to grain boundary diffusion, other parallel mass transport mechanisms with different activation energies coexist.

| Mass transport mechanism  | $E_a(eV)$ |

|---------------------------|-----------|

| Lattice diffusion         | 1.4       |

| Grain boundary diffusion  | 0.4-0.5   |

| Grain boundary to bulk    | 0.63      |

| Defects to bulk diffusion | 0.62      |

| Surface diffusion         | 0.28      |

Table 3-2: Mass transport mechanisms in thin aluminium films

These are summarised in Table 3–2. Hence the activation energy of 0.8 eV may be considered as an appropriate average.

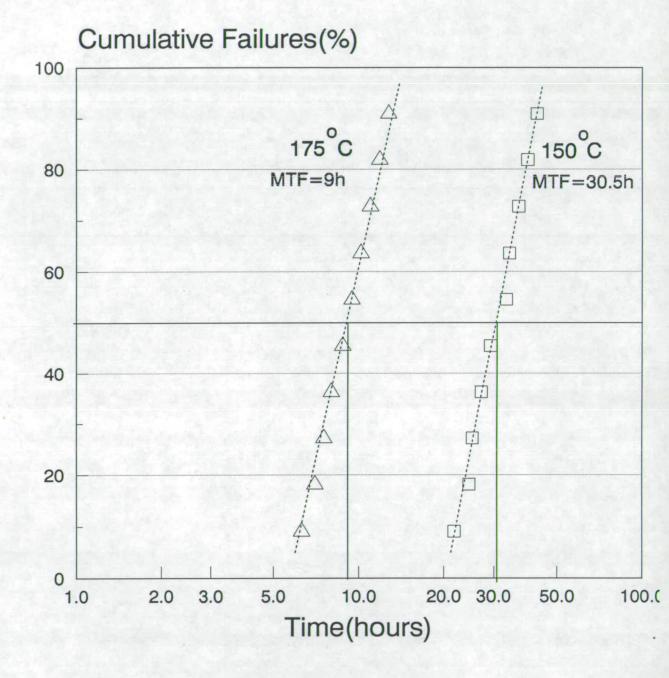

The reliability specifications are commonly given in terms of FITs and hence, the MTF data is translated into failure rate versus time curves as shown in Figure 3-3. This prediction is for a  $3\mu$ m width line and under the following operating conditions: normal operating current density  $1 \times 10^5$  A/cm<sup>2</sup> and normal operating temperature 40°C. Also, the commonly used value of x=1 for this current density was used in Black's equation (see section 2.4.1).

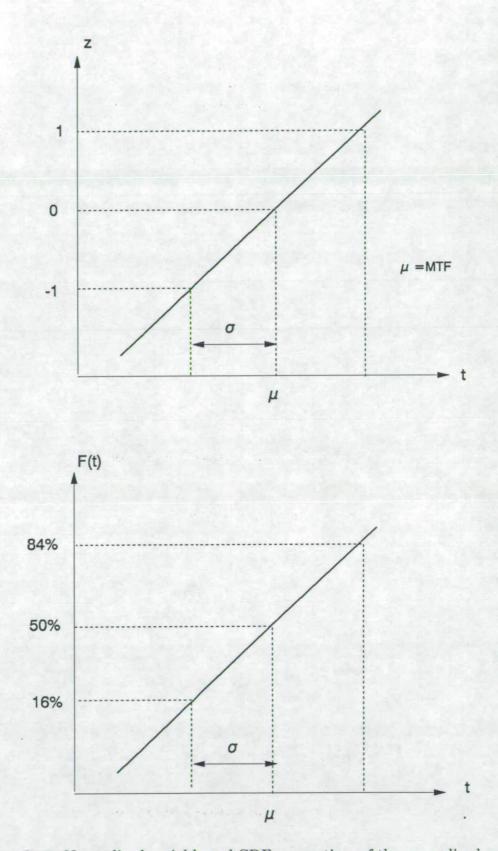

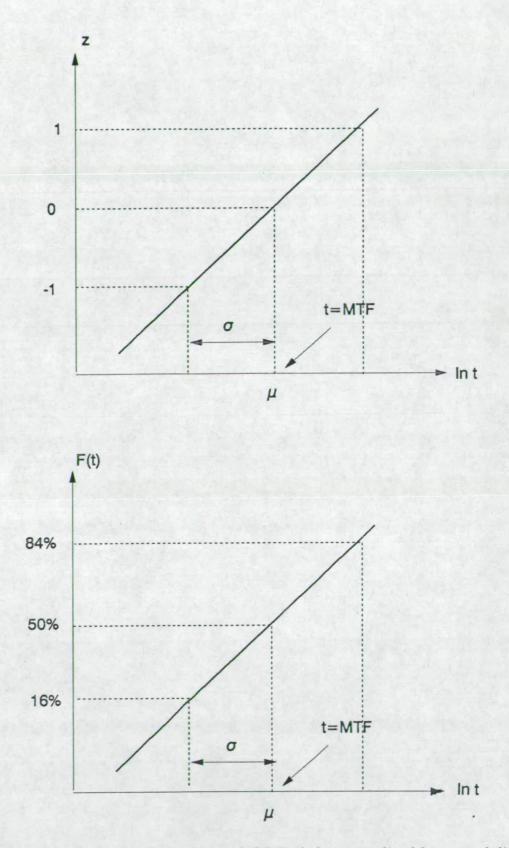

The failure rate as a function of time is calculated using the probability density function and cumulative distribution function of the lognormal distribution described in Appendix C. The expression for the failure rate is given below.

$$\lambda(t) = \frac{\exp\left[-\frac{(\ln t - \mu)^2}{2\sigma^2}\right]}{t \int_t^\infty \frac{1}{t} \exp\left[-\frac{(\ln t - \mu)^2}{2\sigma^2}\right]} dt$$

(3.7)

Figure 3-3: Estimated failure rate versus time of EMF metallisation under normal operating conditions

#### Chapter 3. Review of Measurement Techniques

where,

$\lambda$  (t) = failure rate as a function of time t = time  $\mu = \ln(MTF)$  $\sigma = \ln[MTF/t_{16}]$  $t_{16}$  = time for 16% cumulative failures

Figure 3-3 shows that when linewidth is  $\leq 3\mu$ m it may become increasingly difficult to meet the future reliability requirements. The failure rate may far exceed (by a factor of about 500) the minimum acceptable limit of 10 FITs for 20 years.

There are many ways to meet the reliability demands of high reliability device users. One method is to reduce the operating current density. This is not a real option because it puts stringent constraints on the circuit designer. The second way is the technological solution; addition of copper to the aluminium-silicon alloy film or multilayer metallisation systems with refractory metals which give order of magnitude improvement in MTF and hence a significant reduction in failure rate to meet or exceed the requirement for 10 FITs for 20 years. However, this may bring in other technological process problems as discussed in chapter 2 (section 2.3.5). The most attractive solution is to increase the MTF by grain structure modifications such as 'bamboo' structures. This means the process should be well controlled and should be continuously monitored to ensure that all the wafers meet the target reliability specifications. There are some fundamental limitations with MTF measurement as a process control monitor and these are discussed in chapter 4.

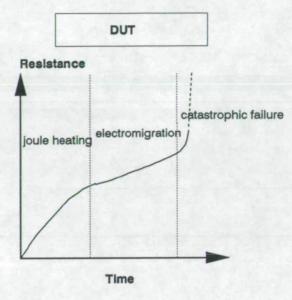

Figure 3-4: Schematic representation of resistance change with time of a metallisation line during electromigration stress experiments

# 3.4 Resistometry [15-24]

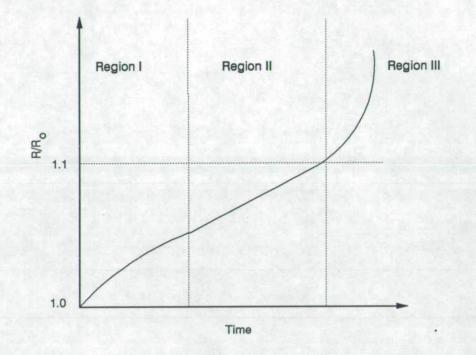

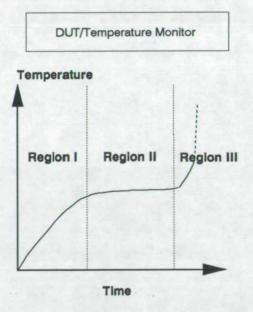

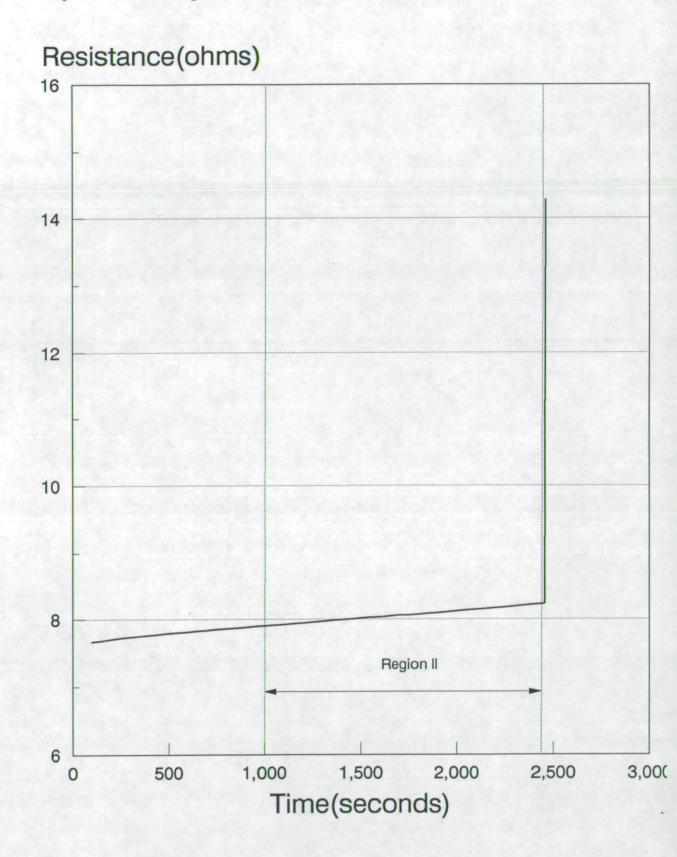

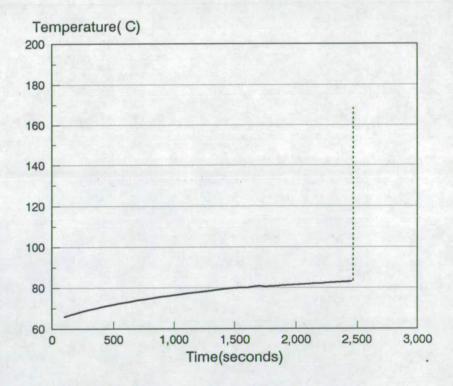

This method measures the fractional change in resistance  $\left(\frac{R}{R_o}\right)$  with time caused by material accumulation and depletion as a result of electromigration. The technique has the advantage of being simple and resistance changes can be measured accurately. The resistance change with time during electromigration stress experiments usually looks like 3–4. It consists of three regions:

Region I: joule heating Region II: mass transport due to electromigration Region III: catastrophic failure processes

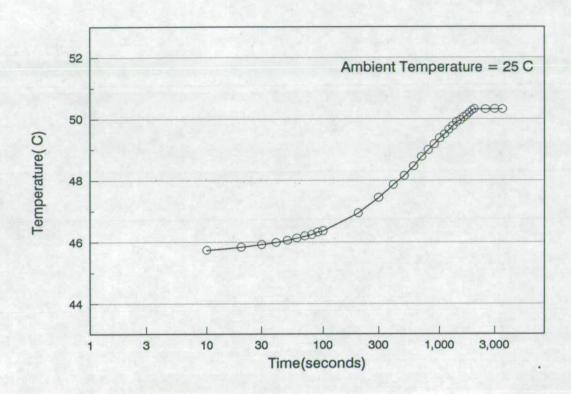

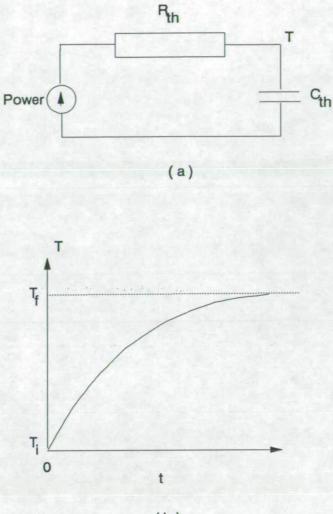

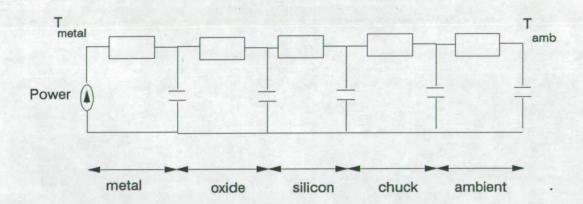

In region I the temperature of the metallisation increases due to self-heating. The thermal stabilization time depends on various thermal time constants. For example, thermal time constant of the metallisation/oxide; oxide/substrate; substrate/chuck etc.

### Chapter 3. Review of Measurement Techniques

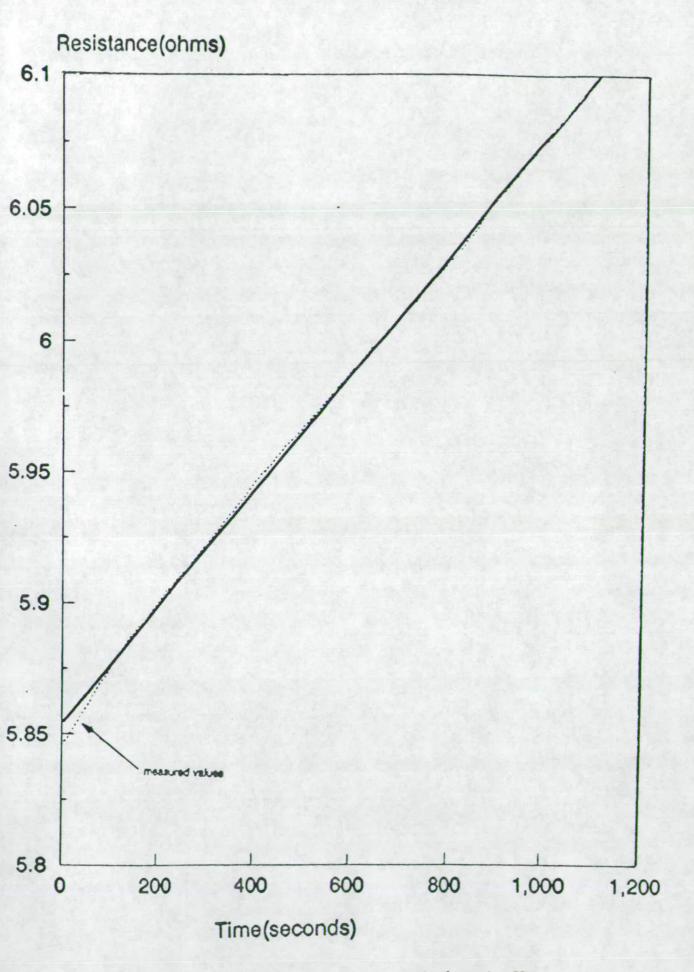

In region II the resistance increases gradually due to mass transport. Typically a near linear resistance increase has been reported by many researchers. Electromigration parameters like activation energy, the pre-exponential constant in Black's equation, and estimation of MTF are usually obtained by analysing this region.

In region III resistance increases rapidly and within a short time the structure fails ("opens"). The mechanisms leading to the ultimate failure of the line are quite complex, involving increase in current density, temperature and void growth. The exact point on the resistance versus time curve at which these catastrophic failure processes take over is not yet resolved, typically it is taken as that corresponding to 5-10% increase in resistance.

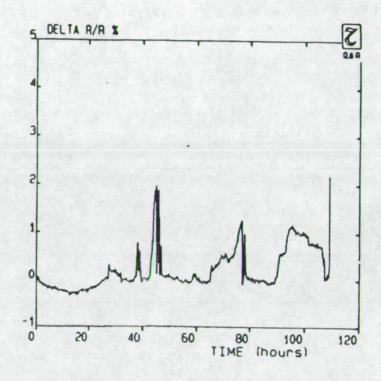

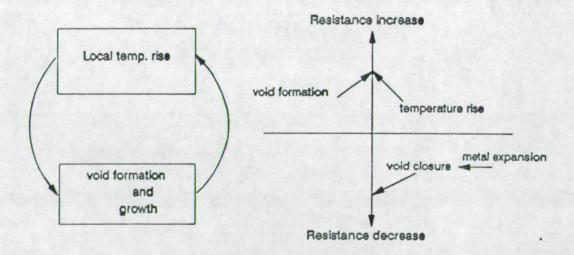

Figure 3-4 shows a smooth resistance versus time curve, but this may not be the case in practice and multiple spikes may occur to further complicate the analysis. This problem is discussed in section 3.4.2.

While the time to failure is determined by the failure time of a worst site along the stripe length, all the grain boundaries at which electromigration is taking place contribute to the resistance change and hence the rate of resistance change is considered to be an appropriate average over the entire stripe. These measurements are carried out before the catastrophic failure processes occur and an understanding of the mechanisms of solid state transport is only possible through measurements carried out in the earlier stages of electromigration damage.

Resistometry has been used to obtain many important electromigration parameters like activation energy, effects of material/processing on the pre-exponential constant in the MTF equation, and also MTF.

# 3.4.1 Resistometry Types

Resistometric measurements have been carried out under three types of stress conditions:

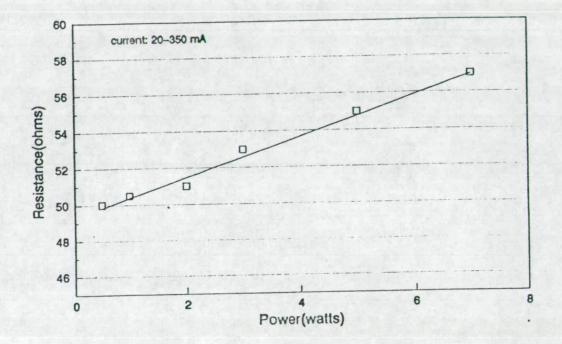

1. High ambient temperature but negligible initial joule heating— This is the simplest of the three types. Samples are subjected to constant current density stress at high temperatures. Current density values are such that the temperature rise is usually small (5 to10°C). Using a minor alteration of this technique, activation energies have been obtained using a single sample by suddenly changing the ambient temperature, but keeping the same current density and noting the ratio of rate of change of resistance.