# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# Characterizing and Exploiting Application Behavior Under Data Corruption

Georgios Stefanakis

Master of Philosophy Institute of Computing Systems Architecture School of Informatics University of Edinburgh 2015

### Abstract

Shrinking semiconductor technologies come at the cost of higher susceptibility to hardware faults that render the systems unreliable. Traditionally, reliability solutions are aimed to protect equally and exhaustively all hardware parts of a system. This is in order to maintain the illusion of a correctly operating hardware. Due to the increasing error rates that induce higher reliability costs, this approach can no longer be sustainable.

It is a fact that hardware faults can be masked by various levels of fault-masking effects. Therefore, not all hardware faults manifest as the same outcome on an application's execution. Motivated by this fact, we propose a shift to vulnerability-driven unequal protection of a given structure (or same-level structures), where the less-vulnerable parts of a structure are protected less than their more-vulnerable counterparts.

For that purpose, in this thesis, we quantitatively investigate how the effect of hardware-induced data corruptions on application behavior varies. We develop a portable software-implemented fault-injection (SWIFI) tool. On top of performing singlebit fault injections to capture their effects on application behavior, our tool is also datalevel aware and tracks the corrupted data to obtain more of their characteristics. This enables to analyze the effects of single-bit data corruptions in relation to the corrupted data characteristics and the executing workload. After a set of extensive fault-injection experiments on programs from the NAS Parallel Benchmarks suite, we obtain detailed insight on how the vulnerability varies; among others, for different application data types and for different bit locations within the data.

The results show that we can characterize the vulnerability of data based on their high-level characteristics (e.g. usage type, size, user and memory space location). Moreover, we conclude that application data are vulnerable in parts. All these show that there is potential in exploiting the application behavior under data corruption. The exhaustive equal protection can be avoided by safely shifting to vulnerability-driven unequal protection within given structures. This can reduce the reliability overheads, without a significant impact on the fault coverage. For that purpose, we demonstrate the potential benefits of exploiting the varying vulnerability characteristics of application data in the case of a data cache.

### Lay Summary

Computer applications are executing on computer hardware and manipulate data stored in the computer hardware to perform computations and decisions according to their intended functionality. Unfortunately the underlying computer hardware is becoming increasingly unreliable due to a variety of physical effects. Such occurrences of hardware faults may unpredictably change the values of the application data causing the computer applications to potentially have unexpected behavior.

Interestingly though, the hardware faults do not affect the executing application always in the same manner; there are many different effects that a hardware fault may have on the behavior of an application. E.g., the application may stop operations, it may complete but compute a wrong output, it may complete successfully, etc.

One of the goals of this thesis is to investigate *how an application behaves under the presence of hardware faults that corrupt the application data*. For that purpose we develop a framework that emulates hardware faults in application data during the execution of an application and captures the resulting behavior of the application. After performing extensive tests on a set of applications, among other things, we can observe which application data are less likely than others to affect the application behavior if corrupted.

Based on this vulnerability insight, we propose that we can *exploit the application data vulnerabilities* to our benefit. As it is imperative that computing systems behave correctly, it has been common to protect fully the computing systems against as many hardware faults as possible. Such exhaustive protection though comes at the cost of increased operating costs and decreased performance in the effort to maximize the system's reliability.

As we find out that not all application data are equally vulnerable, we propose that it is not necessary to fully protect a computing system. Instead we can unequally protect a system by decreasing the protection of the areas that are less vulnerable if a hardware fault occurs there. That way we can reduce the protection overheads with a minimum effect on the system's reliability. As a mean to motivate such a design, we demonstrate the magnitude of potential benefits of unequal protection in the case of one hardware structure in particular, a data cache.

### Acknowledgements

First, I would like to acknowledge the contribution of my supervisors, Marcelo Cintra and Vijay Nagarajan, to this work and to my personal development. Without their effort and guidance, this work wouldn't have been possible and, without their presence, I wouldn't have got where I am today. It is because of them that I got the opportunity to gain valuable research skills and life experience on the inner workings of the academic community.

I would also like to thank the examiners, Boris Grot and Yannis Andreopoulos, for their valuable comments and constructive suggestions on improving the quality of this thesis. Equally important were the rest members of the institute. In particular, I would like to thank the ICSA Directors, Murray Cole and Mike O'Boyle, for all their help and support. Also, my kindest regards go to all the fellow students of the group and to the fellow New Texas residents over the years. Many thanks to all of you Andrew, Fabricio, Karthik, Luna, Murali and Vassilis, who slowly became Kiran, Praveen, Rui, Stan and Ursula.

An extra special thank you goes to all of those that our time overlapped in Edinburgh and got close enough to consider them my friends, made my time in Edinburgh more fun, were kind enough to tolerate me and kept me sane too. Here's a big one for Andrew, George, Konstantina, Lito, Natasa, Nikolas, Salvatore and Vassilis. The same goes for all of those that have kept in touch with me over the years. I may not mention you by name but I am nevertheless very grateful for being there for me and remaining friends throughout the years.

This would not be a proper acknowledgement section without a hello to Jason Isaacs and a shout-out to the EPT/PDT/ETT members. Alexi, Anastasia, Evripidi and Stavre, there is a state-sized thank you coming your way. I cannot picture life without your wisdom, wittiness, bickering, wittering, reposting and five nines availability.

Before concluding this list, I want to state my gratitude to my parents for their support. Last but not least, I would like to thank my dear brother, Filippos, for coping, for being understanding and for being mature enough to handle things in my stead. More so for not making me feel too bad that I hadn't been physically there for him to watch him grow up, all while making me immensely proud of him.

Finally, many thanks to the anonymous EU/UK taxpayer that through its involuntary contribution made it possible to fund this research. I sincerely hope that one day the findings will affect your everyday life in a meaningful manner.

### **Declaration**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified. Some of the material used in this thesis has been published in the following paper:

• Georgios Stefanakis, Vijay Nagarajan, and Marcelo Cintra. Understanding the Effects of Data Corruption on Application Behavior Based on Data Characteristics, In *Proceeding of the 34th International Conference on Computer Safety, Reliability & Security (SAFECOMP)*, September 2015.

(Georgios Stefanakis)

## **Table of Contents**

| Li | List of Figures |                                                               |    |  |

|----|-----------------|---------------------------------------------------------------|----|--|

| Li | List of Tables  |                                                               |    |  |

| 1  | Introduction    |                                                               |    |  |

|    | 1.1             | Fault Masking                                                 | 3  |  |

|    | 1.2             | Problem Statement                                             | 5  |  |

|    | 1.3             | Thesis Goals and Approach                                     | 7  |  |

|    | 1.4             | Thesis Contributions                                          | 9  |  |

|    | 1.5             | Thesis Overview                                               | 10 |  |

| 2  | Cha             | racterization Framework                                       | 13 |  |

|    | 2.1             | Framework Overview                                            | 14 |  |

|    | 2.2             | Single-Fault Injection Tool                                   | 15 |  |

|    |                 | 2.2.1 Fault Trigger                                           | 16 |  |

|    |                 | 2.2.2 Fault Injection and Fault Model                         | 16 |  |

|    |                 | 2.2.3 Monitoring, Data Tracking and Reporting                 | 18 |  |

|    |                 | 2.2.4 Benefits of Binary Instrumentation                      | 22 |  |

|    | 2.3             | Summary                                                       | 23 |  |

| 3  | Арр             | lication Behavior Characterization Under Data Corruption      | 25 |  |

|    | 3.1             | Experimental Setup                                            | 26 |  |

|    | 3.2             | Workload-Related Vulnerability Variation                      | 30 |  |

|    | 3.3             | Application Data Vulnerability Variation                      | 31 |  |

|    |                 | 3.3.1 Per-Bit Vulnerability Variation within Application Data | 34 |  |

|    | 3.4             | Memory Space Vulnerability Variation                          | 40 |  |

|    | 3.5             | Register File Vulnerability Variation                         | 43 |  |

|    | 3.6             | Instruction-Level Vulnerability Variation                     | 47 |  |

|   |                                                                                                                                 | 3.6.1                                                                                                           | Per Instruction Type at Fault Injection                                                                                                                                                                                                                   | 48                                                                                                                                           |

|---|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                                                                 | 3.6.2                                                                                                           | Per Instruction Type at First Consumption                                                                                                                                                                                                                 |                                                                                                                                              |

|   |                                                                                                                                 |                                                                                                                 | of Corrupted Operand                                                                                                                                                                                                                                      | 52                                                                                                                                           |

|   |                                                                                                                                 | 3.6.3                                                                                                           | Program Space Vulnerability                                                                                                                                                                                                                               | 56                                                                                                                                           |

|   |                                                                                                                                 | 3.6.4                                                                                                           | Program Vulnerability Phases                                                                                                                                                                                                                              | 59                                                                                                                                           |

|   | 3.7                                                                                                                             | Summ                                                                                                            | ary                                                                                                                                                                                                                                                       | 62                                                                                                                                           |

| 4 | Exp                                                                                                                             | loiting A                                                                                                       | Application Behavior Characterization                                                                                                                                                                                                                     | 65                                                                                                                                           |

|   | 4.1                                                                                                                             | Exploi                                                                                                          | tation Alternatives                                                                                                                                                                                                                                       | 66                                                                                                                                           |

|   |                                                                                                                                 | 4.1.1                                                                                                           | Identifying Areas of High Exploitability Potential                                                                                                                                                                                                        | 72                                                                                                                                           |

|   | 4.2                                                                                                                             | Data C                                                                                                          | Cache Content Profiling                                                                                                                                                                                                                                   | 75                                                                                                                                           |

|   |                                                                                                                                 | 4.2.1                                                                                                           | Data Cache Content Profiler                                                                                                                                                                                                                               | 75                                                                                                                                           |

|   |                                                                                                                                 | 4.2.2                                                                                                           | Experimental Setup and Profiling Results                                                                                                                                                                                                                  | 79                                                                                                                                           |

|   | 4.3                                                                                                                             | Per-Bi                                                                                                          | t Data-Level Vulnerability Exploitation Benefits in a Data Cache                                                                                                                                                                                          | 83                                                                                                                                           |

|   |                                                                                                                                 | 4.3.1                                                                                                           | Strongly-Protected Surface Trade-Offs Against Fault Coverage                                                                                                                                                                                              | 86                                                                                                                                           |

|   |                                                                                                                                 | 4.3.2                                                                                                           | Practicality Issues of This Case Study                                                                                                                                                                                                                    | 94                                                                                                                                           |

|   | 4.4                                                                                                                             | Summ                                                                                                            | ary                                                                                                                                                                                                                                                       | 96                                                                                                                                           |

|   |                                                                                                                                 |                                                                                                                 | •                                                                                                                                                                                                                                                         |                                                                                                                                              |

| 5 | Rela                                                                                                                            | ted Wo                                                                                                          | rk                                                                                                                                                                                                                                                        | 99                                                                                                                                           |

| 5 | <b>Rela</b><br>5.1                                                                                                              |                                                                                                                 | rk                                                                                                                                                                                                                                                        | <b>99</b><br>101                                                                                                                             |

| 5 |                                                                                                                                 |                                                                                                                 |                                                                                                                                                                                                                                                           |                                                                                                                                              |

| 5 |                                                                                                                                 | Monito                                                                                                          | oring Behavior Under Data Corruption                                                                                                                                                                                                                      | 101                                                                                                                                          |

| 5 |                                                                                                                                 | Monito<br>5.1.1<br>5.1.2                                                                                        | DescriptionDescriptionDescriptionDescriptionAnalytical TechniquesDescriptionDescription                                                                                                                                                                   | 101<br>101                                                                                                                                   |

| 5 | 5.1                                                                                                                             | Monito<br>5.1.1<br>5.1.2<br>Observ                                                                              | DescriptionDescriptionDescriptionDescriptionAnalytical TechniquesDescriptionDescriptionDescriptionExperimental TechniquesDescriptionDescriptionDescription                                                                                                | 101<br>101<br>102                                                                                                                            |

| 5 | 5.1<br>5.2                                                                                                                      | Monito<br>5.1.1<br>5.1.2<br>Observ<br>Shiftin                                                                   | DescriptionDescriptionDescriptionDescriptionAnalytical TechniquesAnalytical TechniquesAnalytical TechniquesExperimental TechniquesFault InjectionAnalytical Analytical TechniquesVing Vulnerability VariationsAnalytical Analytical Analytical Techniques | 101<br>101<br>102<br>104                                                                                                                     |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                                                                                   | Monito<br>5.1.1<br>5.1.2<br>Observ<br>Shiftin<br>Fault-T                                                        | oring Behavior Under Data Corruption                                                                                                                                                                                                                      | 101<br>101<br>102<br>104<br>107                                                                                                              |

| 5 | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul>                                                     | Monito<br>5.1.1<br>5.1.2<br>Observ<br>Shiftin<br>Fault-T                                                        | oring Behavior Under Data Corruption                                                                                                                                                                                                                      | 101<br>101<br>102<br>104<br>107<br>110<br>115                                                                                                |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul>                                                     | Monito<br>5.1.1<br>5.1.2<br>Observ<br>Shiftin<br>Fault-7<br>Summ                                                | oring Behavior Under Data Corruption                                                                                                                                                                                                                      | 101<br>101<br>102<br>104<br>107<br>110                                                                                                       |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>Con</li> </ul>                                        | Monito<br>5.1.1<br>5.1.2<br>Observ<br>Shiftin<br>Fault-7<br>Summ<br><b>clusion</b><br>Summ                      | oring Behavior Under Data Corruption                                                                                                                                                                                                                      | <ol> <li>101</li> <li>101</li> <li>102</li> <li>104</li> <li>107</li> <li>110</li> <li>115</li> <li>117</li> </ol>                           |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>Con</li> <li>6.1</li> </ul>                           | Monito<br>5.1.1<br>5.1.2<br>Observ<br>Shiftin<br>Fault-7<br>Summ<br><b>clusion</b><br>Summ<br>Contril           | bring Behavior Under Data Corruption   Analytical Techniques   Experimental Techniques - Fault Injection   Ving Vulnerability Variations   g to a Hardware/Software Co-Approach   Folerant Cache Design   ary                                             | <ol> <li>101</li> <li>101</li> <li>102</li> <li>104</li> <li>107</li> <li>110</li> <li>115</li> <li>117</li> <li>118</li> </ol>              |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>Con</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> </ul> | Monito<br>5.1.1<br>5.1.2<br>Observ<br>Shiftin<br>Fault-7<br>Summ<br><b>clusion</b><br>Summ<br>Contril<br>Future | bring Behavior Under Data Corruption   Analytical Techniques   Experimental Techniques - Fault Injection   Ving Vulnerability Variations   g to a Hardware/Software Co-Approach   Colerant Cache Design   ary                                             | <ul> <li>101</li> <li>101</li> <li>102</li> <li>104</li> <li>107</li> <li>110</li> <li>115</li> <li>117</li> <li>118</li> <li>120</li> </ul> |

# **List of Figures**

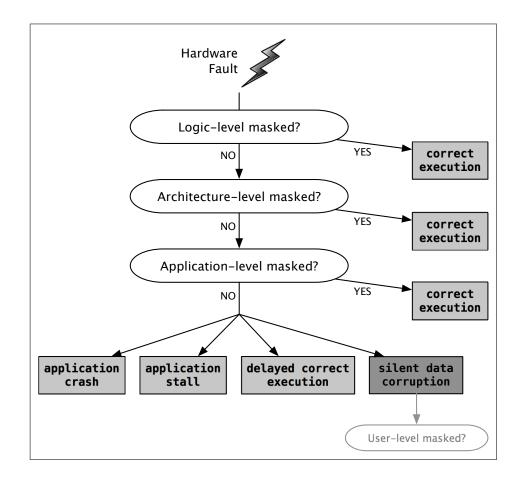

| 1.1  | Visualization of fault-masking effects and corruption outcomes          | 5  |

|------|-------------------------------------------------------------------------|----|

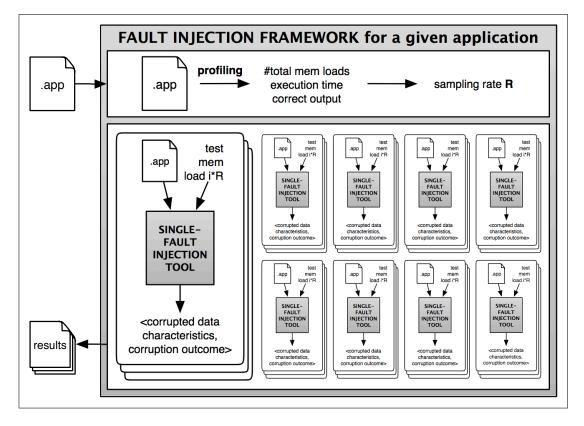

| 2.1  | Complete SWIFI framework overview                                       | 15 |

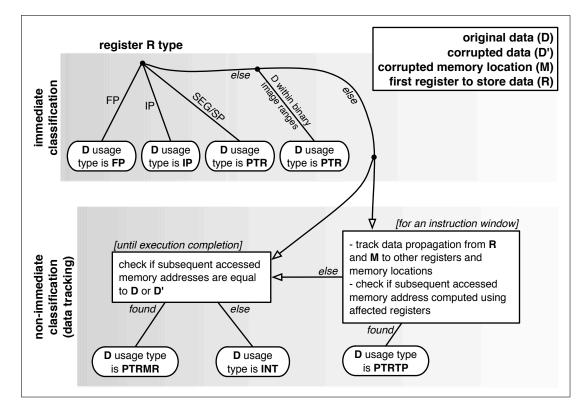

| 2.2  | Decision tree for determining application data usage type               | 18 |

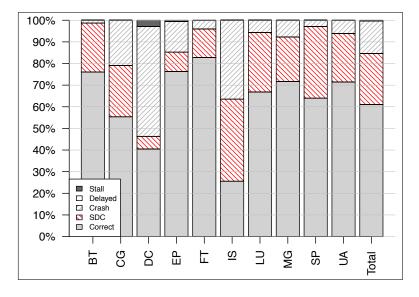

| 3.1  | Workload-related vulnerability variation (Full NPB)                     | 31 |

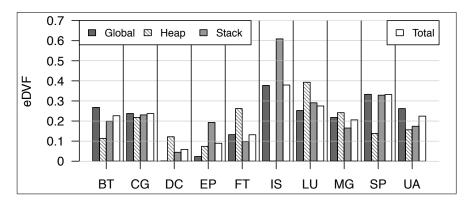

| 3.2  | Data memory location related vulnerability variation (Full NPB)         | 32 |

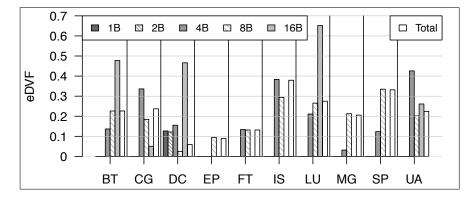

| 3.3  | Data size related vulnerability variation (Full NPB)                    | 32 |

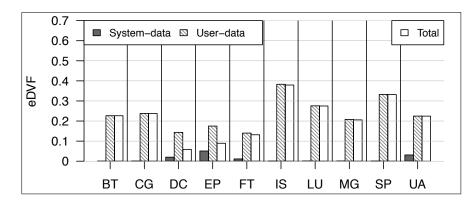

| 3.4  | Data user related vulnerability variation (Full NPB)                    | 33 |

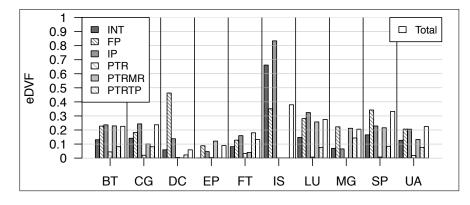

| 3.5  | Data usage type related vulnerability variation (Full NPB)              | 33 |

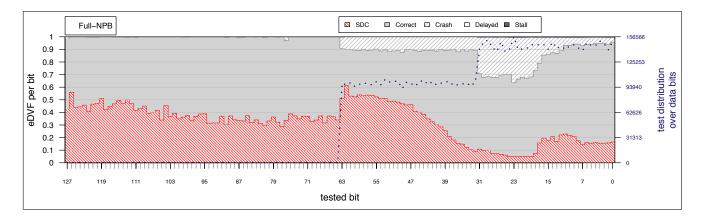

| 3.6  | Per-bit vulnerability variation (Full NPB)                              | 35 |

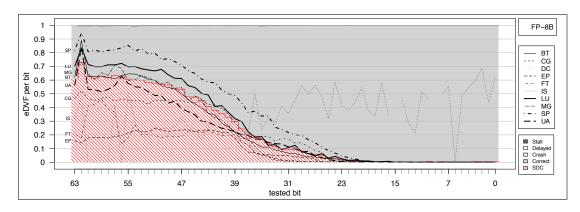

| 3.7  | Per-bit vulnerability variation of FP 8 byte data (Full NPB)            | 36 |

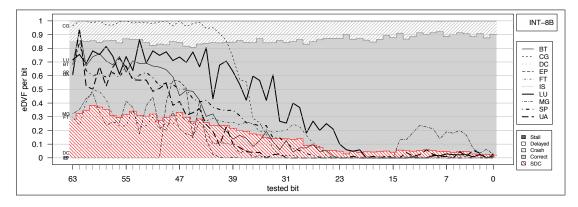

| 3.8  | Per-bit vulnerability variation of INT 8 byte data (Full NPB)           | 36 |

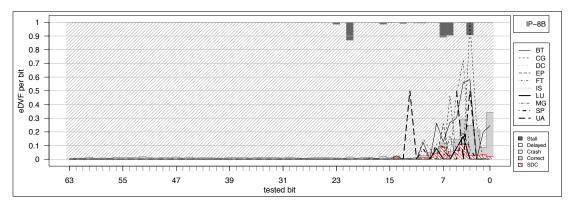

| 3.9  | Per-bit vulnerability variation of IP 8 byte data (Full NPB)            | 37 |

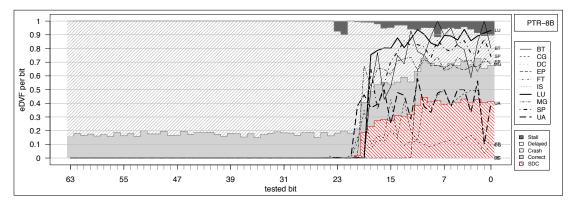

| 3.10 | Per-bit vulnerability variation of PTR 8 byte data (Full NPB)           | 37 |

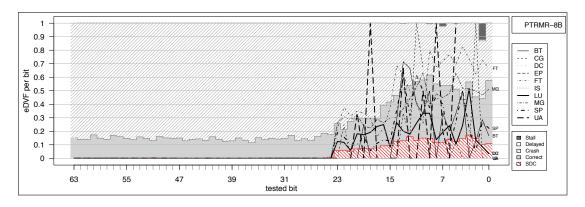

| 3.11 | Per-bit vulnerability variation of PTRMR 8 byte data (Full NPB)         | 38 |

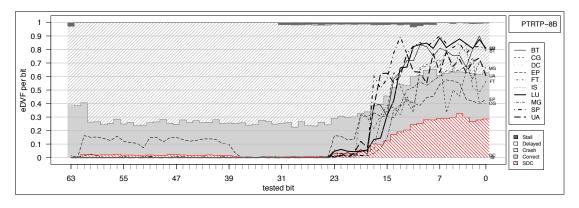

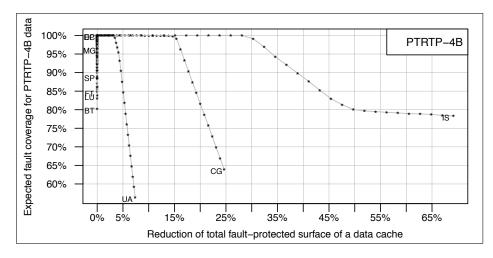

| 3.12 | Per-bit vulnerability variation of PTRTP 8 byte data (Full NPB)         | 38 |

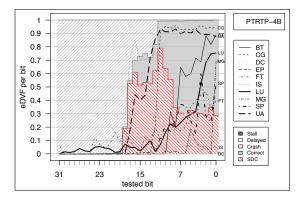

| 3.13 | Per-bit vulnerability variation of PTRTP 4 byte data (Full NPB)         | 39 |

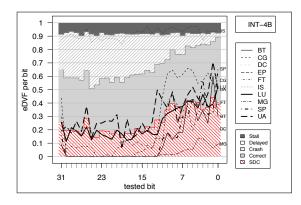

| 3.14 | Per-bit vulnerability variation of INT 4 byte data (Full NPB)           | 39 |

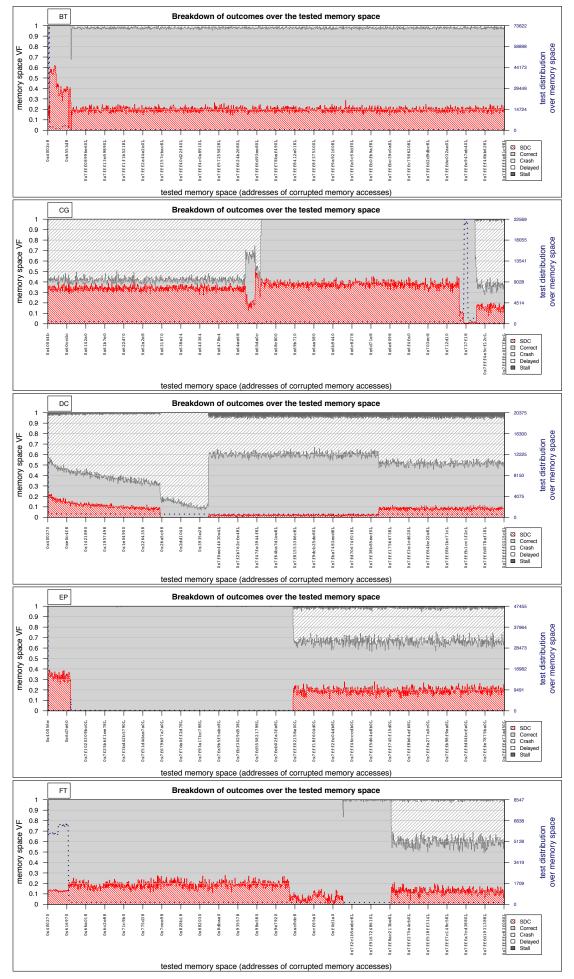

| 3.15 | Memory space vulnerability variation (BT, CG, DC, EP, FT)               | 41 |

| 3.16 | Memory space vulnerability variation (IS, LU, MG, SP, UA)               | 42 |

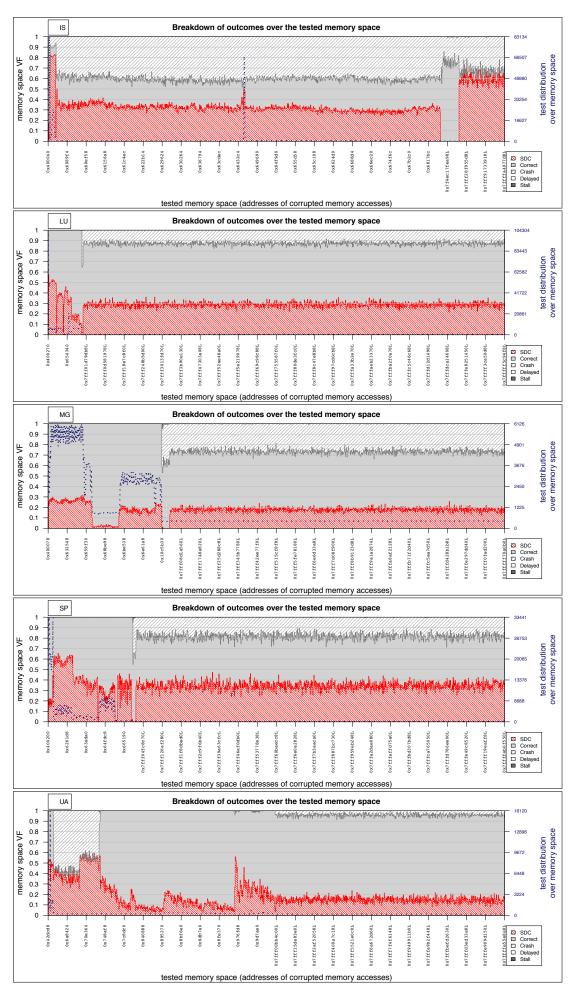

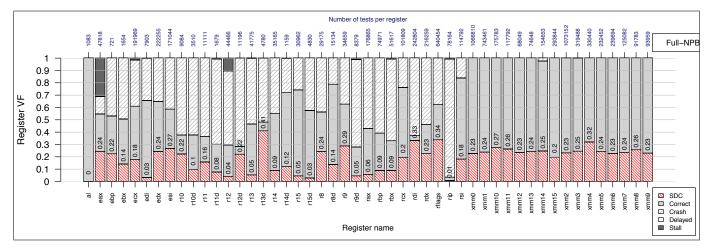

| 3.17 | Register file vulnerability variation (Full NPB)                        | 44 |

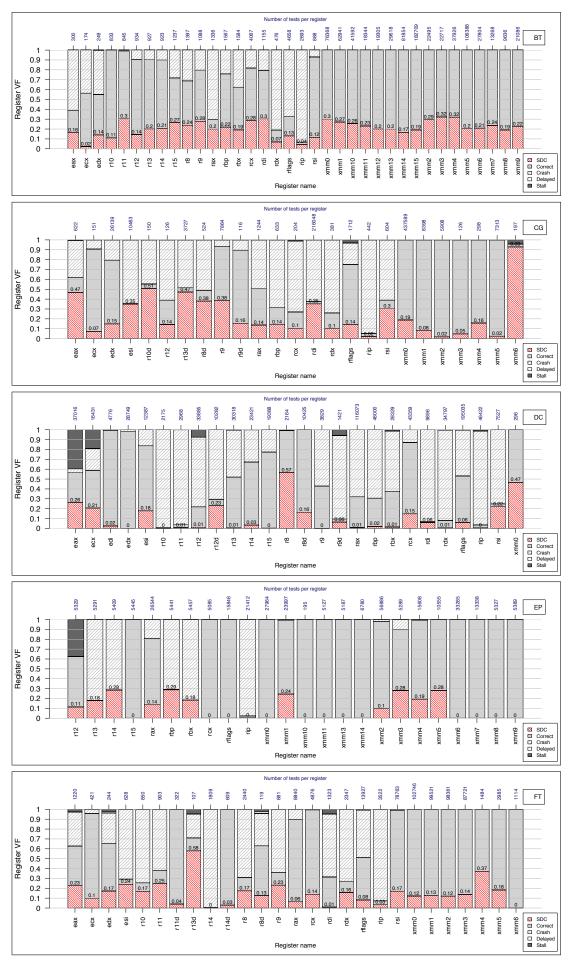

| 3.18 | Register file vulnerability variation (BT, CG, DC, EP, FT)              | 45 |

| 3.19 | Register file vulnerability variation (IS, LU, MG, SP, UA)              | 46 |

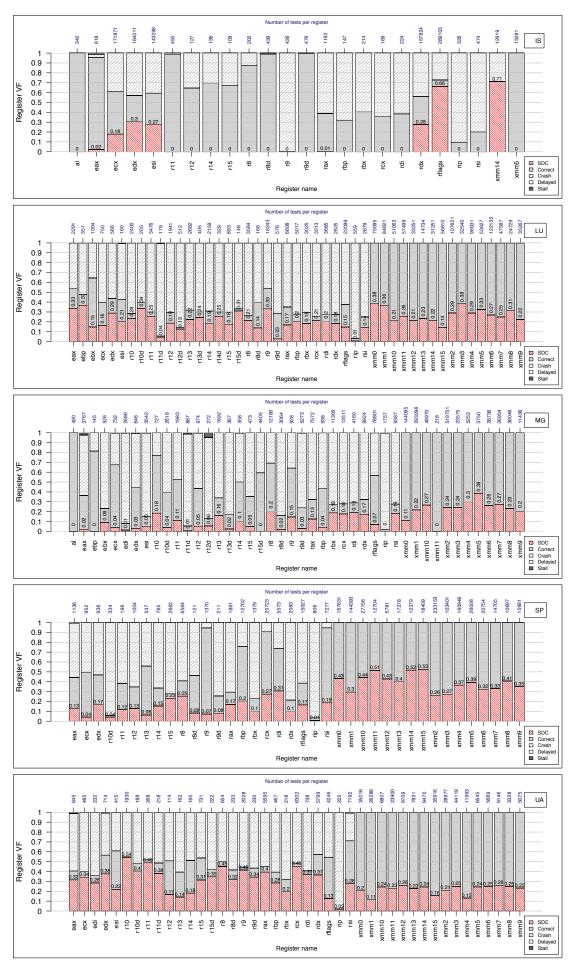

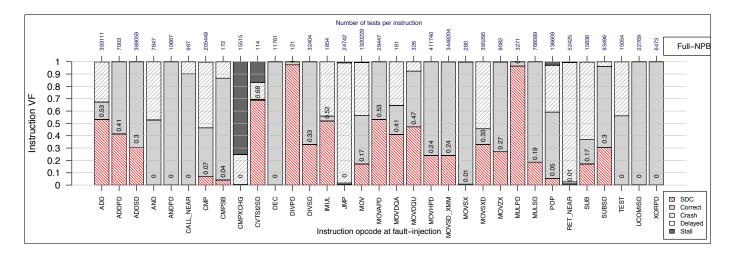

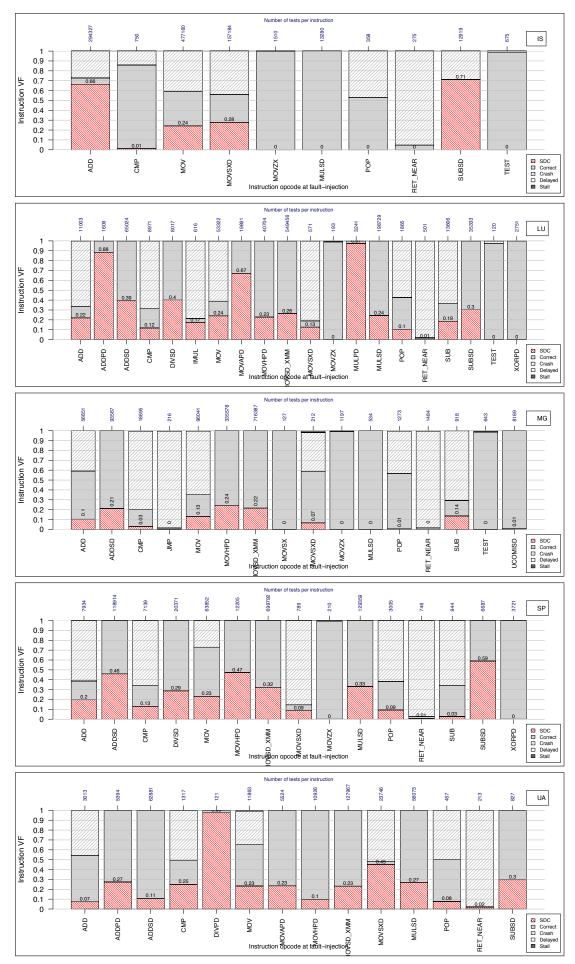

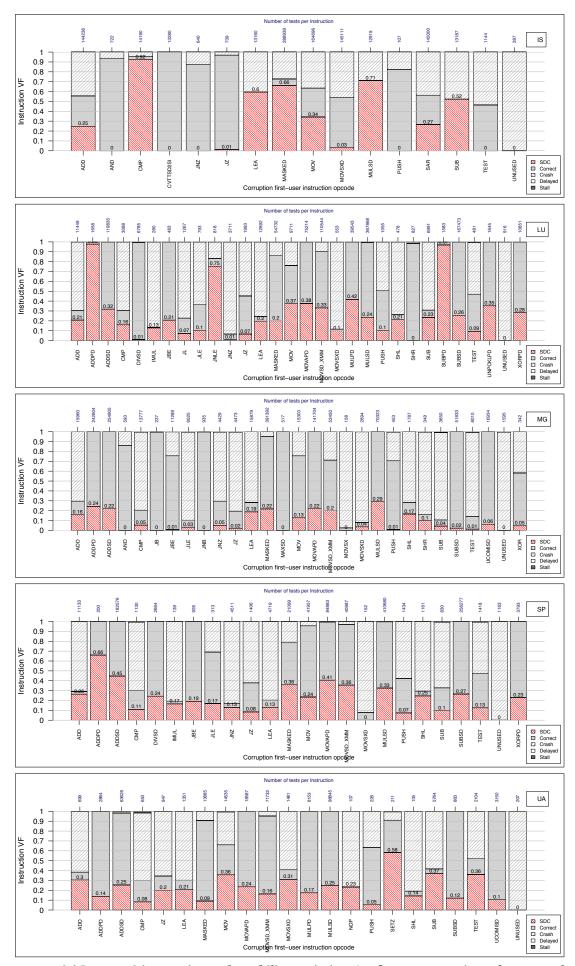

| 3.20 | Instruction vulnerability variation at fault injection (Full NPB)       | 48 |

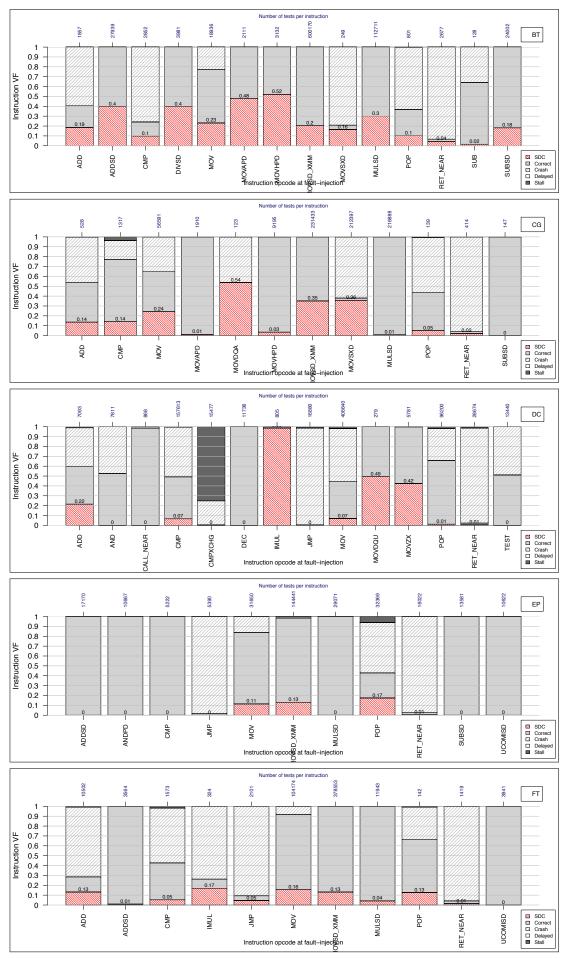

| 3.21 | Instruction vulnerability variation at fault injection (BT, CG, DC, EP, |    |

|      | FT)                                                                     | 49 |

| 3.22 | Instruction vulnerability variation at fault injection (IS, LU, MG, SP, |    |

|------|-------------------------------------------------------------------------|----|

|      | UA)                                                                     | 50 |

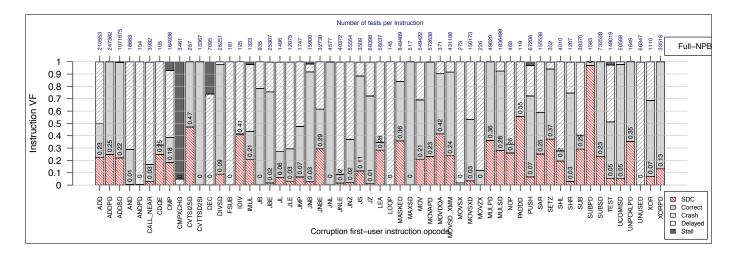

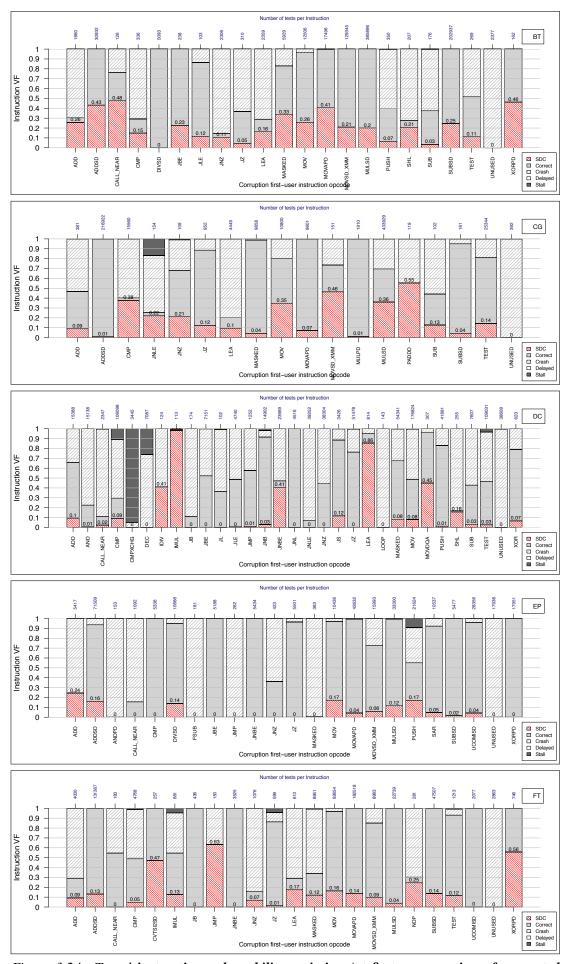

| 3.23 | Instruction vulnerability variation at first consumption of corrupted   |    |

|      | operand (Full NPB)                                                      | 52 |

| 3.24 | Instruction vulnerability variation at first consumption of corrupted   |    |

|      | operand (BT, CG, DC, EP, FT)                                            | 53 |

| 3.25 | Instruction vulnerability variation at fault consumption of corrupted   |    |

|      | operand (IS, LU, MG, SP, UA)                                            | 54 |

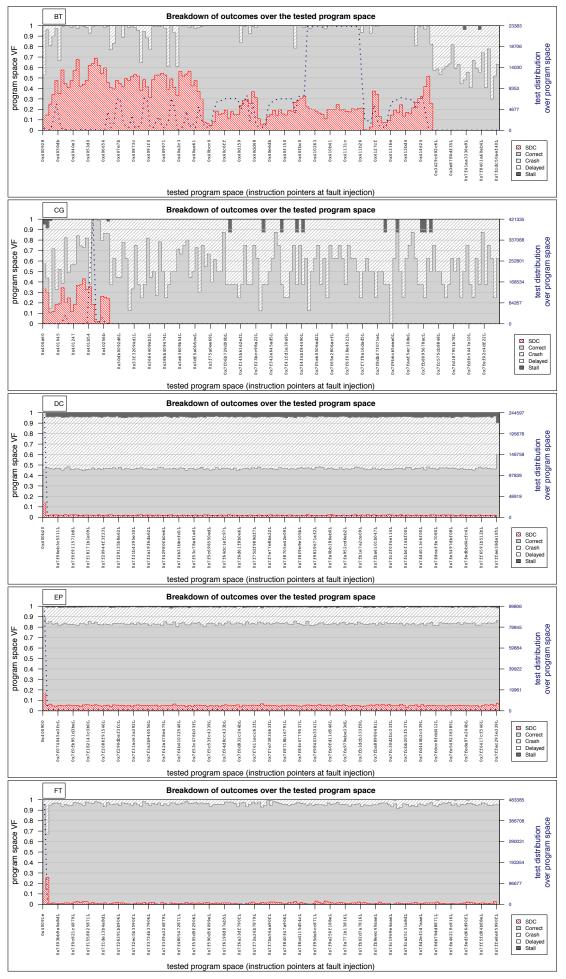

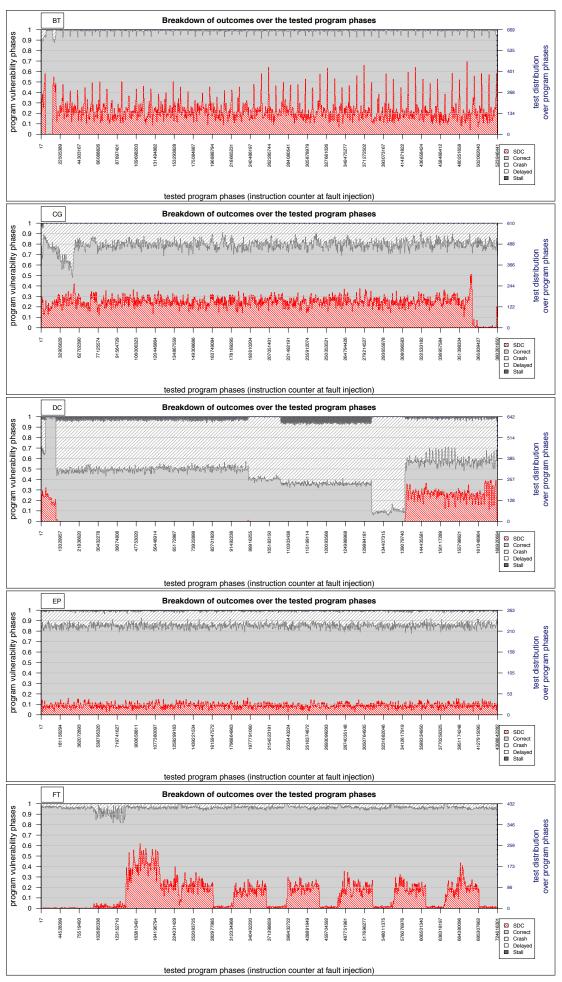

| 3.26 | Program space vulnerability variation (BT, CG, DC, EP, FT)              | 57 |

| 3.27 | Program space vulnerability variation (IS, LU, MG, SP, UA)              | 58 |

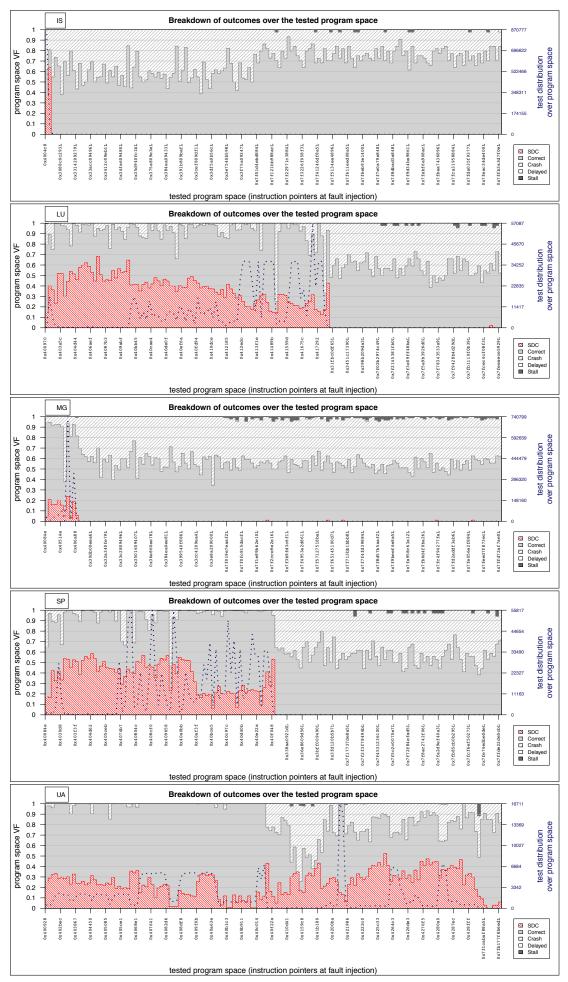

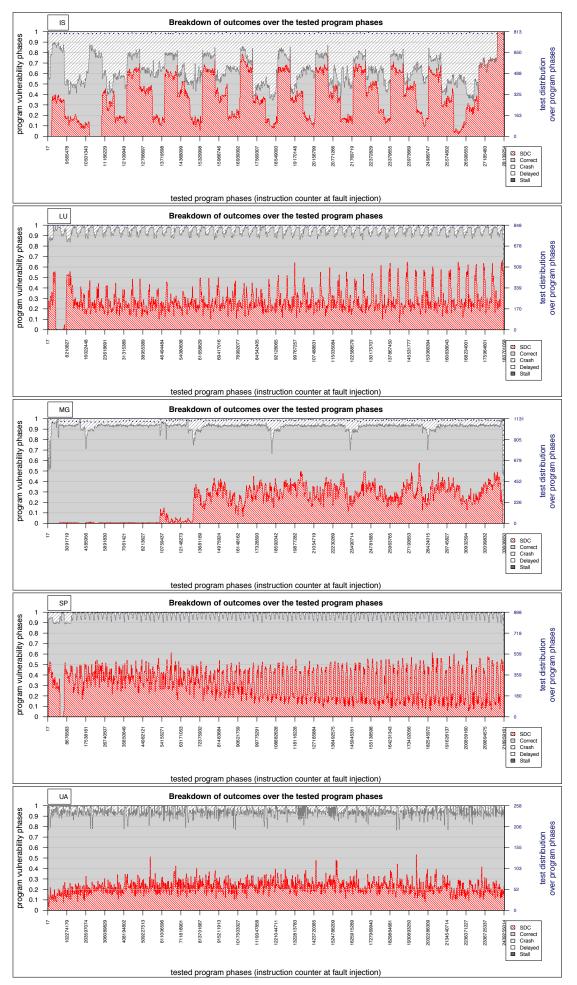

| 3.28 | Program vulnerability phases (BT, CG, DC, EP, FT)                       | 60 |

| 3.29 | Program vulnerability phases (IS, LU, MG, SP, UA)                       | 61 |

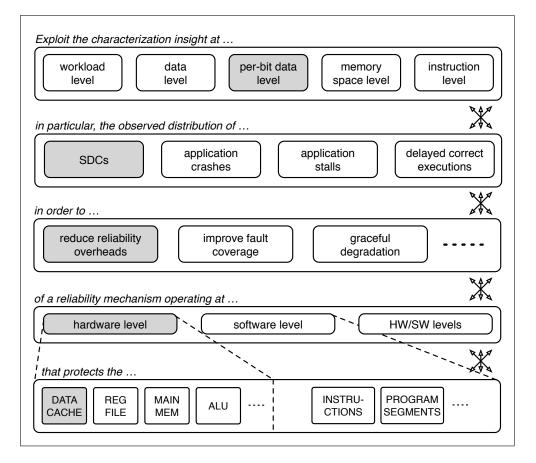

| 4.1  | Visualization of the exploitation alternatives                          | 67 |

| 4.2  | Management of concurrent usage type classification for in-order data    |    |

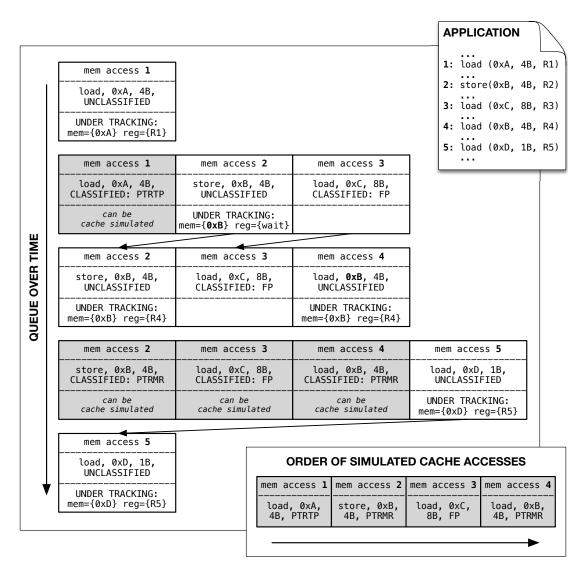

|      | cache content profiling                                                 | 78 |

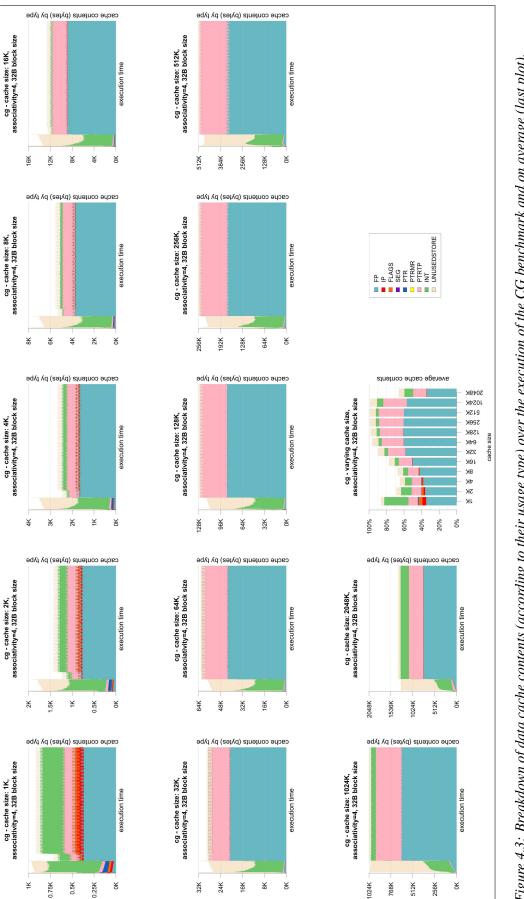

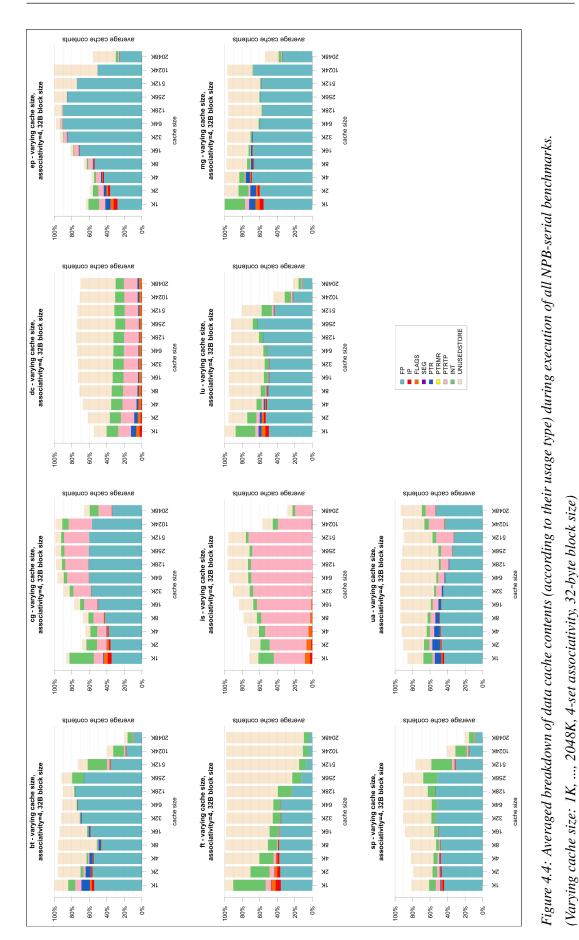

| 4.3  | Data cache content profiling per usage type (over execution time) (CG)  | 81 |

| 4.4  | Data cache content profiling per usage type (averaged) (Full NPB)       | 82 |

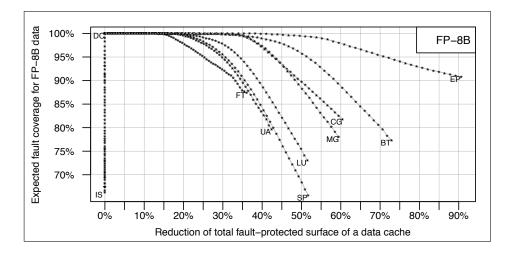

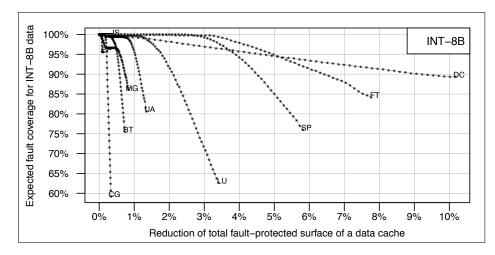

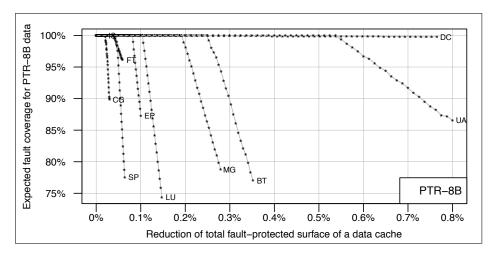

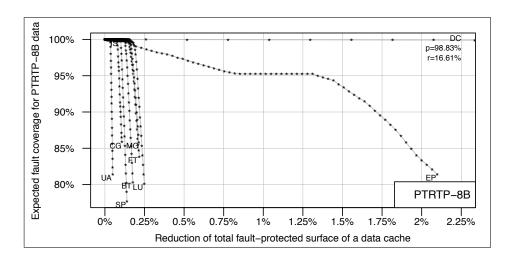

| 4.5  | Trading-off fault coverage of FP 8 byte data (Full NPB)                 | 89 |

| 4.6  | Trading-off fault coverage of INT 8 byte data (Full NPB)                | 90 |

| 4.7  | Trading-off fault coverage of PTR 8 byte data (Full NPB)                | 90 |

| 4.8  | Trading-off fault coverage of PTRTP 8 byte data (Full NPB)              | 91 |

| 4.9  | Trading-off fault coverage of PTRTP 4 byte data (Full NPB)              | 92 |

## **List of Tables**

| 2.1 | Reported corruption characteristics                               | 20 |

|-----|-------------------------------------------------------------------|----|

| 2.2 | Reported corruption effects                                       | 21 |

| 3.1 | Profiling and sampling information for each tested benchmark      | 29 |

| 4.1 | Breakdown of data cache contents per data type and data size (64K |    |

|     | cache) (Full NPB)                                                 | 85 |

| 4.2 | 'Unused' data cache contents/space (64K cache) (Full NPB)         | 93 |

## **Chapter 1**

### Introduction

Hardware reliability challenges have always been present in all parts of a system (logic, interconnects, memory elements). Examples include wire-induced noise corrupting data communicating over the interconnects, operating voltage/frequency scaling causing timing violations, gamma ray and alpha particle strikes flipping values in transistors, ageing or manufacturing defects causing deterioration of chips and systems.

All such occurrences of anomalous physical conditions are called *hardware faults* [45]. According to their duration, hardware faults can be classified into (a) *transient faults* (soft errors or single event upsets) that occur only once and do not persist, (b) *permanent faults* (hard faults) that occur at some point in time and persist from that time onward and (c) *intermittent faults* that occur repeatedly but not continuously in the same location.

Once a hardware fault occurs, it is upsetting logic values. Therefore, regardless of the cause or the duration of hardware faults, all of them essentially lead to data corruption. As data corruptions affect a system's dependability, hardware faults must be dealt with to ensure the hardware's reliability.

Hardware faults are not a recent challenge and extensive research work is already present to enable fault-tolerant features in a system. The purpose of *fault-tolerant design* is to improve dependability by enabling a system to perform its intended behavior in the presence of a given number of faults [32].

As such, hardware faults need to be detected and corrected to ensure the correct operation of a system. The approach to tolerate a fault depends on its type. Generally, a set of up to four steps needs to be followed in order to tolerate a fault [45]: (1) *Error detection*, where the system becomes aware of the presence of a fault, (2) *Error*

*recovery* (error correction), where the system tries to mask the fault's effect and set the correct expected behavior, (3) *Fault diagnosis*, where the type and location of the fault is identified (not for transient faults), and (4) *Self repair*, where the system is repaired or reconfigured to avoid the diagnosed fault.

Each step requires a form of redundancy in terms of extra hardware and/or computations. Thus, reliability solutions always come with associated performance and cost overheads in their effort to ensure the highest possible fault coverage.

As it is desirable for systems to maintain their expected functionality, even in the presence of faults, hardware reliability and correctness has become a design target equally important to high performance and low cost. Due to the necessity of a correctly operating infrastructure, especially on safety and mission critical systems, a common approach has been to deal with hardware faults exclusively at the hardware level. In that effort to ensure that the hardware operates correctly, all system components are protected equally, exhaustively and transparently between the hardware/software stack levels. Not unexpectedly, adding the necessary redundancy comes with an overhead of extra operating costs and/or reduced performance. Such reliability-associated costs are not an issue for the safety and mission critical systems.

As we move into deep submicron fabrication technologies the reliability challenges start to appear in an ever-increasing rate [40]. As a result reliability concerns now arise in commodity systems too. Once more the general consensus is to protect all system components equally, exhaustively and transparently between the hardware/software levels. This time though, due to the cost concerns in commodity systems, the various proposed reliability mechanisms aim to maximize dependability under a minimum performance/cost penalty. As such, most existing reliability approaches focus on reducing these reliability associated overheads by tinkering with the implementation details. All these while ensuring that the hardware faults are hidden from the upper architectural/software layers in order to still provide them with the behavior of a fault-free hardware layer.

Unfortunately, due to the increasing error rates in successive process generations, this black box approach cannot be maintained for much longer [9]. We are reaching the point where it will be unsustainable to deal with all the faults at the hardware level transparently. It will become prohibitively expensive, both in terms of power/area cost and performance to tolerate all hardware faults and guarantee a fully protected underlying hardware.

All these lead to the general problem that motivated this thesis; *increasing error rates inducing unsustainable higher reliability costs, especially due to the equal and exhaustive protection.*

The rest of this introductory chapter is organized as follows: Section 1.1 introduces the natural fault-masking effects that are the motivation to our proposed solution to the problem of unsustainably increasing reliability costs. Section 1.2 shifts the original problem into the two new problems that this thesis intends to tackle in order to reduce the reliability costs. Section 1.3 states the goals of this thesis and overviews our approach to achieve them. Section 1.4 states our main contributions. Finally, Section 1.5 concludes this chapter with an overview of this thesis.

#### 1.1 Fault Masking

Interestingly, not all hardware faults end up manifesting as errors in the system's behavior and the executing application's behavior.

In fact, depending on the fault characteristics (location, type, timing, duration), the executing workload and the underlying hardware, a hardware fault may get masked for a variety of reasons by various levels of fault-masking effects [45]:

- *Logic-level masking*, where a hardware fault may get masked at logic gate level before becoming an error, e.g., a 2-input AND gate's output will not change if it has a fault in one input and a zero in its other input.

- *Architecture-level masking*, where a hardware fault is not logically masked but may never propagate to the architectural state, e.g., a hardware fault in memory in the non-opcode bits of a NOP instruction or a hardware fault in the branch predictor.

- *Application-level masking*, where a hardware fault is not architecturally masked but may never propagate to the application's output, e.g., a hardware fault in a memory location that is never to be accessed again.

Once a fault does get masked by any fault-masking level, then the system and the executing application behave as expected resulting into a *correct application execution*. If a hardware fault does not get masked and becomes an error, the effect on the executing application varies and may be one of the following:

- *Application crash*, where the not-masked hardware fault leads to an invalid operation that causes the application to crash.

- *Application stall*, where the not-masked hardware fault causes the application to wrongly wait for an event that will never occur or lead the application to enter an infinite execution.

- *Delayed correct execution*, where the not-masked hardware fault does not corrupt the application output but causes the computation to complete in a larger-than-usual delay.

- *Silent data corruption (SDC)*, where the not-masked hardware fault propagates to the application output causing it to be different than the expected one. Contrary to all the previous execution upsets that are observable when they occur, these cases where the output is wrong are unobservable execution upsets. They can be identified *only* after application completion by comparing the effective application output to the expected correct one. This non-observability of SDCs make them the most severe case of possible execution outcomes under hardware faults. There is also a special case of SDCs, that will not be considered by this thesis, where the output corruption is masked at user level by not being perceived as a wrong output, e.g., a single wrong pixel color in a frame of a video.

Fig. 1.1 visually depicts the possible fault-masking levels and the possible corrupted execution outcomes. To summarize, depending on the fault characteristics (location, type, timing, duration), the executing workload and the underlying hardware, faults can either (a) get masked by various levels of fault-masking effects (logic-, architectural-, application-level) and result in a correct execution with no visible effects or (b) not get masked and result either in an observable execution upset (application crash, stall or delay) or an unobservable output corruption (silent data corruption).

All these fault-masking effects have been widely documented by prior works, especially those that experimentally evaluate the dependability of fault-tolerant approaches. In such works a breakdown of possible execution outcomes is usually presented and the fault coverage is commonly measured as the percentage of the resulting SDCs.

Generally, the focus has always been on reducing the occurrence of SDCs because they are the most severe ones. SDCs are the only execution outcome that is undetectable online by any means and that does not provide any indication that something happened out of the ordinary. All other corruption outcomes are observable and detectable by conventional methods, e.g., software-visible symptom-based fault detection [50, 27, 37, 13, 8] monitors for suspicious behaviors/symptoms, such as violating likely program invariants, memory exceptions, cache misses, branch mispredictions, fatal exceptions, program crashes, high OS activity, hangs.

Figure 1.1: A hardware fault possibly getting masked by different levels of fault-masking effects and resulting into different possible corruption outcomes.

#### 1.2 Problem Statement

As mentioned, reliability solutions face the problem of the unsustainably increasing overhead costs as the hardware fault error rates increase, especially due to the tendency to protect all hardware and software components equally and exhaustively.

Mainly motivated by the aforementioned fact that not all hardware faults manifest as the same symptom in an application's execution and can be masked by various levels of fault-masking effects, this thesis proposes a solution to the unsustainable reliability costs. We propose that we can avoid protecting equally and exhaustively the underlying hardware. Instead we suggest a shift to vulnerability-driven unequal-protection mechanisms, where the protection strength is assigned according to the error sensitivity of the components under protection. Our proposed shift to unequal protection will be targeting a given structure or same-level structures.

Given that the end-to-end effect of a hardware fault on the application output is what matters and, in particular, since only faults that lead to SDCs are what need to be protected against, the area that needs to be protected strongly against faults can be reduced. This intuitively translates into reliability overhead reductions without affecting the fault coverage. Alternatively, this points out that for the same overhead the fault coverage can be increased and help sustain the increasing error rates. This is contrary to most of existing fault-tolerance approaches that tend to be conservative and do not leverage the inherent masking of hardware faults.

As what we propose is to assign protection to hardware/software components according to their likelihood that a fault occurring there will cause an SDC to the final execution outcome, this thesis intends to tackle the problem of driving and implementing vulnerability-driven reliability mechanisms.

This means that in order to solve the original problem of high unsustainable reliability costs we shift the problem into:

- observing and characterizing the exact end-to-end effects of hardware faults on application behavior, and

- exploiting the gained insight in a vulnerability-driven reliability mechanism to reduce the reliability overheads in a given structure or same-level structures.

Generally we expect that useful insight can be gained by characterizing the application behavior under hardware-induced data corruption conditions. In particular, we expect that application behavior under unreliable conditions will vary and we intend to exploit these variations to our benefit. Given the expected error sensitivity variations, we will use this to avoid exhaustive equal protection and reduce the reliability overheads, without a significant reliability impact, by shifting to a class of vulnerability-aware unequal-protection architectures, where less-vulnerable application data are protected less against corruption than their more-vulnerable counterparts.

#### 1.3 Thesis Goals and Approach

Our proposed thesis goals revolve around investigating how the effect of hardwareinduced data corruptions on application behavior varies with the purpose of identifying exploitable insight in order to reduce the reliability costs by shifting into a vulnerability-aware protection paradigm.

The goals of this thesis relate exactly to the twofold problem we intend to tackle. Generally speaking, the research goal of this thesis is to answer the following questions: (1) *Can application behavior under data corruption be characterized based on the characteristics of the corrupted data (type, bit, location, etc.) and what data-level error-sensitivity observations can be made?* (2) *How can this characterization insight be exploited to drive the design of lower-cost vulnerability-aware unequally-protected architectures?*

To characterize the effects of hardware-induced data corruption on application behavior based on the corrupted data characteristics and the executing workload, we use software-implemented fault injection (SWIFI). This is to model transient fault data corruption in memory locations, during the operation of an application in a unprotected system, and to capture the effect of the corruption on the execution.

As our focus is on gaining detailed error-sensitivity insight of application data types, we develop a portable instrumentation-based SWIFI tool that operates at *application data level*. Given an application binary, without need of its source code, the SWIFI tool can finely control the location of the corruption in the application's memory address space without further intruding the application behavior. Once a fault is injected at runtime, without need for binary file modifications per injection test, it tracks the corrupted data to classify them according to their use by the application. Meanwhile it monitors the execution's state and outcome to report back many diagnostics regarding the corruption and the corruption outcome. Since we monitor the full application behavior under data corruption until completion, we capture all higher levels of fault-masking effects and all possible outcomes of a data corruption (ranging from silent data corruption on one side of the spectrum to correct execution with no visible effects on the other side).

SWIFI is an established method commonly used in the literature as it is a straightforward, fast and easy to deploy way to inject realistic faults in real systems, while allowing for more detailed monitoring/reporting. It has been used mainly for systemlevel dependability assessment of reliability mechanisms [20, 42, 48, 7, 39] but usually without further elaboration on the vulnerabilities of individual hardware/software structures. Other non fault-injection approaches do vulnerability estimation through detailed modeling to analyze the behavior of only higher-level hardware structures [31, 46, 47]. Instead, we employ SWIFI in order to gain detailed *error sensitivity insight* at a lower *application data level*.

The main value of our study stems from investigating data-level (down to bitlevel) vulnerability variations. As we can perform an extensive set of individual faultinjection tests that report many diagnostic information, we can thoroughly characterize the data corruption effects on application behavior based on the characteristics of the corrupted data; namely, among others, their location within the memory address space, their size, their type as used by the application and, even, the exact bit location of the corruption. This enables us to quantitatively investigate how the acuteness of the effect of a hardware-induced data corruption on application varies. As a result we can observe the *actual* varying vulnerability characteristics at application *data-level*, down to identifying bit ranges within specific types of application data that if corrupted by a single-event-upset are less prone to manifest as SDCs. This approach is more detailed compared to existing studies, that also focus on vulnerability estimation, but are limited due to investigating higher abstraction structures (e.g., specific hardware structures [31, 46], code segments [13], instructions [6, 29]) or due to using limited assumptions for estimating the vulnerabilities (e.g., characterizing individual memory locations only by their liveliness attributes [29]). Moreover, as hardware functionality is largely visible through software, the injected faults can emulate faults at various levels of a system and not only at application data level. As such we can extrapolate the insight to error sensitivity of instructions, memory address space and registers too.

After correlating the corruption characteristics to the reported corruption effects on the application behavior, we gain statistical insight into the application data vulnerabilities per tested workload. It is observed that there are vulnerability variations between application data, even within bit ranges of specific application data types.

Given that the gained insight from the characterization study essentially estimates *data-level vulnerability factors* for a given workload, it can be **exploited by shift-ing to vulnerability-driven unequally-protected architectures** where the application data are protected unequally according to their expected vulnerability. Moving down into characterizing data-level vulnerabilities, instead of higher-level hardware/software

structures, results into deeper and more exploitable insight by a variety of protection schemes.

One promising way to exploit such insight is for reducing the cost of existing faulttolerant mechanisms that tend to protect everything equally. We argue that such a shift is highly beneficial; the protection overhead can be reduced without a significant impact on fault coverage, as we reduce the fault-protected surface by avoiding the excessive full protection of the previously identified less-vulnerable application data. This is contrary to traditional reliability approaches that either unnecessarily protect all parts equally and exhaustively [16, 19, 52, 11] or offer unequal protection agnostic to the actual distribution of likelihood of the application's data to corrupt the execution output [55, 22, 23].

Achieving these goals will allow to sustain the same reliability QoS as before but for lower operating costs or higher performance. This can be translated also into sustaining a reliable operation of applications on the increasingly unreliable hardware.

Moreover, as our proposed class of vulnerability-aware fault-tolerant architectures can have varying fault protection levels, it lends itself naturally to offer various degrees of *reliability QoS* for trading off reliability against performance/cost. Considering that our characterization study goes down to bit-level vulnerability estimation, the performance/cost benefits can be maximized for an even smoother trading off against reliability. This also enables graceful degrading architectures where for a given error rate we may achieve better metrics than existing techniques and guarantee a minimum set of executing functions.

Finally, vulnerability-aware unequal protection is orthogonal to the specifics of fault-tolerant approaches. It may be applied to any kind of software- or hardware-level fault tolerance method to reduce the total area under protection and, subsequently, their reliability overhead.

As an instance to demonstrate the applicability and potential of exploiting the varying vulnerability characteristics of application data, we assume a data cache design that can unequally protect its contents driven by our characterization insight and we observe the trade-offs between the fault-protected surface reduction against the fault coverage.

#### 1.4 Thesis Contributions

In this thesis, we make the following main contributions:

• We establish an easy-to-deploy instrumentation-based SWIFI framework that

can perform extensive tests on target binaries for a data-aware characterization study of the exact data corruption effects on application behavior, where all possible levels of fault-masking effects are captured.

- After extensive experimental fault-injection tests, we observe different levels of vulnerability variations. The most promising among them is the workload-related vulnerability variation of application data of the NPB-serial benchmarks based on their characteristics, along with the vulnerability variation within parts of application data. For given application data characteristics, we identify clear patterns of less-vulnerable bit ranges that if corrupted are less likely to cause SDCs, e.g., up to 32 LSBs of floating-point data in the CG (Conjugate Gradient) benchmark have each less than 1% probability to cause an SDC. The other observed vulnerability variations are in areas such as the memory space, the register file, individual instructions and the program space.

- We demonstrate the potential exploitability of our data-level characterization findings in a generic fault-tolerant data cache running the NPB-serial benchmarks. Assuming a vulnerability-aware unequal-protection mechanism we show how much we can exploit the vulnerability characteristics of application data and to what effect on the reliability QoS level, e.g., the fault-protected surface of a 64K data cache can be reduced by 41% with a less than 0.01% drop in the fault coverage just by avoiding protection of the less-vulnerable bit ranges of floating-point data in the EP (Embarrassingly Parallel) benchmark.

#### 1.5 Thesis Overview

The remainder of this thesis is structured as follows:

In **Chapter 2** we describe our SWIFI-based framework for enabling our data-aware characterization study of the exact data corruption effects on application behavior. Additional relevant supplementary material is detailed in **Appendix A**.

In **Chapter 3** we present and analyze the characterization results after invoking our SWIFI framework to extensively test the NAS Parallel Benchmarks. The application behavior variation is observed in relation to different levels of corruption characteristics; application data characteristics (usage type, size, location in memory space, bit location corrupted, etc.), memory space characteristics, register-level characteristics and instruction-level characteristics.

In **Chapter 4** we discuss the importance of our characterization findings and on the ways they can be exploited for vulnerability-driven protection of a given structure or same-level structures. Then we demonstrate the potential of shifting to a class of vulnerability-aware unequal-protection architectures by exploiting our insight in a fault-tolerant data cache with two distinct levels of protection strength.

In **Chapter 5** some background information on fault tolerance is discussed followed by relevant prior works. The presented relevant studies generally relate to methods that investigate the varying vulnerabilities of hardware and software components, methods that attempt to unequally protect a system and methods that trade-off reliability against cost/performance.

Finally, **Chapter 6** concludes this thesis by summarizing its approach and contributions, before presenting some grounds for future works.

## **Chapter 2**

### **Characterization Framework**

In this chapter we present our instrumentation-based software-implemented fault-injection (SWIFI) framework that can perform extensive data-level aware fault-injection tests. Its end purpose is to capture the exact effects of hardware-induced data corruption on application behavior, mainly in relation to the corrupted data characteristics and the executing workload.

To do so, we employ SWIFI to model transient single-bit fault in memory locations, during application execution in an unprotected system, and to capture the corruption effect on the execution. As we focus mainly on characterizing the effects of data corruption at data level, we develop a portable instrumentation-based SWIFI tool that is data-level aware. Given an application binary, without need of its source code, our tool can finely control the location of the corruption in the application's memory space without further intruding the application behavior. Once a fault is injected at runtime, without need for binary file modifications per test, on top of traditional fault-injection approaches, it tracks the corrupted data to gather more information regarding them. Meanwhile it keeps monitoring the execution to report back more diagnostics relating to the corruption characteristics and the corruption outcome.

We opted to perform the characterization study through fault injection testing, instead of modeling-based methods. Fault injection is a straightforward technique that allows us to quickly set a toolchain to capture all possible end-to-end effects of data corruption down to bit-level granularity, in real applications in real systems. If we were to use analytical techniques, the propagation of every bit of every used data would have to be modeled through a detailed hardware/software data flow analysis. Then, to obtain the desired vulnerability characteristics, a slow detailed microarchitectural simulation of the tested application would have to be performed. Despite the time effort, this analytical approach would still not be able to capture all the detailed corruption characteristics and effects, as we intend.

Moreover, due to implementing the SWIFI framework using binary instrumentation in particular, the close monitoring of the application execution status is possible without requiring all of the above. Dynamic instrumentation is an easy to deploy, portable and efficient way to alter and monitor an application's execution. On top of modeling the desired corruption and capturing the exact execution outcome of real applications in real systems, fault injection by instrumentation also allows us to finely control the location of corruption, to closely observe the execution and to capture even finer details of the corruption characteristics and the corruption effects.

In the rest of this chapter, first, we present an overview of our framework in Section 2.1. Then, to show how we can capture all the desired properties of our experiments, in Section 2.2 we elaborate on the details of the individual single-fault injection process, focusing on the chosen injected fault model and the data-tracking capabilities of the implemented tool.

#### 2.1 Framework Overview

Our proposed **SWIFI framework** (Fig. 2.1) operates as follows on a given applicationunder-test to characterize its behavior under data corruption:

- First, a golden run of the target binary is profiled, without introducing data corruption, to obtain (a) its expected correct output (for SDC detection), (b) its normal execution time when under instrumentation by our tool (for delayed/stalled execution detection) and (c) its total number of memory load accesses (for deciding the sample rate to drive the tests uniformly over the test space).

- Then a *single-fault injection tool* is repeatedly invoked on a clean instance of the target application, each time corrupting a different memory load operation. In every test, the application-under-test is re-executed, a bit-flip is injected at a random bit of a different specified memory load access and the rest of the execution is closely monitored to capture/report the details of the corrupted data characteristics and of the exact corruption effects. Given a sample rate, we drive the tests uniformly over the test space of all possible memory locations and times.

Figure 2.1: Our proposed framework that captures an application's behavior under data corruption through extensive multiple single-fault injection experiments.

• Finally, once all tests complete, the extensive reported execution results are aggregated to relate the corruption outcome to the corrupted data characteristics (Chapter 3).

Once we set up the framework, it will run extensive fault injection tests over given applications. Due to the volume of our experiments and the detailed reported diagnostics, after aggregating our results and studying them, we will be able to confidently relate in many ways the corruption attributes and the resulting corruption effect on the application. Among the gained insight, we expect to be able to elaborate on the varying vulnerability factors of application data depending on their characteristics, down to even identifying different vulnerability levels within bit ranges of application data.

#### 2.2 Single-Fault Injection Tool

At the heart of our framework is the **single-fault injection tool** that operates following the established fault injection methodology. In each test once the **fault trigger** condition is reached, a **fault injection** is performed according to the chosen **fault model**  and the rest of the execution is **monitored** to **report** the exact end-to-end effect of the corruption. Since we opted for SWIFI these operations are performed using special software to emulate the behavior of expected hardware faults during the application operation only (and not the kernel).

To briefly outline the operation of the single-fault injection tool, it performs and monitors the fault injection tests by dynamic binary instrumentation of the applicationunder-test. In each test just before a specified memory load access a random bit of the accessed data is flipped to emulate a single-bit transient fault in the particular memory location. Then the execution is monitored and, on top of usual SWIFI approaches, the corrupted data are tracked in order to report more detailed corruption characteristics (Table 2.1) and corruption effects (Table 2.2).

#### 2.2.1 Fault Trigger

First, the single-fault injection tool starts by instrumenting the application-under-test until the execution reaches the specified memory load access to be corrupted. The memory load access to be corrupted will be chosen uniformly out of the total memory load accesses of the tested workload.

The specified memory load access acts as both a spatial and a temporal fault trigger to invoke the injection routine just before the load operation. Instead of corrupting random memory locations in the whole address space at random times, using the memory load access as a fault trigger captures all possible times that a transient fault could occur and all possible live memory locations that could get corrupted by a transient fault. Thus it simplifies driving where/when to inject a fault as it narrows down to selecting a memory load access, without having to rely on external events. Also its inject-before-load policy reduces the testing space by avoiding the unnecessary testing of dead memory locations.

#### 2.2.2 Fault Injection and Fault Model

Once the instrumentation code detects that the fault trigger condition has been reached, the fault-injection routine is invoked in a manner similar to a software trap. Then, complying to our fault model, it injects a random bit-flip in the accessed data just before they are accessed.

The chosen injected fault model emulates *single-bit transient faults in memory locations* by randomly flipping a bit of the accessed data just before they are accessed

by a memory load operation. The bit-flip is performed by storing the corrupted value to the same memory location without further intruding the application's original behavior. This is to force the execution to behave as if a different value was already there and avoid activating any reliability mechanisms of the system that would skew our intended vulnerability insight.

Software-injected high-level faults model lower-level hardware-induced data corruption to make the system behave as if a hardware fault was present in order to monitor the application behavior. Therefore, it is important in fault-injection testing for dependability assessment to choose fault models that closely resemble the naturally occurring hardware faults. Given that we focus on error sensitivity of application data, the chosen fault model suffices for our purposes to capture the application behavior under corrupted application data without a need for precise realistic hardware fault models. Plus, due to the instrumentation-based SWIFI the fault model does not need to be adapted per target system but only to have the necessary high-level characteristics (type, duration, location) required by our application data level investigation.

In particular, we chose a bit-flip *fault type* instead of stuck-at-zero or stuck-at-one to ensure that application data will always be corrupted at every injection test.

Moreover, the inject-before-load policy enforces emulation of transient faults as the injected corruption will not persist after the corrupted location is overwritten. Modeling transient *fault duration* fits better our purposes as they affect only a single memory object. On the contrary, permanent/intermittent (or multi-bit) faults in memory locations, besides being harder to emulate in software, corrupt different data over time (or multiple bits). In that case it would be indistinguishable which corrupted data (or bits) are responsible for the reported outcome.

Finally, the injected *fault location* is in main memory and it suffices for our dataaware error sensitivity investigation. Although we inject fault at main memory locations, our chosen fault model is not limited to emulating hardware faults only in memory. Depending on the system and how the fault is propagated, it may translate to emulating faulty behavior in other locations too, such as the register and the cache location where the corrupted value is loaded, or faulty behavior of communication wires and CPU instructions that use the corrupted value.

Figure 2.2: Decision tree used by the single-fault injection tool to classify the corrupted application data according to their use by the application.

#### 2.2.3 Monitoring, Data Tracking and Reporting

Once the fault has been injected the rest of the application execution is still instrumented and analyzed to monitor and report the effects of the data corruption. As the instrumentation and analysis are transparent to the original binary behavior, the faultinjection software does not intrude the application space/behavior and guarantees the non-intrusiveness of the SWIFI tool.

Due to the chosen fault trigger, fault model and instrumentation-based injection we can perform data-level aware fault injection and data-aware characterization of corruption effects. Once the memory location is corrupted and then loaded, we can track it as an application variable to get its detailed usage characteristics and relate them to the outcome to capture the varying vulnerabilities of application data.

More precisely, at the moment of the fault injection, the tool tries to finely identify as many characteristics of the corrupted data as possible (Table 2.1). Attributes such as their location in the memory address space (global, heap or stack), size and user (system or user data) can be identified immediately.

Classifying the type of the corrupted data according to their use by the application

(Fig. 2.2) can be either immediate (e.g., floating-point data, instruction pointer, etc.) or it may require tracking the data through the execution until a first meaningful use (e.g., to determine if they are used for addressing memory or not).

To elaborate, at fault injection which always happens just before a memory load operation, we can identify the first register (R) where the corrupted data (D') are stored. If it is a floating-point register, the instruction counter or a segment/stack pointer register, we can classify immediately the corrupted data as floating-point (FP), instruction pointer (IP) or memory addressing data (PTR) respectively. Otherwise, we check if the original uncorrupted data (D) hold a value within the address ranges of the application binary image and, if they do, we identify them as memory addressing data (PTR).

If the data usage type cannot be determined immediately, data tracking and close monitoring of the execution are used to determine their usage. The corrupted (and the uncorrupted) value is checked against all subsequent accessed effective memory addresses to check if the corrupted data are used for memory addressing (PTRMR).

Meanwhile, for a specified instruction window, we use *dynamic taint analysis* [56] to track the data propagation from the first register (R) to hold the corrupted data and from the corrupted memory location (M). We model our problem as a dynamic taint analysis problem where the taint sources are the register R and the bytes in M. After every instruction, we track accordingly the taint propagation to other registers and memory locations.

To do so, for every executed instruction, we obtain a list of the input/output registers and input/output memory locations accessed by the instruction and:

- If the instruction clears an output register (e.g., sub R1, R1, R1), then the output register gets untainted in case it was tainted already.

- If the instruction outputs to registers/memory locations:

- If *any* of the input registers/memory locations is tainted, then *all* output registers/memory locations must get tainted.

- Otherwise, if *all* of the input registers/memory locations are untainted, then *all* output registers/memory locations must get untainted.

- If the instruction does not output to any register/memory location:

- No taint propagation for this instruction.

|                                          | Characteristics of corrupted data                                                          |  |  |

|------------------------------------------|--------------------------------------------------------------------------------------------|--|--|

| Injected bit-flip location               |                                                                                            |  |  |

| Memory address of corrupted data         |                                                                                            |  |  |

| Memory space location                    | global, heap or stack                                                                      |  |  |

| Size                                     | 1, 2, 4, 8 or 16 bytes                                                                     |  |  |

| User                                     | System library data or application-space (user) data                                       |  |  |

| Usage type                               | FP: floating-point data (immediate classification)                                         |  |  |

|                                          | IP: instruction pointer (immediate classification)                                         |  |  |

|                                          | PTR: memory addressing data (immediate classification)                                     |  |  |

|                                          | PTRMR: memory addressing data (classification by checking subsequent accessed              |  |  |

|                                          | memory addresses)                                                                          |  |  |

|                                          | PTRTP: memory addressing data (classification by data tracking until first use as          |  |  |

|                                          | memory addressing data within an instruction window)                                       |  |  |

|                                          | INT: integer data (if none of the above)                                                   |  |  |

|                                          | Other corruption characteristics                                                           |  |  |

| Corrupted memory load access numb        | er                                                                                         |  |  |

| First register to store the corrupted da | ta                                                                                         |  |  |

| Corrupted instruction                    | Instruction pointer, opcode and time at corruption                                         |  |  |

| First use of corrupted data              | Instruction pointer, opcode and time at first use of first register to store the corrupted |  |  |

|                                          | data                                                                                       |  |  |

| If usage type                            | e identified as memory addressing data (PTRMR or PTRTP)                                    |  |  |

| Time until first use as memory addres    | ssing data                                                                                 |  |  |

| Taint propagation of corrupted data      | Number (and total cumulative number) of registers and memory bytes where the               |  |  |