## **High Speed Simulation of Microprocessor Systems**

using

LTU Dynamic Binary Translation

Daniel Jones

Doctor of Philosophy Institute for Computing Systems Architecture School of Informatics University of Edinburgh

2010

## Abstract

This thesis presents new simulation techniques designed to speed up the simulation of microprocessor systems. The advanced simulation techniques may be applied to the simulator class which employs dynamic binary translation as its underlying technology. This research supports the hypothesis that faster simulation speeds can be realized by translating larger sections of the target program at runtime. The primary motivation for this research was to help facilitate comprehensive design-space exploration and hardware/software co-design of novel processor architectures by reducing the time required to run simulations.

Instruction set simulators are used to design and to verify new system architectures, and to develop software in parallel with hardware. However, compromises must often be made when performing these tasks due to time constraints. This is particularly true in the embedded systems domain where there is a short time-to-market. The processing demands placed on simulation platforms are exacerbated further by the need to simulate the increasingly complex, multi-core processors of tomorrow. High speed simulators are therefore essential to reducing the time required to design and test advanced microprocessors, enabling new systems to be released ahead of the competition.

Dynamic binary translation based simulators typically translate small sections of the target program at runtime. This research considers the translation of larger units of code in order to increase simulation speed. The new simulation techniques identify large sections of program code suitable for translation after analyzing a profile of the target program's execution path built-up during simulation.

The average instruction level simulation speed for the EEMBC benchmark suite is shown to be at least 63% faster for the new simulation techniques than for basic block dynamic binary translation based simulation and 14.8 times faster than interpretive simulation. The average cycle-approximate simulation speed is shown to be at least 32% faster for the new simulation techniques than for basic block dynamic binary translation based simulation and 8.37 times faster than cycle-accurate interpretive simulation.

## Acknowledgements

I wish to thank my adviser Professor Nigel Topham for his support and advice, and for sharing his knowledge of microprocessor architectures during my research.

I would also like to thank all my colleagues within the Institute for Computing Systems Architecture at the University of Edinburgh for their support and encouragement, especially Dr Björn Franke, Professor Mike O'Boyle and Dr Marcelo Cintra.

## **Declaration**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification. Some of the material presented in this thesis has been published in the following papers:

D. Jones and N. Topham, "High Speed CPU Simulation using LTU Dynamic Binary Translation", in *HiPEAC '09: Proceedings of the 4th International Conference on High Performance and Embedded Architectures and Compilers*, Paphos, Cyprus, 2009.

N. Topham and D. Jones, "High Speed CPU Simulation using JIT Binary Translation", in *MoBS '07: Proceedings of the 3rd AnnualWorkshop on Modeling, Benchmarking and Simulation*, San Diego, CA, USA, 2007.

# **Table of Contents**

| 1 | Intr | oduction                          | 1  |

|---|------|-----------------------------------|----|

|   | 1.1  | The High Speed Simulation Problem | 5  |

|   | 1.2  | Large Translation Unit Solution   | 10 |

|   | 1.3  | Research Contributions            | 11 |

|   | 1.4  | Thesis Outline                    | 12 |

| 2 | Sim  | ulation Techniques                | 14 |

|   | 2.1  | Overview                          | 14 |

|   | 2.2  | Interpretation                    | 15 |

|   | 2.3  | Binary Translation                | 16 |

|   |      | 2.3.1 Static Binary Translation   | 18 |

|   |      | 2.3.2 Dynamic Binary Translation  | 23 |

|   | 2.4  | Sampling                          | 25 |

|   | 2.5  | Summary                           | 26 |

| 3 | Rela | nted Work                         | 28 |

|   | 3.1  | Binary Translation Simulators     | 28 |

|   |      | 3.1.1 Static Binary Translation   | 28 |

|   |      | 3.1.2 Dynamic Binary Translation  | 35 |

|   | 3.2  | Summary                           | 41 |

| 4 | Edir | nburgh High Speed Simulator       | 42 |

|   | 4.1  | Overview                          | 42 |

|   | 4.2  | Simulator Features                | 44 |

|   | 4.3  | Normal Simulation Mode            | 46 |

|   |      | 4.3.1 The Decode Cache            | 47 |

|   | 4.4  | Fast Simulation Mode    4             | 48         |  |  |  |  |  |

|---|------|---------------------------------------|------------|--|--|--|--|--|

|   |      | 4.4.1 The Translation Cache           | 49         |  |  |  |  |  |

|   | 4.5  | Instruction Level Simulation          | 50         |  |  |  |  |  |

|   | 4.6  | Cycle Accurate Simulation             | 50         |  |  |  |  |  |

|   |      | 4.6.1 The Pipeline Model              | 50         |  |  |  |  |  |

|   |      | 4.6.2 The Memory Model                | 51         |  |  |  |  |  |

|   | 4.7  | System Simulation                     | 55         |  |  |  |  |  |

|   | 4.8  | Future Development                    | 56         |  |  |  |  |  |

|   | 4.9  | Summary                               | 57         |  |  |  |  |  |

| 5 | Eval | luation Methodology                   | 58         |  |  |  |  |  |

|   | 5.1  | Target System   5                     | 58         |  |  |  |  |  |

|   | 5.2  | Simulation Environment                | 50         |  |  |  |  |  |

|   | 5.3  | Performance Metrics                   | 51         |  |  |  |  |  |

| 6 | Larg | Large Translation Units 6             |            |  |  |  |  |  |

|   | 6.1  | Overview                              | 53         |  |  |  |  |  |

|   | 6.2  | Translation Unit Types                | 54         |  |  |  |  |  |

|   | 6.3  | Runtime Profiling                     | 56         |  |  |  |  |  |

|   | 6.4  | Program Simulation                    | 57         |  |  |  |  |  |

|   |      | 6.4.1 Dynamic Binary Translation      | 59         |  |  |  |  |  |

|   | 6.5  | Cycle Accurate Simulation             | 70         |  |  |  |  |  |

| 7 | Inst | ruction Level Simulation              | 73         |  |  |  |  |  |

|   | 7.1  | Overview                              | 73         |  |  |  |  |  |

|   | 7.2  | Instruction Level Simulation Analysis | 74         |  |  |  |  |  |

|   |      | 7.2.1 Performance                     | 74         |  |  |  |  |  |

|   |      | 7.2.2 Instruction Emulation           | 77         |  |  |  |  |  |

|   |      | 7.2.3 Dynamic Binary Translation      | 77         |  |  |  |  |  |

|   |      | 7.2.4 Simulator Tasks                 | 79         |  |  |  |  |  |

|   |      | 7.2.5 Translated Functions            | 82         |  |  |  |  |  |

|   | 7.3  | Translation Cache Size                | <u>8</u> 9 |  |  |  |  |  |

|   | 7.4  | Workload Sensitivity                  | <u>8</u> 9 |  |  |  |  |  |

|   | 7.5  | Translation Unit Fragmentation        | 90         |  |  |  |  |  |

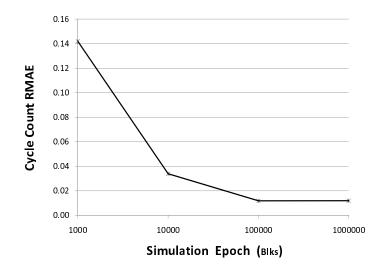

|    | 7.6   | Simula   | ation Epoch Size                            | 93  |

|----|-------|----------|---------------------------------------------|-----|

|    | 7.7   | Compa    | arison with State-of-the-Art Simulators     | 97  |

|    | 7.8   | Summ     | ary                                         | 99  |

| 8  | Cyc   | le Timiı | ng Simulation                               | 101 |

|    | 8.1   | Overvi   | iew                                         | 101 |

|    | 8.2   | Cycle    | Accurate Simulation Analysis                | 102 |

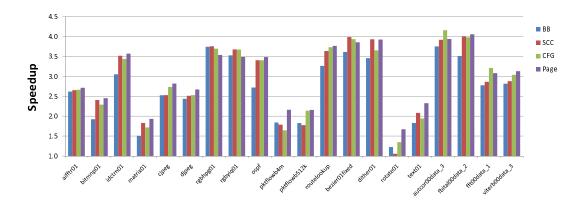

|    | 8.3   | Cycle    | Approximate Simulation Analysis             | 108 |

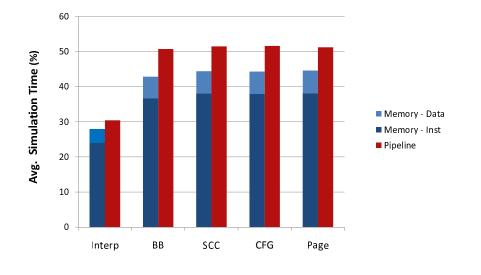

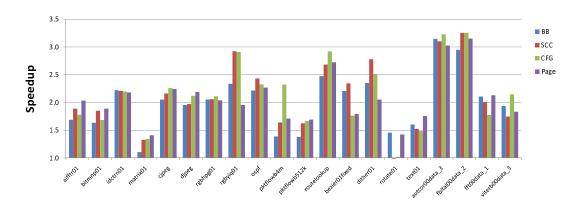

|    |       | 8.3.1    | The Pipeline Model                          | 108 |

|    |       | 8.3.2    | The Memory Model                            | 110 |

|    |       | 8.3.3    | The System Model                            | 112 |

|    |       | 8.3.4    | Comparison with Sampling                    | 115 |

|    | 8.4   | Summ     | ary                                         | 115 |

| 9  | Con   | clusion  |                                             | 116 |

|    | 9.1   | Contri   | butions to Research                         | 116 |

|    |       | 9.1.1    | High Speed Simulation Techniques            | 117 |

|    |       | 9.1.2    | Analysis of Simulation Techniques           | 117 |

|    |       | 9.1.3    | Instruction Level Performance               | 118 |

|    |       | 9.1.4    | Cycle Approximate Performance and Accuracy  | 119 |

|    |       | 9.1.5    | Comparison with State-of-the-Art Simulators | 119 |

|    | 9.2   | Critica  | l Analysis                                  | 120 |

|    | 9.3   | Future   | Research                                    | 120 |

|    |       | 9.3.1    | Runtime Profiling                           | 120 |

|    |       | 9.3.2    | Cycle Approximate Simulation                | 121 |

|    |       | 9.3.3    | Simulation Characterization                 | 122 |

| A  | Glos  | ssary    |                                             | 123 |

| Bi | bliog | raphy    |                                             | 125 |

# **List of Figures**

| 1.1 | DBT Simulation Overview.   8                     |

|-----|--------------------------------------------------|

| 2.1 | Virtual Machines                                 |

| 2.2 | Interpretive Simulator Code                      |

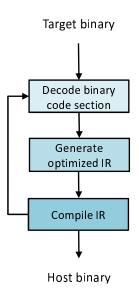

| 2.3 | Processes involved in Static Binary Translation  |

| 2.4 | Compiled Simulator Code                          |

| 2.5 | Compiled Simulator Code for Large Programs       |

| 2.6 | Processes involved in Dynamic Binary Translation |

| 2.7 | DBT Simulator Code                               |

| 4.1 | Interpretive Simulation Loop                     |

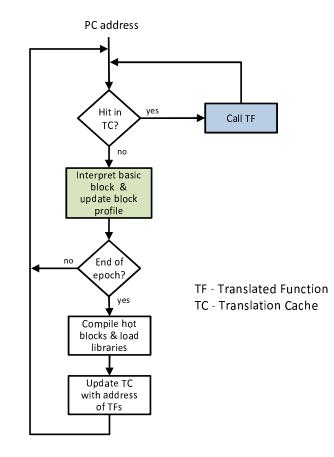

| 4.2 | DBT Simulation Loop                              |

| 4.3 | Processor Pipeline                               |

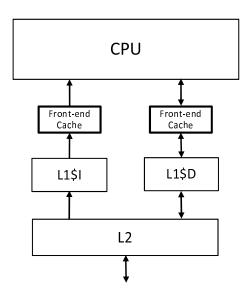

| 4.4 | L1 Front-End Cache                               |

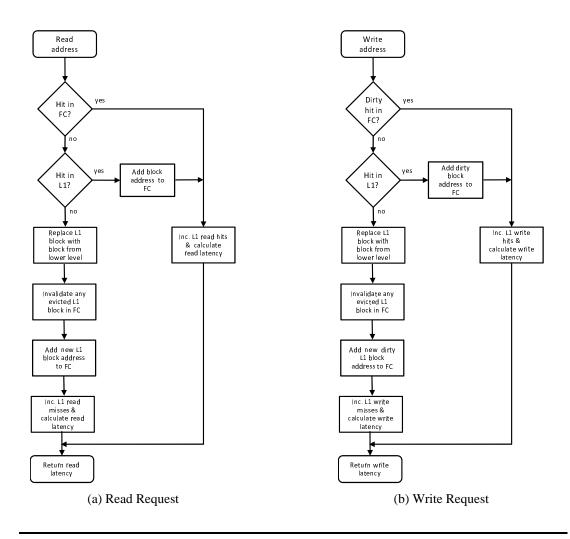

| 4.5 | L1 Front-End Cache Operation                     |

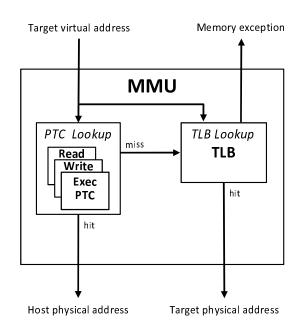

| 4.6 | MMU Page Translation Caches                      |

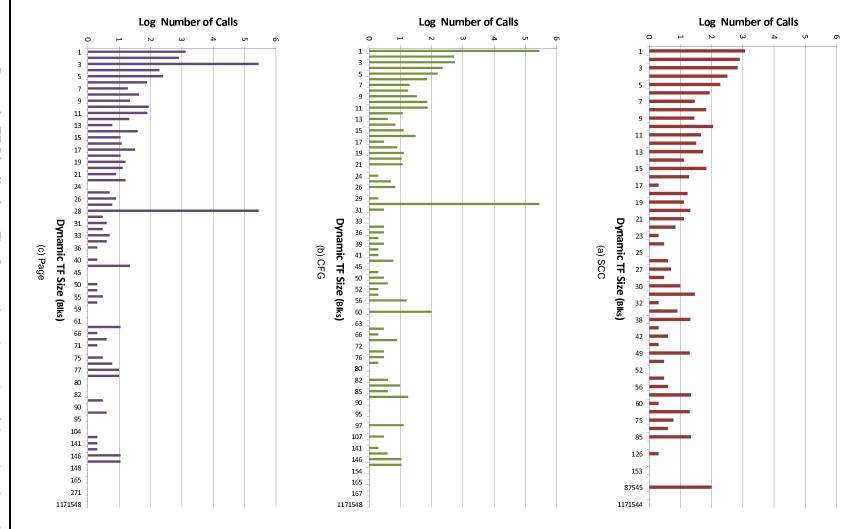

| 6.1 | Translation Units.                               |

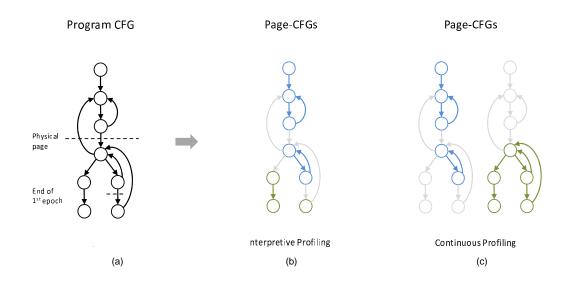

| 6.2 | Page-CFG Configurations                          |

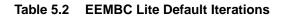

| 6.3 | LTU DBT Simulation Loop                          |

| 6.4 | LTU Translated Function                          |

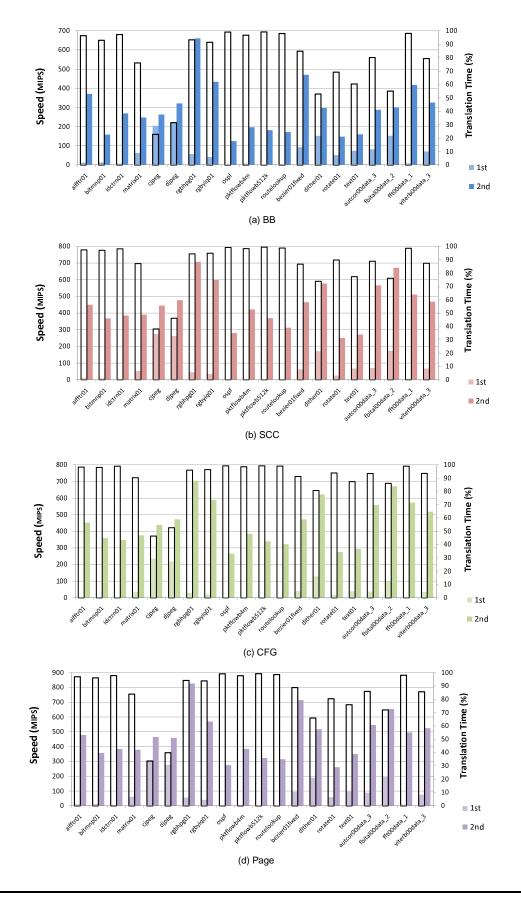

| 7.1 | Instruction Level Simulation Profile             |

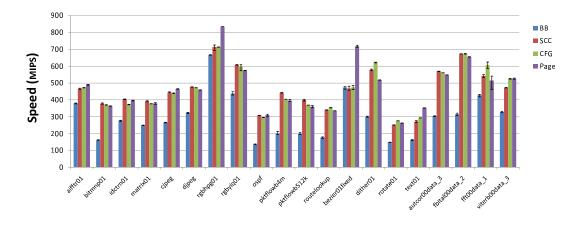

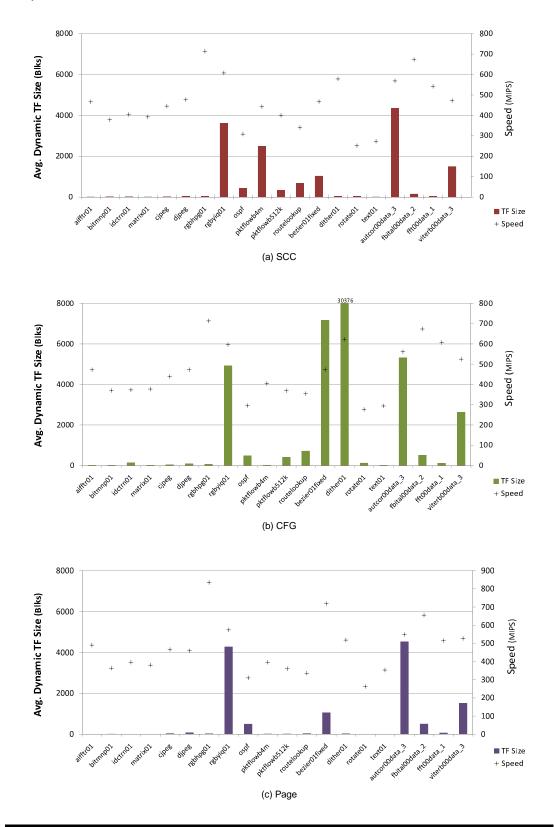

| 7.2 | DBT Instruction Level Speed                      |

| 7.3 | LTU DBT Instruction Level Speedup                |

| 7.4 | EHS Simulation Tasks.    81                      |

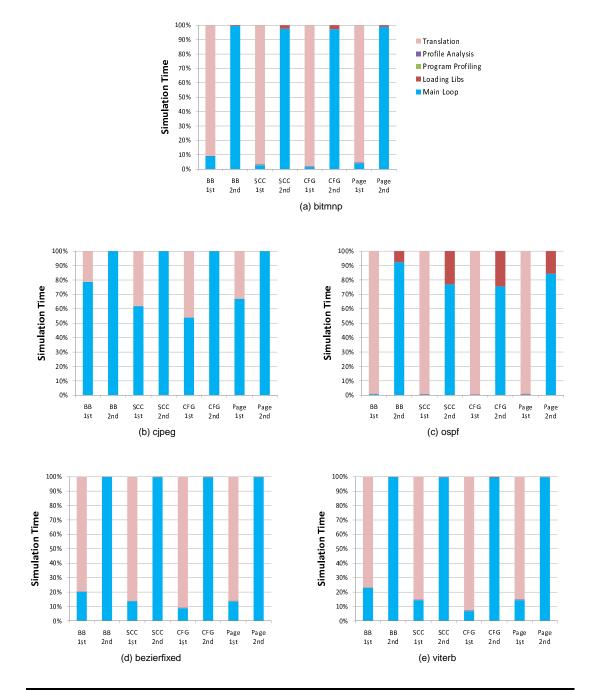

| 7.5 | LTU Dynamic TF Size and Simulation Speed         |

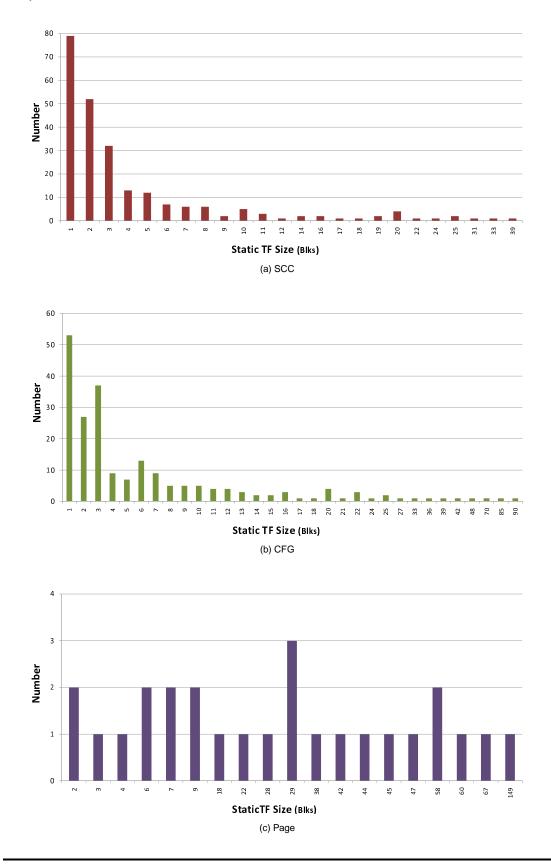

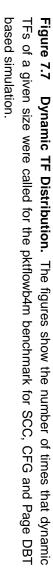

| 7.6  | Static TF Distribution                       | 5 |

|------|----------------------------------------------|---|

| 7.7  | Dynamic TF Distribution                      | 7 |

| 7.8  | Translation Unit Fragmentation               | 1 |

| 7.9  | Translation Unit Profiling Techniques.    93 | 3 |

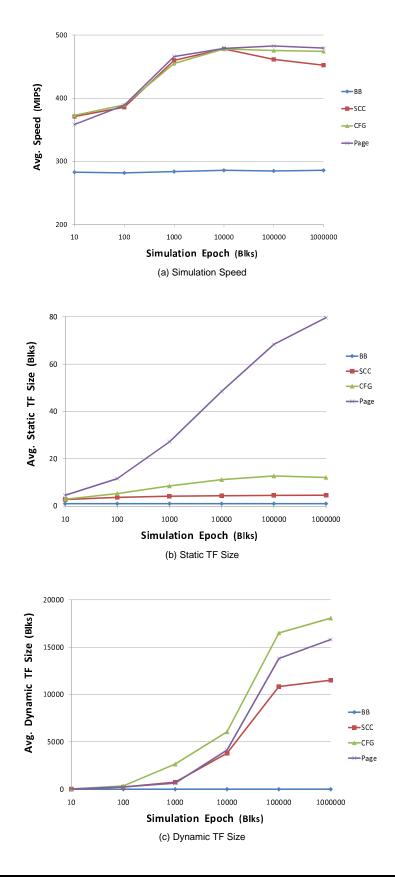

| 7.10 | Simulation Speed and TF Profiles             | 5 |

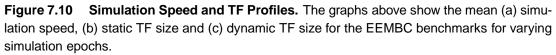

| 7.11 | EHS, Simit-ARM and QEMU Simulation Speeds    | 3 |

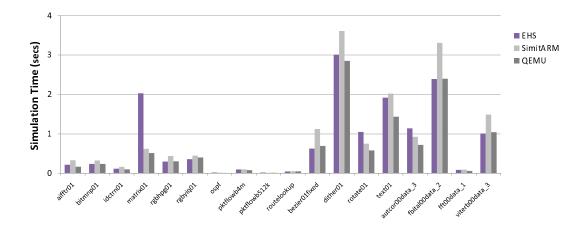

| 7.12 | EHS, Simit-ARM and QEMU Simulation Times     | 3 |

| 8.1  | Cycle Accurate Pipeline Model                | 3 |

| 8.2  | Cycle Accurate Simulation Profile            | 4 |

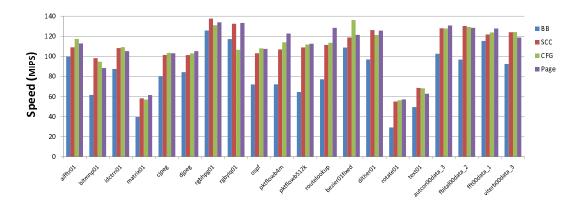

| 8.3  | Cycle Accurate Simulation Speed              | 5 |

| 8.4  | Cycle Accurate Simulation Speedup            | 5 |

| 8.5  | Cycle Accurate Pipeline and Memory Models    | 3 |

| 8.6  | Cycle Approximate Pipeline Model             | 9 |

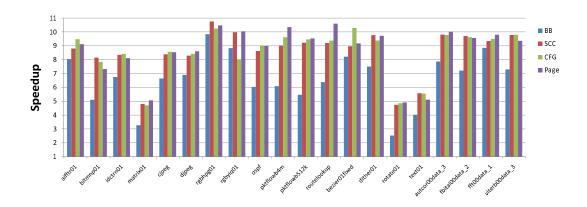

| 8.7  | Cycle Approximate Pipeline Speedup           | ) |

| 8.8  | Cycle Approximate Memory Speedup             | 1 |

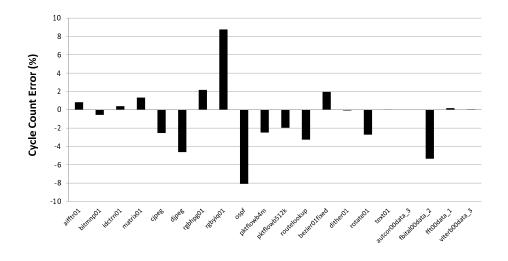

| 8.9  | Cycle Approximate Memory Cycle Count Error   | 2 |

| 8.10 | Cycle Approximate System Simulation Speed    | 3 |

| 8.11 | Cycle Approximate System Speedup             | 3 |

| 8.12 | Cycle Approximate System Cycle Count Errors  | 4 |

# **List of Tables**

| 1.1 | Simulator Classes.                                | 7   |

|-----|---------------------------------------------------|-----|

| 5.1 | Target System Architecture                        | 59  |

| 5.2 | EEMBC Lite Default Iterations                     | 59  |

| 5.3 | Simulation Host Machine                           | 60  |

| 5.4 | EHS Simulator Configuration                       | 60  |

| 7.1 | Instruction Level Simulation Performance Summary. | 76  |

| 7.2 | Static and Dynamic Translated Functions.          | 83  |

| 7.3 | EHS, Simit-ARM and QEMU Performance Summary.      | 99  |

| 8.1 | Cycle Accurate Performance Summary.               | 107 |

| 8.2 | Cycle Approximate Pipeline Performance Summary    | 109 |

| 8.3 | Cycle Approximate Memory Performance Summary      | 111 |

| 8.4 | Cycle Approximate System Performance Summary.     | 112 |

## **Chapter 1**

## Introduction

The research presented in this thesis investigates some novel, high speed simulation techniques which were developed to help facilitate comprehensive design-space exploration (DSE) and hardware/software co-design of microprocessor architectures. Thorough exploration of the design-space is often not performed in situations where a new system must be designed within a limited period of time. As a consequence sub-optimal system designs may be selected for manufacture. This problem is particularly acute in the embedded processor domain where companies work within tight schedules to release new systems to market. Faster simulators allow the design-space to be explored in more detail within the time available. They are therefore very important in the microprocessor design process as they enable the best system architectures to be discovered.

Simulators are used to accurately predict the performance characteristics, such as speed and power consumption, of new processor architectures so that the most efficient design can be selected for fabrication. Simulators are also used to test experimental instructions set architectures (ISAs), for hardware/software co-design and verification, and in the development and debugging of new compilers and applications. Simulation platforms are vital to industry because they enable the engineering tasks involved in the development of a new microprocessor to be performed in parallel, thus reducing the time to release.

The design-space for a new microprocessor architecture is typically very large. Its size will depend on a number of different factors such as the ISA, pipeline design, register

#### Chapter 1. Introduction

file size, functional unit type and quantity, number of processor cores, on-chip network, cache hierarchy and configuration, and application domain. In most embedded system research and design groups, not only are the design goals very exact, in terms of the performance criteria that must be met, there is also limited time available in which to design, test and fabricate a system. Time constraints may necessitate a reduction in the size of the design-space in order that a new system can be released on schedule. System designers may be required to make assumptions about individual micro-architecture parameters or to chose less representative applications with which to test the system. However, a reduced design-space is less likely to contain the best design point.

The design-space may be reduced by decreasing the number of micro-architecture parameters and configuration values to be explored for the target system. Whilst this will cut the overall simulation time it may result in the selection of a sub-optimal design. The design-space may also be reduced by decreasing the number and size of the programs simulated. Small benchmarks may be run instead of real-world programs in an attempt to replicate real application behaviour and at the same time reduce the overall simulation time. However, benchmarks can not imitate real-world programs perfectly and this may also result in the selection of a sub-optimal system design.

The need to model new, advanced system designs has increased the processing demands placed on simulators. In addition to accurately modelling increasingly complex, multi-core systems, simulators must also maintain statistics on a range of system indicators. The degree of modelling detail, accuracy and instrumentation may also be reduced in order to speed up simulation, but this will generate less reliable data from which to select the best design.

Comprehensive design-space exploration therefore involves testing every design point with the simulation of real-world programs. However, rigorous design-space exploration conflicts with the manufacturers natural desire to ship leading-edge systems ahead of the competition. As outlined, simulators play an important role in determining the optimal system design. The simulation speed directly affects the time required to design and to test new system designs and hence it indirectly affects the accuracy of the predicted performance results. For this reason, state-of-the-art high speed simulation techniques remain an active field of research.

In order to perform comprehensive design-space exploration and verification a sim-

ulator needs not only to be fast, it must also satisfy the requirements of a research simulator. This means that the simulator be flexible in both its configuration and operation. It should be capable of modelling any target system architecture and offer a number of different simulation modes.

A flexible research simulator should fulfil the following criteria:

- High Speed Simulation. The design-space needs to be comprehensively explored if the optimal system design is to be found. A linear increase in the number of micro-architecture design parameters results in exponential expansion of the design-space. Vast design spaces, coupled with the need to accurately model complex systems and the desire to run real-world programs demands a lot of processing power. Therefore, high speed simulators are required to explore the design-space as thoroughly as possible, in as short a time as possible.

- Accurate Modelling. The simulator must be capable of modelling the target system at the required level of abstraction and with the desired degree of accuracy in order to confidently predict the behaviour of the real system. It should incorporate instruction level and cycle-accurate modes of operation to facilitate high and low level DSE.

- **Instrumentation**. The performance of the target system can only be evaluated if the simulator is instrumented to return statistics on the system indicators of interest. For example, the simulator may be instrumented to provide instruction counts, program execution cycles, instruction execution profiles, L1 hits and misses, and power consumption figures.

- State Observability. The ability to capture all architecturally-visible CPU state changes at instruction commit is necessary in order to support hardware/software co-design and verification.

- System Simulation. To accurately model the target system's behaviour, the simulation environment should be setup to precisely mirror that anticipated for the real system. A research simulator should therefore pos-

sess the ability to simulate standalone applications and full operating systems (OSs) or embedded system runtimes. User level simulation requires emulation of all system calls, whilst system level simulation requires comprehensive modelling of the system's hardware and I/O devices.

- Simulation Flexibility. Simulators which possess a variety of simulation modes offer greater flexibility for performing DSE. The appropriate level of abstraction, speed and accuracy of simulation may be chosen by designers so as to satisfy the optimal exploration strategy for a particular project. Exploration may be focused on specific regions of code that are of interest by employing a mixture of fast-forwarding and sampling.

- Target System Configuration. To be of use, the simulator must be capable of modelling all of the target systems present in the design-space. It should possess a straightforward method of building complex system models and facilitate detailed configuration of all micro-architecture parameters.

- **Retargetable**. The simulator needs to support different target ISAs and the extension of ISAs so that the benefits of experimental ISAs can be investigated. It should employ a standardized means of defining the target instruction set and the pipeline model.

Instruction set simulators (ISSs) are important software tools which are used to design the advanced processor architectures of tomorrow. They enable the trade-offs between different micro-architecture models to be explored so that the best system design can be selected for production. They also facilitate the development, verification and debugging of hardware and software.

The new simulation techniques detailed in this thesis are applicable to Dynamic Binary Translation (DBT) based simulators. Dynamic binary translation is a high speed emulation technique [Altm 00, Altm 01] which has applications across many domains. Dynamic binary translation based simulators typically run programs up to four times faster than the corresponding field-programmable gate array (FPGA) setup. This research is concerned with high speed research simulators which can be used to carry out DSE and hardware/software co-design and verification of novel processor architectures. In order to perform these tasks the simulator must be capable of high speed instruction level and cycle-accurate simulation, and support observable modelling of the processor state. A glossary of the main simulation terms used throughout this thesis are listed in appendix A.

### 1.1 The High Speed Simulation Problem

Intense competition amongst embedded system designers has led to more leading-edge processors being released to market more frequently. Modern processors incorporate many novel technologies which are designed to increase execution speed and to reduce the power consumption and thermal output. As the complexity and number of cores in future systems increase, the time necessary to run simulations of such systems also increases, at the same time deadlines are becoming tighter.

Superscalar processors incorporate a number of advanced micro-architecture technologies which increase performance. Processors may employ long pipelines, wide instruction issue, out-of-order processing, speculative execution or a trace cache. A simulator must model all of these novel components in addition to emulating complex events such as interrupts and exceptions. Even embedded processors incorporate Memory Management Units (MMUs) to support multi-tasking operating systems.

Chip Multi-Processors (CMPs) are rapidly becoming the preferred processor model as manufacturers strive to make the most effective use out of the ever increasing silicon area available to them [Oluk 96]. Dual-core (AMD Athlon X2; IBM POWER6; Intel Itanium, Core 2 Duo) and quad-core (AMD Phenom X4, Opteron; Intel Core 2 Quad, Core i7) processors are already in mainstream use and the number of on-chip cores is set to increase many fold in the near future. A CMP may contain heterogeneous or homogeneous cores. IBM's CELL processor [Kahl 05] is a heterogeneous CMP designed for the games market and consists of a single general-purpose PowerPC core and 8 special-purpose digital signal processing cores.

Sun Microsystems' UltraSPARC T1 processor [Kong 05] is a homogeneous Chip Multi-

#### Chapter 1. Introduction

Threaded (CMT) processor which has 8 cores, each of which is 4-way multi-threaded, providing a total of 32 hardware thread contexts or logical processors. The processing demand on simulators rises dramatically as the number of processor cores is increased. Simulators will soon be required to emulate systems with hundreds - if not thousands - of cores as well as model the associated on-chip network, cache hierarchy, coherency protocols and I/O.

In order to discover the optimal system design, the effect of all interesting microarchitecture parameters should be evaluated during DSE. However, the consideration of a large number of parameters increases the size of the design-space and thus requires significantly more time to explore. To accurately predict the behaviour of the real system, the simulation environment must be setup to reflect the real system environment. This may involve running real-world programs and operating systems which also take time to simulate.

Table 1.1 provides definitions of the main simulator classes. Most interpretive simulators achieve modelling accuracy by operating at the register transfer level (RTL), but such simulators are very slow. However, compiled simulators, which are many orders of magnitude faster than interpretive simulators, do not provide processor state observability. They can also only be used in situations where the binary code to be simulated is known in advance and are therefore unable to emulate self-modifying code. Sampling simulators on the other hand can perform cycle-accurate simulation at speed, but their functional simulation speed is similar to that of interpretive simulators.

Dynamic binary translation based simulators, which perform a mixture of interpretation and compilation at runtime, are both fast and flexible. Dynamic binary translation is the process of translating source code, which performs a specific task, into the equivalent binary code which runs on the host machine. When executed, the translated code performs the same task but at much greater speed. Dynamic binary translation based simulators are also capable of simulating self-modifying programs and support observability of the processor state.

Dynamic binary translation based systems are very flexible as they enable extensive runtime control over program modification. They are able to react to unforeseen events by generating code which is translated on-the-fly to deal with a new situation. Software employing DBT technology is used across many different application domains such as

| Simulator Class | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | High<br>Speed | Self-<br>modif. | State<br>Observ. |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------|------------------|

| Interpretive    | The target program is simulated by re-<br>peatedly fetching, decoding and emulat-<br>ing the next instruction in the execution<br>stream. Interpretive simulators are flexible<br>and support the running of self-modifying<br>code. Decode caches are used to reduce<br>the overhead of instruction decoding, but<br>interpretive simulators are still compara-<br>tively slow.                                                                                                                                             | No            | Yes             | Yes              |

| Compiled        | A statically compiled simulator is gener-<br>ated by translating the target binary into<br>an executable which when run simulates<br>the target program. This class of simulator<br>is optimized for speed but lacks flexibility<br>and typically can not run self-modifying<br>code.                                                                                                                                                                                                                                        | Yes           | No              | No               |

| DBT             | The simulator switches between interpre-<br>tive simulation and 'translated' simulation<br>in which host code functions are called to<br>emulate sections of the target program at<br>high speed. Whilst interpreting instruc-<br>tions, sections of the program are iden-<br>tified for translation into host code func-<br>tions. If the simulator detects that code has<br>been modified it discards the correspond-<br>ing translations. Dynamic binary trans-<br>lation based simulators are both fast and<br>flexible. | Yes           | Yes             | Yes              |

| Sampling        | Sampling is used to perform fast cycle-<br>approximate simulation. The simulator<br>alternates between functional simulation<br>and cycle-accurate simulation. Cycle-<br>approximate simulation is fast when the<br>fast-forwarding interval is many times<br>larger than the sampling interval. The data<br>gathered in each sampling interval is used<br>to generate the simulation statistics. How-<br>ever, state observability is typically not<br>maintained during the fast-forwarding in-<br>tervals.                | No            | Yes             | No               |

**Table 1.1** Simulator Classes. This table lists the main simulator classes and shows whether they feature high speed instruction level simulation, emulation of self-modifying code and state observability.

resource virtualisation, system resilience, network security, dynamic code patching and optimization, and system emulation.

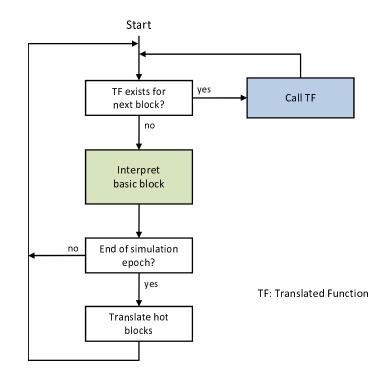

Dynamic binary translation based simulation is a high speed simulation technique in which target instructions, or more typically blocks of instructions, are translated at runtime into equivalent host code functions (translated functions). The translated functions are then called to emulated the basic blocks at high speed within the simulated microprocessor model. In most simulations, the overhead of performing translation is more than offset by the time saved through faster simulation. Figure 1.1 provides an overview of the tasks involved in DBT based simulation.

**Figure 1.1 DBT Simulation Overview.** Basic blocks are interpreted for a defined period (simulation epoch). At the end of each simulation epoch the frequently executed blocks are translated into host code functions (translated functions). If the next block to be simulated has previously been translated, the translated function for the block is called, else the block is interpreted as usual.

High speed cycle-accurate simulation is required in order to perform low level designspace exploration. However, because DBT based simulators perform instruction level simulation very efficiently, there exists little scope for increasing the speed of cycleaccurate simulation through optimizations in areas other than cycle-accurate modelling. Therefore significant speed-ups in DBT based cycle-accurate simulation may only be realized by deploying simplified models of target system components.

There are limitations associated with all of the main simulation techniques. Whilst interpretive simulators are flexible, they are also slow. Compiled simulators on the other hand are fast but place restrictions on the type of programs that may be simulated. Sampling simulators can perform cycle-approximate simulation at high speed but do not provide state observability. Dynamic binary translation based simulators feature high speed instruction level simulation, emulation of self-modifying code and processor state observability.

High speed ISSs contribute towards reducing the time needed to carry out DSE. As outlined previously, the time required to perform DSE is dictated by the size of the designspace, the complexity of the system to be modelled, the need to simulate real-world programs and the scheduled system release date. The processing demands placed on simulators are set to increase substantially in the near future as designers seek to model advanced new multi-core CPUs. The central challenge for today's system designers, of achieving high speed simulation whilst retaining absolute modelling accuracy, is therefore becoming increasingly difficult to satisfy.

The main simulation issues which are addressed in this thesis are:

- **High Speed Instruction Level Simulation**. Simulators must be capable of performing high speed instruction-level simulation in order to facilitate comprehensive high level DSE.

- High Speed Cycle Accurate Simulation. Simulators must be capable of performing high speed cycle-accurate simulation in order to facilitate comprehensive low level DSE. Cycle-approximate models of the target system are typically used to speed-up simulation at the expense of introducing small degrees of error into the simulation results.

- State Observability. The processor state must be accessible at all observation points so that high and low level hardware/software co-design and verification can be performed. The hardware model is validated

against the golden reference model using the simulator's co-simulation API.

• **Realistic Simulation**. Simulators must be capable of running realworld programs within a realistic simulation environment if they are to accurately predict system behaviour. This implies that the simulator should support the running of stand-alone applications, self-modifying programs and operating systems.

### 1.2 Large Translation Unit Solution

This thesis proposes that the simulation speed of DBT based simulators can be increased by identifying large translation units at runtime. By profiling the target program's execution path during simulation it is possible to identify large sections of code which span multiple basic blocks and which are suitable for translation. If the translator has a larger section of target code to analyze it will be better able to optimize the translated code produced for speed of execution.

Large translation units not only contain more target instructions they also have more branches and jumps to instructions within the same translation unit. Indeed, entire loops, even nested loops may be contained within a single translation unit. This means that more instructions will be simulated per translated function call and control will be returned to the main simulation loop less frequently. This results in an overall increase in simulation speed as less time is spent in the slower main loop.

This thesis investigates the performance benefits of translating three different types of large translation unit, or LTU. The different LTUs are based on the standard computer software objects listed below.

- SCC : Strongly Connected Component

- **CFG** : Control Flow Graph

- Page : Physical Page

The DBT simulation process is divided into a number of simulation epochs. During each simulation epoch the simulator builds up a profile of the target program's execution path. At the end of each epoch the execution path profile is analyzed to identify the LTUs and to determine which LTUs should be translated. In subsequent epochs, large sections of the target program may be simulated at high speed by calling the corresponding translated function.

### 1.3 Research Contributions

The Edinburgh High Speed (EHS) simulator, developed at the University of Edinburgh, is a high speed DBT based simulator and is the platform on which all of the simulations were performed for the research presented in this thesis.

This thesis contributes to the knowledge of high speed DBT based simulation as follows:

#### Novel High Speed Simulation Techniques

This thesis shows that LTUs can be deployed to increase the simulation speed of DBT based simulators. The techniques used to profile target programs and to identify and translate LTUs at runtime are unique to the Edinburgh High Speed simulator and are outlined in chapter 6.

The EHS simulator was designed as a research simulator suitable for performing DSE and hardware/software co-design of novel microprocessor architectures. The processor state is updated after each instruction is emulated and is observable at every translation unit boundary. The simulator also incorporates advanced management of translations so that self-modifying code can be simulated.

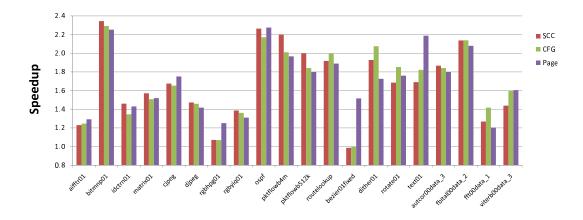

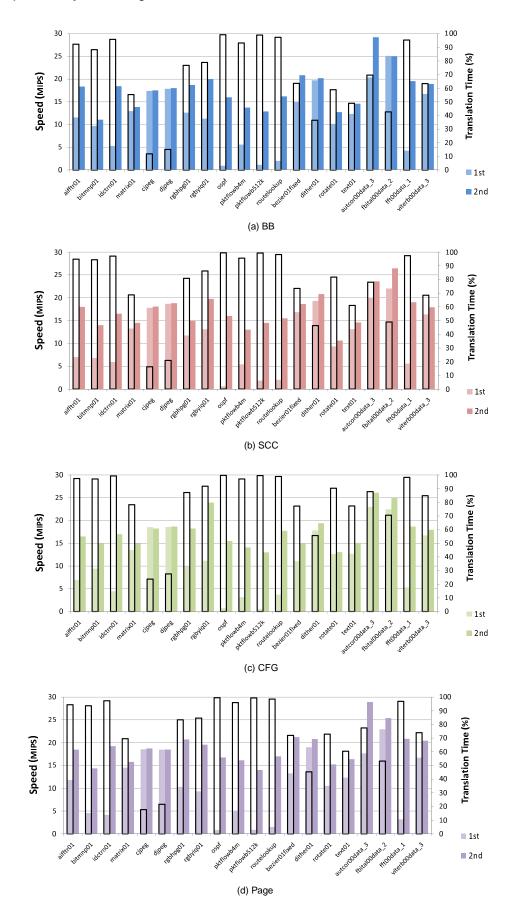

#### • Quantitative Analysis of Simulation Techniques

The performance of the different LTU DBT simulation modes are analyzed in chapters 7 and 8 and provide an insight into their effectiveness and future potential as high speed simulation techniques. Many aspects of LTU DBT based simulation are investigated in detail, including analysis of the number of instructions emulated by translations on the first and second simulation runs; the time spent performing the different simulation tasks; the size and number of translation units generated; the size and frequency of the translated functions called; the factors which cause translation unit fragmentation and the effects of varying the size of the simulation epoch.

#### • Instruction Level Performance Analysis

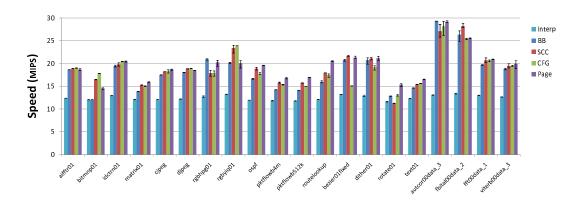

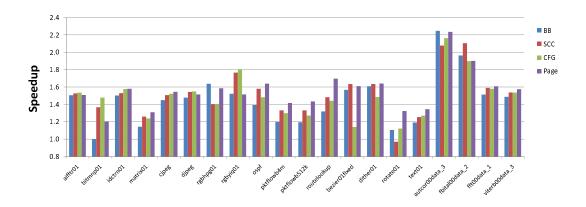

The instruction level simulation performance of the different LTU DBT simulation modes are compared in chapter 7. The results show that all of the LTU DBT simulation modes are on average at least 1.63 times faster than basic block DBT based simulation.

#### Cycle Approximate Performance and Accuracy Analysis

The cycle-approximate simulation performance of the different LTU DBT simulation modes are compared in chapter 8. The results - using simplified models for the target pipeline and memory sub-system - show that all of the LTU DBT simulation modes are on average at least 1.32 times faster than basic block DBT based simulation. The simplified system model is shown to introduce an average error of 2.4% into the cycle count.

#### • Comparison with State-of-the-Art Simulators

Chapter 7 demonstrates that, in addition to being a flexible research simulator, the EHS simulator is capable of performing instruction level simulation at speeds comparable with other state-of-the-art simulators which were designed purely for speed. The EHS simulator completed simulation of a set of benchmarks on average 1.07 times quicker than Simit-ARM and 1.26 times slower than QEMU (ARM).

### 1.4 Thesis Outline

This thesis is divided into nine chapters. Chapter 2 provides an overview of the main simulation techniques used in simulating microprocessor systems. Chapter 3 summarizes related work in the field of static and dynamic binary translation based simulators

and Chapter 4 describes the design and operation of the Edinburgh High Speed simulator used in this research.

Chapter 5 outlines the benchmarking methodology used to asses the performance of the different DBT simulation modes and Chapter 6 describes the different types of Large Translation Unit and details how they are identified and translated at runtime.

Chapters 7 and 8 analyze the performance of the instruction level and cycle-accurate simulation modes respectively. The simulation speed of each LTU DBT mode is presented and compared with that of basic block DBT based simulation. Chapter 7 also analyzes the characteristics of the different LTUs generated and compares the performance of the EHS simulator with two start-of-the-art functional simulators. Finally, chapter 9 presents the conclusions and outlines future work which naturally follows on from this research.

## **Chapter 2**

## **Simulation Techniques**

This chapter describes the simulation techniques employed in instruction set simulators which can be used to perform design-space exploration of microprocessor systems. The different simulation techniques used define a simulator's strengths and weaknesses, and therefore its application domain. Whilst slower simulators tend to provide flexibility of operation, the fastest simulators are restricted in their use. Hybrid simulators on the other hand, which employ a combination of simulation techniques, have the potential to be both fast and flexible and are therefore ideal for carrying out research.

### 2.1 Overview

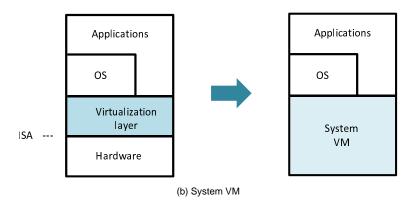

Simulators simulate programs by emulating each target instruction within a model of the target system running on the host machine. The simulation environment must model all of the lower-level components present in the target program's native execution environment. Therefore, all simulators form a virtualisation layer [Gold 73, Pope 74, Smit 05a, Smit 05b] between the simulated application and the host platform.

The two types of virtualisation layer are shown in figure 2.1. Process virtualisation supports the execution of a single process, or single-threaded application, by abstracting the Application Binary Interface (ABI). Process virtual machines (VMs) emulate user-level instructions and operating system calls, and are initiated when a process is

**Figure 2.1** Virtual Machines The two figures show the virtualisation layers used to simulate a) a process and b) an entire system.

## 2.2 Interpretation

Traditional interpretive simulators, such as SimpleScalar [Burg 96, Burg 97, Aust 02] and Bochs [Lawt 96], start by loading the target binary into simulated target memory. The simulator then fetches, decodes and emulates the next instruction in the execution

#### Chapter 2. Simulation Techniques

path [Half 94]. The fetching, decoding and execution tasks are usually performed in a monolithic function. After fetching and decoding the next instruction opcode from memory, the simulator calls an instruction specific function which emulates the instruction's behaviour. The function carries out the instruction operation within the processor model, updating the processor state, general purpose registers and main memory as required. Instrumentation functions may also be called to gather data on indicators such as the instruction count, total execution cycles and power usage statistics.

Figure 2.2 shows how a basic interpretive simulator might be implemented in C code. The main simulation loop is represented by the while statement, with the switch statement directing control to the next instruction to be emulated. The next instruction opcode is fetched and decoded by calling the decode\_opcode function. This function will search a decode cache in order to return previously decoded instructions as quickly as possible. The decoded instruction is then matched with the corresponding case statement which emulates the instruction and updates the program counter (PC). The break statement marks the end of each instruction and transfers control back to the main simulation loop.

Hardware decoders are fast, but instruction opcode decoding in software is a very time consuming process. This is because each opcode must be bit tested in order to ascertain the instruction operation, addressing mode, source and destination operands, data size (16/32 bit), indexing mode and any conditional execution flags to be tested. Interpretive simulators typically execute between 10 and 100 host instructions per target instruction [May 87]. However, interpretive simulation is flexible and enables accurate modelling of the target processor, albeit at relatively slow speeds.

### 2.3 Binary Translation

Binary translation [Cifu 96] is a technique used to convert binary code (target), which has been compiled [Aho 86, Torc 07] to run on one processor architecture, into binary code (host) which can be run on a different - or the same - processor architecture. When executed, the host binary reproduces the behaviour of the target binary within the simulated target environment. The host binary generated is capable of emulating the target

```

while (!end_of_simulation) {

inst = decode_opcode(PC);

switch (inst) {

case ADD:

*a = *b + *c;

PC++;

cycles++;

stats[ADD]++;

break;

case MPY:

*a = *b x *c;

PC++;

cycles+=2;

stats[MPY]++;

break;

case J:

PC = *c;

cycles++;

stats[J]++;

break;

. . .

}

}

```

**Figure 2.2** Interpretive Simulator Code. The next target instruction is fetched from memory address PC and decoded by calling the decode\_opcode function within the main simulation loop. The decoded instruction opcode is then matched with an instruction case statement which emulates the instruction by updating the simulation environment. Variables a,b and c are pointers to general purpose registers which are assigned at instruction decode. The execution cycle count is maintained in the cycles variable and instruction profiling is achieved using the stats variable.

program up to 11 times faster than is possible with interpretive simulation. Chapter 3 covers the work carried out by others into binary translation based simulation.

There a two main types of binary translation: static binary translation and dynamic binary translation.

• Static Binary Translation (Compiled). The target binary is parsed by a translator which analyzes it to discover all possible execution paths and then generates the simulator executable. The simulator is then run on the host machine to simulate the target program at high speed. Some

compiled simulators incorporate a fallback interpreter to deal with instructions which were not identified during compilation.

• Dynamic Binary Translation. The target binary opcodes are fetched, decoded, emulated and profiled by the simulator. Frequently emulated sections of the target binary are then translated at runtime into host code functions. The host code functions are then called to emulate the same sections of program code at high speed. Although not as fast as static binary translation based simulators, DBT based simulators are capable of simulating any target program including self-modifying applications.

Simulators which employ binary translation have been used to port legacy applications across to new systems with minimal effort. This has enabled individuals to continue to benefit from their software investment. Rebuilding or possibly rewriting applications can be very time consuming and may require in-depth knowledge of the compilation process, assuming one even has access to the source code. However, whilst binary translation based simulators are many times faster than interpretive simulators, native compilation of the source code remains the fastest way to run a program. This is primarily because the native compiler can view the target program in its entirety and at a higher level of abstraction. This enables the compiler to better optimize the program executable for speed.

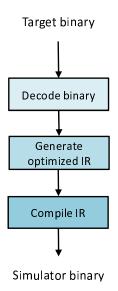

#### 2.3.1 Static Binary Translation

The processes involved in static binary translation are shown in figure 2.3. The frontend is responsible for loading and decoding the target binary. The decoded instructions are then translated into an optimized intermediate representation (IR) which is computer and operating system independent. The back-end compiles the intermediate code to generate the simulator executable. The simulator produced is a self-contained executable which when run simulates the target binary.

A compiled instruction set simulator spends most of its time emulating target instructions and is consequently much faster than an interpretive simulator. One straightforward compiled simulator design uses in-line macro expansion [Mill 91] present in

many programming languages such as C. The target target binary is statically translated into a host binary which is then run directly.

A macro is created for each target assembly language instruction. The macro defines the high-level emulation function for each target instruction. For example, macros for the add (ADD), branch on equal to zero (BEQ) and jump (J) instructions may be defined as:

```

#define ADD(a,b,c) (a) = (b) + (c); cycles++; stats[ADD]++;

#define BEQ(disp) PC += (disp); cycles++; stats[BEQ]++;

#define J(target) PC = (target); cycles++; stats[J]++;

```

Control instructions, such as direct branches and jumps, with destination addresses that can be computed statically may be modelled using GOTO statements and address labels placed before the target instructions. However, control instructions with destination addresses which are computed at runtime can not use such a method. Indirect branch and jump instructions, as well as returns from subroutine calls fall into this category. A switch statement can be used to model the execution path at runtime if each instruction macro is defined as a case statement, where the case statement value is equal to the instruction address. The example instruction macros now look as follows:

```

#define ADD(addr,a,b,c) case (addr): (a) = (b) + (c); \

cycles++; \

stats[ADD]++;

#define BEQ(addr,disp) case (addr): cycles++; \

stats[BEQ]++; \

if (status_flag(ZERO)) { \

PC = (addr) + ((disp); \

break; \

}

#define J(addr,target) case (addr): PC = (target); \

cycles++; \

stats[J]++; \

break;

```

Figure 2.4 shows example C code for a statically compiled simulator. Each target instruction is represented by an instruction macro placed within the main simulation loop (while statement). The switch statement controls the next instruction to be emulated based on the value of the PC. The figure shows that the first instruction in the target program is an ADD instruction at address 0x1000 which adds together source registers r2 and r3, and places the result in destination register r1.

```

while (!end_of_simulation) {

switch (PC) {

ADD(0x1000,r1,r2,r3);

ADD(0x1004,r5,r4,r1);

BEQ(0x1008,0x0008);

MPY(0x100C,r7,r5,r6);

ADD(0x1010,r5,r1,r7);

J(0x1014,r5);

...

}

}

```

Figure 2.4 Compiled Simulator Code. This figure shows the target instruction macros placed within the switch statement.

After a non-control instruction, simulation passes on to the next sequential instruction (following case statement) as non-control instructions do not end with a break state-

ment. The PC is updated with the target address for control instructions which are taken, a break statement then forces control back to the main simulation loop. The PC is not incremented after non-control instructions, or not taken control instructions, in order to increase the simulation speed. The switch statement is compiled by gcc into a set of indexed indirect jumps (jump table) which point to the different case statements. This is an efficient way to reference target instructions and enables changes in the control flow to be simulated at speed.

It is possible for large target programs to exceed the maximum code size (compiler dependent limit) allowed within a switch statement. If this is the case. the target program can be broken up into smaller sections, with each section being placed within a separate switch statement as shown in Figure 2.5.

```

while (!end_of_simulation) {

switch (PC) {

ADD(0x1000,r1,r2,r3);

. . .

PC = 0x1234;

default: break;

}

switch (PC) {

MPY(0x100C,r7,r5,r6);

. . .

PC = 0x2FDC;

default: break;

}

switch (PC) {

ADD(0x1010,r5,r1,r7);

. . .

HALT;

default: break;

}

}

```

**Figure 2.5** Compiled Simulator Code for Large Programs. Multiple switch statements are used to overcome compiler dependent switch size limits. The last instruction within a switch statement sets the PC value to equal the instruction address of the next consecutive instruction (first instruction within the following switch statement).

The PC is set to the next instruction address after the last instruction within a switch statement has been emulated. If the previous instruction was a non-control instruction, simulation continues with the first instruction in the following switch statement.

#### Chapter 2. Simulation Techniques

Control instructions are emulated as before, although they may now have to traverse a number of switch blocks before finding a matching target address. The overhead of searching across switch blocks for a target address increases with program size, but the associated performance degradation is negligible.

If the same target program is to be simulated many times, which is often the case, then compiled simulation is much faster than interpretive simulation. The initial cost of translating the target program is more than offset by the increased simulation speed. However, compiled simulators do not normally model a processor's internal state, including the PC, as accurately as an interpretive simulator for performance reasons.

Compiled simulators can only be used if all of the program code to be simulated can be identified at the time translation is performed. In other words, the target program code must be statically discoverable in order for it to be successfully simulated. This pre-condition excludes simulation of target programs which are self-modifying. Multitasking OSs can not be simulated as different processes may occupy the same address space. Operating system simulation is further complicated by the need to model asynchronous events such as interrupts.

Most embedded systems rely on some form of OS to schedule workloads across multiple processor cores and to control peripheral devices. Although compiled instruction set simulators are much faster than interpretive simulators, their use is restricted to stand-alone programs, which is not sufficient to model the complex hardware/software interfaces present in modern embedded systems.

The process of static binary translation is complicated by the existence of instructions and data within the same address space, and by the presence of indirect branches. Control-flow and register analysis are issues which static binary translation based simulators have to address in much the same way as disassemblers and compilers. The initial parsing of a target executable may not be able to resolve all instructions and data during translation. Hybrid static binary translation based simulators overcome any restrictions by calling a fallback interpreter to emulate target instructions, which for whatever reason, were not previously identified during translation or have been modified.

### 2.3.2 Dynamic Binary Translation

The processes involved in dynamic binary translation are shown in figure 2.6. The front-end is invoked at runtime to decode regions of target code which have not previously been translated. The decoded code is then optimized and translated into an intermediate representation. The back-end compiles the intermediate code into host code functions which are called to emulate the code sections. It may be discovered during emulation that certain host code functions lie on a critical path. In this case, the corresponding sections of code may be re-translated using a more aggressive optimization policy.

**Figure 2.6 Processes involved in Dynamic Binary Translation** Dynamic binary translation is performed at runtime.

Simulators which employ dynamic binary translation can emulate any type of application, including full operating systems, and are almost as fast as static binary translation based simulators. A DBT based simulator translates frequently executed sections of the target code - typically basic blocks - into code which when executed on the host machine emulates the same instructions within the simulation environment. High speed simulation is achieved by combining DBT with translation caching. If self-modifying code is detected at runtime, any translations which emulate the modified program region are discarded. Binary translation is a processor intensive task which can slow down simulation significantly on the first simulation run. To reduce the translation overhead some simulators perform emulation and translation in parallel.

Figure 2.7 shows a basic implementation of the main simulation loop for a DBT based simulator. The simulator calls the fetch\_translation function which searches the translation cache to see whether a translation exists for a basic block with start address equal to the PC. If a translation exists, the pointer to the translated function (trans\_func) is returned to the main loop. The translated function is then called to emulate the block at high speed. A pointer to the processor state is passed to the translated function so that it can update any status flags and registers whilst emulating the instructions within the block.

```

while (!end_of_simulation) {

trans_func = fetch_translation(cpu_state->PC);

if (trans_func)

(*trans_func)(cpu_state);

else

interpret_block(cpu_state);

if (end_of_epoch)

perform_translation();

}

```

**Figure 2.7 DBT Simulator Code.** This figure shows the C code skeleton for the main loop of a basic block DBT based simulator.

If a translation does not exist for the basic block, the fetch\_translation function returns a NULL pointer. The simulator then calls the interpret\_block function which interprets the basic block and maintains a profile of how many times the block has been emulated. The simulator continues emulating consecutive basic blocks in this manner for a fixed number of blocks - the simulation epoch. At the end of each simulation epoch, the perform\_translation function is called which scans the basic block profiles to identify those blocks which were frequently executed. After translating the hot blocks, the function then adds the newly created translated functions to the translation

cache.

A DBT based simulator can also gather profiling information (control-flow, register contents) on the target program whilst simulating it, something which is not possible with a static binary translation based simulator. This means that frequently executed code regions may be sent for highly optimized translation. Dynamic binary translation is lazy. This is an advantage as it guards against translating sections of the target binary which are never executed or which contain only data.

### 2.4 Sampling

Sampling is a technique which is used to speed up cycle-accurate simulation. A sampling based simulator collects accurate simulation data for a small subset (sample) of the entire benchmark simulation period (population), fast-forwarding through the remainder of the benchmark. Statistical analysis is then performed on the data collected to produce approximate figures for the simulation. During fast-forwarding, full observability is typically not supported, therefore sampling is not suitable for performing hardware/software co-design.

The Sampling Microarchitecture Simulation (SMARTS) framework [Wund 03] uses statistical sampling. It has been shown to speed up the simulation of 8-way and 16-way out-of-order processors by a factor of 35 and 60 times respectively compared to full cycle-accurate simulation. SMARTS can calculate the clock cycles per instruction (CPI) to within  $\pm 3\%$  for 41 of the SPEC2000 benchmarks. SMARTS applies statistical sampling theory to work out the optimal sampling strategy that will capture a programs' variability and produce results with the required degree of accuracy. The sampling strategy requires taking a large number of small samples from the population. By selecting a minimal, but representative sample, the nature of a particular benchmark can be accurately modelled.

SMARTS samples a tiny fraction of a benchmark's execution stream using detailed cycle-accurate simulation. The rest of the time it fast-forwards through the benchmark using functional simulation. The desired micro-architectural data is collected during sampling, whereas only the program-visible architectural state is updated during fast-

#### Chapter 2. Simulation Techniques

forwarding. Systematic sampling is used where the samples, which consist of a relatively small number of consecutive instructions, are separated by sampling intervals, which consist of a large number of consecutive instructions.

Whilst SMARTS maintains the processor state between samples with functional simulation, the state of the system micro-architecture is left to become stale. If the microarchitecture state is not up-to-date prior to sampling then large errors appear in the detailed data collected. To combat this, the micro-architecture state is updated by the inclusion of a cycle-accurate warm-up period just prior to sampling. However, it is difficult to know how long to make the warm-up phase as some micro-architecture states may require many simulation cycles before they are representative of the true cycle-accurate states.

Another sampling technique, SimPoint [Sher 02], can summarize the large-scale behaviour of programs relatively quickly. It achieves this by offline analysis of the basic blocks within large representative sample traces - 100 million instructions - taken from the program trace. The assumption is that samples with matching dynamic basic block profiles exhibit similar behaviours. However, SimPoint does not provide a formal method for quantifying the accuracy of the results returned.

### 2.5 Summary

This chapter outlines the main simulation techniques used in instruction level and cycle-accurate simulation of microprocessor systems. Whilst interpretive simulation is flexible, in that it provides observability and can simulate any target binary, it is very slow at performing instruction level simulation compared to the different binary translation based simulation techniques. Dynamic binary translation is the best simulation technique for performing instruction level simulation as it is not only very fast, it also provides state observability and can simulate self-modifying programs. This makes DBT based simulation ideal for carrying out high level DSE and for performing hardware/software co-design and verification.

Sampling based simulation techniques are superior for performing cycle-approximate simulation. Sampling based simulation is many times faster than interpretive or binary

#### Chapter 2. Simulation Techniques

translation based simulation techniques as it fast forwards through the majority of the simulation, needing only to simulate very small sections of the target program in detail. The inaccuracies introduced are small and can in some cases be quantified which makes sampling ideal for carrying out low level DSE in situations where there is a very large design-space. However, DBT based simulation remains the best simulation technique for performing cycle-accurate hardware/software co-design and verification of microprocessor architectures.

# **Chapter 3**

# **Related Work**

This chapter describes the simulation techniques used in previous work which are relevant to the field of high speed binary translation based simulation.

## 3.1 Binary Translation Simulators

This section looks at the translation techniques employed in static and dynamic binary translation based simulators [Cifu 96].

### 3.1.1 Static Binary Translation

The first static binary translation simulators were used to port legacy software across to newer, faster RISC based systems [Patt 85, Stal 90]. Static translators operate like compilers, translating the target binary into an equivalent host code binary image. Compiled simulators spend most of their time emulating target instructions and are consequently much faster than interpretive simulators. Interpretive simulators are slow because they spend most of their time, in the main simulation loop, fetching and decoding each instruction. Even if interpretive simulators employ a decode cache, the emulation of instructions is still slow.

#### 3.1.1.1 HP Object Code Translator

When Hewlett Packard released its MPE XL operating system for its new HP Precision Architecture (RISC) series of computers it incorporated a Compatibility Mode (CM) environment [Berg 87]. The CM environment enabled program binaries from the previous family of HP 3000 computers (stack-orientated CISC, MPE V operating system) to run on the Precision Architecture platform. The CM environment uses two subsystems: the HP 3000 emulator and the static binary translator, called the HP 3000 Object Code Translator (OCT).

The emulator is capable of running HP 3000 binary code on HP Precision Architecture platforms without modification. However, the OCT first translates the HP 3000 binary code into native code which is then executed. The OCT binary translator can simulate HP 3000 programs up to five times faster than the emulator.

The OCT translates HP 3000 binary code segments into native code modules. The translator also tries to discover all of the node points within the program code and creates a node mapping table. The node mapping table holds the translated code addresses, within the modules, which correspond to the node addresses within the code segments. When a branch target address can not be statically determined it is looked up at runtime in the node mapping table. If a target address is not found within the node mapping table the emulator is invoked until the PC value equals a module entry-point at which point execution is returned to the translated code.

### 3.1.1.2 Hunter Systems DOS to Unix Translator

Hunter Systems used object code translation to port MS-DOS binaries (8086) into executable files which run on UNIX systems [Hunt 89, Wirb 88]. A number of different translator back-ends made translation to different host architectures possible. However, the program analyser required manual intervention in order to deal with complex code, such as self-modifying code, and to compute indirect jump target addresses.

#### 3.1.1.3 Tandem Accelerator Object Code Translator

Tandem wanted an easy way to migrate software from its proprietary TNS CISC machines to its new TNS/R RISC machines based on the MIPS processor. The OCT developed by Tandem, called the Accelerator [Andr 92], enabled all existing TNS software to be run immediately and at high speed on the TNS/R machines. The Accelerator was also used to translate Tandem's Guardian 90 operating system and produce the first RISC release. This contributed to bringing Tandem's new RISC machines to market many years earlier than would otherwise have been possible.

The Accelerator emulates TNS CISC binary programs on TNS/R RISC machines by using a combination of translation and interpretation. It augments the target binary with translated code sections and a PMap table, which is a map of CISC to RISC instruction addresses, in advance of simulation. The Accelerator acts like any optimizing compiler except that it tightly controls TNS/R register and stack frame usage so that it can easily switch between accelerated and interpreted simulation modes.

After disassembling the CISC (TNS) target binary the Accelerator performs static control-flow analysis in which it attempts to identify all of the branch paths. Jumps through pointer variables or calculated addresses are explicitly marked and if the target address is unknown at runtime - not found in a PMap table - a switch is made to the interpreter. The Accelerator translates the CISC instructions within each basic block, on a per CISC subroutine basis, into a preliminary sequence of RISC instructions. CISC subroutine calls lookup the target address in a jump table which is replaced by a direct jump into translated RISC code. Returns back to the caller must also be looked up in the PMap table. Standard optimization techniques are then applied to the translated code within and across the basic blocks, including reordering the instructions within each block to minimize pipeline stalls.

Four different programs (TAL compiler, TAL-coded Dhrystone, Axcel and ET1) were used as benchmarks to measure the performance of the Accelerator. The benchmarks were run natively on a NonStop Cyclone, 22.3MHz superscalar CISC machine and compared with OCT emulation of the same benchmarks on a NonStop Cyclone/R, 25 MHz machine. The average benchmark simulation speed was 78% of the average native execution speed, and the simulation speed for the Axcel benchmark was 8% faster than native execution.

It was shown that translated code ran 5 to 8 times faster than interpretation and that interpretation accounted for less than 1% of the emulation time. On average, the number of RISC instructions generated per CISC instruction was 1.6, and the accelerated code file (CISC binary plus translated code plus PMap) was 5 times larger than the original CISC binary.

#### 3.1.1.4 Digital VEST Binary Translator

In 1988, Digital wanted to run legacy code which had previously been executed on its VAX machines [Brun 91] on its latest Alpha AXP processor [Site 93a, Site 95], but it was not simply a case of recompiling the applications for the new architecture. Large and complex applications typically rely on a spectrum of different OS libraries and services, and the time required to rebuild everything from scratch would have been prohibitive. It was therefore necessary to run as much as possible in the old environment, with system calls being redirected to the newly ported OpenVMS AXP [Kron 93] operating system. The Alpha AXP team decided to use static binary translation to enable not just their existing VAX code base, but also their MIPS code [Kane 88] code base, to be run on the Alpha processor.

Digital developed the VAX Environment Software Translator (VEST) binary translator to translate an OpenVMS VAX binary image into a OpenVMS AXP binary image [Site 93b]. VEST disassembles the VAX code starting at standard entry points, such as global sub-routines, and traces the program building-up a control-flow graph of basic blocks. After analysing the CFG, VEST generates an optimized host binary. The mapping between architectures is simplified by the fact that the AXP processor has more registers than the VAX processor. VAX condition codes, which are not implemented in the AXP processor, are mapped on to spare AXP registers. Each VAX instruction gets translated into zero or more AXP instructions.

VEST inserts jump instructions within the host binary to emulate direct branches and jumps. However, in order to emulate branches and subroutine calls to unknown target addresses, VEST inserts calls to a runtime look-up routine. The routine uses a look-up table which maps VAX instruction addresses to the corresponding translated Alpha

AXP instruction addresses. If the destination address is found in the look-up table then control is passed to the corresponding address in the host code. If it is not found, control is passed back to the runtime environment.

The Translated Image Environment (TIE) is the runtime environment which executes the translated image. The TIE employs open-ended translation and emulates the Open-VMS VAX environment by using wrappers to map library and system calls to the corresponding OpenVMS AXP calls. Target binary instructions which were either not discovered, or which did not exist at translation (self-modifying code), are caught and then simulated by TIE's built-in interpreter.

Digital used binary translation as an interim solution to enable users to run existing VAX/MIPS binaries on the Alpha processor with minimal effort. Over time, all legacy applications and dependent libraries were ported over to the new platform. By utilizing binary translation, Digital were able to run translated applications on Alpha AXP systems as fast, or faster, than the original applications ran on VAX systems.

### 3.1.1.5 Digital FreePort Translator

FreePort Express [Free 95] is a free program developed at Digital Research which translates SunOS 4.1.x user-mode binaries into executable files which can be run on DEC Unix 3.0 and later systems. It was the first translator from Digital which converted binaries from a non-Digital OS platform. FreePort Express translates the target binary prior to execution and incorporates a fallback interpreter. It was first demonstrated at SunWorld '95 where translated SunOS applications were shown to run as fast, or faster, on an AlphaStation 400 4/233 system than natively on a SPARC 20/71 system.

### 3.1.1.6 Digital FX!32 Emulator

Digital developed the FX!32 emulator [Thom 96, Hook 97a, Cher 98] in order to increase the popularity of its Alpha RISC platform by ensuring that a large number of applications would be available to run on it. FX!32 enabled all x86 32-bit Windows NT 4.0 programs to be run on the Alpha Windows NT 4.0 system. The FX!32 was the first emulator to use a combination of interpretation and profile-directed translation to

#### Chapter 3. Related Work

provide fast simulation [Hook 97b] of x86 programs on the Alpha platform. The translation of x86 code into native Alpha code is performed in the background. Parallel translation means that the translated code can be optimized for speed without affecting the simulation speed.

The FX!32 runtime is started automatically whenever an x86 executable is run. The runtime loads the x86 image into memory and then calls the emulator which interprets the whole program the first time it is run. At the same time the emulator generates profile data on CALL instruction target addresses, and source and target address pairs for indirect jumps, which it stores in a database for use later by the translator.

The translator uses the execution profile information gathered during emulation to translate the target binary into a collection of native code images. The unit of translation is the assembly code routine. The translator divides the target image into separate routines that have entry points at each call target address. The routines are created using the control-flow profile information which includes known target addresses for indirect jumps. A routine is a collection of one or more regions which consist of a contiguous set of instructions. Direct entry is permitted to any region within a routine.

A hash table is generated which maps target binary addresses to entry points within the translated routines. If the emulator finds that the next instruction address is mapped to an entry point, the corresponding translated routine is called. As it is generally impossible to statically analyse all program execution paths, the emulator is invoked as a backup when no translated routine mapping exists for a target address.

Digital's FX!32 emulator transparently emulates x86 binaries on the Alpha platform at high speed. The performance of a set of x86 benchmarks running on a 200MHz Intel Pentium Pro and a 500MHz Alpha system under FX!32 were compared. The results showed that the x86 applications ran as fast on the Alpha (second emulation run) as they did on the Intel machine.

#### 3.1.1.7 Ultra-fast Instruction Set Simulator

A number of research groups are now developing retargetable instruction set simulators. The Ultra-fast Instruction Set Simulator [Zhu 99, Zhu 02] improves the performance of statically compiled simulation by aggressively utilizing low level machine resources to take full advantage of the host architecture. The low level simulation techniques were shown to increase the simulation speed by a factor of 2.7 on average over traditional compiled simulation techniques which generate C code.

### 3.1.1.8 Static Scheduling Simulator

The static scheduling simulation technique [Brau 01] applies static compilation to instruction decoding and instruction scheduling in retargetable simulators. Whilst static instruction scheduling increases the simulation speed of cycle-accurate simulators it also restricts flexibility of operation. Compiled simulators were generated from model descriptions of TI's TMS320C54x processor (cycle accurate model) and the ARM7 processor (functional model). A FIR filter was used to benchmark both processor models running on an 800MHz Athlon PC. The simulation results for the TMS320C54X processor, showed that static scheduling led to an increase in speed by almost a factor of 4 compared to dynamically scheduled simulation. Static scheduling resulted in a speed-up by a factor of 7 for the ARM7 processor, from 5 MIPS to 35.5 MIPS.

### 3.1.1.9 JIT-CCS Simulator

Just-In-Time Cache Compiled Simulation (JIT-CCS) [Nohl 02, Brau 04] can be used to create retargetable functional and cycle-accurate simulators. The JIT-CCS simulator references an array of built-in, pre-compiled instruction functions which emulate the behaviour of the different target instructions. When a target instruction is decoded a reference to the corresponding compiled instruction function is stored in the translation cache. If the simulator finds a matching translation cache entry for the next target instruction it calls the corresponding instruction function. If the simulator detects that an instruction has been modified, it decodes it and then calls the corresponding compiled instruction function.

Simulation results for cycle-accurate simulation of an ARM7 processor showed that JIT-CCS simulation is four time faster than interpretive simulation and only 5% slower than compiled simulation. The simulation performance results for the jpeg200 codec benchmark were: compiled simulation 7.2 MIPS; JIT-CCS simulation 7.0 MIPS; interpretive simulation 1.8 MIPS.

### 3.1.1.10 IS-CS Simulator