# Proof Planning for Automating Hardware Verification

Francisco J. Cantu-Ortiz

Ph.D. University of Edinburgh 1997

## Abstract

In this thesis we investigate the applicability of *proof planning* to automate the verification of hardware systems. Proof planning is a meta-level reasoning technique which captures patterns of proof common to a family of theorems. It contributes to the automation of proof by incorporating and extending heuristics found in the *Nqthm* theorem prover and using them to guide a tactic-based theorem prover in the search for a proof. We have addressed the automation of proof for hardware verification from a proof planning perspective, and have applied the strategies and search control mechanisms of proof planning to generate automatically customised tactics which prove conjectures about the correctness of many types of circuits.

The contributions of this research can be summarised as follows: (1) we show by experimentation the applicability of the proof planning ideas to verify automatically hardware designs; (2) we develop and use a methodology based on the concept of proof engineering using proof planning to verify various combinational and sequential circuits which include: arithmetic circuits (adders, subtracters, multipliers, dividers, factorials), data-path components (arithmetic logic units, shifters, processing units), and a simple microprocessor system; and (3) we contribute to the profiling of the *Clam* proof planning system by improving its robustness and efficiency in handling large terms and proofs.

In verifying hardware, the user formalises a problem by writing the specification, the implementation and the conjecture, using a logic language, and asks *Clam* to compose a tactic to prove the conjecture. This tactic is then executed by the *Oyster* prover. To compose a tactic, *Clam* uses a set of *methods* which implement heuristics that specify general-purpose tactics, and AI planning mechanisms. Search is controlled by a type of annotated rewriting called *rippling*, which controls the selective application of rewrites called *wave* rules. We have extended some of the *Clam*'s methods to verify circuits. The size of the proofs were orders of magnitude larger than the proofs that had been attempted before with proof planning, and are comparable with similar verification proofs obtained by other systems, but using fewer lemmas and less interaction.

Proof engineering refers to the application of formal proof for system design and verification. We propose a proof engineering methodology which consists of partitioning the automation of formal proof into three different kind of tasks: user, proof and systems tasks. User tasks have to do with formalising a particular verification problem and using a formal tool to obtain a proof. Proof tasks refer to the tuning of proof techniques (e.g. methods and tactics) to help obtain a proof. Systems tasks have to do with the modification of a formal tool system. By making this distinction explicit, proof development is more manageable. We conjecture that our approach is widely applicable and can be integrated into formal verification environments to improve automation facilities, and be utilised to verify commercial and safety-critical hardware systems in industrial settings.

## Acknowledgements

First and foremost I would like to express my deep gratitude to my supervisors Prof. Alan Bundy, Dr. Alan Smaill and Prof. David Basin. Their support, advice, friendship and encouragement, often beyond duty, have been invaluable. I would like to express my appreciation to Toby Walsh and James Molony for their comments and discussions on drafts of the thesis; to Andrew Ireland, Ian Green, Gordon Reid, Raul Monroy, Hugo Terashima and Santiago Negrete for all the support provided; and to the members of the Mathematical Reasoning Group who created such a productive and research environment. I thank Peter and Florence Sinclair through whom I met the superb Scottish hospitality. I would like to express my deep gratitude to Dr. Fernando J. Jaimes (ITESM) for his support, encouragement and patience during my graduate studies. I thank Leticia Rodriguez, Moraima Campbell, Manuel Valenzuela, Rogelio Soto, Jose Escamilla, Pablo Ramirez, Ramon Brena and the members of the Center for Artificial Intelligence at ITESM; I am indebted to my mother Raquel, my brother Humberto and my sisters Hilda, Maria de la Luz and Raquel; my parents-in-law Hector and Carmen and all the members of my family. I thank my examiners Prof. Michael Gordon, University of Cambridge and Prof. Michael Fourman, University of Edinburgh for their thoughtful comments and feedback on the thesis. Finally, I gracefully acknowledge the financial support of CONACYT and ITESM. God bless you all.

## Dedication

I dedicate this thesis to Carmen, my wife, and to our children Francisco, Hector, Eduardo and Marycarmen. My deepest thanks for your love, patience, prayers and care, which made this dream a reality.

## Declaration

I hereby declare that I composed this thesis entirely myself and that it describes my own research. Portions of the work described here have been published previously in [Cantu *et al* 96].

> Francisco J. Cantu-Ortiz Edinburgh June 12, 1997

# **Table of Contents**

| 1. | Intr | oducti  | on                                        | 1  |

|----|------|---------|-------------------------------------------|----|

|    | 1.1  | Overv   | iew                                       | 1  |

|    | 1.2  | Motiv   | ation                                     | 4  |

|    | 1.3  | Contri  | butions                                   | 6  |

|    | 1.4  | Organ   | isation                                   | 6  |

| 2. | Bac  | kgroui  | ıd                                        | 8  |

|    | 2.1  | Verific | ation                                     | 8  |

|    |      | 2.1.1   | Hierarchical Verification                 | 9  |

|    | 2.2  | Comp    | onents                                    | 0  |

|    |      | 2.2.1   | Specification                             | 0  |

|    |      | 2.2.2   | Implementation                            | 12 |

|    |      | 2.2.3   | Relationship                              | 15 |

|    |      | 2.2.4   | Functional versus relational verification | 6  |

|    | 2.3  | Appro   | aches to Formal Verification              | 9  |

|    |      | 2.3.1   | Logic                                     | 9  |

|    |      | 2.3.2   | Propositional Logic                       | 21 |

|    |      | 2.3.3   | First-Order Logic                         | 22 |

|    |      | 2.3.4   | Boyer-Moore Computational Logic           | 22 |

|    |     | 2.3.5   | Higher-Order Logic                        | 24 |

|----|-----|---------|-------------------------------------------|----|

|    |     | 2.3.6   | Intuitionistic Logic                      | 25 |

|    |     | 2.3.7   | Modal Logic                               | 25 |

|    |     | 2.3.8   | Mu Calculus                               | 26 |

|    |     | 2.3.9   | Other Approaches to Hardware Verification | 26 |

|    | 2.4 | Verific | cation Environments                       | 29 |

|    |     | 2.4.1   | Theorem provers                           | 29 |

|    |     | 2.4.2   | Model/equivalence checkers                | 33 |

|    | 2.5 | Summ    | nary                                      | 35 |

| 3. | Pro | of Pla  | nning                                     | 36 |

|    | 3.1 | Metho   | ods                                       | 36 |

|    | 3.2 | Induct  | tive Proof Planning                       | 43 |

|    |     | 3.2.1   | Rippling                                  | 44 |

|    |     | 3.2.2   | Fertilisation                             | 52 |

|    | 3.3 | An ex   | ample                                     | 54 |

|    | 3.4 | Clam-   | <i>Oyster</i>                             | 57 |

|    |     | 3.4.1   | Oyster                                    | 57 |

|    |     | 3.4.2   | <i>Clam</i>                               | 58 |

|    | 3.5 | Summ    | nary                                      | 59 |

| 4. | Har | dware   | Verification                              | 60 |

|    | 4.1 | Basic   | elements                                  | 60 |

|    |     | 4.1.1   | Types                                     | 60 |

|    |     | 4.1.2   | Operations                                | 63 |

|    |     | 4.1.3  | Conversion functions                                                                               | 65  |

|----|-----|--------|----------------------------------------------------------------------------------------------------|-----|

|    | 4.2 | A non  | -inductive proof                                                                                   | 66  |

|    |     | 4.2.1  | Formalisation                                                                                      | 66  |

|    |     | 4.2.2  | Verification                                                                                       | 67  |

|    | 4.3 | An ine | ductive proof                                                                                      | 69  |

|    |     | 4.3.1  | Formalisation                                                                                      | 69  |

|    |     | 4.3.2  | Verification                                                                                       | 71  |

|    | 4.4 | Summ   | nary                                                                                               | 74  |

| 5. | ΑN  | lethoo | dology                                                                                             | 75  |

|    | 5.1 | A Pro  | oof Engineering based Methodology                                                                  | 76  |

|    | 5.2 | Comb   | inational circuits                                                                                 | 79  |

|    |     | 5.2.1  | An $n$ -bit adder $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 79  |

|    |     | 5.2.2  | Arithmetic Logic Unit                                                                              | 83  |

|    |     | 5.2.3  | Multiplier                                                                                         | 88  |

|    | 5.3 | A sequ | uential circuit                                                                                    | 91  |

|    |     | 5.3.1  | User tasks                                                                                         | 93  |

|    |     | 5.3.2  | Proof tasks                                                                                        | 105 |

|    |     | 5.3.3  | Systems tasks                                                                                      | 107 |

|    | 5.4 | Exten  | dability and Scalability                                                                           | 108 |

|    |     | 5.4.1  | Extendability                                                                                      | 108 |

|    |     | 5.4.2  | Scalability                                                                                        | 109 |

|    | 5.5 | Summ   | nary                                                                                               | 110 |

| 6. | $\mathbf{Ext}$ | ension | s to Proof Planning                   | 112   |

|----|----------------|--------|---------------------------------------|-------|

|    | 6.1            | Proof  | level                                 | . 113 |

|    |                | 6.1.1  | Methods and tactics                   | . 115 |

|    |                | 6.1.2  | Induction Schemes                     | . 119 |

|    |                | 6.1.3  | Equations                             | . 120 |

|    | 6.2            | Syster | ms level                              | . 120 |

|    |                | 6.2.1  | Predicates                            | . 121 |

|    |                | 6.2.2  | Debugging and versions of <i>Clam</i> | . 121 |

|    | 6.3            | Summ   | nary                                  | . 122 |

| 7. | Res            | ults   |                                       | 123   |

|    | 7.1            | Exper  | iments                                | . 123 |

|    | 7.2            | -      | sis                                   |       |

|    | 1.2            | Ū      |                                       |       |

|    |                | 7.2.1  | Analysis of human timings             | . 126 |

|    |                | 7.2.2  | Analysis of experiments               | . 127 |

|    |                | 7.2.3  | Analysis of object-level times        | . 134 |

|    |                | 7.2.4  | Analysis of hierarchical proofs       | . 135 |

|    |                | 7.2.5  | Analysis of lemmas                    | . 135 |

|    | 7.3            | Summ   | nary                                  | . 141 |

| 8. | $\mathbf{Rel}$ | ated a | nd future work                        | 142   |

|    | 8.1            | Relate | ed work                               | . 142 |

|    |                | 8.1.1  | NQTHM                                 | . 143 |

|    |                | 8.1.2  | НОГ                                   |       |

|    |                |        |                                       |       |

|    |                | 8.1.3  | PVS                                   | . 145 |

|    |     | 8.1.4   | VERIFY                                    | 45 |

|----|-----|---------|-------------------------------------------|----|

|    |     | 8.1.5   | MONA                                      | 46 |

|    |     | 8.1.6   | VOSS                                      | 46 |

|    |     | 8.1.7   | Comparison                                | 47 |

|    | 8.2 | Future  | Work                                      | 48 |

|    |     | 8.2.1   | Interface with other provers              | 49 |

|    |     | 8.2.2   | Temporal logic                            | 52 |

|    |     | 8.2.3   | Heuristic search                          | 54 |

|    |     | 8.2.4   | Interface to a HDL                        | 54 |

|    |     | 8.2.5   | Propositional reasoning                   | 55 |

|    |     | 8.2.6   | Lemma speculation                         | 55 |

|    |     | 8.2.7   | Automatic generation of induction schemes | 55 |

|    |     | 8.2.8   | Higher-order rippling                     | 56 |

|    |     | 8.2.9   | Relational verification                   | 56 |

|    |     | 8.2.10  | Microprocessor verification               | 56 |

|    | 8.3 | Summ    | ary                                       | 57 |

| 9. | Con | clusion | ns 18                                     | 58 |

| A. | Obj | ect lev | vel definitions 12                        | 79 |

|    | A.1 | Types   |                                           | 79 |

|    | A.2 | Operat  | tions on types                            | 79 |

|    |     | A.2.1   | Booleans                                  | 79 |

|    |     | A.2.2   | Natural numbers                           | 80 |

|    |     | A.2.3   | Lists                                     | 81 |

|               |             | A.2.4 Words           | 181 |

|---------------|-------------|-----------------------|-----|

|               | A.3         | Conversion functions  | 181 |

|               | A.4         | Conditional functions | 182 |

| В.            | Non         | recursive circuits 1  | 183 |

|               | B.1         | Half adder            | 183 |

|               | B.2         | Full adder            | 183 |

|               | B.3         | 1-bit ALU             | 184 |

|               | <b>B.</b> 4 | 4-1 Multiplexer       | 184 |

| $\mathbf{C}.$ | Incr        | rementer 1            | 186 |

|               | С.1         | Formalisation         | 186 |

|               | C.2         | Proof plan            | 186 |

|               | С.3         | Proof                 | 188 |

|               | C.4         | Methods               | 188 |

| D.            | Mul         | tiplier 1             | 189 |

|               | D.1         | Formalisation         | 189 |

|               | D.2         | Lemmas                | 189 |

|               | D.3         | Proof                 | 190 |

|               | D.4         | Methods               | 190 |

| Е.            | Gor         | don computer 1        | 191 |

|               | E.1         | Formalisation         | 191 |

|               | E.2         | Proof plan            | 201 |

|               | E.3         | Proof                 | 205 |

|               | E.4         | Methods               | 206 |

| F. | Oth       | er circuits                                                                                               | 207   |

|----|-----------|-----------------------------------------------------------------------------------------------------------|-------|

|    | F.1       | Adder                                                                                                     | . 207 |

|    |           | F.1.1 Explicit parameter                                                                                  | . 207 |

|    |           | F.1.2 Big endian                                                                                          | . 207 |

|    | F.2       | ALU                                                                                                       | . 208 |

|    |           | F.2.1 Explicit parameter                                                                                  | . 208 |

|    |           | F.2.2 Big endian                                                                                          | . 208 |

|    | F.3       | Shifter                                                                                                   | . 209 |

|    | F.4       | Processing unit                                                                                           | . 210 |

|    | F.5       | Other arithmetic operations                                                                               | . 210 |

|    |           | F.5.1 Adder $\ldots$     | . 210 |

|    |           | F.5.2 Multiplier                                                                                          | . 211 |

|    |           | F.5.3 Exponentiator                                                                                       | . 211 |

|    |           | F.5.4 Factorial $\ldots$ | . 211 |

|    |           | F.5.5 Subtracter                                                                                          | . 211 |

|    |           | F.5.6 Divider                                                                                             | . 212 |

|    |           | F.5.7 Counter $\ldots$   | . 212 |

| G. | ${f Met}$ | hods                                                                                                      | 213   |

|    | G.1       | Symbolic evaluation                                                                                       | . 213 |

|    | G.2       | Generalise                                                                                                | . 214 |

|    | G.3       | Normalise                                                                                                 | . 214 |

|    | G.4       | Induction strategy                                                                                        | . 215 |

|    | G.5       | Elementary                                                                                                | . 215 |

|    | G.6       | Use of equation in hypothesis                                                                             | . 216 |

| G.7  | Evaluate definition                                                                                                       |

|------|---------------------------------------------------------------------------------------------------------------------------|

| G.8  | Term cancellation $\ldots \ldots 217$ |

| G.9  | Boolean case analysis                                                                                                     |

| G.10 | Memoise recursive function                                                                                                |

| G.11 | Weak fertilise                                                                                                            |

# List of Figures

| 2-1   | Modelling the structure of a device                                                                                                  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|

| 3–1   | Method components                                                                                                                    |

| 3-2   | Data base of methods                                                                                                                 |

| 3–3   | $Method eval\_def \dots \dots$ |

| 3-4   | A Proof Plan for Induction                                                                                                           |

| 3–5   | Structure of proof plan                                                                                                              |

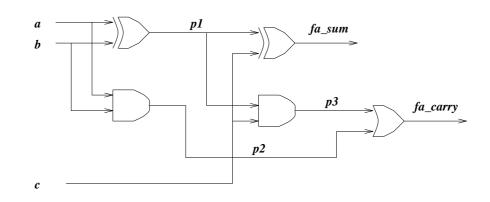

| 4-1   | 1-bit Full adder                                                                                                                     |

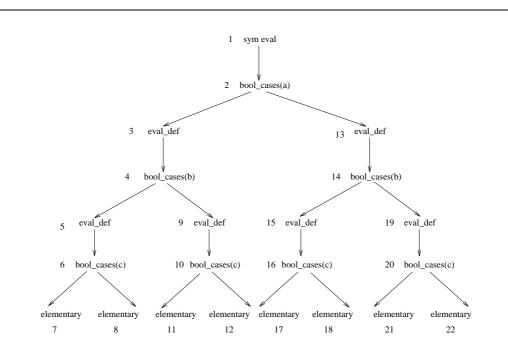

| 4-2   | Structure of proof plan for verifying the full adder                                                                                 |

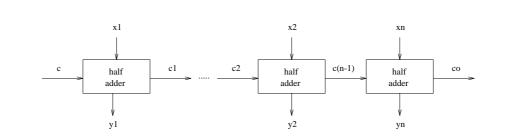

| 4–3   | Implementation of n-bit incrementer                                                                                                  |

| 4-4   | Structure of the proof plan for n-bit incrementer                                                                                    |

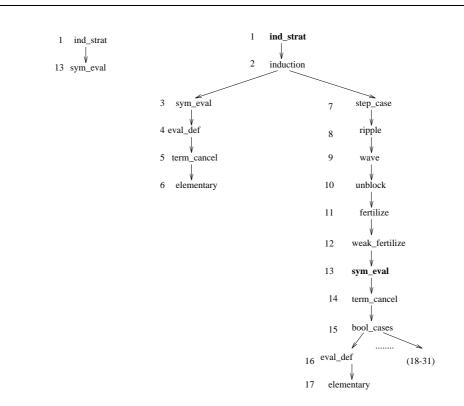

| 5 - 1 | Proof plan for the <i>n</i> -bit Adder $\ldots$ 81                                                                                   |

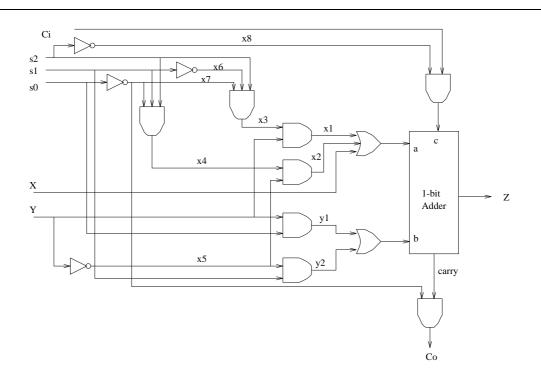

| 5-2   | Hardware Design of a 1-bit ALU                                                                                                       |

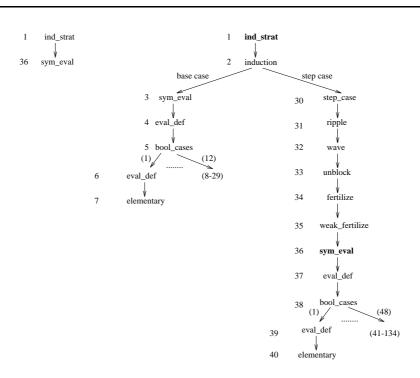

| 5–3   | Proof plan for the <i>n</i> -bit ALU $\ldots \ldots $ 86              |

| 5 - 4 | Proof plan for the $nm$ -bit multiplier                                                                                              |

| 5 - 5 | Specification of the Gordon computer                                                                                                 |

| 5-6   | Register-transfer level implementation of the Gordon computer 96                                                                     |

| 5 - 7 | Proof plan for the Gordon computer                                                                                                   |

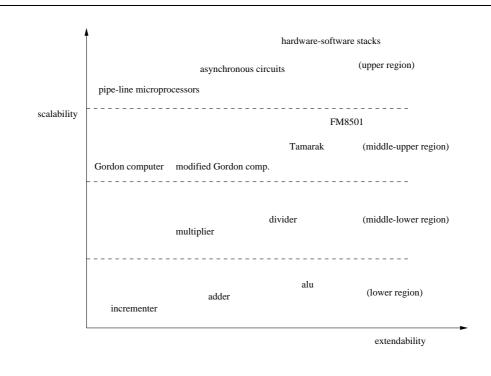

| 5-8 | Extendability and scalability of proof planning  |

|-----|--------------------------------------------------|

| 6–1 | Verify: set of methods for hardware verification |

| 6–2 | Method for term cancellation                     |

| 6–3 | Method for Boolean case analysis                 |

| 6-4 | Method for memoisation                           |

| 8-1 | LAMBDA proof for the associativity of addition   |

| 8-2 | Proof plan for the associativity of addition     |

| 9-1 | Extendability and scalability of proof planning  |

## Chapter 1

# Introduction

## 1.1 Overview

This thesis is about the application of *proof planning* to the automation of formal verification in the hardware domain. Given an implementation of a circuit and a specification of its behaviour, formal verification shows that the implementation meets the specification. The specification and the implementation are expressed as formulae in a formal system, the relationship between the specification and the implementation meets the specification is stated by a conjecture and the proof that the implementation meets the specification is obtained by using a calculus associated to the formal system.

Proof planning is a meta-level reasoning technique for the global control of search in automatic theorem proving. A proof plan captures common patterns of reasoning in a family of similar proofs and is used to guide the search for new proofs in the family. Proof planning combines two standard approaches to automated reasoning: the use of tactics and the use of meta-level control. The meta-level control is used to build large complex tactics from simpler ones and also abstracts the proof, highlighting its structure and the key steps. The main component of proof planning is a collection of methods. A *method* is a specification of a tactic. A tactic is a program that applies one or more rules of inference during a proof. A method consists of an input formula (a sequent), preconditions, output formulae, postconditions, and a tactic. A method is *applicable* if the goal to be proved matches the input formula of the method and the method's preconditions hold. The preconditions, formulated in a meta-logic, specify syntactic properties of the input formula and contain heuristics to constrain search. Using the input formula and preconditions of a method, proof planning can predict if a particular tactic will be applicable without actually running it. The output formulae (there may be none) determine the new subgoals generated by the method and give a schematic description of the formulae resulting from the tactic application. The postconditions specify further syntactic properties of these formulae. For each method there is a corresponding general-purpose tactic associated to that method. Methods can be combined at the meta-level in the same way tactics are combined using tacticals. The process of reasoning about and combining methods is called proof planning. When planning is successful it produces a tree of methods, called a proof plan. A proof plan yields a composite tactic, which is built from the tactics associated with each method, custom designed to prove the current conjecture. Proof plan construction involves search. However, the planning search space is typically many orders of magnitude smaller than the object-level search space. One reason is that the heuristics represented in the preconditions of the methods ensure that backtracking during planning is rare. Another reason is that the particular methods used have preconditions which strongly restrict search, though in certain domains they are very successful in constructing proofs. There is of course a price to pay: the planning system is incomplete. However, this has not proved a serious limitation of the proof planning approach in general [Bundy et al 91] nor in our work where proof plans were found for all experiments we tried. The plan formation system upon which our work is built is called *Clam*. Methods in *Clam* specify tactics which build proofs for a theorem proving system called *Oyster*, which implements a type theory similar to Nuprl's [Bundy et al 90].

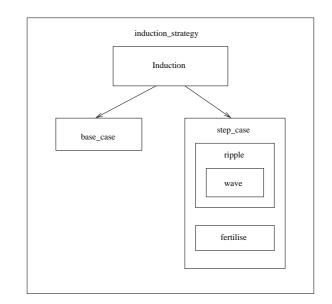

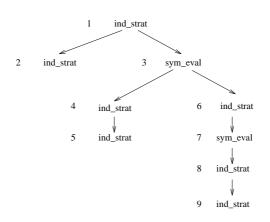

A number of methods have been developed in *Clam* for inductive theorem proving and we used these extensively to prove theorems about parameterised hardware designs. Induction is particularly difficult to automate as there are a number of search control problems including selection of an induction rule, deciding a case split, possible generalisations and lemma speculation, etc. It turns out, though, that many induction proofs have a similar shape and a few tactics can collectively prove a large number of the standard inductive theorems. The induction strategy ind\_strat is a method for applying induction and handling subsequent cases. After the application of induction, the proof is split into one or more base and step cases. The sym\_eval method attempts to solve the base case using simplification and propositional reasoning. If necessary, another induction may be applied. The step\_case method consists of two parts: rippling and fertil*isation*. The first part is implemented by the **ripple** method. Rippling is a kind of annotated rewriting where annotations are used to mark differences between the induction hypothesis and conclusion. Rippling applies annotated rewrite rules (called *wave-rules* which are applied with the wave method) which minimise these differences. Rippling is goal directed and manipulates just the differences between the induction conclusion and hypothesis while leaving their common structure preserved; this is in contrast to rewriting based on normalisation, which is used in other inductive theorem provers such as Nqthm [Boyer & Moore 79]. Rippling also involves little search, since annotations severely restrict rewriting. The second part of the step case, fertilisation, can apply when rippling has succeeded (e.g. when the annotated differences are removed or moved 'out of the way', for example, to the root of the term). The fertilise method then uses the induction hypothesis to simplify the conclusion.

The research reported in this thesis investigates how all these features of proof planning can be transported and extended to deal with the multiple problems that arise in automating hardware verification.

## 1.2 Motivation

Fabrication of hardware systems has become an increasingly difficult activity due to the growing complexity of the tasks the systems perform. Detecting errors after a commercial circuit has been fabricated may represent important economic losses for a hardware company. A recent example of this situation is the design error in the division algorithm of Intel's Pentium microprocessor that was detected after fabrication and when the product was in the market. Simulation, the traditional technique used to test circuit designs cannot validate all of the enormous amount of inputs that exist in an typical circuit because of the combinatorial explosion of the search space. Formal methods promise to overcome this problem by developing mathematical proofs of correctness which are independent of the size of the circuit, increasing in this way the confidence in the correctness of the hardware designs. For instance, formal verification has been used post hoc to detect the error in the division algorithm of the Pentium microprocessor [Moore et al 96, Rueß et al 96]. Although mathematical proof is a desirable feature, formal methods face their own difficulties which prevent them from being widely accepted and used by industry in a regular way [Saiedian 96]. Interest of industry in formal methods has centred mainly on 'push-button' systems based on model checking where weak decidable logics and efficient algorithms are used for problem specification and verification, but these systems are limited and cannot be applied to many important classes of problems such as those requiring hierarchical representations. On the other hand, systems based on more expressive logics are often resisted because translating the specification and the implementation requires expertise in logic, proof construction is not automated, and most companies are not willing to invest time and money in technologies which are still in an embrionic stage as in the case interactive theorem proving.

To increase the acceptance of formal methods in domains with undecidable verification problems, we must automate proof construction as much as is practically possible [Rushby 96]. One of the main problems to overcome is the large search space for proofs. Even when semi-decision procedures like resolution are available, completely automated theorem proving is not viable because such techniques are too general and cannot exploit structure in the problem domain to restrict search. Heuristics, combined with user interaction to overcome incompleteness have become a useful resource. One example of this is the system *NQTHM* [Boyer & Moore 88], which uses a fixed set of heuristics to automate the construction of proofs by induction. Proof construction is automated but sometimes the user must interrupt the prover and suggest lemmas to stop it from exploring an unsuccessful branch. A second example is embodied by tactic-based proof development systems like *HOL*, *LAMBDA*, *PVS*, and *NUPRL* (described in section 2.4), where users themselves raise the level of automation by writing tactics for particular problem domains. Incompleteness is addressed by interactive proof construction, whereby, instead of writing a 'super-tactic' which works in all cases, users interactively combine tactics to solve the problem at hand and directly provide heuristics.

Our motivation comes from the desire to combine the best of these two approaches, providing automation comparable to systems like NQTHM and offering increased flexibility by supplying heuristics and new domain specific proof procedures like in the tactic approach. Proof planning attempts to automate decisions like the choice of induction scheme and variables, case splits, generalisations, lemma speculation, and the like, which are usually specified by the user when writing tactics, as well as the process of assembling a particular tactic for a given conjecture by using AI planning techniques. We will explore how these features of proof planning can be utilised to guide *Oyster*, a theorem prover similar to *NUPRL*, in verifying hardware.

### **1.3** Contributions

The main contribution of this thesis is in the area of proof automation for the hardware verification domain in a tactic-based setting: we demonstrate by experimentation the viability of using proof planning for guiding the automatic construction of customised tactics for the verification of hardware designs of small and medium size scale, and conjecture that proof planning can be scaled-up to verify more complex circuits of the type typically found in modern commercial applications. We develop a proof engineering methodology using proof planning to verify various combinational and sequential circuits which include: arithmetic circuits (adders, subtracters, multipliers, dividers), data-path components (arithmetic logic units, shifters, processing units), and a simple microprocessor system, using few lemmas compared to other systems. We also contribute to the profiling of the *Clam* proof planning system to improve its robustness and efficiency in handling large terms and proofs.

## **1.4 Organisation**

The thesis is organised as follows: chapter 2 presents the background and a survey on formal methods for hardware verification; chapter 3 presents an overview of proof planning and its application to inductive theorem proving; chapter 4 uses two examples to introduce the basic ideas of proof planning for hardware verification; chapter 5 describes a methodology for hardware verification based on proof planning and the concept of proof engineering; chapter 6 describes the extensions to proof planning for verifying hardware; chapter 7 presents experiments for hardware verification, statistics of the experiments and an analysis of the statistics as well as a description of the experiments; chapter 8 describes related and future work; and chapter 9 presents conclusions. Appendix A describes some basic elements for hardware verification: types, operations on types, conversion functions and conditional functions. The rest of the appendices describe the main experiments in verifying hardware with proof planning: appendix B describes non-recursive combinational circuits; appendix C explains a bit incrementer; appendix D describes a multiplier; appendix E describes the Gordon computer; and appendix F describes other circuits. Finally, appendix G displays the main methods used in the proofs.

## Chapter 2

# Background

Formal methods for hardware verification is an active area of research and efforts are being made to transfer its techniques to solve problems of industrial scale. In this chapter we present a summary of basic concepts and a brief survey of formal methods for hardware verification. More comprehensive and extended surveys are presented in [Yoeli 90] and [Gupta 91]. Section 2.1 describes formal verification; section 2.2 characterises the components of the verification problem; section 2.3 describes the approaches to formal hardware verification; section 2.4 describes the main hardware verification environments and the work done in them; and section 2.5 presents a summary of the chapter.

## 2.1 Verification

Verification consists of establishing a formal relationship between a specification and an implementation of a system. That is, showing that:

$$\forall x_1 : \tau_1 \dots \forall x_n : \tau_n. \ Cond \to \mathcal{S}(x_1 \dots x_n) \ \mathcal{R} \ \mathcal{I}(x_1 \dots x_n)$$

where  $x_1 \ldots x_n$  are variables of type  $\tau_1 \ldots \tau_n$  respectively which represent inputs or outputs to the system.  $\mathcal{R}$  is some mathematical relation like equivalence, implication or equality and some others. *Cond* represent some conditions,  $\mathcal{S}(x_1 \ldots x_n)$ represents the specification and  $\mathcal{I}(x_1 \ldots x_n)$  the implementation. This is known as the verification problem. Formal here means the use of a mathematical framework for describing and solving the problem. A formal system is a mathematical framework for reasoning about a problem and its possible solutions. It provides a mathematical description language, and a calculus (or proof system) for proving conjectures in the theory associated with the formal system. The verification problem is given as a conjecture where the specification  $\mathcal{S}$ , the implementation  $\mathcal{I}$ , and the relationship  $\mathcal{R}$  between  $\mathcal{S}$  and  $\mathcal{I}$  are expressed using the language of the formal system, and the calculus is used to prove that the implementation and the specification satisfy the relationship. Two important aspects of the mathematical language are its syntax and its semantics. The former has to do with the rules for writing valid formulae, the latter is concerned with the meaning of formulae. A deductive calculus formed by a set of axioms and a set of inference rules, is the best well-known technique for proving conjectures in the formal system and has been widely applied to the verification problem.

### 2.1.1 Hierarchical Verification

System complexity is frequently dealt with by recursively decomposing the system into simpler interrelated systems yielding a hierarchy of components at different levels of abstraction. A specification and implementation of the system is given for each level. In this hierarchy, a system implementation at a certain level serves as the specification of the system at the next level in the hierarchy. The verifications of the system at two consecutive levels in the hierarchy can then be composed to give a verification of a system implementation with respect to a more abstract specification. This procedure can be extended to other levels to achieve a verification of the bottom level implementation with respect to the top level specification. In [Moore 89], J Moore presents such a methodology for the hierarchical verification of systems specified in the Boyer-Moore logic.

## 2.2 Components

There are three components of the verification problem: the specification, the implementation and the relationship between them. In this section we characterise each of these components.

### 2.2.1 Specification

The specification of a system describes *what* the system should do. It is an abstract description of its external behaviour. Details about the internal working of the system are ignored by the specification and left to the implementation. The specification must include external inputs and outputs which are relevant to the designer, and a relation between inputs and outputs. The following aspects which help the designer in understanding the specification will now be discussed: abstraction mechanisms, properties, verifiable specifications, executable specifications, and representation formalisms.

#### Abstraction

Abstraction mechanisms for hardware verification were first identified by Melham and are described in [Melham 88]. These include the following:

- *Structural.* This type of abstraction consists of hiding internal connections and components of a system, displaying just the external aspects;

- Behavioural. This type of abstraction allows the designer to write partial specifications of a system. This means that there are inputs of the system which are left undefined and treated as "don't cares";

- Data. This type of abstraction allows the designer to map one data type (e.g. binary numbers) into another data type (e.g. decimal numbers)

• Temporal. This type of abstraction allows the designer to map a time-scale (e.g. micro-operations time scale) into another time scale (e.g. programming instruction time scale)

#### System properties

The specification of a system describes properties of the system which are of particular interest. This includes *safety* properties, e.g. two devices cannot access simultaneously their bus; *liveness* properties, e.g. a device will eventually be allowed to access its bus; and *timing* properties, e.g. a device will access its bus within 5 seconds. These properties are modelled using logics to reason about time and events.

#### Verifiable specifications

A specification can either be assumed correct or can be verified with respect to given criteria. This defines a hierarchy of specifications, as these criteria can in turn be verified with respect to more abstract criteria, until we reach a criterion which is assumed correct.

#### Expressive specifications

Expressiveness is determined by the kind of formalism employed to write the specification. With some formal languages, we can express more facts than we can with others. As we will see in section 2.3, higher-order logic is more expressive than first-order logic, which is more expressive than propositional logic. High expressivity is an important feature, because it allows the designer to write compact and broad definitions, facilitating in this way the formalisation task from the user point of view, although transferring the verification effort to the machine.

#### Executable specifications

A specification can be described in a language which is executable, and tested on concrete input data, e.g. a set of definitions given in Lisp. This feature helps the designer in writing and debugging the specifications. But there is a trade-off since, in general, executable specifications tend to be less expressive than non-executable specifications.

#### **Representation formalisms**

Many representation formalisms exist for describing specifications. Among the most common are logical formulae (functional or relational), finite-state machines (either automata or state-transition graphs), and trace structures [Yoeli 90]. Which formalism is used determines the type of proof methods that can be used to reason about the specification.

#### 2.2.2 Implementation

The implementation of a system indicates *how* the system does what it should do. For a hardware system this may be a design displaying its components, inputs and outputs, and connections between the components. Hierarchical layers, timing, and synchronicity among devices (that is, when to send or receive data from other device) are aspects of interest to the designer, and will now be discussed.

#### Hierarchical implementations

As we mentioned above, system complexity is usually tackled by decomposing the system into simpler components organised in hierarchical levels, treating each level separately, and composing the solutions of each layer into an integrated solution. This is commonly done for hardware systems. Layers spread from the modelling of physical characteristics of components, such as speed, capacitance, voltage, current, etc., all the way up to the program level. The following is a description of the main layers:

- *Physical.* The physical level deals with electrical properties (Current, voltage, speed, delays) of basic electronic components (transistors, resistors, diodes).

- Switch. The switch level uses the transistor as its basic element to build electronic systems. Systems verified at this level are electronic circuits made up of transistor, resistors, diodes and other components that implement some type of device, such as boolean gates.

- *Gate.* The gate level uses the gate as its basic element to build combinational and sequential circuits. Systems verified at this level are circuits which are made up of various kinds of gates (AND, OR, XOR, INVERTER, etc). Among these circuits are several kinds of combinational and sequential functions: adders, decoders, multiplexors, flip-flops, load-registers, counters, etc.

- Register transfer. The register transfer level uses the register as its basic element and micro-operations to process data in the registers. A registertransfer logic provides a language to describe valid operations among registers. This level is used to describe the implementation of microprocessor architectures.

- Assembly program. The assembly program level provides programming instructions to write assembly programs. A description of this level is given in terms of the semantics of the individual programming instructions. Each instruction is implemented by a set of micro-operations which are executed at the register-transfer level.

#### Combinational or sequential

A circuit can be either combinational or sequential. In a combinational circuit all the calculations are considered to occur instantly with no delays in data propagation. Combinational circuits use Boolean gates to compute Boolean functions. Sequential circuits use storage elements which can be either flip-flops or registers, combinational circuits which compute inputs to the flip-flops, and feedback loops.

#### Synchronous or asynchronous

A sequential circuit can be either synchronous or asynchronous. In a synchronous circuit signal processing is regulated by the pulses of a clock which is global to circuit components. Time is usually considered discrete, and outputs at time t + 1 are calculated from the inputs at time t.In an asynchronous circuit signal processing, transmission and storage can occur at any instant of time.

#### **Representation** issues

The following aspects of representation are relevant to the implementation: circuit representation by functions or relations, word representation by lists or functions, and parameterised representation of circuits. The first aspect is discussed in subsection 2.2.4.

- Parameterised representation. Hardware representations are sometimes parameterised by an attribute of the circuit. Word size is an example of an attribute that is frequently used as a parameter in representations of various hardware devices.

- Word representation. Words can be modelled using either lists or functions. Lists are commonly used by many verification tools for representing and manipulating words.

#### Hardware description languages

Hardware description languages (HDL) have been developed, standardised, and utilised by the hardware industry to describe and simulate hardware designs [IEEE 88]. These languages have become popular and are used by design engineers in a regular basis. However formal reasoning about the designs is very difficult because the semantics of the language is not clearly defined. Subsets of HDLs with a well established semantics have been defined for formal reasoning in verification environments, although their use remains limited [Gordon 95].

### 2.2.3 Relationship

#### Type of relationship

The relationships between the specification and the implementation may include the following:

- equality. The implementation and the specification are represented by functions: imp = spec

- implication. The implementation and the specification are represented by relations; the specification is a partial description of system behaviour, so the implementation which contains more information, implies the specification: ∀x imp(x) → spec(x)

- equivalence. The implementation and the specification are represented as relations; both contain the same amount of information, so the implementation implies the specification and vice-versa:  $\forall x \ imp(x) \equiv spec(x)$

- subset. The language representing the implementation is a subset of the language representing the specification. The language refers to the one accepted by a finite-state machine: L(imp) ⊂ L(spec)

- logical implication The implementation provides a semantic model with respect to which the specification is satisfied:  $imp \models spec$

#### **Proof** methods

The proof methods used to establish the relationship may include: theorem proving, model checking, equivalence checking, and language containment. These methods are further explained in section 2.3.

### 2.2.4 Functional versus relational verification

The verification problem can be formalised using either a functional or a relational description. A full account of system verification using functional and relational representations is given in [Camilleri 88]. Here we present a summary of this topic because it is relevant for the experiments with hardware verification that we will present later.

#### **Functional Verification**

Functional verification is characterised as follows:

- circuit components are represented by total functions where the inputs of the component are the arguments of the function and the value of the function itself represents one of the possible outputs of the component.

- component interconnections also called internal wires as well as the overall structure of the circuit are represented by function composition, where a term is passed as an argument to another function.

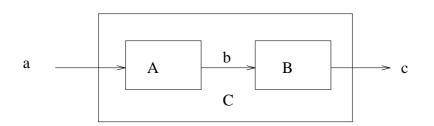

Figure 2–1 describes these characteristics.

Figure 2-1: Modelling the structure of a device

n

The functional representation of this device is as follows:

$$C_{fun}(a) = B_{fun}(A_{fun}(a))$$

$C_{fun}$  is the functional representation of the device with input a, output c, internal components A and B.  $A_{fun}$  and  $B_{fun}$  are functional representations of components A and B. Value b is computed by A and passed to B.

To prove that implementation I meets specification S we must prove a theorem of the form:

$$\forall i_1, \dots, i_n.Abs_1(I_{fun}(i_1, \dots, i_n)) = Abs_2(S_{fun}(Abs(i_1, \dots, i_n)))$$

where Abs,  $Abs_1$  and  $Abs_2$  are data abstraction functions. Abs is required to convert data representations of the implementation to that of the specification. Furthermore, the function definitions need not be equal for all valid data values and so data abstractions  $Abs_1$  and  $Abs_2$  are also required to restrict and select the data for which the specification and implementation descriptions can be shown to be equal. The use of data abstractions to select and restrict the domain of a function is analogous to defining partial specifications when using relations.  $S_{fun}$  and  $I_{fun}$  are the specification and the implementation respectively given as functions.

#### **Relational Verification**

The relational representation approach is characterised as follows:

- circuit components are represented by predicates where the inputs and outputs of the component are the arguments of the predicate. The predicate constrains the values of these parameters so that the predicate is true.

- component interconnections also called internal wires are represented by shared existentially quantified variables.

- the overall structure of the circuit is represented by the conjunction of the predicates and shared variables.

Figure 2–1 also illustrates this modelling technique. The relational representation of this device is as follows:

$$C_{rel}(a,c) \equiv \exists b. A_{rel}(a,b) \land B_{rel}(b,c)$$

$C_{rel}$  is the relational representation of the device with input a, output c, internal components A and B, and internal wire b.  $A_{rel}$  and  $B_{rel}$  are relational representations of components A and B. Value b is hidden by an existential quantifier.

To prove that implementation I meets specification S we must prove a theorem of the form:

$$\forall i_1, \dots, i_n, o_1, \dots, o_m. I_{rel}(i_1, \dots, i_n, o_1, \dots, o_m) \to S_{rel}(Abs(i_1, \dots, i_n, o_1, \dots, o_m))$$

where again, Abs is required to convert data representations of the implementation to that of the specification.  $S_{rel}$  is the specification given as a relation. Similarly  $I_{rel}$  is the implementation given as a relation.

Functional representations in general carry more information than relational representations, especially when the relational descriptions are partial or when extra information is required to specify the outputs in the functional case. Therefore, in these cases it is not possible to prove the equivalence between both representations, except when both representations carry the same amount of information. Otherwise, the following relationship will hold:

$$\forall i_1,\ldots,i_n,o_1,\ldots,o_m$$

$$((o_1,\ldots,o_m) = Rep_{fun}(i_1,\ldots,i_n)) \to Rep_{rel}(i_1,\ldots,i_n,o_1,\ldots,o_m)$$

Here  $Rep_{fun}$  and  $Rep_{rel}$  mean functional and relational representations where these representations can be either specifications or implementations. Camilleri has shown this theorem in verifying various types of combinational hardware [Camilleri 88].

The advantages and disadvantages of each representation can be summarised as follows:

- Relational representations allow the description of only the features of a device which are of interest, thus forming a partial specification.

- Relational representations allow the definition of bidirectional devices by merely defining relations between ports without distinguishing inputs from outputs.

- Functional representations require the definition of total functions, although in principle, partial functions could also be used but with more difficulty.

- Functional representations can be executed given a suitable interpreter.

- Functional representations are easier to reason about than their relational counterparts (e.g. mathematical induction).

- Relational representations are more expressive, while functional representations are computationally more efficient for system verification.

## 2.3 Approaches to Formal Verification

In this section we describe the main approaches to formal verification. These approaches are typically based on logic, and on other formalisms e.g. finite-state machines and trace structures.

#### 2.3.1 Logic

Logic studies the principles of reasoning, and is a science that has as a wide range of applications in many disciplines which include computer science and artificial intelligence [Gallier 86,Genesereth & Nilsson 87].

There are two aspects of logic: its syntax and its semantics. The syntax of logic can be described in terms of a formal system where the language consists of a set of well-formed formulae made of symbols from an alphabet (constants, variables, functions, predicates, connectives) and rules for constructing the formulae; and the calculus (or proof system) associated to the formal system consists of a set of axioms, and a set of rules of inference for deductive reasoning. A formula  $\alpha$  which is derived from the axioms by a sequence of inference rules applications is called a theorem and is denoted by:  $\vdash \alpha$ . If  $\alpha$  is derived from a set of formulae  $\Gamma$  we write  $\Gamma \vdash \alpha$  which is read  $\alpha$  is deduced from  $\Gamma$ .

The semantics of classical logic assigns meaning to the formulae by means of an interpretation. An interpretation consists of a domain and a mapping from elements, functions, and relations of the domain to constant, variables, function and predicate symbols in the formula. Constants, variables, and terms denote elements of the domain. A formula can take the values true or false. A model  $\mathcal{M}$ is an interpretation that makes a formula  $\alpha$  true and is denoted:  $\mathcal{M} \models \alpha$ , which is read " $\mathcal{M}$  satisfies  $\alpha$ ". A formula  $\alpha$  is valid if it is true for every interpretation, and denoted by  $\models \alpha$ . A formula is satisfiable if it has a model and is a contradiction if it is false for every interpretation. A set of formulae  $\Gamma$  is satisfiable if there is an interpretation that satisfies every formula in  $\Gamma$ . The fact that, every interpretation that satisfies a set of formulae  $\Gamma$  also satisfies a formula  $\alpha$ , is denoted by  $\Gamma \models \alpha$ and read " $\Gamma$  logically implies  $\alpha$ ".

Soundness and completeness are two attributes of a proof system with respect to semantics. Soundness means that any theorem deduced by the proof system is valid. Completeness means that any valid formula can be proved by the proof system. The completeness theorem establishes the relationship between deduction and logical implication:

$$\Gamma \models \alpha \leftrightarrow \Gamma \vdash \alpha$$

which establishes the equivalence between  $\models$  and  $\vdash$ .

Theorem proving has to do with establishing that a formula is a theorem in a formal system. Automatic theorem proving is concerned with the mechanisation by computer of the deduction process. Theorem proving has been used to verify hardware. The specification and the implementation are given as formulae in logic and the relationship is either an implication or an equivalence. Alternatively, the specification and the implementation can be given as terms with the relationship being an equality. Model checking has to do with establishing that an interpretation is a model of a formula, and has also been used to verify hardware. The specification is given as a formula, the implementation is given as an interpretation and the relationship is a logical implication. Model checking tries to establish that the implementation is a model of the specification.

Many types of logics can and have been derived, depending upon the constraints imposed on the syntax and semantics of the logic. Without being exhaustive, we survey some of the logics that have been used for hardware verification: propositional logic, first-order logic, higher-order logic, intuitionistic logic, modal-temporal logic.

## 2.3.2 **Propositional Logic**

Propositional logic consists of a set of logical symbols with a fixed meaning (connectives, parentheses), and a set of non-logical symbols with variable meaning (predicate symbols of arity zero called propositions) with which well-formed formulae (wffs) can be constructed. A truth assignment (or interrelation) assigns wffs one of the values true or false. Valid formulae are called tautologies. Propositional logic was one of the first logics used to model digital systems and represent Boolean functions, and is well known among design engineers. Propositional logic is a convenient way of representing and reasoning about gate-level combinational circuits but is inappropriate for modelling time and feedback loops. Propositional logic is decidable and there are tautology checkers for establishing the validity of a formula (e.g. truth tables). However, the problem of satisfiability for propositional logic is known to be NP-complete. Finding a model which satisfies a formula is known as the SAT problem [Gallier 86].

### **Binary Decision Diagrams**

Binary decision diagrams (BDDs) are a data structure for the efficient manipulation of Boolean functions which include testing for validity of formulae and equivalence of functions. BDDs are represented by acyclic graphs which can represent Boolean functions in a concise way [Akers 78]. R. Bryant introduced a restricted form of BDDs called Ordered Binary Decision Diagrams (OBDDs), found a canonical representation of functions, and developed efficient algorithms for validity and equivalence operations [Bryant 86]. Some theorem provers (e.g. PVS) and model checkers (e.g SMV) have implemented a variation of BDDs for tautology checking.

### 2.3.3 First-Order Logic

Universal and existential quantification runs just over elements of the domain which can be any set. A term denotes an element of the domain, predicates can take one of the values true or false. First-order logic is more expressive than propositional logic and digital systems can be better described. Proof systems for first-order logic have been developed which are sound and complete, although when one introduces particular theories (e.g. lists, arithmetic), a proof system may be incomplete. Proof systems in general are semi-decidable, which means that if a formula is valid there are proof methods which will establish this fact, but if the formula is not valid, these same methods may run forever without detecting this fact. First-order logic has found many types of application including program and hardware verification.

## 2.3.4 Boyer-Moore Computational Logic

The Boyer-Moore Computational Logic is a subset of first-order predicate logic with implicit universal quantification, equality, and the inference rule for a type of Noetherian induction, developed for reasoning about computations. The logic exploits the duality between inductive reasoning and recursive definitions. It also includes the *shell principle* for introducing and axiomatising new inductively defined types by defining a recogniser function, a constructor function, and an accessor function for elements of the type. The *principle of definition* allows the user to define new functions and avoid possible inconsistencies either by defining non-recursive functions in terms of pre-defined functions or by making sure that a well-founded order exists on a measure of the arguments that decreases on each recursive call. The logic includes built-in shells that axiomatise the natural numbers, integers, lists, and strings. The proof system associated with the logic comprises a pre-defined proof strategy consisting of the consecutive application of pre-defined basic proof techniques which are inference rules supported by powerful heuristics [Boyer & Moore 79].

Mathematical induction is required for reasoning about object and events containing repetition. Since repetition is ubiquitous in many application areas and inductive reasoning is very difficult to automate, research has focussed on the automation of proof for mathematical induction. Inductive proofs are characterised by the application of induction rules such as Peano induction and structural induction on lists and other data structures. All these forms of induction are subsumed by a single, general schema of well-founded induction:

$$\frac{\forall x : \tau. (\forall y : \tau. x \succ y \rightarrow P(y)) \rightarrow P(x)}{\forall x : \tau. P(x)}$$

where  $\succ$  is some well-founded relation on the type  $\tau$ , *i.e.* there is no infinite descending sequence:  $a_1 \succ a_2 \succ a_3 \succ \ldots$ . The data-structure, control flow, time step, *etc.*, over which induction is to be applied, is represented by the type  $\tau$ . The inductive proof is formalised in a many-sorted or typed logical system.

Success in proving a conjecture, P, by well-founded induction is highly dependent on the choice of x,  $\tau$  and  $\succ$ . For many types,  $\tau$ , there is an infinite variety of possible well-orderings,  $\succ$ . Thus choosing an appropriate induction rule to prove a conjecture is one of the most challenging search problems to be solved in automating inductive inference.

The automation of inductive inference raises a number of unique difficulties in search control:

Synthesis of induction rules: To prove a theorem by induction, one of the infinite number of possible induction rules must be synthesised and the induction variables chosen;

- **Conjecturing lemmata:** Sometimes a lemma required to complete the proof is not already available and must be conjectured and then proved;

- Generalisation of induction formulae: Sometimes a theorem cannot be proved without first being generalised on one of its terms.

In addition to these special search problems all the standard problems also manifest themselves, *e.g.* deciding when to make a case split, determining the witness for an existential quantifier, etc.

## 2.3.5 Higher-Order Logic

In Higher-order logic (HOL) variables range over predicates and functions as well as over individuals of the domain. This means that predicates and functions can be quantified, given as arguments of other predicates or functions, and be outputs of other predicates and functions as well. This makes higher-order logic very expressive, mathematically elegant, and permits a concise description of complex problems. But this increased complexity makes reasoning more difficult as the logic becomes undecidable, inconsistencies can be introduced, and proof systems also become incomplete. To alleviate these problems, the domain is usually constrained to have decidable or semi-decidable sub-classes, a type discipline is used to avoid inconsistencies (e.g. Russell's paradox) by introducing hierarchies among the elements of the domain, and heuristics are developed to cope with incompleteness. With these amendments that retain its advantages, higher-order logic has become very popular for describing and verifying hardware systems [Gordon 86].

One restricted higher-order logic is monadic second-order logic, a decidable logic for reasoning about strings. It has been used for verifying parameterised hardware, as well as generalising standard BDDs hardware verification capabilities [Basin & Klarlund 95].

### 2.3.6 Intuitionistic Logic

In intuitionistic logic the fact that a formula is either true or false does not hold in general. To prove an existential conjecture it is not sufficient to negate the conjecture and arrive at a contradiction, we need to construct explicitly an element (witness) which satisfies the conjecture. This constructive approach has been found very useful in program synthesis and has also been applied to the synthesis of circuits [Basin 91].

### 2.3.7 Modal Logic

Modal logic extends the scope of predicate logic with the notion of change and introduces new modal operators to express variability [Hughes & Cresswell 90]. In propositional logic predicates (propositions) are either true or false; in predicate logic the truth of a predicate depends on the elements of the domain within a static world; in modal logic it is possible to change from a world into another world by means of an accessibly relationship, where the truth of a predicate also depends on the world in which it is applied. Worlds can be seen as states in which a system can be. The accessibility relationship is characterised by modal operators which describe properties which remain true when going from one state to another state. The basic modal operators are the necessity operator  $\Box P$  which means that  $\Box P$  is true in a state s if P is true in all states accessible from s; the possibility operator  $\Diamond P$  which means that  $\Diamond P$  is true in a state s if P is true in some state accessible from s; the next operator  $\bigcirc P$  which, for linear logics, means that  $\bigcirc P$  is true in a state s if P is true in the next state from s; and the until operator  $P \cup Q$ which means that  $P \cup Q$  is true in a state s if either Q is true in s or it is true in some other state accessible from s with P being true in every intermediate state [Galton 87].

### Temporal Logic

Temporal logic is a type of modal logic. It was developed for reasoning about time in the verification of concurrent programs and has found a wide variety of applications in studying time-dependent systems [Pnuelli 77]. The four modal operators are referred as the Always, Sometimes, Next-time, and Until operators respectively in temporal logic terminology. Correctness properties of time-dependent systems can easily be expressed in temporal logic. These include Safety properties which state that nothing bad happens  $\models \Box P$  (e.g. two devices do not access the bus simultaneously); liveness properties which state that eventually something good happens  $\models P \rightarrow \Diamond Q$  (e.g. a device will eventually access the bus); and precedence properties which grants orders of events  $\models P \cup Q$  (e.g. two devices access the bus in the order their requests are done).

Temporal logic can be seen from different perspectives yielding different types of temporal logics. In one view the truth of a formula can be defined with respect to the interval between two states or with respect to a state. In the first case, we have interval temporal logic (ITL) [Moszkowski 85]. In the second case, time can be seen from two different views. In one case, time is a linear sequence of events which results in linear-time temporal logic (LTTL) [Manna & Pnuelli 81]. In the second case time has a branching structure of events which results in what is called branching-time temporal logic (BTTL). Computation tree logic (CTL) is a version of BTTL that has been applied extensively to the formal verification of sequential circuits [Clarke & Emerson 81].

### 2.3.8 Mu Calculus

The Mu Calculus extends the expressiveness of propositional temporal logic by adding operators for denoting fixed points of predicate transformers (i.e functions from relations to relations). It was developed independently of temporal logic and various versions have been studied in the context of program verification and has also been applied to the hardware domain [Emerson & Lei 86].

### 2.3.9 Other Approaches to Hardware Verification

There are other approaches for hardware verification which traditionally are not regarded as part of logic like finite-state machines, although they keep a close connection with logic. For instance, the notion of regularity which is observed in certain types of parameterised circuits (e.g. adders, ALUs, counters) and which have been formalised using automata for which decision procedures for a type of second-order logic on strings exist.

### Finite-state machines

An automaton is a mathematical structure for accepting or rejecting input sequences of symbols which correspond to words in a language. Starting at an initial state, the automaton applies a transition for each symbol of the input sequence giving new states. When the last input symbol is read, if the resulting state corresponds to a designated final state then the input sequence is accepted, otherwise it is rejected. This assumes a finite automaton where the input sequence is finite. Some concurrent/reactive systems may require automata over infinite sequences. A finite-state machine is an automaton extended with an output alphabet to form output sequences rather than just an accept/reject condition. Given a state, if a transition produces a single new state, then the machine is deterministic, otherwise it is non-deterministic. Moore and Mealy machines are commonly studied in automata theory. In a Moore machine the output sequence is a function of a state. In a Mealy machine the output is a function of the state and the input [Hopcroft & Ullman 79]. Finite-state machines have been used to represent both the specification and the implementation of the verification problem, and several techniques have been developed to establish the relationship between the two which include:

• Machine equivalence. Establishes the equivalence of two finite-state machines by composing a machine which accepts the exclusive-or of the two corresponding languages. If the composite language accepts just the empty language then the two machines are equivalent. Since this algorithm is computationally expensive, other techniques based on extracting a state-transition graph from each machine, composing the graphs, and developing efficient algorithms for its manipulation have been attempted [Devadas et al 87].

- Language containment. The relationship between the implementation and the specification is that of language subset rather that equivalence. Here it is shown that the language generated from the machine that describes the implementation is contained in the language generated by the machine that describes the specification [Kurshan 87]

- Trace theory. A trace is a sequence of transitions in a finite-state machine. A trace structure consists of a set of input and output wires, a set of traces representing a circuit's behaviour on legal inputs, and a set of traces representing a circuit's behaviour on invalid inputs. Trace theory represents the behaviour of a system as a set of traces and has been used to model asynchronous systems [Hoare 78], delay-insensitive circuits, and speed-independent circuits [Dill 89]. The specification and the implementation of speed-independent circuits are described by trace structures, and the relationship corresponds to the concept of safe substitution. An implementation is correct if it preserves the correctness of a larger context when substituted for the specification in that context. A context is an expression in trace theory containing a free variable and is denoted by  $\epsilon$ []. A trace structure  $\mathcal{T}$  is said to conform to another structure  $\mathcal{M}$ , denoted by  $\mathcal{T} \leq \mathcal{M}$ , if for every context  $\epsilon[]$ , if  $\epsilon[\mathcal{M}]$  is failure-free then so is  $\epsilon[\mathcal{T}]$ . A trace structure is failure-free if its failure set is empty. Since it is not possible to test an infinite number of contexts, a worstcase context called the *mirror* of  $\mathcal{M}$  can be defined, such that  $\mathcal{T} \leq \mathcal{M}$  holds if and only if the composition of  $\mathcal{T}$  and the mirror of  $\mathcal{M}$  is failure-free. Thus, the mirror of a trace structure represents the strictest environment conditions under which the trace structure is expected to operate correctly. Then, if an implementation operates correctly when composed with the mirror of the specification, then it is a safe substitution under all environments.

The main advantage of trace structures is the ability to perform hierarchical verification by using the same representation formalism (trace structures) of specifications and implementations, and by defining hierarchical operations on traces such as hiding, composition, and renaming. Its main disadvantage, is the need for the explicit construction of a state-transition graph associated with the composite trace structure.

# 2.4 Verification Environments

In this section we present some of the environments used for hardware verification and the type of systems they have been applied to. There are many ways in which these environments could be classified, depending upon features of interest. One such classification considers the type of proof construction method employed, grouped into theorem proving, and model/equivalence checkers. This grouping also reflects a current trend in the use of proof environments in both academic and industrial organisations nowadays.

## 2.4.1 Theorem provers

There are many proof construction methods in the theorem proving arena. Three popular approaches based on seminal works from the 60s and 70s are resolution [Robinson 65], tactics [Gordon *et al* 79], as well as approaches that emphasise a particular sort of inference, like mathematical induction [Boyer & Moore 79]. To raise the level of automation of equational and tactic-based provers, meta-level reasoning methods that reason about equations or tactic formation, have also been developed [Bundy 88,Silver 85].

The NQTHM theorem prover is based on the Boyer&Moore computational logic to automate proof by mathematical induction [CLINC 96]. It uses a subset of Lisp as the specification language of the designs, thus making the the specifications executable. It uses a fixed set of proof techniques, namely, simplification, destructor elimination, cross-fertilisation, generalisation, elimination of irrelevance and induction. The techniques are tried in the order listed on each remaining formula with hardly no backtracking, until all formulae have been proved or all the techniques fail. Users can guide the prover by providing lemmas or suggesting sets of rewrite rules [Boyer & Moore 88]. NQTHM has been used to verify a net-list implementation of the FM9001, a 32-bit general-purpose microprocessor which was fabricated as a CMOS gate array by LSI Logic Inc., and which serves as the basis of the *CLINC* stack [Bishop *et al* 95]. The elements of the stack which include a simple applications program in a high-level language a compiler, an assembler, a linker, and a simple multitasking operating system have also been verified using NQTHM [Moore 89]. The system is a stack in the sense that each upper layer is an abstract machine implemented on top of the lower layer. The stack is short only by comparison to systems of practical interest. The *ACL2* theorem prover is an industrial-strength implementation of the Boyer-Moore logic and a descendant of *Nqthm* that has been used to verify the correctness of the kernel of the  $AMD5_K 86^{tm}$  floating-point division algorithm [Moore *et al* 96].