# A Clustered VLIW Architecture Based on Queue Register Files

Marcio Merino Fernandes

Doctor of Philosophy University of Edinburgh 1998

To my parents, Armirdo and Lourdes

### Abstract

Instruction-level parallelism (ILP) is a set of hardware and software techniques that allow parallel execution of machine operations. Superscalar architectures rely most heavily upon hardware schemes to identify parallelism among operations. Although successful in terms of performance, the hardware complexity involved might limit the scalability of this model. VLIW architectures use a different approach to exploit ILP. In this case all data dependence analyses and scheduling of operations are performed at compile time, resulting in a simpler hardware organization. This allows the inclusion of a larger number of functional units (FUs) into a single chip. In spite of this relative simplification, the scalability of VLIW architectures can be constrained by the size and number of ports of the register file. VLIW machines often use software pipelining techniques to improve the execution of loop structures, which can increase the register pressure. Furthermore, the access time of a register file can be compromised by the number of ports, causing a negative impact on the machine cycle time. For these reasons, we understand that the register file required by a wide-issue unclustered machine could compromise the benefits of having parallel FUs, which have motivated the investigation of alternative machine designs.

This thesis presents a scalable VLIW architecture comprising clusters of FUs and private register files. Register files organized as queue structures are used as a mechanism for inter-cluster communication, allowing the enforcement of fixed latency in the process. This scheme presents better possibilities in terms of scalability as the size of individual register files is not determined by the total number of FUs, suggesting that the silicon area may grow only linearly with respect to the number of FUs. However, the effectiveness of such an organization depends on the efficiency of the code partitioning strategy. We have developed an algorithm for a clustered VLIW architecture integrating both software pipelining and code partitioning in a single procedure. Experimental results show it may allow performance levels close to an unclustered machine without communication constraints. Finally, we have developed silicon area and cycle time models to quantify the scalability of performance and cost for this class of architecture.

### Acknowledgements

My greatest gratitude goes to Dr. Nigel Topham, my supervisor. This work would not exist without him.

Many thanks to Josep Llosa of UPC for his contributions and fruitful discussions, and Prof. Roland Ibbett, for his guidance during the first stages of this work.

Special people have made my years in Edinburgh a great time: Hazel, Ann, Susan, Thereza, Carol, Alberto, Goretti, Jitka, Nils, and many others, including fellow doctoral students, members of basketball clubs, the ceilidh crowd, and the local Brazilian society.

Finally, the unique opportunity for being here was made possible by the financial support from CAPES-Brasil, and my family.

### Declaration

I declare that this thesis was composed by myself and that the work contained therein is my own, except where explicitly stated otherwise in the text. Some of the material in this thesis has already been published in:

- M. Fernandes, J. Llosa, and N. Topham. Distributed Modulo Scheduling. In *HPCA-5*, 5th *IEEE International Symposium on High Performance Computer Architecture*, Orlando, USA, 1999.

- M. Fernandes, J. Llosa, and N. Topham. Partitioned schedules for clustered VLIW architectures. In IPPS'98, 12th IEEE/ACM International Parallel Processing Symposium, Orlando, USA, 1998.

- M. Fernandes, J. Llosa, and N. Topham. Allocating lifetimes to queues in software pipelined architectures. In *EURO-PAR'97*, 3rd International Euro-Par Conference, Passau, Germany, 1997.

- M. Fernandes, J. Llosa, and N. Topham. Extending a VLIW architecture model. Technical Report ECS-CSG-34-97, University of Edinburgh, Department of Computer Science, 1997.

- M. Fernandes, J. Llosa, and N. Topham. Using queues for register file organization in VLIW architectures. Technical Report ECS-CSG-29-97, University of Edinburgh, Department of Computer Science, 1997.

### Table of Contents

| List of | Figure  | es es                                   | V    |

|---------|---------|-----------------------------------------|------|

| List of | Tables  | 5                                       | viii |

| Chapte  | er 1 I  | ntroduction                             | 1    |

| 1.1     | Work    | Context                                 | 1    |

| 1.2     | Work    | Overview                                | 2    |

|         | 1.2.1   | Queue Register Files                    | 3    |

|         | 1.2.2   | Unclustered VLIW Architectures          | 3    |

| _       | 1.2.3   | Clustered VLIW Architectures            | 4    |

| •       | 1.2.4   | Distributed Modulo Scheduling Algorithm | 4    |

| 1.3     | Thesis  | Structure                               | 4    |

| Chapte  | er 2 B  | Background                              | 6    |

| 2.1     | Instruc | ction-Level Parallelism                 | 6    |

|         | 2.1.1   | Hardware-Centric ILP: Superscalar       | 7    |

|         | 2.1.2   | Software-Centric ILP: VLIW              | 8    |

| 2.2     | VLIW    | Architecture                            | 9    |

| 2.3     | Registe | er Files for VLIW Machines              | 10   |

|         | 2.3.1   | Register File Requirements              | 11   |

|         | 2.3.2   | Monolithic Register Files               | 13   |

|         | 2.3.3   | Partitioned Register Files              | 15   |

|         | 2.3.4   | Other Register File Organizations       | 18   |

| 2.4     | VLIW    | Compilation Issues                      | 19   |

|         | 2.4.1   | Overview of the Compilation Process     | 20   |

|         | 2.4.2   | VLIW Scheduling                         | 25   |

|         | 2.4.3   | Register Allocation                     | 28   |

|         | 2.4.4   | Code Generation                         | 29   |

| 2.5     | Comm    | ercial VLIW Machines                    | 30   |

| Chapte | er 3 H | Basic Experimental Framework                       | 32 |

|--------|--------|----------------------------------------------------|----|

| 3.1    | Machi  | ne Model                                           | 33 |

|        | 3.1.1  | Functional Units                                   | 33 |

|        | 3.1.2  | Local Register File                                | 36 |

|        | 3.1.3  | Unclustered Machine                                | 37 |

| 3.2    | Workl  | oad                                                | 37 |

|        | 3.2.1  | Perfect Club Benchmark                             | 38 |

|        | 3.2.2  | Selection of Loops and Compiler Optimizations      | 39 |

|        | 3.2.3  | Data Dependence Graph                              | 40 |

| 3.3    | Modu   | lo Scheduling Algorithm                            | 41 |

|        | 3.3.1  | Minimum Initiation Interval - MII                  | 43 |

|        | 3.3.2  | Iterative Modulo Scheduling - IMS                  | 46 |

|        | 3.3.3  | Scheduling Example                                 | 52 |

| 3.4    | Regist | ser Allocation                                     | 53 |

| 3.5    | Outpu  | ıt Information                                     | 56 |

|        | 3.5.1  | Direct Parameters                                  | 56 |

|        | 3.5.2  | Derived Parameters                                 | 56 |

|        | 3.5.3  | Results Presentation                               | 58 |

| Chapte | er 4 ( | Queue Register Files                               | 59 |

| 4.1    | QRF    | Organization                                       | 59 |

| 4.2    | Transf | forming Multiple-Use Lifetimes                     | 62 |

| 4.3    | Overh  | ead Due to Copy Operations                         | 66 |

| 4.4    | Alloca | ating Lifetimes to a QRF                           | 68 |

|        | 4.4.1  | Q-Compatibility Test                               | 71 |

|        | 4.4.2  | Register Allocation Using the Q-Compatibility Test | 76 |

| 4.5    | Analy  | tical Model for Register Files                     | 79 |

|        | 4.5.1  | Silicon Area Model                                 | 79 |

|        | 4.5.2  | Cycle Time Model                                   | 80 |

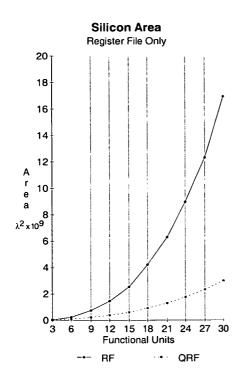

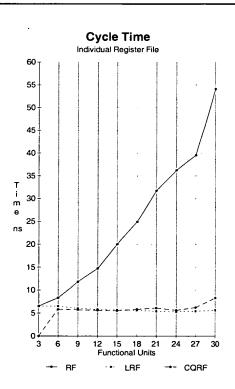

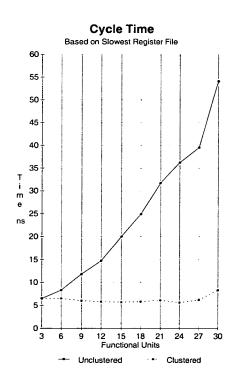

|        | 4.5.3  | Comparing Register File Organizations              | 81 |

| 4.6    | Summ   | nary of Results and Conclusions                    | 83 |

| Chapte | er 5 U | Jnclustered Architectures                          | 84 |

| 5.1    | Increa | sing ILP with Loop Unrolling                       | 85 |

| 5.2    |        | imental Framework Update                           | 88 |

| 5.3    | Exper  | imental Results                                    | 91 |

|        | 5.3.1  | Performance Analysis                               | 91 |

|        | 5.3.2  | Machine Resources Analysis                         | 94 |

|        | 5.3.3  | Summary of Results and Conclusions                     | 102              |

|--------|--------|--------------------------------------------------------|------------------|

| Chapte | er 6 ( | Clustered Architectures                                | 103              |

| 6.1    | Cluste | ered Architecture Organization                         | 103              |

| 6.2    | Exper  | rimental Framework Update                              | 107              |

| 6.3    | Partit | ioning Heuristics                                      | 108              |

|        | 6.3.1  | Find Slot Function for a Clustered Machine             | 109              |

|        | 6.3.2  | Backtracking Function for a Clustered Machine          | 111              |

|        | 6.3.3  | Complexity of the New Heuristics                       | 113              |

| 6.4    | Exper  | rimental Results                                       | 113              |

|        | 6.4.1  | Partitioning Effectiveness                             | 114              |

|        | 6.4.2  | Performance Analysis                                   | 116              |

|        | 6.4.3  | Machine Resources Analysis                             | 118              |

|        | 6.4.4  | Summary of Results and Conclusions                     | 123              |

| Chapte | er 7 I | Distributed Modulo Scheduling                          | 124              |

| 7.1    | Overv  | view of the DMS Algorithm                              | 125              |

|        | 7.1.1  | Chains of Move Operations                              | 127              |

|        | 7.1.2  | Scheduling Chains and their Consumer Operations        | 133              |

|        | 7.1.3  | Unscheduling Operations                                | 135              |

|        | 7.1.4  | Complexity of DMS                                      | 137              |

|        | 7.1.5  | Using DMS with Other Machine Models                    | 138              |

| 7.2    | Exper  | imental Framework Update                               | 139              |

| 7.3    | Exper  | rimental Results                                       | 140              |

|        | 7.3.1  | Partitioning Effectiveness                             | 140              |

|        | 7.3.2  | Performance Analysis                                   | 142              |

|        | 7.3.3  | Machine Resources Analysis                             | 144              |

|        | 7.3.4  | Summary of Results and Conclusions                     | 149              |

| Chapte | er8 S  | Scalability of Performance and Cost for Clustered VLIW | <sup>7</sup> 150 |

| 8.1    | Scalal | bility and Technology Trends                           | 151              |

| 8.2    | Exper  | imental Framework Update                               | 152              |

| 8.3    | Exper  | imental Results                                        | 152              |

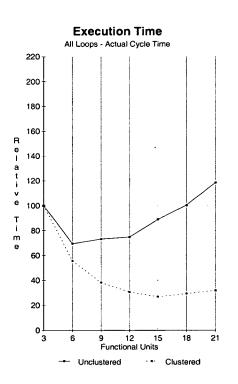

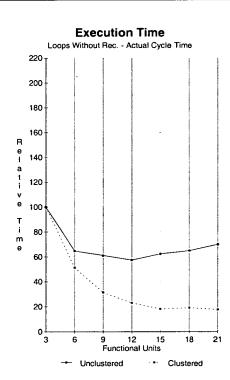

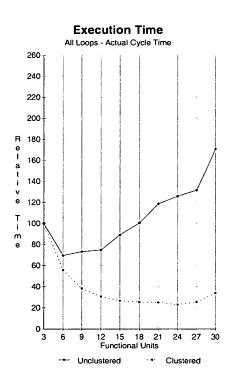

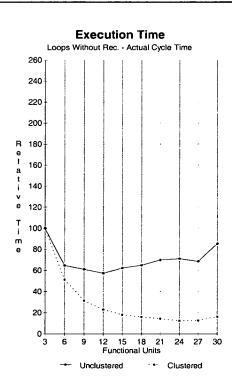

|        | 8.3.1  | Performance Analysis                                   | 152              |

|        | 8.3.2  | Scalability of Performance                             | 155              |

|        | 8.3.3  | Summary of Results and Conclusions                     | 157              |

| Chapte  | er 9 Conclusions    | 159 |

|---------|---------------------|-----|

| 9.1     | Main Findings       | 159 |

| 9.2     | Thesis Contribution | 161 |

| 9.3     | Future Work         | 161 |

| Bibliog | graphy              | 163 |

## List of Figures

| 2.1  | Basic structure of a VLIW processor                      | 10 |

|------|----------------------------------------------------------|----|

| 2.2  | Example of an instruction word for a VLIW processor      | 10 |

| 2.3  | Register pressure resulting from loop unrolling          | 12 |

| 2.4  | Register pressure resulting from software pipelining     | 12 |

| 2.5  | Area of a monolithic register file                       | 14 |

| 2.6  | Subdividing a monolithic register file                   | 16 |

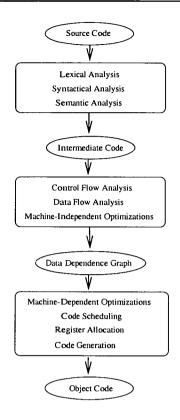

| 2.7  | Phases of an optimizing VLIW compiler                    | 21 |

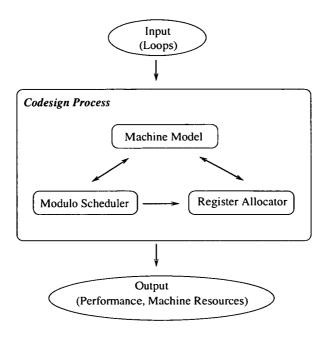

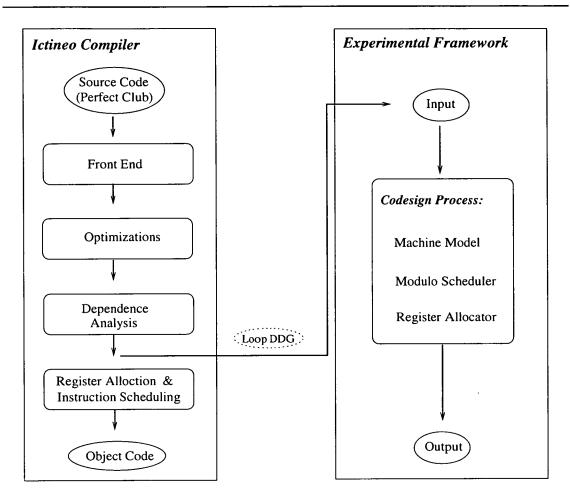

| 3.1  | Hardware/Software codesign process                       | 33 |

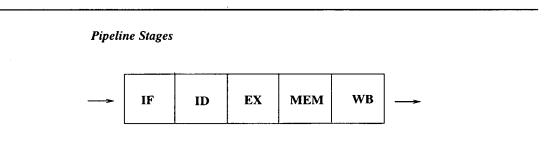

| 3.2  | Generic organization of a microprocessor pipeline        | 34 |

| 3.3  | VLIW unclustered machine                                 | 37 |

| 3.4  | Extracting loops from the benchmark                      | 38 |

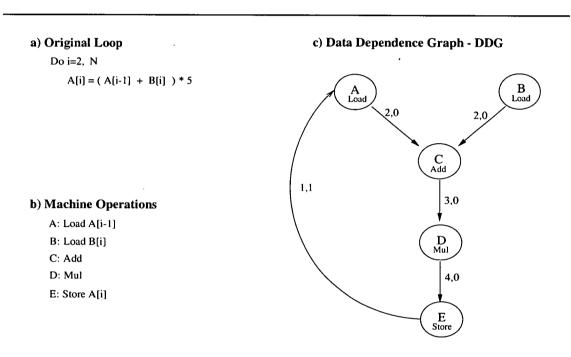

| 3.5  | Innermost loop and data dependence graph                 | 41 |

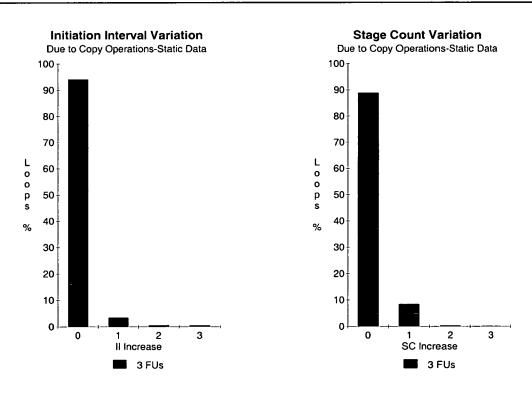

| 3.6  | Modulo Reservation Table                                 | 47 |

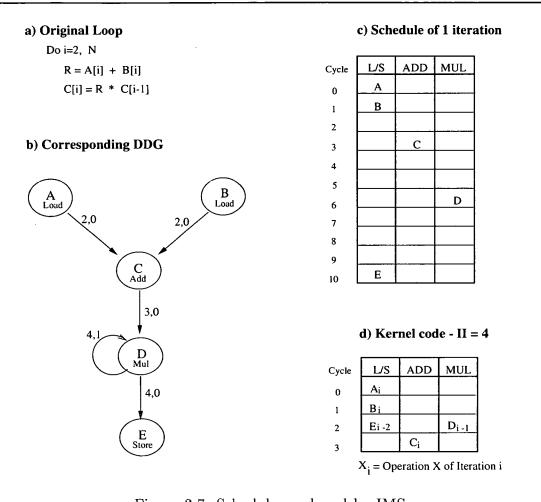

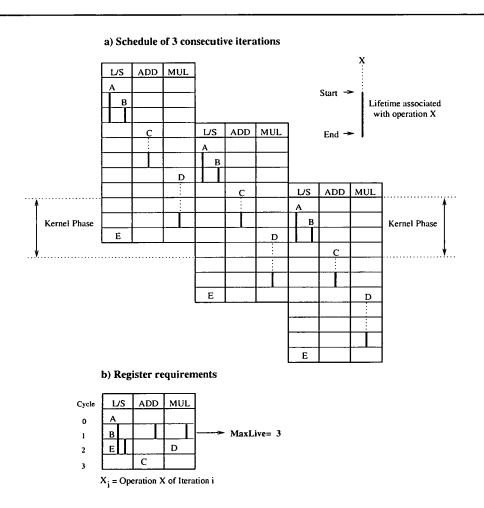

| 3.7  | Schedule produced by IMS                                 | 53 |

| 3.8  | Register requirements - MaxLive                          | 55 |

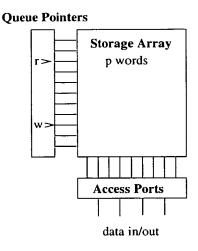

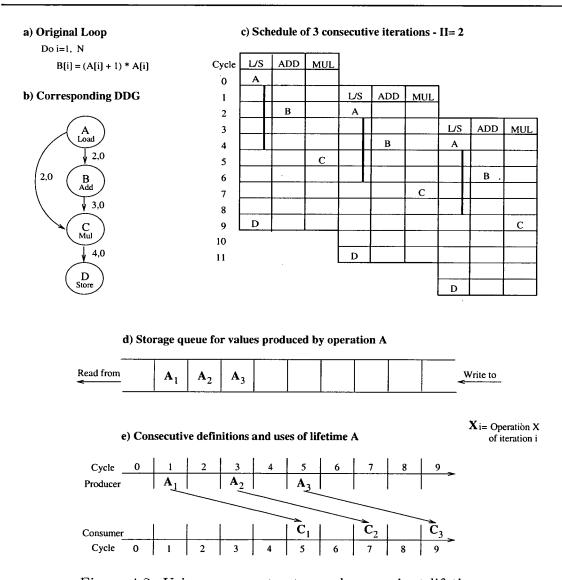

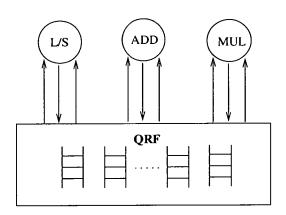

| 4.1  | QRF block diagram                                        | 60 |

| 4.2  | Using a queue to store a loop variant lifetime           | 61 |

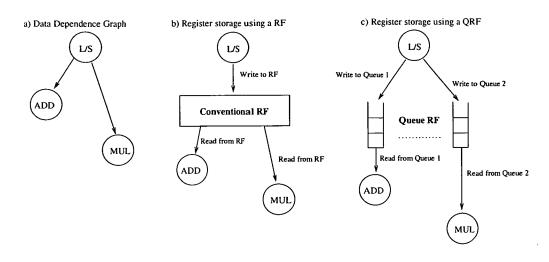

| 4.3  | Register storage                                         | 63 |

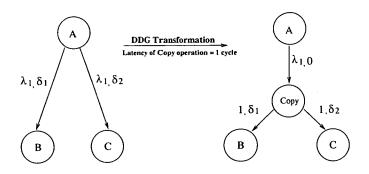

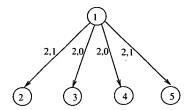

| 4.4  | DDG transformation to include a copy operation           | 63 |

| 4.5  | Inserting copy operations in a DDG                       | 66 |

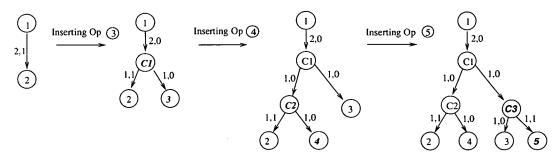

| 4.6  | II Variation-Copy Op                                     | 67 |

| 4.7  | SC Variation-Copy Op                                     | 67 |

| 4.8  | Using one queue to store lifetimes of the same length    | 69 |

| 4.9  | Using one queue to store lifetimes of distinct lengths   | 70 |

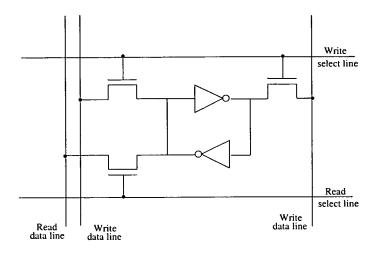

| 4.10 | Dual-ported register cell                                | 80 |

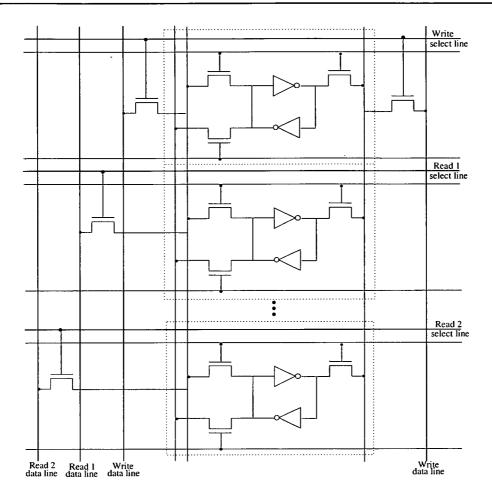

| 4.11 | Implementation of a QRF using dual-ported register cells | 81 |

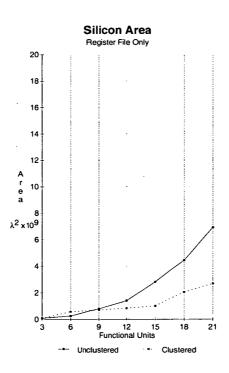

| 4.12 | Silicon area                                             | 83 |

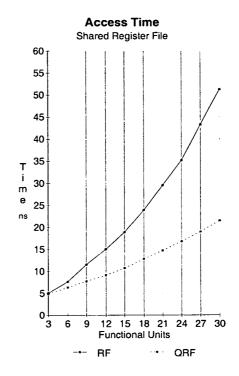

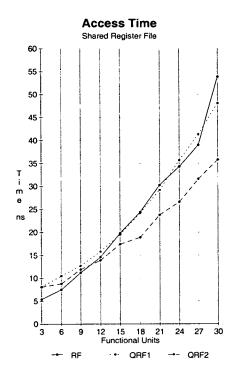

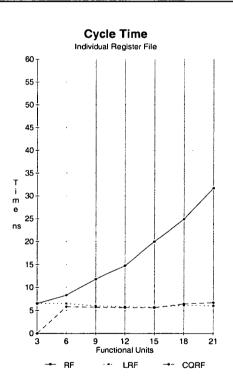

| 4 13 | Access time                                              | 83 |

| 5.1  | Unclustered machine using a QRF                             | 84  |

|------|-------------------------------------------------------------|-----|

| 5.2  | Optimizing the use of machine resources with loop unrolling | 86  |

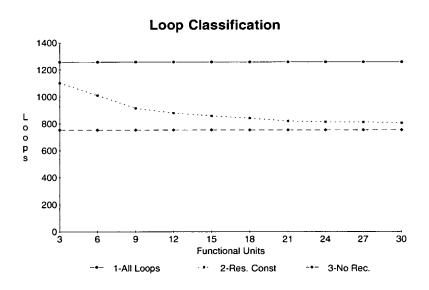

| 5.3  | Number of loops in each class                               | 90  |

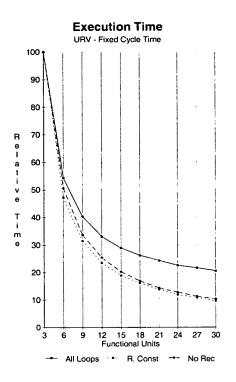

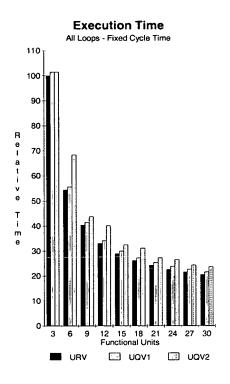

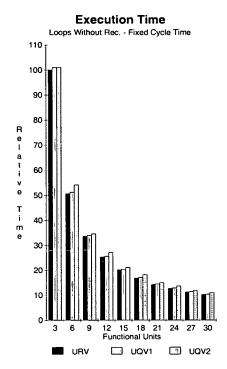

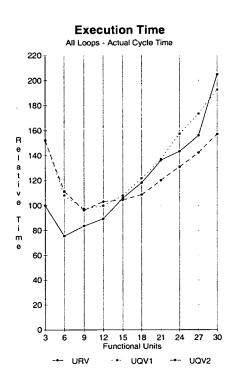

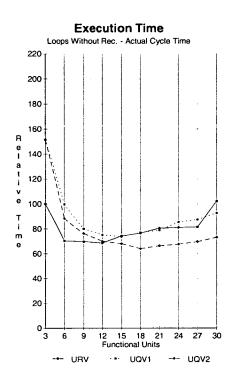

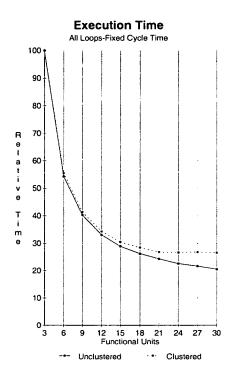

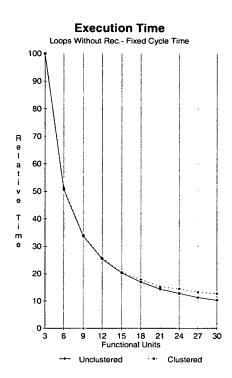

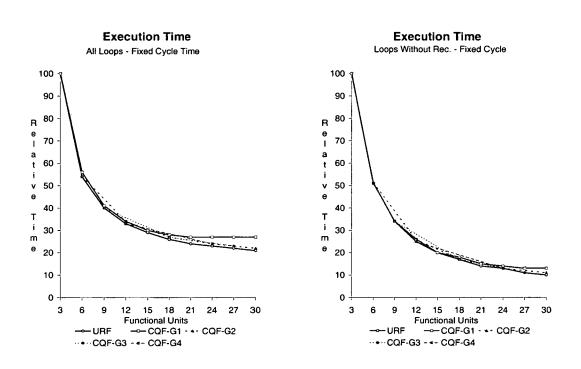

| 5.4  | Execution time-Fixed cycle                                  | 93  |

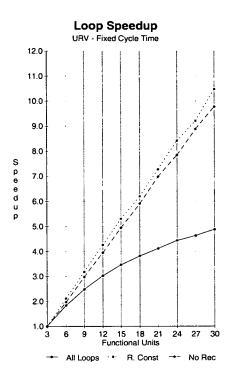

| 5.5  | Loop speedup-Fixed cycle                                    | 93  |

| 5.6  | Copy overhead-Class 1                                       | 94  |

| 5.7  | Copy overhead-Class 3                                       | 94  |

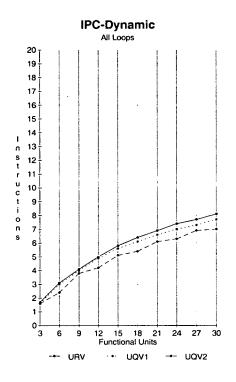

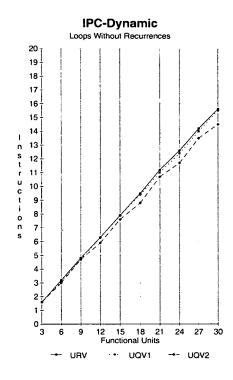

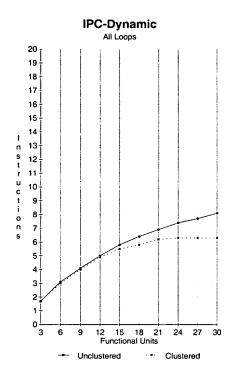

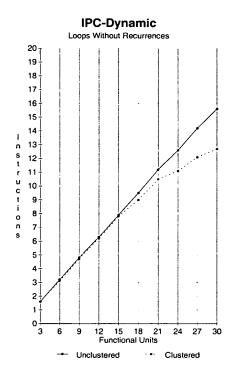

| 5.8  | IPC Dynamic-Class 1                                         | 95  |

| 5.9  | IPC Dynamic-Class 3                                         | 95  |

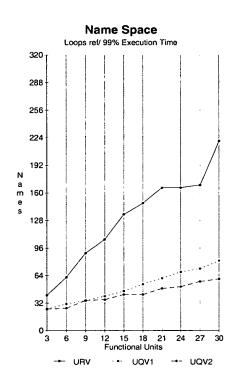

| 5.10 | Name space                                                  | 96  |

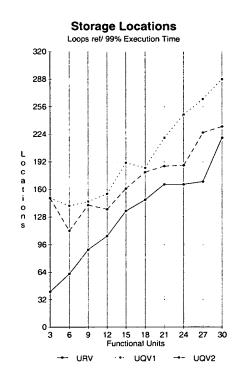

| 5.11 | Storage locations                                           | 96  |

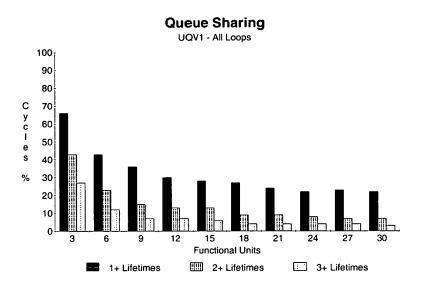

| 5.12 | Lifetimes sharing a queue                                   | 97  |

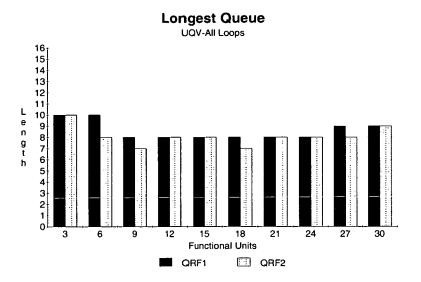

| 5.13 | Maximum queue length                                        | 98  |

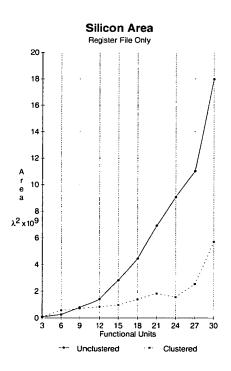

| 5.14 | Silicon area                                                | 100 |

| 5.15 | Cycle time                                                  | 100 |

| 5.16 | Execution time-Class 1                                      | 101 |

| 5.17 | Execution time-Class 3                                      | 101 |

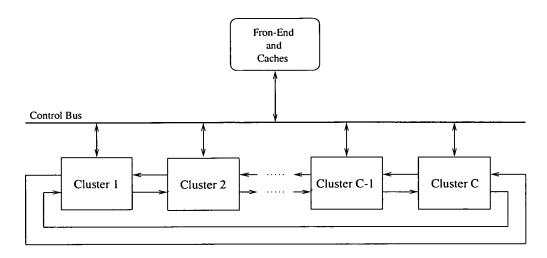

| 6.1  | Clustered machine                                           | 104 |

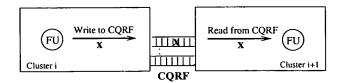

| 6.2  | Communication between adjacent clusters using a CQRF        | 105 |

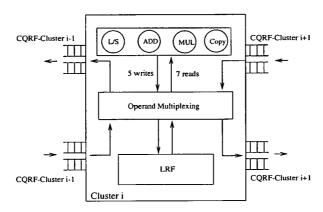

| 6.3  | Cluster organization                                        | 106 |

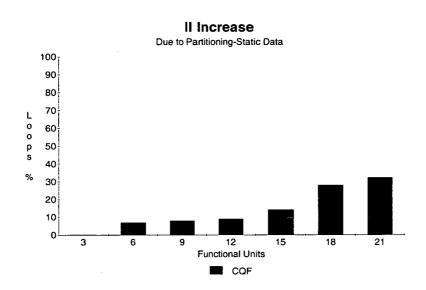

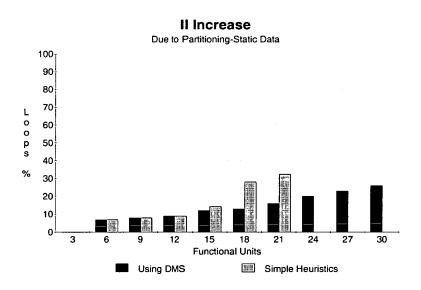

| 6.4  | Loops with a larger II due to partitioning                  | 115 |

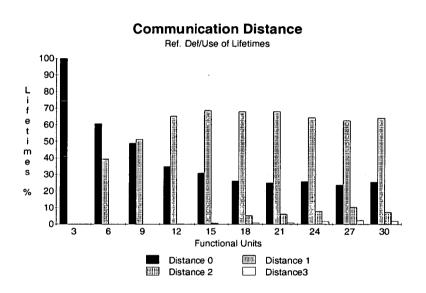

| 6.5  | Communication distance after partitioning                   | 116 |

| 6.6  | Number of cycles-Class 1                                    | 117 |

| 6.7  | Number of cycles-Class 3                                    | 117 |

| 6.8  | IPC Dynamic-Class 1                                         | 118 |

| 6.9  | IPC Dynamic-Class 3                                         | 118 |

| 6.10 | Total silicon area of register files                        | 120 |

| 6.11 | Cycle time of reg. files                                    | 121 |

| 6.12 | Machine cycle time                                          | 121 |

|      | Execution time-Class 1                                      | 122 |

|      | Execution time-Class 3                                      | 122 |

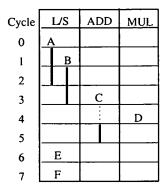

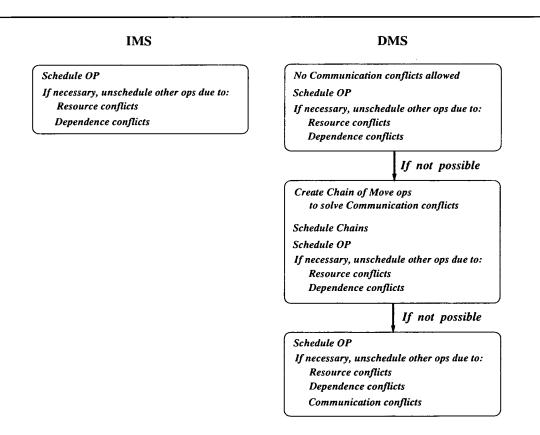

| 7.1  | Overview of IMS and DMS algorithms                          | 125 |

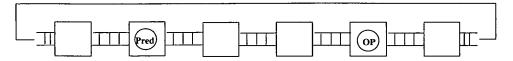

| 7.2  | Options to create a chain                                   | 128 |

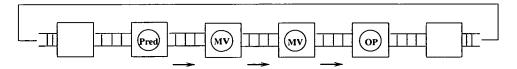

| 7.3  | DDG transformation to insert a chain                        | 133 |

| 7.4  | Typical use of a move operation                             | 139 |

| 7.5  | Loops with a larger II due to DMS partitioning              | 141 |

|      | <u> </u>                                                    |     |

| 7.6  | Communication distance after partitioning with DMS 14 | 12 |

|------|-------------------------------------------------------|----|

| 7.7  | Number of cycles-Class 1                              | 13 |

| 7.8  | Number of cycles-Class 3                              | 13 |

| 7.9  | IPC Dynamic-Class 1                                   | 14 |

| 7.10 | IPC Dynamic-Class 3                                   | 14 |

| 7.11 | Total silicon area of register files                  | 16 |

| 7.12 | Cycle time of reg. files                              | 17 |

| 7.13 | Machine cycle time                                    | 17 |

| 7.14 | Execution time-Class 1                                | 18 |

| 7.15 | Execution time-Class 3                                | 18 |

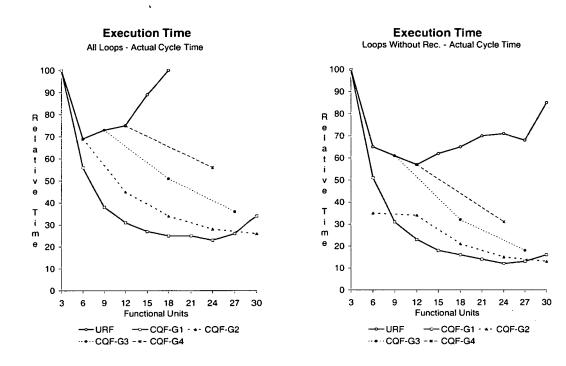

| 8.1  | Number of cycles-Class 1                              | 53 |

| 8.2  | Number of cycles-Class 3                              | 53 |

| 8.3  | Machine cycle time                                    | 54 |

| 8.4  | Execution time-Class 1                                | 55 |

| 8.5  | Execution time-Class 3                                | 55 |

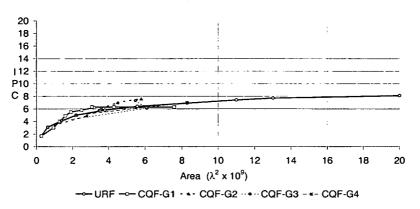

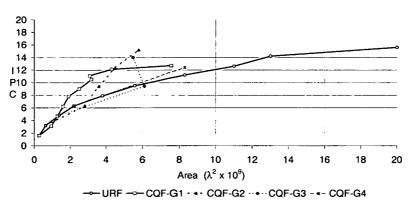

| 8.6  | IPC vs Area-Class 1                                   | 56 |

| 8.7  | IPC vs Area-Class 3                                   | 56 |

| 8.8  | Performance vs Area-Class 1                           | 57 |

| 8 Q  | Performance vs Area-Class 3                           | Ś  |

### List of Tables

| 3.1 | Functional unit characteristics                        | 36         |

|-----|--------------------------------------------------------|------------|

| 3.2 | Register file access port requirements                 | 36         |

| 3.3 | Loops extracted from the Perfect Club benchmark        | 39         |

| 3.4 | Instruction mix of the selected loops                  | <b>3</b> 9 |

| 4.1 | Register file configurations                           | 82         |

| 5.1 | Unclustered machine configurations used in experiments | 91         |

| 5.2 | URV register requirements                              | 98         |

| 5.3 | UQV register requirements                              | 99         |

| 6.1 | Machine configurations used in experiments             | 14         |

| 6.2 | URF register requirements                              | 19         |

| 6.3 | CQF register requirements                              | 20         |

| 7.1 | Machine configurations used in experiments with DMS 1  | 40         |

| 7.2 | URF register requirements                              | 45         |

| 7.3 | CQF register requirements                              | 45         |

| 8.1 | SIA predictions of device capabilities (1997)          | 51         |

### Chapter 1

### Introduction

Performance of computer systems has evolved continuously since the first machine was built. The availability of faster machines encourages the development of new and sophisticated applications, leading to ever increasing performance requirements. Advances in computer design and implementation technology have allowed those improvements. Computer systems in 1998 are based on microprocessors, which have grown in performance at an annual rate of over 50% [45]. One of the latest trends in microprocessor architecture design is called *Very Long Instruction Word* (VLIW). Machines of this kind are able to exploit parallelism at the level of machine instructions. This thesis presents a clustered VLIW architecture model able to achieve high performance and exhibiting a good potential for scalability. It was developed using a hardware/software codesign process to design a number of features, including a novel register file organization based on queues, register allocation schemes, a clustered organization, and algorithms for code scheduling and partitioning.

### 1.1 Work Context

The microprocessor technology of 1998 relies on two basic approaches to improve performance. One is to increase clock rates, resulting in faster execution of machine operations. The other is instruction-level parallelism (ILP), a set of hardware and software techniques that allows parallel execution of machine operations [84]. Superscalar architectures [51] rely most heavily upon hardware schemes to identify parallelism among operations. Although this approach offers advantages in terms of code compatibility, the hardware complexity involved poses some limitations in terms of scalability. Increasing the number of functional units (FUs) in current superscalar microprocessors would require even more sophisticated schemes to find and schedule independent operations. Using a VLIW

architecture is another possibility to exploit ILP. In this case all data dependence analyses and scheduling of operations are performed at compile time, resulting in a simpler hardware organization. This allows the inclusion of a larger number of FUs into a single chip, increasing the possibilities of parallelism exploitation. In spite of this relative simplification, the scalability of VLIW machines can be constrained by the complexity and size of the required register file (RF). Ideally, a VLIW machine would have a number of parallel functional units connected to a common register file able to perform two reads and one write operation per FU in each cycle [14]. This implies that each FU requires three access ports to the register file.

The available processing power of a very wide issue machine can be fully exploited when executing loop structures, which in many cases accounts for the largest share of the total execution time of a program. Several compiling techniques have been developed to schedule loops in ILP machines. Software pipelining [16], for instance, is a scheme that allows the initiation of successive loop iterations before prior ones have completed. In this scheme, consecutive data values produced by the same operation may coexist, requiring distinct storage locations and thus increasing register pressure [64]. High register pressure results in register file requirements that are difficult to realize, taking into account current technology trends. The size of shared register files grows in proportion to the square of the number of ports, and hence also the number of FUs [13]. If software pipelining is performed it can grow in proportion to the cube of the number of FUs (Section 2.3.2). The size of the register file alone can be a problem in the machine design. Furthermore, the access time of such an RF can be compromised by the number of ports, causing a negative impact on the cycle time of the machine. For these reasons we understand that the register file required by a wide-issue unclustered machine can compromise the benefits resulting from aggressive ILP scheduling. This has motivated us to investigate alternative machine designs.

### 1.2 Work Overview

This thesis proposes a scalable VLIW architecture comprising clusters of functional units and private register files, using queue structures to implement a mechanism for inter-cluster communication. We believe this scheme presents better possibilities in terms of scalability as the size of individual RFs is not influenced by the total number of FUs, suggesting that the silicon area may grow only linearly with respect to the number of FUs. Technology trends indicate the future

possibility of building systems integrating powerful processors and main memory on a single chip [53]. This may address some design issues concerning the memory subsystem of our machine model, a problem also common to other microarchitectures. However, the effectiveness of such an organization also depends on the scheduling and code partitioning strategy. We have developed a scheme to produce software pipelined code for a clustered VLIW machine model aiming to achieve performance levels similar to an unclustered machine without communication constraints. The main developments and contributions of this research work are outlined in the next subsections.

### 1.2.1 Queue Register Files

Software pipelining generally increases register pressure in VLIW machines. The register file required in such cases may compromise scalability, which has motivated us to develop a Queue Register File (QRF). Register files organized by means of FIFO queues, with limited read and write access, are believed to be less complex than conventional organizations. That should be the case because it could be implemented using simple dual-ported individual register cells, and a possibly less complex address decoding logic. On the other hand, this simplification in hardware imposes new constraints on the register allocator, requiring new techniques to efficiently exploit this organization. Software pipelined loops generate a regular pattern of production and consumption of lifetimes. We have taken advantage of this fact to deduce and prove a Q-Compatibility Test to decide which lifetimes can share a given storage queue, based on their relative production and consumption order. The Q-Compatibility Test enables efficient register allocation to the QRF. Analytical models show that QRFs are in general more efficient than conventional organizations in terms of silicon area and access time.

#### 1.2.2 Unclustered VLIW Architectures

We developed a VLIW machine model organized as a single cluster of functional units, all of them connected to a common register file. This model allow us to quantify the achievable ILP for the architecture and compilation techniques employed. Two types of register files have been used: a conventional RF, and a QRF. The advantage of using a QRF with software pipelined loops has been confirmed through experimental analysis. Nonetheless, it has also been confirmed that unclustered machines do not scale well, mainly due to the size and number of ports of the shared register file. In this case, all benefits achieved by an aggressive ILP scheduling can be lost due to a long register file cycle time.

#### 1.2.3 Clustered VLIW Architectures

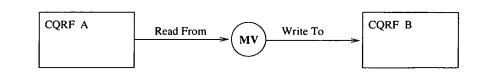

Including additional functional units in a unclustered VLIW architecture is not a straightforward design issue. New register file access ports can severely compromise the machine cycle time. This thesis proposes a VLIW architecture comprising clusters of functional units and private conventional register files. Each cluster should have a small number of FUs to avoid increasing the register file complexity. Clusters are interconnected using a bi-directional communication ring. We developed a scheme using QRFs to implement data communication between adjacent clusters. In this case a communication queue register file (CQRFs) is placed between two clusters. Sending a value from one cluster to another requires only one write and one read operation to the appropriate CQRF. We found through experimental analysis that the silicon area required to implement this scheme may grow only linearly with respect to the number of FUs.

### 1.2.4 Distributed Modulo Scheduling Algorithm

A clustered organization can address some of the issues related to the hardware complexity of a VLIW architecture. However, a single thread of control implies that operations scheduled in distinct clusters may be data dependent with each other, requiring inter-cluster communication. This might impose additional constraints on the scheduler and register allocator, possibly compromising the machine performance. We developed a software pipeline scheduling algorithm targeting clustered VLIW architectures. The scheme, called Distributed Modulo Scheduling, performs in a single step both scheduling and partitioning of operations among clusters. The objective is to produce code achieving performance levels close to a single cluster machine without communications constraints. Several experiments investigated the effectiveness of the scheme for machine configurations up to 10 clusters, and a total of 30 functional units. Furthermore, the scalability of the proposed clustered architecture was assessed, taking into account performance and cost aspects, along with future technology trends.

### 1.3 Thesis Structure

The thesis structure presented in this section generally reflects the chronological order in which this research work was carried out. Some of the findings and experiments performed in early stages of the work are omitted, being replaced by later developments. A number of hardware and software issues have been addressed, however the interrelation among them requires that they are presented

together. We tried to produce a single presentation format for the work methodology, design considerations, experimental results and discussions. Finally, a summary of the main objectives and contents of each chapter is described below:

- Chapter 1: Motivation and work overview.

- Chapter 2: Bibliographic survey related to this thesis. Topics discussed include ILP, hardware support for ILP, VLIW architectures, register file organizations, compilation and scheduling techniques for VLIW, and similar architectures developed elsewhere.

- Chapter 3: Description of the experimental framework used to perform quantitative analyses throughout the work. A basic machine model is defined, along with the benchmark loops employed. A software pipeline scheduling algorithm is at the core of the compilation process. A number of figures regarding performance and machine resources are generated.

- Chapter 4: A queue register file is proposed as an alternative organization to deal with high register pressure. A novel technique is presented to perform register allocation, which includes a theorem (Q-Compatibility Test) and the corresponding proof. Comparisons with conventional organizations are made in terms of silicon area and access time.

- Chapter 5: Defines an unclustered VLIW machine, using either a RF or QRF. The potential to exploit ILP, and the implications of using a shared register file are investigated by means of experimental analysis.

- Chapter 6: A clustered VLIW machine and the corresponding scheduling algorithm is proposed to address scalability issues. The main motivation is to keep register files small enough to result in a short cycle time. Queue register files are used to implement a communication mechanism between clusters.

- Chapter 7: Presents DMS, an integrated scheduling/partitioning algorithm targeting a clustered VLIW machine. The scheme is able to deal efficiently with communication constraints for a range of machine configurations.

- Chapter 8: Analyses the scalability of performance and cost of clustered VLIW machines. Compares several configurations of the proposed architecture, trying to predict its viability according to current technology trends.

- Chapter 9: Final conclusions and suggestions for future work.

### Chapter 2

### Background

### 2.1 Instruction-Level Parallelism

Instruction-level parallelism is a set of processor and compiler design techniques that allows a sequence of machine operations to be parallelized for execution on multiple pipelined functional units. The operations are similar to the ones usually found in a RISC microprocessor, such as memory loads and stores, additions, multiplications, and branch instructions. The main advantage of ILP is the possibility of exploiting parallelism with no need of code rewriting, working with existing programs. Sequential programming style still dominates the software base currently in use, and also new developments. This is unlikely to change in the foreseeable future, which emphasizes the commercial value of ILP.

Several studies have pointed out the existence of large amounts of available ILP to be exploited in existing programs. Some studies concluded that the available ILP is modest, ranging between 2 and 5. However those studies did not consider program transformations able to expose ILP [84], such as loop interchange, trace scheduling, loop unrolling, and software pipelining, among others [7]. Wall carried out an extensive study, using speculative execution, memory disambiguation and other techniques to enhance ILP [94]. He concluded the available parallelism ranges between 2 and 60, depending on the execution model employed. A new version of this study was later conducted, considering a much larger set of techniques to expose ILP [95]. That report presents simulations of test programs under 375 models of available parallelism. It was found that relying only on the technology available at the time (1993), it was possible to consistently obtain ILP between 4 and 10 for most of the programs. Using branch prediction with speculative execution the range would shift to 7-13. It was also concluded that vectorizable programs could attain much higher levels. Another study on available ILP focused on methods to eliminate control flow barriers [55]. It was

found that the parallelism in non-numeric programs ranges between 18 and 400. Numeric applications could go even further. It is expected that new compiler optimizations will expose even larger amounts of parallelism to be exploited by aggressive machine configurations.

On the other hand, continuous improvements in VLSI design enables the integration of more functional units into a single chip. Furthermore, higher clock speeds may result in more deeply pipelined functional units. These factors contribute to increase the available hardware parallelism. The task of keeping an ILP processor busy can rely most heavily either on hardware or software schemes. This constitutes the basis upon which modern ILP processors can be classified, which is discussed in the next subsections.

### 2.1.1 Hardware-Centric ILP: Superscalar

Superscalar processors [51] have complex hardware structures to decide at runtime which operations have no dependences with each other, so they can be executed in parallel. Dynamic scheduling of operations are also performed by hardware. Scoreboarding [92] is a dynamic scheduling technique that allows instructions to execute out-of-order. Another approach, called Tomasulo Algorithm [93] combines out-of-order execution with register renaming. These and other related techniques try to avoid stalls in the pipeline by preventing data hazards. Hardware branch prediction schemes can also be implemented to avoid control hazards [90]. As a side effect, increasing the number of operations in flight (issued but not yet completed) can make the number of architectural visible registers insufficient, requiring register renaming techniques [98].

The possibility of having object code compatibility is one of the main advantages of superscalar processors, allowing applications to run in faster machines without recompilation. For this reason, general purpose superscalar processors have reached the mainstream market. The drawback of this approach is that implementing those and other hardware schemes can be expensive in terms of silicon area and clock cycle. Contemporary machines of 1998 can issue about four operations per cycle [75, 37]. However, there is a general perception that hardware complexities may prevent the expected performance gains if the current instruction issue rate is increased by a significant factor. For this reason new ILP designs, in the form of VLIW processors, move into the compiler some of the tasks performed by hardware in superscalar architectures.

#### 2.1.2 Software-Centric ILP: VLIW

VLIW machines provide hardware parallelism in the form of multiple and deep pipelined functional units. However, they have a relatively simple control logic, releasing more silicon area to implement functional units. This should result in higher levels of hardware parallelism than found in superscalar machines. Simpler hardware may result in lower cost per chip and less power consumption, important features for embedded computing and portable devices, among others. The counterpart of these advantages is the need of sophisticated compiler techniques to identify parallelism and schedule operations among functional units. The program for a VLIW machine specifies precisely which functional unit should execute a given operation, and when an operation should be issued in order to enforce dependence constraints [84]. Comparing to dynamic scheduling schemes, a compiler can work with a larger window of candidate operations to be parallelized. This improves the possibilities of keeping the available functional units busy. However, the compiling techniques involved are complex, still evolving and presenting challenges.

Detailed description of the target processor is necessary to achieve the best performance with static scheduling. In this case object code compatibility may not be possible among distinct machine generations, requiring program recompilation. Complexity and program size can result in long compilation times. To alleviate this problem the compiler can subdivide a program, performing tasks of manageable sizes [44]. The nature of some application fields make them less sensitive to this problem, such as scientific programs and digital signal processing (DSP) [23]. However, this is an important issue for general purpose computers and applications. A research group at IBM proposed a solution for this problem, organizing operations into tree-instructions [72]. Another work proposed dynamic scheduling of operations for VLIW machines [77]. Although a number of compiling issues are still open, VLIW architectures are beginning to establish itself in some niche markets, specially in the DSP area. The technology can also be effective to support multimedia applications, an area of increasing interest [76]. However, to have a broad impact on the mainstream market, VLIW processors must accelerate the non-vectorizable scalar code prevalent in most applications [86]. An indication of the viability of this technology is the announcement by Intel of the first general purpose VLIW-like processor [43], to be released in late 1999. The next sections of this chapter discuss VLIW architectures and related compilation issues, followed by a brief presentation of some commercial VLIW machines.

### 2.2 VLIW Architecture

A VLIW architecture is characterized by a wide instruction word controlling the action of all functional units. A single control unit can issue a new instruction every cycle. Data dependences and scheduling of instructions are resolved statically at compiling time, so the hardware has to perform no further checking to ensure program correctness. The first VLIW architecture was proposed by Fisher at Yale University [33]. Since then a growing interest in this technology has motivated a number of hardware and software developments to support the new paradigm.

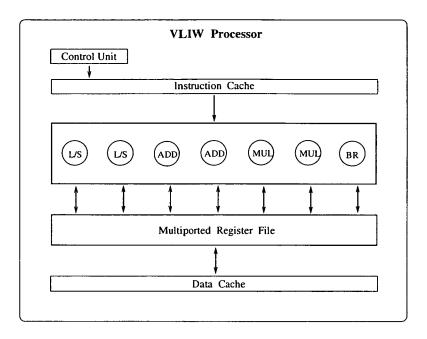

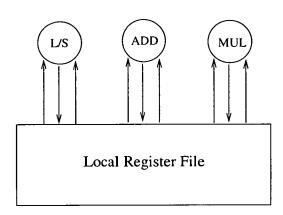

The ideal VLIW machine has a number of concurrent FUs, connected to a register file able to perform two reads and one write operation per functional unit in each cycle [14, 21]. A control unit, instruction and data caches complete the basic VLIW design, as seen in Figure 2.1. The diagram shows a hypothetical machine with functional units capable to perform memory load and store access (L/S), arithmetic and logic operations (ADD), multiplication and divisions (MUL), and a branch unit (BR). Static scheduling and a single thread of control impose strict synchronization constraints among functional units, which should operate in lockstep [45, 40]. This may result in one single cache miss stalling all FUs, stressing the importance of the memory subsystem. However, the pattern of memory access of some DSP applications may result in a high rate of cache misses, motivating the use of alternative designs such as local memories or prefetching buffers [23]. Future trends suggest that it will be possible to integrate processing elements and main memory in a single chip [53], greatly simplifying this issue.

A long instruction word should contain, for each functional unit, the operation code, the source and the destination registers used, as shown in the example in Figure 2.2. No-operations (NOPs) may be inserted in the long instruction if there are not enough operations to be issued in parallel in a given cycle. Practical VLIW machines have been implemented using instruction words up to 1024 bits wide [83, 66]. Uncompressed encodings explicitly store NOPs in the instruction word. This simplifies the hardware organization, but at the expense of poor memory utilization due to increase in code size. Compressed encodings do not store NOPs, using variable size instructions, allowing greater effective memory bandwidth [17].

The need to execute some time-critical instructions might be known only at run time, which is often associated with the outcome of a branch operation. Nevertheless, the compiler can schedule those instructions *speculatively*, as long as some hardware support is provided to ignore the effects of executing unnecessary

Figure 2.1: Basic structure of a VLIW processor

| Single instruction word controlling all functional units |              |                 |       |                   |       |        |  |

|----------------------------------------------------------|--------------|-----------------|-------|-------------------|-------|--------|--|

| L/S 1                                                    | L/S 2        | ADD 1           | ADD 2 | MUL 1             | MUL 2 | BR     |  |

| LD R3, 0(R1)                                             | LD R5, 0(R2) | ADD R10, R8, R9 | NOP   | MUL R20, R17, R18 | NOP   | JR R30 |  |

Figure 2.2: Example of an instruction word for a VLIW processor

operations [21, 83, 52]. Predicated execution determines the execution of an operation according to a Boolean input [47]. Some schemes employ extra poison bits to indicate if the contents of a register is valid [45]. Other methods buffer the result of an speculative instruction until deciding if it is needed or not. Branches can be eliminated from an acyclic region of a control flow graph using if-conversion [4] and predicated execution, as showed by Dehnert [18]. These and other special hardware features can be used to optimize the performance of a VLIW machine.

### 2.3 Register Files for VLIW Machines

Performance reasons dictate that operations other than memory access should be register-register [45]. Those operations use destination and source operands stored in the on-chip register file. Memory operations can be made through load and store operations. All functional units of a VLIW machine operate in lockstep. If one of them stalls due to a memory operation, all the others must also stop executing. Data communication among functional units should always take place thorough a centralized register file. A VLIW processor should provide a register file with enough capacity and bandwidth to support the intended instruction issue. Occasional on-chip cache access to deal with spill code could be tolerated, however frequent cache misses can seriously compromise the machine performance. For this reason the design of the register file is one of the crucial aspects of a VLIW machine, being able to determine the machine cycle time [25].

In this section we show that register file requirements for wide-issue VLIW machines are high and complex. As a result, conventional designs may not be well suited to address the problem. Thus, performance and scalability issues may lead to alternative hardware organizations and compilation techniques

### 2.3.1 Register File Requirements

There are two main factors that make register file requirements for VLIW machines complex:

- Number of registers

- Number of access ports

Compiler optimizations employed to exploit ILP machines often require a large number of registers. Predication and speculative execution generate extra data values that must be kept without knowing if they are necessary or not. Loop unrolling and software pipelining can also increase register pressure dramatically.

The *lifetime* of a value is the time span ranging from its definition up to the last use of it. It can also be referred to as *lifetime length*. The precise definition of the first and the last cycle of a lifetime depends on architecture details, and is not relevant at this point of the discussion. Two types of lifetimes can be found in a loop: A *loop invariant* lifetime spans the whole loop execution. Usually it is initialized before entering loop execution and remains fixed until exiting. For this reason they need only one storage position. On the other hand, a *loop variant* is a lifetime produced by successive iterations of a loop, usually having its value changed.

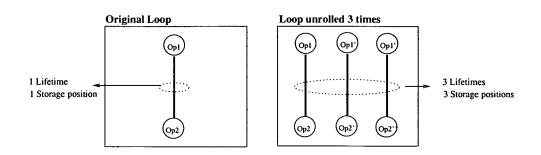

Loop unrolling [20] is a well known compiler optimization that replicates the body of a loop some number of times. This allows simultaneous scheduling of more than one iteration at a time, resulting in a larger number of operations to

exploit machine resources. New lifetimes are also generated, possibly requiring distinct storage positions, as shown in the example in Figure 2.3.

Figure 2.3: Register pressure resulting from loop unrolling

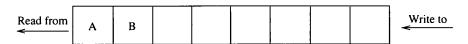

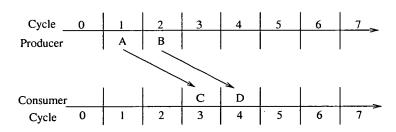

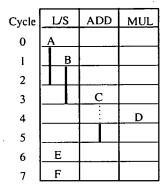

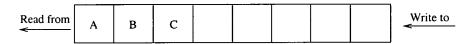

Software pipelining can also be very demanding due to the overlapping of lifetimes produced by the same operation from distinct loop iterations. In this scheme a new iteration starts before prior ones have fully completed. A given lifetime length can be longer than the time between the initiation of two or more successive iterations. In this case an operation produces a new value before previous ones have been consumed, thus requiring distinct storage locations (Figure 2.4).

Figure 2.4: Register pressure resulting from software pipelining

Register requirements for ILP architectures have been studied by several authors. A theory for assessing register requirements of pipelined processors with various issue widths was developed by Mangione-Smith and others [69]. The technique is intended to help in evaluating trade-offs in machine designs. The study concentrates on the execution of innermost loops from scientific programs. Llosa

performed a quantitative analysis on register requirements of software pipelined loops and their effect on performance [64]. This study focused on loop variants as they account for the most significant fraction of register requirements for numeric applications. It was found that 64 registers are enough to avoid spill code for at least 90% of the loops, however a lot more is required by a few loops [65]. Furthermore, those loops account for a significant fraction of the total execution time of the benchmark, which emphasizes the relative importance of them. Farkas produced a study on register files for dynamically scheduled ILP processors, with some findings that can also be extended to VLIW machines [25]. It was concluded that a four-issue machine requires at least 80 registers. An eight-issue processor would require at least 128 registers. Those and other works have confirmed that aggressive exploitation of ILP requires a large number of registers.

It has been shown that ILP machines executing non-numeric applications would require RFs with a small number of access ports [71]. However, numeric applications, often the target of wide-issue machines, are much more demanding. The number of access ports required by a register file for VLIW architectures further complicates its implementation and performance. As already said, each functional unit requires 2 read and 1 write register file access ports to sustain the achievable issue. The area of shared register files grows in proportion to the square of the number of ports, and hence also the number of FUs [13, 25], which has motivated a number of alternative organizations, as shown in the next sections.

### 2.3.2 Monolithic Register Files

A monolithic register file can be implemented using a register cell with multiple read and write ports. It allows multiple access to the same register in any given clock period [58]. This is the organization used by most of the ILP machines built until 1998. However it can constitute a barrier for scalability. If software pipelining is performed, as often happens in ILP machines, we have found that the register file size can grow in proportion to the *cube* of the number FUs.

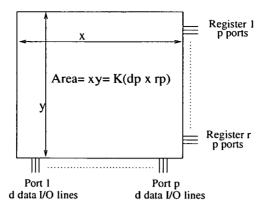

Let us assume that a p ported register file, containing r registers of d bits each is fully connected to a collection of f functional units, each having a latency of l cycles. The silicon area required to implement such a register file is shown diagrammatically in Figure 2.5. It can be inferred that, for some constant value K, the expression to calculate the area A of that register file is:

$$A = Krdp^2 = \Theta(rp^2) \tag{2.1}$$

Figure 2.5: Area of a monolithic register file

In a software pipelined loop each operation in flight reserves n register names, where n is the number of software pipe-stages straddled by each lifetime. The number of operations in flight is determined by the product of the instruction issue width and the pipeline lengths. This equals the number of independent functional units, f, multiplied by the number of pipeline stages of each FU, l. Thus, assuming that n is a constant, the number of registers r required to execute a software pipelined loop in a VLIW machine is:

$$r = nfl = \Theta(fl) \tag{2.2}$$

To sustain an average issue rate of s instructions per cycle it may be necessary to have a register bandwidth of at least 2s reads and s writes per cycle, requiring 2 read ports and 1 write port per instruction. Under the reasonable assumption that  $s = \Theta(f)$  we can say:

$$p = \Theta(f) \tag{2.3}$$

Using equations 2.2 and 2.3 the register file area can be expressed in terms of the number of functional units:

$$A = \Theta(lf^3) \tag{2.4}$$

We have found that the area of a register file to support software pipelining execution is proportional to the cube of the number of functional units. This result clearly shows that designs employing a large multiported register file can constrain the scalability of VLIW architectures.

A further complicating factor is the access time of multiported register files: it grows approximately linearly with the number of ports [23]. The register file may well determine the cycle time of a VLIW machine. One study found that when the issue rate scales up from 4 to 8, the performance improvement achieved is only 20%. The main reason for this is the complexity of the enlarged register file, specially in regard to the number of access ports [25].

We have shown that conventional register file organizations may not be suitable for ILP architectures. This could be even more problematic for wide-issue VLIW machines, which has motivated the development of decentralized architectures, as presented in the next section.

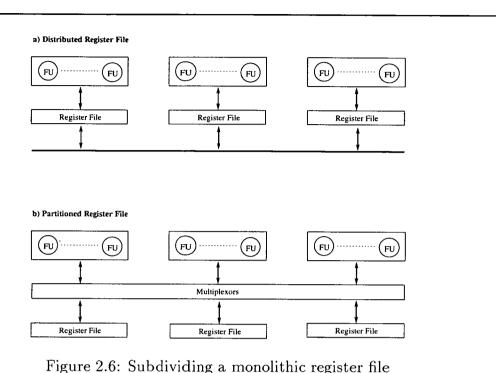

### 2.3.3 Partitioned Register Files

As discussed in Section 2.3.1, exploiting a high degree of parallelism also requires parallel access to a possibly large set of registers. A single multiported register file is the simplest solution to the problem, however access time and silicon area may inhibit its use by wide-issue VLIW machines. The technology available in 1998 allows one to build register files with around 10-15 ports at reasonable cost and speed [23]. This configuration would be suitable for machines with up to 5 FUs, however higher degrees of hardware parallelism are already possible. To overcome this problem, some processor architectures may incorporate distributed or partitioned register files, each of them providing access to a smaller set of functional units. This reduces the port requirements of individual RFs, and should also reduce the size of them. Multiple banked register file organizations can be used by dynamically scheduled processors. One way to deal with the new organization is by using register renaming [96]. Statically scheduled processors require complex compiling techniques to distribute operands among RF banks, each of them dependent on the architectural model adopted.

As defined in [58], in a distributed RF configuration each set of functional units has direct access to one register file only (Figure 2.6a), resulting in a clustered structure [50]. Access to non-local register files may stall the processor or require register copy operations, as discussed later in this section. A partitioned register file provides less connectivity between FUs and registers (Figure 2.6b), however each FU has still direct access to any register [50]. Copy operations are not

necessary, although conflict access may arise. This approach has been successfully used in vector processors [58].

Significant performance degradation may occur if code partitioning is not properly done. According to Faraboschi [23], three distinct architectural scenarios may be possible when register files are partitioned or distributed:

- 1. The register file clustering is architecturally invisible. In this case the compiler assumes a unified register space. Local register access operations occur as usual. However, access to a register file located in another cluster may be necessary. In this case, hardware support should be available to stall the processor while register contents are moved across non-local elements. This approach does not impose extra complexities to the compiler, however significant performance penalties may occur due to excessive stalls.

- 2. The register file clustering is architecturally visible, with complete connectivity between FUs and RFs. In this case local and non-local RF access have distinct latencies. A non-local access is actually implemented using a copy operation, which must be scheduled together with the operation requiring the access to the RF. This creates an indivisible "operation-copy" pair. The advantage here is the possibility of minimizing the overhead due to copy operations by scheduling them out of the critical path.

3. The register file clustering is architecturally visible, with limited connectivity between FUs and RFs. This case is similar to the previous one, however the compiler must schedule copy operations explicitly, but not necessarily together. Better schedules might be produced, at a cost of a more complex compilation process.

Previous works have proposed distributed or partitioned register files for wideissue machines. Whatever organization is used, compilation for these type of machines is difficult, resulting in severe performance loss if not properly handled.

The Multiflow Trace VLIW machines were commercially available as general purpose systems in the late 1980s. Configurations capable of issuing up to 28 operations simultaneously were built [66]. The architecture was designed using clusters of functional unit and distributed private register files. Global shared buses were used to connect non-local register banks, which increases operation latencies. The approach used to minimize the amount of data transfer latency is derived from the Bottom Up Greedy (BUG) algorithm [22]. It is used as a prescheduling step to assign operations to functional units and register banks [66]. The actual latency of an operation is determined by the register bank of the destination operand. If it is local, no extra delay is necessary. Otherwise, the functional unit has also to perform a sort of copy operation to access the non-local register file using the global bus.

Capitanio and others proposed a Limited Connectivity VLIW architecture, employing distributed register files [14]. Although originally called "partitioned", this structure is more closely related to our definition of "distributed" register file. We attribute this denomination conflict to the lack of a widely accepted classification of register file organizations. The processor in this machine model is partitioned into clusters of functional units fully connected to a private register file. Communication between clusters take place through global buses. The compiler schedules move operations when non-local register file access is required. The compilation process uses a three step scheduling process: code is first generated for an ideal VLIW, assuming a monolithic register file. Then an algorithm is applied to distribute data among clusters, minimizing a given cost function related to communication delays. Finally the required move operations are inserted and the code is recompacted.

The Transport Triggered Architecture (TTA) is a VLIW machine using partitioned register files [50]. No extra copy or move operations are needed, however the register allocator has to prevent access conflicts due to a limited number of ports. A conventional register allocator maps architectural registers to machine

registers. Further actions must be taken if the number of physical registers is insufficient. The register allocator for a TTA must also take into account the limited number of ports. The authors proposed several methods for this task.

Another approach has being reported recently by HP Laboratories [19]. The target machine is a clustered VLIW architecture, using distributed register files. The code partitioning strategy can be seen as an extension of the techniques used by the Multiflow architecture. However, a distinct architecture model allows the compiler to explicitly schedule copy operations between clusters. The algorithm distributes operations among clusters, trying to avoid the inclusion of copy operations in the critical path. This should minimize increases in the schedule length due to partitioning. Register allocation is also taken into account during the partitioning phase, avoiding further complications due to eventually required spill code.

### 2.3.4 Other Register File Organizations

Alternative register file organizations have been proposed in addition to the ones described above. The Cydra 5 was designed as a VLIW machine to achieve high performance when executing innermost loops [83]. A set of rotating register files supports the execution of software pipelined loops. The rotating register file is addressed using an iteration frame pointer (IFP), which is decremented on each iteration [18]. The result is that a particular register reference actually refers to a distinct physical register on each iteration. The rotating register file concept is an effective technique to deal with overlapped lifetimes produced by software pipelining schedules. However, it does not address access conflicts and register port requirements, which can be high for wide issue machines. Furthermore, the Cydra 5 architecture employed a crossbar interconnection among FUs and RFs, which is not a scalable solution.

The regularity in memory access patterns found in some classes of applications, like DSP, has motivated the design of other storage structures. Aloquely and Chen proposed queues and stacks to store values not requiring random access [5]. They are implemented using chains of shift registers. Storage structures resembling FIFO (first-in first-out) or LIFO (last-in first-out) queues may reduce the access time and hardware costs. This can be accomplished because there is no need of address generation and decoding logic to access intermediate positions. However, those organizations require register allocation schemes more complex than conventional ones. A similar approach was proposed using circular queues [9], also using shift registers. This implementation may impose further

constraints to the register allocator: values must be written to and read from fixed physical locations, at the end points of the storage structure. It can be possible that the first logical value in a queue is not stored in the first physical location in the queue, requiring extra cycles to perform shift operations. This may delay the schedule of an operation dependent on that value. This problem can be tackled using a structure called sequential read-write memory (SRWM) [46]. A register bit is used to control which memory location should be accessed, eliminating the need for global shifts of values. These structures have been reported as more efficient in terms of silicon area and power consumption than the ones using shift registers [36]. All of those works proposed register allocation schemes exploiting particular characteristics of the application programs, enabling the use of the non-conventional RF organizations.

### 2.4 VLIW Compilation Issues

The ultimate goal of a compiler is to produce code that minimizes the total execution time of a program (runtime). Compiler optimizations for sequential RISC processors accomplish this by minimizing the instruction count (number of operations executed). For ILP processors the correlation between these two factors is not necessarily the same. Some schemes actually increase the number of operations executed in order to minimize runtime. Producing code for ILP architectures requires knowledge of the available parallelism at both software and hardware levels. This allows the compiler to transform the program in order to optimize the use of machine resources, reducing the cycle count (number of cycles to complete the program execution).

Programs are often represented as graph structures, which expose data dependence among operations, and also opportunities for parallelism exploitation. A target machine model, similar to the actual hardware of the target machine, should feed the compiler with the available hardware parallelism. A detailed machine model description [42] may allow the compiler to produce better quality code. However, this exposes one of the drawbacks of statically scheduled ILP machines: a new recompilation is required for every distinct configuration of a given architecture.

Compilers for ILP architectures must find enough parallelism to exploit the available machine resources. This involves several program analyses and transformations. Some designs focus on optimizing code for numeric applications, often accelerating loop execution, using techniques such as software pipelining [16].

General purpose machines must deal with non-numeric (scalar) code. Although some attempts have produced acceptable results [32], research is far from complete in this area.

### 2.4.1 Overview of the Compilation Process

The quality of compiler parallelization techniques can potentially make a difference of an order of magnitude in the performance of processors exploiting ILP. In order to parallelize a program, three tasks must be performed by a compiler:

- Analyze the program to determine dependences between instructions.

- Perform optimizations to remove those dependences.

- Schedule instructions to be executed in parallel.

A simplified representation of the phases constituting an optimizing compiler for a VLIW machine can be seen in Figure 2.7. The front end takes the source code and performs lexical, syntactical, and semantic analysis [3], translating the program into an *intermediate code*. Control and data flow analysis is then performed, providing the information required to apply machine-independent and machine-dependent *optimization* techniques [7]. Parallelism among instructions can be represented by a data dependence graph, which is used by sophisticated code scheduling techniques. Finally, the code generator produces the object code for the target architecture. Optimization techniques can interact with each other, so the order in which they are performed can change significantly the final effect. For this reason, compiler implementations employing the same optimizations can adopt a distinct *phase ordering*.

#### 2.4.1.1 Dependence analysis

Optimizing compilers rely most heavily in a technique called dependence analysis [8]. A dependence is a relationship between two computations that places constraints on their execution order. Dependence analysis is used to determine whether a particular program transformation can be applied without changing the program behaviour.

Deciding which operations can execute in parallel requires knowledge about which operations must follow other ones. A dependence exists between two operations if interchanging their order changes the results. In the following examples we assume that executing  $Op_1$  before  $Op_2$  ensures the correct semantics. Dependence analysis can be used to verify whether that ordering can be changed.

Figure 2.7: Phases of an optimizing VLIW compiler

Dependences can be one of two types: data dependence and control dependence [8]. Data dependences can be further subdivided into three types:

• True dependence: It is said that  $Op_2$  has a true dependence on  $Op_1$  if  $Op_1$  writes a variable that is read by  $Op_2$ . In the following example the dependence exists because of  $R_1$ , which must be calculated  $(Op_1)$  before it is used  $(Op_2)$ . True dependences are due to the program semantics, imposing a serialization in the program execution. However, a technique called data value speculation may avoid this constraint by predicting the values that flow among data dependent instructions [60, 38].

$Op_1: \qquad \mathbf{R_1} = R_2 * 4$

$Op_2: R_3 = \mathbf{R_1} + 5$

• Antidependence: It is said that  $Op_2$  has a antidependence on  $Op_1$  if  $Op_2$  writes a variable that is read by  $Op_1$ . This example shows an antidependence because of  $R_5$ , which must be read  $(Op_1)$  before it is written over  $(Op_2)$ . This dependence can be avoided if  $Op_1$  and  $Op_2$  use two distinct memory locations for  $R_5$ .

$$Op_1: R_4 = R_5 - 1$$

$Op_2: R_5 = R_6 * 2$

• Output dependence: An output dependence refers to two operations  $Op_1$  and  $Op_2$  writing the same variable. The example shows two instructions using the same variable  $(R_7)$ , to store the result of both computations. Output dependences can also be avoided using distinct memory locations.

$$Op_1: R_7 = R_8 + 1$$

$Op_2: R_7 = R_9 - 3$

Scalar variable references explicitly refer to a name, with each statement being executed at most once. This simplifies the dependence analysis process. In loops each statement may be executed many times, thus a more elaborated dependence analysis is required. Dependences between operations from the same iteration are called *intra-iteration* dependences. Other complex dependences may be found in loop structures:

• Loop-carried dependence: They occur between operations from distinct iterations. If on a given iteration i the loop refers to an element with index i-k, the dependence distance is said to be k. The following example shows a simple loop without any dependence within a single iteration. However there is a dependence between two iterations:  $Op_2$  reads a variable (A[i-2]) written by  $Op_1$  from the second previous iteration. In this case the dependence distance is said to be 2.

Do i=1, 100

$$Op_1: A[i] = C[i] + 1$$

$$Op_2: B[i] = A[i-2] - 5$$

• Recurrence. This is a particular form of loop-carried dependence. It occurs when a variable is defined based on the value of that variable in an earlier iteration. The following example shows a recurrence with distance 1. In this case  $Op_1$  reads a variable produced by itself one iteration before.

Do i=1, 100

$$Op_1: A[i] = A[i-1] + 5$$

The last type of dependence described refers to the program control flow:

• Control dependence: This type of dependence occurs when a given  $Op_1$  determines whether  $Op_2$  should be executed or not. A typical example of a control dependence is the conditional construct if, as the following example shows. Control dependences also impose a serialization in the program execution, which may be avoided with branch prediction schemes [45].

$$Op_1:$$

if  $(R_{10}=5)$

$Op_2:$  then  $R_{11}=R_{12}$

Control dependences can be converted into data dependences, using a transformation called if-conversion [4]. If-conversion can be applied by using predicated instructions. In this case, an instruction is executed only if the value of a third operand is equal to zero. A predicated instruction (in pseudo-assembly) for the above example is shown below. The instruction copies the contents of register  $R_{11}$  into  $R_{12}$ , according to the value of  $R_{40}$ .

CMOVZ

$$R_{11}$$

,  $R_{12}$ ,  $R_{40}$

#### 2.4.1.2 Optimizations

Optimizing a program often requires some sort of *transformation*, which may involve inclusion, elimination, and reordering of instructions. A compiler must perform three steps to apply an optimization [7]:

- Decide the region of a program to apply a given optimization.

- Verify that the required transformation does not change the program semantics.

- Transform the program.

Optimizations can be classified into machine-independent and machine-dependent. They can be further classified into local (within a single basic block) and global (across basic blocks). A basic block is a sequence of instructions with no branches into or out of the block, apart from the entry and exit boundaries. The goals

of these optimizations are to improve the execution speed and reduce the size of program. For ILP machines they can also increase the amount of parallelism to be exploited by the scheduler. Some of the most common machine-independent optimizations [67] are:

- Constant propagation

- Forward/Backward copy propagation

- Memory copy propagation

- Arithmetic common subexpression elimination

- Redundant load/store elimination

- Dead code removal

Loop structures can be the most significant factor affecting the total execution time for many classes of applications [59]. This has motivated the development of several loop-oriented optimizations [7]. Some of them are machine-independent, capable of reducing loop overhead, improving register usage and data cache locality, among other features. A few of them are listed below:

- Invariant code removal

- Global variable migration

- Induction variable strength reduction

- Induction variable elimination

Machine-dependent optimizations take into account hardware resources of the target machine to make program transformations to further expose parallelism and exploit efficiently machine resources. The following are included among these optimizations:

- Static branch predication

- Speculative Execution

- Loop unrolling

- Loop interchange

- Loop distribution

- Software pipelining

### 2.4.2 VLIW Scheduling

Scheduling algorithms can be classified into three types [84], according to the control flow graph of the region being scheduled:

- Local scheduling

- Global acyclic scheduling

- Global cyclic scheduling

#### 2.4.2.1 Local scheduling

This class of algorithms work with a single basic block at a time. A number of efficient techniques have been proposed to schedule basic blocks. One of the most popular is list scheduling [2], a scheme that schedule operations according to a given priority list, such as highest-level-first. However, local schedulers have a fundamental problem that prevents them from being used effectively with ILP machines: the size of a basic block. Several studies have confirmed that on average the size of a basic block ranges between 5-20 operations, limiting the possibilities of parallelism exploitation. It has been found that limiting parallelism extraction to a single basic block would yield a maximum speedup between two and four [94, 59], an unacceptable limitation for wide-issue VLIW machines. For this reason high performance can only be achieved if ILP is exploited across multiple basic blocks.

#### 2.4.2.2 Global Acyclic Scheduling

Global scheduling operates on multiple basic blocks simultaneously, identifying windows of operations to be scheduled. A window is typically composed by entire procedures or regions from a procedure [86]. Global acyclic scheduling selects regions with no back edges in the control flow, a structure typically found in loops. Doing so they target mainly the loop-free stretches of code prevalent in many general purpose programs. Possibly the most well known algorithm of this class is trace scheduling [32]. A trace scheduler selects regions of code that could be taken according to the output of branch operations. These regions are then scheduled as if they were a single basic block. The larger the size of a region the better the possibilities of finding parallelism. However there is an implicit trade-off: a large region requires a long compilation time, and may also result in inefficient schedules due to wrong paths speculatively taken. Traces are scheduled according to their execution frequency, which can be determined using profile

information or static branch prediction. The scheduler attempts to optimize the execution time of frequently executed traces, at the expense of the least frequent ones. The insertion of compensation code might be necessary in order to correct the outcome of wrongly executed paths. That may generate excessive code replication, resulting in code size explosion. A detailed implementation of this algorithm can be found in [22].

Superblock Scheduling is an algorithm derived from trace scheduling [49]. A superblock is a trace without control entries into it, except at the top, although it still allows intermediate exit points. Intermediate entry points are eliminated using tail duplication, a technique that creates a copy of the trace below the entry point, redirecting the control path to it if necessary. Each trace in a superblock is scheduled using list scheduling.

Hyperblock Scheduling also create structures with a single entry at the top, and possibly multiple exits [68]. The control flow is if-converted [4] to remove control dependences, resulting in a code with a single entry point and multiple exits. Then list scheduling is performed, followed by reverse if-conversion. The later may result in code size explosion, as portions of the schedule in which m predicates are active yield  $2^m$  versions of the code.

### 2.4.2.3 Global cyclic scheduling

Algorithms of this type use basic blocks taken from multiple iterations of a loop structure. Efficient schemes have been proposed to perform cyclic scheduling of numeric applications, as most of their execution time is often spent executing loops. Trace scheduling [32] can also be used to schedule loops. In this scheme back edges in the loop control flow graph are eliminated by performing loop unrolling [20] of the loop body. Although effective, this strategy can generate code size explosion, and also inefficient processing at the start and end points of each series of unrolled iterations. Other acyclic scheduling algorithms can also be used in a similar way, however they also show this limitation.

A scheme specially developed to schedule loop structures for ILP machines is software pipelining [16]. The concept is similar to a hardware pipeline: successive iterations start before previous ones have completed. This is possible because the execution of operations from distinct loop iterations is overlapped, taking advantage of the available hardware parallelism. Software pipelining algorithms have to deal with machine resource constraints and data dependences among operations in the loop body. In this context, generating optimal schedules of loops with arbitrary data dependence graphs is known to be a NP-complete problem [54].

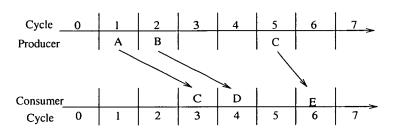

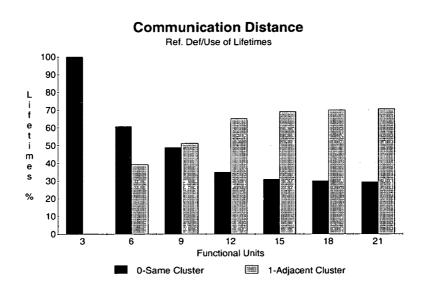

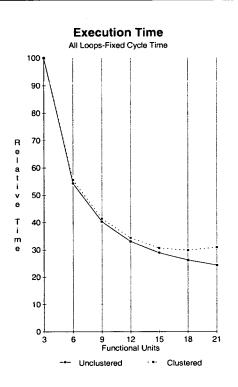

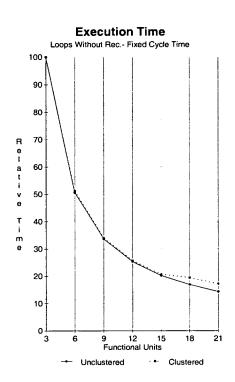

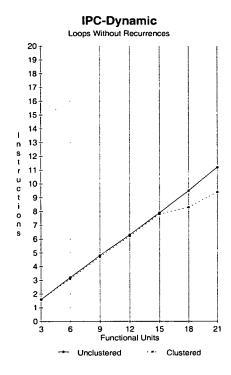

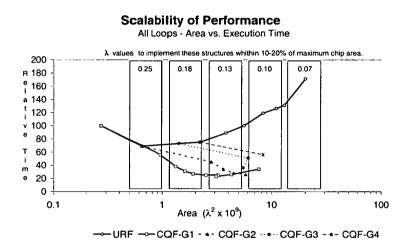

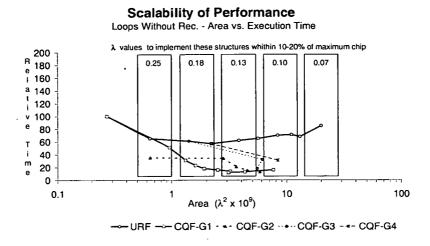

Optimal schedules can be generated using integer linear programming, a technique that employs precise definitions of objectives and constraints of the schedule. Some techniques assume the use of unlimited machine resources [35]. Others are realistic enough to model resource constraints and minimize register requirements [39]. Although very effective to find the best possible schedule, the complexity of methods based on integer linear programming prevent them from being used in production compilers. However, they can be a valuable tool to evaluate the effectiveness of other approaches.