# SCHOOL OF INFORMATICS EDINBURGH UNIVERSITY

# PhD Thesis

# **Increasing the Efficacy of Automated Instruction Set Extension**

Author:

Richard Vincent BENNETT

Supervisor: Prof. Nigel TOPHAM

Secondary Supervisor: Dr. Björn Franke

#### **Abstract**

The use of Instruction Set Extension (ISE) in customising embedded processors for a specific application has been studied extensively in recent years. The addition of a set of complex arithmetic instructions to a baseline core has proven to be a cost-effective means of meeting design performance requirements. This thesis proposes and evaluates a reconfigurable ISE implementation called "Configurable Flow Accelerators" (CFAs), a number of refinements to an existing Automated ISE (AISE) algorithm called "ISEGEN", and the effects of source form on AISE.

The CFA is demonstrated repeatedly to be a cost-effective design for ISE implementation. A temporal partitioning algorithm called "staggering" is proposed and demonstrated on average to reduce the area of CFA implementation by 37% for only an 8% reduction in acceleration.

This thesis then turns to concerns within the ISEGEN AISE algorithm. A methodology for finding a good static heuristic weighting vector for ISEGEN is proposed and demonstrated. Up to 100% of merit is shown to be lost or gained through the choice of vector. ISEGEN early-termination is introduced and shown to improve the runtime of the algorithm by up to 7.26x, and 5.82x on average. An extension to the ISEGEN heuristic to account for pipelining is proposed and evaluated, increasing acceleration by up to an additional 1.5x. An energy-aware heuristic is added to ISEGEN, which reduces the energy used by a CFA implementation of a set of ISEs by an average of 1.6x, up to 3.6x. This result directly contradicts the frequently espoused notion that "bigger is better" in ISE.

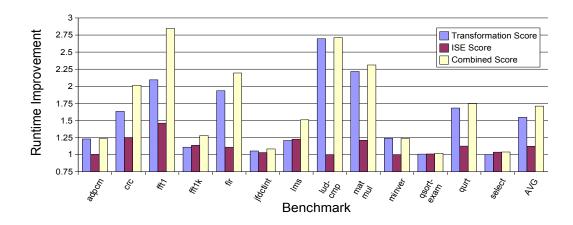

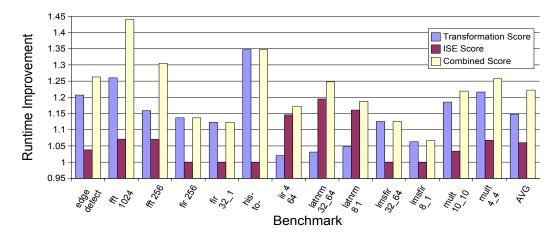

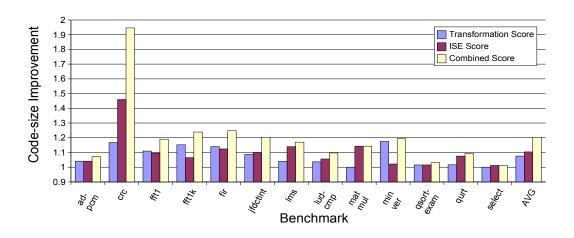

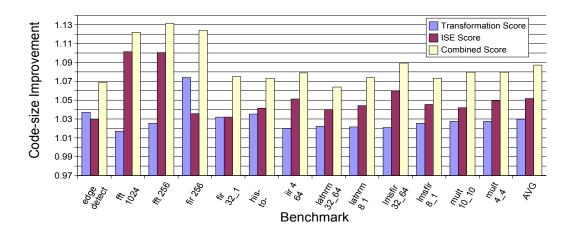

The last stretch of work in this thesis is concerned with source-level transformation: the effect of changing the representation of the application on the quality of the combined hardware-software solution. A methodology for combined exploration of source transformation and ISE is presented, and demonstrated to improve the acceleration of the result by an average of 35% versus ISE alone. Floating point is demonstrated to perform worse than fixed point, for all design concerns and applications studied here, regardless of ISEs employed.

# Acknowledgements

Special thanks is given to the following people:

"A master can tell you what he expects of you. A teacher, though, awakens your own expectations."

#### - Patricia Neal

Nigel Topham; for the opportunities, understanding, and sage advice.

Björn Franke; for front-line support, patience, and keen insight.

Without both of your help I would not have been able to navigate the strange world of academic computer science.

"I love being married. It's so great to find that one special person you want to annoy for the rest of your life."

# - Rita Rudner

To Kate Weaver-Bennett; for making me whole.

"A scientist's aim in a discussion with his colleagues is not to persuade, but to clarify."

#### - Leo Szilard

Oscar Almer, Igor Böhm, Christophe Dubach, Salman Khan, Stephen Kyle, Hugh Leather, Alastair Murray, Mike O'Boyle, Freddie Qu, Chris Thompson, George Tournavatis, and Marcela Zuluaga; for providing countless hours of productive discussion, countless further hours of unproductive discussion, and travelling companionship across the world.

"You are the bows from which your children as living arrows are sent forth."

# - Kahlil Gibran

Paul and Wendy Bennett; for getting me as far as you did, and many words of encouragement. Patricia Curtis and Brian Weaver; for raising your daughter, and for providing a level of support that astounds me on a daily basis.

"A good friend is a connection to life - a tie to the past, a road to the future, the key to sanity in a totally insane world."

#### -Lois Wyse

Luke Bennett, Gemma Bennett, Thomas James, Jonathan Gray, Tom Feist, Charles Leahy, Thomas Haddow, James Hanlon, Alexandra Nagy, Douglas Llewellyn, Barbara Hind, John Turner, Rachel McKerrow, Eugene Hopkinson, Andreas Learch, David Weigl, James Addison, Courtney Fox, Matthew Mossman, Ryan Barton, Erin Roherty, Taylor Seymour, Colin McEwan, Adam Lion, Jim Rutherford, Glynn Weaver, Amanda Weaver, and countless others.

This thesis is dedicated to the memories of Colin Bennett and Alan Smith

# **Declaration**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified. The following work with which this thesis shares content was published:

- R.V. Bennett, A.C. Murray, B. Franke, and N. Topham "Combining source-to-source transformations and processor instruction set extension for the automated design-space exploration of embedded systems". In: *Proceedings of Languages Compilers and Tech*nology for Embedded Systems (LCTES), 2007.

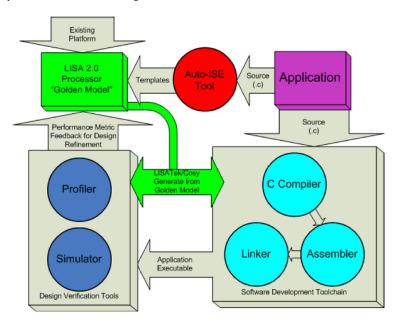

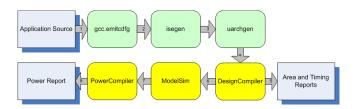

- O. Almer, R.V. Bennett, I. Böhm, A.C. Murray, X. Qu, M. Zuluaga, B. Franke and N.P. Topham "An End-to-End Design Flow for Automated Instruction Set Extension and Complex Instruction Selection based on GCC". In: *Proceedings of the 1st International Workshop on GCC Research Opportunities (GROW)*, 2009.

(D. )

(Richard Vincent Bennett)

# **Document Conventions**

Throughout the text of this document, the use of the following terms and abbreviations are made use of in an effort to increase its accuracy and clarity.

- AISE Automated Instruction Set Extension.

- ASIC Application Specific Integrated Circuit.

- ASIP Application Specific Instruction-set Processor.

- CCA Configurable Compute Accelerator.

- CFA Configurable Flow Accelerator.

- CDFG Control and Data Flow Graph.

- DFG Data Flow Graph.

- DII Data Initiation Interval (issue latency).

- DSE Design Space Exploration.

- FPGA Field Programmable Gate Array.

- ILP Integer Linear Programming.

- ISA Instruction Set Architecture.

- ISE Instruction Set Extension.

- LUT Look Up Table.

- NoC Network On Chip

- OLP Operator Level Parallelism (sometimes referred to as Instruction Level Parallelism in other works, but herein we refer to the phenomenon at a higher level in the IR).

- ML Machine Learning.

- RFU Reconfigurable Functional Unit.

- SoC System On Chip

The meaning of some of these terms is expanded in the text of the document where appropriate.

# **CONTENTS**

| 1              | Intr | roduction               |                                     |    |  |

|----------------|------|-------------------------|-------------------------------------|----|--|

|                | 1.1  | Instruc                 | ction Set Extension                 | 3  |  |

|                | 1.2  | The Pr                  | oblem                               | 4  |  |

|                |      | 1.2.1                   | Engineering Time                    | 4  |  |

|                |      | 1.2.2                   | Acceleration                        | 5  |  |

|                |      | 1.2.3                   | Area                                | 6  |  |

|                |      | 1.2.4                   | Energy                              | 7  |  |

|                | 1.3  | Contri                  | butions                             | 8  |  |

|                | 1.4  | Docum                   | nent Structure                      | 11 |  |

|                | 1.5  | Summ                    | ary                                 | 11 |  |

| 2              | Bacl | kground                 | 1                                   | 14 |  |

|                | 2.1  | Embed                   | Ided Processors                     | 14 |  |

|                |      | 2.1.1                   | Extensible Processors               | 15 |  |

|                |      | 2.1.2                   | Reconfigurable Processors           | 16 |  |

|                | 2.2  | Design                  | Space Exploration                   | 17 |  |

|                | 2.3  | Instruc                 | etion Set Extension                 | 18 |  |

|                |      | 2.3.1                   | Abstract Problem Definition         | 19 |  |

|                |      | 2.3.2                   | The Software Emulation Fallacy      | 20 |  |

|                |      | 2.3.3                   | Separation of Concerns              | 21 |  |

|                |      | 2.3.4                   | Amdahl Limit                        | 23 |  |

|                |      | 2.3.5                   | Micro-architecture                  | 23 |  |

|                |      | 2.3.6                   | ISE Example                         | 27 |  |

|                | 2.4  | 2.4 Automated Synthesis |                                     |    |  |

|                |      | 2.4.1                   | Automated Instruction Set Extension | 29 |  |

|                |      | 2.4.2                   | ISEGEN Algorithm                    | 31 |  |

|                |      | 2.4.3                   | HDL Synthesis and Analysis          | 36 |  |

|                | 2.5  | Resour                  | rce Sharing                         | 37 |  |

|                | 2.6  | Compi                   | ler Transformations                 | 38 |  |

|                | 2.7  | 7 Summary               |                                     |    |  |

| 3 Related Work |      |                         | rk                                  | 41 |  |

|                | 3.1  |                         |                                     |    |  |

|                |      | 3.1.1                   | Verilog                             | 41 |  |

|                |      | 212                     | VIDI                                | 42 |  |

|     | 3.1.3  | SystemC                                                     | 43 |

|-----|--------|-------------------------------------------------------------|----|

|     | 3.1.4  | SA-C                                                        | 44 |

|     | 3.1.5  | Handel-C                                                    | 45 |

|     | 3.1.6  | ROCCC                                                       | 46 |

|     | 3.1.7  | SPARK                                                       | 47 |

|     | 3.1.8  | DWARV                                                       | 47 |

|     | 3.1.9  | LISA                                                        | 48 |

|     | 3.1.10 | MESCAL                                                      | 49 |

|     | 3.1.11 | Lime & Liquid Metal                                         | 50 |

|     | 3.1.12 | Trimaran                                                    | 51 |

|     | 3.1.13 | Other Languages and Frameworks                              | 52 |

| 3.2 | Autom  | ated Instruction Set Extension                              | 53 |

|     | 3.2.1  | Linear-Complexity MISO Identification                       | 53 |

|     | 3.2.2  | Linear-Complexity MIMO Identification                       | 54 |

|     | 3.2.3  | Integer-Linear Programming Methodology                      | 55 |

|     | 3.2.4  | Fast Clustering AISE Algorithm                              | 56 |

|     | 3.2.5  | Polynomial-Complexity Identification and Selection          | 57 |

|     | 3.2.6  | Tensilica XPRES                                             | 58 |

|     | 3.2.7  | Other Algorithms                                            | 59 |

| 3.3 | Microa | architectural Solutions                                     | 62 |

|     | 3.3.1  | Field Programmable Gate Arrays                              | 62 |

|     | 3.3.2  | MOLEN                                                       | 63 |

|     | 3.3.3  | Custard                                                     | 64 |

|     | 3.3.4  | ADRES                                                       | 65 |

|     | 3.3.5  | Annabelle and Montium: Chameleon                            | 65 |

|     | 3.3.6  | QuickSilver Adaptive Computing Machine                      | 66 |

|     | 3.3.7  | XTENSA                                                      | 67 |

|     | 3.3.8  | Stretch                                                     | 69 |

|     | 3.3.9  | Other Microarchitectures                                    | 70 |

| 3.4 | This W | Vork In Context                                             | 70 |

|     | 3.4.1  | The Need For Predictable Microarchitecture Cost and Benefit | 71 |

|     | 3.4.2  | Reducing Engineering Time                                   | 71 |

|     | 3.4.3  | Reducing Area                                               | 72 |

|     | 3.4.4  | Improving Acceleration                                      | 72 |

|     | 3.4.5  | Reducing Energy Requirements                                | 73 |

|     | 3.4.6  | Software and Hardware: Chicken and Egg                      | 73 |

| 3.5 | Summa  | ary                                                         | 74 |

| 4 | The  | Real W   | orld: Enabling and Optimising Hardware Synthesis                  | <b>76</b> |

|---|------|----------|-------------------------------------------------------------------|-----------|

|   | 4.1  | Introdu  | ction                                                             | . 76      |

|   | 4.2  | Configu  | urable Flow Accelerators                                          | . 78      |

|   |      | 4.2.1    | Introducing the CFA                                               | . 78      |

|   |      | 4.2.2    | CFA Design Space Exploration Methodology                          | . 83      |

|   |      | 4.2.3    | Analysis of the Efficacy of CFA                                   | . 86      |

|   |      | 4.2.4    | Conclusions                                                       | . 93      |

|   | 4.3  | CFA St   | aggering Methodology                                              | . 94      |

|   |      | 4.3.1    | Trading off Space for Time                                        | . 94      |

|   |      | 4.3.2    | Comparison to Other Techniques                                    | . 96      |

|   |      | 4.3.3    | Determining the Efficacy of Staggering                            | . 98      |

|   |      | 4.3.4    | Evaluation of Staggering Efficacy                                 | . 99      |

|   |      | 4.3.5    | Conclusions                                                       | . 104     |

|   | 4.4  | Summa    | ury                                                               | . 105     |

| 5 | Brid | ging the | e Gap: Improving ISE Identification                               | 107       |

|   | 5.1  | Introdu  | ction                                                             | . 107     |

|   | 5.2  | ISEGE    | N Heuristic Weighting Analysis                                    | . 109     |

|   |      | 5.2.1    | The ISEGEN Heuristic Weighting Vector                             | . 109     |

|   |      | 5.2.2    | Weighting Vector Space Exploration Methodology                    | . 110     |

|   |      | 5.2.3    | Evaluation: Analysis of Parameter Space                           | . 112     |

|   |      | 5.2.4    | Conclusions                                                       | . 121     |

|   | 5.3  | Search   | Early Termination                                                 | . 122     |

|   |      | 5.3.1    | Faster ISE Analysis Through Shortcuts                             | . 122     |

|   |      | 5.3.2    | Validation and Evaluation of Early Termination Approach           | . 125     |

|   |      | 5.3.3    | Evaluation of Validatory Results                                  | . 127     |

|   |      | 5.3.4    | Conclusions                                                       | . 134     |

|   | 5.4  | Pipelin  | e Aware Identification                                            | . 135     |

|   |      | 5.4.1    | When Serial is also Parallel                                      | . 135     |

|   |      | 5.4.2    | Pipeline Model and Scheduling Heuristic                           | . 137     |

|   |      | 5.4.3    | Determining the Efficacy of the Pipelining Heuristic              | . 138     |

|   |      | 5.4.4    | Pipeline Heuristic Results and Evaluation                         | . 140     |

|   |      | 5.4.5    | Conclusions                                                       | . 153     |

|   | 5.5  | Energy   | Aware Identification                                              | . 155     |

|   |      | 5.5.1    | Better Value ISE: Making ISEGEN Optimise for Energy               | . 155     |

|   |      | 5.5.2    | Determining the Efficacy of the CFA Energy Optimisation Heuristic | . 156     |

|   |      | 5.5.3    | Energy Heuristic Results and Evaluation                           | . 157     |

|   |      | 554      | Conclusions                                                       | 167       |

|    | 5.6         | Summ                            | ary                                                  | . 169 |  |  |

|----|-------------|---------------------------------|------------------------------------------------------|-------|--|--|

| 6  | Fori        | n Over                          | Function: Source Transformation                      | 171   |  |  |

|    | 6.1         | Introdu                         | uction                                               | . 171 |  |  |

|    | 6.2         | 6.2 Transform Space Exploration |                                                      |       |  |  |

|    |             | 6.2.1                           | The Need for Source-to-Source Transformations in ISE | . 173 |  |  |

|    |             | 6.2.2                           | Transform Space Exploration Methodology              | . 175 |  |  |

|    |             | 6.2.3                           | Evaluation                                           | . 181 |  |  |

|    |             | 6.2.4                           | Conclusions                                          | . 192 |  |  |

|    | 6.3         | Floatir                         | ng versus Fixed Point                                | . 193 |  |  |

|    |             | 6.3.1                           | Introduction                                         | . 193 |  |  |

|    |             | 6.3.2                           | Methodology                                          | . 194 |  |  |

|    |             | 6.3.3                           | Evaluation                                           | . 195 |  |  |

|    |             | 6.3.4                           | Conclusions                                          | . 215 |  |  |

|    | 6.4         | Summ                            | ary                                                  | . 216 |  |  |

| 7  | Conclusions |                                 |                                                      |       |  |  |

|    | 7.1         | Contri                          | butions                                              | . 217 |  |  |

|    | 7.2         | EnCor                           | e and CFA integrated: Castle                         | . 220 |  |  |

|    | 7.3         | Furthe                          | r Work                                               | . 221 |  |  |

| Bi | bliogi      | aphy                            |                                                      | 225   |  |  |

# 1 Introduction

"The last thing one knows in constructing a work is what to put first."

#### - Blaise Pascal

We are now living in the Information Age, where those who cooperate with the legion of digital information services can improve both productivity and quality of life. There is a trend towards increasingly more personalised management and delivery of information. The markets have concluded the only logical outcome of this trend is the development of more ubiquitous and faster embedded computing. Moving away from the "Desktop Model" created by such companies as Microsoft, IBM, and Intel has begun to dominate the microelectronics market. The struggle between high performance and low cost will continue for the foreseeable future, and will only be mitigated with the introduction of new, more cost-effective design innovation and automation.

The progression of commercially adopted computer architecture has always been largely guided by two factors:

- The productivity of the applications programmer.

- The maximum throughput or speed of execution obtainable.

The maximisation of both of these factors is the principle concern, as they govern two critical financial concerns to stakeholders in application development, namely:

- The cost of developing the application.

- The size and quality or domain of applications which may be developed; hence the markets which may be exposed and exploited by application development.

Computers exist solely for the purpose of the applications which run on them. Such applications were originally written directly in the machine code, and later the assembly languages of the machines which they ran on. This small addition of mnemonics as assembly language was a small luxury afforded by the feasibility of creating assemblers, the possibility itself created by advances in the hardware architecture. This was the first iteration of the evolutionary cycle, wherein we connected streams of ones and zeroes to Hindu-Arabic numerals and letters in the Roman alphabet.

Next came compilers, and the ensuing language debate. Whilst the issue of which language to use in software design is far from resolved, at least in our particular branch of this story there is a clear winner in terms of tried and tested efficacy; the imperative language C. Imperative programming in general has several advantages over other language paradigms from a practical point of view, for example:

- Imperative programming lends itself to natural, object-oriented, behavioural descriptions.

- Imperative programming is readily mapped to RISC execution, which are essentially imperative execution engines.

For these reasons and more, the majority of compiler research efforts at present focus on objectoriented and/or imperative languages such as C, C++, and Java. As the hardware which runs a compiler evolves, the ability to map from our high level languages to complex computer systems grows also.

The success of RISC is largely as a product of the increase in compiler design complexity and the decrease in memory cost, allowing the necessary fine grain control. Further along the explicit control axis, one finds architectures such as VLIW. With VLIW more effort must be put into code quality and scheduling in order to obtain greater performance (speed) for less cost (power, die area) [1]. Around the time that VLIW architectures were being commercialised, the idea of Hardware/Software co-design [2] came to light as a good engineering formulation, when designing embedded systems with performance constraints. Design becomes a process of mapping between the hard and soft elements of the system; allocating hardware resources where performance is critical, and software otherwise especially where flexibility is required.

During the 1990's there was a move towards electronic system design, utilising a degree of design automation in order to perform tasks which were becoming less and less tractable to human engineers due to their sheer size and complexity. The Verilog language became the industry standard for ASIC design specification and verification, largely as a product of its support for fast simulation of a design which allowed for engineers to test their designs before they were committed to silicon. More importantly, the language was able to be directly synthesised, meaning that a single description of an ASIC could be used throughout the design process. From this basis comes the idea of an iterative process of design, whereby the concerns of a design are worked in from the top level of abstraction (the system level view) down to the bottom (silicon layout, i.e. GDS-II). This is achieved through compiling a language such as Verilog down to a lower level of abstraction, then examining what further efforts are needed to make the design meet the more complex requirements of the lower levels of abstraction.

The previous GPP stage of evolution has failed in recent years; we are unable to arbitrarily increase clock speed, and so we must map more hardware instead. General purpose execution has very much taken the high(-level) road, in that it looks to byte-code languages such as Java, and C#, choosing C or C++ only when performance is absolutely critical. This constant raising of the abstraction level makes an efficient mapping to thread-level parallelism more readily accessible to programmers, but is expensive. Over-specification in the multi-core dimension is both costly and hard to program. Methods such as clock gating [3] have been proposed to help reduce the problem in terms of power and energy efficiency, but these do nothing to address

the ever increasing GPP real-estate.

It is as of yet unclear whether the multi-core trend will ultimately be the saviour of GPP. The big players like AMD and Intel are embracing the multi-core idea, putting more and more cores on a chip in an attempt to exploit the available silicon. One fact remains that prevent GPPs from gaining extensive foothold in the embedded domain: their performance is extremely expensive in terms of both power and die area.

The techniques and skill that have gone into GPP design have been both forward-looking and effective in achieving their goal: performance at whatever cost. The trend towards low power, limited function, mobile devices does require a rethink of this entire methodology. Suddenly engineers are presented with a very concrete limit to the amount of silicon and energy that may be used. The situation is now that for the specific functions of a mobile device the execution speed is expected to be at least equal to GPP. Audio and video decoding, encryption, rendering in both 2D and 3D, and automated control purposes are all good examples of domains which are driving the need for faster, cheaper embedded processing.

The focus of this thesis is therefore that of embedded applications hardware-software codesign, that having been one basic remit of ICSA for the last nine years. The inclusion of the compiler into the hardware-software co-design process has brought about a new way of thinking about architectural design; that of using an application to guide the design process automatically based on features and structures used in its execution. This design methodology is now introduced in more depth in the following section.

#### 1.1 Instruction Set Extension

Many methodologies for hardware-software co-design will include Instruction Set Extension (ISE) as a core component of their design space [4]. ISE is a technique for processor customisation wherein the architecture (and often also the microarchitecture) are extended specifically with the computing requirements of the application software in mind. The architectures used with ISE are most often Reduced Instruction Set Computers (RISC), and hence the complexity of the instructions in the baseline core will be low, maintaining the generality of the instruction set in question. Low-complexity RISC-style instructions are also generally not the most efficient way of executing a given application, and so additional instructions (ISEs) will be added to this baseline in order to provide a better fit between the application in question, and the target architecture. ISE design introduces a dependency between the software and the hardware, requiring that the application software or at least its critical kernels be somewhat stable before hardware design gets underway. More stability is generally required with larger ISEs; smaller ISEs can be retargeted more readily due to lower complexity. This is generally at odds with the "old-fashioned" embedded application development methodology, wherein a prefabricated target architecture would be selected on the basis of much more high-level specifications, such

as the potential for executing DSP or control-flow dominated algorithms well. ISEs are generally far more specific than this, although the selection of a suitable prefabricated baseline is still important. ISEs require fine-grain structural design decisions in order to properly exploit their potential. A number of algorithms have been created in order to identify ISEs automatically based on the source code of an application, handling the fine-grain decisions by way of heuristic merit functions. These algorithms have enabled the rapid construction of ISEs for a particular application, putting the problem into computational costs rather than engineering. Both AMD and Intel have recently produced ISEs in the form of XOP [5] and AVX [6] respectively, demonstrating the relevance of application-specific instructions even with GPPs. These GPP ISEs are not as complex as those considered for ASIPs, and focus more on vectorising common complex operations than creating instructions with a single purpose. In this thesis ISE is examined relative to low-complexity baseline RISC architectures.

### 1.2 The Problem

The major concern with using ISE when constructing a combined hardware-software design is that of the speed and quality of the design work that can be achieved. The major challenge for increasing the efficacy of ISE is to:

- Reduce the time taken to produce a working system (architecture, microarchitecture, and tool-chain) through design automation.

- Increase the quality (lower area, lower energy, higher acceleration) of the specialised system.

At the time of writing this thesis, there are still engineers employed at companies such as ARM and ST Microelectronics who perform application-specific ISE design on a manual basis. The manual approach represents the slowest but highest-quality trade-off in engineering cost versus design quality. Automated synthesis of ISEs including identification, implementation, and exploitation is an extremely important avenue of research, to reduce the manual effort and hence engineering cost of utilising the technique. It is the central goal of AISE research to increase the efficacy of the methodology until it equals, and eventually surpasses that possible by manual design. The following sub-sections give more detail on the concerns in question when considering automatically synthesised ISEs.

# 1.2.1 Engineering Time

The manual effort required in order to include ISEs in a design is considerable, and requires several distinct "deliverables" to be produced in order to be part of a practical design solution:

• The semantics of ISEs including instruction encoding (dependant on the baseline architecture), function (usually a collection of "data-flow" as directed graphs), and assembler

mnemonic syntax.

- An implementation of ISEs as a structural extension to the baseline architecture, usually via a pre-defined extension interface. These must implement the semantics defined above.

- Additional tool-chain support for mapping the application software to the extended hardware, and potentially simulation of the extended hardware for testing & verification.

Time to market constraints often dominate the engineering trade-offs made in the design, with embedded applications requiring a fast turn-around from the conception of the application to the realisation of the device. Automated ISE (AISE) accelerates not only the application in question but the generation of the above deliverables also. This makes AISE especially attractive where the automated process can derive instructions of a suitably high quality with respect to design concerns compared to the manual approach. The major limiting factor to AISE is the tractability of the search problem. In its most naive form the identification problem alone has a search space size of  $2^n$ , where n is the number of operators in the basic block being analysed. This intractability of the search space as a whole gives rise to the need for heuristics and search-space pruning; two methodologies used extensively in AISE algorithms.

### 1.2.2 Acceleration

Acceleration of the application when executing on the extended architecture has for a long time been the principal concern of ISE methodologies, despite it being only one of several design concerns for real-world solutions. The individual ISEs will cover a number of operations that would otherwise have been performed via the baseline RISC instruction set. This in effect packs sets of operators together in a manner which exploits a combination of serial and parallel acceleration. Serial acceleration is possible when two or more operators in sequence have the ceiling of the sum of their latencies less than the sum of the latencies of the RISC instructions required to execute them. Parallel acceleration is the more classical case similar to instruction-level parallelism as considered in VLIW, wherein multiple operators are independent from one-another and have their inputs available in an overlapping time-frame; referred to henceforth as "Operator Level Parallelism" (OLP).

Second-order speedup effects are possible, such as reduction of register pressure and hence spill code due to ISE-internal values being passed by wire, rather than via the register set. ISEs can also be combined with scratch-pad memories, further reducing the pressure on the register file. When taken together, this plethora of potential customisation can lead to a significant acceleration of the application; assuming a suitable portion of the application lies in frequently executed loops which are of a form suitable for ISE mapping.

#### 1.2.3 Area

The process of reducing the area that ISEs utilise has not been neglected by researchers. Whether area is FPGA slices or millimetres of silicon area is an important contributor to the bottom line. Higher silicon area can contribute two-fold to higher monetary costs:

- In silicon the area has a direct price-tag attached per unit consumed, although often there

is a specific limit which engineers are encouraged to get as close to as possible but not

exceed.

- The larger an ASIC design is, the more likely an individual unit is to contain a fabrication flaw which will render that unit useless or lesser-functioned.

Several factors interact to determine the merit of using FPGA instead:

- FPGA implementation is generally a lot more expensive than ASIC when considered in high-volume, as most application-specific designs are.

- Regardless of volume, the size of the hardware design will determine the size of the FPGA required to contain it.

- Baseline processors in FPGA can lead to better baseline performance, but ISEs within a standard LUT FPGA will be of very poor performance.

- Some FPGA units contain a selection of arithmetic units as hard macros, and so fitting the design not only to the area but to the FPGA microarchitecture becomes essential.

ISE in FPGA is generally of lower efficacy than ISE in ASIC standard-cell technology. There is no reason to discount FPGA entirely as industry is making good progress in increasing the number of hard-macros available and the routing hierarchies. This thesis concentrates on silicon implementation, and hence any reference to area is standard cell area, in a commercial 130nm process.

Resource-sharing is absolutely essential to improve the cost-benefit performance of ISE. There are two major scenarios in ISE to exploit through resource sharing: Inter-ISE resource sharing wherein units from one ISE are shared with another, and intra-ISE resource sharing, wherein units are time-multiplexed between temporally separate sections of the ISE. These two methods are henceforth referred to as "spatial" and "temporal" resource sharing. Another area reduction technique, less beneficial but still substantial enough to note is that of replacing units not on the critical path of an ISE with higher latency, lower area equivalents. This is considered here to be more of a concern to developers of products such as DesignWare, than those using them to produce ISEs.

ISE is inherently an *extension* technique and therefore will never reduce the area of the baseline core under extension. However, the design space as seen by application engineers

should include a number of potential baseline cores. ISE could produce a solution which when compared to an equivalently performing (acceleration and energy) general purpose core does have lesser area. This is due to a better fit between the hardware and software, meaning the hardware does not have to use generalised acceleration techniques such as out-of-order execution which can add a large amount of area. Dynamic scheduling hardware is a major contributor to the inefficiencies of GPP.

Regardless of whether area is represented by FPGA cells or silicon area, there will generally be an increase in power consumption for an increase in area. Power consumption alone is generally not of great importance other than ensuring the source is not overloaded by any peak consumption. Power though, is a direct contributor to energy consumption.

# **1.2.4** Energy

When purchasing a mobile device, one of the primary concerns is often the question of how long the battery will last. As mobile devices shrink in size and their functional complexity increases, this inevitably places more and more drain on batteries. The SoC components of a mobile device such as a cell phone is not necessarily the entirety of its energy consumption; analogue components also play a large part in many instances. The SoC components do consume a significant enough proportion to warrant addressing the energy costs of executing an application. In addition, newer techniques such as software radio are placing more and more of the functional burden on the digital elements; this will further push SoC components into the fore in energy considerations.

The scenario is further complicated by developments in process technology tending towards the lower (sub-micron and beyond) nodes, changing the rules of thumb engineers can use when designing circuits. The progress in fabrication makes the problem of balancing energy consumption with other concerns an ever more complex one. The major shift is in the ratio of dynamic versus static power consumption, with dynamic power largely being handled with clock gating and static power requiring ever more audacious techniques to reduce it as it becomes more and more the dominant factor. This thesis largely focuses on the 130nm technology node, and leaves tackling newer process sizes to further work.

ISE can be used in reducing the energy consumption of an ASIP, but the process must be carefully managed so that the ISEs actually benefit rather than reduce the energy performance. If large ISEs are employed, the possibility that they will not lend themselves well to resource sharing is a real concern. Without efficient resource sharing, ISEs can bloat a design and result in a considerably worsened cost-benefit than just selecting a more capable baseline core. The energy cost is one of the concerns which can be worsened by poorly designed or implemented ISEs. In order to improve the efficacy in terms of energy consumption therefore, we need both a microarchitecture capable of efficient resource sharing and an algorithm capable of measuring and manipulating those microarchitectural elements with an impact on energy.

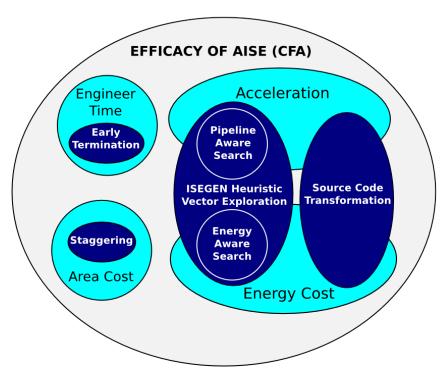

Fig. 1.1: A diagram showing how the different contributions cover the efficacy concerns of AISE. Light blue areas are concerns, and the dark blue areas are the contributions made in this thesis.

#### 1.3 Contributions

The contributions made in this thesis are in several categories spanning the levels of design consideration in a hardware-software co-design.

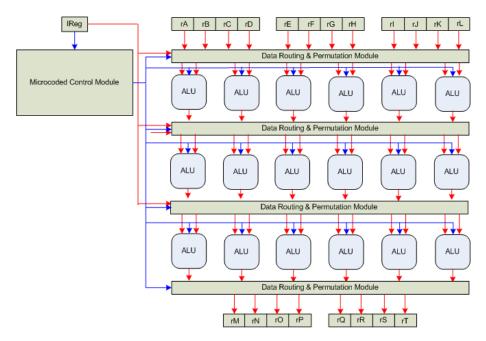

In order to derive the low level performance of a realistic implementation, a microarchitectural solution to ISE dubbed the "Configurable Flow Accelerator" (CFA) is introduced and used as the basis for later exploration and analysis. The properties of this accelerator are explored in order to demonstrate that it is a viable design for implementing ISEs, and to determine the potential for performance improvement across the axes of design concern. *The CFA is demonstrated repeatedly to be a cost-effective design for ISE implementation*.

Introduced alongside the CFA is a process of temporal partitioning dubbed "CFA Staggering", due to its similarities with loop staggering (software pipelining). *Staggering is demonstrated on average to reduce the area of CFA implementation by 37% for only an 8% reduction in acceleration.*

Following the exploration of cost mitigation within the proposed CFA microarchitecture, this work moves to address the issues of identification, in particular determining whether the heuristics used within the ISEGEN algorithm are in fact efficacious in identifying ISEs which are implemented as CFAs. The first effort in this vein is concerned with the original algorithm, and is divorced from the idea of CFAs. There is a weighting vector located at the heart of

the ISEGEN algorithm which has previously been cited [7] as having a single static optimal value. A methodology for finding a good static weighting vector for ISEGEN is proposed and demonstrated. Up to 100% of merit is shown to be lost or gained through the choice of vector. Also demonstrated is that good ISEGEN weighting vectors are application-specific, and that in order to use a single vector across multiple benchmarks a small amount of performance must be lost from some of them. This motivates the use of feature-based dynamic vector selection, although this is not explored in this thesis. A maximally efficacious vector is located for the set of benchmarks and architecture targeted herein, to demonstrate that the vector is different from that given in [7] and to provide a suitably tuned heuristic for later work in this thesis.

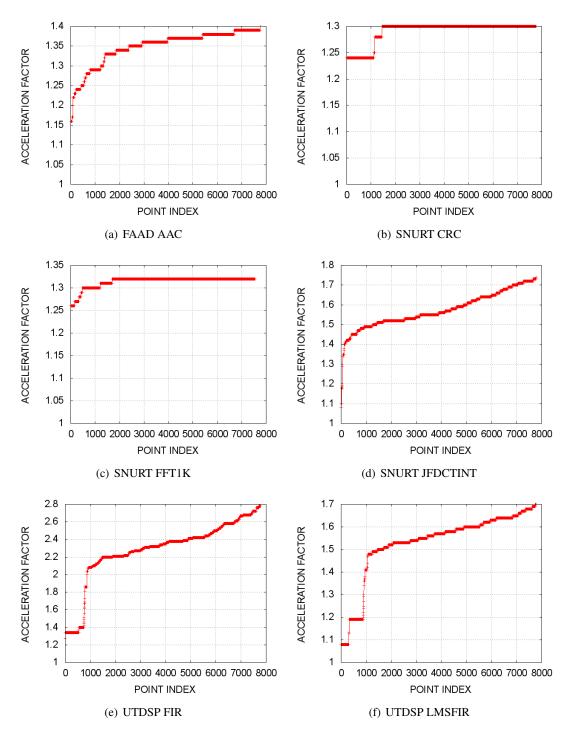

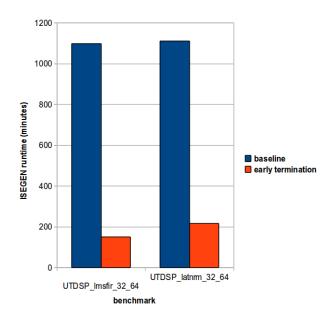

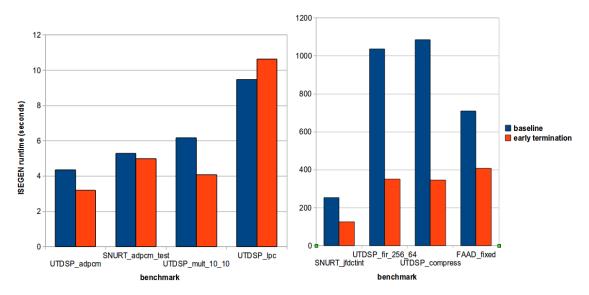

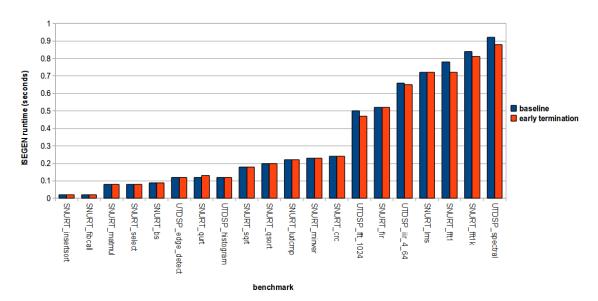

The original ISEGEN algorithm is prone to performing a considerable amount of fruitless search, due to being unaware of when an invalid ISE will converge on a valid solution during the algorithm's execution. This thesis presents an early-termination modification which greatly reduces the ISEGEN algorithm's execution time, especially in the presence of larger graphs where the early termination heuristic is particularly efficacious. *ISEGEN early-termination is shown to improve the runtime of the algorithm by up to 7.26x, and 5.82x on average.* It is shown that whilst there are pathological conditions in which the early termination may reduce the quality of a result, these conditions do not occur in any of the benchmarks tested. This modification of the ISEGEN algorithm contributes to the concerns involving the time of the designer or engineer, as it reduces the amount of time taken for an engineer to evaluate a particular instance of an application's source code for suitable ISEs.

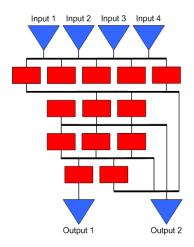

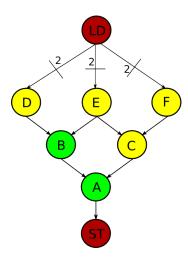

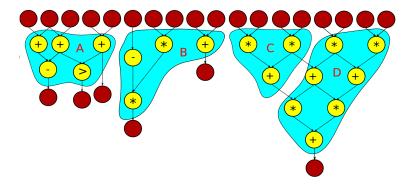

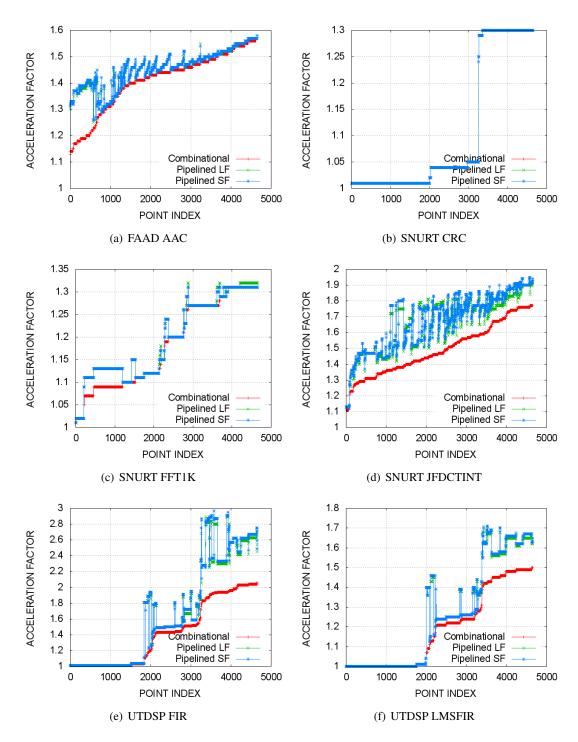

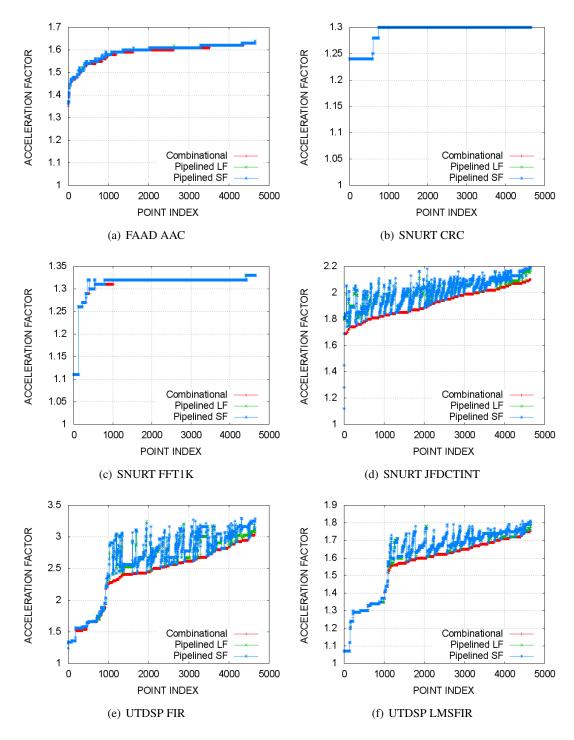

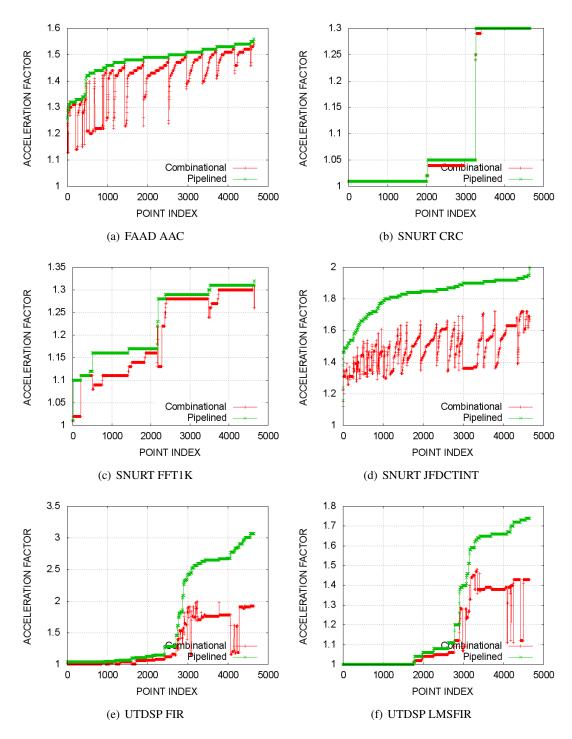

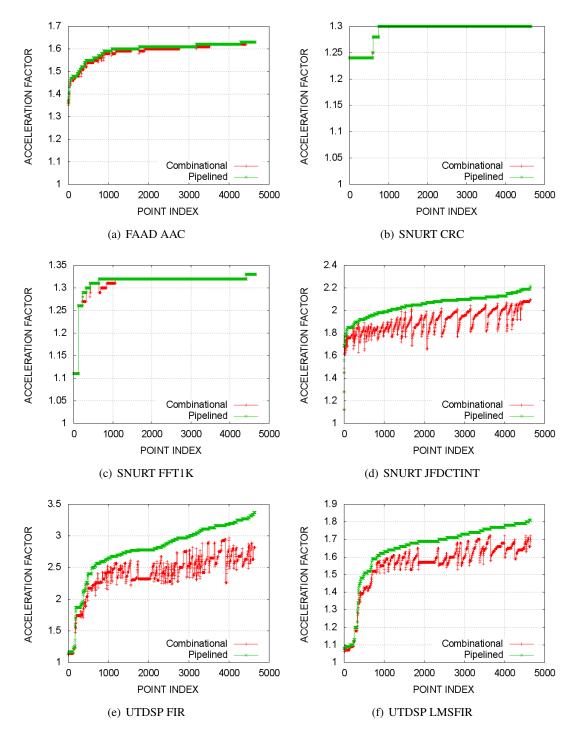

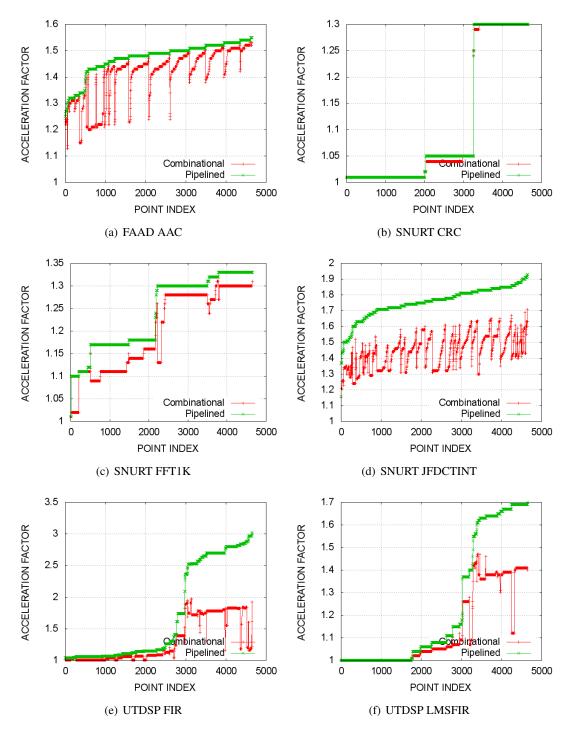

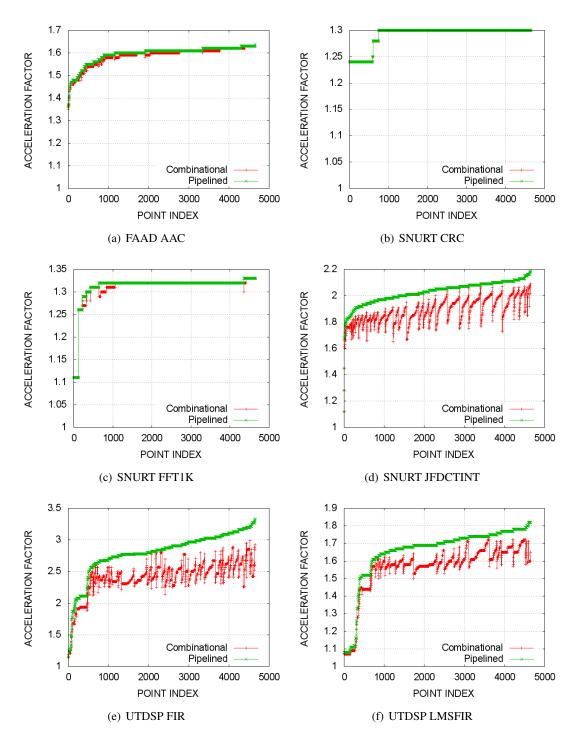

The CFA microarchitecture is pipelined with the potential to initiate operations with an issue latency of one cycle. Modelling the performance impact of overlapping independent ISEs in a CFA is investigated as a potential alternative to other I/O pipelining techniques. Instead of giving inputs and reading outputs for a single large ISE over several cycles, each ISE must only use a single cycle to perform input or output, and will generally be smaller for a given I/O constraint. If smaller ISEs can be used, area and energy consumed will be less and the efficacy of the ISE solution will be increased. New heuristics are produced to allow the ISEGEN algorithm to be aware of the additional acceleration obtained through overlapping templates, hence making it able to better exploit the temporal parallelism in the ISEs it produces. *Pipelining is shown to increase acceleration by up to an additional 1.5x.* The new pipeline heuristic is also shown to have better stability with regards to the weighting vector used versus the original combinational heuristic, in addition to producing better results. Two pipeline scheduling heuristics are evaluated within the greater context of the new pipeline merit heuristic, and a "shortest-first" policy is demonstrated to generally produce better schedules in the benchmarks evaluated.

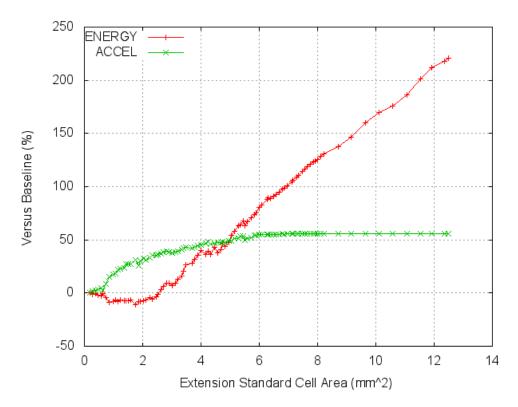

In the earlier work to demonstrate the use of the CFAs in several applications, a near-linear correlation is demonstrated between the power consumed by a CFA and its standard cell area. It is also shown that CFAs can have a beneficial or detrimental effect on the energy perfor-

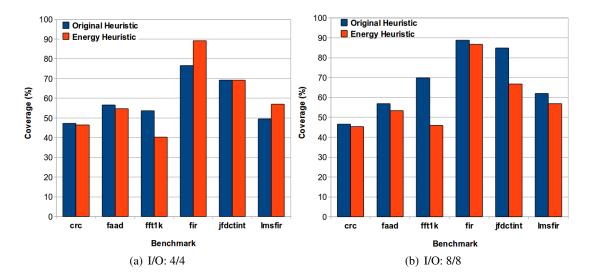

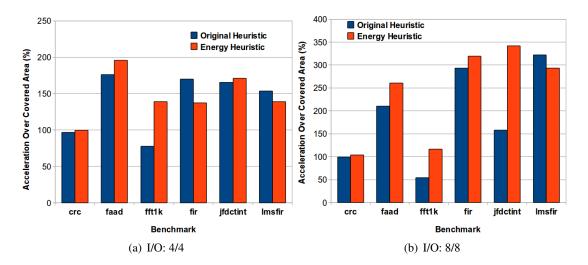

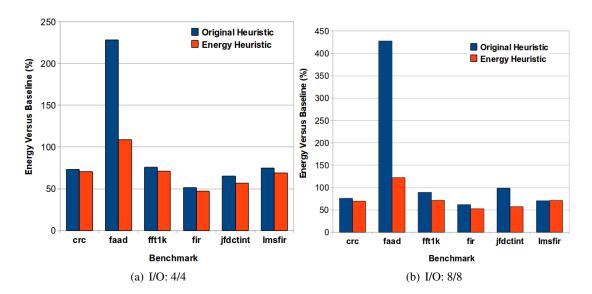

mance of a particular hardware-software co-design. In order to make the ISEGEN algorithm aware of the potential energy effects, a heuristic is produced using the relationship described in the earlier section 4.2. The new heuristic can be used to determine the "energy merit" of a particular ISE, utilising the integral of power versus time to model the energy cost of using a particular ISE when implemented as a CFA. The new heuristic is placed into the ISEGEN algorithm and evaluated with regards to several benchmarks, and found to produce better solutions across nearly all of them. The energy-aware heuristic reduces the energy used by a CFA implementation of a set of ISEs by an average of 1.6x, up to 3.6x. In fact, even though the CFAs are not constrained with regards to area, the new heuristic actually manages to produce a better acceleration for most of the applications than the original combinational heuristic does. The socalled energy heuristic actually makes improvements in acceleration, area, power, and energy in most benchmarks. This improvement does not come at the cost of engineering time either, as coincidentally the new heuristic is found to take less time to converge on its solution than the original combinational heuristic. The same process as before is used to demonstrate that a common and stable weighting vector exists for this heuristic, and like the pipeline heuristic this common vector is shown to be more stable than the combinational heuristic.

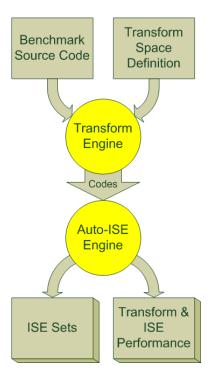

Compiler transformations are an important source of potential optimisation, and their effects when combined with ISEs are only just beginning to be understood. This thesis presents a transformation-space exploration, in which ISEs are produced after a range of source-code transformations are performed. The methodology for combined exploration of source transformation and ISE is demonstrated to improve the acceleration of the result by an average of 35% versus ISE alone. It is also demonstrated that there is a critical link between the efficacy of source transformation and the efficacy of the resulting ISE identification. Transformation and ISE overlap in where they obtain performance improvement from. Wherever transformations are ineffective, ISEs are shown to be generally more effective in accelerating. Source transformation comes with a lower cost than ISE, so this work shows that it is important to perform a zealous evaluation of potential software transformations in tandem with ISE identification.

Low-power embedded processors used for media applications often perform calculations for fractional numbers using fixed-point representations. This thesis performs an evaluation of applications implemented in both fixed- and floating-point arithmetic, with regards to the absolute performance of the solution that would be produced in a design utilising ISE. *It is demonstrated that the fixed point designs provide the best trade-off in execution time, area, power, and energy.* With the higher baseline power and energy performance of the floating point solution, benefits from ISEs in energy consumption are relatively greater for floating point than for fixed point. It is therefore shown that wherever floating point is utilised, ISEs can be used to significantly reduce both the execution time and energy cost of a design.

Contributions have been made across the spectrum of concerns for ISE; the efficacy of all design concerns have been addressed in one form or another, and improvements made in all

cases. Exploration into the ancillary concerns of ISE design such as source transformation has been produced, promoting a holistic approach to ISE wherever possible: In a hardware-software co-design utilising ISE, both sides of the design must be evaluated together in order to produce a better design.

## 1.4 Document Structure

This thesis is organised as follows:

- Chapter 2 introduces and describes the background material (empirical, practical and theoretical) required to understand the motivation and implementation of the work of this thesis.

- Chapter 3 describes efforts in the field of specialised computer architecture, specifically those relevant or related to the work performed in this thesis.

- Chapter 4 introduces the Configurable Flow Accelerator (CFA) ISE implementation, explores the strengths and weaknesses of the implementation as originally conceived, and introduces a temporal-partitioning algorithm for compressing the latency and resources of a CFA implementation.

- Chapter 5 looks at an existing high performance ISE identification algorithm (ISEGEN), with an eye towards increasing its efficacy for both the "classic" combinational ISE exploration and more specific situations such as energy optimisation and pipelined microarchitecture. In addition to improving the scenario-specific quality of the algorithm's output, the runtime of the algorithm itself is reduced by introducing search early termination.

- Chapter 6 is concerned with the form in which an application's software is delivered to the AISE methodology, in particular with regards to the software transformations and number formats utilised. In the latter case techniques from chapter 5 are applied as appropriate to determine if they are more or less efficacious than the original combinatorial methodology.

- Chapter 7 concludes this thesis with a critical analysis of the work performed therein and suggestions for future continuation of this effort.

# 1.5 Summary

In this chapter, a general introduction to the contents of this thesis has been covered. Special consideration has been given to design concerns this work is intended to address by improving the efficacy of ISE:

- Engineering Time.

- Acceleration.

- Area Cost.

- Energy Cost.

This chapter has introduced and motivated the process of processor specialisation via ISE, in particular the engineering concerns that will be encountered, so that these may be directly addressed in later chapters. Contributions made in addressing these concerns and the structure of this thesis hereon have been covered, and now we progress to providing the background information necessary to understand this thesis.

# 2 BACKGROUND

"I was born not knowing and have had only a little time to change that here and there."

#### - Richard Feynman

This chapter covers a review of the material necessary as background to understand the motivation and implementation of the efforts contained in this thesis.

### 2.1 Embedded Processors

General purpose processors (GPP) tend towards high-power, deep pipelining, large die-size, and high clock frequency; embedded processors on the other hand tend towards the exact opposite:

- Pipeline depths tend to be limited in order to reduce the cost of a flush; the degree of speculative hardware used in GPP is much greater than embedded cores, which tend towards simpler branch prediction schemes.

- Clock frequencies tend to be lower as a product of the shorter pipelines, as deeper pipelines also tend to burn a lot more static power through driving feedback in latches.

- On-die sizes of embedded processors tend to be smaller, as in general embedded processors are not provided as fabricated products; rather as IP blocks for integration in a system-on-chip design.

Embedded processors can largely be divided into three classes, although there is some overlap:

- Non-extensible, Non-reconfigurable cores. These are a slowly dying breed of cores which tend to favour higher performance serial processing and general purpose execution to some degree. These may include some application- or domain-specific acceleration functions. Examples include the Pentium-M at the high end of performance and cost, or the ARM 7TDMI at the lower end. These cores can generally only be externally accelerated, through the use of co-processors.

- Extensible Cores. These cores may undergo extensions to the architecture and microarchitecture pre-fabrication, in order to accelerate a particular application or domain.

These are usually referred to as ASIP.

- Configurable Cores. These cores are defined with computing fabrics at the microarchitectural level which are reconfigurable post-fabrication. The degree of reconfigurability

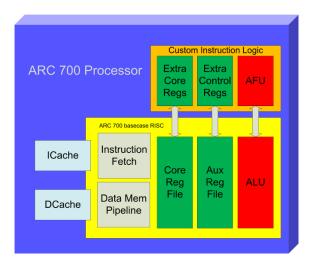

Fig. 2.1: A simplified system-level view of ARC 700 family architecture, demonstrating the pre-verified baseline core and its connection to ISE hardware through custom registers and arithmetic units.

varies from the less mutable microcode specification, to fully dynamically reconfigurable architectures.

The following sections cover the relevant details of the latter two classes, with respect to the problems addressed by the research detailed herein.

### 2.1.1 Extensible Processors

Extensible processors contain a number of variable components, essentially opening up design spaces inside the processor core for exploration by the designer of an ASIP-based system. Extensions to registers and supporting arithmetic logic are implemented outside of a prefab baseline core, the latter implementing all of the expected basic RISC functionality. In this manner, users may make the best use of the degrees of freedom provided, with the knowledge that their extensions will not make unpredictable timing changes to the core as a whole. Architectures are extended by implementing extensions in SystemC or Verilog with respect to the architecture's extension interface. Some extensible processors have supporting tool-chains which allows for an engineer-guided exploration of the application to determine a partitioning between software execution on the original architecture, and hardware execution through ISEs. Examples of Extensible processors include the ARC 700 (See figure 2.1), Tensilica's XTensa, and Altera's NiosII.

The intention with extensible processors is to create architectural extensions prior to fabrication, which are thereon fixed in their purpose to accelerate specific application components. Whilst this approach appears on the surface to provide the best potential for cheaply minimising the area-delay products and other such metrics, there is a widely recognised problem in the design process. Application sources must be mature or predictable enough to permit an

early specialisation of the architecture through extension. Once the hardware design is fixed, any changes to the application may invalidate previous assumptions about timing and data-flow which contributed to the efficacy of the overall HW/SW combination. The problem of the flexibility of an architecture becomes key, and therefore precludes very complex data-flow acceleration due to a possible mismatch between the identified extensions and an application at a later stage of its development. The Tensilica XTensa approach to this problem is to create a range of complexity in the ISEs generated. When the application drifts from its original specification the less complex ISEs are still able to be mapped for a performance advantage. At this point though, the benefit of the larger ISEs is lost entirely. The static ISEs cannot be reconfigured to match the structure of the new software.

# 2.1.2 Reconfigurable Processors

Reconfigurable Processors are an attempt to address the problems of application drift during the design process, as they allow for more flexibility in the acceleration microarchitecture at the cost of more control logic. Examples include the Xilinx combined FPGA/PowerPC, the Stretch S5000 and S6000 processors, and the ARM OptimoDE. This list is given in order of granularity; that is the level at which reconfiguration is possible. Without doubt, the most flexible in terms of achievable function space is the FPGA solution, wherein ISEs are implemented in an FPGA surrounding a hard-macro processor core. There are several inefficiencies to the FPGA approach, all stemming from the high degree of complexity and latency inherent in the interconnect of the gate array.

DSP applications will include a great deal of integer (fixed-point) and potentially floating point arithmetic, for which the mapping from an FPGA to the required structure is rather inefficient when compared to the direct gate-implementation of an ALU for that operation. The bitstream required in order to maintain the instance of such a direct implementation of an operator versus the FPGA equivalent will always be far smaller, as all that is required is potentially a mode (operation select) as opposed to a bitstream maintaining the entire structure of the ALU. The next level of architectural flexibility is based off this coarse-grained FPGA idea, providing a regular collection of arithmetic operators with a mesh routing fabric. The approach of combining both high and low flexibility components gives such products a considerable advantage in cost-benefit in their targeted domain versus FPGA alternatives.

Most reconfigurable processors at present require the engineer to manually select and replace sections of source code with ISEs that utilise the various reconfigurable fabrics available to the architecture. The addition of design automation in this process can, if it provides solutions of equal quality or better than an engineer in a manual process in the same time, provide a great improvement in design cost.

# 2.2 Design Space Exploration

Hardware / Software Co-design [2] is the phrase used to describe the inclusion of both hardware and software elements simultaneously in the design of an embedded system. It was the original idea from which more recent topics such as Design Space Exploration (DSE) [8] were inspired, and fundamentally forms the basis on which this thesis rests. A number of engineering methodologies [2] for the combined system-level design of hardware and software have been published. Such methodologies tend to involve manual analysis of the constraints of a particular problem, and really do not provide much in the way of design automation. Through a structured and methodical design process centered around the preservation of design flexibility and efficiency the designer performs all of the trade-offs themselves. Whilst this approach offered a considerable advantage over classical software engineering for embedded system level integration, it does not attempt to address the dwindling efficiency of the engineer themselves. With ever increasing numbers of design trade-offs available, the engineer is swamped with complexity.

Design-Space Exploration [8] is an attempt to properly formalise the trade-offs inherent in an embedded application design. Constraints such as execution speed, power use, cost, and complexity are made functions of axes of design, which represent the potential dimensions in which a design may develop. There is a space defined by these dimensions, but by no means is this space straightforward to explore. A large degree of trial-and-error is required in the process, placing a premium on making small changes to a design and observing the effects that has on its various performance metrics. In addition, the various levels of hardware and software co-design spread the space across multiple levels of abstraction, further increasing the complexity of attributing performance to particular "features" of the design. What is more, performance functions over the space are often exceptionally discontinuous and non-linear for continuous regions of the space. Whilst original efforts in manual design space exploration have been very promising, generally these efforts were reduced to a mechanised brute-force evaluation of contiguous regions of the design space at-once, with a degree of controlled iteration and movement within the space provided by the engineer atop the design process. It soon became apparent that there were more effective means of automating this process by taking the engineer out of the loop in order to make a wider guided evaluation of the space.

Meeting speed constraints means that no further increase in speed is useful for its own sake. In certain cases excess speed may be "spent" in reducing other design costs. So long as hardware and software together meet the minimum speed requirements, application deadlines will be met and the system built around the core will be able to communicate and process data. No stalls will occur due to system-level deadlines missed by the core, and power will have been reduced overall. For example, if execution speed exceeds requirements, the clock speed of the ASIP may be reduced, reducing power and hence energy consumption. These secondary concerns have additional design spaces of the configurable core available to be explored for

satisfactory areas; for example clock gating [3], dynamic voltage scaling [9], and unit pruning. The "second order" effects of core extension are not always beneficial and often hard to predict with any accuracy. Adding more logic to a core can for example increase the critical path and force a reduction in the overall clock speed. Such a complicated web of non-orthogonal tradeoffs forms a space which can only be explored efficiently through the aid of iterative automated means.

#### 2.3 Instruction Set Extension

Instruction Set Extension (ISE) is the process of adding new instructions to a baseline core in order to improve the performance of the core with respect to a particular application or set of applications (domain). The approach requires work in a number of distinct areas: those of architecture (instruction set design), microarchitecture (the hardware implementing the architecture), and compiler (in order to map applications to the new architecture). These three problems have been addressed manually for some time, with engineers using profiling and manual inspection of application code to determine the best application of ISE. RISC architectures have formed the basis of most ISE-driven approaches for a considerable time. Their basic architecture is able to efficiently cover the non-ISE component of the application without expending excessive amounts on resources attacking things like dynamic instruction-level parallelism. Most high-performance execution is performed by ISEs and not by the general purpose component of the design, which makes dynamic OLP-exploiting hardware redundant.

ISE affects all the main axes of design concern (acceleration, area, power, energy, engineering cost). The guiding metric in deriving extensions is often still application execution speed; designers will add ISEs that "cover" the hottest (most frequently executed) sections of their application code. The intention is that by partitioning of the application code into areas covered and not by ISEs, sections of microarchitecture can be dedicated to the servicing of these new ISEs. This is an example of the application of Amdahl's law; by covering the dominating areas of program code with acceleration the useful effect of the optimisation is maximised for a given application. This approach is ostensibly one of design-space exploration, but in a less classical sense since the opportunities for extension are not bounded so much by design space constraints as by the data-flow structures present in the application code and their potential for mapping to specialised microarchitecture, often referred to as an "Application Functional Unit" (AFU). This aside, there are some constraints which can be thought of as defining the design space when considered with the structure of the application code; these are:

- The number of register file ports for input and output; this ultimately defines the bandwidth to and from the ISE hardware, giving the number of words that can be read to and written from an ISE per cycle. This is commonly referred to as the "I/O Constraint".

- That the data-flow covered by an ISE is able to be scheduled; more specifically that

there are no mutual dependencies introduced by new instructions (i.e. an instruction that both reads from and writes to another instruction, ISE or otherwise). This is commonly referred to as the "Convexity Constraint", as it is represented by the convexity of the data-flow graphs commonly used to define ISEs structurally.

- That the number of ISEs defined can actually be encoded in the space available in the instruction word fields. E.g. there exist opcodes or sub-opcodes free for defining as instruction set extensions, and the number of these is statically finite. This is somewhat relaxed where dynamic hardware reconfiguration is possible, as opcodes can be re-used during execution.

- That the power and energy consumed by ISEs does not excessively overload or drain the supply available to the core.

- That the resources employed by ISEs, in cells or silicon area, does not exceed the maximum allowable by the particular technology and budget in question.

These constraints are derived from different levels in the design hierarchy; convexity being a requirement of the compiler, encoding space being a requirement of the architecture, I/O being a requirement of the microarchitecture. Some constraints are set purely by the cost of producing a given design, and a further meta-constraint is that the time cost of deriving the instructions does not exceed whatever limit is set by the desired time-to-market and human resources budget. Given that the finally selected architecture (instruction set) impacts all elements of the hardware-software co-design, care must be taken to fix each constraint only as it is found to be either necessary or beneficial to the outcome. This represents a "Phase Ordering" problem in the design flow: What constraints should be fixed and what should remain mutable at what stage in the design process. The proper division of the design space into (preferably orthogonal) concerns is essential for determining an answer to this problem.

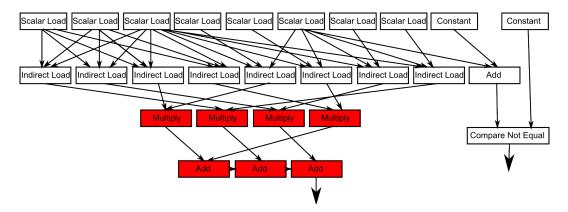

# 2.3.1 Abstract Problem Definition

For the sake of both manual and automated analysis, it is necessary to define an abstract formalism of the data-flow which will be examined for ISE candidates. Since the aim of ISE is to take a section of code and convert it to a structural representation, a structural graph representation is a good formalism for this purpose. Application code and ISEs are themselves represented as a Data-Flow Graph (DFG). Application code DFGs are derived directly from basic blocks from within the compiler representation of the application. DFGs are defined as G = (V, E), wherein V is the set of vertices representing operations and E is the set of data-flow edges connecting the operations in G. Vertices of DFG are referred to as "nodes", which may or may not be coverable by the particular ISE methodology in question. For example, throughout this thesis memory operations are not coverable, and so will never be included in an ISE. Other nodes

are not represented in the DFG, specifically those involved in control-flow. For this reason, all performance figures given in this thesis with regards to this model are concerned only with the data-flow portion of an application, not the control-flow.

When calculating the impact of an ISE formalised in this fashion, the difference between the sum of the latencies of all the nodes in an ISE minus the sum of the latencies of all the nodes in the critical path of the ISE constitutes the speedup in cycles. The software and hardware latencies of a particular node reflect the number of cycles the node will take to execute on the baseline RISC processor and as a synthesised functional unit in an ISE, respectively. The hardware latency is generally lower than the software latency in standard-cell approaches, but in FPGA the extension logic can sometimes be slower than the baseline processor. The speedup of implementing a particular DFG *G* as an ISE is calculated as follows:

$$\lambda\_sw(G)$$

= Sum of all software latencies of nodes  $\in G.V$

$\lambda\_hw(G)$  = Sum of all hardware latencies of nodes  $\in$  critical path of  $G.V$

$speedup\_cycles(G) = \lambda_{sw}(G) - \lambda_{hw}(G)$

The total software cycles taken by an application in the data-flow domain is calculated in a similar manner. First the application is profiled to get per-basic-block execution frequencies. For each basic block, the number of software cycles is calculated by summing the software latencies of all the nodes in the DFG for that basic block. This value is multiplied by the profiled execution-count for that basic block and is added to the total. Taking the same approach but including the speedups calculated as above, the ISE-accelerated cycle count can be calculated. This is the method used in all experiments in this thesis. In all experiments in this thesis other than that of section 6.2 the node latencies are set to those of the EnCore processor [10]: both hardware and software latencies are the same, due to the baseline and extension being implemented in the same standard-cell technology.

### 2.3.2 The Software Emulation Fallacy

When performing ISE for any given baseline core, we are weighing up the cost of the new extensions (in area or power) versus the benefit (in acceleration or power). It is very important to keep in mind what you are using for a baseline, and the continuum of design from that baseline to any other design point currently under consideration.

Wherever a baseline has simple RISC-like operations which are not covered by hardware functional units, software emulation is usually used to provide these operations to compilers. An example of this is the GNU libfpe (Floating Point Emulation Library) provided as a part of the GCC compiler infrastructure. The libfpe software provides floating point operations in terms of a series of integer operations. Most architectures will then be able to use to provide floating point calculation in the absence of floating point functional units. When the cyclecounts for software-emulated operations are included as the software latencies of nodes in ISE,

the resulting speedup when considering a single ISE design point is grossly misrepresented. In order for ISE identification algorithms (or indeed manual ISE) to honestly represent the merit of ISE, the baseline for extension should always consider the software latency of each operation represented as being the integer ceiling of an individual hardware functional unit that could be included. ISE as represented in the literature (see section 3.2) does not generally consider the simple instructions which could be added, rather opting to cover as large an array of complex arithmetic as possible in order to obtain a design point of high merit.

It is important when designing an ASIP to perform some degree of design-space exploration outside ISE, both before and after the ISE is performed and often with a degree of iteration. Citing the speedup obtained by complex ISEs when software-emulated operations are included in the software latency calculations will invariably provide an extremely high speedup where these operations are included in ISEs. Including a scalar hardware functional unit to cover the software emulated functions would provide a large degree of this speedup. Even the design-space of a single scalar functional unit is complex and results in a number of potential solutions; a simple integer multiplier itself has several potential structures for implementation at different cost/benefit points. For this reason and others, ISE alone is not a holistic solution to designing ASIP, but instead one powerful technique within a number of other techniques which overlap with regards to their impact on the function of cost versus benefit. In this work, software latencies are always assumed to be as if there were a scalar hardware functional unit; this avoids misrepresenting the speedups by including the benefit from simple scalar extensions before addressing the complex approach of ISE.

# 2.3.3 Separation of Concerns

As discussed earlier, ISE design is a DSE problem at heart, and one with various separable concerns; acceleration, power, energy, area, code size, and engineering time. It has been demonstrated that the orthogonalisation of concerns [11] is necessary for a thorough exploration of the potential design points.

With regards to acceleration, the following properties of an ISE design will contribute to its efficacy:

- Operation-level/Spatial parallelism. Parallel instances of arithmetic hardware are used in order to perform multiple operations at-once, as allowed by dependencies.

- Aggregation of clock period surplus present in most arithmetic functions. In particular, bitwise functions have a hardware latency far below the clock period in most cases.

- Issue latency between data-independent ISEs. Scheduling ISEs to have the minimum

possible distance between independent instances will allow these to be temporally parallel

• Reduced register-transfer overhead, due to the increased locality of communication within the functional unit used to represent the ISEs. Wherever a value is passed between nodes in an ISE, register pressure is reduced. The opposite may occur with wider ISEs, which may actually increase the pressure through requiring a large number of live registers for input and output.

Power and energy performance will depend heavily on the microarchitectural implementation selected, and the size of ISEs used. Some work (see section 4.2.1 for a review) has been done by others to characterise the power and energy concerns of ISEs. The following properties of an ISE design point will effect these concerns:

- Number and complexity of arithmetic units used in ISE microarchitecture. Dominant in non-sub-micron designs, power will depend on the number of concurrently processing arithmetic units. This is naturally at odds with the spatial parallelism described under acceleration above, and adding more arithmetic units will always increase power. Power though, is only one factor of energy. Addition of more arithmetic units may decrease energy through acceleration. This trade-off is investigated in later sections 4.2, 5.5, and 6.3.

- Number and width of flip-flops used in ISE microarchitecture. Dynamic and static power are the dominant factors in processor power consumption, and the registers used in making a synchronous circuit are the source of these factors. Dynamic power is the major contributor in designs above 90nm, with static power becoming dominant below this technology node. Deeper pipelines are a major contributor to the power and energy consumed by a design.

- Clock Gating. The granularity of clock gating is of particular importance to ISE, and will have a large impact on the efficacy of maintaining both low power and energy consumption when using ISE.

- **Power Gating.** whilst harder to apply than clock gating and not yet investigated at all in the context of ISE, power gating should prove useful in the future for shutting down ISE when not in use.

Code size is generally impacted positively by ISE where the baseline architecture is RISC with a single instruction word size (by far the most common case). Each instance of an extension instruction should cover at least two operations, so wherever an ISE is used it will bring down the overall number of instructions directly. The decrease in register pressure covered under acceleration above will also contribute a reduction in code-size where spill code is removed.

Engineering time is not really a function of any point in the design space, but is still a relevant design concern for any practical application of ISE. The use of ISE in a purely manual design methodology is fairly impractical for all but the simplest efforts, due to the effort involved. Both time-to-market deadlines and human resource limitations will govern the amount of time that can be spent designing any application of embedded computing. Design automation is absolutely critical in order to make ISE an industrially viable technique; the production of extended architecture, microarchitecture, and compiler by automated means is a major goal of ISE research. Automating as much of the design process as possible frees up human resources for more creative tasks, decreases the time-to-market, and delivers a higher quality through reducing error from the human element. SoC are becoming more and more complex, with the human designer being placed higher and higher atop a pyramid of abstractions allowing them to govern the design through high level specifications and constraints. The transition from manual to automated design echoes similar developments elsewhere in computing and manufacturing across history, and is a sign of increasing technological maturity.

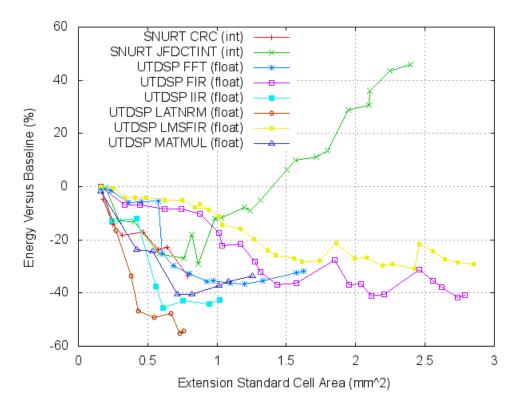

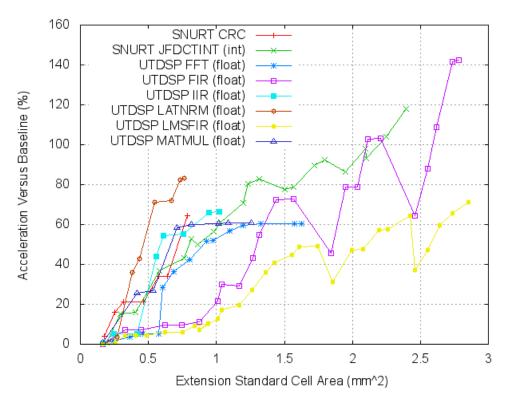

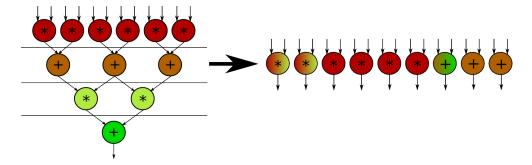

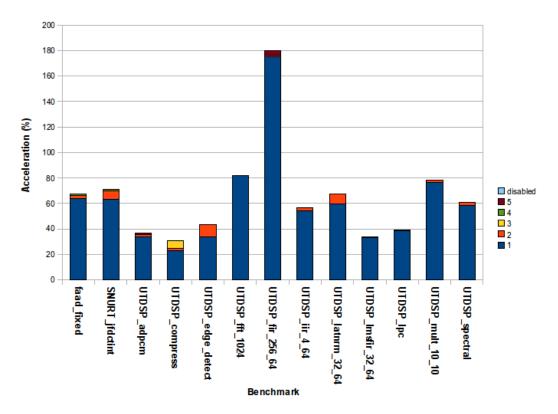

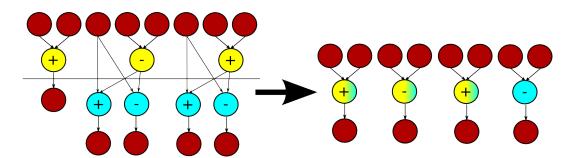

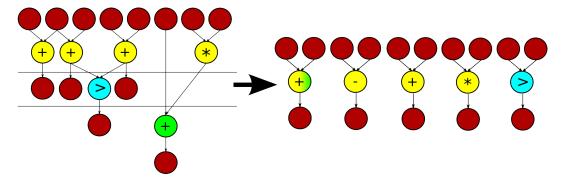

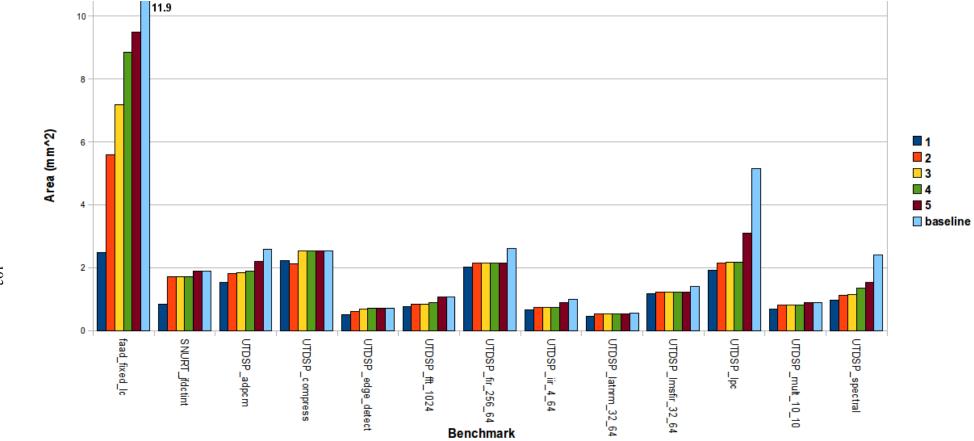

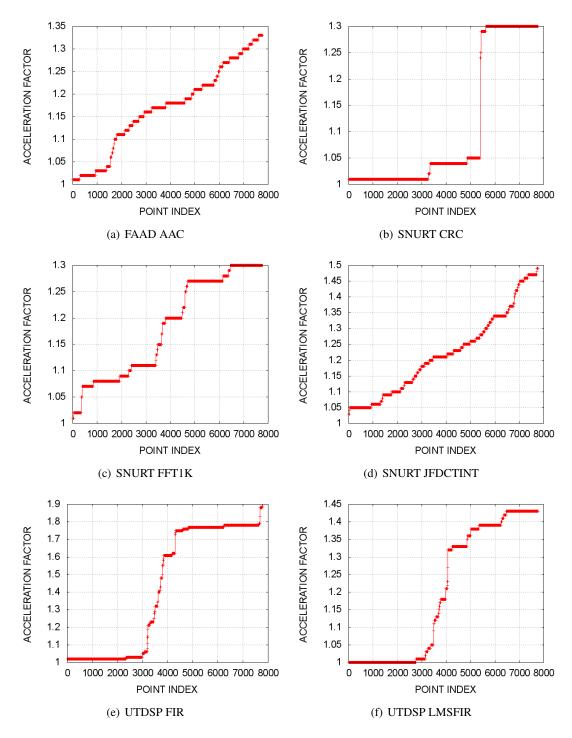

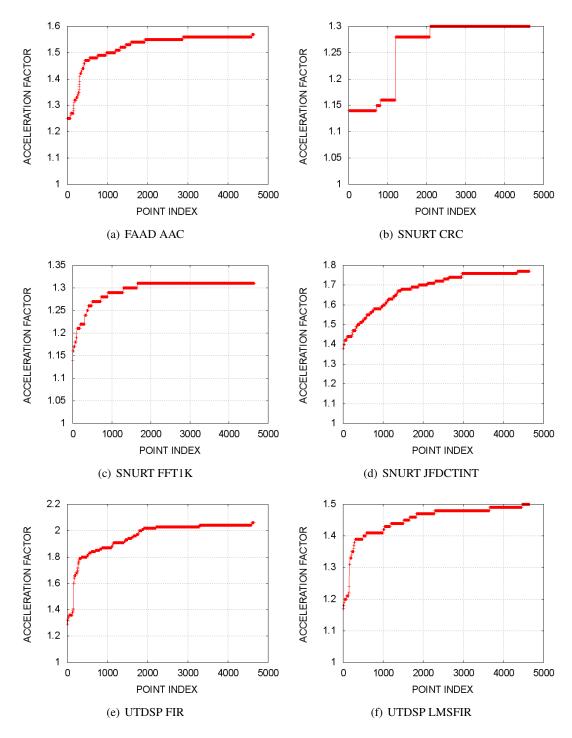

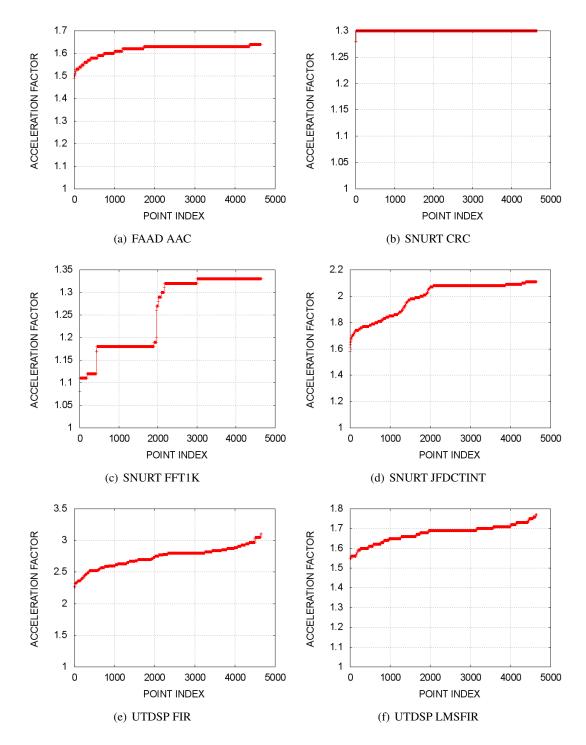

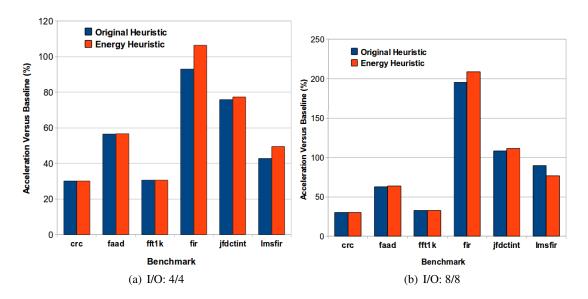

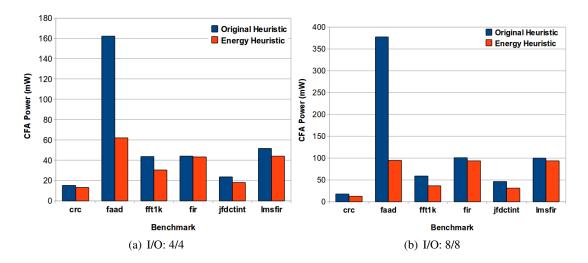

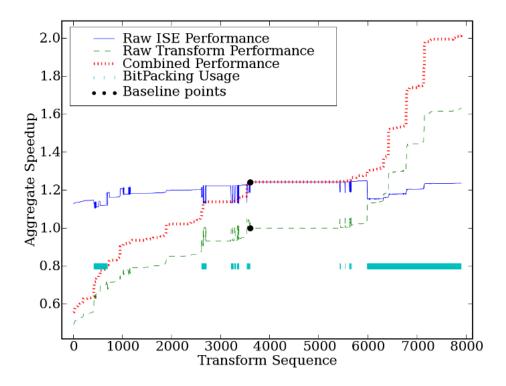

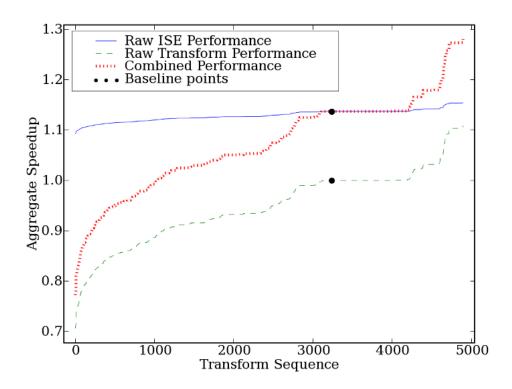

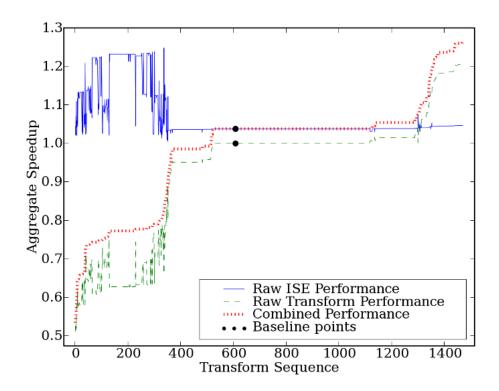

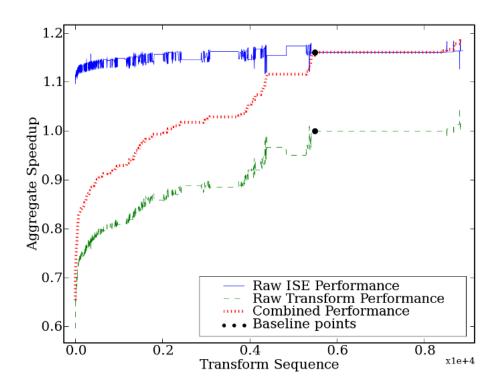

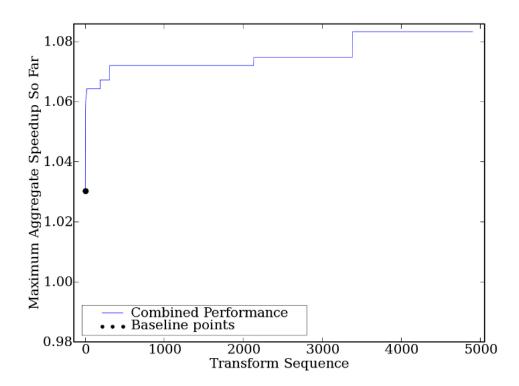

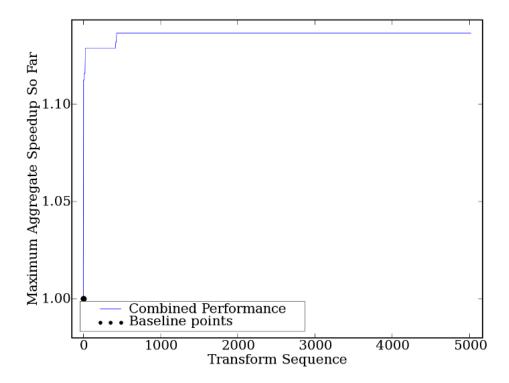

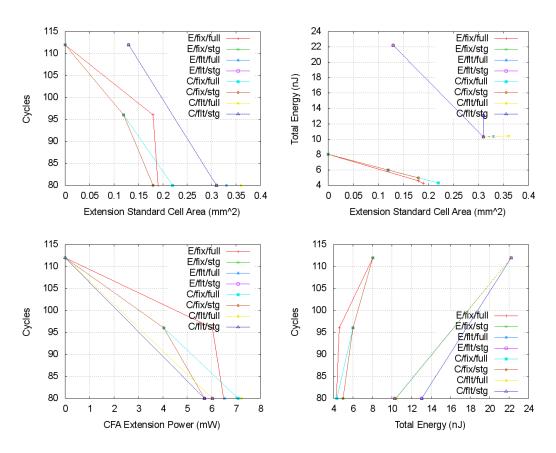

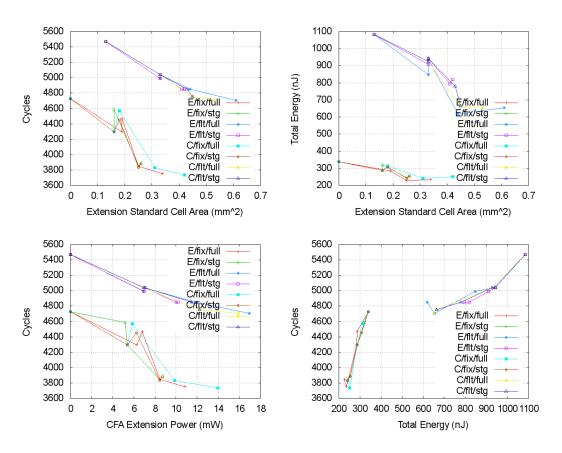

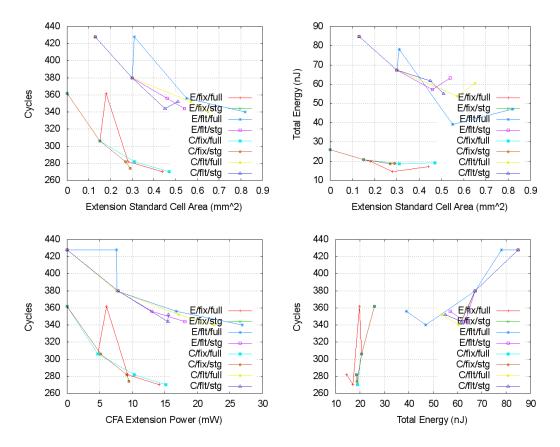

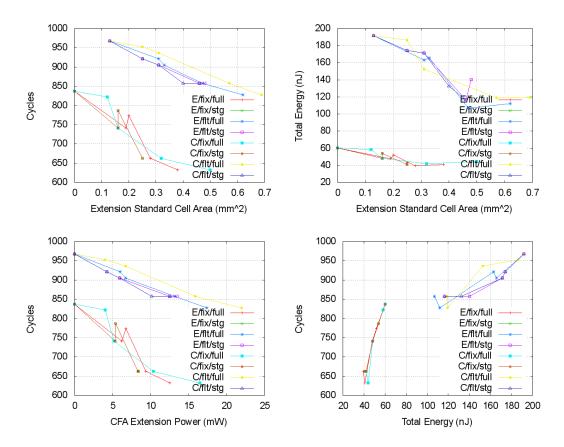

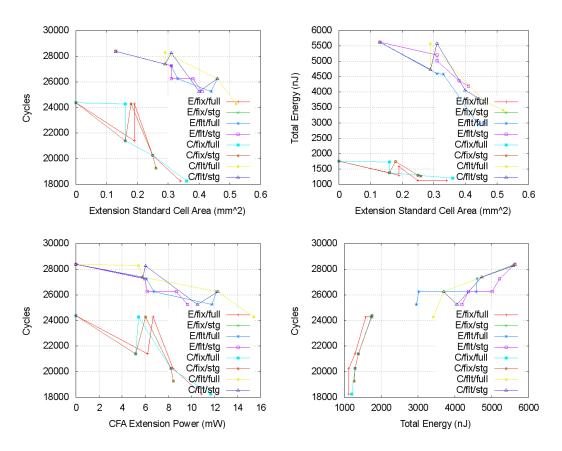

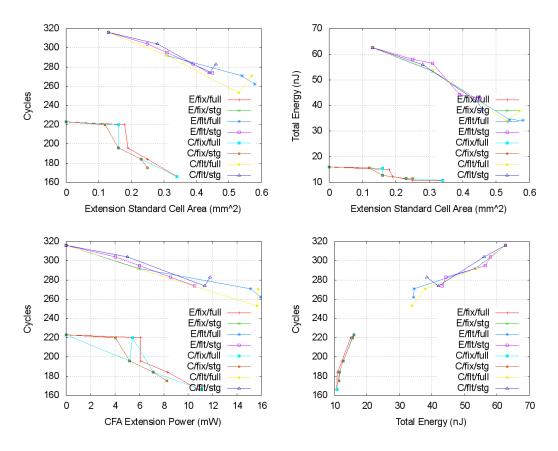

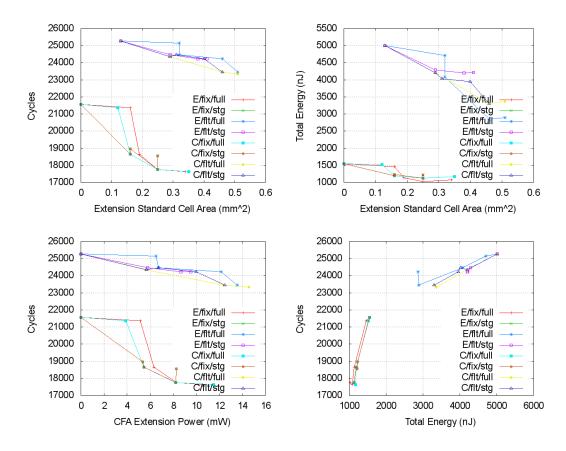

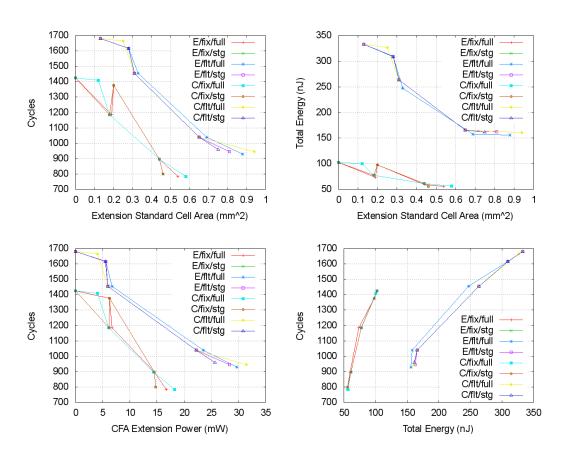

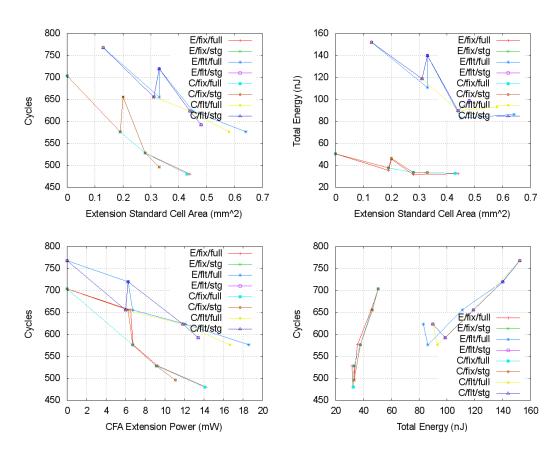

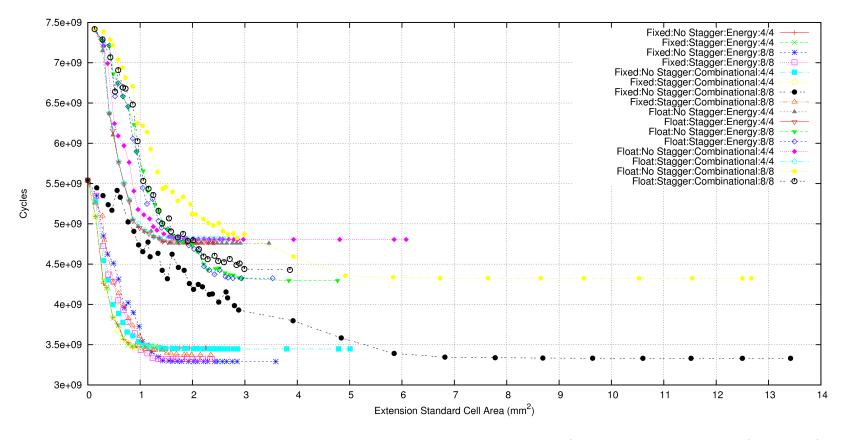

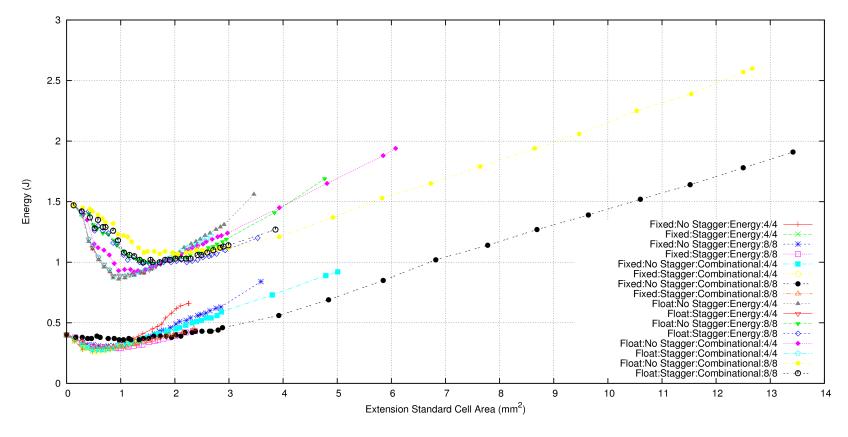

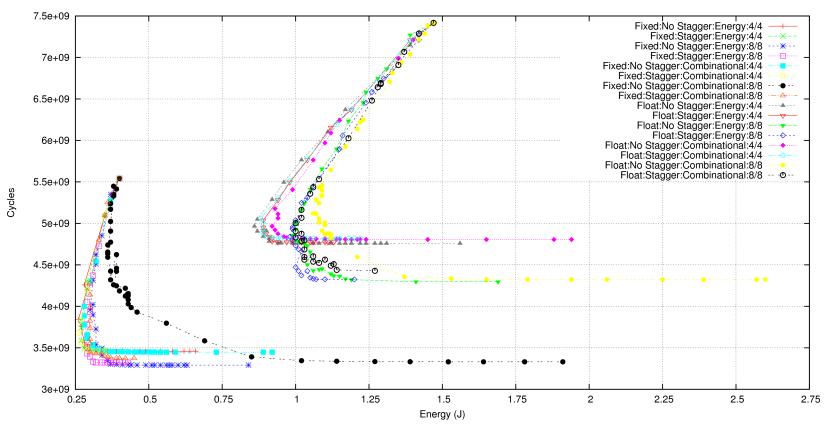

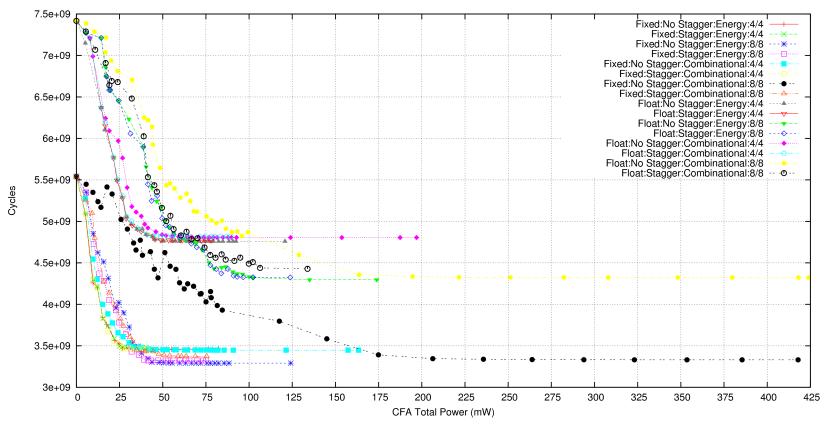

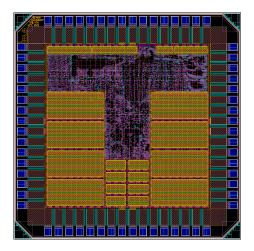

### 2.3.4 Amdahl Limit