# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# **Autonomous Smart Antenna Systems for Future Mobile Devices**

Wei Zhou

A thesis submitted for the Degree of Doctor of Philosophy The University of Edinburgh 2014

# **DECLARATION**

I hereby declare that this thesis has been composed by myself and that except where stated, the work contained is my own. I also declare that the work contained in this thesis has not been submitted for any other degree or professional qualification except as specified.

Wei Zhou

August 2014

Edinburgh, UK

# **ACKNOWLEDGEMENTS**

First of all, I wish to express my greatest gratitude to my supervisor, Professor Tughrul Arslan for his invaluable support, constant encouragement and incisive guidance throughout this study.

I wish also like to extend my appreciation to my second supervisor Dr. Khaled Benkrid, for his useful comments and suggestions in this research. I would like to thank Dr. Brian W. Flynn, Dr. Ahmed O. El-Rayis, Dr. Nakul Haridas, Dr. Ahmet T. Erdogan, and Mrs. Susan Kivlin for their support and help during my PhD study.

To the members of the System Level Integration Group (SLIG) and Advanced Smart Antenna Technologies (ASAT) research group, I owe sincere and earnest thankfulness for the unforgettable and unique experience of my life.

I would also like to thank all my colleagues in the Sofant Technologies for their friendship and support.

I am extremely grateful to my family and my girl friend, Miss Dixiao Shen, for their understanding, patience and support during the research and the preparation of this thesis.

# **ABSTRACT**

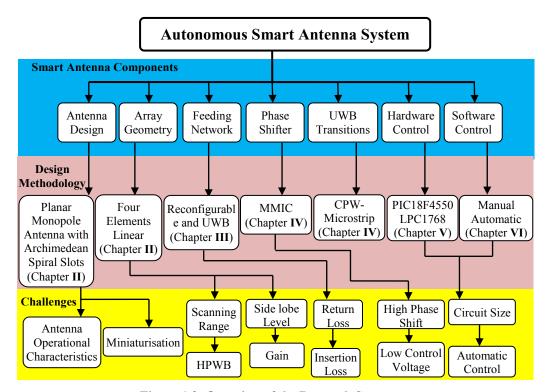

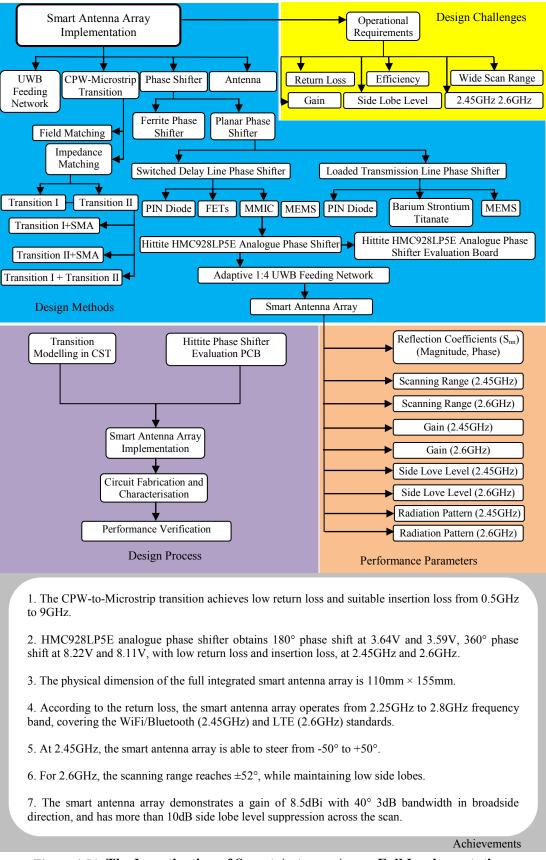

Along with the current trend of wireless technology innovation, wideband, compact size, low-profile, lightweight and multiple functional antenna and array designs are becoming more attractive in many applications. Conventional wireless systems utilise omni-directional or sectored antenna systems. The disadvantage of such antenna systems is that the electromagnetic energy, required by a particular user located in a certain direction, is radiated unnecessarily in every direction within the entire cell, hence causing interference to other users in the system. In order to limit this source of interference and direct the energy to the desired user, smart antenna systems have been investigated and developed. This thesis presents the design, simulation, fabrication and full implementation of a novel smart antenna system for future mobile applications.

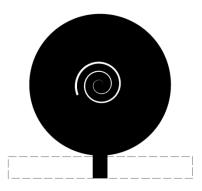

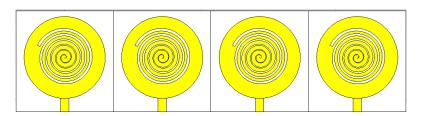

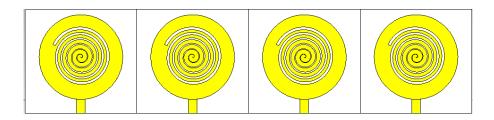

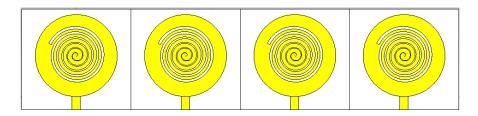

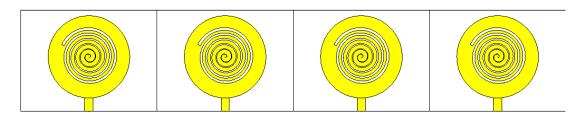

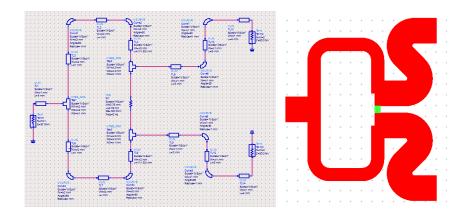

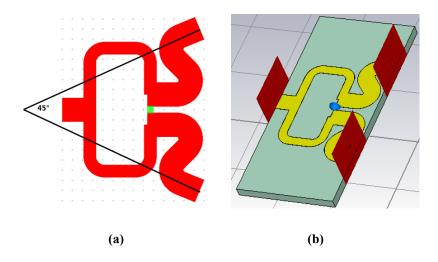

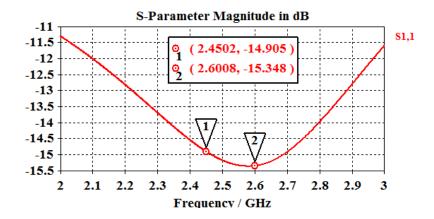

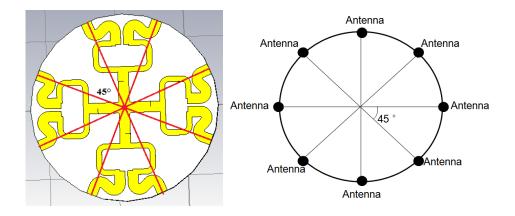

The design and characterisation of a novel antenna structure and four-element liner array geometry for smart antenna systems are proposed in the first stage of this study. Firstly, a miniaturised microstrip-fed planar monopole antenna with Archimedean spiral slots to cover WiFi/Bluetooth and LTE mobile applications has been demonstrated. The fundamental structure of the proposed antenna element is a circular patch, which operates in high frequency range, for the purpose of miniaturising the circuit dimension. In order to achieve a multi-band performance, Archimedean spiral slots, acting as resonance paths, have been etched on the circular patch antenna. Different shapes of Archimedean spiral slots have been investigated and compared. The miniaturised and optimised antenna achieves a bandwidth of 2.2GHz to 2.9GHz covering WiFi/Bluetooth (2.45GHz) and LTE (2.6GHz) mobile standards. Then a four-element linear antenna array geometry utilising the planar monopole elements with Archimedean spiral slots has been described. All the relevant parameters have been studied and evaluated. Different phase shifts are excited for the array elements, and the main beam scanning range has been simulated and analysed.

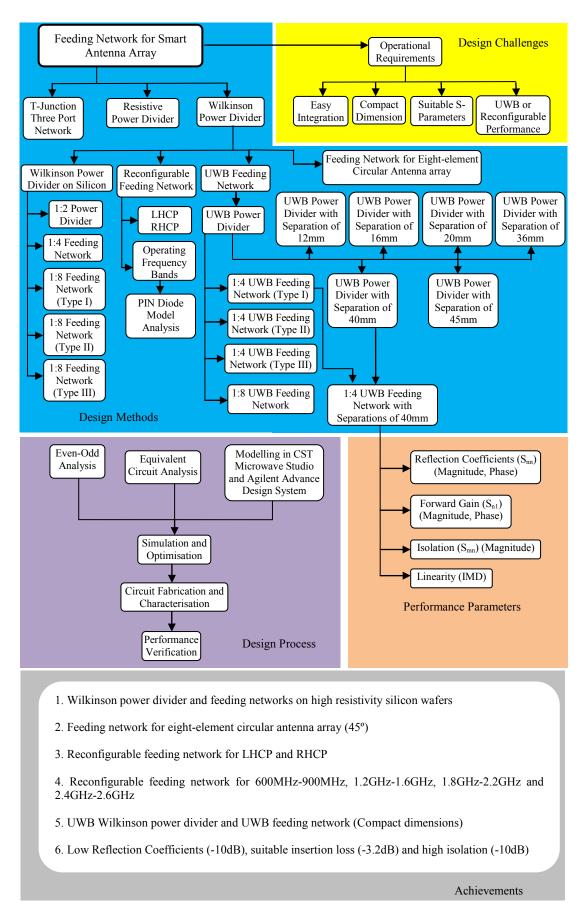

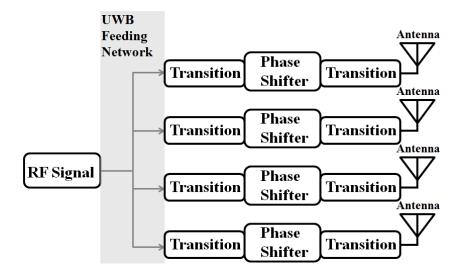

The second stage of the study presents several feeding network structures, which control the amplitude and phase excitations of the smart antenna elements. Research begins with the basic Wilkinson power divider configuration. Then this thesis presents a compact feeding network for circular antenna array, reconfigurable feeding networks for tuning the operating frequency and polarisations, a feeding network on high resistivity silicon (HRS), and an ultrawideband (UWB) feeding network covering from 0.5GHz to 10GHz. The UWB feeding network is used to establish the smart antenna array system.

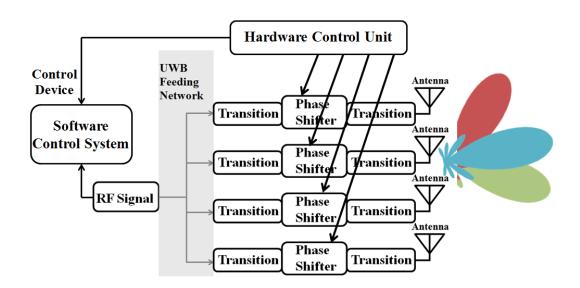

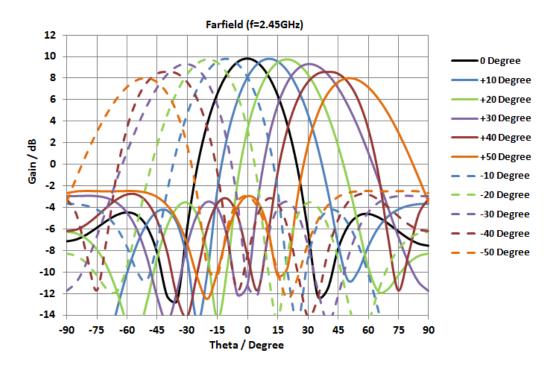

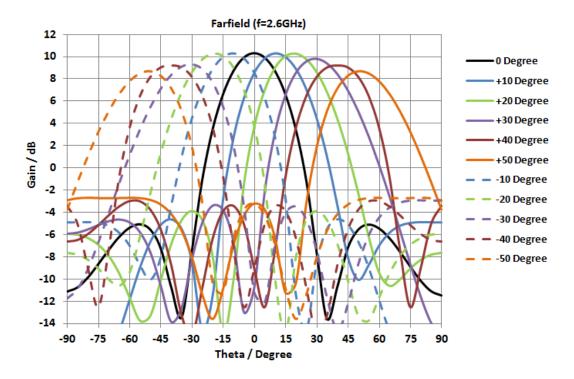

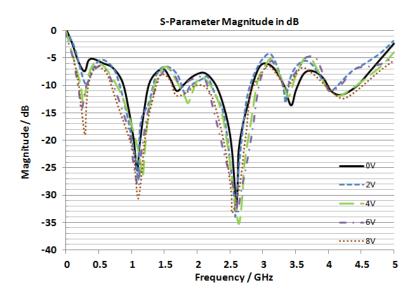

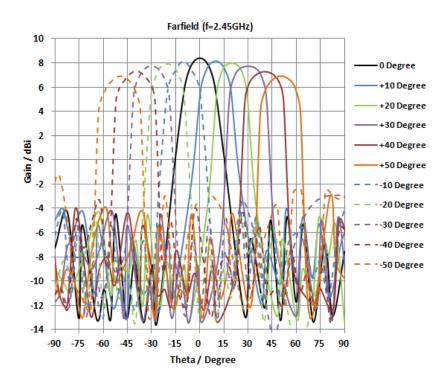

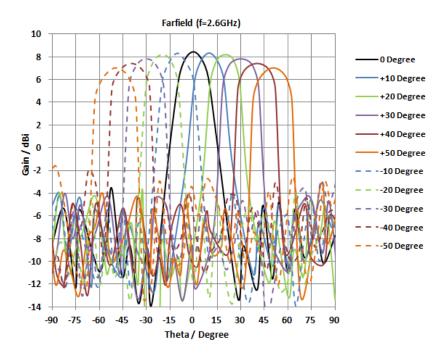

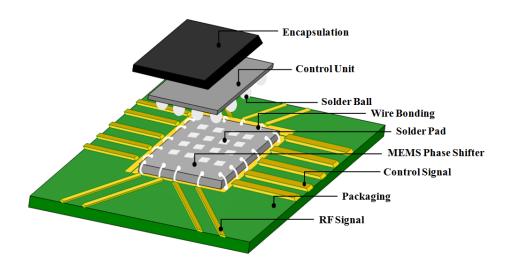

Different topologies of phase shifters are discussed in the third stage, including ferrite phase shifters and planar phase shifters using switched delay line and loaded transmission line technologies. Diodes, FETs, MMIC and MEMS are integrated into different configurations. Based on the comparison, a low loss and high accurate Hittite MMIC analogue phase shifter has been selected and fully evaluated for this implementation. For the purpose of impedance matching and field matching, compact and ultra wideband CPW-to-Microstrip transitions are utilised between the phase shifters, feeding network and antenna elements. Finally, the fully integrated smart antenna array achieves a 10dB reflection coefficient from 2.25GHz to 2.8GHz, which covers WiFi/Bluetooth (2.45GHz) and LTE (2.6GHz) mobile applications. By appropriately controlling the voltage on the phase shifters, the main beam of the antenna array is steered  $\pm 50^{\circ}$  and  $\pm 52^{\circ}$ , for 2.45GHz and 2.6GHz, respectively. Furthermore, the smart antenna array demonstrates a gain of 8.5dBi with  $40^{\circ}$  3dB bandwidth in broadside direction, and has more than 10dB side lobe level suppression across the scan.

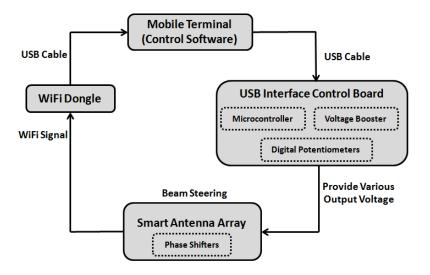

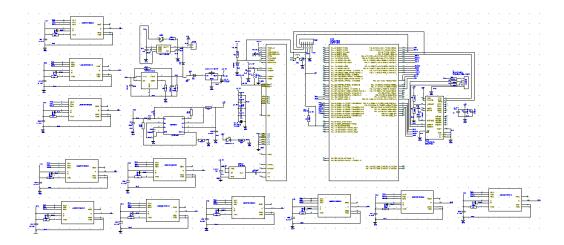

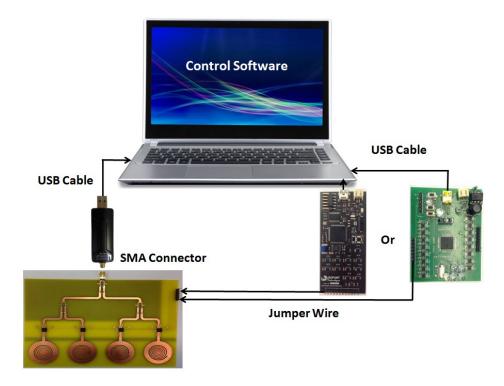

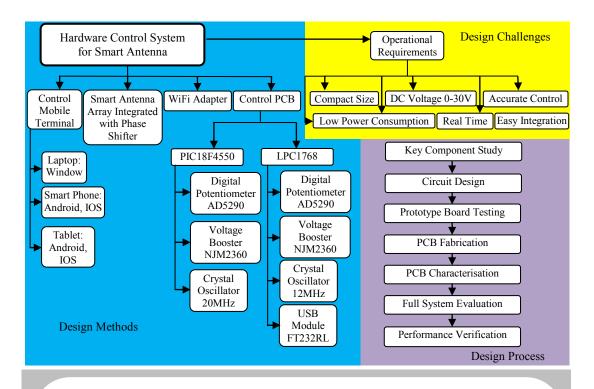

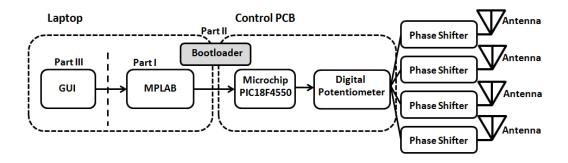

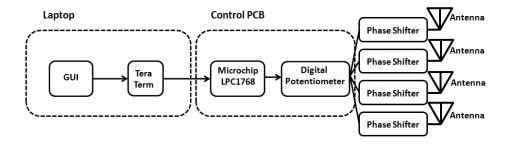

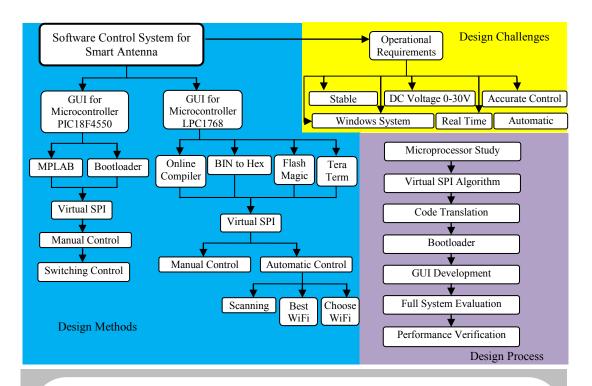

The final stage of the study investigates hardware and software automatic control systems for the smart antenna array. Two microcontrollers PIC18F4550 and LPC1768 are utilised to build the control PCBs. Using the graphical user interfaces provided in this thesis, it is able to configure the beam steering of the smart antenna array, which allows the user to analyse and optimise the signal strength of the received WiFi signals around the mobile device.

The design strategies proposed in this thesis contribute to the realisation of adaptable and autonomous smart phone systems.

# TABLE OF CONTENTS

| DECL   | ARATIO   | N                                            | II    |

|--------|----------|----------------------------------------------|-------|

| ACKN   | OWLED    | GEMENTS                                      | III   |

| ABST   | RACT     |                                              | IV    |

| TABL   | E OF CO  | NTENTS                                       | VI    |

| List ( | of Figui | RES                                          | XI    |

| List ( | OF TABL  | ES                                           | XXIII |

| List ( | OF ACRO  | DNYMS AND ABBREVIATIONS                      | XXV   |

| Снар   | TER 1: 1 | INTRODUCTION                                 | 1     |

| 1.1    | Resea    | rch Motivation                               | 1     |

| 1.2    | Resea    | rch Investigations                           | 3     |

| 1.     | 2.1 Des  | sign Challenges                              | 3     |

|        | 1.2.1.1  | Antenna Design                               | 3     |

|        | 1.2.1.2  | Array Geometry                               | 4     |

|        | 1.2.1.3  | Feeding Network Structure                    | 4     |

|        | 1.2.1.4  | Phase Shifter Implementation                 | 5     |

|        | 1.2.1.5  | Hardware Control                             | 5     |

|        | 1.2.1.6  | Software Control                             | 6     |

| 1.     | 2.2 Res  | search Objectives                            | 7     |

| 1.3    | Overv    | view of Thesis                               | 7     |

| 1.4    | Key C    | Contributions of the Thesis                  | 9     |

| 1.5    | Public   | eations Arising from This Research           | 9     |

| Снар   | TER 2: 1 | NOVEL ANTENNA DESIGN FOR SMART ANTENNA ARRAY | 11    |

| 2.1    | Introd   | luction                                      | 11    |

| 2.2    | Anten    | nna Theory                                   | 12    |

| 2.     | 2.1 An   | tenna Introduction                           | 12    |

| 2.     | 2.2 An   | tenna Properties                             | 15    |

| 2.     | 2.3 An   | tenna Fundamental Parameters                 | 16    |

|        | 2.2.3.1  | Radiation Pattern                            | 16    |

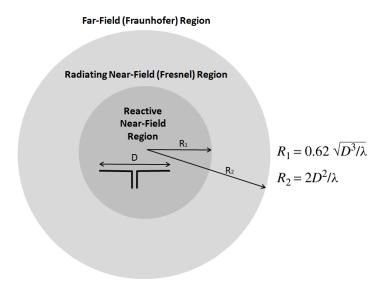

|        | 2.2.3.2  | Field Regions                                | 17    |

|        | 2.2.3.3  | Radiation Power Density                      | 18    |

|        | 2.2.3.4  | Radiation Intensity                          | 18    |

|        | 2.2.3.5  | Directivity                                  | 19    |

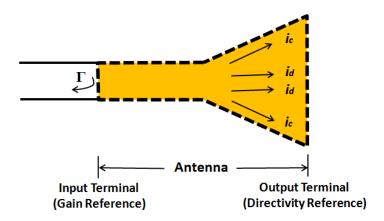

|        | 2.2.3.6  | Gain                                         | 19    |

| 2.2     | A.3.7 Antenna Efficiency                                                        | 19  |

|---------|---------------------------------------------------------------------------------|-----|

| 2.2     | .3.8 Beam Efficiency                                                            | 20  |

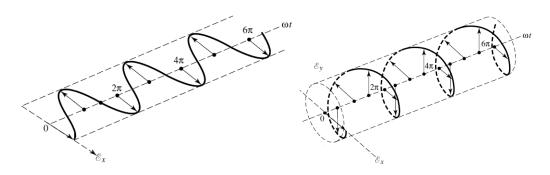

| 2.2     | 2.3.9 Polarisation                                                              | 21  |

| 2.3     | Novel Planar Monopole Antenna Design with Archimedean Spiral Slots              | 21  |

| 2.3.1   | Introduction                                                                    | 21  |

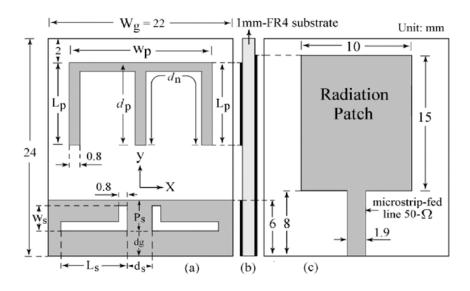

| 2.3.2   | Antenna Structure Design                                                        | 24  |

| 2.3.3   | Equivalent Circuit of the Antenna Structure                                     | 27  |

| 2.3.4   | Simulation and Experimental Results                                             | 29  |

| 2.4     | Antenna Array Theory                                                            | 40  |

| 2.4.1   | Antenna Array Introduction                                                      | 40  |

| 2.4.2   | Antenna Array Fundamental Parameters                                            | 41  |

| 2.4     | -2.1 Array Factor                                                               | 41  |

| 2.4     | -2.2 Radiation Pattern.                                                         | 42  |

| 2.4     | .2.3 Directivity                                                                | 42  |

| 2.5     | Array Geometry for Smart Antenna System                                         | 42  |

| 2.5.1   | Antenna Array Structure                                                         | 42  |

| 2.5.2   | Antenna Array Simulation and Experimental Results                               | 43  |

| 2.5.3   | Antenna Array with Simulated Phase Excitation                                   | 48  |

| 2.6     | Summary                                                                         | 51  |

| Снартен | 3: RECONFIGURABLE AND ULTRA-WIDEBAND FEEDING NETWORK                            | FOF |

| SMART A | NTENNA ARRAY                                                                    | 54  |

| 3.1     | Introduction                                                                    | 54  |

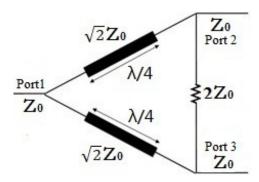

| 3.2     | Fundamental Wilkinson Power Divider Design                                      | 55  |

| 3.2.1   | Introduction                                                                    | 55  |

| 3.2.2   | T-Junction Power Divider Structure                                              | 55  |

| 3.2.3   | Resistive Power Divider Configuration                                           | 59  |

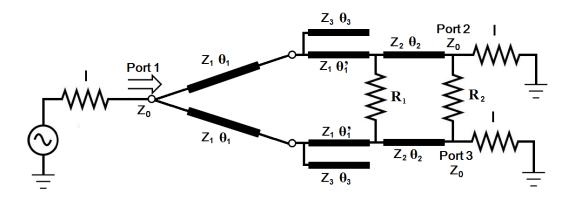

| 3.2.4   | Wilkinson Power Divider Introduction                                            | 60  |

| 3.2.5   | Wilkinson Power Divider Equivalent Circuit Analysis                             | 62  |

| 3.2.6   | Wilkinson Power Divider Design                                                  | 65  |

|         | Enhanced Wilkinson Divider on Si Substrate for Energy Efficient Microwave tions | 68  |

| 3.3.1   | Introduction                                                                    | 68  |

| 3.3.2   | Enhanced Wilkinson Power Divider Geometry                                       | 69  |

| 3.3.3   | Enhanced Wilkinson Power Divider Fabrication and Characterisation               | 73  |

| 3.4     | A WiFi/LTE Compact Feeding Network for an 8-Element Circular Antenna Array      | 75  |

| 3.4.1   | Introduction                                                                    | 75  |

| 3.4.2   | Individual Modified Wilkinson Power Divider Geometry                            | 76  |

| Feeding Network Configuration.                                                  | 78                                                                                                                                             |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| A Reconfigurable Feeding Network for a Dual Circularly Polarised Antenna Array  | 82                                                                                                                                             |

| Introduction                                                                    | 82                                                                                                                                             |

| Individual Wilkinson Power Divider Architecture                                 | 83                                                                                                                                             |

| Design of the Reconfigurable Feeding Network                                    | 87                                                                                                                                             |

| Circuit Fabrication and Characterisation                                        | 91                                                                                                                                             |

| Reconfigurable Feeding Network for GSM/GPS/3G/WiFi and Global LTE               | 02                                                                                                                                             |

|                                                                                 |                                                                                                                                                |

|                                                                                 |                                                                                                                                                |

|                                                                                 |                                                                                                                                                |

|                                                                                 |                                                                                                                                                |

|                                                                                 |                                                                                                                                                |

|                                                                                 |                                                                                                                                                |

|                                                                                 |                                                                                                                                                |

|                                                                                 |                                                                                                                                                |

| -                                                                               | .107                                                                                                                                           |

| urements                                                                        | .119                                                                                                                                           |

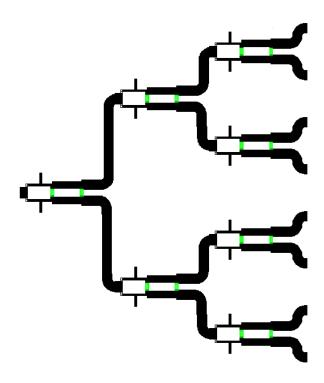

| 1:4 UWB Feeding Network for Smart Antenna Array                                 | .122                                                                                                                                           |

| Summary                                                                         | .124                                                                                                                                           |

| R 4: SMART ANTENNA ARRAY IMPLEMENTATION                                         | 127                                                                                                                                            |

| Introduction                                                                    | .127                                                                                                                                           |

| Phase Shifter Introduction                                                      | .128                                                                                                                                           |

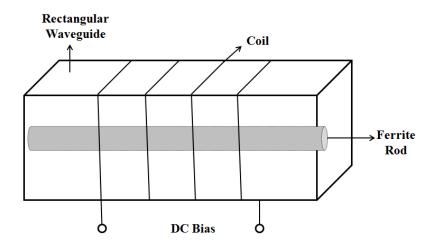

| Ferrite Phase Shifter                                                           | .129                                                                                                                                           |

| Planar Phase Shifter                                                            | .130                                                                                                                                           |

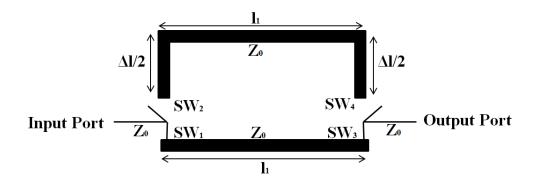

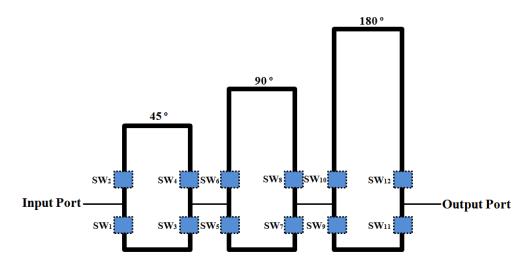

| 2.1 Switched Delay Line Phase Shifter                                           | .130                                                                                                                                           |

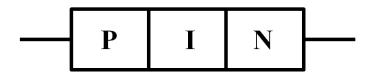

| 4.2.2.1.1 PIN Diodes Switched Delay Line Phase Shifter                          | .132                                                                                                                                           |

| 4.2.2.1.2 FETs Switched Delay Line Phase Shifter                                | .132                                                                                                                                           |

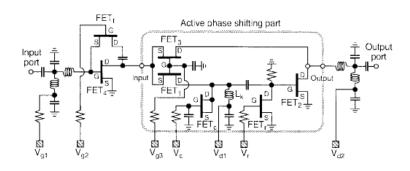

| 4.2.2.1.3 MMIC Phase Shifter                                                    | .133                                                                                                                                           |

| 4.2.2.1.4 MEMS Phase Shifter                                                    | .134                                                                                                                                           |

| .2.2 Loaded Transmission Line Phase Shifter                                     | .136                                                                                                                                           |

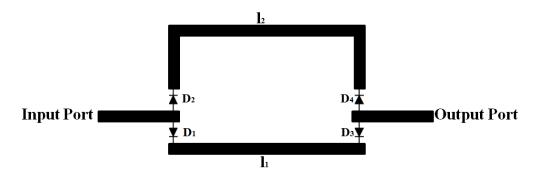

| 4.2.2.2.1 Diode Distributed Transmission Line Phase Shifter                     | .138                                                                                                                                           |

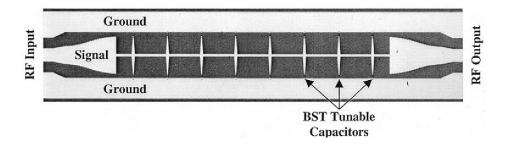

| 4.2.2.2.2 Barium Strontium Titanate Distributed Transmission Line Phase Shifter | .138                                                                                                                                           |

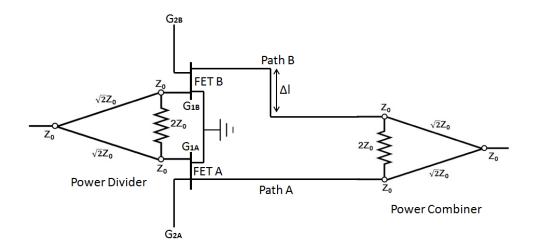

| 4.2.2.2.3 Distributed MEMS Transmission Line Phase Shifter                      | .139                                                                                                                                           |

| Hittite Analogue Phase Shifter Evaluation                                       |                                                                                                                                                |

| Hittite Analogue Phase Shifter Description                                      |                                                                                                                                                |

| Hittite Analogue Phase Shifter Characterisation                                 | .146                                                                                                                                           |

|                                                                                 | A Reconfigurable Feeding Network for a Dual Circularly Polarised Antenna Array. Introduction.  Individual Wilkinson Power Divider Architecture |

|   | 4.4    | UWB CPW-to-Microstrip Transition Structure            | 150 |

|---|--------|-------------------------------------------------------|-----|

|   | 4.4.1  | Field Matching                                        | 150 |

|   | 4.4.2  | Impedance Matching                                    | 151 |

|   | 4.4.3  | UWB CPW-to-Microstrip Transition Characterisation     | 153 |

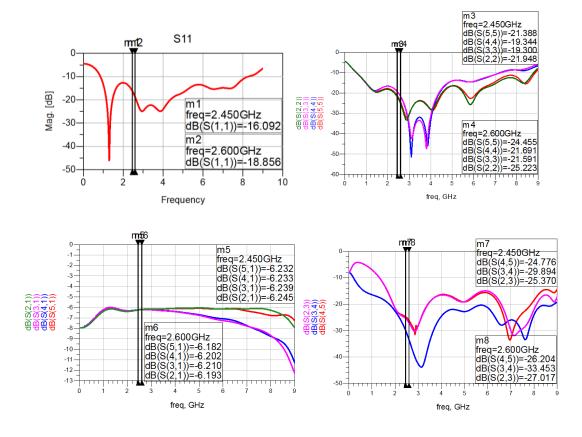

|   | 4.5    | Smart Antenna Array Implementation                    | 157 |

|   | 4.5.1  | Adaptive 1:4 UWB Feeding Network Integration          | 157 |

|   | 4.5.2  | Smart Antenna Array Integration and Characterisation  | 160 |

|   | 4.6    | Summary                                               | 165 |

| ( | СНАРТЕ | R 5: HARDWARE CONTROL SYSTEMS FOR SMART ANTENNA       | 167 |

|   | 5.1    | Introduction                                          | 167 |

|   | 5.2    | Key Components Characterisations                      | 168 |

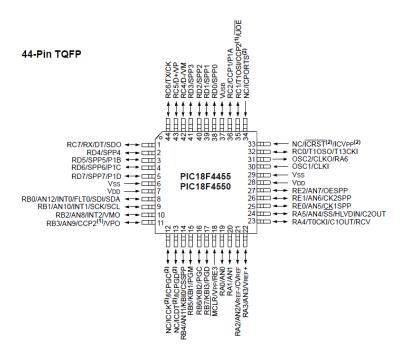

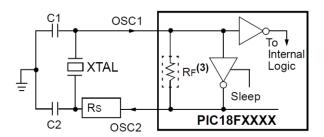

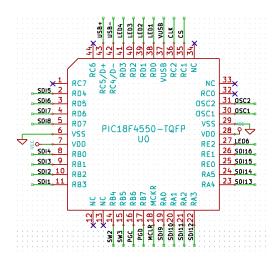

|   | 5.2.1  | Microcontroller PIC18F4550                            | 169 |

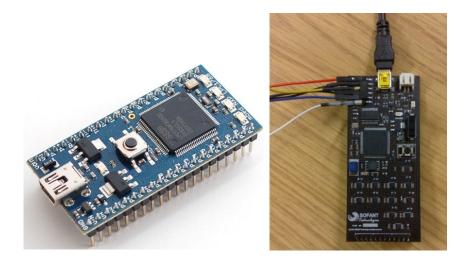

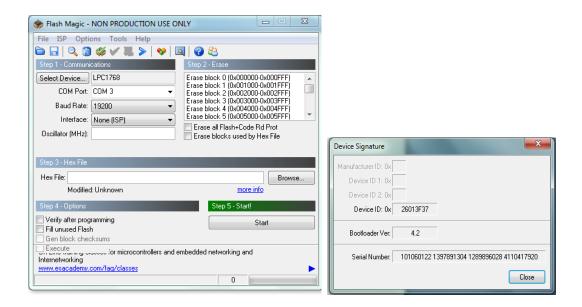

|   | 5.2.2  | Microcontroller LPC1768                               | 172 |

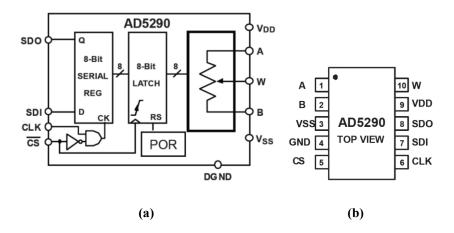

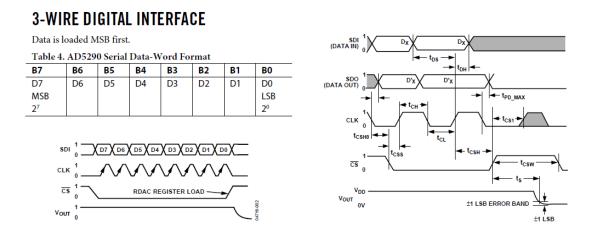

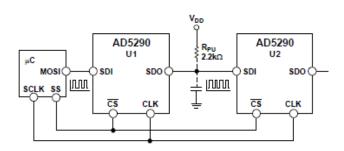

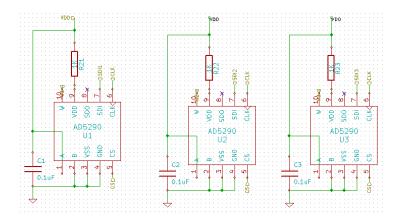

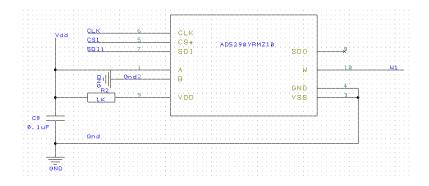

|   | 5.2.3  | Digital Potentiometer AD5290.                         | 174 |

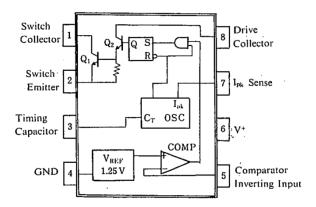

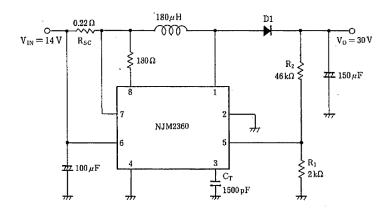

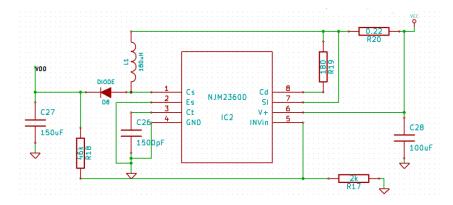

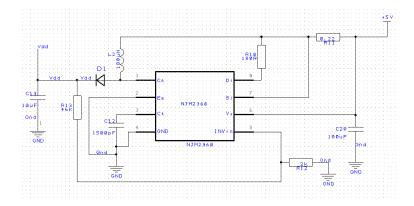

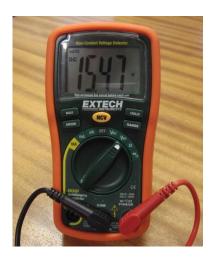

|   | 5.2.4  | Voltage Booster NJM2360                               | 177 |

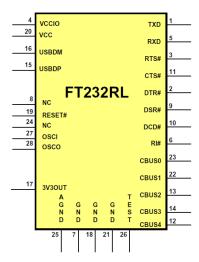

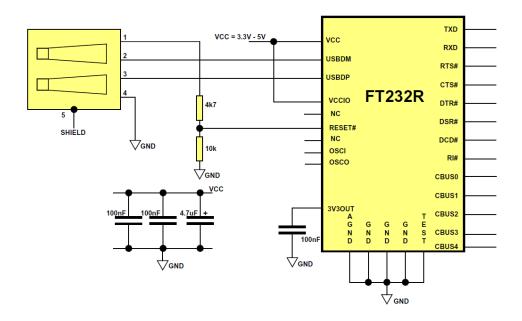

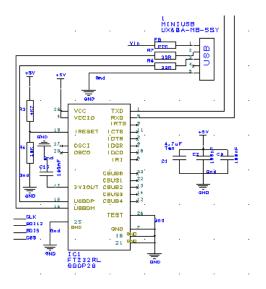

|   | 5.2.5  | USB to UART Interface FT232RL                         | 178 |

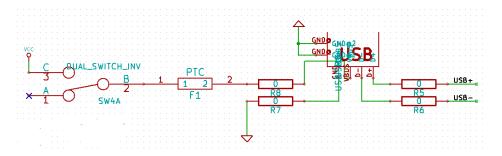

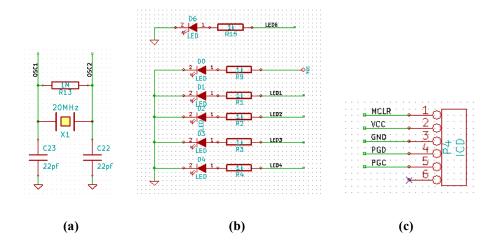

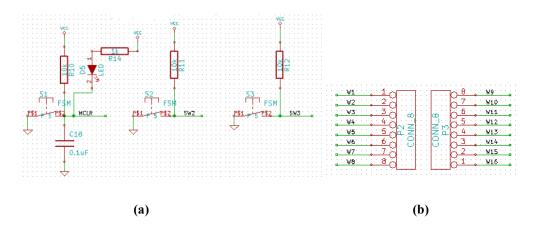

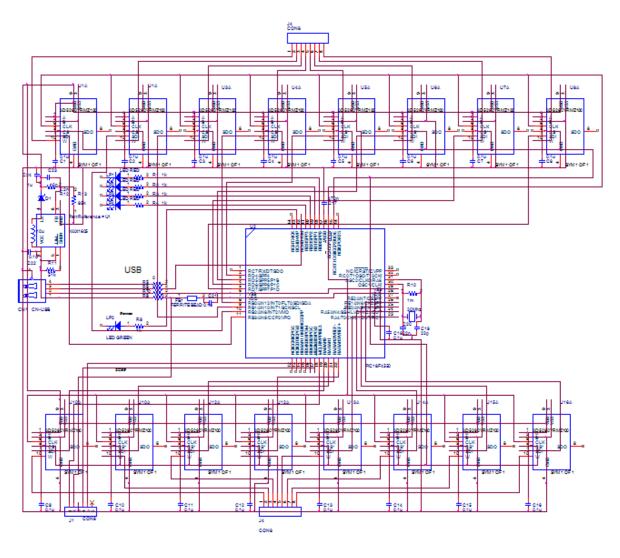

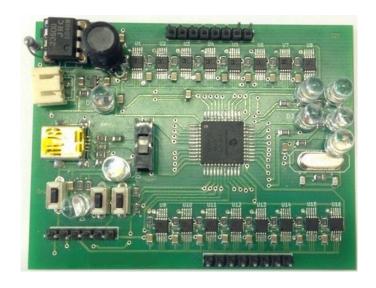

|   | 5.3    | Control PCB Implementation Using PIC18F4550           | 179 |

|   | 5.3.1  | Circuit Diagram.                                      | 179 |

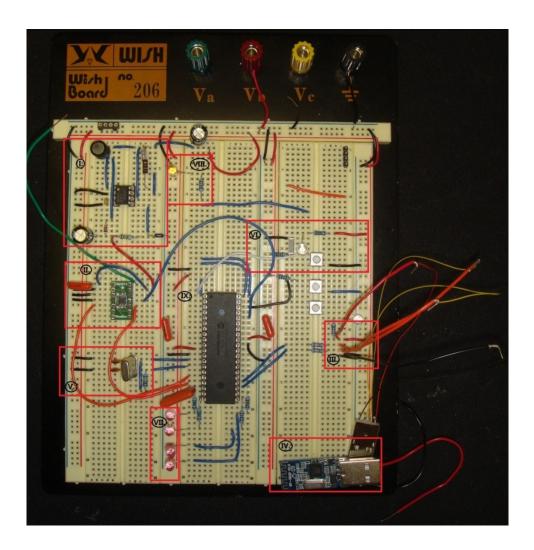

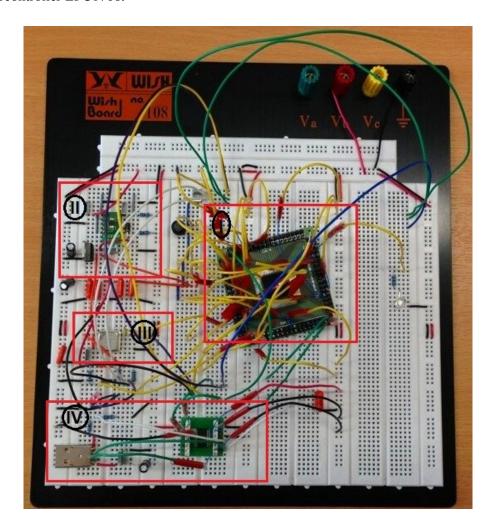

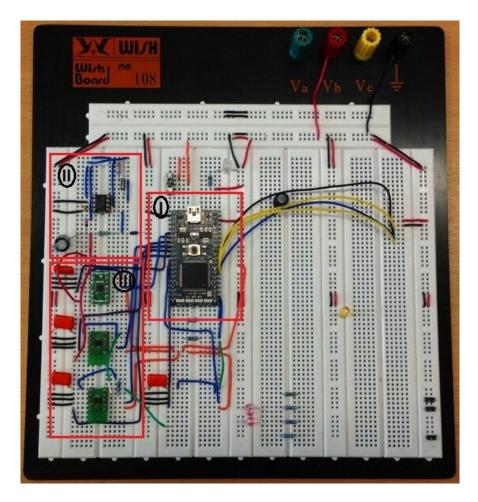

|   | 5.3.2  | Breadboard Testing                                    | 183 |

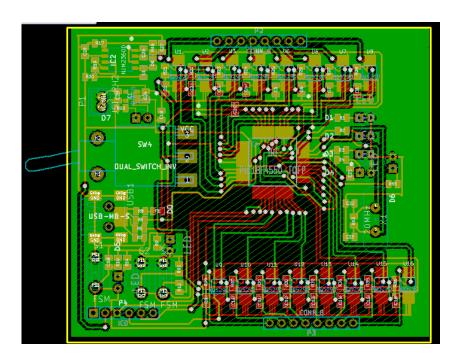

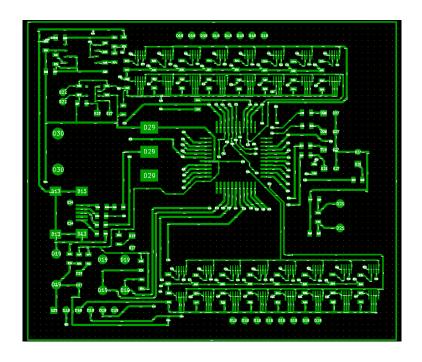

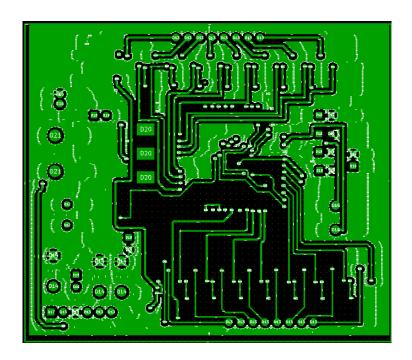

|   | 5.3.3  | PCB Fabrication                                       | 185 |

|   | 5.3.4  | PCB Evaluation                                        | 189 |

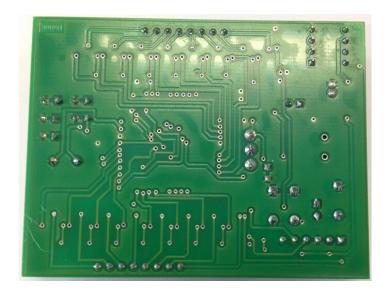

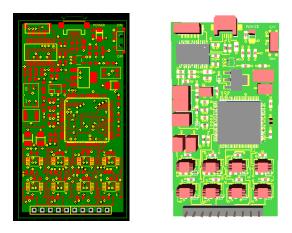

|   | 5.4    | Control PCB Implementation Using LPC1768              | 192 |

|   | 5.4.1  | Circuit Diagram                                       | 192 |

|   | 5.4.2  | Breadboard Testing                                    | 195 |

|   | 5.4.3  | PCB Fabrication                                       | 198 |

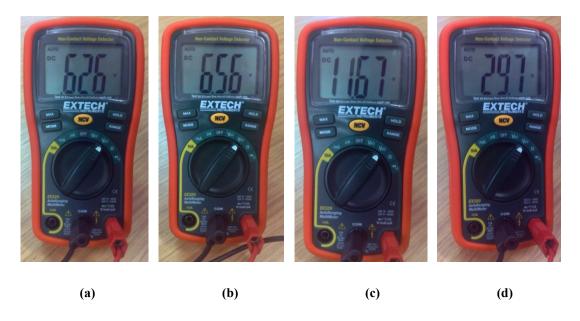

|   | 5.4.4  | PCB Evaluation                                        | 201 |

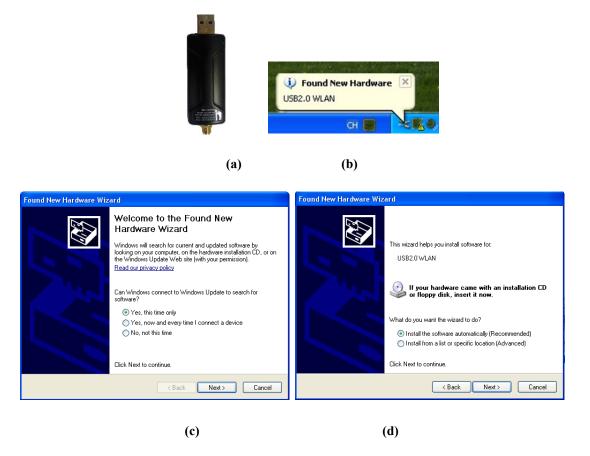

|   | 5.5    | EDUP WiFi Adapter                                     | 203 |

|   | 5.6    | Summary                                               | 205 |

| ( | НАРТЕ  | R 6: SOFTWARE CONTROL SYSTEMS FOR SMART ANTENNA       | 207 |

|   | 6.1    | Introduction                                          | 207 |

|   | 6.2    | Software Implementation for PIC18F4550 Control System | 208 |

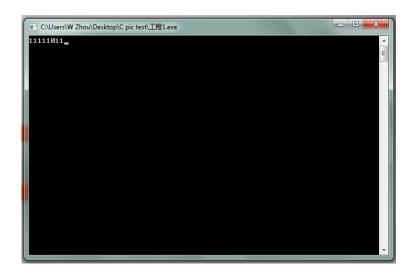

|   | 6.2.1  | Programme PIC18F4550                                  | 209 |

|   | 6.     | 2.1.1 SPI Communication                               | 209 |

|   | 6.     | 2.1.2 Manual Control                                  | 210 |

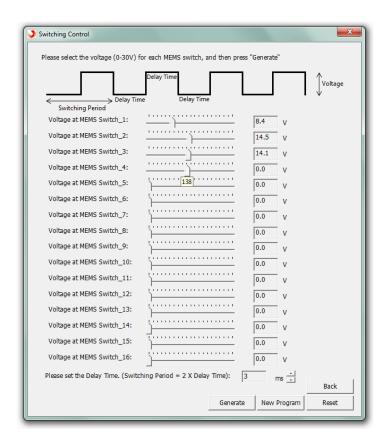

|   | 6.     | 2.1.3 Switching Control                               | 213 |

|   | 6.2.2  | Graphical User Interface for PIC18F4550               | 214 |

|   | 6.     | 2.2.1 Manual Control                                  | 215 |

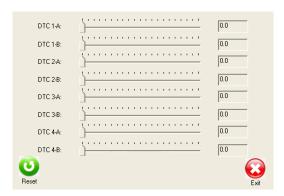

| 6.2     | .2.2 Switching Control                             | 216 |

|---------|----------------------------------------------------|-----|

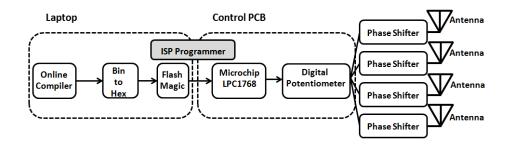

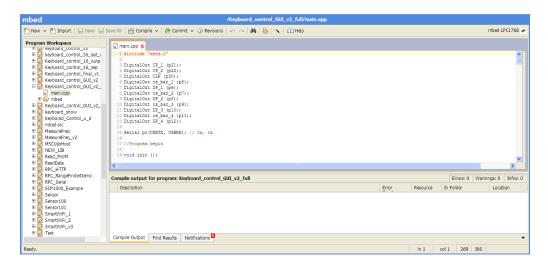

| 6.3     | Software Implementation for LPC1768 Control System | 218 |

| 6.3.1   | Programme LPC1768                                  | 218 |

| 6.3.2   | Graphical User Interface for LPC1768               | 220 |

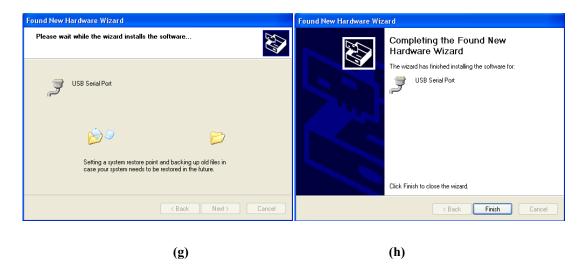

| 6.3     | .2.1 Driver Installation                           | 220 |

| 6.3     | .2.2 Manual Control                                | 223 |

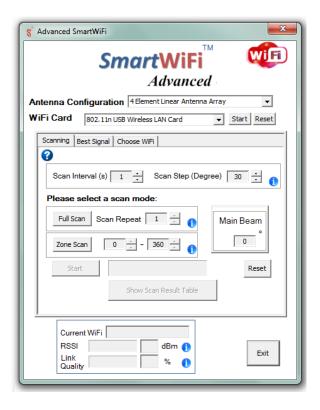

| 6.3     | .2.3 Automatic Control                             | 227 |

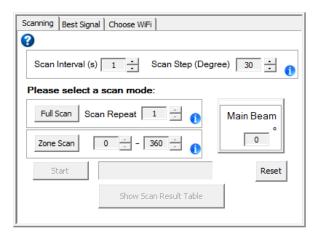

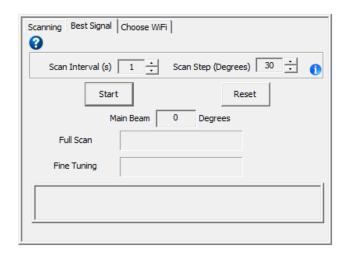

| (       | 5.3.2.3.1 Scanning Function                        | 229 |

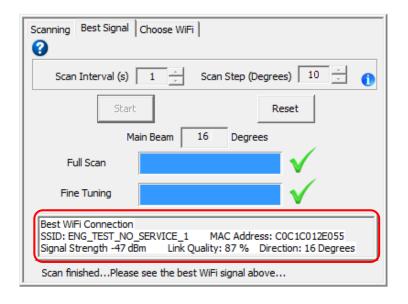

| (       | 5.3.2.3.2 Best Signal Function                     | 231 |

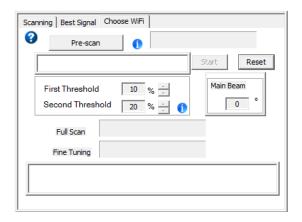

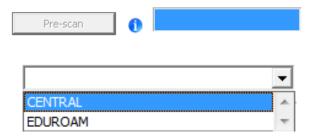

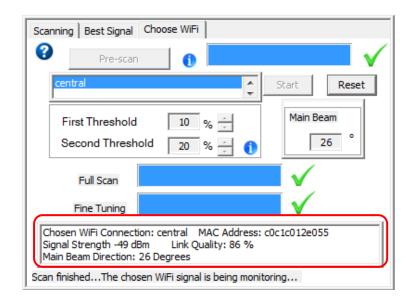

| (       | 5.3.2.3.3 Choose WiFi Function                     | 232 |

| 6.4     | Summary                                            | 235 |

| Снартег | 7: Conclusions                                     | 237 |

| 7.1     | Summary and Conclusions                            | 237 |

| 7.2     | Summary of Contributions                           | 240 |

| 7.2.1   | Miniaturised and Multiband Antenna Design          | 240 |

| 7.2.2   | Adaptive Array Geometry with Wide Scanning Range   | 240 |

| 7.2.3   | Reconfigurable and UWB Feeding Network             | 241 |

| 7.2.4   | Phase Shifter Evaluation                           | 242 |

| 7.2.5   | UWB CPW-to-Microstrip Transition                   | 242 |

| 7.2.6   | Smart Antenna Hardware Implementation              | 242 |

| 7.2.7   | Smart Antenna Software Control System              | 243 |

| 7.2.8   | Complete Smart Antenna System Integration          | 243 |

| 7.3     | Future Work                                        | 243 |

| 7.3.1   | Antenna Design                                     | 243 |

| 7.3.2   | Array Geometry                                     | 243 |

| 7.3.3   | Feeding Network Structure                          | 244 |

| 7.3.4   | Phase Shifter Investigation                        | 245 |

| 7.3.5   | Hardware Control                                   | 245 |

| 7.3.6   | Software Programming                               | 247 |

| 7.4     | Final Comments                                     | 247 |

| REFEDEN | CES                                                | 248 |

# **LIST OF FIGURES**

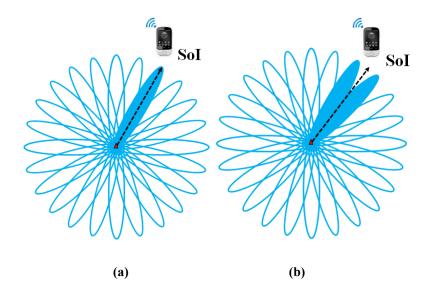

| Figure 1.1: (a) Predefined Switched Beam Antenna (b) Low Resolution of the Main Beam.                  | 2    |

|--------------------------------------------------------------------------------------------------------|------|

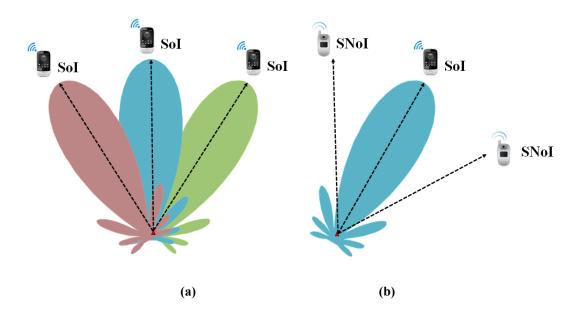

| Figure 1.2: Adaptive Antenna (a) Arbitrary Steering (b) Adaptive Beamforming                           | 2    |

| Figure 1.3: Overview of the Research Structure                                                         | 6    |

| Figure 1.4: Block Diagram of the Autonomous Smart Antenna System                                       | 8    |

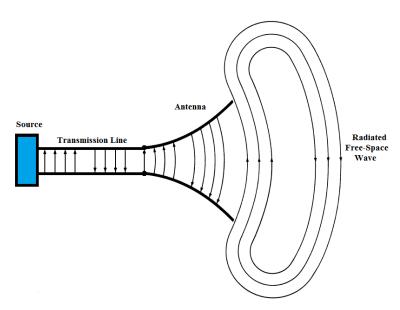

| Figure 2.1: Antenna Operates as a Transition Device [22]                                               | . 12 |

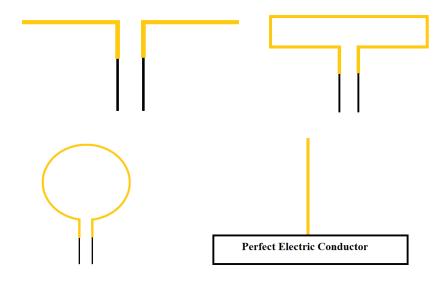

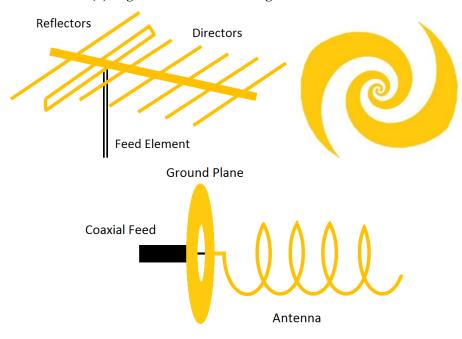

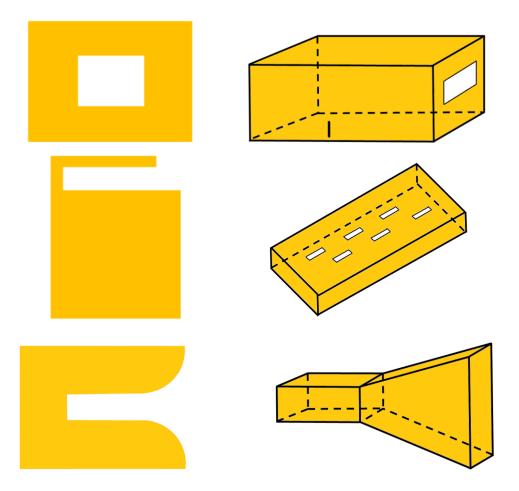

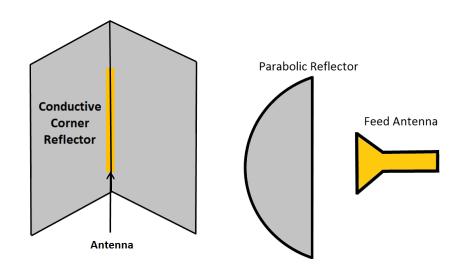

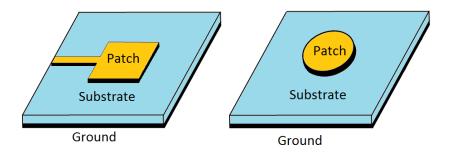

| Figure 2.2: Antenna Types: (a) Wire Antennas, (b) Log-Periodic Antennas, (c) Travelling                |      |

| Wave Antennas, (d) Aperture Antennas, (e) Reflector Antennas, and (f) Microstrip Antenna               | as   |

|                                                                                                        | 15   |

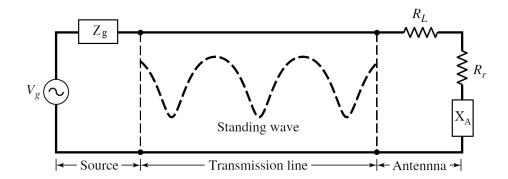

| Figure 2.3: Transmission-Line Thevenin Equivalent of a Transmitting Antenna [22]                       | 15   |

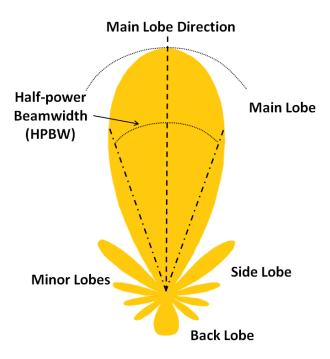

| Figure 2.4: Directional Radiation Pattern                                                              | . 17 |

| Figure 2.5: Antenna Radiation Field Regions [22]                                                       | 18   |

| Figure 2.6: Antenna Terminals and Losses                                                               | 20   |

| Figure 2.7: Linear Polarisation and Circular Polarisation                                              | 21   |

| Figure 2.8: UWB Printed Monopole Antenna with a Pair of L-Shaped Slots [29]                            | 22   |

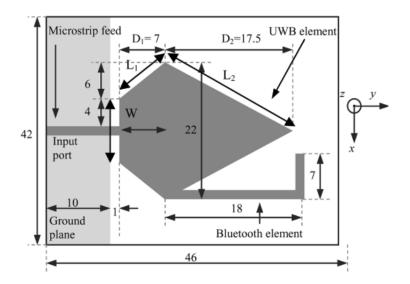

| Figure 2.9: Microstrip-Fed Integrated Bluetooth/UWB Antenna [30]                                       | 23   |

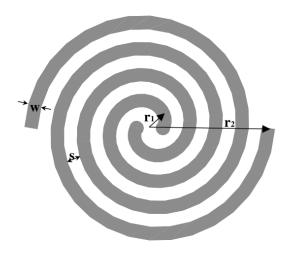

| Figure 2.10: Conventional Archimedean Spiral Antenna Structure                                         | 23   |

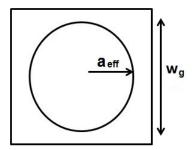

| Figure 2.11: Geometry of the Fundamental Antenna                                                       | 24   |

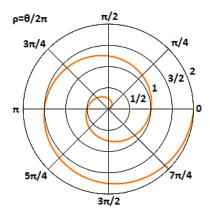

| Figure 2.12: Archimedean Spiral Represented on a Polar Graph                                           | 26   |

| Figure 2.13: Geometry of the Proposed Antenna                                                          | 26   |

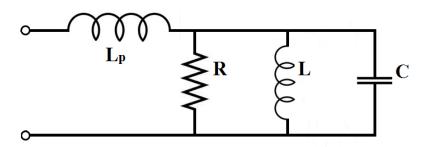

| Figure 2.14: Equivalent Circuit of the Patch Antenna                                                   | 27   |

| Figure 2.15: Equivalent Circuit of the Planar Monopole Antenna with Archimedean Spiral                 |      |

| Slots                                                                                                  | . 28 |

| Figure 2.16: Equivalent Circuit of the Planar Monopole Antenna with Archimedean Spiral                 |      |

| Slots in ADS                                                                                           | . 28 |

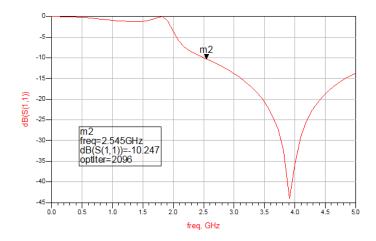

| Figure 2.17: Simulation Results of the Antenna Equivalent Circuit in ADS                               | 29   |

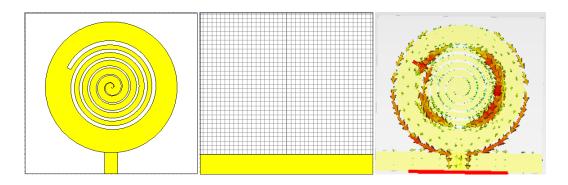

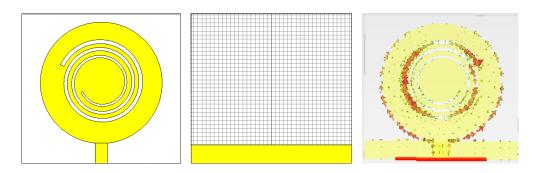

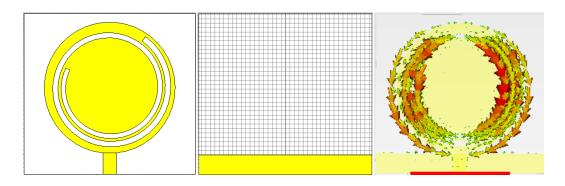

| Figure 2.18: Planar Monopole Antenna with Archimedean Spiral Slots ( $t = 0 \sim 0.5$ mm), From        | nt   |

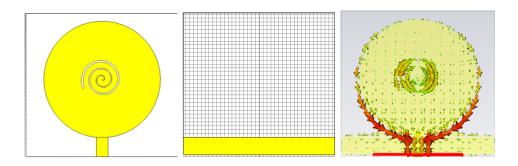

| View, Back View, and its Corresponding Surface Current Distribution                                    | 30   |

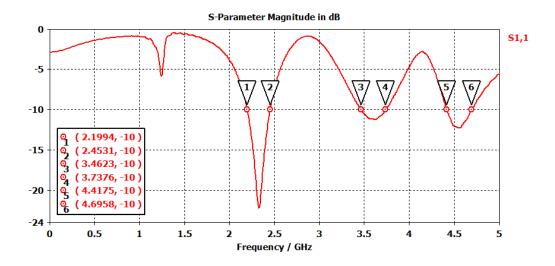

| Figure 2.19: Simulated Reflection Coefficient of the Planar Monopole Antenna with                      |      |

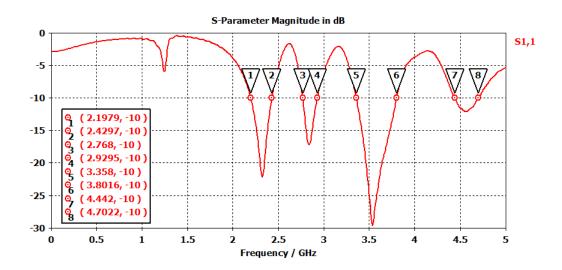

| Archimedean Spiral Slots ( $t = 0 \sim 0.5 \text{mm}$ )                                                | 30   |

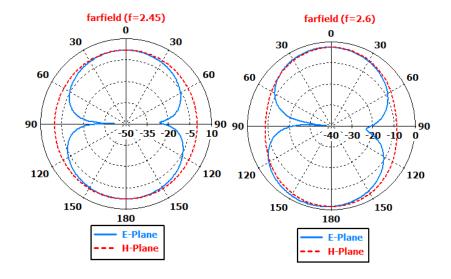

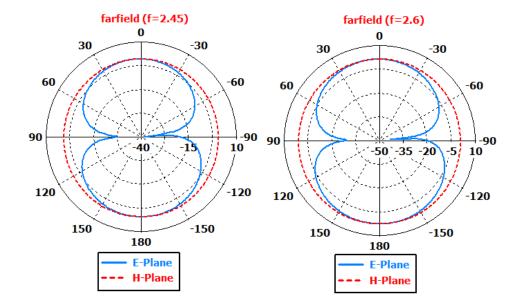

| Figure 2.20: Simulated Radiation Pattern of the Planar Monopole Antenna with Archimede                 | an   |

| Spiral Slots (t = 0~0.5mm), at 2.45GHz and 2.6GHz, in E-Plane and H-Plane                              | 30   |

| Figure 2.21: Planar Monopole Antenna with Archimedean Spiral Slots ( $t = 0 \sim 1 \text{mm}$ ), Front |      |

| View, Back View, and its Corresponding Surface Current Distribution                                    | 31   |

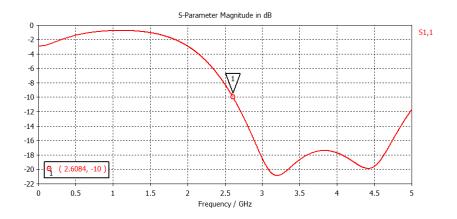

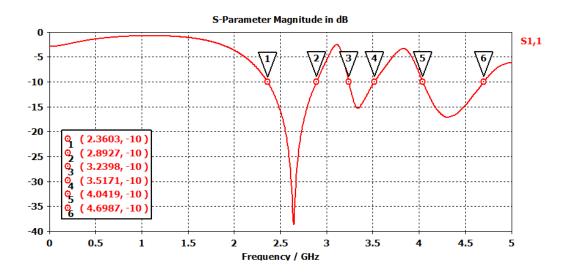

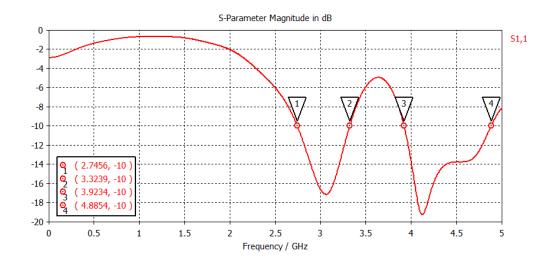

| Figure 2.22: Simulated Reflection Coefficient of the Planar Monopole Antenna with            |       |

|----------------------------------------------------------------------------------------------|-------|

| Archimedean Spiral Slots ( $t = 0 \sim 1 \text{mm}$ )                                        | 31    |

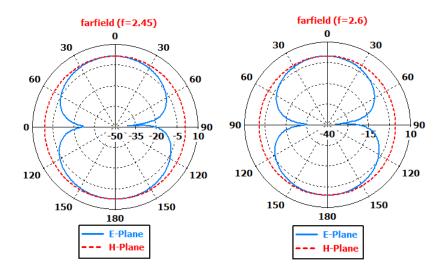

| Figure 2.23: Simulated Radiation Pattern of the Planar Monopole Antenna with Archime         | edean |

| Spiral Slots ( $t = 0 \sim 1 \text{ mm}$ ), at 2.45GHz and 2.6GHz, in E-Plane and H-Plane    | 31    |

| Figure 2.24: Planar Monopole Antenna with Archimedean Spiral Slots ( $t = 0 \sim 1.3$ mm), F | ront  |

| View, Back View, and its Corresponding Surface Current Distribution                          | 32    |

| Figure 2.25: Simulated Reflection Coefficient of the Planar Monopole Antenna with            |       |

| Archimedean Spiral Slots ( $t = 0 \sim 1.3$ mm)                                              | 32    |

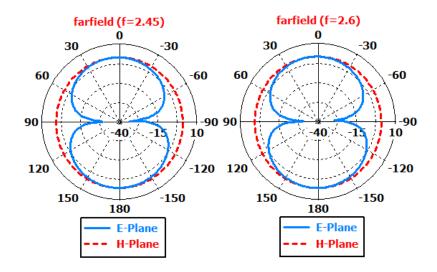

| Figure 2.26: Simulated Radiation Pattern of the Planar Monopole Antenna with Archime         | edean |

| Spiral Slots ( $t = 0 \sim 1.3$ mm), at 2.45GHz and 2.6GHz, in E-Plane and H-Plane           | 32    |

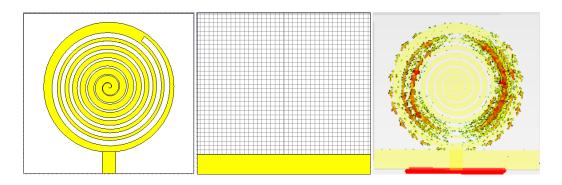

| Figure 2.27: Planar Monopole Antenna with Archimedean Spiral Slots (t = 0.5~1mm), F          | ront  |

| View, Back View, and its Corresponding Surface Current Distribution                          | 33    |

| Figure 2.28: Simulated Reflection Coefficient of the Planar Monopole Antenna with            |       |

| Archimedean Spiral Slots (t = 0.5~1mm)                                                       | 33    |

| Figure 2.29: Simulated Radiation Pattern of the Planar Monopole Antenna with Archime         | edean |

| Spiral Slots ( $t = 0.5 \sim 1 \text{mm}$ ), at 2.45GHz and 2.6GHz, in E-Plane and H-Plane   | 34    |

| Figure 2.30: Planar Monopole Antenna with Archimedean Spiral Slots ( $t = 1 \sim 1.3$ mm), F | ront  |

| View, Back View, and its Corresponding Surface Current Distribution                          | 34    |

| Figure 2.31: Simulated Reflection Coefficient of the Planar Monopole Antenna with            |       |

| Archimedean Spiral Slots ( $t = 1 \sim 1.3$ mm)                                              | 34    |

| Figure 2.32: Simulated Radiation Pattern of the Planar Monopole Antenna with Archime         | edean |

| Spiral Slots ( $t = 1 \sim 1.3$ mm), at 2.45GHz and 2.6GHz, in E-Plane and H-Plane           | 35    |

| Figure 2.33: Photo of the Fabricated Antenna Designs, Front View and Back View               | 36    |

| Figure 2.34: HP8753C Vector Network Analyser                                                 | 36    |

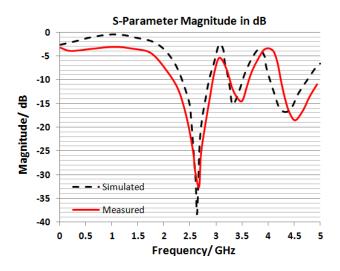

| Figure 2.35: Simulated and Measured Reflection Coefficient of the Proposed Antenna           | 36    |

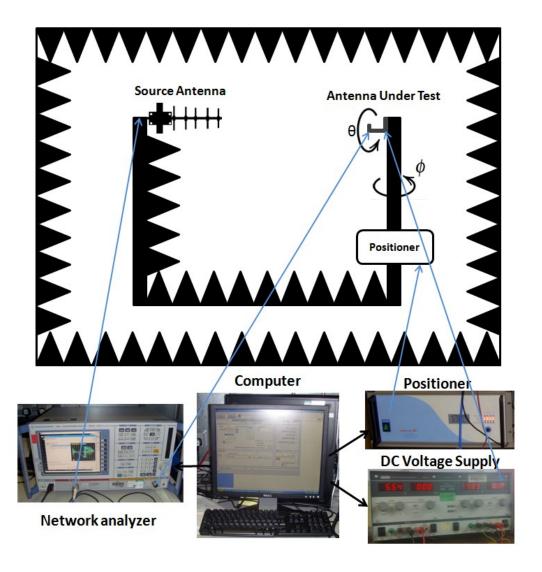

| Figure 2.36: Radiation Pattern Measurement Setup                                             | 37    |

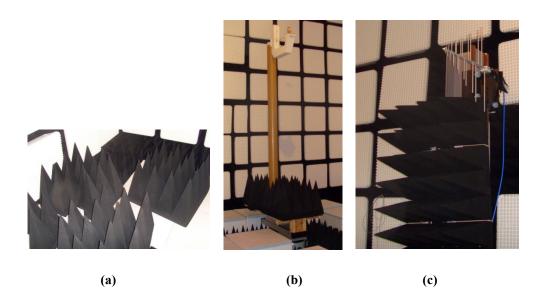

| Figure 2.37: (a) RF Absorbers (b) Antenna under Test (c) Source Yagi Antenna                 | 38    |

| Figure 2.38: Photo of the Radiation Pattern Measurement Setup                                | 38    |

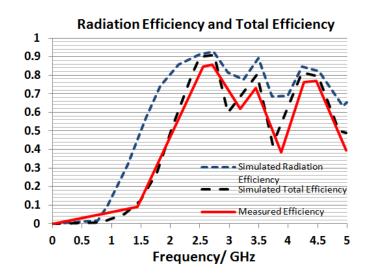

| Figure 2.39: Simulated Radiation Efficiency, Simulated Total Efficiency and Measured         |       |

| Efficiency of the Proposed Antenna Structure                                                 | 39    |

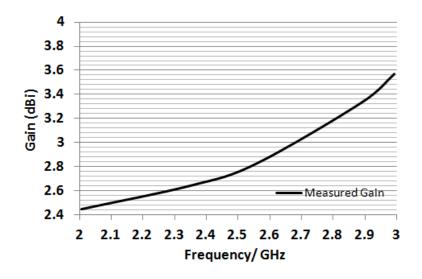

| Figure 2.40: Measured Gain of the Proposed Antenna Structure                                 | 39    |

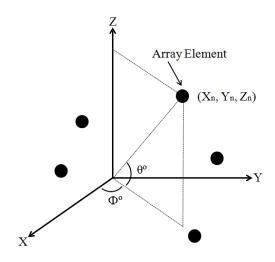

| Figure 2.41: Arbitrary Antenna Array Geometry                                                | 41    |

| Figure 2.42: Four-Element Linear Planar Antenna Array                                        | 42    |

| Figure 2.43: Antenna Array with Inter-Element Spacing S=32mm                                 | 43    |

| Figure 2.44: Antenna Array with Inter-Element Spacing S=36mm                                 | 43    |

| Figure 2.45: Antenna Array with Inter-Element Spacing S=40mm                                 | 44    |

| Figure 2.46: Antenna Array with Inter-Element Spacing S=45mm                                 | 44    |

| Figure 2.47: Antenna Array with Inter-Element Spacing S=50mm                                          | 44 |

|-------------------------------------------------------------------------------------------------------|----|

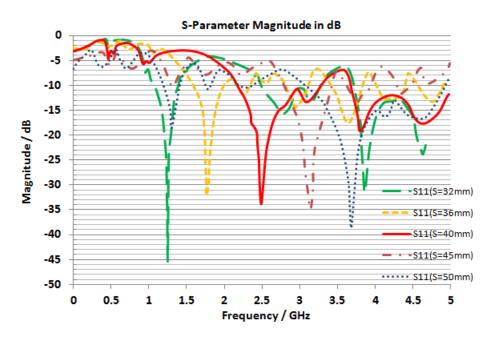

| Figure 2.48: Simulated Reflection Coefficient (S <sub>11</sub> ) Corresponds to Inter-Element Spacing |    |

| Figure 2.49: Simulated Mutual Coupling of the Proposed Antenna Array                                  |    |

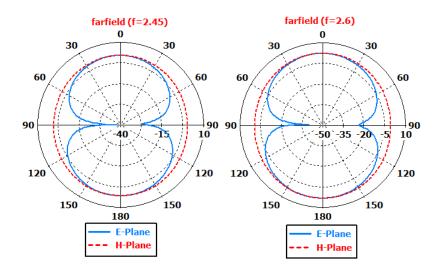

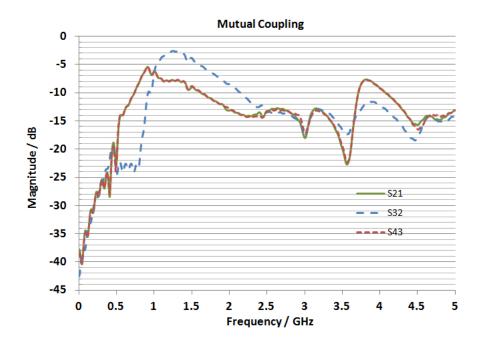

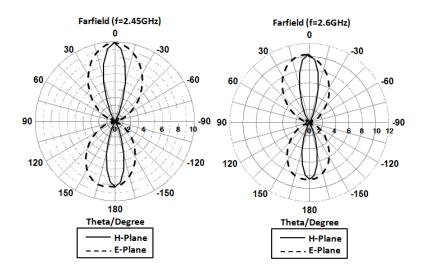

| Figure 2.50: Simulated Radiation Pattern of the Proposed Four-Element Linear Planar                   |    |

| Antenna Array at 2.45GHz and 2.6GHz in H-Plane and E-Plane                                            | 46 |

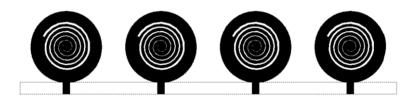

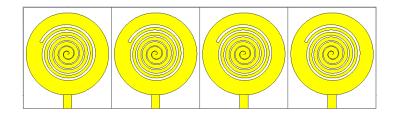

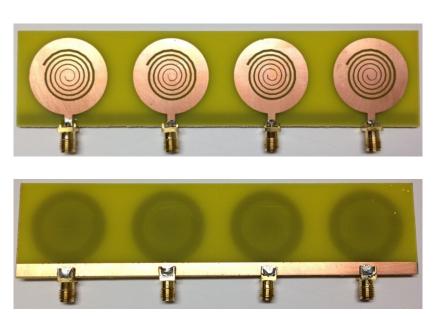

| Figure 2.51: Photo of the Fabricated Antenna Array, Front View and Back View                          | 46 |

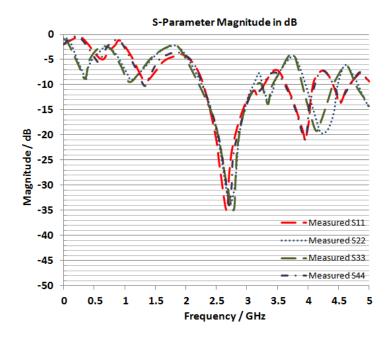

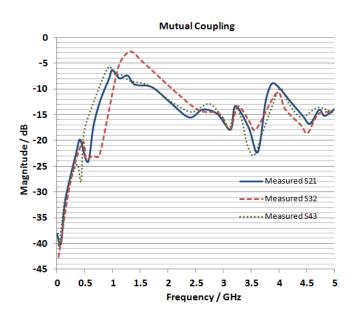

| Figure 2.52: Measured Reflection Coefficient of the Proposed Antenna Array                            | 47 |

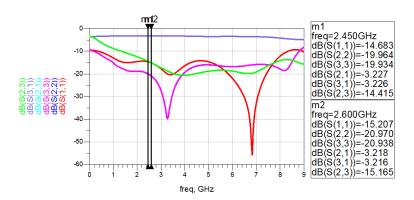

| Figure 2.53: Measured Mutual Coupling of the Proposed Antenna Array                                   | 47 |

| Figure 2.54: Simulated Gain vs. Theta in the H-Plane for Different Scanning Angles, at                |    |

| 2.45GHz                                                                                               | 49 |

| Figure 2.55: Simulated Gain vs. Theta in the H-Plane for Different Scanning Angles, at                |    |

| 2.6GHz                                                                                                | 49 |

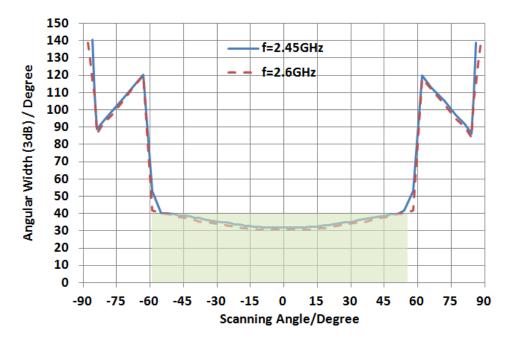

| Figure 2.56: Full Wave Simulation Results of Angular Width (3dB)                                      | 50 |

| Figure 2.57: Full Wave Simulation Results of Side Lobe Level                                          | 50 |

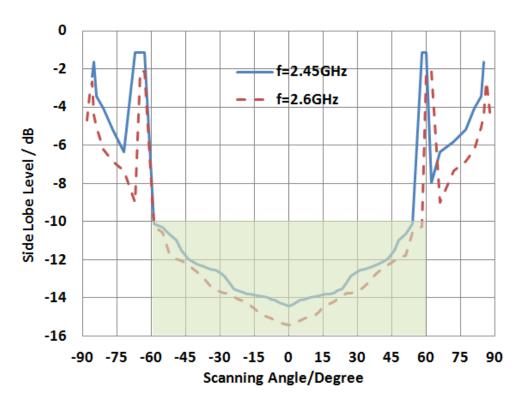

| Figure 2.58: Investigation of Planar Monopole Antenna with Archimedean Spiral Slots                   | 52 |

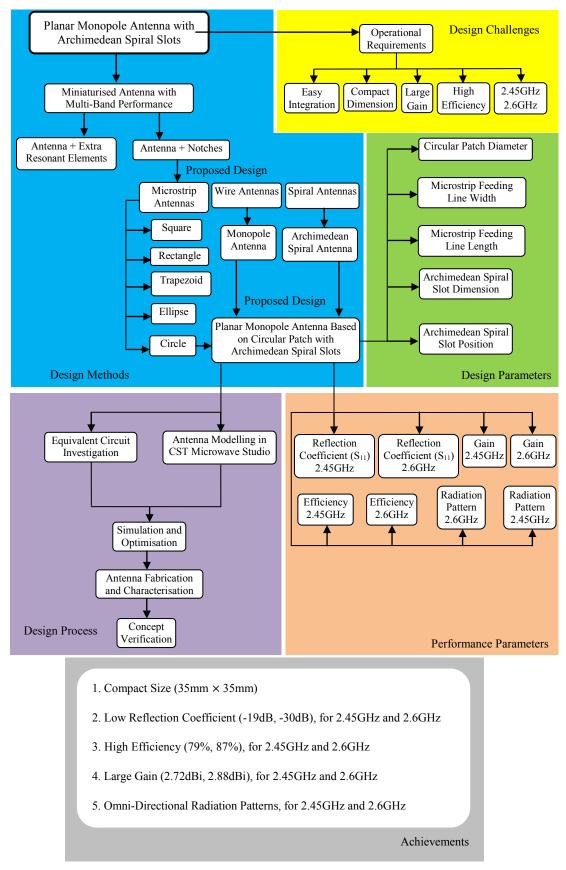

| Figure 2.59: Investigation of Four-Element Linear Antenna Array                                       | 53 |

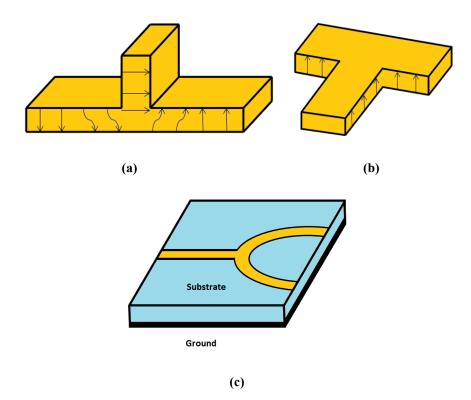

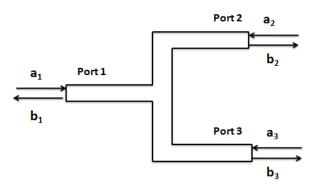

| Figure 3.1: (a) Power Division (b) Power Combination [37]                                             | 55 |

| Figure 3.2: Various T-Junction Power Dividers: (a) E-Plane Waveguide (b) H-Plane                      |    |

| Waveguide (c) Microstrip T-Junction                                                                   | 56 |

| Figure 3.3: Transmission Line Model of a Lossless T-Junction [37]                                     | 57 |

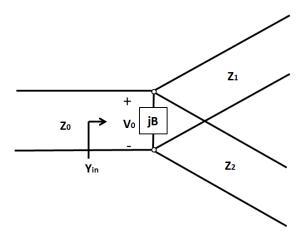

| Figure 3.4: A Reciprocal, Lossless Three-Port Network Matched at Port 1 and 2 [37]                    | 59 |

| Figure 3.5: Equal-Split Three-Port Resistive Power Divider [37]                                       | 59 |

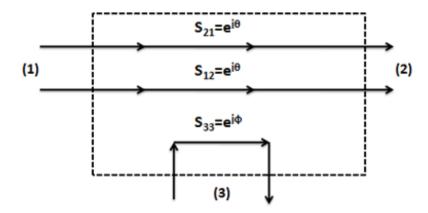

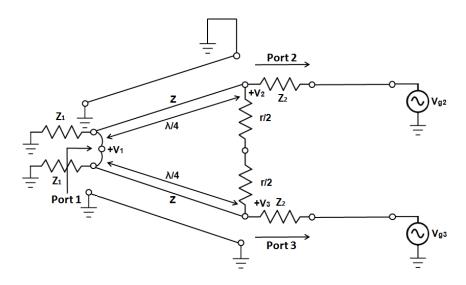

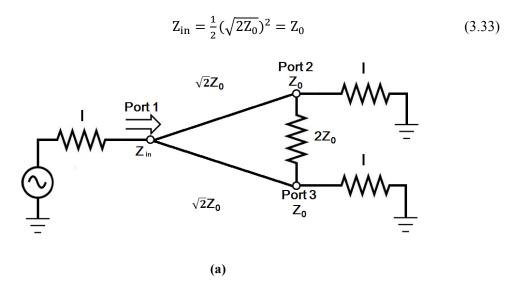

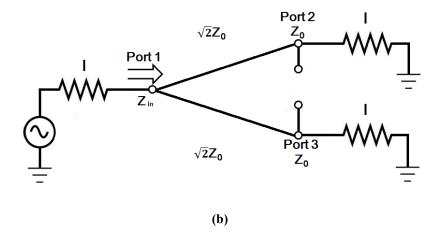

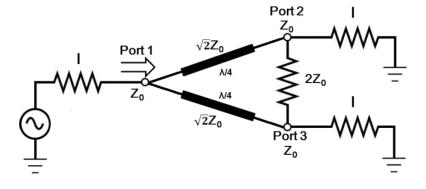

| Figure 3.6: Wilkinson Power Divider Equivalent Transmission Line Circuit                              | 62 |

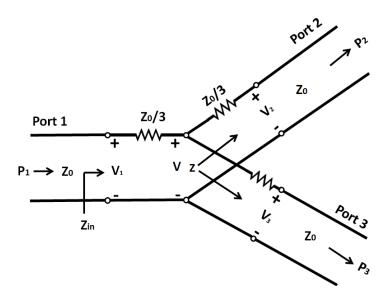

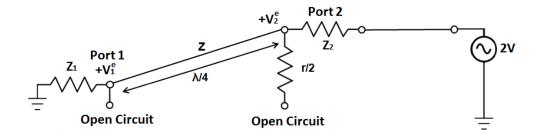

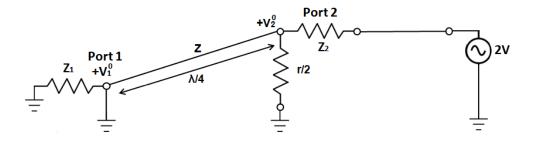

| Figure 3.7: Wilkinson Power Divider in Normalised and Symmetric Form [37]                             | 62 |

| Figure 3.8: Bisection of the Circuit for Even Mode Excitation [37]                                    | 63 |

| Figure 3.9: Bisection of the Circuit for Odd Mode Excitation [37]                                     | 64 |

| Figure 3.10: (a). Terminated Wilkinson Power Divider (b). Bisection Wilkinson Power                   |    |

| Divider [37]                                                                                          | 65 |

| Figure 3.11: Structure of the Wilkinson Power Divider [47]                                            | 65 |

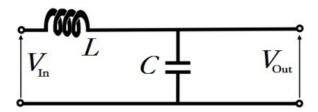

| Figure 3.12: Equivalent Lumped Component Circuit of Lossless Transmission Line [48]                   | 66 |

| Figure 3.13: S-Parameter Relationships                                                                | 67 |

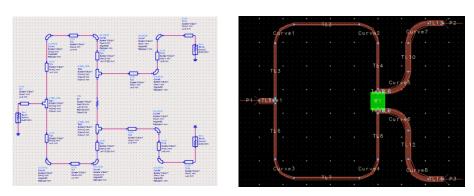

| Figure 3.14: Enhanced Wilkinson Power Divider (a) Schematic (b) Layout [59]                           | 69 |

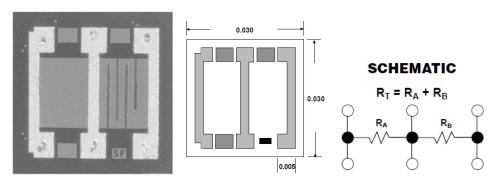

| Figure 3.15: Thin Film, Centre-Tapped Resistors (CTR)                                                 | 69 |

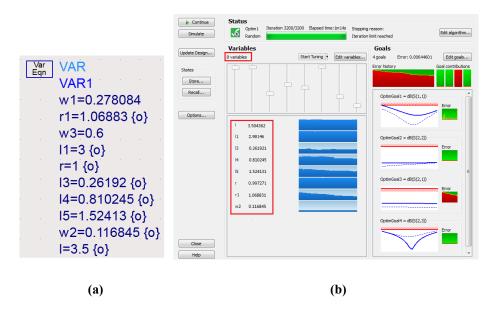

| Figure 3.16: (a) Wilkinson Power Divider Design Parameters (b) Optimisation Results                   | 70 |

| Figure 3.17: 3D View of the Optimised Enhanced Wilkinson Power Divider                                | 70 |

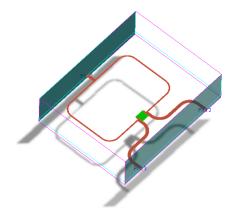

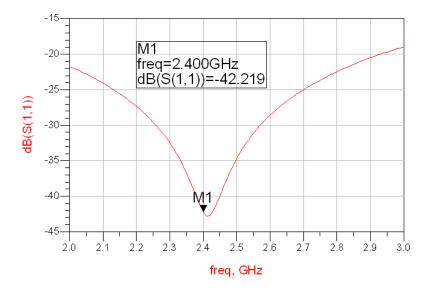

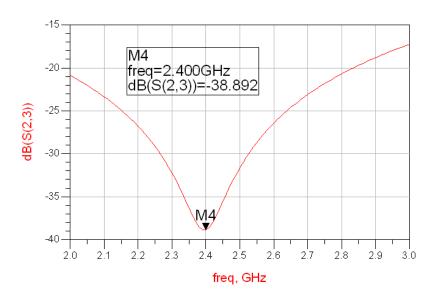

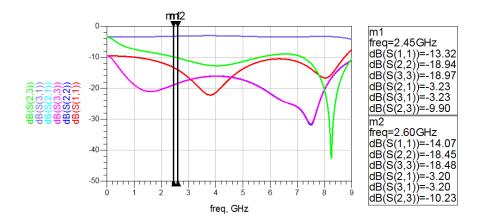

| Figure 3.18: Simulated Reflection Coefficient ( $S_{11}$ ) at the Input Port is -42.219dB at 2.4GF       | łz   |

|----------------------------------------------------------------------------------------------------------|------|

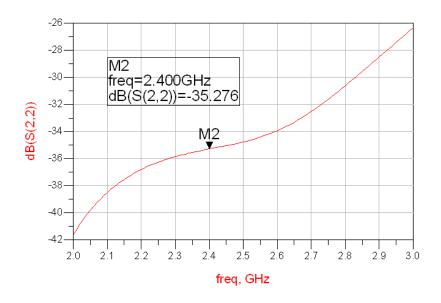

|                                                                                                          | . 71 |

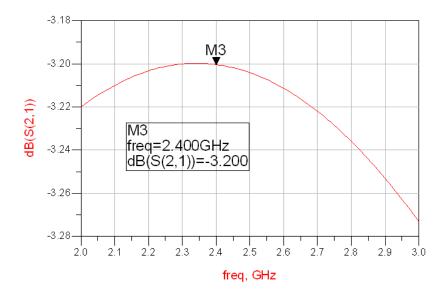

| Figure 3.19: Simulated Reflection Coefficient (S <sub>22</sub> ) at the Output Port is -35.276dB at 2.40 |      |

| Figure 3.20: Simulated Insertion Loss between Port 2 and Port 1 is 3.2dB at 2.4GHz                       |      |

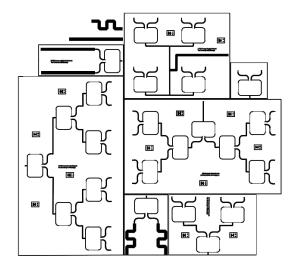

| Figure 3.21: A Good Isolation (S <sub>23</sub> ) is Achieved (-38.892dB) Between Output Ports            | . 72 |

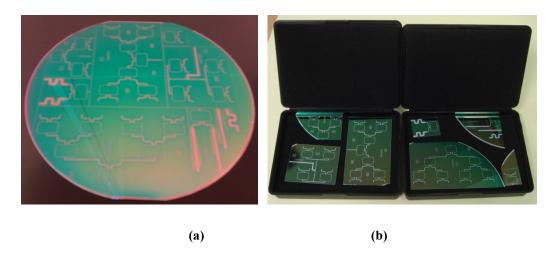

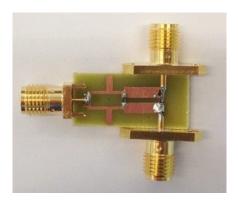

| Figure 3.22: Silicon Wafer Layout                                                                        | . 73 |

| Figure 3.23: (a) Original Wafer (b) Test Components after Dicing                                         | . 73 |

| Figure 3.24: Vector Network Analyser, PC, Microscope and RF Probe Station                                | . 74 |

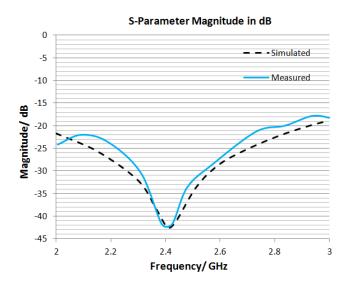

| Figure 3.25: The Fabricated Divider and RF Probes Measurement                                            | . 74 |

| Figure 3.26: Measured $S_{11}$ of the Enhanced Wilkinson Power Divider: $S_{11}$ is -41.637dB at         |      |

| 2.4GHz                                                                                                   | . 74 |

| Figure 3.27: Individual Wilkinson Power Divider                                                          | . 77 |

| Figure 3.28: (a) Modified Wilkinson Power Divider (b) Optimised Structure Based on the                   |      |

| Modified Wilkinson Power Divider                                                                         | . 77 |

| Figure 3.29: Simulated Reflection Coefficient ( $S_{11}$ ) of the Proposed Optimised Wilkinson           |      |

| Power Divider                                                                                            | . 78 |

| Figure 3.30: Structure of the Circular Feeding Network                                                   | . 79 |

| Figure 3.31: Geometry of the Circular Feeding Network with Meandered Input                               | . 79 |

| Figure 3.32: Photo of the Fabricated Prototype of the Circular Feeding Network                           | . 79 |

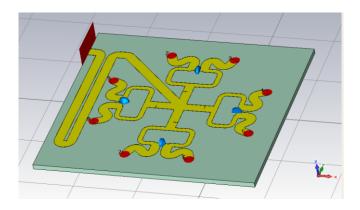

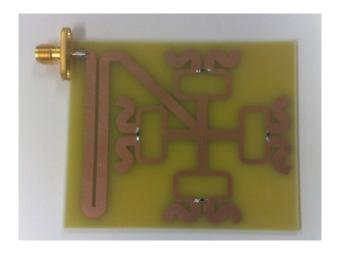

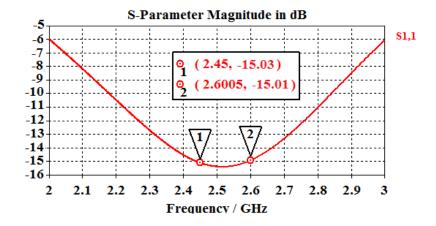

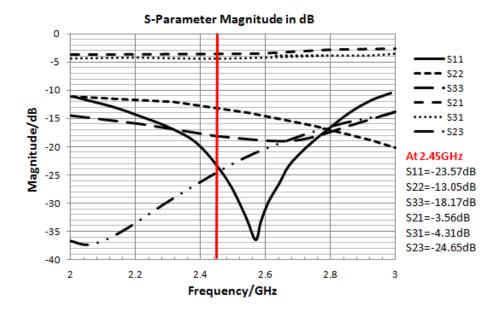

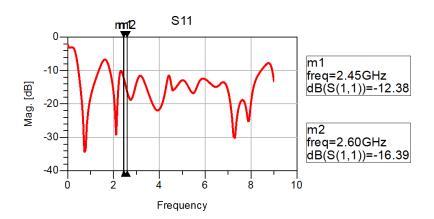

| Figure 3.33: Simulated $S_{11}$ : $S_{11}$ is -15.03dB and -15.01dB at 2.45GHz and 2.6GHz                | . 80 |

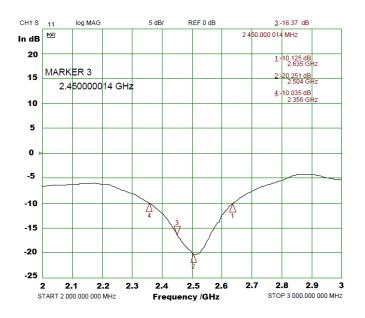

| Figure 3.34: Measured $S_{11}$ Parameter: $S_{11}$ is -16.37dB and -12.34dB at 2.45GHz and 2.6GHz        |      |

| Figure 3.35: Wilkinson Power Divider with 90° Phase Shift                                                |      |

| Figure 3.36: Wilkinson Power Divider with 180° Phase Shift                                               |      |

| Figure 3.37: Simulated S-Parameters (Magnitude) of Wilkinson Power Divider with 90°                      |      |

| Phase Shift                                                                                              | . 85 |

| Figure 3.38: Simulated S-Parameters (Phase) of Wilkinson Power Divider with 90° Phase                    |      |

| Shift                                                                                                    | . 85 |

| Figure 3.39: Simulated S-Parameters (Magnitude) of Wilkinson Power Divider with 180°                     |      |

| Phase Shift                                                                                              | . 86 |

| Figure 3.40: Simulated S-Parameters (Phase) of Wilkinson Power Divider with 180° Phase                   | ;    |

| Shift                                                                                                    |      |

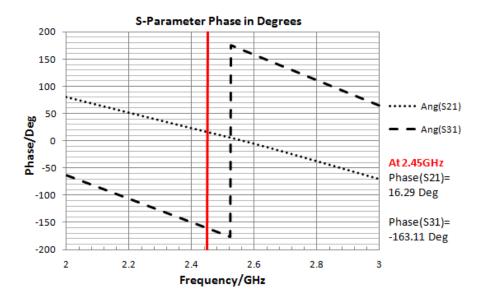

| Figure 3.41: Schematic of the Reconfigurable Feeding Network                                             |      |

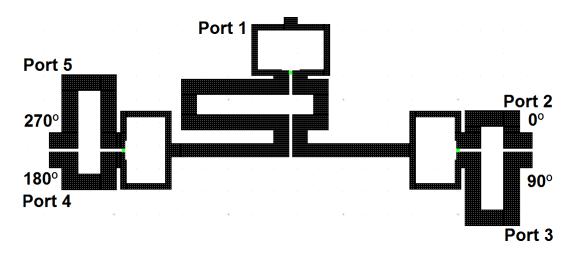

| Figure 3.42: Configuration of the Proposed Feeding Network                                               |      |

| Figure 3.43: Circuit Configuration for Left-Hand Circular Polarisation (LHCP)                            |      |

| Figure 3.44: Circuit Configuration for Right-Hand Circular Polarisation (RHCP)                           | . 89 |

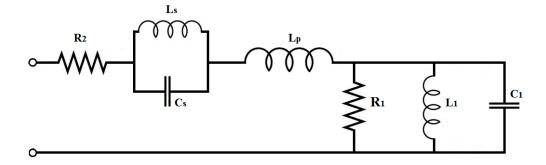

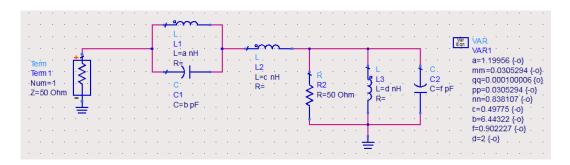

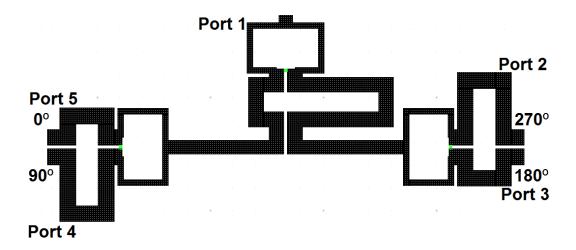

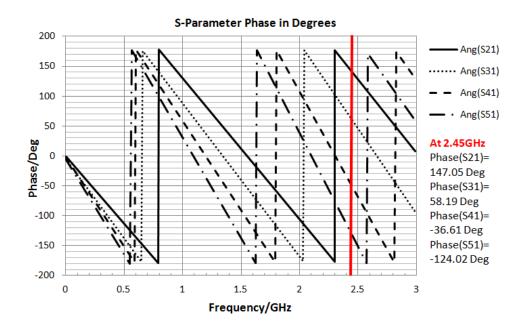

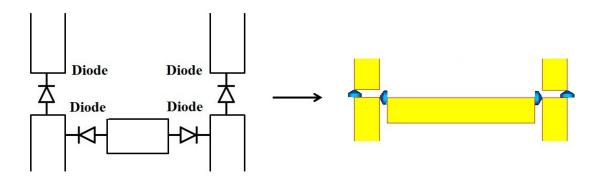

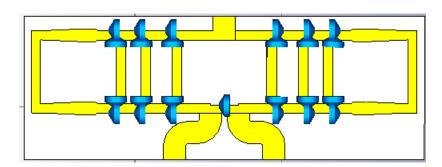

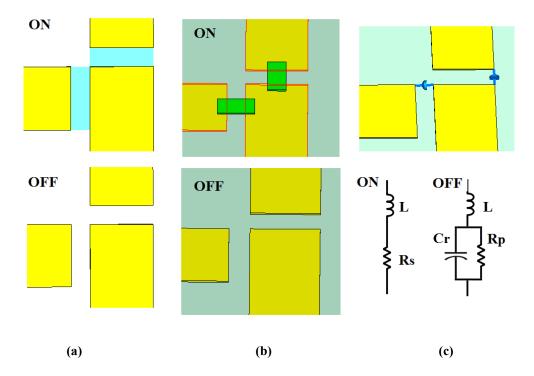

| Figure 3.45: (a) PIN diodes Arrangement (b) Equivalent RLC Circuit of PIN Diode (c) Pl           | N   |

|--------------------------------------------------------------------------------------------------|-----|

| Diode Simulation Model in Agilent ADS                                                            | 89  |

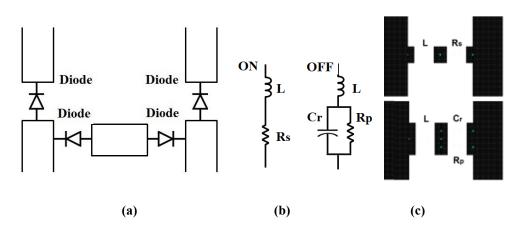

| Figure 3.46: Simulated S-Parameter (Phase) of LHCP                                               | 90  |

| Figure 3.47: Simulated S-Parameter (Phase) of RHCP                                               | 91  |

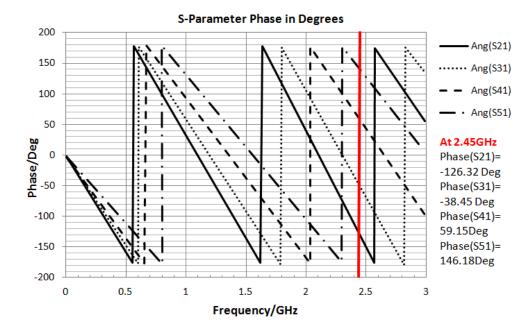

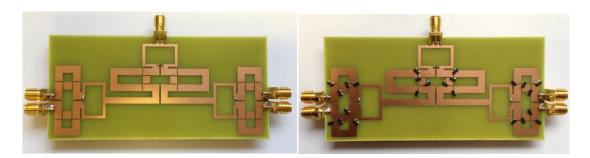

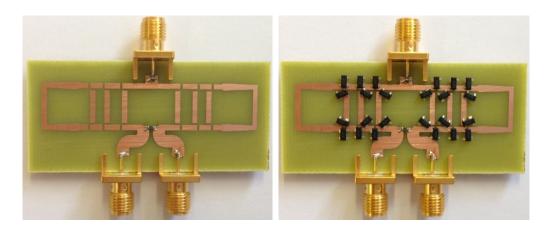

| Figure 3.48: Photo of the Fabricated Structure (with and without PIN Diodes)                     | 91  |

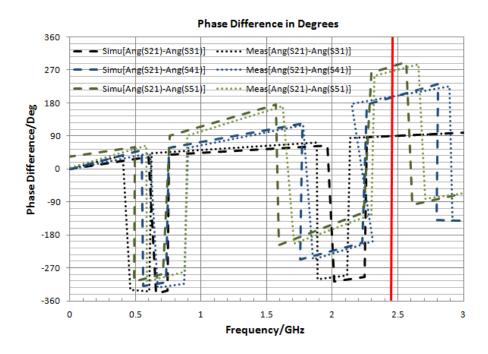

| Figure 3.49: Simulated and Measured Phase Difference for LHCP                                    | 92  |

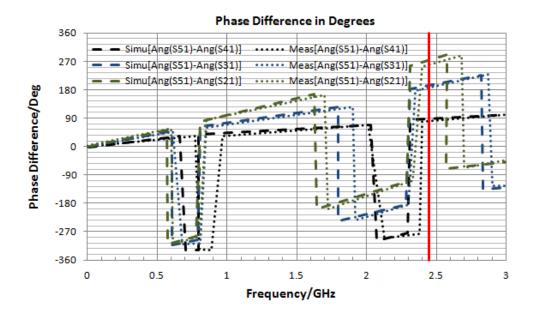

| Figure 3.50: Simulated and Measured Phase Difference for RHCP                                    | 93  |

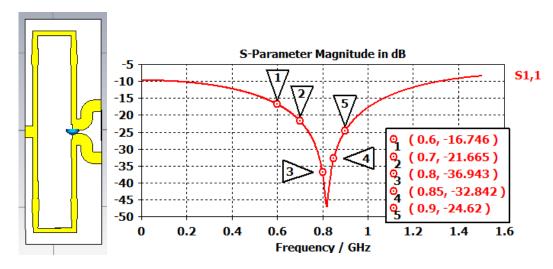

| Figure 3.51: Wilkinson Divider with Frequency Band 600MHz-900MHz                                 | 95  |

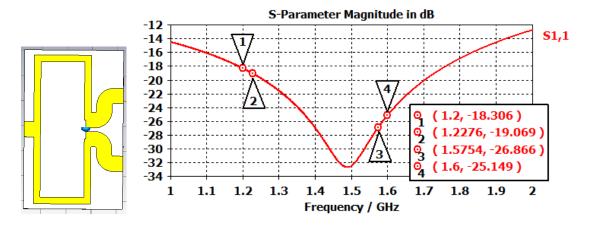

| Figure 3.52: Wilkinson Divider with Frequency Band 1.2GHz-1.6GHz                                 | 95  |

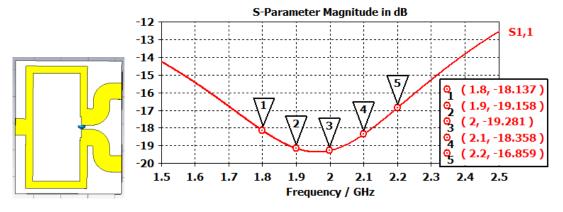

| Figure 3.53: Wilkinson Divider with Frequency Band 1.8GHz-2.2GHz                                 | 95  |

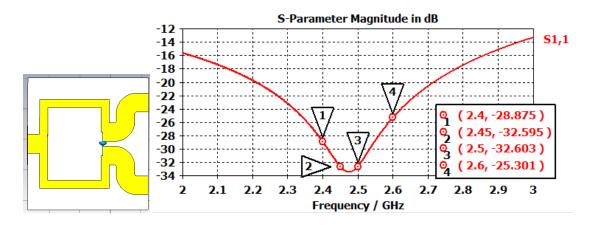

| Figure 3.54: Wilkinson Divider with Frequency Band 2.4GHz-2.6GHz                                 | 96  |

| Figure 3.55: Schematic of the Reconfigurable Feeding Network                                     | 97  |

| Figure 3.56: PIN Diodes Arrangement                                                              | 97  |

| Figure 3.57: Configuration of the Proposed Design in CST Microwave Studio                        | 97  |

| Figure 3.58: Schematic of a PIN Diode                                                            | 98  |

| Figure 3.59: (a) PEC PIN Diode Model (b) Metal Strip PIN Diode Model (c) Equivalent l            | RLC |

| Circuit of PIN Diode                                                                             | 99  |

| Figure 3.60: Photo of the Fabricated Configuration (With and Without PIN Diodes)                 | 100 |

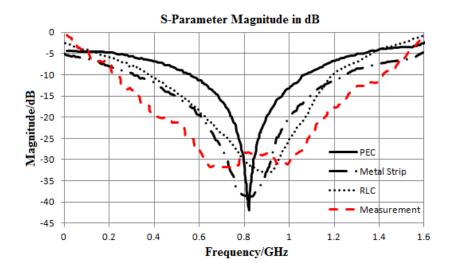

| Figure 3.61: Simulated and Measured Reflection Coefficients (S <sub>11</sub> ) for 600MHz-900MHz | 100 |

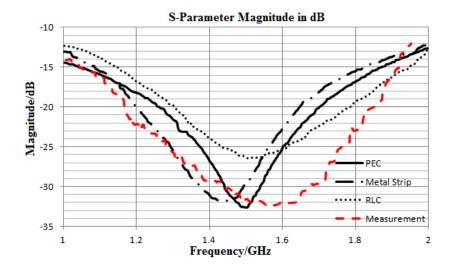

| Figure 3.62: Simulated and Measured Reflection Coefficients ( $S_{11}$ ) for 1.2GHz-1.6GHz       | 101 |

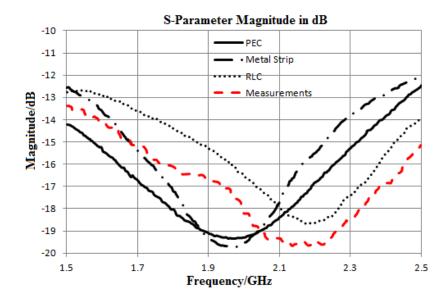

| Figure 3.63: Simulated and Measured Reflection Coefficients ( $S_{11}$ ) for 1.8GHz-2.2GHz       | 101 |

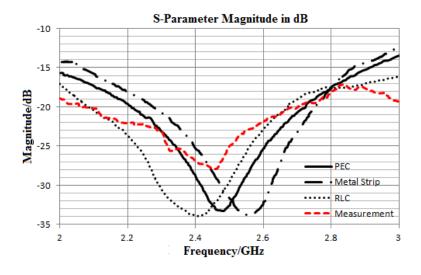

| Figure 3.64: Simulated and Measured Reflection Coefficients ( $S_{11}$ ) for 2.4GHz-2.6GHz       | 101 |

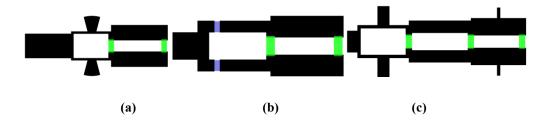

| Figure 3.65: Structure of the UWB Wilkinson Power Divider                                        | 103 |

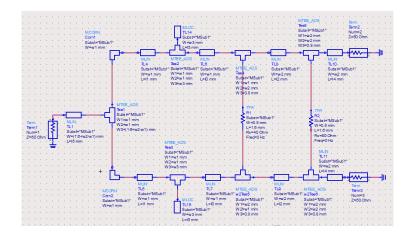

| Figure 3.66: Schematic of the UWB Wilkinson Power Divider                                        | 105 |

| Figure 3.67: Configuration of the UWB Wilkinson Power Divider                                    | 105 |

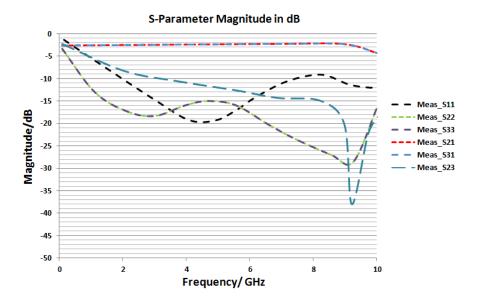

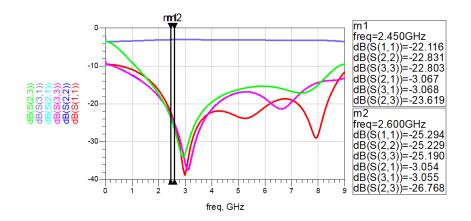

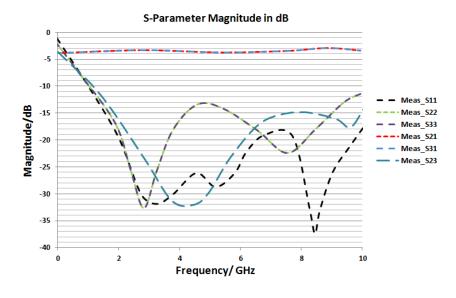

| Figure 3.68: Simulated S-Parameters (Magnitude) of the UWB Wilkinson Power Divider.              | 105 |

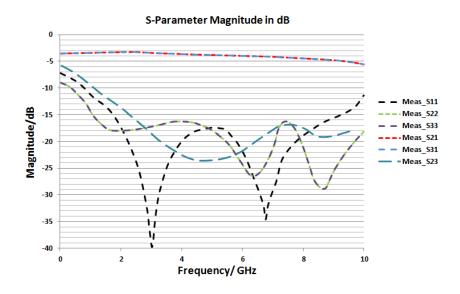

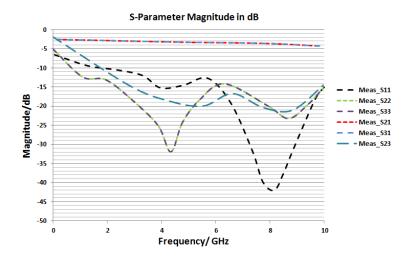

| Figure 3.69: Photo of the Fabricated UWB Wilkinson Power Divider                                 | 106 |

| Figure 3.70: Measured S-Parameters (Magnitude) of the Fabricated UWB Wilkinson Pow               | er  |

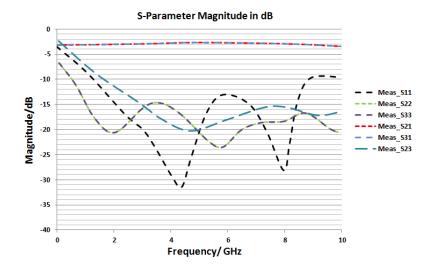

| Divider                                                                                          | 106 |

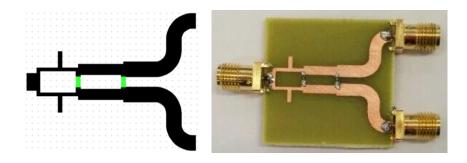

| Figure 3.71: Schematic of the Modified UWB Wilkinson Power Divider                               | 107 |

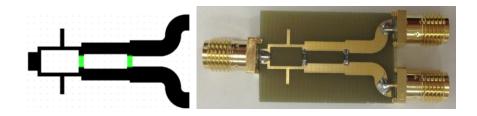

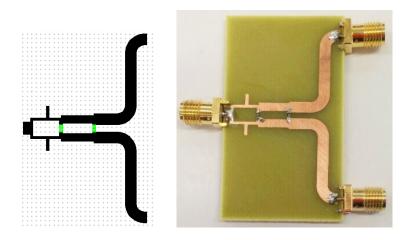

| Figure 3.72: Modified UWB Wilkinson Power Divider with Separation of 12mm                        | 108 |

| Figure 3.73: Simulated S-Parameters (Magnitude) of Modified UWB Wilkinson Power                  |     |

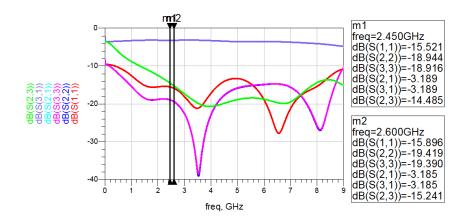

| Divider with Separation of 12mm                                                                  | 108 |

| Figure 3.74: Measured S-Parameters (Magnitude) of Modified UWB Wilkinson Power                   |     |

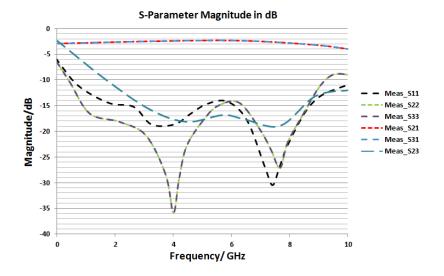

| Divider with Separation of 12mm                                                                  | 108 |

| Figure 3.75: Modified UWB Wilkinson Power Divider with Separation of 16mm                        | 109 |

|                                                                                                  |     |

| Figure 3.76: Simulated S-Parameters (Magnitude) of Modified UWB Wilkinson Power     |       |

|-------------------------------------------------------------------------------------|-------|

| Divider with Separation of 16mm                                                     | . 109 |

| Figure 3.77: Measured S-Parameters (Magnitude) of Modified UWB Wilkinson Power      |       |

| Divider with Separation of 16mm                                                     | . 109 |

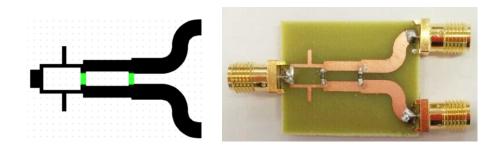

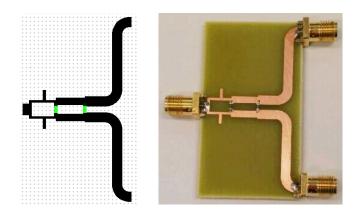

| Figure 3.78: Modified UWB Wilkinson Power Divider with Separation of 20mm           | . 110 |

| Figure 3.79: Simulated S-Parameters (Magnitude) of Modified UWB Wilkinson Power     |       |

| Divider with Separation of 20mm                                                     | . 110 |

| Figure 3.80: Measured S-Parameters (Magnitude) of Modified UWB Wilkinson Power      |       |

| Divider with Separation of 20mm                                                     | . 110 |

| Figure 3.81: Modified UWB Wilkinson Power Divider with Separation of 36mm           | . 111 |

| Figure 3.82: Simulated S-Parameters (Magnitude) of Modified UWB Wilkinson Power     |       |

| Divider with Separation of 36mm                                                     | . 111 |

| Figure 3.83: Measured S-Parameters (Magnitude) of Modified UWB Wilkinson Power      |       |

| Divider with Separation of 36mm                                                     | . 111 |

| Figure 3.84: Modified UWB Wilkinson Power Divider with Separation of 40mm           | . 112 |

| Figure 3.85: Simulated S-Parameters (Magnitude) of Modified UWB Wilkinson Power     |       |

| Divider with Separation of 40mm                                                     | . 112 |

| Figure 3.86: Measured S-Parameters (Magnitude) of Modified UWB Wilkinson Power      |       |

| Divider with Separation of 40mm                                                     | . 112 |

| Figure 3.87: Modified UWB Wilkinson Power Divider with Separation of 45mm           | . 113 |

| Figure 3.88: Simulated S-Parameters (Magnitude) of Modified UWB Wilkinson Power     |       |

| Divider with Separation of 45mm                                                     | . 113 |

| Figure 3.89: Measured S-Parameters (Magnitude) of Modified UWB Wilkinson Power      |       |

| Divider with Separation of 45mm                                                     | . 113 |

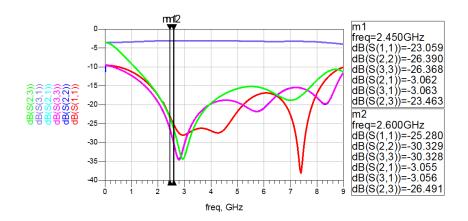

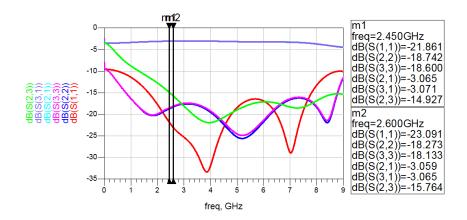

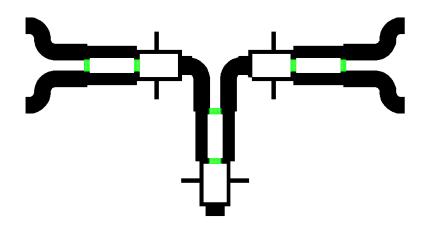

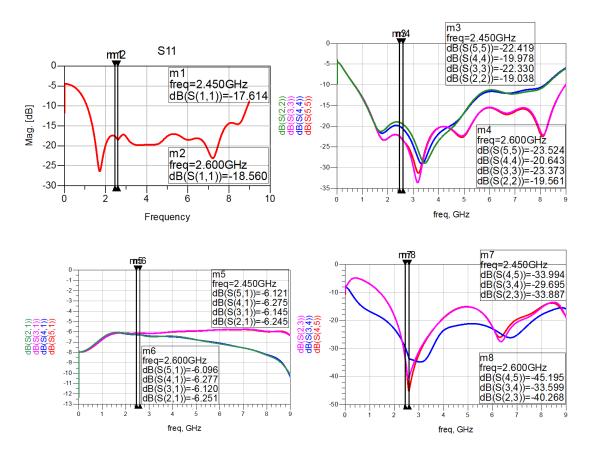

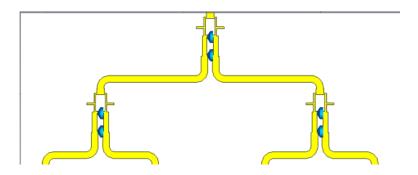

| Figure 3.90: 1:4 UWB Feeding Network (Type I) with Separations of 12mm              | . 114 |

| Figure 3.91: Simulated S-Parameters of 1:4 UWB Feeding Network (Type I) with Separa | tions |

| of 12mm                                                                             | . 114 |

| Figure 3.92: 1:4 UWB Feeding Network (Type II) with Separations of 12mm             | . 115 |

| Figure 3.93: Simulated S-Parameters of 1:4 UWB Feeding Network (Type II) with       |       |

| Separations of 12mm                                                                 | . 115 |

| Figure 3.94: 1:4 UWB Feeding Network (Type III) with Separations of 12mm            | . 116 |

| Figure 3.95: Simulated S-Parameters of 1:4 UWB Feeding Network (Type III) with      |       |

| Separations of 12mm                                                                 | . 116 |

| Figure 3.96: 1:8 UWB Feeding Network with Separations of 12mm                       | . 117 |

| Figure 3.97: Simulated S-Parameters of 1:8 UWB Feeding Network with Separations of  |       |

| 12mm                                                                                | . 118 |

| Figure 3.98: Other UWB Wilkinson Power Divider Geometries                           | . 118 |

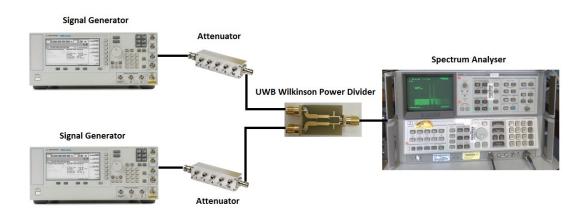

| Figure 3.99: Intermodulation Distortion Measurement Setup                              | 119   |

|----------------------------------------------------------------------------------------|-------|

| Figure 3.100: Signal Generators (HP83732A and HPE4400A) and Spectrum Analyser          |       |

| HP8566B                                                                                | . 120 |

| Figure 3.101: Attenuator and UWB Power Divider under Test                              | . 120 |

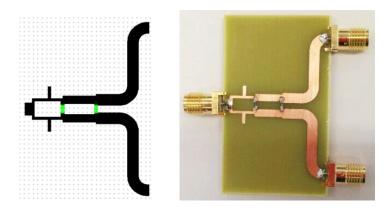

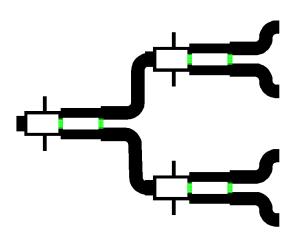

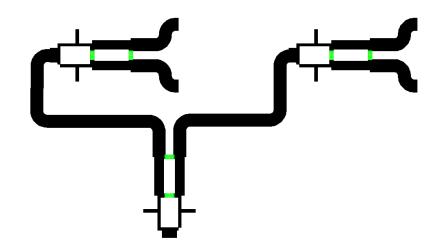

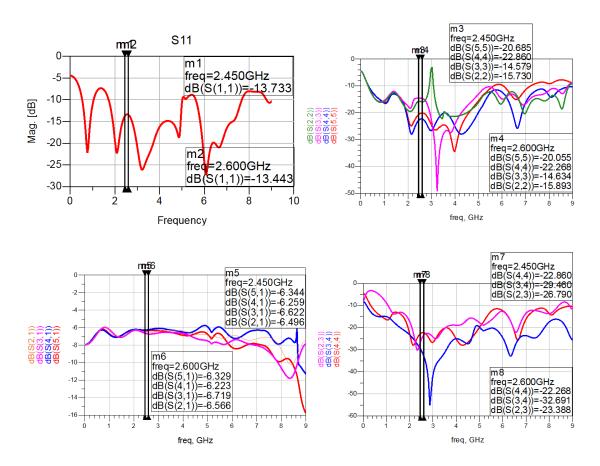

| Figure 3.102: Configuration of the UWB Feeding Network for Smart Antenna Array         | . 122 |

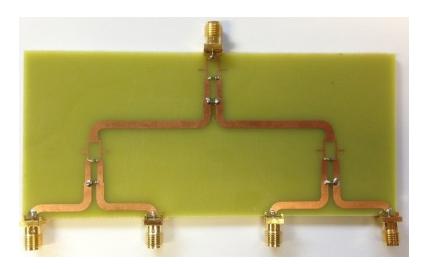

| Figure 3.103: Photo of the Fabricated UWB Feeding Network for Smart Antenna Array      | 122   |

| Figure 3.104: The Investigation of Feeding Network for Smart Antenna Array             | 126   |

| Figure 4.1: Smart Antenna Array System Layout                                          | 128   |

| Figure 4.2: Ferrite Rod in Rectangular Waveguide                                       | . 129 |

| Figure 4.3: YIG Phase Shifter Measurement Setup [115]                                  | 130   |

| Figure 4.4: Basic Schematic of Switched Delay Line Phase Shifter                       | 131   |

| Figure 4.5: 3-Bit Switched Delay Line Phase Shifter                                    | 132   |

| Figure 4.6: Series Diode Switched Line Phase Shifter                                   | 132   |

| Figure 4.7: Schematic of Dual Gate FET (DGFET) Phase Shifter [110]                     | 133   |

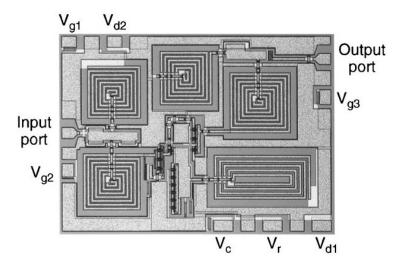

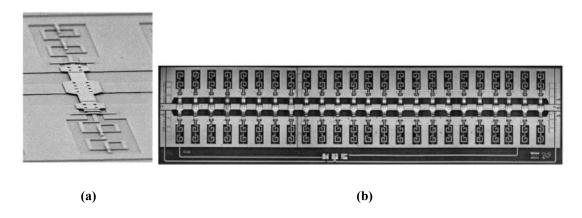

| Figure 4.8: MMIC Circuit Configuration [119]                                           | 134   |

| Figure 4.9: Photo of the Fabricated MMIC [119]                                         | 134   |

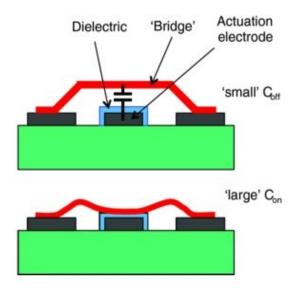

| Figure 4.10: RF MEMS Switch, ON and OFF State                                          | 135   |

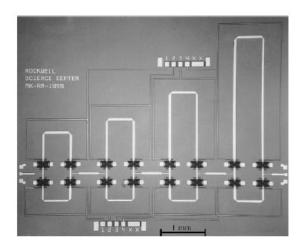

| Figure 4.11: 4-Bit RF MEMS Switched Delay Line Phase Shifter [112]                     | 135   |

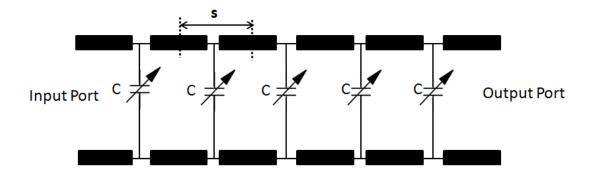

| Figure 4.12: Loaded Transmission Line Phase Shifter with Shunt Varactors               | 136   |

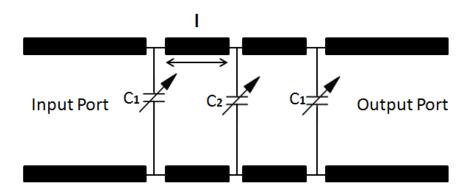

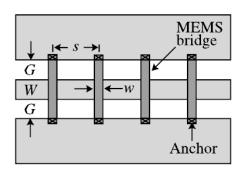

| Figure 4.13: Distributed MEMS Transmission Line Phase Shifter                          | 136   |

| Figure 4.14: Lumped-Element Periodically Loaded Transmission Line Model [120]          | 137   |

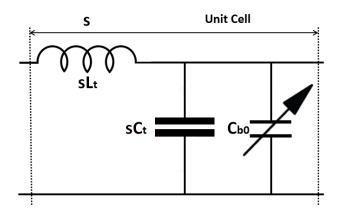

| Figure 4.15: (a) Schematic of the Schottky Diode Varactor Loaded CPW Transmission L    | ine   |

| (b) SEM Photographs of the Fabricated Phase Shifter [121]                              | . 138 |

| Figure 4.16: Fabricated Distributed Transmission Line Phase Shifter Using BST Parallel | Plate |

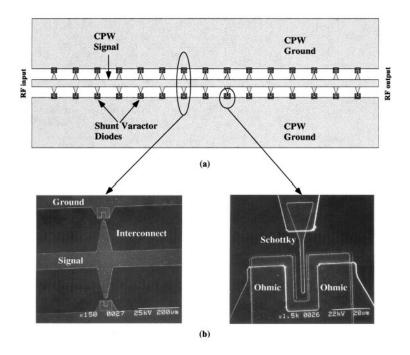

| Capacitor [122]                                                                        | 139   |

| Figure 4.17: Fabricated Distributed Transmission Line Phase Shifter Using BST Inter-Di | gital |

| Capacitor [123]                                                                        | 139   |

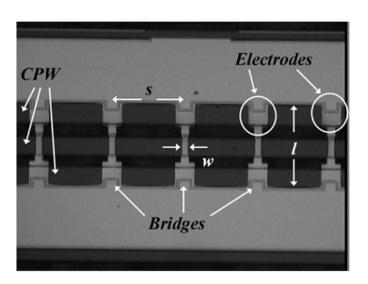

| Figure 4.18: Distributed MEMS Transmission Line Phase Shifter [112]                    | . 139 |

| Figure 4.19: (a) Photograph of the Unit Cell of a Phase Shifter with MEMS Bridge (b)   |       |

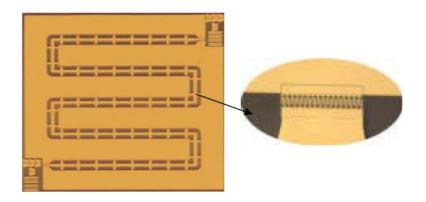

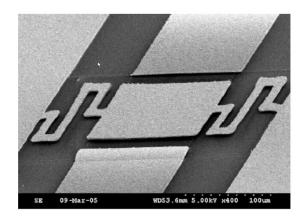

| Photograph of the Fabricated MEMS Phase Shifter, on Quartz Substrate [124]             | 140   |

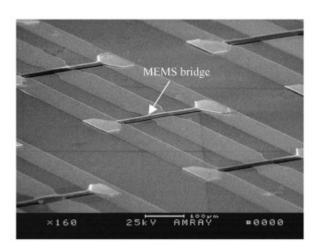

| Figure 4.20: SEM Photograph of the Fabricated Phase Shifter on Silicon Substrate       | . 140 |

| Figure 4.21: SEM Photograph of the Fabricated MEMS Device with Meander-Hinge           |       |

| Switches [126]                                                                         | 141   |

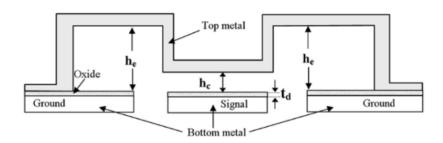

| Figure 4.22: High Tuning Two-Levelled Bridge Capacitor Profile [116]                   | . 141 |

| Figure 4.23: Photograph of the Fabricated Phase Shifter [116]                          | . 141 |

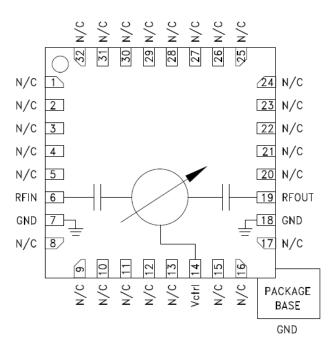

| Figure 4.24: HMC928LP5E MMIC Analogue Phase Shifter Functional Diagram [127]           | 142   |

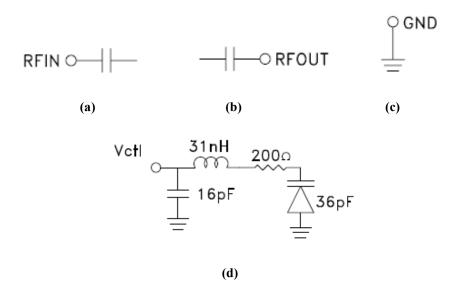

| Figure 4.25: Interface Schematic of the Pins of HMC928LP5E MMIC Analogue Phase S       | Shifter |

|----------------------------------------------------------------------------------------|---------|

| (a).RFIN (b).RFOUT (c).GND (d).Control Voltage                                         | 143     |

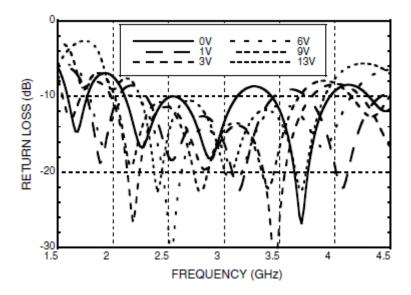

| Figure 4.26: Input Return Loss of the HMC928LP5E MMIC Analogue Phase Shifter, for      | r       |

| Vctl=0-13V [127]                                                                       | 144     |

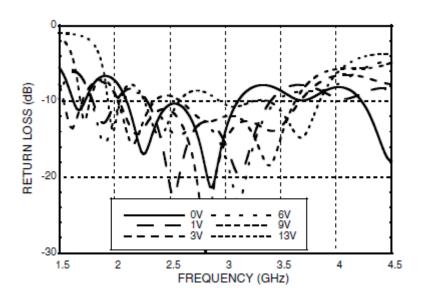

| Figure 4.27: Output Return Loss of the HMC928LP5E MMIC Analogue Phase Shifter,         | for     |

| Vctl=0-13V [127]                                                                       | 144     |

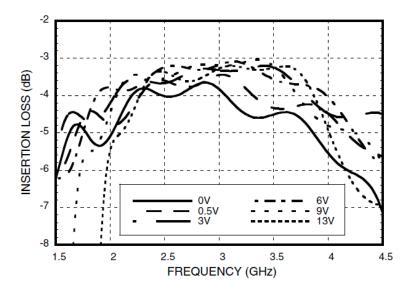

| Figure 4.28: Insertion Loss of the HMC928LP5E MMIC Analogue Phase Shifter, for Vo      | ctl=0-  |

| 13V [127]                                                                              | 145     |

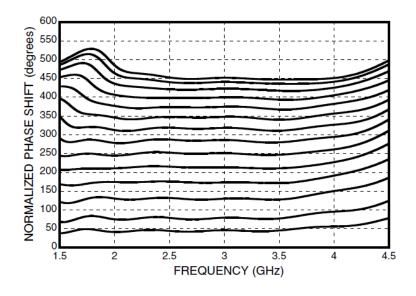

| Figure 4.29: Phase Shift vs. Frequency, for Vctl = 0-13V [127]                         | 145     |

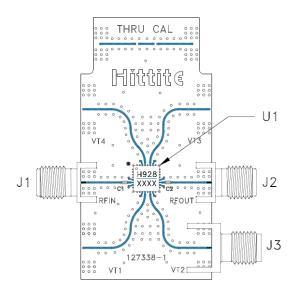

| Figure 4.30: HMC928LP5E MMIC Analogue Phase Shifter Evaluation PCB [127]               | 146     |

| Figure 4.31: (a) Standard Evaluation PCB for HMC928LP5E MMIC Analogue Phase S          | hifter  |

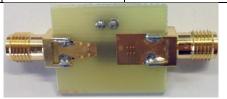

| (b) Top Layer (c) Bottom Layer                                                         | 146     |

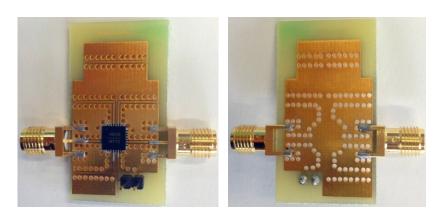

| Figure 4.32: Photo of the Fabricated Standard Evaluation PCB for HMC928LP5E MMI        | C       |

| Analogue Phase Shifter: Front View and Back View                                       | 147     |

| Figure 4.33: Digital Power Supply to Control the Analogue Phase Shifter                | 147     |

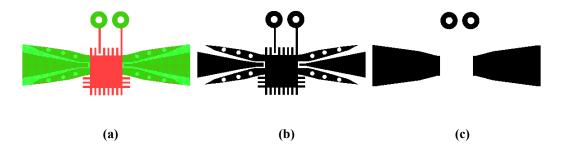

| Figure 4.34: (a) Modified Evaluation PCB for HMC928LP5E MMIC Analogue Phase S          | hifter  |

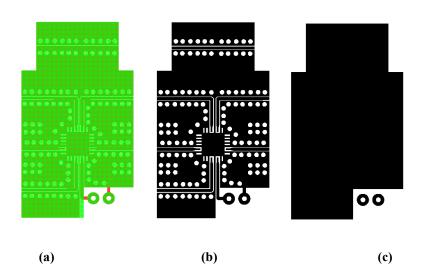

| (b) Top Layer (c) Bottom Layer                                                         | 148     |

| Figure 4.35: Photo of the Fabricated Modified Evaluation PCB for HMC928LP5E MMI        | C.      |

| Analogue Phase Shifter: Top View and Back View                                         | 149     |

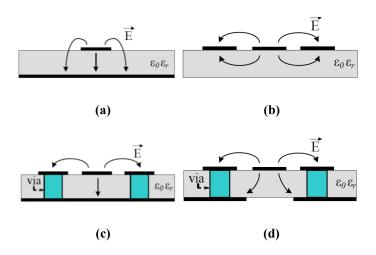

| Figure 4.36: Electric Field Lines at Each Cross-Section along the Transitions [128]    | 150     |

| Figure 4.37: (a) Proposed UWB Transition between the Feeding Network and Phase Sh      | ifter   |

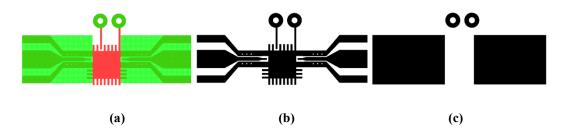

| (Transition I) (b) Top Layer (c) Bottom Layer (d) Side View                            | 151     |

| Figure 4.38: (a) Proposed UWB Transition between Phase Shifter and Monopole Anten      | ına     |

| (Transition II) (b) Top Layer (c) Bottom Layer (d) Side View                           | 152     |

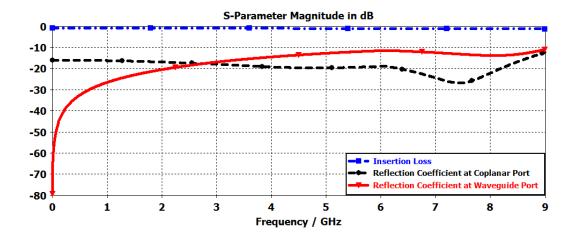

| Figure 4.39: Simulated S-Parameters (Magnitude) of the Proposed UWB Transition between | ween    |

| the Feeding Network and Phase Shifter (Transition I)                                   | 152     |

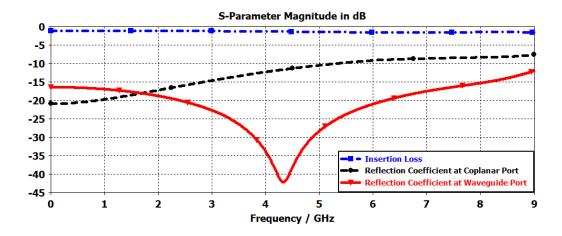

| Figure 4.40: Simulated S-Parameters (Magnitude) of the Proposed UWB Transition between | ween    |

| the Phase Shifter and Monopole Antenna (Transition II)                                 | 153     |

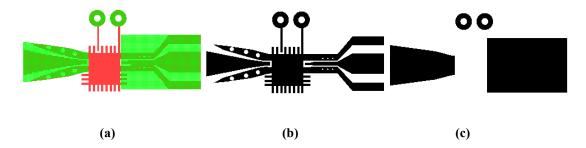

| Figure 4.41: (a) Geometry of the Evaluation PCB for Testing the Transition between the | ;       |

| Feeding Network and Phase Shifter (Transition I) (b) Top Layer (c) Bottom Layer        | 153     |

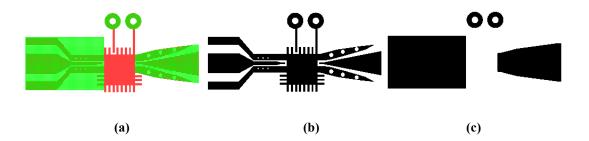

| Figure 4.42: (a) Geometry of the Evaluation PCB for Testing the Transition between the | ;       |

| Phase Shifter and Monopole Antenna (Transition II) (b) Top Layer (c) Bottom Layer      | 153     |

| Figure 4.43: Photo of the Fabricated Evaluation PCB for Testing the Transition between | the     |

| Feeding Network and Phase Shifter (Transition I): Top View and Back View               | 154     |

| Figure 4.44: Photo of the Fabricated Evaluation PCB for Testing the Transition between | the     |

| Phase Shifter and Monopole Antenna (Transition II): Top View and Bottom View           | 154     |

| Figure 4.45: (a) Geometry of the Evaluation PCB for Testing the Two Transitions (b) To  | p                |

|-----------------------------------------------------------------------------------------|------------------|

| Layer (c) Bottom Layer                                                                  | 155              |

| Figure 4.46: Photo of the Fabricated Evaluation PCB for Testing the Two Transitions: To | эр               |

| View and Bottom View                                                                    | 156              |

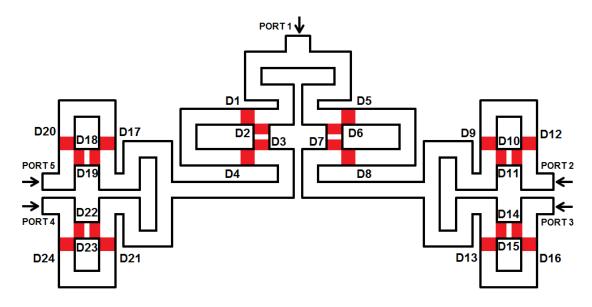

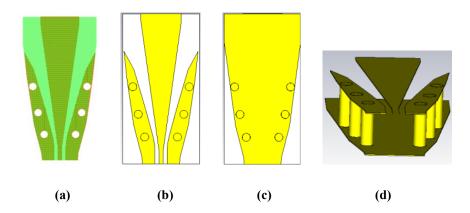

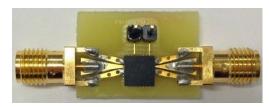

| Figure 4.47: (a) Geometry of Adaptive 1:4 UWB Feeding Network (b) Top Layer (c) Bo      | ttom             |

| Layer                                                                                   | 158              |

| Figure 4.48: Photo of the Fabricated 1:4 Adaptive UWB Feeding Network: (a) Top View     | <sup>7</sup> (b) |

| Bottom View                                                                             | 158              |

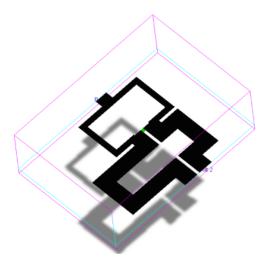

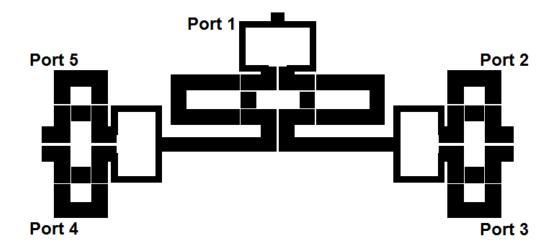

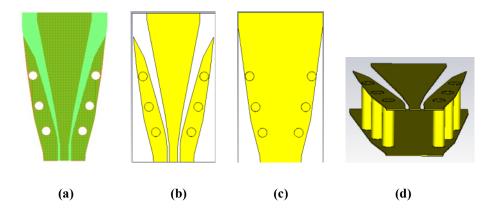

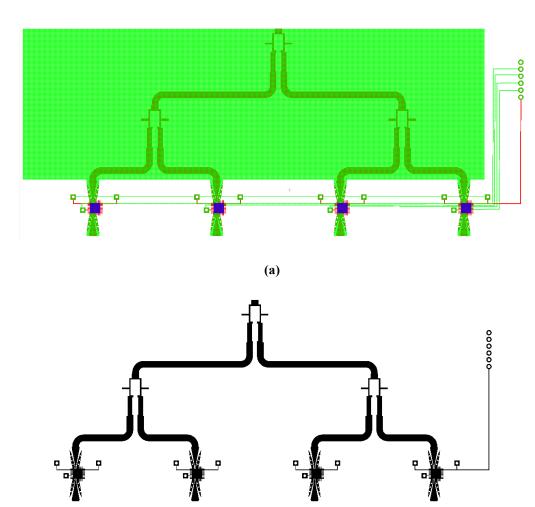

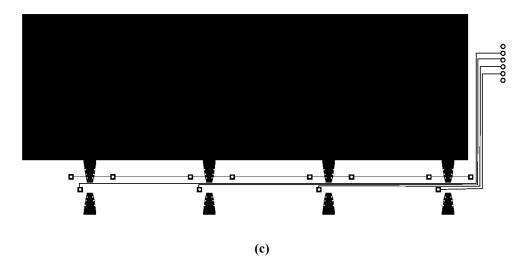

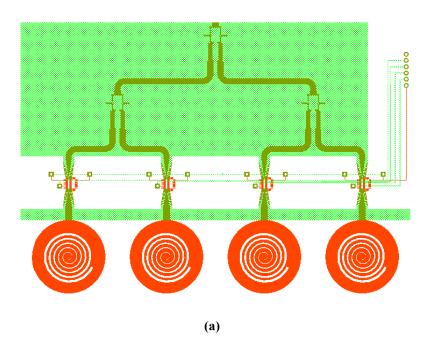

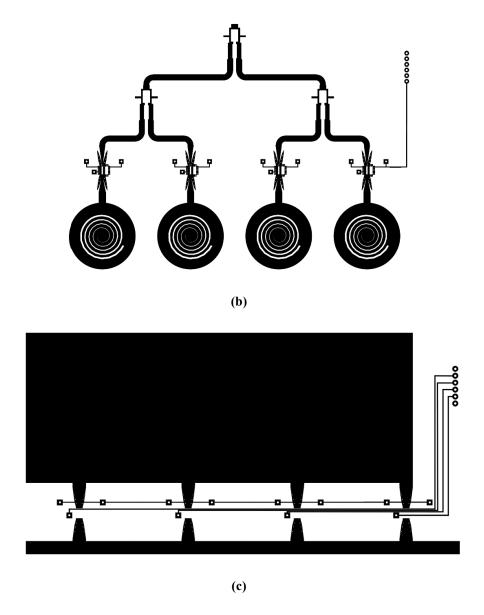

| Figure 4.49: (a) Geometry of the Fully Integrated Smart Antenna Array (b) Top Layer (c  | :)               |

| Bottom Layer                                                                            | 161              |

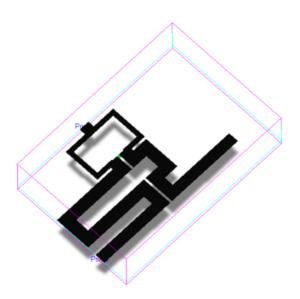

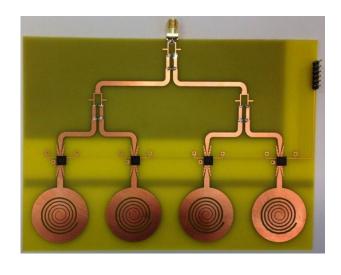

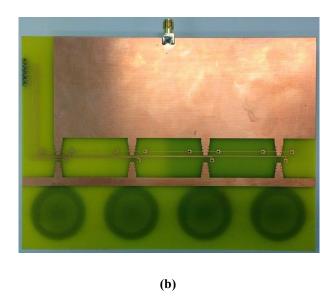

| Figure 4.50: Photo of the Fabricated Smart Antenna Array (a) Top View (b) Bottom View   | w 162            |

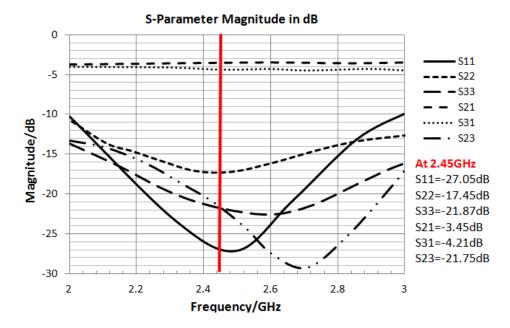

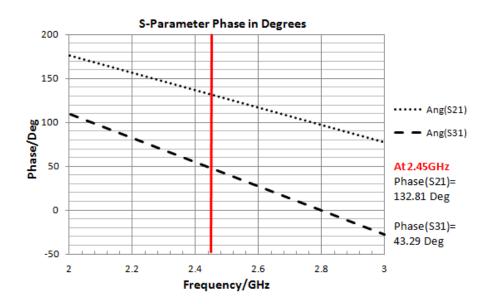

| Figure 4.51: Measured Reflection Coefficient of the Proposed Smart Antenna Array with   | ı DC             |

| Bias 0V, 2V, 4V, 6V and 8V                                                              | 162              |

| Figure 4.52: Measured Gain vs. Theta in the H-Plane for Different Scanning Angles, at   |                  |

| 2.45GHz                                                                                 | 163              |

| Figure 4.53: Measured Gain vs. Theta in the H-Plane for Different Scanning Angles, at   |                  |

| 2.6GHz                                                                                  | 163              |

| Figure 4.54: The Investigation of Smart Antenna Array Full Implementation               | 166              |

| Figure 5.1: System Block Diagram of the Smart Antenna Array System                      | 168              |

| Figure 5.2: PIC18F4550 PIN Diagram [130]                                                | 169              |

| Figure 5.3: Oscillator Pin Connections [130]                                            | 170              |

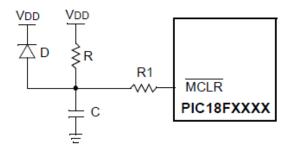

| Figure 5.4: External Power Reset Circuit [130]                                          | 171              |

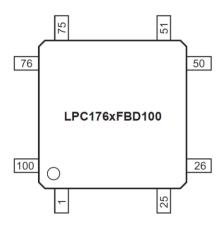

| Figure 5.5: LPC1768 PIN Configuration [131]                                             | 172              |

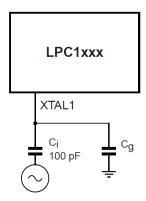

| Figure 5.6: Oscillator Circuit Diagram [131]                                            | 173              |

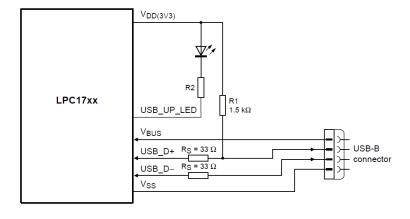

| Figure 5.7: LPC1768 USB Connection [131]                                                | 173              |

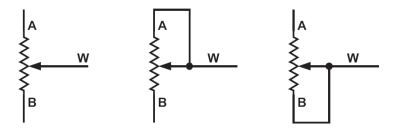

| Figure 5.8: (a) AD5290 Functional Block Diagram (b) AD5290 PIN Configuration [132]      | . 174            |

| Figure 5.9: Rheostat Mode Configuration [132]                                           | 174              |

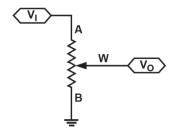

| Figure 5.10: Voltage Divider Mode Circuit Diagram [132]                                 | 175              |

| Figure 5.11: AD5290 Timing Diagram [132]                                                | 176              |

| Figure 5.12: AD5290 Daisy-Chain Operation [132]                                         | 176              |

| Figure 5.13: NJM2360 Block Diagram [133]                                                | 177              |

| Figure 5.14: Voltage Booster Step-Up Circuit                                            | 177              |

| Figure 5.15: FT232RL Pin Configuration [134]                                            | 178              |

| Figure 5.16: FT232RL to USB Configuration [134]                                         | 179              |

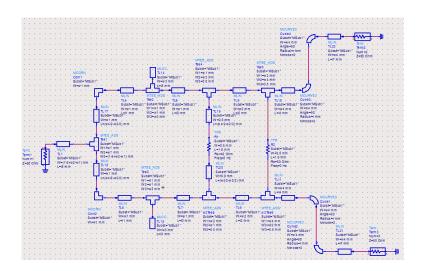

| Figure 5.17: Microcontroller 18F4550 Circuit Diagram                                    | 180              |

| Figure 5.18: Digital Potentiometer AD5290 Circuit Diagram                               | 180              |

| Figure 5.19: Voltage Booster NJM2360 Circuit Diagram                                    | 181              |

| Figure 5.20: USB Module Circuit Diagram                                            | 181    |

|------------------------------------------------------------------------------------|--------|

| Figure 5.21: (a) Crysital Oscillator (b) Testing LEDs (c) 6-Pin ICSP Connector     | 182    |

| Figure 5.22: (a) Reset Switches (b) Output Voltage Pins                            | 182    |

| Figure 5.23: Schematic of Control PCB Using PIC18F4550                             | 183    |

| Figure 5.24: Breadboard Testing of Control Board Using PIC18F4550                  | 184    |

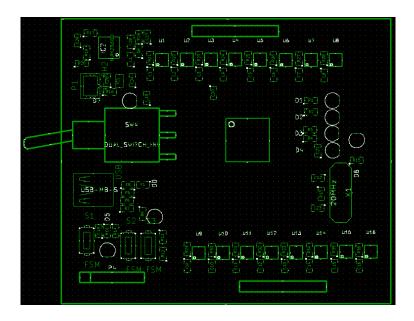

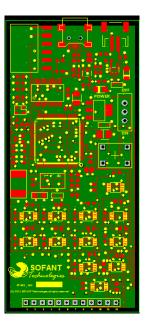

| Figure 5.25: PCB Design Using Microcontroller PIC18F4550                           | 186    |

| Figure 5.26: Front Layer of PCB Design Using Microcontroller PIC18F4550            | 187    |

| Figure 5.27: Back Layer of PCB Design Using Microcontroller PIC18F4550             | 187    |

| Figure 5.28: Silk Document of PCB Design Using Microcontroller PIC18F4550          | 188    |

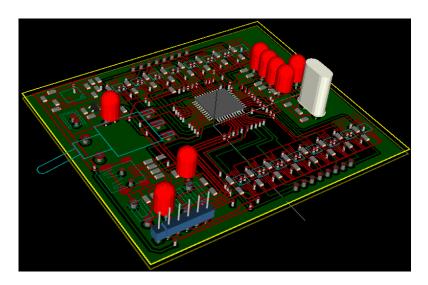

| Figure 5.29: 3D View of the PCB Design Using Microcontroller PIC18F4550            | 188    |

| Figure 5.30: Fabricated PCB Design Using Microcontroller PIC18F4550 (a) Front View | w (b)  |

| Back View                                                                          | 189    |

| Figure 5.31: PICSTART Plus Programmer [136]                                        | 190    |

| Figure 5.32: PIC-PG2 Programmer                                                    | 190    |

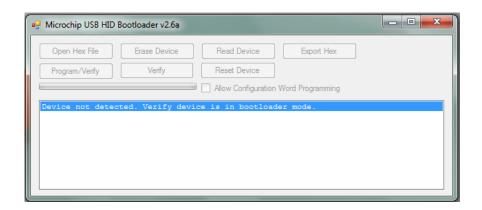

| Figure 5.33: Bootloader Program Interface                                          | 191    |

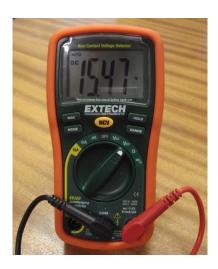

| Figure 5.34: Stable DC Output Voltage from PCB Design Using Microcontroller PIC18  | 3F4550 |

|                                                                                    | 192    |

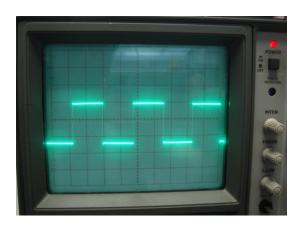

| Figure 5.35: Square Wave Output Signal from PCB Design Using Microcontroller       |        |

| PIC18F4550                                                                         | 192    |

| Figure 5.36: Microcontroller LPC1768 Circuit Diagram                               | 193    |

| Figure 5.37: Digital Potentiometer AD5290 Circuit Diagram                          | 193    |

| Figure 5.38: Voltage Booster NJM2360 Circuit Diagram                               | 194    |

| Figure 5.39: FT232RL Circuit Diagram                                               | 194    |

| Figure 5.40: Schematic of Control PCB Using LPC1768                                | 195    |

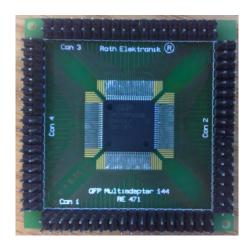

| Figure 5.41: LPC1768 Microcontroller and Adapter                                   | 196    |

| Figure 5.42: Breadboard_I to Test Control Board Using LPC1768                      | 196    |

| Figure 5.43: Breadboard_II to Test Control Board Using LPC1768                     | 197    |

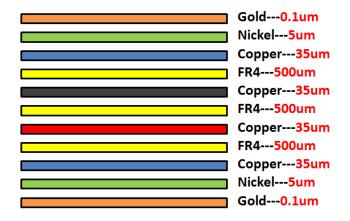

| Figure 5.44: Four Layers PCB Structure                                             | 198    |

| Figure 5.45: Detailed Multi-Layer PCB                                              | 198    |

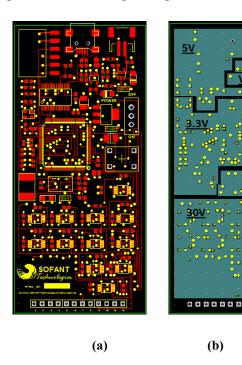

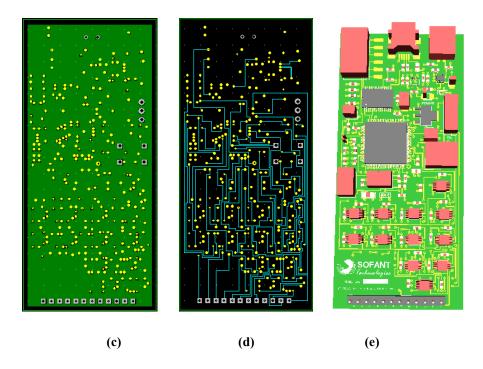

| Figure 5.46: PCB Design Using Microcontroller LPC1768                              | 199    |

| Figure 5.47: PCB Layout Using Microcontroller LPC1768 (a) Top Copper Layer (b) Pc  | ower   |

| Layer (c) Ground Layer (d) Bottom Copper Layer (e) 3D View                         | 200    |

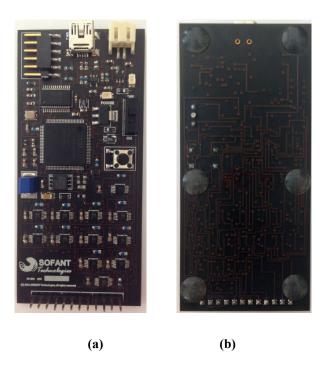

| Figure 5.48: Fabricated PCB Design Using Microcontroller LPC1768 (a) Top View (b)  | )      |

| Bottom View                                                                        | 200    |

| Figure 5.49: Mbed LPC1768 Evaluation Kit and the PCB Under Programmed              | 201    |

| Figure 5.50: Flash Magic to Initialise Microcontroller LPC1768                     | 202    |

|                                                                                    |        |

| Figure 5.51: Stable DC Output Voltage from PCB Design Using Microcontroller LPC1768 |           |

|-------------------------------------------------------------------------------------|-----------|

| (a)0.626V (b)6.56V (c)11.67V (d)29.7V                                               |           |

| Figure 5.52: Square Wave Output Signal from PCB Design Using Microcontroller L      | PC1768    |

|                                                                                     | 203       |

| Figure 5.53: EDUP Wireless USB Adapter with SMA Connector                           | 203       |

| Figure 5.54: Smart Antenna System Hardware Implementation                           | 204       |

| Figure 5.55: The Investigation of Hardware Control Systems for Smart Antenna        | 206       |

| Figure 6.1: Functional Block Diagram for PIC18F4550                                 | 208       |

| Figure 6.2: Digital Potentiometer AD5290 Timing Diagram [132]                       | 209       |

| Figure 6.3: C Code Result for SPI Communication                                     | 211       |

| Figure 6.4: Measurement Result of PIC18F4550 Manual Control                         | 213       |

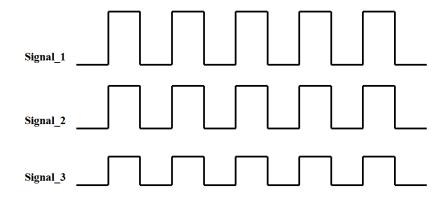

| Figure 6.5: Square Waveforms from Switching Control                                 | 213       |

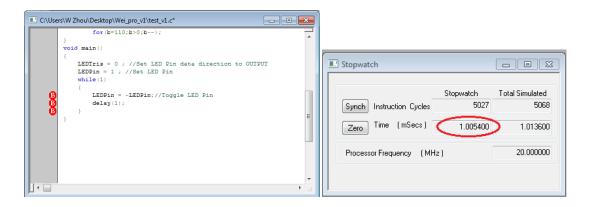

| Figure 6.6: Delay Time Simulation in MPLAB                                          | 214       |

| Figure 6.7: Measured Result of the Switching Control                                | 214       |

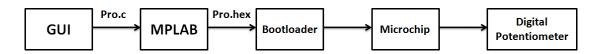

| Figure 6.8: Control Loop between GUI and Microchip                                  | 214       |

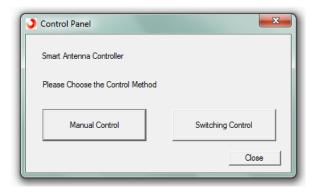

| Figure 6.9: GUI Main Window for PIC18F4550                                          | 215       |

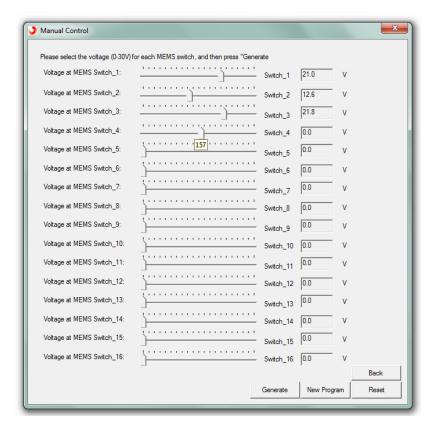

| Figure 6.10: Manual Control GUI for PIC18F4550                                      | 216       |

| Figure 6.11: Output Square Waveforms                                                | 217       |

| Figure 6.12: Switching Control GUI for PIC18F4550                                   | 217       |

| Figure 6.13: LPC1768 Programming Block Diagram                                      | 218       |

| Figure 6.14: LPC1768 Online Compiler                                                | 218       |

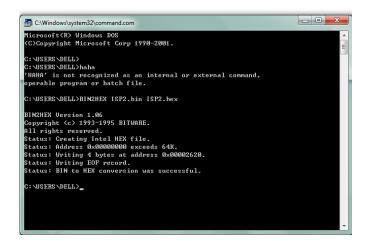

| Figure 6.15: LPC1768 BIN to HEX Transformer                                         | 219       |

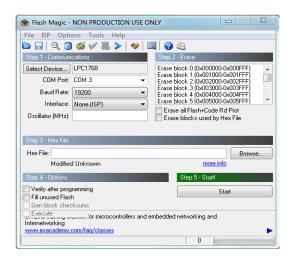

| Figure 6.16: Flash Magic to Program LPC1768                                         | 219       |

| Figure 6.17: Real Time LPC1768 Communication Block Diagram                          | 220       |

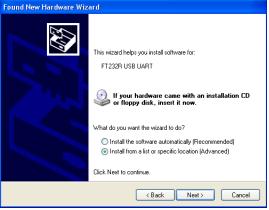

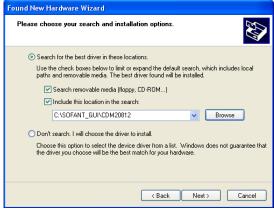

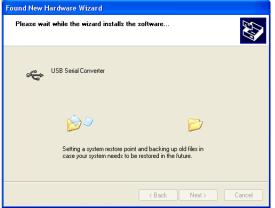

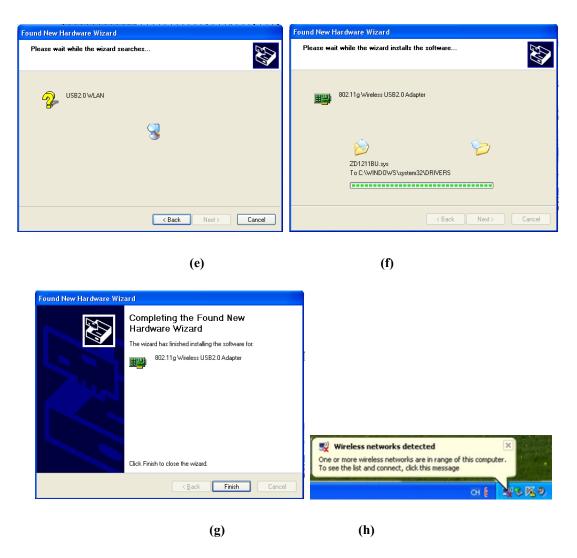

| Figure 6.18: FT232RL Diver Installation                                             | 222       |

| Figure 6.19: WiFi Adapter Driver Installation                                       | 223       |

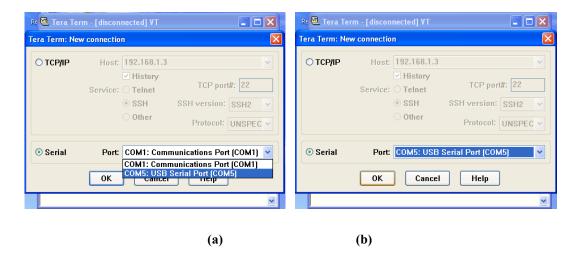

| Figure 6.20: Tera Term Connection Setup                                             | 224       |

| Figure 6.21: Manual Control GUI Start Screen for LPC1768                            | 224       |

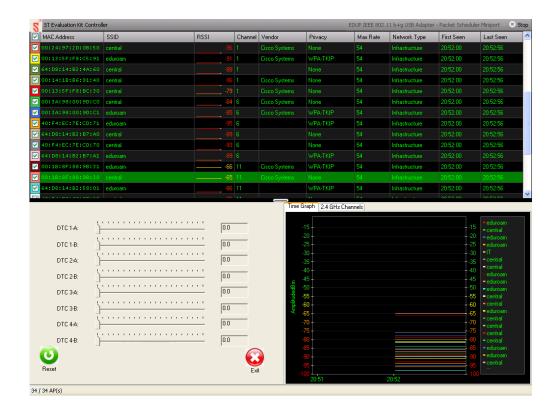

| Figure 6.22: Manual Control GUI Main Screen for LPC1768                             | 225       |

| Figure 6.23: Wireless Adapter Selection for LPC1768                                 | 225       |

| Figure 6.24: WiFi Information of the GUI for LPC1768                                | 225       |

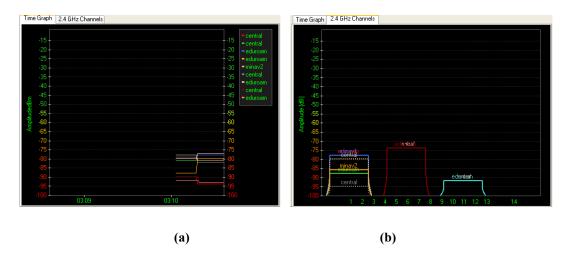

| Figure 6.25: (a) WiFi Signal Strength Real Time Curve (b) WiFi Signal Strength in   | Different |

| Channels                                                                            | 226       |

| Figure 6.26: Real Time Control Slider for LPC1768                                   |           |

| Figure 6.27: Manual Control Evaluating Results for LPC1768                          | 227       |

| Figure 6.28: Automatic Control GUI for LPC1768                                      | 227       |

| Figure 6.29: Antenna Array and WiFi Adapter Selection                               | 228       |

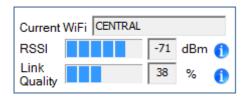

| Figure 6.30: Current Connected WiFi Information                                   | 228 |

|-----------------------------------------------------------------------------------|-----|

| Figure 6.31: RSSI Description                                                     | 228 |

| Figure 6.32: Link Quality Description                                             | 228 |

| Figure 6.33: Scanning Function of the GUI for LPC1768                             | 229 |

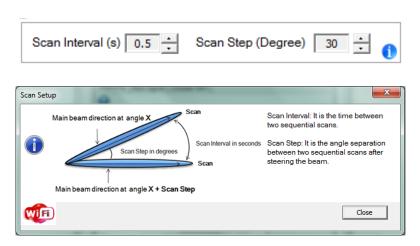

| Figure 6.34: Scan Interval and Scan Step Definition                               | 229 |

| Figure 6.35: Scan Mode Selection.                                                 | 230 |

| Figure 6.36: Status Bar and Current Main Beam Direction                           | 230 |

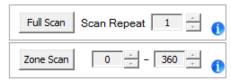

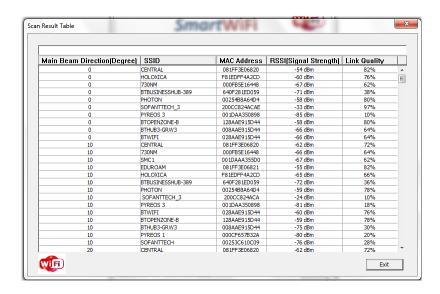

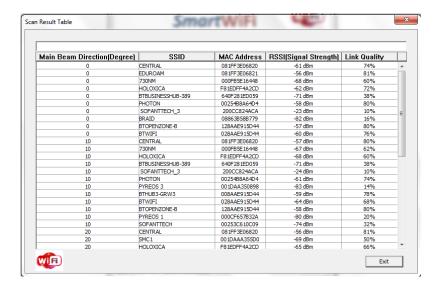

| Figure 6.37: Full Scan Results Using Four-Element Linear Antenna Array            | 230 |

| Figure 6.38: Zone Scan Results Using Four-Element Linear Antenna Array            | 231 |

| Figure 6.39: Best Signal Function of the GUI for LPC1768                          | 232 |

| Figure 6.40: Best Signal Scan Results Using Four-Element Linear Antenna Array     | 232 |

| Figure 6.41: Choose WiFi Function of the GUI for LPC1768                          | 233 |

| Figure 6.42: Pre-Scan in Choose WiFi Function.                                    | 233 |

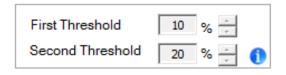

| Figure 6.43: Threshold in Choose WiFi Function                                    | 233 |

| Figure 6.44: Choose WiFi Scan Results Using Four-Element Linear Antenna Array     | 234 |

| Figure 6.45: The Investigation of Software Control Systems for Smart Antenna      | 236 |

| Figure 7.1: Miniaturised PCB Control Unit Using Microprocessor LPC1768            | 246 |

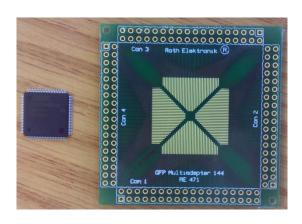

| Figure 7.2: Control System Package Level Integration through Flip Chip Technology | 246 |

| Figure 7.3: Prototype WiFi Analyser on Android 4.4.4 System                       | 247 |

# LIST OF TABLES

| Table 2.1: Simulated Efficiency and Gain                                           | 35        |

|------------------------------------------------------------------------------------|-----------|

| Table 2.2: Simulated Efficiency and Gain.                                          | 45        |

| Table 2.3: Phase Excitation of the Antenna                                         | 48        |

| Table 3.1: S-Parameters of the Enhanced Wilkinson Power Divider                    | 75        |

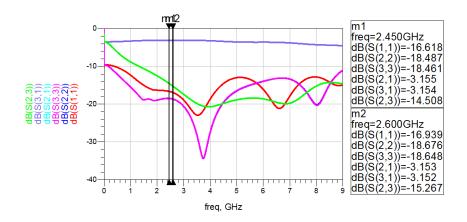

| Table 3.2: Simulated S-Parameters of the Optimised Wilkinson Power Divider         | 78        |

| Table 3.3: Simulated and Measured S-Parameters for Circular Feeding Network        | 81        |

| Table 3.4: Simulated and Measured S-Parameters                                     | 91        |

| Table 3.5: Simulated and Measured Forward Gain (S <sub>21</sub> )                  | 102       |

| Table 3.6: Third Order Intermodulation Distortion Measurements of UWB Wilkinson    | 1 Power   |

| Divider                                                                            | 121       |

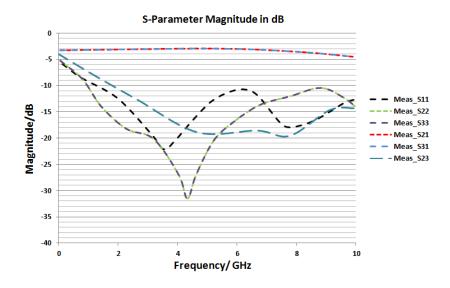

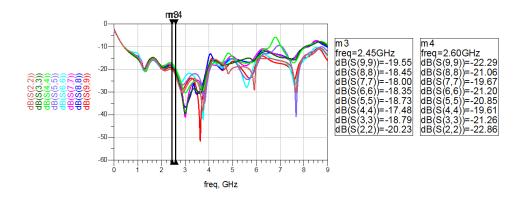

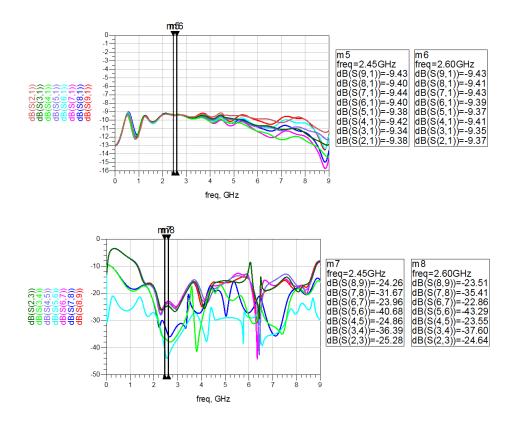

| Table 3.7: Simulated and Measured S-Parameters of UWB Feeding Network for Sma      | ırt       |

| Antenna Array                                                                      | 123       |

| Table 4.1: Measured S-Parameters of the Standard Phase Shifter Evaluation PCB at 2 | 2.45GHz   |

|                                                                                    | 148       |

| Table 4.2: Measured S-Parameters of the Standard Phase Shifter Evaluation PCB at 2 | 2.6GHz    |

|                                                                                    | 148       |

| Table 4.3: Measured S-Parameters of the Modified Phase Shifter Evaluation PCB at   | 2.45GHz   |

|                                                                                    | 149       |

| Table 4.4: Measured S-Parameters of the Modified Phase Shifter Evaluation PCB at   | 2.6GHz    |

|                                                                                    | 149       |

| Table 4.5: Measured S-Parameters of the Fabricated Evaluation PCB for Testing the  |           |

| Transition between the Feeding Network and Phase Shifter at 2.45GHz                | 154       |

| Table 4.6: Measured S-Parameters of the Fabricated Evaluation PCB for Testing the  |           |

| Transition between the Feeding Network and Phase Shifter at 2.6GHz                 | 154       |

| Table 4.7: Measured S-Parameters of the Fabricated Evaluation PCB for Testing the  |           |

| Transition between the Phase Shifter and Monopole Antenna at 2.45GHz               | 155       |

| Table 4.8: Measured S-Parameters of the Fabricated Evaluation PCB for Testing the  |           |

| Transition between the Phase Shifter and Monopole Antenna at 2.6GHz                | 155       |

| Table 4.9: Measured S-Parameters of the Fabricated Evaluation PCB for Testing the  | Two       |

| Transitions at 2.45GHz.                                                            | 156       |

| Table 4.10: Measured S-Parameters of the Fabricated Evaluation PCB for Testing the | e Two     |

| Transitions at 2.6GHz                                                              | 156       |

| Table 4.11: Measured S-Parameters of the Fabricated 1:4 Adaptive UWB Feeding No.   | etwork at |

| 2.45GHz                                                                            | 159       |

| Table 4.12: Measured S-Parameters of the Fabricated 1:4 Adaptive UWB Feeding Networ | k at |

|-------------------------------------------------------------------------------------|------|

| 2.6GHz                                                                              | 159  |

# LIST OF ACRONYMS AND ABBREVIATIONS

1D = 1 Dimensional

2D = 2 Dimensional

3D = 3Dimensional

3G = Third Generation

4G = Fourth Generation

ACPS = Asymmetric Coplanar Stripline

ADC = Analogue to Digital Converter

ADS = Advanced Design System

AF = Array Factor

AM = Amplitude Modulation

BE = Beam Efficiency

BST = Barium Strontium Titanate

CBCPW = Conductor Backed Coplanar Waveguide