IC Optimisation using Parallel Processing and Response Surface Methodology

> Thesis submitted by Godfrey Jonathan Gaston for the degree of Doctor of Philosophy

Edinburgh Microfabrication Facility Department of Electrical Engineering University of Edinburgh Scotland

October 1992

### Abstract

Simulation software has become an essential tool in the design and development of integrated circuits. The key to the rapid and efficient designs required in the competitive industry lies with the use of these simulators with statistical optimisation methods. This is necessary if companies are to survive in the aggressive IC marketplace. The linking of simulation and statistics not only results in rapid development times, but also in robust, highly manufacturable products.

In this work an automated software system is presented where the benefits of simulation and statistical techniques can be readily made available. The efficiency of the system is increased further by utilising parallel processing techniques. Using one system built around the INMOS transputer and one using Intel i860 processors, the time taken to obtain simulation results is greatly reduced.

Two statistical methods are investigated, namely Response Surface Methodology (RSM) and Taguchi analysis. In order to illustrate how these approaches can be utilised in the field of semiconductors, part of a  $1.5\mu$ m nMOS process is optimised in relational to some specified device parameters. A comparison is made between both techniques, with good agreement being obtained.

Finally devices have also been fabricated using the same experimental design as for the RSM simulation analysis. This facilitated a verification of the simulation optimisation with reality. Both simulated and fabricated devices suggested the same improved optimised conditions when compared to the existing process parameters.

# Acknowledgements

I wish to express my thanks to all those people who helped in any way towards this PhD. In particular, I would like to thank my supervisor, Dr A J Walton, for his constant help and guidance throughout the last three years.

A special word of thanks must also go to Mr Z Chen, whose advice, counsel and encouragement were never ending. I would also like to thank Dr W J C Alexander for answering so many of my pleas for help and to Dr L Clarke for helping me down the parallel processing road.

I am also indebted to the staff of the Edinburgh Microfabrication Facility (EMF) for all their help in fabricating the silicon wafers and to my fellow PhD students for their support and assistance in this work.

Last, and definitely by no means least, I wish to express my thanks to my parents whose inspiration and example have always been an encouragement to me, and to my wife, Julia, who laboriously typed this thesis and who was always there when things weren't going so well. Maybe I'm most indebted of all to my baby son Matthew, whose arrival ensured prompt completion of this thesis.

I conclude with an acknowledgement to the Department of Education for Northern Ireland, who funded this research.

# **Table of Contents**

| 1. | Intr | oduction                                  | 1    |

|----|------|-------------------------------------------|------|

|    | 1.1  | Quality considerations in the IC industry | 3    |

|    | 1.2  | Motivation                                | 4    |

|    | 1.3  | Thesis outline                            | 4    |

| 2. | Pro  | cess Simulation                           | 6    |

|    | 2.1  | Introduction                              | . 6  |

|    | 2.2  | Operation of SSUPREM4                     | . 7  |

|    |      | 2.2.1 Grid Definition                     | . 8  |

|    |      | 2.2.2 Implantation                        | . 11 |

|    |      | 2.2.3 Diffusion and Oxidation             | . 13 |

|    |      | 2.2.4 Deposition and Etching              | . 17 |

|    |      | 2.2.5 SSUPREM4 Interface                  | . 18 |

|    | 2.3  | Software Review                           | . 19 |

| 3. | Dev  | vice Simulation and Parameter Extraction  | 21   |

|    | 3.1  | Device Simulation                         | . 21 |

|    |      | 3.1.1 Introduction                        | . 21 |

|    |      | 3.1.2 Semiconductor Equations             | . 22 |

|    | 3.2 | Operation of SPISCES-2B                    | 23 |

|----|-----|--------------------------------------------|----|

|    |     | 3.2.1 Input from process simulation        | 24 |

|    |     | 3.2.2 Refining the Mesh                    | 25 |

|    |     | 3.2.3 Solution Methods                     | 27 |

|    |     | 3.2.4 Device Characteristics               | 29 |

|    | 3.3 | Parameter Extraction                       | 31 |

|    |     | 3.3.1 Operation of TOPEX                   | 32 |

|    | 3.4 | Integrated CAD Tools                       | 33 |

| 4. | Exp | perimental Design and Process Optimisation | 39 |

|    | -   |                                            |    |

|    | 4.1 | Introduction                               | 39 |

|    | 4.2 | Statistical Methods                        | 42 |

|    |     | 4.2.1 Screening                            | 42 |

|    |     | 4.2.2 Response Surface Methodology         | 44 |

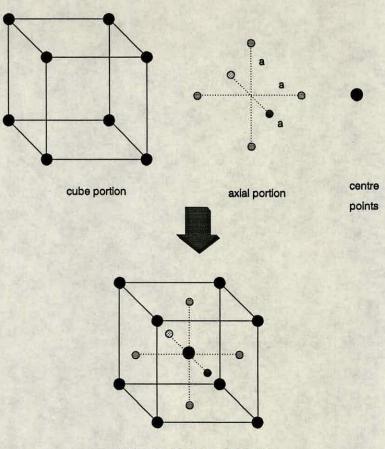

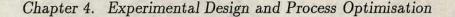

|    |     | 4.2.3 Central Composite Designs            | 47 |

|    |     | 4.2.4 D-optimal Designs                    | 49 |

|    |     | 4.2.5 Box-Behnken Designs                  | 50 |

|    |     | 4.2.6 Taguchi Methods                      | 51 |

|    | 4.3 | Experimental design and semiconductors     | 54 |

|    |     | 4.3.1 Tools of the trade                   | 56 |

|    | 4.4 | Conclusions                                | 67 |

| -  | -   |                                            | 00 |

| 5. | Par | allel Computing                            | 68 |

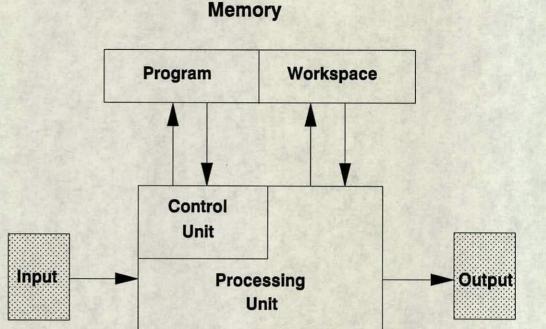

|    | 5.1 | Introduction                               | 68 |

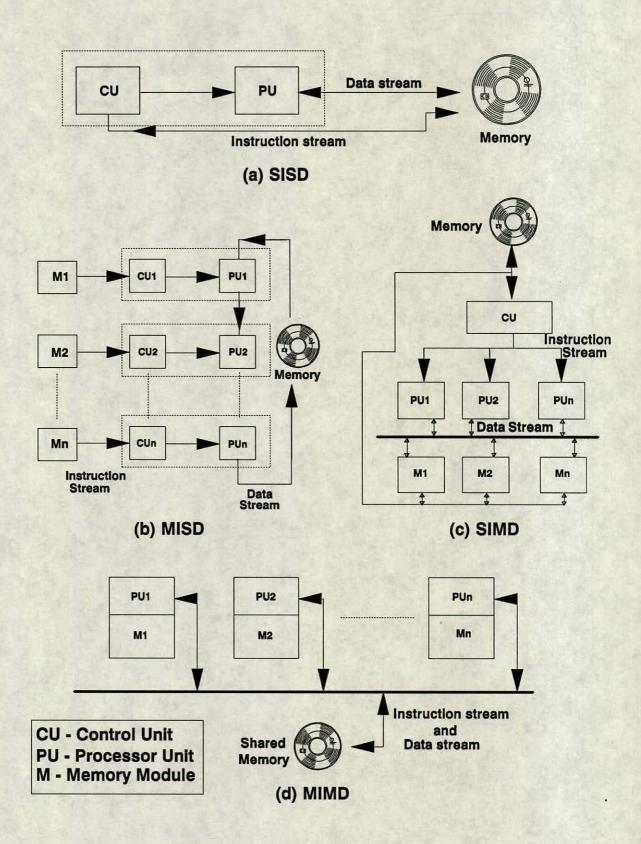

|    | 5.2 | Classification of parallel computers       | 70 |

|    |     | 5.2.1 SISD                                                    | 72 |

|----|-----|---------------------------------------------------------------|----|

|    |     | 5.2.2 SIMD                                                    | 73 |

|    |     | 5.2.3 MISD                                                    | 73 |

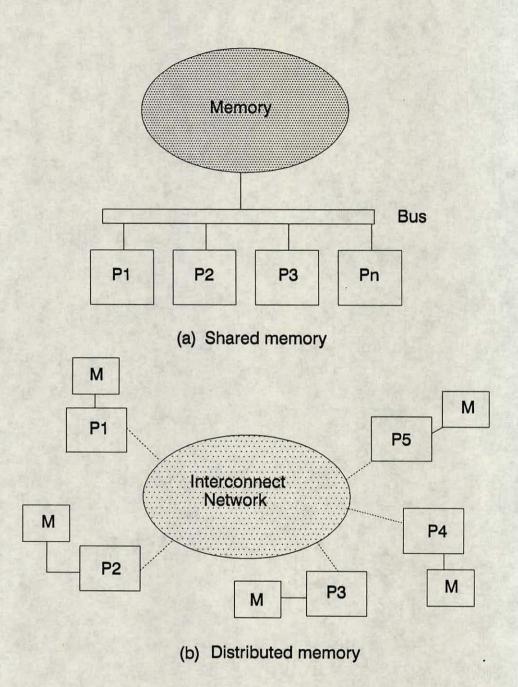

|    |     | 5.2.4 MIMD                                                    | 74 |

|    | 5.3 | Message Passing Systems                                       | 78 |

|    |     | 5.3.1 Tiny                                                    | 78 |

|    |     | 5.3.2 CS Tools                                                | 78 |

|    |     | 5.3.3 Linda                                                   | 79 |

|    |     | 5.3.4 Strand                                                  | 79 |

|    |     | 5.3.5 Express                                                 | 79 |

|    |     | 5.3.6 Helios                                                  | 80 |

|    | 5.4 | Software Design and Parallel Algorithms                       | 80 |

|    |     | 5.4.1 Parallel Algorithms                                     | 82 |

|    | 5.5 | The transputer                                                | 85 |

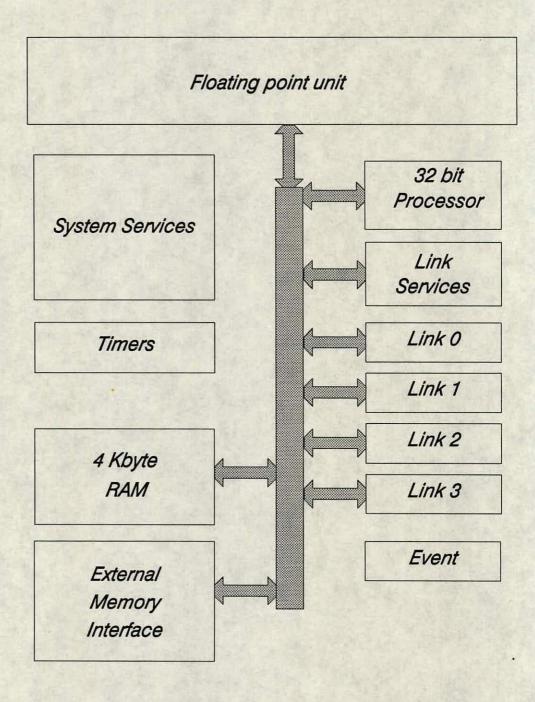

|    |     | 5.5.1 Introduction                                            | 85 |

|    |     | 5.5.2 Architecture and hardware                               | 85 |

|    |     | 5.5.3 Software tools                                          | 87 |

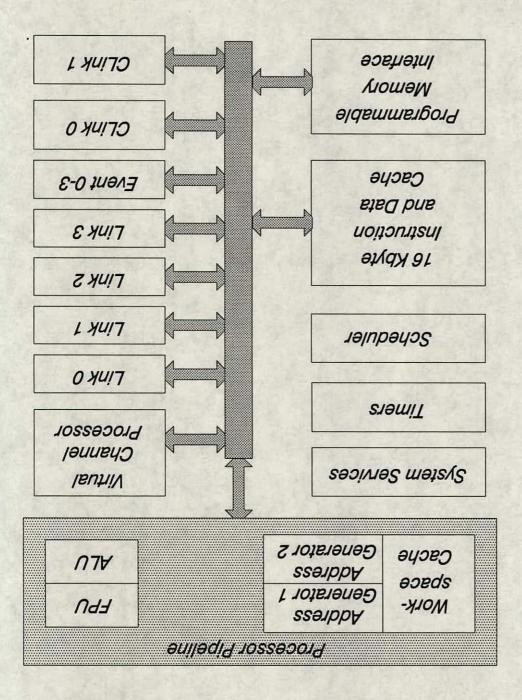

|    |     | 5.5.4 T9000                                                   | 89 |

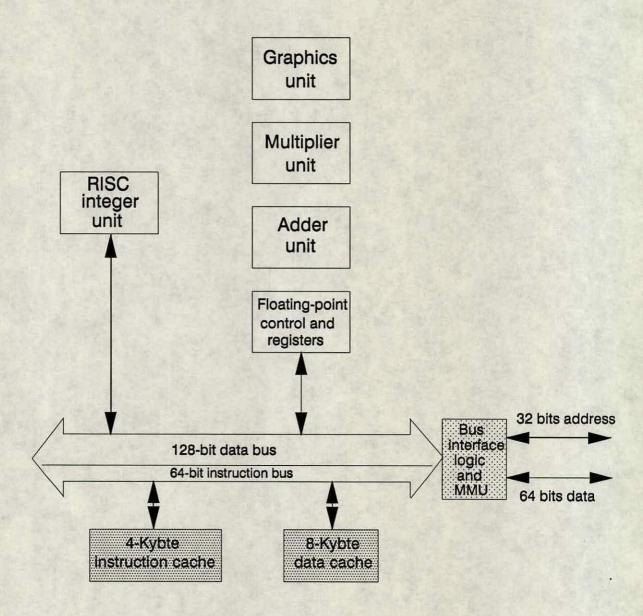

|    | 5.6 | Intel i860 - A brief overview                                 | 91 |

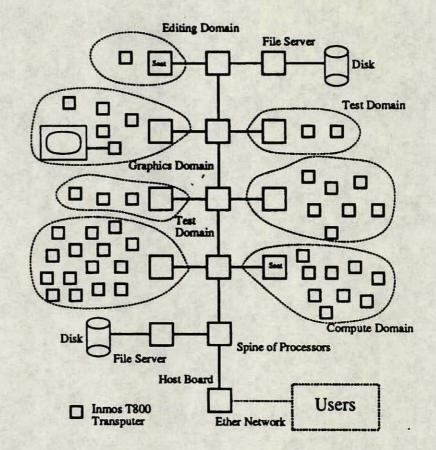

|    | 5.7 | Parallel Computing at the Edinburgh Parallel Computing Centre |    |

|    |     | (EPCC)                                                        |    |

|    | 5.8 | Future trends in parallel computing                           | 94 |

| 5. | Pro | cess Optimisation using Parallel Computing                    | 96 |

|    | 6.1 | Introduction                                                  | 96 |

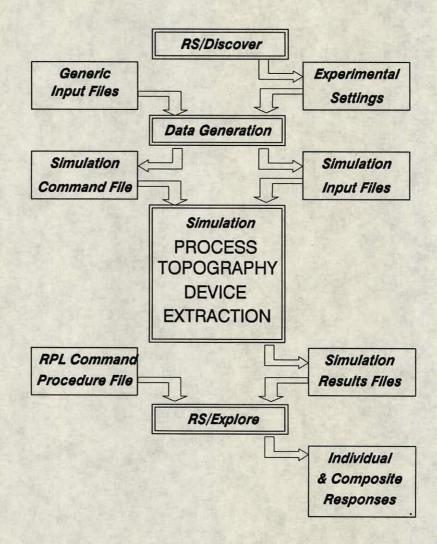

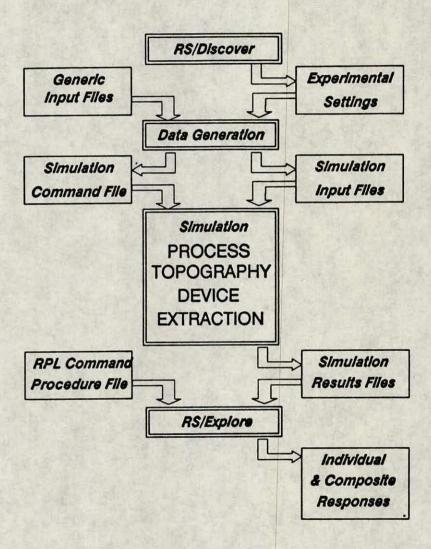

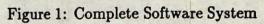

|    | 6.2 | Softwa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | are system                                                                                              | 97 |

|----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----|

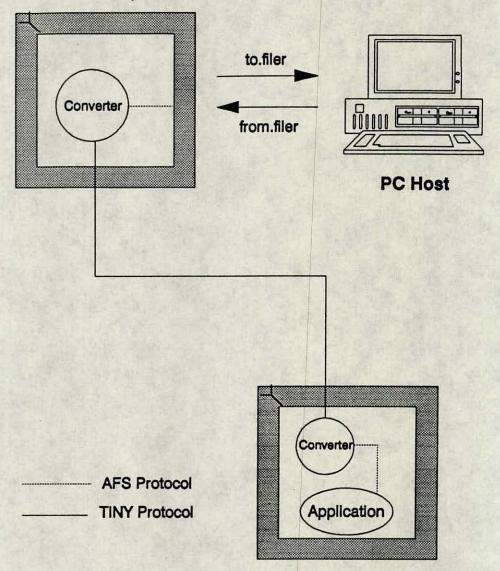

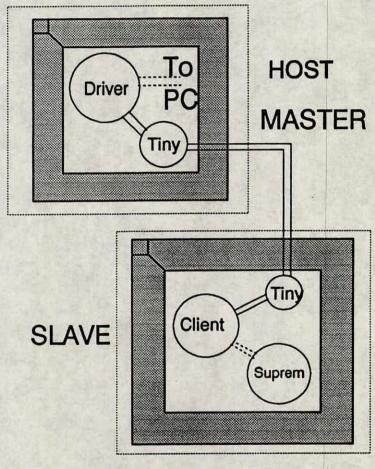

|    | 6.3 | A gene                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | eral transputer taskfarm                                                                                | 03 |

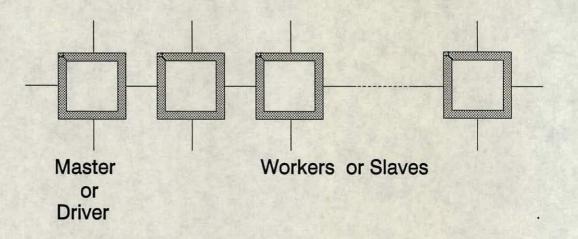

|    |     | 6.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | General taskfarm outline                                                                                | 03 |

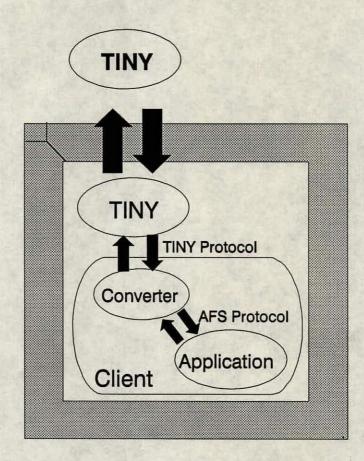

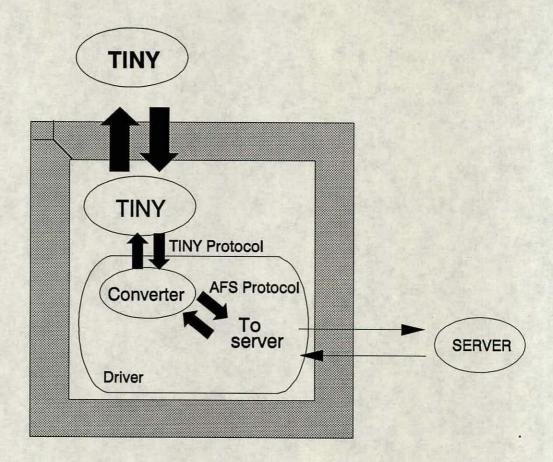

|    |     | 6.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TINY                                                                                                    | 06 |

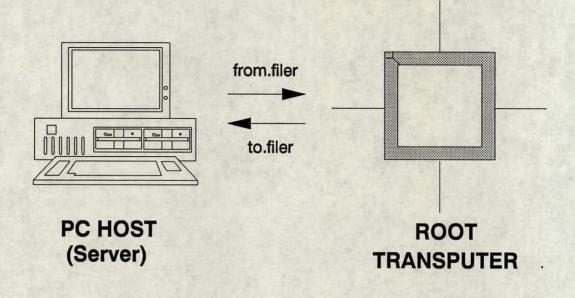

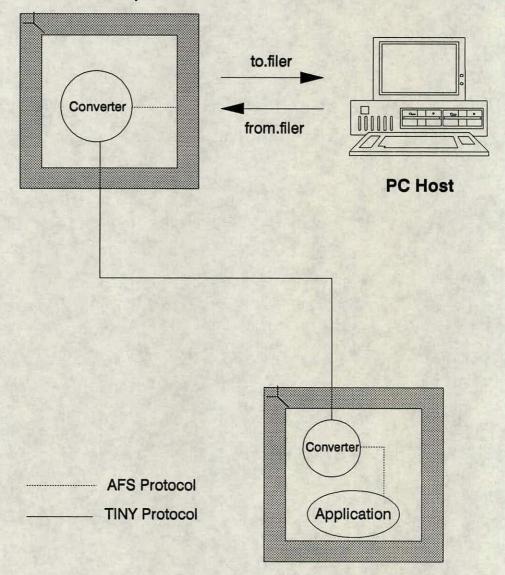

|    |     | 6.3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Afserver                                                                                                | 07 |

|    |     | 6.3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | General taskfarm operation                                                                              | 10 |

|    |     | 6.3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | System control                                                                                          | 16 |

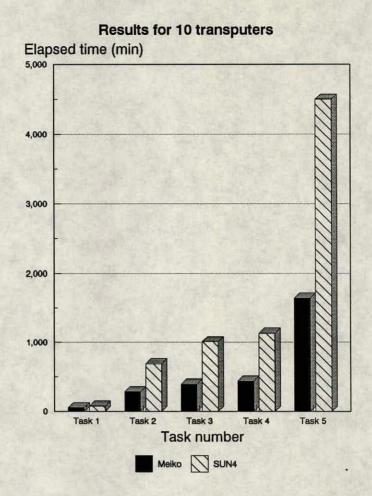

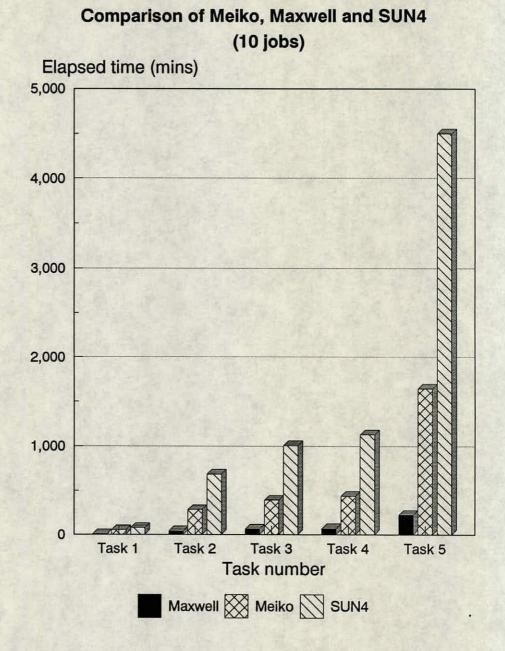

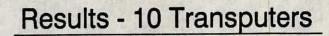

|    |     | 6.3.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | System Results                                                                                          | 16 |

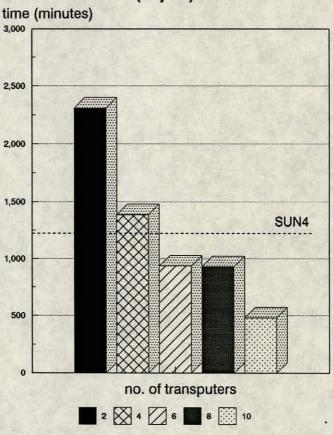

|    |     | 6.3.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Timing results                                                                                          | 19 |

|    | 6.4 | A para                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | allel taskfarm using Intel i860's                                                                       | 26 |

|    |     | 6.4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | General operation of the taskfarm                                                                       | 27 |

|    |     | 6.4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Running the taskfarm                                                                                    | 29 |

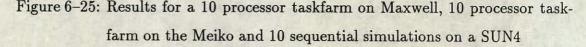

|    | 6.5 | SUN v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | workstation Networking $\ldots \ldots 1$ | 31 |

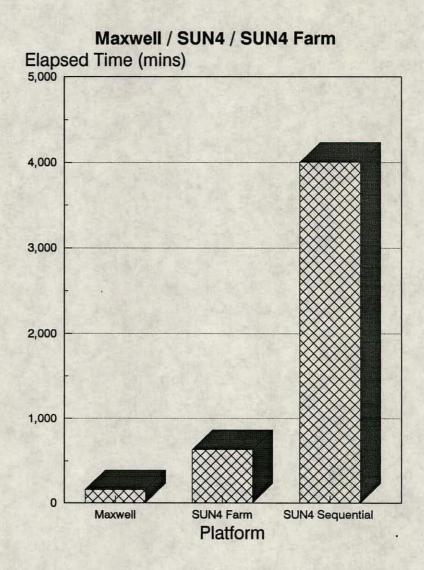

|    | 6.6 | A com                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | parative study of hardware platforms                                                                    | 32 |

|    | 6.7 | Conclu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | usions $\ldots$ $\ldots$ $\ldots$ $1$                                                                   | 34 |

| 7. | Sim | ulatio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | n and 1.5 $\mu$ m nMOS process optimisation 13                                                          | 36 |

|    | 7.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | luction                                                                                                 |    |

|    | 7.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | imental objectives and tradeoffs                                                                        |    |

|    | 7.3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | nMOS response parameters                                                                                |    |

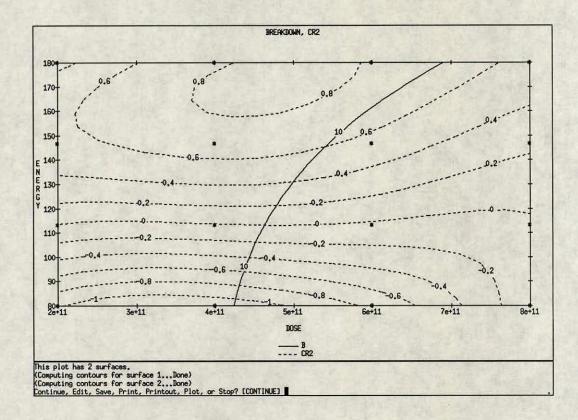

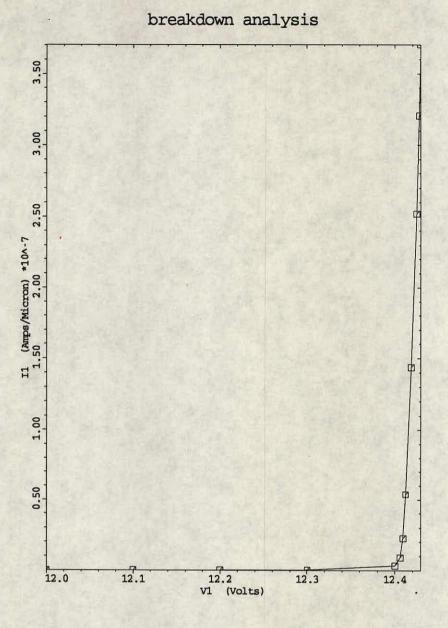

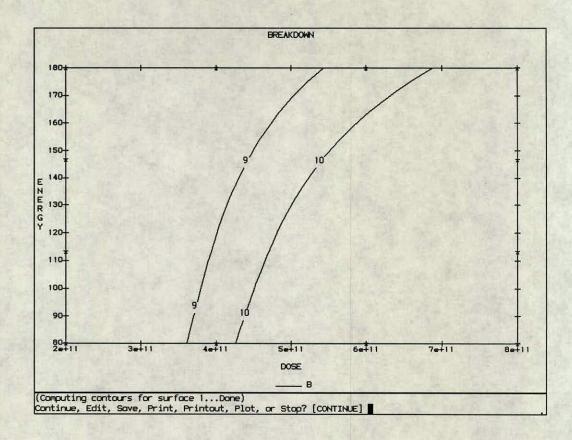

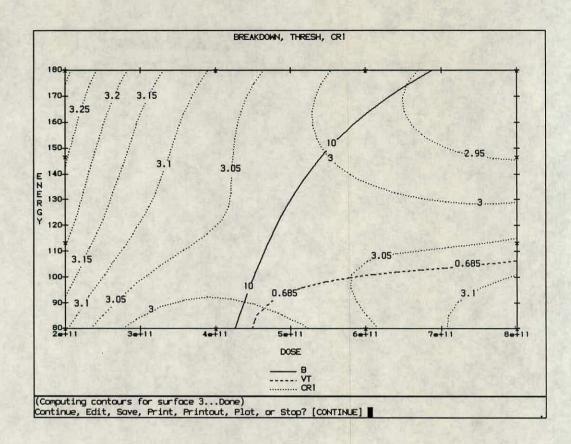

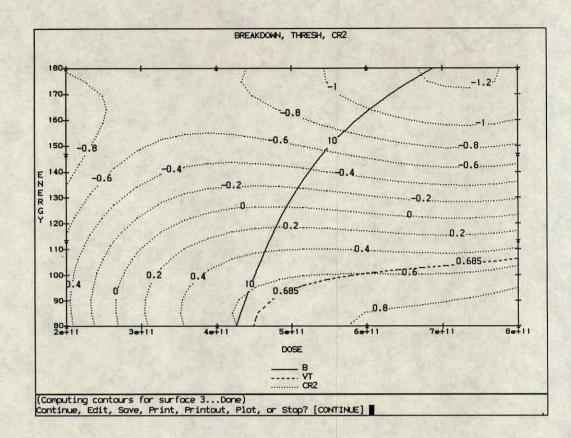

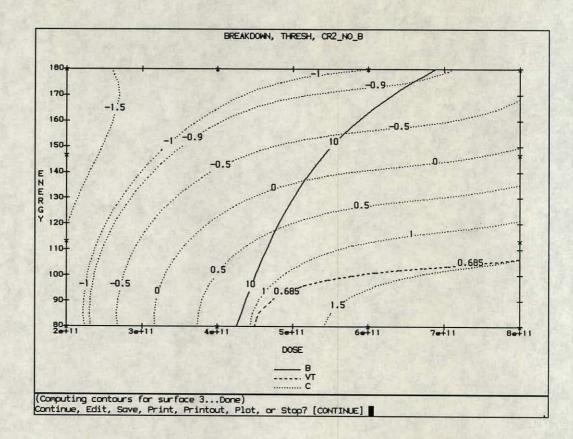

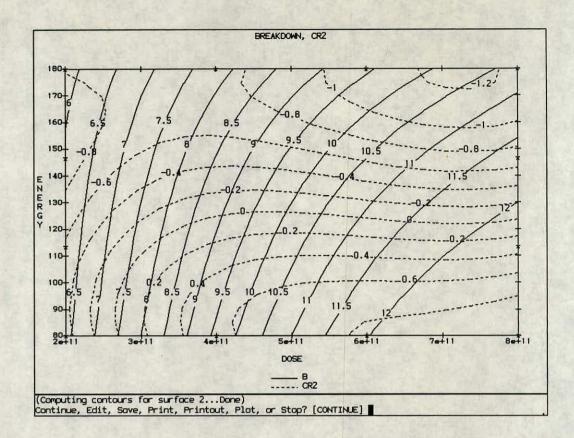

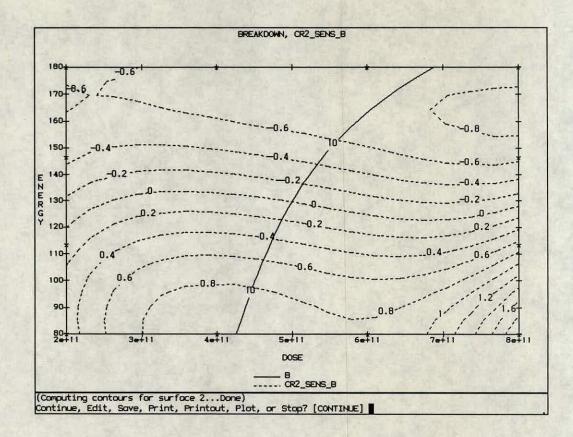

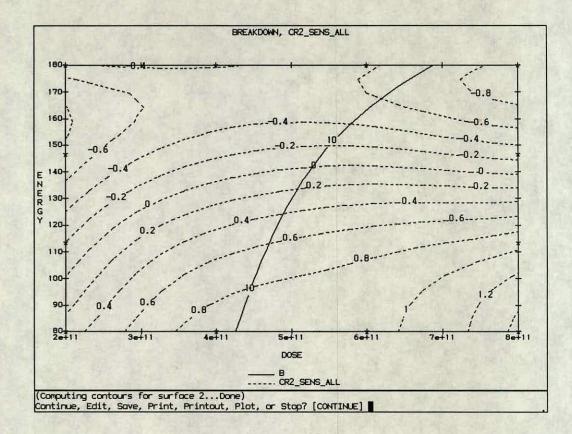

|    |     | 7.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Breakdown                                                                                               |    |

|    |     | 7.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Punchthrough                                                                                            |    |

|    |     | 7.3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Avalanche breakdown                                                                                     |    |

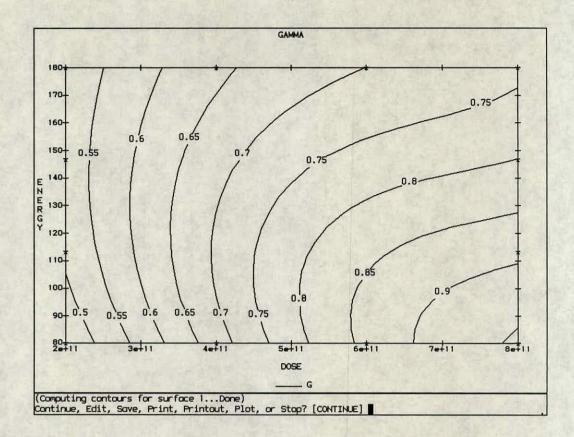

|    |     | 7.3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Gamma (body effect coefficient)                                                                         |    |

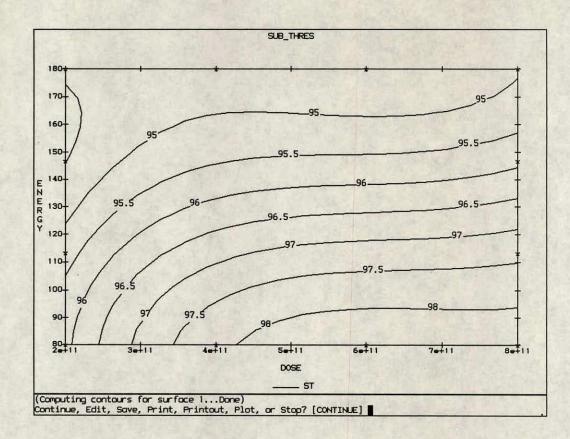

|    |     | 7.3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Subthreshold swing                                                                                      |    |

|    | -   | and the second sec |                                                                                                         |    |

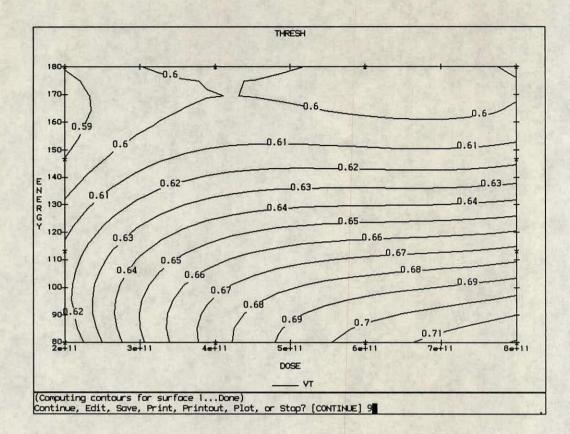

|    |      | 7.3.6   | Threshold voltage                                      | 46 |

|----|------|---------|--------------------------------------------------------|----|

|    | 7.4  | Definit | g the experiment                                       | 47 |

|    |      | 7.4.1   | Response Surface Analysis                              | 47 |

|    |      | 7.4.2   | Taguchi analysis                                       | 51 |

|    | 7.5  | Simula  | tion Procedure                                         | 51 |

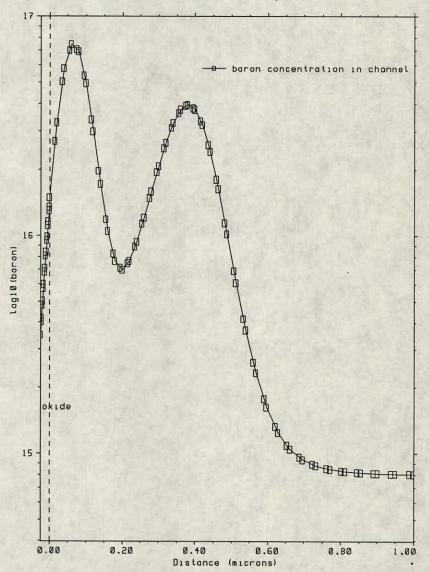

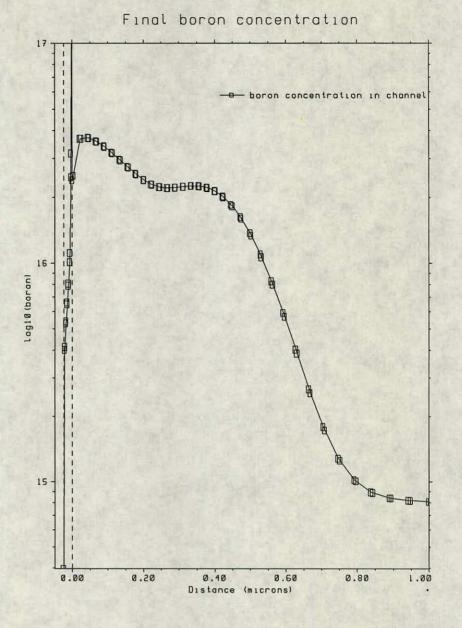

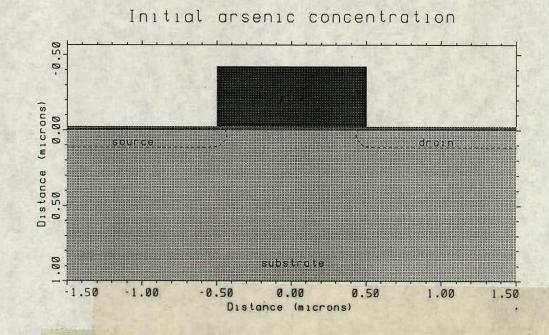

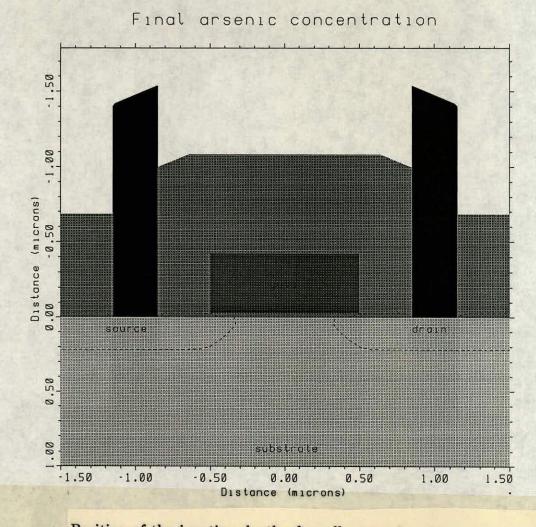

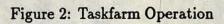

|    |      | 7.5.1   | SUPREM4 Analysis                                       | 53 |

|    |      | 7.5.2   | Device analysis                                        | 59 |

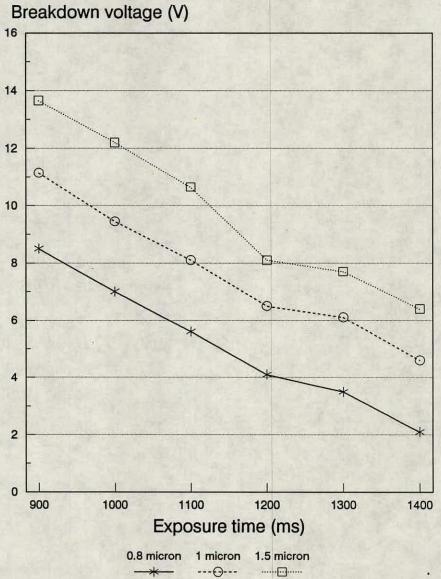

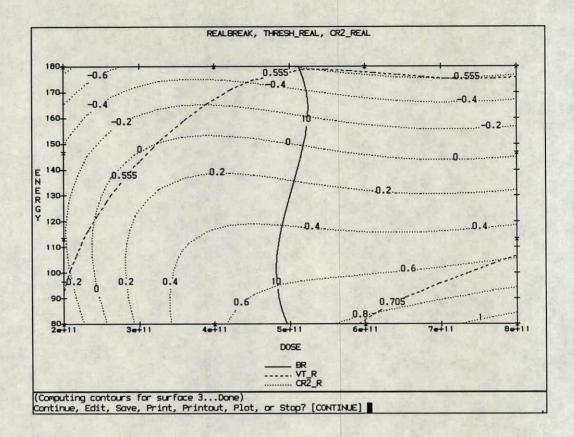

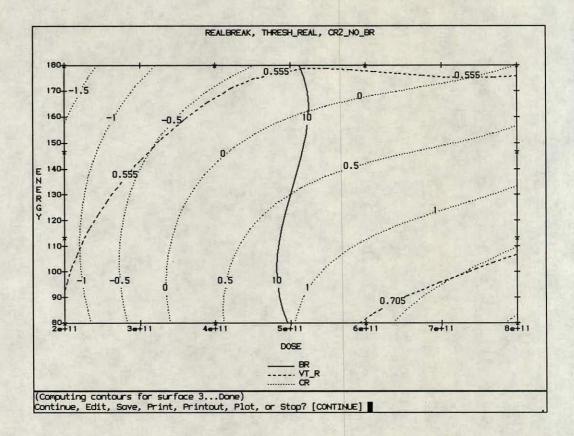

|    |      | 7.5.3   | Breakdown voltage simulation                           | 60 |

|    |      | 7.5.4   | Gamma simulation                                       | 61 |

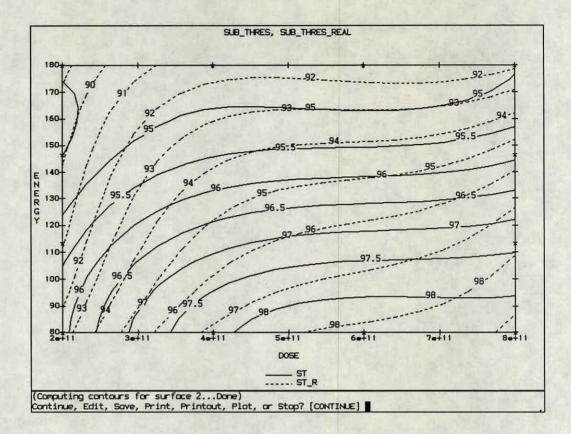

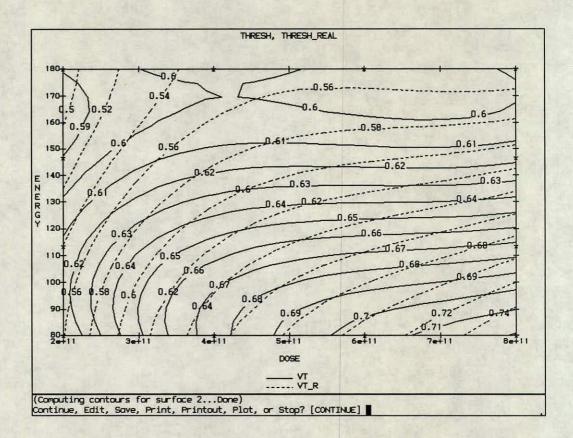

|    |      | 7.5.5   | Threshold and subthreshold simulation                  | 63 |

|    | 7.6  | Analy   | is of results                                          | 64 |

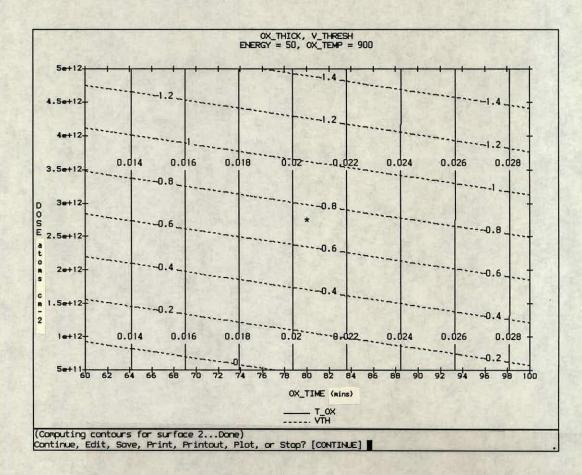

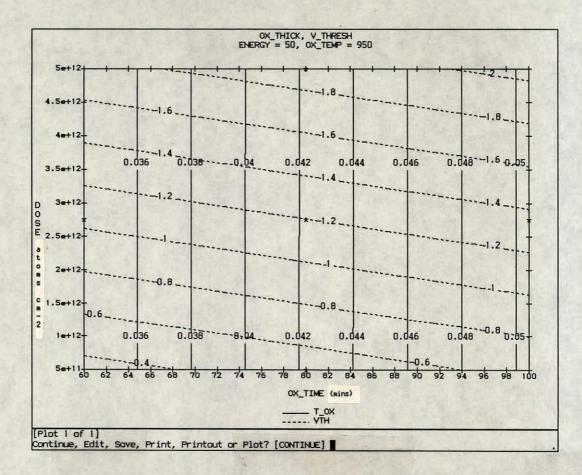

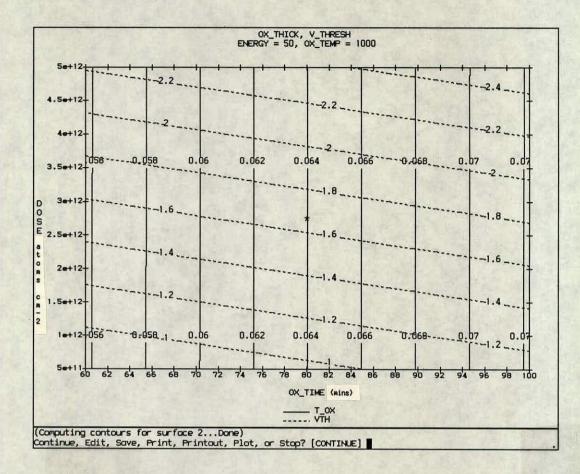

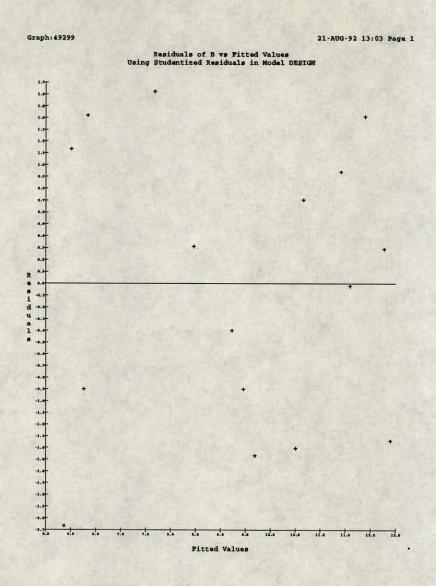

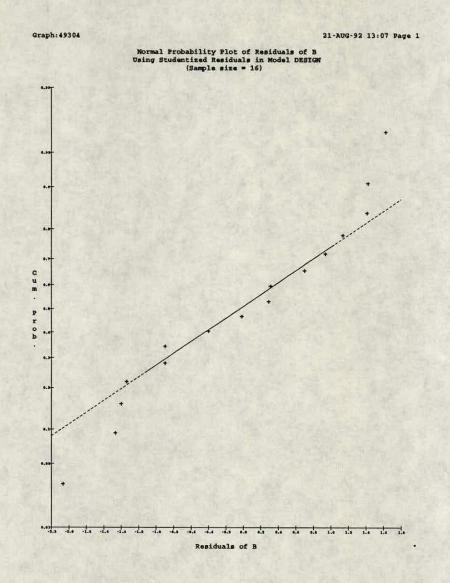

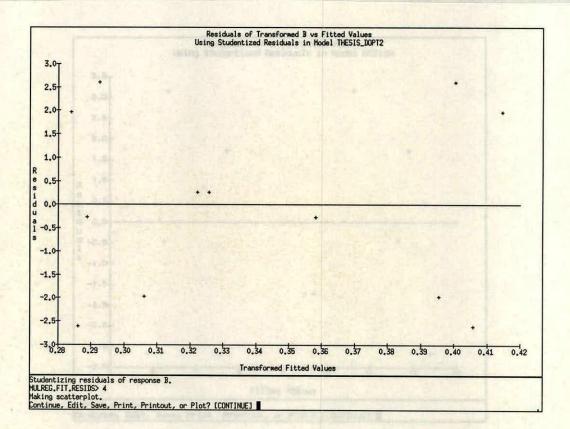

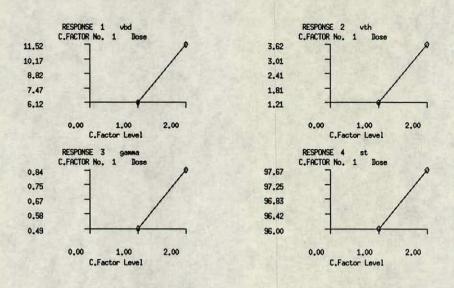

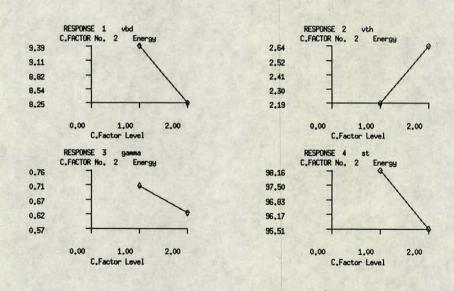

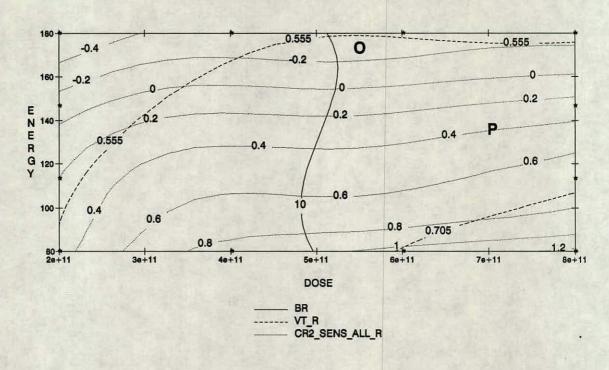

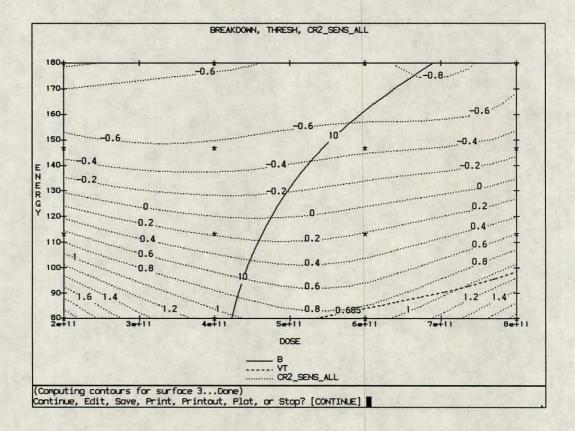

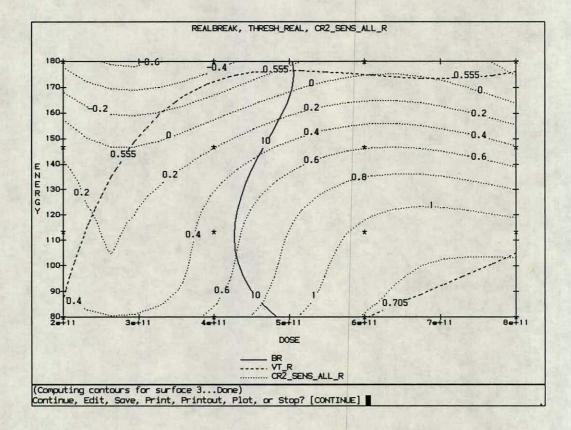

|    |      | 7.6.1   | RSM analysis                                           | 65 |

|    |      | 7.6.2   | Optimum operating conditions                           | 68 |

|    |      | 7.6.3   | Sensitivity analysis                                   | 73 |

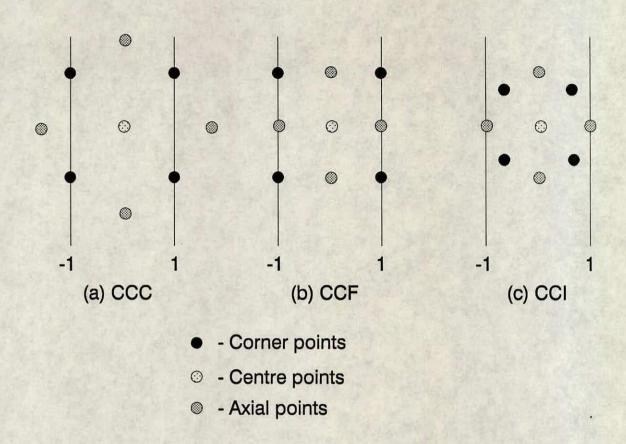

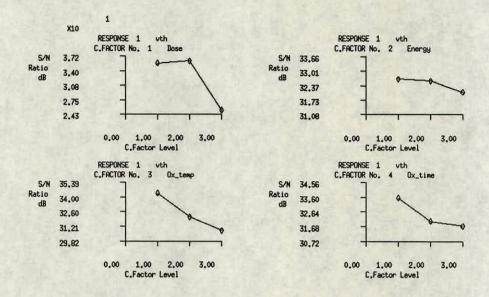

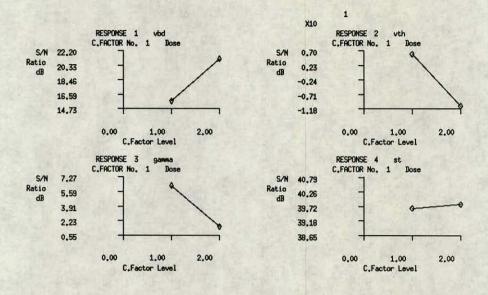

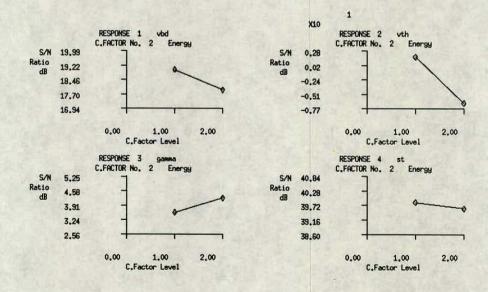

|    |      | 7.6.4   | A comparison of Taguchi and RSM                        | 76 |

|    | 7.7  | Conch   | sions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$ | 81 |

| 3. | Test | t resul | s and analysis 18                                      | 82 |

|    | 8.1  | Introd  | uction                                                 | 82 |

|    | 8.2  | The 1   | 5µm nMOS process                                       | 83 |

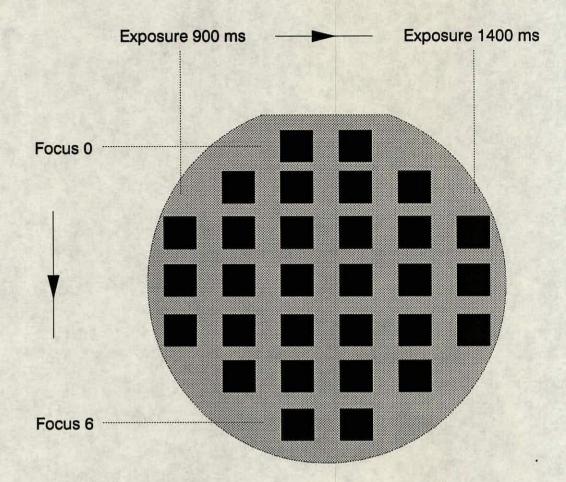

|    | 8.3  | Wafer   | processing                                             | 84 |

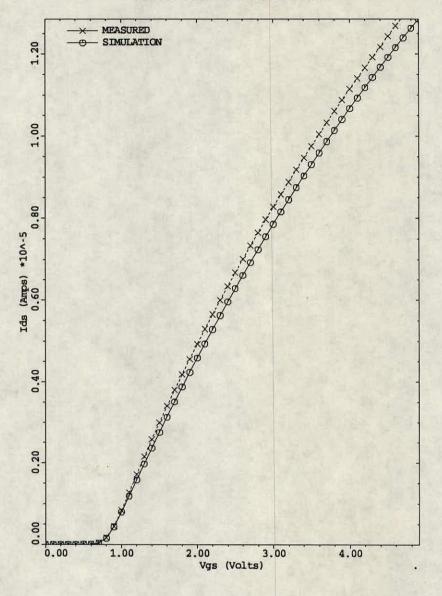

|    | 8.4  | Test r  | esults                                                 | 86 |

|    | 8.5  | Analy   | is of results                                          | 87 |

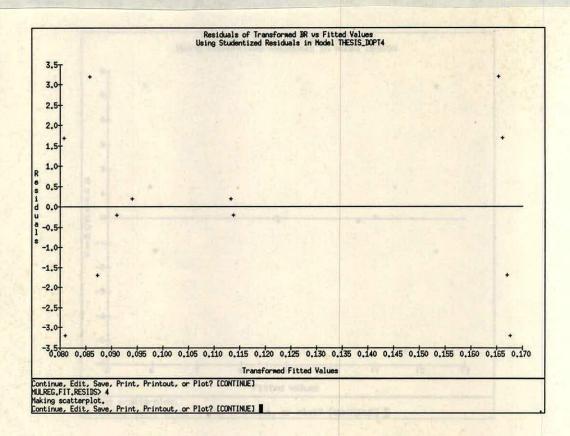

|    |      | 8.5.1   | RSM analysis                                           | 87 |

|    |      | 8.5.2   | Optimum operating conditions                           | 91 |

|     | 8.5.3 | Sensitivity analysis                       |

|-----|-------|--------------------------------------------|

|     | 8.5.4 | Comparison of D-optimal and full-factorial |

| 8.6 | Concl | usions                                     |

## 9. Conclusions

200

# List of Figures

| 1–1 | Trends in fabrication of DRAM's                                   | 2  |

|-----|-------------------------------------------------------------------|----|

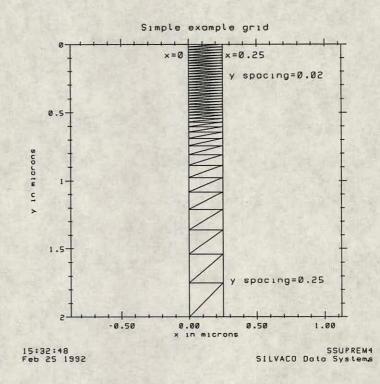

| 2–1 | An example of a simple grid generated by SSUPREM4                 | 10 |

| 2-2 | An example of a SSUPREM4 grid used to simulate a small geometry   |    |

|     | process                                                           | 11 |

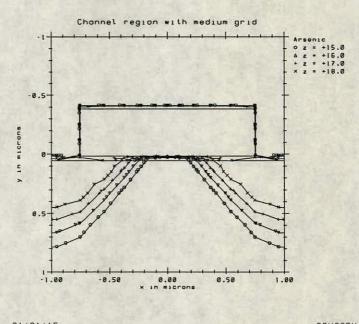

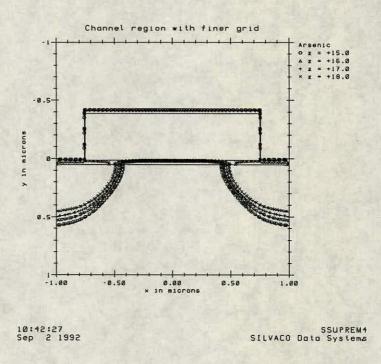

| 2–3 | Channel region using a coarse grid                                | 12 |

| 2-4 | Channel region using a finer grid                                 | 12 |

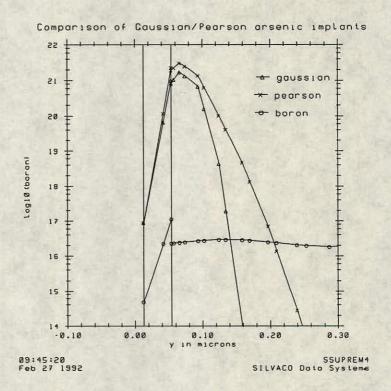

| 2–5 | A comparison of Gaussian and Pearson distributions for an arsenic |    |

|     | implant                                                           | 13 |

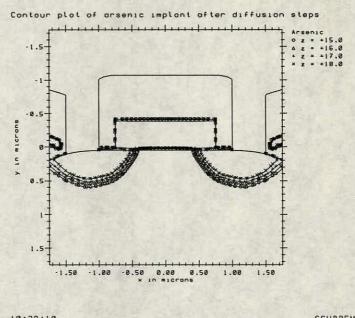

| 2-6 | Concentration contour plot for the source drain implant of a MOS  |    |

|     | transistor                                                        | 14 |

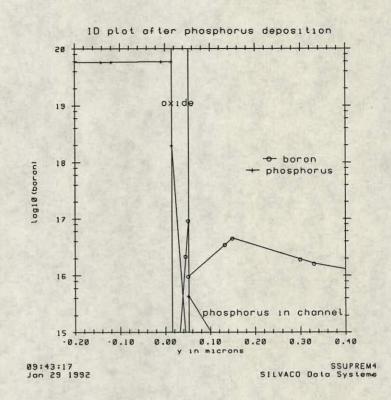

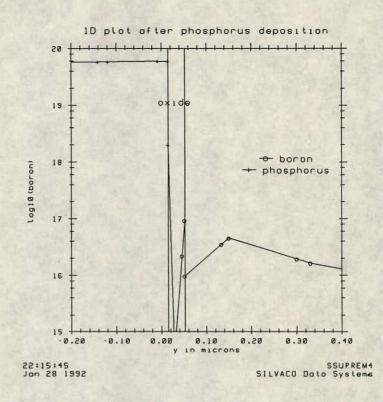

| 2-7 | Phosphorus diffusion using default coefficients                   | 16 |

| 2–8 | Phosphorus diffusion using calibrated coefficients                | 17 |

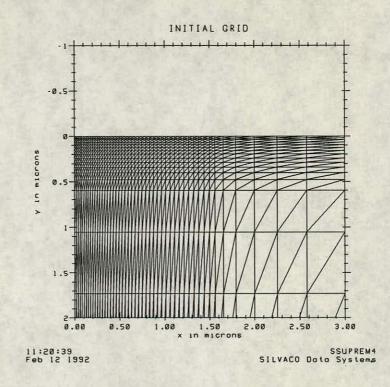

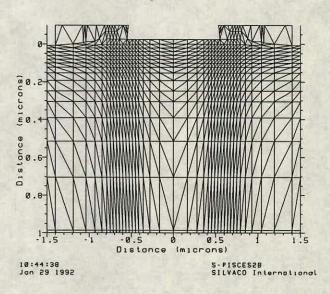

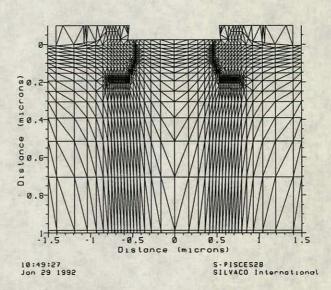

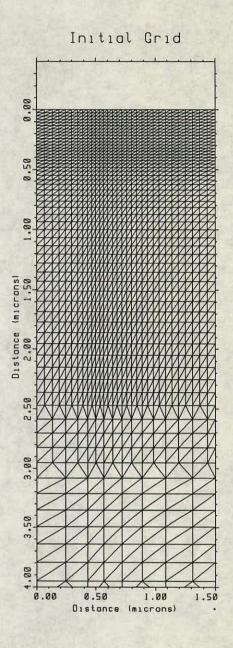

| 3–1 | Initial grid definition                                           | 26 |

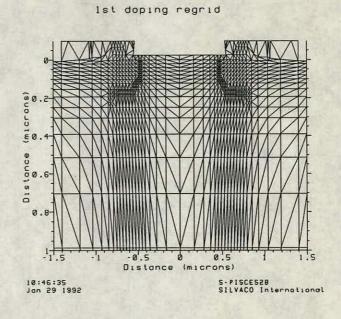

| 3–2 | First doping regrid                                               | 27 |

| 3–3 | Second doping regrid                                              | 27 |

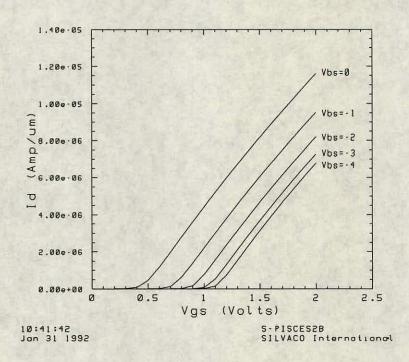

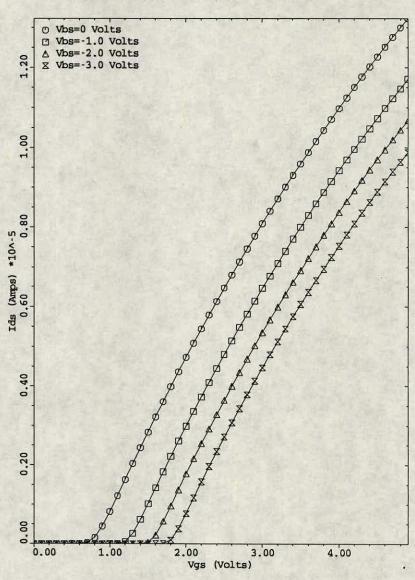

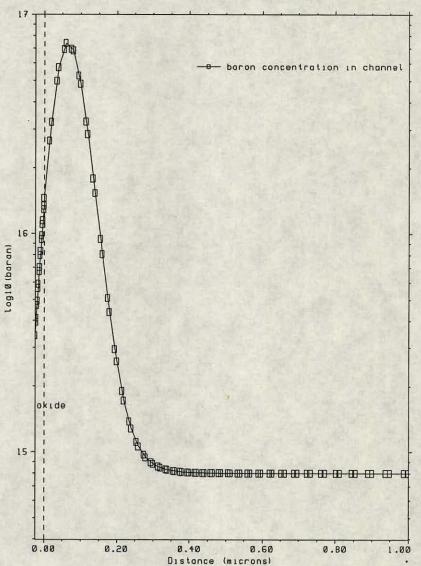

| 3–4 | $I_d$ versus $V_{gs}$ for different $V_{bs}$                      | 29 |

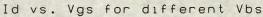

| 3–5 | $I_d$ versus $V_{ds}$ for different $V_{gs}$                      | 30 |

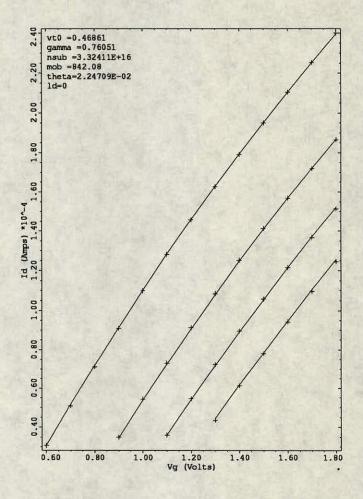

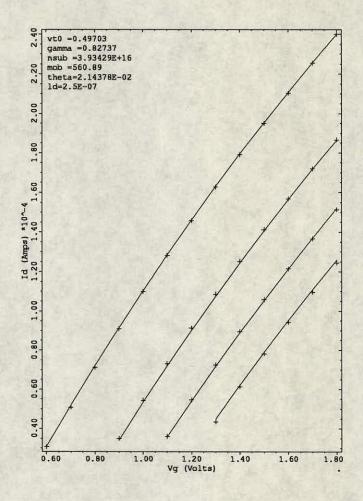

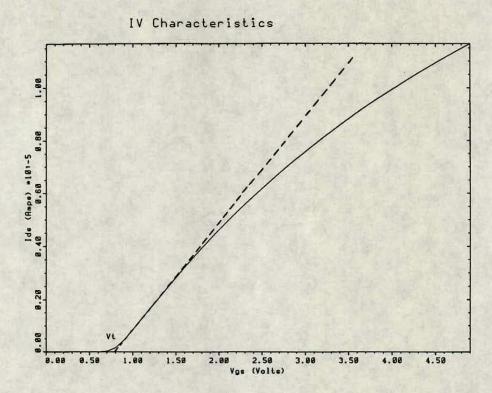

| 3–6 | Topex fit showing unrealistic value for Ld                        | 33 |

| 3-7 | Topex fit showing realistic value for Ld                          | 34 |

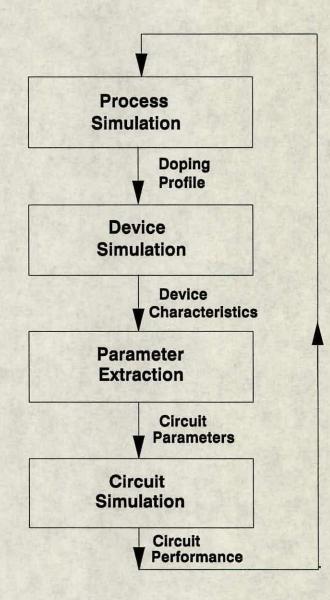

| 3-8  | Integration of process, device, parameter extraction and circuit sim-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | ulation tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35 |

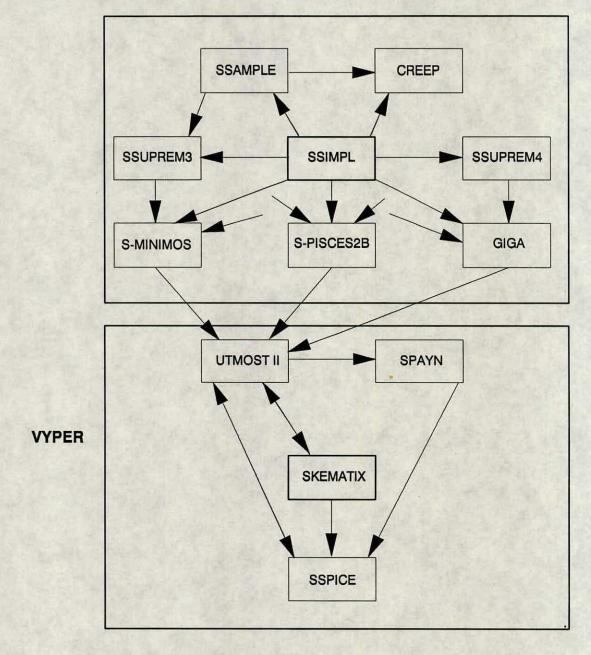

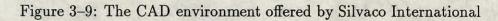

| 3–9  | The CAD environment offered by Silvaco International                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 37 |

| 3–10 | The CAD environment offered by Technology Modeling Associates .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 38 |

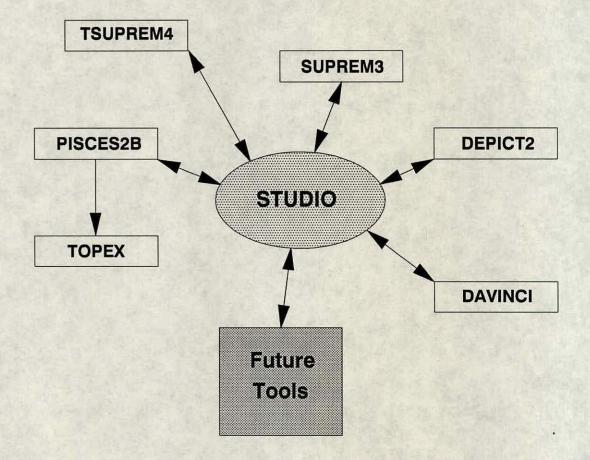

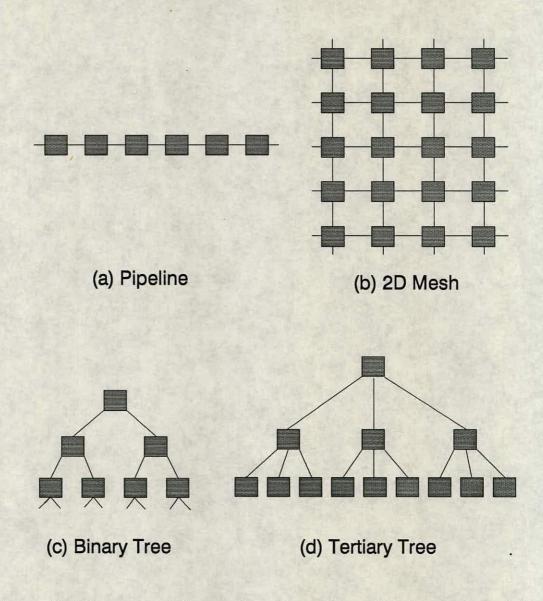

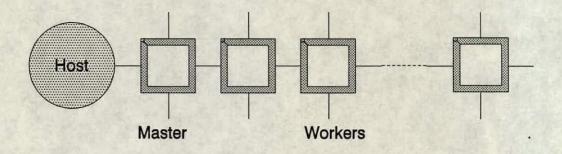

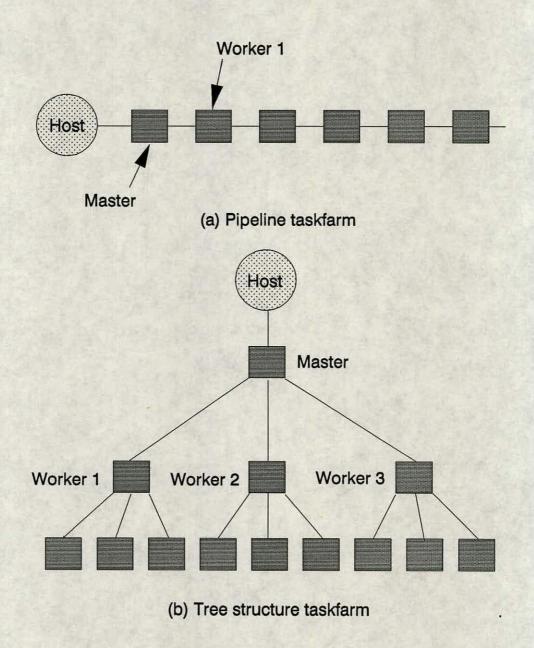

| 4–1  | Graphical representation of the experimental design process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41 |

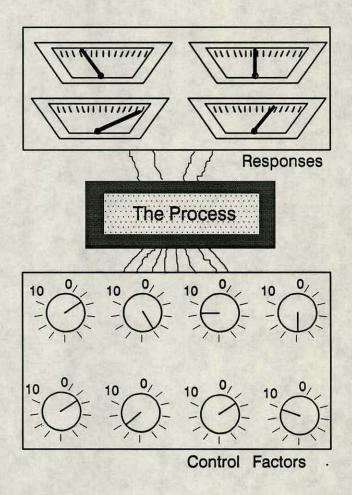

| 4-2  | The comparative effects of interactions and no interactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43 |

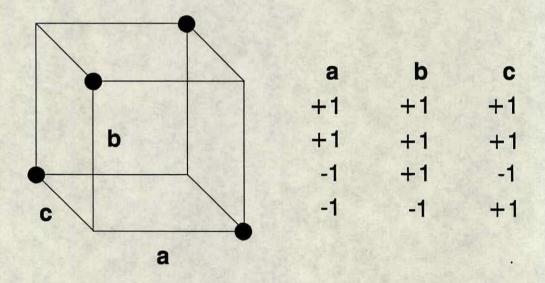

| 4–3  | A fractional factorial design for 3 variables and two levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 43 |

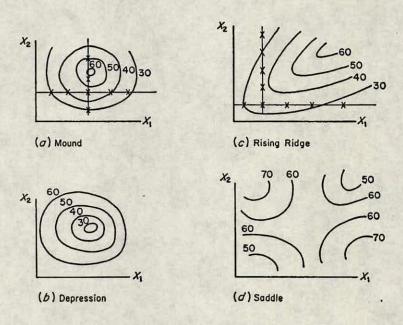

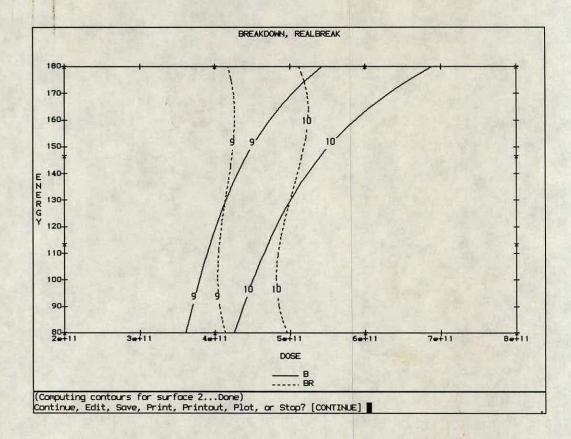

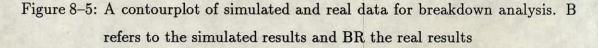

| 4-4  | An example of a typical response surface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45 |