## **Application of CMP and Wafer Bonding for Integrating CMOS and MEMS Technology**

Huamao Lin

A thesis submitted for the degree of Doctor of Philosophy. The University of Edinburgh. November 2007

## Abstract

Microelectromechanical systems (MEMS) can provide an interface between the digital electronic world and the analog physical world. Depended on the transduction mechanisms, various micromechanical structures are designed to ensure the transductions with highest efficiency. As a consequence, MEMS devices have to be fabricated using a broad range of techniques, and often require integration with the CMOS circuitry.

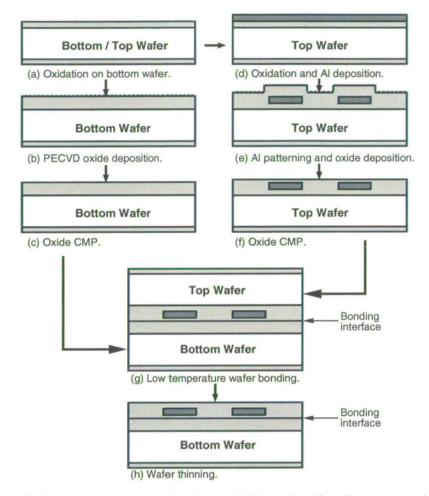

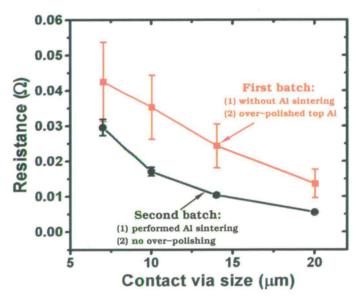

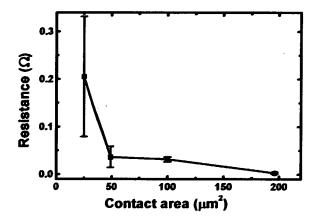

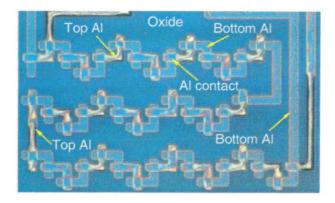

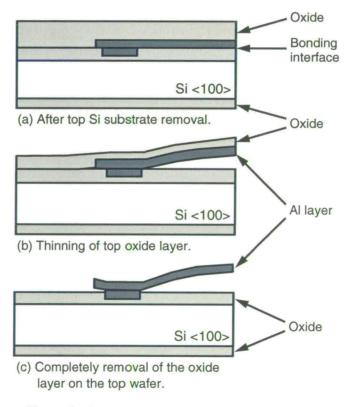

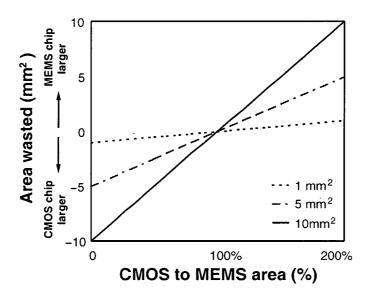

The feasibility of a new fabrication approach has been investigated in this thesis, which uses chemical mechanical polishing (CMP) and oxygen plasma assisted low temperature wafer bonding, to integrate prefabricated MEMS and CMOS devices. Fabricating MEMS and CMOS devices on separate wafers enables the optimisation of each technology separately. However, to integrate them requires low temperature bonding of processed wafers, connecting the bonded wafer pair and bringing the electrical signals to the top surface. Test structures have been used to investigate the feasibility of bonding MEMS and CMOS wafers to create an integrated system with electrical connections. Bonding and thinning of prefabricated wafers has been demonstrated using a CMP enabled surface planarisation process and plasma assisted low temperature wafer bonding. Inter-wafer connections can be achieved using two fabrication methods. With oxide to oxide bonding method, resistances of  $3.8 - 5.2 \Omega$  have been obtained for the via chain test structures with 9-13 contact vias, whilst an average specific contact resistivity of  $1.7 \times 10^{-8}\Omega \cdot cm^2$  has been achieved from the single via test structure. Direct electrical connections between wafers has also been implemented during the bonding anneal stage with an average contact resistance of  $2.6 \times 10^{-8} \Omega \cdot cm^2$ .

## Declaration of originality

I hereby declare that the research recorded in this thesis and the thesis itself was composed and originated entirely by myself in the School of Engineering and Electronics at The University of Edinburgh. This work has not been submitted for any other degree or professional qualification.

Huamao Lin

## Acknowledgements

First, I would like to thank Professor Anthony Walton for his guidance, encouragement and support throughout the course of my research. I would also like to thank all the people I have worked with at the Scottish Microelectronics Centre, most of you have had contribution and influence on this work: Tom Stevenson, Alan Gundlach, Camelia Dunare, Alec Ruthven, Stewart Smith, Jennifer McGregor, Joanna Venkov, Jon Terry, Ewan MacDonald, Gerry McDade, Bill Parkes, Andrew Bunting, Alan Ross, Richard Blair, Ann Cunningham, Rebecca Cheung, Peter Ewen, Les Haworth, Tony Snell, Kevin Tierney and David Archibald. This work would not be completed without the help and assistance from other students and friends, who have also made my life in Edinburgh more enjoyable. Therefore, thanks must also go to Liudi Jiang, Kin-Kiong Lee, Yifan Li, Peng Li, Martin Dicks, Stefan Enderling, Louise Teo, Natalie Plank, Gerard Cummins, Byron Shulver, Mark Muir, Keith Muir, Keith Baldwin, Petros Argyrakis, Tong-Boon Tang and Andreas Tsiamis. I am also grateful for the funding provided by the Applied Materials, without its support this dissertation would not be made possible.

A special thank you to my parents, sister and other family members for their constant encouragement and support. The most important person I wish to thank is my wife, Huihong Li, for always being there with love and support over the last four years, even though it has meant many sacrifices. I would never have managed to finish this work without her encouragement, patience and understanding.

## Publications

Publications by the author relevant to this work include:

1. H. Lin, J.T.M. Stevenson, A.M. Gundlach, C.C. Dunare, and A.J. Walton, "Application of CMP for Integrating MEMS and CMOS Technology", *16<sup>th</sup> European Workshop on MicroMechanics*, pp. 207-210, 2005.

2. H. Lin, A.J. Walton, C.C. Dunare, J.T.M. Stevenson, A.M. Gundlach, S. Smith, and A.S. Bunting, "Test Structure for the Characterization of MEMS and CMOS Integration Technology", in *Proceeding of IEEE International Conference on Microelectronic Test Structures*, pp. 143-148, 2006.

3. S. Enderling, H. Lin, J.T.M. Stevenson, A.S. Bunting, and A.J. Walton, "Characterisation of a CMP Nanoscale Planarisation-based Process for RF MEMS Resonators", *Proceeding of SPIE: Micro- and Nanotechnology - Materials, Processes, Packaging, and Systems III*, vol. 6415, p. 64150G, 2006.

4. A. J. Walton, J. T. M. Stevenson, I. Underwood, J.G. Terry, S. Smith, W. Parkes, C. Dunare, **H. Lin**, Y. Li, R. Henderson, D. Renshaw, K. Muir, M. Desmulliez, B. Flynn, A. F. Murray, T.B. Tang, A. Bunting, and A.M. Gundlach, "Integration of IC technology with MEMS: Silicon<sup>+</sup> technology for the future", *IET Seminar on Micro-Electro-Mechanical Systems, MEMS Technology*, pp. 1-11, 2007.

5. H. Lin, J.T.M. Stevenson, A.M. Gundlach, C.C. Dunare, and A.J. Walton, "Direct Al-Al Contact using Low Temperature Wafer Bonding for Integrating MEMS and CMOS Devices", in *Proceeding of 33rd International Conference on Micro- and Nano-Engineering*, pp. 357-358, 2007.

6. **H. Lin**, S. Smith, J.T.M. Stevenson, A.M. Gundlach, C.C. Dunare, and A.J. Walton, "An Evaluation of Test Structures for Measuring the Contact Resistance of 3-D Bonded Interconnects", accepted by *IEEE International Conference on Microelectronic Test Structures 2008*.

7. H. Lin, A.J. Walton, C.C. Dunare, J.T.M. Stevenson, A.M. Gundlach, S. Smith, and A.S. Bunting, "Test Structures for the Characterisation of MEMS and CMOS Integration Technol-

ogy", accepted by IEEE Transactions on Semiconductor Manufacturing.

8. **H. Lin**, J.T.M. Stevenson, A.M. Gundlach, C.C. Dunare, and A.J. Walton, "Direct Al-Al Contact using Low Temperature Wafer Bonding for Integrating MEMS and CMOS Devices", manuscript submitted to journal *Microelectronic Engineering*.

## Contents

| 1 |      | Declaration of originality       iii         Acknowledgements       iv         Publications       vi         Contents       vi         List of figures       xiv         xit of tables       xiv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | v        |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1 |      | Publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| 1 |      | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| 1 |      | List of figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 1 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 1 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -        |

| 1 |      | A second and the second s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| 1 |      | Acronyms and abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| 1 |      | Nomenclature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1        |

| • | Intr | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1        |

|   | 1.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I        |

|   | 1.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1        |

|   | 1.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4        |

|   | 1.4  | internation and oropy of the international states of the s | 5        |

|   | 1.4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <i>,</i> |

| 2 | CM   | ob una billito lintegi anon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7        |

|   | 2.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7        |

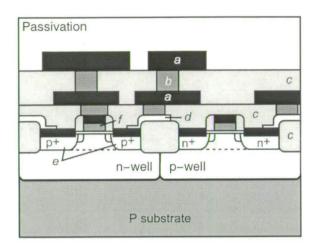

|   | 2.2  | CMOS IC fabrication technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7        |

|   |      | 2.2.1 CMOS IC fabrication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7        |

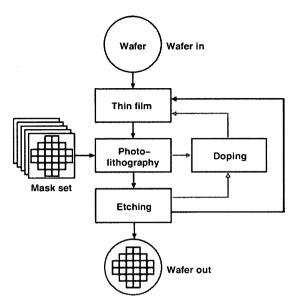

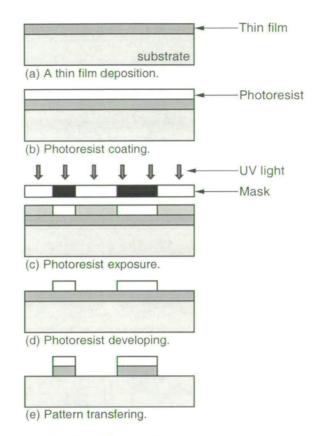

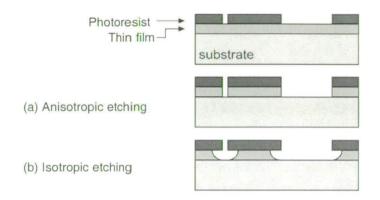

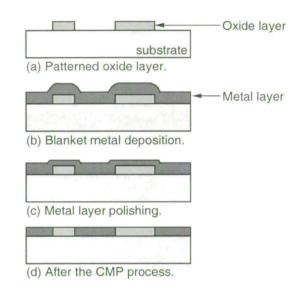

|   |      | 2.2.2 Basic fabrication processes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9        |

|   | 2.3  | MEMS fabrication technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3        |

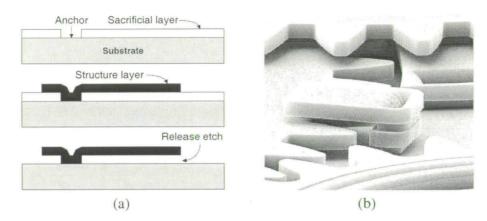

|   |      | 2.3.1 Surface micromachining                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3        |

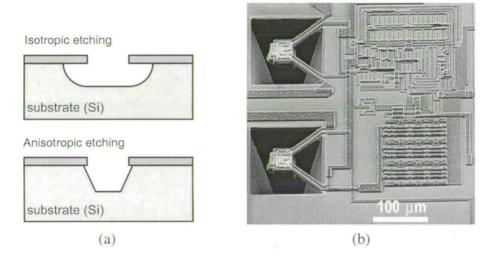

|   |      | 2.3.2 Bulk micromachining                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4        |

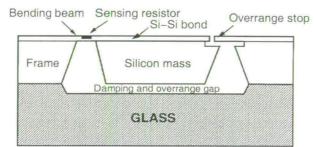

|   |      | 2.3.3 Wafer bonding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5        |

|   | 2.4  | Integration of MEMS and CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6        |

|   |      | 2.4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6        |

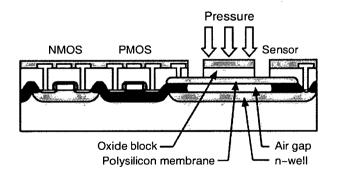

|   |      | 2.4.2 Pre-CMOS micromachining                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8        |

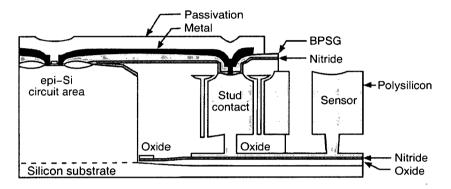

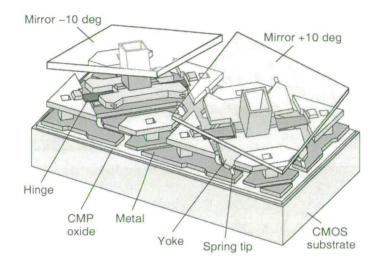

|   |      | 2.4.3 Fully integrated micromachining                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9        |

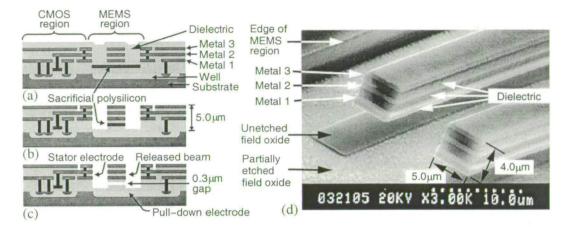

|   |      | 2.4.4 Post-CMOS micromachining                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1        |

|   |      | 2.4.5 Chip-level integration and multi-chip modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4        |

|   | 2.5  | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

|   | 2.0  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 3 | Che  | mical Mechanical Polishing 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

|   | 3.1  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

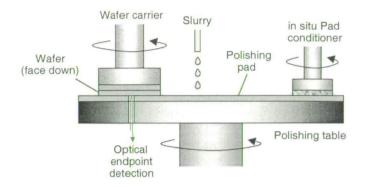

|   | 3.2  | Introduction of the CMP process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5        |