# Automated Synthesis of Delay-Insensitive Circuits

Roger Anthony Sayle

Doctor of Philosophy

Department of Computer Science

University of Edinburgh

1996

## Abstract

The technological trend towards VLSI circuits built from increasing numbers of transistors continues to challenge the ingenuity of both designers and engineers. The use of asynchronous design techniques presents a method for taming the complexity of large concurrent VLSI system design and offers a number of attractive advantages over conventional design styles. In this thesis, we concentrate on the useful class of *delay insensitive* asynchronous circuits. These have the property that their correct operation is independent of the speed of the individual elements and the delays in the connecting wires.

Traditionally, asynchronous circuits are considered much harder to design than their synchronous equivalents due to their inherent nondeterminism. The use of automated formal methods for generating such circuits shields the designer from this complexity. This allows the designer to abstract away from implementation issues and reason about the system behaviour in terms of concurrent processes or high level programs. Because each step of the compilation process can be shown to be sound, the resulting circuits are correct-by-construction.

This thesis presents a compilation methodology for designing delay insensitive VLSI systems from behavioural specifications. The synthesis method makes use of a graph-based representation of the circuit's behaviour. Optimization of the global behaviour, by graph transformation, enables the generation of more efficient circuits than those produced by previous asynchronous circuit compilers based on syntax-directed translation. The resulting circuits are further improved by semantics-preserving circuit transformations. A compiler has been constructed that automatically performs the translation and transformation.

# Acknowledgements

Although this page is considered unimportant and is often skipped by the reader, to the author it is perhaps the most important page of all. The work in this thesis would not have taken its final form without the help and friendship of the people mentioned below.

Foremost I would like to thank my thesis supervisor Mike Fourman, for his guidance and for the exceptional creative freedom I have been allowed. I would also like to thank Jo Ebergen, Mark Josephs and Jan Tijmen Udding for many constructive conversations. But most of all I would like to thank my examiners, Julian Bradfield and Graham Birtwistle for their many recommendations that have resulted in a much improved thesis.

Thanks also go to Delia Johnson for her continual support and encouragement.

This work has been financially supported by funding from the Science and Engineering Research Council.

# Table of Contents

| Abstract |                             |        |                             |      |  |  |  |  |

|----------|-----------------------------|--------|-----------------------------|------|--|--|--|--|

| D        | eclar                       | ation  |                             | ii   |  |  |  |  |

| A        | ckno                        | wledge | ements                      | iii  |  |  |  |  |

| 1.       | Introduction                |        |                             |      |  |  |  |  |

|          | 1.1                         | Thesis | s Overview                  | . 1  |  |  |  |  |

|          | 1.2                         | Async  | chronous Circuits           | . 3  |  |  |  |  |

|          | 1.3                         | Motiv  | ation                       | . 5  |  |  |  |  |

|          | 1.4                         | Backg  | round and Related Work      | . 8  |  |  |  |  |

|          |                             | 1.4.1  | Bounded Delay Model         | . 8  |  |  |  |  |

|          |                             | 1.4.2  | Unbounded Gate-Delay Model  | . 10 |  |  |  |  |

|          |                             | 1.4.3  | Unbounded Wire-Delay Model  | . 13 |  |  |  |  |

|          |                             | 1.4.4  | Module Based Synthesis      | . 16 |  |  |  |  |

| 2.       | Behavioural Specification 2 |        |                             |      |  |  |  |  |

|          | 2.1                         | Abstra | act Circuit Model           | . 20 |  |  |  |  |

|          |                             | 2.1.1  | Labelled Transition Systems | . 20 |  |  |  |  |

|          |                             | 2.1.2  | Operational Behaviour       | . 22 |  |  |  |  |

|          | 2.2                         | Circui | t Specification             | . 24 |  |  |  |  |

|          |                             | 2.2.1  | Process Algebra             | . 24 |  |  |  |  |

|    |     | 2.2.2   | Trace Theory                        |  |

|----|-----|---------|-------------------------------------|--|

|    |     | 2.2.3   | Petri Nets                          |  |

|    | 2.3 | Circui  | t Composition                       |  |

|    | 2.4 | Imple   | mentation Relation                  |  |

|    | 2.5 | Delay   | Insensitivity                       |  |

|    | 2.6 | Interfa | ace Partitioning                    |  |

|    | 2.7 | Comp    | iler Representation                 |  |

| 3. | Bas | ic Con  | aponents 51                         |  |

|    | 3.1 | Hands   | haking                              |  |

|    | 3.2 | Primit  | sive Components                     |  |

|    |     | 3.2.1   | Merge                               |  |

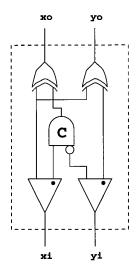

|    |     | 3.2.2   | Muller C-element                    |  |

|    |     | 3.2.3   | Keller Select                       |  |

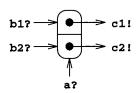

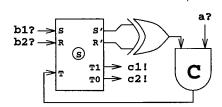

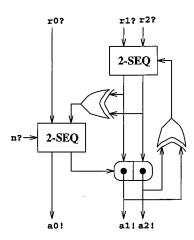

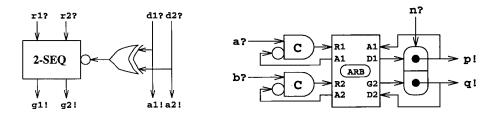

|    |     | 3.2.4   | Decision-wait elements              |  |

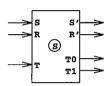

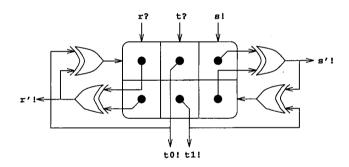

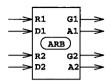

|    |     | 3.2.5   | RGDA Arbiter                        |  |

|    | 3.3 | Standa  | ard Components                      |  |

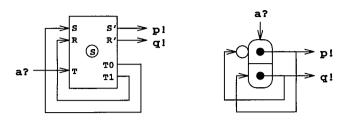

|    |     | 3.3.1   | IWire 58                            |  |

|    |     | 3.3.2   | Toggle                              |  |

|    |     | 3.3.3   | Call Element                        |  |

|    |     | 3.3.4   | Conventional Logic Gates            |  |

|    |     | 3.3.5   | Choice Element                      |  |

|    | 3.4 | Genera  | alized Components                   |  |

|    |     | 3.4.1   | N-Input C-Elements                  |  |

|    |     | 3.4.2   | <i>N</i> -Input Merges              |  |

|    |     | 3.4.3   | Generalized Call Components         |  |

|    |     | 3.4.4   | Generalized Select Element          |  |

|    |     | 3.4.5   | $N \times 1$ Decision Wait Elements |  |

|    |                         | 3.4.6                             | $N \times M$ Decision Wait Elements | 67 |  |  |  |

|----|-------------------------|-----------------------------------|-------------------------------------|----|--|--|--|

|    |                         | 3.4.7                             | N-TOGGLE Circuits                   | 70 |  |  |  |

|    | 3.5                     | Arbitr                            | ration Protocols                    | 75 |  |  |  |

|    |                         | 3.5.1                             | Mutual Exclusion Element            | 75 |  |  |  |

|    |                         | 3.5.2                             | RGD Arbiter                         | 76 |  |  |  |

|    |                         | 3.5.3                             | k-SEQ Component                     | 77 |  |  |  |

|    | 3.6                     | Initial                           | Conditions                          | 79 |  |  |  |

|    | 3.7                     | Asynchronous VLSI Circuits        |                                     |    |  |  |  |

|    | 3.8                     | Transi                            | stor-level Implementation           | 82 |  |  |  |

| 4. | Stal                    | ole Sta                           | te Synthesis Methodology            | 34 |  |  |  |

|    | 4.1                     | Stable                            | State Theory                        | 84 |  |  |  |

|    |                         | 4.1.1                             | Stable States                       | 85 |  |  |  |

|    |                         | 4.1.2                             | Stable State Graphs                 | 87 |  |  |  |

|    |                         | 4.1.3                             | Unstable Initial States             | 39 |  |  |  |

|    |                         | 4.1.4                             | Terminal States                     | 90 |  |  |  |

|    | 4.2                     | Properties of Stable State Graphs |                                     |    |  |  |  |

|    | 4.3                     | Signal                            | Instance Graphs                     | 95 |  |  |  |

|    | 4.4                     | Generi                            | c Implementation Strategy           | 97 |  |  |  |

|    | 4.5                     | Improv                            | ved Generic Solution                | 00 |  |  |  |

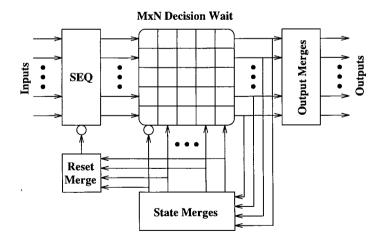

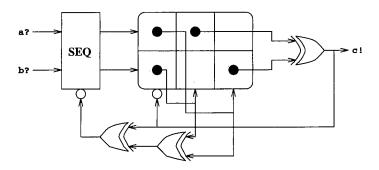

|    |                         | 4.5.1                             | Decision Wait Improvements          | 00 |  |  |  |

|    |                         | 4.5.2                             | SEQ element Improvements            | )2 |  |  |  |

|    | 4.6                     | Propos                            | sed Synthesis Methodology           | )3 |  |  |  |

|    |                         | 4.6.1                             | Implementation Model                | )3 |  |  |  |

|    |                         | 4.6.2                             | The Committee Problem               | Э6 |  |  |  |

| 5. | Circ                    | cuit Sy                           | nthesis 10                          | )9 |  |  |  |

|    | ntial Circuit Synthesis | <b>)</b> 9                        |                                     |    |  |  |  |

|    |                       | 5.1.1   | Stateless Sequential Circuits     |  |  |  |

|----|-----------------------|---------|-----------------------------------|--|--|--|

|    |                       | 5.1.2   | State-Holding Sequential Circuits |  |  |  |

|    | 5.2                   | Non-C   | Concurrent Circuits               |  |  |  |

|    |                       | 5.2.1   | Non-Concurrent Routing Synthesis  |  |  |  |

|    |                       | 5.2.2   | Disjoint Transitions              |  |  |  |

|    |                       | 5.2.3   | Distinct Transitions              |  |  |  |

|    |                       | 5.2.4   | Partitioned Transitions           |  |  |  |

|    |                       | 5.2.5   | Synchronization Decomposition     |  |  |  |

|    | 5.3                   | Concu   | rrent Circuits                    |  |  |  |

|    |                       | 5.3.1   | Static Non-determinism            |  |  |  |

|    |                       | 5.3.2   | Premature Concurrency             |  |  |  |

|    |                       | 5.3.3   | Classical Concurrency             |  |  |  |

|    |                       | 5.3.4   | Simple Concurrency                |  |  |  |

|    |                       | 5.3.5   | Synchronization Rollback          |  |  |  |

|    |                       | 5.3.6   | General Arbitration               |  |  |  |

| 6. | Advanced Synthesis 15 |         |                                   |  |  |  |

|    | 6.1                   | Circuit | t Level Optimization              |  |  |  |

|    |                       | 6.1.1   | Component Generalization          |  |  |  |

|    |                       | 6.1.2   | Circuit Identities                |  |  |  |

|    |                       | 6.1.3   | Common Subexpression Elimination  |  |  |  |

|    |                       | 6.1.4   | Technology Mapping                |  |  |  |

|    |                       | 6.1.5   | Row/Column Elimination            |  |  |  |

|    |                       | 6.1.6   | Row/Column Compression            |  |  |  |

|    |                       | 6.1.7   | Decision Wait Splitting           |  |  |  |

|    |                       | 6.1.8   | Serial-Parallel Tradeoffs         |  |  |  |

|    |                       | 6.1.9   | Standard Logic Gates              |  |  |  |

|    |                       | 6 1 10  | N-Toggle Optimization 163         |  |  |  |

|             |        | 6.1.11                        | CSG Optimization              | • | 10 | 65        |

|-------------|--------|-------------------------------|-------------------------------|---|----|-----------|

|             |        | 6.1.12                        | Constant Time Counters & CSGs |   | 10 | 69        |

|             | 6.2    | .2 Behavioural Transformation |                               |   | 1' | 70        |

|             |        | 6.2.1                         | Input Clustering              |   | 1' | 70        |

|             |        | 6.2.2                         | State Collapsing              |   | 1' | 71        |

|             |        | 6.2.3                         | State Combining               |   | 1' | 73        |

|             |        | 6.2.4                         | Initial State Combining       |   | 1' | 75        |

| 7.          | Case   | e Stud                        | ies                           |   | 17 | 76        |

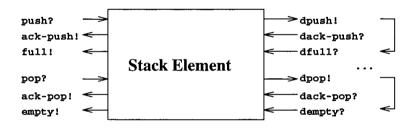

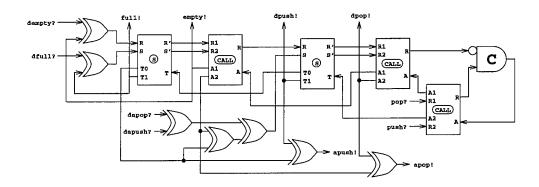

|             | 7.1    | Stack I                       | Element                       |   | 1' | 76        |

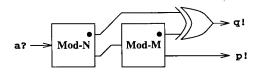

|             | 7.2    | Module                        | lo- $N$ Counters              |   | 17 | 78        |

|             | 7.3    | One Pl                        | lace Buffer                   |   | 18 | 33        |

| 8.          | Con    | clusior                       | ns                            |   | 18 | <b>35</b> |

|             | 8.1    | Summa                         | ary                           |   | 18 | 35        |

|             | 8.2    | Evalua                        | ation                         |   | 18 | 87        |

|             | 8.3    | Future                        | e Work                        | • | 18 | 39        |

| Gl          | ossaı  | <b>·y</b>                     |                               |   | 19 | 91        |

| $R\epsilon$ | eferei | nces                          |                               |   | 19 | 93        |

# Chapter 1

## Introduction

The complexity of VLSI circuits makes it difficult for designers to ensure their correct operation. This problem is aggravated by the continual reduction of transistor size and growth of circuit size. The use of asynchronous circuits offers a possible solution to the first issue and the use of automated formal methods as a solution to the second. Automated asynchronous circuit synthesis can reduce both the time and expense of producing correct and reliable circuits. In this thesis, we present such a design method for a useful class of asynchronous circuits.

## 1.1 Thesis Overview

This thesis is organized such that the reader who is not interested in the details of the theorems can skip them and still understand the important points. Each chapter includes a set of examples to illustrate the concepts described in that chapter. A glossary containing definitions of the more commonly used technical terms is presented at the end of the thesis. The rest of this first chapter describes what are asynchronous circuits, and particularly delay insensitive circuits are. This is followed by a section motivating their use and finally by a review of previous work on asynchronous circuit design.

Chapter 2 begins by introducing an abstract model of asynchronous circuit. This model describes the observable operational model of an asynchronous circuit in terms of labelled transition systems (LTSs). This model is then related to other formalisms for describing asynchronous circuit behaviour, including process algebra, trace theory and Petri nets. An improved implementation (or satisfaction)

relation is then defined on these transition systems that holds between a specification and a valid implementation of that specification. Automated techniques are then discussed for translating specifications into LTSs, checking (and correcting) their delay insensitivity and finally converting it into a minimized normal form.

Chapter 3 describes the basic target components used by the synthesis method. The chapter starts by introducing a number of 'primitives' that form a component basis for the synthesis method. Using these primitives, more useful components (commonly used by other researchers) are defined. The chapter goes on to define larger parameterizable 'macro' components that are used by the circuit compilation method. The correctness requirements for transistor level implementations of these components are then discussed. The constraints insure that composition of the physical transistor level implementations obey the abstract model. The chapter ends with a section on initialization conditions and implementation issues for transistor (or gate) level implementation of DI modules.

Chapter 4 presents an introduction and overview of the automated delay insensitive circuit synthesis methodology. This chapter introduces the 'stable state' model of delay insensitive circuit behaviour. This model then provides the formal basis of an useful abstraction of delay insensitive transition systems, called stable state graphs (SSGs). This representation takes advantage of the properties of delay insensitive behaviours to reduce the complexity of representing circuit behaviour, and acts as an underlying formalism for the circuit synthesis method. A classification of stable states and several other properties of SSGs are then defined that are used during circuit synthesis. Next, an improved generic implementation strategy is described that forms the basis for the proposed compilation method. Finally, the chapter ends with a short overview of the steps involved in the proposed compilation (decomposition) method and the target implementation model for this approach.

Chapter 5 contains the detailed description of the proposed synthesis methodology. The chapter is arranged sequentially, presenting decomposition strategies for larger and larger classes of circuit behaviours. This organization allows the exposition of simple concepts and examples first, before proceeding to more complex cases and problems. Chapter 6 describes a number of improvements to the synthesis method given in the previous section. These optimizations and transformations are discussed separately from the main method for clarity. The various improvements presented in this chapter are divided into two groups; circuit trans-

formations and behavioural transformations. Circuit transformations are 'peep-hole' optimizations that may be applied to the generated circuit to improve the resultant design. Behavioural transformations are semantics preserving transformations that modify the circuit specification as a preprocessing step (or first pass) to the automated compilation method.

Chapter 7 describes the application of the proposed circuit synthesis method to several example circuit specifications. The case studies have been defined by other researchers, and provide a set of common benchmarks in the field of delay insensitive circuit design. Finally, Chapter 8 contains a summary of the thesis. It reviews the main achievements of this research, and proposes some suggestions for future work in this area. This chapter also compares the developed delay insensitive circuit synthesis methodology to the results of similar related work by other researchers.

## 1.2 Asynchronous Circuits

In classical logic design, digital circuits are classified as being either *combinational* or *sequential*, distinguished by the existence of feedback signals within the circuit. Combinational circuits are those without feedback and are therefore stateless. Each of the circuit's outputs is a (delayed) boolean function of the circuit's inputs. To do more complex computations, state holding sequential circuits must be used. Timing is a central problem in such circuits, especially those using feedback signals, as the design must ensure that a computation does not begin until earlier computations have been completed.

In conventional synchronous design, storage elements are used to decouple the feedback signals and break the circuit into combinational logic separated by latches. These latches capture their inputs on the tick of a global synchronization 'clock' signal. The correct operation of the circuit is ensured by spacing the clock ticks by more than the delay of each combinational block. Synchronous design typically also assumes that the inputs to the circuit change on or shortly after each clock tick, and then remain constant until the next tick.

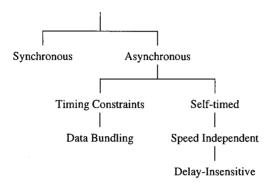

The alternative to this almost universal approach is to use unclocked asynchronous design styles. Asynchronous circuits are divided into those that avoid timing problems by carefully co-ordinating the various delays in the circuit and self-timed circuits that use synchronization signals between circuits. A classification of these various timing paradigms is given in figure 1–1.

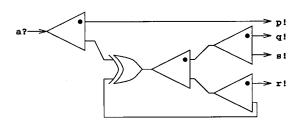

Figure 1-1: Classification of circuit timing paradigms.

The most common form of timing constraint used in asynchronous design is the data bundle. A 'bundle' of data wires, or bus, is associated with a single set of control wires that show the validity of the value on the data bundle. The bundling constraint requires that the data value be observed at the receiver before a signal appears on a control wire. This may be achieved by constructing delays in the control wires. Bundling allows data values to be transmitted over buses without the wiring and circuitry overhead of using complex encoding techniques. Bundled data paths are commonly used with self-timed control circuitry. These circuits can make use of standard combinational logic components, such as adders and multipliers. Other forms of timing constraint used in asynchronous design include assumptions about the upper and lower bounds on component delays and assumptions about the maximum ratios of these bounds.

Interest in self-timed circuits has been centered on speed independent circuits, those that do not depend on the delays of the individual components within the circuit. Speed independent circuits form pure concurrent systems and are therefore particularly amenable to mathematical methods. These circuits consist of a fixed set of processes (modules) communicating over a fixed set of unbuffered channels (wires). All synchronization between modules is by explicit handshaking protocols over these channels. The complexity caused by the nondeterministic behaviour of such concurrent systems is the principal reason for the popularity of synchronous design styles.

In this thesis we concentrate on *delay insensitive* circuits, a subclass of speed independent circuits. A digital circuit is delay insensitive if its correct operation is

independent of the delays in both the individual components and the interconnecting wires of the circuit, except that those delays be finite. This tolerance to wire propagation delays eliminates several of the technical problems currently facing circuit designers.

Digital circuits cannot always be classified as either totally synchronous or asynchronous. A large system is often designed at several different levels of abstraction. At each level, the use of a different timing paradigm may be appropriate. For example, a single global clock signal is better suited to gate level abstractions than to large computing systems, whereas delay insensitive techniques are inapplicable to transistor level circuit abstractions. An example of a multi-paradigm design style is the use of several independent clocks within a single design, called self-clocked design. Conventional synchronous methods are used within each clock domain, and these domains communicate between one another asynchronously. Similarly, an asynchronous circuit may be used within a conventional synchronous (clocked) design by either estimating or measuring the upper bound on the computation delay.

## 1.3 Motivation

As the technological trend to scale down the feature size of transistors and increase the size of each chip continues, conventional synchronous circuit design encounters several serious, fundamental limitations. Some of these problems relate to the difficulty in synchronization and transfer of information between subcircuits within a single clock period, while others are caused by the complexity of managing large designs [84].

Seitz [106] argues that as the physical size of the circuit is reduced, the parameters determining its behaviour do not scale uniformly. The relationship between wire delay and switching delay changes such that the delays in the connecting wires increasingly dominate the transistor switching times. As the cost of communications becomes ever more important, a change of design discipline is required. The serious problem of *clock skew* which is facing current designers is caused by the difficulty of distributing global clock signals. Transmission delays cause clock ticks that are supposed to be simultaneous, to occur at significantly different times.

The ability to isolate and abstract the implementation timing from the logical design of a circuit is a useful property of a hardware design method. It allows both the behaviour and the correctness of a design to be reasoned about, without reference to the physical properties of a specific implementation. Delay insensitive circuits allow this separation between design and engineering issues and are therefore attractive for analysis by formal methods and particularly automated synthesis.

Delay insensitive circuits also have several advantages over conventional synchronous design that are attractive to engineers and designers.

Performance Asynchronous circuits are potentially faster than their equivalent clocked designs. A synchronous system is composed of several parts that carry out specific computations. The correct behaviour of the system requires the clock rate to be slowed to the speed of the slowest subcomputation. This clock period must also take into account the worst case execution time and propagation delays under worst case operating conditions. In, comparison, Self-timed circuits operate at a rate determined locally by component and wire delays, and this tends to reflect average case rather than worst case delay for the circuit.

Power Consumption Asynchronous circuits typically have a much lower power consumption for two principal reasons. Firstly, no power is dissipated by driving a global clock signal at high frequencies. Secondly, transistors in an asynchronous circuit only fire when they contribute to a computation. A related engineering benefit is that power dissipation is distributed over time rather than concentrated at rising and falling clock edges. This property leads to a reduction in electromagnetic interference.

Modularity Self-timed circuits have useful composition properties that simplify the process of system design. Large complex systems can be split into independent modules without interface timing constraints. Self-timing also allows efficient circuits to be collected to form libraries and re-used within designs. This modularity also allows any component within a design to be replaced safely by a functionally equivalent one, with improved properties such as performance or cost, without compromising the circuit's correct behaviour.

Robustness Delay insensitive circuit behaviour is less sensitive to variations in the environment. Physical factors such as temperature, process spread and power supply variations tend to affect the relative delays in the circuit rather than its logical correctness. Reducing the temperature of a delay insensitive circuit increases the observable speed of the circuit. Asynchronous circuits also suffer less from other effects, such as switching noise. Tolerance of these parameters is typically difficult to assess before fabrication and to detect during testing.

Implementation The low level physical design of delay insensitive circuits is also much simplified. Routing constraints on the physical layout of the circuit and geometry of the circuit are relaxed. Transistor sizing and placement optimization can be performed, provided the functionality of the primitive components is maintained. Reimplementation of the design at a different feature size or in a different fabrication process requires only redesign of the primitive components. This allows designs to be reused and to take advantage of improvements in implementation technology with minimum effort.

Metastability Another benefit is the reliability of circuits containing components with metastable behaviour. Metastability is an unstable equilibrium in the state of an electrical circuit. A metastable circuit can remain in a metastable equilibrium for an indefinite period of time before resolving into a stable state. This can cause functional errors in synchronous circuits when the duration of the metastability lasts longer than a single clock period. This 'glitch' phenomenon, first discovered by Chaney and Molnar [25], is fundamental to arbiter and synchronizer circuits. Indeed, Mendler and Stroup [85] show that any such device built on Newtonian principles (that voltage changes are continuous) will behave incorrectly with the appropriate inputs. Self-timed circuits avoid this problem as the circuit waits until the element has settled into a stable state before the computation proceeds.

**Testability** Delay insensitive circuits are completely self-checking for single and multiple *stuck-at-faults*. The occurrence of a break in any of the circuit's wires will eventually halt the operation of the circuit. This property means that deterministic delay insensitive circuits are fully testable for stuck-at-faults. Any test computation that fails to complete within a maximum permitted time limit indicates a fault within the circuit. It is also possible to build fault tolerant systems by using a

'watchdog' time-out signal, where the absence of a result from a subcircuit within a time limit causes the system to detect that the subcircuit is malfunctioning.

## 1.4 Background and Related Work

Previous work on asynchronous circuit design methodologies can be categorized by the 'delay-model' used in the circuit abstraction. The organization is chronological from the date of the model's introduction. The first work on asynchronous circuit design assumed an upper limit on the delays in both the components and the wires of the circuit. This was followed by speed independent circuit design, using the assumption that component delays were unbounded and that wire delays are negligible. This is equivalent to stating that all wire delays are concentrated at the outputs of the components. The most recent delay model is that used for delay insensitive circuit design, which allows unbounded delays in both components and wires. As with most classifications, some works may be placed in more than a single class or group.

Similar reviews of the field of asynchronous circuit design have been published by several authors [4,50,51].

## 1.4.1 Bounded Delay Model

#### **Asynchronous State Machines**

Early work on asynchronous circuit design concentrated on the design of asynchronous state machines, referred to as *Huffman circuits* [56,57]. These state machines are implemented as combinational logic with delayed feedback signals to maintain the current state. The circuit is assumed to operate in *fundamental mode* [83] where the interval between successive input changes is long enough for the circuit to complete its transition to the next stable state.

The principal difficulty in asynchronous state machine synthesis is the state assignment problem. For a synchronous finite state machine (FSM),  $\lceil \log_2 n \rceil$  state variables are both necessary and sufficient for representing n states. As long as each state code is unique, the assignment of codes to states may be made arbitrarily without affecting the correct operation of the FSM. However, this is not the case

for asynchronous state machines where a 'critical-race-free' state assignment is required, which may need more than  $\lceil \log_2 n \rceil$  variables. A race is said to occur when two or more state variables change during a state transition. This race is termed *critical* if the final state reached depends on the ordering of the changes.

Algorithms for these critical-race-free state assignments have been suggested by several authors [43,73,111] and techniques permitting non-fundamental mode operation have also been suggested [116]. Detailed reviews of early asynchronous state machine synthesis may be found in the text books by Unger [115] and Friedman and Menon [44]. Enhancements to the asynchronous state machine model have been developed by Hayes [52], Hollaar [55] and Molnar [91]. More recently, asynchronous state machine synthesis based on burst mode operation has been suggested [31]. This alternative to fundamental mode operation allows construction of fast and efficient control circuits. The principal disadvantage of the state machine model is that their behaviour is strictly sequential and concurrent operation cannot be described.

#### Self-clocked Design

Seitz, in his chapter 'System Timing' in Mead and Conway's text book [106], proposes self-clocked design as one approach to asynchronous circuit design. Small self-timed elements are designed as synchronous systems with internal clocks, in equipotential regions inside which wire delays are considered negligible. The design may be made free of synchronization failure by using 'universal clocks' that may be stopped and restarted asynchronously. This retains the advantages of synchronous design under those conditions in which it is workable. Rosenberger [101] describes a similar design style called Q-Modules, where local clock ticks are suspended until all storage elements have settled into the next state.

#### Micropipelines

In his 1988 Turing Award Lecture, Sutherland [110] described another asynchronous design style based on the bounded gate-delay model. This style, termed micropipelines, uses fine grain pipelines where each stage communicates asynchronously with its neighbours. In addition to a single completion signal, these stages have another signal to acknowledge the receipt of the start request and permit another request to be sent. In conventional self-timed design, acknowledgement

takes place only after the processing has been completed. The micropipelined paradigm can achieve high speed throughput by overlapping operations, with different stages operating concurrently. Sutherland's approach traditionally uses a four phase bundled datapath with two phase handshaking. Furber and his colleagues at the University of Manchester have used this approach to implement a self-timed RISC processor [45,47].

## 1.4.2 Unbounded Gate-Delay Model

#### Speed Independence

Although most early interest was in this state machine model of asynchronous circuits, the roots of the theory of self-timed circuits go back as far as the early 1950s. Muller and his colleagues at the University of Illinois developed a fundamental algebraic theory of circuits whose observable behaviour does not depend on the relative speeds of their elements [92]. It was in this seminal paper that the term speed independent circuit was first coined. However the relevance of this work, and a similar later paper by Armstrong, Friedman and Menon [2], was not recognized until much later. It was in this second publication that the self-checking properties of self-timed circuits were first mentioned.

Independent research in the Soviet Union during the 1950s and 1960s tackled the problem of the variable delays in standard SSI and MSI IC packages. The best case gate delays of identical commercially available circuits were four or five times better then their worst case delay. A theory of speed independent circuits, termed aperiodic circuits in translation, was developed by Varshavsky and Rosenblum [126] based on earlier work on asynchronous circuits by Gavrilov [48]. Varshavsky et al. [125] showed that any four-phase asynchronous state machine can be implemented speed independently from AND-OR-NOT components. Originally, implementations required these 'antitone' components of arbitrary complexity. However subsequent work describes implementations in a finite basis of primitive components [124]. Synthesis from event-based specifications, rather than state transition diagrams, was first suggested by Starodubtsev [107]. His doctoral thesis [108] contains efficient synthesis and analysis methods for arbitrary autonomous circuits described by taxograms, where events are labelled by signal transitions.

#### Petri Net Modules

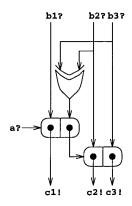

A module based approach to the implementation of speed independent circuits was investigated during the 1970s by Dennis' group of project MAC at the Massachusetts Institute of Technology [32]. They used Petri nets to model the behaviour of speed independent circuits. The Petri net is a widely used model of concurrent systems developed by Carl Petri. A Petri net is a bipartite directed graph with two types of nodes: places and transitions. Places within the net are capable of containing some number of 'tokens' or 'markers', such that a condition (place) is said to hold or be true if a token is present in it. Places are connected by directed arcs, via transitions, along which tokens may pass. The movement of tokens along the arcs is controlled by the occurrence of a 'firing' of a transition, known as an event. A transition may only fire when there is a token in each input state, when a single token is removed from each of its input states and placed in each of its output states.

Patil [96] proposed implementing speed independent circuits that resembled the Petri net itself. The Petri net was structurally realized by modules that performed the roles of the places, transitions and arcs of the Petri net. The main drawback with this approach is that it resulted in very large implementations for relatively simple circuit behaviours. Misunas [90] improved upon this idea by using modules of common Petri net functions. These basic functions are then composed to implement the behaviour of the specification Petri net. Using this relatively simple approach Misunas was able to design a speed independent processor based on the design of a CDC 6600. More recently, Lister and Alhelwani have proposed a similar method for implementing speed independent circuits from data-flow Petri nets [72].

#### Signal Transition Graphs

The signal transition graph (STG), originally called a 'signal graph', was first introduced as a formal model of asynchronous circuit behaviour by Rosenblum and Yakovlev [102,103,128]. Similar work on STGs has been independently introduced by Chu [26] and Molnar et al. [91] under the name 'I-Nets'. An STG is an 'interpreted Petri net' where the transitions are interpreted as signal transitions. STGs formally model the causal relationships between the circuit and the environment in which it operates.

The synthesis of asynchronous circuits from STGs involves finding both a state assignment and a hazard-free implementation of the circuit using the appropriate delay-model. The problem of state assignment, assigning a binary coding to each state, is similar to that in asynchronous state machines. An STG has a unique state coding (USC) property if the binary code assigned to each state is distinct from the codes assigned to every other state. An STG has the weaker complete state coding (CSC) property, if any two markings that enable different sets of output signals have distinct state codes. A CSC state assignment often permits a more efficient implementation that a USC state coding, as distinct states may have the same coding allowing states to be represented by shorter binary codes. Different synthesis techniques require the STG to satisfy either the USC or CSC property.

Algorithms for modifying the STG by adding state variables to obtain both the above properties have been given by several authors [71,86,123,129]. The chosen state assignment must also have a boolean implementation that is free from both critical races and hazards. A hazard in an asynchronous circuit is an unexpected 'glitch' of a signal value that is a transition that is not allowed by the specification. Hazards are typically caused either by the delays in the circuit's feedback signals or the differences in the gate delays of the circuit. The use of STGs with bounded-wire delay models has been investigated by Lavagno et al. [68,69].

### CalTech Design Method

Alain Martin [76,78,80] has developed a design method for speed independent circuits that produces very efficient implementations. His method is based on a sequence of transformations from a specification of communicating processes to a transistor level implementation. The final implementations contain isochronic forks but are independent of transistor switching delays. A fork or branch of a wire is considered *isochronic* if the difference in propagation delays between the two branches is negligible. This assumes all wire delays are concentrated at gate outputs, and hence circuits are speed independent but not delay insensitive.

Martin specifies the desired behaviour of the circuit using a language based on Hoare's CSP [53] and Dijkstra's guarded command language [33], called Communicating Hardware Processes (CHP). In addition, CHP contains assignments, arrays, functions, procedures and a 'probe' construct that allows a process to determine if there are any incoming communications pending [75]. The synthesis

method begins by decomposing the processes into small, sequential processes with explicit handshaking between them. All communication is assumed to be fourphase using dual-rail encoding. After a state assignment similar to those described above, each process is translated into a set of production rules, which form a compact representation for CMOS transistor networks. Production rules are selected that ensure the correct sequential behaviour of the circuit and minimize the number of state holding operators required. Burns and Martin have also developed an algorithm for automatic transistor sizing for the generated circuits [22]. This technique has been used on a number of complex designs including a fast asynchronous microprocessor [77]. Methods based upon production rules have also been investigated by several other authors [109,117].

## 1.4.3 Unbounded Wire-Delay Model

#### Macromodules

The first attempt to construct circuits that were independent of wiring delays was made by the Macromodules project at Washington University around 1970 [27]. It was this research that first coined the term 'delay insensitive circuit'. The aims of the project were to investigate computer architecture using modular building blocks that performed specific operations. Physical implementation issues demanded that regular interfaces be used to plug modules together and their operation be independent of wiring delays between the racks that held the modules. Around 16 types of module were implemented including modules for ALUs, registers, adders and ferrite core memory. Communication between modules used transition signalling for the control paths and bundled data paths. This design approach led to ease of reconfiguration and no natural limit to the size of the design.

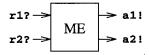

Following the work of the Macromodules project, Keller [64] attempted to determine a minimum set of primitive delay insensitive modules that were 'universal' to the class of speed independent or delay insensitive circuits. That is, all such circuits can be implemented entirely from a restricted set of basic elements. This is similar to the property that any synchronous design may be implemented using just NAND or NOR gates. Keller showed that only three components (the merge, the select and the arbitrating test and set) are required for all four-phase speed independent circuits. However, no attempt was made to formalize either the composition semantics or the class of circuits covered by the method.

Recent results by Seger [105], Brzozowski and Ebergen [16,17], Martin [79] and Leung and Li [70] have shown that the class of purely delay insensitive circuits is extremely restricted. This proof, called the Unique Successor Set (USS) property, states that circuits of components with only single outputs are either sensitive to wire delays or perform trivial computations. This result requires primitive component bases for general delay insensitive circuits to contain elements with multiple outputs. Implementations of these elements using transistors (or conventional logic gates) must make use of timing constraints, such as isochronic forks.

#### Trace Theory and Process Algebra

The first formal model of delay insensitive circuits was developed at the Technical University of Eindhoven [99,121]. Trace theory, first proposed by Hoare [54], represents the behaviour of an asynchronous circuit as the sequence of voltage transitions at its interface. Directed trace structures classify each observable wire as either an input or an output, and specify all permissible orderings of events on these wires. These orderings, or traces, specify the correct operation of a circuit and also constrain the circuit's environment. A circuit is delay insensitive if its wires are free from computation interference and transmission interference. Computation interference occurs when a signal arrives before a receiver is ready for it and transmission interference occurs when two signals on the same wire interfere.

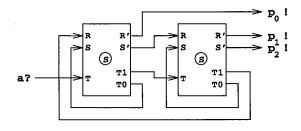

Snepscheut [122] defines a composition operator for directed trace structures, called agglutination, that places an explicit delay in wires connecting outputs to inputs. Because this operator allows an unbounded number of messages per wire, explicit handshaking signals must be added to avoid transmission interference. Snepscheut implements trace structures as a network of communicating asynchronous state machines whose interconnections are independent of wiring delays. Each state machine is constructed from a programmable logic array (PLA), flip-flops and c-elements and is assumed small enough to be embedded in an isochronic region.

Udding [112,113] presented a formal definition of the delay insensitivity of a component as a set of constraints on the component's trace structure. These rules also lead to system of classification of delay insensitive circuits. Udding also states necessary conditions for a composition of trace structures to be free from computation and transmission interference and proves that the class of delay insensitive circuits is closed under composition.

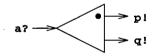

In his doctoral thesis Ebergen [36,38] presents an alternative formalization of delay insensitivity which he proves equivalent to Udding's rules. Ebergen also introduces a more general (de)composition operator for delay insensitive networks that reflects the permissible behaviour of the circuit's environment. Using this definition, an automatic method for synthesis for delay insensitive circuits is presented for a restricted class of circuit specifications. This syntax directed approach produces a delay insensitive network of primitive components from a predefined (but infinite) basis.

Dill [34] suggests the use of trace theory for the automatic hierarchical verification of speed independent circuits. His LISP model checker uses a state based approach to verify 'safety' properties, such as the delay insensitivity of a circuit. He also defines an implementation equivalence between two trace structures that holds when one may be safely replaced by the other.

The prefix-closed trace structures described fail to capture properties such as the 'liveness' and 'fairness' of a circuit [46]. Black [8] extends trace theory to include infinite traces which may be used to describe the behaviour of fair arbiters. A similar approach using non-prefix-closed sets of finite and infinite traces, termed complete trace structures, has been described by Dill to cover both liveness and fairness [34].

An alternative to the use of trace theory is to describe the behaviour of an asynchronous circuit as a set of communicating sequential processes using a process algebra such as CSP [53] or CCS [89]. This model of computation considers a static set of concurrent processes that interact via input and output commands on shared communication channels. Josephs and Udding [58,59] have developed a delay insensitive process algebra, based on CSP, that expresses the properties of delay insensitive circuits. The formalism contains algebraic laws for modelling interference that can be shown equivalent to Udding's original rules. The laws of the DI algebra allow expressions to be transformed into a normal form [49] and semantically equivalent forms. This system of manual transformations provides a basis for algebraically specifying and verifying component behaviours but is unsuitable for an automatic synthesis methodology.

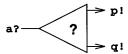

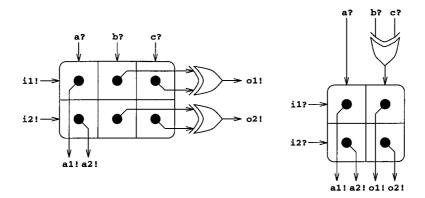

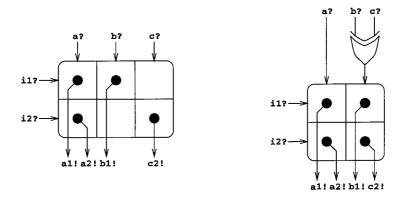

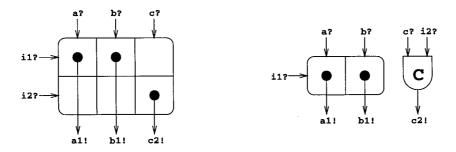

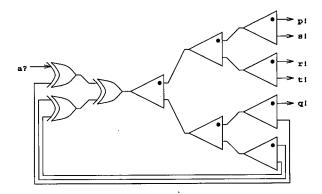

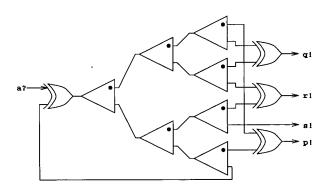

### 1.4.4 Module Based Synthesis

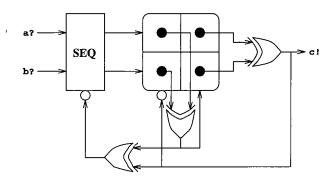

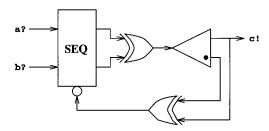

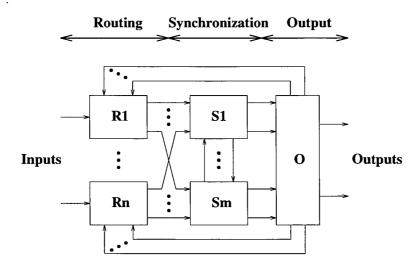

Several systems have been developed to automate the synthesis of delay insensitive circuits from behavioural specifications. These circuit compilers translate a process based description of the desired behaviour into a network of primitive elements. A process based specification is either the composition of simpler processes or a primitive process. Typically a source language will contain constructs for sequential, parallel and conditional composition, alternation and repetition. All of the compilers described below use syntax directed translation techniques [1], where each syntactic construct of the source language generates a fixed set of components and wires. Using this method, an implementation is given for each of the primitive processes of the language and a circuit composition rule is given for each construct of the specification language. For a compound specification of a process and valid implementations of its subprocesses, these rules should generate a valid implementation of the whole construct.

A restrictive communications protocol is imposed on each process to ensure the semantics of circuit composition is equivalent that of the specification language. Typically each process is viewed as a module that begins execution upon the receipt of a request signal and indicates completion by an acknowledge signal. These processes may then be connected/composed to create larger circuits with similar request and acknowledge signals. Synchronization and communication between concurrent processes is by implicit handshaking circuitry. In this way, the source specification may be used to describe the hierarchical structure of the implementation. This simplistic translation may produce relatively large and inefficient circuits.

#### Burns

The first automated asynchronous circuit compiler was developed by Burns and Martin [21]. This program automated the CalTech design methodology described earlier. The translation is from a variant of CSP that includes the *probe* construct [75]. The addition of the probe allows CSP to specify 'fair' arbiters. Several possible rules are given for each construct allowing trade-offs between cost and performance. For example the guards of the ALT construct may be tested either sequentially or concurrently (possibly using arbiters to ensure mutual exclusion). The compiler also performs a significant amount of optimization at both the source and circuit level. Source level optimizations involve testing invariants that guide

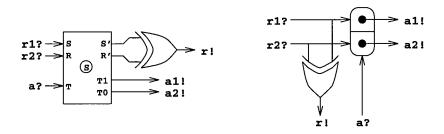

the selection of transformation rules. Circuit level, or *peep-hole*, optimizations remove locally redundant components from the final circuit. The resulting circuits use four phase handshaking and consist of six basic components. These are the standard logic gates, AND, OR and NOT, and three state holding components; the Muller c-element, the synchronizer and the set/reset flip-flop.

Because this design style requires isochronic forks, the generated circuits are speed independent but not delay insensitive. A full description of the translation rules and optimizations is given in Burns' masters thesis [20]. The complete system consists of about 800 PROLOG clauses. The compiled circuits are typically no more than three times the size of those derived by hand. This inefficiency is caused by the compiler not detecting all cases where explicit sequencing can be removed.

#### **Brunvand**

A similar approach has been used by Brunvand and Sproull [14]. Their compilation uses similar techniques to generate circuits that consist of delay insensitive control units that direct the flow of data of bundled data paths. All control signals within the target design use transition signalling. The source language to the compilation system is a large subset of the Occam programming language [81] given in a LISP-like syntax. The synthesis system also includes an Occam interpreter that allows behavioural simulation and debugging of specifications prior to their compilation [11]. The details of the nine translation rules are given in Brunvand's doctoral thesis [13].

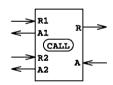

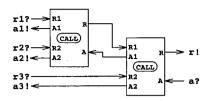

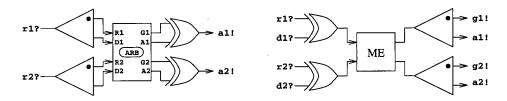

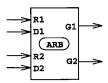

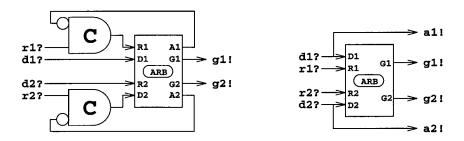

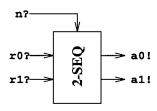

Except for the data path operators, the synthesis method requires only 11 primitive modules. The complete list of primitive components includes the merge element, the c-element, the toggle element, the arbiter and several kinds of storage element including the select and call modules. All of the required components have been implemented as standard cells requiring only a small number of transistors [12]. The state holding components respond to a global 'clear' signal to reset them to an initial known state. The major advantage of data bundling is that standard library components are used to implement the data path, such as adders and multipliers.

Brunvand's compiler, like Burns', improves the generated designs using semantics preserving circuit-to-circuit transformations, similar to the peep-hole optimizations used in conventional compilers. This pass substitutes inefficient subcircuits by more efficient implementations by identifying common module topologies.

These local improvements overcome some of the disadvantages of the relatively simplistic translation method. Brunvand proves the validity of the circuit transformations by showing their conformance equivalence using Dill's trace tools [34].

#### Brown

The first attempt at produce a truly delay insensitive circuit compiler was made by Brown [10]. His system used a variable free subset of the Occam programming language as the specification language. The absence of variables removes the assignment, conditional and data communication commands from the language. The design of circuits without data paths avoids the need for either data bundling constraints or isochronic forks. The compilation process requires only ten rules to generate delay insensitive circuits from their specifications. The target circuits use transition signalling and are composed of six types of primitive component. These components are the merge, the c-element, the select, two types of call module and an arbitrating test-and-set module.

#### van Berkel

A far more advanced delay insensitive circuit compiler has been developed by van Berkel and the group at Philips Research Labs [119,117]. The source language to their synthesis system, called *Tangram*, is based heavily upon Hoare's CSP. In addition to the constructs of Occam, Tangram supports finite iteration, guarded commands, arrays, tuples, arithmetic operators, broadcast communication, functions and procedures. Recently, the syntax of the Tangram programming language has developed a Pascal-like syntax to make the notation more accessible to designers.

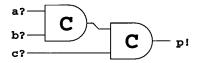

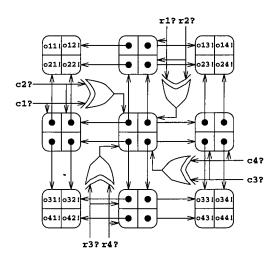

The first phase of the Tangram compilation process is the syntax directed translation of the source description into a graphical intermediate representation, called handshake circuits. A handshake circuit is a graph representing both the structure and behaviour of the circuit. Each vertex of the graph is a handshake component and control and data flow is explicitly represented by arcs between nodes. These delay insensitive channels form the only interaction between handshake components. This representation abstracts the communication actions away from specific handshaking protocols and data encodings. The full implementation of Tangram requires about two dozen types of handshake component, many of which are parameterized on word width. The Tangram compiler includes a peephole optimization

pass that identifies subcircuits of the handshake circuit and replaces them with cheaper equivalents.

The final stage of the compilation process implements the handshake circuit as a CMOS VLSI circuit. Currently, the Tangram compiler synthesizes circuits with four phase handshaking and dual rail encoding, and the corresponding speed independent gate-level decompositions of the handshake components. The realizations of handshake components allow all components in the circuit to be initialized by forcing the electrical inputs low. This property called *weakly initializable* avoids the need for reset circuitry. More recently a testability option has been added to the compiler, which generates test circuitry for a restricted class of circuits [100]. This test strategy allows circuits to be tested effectively in polynomial time.

The Tangram compiler is part of an integrated tool set. The Tangram source program can be compiled into a C-code simulator that will generate a coarse timed trace of the circuit's behaviour or the intermediate handshake circuit may be translated to VHDL to generate more detailed timing information. The 'backend' of the compiler produces standard cell net lists that may be input to Philips' VLSI layout tools. At a more abstract level, the VOC project at Eindhoven University of Technology have produced a front end to the system that generates regular language acceptors [7].

# Chapter 2

# Behavioural Specification

The design process can be seen as a translation of notation, starting with an abstract descriptive specification and ending with a more concrete realization or implementation of that specification. A synthesis method is a theory for constructing realizations that are guaranteed to be correct with respect to their specifications and therefore do not require debugging or verification. The foundations of any synthesis method must contain a model for reasoning about a system's behaviour. Several different models have been suggested for describing the concurrent behaviour of asynchronous circuits, including process algebra [23], Petri nets [26], temporal logic [74] and trace theory [122]. In this thesis, a mathematical model based on labelled transition systems is proposed to describe the behaviour of delay insensitive circuits.

## 2.1 Abstract Circuit Model

## 2.1.1 Labelled Transition Systems

Labelled transition systems use an *interleaving* model of concurrency where simultaneous actions can occur in any temporal ordering, thus reducing concurrency to non-deterministic interleaving. Models based upon *true concurrency*, such as Petri nets, describe concurrent operation by explicit causal independence. Although truly concurrent formalisms have greater discriminating power than interleaving models, the 'observable' behaviour of an asynchronous system is a chronological sequence of events. Hence, an interleaving model is a suitable formalism for behavioural specification, which need not distinguish between underlying causal models.

It is the design methodology's task to find an implementation with a suitable causal mechanism.

**Definition 1** A directed labelled transition system is a structure  $(S, s_0, I, O, T)$  where S is a finite non-empty set of states,  $s_0 \in S$  is an initial state, I and O are disjoint sets of input and output labels respectively and  $T \subseteq S \times (I \cup O) \times S$  is the transition relation.

Usually we write  $s \stackrel{a}{\to} s'$  instead of  $(s, a, s') \in T$ , and  $s \to s'$  when  $\exists a \quad s \stackrel{a}{\to} s'$ . The set of labels  $I \cup O$  is sometimes called the alphabet of the directed labelled transition system (DLTS). Labels from the set of input labels, I, are distinguished by suffixing with a question mark and output labels, O, by suffixing with an exclamation mark. For a transition t = (s, a, s'), s is called the prestate of t, and s' is called the poststate.

At any moment in time, the asynchronous process described by a directed labelled transition system can be in one, and only one, state or situation. Time is introduced into our descriptive model by the transition relation T which describes the sequential evolution of the asynchronous process. The definition of T as a relation rather than a function expresses the non-determinism inherent in a process' specification. Typically the transition relation is non-reflexive.

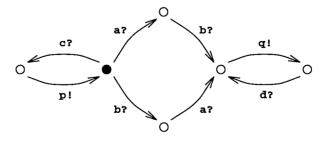

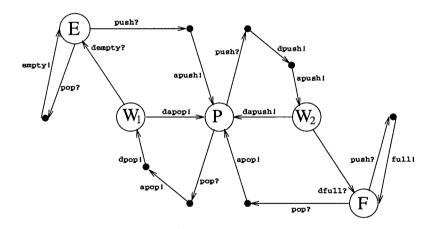

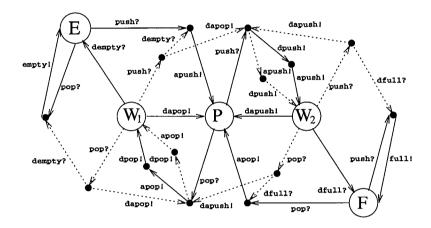

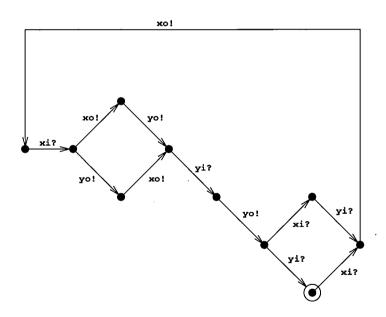

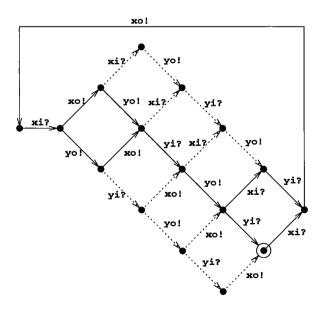

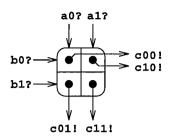

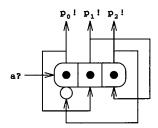

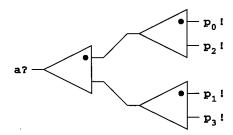

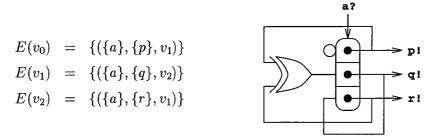

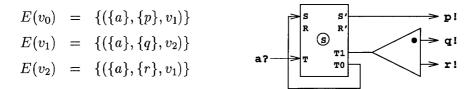

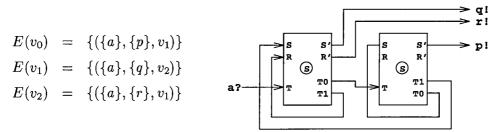

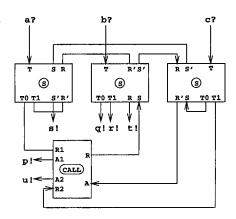

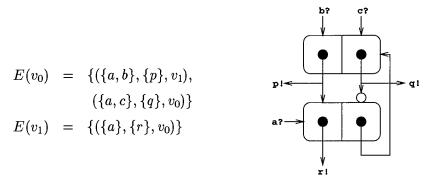

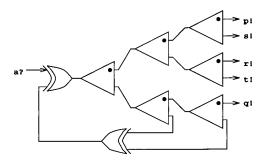

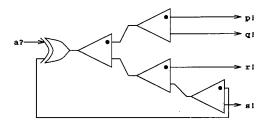

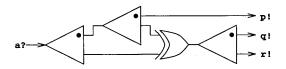

This definition of a directed labelled transition system leads to the usual graphical representation as a directed transition graph. The vertices of the transition graph are used to denote the states of the transition system, and labelled arcs represent the transition relations between them. Usually, the vertex of the transition graph that denotes the initial state,  $s_0$ , is emphasized to distinguish it from the remaining states. An example of a transition graph is given in figure 2–1.

Figure 2–1: Graphical representation of a directed labelled transition system.

The common notion of *bisimulation* [88,95] can be used to define an equality relation on labelled transition systems. Two labelled transition systems are equivalent if their initial states are bisimilar.

**Definition 2** The two states P and Q, of labelled transition systems P and Q respectively, are bisimilar, written  $P \sim Q$ , iff, for all a,

- i) Whenever  $P \xrightarrow{a} P'$  then, for some Q',  $Q \xrightarrow{a} Q'$  and  $P' \sim Q'$

- ii) Whenever  $Q \stackrel{a}{\rightarrow} Q'$  then, for some P',  $P \stackrel{a}{\rightarrow} P'$  and  $P' \sim Q'$

This notion of equivalence is not the same as transition graph isomorphism. Although graph isomorphism implies transition system equivalence, equal transition systems may not have isomorphic transition graphs. This notion of equality can be used to define a normal or canonical form for directed labelled transition systems. The normal form of a DLTS is the coarsest member of the bisimulation equivalence class, i.e. the equivalent transition system which has the minimum number of states.

Of special interest in behavioural specification is the class of strongly determinate directed labelled transition systems. This is the class of transition systems that do not make non-deterministic choices between transitions with the same label. This restricted class of behaviours may be completely specified by trace structures.

**Definition 3** The state s of the directed labelled transition system  $(S, s_0, I, O, T)$  is strongly determinate iff for all states  $s_1, s_2 \in S$ , if  $s \stackrel{a}{\to} s_1$  and  $s \stackrel{a}{\to} s_2$  for any label  $a \in I \cup O$ , then  $s_1$  and  $s_2$  are bisimilar,  $s_1 \sim s_2$ . A DLTS is called strongly determinate if all its states are strongly determinate.

## 2.1.2 Operational Behaviour

An digital circuit has associated with it a finite set of terminals (or ports) used to communicate with its environment. These terminals are partitioned into a set of input ports I and a set of output ports O. The observable behaviour of such a circuit can be represented by a directed labelled transition system  $(S, s_0, I, O, Tran)$  where each terminal of the circuit's interface is denoted by a unique label.

Each state of the transition system represents an instant in the behaviour of the component, with initial state representing the starting state of the circuit. Each state transition represents a possible communication action, or *signal*, between

the circuit and environment on the terminal denoted by the transition's label. The transitions from a given state specify the set of permissible actions that may be produced at that point in the circuit's behaviour, and by whom. Transitions labelled by elements of I mean that the environment may produce that communication signal next, and those labelled by O allow the circuit to generate the corresponding output action next. Once the communication has taken place, the behaviour of the circuit is represented by the poststate of the performed transition. In addition to above safety constraint, the behavioural specification of a component also contains a liveness constraint. A safety property asserts that "nothing bad will happen", while a liveness property asserts that "something good will happen". If in a given state, there exists a transition from that state labelled by O, then the behavioural state of the circuit must eventually advance. This progress requirement guarantees that the environment can never wait indefinitely for a valid output to be produced.

Operationally, the occurrence of a communication action represents a change of voltage, a transition, at the corresponding terminal. No distinction is made between rising and falling voltage transitions. Hence the same state transition may correspond to both low-to-high and high-to-low voltage transitions. Although it is possible to 'unfold' a transition system such that each label denotes either a rising or falling transition, specifications that do not make this distinction tend to be much smaller. By convention, all terminals of a circuit are considered to initially low, unless stated otherwise.

The complete labelled transition system contains all communication behaviours that may take place between the component and its environment. The specification of the boundary between component and environment acts as a contract between them. The correct behaviour of the component should be guaranteed, provided the environment behaves only as prescribed. Hence the behavioural specification both defines the correct behaviour of a circuit and restricts the behaviour of the environment.

As behavioural specifications detail the permitted observational behaviour of a circuit's environment, they may be used to specify the class of correct 'environment components'. The specification for a live environment may be found by reflecting the directed labelled transition system. The reflection of a strongly determinate DLTS L, denoted by  $\overline{L}$ , is obtained by exchanging the elements of the sets I and O. In this way, every output action of the circuit becomes an input action of the environment and vice versa.

This interpretation of the permissible interface behaviour is similar to the use of the *must* and *may* modalities of modal transition systems [67]. In this framework, an implementation must be able to accept all the inputs and may generate any of the outputs that are prescribed in the specification. In this case, the transitions  $\stackrel{a?}{\to}$  and  $\stackrel{a!}{\to}$  can be seen as variants of the  $\to_{\square}$  and  $\to_{\Diamond}$  relations.

Asynchronous circuit behaviours that are not 'strongly determinate' pose interesting problems. Consider the three states  $s_1$ ,  $s_2$  and  $s_3$  of a DLTS such that  $s_1 \stackrel{a}{\to} s_2$  and  $s_1 \stackrel{a}{\to} s_3$  for any symbol a where the states  $s_2$  and  $s_3$  are not bisimilar  $s_2 \not\sim s_3$ . After the communication action a, the circuit is in one of two states, indistinguishable by the environment. To ensure correct operation in such an event, the environment may only send input signals that may be received in all such indistinguishable states and must be able to accept output communication actions from any such state. Hence, for any non-strongly determinate DLTS it is possible to determine an 'equivalent' strongly determinate behaviour that ensures safe operation. The proposed design methodology assumes (ensures) that a DLTS specifies the 'safe' strongly determinate behaviour of an asynchronous circuit, and issues an error (warning) otherwise.

## 2.2 Circuit Specification

Directed labelled transition systems serve as suitable abstract model of asynchronous circuit behaviour, but lack a convenient notation for a specification formalism. For this reason, we give a labelled transition system semantics to a number of common circuit specification styles. This allows the use of conventional descriptions to clearly and concisely define required circuit behaviours. Note that some of the formalisms mentioned below are less expressive than DLTSs and hence are used to describe restricted classes of circuit behaviour.

## 2.2.1 Process Algebra

Process algebra [53,89] provides a framework for describing the modular structure of concurrent systems (or *processes*) and also details their operational behaviour. Syntactically, processes form a term algebra, where terms are built by a given set of operators that typically include a parallel composition operator.

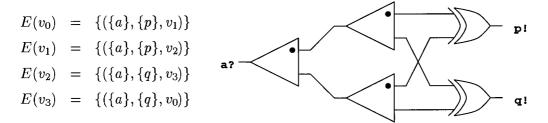

In this thesis, circuit specifications are given in a small subset of Milner's Calculus of Communicating Systems (CCS) [89]. This subset has sufficient expressive power to allow the description of any directed labelled transition system. The agent, or process, Nil can perform no communication action. The prefix operator, a.E., where a is an action label and E represents an agent expression, performs the communication action a before evolving into the process E. By convention, communication labels begin with a lower case letter. The choice, or sum, of two agents  $E_1$  and  $E_2$ , written  $E_1 + E_2$ , non-deterministically behaves like either  $E_1$  or  $E_2$ . Action prefixing binds tighter than the choice operator. We shall assume a set of agent identifiers, which may be bound to an agent expression that may contain a reference to itself. This enables the definition of recursive processes. By convention, agent identifiers are labels beginning with an upper case letter (unique from Nil). An agent definition has the form bi AE, where the identifier A is associated with the agent expression E. This syntax is the same as that used by the original version Concurrency Workbench process algebra tool [30].

The directed labelled transition system describing the observable behaviour of an agent can be determined using the structural operational semantics (SOS) rules of that process algebra [98]. The initial agent, by convention the first agent identifier defined in a circuit specification, is associated with the initial state  $s_0$  of the DLTS. If the agent P, associated with a state  $s_1$  of a labelled transition system, can perform a communication action  $\alpha$ , then the DLTS has a state  $s_2$  that denotes the  $\alpha$ -derivative of P, and  $s_1 \stackrel{\alpha}{\to} s_2$ . The process  $\alpha . E$  has the  $\alpha$ -derivative E. If P has an  $\alpha$ -derivative P', then so do the agents P + E and E + P, for any agent E and communication action (label)  $\alpha$ . This definition allows the derivation of a directed labelled transition system by syntactic search for reachable states.

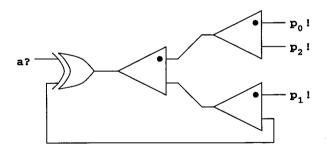

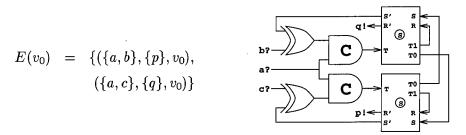

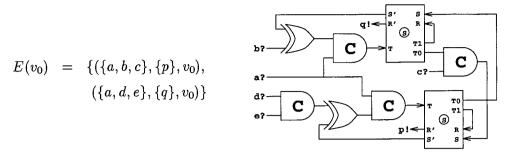

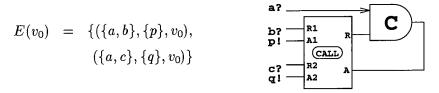

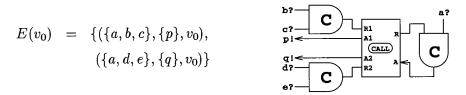

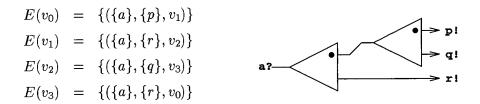

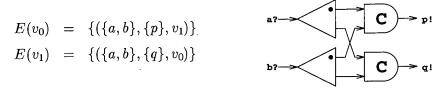

For example, the directed labelled transition system described by the transition graph in figure 2–1 is given by the CCS specification in figure 2–2 below.

```

bi S0 a?.b?.S1 + b?.a?.S1 + c?.p!.S0

bi S1 q!.d?.S1

```

Figure 2-2: Example CCS circuit specification

It is trivial to extend this technique to allow asynchronous circuit specifications to be given in the complete CCS syntax, including restriction, relabelling and various composition operators. Similarly, for other process algebras such as CSP [53,

59], Circal [87], Esterel [6], ACP [3] and LOTOS. The principal advantage of this approach over the formalisms used by other circuit synthesis methodologies is that the semantics of the process algebra's operators need not be that of circuit composition. This allows the specification to describe the circuit's required observational behaviour without determining its structure.

### 2.2.2 Trace Theory

The most common formalism for describing delay insensitive circuit behaviour is trace theory [36,112,122]. Trace theory specifies circuit behaviour by explicitly stating all permissible sequences of communication actions that may take place between a circuit and its environment.

**Definition 4** A directed trace structure T is a pair  $\langle \mathbf{a}T, \mathbf{t}T \rangle$  in which  $\mathbf{a}T$  is a finite set of symbols partitioned into two sets  $\mathbf{i}T$  and  $\mathbf{o}T$ , and  $\mathbf{t}T$  is a set of finite-length prefix-closed sequences of elements of  $\mathbf{a}T$ , which are called traces.

The set of symbols  $\mathbf{a}T$  is referred to as the alphabet of T, which is split into the input alphabet,  $\mathbf{i}T$ , and the output alphabet,  $\mathbf{o}T$ . The trace set,  $\mathbf{t}T$  specifies all permissible communication sequences at the mechanism's interface with its environment. Since trace sets are often infinite, representation by enumeration of their elements is unreasonable, so traces structures are often defined using a program notation based on regular expressions called commands.

**Definition 5** A trace command over the alphabet of symbols (or labels)  $\Sigma$  is either  $\epsilon$ , any symbol  $a \in \Sigma$ , or any expression of the form S;T, [S], S|T, S|A, S|T or pref S where S and T are trace commands over  $\Sigma$ , and A is a set of symbols.

Each trace command E over an alphabet  $\Sigma$  denotes a directed trace structure  $\langle \mathbf{a}E, \mathbf{t}E \rangle$  where  $\mathbf{a}E \subseteq \Sigma$ . The command  $\epsilon$  denotes the trace structure  $\langle \emptyset, \{\epsilon\} \rangle$  (where  $\{\epsilon\}$  is the set containing the empty trace), the atomic command  $a \in \Sigma$  denotes the trace structure  $\langle \{a\}, \{a\} \rangle$  and each of the concatenation, union, repetition, prefix closure, projection and weaving operators is defined as follows.

$$S;T = \langle \mathbf{a}S \cup \mathbf{a}T, \{st \mid s \in \mathbf{t}S \land t \in \mathbf{t}T\} \rangle$$

$$S|T = \langle \mathbf{a}S \cup \mathbf{a}T, \mathbf{t}T \cup \mathbf{t}S \rangle$$

$$[S] = \langle \mathbf{a}S, (\mathbf{t}S)^* \rangle$$

```

\begin{aligned} \operatorname{pref} S &= \langle \mathbf{a}S, \{s \mid \exists t.st \in \mathbf{t}S\} \rangle \\ S \upharpoonright A &= \langle \mathbf{a}S \cap A, \{s \lceil A \mid s \in \mathbf{t}S\} \rangle \\ S \lVert T &= \langle \mathbf{a}S \cup \mathbf{a}T, \{t \in (\mathbf{a}S \cup \mathbf{a}T)^* \mid t \lceil \mathbf{a}S \in \mathbf{t}S \wedge t \lceil \mathbf{a}T \in \mathbf{t}T\} \rangle \end{aligned}

```

where  $t \mid A$  is the trace t from which all symbols not in set A have been removed. To save parentheses, unary operators have the highest priority, followed be weaving, concatenation, union and finally projection has the lowest priority. Snepscheut [122] presents proofs for several interesting properties for these trace operators. Ebergen [36] extends this notation to include general tail recursion, similar to the agent identifiers used in process algebras.

We can introduce the notion of states of a trace structure by determining an equivalence relation  $\sim_R$  on traces of a prefix closed trace T. The relation  $t \sim_R s$  holds iff for any trace  $r \in \mathbf{a}T$ ,  $tr \in \mathbf{t}T \Leftrightarrow sr \in \mathbf{t}T$ , i.e. the  $\sim_R$  relation holds between traces with the same continuations. The equivalence classes of this relation form the states of the trace structure T. The state containing the trace t is denoted by  $[\![t]\!]$ . The directed labelled transition system representing the directed trace structure T, has input label set  $\mathbf{i}T$ , output label set  $\mathbf{o}T$  and initial state  $[\![\epsilon]\!]$ . There is a transition  $[\![s]\!] \stackrel{a}{\to} [\![t]\!]$  for any label  $a \in \mathbf{a}T$  iff  $sa \sim_R t$ . One corollary of this definition is that any directed labelled transition system described by a trace structure is strongly determinate. As an example, the trace command  $\operatorname{pref}([c?; p!]; (a?||b?); [q!; d!])$  denotes the directed labelled transition system of figure 2-1 on page 21.

A similar notation, based on regular expressions, is used by several asynchronous circuit researchers to describe directed labelled transition system that do not have a branching structure. These notations are called *cyclograms* or *taxograms* by Starodubtsev [107] and *handshaking expansions* by Martin [76]. The syntax of both notations annotate transitions depending on whether the signal is rising or falling. Martin suffixes output signals with '\' for low-to-high transitions, and the suffix '\' for high-to-low transitions. The input actions of a circuit are described syntactically as boolean expressions of signal names enclosed square brackets (not to be confused with the repetition operator of trace commands) called *wait conditions*. A handshaking expansion is an alternating sequence of input and output communication actions separated by semi-colons enclosed by a repetition operator \*[...]. An example handshaking expansion is given in figure 2-3 below.

```

*[[li]; ro\uparrow; [ri]; ro\downarrow; [\neg ri]; lo\uparrow; [\neg li]; lo\downarrow]

```

Figure 2-3: Example handshaking expansion

Translating this syntax into a directed labelled transition system is straightforward; the example given above specifies the same DLTS as the trace command pref [li?; ro!; ri?; ro!; ri?; lo?; li?; lo!]. Starodubtsev uses an almost identical syntax using the characters '+' and '-' to denote transition polarity and delimiting the repetition sequence by -> and <-. However, cyclograms may also contain an initial sequence of communication actions that are only performed once.

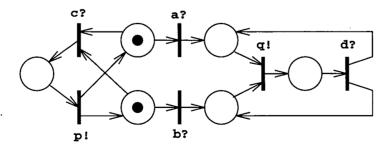

#### 2.2.3 Petri Nets