# Characterisation of organometallic materials for IC processes

Martin H Dicks

A thesis submitted for the degree of Doctor of Philosophy

Characterisation of organometallic materials for IC processes

# **Abstract**

UE to their low resistivity, metals have been a subject of great interest in semiconductor manufacturing, primarily for use as a material for interconnects. Besides, the continuous reduction of feature sizes on silicon based integrated circuits is expected to cause a switch from silicide gates on silicon dioxide to metal gates on advanced dielectrics.

The shrinking of semiconductor structures and emerging new technologies demand for new metallisation processes which overcome the limitations of existing solutions and meet new requirements.

This thesis reports on the characterisation of platinum features which were deposited and patterned using UV (ultra violet) exposure of a solid photosensitive organometallic material through a mask. The work aims to evaluate the process for its use in present and future semiconductor technology.

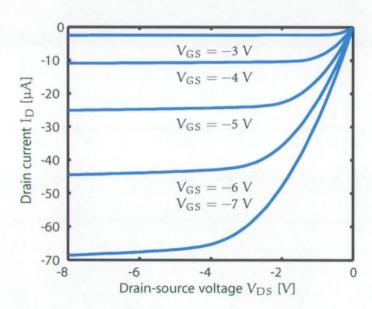

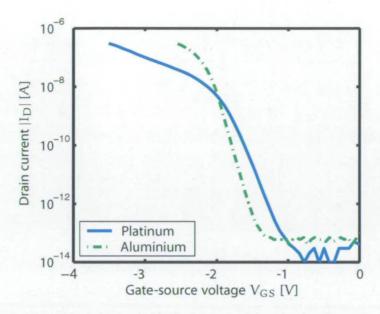

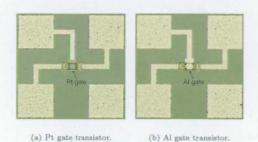

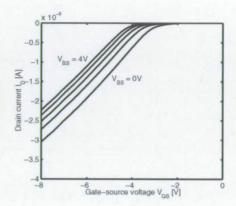

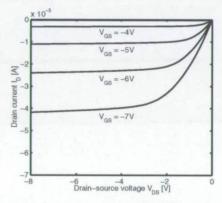

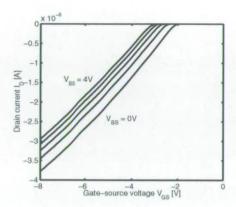

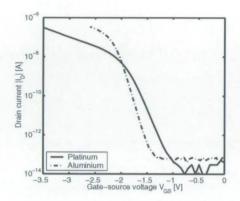

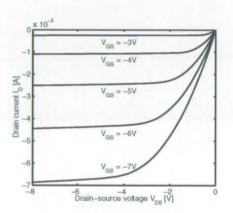

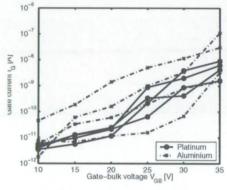

A range of devices including resistive and capacitive test structures as well as MOS transistors were produced using platinum deposited by the organometallic process and characterised by standard methods. The deposited films were found to be metallic and have a good adhesion to silicon dioxide, although their resistivity is higher than the one of bulk platinum. Measurements on platinum MOS capacitors showed their capacitance curves to agree well with curves from aluminium capacitors on the same substrate albeit the curves of capacitors on chips which incorporated MOS transistors indicated interface traps. Threshold and source-drain characteristics of platinum gate transistors are presented and these results are compared with aluminium gate transistors manufactured on the same substrate. Both sets of characteristics are very similar with the major difference being that the platinum gate devices have a lower sub-threshold slope, an effect which was attributed to trap charges at the silicon/silicon dioxide interface. The work also found that structures produced were generally larger than expected and spectroscopy methods showed contaminants to be present in the films.

The findings of this research indicate that many properties of the platinum films reported herein are superior to those of films deposited by similar means found in the literature. However, the work also identified problems concerning the microstructure of the films and accurate control of feature size which need to be solved before the films can be integrated into a modern semiconductor process.

# **Contents**

|   |       | Contents v                                                             |

|---|-------|------------------------------------------------------------------------|

|   |       | List of figures viii                                                   |

|   |       | List of tables xi                                                      |

|   |       | Acronyms and abbreviations xii                                         |

|   |       | Nomenclature xiii                                                      |

|   |       | Preface xv                                                             |

| 1 | Intro | oduction 1                                                             |

|   | 1.1   | Motivation 1                                                           |

|   | 1.2   | Scope and objectives of this work 3                                    |

| 2 | Histo | orical background and review of subject 6                              |

|   | 2.1   | Semiconductor devices 6                                                |

|   | 2.2   | Process technology 9                                                   |

|   |       | 2.2.1 Early processes 9                                                |

|   |       | 2.2.2 Invention of the integrated circuit 10                           |

|   |       | 2.2.3 Planar process 10                                                |

|   |       | 2.2.4 Device scaling 10                                                |

|   |       | 2.2.5 Modern VLSI technology 13                                        |

|   |       | 2.2.6 Future technologies 16                                           |

|   | 2.3   | Organometallic materials in semiconductor manufacturing 19             |

|   |       | 2.3.1 Organometallic processes 19                                      |

|   |       | 2.3.2 Properties of metal features deposited from an organometallic 20 |

|   | 2.4   | Platinum in semiconductor processes 21                                 |

|   |       | 2.4.1 Applications of platinum in semiconductor manufacturing 21       |

|   |       | 2.4.2 Influence of platinum on semiconductor structures 21             |

| 3 | Orga  | anometallic compound and process 22                                    |

|   | 3.1   | Organometallic compound 22                                             |

|   |       | 3.1.1 Bonding mechanism 23                                             |

|   |       | 3.1.2 Photochemical reaction 26                                        |

|   | 3.2   |                                                                        |

|   |       | 3.2.1 Deposition 27                                                    |

|   |       | 3.2.2 Exposure 28                                                      |

|   |       | 3.2.3 Heat treatment 28                                                |

| _ | 3.3   | Discussion 32                                                          |

| 1 |       | chips 33                                                               |

|   | 4.1   | Test chip UDEA VO 33                                                   |

|   |       | 4.1.1 Layout 33                                                        |

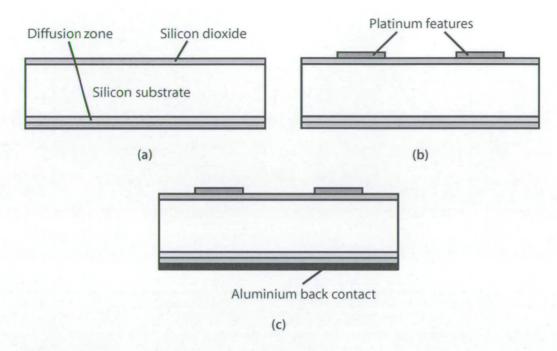

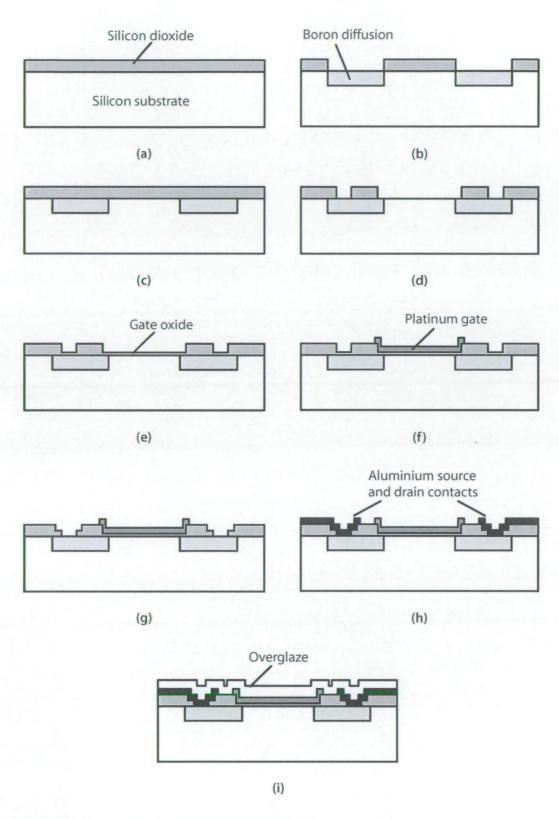

|   | 4.0   | 4.1.2 Process 34                                                       |

|   | 4.2   | Test chip UDEA V1 36                                                   |

|   |       | 4.2.1 Layout 36                                                        |

|   | 12    | 4.2.2 Process 38 Discussion 39                                         |

| = | 4.3   | stance and dimensional measurements 42                                 |

| 5 | 5.1   | Basics 43                                                              |

|   | J. I  | Dasils 43                                                              |

|   |      | 5.1.1 Sheet resistance and resistivity 43                                             |

|---|------|---------------------------------------------------------------------------------------|

|   |      | 5.1.2 Contact resistivity 45                                                          |

|   |      | 5.1.3 Linewidth measurements 45                                                       |

|   |      | 5.1.4 Resistivity of thin films 47                                                    |

|   | 5.2  | Materials and methods 49                                                              |

|   |      | 5.2.1 Test structures 49                                                              |

|   |      | 5.2.2 Measurement setup 49                                                            |

|   |      | 5.2.3 Measurement procedure 49                                                        |

|   | 5.3  | Results and Discussion 50                                                             |

| 6 | Capa | acitance measurements 58                                                              |

|   | 6.1  | Basics 58                                                                             |

|   |      | 6.1.1 MOS capacitor 59                                                                |

|   |      | 6.1.2 Definition and sign conversion of potentials 59                                 |

|   |      | 6.1.3 Ideal MOS capacitor 60                                                          |

|   |      | 6.1.4 Real MOS capacitor 62                                                           |

|   |      | 6.1.5 Capacitance of MOS capacitor 66                                                 |

|   |      | 6.1.6 Gate voltage 72                                                                 |

|   |      | 6.1.7 Impact of different factors on C-V curves 72                                    |

|   | 6.2  | Materials and methods 73                                                              |

|   |      | 6.2.1 Test structures 73                                                              |

|   |      | 6.2.2 Measurement setup 74                                                            |

|   | 6 2  | 6.2.3 Extraction of MOS properties from C-V measurements 74 Results and discussion 80 |

| 7 | 6.3  | sical characterisation 86                                                             |

| , | 7.1  | Basics 86                                                                             |

|   | 7.1  | 7.1.1 Auger electron spectroscopy (AES) 86                                            |

|   |      | 7.1.2 X-ray photoelectron spectroscopy (XPS) 87                                       |

|   | 7.2  | Materials and methods 87                                                              |

|   | ,    | 7.2.1 Sample preparation 87                                                           |

|   |      | 7.2.2 Measurement setup 87                                                            |

|   | 7.3  | Results and discussion 88                                                             |

|   |      | 7.3.1 AES 88                                                                          |

|   |      | 7.3.2 XPS 89                                                                          |

|   |      | 7.3.3 Discussion 91                                                                   |

| 8 | Cha  | racterisation of MOS transistors 92                                                   |

|   | 8.1  | Basics 92                                                                             |

|   | 8.2  | Materials and methods 97                                                              |

|   |      | 8.2.1 Test structures 97                                                              |

|   |      | 8.2.2 Measurement setup 98                                                            |

|   |      | 8.2.3 MOS transistor parameter extraction 98                                          |

|   | 8.3  | Results and Discussion 99                                                             |

| 9 |      | ew, discussion and future work 103                                                    |

|   | 9.1  | Review of experimental findings 103                                                   |

|   | 9.2  | Implications 105                                                                      |

|   | 9.3  | Further work 108                                                                      |

| A |      | structures 109                                                                        |

|   | A.1  | UDEA V0 109                                                                           |

|   | A.2   | UDEA V1 | 111 |

|---|-------|---------|-----|

| В | Proce | ss 116  |     |

B.1 UDEA V0 116

B.1.1 Runsheet 116

B.2 UDEA V1 119

- B.2.1 Runsheet 119

- B.2.2 Design rules 123

- B.2.3 Mask nomenclature and sequence 125

- C Errors introduced by profilometer tip 126

- D Published papers 129

- D.1 International Conference on Semiconductor Test Structures (Monterey, USA, 2003) 130

- D.2 International Conference on Semiconductor Test Structures (Awaji, JP, 2004) 136

- D.3 IEEE Transactions on Semiconductor Manufacturing (vol. 17, may 2004) 142 References 150

# **List of Figures**

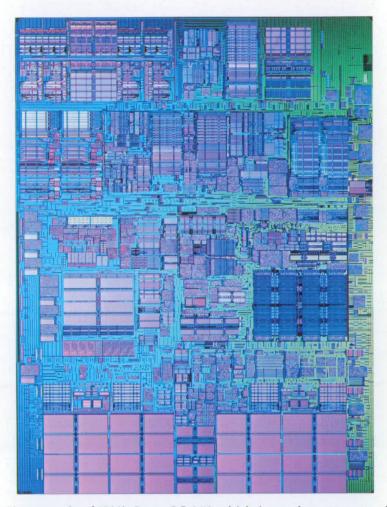

- 1.1 Photograph of IBM's PowerPC 970 which is used as processor in Apple's G5 computers [7]. The chip size is 118 mm<sup>2</sup>. 2

- 1.2 Cross section showing the transistor level and one layer of copper interconnect of a PowerPC 970 chip [7]. 2

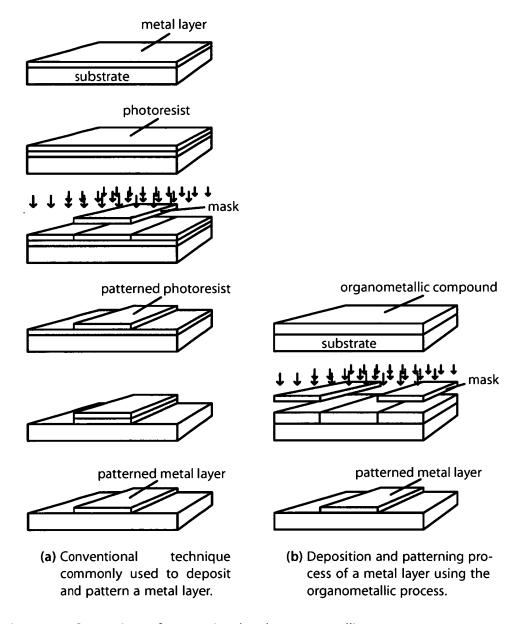

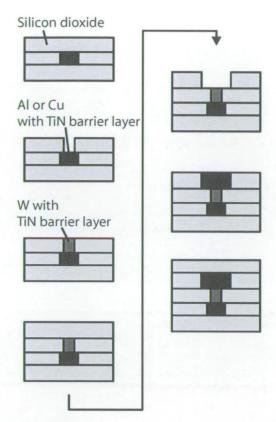

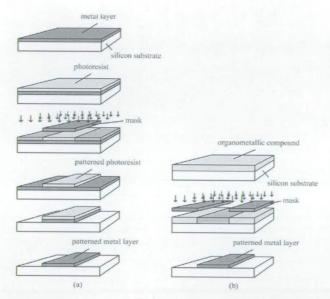

- 1.3 Comparison of conventional and organometallic process.

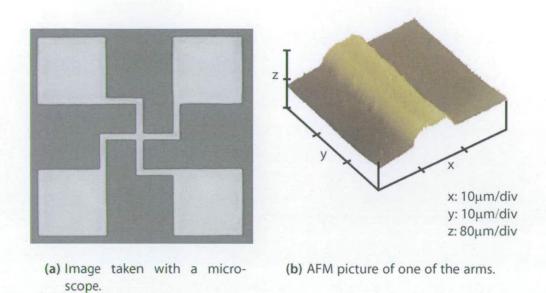

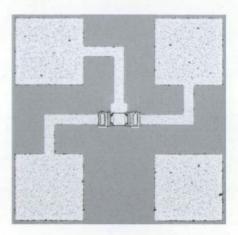

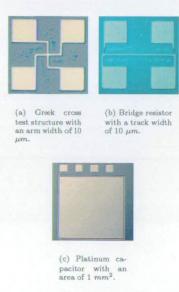

- 1.4 A Greek cross test structure produced using UV exposure of a solid organometallic material. 5

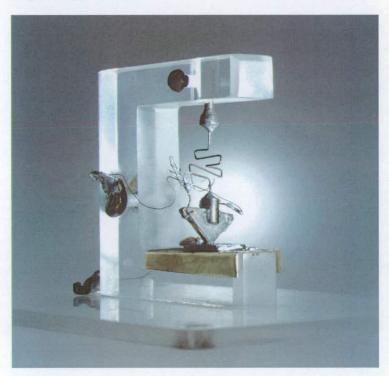

- 2.1 The first bipolar transistor as it was built by Bardeen and Brattain at Bell Laboratories [12]. 7

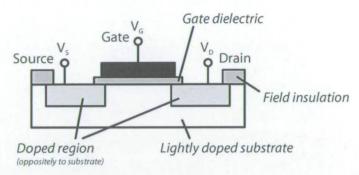

- 2.2 Typical structure of a MOS transistor.

- 2.3 Typical structure of a double gate MOS transistor. 8

- 2.4 Steps involved in the alloy junction technology.

- 2.5 The planar process as it was developed by Hoerni to produce transistors.

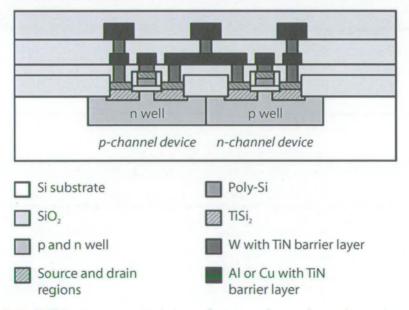

- 2.6 A CMOS structure consisting of a n- and a p-channel transistor fabricated using modern manufacturing methods. 13

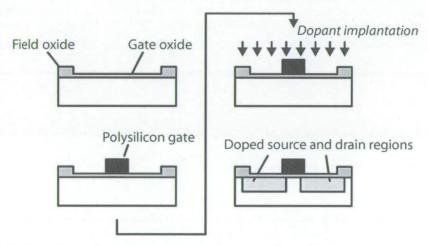

- 2.7 Definition of source and drain regions by the self-aligned process. 14

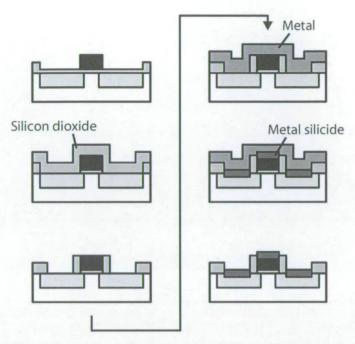

- 2.8 Creation of source and drain contacts by the self-aligned silicide process. 15

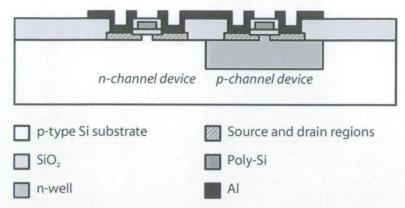

- 2.9 A CMOS structure consisting of a n- and a p-channel transistor as it was commonly fabricated in the 80s. 16

- 2.10 Damascene process. 17

- 2.11 Dual damascene process. 17

- 2.12 Possible positions of materials in the silicon band. 18

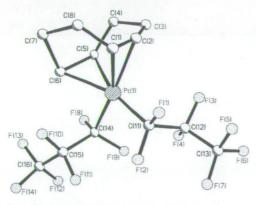

- 3.1 Structure of the organometallic material. 23

- 3.2 Hydrogen atom 1s orbital. 24

- 3.3 Hydrogen atom 2p orbitals. 25

- 3.4 Hydrogen atom 3d orbitals. 25

- 3.5 The two different types of backbonding mechanisms. 25

- 3.6 The two different types of backbonding mechanisms applied to the organometallic material. 27

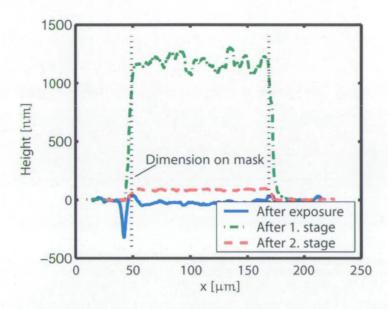

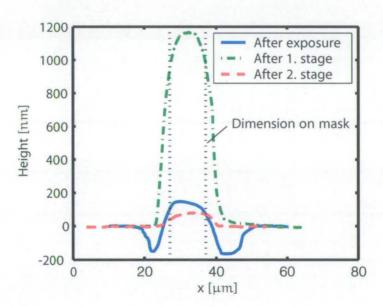

- 3.7 Change of the film topology during the heat treatment. 29

- 3.8 Platinum features manufactured at the University of Dundee using the organometallic process and a test chip mask designed for this work at University of Edinburgh. 30

- 3.9 Setup used to process the samples in the oven. 31

- 3.10 Platinum features manufactured at the University of Edinburgh using the organometallic process. Note that in contrast to the structures in Figure 3.8, the pads are made of aluminium. 31

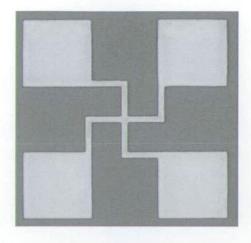

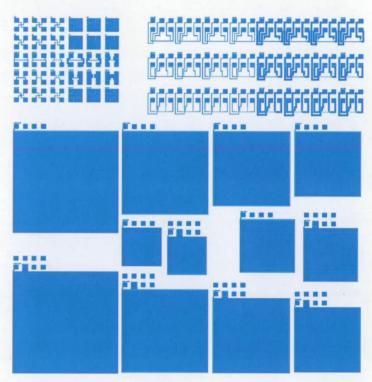

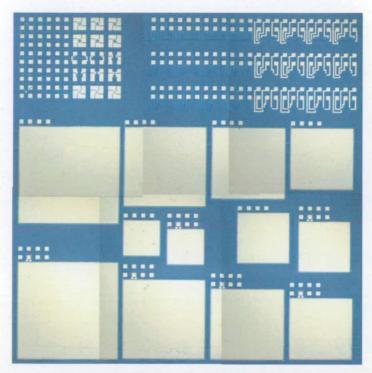

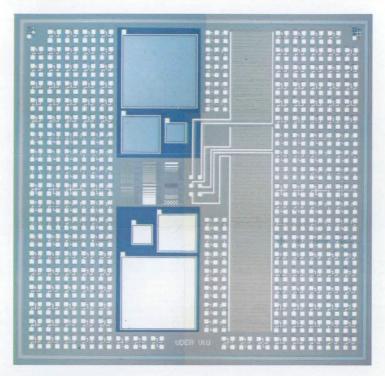

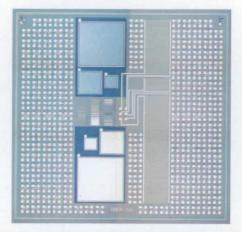

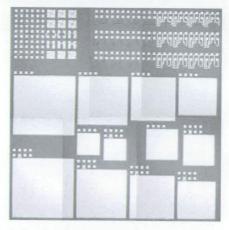

- 4.1 Layout of the test chip UDEA V0. The resistivity structures are situated in the upper left-hand corner, linewidth test structures in the upper right-hand corner and the capacitors below. 34

- 4.2 Process used to manufacture UDEA VO. 36

- 4.3 Test chip UDEA V0. 37

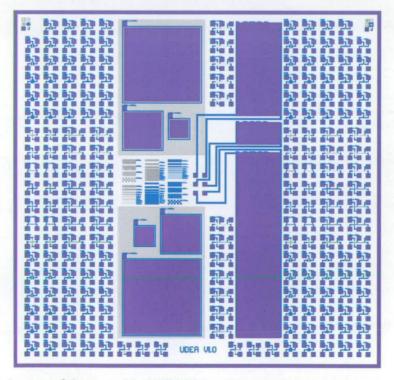

- 4.4 Layout of the test chip UDEA V1. 37

- 4.5 Process used to manufacture UDEA V1. 40

- 4.6 Test chip UDEA V1. 4

- 5.1 Bridge resistor test structure. 44

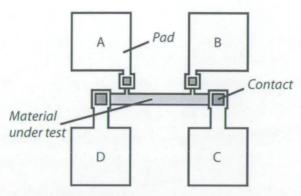

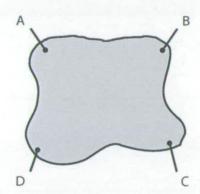

- 5.2 Arbitrary shaped sample connected for van der Pauw resistivity measurements. 44

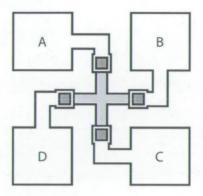

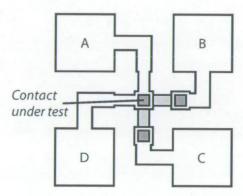

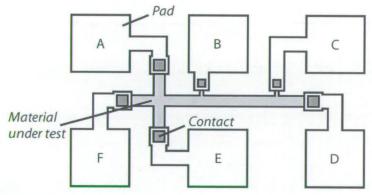

- 5.3 Greek cross test structure. 45

- 5.4 Kelvin test structure used for contact resistivity measurements. 46

- 5.5 Line width test structure. 46

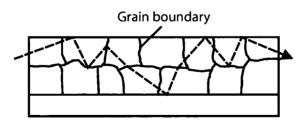

- 5.6 Scattering of an electron at the film surfaces and grain boundaries. 48

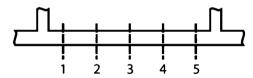

- 5.7 The positions of the five profiles obtained from each bridge structure to calculate the average area of the cross section. 51

- 5.8 Profiles of bridge resistor structures on UDEA V0 obtained by a profilometer. 52

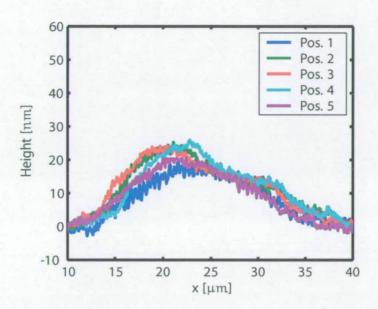

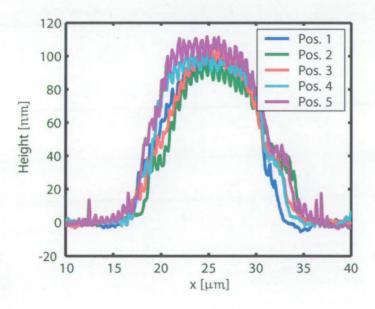

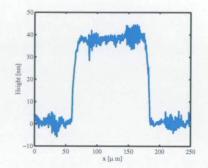

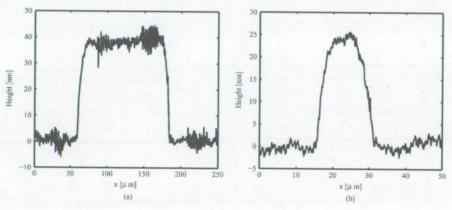

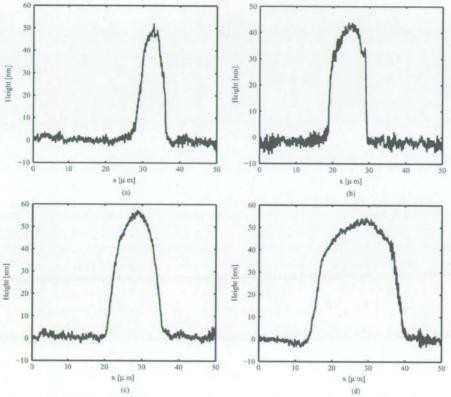

- 5.9 Profiles of bridge resistor structures on UDEA V0 obtained by a profilometer. 53

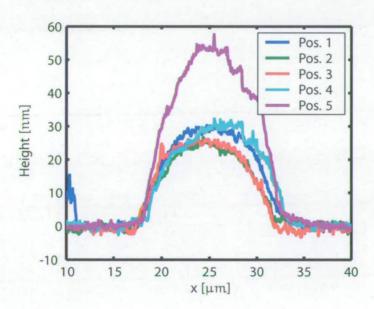

- 5.10 Profiles of bridge resistor structures on UDEA V1 obtained by a profilometer. 54

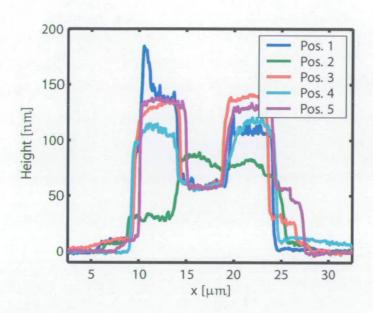

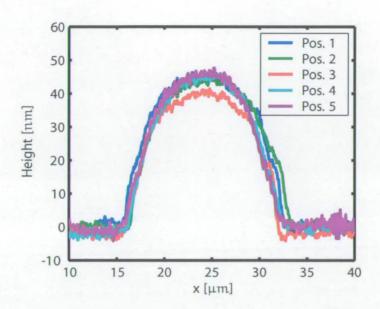

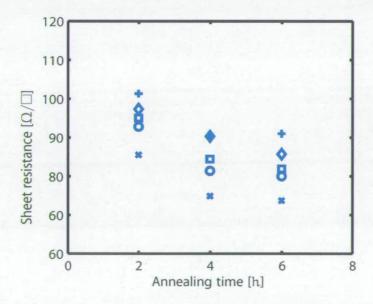

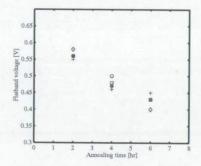

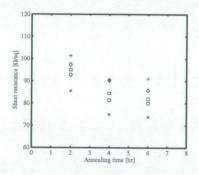

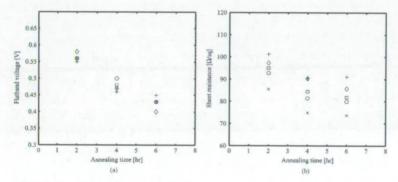

- 5.11 Influence of annealing time on the sheet resistance of the deposited films. The data was obtained from measurements at different locations on a wafer. 55

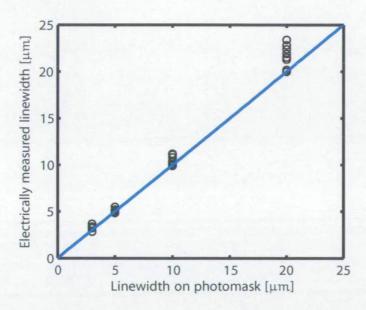

- 5.12 Comparison of the linewidth measured electrically and the linewidth on the mask.

The circles represent measurements at different positions on the wafer. 56

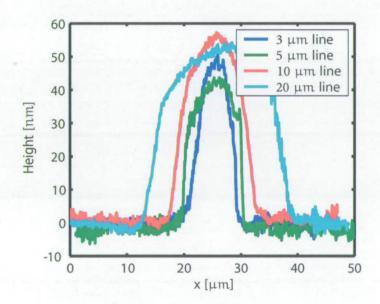

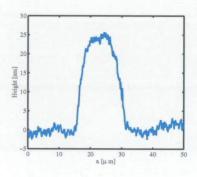

- 5.13 Profiles of lines of different width measured with a profilometer. 57

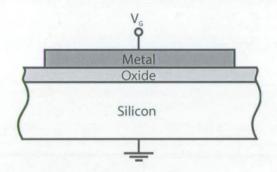

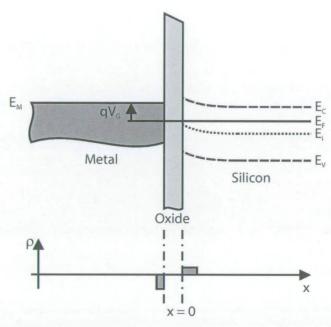

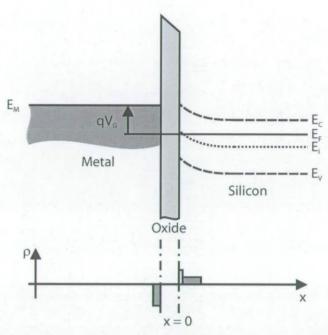

- 6.1 MOS capacitor. 59

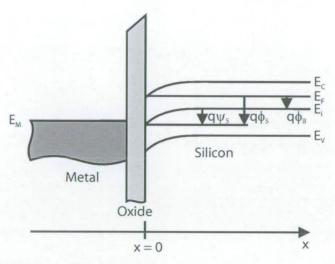

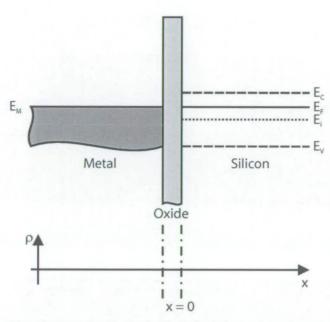

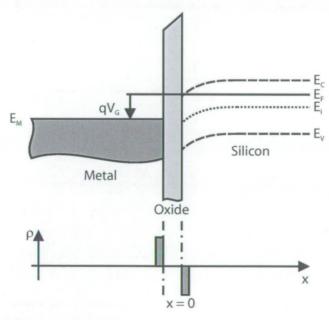

- 6.2 Potentials in a MOS structure. 60

- 6.3 Band diagram of a MOS structure at flatband condition (n-type substrate). 61

- 6.4 Band diagram of a MOS structure in accumulation (n-type substrate). 61

- 6.5 Band diagram of a MOS structure in depletion (n-type substrate). 62

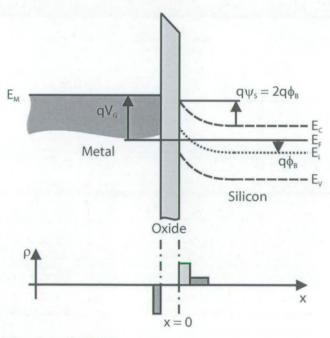

- 6.6 Band diagram of a MOS structure in weak inversion (n-type substrate). 63

- 6.7 Band diagram of a MOS structure in strong inversion (n-type substrate). 63

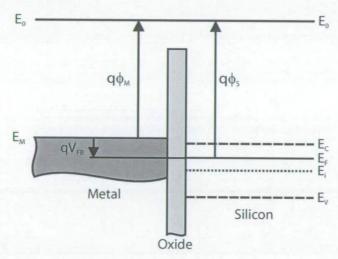

- 6.8 Workfunction difference. 64

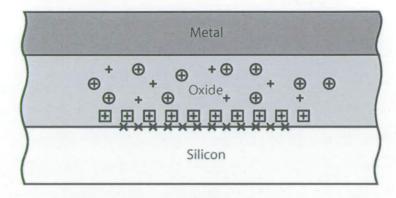

- 6.9 Charges in the MOS structure 65

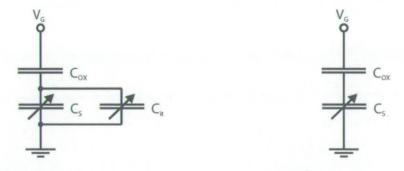

- 6.10 Equivalent circuit of a MOS capacitor with interface traps at both low and high frequencies. 65

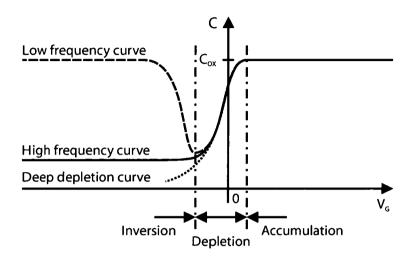

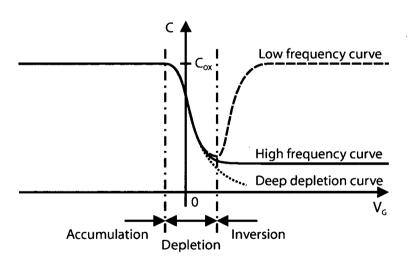

- 6.11 Typical C-V curves of capacitors on different substrates. 67

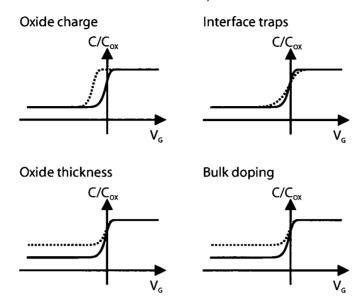

- 6.12 Influence of different factors on the C-V curve of a capacitor on a n-type substrate. 73

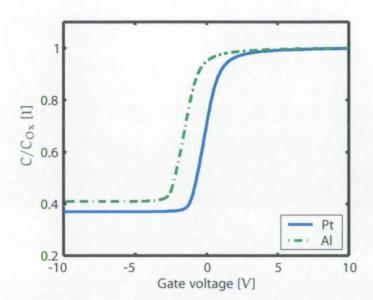

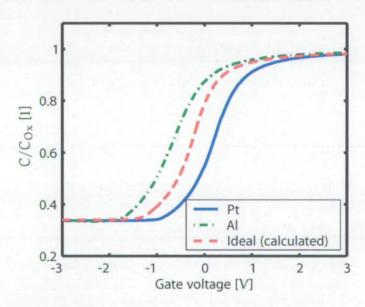

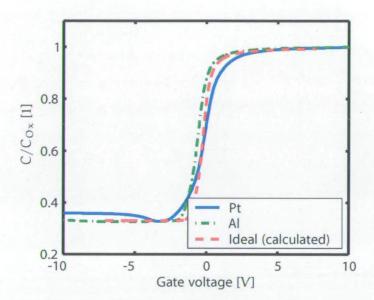

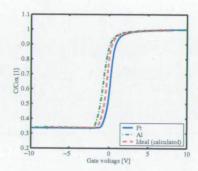

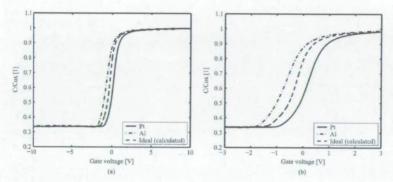

- 6.13 Typical C-V curves obtained at 1 MHz of both a Pt (film a, deposited using the organometallic process) and an Al (deposited by sputtering) capacitor on the n-type substrate of UDEA V0. 81

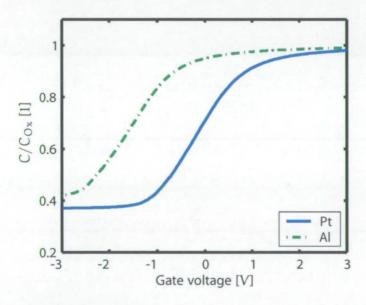

- 6.14 Typical C-V curves obtained at 1 MHz of both a Pt (film b, deposited using the organometallic process) and an Al (deposited by sputtering) capacitor on the n-type substrate of UDEA VO. A calculated ideal curve is also shown for comparison. 82

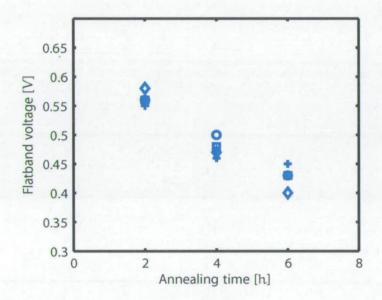

- 6.15 Workfunction versus annealing time. The data was obtained from measurements at different locations on a wafer. 83

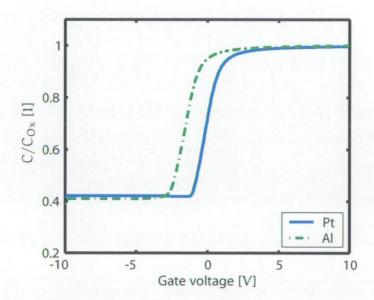

- 6.16 Typical C-V curves obtained at 1 MHz of both a Pt (film c, deposited using the organometallic process) and an Al (deposited by sputtering) capacitor on the n-type substrate of UDEA VO. 84

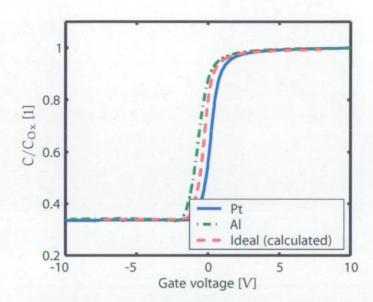

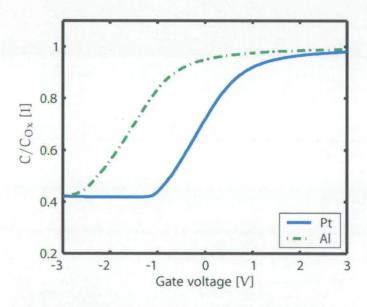

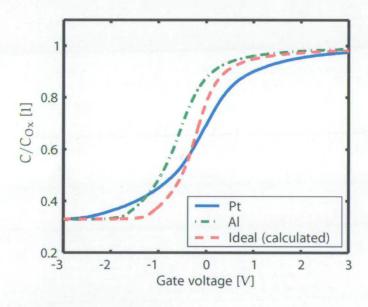

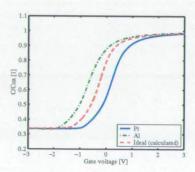

- 6.17 Typical C-V curves obtained at 1 MHz of both a Pt (film e, deposited using the organometallic process) and an Al (deposited by sputtering) capacitor on the n-type substrate of UDEA V1. A calculated ideal curve is also shown for comparison. 85

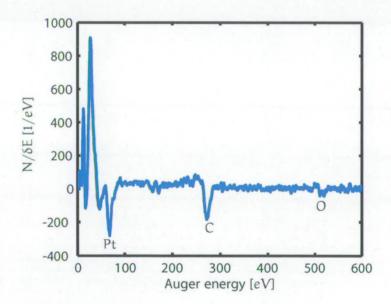

- 7.1 AES spectra of the platinum film before sputtering. 88

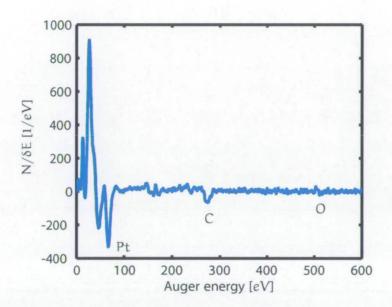

- 7.2 AES spectra of the platinum film after sputtering. 89

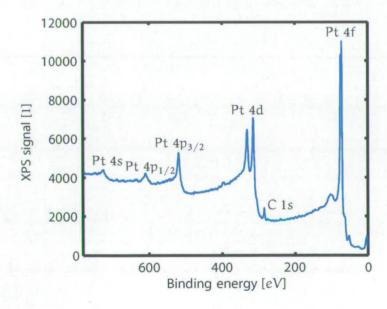

- 7.3 XPS spectra of the platinum film after sputtering. 90

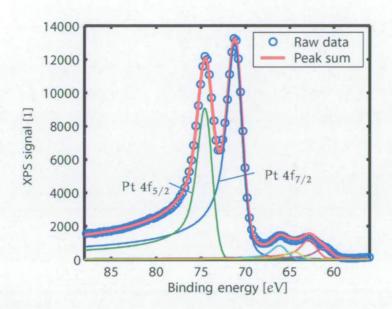

- 7.4 Pt4 $f_{7/2}$  and Pt4 $f_{5/2}$  peaks of the platinum film after sputtering. 91

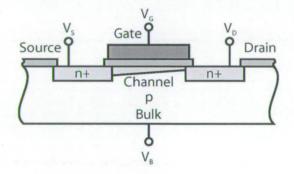

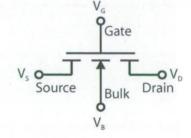

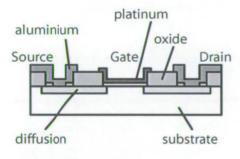

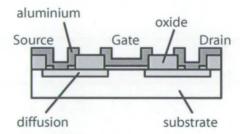

- 8.1 MOS transistor. 92

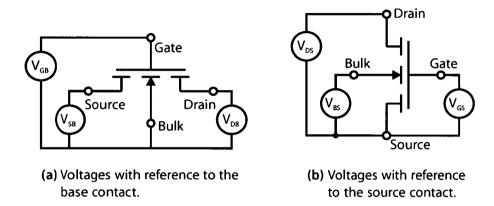

- 8.2 Voltages at the MOS transistor. 93

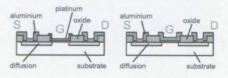

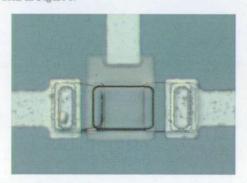

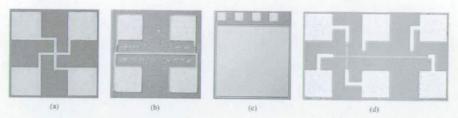

- 8.3 Devices with gate length of 20  $\mu$ m and width of 20  $\mu$ m. 97

- 8.4 Cross sections of the two transistor types. 97

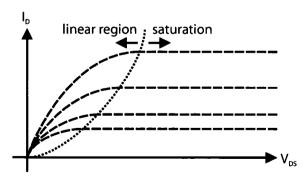

- 8.5 Operating regions of the MOS transistor. 98

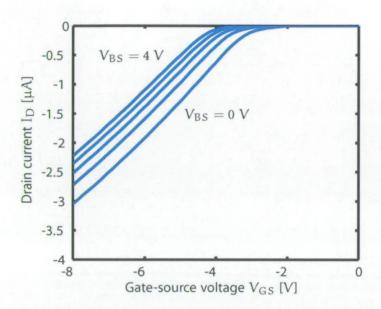

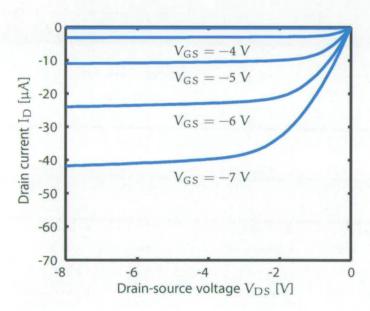

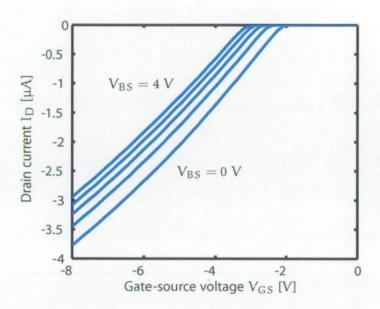

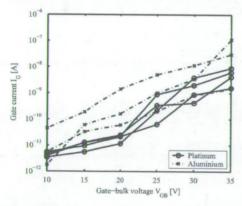

- 8.6 Characteristics of a platinum gate transistor with a gate length of 20  $\mu$ m and a width of 20  $\mu$ m. 100

- 8.7 Characteristics of an aluminium gate transistor with a gate length of 20  $\mu$ m and a width of 20  $\mu$ m. 101

- 8.8 Subthreshold characteristic of transistors with a gate length of 20  $\mu m$  and a width of 20  $\mu m$ . 102

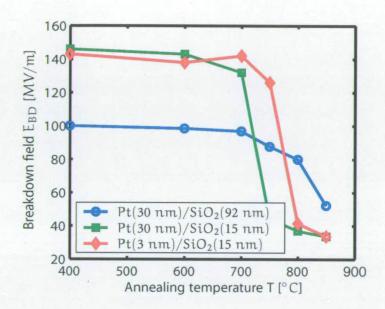

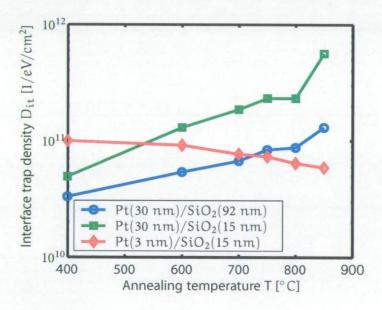

- 9.1 Influence of annealing temperature on oxide breakdown field and interface trap density of a MOS structure [50]. 107

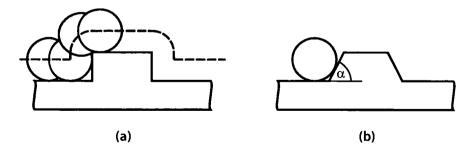

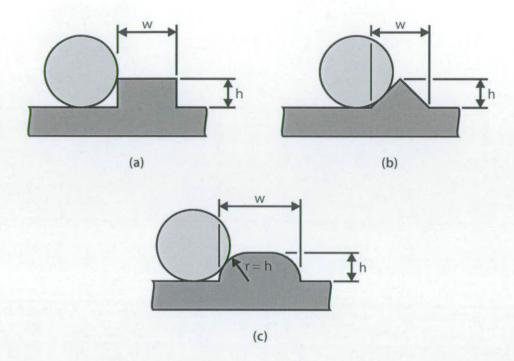

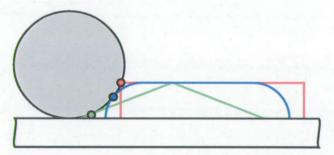

- C.1 Illustration (a) shows a profile (solid line) and the curve resulting from a measurement with a ball-shaped profilometer tip (dashed line). The angle  $\alpha$  used to investigate the error is depicted in (b). 126

- C.2 Profiles used to investigate the errors caused by the tip of the profilometer. 127

- C.3 The points of maximum error for the three different feature shapes discussed in this chapter. 127

# **List of Tables**

- 2.1 Dependence of scaling factor  $\alpha$  on the circuit performance and interconnect lines. 12

- 2.2 Properties of different gate and interconnect materials. 13

- 2.3 Properties of some of the organometallic processes reported in the literature. 20

- 2.4 Resistivities of some metals. 20

- 4.1 Names given to the deposited platinum films for UDEA VO. 35

- 4.2 Names given to the deposited platinum films for UDEA V1. 39

- 5.1 Electron mean free path of some metals. 48

- 5.2 Resistivities for the different films measured using Greek cross and bridge resistor test structures on UDEA VO. 50

- 5.3 Resistivities for the different films measured using Greek cross and bridge resistor test structures on UDEA V1. 51

- 5.4 Calculated resistivities of the different films based on the cross-section area measured at five positions of a bridge resistor on UDEA V0. 53

- 5.5 Calculated resistivities of the different films based on the cross-section area measured at five positions of a bridge resistor on UDEA V1. 53

- 7.1 Position of the photoelectron lines of Pt [103]. 90

- 7.2 Position and intensity of X-ray satellites from Mg targets [103]. 90

- C.1 Maximum errors expected for structures characterised using a profilometer with a tip radius of 2.5  $\mu$ m. A value of 5  $\mu$ m was used for the width w shown in Figure C.2. 128

# Acronyms and abbreviations

AES Auger Electron Spectroscopy

AFM Atomic Force Microscopy

CMOS Complementary Metal Oxide Semiconductor

CMP Chemical Mechanical Polishing

COD Cycloocta-1,5-diene

EOT Equivalent Oxide Thickness

FET Field Effect Transistor

HOMO Highest Occupied Molecular Orbital

IC Integrated Circuit

ITRS International Technology Roadmap for Semiconductors

JFET Junction Field Effect Transistor

LUMO Lowest Unoccupied Molecular Orbital

MEMS Microelectromechanical Systems

MIS Metal Insulator Semiconductor

MOS Metal Oxide Semiconductor

MPU Mathematical Processing Unit

PVD Physical Vapour Deposition

SOI Silicon On Insulator

TLM Transmission Line Model

UV Ultra Violet

VLSI Very Large-Scale Integration

XPS X-ray Photoelectron Spectroscopy

# Nomenclature

| C                  | Capacitance                                          |

|--------------------|------------------------------------------------------|

| $C_{FB}$           | Flatband capacitance                                 |

| $C_{it}$           | Interface trap charge                                |

| $C_{max}$          | Maximum capacitance                                  |

| $C_{min}$          | Minimum capacitance                                  |

| $C_{Ox}$           | Oxide capacitance                                    |

| $C_S$              | Depletion layer capacitance                          |

| $E_C$              | Minimum energy of an electron in the conduction band |

| $E_F$              | Fermi energy                                         |

| $E_{\mathbf{i}}$   | Intrinsic Fermi energy                               |

| $E_{M}$            | Metal Fermi energy                                   |

| $E_0$              | Vacuum energy                                        |

| $E_{oldsymbol{V}}$ | Maximum energy of an electron in the valence band    |

| $F_S$              | Electrical field at the silicon surface              |

| h                  | Plank's constant                                     |

| $I_D$              | Drain current                                        |

| k                  | Boltzmann constant                                   |

| L                  | Transistor gate lenght                               |

| n                  | Electron concentration                               |

| $n_S$              | Electron concentration at the silicon surface        |

| $N_A$              | Acceptor density                                     |

| $N_D$              | Donor density                                        |

| p                  | Hole concentration                                   |

| $p_S$              | Electron concentration at the silicon surface        |

| $Q_D$              | Depletion layer charge                               |

| $Q_{f}$            | Oxide fixed charge                                   |

| $Q_{\rm I}$        | Inversion layer charge                               |

| $Q_{it}$           | Interface trapped charge                             |

| $Q_{\mathfrak{m}}$ | Mobile ionic charge                                  |

| Qo                 | Oxide charge                                         |

| $Q_{ot}$           | Oxide trapped charge                                 |

| $Q_S$              | Surface charge                                       |

| q                  | Electron charge                                      |

| t                  | Time                                                 |

| $t_{Ox}$           | Oxide thickness                                      |

$\begin{array}{lll} T & & \text{Temperature} \\ V_{FB} & & \text{Flatband voltage} \\ V_{G} & & \text{Gate voltage} \\ V_{Ox} & & \text{Oxide voltage} \\ V_{TH} & & \text{Threshold voltage} \\ w & & \text{Depletion layer width} \end{array}$

wmax Maximum depletion layer width

$\begin{array}{ll} W & \quad \text{Transistor gate width} \\ \varepsilon_0 & \quad \text{Vacuum permitivity} \\ \varepsilon_{Ox} & \quad \text{Oxide permitivity} \\ \varepsilon_{Si} & \quad \text{Silicon permitivity} \end{array}$

$\lambda_n$  Debye length (for n-type material)  $\lambda_p$  Debye length (for p-type material)

μ Mobility

ρ Charge density

Φ Potential between Fermi level and intrinsic Fermi level

φ<sub>B</sub> Bulk potential

φ<sub>M</sub> Metal workfunctionφ<sub>MS</sub> Workfunction difference

$\begin{array}{ll} \varphi_S & \quad \text{Surface potential} \\ \varphi_{Si} & \quad \text{Silicon workfunction} \end{array}$

ψ Band bending

$\psi_S$  Band bending at the silicon surface

## **Preface**

HIS thesis is the result of my studies for a PhD degree from the University of Edinburgh in Scotland (UK). It is based on work done between August 2000 and July 2004 at the Institute for Micro- and Nanosystems at the Scottish Microelectronics Centre in Edinburgh which has partly been published in two conference papers [1,2] and a journal paper [3].

### Outline of the thesis

This thesis can roughly be divided into three main parts. The first part, the introductory chapters, consists of an introduction and a review of semiconductor processes. Part two, the experimental part, includes descriptions of the organometallic process and the manufacturing of the test structures, together with chapters regarding the measurements. The thesis finishes with a chapter concluding this research and giving details about possible future work.

Throughout the thesis, special care has been placed upon the consistent use of nomenclature and abbreviations, the excellent book about the MOS transistor by Tsividis [4] was hereby taken as an example. The nomenclature used corresponds widely with the one used by Nicollian and Brews in their standard reference book on the MOS capacitor [5] and was extended to the MOS transistor.

The figures in the thesis were deliberately kept simple. However, this means that silicon dioxide layers produced by oxidation, for example, are represented by a layer on top of the silicon substrate and it is not shown that silicon is consumed into the oxide during this process. Also, rectangles were used to draw structures and rounded shapes only employed where they were necessary for better understanding.

In the following, the chapters of this dissertation are briefly outlined.

Chapter one. In chapter one a brief introduction is given and the motivation and the objectives of this work are described.

Chapter two. The second chapter of this thesis starts with the historical background to this work, explaining not only the development of semiconductor processes and devices in the past but also giving an outlook into the future. The process steps involved in the manufacturing of modern integrated circuits are described and problems likely to arise are extracted from the ITRS 2003 (International Technology Roadmap for Semiconductors 2003) [6]. It is then focused onto the use of organometallic materials and platinum in semiconductor processing, which are areas of special interest for this project.

Chapter three. Chapter three explains the chemistry of the organometallic material which includes the bonding mechanisms holding the molecule together and the photochemical process which makes this particular compound so useful. Also, the organometallic process is described and platinum structures produced are shown.

Chapter four. Chapter four delineates the design and manufacturing of two test chips, both of which were used for the measurements in the following chapters.

Chapter five. The fifth chapter deals with resistive and dimensional measurements. It starts with the theory necessary to understand resistive test structures as well as mechanisms responsible for the resistance of thin films. Electrical linewidth measurements are then explained and results are shown.

Chapter six. The voltages at the MOS stack and the theory around the capacitance of a MOS structure are introduced in chapter six. The extraction of parameters from C-V curves is described and results obtained from capacitance measurements at capacitors produced using the organometallic process are presented.

Chapter seven. Chapter seven begins by explaining AES (Auger Electron Spectroscopy) and XPS (X-ray Photoelectron Spectroscopy). Spectres obtained using this characterisation methods are then shown, evaluated and the results discussed.

Chapter eight. The characterisation of transistors with a gate manufactured using the organometallic process is reported in chapter eight. Besides, formulas describing the MOS transistor are developed and a model derived which is used for fitting curves to the ones obtained from the transistors manufactured.

Chapter nine. The final chapter reviews the whole thesis in brief, discusses the results and their implications on the state of the art. Besides, possible future work is proposed.

# **Acknowledgements**

I would, of course, not have been able to finish this thesis, had it not been for the help of others.

First of all, I wish to thank my supervisor Anthony Walton for suggesting this work and his guidance throughout the project. I would also like to express gratitude to AMCET Ltd for funding two years of my PhD and Hansjörg Wirz for providing a reference which made this study in Edinburgh possible. I am also deeply in debt to all the people at the Scottish Microelectronics Centre and at the University of Dundee for their valuable suggestions, the synthe-

sis of the organometallic material and help with the processing of the test structures which I characterised during my work. Beside others, I would particularly like to thank Gareth Broxton, Alan Gundlach, Tom Stevenson and James Thomson who were greatly involved in this project and all spent a considerable amount of time helping me with my tasks.

I am especially indebted to the people who provided the social environment at my working place by being good friends, company during the coffee breaks and participants at events outside the university, namely Stefan Enderling, Natalie Plank, Louise Teo, Huamao Lin and Yifan Li from the ranks of the PhD students and Liudi Jiang, a post-doc.

There were also people not directly associated with the project or the Scottish Microelectronics Centre who I would like to mention. First of all, I would like to thank my wife Nanako for her tolerance during the final year of my studies. I do not know how many times we had to change our plans due to delays with my experiments. I also gratefully recognise my family and friends in Switzerland and Japan, who supported me very well and provided something like a backbone by letting me know that I could always count on their help. A special thank goes to Shinya Katsumata who started his PhD studies at the same time as I and was a fast friend over the whole four years.

Besides the people, there were also tools and things which did their part in helping me accomplish my tasks. The toolset that was available at the SMC provided the opportunity to undertake this work but at the same time presented a challenge in terms of both its operation and maintenance. The Sun workstation running Solaris which occupied big parts of my desk always provided the computing power I needed to do my work. I also want to thank Google (http://www.google.com) for its great search results and Leo (http://dict.leo.org) for its translations between German and English which helped to solve many language problems. Finally, there was Matlab which automated the creation of graphs and Language profiled to be the perfect tool to write this thesis.

## **Declaration of originality**

I hereby declare that the research recorded in this thesis is my own work, unaided except where otherwise acknowledged in the text, and the thesis itself was composed entirely by myself in the School of Engineering and Electronics at the University of Edinburgh. This work has not been submitted for any other degree or professional qualification.

# Introduction

### Contents

- 1.1 Motivation

- 1.2 Scope and objectives of this work

3

tors. Semiconductor and especially silicon technology lies at the core of the majority of computer systems today and made the Internet possible. The silicon industry is of immense proportions and often used as an indicator for the state of the world economy. It is therefore not surprising that a lot of research is undertaken in the field of semiconductors, allowing this sector of industry to maintain a very high speed in which new technologies are developed.

Figure 1.1 and Figure 1.2 show the present state of the art by depicting a PowerPC 970 processor developed by IBM [7]. Its circuitry incorporates 52 million transistor on a 118 mm<sup>2</sup> die and it is manufactured on 300 mm wafers using 0.13  $\mu$ m SOI (Silicon On Insulator) technology with eight layers of copper interconnect.

### 1.1 Motivation

In early integrated circuits based on MOS (Metal Oxide Semiconductor) structures, metals were used for both, gates and interconnects. Later, the metal for the gates was replaced by polysilicon and silicides, thus allowing the channel to be formed using the self-aligned process described later in Chapter 3. However, it was forecasted [6] that in the near future, metals will be used again for gates. The reasons for this are, among other things, the low resistivity of metals compared to polysilicon, the various workfunctions of different metals and their compatibility with novel dielectrics. There are, however, drawbacks linked to the use of metals. First of all, many metals have low melting points or form silicide when in contact with silicon at temperatures as low as 250 °C, making a high-temperature step impossible to follow the metal deposition. Another difficulty is the deposition and patterning of metals which is more complicated than the one of materials commonly used in present-day semiconductor processing.

Despite the problems likely to arise with the use of metals, the replacement of silicon based gate materials by metals seems to be inevitable and it is therefore of high interest to find

Figure 1.1: Photograph of IBM's PowerPC 970 which is used as processor in Apple's G5 computers [7]. The chip size is 118 mm<sup>2</sup>.

Figure 1.2: Cross section showing the transistor level and one layer of copper interconnect of a PowerPC 970 chip [7].

new processes to deposit and pattern metals which comply with modern integrated circuit manufacturing methods.

### 1.2 Scope and objectives of this work

This research looks at a new process to deposit patterned platinum layers by UV (ultra violet) light exposure of a solid organometallic material. A platinum compound was choosen because it was the only material available at the start of this work. It is possible to produce organometallics based on other metals, some of which possess properties superior to the ones of platinum.

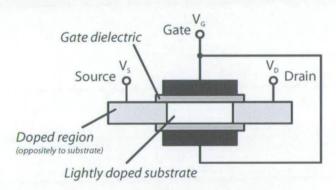

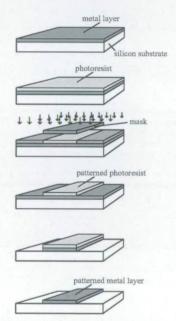

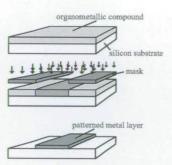

In conventional semiconductor processes, a patterned metal layer can be produced using the steps shown in Figure 1.3(a). It starts with the deposition of a metal layer on a substrate and putting photoresist on top of it. The photoresist is then exposed and developed and used as a mask to etch the metal. Finally, the photoresist is removed thus leaving behind the metal features.

The organometallic process depicted in Figure 1.3(b) works in a very different way and can be divided into three main parts, namely deposition, exposure and heat treatment. The solid organometallic compound can be spun onto a substrate or deposited using methods like PVD (Physical Vapour Deposition) and sputtering. After the deposition, the layer of organometallic material is exposed using either UV, e-beam or ion-beam lithography. The material behaves like a negative resist and therefore requires a dark field mask for exposure. To finalise the process, the unexposed organometallic material and organic residue are removed using a three-stage heat treatment. The three stages perform different tasks in defining and purifying the metal and are conducted at different temperatures in air or in a hydrogen/nitrogen environment (for a detailed description see Chapter 3). A Greek cross structure [8] made of platinum manufactured from an organometallic material is shown in Figure 1.4(a) and an AFM (Atomic Force Microscopy) image of one of the arms in Figure 1.4(b).

It can be seen that the organometallic process requires less process steps and works without etch steps or solvents, which is favourable from a manufacturing viewpoint.

This thesis investigates the integration of an organometallic compound into the manufacturing process of semiconductor structures. The organometallic materials and associated processes were developed at the University of Dundee under the direction of James Thomson. Throughout the project, parts of the experiments closely related to the organometallic process were performed in collaboration with researchers at the University of Dundee who also synthesised and supplied the organometallics. The work reported herein concerns itself with the application of organometallic compounds and deals only briefly with their chemistry. The design and production of test chips with standard semiconductor test structures as well as MOS transistors are described and their characterisation explained. The results are

Figure 1.3: Comparison of conventional and organometallic process.

Figure 1.4: A Greek cross test structure produced using UV exposure of a solid organometallic material.

then used to evaluate the suitability of the organometallic process for the manufacturing of present and future integrated circuits, which is the main objective of this work.

# Historical background and review of subject

### **Contents**

| 2.1 | .1 Semiconductor devices 6 |                                                                  |  |

|-----|----------------------------|------------------------------------------------------------------|--|

| 2.2 | Proces                     | s technology 9                                                   |  |

|     | 2.2.1                      | Early processes 9                                                |  |

|     | 2.2.2                      | Invention of the integrated circuit 10                           |  |

|     | 2.2.3                      | Planar process 10                                                |  |

|     | 2.2.4                      | Device scaling 10                                                |  |

|     | 2.2.5                      | Modern VLSI technology 13                                        |  |

|     | 2.2.6                      | Future technologies 16                                           |  |

| 2.3 | Organo                     | ometallic materials in semiconductor manufacturing 19            |  |

|     | 2.3.1                      | Organometallic processes 19                                      |  |

|     | 2.3.2                      | Properties of metal features deposited from an organometallic 20 |  |

| 2.4 | Platinu                    | im in semiconductor processes 21                                 |  |

|     | 2.4.1                      | Applications of platinum in semiconductor manufacturing 21       |  |

|     | 2.4.2                      | Influence of platinum on semiconductor structures 21             |  |

HIS chapter gives an introduction to semiconductor processes and provides an outlook on future technologies and arising challenges. First, some semiconductor devices are described in order to facilitate the understanding of the following sections concerning process technology. Here, emphasis is placed on areas which are of importance to this project, namely gate materials and interconnect technology. The use of organometallic materials and platinum in semiconductor processing are then examined thus further focusing on the topic of this work which deals with platinum films deposited from an organometallic material.

A lot of the historical information found in this chapter is based on the book written by Plummer et al. [9].

### 2.1 Semiconductor devices

The PN diode is the simplest semiconductor device and was one of the earliest semiconductor devices developed. A PN diode can be produced by bringing a n-type semiconductor material in contact with a p-type one.

The bipolar transistor was invented by Bardeen and Brattain in December 1947 at Bell Laboratories [10]. It was built using the point contact method and is shown in Figure 2.1. Soon

afterwards, Shockley developed the theory behind the function of the bipolar transistor [11]. The bipolar transistor was the most important semiconductor device in early integrated circuits but was later replaced by the field effect transistor. Most of modern integrated circuits are based on the field effect transistor but the bipolar transistor is still used for high-speed logic and other special applications.

Figure 2.1: The first bipolar transistor as it was built by Bardeen and Brattain at Bell Laboratories [12].

Although the basic principle and structure of the field effect transistor was reported earlier, the first transistor taking advantage of the field effect was not built until 1953 when the JFET (Junction Field Effect Transistor) was invented [13] whose theory was developed a year earlier by Shockley [14]. A MIS (Metal Insulator Semiconductor) structure was reported in 1959 [15] and a working MOS (Metal Oxide Semiconductor) transistor was demonstrated in 1960 [16, 17].

Since then, the basic structure of the transistor depicted in Figure 2.2 did not change significantly, although modern devices are the product of lots of scaling (see Section 2.2.4) and, according to the ITRS 2003 (International Technology Roadmap for Semiconductors 2003) [6], the physical gate length of a transistor of a MPU (Mathematical Processing Unit) will be 28 nm by the year 2006.

Recently, emerging problems with further scaling led to lots of research into new devices. One of the main issues are short channel effects which appear when the depletion layer width

Figure 2.2: Typical structure of a MOS transistor.

of the source and drain junctions becomes comparable to to the channel length. This causes the potential distribution in the channel to be dependent on both the gate and the drain voltage, thus changing the device behaviour. Short channel effects can be minimised by strictly sticking to the scaling rules described in Section 2.2.4 but shrinking device dimensions will in the near future make it difficult to follow these rules. Two of the main reasons for this are very shallow junctions and ultrathin oxide layers. Former are difficult to manufacture while very thin oxide layers lead to high leakage currents due to direct tunneling.

The double gate transistor shown in Figure 2.3 seems to eliminate some difficulties [18,19]. Its two gates effectively shield the channel from the drain field and result in a better scalability of the device. Recently, CMOS structures based on double gate transistors with gate lengths down to 10 nm have been reported [20,21].

Figure 2.3: Typical structure of a double gate MOS transistor.

A lot of work is also spent in the field of nanotechnology, for example on the carbon nanotube FET [19, 22]. Here, a carbon nanotube forms the channel between the source and the drain contacts. However, one of the drawbacks of devices with structures very different from present MOS transistors is their unfamiliar behaviour which requires to be understood before an integration into an integrated circuit technology is possible. Carrier transport in carbon nanotubes is very dissimilar to the one in a semiconductor like silicon and scaling needs to be addressed.

### 2.2 Process technology

The techniques used to produce semiconductor devices and integrated circuits changed significantly since the early years of semiconductors. This chapter gives a historical outline of the manufacturing methods and describes a modern semiconductor process as it is used for current VLSI (Very Large Scale Integrated) circuits.

#### 2.2.1 Early processes

The first transistors were built using point contact technology and polycrystalline germanium. Shortly afterward it was moved to silicon and single-crystal material which allowed more uniform and reproducible device characteristics.

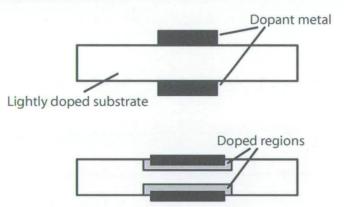

By the mid 1950s the grown junction and alloy junction technology had been developed by Shockley [10] and were widely used to produce transistors. For the grown junction technology, a single crystal was grown which contained a thin zone of material with opposite doping to the main part of the crystal. The crystal was then sawn into pieces so as to create pnp or npn structures, which could be connected using wires. In the alloy junction technology (Figure 2.4) a semiconductor material was taken and a metal was placed on it. The structure was then heated and the metal melted in order to diffuse the metal into the semiconductor. Materials commonly used for this process were germanium as semiconductor and indium as metal. Indium is a p-type dopant and a pn region is therefore created when it diffuses into an n-doped germanium semiconductor.

Figure 2.4: Steps involved in the alloy junction technology.

A next step towards multitransistor integrated circuits was the phase diffusion process developed at Bell Laboratories in 1957. The creation of a npn structure using this method involved the diffusion of a p-type dopant, which is in the gas phase, into a n-type substrate and the repetition of this step with a n-type dopant.

### 2.2.2 Invention of the integrated circuit

In 1959 Kilby built a circuit which integrated transistors, capacitors and resistors on a germanium substrate and therewith invented the integrated circuit [23]. Before his development, capacitors and resistors used in circuits were discrete elements manufactured without the use of semiconductors. Kilby's circuit still employed discrete wires to connect the devices on the substrate.

### 2.2.3 Planar process

In 1960 Hoerni presented the planar process which used patterned silicon dioxide layers to produce geometrically defined n- or p-type regions. Beforehand, people had started working with silicon dioxide and discovered the good interface between it and silicon. Silicon dioxide has also other properties which make it a very suitable material for the proposed process. First of all, it can easily be produced by oxidation of silicon in a furnace. Even more important is its ability of masking underlying material against the diffusion of dopants when creating doped regions.

Besides the use of silicon dioxide layers as masks for diffusion, the planar process developed by Hoerni also offered the capability of creating patterned metal interconnects between the devices on the substrate.

The manufacturing steps necessary to produce a npn bipolar transistor using the process developed by Hoerni is shown in Figure 2.5. A n-type silicon substrate is the starting material which is oxidised and patterned by etching so as to create a mask for the following diffusion using a p-type dopant. After diffusion the oxide is patterned again and a n-type dopant diffused into the silicon which finishes the creation of the required npn structure. The contact to the base of the transistor is made via a ring-shaped electrode, drain and source contacts are in the middle of the ring-electrode and at the back of the structure, respectively.

### 2.2.4 Device scaling

Since the development of the bipolar transistor, MOS transistor and planar process, the semiconductor industry continuously decreased feature sizes in integrated circuits. There are two main reasons why the industry is interested in reduced feature dimensions. First of all, it makes it possible to fit more structures onto a certain area, thus being able to manufacture more structures at the same time which reduces cost. Secondly, the speed of an integrated circuit is strongly influenced by its dimensions and electrical properties for reasons which are described using Equation 5.1 in Chapter 5.

The shrinking of devices, of course, created problems which were most of the time anticipated and solved by manufacturers. The FET is the dominant device in present-day integrated circuits due to its simple construction and good suitability for the planar process. A

Figure 2.5: The planar process as it was developed by Hoerni to produce transistors.

| Dimension                                   | Scaling factor |

|---------------------------------------------|----------------|

| Gate length l                               | 1/α            |

| Gate width w                                | $1/\alpha$     |

| Oxide thickness t <sub>Ox</sub>             | $1/\alpha$     |

| Doping concentration N <sub>A</sub>         | α              |

| Operating voltage V                         | $1/\alpha$     |

| Drive current I                             | 1/α            |

| Oxide capacitance C <sub>Ox</sub>           | $1/\alpha$     |

| Delay time per circuit VC/I                 | $1/\alpha$     |

| Power dissipation per circuit P             | $1/\alpha^2$   |

| Power density P/A                           | 1              |

| Interconnect line resistance R <sub>L</sub> | α              |

| Line response time R <sub>L</sub> C         | 1              |

| Line current density I/A                    | α              |

**Table 2.1:** Dependence of scaling factor  $\alpha$  on the circuit performance and interconnect lines.

good way to decrease the size of the device, while keeping its characteristic behaviour, is to reduce all dimensions and voltages so that the electrical fields in the device are the same as of a larger device. Some of the consequences of device scaling according to the constant-field method are given in Table 2.1 [24]. However, it must be noted that in practice, it is often impossible to comply with all scaling rules. Supply and threshold voltage cannot be choosen arbitrary because of compatibility issues and power dissipation [25]. This results in large electrical fields which increase oxide leakage and lead to bad performance of the transistor unless new materials and processes could be developed to overcome these limitations. The problems associated with small devices described in Section 2.1 further complicate the application of the scaling rules. Table 2.1 has therefore only limited validity for very short devices as they are manufactured presently by the semicoductor industry.

The impact of device scaling on the device speed, namely the gate delay, is one of the major concerns in semiconductor manufacturing. The gate delay of a semiconductor device depends on the gate resistance and the capacitance of the gate stack. Early devices used aluminium as a gate material which possessed a low resistivity and was easy to deposit using PVD (Physical Vapour Deposition). However, aluminium was soon replaced by polysilicon (heavily doped silicon) which withstands the high temperatures that are used in the self-aligned gate process [24] described later. Further device scaling required lower resistivities which were achieved by using metal silicides for gate applications [26] (see Table 2.2). Aluminium and, more recently, copper are used as interconnect material in modern IC processes.

| Material        | Sheet resistance      | Properties                                                 |

|-----------------|-----------------------|------------------------------------------------------------|

| Polysilicon     | $20-30\Omega/\square$ | suitable for self-aligned process<br>low threshold voltage |

|                 |                       | self-passivation                                           |

|                 |                       | high temperature stability                                 |

| Metal silicides | $1\Omega/\Box$        | suitable for self-aligned process                          |

|                 |                       | high temperature stability                                 |

|                 |                       | high electromigration resistance                           |

| Metal           | $0.05\Omega/\Box$     | easy deposition (evaporation or sputtering)                |

|                 |                       | low resistance ohmic contacts to silicon                   |

Table 2.2: Properties of different gate and interconnect materials.

### 2.2.5 Modern VLSI technology

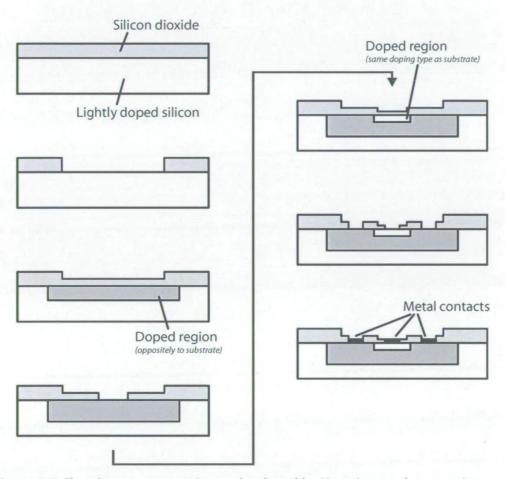

The invention of the integrated circuit and the planar process in the late fifties and early sixties, respectively, led to the processes used to produce modern integrated circuits. Since their development, the main concepts did not significantly change but were merely refined. Modern VLSI circuits have features with dimensions down to 130 nm and possess up to eight layers of interconnects. Figure 2.6 is a simplified illustration of a structure as it can be found in present-day integrated circuits.

**Figure 2.6**: A CMOS structure consisting of a n- and a p-channel transistor fabricated using modern manufacturing methods.

The main differences compared to early MOS processes lie in the gate material, the formation of the source and drain regions and interconnect technology. As mentioned earlier,

the first MOS transistors used metal gates. However, device scaling required short channels which could not be manufactured using the standard process as described by Hoerni. The self-aligned process (Figure 2.7) supplied a solution to the problem by the definition of the drain and source regions by the gate itself [24]. This required a gate which masks the underlying substrate when creating the drain and source regions by dopant implantation and could withstand the high temperatures involved in the following heat treatment. This heat treatment is necessary to activate and diffuse the dopant. It was found that heavily doped polysilicon (polycrystalline silicon) met the requirements for the process. The fabrication begins with growing a field oxide which is then patterned to define the active device region. The gate oxide is then grown and the polysilicon gate created. A dopant diffusion is thereafter performed to create the drain and source regions. As a result of this process, the drain and source are perfectly aligned to the gate. The metallisation is done in the conventional way by depositing a dielectric, etching contact holes, depositing a metal layer and patterning it.

Figure 2.7: Definition of source and drain regions by the self-aligned process.

A further development was the self-aligned silicide (salicide) process to form drain and source contacts together with a low resistance silicide gate as depicted in Figure 2.8. The starting point is a transistor with a polysilicon gate and source/drain regions formed by the self-aligned gate process. To avoid a connection between the gate and the source/drain contacts, it is necessary to create sidewall spacers on the gate. This is usually done by depositing a silicon-dioxide layer and a following anisotropic etch. A metal layer is then deposited onto the wafer and the structure annealed. This results in the formation of metal-silicide in areas where the metal was in contact with silicon but not at locations where it was lying on top of silicon dioxide. The unreacted metal can then be easily removed using a selective wet etch process.

Figure 2.8: Creation of source and drain contacts by the self-aligned silicide process.

Modern integrated circuits are often built of millions of transistors which have to be wired together using local and global interconnects. The layers of interconnects, the vias used to connect them together and the dielectric layers are referred to as back-end technology. While the speed of early circuits mainly depended on transistor speed, the delay of the interconnects is nowadays dominant. Improving the back-end technology is therefore a key-issue in the quest for better integrated circuit performance.

As mentioned earlier, modern VLSI circuits consist of up to eight layers of interconnects. These are nowadays being produced using either the damascene or the double damascene process [9, 27]. Both these techniques use CMP (Chemical Mechanical Polishing) to obtain a flat surface even after many metal layers. The conventional approach used before resulted in non-planar topography and was not suited for many interconnect layers. This is mainly caused by lithography and step coverage limitations. Lithography limitations arise because of the restricted focus depth of exposure tools. The step coverage becomes a problem if deposited layers are not continuous or do not have the thickness required as a consequence of poor deposition on sidewalls resulting from many deposition processes.

Figure 2.9 shows the approach used in early multilayer interconnect structures. First, a contact hole to the lower level is opened in the dielectric. The metal is then deposited and patterned, forming the vias and interconnects. If more layers are required, a dielectric is deposited on top and the procedure repeated. It is obvious that this method works fine for a few interconnect layers but the process becomes more difficult with an increasing number of levels due to the topography created.

Figure 2.9: A CMOS structure consisting of a n- and a p-channel transistor as it was commonly fabricated in the 80s.

Unlike the conventional method, the damascene process employs a planarisation step to get a planar surface even after creation of many interconnect layers. The technique, which is shown in Figure 2.10, starts with the etching of contact holes to the lower level and the deposition of a tungsten blanket. An etchback is then done to remove the tungsten on the dielectric. After the creation of the via, the dielectric is deposited, the trenches for the metal lines are defined and filled with metal. The metal is then planarised after which another dielectric layer can be deposited and the procedure repeated to create more interconnect levels.

The dual-damascene process (Figure 2.11) works in a similar way. However, the via plug is filled in the same step as the metal line thus reducing the number of steps involved.

### 2.2.6 Future technologies

The ITRS 2003 (International Technology Roadmap for Semiconductors 2003) [6] mentions several technology trends and challenges which might occur in VLSI technology in the next 15 years. Many of the technologies required to keep up with Moore's law are already known but solutions to some problems still have to be found. A few of the main future trends are described in the following along with relating material and process requirements.

According to the roadmap the number of interconnect layers will continue to increase, adding extra cost to the manufacturing and decreasing the yield. The high number of interconnect layers and devices will increase the overall interconnect length on the chip and lead to cooling problems. The distance between the top of the chip and the layer with the active devices will grow, thus making an efficient heat transfer more difficult. Furthermore, the increasing device density will concentrate the heat on a small area and make power dissipation an even bigger problem.

There are a number of things which can be done to reduce the power dissipation problem. First of all, the devices can be operated at a lower voltage and consequently the power de-

Figure 2.10: Damascene process.

Figure 2.11: Dual damascene process.

creased. Secondly, it can be tried to reduce the resistance of the interconnects by choosing a material with a lower resistivity.

One of the trends predicted and communicated in the ITRS 2001 is the introduction of advanced gate dielectrics (high- $\kappa$ ) to reduce the RC delay. However, most of the dielectrics reported require the use of metal rather than polysilicon as a gate material [28]. This is because many of the dielectrics investigated are metal-oxides and react with silicon.

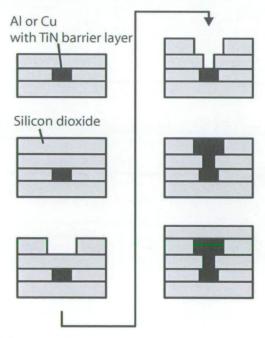

Metals have a further advantage compared to polysilicon due to their widely different work functions. Polysilicon gates can be doped to adjust the threshold voltage of the MOS devices but this requires an activation anneal thus increasing the overall thermal energy. Metals can be chosen according to their work function so that no channel doping is needed [28]. There are two ways to accomplish this which are depicted in Figure 2.12. Firstly, a metal or conductor with a work function leading to a Fermi level in the middle of the silicon bandgap (TiN for example) can be employed (midgap metal gate). This results in the same threshold voltage for both a n-channel and a p-channel device. Also, the number of masks required is reduced because all gates of a CMOS circuit can be created in the same process step. The second method makes use of two different metals (such as aluminium and platinum) for the gates of the n-channel and the p-channel device (double metal gates).

Figure 2.12: Possible positions of materials in the silicon band.

According to the ITRS 2003, metal gates could delay the introduction of high- $\kappa$  dielectrics until the year 2009 while, with polysilicon gates, they are expected to be necessary from 2006. In present CMOS processes, heavily doped polysilicon is used as the gate material. However, it is difficult to create a high dopant concentration at the interface between the gate and the dielectric. This causes the lower part of the gate electrode to be depleted when the MOS transistor is switched on and this means that the actual dielectric thickness is increased. The increase of the equivalent oxide thickness (EOT) due to gate depletion is typically in the range of  $0.4-0.5~\rm nm$  [19], which is a significant amount considering an equivalent physical oxide thickness of 1 nm for the 70 nm technology suggested by the roadmap. The gate

depletion is expected to become a problem for polysilicon gates with a dopant density of  $1 \cdot 10^{20}$  cm<sup>-3</sup> in 2006. Besides the thickness of the depletion region in the polysilicon gate, the EOT also consists of a contribution from quantum effects in the channel. The maximum of the carrier density under the dielectric lies a short distance from the interface in the substrate and enlarges the EOT. An increase of the effective oxide thickness therefore also occurs even when metal gates are used.

A major issue when using metal gates is the low melting point of most metals and their interaction with other materials at low temperatures. The self-aligned gate process described earlier requires high temperature to activate the implanted dopants. A possible solution to the problem is the replacement gate process [29]. Here, a polysilicon dummy gate is used to define the source and the drain regions. The polysilicon is then removed and replaced by a metal gate.

### 2.3 Organometallic materials in semiconductor manufacturing

### 2.3.1 Organometallic processes

Organometallic materials are widely used in the repair of photolithography masks and integrated circuits. The method usually employed is the focused ion-beam induced deposition of metals using an organometallic precursor gas. To produce a metal feature, the gas is injected into a vacuum chamber via a needle which ends close to the sample surface. The ion beam decomposes the gas and leaves behind a metal film. A review of this technique was written by Prewett [30]. Its applications in the semiconductor field range from the creation of cross-sections of integrated circuits to the repair of microchips by removing or depositing material. The deposition of platinum from an organometallic material was reported by Tao et al. in the early nineties [31].

Other research focused on the direct laser-writing of a metal pattern from a metal containing organic compound which was either solid [32, 33, 34, 35] or in the liquid phase [36, 37] by means of photothermal (pyrolitic) decomposition. In some cases, the sample needs to be rinsed in a liquid after exposure in order to remove organic residue.

Finer and more controllable features can be realised by photochemical (photolitic) decomposition. This principle was employed to deposit and pattern metal by irradiation of a solid organometallic material through a photolithographic mask [38, 39, 40, 41] or by laser-writing [42]. Some of the processes reported require the use of solvents in order to remove organic residue from the exposed film. Also, the photochemical decomposition of a gaseous precursor by exposure using a UV lamp and lasers has been employed to produce copper [43].

Another possible process is the deposition of a thin patterned metal layer from an organometallic material which is then used as a catalyst for the following electroless plating of a conductor [44].

| Metal | Precursor                                 | Exposure<br>method                                                             | Feature<br>size<br>[µm]      | Film<br>thickness<br>[nm]    | Resistivity $[10^{-8}\Omega m]$          | Ref.                                 |

|-------|-------------------------------------------|--------------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------------------|--------------------------------------|

| Al    | liquid                                    | laser writing                                                                  | 3                            | 1000                         | 5.6                                      | [36]                                 |

| Cu    | solid                                     | laser writing                                                                  | _                            | _                            | <10                                      | [35]                                 |

| Pd    | liquid<br>solid                           | laser writing<br>laser writing                                                 | 10<br>1.8                    | _                            | -<br>40-240                              | [37]<br>[34]                         |

| Pt    | gas<br>solid                              | ion-beam writing laser writing                                                 | 0.3                          | -<br><100                    | 70<br>< 200                              | [31]<br>[33]                         |

| Au    | solid<br>solid<br>solid<br>solid<br>solid | UV light and mask UV light and mask e-beam writing laser writing laser writing | 1.2<br><1<br>0.5<br>-<br>3.5 | -<br>15<br>100<br>1500<br>40 | 40<br>-<br>2.3 <sup>a</sup><br>12<br>4.5 | [41]<br>[38]<br>[39]<br>[45]<br>[42] |

ameasured on conducting substrate

Table 2.3: Properties of some of the organometallic processes reported in the literature.

| Metal | Resistivity at 293 K [46] $[10^{-8} \Omega m]$ |

|-------|------------------------------------------------|

| Al    | 2.6548                                         |

| Cu    | 1.6730                                         |

| Pd    | 10.8                                           |

| Pt    | 10.6                                           |

| Au    | 2.35                                           |

Table 2.4: Resistivities of some metals.

While organometallic materials have a broad use in the repair of small numbers of circuits and masks, they do not yet have an application in modern IC manufacturing.

### 2.3.2 Properties of metal features deposited from an organometallic

The feature sizes and resistivities achieved by different authors differ widely and are summarised in Table 2.3. For comparison, known bulk resistivity values for some metals are listed in Table 2.4. The resistivity of most films reported lies well above the bulk resistivity, the cause of which can be attributed to inhomogeneity and thin film effects as described in Chapter 5. The exceptionally low resistivity of  $2.3 \cdot 10^{-8} \ \Omega m$  (bulk resistivity of gold:  $2.35 \cdot 10^{-8} \ \Omega m$ ) measured for gold films created by e-beam exposure of a solid organometallic material is questionable due to the film being deposited on a conducting surface and should therefore not be included when comparing films.

## 2.4 Platinum in semiconductor processes

## 2.4.1 Applications of platinum in semiconductor manufacturing

Platinum has many applications in semiconductor processes, especially as barrier layers [47] or as a component in the formation of silicides [26]. Barrier layers are used in integrated circuits so as to avoid the diffusion of one material into another. Aluminium for example forms a compound with a silicon content of approximately 0.5% when in contact with silicon and heated to 450 °C [48]. This is a major problem and causes spikes to be formed at aluminium/silicon junctions which can result in the failure of a device. Platinum, in the form of a silicide (e.g. PtSi), effectively prevents the interdiffusion of aluminium and silicon. In modern semiconductor processes, TiN is the most popular barrier layer.

## 2.4.2 Influence of platinum on semiconductor structures

One of the issues of interest for this work is the impact of platinum on underlying layers in a MOS stack. The influence of platinum on the silicon/silicon dioxide interface was studied early [49] and a shift of the C-V curve (see Chapter 6) of a MOS structure was observed after diffusion of platinum in nitrogen at a temperature of 900 °C. An investigation into the degradation of the silicon dioxide layer of a platinum/silicon dioxide/silicon structure due to annealing in nitrogen at temperatures between 400 °C and 850 °C was reported in the nineties [50]. It was found that, when annealing at temperatures above 600 °C, the breakdown voltage decreases significantly. Also, the interface state density at the silicon/silicon dioxide layer was thought to increase because of thermally induced stress. Based on their findings, the authors excluded the possibility of platinum being used as a gate material for MOS devices. The reaction of platinum with silicon dioxide substrates in a hydrogen environment was described by Lamber et al. [51].

When platinum is in contact with silicon and heated to a temperature of about 350  $^{\circ}$ C, it forms platinum silicide PtSi in a two stage process via the intermediate Pt<sub>2</sub>Si. It was shown that reactions between the two materials already take place at temperatures as low as  $170 ^{\circ}$ C [52].

## Organometallic compound and process

## Contents

- 3.1 Organometallic compound 22 23 3.1.1 Bonding mechanism 3.1.2 Photochemical reaction

- 26

- 3.2 **Process**

- 3.2.1 Deposition 27

- 3.2.2 Exposure 28

- 3.2.3 Heat treatment 28

- 3.3 Discussion 32

THE organometallic process used in this research is based on two photosensitive organometallic materials which can be exposed using UV, e-beam or ion-beam lithography in order to photolitically form the required metal pattern. This chapter describes the chemical structure and photochemical reaction associated with the organometallic compounds as well as the process used to create patterned metal layers on a substrate.

The organometallic material and the associated process used in this work were developed at the University of Dundee [53]. An analysis of the material and study of the chemistry of the compound and the platinum films produced are reported elsewhere [54].

#### 3.1 Organometallic compound

It is important to point out at the beginning of this section that the bonding mechanism and the photochemical reaction described in the following are possible explanations only and research into the exact mechanisms behind the organometallic process is still under way.

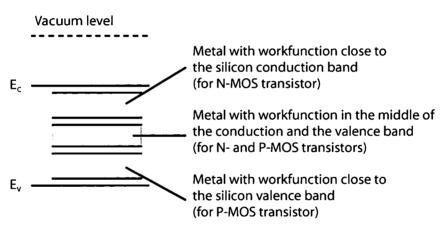

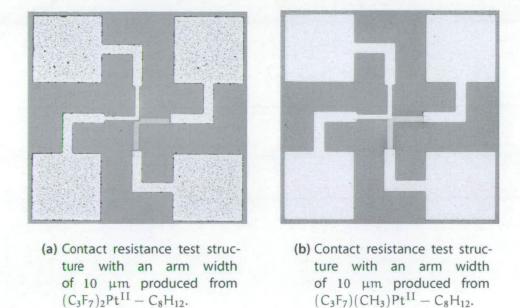

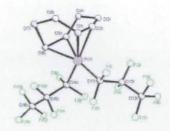

An organometallic is a compound containing at least one metal-carbon bond. The fluoro platinum complexes  $(C_3F_7)_2Pt^{11}-C_8H_{12}$  (cis bis-(normal-perfluoropropyl) platinum(II) 1,5-cyclooctadiene) [53] and  $(C_3F_7)(CH_3)Pt^{II} - C_8H_{12}$  (cis methyl iso-perfluoropropyl platinum(II) 1,5-cyclooctadiene) used for this work are such compounds and the chemical structure of the former is shown in Figure 3.1.

It can be seen that the molecule of  $(C_3F_7)_2Pt^{II} - C_8H_{12}$  consists of a platinum atom to which two C<sub>3</sub>F<sub>7</sub> groups are attached on one side and a C<sub>8</sub>H<sub>12</sub> group (cycloocta-1,5-diene or COD) on the other. The second organometallic has one of the C<sub>3</sub>F<sub>7</sub> groups replaced by a CH<sub>3</sub> group.

Figure 3.1: Structure of the organometallic material.

It should be noted that, although this research utilises a platinum organometallic, similar compounds based on other metals such as silver, gold, molybdenum, hafnium, tantalum and tungsten can be produced.

## 3.1.1 Bonding mechanism

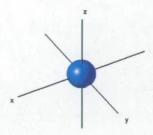

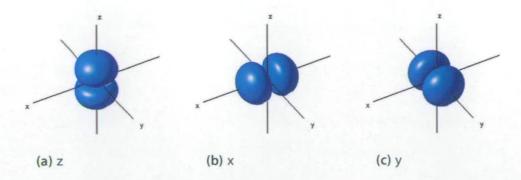

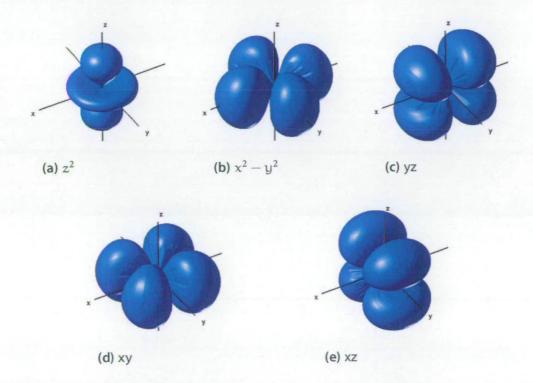

The possible bonding mechanisms related to the organometallic material  $(C_3F_7)_2Pt^{II}-C_8H_{12}$  can best be explained using electron orbitals which are probability densities for electrons around a nuclei. Orbitals for the 1s, 2p and 3d shell calculated from eigenfunctions for one-electron atoms [55] are shown in Figure 3.2, Figure 3.3 and Figure 3.4, respectively.

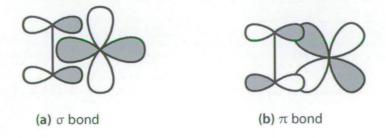

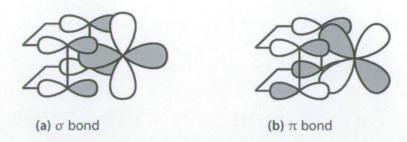

The bond between the platinum atom and the cycloocta-1,5-diene is made via backbonding [56] as depicted in Figure 3.5. The cycloocta-1,5-diene acts as a  $\sigma$  donor/ $\pi$  acceptor ligand and is also called  $\eta^4$ -cycloocta-1,5-diene due to it having an hapticity of 4 (it has 4 electrons which can be bonded directly to the metal). The  $\sigma$  bond is created by electrons from the COD which fill the bonding orbital. Backbonding occurs if electrons from the metal fill the empty antibonding  $\pi$ -orbitals of the C-C bond, thus weakening it (its length can then similar to a single bond) and creating two metal-carbon bonds which can be represented by  $\sigma$  bonds.

Pt<sup>II</sup>, as it occurs in the compound, possesses a  $(d)^8$  metal centre and therefore forms a square-planar coordination complex. In a free atom, the five d orbitals, which are shown in Figure 3.4, have the same energy. If a ligand is present, ligand field splitting occurs and the  $d_{x^2-y^2}$  orbital situated in the xy plane pointing directly at the ligand  $(e_g$  set) has a higher

Figure 3.2: Hydrogen atom 1s orbital.

energy than the remaining four d orbitals ( $t_{2g}$  set). It is energetically advantageous for the electrons of the COD to occupy the  $\sigma$  bonding molecular orbitals. At the same time, the  $e_g$  set of the metal is formed by the antibonding levels of the COD. The empty antibonding orbitals of the COD also lower the  $t_{2g}$  set which is subsequently filled with electrons from the metal.

The bonding of the two  $C_3F_7$  groups to the Pt<sup>0</sup> can be explained as follows.  $C_3F_7$  needs a single electron to complete an octet and can therefore accept an electron. Pt<sup>0</sup>, which has an electron configuration of  $[Xe](4f)^{14}(5d)^9(6s)^1$ , has ten valence electrons and can donate electrons. We thus have electron pair bonds between Pt<sup>0</sup> and the  $C_3F_7$  groups. The bond is a single bond which means that it is a  $\sigma$  bond. Owing to the removal of two electrons from the platinum, it is in the oxidation state Pt<sup>II</sup> which has an electron configuration of  $[Xe](4f)^{14}(5d)^8$ . The  $C_3F_7$  groups have a high electron affinity and thus weaken the Pt -  $C_8H_{12}$  bond. It is possible to replace the  $C_3F_7$  by some other group in order to adjust the bond strength, which has been done in the case of the  $(C_3F_7)(CH_3)Pt^{II}-C_8H_{12}$  compound.

The resulting molecule is a coordination complex, a geometrical isomer called cis, and is likely to be stable due to it complying with the 16-electron rule for square-planar molecules [56]. There are four electrons from the  $C_8H_{12}$  ligand, ten electrons from the  $Pt^0$  and one electron from each of the  $C_3F_7$  groups.

The bonding effects related to the  $(C_3F_7)(CH_3)Pt^{\rm II}-C_8H_{12}$  compound are the same as described above, with the exception of the  $CH_3$  group which replaces one of the  $C_3F_7$

Figure 3.3: Hydrogen atom 2p orbitals.

Figure 3.4: Hydrogen atom 3d orbitals.

Figure 3.5: The two different types of backbonding mechanisms.

groups. CH<sub>3</sub> also requires a single electron to complete an octet and is therefore bonded to the electron-donating platinum. Thus, there will again be 16 electrons around the platinum atom which predicts that the molecule is stable.

#### 3.1.2 Photochemical reaction

It is thought that the bonds between the COD and the Pt of  $(C_3F_7)_2$ Pt<sup>II</sup>  $- C_8H_{12}$  can photochemically be broken by a pericyclic reaction according to a set of rules which are called the Woodward-Hoffmann rules [57]. A pericyclic reaction is a reaction whereby a reorganisation of the bonds of a structure takes place at the same time and without going through intermediate compounds.

The Woodward-Hoffmann rule for a thermal pericyclic reaction [58].