## Can deep-sub-micron device noise be used as the basis for probabilistic neural computation?

Nor Hisham Hamid

A thesis submitted for the degree of Doctor of Philosophy. **The University of Edinburgh**. March 2006

## Abstract

This thesis explores the potential of probabilistic neural architectures for computation with future nanoscale Metal-Oxide-Semiconductor Field Effect Transistors (MOSFETs). In particular, the performance of a Continuous Restricted Boltzmann Machine (CRBM) implemented with generated noise of Random Telegraph Signal (RTS) and 1/f form has been studied with reference to the 'typical' Gaussian implementation. In this study, a time domain RTS based noise analysis capability has been developed based upon future nanoscale MOSFETs, to represent the effect of nanoscale MOSFET noise on circuit implementation in particular the synaptic analogue multiplier which is subsequently used to implement stochastic behaviour of the CRBM. The result of this thesis indicates little degradation in performance from that of the typical Gaussian CRBM. Through simulation experiments, the CRBM with nanoscale MOSFET noise shows the ability to reconstruct training data, although it takes longer to converge to equilibrium. The results in this thesis do not prove that nanoscale MOSFET noise can be exploited in all contexts and with all data, for probabilistic computation. However, the result indicates, for the first time, that nanoscale MOSFET noise has the potential to be used for probabilistic neural computation hardware implementation. This thesis thus introduces a methodology for a form of technology-downstreaming and highlights the potential of probabilistic architecture for computation with future nanoscale MOSFETs.

## Declaration of originality

I declare that this thesis has been completed by myself and that, except where indicated to the contrary, the research documented in this thesis is entirely my own.

Nor Hisham Hamid

## Acknowledgements

First of all, I would like to thank God, the Almighty, for having made everything possible by giving me the strength and courage to pursue this PhD.

I would like to thank my supervisors Prof. Alan F. Murray and Dr. Martin Reekie for their advise, guidance, and encouragement, throughout the course of this PhD. I am particularly indebted to Prof. Alan Murray, whose expertise, understanding, dedication and patience has greatly contributed toward the completion of this thesis.

I would also like to thank my family for their inspiration, love, moral and financial support, and prayers over these past four years. In particular, I am forever indebted to my wife Mazni, without her love, encouragement, patience, and understanding, I would never have completed this thesis.

I greatly appreciate Dr. David Laurenson and Prof. Steve McLaughlin (IDCOM) of University of Edinburgh, and Prof. Asen Asenov, Dr. Scott Roy, Dr. Jeremy Watling, and all members of Device Modelling Group of University of Glasgow, for their technical support and expertise toward the understanding and implementation of noisy nanoscale MOSFET model.

A very special thank to Dr. Thomas Koickal, Tong Boon, Mark, and Katherine who carefully proof read my papers and thesis, and politely pointed out mistakes. I also would like to thank all SEE computing staff in particular David Stewart for their dedication in ensuring a first class IT support. Finally, I would like to thank all whose direct and indirect support helped me completing this thesis.

I acknowledge the Universiti Teknologi Petronas for providing scholarships to pursue this PhD work.

I dedicate this thesis to my wife, my son Haziq, my daughters Aqeela and Faqeeha.

iv

## Contents

|   |     | Declaration of originality                          | iv  |

|---|-----|-----------------------------------------------------|-----|

|   |     | List of figures                                     |     |

|   |     | 0                                                   | xii |

|   |     |                                                     |     |

| 1 |     | roduction                                           | 1   |

|   | 1.1 | Motivation                                          | 1   |

|   | 1.2 | Contribution to knowledge                           | 3   |

|   | 1.3 | Chapter layout                                      | 4   |

| 2 | Low | v Frequency Noise in Nanoscale MOSFETs              | 7   |

|   | 2.1 | Introduction                                        | 7   |

|   | 2.2 | Random Telegraph Signal (RTS) Noise                 | 8   |

|   |     | 2.2.1 Origin of traps                               | 8   |

|   |     | 2.2.2 RTS noise amplitude                           | 10  |

|   |     | 2.2.3 RTS average capture and average emission time | 11  |

|   |     | 2.2.4 Discussion                                    | 12  |

|   | 2.3 | Flicker $(1/f)$ Noise                               | 14  |

|   |     | 2.3.1 $1/f$ noise model                             | 14  |

|   |     | 2.3.2 Discussion                                    | 15  |

|   | 2.4 | Summary                                             | 16  |

| 3 | Mod | delling 'Noisy' MOSFETs                             | 17  |

| - | 3.1 |                                                     | 17  |

|   | 3.2 |                                                     | 18  |

|   | 3.3 |                                                     | 20  |

|   |     | ÷                                                   | 20  |

|   |     |                                                     | 21  |

|   | 3.4 |                                                     | 23  |

|   |     |                                                     | 24  |

|   |     | •                                                   | 25  |

|   |     |                                                     | 27  |

|   |     |                                                     | 29  |

|   |     |                                                     | 31  |

|   | 3.5 |                                                     | 35  |

|   | 3.6 |                                                     | 40  |

|   | 3.7 |                                                     | 45  |

| 4 | Noi                  | sy Circuit Implementation                       | 46       |  |  |  |

|---|----------------------|-------------------------------------------------|----------|--|--|--|

|   | 4.1                  | Noisy 2-Quadrant Multiplier                     | 46       |  |  |  |

|   |                      | 4.1.1 Circuit Description                       | 46       |  |  |  |

|   |                      | 4.1.2 Circuit Implementation                    | 48       |  |  |  |

|   |                      | 4.1.3 Simulation Results and Discussion         | 48       |  |  |  |

|   | 4.2                  | Noisy 4-Quadrant Multiplier                     | 49       |  |  |  |

|   |                      | 4.2.1 Circuit Description                       | 51       |  |  |  |

|   |                      | 4.2.2 Circuit Implementation                    | 53       |  |  |  |

|   |                      | 4.2.3 Simulation Results and Discussion         | 53       |  |  |  |

|   | 4.3                  | Summary                                         | 56       |  |  |  |

| 5 | Pro                  | babilistic Neural Computation                   | 60       |  |  |  |

| 5 | 5.1                  | •                                               | 60       |  |  |  |

|   | 5.2                  | Introduction                                    |          |  |  |  |

|   | 5.2                  | Continuous Restricted Boltzmann Machine (CRBM)  | 61       |  |  |  |

|   |                      |                                                 | 61       |  |  |  |

|   |                      | 5.2.2 A continuous stochastic neuron            | 62       |  |  |  |

|   |                      | 5.2.3 CRBM training                             | 63       |  |  |  |

|   |                      | 5.2.4 CRBM in VLSI                              | 65       |  |  |  |

|   | 5.3                  | Summary                                         | 66       |  |  |  |

| 6 | Noise in the CRBM 67 |                                                 |          |  |  |  |

|   | 6.1                  | Introduction                                    | 67       |  |  |  |

|   | 6.2                  | Zero-mean Gaussian noise in CRBM                | 68       |  |  |  |

|   | 6.3                  | Non-zero mean Gaussian noise in CRBM            | 69       |  |  |  |

|   | 6.4                  | Non-Gaussian 'Pseudo-RTS' noise in the CRBM     | 74       |  |  |  |

|   | 6.5                  | CRBM with noise in Multiplier                   | 76       |  |  |  |

|   | 6.6                  | Summary                                         | 78       |  |  |  |

| 7 | CRI                  | 3M with Nanoscale MOSFET Noise                  | 81       |  |  |  |

|   | 7.1                  | Methodology                                     | 81       |  |  |  |

|   |                      | 7.1.1 Noise data in look-up table               | 82       |  |  |  |

|   |                      | 7.1.2 Data look-up                              | 84       |  |  |  |

|   | 7.2                  | Modelling data with non-symmetric distribution  | 85       |  |  |  |

|   |                      | 7.2.1 4-traps                                   | 86       |  |  |  |

|   |                      | 7.2.2 10-trap and 100-trap RTS in a CRBM        | 87       |  |  |  |

|   | 7.3                  | Summary                                         | 90       |  |  |  |

| 8 | Sum                  | mary and Conclusion                             | 92       |  |  |  |

| Č | 8.1                  |                                                 | 92<br>92 |  |  |  |

|   | 8.2                  | Conclusion                                      |          |  |  |  |

|   | 8.2<br>8.3           | Future work                                     | 93       |  |  |  |

|   | 0.5                  |                                                 | 95       |  |  |  |

| A |                      | SFET Channel Voltage Approximation              | 96       |  |  |  |

|   | A.1                  | Approximating the Quasi-Fermi Potential, $V(y)$ | 96       |  |  |  |

|    | A.2        | Approximating Surface Potential, $\psi_S$ | 98  |

|----|------------|-------------------------------------------|-----|

| B  | Publ       | lication list                             | 100 |

| Re | References |                                           | 101 |

# List of figures

.

•

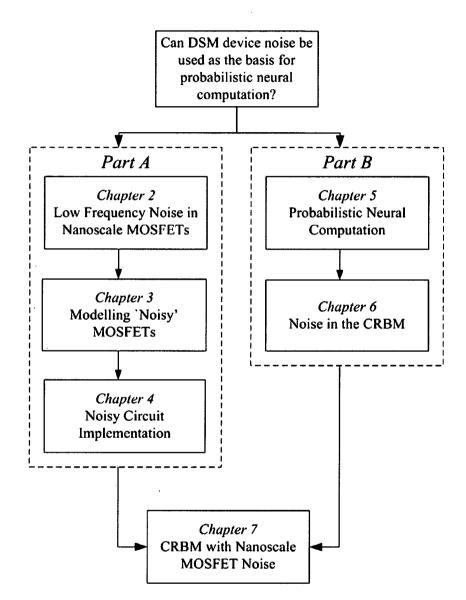

| 1.1                               | The flowchart illustrating the chapter flow in this thesis                                                                                                                                                                                                                                                                                                                      | 6        |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

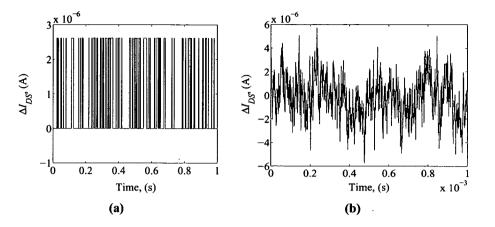

| 2.1                               | Sample of (a) single trap RTS and (b) flicker noise.                                                                                                                                                                                                                                                                                                                            | 8        |

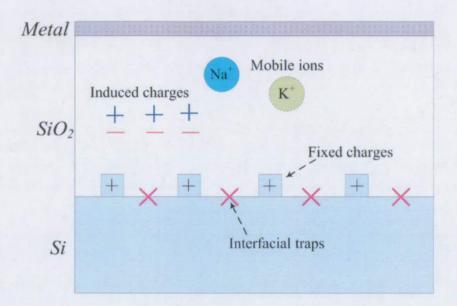

| 2.2                               | An illustration of the traps and charges in $Si - SiO_2$ structures. (Adapted from [1]).                                                                                                                                                                                                                                                                                        | 9        |

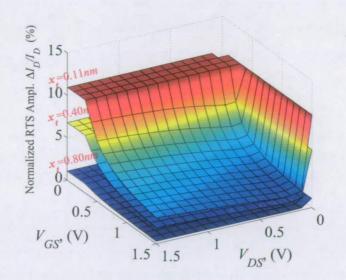

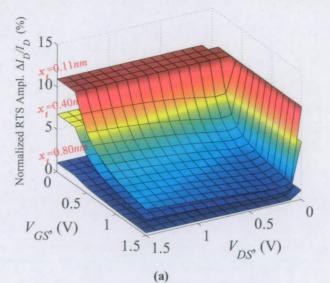

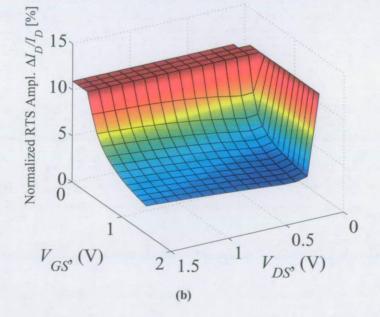

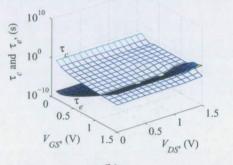

| <ul><li>2.3</li><li>2.4</li></ul> | RTS noise amplitude variation with gate $V_{GS}$ and drain $V_{DS}$ voltages for three<br>different trap depths ( $x_t = 0.11, 0.40, 0.80 \ nm$ ) located in the middle of gate<br>( $y_t = 16nm$ ) for an implementation based on $35nm$ NMOS modelled in [2].<br>Average capture $\bar{\tau}_c$ and average emission $\bar{\tau}_e$ vs gate $V_{GS}$ and drain $V_{DS}$ volt- | 11       |

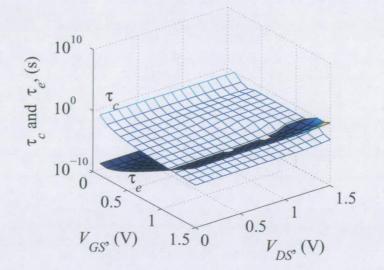

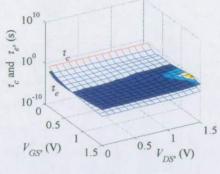

|                                   | ages for trap located at $x_t = 0.11nm$ and $y_t = 16nm$ for an implementation<br>based on $35nm$ NMOS modelled in [2].                                                                                                                                                                                                                                                         | 13       |

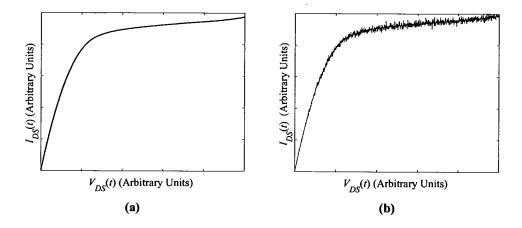

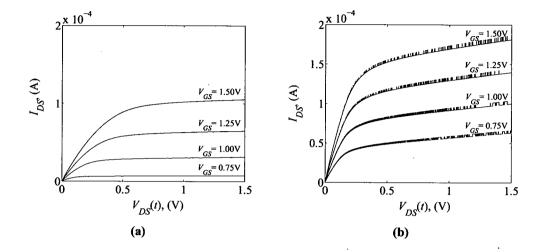

| 3.1                               | (a) Standard n-channel MOS drain-source current $I_{DS}$ for a given $V_{GS}$ voltage. (b) noisy n-channel MOS drain current for a given $V_{GS}$ voltage.                                                                                                                                                                                                                      | 18       |

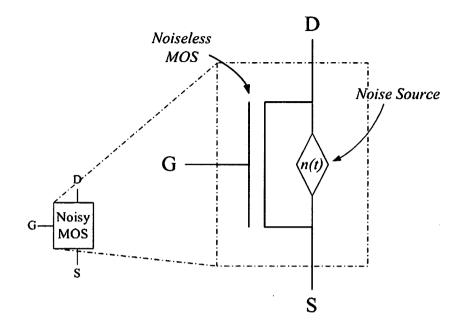

| 3.2                               | Noisy MOSFET components. The noiseless MOSFET is a standard MOS-<br>FET having a typical I-V characteristic corresponding to the technology used.                                                                                                                                                                                                                               | 10       |

|                                   | The noise source $n(t)$ generates noise data with the specific physical charac-<br>taristics of the low frequency poise it models                                                                                                                                                                                                                                               | 10       |

| 3.3                               | teristics of the low frequency noise it models                                                                                                                                                                                                                                                                                                                                  | 19<br>22 |

| 3.4                               | (a) Single trap RTS noise Power Spectral Density, $S(f)$ generated using                                                                                                                                                                                                                                                                                                        | ZZ       |

| 5.1                               | Eq.(2.5). (b) Time domain RTS noise generated from Power Spectral Density                                                                                                                                                                                                                                                                                                       |          |

|                                   | S(f) using Sum-of-Sinusoids techniques.                                                                                                                                                                                                                                                                                                                                         | 29       |

| 3.5                               | (a) Single trap RTS noise. (b) multi(3)-trap RTS noise.                                                                                                                                                                                                                                                                                                                         | 32       |

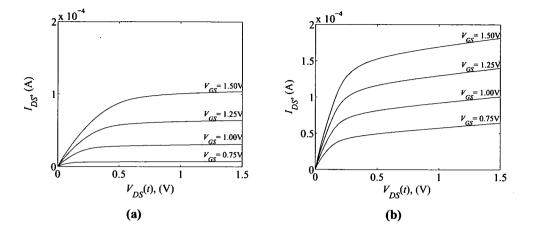

| 3.6                               | I-V characteristic for (a) $0.35\mu m$ (L= $0.35\mu m$ , W= $1\mu m$ ), and (b) $35\ nm$                                                                                                                                                                                                                                                                                        | 0-       |

|                                   | $(L=35nm, W=0.1\mu m)$ 'noiseless' MOSFET.                                                                                                                                                                                                                                                                                                                                      | 35       |

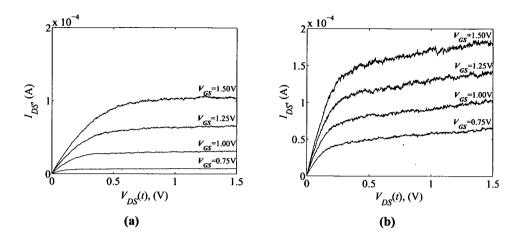

| 3.7                               | I-V characteristic for $1/f$ based noisy (a) $0.35\mu m$ (L= $0.35\mu m$ , W= $1\mu m$ ), and                                                                                                                                                                                                                                                                                   |          |

|                                   | (b) $35 nm$ (L= $35nm$ , W= $0.1\mu m$ ) NMOS.                                                                                                                                                                                                                                                                                                                                  | 36       |

| 3.8                               | I-V characteristics for RTS based noisy (a) $0.35 \mu m$ (with L= $0.35 \mu m$ , W= $1 \mu m$ ,                                                                                                                                                                                                                                                                                 |          |

|                                   | trap depth $x_t = 1.1nm$ and lateral location $y_t = 160nm$ ) and (b) 35 nm                                                                                                                                                                                                                                                                                                     |          |

|                                   | (L=35nm, W=0.1 $\mu$ m, trap depth $x_t = 0.11nm$ and lateral location $y_t =$                                                                                                                                                                                                                                                                                                  |          |

|                                   | 16nm) MOSFETs. The values $\sigma_0$ , $\Delta E_B$ , $\Delta E_{CT}$ and trap $V_{GS}$ were selected                                                                                                                                                                                                                                                                           |          |

| •                                 | from Table 3.1 corresponding to trap depth $x_t$ 1.1 $nm$                                                                                                                                                                                                                                                                                                                       | 37       |

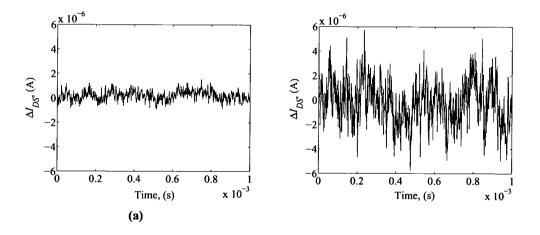

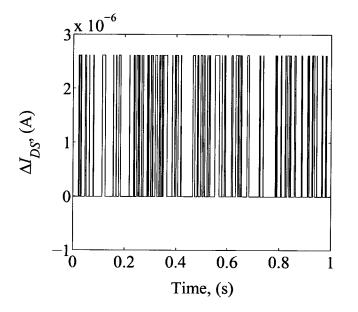

| 3.9                               | Time domain noise generated by (a) $0.35\mu m$ and (b) $35 nm$ noisy MOSFET                                                                                                                                                                                                                                                                                                     |          |

|                                   | simulated at static bias conditions ( $V_{DS} = 1.5V$ and $V_{GS} = 1V$ ) for $1ms$ .                                                                                                                                                                                                                                                                                           | 37       |

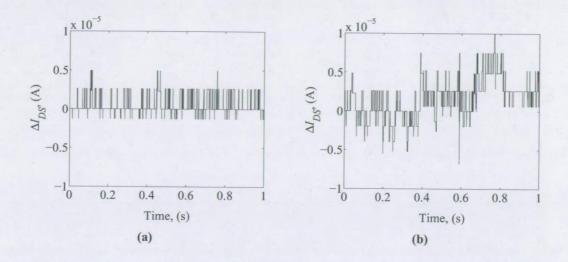

| 3.10 | The Drain-Source current noise ( $\Delta I_{DS}$ ) for a 35nm (L=35nm, W=0.1 $\mu$ m)                                                                   |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | single trap RTS, based noisy MOSFET biased at $V_{GS} = 1.0V$ and $V_{DS} =$                                                                            |    |

|      | 0.6V. The drain current with DC value ( $I_{DS} = 84\mu A$ ) removed. (Note that a                                                                      |    |

|      | longer simulation time (1 second) was needed in order to capture more RTS                                                                               |    |

| •    | noise). Based on the fixed bias conditions, $\Delta I_{DS}$ , $\bar{\tau}_c$ and $\bar{\tau}_e$ in the RTS based                                        |    |

|      | noisy MOSFET were generated to be 2.62e-6 A, 2.918e-3 s, and 1.279e-2 s,                                                                                |    |

|      | respectively.                                                                                                                                           | 38 |

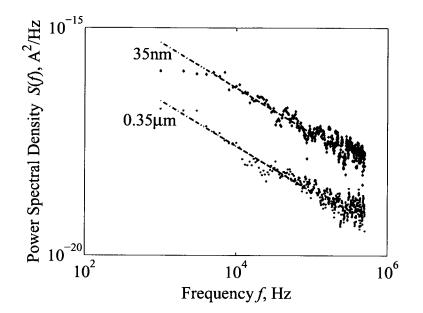

| 3.11 | The Power Spectral Density (PSD), $S(f)$ corresponding to the time domain<br>noises shown in Fig.3.9. The dash-dot lines are $1/f$ PSDs generated using |    |

|      | Eq.(2.7).                                                                                                                                               | 39 |

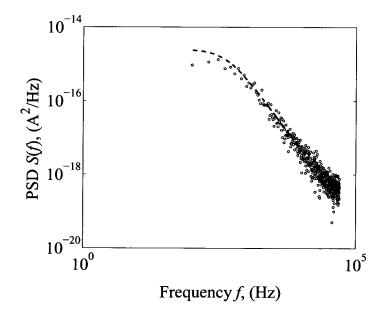

| 3.12 | The Power Spectral Density (PSD), $S(f)$ of a single trap RTS plotted in                                                                                |    |

|      | Fig.3.10. The dashed-line is the calculated PSD based on Eq.(2.5)                                                                                       | 39 |

| 3.13 | (a) Normalised $(\Delta I_D/I_D)$ RTS amplitude for three different trap depths $x_t$ =                                                                 |    |

|      | 0.11nm, 0.4nm, 0.8nm with trap lateral position (measured from source)                                                                                  |    |

|      | fixed at $y_t = 16nm$ . (b) Normalised $(\Delta I_D/I_D)$ RTS amplitude for three differ-                                                               |    |

|      | ent trap lateral positions (measured from source) $y_t = 5nm$ , $16nm$ , $30nm$ with                                                                    |    |

|      | trap depth fixed at $x_t = 0.11nm$ . The simulation was based upon parameters                                                                           |    |

|      | corresponding to $x_t = 1.1nm$ in Table 3.1.                                                                                                            | 41 |

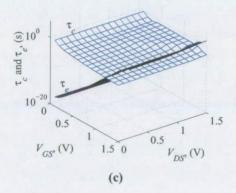

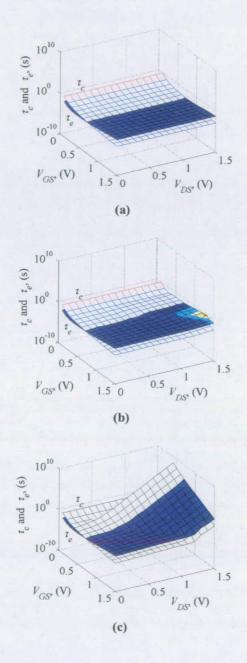

| 3.14 | Mean capture and emission times for three different trap depths with fixed                                                                              |    |

|      | $y_t = 16nm$ (a) $x_t = 0.11nm$ , (b) $x_t = 0.4nm$ , (c) $x_t = 0.8nm$ .                                                                               | 42 |

| 3.15 | Mean capture and emission times for three different trap lateral locations with                                                                         |    |

|      | fixed $x_t = 0.11nm$ (a) $y_t = 5nm$ , (b) $y_t = 16nm$ , (c) $y_t = 30nm$ .                                                                            | 43 |

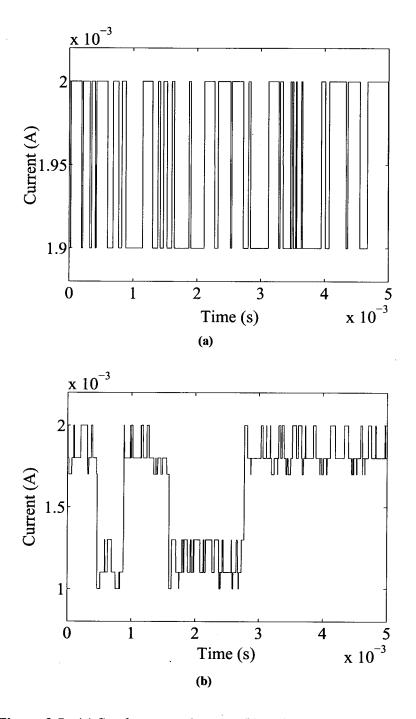

| 3.16 | RTS noise generated by noisy MOSFET implemented with (a) 3 Traps and (b)                                                                                |    |

|      | 10 Traps. Trap parameters were based on the value in Table 3.1 corresponding                                                                            |    |

|      | to $x_t = 1.1nm$ . $V_{DS}$ and $V_{GS}$ were set to 0.6V and 1V respectively.                                                                          | 44 |

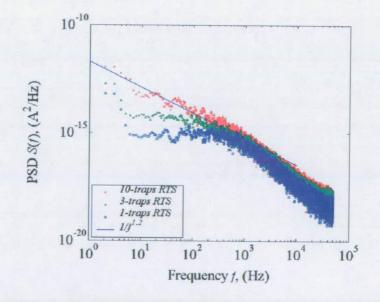

| 3.17 | Power Spectral Density of 1-trap, 3-trap, and 10-trap RTS noise. Dashed-line                                                                            |    |

|      | indicates the $1/f$ noise PSD.                                                                                                                          | 44 |

|      |                                                                                                                                                         |    |

| 4.1  | 2-quadrant Chible multiplier                                                                                                                            | 47 |

| 4.2  | 35nm CMOS technology 2-quadrant multiplier output current $I_{out}$                                                                                     | 49 |

| 4.3  | 35nm CMOS technology 2-quadrant multiplier output current with $M_{n1}$ , $M_{n4}$ ,                                                                    |    |

|      | and $M_{n5}$ replaced with (a) $1/f$ and (b) single trap RTS based noisy n-MOSFETs.                                                                     | 50 |

| 4.4  | (a) $1/f$ and (b) single trap RTS based noisy MOSFET transient plot with                                                                                |    |

|      | $V_{DD}$ , $V_w$ , $V_{in}$ , $V_{ref}$ were set to 1.5V, 1V, 0.6V, and 0.75V, respectively. Note                                                       |    |

|      | that longer simulation time was necessary for RTS noise in order to capture                                                                             |    |

|      | more noise data                                                                                                                                         | 50 |

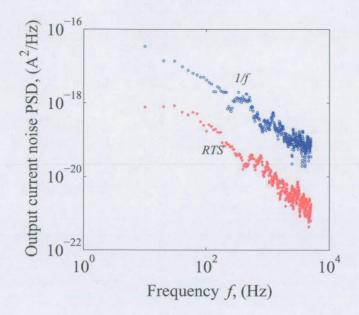

| 4.5  | Power spectral density generated from time domain noise data in Fig.4.4.                                                                                | 51 |

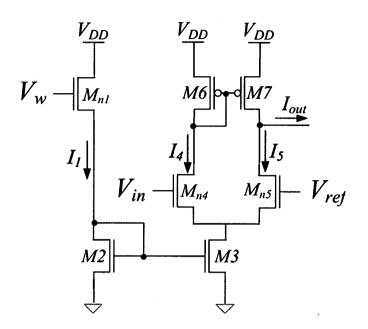

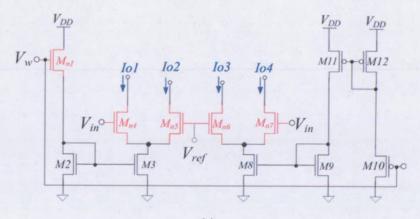

| 4.6  | The modified Chible 4-quadrant multiplier adopted from [3]. (a) one- com-                                                                               |    |

|      | puting cell of the modified Chible multiplier (b) the full 4-quadrant multiplier                                                                        |    |

|      | circuit composed of two computing cells.                                                                                                                | 52 |

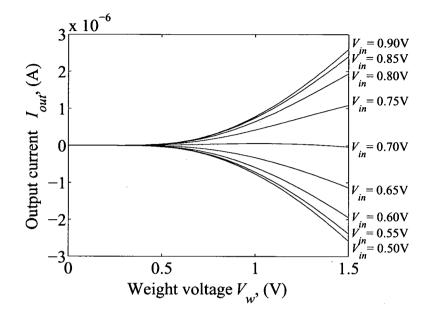

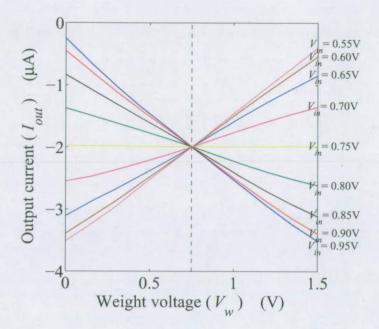

| 4.7  | 35nm CMOS technology 4-quadrant multiplier output current Iout.                                                                                         | 54 |

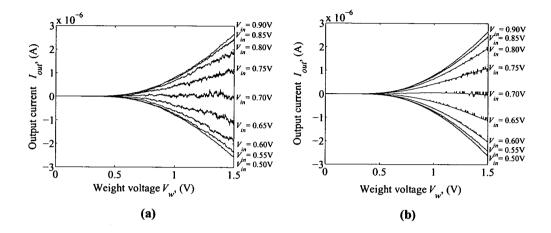

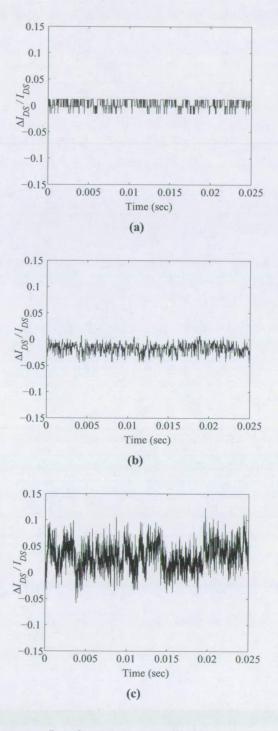

| 4.8  | The output current $I_{out}$ for (a) 4-trap, (b) 10-trap, and (c) 100-trap 4-quadrant                                                                   |    |

|      | noisy multiplier simulated for $250ms$ with $1\mu s$ time step                                                                                          | 55 |

|      |                                                                                                                                                         |    |

.

.

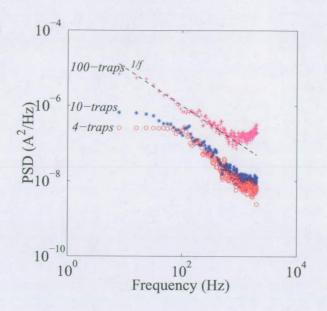

| <ul><li>4.9</li><li>4.10</li></ul> | The power spectral densities (PSDs) of the time domain noise data shown in Fig.4.8, generated using periodogram function in Matlab                                                                           | 56             |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

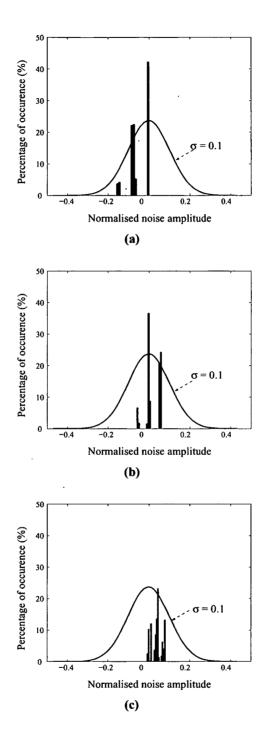

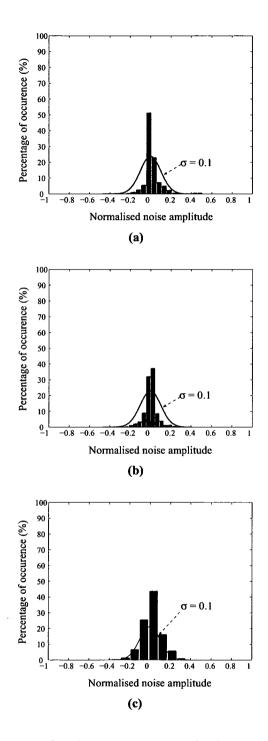

| 4.11                               | $0.3V \& V_{in} = 0.65V$ (b) $V_w = 0.6V \& V_{in} = 0.7$ (c) $V_w = 1.05V \& V_{in} = 0.8V$ .                                                                                                               | 57             |

|                                    | plemented with (a) 4-trap (b) 10-trap (c) 100-trap.                                                                                                                                                          | 58             |

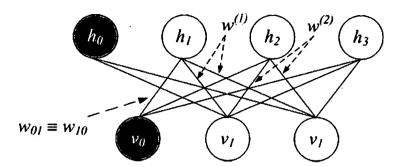

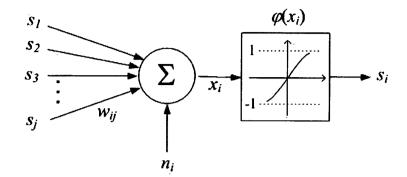

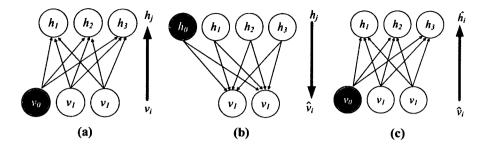

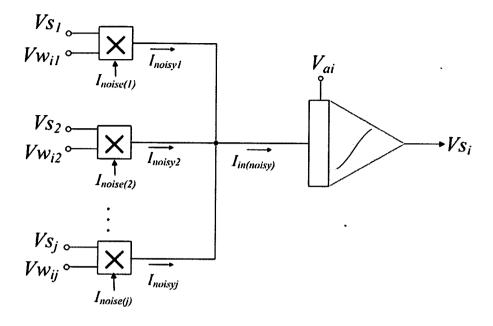

| 5.1<br>5.2<br>5.3                  | CRBM network with 3 visible neurons and 4 hidden neurons                                                                                                                                                     | 62<br>63<br>64 |

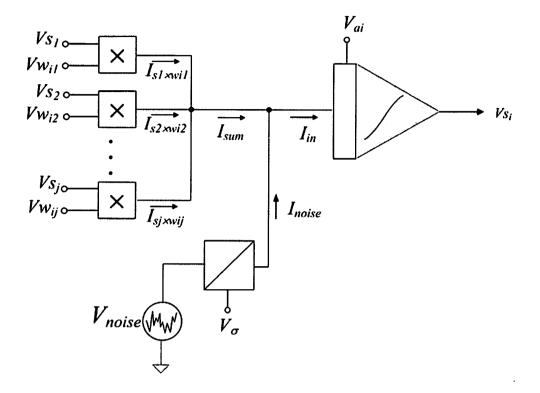

| 5.4                                | Typical CRBM neuron circuit implementation.                                                                                                                                                                  | 64<br>65       |

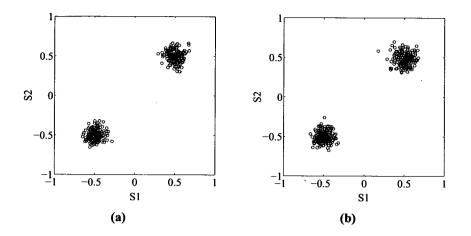

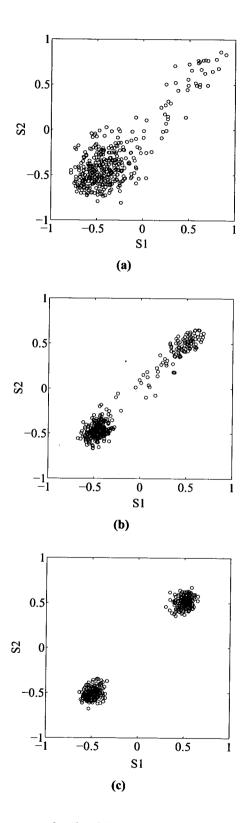

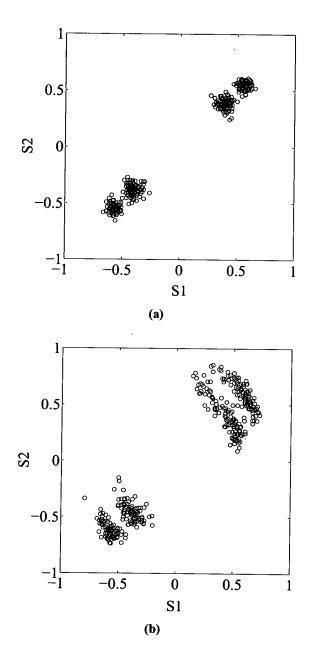

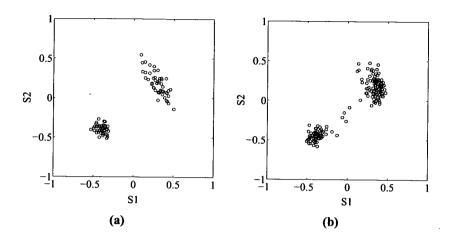

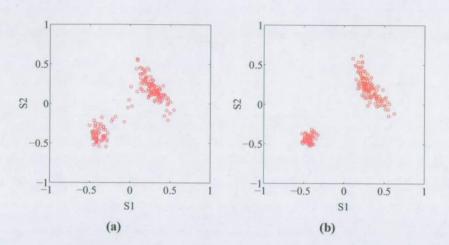

| 6.1                                | (a) Training data. (b) 20-step reconstruction of the CRBM with zero mean Gaussian noise.                                                                                                                     | 68             |

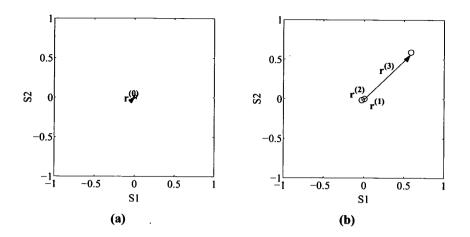

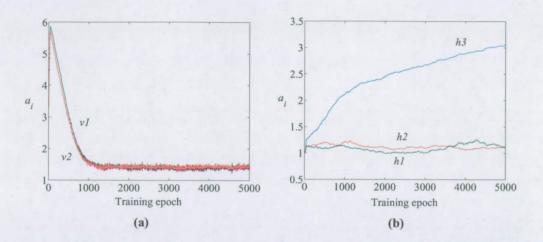

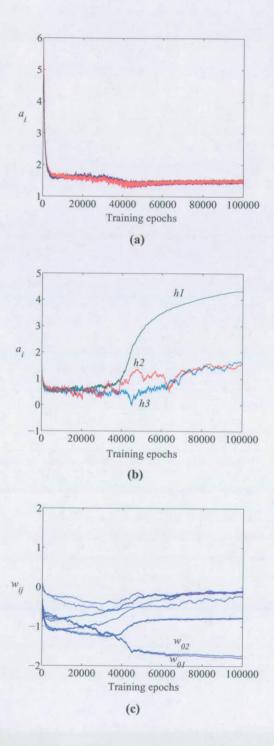

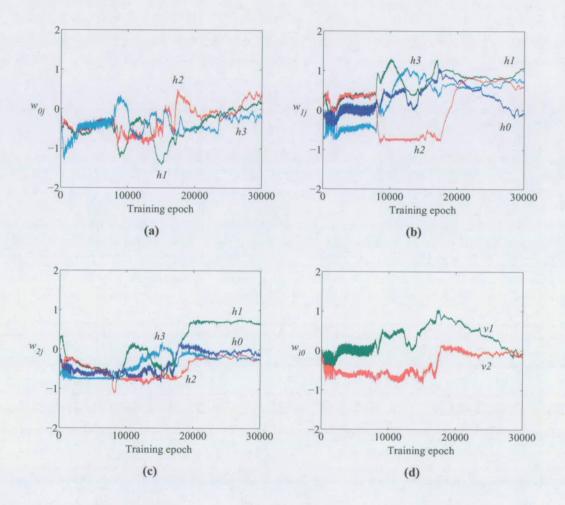

| 6.2<br>6.3                         | <ul><li>(a) Weight vector for bias neuron (b) Weight vector for hidden neurons.</li><li>(a) Visible neurons and (b) Hidden neurons noise control parameters evolu-</li></ul>                                 | 69             |

| 6.4                                | tion with training epoch                                                                                                                                                                                     | 70<br>71       |

| 6.5                                | 20-step reconstruction by the CRBM injected with non-zero mean ( $\bar{n}_i = 2$ )<br>Gaussian noise (a) after 500 training epochs (b) after 30000 epochs (c) after                                          |                |

| 6.6                                | 40000 epochs. $\{a_i\}$ for (a) visible, (b) hidden neurons, and (c) hidden-visible weight evolutions during training. $w01$ and $w02$ in (c) indicate the biased hidden neurons                             | 72             |

| 6.7                                | weight to visibles                                                                                                                                                                                           | 73             |

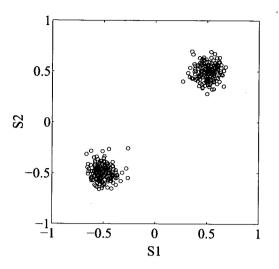

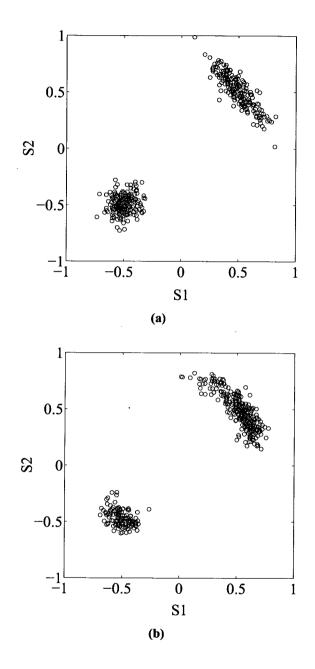

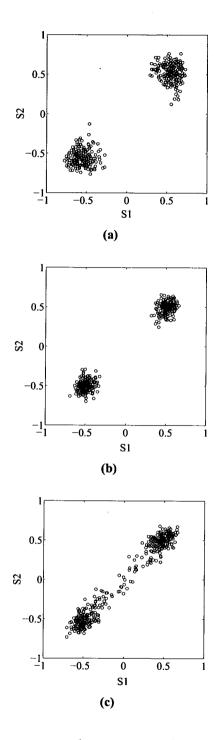

| 6.8<br>6.9                         | epochs. Artificially generated non-Gaussian noise. 20-step reconstruction of CRBM injected with non-Gaussian noise after 10000 epochs for (a) symmetric distribution (b) non-symmetric distribution training | 75<br>76       |

|                                    | data                                                                                                                                                                                                         | 77<br>78       |

| 6.11                               | 20-step reconstruction with zero-mean Gaussian noise injected into every synaptic multiplier with noise variance set to (a) $0.1$ (b) $0.05$ (c) $0.01$                                                      | 79             |

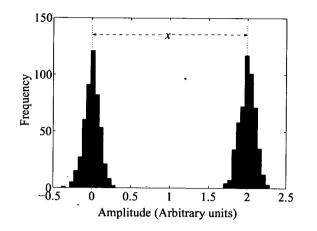

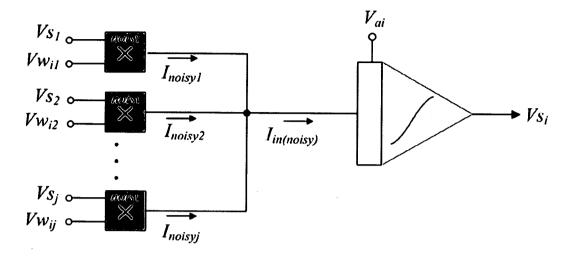

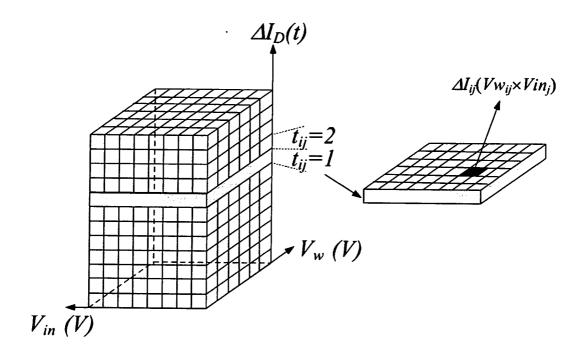

| 7.1<br>7.2<br>7.3                  | CRBM neuron with noisy synaptic multiplication                                                                                                                                                               | 82<br>83       |

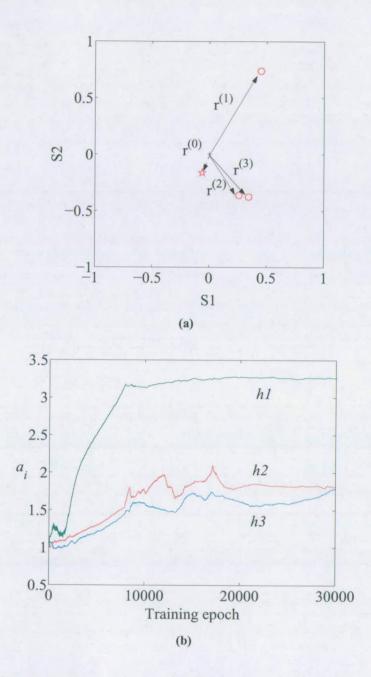

| 7.4                                | to $w_{ij}$ and $s_j$ respectively                                                                                                                                                                           | 86<br>87       |

|                                    |                                                                                                                                                                                                              |                |

| 7.5 | CRBM with 4-trap implementation weights $\{w_{ji}\}$ evolution for 30000 epochs where visible neuron <i>i</i> and hidden neuron <i>j</i> and index 0 represents bias neu- |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | rons during training.                                                                                                                                                     | 88 |

| 7.6 |                                                                                                                                                                           |    |

|     | parameters $\{a_i\}$ for hidden neurons, during training.                                                                                                                 | 89 |

| 7.7 |                                                                                                                                                                           |    |

|     | trap noisy synaptic multiplier output noise after 30000 epoch                                                                                                             | 90 |

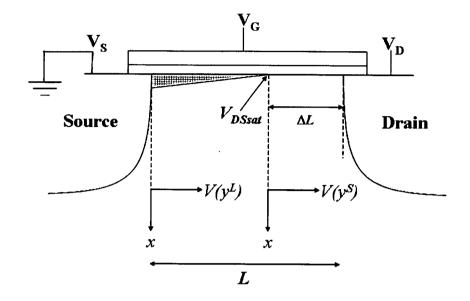

| A.1 | MOSFET cross-section for saturation operation with channel length modula-                                                                                                 |    |

|     | tion. The pinch-off point is defined when $V_{DS} = V_{GS} - V_{th}$ and denoted by                                                                                       |    |

|     | · · · · · · · · ·                                                                                                                                                         | 97 |

•

## List of tables

| 3.1 | Fitting parameters $\sigma_0$ , $\Delta E_B$ , $\Delta E_{CT}$ , for seven room temperature traps observed in 0.4 $\mu$ m <sup>2</sup> n-channel MOSFETs with corresponding estimated trap |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | depth $x_t$ [4, 5].                                                                                                                                                                        | 31 |

| 7.1 | Mapping noisy multiplier input bias voltage (hardware) to Matlab (software).                                                                                                               | 84 |

•

## Chapter 1 Introduction

This thesis explores the prospects of using future nanoscale MOSFETs to implement probabilistic computation in hardware, based on modelled future nanoscale MOSFETs and specific probabilistic neural computation architecture. The word 'future' refers to MOSFETs which are not yet available although their performance is predictable through current research efforts, while the word 'nanoscale' refers to MOSFETs with dimensions less than 10nm (sub-10nm) in physical gate length. The motivation of this research is described in Sec.1.1, and the contribution to knowledge is clarified in Sec.1.2. Finally, the structure of this thesis is described in Sec.1.3.

## **1.1 Motivation**

The success of metal-oxide-semiconductor field-effect transistors (MOSFETs) as the basic building block of most digital and analogue very large scale integrated (VLSI) circuits is predicted to continue for some years. Currently, 90nm (with a physical gate length of 50nm) is the state-of-the-art MOSFET process technology and it is projected that by 2018, sub-10nm physical gate length MOSFETs will be available [6]. The drive toward miniaturisation is led by the promise of improved circuit performance, reduced chip sizes, and the potential of higher levels of integration. However, as MOSFET dimensions continue to shrink, consider-able challenges arise in the area of device performance and reliability uncertainty [7, 8].

One of the contributing factors towards performance and reliability uncertainty is the increase in low frequency drain current noise. Drain current noise in MOSFETs is predicted to increase as the channel length shrinks [9–12]. Random Telegraph Signal (RTS) noise and 1/f noise are the primary forms of low frequency noises that are predicted in future nanoscale MOSFETs. In current technology these are minimised or suppressed through design and/or additional fabrication steps. As MOSFET dimensions continue to shrink, their presence will become increasingly significant. Recent studies show low frequency drain current noise amplitudes in excess of 60% in Deep Sub-Micrometer (DSM) MOSFET<sup>1</sup> [13]. As MOSFETs continue to scale, the low frequency drain current noise in nanoscale MOS-FETs<sup>2</sup> is expected to become a serious issue [14], leading to severely limited functionality, performance, and compromised reliability. A conventional solution would avoid or minimise nanoscale MOSFET noise through additional fabrication processes. For large MOSFETs, fabrication processes may be controlled to reduce noise [6]. However, in nanoscale fabrication process, precise fabrication process control may be impossible and the performance gain of nanoscale MOSFETs may not justify the enormous fabrication cost. Furthermore, many of the sources of noise and unreliability in DSM MOSFETs are fundamental and will not yield to improved or more careful processing. Solutions based on alternative architectural paradigms, such that the unreliable performance of these nanoscale MOSFETs could be tolerated or useful, become very attractive. For example, the architectures proposed in [15–17] use redundant circuits to form error correction to deal with this uncertainty. Other approaches are adaptive (neural network and probabilistic computing), forcing errors introduced by these nanoscale MOSFETs noise to adapt to a known (trained) system outcome or acceptable-error marked [18–20]. These fault tolerant architectural approaches provide reliability via redundancy, at the expense of circuit area and speed. An unconventional architectural approach that allows for stochasticity, or that even exploits nanoscale MOSFET noise, is therefore an exciting alternative.

Solving the nanoscale MOSFET noise issue requires something of a paradigm shift, wherein noise is viewed as a necessary element of useful computation. This is different from the approach reported in [16–18] where artificial neural networks are used because of their inherent hardware redundancy, error tolerance and self-organisation features, offering a very effective means to counteract the inherent weaknesses of nanoscale MOSFETs. Naturally, it would be unwise to claim that the proposed approach will solve all conventional computing problems. Rather, it provides an opportunity for new computation architectures such as a probabilistic neural architecture to be implemented in hardware more efficiently, extending

<sup>&</sup>lt;sup>1</sup>Deep Sub-Micrometer (DSM) refers to MOSFET with physical gate length less than 100nm but greater than 10nm.

<sup>&</sup>lt;sup>2</sup>Low frequency noise in nanoscale MOSFETs will henceforth be referred to as nanoscale MOSFET noise.

the compatibility of nanoscale MOSFETs to specific real-world application.

The Continuous Restricted Boltzmann Machine (CRBM) aims to deal with real-time data in a noisy environment; potentially for a complex multi-sensory micro-system implementation such as a Lab-On-Chip system [21, 22], coincidentally an area where nanoscale technology may be highly desirable for reasons of size. Data often encodes biological or chemical information, of relatively low bandwidth. Probabilistic neural systems are arguably wellpositioned to address nanoscale MOSFET noise as they use stochasticity to extract and to classify important features in real-world data. This project explores the use of nanoscale MOSFET noise in a probabilistic neural architecture which has been shown great potential for realising intelligent embedded system [21–24].

The work therefore must build a bridge between future nanoscale MOSFET physics and this probabilistic neural computation, in order to determine whether intrinsic low frequency drain current noise in future nanoscale MOSFETs is useful for probabilistic computation. If unreliable nanoscale MOSFETs can be shown to be useful in such an application, the technological and economic consequences of their practical implementation may become extremely significant. Furthermore, the methodology developed to make this study has more generic usefulness, as will be discussed in this thesis.

## **1.2 Contribution to knowledge**

This project sets out to explore the suggestion that :-

Low frequency drain current noise in future nanoscale MOSFETs can underpin useful probabilistic computation.

In examining this hypothesis, the project will develop new methods to link DSM device physics, through compact circuit models, to behavioural-level simulations of a relativelywell-understood probabilistic paradigm.

The Continuous Restricted Boltzmann Machine (CRBM) has been chosen as an experimental platform. While both nanoscale MOSFET noise [10–12, 25–29] and CRBM [3, 21–24, 30–

32] have been the subject of extensive research, the use of nanoscale MOSFET noise for computation in the CRBM has not been studied, and it is hoped that this project will point the way towards hardware implementations of nano-embedded intelligent systems.

To achieve the objective of this project, temporal fluctuations of nanoscale MOSFET noise must be incorporated into the CRBM. Unfortunately, nanoscale devices are at least a decade away from everyday reality [6]. To pursue this project, temporal fluctuations in nanoscale MOSFETs will be simulated, based upon theoretical compact models of nanoscale MOS-FETs extracted from atomistic simulation [25–27, 33]. Current simulators cannot support the requirement for time domain noise analysis based on nanoscale MOSFET noise characteristics (RTS). Therefore, in order to still pursue on the main objective of this project, a time domain RTS noise based simulation capability must be developed.

## **1.3 Chapter layout**

This thesis can be separated into two relatively independent sections, A and B as illustrated by Fig.1.1. Part A deals with nanoscale MOSFET noise while part B discusses the chosen probabilistic neural model, the CRBM. Chapter 7 brings these together, linking nanoscale MOSFET characteristics and probabilistic neural computation into one common goal, providing useful computation. The chapters are:-

- Chapter 2 reviews the nanoscale MOSFET drain current low frequency noise: RTS and 1/f noise.

- Chapter 3 discusses the modelling of a noisy MOSFET for time domain noise analysis capability.

- Chapter 4 analyses the time domain output noise of the noisy analogue multipliers implementation, based on the capability developed in Chapter 3.

- Chapter 5 reviews the CRBM algorithm and architecture.

- Chapter 6 analyses the effect of noise on the CRBM performance.

- Chapter 7 presents the CRBM with nanoscale MOSFET noise implementation, and explore the performance of this implementation.

- Chapter 8 concludes the contribution and the future work of this research.

DSM : Deep-Sub-Micrometer

**CRBM : Continuous Restricted Boltzman Machine**

Figure 1.1: The flowchart illustrating the chapter flow in this thesis.

# Chapter 2 Low Frequency Noise in Nanoscale MOSFETs

## 2.1 Introduction

Low frequency noise becomes a dominant limiting factor in the practical use of MOSFETs in a circuit implementation as the devices enter nanoscale dimensions. It sets a lower limit to the level of signal that can be reliably processed by the circuit. Excessive low frequency noise could lead to serious performance and functionality limitations. Therefore, low frequency noise in MOSFETs has been studied extensively in the last few decades [4, 9, 11–14, 27, 34, 35].

Random Telegraph Signal (RTS) noise and 1/f noise are the two forms of low frequency noise that are predicted to dominate future nanoscale MOSFETs [9, 11, 12, 14]. In current technology, their existence is insignificant, and in most cases minimised or suppressed through either design or additional fabrication processes [6]. As MOSFET dimensions continue to shrink, their presence (noise) is predicted to become increasingly significant. Recent studies have shown low frequency drain current noise amplitude in excess of 60% in Deep-Sub-Micrometer (DSM) MOSFETs [13].

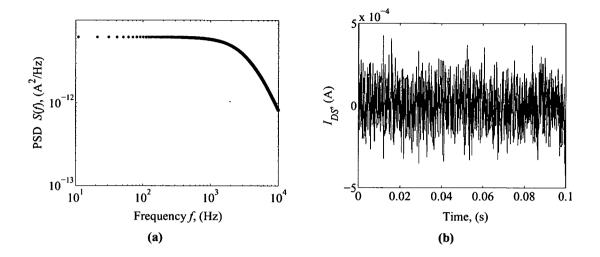

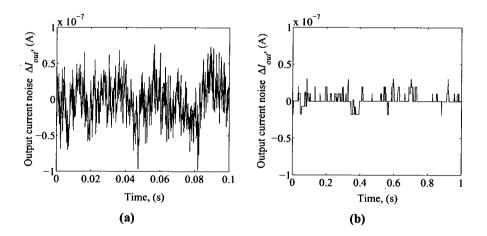

Fig.2.1 shows an example of simulated time domain 1-trap RTS and 1/f noise for a 35nm gate-length NMOS transistor based on a noisy MOSFET model developed in [2]. In reality, 1/f noise in general is more relevant to larger MOSFETs (>5-10  $\mu m^2$ [11]), while as MOS-FETs shrink to nanometer scale, RTS noise becomes dominant [4]. It is commonly agreed that the superposition of multiple RTS noise sources gives rise to 1/f noise. Understanding the microscopic origin of RTS noise therefore contributes to the understanding of the origin of 1/f noise.

Figure 2.1: Sample of (a) single trap RTS and (b) flicker noise.

## 2.2 Random Telegraph Signal (RTS) Noise

Recent studies show that the low frequency performance of nanoscale MOSFETs is dominated by RTS noise [11, 13]. RTS noise arises from the capture and emission (trapping and detrapping) of hot electrons in the channel by traps (defects) at the interface of  $Si - SiO_2$ , causing discretised drain current fluctuations, as seen in Fig.2.1(a) [2].

RTS noise is characterised by three parameters: the average amplitude of fluctuation  $\Delta I_D$ , the mean capture time  $\bar{\tau}_c$ , and the mean emission time  $\bar{\tau}_e$ . All these parameters vary over wide ranges with devices sizes, temperature, and bias conditions, where models to describe their dependencies have been developed [4, 27, 28, 36].

#### 2.2.1 Origin of traps

There are four kinds of defects or traps commonly associated with a  $Si - SiO_2$  interface: mobile ions, fixed charges, interfacial traps, and induced charges [1]. Illustrated by Fig.2.2, the defects/traps are briefly described below based on the detailed descriptions in [1].

• Mobile ions, typically  $Na^+$  and  $K^+$ , lying within the  $SiO_2$  interface are introduced through contamination during the fabrication process. They move around or redistribute under bias-temperature stressing, producing instability in the MOSFET's char-

**Figure 2.2:** An illustration of the traps and charges in  $Si - SiO_2$  structures. (Adapted from [1]).

acteristics.

- Fixed charges exist due to excess ionic silicon that has broken away during the oxidising reaction at the Si - SiO<sub>2</sub> interface. This explains the location of fixed charges in SiO<sub>2</sub>. Unlike mobile ions, these fixed charges are consistent for a given set of fabrication conditions.

- Interfacial traps, which are situated at the  $Si SiO_2$  interface, are believed to arise from unsatisfied chemical bonds, or so-called "dangling bonds", at the surface of the Si during thermal formation of the  $SiO_2$  layer. The interfacial traps introduce energy levels in the forbidden band gap at the  $Si - SiO_2$  interface and remain fixed in energy relative to the conduction band and valence band energies.

- Induced charges are introduced into the SiO<sub>2</sub> due to ionising radiation, or hot carrier stress. The induced charges may be positively or negatively charged. They influence the MOSFET's characteristics by increasing or reducing the threshold voltage.

Interface traps and induced charges, unlike the mobile ions and fixed charges, are readily influenced by the bias conditions of the MOSFET. If they are within the tunnelling distance

$(\leq 2 nm)$  of the hot electrons, they can be charged or discharged, creating fluctuations in the MOSFET's characteristics (i.e. the drain current  $I_{DS}$ ), of the form of RTS.

#### 2.2.2 RTS noise amplitude

The discretised drain current noise in a nanoscale MOSFETs is the combined effect of carrier number fluctuations and carrier mobility fluctuations [9, 37]. The normalised amplitude of this discrete fluctuation is described in the following general relation:

$$\frac{\Delta I_D}{I_D} = \frac{\Delta N}{N} \pm \frac{\Delta \mu}{\mu},\tag{2.1}$$

where N is the number of channel carriers per unit area and  $\mu$  is carrier mobility. The term  $\left(\frac{\Delta\mu}{\mu}\right)$  in Eq.(2.1) describes the effect of mobility fluctuations caused by Coulombic scattering of the charged traps [4, 37–39]. The sign (±) indicates the electronic state of the traps (i.e. charged (+) or neutral (-)) [36], after capturing electrons [37]. A trap that is charged after capturing an electron increases the scattering effect which subsequently increases the noise amplitude  $\Delta I_D$  [37]. If a trap becomes neutral after capturing an electron (charged when empty), the Coulombic scattering becomes weaker, reducing the noise amplitude  $\Delta I_D$  [37]. As the MOSFET enters nanoscale dimensions, the carrier number fluctuations ( $\frac{\Delta N}{N}$ ) become dominant [9]. Therefore, the term  $\left(\pm\frac{\Delta\mu}{\mu}\right)$  in Eq.(2.1) can be dropped.  $\left(\frac{\Delta N}{N}\right)$  describes the carrier number fluctuations caused by the capture and emission of electrons by the trap. When a trap captures an electron from the channel, the effective drain to source current increases. The normalised amplitude ( $\Delta I_D/I_D$ ) dominated by ( $\frac{\Delta N}{N}$ ) can therefore be described by [40, 41]:

$$\frac{\Delta I_D}{I_D} = \alpha \frac{g_m}{I_D} \cdot \frac{q}{WLC_{ox}} \left(1 - \frac{x_t}{t_{ox}}\right),\tag{2.2}$$

where  $g_m$  is channel transconductance, W is channel width, L is channel length,  $C_{ox}$  is gate oxide capacitance,  $t_{ox}$  is gate oxide thickness,  $x_t$  is trap depth measured from the  $Si - SiO_2$ interface.  $\alpha$  in Eq.(2.2) is a semi-empirical parameter used to account for the wide variation

**Figure 2.3:** *RTS noise amplitude variation with gate*  $V_{GS}$  *and drain*  $V_{DS}$  *voltages for three different trap depths (* $x_t$ = 0.11, 0.40, 0.80 nm) *located in the middle of gate (* $y_t$ = 16nm) for an implementation based on 35nm NMOS modelled in [2].

of RTS amplitude [40] caused by the short channel effect in MOSFETs operating in weak inversion [41].  $\alpha$  is in the range of 0.1 to 100 [42].

The dependence of typical RTS noise amplitudes on bias is shown in Fig.2.3. The noise amplitudes peak at low gate voltages (weak inversion), while at higher gate voltages, the amplitudes decrease. Recent studies have shown that RTS noise amplitudes vary by some 40% in weak inversion compared to 5% for strong inversion [27]. In addition, it has been reported that shallower traps (small  $x_t$ ) produce a larger RTS noise amplitude [37], which is in agreement with Eq.(2.2).

#### 2.2.3 RTS average capture and average emission time

The capture and emission of electrons cause fluctuations in channel conductance, which in turn causes the drain current to fluctuate. Capture and emission are stochastic events, obeying Poisson statistics, and are normally described by the average values of  $\bar{\tau}_c$  and  $\bar{\tau}_e$ , respectively [36].  $\bar{\tau}_c$  represents the mean time that a trap is empty before capturing an electron and  $\bar{\tau}_e$  represents the mean time in which a trapped electron is freed. Eq.(2.3) and Eq.(2.4) [4]

describe the basic empirical model for  $\bar{\tau}_c$  and  $\bar{\tau}_e$  that are used in this work.

$$\bar{\tau}_c = \frac{\exp\left(\frac{\Delta E_B}{kT}\right)}{\sigma_0 v_{th} n} \tag{2.3}$$

$$\bar{\tau}_e = \frac{\exp\left[\left(\Delta E_B + \Delta E_{CT}\right)/kT\right]}{g\sigma_0 v_{th} n} \tag{2.4}$$

In Eq.(2.3) and Eq.(2.4),  $\sigma_0$  is the trap cross-section pre-factor,  $\Delta E_B$  is the barrier energy for capture (also known as activation energy for capture),  $\Delta E_{CT}$  is the trap binding energy,  $\Delta E_B + \Delta E_{CT}$  is the emission activation energy,  $v_{th}$  is the average thermal velocity, n is the channel electron concentration, k is the Boltzmann constant, T is the absolute temperature, and g is the degeneracy factor which is normally set to 1 [4].

The capture and emission time are thermally activated processes which are inversely proportional to temperature, as described in both Eq.(2.3) and Eq.(2.4). For a fixed operating temperature, the capture and emission time are affected by bias conditions through  $\sigma_0$ ,  $\Delta E_B$ , and  $\Delta E_{CT}$ . It has been reported that  $\sigma_0$  and  $\Delta E_{CT}$  depend strongly and positively on gate voltage,  $V_{GS}$  while  $\Delta E_B$  does not depend on either  $V_{GS}$  or  $V_{DS}$  [4, 5, 28]. The channel electron concentration's, dependence on drain voltage,  $V_{DS}$ , is strongly influenced by the position along the channel at which the trap is located. For an n-MOSFET, *n* near the source is not affected by  $V_{DS}$  while *n* near the drain shows a strong inverse relationship with  $V_{DS}$  [2]. An example of mean capture and emission time variation with bias conditions for a trap near the  $Si - SiO_2$  interface ( $x_t = 0.11nm$ ) located in the middle of the channel ( $y_t = 16nm$ ) is shown in Fig.2.4.

#### 2.2.4 Discussion

The capture and emission (trapping and de-trapping) of channel hot electrons by a trap (defect) at the interface of  $Si - SiO_2$ , causes discretised drain current fluctuations with amplitude exhibiting a non-Gaussian distribution [11]. The power spectral density (PSD) of 1-trap RTS noise exhibits a Lorentzian spectrum, described by [4, 28, 29]:

**Figure 2.4:** Average capture  $\bar{\tau}_c$  and average emission  $\bar{\tau}_e$  vs gate  $V_{GS}$  and drain  $V_{DS}$  voltages for trap located at  $x_t = 0.11$ nm and  $y_t = 16$ nm for an implementation based on 35nm NMOS modelled in [2].

$$S(f) = \frac{4 \left(\Delta I_D\right)^2}{\left(\bar{\tau}_c + \bar{\tau}_e\right) \left[ \left(\frac{1}{\bar{\tau}_c} + \frac{1}{\bar{\tau}_e}\right)^2 + (2\pi f)^2 \right]},$$

(2.5)

The number of discrete levels of drain current clearly depends on the number of traps. In practical MOSFETs of  $1.0 \times 0.15 \ \mu m^2$  dimensions, the number of interface trap densities are usually in the order of  $10^{10} \text{eV}^{-1} \cdot \text{cm}^{-2}$  [43], of which several could be active (i.e. energy level within kT) causing multi-level RTS noise. For multi-trap RTS, Eq.(2.5) is generalised to [4]:

$$S_{I}(f) = \sum_{k=1}^{N_{traps}} \frac{4 \left(\Delta I_{D}\right)_{k}^{2}}{\left(\bar{\tau}_{c} + \bar{\tau}_{e}\right)_{k} \left[ \left(\frac{1}{\bar{\tau}_{c}} + \frac{1}{\bar{\tau}_{e}}\right)_{k}^{2} + \left(2\pi f\right)^{2} \right]}$$

(2.6)

where  $N_{traps}$  represents the total number of active traps contained within the  $Si - SiO_2$ interface and  $S_I(f)$  is the current noise power spectral density summed over all traps  $k = 1, 2, 3, ..., N_{traps}$ . For a large number of active traps,  $N_{traps}$ , uniformly distributed (both throughout the oxide and in energy [44]) with a wide distribution of time constant ( $\bar{\tau}_c$  and  $\bar{\tau}_e$ ), the superposition of Lorentzian spectra in Eq.(2.6) gives rise to  $S_I(f)$  with a 1/f form [4, 12]. This provides a physical justification that the superposition of several RTS noises gives rise to 1/f noise in MOSFETs.

## **2.3** Flicker (1/f) Noise

The origin of 1/f noise in MOSFETs has been extensively studied for more than a decade [9, 14, 44–46]. It has been agreed recently that 1/f noise in MOSFETs is associated with both carrier number fluctuations and correlated carrier mobility fluctuations [4, 47]. Carrier number fluctuations come from the random trapping and detrapping of free carriers in the oxide traps near the  $Si - SiO_2$  interface, where the trapped carriers limit the mobility of the free carriers near the interface by Coulombic scattering [4].

### **2.3.1** 1/f noise model

In practice, MOSFET drain current 1/f noise is commonly described by its Power Spectral Density (PSD). A typical MOSFET drain current 1/f noise PSD has the following form [48]:

$$S(f) = \frac{K_f I_{DS}^{af}}{C_{ox} L_{eff}^2 f^{ef}},$$

(2.7)

where  $K_f$  and  $a_f$  are process-dependent constants and may vary from sample to sample. The noise exponent  $a_f$  is typically between 0.5 and 2 [49]. The 1/f noise coefficient  $K_f$  was claimed in [47] to be bias-dependent but in common practice [48],  $K_f$  is considered constant. The frequency exponent,  $e_f$ , is a bias-dependent parameter with a typical value ranging between 0.7 and 1.2 [50].  $C_{ox}$  is the gate oxide capacitance and  $L_{eff}$  is the effective channel length of a MOSFET.

A unified model of a MOSFET's drain current 1/f noise PSD incorporating both carrier number fluctuation and mobility fluctuation has been proposed by Hung [45]. The widely adopted analytical expression of the unified model in strong inversion is given by [48]

$$S(f) = \frac{kTq^2 I_{DS} \mu_{eff}}{\gamma f^{ef} L^2 C_{ox}} \left[ A \ln \frac{N_O + N^*}{N_L + N^*} + B \left( N_O - N_L \right) + \frac{1}{2} C \left( N_O^2 - N_L^2 \right) \right] \\ + \Delta L_{clm} \frac{kT I_{DS}^2}{\gamma f^{ef} W L^2} \times \frac{A + B N_L + C N_L^2}{\left( N_L + N^* \right)^2},$$

(2.8)

where

$$qN_O = C_{ox} \left( V_{GS} - V_{th} \right) \tag{2.9}$$

$$qN_L = C_{ox} \left( V_{GS} - V_{th} - V_{DS} \right)$$

(2.10)

and  $N^* = (kT/q^2) (C_{ox} + C_d + C_{it})$ .  $C_d$  and  $C_{it}$  are depletion layers and interface trap capacitance respectively.  $\gamma$  is the attenuation coefficient of the electron wave function in the oxide, with a typical value of  $10^8 cm^{-1}$ [48]. A, B, and C are technology-dependent model parameters.  $\Delta L_{clm}$  refers to the electrical channel length reduction due to channel length modulation.  $N_O$  and  $N_L$  are the charge densities at the source and the drain ends of the channel respectively.

#### 2.3.2 Discussion

Eq.(2.7) is a simple model of the MOSFET's drain current 1/f noise PSD, used largely for 'long channel' MOSFETs [47]. Nevertheless, it is able to explain the general frequency and size dependence of 1/f noise in any MOSFET correctly. In practice, Eq.(2.7) is much easier to understand and implement, especially for the initial low frequency noise characteristic approximation of a MOSFET.

The approach to carrier trapping-detrapping 1/f noise provides a better physical explanation of 1/f noise in MOSFETs. Eq.(2.8) is a complex model based on this approach and is con-

sidered to be a 'complete' model, capable of expressing 1/f noise in all MOSFET operation regions in strong inversion. In the absence of technology-dependent model parameters and charge density estimations, Eq.(2.8) may not be immediately useful to describe 'accurate' low frequency noise in MOSFETs. In this case, Eq.(2.7) provides a reasonable approximation of Eq.(2.8).

### 2.4 Summary

This chapter has drawn together results from the extensive research and literature of Deep-Sub-Micrometer (DSM) noise modelling. It has been established that an approach based on the capture and emission of electrons by traps near the vicinity of the  $Si - SiO_2$  interface provides a clear and simple explanation of dominant low frequency noise sources (RTS and 1/f) in nanoscale MOSFETs, which accounts for both the effect of carrier number fluctuation and carrier mobility fluctuation. In general, low frequency noise is inversely proportional to MOSFET gate area. For a small MOSFET, RTS noise dominates the low frequency, producing discretised drain current. For large MOSFETs, the superposition of RTS noise gives rise to 1/f noise.

# Chapter 3 Modelling 'Noisy' MOSFETs

This thesis aims to demonstrate the principle that nanoscale MOSFET low frequency noise can underpin useful probabilistic behaviour. The low frequency noise is used as a source of probabilistic behaviour in a modelled nanoscale silicon 'neuron' that adapts to the natural variability in input data. For this purpose, a noisy MOSFET model that accurately represents the temporal fluctuation of a real nanoscale MOSFET is required. This chapter describes the method used to model the noisy MOSFET. The capability to represent the dominant nanoscale MOSFET low frequency noises (RTS and 1/f) will be demonstrated and verified. The noisy MOSFET model will be used to implement a key circuit for the silicon 'neuron' in Chapter 4.

### 3.1 Introduction

The aim of this study is to develop a SPICE-based behavioural model of a 'noisy' MOS-FET, preserving the underlying, essential MOSFET transfer characteristics, as illustrated in Fig.3.1.

A credible, computationally-simple noisy MOSFET model is critical to this work. At this concept-proving stage, however, simplicity and simulation speed are more important than great accuracy. It is not, therefore, the objective of this study to develop a complex, arbitrarily accurate noisy DSM MOSFET model. Rather, the focus is to develop a model that produces a correct form of noise behaviour, valid in all operating regimes, and is easy to implement in a readily-available circuit simulator.

The work described in this chapter focuses on two low frequency MOSFET noise models: 1/f noise and RTS noise. 1/f noise in general is more relevant to the larger area MOSFETs

Figure 3.1: (a) Standard n-channel MOS drain-source current  $I_{DS}$  for a given  $V_{GS}$  voltage. (b) noisy n-channel MOS drain current for a given  $V_{GS}$  voltage.

$(>5-10\mu m^2$  [11]), while as the MOSFET shrinks to nanometer scale, the RTS noise become dominant [11, 36]. Current models predict that the superposition of RTS noise produces 1/f noise, and that the transition from a 1/f -dominated regime to that of true RTS noise is gradual—not in the form of a first-order 'phase transition' [4, 11, 45].

## 3.2 Methodology Overview

The noisy MOSFET was modelled by augmenting a conventional noiseless MOSFET with a noise source, n(t) (Fig.3.2). In this study, the initial MOSFET model was that for a  $0.35\mu m$  AMS CMOS technology. However, the overall and final implementation of the noisy MOS-FET was based upon a 35nm gate length MOSFET, for 90nm CMOS technology node, extracted from atomistic simulation [25, 26, 33].

The noiseless MOSFET is used to generate the  $I_{DS}$  response of the noisy MOSFET at a particular time instance t, for the given bias conditions ( $V_{GS}$  and  $V_{DS}$ ). As bias conditions change in time, the noisy MOSFET drain current therefore changes correspondingly. The methodology uses  $I_{DS}$  static model in transient analysis. This is valid as the  $I_{DS}$  reaches steady state in pico-seconds [51] while the low frequency noise fluctuates in micro-seconds.

Figure 3.2: Noisy MOSFET components. The noiseless MOSFET is a standard MOSFET having a typical I-V characteristic corresponding to the technology used. The noise source n(t) generates noise data with the specific physical characteristics of the low frequency noise it models.

The noise source n(t) represents the 1/f or RTS behaviour of the noisy MOSFET. Timedomain models of 1/f noise are calculated from the 1/f Power Spectral Density (PSD) (described in Sec.2.3.1) generated for each bias point of the MOSFET. For RTS noise, timedomain models are developed using RTS parameters (amplitude and time statistics) calculated at each bias point of the MOSFET. Details are illustrated in Sections 3.3 and 3.4.

To ensure that the methodology used for generating noise does indeed produce time-domain noise with the intended spectral characteristics, the PSD of the generated time-domain noise is calculated using a PSD extraction algorithm.

In general, the DC drain-source current,  $I_{DS}$ , generated at a given time t, is used by the noise source n(t) to generate *one* noise datum. The noise data generated in time space have the correct *form* of noise behaviour that the noise source n(t) is supposed to model. If bias conditions change in time, the noise source n(t) generates non-stationary noise data corresponding to the changing DC response of the noiseless MOSFET. The noisy MOSFET model is used as a 'standard' component in circuits. It is essential that the method of generating noisy drain current does not otherwise disrupt the use of the circuit simulation under transient analysis. Therefore, a high-level analogue behavioural language, called Verilog-A, is used to model the noisy MOSFET. Implementation using Verilog-A allows full control of the noisy MOSFET behaviour, in addition to implementation flexibility for future modification.

## **3.3** Generating 1/f Noise

The objective of generating time-domain 1/f noise is somewhat different from that of most other work [52, 53]. Although the method chosen has been used to develop commercial transient noise analysis [53], this is not the aim of this work. The aim is to model a noisy MOSFET in a circuit implementation of a particular computational architecture, in order to explore the effects of noise on its performance.

### **3.3.1** Methodology: 1/f noise

The critical part in modelling the noisy MOSFET is the implementation of the 1/f noise source, n(t). The 1/f noise source should exhibit the correct *form* of noise characteristic corresponding to the MOSFET technology and bias conditions.

In this work, 1/f noise was generated based on the Sum-of-Sinusoids technique adapted from [52]. This is the best approach for the use with Verilog-A implementation, even though other approaches are possible. The technique generates the time domain 1/f noise data, n(t), by summing a fixed number  $N_f$  of random phase sinusoids in a specified frequency band [52]:

$$n(t) = \sum_{i=1}^{N_f} a_i(t) \sin(2\pi f_i t + \varphi_i),$$

(3.1)

where  $a_i$  is the magnitude,  $f_i$  is the frequency and  $\varphi_i$  is the random phase defining the  $i^{th}$  sinusoid.

$N_f$  represents the number of sinusoids used to approximate noise data at a given time t. For a fixed frequency band (band-limited) PSD S(f) (Eq.(2.7)),  $N_f$  depends on the division of the frequency band into frequency steps,  $\Delta f$ . A smaller  $\Delta f$  means more sinusoids, better n(t) approximation, and longer transient data representation. Depending on the shape of S(f), the frequency band may be divided linearly or logarithmically.

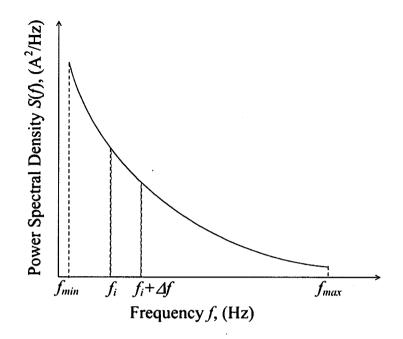

For each frequency interval  $f_i$  and  $f_i + \Delta f$  of a given PSD S(f) shown in Fig.3.3, the magnitude  $a_i$  is approximated as:

ł

$$a_i = \sqrt{2 \int_{f_i}^{f_i + \Delta f} S(f) df}.$$

(3.2)

During simulation, as bias conditions change, S(f) changes accordingly. For 1/f noise, the PSD is proportional to the drain-source current,  $I_{DS}$ , as described by Eq.(2.7) in Sec.2.3.1. Consequently, according to Eq.(3.2), the magnitude  $a_i$  will also change. The values for  $a_i$  are updated at each time step to cater for changes in bias conditions. Changes in bias conditions therefore affect generated 1/f noise magnitude and spectrum characteristics through Eq.(3.2) and Eq.(3.1). This enables the modelled noise generated to be of non-stationarity characteristics in the case where bias conditions change with time, at the expense of lengthy simulations.

$f_i$  represents the frequency of the  $i^{th}$  sinusoid.  $\varphi_i$  is a random phase angle, uniformly distributed between 0 and  $2\pi$ .  $\varphi_i$  values are unique for each sinusoid across t.

### **3.3.2** Implementation: 1/f noise

The initial n-channel MOSFET (NMOS) used to establish our methodology was based upon a  $0.35\mu m$  AMS CMOS model. Gate length L, width W, and oxide thickness  $T_{ox}$  were set to  $0.35\mu m$ ,  $1\mu m$ , and 7.7nm, respectively. The 1/f noise coefficient  $K_f$ , exponent  $a_f$ , and frequency exponent  $e_f$  values were set to 2.81e-27  $A \cdot F$ , 1.4, and 1, respectively. These values were taken from the AMS CMOS technology file used in simulation. In order to generate statistically significant noise amplitudes useful for this work,  $K_f$  was arbitrarily increased to 2.81e-23  $A \cdot F$ .

**Figure 3.3:** Illustration of 1/f power spectral density S(f).

DSM implementation was based upon a 35nm gate length NMOS model developed using atomistic simulation. We set L=35nm,  $W=0.1\mu m$ ,  $T_{ox}=0.88nm$ . The flicker noise parameters were not available in this 35nm NMOS model. Therefore, in this study, the values used for  $0.35\mu m$  CMOS technology were re-used for the 35nm NMOS implementation.

These values and this approach are not acceptable for a thorough exploration of noise in 35nm MOSFETs. However as explained in Sec.3.3, they are more than adequate for the aims of this study, capturing as they do the most important characteristics of DSM noise at circuit level.

Using these parameters, the 1/f noise source n(t) was implemented based on the method in Sec.3.3.1. It is thought that 1/f noise is important below 10kHz [9, 46], and we chose to generate 1/f noise between 100 Hz ( $f_{min}$ ) and 10 kHz ( $f_{max}$ ). So, for a given bias conditions (i.e.  $I_{DS}$ ), frequency band, and MOSFET parameters, a corresponding PSD can be generated based on Eq.(2.7).

This PSD is then used to generate the amplitudes of the sinusoids in Eq.(3.1) using Eq.(3.2). The frequency band was initially divided linearly with  $\Delta f$  set to 100 Hz. Therefore, based

upon the set frequency band and frequency step, there are 99 terms in equation Eq.(3.1).

It should be noted that this calculation is performed to generate *one* noise datum at a particular time instance t and then the noise datum,  $\Delta I_{DS}(t)$ , is added to generate  $(I_{DS}(t) + \Delta I_{DS}(t))$ . At the next simulation time step, the process is repeated.

The implementation steps for generating time domain 1/f noise are summarised as follows:

1. At t = 0 (initialisation)

- Set the lowest frequency  $f_{min}$  and highest frequency  $f_{max}$ .

- Set the frequency step  $\Delta f$  for dividing the band-limited PSD S(f).

- Calculate the number of sinusoids:  $N_f = \frac{f_{max} f_{min}}{\Delta f}$ .

- Generate  $N_f$  random phase angle using random number generator.

- 2. Probe the noiseless MOSFET drain-source current  $I_{DS}$  at time t.

- 3. Use the  $I_{DS}$  to generate band-limited  $(f_{min} \rightarrow f_{max})$  PSD S(f) using Eq.(2.7).

- 4. Approximate the magnitude  $a_i$  for each frequency interval  $f_i$  and  $f_i + \Delta f$  using Eq.(3.2).

- 5. Calculate the noise datum n(t) using Eq.(3.1).

- 6. Add the noise datum n(t) to  $I_{DS}$  to produce noisy  $I_{DS}$ .

- 7. Repeat 1-6 until the end of simulation time.

## 3.4 Generating RTS Noise

RTS noise in MOSFETs has been accepted and studied for some time [4, 37, 54, 55]. Most agree that the physical origin of RTS noise is the trapping and de-trapping of electrons by traps located at or near the vicinity of the  $Si - SiO_2$  interface [28, 43] and RTS noise causes discretised drain current fluctuations. However, a 'standard' and generally accepted model for RTS noise that is valid for all operating regimes does not yet exist [28].

The number of discrete values of  $I_{DS}$  depends on the number of traps [38]. Most RTS noise models are based upon single trap capture and emission activity [4, 28], and restricted to room temperature operation in ohmic regimes at strong inversion [4, 28, 43].

In this work, we assembled a more wide-ranging RTS model based upon previously-published work [4, 28, 36, 37, 41, 55–57], and made some pragmatic assumptions to enable the models to be used in our circuit and target architecture.

#### 3.4.1 Assumptions: RTS noise

The RTS noise is generated based upon existing models, which were developed and extended, with the following assumptions and restrictions:-

- 1. Only electron traps are considered and the noisy-MOSFET modelling was limited to n-type devices at this stage, as very few models of hole traps have been reported.

- 2. All traps are considered neutral when empty. Attractive and neutral traps have larger cross-sections (in the range of  $10^{-14} 10^{-12}cm^2$  and  $10^{-18} 10^{-14}cm^2$ , respectively) than do repulsive (negative) traps with a cross-section smaller than  $10^{-18}cm^2$ , and a concomitantly low capture probability [58]. Neutral traps produce larger RTS amplitudes compared to the attractive traps and therefore representing the normally observable, hence analyzable RTS noise [37].

- 3. Active traps reside in the volume between the  $Si SiO_2$  interface and oxide at depth within the tunnelling distance ( $\leq 2 nm$ ) of any hot electrons, limited by gate oxide thickness  $t_{ox}$ .

- 4. Adjacent traps are at least 2nm apart. This is important to ensure that traps are electrostatically isolated [34], and thus there is no interaction such as tunnelling between traps [4].

- 5. The capture and emission of an electron by a single trap are mutually exclusive events.

- 6. Only one electron can be trapped by each trap at any particular time. It was reported

by [4] that RTS noise due to multi-electron trapping by a single trap can occur for traps located in Si rather than the  $Si - SiO_2$  interface.

- No Coulombic scattering effect (channel blocking). Coulombic scattering would cause trapped electrons to become a mid-filter that repels the further capturing process of electrons. This effect is mainly prominent in strong inversion and in very weak inversion [4].

- 8. It is assumed that capture and emission time are not affected by electron temperature. However, according to [4], by applying a drain-source voltage, the electron temperature can be raised above the underlying lattice temperature, giving rise to temperaturedependent capture and emission as evident by Eq.(2.3) and Eq.(2.4). By ignoring the effects of electron temperature, this assumption introduces inaccuracy to capture and emission time approximation especially for high bias conditions.

- 9. The amplitude of RTS is not affected by lateral trap position along the channel region.

With these assumptions, a suitably accurate *form* of RTS noise, valid for low bias conditions and typical temperatures can be generated while at high bias conditions and corresponding high temperatures, the accuracy will be compromised. It is acknowledged again that RTS noise thus generated may not be a completely accurate representation of real RTS noise in MOSFETs. As stated in Sec.3.1, that is not the main aim of this study.

### 3.4.2 RTS Amplitude

When a trap captures an electron from the channel, the effective drain to source current drops. When the trapped electron is released into the channel, the effective drain to source current increases. The normalised amplitude  $(\Delta I_D/I_D)$  of current fluctuation between the capture and emission of an electron by the trap is described by Eq.(2.2) in Sec.2.2.2 [40, 41]

Eq.(2.2) assumes RTS noise amplitude does not depend on the position of the trap along the channel region. Evidently, this assumption is not wholly accurate [27, 57]. The RTS amplitude has been shown to peak when the trap is located at the centre of the channel region,

and reduces for locations toward the source or drain [27, 57]. However, for simplicity, in this study it is assumed that Eq.(2.2) is sufficient to describe RTS amplitude that depends solely on trap depth  $x_t$ . It is acknowledged that it is crucial to refine Eq.(2.2) to include the effect of trap position along the channel on noise amplitude in future models. From Eq.(2.2), the deeper the trap location into the oxide from the  $Si-SiO_2$  interface, the smaller the amplitude. The maximum amplitude occurs when the trap lies at the interface,  $x_t = 0$ , where Eq.(2.2) reduces to:

$$\frac{\Delta I_D}{I_D} = \alpha \frac{g_m}{I_D} \cdot \frac{q}{WLC_{ox}}.$$

(3.3)

RTS amplitude varies by some 40% in weak inversion compared to 5% for strong inversion [27]. This suggests that RTS noise will depend strongly on the bias point of the MOSFET. In Eq.(2.2), the bias dependence of RTS amplitude is modelled through the channel transconductance  $g_m$ .