## Low Power Architectures for MPEG-4 AVC/H.264 Video Compression

#### Asral Bahari

A thesis submitted for the degree of Doctor of Philosophy.

The University of Edinburgh.

July 24, 2008

#### Abstract

Multimedia communication will be an important application in future wireless communication. The second-generation mobile communication systems already support basic multimedia services such as voice, text-messaging services and still-imaging communication. However, next generation wireless communication technology combined with advances in integrated circuit design and process fabrication technology will allow more data to be processed and transmitted through wireless channels. This will lift the current barriers and enable more demanding multimedia applications such as video telephony, video conferencing and video streaming.

Video compression plays an important role in today's wireless communications. It allows raw video data to be compressed before it is sent through a wireless channel. However, video compression is compute-intensive and dissipates a significant amount of power. This is a major limitation in today's portable devices. Existing multimedia devices can only play video applications for a short time before the battery is depleted. This limits the user's entertainment experience and becomes a major bottleneck for the development of more attractive applications.

The focus of this thesis is to design a low power video compression system for wireless communication. In this thesis, we propose techniques to minimise the power consumption at the algorithmic and architectural level. The low power is achieved by minimising the switching power between interacting modules that contribute to major the power consumption in H.264 standard.

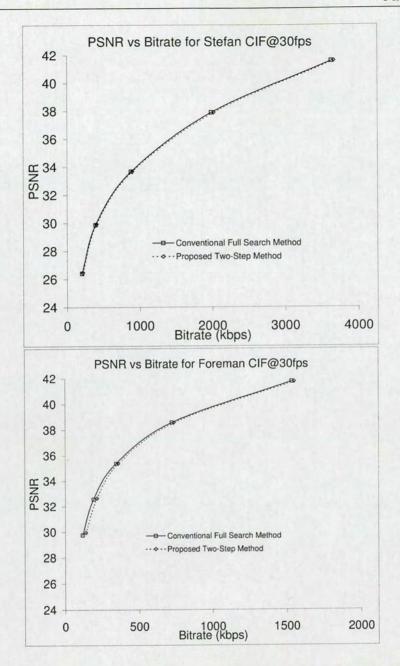

Motion estimation (ME) has been identified as the main bottleneck in MPEG video compression, including in the H.264 system where it takes up to 90% of the coding time. To reduce the power consumption in motion estimation hardware architecture, we have proposed a two-step algorithm that minimises the memory bandwidth and computational load of the ME. In this technique, the search is performed in low resolution mode at the first stage followed by high resolution mode in the second stage. This method reduces the total computation and memory access compared to the conventional method without significantly degrading the picture quality. The simulation results show that the proposed method gives good PSNR as compared to the conventional full search with PSNR drop < 0.5dB.

An energy efficient hardware for implementing the proposed two-step method is suggested. The architecture is able to perform both low resolution and high resolution searches without significantly increasing the area overhead. With a unique pixel arrangement, the proposed method is able to perform at both low resolution and high resolution while still being able to reduce the memory bandwidth. The results show that the proposed architecture is able to save up to 53% energy as compared to the conventional full search architecture.

In addition, video compression is a data intensive application where the data need to be read and stored between the main memory and the computational unit. In this thesis, we have proposed a method to reduce the bus switching activity on off-chip busses due to multiple search area requirements during motion prediction in H.264. An interframe bus encoding that exploits the high correlation between frames achieved significant power saving as compared to the conventional method. The proposed technique is able to reduce the off chip bus switching activity by 53%, which is equivalent to a 38% reduction of power consumption on a typical off-chip wire capacitance.

Finally, the proposed low power ME architecture and bus encoding technique were implemented on the H.264 system. The results show that the two-step algorithm is able to save 40% energy over the conventional system, while the interframe bus encoding technique saves 58% energy when transferring search area pixels on the 32-bit bus compared to the unencoded bus.

#### Publication

#### **Refereed Papers**

- 1. A. Bahari, T. Arslan, and A. T. Erdogan, "Interframe bus encoding technique for low power video compression," 20th International Conference on VLSI Design, pp. 691 698, Jan 2007.

- 2. A. Bahari, T. Arslan, and A. T. Erdogan, "Low power variable block size motion estimation using pixel truncation," IEEE International Symposium on Circuits and Systems, pp. 3663 3666, May 2007.

- 3. A. Bahari, T. Arslan, and A. T. Erdogan, "Reduced computation and memory access for VBSME using pixel truncation," 20th IEEE International SOC Conference, Sep 2007.

- 4. A. Bahari, T. Arslan, and A. T. Erdogan, "Low computation and memory access for variable block size motion estimation using pixel truncation," IEEE Workshop on Signal Processing Systems, pp.681 685, Oct 2007.

- 5. A. Bahari, T. Arslan, and A. T. Erdogan, "Low power hardware architecture for VBSME using pixel truncation," 21st International Conference on VLSI Design, pp.389 395, Jan 2008.

#### **Submitted Papers**

1. A. Bahari, T. Arslan, and A. T. Erdogan, "Interframe bus encoding technique for low power H.264 video compression," Submitted to 21st IEEE International SOC Conference.

2. A. Bahari, T. Arslan, and A. T. Erdogan, "Low power H.264 video compression architectures for mobile communication," Submitted to IEEE Transactions on Very Large Scale Integration (VLSI) Systems.

### Acknowledgements

I would like to thank my supervisor, Professor Tughrul Arslan, for his excellent guidance and expertise throughout my research work.

I would also like to thank my second supervisor, Dr. Ahmet T. Erdogan, for his help and advice during different stages of my PhD.

Many thanks to those in the School of Electronics and Engineering, University of Edinburgh, especially in the System Level Integration Group (SLIG), for those memorable years.

My thanks go to my sponsor, the Government of Malaysia, for funding my studies.

Many thanks are also due to my parents for their guidance and support.

Special thanks to my wife for her love, care and encouragement during my studies. Thank you to my sons for making my life so wonderful.

## Contents

|   |      | Publication iv                                      |  |  |  |  |  |  |  |

|---|------|-----------------------------------------------------|--|--|--|--|--|--|--|

|   |      | Declaration of originality vi                       |  |  |  |  |  |  |  |

|   |      | Acknowledgements vii                                |  |  |  |  |  |  |  |

|   |      | Contents                                            |  |  |  |  |  |  |  |

|   |      | List of figures                                     |  |  |  |  |  |  |  |

|   |      | List of tables xiii                                 |  |  |  |  |  |  |  |

|   |      | Acronyms and abbreviations                          |  |  |  |  |  |  |  |

|   |      | Nomenclature                                        |  |  |  |  |  |  |  |

| 1 | Intr | oduction 1                                          |  |  |  |  |  |  |  |

| - | 1.1  | Motivation                                          |  |  |  |  |  |  |  |

|   | 1.2  | Thesis Contribution                                 |  |  |  |  |  |  |  |

|   | 1.3  | Thesis Structure                                    |  |  |  |  |  |  |  |

|   | 1.4  | Summary                                             |  |  |  |  |  |  |  |

|   | 1.4  | Summary                                             |  |  |  |  |  |  |  |

| 2 | Low  | Low Power CMOS VLSI Design 6                        |  |  |  |  |  |  |  |

|   | 2.1  | Introduction                                        |  |  |  |  |  |  |  |

|   | 2.2  | Low Power Electronics Design                        |  |  |  |  |  |  |  |

|   | 2.3  | Sources of CMOS Power Consumption                   |  |  |  |  |  |  |  |

|   |      | 2.3.1 Switching Power                               |  |  |  |  |  |  |  |

|   | 2.4  | General Low Power Design Techniques for VLSI Design |  |  |  |  |  |  |  |

|   | 2.5  | Power Estimation Techniques                         |  |  |  |  |  |  |  |

|   | 2.6  | Design Flow                                         |  |  |  |  |  |  |  |

|   | 2.7  | Summary                                             |  |  |  |  |  |  |  |

| 3 | Vid  | eo Compression 24                                   |  |  |  |  |  |  |  |

| 3 | 3.1  | Introduction                                        |  |  |  |  |  |  |  |

|   | 3.2  | Video Data                                          |  |  |  |  |  |  |  |

|   | 3.3  | Video Compression                                   |  |  |  |  |  |  |  |

|   | 3.3  | 3.3.1 Motion Prediction                             |  |  |  |  |  |  |  |

|   |      | 3.3.2 Transform Coding                              |  |  |  |  |  |  |  |

|   |      | 5.5.2 Hansiothi Coung                               |  |  |  |  |  |  |  |

|   |      | 5.5.5 Entropy Coding                                |  |  |  |  |  |  |  |

|   |      | 5.5.4 Rate Control and Quantisation                 |  |  |  |  |  |  |  |

|   |      | J.J.J Deblocking I itel                             |  |  |  |  |  |  |  |

|   | 3.4  | 11.204 video Compression Standard                   |  |  |  |  |  |  |  |

|   | 3.5  | 11.204 Computational Load                           |  |  |  |  |  |  |  |

|   | 3.6  | Video Quality Measures                              |  |  |  |  |  |  |  |

|   | 37   | Summary 50                                          |  |  |  |  |  |  |  |

| 4 | Low  | Power Works on Video Compression                                      | 51  |

|---|------|-----------------------------------------------------------------------|-----|

|   | 4.1  | Introduction                                                          | 51  |

|   | 4.2  | Low Power Motion Estimation                                           | 52  |

|   | 4.3  | Low Power Transform Coding                                            | 54  |

|   | 4.4  | Low Power MPEG-4 System                                               | 54  |

|   | 4.5  | Low Power Memory for Video Compression                                | 56  |

|   | 4.6  | Further Discussion                                                    | 58  |

|   | 4.7  | Summary                                                               | 59  |

| _ | Low  | Computation and Memory Access for Variable Block Size Motion Estima-  |     |

| 5 |      | using Pixel Truncation                                                | 60  |

|   | 5.1  | Introduction                                                          | 60  |

|   | 5.2  | Low Resolution Motion Estimation                                      | 61  |

|   | 5.3  | The Effect of Pixel Truncation for VBSME                              | 63  |

|   | 5.4  | Two-Step Algorithm                                                    | 67  |

|   | 5.5  | Results and Discussion                                                | 73  |

|   | 5.6  | Summary                                                               | 80  |

|   |      |                                                                       |     |

| 6 |      | gy Efficient Motion Estimation Architecture for H.264 VBSME using The | 0.1 |

|   |      | -Step Algorithm                                                       | 81  |

|   | 6.1  | Introduction                                                          | 81  |

|   | 6.2  | Motion Estimation Implementation                                      | 82  |

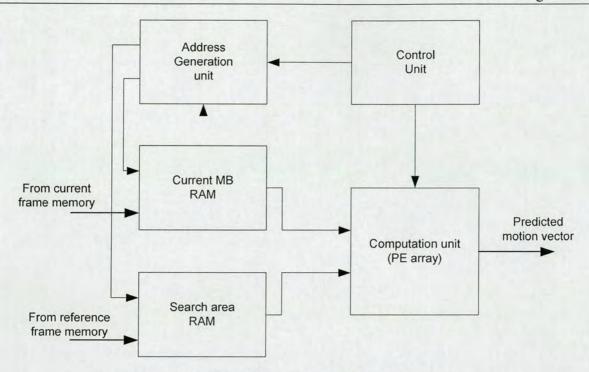

|   |      | 6.2.1 General Motion Estimation Architecture                          | 83  |

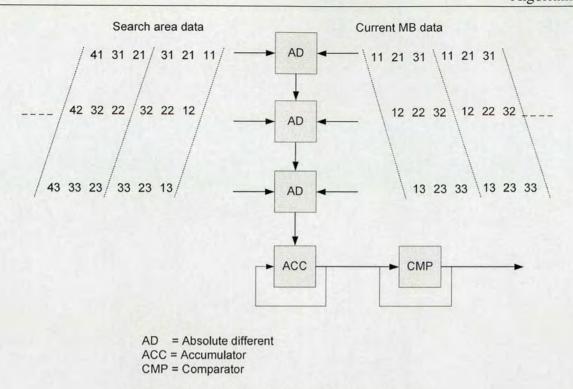

|   |      | 6.2.2 One-dimensional Motion Estimation (1D ME)                       | 85  |

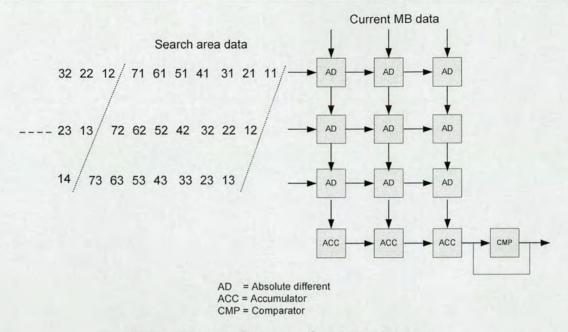

|   |      | 6.2.3 Two-dimensional Motion Estimation (2D ME)                       | 86  |

|   | 6.3  | Methodology and Hardware Design                                       | 87  |

|   |      | 6.3.1 Computation Unit                                                | 88  |

|   |      | 6.3.2 Memory Architecture                                             | 93  |

|   |      | 6.3.3 Overall Architecture                                            | 95  |

|   | 6.4  | Results                                                               | 96  |

|   | 6.5  | Summary                                                               | 99  |

| 7 | Into | rframe Bus Encoding Technique for Low Power Video Compression         | 100 |

| ' | 7.1  | Introduction                                                          |     |

|   | 7.1  | Bus Encoding                                                          |     |

|   | 7.3  | Previous Work                                                         |     |

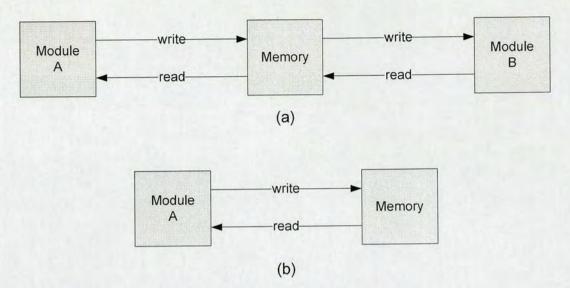

|   |      | Intraframe Decorrelation                                              | 107 |

|   | 7.4  | Interframe Decorrelation                                              | 109 |

|   | 7.5  |                                                                       |     |

|   | 7.6  | Results and Discussion                                                |     |

|   | 7.7  | Summary                                                               | 11/ |

| 8 | Low  | power 11.204 System                                                   | 118 |

|   | 8.1  | Introduction                                                          | 118 |

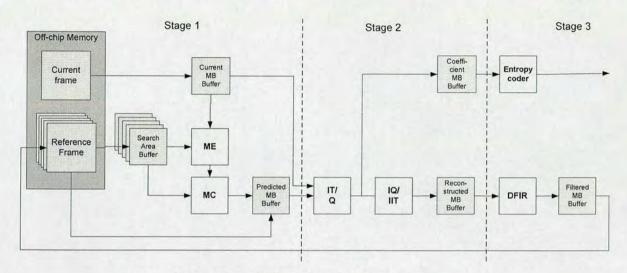

|   | 82   | H.264 Architecture                                                    | 119 |

|    |        | 8.2.1   | Motion Estimation                          | . 122 |

|----|--------|---------|--------------------------------------------|-------|

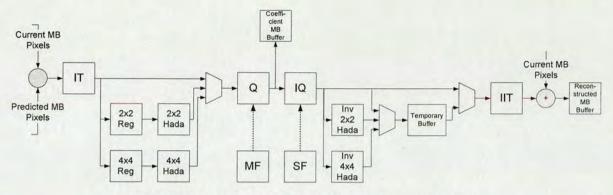

|    |        | 8.2.2   | Transform and Quantiser Module             | . 123 |

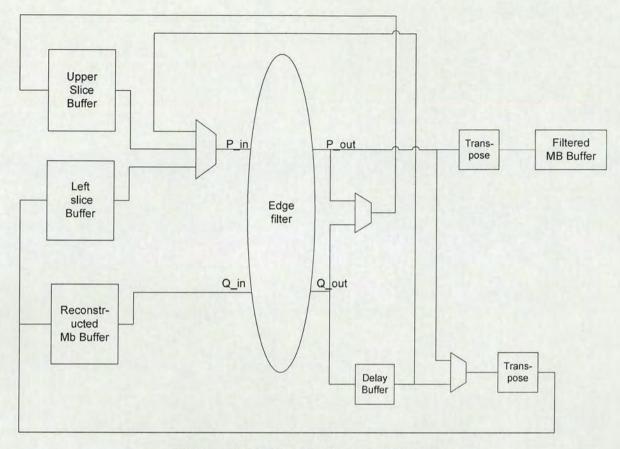

|    |        | 8.2.3   | Deblocking Filter                          | . 124 |

|    |        | 8.2.4   | Entropy Coding                             | . 126 |

|    | 8.3    |         | ower H.264 System                          | . 127 |

|    |        | 8.3.1   | Two-step Search                            | . 127 |

|    |        | 8.3.2   | Interframe Bus Encoding                    | . 128 |

|    | 8.4    | Results |                                            | . 131 |

|    |        | 8.4.1   | Conventional H.264 Architecture            | . 132 |

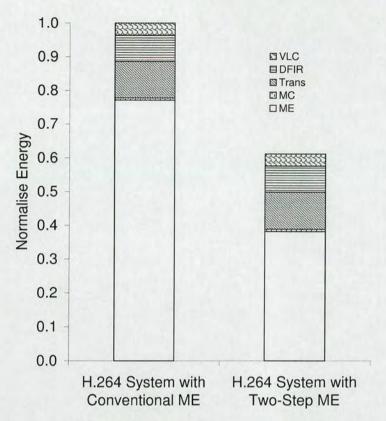

|    |        | 8.4.2   | Two-Step Motion Estimation in H.264 System | . 133 |

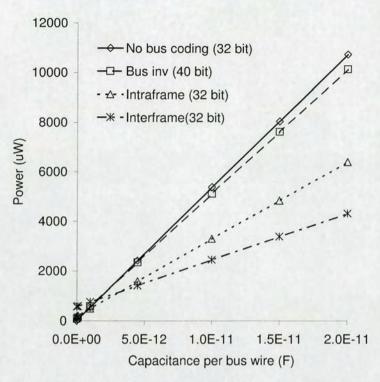

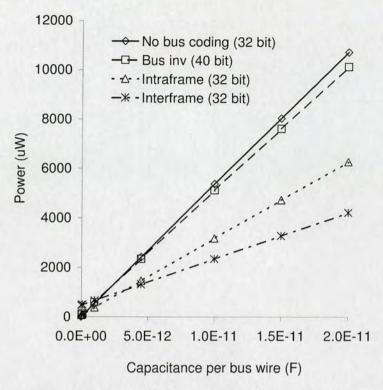

|    |        | 8.4.3   | Interframe Bus Encoding in H.264 System    | . 135 |

|    |        | 8.4.4   | Overall Energy saving                      | . 139 |

|    | 8.5    | Summ    | ary                                        |       |

| 9  | Con    | clusion |                                            | 142   |

|    | 9.1    |         | uction                                     | . 142 |

|    | 9.2    | Thesis  | Conclusion and Discussion                  | . 142 |

|    | 9.3    | Summ    | ary of Achievements                        | . 144 |

|    | 9.4    | Future  | : Work                                     | . 145 |

|    | 9.5    | Final C | Comment                                    | . 146 |

| Re | eferen | ces     |                                            | 147   |

|    |        |         |                                            |       |

## List of figures

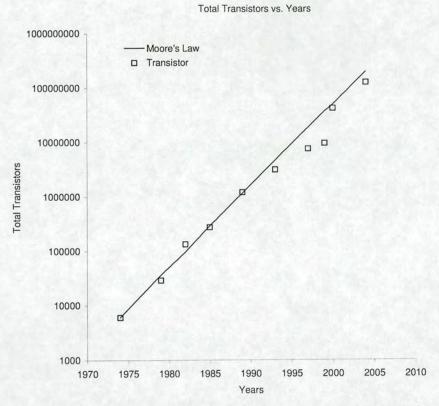

| 2.1  | Total transistors vs. time for Intel processors. [6]                        | 8        |

|------|-----------------------------------------------------------------------------|----------|

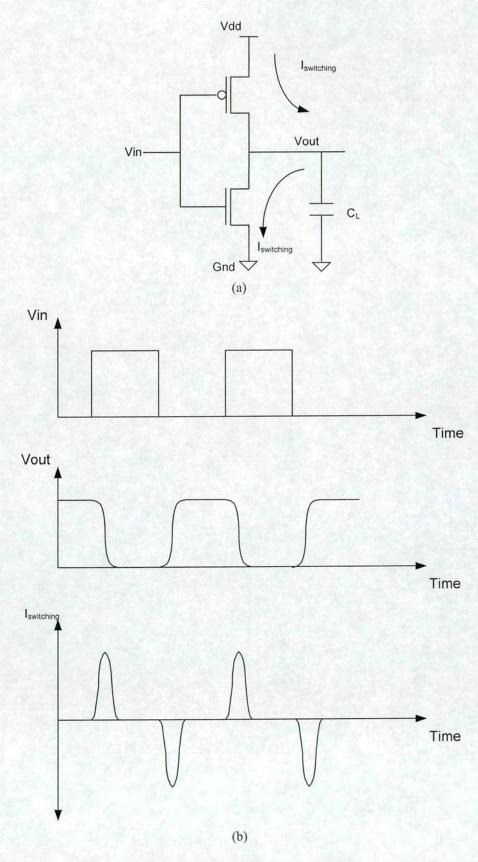

|      | output voltage/current                                                      | 13       |

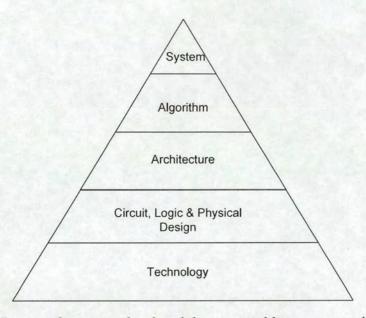

| 2.3  | Design abstraction level and the potential low power techniques [13]        | 14       |

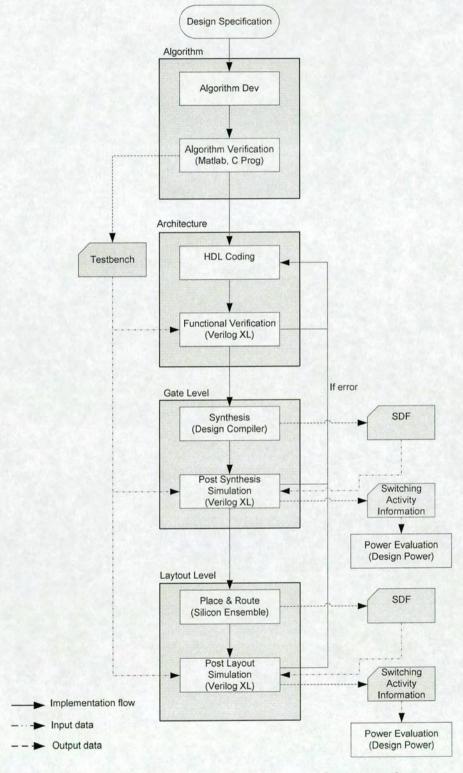

| 2.4  | Design flow for hardware implementation, verification and power evaluation. | 20       |

| 3.1  | Video camera system                                                         | 26       |

| 3.2  | Picture element (pixel)                                                     | 26<br>30 |

| 3.3  | Video coding standard history [43]                                          | 32       |

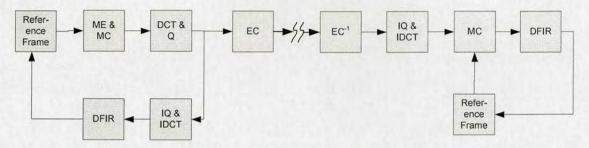

| 3.4  | Generic video encoder-decoder block diagram                                 | 32       |

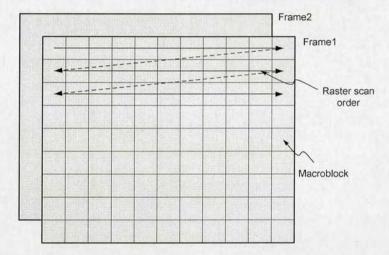

| 3.5  | MB raster scan                                                              | 34       |

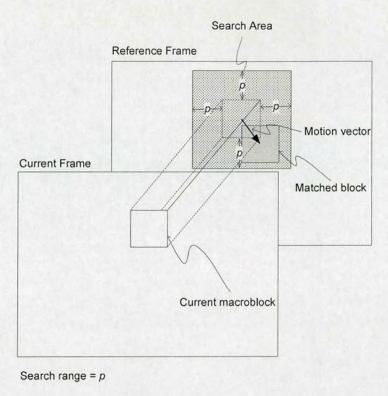

| 3.6  | Search area                                                                 | 36       |

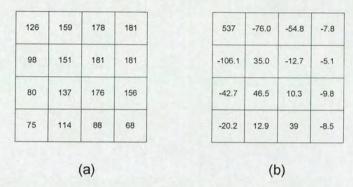

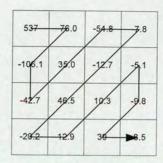

| 3.7  | Transform coding (a) image data (b) DCT coefficient values                  | 37       |

| 3.8  | Zig-zag scanning of coefficient data                                        | 42       |

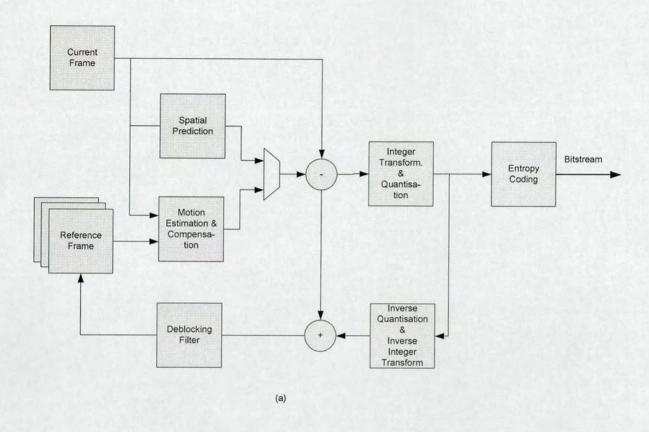

| 3.9  | H.264 block diagram (a) encoder (b) decoder                                 | 49       |

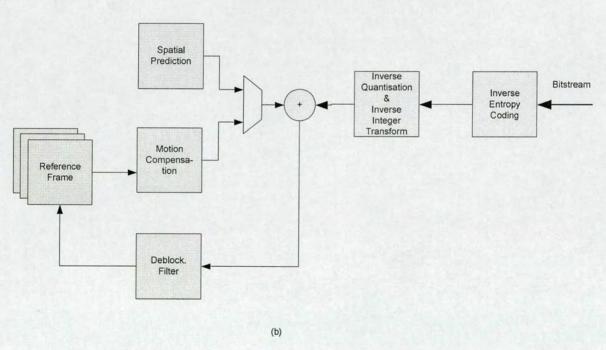

| 3.10 | MPEG video sequences snapshots                                              | 4)       |

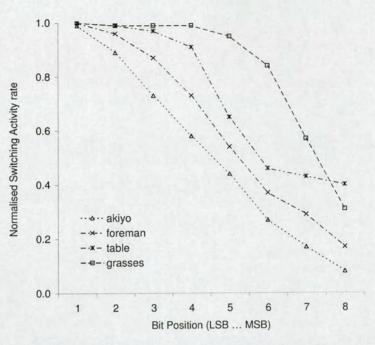

| 5.1  | Bit switching activity for video data.                                      | 64       |

| 5.2  | Total switching activity vs. number of truncated LSBs                       | 64       |

| 5.3  | Pixel truncation for Foreman sequences                                      | 66       |

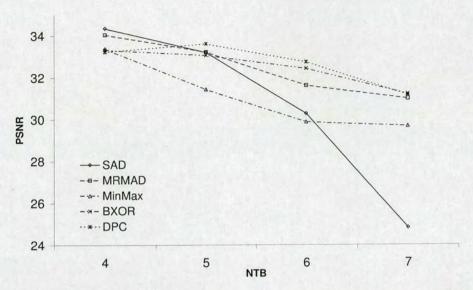

| 5.4  | Pixel truncation algorithm using two step approach                          | 68       |

| 5.5  | Average PSNR vs. NTB for different block matching criteria using 8x8 block  |          |

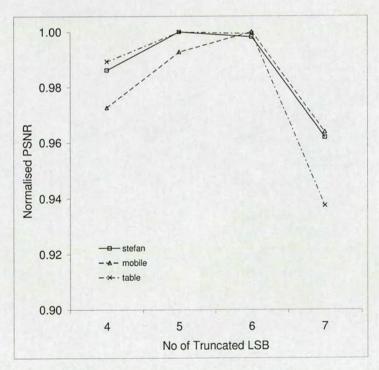

|      | size (50 Foreman frame sequences, QCIF@30fps, search range, p=[-8,7]).      | 70       |

| 5.6  | Normalised PSNR vs. NTB using DPC as matching criteria on 8x8 block size    |          |

|      | (Stefan, Mobile and Table Tennis sequences, 50 frames each, QCIF@30fps,     | 44       |

|      | search range, p=[-8,7])                                                     | 70       |

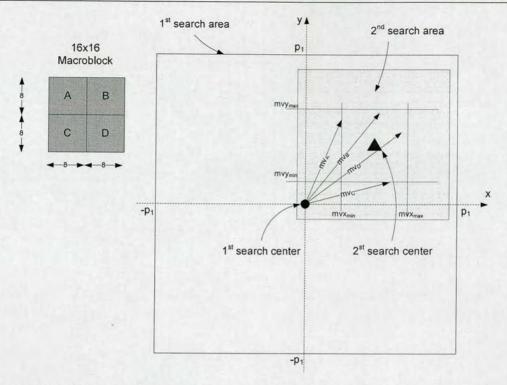

| 5.7  | Defining the second search area for the proposed two-step algorithm         | 73       |

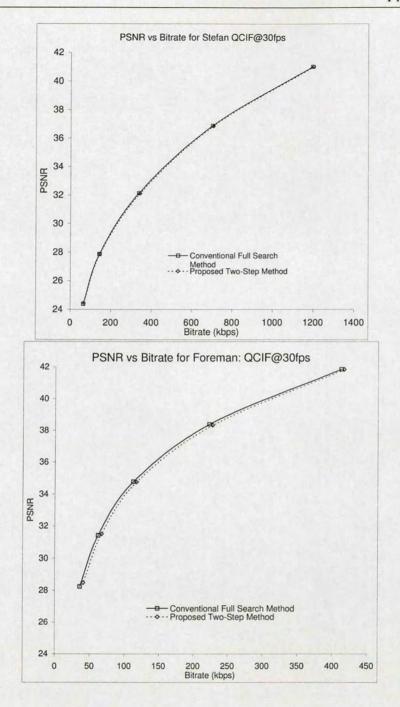

| 5.8  | PSNR vs. Bitrate using the proposed 2-Step method for QCIF@30fps            | 78       |

| 5.9  | PSNR vs. Bitrate using the proposed 2-Step method for CIF@30fps             | 79       |

| 6.1  | General motion estimation architecture                                      | 84       |

| 6.2  | One-dimensional motion estimation.                                          | 85       |

| 6.3  | Two-dimensional motion estimation.                                          | 87       |

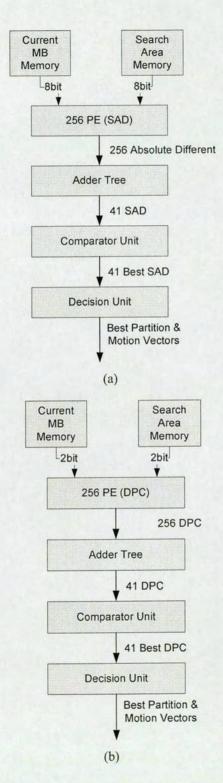

| 6.4  | Block diagrams for (a) me_sad (b) me_dpc                                    | 89       |

| 6.5  | Processing element (PE) to support (a) SAD and (b) DPC                      | 90       |

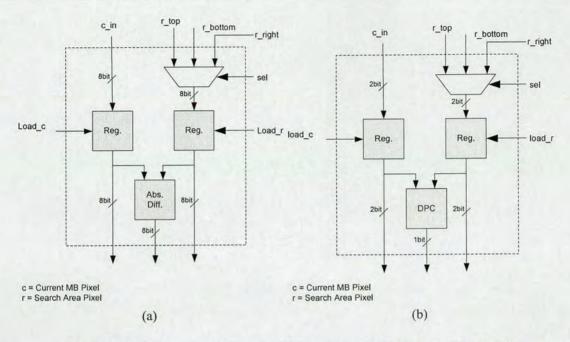

| 6.6  | Computational unit: (a) me_split (b) me_combine                             | 92       |

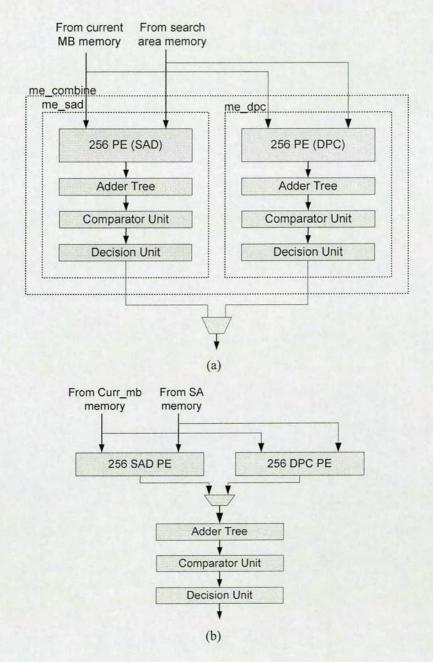

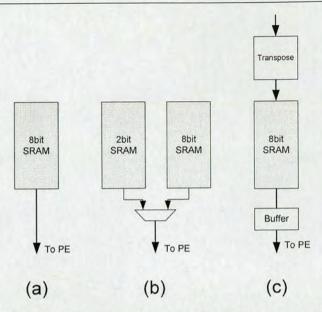

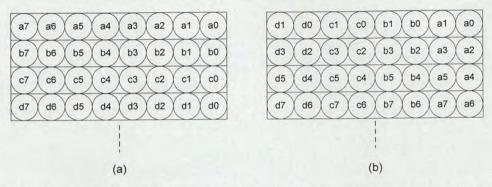

| 6.7  | SA memory arrangement (a) mem8 (b) mem28, (c) mem8pre                       | 94       |

| 6.8  | Storing 8bit pixel in 8bit memory (a) conventional arrangement (b) mem8pre  | 95       |

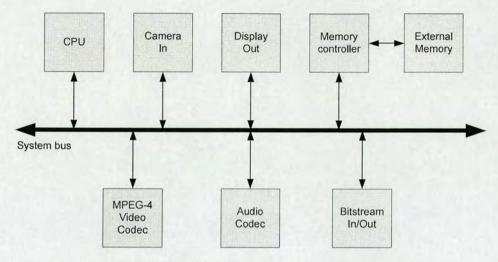

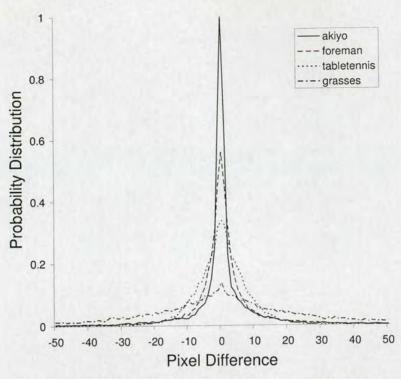

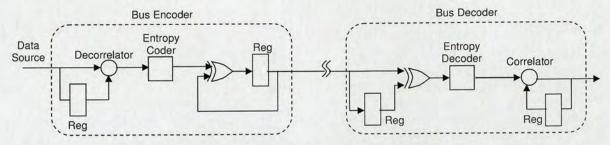

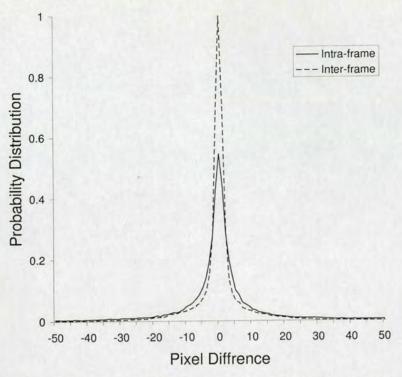

| 7.1  | Typical video communication system                                            |

|------|-------------------------------------------------------------------------------|

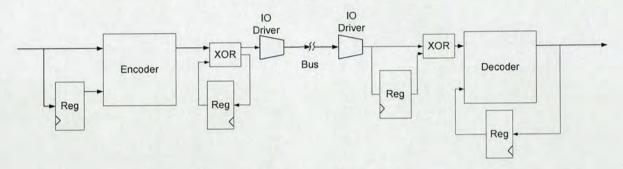

| 7.2  | Generic bus encoder                                                           |

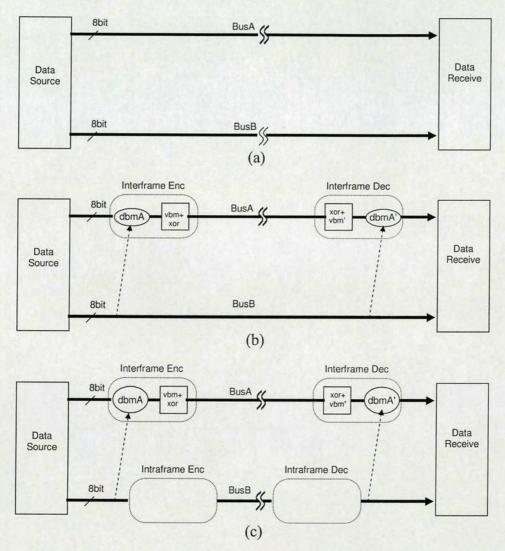

| 7.3  | Bus transmission scenario                                                     |

| 7.4  | Intraframe decorrelation using adjacent pixel                                 |

| 7.5  | dbm-vbm bus encoder and decoder                                               |

| 7.6  | Interframe vs. intraframe decorrelation for Foreman sequence                  |

| 7.7  | Experiment setup: (a) Unencoded buses (b) Encoding BusA using interframe      |

|      | (c) Encoding BusA and BusB                                                    |

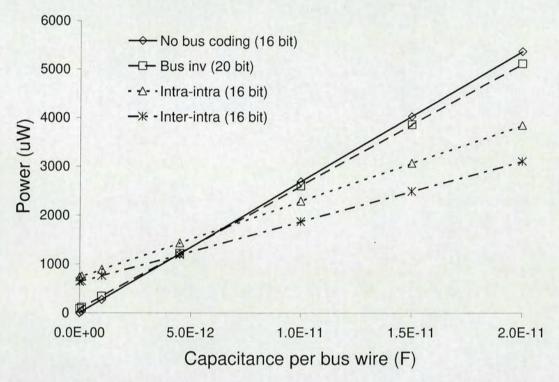

| 7.8  | Total bus power consumption vs. wire capacitance                              |

| 0.1  | 120                                                                           |

| 8.1  | MPEG system 3 stage pipeline                                                  |

| 8.2  | Integer transform and quantiser architecture                                  |

| 8.3  | Deblocking filter architecture                                                |

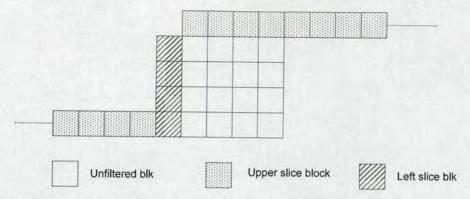

| 8.4  | Arrangement of blocks for deblocking filter: unfiltered blocks of current MB, |

|      | upper slice blocks and left slice blocks                                      |

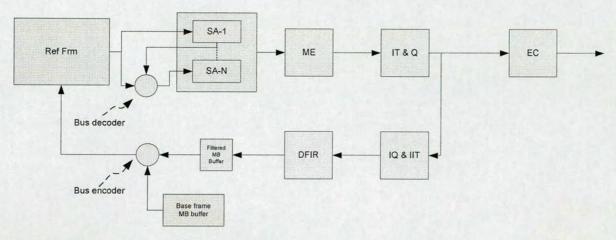

| 8.5  | H.264 system modified to include an interframe bus coder                      |

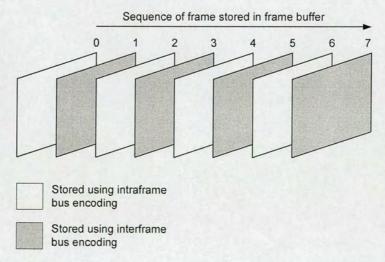

| 8.6  | Reference frame arrangement of external buffer and the type of bus encoding   |

|      | applied to it                                                                 |

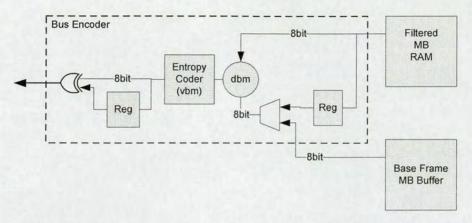

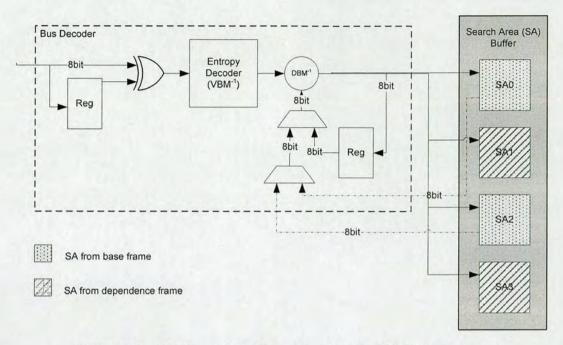

| 8.7  | Interframe-intraframe encoder for H.264 hardware                              |

| 8.8  | Interframe-intraframe decoder for H.264 hardware                              |

| 8.9  | Energy comparison of H.264 system using conventional and two-step ME          |

|      | using one reference frame                                                     |

| 8.10 | Power consumption of 32 bit bus at 6MHz when transferring pixels into the     |

|      | external reference frame memory                                               |

| 8.11 | Power consumption of 32 bit bus at 6MHz when loading pixels from the          |

|      | external reference frame memory                                               |

|      |                                                                               |

## List of tables

| 3.1<br>3.2<br>3.3                      | Typical frame size and rates  YUV Format  H.264 Profiles                                                                                                                                                                                                                                            | 27<br>29<br>40                   |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9 | H.264 Level and the corresponding picture type, frame rate and bitrates [52]  [53]                                                                                                                                                                                                                  | 40<br>40<br>41<br>45<br>48<br>48 |

| 5.1<br>5.2                             | Percentage of matched candidates with $SAD=0$ during motion estimation using Foreman sequence (search range, p = $\pm 8$ )                                                                                                                                                                          | 65                               |

| 5.3                                    | (search range, $p = \pm 8$ )                                                                                                                                                                                                                                                                        | 67                               |

| 5.4                                    | candidate, respectively)                                                                                                                                                                                                                                                                            | 71<br>74                         |

| 5.5                                    | 8,7]                                                                                                                                                                                                                                                                                                | 74                               |

| <ul><li>5.6</li><li>5.7</li></ul>      | Total number of memory access and matching computation for fs_p4, fs_p8, and $2\text{step}16$ ( $p$ represents the search range; $q$ and $r$ are the numbers of memory access and matching computation per candidate, respectively) Average PSNR drop (dB) for several motion estimation techniques | 75<br>77                         |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6 | me_sad and me_dpc area (mm²) and power (mW)                                                                                                                                                                                                                                                         | 91<br>95<br>97<br>98<br>99       |

| 7.1<br>7.2<br>7.3                      | QCIF, CIF and 4CIF frame buffer size YUV420 in MByte                                                                                                                                                                                                                                                | 102<br>103                       |

|                                        | percentage of transition reduction when compared with unencoded bus (Sav)                                                                                                                                                                                                                           | 113                              |

| 7.4  | Total number of transitions (Trans) for different frame distances applied to interframe bus encoding, and percentage of transition reduction when com- |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | pared with unencoded bus (Sav)                                                                                                                         |

| 7.5  | Total number of transitions (Trans) for different bus codings implemented on                                                                           |

|      | BusA and BusB, and percentage of transition reduction when compared with                                                                               |

| 7.   | unencoded bus (Sav)                                                                                                                                    |

| 7.6  | mented on BusA and BusB                                                                                                                                |

| 8.1  | Clock cycle requirements for each module                                                                                                               |

| 8.2  | Pipeline buffer's size and type and the total number of SRAM required 122                                                                              |

| 8.3  | Area for conventional H.264 architecture                                                                                                               |

| 8.4  | Energy consumption (nJ) for the conventional H.264 architecture at 6MHz                                                                                |

|      | for one reference frame                                                                                                                                |

| 8.5  | Area for the proposed H.264 low power architecture                                                                                                     |

| 8.6  | Energy consumption (nJ) for the proposed H.264 low power architecture at                                                                               |

|      | 6MHz for one reference frame                                                                                                                           |

| 8.7  | The bus encoding area and power overhead required to implement the interframe-                                                                         |

|      | intraframe bus coding on a 32 bit bus at 6MHz                                                                                                          |

| 8.8  | The bus decoding area and power overhead required to implement the interframe-                                                                         |

|      | intraframe bus coding at 6MHz                                                                                                                          |

| 8.9  | Total energy consumption on 32bit bus at 6MHz with 15pF per bus wire when                                                                              |

|      | sending one filtered MB to external frame buffer                                                                                                       |

| 8.10 | Total energy consumption on 32-bit bus at 6MHz with 15pF per bus wire                                                                                  |

|      | when receiving one search area from external frame buffer for one reference                                                                            |

|      | frame                                                                                                                                                  |

| 8.11 | Overall energy consumption (nJ) when implement bolth the low power mo-                                                                                 |

|      | tion estimation and interframe bus encoding technique into the H.264 system. 139                                                                       |

| 8.12 | Comparison with other H.264 encoders                                                                                                                   |

|      |                                                                                                                                                        |

### Acronyms and abbreviations

1BT One-Bit Transform

1D One-Dimension

2BT Two-Bit Transform

2D Two-Dimension

3SS Three Step Search

APBI Adaptive Partial Bus Invert

ASIC Application Specific Integrated Circuit

AVC Advance Video Coding

BF Base Frame

BI Bus Invert Technique

BXOR Binary XOR

CAVLC Context Adaptive Variable Length Codes

CCD Charge-coupled Device

CDF Cumulative Density Function

CIF Common Intermediate Format

CMB Current Macroblock

CMOS Complementary Metal Oxide Semiconductor

CPL Complementary Pass Logic Circuits

CPU Central Processing Unit

DC Direct Current

DCT Discrete Cosine Transform

DA Distributed Arithmetic

DF Dependence Frame

DFIR Deblocking Filter

dbm Difference Based Map

DMA Direct Memory Access

DPC Difference Pixel Count

DPM Dynamic Power Management

DS Diamond Search

DSP Digial Signal Processor DVD Digital Video Disc

DVS Dynamic Voltage Scaling

EC Entropy Coder FIFO First In First Out

GIP Giga Instruction Persecond

H.264 Recommendation of ITU Telecommunication Standardization Sector

HADA Hadamard transform

HDL Hardware Description Language

HDTV High Definition TV HVS Human Visual System

IDCT Inverse Discrete Cosine Transform

IQ Inverse Quantizer

LRQME Low Resolution Quantize Motion Estimation

LSB Low Significant Bits

MAD Mean Absolute Different

MB Macroblock

MC Motion Compensation

ME Motion Estimation

MF Multiplication Factor

MIPS Million Instruction Persecond MMS Multimedia Messaging Service MPEG Motion Picture Expert Group

MRMAD Mean Reduce MAD MSB Most Significant Bits

MV Motion Vector

NMOS P-channel Metal Oxide Semiconductor Field-Effect Transistor

NTB Number of Truncated Bits NTSS New Three Step Search

PBI Partial Bus Invert

PDA Personal digital assistant PE Processing Element

PMOS P-channel Metal Oxide Semiconductor Field-Effect Transistor PMVFAST Prediction Motion Vector Field Adaptive Search Technique

PNR Place and Route

PSNR Peak Signal to Noise Ratio

Q Quantiser

OCIF Quarter Common Intermediate Format

QP Quantiser Parameter

RAM Random Access Memory

RC Rate Control RD Rate-Distortion

RGB Red/Green/Blue Colour Format

RISC Reduced Instruction Set Computing

RTL Register Transfer Level

SA Search Area

SAD Sum of Absolute Difference SDF Standard Delay Format

SDRAM Synchronous Dynamic Random Access Memory

SF Scaling Factor SOC System on Chip SOI Silicon on Insulator

SPICE Simulation Program with Integrated Circuit Emphasis

SRAM Static Random Access Memory

UMC United Microelectronics Corporation

vbm Value Based Map

VBSME Variable Block Size Motion Estimation

VCEG Video Coding Expert Group VLC Variable Length Codes

VLSI Very Large Scale Integrated Circuit

WMV Windows Media Video

YUV Luminance/Blue chrominance/Red chrominance Colour Format

## Nomenclature

| $\alpha$    | switching activity                                                                   |

|-------------|--------------------------------------------------------------------------------------|

| $\bar{p}$   | Current MB mean                                                                      |

| $\pi$       | Pi, the ratio of the circumference of a circle to its diameter (Value = 3.141592654) |

| B           | Blue color signal                                                                    |

| C(k,l)      | Current macroblock pixel                                                             |

| $C_i$       | Load Capacitance                                                                     |

| $C_L$       | Capacitance Load                                                                     |

| dbm         | Difference Based Map                                                                 |

| f           | Clock frequency                                                                      |

| G           | Green color signal                                                                   |

| Gnd         | Electrical Ground                                                                    |

| H           | Search area height                                                                   |

| i           | Horizontal coordinate in the image data sample                                       |

| j           | Vertical coordinate in the image data sample                                         |

| J           | Frame rate                                                                           |

| M           | Macroblock height                                                                    |

| MSE         | Mean squared error                                                                   |

| mvx         | Horizontal motion vector of a macroblock                                             |

| $mvx_A$     | Horizontal motion vector for top-left 8x8 partition of a macroblock                  |

| $mvx_B$     | Horizontal motion vector for top-right 8x8 partition of a macroblock                 |

| $mvx_C$     | Horizontal motion vector for bottom-left 8x8 partition of a macroblock               |

| $mvx_D$     | Horizontal motion vector for bottom-right 8x8 partition of a macroblock              |

| $mvx_{min}$ | Minimum horizontal motion vector for 8x8 partitions of a macroblock                  |

| $mvx_{max}$ | Maximum horizontal motion vector for 8x8 partitions of a macroblock                  |

| mvy         | Vertical motion vector of a macroblock                                               |

| $mvy_A$     | Vertical motion vector for top-left 8x8 partition of a macroblock                    |

| $mvy_B$     | Vertical motion vector for top-right 8x8 partition of a macroblock                   |

| $mvy_C$     | Vertical motion vector for bottom-left 8x8 partition of a macroblock                 |

| $mvy_D$     | Vertical motion vector for bottom-right 8x8 partition of a macroblock                |

| $mvy_{min}$ | Minimum vertical motion vector for 8x8 partitions of a macroblock                    |

| $mvy_{max}$ | Maximum vertical motion vector for 8x8 partitions of a macroblock                    |

| N           | Macroblock width                                                                     |

| p           | Search range                                                                         |

| p(i,j)      | Pixel vlaue of the current macroblock                                                |

| $p_1$       | First search range                                                                   |

| $p_2$       | Second search range                                                                  |

$P_{CL}$  Power consume by the capacitance load  $P_{Dec}$  Bus decoder circuit power consumption  $P_{Enc}$  Bus encoder circuit power consumption

$egin{array}{ll} P_{leakage} & & \ Leakage \ power \ P_{short-circuit} & \ Short-circuit \ power \ P_{switching} & \ Switching \ power \ P_{T} & \ Total \ power \ \end{array}$

$p_i(x_i)$  Transition probability at node x  $P_{total}$  Total power consumption

PMAX The maximum possible pixel value of the image data

R Red color signal

R(i+k, j+l) Candidate macroblock pixel SAD(i, j) Sum of absolute difference

first quantisation threshold for LRQME

Second quantisation threshold for LRQME

Third quantisation threshold for LRQME

$egin{array}{lll} V_{dd} & ext{Power supply} \\ vbm & ext{Value Based Map} \\ W & ext{Search area width} \\ \end{array}$

x Horizontal Coordinate in the transform domain

$X_{ij}$  Image sample

y Vertical Coordinate in the transform domain

Y Luminance signal  $Y_{xy}$  Coefficient value

## Chapter 1 **Introduction**

#### 1.1 Motivation

Multimedia will be an important application in future wireless communication [1]. Second-generation mobile communication systems already support basic multimedia services such as voice, text-messaging services and still-imaging communication [2]. However, next generation wireless communication technology combined with advances in integrated circuit design and process fabrication technology will allow more data to be processed and transmitted through wireless channels. This will lift the current barriers and enable more demanding multimedia applications such as video telephony, video conferencing and video streaming [3].

Video compression plays an important role in today's wireless communications. It allows raw video data to be compressed before it is sent through a wireless channel. However, video compression is compute-intensive and dissipates a significant amount of power. This is a major limitation in today's portable devices. Existing multimedia devices can only play video applications for a short time before the battery is depleted. This limits the user's entertainment experience and becomes a major bottleneck for the development of more attractive applications.

The latest video compression standard, MPEG-4 AVC/H.264 [4], gives a 50% improvement in compression efficiency compared to the previous standard. However, the coding gain

comes at the expense of increased computational complexity at the encoder. The introduction of variable block size partitions and multiple reference frames in the standard resulted in large increases in computational power and memory bandwidth during motion prediction. This thesis proposes several new implementations that reduce the power consumption in video compression systems such as in H.264.

#### 1.2 Thesis Contribution

This thesis investigates low power techniques for the MPEG-4 system at an algorithmic and architectural level. The low power is achieved by minimising the switching power between interacting modules which contribute to the major part of the power consumption.

Motion estimation (ME) has been identified as the main bottleneck in MPEG video compression, including in the H.264 system where it takes up to 90% of the coding time. To reduce the power consumption in the motion estimation hardware architecture, a two-step algorithm that minimises the memory bandwidth and computational load of the ME is proposed. In this technique, the search is performed in low resolution mode at the first stage followed by high resolution mode in the second stage. This method reduces the total computation and memory access, as compared to the conventional method, without significantly degrading the picture quality.

This work has led to the development of energy efficient hardware to perform the two-step algorithm. The proposed hardware requires minimal additional area on top of the conventional architecture, where it can perform both the conventional full search and the proposed

two-step method. With unique data arrangement, the proposed method is able to perform both low resolution and high resolution search while still being able to reduce the memory bandwidth. This allows the system to select the required ME computational load depending on the video data characteristics.

In addition, video compression is a data intensive application where the data need to be read and stored between the main memory and the computational unit. In this thesis, a method to reduce the bus switching activity on off-chip buses due to multiple search area requirements during motion prediction in H.264 is proposed. The interframe bus encoding exploits the video data characteristics to achieve significant power saving compared to the conventional method.

Finally, the proposed two-step method and the bus encoding technique are implemented on the MPEG-4 system. Due to the way in which data is stored and accessed to/from the external frame memory, the implementation of interframe bus encoding for H.264 system is also proposed. The power saving from these techniques is evaluated and compared with the conventional architecture. The results show that the proposed methods achieve significant energy savings compared to the conventional architecture.

#### 1.3 Thesis Structure

The rest of the thesis is organised as follows:

Chapter 2 discusses the sources of power consumption in CMOS VLSI design. Since the switching power is the main contributor in the total power consumption, the existing tech-

niques to minimise the power at different levels of design abstraction are discussed in this chapter.

Chapter 3 describes the existing video coding algorithms. While various video coding standards have been released, the main functional blocks are still common in most standards. These essential blocks are highlighted in this chapter. The existing video coding standards are reviewed, including the new features of H.264.

Chapter 4 discusses the existing low power strategy for video compression. In this chapter, low power techniques for essential modules are reviewed. Low power techniques at the system level and memory communication are also considered, since these modules consume a significant amount of power.

Chapter 5 presents the proposed technique to reduce the power consumption in motion estimation and the memory unit. As a result, the two-step algorithm is proposed in this chapter. The justification of this algorithm for variable block size motion estimation is first analysed. Then, the proposed algorithm is described in detail. The simulation results which show the effectiveness of this technique are discussed in this chapter.

Chapter 6 presents the proposed energy efficient hardware that utilises the proposed twostep algorithm. The existing conventional hardware for motion estimation is discussed. The performance of the proposed hardware against the conventional architecture is also presented.

Chapter 7 presents our proposed technique to reduce bus switching activity for off-chip busses in the H.264 system. Existing off-chip bus encoding techniques are first introduced. A comparison of the switching activity reduction is shown against existing methods.

Chapter 8 discusses the integration of the proposed methods into the H.264 system. The power saving is compared against the existing conventional architecture. The effectiveness of these methods in minimising the overall H.264 power consumption is discussed.

Chapter 9 summarises and concludes this thesis. In addition, the contribution of this thesis is re-highlighted and further research based on the techniques developed in this thesis is suggested.

#### 1.4 Summary

Multimedia will be important in future wireless communication. With the widespread use of this application, video compression is indispensable to allow the video data to be transmitted or stored in electronic devices. Since video compression requires high computational power, a low power solution is critical, especially for battery operated devices. This thesis proposes low power methods for minimising power in the H.264/MPEG-4 standard. This thesis focuses on the main power contributors in the H.264 system at the algorithmic and architectural levels. Particular attention is given to the interaction between modules such as motion prediction and frame memories, since they consume significant power.

## Chapter 2 Low Power CMOS VLSI Design

#### 2.1 Introduction

Low power design is becoming important in today's consumer electronics. With the increased popularity of portable devices, more electronic appliances are depending on energy supply from the battery. Furthermore, as more functions are embedded in the chip and more complex algorithms are introduced to improve the services, the chip power consumption increases dramatically. To overcome this problem, low power design is indispensable in today's electronics design. This makes today's design task more challenging since additional parameters have to be considered from the early stage of design.

This chapter discusses the source of power consumption in today's VLSI design. The evolution of technology toward CMOS technology is first reviewed to see how design trends affect power consumption in electronics devices. The main power source in today's CMOS circuit is reviewed, since this has become the main bottleneck in designing low power systems. Switching activity has been identified as the main contributor for power consumption. Existing techniques for minimising this power use are discussed in this chapter. In order to facilitate low power design, power estimation techniques are important in identifying the main power consumption in the design to be implemented. Thus, existing power estimation techniques are also discussed. Finally, the standard design flow that is used in this thesis is described.

This chapter is organised as follows. Section 2.2 reviews the background of low power electronics design. Section 2.3 discusses the main power consumption in CMOS technology. Existing low power techniques to minimise switching power consumption are discussed in Section 2.4. Power estimation techniques are discussed in Section 2.5. Section 2.6 discusses the design flow used in this thesis. Finally, section 2.7 concludes this chapter.

#### 2.2 Low Power Electronics Design

The electronics device design has evolved since the mid-20th century. Starting from the electromechanically based machines, the technology shifted to vacuum tube, before becoming dominated by bipolar transistors. The invention of the integrated circuit and complementary metal-oxide semiconductor (CMOS) technology have greatly revolutionised the way today's devices are being designed in terms of area and power consumption.

Today, CMOS is a dominant technology widely used by the industry. Compared to bipolar technology, CMOS offers better device integration and lower power consumption. At the early introduction of CMOS technology, its speed was much slower compared to bipolar. As the technology improved, the speed has now become almost comparable to that of bipolar. Furthermore, CMOS offers easier circuit design that allows automation in most design stages. This helps designers to easily integrate more transistors on a single chip.

Since its introduction, CMOS technology has seen a dramatic improvement in terms of speed, area and power. Due to reduced feature size, effective chip area has increased. Thus, area is becoming less important than before and is traded-off to reduce power [5]. Figure 2.1

Figure 2.1: Total transistors vs. time for Intel processors. [6]

shows various processors developed by Intel Corporation [6]. As seen in the graph, the number of transistors are doubled every two years as predicted by Moore's law. Processors' operation becomes more complex and more functions are added onto the chip. This results in an increased number of transistors per chip and more power dissipated on a single chip. The power consumption is becoming more serious as the design is moving toward system-on-chip (SOC).

While CMOS has advantages in improved speed, area, and power consumption driven by aggressive technology scaling, this technology will reach its limit just as did its predecessors. Many experts agree that CMOS will reach the end of its progression in about 15 years - hitting physical, technological and economic limits [7]. Thus, many studies have been done to find

other alternatives to replace CMOS. However, up to now, no feasible solution has been found that can replace the CMOS technology completely [8]. Until a better solution can be found, the power dissipation in CMOS has to be dealt with in the early design stages.

In summary, there are several reasons why low power is important in today's VLSI design. One of the main factors is the increasing demand for portable devices since the early 1990s. Since these devices are operated using battery energy, longer battery lifetime is crucial. However, while the increase of computational power is doubled every two years, the improvement in battery capacity is slow, such as 6-7% per annum for Lithium Ion (Li-ion) [9]. If low power design is not adopted, the battery energy life time will be very short, or larger batteries will be required to cope with the computational demand.

Furthermore, as the fabrication technology improves, more devices can be integrated into a single chip. This results in increases in chip temperature. Thus, more expensive packing and cooling systems are required to cope with the problem. Another serious problem due to increase of temperature is device reliability. The increase of  $10^{0}C$  results in double the device failure rate [10] and performance decreases by approximately 3% [11]. The high temperature causes problems such as electromigration, junction fatigue and dielectric breakdown.

In the following section, the main sources of power consumption in CMOS technology will be discussed. Then, the general techniques used to minimise the power consumption in CMOS circuits will be reviewed.

#### 2.3 Sources of CMOS Power Consumption

There are three main sources of power dissipation in CMOS circuits. This can be summarised as follows [5]:

$$P_{total} = P_{leakage} + P_{short-circuit} + P_{switching}$$

(2.1)

where  $P_{total}$  is the total power dissipation of a CMOS circuit,  $P_{leakage}$  is the leakage power,  $P_{short-circuit}$  is the short circuit power and  $P_{switching}$  is the switching power.

These uses of power can be categorized as dynamic or static. Dynamic power is used when the circuit is active, and largely depends on the behaviour of the switched signal, whereas static power is consumed even if the circuit is not active, i.e. in standby mode. In Equation 2.1,  $P_{leakage}$  is considered as static power, while  $P_{short-circuit}$  and  $P_{switching}$  contribute toward dynamic power. Each of these components will be discussed in the following sections.

Leakage power occurs when there is unwanted current flow in the circuit due to the physical properties of the semiconductor devices. While the value is very small, it could be a problem for battery operated devices. Any battery operated device will run out of energy, even if it is idle most of the time.

Short circuit power is used when there is a direct path from  $V_{dd}$  to Gnd. A CMOS circuit operates based on a pull-up and pull-down concept, depending on the input voltage. The pull-up and pull-down circuit is built using PMOS and NMOS networks, respectively. For a CMOS circuit to be an ideal switch, only one network is turned on at any given time.

However, in practical use, the input voltage requires a finite amount of time to change its state from  $0 \to 1$  or  $1 \to 0$ . During switching of the input, there is a time when both NMOS and PMOS networks are turned on simultaneously. This creates a path for current to flow directly between Vdd and Gnd. To reduce short-circuit power, it is important to keep the signal rise and fall times during the transition as small as possible, or at least keep both rise and fall times equal [12]. This can be done by properly sizing the transistors or by adjusting the capacitance load.

#### 2.3.1 Switching Power

Switching current causes the highest power dissipation in CMOS circuits. In some designs, it consumes about 90% of the total power [13]. Switching power occurs when the capacitance load must be charged or discharged in response to the input changing.

Fig 2.2 shows typical CMOS inverter operation with the input constantly toggled. When the input is low, the PMOS transistor is turned on and the NMOS transistor is turned off. This causes current to flow from the  $V_{dd}$ , charging up the load  $C_L$ . When the input is switched to high, the PMOS is turned off and the NMOS is turned on. Since there is a potential difference between  $C_L$  and Gnd, current flows from  $C_L$  to Gnd. On average, the switching power consumed by the inverter is given by [5]:

$$P_{switching} = C_L V_{dd}^2 f (2.2)$$

where  $C_L$  is the load capacitance,  $V_{dd}$  is the power supply and f is the rate of the toggled

input.

In synchronous digital circuits, the rate of input switching depends on the clock frequency. However, it may not toggle at the same rate as the clock. Thus, to take this into account, the input switching probability,  $\alpha$ , is used to modify Equation 2.2:

$$P_{switching} = C_L V_{dd}^2 f \alpha \tag{2.3}$$

From Equation 2.3, since power is only consumed when the capacitive load is being charged or discharged, the term  $C_L\alpha$  is known as effective capacitance. Capacitive load that is not charged or discharged will not consume any power. It is obvious that the switching power is proportional to  $V_{dd}^2$ , f and  $C_L\alpha$ . Thus the switching power can be minimised by reducing these parameters. The following section discusses how these parameters can be utilised to reduce total power and how this affects design.

# 2.4 General Low Power Design Techniques for VLSI Design

As discussed in the previous section, switching power consumes the majority of the power consumption in digital CMOS circuits. For CMOS technology with 45nm and below, leakage power will dominate the power consumption [14]. Various techniques at circuit and technology levels such as transistor stacking, multi threshold voltage CMOS, and transistor body biasing can be applied to reduce this power [15]. This thesis focuses on minimising

**Figure 2.2:** Switching current of a CMOS inverter (a) circuit schematic (b) input and output voltage/current 13

**Figure 2.3:** Design abstraction level and the potential low power techniques [13]

switching power that is applicable at algorithmic and architectural levels.

Many research studies have focused on reducing switching power, mainly by reducing the operating voltage, physical capacitance, and switching activity. In most cases, reduction of these parameters results in degradation of other performance criteria such as speed and area. For example, reducing the supply voltage results in quadratic power reduction, but increases the propagation delay in the circuit which results in reduced speed. Thus, a careful balance between power reduction and overall system performance is crucial.

Power consumption can be tackled at different levels of design abstraction as shown in Fig 2.3. The earlier the problem is addressed at the design stage, the greater the impact on power savings for the whole system. In this section, the general methods to reduce power consumption will be reviewed, starting from the system level and proceeding all the way to the technology level.

At the system level, the objective of power minimisation is to reduce the workload between

interacting modules. Since different modules require different workloads, these modules can be controlled to manage their operations. This is the basic reason for implementing dynamic power management (DPM), commonly used in communication systems and interactive devices. To minimise power consumption, the system operates in different states, such as active, idle and sleep mode. The transition between these states is controlled by a power manager such as timeout policy [16] and predictive policy [17].

While DPM selectively forces components into a low-power state, dynamic voltage scaling (DVS) changes processor speed and voltage at run time depending on needs. The voltage is reduced only when this will not result in noticeable degradation of performance. In DVS, the voltage and speed are controlled by a set of algorithms such as based on the processor utilisation within fixed intervals [18][19] or by analysing application requirements [20].

At the algorithmic level, low power design is achieved by transforming the computation method so that an optimum operation can be performed. This optimisation includes computation modules and sequence of operations. One of the transformations is operation reduction, where the operation is recomposed to reduce the number of operations needed which leads in reduction of switched capacitance [21]. Since certain operations require less energy than others, lower power operations can be substituted to minimise power consumption [21].

Another means to reduce power consumption is at the architectural level. This approach minimises the power consumption resulting from the structure of the architecture. Compared to the previous two hierarchies, where the power saving is achieved at a larger scale, this approach reduces power consumption at the specific module that is being implemented. Several techniques that are available at this level are parallelism [22], pipelining [23], low power data

representation [5] and clock gating [24, 25].

At the logic and circuit level, designers have greater control over final circuit performance. One of the important decisions is the type of logic implementation. Since the amount of capacitance depends on the total number of transistors, the decision on logic implementation greatly affects the total power consumption. In CMOS circuits, the inputs are connected to the transistor gates, which results in high input capacitance due to gate, drain and source capacitance. In contrast, complementary pass logic circuits (CPL) [26] have lower input capacitance since the input is connected through the drain or source and fewer transistors are used to implement important logic. The result in [27] shows that CPL can give 30% power reduction. Other methods such as logic optimisation [5], transistor sizing [28] and power aware placement and routing can be used to minimize power at the circuit level.

At the technology level, technology scaling has been shown to be very effective in reducing overall power during the last four decades. This technique scales the voltage and feature size according to the constant-field scaling law [29]. This approach results in improvements in power consumption, chip density and circuit performance. The technology reduces in scale by a factor of two every three years. However, this method is limited by how much lower threshold voltage can be scaled without causing serious leakage current [30]. Apart from technology scaling, other technology improvement, such as Silicon on Insulator (SOI), reduces the parasitic capacitance in the circuit by 30% compared to CMOS technology [31].

#### 2.5 Power Estimation Techniques

Power estimation is important since it helps designers identify the main power bottlenecks so that the appropriate corrective measures can be taken in the early design stages. Power estimation can be performed at several stages of the design: algorithm, architecture, gate level and circuit level. The power estimation accuracy at higher design levels is less accurate than when the design abstraction is closer to the silicon implementation. Most power estimations trade off accuracy for improvements in run time and capacity.

At the behavioural level, the power estimation depends on the execution of the algorithm since it lacks hardware structure. In information-theoretic models, measures such as entropy are used to estimate power consumption [32]. Higher switching activity results from higher entropy. Complexity based model [33] estimates the power based on circuit complexity parameters, such as amount and type of arithmetic, number of states and Boolean expressions.

At the architectural level or register transistor level (RTL), the design has been divided into sub blocks and each functional unit has been identified. Thus estimating power consumption at this level is crucial since it can be used to gain insight into which modules consume the most power. The power estimation tool utilises lines of code to understand the design structure and estimate the power. Several power estimation methods are available at this level. In the gate count approach, the consumed power is estimated based on the equivalent gate count [34]. Another technique is the power factor approximation method [35] which is based on previously characterised functional blocks. Estimating tools such as WattWatcher claim to be within 20% to 25% of actual silicon power requirements at a good execution speed [36].

At the gate level, the design are represented by technology dependent logic gates. The probability method calculates power using the input probability where this will be propagated into other nodes. The average power is calculated using:

$$P_{switching} = \frac{1}{2} f V_{dd}^2 \sum_{i=1}^{n} C_i p_t(x_i)$$

where  $C_i$  represents the total capacitance load and  $p_t(x_i)$  represents the transition probability at node x. This approach has the advantage of being test pattern independent, and is fast since it only requires a single analysis to be run. While this method is suitable for combinational circuits, it is difficult to apply it to sequential circuits [37]. Furthermore, this method depends on a simplified delay model. Better accuracy can be achieved, at the expense of computing time, by considering the correlation among the internal nodes.

In the event driven simulation method, the average power is calculated based on the number of transitions that occur and the amount of power consumed per transition [38]. The accuracy of this technique depends strongly on how accurately the technology library has been characterised for power consumption. Thus, the library must be precharacterised for static and dynamic power at various input slopes and output loads. Typically, the calculation is done using a circuit simulator such as SPICE. This provides a convenient method and can be used on any design and technology that has a precharacterised library for power. While this approach can give better accuracy compared to the probability method, the result depends on the given input test pattern. Thus, the input must be chosen to match the closest real world implementation. Furthermore, this method requires longer execution times especially for large circuits.

For highest power estimation accuracy, a circuit level simulator, such as SPICE, provides the best approach. In this method, the actual physical device model, such as transistor, capacitor or resistor, is used during the simulation. Since the actual physical model is used, this method can accurately calculate non-linear behaviour that is often missed by the higher level power approximation techniques. It also calculates the actual leakage, short circuit and dynamic power. But while this method provides the best accuracy and is easy to use for smaller circuits, it is very time consuming for larger circuits. Furthermore, the power dissipation result depends on input test pattern.

#### 2.6 Design Flow

The design flow shown in Figure 2.4 is adopted throughout this thesis. In this work, the design starts from the algorithm specification and continues up to the place and route (PNR) stage. The algorithm is validated using Matlab since it provides a good environment for image and video processing. It is more convenient to explore various solutions at the algorithm stage since it can be modified and verified quickly.

Once the algorithm is validated, test benches are created from the algorithm simulation to assist during hardware verification. This test bench is sometimes called the golden test bench since it is used as a reference throughout the design flow. This is important to ensure that the design performs correctly at each design stage.

Transferring from algorithm to hardware requires careful partitions to ensure an efficient implementation. Division between data path, memory and control is made at this stage. The

Figure 2.4: Design flow for hardware implementation, verification and power evaluation.

hardware is coded using the Verilog language and simulated using Verilog XL from Cadence Design System. At this stage, the golden test bench is used to verify the hardware.

Once the hardware coding is verified, it is mapped onto a technology dependent library using Design Compiler, a logic synthesis tool from Synopsys Inc. In this work, the UMC  $0.13\mu m$  CMOS library, which consists of 557 cells and a memory compiler for 1-port, 2-port, and dual-port memories [39], is used. The gate level netlist is verified using the golden test bench and the switching activity is extracted. After the post synthesis simulation, the switching activity is used by the Power Compiler to calculate the power consumption.

While post-synthesis gate level power evaluation can give good power estimation, the interconnect capacitances are based on the wire load models provided by the technology library. For more accurate interconnect capacitance estimation, the post layout data are obtained. Silicon Ensemble, an automatic PNR tool, is used for routing the verified gate level netlist. The output is a netlist with more accurate interconnect capacitance extracted from the layout.

Throughout the design process, power consumption can be monitored at different design phases, such as after synthesis or after PNR. For fast comparison of different architectures, the post synthesis power estimates are used. For more accurate comparison in the final stage of the design, the power estimation is based on post-layout netlist.

As discussed in the previous section, power estimator provides a convenient way to estimate total power consumption of a design. However, for an event-driven power calculator such as the Power Compiler used in this work, the following factors affect its accuracy:

#### 1. testbench dependency

- 2. cell library accuracy

- 3. assumption of constant operating environment such as voltage supply, temperature, fabrication process and electrically noiseless environment

While designers can tackle problem (1) by using a wide range of testbenches that reflect real world implementation, factors (2) and (3) are highly dependent on the accuracy of the technology library provided by silicon vendors, and the actual operating conditions when the chip is used. Despite these shortcomings, these tools provide very useful input for low power design. This is because the information provided by the power estimation tools allows designers to make power comparison between different architectures and offers good insight into how different architectures contribute to total power consumption. Furthermore, these tools give designers good estimation of the final power consumption with claimed accuracy of 5% to 17% of silicon results [40].

#### 2.7 Summary

This chapter discussed the main sources of power dissipation in CMOS circuits and the existing solutions to minimise the problem. Throughout the history of electronics, the rapid advancement in human knowledge and creativity always pushes the existing technology to its maximum limit. This phenomenon has been happening to CMOS technology and power consumption has become the main problem in today's multi-million transistor designs. The main sources of power consumption in CMOS circuits are leakage, short circuit and switching power.

Many techniques have been proposed to reduce this power. This chapter reviewed some of the popular methods that have been shown to be effective in minimising CMOS switching power. The low power optimisation techniques can be performed at different levels of design abstraction such as algorithm, architecture, logic and technology. The sooner the problem is tackled during the design stages, the greater the power saving impact. Power estimation techniques were also reviewed in this chapter since they are crucial to determine the main bottlenecks in the design. In power estimation, accuracy is often traded off for faster run time. Finally, this chapter discussed the design flow that is used to evaluate power consumption throughout the thesis.

# Chapter 3 Video Compression

#### 3.1 Introduction

Digital multimedia applications have shown significant growth in the last few years. From personal computers, the application has become increasingly popular in mobile terminals such as mobile phones and personal digital assistance (PDA). One of the examples is mobile multimedia services (MMS) which have been widely adopted to send a short video message. This trend will advance further in the next generation wireless communication as video communication and wireless video distribution become widely available to the consumer market.

Video compression plays an important role in ensuring the success of today's video communication. It allows raw video data to be transmitted in current available transmission bandwidth or stored in minimal storage capacity. The success of video compression has allowed many other high quality video base applications to be widely available to the consumer such as video streaming, video broadcasting and video content distribution. It can be found in many electronics devices such as digital camcorders and DVD players.

This chapter presents an overview of video compression systems. While many video compression standards have been developed over the last two decades, the important principles and algorithms, which are similar among these standards, are highlighted in this chapter. The latest video coding standard, H.264, is reviewed and its impact on software and hardware

computational load is discussed to justify the requirement for a low power design. Since performance comparison between different algorithms is important to determine their efficiency, this chapter discusses benchmarking techniques and data that are widely used by the video coding community.

This chapter is organised as follows. Section 3.2 describes the typical raw video data and various formats used in video coding. The main building blocks for video compression are described in Section 3.3. Sections 3.4 and 3.5 describe new features in H.264 and how they affect the computational cost. Section 3.6 discusses benchmarking methods to compare video coding algorithms. Finally, Section 3.7 summarises the chapter.

#### 3.2 Video Data

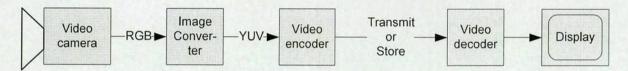

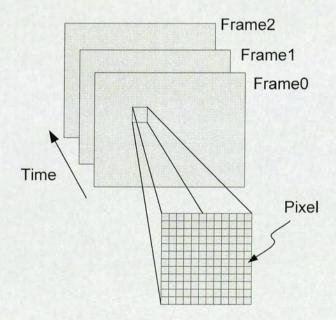

The basic element of video data is a series of still pictures that are captured at a specific time interval. Figure 3.1 shows a typical video camera system. When the picture is captured by a digital video camera, the source light falls onto a light sensor, such as a charge-coupled device (CCD) which is made up of tiny light-sensitive semiconductor diodes arranged in 2D. Each diode converts the light into an electrical signal recording the level of light intensity. This diode forms the basic unit of a picture which is called a picture element or pixel as shown in Figure 3.2 [41]. The quality of the picture depends on the number of sensors available. The denser the sensors are, the better the picture is, because more light can be captured per unit length. The pixel data is then stored into memory or displayed on screen.

The raw video data is differentiated by its frame's size and rate. The frame size is determined

Figure 3.1: Video camera system

Figure 3.2: Picture element (pixel)

| Typical                  | QCIF             | CIF              | 4CIF             | VGA              |

|--------------------------|------------------|------------------|------------------|------------------|

| frame size               | $176 \times 144$ | $352 \times 288$ | $704 \times 576$ | $640 \times 480$ |

| Typical frame rate (fps) | 7.5,15, 30, 60   |                  |                  |                  |

Table 3.1: Typical frame size and rates

by total number of pixels, while the frame rate is the frequency at which the picture is captured (often expressed in frames per second, fps). The higher the frame rate, the smoother the object transition will be when perceived by the viewer. Some typical frame sizes and rates are shown in Table 3.1.

The original video colour is represented by red, blue and green (RGB). The combinations of these colours produce many other colours. In RGB format, all three colour components have equal importance. Thus, all three components need to be stored using the same resolution.

To reduce the amount of memory needed to store these colours, YUV format is introduced (also known as YCbCr). This format exploits the human visual system (HVS) which is more sensitive to brightness (luminance or luma) than to the colour component (chroma). It is more efficient to separate luminance from chroma, then represent the luminance using higher resolution than chroma. Thus, this format has the advantage of reducing the amount of stored data compared to the *RGB* format.

The overall brightness or luminance signal (Y) is achieved by adding the weighted R, G, and B colours using different factors. The colour components consist of two parts: U and V. The U signal is obtained by subtracting Y from B, followed by scaling, while the V is created by subtracting Y from R followed by scaling but using a different factor. Using the ITU-R recommendation BT.601, the conversion from RGB to YUV and YUV to RGB is given as follows [42]:

RGB to YUV:

$$Y = 0.299R + 0.587G + 0.114B \tag{3.1}$$

$$U = 0.564(B - Y) \tag{3.2}$$

$$V = 0.713(R - Y) (3.3)$$

YUV to RGB:

$$R = Y + 1.402V \tag{3.4}$$

$$G = Y - 0.344U - 0.714V (3.5)$$

$$B = Y + 1.772U (3.6)$$

Several types of YUV formats are normally used depending on the resolution of the chroma per frame. Table 3.2 summarizes the existing YUV formats. The Hor and Ver columns show the ratio of chroma with respect to the luminance [43]. In this thesis, YUV 4:2:0 is used with

| YUV   | Hor(%) | Ver(%) |

|-------|--------|--------|

| 4:4:4 | 100    | 100    |

| 4:2:2 | 50     | 100    |

| 4:2:0 | 50     | 50     |

Table 3.2: YUV Format

8 bits per pixel since it is widely used in mobile video applications while delivering good picture quality. In this format, U and V each have half the horizontal and vertical resolution of Y. Thus this format requires half of the sample compared to RGB.

#### 3.3 Video Compression

A five minutes video clip with appropriate size for a hand held mobile terminal (YUV420, CIF@15fps) requires about 648 Megabytes of data requiring a transfer rate of 18.2 MBits/s. This obviously shows that storing and transmitting raw video data is almost impractical using current devices. Thus, this data needs to be compressed before it can be transmitted through a wireless channel.

Video coding reduces the raw video data by exploiting the temporal and spatial relationship of video data. When the frame rate is sufficiently high, the data between neighbouring frames are highly correlated and have very small differences. This makes it feasible to compress video data by removing the redundancy between frames. The compressed video must be decodable and capable of handling any error during storage or transmission.

With the wide use of video applications, standardizing the video coding method is crucial to ensure interoperability between different devices and platforms [2]. Thus, video coding

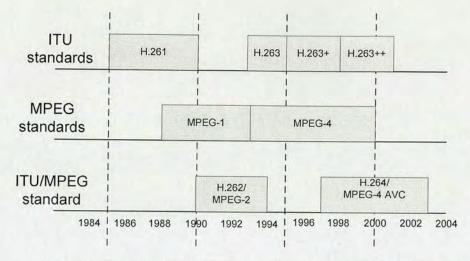

Figure 3.3: Video coding standard history [43]

standards have been introduced to the industry to allow a more efficient way to exchange video files between different parties. This permits various attractive applications and services to be offered to consumers. Furthermore, with wide acceptance of the standards, large scale production will follow which guarantees reduction in cost.

Video coding standards have seen a great improvement since its introduction in the last two decades. There are two main bodies actively involved in developing these standards: Motion Picture Expert Group (MPEG) and Video Coding Expert Group (VCEG). Figure 3.3 shows various video coding standards that have been introduced by these organisations.