# LOW BIT RATE SPEECH COMMUNICATION BASED ON CHARGE COUPLED DEVICE FOURIER TRANSFORM PROCESSORS

A thesis submitted to the Faculty of Science of the

University of Edinburgh, for the degree of

Doctor of Philosophy

bу

M. C. DAVIE, B.Sc.

Department of Electrical Engineering

Sept 1979

# DECLARATION OF ORIGINALITY

This thesis, composed entirely by myself, reports on work conducted by myself in the Department of Electrical Engineering, University of Edinburgh, and the Advanced Development Division, Racal Group Services, Reading.

#### ACKNOWLEDGEMENTS

The author would like to express his sincere gratitude to Dr.P.M.Grant, Mr.R.J.Preston, Dr.M.A.Jack, Dr.J.M.Hannah and Professor J.H.Collins for their supervision and encouragement given throughout this work. He would like to acknowledge Racal Group Services Ltd., Reading and the Science Research Council for financial assistance.

Sincere thanks are also due to the many friends and members of staff, both in the Department and at Racal for their useful comments relating to this work. The advice and help given by Mr.J.N.Holmes and his colleagues at the Joint Speech Research Unit, Cheltenham are gratefully acknowledged. Finally, thanks are due to Mrs.M.C.Davie for her patience and help.

# C O N T E N T S

| Title Page  |                                     | i   |

|-------------|-------------------------------------|-----|

| Abstract    |                                     | ii  |

| Declaration | of Originality                      | iii |

| Acknowledge | ments                               | iv  |

| Contents    | •                                   | V   |

| Glossary of | Abreviations                        | х   |

|             |                                     |     |

|             |                                     |     |

| CHAPTER 1:  | INTRODUCTION                        | 1   |

|             |                                     |     |

| 1.1         | Advanced Analogue Signal Processing | 1   |

|             |                                     |     |

| 1.2         | Layout of Thesis                    | 3   |

|             |                                     |     |

|             |                                     |     |

| CHAPTER 2:  | SPEECH AND VOCODERS                 | 5   |

|             | •                                   |     |

| 2.1         | Human Speech Production             | 6   |

|             |                                     |     |

| 2.2         | Pitch Detection                     | 11  |

|             | /                                   |     |

| 2.3         | The Channel Vocoder                 | 18  |

|             |                                     |     |

| 2.4         | The Linear Predictive Vocoder       | 27  |

| 2.5        | Other Vocoder Principles          | 29  |

|------------|-----------------------------------|-----|

|            | . ·                               |     |

| CHAPTER 3: | THE CHARGE COUPLED DEVICE         | 33  |

| 3.1        | Basic Principles                  | 34  |

| 3.2        | Charge Input and Output           | 38  |

| 3.2.1      | Input Techniques                  | 39  |

| 3.2.2      | Output Techniques                 | 4 2 |

| 3.3        | Device Limitations and Defects    | 45  |

| 3.3.1      | Transfer Efficiency               | 46  |

| 3.3.2      | Noise                             | 48  |

| 3.3.3      | Dark Current                      | 49  |

| 3.3.4      | Peripheral On-chip Circuitry      | 50  |

| 3.4        | The Transversal Filter            | 51  |

| CHAPTER 4: | CCD FOURIER TRANSFORM PROCESSORS  | 53  |

| 4.1        | Conventional Spectrum Analysers   | 54  |

| 4.2        | The Fourier Transform             | 56  |

| 4.2.1      | The Discrete Fourier Transform    | 58  |

| 4.2.2      | The Fast Fourier Transform        | 6 2 |

| 4.2.3      | On the Use of Weighting Functions | 66  |

| 4.3        | The Chirp-z Transform                      | 69  |

|------------|--------------------------------------------|-----|

| 4.3.1      | Derivation                                 | 69  |

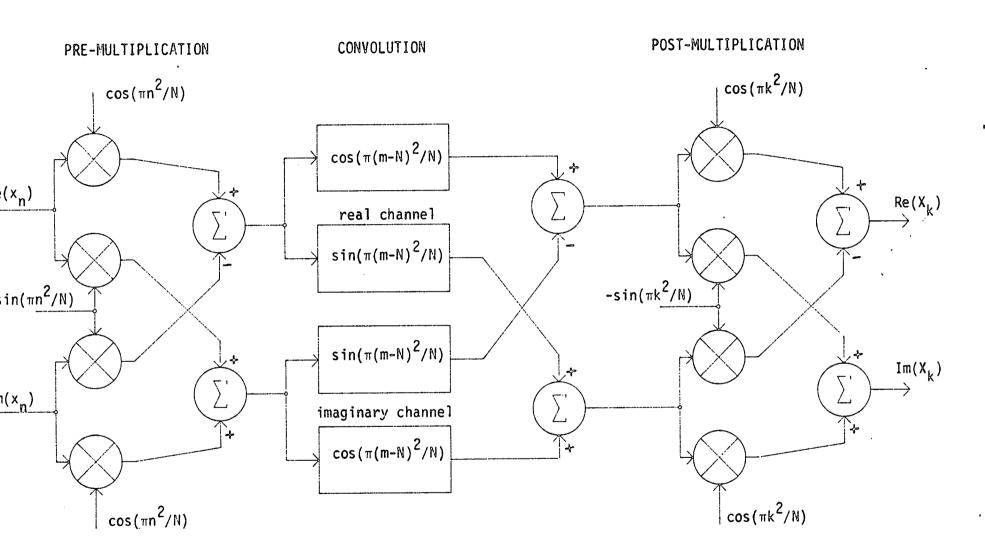

| 4.3.2      | Implementation                             | 7 4 |

| 4.3.3      | Hardware Reduction                         | 77  |

| 4.3.4      | Inaccuracies and Limitations               | 8 2 |

| 4.4        | The Sliding Chirp-z Transform              | 8 4 |

| 4.5        | The Prime Transform                        | 86  |

| 4.5.1      | Derivation                                 | 86  |

| 4.5.2      | Implementation                             | 88  |

| 4.5.3      | Hardware Reduction                         | 89  |

| 4.5.4      | Errors and Limitations                     | 90  |

| 4.6        | Comparison of Real-time Spectrum Analysers | 91  |

|            | •                                          |     |

| CHAPTER 5: | THE DESIGN AND CONSTRUCTION OF A CCD       |     |

|            | CHIRP-Z TRANSFORM PROCESSOR                | 94  |

| 5.1        | Design Objectives                          | 94  |

| 5.2        | Computer Simulation                        | 95  |

| 5.2.1      | Graphical Analysis of the CZT              | 97  |

| 5.2.2      | Premultiplier Quantisation Errors          | 103 |

| 5.2.3      | CCD Tap Weight Tolerance                   | 106 |

| 5.2.4      | Charge Transfer Efficiency                 | 107 |

| 5.2.5      | Analogue Multiplier Accuracy               | 111 |

| 5.2.6      | Phase Shifter Errors                       | 111 |

| 5.2.7      | Summary of Simulation Results            | 113 |  |  |

|------------|------------------------------------------|-----|--|--|

| 5.3        | Implementation                           | 115 |  |  |

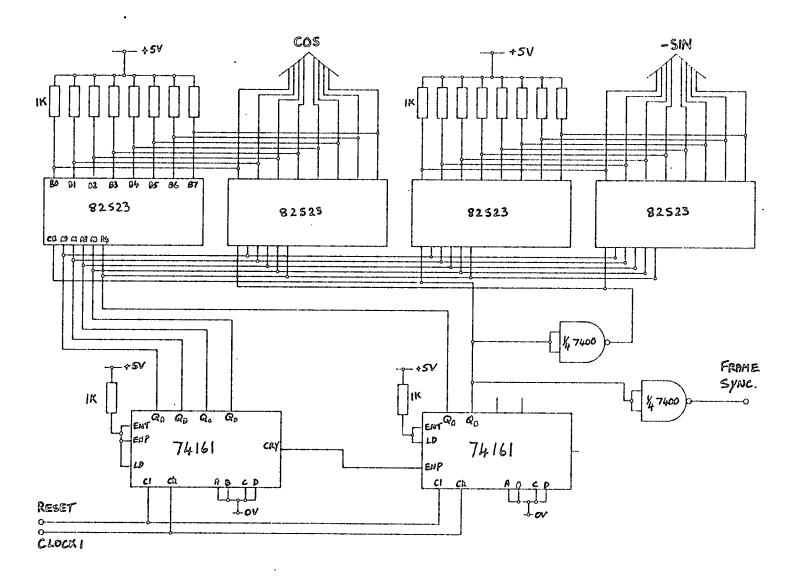

| 5.3.1      | The Premultiplier                        |     |  |  |

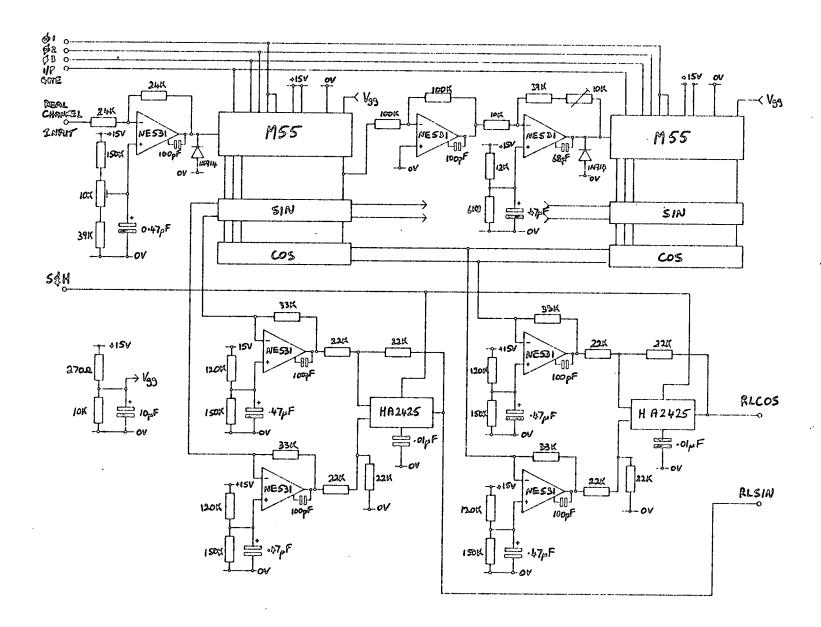

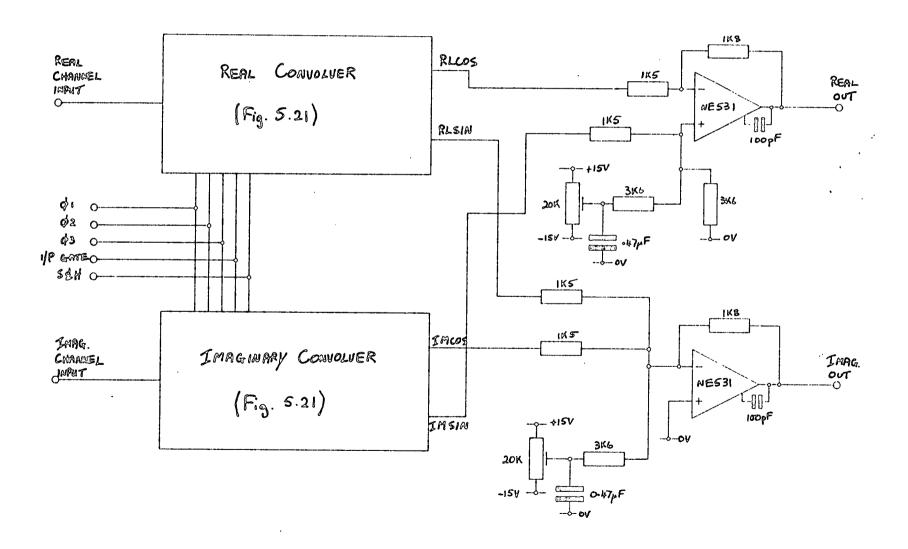

| 5.3.2      | The Convolver                            |     |  |  |

| 5.3.3      | Post Circuitry                           | 120 |  |  |

| 5.3.4      | Timing                                   |     |  |  |

| 5.3.5      | 90-Degree Phase Difference Network       |     |  |  |

| 5.3.6      | Low-pass Filter                          |     |  |  |

| 5.3.7      | Physical Construction                    | 135 |  |  |

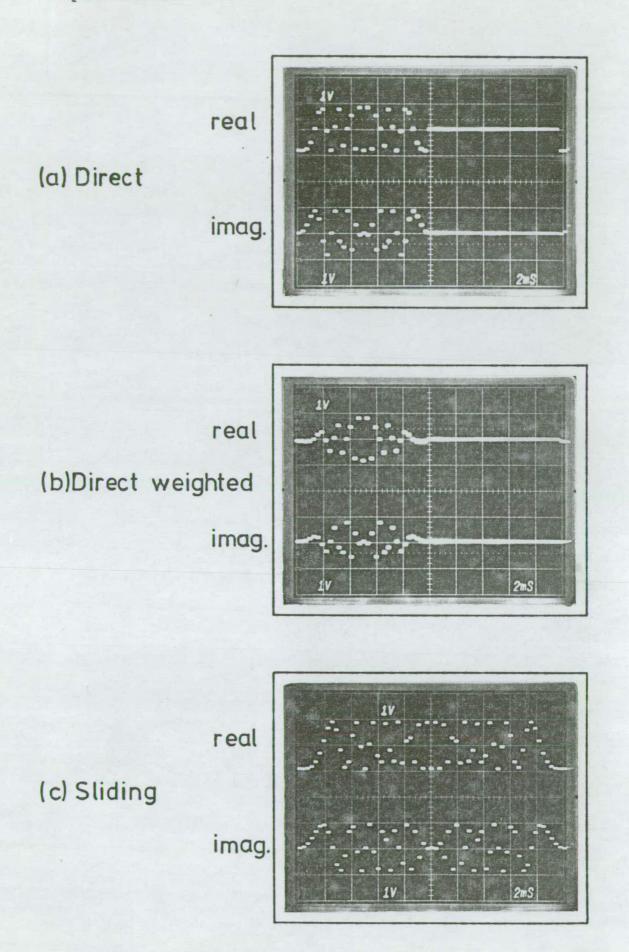

| 5.4        | Hardware Performance                     | 140 |  |  |

| CHAPTER 6: | THE ON-LINE COMPUTER SIMULATION OF A CCD |     |  |  |

|            | CHANNEL VOCODER                          | 151 |  |  |

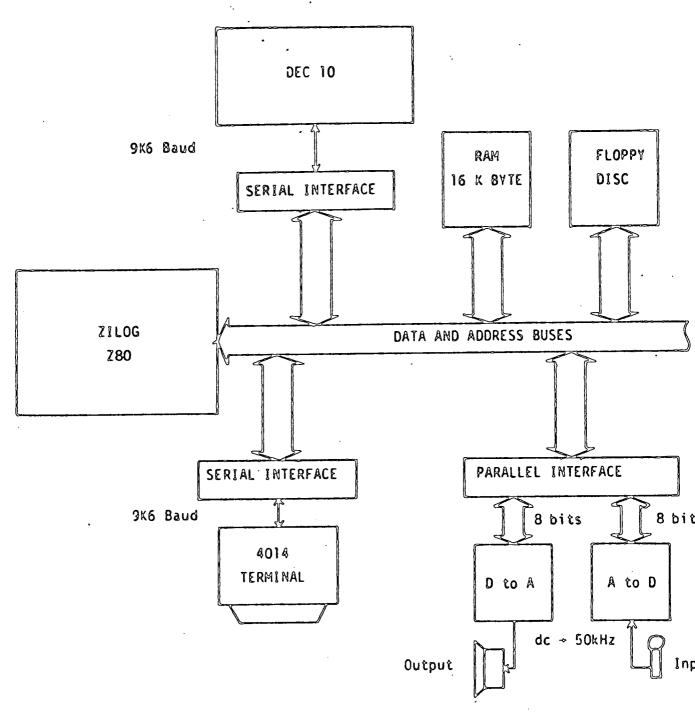

| 6.1        | Computing Facilities                     | 151 |  |  |

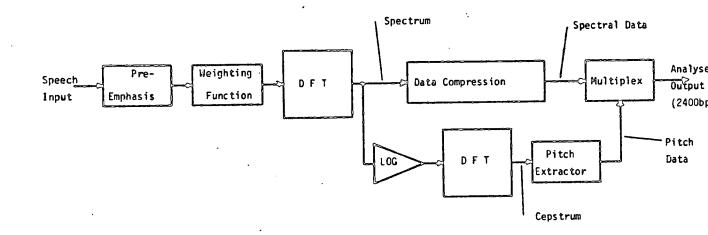

| 6.2        | The Channel Analyser                     | 155 |  |  |

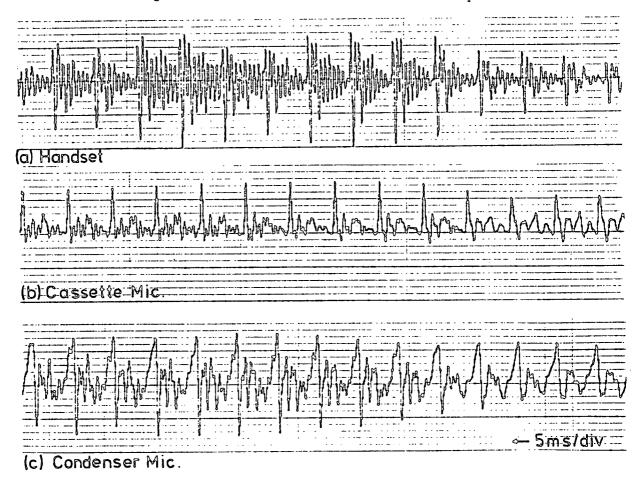

| 6.2.1      | Speech Input                             |     |  |  |

| 6.2.2      | Spectrum and Cepstrum Computation        |     |  |  |

| 6.2.3      | Data Reduction and Quantisation          |     |  |  |

| 6.2.4      | Pitch Extraction                         |     |  |  |

| 6.2.5      | Performance Comparison                   | 186 |  |  |

| 6.2.6      | Summary of Analyser Simulation           |     |  |  |

|            | Conclusions                              | 191 |  |  |

| 6.3        | Channel Synthesiser Simulation           | 192 |  |  |

| 6.3.1      | Impulse Response Generation       | 193 |

|------------|-----------------------------------|-----|

| 6.3.2      | Synthesiser Excitation Sources    | 197 |

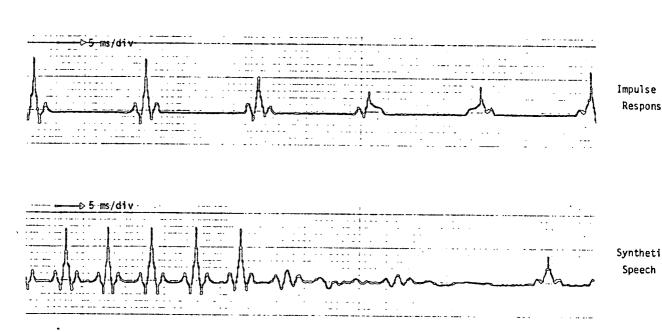

| 6.3.3      | Reconstruction by Convolution     | 198 |

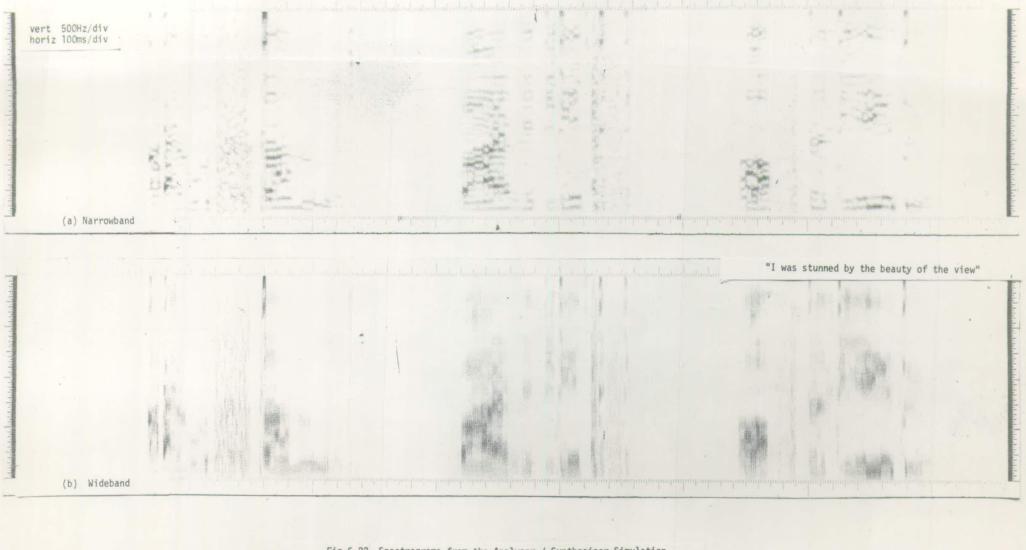

| 6.3.4      | Synthesiser Performance           | 202 |

| 6.3.5      | Summary of Synthesiser Simulation |     |

|            | Conclusions                       | 206 |

|            |                                   |     |

| CHAPTER 7: | THE OPTIMAL DESIGN OF A CCD BASED |     |

|            | CHANNEL VOCODER                   | 208 |

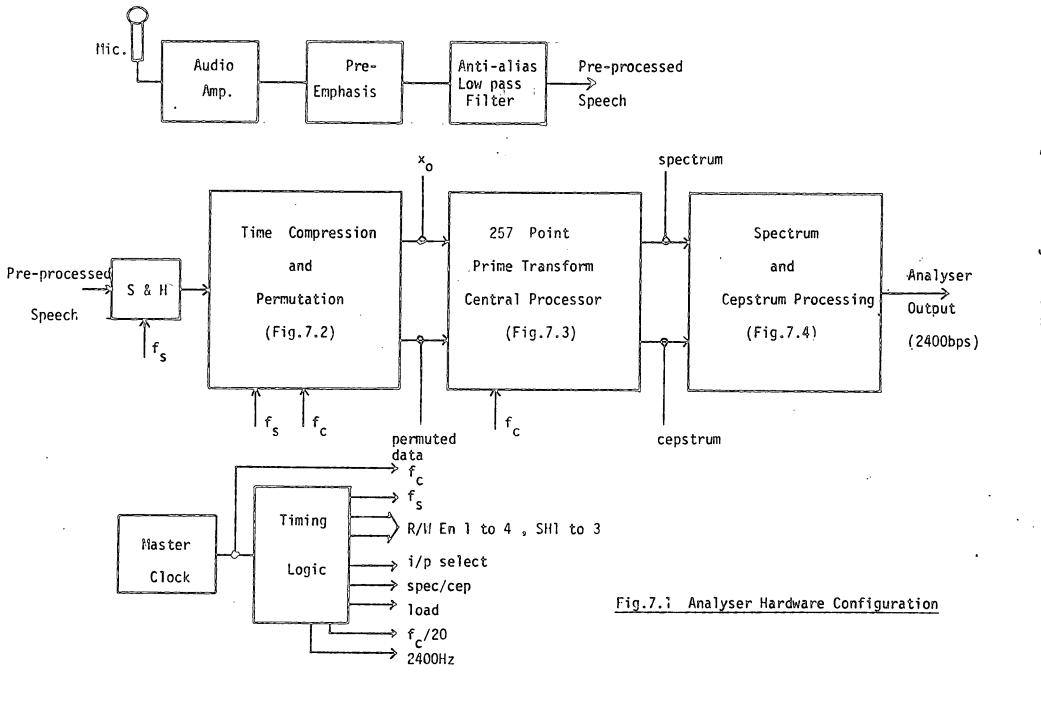

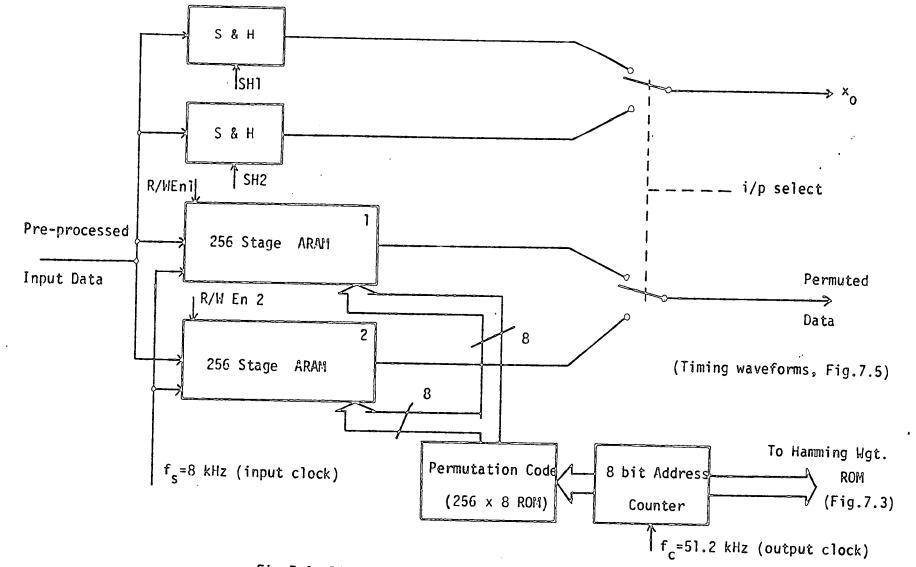

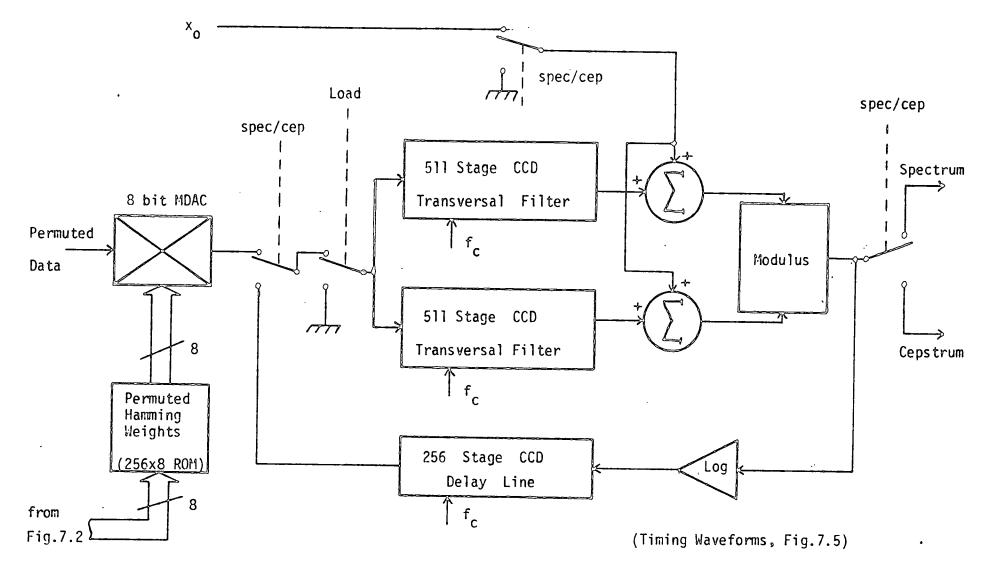

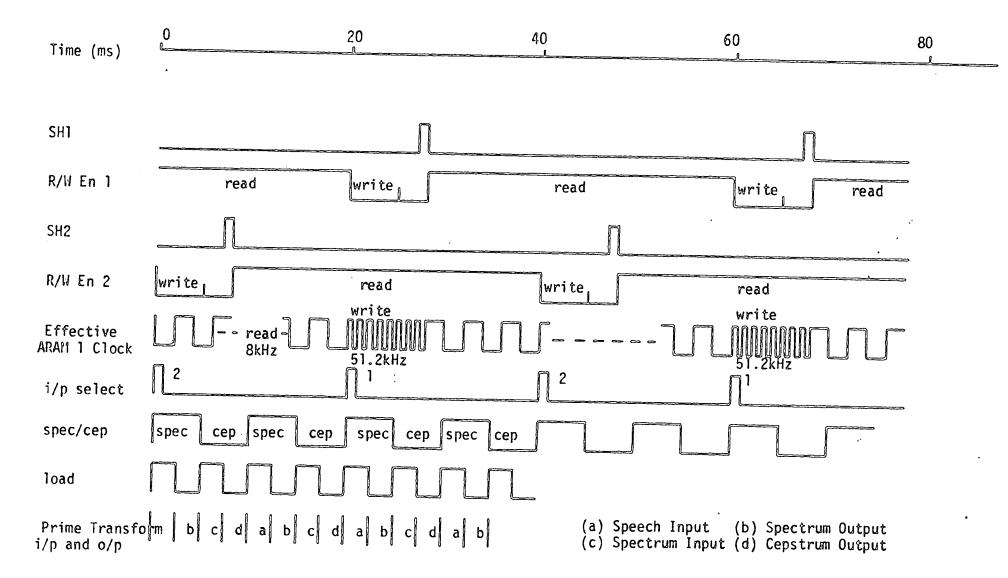

| 7.1        | Analyser Configuration            | 208 |

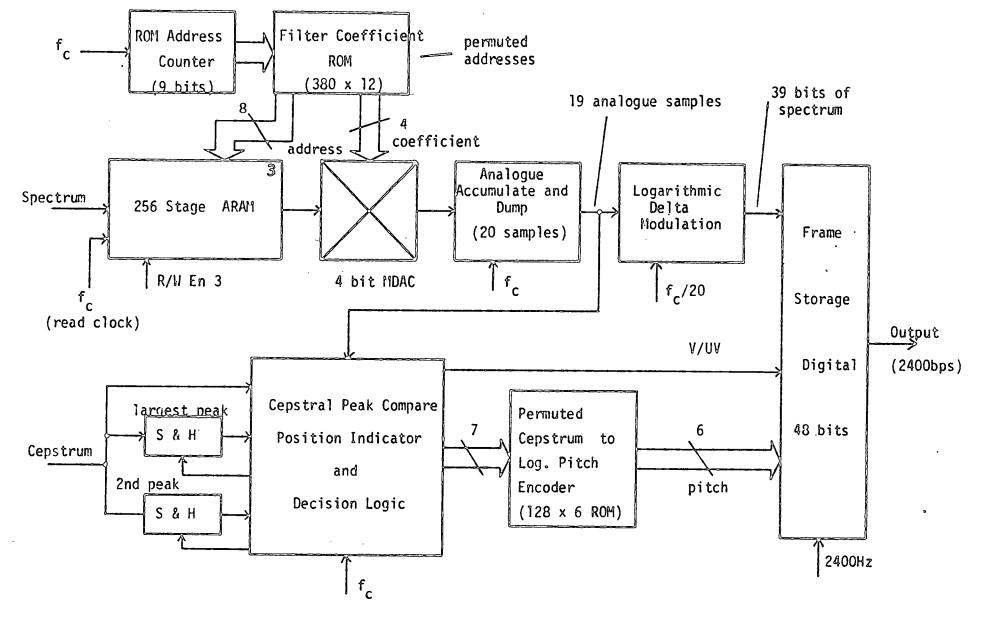

| 7.2        | Synthesiser Configuration         | 217 |

| 7.3        | Comparison with a CCD Parallel    |     |

|            | Filter Bank Vocoder               | 222 |

|            |                                   |     |

| CHAPTER 8: | CONCLUSIONS                       | 226 |

|            |                                   |     |

| References |                                   | 230 |

| Appendix A |                                   | 238 |

| Appendix B |                                   | 242 |

| Appendix C |                                   | 247 |

#### GLOSSARY OF ABBREVIATIONS

age automatic gain control

ARAM Analogue Random Access Memory

BBD Bucket Brigade Device

bps bits per second

CCD Charge Coupled Device

CMOS Complementary Metal Oxide Silicon

CTD Charge Transfer Device

CZT Chirp Z-transform

DCT Discrete Cosine Transform

DFT Discrete Fourier Transform

DSAT Double Sample Alternate Tap

FFT Fast Fourier Transform

FILO First In Last Out

FIR Finite Impulse Response

FM Frequency Modulation

FT Fourier Transform

FTP Fourier Transform Processor

IDFT Inverse Discrete Fourier Transform

IF Intermediate Frequency

IFT Inverse Fourier Transform

LSB Least Significant Bit

MDAC Multiplying Digital to Analogue Convertor

MOS Metal Oxide Semiconductor

N/S Noise to Signal Ratio

PCM Pulse Code Modulation

PE/N Peak Error to Noise ratio

| PT  | Detino | Transform |

|-----|--------|-----------|

| K L | Prine  | iranstorm |

RAM Random Access Memory

rms root mean square

ROM Read Only Memory

SCZT Sliding Chirp Z-transform

SIPO Serial-In-Parallel-Out

TF Transversal Filter

TRF Tuned Radio Frequency

TTL Transistor-Transistor Logic

VLSI Very Large Scale Integration

V/UV Voiced/Unvoiced decision

To Moira

#### CHAPTER 1

## INTRODUCTION

## 1.1 ADVANCED ANALOGUE SIGNAL PROCESSING

Low bit rate speech communication systems (vocoders) available for many years  $now_{\varrho}$  but their been application areas have always remained extremely specialised. One of the main reasons for this trend has been the large size and expense associated with such equipments, especially when the synthetic speech quality achieved is rather poor. Within the last few years, however, vocoder interest has been rekindled and stimulated by the demand for digital communications. Efficient data compression techniques are necessary since the increased bandwidth inherent in digital coding is contrary to overriding philosophy that bandwith conservation is requisite [1].

At present, the two established systems for low bit rate (2400bps) speech compression are the channel vocoder [2] and the linear predictive vocoder [3]. The linear predictive vocoder is becoming increasingly popular because of its more elegant digital implementation. However, recent advances in analogue signal processing may yet produce a channel vocoder which is even more attractive in terms of engineering premiums.

One technology which offers high density analogue signal processing is the Charge Coupled Device (CCD) [4]. The CCD is a shift register which stores samples of analogue information directly as charge packets. These packets can be transferred along the register under control of an external clock to form a variable delay line Further, by adding a non-destructive structure. CCD permits technique, fabrication of very Transversal Filters (TFs) [5] which form the basic building blocks for many powerful signal processing modules [6].

Since the conception of CCD at the turn of the decade, industry's acceptance of CCD for analogue signal processing has been laboured. This has been due to factors which include (a) the increased competition from digital componentry (d) limited the CCD operating characteristics and (c) the slow development of peripheral integration. However, the CCD is now being manufactured as a fully modular 'black box' which frees the from many of the 'setting-up' problems, and advanced components such as Fourier Transform Processors (FTPs) [6], adaptive filters [7] and correlators [8] are finding extensive real-time application.

The intention of this thesis is to examine and demonstrate the potential of analogue CCD in the realisation of complex signal processing systems. In particular, the application of CCD FTPs in a low bit rate channel vocoder is

investigated, since the market for a low power, small size and low cost vocoder is potentially vast.

### 1.2 LAYOUT OF THESIS

Chapter 2 gives an introduction to the subject of speech and vocoders, highlighting the particular areas in which CCD may have application. The channel vocoder is described in detail since this algorithm is examined in later chapters. Some of the basic CCD principles are explained in chapter 3, along with a summary of the most important operational characteristics. The transversal filter, one of the most powerful analogue signal processing blocks, is introduced in this chapter.

Chapter 4 investigates several of the many algorithms have been proposed for real-time Fourier transformation and, in particular, compares the advantages and disadvantages of the CCD Chirp-Z Transform (CZT) and the Prime Transform (PT). The detailed desian and construction of a CCD CZT processor together with the performance limitations are presented in chapter 5。 Practical aspects of CCD system design are emphasised.

In chapter 6, an extensive computer simulation of a novel channel vocoder is reported. Both the analyser and the synthesiser are based upon discrete Fourier transform

processors. The simulation involved the design and construction of a specialised 'intelligent' computer terminal and this is described briefly. Practical experience in CCD processors and the results of the above simulation are merged in chapter 7 to suggest an optimal hardware configuration for a CCD channel vocoder.

Finally, the most important achievements of this work are summarised in chapter 8, and the conclusions suggest suitable areas for research continuation.

# S P E E C H A N D V O C O D E R S

The advantages of digital communication are well known. For example, binary waveforms may be regenerated at stages along the transmission path without cumulative addition of noise and distortion. Also, the user is free to "scramble" the message in complex ways for secure or private transmission. The price paid for these important advantages is additional transmission bandwidth. In order to transmit a speech signal with 3kHz bandwidth and 40dB signal to noise ratio using direct Pulse Code Modulation (PCM), a data rate of approximately 64000 bits per second (bps) is required. A normal 3kHz analogue communication channel will handle only 2400 bps without equalisation.

The solution is therefore to find an efficient coding algorithm for speech, which permits more economical use of the spectrum. If one examines the information content speech, assuming a vocabulary of 2 4 words and a speaking rate of 10 words per second, only 140 bps are required. course, this figure does not include other information such as emotional content and speaker characteristic. Nevertheless, it is clear that the analogue speech signal contains considerable redundancy because the human vocal mechanism generates sounds by relatively slow articulatory movements. A system which attempts to exploit redundancy is called a vocoder (short for voice coder).

general, a vocoder operates by analysing speech in the transmitter, generating a set of control parameters at a much lower bit rate and synthesising the original speech in the receiver. The amount of information which can be thrown away depends on the application: military systems might require only intelligibility whereas telephone systems demand high quality.

Section 2.1 reviews briefly the most important characteristics of the human speech mechanism. This is necessary since any vocoder algorithm must capitalise various aspects of speech production; the optimum vocoder will modelthe human mechanism exactly. Section examines pitch detection algorithms which are vital for good quality vocoding, and sections 2.3 through 2.5 summarise some of the most important, established low-bit rate vocoder techniques. Other speech coding algorithms such as adaptive delta modulation [9] and time encoded digital speech [10], which are generally considered to have application in higher bit-rate communication channels (i.e. 4800 - 16000bps), are not considered here.

# 2.1 HUMAN SPEECH PRODUCTION [11,12]

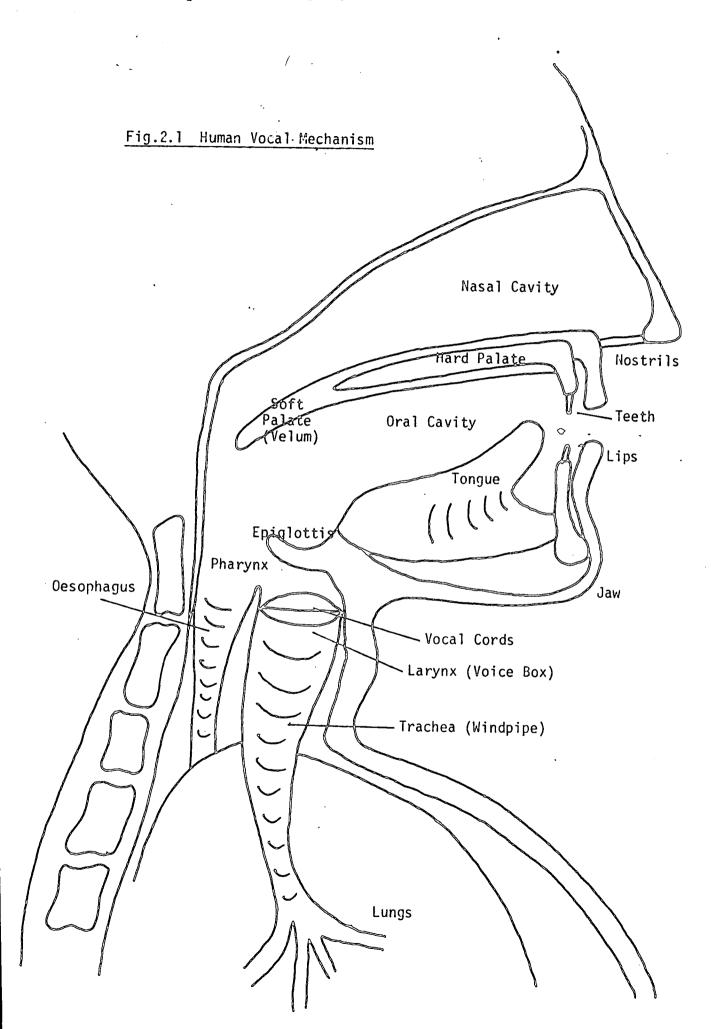

A cross-section through the human vocal mechanism is shown schematically in Fig.2.1. The main vocal tract is a non-uniform acoustical tube which starts at the pharynx and terminates at the lips. It can be deformed by four

articulators, namely the lips, the tongue, the jaw and the velum, to provide the resonances and anti-resonances (poles and zeroes) which modify the energy/frequency distribution of the excitation source. The resonances of the vocal tract are normally known as the "formants" of speech. An ancillary path for sound transmission is formed by the nasal tract, extending from the velum to the nostrils, and has essentially fixed characteristics.

The excitation for the vocal tract is a controlled flow of air from the lungs which first passes through the larynx or voice-box. The larynx has a cartilage frame and houses two lips of ligament and muscle called the vocal cords.

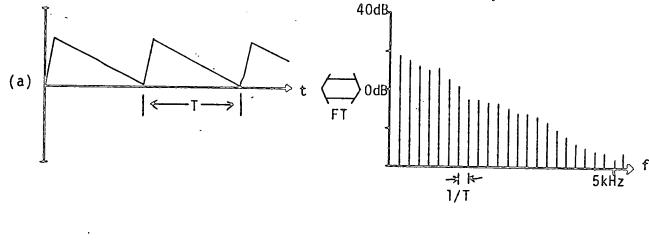

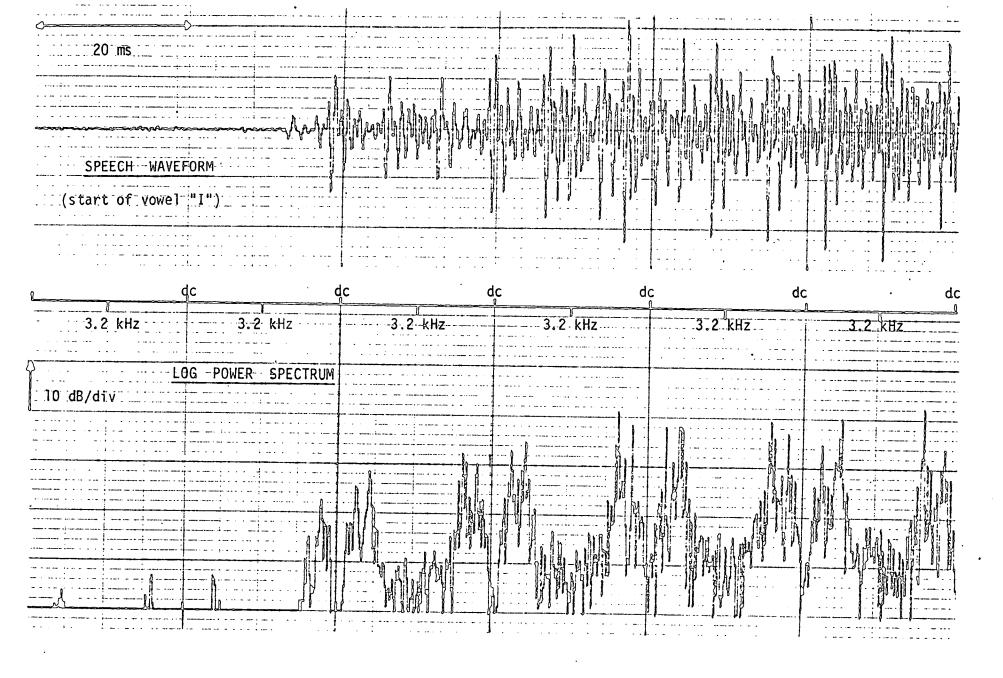

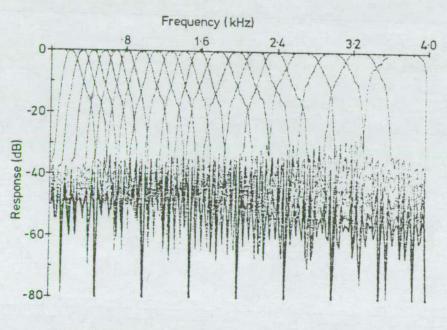

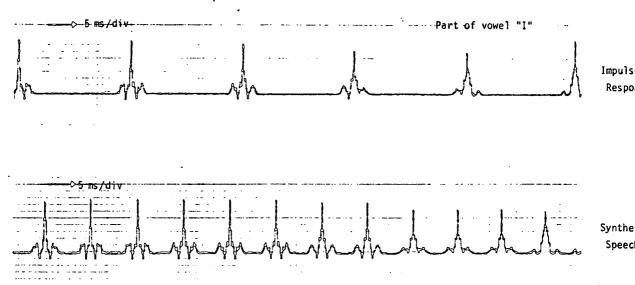

When "voiced" speech is produced, the vocal cords held tensioned by cartilages and the Bernoulli effect makes the slit between the cords (the glottis) open and close at a rate determined by both the sub-glottal pressure and the cord tension. The quasi-periodic pulses of air have triangular shape and the repetition rate, which is closely related to the perceived "pitch" of the speech, lies between and 400 times per second. Because of the triangular shape, the vocal cord excitation source has a line spectrum falls which off at approximately -12dB/octave (Fig.2.2a). Voiced speech includes the vowels and several consonants such as /1,r,m,n/ and a typical speech segment is shown in Fig. 2. 2c.

- (a) excitation source

- (b) vocal tract impulse response and transfer function

- (c) speech waveform (a) \* (b)

Fig.2.2 Typical Voiced Speech Segment (vowel /i/)

The second main excitation source is random noise and is used in the production of "unvoiced" speech. In this case the vocal cords are held wide apart and the air passes uninterrupted through the larynx. A subsequent stricture in the tract causes turbulent air flow creating acoustic random noise. An example of unvoiced speech is the fricative consonant /f/ which is produced by a labio-dental stricture (upper teeth on lower lip). Another group of speech sounds, call "voiced fricatives" (e.g. /z,v/), uses both the turbulent and the vocal cord sources simultaneously.

The final type of excitation results from the build - up of pressure that occurs when the vocal tract is completely closed at some point. A sudden release of this pressure causes a transient excitation of the vocal tract. If the vocal cords were vibrating immediately before the closure, the sound is called a "voiced stop consonant" (e.g. /b,d/) and if the closure is preceded by silence, an "unvoiced stop consonant" is produced (e.g. /p,t/).

Speech production represents only half of the human communication system; the acoustic signal has to be received by the ear and decoded into the appropriate neural stimuli. Several aspects of the receiving process give an insight into speech waveform redundancy. The acoustic pressure wave received by the ear is converted into a mechanical vibration by the tympanic membrane (eardrum) in the middle ear. This

vibration is amplified and transmitted to the cochlea in the inner ear by a system of levers. The fluid filled cochlea is partitioned by the basilar membrane which tapers in width from base to apex. Because the cochlea is rigid the input vibrations pump the cochlea fluid back structure and forward and the basilar membrane vibrates at a position dependent on the frequency. The organ of Corti, which rests along the length of the basilar membrane and contains some 30,000 sensory cells, detects and converts the vibration into electrical pulses to be fed in parallel along the auditory nerve to the brain. How the brain decodes these pulses is still unknown. However, it is clear that the effectively performs a spectrum analysis and passes spectral amplitude information to the brain. Both the frequency and amplitude are logarithmically resolved. In addition, it has been shown that the relative phase of the input signal does not affect human hearing[]].

## 2.2 PITCH DETECTION

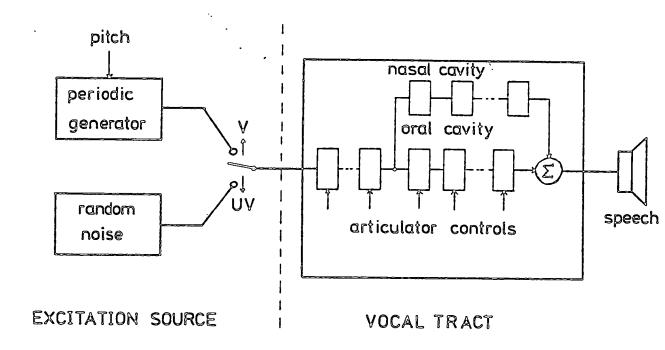

In almost all speech synthesisers, use is made of the fact that, to a first approximation, the excitation source and the vocal tract may be treated independently; electrical models of speech production consist of a set of waveform generators feeding a filter bank which represents the vocal tract (Fig. 2.3). The excitation source in Fig. 2.3 does not cater for voiced fricatives and stops, because in general,

Fig. 2.3 Electrical Model for Speech Synthesis

the extra complexity does not provide a significant speech quality improvement. Recognition of these sounds is left to human perception.

Two control parameters are required for the synthesiser excitation source: (a) a voiced/unvoiced (V/UV) input to select the appropriate waveform generator and (b) a number representing the pitch period for the voiced generator. In a vocoder, the analyser has to estimate automatically these parameters. The V/UV decision can either be computed separately or can be a by-product of the pitch detection. The most common V/UV detector compares the speech energy in two frequency bands. For example, a typical system might compare the energy in the band 200-600Hz with that in the

range 5000-7000Hz [13]. A high ratio of low frequency to high frequency indicates voiced sound and a low ratio (<<1) indicates unvoiced sound.

At first glance, it would appear that the accurate reliable measurement of pitch period is relatively straightforward. However, this is not the case for several and, in fact, turns out to be one of the most reasons difficult vocoder operations. In principle, the fundamental frequency may be extracted by a low-pass filter. In practice, the fundamental frequency varies over octaves so that a fixed low-pass filter often extracts more than the fundamental. Also, in many practical situations, fundamental frequency is not present or is greatly attenuated (e.g. 300-3000Hz telephone channel). reason for pitch detector inaccuracy is that the glottal excitation waveform is not a perfect train of periodic This results in a speech waveform varying both in period and in the detailed structure within a period.

Over the years, considerable effort has been invested in the search for a reliable pitch detector. The reason for this quest is that the intonation and intelligibility speech depends to a large extent on the correct synthetic pitch. detector errors cause very objectionable Pitch effects. for example, the pitch detector selects the If, second harmonic instead of the fundamental, the resultant not only sounds unnatural but causes the listener "squeak"

to lose concentration temporarily, thereby masking a longer section of the speech.

Pitch extraction techniques may be classed in two categories: (a) time domain and (b) frequency domain. The most common time domain pitch detector in an analoque implementation is a tracking band-pass filter. This attempts to follow the fundamental frequency by assuming fundamental that the component has the largest amplitude. If the input speech is high quality (wide-band) with a signal to noise ratio, then reasonable performance can be maintained over a limited frequency range. However, because filter response time, fast pitch inflexions may temporarily unlock the filter.

Another pitch detector makes use of parallel processing in the time domain [15] and relies on the philosophy that one simple measurement is unlikely to be satisfactory but, by combining the results of several measurements performed in parallel and taking a majority vote, a reliable answer is obtained. The pitch detector in Ref.[15] low-pass filters the input speech to 900Hz and makes six parallel estimates of the pitch, based on peak and valley measurements.

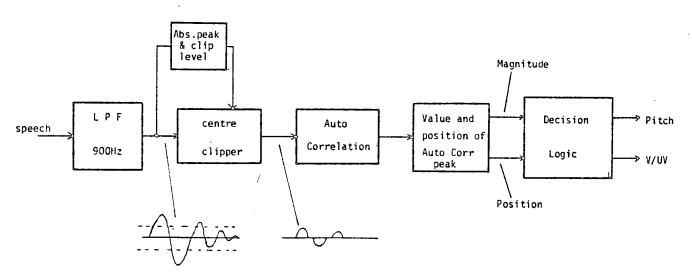

In recent years, autocorrelation pitch detectors have become popular in digital systems. There are many variations on this basic theme, but perhaps the most successful is autocorrelation of centre clipped speech [16]. The centre clipping tends to remove the formant structure of

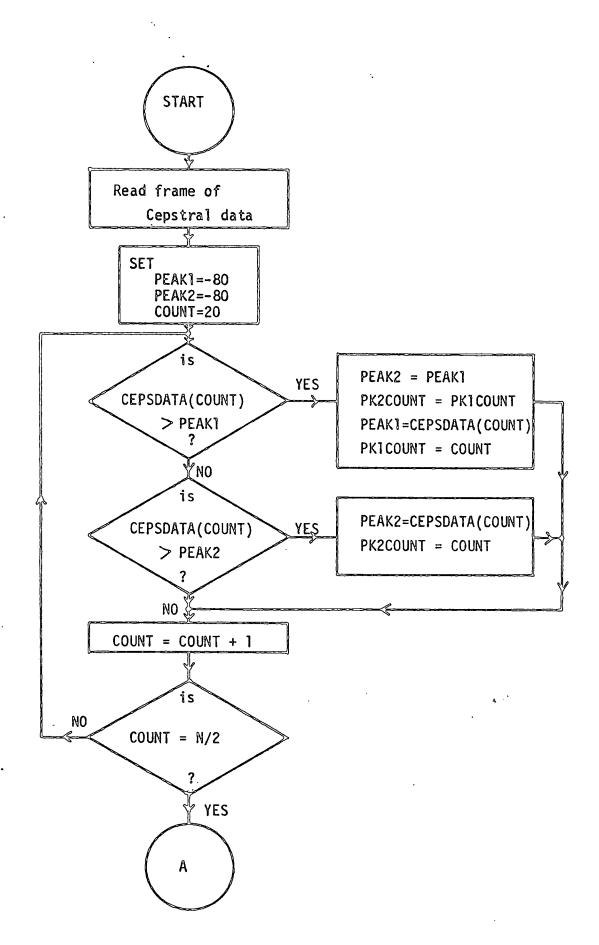

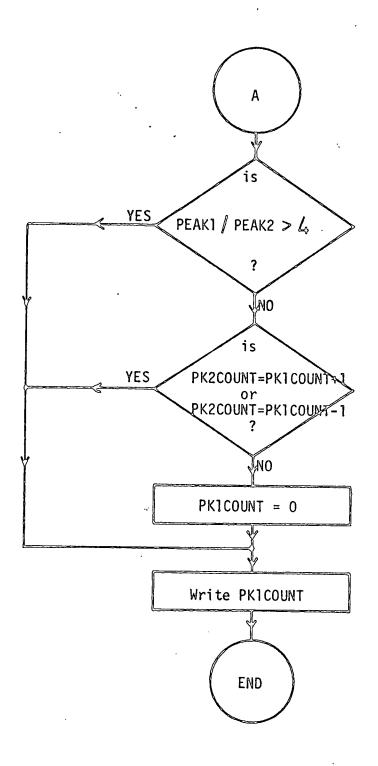

the speech and effectively flattens the spectrum. It is then much easier to resolve the autocorrelation peak due to pitch (i.e. autocorrelation peaks due to the formants are suppressed). The pitch period is measured as the time lag from a reference to the largest autocorrelation peak and, normally, logic circuits after the correlator check the validity of the measurement (Fig. 2.4).

Fig. 2.4 Centre Clipped Auto-correlation Pitch Detector

A hardware implementation of the above approach has been reported [17] which uses both centre clipping and infinite clipping to ease computational problems. Another approach computes the average magnitude difference function [18] instead of the autocorrelation function SO that multiplications are replaced by additions.

The final time domain technique of significance makes use of adaptive filtering. In one example, the coefficients of a digital filter are updated to minimise the mean square error function and the resulting residue approximates to the glottal pulse train [19]. One advantage of this technique linear predictive vocoder (section 2.4) the in a filter structure already exists and the pitch period by-product. A slightly different technique a based on adaptive principles employs a recursive comb filter which homes in on the speech line spectrum by minimising the mean square output of the filter [20]. Since this method involves only addition, it is faster than the inverse filtering method.

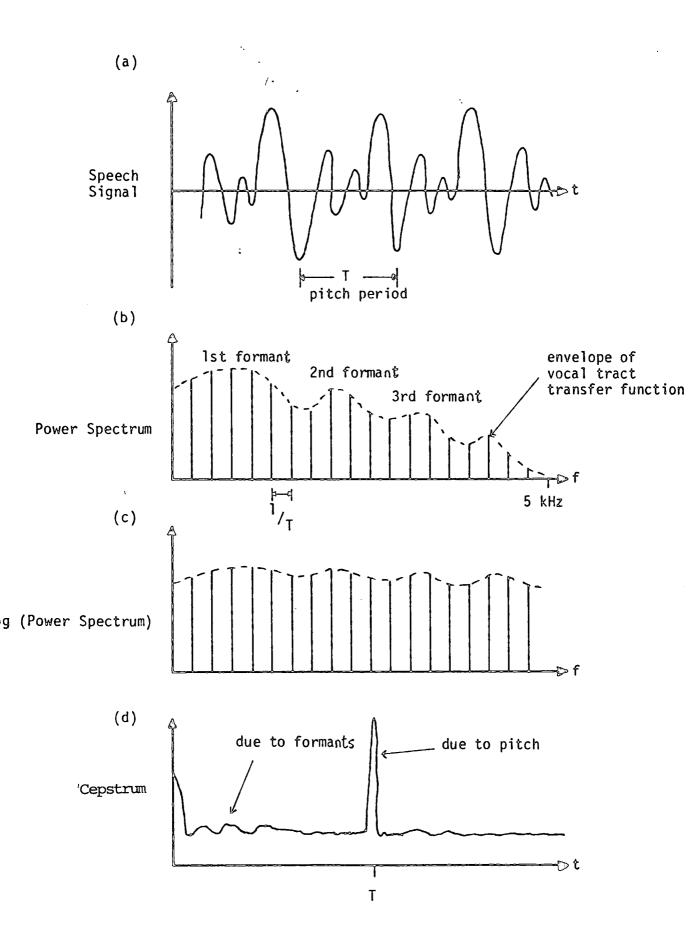

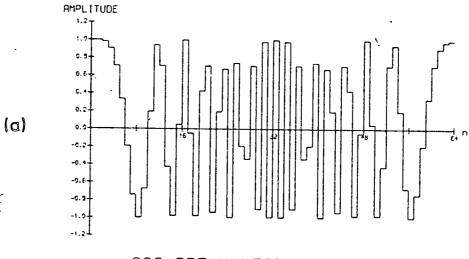

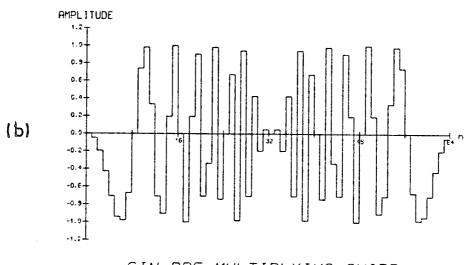

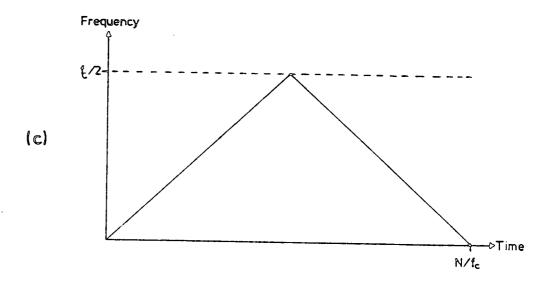

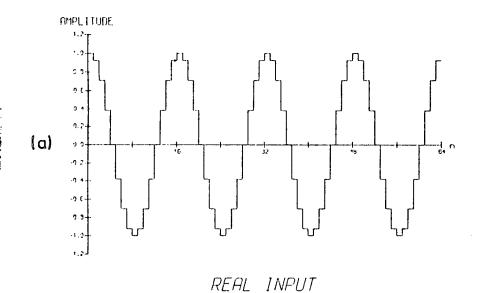

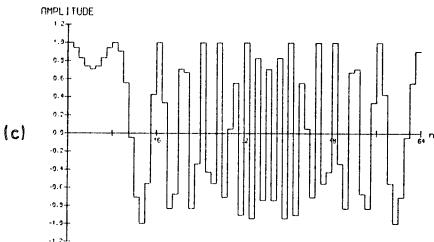

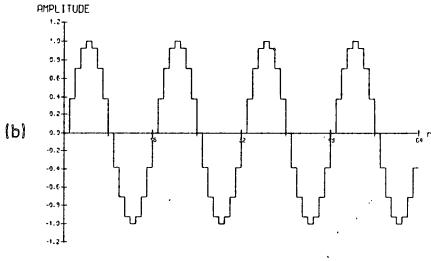

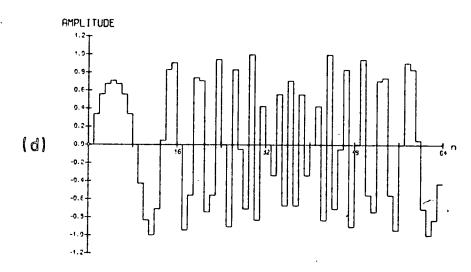

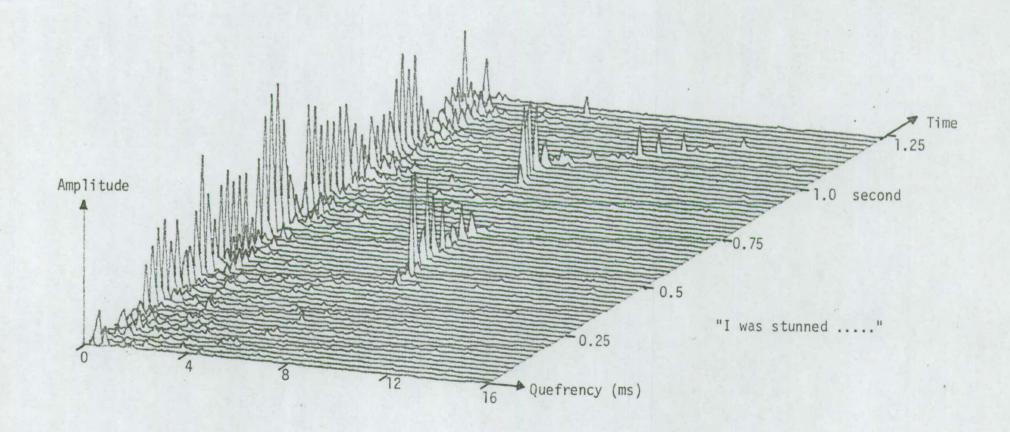

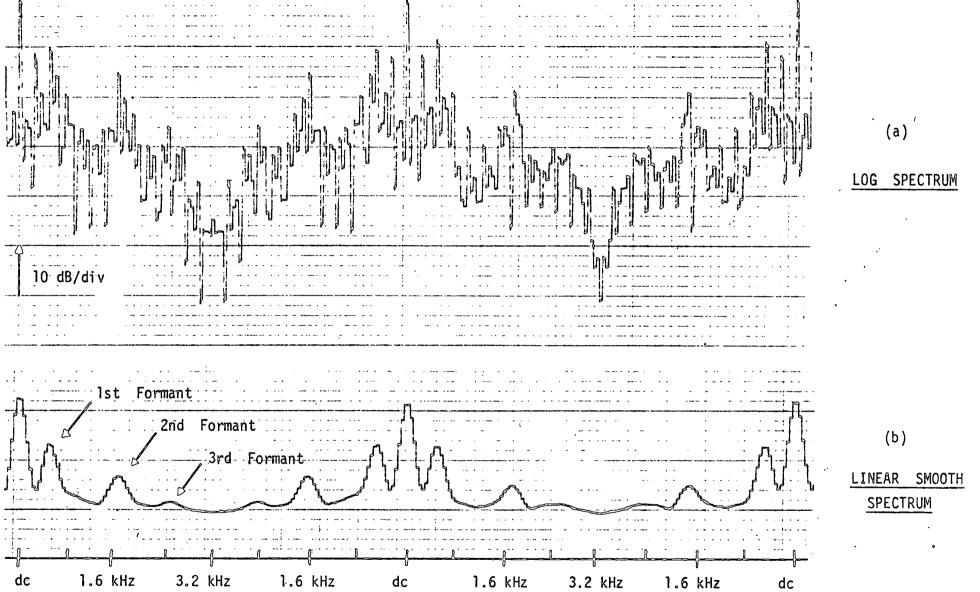

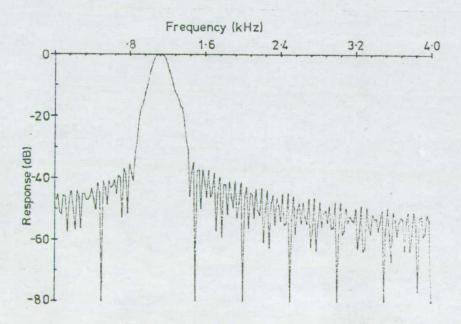

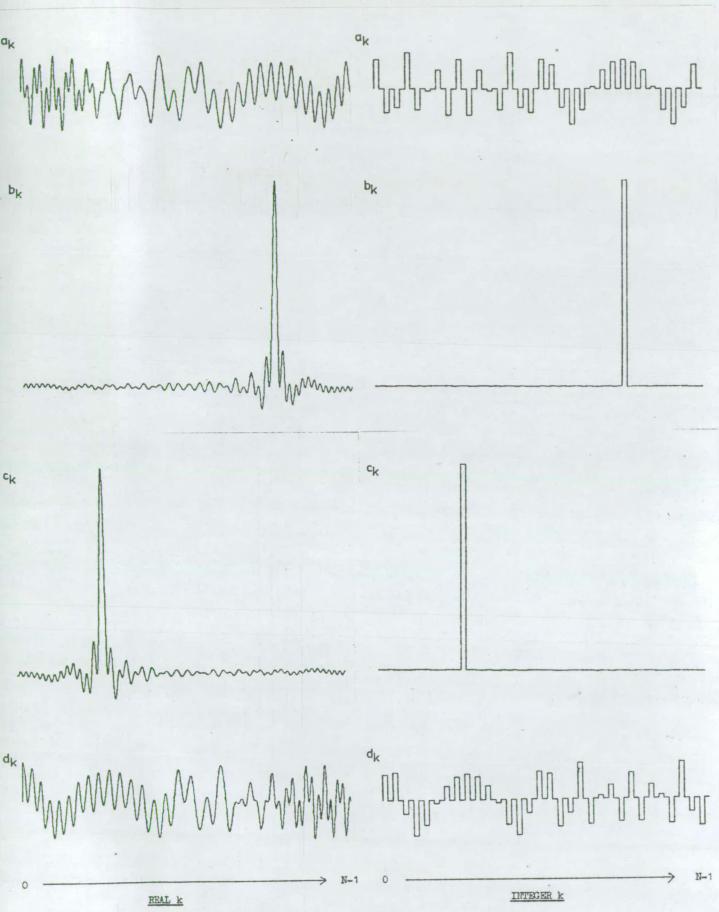

A frequency domain pitch extractor has been described by Noll [21] and is based on the cepstrum of speech, which is defined as the Fourier transform of the logarithm of spectrum. non-linear operation on the spectrum The equalises the line harmonic amplitudes and effectively the formant structure. Mathematically, the de-emphasises log operation deconvolves the effect of the vocal tract the excitation source. The second transform measures periodicity in the frequency domain. Fig. 2.5 illustrates the involved in the cepstral computation. operations time domain signal in Fig.2.5a is transformed to Fig. 2.5b which spectrum in is subsequently logged (Fig. 2.5c) and Fourier transformed a second time to provide the (Fig. 2.5d). (The cepstrum variable is called cepstrum

Fig. 2.5 Illustration of the Cepstrum

"quefrency" and has units of time). The cepstrum has a main due to the speech periodicity and a series of smaller peaks at high quefrencies due to the compressed formants. When the cepstrum is computed for unvoiced speech, there is no line spectrum and therefore no cepstral pitch peak, automatic V/UV decision can be made. As in the autocorrelation technique, logic circuits are usually necessary to decide if the pitch measurement is feasible. It is generally considered that the cepstrum is an extremely powerful technique because the input signal does not require to be high quality.

A comparative performance study of several of the above pitch detectors was carried out by Rabiner et. al.[22]. The conclusion was that each detector has its own strengths and weaknesses and no single detector was top ranked for all cases of input signal. For example, the cepstrum was poor on high pitch speakers whereas time domain techniques were poor on low pitch speakers. Overall, the cepstrum technique proved to be the best all-round performer but was probably the most inefficient in terms of hardware implementation.

#### 2.3 THE CHANNEL VOCODER

Historically, the channel vocoder was invented in 1939 by Homer Dudley [23] of Bell Telephone Laboratories. During the 1940's and 1950's it was realised that vocoders might

have a useful role in communication systems and by the late 1950°s, practical systems were being developed. The basic principles described by Dudley in 1939 remain today as an established speech compression technique.

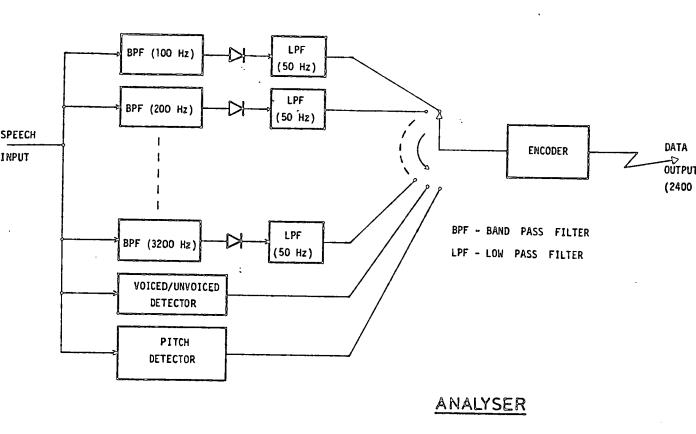

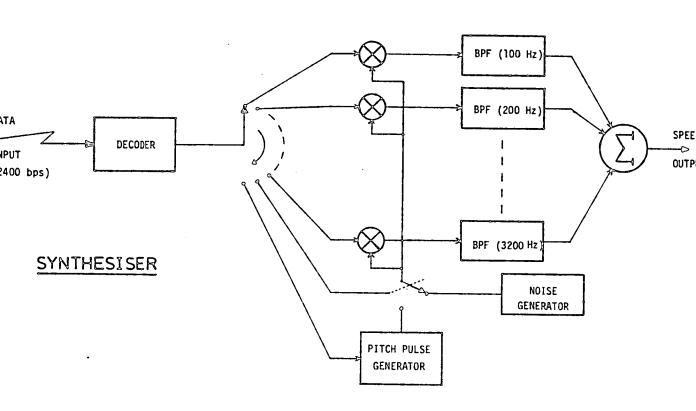

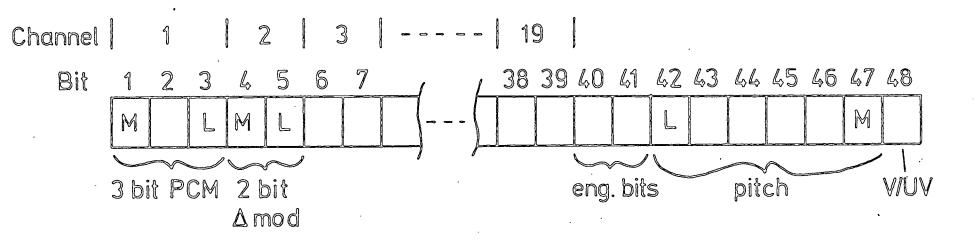

A block diagram of the channel vocoder is shown in In the analyser, the main processing block is a bank of contiguous band-pass filters arranged to cover continuously the speech bandwidth of interest. The outputs from these filters are rectified and low-pass filtered that an approximation to the short-time spectral envelope [11] of the speech is available. Normally, the amplitude components of the smoothed spectral envelope are sampled, quantised logarithmically, multiplexed with pitch and voicing information (section 2.2) into frames and transmitted serially to the synthesiser. Data reduction is achieved because:

- 1. phase information is not transmitted

- 2. only the smoothed envelope of the voiced speech line spectrum is transmitted (in addition to the line spectrum fundamental)

- both amplitude and frequency are logarithmically quantised.

In the synthesiser, the received data are inversly decoded and fed in parallel to the appropriate circuit

Fig. 2.6 The Channel Vocoder

elements. Speech is synthesised by summing the outputs from a contiguous filter bank, similar to that in the analyser, which has been input with weighted versions of an excitation source. The particular source is selected by the voicing control and the period of the periodic source is given by the received pitch information. Finally, the synthetic speech is filtered to remove the analyser pre-equalisation and to compensate for the non-triangular excitation source.

It is generally accepted that the minimum data rate which can be achieved by a channel vocoder (without special coding techniques [24]) is in the order of 2400 bps. At this data rate, the speech has a mechanical quality but still maintains good intelligibility [2].

The channel vocoder fidelity depends on the design of contiguous filter banks [2]. Ideally, these should consist of steep-sided filters narrow enough for no more than a single harmonic to enter any one filter during voicing. The spectrum envelope generated would thus be correct measure of the speech spectral energy at that time and synthetic speech could be constructed exactly from The disadvantage of this filter bank, disregarding practical considerations, would be that relatively bandwidth compression would result. For example, if the lower limit of the pitch frequency is 50Hz then 80 parallel filters are required to analyse a 4kHz bandwidth. As the

filter bandwidths are increased so that the total number of filters can be reduced, a spectral distortion becomes evident. This is because more than one harmonic appears in some of the filters at low pitch frequencies. It is exceptionally difficult to quantify this distortion in terms of synthetic speech quality and generally, the number of filters in the bank is chosen through practical experience. Channel vocoder designs typically employ between 16 and 32 logarithmically spaced filters to cover a 4kHz bandwidth. The filter characteristics for a 19-channel vocoder are given in Table 2.1 [25].

individual filter characteristic is also an important consideration. It can be deduced that sharp cut-off filters will give a more accurate spectral measurement; in practice, sharp cut-off filters have long settling times so that their use would result in a smearing rapid spectral changes and subsequent reverberation o£ effects in the synthetic speech. Unequal filter time might be the case if different channels employ different bandwidths, also give rise to a temporal smearing effect. The compromise utilised by most channel vocoders is a 2-pole Butterworth characteristic [2].

The cut-off frequencies of the low-pass filters which smooth or average the rectified band-pass filter outputs have to be chosen to follow the slowly varying spectral content of speech. Practical experience [26] has shown that

| Channel<br>Number | Filter Centre<br>Freq. (Hz) | Analysis Filter<br>BW (Hz) | Synthesis Filter<br>BW (Hz) |

|-------------------|-----------------------------|----------------------------|-----------------------------|

| 1                 | 240                         | 120                        | 40                          |

| 2                 | 360                         | 120                        | 40                          |

| 3                 | 480                         | 120                        | 40                          |

| 4                 | 600                         | 120                        | 40                          |

| 5                 | 720<br>:                    | 120                        | 40                          |

| 6                 | 840                         | 120                        | 40                          |

| 7                 | 1000                        | 150                        | 40                          |

| 8                 | 1150                        | 150                        | 40                          |

| 9                 | 1300                        | 150                        | 40                          |

| 10                | 1450                        | 150                        | 40                          |

| 11                | 1600                        | 150                        | 40                          |

| 12                | 1800                        | 200                        | 60                          |

| 13                | 2000                        | 200                        | 60                          |

| 14                | 2200                        | 200                        | 60                          |

| 15                | 2400                        | 200                        | 60                          |

| 16                | 2700                        | 300                        | 60                          |

| 17                | 3000                        | 300                        | 60                          |

| 18                | 3300                        | 300                        | 60                          |

| 19                | 3760                        | 500 (f <sub>o</sub> 36     | 00)60                       |

| 19a               | -                           | - (f <sub>o</sub> 37       | 50)500                      |

Analysis Filters are second order Butterworth

Synthesis Filters are single tuned with alternate outputs summed in antipha

- Note: (a) Only 19 analysis channels

(b) Synthesis filter 19 excited during voiced sounds

(c) Synthesis filter 19a excited during unvoiced sounds

Table 2.1 Parameters for a 19 Channel Vocoder

the spectral content of speech is fairly constant for periods of 20mS but has probably changed significantly after 40mS. The smoothing filter is usually chosen to have a 3dB attenuation at 25-35Hz and an 18dB/octave roll-off [2].

other speech processing systems, large the dynamic range (> 60dB) associated with speaker variations and conditions causes practical circuit problems in vocoder implementations. Several techniques are used to ease situation. the Pre-equalisation in the analyser is designed to boost the high frequencies so spectral energy spread more evenly between the is channel filters. This boost is typically 6dB/octave (The vocal cord excitation source has a general lkHz [25]. trend of approximately -12dB/octave which is differentiated acoustic pressure wave is launched from the human when the lips [11] so that the input speech to a vocoder has general trend of -6dB/octave). Automatic gain control (agc) may be applied to save up to 20dB dynamic range [27] practice is not generally desirable since agc distorts the speech and the vocoder is a non-linear system.

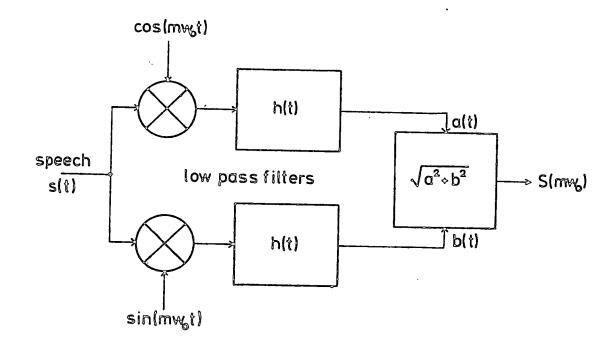

More recently, fully digital implementations οf channel vocoder have been reported. In one example [28], use is made of the filtering structure in Fig. 2.7a. Speech simultaneously modulated by two quadrature sine waves of is the same frequency and the resultant waveforms are separately low-pass filtered. The modulus of the quadrature

(a) Heterodyne Analyser

(b) 2nd Order Recursive Filter

Fig. 2.7 Digital Filtering for the Channel Vocoder

channels gives the spectral amplitude of the speech input evaluated at the frequency of the modulating sinewaves. By sequentially filtering the same segment of speech using different modulating frequencies, an equivalent to the channel vocoder filter bank is achieved. In digital hardware, the modulating frequencies are stored in read only memory and the low-pass filters are accumulate and dump algorithms.

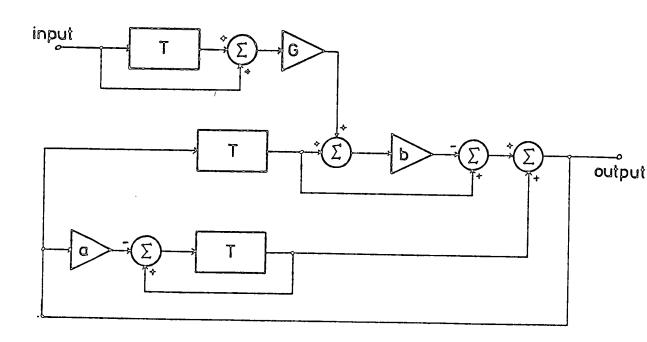

An alternative digital channel vocoder [29] operates by multiplexing a recursive band-pass filter. The filter shown in Fig. 2.7b has a Z transfer function given by

$$H(z) = \frac{-G b (1 - z^2)}{1 - (2 - a - b) z^{-1} + (1 - b) z^{-2}} \dots (2.1)$$

which has a centre frequency and a Q-factor approximately proportional to  $\sqrt{a}$  and  $\sqrt{a/b}$  respectively. Using a filter of this type it is relatively straightforward to update the filter coefficients (stored in read only memory) and produce a logarithmically spaced filter bank.

Both of these digital filtering techniques have potential for Very Large Scale Integration (VLSI) and must be considered serious contenders for the single chip vocoder. However, at the present time, typical digital vocoder implementations employ in the region of 200 discrete integrated circuits and consume 15W of power [28]

One other channel vocoder implementation has recently been reported [30]. Here the filter bank is fabricated as a single integrated circuit using 19 parallel finite impulse response (FIR) CCD filters. This approach to the CCD channel vocoder will be discussed in more detail in chapter 7 and compared to the alternative CCD channel vocoder studied by the author.

# 2.4 THE LINEAR PREDICTIVE VOCODER

An increasingly popular technique for low bit rate speech analysis and synthesis employs the properties of linear prediction [31]. This method is suited to sampled-data implementation and utilises either an all-pole recursive filter [3] or a lattice filter [32] to synthesise the speech. The filter coefficients represent a linear prediction of the analyser input speech.

Briefly, linear prediction consists of predicting or estimating the present value of a signal using a linear weighted sum of delayed signals. The linear weights that minimise, for example, the least mean square predictor error are then information parameters which characterise the properties of the signal under analysis. These linear weights or predictor values can be transmitted directly or can be further processed in a variety of ways for different applications [3].

A useful by-product of the prediction process is that once the weights have converged, the error signal is an approximation to the excitation source. Pitch information and a V/UV decision can therefore be derived by means of a peak picking algorithm.

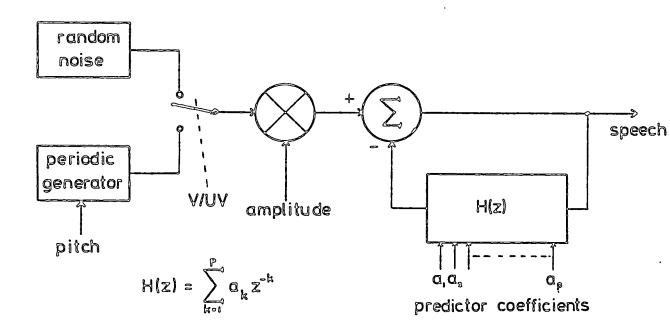

Speech synthesis from a recursive digital filter using linear prediction is shown in Fig.2.8 [3].

Fig. 2.8 Linear Predictive Synthesis

The excitation source is selected in exactly the same manner as in the channel vocoder (section 2.3) and is input to the filter via an amplitude control. The amplitude level is derived from the rms value of the analyser input speech and is necessary since the predictor coefficients contain only information concerning the spectral shape.

Due consideration to the quantisation of control parameters [33] results in vocoders which operate down to 2400 bps with more natural sounding synthetic speech than the equivalent channel vocoder[33]. The predictor typically requires 10-12 coefficients and a sample rate of 10kHz for good quality speech. Charge coupled device programmable transversal filters (chapter 3) are suitable for use in this application, but, because only 10-12 taps are required, it seems likely that digital implementations will almost always be preferred.

## 2.5 OTHER VOCODER PRINCIPLES

Since the introduction of the digital computer which facilitated simulation studies of complex systems, the interest in speech research has grown enormously and many other vocoding techniques have been reported. Some of these are still too complex for real-time hardware implementation, but others are now realistic.

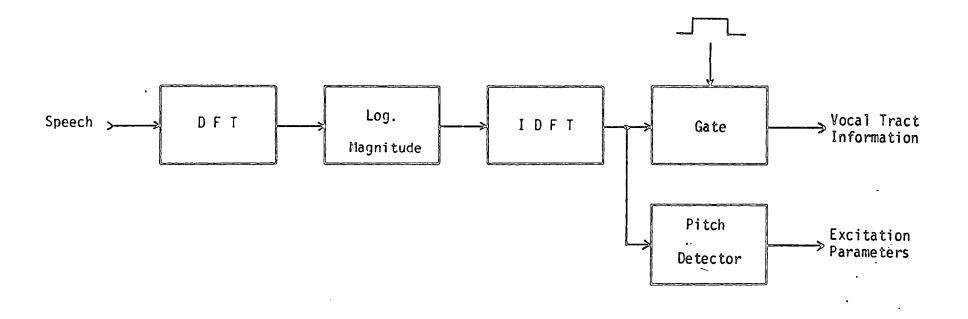

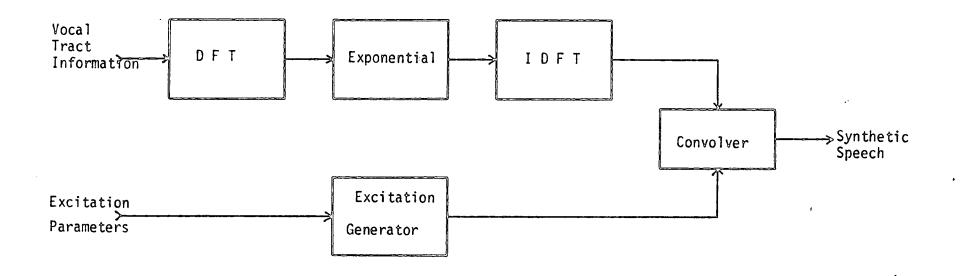

One such system is the homomorphic vocoder [34] which has the potential for real-time hardware implementation using charge coupled devices. It relies on the deconvolution of the speech excitation source and the vocal tract impulse response by homomorphic filtering [35]; homomorphic filtering is based on the computation of the cepstrum. The vocoder's block diagram is shown in Fig.2.9 where it can be seen that the analyser is identical to the

cepstral pitch detector (section 2.2) except for operation which extracts the quefrencies due to the vocal tract (Fig.2.5d). These quefrencies are then coded transmitted to the synthesiser where the vocal tract impulse response is constructed by an inverse set of operations. Synthetic speech is produced by convolving the vocal tract impulse response with the excitation source. [34] have shown that high quality speech may be reconstructed at 7800 bps and compression to 4000 bps may be more complex coding [36]. obtained by Simplification in synthesiser hardware and a bit rate reduction to less than 2000 bps are possible by using a log magnitude approximation filter [37].

A vocoder technique which promises to give optimum bit rate reduction (600 bps) is the formant vocoder. Research has been continuing for many years but solution has practical been found. The principle is to extract the centre frequencies and bandwidths of the (there are three in male speech below 3kHz) and to formants use this information to control a resonant model ο£ production [11]. Formant extraction techniques generally rely on formant tracking algorithms which are based accumulated and detailed experience of speech waveforms. These algorithms have been designed to operate on short-time spectra of speech [38], autocorrelation functions [39] and linear prediction spectra [40], but, in the complex formant movements create problems. Another

Fig.2.9 The Homomorphic Vocoder

philosophy that applies to formant extraction is analysis-by-synthesis. Here an educated guess is made of the formant parameters and a spectrum is generated which compared to the actual speech spectrum. The formant parameters are then varied until the difference between the two is minimised according to some criterion [41]. latter technique has some advantages because the entire spectral shape is considered and not simply the spectral peaks.

#### CHAPTER 3

## THE CHARGE COUPLED DEVICE

The Charge Coupled Device (CCD) is essentially an analogue shift register which can be fabricated as an integrated circuit using Metal Oxide Silicon (MOS) technology. Discrete samples of input signal are stored as charge packets in potential wells and these may be moved along the CCD register by applying a sequence of clock pulses. The CCD therefore provides the flexibility of a time-quantised, clock variable system which does not require analogue to digital conversion.

The CCD was first reported by Boyle [42] in 1970 and is a member of the more general Charge Transfer Device (CTD) family which includes the earlier Bucket Brigade Device (BBD) [43]. In recent years the CCD has become important because:

- the technology (MOS) is standard and hence is low cost

- 2. the silicon area required per stage is very small

- the CCD can be used to process either analogue or digital electrical signals, or optical signals

- 4. the range of applications is very wide.

Section 3.1 explains the basic principles of CCD charge storage and charge transfer whilst section 3.2 discusses the merits of several methods of charge input and output. The third section summarises the main defects and causes of degradation in CCDs and, finally, section 3.4 describes one of the most powerful analogue signal processing blocks, the transversal filter.

# 3.1 BASIC PRINCIPLES

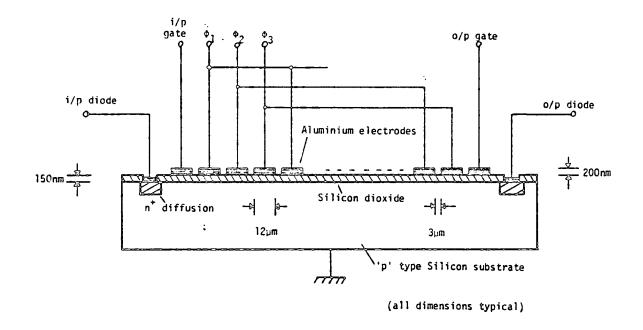

The fundamental concepts of CCD operation [4,44] have been developed directly from the established theory of MOS transistors [45] and, as shown in Fig.3.1, the basic CCD delay line structure resembles a rather large multi-gate MOS transistor. The input diffusion converts a sample of the input signal into a charge packet of minority carriers, which is subsequently transferred along the register at a rate controlled by the clock waveforms. After some delay, this charge packet can be sensed at the output diffusion.

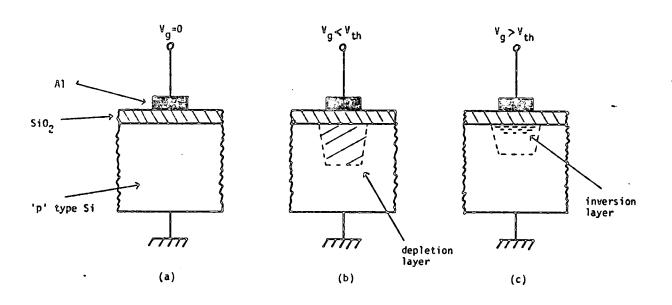

To understand the CCD operation it is best to start by examining the basic CCD storage element [45], the MOS capacitor shown in Fig. 3.2. With zero potential on the gate there is a uniform distribution of majority carriers (holes in this case) in the "p type" semiconductor. When the gate terminal is pulsed more positive than the substrate, majority carriers from the silicon/silicon dioxide (Si/SiO2) interface immediately below the gate are repelled, thereby

Fig.3.1 Cross Section of CCD Delay Line

Fig. 3.2 The CCD Storage Element

creating a depletion region (Fig. 3.2b). If the pulse amplitude exceeds the threshold voltage, Vth, carriers (electrons) can be attracted towards the interface form an extremely thin "inversion layer" (Fig. 3.2c). the amount of charge stored is increased, the extent of depletion region must decrease to preserve charge neutrality The creation of this in the system. layer corresponds the formation of a channel in a MOS transistor. minority carriers can be stored in the inversion layer typically hundreds of milli-seconds before thermally generated minority carriers from within the depletion region significantly distort the charge packet.

An extremely useful model for visualising the operation of CCD structures results from the "potential well" concept If a potential well is formed by applying a [46]. gate threshold voltage, then greater than the introduction of minority carriers is analogous to being poured into a well. The maximum quantity of charge which can be stored in the structure (typically lpC) depends the volume of the potential well; the depth of the well is related to both the magnitude of the gate pulse and the oxide thickness, and the area of the well is defined by the electrode area.

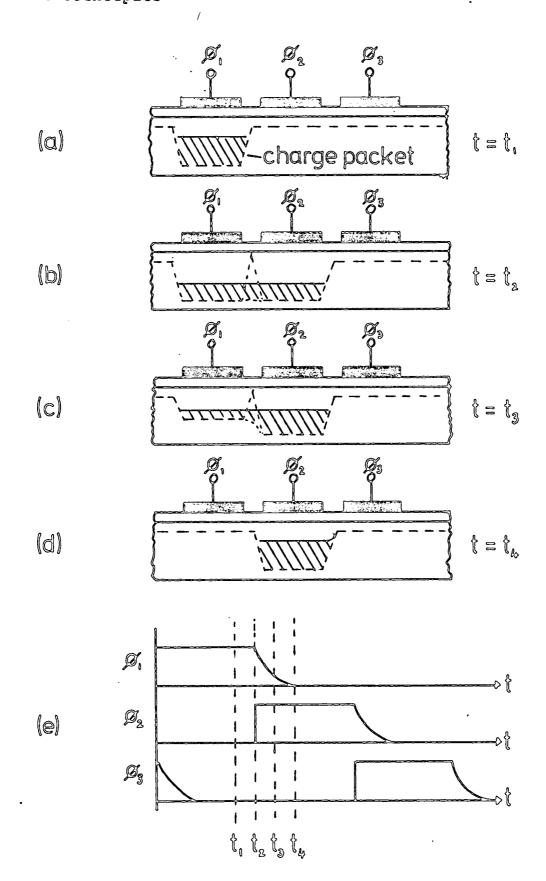

The next operation is to transfer the stored packet of charge to an adjacent CCD element. Consider the structure

Fig. 3.3 Charge Transfer in CCD

illustrated in Fig.3.3a where there is a charge packet under the Øl electrode. If each electrode physically very close to its neighbour (<3µm separation), then when  $\emptyset 2$  turns on, the depletion regions under  $\emptyset 1$  and  $\emptyset 2$ will merge and the charge will redistribute (Fig. 3.3b). Βy slowly reducing the potential on  $\emptyset$ 1, the charge remaining under 01 will spill over into the 02 well make the transfer complete at time t4. It is therefore possible to transfer charge packets along an entire register by applying the appropriate time sequence of pulses. In the simple structure shown in Fig. 3.3, a three phase clocking system is necessary to propagate the charge unambiguously in direction. This structure has, however, limitations (some of practical which are discussed section 3.3) and many other more sophisticated electrode arrangements have been developed [43].

#### 3.2 CHARGE INPUT AND OUTPUT

When the CCD is used in an analogue mode, the linearity of charge input and output is extremely important. In the following section, four serial input schemes of varying complexity and performance will be compared and three output techniques, one serial and two parallel, will be discussed.

## 3.2.1 Input Techniques

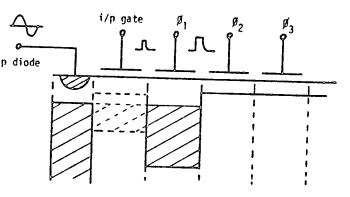

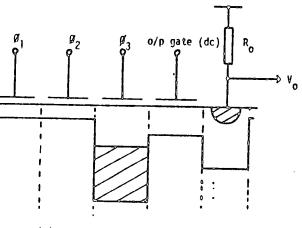

Dynamic current injection [47], which uses the input in Fig.3.4a, is one of the simplest input The input signal is applied to the input diffusion and the input gate is held at a relatively low When the Øl potential well potential. is created, charge flows from the diffusion across the gate into the well. The size of the injected charge packet is determined input diode potential, the channel conductance and the available injection time (governed by the CCD clock). process is inherently non-linear and the resulting distortion is quite severe. For a sinusoidal input giving full well capacity, the 2nd harmonic typically at -16dB and the third harmonic at 15 -30dB [48].

In a diode cut-off scheme [49] (Fig. 3.4b), the signal normally capacitively coupled to a reverse biassed input During  $\emptyset l_i$  the input gate is pulsed on to allow minority carriers from the diffusion to flow into the  $\emptyset$ 1 potential well. The surface potential is therefore directly by the diode potential and the sample is trapped when the input gate is turned off. The trailing edge of the gate pulse has to be designed carefully because: (a) if the channel is cut-off too quickly, some charge from within will be emptied into the signal packet (partition noise) and (b) if the channel is cut-off too slowly, the sampling instant will depend on the signal level. exact

(a) Dynamic Current Injection

(b) Diode Cut-off

(d) Feedback Linearisation

However, even with an ideal gate cut-off, this method still has an inherent non-linearity due to the depletion capacitance changing with the diode potential. These effects give rise to second harmonics in the order of -26dB [48].

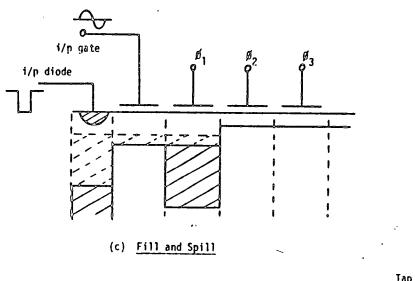

A significant improvement in linearity may be obtained using a fill and spill method [50] of charge input. the variation shown in Fig. 3.4c, the input signal is applied the control gate and the input diode is pulsed to a low potential to fill the well created under  $\phi$ 1. When this is returned to a high potential, the excess charge drains back into the diffusion, leaving a charge packet proportional to the gate potential. Two second order distortions are present: (a) spurious noise on the driving waveform enters the signal packet directly and (b) the signal dependent fringe field from the input gate alters the effective area of the  $\phi$ 1 potential well. However, both of these problems may be eliminated by a more complex "pump priming" method of fill and spill [51]. Second harmonic distortion components of less than -40dB have been reported [50].

The technique described above helps to linearise the .

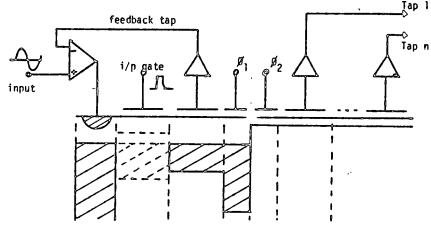

CCD input structure; feedback linearisation [52], however, attempts to linearise the complete CCD input to output transfer function. An essential feature of the input

in Fig. 3.4d is the inclusion of extra non-destructive output tap to monitor the input charge. output is compared with the original signal to generate an error which subsequently corrects the stored charge. If the monitoring tap is electrically identical to all the other output taps, the CCD transfer function will tend to be linearised and the total harmonic distortion theoretically be reduced by the open loop gain of the system (in practice to less than -40dB [53]). The disadvantage of this technique is the need for a high quality differential amplifier which may be difficult to integrate with the CCD.

# 3.2.2 Output Techniques

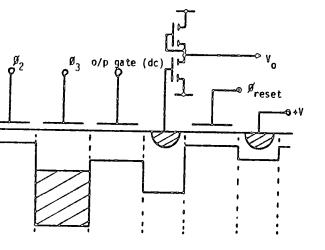

When the CCD is used as a serial delay line, an output diffusion [46] (Fig.3.5a) senses the magnitude of the charge The pn junction is normally held reverse biassed is positioned so that its depletion region couples with that of the last storage element. An extra gate held constant bias is generally included to help capacitive pick-up from the last transfer electrode. Ø3 is turned off, any charge in the  $\phi$ 3 potential well will be collected by the output diode to appear as current output circuitry. A voltage output can be in the simply by incorporating a resistor. However, output changes are very small because of the minute charge packets and, except in wideband application, it is desirable

Output Diffusion

Floating Output Diffusion with Reset

(c) Plan View of Split Gate CCD

Fig.3.5 Charge Output Techniques

to perform on-chip amplification. This is best accomplished by a MOS transistor with its gate connected directly to the sense diffusion. Since in this case the sense diffusion is floating, an extra diffusion and control gate are required to reset the sense diffusion after the detection of each charge packet (Fig. 3.5b).

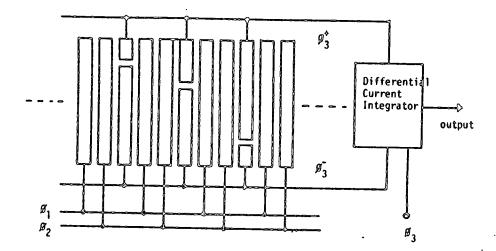

Split electrode tapping [54] is an extremely elegant method for the implementation of fixed weight transversal filters (section 3.4). The basic split electrode arrangement for use in a 3 phase CCD is shown in Fig. 3.5c. Here the third electrode in each cell is divided into sections and each is connected to either the  $\emptyset 3+$  or the  $\emptyset 3$ clock lines. As charge transfers into the region under a gate, an opposite charge is induced onto the electrode from the clock line. Assuming that the oxide capacitance is very greater than the depletion capacitance and that the latter may be considered constant, the induced current in line due to one section of a split electrode is clock proportional to the amount of charge in that potential times the area of the section. The transversal filter is obtained by differencing the total current change in each clock line. Thus a split in the middle of an electrode corresponds to a weighting factor of zero. This technique does not interfere with the signal charge packet in any way and is therefore non-destructive.

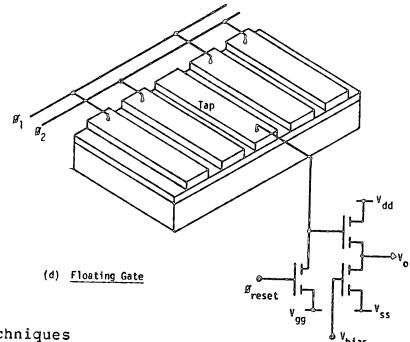

A very powerful and flexible mode of CCD operation is made possible by the floating gate tapping technique [55,56]: serial charge packets may be sensed non-destructively and their magnitudes output in parallel. The applications of this configuration include programmable transversal filtering [57], correlation [8] and adaptive filtering [8].

Fig. 3.5d shows the floating gate tap schematic for a three phase CCD with pseudo two phase clocking. The CCD tap electrode is directly connected to the gate of a sense transistor and also to a reset diffusion. Assuming that the reset transistor is off and that the tapped CCD electrode is floating at a potential of Vgg, the transfer of minority carriers into the potential well below this electrode induces a charge redistribution which causes a related change in electrode potential. This voltage change is buffered by a MOS source follower to provide an output signal at a low impedance. After transfer of this charge packet to the next potential well (under  $\emptyset$ 1), the reset transistor is pulsed on to reset the tap electrode potential in preparation for the next cycle.

## 3.3 DEVICE LIMITATIONS AND DEFECTS

## 3.3.1 Transfer Efficiency

The charge transfer efficiency is an important measure of device performance in analogue signal processing. When a charge packet is transferred from under one electrode to the next, some of the charge is left behind and some lost completely. Two main effects are responsible for this inefficiency, the first of which is due to "interface states" at the Si/SiO2 boundary [58]. As each charge packet is passed along the device, interface states are filled almost instantaneously by minority carriers and then, the charge packet moves on, the states are emptied much more slowly. Some of the emitted charges return to the correct packet but others empty into trailing packets. The primary effect of these states can be reduced considerably by passing a background charge or "fat zero" continuously along the device. The second source of inefficiency is caused by transfer mechanism itself [59]. When the transfer process begins, minority carriers move across quickly under influence of a drift field. As the charge in the new builds up, the drift field is reduced and the predominant transfer process becomes thermal diffusion, which is a relatively slow process characterised by a time constant defined by the electrode length and the carrier mobility. This time constant therefore gives a trade-off between clock frequency and transfer efficiency. efficiency can be maximised by careful design of the driving waveforms and by making the interelectrode spacing as small

as possible.

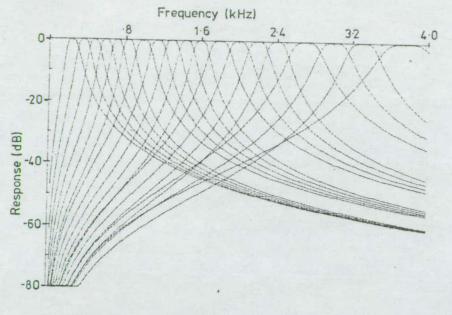

The effect of charge transfer efficiency can visualised by impulsing a CCD delay line. The delayed output will consist of an attenuated version of the original pulse, followed by a time series of smaller residual pulses. In practical CCD delay lines only the first residual is normally significant. This smearing gives rise to a low pass filter characteristic in the frequency domain reducing device bandwidth. A simple analytical expression the relating the transfer efficiency to the frequency response been developed by Vanstone et. al. [60] using Z-transforms. The amplitude response at the nth output stage is

$$\mathbb{A}_{n}(w) = \left[\frac{2}{1+\xi^{2}-2 \, \xi \, \cos(wT)}\right]^{n/2} \qquad \dots (3.1)$$

and the phase response is given by

$$\phi_{n}(w) = \tan^{-1} \left[ \frac{n \sin(wT)}{\varepsilon - \cos(wT)} \right]$$

... (3.2)

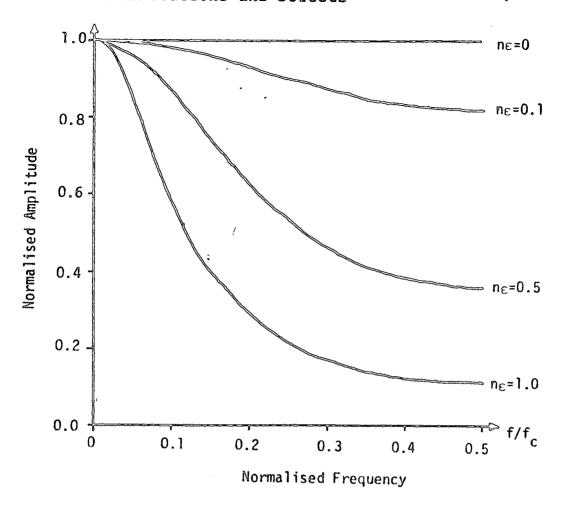

where  $\propto$  is the transfer efficiency per stage,  $\in$  is the transfer inefficiency ( $\in$ =1- $\propto$ ), T is the sampling period and w is the angular frequency of the input. Fig.3.6 shows a plot of the normalised amplitude transfer function for various values of the transfer inefficiency product n $\in$

In current CCDs, charge transfer inefficiency is in the order of 0.0001 which restricts the number of serial stages to 1000. However, this depends to a great extent on the

Fig. 3.6 CCD Amplitude Frequency Response

application and the amount of permissible signal degradation. Several techniques have been developed to compensate for charge transfer inefficiency [61,62,63], but in general these result in considerable circuit complexity or redundancy.

## 3.3.2 Noise [64]

Noise sources can be classified into four different categories; input, storage, transfer and output. The combined effect of all noise sources is to limit the dynamic

range.

The input and output noise sources depend largely on the particular techniques used. For example, dynamic current injection suffers from random fluctuations in voltage levels and pulse jitter in the clocking waveforms whereas dynamic cut-off has associated partition noise and sampling jitter. In the split electrode tapping technique, the summing amplifier noise tends to dominate all other sources.

Of the inherent noise groups, storage and transfer, the most significant sources are due to the shot noise in dark current (storage) and the fluctuating trapping of fast interface states (transfer). In typical signal processing applications, this last source causes most concern and may be minimised by careful design. Signal to noise ratios in the order of 70-80dB have been achieved in current devices.

## 3.3.3 Dark Current [44]

Dark current is the equivalent of "leakage current" in MOS transistors and is caused by the thermal generation of minority carriers both in the bulk semiconductor and at the Si/SiO2 interface. This extra charge accumulates in the potential wells, thereby degrading the stored information. At normal temperatures, dark current limits the maximum storage time to several hundred milli-seconds. In

continuously clocked delay lines, the dark current effect simply reduces the dynamic range, whereas in transversal filters (SIPO) there is a non-uniform noise distribution. The level of dark current approximately doubles for every ten degrees centigrade increase in substrate temperature, necessitating careful consideration of the total on-chip power dissipation.

## 3.3.4 Peripheral On-chip Circuitry

To make the CCD appear as a "black box" which may be readily configured for any system, it is highly desirable to integrate along with the CCD many of the necessary peripherals. For example, the operation of a CCD requires clock drivers, timing logic, input and output amplifiers, anti-aliasing filters and sample and hold gates. All of these functions have, of course, to be realisable in a compatible technology.

The integration of the clock drivers and timing logic is relatively easy, but their inclusion normally limits the maximum operating frequency to about lMHz. This limit is due to the power dissipated when driving capacitive clock lines. MOS amplifiers have been improved considerably in recent years and suitable amplifier designs have been reported [65] which operate at over lMHz bandwidth with very low d.c. drift. The anti-aliasing filters and sample and hold circuits should be clock variable; switched capacitor

... (3.3)

techniques [66] provide suitable characteristics at audio frequencies.

#### 3.4 THE TRANSVERSAL FILTER

The transversal filter structure shown in Fig. 3.7 is an extremely powerful and flexible building block in analogue (and digital) signal processing [5].

Fig. 3.7 Transversal Filter Schematic

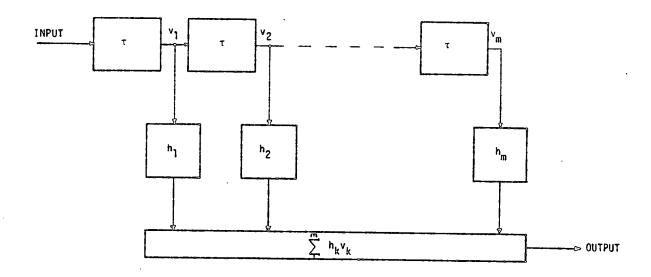

It consists of an N-stage shift register with non-destructive taps after each delay, T. Each tap output is multiplied by a weighting coefficient,  $h = (k=1,2,\ldots m)$  and the results are summed. The filter output is given by

$$V_o(nT) = \sum_{k=1}^m V_i (nT - kT + T) h_k$$

which is the discrete convolution of the input with an impulse response function (correlation may be obtained by time reversing the impulse response). The frequency response of this filter is given by the discrete Fourier transform of the weighting coefficients. Therefore, by modifying the weights appropriately, any linear Finite Impulse Response (FIR) filter [67] can be constructed.

Split electrode weighting (see section 2.2.2) is an extremely efficient technique for the implementation of fixed weight transversal filters in CCD, and one powerful application of these filters is in the CCD Chirp-Z transform processor (chapters 4 and 5). If, however, the weights are made electrically programmable, then a vast range of sophisticated analogue signal processing applications is possible e.g. time variant adaptive filtering [7] and programmable correlation [8,68].

## CHAPTER 4

#

When analysing electrical signals, it is most common to display the waveform in the time domain. This gives the necessary amplitude and timing information. However, in certain cases, it can be more illuminating to picture the same information from an entirely different viewpoint, i.e. from in the frequency domain. In much the same way, it is sometimes much more powerful to perform signal processing in the frequency domain.

This chapter discusses the advantages and disadvantages of several techniques for time to frequency domain conversion (and the inverse) when applied to processing. Section 4.1 reviews the conventional filtering spectrum analysers, one of which has recently implemented in CCD. The fundamental mathematical tools relating the domains, となり both theoretically practically, are summarised in section 4.2 along with an efficient discrete transform algorithm suited to microprocessor implementation. Sections 4.3, 4.4 and 4.5 investigate three algorithms which can be realised efficiently using CCD transversal filters to give real-time operation up to several megahertz. The final section compares their performance.

#### 4.1 CONVENTIONAL SPECTRUM ANALYSERS

One of the first systems used to resolve the frequency components of time domain signals employed a variable centre frequency filter to scan the temporal signal. This type of analyser, known as a Tuned Radio Frequency (TRF) analyser, is simple and inexpensive but suffers from several disadvantages. Firstly, because the TRF analyser has a swept filter, its sweep width is limited (usually one decade); secondly, since the swept filter bandwidth is not normally constant with frequency, the resolution is dependent on frequency.

A significant development in spectrum analysis was initiated by the invention of the heterodyne principle. In contrast to the TRF analyser, the heterodyne spectrum analyser uses a bandpass filter with fixed characteristics. The input signal is mixed with a swept local oscillator before being filtered. An output from the filter will be present only when the difference frequency (or the sum frequency) falls within the passband. The advantages of this technique are considerable. It obtains high sensitivity through the use of IF amplifiers and many decades in frequency can be covered. Also, the resolution can be varied by changing the bandwidth of the IF filter and the sweep rate of the local oscillator.

Both the TRF and heterodyne analysers discussed so far are swept tuned and hence the frequency components of a

sampled are sequentially in time. This is "off-line" sufficient for spectrum analysis, to transform signals continuously "on-line", the output rate of the processor has to be the same as or greater than the input rate. Equivalently, the processor's bandwidth must be least that at the input signal. Such processors are o£ normally termed real-time.

One way of achieving this real-time performance use bank of staggered band-pass filters, each with equal bandwidth, and to process the input signal in parallel. frequency range and resolution of this analyser is normally restricted by the amount of hardware required and applications (e.g. the channel vocoder) have fewer than 30 resolution bins across the bandwidth. The contiguous filter bank arrangement obviously lacks flexibility and is always used with fixed parameters. More recently, many of the engineering disadvantages of this approach have relieved. For example, an integrated circuit has been reported [30] which houses 19 parallel CCD FIR filters. Alternatively, switched capacitor filters [66] may be in audio frequency applications.

Another technique, similar to the analogue filter bank but rather more flexible, is the multiplexed digital filter. The filter coefficients are stored in Read Only Memory (ROM) and accessed when required. For a single integrated circuit realisation, the serial digital processing restricts the

real-time operation, at present, to several kilohertz. Hardwired versions may be constructed to operate considerably faster (hundreds of kilohertz in real-time) but the power consumption and physical size increase accordingly.

#### 4.2 THE FOURIER TRANSFORM

The principle mathematical tool for time to frequency domain conversion is the Fourier Transform (FT). The definition given in equation 4.1 transforms the time domain signal, f(t), into its frequency domain counterpart F(w). The inverse process, from the frequency to the time domain, is given by the Inverse Fourier Transform (IFT) in equation 4.2. These equations are used widely in communication theory and are fundamental to spectrum analysis.

$$F(w) = \int_{-\infty}^{\infty} f(t) e^{-jwt} dt \qquad ... (4.1)$$

$$f(t) = \frac{1}{2 \pi} \int_{-\infty}^{\infty} F(w) e^{jwt} dw \qquad \dots (4.2)$$

In general, F(w) and f(t) are complex quantities. The amplitude and phase components may be extracted by taking the modulus and argument in the usual way, i.e. for a complex number x=a+jb

$$|x| = \sqrt{a^2 + b^2} \qquad \cdots \qquad (4.3)$$

$$\phi(x) = \tan^{-1} (b/a)$$

... (4.4)

and

The FT pair are well defined for most signals encountered in practical systems. One sufficient but not necessary condition for the existence of the FT is that the time signal, f(t), should have finite energy. Periodic signals, commonly represented by the Fourier series, have infinite energy and are therefore excluded by this condition. However, by the introduction of the Dirac impulse function, S(t), which has an infinite amplitude, an infinitesimal width and unit area, it can be shown [69] that the FT of both periodic and singular functions can be defined.

If the time signal, f(t), is zero for all negative time, then the FT is equivalent to the evaluation of the Laplace transform on the imaginary axis in the "s" plane (complex frequency). The FT is therefore a special case of the more general Laplace transform.

One reason for the popularity of the FT pair is its wide range of useful properties [70]. Possibly the most important of these is given by the convolution theorem. If h(t) is the linear, time-invariant impulse response of a system, and this system is excited by the input signal, x(t), then the output, y(t), is given by the convolution integral

$$y(t) = \int_{-\infty}^{\infty} x(\tau') h(t = \tau) d\tau \qquad \dots (4.5)$$

The convolution theorem states that the FT of the output,

Y(w), is equal to the product of the system transfer function, H(w), and the transformed input signal, X(w), viz.

$$Y(w) = X(w) H(w) \qquad \dots \qquad (4.6)$$

Therefore, convolution in the time domain is the same as multiplication in the frequency domain. In addition, it can be shown that convolution in the frequency domain is equivalent to multiplication in the time domain.

## 4.2.1 The Discrete Fourier Transform

When there is a need to calculate the FT by computer, the definition given in equation 4.1 must be modified because it requires an infinite amount of processing. Firstly, the input function has to be band-limited and sampled at discrete time instants, and secondly, this sequence has to be time truncated to say N points. The resulting definition is an approximation to the FT and is called the Discrete Fourier Transform (DFT). The DFT pair corresponding to equations 4.1 and 4.2 is given by

$$x_k = \sum_{n=0}^{N-1} x_n e^{-j2\pi nk/N}$$

k=0,1..N-1 ...(4.7)

$$x_n = \sum_{n=0}^{N-1} X_k e^{j2\pi nk/N}$$

$k=0,1..N-1$  ...(4.8)

where  $x_k$  is the kth Fourier coefficient,  $x_n$  is the nth sample of the input data and N is the number of points in the

transform.

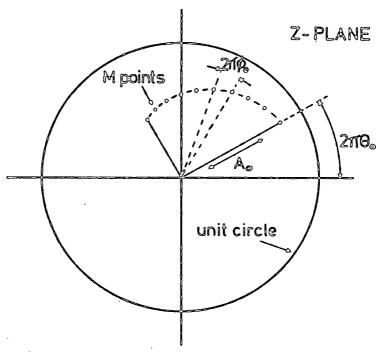

In discrete sampled data analysis, the Z-transform same role as does the Laplace transform in the continuous analysis. The s plane is related to through the expression z=exp(st) and the imaginary plane axis in the s plane maps to the unit circle in the z plane. The equivalence of the FT and the Laplace transform evaluated on the imaginary axis is therefore analogous with of the N-point DFT and the Z-transform evaluated at N equidistant points round the unit circle.

To find out how closely the DFT approximates to the continuous FT it is necessary to examine each stage in the development of the DFT. Firstly, consider the effect of sampling in the time domain. If the sampling period is Ts, then the output spectrum will contain not only the correct result, but also an infinite number of aliased replicas each separated in frequency by fs, where fs=1/Ts. As long as the input function is band-limited to fs/2 (Nyquist), the aliased spectra will not overlap and there will be no distortion. In the practical case, the band-limiting filter cannot have an infinitely sharp cut-off and so it is usual to sample several times faster than the Nyquist limit. For a fixed filter, the only way to reduce aliasing errors is to increase the sample rate.

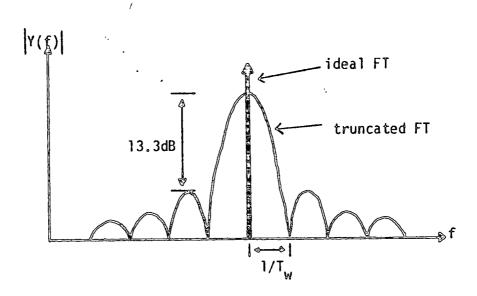

Secondly, the input data are truncated to N points. This is equivalent to multiplying the time signal by a

rectangular window of length N.Ts and its effect convolve the true FT with a (sin x)/x response (which is the FT of a rectangular window). Fig.4.1 compares the true of a sinewave (impulse function) with that of the windowed version. It can be seen that the (sin x)/x main lobe width the frequency resolution i.e. the transform's ability to distinguish between adjacent frequencies. main lobe width is inversely proportional to the time domain window length and to increase the inherent frequency resolution therefore requires an increase in window length. (Note that if the window is increased to infinity then the ideal impulse function results). In addition, the ( $\sin x$ )/x sidelobes create a "leakage" effect and this limits the amplitude resolution. The most significant sidelobes are the first pair, their amplitudes being -13dB with respect to lobe peak. However, weighting functions (section main 4.2.3) can be employed to increase the amplitude resolution at the expense of frequency resolution.

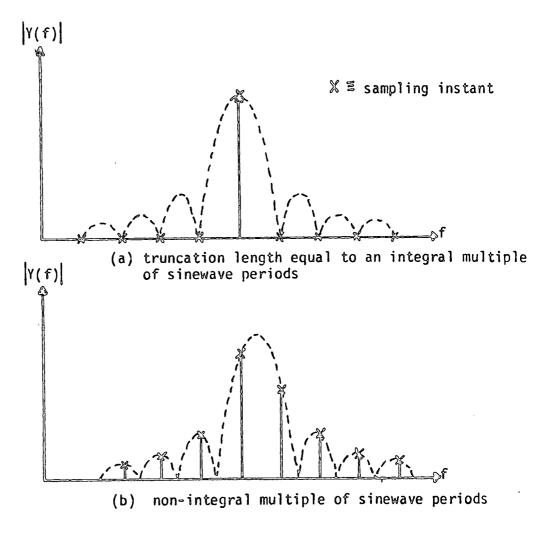

The final modification necessary to obtain the sampling in the frequency domain. This is achieved by assuming that N samples of the input function are one period a periodic waveform. The output spectrum will then o£ discrete samples, each consist o £ spaced by 1/(N.Ts) = fs/N.Мо information is lost by this sampling but great care has to be exercised in the interpretation of spectra. For example, consider the DFT of a sinewave. If the sinewave is a basis vector (i.e. it has an integral

Fig. 4.1 The Infinite and the Truncated Fourier Transform

Fig.4.2 DFT of a Sinewave

number of periods within the truncation window) then the resulting frequency domain  $(\sin x)/x$  will fall exactly on the sampling grid (Fig. 4.2a) and the output sequence will be all zeroes except for a "1" at the appropriate frequency sample. If, however, the sinewave is not a basis vector, the  $(\sin x)/x$  will be offset from the sampling grid to give an output similar to that shown in Fig. 4.2b.

# 4.2.2 The Fast Fourier Transform

It can be seen from equation 4.7 that N<sup>2</sup> complex multiplications and associated additions are required to compute an N-point DFT. Since the processing time and hence the cost are usually proportional to the number of multiplications, the DFT calculation for large N (>64) becomes prohibitive. A Fast Fourier Transform (FFT) is an algorithm which significantly reduces the number of multiplications needed to calculate the exact DFT.

The first FFT algorithm to achieve widespread acclaim was developed by Cooley and Tukey [71] in 1965 and remains today as the foundation for most other FFT algorithms. The mechanics of the 'Cooley-Tukey FFT algorithm are well documented [72] and it is sufficient to note that the key to its efficiency results from the periodicity of the function W in N, where

$$W = e^{-j2\pi/N} \qquad ... (4.9)$$

Using the properties

$$\mathbb{W}^{nk} = 1$$

for all  $nk = p\mathbb{N}$ ,  $p=0,1..\mathbb{N}$

$$\mathbb{W}^{nk+\mathbb{N}/2} = -\mathbb{W}^{nk}$$

$$\mathbb{W}^{nk} = \mathbb{W}^{nk} \mod \mathbb{N}$$

and

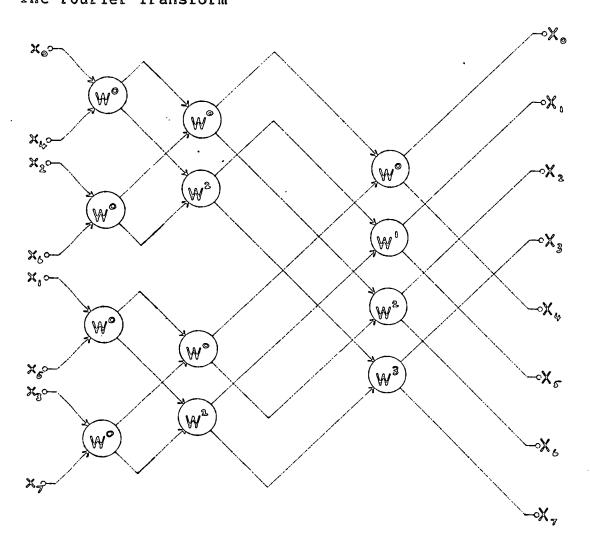

where nk modulo(N) is the remainder upon division of nk by N<sub>o</sub> it is possible to structure the DFT to minimise the number of multiplications. Fig. 4.3a shows the flow diagram for a decimation in time radix-2 FFT algorithm with N=8. The fundamental operation in this algorithm is the "butterfly" represented by a circle in the flow diagram. Each butterfly takes two complex inputs A and B<sub>o</sub> and combines them to give P and Q through the operations

$$P = A + W_N^r B$$

... (4.10)

$$Q = A - W_N^r B$$

... (4.11)

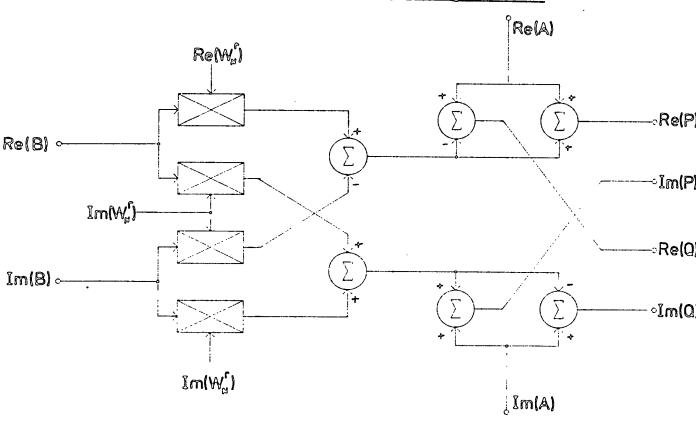

where  $W_N^r$  are the so called "twiddle factors". To evaluate the complex P and Q using real arithmetic involves four multiplications, three additions and three subtractions (Fig. 4.3b).

The complex input sequence  $\{x_n\}$ , n=0,1...N-1, is initially reordered and the first set of butterflies performs what is essentially a 2-point DFT on pairs of input data. The second set of butterflies combines the 2-point DFTs using twiddle factors to give two 4-point DFTs of the even and odd numbered input data. Finally, these are combined to achieve the 8-point DFT.

Fig.4.3a 8-point, Radix-2, Decimation in Time FFT

Fig. 4.3b Implementation of a Radix-2 Butterfly

From this description, it is clear that N must be restricted to an integral power of 2 for efficient implementation i.e.  $N=2^{V}$ , where V is an integer. There are therefore V or  $\log_2 N$  stages each with N/2 complex butterflies so that a total of  $(N/2)\log_2 N$  complex butterflies are required to provide the N-point DFT. In terms of real arithmetic, this is a total of  $2N\log_2 N$  multiplications, which compares with  $4N^2$  for the direct calculation of the DFT. For N=1024,  $2N\log_2 N=20,480$  and  $4N^2=4,194,304$ ; in this case, a saving of approximately 200:1 in processing time has been achieved.

The FFT accuracy is limited by the finite word lengths used in digital machines [73]. The error sources can be divided into three categories: (1) the analogue input quantisation, (2) the finite word lengths used to represent the twiddle factors and (3) the truncation and round-off within the butterflies. The last error source is the most important because its effects are cumulative and depend on the transform length. Each Fourier coefficient is processed through log<sub>2</sub> N butterfly operations, which indicates that higher accuracy is necessary for longer transforms.

. Many other FFT algorithms have since been developed either to capitalise on particular properties of the input data or to optimise the speed-storage trade-off. For example, if a larger memory is tolerable, a faster transform

may be obtained by increasing the FFT radix [67].

An FFT algorithm can be implemented in one of two ways: (a) software on in general а purpose minimicro-computer, or (b) as a specialised hardware structure. implementations The software tend to be used for non-real-time applications as the transform rate is limited (typically 600ms for 1024 complex points on microprocessor based systems [74]). Hardware structures commonly employ a single multiplexed high-speed butterfly [75] or make use of pipelining to achieve a transform rate of up to 0.65mS 1024 complex points [76]. However, the cost, consumption and size of these array processors greatly restrict the range of possible applications.

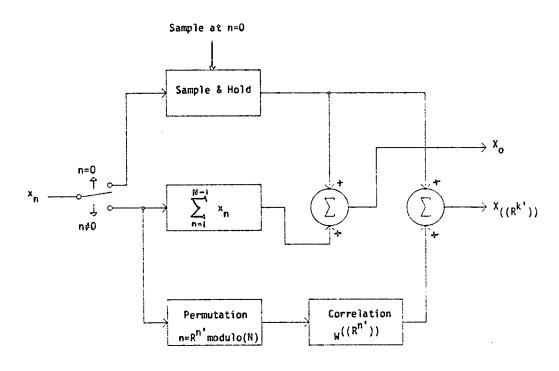

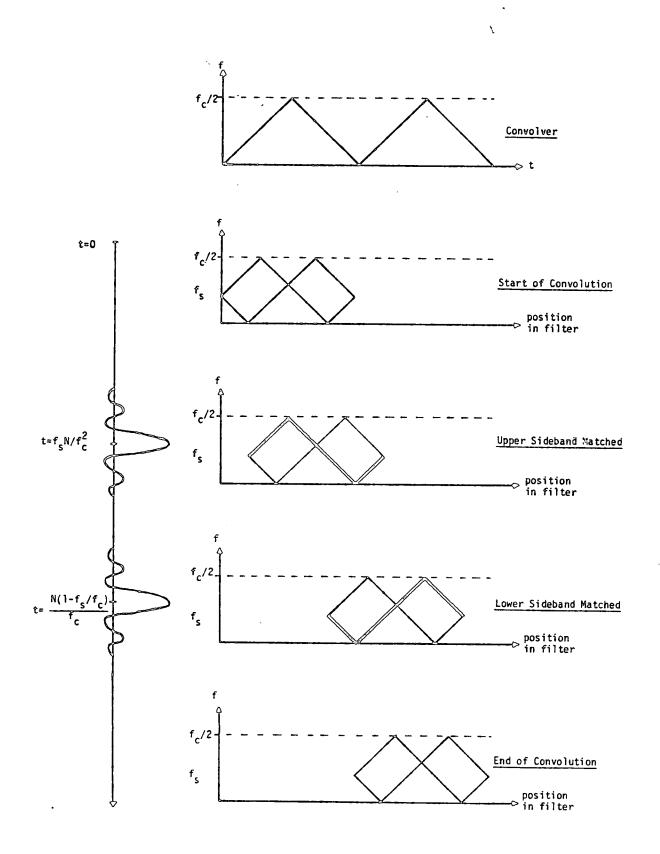

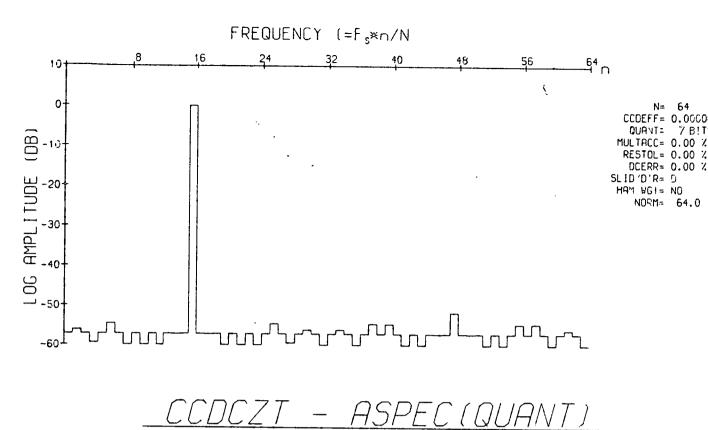

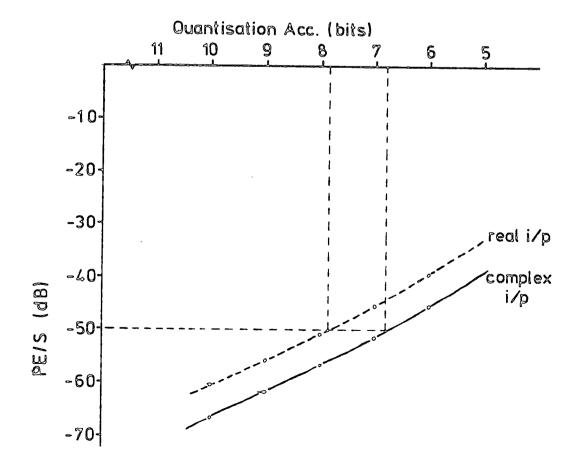

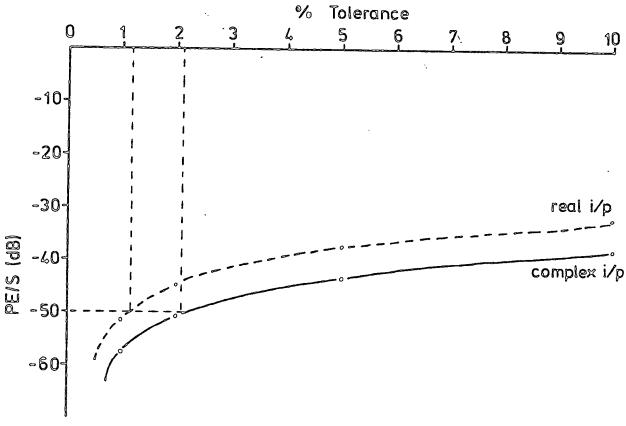

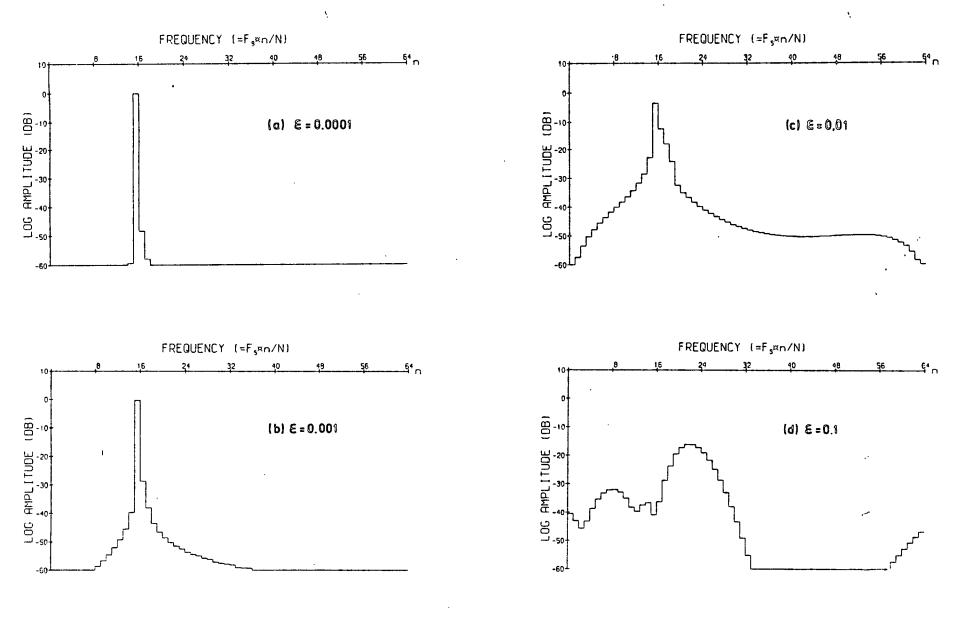

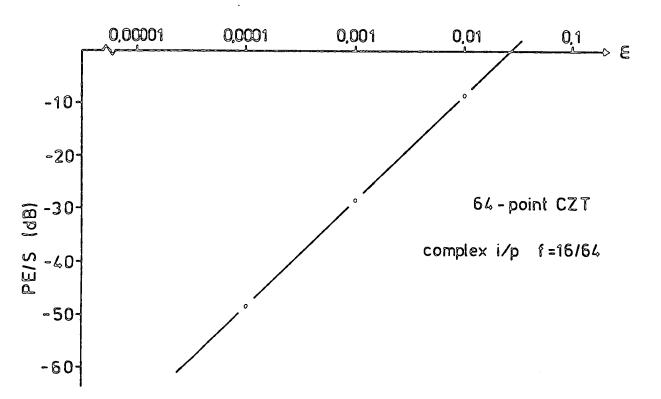

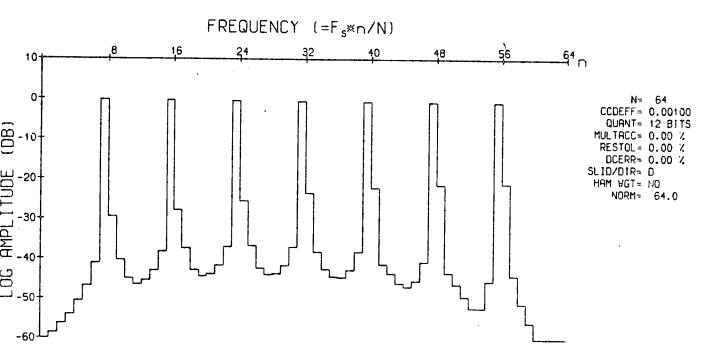

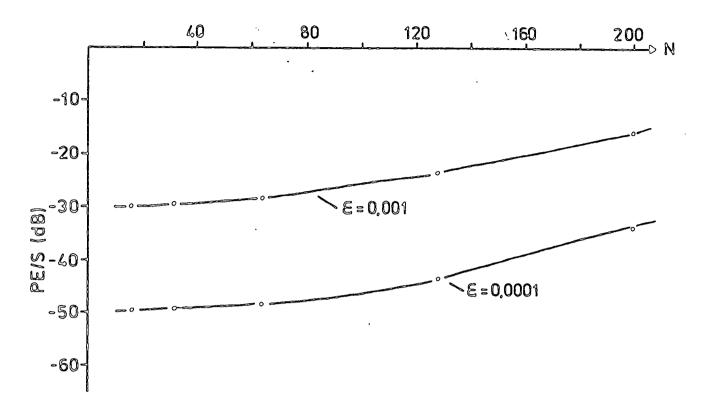

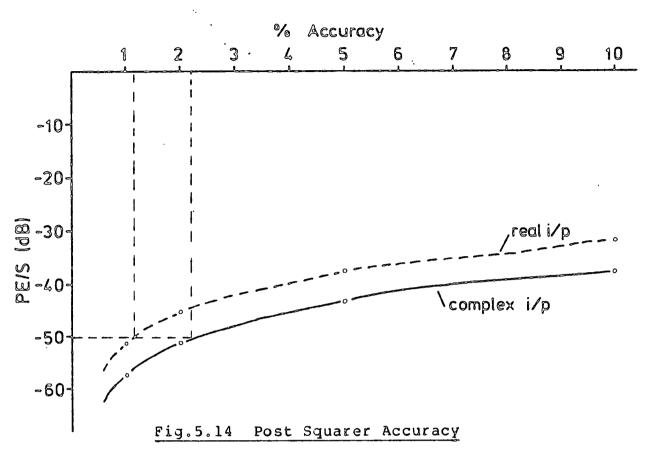

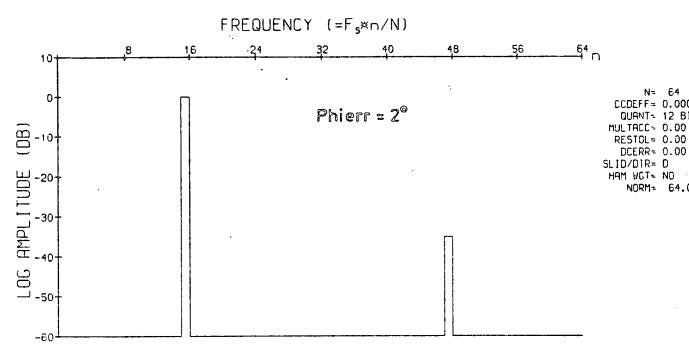

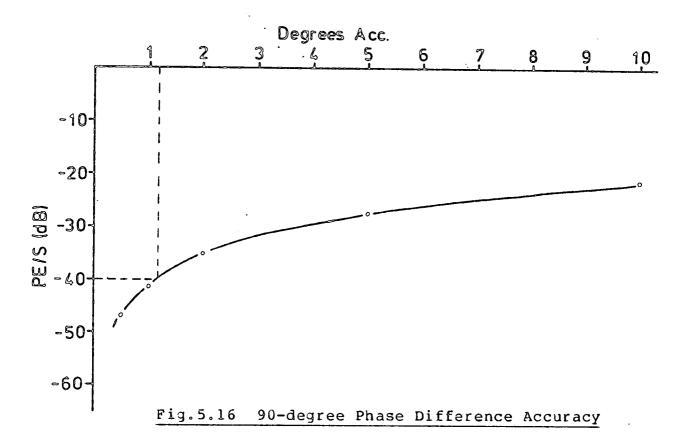

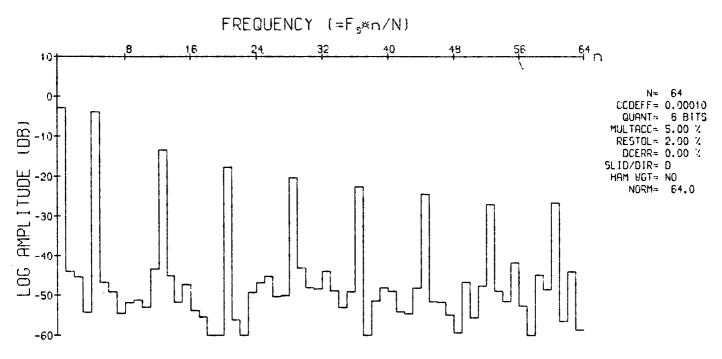

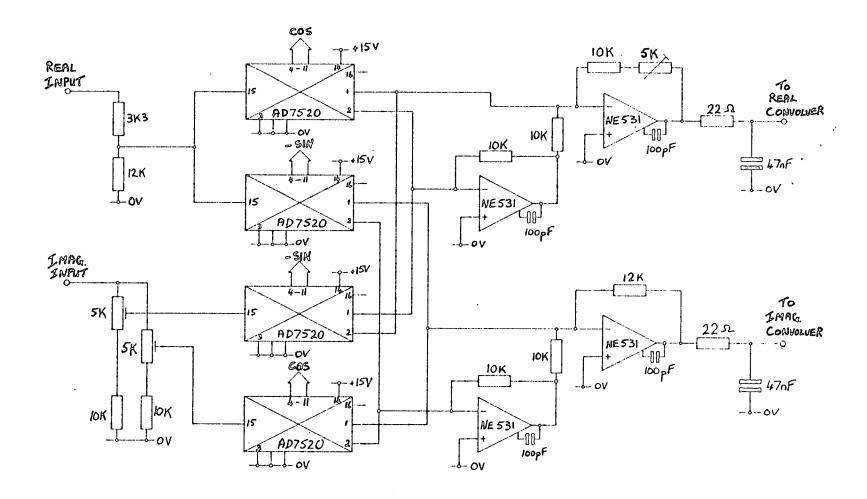

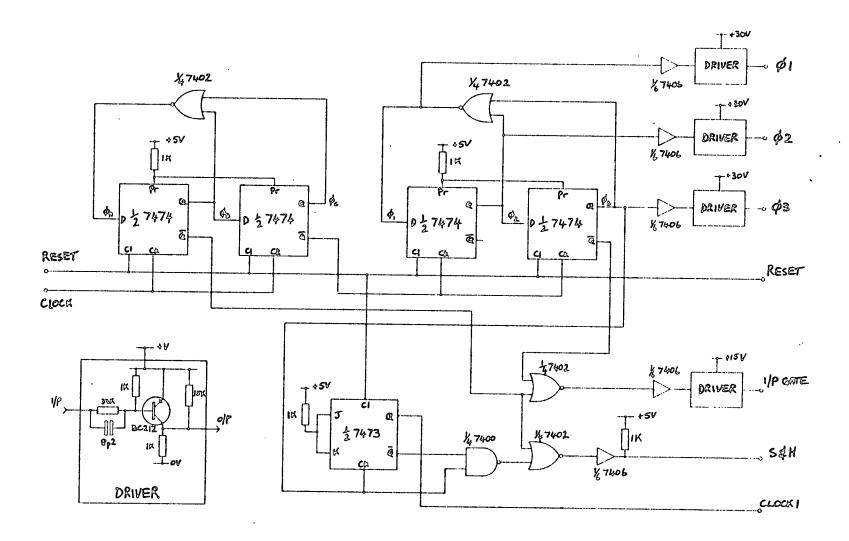

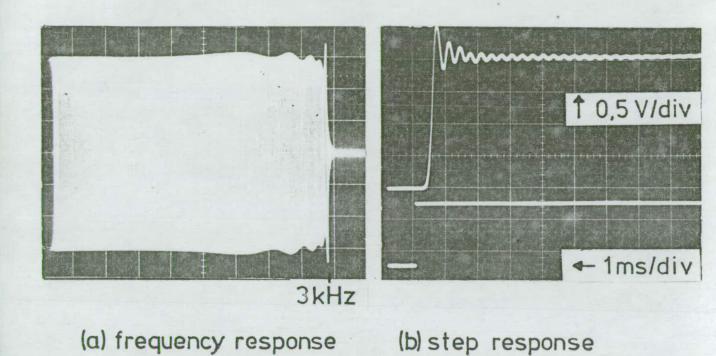

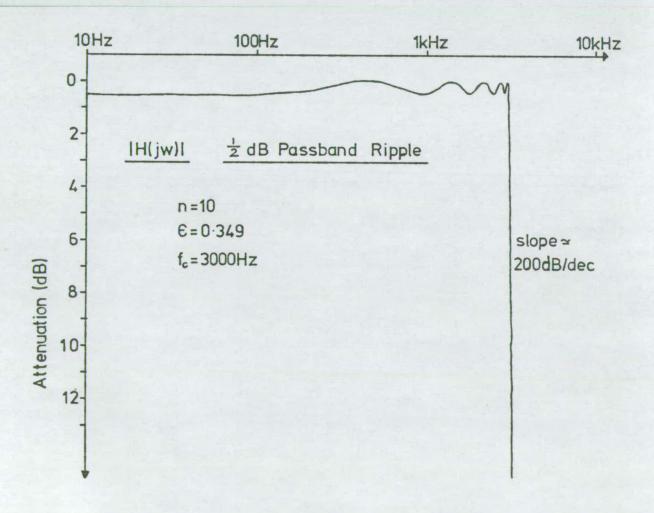

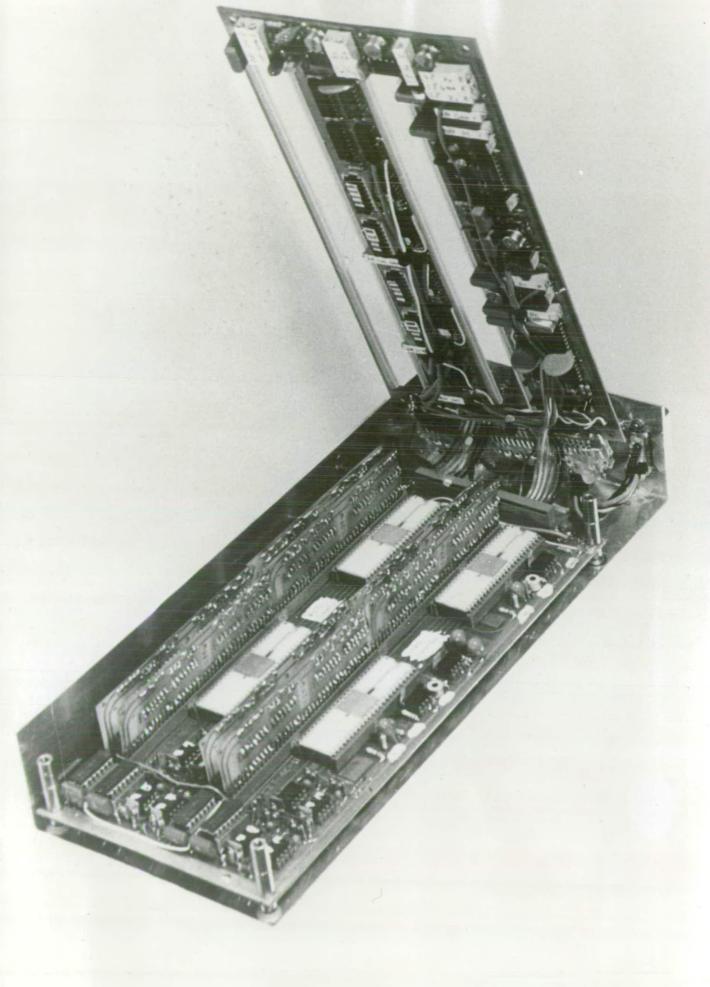

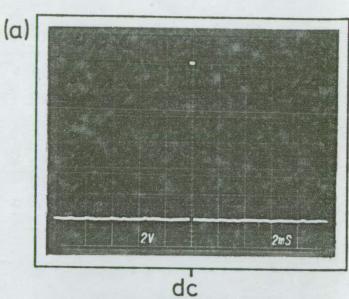

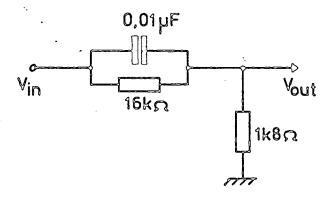

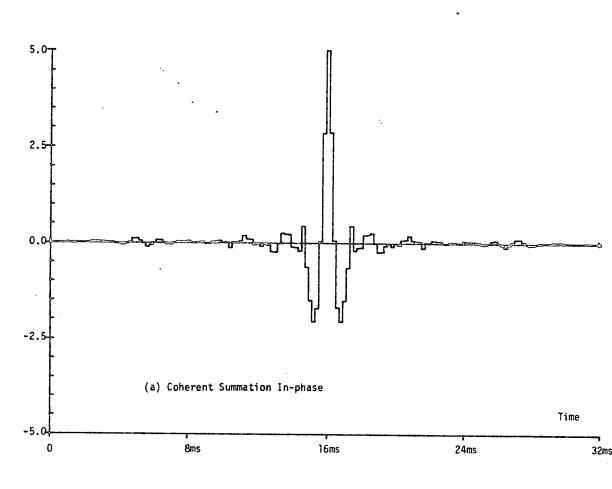

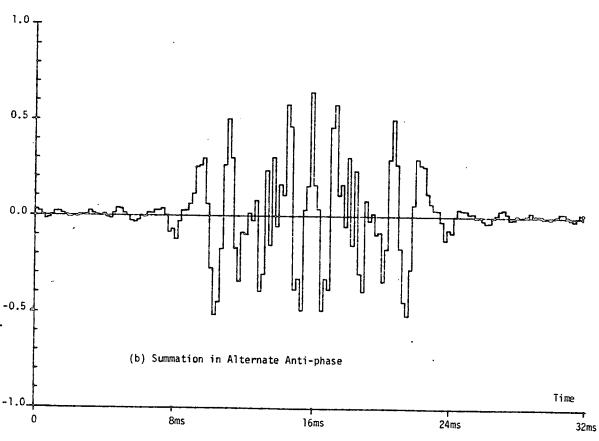

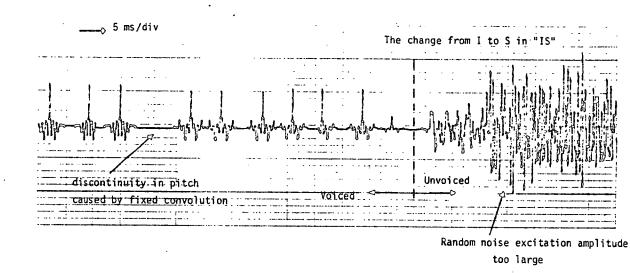

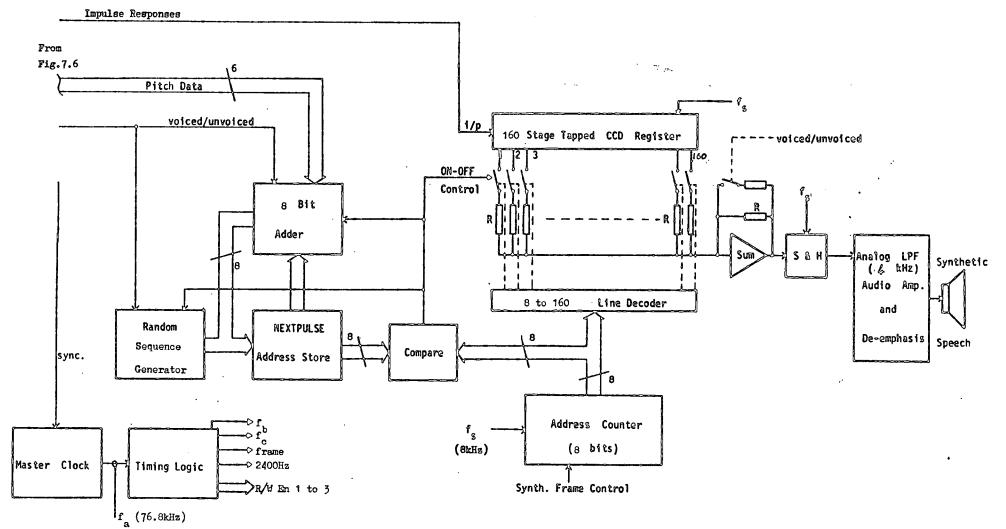

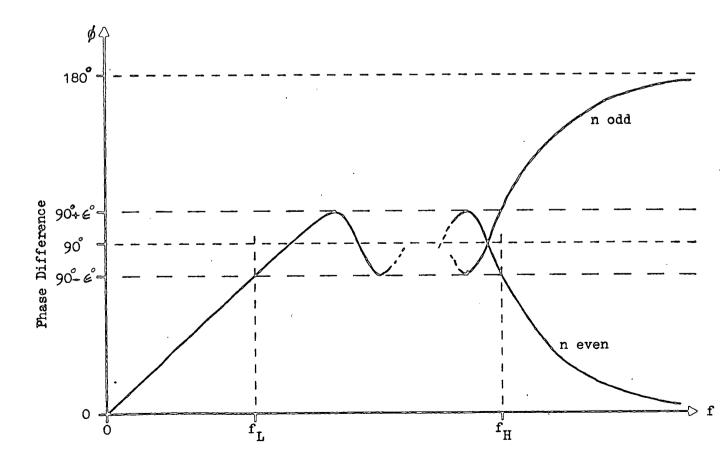

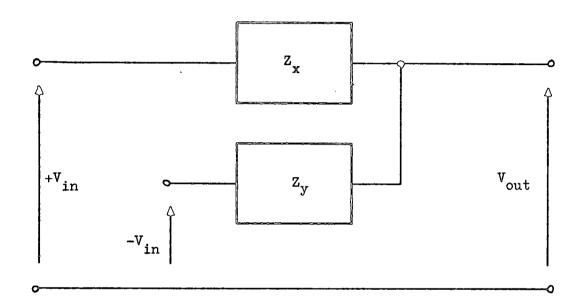

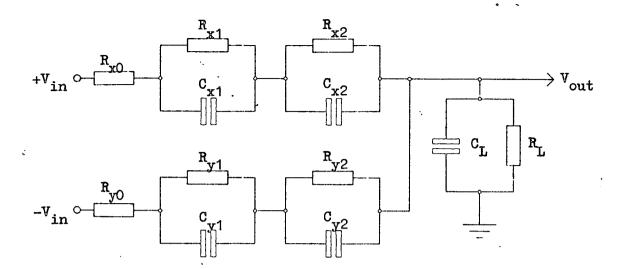

# 4.2.3 On The Use Of Weighting Functions