# Gallium Arsenide Bit-Serial Integrated Circuits

by

S. C. K. Lam

A thesis submitted to the Faculty of Science,

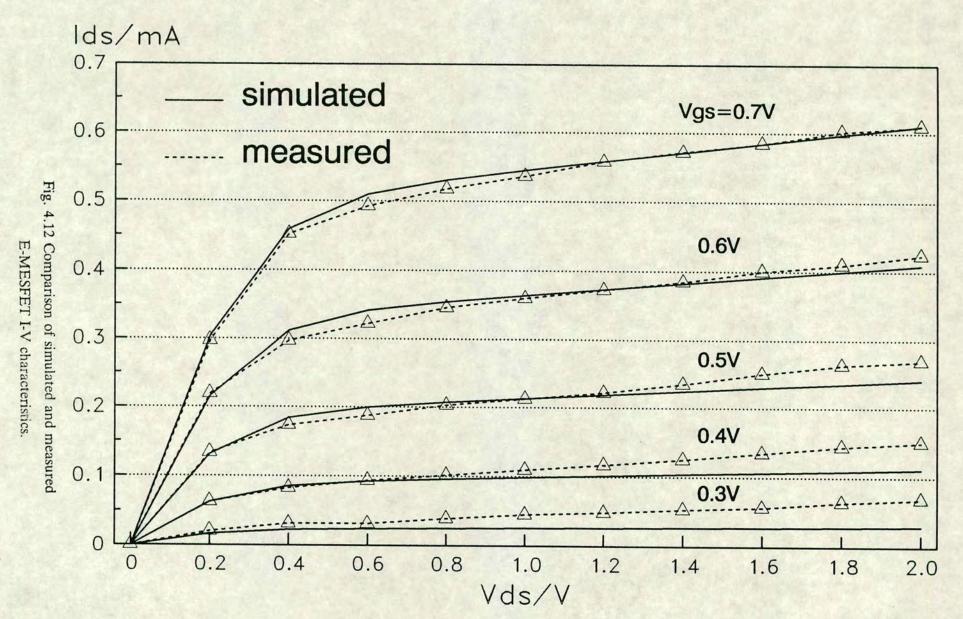

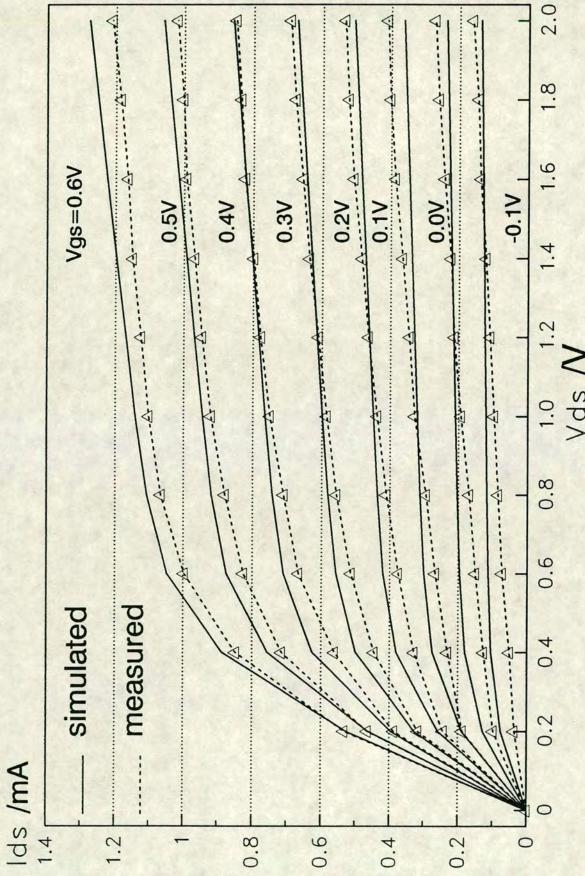

University of Edinburgh,

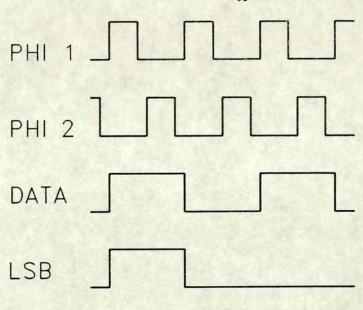

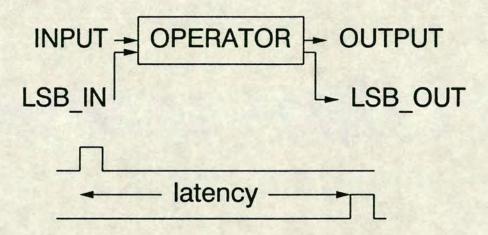

for the degree of

Doctor of Philosphy

Department of Electrical Engineering 1990

#### Abstract

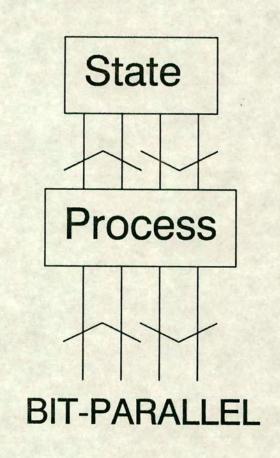

Bit-Serial architecture and Gallium Arsenide have essentially been mutually exclusive fields in the past. Digital Gallium Arsenide integrated circuits have increasingly adopted the conventional approach of bit-parallel structures that do not always suit the properties and problems of the technology. This thesis proposes an alternative by using a least significant bit first bit-serial architecture, and presents a group of "cells" designed for signal processing applications.

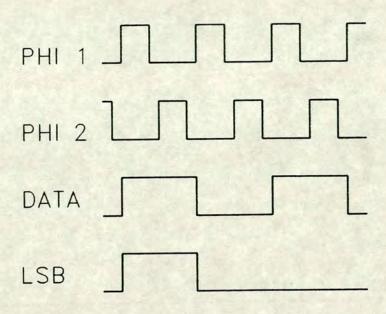

The main features of the cells include the extensive use of pseudo-dynamic latches for pipelining, modularity, and programmability. The logic circuits are mainly based on direct-coupled FET logic. They are also compatible with silicon ECL circuits. The target clock rate for these cells are 500MHz, at least ten times faster than previous silicon bit-serial circuits. The differences between GaAs and silicon technologies meant that the cells were designed from circuit level upwards.

Further to these cells, a multi-level signaling scheme has been developed to substantially alleviate off-chip signaling. Synchronisation between signals is simplified, improving even further on the conventional bit-serial system, especially at the high bit-rates encountered in GaAs circuits.

For on-chip signals, a single phase clock scheme has been developed for the GaAs cells, which maintains the low clock loading and high speed characteristics of the pseudo-dynamic cells, while substantially simplifying clock distribution and generation. Two novel latch designs are proposed for this scheme.

Test results available have already proved the concepts behind the two-phase clocking scheme, the latches, and the multi-level signaling scheme. Further tests are taking place to establish their speed performance.

#### **Declaration of Originality**

This thesis was composed entirely by myself. All the circuit design work described in this thesis, including the software modifications in Chapter 4, were carried out solely by myself, when I was a member of a research group in the Department of Electrical Engineering, University of Edinburgh.

#### Acknowledgement

The author is most grateful to my Supervisor, Dr. Martin Reekie, whose help, inspiration, and patience, have made it possible to finish this work. I am very grateful to my second Supervisor, Dr. Brian Flynn, who gave me a great deal of help and support over the years. I would also like to thank Professor John Mavor, whose kind support in extending my contract has enabled me to complete my thesis.

Numerous colleagues in the Department have helped me in the past. In particular, I would like to thank Bob Mhar and Dr. C. H. Lau, for their help and friendship. Thanks are also due to Dr. Alan Murray for help with the diagrams, to Mrs. Caroline Burns for providing photocopying facilities, and to Bruce Hassall and David Stewart for keeping the computers going.

Finally, I would like to thank Dr. Ross McTaggart and Honeywell for circuit fabrication and testing.

S. C. K. Lam

# Contents

| ABSTRACT i                                              |

|---------------------------------------------------------|

| DECLARATION OF ORIGINALITY                              |

| ACKNOWLEDGEMENT ii                                      |

| CONTENTS iii                                            |

| CHAPTER 1: Introduction                                 |

| CHAPTER 2: Introduction to GaAs and Bit-serial circuits |

| 2.1. GaAs integrated circuit technology                 |

| 2.1.1. Material properties 5                            |

| 2.1.2. Device constraints in GaAs 7                     |

| 2.1.3. Logic circuit configurations                     |

| D-MESFET logic 11                                       |

| E-MESFET/D-MESFET (E/D) logic families                  |

| 2.1.4. Circuits and systems                             |

| Signal processing 24                                    |

| Arithmetic logic                                        |

| Memories                                                |

| Mi croprocessors                                        |

| Application specific processors                         |

| Communications circuits                                 |

| Supercomputers 35                                       |

| Gate array and standard cells                           |

| Test and measurement systems                            |

| 2.2. Bit serial circuits and systems                    |

| 2.3. Discussion                                         |

| CHAPTER 3: GaAs DCFL design                             |

| 3.1. The DCFL inverter and NOR gate 49                  |

| 3.2. Other logic gates 57                               |

| 3.3. Delay optimisation and interconnections            | 57   |

|---------------------------------------------------------|------|

| 3.4. ECL compatibility                                  | 58   |

| 3.5. Conclusion                                         | 59   |

| CHAPTER 4: GaAs MESFET device and SPICE modelling       | 60   |

| 4.1. GaAs MESFET device operation                       | 60   |

| The MOSFET device                                       | 60   |

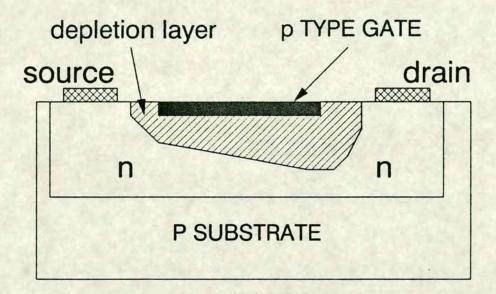

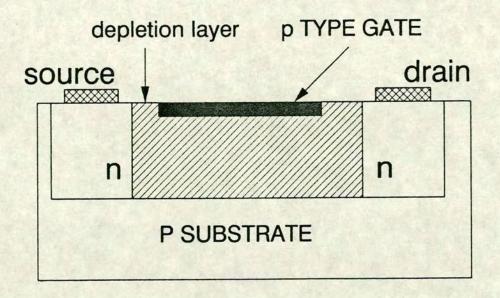

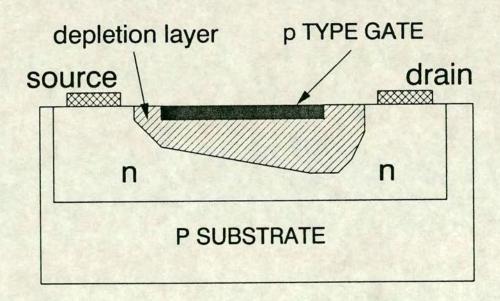

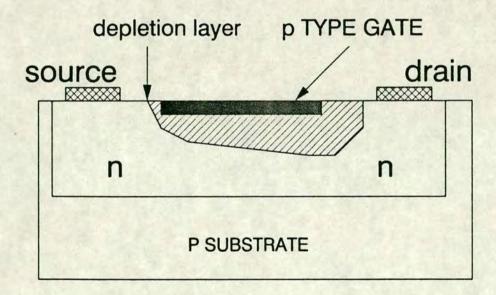

| The JFET structure                                      | 61   |

| The GaAs MESFET structure                               | . 64 |

| 4.2. GaAs MESFET processing                             | . 67 |

| 4.3. Electrical properties of the GaAs MESFET device    | . 71 |

| Process control and noise margin                        |      |

| Yield hazards in processing                             | . 74 |

| 4.3.1. Detrimental device properties of the GaAs MESFET |      |

| Channel-widening effect                                 | . 75 |

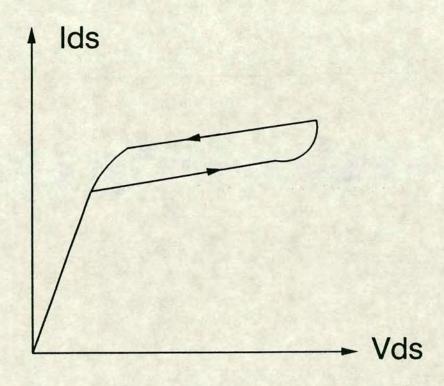

| Hysteresis in I-V characteristics                       | . 76 |

| Backgating/sidegating effect                            | . 77 |

| Short channel effects                                   | . 78 |

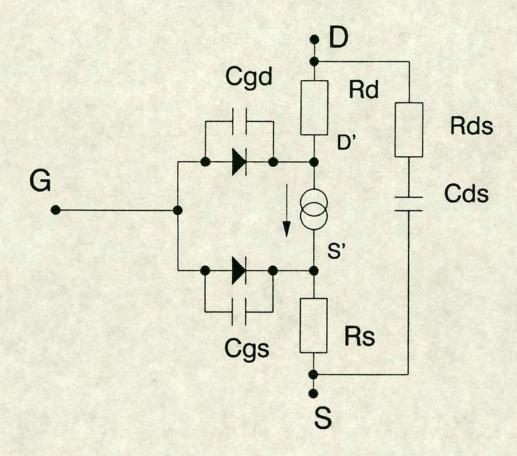

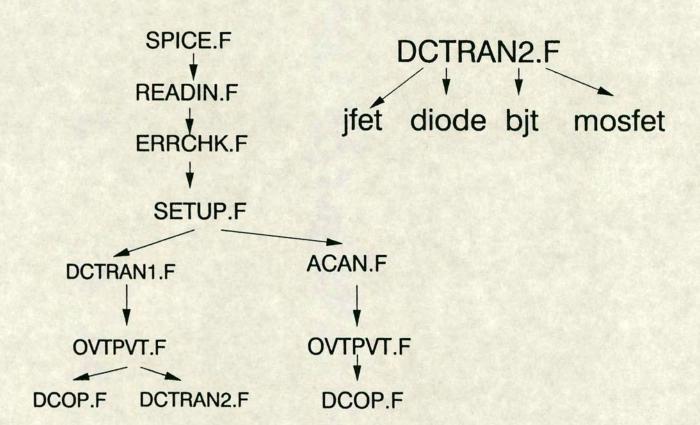

| 4.4. SPICE modelling of the MESFET model                | 70   |

| 4.4. SPICE modelling of the MESFEI model                |      |

| 4.4.2. SPICE modifications                              |      |

| 4.4.2. SPICE modifications                              |      |

|                                                         |      |

| CHAPTER 5: GaAs Bit-Serial Cells and Systems            | . 94 |

| Conventions                                             | . 95 |

| 5.1. Latch structure requirements                       | . 97 |

| Pipelining timing constraints                           | . 97 |

| Latch properties                                        | . 98 |

| 5.2. Comparison of latch structures                                | .00 |

|--------------------------------------------------------------------|-----|

| Fully static latches 1                                             | 00  |

| Fully-dynamic and pseudo-dynamic latches                           | 01  |

| Pseudo-dynamic latches                                             | 103 |

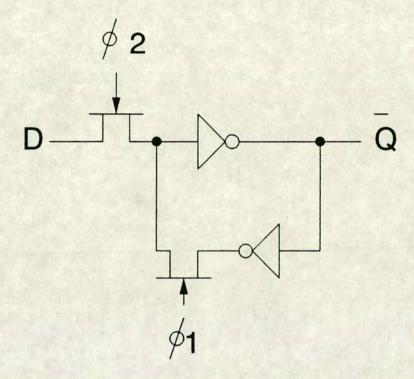

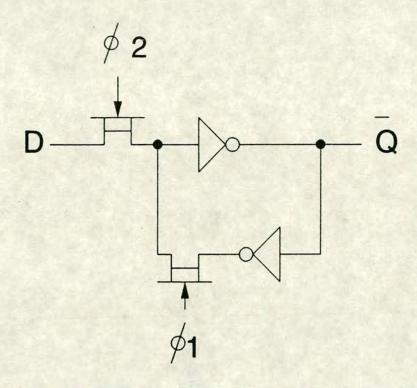

| The E-MESFET pass transistor latch                                 | 104 |

| The D-MESFET pass transistor latch                                 | 113 |

| 5.3. Variations of the D-MESFET pseudo-dynamic latch               | 118 |

| 5.4. A silicon NMOS study of the pseudo-dynamic latch              | 121 |

| 5.5. The GaAs Cell Designs                                         | 127 |

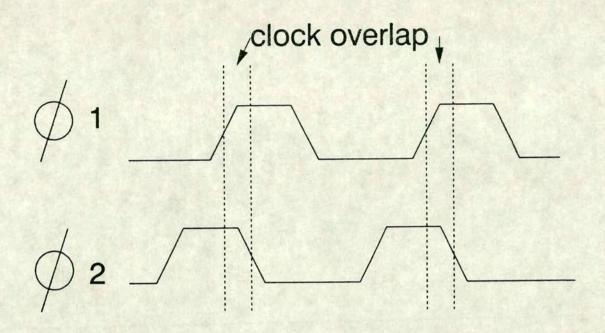

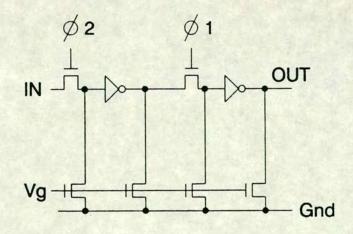

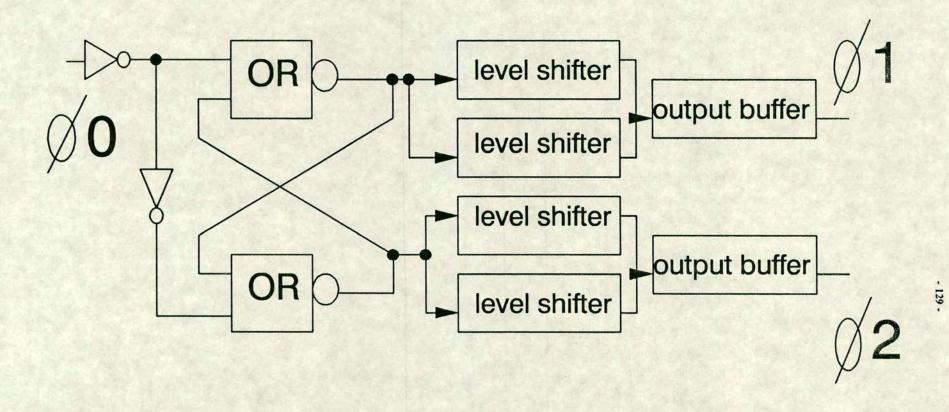

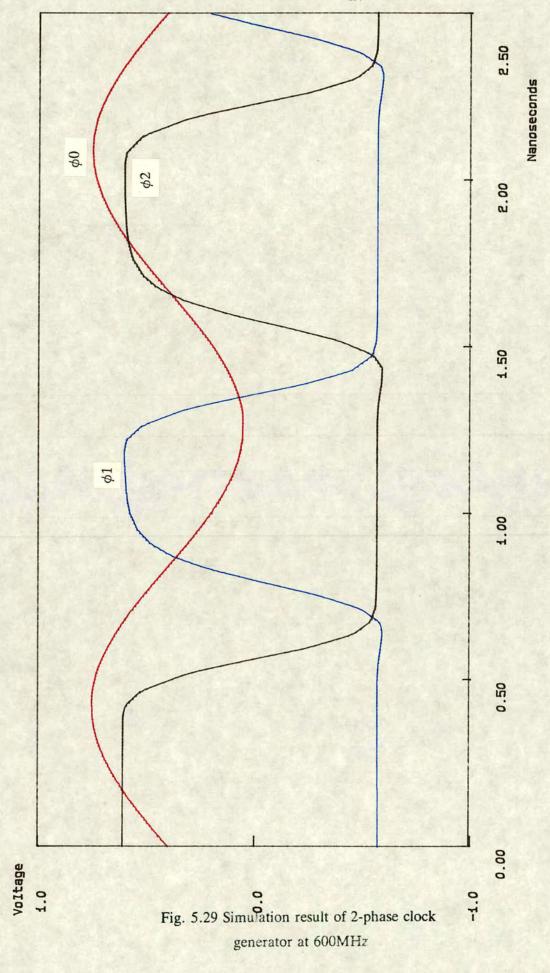

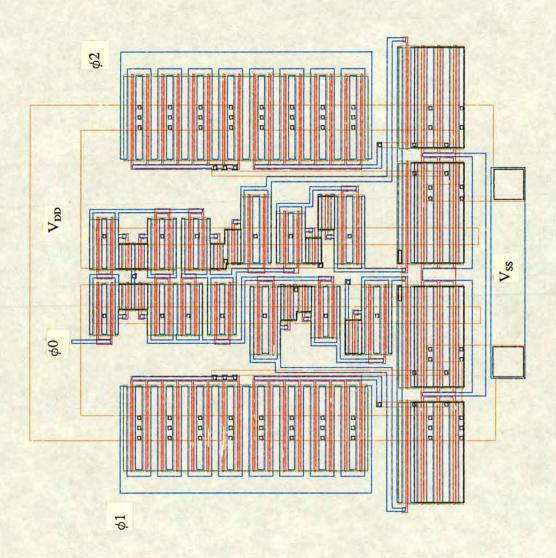

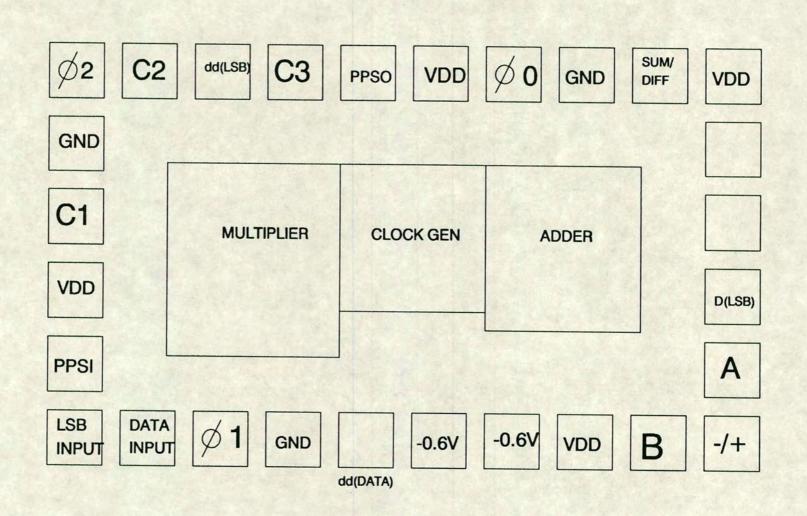

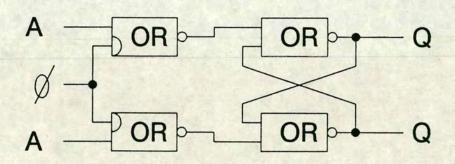

| 5.5.1. The 2-phase clock generator                                 | 128 |

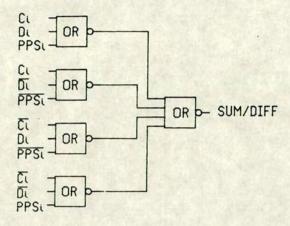

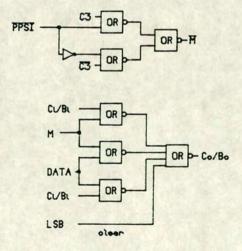

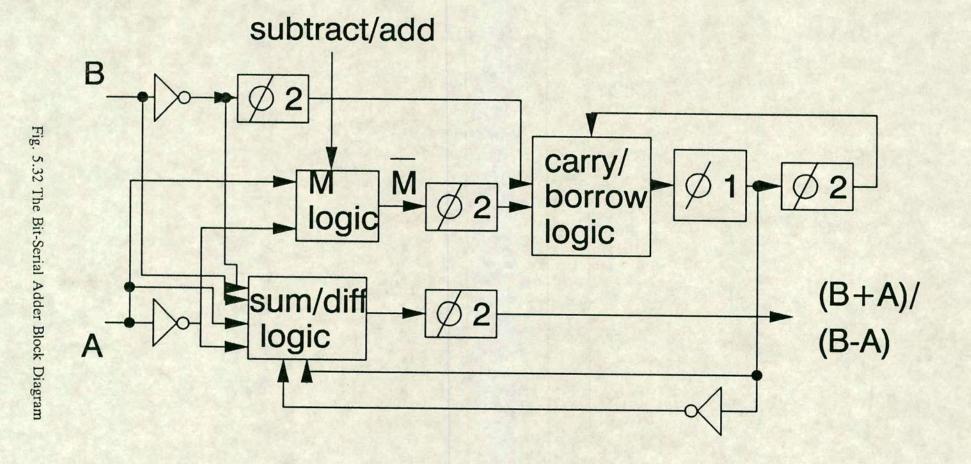

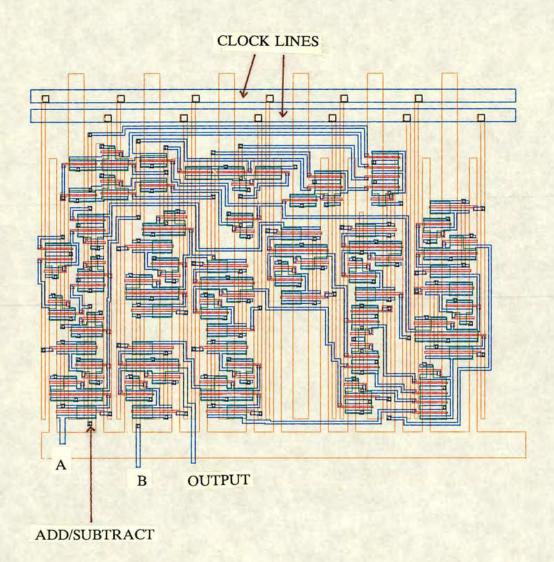

| 5.5.2. The bit-serial adder                                        | 136 |

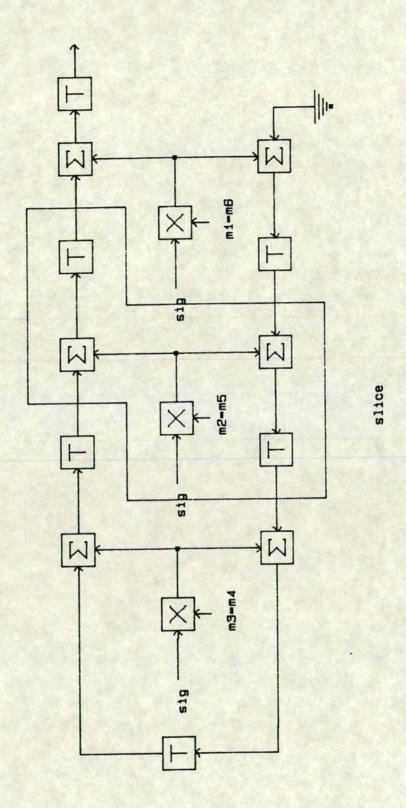

| 5.5.3. The Multiplier                                              | 141 |

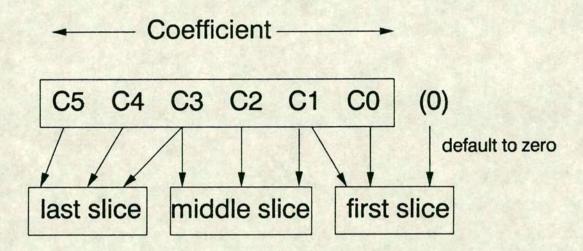

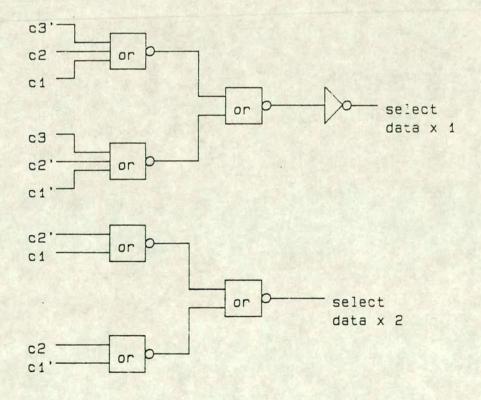

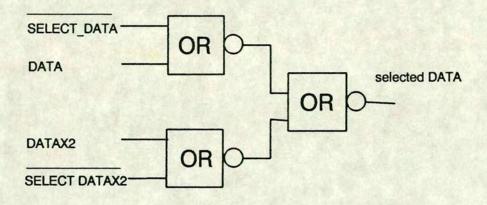

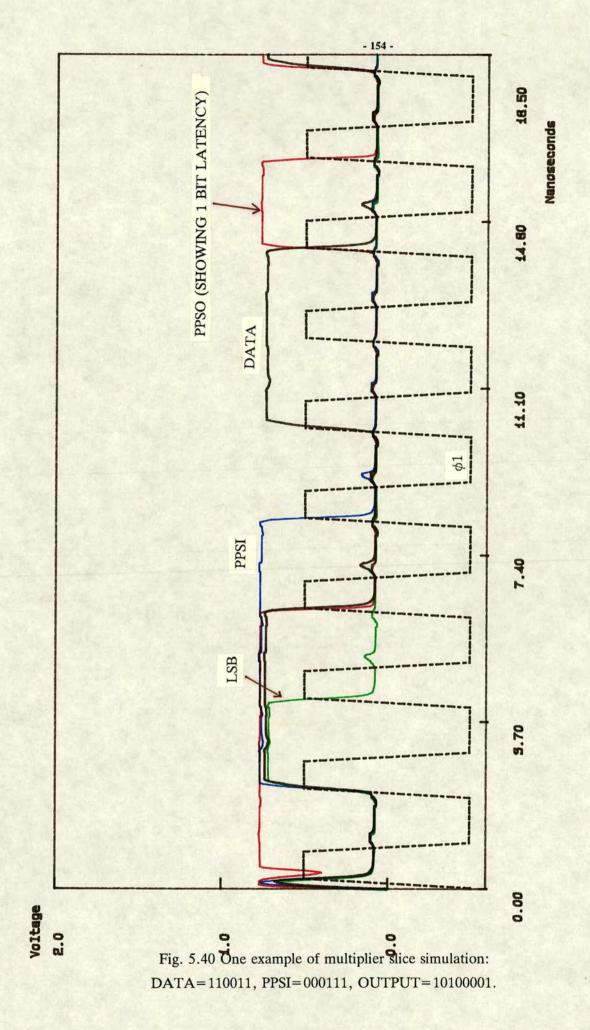

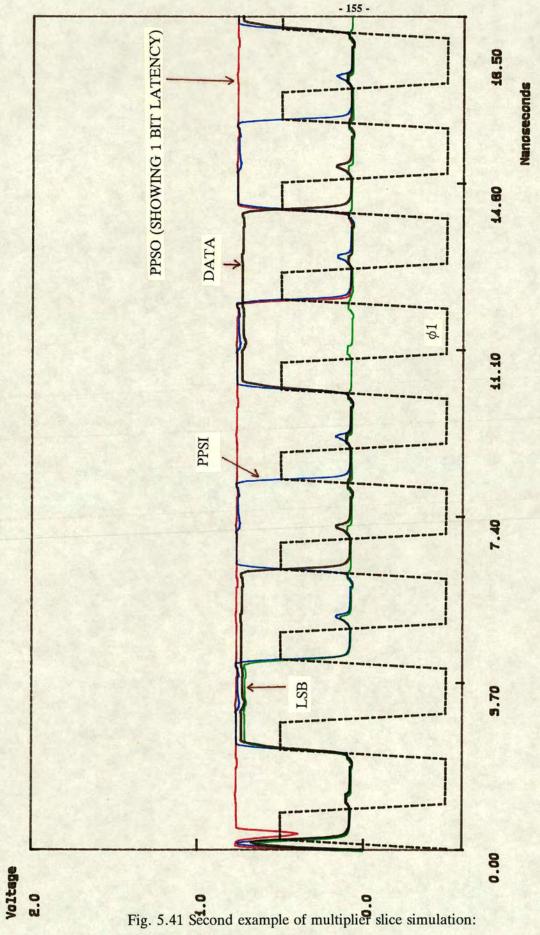

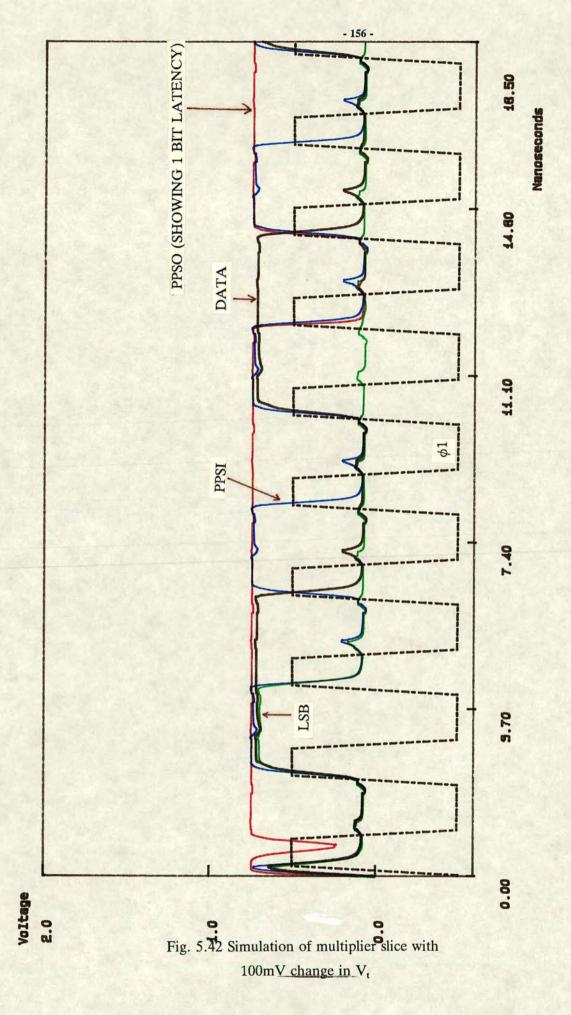

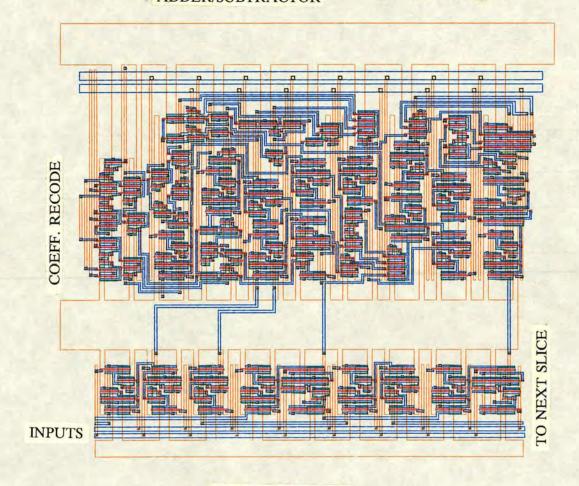

| The multiplier slice design                                        | 145 |

| Multiplier product rounding                                        | 148 |

| Multiplier slice logic schematics                                  | 150 |

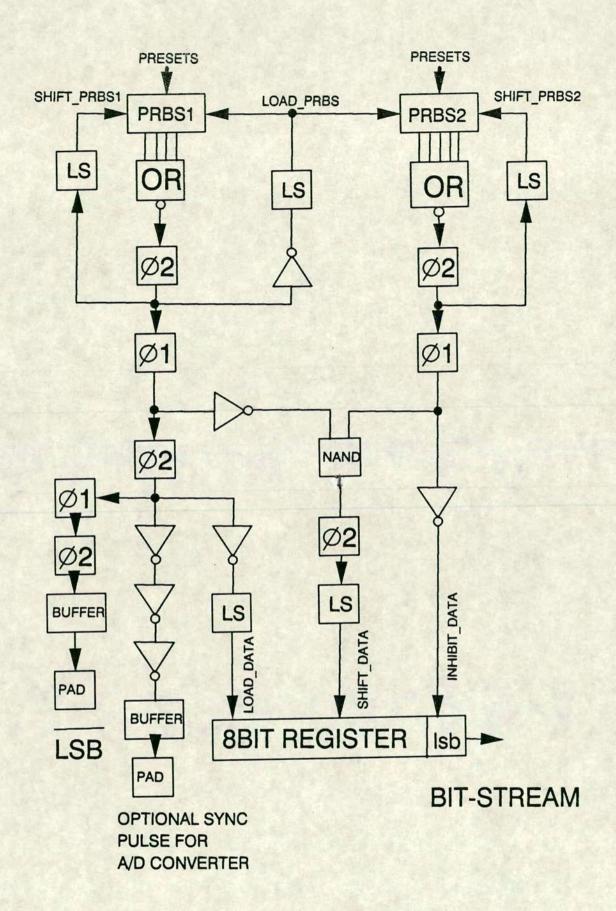

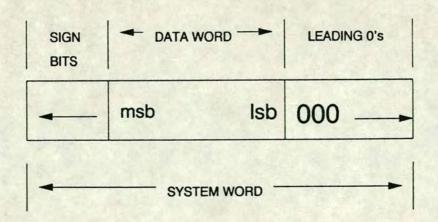

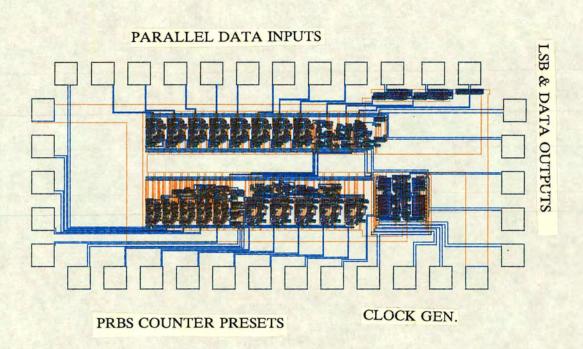

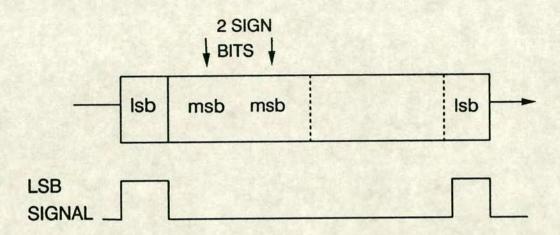

| 5.5.4. The Parallel to Serial Converter (P/S converter)            | 157 |

| 5.5.5. The Serial to Parallel Converter (S/P converter)            | 168 |

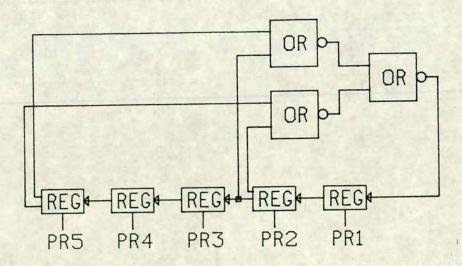

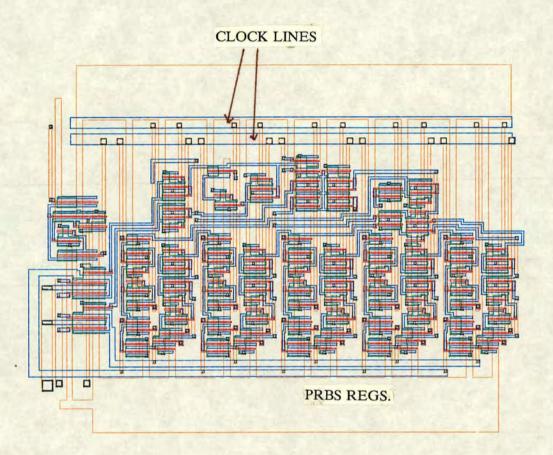

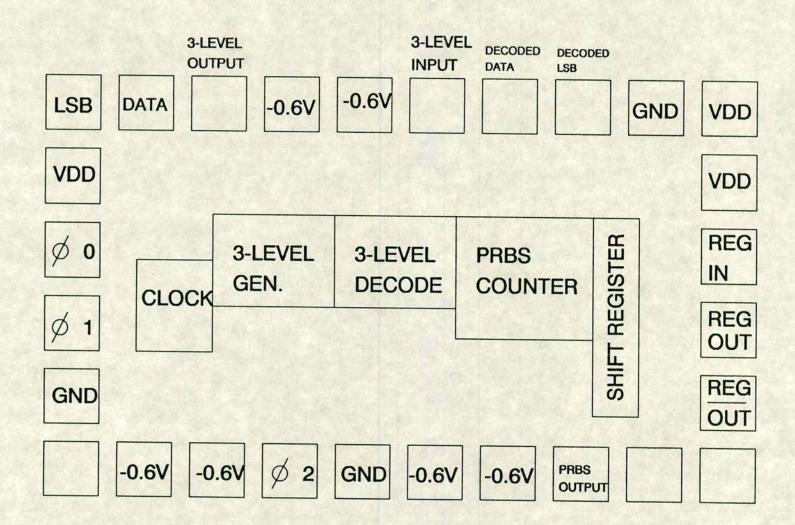

| 5.5.6. The PRBS counter chip                                       | 174 |

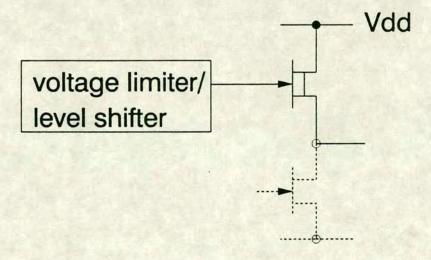

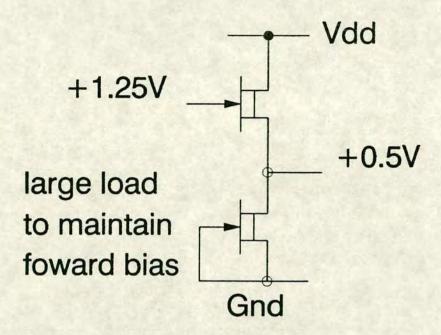

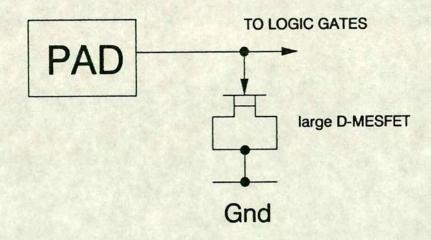

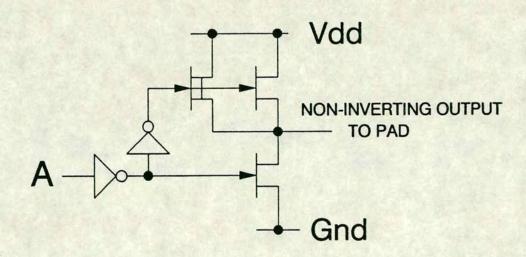

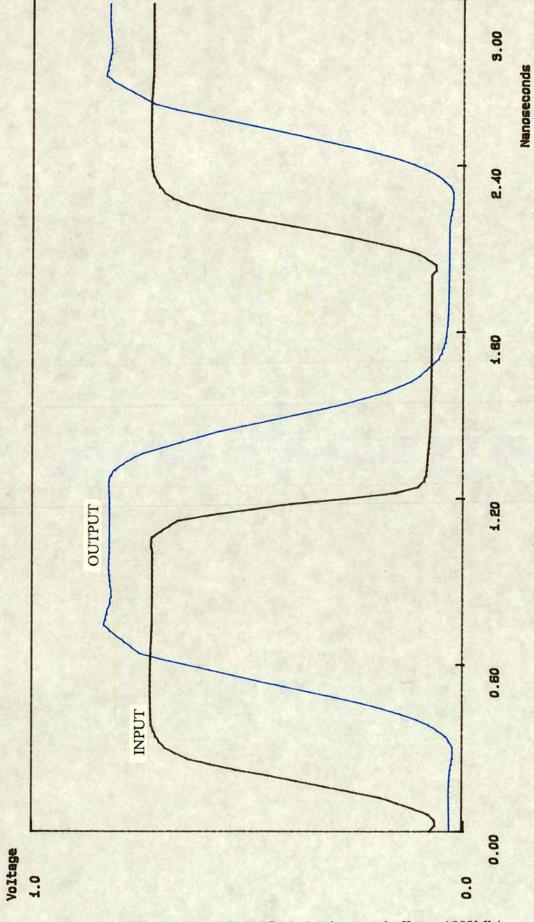

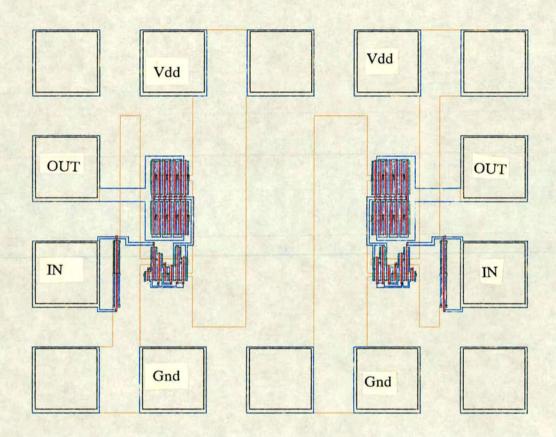

| 5.5.7. I/O buffers                                                 | 177 |

| 5.5.7.1. A low speed ECL level output buffer                       | 177 |

| 5.5.7.2. Other I/O buffers                                         | 178 |

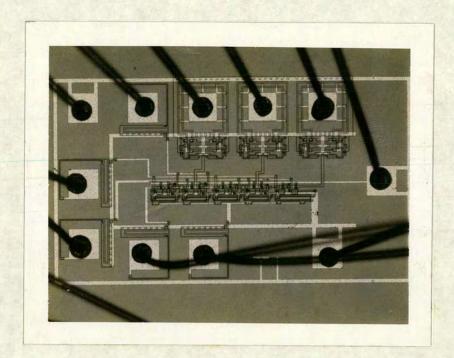

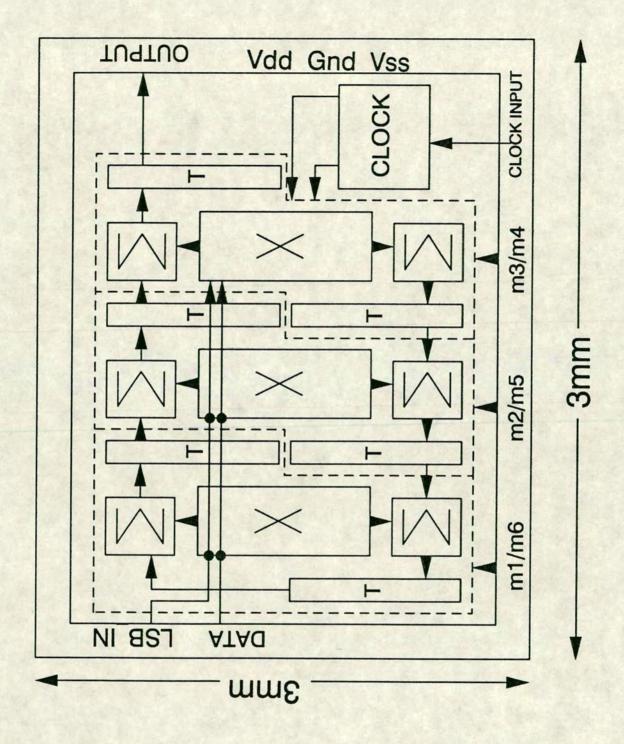

| 5.6. The Layouts                                                   | 181 |

| 5.7. The MODFET mask set                                           | 190 |

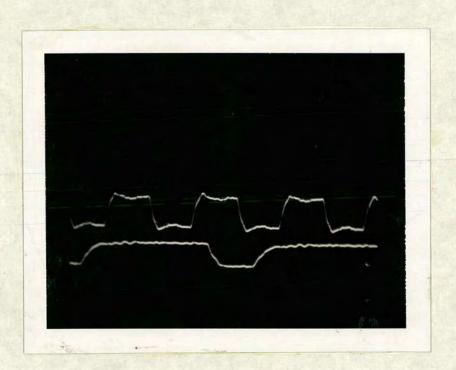

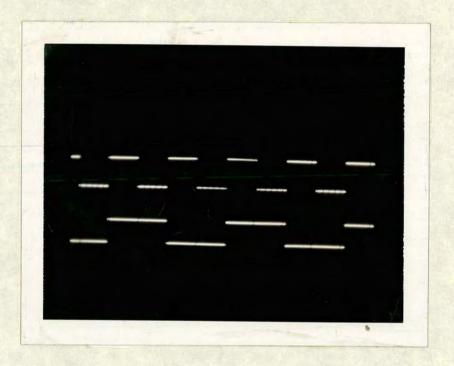

| 5.8. Test results                                                  | 194 |

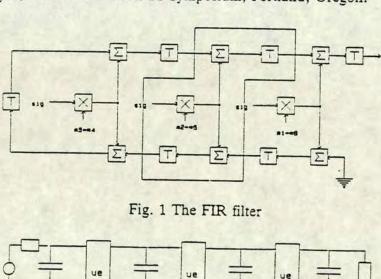

| FIR implementation study                                           | 194 |

| 5.9. Summary                                                       | 194 |

| 5.10. Performance enhancement                                      | 198 |

| CHAPTER 6: Multi-level signaling and single-phase clocking schemes | 199 |

| 6.1. Overview of multi-level signals and systems                  | 199 |

|-------------------------------------------------------------------|-----|

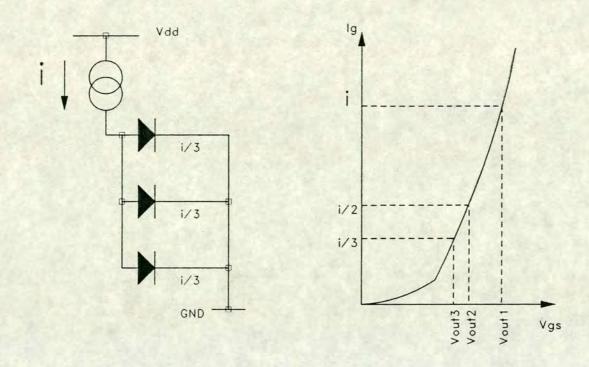

| Silicon implementations of multi-level signals                    | 202 |

| Feasibility of GaAs multi-level circuits                          | 203 |

| 6.2. The off-chip 3-level signaling scheme                        | 205 |

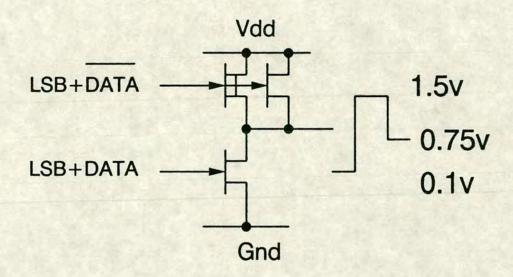

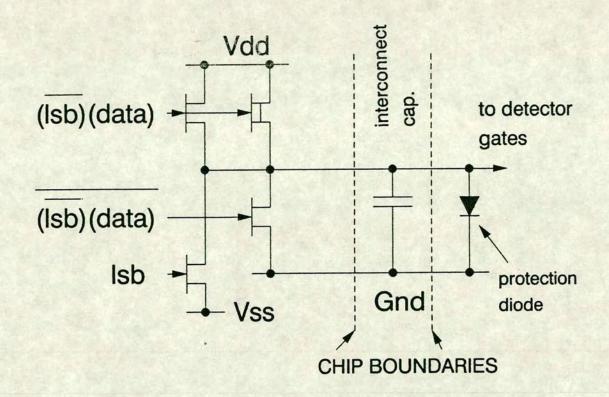

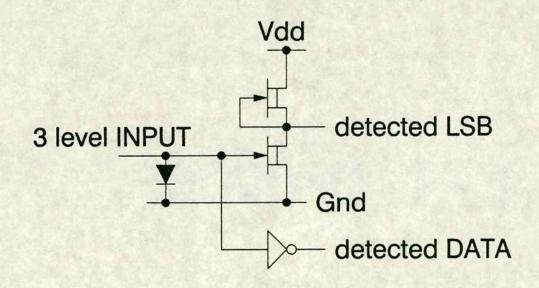

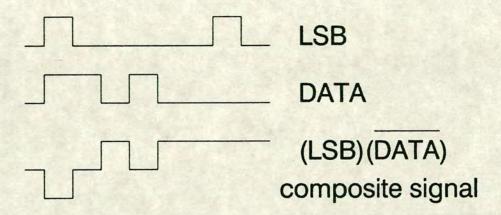

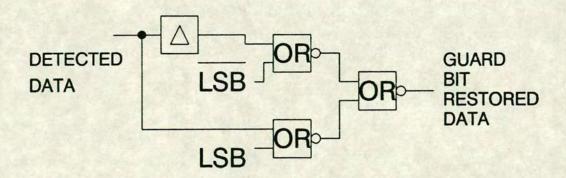

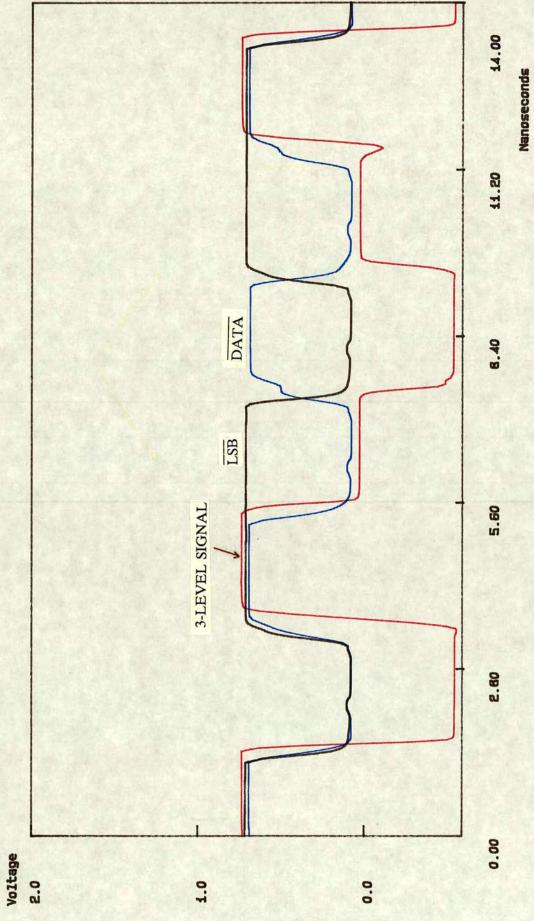

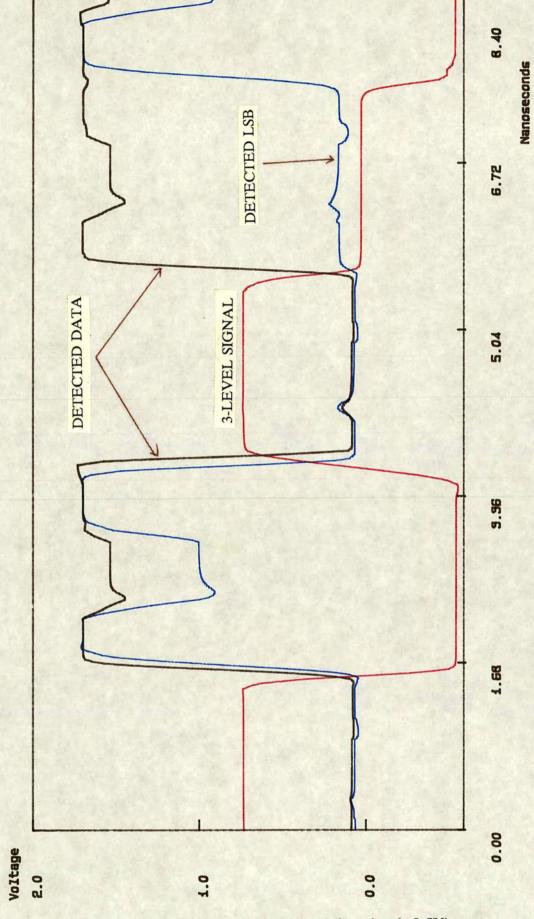

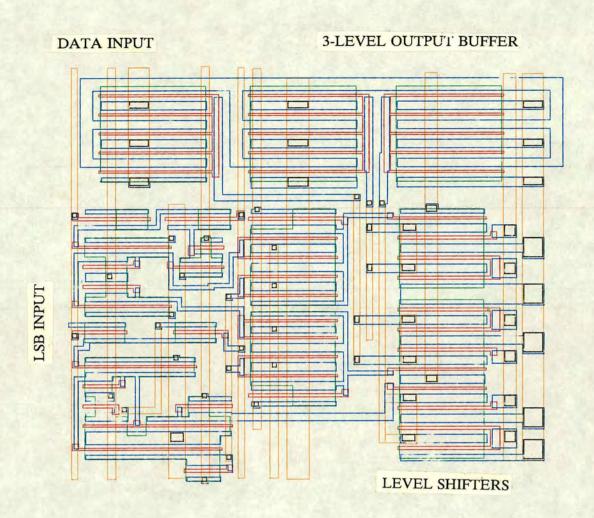

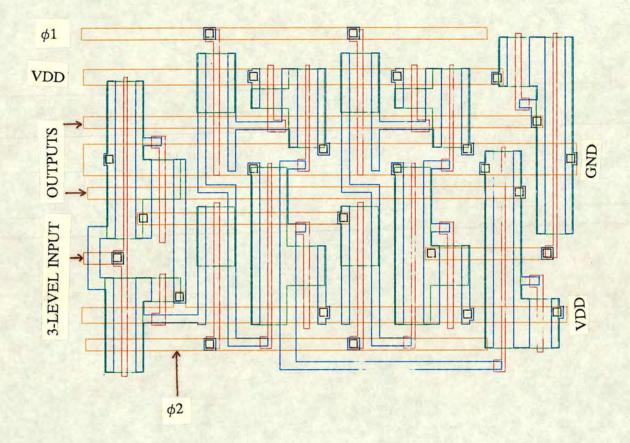

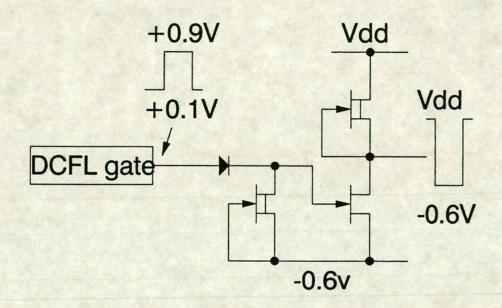

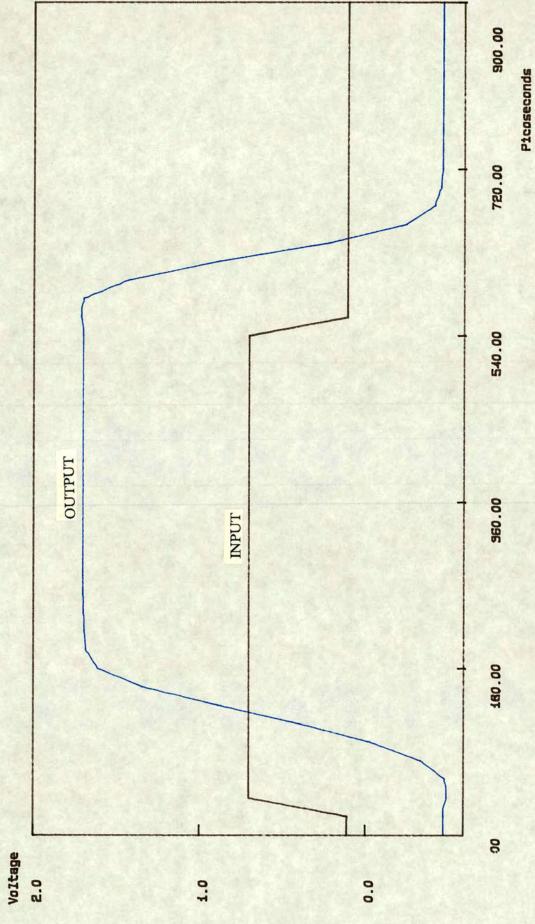

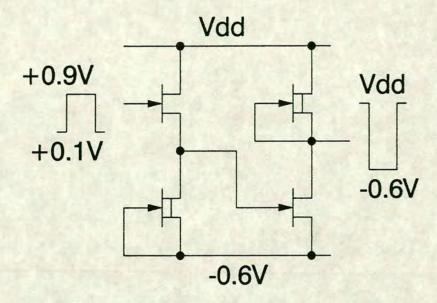

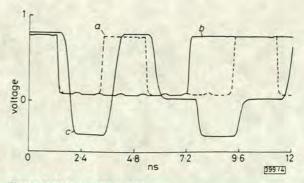

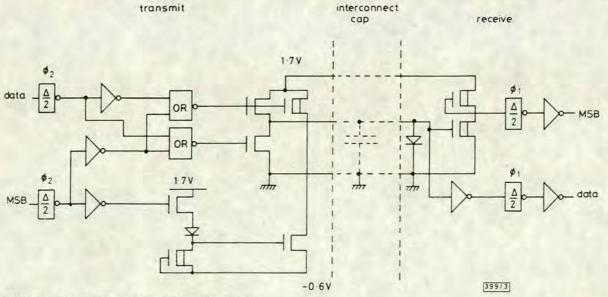

| The circuit details and simulation results                        | 211 |

| Test results                                                      | 213 |

| 6.3. Extensions of the 3-level scheme                             | 213 |

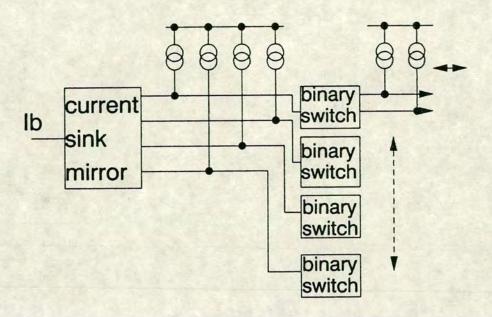

| 6.3.1. 4-level off-chip signaling                                 |     |

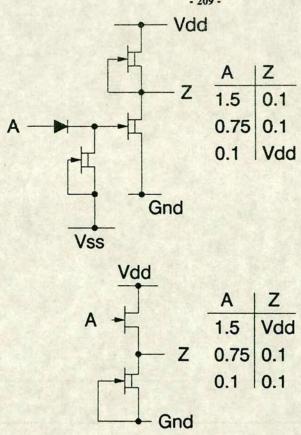

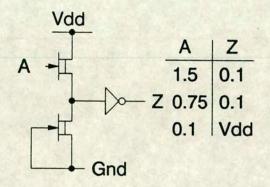

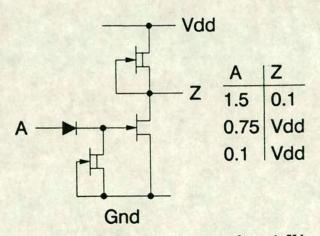

| 4-level signal detection                                          | 226 |

| 6.3.2. Higher radix representations using multi-level signals     |     |

|                                                                   |     |

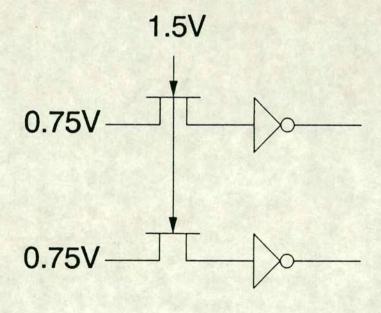

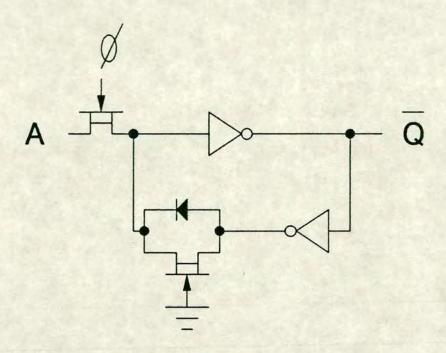

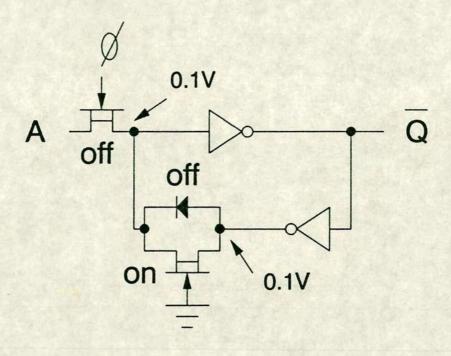

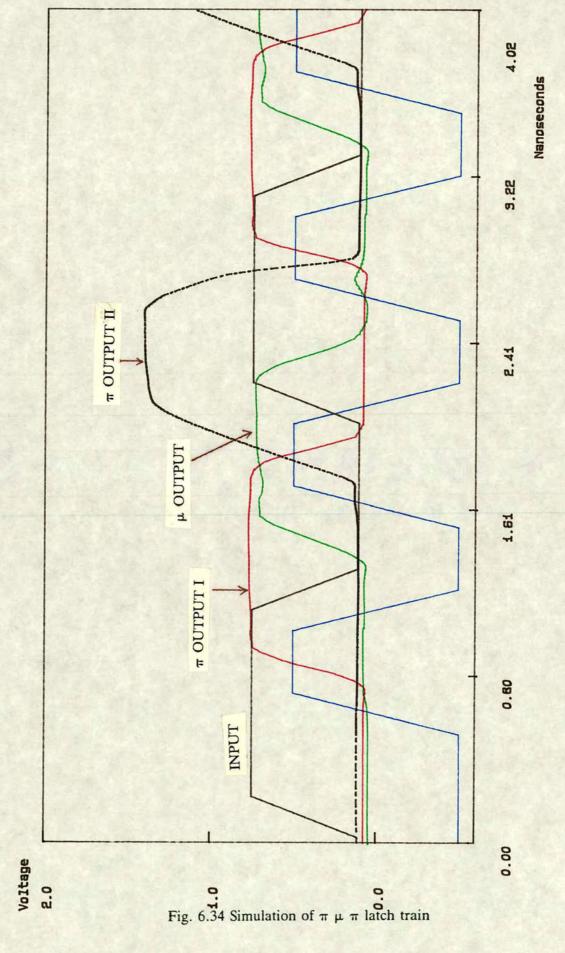

| 6.4. GaAs single phase clocking                                   | 237 |

| The $\pi$ and $\mu$ latch designs                                 | 238 |

| 6.5. Conclusion                                                   | 247 |

| CHAPTER 7: Discussion and conclusion                              | 248 |

| Conclusion                                                        | 249 |

| APPENDIX 1: Modified SPICE JFET subroutine                        | 251 |

| APPENDIX 2: Derivation of Gds and Gm equations                    | 259 |

| APPENDIX 3: UNIX 'makefile' for compiling modified-SPICE routines | 260 |

| APPENDIX 4: Clock generator SPICE input file                      | 262 |

| APPENDIX 5: Multiplier slice SPICE input file                     | 265 |

| APPENDIX 6: Parallel-to-serial converter SPICE input file         | 273 |

| APPENDIX 7: Serial-to-parallel converter SPICE input file         | 278 |

| APPENDIX 8: PRBS counter SPICE input file                         | 283 |

| APPENDIX 9: GaAs-to-ECL output buffer SPICE input file            | 286 |

| APPENDIX 10: GaAs output buffer SPICE input file        | 287 |

|---------------------------------------------------------|-----|

| APPENDIX 11: 3-level circuit SPICE input file           | 288 |

| APPENDIX 12: 4-level circuit SPICE input file           | 292 |

| APPENDIX 13: 4-level detection circuit SPICE input file | 293 |

| APPENDIX 14: Single phase latches SPICE input file      | 294 |

| APPENDIX 15: GaAs circuit test results                  | 295 |

| BIBLIOGRAPHY                                            | 302 |

| AUTHOR'S PUBLICATIONS                                   | 315 |

# Chapter 1

#### Introduction

This thesis is the result of two and a half years of research carried out in this Department on gallium arsenide (GaAs) digital ICs. The main objectives of this work were to design a library of cells, based on GaAs MESFET technology, and combine it with a bit-serial architecture to produce highly modular and efficient integrated circuits for signal processing. The original work in this thesis can be divided into three main parts: bit-serial GaAs cells, multi-level signaling, and single-phase latches. The cell designs were partly based on direct-coupled field effect transistor logic (DCFL), and adopted a unified bit-serial approach, tightly pipelined logic, and psuedo-static latches.

Although this project was essentially based on GaAs metal-semiconductor field effect transistor (MESFET) technology, the circuit techniques and system architecture are also applicable to modulation doped field effect transistors (MODFETs) or high electron mobility transistors (HEMTs) technologies. MODFETs are GaAlAs heterojunction FETs that are very similar to GaAs MESFET technology. Converting MESFET based circuits for MODFET/HEMT fabrication only requires minor modifications at the circuit level. Some of the cells in this work were appropriately modified for fabrication (Chapter 5), illustrating their flexibility.

To summarise the scope of this project, a library of cells had been designed and an FIR filter was used as a case study of integrating these cells. Work was done to incorporate a suitable model into SPICE2G.6. The verification of the designs were mostly done by the SPICE simulations. Some of the cells were fabricated at a late stage of the project and some testing is still under way in the United States. A test IC was fabricated in NMOS in silicon to demonstrate the special registers used for the cells. A single wire 3-level chip-to-chip signaling technique was developed to minimise synchronisation problems of off-chip signals without sacrificing throughput. A two wire scheme, each having 3 voltage levels, was also investigated as an extension of the concept, leading towards radix-8 data representations.

With a project of such a time span, a brief history of the events that led to its present and final form is appropriate. Initial interests in digital GaAs ICs in this Department stemmed from work done by Dr. A. David Welbourn and Dr. Brian W. Flynn in 1983. An SERC funded project was initiated in 1986, with Standard Telecommunications Laboratories (STL) agreeing to provide free fabrication. Owing to a management commercial decision at STL in 1987, the processing facilities were no longer available. (This also applied to other research projects related to STL at the time.) Subsequent to this setback, limited unofficial links with Honeywell Sensors and Signal Processing Laboratory (SSPL) were obtained. Delays in obtaining mask insertion meant that in the present state of this project, some of the cells were fabricated in a non-standard Honeywell MESFET process (Chapter 5), and they will be fully assessed at SSPL. Export restrictions also meant that the test ICs are unlikely to be available for full assessment in this country within the time available. However, the low speed test results obtained so far have been positive and support the simulations. The test results are included in an Appendix at the end of this thesis. The circuits that have not been fabricated are therefore supported by simulation results only, using the modified SPICE2G.6 program, discussed in Chapter 4.

GaAs has always been considered a high risk material for making ICs simply because of its possible obsolescence from competing compound materials and from the well established Si ECL technology. The arguments on GaAs versus Si have continued if not heightened during the course of this project and Chapter 2 will highlight some of the recent developments in high speed ICs and make observations on the future of GaAs in the various application areas reviewed. Research in bit-serial computation in silicon are also reviewed in Chapter 2. The Chapter ends with a discussion on the reasons for combining GaAs and bit-serial techniques.

Chapter 3 provides an introduction to basic GaAs DCFL design. The similarities and important differences between DCFL and silicon NMOS are highlighted, allowing silicon designers to transfer to DCFL design, and provide background to the circuits discussed in later Chapters.

In Chapter 4, the operation of the GaAs MESFET, device structure, and its modelling are discussed in more detail. Its operation is compared to the common silicon MOSFET and JFET devices to further emphasise its different properties and problems. A Honeywell model and its incorporation into the SPICE FORTRAN source code, and comparison with measured data, are discussed in detail.

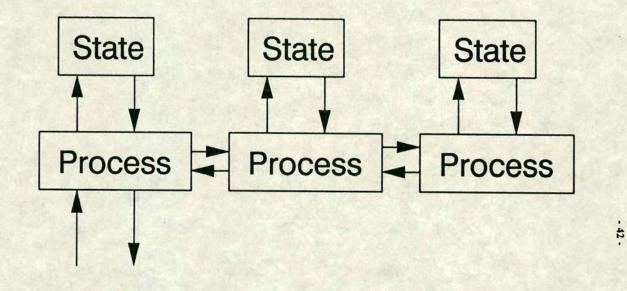

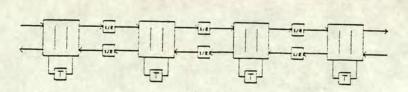

The rest of the thesis centres on the original circuit design work. Chapter 5 describes in detail the adopted bit-serial architecture, the design of the register structure, and the GaAs cells. The layouts of the cells as multi-project chips and their simulations are also shown. Modifications for a real MODFET process were also discussed to show the flexibility of the designs. To illustrate the application of the cells, a brief case study of an FIR filter is then discussed.

In Chapter 6, a novel 3-level voltage signaling technique and its associated decoding/encoding circuitry are described. This approach was also extended into the 2-wire radix-8 technique mentioned above and its properties and circuitry are discussed in detail. Timing limitations of two-phase clocks systems are substantially reduced by single-phase clocking. Two unique single-phase pipelining latch designs are proposed in this Chapter.

Finally, the thesis is concluded in Chapter 7 by identifying the limitations of the GaAs cells as they stand, and suggest possible future extensions of this work. The results and achievements of this work are also summarised.

# Chapter 2

### Introduction to GaAs and Bit-serial circuits

The two main areas of interest in this work, GaAs and bit-serial circuits, had previously been separate major subjects in their own right, and a fair amount of literature exist in both areas. The scope and structure of this survey is defined by the following objectives: to introduce the basic concepts of GaAs and bit-serial circuits, review previous important developments in each field, and focus on the idea of combining GaAs technology and bit-serial techniques.

The survey consists of three main sections: GaAs integrated circuits, bit-serial circuits, and a final discussion. In each of the first two main sections, initial discussions cover some historical aspects of the subject, fundamental concepts, and their advantages and disadvantages compared to other technologies or circuit architectures. In the case of GaAs, the basic concepts will also include some material and device properties, and common circuit configurations. They serve to provide a silicon designer familiar with metal-oxide-semiconductor FET (MOSFET) and junction FET (JFET) technologies with the basic background to "transfer" to GaAs devices. More detailed discussions of device operation, fabrication, and modelling are dealt with in Chapter 4. Recent and important developments are discussed to indicate possible future trends of research in each area. These will include some products and systems available commercially or under development. They are especially relevant to GaAs, owing to its continuing "high risk" designation and limited acceptance within the semiconductor industry, and the continuous threat from silicon to its survival.

Finally, the third section of this chapter makes observations based on the previous sections concerning the problems of GaAs VLSI utilisation in systems, and puts forward the case for combining bit-serial architecture and GaAs as an alternative, thus laying the basic foundation of this work.

### 2.1. GaAs integrated circuit technology

Since the early 60's, GaAs has been known to possess certain electrical properties which make it attractive for three main categories of integrated circuits: high speed digital, analogue, and microwave [71,127]. The second type covers wide bandwidth operational amplifiers, and data converters. Switched-capacitor filters have also recently been of interest [141]. The third type covers microwave amplifier stages, mixers, and oscillators, and are often called monolithic microwave integrated circuits (MMICs). While noting the significant overlap in device modelling and fabrication between the three categories, this thesis shall concentrate on digital circuits. Wherever appropriate, comparisons are made to silicon circuits to highlight the state of development and viability of GaAs in a particular area.

In the next sub-section, the basic properties of GaAs materials, devices, and common circuit configurations are first introduced to provide the background for later discussions.

### 2.1.1. Material properties

The basic material properties of GaAs have been well known. Along with Indium Phosphide (InP), GaAs is a binary III-V compound semiconductor which promises dramatic advantages over silicon. A number of quantitative comparisons of its properties are available in the literature [43,127]. A mainly qualitative summary of several of its properties in comparison with silicon illustrates its fundamental attractions:

- (i) 6 times higher electron mobility;

- (ii) 1.5 times higher electron saturation velocity;

- (iii) High resistivity, semi-insulating substrate;

- (iv) Higher electron band gap energy;

- (v) Large velocity overshoot at low electric fields;

- (vi) Direct band gap structure;

- (vii) Higher radiation hardness.

The advantages of higher mobility and saturation velocity are self-evident. The higher band gap energy implies a wider operating temperature range. The semi-insulating substrate promises lower device to substrate and interconnect to substrate parasitic capacitances, and simpler device isolation. For MMICs, these also mean that inductors, capacitors, and resistors can all be compactly placed on the same substrate (hence monolithic).

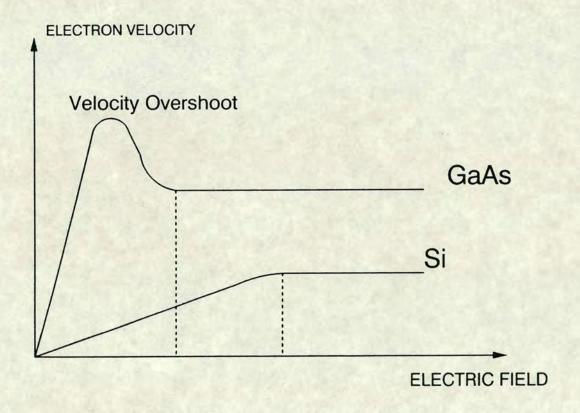

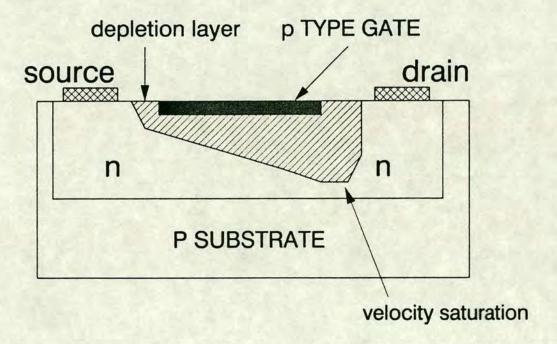

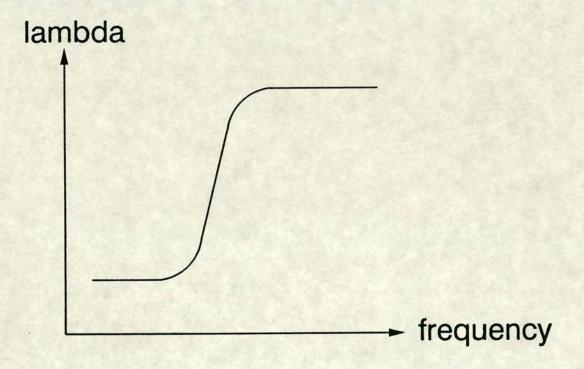

Velocity overshoot is a particularly significant phenomenon in III-V compound semiconductors, such as GaAs and InP [13,71]. This is qualitatively illustrated in Fig. 2.1. The amount of overshoot can be quite marked — as high as two to three times of the saturation velocity — and was found to be very sensitive to channel doping, electric field, initial injection energy, and transient distance. Note that from the diagram that overshoot occurs at a much lower field in GaAs than in silicon. This phenomenon is most applicable to field effect transistors at submicron and ultra-submicron levels of gate/channel lengths, and was found to be small in silicon.

Fig. 2.1 Electron drift velocity vs. electric field in GaAs and Si

The direct band gap structure of GaAs results in its ability to emit infra-red light, and in theory fully integrated opto-electronic circuits can be realised [43]. In addition, GaAs is sensitive to radiation in the microwave frequency range. These

properties make it attractive for fibre-optic systems.

Offsetting these advantages over silicon, GaAs unfortunately has several detrimental material properties:

- (i) 2 times lower thermal conductivity;

- (ii) Brittleness;

- (iii) Lower hole mobility;

- (iv) Orientation dependency of electrical properties.

The implications of (i) and (ii) are generally higher manufacturing costs. The low hole mobility (lower than that of silicon) rules out complementary structures where speed is of major concern. Orientation dependency implies less scope for layout compaction, because all active devices have to be parallel to each other.

Although the advantages of GaAs materials over silicon mentioned above are impressive, they do not indicate how or whether they can be utilised to the same degree in circuits and systems. In practice, factors such as device geometry, and circuit and system architectures, limit the speed advantage to much less than that suggested by the 6 times higher electron mobility. Examples of direct comparative studies have been published and will be discussed. First, the fundamental difference between silicon and GaAs IC technologies — the active device — is discussed.

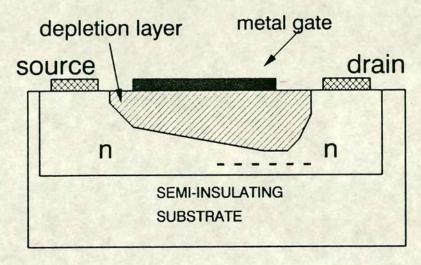

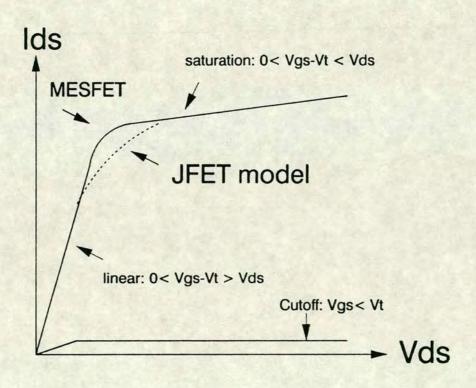

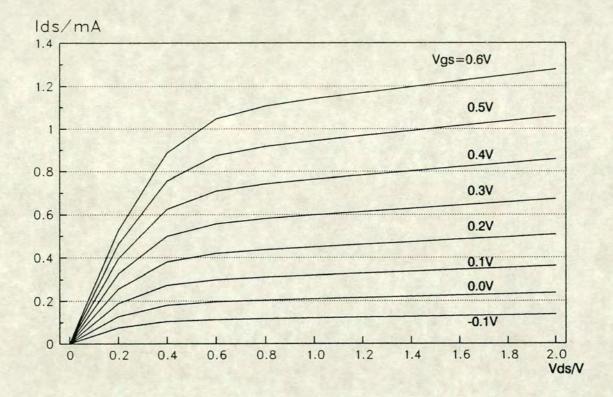

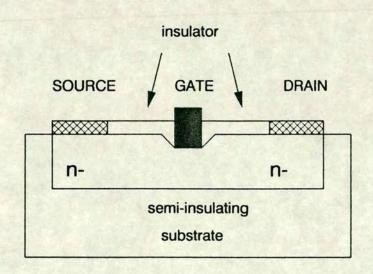

#### 2.1.2. Device constraints in GaAs

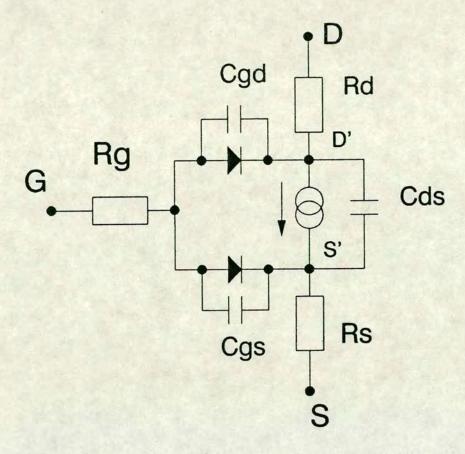

The early stages of an IC technology is inevitably entirely driven by device research and fabrication. The first and most important distinction between GaAs and silicon devices is the unavailability of a good quality oxide in GaAs, making insulated gate field effect transistors (IGFET) impractical, though not entirely impossible [32,36]. As a result, present digital GaAs circuits are based on the MESFET and the JFET, with the former being dominant. The operational and modelling problems of the MESFET are dealt with in more detail in the next Chapter. It is sufficient in this discussion to note this important difference and the immediate consequences of using a MESFET. First consider the fundamental differences in the switching behaviour between the MESFET and the two currently dominant devices in silicon, the MOSFET and the bipolar junction transistor (BJT). Table 2.1 below gives such a comparison.

| Characteristic     | MESFET           | MOSFET                      | ВЈТ         |

|--------------------|------------------|-----------------------------|-------------|

| gate-source/drain  | Schottky barrier | Insulated gate              | pn junction |

| conduction         | unipolar         | unipolar                    | bipolar     |

| switching/clamping | Schottky barrier | No clamping                 | pn junction |

| input impedance    | low when ON      | capacitive, high resistance | low when ON |

Table 2.1 Qualitative comparison of MESFET, MOSFET, and BJT.

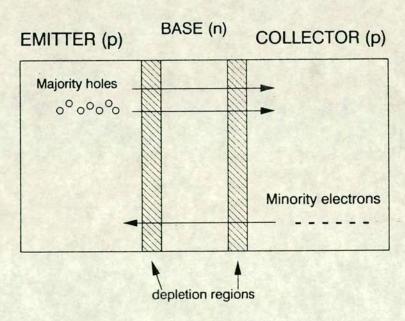

Fig. 2.2 illustrates schematically the different conduction mechanisms in the three devices. It is clear from these that, as a switch, the MESFET is very different from a MOSFET, even though both are FET devices, but shares some similarity to the BJT owing to its gate-source/drain junction. However, whereas a BJT has two pn junctions, the MESFET has one depletion region directly underneath the channel which also controls the flow of majority carriers between the drain and source. Also, the Schottky barrier has a different turn on characteristic compared to a pn junction, and has a lower forward biased voltage (Von).

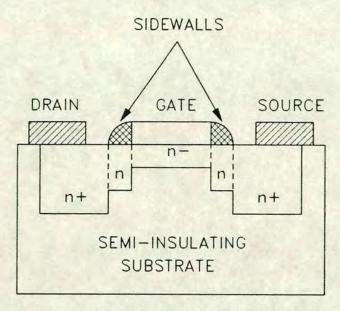

One device that does have many similarities to the MESFET is the JFET. The JFET was the precursor to the MESFET and was proposed as early as 1951 by Shockley. The first successful device was fabricated 7 years later [90]. In a JFET, a pn junction exists between the gate and the channel, instead of the metal/semiconductor contact in a MESFET. As a result, the JFET has a higher barrier height than the MESFET and has a larger gate voltage swing. The JFET is quite widely used for input stages in precision silicon operational amplifiers, such as a number of precision amplifiers available from Analog Devices.

The JFET was initially found to be less manufacturable in GaAs, and a simpler and more planar structures was sought after in the early stages of the technology. The GaAs MESFET was invented in 1965 by Carver Mead [24]. (The first silicon MOSFET was made in 1960 for similar reasons.) While the JFET has been used

Fig. 2.2 Conduction mechanisms in MESFET, MOSFET, and BJT devices

increasingly in GaAs, the MESFET device still dominates in VLSI.

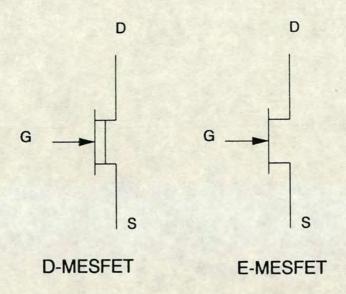

With the GaAs MESFET, both enhancement and depletion devices are available. Depending on the process and application, threshold voltages vary from -2 V to -0.5V for the depletion device, and +0.1 V to +0.3 V for the enhancement device. The symbols adopted for this and all subsequent discussions for these two MESFET's are shown in Fig. 2.3.

Fig. 2.3 Symbols used for D-MESFET and E-MESFET.

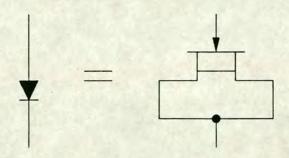

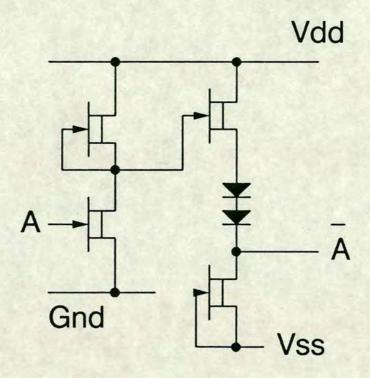

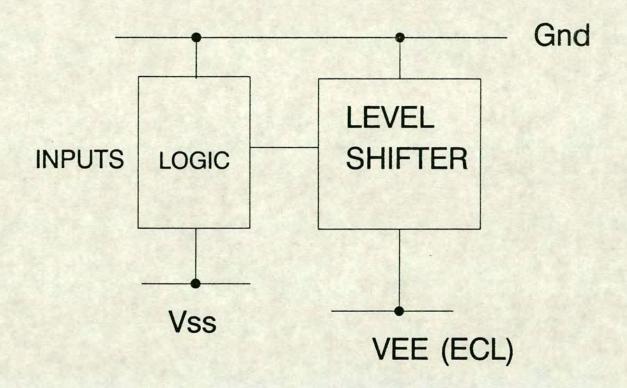

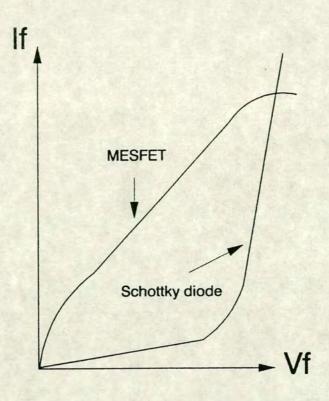

The other important active device is the Schottky diode, used extensively in level shifting and switching. It is commonly formed by a shorted MESFET, as shown in Fig. 2.4. If it is used for switching rather than level shifting, a separate mask may be introduced for the anode for compactness [24]. A reversed biased diode can also be used as a capacitor for level shifting [150], as will be seen later.

Passive devices such as resistors, capacitors, and inductors are mainly used in opamps and MMICs, and are not discussed here. The next section will discuss the various logic circuit configurations centred on the MESFET and Schottky diode.

Fig. 2.4 Schottky diode made from a D-MESFET.

# 2.1.3. Logic circuit configurations

The relatively recent expansion of GaAs research predictably resulted in a fair number of different logic configurations generally aiming to find a suitable compromise between the often conflicting requirements in speed, power, and size. Owing to the limited number of devices available in GaAs, most logic families can be divided into two broad categories: D-MESFET only, and both E-MESFET and D-MESFET. They will be denoted as D-MESFET and E/D-MESFET logic respectively. The latter includes complementary logic circuits (both p and n channel devices).

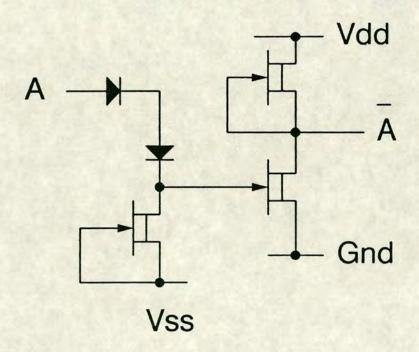

#### **D-MESFET logic**

In this type of logic, level shifting is invariably required between logic stages in order to switch off the D-MESFET. The most common family is the Buffered FET Logic (BFL). The basic gate is made up of a logic block followed by a level-shifting buffer, as shown in Fig. 2.5. The number of level shifting diodes (made up of D-MESFET's) depend on the threshold voltage of the particular process. Most of the power is dissipated in the buffer stage, which has quiescent current flowing from  $V_{dd}$  to a negative  $V_{ss}$  for both HIGH and LOW output states. The power of the first stage is small provided that the pull-down D-MESFET is not forward biased. With this two-stage structure, the output of the first stage is effectively decoupled from fanout gate and interconnect capacitances, and the overall propagation delay is very small. The large voltage swing and the buffered output ensure good noise margins and fanout capability. To offset these, the normally-on buffer stage results in low power efficiency. Values of 34ps at 0.5µm gate lengths [150] are attainable with this

structure and is therefore most suitable for applications where ultimate speed is required. The high power dissipation, ranging from several milliwatts to 50mW per gate depending on speed, and the large number of components per gate, exclude it from levels of integration higher than LSI. Low power versions of BFL (LP-BFL), using less level shifting diodes and D-MESFET's with higher (less negative) threshold voltages, tend to have little speed advantage over other logic families reviewed later on.

Fig. 2.5 Buffered FET logic (BFL).

To overcome the high power dissipation of BFL, several alternatives had been introduced. These include unbuffered FET logic (UFL) [74], Schottky diode FET logic (SDFL) [24], and Capacitor-coupled FET Logic (CCL) [75].

In UFL, the pull-up D-MESFET device in the BFL output buffer is removed to save power, at the expense of fanout capability. It is identical to BFL in all other respects. For low fanout logic, this was found to be a good alternative to BFL.

SDFL is similar in principle to UFL. But unlike BFL and UFL where logic switching is performed by a NOR gate with multiple pull-down D-MESFETs, level shifting and input logic switching are combined by using Schottky diodes and a D-MESFET, which now forms the input stage, as shown in Fig. 2.6. The output stage

is an inverter which produces a maximum possible swing of up to V<sub>dd</sub>. A NOR gate is formed if more than one switching diodes are connected in parallel at the input stage. A negative V<sub>ss</sub> supply is again necessary. Additional level shifting diodes may be necessary if the D-MESFETs have very negative threshold voltages. The input diodes are usually small area Schottky diodes while the level shifting diode is made from a D-MESFET [24,25]. Significant power and size reductions resulted from SDFL, but with longer delays compared to BFL. Typical figures of propagation delay and power are 75ps and 0.3mW respectively [151]. SDFL has similar insensitivity to device threshold voltage variations, but has worse fanout capability due to the unbuffered output. Fanin, however, is substantially better than BFL. (Here fanin is defined as the number of inputs in a NOR gate and fanout is the number of logic gates of the same size being driven.) A recently published chip consisting of 2000 gate array cells [147], which also used a push-pull output stage, demonstrated high integration and low power. Unfortunately, gate delay was too large compared to even silicon bipolar gate arrays. The speed/power compromise might have been too severe in this particular case.

Fig. 2.6 Schottky diode FET logic (SDFL).

One interesting variation of SDFL exists, and is called inverted common drain logic (ICDL) [1]. This has essentially the same structure as SDFL, but uses an ion implanted resistor instead of small area diodes. The reasons for using a resistor

were ease of process control and lower power dissipation. Experimental results showed that although speed-power product was reduced, speed suffered as result.

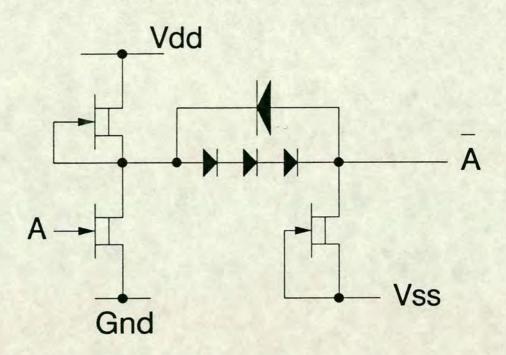

Another important attempt at solving the level shifting problem was the use of capacitor coupling between logic gates, initially called capacitor-coupled logic (CCL) [75]. Instead of forward biased diodes, reversed biased Schottky diodes are used as capacitors, as shown in Fig. 2.7. With a correctly chosen diode to MESFET ratio, charges are transferred as the input level changes, providing level shifting with minimal static power dissipation, and without the need for an extra negative supply. It was also designed to be insensitive to device variations, and produced figures of 55ps gate delay at 3.5mW/gate from ring-oscillator results [150]. Initial charging of the capacitors is necessary and a lower cut-off frequency exists. These were not considered to be major drawbacks for telecommunication applications at which it was aimed at. The ratio of the reverse biased diode capacitance to the total load capacitance determines charge transfer efficiency and hence fanout capability. With large fanouts, penalty is paid in the form of large diodes, with significant parasitics which need to be charged by the input gate during a transition. Since the output is also unbuffered, as in SDFL, CCL gate delay is more sensitive to fanout compared to BFL.

Fig. 2.7 Capacitor-coupled FET logic (CCL).

A variation of the basic CCL principle, called Capacitor diode-coupled FET logic (CDFL), improved on the speed and power performance further, and was adopted for a high speed logic family [25]. In the CDFL, extra diodes and pull-down device are added between stages to improve fanout capability. A CDFL inverter gate is shown in Fig. 2.8. A further variation of CDFL, super capacitor FET logic (super-CFL), uses a super buffer stage to further improve output current drive [76]. All versions of CCL are capable of higher integration than BFL (up to LSI), and have better speed-power products, but cannot match BFL in ultimate speed.

Fig. 2.8 Capacitor diode FET logic (CDFL).

All the D-MESFET logic discussed so far operate in voltage mode. The GaAs equivalent of silicon ECL is generally called source-coupled FET logic (SCFL). Its basic structure, shown in Fig. 2.9, consists of source-coupled pairs and current sources biased by voltage references, with the outputs buffered by source following level shifters, similar to those in BFL. This implies that the output is in voltage mode while the logic block operates in current mode. As a result, it is also insensitive to threshold variations, and has all the advantages of current mode logic [127]. Recent results [44,53,148] appeared to be very favourable both in power and speed compared to BFL, producing figures of 50ps of propagation delay for a NOR gate (fanout unknown). A low power version called LSCFL gave figures of 24ps and 2.4mW/gate [55] for a fanout of 1, 0.4μm gate length, plus 255 μm of interconnect. The buffered outputs ensured low fanout sensitivity. The SCFL family is relatively new compared to BFL, and is clearly a major contender at the MSI to

A Vref2 A A

LSI level, where high speed and acceptable power dissipation are required.

Fig. 2.9 Source-coupled FET logic (SCFL).

Vss

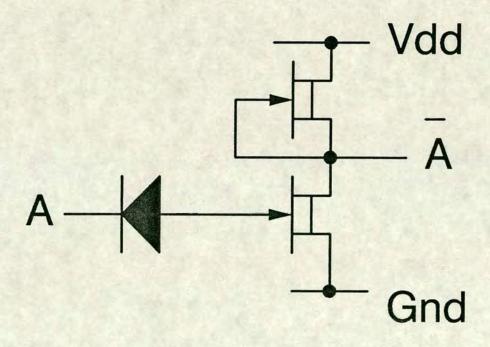

Finally, an important issue worth mentioning is compatibility between the different D-MESFET logic structures, and between GaAs and silicon ECL. In the former case, all the D-MESFET configurations discussed above require two supply rails (V<sub>dd</sub> and V<sub>ss</sub>), and are directly compatible to each other with the same process. In a custom design, they can be mixed at will to optimise area, speed, and power on the same chip. Where ECL compatibility is necessary, the V<sub>ss</sub> supply rails can be split and level-shifted, as shown in Fig. 2.10, to share the conventional ECL rails. A total of two or more power supplies are normally necessary, depending on the silicon ECL family used. Since D-MESFET logic is generally process tolerant and has a large logic swing, the level-shifted supply rails are not detrimental to noise margins.

Fig. 2.10 Level-shifted supply rails for ECL compatibility.

# E-MESFET/D-MESFET (E/D) logic families

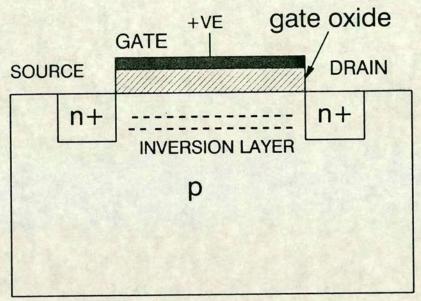

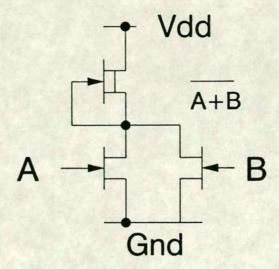

The major drawbacks of D-MESFET logic are clearly the high power dissipation and component count per gate. For commercial survival, high integration and functionality are mandatory. Although low power D-MESFET logic families such as SDFL and SCFL did go some way in improving speed-power product, they are all generally considered to be too large for VLSI. The simplest solution is to have silicon NMOS-like static logic, using both E-MESFET and D-MESFET devices — direct-coupled FET logic (DCFL).

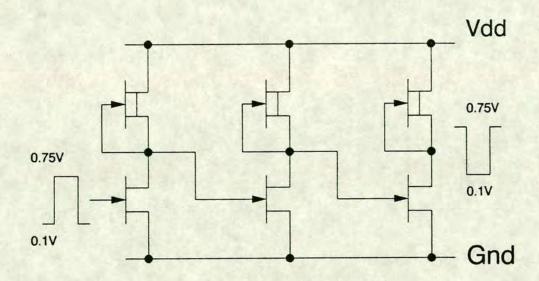

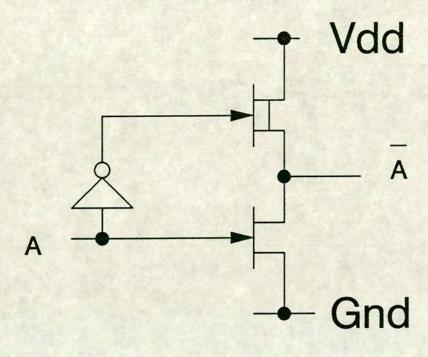

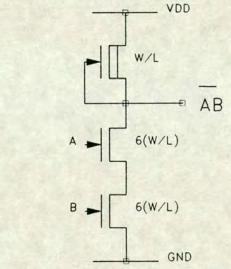

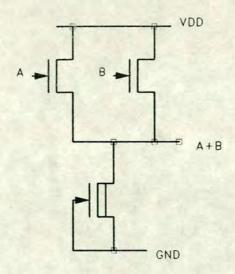

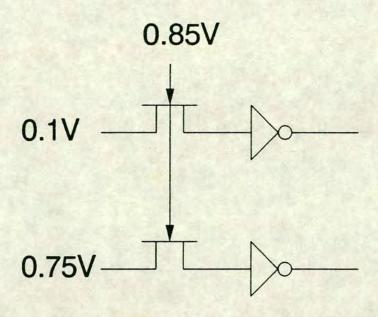

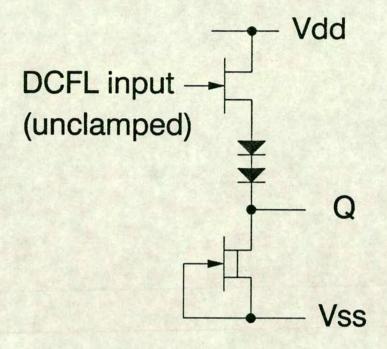

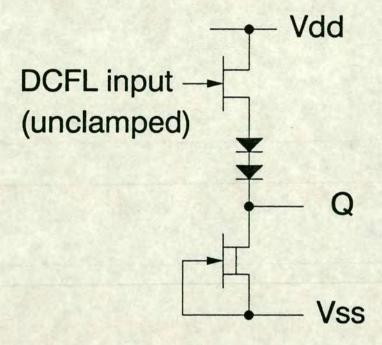

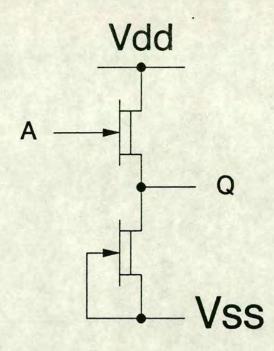

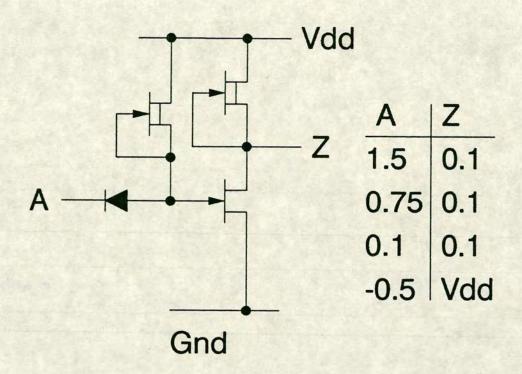

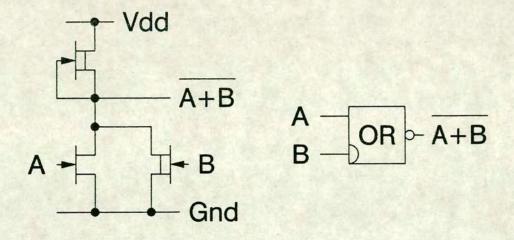

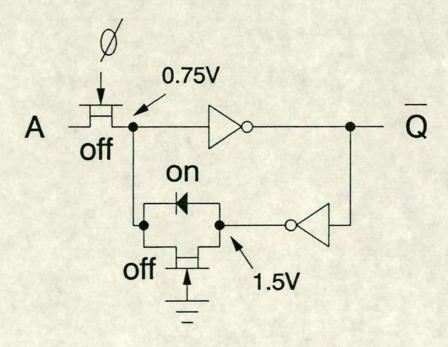

The basic DCFL inverter is shown in Fig. 2.11. The pull-down E-MESFET avoids the need for level shifting between stages, hence the name. The voltages shown in Fig. 2.11 are for a DCFL gate with a non-zero fanout. If the gate is not clamped, as might be the case when it is driving a source follower, then the output HIGH voltage can rise to  $V_{\rm dd}$ . The immediate advantages are small size, low power, and single supply operation. It is therefore widely accepted as the most suitable logic family for VLSI in GaAs.

Fig. 2.11 Direct-coupled FET logic (DCFL) inverter chain.

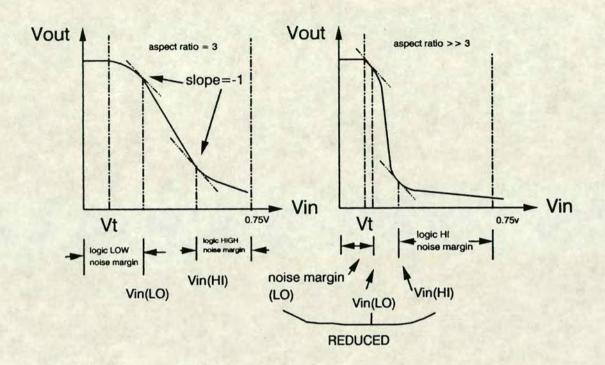

In DCFL, major drawbacks caused by the unavailability of a IGFET device are small logic swing (typically 0.1V to 0.75V), low fanin and hence functionality per gate, and high fanout sensitivity. Stringent process control over threshold voltage is also crucial. Together with high costs, lower yields, and lower noise margins compared to D-MESFET logic families, DCFL was considered to be too high a risk to adopt as a standard logic family until recently. Self-aligned gate ion implanted E/D processes have improved to such an extent in the last two to three years that DCFL has become a viable commercial alternative to silicon ECL [73]. The basics of DCFL design are discussed in more detail in the next Chapter.

Although DCFL was primarily envisaged for VLSI rather than ultimate speed, impressive figures of under 100ps gate delay at 0.3mW/gate were achievable even from a gate array [73]. The high fanout sensitivity would increase delay closer to 200ps, comparable to the better silicon ECL gate arrays. The most important advantage of GaAs, however, is the much lower power dissipation. A more detailed look at silicon ECL performance later on will confirm that GaAs DCFL is commercially viable mainly because of its power advantage.

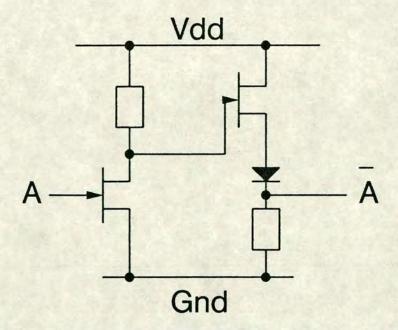

In order to reduce its fanout sensitivity, various forms of buffering were introduced. One method used a super-buffer output stage, and is called super-buffered FET logic (SB-DCFL) [73]. The basic super-buffer is similar to its silicon NMOS

counterpart, and is shown in Fig. 2.12. Because of the shared gate terminal between the two stages of the buffer, a compact layout of the logic gate is possible, despite its apparent complexity.

Fig. 2.12 E/D super-buffer used in super-buffered FET logic (SB-DCFL).

Other forms of output buffering use source followers, increasing fanout capability at the expense of dc power dissipation. This is used in one of the various forms of a logic family called low pinch-off FET logic (LPFL) [101]. LPFL was envisaged as a compromise between DCFL and BFL, and used MESFET's with threshold voltages close to 0V and single supply operation. At least six forms of LPFL had been proposed [151]. They follow the lines of modified forms of D-MESFET logic families such as BFL, UFL, SDFL, and ICDL. One example, which uses source follower buffering, is shown in Fig. 2.13. They generally have the BFL advantages of process tolerance and good fanout capability, and lie between BFL and DCFL in terms of speed, power, and size. The output swing is about 100mV higher than DCFL. This was especially attractive in the early stages of DCFL development when the swing was as low as 500mV due to the low Schottky forward voltage (V<sub>on</sub>). Noise margins were also improved with LPFL. However, an examination of recent GaAs circuits showed that the interest in LPFL had declined owing to improvements in processing, although the concept was clearly a significant one.

Fig. 2.13 One form of low pinch-off FET logic (LPFL).

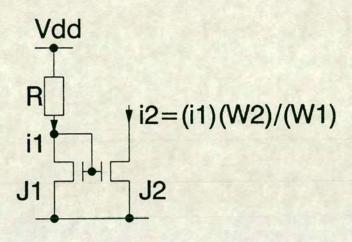

In current mode form, one notable attempt was to use SCFL with an E/D-MESFET process. The basic concept remained unchanged, but with E-MESFET replacing most of the D-MESFET devices in the differential pairs and voltage references. Simulated results showed that an E/D SCFL frequency divider operated up to 3 GHz at 3 times power dissipation and same circuit density, compared to the DCFL equivalent operating up to 1.5 GHz [148]. Although 4-bit digital-to-analogue and analogue-to-digital converters were designed and tested successfully using E/D SCFL, full test results were not disclosed and simulated advantages could not be confirmed. The increased speed was largely attributed to the much better fanout capability, at the expense of power. Another important feature was the ease of integrating digital, analogue, and even microwave circuits on the same chip. The first two of these had been demonstrated by the converters already mentioned.

These different variations of E/D logic had aimed at striking a reasonable compromise between the low power of DCFL and the high speed of BFL. Although the hole mobility of GaAs is lower than that of silicon, quasi-complementary and complementary logic had been used in GaAs to reduce power even further than conventional DCFL. Particular areas of interest are memories and gate arrays.

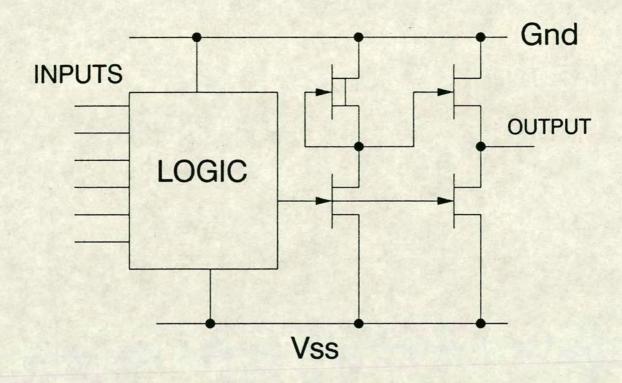

In the gate array sector, a quasi-complementary output stage was used with a custom input logic block. This logic is called Gain FET logic (GFL) (named after the company), and is shown in block form in Fig. 2.14. Power is reduced by avoiding a dc current path in the output stage. Full details of the input logic block were not disclosed, and was claimed to have better input noise margins than DCFL. Performance figures of 180ps at 700μW/gate for an inverter were also quoted. Although these appear to be worse than conventional DCFL, the increased fanin and fanout capability and the resulting higher functionality per gate meant that much less gates are needed than DCFL for the same logic function. An earlier comparison of quasi-complementary logic [151] showed that for large fanouts, this approach was fastest compared to inverters with resistive and D-MESFET pull-up loads. Unfortunately, it also had the worst fanin capability. GFL had apparently solved the fanin problem, while inevitably increasing total propagation delay through the gate, confirmed by the quoted figures. In terms of size, direct comparison was not available. The largest array offered has 1444 cells. A 14 × 16 cross-point switch was fabricated and worked up to 500Mbits/s into 50 $\Omega$ , at a power dissipation of 1.1W. Other GaAs gate arrays are reviewed in a later section.

In the case of complementary logic, the most notable attempts were SRAMs ranging from 4K to 16K [70,146]. Apart from the reduction in power by using n and p channel devices, the other distinguishing feature of these designs is the use of JFETs rather than MESFETs. Figures for the 16K SRAMs were 16.1ns access time, 678mW dissipation, and 3% yield. Much better access times are possible in GaAs RAMs which used non-complementary logic, but the low power and good yield may prove complementary logic to be viable. However, it has not been adopted for other types of circuits. A 32-bit RISC microprocessor made with the same JFET process used n-channel devices only [45]. The speed degradation was clearly considered to be unacceptable for most circuits.

Finally, in terms of compatibility, the problem of different supply voltages is less severe owing to the lower currents involved, compared to D-MESFET logic. In DCFL and its variations described so far,  $V_{dd}$  is normally chosen to be sufficiently high to saturate the D-MESFET pull-up device, but low enough to minimise dc power. Values can range from +1V to +2V, and are therefore not directly compatible with any silicon technology. A simple solution had been to use the same supplies as silicon CMOS or ECL, and connect external resistors in series between the GaAs supply terminal and the board  $V_{dd}$ . This is clearly inefficient if a large number of DCFL chips are involved, and an extra rail with on-chip level translators would be necessary in such cases, as with the D-MESFET logic families

Fig. 2.14 Block diagram of gate array cell with quasi-complementary output stages.

discussed above. (ECL compatibility is discussed in more detail in Chapter 3.)

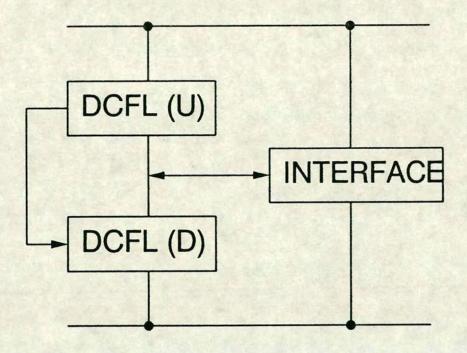

One interesting configuration that avoided either of these board level adaptations is the stacked DCFL logic [121]. This consisted of upper and lower DCFL blocks with an interface block referenced to a virtual ground (VG). The block diagram is shown in Fig. 2.15. Test results of a prescaler IC, using a V<sub>dd</sub> voltage of 3.3V, showed 31% reduction in circuit current compared to the resistor and conventional DCFL arrangement. The IC operated up to 900MHz. A three-stack structure was considered to be possible and should reduce current even further. Direct comparison of speed was not available. The main disadvantage of stacked circuits is clearly gate size, limiting integration level.

Fig. 2.15 Stacked DCFL logic structure.

# 2.1.4. Circuits and systems

In the last sub-section, a fair number of logic families, spanning the two extremes of D-MESFET BFL and complementary E/D JFET logic, were discussed. It is clear that no one single family can dominate and the application in question ultimately dictates what combinations or variations of these families should be used. In this section, recent results of GaAs circuits, some of which are commercially available, are reviewed according to their functional areas. There are four main application areas in which digital GaAs ICs are used:

- (i) Signal processing.

- (ii) Communications.

- (iii) Test and measurement.

- (iv) Supercomputers.

Signal processing and communications are closely related areas, while the other areas also overlap with the others. Although no sharp distinction shall be made on the applications of GaAs circuits in this review, a few words on signal processing are appropriate here.

### Signal processing

Owing to military interests in the States and Europe and commercial interests in Japan, communications and signal processing are the major areas that attracted funding for GaAs. These have made possible advances such as the jump from 4K to 16K SRAMs in 2 years. The material advantages of GaAs in terms of radiation hardness and potential speed were the fundamental attractions, although silicon advances, in response to GaAs, have forced the speed argument more and more towards lower power.

Signal processing covers a wide range of circuit functions, ranging from custom FFT processors to general purpose microprocessors. These include:

- (i) Arithmetic logic, such as multipliers and adders, and registers.

- (ii) Memories.

- (iii) Microprocessors.

- (iv) Application specific processors.

Other equally important SSI to MSI circuits are A/D and D/A converters, and sample and holds. Due to their semi-analogue nature, they are not reviewed here. The next section will first review the core of all signal processing systems.

#### Arithmetic logic

The most important elements in arithmetic are the adder and the multiplier. Apart from their obvious functions, the multiplier is often used to assess a certain new process or logic configuration due to its circuit complexity. The speed of the multiplier also determines the processing power of a system for the same reason. Recent published results on adders and multipliers are summarised in Table 2.2.

It can been seen from this Table that low power, medium to high speed, 4-bit circuits were most developed. Two of the circuits, the 32-bit adder and 8×8 multiplier, exceeded 1W in power dissipation, as a direct result of using D-MESFET logic.

Assuming good accuracy of manufacturer's figures, a comparison of off-the-shelf products between silicon and GaAs should indicate possible real system advantages. For a silicon ECL 100K series 4-bit ALU [94], the worst case adder propagation delay from input to carry output was quoted at 8.3ns (excluding setup and hold times), with a power dissipation of 920mW. Worst case test figures for the Vitesse 4-bit slice ALU listed in the Table, also available commercially, were 4.7ns at 240mW power dissipation for the same function. Whereas these figures point towards significant improvements by using the GaAs parts, a customised silicon ECL ALU may match them in speed. The greater than 3 times power advantage is more significant in the context of a complete system, as other GaAs system comparisons will confirm in later discussions.

| Circuit and performance (worst delay/power)               | Ref.   |

|-----------------------------------------------------------|--------|

| (1) 4-bit carry look-ahead generator, 1.55ns, 34mW, DCFL. | [117]. |

| (2) 4-bit ripple carry adder, 1.25ns, 180mW, lp-BFL.      | [107]. |

| (3) 4-bit adder-accumulator, 340 MHz, 500mW, BFL.         | [26].  |

| (4) 8-bit adder, 11ns, 236mW, SDFL.                       | [147]. |

| (5) 32-bit adder, 2.9ns, 1.2 W, BFL.                      | [157]. |

| (6) 4X4 multiplier, 2.5ns, 40mW, DCFL.                    | [23].  |

| (7) 4X4 multiplier, 1.4ns, 1.6 W, CDFL.                   | [76].  |

| (8) 5X5 multiplier, 4ns, 133 μW/gate, DCFL.               | [17].  |

| (9) 8X8 multiplier, 5.25ns, 1-2mW/gate, SDFL.             | [24].  |

| (10) 8X8 multiplier, 6ns, 876mW, JFET DCFL.               | [40].  |

| (11) 16X16 multiplier, 10.5ns, 952mW, DCFL.               | [96].  |

| (12) 4-bit slice ALU, 4.7ns, 240mW, DCFL.                 | [49].  |

Table 2.2 Performance of arithmetic logic elements

In contrast to this favourable comparison of "standard" products, a laboratory silicon CMOS 16×16 multiplier, based on 0.6µm gate lengths, gave a typical multiply time of 7.4ns and dissipated 400mW [103]. This is significantly better than the GaAs DCFL multiplier figure of 10.5ns worst case delay, achieved 4 years earlier

(Table 2.2). A more detailed examination revealed that the GaAs multiplier used a classic parallel array architecture, while the CMOS circuit used a Booth's algorithm array scheme to reduce the number of adder stages (Chapter 6). Also, the GaAs MESFETs used in this example had gate lengths of 2μm. Projected performance with 1μm gate lengths was 6.5ns. Unfortunately, attempts at improving on the GaAs figures are not available in recent publications and therefore an up-to-date speed comparison cannot be made. Nevertheless, these results demonstrate that at this LSI level, the well known advantages of GaAs materials over silicon do not guarantee correlation with circuit performance, and that circuit architecture becomes more and more important as integration level increases.

#### Memories

The fabrication of memory components has traditionally been the most difficult for any process owing to the need for small feature sizes and high yield. Interests in GaAs have been mainly in SRAMs. Table 2.3 below summarises a number of recent achievements.

Referring to the Table, it can be seen that DCFL based logic dominated all sizes. In the 1K category, fastest access time was 1ns with the second lowest power of 300mW. Lowest power was achieved with a 0.7µm process. In the 4K category, best access time was again 1ns. Lowest power was achieved at 200mW with a complementary JFET process. The largest memory size in GaAs is 16K, and produced best access time of 7ns at 2.1W. Lowest power was again from a complementary JFET process, which was also the slowest. Overall, no GaAs SRAM could achieve subnanosecond access time, and power covers a range of 200mW to 2.1W. For comparison, a 4K high electron mobility transistor (HEMT) RAM was capable of 0.5ns access time, but at a high power of 5.7W (Table 2.3).

In GaAs, the processing problems that most affected memory ICs are temperature gradients in annealing furnaces, handling damage, surface contamination, residual polishing damage, and the small diameter of wafers [140]. The effects of the high dislocation density in un-doped GaAs wafers were less clear, and were thought to affect E/D-MESFET memories more than D-MESFET circuits [125]. Indium doped wafers were found to reduce dislocations by at least 4 times. They were also more expensive and brittle, restricting their general acceptance.

In terms of circuit design, several problems have hampered the acceptance of large SRAMs in GaAs [137]. These include non-standard power supplies, low tolerance to supply, temperature, and process variations. Together with typical yield figures of

1% to 3% for 16k SRAMs, they are still a significant way from widespread system replacement of silicon parts.

In contrast, 1K SRAMs are relatively well developed, with parts available commercially that can directly replace silicon ECL 100K and TTL memories. A silicon ECL 256×4 bit SRAM gave worst case read access time of 10ns and power dissipation of 1W [88]. Test results of pin compatible GaAs parts produced figures of 2.5ns and 1.5W [137]. Therefore the GaAs SRAMs have a better speed-power product, but higher power dissipation. This was likely to be the result of using some current-mode logic in this GaAs SRAM. Yield was high at 30%. Other laboratory results have shown much better speed-power product than these standard parts. It was found to be generally true that when ECL or TTL compatibility are necessary, power had to be sacrificed.

| Circuit and performance (read access time/power)                   | Ref.   |

|--------------------------------------------------------------------|--------|

| (1) 1K SRAM, 3.6ns, 68mW, 2µm DCFL.                                | [157]. |

| (2) 1K SRAM, 1.3ns(min.), 1.4W, DCFL.                              | [86].  |

| (3) 1K SRAM, 1ns, 300mW, DCFL.                                     | [134]. |

| (4) 1K SRAM, 3.6ns (worst), 1.9W, E/D CDFL.                        | [31].  |

| (5) 1K SRAM, 2.5ns (min.), 1.5W, DCFL, TTL/ECL pin compatible.     | [137]. |

| (6) 1K SRAM, 1.4ns (min.), 210mW, 0.7μm DCFL.                      | [35].  |

| (7) 1K SRAM, 2.3ns (mean), 550mW, 1μm DCFL.                        | [48].  |

| (8) 4K SRAM, 2.6ns (mean), 890mW, 1µm DCFL.                        | [48].  |

| (9) 4K SRAM, 1ns, —, 0.7μm,DCFL.                                   | [82].  |

| (10) 4K SRAM, 0.5ns, 5.7W, 0.5μm, HEMT                             | [99].  |

| (11) 4K SRAM, 10ns (typical), 200mW (typical), complementary JFET. | [100]. |

| (12) 4K ROM, 1.2ns, 3.75W, 0.5μm,DCFL.                             | [56].  |

| (13) 4K SRAM, 7ns (worst), 850mW, 1µm DCFL.                        | [79].  |

| (14) 4K ROM, 1.2ns, 1.9W, 1µm CDFL.                                | [16].  |

| (15) 4K DRFM, 1.4ns (min.), 1.5W, DCFL.                            | [153]. |

| (16) 16K SRAM, 20ns (typical), 1W, 1µm, D-MESFET.                  | [143]. |

| (17) 16K SRAM, 22.5ns (worst), 678mW, complementary JFET.          | [146]. |

| (18) 16K SRAM, 7ns, 2.1W, 0.7μm DCFL.                              | [81].  |

Table 2.3 GaAs Memories.

At the 4K-bit size, a comparison of manufacturers' figures of standard parts is favourable towards GaAs. The silicon ECL 10474-15 4K RAM achieved worst case chip select access time of 8ns [88], compared to 3.5ns of the Vitesse GaAs VE12G474 of the same memory size [18].

Moving away from standard parts, the comparisons are not as clear cut. One example of silicon performance is a 5K ECL SRAM with a best access time of 0.85ns at 2.4W [14]. The technology used was an advanced self-aligned 1.2µm process. At a similar time, two independent GaAs 4K SRAM produced figures of 1.3ns and 1.4W [86], and 2.2ns and 890mW [48], for minimum access times and power respectively. The larger size of the ECL RAM implies that it has slight advantage over GaAs on both speed-power product and speed. The relative states of development of the three processes involved are difficult to assess. In the case of 16K SRAMs, the 3.5ns and 2W performance of one silicon example [51] compares favourably to the 7ns and 2.1W of a GaAs SRAM [81]. These laboratory results imply that at the present state of GaAs development, it has no advantage over silicon in memories larger than 4K bit.

#### Microprocessors

The first major initiative in GaAs microprocessors was the 32-bit reduced instruction set computer (RISC) program, started in 1984 by the Defence Advanced Research Projects Agency (DARPA). This processor was targeted specifically for the advanced on-board signal processor (AOSP) for a broad range of military missions [91]. The RISC architecture, as opposed to CISC (complex instruction set computer) popular in silicon, was considered to be the only viable one, owing to the limited integration level, fast switching speed, high dependency of fanin and fanout, and the non-existence of dynamic logic of GaAs technology available at the time. More importantly, this program had drawn attention to the need for different architectural approaches to GaAs VLSI in general.

Other efforts at making GaAs microprocessors include 4-bit slice and 8-bit slice processors. Test results of these efforts and the 32-bit RISC processor are listed in Table. 2.4 below.

| Processor                           | Comment                                       | Ref.  |

|-------------------------------------|-----------------------------------------------|-------|

| (1) 4-bit slice processor chip set. | ALU: 6.5ns t <sub>pd</sub> ,1W.               | [49]. |

| (2) 8-bit slice.                    | 150 MIPS (6.6ns),<br>9.2W, D-MESFET.          | [37]. |

| (3) 32-bit RISC.                    | 60MIPS (16.5ns clock cycle), 4.7W, JFET DCFL. | [45]. |

Table 2.4 GaAs microprocessors

The 4-bit slice chip set consisted of a central processor, a carry-look-ahead generator, a microcontroller, and a 4K SRAM. They were designed as direct replacements of Am2900 (Advanced Microdevices) series silicon ECL chip set. This effort was therefore significant within the GaAs industry as the first to offer such a chip set. Projected performance of 4×4-slice system was 55MHz clock rate. Direct experimental comparison with a silicon system is not available. However, judging from the low clock rate with 4 cascaded 4-bit slices, speed advantage over 16-bit silicon CMOS microprocessors is likely to be limited. The projected performance for an integrated 16 bit processor was more practical at 125 MHz. These figures do demonstrate that advantages from fast switching speeds on-chip are easily crippled by going off-chip.

The other two processors were directed more at military systems. Both the 8-bit and 32-bit processors improved on the 4-bit processor by a significant amount. The 32-bit RISC processors also demonstrated VLSI capability in GaAs, particularly using direct-coupled FET logic (DCFL) — the MD484 (McDonnell Douglas) CPU contained 21606 transistors and was fully functional.

Communication between processors in multi-processor systems is an important issue in both GaAs and silicon microprocessors. Two GaAs circuits in this area have been published. The first is a 32-bit asynchronous serial data transceiver chip set [102]. The chips have been tested at 500Mb/s using 16 32-bit silicon microprocessors. Power was rated at 1W. The other circuit is an 8-bit bus logic IC designed specifically for a parallel data transfer network [64]. A test cycle time of 10ns has been achieved, at a high power dissipation of 7W. By using 48 ICs, 4Gb/s transfer rate was considered to be possible.

In terms of speed, the 60MIPS GaAs RISC chip compares favourably with the 10MIPS achievable in 32-bit silicon chips at present. But a commercially available 64-bit RISC chip from Integraph [29] is already capable of 50MHz clock rate and 20MIPS in CMOS. Its ECL version under development is aimed at 100MHz and 80MIPS. Therefore the speed advantage of GaAs in this area is not clear cut. The availability of supporting software is clearly also a major factor in the acceptance of a new microprocessor. It is likely that future GaAs circuits will need to take this into account if they are to compete with silicon.

### **Application specific processors**

Most of the ICs mentioned so far were designed for one general functionality per chip, such as multiplication or memory. Very few published results were available on dedicated signal processing circuits and systems, while noting that some military circuits are not publishable. (Optical fibre transmission circuits are discussed in a later section.) Table. 2.5 lists 3 recent examples.

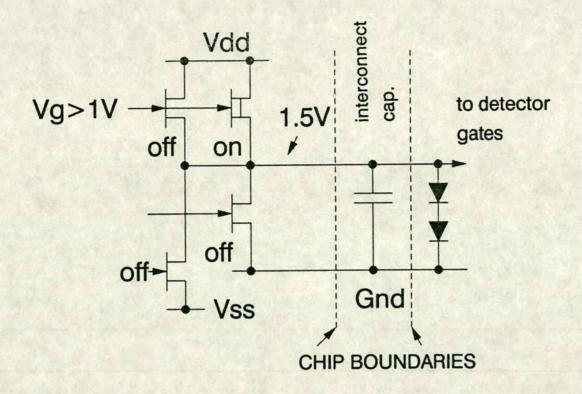

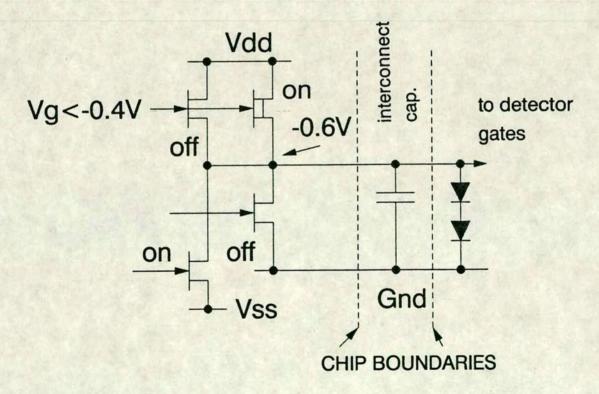

Among these systems, the highest integration level was used in the FIR filter, which utilised 13376 sites in a gate array IC, and a 4K SRAM. The 400MHz clock rate achieved has demonstrated the practicality of GaAs gate arrays in a high speed system, while noting that such speed should be achievable with silicon ECL gate arrays. More importantly, it was noted that higher performance and lower power dissipation resulted from using a unique GaAs I/O structure, rather than traditional ECL or TTL levels. Full details of this structure were not disclosed.

The third project in the Table was impressive in its scope. In terms of performance, the most notable was the half-FFT butterfly in achieving 500MHz clock rate with 88 custom SSI and MSI GaAs ICs. The operations involved two  $16\times8$  complex multiplications, additions, subtractions, and serial-parallel shifts. All the ICs had ECL interfaces, driving  $100\Omega$  loading. An RF memory in the Table [22] has also demonstrated 1GHz capability in signal processing by using a number of GaAs ICs.

| Circuit/system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| (1) Numerically controlled oscillator IC for direct digital frequency synthesis and phase modulation. Consists of pipelined accumulator, phase modulator, phase adder, two ROMs, and waveform generator. DCFL-based. Tested functional, speed unknown.                                                                                                                                                                                                                                                                                   | [80]. |

| (2) Low pass filter (2 ICs) in sub-band tuner for adaptive tuning to narrow band signals. Custom FIR made from a 4K SRAM and a 10K gate array. 400 MHz clock rate. DCFL-based.                                                                                                                                                                                                                                                                                                                                                           | [8].  |

| <ul> <li>(3) 7 ICs</li> <li>(i) Radio frequency memory. Tested to 1GHz, 35 GaAs ICs.</li> <li>(ii) Half FFT butterfly. Tested to 500MHz, 88 GaAs IC.</li> <li>(iii) Digital convolver.</li> <li>(iv) Phase shift keying code generator.</li> <li>(v) Timing incoming detector.</li> <li>(vi) 8-bit A/D processor.</li> <li>(vii) Fibre-optic transmission system, Tested to 700MHz, 40 GaAs ICs.</li> <li>Microstrip boards made with up to 88 GaAs ICs (custom D flip-flops, 4-bit universal shift register, serial-parallel</li> </ul> | [22]. |

Table 2.5 Signal processing systems

It would appear from these different examples that custom high integration ICs with GaAs I/O levels would combine to produce systems performing complex signal processing functions at 1GHz clock rates or above.

#### Communications circuits

Telecommunication is one area that sees continuous growth. The optical properties of GaAs, already mentioned earlier, and its high switching speed have been a major focus for integrated optical transmit/receive (transceiving) systems. Some the circuit and system achievements are listed in Table. 2.6 below.

Most of the chips or chip sets listed have been tested in a real transmission environment. For example, the 2.4Gb/s chip set from BTRL has been tested in a 50km link using single-mode fibres [130].

Apart from systems, a number of frequency dividers, flip-flops, multiplexers (MUX), and demultiplexers (DEMUX) have been reported to demonstrate the suitability of GaAs for telecommunication. Figures of 1.2Gb/s for multiplexers [150] and 10GHz for frequency division [116] had already been achieved in 1983/84. More recent circuits include a 26.5 GHz BFL 1/2 divider based on 0.2μm MESFETs [63], and 4 Gb/s 16:1 and 1:16 MUX/DEMUX circuits [53]. Other switching circuits included 12Gb/s 2-bit MUX/DEMUX ICs [58], and 16×16 [5], 8×8 [47], and 4×4 [96] cross-point switches at up to 3Gb/s input data rate. The 16×16 cross-point switch contained 10000 transistors and dissipated only 800mW.

Existing optical fibre systems have been based on 140Mb/s, 565Mb/s, 1.6Gb/s, and 1.7Gb/s rates [130,46], and were built from discrete silicon components at the higher bit rates. The GaAs circuits have been concentrating on the imminent standard of 2.4Gb/s and above. In all cases, high reliability, low power, and low cost are the most important issues. Reliability is particularly important in the high current laser drivers.

| Circuit and test results.                                                             | Ref.   |

|---------------------------------------------------------------------------------------|--------|

| (1) PRBS generator/error detector. 1023 bits at 2Gb/s, UFL.                           | [74].  |

| (2) Fibre-optic system.  Prototype made with 40 GaAs ICs, 350MHz, BFL.                | [22].  |

| (3) Optical transmitter.  1.1Gb/s, 20mA peak current, SCFL.                           | [144]. |

| <ul><li>(4) Buffer store for optical transmission.</li><li>2Gb/s,,1μm CDFL.</li></ul> | [122]. |

| (5) opto-electronic receiver.  Photodetector, amplifier, demux, 6GHz, DCFL.           | [98].  |

| (6) complete transmit/receive chip set.  2.4GHz                                       | [34].  |

| (7) optical transmission system. 2.4Gb/s, CDFL.                                       | [130]. |

| (8) Transceiver chip set for computer networks (HOT ROD). 1Gb/s.                      | [19].  |

Table 2.6 Optical communication circuits

Most ambitious among the 2.4Gb/s systems was the complete GaAs chip set from Hitachi (Item 6 [34]), available commercially since late 1988. This consisted of seven chips, which included laser driver, 4:1 MUX, 1:4 DEMUX, decision circuit, pre-amp, AGC amp, and main amp. Maximum operating frequency of 3GHz was achieved by the 1:4 DEMUX, at a power dissipation of 1.5W. 0.8m gate lengths were used, although the logic configuration was unclear. A commercial silicon bipolar chip set was not available for direct comparison. However, a review of laboratory circuits based on "standard" 2µm silicon bipolar processes [113], showed that silicon was well capable of the necessary speed, and in the case of 2.4Gb/s, dissipated less power with the laboratory samples. Although the comparative study gave no indication as to the practical utilisation, reliability, and cost of these laboratory chips, it would appear that in a multi-chip system, GaAs chips do not have conclusive advantages over silicon at the 2.4Gb/s rate.

Above 2.4Gb/s, 9.95Gb/s was considered to be a possible future requirement [58,113]. Silicon was also considered to be suitable for this bit rate by using advanced self-aligned gate processes [113]. GaAs laboratory circuits have already demonstrated their capability with circuits such as the 26GHz frequency divider and 12Gb/s 2-bit MUX/DEMUX mentioned earlier. Silicon have produced 5.8Gb/s 2-bit MUX and 8 Gb/s frequency divider ICs. From these figures, one can conclude that silicon has not yet achieved 10Gb/s, but has the necessary potential.

The possibility of integrating optical and logic functions onto the same GaAs substrate may prove to be more important than ultimate circuit speed at the moment commercially. This had been realised in the 6GHz integrated receiver (Item 5, [98]). The chip consisted of a photodetector, a three-stage amplifier, and a DCFL-based demultiplexer. This was not possible in silicon, and should point the way forward for ICs where opto-electronics, switching, and even MMIC functions exist on the same chip.

On the computer networking front, two GaAs ICs provide the fastest serial data link commercially available in any technology. The "Hot Rod" chip set (Item 8, [19]) consists of a GA9011 transmitter and GA9012 receiver, based on a proprietary TTL-compatible GaAs technology from Gazelle. They were capable of transceiving data at 1Gb/s, compared to the 175Mb/s of the fastest silicon chip set from Advanced Micro Devices [3]. The silicon chip set is based on the Fibre Distributed Data Interface (FDDI) standard, defined by an ANSI committee [61]. The GaAs chips were designed on a similar standard, but with a 40-bit interface, rather than 10-bit of the silicon chip set. They were aimed at easing communication bottlenecks between workstations in a distributed network, and at critical server nodes. The next generation Hot Rod will aim at 10Gb/s.

Objectively, the lack of comparable circuits means that this chip set may well be ahead of its time, and may have difficulty in finding networks that require this bit rate. Also, from earlier discussions concerning optical fibre transmission, present silicon technology is well capable of achieving similar bit rates. On the other hand, since all the error encoding and decoding functions are fully integrated into the GaAs chips, it can be used by any networking protocol designed for 1Gb/s bit rates or beyond. Therefore the chip set may have a new standard all to itself until a faster chip set is available. This was the case when the AMD chip set was introduced.

### **Supercomputers**

Supercomputers and mini-supercomputers have found wider general use in the 80's in numerically intensive computing, interactive design and graphics. They have been based on massively parallel architectures and large number of silicon ECL processors and physical memories, and usually require liquid cooling systems. The processors are normally LSI to MSI integrated circuits designed for highest switching speed at the expense of power dissipation. GaAs was therefore considered to be particularly suitable, owing to its speed potentials.

Two systems have been announced that will use GaAs technology. They are listed in Table 2.7 below, together with their projected performance. The subject of computer benchmarking is complex and the figures should be treated only as a guideline. Cray-3 was claimed to be the fastest supercomputer if the figures are realised. The Prisma system is targeted for the mini-supercomputer market. The fact that the maker of the first supercomputer is strongly backing the use of GaAs is in itself significant, even though its real market potential is likely to be small compared to other GaAs applications.

| Computer | Description                       | Ref.  |

|----------|-----------------------------------|-------|

| Cray-3   | 16 processors, 16 giga-flops.     | [68]. |

| Prisma   | Based on Sparc<br>RISC, 250 MIPS. | [50]. |

Table 2.7 Supercomputer systems

The backing of GaAs for Cray-3 was based on a comparative study with silicon ECL [68]. The study found that silicon could match a GaAs system in performance only by using more chips and power. In addition, it was considered that experience learned from designing the Cray-3 would be useful for Cray-4, possibly based on a MODFET or HEMT technology (the theory of MODFET/HEMT can be found in [30]), which have many similarities to GaAs MESFET technology.

Test results are not yet available on either system. Cray-3 has been delayed by circuit design and board level problems [59]. GaAs circuit yield, however, was not found to be a problem. The success or failure of these computers will essentially determine the future prospects of GaAs in this area.

### Gate array and standard cells

Apart from custom military and civil communication circuits, gate arrays and related semi-custom have also been a major focus of GaAs foundries, especially for start-ups like Vitesse and TriQuint. For those companies which do not manufacture silicon, it is a commercial necessity to diversify.

In silicon, gate arrays have been used in all types of applications that require a fast design turnaround time. A fair number of GaAs standard cell and gate array families have been published. Most of them are commercially available to compete head-on with silicon. One example of laser programmable logic devices (PLD) also exists. These are listed in Table. 2.8 below.

| Details                                                                                                                                | Commercial availability/Ref. |

|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| (1) 6K gates, SDFL. 1.1ns, 500μW/gate at fanout=2 plus 1500μm line. 12×12 multiplier, 82.5ns and 1.7W.                                 | No.[105].                    |

| (2) 15K gates, DCFL. 68ps unloaded. D-flip flops, 450ps delay.                                                                         | Vitesse.[73].                |

| (3) 3K gates, E/D BFL. 125ps unity fanout. divider at 1 GHz, control chip for test system at 750MHz, ECL/TTL compatible.               | TriQuint.[119].              |

| (4) 500 gates, 0.5μm BFL. 44ps unloaded, 5mW. counter at 4.1GHz, 2:1 MUX at 4.6Gb/s, 1:2 DEMUX 5Gb/s, 4:1 MUX 3.6Gb/s, ECL compatible. | NEC.[50].                    |

| (5) 6K, CDFL. 76ps unloaded, 1.2mW. 16-bit serial/parallel circuit at 852MHz and 952mW, ECL compatible.                                | Toshiba.[136].               |

Table 2.8 GaAs gate arrays

| Details                                                                                                                                                             | Commercial availability/Ref. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| STANDARD CELLS                                                                                                                                                      |                              |

| <ul><li>(1) BFL gates, buffers, flip-flops. 80ps unity fanout, 5mW.</li><li>4-bit serial/parallel register at 1.3GHz, flip-flops at 2GHz, ECL compatible.</li></ul> | Thomson.[118].               |

| (2) 22K gates max., logic, I/O, RAM, ROM, ALU, register file. DCFL, 100ps, 0.3mW 2-input NOR. 3.5GHz clock rate.                                                    | Vitesse.[138].               |

| MACROCELL ARRAYS                                                                                                                                                    |                              |

| (3) 250 gates, SCFL. 74ps loaded delay, 2.4mW/gate. Flip-flops at 7.5GHz, 2×2X-point switch at 2GHz, ECL compatible.                                                | No.[55].                     |

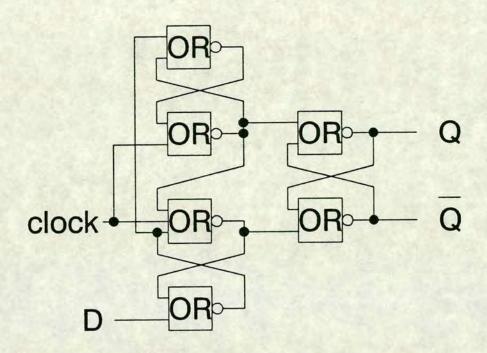

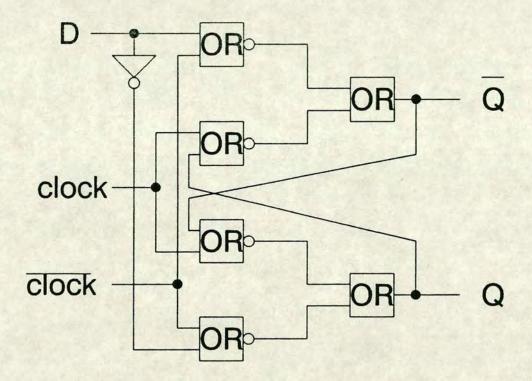

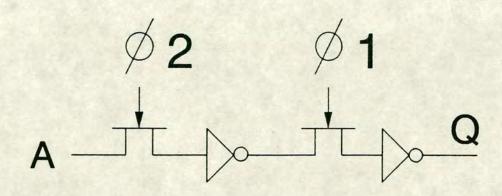

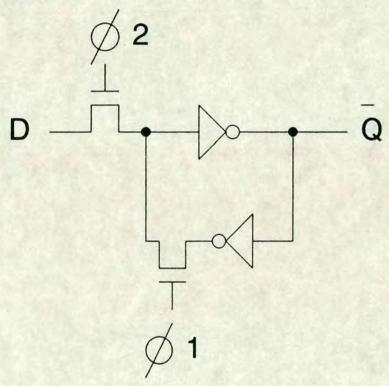

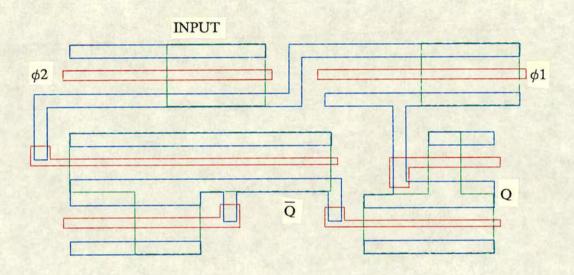

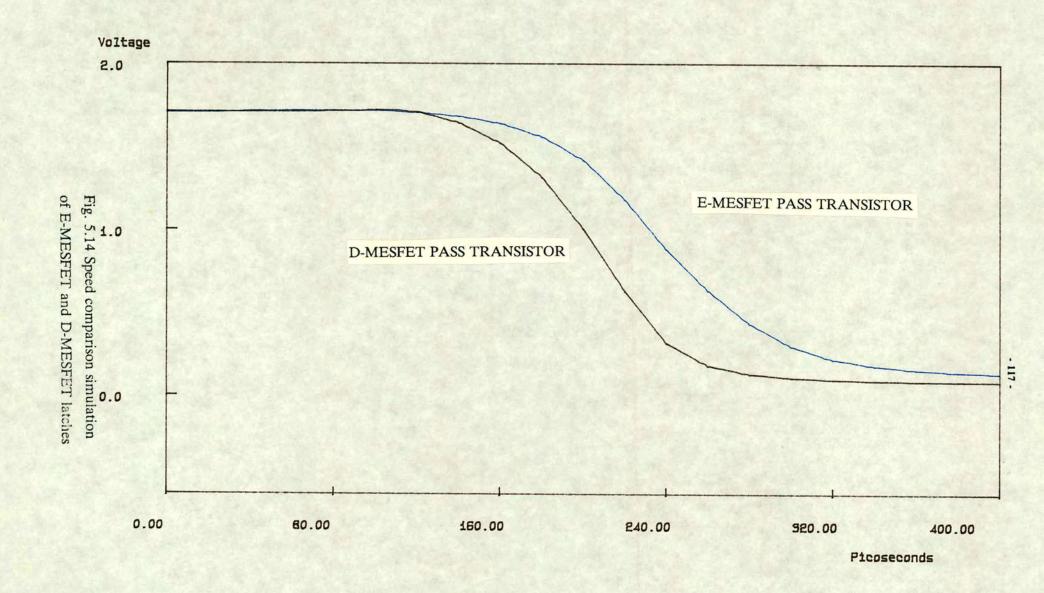

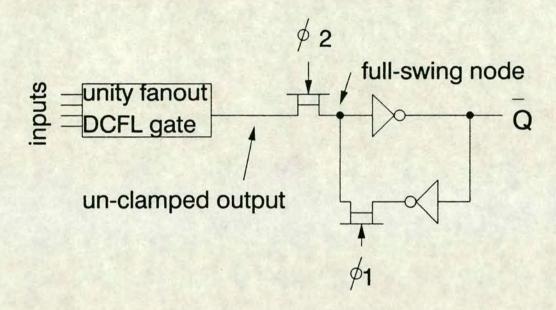

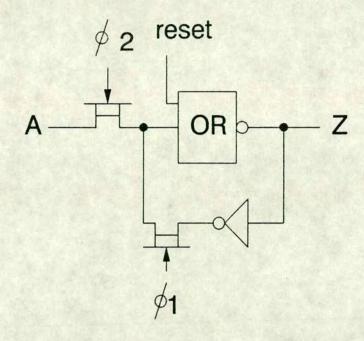

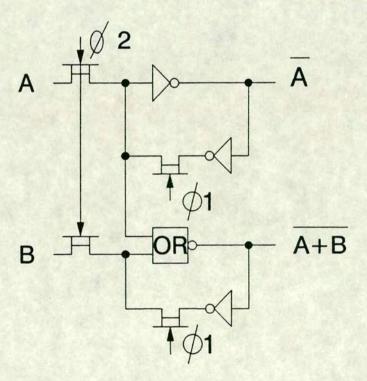

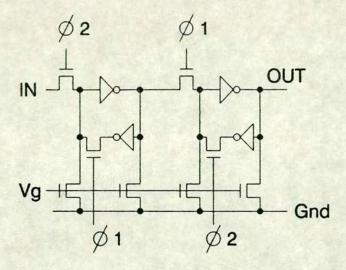

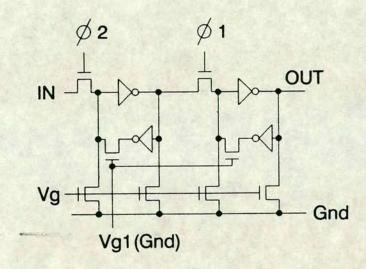

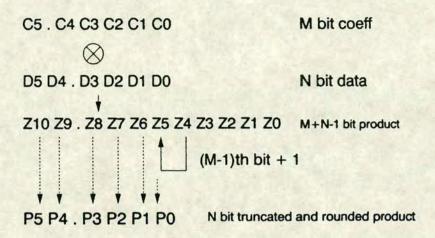

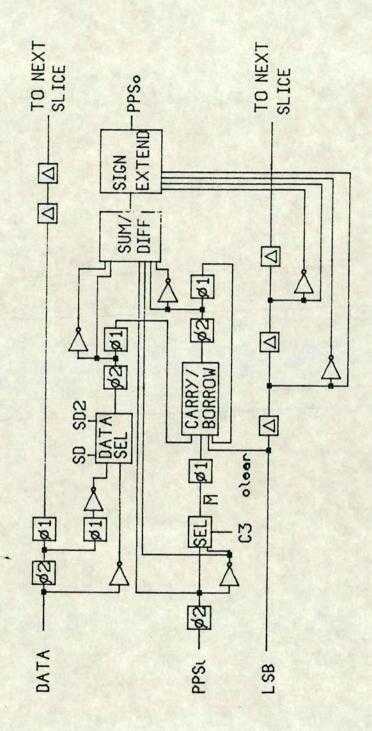

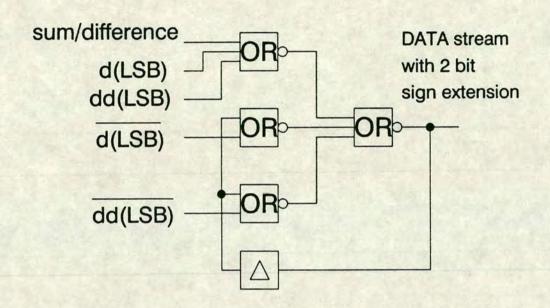

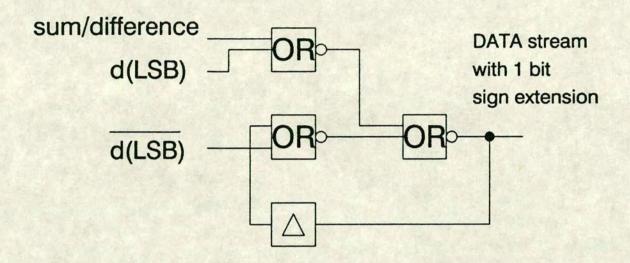

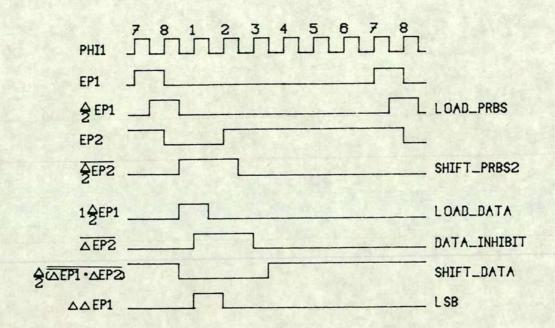

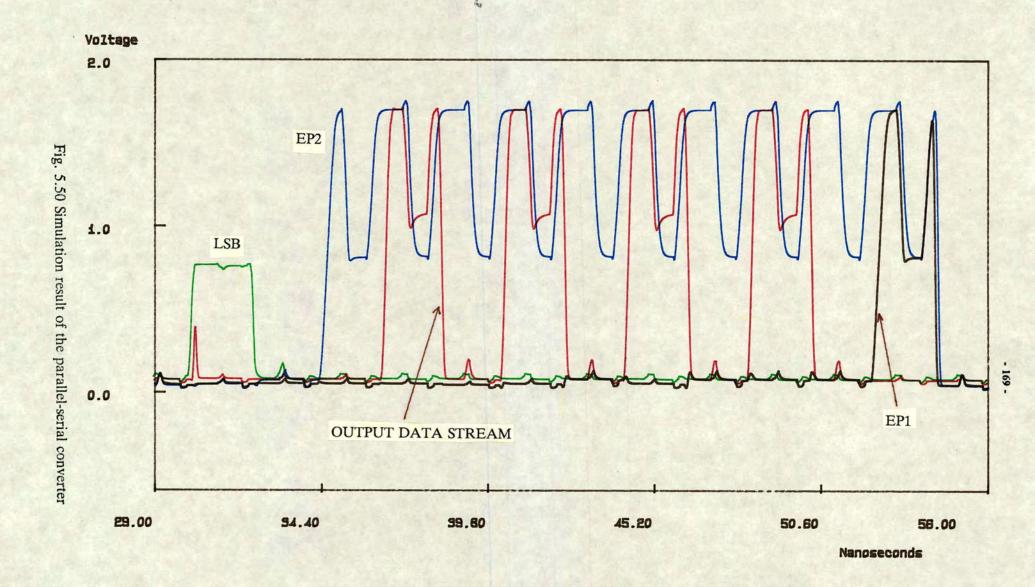

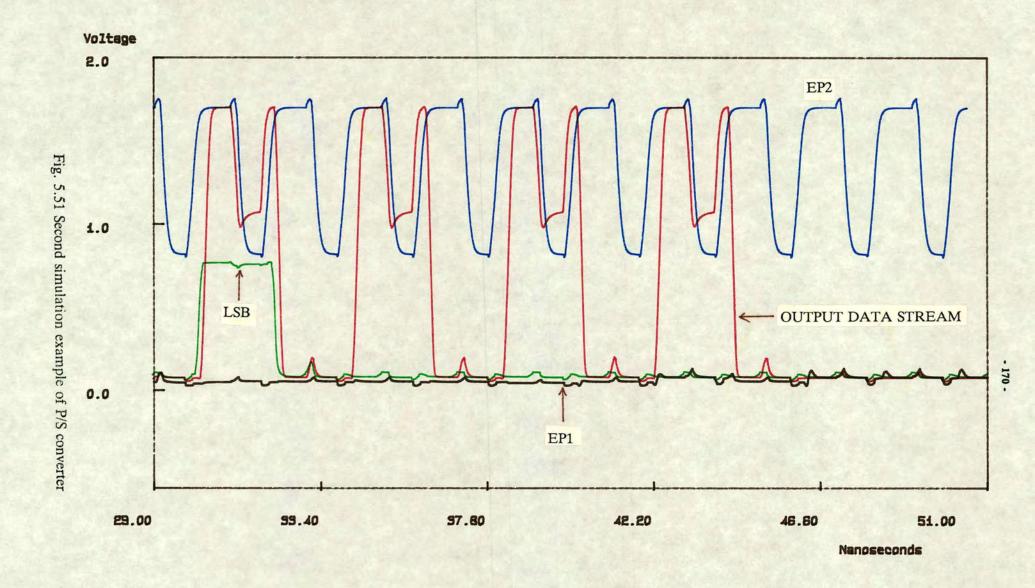

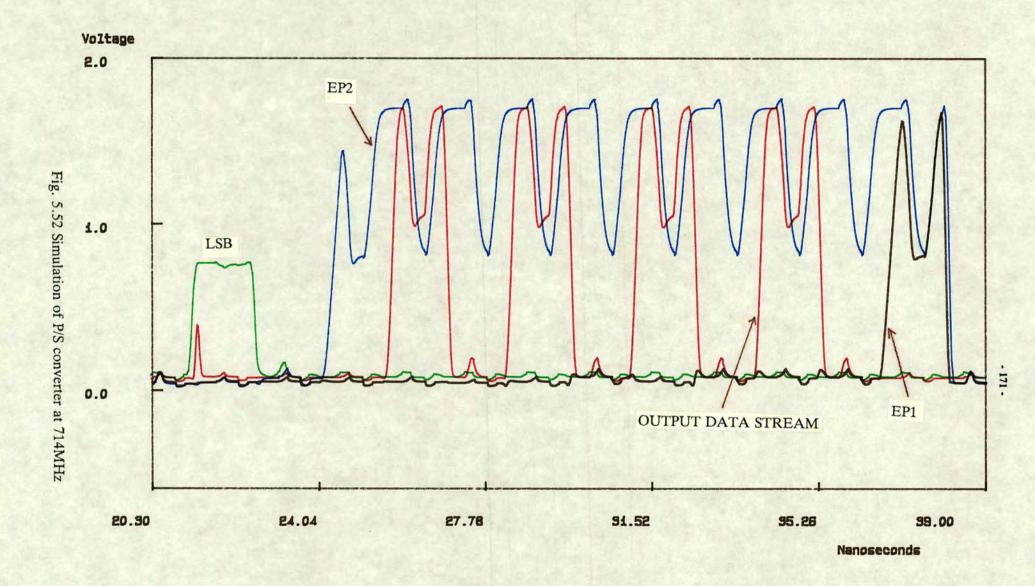

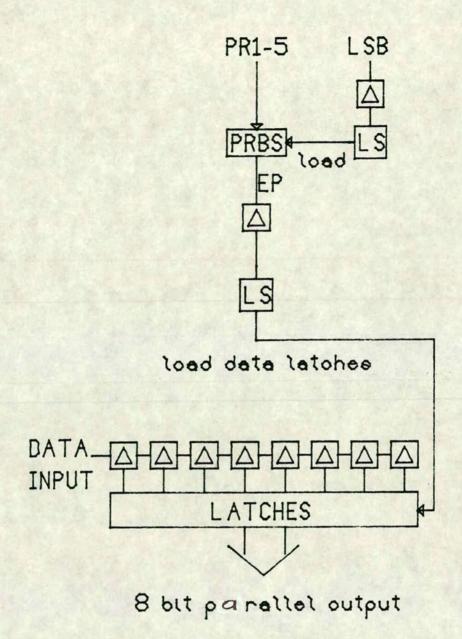

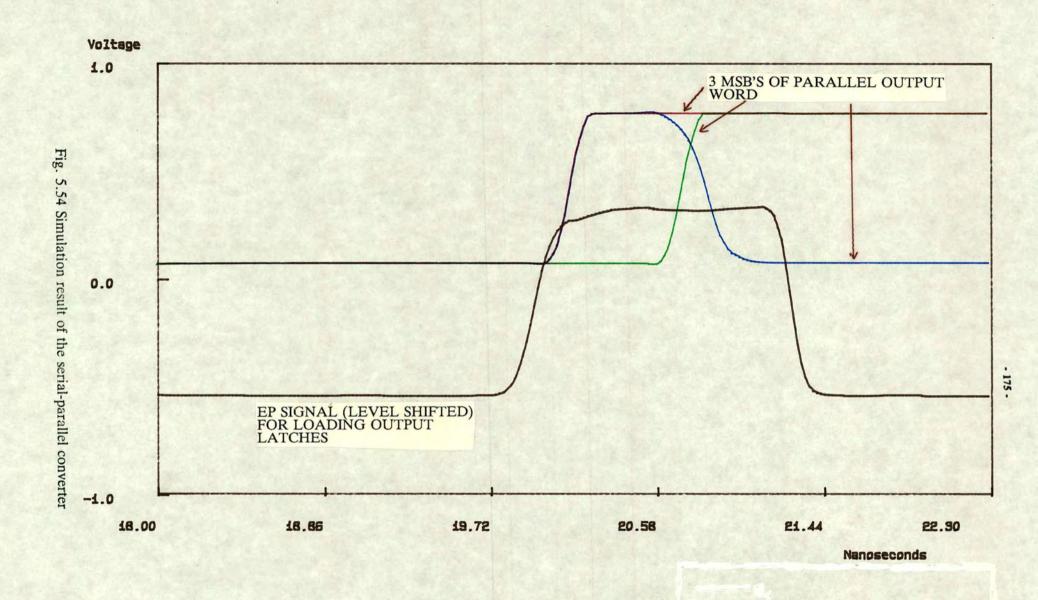

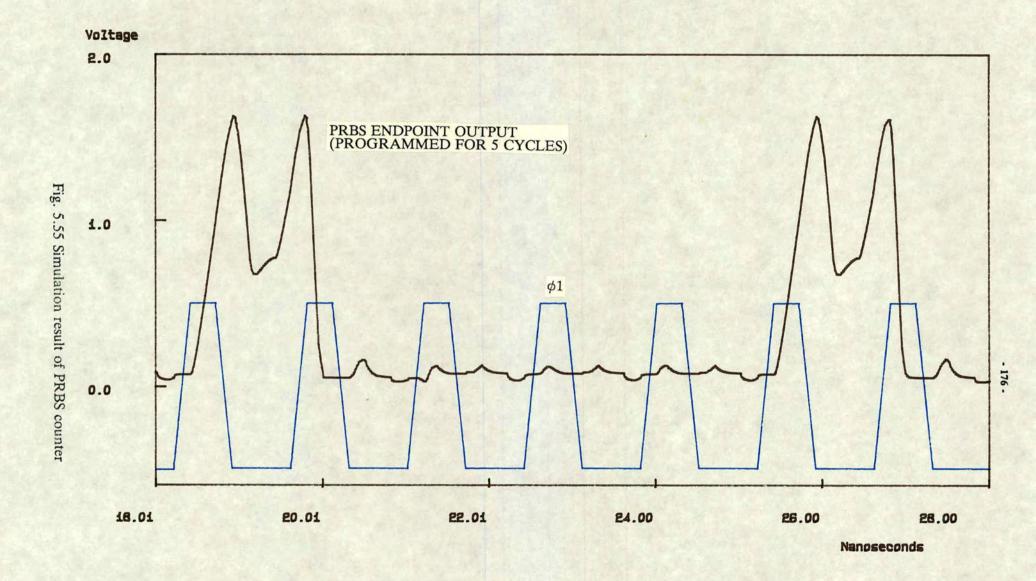

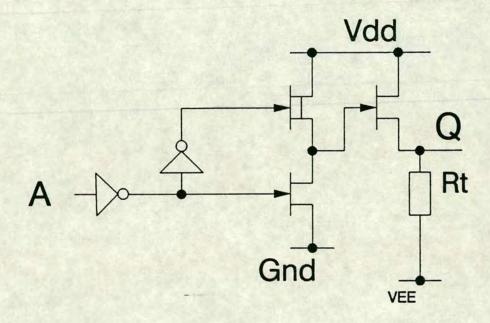

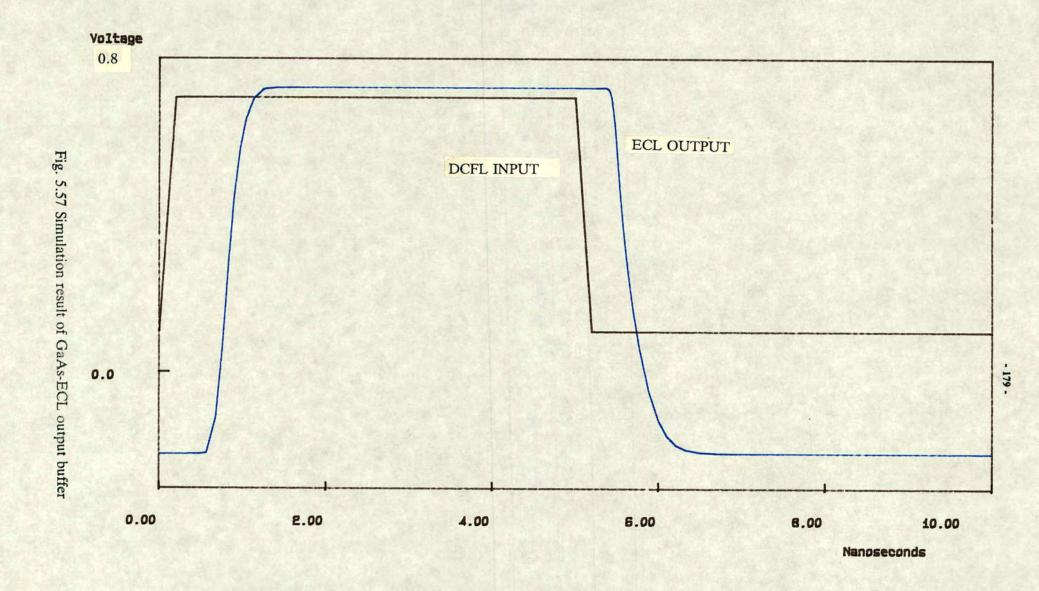

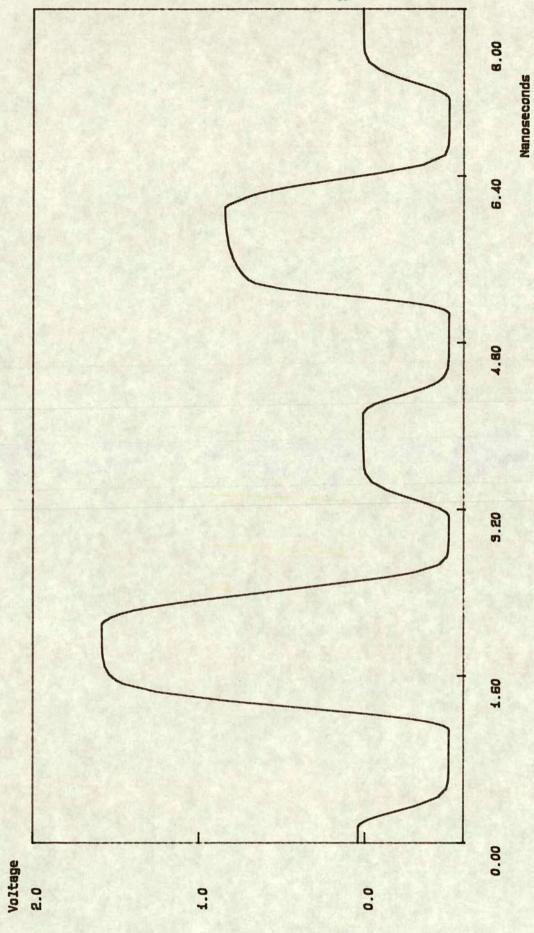

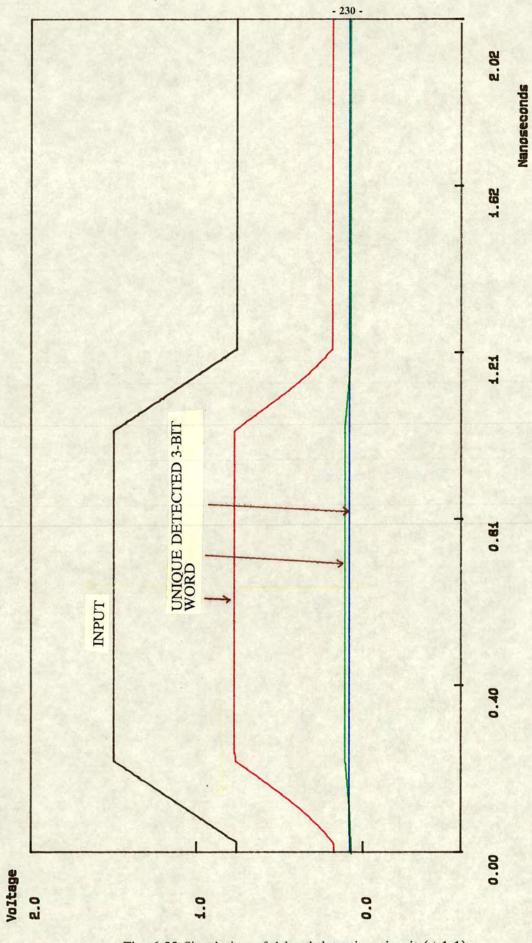

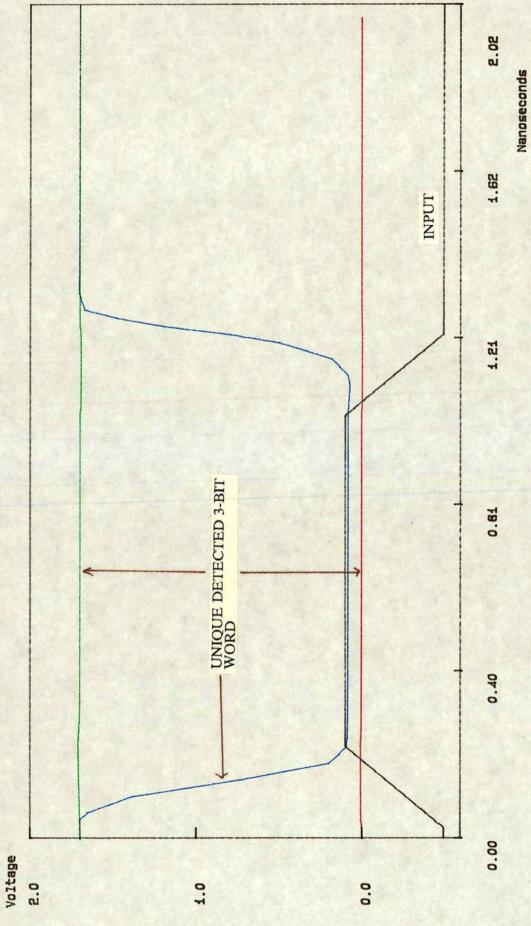

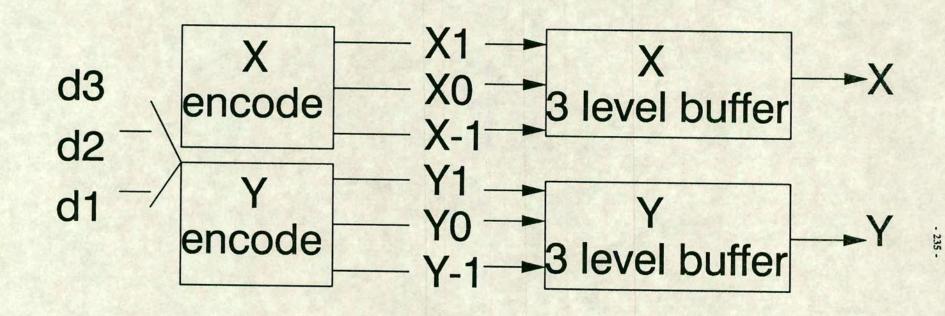

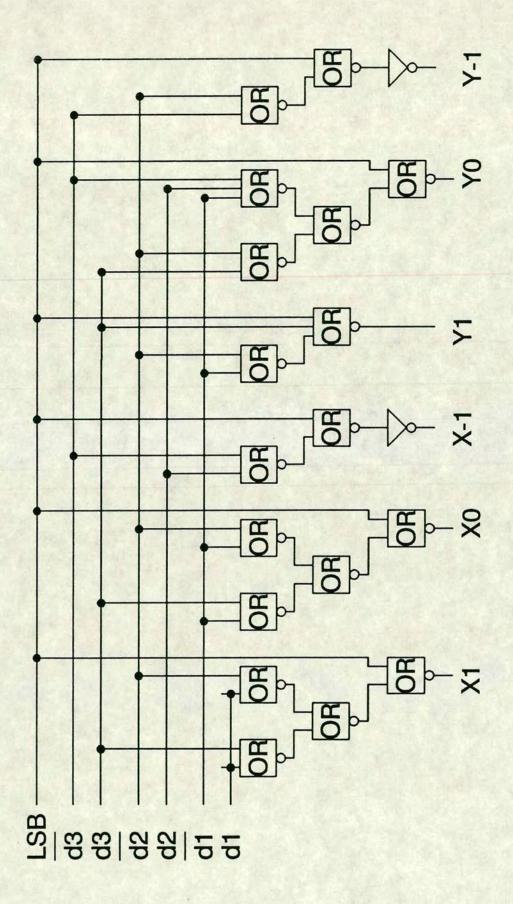

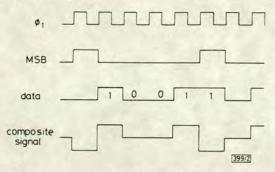

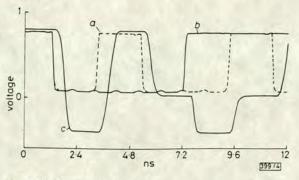

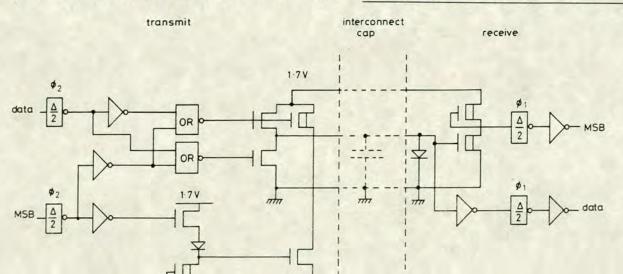

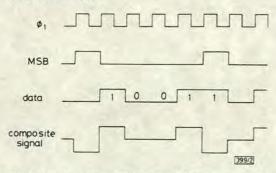

| PROGRAMMABLE LOGIC DEVICES (PLD)                                                                                                                                    | y                            |