# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# **Customising Compilers for Customisable Processors**

Alastair Colin Murray

Doctor of Philosophy

Institute of Computing Systems Architecture

School of Informatics

University of Edinburgh

2011

### **Abstract**

The automatic generation of instruction set extensions to provide application-specific acceleration for embedded processors has been a productive area of research in recent years. There have been incremental improvements in the quality of the algorithms that discover and select which instructions to add to a processor. The use of automatic algorithms, however, result in instructions which are radically different from those found in conventional, human-designed, RISC or CISC ISAs. This has resulted in a gap between the hardware's capabilities and the compiler's ability to exploit them.

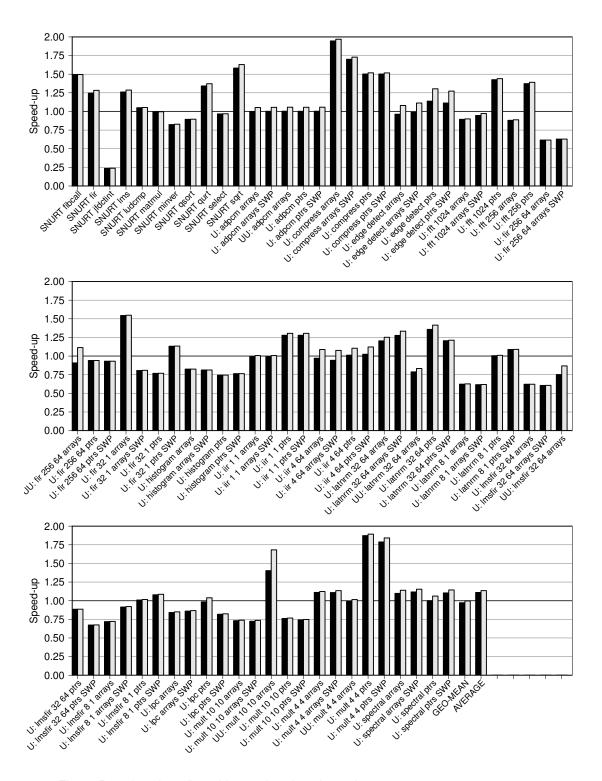

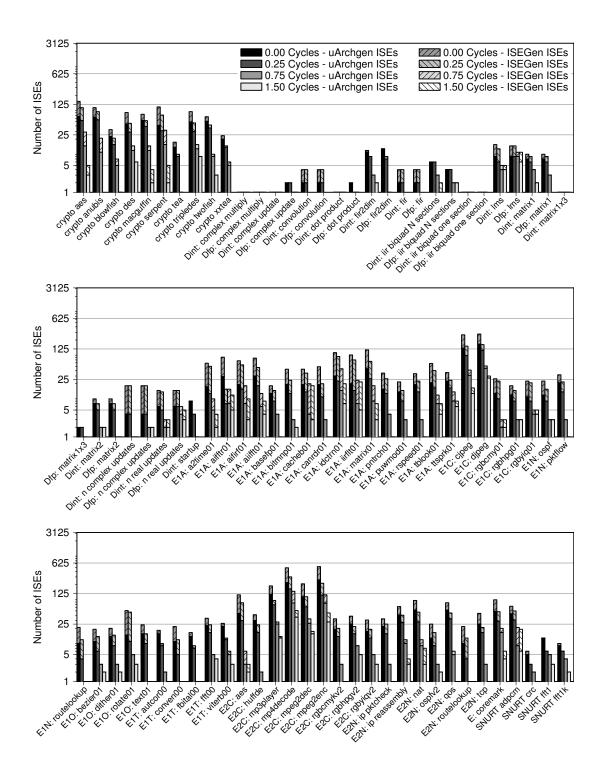

This thesis proposes and investigates the use of a high-level compiler pass that uses graph-subgraph isomorphism checking to exploit these complex instructions. Operating in a separate pass permits techniques to be applied that are uniquely suited for mapping complex instructions, but unsuitable for conventional instruction selection. The existing, mature, compiler back-end can then handle the remainder of the compilation. With this method, the high-level pass was able to use 1965 different automatically produced instructions to obtain an initial average speed-up of 1.11x over 179 benchmarks evaluated on a hardware-verified cycle-accurate simulator.

This result was improved following an investigation of how the produced instructions were being used by the compiler. It was established that the models the automatic tools were using to develop instructions did not take account of how well the compiler could realistically use them. Adding additional parameters to the search heuristic to account for compiler issues increased the speed-up from 1.11x to 1.24x. An alternative approach using a re-designed hardware interface was also investigated and this achieved a speed-up of 1.26x while reducing hardware and compiler complexity.

A complementary, high-level, method of exploiting dual memory banks was created to increase memory bandwidth to accommodate the increased data-processing bandwidth provided by extension instructions. Finally, the compiler was considered for use in a non-conventional role where rather than generating code it is used to apply source-level transformations prior to the generation of extension instructions and thus affect the shape of the instructions that are generated.

### **Acknowledgements**

I would like to thank my supervisor, Björn, for his help with guiding the direction of the research that eventually resulted in this thesis.

I would like to thank Nigel for helping to get me involved in the PASTA project.

Everyone involved in the PASTA project deserves a mention, but those who were involved with *ArcSim* especially – my research wouldn't have been possible without it.

Within PASTA Richard deserves a special mention, for all the parts of the pie-g toolchain he created, especially *ISEGen*— another tool that my research wouldn't have been possible without.

Finally, I would like thank my proof readers: Claire and Colin.

### **Declaration**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified. Some of the material used in this thesis has been published in the following papers:

- Richard V. Bennett, Alastair C. Murray, Björn Franke, and Nigel Topham. Combining source-to-source transformations and processor instruction set extensions for the automated design-space exploration of embedded systems. In *Proceedings of the ACM SIG-PLAN/SIGBED Conference on Languages, Compilers, and Tools for Embedded Systems* (LCTES '07), pages 83–92, June 2007.

- Alastair Murray and Björn Franke. Fast source-level data assignment to dual memory banks. In *Proceedings of the 11th International Workshop on Software and Compilers* for Embedded Systems (SCOPES '08), pages 43–52, March 2008.

- Alastair C. Murray, Richard V. Bennett, Björn Franke, and Nigel Topham. Code transformation and instruction set extension. *ACM Transactions on Embedded Computing Systems (ACM TECS)*, 8(4):1–31, 2009.

- Oscar Almer, Richard Bennett, Igor Böhm, Alastair Murray, Xinhao Qu, Marcela Zuluaga, Björn Franke, and Nigel Topham. An end-to-end design flow for automated instruction set extension and complex instruction selection based on GCC. In *Proceedings of the First International Workshop on GCC Research Opportunities (GROW '09)*, pages 49–60, January 2009.

- Alastair Murray and Björn Franke. Using genetic programming for source-level data assignment to dual memory banks. In *Proceedings of the 3rd Workshop on Statistical and Machine Learning Approaches to Architectures and Compilation (SMART '09)*, pages 75–89, January 2009.

- Alastair Murray and Björn Franke. Compiling for automatically generated instruction set extensions. In *Proceedings of the International Symposium on Code Generation and Optimization (CGO '12)*, April 2012b.

- Alastair Murray and Björn Franke. Adaptive source-level data assignment to dual memory banks. ACM Transactions on Embedded Computing Systems (ACM TECS), 11S(1), June 2012a.

(Alastair Colin Murray)

For Claire.

# **Table of Contents**

| Pr | eamb | le               |              |           |         |       |      |      |      |    |       |  |  |  | i   |

|----|------|------------------|--------------|-----------|---------|-------|------|------|------|----|-------|--|--|--|-----|

|    | Abst | ract             |              |           |         |       |      |      |      |    |       |  |  |  | iii |

|    | Ack  | nowledgemer      | ıts          |           |         |       |      |      |      |    |       |  |  |  | v   |

|    | Decl | aration          |              |           |         |       |      |      |      |    |       |  |  |  | vii |

|    | Tabl | e of Contents    |              |           |         |       |      |      |      |    | <br>• |  |  |  | ix  |

| 1  | Intr | oduction         |              |           |         |       |      |      |      |    |       |  |  |  | 1   |

|    | 1.1  | Specialised      | Processors   |           |         |       |      |      |      |    |       |  |  |  | 2   |

|    | 1.2  | The Probler      | n            |           |         |       |      |      |      |    |       |  |  |  | 4   |

|    | 1.3  | Contribution     | ns           |           |         |       |      |      |      |    |       |  |  |  | 6   |

|    | 1.4  | Structure .      |              |           |         |       |      |      |      |    |       |  |  |  | 7   |

|    | 1.5  | Summary          |              |           |         |       |      |      |      |    |       |  |  |  | 8   |

| 2  | Bacl | kground and      | Infrastruc   | cture     |         |       |      |      |      |    |       |  |  |  | 9   |

|    | 2.1  | Embedded I       | Processors   |           |         |       |      |      |      |    |       |  |  |  | 9   |

|    |      | 2.1.1 Eml        | oedded Pro   | cessor F  | Familie | es .  |      |      |      |    |       |  |  |  | 10  |

|    |      | 2.1.2 App        | olication Sp | ecific Ir | ıstruct | ion-s | et P | roce | esso | rs |       |  |  |  | 10  |

|    | 2.2  | Infrastructu     | re           |           |         |       |      |      |      |    |       |  |  |  | 13  |

|    |      | 2.2.1 <i>EnC</i> | Core         |           |         |       |      |      |      |    |       |  |  |  | 14  |

|    |      | 2.2.2 EnC        | Core Extens  | ion Inte  | rface   |       |      |      |      |    |       |  |  |  | 14  |

|    |      | 2.2.3 <i>ISE</i> | Gen and uA   | rchGen    | ٠       |       |      |      |      |    |       |  |  |  | 17  |

|    | 2.3  | Automated        | Instruction  | Set Ext   | ensior  | ı     |      |      |      |    |       |  |  |  | 17  |

|    |      | 2.3.1 Ata        | su AISE Al   | gorithm   | 1       |       |      |      |      |    |       |  |  |  | 17  |

|    |      | 2.3.2 HW         | /SW Codes    | sign .    |         |       |      |      |      |    |       |  |  |  | 19  |

|    | 2.4  | Design-Spa       | ce Explorat  | ion .     |         |       |      |      |      |    |       |  |  |  | 19  |

|    |      | 2.4.1 Aut        | omated Inst  | truction  | Set E   | xtens | sion |      |      |    |       |  |  |  | 21  |

|    | 2.5  | Dual Memo        | ry Banks     |           |         |       |      |      |      |    |       |  |  |  | 22  |

|    |      | 2.5.1 DSI        | P-C and Em   | ıbedded   | С.      |       |      |      |      |    |       |  |  |  | 23  |

|    | 2.6  | Genetic Pro      | gramming i   | in Com    | pilers  |       |      |      |      |    |       |  |  |  | 23  |

|   | 2.7  | Graph   | Theory                                                | 24 |

|---|------|---------|-------------------------------------------------------|----|

|   |      | 2.7.1   | The Basics                                            | 24 |

|   |      | 2.7.2   | Specific Problems                                     | 25 |

|   | 2.8  | Bench   | marks                                                 | 25 |

| 3 | Rela | ited Wo | rk                                                    | 27 |

|   | 3.1  | Compl   | lex Instruction Mapping                               | 27 |

|   | 3.2  | Compi   | ilation for Dual Memory Banks                         | 30 |

|   | 3.3  | Transf  | Formations Affecting AISE                             | 33 |

|   |      | 3.3.1   | Source-to-Source Transformations for Embedded Systems | 33 |

| 4 | Cod  | e Genei | ration for Complex Instructions                       | 35 |

|   | 4.1  | Motiva  | ation                                                 | 36 |

|   | 4.2  | Mappi   | ng by Graph-Subgraph Isomorphism Checking             | 36 |

|   |      | 4.2.1   | Overview                                              | 36 |

|   |      | 4.2.2   | Integration into GCC                                  | 38 |

|   |      | 4.2.3   | Construction of Graphical Intermediate Representation | 39 |

|   |      | 4.2.4   | Matching Subgraphs                                    | 40 |

|   |      | 4.2.5   | Determining if Two Nodes are Equivalent               | 42 |

|   |      | 4.2.6   | Exploiting Matches                                    | 44 |

|   | 4.3  | Alloca  | tion of Vector-Registers                              | 44 |

|   | 4.4  | Permu   | tation of Vector-Register Elements                    | 45 |

|   | 4.5  | Elimin  | nating Poor Mappings                                  | 46 |

|   | 4.6  | Evalua  | ation Methodology                                     | 46 |

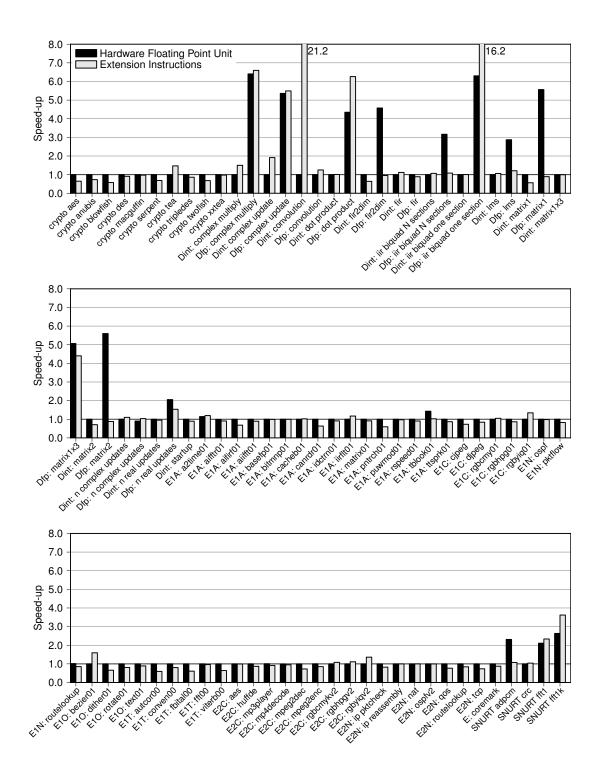

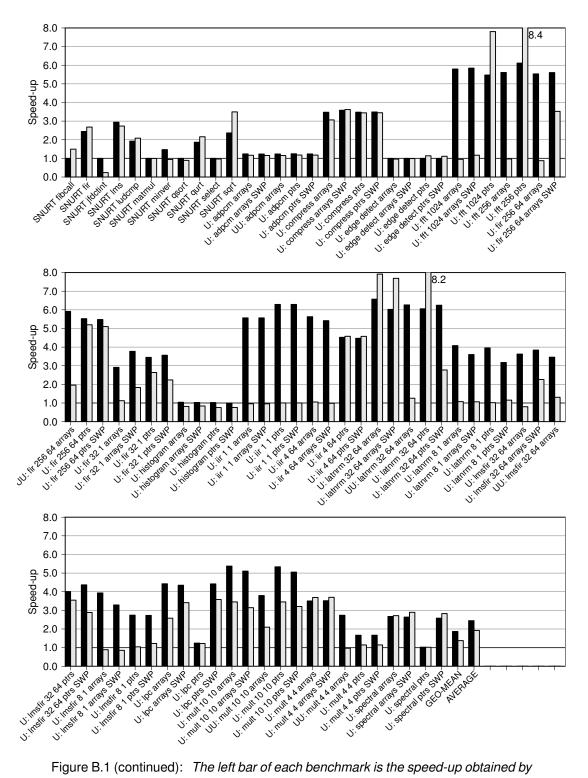

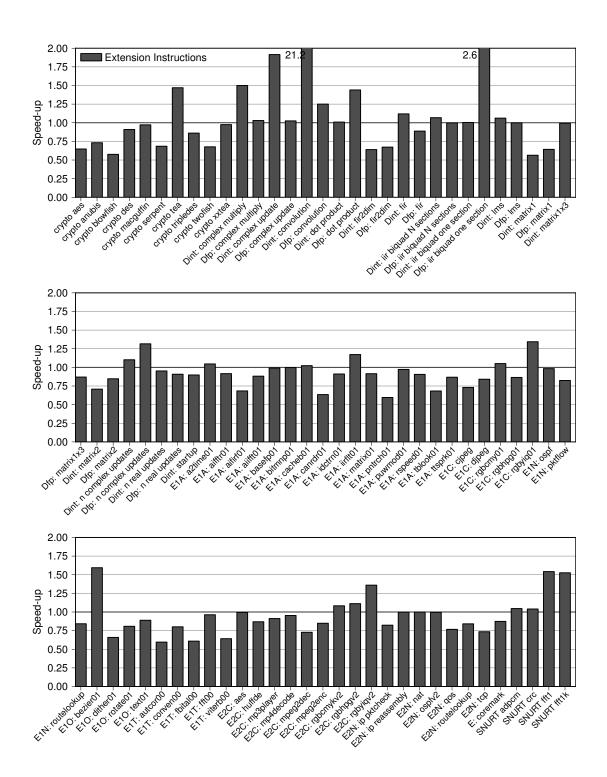

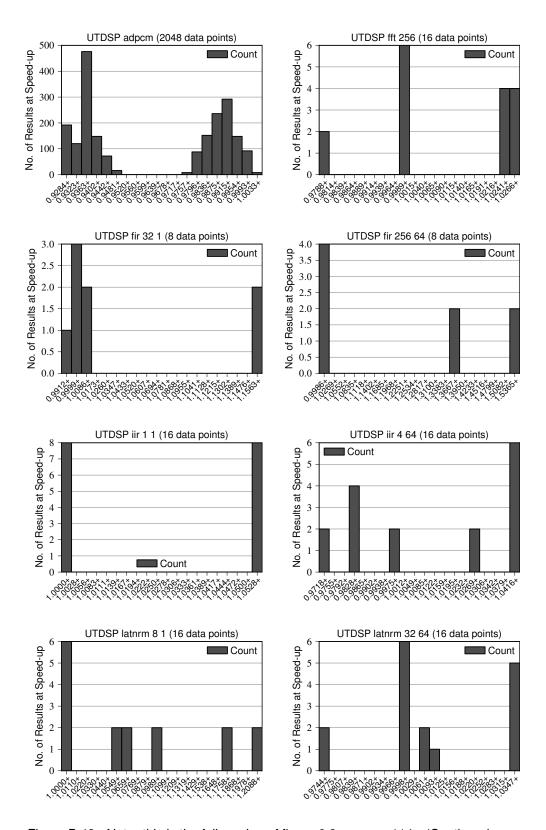

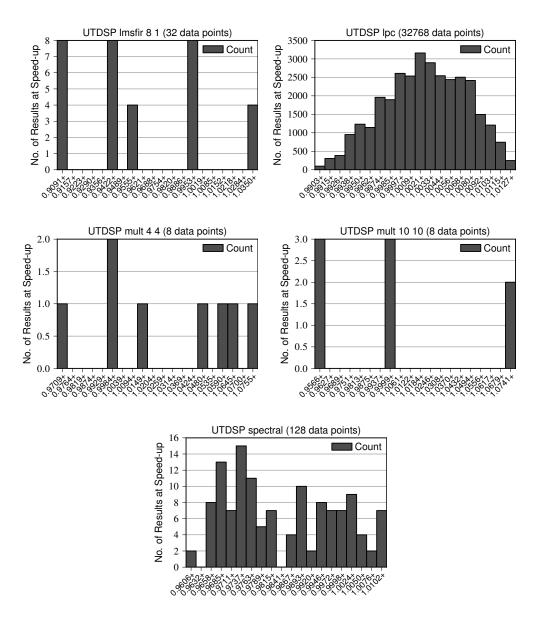

|   |      | 4.6.1   | Presentation of Results                               | 47 |

|   |      | 4.6.2   | Consideration of Floating Point Hardware              | 47 |

|   | 4.7  | Result  | s                                                     | 49 |

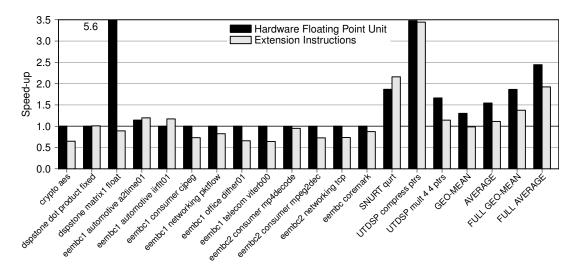

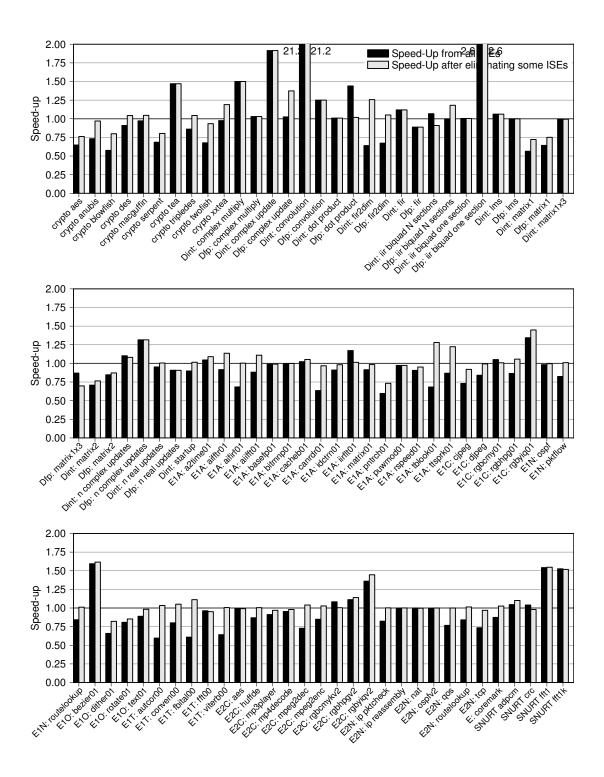

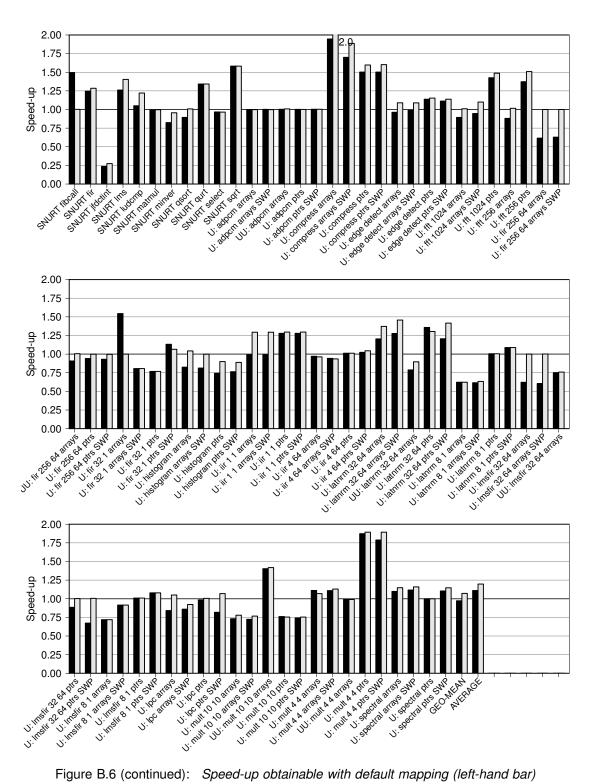

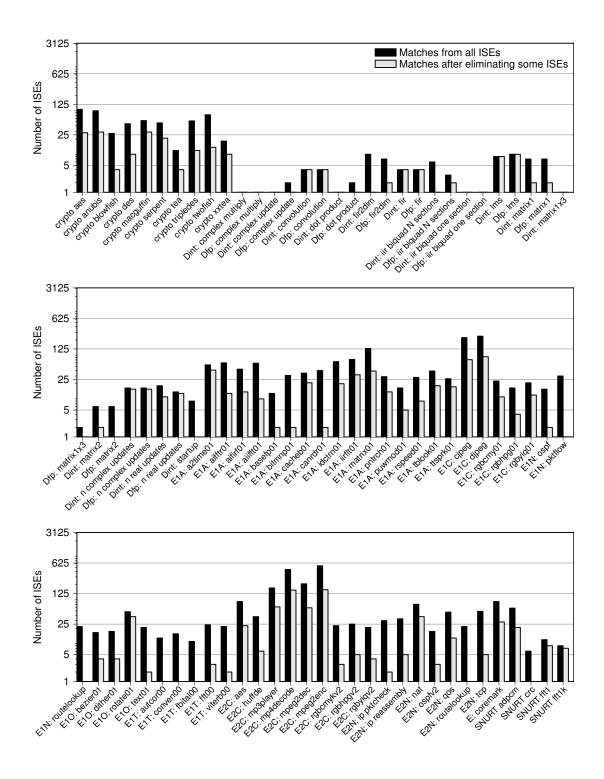

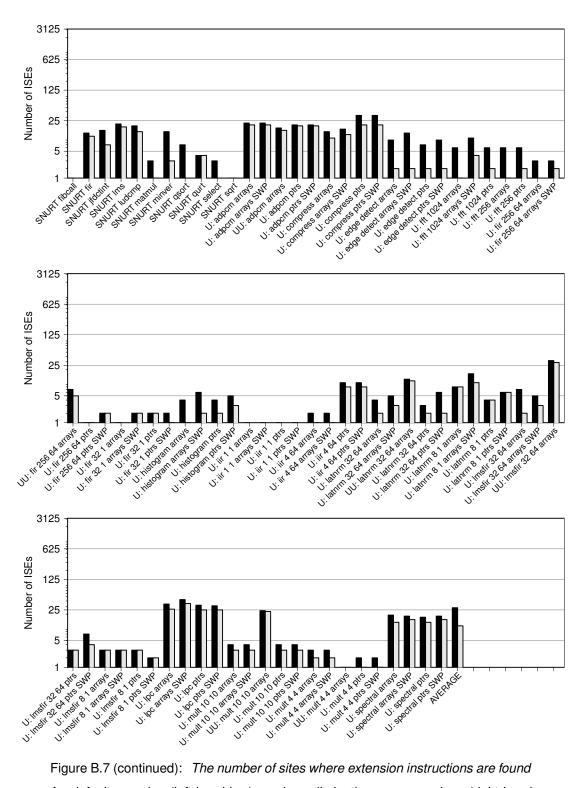

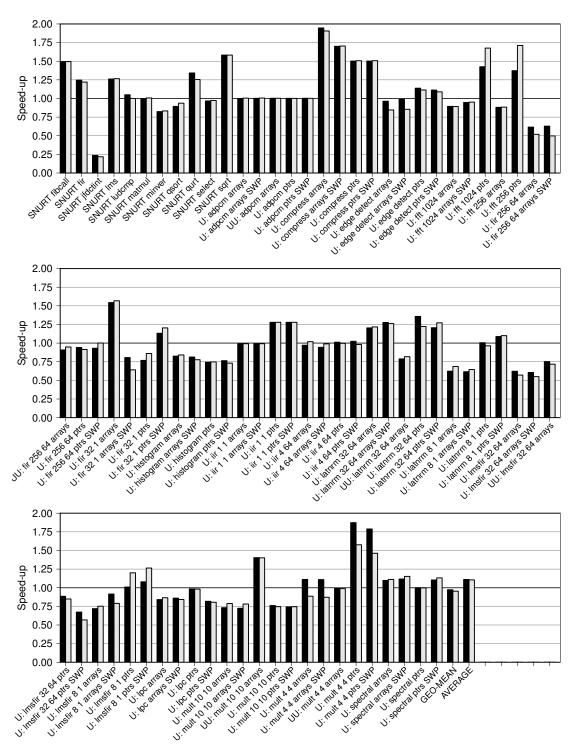

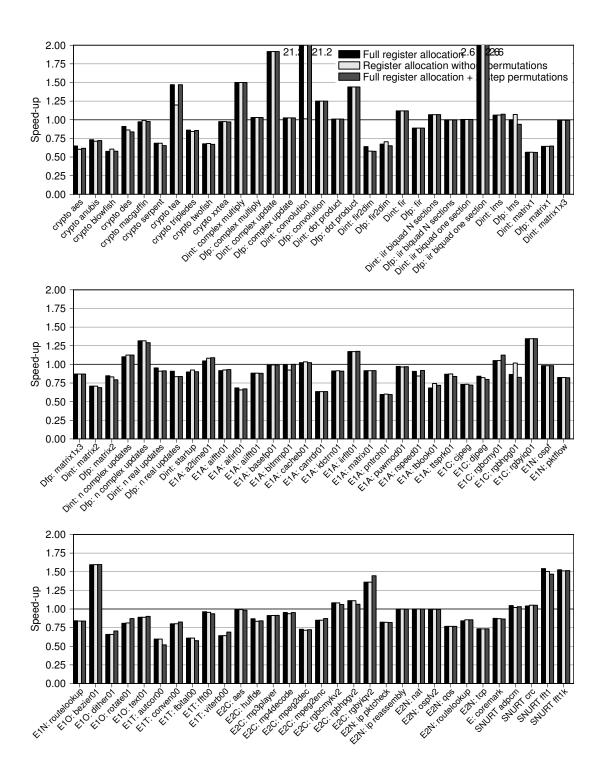

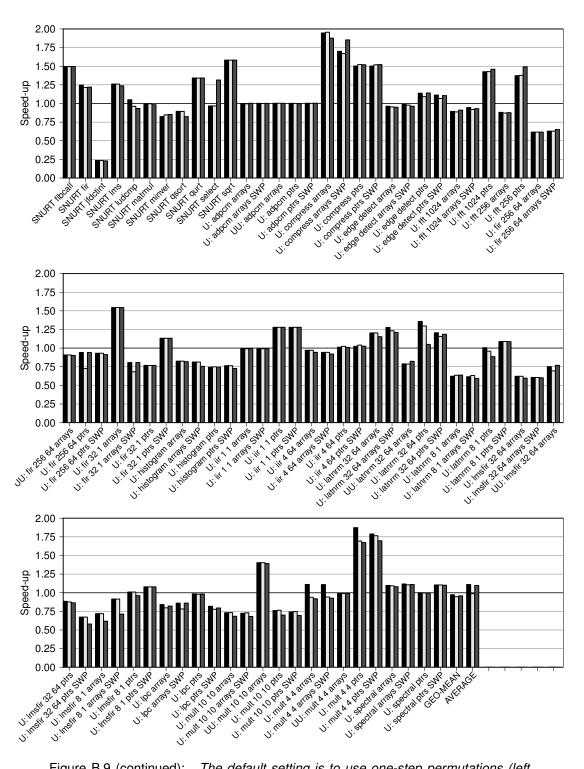

|   |      | 4.7.1   | Default Mapping                                       | 49 |

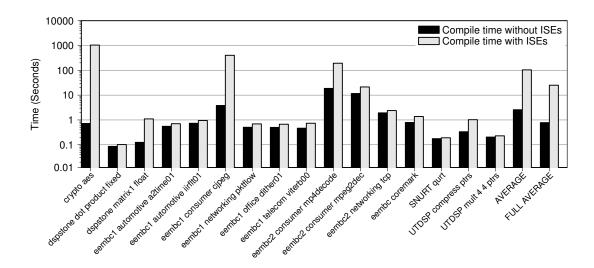

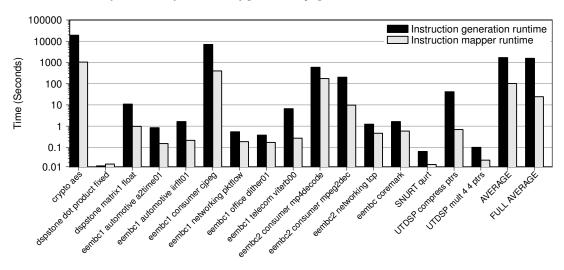

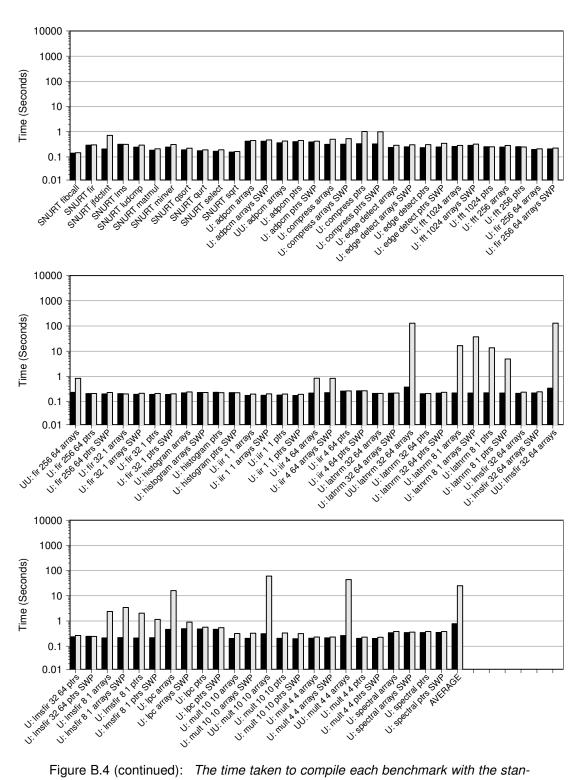

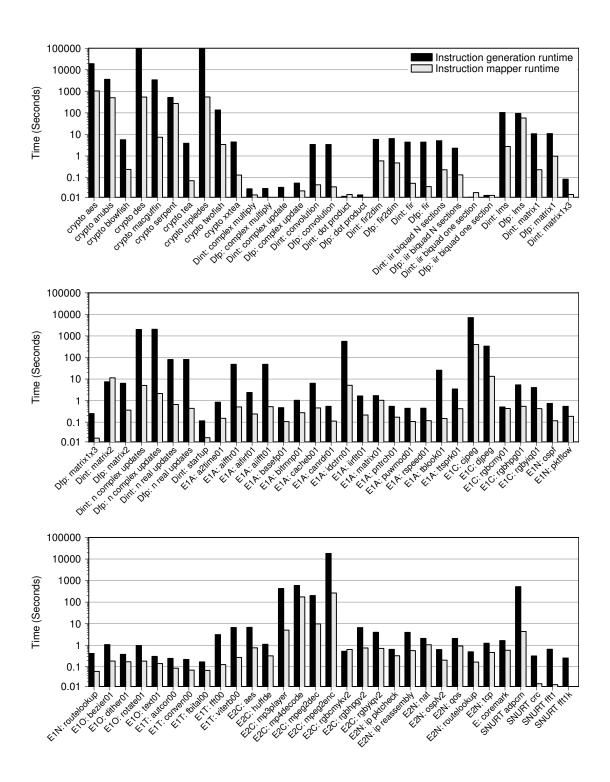

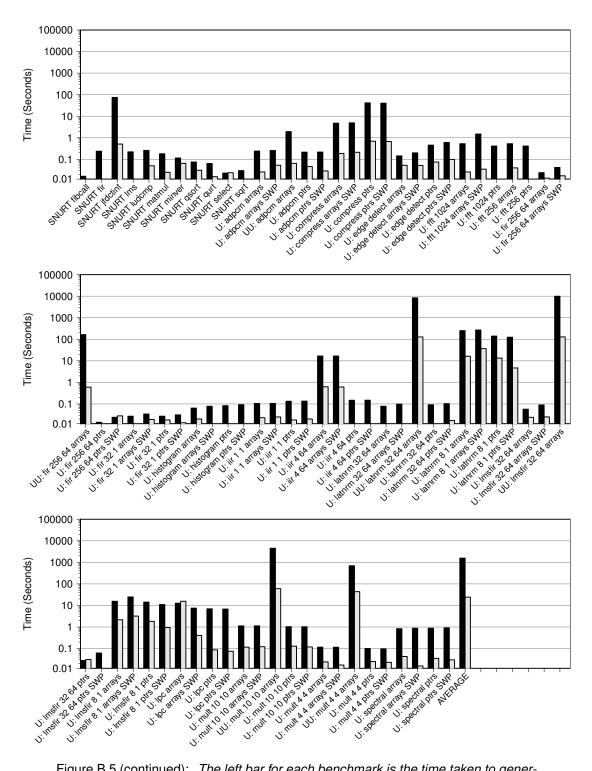

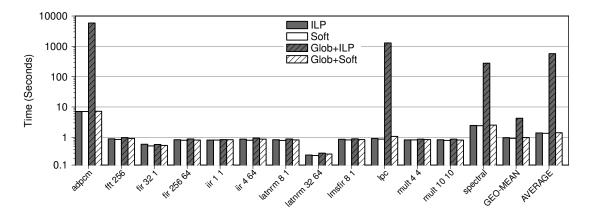

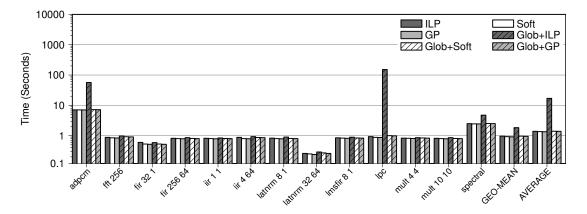

|   |      | 4.7.2   | Timings                                               | 51 |

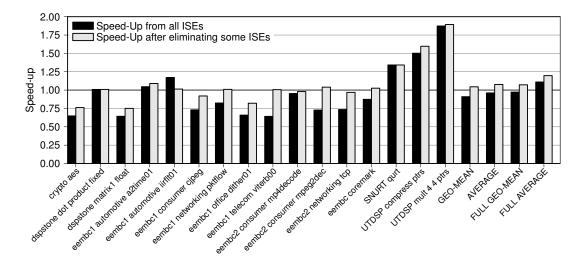

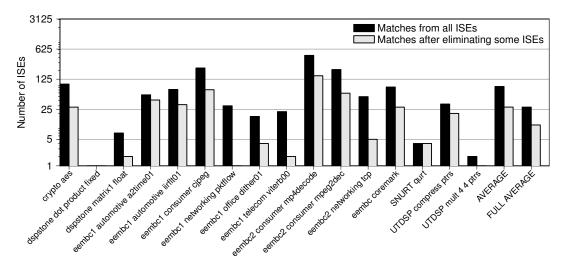

|   |      | 4.7.3   | Eliminating Poor Mappings                             | 52 |

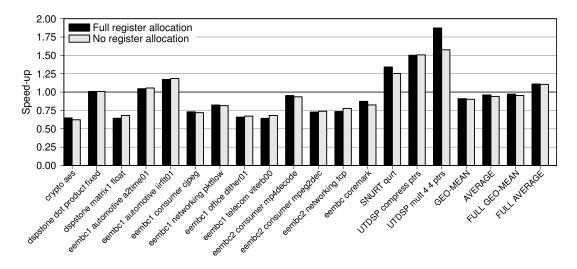

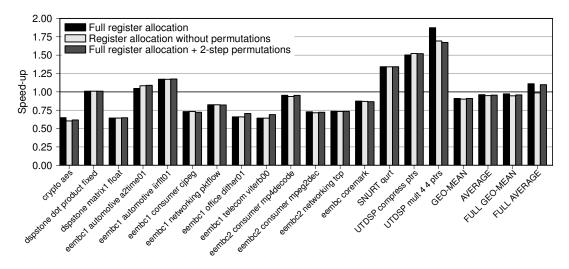

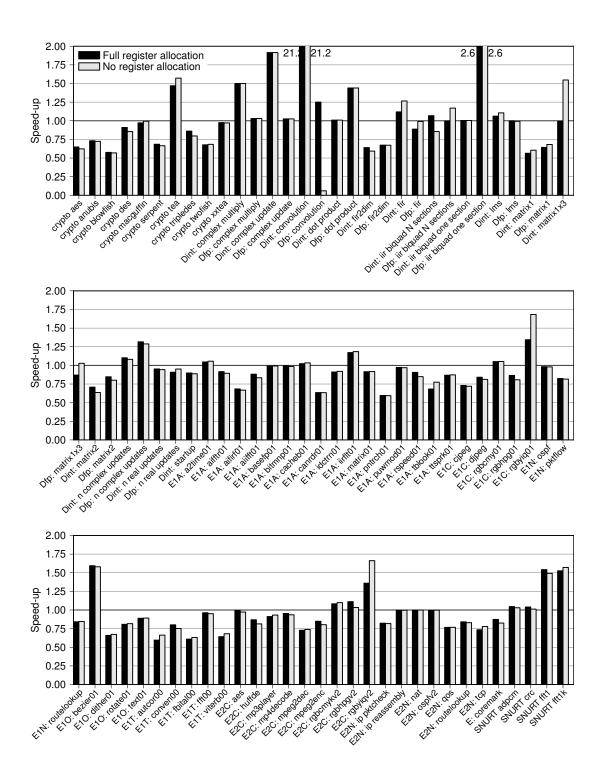

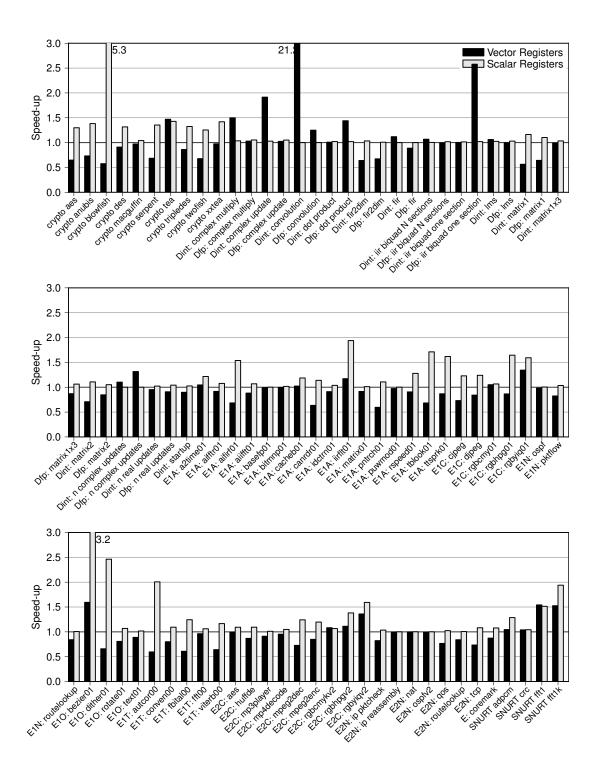

|   |      | 4.7.4   | Register Allocation Variations                        | 54 |

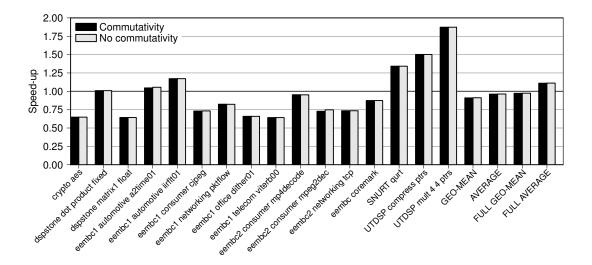

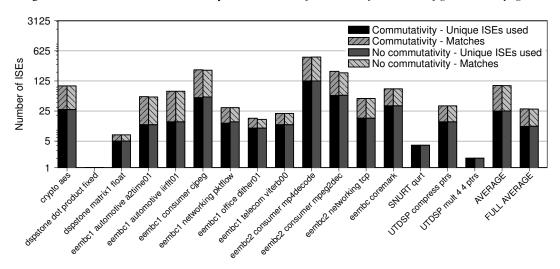

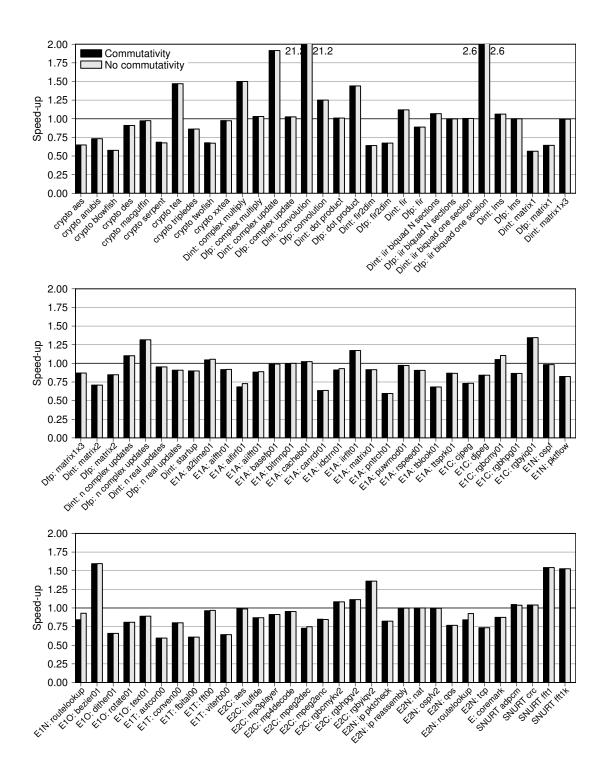

|   |      | 4.7.5   | Commutativity Variations                              | 56 |

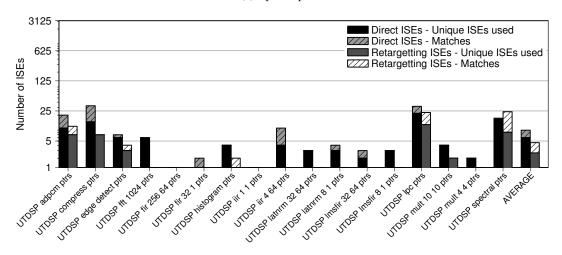

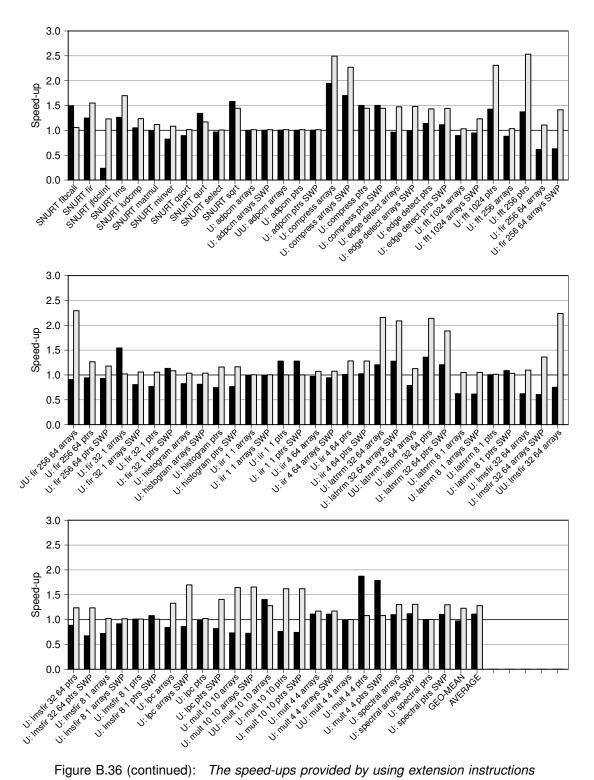

|   | 4.8  | Result  | s - Retargeting Extension Instructions                | 56 |

|   |      | 4.8.1   | Compiler Differences                                  | 59 |

|   |      | 4.8.2   | Modifying Programs                                    | 59 |

|   |      | 4.8.3   | Using Different Implementations                       | 59 |

|   |      | 4.8.4   | Combining Programs                                    | 60 |

|   | 4.9  | Critica | al Evaluation                                         | 61 |

|   |       | 4.9.1    | ISEGen Issues                                 | 62 |

|---|-------|----------|-----------------------------------------------|----|

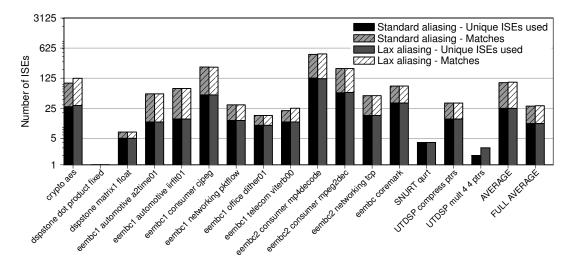

|   |       | 4.9.2    | Effect of Aliasing Differences on Performance | 66 |

|   |       | 4.9.3    | Matching Issues                               | 68 |

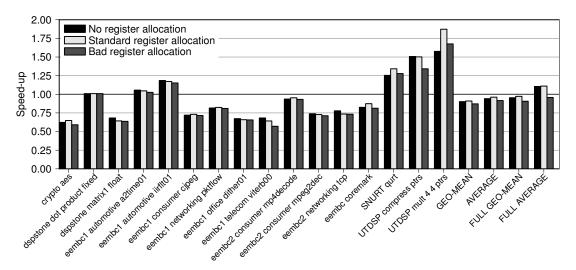

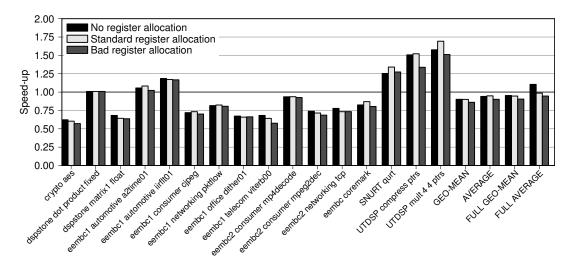

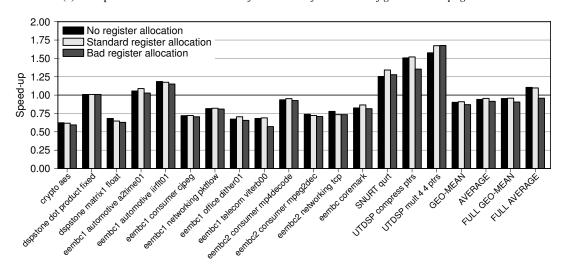

|   |       | 4.9.4    | Register Allocation Issues                    | 68 |

|   | 4.10  | Summa    | ary and Conclusions                           | 70 |

|   |       | 4.10.1   | Future Work                                   | 70 |

|   |       | 4.10.2   | Summary                                       | 72 |

| 5 | Instr | uction S | Set Extension and Code Generation             | 73 |

|   | 5.1   | Reduci   | ng Register Pressure                          | 73 |

|   |       | 5.1.1    | Reducing the Number of I/O Ports              | 74 |

|   |       | 5.1.2    | Hard-Wiring Constant Values                   | 74 |

|   |       | 5.1.3    | Modifying the ISEGEN Heuristic Parameters     | 74 |

|   | 5.2   | Wide M   | Memory Bus for Wide Registers                 | 74 |

|   |       | 5.2.1    | Evaluation Methodology                        | 75 |

|   | 5.3   | Replaci  | ing Wide Registers with Wide Instructions     | 76 |

|   |       | 5.3.1    | Avoiding Extremely Wide Instructions          | 77 |

|   |       | 5.3.2    | Evaluation Methodology                        | 78 |

|   | 5.4   | Results  | - Reducing Register Pressure                  | 79 |

|   |       | 5.4.1    | Reducing the Number of I/O Ports              | 79 |

|   |       | 5.4.2    | Hard-Wiring Constant Values                   | 79 |

|   |       | 5.4.3    | Modifying the ISEGEN Heuristic Parameters     | 80 |

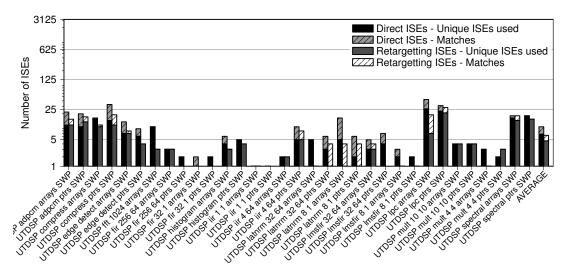

|   |       | 5.4.4    | Combining Techniques                          | 81 |

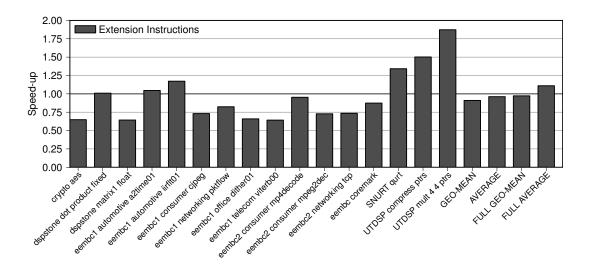

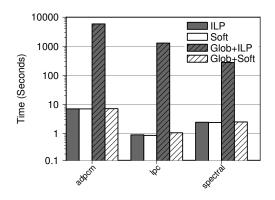

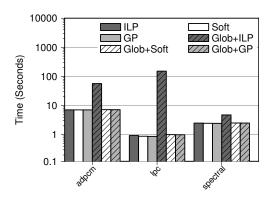

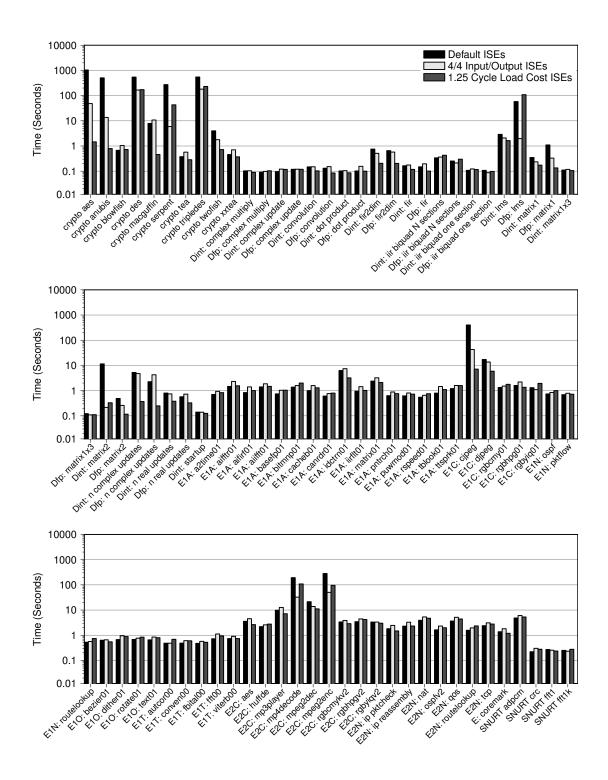

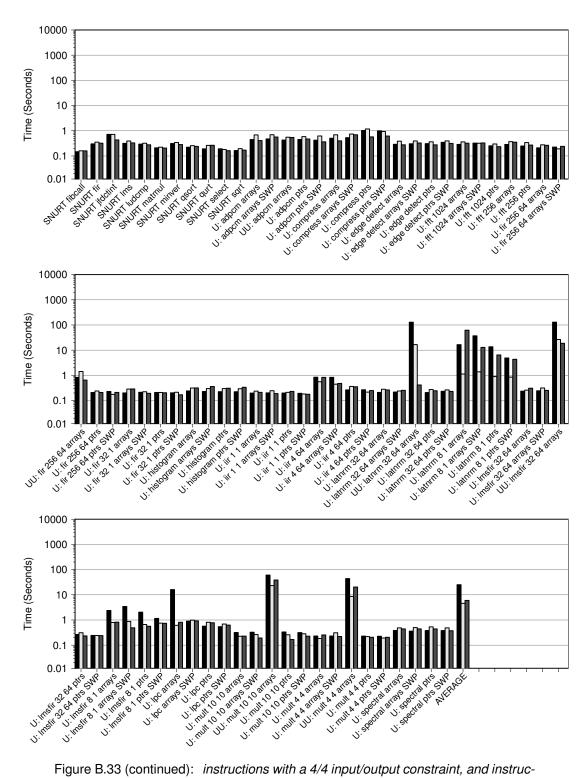

|   |       | 5.4.5    | MapISE Timing                                 | 85 |

|   | 5.5   | Results  | - Wide Memory Bus                             | 85 |

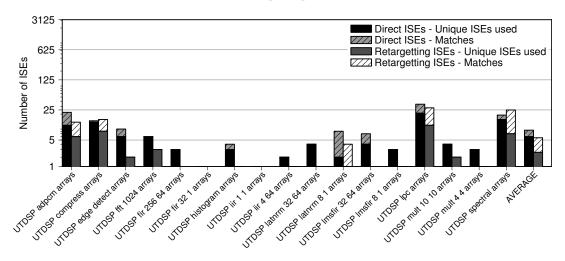

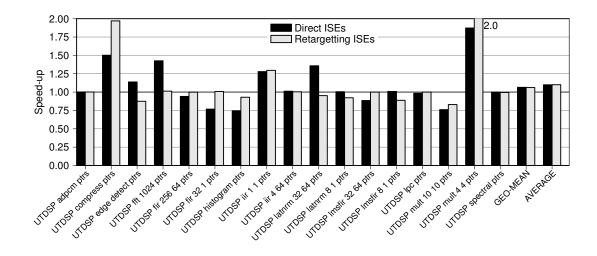

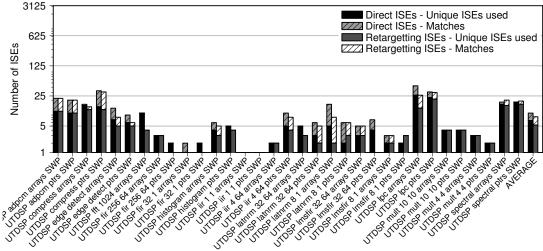

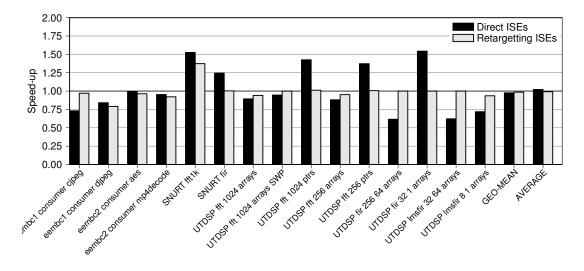

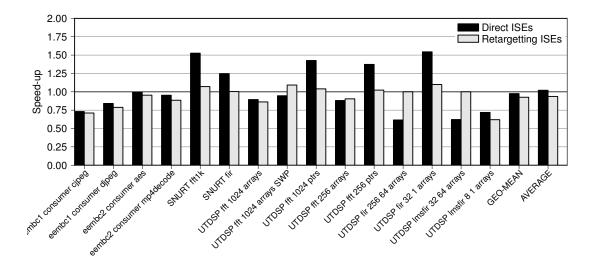

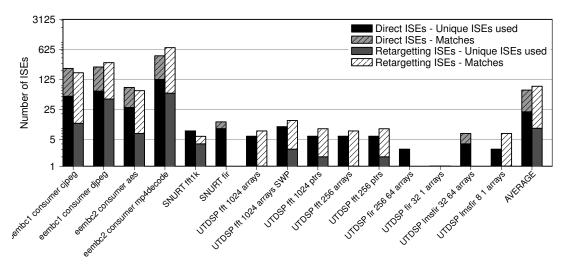

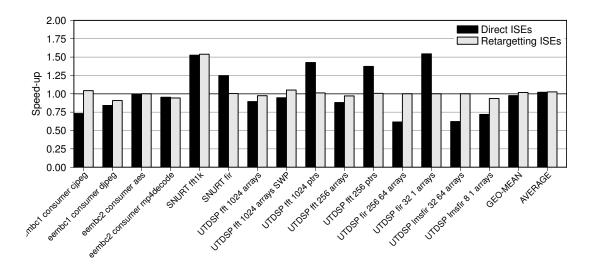

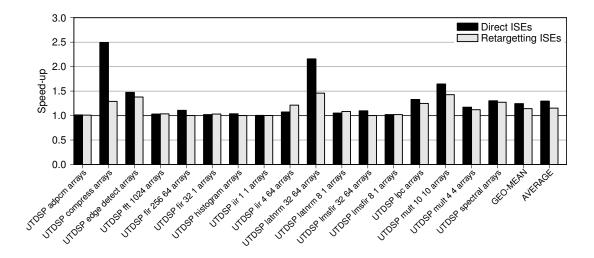

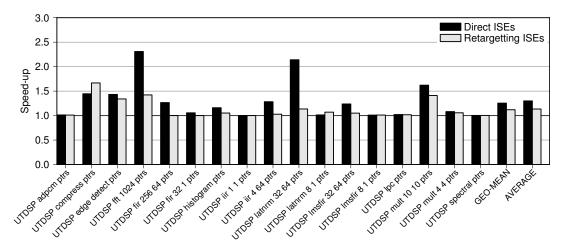

|   | 5.6   | Results  | - Wide Instructions                           | 86 |

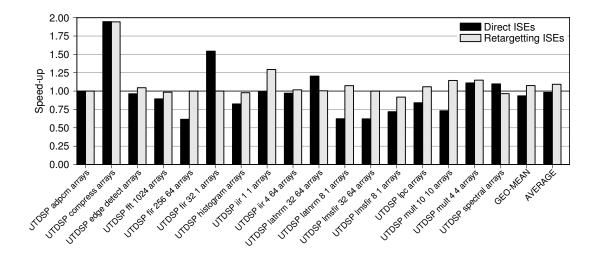

|   | 5.7   | Results  | - Retargeting Extension Instructions          | 89 |

|   | 5.8   | Critical | Evaluation                                    | 90 |

|   |       | 5.8.1    | Reevaluation of ISEGEN Issues                 | 90 |

|   | 5.9   | Summa    | ary and Conclusions                           | 92 |

|   |       | 5.9.1    | Future Work                                   | 92 |

|   |       | 5.9.2    | Summary                                       | 92 |

| 6 | Incre | easing N | <b>Memory Bandwidth: Dual Memory Banks</b>    | 93 |

|   | 6.1   | Feasibi  | lity Study                                    | 94 |

|   | 6.2   | The Pro  | oblem                                         | 95 |

|   |       | 6.2.1    | Difficulty of the Problem                     | 95 |

|   | 6.3   | Method   | lology                                        | 96 |

|   |      | 6.3.1   | Group Forming                               |

|---|------|---------|---------------------------------------------|

|   |      | 6.3.2   | Interference Model                          |

|   |      | 6.3.3   | Partial Pre-assignments                     |

|   | 6.4  | ILP Co  | olouring                                    |

|   |      | 6.4.1   | Single Solution                             |

|   |      | 6.4.2   | Multiple Solutions                          |

|   | 6.5  | Soft Co | olouring                                    |

|   |      | 6.5.1   | Single Solution                             |

|   |      | 6.5.2   | Changes To Interference Graph               |

|   |      | 6.5.3   | Multiple Solutions                          |

|   | 6.6  | Geneti  | c Program Colouring                         |

|   |      | 6.6.1   | Single Solution                             |

|   |      | 6.6.2   | Multiple Solutions                          |

|   | 6.7  | Evalua  | tion Methodology                            |

|   |      | 6.7.1   | Platform and Benchmarks                     |

|   |      | 6.7.2   | Evaluating Genetic Programming              |

|   | 6.8  | Results | s                                           |

|   |      | 6.8.1   | Scalability                                 |

|   | 6.9  | Summa   | ary and Conclusions                         |

|   |      | 6.9.1   | Critical Evaluation                         |

|   |      | 6.9.2   | Future Work                                 |

|   |      | 6.9.3   | Summary                                     |

| 7 | Code | e Trans | formation and Instruction Set Extension 121 |

|   | 7.1  | Limita  | tions of Methodology                        |

|   | 7.2  | Motiva  | ating Example                               |

|   |      | 7.2.1   | Combined Design-Space                       |

|   | 7.3  | Experi  | ment Methodology                            |

|   |      | 7.3.1   | Selection of Transformations                |

|   |      | 7.3.2   | Extension Instruction Identification        |

|   |      | 7.3.3   | Performance Evaluation                      |

|   | 7.4  | Evalua  | tion Methodology                            |

|   | 7.5  | Results | s                                           |

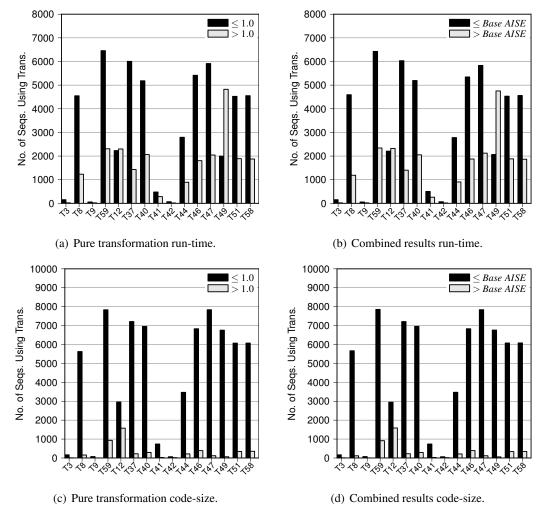

|   |      | 7.5.1   | Performance and Code Size Results           |

|   |      | 7.5.2   | Application-Oriented Evaluation             |

|   |      | 7.5.3   | Transformation-Oriented Evaluation          |

|   | 7.6  | Summa   | ary and Conclusions                         |

|   |      | 761     | Critical Evaluation 141                     |

|     |        | 7.6.2    | Future Work                       | . 141 |

|-----|--------|----------|-----------------------------------|-------|

|     |        | 7.6.3    | Summary                           | . 141 |

| 8   | Conc   | clusion  |                                   | 143   |

|     | 8.1    | Contrib  | outions                           | . 143 |

|     |        | 8.1.1    | Compiling for AISE                | . 143 |

|     |        | 8.1.2    | AISE for Compiling                | . 143 |

|     |        | 8.1.3    | Exploiting Dual Memory Banks      | . 144 |

|     |        | 8.1.4    | Transformation-Based DSE and AISE | . 144 |

|     | 8.2    | Critical | l Evaluation                      | . 144 |

|     |        | 8.2.1    | Integration                       | . 144 |

|     |        | 8.2.2    | Limits of AISE                    | . 145 |

|     | 8.3    | Insight  | s                                 | . 146 |

|     | 8.4    | Future   | Work                              | . 147 |

| A   | SUII   | Transi   | formation List                    | 149   |

|     | A.1    | Most I   | mportant Transformations          | . 149 |

|     | A.2    | Additio  | onal Transformations              | . 151 |

| В   | Full   | Results  |                                   | 155   |

| C   | Reta   | rgeting  | <b>Extension Instructions</b>     | 243   |

|     | C.1    | Reduci   | ng the Number of I/O Ports        | . 243 |

|     | C.2    | Hard-V   | Viring Constant Values            | . 249 |

|     | C.3    | Wide I   | nstructions                       | . 254 |

| Bil | oliogr | aphy     |                                   | 257   |

| Inc | dex    |          |                                   | 265   |

### Chapter 1

### Introduction

"I have no data yet. It is a capital mistake to theorise before one has data. Insensibly one begins to twist facts to suit theories, instead of theories to suit facts."

— Sherlock Holmes, fictional character created by Sir Arthur Conan Doyle, 1859–1930.

The designers of embedded computer systems are under pressure to produce high quality products which meet multiple conflicting constraints: low cost, low power, short time-to-market but still high performance. For embedded computing systems the performance requirement, at a high-level, is usually a fixed target (e.g. a Blu-ray player must be able to decode H.264 video streams and an accompanying audio stream at a specified peak bit-rate). The selection of processors, however, that may be designed, licensed or purchased to meet this performance requirement is huge, and there is frequently an existing processor that will perform sufficiently. For example, a top-of-the-line multi-core Intel processor would be able to perform the tasks of virtually any embedded processor from a performance perspective, but financial cost and power requirements make this uneconomical for an embedded system. Thus, designing an embedded computing system is about meeting the performance requirements for the lowest cost and power requirements, and to do this before your competitors release a similar product.

The advantages of developing a low cost product with a short time-to-market in the highly competitive embedded computing system market are obvious; if you are the first to meet a given performance/power requirement you can capture the market, and once multiple manufacturers have products the lowest-priced item will sell the most. The primary requirement for low power is that portable battery-operated devices must be able to function for significant periods without recharging; a smart-phone with only a few hours of battery life is of little use to anyone. The secondary low power requirement is the need for minimal heat output, a hand-held device must never be more than warm to the touch, must be cooled passively and is frequently sealed in a plastic enclosure. Static embedded systems must also have low heat output (and thus be low power, even when they are connected to mains electricity) as passive cooling is still highly

desirable, e.g. a wireless router is expected to operate silently, noise from fans is undesirable. Consequently, to meet these conflicting requirements the system designers either take standard components and combine them into a Multi-Processor System-on-Chip (MPSoC) and/or design custom pieces of hardware – in both cases they are creating a system specialised for a specific domain or application.

### 1.1 Specialised Processors

Specialising processors for a particular domain is an effective way of increasing the performance achievable for a given level of power consumption. The most obvious examples of this are the different processor families for different domain areas. Digital Signal Processors (DSPs) are based on VLIW or static superscalar designs (effective on highly data-parallel tasks), with scratchpad memories (effective on streaming data where standard caches are not) and specialised instructions (e.g. a multiply-accumulate, MAC, which are common in DSP tasks). Together these features allow effective digital signal processing (DSP) where highly data-parallel streaming data is processed. Other processor families include Network Processors, or general purpose embedded processors ranging from microcontrollers, used in everything from hard-disk drives to cars to washing machines, up to high performance processors used in portable media players, smartphones, netbooks, etc.

Within most families of embedded processors there are many more design-time configuration options that allow a processor to be tuned to a specific task. As an example, the ARM processor family [ARM, 2011] may be configured with: an optional scratchpad memory; different cache sizes; an optional Memory Management Unit (MMU); different bus interfaces; optional mixed 16/32-bit mode instructions; optional additional DSP instructions; optional floating-point calculation hardware; optional Single-Instruction Multiple-Data (SIMD) units; different process geometries (e.g.  $90nm^2$  or  $65nm^2$ ); different clock frequencies; and other more esoteric options. These options can either be thought of as additions to a baseline to improve performance, or as removing unnecessary components from a complete processor to reduce die-area and static power draw. In either case the engineer is tuning the processor to a specific task.

While selecting the correct processor from the correct family and then configuring it appropriately results in a processor well-matched to a task, designing custom hardware can dramatically reduce the power required for the targeted task [Ienne and Leupers, 2007]. Taking this idea to its full extent results in Application Specific Integrated Circuits (ASICs), which are very high performance and low power, but take time and effort to develop so they are neither low cost nor have a short time-to-market. Additionally, once they have been deployed their functionality is set, new features may not be implemented and bugs cannot be fixed. An in-

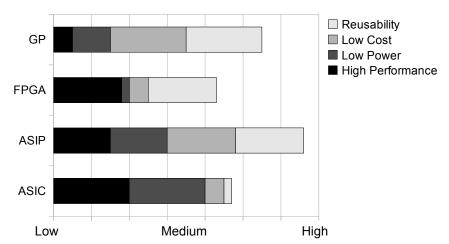

Figure 1.1: A comparison of the merits of general purpose processors and different types of customisable embedded processors. Each type has some advantages, but ASIP is the only type that scores well in every criteria.

creasingly popular compromise between ASICs and general purpose embedded processors are Application Specific Instruction-set Processors (ASIPs). These processors take a pre-verified baseline processor as a core and add extension instructions, thus standard tasks can use the baseline processor but critical kernels can be programmed to use the extension hardware. This strikes a balance between performance and time-to-market, and the pre-verified baseline avoids much of the risk involved in developing new hardware. See figure 1.1 for a visual comparison of the merits of ASICs, ASIPs and also general purpose processors and field programmable gate arrays (FPGAs).

Manually designed ASIPs can out-perform general purpose embedded processors, use less power and are quicker and cheaper to design than ASICs [Keutzer et al., 2002]. Using automated instruction set extension (AISE) to automatically design ASIPs, however, improves on this yet again. Manually designing an ASIP requires an engineer to spend a significant period of time analysing the target application, designing instructions and then implementing them in hardware. A set of automated tools, however, can do this by profiling the application to find "hot-spots" and analysing the data-flow at these spots to produce instruction definitions. These definitions can then be used to automatically create the hardware based on the data-flow graphs. This task would likely take an experienced engineer weeks or months to complete, but the automated tools can do the same thing in minutes or hours [Biswas et al., 2006a]. This approach reduces the cost of designing an ASIP and significantly reduces the time-to-market. There are many processors now on the market that allow the addition of customised extension instructions, allowing them to be used as the core of an ASIP. Examples of these baseline processors are the ARC 600 and 700 series, the Tensilica Xtensa, the ARM OptimoDE and the

4

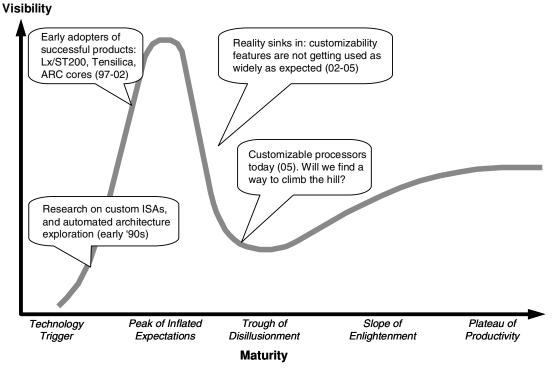

Figure 1.2: Fisher, Faraboschi and Young's view of Gartner's "Hype Cycle" [lenne and Leupers, 2007, Figure 3.4].

MIPS Pro series.

### 1.2 The Problem

Fisher, Faraboschi and Young take an extremely cautious view on the future of customisable processors [Ienne and Leupers, 2007, Chapter 3]. Their reasons are related to customisable processors in general rather than focusing on extension instructions, but much of what they say also relates to AISE extended processors. Specifically, they present a view of Gartner's "Hype Cycle" [Linden and Fenn] which is shown here in figure 1.2. They state that in the 1990's there was a lot of hype regarding the potential of customised hardware. By 2005, however, it had been realised how hard it would be to bring customisability to anything like its full potential and the hype fell into a "Trough of Disillusionment". It is now 2011 and it does not seem as though the field has left the "trough" yet. It is the premise of this thesis that effective compiler technology is key to progressing to the "Slope of Enlightenment".

Others have already shown that using AISE to design ASIPs is an effective way to design hardware [Galuzzi and Bertels, 2008]. The problem, however, is that as with almost every hardware advance in the history of computing, the capabilities of compilers lag behind the features of the hardware. This thesis, therefore, investigates how the compiler can effectively

1.2. The Problem 5

use an AISE produced processor.

The current standard methodology for using extension instructions within programs is for the AISE tool to note where it finds each extension. Generally, the tool will then modify the input code to eliminate the covered operations and replace them with either inline assembly code or *compiler known functions*. This is acceptable in the situation where a single program is being accelerated, but it creates an issue if the program needs to be changed after the processor has been fabricated. Re-running the AISE tool may generate different instructions requiring an engineer to manually map the old extensions to the new code, which is both time-consuming and error-prone [Ienne and Leupers, 2007, Section 6.5]. It would be more appropriate for the compiler to automatically perform the mapping for the engineer.

This, however, turns out to be a difficult task. The instruction set extensions (ISEs) produced by AISE are often far too complicated for conventional tree-based instruction selection (indeed, the instructions are often directed acyclic graphs, not trees), and they are often far too large for peephole-based instruction selection. Some form of graph-based instruction mapping is required instead; this has been investigated previously, but for much smaller instructions than those produced by AISE. Systems based on Architecture Description Languages (ADLs), for example, generally just produce compilers with standard tree-based back-ends. These are sometimes able to combine trees during matching to exploit small (e.g. two-node) instructions, but are unable to exploit larger instructions.

Not all extension instructions are automatically generated; many instruction set architectures (ISAs) have had additional instructions added that interact with the core processor via some extension interface. For example, the x86 ISA has the MMX and SSE extensions. These are used in the standard instruction stream, but interact with the baseline x86 instructions through additional vector registers. These instructions are designed to be used with highly regular, data-parallel code, such as that commonly found in multimedia applications. Successfully enabling a compiler to use them, however, is difficult. Techniques exist that "vectorise" loops to use these instructions [Allen and Kennedy, 2001], but they frequently fail to produce efficient code. In fact, code that can heavily exploit MMX and SSE instructions is one of the few areas in the x86 world where hand-written assembly is still considered worthwhile. For example, in the FFmpeg [Various, 2011a] and x264 [Various, 2011b] video codecs every critical kernel is hand-written in MMX or SSE assembly. MMX and SSE instructions are graph-shaped but repeat a very small, regular pattern two or four times, e.g. grouping four multiplies together. Extension instructions produced by AISE are also graph-shaped, but are not guaranteed to be regular. Thus, these instructions are a superset of the regular extension instructions and compiling for them will be at least as difficult, if not more so. This thesis, therefore, investigates how effectively the compiler can use these AISE produced extension instructions.

### 1.3 Contributions

The contributions of this thesis are many, as the research was undertaken using an iterative approach where each step directed the next, leading to some interesting results.

The first major contribution is a method for mapping arbitrary graph-shaped instructions (both disjoint and not) to arbitrary programs. The novel aspects of the mapper are that it performs instruction mapping in the middle-end instead of the back-end. This allows it to focus only on extension instructions, which the back-end cannot exploit. The mature and tuned back-end performs effective instruction selection for the code which is not mapped to extension instructions. Additionally, the instruction mapper is able to target a new extension interface based on vector instructions complete with vector permutation units [Almer et al., 2009].

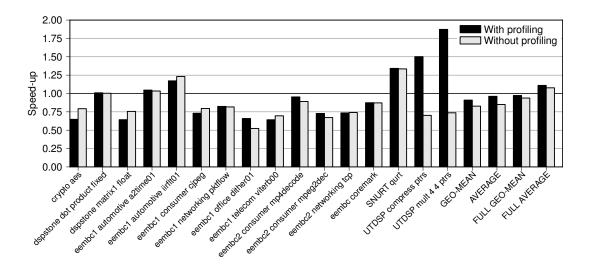

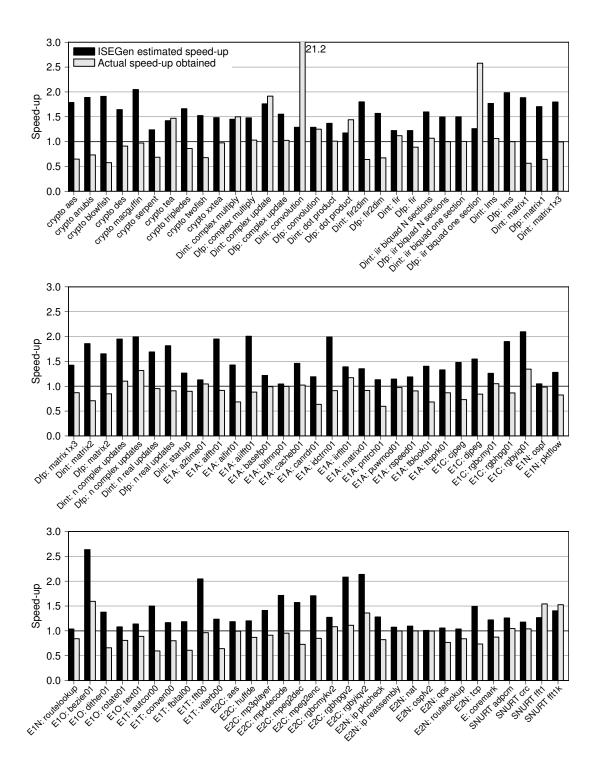

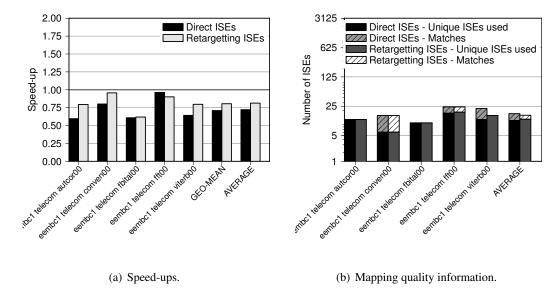

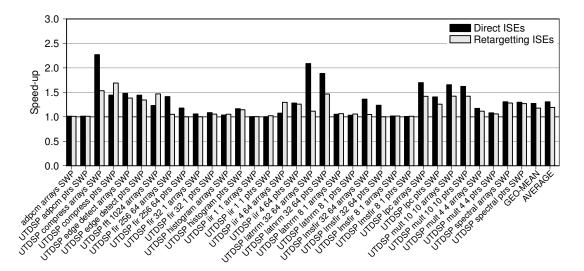

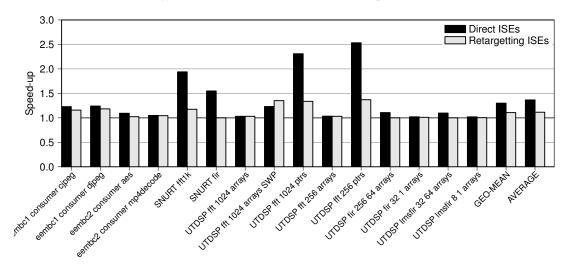

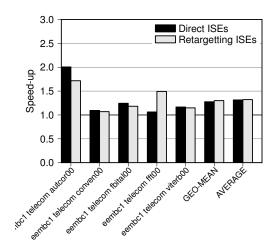

An extensive evaluation is performed using 179 benchmarks from seven benchmark suites obtained from five sources. Results are generated using a hardware-verified cycle-accurate simulator. Additionally, the instruction mapper is evaluated using extension instructions generated for programs which are similar (but not identical to) the programs which they are mapped to. Changes include dropping profiling data, modifying programs or using completely different implementations of an algorithm.

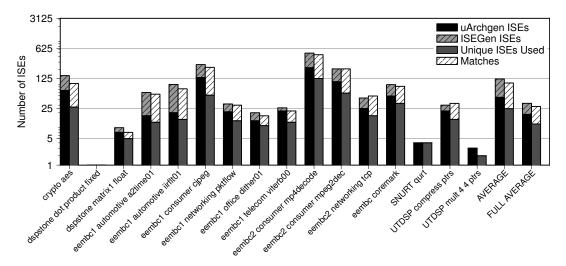

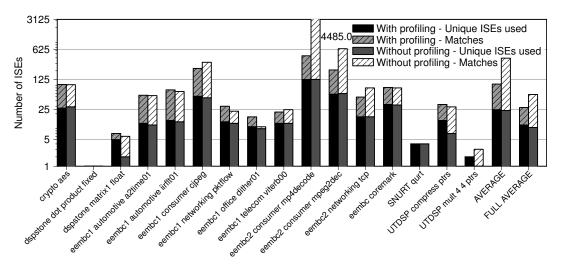

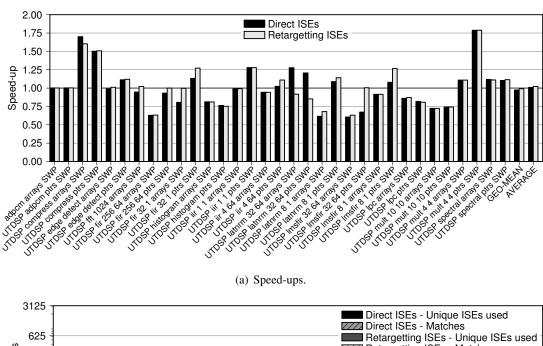

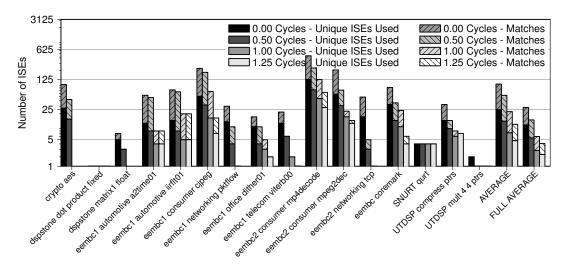

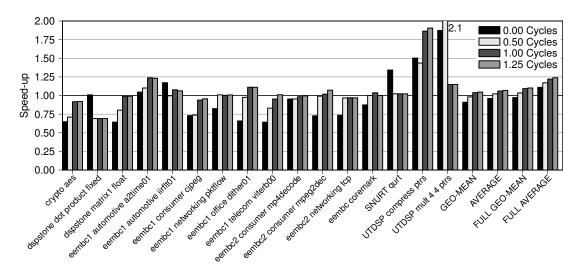

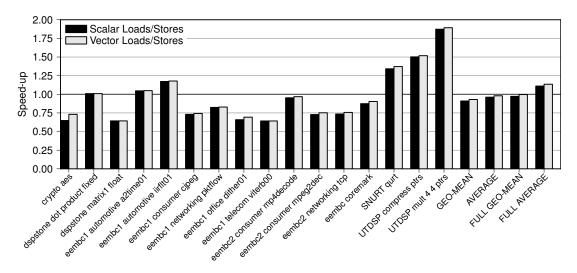

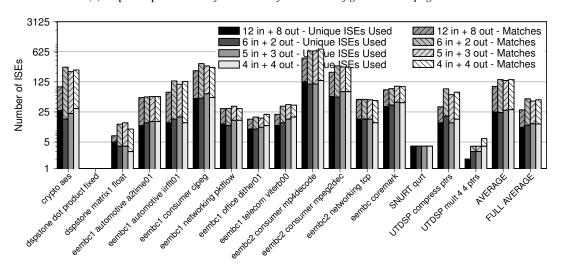

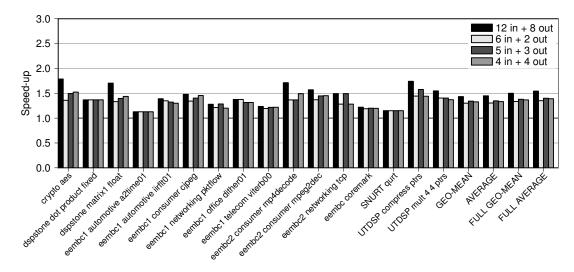

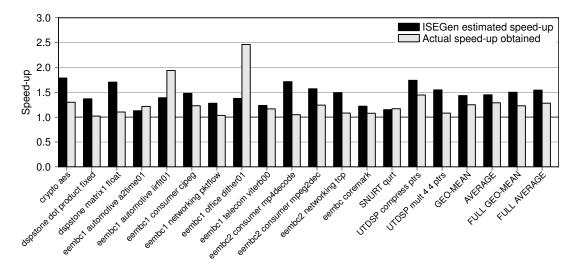

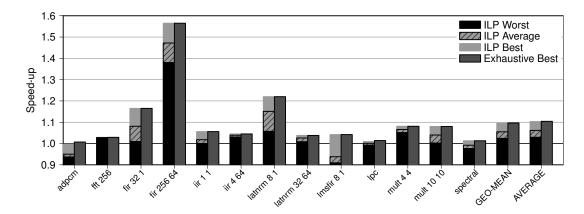

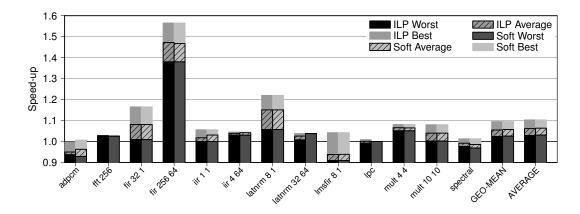

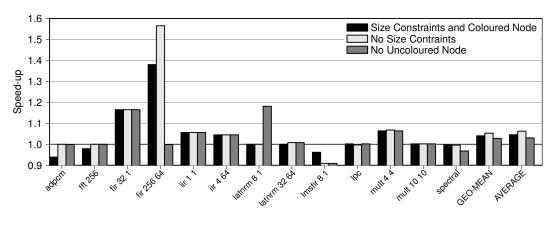

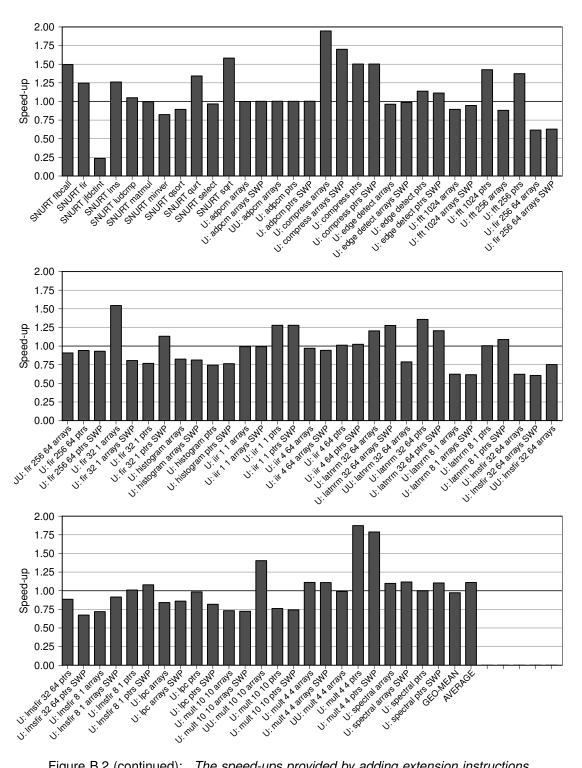

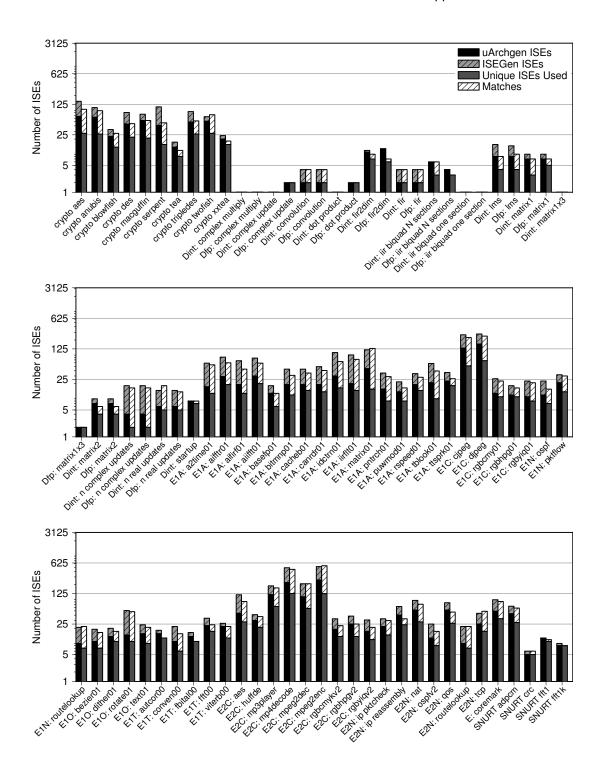

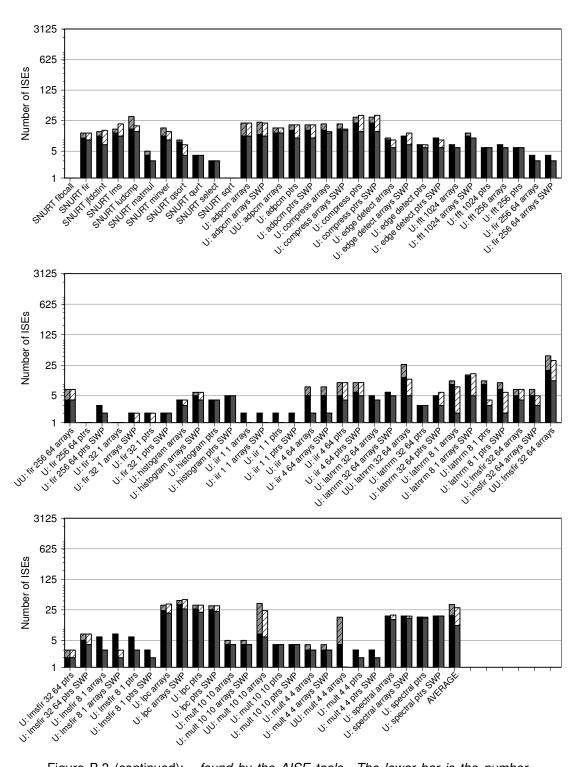

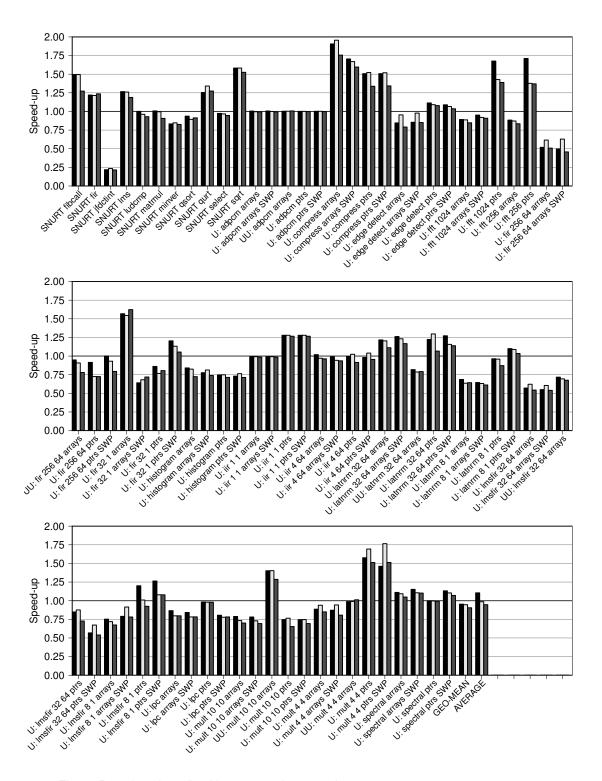

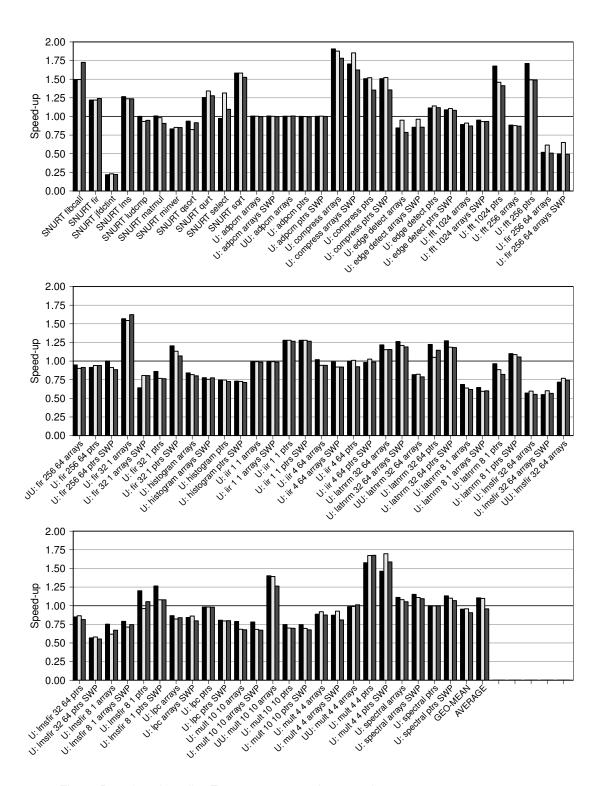

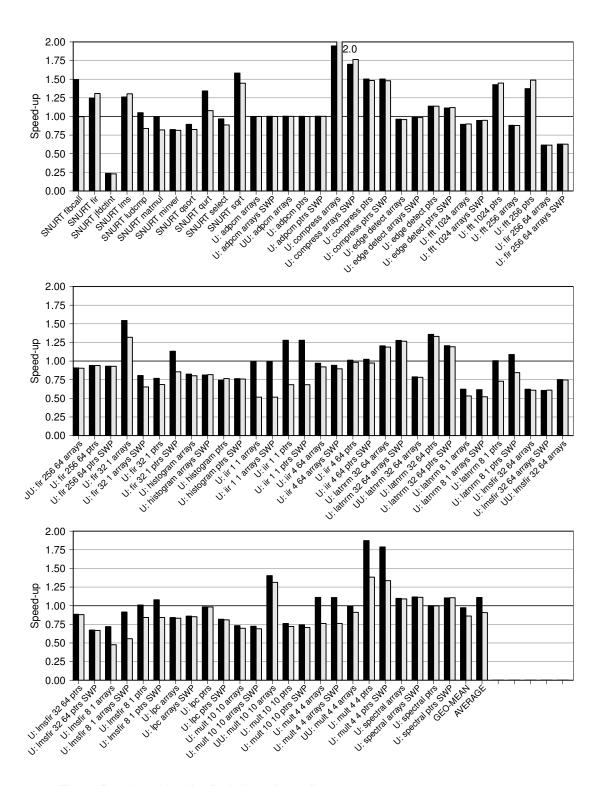

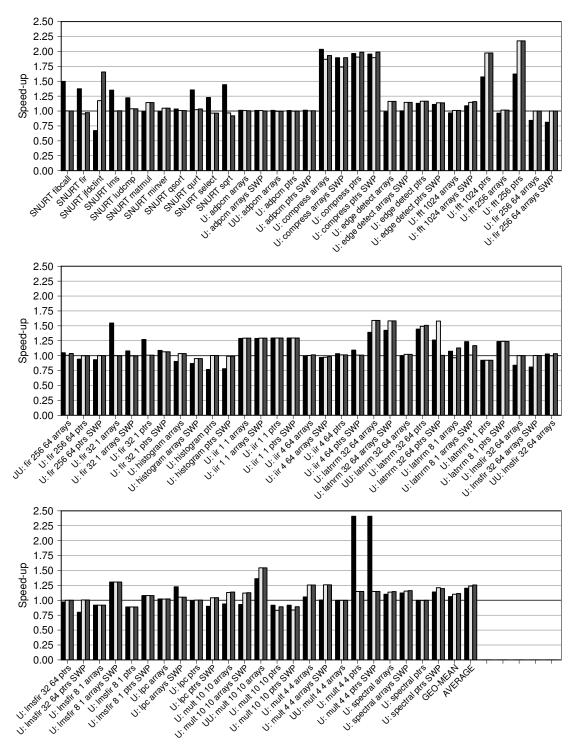

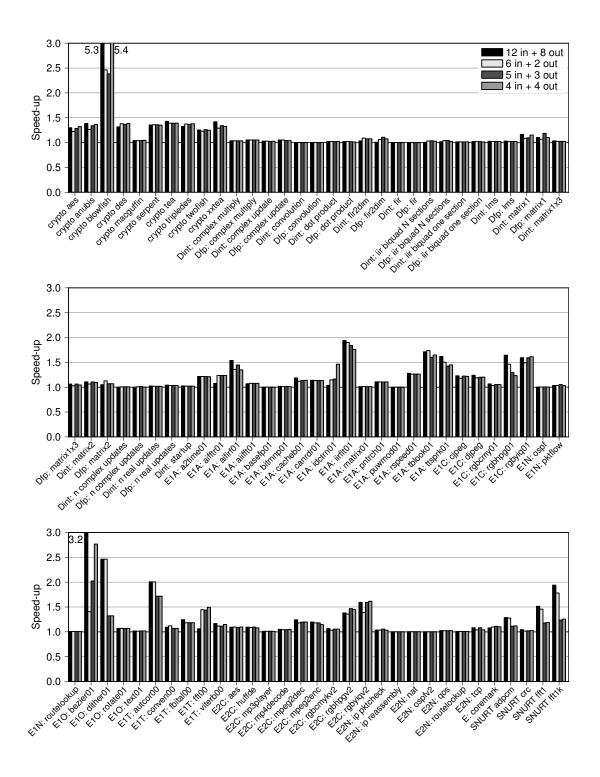

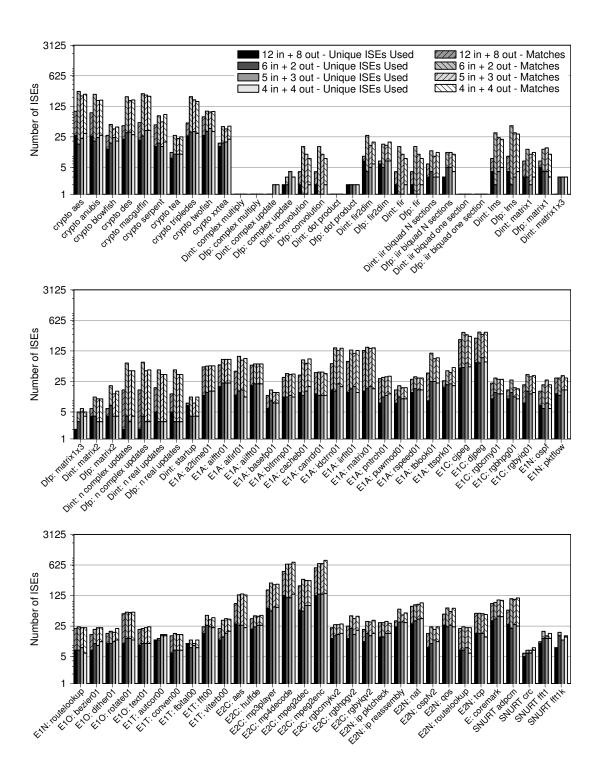

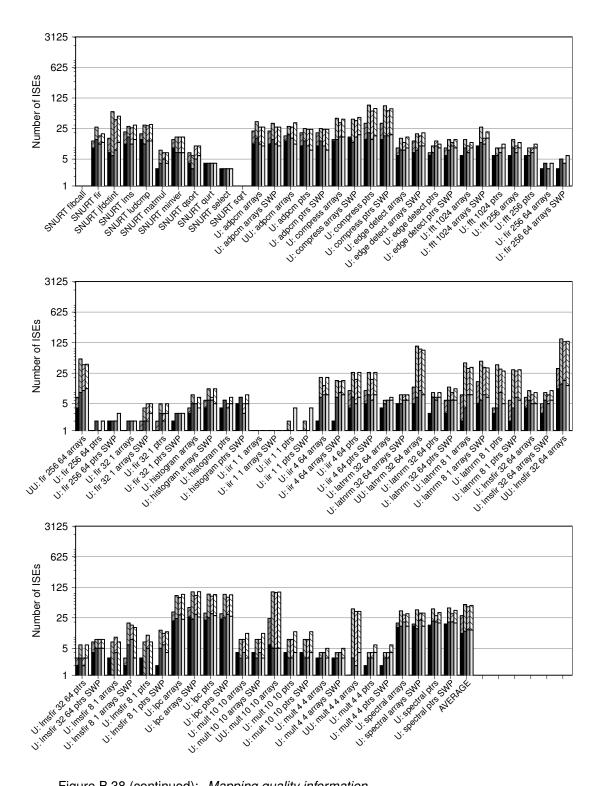

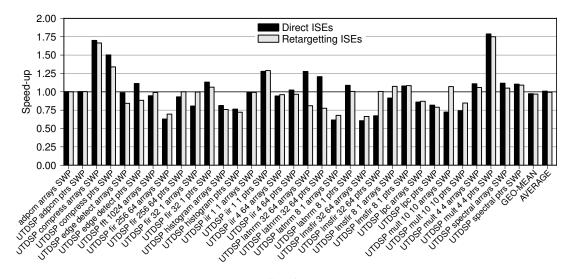

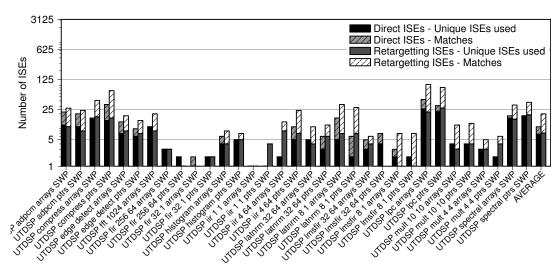

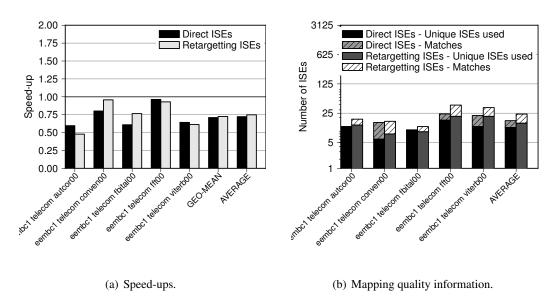

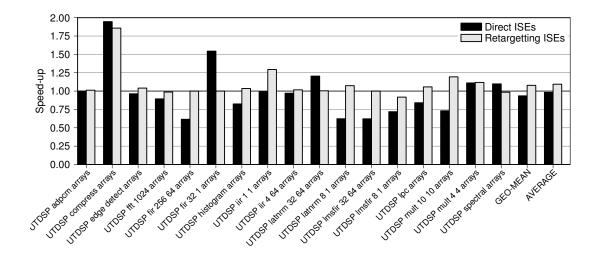

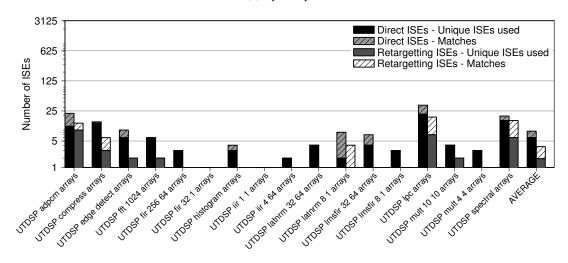

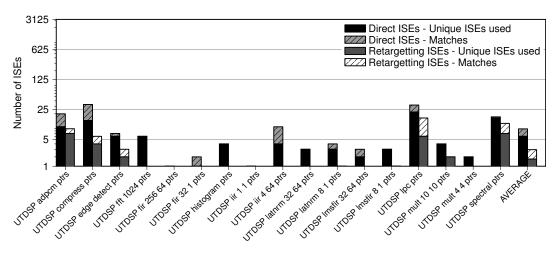

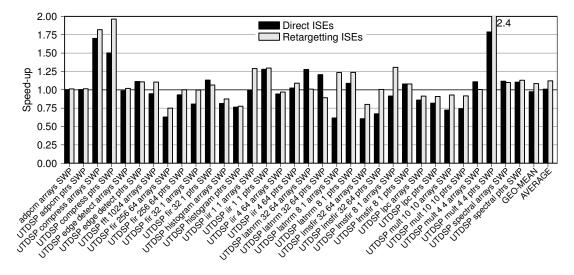

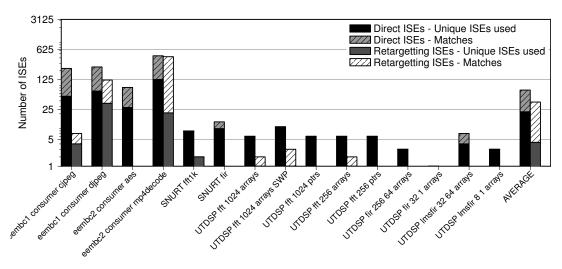

The instruction mapper was able to find 84.5% as many extension instruction mappings as the AISE tools predicted. The more interesting results at this stage, however, are the negative results – as they lead to interesting conclusions about the role the compiler should play in an AISE based framework. The instruction mapper only uses 60% of the extension instructions that the AISE tool generates and only achieves an average speed-up of 1.11x. Additionally, 110 of 179 benchmarks actually run more slowly when using extension instructions. This is found to be due to the costs of mismatch between regular vectors and irregular extension instructions.

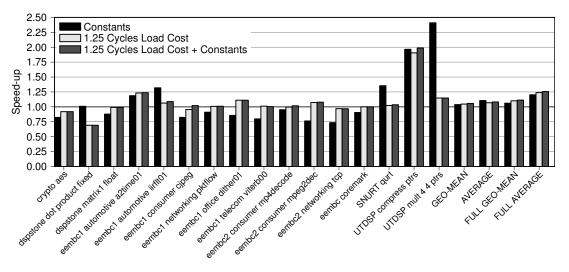

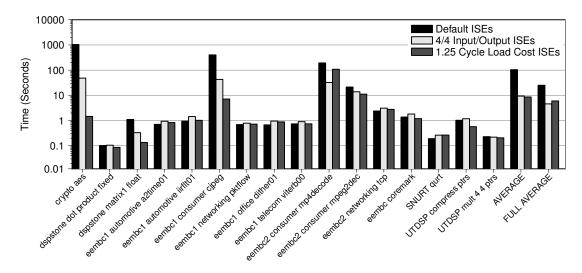

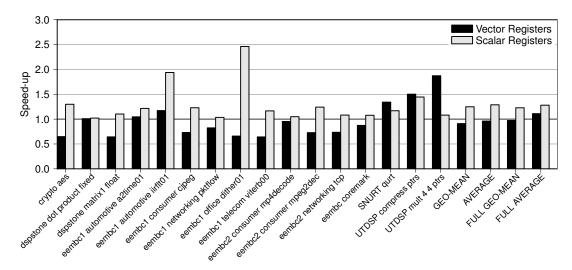

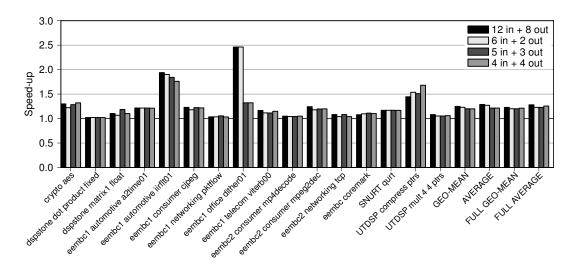

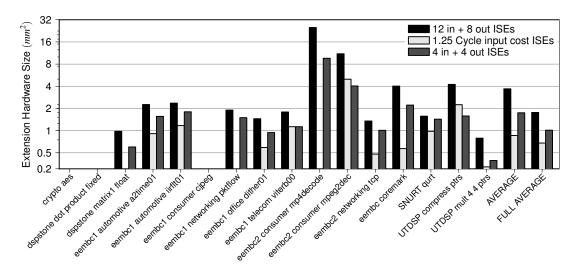

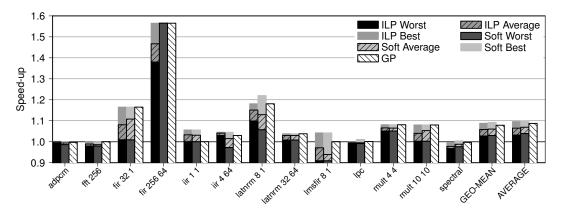

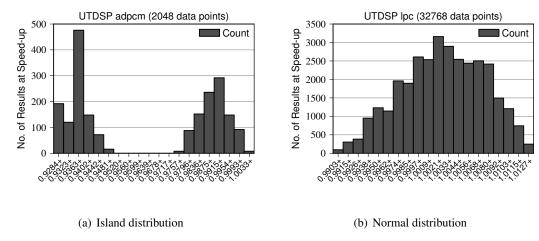

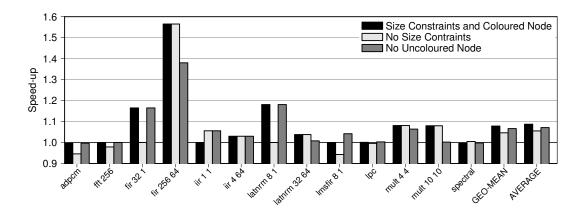

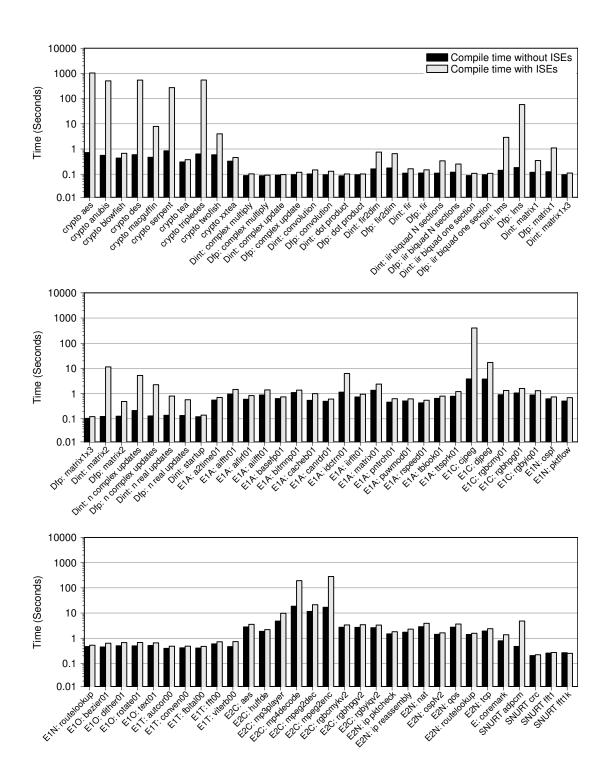

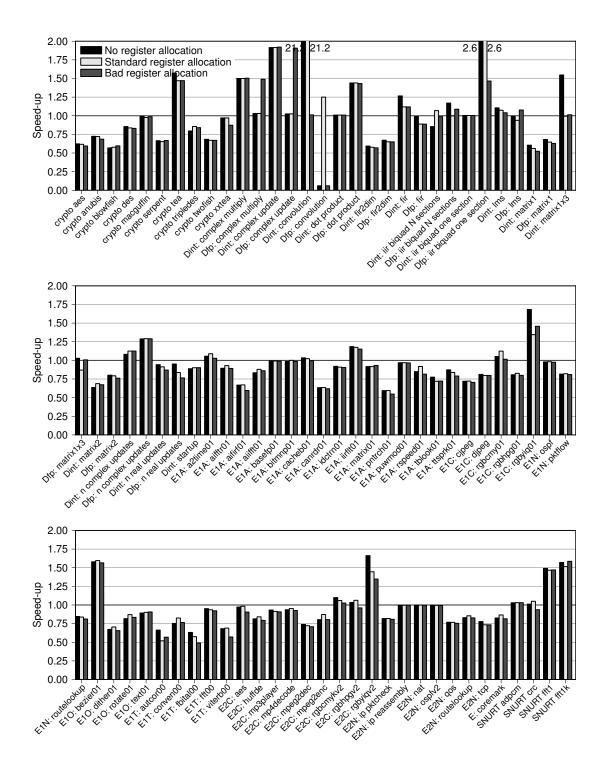

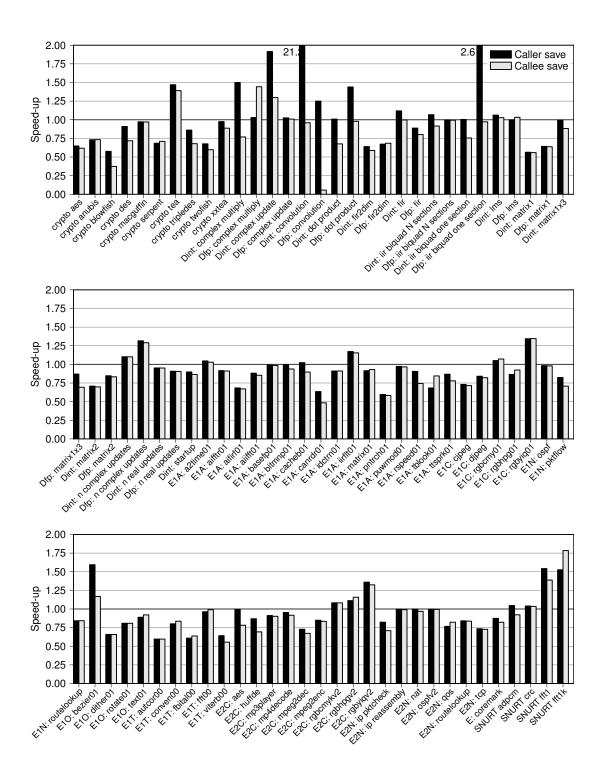

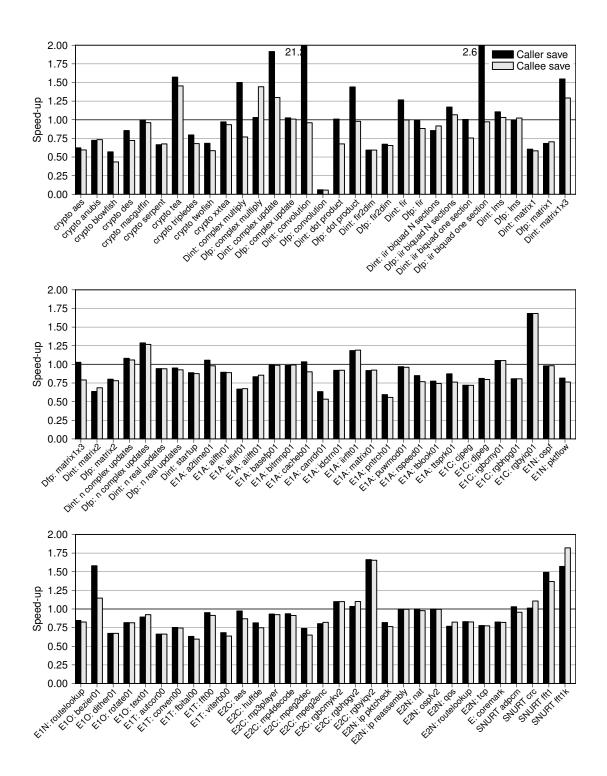

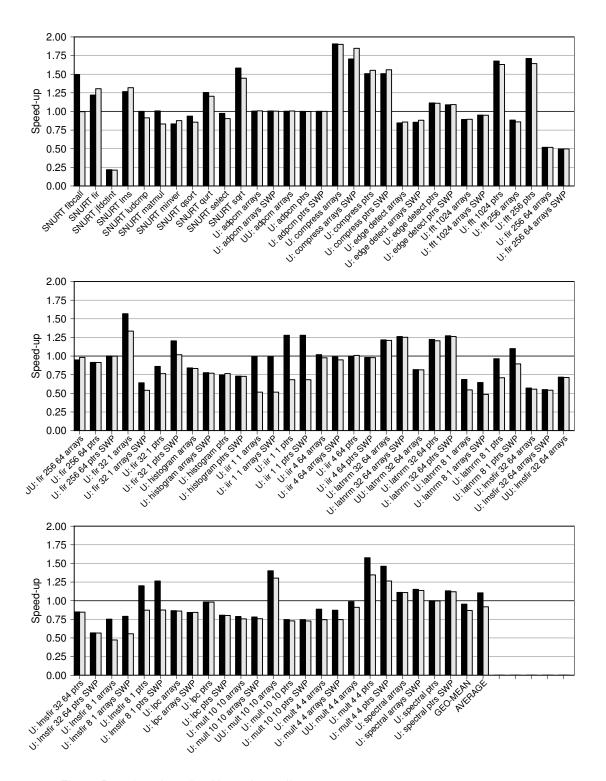

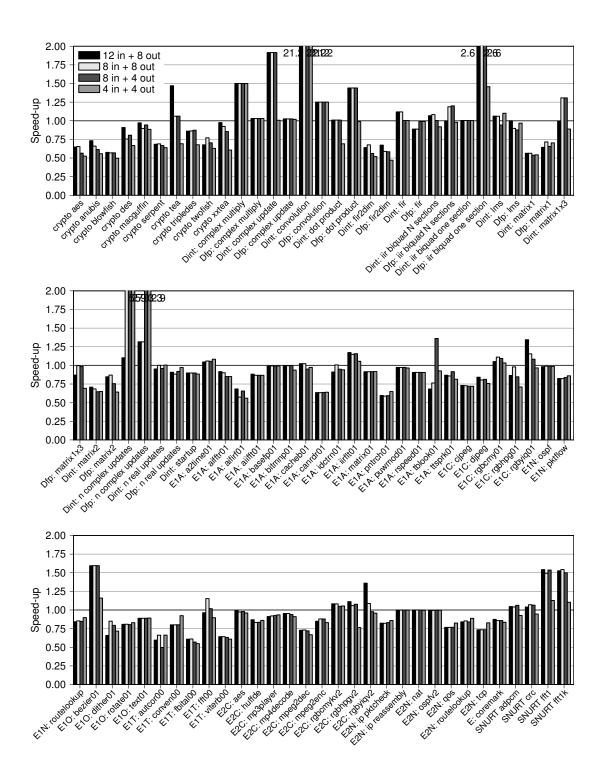

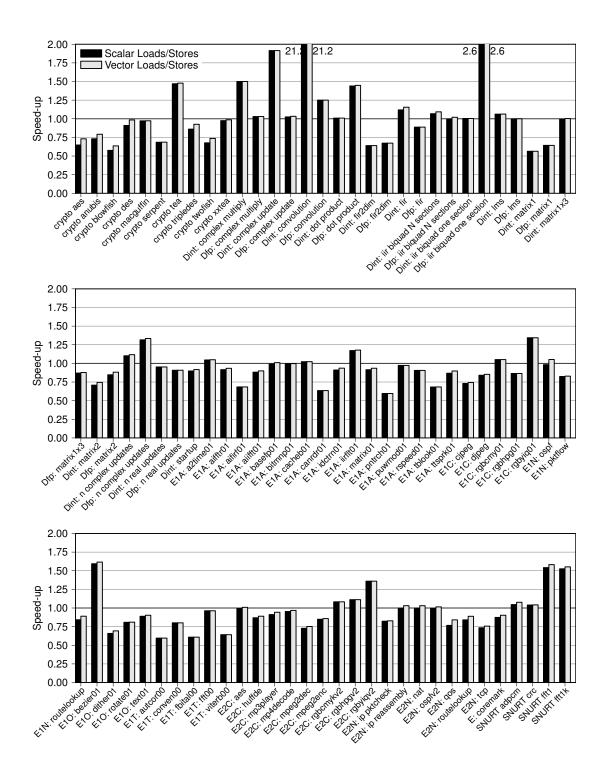

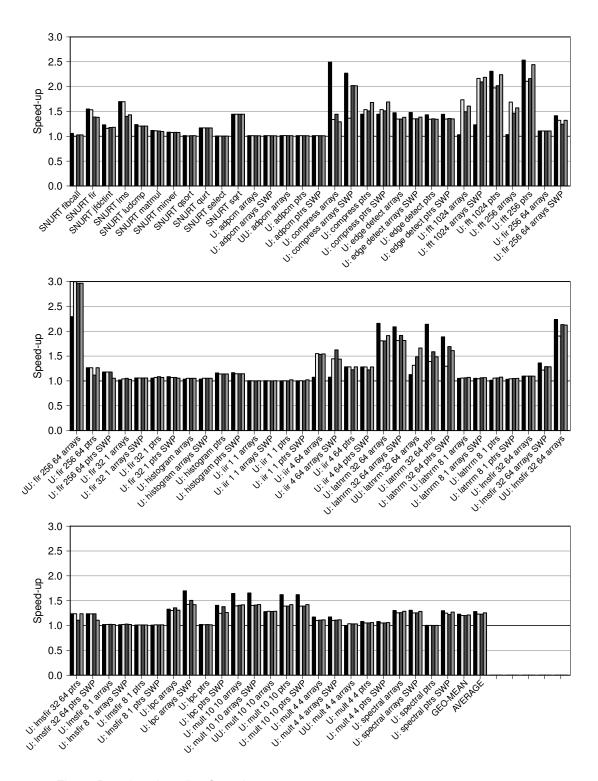

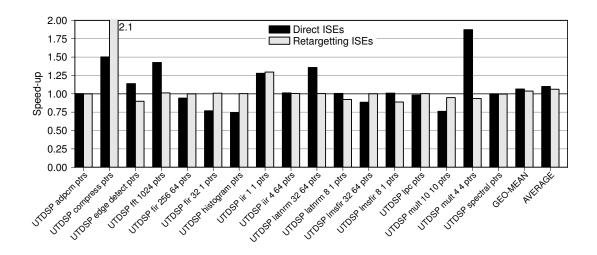

These results lead to modifications that arguable represent the most important contributions of this thesis. Several changes are made, but they are evaluated independently from each other. The first change allows the compiler to ignore extension instructions where the irregular-regular mismatch cost is likely to outweigh the instructions benefits. This increases the average speed-up to 1.20x and only 66 of 179 benchmarks slow-down. Hard-wiring some constants into extension instructions also increases the average speed-up to 1.20x. Using smaller extension instructions can increase the average speed-up up to 1.13x. Adding an additional parameter to the AISE model to represent the irregular-regular mismatch cost can increase the average speed-up to 1.24x with only 52 benchmarks slowing-down. The most effective change is to abandon the vector registers completely and thus discard all issues regarding irregular-regular data mismatches. Evaluated using the same terms as the rest of this paragraph this results in an average speed-up of 1.28x and zero benchmarks slowing down (though six do not experience a speed-up). This would have some unrealistic hardware requirements though, but reducing the hardware demands only lowers the speed-up to 1.26x (while still resulting in zero slow-downs).

1.4. Structure 7

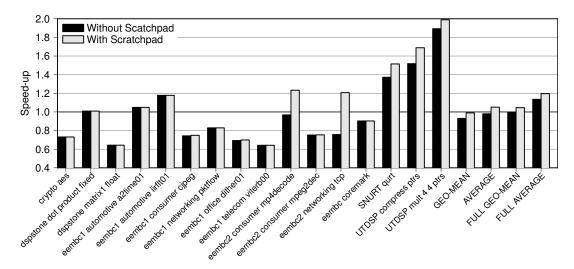

Vector loads and stores are also found to be likely to provide a small benefit (increases average speed-up to 1.14), but to increase bandwidth in a system without vector registers dual memory banks are evaluated. A source-level memory partitioning scheme based on genetic programming was able to produce better results in far less time than an "optimal" integer linear programming based approach when operating at the source-level. The source-level approach itself is also a novel contribution which required the development of a C-to-DSP-C source-to-source compiler.

Finally, the compiler is used to modify the shape of programs before the AISE tool processes them. 59 transformations are used to create a large transformation space. An extensive random sample of this space is taken and is used to produce a reduced space which covers short sequences of the most important transformations. This reduced space is then exhaustively enumerated. This approach found that the combined speed-up of transformations followed by AISE could be greater than the product of the two separately. Additionally key transformations for AISE are identified.

### 1.4 Structure

The rest of the thesis is structured as follows.

**Chapter 2** provides background information to aid in the understanding of the thesis. It primarily presents tools and techniques that later chapters use but do not improve upon.

**Chapter 3** examines prior work attempting to solve the problems directly related to the issues explored by this thesis. The specific areas of previous work considered are: classical instruction selection, complex instruction mapping, compilation for dual memory banks and compiler transformations, as they apply to instruction set extension.

Chapters 4–7 present and evaluate the techniques developed for this thesis. **Chapter 4** specifically examines how to map extension instructions onto programs by use of a graph-subgraph isomorphism checker and how to perform register allocation for the vector registers used by the extension interface. These techniques are evaluated, both directly and by re-using extension instructions in programs similar, but not identical, to the programs for which they were generated. While this shows that the tool is effective at exploiting extension instructions, the results are sometimes marginal or introduce a reduction in performance.

**Chapter 5**, therefore, investigates various ways of increasing the effectiveness of extension instructions. Firstly, by changing the heuristic parameters for extensions generation. Secondly, two independent hardware modifications to ease the use of extension instructions are proposed; one using vector loads and stores with the vector registers and the other eliminating vector registers entirely.

Chapter 6 takes the two hardware modifications proposed in chapter 5 and unifies the

idea of increasing memory bandwidth (through vector loads and stores) with the clear benefits of eliminating the use of vector registers. This is achieved by proposing another hardware extension: dual on-chip scratchpad memories. Multiple techniques to split data between the two memory banks are proposed and evaluated.

The previous chapters presented techniques to enable the compiler to use extension instructions. **Chapter 7** uses the compiler to enhance extension generation. Source-to-source transformations are used to modified programs before they are presented to the AISE tool and certain key transformations were found to improve the quality of the extension instructions produced.

Chapter 8 concludes the thesis by summarising the results and contributions presented in earlier chapters and by providing a high-level critical evaluation that considers broad issues that were not specifically related to any single chapter.

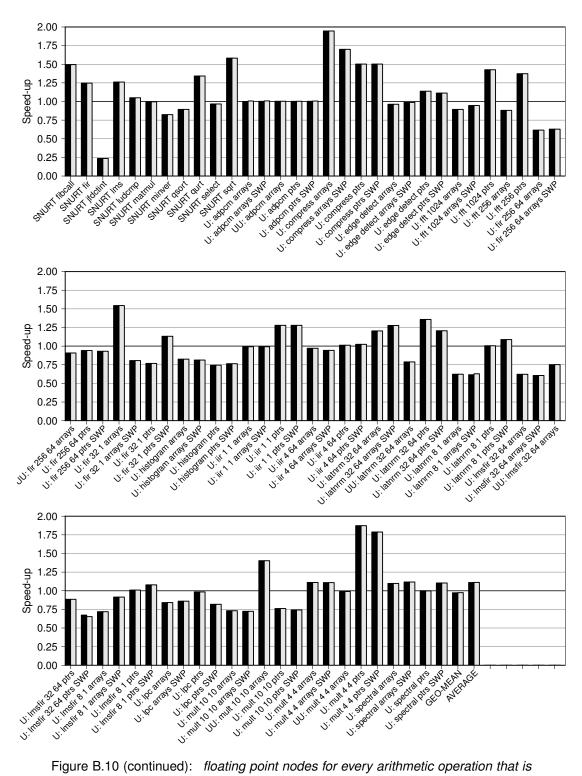

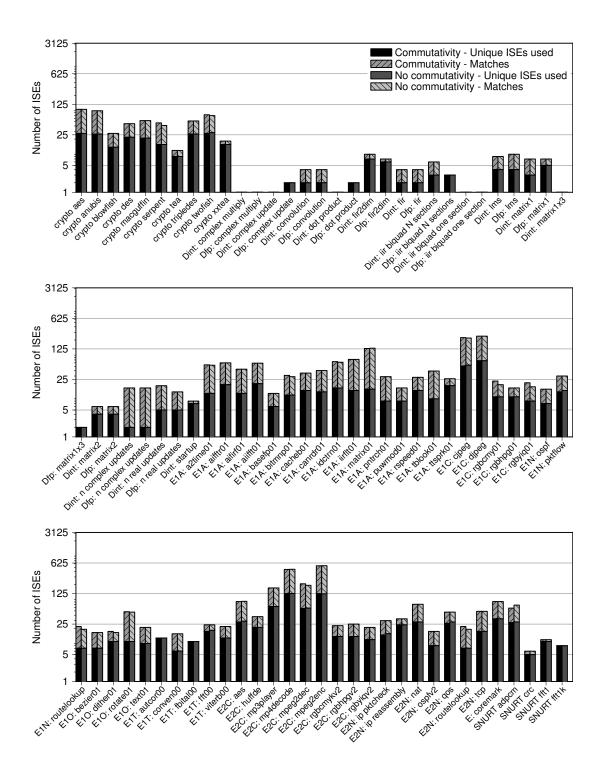

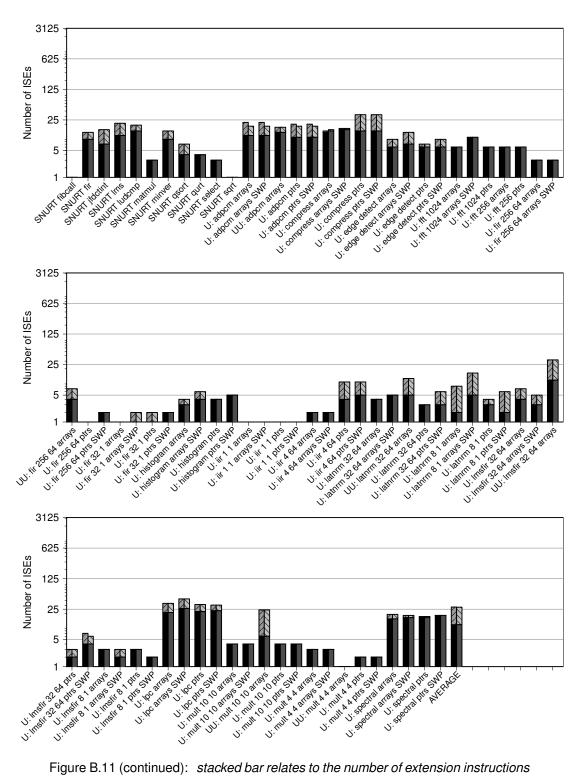

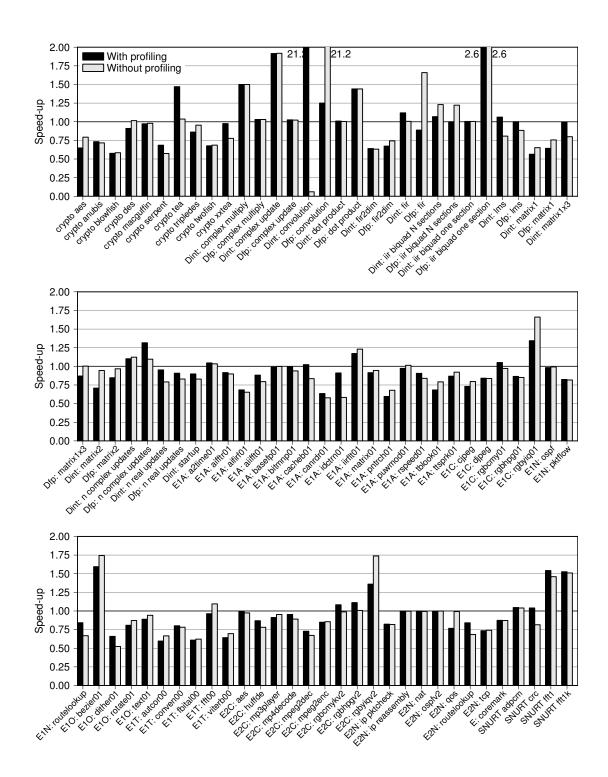

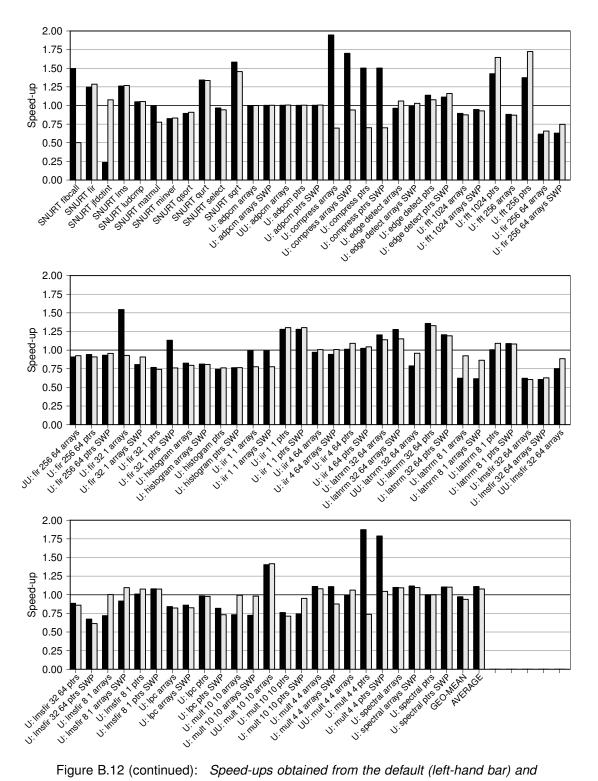

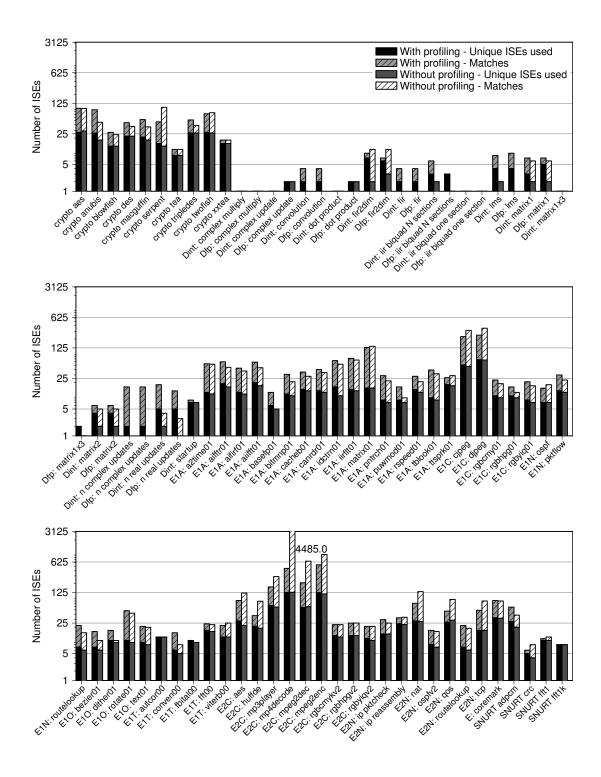

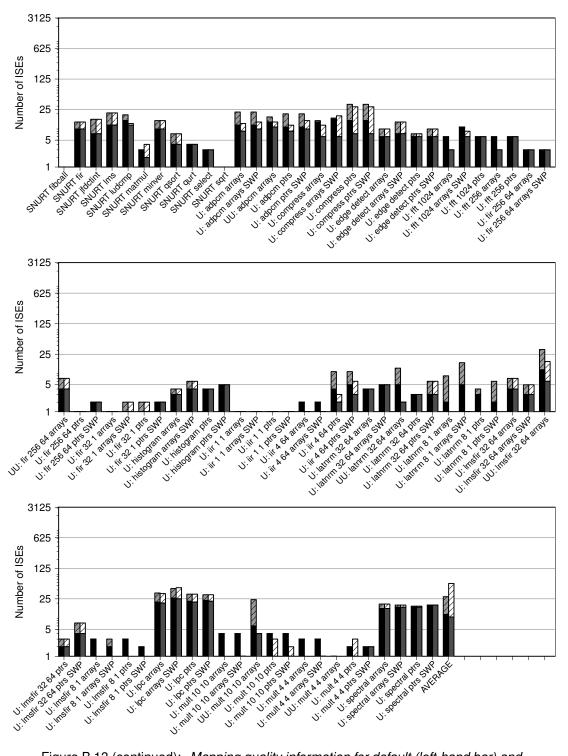

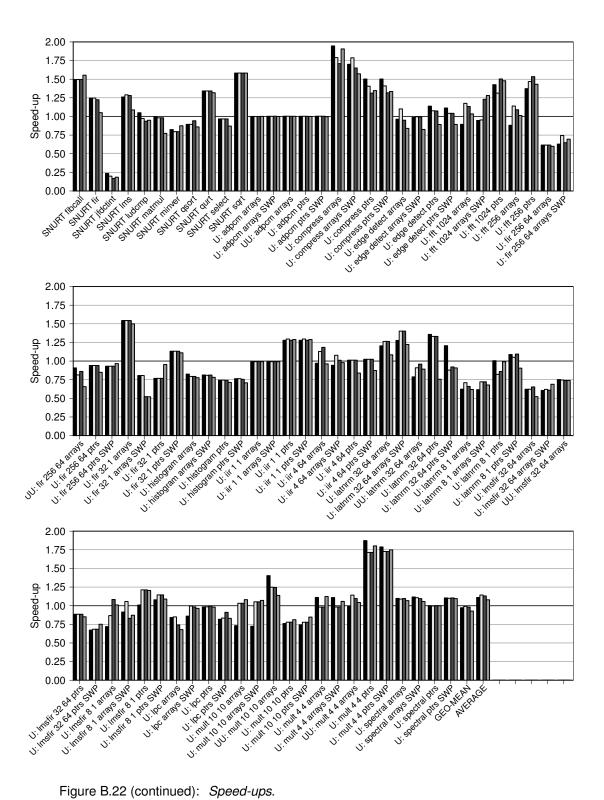

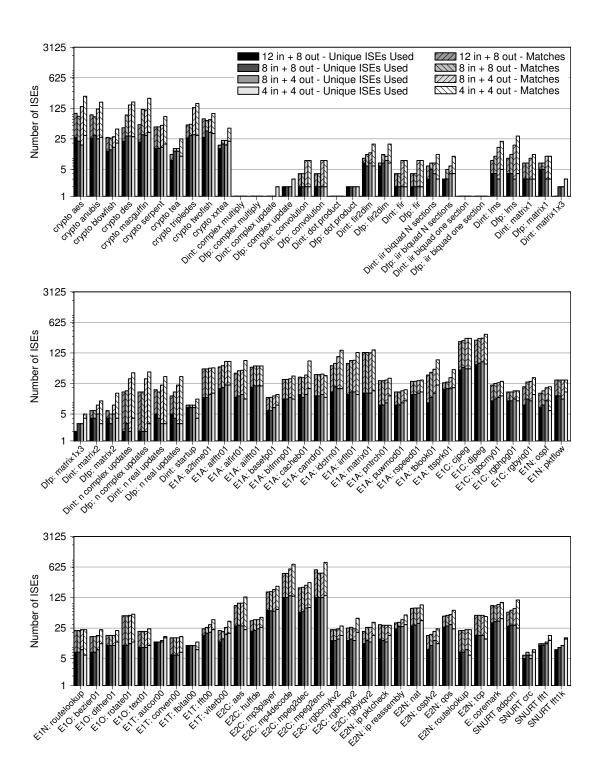

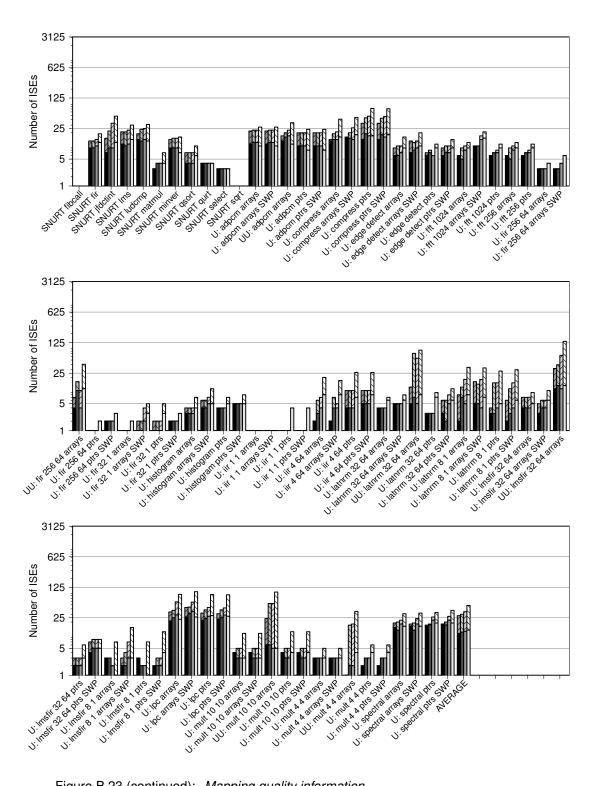

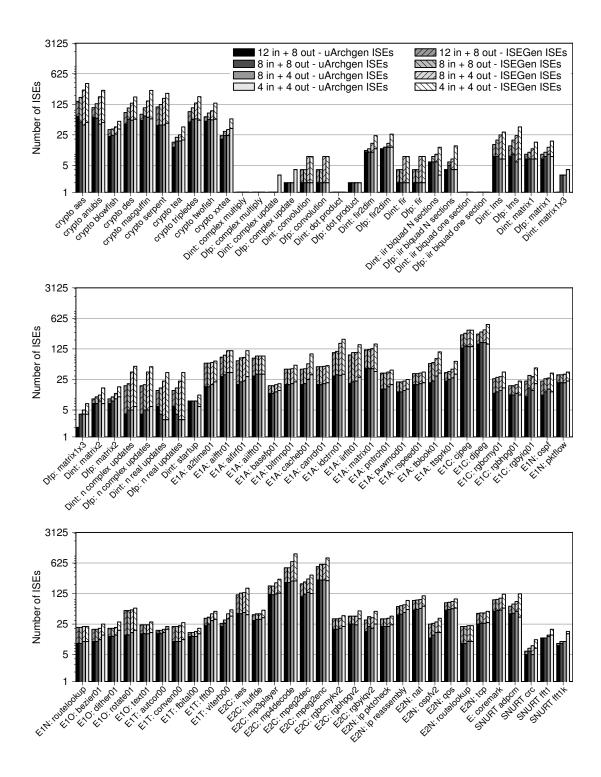

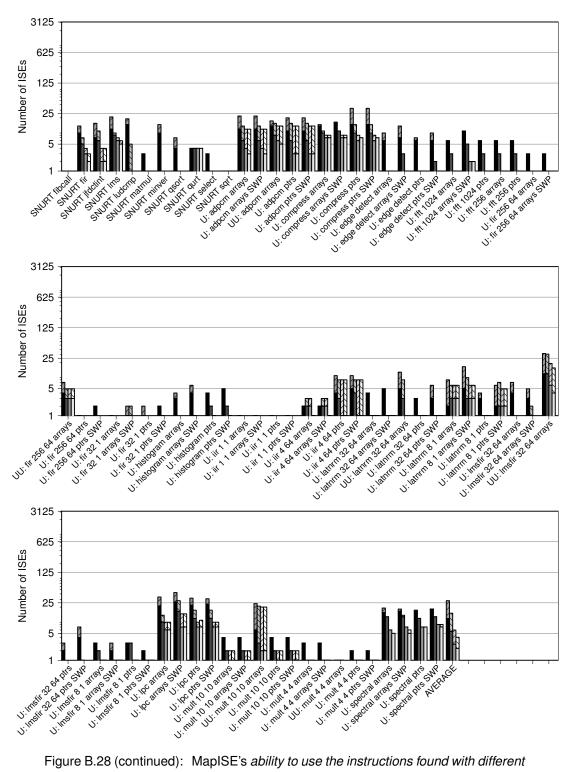

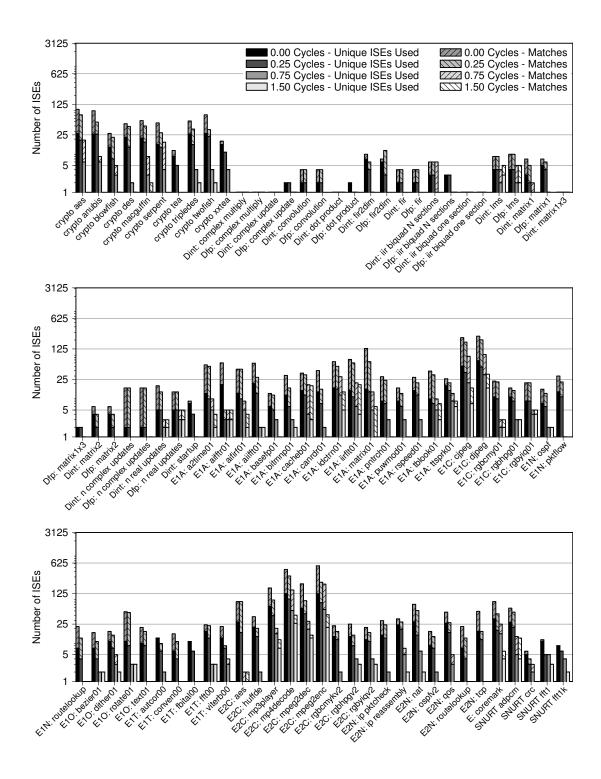

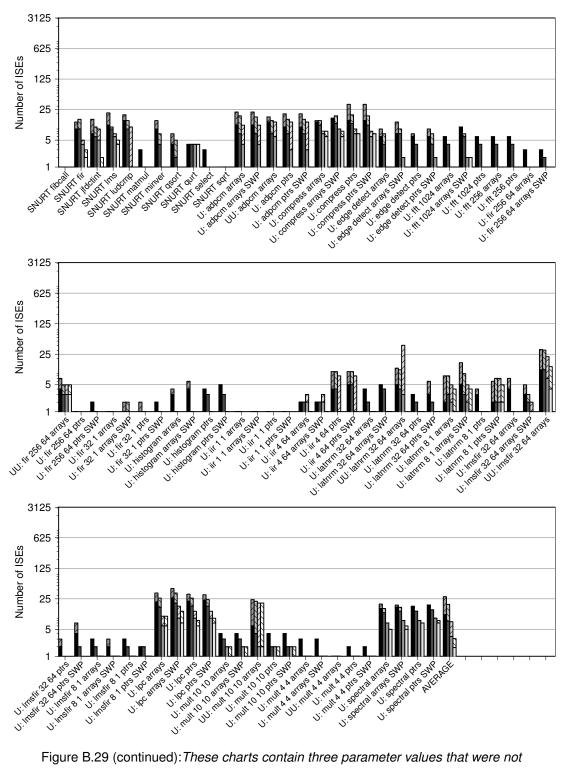

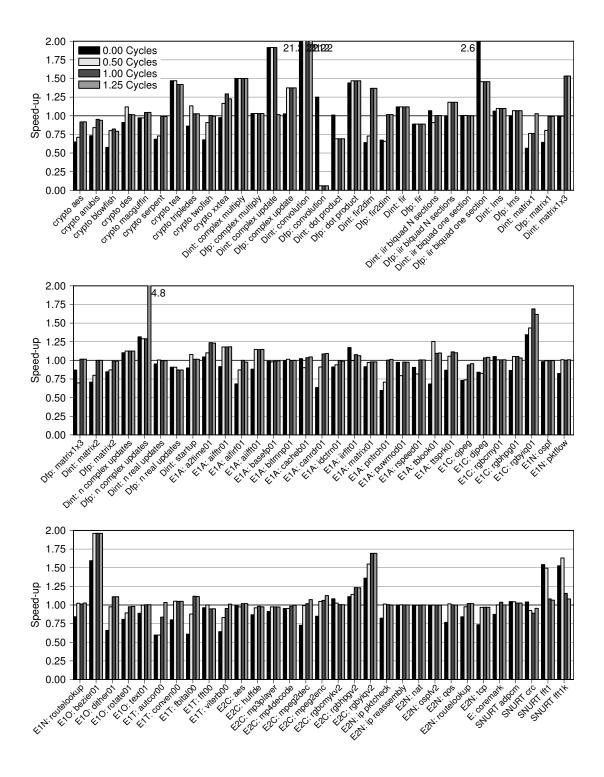

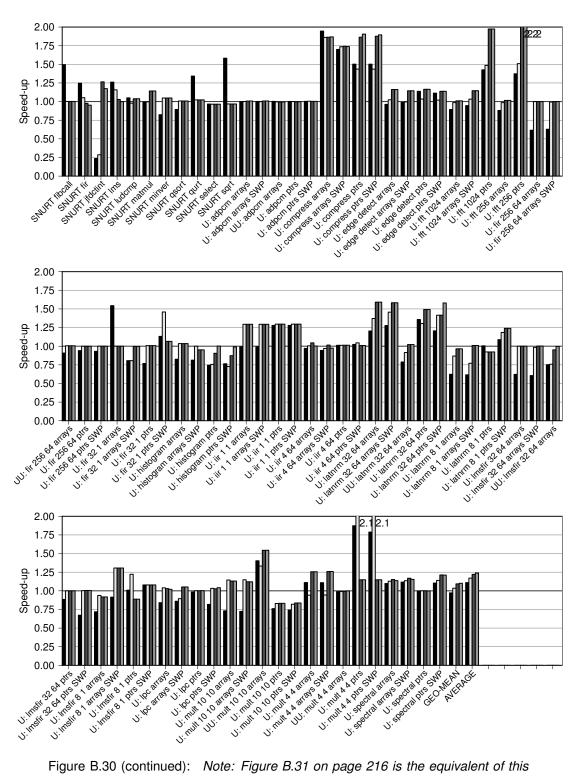

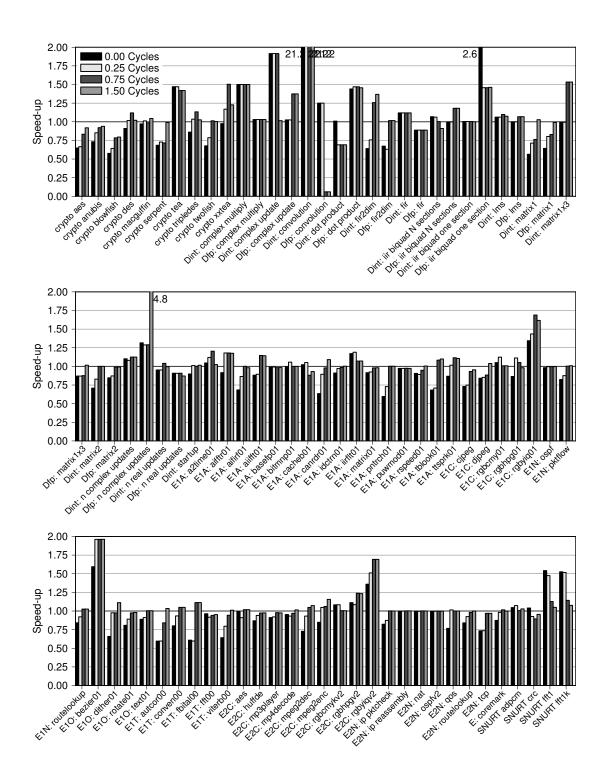

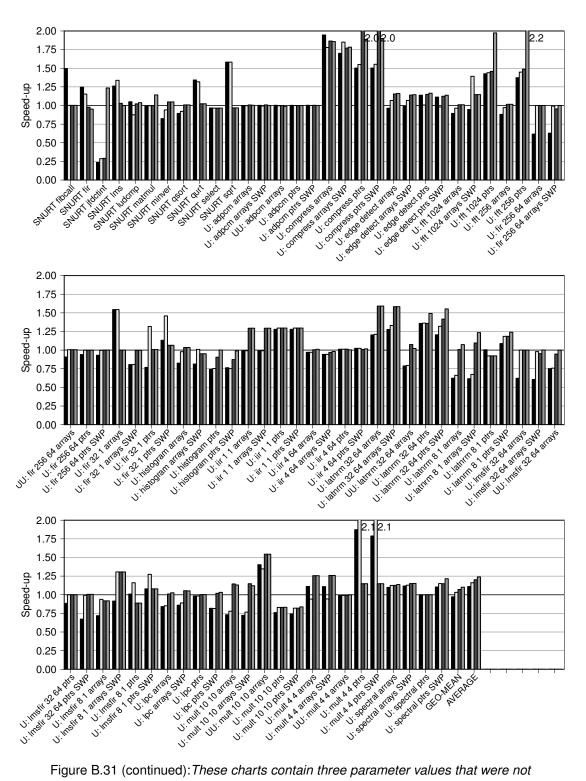

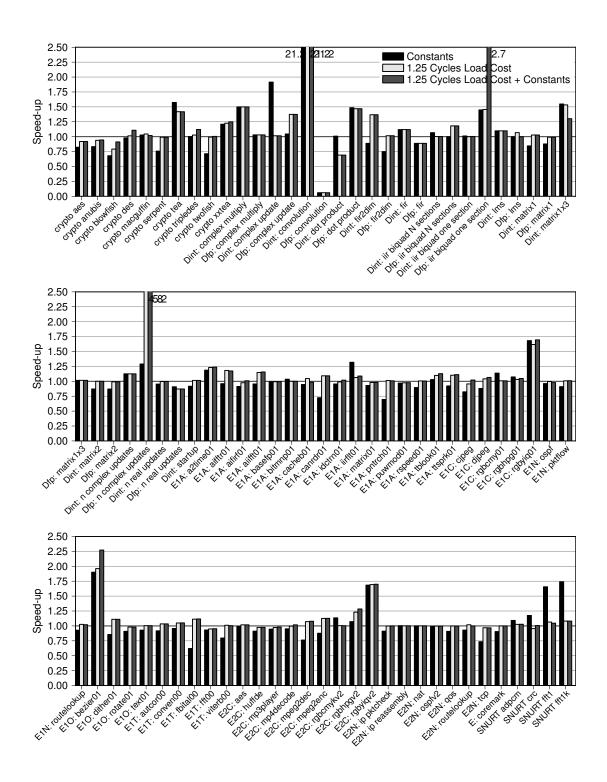

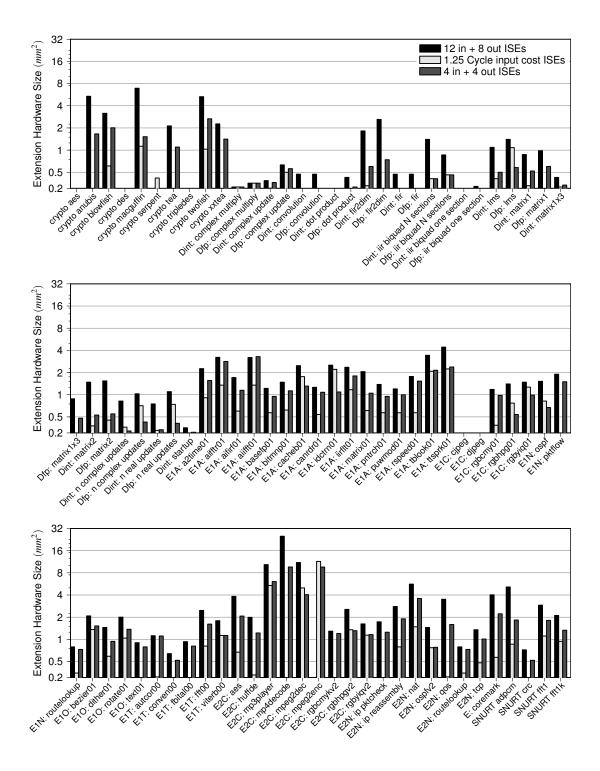

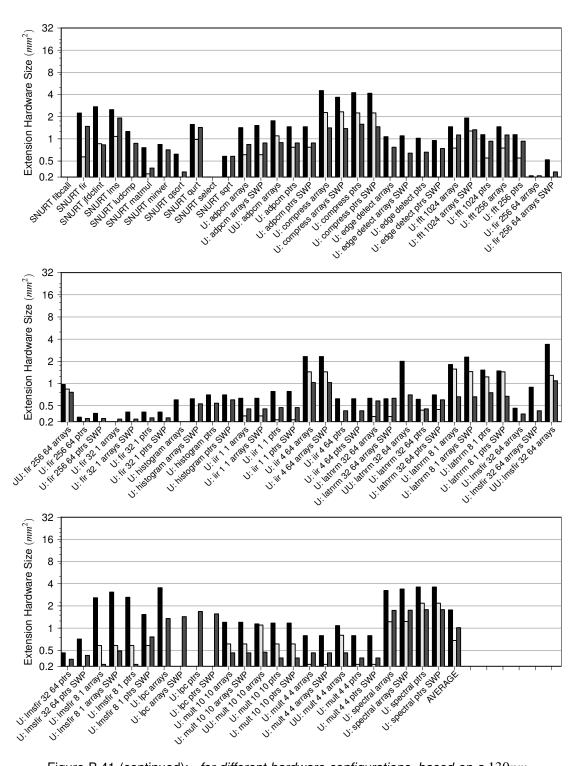

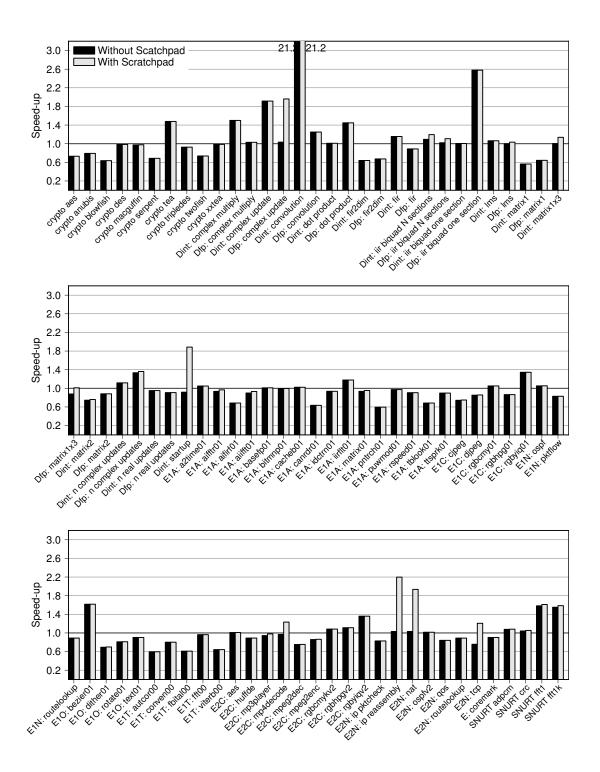

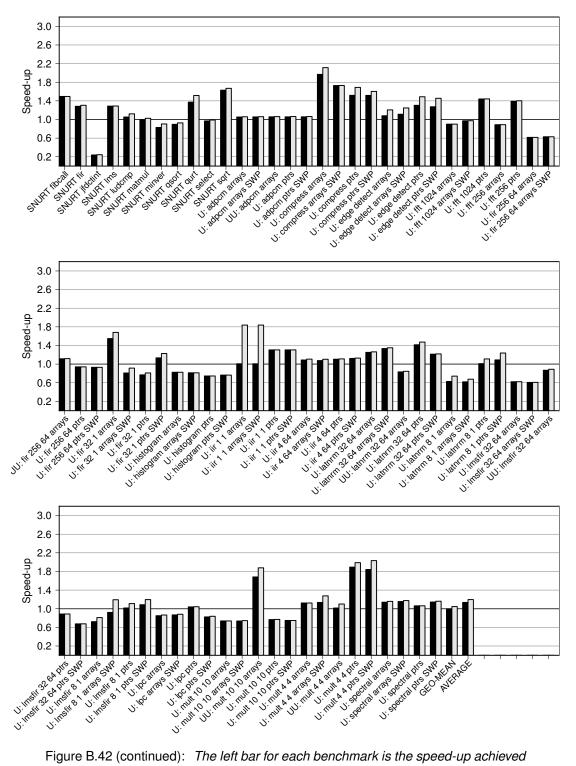

Finally, **appendix A** contains a list of the source-to-source transformations used in chapter 7 and **appendix B** has the complete versions of the charts shown in previous chapters.

### 1.5 Summary

This chapter has introduced the thesis by motivating the use of ASIPs in embedded computer systems but also outlining the compiler issues that they introduce. The contributions of this thesis were summarised and the structure of the thesis was described by means of a brief walk-through which showed how each chapter is motivated by the results of previous chapters.

## **Chapter 2**

# **Background and Infrastructure**

"It would appear that we have reached the limits of what it is possible to achieve with computer technology, although one should be careful with such statements, as they tend to sound pretty silly in five years."

— John Von Neumann, mathematician, 1903–1957. Quote from circa 1949.

This chapter provides a short overview of the technologies and techniques relevant to the work of this thesis and is organised as follows: section 2.1 introduces embedded processors and highlights the various design options offered by these devices; section 2.2 covers the toolchain used in this thesis; section 2.3 outlines an automated instruction set exploration (AISE) algorithm; section 2.4 explains the concept of Design Space Exploration and section 2.5 describes Dual Memory Banks. Section 2.6 summarises Genetic programming relating to the work of this thesis, section 2.7 introduces Graph Theory, and finally and section 2.8 sets out the benchmark suites used for evaluation.

### 2.1 Embedded Processors

A complete description of embedded processors would be too large for this thesis. Therefore, a short summary is provided here, more complete descriptions have been written by Fisher et al. [2005, Chapter 1] or Ienne and Leupers [2007].

As described in chapter 1, embedded processors are required to be low cost, low power and small:

- Low cost: embedded processors must be cheap to produce. Despite the importance of the processor they usually only account for a small portion of the overall design budget.

- Low power: hand-held devices are battery operated and even in static devices low heat output is essential.

- Small: hand-held devices have limited space for electronics, the smaller the size of the packaged processor the better. This is helped by increasing transistor density, which

allows multiple processors to be included on a single die, i.e. System-on-Chip.

#### 2.1.1 Embedded Processor Families

There are several different families of embedded processors:

- General Purpose Embedded Processors are designed to be usable in a wide-range of scenarios. Many started as scaled down versions of general purpose workstation processors. They can be used as stand-alone processors, but are often licensed as an IP-block for use within a system- on-chip.

- Microcontrollers are contained in most industrial electronics, from washing machines

to cars. They operate as stand-alone processors controlling mechanical processes. Their

design is often descended from older 8-bit and 16-bit architectures.

- VLIW and DSP are specialised for digital signal processing and multimedia functionality, they are effective for highly data-parallel processing. Their specialised design means they sometimes have to be paired with a general purpose processor.

- **Reconfigurable Processors** are processors that allow partial run-time reconfiguration. This is achieved with a microcode programmable micro-architecture, an FPGA is the full realisation of this. This fabric is not power efficient so reconfigurable processors rely on coarse-grain specialisation to exploit the reconfigurable fabric and save power.

- Application Specific Integrated Circuits (ASICs) are fully custom-designed pieces of hardware that can perform one task extremely efficiently. They have a very high design cost which unlike general purpose processors cannot be amortised across applications.

- Application Specific Instruction-set Processors (ASIPs) are normally general purpose

embedded processors with additional application specific instructions, though any kind

of processor can be used as a baseline. The use of a standard baseline means that their

design-cost is much lower than that of an ASIC.

### 2.1.2 Application Specific Instruction-set Processors

Designers of embedded processors are increasingly using techniques that were previously only used in general purpose processors to trade-off processor size for performance. As processor fabrication capabilities improve embedded processors designers are able to use the extra die-space to design more complicated processors with deep pipelining and superscalar processing. For example, the ARM Cortex-A8 processor has a 13-stage pipeline and is dual-issue superscalar [ARM Ltd., 2010a]. Additionally, the ARM Cortex-A9 uses out-of-order execution [ARM Ltd., 2010b].

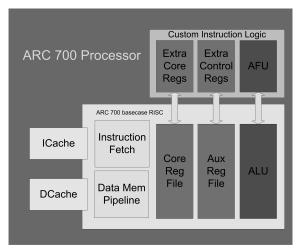

Figure 2.1: A simplified system-level view of ARC700 family architecture, demonstrating the pre-verified baseline core and its connection to an instruction set extension through custom registers and arithmetic units.

These general-purpose modifications will improve performance for almost every kind of program, either by allowing higher frequencies (deep pipelining), or by increasing the number of operations completed per-cycle (superscalar and out-of-order execution). Their generality, however, means they are power-hungry. In the situation were a specific set of applications are being targeted it is possible to use the information this provides to produce a specialised processor that is more power-efficient.

Historically the standard way of exploiting application specialism was to build an ASIC. As the tasks required of embedded computers have been increasing in complexity however, the cost and time required to design an ASIC has grown [Keutzer et al., 2002]. For most situations it is now preferable to build an application specific instruction-set processor (ASIP). These are cheaper and quicker to design because they are centred around a general-purpose baseline core which can be extended in an application-specific manner.

Extensible processors are based on the premise that processor speed, die area, and power consumption can be improved if the architecture of the processor is extended to include some features that are application-specific. This approach requires an ability to extend the architecture and its implementation, as well as the compiler and associated binary utilities, to support the application-specific extensions. It may seem counter-intuitive that adding to a processor will save die area, but application-specific extensions are more efficient than general purpose enhancements.

Processors may be extended *statically* or *dynamically*. A processor can be extended statically by augmenting the Verilog description of the processor prior to synthesis. Once the extensions have been incorporated, and the design has been fabricated, the extensions cannot be modified or further extended. A dynamically-extensible processor must be implemented,

either wholly or partly, in some form of field programmable logic fabric [Stretch Inc., 2007].

The simplest forms of extension, which are perhaps more properly considered to be forms of configuration, are the micro-architectural modifications that can be made to caches and their associated bus structures. Most embedded microprocessor cores provide the capability to adjust level-1 cache size, associativity and sometimes also block size and memory bus width. These all have a significant impact on performance, die area and power consumption. They are also relatively easy to exploit, as they require no changes to the instruction set architecture.

True architecture extensions begin with the capability to add custom instructions to a base-line instruction set. In their simplest form these may be predefined *packs* of add-on instructions, such as the ARM DSP-enhanced extensions included in the ARM9E [Francis, 2001], the various flavours of MIPS Application Specific Extensions [MIPS Technologies, 2007], or ARC's floating-point extensions to the ARCompact instruction set [ARC International, 2007].

These are domain-specific extensions, they can be used across many related tasks. Application-specific instruction set extensions are not predefined by the processor vendor but are instead identified by the system integrator through analysis of the application. To allow such instructions to be incorporated into a pre-existing processor pipeline, there must be a well-defined extension interface. From a high-level architecture perspective this interface will allow the extension to operate as a "black-box" functional unit at the execute (EX) stage of a standard RISC pipeline. This is an over simplification though, standard RISC instructions are two-input and one-output. Effective extension instructions require this constraint to be relaxed as extensions exploit the parallelism available in large instructions. This, therefore, generally requires an extended or additional register file, hence the need for an extension interface.

Practical extensible processors for the embedded computing market, such as those from ARC and Tensilica, normally have single-issue in-order pipelines of 5–7 stages. This permits operating frequencies in the range 400MHz to 700MHz at the 90nm technology node. Extension instructions may be constrained to fit within a single clock cycle, or may be pipelined to operate across multiple cycles. Current dynamically-extensible cores that use FPGA fabrics to implement the extension instructions cannot operate at these speeds. For example, extension instructions in the Stretch S5000 [Stretch Inc., 2007] operate at one-third of the clock rate of the processor.

The representation of instruction set extensions varies from one vendor to another, but essentially describes the encoding and semantics of each extension instruction in ways that can be understood by both a processor generator tool and all of the software tools (e.g. compilers, assemblers and simulators). There follows a process of translating the abstract representation of the extension instructions to structural form using a Hardware Description Language (HDL) such as Verilog or VHDL. This is then incorporated into the overall HDL definition of the processor, which is then synthesised to the target silicon technology or perhaps to an FPGA.

2.2. Infrastructure

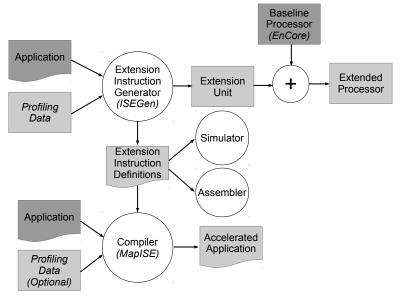

Figure 2.2: How the different tools in PASTA interact.

### 2.2 Infrastructure

The research presented in this thesis was undertaken within the PASTA project: Processor Automated Synthesis by iTerative Analysis. This was a large, multi-person project that aimed to automatically produce application specific processors and their associated tools. An application which is to be accelerated is provided and the PASTA toolchain produces a processor designed to accelerate that application as well as a compiler and a simulator that support the accelerated processor.

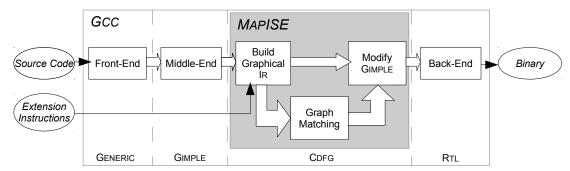

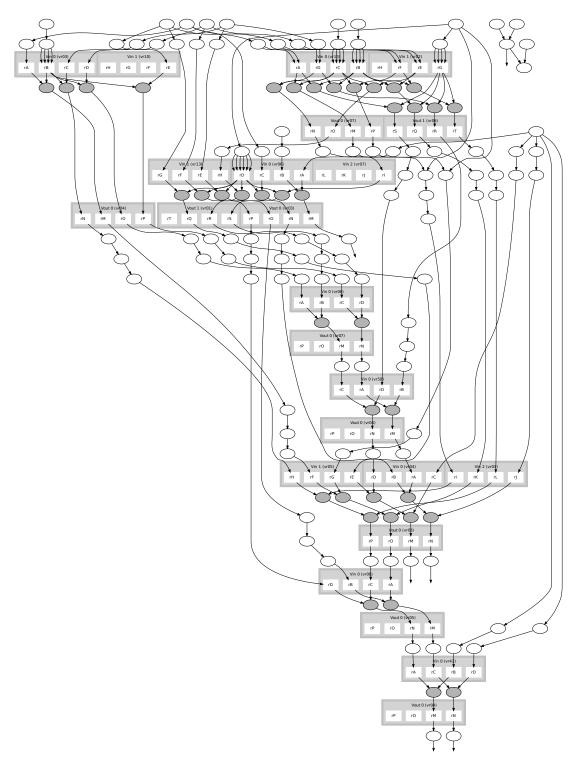

Figure 2.2 shows how the key components of the PASTA project interact. The target application and associated profiling data is passed to the extension instruction generator (*ISEGen*). This produces an XML specification of the generated extension instructions and a Verilog implementation of the extension unit. This Verilog extension unit can then be integrated with the *EnCore* baseline processor to produce an extended processor. The XML extension instruction specification is used to produce a new assembler and a simulator that supports the newly specified processor. Finally, this same XML specification is provided to the *MapISE* compiler along with an application (potentially the original target) and profiling data so as it can produce an accelerated application which will run on the extended processor.

**Disclaimer.** Of the components described in figure 2.2 only the compiler (*MapISE*) is presented as a contribution of this thesis. Specifically *ISEGen*, the simulator and *EnCore* were not developed by the author of this thesis but by other members of the PASTA project.

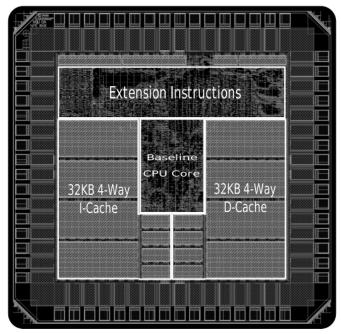

Figure 2.3: A specific instantiation of an EnCore processor with an extension unit.

### 2.2.1 EnCore

The extensible processor used in this thesis is the *EnCore*. This processor is an implementation of the ARCompact ISA. The ARCompact ISA is a 32-bit RISC ISA with 16/32-bit mixed mode instructions and optional extensions for digital signal processing, floating point operations and dual memory banks. The *EnCore* implementation is both low power and high performance: using a generic 130nm process it operates at a frequency of up to 375MHz, or up to 600MHz using a 90nm process. In terms of customisability: *EnCore* has configurable caches, it may be specified with 16, 32 or 64 general purpose registers and it has an extensive extension interface. Figure 2.3 shows the layout of a 90nm *EnCore* processor with a five stage pipeline, two 32Kb caches, 64 general purpose registers and additional extension instructions.

#### 2.2.2 EnCore Extension Interface

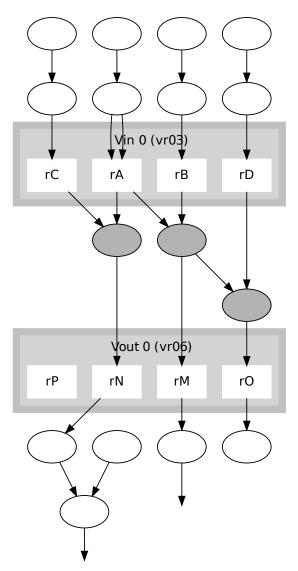

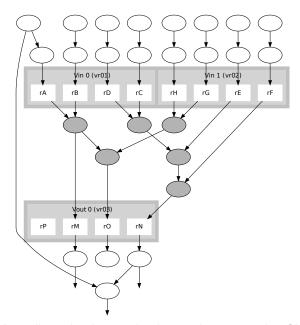

*EnCore's* extension interface is an addition which is not present in the original ARCompact ISA. It supports up to 255 extension instructions which read and write data via vector registers (four elements each). Extension instructions are used via a vextNNN mnemonic, e.g. vext001, vext002 etc. Each use of a vext instruction may use up to three input vectors and two output vectors, e.g.

This means that an extension instruction may have up to twelve input values and eight output values. For instructions which do not require every vector the register vr00 is used in

2.2. Infrastructure 15

| Vector |     | Scala | ar Registers |     |

|--------|-----|-------|--------------|-----|

| vr01   | r35 | r34   | r33          | r32 |

| vr02   | r39 | r38   | r37          | r36 |

| vr03   | r43 | r42   | r41          | r40 |

| vr04   | r47 | r46   | r45          | r44 |

| vr05   | r51 | r50   | r49          | r48 |

| vr06   | r55 | r54   | r53          | r52 |

| vr07   | r59 | r58   | r57          | r56 |

Table 2.1: The mapping of scalar registers to vector registers on EnCore.

the mnemonic as this is a read-only register that is hard-wired to all zeroes, writing to it has no effect. If an instruction does not need to read or write an entire vector then elements may be ignored by unsetting a bit in the read or write mask that is hard-coded into the instruction's hardware implementation. This is especially important when writing to vectors as otherwise register contents will be unnecessarily "clobbered" (i.e. live-ranges are interrupted and the compiler will need to spill any live values stored in those registers). There is also a special vmov instruction (or vext000) which is the vector register equivalent of a RISC mov instruction.

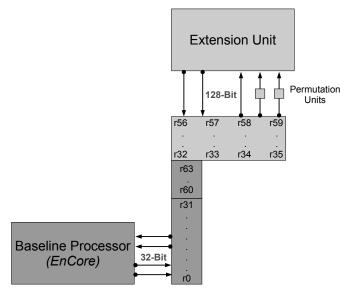

The extension unit interface in *EnCore* is only connected to the vector registers, extension instructions are not capable of accessing individual scalar registers. *EnCore* has seven physical vector registers, each of which contains four 32-bit elements. Each of these 28 elements are mapped to the upper-half of the general purpose register file, as shown in table 2.1. In the ARCompact ISA registers r00-r31 are already used for standard compilation and r60-r63 are used for specific purposes. This leaves registers r32-r59 for mapping to the vector register file. When these are arranged into four element vectors the limit of seven physical vector registers is created.

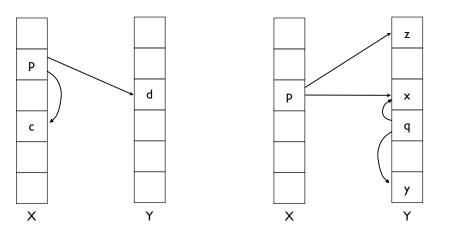

The baseline *EnCore* processor, however, can access any register r00–r63 including the registers r32–r59 which are mapped to vector registers. The baseline processor cannot access an entire vector at once, it can only access individual elements. Figure 2.4 shows the two separate register interfaces that are used to make this work. The baseline processor uses 32-bit ports to access single scalar registers and is connected to the entire register file with two read and two write ports. The extension interface uses 128-bit ports to access entire vectors at once and is connected to the extension register file with three read and two write ports. The reduced wiring complexity due to only having seven vector registers makes the third read port viable.

Figure 2.4 also shows that two of the vector register read ports have "permutation units". These allow the extension instructions to access the elements of vector registers in a different order than in which they are stored. Due to limited space in the instruction encoding only

Figure 2.4: Extension instructions interface with EnCore via vector registers.

| Vector | Permutation    | Scalar Registers |     |     |     |  |  |  |

|--------|----------------|------------------|-----|-----|-----|--|--|--|

| vr01   | Identity       | r35              | r34 | r33 | r32 |  |  |  |

| vr08   | Swap Central 2 | r35              | r33 | r34 | r32 |  |  |  |

| vr09   | Swap 2 Ends    | r32              | r34 | r33 | r35 |  |  |  |

| vr10   | Swap Pairs     | r34              | r35 | r32 | r33 |  |  |  |

| vr11   | Swap Left Pair | r34              | r35 | r33 | r32 |  |  |  |

| vr12   | Reverse        | r32              | r33 | r34 | r35 |  |  |  |

| vr13   | Rotate Left    | r34              | r33 | r32 | r35 |  |  |  |

| vr14   | Rotate Right   | r32              | r35 | r34 | r33 |  |  |  |

| vr15   | Rotate by 2    | r33              | r32 | r35 | r34 |  |  |  |

Table 2.2: The permutations available for vr01 on EnCore. vr16-vr63 provide equivalent permutations for vr02-vr07.

9 of the possible 24 permutations are available, these are shown in table 2.2. These nine permutations were chosen such that the other permutations are accessible by combining two permutations. This is done by using a vmov instruction to apply the first permutation and apply the second permutation via the vext instruction. The intention of the permutation units is to make it easier to use the output of one extension instruction as the input to another, especially in the context of loops.

### 2.2.3 ISEGen and uArchGen

The *ISEGen* tool generates a specification for a set of extension instructions to accelerate a provided target application by means of the ISEGEN algorithm [Biswas et al., 2006a]. The generation of the Verilog implementation of the extension unit is actually done by a second tightly coupled program called *uArchGen*.

uArchGen can optionally use resource sharing when creating the extension unit. This means that if two instruction implement the same operator the can share the same hardware (e.g. they both contain a multiply then the same hardware multiplier could be used for both). This can reduce performance, however, as the extension instructions are implemented over three of En-Core's five pipeline stages so as to avoid large instructions decreasing the maximum achievable clock frequency. This means that if two instructions want to access a shared resource at the same time a pipeline bubble will occur. uArchGen can also fit the extension unit into a target die area, but it does that by excluding some of the instructions that ISEGen finds. As this thesis is evaluating the compiler and not the hardware implementation, uArchGen is used in its default mode of not using resourcing sharing and allowing unlimited die size.

*ISEGen*, however, has many heuristic parameters. The core ISEGEN algorithm uses seven heuristic weights that affect the search process. These are all left at their default values for this thesis as small changes can drastically slow down the algorithm. Other parameters are safer to use, such as changing the maximum number of input and outputs that an instruction may have or changing the expected costs of implementing certain operations in hardware.

### 2.3 Automated Instruction Set Extension

An AISE algorithm used in this thesis is described below, but many others exist, Galuzzi and Bertels [2011] provide an overview of the topic with references to many other algorithms. There are actually two AISE algorithms implemented by the tools used in this thesis. The simpler algorithm is described below while also outlining AISE methodology. The more advanced algorithm is described by Biswas et al. [2006a].

### 2.3.1 Atasu AISE Algorithm

Atasu et al. [2005a] implemented an integer linear programming based automated instruction set extension tool to find optimal extensions. Each basic block was defined as an integer linear program, along with the input and output dependencies of the block. Additional constraints were then added to the model such as the maximum number of inputs or outputs an instruction may have and enforcing the convexity constraint. The convexity constraint states that if a custom instruction provides an input to some node, and uses the output of the same node then that node must be contained within the custom instruction or the instruction is invalid. Without

this the node may need to be scheduled both before and after the custom instruction, which is clearly impossible. Every node in the basic block implements some simple operation, in the model there are hardware and software costs for each operation. The hardware cost is the fraction of a cycle (maybe greater than 1 cycle) that it takes to perform the operation. The software cost is the number of cycles the standard instruction that performs this operation takes to complete. The integer linear program is then used to find the single instruction which results in the greatest reduction in schedule length from implementing that set of nodes in hardware. Once an instruction is found, all the nodes implemented by that instruction are collapsed into a single node and the algorithm is re-run to find another instruction (the collapsed node may not be included in another instruction). This means given the already picked instructions the next instruction picked will be genuinely optimal – however the overall set of instructions isn't necessarily optimal.

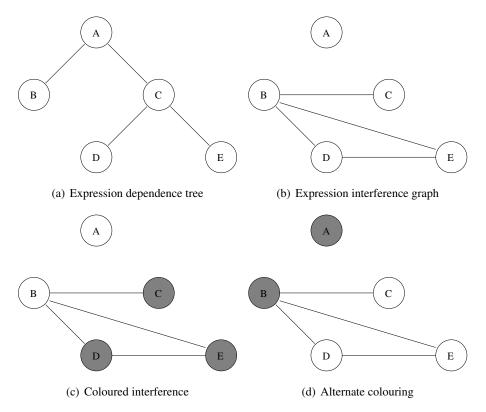

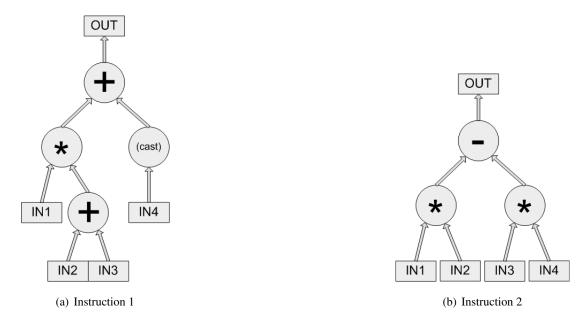

The ILP AISE algorithm generates data-flow-graph templates through the conversion of basic blocks to a set of constraints in an *Integer Linear Program (ILP)* and solution of that program. For the implementation used in chapter 7 a tool built into a CoSy compiler uses the *lp\_solve* library [Berkelaar, 2008] to solve such problems and generate a set of candidate templates for an entire program. Constraints are declared for each basic block to generate a template such that:

- 1. The template is **convex** (i.e. there is no dataflow path between two operations in the template that includes an operation that isn't in the template), so that it may be scheduled.

- 2. Input and output **port constraints** are met (i.e. the number of register input and output ports are sufficient), so that it may be implemented.

In addition to the constraints, a goal function is also expressed. For this algorithm, the goal is the estimated serial time of execution in cycles of the instructions covered by the template, minus the estimated critical path of the template. The former is denoted the "software" execution time, and is indicative of the time the instruction would take to execute on the unextended architecture. The latter is denoted the "hardware" execution time, and is a real-valued factor of the cycle time taken to execute the template as a single instruction. A cycle time for each software and hardware operation is specified to the tool a-priori to ILP construction, to allow for the constraints to be generated. The per-template difference between software and hardware execution time is the per-execution gain in cycles to an architecture implementing that template. Following the generation of templates from basic blocks, the templates are checked for isomorphism with one another using the *NAUTY* [McKay, 2008] graph isomorphism library, then ranked using the product of their estimated usage and per-execution gain. The top four of these instructions are then recorded alongside their performance estimates for inclusion in results.

### 2.3.2 HW/SW Codesign

HW/SW Codesign was an active research area in the 1990's and has inspired subsequent work on Electronic System Level Design, e.g. [Keutzer et al., 2000; Balarin et al., 2003]. A comprehensive summary of research directions, approaches and tools has been written by Rozenblit and Buchenrieder [1995]. This work covers a broad scope of issues, typically ranging from the analysis of constraints and requirements down to system evaluation and design verification. In contrast, this thesis focuses on a more specific, individual problem, namely that of HW/SW partitioning in the context of extensible application-specific processors. The primary feature that distinguishes HW/SW Codesign from AISE HW/SW Partitioning is software synthesis. In HW/SW Codesign a problem definition is used to synthesise both hardware and software, in AISE HW/SW Partitioning portions of the software are implemented in hardware.

### 2.4 Design-Space Exploration

Design-space exploration is an optimisation process in the design flow of a System-on-Chip. Typically, the search has multiple constraints (performance, power, cost etc.), and targeting an often multi-dimensional and highly non-linear optimisation space. Multiple dependent levels (algorithm, SW, and HW design space exploration) of interaction make it difficult to employ isolated local search approaches, but require a combined effort crossing the traditional boundaries between design domains, providing feedback paths and integrating tools into larger frameworks.

Configurable and extensible processor cores such as the ARC 600 and 700 have a number of capabilities to allow their instruction set and micro-architecture to be optimised for a particular application. Design concerns guiding the exploration are often reduced to metrics such as execution speed, power usage, and die area; each of these metrics has an accompanying relevant design space in the configuration and extension domain.

Meeting the main execution speed requirement means that no further increase in speed is generally useful, other than to provide an overhead for development. Application deadlines will be met and the system built around the core will be able to communicate and process data without stalling due to system-level deadlines missed by the core.

Once execution speed requirements have been met the focus of designers may be switched to secondary axes of design concern, such as power usage. Efforts in addressing one axis of design concern may make use of excesses in other axes. For example if performance exceeds requirements the clock speed of the ASIP may be reduced, reducing the power consumption. These secondary concerns have additional design spaces of the configurable core available to be explored for satisfactory areas; for example clock gating, dynamic voltage scaling, and unit pruning. These are, however, outside the scope of instruction set extension and are not covered

here.

Unfortunately the "second order" effects of core extension are not always beneficial and are often hard to predict with any accuracy. Adding more logic to a core can increase the critical path and force a reduction in the overall clock speed. A complicated web of non-orthogonal trade-offs forms a space which can only be explored efficiently with iterative, automated help.

Instruction set extensions affect all three of the aforementioned axes of design concern. The guiding metric in deriving extensions is often still application execution speed; designers will add instructions that "cover" the hottest (most frequently executed) sections of their application code. The intention is that by partitioning the application code into areas covered by extension instructions, subsections of micro-architecture can be dedicated to the servicing of these new instructions. In this highly application-specific design space, several sources of micro-architectural optimisation are currently brought to bear on the hardware performance of the new instruction:

- 1. **Operation-level/Spatial parallelism**; Parallel instances of arithmetic hardware in order to perform multiple operations at-once, as allowed by dependencies.

- 2. **Reduced register-transfer overhead**, due to the increased locality of communication within the functional unit used to represent the new instruction.

- Aggregation of clock period surplus present in most arithmetic functions. In particular, bit-wise functions have a hardware latency far below the clock period in most cases.

This growing catalogue of optimisation aims to ensure that the "hot-spot" represented by the new instruction achieves the maximum speed possible, by trading off die area for an increase in execution speed, a decrease in power usage, and a decrease in code-size. Often these extensions correlate to very frequently executed sections of code, and so the benefits for a relatively small increase in die-size can be very tempting to designers. The problem remains to find a way to accurately model both the existing architecture and the full range of potential extensions in such a way as to efficiently automate exploration.

It has been shown [Bonzini and Pozzi, 2006] that new search methods and heuristics can be developed to control the application of transformations, with respect to the new set of goals inherent in AISE as compared to code generation. Transformations once targeted at the backend would attempt to limit increasing basic block size due to register pressure, e.g. [Gupta and Bodik, 2004]. Now in instruction set extension the drive is towards the largest possible basic block size for analysis.

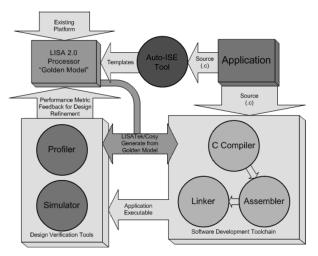

Figure 2.5: The Compiler-in-loop methodology for ASIP design space exploration.

#### 2.4.1 Automated Instruction Set Extension

Automated instruction set exploration (AISE) has been actively studied in recent years, leading to a number of algorithms [Peymandoust et al., 2003; Biswas et al., 2006a; Atasu et al., 2005b; Pozzi et al., 2006] which derive the partitioning of hardware and software under microarchitectural constraints. Work is still underway in defining the full space of exploration even in purely arithmetic instruction set design [Verma and Ienne, 2006]. Work to include better models in tools has allowed for better decisions about the performance and feasibility of extensions [Pozzi and Ienne, 2005].

The current exploration approach of using a range of tools operating on a canonical systemlevel ADL, is described as "Compiler-in-Loop Design-Space Exploration" [Hohenauer et al., 2004]. It was originally motivated [Glökler et al., 2003] through the discovery that iterative and methodical exploration of ASIP design is very beneficial in decreasing time-to-market. The CoSy [ACE Associated Compiler Experts, 2011] and Processor Designer [CoWare, 2007] tools feature in many such frameworks; figure 2.5 illustrates such a combination. The compiler, binary utilities such as assembler and linker, profiler, and simulator are generated from a single "Golden Model" written in LISA 2.0. This toolchain may then be used to evaluate the performance of the architecture described by the model. The application for which the model is intended is compiled, assembled, linked, simulated and profiled for run-time and other statistics. The Automated Instruction Set Extension tool is run over the application to determine a set of effective instructions to add to the model. The designer selects a subset of these instructions to add, and is able to use the generation facilities of the compiler-in-loop framework to generate a new toolchain for further performance analysis of the program. The designer is then free to modify the constraints imposed on the AISE tool (such as register file input / output) and repeat the loop to further explore the design space of the application specific processor

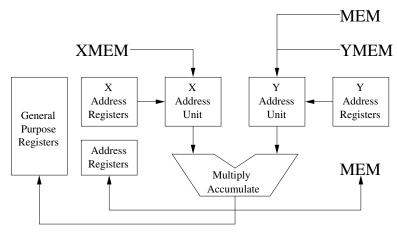

Figure 2.6: Example DSP processor architecture with dual-input memory data path and MAC unit.

described by the Golden Model. In this way, the designer is freed from many drawbacks inherent in design space exploration without such a framework. They may directly test the impact of a design decision without the need to manually re-implement a simulation and compilation toolchain. This top-down automated approach to design exploration and evaluation has been proven successful in case studies such as those cited in Hohenauer et al. [2004].

# 2.5 Dual Memory Banks

Digital signal processors are often required to process "infinite streams", e.g. decoding an incoming television signal or encoding a mobile telephone call. For these tasks the input data will keep on arriving for an unknown period of time, so the processor must be able to process the stream constantly in real-time.

A key performance bottleneck when doing this is memory bandwidth. To address this most digital signal processors have dual memory banks. For example, the TigerSHARC DSP platform that is used in chapter 6 is a hybrid VLIW/superscalar processor — this means it can issue multiple instructions per cycle. It also has dual memory banks (called "X/Y Memory"), this means it can issue two loads or two stores each cycle as long as the accesses are not to the same memory bank (i.e. it can access bank X once a cycle and bank Y once a cycle). This requires the compiler to split the program's data between the two banks in a way that maximises the possibilities for parallel accesses.

Figure 2.6 shows a generic DSP architecture with dual memory banks *X* and *Y*. These two banks are accessed via the *X* and *Y* addressing units, which may support DSP specific post-increment addressing modes. TigerSHARC's memory architecture fits this generic design.

#### 2.5.1 DSP-C and Embedded C

Programmers can use dual memory banks directly with *DSP-C* [ACE Associated Compiler Experts, 1998], or its later extension *Embedded C* [JTC1 et al., 2004; Beemster et al., 2005]. These are sets of language extensions to the ISO C programming language that allow application programmers to describe the key features of DSPs that enable efficient source code compilation. As such, DSP-C includes C-level support for fixed point data types, circular arrays and pointers, and, in particular, divided or multiple memory spaces.

DSP-C uses address qualifiers to identify specific memory spaces in variable declarations. For example, a variable declaration like

defines an integer array of size 32, which is located in the *X* memory. In a similar way, the address qualifier concept applies to pointers, but now up to two address qualifiers can be provided to specify where the pointer and the data it points to is stored. For example, the following pointer declaration

int

$$X * Y p$$

;

describes a pointer p that is stored in Y memory and points to integer data that is located in X memory. For unqualified variables a default rule will be applied (e.g. to place this data in X memory).

# 2.6 Genetic Programming in Compilers

There is a growing research field which makes use of machine learning in compilers. For example: early work was undertaken by Agakov et al. [2006], Wang and O'Boyle [2010] use machine learning for automatic parallelisation and Fursin et al. [2008] produced a complete machine learning compiler. For the purposes of this thesis, only one technique will be considered: genetic programming (GP) which is used in chapter 6.

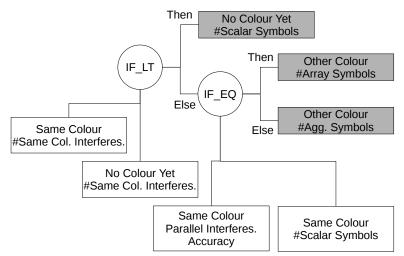

Genetic programming is based on the same evolutionary principles as genetic algorithms. Instead of mutating and breeding strings, however, trees are used to represent functions [Cramer, 1985; Koza, 1992]. Trees are mutated and are allowed to survive by their "fitness", the higher their "fitness" the higher the probability that they will make it into the next generation. To breed two trees, one of each of their sub-trees are swapped and to mutate a tree, a sub-tree is replaced with a randomly generated sub-tree.

The algorithm is initialised with a population of entirely random trees. Each member of the population is then assigned a fitness by a provided fitness function. The next generation will be the same size as the current generation, X% of its members will be produced by breeding and 100 - X% will be produced by mutation -90 is a typical figure for X. Members are selected for breeding or mutation based on their fitness, there are many ways of doing this but

the experiments in this chapter use tournament selection. A set of size N is picked entirely at random with no bias towards fitter candidates, then the fittest of the N is selected. This means that the N-1 least fit candidates will never be chosen and the larger N is the stronger the bias towards fitter candidates becomes. Once the new generation has been formed the old one is discarded and the process starts-over with the new generation until some generational limit is reached, then the fittest candidate in the current generation is returned.

Stephenson et al. [2003b] used genetic programming in a compiler. They use genetic programming to generate heuristics for priority functions related to hyperblock formation, register allocation and data prefetching. Although many of the results they report are due to evaluating the heuristics on their own training data they also present results for separate test benchmarks. They were able to improve on the existing heuristic in a mature compiler by 9% on average for hyperblock formation across many SPEC benchmarks, demonstrating that genetic programming has potential within compilers.

Leather et al. [2009] take a different approach and use genetic programming to search a feature space as defined by a grammar. The work of Stephenson et al. [2003b] (and the work in chapter 6) both use GP to generate compiler heuristics, Leather et al. [2009] generate "features" which are then used by heuristics. This technique outperformed both the default *GCC* heuristic and a support vector machine (SVM) approach.

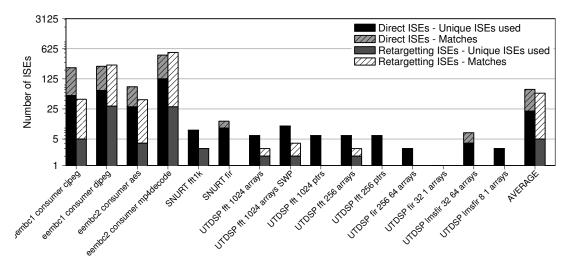

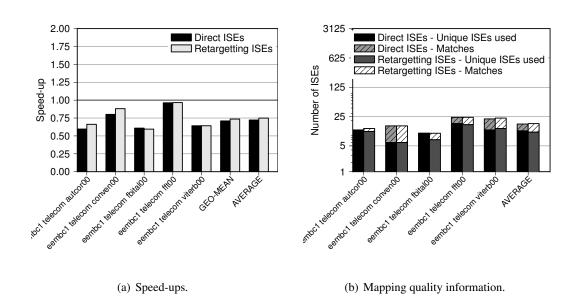

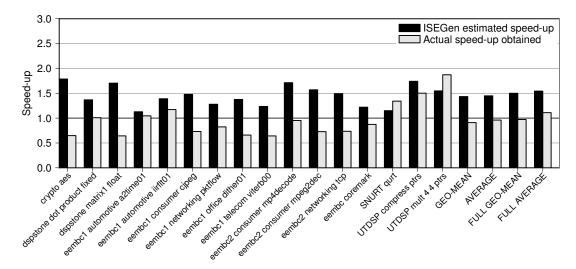

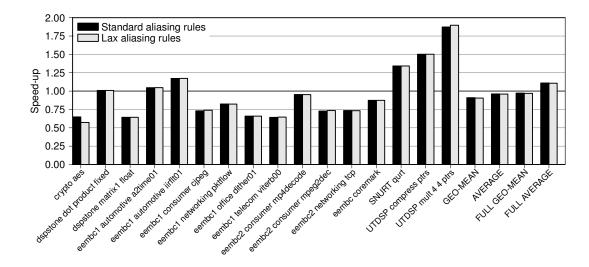

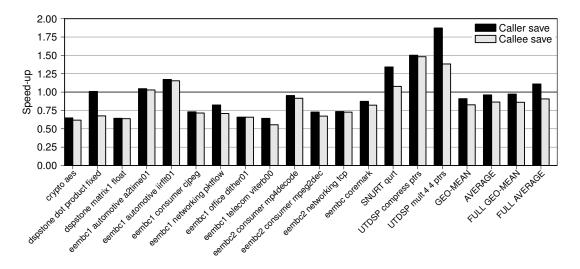

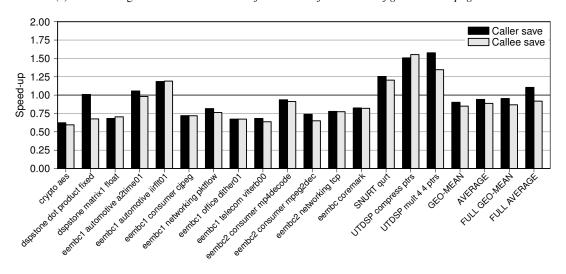

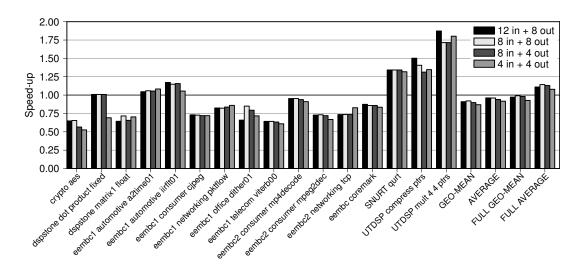

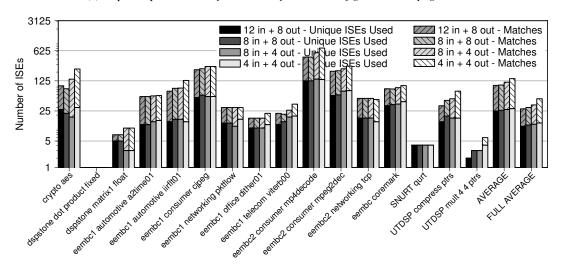

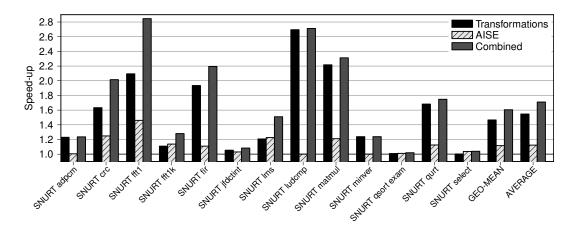

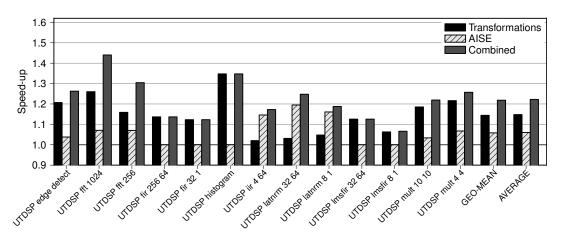

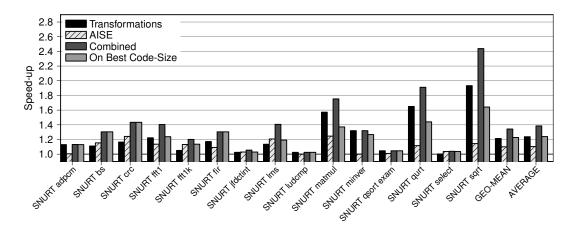

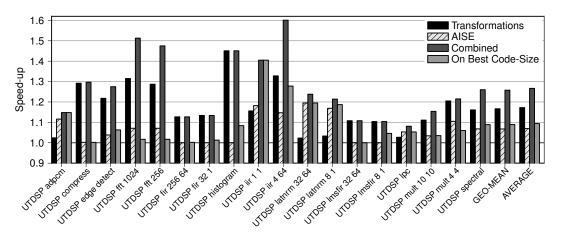

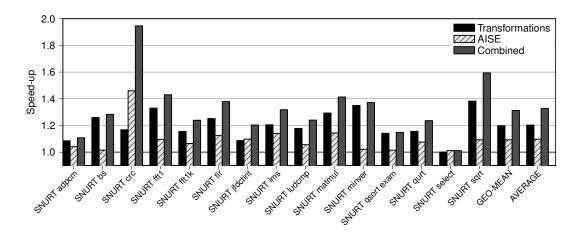

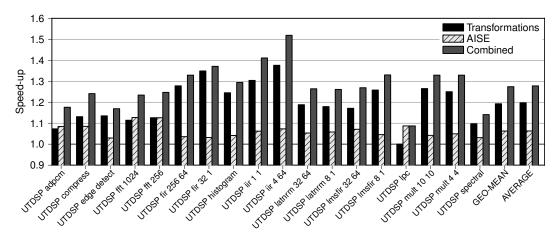

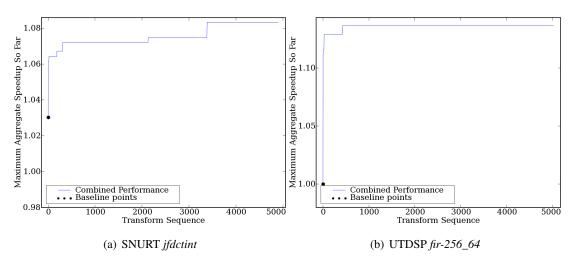

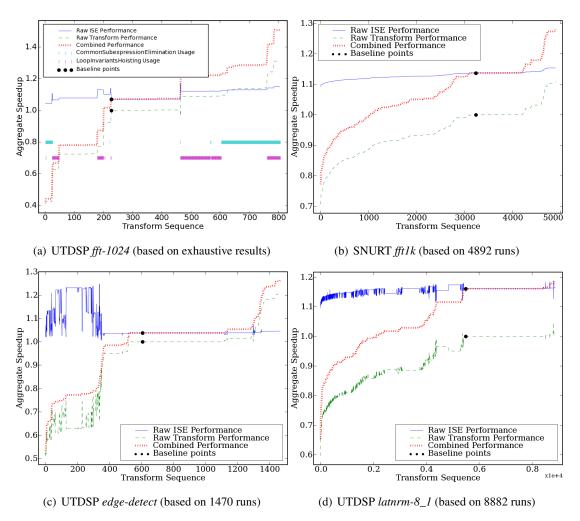

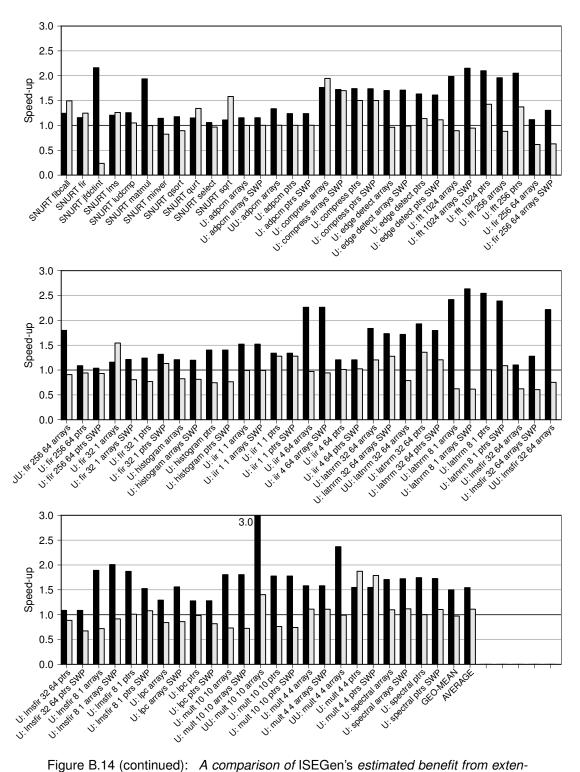

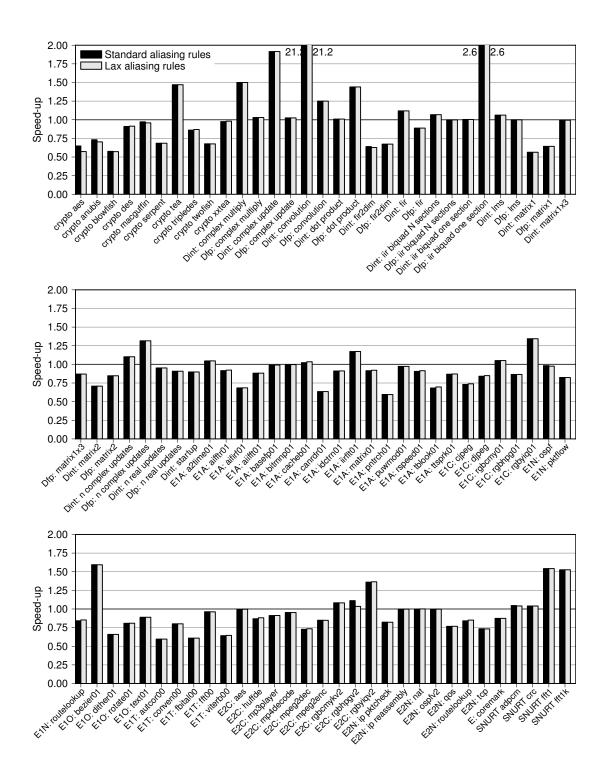

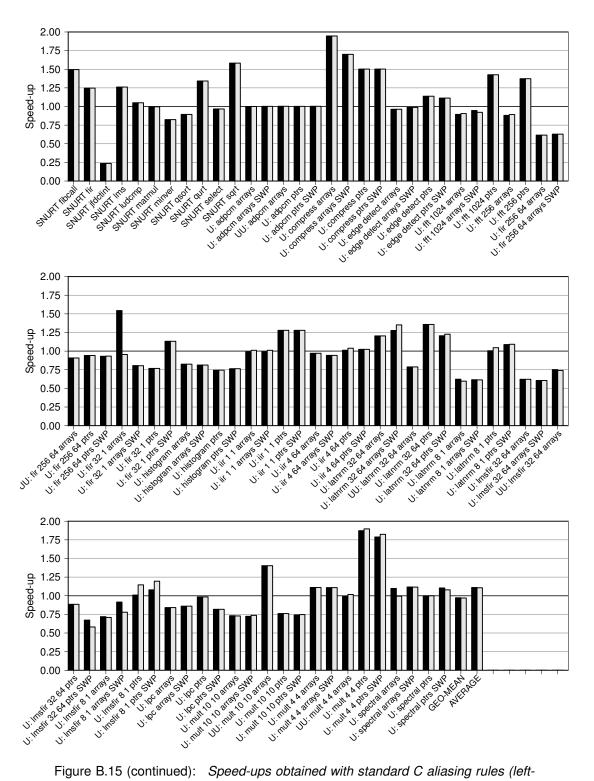

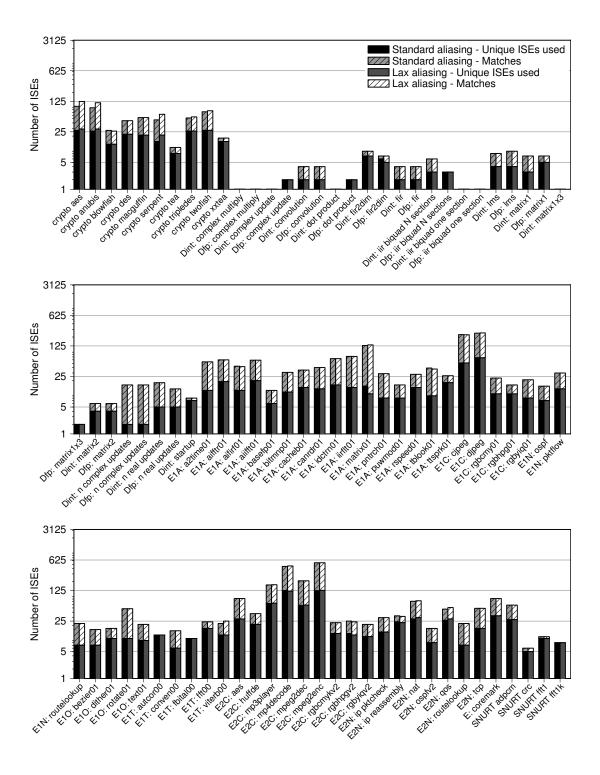

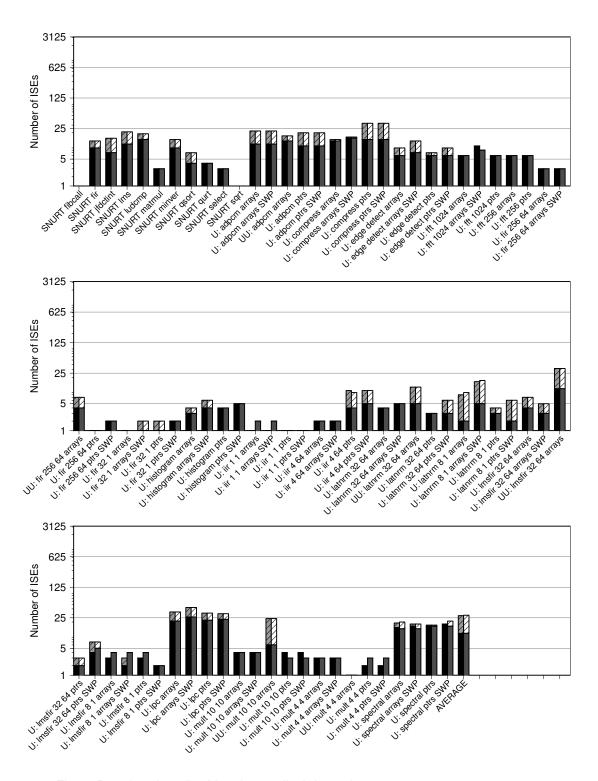

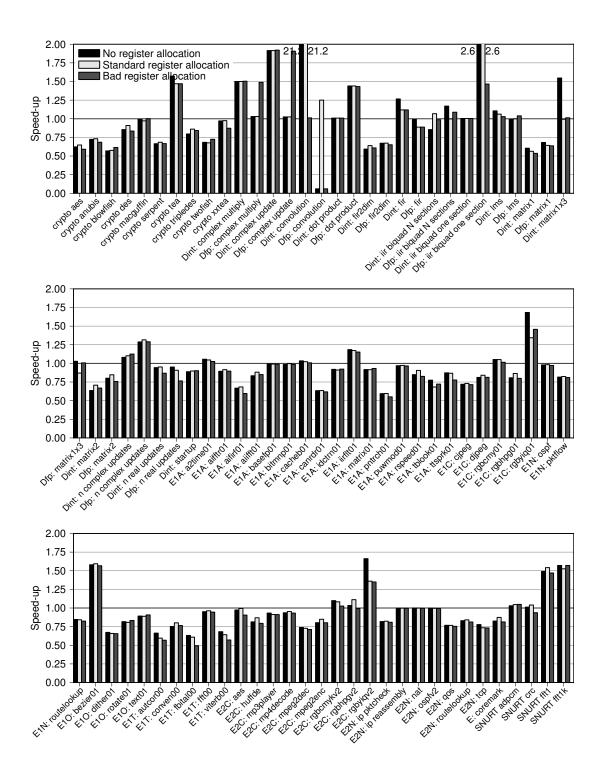

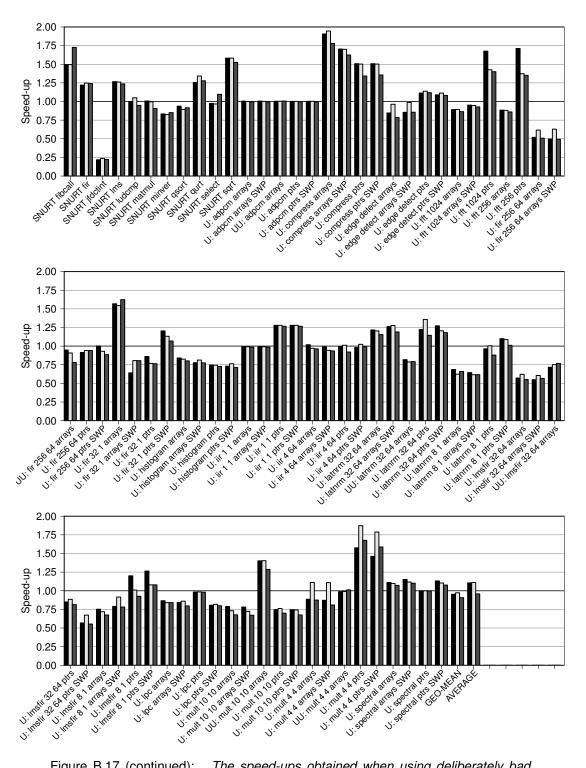

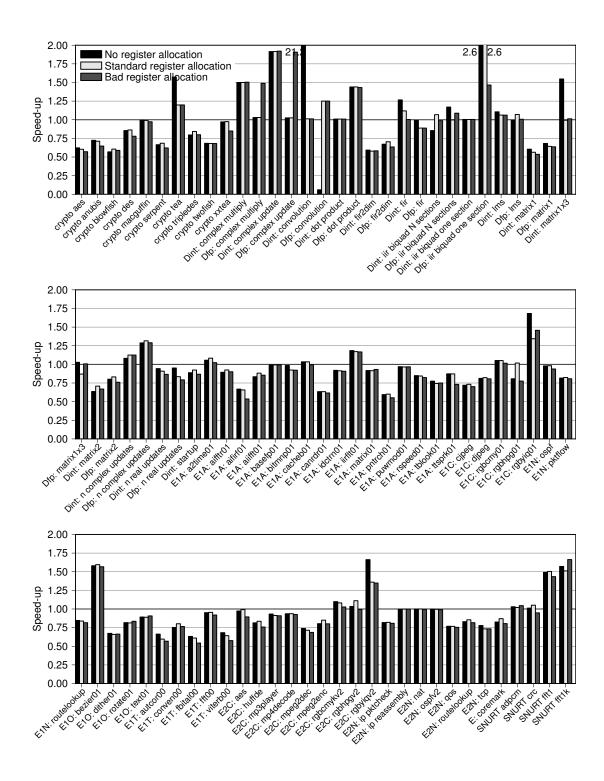

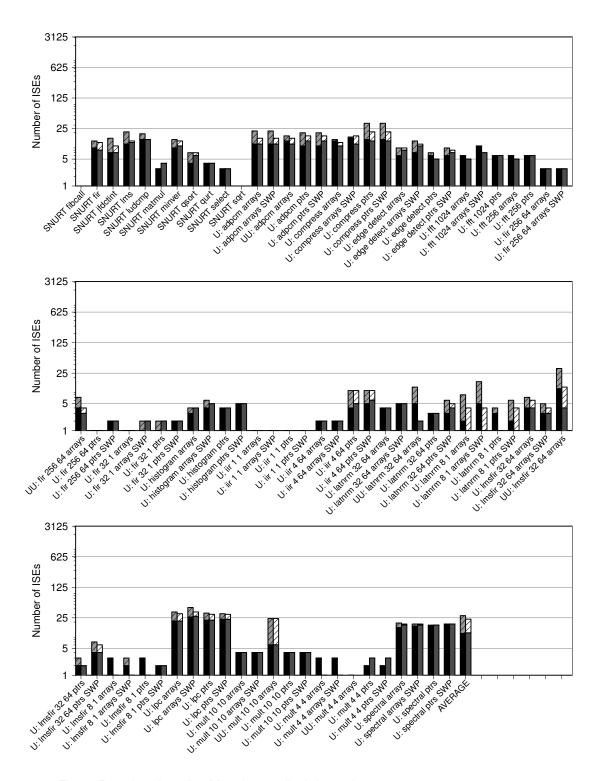

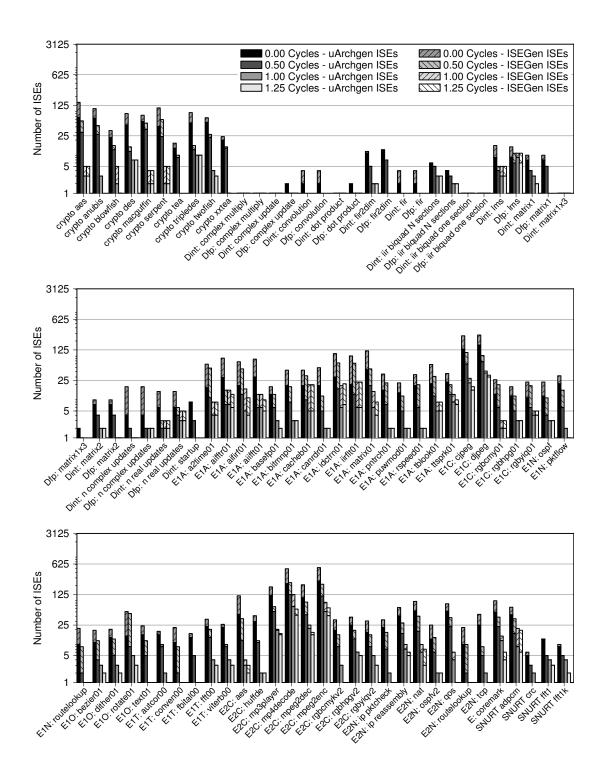

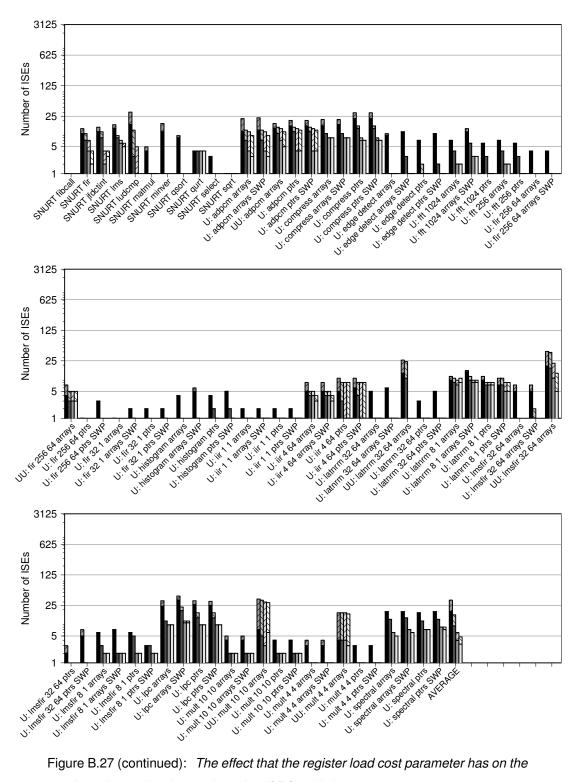

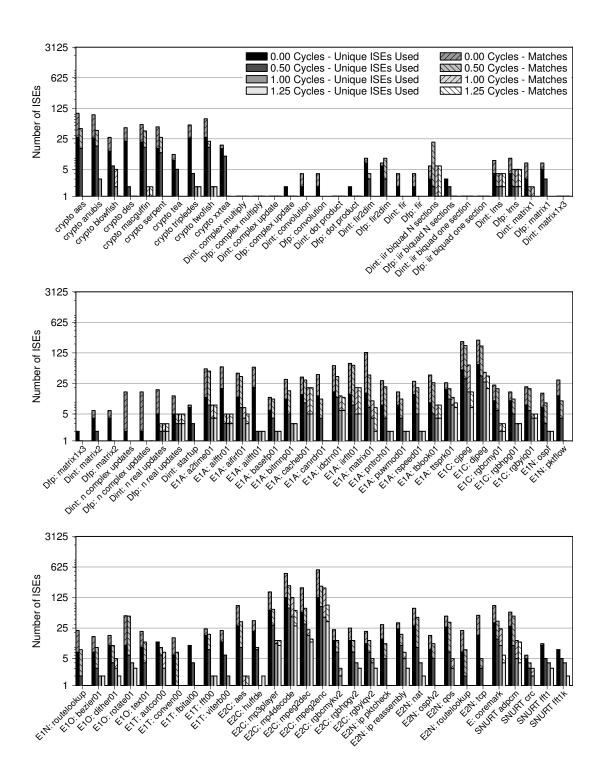

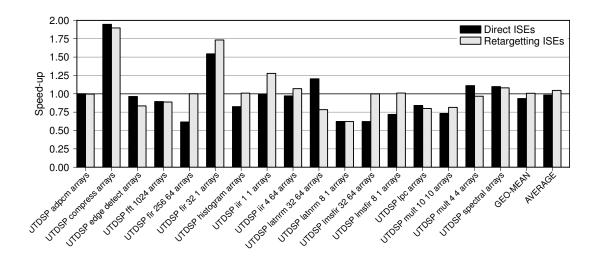

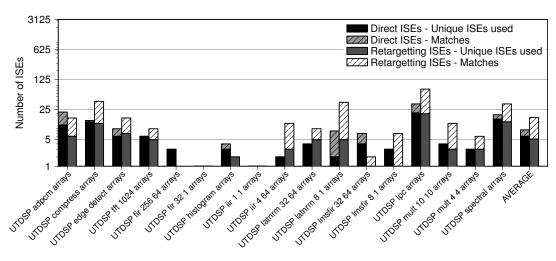

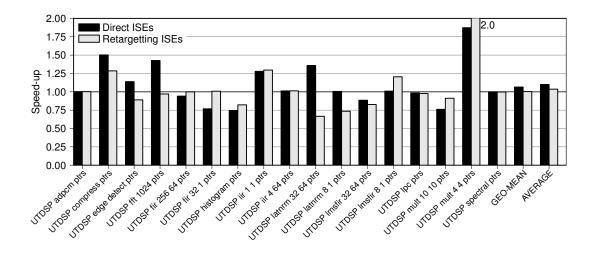

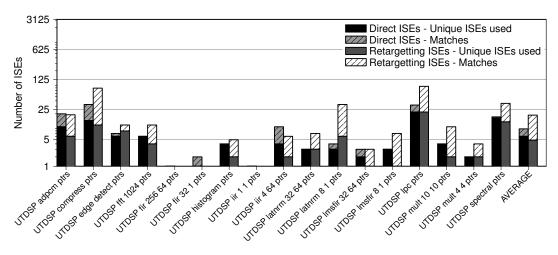

# 2.7 Graph Theory