# A VLSI SMART SENSOR-PROCESSOR FOR FINGERPRINT COMPARISON

by

**Stuart Anderson**

A thesis submitted to the Faculty of Science, University of Edinburgh, for the degree of Doctor of Philosophy

Department of Electrical Engineering, 1993

# **Abstract of Thesis**

Image processing techniques are increasingly being applied to new applications beyond their traditional uses for remote sensing image data enhancement. These new areas, such as machine vision for automated production line monitoring and control and financial transaction security, require low-cost compact but highly reliable systems. This thesis discusses some of the problems in achieving this goal and presents a novel approach to the implementation of low-cost real-time image processing systems.

The method presented in this thesis utilises the usual system design leverage offered by VLSI of reduced cost, power, size and weight; achieved as a result of the freedom to efficiently map algorithms to hardware. In addition, substantial further advantages are obtained by integrating the image sensor and preprocessing interface circuits onto the same silicon substrate.

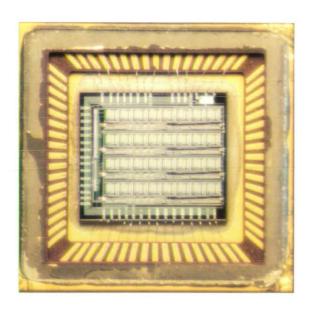

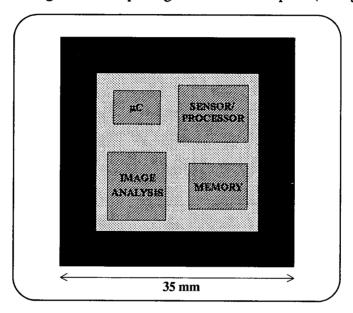

During the course of this work three custom integrated circuits for real-time image processing were designed, simulated, fabricated and tested. Two of the devices form the image processing core of an entirely new, working, fingerprint based access control system. These designs then led to the development of the third device and the main focus of this thesis, a highly integrated sensor-processor for fingerprint comparison. This device has applications in many fields where personal identification is vital such as physical access control, financial transactions and health care. The architecture can also be adapted to address more general pattern recognition tasks. It is shown that through architectural enhancement of the fingerprint comparison system increased processing performance is obtained. Efficient integration of the sensing, processing and memory elements also provides the potential for reduced manufacturing costs.

# **Declaration**

Unless otherwise stated, the material contained herein was researched and composed entirely by myself in the Department of Electrical Engineering at the University of Edinburgh, between October 1987 and March 1993.

Stuart Anderson

# Acknowledgements

I wish to express my thanks to all those people who have helped in any way towards this thesis.

In particular I would like to thank my supervisor, Dr. D. Renshaw, for his technical guidance and constant encouragement throughout this work. I am also indebted to W.H. Bruce and Prof. P.B. Denyer for describing the intricacies and minutiae of the fingerprint comparison algorithm. A special word of thanks must go to G. Wang for his advice and technical support in the development of the custom image sensor.

Finally, I would like to thank Dr. Y.V. Roberts for her invaluable suggestions and comments during the final preparation of this thesis.

I conclude with an acknowledgement to the following organisations, De La Rue Plc., VLSI Vision Ltd., and the SERC, whose funding has made this research possible.

# **Table of Contents**

| 1. | INTRODUCTION                     | 1  |

|----|----------------------------------|----|

|    | 1.1 MOTIVATIONS                  | 1  |

|    | 1.2 OBJECTIVES                   | 4  |

|    | 1.3 THESIS SUMMARY               | 6  |

| 2. | VLSI FOR IMAGE PROCESSING        | 8  |

|    | 2.1 IMAGE PROCESSING             | 8  |

|    | 2.2 ARCHITECTURES                | 10 |

|    | 2.2.1 Software                   | 10 |

|    | 2.2.2 SISD                       | 11 |

|    | 2.2.3 SIMD                       | 11 |

|    | 2.2.4 MISD                       | 12 |

|    | 2.2.5 MIMD                       | 12 |

|    | 2.2.6 Hybrid                     | 13 |

|    | 2.3 VLSI FOR IMAGE PROCESSING    | 13 |

|    | 2.3.1 General Purpose            | 14 |

|    | 2.3.2 Function Specific          | 16 |

|    | 2.3.3 Application Specific       | 17 |

|    | 2.3.4 Smart Sensor-Processors    | 17 |

| 3. | BIOMETRICS                       | 21 |

|    | 3.1 INTRODUCTION                 | 21 |

|    | 3.2 RECOGNITION AND VERIFICATION | 21 |

|    | 3.3 AUTOMATED VERIFICATION       | 23 |

|    | 3.4 BIOMETRIC VERIFIERS          | 24 |

|    | 3.5 PERFORMANCE MEASURES         | 27 |

|    | 3.6 BIOMETRIC DESCRIPTORS        | 29 |

|    |     | 3.6.1   | Eye - Retina                      | 30 |

|----|-----|---------|-----------------------------------|----|

|    |     | 3.6.2   | Eye - Iris                        | 31 |

|    |     | 3.6.3   | Face                              | 31 |

|    |     | 3.6.4   | Fingerprint                       | 31 |

|    |     | 3.6.5   | Hand                              | 32 |

|    |     | 3.6.6   | Keystroke Dynamics                | 33 |

|    |     | 3.6.7   | Signature Dynamics                | 33 |

|    |     | 3.6.8   | Voice                             | 34 |

|    | 3.7 | FUTURI  | E DIRECTIONS                      | 35 |

| 4. | FIN | GERPRI  | NT VERIFICATION                   | 37 |

|    | 4.1 | INTROL  | DUCTION                           | 37 |

|    | 4.2 | FINGE   | RPRINT VERIFICATION UNIT          | 37 |

|    | 4.3 | EDINB   | URGH ALGORITHM                    | 41 |

|    |     | 4.3.1   | Print Capture                     | 42 |

|    |     | 4.3.2   | Preprocessing                     | 43 |

|    |     | 4.3.3   | Signature Extraction              | 44 |

|    |     | 4.3.4   | Pattern Matching                  | 46 |

|    | 4.4 | ASIC FU | JNCTIONS AND ARCHITECTURES        | 47 |

|    |     | 4.4.1   | Overview                          | 47 |

|    |     | 4.4.2   | Microcontroller Interface         | 49 |

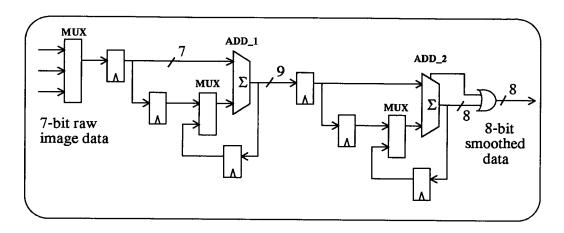

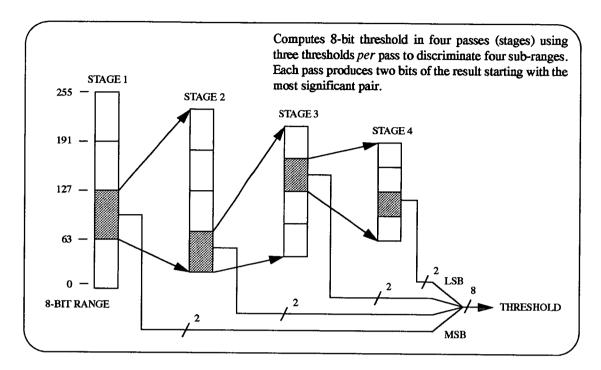

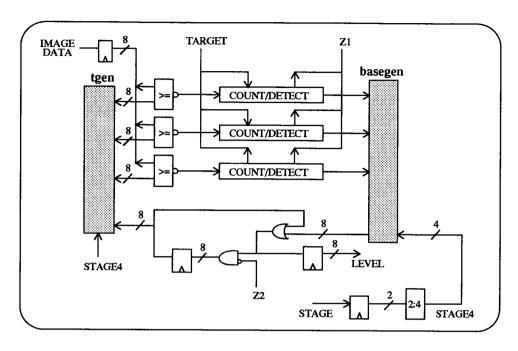

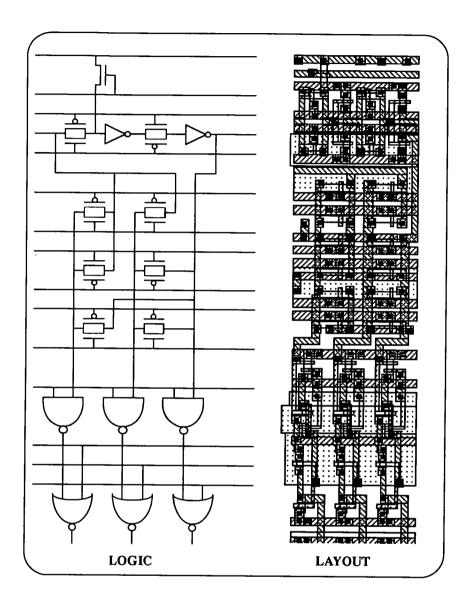

|    |     | 4.4.3   | Smoothing Filter and Thresholding | 51 |

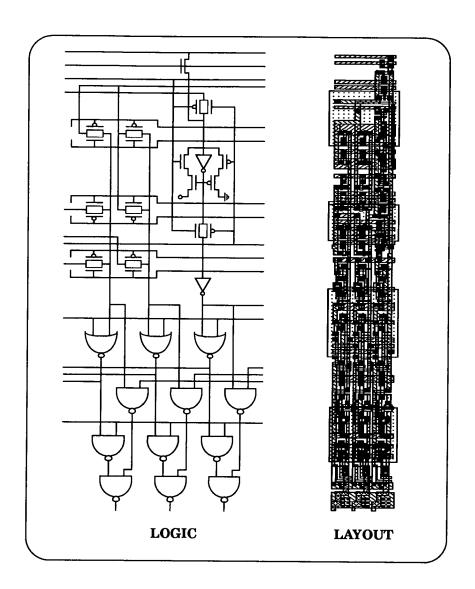

|    |     | 4.4.4   | Correlation                       | 57 |

|    |     | 4.4.5   | Correlation Array                 | 58 |

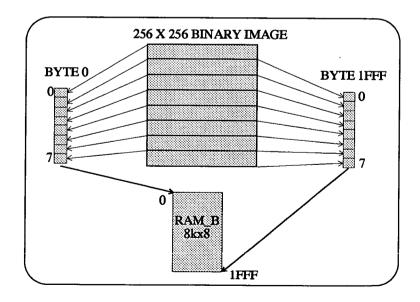

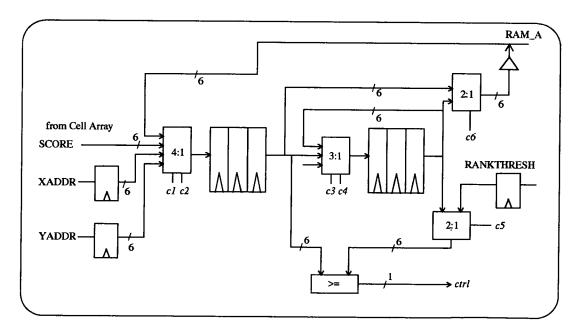

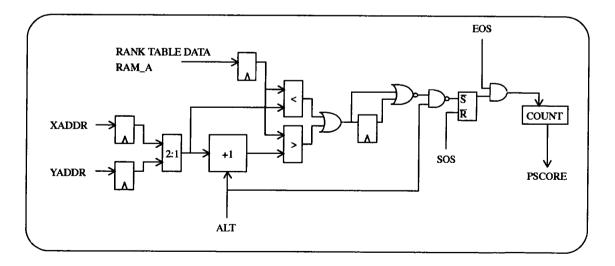

|    |     | 4.4.6   | Rank Value Filter                 | 61 |

|    |     | 4.4.7   | Polling                           | 63 |

|    | 4.5 | ASIC IM | PLEMENTATION                      | 64 |

|    |     | 4.5.1   | Parcor1                           | 64 |

|    |     | 4.5.2   | Parcor2                           | 67 |

|    | 4.6 | DISCUS  | SION AND CONCLUSIONS              | 69 |

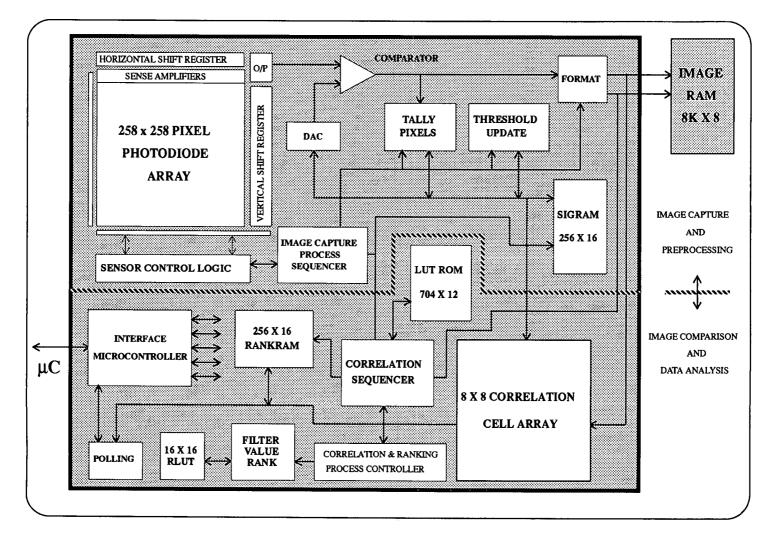

| 5. | MAGE SENSOR-PROCESSOR                    | <b>7</b> 1 |

|----|------------------------------------------|------------|

|    | 5.1 MACRO-ARCHITECTURAL SPECIFICATION    | 71         |

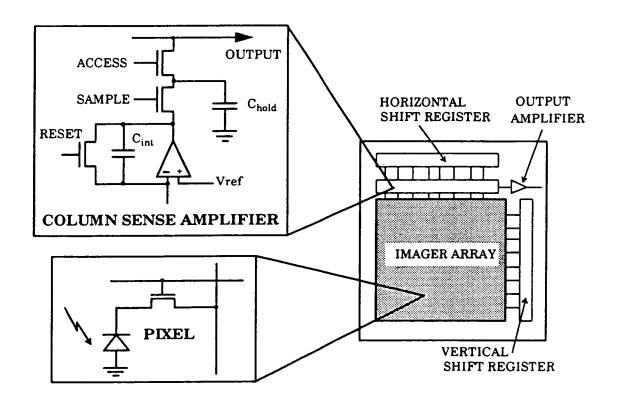

|    | 5.2 CMOS IMAGE SENSORS                   | 75         |

|    | 5.3 IMAGE SENSING AND PRE-PROCESSING     | 78         |

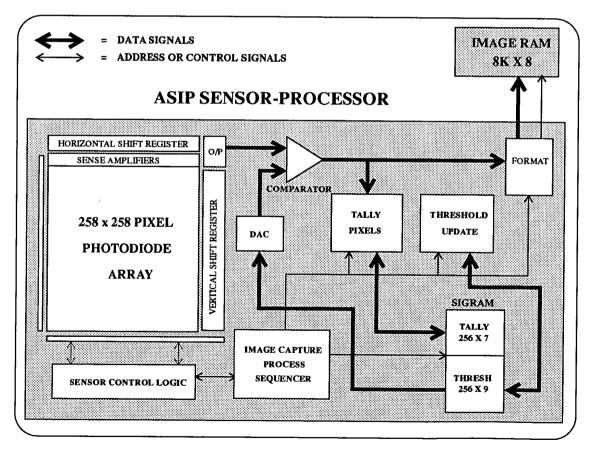

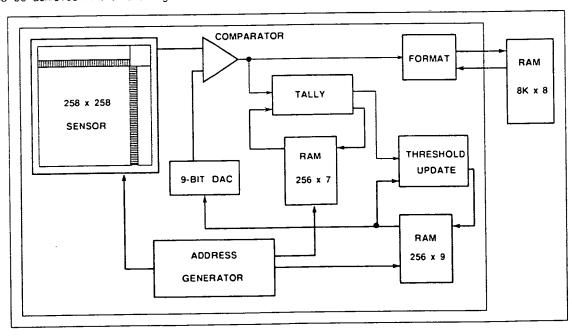

|    | 5.3.1 Architectural Overview             | 79         |

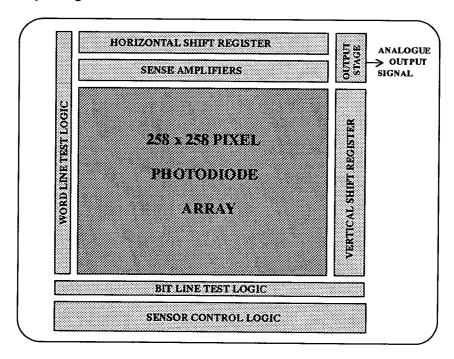

|    | 5.3.2 Sensor and Filter                  | 81         |

|    | 5.3.3 Sensor Controller                  | 85         |

|    | 5.3.4 Sequencer                          | 86         |

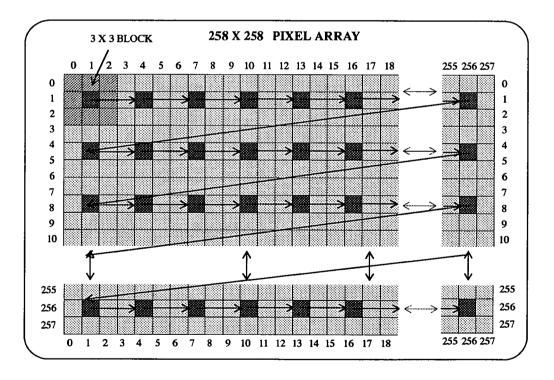

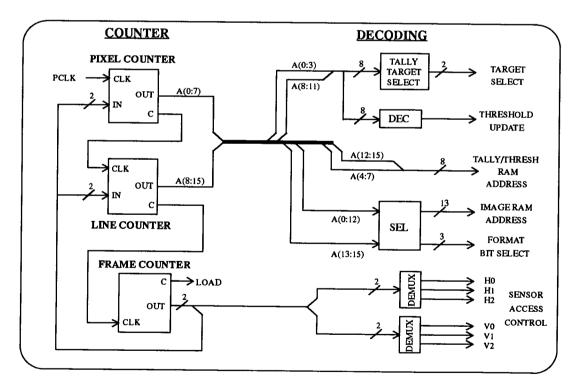

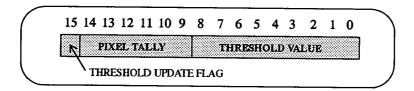

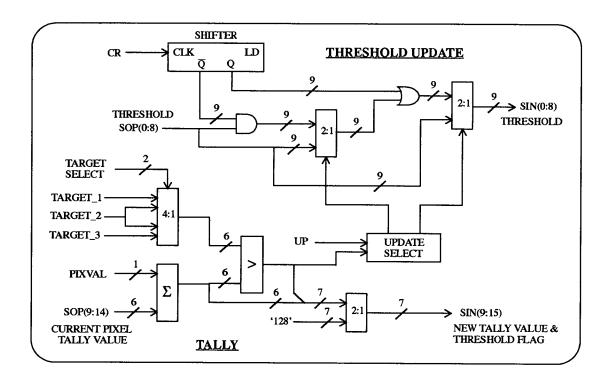

|    | 5.3.5 Tally and Threshold Calculation    | 89         |

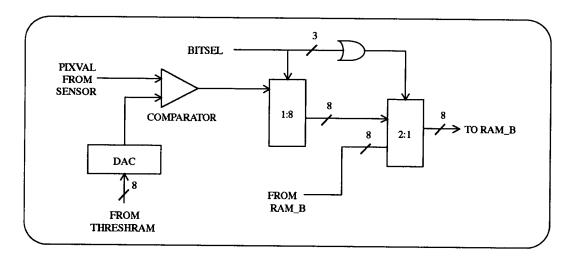

|    | 5.3.6 Threshold and Format               | 92         |

|    | 5.4 IMAGE COMPARISON AND RESULT ANALYSIS | 93         |

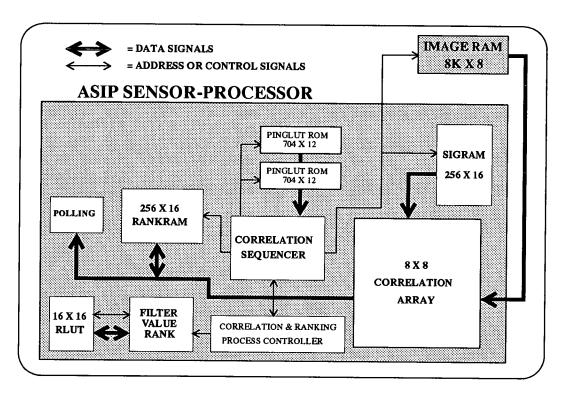

|    | 5.4.1 Overview                           | 93         |

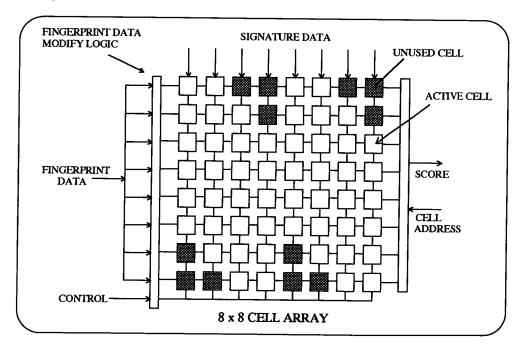

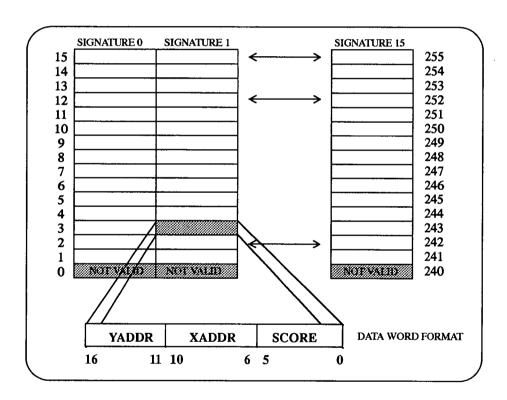

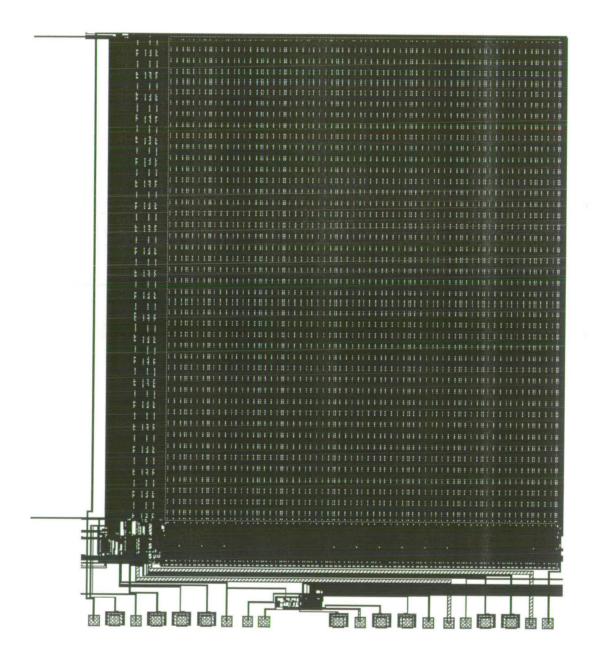

|    | 5.4.2 Correlation Cell Array             | 96         |

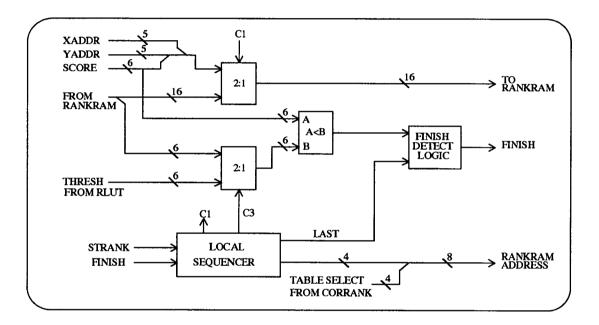

|    | 5.4.3 Rank Value Filter                  | 97         |

|    | 5.4.4 Polling                            | 99         |

|    | 5.5 COMPARISON OF ARCHITECTURES          | 101        |

|    | 5.6 SUMMARY                              | 104        |

| 6. | MPLEMENTATION                            | 105        |

| 0. |                                          | 103        |

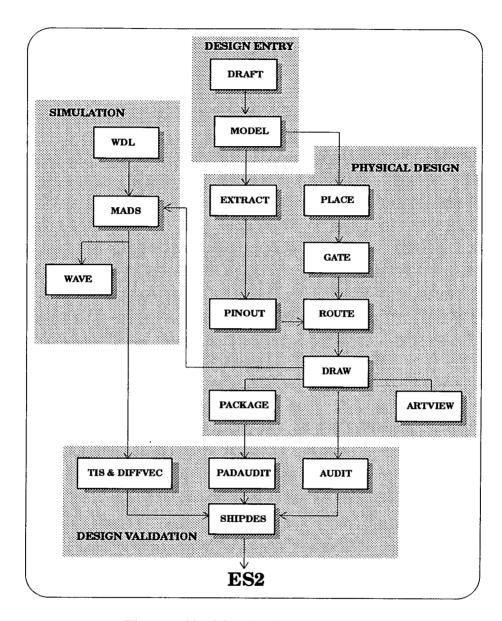

|    | 6.1 IMPLEMENTATION METHODOLOGY           | 105        |

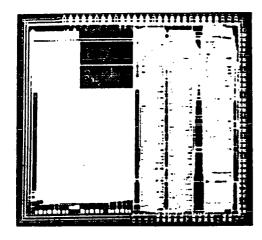

|    | 6.2 DESIGN PARTITIONING                  | 107        |

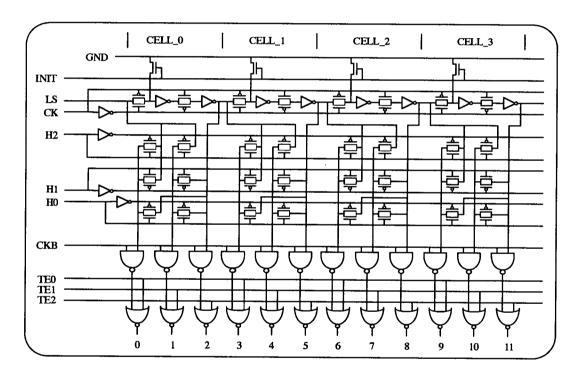

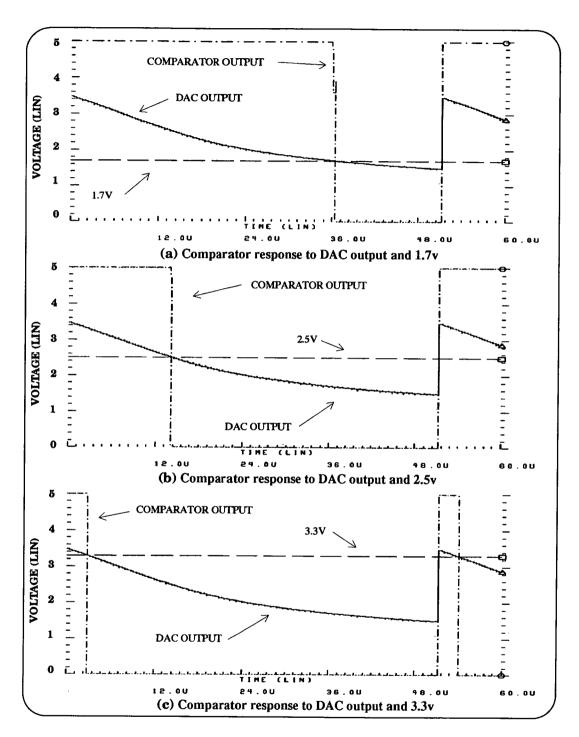

|    | 6.3 DAC AND COMPARATOR                   | 109        |

|    | 6.3.1 DAC Architecture                   | 109        |

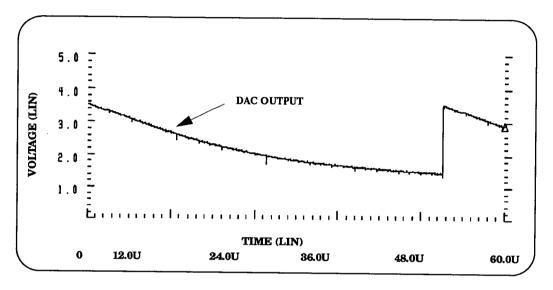

|    | 6.3.2 DAC Layout and Simulation          | 110        |

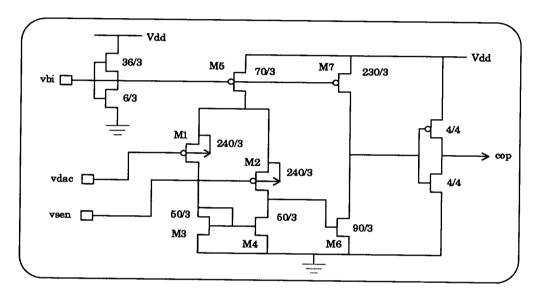

|    | 6.3.3 Comparator Architecture            | 112        |

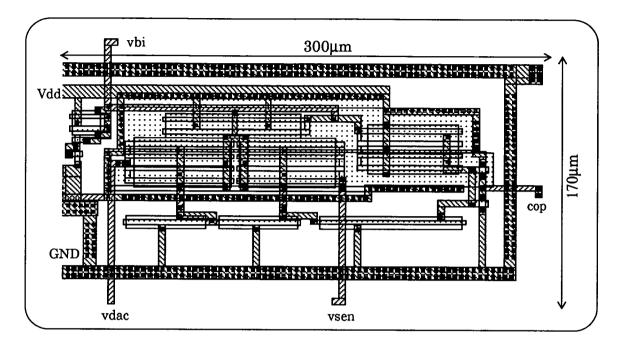

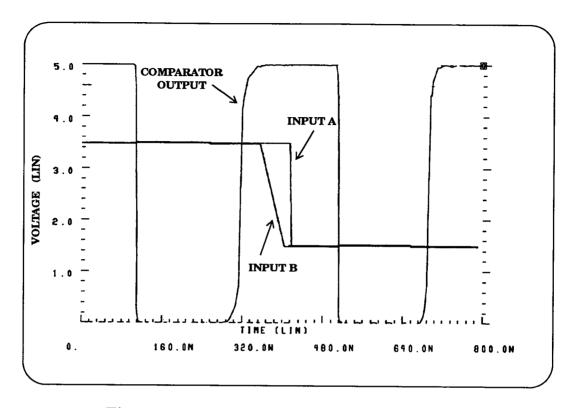

|    | 6.3.4 Comparator Layout and Simulation   | 113        |

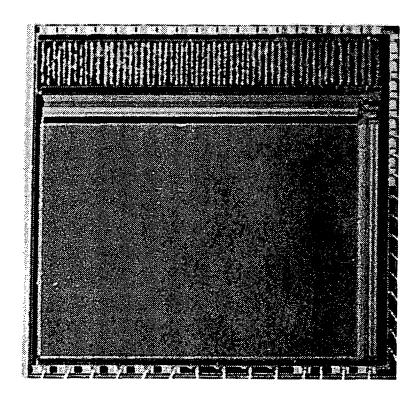

|    | 6.4 CUSTOM SENSOR                        | 117        |

|    | 6.5 CUSTOM BLOCK AND I/O PADS            | 120        |

|    | 6.6 DIGITAL LOGIC AND COMPILED MEMORY    | 122        |

| 7. | FAB           | RICATION AND TESTING             | 125 |

|----|---------------|----------------------------------|-----|

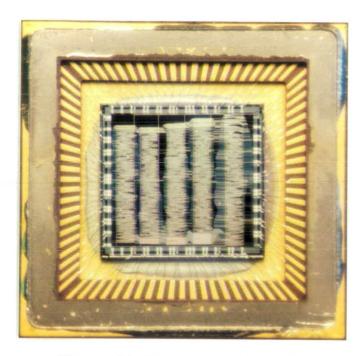

|    | 7.1           | FABRICATION                      | 125 |

|    | 7.2           | TEST PROCEDURE                   | 126 |

|    | 7.3           | MEMORY TESTS                     | 130 |

|    | 7.4           | DAC AND COMPARATOR               | 134 |

|    | 7.5           | SENSOR                           | 135 |

|    | 7.6           | IMAGE CAPTURE AND PROCESSING     | 138 |

|    | 7.7           | SUMMARY                          | 139 |

| 8. | SUM           | MARY, DISCUSSION AND CONCLUSIONS | 141 |

|    | 8.1           | A BRIEF REVIEW                   | 141 |

|    | 8.2           | CONCLUSIONS                      | 142 |

|    | 8.3           | FUTURE RESEARCH                  | 147 |

| RI | EFERI         | ENCES                            | 150 |

| ΡĪ | IRLJ <i>C</i> | ATIONS                           | 150 |

## Chapter 1. INTRODUCTION

#### 1.1 MOTIVATIONS

The use of image processing techniques to solve monitoring and control problems has, until recently, been restricted to military, space and a few hazardous industrial applications where low-cost solutions were of secondary importance to system performance. The main problem has not been one of algorithmic development but the cost of the processing hardware necessary to cope with the inherently high computational requirements of image processing.

With the advances in implementation technologies over the last two decades, providing ever greater levels of processing power *per* pound, many new application areas, especially in manufacturing situations, can now be addressed. The continuing development of ever lower cost computing platforms, with increased processing capability, has reached the point where commercial and domestic image processing systems are becoming economically viable. The possible applications for low-cost image processors cover a wide range of products and functions such as traffic speed control, video-telephones, identity verification and production-line monitoring.

Hardware solutions to these types of image processing problems are normally achieved in one of two ways. The first makes use of general purpose image processors, or function specific integrated circuits, with additional glue-logic and high-level control circuitry to perform the desired function. Problems associated with this approach are numerous. They include difficulty in finding suitable devices to implement the given

algorithm, or inefficient implementation due to circuit redundancy, performance bottlenecks and accuracy considerations given the limited set of available functions.

The other approach is to produce a custom solution in one or more VLSI devices using appropriate functional modules to implement the required processes. The use of custom ASICs helps to reduce the problems associated with the former approach and can produce an efficient mapping of the algorithm to an architecture optimized for area, algorithmic accuracy or speed and also has weight and cost advantages. One perceived disadvantage of the ASIC based approach is the algorithm is essentially frozen at the time of implementation and cannot be enhanced without a hardware redesign.

Typically, VLSI design methodologies have only been used to integrate the computationally intensive digital elements of image processing systems such as correlators, array operators, and data compressors. These devices only provide the data processing component of a complete image processing system.

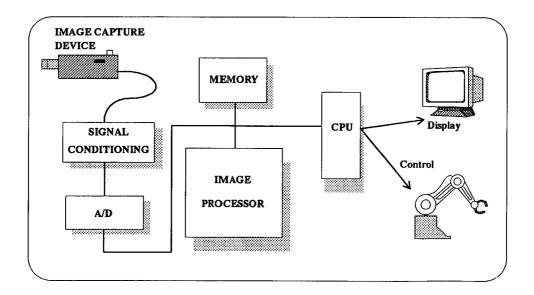

Figure 1.1 Generic Image Processing System

A generic image processing system for the analysis and recognition of images, see figure 1.1, presently consists of five main elements:- an image sensor; a data preprocessor; image analysis hardware; memory; and a microprocessor.

The input medium to this class of system is visible electromagnetic radiation which is sensed and converted into an analogue electrical representation of the image. The sensor is usually based on vidicon or solid-state CCD or MOS technology. The electrical signal often corresponds to some standard format, such as CCIR or NTSC video, in order to simplify the interfacing to various systems, or it may simply be a raster scan read-out. A preprocessor stage then performs global functions such as spatial noise filtering, analogue-to-digital conversion and image normalisation before the main image processing task is carried out. The core of the system can be either a high-performance, single-chip DSP or, for real-time operation, an array of general purpose processors or dedicated image array-processors. Memory is required to buffer images, and to store reference data and results for post-analysis. The final component of a generic image processing system is a low-bandwidth (when compared with the capability of the image processor) microprocessor which is needed to perform system control functions and analysis of results. An inherent performance bottleneck exists with systems of this type due to the serial nature of the transfer of the data from the sensor to the data processing system. The emergence a new type of VLSI device, called a smart sensor-processor, provides a possible solution to this problem and other limitations of existing image processing hardware such as cost, power consumption and size.

It is proposed that, through integration of image sensing and signal conditioning elements with the core digital processing greater architectural performance can be achieved without detriment to the usual design leverage offered by VLSI. The available architectural flexibility can be used to efficiently match the hardware to the required function. The economic and performance pay-off of this approach will provide an commercially viable method for the development of powerful, compact and reliable solutions to machine vision problems in manufacturing and enable a wide range of new consumer products based on the smart-sensor concept to be created.

#### 1.2 OBJECTIVES

The objectives of this thesis are firstly to investigate and develop architectures for application specific image processing, including the integration of image sensors to create smart sensor-processors. Secondly, to design a hardware solution for a real-world application which will be used as a vehicle to demonstrate the technical and economic practicality of the proposed implementation technique. The design example will also highlight the degree of system integration which can be achieved with currently available VLSI technologies and integrated circuit design software. Engineering trade-off decisions covering design time, algorithmic mapping and implementation architecture will be combined to form a measure of the efficiency of a particular design approach. These elements, along with the obvious physical and performance characteristics of the integrated device, will be compared with examples of the traditional system implementation approach described earlier.

The practical work presented in this thesis will describe the design and implementation of a fingerprint comparison system for automated personal identity

verification as a single chip smart sensor-processor. The choice of this application to demonstrate the viability of the proposed implementation method has been made for a number of reasons. Firstly, the system is commercially relevant. With the explosion in electronic financial transaction systems available for use by the general public, the need for secure and accurate identity verification has become vital to minimise fraud. The use of human biometrics such as handwriting, fingerprints and voice patterns are considered as potential solutions to this problem. Unfortunately, many of the algorithms which have been developed with sufficient discriminatory accuracy have had their practical use limited by hardware implementation costs.

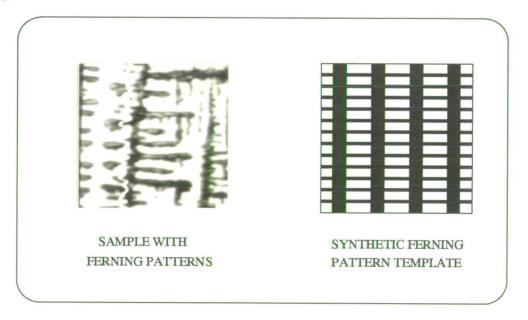

Secondly, the algorithm forming the core of the proposed system has been well defined and a detailed description is available. Although the algorithm has been tuned for fingerprint comparison, the basic functional blocks implementing the algorithm can easily be adapted to other image processing tasks of a similar nature. An example of the algorithm's flexibility is its proposed use for fertility screening by matching ferning patterns in smear samples. This application is briefly described in chapter 8

Finally, a real-time prototype access control system based on the same algorithm has been developed which contains all the basic elements of a generic image processing system as described earlier, *i.e.* sensor, signal preprocessor, and a computationally intensive image processor. The prototype system provides a set of physical, performance and economic measurements which can be compared with those of the proposed integrated sensor-processor. This makes the fingerprint comparison application a particularly suitable demonstrator for the smart sensor-processor implementation approach.

#### 1.3 THESIS SUMMARY

Chapter 2 briefly reviews the history of implementation methods and technologies for image processing systems highlighting the limitations of each type. Examples of current progress in the development of VLSI circuits for image processing are presented. These include general purpose image processors, function specific and application specific circuits, and smart sensors.

Chapter 3 provides an overview of the application area of the demonstration system, personal identity verification using human biometrics. A variety of different commonly used biometric features are described, comparing their usefulness for automated identity verification. A summary of commercially available identity verifiers is also provided, giving details of performance and system cost where possible.

Chapter 4 presents a brief description of the prototype fingerprint based identity verifier system and the fingerprint comparison algorithm it implements. At the core of the system are two high performance image processing ASICs. The architectures used to implement the preprocessing and comparison algorithms are given, along with details of their physical and performance characteristics.

Chapter 5 describes the architectures used to implement the functional elements of the prototype fingerprint comparison system to a single-chip smart sensor-processor. A sensor technology using standard low-cost digital ASIC processing has enabled the integrated sensor-processor design approach to be considered. The background to the development of this technology and its main design characteristics are also presented in this chapter. At the end of Chapter 5 the architectural advantages, such as increased performance and reduced memory requirements, of the single-chip design approach are

discussed.

Chapter 6 briefly describes the two different VLSI design methods, full custom and silicon compilation, that have been used to implement the fingerprint comparison architecture presented in the previous chapter. The rest of the chapter details the implementation and simulation of each of the functional blocks, and their integration to form a single-chip smart sensor-processor.

Chapter 7 describes the post-fabrication test procedures used to verify circuit operation and presents the results of these initial tests on a prototype batch of integrated sensor-processors.

Finally, Chapter 8 provides a discussion of the successes and failures of the design approach as a solution to the economic implementation of real-time image processing systems using VLSI in the form of smart sensor-processors.

# Chapter 2. VLSI FOR IMAGE PROCESSING

In order to set the scene for the work presented in this thesis it is necessary to review the available hardware implementation alternatives for image processing systems. This chapter provides a very brief review of hardware architectures used to implement image processing functions and surveys a range of VLSI devices designed specifically for use in image processing systems. Chapter 3 reviews biometric techniques and applications, justifying the choice of a fingerprint comparison based identity verifier as a technically and commercially relevant demonstration vehicle for the VLSI smart sensor-processor design approach.

#### 2.1 IMAGE PROCESSING

Image processing is principally the interpretation of pictorial information for autonomous system control or the improvement of image quality. One early form of image processing involved the Trans-Atlantic transmission of coded newspaper pictures by submarine cable and their subsequent reconstruction using a special telegraph printer. This system, known as the Bartlane cable picture system, was introduced in the early 1920s. The real stimulus to the development of image processing techniques came with the space programme in the 1960s. The requirements of space exploration produced technologies enabling the construction of powerful digital computers for control systems and data analysis. Work at the Jet Propulsion Laboratory to enhance pictures returned from early missions to the moon formed the starting point of the rapid development of image processing techniques and application areas which continues today. Looking back to the Bartlane picture transmission system of the 1920s

it is interesting to note that, today, one of the fastest expanding application areas for image processing is multi-media information technology *i.e.* the transmission of information and pictures. Other fields where image processing algorithms are used to enhance picture quality, or facilitate understanding of the information contained within the image include biology, archeology, geography, physics, medicine and law enforcement.

Increasingly, image processing techniques and technologies are being applied to the automatic interpretation analysis of the data within a scene, not just image enhancement for human analysis. This type of image processing technique is widely used in field of medicine where automated systems are being developed to aid the analysis of cervical smears<sup>[44]</sup>, blood samples<sup>[28]</sup> and to automatically classify chromosomes<sup>[40]</sup>. Other areas where automated image analysis techniques are being utilised include military applications such as reconnaissance, weapons guidance systems, and law enforcement for automatic fingerprint comparison<sup>[11]</sup> and car registration plate recognition<sup>[32]</sup>. A further area where image processing is beginning to make an impact is in production line monitoring and quality control applications, commonly known as machine vision<sup>[34], [36], [37]</sup>.

The continued expansion of image processing into higher volume commercial and domestic systems is currently limited by the cost of the processing power required to implement reliable solutions to real-world image processing problems. This situation can only be addressed by the development of appropriate architectures and technologies to allow the efficient implementation of image processing algorithms. A brief review of the computer architectures which have been used to implement image processing algorithms is presented in the next section.

#### 2.2 ARCHITECTURES

It is has been widely stated<sup>[29],[30],[39]</sup> that no single processing architecture is capable of efficiently handling all types of image processing function. Before deciding whether or not to concur with this view it is necessary to look at some of the possible implementation methods for image processing algorithms.

#### 2.2.1 Software

The development of software to implement image processing algorithms is the traditional method used to solve vision applications. This approach is particularly flexible, allowing modifications and enhancement of the algorithm to be made quickly and inexpensively. The major drawback of this implementation approach is the inability of general purpose, von Neumann type, computing platforms to deliver the necessary processing power to cope with the huge quantities of data generated by image processing tasks. A further penalty of such vision processing systems is that they are not capable of real-time operation, severely limiting their usefulness for practical vision applications.

One solution to the processing bottleneck of von Neumann based computer architectures is to introduce parallelism in various forms to increase data throughput. Parallel architectures are particularly useful for the implementation of low-level, pixel-oriented, image processing functions such as neighbourhood processing, edge detection and convolution functions. Classification and comparison of the vast number of different parallel computing architectures is not easy. One taxonomy which is widely used for general purpose parallel computing architectures, proposed by Flynn<sup>[27]</sup>, classifies systems by the relationships between the data and instruction streams within

the system. The Flynn taxonomy is also used to classify image processing system architectures. The four classifications established by Flynn are SISD - Single Instruction Single Data, SIMD - Single Instruction Multiple Data, MISD - Multiple Instruction Single Data and MIMD - Multiple Instruction Multiple Data.

#### 2.2.2 SISD

The SISD class of machine is the conventional von Neumann type of architecture in which a single processor executes instructions on a single data set. This architecture is widely used and can be found in a large variety of computing platforms from a desktop P.C. to supercomputers like the Cray-x series. The SISD model as been extended to include pipelined processor architectures where individual processes were implemented as separate functional units. As a data set passes from one serial processor to the next, a new data set is consumed by the previous processor.

#### 2.2.3 **SIMD**

The SIMD type of parallel processing architecture is particularly appropriate for implementing low-level image processing functions such as neighbourhood processing, convolution, thresholding, and edge-detection. SIMD processors are formed by constructing an array of identical processors controlled by a master. The controlling processor transmits an instruction to each processor in the array which performs the instruction on its local data. Processor to processor communication depends on the particular system but is typically nearest neighbour only. Unfortunately, SIMD systems are not particularly suitable for higher level image processing functions such as histogramming, ranking, feature extraction, or object matching.

#### 2.2.4 MISD

Although there is little evidence of current processing systems which can be classified as MISD, architectures of this type may still be of use in image processing systems. An architecture where the incoming data stream is processed in a parallel manner by independent processors, each performing a unique function, can be envisaged. For example, this type of system could be used to extract edge, texture, shape, and image difference information simultaneously from a single input data stream.

#### 2.2.5 MIMD

MIMD systems have an array of processors often arranged in a similar manner to those in SIMD machines, but with the ability for each processor to be executing different instructions on its local data set. MIMD systems are capable of implementing a wide range of image processing functions but with varying degrees of efficiency. Unfortunately, the effort required to write and debug programs for this class of machine and the interprocessor communication overhead limit the usefulness of current MIMD architectures according to Cypher<sup>[41]</sup>. The application independent design emphasis adopted by all these parallel processing architectures is a limitation to their economic practicality. Inherent in their generality is the inefficient mapping of specific image processing algorithms to the available processing resources. As Hummel<sup>[41]</sup> has stated in a discussion on the topic of parallel architectures for vision algorithms, "It is a shame to pay for 64,000 processors and then at any given time only use a fraction of the processors to do useful work". This observation applies to any processor whose function is linked to a specific pixel or group of pixels. This suggests that for an efficient implementation of an image processing algorithm a multi-level processing architecture

is the most suitable. This type of system could include processor architectures from any of the Flynn classifications. For this reason an extension to the taxonomy is required to accommodate these multi-architectural processing systems.

#### **2.2.6** Hybrid

Hybrid systems combine parallel array processors for low level pixel-oriented functions, special purpose devices for feature based functions (e.g. edge detection, object matching) and general purpose microprocessors for high level analysis and decision making. Examples of this type of hybrid multiprocessor system have been described by Sousa<sup>[42]</sup>, Kioi<sup>[80]</sup> and Vellacott<sup>[45]</sup>.

Although the hybrid processor architecture is seen as a solution to the efficient implementation of general purpose image processing systems, it does not provide a complete technology for the production of low-cost systems suitable for high-volume commercial or domestic image processing based products. However, when combined with cost, size, and power leverage of VLSI design techniques it could provide a method of implementing low-cost image processing solutions.

#### 2.3 VLSI FOR IMAGE PROCESSING

The concept of multi-architectural hybrid image processing systems, combined with the design leverage afforded by the latest generation of VLSI CAD software, offers the possibility a low-cost, real-time solution to the implementation of image processing algorithms. This section reviews existing VLSI devices which have been designed for use in image processing systems. There are four main categories of VLSI

image processing chips:

General Purpose - these devices implement several processing elements (PEs) and, when cascaded, form the cores of massively parallel processing systems. The PE structure can be of various types but generally consists of an ALU, datapath, registers, and possibly some distributed data memory.

Function Specific - This class of device typically implements a single general purpose image processing function such as correlation, image warping or convolution.

Application Specific - For this taxonomy, application specific devices are those which have been optimised for one particular application area such as character recognition or fingerprint comparison. The complete algorithm required to process and analyse the image data for the application is implemented as one or more custom VLSI devices.

Smart Sensor-Processors - This class of device not only includes the digital processing elements of the application specific devices but also the image sensor itself, and associated image pre-processing such as signal conditioning and digitisation.

## 2.3.1 General Purpose

MasPar Corporation's MP-1<sup>[31]</sup> is a typical example of a general purpose massively parallel processing architecture. The core of this system is formed from an

array of processor elements (PEs) configured for SIMD operation. This architecture is typical of other, earlier, SIMD machines such as University College of London's CLIP4 (Cellular Logic Image Processor), Goodyear's MPP<sup>[38]</sup> (Massively Parallel Processor) and AMT's DAP (Distributed Array Processor) except that the MP-1 has distributed memory allowing the PEs to simultaneously access different memory locations. The MP-1 processor array contains from 1,024 to 16,384 separate units, giving the system a claimed performance of up to 26,000 million instructions *per* second (MIPS) and 1,300 floating-point operations *per* second (MFLOPS). Each of the processor elements (PEs) consists of a datapath, arithmetic logic unit, registers and in the case of MP-1, 16 kilobytes of local data memory. The array has been formed from full-custom CMOS VLSI devices, each implementing 32 PEs, and their dedicated memory.

The cost for this level of performance is in the region of £140,000 to £500,000 depending on the system configuration. Other examples of VLSI being used to implement the custom PEs for massively parallel cores of real-time image processing systems include GRID<sup>[49]</sup>, SCAPE<sup>[59]</sup>, DSA-1<sup>[60]</sup> and ISMP<sup>[63]</sup>.

Pipeline architectures are a form of SISD processor where the successive steps of the algorithm are distributed over a number of cascaded processors. The image data is fed (usually in raster-scan format) sequentially into the pipeline to be processed.

Another architecture used for general purpose image processing is known as a dataflow architecture. Here the sequence of operations is defined by the data being processed. Examples of processor elements designed using the dataflow type of architecture have been described by Quenot<sup>[64]</sup> and Kurokawa<sup>[35]</sup>.

#### 2.3.2 Function Specific

Function specific integrated circuit architectures implement particular image processing operations. Devices have been fabricated for a number of functions including segmentation<sup>[52]</sup>, motion estimation<sup>[53]</sup>, image compression<sup>[70]</sup>, contour line filtering<sup>[54]</sup>, edge detection<sup>[50]</sup>, thinning<sup>[66]</sup>, convolution<sup>[56],[58],[67]</sup>, template matching<sup>[25]</sup>, and correlation<sup>[55],[65]</sup>. A good example of function specific VLSI is the set of eight devices from Ruetz and Brodersen<sup>[68]</sup> which implement a variety of image processing algorithms. Specifically, they implement a 3 x 3 linear convolver, a 3 x 3 sorting filter, a 7 x 7 logical convolver, a contour tracer, a look-up-table ROM, and two post processors for the linear convolver. The complete system is controlled by a SUN workstation and can work at frame rates of up to 15 *per* second on 512 x 512-pixels. More recent work by Reutz<sup>[69]</sup> has produced a set of function specific devices with the design emphasis on producing architectures with a high degree of programmability, to allow them to be used over a wide range of applications.

Beyond these function specific devices, increased levels of integration produce chips which contain several image processing functions, and are optimised for a particular class of image processing application. An example of this type of device is the OPTIC image processor<sup>[62]</sup>. Although described as a processor for use in general purpose real-time vision systems, its functionality makes it particularly appropriate for production line inspection and robotic control. The device implements filter functions (typically used for 'salt and pepper' noise suppression), dynamic thresholding and correlation with a binary template and grey-level image data. The resulting VLSI device contains 80k transistors and has been fabricated using a 1.5µm CMOS process.

## 2.3.3 Application Specific

Although VLSI has been used to implement particular image processing functions or groups of functions, little evidence exists of the generation of application specific image processing chips where the complete algorithm for an image processing problem is implemented as one or more custom integrated circuits. This seems to be due to the fact that most research has concentrated on developing architectures for general purpose image processing systems. As stated earlier, to enable image processing techniques to be used in consumer products, system size and cost have to fall dramatically without loss of processing performance. Only through the use of VLSI technology can all of these goals be achieved. An example of application specific VLSI devices for image processing is the two device chipset, developed by the author, implementing the core functions of the prototype fingerprint comparison identity verification system described in chapter 4 The first device performs various real-time image preprocessing and data analysis functions such as image smoothing, dynamic thresholding, and rank-value filtering while the second device implements a high throughput two-dimensional binary correlation array. Other application specific devices have been reported recently, but they integrate an image sensor as well as image processing functions and are therefore included in the following section.

#### 2.3.4 Smart Sensor-Processors

This final classification of this brief review of VLSI image processing devices is an area in which there is rapidly increasing activity design activity. In general terms a smart sensor-processor is some form of sensor (optical, heat, pressure) integrated onto the same substrate as the data processing hardware. This review will concentrate on devices with sensors working in the visible part of the electromagnetic spectrum. An

overview of smart sensor technology can be found elsewhere<sup>[82]</sup>. Integrating the image sensor with the processing functions allows the designer a great deal more flexibility in the design of efficient solutions to image processing problems. In particular it eliminates the design constraint of raster-scan data transfer between the sensor and the processor, which often results in the need for buffering of image data before consumption by the data processor. The integration of the sensor allows the designer a choice in the pixel array size, pixel aspect ratios, and sensor data read-out methods. All of these help to optimise the performance of the image processing system. Further architectural optimization opportunities exist in such systems with the removal the architectural partition between the image sensor and image processor. In sensor-processor architectures the image data pre-processing functions of the system can be more closely coupled with the image sensor.

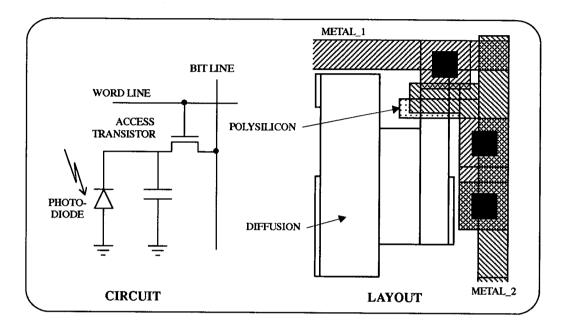

A major barrier to the production of practical integrated sensor-processors is the incompatibility of the implementation technologies. Conventional VLSI image sensors are typically fabricated using CCD processing technology<sup>[51]</sup> while low-cost CMOS processes have been developed for the design of low-power digital processing circuits. Although it is possible to implement logic using CCD processes, the performance, complexity and cost of such circuits is not economic when compared with CMOS based logic. An example of this design approach is the CCD sensor produced by Kemeny, et al.<sup>[79]</sup> which includes image reformatting circuitry for some basic neighbourhood processing on the output image data. The additional circuitry occupies 2% of the active chip area. An example of device combining the qualities of CCD and CMOS technologies on the same substrate has been reported by Hakkarainen and Lee<sup>[77]</sup>. Another smart sensor-processor has been described by Kioi, et al.<sup>[80]</sup> which uses a novel three-dimensional processing technology, SOI (Silicon On Insulator), to create a

4-level image processing chip for character recognition. The top layer is a 5040 pixel image sensor, the next layer down implements digitisation and magnitude comparison functions, the third layer contains data buffering and mask registers, and the final layer contains template information. The device contains 0.22 million transistors on a 14.3 mm square die. Although this type of device has potential for the efficient implementation of hybrid image processors the current device densities and the high cost of the unique processing technology limit its usefulness as a low-cost image processing hardware solution.

Work in the 1980s by Lyon<sup>[81]</sup>, Mead<sup>[83]</sup>, and Renshaw<sup>[87],[85]</sup>, among others, in developing photo-receptors and on-chip amplification circuits suitable for implementation using standard CMOS processes, has lead to the development of image sensors that are nearing the quality and performance of CCD devices. This technology has enabled the development of an increasing number of CMOS based sensor-processor devices. One of the earliest was a simple correlating optical motion detector designed by Tanner and Mead<sup>[88]</sup>. This device integrates a linear 16-pixel sensor and analogue and digital processing on the same substrate to perform correlation between successive image frames. An optical mouse was the proposed application for this chip. Another CMOS linear sensor array with processing logic fabricated on the same substrate is the LAPP<sup>[76]</sup> designed by a group at Linkoping University.

Recent work at the University of Edinburgh has resulted in highly integrated image sensors with two-dimensional photodiode arrays of up to 312 x 287 pixels incorporating on-chip sense-amplification and electronic exposure control logic by Wang, et al. [91]. It is particularly interesting to note that these devices are fabricated using a standard low-cost digital CMOS ASIC process. This technology is described in

further detail in Section 5.2. The PASIC sensor and bit-slice processor reported by Chen, et al.<sup>[74]</sup> in 1990, and the MAPP2200 256 x 256 pixel sensor with on-chip A/D conversion reported by Jansson, et al.<sup>[78]</sup> in 1992 are further examples of the development of CMOS based sensor-processors. Other recent VLSI sensor-processors developments include the 65 x 75 pixel NCP Retina<sup>[73]</sup>, a 32 x 32 pixel resistive-fuse processor<sup>[92]</sup> and a 53 x 52 pixel image contrast enhancement sensor-processor reported by Shimmi, et al.<sup>[89]</sup>, and a neural network based cheque reader manufactured by Synaptics<sup>[43]</sup>. This final group of devices are good examples of the type architectures that can be created when implementing image processing functions as integrated mixed signal (analogue and digital) sensor-processors.

VLSI smart sensor-processors provide a flexible design technology for the implementation of hybrid processor architectures. Through the efficient mapping of image processing algorithms to silicon architectures, low-cost application specific image processing systems are now possible. The next chapter provides a review of biometric techniques and applications, justifying the choice of a fingerprint comparison based identity verifier as a technically and commercially relevant demonstration vehicle for the VLSI smart sensor-processor design approach.

# Chapter 3. BIOMETRICS

#### 3.1 INTRODUCTION

The requirement for reliable identification of individuals has grown with the rapid expansion of information technology based financial transaction services. The proliferation of automated teller machines (ATMs), electronic funds transfer at point of sale (EFTPOS) systems, home banking facilities, and telephone calling cards are examples of systems which have the need for secure identification. International travel, secure industrial and governmental facilities, sport centres, vehicle security, and logical access points (computer terminals and databases) are further areas where personal identity verification is required.

This chapter will outline a class of solution to these security problems known as automated biometric verification, and review its techniques, application areas and implementation technologies. The review will also provide an application context for the practical implementation of the architectural studies presented in this Thesis.

#### 3.2 RECOGNITION AND VERIFICATION

Biometrics, in this context, can be defined as the use of any measurable human physiological or behavioural characteristic to reliably confirm a person's identity.

Through the comparison of biometric descriptors identification can be achieved by either *recognition* or *verification*. When a feature is used to determine an individual's identity from a group of known references the process is called *recognition*. Human interaction relies on this type of identification, most commonly using face and voice

characteristics to determine identity and relationships. Law enforcement agencies have utilized the uniqueness of human fingerprints in solving crime for over a hundred years. Historically, this form of recognition was achieved by experts manually comparing the print recovered from the scene of the crime with those of suspects stored as a file of inked fingerprint reference cards. Today, powerful, and expensive <u>automated fingerprint identification systems</u> (AFIS) can compare a print with tens of thousands of references *per* second in order to determine the probable identity of the criminal.

The second way in which biometrics can be used to identify people is where it is necessary to *verify* an individual's claimed identity. Here the individual's characteristic is compared only with the reference template of the person he claims to be. The reference can be either selected from a database by some form of identifier such as a PIN, or provided by the claimant and encoded electronically on a smart card. Verification has an advantage over recognition approaches, in that the claimant has to make a conscious identity claim before verification. In certain applications (such as point of sale) this is seen as a useful additional imposter deterrent. The verification approach also has the added benefit of substantially reducing the computation required to determine identity.

The target identification application areas for automated biometric verifiers are physical access control, logical access control, personal verification. A partial list of possible applications is provided in table 3.1. All of these applications require biometric verifiers which are compact, functionally reliable, user friendly and, most of all, inexpensive.

| Physical Access Control                                                                                                                                                                          | Logical Access Control                          | Personal Verification                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| . Factories, industrial sites . Government facilities - offices - embassies - consulates . International travel . Sports facilities . Vehicle security . Military sites . Hotels . Leisure parks | . Computers . Databases . Home banking . Pay TV | Personal verification  Prisoner release  Health care  medication control infant identification  EPOS  EFTPOS  Border control Telephone charge cards |

| . Clubs                                                                                                                                                                                          |                                                 |                                                                                                                                                     |

Table 3.1 Typical Verification Applications

## 3.3 AUTOMATED VERIFICATION

Before looking in more detail at specific biometric techniques and applications it is worth differentiating between *manual* and *automated* forms of identity verification. In this context manual methods typically involve the comparison of features by human visual inspection or aural comparison. In automated biometric systems feature comparison is automatically performed by electronic systems utilizing custom image processing hardware and software.

For centuries, access control and identity verification methods have relied on the allocation of a portable device or token whose ownership is verified by a secret key or password. A classic example of this token and password approach to security is handwriting, in the form of a personal signature or mark. Here, identity is verified by manually comparing the example signature on the token (e.g. cheque card, credit card,

membership card, driving licence) with a live signature provided by the claimant. Photo identity cards and passports are another common form of manual verification device. These manual forms of personal verification are particularly prone to error or abuse, since the comparison is often performed by relatively unskilled and poorly paid personnel. Tedium is another factor which leads to higher error rates.

With the increasing use of ATMs and other unmanned self-service transaction systems, the requirement for reliable remote verification has become much more important. In this type of application magnetic strip cards combined with personal identification numbers (PINs) are the most widely accepted method of access control.

The existing approaches to identification all have their weak points; cards can be stolen; signatures easily forged; and passwords and PINs forgotten. For these reasons present methods are deemed inadequate. Automated biometric verification technologies are an attempt to create a reliable solution which can easily be tailored to fit a wide variety of security applications.

Biometric systems can additionally provide an audit trail through data logging, of both genuine and imposter access attempts. In the case of fingerprint systems, the captured fingerprint can be used in subsequent criminal investigations (although this feature is not normally advertised to users, legally they must be told).

#### 3.4 BIOMETRIC VERIFIERS

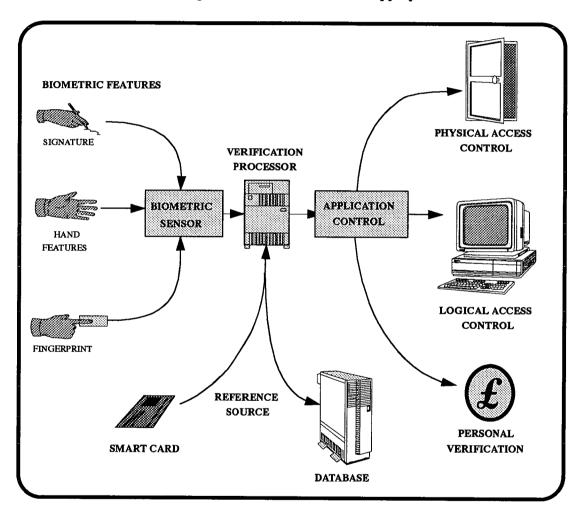

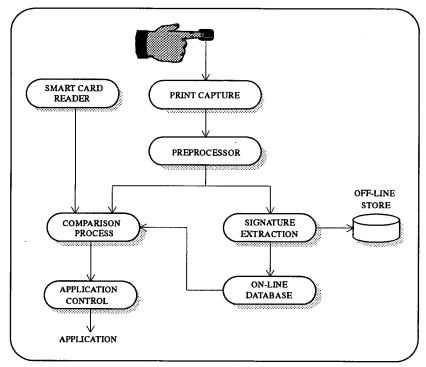

Having outlined the need for low cost, automated biometric verifiers some of the typical features of such systems can be described. Automated biometric identification systems, in general, consist of a mechanism which allows for the sensing and capture

of a particular feature, and a processor which compares the 'live' image with a previously stored reference in order to verify a user's identity (see figure 3.1). The reference is selected from a database by a PIN, or can be provided encoded on a smart card. The comparison is performed by the processor and an authentication decision is made. The claimant is then granted or denied access, as appropriate.

Figure 3.1 Generalized Biometric Verifier

Enrolment is the procedure performed to register or validate a new user on a system. It involves the repeated capture (typically 2 - 5 times) of a particular biometric characteristic, in the presence of a trained enroller. The captured feature is processed to

create a reference template for the user, which is either stored in a database or encoded on a smart card.

A powerful feature used in some biometric systems is the ability to automatically update the reference template for a user, without having to repeat the enrolment process. This adaptive update of references is particularly useful for accommodating minor biometric variations in voice and signature based systems. The update procedure works by tracking the changes between the reference template and the presented live feature. Assuming access is granted, the template can then be modified to more closely match the user's characteristic. The configuration of the main elements of a biometric verifier; the sensor, comparator, controller, and database, is dependent on the needs of the application and available implementation technologies.

Historically, according to Driscoll<sup>[2]</sup>, biometric systems were designed round a centralized architecture, due to the magnitude of the processing task in comparing a biometric sample and reference. In this configuration, the reference template database, comparison processor, and application controller are all part of a central computing resource with only the biometric sensors located at the various access or verification points. With the development of more sophisticated image processing algorithms and new implementation technologies like VLSI, a distributed architecture can now be created. Here, each access point has a dedicated sensor, database, comparator and controller which can operate in isolation, or can be networked to allow data logging or global data updates.

Another feature incorporated into some systems is the ability to determine whether or not the presented biometric characteristic is live. For fingerprints, a simple skin

temperature and non-intrusive blood oxygen test is used in one system<sup>[4]</sup> to reject severed fingers or latex prostheses.

#### 3.5 PERFORMANCE MEASURES

The performance and comparison of biometric devices is normally based on two measures, the <u>false rejection rate</u> (FRR) and the <u>false accept rate</u> (FAR).

The FRR (also described as a Type 1 error, or insult factor) is the ratio of valid attempts (or bids) to the total number of bids. While the FAR (or Type 2 error) is the ratio of successful imposter attempts to the total number of imposter attempts. Most systems allow for the adjustment of the balance between FRR and FAR. If the security against illegal acceptance is increased the likelihood of a genuine user being rejected is also increased. The converse is also true.

Another measure of comparative performance often quoted is the equal error rate (EER), which is the point in a biometric verifier's error curves where FRR = FAR. Unfortunately, the measurement of these ratios and their relationships are not very well defined, which makes for unreliable system comparison based on manufacturers' claimed performance. Directly comparable trials on identical bench marks are very costly. Trials by the Sandia National Laboratories [5],[10],[9], a U.S. government sponsored agency, provide most of the reliable published performance information on existing, commercially available, biometric systems.

The FRR for a particular system can be improved through a combination of careful enrolment, user training, and the use of adaptive template updating. The elimination of errors due to the mistyping of PINs can be achieved by using magnetic or smart cards.

| COMPANY                      | PRODUCT                | BIOMETRIC        | ТҮРЕ       | PER<br>EER%                          | FRR%                                 | NCE<br>  FAR%                        | VERIFY secs. | TEMPLATE                             | UNIT                 | COMMENTS                       |

|------------------------------|------------------------|------------------|------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------|--------------------------------------|----------------------|--------------------------------|

| Fingermatrix                 | Mint 21<br>Mint11      | Fingerprint      | P<br>L     | -                                    | 0.5<br>0.5                           | 0.001<br>0.001                       | <3<br><3     | 400 bytes/finger<br>400 bytes/finger | \$3,500<br>\$3,500   | Error rate source              |

| Identix                      | Touchlock<br>Touchsafe | Fingerprint      | P<br>L     | -                                    | 1.8 <sup>C</sup><br>1.8 <sup>C</sup> | 0 <sub>C</sub>                       | 1-2<br>1-2   | 1 kbytes/finger<br>1 kbytes/finger   | \$3,500<br>\$1,895   | Error rate source              |

| Thumbscan                    | 301                    | Fingerprint      | L          |                                      | 0.5                                  | 0.01                                 | 6-10         | -                                    | \$1,195              | Error rate source              |

| TMS                          | Eagle, Hawk,<br>Falcon | Fingerprint      | v          | •                                    | -                                    | -                                    | 3            | 24 bytes                             | \$2,000              | No live capture<br>Inked cards |

| Alpha<br>Microsystems        | TIS<br>RACS            | Voiœ             | L,C<br>P,C | 6.5 <sup>A</sup><br>6.5 <sup>A</sup> | 5.1 <sup>C</sup><br>5.1 <sup>C</sup> | 2.8 <sup>C</sup><br>2.8 <sup>C</sup> | -            | ~ 8 kbyte/user<br>~ 8 kbyte/user     | \$20,000<br>\$20,000 | Error rate source              |

| VoiceTek                     | Alpha V<br>Alpha VI    | Voiœ             | P,C<br>P,C | -                                    | -                                    | -                                    |              | -                                    | \$19,500<br>\$70,000 | 8 doors<br>>500 doors          |

| International<br>Electronics | VoiceKey               | Voiœ             | P,V        | 8.2 <sup>A</sup>                     | 4.3 <sup>C</sup>                     | 0.9 <sup>A</sup>                     | 2            | 160 bytes/word                       | \$1,190              | Error rate source              |

| Eydentify                    | Model 8.5              | Eye - Retina     | P,L        | 1.5 <sup>A</sup>                     | 0.4 <sup>C</sup>                     | 0 <sup>C</sup>                       | 1.5          | 40 bytes                             | \$4,995              | Error rate source              |

| Pideac                       | MarkIV                 | Hand Geometry    | P          | -                                    | -                                    | -                                    | -            | 2 kbytes                             | \$3,500              |                                |

| Recognition<br>Systems       | ID-3D                  | Hand Geometry    | P          | 0.2 <sup>A</sup>                     | <0.1 <sup>C</sup>                    | 0.1 <sup>C</sup>                     | 2            | 9 bytes                              | \$2,000              | Error rate source              |

| Hand Scan<br>Technologies    | PG2000                 | Hand Print       | P          | -                                    | -                                    | -                                    | -            | 10,000 points                        | \$9,750              |                                |

| Digital<br>Signatures        | Sign/On                | Dyn. Signature   | P,L,V      | -                                    | 2.1 <sup>C</sup>                     | 0.7 <sup>C</sup>                     | 3            | 84 bytes/sig.                        | From<br>\$640        | Error rate source              |

| Cheque Alert                 | DigiScan               | Static Signature | v          | -                                    | 10                                   | 1-15                                 | -            | 18 bytes                             | \$995                | Error rate source              |

Key:

P - Physical access control, L - Logical access control, V - Personal Verification, C - Centralized verification processor and database EER - Equal Error Rate, FRR - False Reject Rate, FAR - False Accept Rate, A - 1 try, B - 2 try, C - 3 try

The FAR is influenced by the particular biometric descriptor being used, and the ability of the verifier to extract and compare its inherent discriminating characteristics. Examples of the performance measures (EER, FAR, FRR, verification times) for several commercial verifiers are given in table 3.2. The most secure systems are based on fingerprint and retina scan. Both return FARs approaching zero under trial conditions. The FRR for the same systems is in the region of 0.5% to 2%. In contrast the worst scores are for a signature geometry based verification system from *Cheque Alert Inc.*<sup>[11]</sup> with a FRR = 10% and FAR = 1%-15%. The human voice is a difficult biometric to discriminate accurately and consistently, and this is reflected in typical system FARs of 1%-2% and FRRs of around 5%.

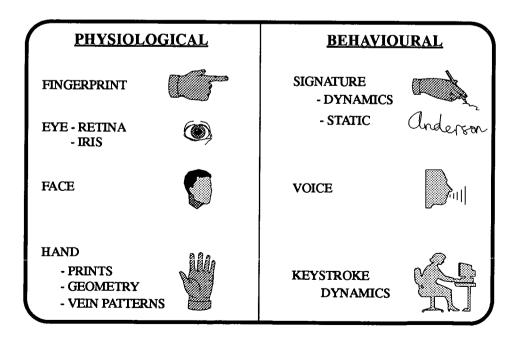

### 3.6 BIOMETRIC DESCRIPTORS

A wide range of biometric features are utilized in such systems which can be classed as either physiological, or behavioural characteristics (see figure 3.2).

Figure 3.2 Common Biometric Descriptors

Commonly used physiological descriptors include fingerprints, hand geometry, faces and eyes. These features are basically invariant over time, except through accidental damage.

Behavioural characteristics, such as speech and handwriting, are a combination of physiological and psychological influences. The characteristics of a voice are not only dependent on a person's size, sex and heredity, but also on their accent, emotional state, and even on their state of health *e.g.* whether or not they have a cold. The remainder of this section will briefly survey the biometric descriptors which are presently used in commercial standard verifiers. Most of the information given below regarding commercial biometric verification systems has been reported by Miller in Personal Identification News (PIN)<sup>[11],[12],[13]</sup> and in papers by Parks<sup>[14],[15]</sup>.

## **3.6.1** Eye - Retina

The blood vessel pattern on the retina and the iris pattern of the human eye are both used as biometric descriptors. *Eydentify Inc*.<sup>[11]</sup> manufactures products based on the retina pattern for both logical and physical access control applications. To gain access, the user positions his head over the unit, focuses on an alignment target consisting of a series of concentric circles, then presses a button to trigger the scan sequence. A low-intensity infrared light source is directed in a circular scan centred on the back of the retina. The reflected light is then sampled, and processed to produce a unique 40 byte template. The sensed pattern relies on the differences in reflectivity of the retinal blood vessels and surrounding tissue. The matching process is performed by an algorithm based on Fourier cross-correlation with phase matching (to compensate for rotation of the user's head) running on a Motorola 32-bit microprocessor.

### 3.6.2 Eye - Iris

A variation on the retina scan system is being developed by  $Eye-D^{[11]}$  which uses the iris pattern of the eye, as opposed to the retina. A feed-back system of lights is used to adjust the pupil size before scanning. This type of system is only likely to be used in high security sites, since the quality of the optics and engineering required precludes low production costs.

### 3.6.3 Face

The use of the face as a biometric identifier is an obvious one since this is how humans perform recognition of individuals. Neural networks are viewed as the most effective method of comparing faces. Research work on a pattern recognition techniques at the Paul Scherrer Institute in Zurich (PSIZ)<sup>[1]</sup>, using edge direction vectors, has been applied to face recognition with some success. The problem of impersonation by the use of photographs is one which will have to be addressed before face recognition will be acceptable for unmanned access applications. There has been much research activity<sup>[3],[18],[20]</sup> into face recognition but, as yet, there has been no commercial exploitation. A system designed to detect potential bank robbers as they enter a bank branch, developed by *NeuroMetric Systems*<sup>[12]</sup>, is likely to be the first commercial use of face recognition.

### 3.6.4 Fingerprint

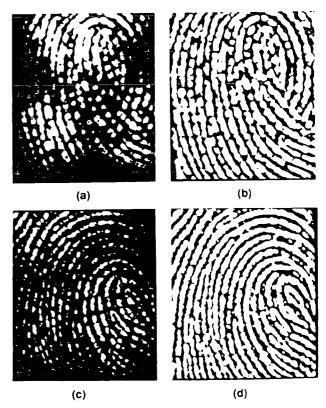

The uniqueness and stability of fingerprints is the longest established biometric, making them particularly appropriate for identity verification. Traditional non-automated methods of fingerprint comparison have been based on the classification of minutiae. Minutiae are the small characteristic whorls (spirals), bifurcations (forks) and

loops, which form a unique fingerprint pattern. This technique has been adapted for use in fingerprint-based, automated identity verifiers from *Identix Inc.* and *Fingermatrix Inc.* Other methods which have been applied to fingerprint verification include the use of Fourier analysis (*France Telecom*<sup>[11]</sup> in Caen), spatial correlation (*University of Edinburgh*<sup>[24]</sup>) and neural pattern matching (*Net-ID Inc.*<sup>[13]</sup> and *University of Essex*<sup>[6]</sup>). Novel approaches to the capture of fingerprint images through the use of tactile sensors (*Tactile Technologies*<sup>[11]</sup>) and high-frequency ultrasound (*Niagra Technology Labs*<sup>[13]</sup>) are also being investigated.

## 3.6.5 Hand

The first commercially available, automated biometric device was installed at Shearson Hamil on Wall Street in 1973. The device, called Identimat, used the lengths of four fingers as a means of discrimination. Although no longer available in its original form, the principle has been developed into a three-dimensional system marketed by Recognition Systems Inc. Another product, from Pideac Inc., also utilizes hand measurement as the basis of identification. This product differs from Recognition Systems' by using software, rather than guide posts or stops, to compensate for variation in hand placement and finger spread.

Creases on finger joints and palms are also used as physiological biometrics. A system from *Biometrics Inc.* uses infrared sensors to detect the pattern of creases on the underside of finger joints to form a 'human bar code'. The creases and lines in a area 1.5" x 1.5" on the palm of the hand is used by a biometric identifier marketed by *Hand Scan Technologies*.

An algorithm, called Veincheck which is based on the blood vessel pattern on the

back of the hand has been developed by Cambridge Consultants Ltd.<sup>[7]</sup>. The hand is illuminated by a tungsten light source, and an image is captured using a CCD camera fitted with an infrared filter. A hexagonal grid is superimposed on the vein pattern and a connectivity matrix is produced. The comparison is performed by analysing matrices for like connections. Hand-feature based approaches are claimed to be particularly appropriate for high throughput access control applications.

## 3.6.6 Keystroke Dynamics

This behavioural descriptor is based on the unique rhythm with which typists enter certain groups of characters. It is claimed that as few as a dozen keystrokes are sufficient to identify a user. The principle is not new; in the days of telegraph using Morse code, operators could identify each other from their typing idiosyncrasies.

The principle of keystroke dynamics has been specifically developed for signing on and off procedures in logical access control applications. It is also the only biometric (with the possible exception of face recognition) which has the potential for continuous assessment of the operators identity. This is achieved by monitoring for frequently entered sequences of characters, and prompting the typist to re-enter a password if the system suspects a change of user. Although appropriate for database protection, keystroke dynamics does not provide a suitable solution for physical access control or ATM security.

## 3.6.7 Signature Dynamics

In business and financial transactions, personal signatures are by far the most widely used method of identity verification, so it is natural that they should be exploited in automated verification systems. Static signature verification is where only the

graphical information contained in the signature is used for comparison. It is interesting to note that the error rate performance is the worst of all biometric systems and is only commonly found as part of bank automated credit and cheque clearing operations. These systems are similar to AFIS systems where the emphasis is on high throughput (tens of thousands of comparisons *per* second) rather than on accuracy and low cost. One company, *Cheque Alert Inc.* produce a signature geometry based system, but with a FAR of between 1% - 15%, depending on the skill of the forger, it is unlikely to provide a successful solution for point of sale applications.

Signature dynamics provide a more robust form of biometric identifier as they are much more difficult to forge and, hence, many companies have developed systems based on this biometric. As well as graphical information comparison, signature dynamics use behavioural spatial and timing information captured while the signature is being written. These systems typically require some form of sensitive writing surface and/or a special hardwired pen to detect the accelerations, directions and forces generated while the signature is being written<sup>[21]</sup>. The use of custom pens render them susceptible to malicious damage, making them suitable only for monitored applications such as point of sale or bank teller transactions.

## 3.6.8 **Voice**

Voice based verification is particularly attractive because of its acceptability to a wide range of users. Peckam<sup>[16]</sup> classifies voice analysis systems as either text-dependent or text-independent. Text-dependent systems require a previously specified word to be spoken which is then matched with stored samples of the same word through non-linear time alignment. In text-independent verification, acoustic measurements are taken from a characterization template for an individual speaker. These descriptors

include pitch, formant frequencies, linear prediction coefficients, energy measurements and Fourier Transforms.

Voice verification systems are usually configured in one of two ways. They can employ custom voice sensor hardware (a telephone!) and a speech analyser at each point of access, stand-alone or networked. Alternatively they may use a centralized voice processor and with a reference database accessed via the existing telephone networks. Tape fraud is a recognized problem with voice verifiers. A partial solution for text-dependent systems is to use random word selection from a fixed library, but this has a penalty of increased enrolment times which may not be acceptable. Voice-based systems do have the potential for hands-off operation which could be useful for access control applications. Companies currently marketing voice based products include Electronic Warfare Associates, Voice Sciences, Alpha Microsystems, International Electronics (formerly Ecco), VoiceTek (formerly Voice Control Systems).

#### 3.7 FUTURE DIRECTIONS

The cost of biometric verifiers in the eighties have fallen from around £7,000 per unit in 1985 to around £1,500 in 1989. According to data published in PIN<sup>[11]</sup>, this rapid decline in system prices has stabilized over the last two years with the average price dropping by only £300 during 1990. At this level biometric verifiers are only suitable for higher value industrial, military, and government applications. To expand the use of biometric products into new markets, such as personal verification for EFTPOS, and domestic applications like vehicle and home security, the unit price will need to fall to the region of £100-£200. This price reduction will be met by a number of improvements to current technology.

One change, applicable to systems targeted at EFTPOS applications, will be the elimination of the requirement for either a local or centralized database, and

consequently the need for a PIN, through the use of smart card technologies. The simplest form of smart card or IC card contains some nonvolatile memory which can be accessed by an external reader. Rather than storing a reference in a local database for each valid user, it is encoded on a smart card which is issued to the user. To gain access the user no longer needs a PIN but simply inserts the smart card into the verifier and, when prompted, provides his biometric feature for verification against the smart card reference. This is particularly useful for remote applications like credit card verification, and unmanned situations like ATMs. More sophisticated cards<sup>[17],[8]</sup> incorporate microprocessors and memory which can perform, on a single card, the functions of several credit cards, debit cards, or cheque guarantee cards, and can also act as an electronic purse.

The error rate performance requirements for the target applications are already being met by most of the existing commercial systems with average FRRs near 1% and near zero FARs for fingerprint, retina scan and hand geometry based systems. The average verification time is currently around 2 secs. In future systems a comparison time of around 0.5 secs. will be perceived by the user as almost instantaneous.

The required system cost reduction and increased performance for the next generation of biometric verifiers will be achieved through the use of application specific VLSI technology. This chapter has described some of the wide range of applications for automated identity verification systems. It has also shown that fingerprints are a particularly useful biometric feature for identity verification, providing a high level of discrimination and, therefore, security. For these reasons the choice of an automated fingerprint comparator provides a practical, commercially relevant demonstrator for the image processing system implementation approach presented in this Thesis. The next chapter describes the fingerprint comparison algorithm and a prototype identity verifier system based on it.

# Chapter 4. FINGERPRINT VERIFICATION

## 4.1 INTRODUCTION

In order to set the scene and provide a framework for the image processing case study presented in the remainder of the thesis, this chapter will outline the algorithm which has been developed at Edinburgh University for capturing and comparing fingerprint patterns. A full and detailed description of the algorithm and its development is available elsewhere<sup>[24],[22],[26]</sup>. A prototype fingerprint verification unit (FVU) for physical access control has been developed<sup>[46]</sup>. This system was chosen because it represented a practical, complex, and industrially relevant example, for which all the details of function and structure were available and well understood.

At the heart of the unit is an ASIC-based subsystem which implements the Edinburgh fingerprint comparison algorithm. This ASIC chipset<sup>[47],[48]</sup> was the precursor to the highly integrated image sensor-processor presented later in this thesis. A brief description of the ASIC architectures and the chip performances will be presented in section 4.4.

## 4.2 FINGERPRINT VERIFICATION UNIT

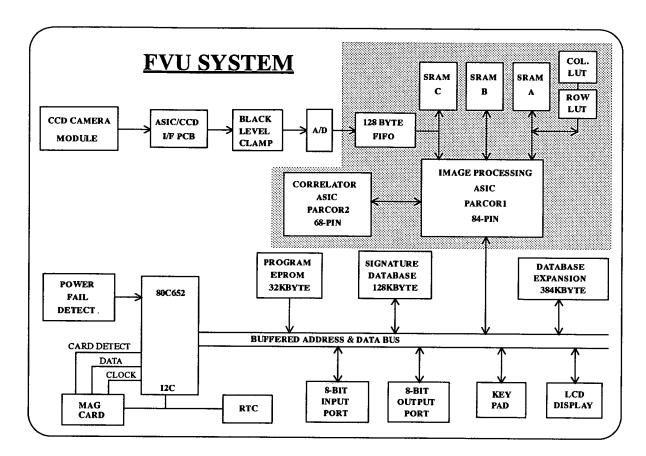

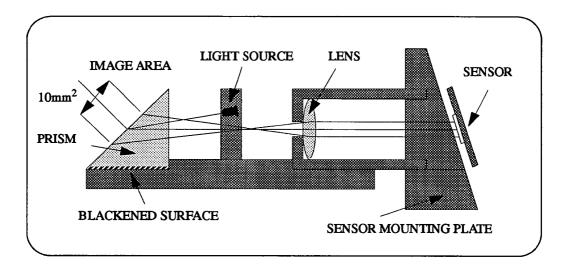

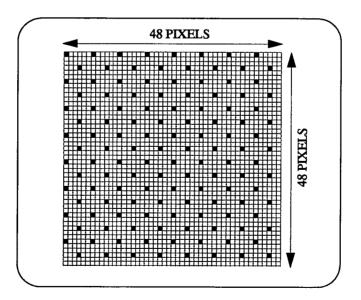

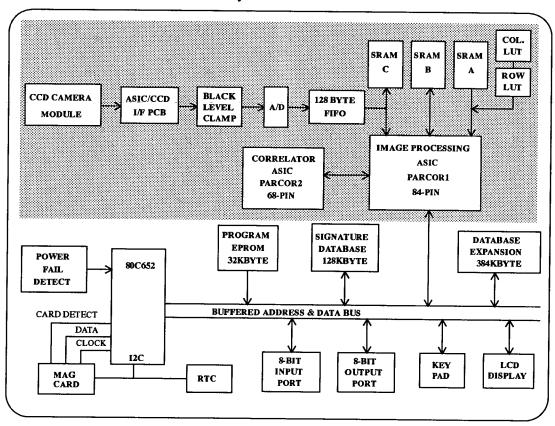

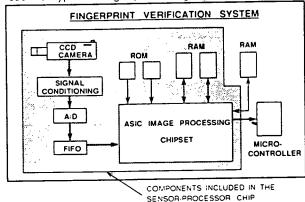

The FVU<sup>[46]</sup> is divided into several functional areas as illustrated in figure 4.1. The video processing system consists of a CCD camera module, a CCD to ASIC interface board, black level clamp circuitry and a 7-bit A/D convertor.

Figure 4.1 FVU Functional Schematic

The interface board generates signals which are used to sample a particular window within the complete image produced by the camera module. The black level clamp circuitry is used to scale the signal for input to the A/D convertor. The output from the A/D is then buffered using a 128 byte FIFO. This is required to even out the 'bursts' of pixel data generated by the camera module.

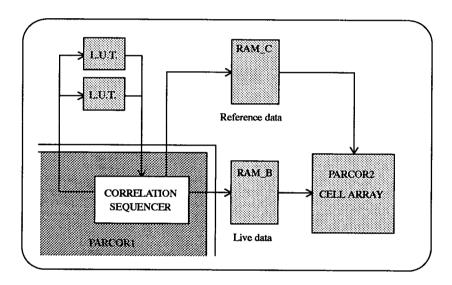

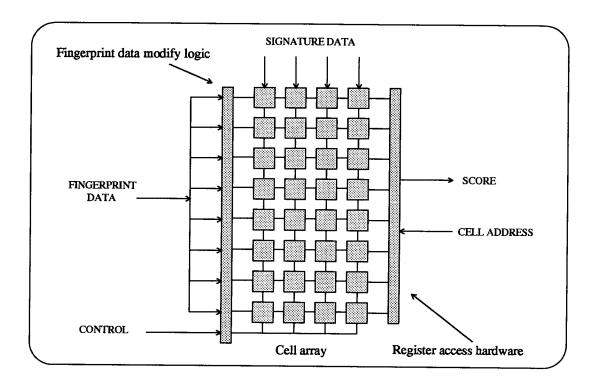

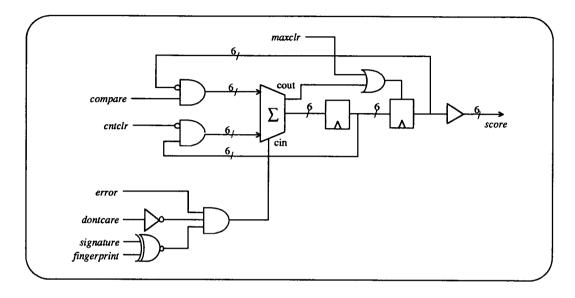

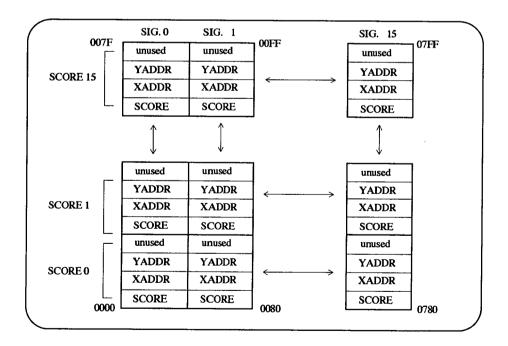

The delay between image lines is used by the first of the two custom ASICs, Parcor1, to empty the FIFO before the next line is digitized. Parcor1 preprocesses the grey-level data, performing filtering and thresholding functions, to produce a normalized black and white representation of the fingerprint image. The binary image is then compared with a pre-stored reference image using an algorithm based upon a modified correlation process. The comparison process is controlled by Parcor1 which sequences the flow of image and reference data to the second ASIC, Parcor2, which performs the correlation function.

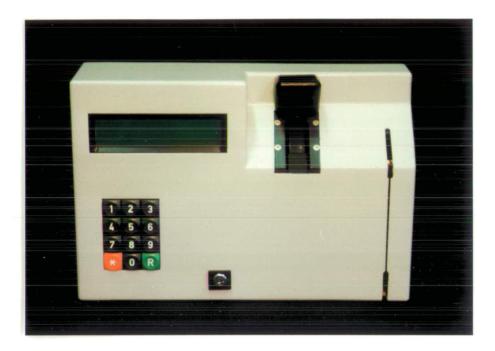

Figure 4.2 FVU General External View

Based on the results of this comparison, a decision is made as to whether or not the captured image sufficiently matches the reference template to allow access. Parcor1 also has an interface which allows communication with an 8-bit microcontroller. The microcontroller provides high-level system control functions linking the ASIC image processing subsystem to the peripheral human interface circuitry (e.g. LCD display, keypad, magnetic card reader). The main processor board also contains 128kbytes of RAM for storing reference fingerprint data (signatures) and other system variables. The system control software, for the embedded microcontroller, is stored in a 32kbyte EPROM.

The user interface consists of keypad which allows a user to enter a PIN code, a magnetic card reader giving an alternative means by which a user can be identified and a LCD display for the presentation of system status messages and user instructions. There is also a finger guide to help position a finger on the fingerprint sensing platen. Figure 4.2 shows the general external make-up of the prototype FVU. Other peripheral circuitry includes a serial communications port (for networking several FVU systems), a real time clock, power fail detection and 8-bit parallel input and output ports.

Table 4.1 provides a summary of some of the physical and performance characteristics of the prototype FVU. This data provides a benchmark to compare the performance of the FVU with the integrated sensor-processor ASIC described in chapters 5 and 6.

| FINGERPRINT VERIFICATION UNIT |                 |  |  |

|-------------------------------|-----------------|--|--|

| No. of ICs (VLSI, LSI)        | 16              |  |  |

| No. of ICs (MSI)              | 37              |  |  |

| No. of discretes              | 400 (approx.)   |  |  |

| Power                         | 6W              |  |  |

| Weight                        | 2kg             |  |  |

| Clock frequency               | 12MHz           |  |  |

| Size (w x h x d)              | 26 x 18 x 12cm  |  |  |

| Template size                 | 512bytes/finger |  |  |

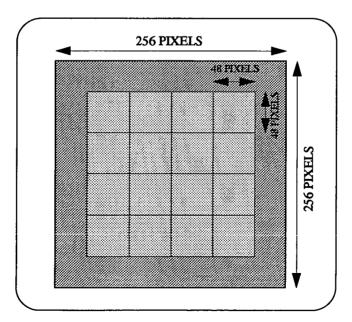

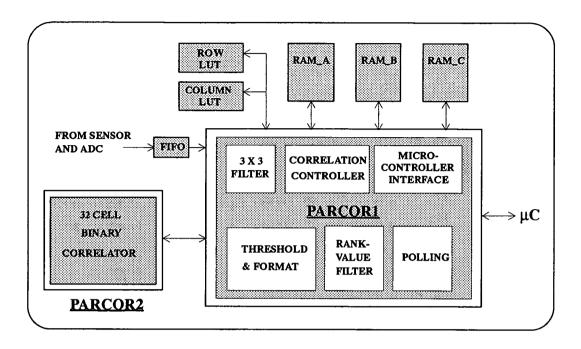

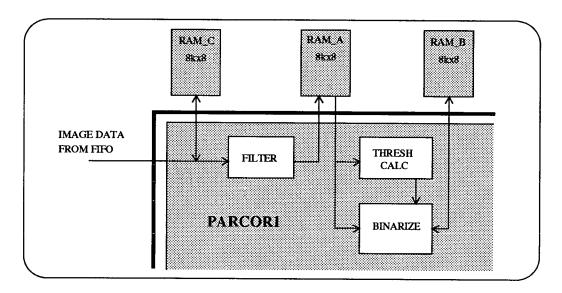

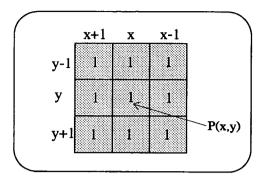

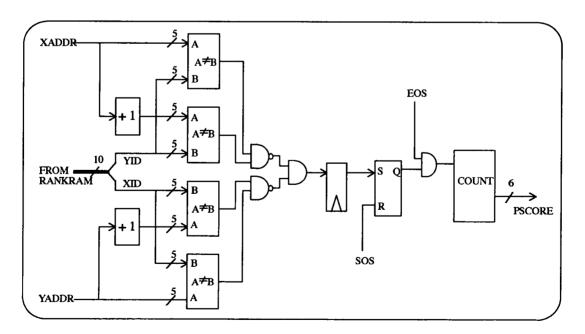

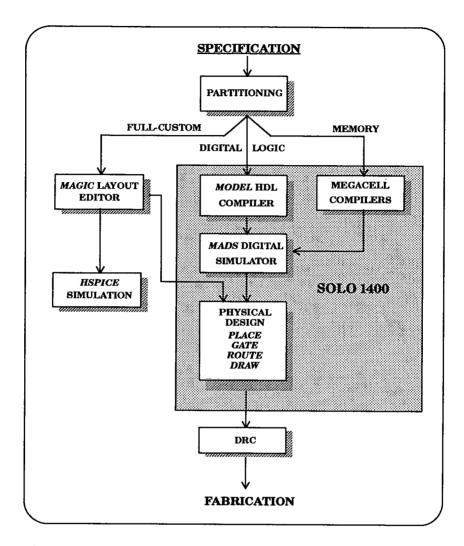

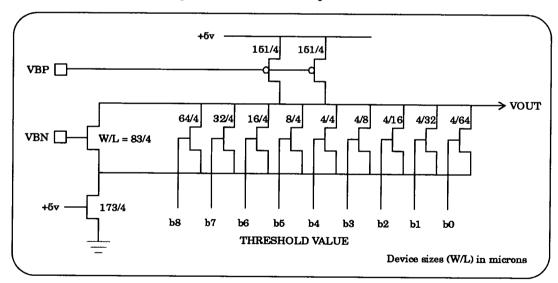

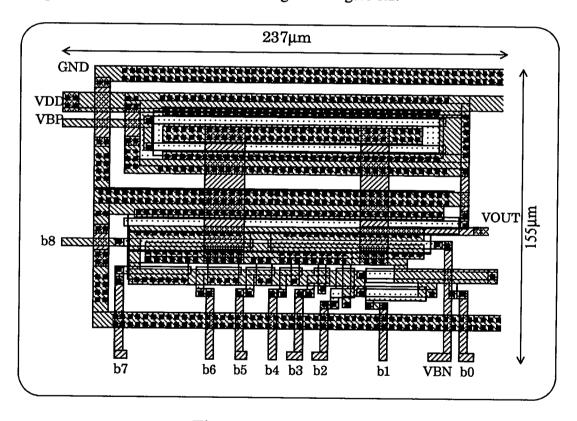

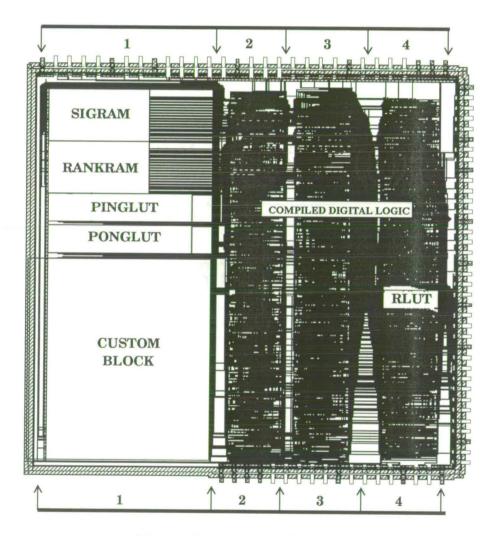

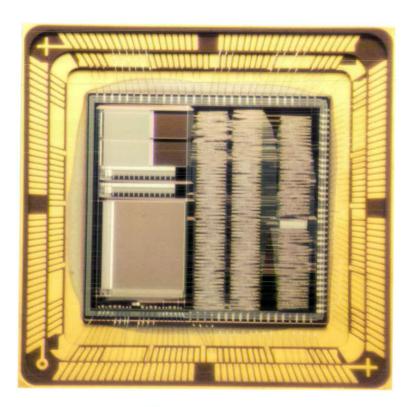

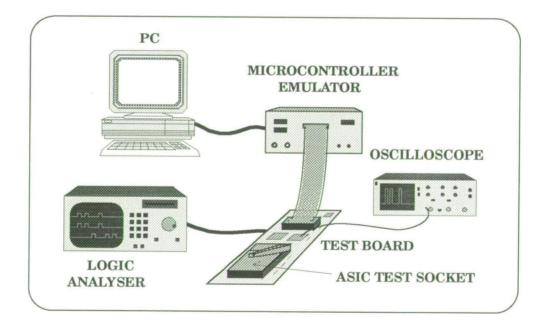

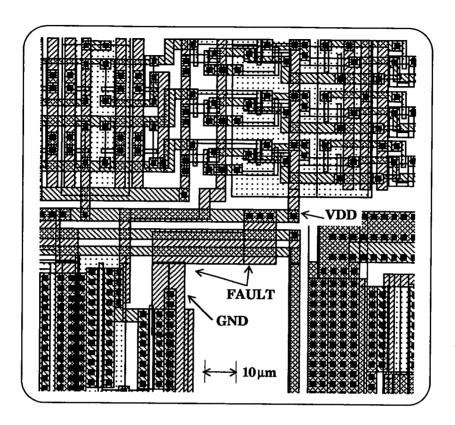

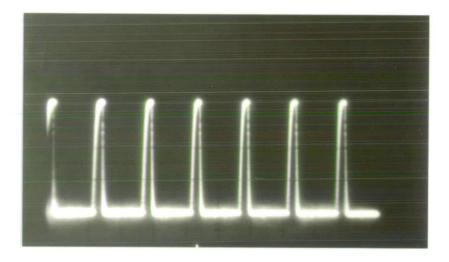

| User database                 | 96              |  |  |