# A RECONFIGURABLE ARCHITECTURE FOR VERY LARGE

# SCALE MICROELECTRONIC SYSTEMS

Wei Chen

Doctor of Philosophy

Department of Electrical Engineering

University of Edinburgh

December 1986

## ABSTRACT

With the inexorable increase in integrated circuit complexity and chip size, an efficient defect tolerant method must be incorporated into the design of large silicon integrated systems to avoid dramatic yield loss. Furthermore, it is highly desirable that future integrated systems be high performance, low cost, and particularly have system level reconfigurability. This thesis introduces an architecture embodied in a large silicon chip, called *superchip*, which can be tailored by the user to a specific system to perform a particular processing task. The methodology of system design using the superchip architecture is presented both at the top level of system organisation and at a lower level of system customisation, through a suite of supporting software. The superchip architecture offers defect/fault tolerant capability and system reconfigurability by incorporating a crossbar switching network in the superchip together to accommodate the required communication. Defect/fault tolerance is achieved by introducing redundancy through the switching network.

Cost-effectiveness is one of the major issues investigated in the thesis. By employing the optimal redundancy predicted by yield models and the redundancy selector developed during this research, a dramatic yield improvement over the yield without redundancy can be achieved. This brings the superchip yield up to an economically acceptable level, while keeping the hardware overhead at a minimum.

Finally, an example is given to illustrate the design and customisation process for implementing an FFT system in the superchip style. High performance and flexibility are achieved by reconfigurability of the architecture. The example system, having  $35 \times 35 \text{ mm}^2$  silicon area, is capable of approximately 150 million arithmetic operations per second. More powerful systems can be achieved by extending the concept to an entire silicon wafer by using the same processing technology, or by increasing the density using a smaller geometry processing technology.

# **Declaration of Originality**

The material contained in this thesis was researched and composed entirely by myself in the Department of Electrical Engineering, University of Edinburgh between March 1984 and December 1986.

Signed

Wei Chen

# **ACKNOWLEDGMENTS**

I would like to thank my supervisors Professor John Mavor and Dr. David Renshaw, and also Professor Peter Denyer for their continuous encouragement and technical guidance throughout the research.

Thanks also go to the members of the Integrated Systems Group, particularly Dr. Kunihiro Asada, David Fletcher, Stewart Smith, and C. H. Lau, for their assistance and conversation. Dr. Gordon Brebner also has my thanks for his interest and contribution on the mathematical proof of NP-completeness for the routing problem. I am grateful to SERC for their silicon brokerage service. Thanks also go to University of Edinburgh and Shanghai Jiao-tong University for their financial support, and CVCP for the ORS award.

Finally, it is a pleasure to acknowledge my parents' support during my stay in Edinburgh.

# CONTENTS

| 1 INTRODUCTION                                                     | 1          |

|--------------------------------------------------------------------|------------|

| Introduction                                                       | 1          |

| A Brief Review of Defect-Tolerant Techniques in Integrated Systems | 4          |

| The Defect/Fault Tolerant Approach Introduced in This Research     | 10         |

| Outline of Thesis                                                  | 10         |

| 2 A RECONFIGURATION AND DEFECT/FAULT TOLERANT                      |            |

| MONOTHIC COMPUTING SYSTEM                                          | 13         |

| Introduction                                                       | 13         |

| Crossbar vs Other Interconnection Networks                         | 13         |

| The FIRST Silicon Compiler                                         | 19         |

| The Superchip Architecture                                         | 20         |

| Summary                                                            | 35         |

| 3 YIELD MODELLING AND REDUNDANCY SELECTION                         | 36         |

| Introduction                                                       | 36         |

| Previous Work on Yield Modelling                                   | 36         |

| Superchip Yield Modelling                                          | 47         |

| Optimal System Block Partitioning Using Crossbar Networks          | <b>7</b> 1 |

| Block Partitioning versus Hierarchical Redundancy                  | 74         |

| Conclusions                                                        | 77         |

| 4 THE PROTOTYPE CROSSBAR SWITCH MATRIX DESIGN                      |            |

| AND EXPERIMENTAL RESULTS                                           | 79         |

| Introduction                                                       | 79         |

| Prototype Design Procedure                                         | 79         |

| Test Procedure of the Prototypes                                   | 83         |

| Test Results                                                       | 87         |

| Design Deficiencies                                                | 107        |

| Summary                                                            | 112        |

|                                                                    |            |

| 5 A MESSAGE ROUTING ALGORITHM FOR THE CROSSBAR SWITCH  |  |

|--------------------------------------------------------|--|

| MATRIX IN THE PRESENCE OF FAULTY SWITCHES 113          |  |

| Introduction 113                                       |  |

| The Problem and Solution Tactics                       |  |

| Goodness Function for Net Assignment 117               |  |

| The Algorithm 123                                      |  |

| Implementation                                         |  |

| An Example 133                                         |  |

| Discussion                                             |  |

| Conclusion 143                                         |  |

| 6 A COLUMN FFT ENGINE USING THE CROSSBAR SWITCH        |  |

| MATRIX - A CASE STUDY 145                              |  |

| Fast Fourier Transform                                 |  |

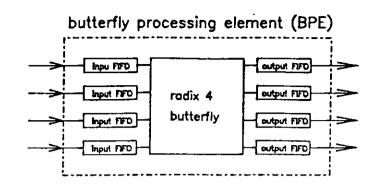

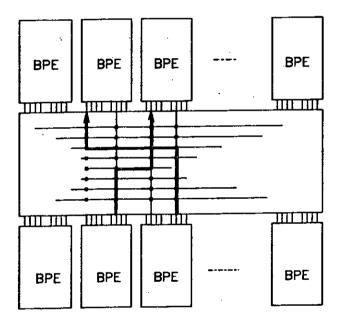

| A Monolithic 64 Point Column FFT System 147            |  |

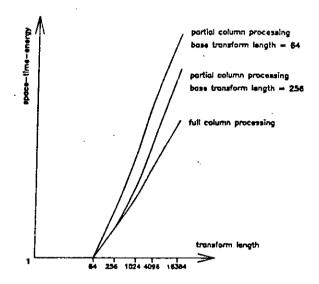

| Expandability of the FFT Superchip 158                 |  |

| Conclusion 168                                         |  |

| 7 CONCLUSION AND RECOMMENDATIONS FOR FURTHER           |  |

| RESEARCH 169                                           |  |

| Summary 169                                            |  |

| Recommended Further Research 171                       |  |

| REFERENCES 176                                         |  |

| APPENDIX A: SOME MATHEMATICAL NOTATION 190             |  |

| APPENDIX B: NP-COMPLETENESS OF THE ROUTING PROBLEM 192 |  |

| APPENDIX C: PUBLICATIONS 197                           |  |

# NOTATION

| ALU     | arithmetic-logic unit                   |

|---------|-----------------------------------------|

| BPE     | butterfly processing element            |

| CAD     | computer-aided design                   |

| CMOS    | complementary metal-oxide-semiconductor |

| CPU     | central processing unit                 |

| CtrlIn  | control input of a processing element   |

| CtrlOut | control output of a processing element  |

| CVD     | chemical vapour deposition              |

| DAS     | digital analysis system                 |

| DFT     | discrete fourier transform              |

| DIF     | decimation-in-frequency                 |

| DSP     | digital signal processor                |

| ECL     | emitter-coupled logic                   |

| EPROM   | erasoble programmable read—only memory  |

| FET     | field-effect transistor                 |

| FFT     | fast fourier transform                  |

| GaAs    | gallium arsenide                        |

| IC      | integrated circuit                      |

| LSB     | least significant bit                   |

| LSI     | large scale integration                 |

| MSB     | most significant bit                    |

| NMOS    | N channel metal-oxide-semiconductor     |

| РСВ     | printed-circuit board                   |

| PE      | processing element                      |

| ROM     | read-only memory                        |

| SA1     | stuck at 1                              |

| SA0     | stuck at 0                              |

| SEM     | scanning electron microscope            |

| SigIn   | signal input of a processing element    |

| SigOut  | signal output of a processing element   |

| S_ON    | stuck on                                |

| S_OP    | stuck open                              |

| SSI     | small scale integration                 |

| ULSI    | ultra-large scale integration           |

| VLSI    | very large scale integration            |

| W SI    | wafer-scale integration                 |

|         |                                         |

#### CHAPTER 1

#### INTRODUCTION

## 1.1. Introduction

The evolution of modern electronic systems from the embryonic stage of vacuum tube realisations at the beginning of this century through discrete transistor, SSI, and LSI realisations to today's VLSI complexity illustrates the trend in system integration towards more compact, cheaper, faster, and more reliable systems. For example, modern VLSI technology has made it possible to integrate hundreds of thousands of transistors on to one small piece of silicon, typically less than 100  $mm^2$ . The integration evolution has matured over the past decade and resulted in the appearance of single chip DSP [1,2] and microprocessors [3,4], very large memory chips [5,6], and so on. Continually, integrated circuit designers have endeavoured to increase chip complexity by integrating more and more circuits on to a single chip with various design styles. The trend nowadays is towards a system-on-a-chip which requires an entire silicon wafer to accommodate the entire electronic system [7,8,9,10]. There are many advantages of having fewer, but larger, IC chips many many many maller ones wired together on a circuit board to form the same system. These include:

• potentially higher speed due to less inter-chip connections. This follows from the fact that on-chip capacitance is much smaller than off-chip capacitance and, therefore, on-chip delay is tess than off-chip delay. For current ECL gate arrays, for example, the internal cells are about 2.5 times faster than the inter-chip delays (including the wiring delay). For CMOS this ratio can be as high as 10 times when the internal cells are close to each other<sup>†</sup> [11, 10].

<sup>†</sup> It might be argued that one can not simply scale this to full wafer products. But generally, as chip complexity increases, this observation still stands.

- lower packaging and assembly cost resulting from the simplification in conventional packaging with fewer bonding pads, gold wires, and package conductor runs, etc. As a result, more silicon is available for computational elements rather than being used for large drivers, required for driving large off-chip capacitive loads [12,13,10]. The pin count per logic function is also reduced for the large single chip system.

- lower power dissipation achieved by having fewer bonding pads. Much lower output capacitances which results lead to the requirement-for smaller output drivers [12,10].

- higher reliability expected-through-having fewer mechanical connections, than is the case when mounting chips on a printed-circuit board [10].

However, problems have emerged in experimental work directed to developing large, single chip, integrated circuits. One of the most important and dominant problems is the rapid degradation in yield which results when the chip size is appreciably increased duction sizes, because, with the increase of integration scale and circuit complexity, catastrophic processing defects on each chip become increasingly likely. These processing defects degrade the overall yield of the chip dramatically and, thus, increase the cost. For example, a well 'tuned' processing line can achieve a defect density of two defects per square centimetre. The probe yield of a typical VLSI chip today with  $5 \times 5$  $mm^2$  size can be around 60%. However, if the chip size is increased to  $15 \times 15 mm^2$ , using the Poisson yield model (which is rather pessimistic in practice but often used as an analytical tool for yield prediction), the new yield could be as low as 1%. The IC industry can not afford such implied yield losses in the exploration for higher levels of integration. This is a prime consideration in setting the optimum size of chip for a particular IC process. Naturally, yield enhancement can be expected by continual improvements in IC processing which lower defect density, but such improvements are gradual and very expensive to achieve. However, today's VLSI technology has made it possible to afford a degree of redundancy, which enables defect tolerance to be included in chips to achieve acceptable yields, that current technology can not offer. Therefore, it is more feasible to enhance yield by designing defect-tolerant integrated systems, than wait for improvements in the technology. So far, the accepted approach to larger chips is to introduce some form of hardware redundancy into the circuits. Thus, affected elements can be switched out via some programmable switches and replaced by fully working

circuit sections.

Besides low yield, there have been some other problems in large integrated systems; one being reliability. With the increase of system complexity, the probability of having an operational fault (often classified  $as_{\Lambda}^{\alpha}$  soft error or transient error) at any time also increases. It has been estimated [14] that a system containing two thousand VLSI chips would suffer from transient failures at a rate of one every 50 hours and permanent hardware failures at a rate of one every 500 hours of operation. For larger silicon chips, occasional operational faults of some elements in the chip are still likely during field operation, although their reliability is better than the same system with smaller chips because of the level of integration. Such occasional faults in some elements may cause a great deal of performance degradation as well as malfunctioning of the whole system. To improve reliability for complex electronic systems, the conventional fault-tolerant approaches, such as TMR (Triple Modular Redundancy) [15, 16], are required. However, due to the large hardware overhead, such a technique will become more and more costly in future.

The approach advocated in this thesis is to achieve fault tolerance for a chip by avoiding the faulty elements whenever they appear, rather than discarding the whole system. To be consistent in terminology throughout the thesis, methods<sup>†</sup> of circumventing defects in the chip are referred to as *defect tolerance*. The method of recovering the system from an operational fault is called *fault tolerance*. The replacement of a faulty element during system operation can be achieved by incorporating hardware redundancy, by introducing a switching network into the system.

Another problem, or perhaps desire, has been the issue of system reconfigurability. There has been a great deal of interest in the design of reconfigurable architectures whose paths between elements (processors, memory and I/O devices) can be reconfigured by some programmable control. Such reconfiguration can be achieved in two ways according to different tasks and interconnection networks. One is to set up interconnection paths once, and prior to the initiation of the tasks, or at compile time<sup>††</sup>; this is here called *static reconfiguration*. The other is to reconfigure the interconnection paths

<sup>†</sup> These expressions are in common use [17].

<sup>&</sup>lt;sup>++</sup> This is derived from an analogy with conventional programming. High-level language programs are compiled to produce executable object code. Similarly, some specification of the communication requirements of an algorithm can be compiled to produce control signals to set up the network prior to execution [18].

'on-the-fly', or at run time; this is here called *dynamic reconfiguration*. The latter is particularly desirable in applications where the communication patterns have to be changed during the operation, or they are data-dependent. To achieve such flexible reconfiguration schemes, a good interconnection network with simple and easy control is desired.

This thesis addresses the key three issues of yield, reliability and system reconfigurability, by incorporating a flexible crossbar switching network into integrated systems. This course should improve yield for very large silicon chips, and achieve system reconfiguration, either statically or dynamically. A general system architecture is proposed which consists of multiple processing elements (PEs) and a crossbar switching network. It is capable of performing a range of tasks by programming the crossbar switching network to customise the system. This programming procedure can be performed either before the system is operational; static reconfiguration, or during operations as well; dynamic reconfiguration. Static reconfiguration is often preferred when only system customisation and/or defect-tolerance are to be achieved. Such initial system interconnection is kept unchanged during the operation. Defect-tolerance is achieved by connecting all the necessary, and working processing elements together using working switches in the crossbar switching network. Dynamic reconfiguration, on the other hand, is usually performed when the connections in the system need to be changed or a fault is found during its operation. The objective of this thesis is to assess the potential of employing a crossbar switching network in very large integrated systems by considering the following factors: interconnection organisation, defecttolerance and fault-tolerance.

# 1.2. A Brief Review of Defect-Tolerant Techniques in Integrated Systems

Processing defects exhibit themselves in many different ways resulting in a variety of fault conditions. These processing defects can be classified in two categories. One is referred to as a point defect. Each such defect is a local phenomenon affecting only the microstructure in its own immediate area. Pinholes in the oxide layer belong to the point defect category. Processing defects in the other category have a size comparable with the geometry of circuit layout. They are usually caused by contamination introduced during the processing, typically, resulting in open- or short-circuit conditions. Typical defects have been analysed and listed by a variety of authors [19,11,20,21,22]. Table 1.1 lists some of the defect types for current double-metal VLSI technology. For

- 4 -

each type of defect the likely mechanism causing the defect is also listed.

| Table 1.1 Classification of Defect Types |                                                                        |  |  |  |  |

|------------------------------------------|------------------------------------------------------------------------|--|--|--|--|

| Fault Condition                          | Equivalent Source Defects                                              |  |  |  |  |

| unexpected opens or shorts among         | large contamination spot                                               |  |  |  |  |

| features on two metal layers             | during the process                                                     |  |  |  |  |

| unexpected opens or shorts among         | contamination during                                                   |  |  |  |  |

| features on polysilicon layer            | processing                                                             |  |  |  |  |

| unexpected opens or shorts among         | contamination and schedule                                             |  |  |  |  |

| features on diffusion layer              | errors in implantation                                                 |  |  |  |  |

| poor contact and via                     | high contact resistance or poor metal<br>coverage over contact regions |  |  |  |  |

| unexpected shorts between features       | poor oxide quality                                                     |  |  |  |  |

| on metal and polysilicon layers          | pinholes in the oxide                                                  |  |  |  |  |

| unexpected shorts between features       | poor oxide quality                                                     |  |  |  |  |

| on metal and diffusion layers            | pinholes in the oxide                                                  |  |  |  |  |

Any of these defects identified in Table 1.1 may cause a logical) malfunctioning of the circuit. However, introducing hardware redundancy in design to replace the defective logic area is the common approach to circumvent such defects. In practice, the part of the circuit affected may be locally circumvented by disconnecting in the whole circuit and connecting (switching in) a working redundant logic part into the circuit. This idea was originally introduced in the design of large memory chips, because they are highly regular in design and densely packed and, therefore, are highly sensitive to defects. However, their highly regular architecture makes it possible to efficiently implement various redundant elements as a standby to replace any affected element. Various large memory designs with different defect tolerant schemes have been presented [23,24,25,26]. The techniques for implementing defect-tolerant schemes vary with the different switch implementations for introducing redundancy. The switches can be classified as *physically programmable* switches or *electrically programmable* switches. The physically programmable switches are realised by incorporating special links on the chip between sections of circuit. The switch setting is performed using non-electrical methods, such as a laser, to make the special links conducting or nonconducting. This approach usually needs special processing steps or programming equipment. The electrically programmable switches are usually realised using transistor structures within the chip. For this approach the switch setting is performed at circuit level by turning on or off transistors using electrical control. Some typical defecttolerant techniques using either physically or electrically programmable switches are summarised in the remainder of this sub-section.

#### 1.2.1 Discretionary Wiring

A large integrated system can be divided into many functional units. These functional units are distributed and processed discretely over a large silicon area like many chips on a wafer. After processing, each functional unit is tested. The discretionary wiring technique is used to generate correct interconnection patterns by linking the working functional units on the silicon to form a desired large integrated system. Defecttolerance is achieved by isolating the defective functional units from the system. When the wiring pattern is complicated, the resulting systems are small, reliable and potentially cheap comparing to the printed-circuit board approach using individual packaged chips. However discretionary wiring requires high quality processing steps to generate metal wiring patterns on the silicon. If these wires are regarded as a set of switch links, then this technique provides non-volatile<sup>†</sup> and non-reversible<sup>††</sup> switching.

One of the earliest attempts to use the discretionary wiring technique to build a large memory chip was in the 1960s, when Texas Instruments Inc. produced a prototype 32K memory product on a 2-inch wafer[7]. With this early approach redundant circuits, implemented on a ceramic substrate, were connected into systems by discretionary

<sup>†</sup> A programmable switch is said to be *volatile* if its control store is volatile, i.e. testing and reconfiguration (switch setting) must be initiated each time power has been removed from the part in question. Otherwise, it is *non-volatile*.

<sup>††</sup> A programmable switch is said to be *reversible* if it can be turned off after it has been turned on, or vice versa.

wiring. Unfortunately, this technique was ahead its time and was not then adopted in production. The reason is that complex wiring processes were not mature at the time of its introduction and, therefore, could not be used to produce economically viable large integrated systems. However, this approach has been recently reintroduced [27] by using modern silicon fabrication and CAD techniques, including E-beam writing, thick film/metal structures with relaxed design rules for wiring patterns, and sophisticated CAD support.

#### 1.2.2. Laser Programming

Laser programming techniques include laser welding and laser cutting. Typically, a high energy laser beam is placed precisely on some points or tracks, like bus or power lines, fuse, or antifuse<sup>†</sup>, etc, to make connections or disconnections. These areas receiving the laser beam usually use special material and include features to help the welding or cutting processes. Defective devices within the system can be disconnected and replaced by a duplicate circuit using this technique. As compared to the discretionary wiring technique, laser programming is easier to achieve and more interactive and flexible to designers, because laser programming facilities are simpler and more accessible to designers. However, it requires some non-standard processing steps.

The Lincoln Laboratory of MIT demonstrated a so-called "restructurable VLSI" architecture [28,29,30] using a laser programmed, vertical metal, H-A-Si (Hydrogenated Amorphous Silicon) sandwich structure to avoid defective elements in the chip. A single wafer, 16-point FFT processor has been designed [31,32] with this approach. Other forms of laser programming include laser-induced CVD conductors [33], and laser programmed polysilicon doping. Laser programming has been used in large commercial memory designs by Bell Laboratories [34,35,36], Hitachi [37], Toshiba [38], and more recently by Mitsubishi [25] and Mostek [39].

- 7 -

<sup>†</sup> Fuse (antifuse) is a linking device. According to its type, it is sensitive to laser, current or voltage with a circuit-opening (circuit-closing) fusible part controlled to disconnect (connect) circuit portions.

#### 1.2.3. E-Beam Programming

Use of an electron-beam programmed transistor switch for performing circuit repairing was suggested by Shaver [40], in which the switch is a floating-gate FET. This type of transistor can be fabricated using conventional processing lines and does not usually require process modification. The programming is performed by applying an electron-beam to the floating gate of the transistor, causing a negative potential to exist on its gate. Such a negative potential can turn on an enhancement-mode p-channel FET, or turn off a depletion-mode n-channel FET. In CMOS, both types of FET can be fabricated, so that both normally "on" or "off" switches are available. A 128K bit NMOS electronically programmable ROM has demonstrated the feasibility of this approach to circuit customisation, as well as to repairing and testing [41,42]. A wafer-scale, pipelined processor system using electron-beam programmable switches has also been reported [43]. As well-as applying an electron-beam on the floating-gate of a special designed transistor to reconfigure the circuit, it is also possible to use an electron-beam or ion-beam to impinge the surface of an IC circuit directly ( monte ) normal transistor structures) to alter some characteristics of the transistors, (So) that system reconfiguration may be achieved [44]. For example, a strong electron-beam can be directed to a normal transistor (not a special designed floating-gate transistor) to change its characteristics, so that the transistor is, possibly permanently, turned "on" or "off" to switch in or out circuit portions.

#### 1.2.4. Transistor Switches

The use of normal transistors to perform programmable, reversible, volatile switches has been widely studied. Because a normal transistor performs as a volatile switch, its switch settings should be initialised every time the power is reapplied. Such switch elements can also be used to configure the system so that the communication pattern can be changed according to different requirements.

Various circuit switching schemes for incorporating redundancy, testing, and restructuring around defective circuitry have been proposed. Early exploitation was made in [45] to use transistor switches to form a spiral from a hexagonal array of processing elements. This work has been further developed by Shute et al [46,47], in which a small crossbar interconnection network acts for both defect-avoidance and for system communication link-up. Similarly, fault-tolerant two-dimensional processor arrays employing transistor switches for defect-tolerance and system configuration [48,49,50,51,52,53] have been reported. Memory designs also use such switching techniques to introduce redundancy, for example, a fast bipolar static RAM by IBM [54].

#### 1.2.5. Other Techniques

WHIP (Wafer Hybrid Interconnection Packaging) technology [55, 56, 57] developed by Mosaic Inc. used two levels of signal wiring, separated by amorphous silicon, to form a general-purpose cross-point switch. This can be electrically (or by laser) programmed to form any desired set of interconnection networks. Pre-tested functional chips are bonded on to a wafer with the signal wiring pattern. Due to the electrical property of amorphous silicon, these wires can be connected to form a particular system by applying a high voltage at the cross-over of any two wires separated by amorphous silicon. The use of a silicon substrate minimises thermal stress, and allows the use of standard IC technology to fabricate dense interconnect wiring. High yield for this signal wiring pattern has been reported [58]. For a very large and complex system (say, more than a 100 chip count) this could be an economic approach as compared to PCB realisation. A similar view has been taken by researchers at Rensselaer Polytechnic [59].

More recently, another hybrid packaging approach was suggested [60] to circumvent the yield and discretionary wiring problems. This advocates putting pre-tested chips into recesses in pre-etched silicon substrates. Thereafter, a normal two layer metallisation is carried out to customise the whole system.

These hybrid packaging approaches have advantages over PCB or discretionary wiring approaches in terms of the flexibility and yield. They also have the potential of mixing MOS and bipolar chips together or even mixing silicon and GaAs chips together, to form larger systems with the flexibility of hybrid integrated circuits and the reliability of monolithic interconnections.

Amongst other approaches are pad relocation [61], MNOS transistors [62,63], floating-gate electrical erasable, chalcogenide glass and bridging-bond links [64]. Table 1.2 gives a summary of various existing switching techniques for defect tolerance.

# 1.3. The Defect/Fault Tolerant Approach Introduced in This Research

There is an increasing demand for more processing power for applications including super-computing, vision and speech recognition, bank or office management, etc. More flexible and powerful processing systems with millions or even billions of gates, having better performance and less cost will be vital in future. The trend from VLSI to ULSI (Ultra Large Scale Integration) and WSI (Wafer Scale Integration) is inevitable. Such high integration levels imply hundreds of processing elements, such as floatingpoint processors, memories, caches, together with the necessary interface circuits, to be integrated on the same silicon substrate. However, efficient communication among these processing elements is crucial to the performance of the whole system. Such communication must have high bandwidth, high reliability and flexible reconfigurability. Defect/fault tolerance is a further factor of equal importance.

In this research, the author believes that the volatility and reversibility of the normal transistor is advantageous to realising defect/fault tolerance and, particularly, system reconfiguration. The switches in other defect-tolerant techniques, such as laser or electron-beam programming, cannot entirely meet the requirements, due to their nonreversibility or their requirement for extra complex programming processes. The architecture advocated in this thesis employs an interconnection network using normal transistors to efficiently achieve the requirements for high performance communication among the processing elements, defect/fault tolerance in the system, and system reconfigurability.

#### 1.4. Outline of Thesis

In Chapter 2, a user-programmable general purpose computational architecture is introduced. This uses a large crossbar switching network for system reconfiguration, system communication, and the defect/fault tolerance medium. The crossbar switching network is detailed in Chapter 3 by developing yield models for various defect situations, such as different defect densities and different levels of redundancy. From this work a redundancy selection scheme is proposed. Results generated by testing the crossbar switching network design are discussed in Chapter 4. In Chapter 5, an automatic message routing algorithm in the presence of faulty switches in the crossbar switching network is presented, along with its implementation in software (C-UNIX). Some trials and their results show the efficiency of the algorithm. In Chapter 6, potential applications of the architecture are discussed. Finally, Chapter 7 summarizes the thesis and some suggestions for further research.

| Table 1.2 Summary of Different Defect-Tolerant Techniques |     |        |               |                       |  |  |

|-----------------------------------------------------------|-----|--------|---------------|-----------------------|--|--|

| Types                                                     | V+  | R+     | switched mode | comments              |  |  |

| discretionary wiring                                      | по  | по     | connect       | need some extra       |  |  |

|                                                           |     |        |               | processing steps      |  |  |

| laser programmed                                          | no  | once   | connect or    | need special          |  |  |

| link                                                      |     |        | disconnect    | fabrication step      |  |  |

| laser induced CVD                                         | no  | no     | connect or    | need special          |  |  |

|                                                           |     |        | disconnect    | fabrication step      |  |  |

| laser or electrical                                       | по  | no     | disconnect    | laser fuse needs      |  |  |

| programmed fuse                                           |     |        |               | special treatment     |  |  |

| laser or electrical                                       | по  | no     | connect       | laser antifuse needs  |  |  |

| programmed antifuse                                       |     |        |               | special treatment     |  |  |

| E-beam floating-                                          | ٥đ  | yes    | connect and   | need special          |  |  |

| gate transistor                                           |     |        | disconnect    | treatment             |  |  |

| MNOS transistor                                           | סת  | yes    | connect and   | need special          |  |  |

|                                                           |     |        | disconnect    | fabrication           |  |  |

| active transistor                                         | yes | yes    | connect and   | no special            |  |  |

|                                                           |     |        | disconnect    | treatment             |  |  |

| amorphous silicon                                         | no  | no.    | connect       | special material and  |  |  |

|                                                           |     |        |               | processing steps      |  |  |

| bridging-bond links                                       | no  | (once) | connect       | no special processing |  |  |

|                                                           |     |        |               | steps involved        |  |  |

\* Due to the limited space, V is for Volatility, and R is for Reversibility.

.

#### **CHAPTER 2**

# A RECONFIGURABLE AND DEFECT/FAULT TOLERANT MONOLITHIC COMPUTING SYSTEM

## 2.1. Introduction

Before discussing the architecture of the monolithic computational system introthe duced here, some issues relating to system interconnection on which the proposed architecture is based should be addressed. As discussed in Chapter 1, normal transistor switches are favoured in this research to achieve defect-tolerance, as well as faulttolerance and system reconfiguration. These factors are thought key to the basic requirements for future large computational systems at VLSI density, and beyond.

#### 2.2. Crossbar vs Other Interconnection Networks

Considerable research has been devoted to evaluating the characteristics of various interconnection networks for more than two decades. Many of them have been reviewed in several survey articles [65,66,67,68,69] to which the reader is referred. Here, emphasis is laid on the crossbar network with some differences from the other interconnection networks being pointed out.

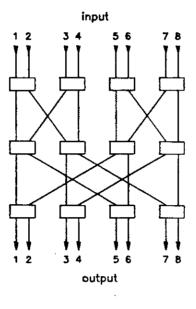

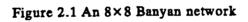

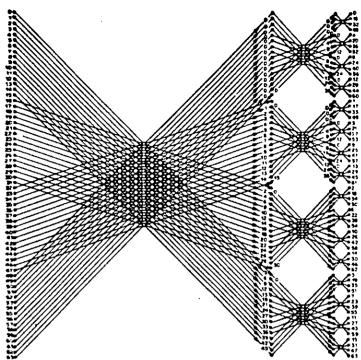

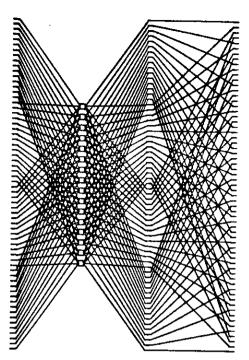

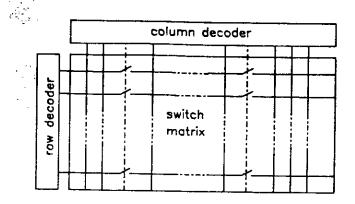

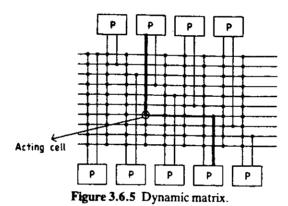

A particular interconnection network can usually be categorised according to four aspects [70]: operation mode, control strategy, switching method, and network topology. By further classifying the network in terms of topology [71], a network can be grouped into two categories: *static* and *dynamic*. In a static topology, links between processing elements are fixed by hardwiring or some similar non-volatile connection so that subsequent reconfiguration is impossible. On the other hand, processing elements in a dynamic topology are linked through a set of active switching elements, whose switching mode can be changed. By setting a particular set of switching elements, reconfiguration can be realised. Multistage [72] and crossbar are the two main types of network in the dynamic group. A three stage banyan network (one kind of multistage interconnection network), and a traditional two-sided normal crossbar network are shown in Figures 2.1 and 2.2, respectively.

Figure 2.2 An 8×8 Traditional crossbar network

The development of the crossbar switching network was originally motivated by the increasing interest in expanding the availability of the common bus structure. The Burroughs D-825 multiprocessor system was among the earliest systems employing the crossbar interconnection network. One of the major research projects involving a crossbar interconnection network earlier was the "C.mm", the Carnegie-Mellon multiminiprocessor [73,74,75]. The crossbar interconnection network provides full interconnection capability between any two connected elements, known as nonblocking. It also provides a fast transfer rate and is flexible in term of possible multiple paths between any two connected elements. Real-time data transfer and computation can be carried out within the network. However, early developments in the crossbar approach exhibited a cost growth of  $O(N^2)^{\dagger}$  for a network having N inputs and N outputs, which is a major obstacle limiting its usage. This is due to the unacceptable implementation cost of  $N^2$ number of switches using MSI (Medium Scale Integration) or LSI (Large Scale Integration). On the other hand, multistage interconnection networks have evolved with slower cost growth over their counterparts in the crossbar network. Various types of multistage interconnection networks have been introduced for connecting N inputs and N outputs. Examples include data manipulator [76], baseline [72,77,78], banyan [79]. omega[80], and delta [81], These multistage interconnection networks have a cost growth of O(NlogN), which has been predicted to be the theoretical lower bound for the growth rate of the switch components in the interconnection networks<sup>††</sup>. However, such an improved cost function is achieved at the expense of increased delay, between inputs and outputs, due to either blocking or the inherent (average) transfer delay<sup>†††</sup> compared to the crossbar approach. In some applications where speed is not of prime importance, this is an acceptable tradeoff. For situations which require high performance, and 100% realisation of required communications amongst PEs at any time, crossbar networks are more suitable than their multistage counterparts. This is particularly true when the interconnection network is used to construct a system (by customisation) rather than just adding more homogeneous processing elements to achieve parallelism.

<sup>†</sup> Consult Appendix A for the definition of the "big-OH".

<sup>††</sup> This argument was given by Shannon [82] in 1950. Interested readers should consult this reference for further details.

the themselves and more switching elements on a single communication route. However, it may be argued that the communication delay of these two type of networks is of the same order [18].

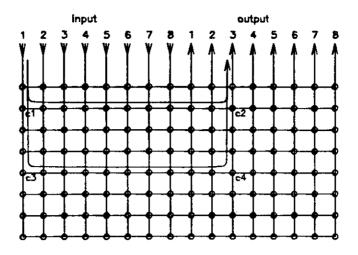

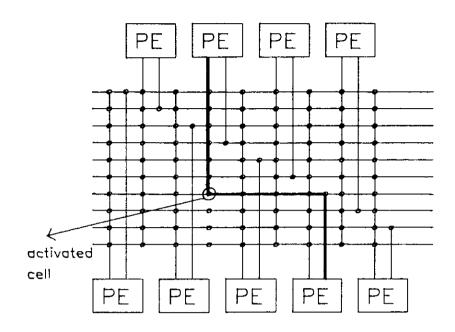

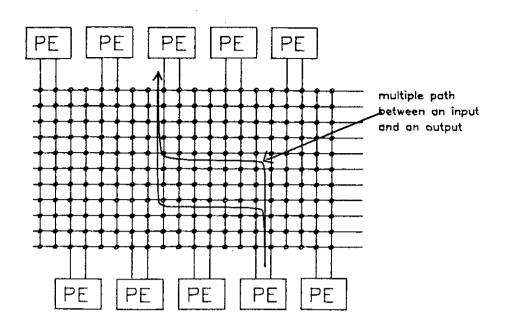

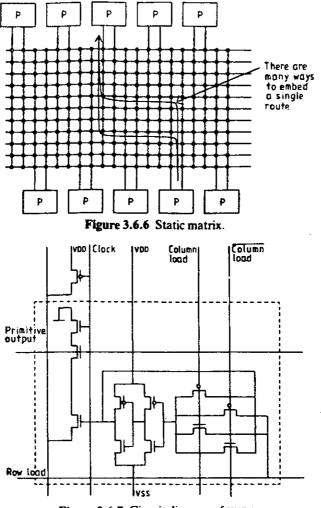

From a defect-tolerance and fault-tolerance point of view, multistage interconnection networks themselves are much more vulnerable to catastrophic defects in the network. This is mainly attributed to the unique-path property that most of the multistage interconnection networks have. To alleviate this, researchers have modified the networks by adding one or more stages of switches and/or redundant links to the networks [83, 84, 85], so that multiple paths between inputs and outputs can be achieved. However, such modification can only tolerate defective switches at certain restricted locations (usually the first and the last stages) rather than for any switch in the network. This can not map the real situation where the defects are randomly distributed and all the switches have an equal chance of being defective. Alternatively, the crossbar interconnection network advocated in this thesis is inherently defect-tolerant and faulttolerant, because of the structure of its multiple-path between any input and output which is able to tolerate defective switches at any location. Due to its regular structure (similar to memory structure), hardware redundancy can be easily and efficiently incorporated into the network. Christos [86] has previously discussed various organisations of the crossbar switching networks to introduce different degrees of fault-tolerance. A conventional two-sided crossbar network is shown in Figure 2.2. The communication path from input 1 to output 3 can be, and only be, made by switching on the switch cell cl. Thus any communication path between a given input and output in this configuration is unique, although free from traffic contention<sup>†</sup>. Such a configuration can not take on a serious defect-tolerance role, because a single failure of any switch cell will rule out one possible input/output communication path. As an alternative, a one-sided duplex crossbar switching network shown in Figure 2.3 introduces the possibility of multiple paths between any input/output pair. With this configuration, all the horizontal conducting tracks serve only internal connections. Inputs and outputs are located either at the top or at the bottom of the network or both. The communication path from input 1 to output 3 can either be made by switching on c1 and c2, or c3 and c4, etc. The number of paths for any input/output pair equals the total number of horizontal conducting tracks.

<sup>†</sup> In multistage network, implementing several connections may require the same route in a certain stage, blocking implementing these connections at the same time. For example, in the  $8 \times 8$  banyan network given in Figure 2.1, if we want to implement connections "input  $1 \rightarrow$  output 1" and "input  $3 \rightarrow$  output 2", then a traffic contention will happen at the second stage, causing blocking.

Figure 2.3 An 8×8 Duplex crossbar network

From a system point of view, the switching elements in a multistage interconnection network need to have more switching states (usually more than two) than that for a crossbar network. They need more involved control circuits to address a set of connections than does the crossbar network. In most of the defect-tolerant schemes, critical defects in control circuits are more crucial than those in the switching circuits, because it is difficult to introduce efficiently redundancy or other defect-tolerant schemes into control circuits. Therefore, it follows that simpler control means higher availability of interconnections. It also indicates that the control overhead for systems employing a crossbar interconnection network is less than that for multistage networks. Moreover, the crossbar structure can easily be expanded to a larger interconnection network with smaller networks. This gives system designers more flexibility in adding additional system functions, and/or improving system performance, without redesigning the whole communication network.

The relatively faster cost growth of crossbar networks appears to be a major problem for implementation in comparison to multistage networks. Fortunately, the manufacturing cost of silicon devices (and, therefore, the unit cost of a switch cell in a crossbar network) has gone down rapidly over the last two decades, and is set to reduce with the progress of VLSI technology. As a result, the cost of such interconnection networks will not become the major cost component in the VLSI era, and beyond. As far as the efficiency of integration is concerned, architectural regularity is more important for cost reduction. The previously established cost measure for crossbar networks is no longer significant in the VLSI era with respect to the cost of multistage networks. Let us consider the banyan switching network as an example of multistage network for comparison with a crossbar network, because many other networks in the multistage network category, such as the Omega network [80], are topologically equivalent to the banyan network [72]. A recent study [87] has already indicated that VLSI realisation of the crossbar network does not necessarily result in a larger silicon area, as compared with the banyan network. They both have a cost growth of  $O(N^2)$ . The time delay through the network, which is technologically dependent, grows as O(N) for crossbar and  $O(N^a(logN)^2)$ , where 0 < a < 1, for the banyan network. This contrasts with traditional results which predict O(NlogN) and O(logN) for the cost and delay growth of a banyan network [79].

In summary, for future integrated systems which demand higher levels of integration, better performance and lower cost, the crossbar switching network is a suitable candidate for the interconnection network for system communication, defect/fault tolerance and system reconfiguration. The features that the crossbar networks offers can be listed as:

- full interconnection capability (allowing any connection from any input to any output),

- non-blocking,

- constant response time,

- simple control,

- possible system expansion, and

- inherent defect-tolerance and fault-tolerance through redundancy.

The approach advocated in this thesis, towards a defect-tolerant and fault-tolerant architecture for ULSI and WSI is to use a large crossbar switching network as a programmable element to achieve both system communication and defect/fault tolerance. The foundation to this research was inspired by the development of bit-serial architecture employed in the FIRST silicon compiler [88].

# 2.3. The FIRST Silicon Compiler

In this section, the FIRST silicon compiler and its architecture are briefly reviewed as a useful background to the research undertaken in this thesis.

## 2.3.1. Bit-Serial Architecture

Bit-serial architectures are distinguished by their communication strategy. Digital signals are transmitted bit sequentially on single wires or busses, as opposed to the simultaneous transmission of the bits of words on parallel busses. This distinction is the key to many inherent advantages of the bit-serial approach as a VLSI strategy. Most significantly, bit-serial transmission leads to efficient communication within and between VLSI chips. This is an outstanding advantage where communication issues dominate, as in many signal processing applications.

As discussed earlier, with the increase in chip size, defect/fault tolerance is a crucial factor in system performance and, particularly, economic production. Owing to the ease of bit-serial communication relative to parallel, the architectural restriction of nearest-neighbour communication need not be imposed, leading to a much greater architectural (and therefore algorithmic) flexibility. Additionally, bit-serial processing elements are generally smaller and therefore intrinsically higher yielding than their bitparallel counterparts. It has been discovered [89] that fault coverage of bit-serial circuits can be high, and may be determined without extensive fault simulation. The cost in silicon, power, complexity and design difficulty is low, leading to a better yield of function per unit silicon area and high fault coverage for the whole system. Furthermore, introducing pipelined processing in bit-serial systems can result in a better *area\*time*<sup>2</sup> measure over its bit-parallel counterparts. Therefore, bit-serial architectures are an attractive proposition, and can offer architectural and defect/fault-tolerant advantages over their bit-parallel counterparts.

## 2.3.2. The FIRST Silicon Compiler [88]

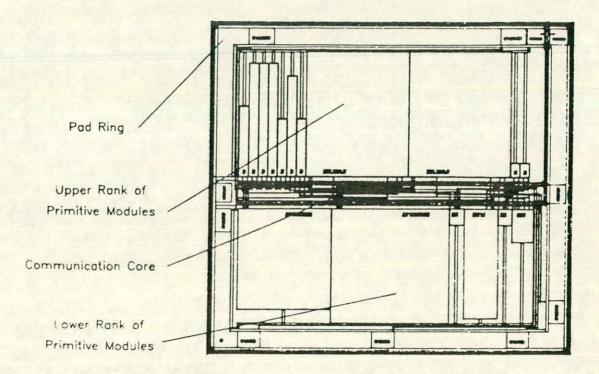

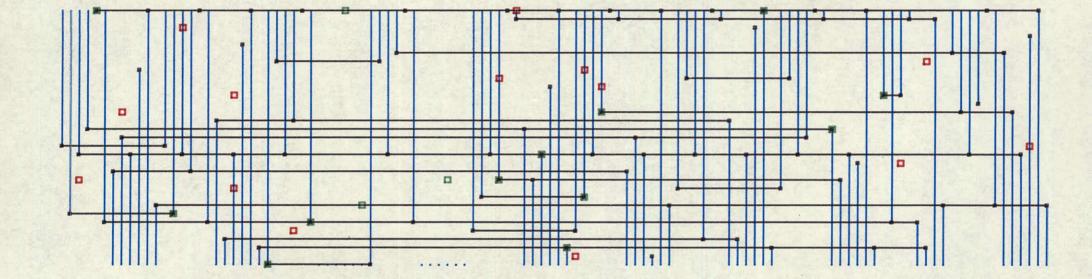

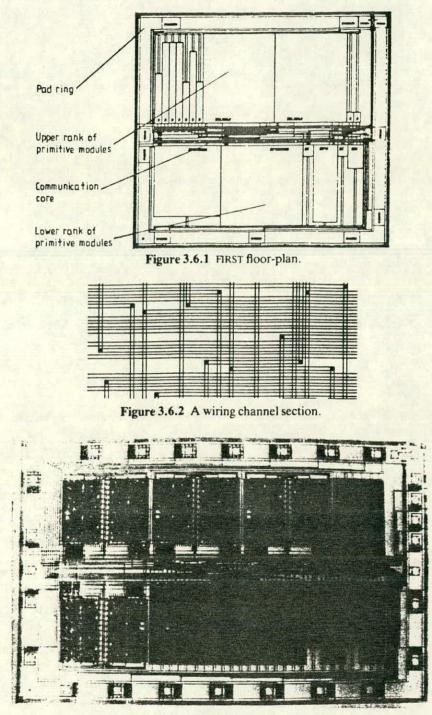

(pilicon compiler is a tool which takes a high level functional description of a system as input but produces, instead of machine code like a conventional compiler, a detailed chip mask geometry. The FIRST (for Fast Implementation of Real-time Signal Transforms) silicon compiler is simply an interpretation at one technology level of the bit-serial approach. A chip generated by FIRST comprises a central communication channel, flanked by two rows of bit-serial primitive modules. Signal routing is only implemented through the central channel, and there is no intimate connection between neighbouring modules, Thus processing elements communicate by receiving and transmitting data via a routing channel. Chip input and output signals are fed to peripheral pads via the ends of the channel. A channel router is used to carry out the inter-PE routing. Figure 2.4 shows a floorplan of an actual design generated by FIRST, in which the characteristic features are identified.

Figure 2.4 The floorplan of a design generated by FIRST

# 2.4. The Superchip Architecture

A system created by FIRST is not reconfigurable; instead, algorithms are hardwired through a central routing channel (interconnection network with static topology). The designer can only change the system configuration during compile-time; variations are impossible at run-time. Further, in line with the familiar yield problem, a single catastrophic fabrication defect will result in abandonment of the entire chip. Finally, the requirement for increasingly large, high performance, low cost signal processing systems implies larger chip sizes. Inevitable fabrication defects limit the practical size of these chips and, thus, the attainable performance level for one substrate.

The approach advocated in this research is to extend the flexibility of the FIRST approach to build arbitrarily complex networks of bit-serial systems. This is to be achieved by integrating a crossbar switching network with a large number of bit-serial PEs. Arbitrary interconnections offered by the crossbar network amongst the bit-serial processing elements contrast with alternative nearest-neighbour-only communication strategies, usually advocated for ULSI and WSI. The chip size required to accommodate the proposed architecture is expected to extend beyond today's usual VLSI chip sizes ( < 100 mm<sup>2</sup>) and, hopefully, to a whole silicon wafer. For convenience in later discussion, the concept of this scale of integration will be referred to as superchip, the proposed architecture implemented with the superchip as superchip architecture, and the adopted crossbar switching network as switch matrix.

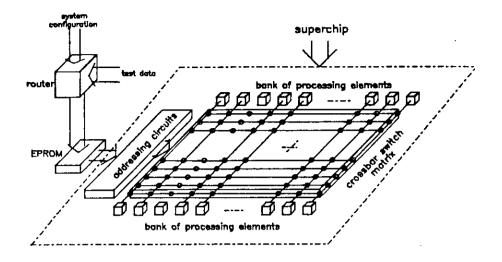

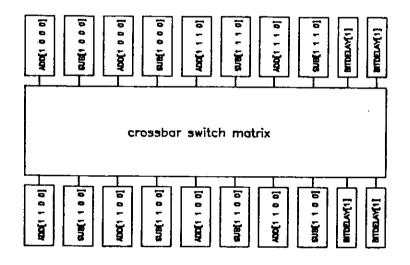

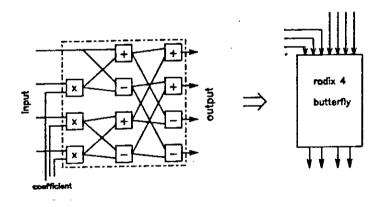

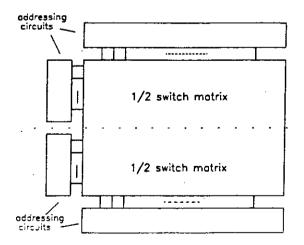

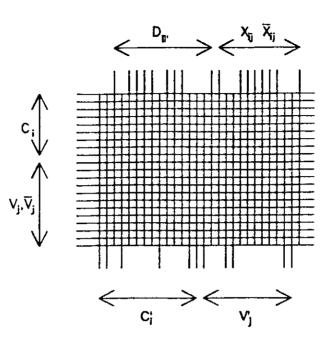

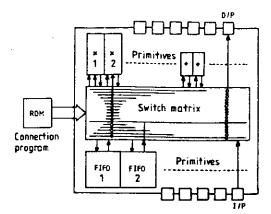

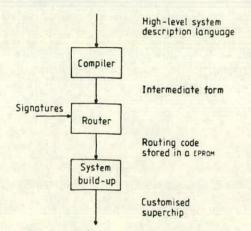

The superchip is a large silicon chip containing many independent bit-serial processing elements. Computational networks are produced by the electrically programmable crossbar switch matrix controlled by the end user. The end user may thus customise superchip to implement a range of signal processing or scientific computational tasks. Figure 2.5 is a schematic diagram illustrating the superchip architecture. Bitserial processing elements are placed in two rows, above and below a crossbar switch matrix. All the processing elements communicate with each other via the crossbar switch matrix. The crossbar switch matrix permits users to program arbitrary functional networks comprising bit-serial processing elements. Redundant processing elements can be introduced easily by adding extra matrix columns to accommodate these redundancies. These can be switched into the system through the switch matrix. Defect/fault tolerance can also be achieved by programming the switch matrix to avoid faulty elements and employing working redundant elements in the chip, whenever necessary. The addressing data stored in EPROM is generated by a software program, called router, which combines the system configuration information and the information about the defective elements in the chip to produce the correct communication paths among the processing elements. A key issue in the superchip architecture is the organisation of the switch matrix and its effect on the performance of the whole system.

- 21 -

Figure 2.5 A schematic of the superchip architecture

#### 2.4.1. Crossbar Switch Cell and Switch Matrix

Two different switch cells have been considered in this research, and their relative features compared. This involved two different crossbar matrix architectures: two-sided and one-sided architectures, already referred to in Figures 2.1 and 2.3.

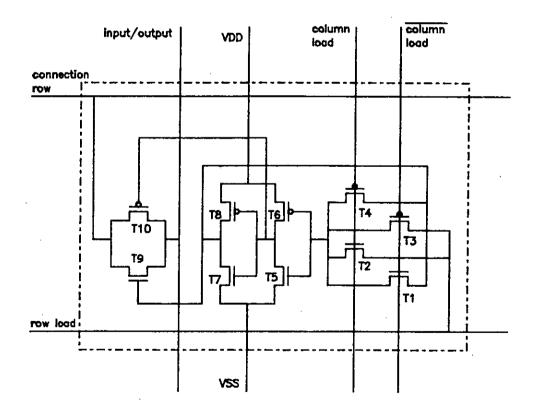

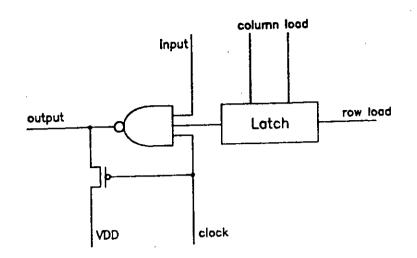

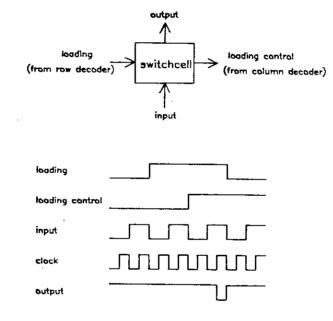

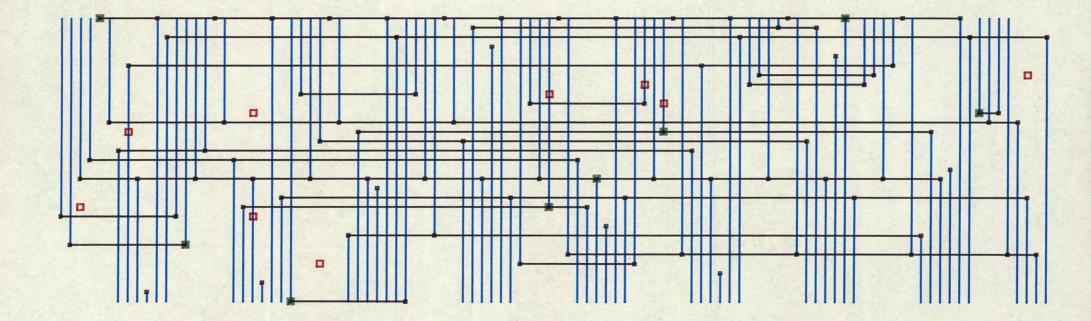

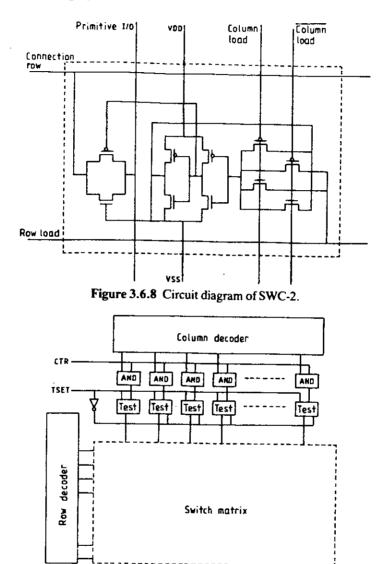

In the two-sided switch matrix architecture, one row of the matrix is exclusively assigned to each output of processing elements. Networks are routed in this architecture by programming connections to the inputs of processing elements. Figure 2.6 illustrates the two-sided switch matrix scheme adopted in the superchip architecture, which is similar to the architecture shown in Figure 2.2 except that in this diagram the actual position of the processing elements and the layout style of the matrix are given. The circuit diagram of the switch cell employed is shown in Figure 2.7. This switch cell, let us call it swc-1, comprises a latch, a dynamic NAND gate, and a control pass-gate controlled by the latch. During the precharge cycle, the matrix column (connected to a processing element input) is charged to a logic one. During the evaluation, the matrix column holds its precharged state if the switch is switched off, or becomes the complement of its matrix row (connected to a processing element output) if the switch is switched on. To turn the switch on or off, "column load" is set to logic one so that the switching information from row decoder ("row load" signal) is written into the latch via

Figure 2.6 Interconnection organisation using traditional crossbar network

Figure 2.7 Circuit diagram of the dynamic switch cell (swc-1)

- 23 -

the pass gate. Otherwise the latch is isolated from other circuits to maintain the current switching state. At the system level operation of the matrix, the output of each processing element drives one horizontal row of the matrix and every processing element input is driven by a column of the switch matrix. Input and output signals enter and leave the superchip via the switch matrix. Thus input pads are assigned one horizontal channel in the matrix, and output pads each come from one switch matrix column. Clearly, because the switch cell only allows an unidirectional pass of the signal, it is particularly suited to the realisation of the two-sided crossbar architecture. Such a matrix architecture is called *normal matrix* in the rest of the thesis, due to its conventional two-sided matrix organisation.

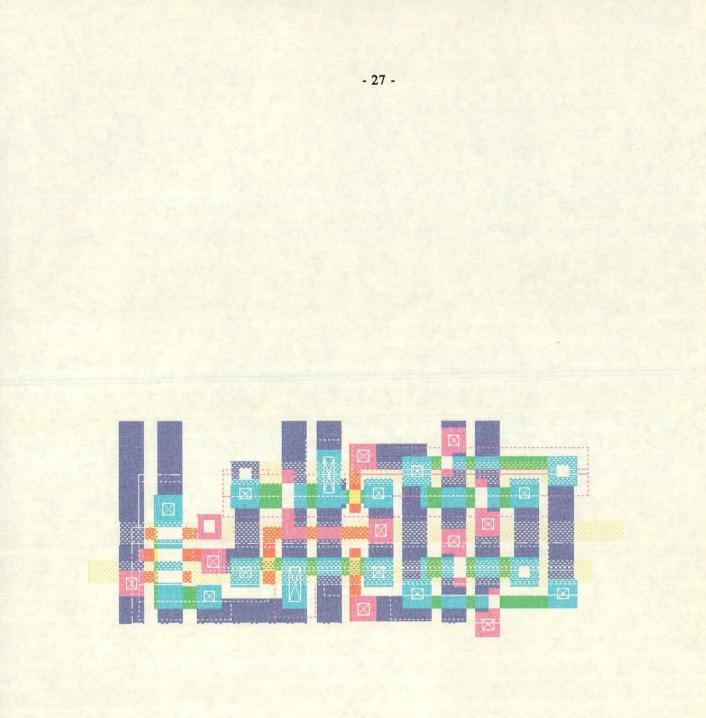

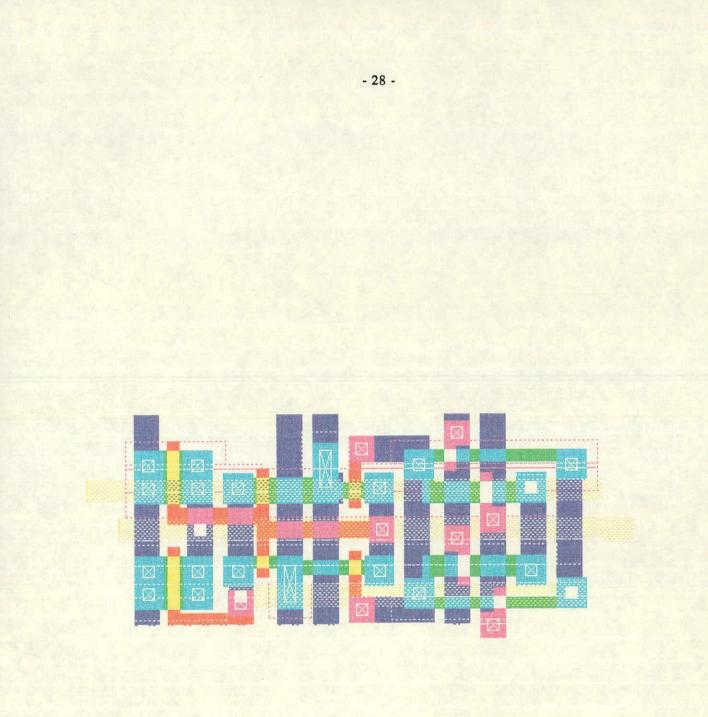

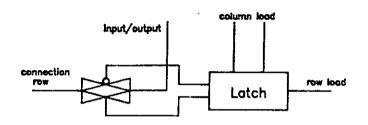

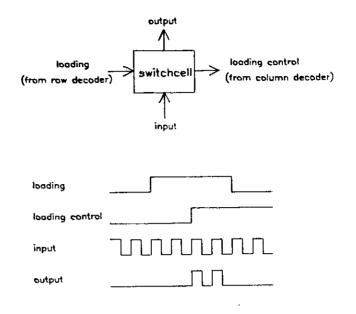

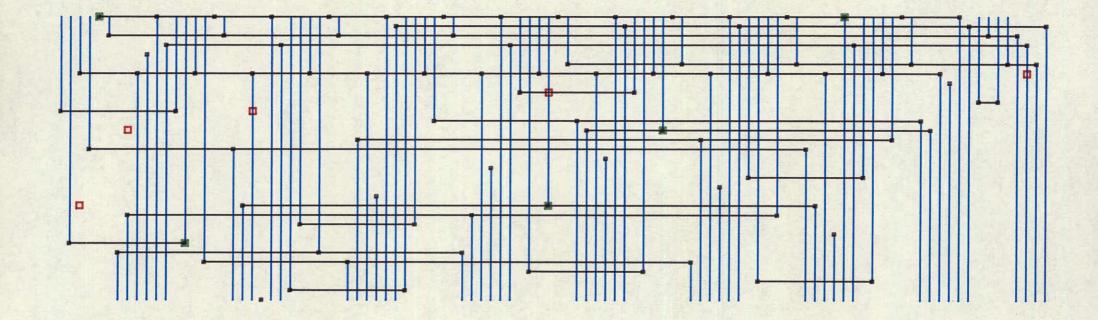

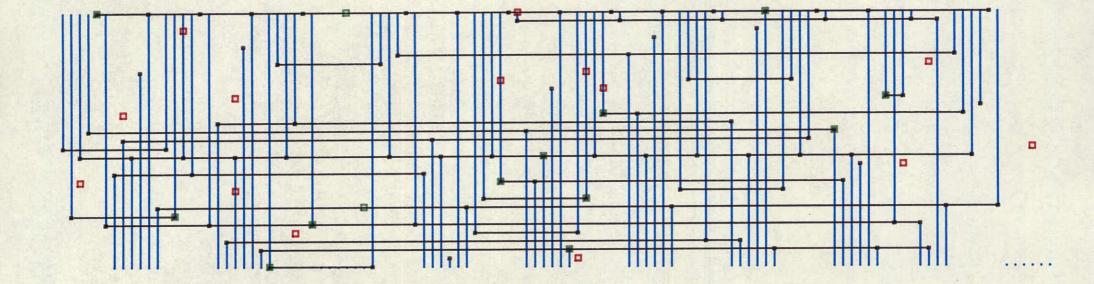

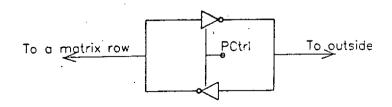

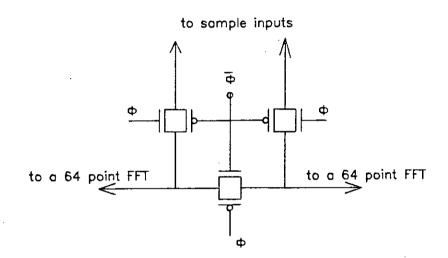

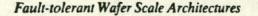

The alternative switch matrix architecture allows programmable assignment of the horizontal rows to the nets in a system for more flexible routing strategies. Figure 2.8 illustrates this scheme which is similar to the architecture shown in Figure 2.3, except that processing elements are placed at both sides of the matrix. The circuit diagram of this switch cell (called swc-2) is shown in Figure 2.9. Compared to the circuit of swc-1, the dynamic NAND gate is replaced here by a bidirectional transmission gate controlled by the output of the latch. Architecturally, instead of connecting the outputs of processing elements to the matrix rows, each input and output of the processing elements are connected to a column of the switch matrix. Input and output signals of all processing elements enter and leave the superchip via particular columns of the switch matrix. Owing to the use of the bidirectional, static, transmission gate as a switching element signals can pass through the switch cell, from either one direction or the other. Therefore, bidirectional I/O pads are assigned to matrix rows so that each processing element can communicate with external signal sources. Compared to the normal matrix, this matrix duplicates the normal matrix in size. In the rest of this thesis, it will be called the duplex matrix.

The performance difference of these two switch cells is determined by the performance of the transmission gate, against that of the dynamic NAND gate. For a quantitative performance comparison, suppose that all the transistors in these two gates have the same parameters, and  $g_m$  is the transconductance for a single transistor. For swc-1, the input node of each processing element is discharged through three transistors in series. Therefore the total conductance of the dynamic NAND gate becomes  $g_m/3$ . Note that precharging is taken to a whole column of the matrix. For swc-2, the total

Figure 2.8 Interconnection organisation using duplex crossbar network

Figure 2.9 Circuit diagram of the static switch cell (swc-2)

- 25 -

. . conductance of a CMOS transmission gate is equal to  $2g_m$  because two transistors are here in parallel. However, because a complete path from an output of a processing element to an input of a processing element passes through two transmission gates in series, then the total conductance of a path is equivalent to the conductance of a single transistor,  $g_m$ . On the other hand, the outputs of the processing elements in swc-1 are not connected directly to the inputs of processing elements. A processing element needs only to drive a long horizontal metal track in the matrix (a row of the matrix). In swc-2, however, an output from a processing element has to drive all its horizontal and vertical metal tracks (a row and two columns of the matrix), because the transmission gates connect outputs of the processing elements directly to the inputs of the processing elements they drive. Therefore, the required driving capability for swc-1 is more independent of the matrix size. In other words, a larger transmission gate is needed for bigger switch matrices.

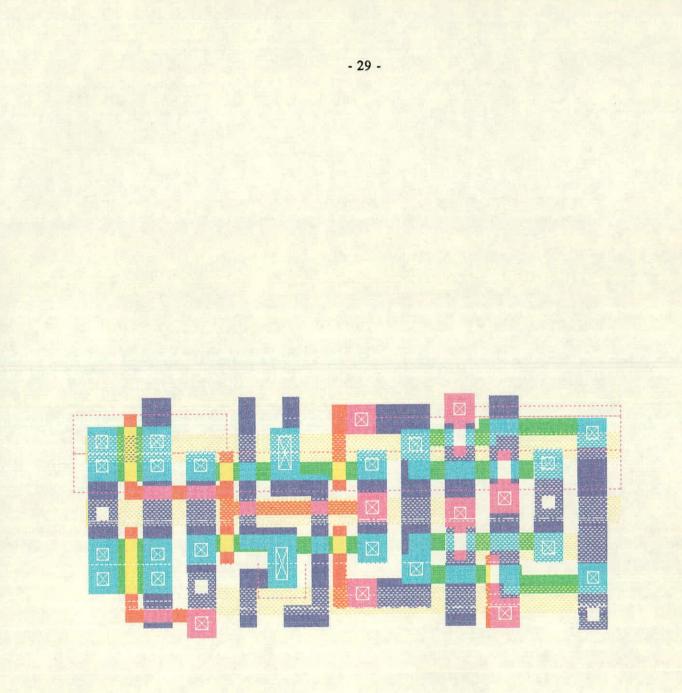

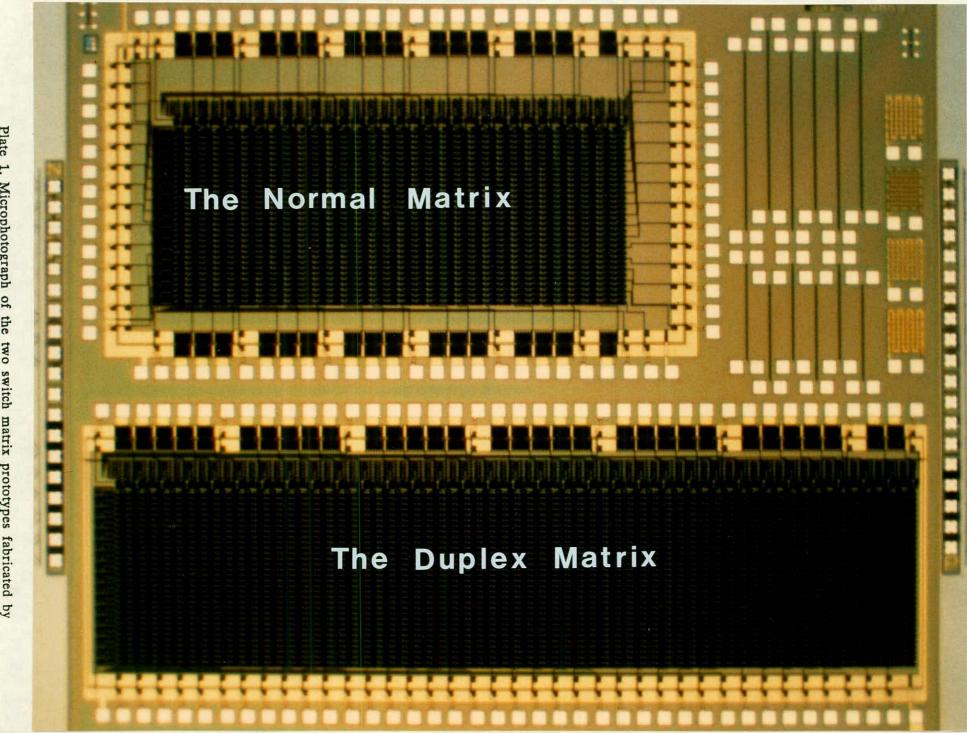

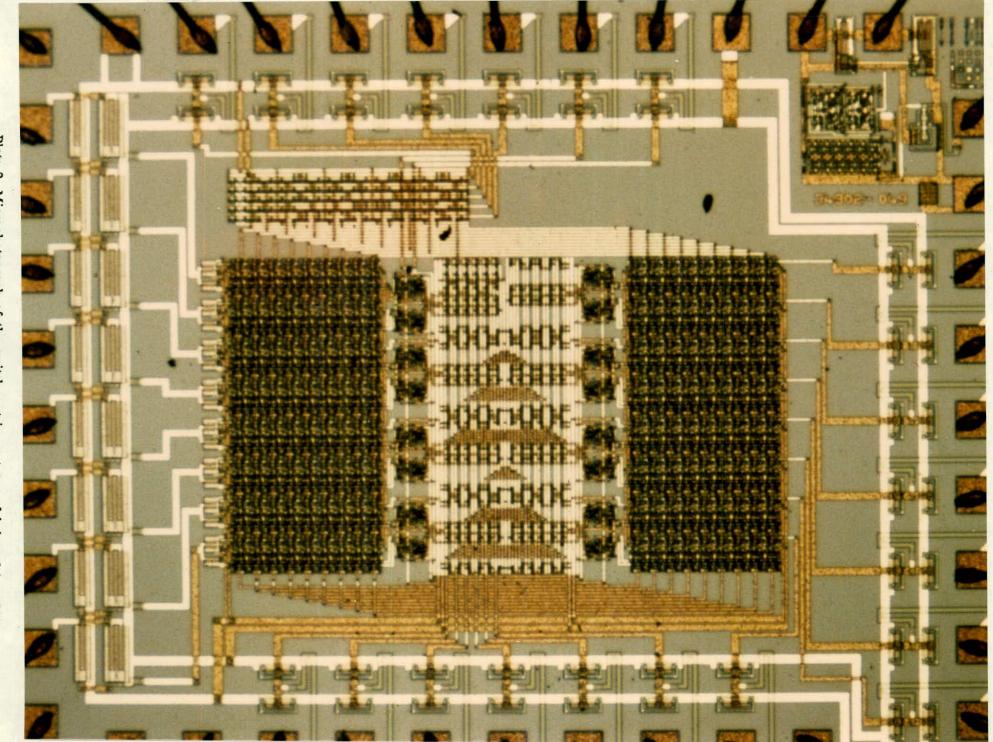

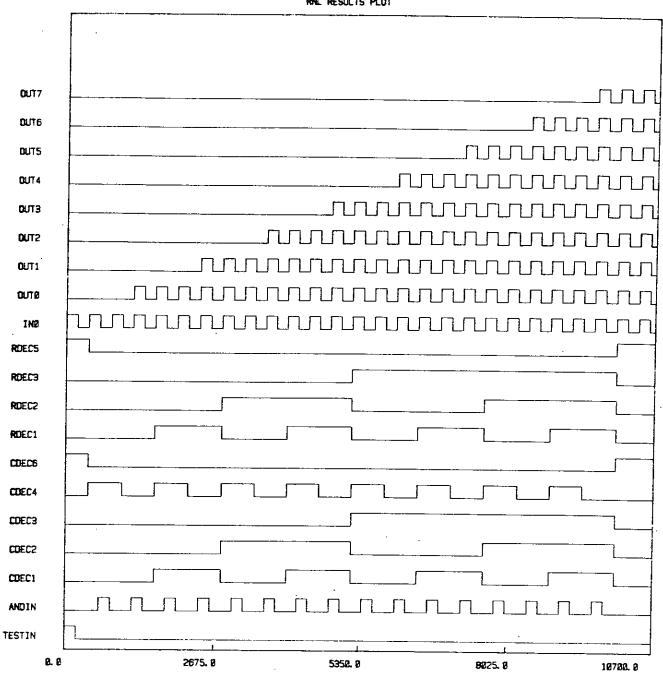

Figures 2.10 and 2.11 illustrate the circuit layout of the two switch cells in  $2.5\mu$ m double-metal CMOS technology, which were fabricated at Plessey. Figure 2.12 shows the circuit layout of swc-2 in  $3\mu$ m double-metal CMOS technology which was fabricated at MCE (Micro-Circuits Engineering Ltd). The results from these designs are presented in Chapter 4.

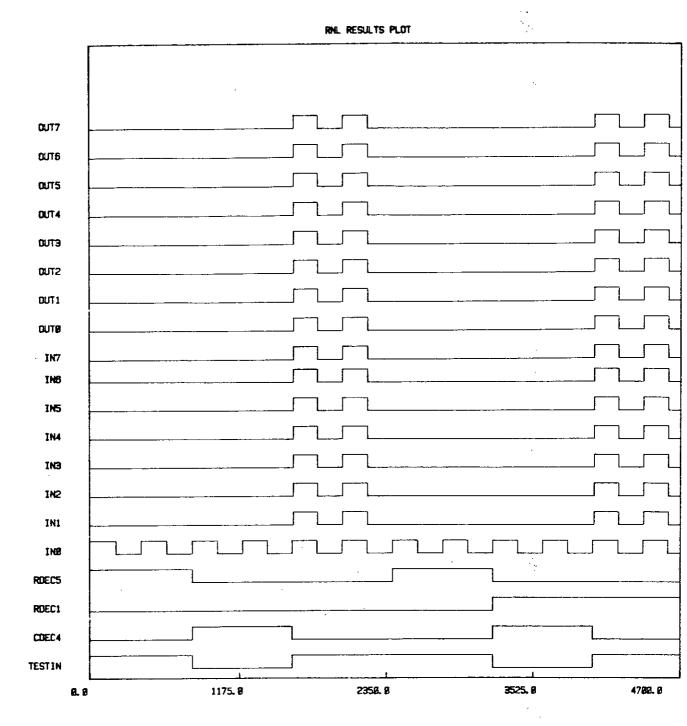

## 2.4.2. Programming Switch Matrix

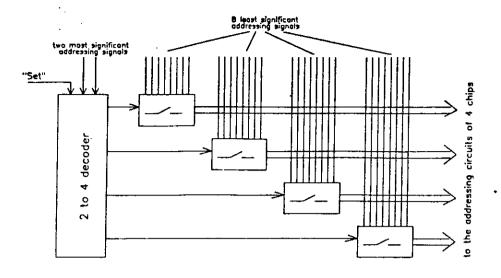

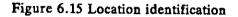

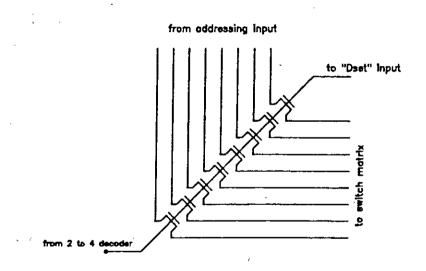

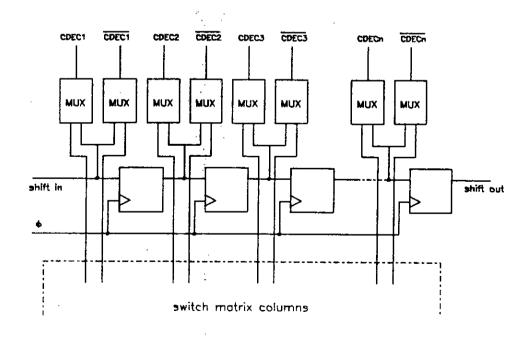

The information for switch setting within the switch matrix is provided by users who commit the superchip to a specific system task. The information governing all the switch settings in a switch matrix is here called the *switching pattern* of the matrix. The control circuits are not only responsible for loading the switching pattern, but also help during the testing of the switch matrix. The overall control path of the switch matrix is shown in Figure 2.13. Two decoders are provided for both matrix column and matrix row addressing. Static CMOS NOR gates are adopted here to form both decoders. Each output of the row decoder is connected to the "row load" of all the switch cells sitting on the row which the row decoder output addresses. Similarly, each output of the column decoder is connected to the "column load" of all the switch cells sitting on the column which the column decoder output addresses. The required input address for the control circuits is the binary form of the actual location of the matrix row or column. For example, the input "1010" to the row decoder will address the 10th row in the

Figure 2.10 Layout of swc-1 (Plessey technology)

Figure 2.11 Layout of swc-2 (Plessey technology)

Figure 2.12 Layout of swc-2 (MCE technology)

switch matrix. Prior to loading a switching pattern, the whole matrix is initialised (every switch cell is set to be "off"). To initialise all the switch cells simultaneously, all the outputs of the row decoder should be set to be at a logic zero at the same time. This is realised by decoding an address which is greater than the existing number of total rows in the matrix. If the total number of rows in the matrix is just the value of two to the power of n (where n is the number of inputs to the row decoder), then a spare input should be added to the row decoder. Thus the number of inputs to the row decoder becomes n+1 to ensure that there is at least one address which can set all the outputs from the row decoder to be logic zero at the same time. Such a condition of the row decoder when all its outputs are logic zero, at the same time, is called the *clearing state*. Every output from the column decoder is fed through a two-input NAND gate. This allows all the outputs from the column decoder. This is controlled by the signal "Dset" applied to one input of all the NAND gates. This state of the column decoder is here called the *disabled state*.

Figure 2.13 Switch matrix control path

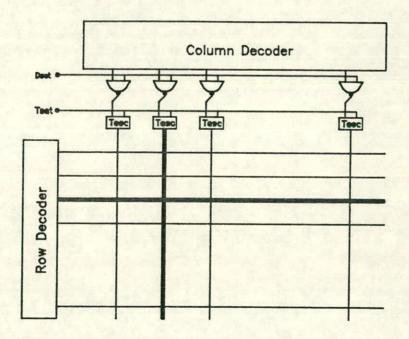

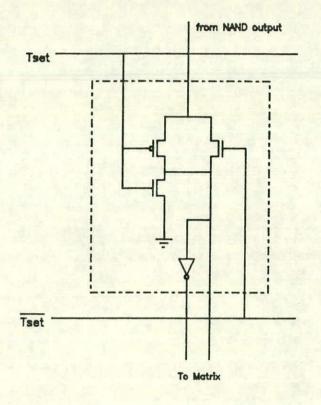

The circuit called "Tesc" in Figure 2.14. is an auxiliary circuit for testing the matrix. During test, all the column addressing lines from the column decoder are

expected to be at a logic one, simultaneously, so that all the switch cells on the same matrix row can be addressed and evaluated at the same time. The "Tset" signal sets the operational mode of the test circuit. When it is logic zero, the signal from the NAND gate simply goes through this test circuit to the matrix. Otherwise, the circuit isolates the matrix from the column decoder and sets all the matrix "column load" lines to logic one. The column decoder (including NAND gates and "Tesc" circuits) is said to be in the "clearing state" when "Tset" is at logic high.

Figure 2.14 "Tesc" circuit diagram

# 2.4.3. System Operation

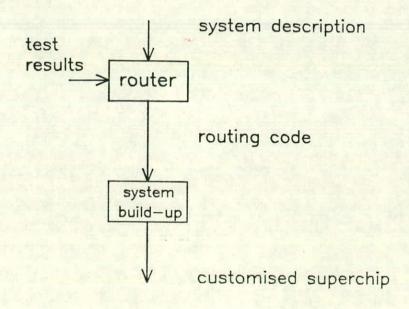

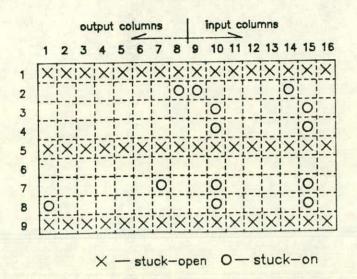

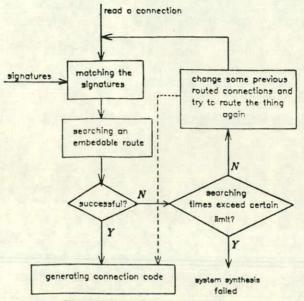

System customisation within the superchip is specified and performed by the end user. The whole procedure from the user's system specification to the physical realisation of the system can be divided into two phases, as illustrated in Figure 2.15. The first phase is message generation for system traffic routing. This takes the user's system specification and the test results of both the processing elements and the switch cells as inputs, to produce a set of routing codes (switching pattern) for the switch matrix. These routing codes are stored in an external EPROM. The test results, showing types of faults and their locations in a superchip, are called the *fault pattern* for any given chip. Defect-tolerance is achieved by connecting working processing elements together using working switch cells in the switch matrix, whilst avoiding defective processing elements and switch cells. Both the routing algorithm and its software implementation will be discussed in detail in Chapter 5. The second phase is system realisation (customisation) which is achieved by loading the switching pattern obtained from the first phase into the switch matrix to realise the interconnections for a specific system.

Figure 2.15 System synthesis procedure within the superchip

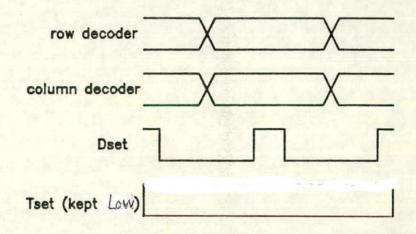

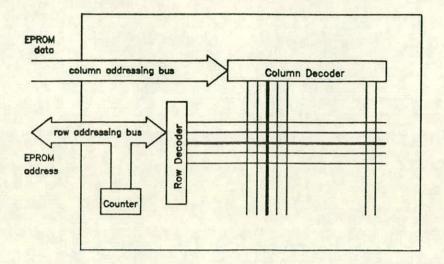

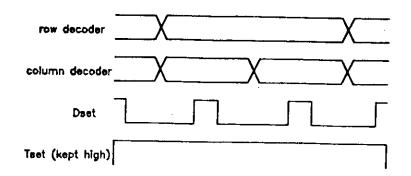

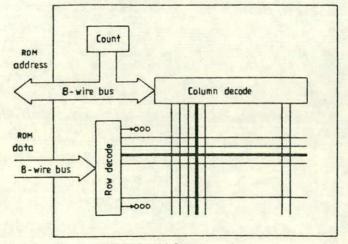

The switching pattern for the switch matrix is loaded on power-up, or in response to a reset request from an external EPROM. Before actually loading the switching pattern, both the row and column decoder are set to the clearing state to initialise the whole matrix, after which all the switch cells in the matrix are non-activated (nonconducting). Although the total number of switch-settings for the switch matrix is large, the embedded information is much smaller, as at most one switch in any column may be active. Thus we need only to store and load a row address for the active switch cell in each column. Row 0 (or any assigned row) is reserved for "no connection" and will be employed by unused processing elements to inhibit their clock connection. Thus, unused processing elements do not need to be active, eliminating unnecessary power consumption. This convention leads to the loading arrangement shown in Figure 2.16, in which a counter is used to address the external EPROM. Each address from the counter is also decoded to activate an associated column in the switch matrix. The active switch for that column is defined by the returned EPROM address generated by the router, which is decoded to drive the relevant "row load" line. Whilst loading a switching pattern, "Tset" is kept low. To prevent possible output signal 'spikes' occurring when the inputs of both row and column decoders change from being incorrectly loaded into switch cells, "Dset" should kept low when addresses from the decoders are being changed. Figure 2.17 shows the waveforms for activating a switch cell in a matrix column. Every time "Dset" goes high, an addressing signal from the row decoder is passed on and loaded into a switch cell, so that a switch cell is set to be active (conducting). The input and output signals are bit-serial, and enter and leave the superchip via the switch matrix. In other words, any element in the superchip can only communicate externally through the switch matrix.

Figure 2.16 A loading scheme for switch matrix

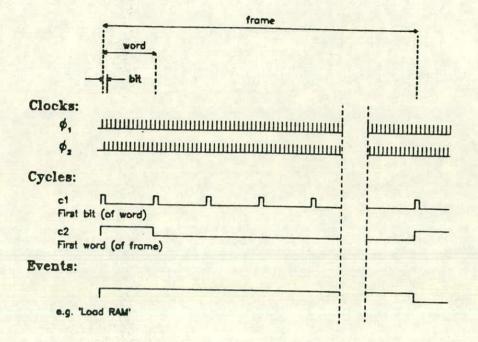

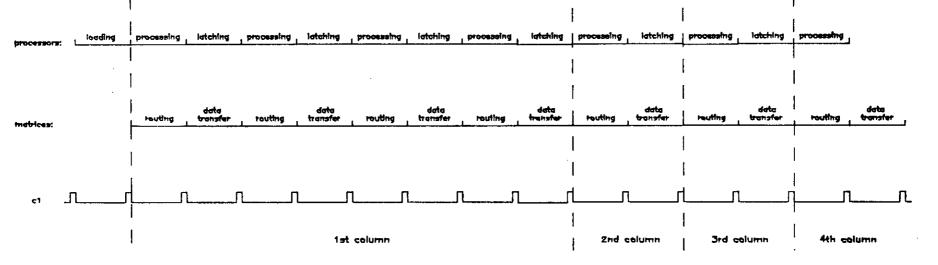

The communication and control conventions for bit-serial systems have been defined by Lyon[90] and Denyer[88]. The lowest level of control is a synchronous bitclock controlling the flow of all data in the system at bit level. This level of control is called cycle 0, or simple c0. One level above this is the cycle indicating the beginning of every new word in a data stream, called c1 control. At a higher level, there will

Figure 2.17 Loading signals for activating one switch cell

probably be a need for levels of control indicating the beginning of every frame of words c2, and the beginning of a group of frames c3, and so on. All these different levels of control signals are generated from an off-chip controller. Figure 2.18 shows a frame of these control signals. The bit-clock control c0 from the controller is globally distributed to all the processing elements in the superchip. Other levels of control (particularly c1) are distributed through a control network in the superchip to adjust various LSB-times of different nodes in the system. The delay elements for such a control network are a part of the processing elements connected to the switch matrix, so that they can be routed (distributed) with correct timing alignment, to any processing element in the superchip.

Synthesizing a system from the superchip can be viewed as a static reconfiguration procedure i.e. the system is configured before operation. However, such a tailored system is also capable of performing dynamic reconfiguration, in which the system configuration can be altered during operation by changing the switch setting in the switch matrix, provided that no communication is required on the connections during the change. In the switch matrix, any connection being reconfigured will not affect communication of other unchanged connections.

Figure 2.18 A frame of control signals at different levels

# 2.5. Summary

A system architecture based on integrating a crossbar switching network and a large number of processing elements on a single piece of silicon was presented in this Chapter. This approach enables a high level of integration, and exhibits better performance and lower cost than conventional integration techniques. Some related design issues have been discussed. Such an approach provides defect/fault tolerance and system reconfiguration by message routing in the switch matrix. More numerical and algorithmical representations for such a approach will be illustrated in the following Chapters.

### **CHAPTER 3**

# YIELD MODELLING AND REDUNDANCY SELECTION

## 3.1. Introduction

From the earliest days of integrated circuit manufacture, it has been observed that yield decreases with increase in chip area with some exponential dependence. The impact of this observation to today's VLSI-density chip is the limitation on the chip size for economic production. However, with the advent of defect tolerant circuit design, introduction of hardware redundancy can improve the situation. The question now is one of choosing the right amount of redundancy which is optimal in terms of costeffectiveness. In this Chapter, discussion will be concentrated on developing a yield model for the superchip, from which an optimal level of redundancy can be derived. Firstly, a brief review of integrated circuit yield modeling is given and, thereafter, these results are applied to the yield modeling of the switch matrix and the superchip.

# 3.2. Previous Work on Yield Modeling

Integrated circuit yield estimation has been studied since the earliest silicon IC processes were introduced, and many yield models have been proposed. At the outset, the fundamental assumption was that defects occur randomly. In other words, they are distributed uniformly across the whole wafer. If this is true, then the defect distribution can described by the Poisson process

$$P_{n} = \frac{(D_{o}A)^{n} e^{-D_{o}A}}{n!}$$

(3-1)

where  $P_n$  is the probability of having n defects in the area A,  $D_o$  is average defect density (defects/area), A is critical area (or susceptible area<sup>†</sup>), and n are the number of defects causing initial electrical failure. The yield is obtained by letting n = 0 (note that 0! = 1)

$$Y = e^{-D_0 A}$$

(3-2)

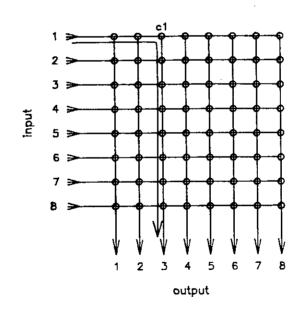

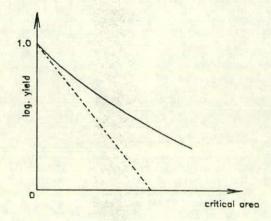

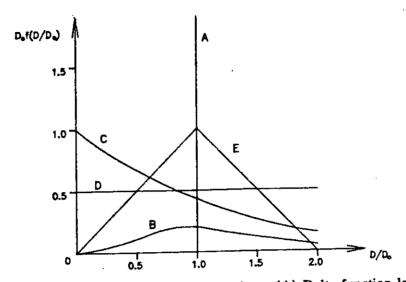

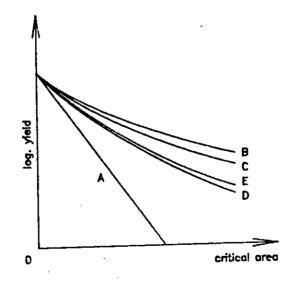

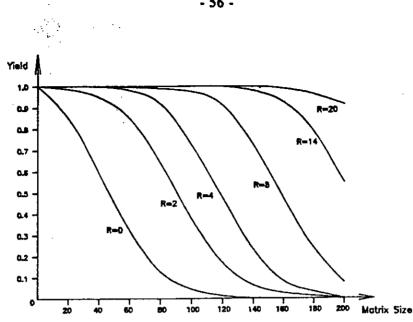

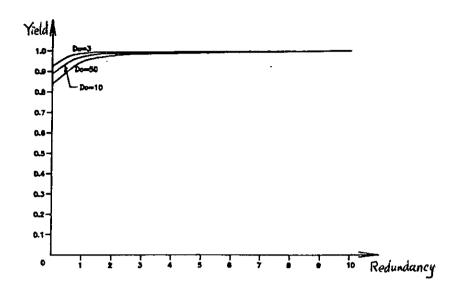

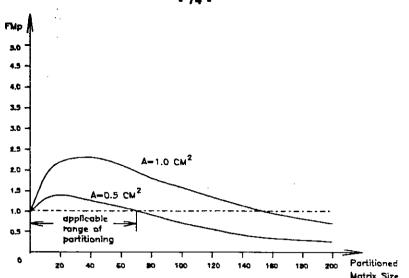

and this expression is widely referred to as the so-called Poisson yield model. The dotted line in Figure 3.1 gives the log yield versus total critical area plot (Y-vs-A) for equation (3-2). Unfortunately, this linear relationship (in the log scale for yield) is contrary to integrated circuit manufacturing experience. It is known in practice that experimental log Y-vs-A plots are usually concave upward, as shown by the solid line in Figure 3.1. This fact has led to many modifications of the basic Poisson yield expression.

Figure 3.1 Yield vs critical area plot

### 3.2.1. Murphy's Modification

In 1964 Murphy [91] recognized that the Poisson distribution is not an accurate description of IC yield vs the total critical area of an IC, and tends to give an increasingly pessimistic yield projection for larger areas. This is because the Poisson process assumes that all the defects are randomly, and uniformly distributed over the surface of the silicon wafer. However, in IC manufacturing the defect density varies from chip to chip as well as wafer to wafer. To relate yield prediction given by equation (3-2) with

<sup>†</sup> critical area is the area within which a single processing defect will cause incorrect logical output of the circuit.

actual manufacturing data, Murphy and some others suggested that the defect density has a long-range non-uniformity expressible by a normalised distribution function (or, in the terminology of probability theory, a *probability density function* f(D)). These are called *mixed Poisson statistics*. The resulting yield expression is given by

$$Y = \int_{0}^{\infty} e^{-DA} f(D) dD$$

(3-3)

which is known as Murphy's yield model. In this expression, Murphy used both triangular and rectangular distribution functions for f(D). The resulting yield formulae derived from these distributions showed that the yield of larger and more complex chips would be higher than was expected from Poisson statistics. However, according to actual data, the log Y-vs-A curve is still too pessimistic (related curves will be shown later in the summary).

Several other forms of distribution function have also been investigated by Seeds [92], Price [93], Stapper [94,95,96], and Hu [97] etc, in addition to the triangular and rectangular distribution functions adopted by Murphy. Each assumed distribution results in a different form of IC yield model.

### 3.2.2. Seed's Yield Model

Seeds [92] selected the exponential probability density function:

$$f(D) = \frac{1}{\alpha} e^{-\frac{D}{\alpha}}$$

(3-4)

which has the interesting feature that the mean and variance are exactly equal to the average defect density. This distribution leads to a yield expression:

$$Y = \frac{1}{1 + DA} \tag{3-5}$$

which is regarded as a Bose-Einstein distribution. Price arrived at equation (3-5) by basic probabilistic arguments in which all the defects concerned are considered to be indistinguishable. Price favoured the use of Bose-Einstein statistics because they result in a yield at large values of chip area that is higher than that given by the Boltzmann exponential relation (Poisson statistics). The main argument against using Bose-Einstein statistics is that they assume that the probability of having a defect on a particular chip is the same as the probability of having a defect in the remainder of the silicon wafer, having a much larger area. However, it is felt intuitively that the probability of having a defect should be proportional to its related area.

For a large DA product, the physical meaning of Seed's model is that the fault distribution function is a square function, and the fault density for a (square area) wafer increases linearly across the wafer from 0 to  $2q_o$ , where  $q_o$  is the average number of fault-causing defects per circuit.

# 3.2.3. Stapper's Model

Stapper suggested [94,95] the use of the gamma function as a probability distribution. The gamma distribution function has the form

$$f(D) = \frac{1}{\Gamma(\alpha)B^{\alpha}} D^{(\alpha-1)} e^{-\frac{D}{B}}$$

(3-6)

where  $\alpha$  and B are two empirical parameters. The mean, variance, and  $\sigma/u$  ratio are given by:

$$D = \alpha B \tag{3-7}$$

$$Var D = \alpha B^2 \tag{3-8}$$

$$\frac{\sigma}{u} = \frac{1}{\sigma r} \alpha \tag{3-9}$$

The resulting yield calculation can be described by the negative binomial distribution:

$$Y = (1 + \frac{DA}{n})^{-n}$$

(3-10)

where

$$n = \left(\frac{u}{\sigma}\right)^2 \tag{3-11}$$

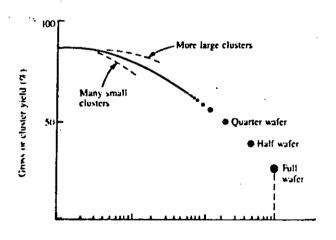

is a clustering effect coefficient representing the degree of clustering. It is an empirical parameter and usually ranges from 0.5 to 4 in practice. By itself n does not denote the balance between on-wafer defect density variation and wafer-to-wafer defect density variation. However, it is a key clustering parameter and determines the overall yield for chips without redundancy. For situations where the defect density can be assumed constant over a small sub-area, the clustering of defects, either because of interaction among themselves, or because of the hospitality of the geographical characteristics of wafer regions, will tend to result in a higher yield than predicted by the Poisson distribution for a given average defect density. This is because more than one catastrophic defect resides on the same area or sub-area of a chip leaving other chips to have less chance of being defective.

### 3.2.4. Hu's Model

By employing different assumptions for the distribution functions in the original Murphy yield expression (equation (3-3)) by Seed, Stapper and Murphy, Hu has proved mathematically [98] three properties of the yield model, expressed by equation (3-3). Firstly, Murphy's model is always concave upwards. Secondly, the initial slope of Murphy's model is the same as that of a Poisson curve with the same defect density. Thirdly, the lower bound for Murphy's model is the Poisson yield model.

Hu derived [97] a yield expression from very basic probabilistic considerations, which turned out to be a binomial yield model:

$$Y = (1 - \frac{A}{S})^{n}$$

(3-12)

where n is equal to DS, A is total critical area of a chip, D is defect density distributed randomly over an area S (A  $\epsilon$  S) which may be a part of or the whole of a silicon wafer, so that

$$Y = \left(1 - \frac{A}{S}\right)^{\frac{S}{A}DA}$$

(3-13)

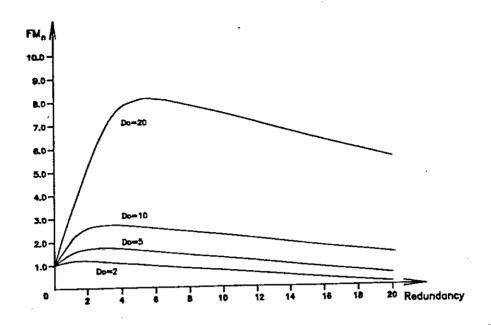

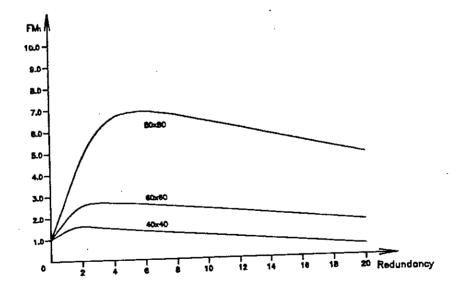

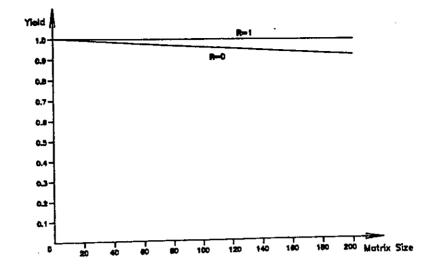

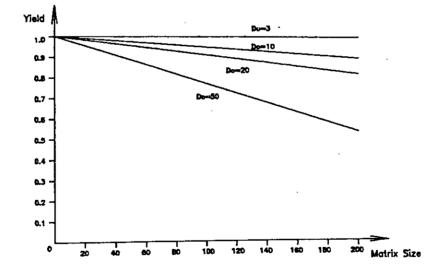

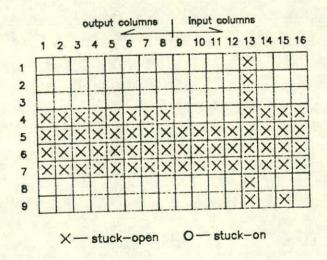

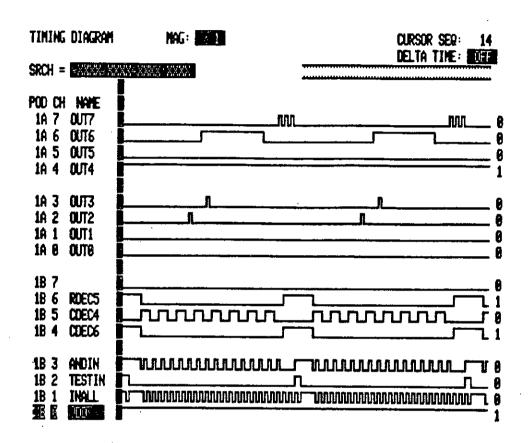

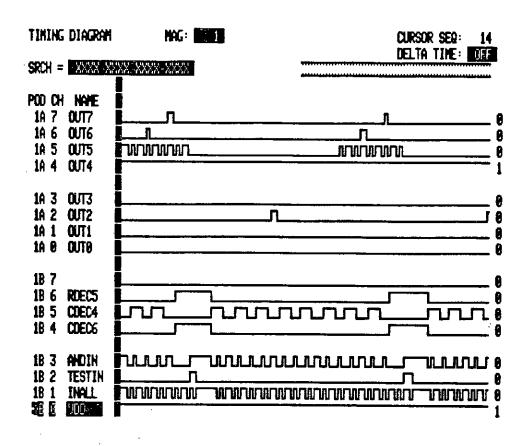

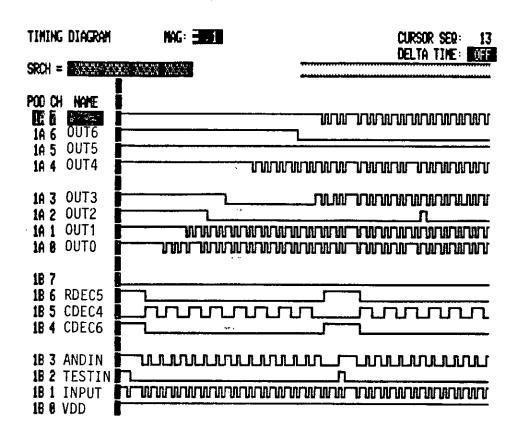

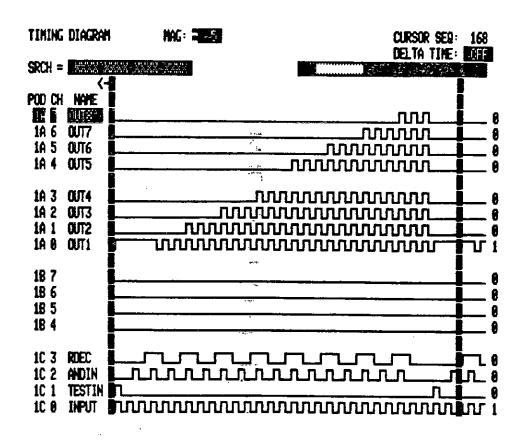

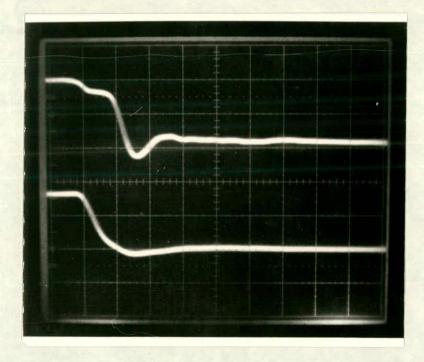

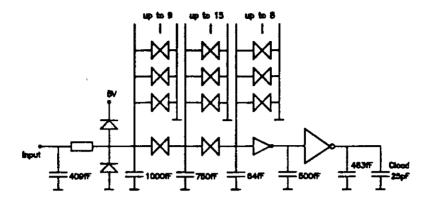

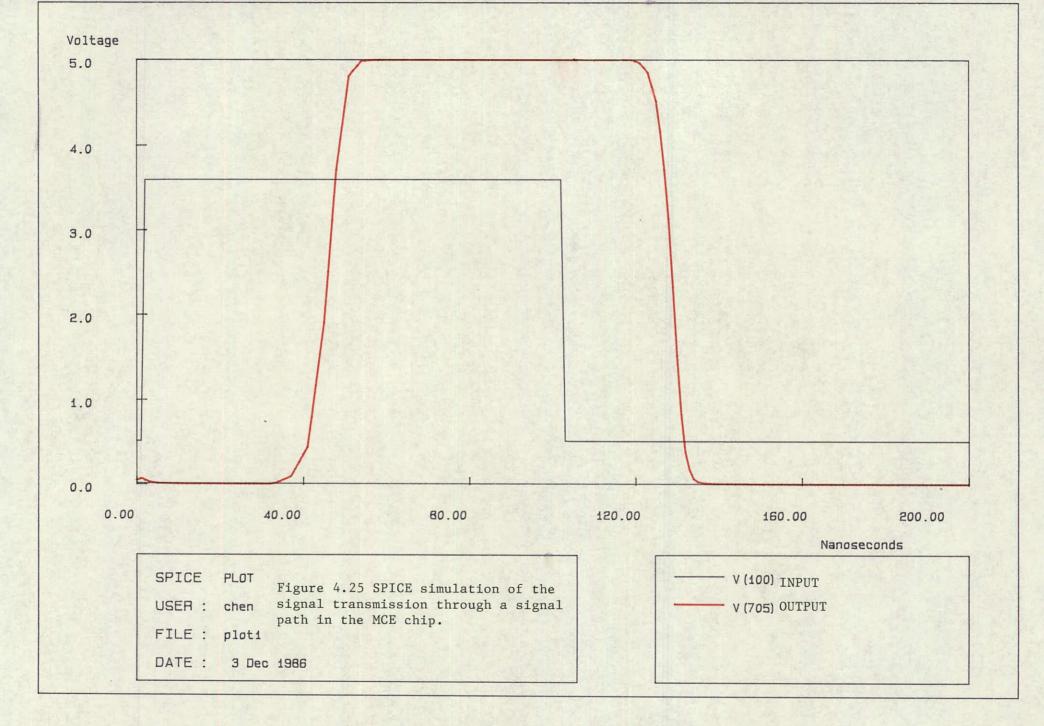

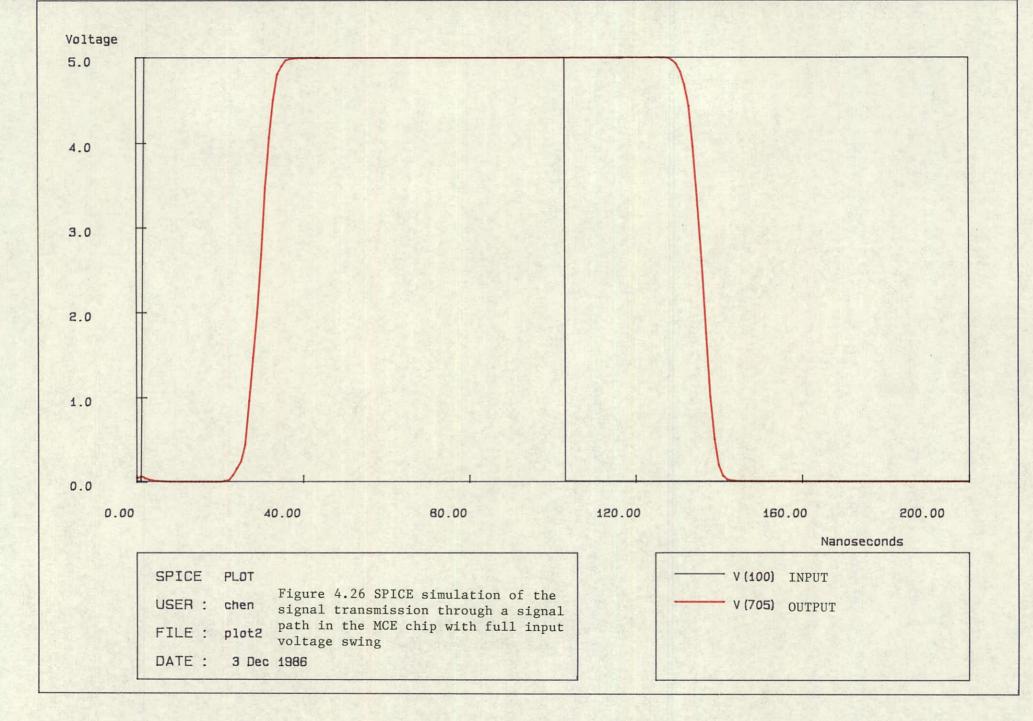

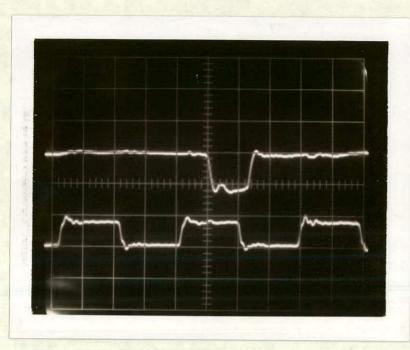

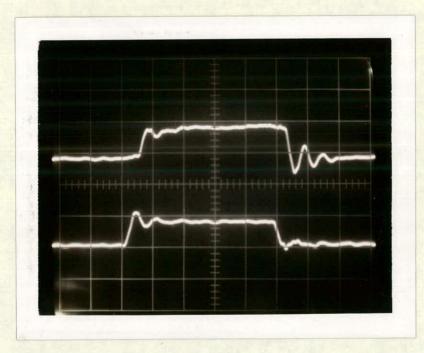

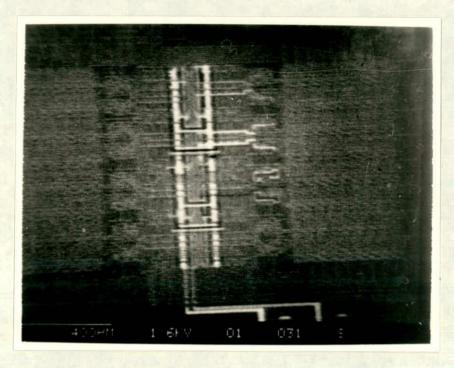

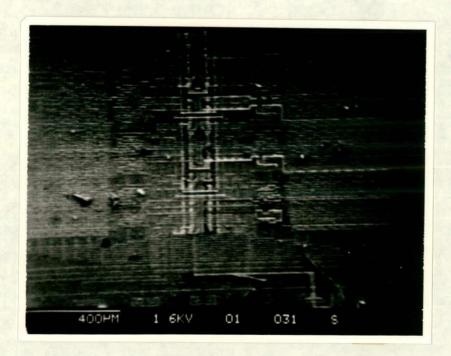

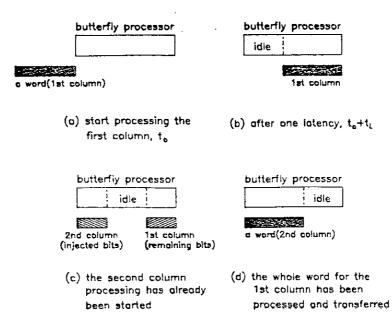

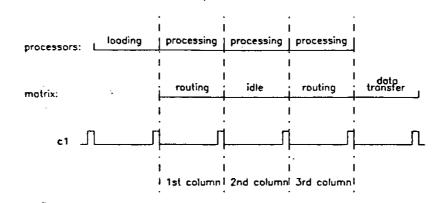

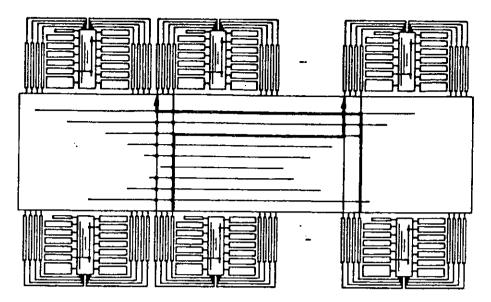

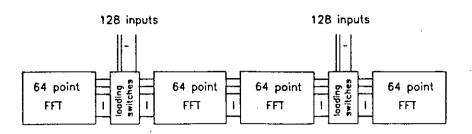

$$= e^{-DA} \qquad \text{for very large } S, \ (\frac{A}{S} \to 0).$$