# Time Interleaved Counter Analog to Digital Converters

Seyed Danesh

2011

A thesis submitted for the degree of Doctor of Philosophy

The University of Edinburgh

### Abstract

The work explores extending time interleaving in A/D converters, by applying a high-level of parallelism to one of the slowest and simplest types of data-converters, the counter ADC. The motivation for the work is to realise high-performance re-configurable A/D converters for use in multi-standard and multi-PHY communication receivers with signal bandwidths in the 10s to 100s of The counter ADC requires only a comparator, a ramp signal, and a digital counter, where the comparator compares the sampled input against all possible quantisation levels sequentially. This work explores arranging counter ADCs in large time-interleaved arrays, building a Time Interleaved Counter (TIC) ADC. The key to realising a TIC ADC is distributed sampling and a global multi-phase ramp generator realised with a novel figure-of-8 rotating resistor ring. Furthermore Counter ADCs allow for re-configurability between effective sampling rate and resolution due to their sequential comparison of reference levels in conversion. A prototype TIC ADC of 128-channels was fabricated and measured in 0.13µm CMOS technology, where the same block can be configured to operate as a 7-bit 1GS/s, 8-bit 500MS/s, or 9-bit 250MS/s dataconverter. The ADC achieves a sub 400fJ/step FOM in all modes of configuration.

Dedicated to my father's memory

## Acknowledgments

Firstly, I would like to thank Robert Henderson, my supervisor, for all his support and help. It has been a pleasure doing this project with you Robert. For sure you know how to get me working at my best. Every technical discussion we had related to this work, and your other activities, have been a great source of learning and pleasure to me. Thank you Robert.

I would like to thank Jed Hurwitz for teaching me so much, and really looking after me over the last couple of years. It's been really great working with you, and I think we've had a lot of fun. We've talked about the craziest of ideas. I'm glad we eventually implemented one of them. Who would've thought Jed, it actually works.

I would like to thank David Renshaw. David, you've looked after me ever since I set foot in this university almost 10 years ago now, through all the undergraduate labs right to today. I appreciate it a huge amount. At times it would've been impossible without your help and support. Thank you.

I would like to thank Keith Findlater. Keith, thank you for all your support, and giving me so much space to really get to working on these crazy ideas. You always looked for ways to help me out, and I hugely appreciate this. I can't imagine working for anyone better.

I would like to thank the whole team at Gigle, especially the analog team, and especially Will, Adria, Ewan and Al. You guys have been a joy to work with, and have each helped in many ways with my research.

I would like to say a special thanks to Steve Maughan, my PhD buddy. I escaped early my friend but I'll never forget those days at that prison like office at KB together, we talking absolute nonsense didn't we.

Finally, I would like to thank my close friends, and my dear family.

# Table of Contents

| Chapter 1 | - Introduction                                   | 1  |

|-----------|--------------------------------------------------|----|

| 1.1 Th    | e growing requirement on communication           | 1  |

| 1.2 Th    | e System on Chip Communication System            | 3  |

| 1.2.1     | Building blocks for a communication system       | 3  |

| 1.2.2     | Example of an multi-tone communication PHY       | 5  |

| 1.2.3     | Design of a Multi-Carrier Communication Standard | 9  |

| 1.2.4     | SoC for communication and Multi-Standard systems | 11 |

| 1.3 A/    | D Converters, and re-configurability             | 13 |

| 1.3.1     | An Overview of Analog to Digital Converters      | 14 |

| 1.3.2     | Comparison of A/D Architectures                  | 15 |

| 1.3.3     | Time Interleaving in A/D Converters              | 18 |

| 1.3.4     | Re-configurability in A/D Converters             | 20 |

| 1.4 Ori   | iginal Contribution of Thesis                    | 22 |

| 1.5 Str   | ructure of Thesis                                | 24 |

| 1.6 Co    | nclusion and Summary                             | 25 |

| Chapter 2 | 2 - Analog to Digital Conversion                 | 27 |

| 2.1 Int   | roduction                                        | 27 |

| 2.2 Spe   | ecifications and Non-idealities in ADCs          | 28 |

| 2.2.1     | Offset                                           | 29 |

| 2.2.2     | Input Range and Gain Error                       | 30 |

| 2.2.3     | Static Non-Linearity in the Transfer Function    | 32 |

| 2.2.4     | Noise in A/D Converters                          | 33 |

| 2.2.5     | ADC Non-idealities in the frequency domain       | 37 |

| 2.2.6     | Sampling Inaccuracy, Jitter and Clock Drift      | 44 |

| 2.3 Tir   | ne Interleaving and non-idealities               | 47 |

| 2.3.1     | Offset mismatch                                  | 48 |

| 2.3.2     | Gain mismatch                                    | 51 |

| 2.3.3     | Input Signal Bandwidth Mismatch                  | 54 |

| 2.3.4     | Sampling Clock Mismatch                          | 60 |

| 2.4 Ca    | libration and Error Correction                   | 65 |

| 2.4.1     | Methods to apply the calibration, Digital or Analog           | 66  |

|-----------|---------------------------------------------------------------|-----|

| 2.4.2     | Regularity: Trim, Foreground or Background                    | 67  |

| 2.4.3     | Quantifying the cost of calibration                           | 69  |

| 2.5 TI,   | Calibration & Re-configurability by Example                   | 70  |

| 2.5.1     | Introduction                                                  | 70  |

| 2.5.2     | Flash converters and calibration                              | 70  |

| 2.5.3     | Pipeline converters, calibration, TI and re-configurability . | 75  |

| 2.5.4     | SAR converters and time interleaving                          | 79  |

| 2.5.5     | Sigma-Delta converters and re-configurability                 | 83  |

| 2.6 Con   | nclusions                                                     | 84  |

| Chapter 3 | - Time Interleaved Counter ADC                                | 86  |

| 3.1 Int   | roduction                                                     | 86  |

| 3.2 Co    | inter ADC                                                     | 87  |

| 3.2.1     | Description of the Counter ADC Architecture                   | 87  |

| 3.2.2     | Implementation of an Counter ADC                              | 88  |

| 3.3 The   | e use of parallel counter ADCs in imaging                     | 90  |

| 3.4 Par   | rallelism with counter ADC block Ping-Ponging                 | 92  |

| 3.5 The   | e Time Interleaving Counter (TIC) ADC                         | 94  |

| 3.5.1     | Defining the TIC ADC                                          | 94  |

| 3.5.2     | The clock frequencies, sampling rate and resolution           | 96  |

| 3.5.3     | Changing the clock frequencies and re-configurability         | 98  |

| 3.6 The   | e Ramp Generation for the TIC                                 | 100 |

| 3.6.1     | The Rotary Resistor Ring Concept                              | 100 |

| 3.6.2     | Building the figure-of-8 rotary resistor ring                 | 101 |

| 3.6.3     | Choice of unit resistor and switch sizes                      | 104 |

| 3.7 Ana   | alog Front End for channels of TIC ADC                        | 105 |

| 3.7.1     | Sample and Hold Circuit                                       | 105 |

| 3.7.2     | Applying the Ramp                                             | 107 |

| 3.7.3     | The requirements on the Comparator                            | 109 |

| 3.8 Sys   | tem Level Digital Counter                                     | 112 |

| 3.9 Bac   | kend Memory and Readout                                       | 113 |

| 3.10 Co   | onclusions                                                    | 116 |

| Chapter 1 | Implementation of a TIC ADC                                   | 117 |

|   | 4.1  | Introduction                                              | 117 |

|---|------|-----------------------------------------------------------|-----|

|   | 4.2  | Defining the specifications and clock frequencies         | 117 |

|   | 4.3  | Top-down Specification and Implementation                 | 120 |

|   | 4.4  | Global Ramp Generator                                     | 122 |

|   | 4.4  | 4.1 Design of a Variable Resolution Global Ramp Generator | 122 |

|   | 4.4  | 4.2 Top-Level Implementation of Global Ramp Generator     | 132 |

|   | 4.4  | 4.3 Custom Latch for Timing of Resistor Ring              | 133 |

|   | 4.4  | 4.4 Unit Resistor and Resistor Ring                       | 134 |

|   | 4.4  | 4.5 Programmable Interpolation Filter                     | 136 |

|   | 4.5  | Sample and Hold and Ramp Front End                        | 136 |

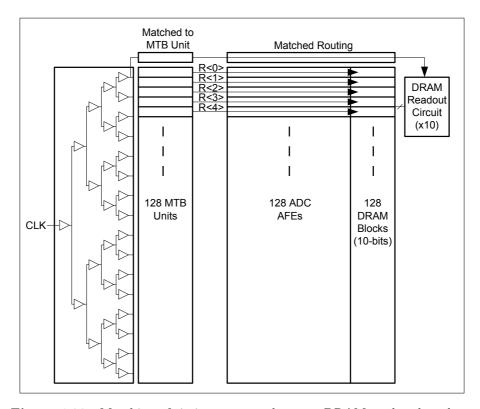

|   | 4.6  | Master Timing Block                                       | 141 |

|   | 4.7  | Comparator Design                                         | 145 |

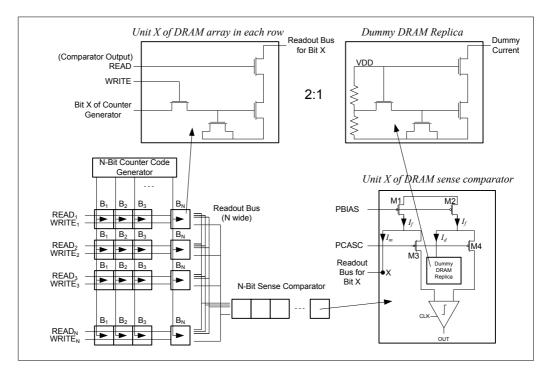

|   | 4.8  | Backend Memory                                            | 150 |

|   | 4.9  | Global count generator                                    | 151 |

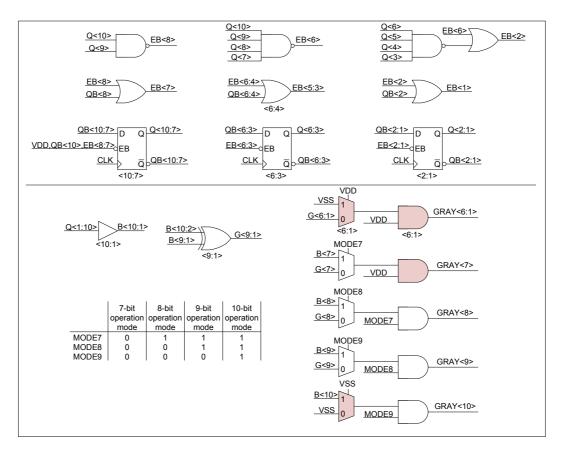

|   | 4.10 | Backend Memory Readout circuit                            | 152 |

|   | 4.1  | 10.1 Task of memory readout                               | 152 |

|   | 4.11 | TIC Top-Level                                             | 154 |

|   | 4.12 | Chip-Level Auxiliary blocks                               | 156 |

|   | 4.1  | 12.1 Introduction                                         | 156 |

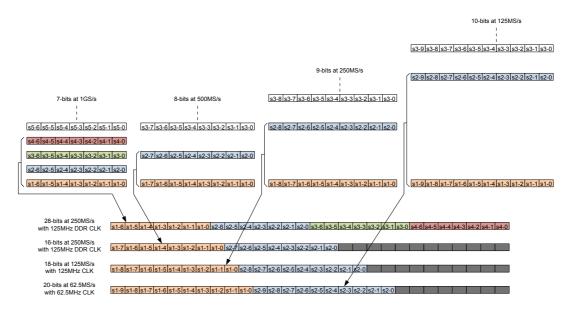

|   | 4.   | 12.2 Data Packer                                          | 157 |

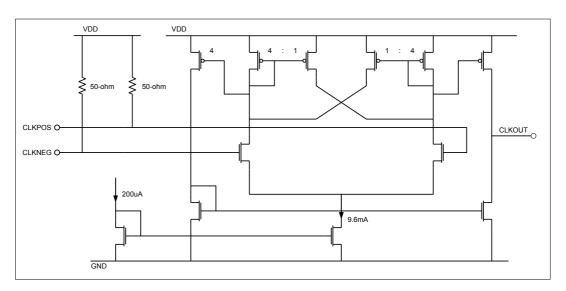

|   | 4.1  | 12.3 Clock Receiver                                       | 158 |

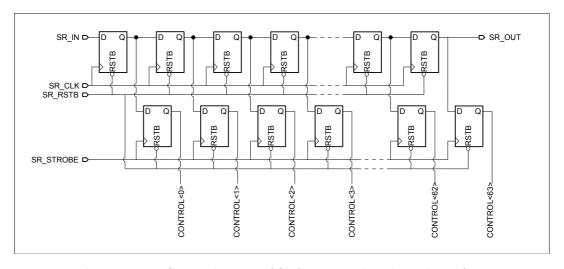

|   | 4.   | 12.4 Serial Interface                                     | 160 |

|   | 4.13 | Top Level Chip Assembly                                   | 160 |

|   | 4.   | 13.1 Number of Pads, Pin-out, and Package choice          | 160 |

|   | 4.14 | Conclusions                                               | 163 |

| C | hapt | er 5 - Measurement Results                                | 166 |

|   | 5.1  | Introduction                                              | 166 |

|   | 5.2  | Test Setup                                                | 166 |

|   | 5.3  | Calibration                                               | 168 |

|   | 5.4  | Block Performance Analysis                                | 171 |

|   | 5.4  | 4.1 DNL and INL, static non-linearities                   | 171 |

|   | 5.4  | 4.2 Frequency domain performance                          | 173 |

|   | 5 5  | Summary of Performance                                    | 179 |

| 5.6    | Conclusions                                   | 180 |

|--------|-----------------------------------------------|-----|

| Chapt  | er 6 - Conclusions                            | 182 |

| 6.1    | Introduction                                  | 182 |

| 6.2    | Critical Assessment of Work                   | 182 |

| 6.     | 2.1 Choice of number of rows and clock speeds | 183 |

| 6.     | 2.2 Design of Ramp Generator                  | 184 |

| 6.     | 2.3 Comparator Design                         | 185 |

| 6.3    | Performance Summary                           | 186 |

| 6.4    | Technology Scaling                            | 188 |

| 6.5    | Architectural Directions                      | 190 |

| 6.6    | Conclusions                                   | 192 |

| Refere | ences:                                        | 194 |

# List of Figures

| Figure | 1.1 – The growing demand for greater network bandwidth and converge                                                                                                                             | 1  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure | 1.2 – Block diagram of a multi-carrier communication system                                                                                                                                     | 4  |

| Figure | ${f 1.3}$ – The breaking of the digital stream into packets for transmission                                                                                                                    | 6  |

| Figure | 1.4 – Bit-loading of carriers and combining to build symbol                                                                                                                                     | 7  |

| Figure | ${\bf 1.5}-{\bf Comparison\ of\ two\ theoretical\ communication\ systems}\dots$                                                                                                                 | 9  |

| Figure | $\textbf{1.6}-\text{Evolution of Multi-Standard/Multi-PHY Digital Comms SoC} \dots \dots$ | .2 |

| Figure | 1.7 – Overview of classical ADC architectures                                                                                                                                                   | .4 |

| Figure | 1.8 – Comparison of classical ADC architectures                                                                                                                                                 | .6 |

| Figure | 1.9 – Comparison of Power Efficiency for different architectures                                                                                                                                | .7 |

| Figure | 1.10 – A Time Interleaving A/D Converter block diagram                                                                                                                                          | .8 |

| Figure | 1.11 – The effect of time interleaving of SAR A/D Converters                                                                                                                                    | .9 |

| Figure | 2.1 – Structure of Chapter 2                                                                                                                                                                    | 28 |

| Figure | 2.2 – Transfer function of an ADC with 3-code output offset                                                                                                                                     | 29 |

| Figure | 2.3 – Positive and Negative gain error in transfer function                                                                                                                                     | 31 |

| Figure | 2.4 – Non-linearity in transfer function, DNL and INL                                                                                                                                           | 32 |

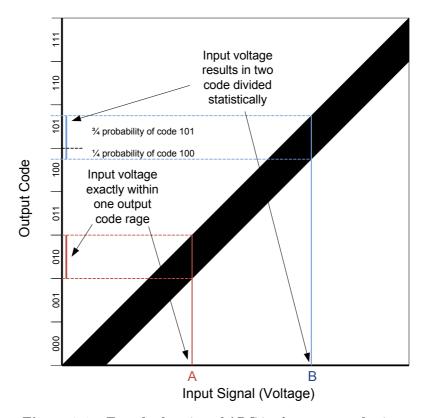

| Figure | 2.5 – Code transition in the presence of noise                                                                                                                                                  | 34 |

| Figure | 2.6 – Transfer function of ADC in the presence of noise                                                                                                                                         | 35 |

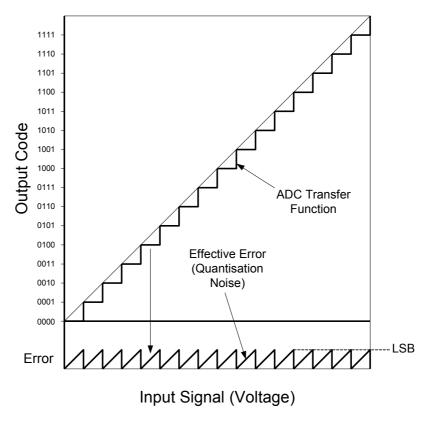

| Figure | 2.7 – Transfer function of ADC with magnitude of quantisation noise                                                                                                                             | 36 |

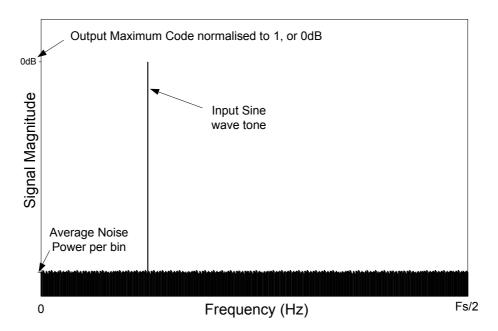

| Figure | ${\bf 2.8}$ – Ideal output spectrum of an n-bit ADC with 1/8 Fs input sine-wave                                                                                                                 | 37 |

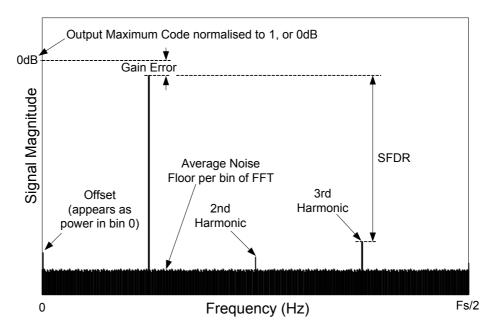

| Figure | ${\bf 2.9}$ – Output spectrum of non-ideal ADC with 1/8 Fs input sine-wave                                                                                                                      | 39 |

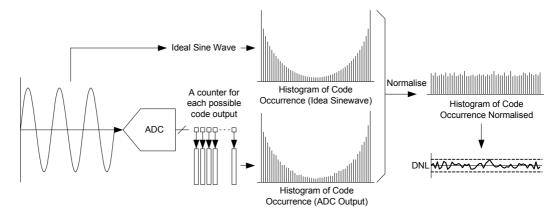

| Figure | $\textbf{2.10}-\text{Calculated Dynamic DNL from sine-wave using histogram} \dots \\ \\ $                                                                                                       | 12 |

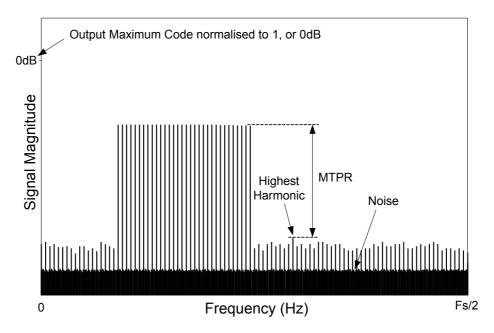

| Figure | 2.11 – Output spectrum for Multi-Tone MTPR test                                                                                                                                                 | 13 |

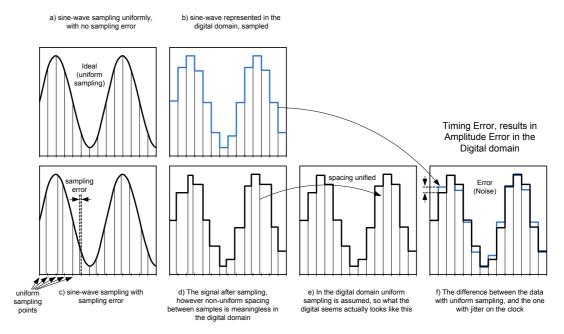

| Figure | 2.12 – Effect of sampling error on overall amplitude error                                                                                                                                      | Ι4 |

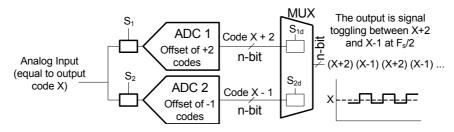

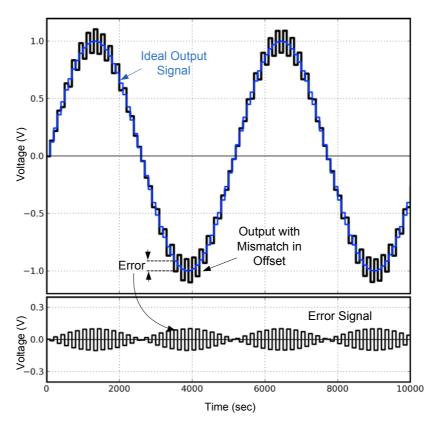

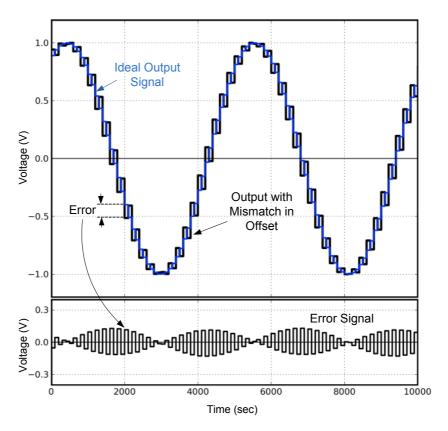

| Figure | ${f 2.13}$ – Example of the effect of offset on time-interleaving ADCs                                                                                                                          | ŀ7 |

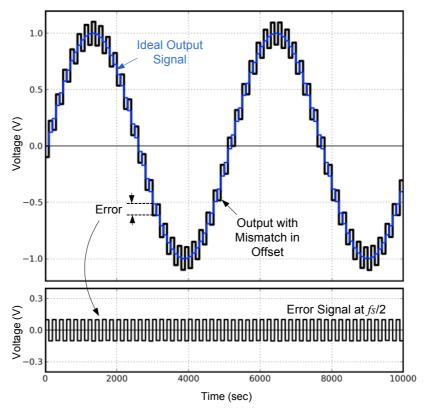

| Figure | 2.14 – Example of the effect of offset on time-interleaving ADCs                                                                                                                                | 18 |

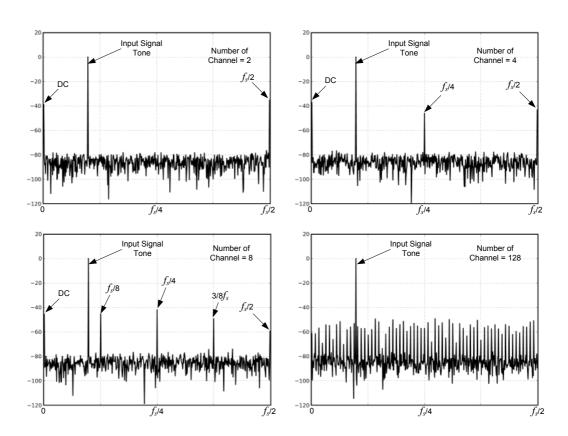

| Figure | 2.15 – Result of offset for sine input for a 2-channel TI ADC                                                                                                                                   | Į9 |

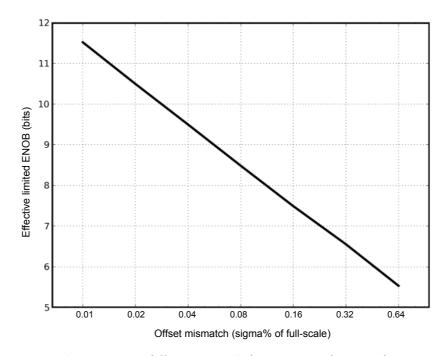

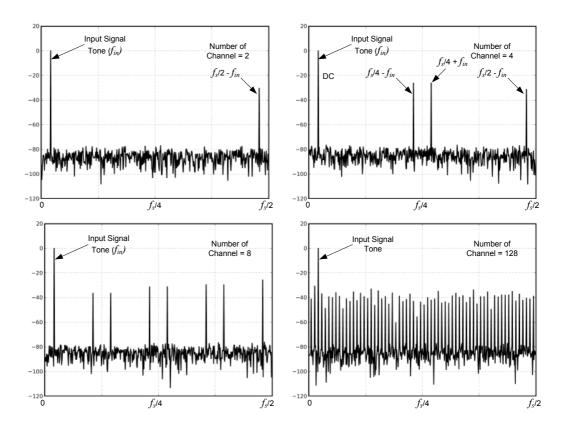

| Figure | 2.16 - Example of output spectrum for TI ADC with offset mismatch                                                                                                                               | 60 |

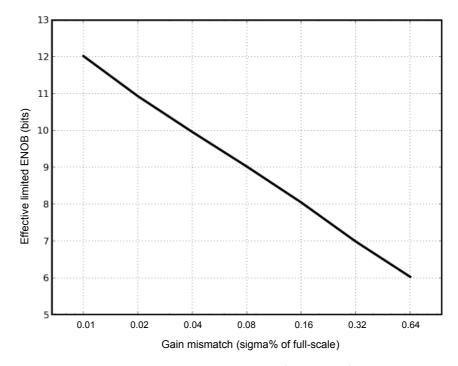

| Figure | 2.17 – Offset mismatch (in percentage) vs. ENOB                                                                                                                                                 | 51 |

| Figure | ${f 2.18}$ – Result of gain mismatch for sine input for a 2-channel TI ADC                                                                                                                      | 52 |

| Figure | ${f 2.19}$ – Result of gain mismatch for sine input for a 2-channel TI ADC                                                                                                                      | 53 |

| Figure | 2 20 - Channel gain-mismatch (percentage) vs ENOR                                                                                                                                               | 54 |

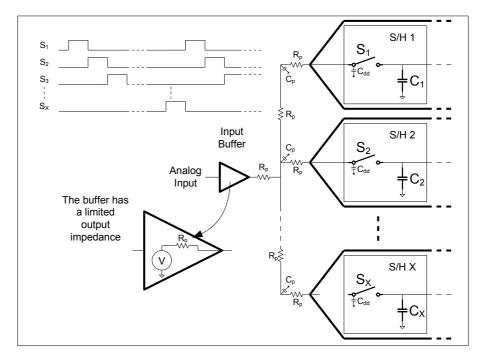

| Figure 2.21 – Input signal routing in time interleaved ADC system                                            |

|--------------------------------------------------------------------------------------------------------------|

| Figure 2.22 - Result of bandwidth mismatch for sine input for a 2-channel TI ADC . 58                        |

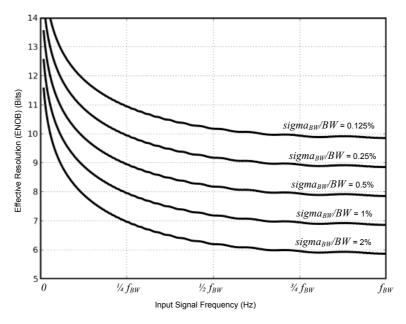

| Figure 2.23 – Noise due to BW mismatch at different input frequencies                                        |

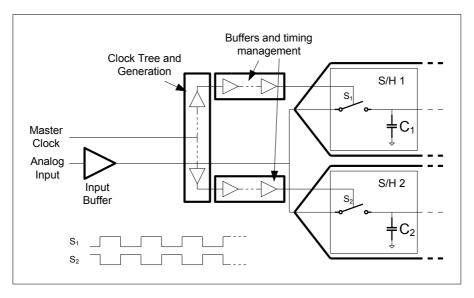

| Figure 2.24 – 2-channel time-interleaving ADC with circuit element in path of clock.                         |

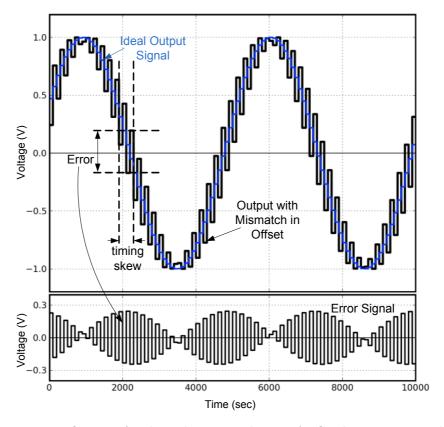

| $ \textbf{Figure 2.25} - \text{Output of 2-channel time-interleaving ADC subject to timing skew} \dots 6 \\$ |

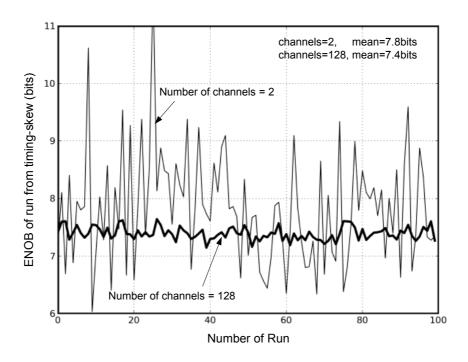

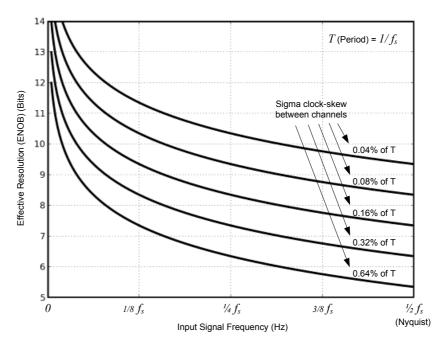

| Figure 2.26 – ENOB of 100 parts with matching sigma for 2 and 128-channels 63                                |

| Figure 2.27 - ENOB vs. timing skew sigma for different input frequency signals 64                            |

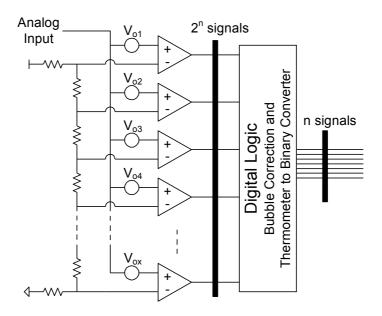

| Figure 2.28 – Flash ADC, with comparator offset                                                              |

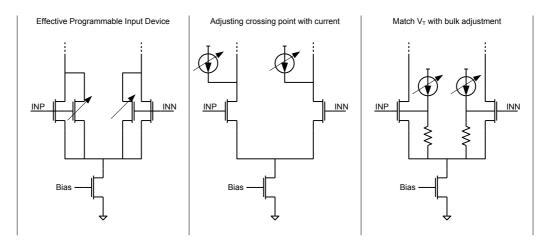

| Figure 2.29 – Calibration methods for input pair                                                             |

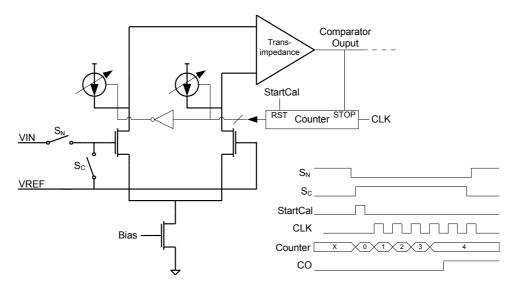

| Figure 2.30 – Digital counter based calibration loop for input pair offset                                   |

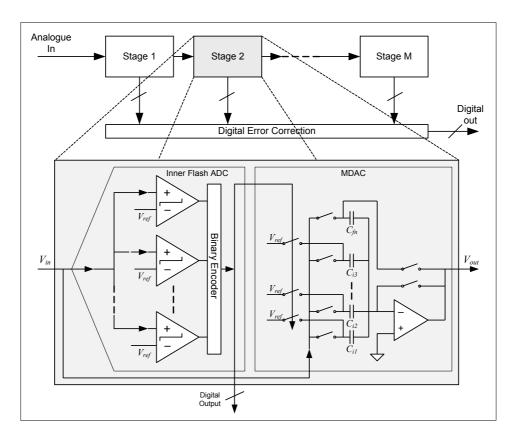

| Figure 2.31 – Pipeline ADC basic block diagram                                                               |

| Figure 2.32 – Pipelined ADC is background calibration algorithm                                              |

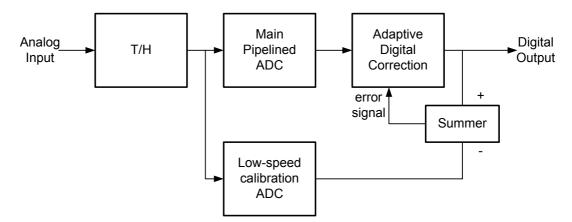

| Figure 2.33 – Reconfigurable Pipelined ADC                                                                   |

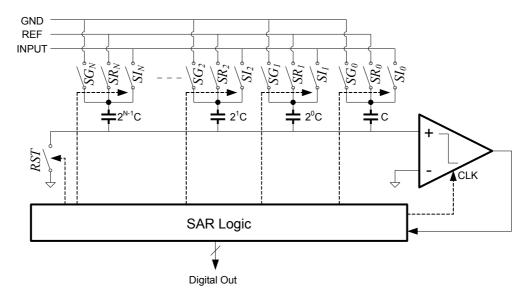

| Figure 2.34 – SAR ADC with Binary Weighted Capacitor DAC                                                     |

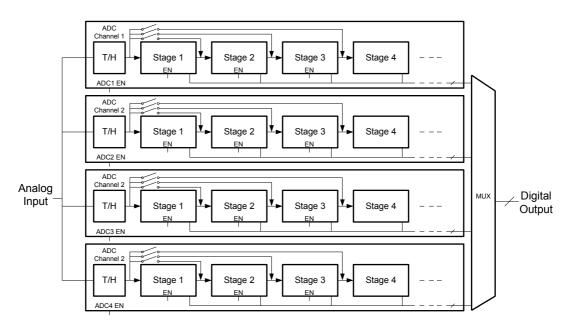

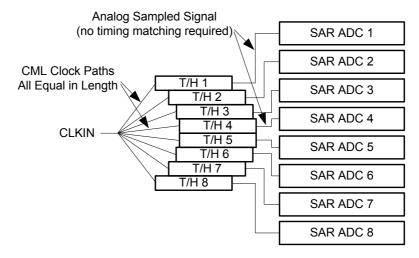

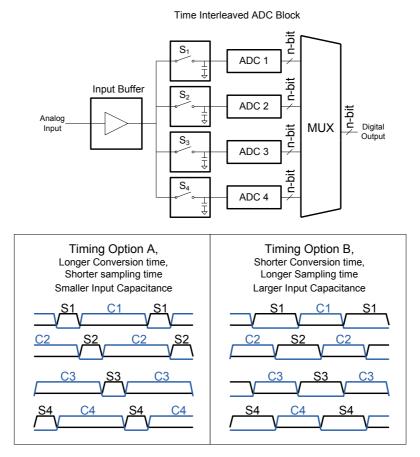

| Figure 2.35 – Layout strategy and motivation for separation of T/H from ADC [9] $82$                         |

| Figure 2.36 – Choice of T/H timing versus conversion timing                                                  |

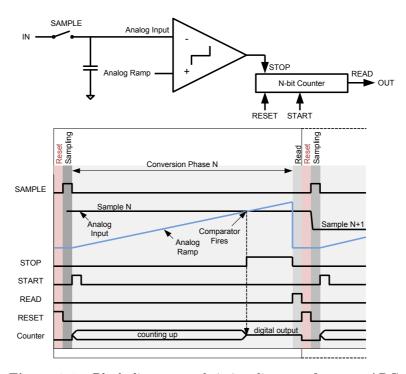

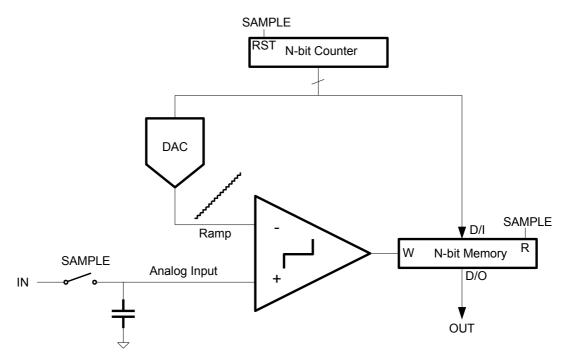

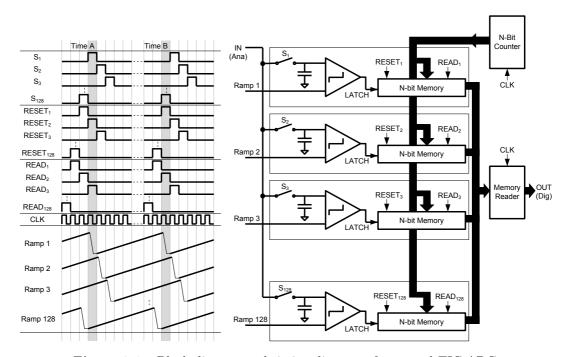

| Figure 3.1 – Block diagram, and timing diagram of counter ADC                                                |

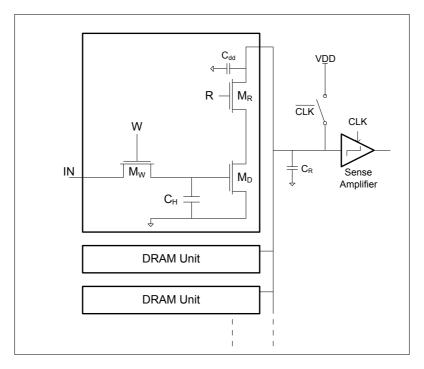

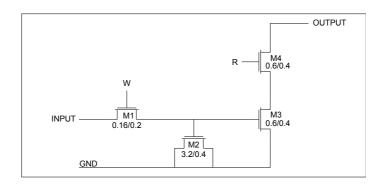

| Figure 3.2 – Practical implementation of a Counter ADC system                                                |

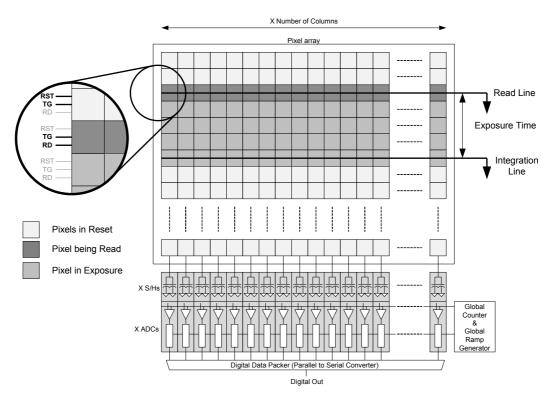

| Figure 3.3 - CMOS image sensor with column ADC readout and converter                                         |

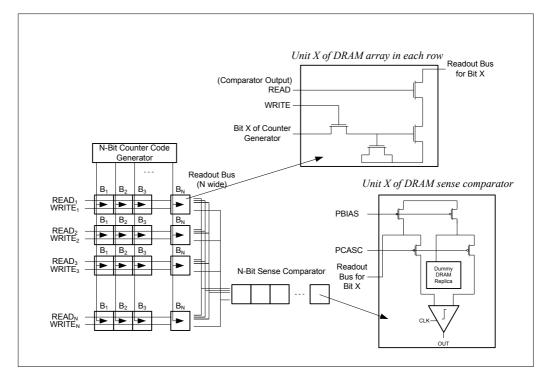

| Figure 3.4 – Counter ADC used in column parallel Architecture                                                |

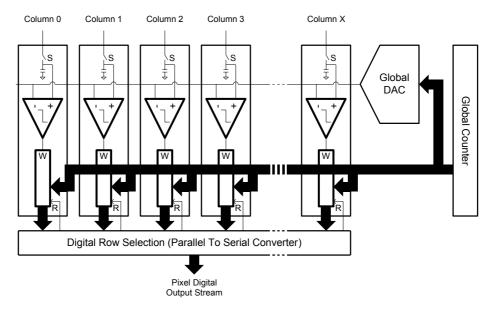

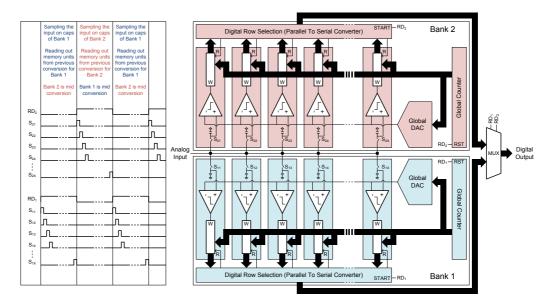

| Figure 3.5 - System diagram and timing diagram of a ping-pong counter ADC95                                  |

| Figure 3.6 – Block diagram and timing diagram of proposed TIC ADC                                            |

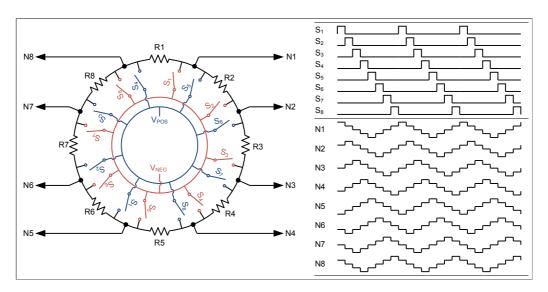

| Figure 3.7 – Rotary Resistor Ring concept circuit and timing diagram                                         |

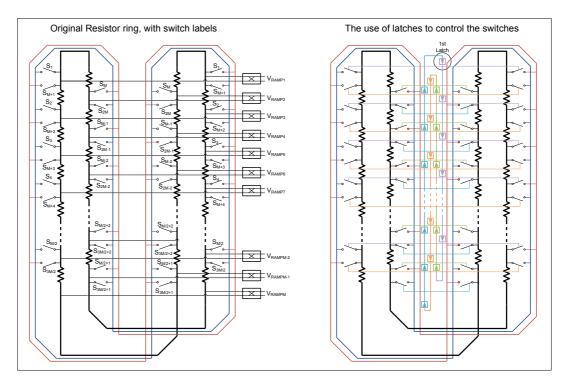

| Figure 3.8 - Circuit diagram of figure-of-8 rotating resistor ring                                           |

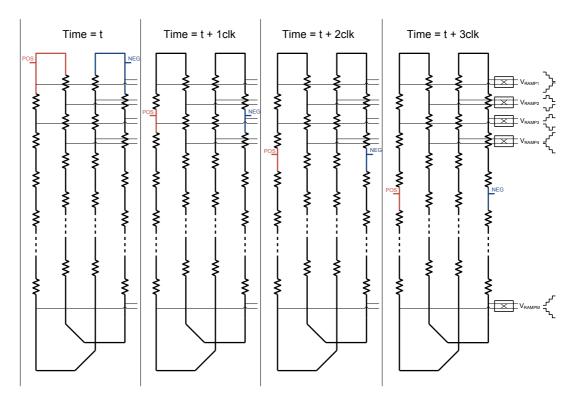

| Figure 3.9 – Example of voltage rotation around resistor ring                                                |

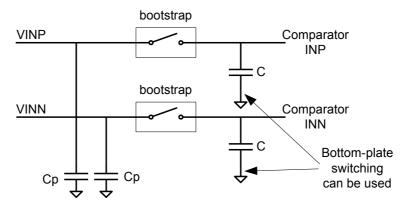

| Figure 3.10 – Sample and Hold switch and capacitor                                                           |

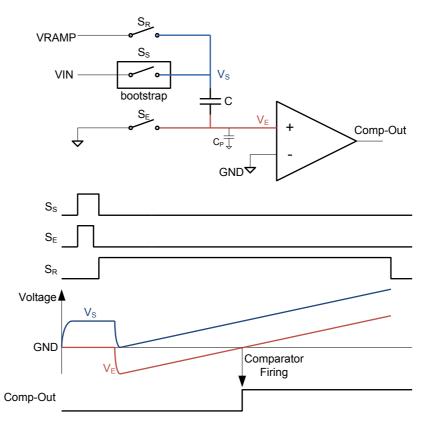

| Figure 3.11 – Bottom-Plate-Ramping technique                                                                 |

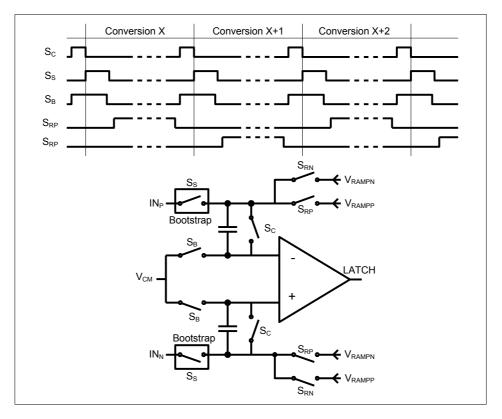

| Figure 3.12 – Fully differential implementation of AFE                                                       |

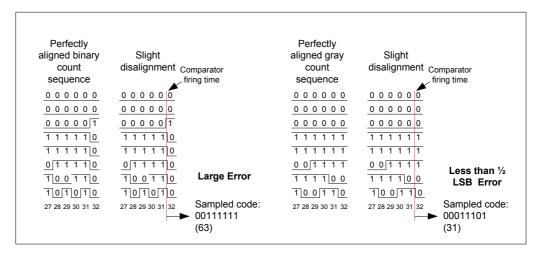

| Figure 3.13 – Error at transition in binary code compared to gray code                                       |

| Figure 3.14 – Unit DRAM and readout circuit                                                                  |

| Figure 3.15 – DRAM unit, with readout circuit with folding                                                   |

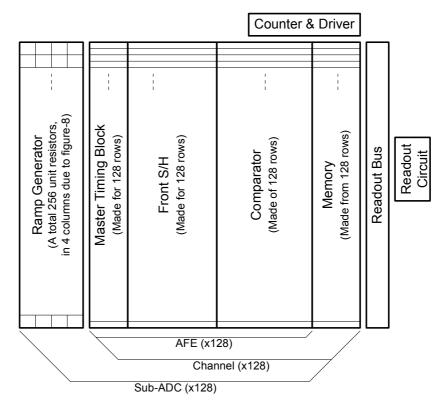

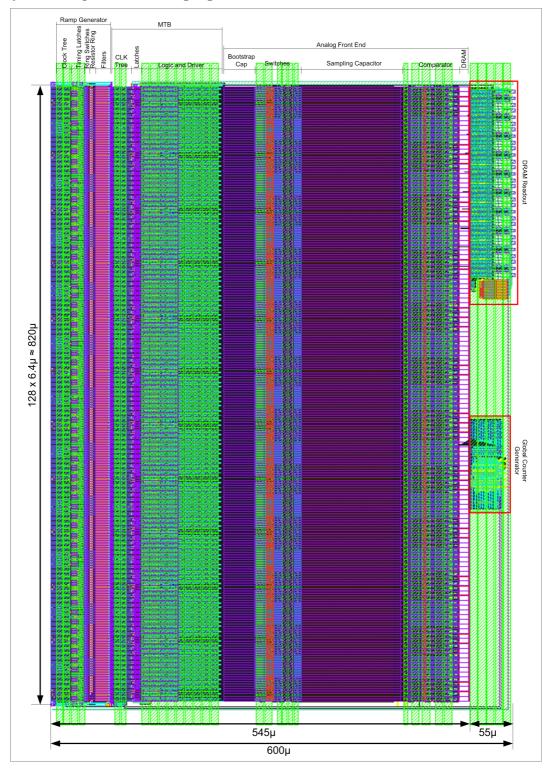

| Figure 4.1 – Top-level building blocks, and layout floorplan                                                 |

| Figure 4.2 – Figure-of-8 rotating resistor ring, with latch timing circuitry 123                             |

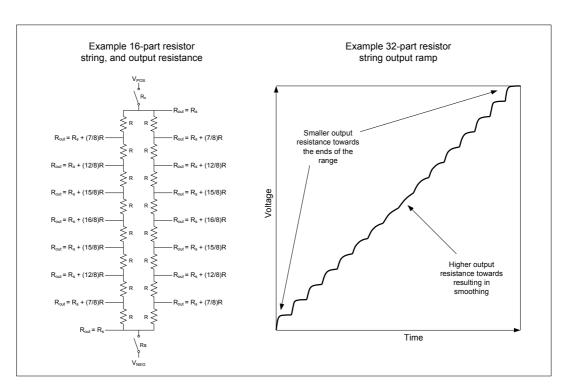

| Figure 4.3 – Example of output resistance effect on output ramp                                              |

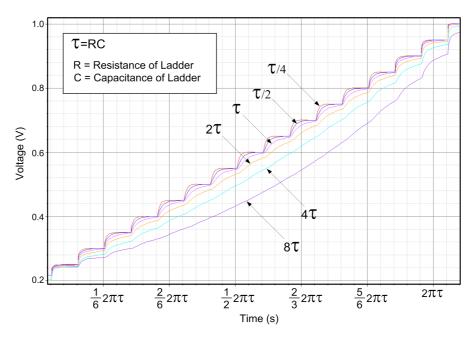

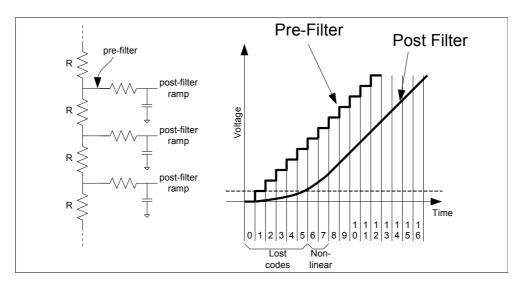

| $ \begin{tabular}{ll} \textbf{Figure 4.4} - \textbf{The effect of different RCs on ramp linearity} & \dots & $ | 125 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

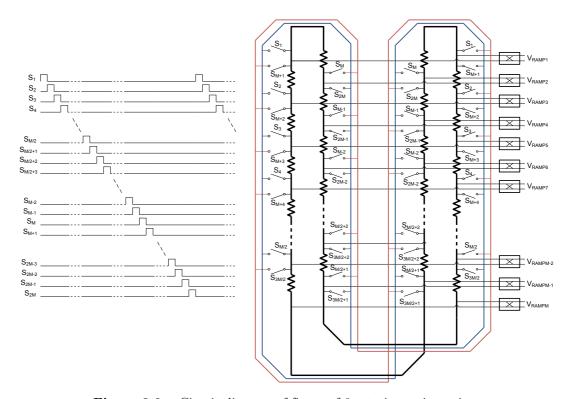

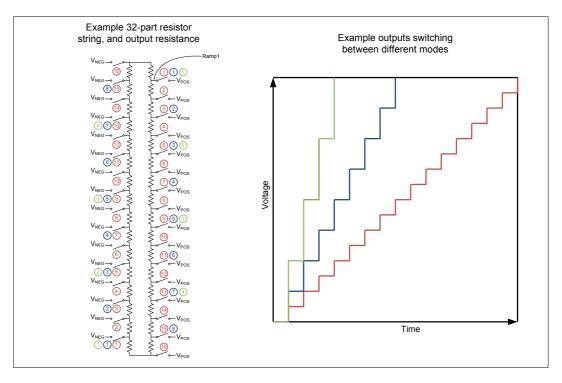

| ${\bf Figure}~{\bf 4.5}-{\rm Example~of~reconfigurable~resistor~ring~with~switch~skipping~}$                                                                                   | 129 |

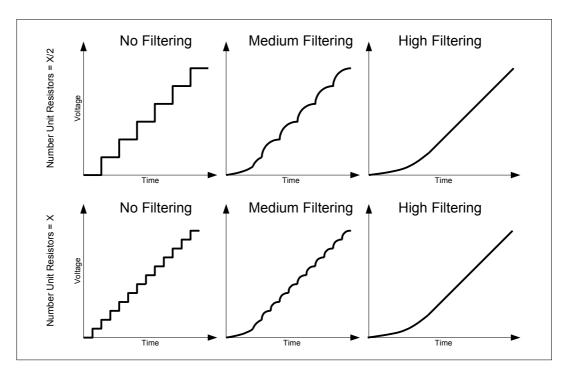

| ${\bf Figure}~{\bf 4.6}-{\rm Different~ramp~resolutions,~and~the~effect~of~filtering}$                                                                                         | 130 |

| Figure 4.7 – The effect of filtering on ramp accuracy                                                                                                                          | 131 |

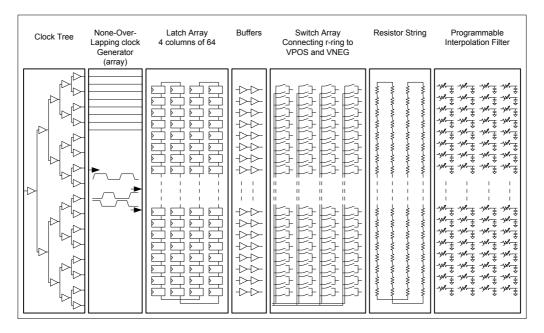

| Figure 4.8 - Top level diagram of rotating resistor ring system                                                                                                                | 133 |

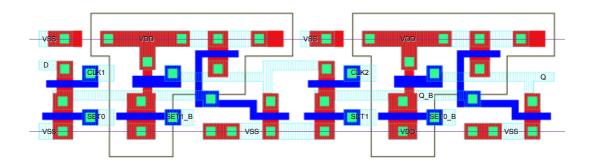

| Figure 4.9 - Circuit diagram of custom latch                                                                                                                                   | 134 |

| Figure 4.10 - Layout of custom latch                                                                                                                                           | 134 |

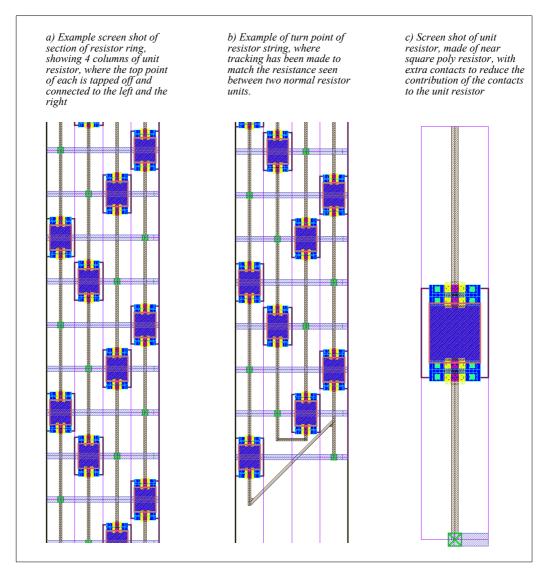

| ${\bf Figure~4.11~-~Examples~of~unit~resistor~and~connection~in~different~parts~of~the~ring}$                                                                                  | 135 |

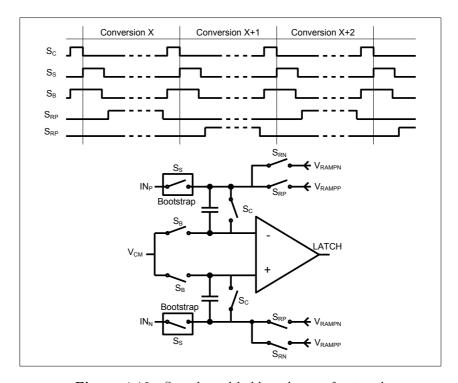

| Figure 4.12 - Sample and hold, and ramp front end                                                                                                                              | 136 |

| Figure 4.13 - Boot-strap switch circuit diagram                                                                                                                                | 139 |

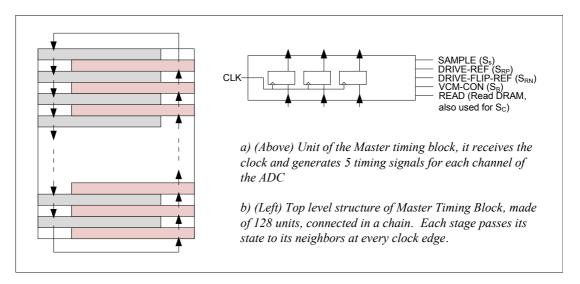

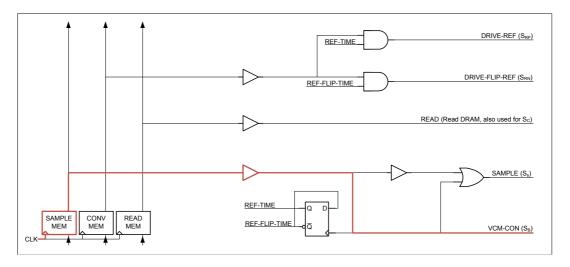

| Figure 4.14 - Top level view, and unit view of Master Timing Block                                                                                                             | 142 |

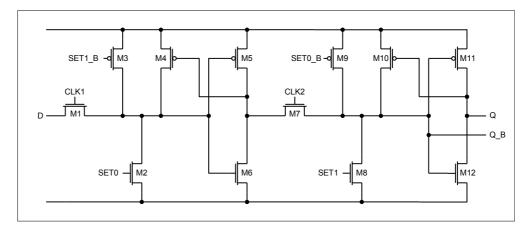

| Figure 4.15 - Circuit diagram of unit MTB                                                                                                                                      | 143 |

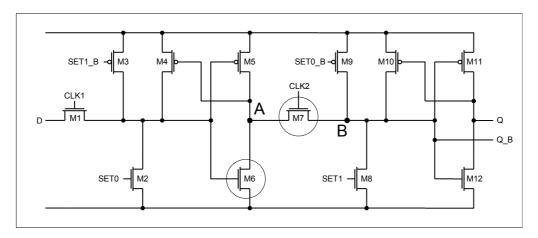

| ${\bf Figure~4.16}-{\rm Circuit~diagram~of~MTB~latch,~with~highlighted~timing~critical~device}$                                                                                | 145 |

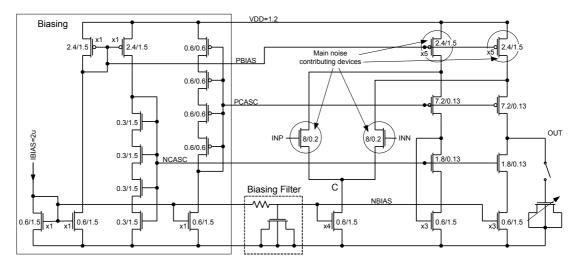

| ${\bf Figure~4.17} \hbox{ - Circuit diagram of folded cascode amplifier used as comparator} \dots \dots \dots$                                                                 | 147 |

| ${\bf Figure~4.18} \hbox{ - Circuit diagram of folded cascode amplifier used as comparator} \dots \dots \dots$                                                                 | 150 |

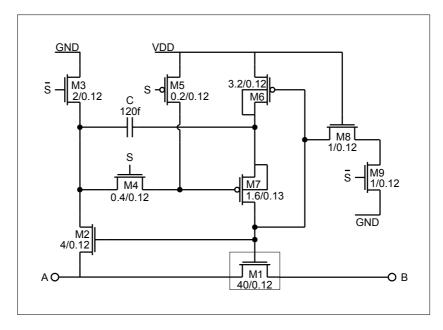

| Figure 4.19 - Unit DRAM, and device sizes                                                                                                                                      | 151 |

| Figure 4.20 - Circuit of Global Counter Generator                                                                                                                              | 152 |

| Figure 4.21 - DRAM readout circuit                                                                                                                                             | 153 |

| Figure 4.22  -  Matching of timing accuracy between DRAM read and readout                                                                                                      | 154 |

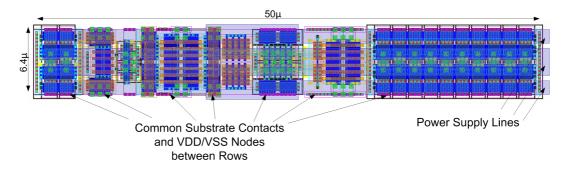

| Figure 4.23  - Top Level view of TIC ADC, showing 128 rows and readout circuitry                                                                                               | 155 |

| Figure 4.24 – Packing algorithms for different modes of operation                                                                                                              | 157 |

| Figure 4.25 - Clock Receiver circuit diagram                                                                                                                                   | 159 |

| Figure 4.26 - Circuit diagram of Shift-Register based serial interface                                                                                                         | 160 |

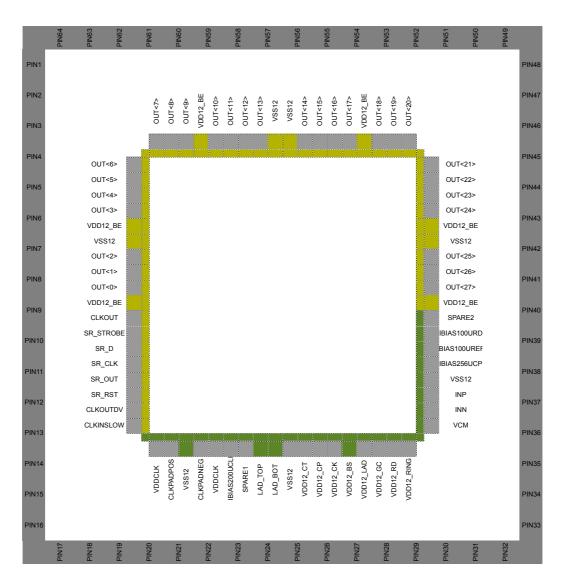

| Figure 4.27 – Chip pin-out and bonding diagram                                                                                                                                 | 161 |

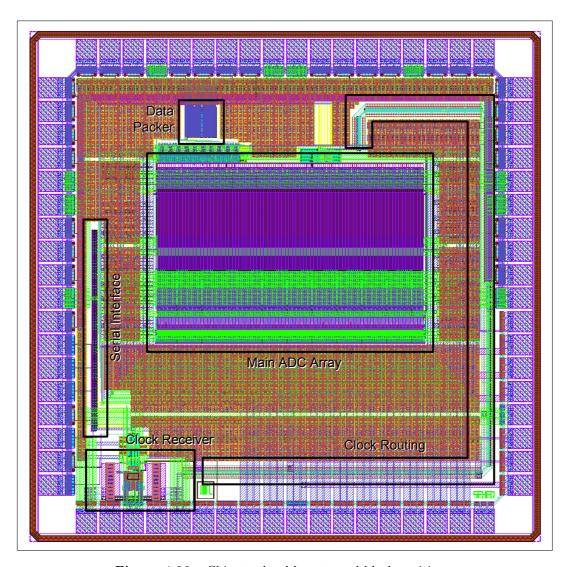

| Figure 4.28 – Chip top-level layout, and block positions                                                                                                                       | 162 |

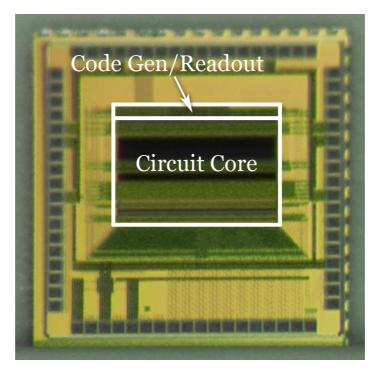

| Figure 4.29 – Die photograph of chip                                                                                                                                           | 163 |

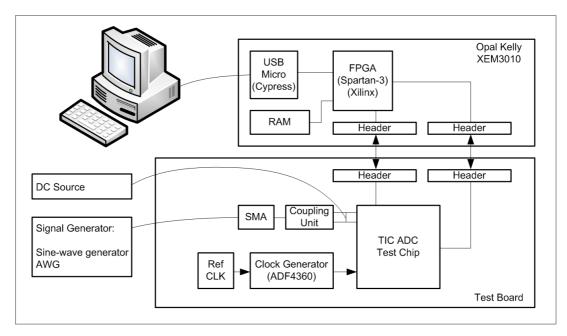

| Figure 5.1 – Test setup developed for testing chip                                                                                                                             | 167 |

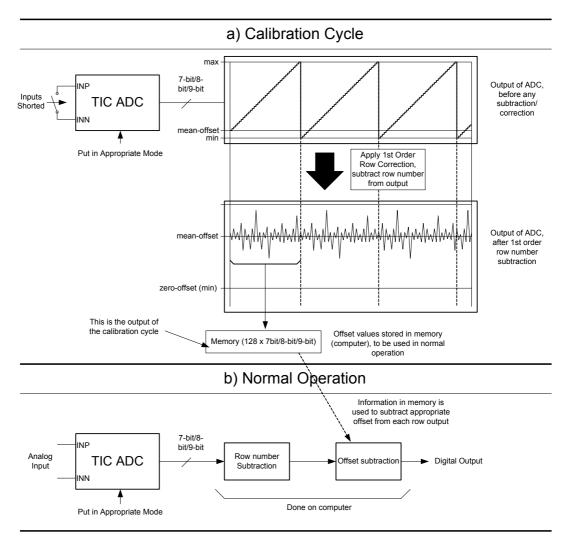

| ${\bf Figure~5.2}-{\bf Calibration~cycle,~and~how~information~is~used~in~normal~operation~}$                                                                                   | 169 |

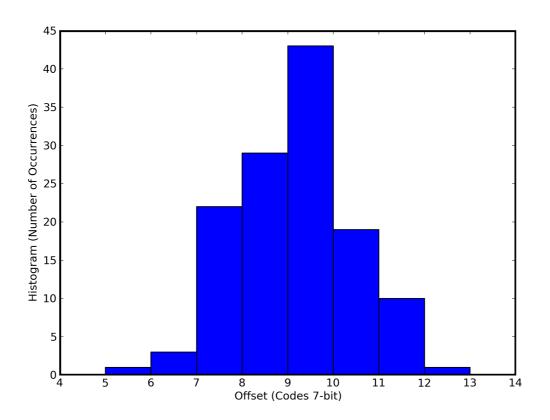

| Figure 5.3 – Histogram of Offsets in codes of 7-bit mode                                                                                                                       | 170 |

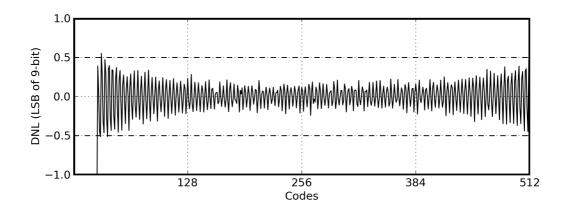

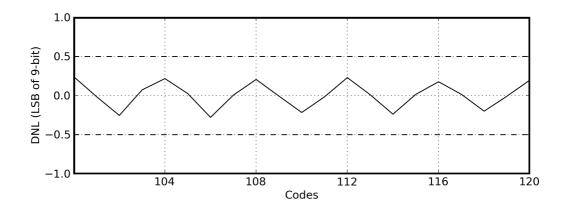

| $ {\bf Figure~5.4} - {\rm Static~DNL~performance~of~TIC~ADC~in~9-bit~Mode} \\$                                                                                                 | 172 |

| Figure 5.5 – Static DNL performance of TIC ADC in 9-bit Mode                                                                                                                   | 172 |

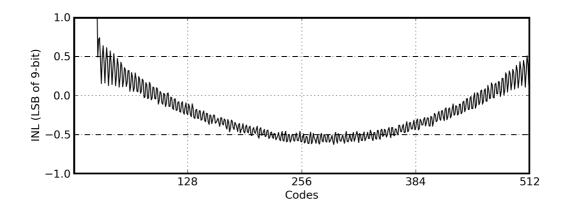

| $ {\bf Figure} \ {\bf 5.6} - {\rm Static} \ {\rm INL} \ {\rm performance} \ {\rm of} \ {\rm TIC} \ {\rm ADC} \ {\rm in} \ 9\text{-bit} \ {\rm Mode} \$                         | 173 |

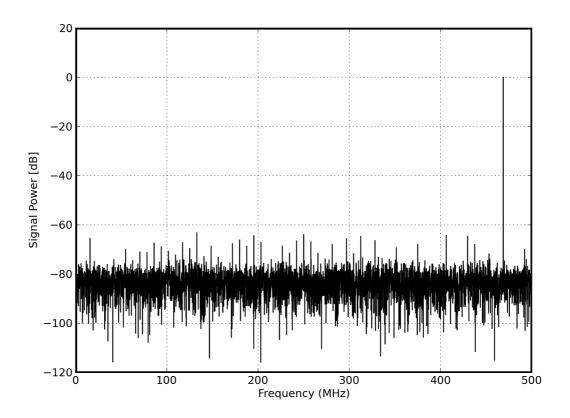

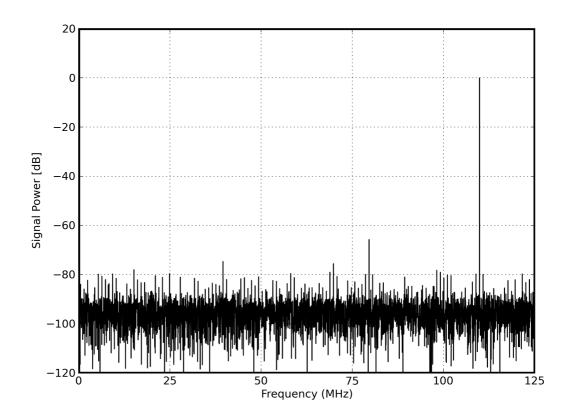

| Figure 5.7 - Output spectrum of ADC with 468.75MHz input frequency                                                                                                             | 174 |

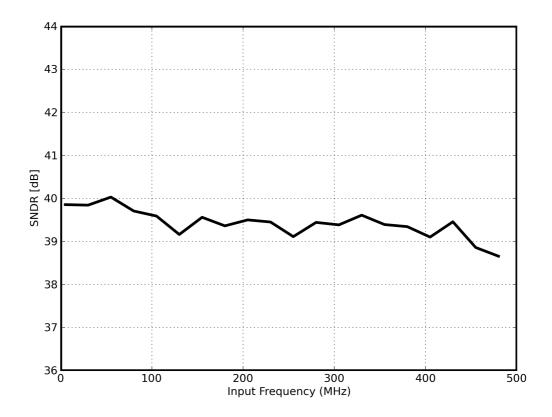

| Figure 5.8 – SNDR of ADC vs. input signal frequency in 7-bit mode                                                                                                              | 175 |

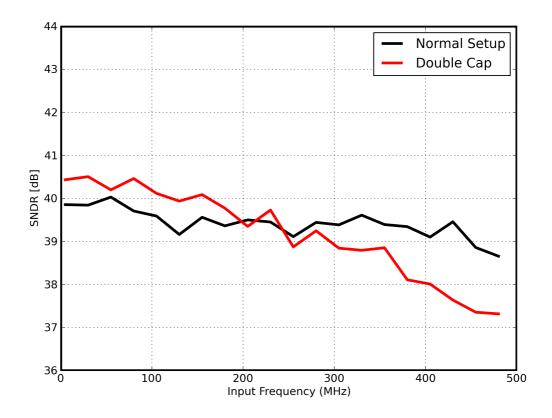

| Figure | <b>5.9</b> – 7-bit SNDR vs. input signal frequency with capacitor adjustment     | 176 |

|--------|----------------------------------------------------------------------------------|-----|

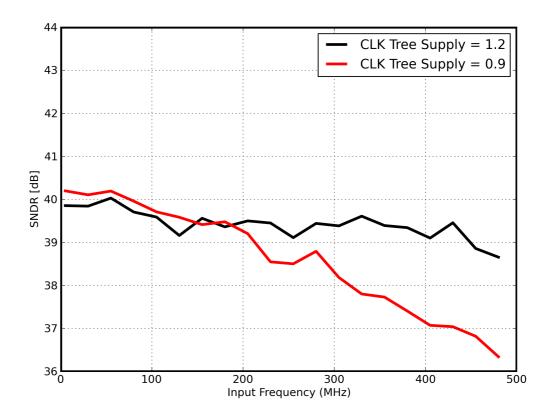

| Figure | ${f 5.10}$ – High-frequency SNDR with reduction in clock-tree supply voltage     | 177 |

| Figure | <b>5.11</b> – Output spectrum of ADC in 9-bit mode with 110MHz input             | 178 |

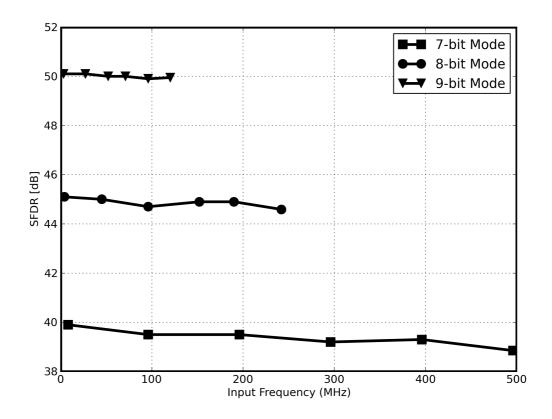

| Figure | <b>5.12</b> – SFDR vs. input frequency for all modes of operation                | 179 |

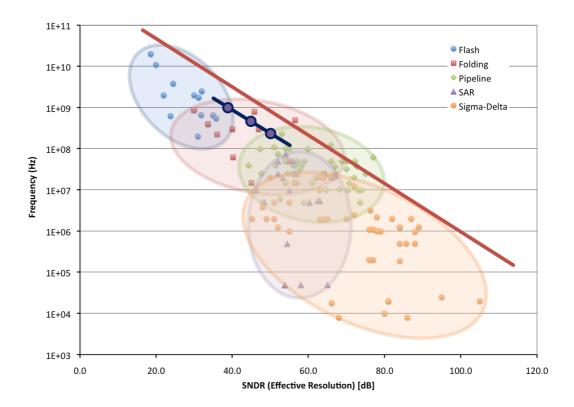

| Figure | <b>6.1</b> – Comparison of implemented ADC verses publish work                   | 187 |

| Figure | ${f 6.2}$ – Comparison of TIC ADC with other architectures for power efficiency. | 188 |

| Figure | 6.3-Performance improvement of TIC ADC with technology scaling                   | 190 |

| Figure | 6.4 – Circuit diagram of single channel for sub-ranging concept                  | 191 |

| Figure | 6.5 – Ramp generation for sub-ranging concept                                    | 191 |

# Chapter 1 - Introduction

# 1.1 The growing requirement on communication

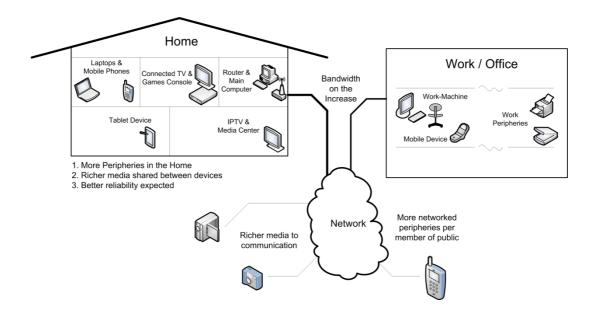

The number of electronic devices in the home from utilities and appliances, to luxury and pleasure, hand-held and mobile devices has increased exponentially in the last 20 years. The ever-growing digital data generated or consumed by these devices has pushed the requirements for in-home digital communication in terms of bandwidth and also coverage and reliability dramatically. Also the cloud computing model, technologies such as IPTV, and our desire to generate content on digital devices outside of our homes and workplaces has increased the requirements on networking bandwidth to these places. In general the use of content rich electronic devices has grown and with this the requirement and expectation of better digital communication between them.

Figure 1.1 – The growing demand for greater network bandwidth and converge

As the resolution of sensors, for imaging or audio, and displays and output devices have grown with Moore's law benefiting from technological advances, digital communication over a given medium within a given bandwidth is bound by Shannon's law [1] and cannot grow as easily. To extend the communication data-rates one is limited to 3 options:

- 1. Increase injected power levels (Improving SNR)

- 2. Use greater bandwidth on the channel

- 3. Use a new medium (new channel)

The first option of increasing the injected power levels is rarely a real option as this level is limited by emission regulations for health reasons, and also limited to prevent interference with communication on other channels due to radiation. Increasing bandwidth is a common option, apart from the huge cost associated with access to new bandwidth space, very rarely a new spectrum is available next to the current one used by a system, and potentially the injected power levels and channel characteristics are different at this new spectrum space and redesign of the digital communication apparatus is required. Exploration of new communication channels, primarily new wireline channels, has enabled growth in digital communication however these are usually difficult and time consuming and require a large investment up front to develop and understand the new channel, to define a suitable communication methodology, and to implement the communication apparatus.

Separate to the huge requirement on increase in communication bandwidth, coverage and reliability have become important factors in the digital lifestyle model. Electronic devices are no longer only used by technical specialists, with an understanding and appreciation of digital networking, but the mass-market model is now members of the public using these devices for pleasure and entertainment or non-electronic professionals in a work environment. The expectation for these rich media devices is to just work, and communicate with one another. Easy to use, simple and reliable software may

be perceived to be the key to this model, but this software can only operate on top of a reliable communication system. In a communication system, to increase coverage we cannot simply increase our injected power levels, apart from regulatory reasons explained above, increasing power levels, in turn increases interference levels, defeating the original point and very rarely increasing coverage and reliability in the long term. The key to reliability is diversity. Diversity can be applied at many different levels for example,

- Diversity by use of different communication mediums (channels), used in combination, or transparent switching in case of failure in one.

- Diversity by use of different spectrum (frequency bands) within one channel, again in combination, or transparent switching in case of failure.

- Diversity by physical location, in wireless systems for example the use of two antennas,

These are some examples of how diversity in communication can be applied. Diversity comes at the cost of complexity, power consumption, and size of apparatus, however implementation of diversity is more common.

## 1.2 The System on Chip Communication System

In recent years the push towards reducing costs, miniaturisation and increased performance has encouraged the movement towards System on Chip (SoC) implementation of communication systems. Before looking at this implementation technique and its implication on communication bandwidth and coverage, a more detailed look at a generic communication system is required.

## 1.2.1 Building blocks for a communication system

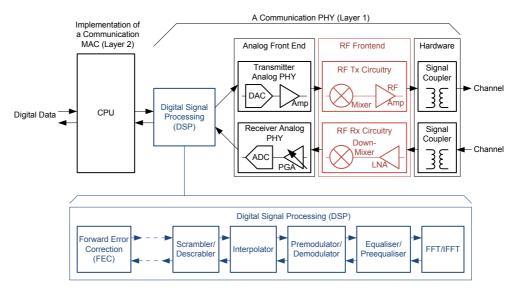

It can be difficult to produce a diagrammatical representation of a communication system that covers all modern systems, since they can be very different in flow and sub-blocks. Figure 1.2 shows the main elements of a frequency and phase modulated communication system, or multi-tone or Orthogonal Frequency Domain Modulation (OFDM) system, which tend to use the frequency bandwidth more efficiently to produce systems closer to the Shannon limit of communication [2].

Not all sub-blocks shown here would be present in all systems. For example a baseband (low frequency) communication system, common in wireline systems, would not require an RF Frontend, and the Analog Front End (AFE) would connect to the hardware system, comprising of filters and signal coupling directly. The AFE in the receive path is tasked to digitise the signal on the channel with the required bandwidth to cover the entire signal of interest and the required resolution (dynamic range) to achieve the noise floor required for the digital signal processing (DSP) to read the original digital codes transmitted.

Figure 1.2 - Block diagram of a multi-carrier communication system

The sub-blocks present in the DSP sub-system can be different for different communication standards, but commonly have these main building blocks however the balance of their complexity can be widely different. The sections of the communication apparatus which deal with physical aspects of the signal, if they were to be modulating, equalising, amplifying, digitising, etc are referred to as the PHY of the communication system. All PHY sub-blocks deal with the signal in a non-abstracted way, if it were to be voltage values, or complex coefficients representing modulated values. The input and output of the PHY sub-system are digital codes, representing the communication signal at the lowest possible layer. In modern communication systems the presence of a CPU sub-system is common, running the instruction codes which manage high-level communication tasks such as synchronisation of the network, order of transmit and receive, etc. This implements the MAC subsystem, which deals with the signal at an abstracted level and controls the operation of a communication PHY. The combination of a MAC and PHY for a particular communication standard over a particular communication medium builds a communication system, which can then be used by an electronic system as a means of communicating with a network.

#### 1.2.2 Example of an multi-tone communication PHY

A digital photo can be easily represented as a series of 1s and 0s. This data can be communicated easily over a digital backplane channel by simply driving the voltage level of the line high and low at a particular clock rate to represent 1s and 0s. With suitable synchronisation circuits, and clock recovery circuits the receiver can receive the digital stream representing the image and reproduce the photo. However to communicate this image over a busy communication channel, where only a small spectrum of frequency is available to the system, can be quite a complex problem, and a further level of abstraction is required since the information cannot be plainly placed on the line as high and low voltages representing the signal. Here we will explain how data can be communicated over a channel only using a limited bandwidth of the channel via a multi-tone communication system, which despite its greater complexity compared to a basic backplane communication system is becoming the more common and modern type of communication specially in limited spectrum systems.

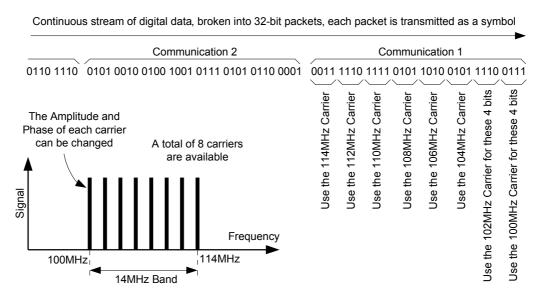

To send an image the data from the image is pre-packed with specially communication information such as the target address, length, type but never the less is a stream of digital 1s and 0s which need to be communicated over a channel. The MAC manages the high-level acknowledgments, synchronisation and turn taking to allow node A to send the digital data stream to node B. For this example we will use a theoretical communication system, where we are only allowed to use the spectrum between 100MHz and 114MHz. In this example we will use 8 frequency carriers in this space, where each is 'bit-loaded' with 4 bits of information. In the example that follows, the DSP sub-system has been heavily simplified. The purpose of this example is to give an appreciation of the type of analog signal passing through a multi-tone communication AFE, and how the requirements on the AFE change for different communication standards.

${\bf Figure~1.3}-{\bf The~breaking~of~the~digital~stream~into~packets~for~transmission}$

The digital data stream is first passed through the Forward Error Correction (FEC) where blocks (words) of the data are coded with redundancy bits, so that in the presence of small errors due to noise and non-linearity in the communication system, the original data stream can be recovered. The output of this block is again a digital stream of 1s and 0s. We now have a stream of 1s and 0s, and we have 8 carriers to use to communicate them. This is shown in Figure 1.3. Based on the standard defined earlier, we are allowed 4-bits per

carrier. Starting from the first bit of the stream, breaking the stream into 4-bit sections, each bit to be communicated on a different carrier. This division continues until 8 packets of 4 bit in length are chosen. This is all the information that can be communicated in the 'Communication 1' period. Now the systems requires to represent the collected bits using the 8-carriers in a unique way.

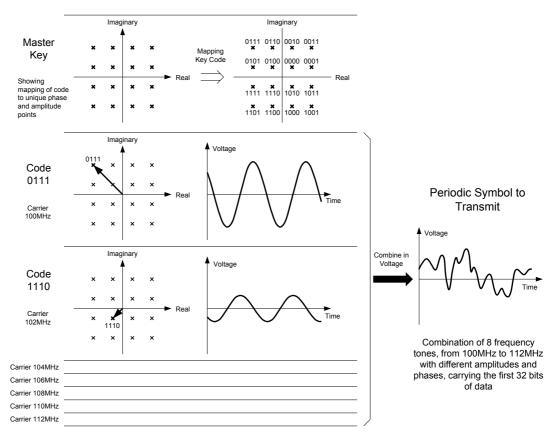

Figure 1.4 – Bit-loading of carriers and combining to build symbol.

On each carrier a Quadrature Amplitude Modulation (QAM) scheme will be used. This will be explained below. The amplitude and phase of each carrier can be adjusted to uniquely represent the code it is transmitting. For the communication system in question, a unique Master Key is defined, which is shown in Figure 1.4. This shows the mapping from a 4-bit code, to a particular amplitude and phase value. This is shown on the real and imaginary axis. For each carrier, using this master key, the amplitude and phase of that carrier can be adjusted to represent the desired 4-bit digital code which is required to be

transmitted. Following this, the 8 carriers are combined (added) in the time domain to build the periodic symbol holding the 32-bits which we require to transmit. This symbol only occupies 14MHz of the channel bandwidth, and when received by the receiver hold 32-bits worth of information.

In reality, the correct QAM constellation for each carrier is constructed as a real and imaginary number in the DSP subsystem, and is passed through an IFFT to build a digital output stream in the time domain. This digital stream is then passed to the analog front-end to be transmitted through a DAC and Line-Driver. In this example no RF circuitry is required, since the band is not modulated to a higher frequency.

The signal passing through the channel will attenuate and may be subject to phase variation. At the receiver, the signal is quantised, and passed to an FFT block where amplitude and phase information for each carrier is obtained. Before the first transmission of real data, a known symbol is transmitted and the receiver uses this to learn the amplitude and phase transfer function of the channel. How the channel changes the amplitude and phase of each carrier is learned from the communication of this known symbol, and for normal operation this correction factor to amplitude and phase is applied prior to decoding of the data. This is known as equalisation. At the output of the FFT after equalisation, the amplitude and phase of each carrier is compared to the Master Key to identify what original 4-bit code was placed on this carrier. amplitude and phase will rarely fall exactly on a QAM constellation point, due to noise, though the nearest point on the Master Key is assumed to be the original code. It is clear that if the noise in the channel, or noise of the AFE, is above a certain effective threshold for each carrier then the de-coding process will be subject to an error, since the amplitude and phases of a carrier may move to a different QAM constellation.

#### 1.2.3 Design of a Multi-Carrier Communication Standard

Design of a multi-carrier communication system involves choosing parameters such as the frequency band used, the number of carriers, carrier spacing, injected power, maximum carrier bit-loading, symbol length, cyclic prefix length, and many others [2]. Some may be variables available to the communication standards designer and some may be pre-determined. The trade-off between these variables is far beyond the scope of this document, some text in [2] and [3] can be found to tackle these trade-offs. The purpose here is to highlight the common physical differences between different communication standards, to appreciate the implications on the design of the AFE.

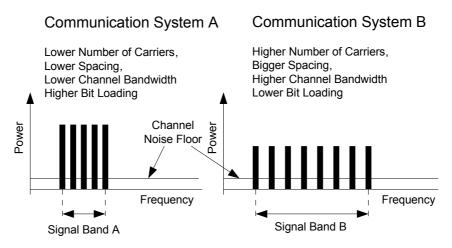

Figure 1.5 – Comparison of two theoretical communication systems

Figure 1.5 shows the spectrums of two theoretical communication systems at the input of the receiver. System A uses fewer carriers, with closer spacing, while System B uses a larger communication bandwidth with a larger number of carrier and more spacing. In this example System A uses a larger bit-loading per carrier compared to System B. In theory the two systems can be design to achieve an equal PHY communication data-rate. If the injected power per carrier were to be reduced in System B compared to A, the injected power over extended signal bandwidth could also be made similar. In this example, one could argue that System A can handle larger channel attenuation, and can hence extend the communication system reliability compared to B, while on the other

hand System B can handle large nulling, variable frequency attenuation and interference better, and hence may have a better system coverage compared to A From this simple example it is clear that communication systems are [2].configured subject to many trade-offs. Clearly System A may be more suited to a particular channel (medium) compared to B, but also even on the same channel A for example may be suited for a particular lower frequency band, while B outperforms A at higher frequency bands. Even one can think that for the same channel and same relative frequency band, system A and B can each out perform the other at different moments of time, depending on the channel Even from this simple example, in the interest of achieving circumstances. higher network converge and reliability, the importance of diversity in of multi-standard, communication systems. and use and multi-PHY communication apparatuses is clearly apparent.

The performance of communication apparatus is commonly limited by the quality of the receiver, since the receiver is required to deal with the attenuated signal, which has been subject to variable noise and variation. The receiver half modem is made from an analog front-end (AFE) section and a digital signal processing section. The dynamic range and accuracy, and signal bandwidth of the digital subsystem can be extended with greater memory depth, gate count, and parallelism respectfully. However extending the dynamic range and bandwidth of the AFE receiver subsection can be challenging and is commonly limited by the technology used for implementation. In this simple example, in the AFE, the noise floor requirement of the PGA in System A and B are equal, limited by the channel noise floor, while System B requires a larger bandwidth, but potentially a smaller gain range, assuming lower injected power and equal attenuation between System A and B. Regarding the ADC, System A requires a high-resolution converter, due to its greater bit-loading per carrier and hence greater Signal-to-Noise Ratio (SNR) per carrier, while System B requires a lower resolution but greater bandwidth and hence sampling rate. It is very clear that the A/D converter for these two example sub-systems have very different requirements.

#### 1.2.4 SoC for communication and Multi-Standard systems

In the last decade there has been a huge drive towards implementing System on a Chip (SoC) solutions for communication apparatus. The motivations here are primarily to reduce cost and size by reducing the Bill of Material (BoM), enabling easier integration into other systems and allowing greater communication between the system's sub-blocks when implemented on a single die. There are many examples of published and commercial available SoC communication devices. These devices primarily comprise a CPU subsystem managing the MAC, the Digital Signal Processing, and an Analog Front End. While SoC in communication are beneficial for the reasons stated above, their main disadvantage is lack or limited re-configurability and versatility. For example in a 3 chip solution, where the CPU, DSP and AFE are implemented as separate entities, to re-configure the system to work to a different standard, that for example requires a different dynamic-range and bandwidth trade-off, the AFE chip could be replaced with an alternative part.

Earlier in this chapter, the importance of extending network coverage through diversity was explained. One of the powerful methods in reaching a high level of diversity is building a system that can operate to different standards of communication, potentially also on different mediums of It was briefly explained, that in multi-carrier systems, communication. standards that use high dynamic range and lower bandwidths, are designed to operate better in different environments compared to those optimised to lower bit-loading and larger bandwidths. Also in a certain environment, for example in the home, a certain channel or spectrum could be suffering from interference while a different channel or spectrum is clean. To build a communication apparatus with a high coverage rate ideally one would like a system that can communicate to many different standards over different channels with real-time re-configurability. At first this may suggest implementing many different complete communication sub-systems on one system.

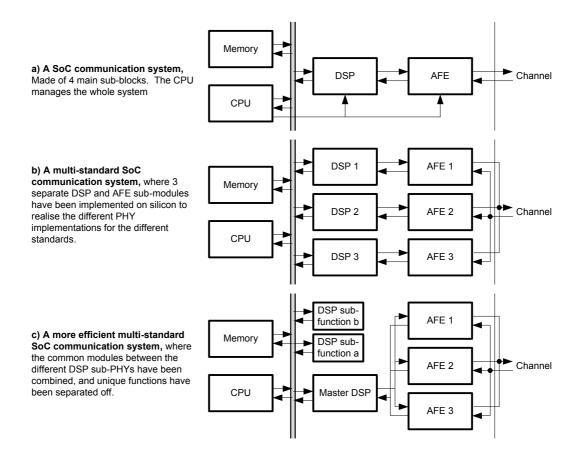

Figure 1.6 – Evolution of Multi-Standard/Multi-PHY Digital Comms SoC

Figure 1.6 shows the evolution of the Multi-Standard to Multi-PHY communication SoC. The CPU and Memory between the different communication standards can be shared. Very quickly similarities between the different DSP sub-modules become clear, and different DSP modules can be merged to build a master DSP system. Some functionalities which are unique to a particular PHY can be separated, and used as part of the DSP system controlled by the CPU effectively building a re-configurable DSP sub-system. Unfortunately, re-use of the key AFE sub-blocks, particularly in the receiver and in particular the ADC has been found to be more challenging, since the requirements on these blocks can be very different for different standards, and this leads to architecturally different blocks. This is looked at in more detail in the next sections.

The important fact to take from this section is that multi-PHY communication systems hold the key to achieving higher coverage and reliability for today's communication needs, however to realistically fulfil this ambition without implications in design time, system size, and inevitably cost, one should explore the possibility of efficient re-configurability within the AFE sub-system, specially in sub-blocks where over designing to meet a super-set of the multi-PHY specifications is not practically possible.

## 1.3 A/D Converters, and re-configurability

Looking back at the 4 main sub-blocks of a communication AFE subsystem, the line-driver (amplifier) and Programmable Gain Amplifier (PGA), when used in closed loop, bandwidth and dynamic range or resolution, commonly measured as linearity can be fundamentally traded-off for a particular circuit, since closed-loop linearity is proportional to open-loop gain, and since the openloop gain-bandwidth product of an amplifier is a constant, so for basic closed loop architectures the feedback factor can be adjusted to trade-off linearity (resolution) for bandwidth. Of course in practice there are many subtleties to this that makes this programmability less than trivial, and also if a less conventional architecture is used the trade-off may not be as practical.

D/A converters for communication with signal bandwidths in the 10s of MHz to 100s of MHz are commonly implemented as a current steering architecture, where their resolution is limited by matching in a particular technology, and output impedance by design [4], where the operation speed is limited by the digital backend speed, and switch driver operation, again limited by a technology. Fundamentally D/A converters are rarely the bottle-neck for speed or resolution in a communication system, and they can be over-designed to a super-set of speed and resolution for a multi-PHY communication system. The A/D converter on the other hand can be one of the hardest blocks to realise reconfigurability in, especially to trade-off speed and resolution over a useful range. The reasons behind this will be explained below.

#### 1.3.1 An Overview of Analog to Digital Converters

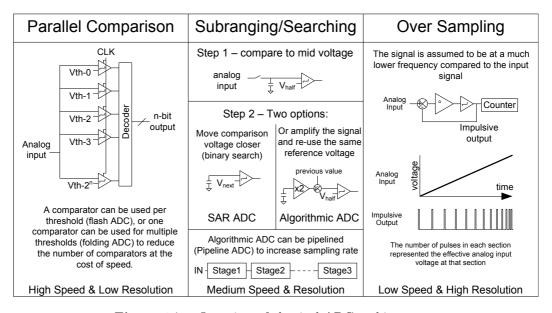

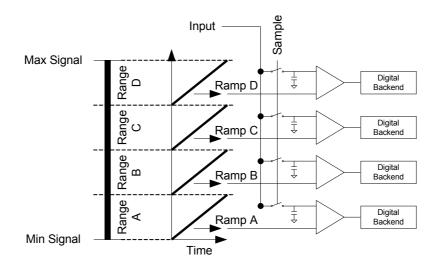

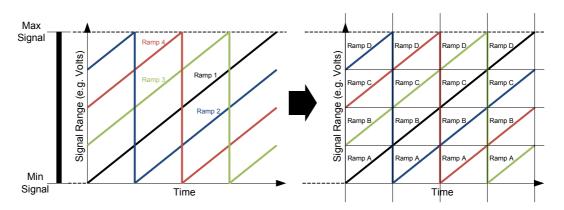

The task of converting an analog signal to a digital signal is an integral part of a digital communication system. Many architectures and approaches to performing this task are available and are used. Some architectures are more conventional or classical, each with their purpose and suited to a particular operation range. Figure 1.7 summarises the main 3 approaches commonly used for digitising of an analog signal. To achieve the highest sampling rate, the best approach is to compare the analog input to all digital threshold levels simultaneously. This builds a Flash ADC. Although Flash ADCs achieve the highest sampling rate, since the number of comparators used are exponentially related to the resolution, they tend to be low-resolution converters. One comparator can be used for multiple comparisons, allowing a first order trade-off of speed and resolution architecturally; this in turn builds a Folding ADC.

Figure 1.7 – Overview of classical ADC architectures

If greater resolution is required, a searching or sub-ranging approach is used, which is primarily similar to a binary search algorithm. These types of converters can be broken into two categories, those that sample the input voltage, and search by moving the comparison threshold voltage, or those which

use 1 threshold comparison voltage and amplify (move) the input signal around the threshold. The former are Successive Approximation Register (SAR) converter, and the latter are Algorithmic converters. Since the input is amplified and re-sampled after each comparison in an Algorithmic converter, it is possible to pipeline the comparisons to increase the overall sampling rate and hence build a Pipelined ADC.

To increase the resolution further, oversampling converters can be used. These converters continuously quantise the input signal, assuming it does not move much between quantisation cycles. The output of this quantiser is effectively subtracted from the input and the result is integrated building a Sigma-Delta quantiser loop. The integrator has a time constant and hence the output of this block is effectively a ramp with a gradient proportional to the analog input. This ramp when crossing a threshold results in a bit-stream where the occurrence of a pulse is proportional to the input signal. The pulse occurrences can be counted to find the digital representation of the input.

Further background on ADC architectures, and more detailed descriptions of different architectures can be found in common converter textbooks [5][6][7]. This text assumes a basic understanding of the common ADC architectures from the reader. The architectures relating to this work are covered with more detail in Chapter 2.

#### 1.3.2 Comparison of A/D Architectures

The specifications for A/D converters published in the major IEEE solidstates circuit conferences in last decade have been collected in a spreadsheet by Boris Murmann, at the University of Stanford that is publicly available [8]. Although data and graphs from [8] are not directly used in this section, the concept and approach here is motivated and heavily influenced by this work and is hence referred to here. In this section a similar approach is used where papers published in the last decade at IEEE International Solid-State Circuits Conference (ISSCC) and IEEE VLSI Symposium on Circuits on A/D converters are collected and papers following the conventional ADC architectures are identified and used to highlight trends in data converters and identify practical limitations of each architecture.

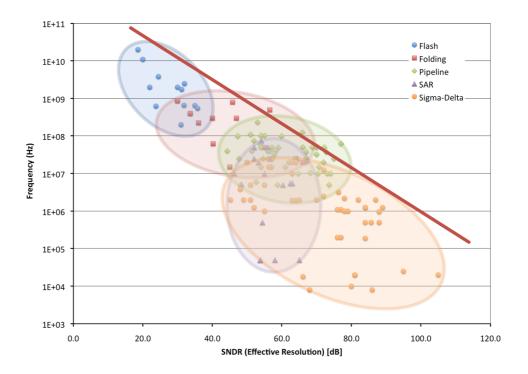

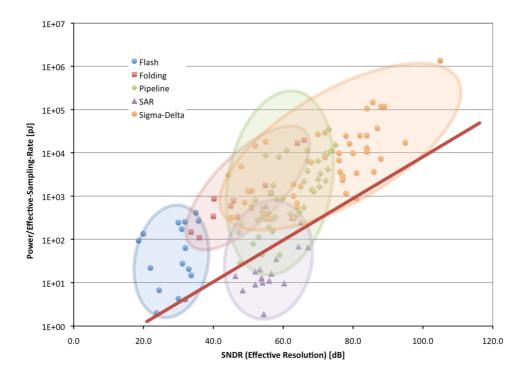

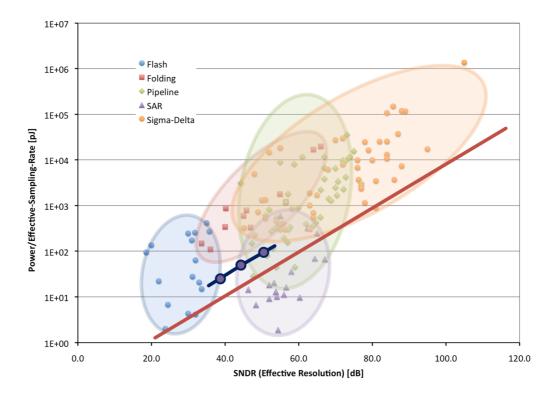

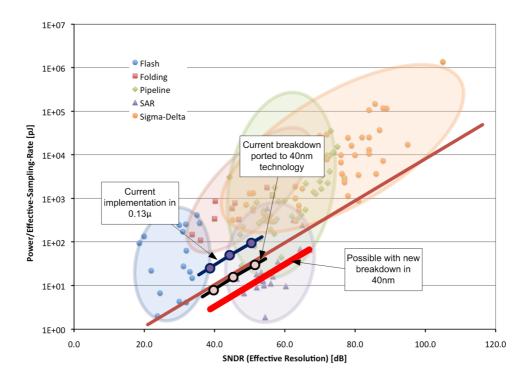

Figure 1.8 – Comparison of classical ADC architectures

Figure 1.8 shows the performance of the different ADC architectures, Flash [69-83], Folding [84-96], Pipelined [97-147], SAR [148-167] and Sigma-Delta [168-210], in the resolution and bandwidth space. For this graph the papers that follow the more classical description of each architecture published in the last 10 years, have been used. Each architecture is suited to a particular speed and resolution space. The red line drawn highlights the limit on the resolution speed product, drawn at a gradient of about 6dB per halving of frequency. This is believed to be the maximum resolution speed product possible limited to about 1ps RMS jitter. The growth in technology has always pushed this number further down, but moving along this theoretical line, to achieve different resolutions and speed ratios one must move between architectures from flash, to folding, to pipeline, to SAR, to sigma-deltas. It is also worth noting that with

advances in technology and work on sigma-delta architectures, the effective bandwidth of these blocks have been increased to new limits, Looking at Figure 1.8 one may conclude that the need for SAR ADCs has been eliminated, however the problem is that this figure only shows half the story. Figure 1.9 shows the effective power-consumption per sampling rate for the different architectures.

Figure 1.9 – Comparison of Power Efficiency for different architectures

This figure shows, in terms of power, how efficient each architecture operates. The red line highlighted is the 100fJ/step Figure of Merit marker placed as a reference. The closer each converter is to this line it is using the power from the supply more efficiently for its conversion. It can be clearly seen that SAR ADCs do significantly better than other architectures for efficiency, and although sigma-delta converters can be designed to have similar resolutions to SAR ADCs published, they can be up to two orders of magnitude less efficient compared to SAR ADCs at doing the conversion.

It is clear that each architecture has its strength and weaknesses. In the previous section it was explained that ideally for multi-PHY networking

applications we would like to trade speed (bandwidth) for resolution for a given block to work with different standards. Referring back to Figure 1.8, it is interesting to note that no one architecture can be used to travel along the full red line. Sigma-Delta converters do cover a large section of the red-line, the bottom half, in the range of MHz to 10s of MHz, however to move along the red-line in the 100s of MHz to GHz space, moving between the architectures is required. With programmability in the sub-blocks in a sigma-delta converter, some trade-offs between resolution and speed may be possible, only at low frequency. This will be looked at in Chapter 2. At higher frequencies (which many wireline standards operate at) no re-configurability seems possible looking at the classical architectures.

#### 1.3.3 Time Interleaving in A/D Converters

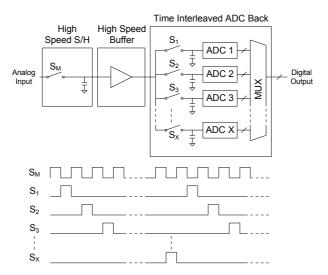

Time interleaving is a technique of using a number of identical converters in parallel with one another, but out of phase, where the input stream is captured and sampled at a higher rate compared to the operation speed of each converter, but as this stream is sampled, consecutive samples are forwarded to different ADCs to quantise, allowing each converter a longer time than the sampling rate for conversion. The digitised values from each converter is collected, and correctly ordered to pass to the output.

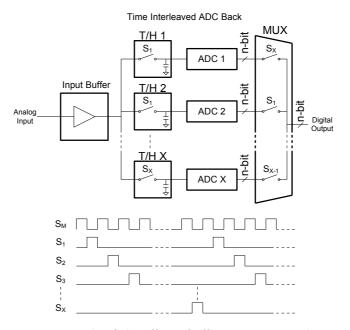

Figure 1.10 – A Time Interleaving A/D Converter block diagram

Figure 1.10 shows the block diagram of a time-interleaved ADC system. The 'Time-Interleaved ADC Block' appears as one high-speed ADC to the outside world, however is constructed from many lower frequency ADC blocks working out of phase from one another.

The presence of a high-speed sample and hold circuit and buffer at the front is not necessary for correct operation, and the sample and hold circuitry itself can be time-interleaved. This will be looked at in the following chapters. Time interleaving is used to push classical architectures outside of their conventional operation region shown previously in Figure 1.8.

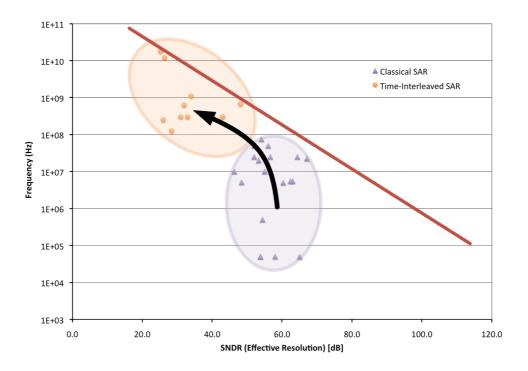

Figure 1.11 – The effect of time interleaving of SAR A/D Converters

As time interleaving can be used to extend the effective operation speed of a converter, it tends to degrade the resolution slightly due to systematic and dynamic errors induced due to mismatch in channels and matching of clock and signal distribution. Not all architectures lend themselves to time-interleaving as well as other. Figure 1.11 shows the effect of time interleaving of SAR ADCs. The devices chosen are all classical SAR ADCs [148-167], in purple, and all time-

interleaved SAR ADCs [211-221], in orange, published at ISSCC and VLSI Symposium in the last 10 year. It is very clear to see how time-interleaving has been used to push the architecture into a new space of operation. SAR ADCs are the most popular choice for time-interleaving, based on publications, among the main ADC architectures, primarily due to their initial efficiency in power consumption. As will be explained in the next chapter, due to matching requirements, time interleaving can result in an increase in the overall power efficiency of the converter, despite the increase in sampling rate. Using an architecture, which is inherently more efficient, will result in a solution with power consumption acceptable for integration in SoC solutions.

It's also interesting to see how almost all time-interleaved SARs published achieve a lower resolution compared to the classical single channel SARs in the last 10 years. This is partially due to the fact that in current technologies it is very difficult for converters to cross the 1ps timing jitter line drawn above, and though time-interleaving has increased the effective sampling rate, the effective resolution will inevitably degrade. Also a time-interleaved ADC may achieve a sampling rate increase by the interleaving factor, compared to the individual channels, however commonly does not achieve the same accuracy of each individual channel at the top-level due to non-idealities at the interleaving top-level. Time interleaving is a very powerful tool to realise new specifications for different architectures, however the technique has many subtleties. The area of time-interleaving will be looked at in more detail in Chapter 2. Here only a short background was provided to help understanding of the following sections.

#### 1.3.4 Re-configurability in A/D Converters

After a data converter is fabricated, the 3 main parameters of the system can theoretically be re-configured in the field. These are Power Consumption, Resolution, and Bandwidth. A reconfigurable ADC is one that allows the system controller to adjust the balance between these 3 factors in real time,

trading Power-Consumption for Resolution or Bandwidth, or trading Resolution for Bandwidth itself. In mobile applications where the system is battery powered, the ability to reduce power-consumption in certain modes of operation is of great use. The loss of resolution at the ADC level, will at the communication level result in less available dynamic range per carrier, and hence lower potential maximum bit-loading per carrier. Making this trade-off can allow the system to adjust power consumption for maximum communication through-put (speed). Another point of re-configurability is the trade-off of power-consumption for operation speed. For time-interleaved ADC, this can be realised by powering down ADC channels, effectively reducing the number of time-interleaved devices, and hence reducing speed and power consumption. Examples of this will be shown in Chapter 2.

The other area of re-configurability is the trade-off of resolution for bandwidth, while maintaining a constant power consumption. This form of reconfigurability as explained in the previous sections allowed the communication AFE to work to different standards of communication and potentially enable greater network coverage. In wireless communication, receivers which can tune to different standards of communication are often referred to as software defined radio systems. These can be realised either by using one very wideband A/D channel, or for certain types of multi-standard systems by realising a reconfigurable ADC that can trade resolution and bandwidth. Re-configurable sigma-delta converters have been developed for use in software defined radio working to many different cellular standards. These will be looked at in Chapter As shown in the graphs of ADC architectures, sigma deltas operate in the range of a few MHz to 10s of MHz, while many wireline standards today operate at much higher frequency bands, closer to 100s of MHz. To the author's knowledge in this frequency space no re-configurable ADC allowing trade-off of resolution and signal bandwidth has been reported to date.

# 1.4 Original Contribution of Thesis

This work aims to improve network coverage of digital communication systems, by exploring the implementation of an A/D converter which is able to trade resolution for bandwidth in the 100s of MHz sampling rate space. Such a data converter would play an integral part of a multi-standard and multi-PHY AFE capable of communicating over different channels to many different standards. The aim of the work is to demonstrate such re-configurability while maintain a near constant power consumption, and hence maintaining a power efficiency Figure of Merit over the whole reconfigurable space.

This converter is realised by extending the idea of time-interleaving to the extreme, applied to one of the slowest and simplest data A/D converter types, which is commonly left out of comparison graphs between data converter architectures. To achieve this, the following original work was carried out:

- Time Interleaving, and its non-idealities have been researched well in academic and industrial institutions, and much work can be found which discuss these non-idealities and apply to build time-interleaved converters. Most mathematical work focuses on the interleaving of 2 to 4 since algebraic work extending beyond this can be difficult. During the course of this work some basic modelling was done to try and understand how the non-idealities of time-interleaved systems manifest themselves when the number of channels is increased to greater than 100 channels. The work follows on from work done by [9][10][11] but further explores the significance of time-interleaving artefacts when the number of channels are increased or when such systems are used to quantise multitone, OFDM style signals, made of many frequency components with larger peak-to-average ratios.

- A new time-interleaved ADC architecture is proposed in this work. It builds on foundation work done in column parallel A/D converters used in CMOS image sensors. The parallel converter used in image sensors is

transformed to a time-interleaved, column serial converter, which can then be used to quantise a serial data stream. In the heart of this architecture is a newly proposed global parallel ramp generator, realised as a figure-of-8 rotating resistor string. Modelling work is carried out to understand the specifications of this block and its non-idealities. The proposed ADC architecture achieves re-configurability in field, allowing trade-off of resolution for sampling rate while maintaining a constant power consumption

- The design requirements of the sub-blocks for the new proposed ADC are analysed and a prototype implementation of the proposed ADC architecture is realised in 0.13µm Standard CMOS technology. The implemented ADC is designed to operate at 1GS/s 7-bit, 500MS/s 8-bit, and 250MS/s 9-bit configurations while maintain a near constant power consumption, and hence near constant figure-of-merit.

During the course of the work the following papers and patents were published and filed:

Danesh, S.; Hurwitz, J.; Findlater, K.; Renshaw, D.; Henderson, R.; "A Reconfigurable 1GSps to 250MSps, 7-bit to 9-bit Highly Time-Interleaved Counter ADC in 0.13µm CMOS", VLSI Symposium on Circuits, Proceedings of, 2011, 25-4

Findlater, K.; Bailey, T.; Bofill, A.; Calder, N.; Danesh, S.; Henderson, R.; Holland, W.; Hurwitz, J.; Maughan, S.; Sutherland, A.; Watt, E.; "A 90nm CMOS Dual-Channel Powerline Communication AFE for Homeplug AV with a Gb Extension", International Solid-State Circuits Conference, 2008, Digest of Technical Papers, p-p 464-628

Danesh, S.; Holland, W.; Hurwitz, J.; Findlater, K.; Henderson, R.; Renshaw, D.; "A non-uniform resolution step GHz 7-bit flash A/D converter for

wideband OFDM signal conversion", International Symposium on Circuits and Systems, 2009, Proceedings of, p-p 964-967

Danesh, S.; Hurwitz, J.; "Analogue-to-Digital Conversion", United Kingdom Patent Application Number 1014418.6. Property of Gigle Networks.

#### 1.5 Structure of Thesis

The work outlined above, and some further analysis and background material is covered in the following chapters. Chapter 2 provides further background to the area of A/D converters, their limitations and methods of quantifying and characterising their relative performances. In this chapter a closer look at time-interleaving will be presented, and results from numerical modelling of highly time interleaved system is presented accompanied by algebraic derivations from the non-idealities in time-interleaved systems. The chapter is concluded with some examples of time-interleaving, re-configurability, and calibration in different ADC architectures.

Chapter 3 will begin to explain the new ADC system, designed to realise large re-configurability in resolution and speed. The architecture and design trade-offs will be explained. The basic concept of the Global time-interleaved ramp-generator will be explained in this chapter. Chapter 4 discusses the implementation of an actual re-configurable ADC to the architecture explained in Chapter 3 in a standard 0.13 $\mu$  CMOS process. The implemented ADC is design to operate at 1GS/s 7-bit, 500MS/s 8-bit, and 250MS/s 9-bit configuration while maintaining a near constant power consumption. The detailed design report is presented in Chapter 4.

Chapter 5 will look at the measurement results from silicon from the device implemented and analysis the results to identify the effect of individual non-idealises in the system. Chapter 6 draws conclusions from the work by looking back over the implementation work during the course of this project, and

tries to assess if we have achieved the goals set out up front and how the architecture developed may help multi-PHY communication systems. A critical analysis of the design shows areas of improvement and in particular looks at technology scaling. Estimations are done on how this architecture would scale with technology, moving forward to 45nm and below, and looks to explore further work that can be done on the architecture to greater advance its performance and potential re-configurability options.

# 1.6 Conclusion and Summary

It is clear that digital communication is advancing in ways to allow better coverage and reliability, and a key part to this is the development of more diversity in the communication apparatus. One powerful method to realise diversity in the communication is the use of multi-standard and multi-PHY systems. With the goal of maintaining low cost and especially lower power consumption, ideally the sub-blocks in the system should be re-configurable to allow transformation of the PHY from operation in one standard to another. This is achieved in the DSP part of the PHY by appropriate segmentation of the system, while in the AFE is commonly achieved either by over-designing some parts of the system or implementing re-configurability in the individual AFE building blocks.

In the Analog Front End, the A/D converter can be difficult to make reconfigurable when signal bandwidths in the 10s to 100s of MHz are present, and for such bandwidths simply over specifying the block to a super-set of performance can be very costly for area and in particular power consumption, if even possible. Time-interleaving has emerged as a key technique to allow ADCs of different architectures to achieve specification parameters they could not initially achieve, and to allow greater sampling rates, sometimes at the cost of linearity. In this work we exploit time-interleaving to a much higher degree compared to work previously published for main-stream communication systems, by exploring and realising a highly time-interleaved system made of units of one

of the slowest type of data-converters which is commonly dismissed from data converter comparisons. To realise this a better understanding of highly time-interleaved systems are required which is obtained through numerical modelling and then combined with new circuitry to build a prototype re-configurable time-interleaved ADC implemented in silicon. The work explains the requirements and implementation work, analyses the results from silicon and draws conclusions on how this architecture will scale with technology.

# Chapter 2 - Analog to Digital Conversion

#### 2.1 Introduction

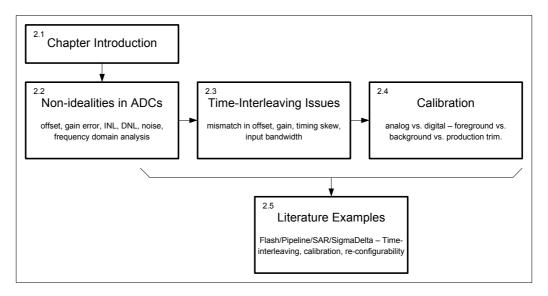

To design A/D converters that meet the requirements of the system they are used in, understanding of the specification and low-level non-idealities is Meeting these specifications will increase the likelihood of the block meeting performance and functional requirements when used in a system. In this section, conventional specifications and performance metrics for A/D converters will be defined, and the common techniques to measure these at the time of design, in simulation, and on the bench for the actual fabricated ADC will be discussed. These specifications can be applied to all A/D converters, including those using time-interleaving concepts, however in time-interleaving systems the implications of low-level specifications on the converters over all performance may be different from that of the individual channel architectures. Following an outline of basic specifications and non-idealities in A/D converters, a close look at the implications of specification mismatch between the channels of a time-interleaved converter will be presented. Algebraic equations previously published, and numerical modelling and curve fitting will help to explain the effect of these differences and help to define requirements on these parameters to meet the overall ADC requirement.

When designing an A/D converter, clearly one attempts to meet all low level specifications necessary to meet the overall converter performance required by the system, however in practice this my not be possible or may come at a huge cost for area or power consumption. One of the techniques, which is becoming more common, to improve the performance of the block after fabrication is the use of calibration. Calibration now plays a key part in A/D converter design. Some calibration techniques may have implications at the

system level, and may only be effective for given length of time. This chapter provideds an overview of different calibration techniques, how the correction amount is identified, how it is applied to the converter and how often correction loops are performed.

Following a high-level over-view of categorisation of different calibration techniques, the many approaches to calibration are explained using examples. The chapter is concluded by looking at the main classical ADC architectures, Flash and Folding, Pipelined converters, SAR ADCs and Sigma-Delta oversampling converters, showing examples of time-interleaving, reconfigurability, and calibration in published work for each architecture.

Figure 2.1 – Structure of Chapter 2

# 2.2 Specifications and Non-idealities in ADCs

The non-idealities of a converter can be looked at in the time domain, or frequency domain. Some non-idealities are easier to see and quantify in the time domain, so even though the converter output may be used in a frequency and phase domain such as in communication systems, some analysis of the converter in the time domain may be useful. Also some non-idealities may have implications for performance in certain applications but not in others. It is

important to understand all these issues, since when used in time-interleaving configurations, some static non-idealities which individually may not affect the performance at the application level, may turn into dynamic and more complex non-idealities which may degrade the performance in a different way. Here the main non-idealities will be reviewed and means of measuring and quantifying each at simulation and chip measurement will be presented.

#### 2.2.1 Offset

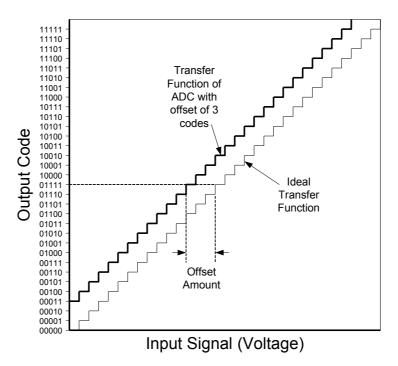

Offset in the ADC transfer function can be clearly identified and measured. Figure 2.2 shows the transfer function of a 5-bit example ADC, its ideal transfer function and that of an ADC with 3-code error in offset.

Figure 2.2 - Transfer function of an ADC with 3-code output offset

The x-axis for all ADC transfer functions is a continuous axis, representing the input analog voltage which is continuous. The y-axis has only discrete values, representing the digital code outputs. Here a 5 bit ADC is used as an example, hence only 2<sup>5</sup> possible values are available on the y-axis. The offset error clearly adds a fixed error to all output codes and is independent of

input signal magnitude. In many applications, which use the output of the ADC in the frequency domain such as frequency and phase based communication systems, this offset error does not effect the accuracy of the converter at first order. For other applications, such as in instrumentation, where the exact analog voltage is in question, this offset directly affects the accuracy [12]. In the calibration section we will look at ways to correct this offset if it cannot be reduced to a sufficiently low values by design. For the transfer function of the converter with offset shown in the Figure 2.2, output code 00000, 00001 and 00010 will never occur. In reality due to the offset we have reduced the output range of the converter, and in fact reduced its effective resolution. This is no longer a 5-bit converter, but in reality a 4.86-bit converter at best.

# 2.2.2 Input Range and Gain Error