## Electrical Test Structures and Measurement Techniques for the Characterisation of Advanced Photomasks

Andreas Tsiamis Ανδρέας Τσιάμης

A thesis submitted for the degree of Doctor of Philosophy. **The University of Edinburgh**. September 30, 2009

### Abstract

Existing photomask metrology is struggling to keep pace with the rapid reduction of IC dimensions as traditional measurement techniques are being stretched to their limits. This thesis examines the use of on-mask probable electrical test structures and measurement techniques to meet this challenge and to accurately characterise the imaging capabilities of advanced binary and phase-shifting chrome-on-quartz photomasks. On-mask, electrical and optical linewidth measurement techniques have highlighted that the use of more than one measurement method, complementing each other, can prove valuable when characterising an advanced photomask process.

Industry standard optical metrology test patterns have been adapted for the direct electrical equivalent measurement and the structures used to characterise different feature arrangements fabricated on standard and advanced photomasks with proximity correction techniques. The electrical measurements were compared to measurements from an optical mask metrology and verification tool and a state-of-the-art CD-AFM system and the results have demonstrated the capability and strengths of the on-mask electrical measurement. For example, electrical and AFM measurements on submicron features agreed within 10nm of each other while optical measurements were offset by up to 90nm. Hence, electrical techniques can prove valuable in providing feedback to the large number of metrology tools already supporting photomask manufacture, which in turn will help to develop CD standards for maskmaking.

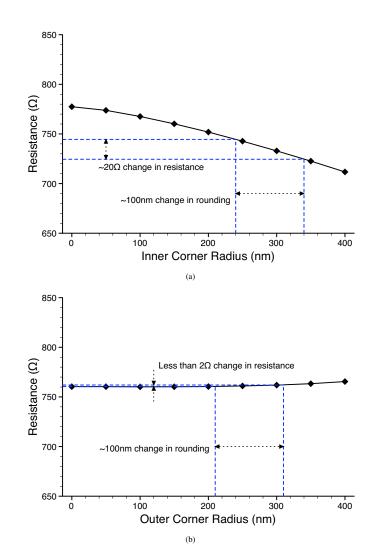

Electrical test structures have also been designed to enable the characterisation of optical proximity correction to characterise right angled corners in conducting tracks using a prototype design for both on-mask and wafer characterisation. Measurement results from the on-mask structures have shown that the electrical technique is sensitive enough to detect the effect of OPC on inner corners and to identify any defects in the fabricated features. For example less than  $10\Omega$  (5%) change in the expected resistance data trends indicated a deformed OPC feature. Results from on-wafer structures have shown that the correction technique has an impact on the final printed features and the measured resistance can be used to characterise the effects of different levels of correction. Overall the structures have shown their capability to characterise this type of optical proximity correction on both mask and wafer level.

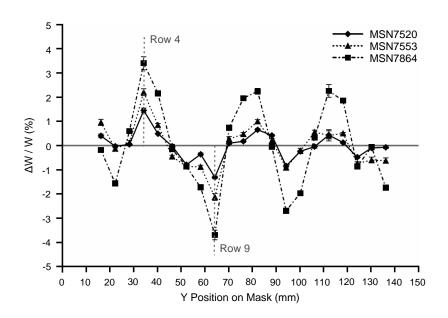

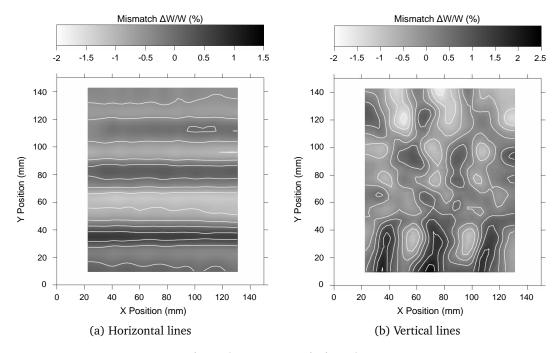

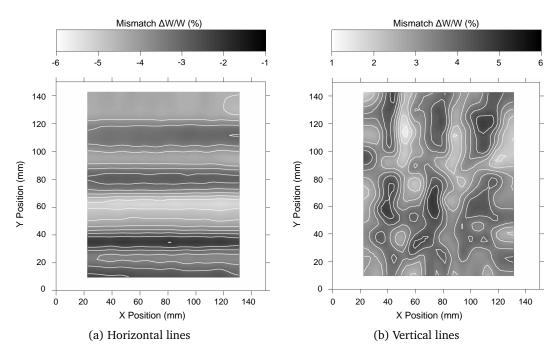

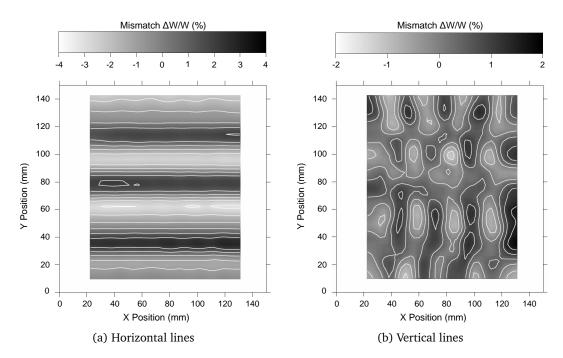

Test structures have also been designed for the characterisation of the dimensional mismatch between closely spaced photomask features. A number of photomasks were fabricated with these structures and the results from electrical measurements have been analysed to obtain information about the capability of the mask making process. The electrical test structures have demonstrated the capability of measuring tool and process induced dimensional mismatches in the nanometer range on masks which would otherwise prove difficult with standard optical metrology techniques. For example, electrical measurements detected mismatches of less than 15nm on 500nm wide features.

## Declaration of Originality

I hereby declare that the research recorded in this thesis and the thesis itself was composed and originated entirely by myself in the School of Engineering at The University of Edinburgh.

List your exceptions here and sign before your printed name.

Optical CD measurements with the MueTec <M5K> were made by Andrew Hourd at Compugraphics.

CD-AFM measurements with the Veeco SXM320 were performed by Ronald Dixson at NIST.

Andreas Tsiamis

### Acknowledgements

Many people have helped me over the four years I have been working towards my PhD, so I apologize if I have left anyone out. First and foremost I wish to thank my supervisor Professor Anthony Walton, without whom none of this would have happened. He has always guided me in the right direction with insight and understanding and for this I would like to express my deepest gratitude. I would like to thank my second supervisor Tom Stevenson, for his advice and support throughout the project. I would also like to thank Stewart Smith for his enthusiasm for this research, his invaluable assistance and for the many hours he has spent advising me through all the stages of the project. I consider him as a supervisor. I would also like to thank everyone I have worked with at the Scottish Microelectronics Centre and who have had some influence on this work. Thanks go out to: Les Haworth who has also been my director of studies in the past, Rebecca Cheung, Peter Ewen, Ian Underwood, Ron Pethig, Camelia Dunare, Andy Bunting, Bill Parkes, Yifan Li, Jon Terry, Iain Hyslop, Alec Ruthven, Kevin Tierney, Richard Blair, Hue Frizell, Ewan MacDonald, Stewart Ramsay, Valerie McDermott, Claire Watson, as well as Alan Ross, Peter Snell and Alan Gundlach who have retired.

Outside the University I have to thank the people I have collaborated with during the course of my research. Firstly, I wish to thank Andrew Hourd, not only for fabricating and optically measuring the photomasks at Compugraphics, but for his great interest and guidance during this project. I would like to thank Martin McCallum at Nikon, his industrial knowledge and support for this project have been invaluable. I would also like to thank Olivier Toublan at Mentor Graphics. Thanks must go to Ronald Dixson, Richard Allen and all the members at NIST for the mask metrology collaboration and for the AFM measurements they have provided. I would also like to thank everyone that I had the opportunity to discuss my work with at the annual International Conference on Microelectronics Test Structures and those whom their work has been helpful at some stage of my research. I also need to thank my good friends and fellow students at the University, who are unfortunately too many to list. Finally, I thank my parents for their unconditional love and support. They have always been there with encouragement for me, more so for the last decade that I have been away from home.

#### In memory of my grandfather Aristoteles

Είς μνήμην του παππού μου Αριστοτέλη

## Contents

|   |      | Declaration of Originality                                             | iii<br>iv |

|---|------|------------------------------------------------------------------------|-----------|

|   |      | Contents                                                               | vi        |

|   |      |                                                                        | ix        |

|   |      |                                                                        | XV        |

|   |      | Acronyms and Abbreviations                                             | xvi       |

|   |      |                                                                        | XVI       |

| 1 |      | oduction                                                               | 1         |

|   | 1.1  | Background                                                             | 1         |

|   | 1.2  | Thesis Structure                                                       | 6         |

| 2 |      | kground                                                                | 8         |

|   | 2.1  | 1 015                                                                  | 8         |

|   | 2.2  |                                                                        | 10        |

|   | 2.3  | Improving Resolution in Optical Lithography                            | 12        |

|   |      | 2.3.1 Introduction                                                     | 13        |

|   |      | 2.3.2 Binary and Phase-Shifting Masks                                  | 14        |

|   |      | 2.3.3 Proximity Correction Techniques                                  | 16        |

|   |      | 2.3.4 Other Resolution Enhancement Techniques                          | 18        |

|   | 2.4  | Photomask Metrology and Requirements                                   | 19        |

|   | 2.5  | Sheet Resistance Measurement                                           | 20        |

|   |      | 2.5.1 Resistivity                                                      | 20        |

|   |      | 2.5.2 Sheet Resistance                                                 | 22        |

|   |      | 2.5.3 Van der Pauw Structure                                           | 22        |

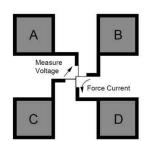

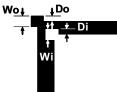

|   |      | 2.5.4 Greek Cross Structure                                            | 24        |

|   | 2.6  | Linewidth Measurement                                                  | 27        |

|   |      | 2.6.1 Optical Metrology                                                | 27        |

|   |      | 2.6.2 Critical Dimension Scanning Electron Microscopy (CD-SEM)         | 29        |

|   |      | 2.6.3 Scanning Probe Microscopy (SPM) and the Atomic Force             |           |

|   |      | Microscope (AFM)                                                       | 30        |

|   |      | 2.6.4 Electrical Test Structures and Measurement Techniques            | 31        |

|   | 2.7  | Other Electrical Test Structures                                       | 35        |

|   |      | 2.7.1 Alignment Test Structures                                        | 35        |

|   |      | 2.7.2 Electrical Test Structure for the Measurement of Contact Holes . | 37        |

|   |      | 2.7.3 Matching Test Structures                                         | 39        |

|   | 2.8  | Conclusions                                                            | 40        |

| 3 | Line | width Measurement Techniques for the Characterisation of Binary and    | l         |

|   |      | rnating Aperture Phase-Shifting Masks                                  | 42        |

|   | 3.1  | Introduction and Early Work Background                                 | 42        |

|   | 3.2  | Test Structures and Photomask Layout                                   | 44        |

|   | 3.3  | •                                                                      | 47        |

|   | 3.4  | -                                                                      | 57        |

|   |      |                                                                        |           |

| 4 | Dev  | elopment of Electrical On-Mask CD Test Structures Based On Optical   |              |

|---|------|----------------------------------------------------------------------|--------------|

|   | Met  | rology Features                                                      | 59           |

|   | 4.1  | Introduction                                                         | 59           |

|   | 4.2  | Test Structures and Photomask Layout                                 | 60           |

|   |      | 4.2.1 Optical Test Structures                                        | 60           |

|   |      | 4.2.2 Electrical Test Structures                                     | 61           |

|   | 4.3  | Measurements and Results                                             | 63           |

|   |      | 4.3.1 Short and Long-Term CD Measurement Repeatability               | 64           |

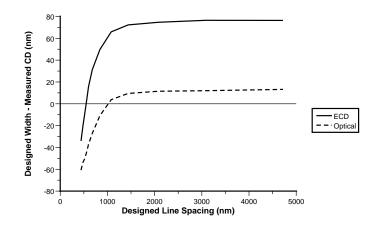

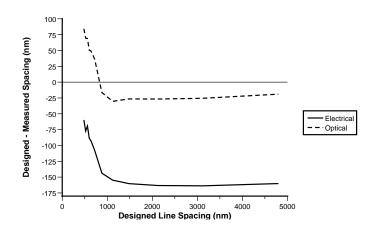

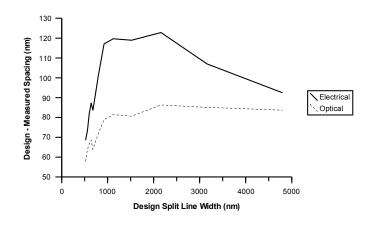

|   |      | 4.3.2 Linewidth Measurements on Isolated and Dense Features          | 65           |

|   |      | 4.3.3 Line-Spacing Measurements on Isolated and Dense Features       | 67           |

|   | 4.4  | Investigation of Resistive and Capacitive Test Structures for the    |              |

|   |      | Characterisation of Optical Features                                 | 69           |

|   |      | 4.4.1 Line End and Corner Patterns                                   | 70           |

|   |      | 4.4.2 Inverse Line End Structure                                     | 74           |

|   | . –  | 4.4.3 Contact and Inverse Contact Structures                         | 76           |

|   | 4.5  | Conclusions                                                          | 79           |

| 5 | Con  | parison of Metrology Techniques for the Characterisation of Advanced |              |

| 5 |      | tomask Processes                                                     | 81           |

|   | 5.1  |                                                                      | 81           |

|   | 5.2  | CD Measurement Techniques for the Characterisation of GHOST          | 01           |

|   |      | Proximity Corrected Features                                         | 82           |

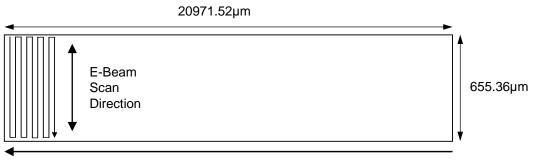

|   |      | 5.2.1 Test Structures and Photomask Fabrication                      | 82           |

|   |      | 5.2.2 Linewidth Measurements on Isolated and Dense Features          | 84           |

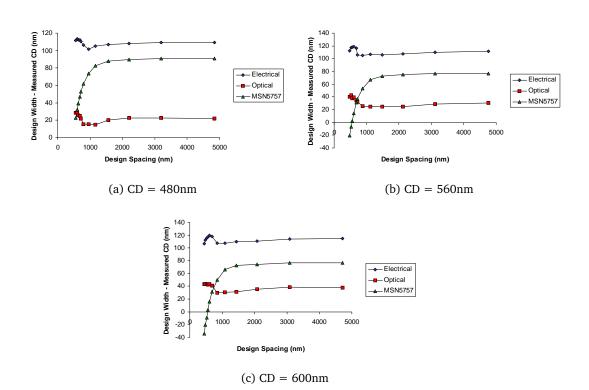

|   |      | 5.2.3 Line-Spacing Measurements on Isolated and Dense Features       | 88           |

|   | 5.3  | Comparison of Measurement Techniques for Sub-micron Linewidth        |              |

|   |      | Photomask Metrology                                                  | 94           |

|   |      | 5.3.1 Test Structures                                                | 94           |

|   |      | 5.3.2 Electrical Measurements                                        | 94           |

|   |      | 5.3.3 Optical Measurements                                           | 95           |

|   |      | 5.3.4 CD-AFM Measurements                                            | 95           |

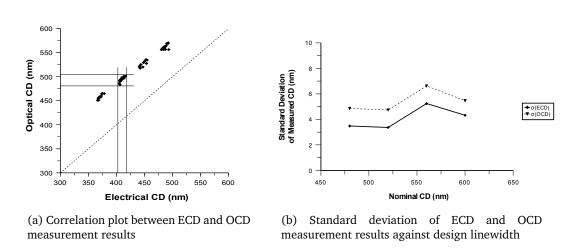

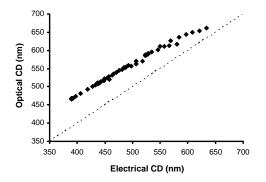

|   |      | 5.3.5 Results                                                        | 97           |

|   |      | 5.3.6 Analysis of Electrical Measurement Uncertainties               | 98           |

|   |      |                                                                      | 103          |

|   | - 4  | 5                                                                    | 103          |

|   | 5.4  | Conclusions and Further Work                                         | 104          |

| 6 | Elec | trical Test Structures for the Characterisation of Optical Proximity | <del>,</del> |

| - |      |                                                                      | 106          |

|   | 6.1  | Introduction                                                         | 106          |

|   | 6.2  |                                                                      | 107          |

|   | 6.3  | c ·                                                                  | 109          |

|   | 6.4  |                                                                      | 112          |

|   |      | 6.4.1 Electrical Measurements                                        | 112          |

|   |      | 6.4.2 Optical Inspection                                             | 113          |

|   |      | 6.4.3 Atomic Force Microscope Inspection                             | 114          |

|   |      | 6.4.4 Focused Ion Beam (FIB) Images                                  | 116          |

|    | 6.5        | On-Wa<br>6.5.1 | afer Test Structures                                                                                                        |          |

|----|------------|----------------|-----------------------------------------------------------------------------------------------------------------------------|----------|

|    |            | 6.5.2          | On-Wafer Electrical Measurements                                                                                            |          |

|    |            | 6.5.3          |                                                                                                                             |          |

|    |            | 6.5.4          | Scanning Electron Microscope Inspection                                                                                     | 119      |

|    | 66         |                | usions and Further Work                                                                                                     |          |

|    | 6.6        | Concit         |                                                                                                                             | 123      |

| 7  |            |                | Resistor Test Structures for the Characterisation of the Photomas<br>n Process                                              | k<br>125 |

|    | <b>7.1</b> |                |                                                                                                                             | 125      |

|    | 7.1        |                | uction                                                                                                                      |          |

|    | 1.2        |                |                                                                                                                             |          |

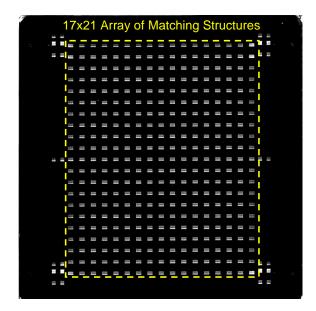

|    |            | 7.2.1          |                                                                                                                             | 126      |

|    |            | 7.2.2          | Measurement Technique                                                                                                       | 127      |

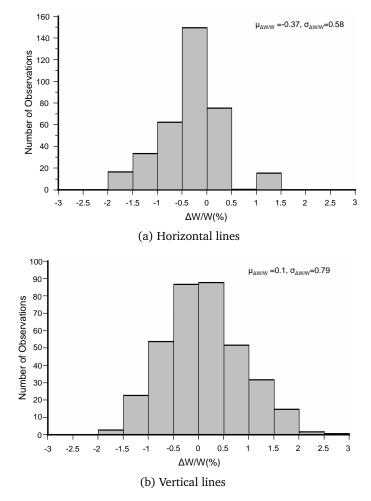

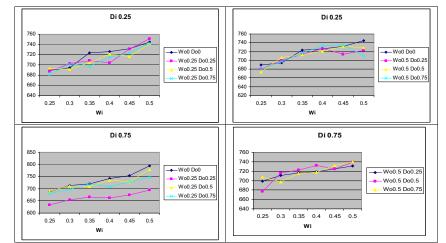

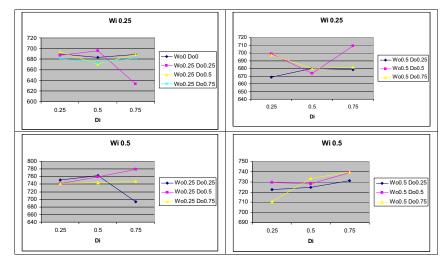

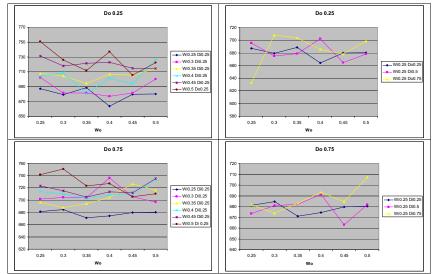

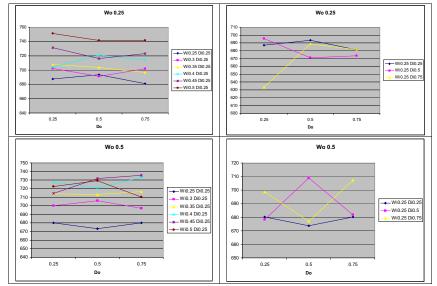

|    |            | 7.2.3          | Measurement Results and Analysis                                                                                            | 128      |

|    | 7 0        | 7.2.4          | Conclusions                                                                                                                 | 135      |

|    | 7.3        |                | ical Characterisation for an Improved Photomask Design                                                                      | 136      |

|    |            | 7.3.1          | Test Structures and Photomasks                                                                                              | 136      |

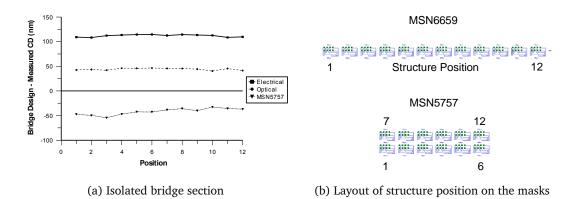

|    |            | 7.3.2          | Measurements and Results                                                                                                    | 137      |

|    |            | 7.3.3          | GHOST Proximity Corrected Photomasks                                                                                        | 141      |

|    |            | 7.3.4          | Results and Analysis                                                                                                        | 141      |

|    |            | 7.3.5          | Conclusions                                                                                                                 | 146      |

| 8  | Con        |                | and Further Work                                                                                                            | 148      |

|    | 8.1        |                | usions                                                                                                                      | 148      |

|    |            | 8.1.1          | Linewidth Measurement Techniques for the Characterisation of                                                                |          |

|    |            |                | Binary and Alternating Aperture Phase-Shifting Masks                                                                        | 148      |

|    |            | 8.1.2          | Development of Electrical On-Mask CD Test Structures Based On                                                               |          |

|    |            |                | Optical Metrology Features                                                                                                  | 149      |

|    |            | 8.1.3          | Comparison of Metrology Techniques for the Characterisation of                                                              |          |

|    |            |                | Advanced Photomask Processes                                                                                                | 150      |

|    |            | 8.1.4          | Electrical Test Structures for the Characterisation of Optical                                                              |          |

|    |            |                | Proximity Correction                                                                                                        | 151      |

|    |            | 8.1.5          | Matching Resistor Test Structures for the Characterisation of the                                                           |          |

|    |            |                | Photomask Fabrication Process                                                                                               | 152      |

|    | 8.2        | Furthe         | er Work                                                                                                                     | 153      |

|    | 8.3        | Final (        | Conclusions                                                                                                                 | 154      |

| Α  | Pub        | licatior       | 15                                                                                                                          | 156      |

|    |            |                | hed Papers                                                                                                                  | 156      |

|    |            |                | $er Work \dots \dots$ |          |

| Re | ferer      | ices           |                                                                                                                             | 188      |

|    |            |                |                                                                                                                             |          |

# List of Figures

| 2.1        | Diagram of an optical projection lithography "stepper" tool used for         |    |

|------------|------------------------------------------------------------------------------|----|

|            | exposing semiconductor wafers                                                | 9  |

| 2.2        | Diagram of a line and space pattern.                                         | 9  |

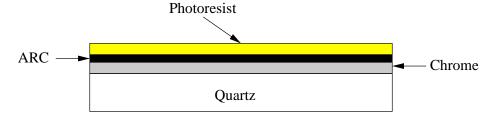

| 2.3        | Layout on an unprocessed photomask (also known as a blank)                   | 11 |

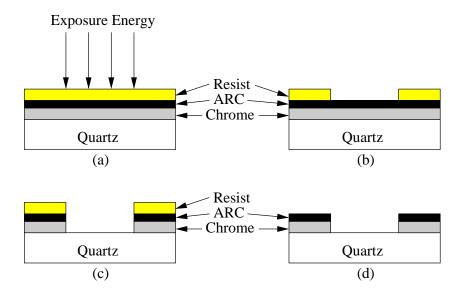

| 2.4        | Fabrication process steps for a binary photomask (a) Pattern generation      |    |

|            | (b) Photoresist development (c) Chrome etch (d) Photoresist strip            | 12 |

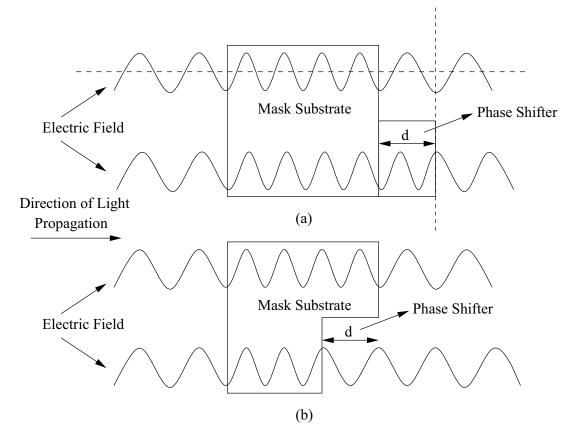

| 2.5        | A phase-shifting layer which is created either by (a) adding an extra layer  |    |

|            | of transmissive material or by (b) etching the mask substrate introduces     |    |

|            | a difference of $\lambda / 2$ (in this case) in the optical path             | 15 |

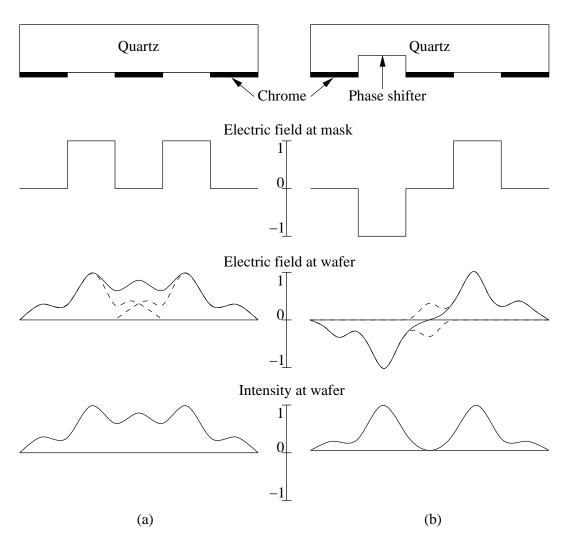

| 2.6        | Comparison of imaging process for (a) a conventional binary mask and         |    |

|            | (b) an alternating aperture phase-shifting mask                              | 16 |

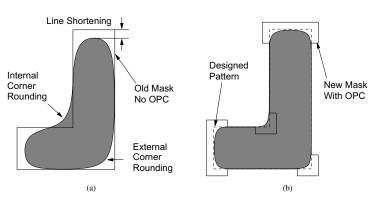

| 2.7        | Section of design (a) with no OPC (b) with OPC.                              | 17 |

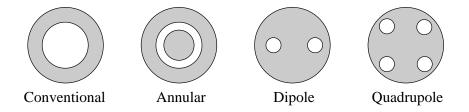

| 2.8        | Examples of light source shapes for the off-axis illumination technique.     |    |

|            | Note that the grey areas are opaque and the white areas are transparent.     | 19 |

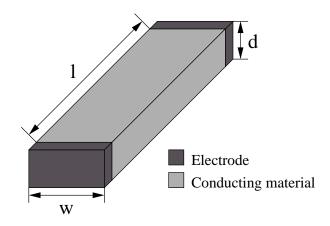

| 2.9        | Diagram demonstrating the dimensions of a bar of conducting material.        | 21 |

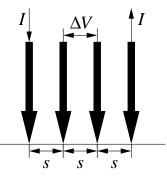

| 2.10       | Setup of four-point probe measurement technique.                             | 21 |

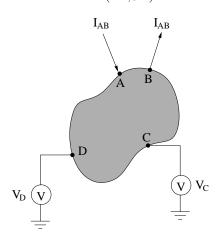

|            | Van der Pauw test structure of arbitrary shape and contact location, used    |    |

|            | to measure the resistivity.                                                  | 23 |

| 2.12       | Layout of four terminal Greek cross sheet resistance test structure          | 25 |

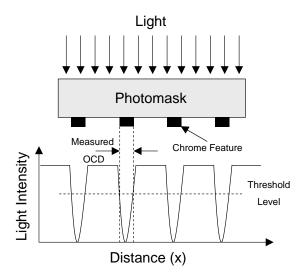

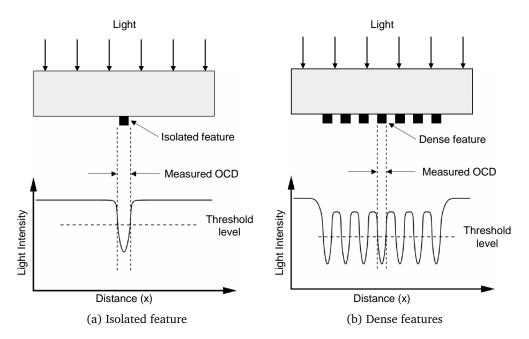

| 2.13       | Optical CD measurement by applying a threshold to a light intensity profile. | 28 |

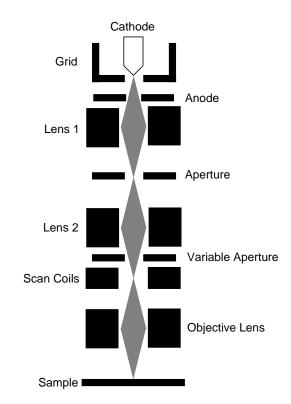

| 2.14       | Cross-sectional schematic of a standard SEM.                                 | 29 |

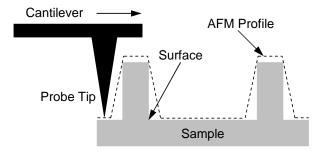

| 2.15       | Schematic illustrating an AFM scan and the resulting surface profile as      |    |

|            | affected by the tip shape                                                    | 31 |

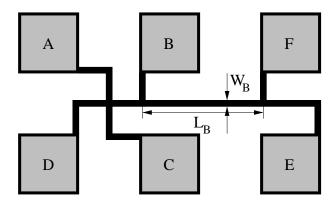

| 2.16       | Diagram of cross-bridge electrical test structure for sheet resistance and   |    |

|            | linewidth measurement.                                                       | 32 |

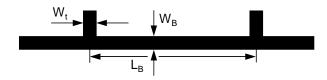

| 2.17       | Schematic of bridge section showing which dimensions need to follow          |    |

|            | the design rules.                                                            | 33 |

| 2.18       | Split-cross-bridge test structure used to measure sheet resistance,          |    |

|            | linewidth and line-spacing.                                                  | 34 |

|            | Schematic layout of an interdigitated capacitor alignment test structure.    | 37 |

| 2.20       | Partial layout of bridge resistor test structures for the measurement of     |    |

|            | contact holes.                                                               | 38 |

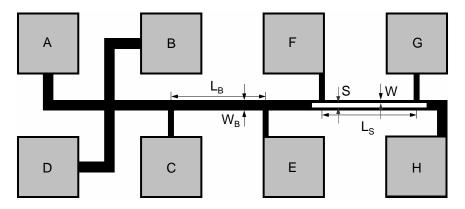

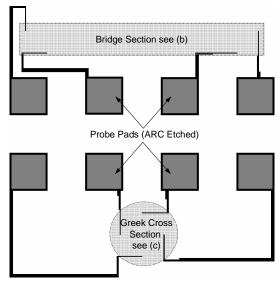

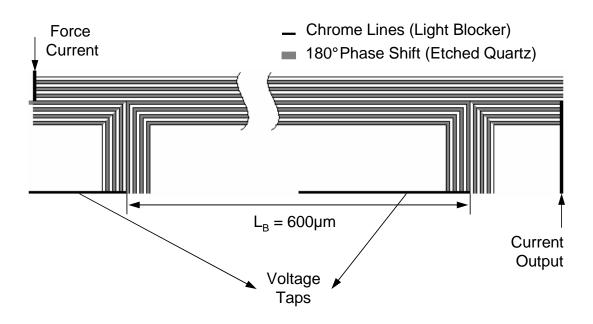

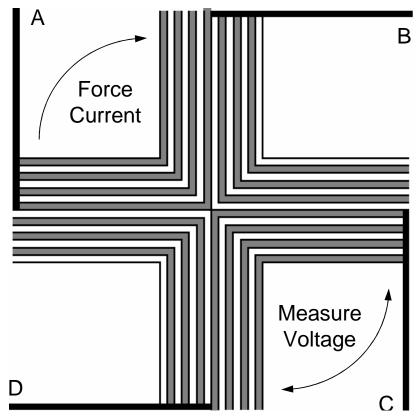

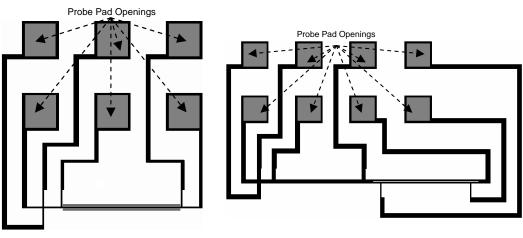

| 91         | Layout and close up view of Cross-bridge on-mask electrical test structure.  | 45 |

| 3.1<br>3.1 | Layout and close up view of Cross-bridge on-mask electrical test structure.  | 45 |

| 5.1        | (continued)                                                                  | 46 |

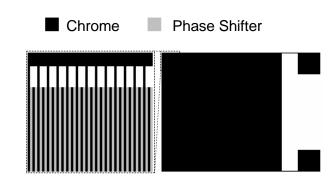

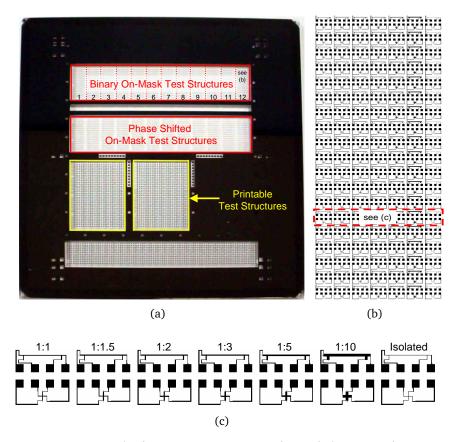

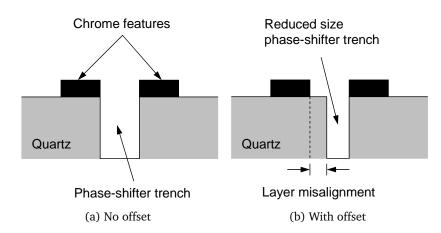

| 3.2        | (a) Layout of alternating aperture phase-shifting masks PSM3920 and          | 40 |

| 5.2        | PSM3926 (b) Block of on-mask test structures (c) Set of on-mask              |    |

|            | structures for one feature dimension.                                        | 47 |

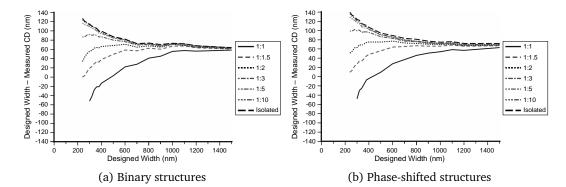

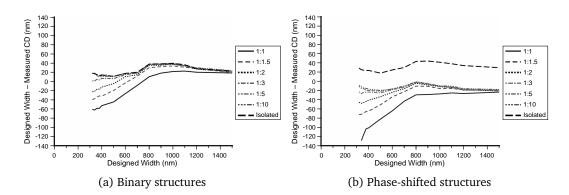

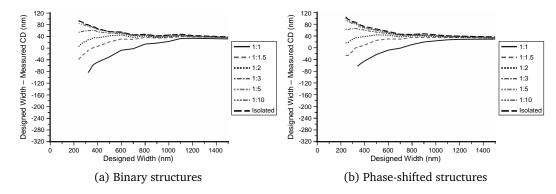

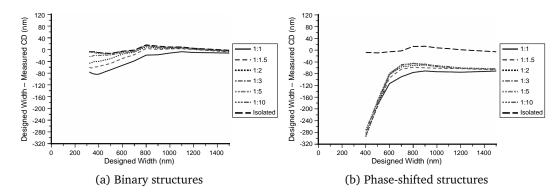

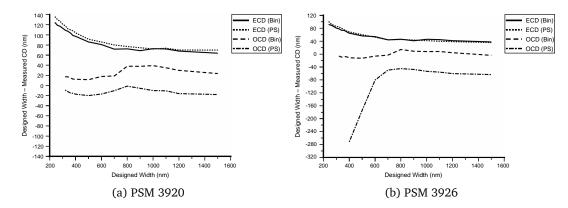

| 3.3        | Electrical CD measurement results from mask PSM3920 for a range of           | 47 |

| 5.5        | line to space ratios                                                         | 48 |

|            |                                                                              | 40 |

| 3.4   | Optical CD measurement results from mask PSM3920 for a range of line      |     |

|-------|---------------------------------------------------------------------------|-----|

|       | to space ratios.                                                          | 49  |

| 3.5   | Electrical CD measurement results from mask PSM3926 for a range of        |     |

|       | line to space ratios.                                                     | 49  |

| 3.6   | Optical CD measurement results from mask PSM3926 for a range of line      |     |

|       | to space ratios.                                                          | 49  |

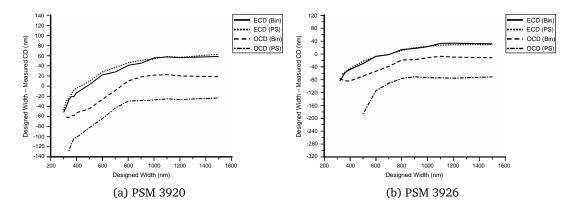

| 3.7   | Comparison of electrical and optical measurement results from binary      |     |

|       | and phase-shifted structures with 1:1 line to space ratio.                | 50  |

| 3.8   | Comparison of electrical and optical measurement results from binary      |     |

|       | and phase-shifted structures with 1:10 line to space ratio.               | 51  |

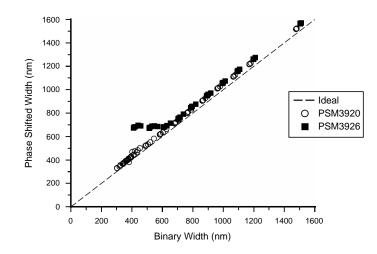

| 3.9   | Illustration of possible sources of errors with optical CD measurements.  | 52  |

| 3.10  | Correlation plot of phase-shifted against binary optical CD measurements. | 53  |

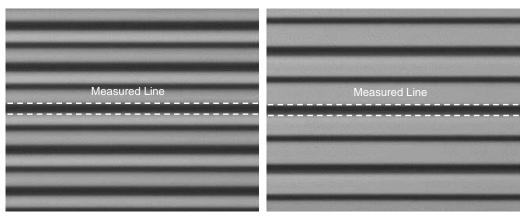

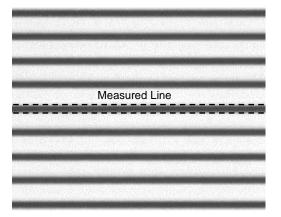

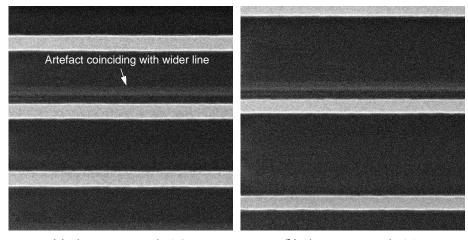

|       | MueTec (M5k) images of phase-shifted structures from mask PSM3926.        | 54  |

|       | MueTec (M5k) image of phase-shifted structure with 1:3 line to space      |     |

|       | ratio from mask PSM3920                                                   | 54  |

| 3.13  | FIB images of phase-shifted structures from mask PSM3926                  | 55  |

|       | Schematic diagrams of phase-shifted structures showing no                 |     |

| 0.11  | misalignment or with misaligned chrome and phase-shifting layers          | 56  |

|       | inibulgiment of with misungited enforme and phase similing layers.        | 00  |

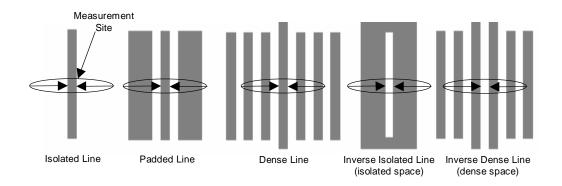

| 4.1   | Layouts of the Mentor Graphics optical test features.                     | 60  |

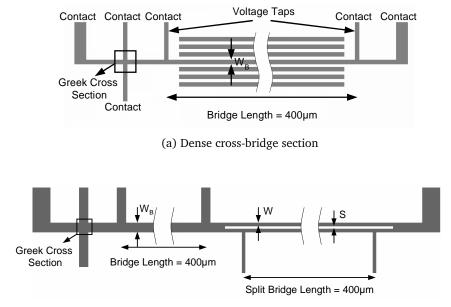

| 4.2   | Schematic layouts of the on-mask test structures.                         | 61  |

| 4.3   | Expanded views of the on-mask test structures.                            | 62  |

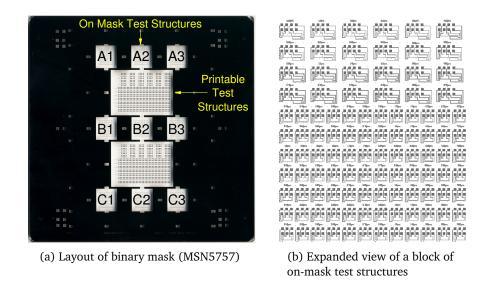

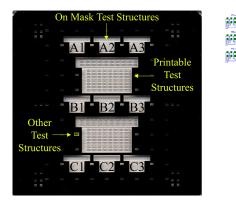

| 4.4   | Layout of binary mask (MSN5757) with a close up view of one block of      |     |

|       | on-mask test structures.                                                  | 63  |

| 4.5   | Comparison of ECD and optical results from isolated structures for a      |     |

|       | range of dimensions.                                                      | 65  |

| 4.6   | Comparison of ECD and optical results from 600nm wide dense               |     |

|       | structures for a range of line to space ratios.                           | 66  |

| 4.7   | Comparison of electrical and optical line-spacing results                 | 67  |

| 4.8   | Comparison of electrical and optical line-spacing results from dense      |     |

|       | structures.                                                               | 68  |

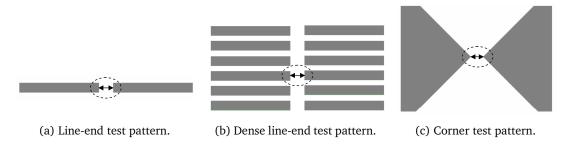

| 4.9   | Mentor Graphics optical test patterns.                                    | 70  |

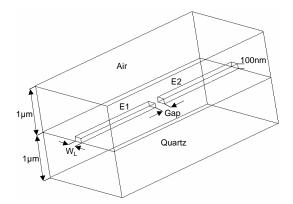

| 4.10  | Three dimensional simulation environment used to model an on-mask         |     |

|       | capacitor test structure for the measurement of the gap between two       |     |

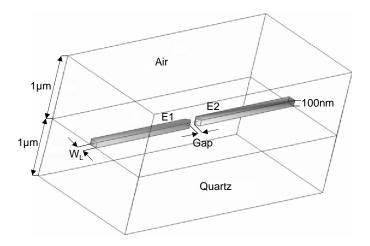

|       | line-ends.                                                                | 71  |

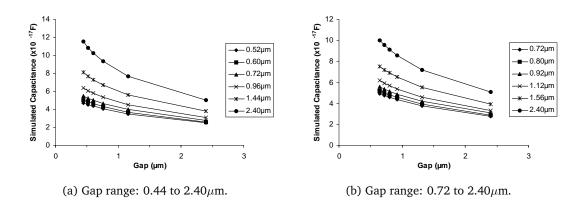

| 4.11  | Simulated capacitance against line-end gap for a range of linewidths      | 71  |

|       | Schematic layout of proposed capacitive test structure for measuring the  | . – |

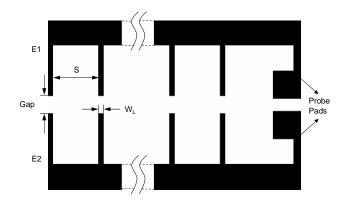

|       | gap between isolated line-end pairs.                                      | 72  |

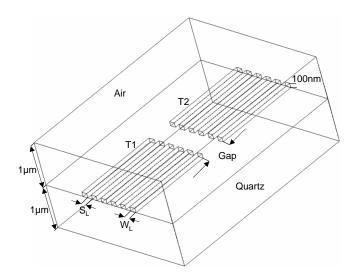

| 4.13  | Three dimensional simulation environment used to model an on-mask         | . – |

| 1120  | capacitor test structure for the measurement of the gap between pairs of  |     |

|       | line-ends.                                                                | 73  |

| 4 14  | Three dimensional simulation environment used to model an on-mask         | , 0 |

| 1.1   | capacitor test structure for the measurement of the gap between two       |     |

|       | corners.                                                                  | 73  |

| 4 1 5 | Schematic layout of an inter-digitated capacitor test structure for       | , 0 |

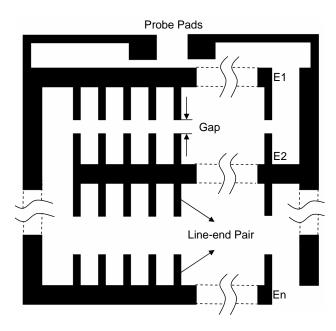

|       | measuring the gap between line-ends, for the line-end, dense line-end     |     |

|       | and corner test patterns                                                  | 74  |

|       | and corner toot putterno                                                  | / T |

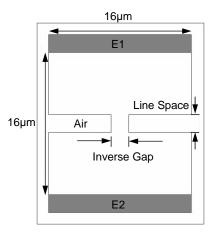

| <ul><li>4.16 Mentor Graphics inverse line-end optical test pattern.</li><li>4.17 2D simulation area used to model an on-mask resistor test structure for</li></ul> | 75  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| the measurement of the gap between the ends of line-spaces                                                                                                         | 75  |

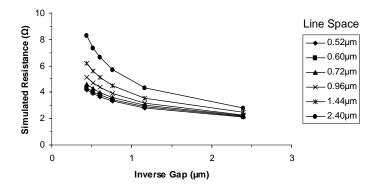

| 4.18 Simulated resistance against inverse gap for a number of different line space dimensions.                                                                     | 76  |

| 4.19 Mentor Graphics optical test patterns.                                                                                                                        | 77  |

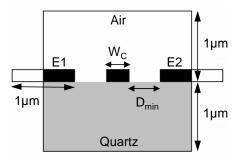

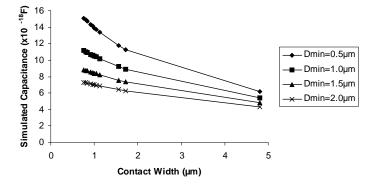

| 4.20 2D simulation area used to model an inter-digitated capacitor test structure for the measurement of the contact width                                         | 77  |

| 4.21 Simulated capacitance against contact width for a number of different                                                                                         |     |

| distance $(D_{min})$ dimensions.                                                                                                                                   | 78  |

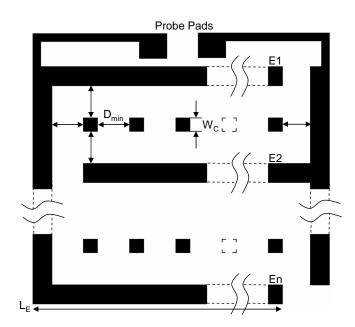

| 4.22 Schematic layout of an inter-digitated capacitor test structure for                                                                                           | , . |

| measuring the contact width.                                                                                                                                       | 79  |

|                                                                                                                                                                    | //  |

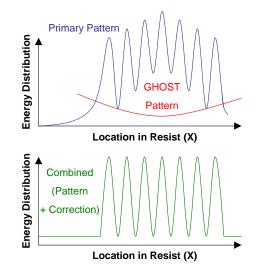

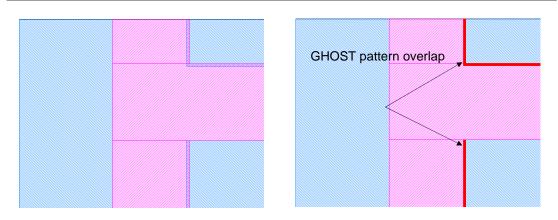

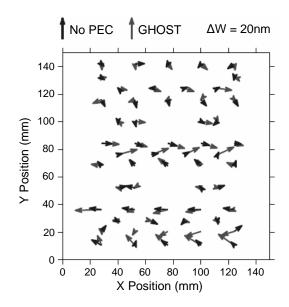

| 5.1 Schematic showing how GHOST can be used for proximity effect correction.                                                                                       | 83  |

| 5.2 Layout of the binary mask with a close up view of one block of on-mask                                                                                         | 00  |

| test structures.                                                                                                                                                   | 84  |

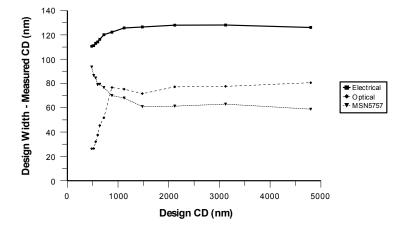

| 5.3 Comparison of ECD and optical results for a set of isolated cross-bridge                                                                                       | 07  |

| structures (GHOSTed MSN6659) with reference ECD measurements                                                                                                       |     |

|                                                                                                                                                                    | 0 - |

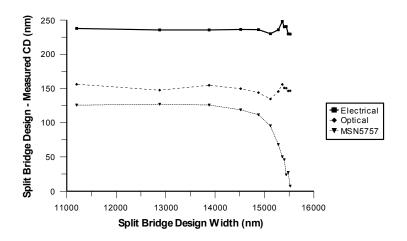

| from a standard exposure mask (MSN5757)                                                                                                                            | 85  |

| 5.4 Comparison of ECD and optical results for a set of 520nm wide dense                                                                                            |     |

| cross-bridge structures (GHOSTed MSN6659) with reference ECD                                                                                                       |     |

| measurements from a standard exposure mask (MSN5757)                                                                                                               | 86  |

| 5.5 Comparison of ECD and optical results for three sets of dense                                                                                                  |     |

| cross-bridge structures (GHOSTed MSN6659) with reference ECD                                                                                                       |     |

| measurements from a standard exposure mask (MSN5757)                                                                                                               | 87  |

| 5.6 Comparison of electrical and optical measurement results for four groups                                                                                       |     |

| of dense features with similarly sized CDs on different duty cycles, on                                                                                            |     |

| MSN6659                                                                                                                                                            | 88  |

| 5.7 Correlation plot between ECD and OCD measurement results (MSN5757).                                                                                            |     |

| 5.8 Comparison of ECD and optical results for the solid bridge section from                                                                                        |     |

| a set of inverse isolated (space) structures (GHOSTed MSN6659) with                                                                                                |     |

| reference ECD measurements from a standard exposure mask (MSN5757).                                                                                                | 80  |

| 5.9 Comparison of ECD and optical results for the split-bridge section from                                                                                        | 07  |

| a set of inverse isolated (space) structures (GHOSTed MSN6659) with                                                                                                |     |

| -                                                                                                                                                                  | 00  |

| reference ECD measurements from a standard exposure mask (MSN5757).                                                                                                | 90  |

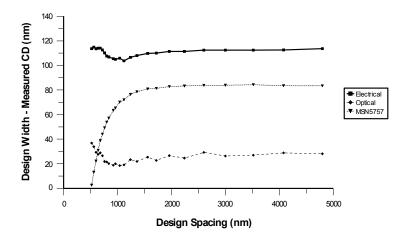

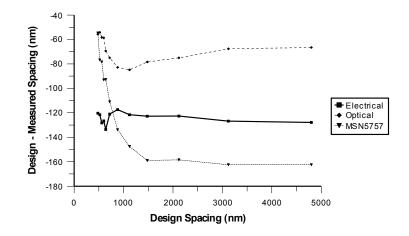

| 5.10 Comparison of electrical and optical line-spacing results from a set of                                                                                       |     |

| inverse isolated (space) structures (GHOSTed MSN6659) with reference                                                                                               |     |

| ECD measurements from a standard exposure mask (MSN5757)                                                                                                           | 91  |

| 5.11 Comparison of ECD results from a set of inverse dense (space) structures                                                                                      |     |

| on a GHOSTed (MSN6659) and a standard exposure mask (MSN5757).                                                                                                     | 92  |

| 5.12 Comparison of electrical line-spacing results from inverse dense                                                                                              |     |

| structures on masks MSN5757 (optical results included for reference)                                                                                               |     |

| and MSN6659                                                                                                                                                        | 93  |

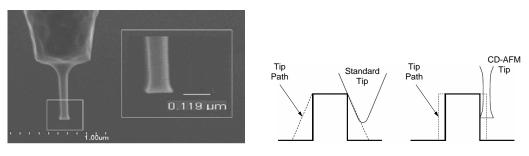

| 5.13 Comparison between standard and CD-AFM probe tips                                                                                                             | 96  |

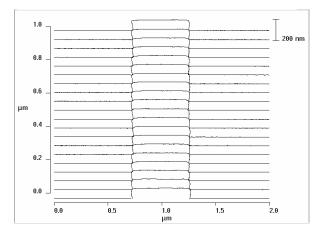

| 5.14 A $2\mu m$ by $1\mu m$ AFM scan area.                                                                                                                         | 96  |

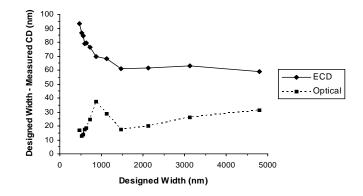

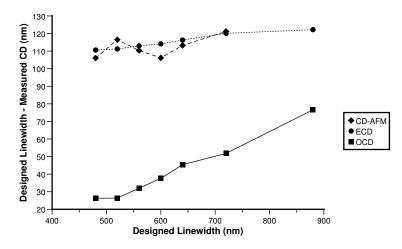

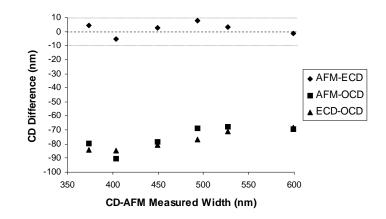

| 5.15 Comparison of optical, electrical and AFM metrology.                                                                                                          | 97  |

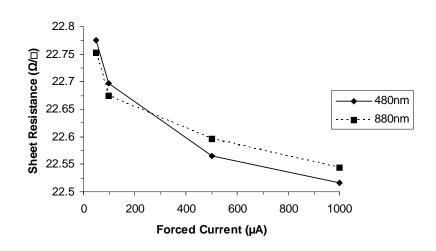

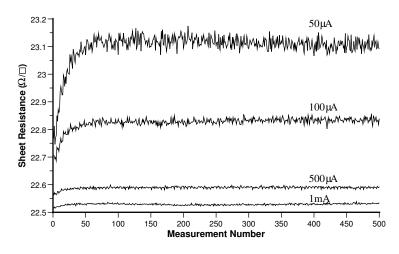

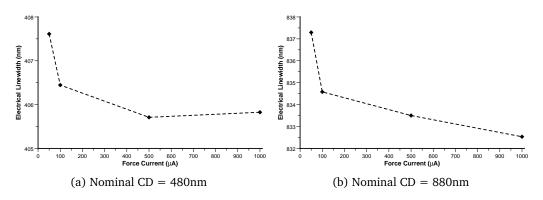

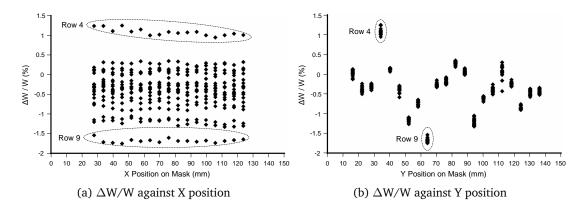

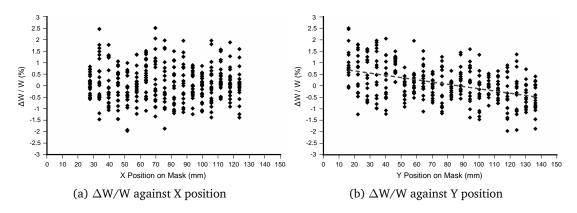

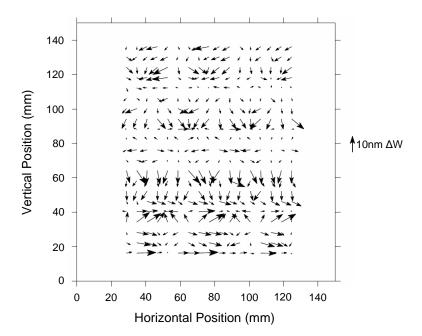

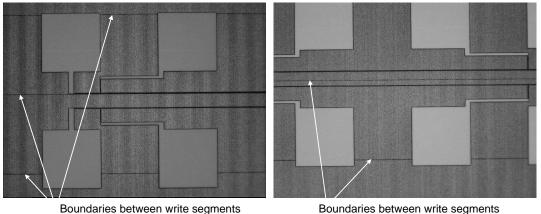

|            | Linewidth measurement offsets for isolated structures. $\ldots$ Sheet resistance plotted against force current for two different Greek crosses. This shows a variation of around 1% over the range of currents | 99         |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 5 10       | used                                                                                                                                                                                                           | 101        |

|            | measurement currents                                                                                                                                                                                           | 101        |

| 5.19       | Electrical linewidth plotted against force current for two different test structures.                                                                                                                          | 102        |

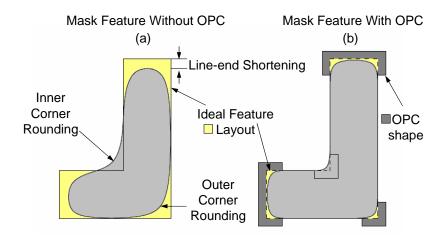

| 6.1        | (a) Layout of feature printed with a mask without OPC. (b) Layout of feature printed with a mask with OPC; the feature matches more closely                                                                    | 105        |

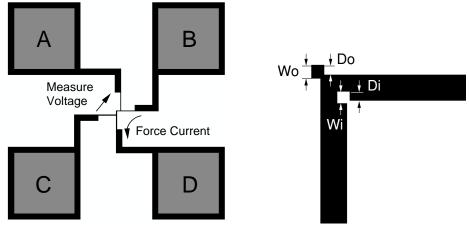

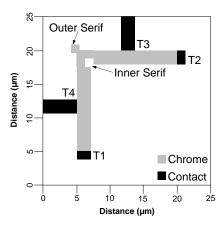

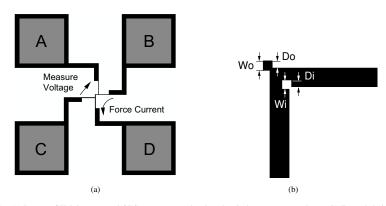

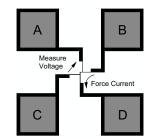

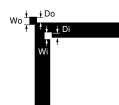

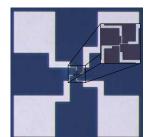

| 6.2        | the desired layout (dashed line)                                                                                                                                                                               | 107        |

| 6.3        | features                                                                                                                                                                                                       | 108        |

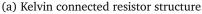

| 6.4        | test structures                                                                                                                                                                                                | 109<br>110 |

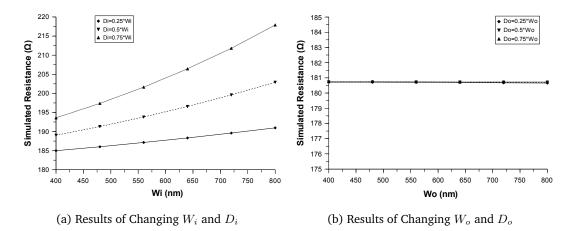

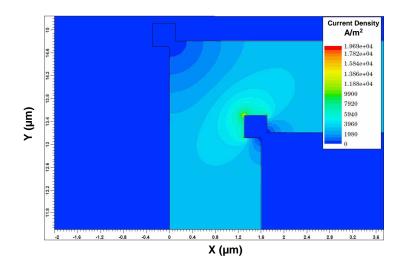

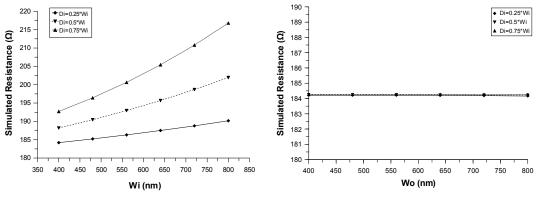

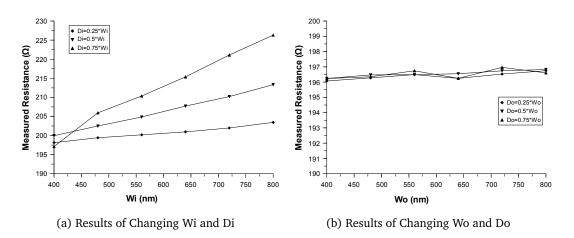

| 6.5        | Simulation results showing the effects of changing the dimensions of the                                                                                                                                       |            |

| 6.6        | OPC features                                                                                                                                                                                                   | 110        |

| 6.7        | inner and outer serifs                                                                                                                                                                                         | 111        |

|            | OPC features for structures with both inner and outer serifs                                                                                                                                                   | 111        |

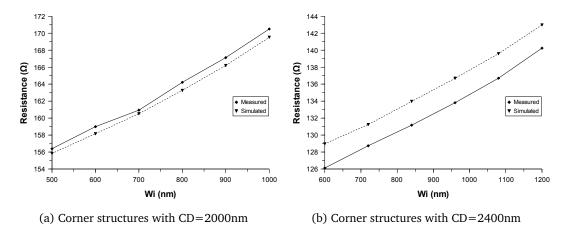

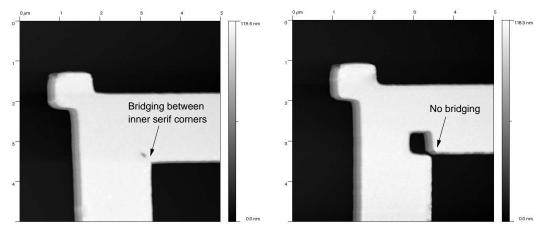

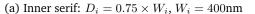

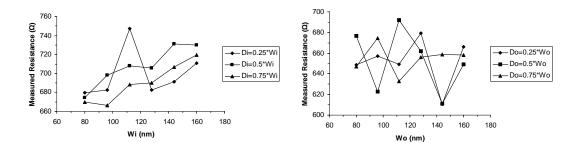

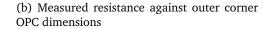

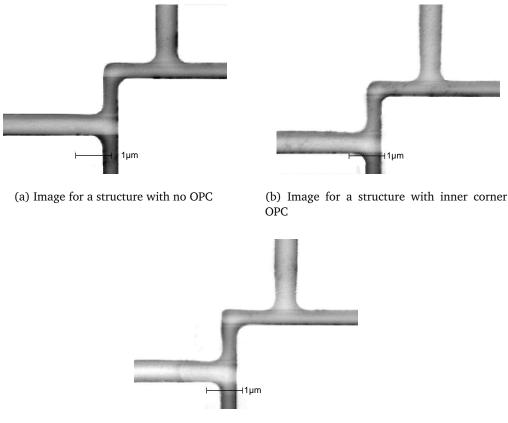

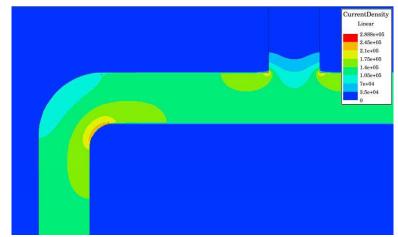

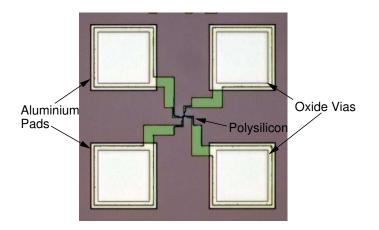

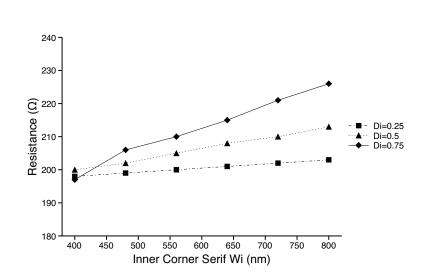

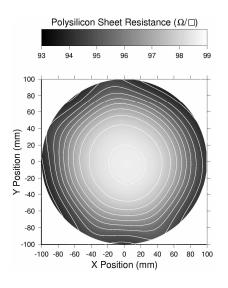

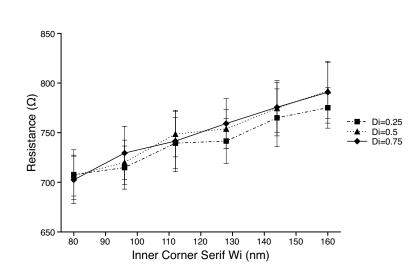

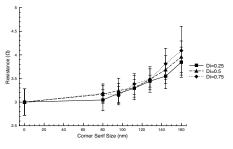

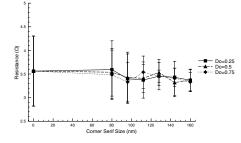

| 6.8<br>6.9 | Comparison of simulation results and on-mask measurements                                                                                                                                                      | 112<br>113 |

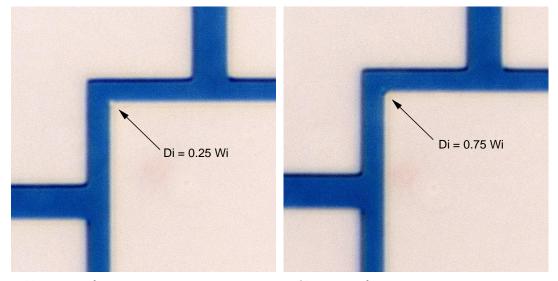

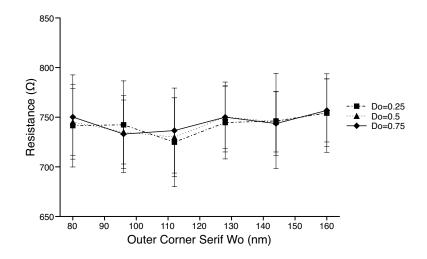

|            | Electrical measurement results obtained from binary mask (MSN6754)<br>Optical images for corner structures with inner OPC features only                                                                        | 113        |

|            | Optical images for structures with inner corner serifs                                                                                                                                                         | 115        |

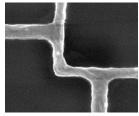

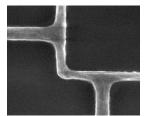

|            | $5\mu m \times 5\mu m$ AFM scans of corner structures with inner and outer OPC                                                                                                                                 | 110        |

|            | features.                                                                                                                                                                                                      | 115        |

| 6.13       | FIB images for structures with inner corner serifs                                                                                                                                                             | 116        |

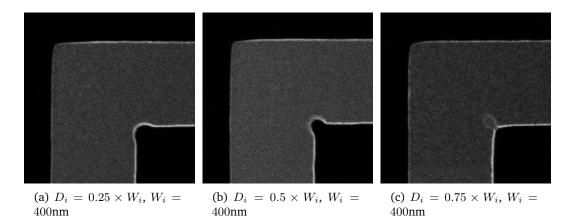

|            | Fabrication process steps for on-wafer test structures                                                                                                                                                         | 117        |

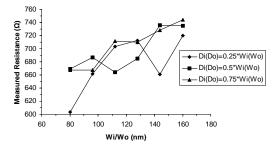

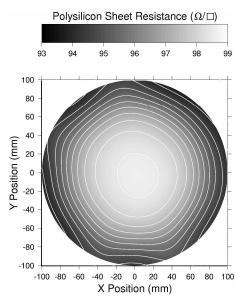

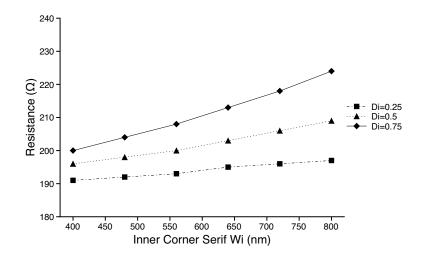

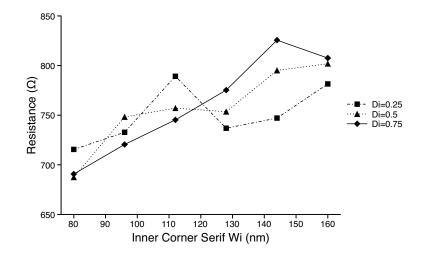

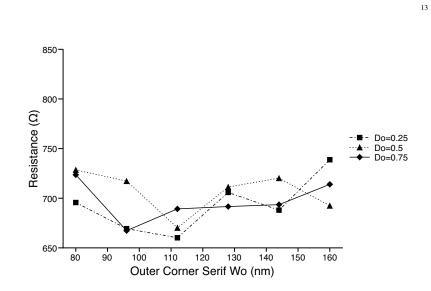

| 6.15       | Resistance measurements for on-wafer structures with inner and outer                                                                                                                                           |            |

| 6.16       | corner OPC arrangements                                                                                                                                                                                        | 118        |

|            | test structures.                                                                                                                                                                                               | 119        |

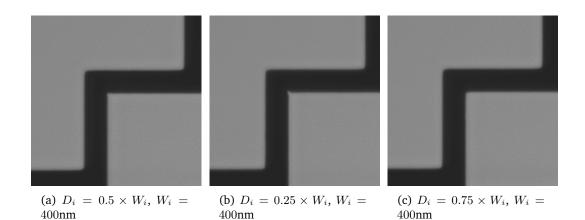

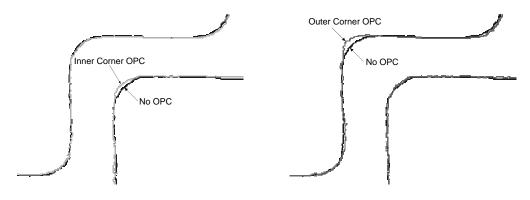

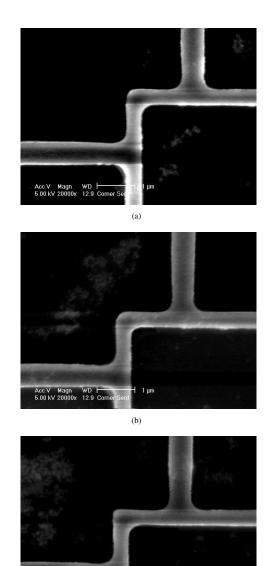

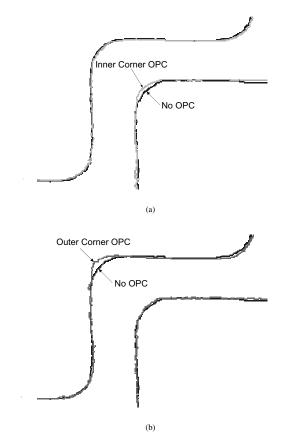

| 6.17       | SEM images of structures with different OPC arrangements                                                                                                                                                       | 120        |

| 6.18       | Overlaid shapes of structures with different OPC arrangements                                                                                                                                                  | 121        |

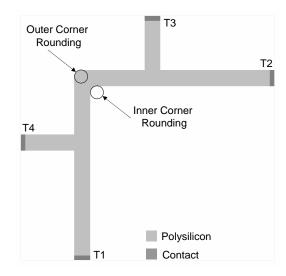

| 6.19       | Layout of structure used to simulate the effect of inner and outer corner                                                                                                                                      | 122        |

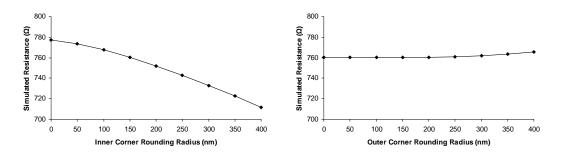

| 6 20       | rounding                                                                                                                                                                                                       | 122        |

| 0.20       | arrangements                                                                                                                                                                                                   | 122        |

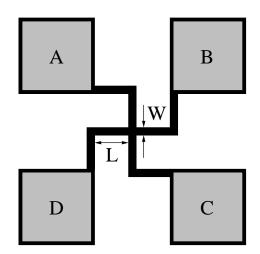

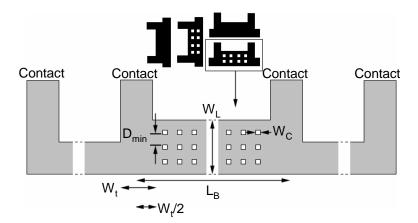

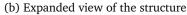

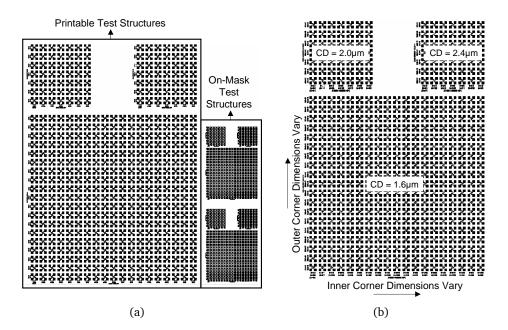

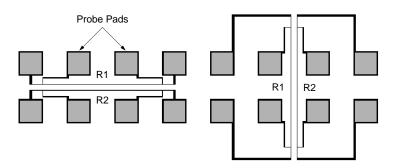

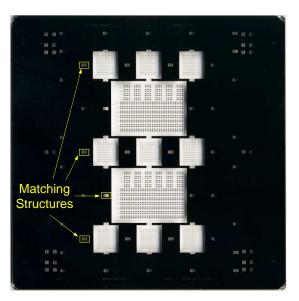

| 7.1        | Layout of mismatch bride resistor test structures.                                                                                                                                                             | 126        |

| 7.2<br>7.3 | Layout of a photomask with the matching structures highlighted<br>Measurement of a Kelvin bridge resistor forming the half section of a                                                                        | 127        |

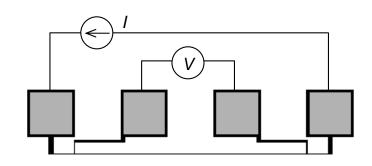

| 7.5        | horizontal matching structure                                                                                                                                                                                  | 128        |

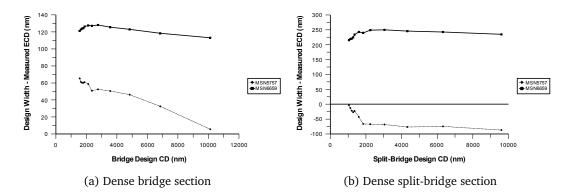

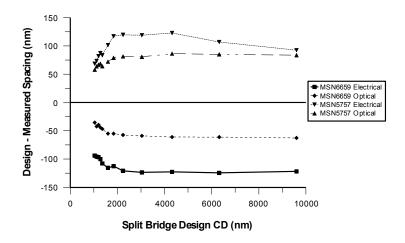

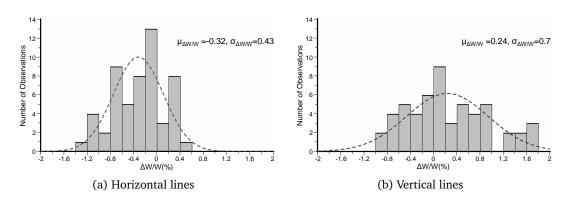

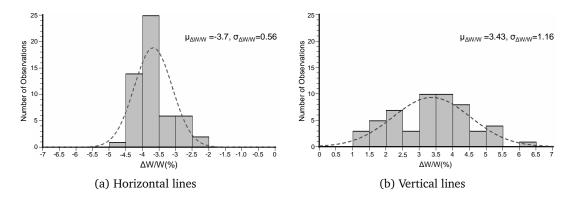

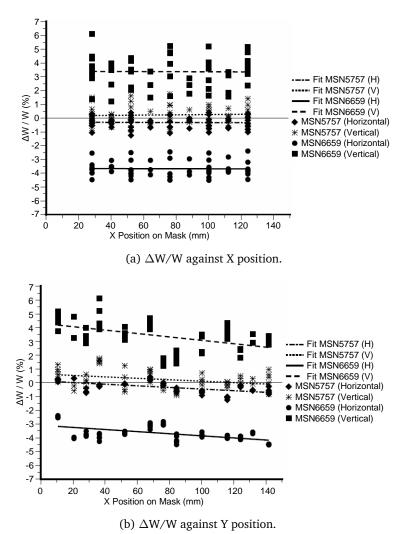

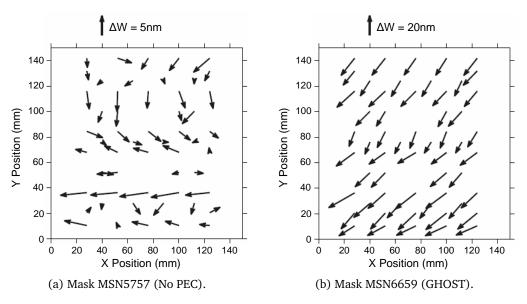

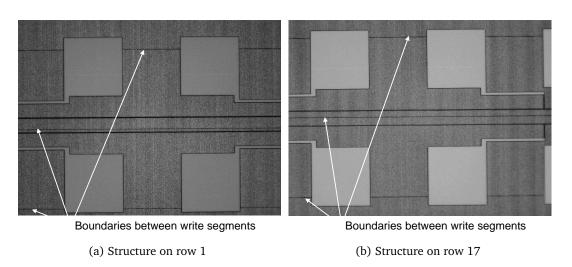

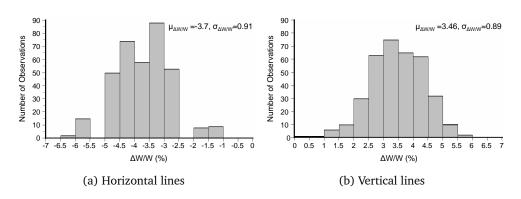

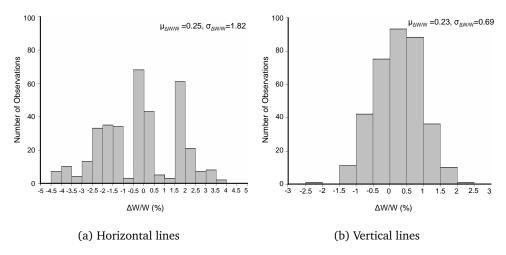

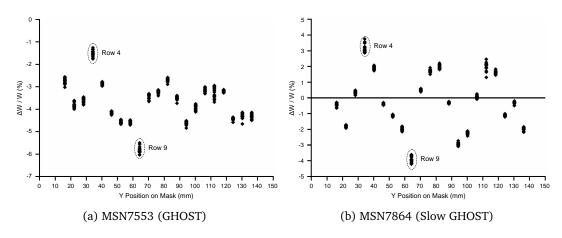

| 7.4        | Histograms of CD mismatch results for MSN5757 (No PEC).                                                                                                                                                        |            |

|            |                                                                                                                                                                                                                | -          |

| 29                                 |

|------------------------------------|

|                                    |

| 30                                 |

|                                    |

| 31                                 |

| 32                                 |

|                                    |

| 33                                 |

| 33                                 |

| 36                                 |

| 37                                 |

|                                    |

| 38                                 |

|                                    |

| 38                                 |

| 39                                 |

|                                    |

| 40                                 |

|                                    |

| 41                                 |

| 42                                 |

| 42                                 |

| 43                                 |

|                                    |

| 44                                 |

| 45                                 |

| 45                                 |

| 46                                 |

|                                    |

|                                    |

| 59                                 |

|                                    |

| 60                                 |

|                                    |

| 51                                 |

|                                    |

| 62                                 |

|                                    |

| 63                                 |

|                                    |

| 64                                 |

|                                    |

| 65                                 |

|                                    |

|                                    |

| 66                                 |

| 56                                 |

| 33 3333 3 33 4 4444 4444 5 6 6 6 6 |

| A.10 Reprint of paper submitted for publication to the IEEE Transactions on  |     |

|------------------------------------------------------------------------------|-----|

| Semiconductor Manufacturing, page 3                                          | 168 |

| A.11 Reprint of paper submitted for publication to the IEEE Transactions on  |     |

| Semiconductor Manufacturing, page 4                                          | 169 |

| A.12 Reprint of paper submitted for publication to the IEEE Transactions on  |     |

| Semiconductor Manufacturing, page 5                                          | 170 |

| A.13 Reprint of paper submitted for publication to the IEEE Transactions on  |     |

| Semiconductor Manufacturing, page 6                                          | 171 |

| A.14 Reprint of paper submitted for publication to the IEEE Transactions on  |     |

| Semiconductor Manufacturing, page 7                                          | 172 |

| A.15 Reprint of paper submitted for publication to the IEEE Transactions on  |     |

| Semiconductor Manufacturing, page 8                                          | 173 |

| A.16 Reprint of paper submitted for publication to the IEEE Transactions on  |     |

| Semiconductor Manufacturing, page 9                                          | 174 |

| A.17 Reprint of paper submitted for publication to the IEEE Transactions on  |     |

| Semiconductor Manufacturing, page 10                                         | 175 |

| A.18 Reprint of paper submitted for publication to the IEEE Transactions on  |     |

| Semiconductor Manufacturing, page 11                                         | 176 |

| A.19 Reprint of paper submitted for publication to the IEEE Transactions on  |     |

| Semiconductor Manufacturing, page 12                                         | 177 |

| A.20 Reprint of paper submitted for publication to the IEEE Transactions on  |     |

| Semiconductor Manufacturing, page 13                                         | 178 |

| A.21 Reprint of paper submitted for publication to the IEEE Transactions on  |     |

| Semiconductor Manufacturing, page 14                                         | 179 |

| A.22 Reprint of paper submitted for publication to the IEEE Transactions on  |     |

| Semiconductor Manufacturing, page 15                                         | 180 |

| A.23 Reprint of paper submitted for publication to the IEEE Transactions on  |     |

| Semiconductor Manufacturing, page 16                                         | 181 |

| A.24 Reprint of paper submitted for publication to the IEEE Transactions on  |     |

| Semiconductor Manufacturing, page 17                                         | 182 |

| A.25 Reprint of paper submitted for publication to the IEEE Transactions on  |     |

| Semiconductor Manufacturing, page 18                                         | 183 |

| A.26 Reprint of four page abstract to be submitted to the IEEE International |     |

| Conference on Microelectronics Test Structures 2010, page 1                  | 184 |

| A.27 Reprint of four page abstract to be submitted to the IEEE International |     |

| Conference on Microelectronics Test Structures 2010, page 2                  | 185 |

| A.28 Reprint of four page abstract to be submitted to the IEEE International |     |

| Conference on Microelectronics Test Structures 2010, page 3                  | 186 |

| A.29 Reprint of four page abstract to be submitted to the IEEE International |     |

| Conference on Microelectronics Test Structures 2010, page 4                  | 187 |

## List of Tables

| Measured and target phase-shift trench depths and phase angles | 53                                                                                                                                                                                       |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                              |                                                                                                                                                                                          |

|                                                                | 134                                                                                                                                                                                      |

| 6 6                                                            | 134                                                                                                                                                                                      |

|                                                                |                                                                                                                                                                                          |

|                                                                | Measured and target phase-shift trench depths and phase angles<br>Measured linewidths at the top, middle and bottom of a feature<br>CD-AFM measurements made at five different positions |

# Acronyms and Abbreviations

| AFM     | Atomic Force Microscope                             |

|---------|-----------------------------------------------------|

| Alt-PSM | Alternating Aperture Phase-Shifting Mask            |

| ARC     | Anti-Reflective Coating                             |

| ArF     | Argon Fluoride                                      |

| Att-PSM | Attenuated Phase-Shifting Mask                      |

| BIM     | Binary Intensity Mask                               |

| BJT     | Bipolar Junction Transistor                         |

| BSE     | Back Scattered Electrons                            |

| CAD     | Computer Aided Design                               |

| CD-SEM  | Critical Dimension Scanning Electron Microscope     |

| CMOS    | Complementary Metal Oxide Semiconductor             |

| Cr      | Chrome                                              |

| CrON    | Chromium Oxynitride                                 |

| DC      | Direct Current                                      |

| DOF     | Depth of Focus                                      |

| DPT     | Double Patterning                                   |

| DUV     | Deep Ultra Violet                                   |

| ECD     | Electrical Critical Dimension                       |

| FIB     | Focused Ion Beam                                    |

| FPP     | Four Point Probe                                    |

| GIMP    | Gnu Image Manipulation Program                      |

| HP      | Half-Pitch                                          |

| IC      | Integrated Circuit                                  |

| ITRS    | International Technology Roadmap for Semiconductors |

| KrF     | Krypton Fluoride                                    |

| LSR     | Line to Space Ratio                                 |

| LWR     | Linewidth Roughness                                 |

| MEEF    | Mask Error Enhancement Factor                       |

| MG      | Mentor Graphics                                     |

|         |                                                     |

| MOS     | Metal Oxide Semiconductor                            |

|---------|------------------------------------------------------|

| MOSFET  | Metal Oxide Semiconductor Field-Effect Transistor    |

| NA      | Numerical Aperture                                   |

| NGL     | Next Generation Lithography                          |

| NIST    | National Institute of Standards and Technology       |

| OAI     | Off-Axis Illumination                                |

| OCD     | Optical Critical Dimension                           |

| OPC     | Optical Proximity Correction                         |

| OPE     | Optical Proximity Effects                            |

| PEC     | Proximity Effect Correction                          |

| PECVD   | Plasma-Enhanced Chemical Vapor Deposition            |

| POT     | Progressional Offset Technique                       |

| PSM     | Phase-Shifting Mask                                  |

| RET     | Resolution Enhancement Technique                     |

| RIE     | Reactive Ion Etch                                    |

| Rim-PSM | Rim Phase-Shifting Mask                              |

| SA-PSM  | Subresolution-Assisted Phase-Shifting Mask           |

| SCCDRM  | Single Crystal Critical Dimension Reference Material |

| SE      | Secondary Electrons                                  |

| SMU     | Source Monitor Unit                                  |

| SPM     | Scanning Probe Microscope                            |

| STM     | Scanning Tunneling Microscope                        |

| Utt-PSM | Unattenuated Phase-Shifting Mask                     |

|         |                                                      |

# Chapter 1 Introduction

#### 1.1 Background

The invention of the point-contact transistor at the Bell Telephone Laboratories by Bardeen and Brattain in 1947 signalled the beginning of the revolution in microelectronics technology. Around the same time Shockley developed the theory behind the bipolar junction transistor (BJT) as part of an effort to replace vacuum tubes with solid states devices [1]. In 1951 the first bipolar transistor was fabricated and by 1954 it was an essential component of the telephone system. The first commercial device to make use of the transistor was a hearing aid and soon after the first transistor radio was put on the market. Although small in size and low in power consumption, transistors were not small enough for some applications which required whole miniaturised circuits. The drive for miniaturisation was the impetus for the work which led to the invention of the integrated circuit (IC).

The concept of the integrated circuit was first conceived by radar scientist Dummer in 1952, who was however unsuccessful in building such a circuit in 1956. The first integrated circuits were manufactured independently by two scientists who were unaware of each other's activities. Kilby of Texas Instruments filed a patent for a "Solid Circuit" made of germanium in 1959, however it was Noyce of Fairchild Semiconductor who was first awarded a patent for a more complex "unitary circuit" made of silicon in 1961 [2]. While Kilby's idea to make all circuit components out of the same semiconductor material was groundbreaking, Noyce's circuit solved several practical problems that Kilby's concept had, mainly the problem of interconnecting all the parts on the chip. This made ICs more suitable for mass production. The first integrated circuits were oscillators and simple digital flip-flops using a few active devices along with the passive elements. By 1971 IC technology had advanced to the stage that the first microprocessor, the 4-bit Intel 4004, was fabricated with 2300 transistors [3].

Over the last 50 years ICs have evolved in terms of complexity and thus are often

classified by the number of transistors they contain. The first integrated circuits, called Small Scale Integration (SSI), were developed in the 1960s and contained only a few transistors numbering in the tens. SSI circuits were crucial to early aerospace projects. The next step in the development of ICs took place in the late 1960s and introduced devices which contained hundreds of transistors. Medium Scale Integration (MSI) circuits were attractive economically, as their fabrication cost was little more than SSI devices, but allowed more complex systems to be produced. Economic factors led to further development and Large Scale Integration (LSI) in the mid 1970s, with tens of thousands of transistors per chip. In the early 1980s circuits with hundreds of thousands of transistors were manufactured and the term Very Large Scale Integration (VLSI) was introduced. To reflect further growth of complexity the term Ultra Large Scale Integration (ULSI) was proposed for chips with more than 1 million transistors.

The growth of complexity of integrated circuits has been following a trend called "Moore's Law" which was described by Moore of Intel in 1965 and predicted that the number of devices in an integrated circuit would double each year [4]. In 1975 Moore amended the law to state that the numbers of transistors in an IC would double every 18 months [5]. Although Moore's law was initially made in the form of an observation and prediction, as it became more widely accepted, the more it served as a goal for an entire industry. This prediction has been successfully followed for the last 40 years and on average, the numbers of transistors in a state-of-the-art chip has doubled every 18 months.

Since the late 1960s, when circuits had linewidths of  $5\mu$ m, to now, where 65nm devices are in mass production, optical lithography has been a key technology for the advancement of IC fabrication and performance. Optical projection lithography is the process used to transfer the patterns that define integrated circuits through a mask onto semiconductor wafers. It is the first choice for mass production in the IC industry as no other technology has approached the same levels of cost-effectiveness and wafer throughput capability [6]. A lithographic system includes an exposure tool, masks, resist, and all of the processing steps required to accomplish pattern transfer.

Continued improvements have enabled the printing of ever finer features which in turn has allowed the industry to produce faster and more powerful semiconductor devices. The drive for smaller feature sizes has pushed optical lithography to its very limits. IBM has recently fabricated distinct and uniformly spaced, high quality line patterns only 29.9nm wide [7] and this is one of the many examples of recent advances. This is less than half the size of the 65nm features now in mass production and below the 32nm that the industry consensus held as the limit for photolithography techniques.

The continuous increase in IC performance has been achieved by the introduction of reduced exposure wavelengths and modern resolution enhancement techniques (RETs), which allow the printing of features much smaller than the wavelength of the exposure light [8]. The resolution of a photolithographic system can be enhanced by methods such as off-axis illumination (OAI) [9], pupil filtering [10, 11] and as devices in the 45nm technology node move from development into production, techniques such as immersion lithography [12–14] and double patterning (DPT) [15] become essential.

Of significant importance is the manufacture of photomasks that are capable of perfectly replicating the artwork generated by the IC designer. To enable the latest technologies to be resolved on wafer, advances in photomask resolution enhancement technologies such as optical proximity correction (OPC) and the various types of phase-shifting masks (PSMs) [16, 17], have been introduced into mask making. In addition the manufacturing process has to result in zero defects and this is a significant challenge with tremendous pricing pressures. This is reflected in the cost of a set of leading-edge mask plates, which is now considerably more than \$1M [18, 19]. Therefore, it comes as no surprise that the ability to accurately test and characterise advanced photomasks, for the purposes of process verification and control, is becoming increasingly important. The increases in complexity and cost have placed a premium on mask metrology, which now has to keep up with the strict requirements introduced by the IC industry.

Mask metrology is a challenging issue for the semiconductor industry and an absolute key if the industry is to successfully follow the requirements for future technologies, as charted by the International Technology Roadmap for Semiconductors (ITRS) [20]. It is an industrial process worth over \$2.5B worldwide that underpins the >\$200B integrated circuit industry, which is solely becoming an area of significant economic and social consequence.

Traditional methods for mask metrology and verification use optical [21, 22], critical dimension scanning electron microscopy (CD-SEM) [23–25] and atomic force

microscope (AFM) measurement systems [26–29]. The progress made in optics fabrication could not have been achieved with out access to appropriate metrology tools. However, in addition to the challenges involved in fabricating advanced masks, the manufacturers are now struggling to characterise them. The established techniques not only require expensive equipment well in the region of \$1.5M, but as dimensions continue to rapidly reduce, they are being stretched to their limits and are unable to meet the requirements for accurate and repeatable results. Optical distortions can confound optical measurements, while charging on fused silica photomasks can adversely affect CD-SEM results. In addition, both of these techniques are effectively subjective and require careful calibration of the measurement tool for meaningful results. On the other hand a high resolution CD-AFM can be an excellent means for CD calibration but it suffers from low throughput which makes it unsuitable for a process inspection environment.

Much of the work in this thesis addresses the challenges involved with the measurement and characterisation of advanced photomasks. These challenges have provided the incentives for the development of alternative measurement approaches. The thesis investigates a novel application of electrical test structures and measurement techniques which are adapted for on-mask metrology. Test structures and measurements techniques were originally developed to characterise the IC manufacturing process and their integration onto advanced masks can take full advantage of the considerable developments of the last 30 years.

While enhancement techniques such as phase-shifting masks are essential to achieve the sub-wavelength dimensions required in advanced CMOS (Complementary Metal Oxide Semiconductor) technologies, approximately 85% [30–33] of all masks currently manufactured are binary and binary masks typically form up to 85-90% of the mask set used in an advanced process. Obviously the electrical measurement approach requires a conductive film such as the chrome used in standard binary photomasks or for example PSMs with the alternating design. The most commonly used form of phase-related, reticle enhancement technology used at present, the attenuated phase-shift [34], or chromeless type masks are not suitable for direct electrical probing. However, the process used to create these masks typically uses a chrome layer as a hard mask during patterning and etching of the phase-shifting features and it should be possible to measure them before the chrome layer is removed. Therefore, the proposed electrical techniques are ideally suited for process control measurements on the most widely used photomask types.

A problem with the inclusion of electrical test structures is that they take up valuable space on a mask which could be occupied by the design of the product. For the purposes of photomask characterisation, the full area of a mask plate can be covered by test patterns, as the development engineers attempt to characterise the fabrication A major attraction to this is that similar structures can be printed and process. measured on-wafer using the same electrical techniques for the characterisation of the photolithographic process. However, in a mature/production process the photomask will include only the minimum number of structures required for the purposes of process verification. The test sites can be located outside the circuit area with the alignment marks, the maskmakers identification marks and other process control/inspection structures. One other issue associated with the adoption of electrical test structures for mask metrology is the perception that the photomask could be damaged during probing in the measurement. In comparison to aluminium, the chromium light blocking film on a standard photomask is extremely scratch resistant and robust, so the probe pads are left unmarked after probing. Delicate ICs on expensive wafers are routinely probe tested as a standard part of the IC manufacturing process and so there is little doubt that masks, which are much less susceptible to probe damage, can be characterised electrically without damage.

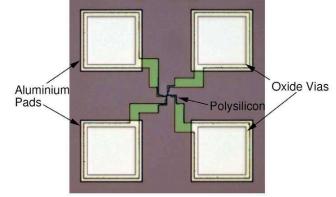

Electrical test structures are connected to the test equipment through metal probe pads (normally 80-120 $\mu$ m square) which are typically arranged in a 2×N array where the pitch of the pads is twice their width. The probe pads can be contacted either with manual probe needles controlled by micro-manipulators or through a probe card. Probe cards are generally used with a probe station which can step the probe tips between test structures. This is integrated with computer controlled measurement equipment to create a complete test system.

Electrical dimensional metrology has the potential to meet the requirements set by the photomask industry whilst it remains a highly repeatable, fast, cost-effective and robust technique. The proposed technique not only can provide an alternative measurement approach, but will also act as a reference point with which to compare traditional measurement methods. In addition, it can provide feedback to help create better calibrations for the large number of metrology tools already supporting photomask manufacture and underpin the requirements for developing CD standards for maskmaking. Finally, the same measurement techniques can be applied equally to on-mask and on-chip features, providing a transferable metrology from mask to wafer.

#### **1.2** Thesis Structure

This section presents a description of the thesis structure and briefly outlines the contents of the chapters which follow.

**Chapter 2: Background.** The fundamentals of optical lithography and resolution enhancement techniques are presented. Special attention is being paid to the operating principles, the correction and enhancement procedures of photomasks. The measurement of sheet resistance and linewidth is described. Traditional linewidth measurement methods are presented, but the main focus is on electrical techniques. Examples from the literature of electrical test structures for the measurement of other important maskmaking parameters are examined.

**Chapter 3: Linewidth Measurement Techniques for the Characterisation of Binary and Alternating Aperture Phase-Shifting Masks.** This chapter briefly describes the earlier work done on electrical test structures for the measurement of photomasks. It then presents the on-mask structure design, fabrication and measurement results from electrical and optical techniques on binary and alternating aperture phase-shifting masks. The advantages and limitations of these mask characterisation techniques are shown.

**Chapter 4: Development of Electrical On-Mask CD Test Structures Based On Optical Metrology Features.** The first part of this chapter investigates the adaptation of standard optical metrology features to electrical equivalents. A prototype mask with the electrical designs is fabricated and the features are electrically and optically measured to investigate the fabrication process and compare the metrology techniques. The second part examines potential electrical on-mask test structures through 2-D and 3-D computer simulations for the characterisation of other important parameters. **Chapter 5: Comparison of Metrology Techniques for the Characterisation of Advanced Photomask Processes.** The first section of this chapter describes the design and fabrication of binary on-mask test structures on a plate written using an e-beam proximity correction technique. Results from electrical and optical measurements made on the structures examine the effectiveness of the correction method and further evaluate the performance of the metrology techniques. The second section presents a comparison of CD-AFM measurements made with a state-of-the-art tool, fully calibrated to a reference standard, with electrical and optical metrology results. An analysis of the uncertainties involved in the different measurement techniques is also presented.

**Chapter 6: Electrical Test Structures for the Characterisation of Optical Proximity Correction.** This chapter begins by examining the use of an on-mask resistive test structure for the characterisation of a corner type of optical proximity correction, using simulations and measurements on a prototype photomask. The photomask is then used to print structures on wafer. Simulations and measurements at wafer level are also performed and a comparison between the two is presented.

**Chapter 7: Matching Resistor Test Structures for the Characterisation of the Photomask Fabrication Process.** This chapter presents the design and fabrication of electrical on-mask test structures for the characterisation of the dimensional mismatch between closely spaced photomask features. A number of photomasks were patterned with these structures and the results have been analysed to obtain information about the capability of the mask making process.

**Chapter 8: Conclusions and Future Work.** In this chapter the conclusions drawn from the work reported in the preceding chapters are reviewed. Suggestions for future work on the topics covered in this thesis are also made.

# Chapter 2 Background

#### 2.1 Optical Lithography Fundamentals

Optical lithography has been the key technology for semiconductor patterning since the early days of integrated circuit production. Although predictions of its demise have been made on many occasions, new techniques have pushed optical lithography beyond the generally accepted theoretical resolution limits. These enhancements have significantly extended the manufacturing capabilities of the IC industry. However, optical lithography does have real physical and economic barriers and an accurate estimation of these limitations is essential for extending its life and preparing for the transition to next generation lithography (NGL) techniques in the future.

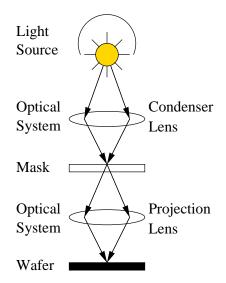

Optical lithography is essentially a photographic process by which a light-sensitive polymer called photoresist is exposed through a master pattern called photomask and developed to form 2D patterns on a substrate [35]. A schematic of an optical projection tool where an image of the photomask is projected onto the substrate is presented in figure 2.1.

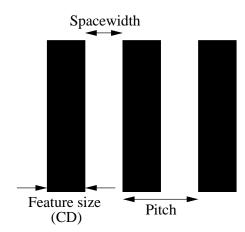

The resolution limit in optical lithography differs depending on the type of feature being printed. The two types of resolution that are used by the IC industry are the minimum printable pitch and feature size (see figure 2.2 [36]). Although related, they have different limits defined by the physics of lithography and different implications in terms of device performance [35]. Feature size resolution determines the characteristics and performance of a transistor. Pitch resolution (the smallest printable linewidth and spacewidth pair) determines how closely transistors can be packed in a chip.

The imaging performance of a photolithographic system is determined by the Rayleigh resolution criterion, developed more than 100 years ago by Lord Rayleigh to describe the diffraction limits of telescopes. It describes the ability of an imaging system to resolve two closely spaced objects and in optical lithography this essentially defines the

Figure 2.1: Diagram of an optical projection lithography "stepper" tool used for exposing semiconductor wafers.

Figure 2.2: Diagram of a line and space pattern.

smallest printable half-pitch (HP). According to Rayleigh's criterion the resolution (*R*) of an optical projection lithography system can be obtained by

$$R = k_1 \frac{\lambda}{NA} \tag{2.1}$$

where ( $\lambda$ ) is the wavelength of the imaging light and (NA) is the numerical aperture of the imagining lens system used in the lithographic process (NA =  $\sin\theta$  is the maximum diffraction angle that a projection lens can capture and use for image formation). The Rayleigh factor ( $k_1$ ) is a constant which depends on the details of the imaging process, such as the configuration of the illumination system and the optical parameters of

the photoresist. Ultimately  $k_1$  can be as low as 0.25 (the fundamental limit) but this requires tremendous effort and is not achievable with conventional lithography.