## The Limits of a Decoupled Out-of-Order Superscalar Architecture

Graham P. Jones

Doctor of Philosophy University of Edinburgh 1999

### Declaration

I declare that this thesis was composed by myself and that the work contained therein is my own, except where explicitly stated otherwise in the text.

(Graham P. Jones)

#### Abstract

This thesis presents a study into a technique for improving performance in outof-order superscalar architectures. It identifies three technological trends limiting superscalar performance; they are the increasing cost of a main memory access, control dependencies and the greater hardware complexity of out-of-order execution.

Decoupling is a technique that can provide higher performance through the mechanism of dynamically reordering, asynchronous instruction streams. It offers the capability to improve ILP, through effective latency hiding and dynamic scheduling, and to reduce hardware complexity, through decentralised logic. This thesis evaluates this capability, by investigating the effectiveness of decoupled out-of-order superscalar architectures.

This thesis identifies the degree to which operations can reorder (the degree of reordering) as the critical dimension to an out-of-order superscalar architecture. It investigates the effectiveness of decoupling by focusing on those design issues that determine the degree of reordering, and relaxes all other architectural constraints. This approach allows us to establish the limitations of decoupled out-of-order superscalar architectures.

This thesis shows that a decoupled architecture, through its dynamically reordering instructions windows, provides a possible solution to the problem of latency hiding and issue logic complexity. This thesis demonstrate that for large memory latencies, a decoupled architecture with 2 instruction streams is less sensitive to increases in memory latency than a conventional single stream superscalar architecture. The results also show that for memory latencies greater than 20 cycles, a decoupled architecture can achieve a higher speedup than a conventional superscalar architecture with twice the individual window sizes of a decoupled unit. An explanation for this effect is provided through the concept of the Effective Window Size.

The thesis also investigates a 3-stream decoupled superscalar architecture, that provides dedicated hardware support for resolving control dependencies. The results show that for the partitioning algorithm used in this thesis, the load balancing is poor and the extra hardware resources are under utilised. For this reason the majority of the thesis focuses on a 2 stream decoupled architecture.

### Acknowledgements

I dedicate this thesis to my wife Kate, our children Jack, Joseph and Rebecca. I would also like to dedicate it to my mother and father, and to Kate's parents. Unfortunately, this work does not do justice to the time and inconvience it has caused them over the years; in this sense the thesis fails, in that their efforts cannot be read in the lines.

I would especially like to thank my supervisor, Nigel Topham, without whose advice and support these acknowledgements would never have been written.

I would also like thank my fellow office mate and friend, Steve Cussack for helping me stay sane during the long days in 3419. In all that time I can not recall a cross word coming between us.

# Table of Contents

| List of Tables |                                                               |    |

|----------------|---------------------------------------------------------------|----|

| List of        | Figures                                                       | vi |

| Chapt          | er 1 Introduction                                             | 1  |

| 1.1            | Thesis methodology                                            | 3  |

| 1.2            | Thesis structure                                              | 4  |

| Chapt          | er 2 Background                                               | 7  |

| 2.1            | A typical superscalar architecture                            | 8  |

| 2.2            | Latency hiding technology                                     | 9  |

| 2.3            | Increasing the degree of reordering                           | 11 |

| 2.4            | Reducing reordering logic complexity                          | 13 |

| 2.5            | The decoupling paradigm                                       | 14 |

| 2.6            | Original contribution                                         | 16 |

| 2.7            | Summary                                                       | 17 |

| Chapte         | er 3 Three Superscalar Architecture Models                    | 18 |

| 3.1            | Multi-streamed decoupled architectures                        | 19 |

| 3.2            | A single stream superscalar architecture                      | 20 |

| 3.3            | The memory system                                             | 21 |

| 3.4            | The design issues for the reordering factors                  | 22 |

| Chapte         | er 4 Description of the Simulation technique                  | 25 |

| 4.1            | Experimental framework                                        | 26 |

|                | 4.1.1 FOrtran Code Annotation Tool (FOCAT)                    | 26 |

|                | 4.1.2 Modelling EnviroNment for Decoupled Out-of-order Super- |    |

|                | scalar Architectures (MENDOSA)                                | 31 |

| 4.2            | Advantages of the simulation technique                        | 32 |

| 4.3            | Disadvantages of the simulation technique                     | 33 |

| 4.4            | Benchmark programs                                            | 34 |

| Chapte | er 5 The Limits of Decoupling                            | 36 |

|--------|----------------------------------------------------------|----|

| 5.1    | A model for latency hiding                               | 37 |

|        | 5.1.1 Write back (WB) cache                              | 39 |

|        | 5.1.2 Write through (WT) cache                           | 39 |

|        | 5.1.3 $\beta$ for the decoupled model                    | 40 |

| 5.2    | Simulation technique                                     | 42 |

| 5.3    | Experimental results                                     | 43 |

|        | 5.3.1 Bandwidth filtering                                | 46 |

|        | 5.3.2 Comparisons of latency hiding efficiency           | 48 |

|        | 5.3.3 Decoupled fetch schemes                            | 50 |

|        | 5.3.4 Temporal behaviour of $\beta^{read}$               | 50 |

| 5.4    | Implications of the experimental findings                | 51 |

| 5.5    | Summary                                                  | 53 |

| Chapt  | er 6 Determining Balanced Configurations for a Decoupled |    |

| Arc    | chitecture                                               | 55 |

| 6.1    | Simulation technique                                     | 55 |

| 6.2    | Experimental results                                     | 56 |

|        | 6.2.1 Estimating good issue width configurations         | 57 |

|        | 6.2.2 IPCR and latency hiding effectiveness              | 58 |

| 6.3    | Summary                                                  | 61 |

| Chapt  | er'7 Design Issues for a Decoupled Architecture          | 67 |

| 7.1    | Design issues                                            | 67 |

| 7.2    | Simulation technique                                     | 70 |

| 7.3    | Experiment results                                       | 71 |

|        | 7.3.1 Data dependency and renaming                       | 72 |

|        | 7.3.2 Memory reordering and barriers                     | 74 |

|        | 7.3.3 Individual program behaviour                       | 76 |

| 7.4    | Design implications for the dual stream system           | 81 |

|        | 7.4.1 Out-of-order decoupled loads                       | 81 |

|        | 7.4.2 Out-of-order decoupled stores                      | 83 |

| 7.5    | Summary                                                  | 84 |

| Chapt  | er 8 Reducing Hardware Complexity through Decoupling     | 86 |

| 8.1    | The effective single window                              | 88 |

| 8.2    | Simulation technique                                     | 88 |

| 8.3    | Issue width                                              | 89 |

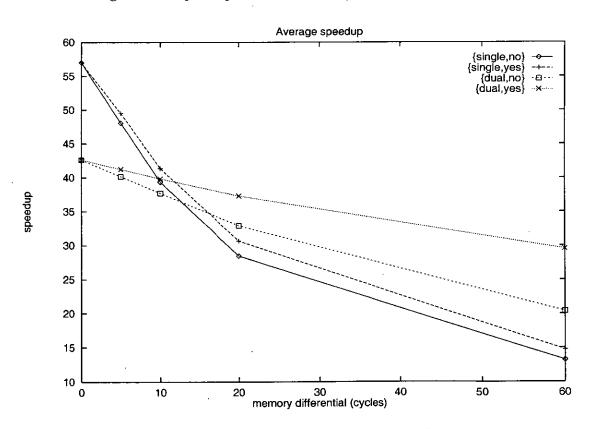

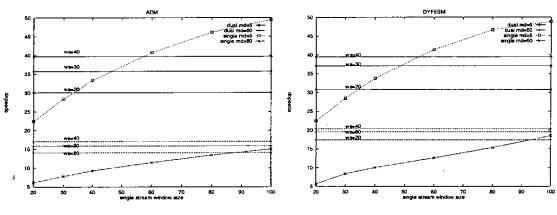

| 8.4     | Windo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | w size and memory latency                          | 93   |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------|

| 8.5     | Reorde                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ering scope and instruction window                 | 98   |

| 8.6     | Summ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ary                                                | 100  |

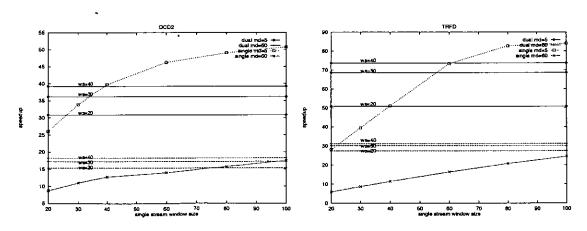

| Chapte  | er 9 R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | educing Hardware Complexity: a Sensitivity Analysi | s104 |

| 9.1     | Experi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | mental results                                     | 104  |

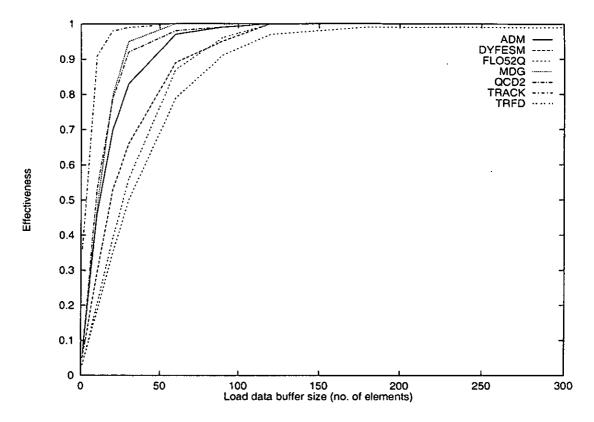

|         | 9.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | The effect of load data buffer capacity            | 105  |

|         | 9.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | The effect of code expansion                       | 107  |

|         | 9.1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Effective communication bandwidth                  | 109  |

|         | 9.1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | The effect of memory reordering                    | 110  |

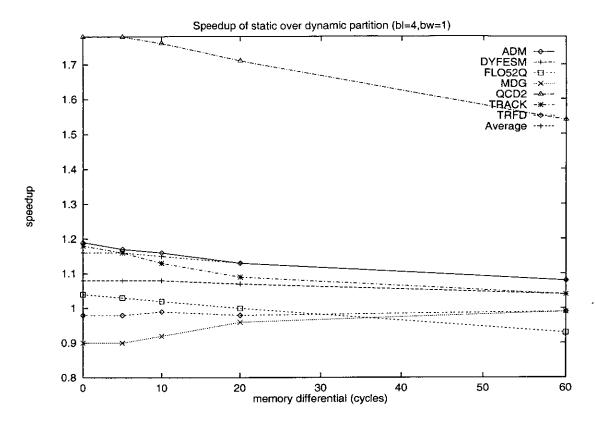

|         | 9.1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Dynamic versus static code partitioning            | 111  |

|         | 9.1.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Speedup and latency hiding effectiveness           | 112  |

| 9.2     | Summa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ary                                                | 113  |

| Chapte  | 3.6 Summary100Apter 9 Reducing Hardware Complexity: a Sensitivity Analysis 1049.1 Experimental results1049.1.1 The effect of load data buffer capacity1059.1.2 The effect of code expansion1079.1.3 Effective communication bandwidth1099.1.4 The effect of memory reordering1109.1.5 Dynamic versus static code partitioning1119.1.6 Speedup and latency hiding effectiveness1129.2 Summary113112 Supter 10 Conclusions1200.1 Thesis findings1200.2 Related work1220.3 Future work12512 Sendix A Program Characteristics12712 Sendix B Derivation of $\beta$ for Two Cache Models129 |                                                    |      |

| 10.1    | Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | findings                                           | 120  |

| 10.2    | Relate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | d work                                             | 122  |

| 10.3    | Future                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | work                                               | 125  |

| Appen   | dix A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Program Characteristics                            | 127  |

| Appen   | dix B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Derivation of $\beta$ for Two Cache Models         | 129  |

| B.1     | $\beta$ for a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | write back cache                                   | 129  |

| B.2     | $\beta$ for a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | write through cache                                | 130  |

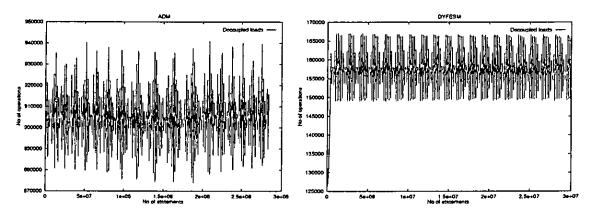

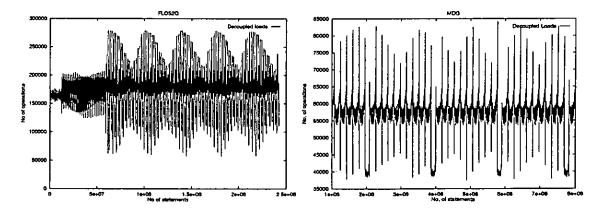

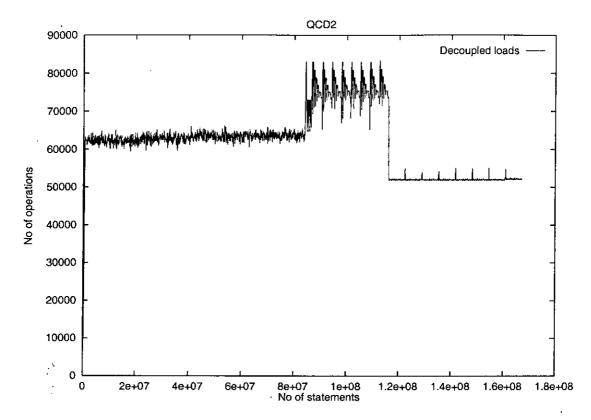

| Appen   | dix C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Simulation Sampling                                | 131  |

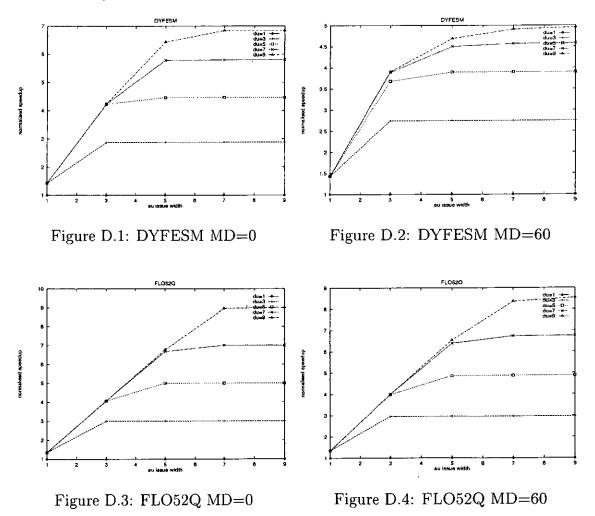

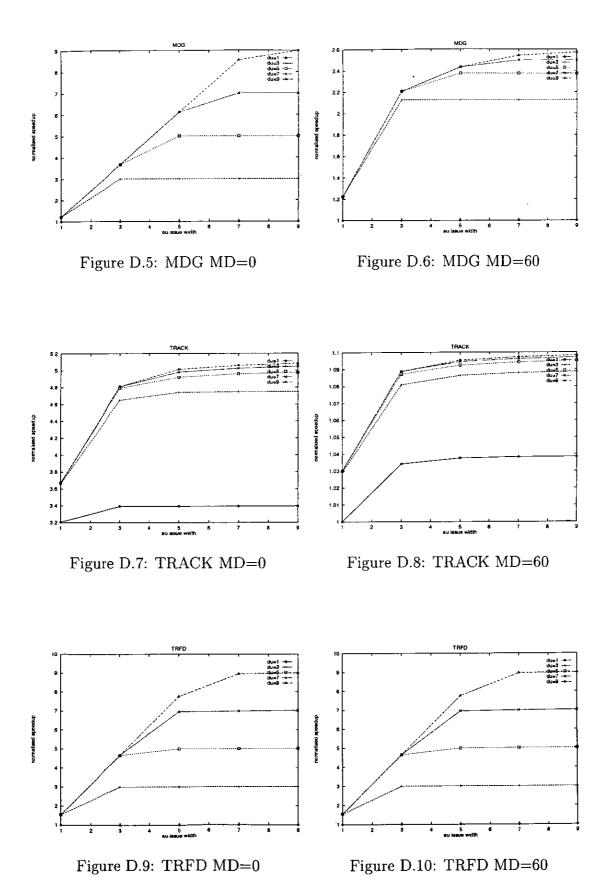

| Appen   | dix D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Balanced Configurations : Additional Data          | 136  |

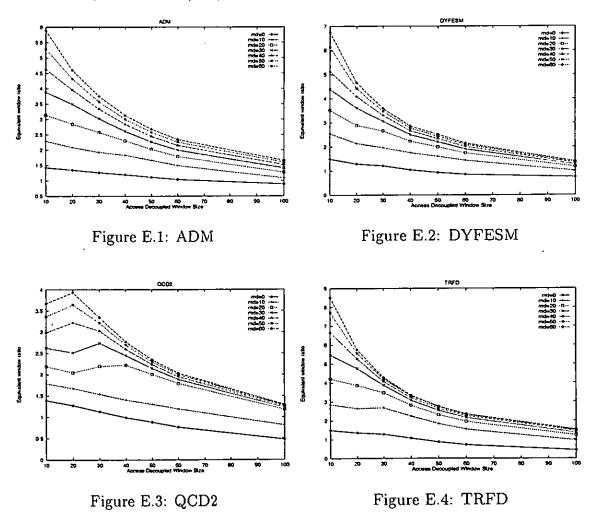

| Appen   | dix E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Reducing Hardware Complexity: Additional Data      | 138  |

| Append  | dix F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Sensitivity Analysis : Additional Data             | 139  |

| Bibliog | raphy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                    | 140  |

# List of Tables

| 3.1 | Design issues for out-of-order machines                             | 23  |

|-----|---------------------------------------------------------------------|-----|

| 4.1 | Critical path times for different annotation tools                  | 32  |

| 4.2 | Benchmark programs from PERFECT club suite                          | 35  |

| 5.1 | Characteristics of the benchmark programs                           | 43  |

| 5.2 | Decoupled loads for benchmark programs                              | 48  |

| 5.3 | $\beta$ versus WB cache hit rate for different block size           | 49  |

| 5.4 | $eta^{read}$ for EIF and LIF schemes                                | 51  |

| 5.5 | Program characteristics                                             | 54  |

| 6.1 | Configurations for the 2-stream decoupled architecture              | 56  |

| 6.2 | Program IPCR                                                        | 57  |

| 6.3 | IPC and LHE for best configurations of AU and DU with and           |     |

|     | without the optimised decoupled memory                              | 66  |

| 7.1 | Configurations for the 2-stream decoupled architecture              | 71  |

| 7.2 | IPC and LHE for different reordering scope; dependency analysis     |     |

|     | is perfect with renaming                                            | 80  |

| 8.1 | Comparison of single and dual instruction streams when RS=3         | 93  |

| 8.2 | Comparison of single and dual instruction streams when RS=6         | 93  |

| 8.3 | Average window size when RS=6                                       | 94  |

| 8.4 | The effect of code expansion on speedup when RS=6                   | 94  |

| 8.5 | IPC and LHE for varying window size (WS)                            | 103 |

| 9.1 | Base-line: architectural configurations for the dual and single     |     |

|     | stream systems                                                      | 105 |

| 9.2 | Sensitivity analysis: architectural configurations for the dual and |     |

|     | single stream systems                                               | 106 |

| 9.3 | Occupancy of the decoupled memory and prefetch buffer               | 107 |

| Q 4 | Effectiveness of various load data buffer capacities                | 108 |

|   | 9.5 | Equivalent single window ratio without code expansion 117              |

|---|-----|------------------------------------------------------------------------|

|   | 9.6 | Equivalent single window ratio with code expansion                     |

|   | 9.7 | Equivalent single window ratio for various bus and memory latencies118 |

|   | 9.8 | Speedup of the dual over the single stream system for various access   |

|   |     | ordering schemes                                                       |

|   | A.1 | Percentage increase in the number of operations executed by the        |

|   |     | dual stream system                                                     |

|   | A.2 | Operation breakdown as percentages                                     |

|   | A.3 | Absolute count of operations ( $\times 10^6$ )                         |

|   | C.1 | Program sampled sections                                               |

|   | C.2 | Program characteristics for different length of simulation (F=full,    |

| • |     | S=sampled, C=continuous)                                               |

|   |     |                                                                        |

.

<u>;</u>

# List of Figures

| 2.1  | Model of execution for a typical superscalar machine            | 9  |

|------|-----------------------------------------------------------------|----|

| 2.2  | Predicted average memory access times for a range of hit ratios |    |

|      | (expressed as percentages)                                      | 10 |

| 3.1  | A 3-stream decoupled architecture                               | 21 |

| 3.2  | A 2-stream decoupled architecture                               | 22 |

| 3.3  | Model of the basic decoupled memory                             | 22 |

| 3.4  | Model of the optimised decoupled memory                         | 23 |

| 3.5  | Single window superscalar machine                               | 24 |

| 4.1  | Basic statement                                                 | 28 |

| 4.2  | After annotation                                                | 28 |

| 4.3  | Code annotation for superscalar architectures                   | 30 |

| 4.4  | Code without WAR dependency                                     | 34 |

| 4.5  | Code with WAR dependency                                        | 34 |

| 5.1  | $\chi$ memory system                                            | 38 |

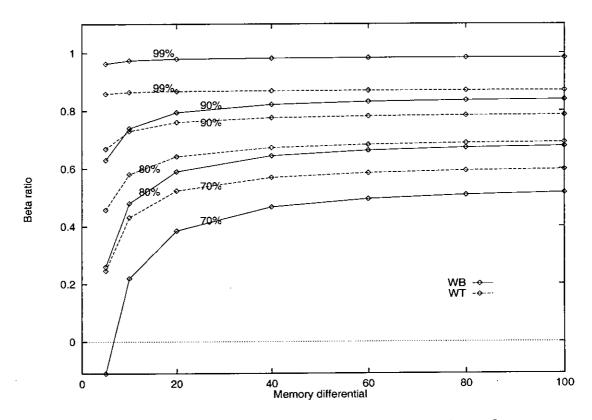

| 5.2  | $\beta$ for WT and WB cache, for various values of $\alpha$     | 40 |

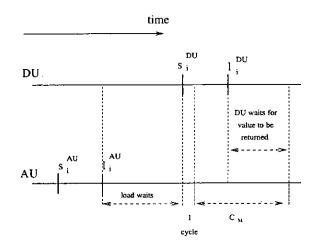

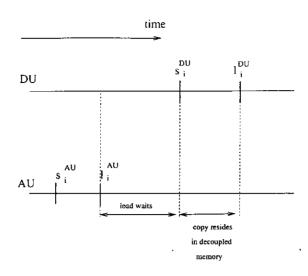

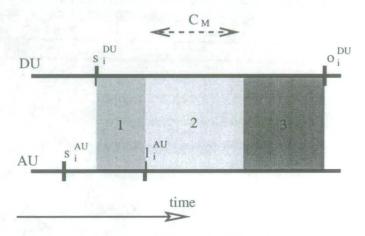

| 5.3, | Time lines for the $i$ th decoupled load during execution       | 42 |

| 5.4  | Basic decoupled memory model; FP latency = 1                    | 44 |

| 5.5  | Optimised decoupled memory; FP latency = 1 cycle                | 45 |

| 5.6  | Optimised decoupled memory; FP latency=5 cycles                 | 46 |

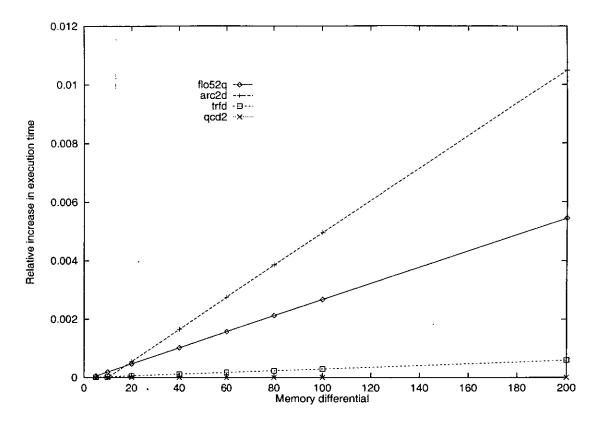

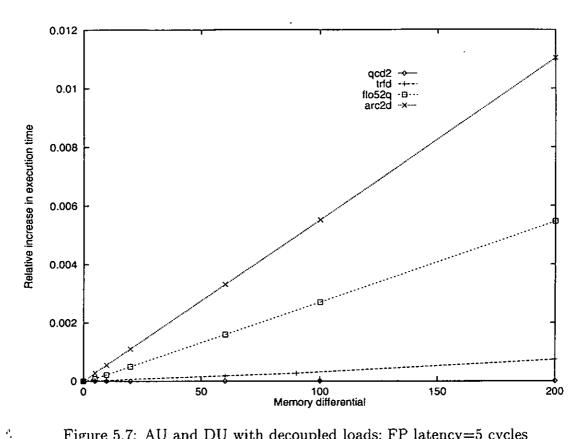

| 5.7  | AU and DU with decoupled loads; FP latency=5 cycles             | 47 |

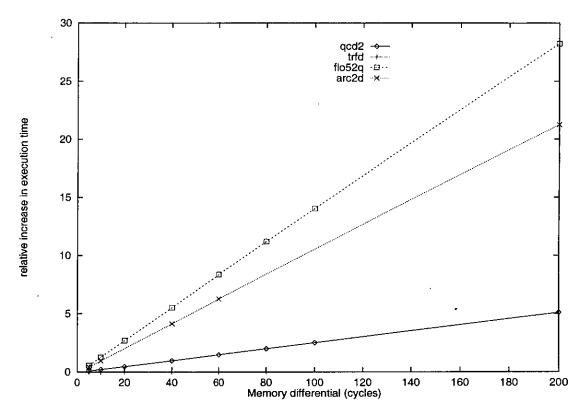

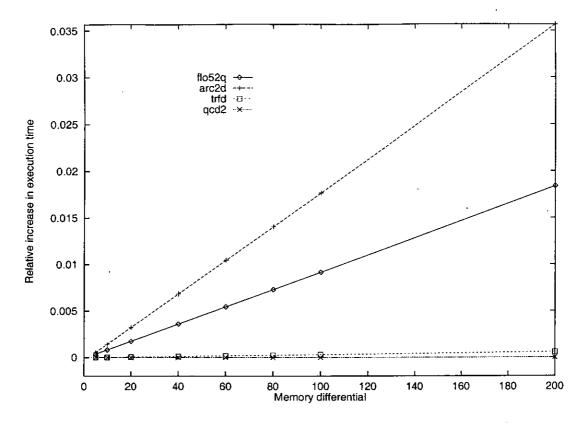

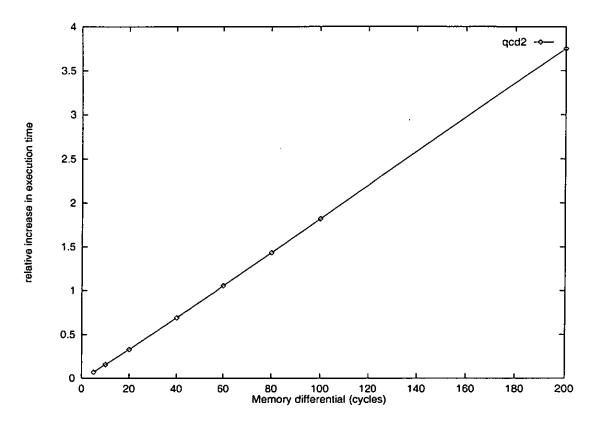

| 5.8  | Relative increase in execution time with no CU for QCD2         | 48 |

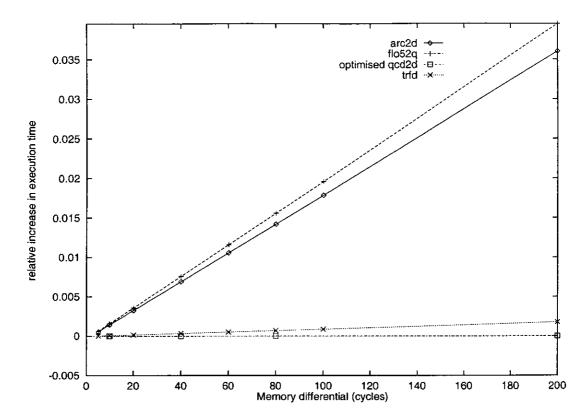

| 5.9  | Relative increase in execution time with no CU                  | 49 |

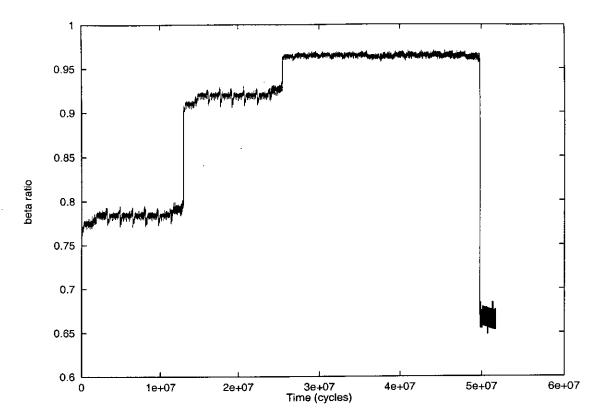

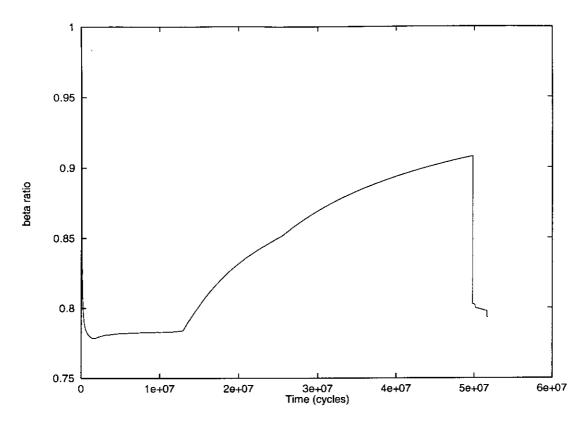

| 5.10 | · ·                                                             | 52 |

| 5.11 | QCD2 : cumulative variation of $\beta^{read}$                   | 53 |

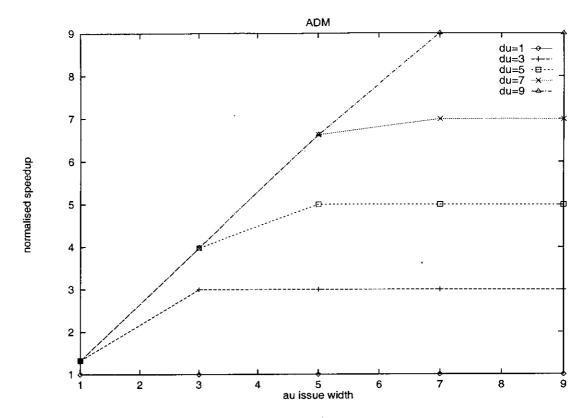

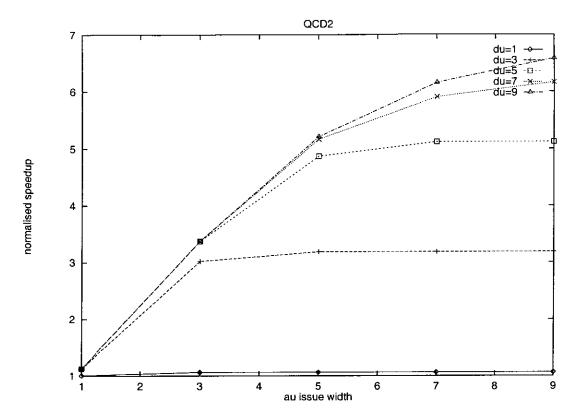

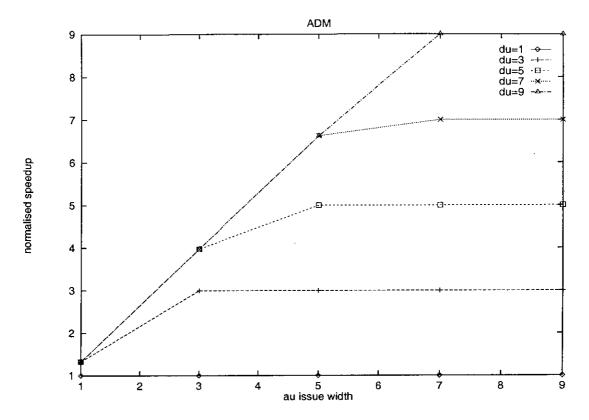

| 6.1  | ADM normalised speedup for MD=0                                 | 60 |

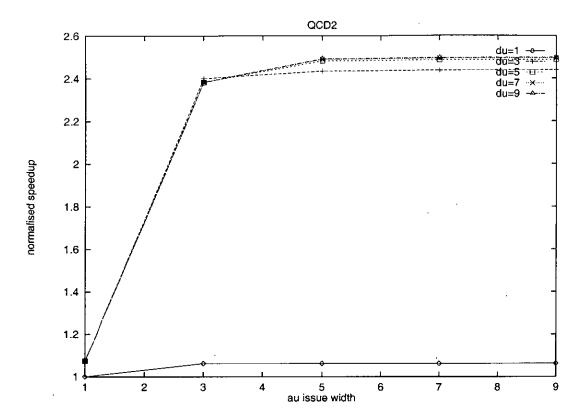

| 6.2  | QCD2 normalised speedup for MD=0                                | 61 |

| 6.3  | ADM normalised speedup for MD=60 cycles                         | 62 |

| 6.4 | QCD2 normalised speedup for MD=60 cycles                           | 63  |

|-----|--------------------------------------------------------------------|-----|

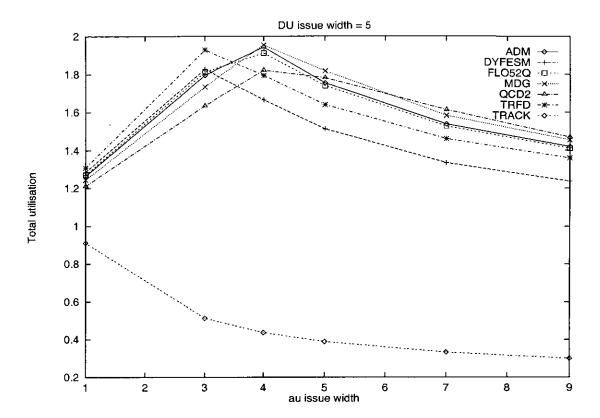

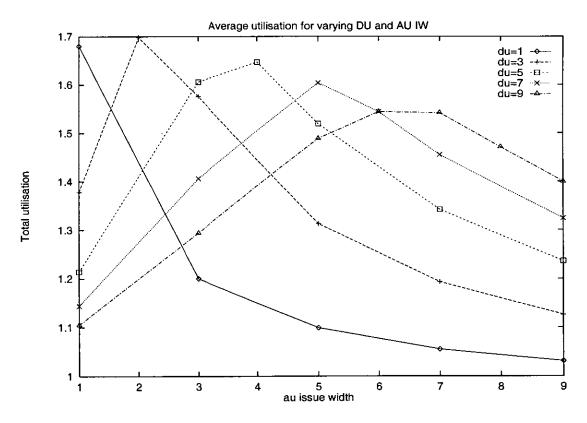

| 6.5 | Issue width utilisation when DU IW = $5 \dots \dots \dots$         | 64  |

| 6.6 | Average IW utilisation                                             | 64  |

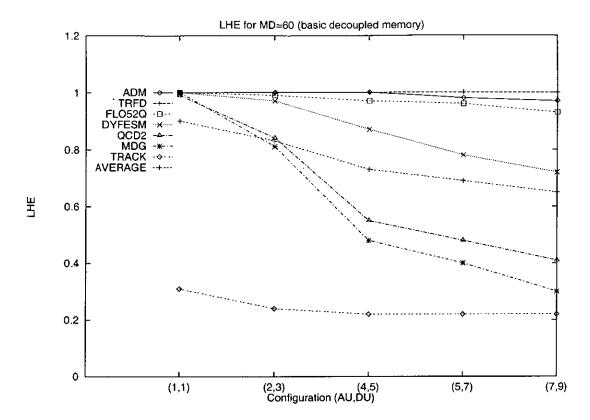

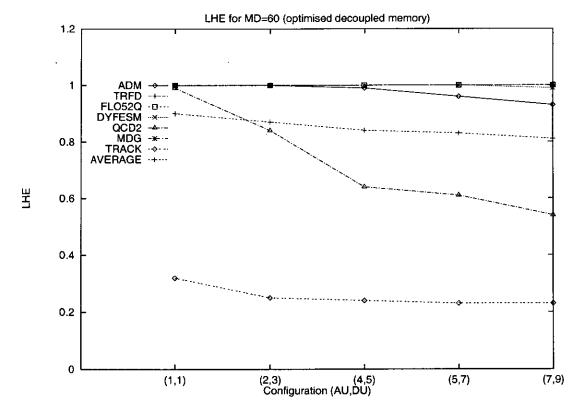

| 6.7 | Latency hiding effectiveness for the basic decoupled memory (MD=60 |     |

|     | cycles)                                                            | 65  |

| 6.8 | Latency hiding effectiveness for the optimised decoupled memory    |     |

|     | (MD=60 cycles)                                                     | 65  |

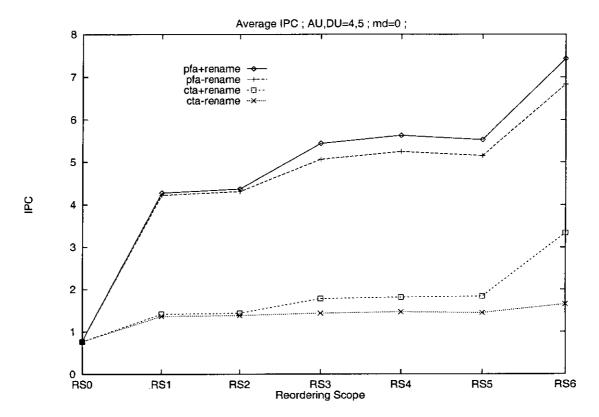

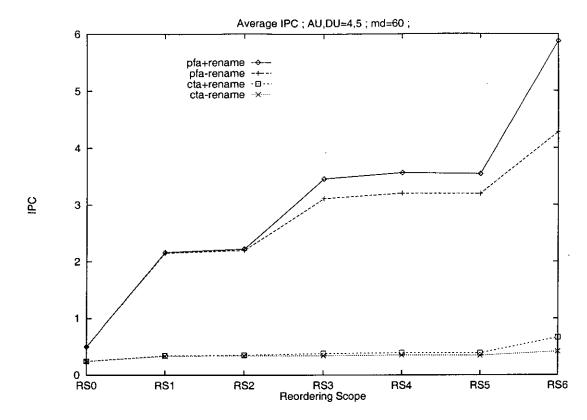

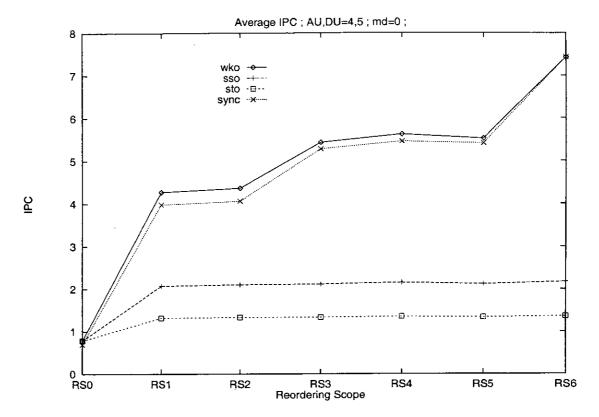

| 7.1 | Average IPC when MD=0                                              | 74  |

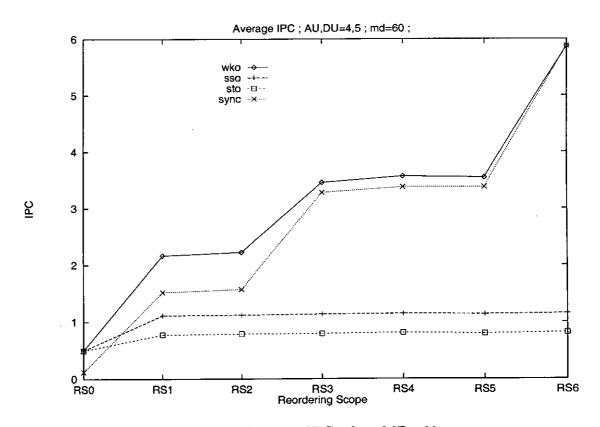

| 7.2 | Average IPC when MD=60                                             | 75  |

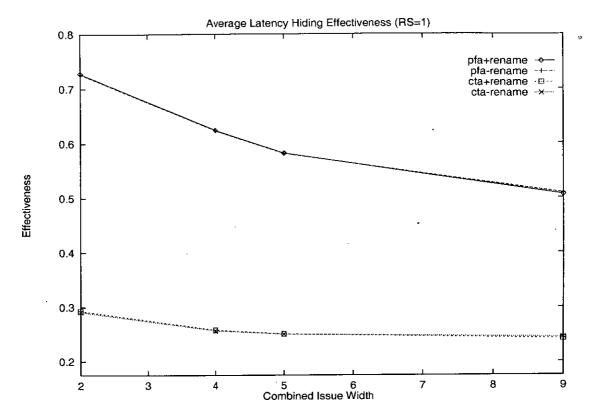

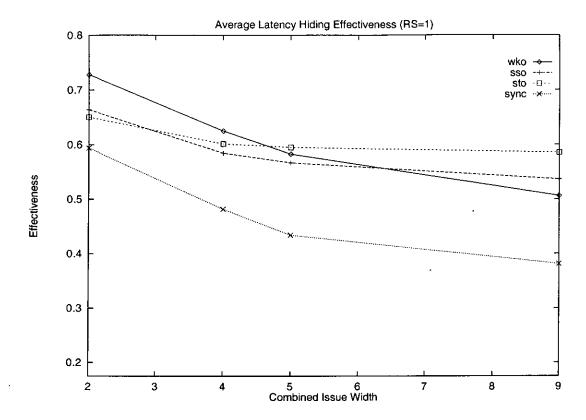

| 7.3 | Average Latency Hiding Effectiveness (RS=1)                        | 76  |

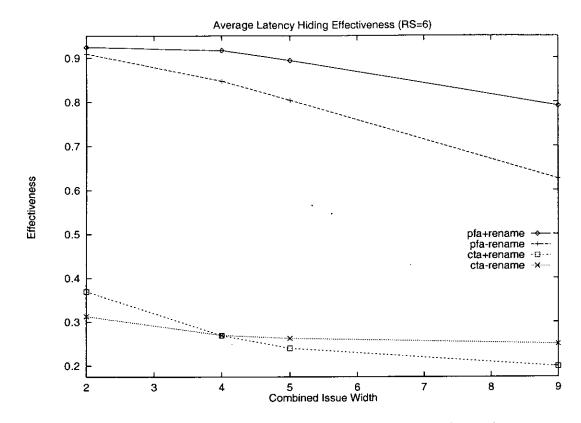

| 7.4 | Average Latency Hiding Effectiveness (RS=6)                        | 77  |

| 7.5 | Average IPC when MD=0                                              | 78  |

| 7.6 | Average IPC when MD=60                                             | 78  |

| 7.7 | Average Latency Hiding Effectiveness (RS=1)                        | 79  |

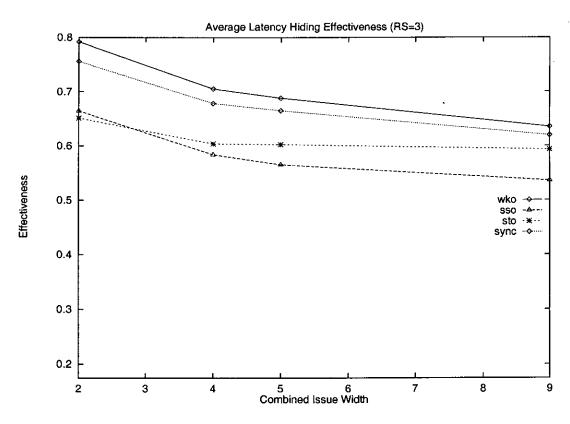

| 7.8 | Average Latency Hiding Effectiveness (RS=3)                        | 79  |

| 7.9 | Support for out of order memory access in a dual stream system .   | 83  |

| 8.1 | Effective single window                                            | 89  |

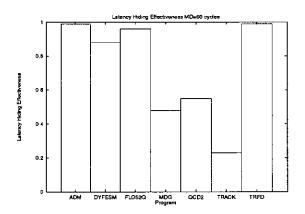

| 8.2 | Latency hiding effectiveness MD=60 cycles                          | 94  |

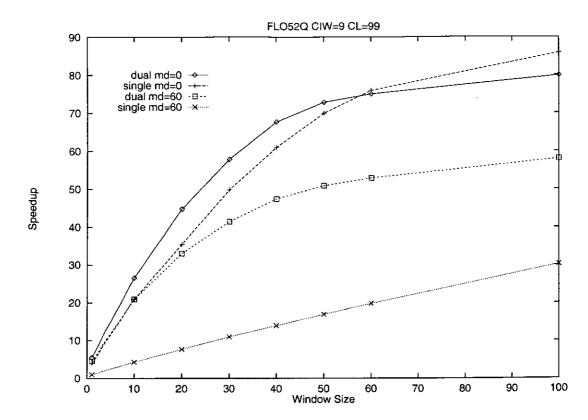

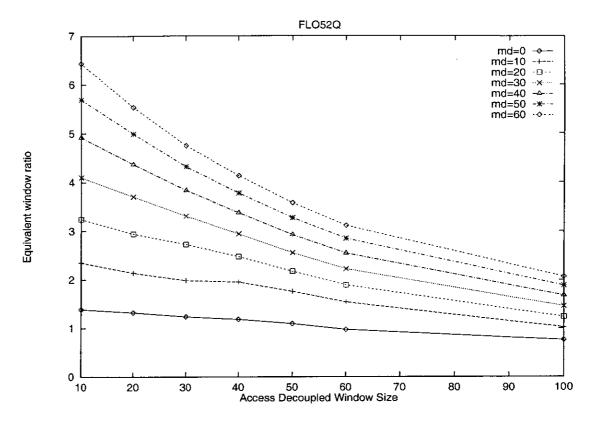

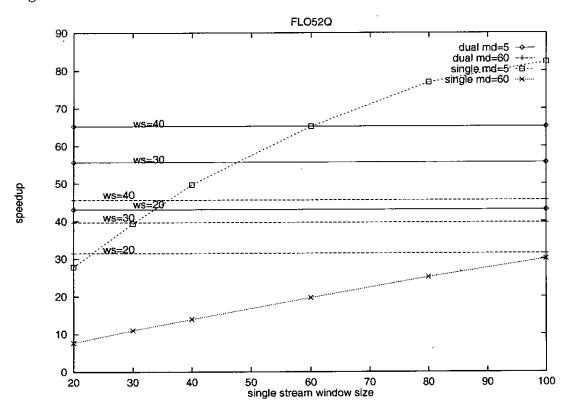

| 8.3 | Speedup of FLO52Q for varying window size                          | 97  |

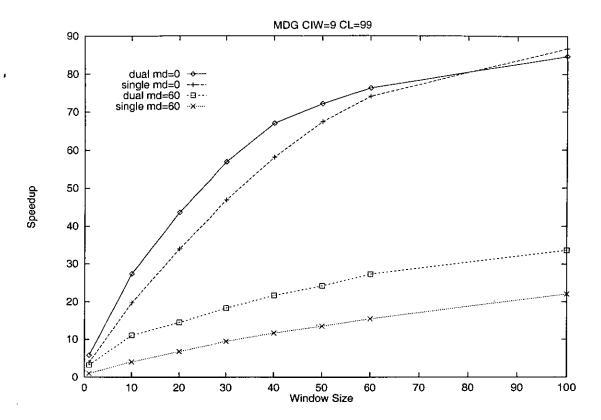

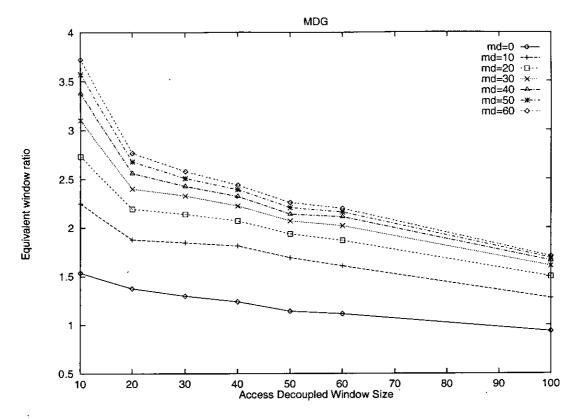

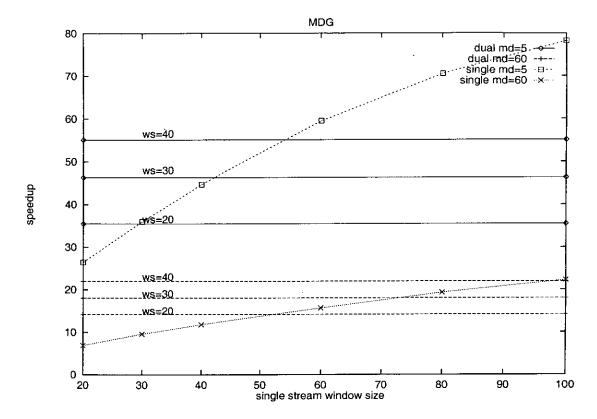

| 8.4 | Speedup of MDG for varying window size                             | 98  |

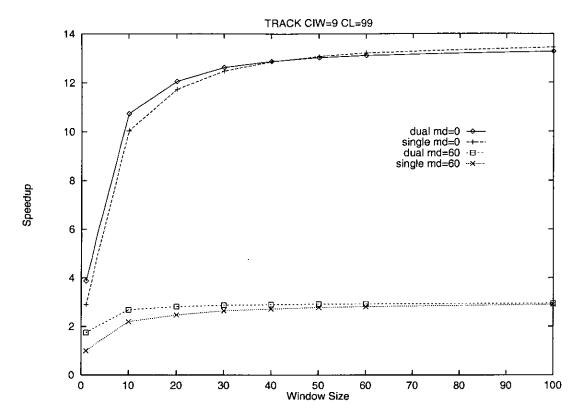

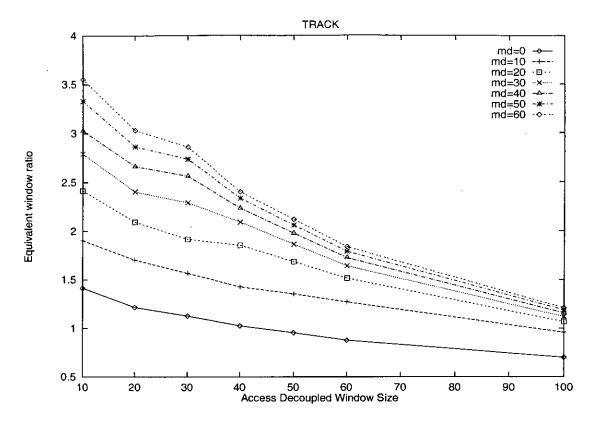

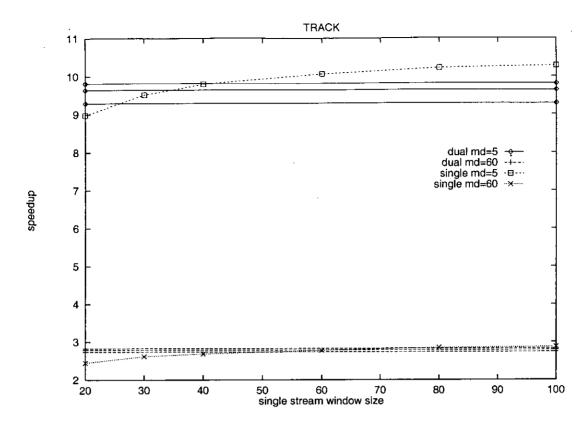

| 8.5 | Speedup of TRACK for varying window size                           | 99  |

| 8.6 | Equivalent window ratio for FLO52Q                                 | 100 |

| 8.7 | Equivalent window ratio for MDG                                    | 101 |

| 8.8 | Equivalent window ratio for TRACK                                  | 102 |

| 9.1 |                                                                    | 108 |

| 9.2 |                                                                    | 113 |

| 9.3 | MDG speedup                                                        | 114 |

| 9.4 | TRACK speedup                                                      | 115 |

| 9.5 | Speedup of static over dynamic code partition                      | 116 |

| 9.6 | Average speedup of baseline dual and single stream systems         | 116 |

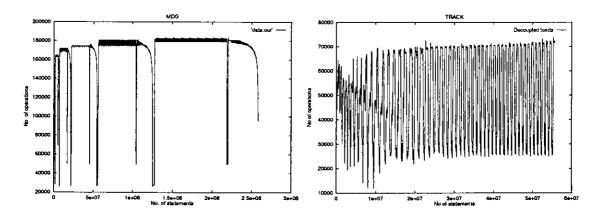

| C.1 | 1                                                                  | 132 |

| C.2 |                                                                    | 132 |

| C.3 | FLO52Q profile of load operations                                  | 132 |

| C.4 | MDG profile of load operations                                     | 132 |

| C 5 | OCD2 profile of load operations                                    | 133 |

| C.6  | TRFD profile of load operations  | 133 |

|------|----------------------------------|-----|

| C.7  | TRACK profile of load operations | 133 |

| D.1  | DYFESM MD=0                      | 136 |

| D.2  | DYFESM MD=60                     | 136 |

| D.3  | FLO52Q MD=0                      | 136 |

| D.4  | FLO52Q MD=60                     | 136 |

| D.5  | MDG MD=0                         | 137 |

| D.6  | MDG MD=60                        | 137 |

| D.7  | TRACK MD=0                       | 137 |

| D.8  | TRACK MD=60                      | 137 |

| D.9  | TRFD MD=0                        | 137 |

| D.10 | TRFD MD=60                       | 137 |

| E.1  | ADM                              | 138 |

| E.2  | DYFESM                           | 138 |

| E.3  | QCD2                             | 138 |

| E.4  | TRFD                             | 138 |

| F.1  | ADM speedup                      | 139 |

| F.2  | DYFESM speedup                   | 139 |

| F.3  | QCD2 speedup                     | 139 |

| F.4  | TRFD speedup                     | 139 |

### Chapter 1

#### Introduction

This thesis presents a study into a technique for improving instruction level parallelism (ILP) and reducing the hardware complexity of out-of-order execution in high performance superscalar architectures. Since the mid-80's we have witnessed a rapid increase in processor performance (on average about 35% per year [45]). To sustain this rate of increase will require innovative techniques capable of detecting greater levels of parallelism and hiding the effect of deleterious technological trends. This thesis explores the application of one such technique, the decoupling paradigm, in superscalar architectures. Decoupling is a technique that provides high ILP and latency tolerance through dynamically reordering, asynchronous instruction streams.

This chapter identifies the technological trends that represent major bottlenecks to superscalar performance. It describes how decoupling could be a potential solution to these problems and outlines the methodology used in the thesis.

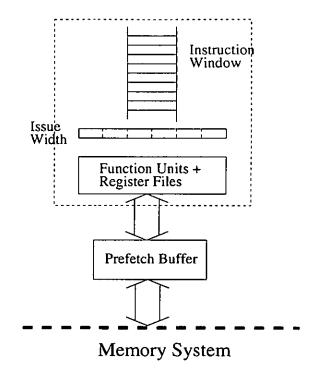

The current generation of superscalar architectures, the Alpha 21264 [42],PA-RISC [27],PowerPC 604 [76],SPARC-64 [85],MIPS R10000 [91], all achieve high performance through a hardware scheduling mechanism. This mechanism dynamically resolves data dependencies, issues operations out-of-order and executes multiple operations per cycle. Decoded instructions are placed in a buffer known as the instruction issue window, where they wait until their operands become available. Arbitration logic then selects and issues ready operations to the function units. The maximum number of instructions issued per cycle is known as the issue width; an architecture with an issue width of size n is also referred to as an n-way superscalar machine. To increase ILP in future machines will require larger instruction issue widths and instruction issue windows; this will need greater hardware complexity and increase the length of paths critical to the processor clock speed [64]. To resolve this problem designers are considering the use of decentralised control logic to increase ILP without effecting clock speed [39, 42, 75, 51, 81]. However

this will not solve some of the other bottlenecks to higher ILP.

The exponentially widening gap between memory and processor speeds means that the cost of a main memory access, in terms of missed instruction issue slots, is becoming more expensive. Wulf [89] has referred to the long term consequences of the speed disparity as hitting the memory wall; the point at which making the processor faster produces no performance gain because memory latencies will dominate. Under one scenario Wulf predicts this could occur shortly after the millennium. In addition, the wider issue widths of future superscalar architectures will place greater pressure on the memory system, requiring high sustained bandwidth and low access latency. For these reasons latency hiding techniques such as non-blocking loads [36], stream buffers [50, 77] and data prefetching [18, 16], will remain an important area for architectural research. In the future software and hardware technology will provide greater opportunities for these techniques to optimise memory accesses and hide latencies.

Another bottleneck to detecting parallelism is control dependencies [57]. These dependencies exist between conditional branches and those operations whose execution is dependent on their outcome. Control dependencies limit the amount of reordering that can take place between operations; in [45] the ratio of conditional statements to other operations for the SPEC92 benchmarks is given as 1 in 5 and 1 in 10 for integer and floating point programs, respectively. To resolve this problem designers have used techniques like loop unrolling, branch prediction and speculative execution.

This thesis postulates that the decoupling paradigm could offer a solution to the three fundamental problems:

- 1. high memory latencies.

- 2. control dependencies.

- 3. issue logic complexity.

The decoupling paradigm comprises two types of decoupling, access and control. Access decoupling [37, 72, 80, 90], the most familiar type of decoupling, is a latency hiding technique that partitions - statically or dynamically - a program into two instruction streams to aggressively prefetch data. One stream executed on an address unit (AU) fetches data for the second stream, executed on a data unit (DU). Memory accesses can then be pipelined to tolerate large memory latencies provided the two streams can decouple sufficiently. The decoupling of the streams is also referred to as the slippage [71].

In [9] it was suggested that the decoupling paradigm could be extended to hide the latency of control operations. This technique requires generating an additional stream of operations responsible for resolving control decisions ahead of the computation streams (AU and DU). This stream, loosely coupled from the computation streams, executes on a control unit (CU). This technique is referred to as control decoupling.

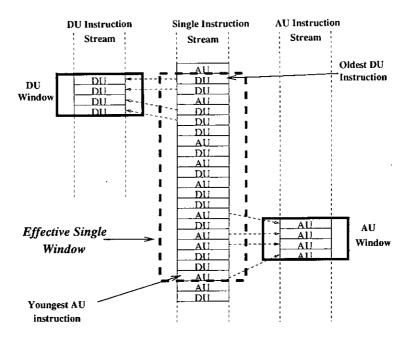

This thesis investigates, for the first time, a decoupled architecture in which the processing units are capable of n-way out-of-order superscalar execution. This means operation reordering can occur between (inter) and within (intra) instruction streams. The former is supported by decentralised control logic which allows the loosely coupled streams to slip relative to each other. The latter is supported through each unit having separate instruction windows and issue logic. Previous work on decoupling [81, 7, 37, 72] had only considered the use of single issue, inorder processing units with the compiler being responsible for generating compact schedules for each stream. In 1997, Tyson's thesis [81], suggested that future work should investigate the use of superscalar units in a decoupled machine. The major contribution of this thesis is to provide a detailed analysis of such an architecture.

#### 1.1 Thesis methodology

The most critical dimension to an out-of-order superscalar machine's performance is the degree to which operations can reorder. The degree of reordering is the distance, measured in numbers of instructions, between the oldest and earliest instruction visible to the issuing hardware. A machine with a large degree of reordering will have greater opportunities for detecting the independent operations necessary for parallel execution. The degree of reordering will determine the memory latency tolerance and the ILP for a given machine.

The approach adopted in this thesis focuses the experimental analysis on those factors that determine the degree of reordering, and hence the ILP, in an out-of-order superscalar machine. These factors are referred to as the reordering factors. Ultimately the ILP and performance is bounded by the algorithms used in the program; there is little short of restructuring the code that can be done to improve on this limit. The ability to reorder operations and hence increase ILP in an out-of-order superscalar architecture is primarily determined by:

1. The number of operations in the instruction window that are visible to the scheduling hardware. A large, densely packed window offers greater opportunities for lookahead, reordering and detecting the independent operations

necessary for parallel execution.

2. The data dependencies that exist between operations in the window. Data dependencies impose a partial ordering on the execution of operations. The importance of data dependencies has been well documented in the literature [65, 10]. Flow dependencies exist between operations that produce and consume data values. They represent the minimum ordering of the program that preserves program semantics. However false dependencies may be introduced because of the complexities of memory disambiguation for array variables [69].

An out-of-order decoupled architecture supports mechanisms for inter and intra stream reordering. This extra complexity introduces additional reordering factors that limit the slippage between streams. These factors are

- 1. The communication traffic and bandwidth between streams. Large levels of communication increase the data dependencies between streams, limiting slippage.

- 2. The frequency of synchronisation points, also known as loss of decouplings (LOD), between the instruction streams.

Other architectural issues, such as the size of the register file and the available memory bandwidth, are also important, but the reordering factors listed above will determine the maximum amount of ILP. As a limitation study, this thesis only considers those design issues that influence the reordering factors and relaxes all other architectural constraints <sup>1</sup>.

The advantage of this approach is that it allows the thesis to focus on the limits of the decoupling paradigm, rather than, as in previous studies [37, 72, 80, 90], a specific implementation of a decoupled architecture. A disadvantage of this approach is that it could be criticised for being too idealistic. However, given the scope of previous work on decoupling [37, 72, 80, 90] and the technological trends described above, the time is right for a quantitative analysis of the limits of decoupled out-of-order superscalar architectures.

#### 1.2 Thesis structure

The narrative of this thesis is presented in the following way. Chapter 2 provides a contextual background to the thesis, reviewing published work on superscalar

<sup>&</sup>lt;sup>1</sup>However, issue widths were constrained to within projected future values for next generation superscalar architectures.

architecture design and latency hiding technology. It also discusses previous work on decoupling and summarises the original contribution of this thesis.

Chapter 3 describes the three out-of-order superscalar architectures modelled in this thesis. The architectures are characterised by the number of instruction streams executed on the superscalar units. It describes a 3-stream and 2-stream decoupled architecture as well as a typical single stream architecture.

Chapter 4 provides a detailed description of the simulation technique, benchmark programs, software tools and experimental methodology. It explains how correctness of the tools was verified by comparing their output with a simulator used in previous published work. This chapter also describes the three architectures modelled in the thesis.

The remaining chapters present the experimental results and findings. Chapters 5 and 6 provide the groundwork to thesis, developing an understanding of the behaviour and characteristics of the out-of-order decoupled architectures. Chapters 7, 8 and 9 draw on this work to present the key findings of the thesis.

Chapter 5 describes a limitation study into access decoupling under maximum ILP and unlimited resources. The purpose of this study is to ascertain whether decoupling is an effective latency hiding technique for large ILP. This chapter introduces a latency hiding model to enable comparisons between different latency hiding techniques. The experiments show control decoupling to be impractical because of it's under-utilisation of the CU. This chapter discusses how the decoupled architecture and simulation technique were revised in the light of the results from the experiments. These results were presented at the EuroPar'97 conference [49].

Chapters 6 extends the work of the previous chapter by considering more realistic architectural constraints. It investigates the effect of superscalar issue width and identifies balanced configurations of AU and DU issue width that maintain maximum throughput. These results were presented at ParCo97 [48].

In Chapter 7 a series of simulations are used to investigate the effect of different levels of compiler and hardware complexity in extracting latent parallelism in a decoupled architecture. This chapter demonstrates the importance of architectural support for out-of-order memory accesses and describes how such a mechanism could be implemented in a decoupled architecture without increasing instruction issue logic complexity.

A single instruction stream, out-of-order superscalar architecture could in principle achieve the same level of reordering as a decoupled out-of-order superscalar machine. Chapter 8 provides a qualitative argument for the use of

decoupling through the notion of the effective single window. This chapter substantiates this notion by using an analytical model and simulation studies to compare performance. It shows that for large latencies there is a significant performance gain from decoupling. The single stream machine is shown to require significantly larger instruction issue windows to achieve equivalent performance. These results were presented at MICRO-30 [47]

The experiments in Chapter 8 relax those design issues particular to decoupled architectures (see Section 1.1 above) in order not to restrict the slippage between streams. Chapter 9 explores the sensitivity of the previous chapter's findings under more realistic conditions for these design issues. Drawing on the findings from Chapter 7, it also examines the sensitivity of the results to memory ordering.

Chapter 10 summarises the major findings of this thesis, discusses their implications in the context of related research and concludes with a discussion of suggested future work.

### Chapter 2

### Background

The potential to overlap the execution of independent instructions is known as instruction level parallelism. Multithreaded [31], VLIW [22, 6] and Superscalar [42] architectures all try to improve performance by exploiting latent ILP. Since the early 1990s out-of-order superscalar <sup>1</sup> architectures have come to dominate single processor high performance computing. In 1995, superscalar technology entered the mass production world of personal computing, with the release of the Pentium Pro [8]. Given the historical success and expertise that has been built around superscalar architectures, it is believed that they will continue to be one of the foremost principles of single processor designs. Section 2.1 describes the typical execution of a superscalar machine with reference to current architectures.

Processor performance since the 1980's has grown exponentially at 35% [45] a year. If that rate of increase is to be sustained, superscalar architectures will have to be designed with faster clock speeds and higher ILP. This will require machines with larger issue widths and a larger degree of reordering (see Section 1.1). However, unless some of the complexity for scheduling operations is migrated to the compiler, this extra complexity will introduce delays critical to the processor clock speed. Section 2.4 describes some of the current techniques being considered to reduce the complexity of future out-of-order machines.

Higher performance is also limited by the exponentially widening gap between memory and processor speeds. This gap means that the cost of a main memory access in terms of missed instruction issues slots is becoming more expensive. Wulf [89] has predicted that without technological shift, future processors are in danger of hitting the memory wall. Section 2.2 explains the notion of the memory wall and outlines some of the techniques currently being used to hide memory latency.

<sup>&</sup>lt;sup>1</sup>This work is only concerned with out-of-order superscalar machines so the prefix out-of-order will not be used in the rest of the thesis

Chapter 1 argued that the degree of reordering was the critical dimension to the performance of a superscalar machine. Section 2.3 presents some of the software and hardware techniques used to increase the degree of reordering.

The author believes that the decoupling paradigm in superscalar architectures could increase the degree of reordering and tolerate large memory latencies. Section 2.5 discusses previous work on decoupling, identifies the benefits of the technique and describes this thesis' original contribution.

#### 2.1 A typical superscalar architecture

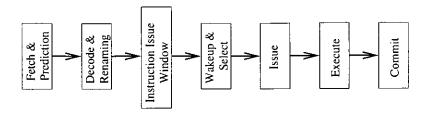

Figure 2.1 <sup>2</sup> shows the model of execution for a typical superscalar machine. Instructions are initially fetched from a cache using branch prediction techniques [59] to reduce the effect of control dependencies. In the next stage, instructions are decoded and their operands renamed to eliminate false register dependencies. Register renaming can be implemented using a mapping from physical to logical registers: as used in the Alpha 21264 [42] and the MIPS R10000 [91]. Renaming can also be implemented using the reorder buffer, as in the PowerPC 604 [76]. After renaming, the decode logic dispatches instructions to the issue window, where operations wait for their operands to become available.

Wake-up logic broadcasts the results of completed operations, and once an operations operands becomes available, it is flagged as ready for execution. Arbitration logic is then used to issue ready operations to the execution units. To reduce the impact of control dependencies many superscalar machines such as the Alpha 21264 [91] now implement speculative execution. Speculative execution is a technique that predicts an operation will be executed even though control dependencies are unresolved [84].

While operations may be issued and speculatively executed out-of-order, the machine state must be updated in-order. This process is known as committing the instruction. An instruction is committed, once it is known that it would have have executed if the program had been executed sequentially. The reason why instructions are committed in-order is to ensure a precise state, if an interrupt should occur. This can be implemented using techniques such as checkpointing [85].

<sup>&</sup>lt;sup>2</sup>This diagram has been taken from Palacharla [77]

Figure 2.1: Model of execution for a typical superscalar machine

#### 2.2 Latency hiding technology

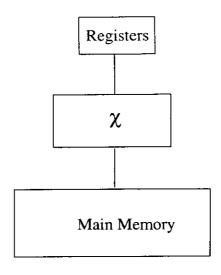

Wulf [89] developed a simple model of program execution that neatly conveyed the critical importance of memory latency to machine performance. Wulf's model used the equation for the average access time  $t_{avg}$  to a data cache

$$t_{avg} = \alpha * t_c + (1 - \alpha) * t_m$$

where  $\alpha$  is the hit ratio, and  $t_c$  and  $t_m$  are the cost of an access to main memory and cache, respectively. Since, typically 1 in 5 operation are memory accesses, when  $t_{avg}$  is greater than 5 cycles the memory latency will dominate the critical path; this point Wulf poetically refers to as hitting the memory wall. Wulf predicts from the base year of 1994 that even with a hit ratio of 99.8%, the memory wall would be reached in 10-12 years.

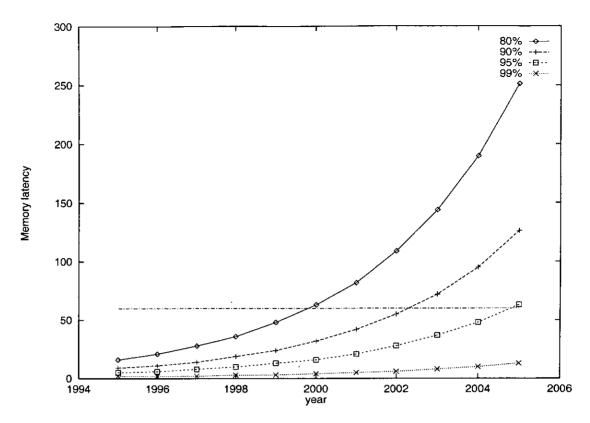

Processor and memory performance are known to be growing at 35% and 7%, respectively [45]. Using Wulf's model Figure 2.2 shows the predicted average access times from the base architecture, the Alpha 21164; the base year is 1995 and the characteristics of the Alpha 21164 [19] are used as an example of a high performance architecture from that year. The 21164 had a clock frequency of 300 MHz and a main memory latency of 253ns  $^3$ . Figure 2.2 also shows that when  $t_{avg}$  is 60 cycles  $^4$ ; it can be seen even with hit rates of 95%, average access times could reach 60 cycles in the year 2005. Wulf's paper and Figure 2.2 clearly show that latency hiding technology will continue to be a pivotal component of future computer architectures.

There are two types of latency hiding techniques, latency tolerance and latency reduction. Latency tolerance techniques try to overlap access and data operations in order to hide latencies. Latency reduction techniques use memory hierarchies to store frequently used data close to the processing unit.

<sup>&</sup>lt;sup>3</sup>Interestingly, the latency for a single DRAM component was only 60ns, but the additional overhead of the memory controller, multiplexing addresses to DRAM and the time to drive the DRAM pins increased the latency by a factor of 4

<sup>&</sup>lt;sup>4</sup>This is the value used in the majority of the simulation studies in this thesis

Figure 2.2: Predicted average memory access times for a range of hit ratios (expressed as percentages)

The cache is the most widely used and successful latency reduction technique. It exploits spatial and temporal locality in order to hide the main memory access time. Superscalar architectures with large issue widths and extensive reordering require support for non-blocking loads and multiple accesses per cycle. Non-blocking loads [74, 36, 30] with lock-up free caches [53] reduce miss penalties by servicing accesses while misses remain in-flight.

Cache technology is also being driven by the need to provide high bandwidth multi-ported caches. A multi-ported cache can be implemented by maintaining multiple copies of the data [42], though to ensure coherence writes must be performed in all banks of the cache. The disadvantage of this technique is the large amount of die space required to duplicate the data. Another multi-ported implementation is the interleaved cache used in the HP PA-8000 [27] and MIPS R10000 [91]. Under this scheme accesses to different banks can be serviced simultaneously but conflicts can occur for poor access patterns. However, Rivers et al. [68] argued that interleaved banking offered the best cost/performance for a multi-ported cache. The frequency of bank conflicts can be reduced through techniques such as access combining [68] and reordering [81].

A scheme for reordering memory references was also proposed in [81] to reduce the effect of bank conflicts. The Alpha 21264 [42] cache operates at twice the clock speed and therefore logically appears as a dual ported cache. However, with growing working set sizes and increasing ILP, the cost of a miss to first and second cache level has grown. To resolve this problem most high performance architectures include latency tolerance techniques such as data prefetching. These schemes allow data to be prefetched so that cache miss penalties can be tolerated.

Data prefetching techniques tolerate memory latencies by overlapping memory and data operations. It can be implemented in either software [16] or hardware [50]. Software prefetching is a compiler driven technique that places non-blocking loads ahead of the actual data reference. The distance between the non-blocking load and the reference is dependent on static analysis of the loop execution time and memory latency [52]. The disadvantage of software prefetching is the extra overhead of the prefetch instructions [17]. To reduce this effect, heuristics can be used to determine those loads that are likely to result in cache miss [62].

Hardware prefetching [50, 77, 18] has the advantage of dynamically prefetching data according to the run-time conditions of the machine. The simplest form of hardware prefetching is to prefetch the next n blocks after a cache [20]. The disadvantage of the hardware scheme is that it increases memory traffic because prefetched data is less likely to be used [17]. To reduce memory traffic techniques have been developed to detect non-unit strides [41] and to filter out unnecessary prefetching using history tables [77].

Results show that software prefetching is less sensitive to increases in memory latency and introduces less memory traffic [17]. In [56] a comparison of software latency hiding techniques found that when memory latencies are large software prefetching outperforms software pipelining and loop unrolling. At low memory latencies, software pipelining outperforms software prefetching due to the overhead associated with the extra prefetch instructions. Although software prefetching does introduce additional overhead by consuming processor cycles, the relative cost is expected to decrease, as issue widths become larger.

#### 2.3 Increasing the degree of reordering

Chapter 1 identified those factors that determine the degree of reordering, namely data dependencies and the number of operations visible to the scheduling hardware. This sections discusses some of the software and hardware techniques that

influence these factors.

Control dependencies limit the scope of operation reordering to a single basic block. For floating point applications the number of operations in basic blocks is typically in the range 1 to 10. This means that for block scheduling ILP is small. The effect of control dependencies has been reported in [57]. Techniques to remove control dependencies can be implemented in hardware and/or software. Branch prediction and speculative execution [59, 84] are commonly used techniques to ensure the instruction pipeline is fully utilised. Compiler directed if-conversion [2], procedure inlining [43] and loop parallelisation techniques [4, 26] allow more operations to be exposed to the reordering hardware. For example, loop unrolling which replicates the body of a loop and transforms the iteration conditions, has been shown to benefit ILP in superscalar architectures [21].

Unresolved data dependencies between memory references force compilers, in the absence of any supporting hardware, to generate conservative code. While compilers can disambiguate scalar references using variable names and equivalence information, array references are difficult to resolve. A range of static data dependency techniques have been developed [5, 92, 87, 67, 14] to disambiguate array references by examining their subscript expressions. However, it has been shown that in scientific applications, a small number of unresolved data dependencies cause large reductions in ILP [65, 10]. One solution is for the compiler to generate conservative and optimised code, and then select the appropriate code, dependent on run-time checks [21, 15].

Dynamic disambiguation is a technique that removes the constraints imposed by statically unresolved memory accesses. Typically this technique works by memory operations being assigned a sequential number in program order. The semantics of the program are preserved by prohibiting loads to reorder before stores that have the same address and lower sequence number. In [3, 72] all loads referencing memory performed an associative compare with active stores held in a queue. However, the weakness of this scheme is that loads can not be reordered before all preceding stores, and stores can not reorder relative to each other.

The difficulty of dynamic disambiguation in an out-of-order machine is that addresses can be only be compared after they have been computed; this may result in loads waiting for stores when no dependence exists between the reference pair. Speculative disambiguation [40, 61] is a technique that allows references to reorder even though load and store references have not been resolved. Franklin [40] proposed a technique known as the Address Reorder Buffer (ARB) that supports multiple accesses per cycle, using distributed bins. References are mapped to

the bins according to their instruction address, and the bins are used to detect memory conflicts using sequence numbers. The ARB is designed to support speculative memory accesses and out-of-order execution of loads and stores. If a load is incorrectly mispredicted to execute before a store, expensive recovery mechanisms roll back the machine state. To reduce the cost of recovery, Moshovos [61] has proposed the use of prediction techniques to detect references that are likely to result in mis-speculation. Interestingly, this paper shows that the cost of misspeculation will become significant as instruction window sizes increase.

Data flow dependencies impose a partial ordering on the operations in a program. However, scientific programs are written in imperative languages that introduce false dependencies; these dependencies introduce unnecessary ordering between operations. Register renaming [73] and array privatisation [23] can be used to remove false dependencies. Array privatisation is a technique that eliminates memory dependencies for scalars and arrays. In a study on the PERFECT club suite it was found that the Polaris compiler could produce speedups comparable to manually written code, when array privatisation was included in the optimisation suite [34].

#### 2.4 Reducing reordering logic complexity

Increasing ILP in an out-of-order superscalar architecture requires larger issue widths and instruction windows. However, Palacharla [77] has shown that delays in components critical to the processor clock speeds vary quadratically with issue width and window size. In his paper, Palacharla emphasised the point that it is the product of IPC and clock speed that designers should maximise. Increased logic complexity can improve IPC, but it may also introduce longer delays into paths critical to the processor clock speed. For this reason, Palacharla analysed delays in those functions in the instruction pipeline whose complexity grows with increasing ILP. These functions were renaming, wakeup/select and bypass. Palacharla's key findings are described below.

- 1. The wakeup and select delay varies quadratically with window size and issue width. This delay was found to dominate at 0.35  $\mu m$  technology, and larger issue width (8-way issue) and window size (64 instructions).

- 2. The bypass delay varies quadratically with issue width. For 0.18  $\mu m$  technology the bypass delay dominates at large issue widths (8-way issue) and window sizes (64 instructions).

Palacharla argues there is a need to consider complexity effective superscalar processors; architecture that can facilitate faster clock speeds without reducing ILP. Palacharla proposed a clustered architecture with centralised decoding and steering logic. Each cluster has a set of FIFO instruction queues that receive operations from the steering logic. The instruction window logic is simplified by only needing to monitor operations at the heads of each queue. The disadvantage of microclusters is the overhead of communicating values between register files and the limited number of operations available for selection. Other work on microclusters [42, 30] has explored the payoffs between simplified hardware and communication hardware.

The Multiscalar [39, 12, 75], MISC [81, 80] and PEW [51] share the common goal of trying to achieve high ILP through decentralised control logic. The MISC and PEW architectures differ from the Multiscalar by using decentralised fetch and decode logic. A detailed description of these architectures is postponed until Chapter 10, where they are discussed in relation to the thesis' findings.

#### 2.5 The decoupling paradigm

Access decoupling [7, 37, 58, 72, 71, 24, 70] is an asynchronous data prefetching technique that tries to hide memory latency by overlapping data and memory operations. Central to all decoupled architectures is an address unit (AU) and a data unit (DU) that communicate, between themselves and memory through the use of queues. Each unit has its own stream of instructions and program counter allowing the AU to run ahead of the DU. The degree to which the AU is ahead of the DU is called the slippage. At certain points in a program's execution, the AU is forced to wait on values from the DU; these points are referred to as a loss of decoupling.

All memory operations are executed by a split load instruction. The address unit computes and sends load and store addresses to memory system via the load and store address queues, respectively. The data from a load is returned from the memory, after some latency, and placed in a data queue where it can be fetched by the data unit. The memory latency can be tolerated, provided the address unit can prefetch data sufficiently far ahead of the data unit. To execute a store operation the address waits in a store address queue until it is matched with a computed value from the data unit, when they are sent to memory.

The early decoupled machines like the ZS-1 [72, 71, 24, 70] and PIPE [37] differed in how they split the instruction stream. The ZS-1 had a single instruction

stream with a splitter whereas PIPE had separate instruction caches for the access and execute unit. The ZS-1, unlike PIPE, also included a data cache. These early studies used synthetic loop kernels to look at the performance of the decoupled architectures for different queue sizes and memory latencies. Recently decoupled machines like the DAE [7], MISC [80, 81] and WM [88] have appeared. The DAE and WM differ from the MISC in their emphasis on providing support for structured data accesses; while the emphasis in the MISC architecture is on the use of decentralised control logic to simplify out-of-order execution.

The DAE [7] includes specialised hardware for efficient address generation of structured data. Efficient generation of addresses is shown to increase slippage, reduce DU stall time and increasing cache utilisation. The technique is similar to the access mechanism in vector machines and therefore subject to the same problems of data dependency analysis described in Section 2.3.

The WM [88] architecture consists of 12 asynchronously executing components that communicate by FIFO queues. An integer and floating point unit execute 1 instruction in-order every cycle. Stream control units are used to execute vector like operations for storing and reading data. The results show a factor of 2-9 increase in performance over a scalar architecture

Farrens [38] made a comparison between an in-order 2-way decoupled and 3-way out-of-order superscalar architecture using the Lawrence Livermore benchmark suite. His study showed that decoupled architectures outperformed superscalar architectures. The reasons given for the improvement were the dynamic loop unrolling through unit slippage, the register renaming and the dynamic out-of-order execution between decoupled units. However, this study limited the amount of reordering in the superscalar architecture by making the instruction window only large enough to hold one loop iteration and not allowing it to perform branch prediction. The study also did not consider wider issue widths, real applications and large memory latencies.

In another study by Kurian [55] a comparison was made between a decoupled architecture and a cache based uniprocessor. Decoupled architectures were observed to be more sensitive to memory latency than cache based systems especially with large memory latencies ( $\approx 15$  cycles) when the memory becomes a bottleneck. A decoupled architecture with a cache to capture locality was found to be the best configuration.

Tyson, in [81, 80], discusses the MISC architecture. The MISC machine has four asynchronous units each with their own instruction cache and a common data cache. The motivation behind the MISC architecture was to use decen-

tralised control logic to increase ILP. MISC is a decoupled microprocessor that exploits instruction level parallelism by executing streams in-order, on single issue processing elements. The architecture relies on the compiler to schedule operations and to partition the code. In his thesis Tyson explored the use of different algorithms for producing balanced work loads for the 4 processors. However, he concluded that in order to utilise all the processors, perfect dependency and inter-procedural analysis was required. Tyson also made a comparison between MISC and an in-order Alpha architecture. His results showed that a 4 processor, 1-way in-order issue MISC architecture can achieve higher performance than 4-way in-order issue on an Alpha 21164. However, these results were obtained with a non-blocking cache for the Alpha. This means that the Alpha will stall shortly after a cache miss, but MISC can continue initiating memory requests until the cache queues are saturated.

Topham [79] performed a limitation study of the effectiveness of decoupling for a range of compiler optimisations. The study was based on the static partitioning algorithm in the OCTAVE compiler and an analytical model of decoupled execution. From profiling information, estimates of the number of loss of decouplings in a program were used to calculate upper bounds on decoupling efficiency. The results showed that for many of the PERFECT club suite it was possible to hide large latencies. The partitioning algorithm differed from Tyson's work by trying to reduce the frequency of loss of decouplings rather than ensuring a balanced work load. This limitation study was however based on a static model and used conservative data dependency analysis to estimate the number of loss of decouplings.

Decoupling has gained currency in superscalar architectures like the MIPS R10000 [91] and PA 8000 [27]. The R10000 is able to support a decoupled mode of operation through out-of-order execution and a separate access instruction queue. The HP PA 8000 has two 28 instruction reorder buffers, for data and memory operations, and a large interleaved non-blocking cache. Both the R10000 and PA 8000 can decouple address and execute operations even though there is no architecturally visible AU and DU.

### 2.6 Original contribution

This thesis is the first known study into the effectiveness of out-of-order execution in decoupled superscalar architectures to improve latency hiding and increase ILP. Exponents of decoupling have typically focused on latency hiding and inter stream

reordering; however, Smith [70] in his early paper argued that an additional benefit of decoupling was the simplification of reordering hardware. This point has been picked up by Tyson [81], but his MISC architecture had multiple streams executing operations in-order. Tyson proposed that future work should consider an out-of-order decoupled architecture. The main contributions of this thesis are:

- 1. To investigate out-of-order decoupled architectures, identifying those design issues critical to their effectiveness at hiding memory latency and increasing ILP.

- 2. To compare the effectiveness of an out-of-order decoupled and single-stream superscalar architecture.

- 3. To investigate how the decoupling paradigm in out-of-order superscalar architectures can reduce issue logic complexity without decreasing performance.

#### 2.7 Summary

This chapter has summarised the strategic problems facing future superscalar designers and the techniques currently being considered to address these issues. It has highlighted the competing tensions between extracting higher ILP and processor complexity, and has emphasised the importance of latency hiding technology.

In summary, it is believed that the design goal for future superscalar archi-

tectures is: to build complexity sensitive [64], large issue width, latency tolerant machines capable of wider degrees of reordering. The following chapters explore whether this design goal can be met using the decoupling paradigm.

### Chapter 3

# Three Superscalar Architecture Models

This chapter describes the three superscalar architectures modelled in this thesis. The architectures are characterised by the number of instruction streams they can support. Each instruction stream executes on a single out-of-order superscalar unit, and each unit has a separate instruction issue window, register file and function units. Section 3.1 describes the 3-stream and 2-stream (also referred to as a dual stream) decoupled architectures. The former implements both control and access decoupling, while the latter only implements access decoupling. Section 3.2 describes a 1-stream (single stream architecture) in which no decoupling occurs.

The benefit of the multi-stream architectures, is that reordering can take place within (intra) or between (inter) instruction streams. However, this benefit is bought at the price of extra of hardware and software complexity. Inter-unit communication are implemented by queues as in previous decoupled machines [37, 72, 80, 90]. Separate instruction caches and fetch and decode mechanisms are required to ensure the maximum amount of slippage.

Extra software complexity is also required in the compiler to partition the code <sup>1</sup>. The 3-stream and 2-stream architecture both rely upon the static code partitioning obtained from the experimental OCTAVE compiler [79]. The OCTAVE compiler uses a set of heuristics that minimise communication and LODs between instruction streams. A full discussion of how the compiler was integrated with the simulation technique is described in Chapter 4.

Section 3.4 discusses the design issues that effect the reordering factors (discussed in Section 1.1) for each of the architectures. This section also describes how these issues shaped the experimental methodology used in this thesis.

<sup>&</sup>lt;sup>1</sup>Partition can also be performed in hardware as in the ZS-1 [72, 71, 24, 70]

#### 3.1 Multi-streamed decoupled architectures

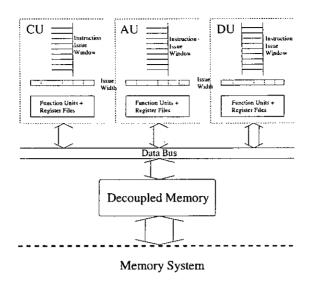

The 3-streamed decoupled superscalar architecture is based on the ACRI machine [9] and is illustrated in Figure 3.1. In this architecture three instruction streams execute on the control unit (CU), address unit (AU) and data unit (DU). Each unit maintains sufficient state to execute independently as an out-of-order superscalar architecture. The bulk of the computational work is performed on the AU/DU pair. The CU is capable of computing conditional branches ahead of the AU/DU pair.

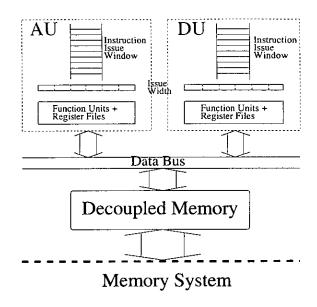

Figure 3.2 shows a 2-stream decoupled architecture similar to the ZS-1 [72] and PIPE [37] machines. This architecture differs from the 3-stream by providing no architectural support for the asynchronous execution of control operations. All operations previously executed on the CU are performed on the AU.

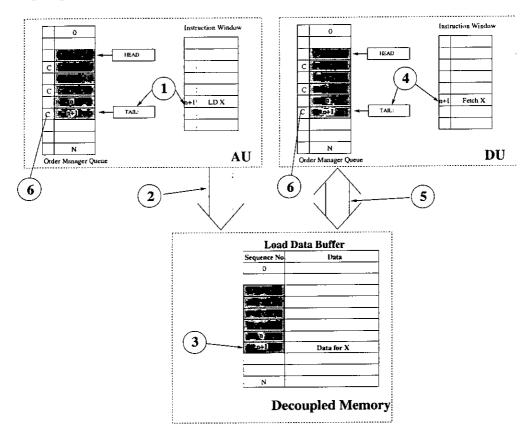

The decoupled memory is capable of sending and receiving data from the AU/DU pair and main memory. The AU and DU can both fetch and write data into the decoupled memory but only the AU can access main memory. This chapter avoids an implementation level description of the decoupled memory, instead concentrating on the semantics necessary to support decoupling <sup>2</sup>

A decoupled load to the DU is performed by way of a split instruction executed on the AU and DU. The AU initiates the load by computing the load address and sending it, via the decoupled memory, to main memory. Once the requested data is returned it waits in the decoupled memory until it is fetched by the DU. The AU is also capable of issuing decoupled self loads in a similar manner.

A decoupled store is performed by the AU sending an address to the decoupled memory, where it waits until the DU computes the data. The decoupled store completes when the address and data are paired and sent to main memory. The CU performs its own accesses via the decoupled memory.