## Evolvable Hardware Platform for Fault-Tolerant Reconfigurable Sensor Electronics

Evangelos F. Stefatos

A thesis submitted for the degree of Doctor of Philosophy The University of Edinburgh May 2007

## Declaration of originality

I hereby declare that the research recoded in this thesis and the thesis itself was composed and originated entirely by myself in the School of Engineering and Electronics at the University of Edinburgh.

**Evangelos Fotiou Stefatos**

2 May 2007

i

## Meaningful Outcome

#### Ιθάκη

Σα βγεις στον πηγαιμό για την Ιθάκη, να εύχεσαι νάναι μακρύς ο δρόμος, γεμάτος περιπέτειες, γεμάτος γνώσεις. Τους Λαιστρυγόνας και τους Κύκλωπας, τον θυμωμένο Ποσειδώνα μη φοβάσαι, τέτοια στον δρόμο σου ποτέ σου δεν θα βρείς, αν μέν' η σκέψις σου υψηλή, αν εκλεκτή συγκίνησις το πνεύμα και το σώμα σου αγγίζει. Τους Λαιστρυγόνας και τους Κύκλωπας, τον άγριο Ποσειδώνα δεν θα συναντήσεις, αν δεν τους κουβανείς μες στην ψυχή σου, αν η ψυχή σου δεν τους στήνει εμπρός σου.

Να εύχεσαι νάναι μακρύς ο δρόμος. Πολλά τα καλοκαιρινά πρωϊά να είναι που με τι ευχαρίστησι, με τι χαρά θα μπαίνεις σε λιμένας πρωτοειδωμένους· να σταματήσεις σ' εμπορεία Φοινικικά, και τες καλές πραγμάτειες ν' αποκτήσεις, σεντέφια και κοράλλια, κεχριμπάρια κ' έβενους, και ηδονικά μυρωδικά κάθε λογής,

#### Ithaca

When you set out on your journey to Ithaca, pray that the road is long, full of adventure, full of knowledge. The Lestrygonians and the Cyclops, the angry Poseidon -- do not fear them: You will never find such as these on your path, if your thoughts remain lofty, if a fine emotion touches your spirit and your body. The Lestrygonians and the Cyclops, the fierce Poseidon you will never encounter, if you do not carry them within your soul, if your soul does not set them up before you.

Pray that the road is long. That the summer mornings are many, when, with such pleasure, with such joy you will enter ports seen for the first time; stop at Phoenician markets, and purchase fine merchandise, mother-of-pearl and coral, amber and ebony, and sensual perfumes of all kinds, as many sensual perfumes as you can; visit many Egyptian cities, όσο μπορείς πιο άφθονα ηδονικά μυρωδικά· σε πόλεις Αιγυπτιακές πολλές να πας, να μάθεις και να μάθεις απ' τους σπουδασμένους.

Πάντα στον νου σου νάχεις την Ιθάκη. Το φθάσιμον εκεί είν' ο προορισμός σου. Αλλά μη βιάζεις το ταξίδι διόλου. Καλλίτερα χρόνια πολλά να διαρκέσει· και γέρος πια ν' αράξεις στο νησί, πλούσιος με όσα κέρδισες στον δρόμο, μη προσδοκώντας πλούτη να σε δώσει η Ιθάκη.

Η Ιθάκη σ' έδωσε το ωραίο ταξίδι. Χωρίς αυτήν δεν θάβγαινες στον δρόμο. Αλλο δεν έχει να σε δώσει πια.

Κι αν πτωχική την βρεις, η Ιθάκη δεν σε γέλασε. Ετσι σοφός που έγινες, με τόση πείρα, ήδη θα το κατάλαβες η Ιθάκες τι σημαίνουν.

Κωνσταντίνος Π. Καβάφης (1911)

to learn and learn from scholars.

Always keep Ithaca in your mind. To arrive there is your ultimate goal. But do not hurry the voyage at all. It is better to let it last for many years; and to anchor at the island when you are old, rich with all you have gained on the way, not expecting that Ithaca will offer you riches.

Ithaca has given you the beautiful voyage. Without her you would have never set out on the road.

She has nothing more to give you.

And if you find her poor, Ithaca has not deceived you.

Wise as you have become, with so much experience,

you must already have understood what Ithacas mean.

Constantine P. Cavafy (1911)

ii

## Acknowledgements

For the completion of my PhD thesis I would like to heartily thank my beloved Elina Kaxamichau. Besides myself, there is no other person that has endeavoured more for the successful completion of this work. Every day, for more than 3 years, she made my life easier and more beautiful. She was the one who patiently endured my frustration and bad-temper during the difficult moments of my research, and I always had someone to love me and help eliminate any problems apart from those of my research. For all the above reasons, I feel that there are no words enough to thank Elina. I cannot dedicate my thesis to her, simply because a significant part of it belongs to her.

Most importantly, I would like to thank my parents (*Foti and Christina*). My strong will to make them proud was the original motivation to start my PhD. The outcome of this research is exclusively dedicated to them, as a small payback for everything they have done for me during my 29 years of life, and as forgiveness for every time I have depressed them. Without the values I have adopted from them, I would have never achieved anything in my life.

In addition, I would like to thank my supervisor, *Prof. Tughrul Arslan*, who trusted me as a person and scientist and gave me the opportunity to implement a PhD in a very interesting and challenging field. We spent three very interesting years together and I

iii

have to say that our collaboration was very close and, above all, productive. I want to thank him for his excellent supervision and for the chance he gave me to travel a lot and present my work at outstanding high-quality scientific conferences, to meet people of important scientific background and gain a lot of invaluable experience. For all these reasons, I feel that it would be a great pleasure for me to collaborate with *Prof. Tughrul* sometime in the future.

Moreover, I would like to acknowledge my second supervisor, *Dr. Alister Hamilton*, because he never refused to give me his prompt assistance and share with me his widespread knowledge, every time I asked for these.

I would also like to acknowledge Dr. Robert (Bob) Thomson for his invaluable guidance during the early stages of my PhD and Mrs. Katherine Cameron for volunteering to proof-read my thesis.

I would also like to thank *all my colleagues* in our group because their technical expertise and professionalism was the best motivation to me and pushed me into working harder every day.

Last but not least, I would like to thank Mrs. Liz Glass for her kind smile every time I asked her assistance. This is a gift of life, it is not a profession.

iv

# Contents

| LIS | T OF TABLES                                                | XII          |

|-----|------------------------------------------------------------|--------------|

| AC  | RONYMS AND ABBREVIATIONS                                   |              |

| NO  | MENCLATURE                                                 | XV           |

| ABS | STRACT                                                     | XVII         |

| СН  | APTER 1 - INTRODUCTION                                     | 1            |

| 1.1 | INTRODUCTION                                               | 1            |

| 1.2 | THESIS ACHIEVEMENTS                                        | 3            |

| 1.3 | THESIS OUTLINE                                             | 4            |

| 1.4 | SUMMARY                                                    | 6            |

| СН  | APTER 2 - JPL/BOEING GYROSCOPE                             | 8 -          |

| 2.1 | INTRODUCTION                                               |              |

| 2.2 | STRUCTURE AND OPERATION OVERVIEW                           | 9 -          |

| 2.3 | CIRCUITS ANALYSIS                                          | 11 -         |

| 2.4 | PREVIOUS WORK AND NEW CHALLENGES                           | 13 -         |

| 2.5 | SUMMARY                                                    | 20 -         |

| СН  | APTER 3 - EVOLVABLE HARDWARE FOR THE DESIGN OF DIGITAL CIR | CUITS - 21 - |

| 3.1 | INTRODUCTION                                               | 21 -         |

| 3.2 | OVERVIEW OF GENETIC ALGORITHMS                             | 22 -         |

| 3.3 | DIFFERENT LEVELS OF EVOLUTION                              | 30 -         |

| 3.4 | DIFFERENT MODES OF EVOLUTION                               | 32 -         |

|     | 3.4.1 Extrinsic                                            |              |

|     | 3.4.2 Intrinsic<br>3.4.3 Mixtrinsic                        |              |

| 3.5 | BACKGROUND THEORY OF THE GYROSCOPE'S ELECTRONICS           |              |

| 5.5 | 3.5.1 Finite Impulse Response filters                      | ·            |

|     | 3.5.2 Proportional Integral Derivative controller          |              |

| 3.6 | CONCLUSIONS                                                |              |

| СН/ | APTER 4 - DESIGNING A STAND-ALONE FAULT-TOLERANT ARCHITECT | 'URE 43 -    |

| 4.1 | INTRODUCTION                                               | - 43 -       |

| 4.2 | SYSTEM DESCRIPTION                                         | 44 -         |

|     | 4.2.1 Computational Layer                                  |              |

|     | 4.2.2 Control Layer                                        | 48 -         |

v

| 4.3        | INTRODUCTION OF FAULTS                                                                         | 50 -          |

|------------|------------------------------------------------------------------------------------------------|---------------|

| 4.4        | RESULTS ANALYSIS                                                                               | 52 -          |

| 4.5        | CONCLUSIONS                                                                                    | 56 -          |

| CH/        | APTER 5 - CUSTOM-RECONFIGURABLE FIR STRUCTURES                                                 | 58 -          |

| 5.1        | INTRODUCTION                                                                                   | 58 -          |

| 5.2        | ZIG-ZAG INTERCONNECTION SCHEME BETWEEN CALBS                                                   | 59 -          |

|            | 5.2.1 Introduction                                                                             |               |

|            | 5.2.2 System Architecture                                                                      | 59 -          |

|            | 5.2.2.1 Addition/Subtraction CALU                                                              |               |

|            | 5.2.2.2 Left/Right Shifting CALU                                                               |               |

|            | 5.2.3 Overflow Protection Mechanism                                                            |               |

|            | 5.2.4 Synthesis Results                                                                        |               |

|            | 5.2.5 Power Analysis                                                                           |               |

|            | 5.2.6 Conclusions                                                                              | 09 -          |

| 5.3        | FIR ARCHITECTURE WITH PROGRAMMABLE TAP-DELAYS WITHIN THE<br>NFIGURABLE ARITHMETIC LOGIC BLOCKS | 70            |

| COr        |                                                                                                |               |

|            | 5.3.1 Introduction                                                                             |               |

|            | 5.3.2 System Architecture                                                                      |               |

|            | 5.3.3 Genetic Algorithm                                                                        |               |

|            | 5.3.3.1 Evolution of Coefficients (time-domain)                                                | <b>-</b> 74 - |

|            | 5.3.3.2 Evolution of Frequency Response (frequency-domain)                                     | 74 -          |

|            | 5.3.4 Simulation Results                                                                       |               |

|            | 5.3.4.1 Results in time-domain                                                                 |               |

|            | 5.3.4.2 Results in frequency-domain                                                            | 78 -          |

|            | 5.3.5 Synthesis and Power Analysis<br>5.3.6 Conclusions                                        |               |

| 5.4<br>CAL | FIR ARCHITECTURE WITH CHAIN INTERCONNECTION SCHEME BETWEE                                      | N             |

|            | 5.4.1 Introduction                                                                             |               |

|            | 5.4.2 System Architecture                                                                      |               |

|            | 5.4.2.1 Reconfigurable Architecture                                                            |               |

|            | 5.4.2.2 Genetic Algorithm                                                                      |               |

|            | 5.4.3 Injection of Anticipated Faults                                                          |               |

|            | 5.4.3.1 Off-line Reconfiguration<br>5.4.3.2 On-line Reconfiguration                            |               |

|            | 5.4.3.2 On-line Reconfiguration                                                                |               |

|            | 5.4.4.1 Off-line Reconfiguration for Faults 5% and 10%                                         |               |

|            | 5.4.4.1 On-line Reconfiguration for Faults 5% and 10%                                          |               |

|            | 5.4.5 Synthesis and Power Analysis                                                             |               |

|            | 5.4.6 Conclusions                                                                              |               |

| 5.5        | DEVELOPMENT OF A FOLDED-TRANSPOSED FORM FIR FILTER                                             |               |

|            | 5.5.1 Introduction                                                                             | . 101 -       |

|            | 5.5.2 Overall Architecture                                                                     |               |

|            | 5.5.2.1 Reconfigurable Hardware Topology                                                       |               |

|            | 5.5.2.2 Architecture of Custom Search Algorithm                                                |               |

|            | 5.5.3 Simulation Results                                                                       | - 110 -       |

|            | 5.5.3.1 Error-free Simulation of FIR Filter                                                    | - 110 -       |

|            | 5.5.3.2 Adaptive Mechanism for Fault-Robustness                                                | - 112 -       |

|            | 5.5.4 Synthesis and Power Analysis                                                             |               |

|            |                                                                                                |               |

|                                                 | 5.5.5          | Conclusions                                            | 116 - |

|-------------------------------------------------|----------------|--------------------------------------------------------|-------|

| 5.6                                             | REC            | CONFIGURABLE ARCHITECTURE FOR REAL-TIME REALIZATION OF |       |

| HIGH-QUALITY AND FAULT-ROBUST FIR FILTERS 117 - |                |                                                        |       |

|                                                 | 5.6.1          | Introduction                                           | 117 - |

|                                                 | 5.6.2          | Reconfigurable Architecture                            | 117 - |

|                                                 | 5.6.3          | Hybrid Evolutionary Technique                          |       |

|                                                 | 5.6.4<br>5.6.4 | Simulation Results                                     |       |

|                                                 | 5.6.4<br>5.6.4 |                                                        |       |

|                                                 | 5.6.4          |                                                        |       |

|                                                 | 5.6.4          |                                                        |       |

|                                                 | 5.6.4<br>5.6.4 |                                                        |       |

|                                                 | 5.6.5          | Synthesis                                              |       |

|                                                 | 5.6.6          | Power Analysis                                         |       |

|                                                 | <b>5.6</b> .7  | Conclusions                                            |       |

| CHA                                             | APTER 6        | - EVOLUTIONARY MECHANISMS                              | 149 - |

| 6.1                                             |                | RODUCTION                                              |       |

| 6.2                                             |                | ITATIONS OF EXISTING EVOLUTIONARY TECHNIQUES           |       |

| 6.3                                             |                | DIFIED CROSSOVER AND MUTATION OPERATIONS               |       |

| <b>6.4</b>                                      |                |                                                        |       |

| 0.4                                             |                | - DLUTIONARY TECHNIQUES                                |       |

|                                                 | 6.4.1<br>6.4.2 | Conventional EA                                        |       |

|                                                 | 0.4.2<br>6.4.3 | Conventional MOEA Generic Gradual Evolution            |       |

|                                                 | 6.4.4          | Incremental Evolutionary Technique                     |       |

|                                                 | 6.4.5          | Combination of Incremental and MOEA                    |       |

| 6.5                                             | SIM            | ULATION ENVIRONMENT                                    | 162 - |

| 6.6                                             | COM            | 1PARISONS                                              | 164 - |

|                                                 | 6.6.1          | 19-tap High-pass Filter                                | 164 - |

|                                                 | 6.6.2          | 26-tap Low-pass Filter                                 |       |

|                                                 | 6.6.3          | 31-tap Low-pass Filter                                 |       |

| 6.7                                             | CON            | ICLUSIONS                                              | 177 - |

| CH/                                             | APTER 7        | -IMPLEMENTATION OF THE.JPL/BOEING GYROSCOPE'S ELECTRON | lics  |

| •••••                                           |                |                                                        | 179 - |

| 7.1                                             | INTI           | RODUCTION 1                                            | 179 - |

| 7.2                                             | EVO            | LUTION OF THE FIR COMPOSING THE CONTROL LOOPS 1        | 180 - |

|                                                 | 7. <i>2.1</i>  | Evolution of Drive Control Loop                        | 180 - |

|                                                 | 7.2.2          | Evolution of the Sense-Rebalance Loop                  | 185 - |

|                                                 | 7.2.3          | Evolution of the Demodulation stage                    | 186 - |

| 7.3                                             | POW            | VER ANALYSIS 1                                         | 190 - |

| 7.4                                             | CON            | CLUSIONS 1                                             | 193 - |

| CHAPTER 8 - SUMMARY AND CONCLUSIONS 195 -       |                |                                                        |       |

| 8.1                                             | INTI           | RODUCTION 1                                            | 195 - |

|                                                 |                |                                                        |       |

vii

| 8.2    | SUMMARY         | 196 - |

|--------|-----------------|-------|

| 8.3    | CONCLUSIONS     | 198 - |

| 8.4    | FUTURE WORK     | 202 - |

| BIBLI  | OGRAPHY         | 205 - |

| APPEI  | NDIX A          | 217 - |

| LIST ( | OF PUBLICATIONS | 217 - |

# **List of Figures**

| FIGURE 2.1: ELECTRON MICROSCOPE PHOTOGRAPH OF THE JPL/BOEING GYROSCOPE [20]                                      | 11 -            |

|------------------------------------------------------------------------------------------------------------------|-----------------|

| FIGURE 2.2: HIGH-LEVEL SCHEMATIC ELECTRONICS OF THE GYROSCOPE'S CONTROL-LOOPS [20]                               | 12 -            |

| FIGURE 3.1: DESIGN FLOW OF A GENERIC GA                                                                          |                 |

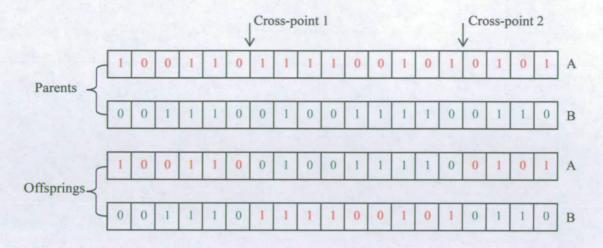

| FIGURE 3.2: PARADIGM OF ONE-POINT CROSSOVER                                                                      | 27 -            |

| FIGURE 3.3: PARADIGM OF TWO-POINT CROSSOVER                                                                      | 28 -            |

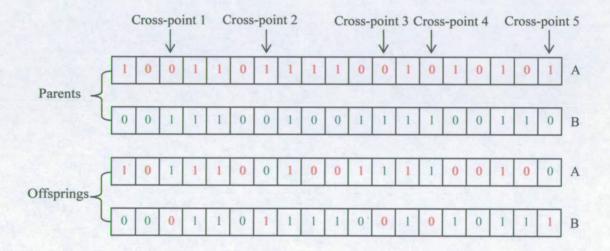

| FIGURE 3.4: UNIFORM CROSSOVER WITH PROBABILITY 25% PER GENE                                                      | 28 -            |

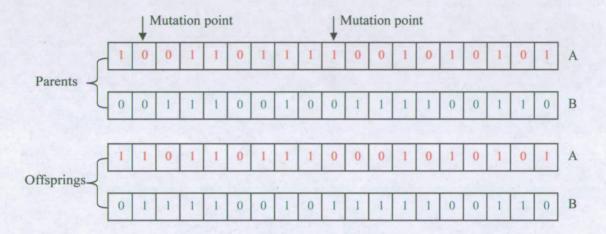

| FIGURE 3.5: MUTATION WITH PROBABILITY 10% PER GENE                                                               | 29 -            |

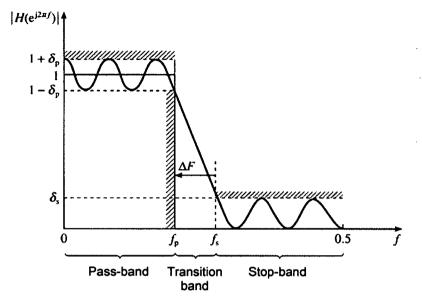

| FIGURE 3.6: FREQUENCY RESPONSE SPECIFICATION OF LOW-PASS FILTER                                                  | 38 -            |

| FIGURE 3.7: FEEDBACK CONTROL SYSTEM                                                                              | 39 -            |

| FIGURE 3.8: PID CONTROLLER                                                                                       |                 |

| FIGURE 3.9: DISCRETE-TIME PID CONTROLLER                                                                         |                 |

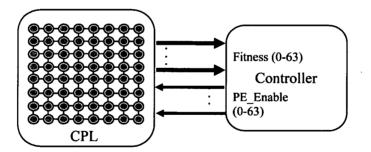

| FIGURE 4.1: TOPOLOGY OF THE PGA AND INTERFACE BETWEEN PES BELONGING IN THE SAME LAYER                            |                 |

| FIGURE 4.2: INTERFACE BETWEEN A UNIQUE CONTROLLER IN CTL AND CPL                                                 |                 |

| FIGURE 4.3: DESCRIPTION OF THE STATES COMPRISING THE FSM OF EACH PE                                              | 48 -            |

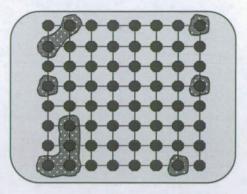

| FIGURE 4.4: POTENTIAL COMBINATIONS OF VALID (GROUPS OF 5 "ALIVE" PES FORMING A CROSS)                            |                 |

| SOLUTIONS                                                                                                        | 50 -            |

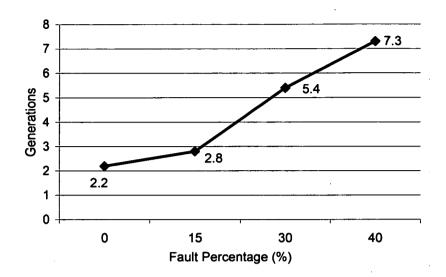

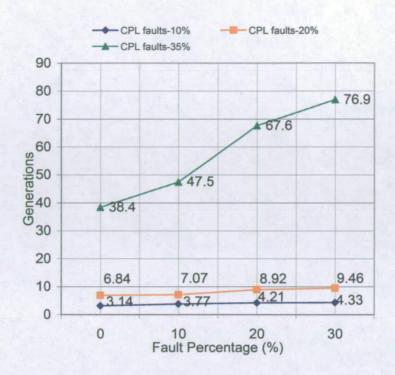

| FIGURE 4.5: MEAN NUMBER OF GENERATIONS THAT CPL NEEDS TO CONVERGE FOR DIFFERENT                                  |                 |

| PERCENTAGES OF FAULTS WITHOUT THE UTILIZATION OF CTL                                                             | 53 -            |

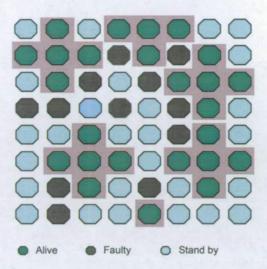

| FIGURE 4.6: SIMULATION SCENARIO FOR PERCENTAGE OF FAULTS 15% (SHADED PES ARE FAULTY)                             |                 |

| FIGURE 4.7: SIMULATION SCENARIO FOR PERCENTAGE OF FAULTS 30% (SHADED PES ARE FAULTY)                             |                 |

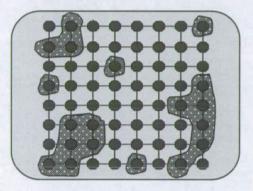

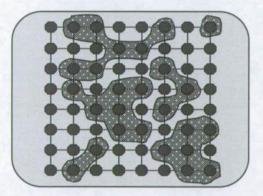

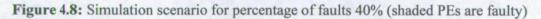

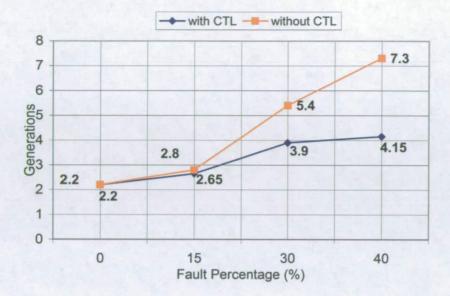

| FIGURE 4.8: SIMULATION SCENARIO FOR PERCENTAGE OF FAULTS 40% (SHADED PES ARE FAULTY)                             | 54 -            |

| FIGURE 4.9: MEAN NUMBER OF GENERATIONS THAT CPL NEEDS TO CONVERGE WITH AND WITHOUT T                             |                 |

| CTL USAGE                                                                                                        | 55 -            |

| FIGURE 4.10: MEAN NUMBER OF GENERATIONS THAT CTL NEEDS FOR DIFFERENT PERCENTAGE OF FA                            | ULTS            |

| IN BOTH LAYERS                                                                                                   |                 |

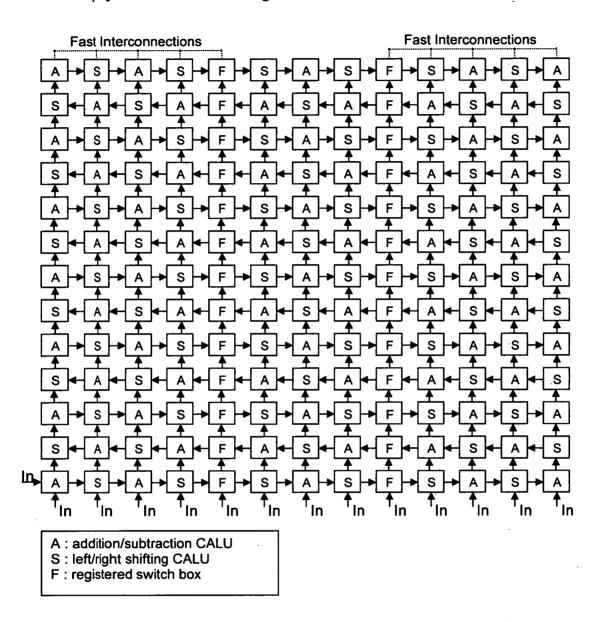

| FIGURE 5.1: TOPOLOGY OF THE RECONFIGURABLE ARRAY                                                                 |                 |

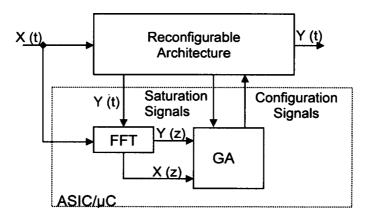

| FIGURE 5.2: OVERALL SYSTEM ARCHITECTURE COMPRISING A RECONFIGURABLE HARDWARE SUBSTR                              |                 |

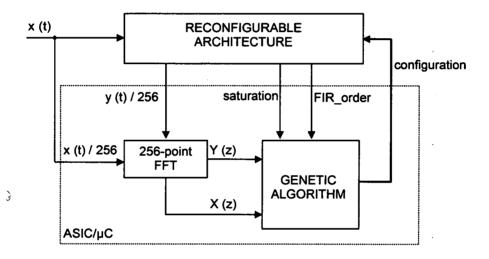

| AND A GA PERFORMING EVOLUTION IN FREQUENCY DOMAIN                                                                | 63 -            |

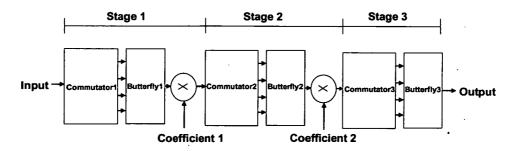

| FIGURE 5.3: THREE STAGES FAST FOURIER TRANSFORM MODULE                                                           | 63 -            |

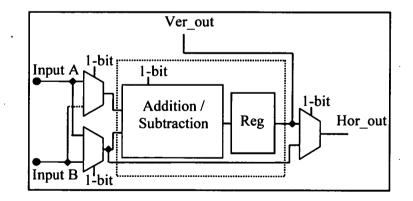

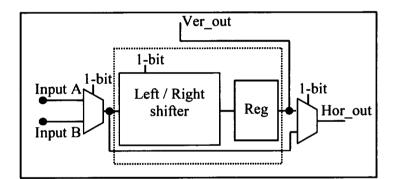

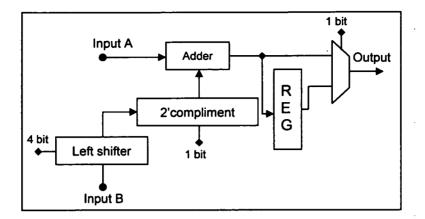

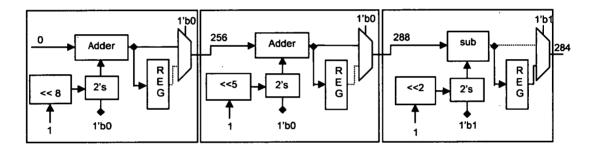

| FIGURE 5.4: ADDITION/SUBTRACTION CALU<br>FIGURE 5.5: BINARY L/R SHIFTER CALU                                     | 64 -            |

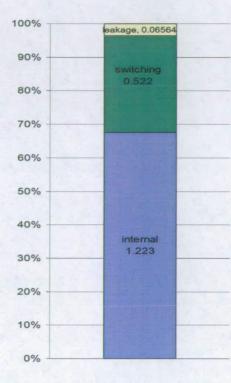

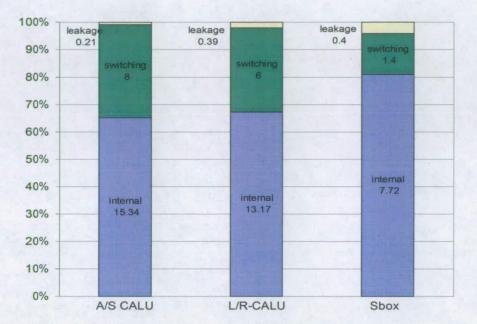

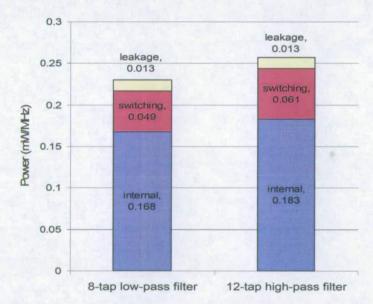

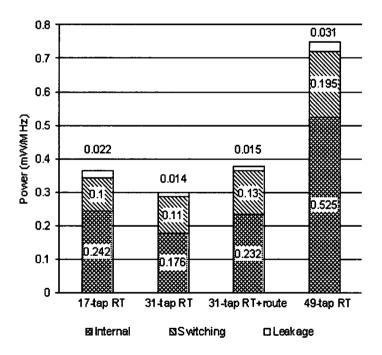

| FIGURE 5.5: BINARY L/R SHIFTER CALU<br>FIGURE 5.6: POWER ANALYSIS OF THE RECONFIGURABLE HARDWARE                 | 65 -            |

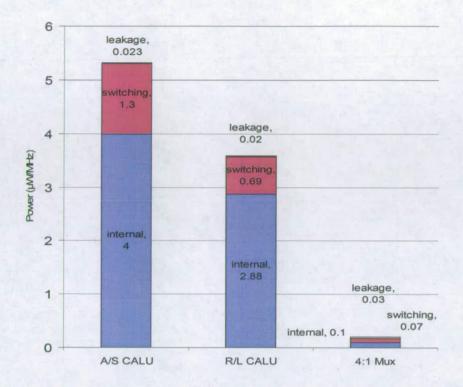

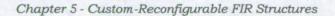

| FIGURE 5.0: FOWER ANALYSIS OF THE RECONFIGURABLE HARDWARE<br>FIGURE 5.7: POWER ANALYSIS OF THE 3 DIFFERENT CALUS | 68 -            |

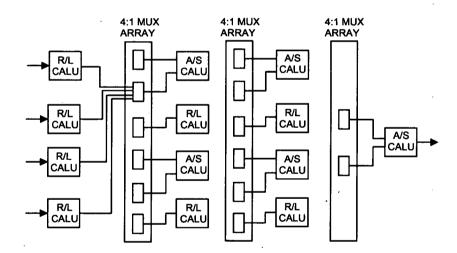

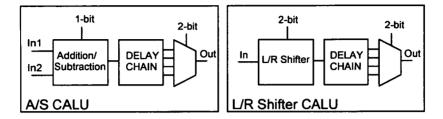

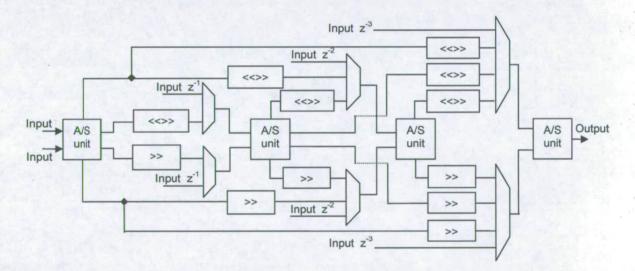

| FIGURE 5.8: CUSTOM RECONFIGURABLE HARDWARE TAILORED FOR THE IMPLEMENTATION OF FIR FIL                            |                 |

| 72 -                                                                                                             | TERS-           |

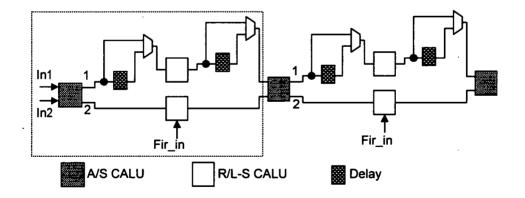

| FIGURE 5.9: HARDWARE DESCRIPTION OF THE TWO EMPLOYED PROGRAMMABLE CALUS                                          | 72              |

| FIGURE 5.10: TRANSFER FUNCTION OF THE 13-TAP LOW-PASS FILTER                                                     |                 |

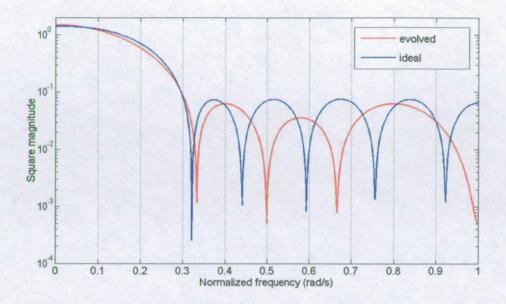

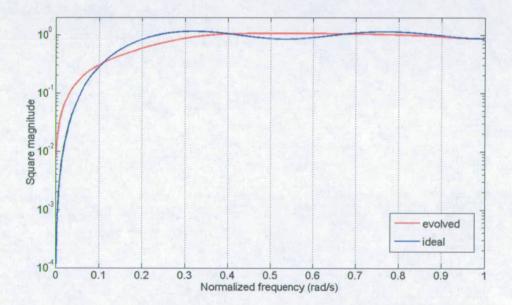

| FIGURE 5.11: TRANSFER FUNCTION OF THE 15-TAP LOW-PASS FILTER                                                     |                 |

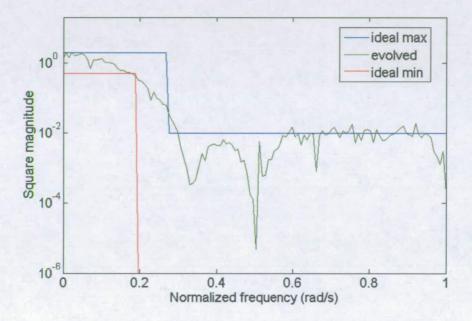

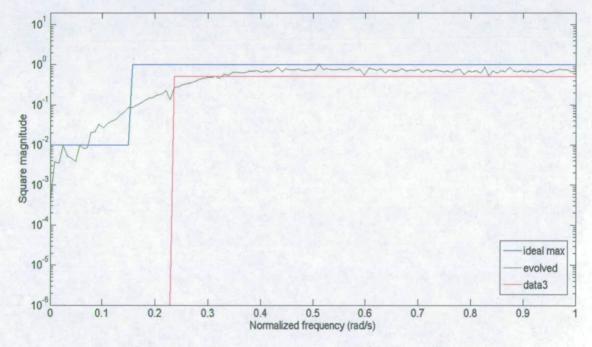

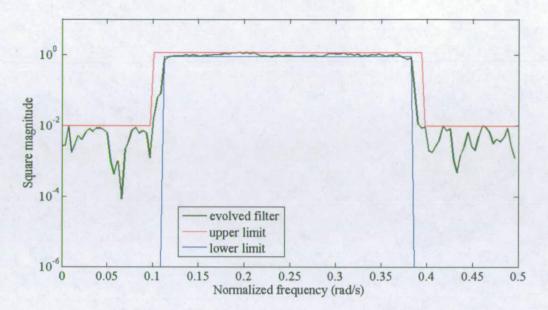

| FIGURE 5.12: MAGNITUDE OF THE EVOLVED LOW-PASS FILTER                                                            |                 |

| FIGURE 5.13: MAGNITUDE OF THE EVOLVED LOW-PASS FILTER                                                            | /9 -            |

| FIGURE 5.14: POWER ANALYSIS OF THE EVOLVED FILTERS                                                               | -00-<br>00      |

| FIGURE 5.15: POWER ANALYSIS OF THE EVOLVED FILTERS                                                               | 02 -<br>Q1      |

| FIGURE 5.16: OVER ANALYSIS OF THE CALOS                                                                          | 04 -            |

| AN EVOLUTIONARY DRIVEN RECONFIGURATION MECHANISM                                                                 |                 |

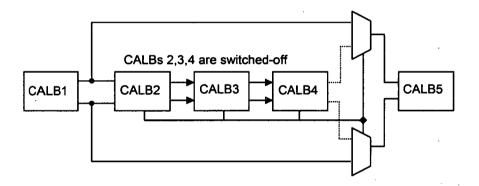

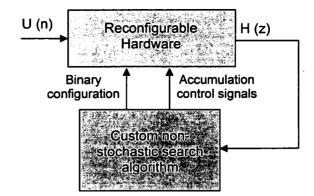

| FIGURE 5.17: FUNCTIONAL DESCRIPTION OF THE CUSTOM RECONFIGURABLE HARDWARE                                        | - 00 -          |

| - TOOLE OF THE OF THE COSTON RECOVERDED BARDWARE                                                                 | , <b>- 07 -</b> |

| FIGURE 5.18: POWER CONTROL MECHANISM - CALBS 2, 3 AND 4 ARE SWITCHED-OFF BECAUSE CALB 1 I            | S          |

|------------------------------------------------------------------------------------------------------|------------|

| VIRTUALLY CONNECTED TO CALB 5. THE CONTROL-BIT OF THE TWO MULTIPLEXERS CONTROL THE                   |            |

| OPERATION OF CALBS 2, 3 AND 4                                                                        |            |

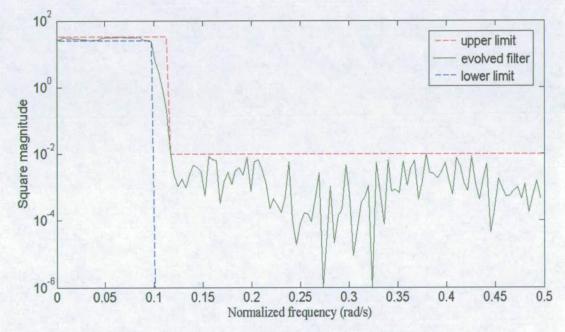

| FIGURE 5.19: LOW-PASS FILTER EVOLUTION WITH 0% FAULTS                                                | -<br>5 -   |

| FIGURE 5.20: PASS-BAND FILTER EVOLUTION WITH 0% FAULTS                                               |            |

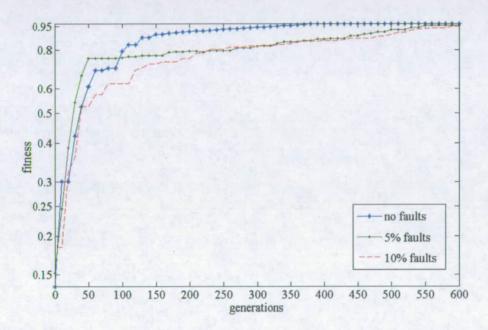

| FIGURE 5.21: EVOLUTION PROCESS OF THE PASS-BAND FILTER FOR FAULTS 0%, 5% AND 10%                     | - 7        |

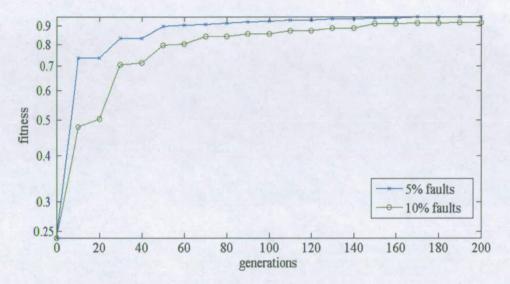

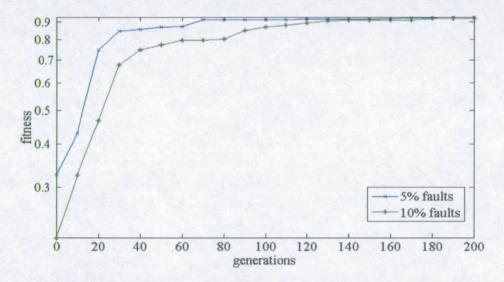

| FIGURE 5.22: ON-LINE PASS-BAND FILTER RECOVERY FOR FAULTS 5% AND 10%                                 |            |

| FIGURE 5.23: ON-LINE LOW-PASS FILTER RECOVERY FOR FAULTS 5% AND 10%                                  |            |

| FIGURE 5.24: POWER SAVINGS FOR THE LOW-PASS AND PASS-BAND FILTERS                                    |            |

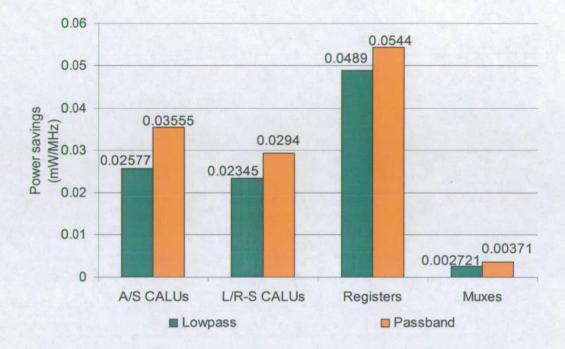

| FIGURE 5.25: BLOCK DIAGRAM OF OVERALL ARCHITECTURE                                                   |            |

| FIGURE 5.26: RECONFIGURABLE HARDWARE TOPOLOGY                                                        |            |

| FIGURE 5.27: HARDWARE ARCHITECTURE AND INTERCONNECTION SCHEME                                        | 5 -        |

| FIGURE 5.28: A/S UNIT IN THE ACCUMULATION BLOCK                                                      |            |

| FIGURE 5.29: ENCODING SCHEME FOR SEARCH ALGORITHM                                                    |            |

| FIGURE 5.30: COMPARISON OF THE EVOLVED AND IDEAL FILTER                                              |            |

| FIGURE 5.31: RECOVERY PROCESS FROM SHE IN USER MEMORY                                                |            |

| FIGURE 5.33: POWER ANALYSIS OF THE 41-TAP FILTER                                                     |            |

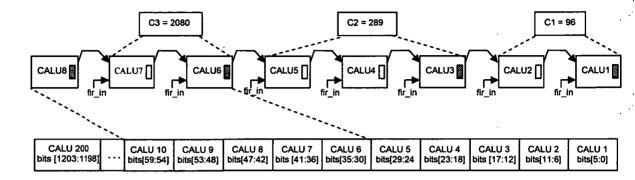

| FIGURE 5.34: HARDWARE TOPOLOGY OF RT VERSION                                                         |            |

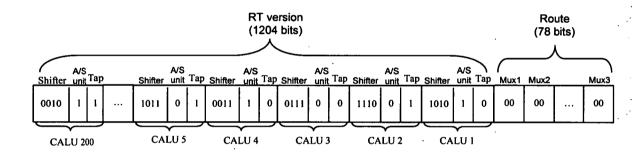

| FIGURE 5.35: HARDWARE TOPOLOGY OF RT+ROUTE VERSION                                                   | 1_         |

| FIGURE 5.36: CALU HARDWARE DESCRIPTION                                                               | 1 -<br>7 - |

| FIGURE 5.37: RELATION BETWEEN REALIZED COEFFICIENTS AND NUMBER OF EMPLOYED CALUS 122                 | 2-         |

| FIGURE 5.38: DESCRIPTION OF SEARCH-AREA MINIMIZATION MECHANISM                                       |            |

| FIGURE 5.39: DIFFERENTIATION IN THE ENCODING BETWEEN THE RT AND RT+ROUTE CHROMOSOME- 126             |            |

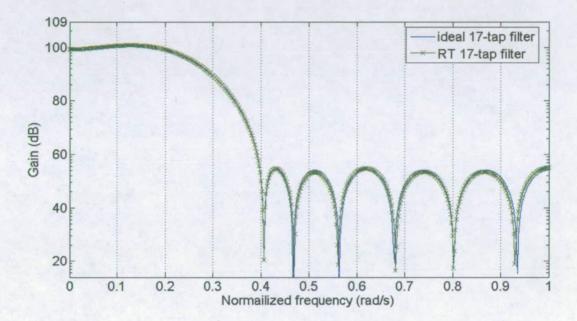

| FIGURE 5.40: COMPARISON OF THE FREQUENCY RESPONSE BETWEEN THE IDEAL AND THE EVOLVED 17-TA            |            |

| LOW-PASS FILTER, USING THE RT VERSION                                                                |            |

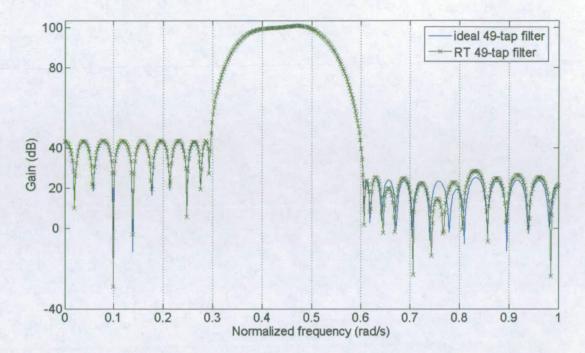

| FIGURE 5.41: COMPARISON OF THE FREQUENCY RESPONSE BETWEEN THE IDEAL AND THE EVOLVED RT 49            |            |

| TAP PASS-BAND FILTER, USING THE RT VERSION                                                           |            |

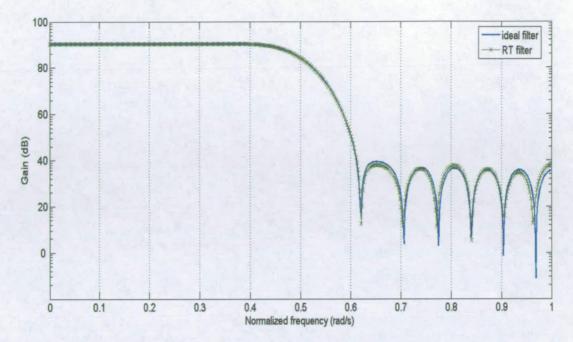

| FIGURE 5.42: COMPARISON OF THE FREQUENCY RESPONSE BETWEEN THE IDEAL AND THE EVOLVED 31-TA            |            |

| LOW-PASS FIR FILTER, USING THE REQUERCE RESIONSE BET WEEK THE IDEAL AND THE EVOLVED STATA            | 11<br>12   |

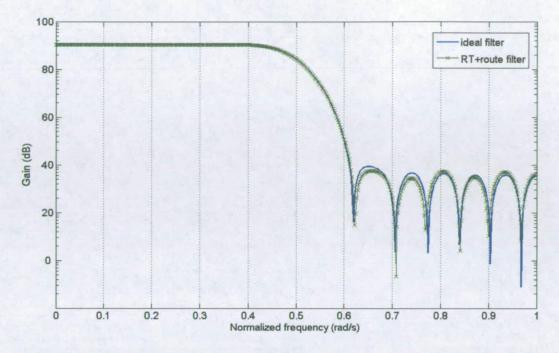

| FIGURE 5.43: COMPARISON OF THE FREQUENCY RESPONSE BETWEEN THE IDEAL AND THE RT + ROUTE               | ,-         |

| FILTER                                                                                               | 4_         |

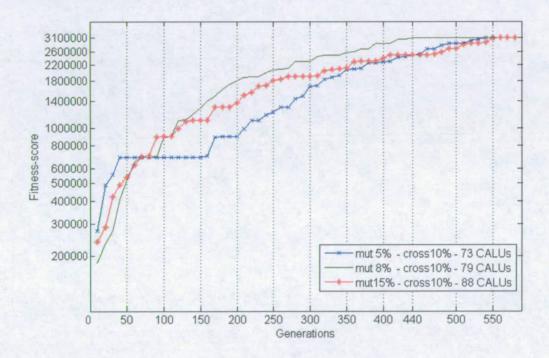

| FIGURE 5.44: RT EVOLUTION PROCESS FOR CROSSOVER RATE 10% AND DYNAMIC MUTATION RATES 5%,              | T -        |

| 10% AND 15%                                                                                          | 5 -        |

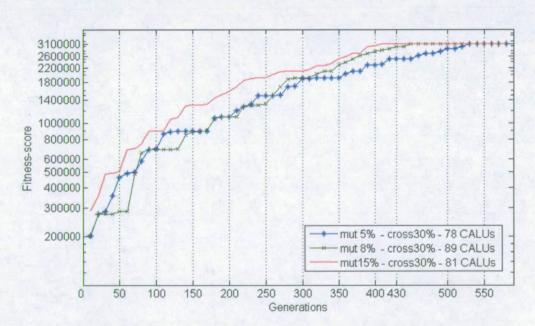

| FIGURE 5.45: RT EVOLUTION PROCESS FOR CROSSOVER RATE 30% AND DYNAMIC MUTATION RATES 5%,              |            |

| 10% AND 15%                                                                                          | 6-         |

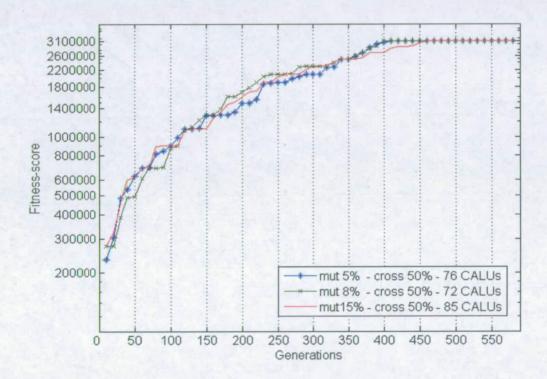

| FIGURE 5.46: RT EVOLUTION PROCESS FOR CROSSOVER RATE 50% AND DYNAMIC MUTATION RATES 5%,              |            |

| 10% AND 15%                                                                                          | 7 -        |

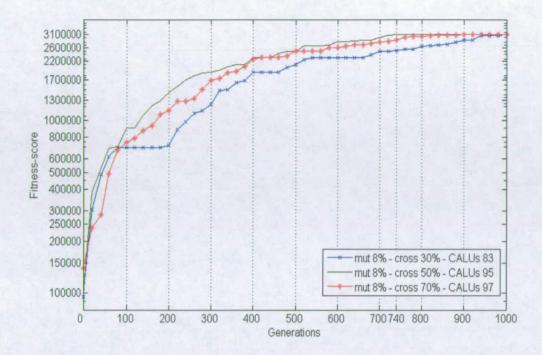

| FIGURE 5.47: RT + ROUTE EVOLUTION PROCESS FOR DYNAMIC MUTATION RATE 8% AND CROSSOVER RATI            | ES         |

| 30%, 50% AND 70%                                                                                     | ₹_         |

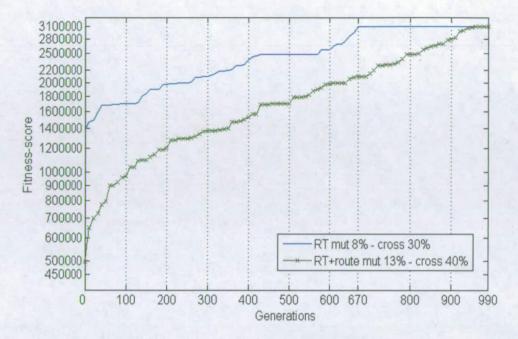

| FIGURE 5.48: ADAPTATION PROCESS OF RT AND RT+ROUTE VERSIONS FOR INJECTION OF 15% FAULTS IN           | ,          |

| THE USER MEMORY                                                                                      |            |

| FIGURE 5.49: ADAPTATION PROCESS OF RT AND RT+ROUTE VERSIONS FOR INJECTION OF 30% FAULTS IN           |            |

| THE USER MEMORY                                                                                      |            |

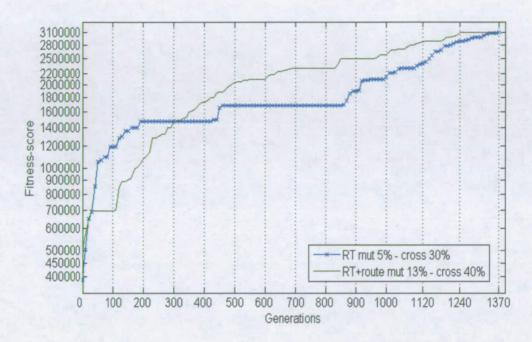

| FIGURE 5.50: ADAPTATION PROCESS OF RT AND RT+ROUTE VERSIONS FOR INJECTION OF 15% FAULTS IN           |            |

| THE CONFIGURATION MEMORY                                                                             |            |

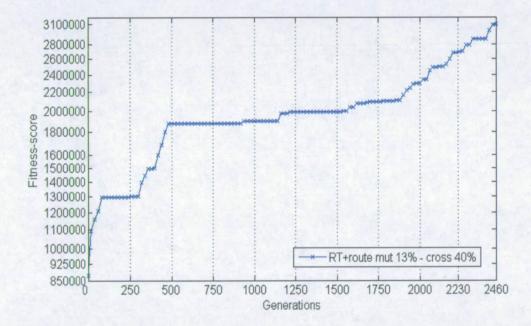

| FIGURE 5.51: ADAPTATION PROCESS OF RT+ROUTE VERSION FOR INJECTION OF 30% FAULTS IN TOTAL IN          |            |

| THE USER AND CONFIGURATION MEMORY                                                                    |            |

| FIGURE 5.52: POWER ANALYSIS FOR THE EVOLVED FILTERS                                                  |            |

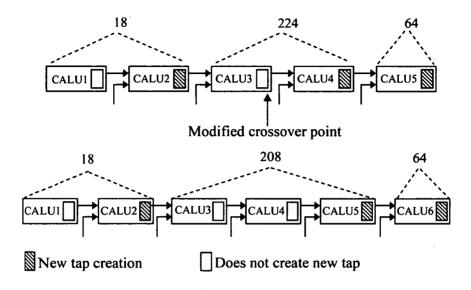

| FIGURE 6.1: DESCRIPTION OF MODIFIED-CROSSOVER OPERATION, WHICH ASSIGNS AN ADDITIONAL CALU            | , -        |

| IN THE REALIZATION OF THE 2 <sup>ND</sup> COEFFICIENT WITHOUT AFFECTING THE CONFIGURATION OF THE RES | ст         |

| COEFFICIENT-SET                                                                                      |            |

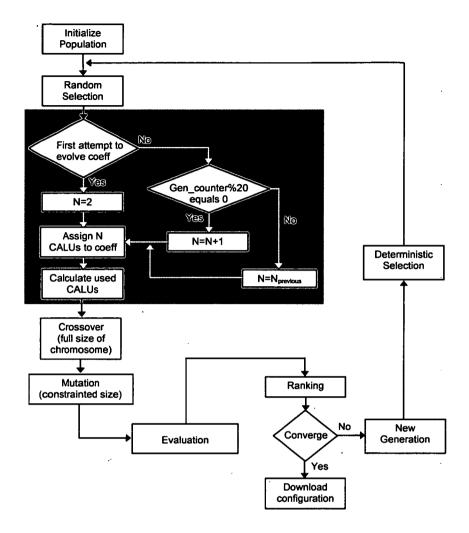

| FIGURE 6.2: FLOW-DIAGRAM OF THE INCREMENTAL EVOLUTIONARY TECHNIQUE                                   |            |

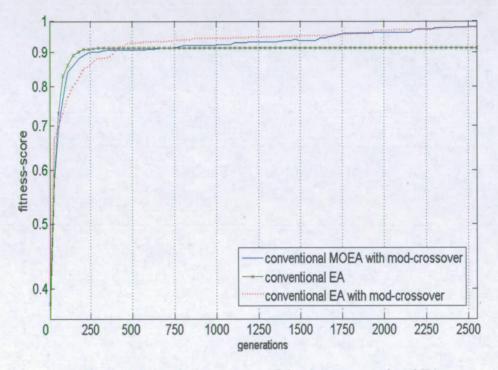

| FIGURE 6.3: EVOLUTION PROCESS OF THE THREE CONVENTIONAL EAS                                          |            |

| 100                                                                                                  |            |

х

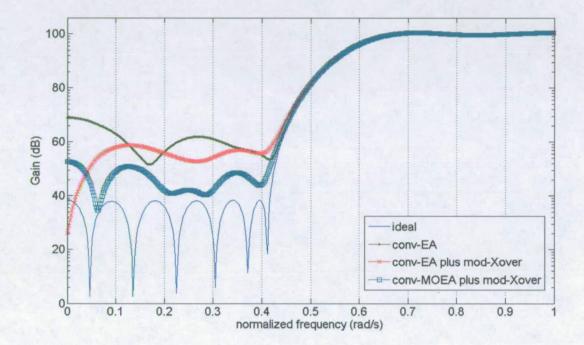

| FIGURE 6.4: EVOLVED FREQUENCY RESPONSE OF THE THREE CONVENTIONAL EAS AFTER 2550                                                                                      |           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| GENERATIONS                                                                                                                                                          | 6 -       |

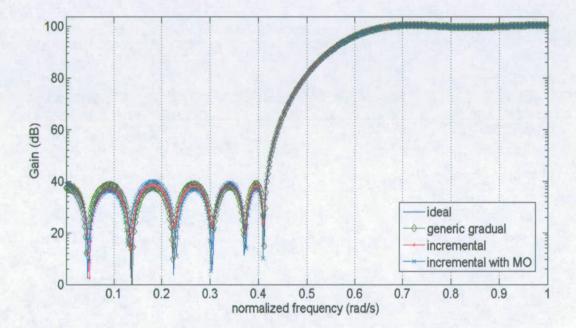

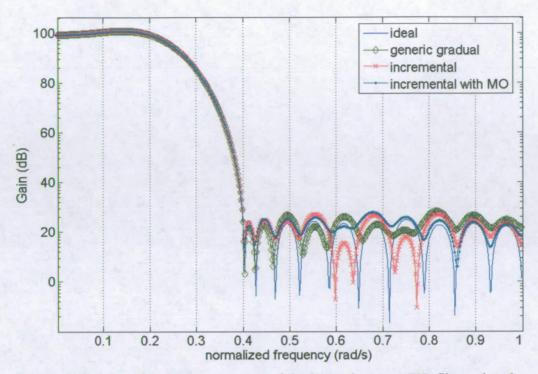

| FIGURE 6.5: EVOLVED FREQUENCY RESPONSE OF THE 19-TAP HIGH-PASS FIR FILTER USING THE THREE EA<br>- 16                                                                 |           |

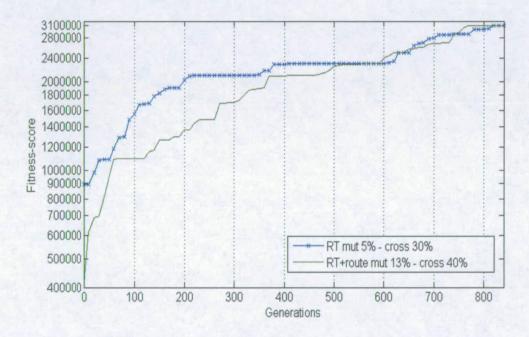

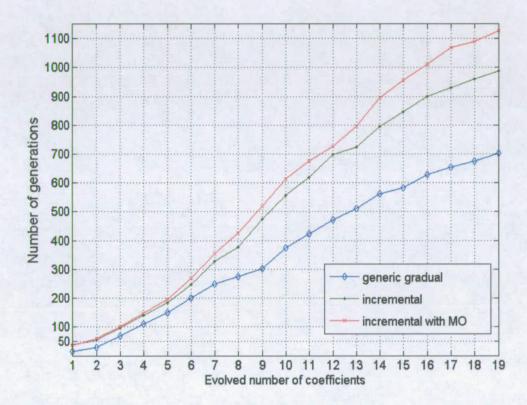

| FIGURE 6.6: EVOLUTION PROCESS OF THE THREE EAS FOR THE EVOLUTION OF THE 19-TAP HIGH-PASS FIF<br>FILTER                                                               | ٢         |

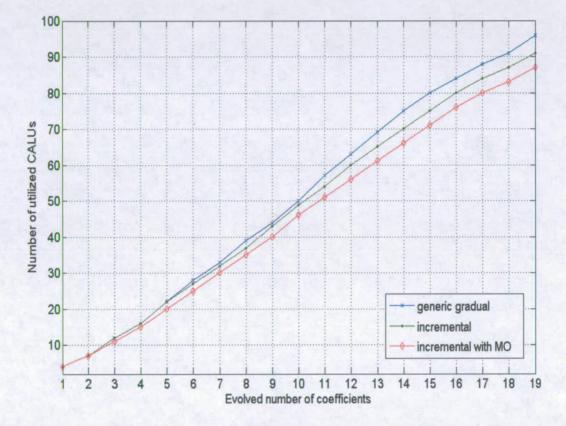

| FIGURE 6.7: HARDWARE UTILIZATION OF THE THREE EAS FOR THE EVOLUTION OF THE 19-TAP HIGH-PASS<br>FIR filter                                                            |           |

| - 17                                                                                                                                                                 | 1 -       |

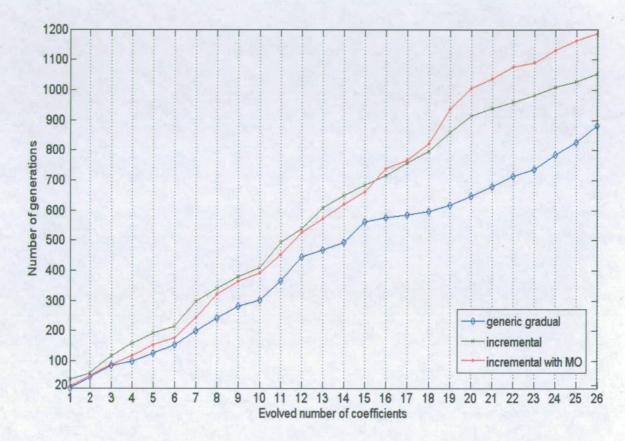

| FIGURE 6.9: EVOLUTION PROCESS OF THE THREE EAS FOR THE EVOLUTION OF THE 26-TAP LOW-PASS FIR FILTER                                                                   |           |

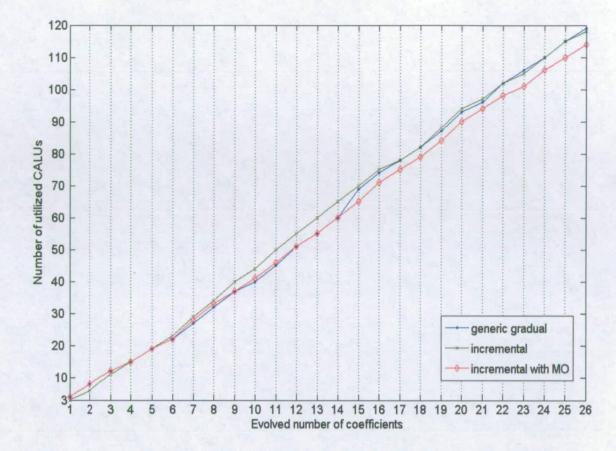

| FIGURE 6.10: HARDWARE UTILIZATION OF THE THREE EAS FOR THE EVOLUTION OF THE 26-TAP LOW-PAS<br>FIR filter                                                             |           |

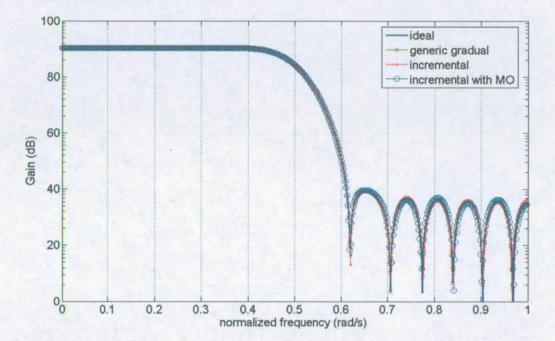

| FIGURE 6.11: EVOLVED FREQUENCY RESPONSE OF THE 31-TAP LOW-PASS FIR FILTER USING THE THREE<br>EAS                                                                     | 4 -       |

| FIGURE 6.12: EVOLUTION PROCESS OF THE THREE EAS FOR THE EVOLUTION OF THE 31-TAP LOW-PASS FI FILTER                                                                   | 5 -       |

| FIGURE 6.13: HARDWARE UTILIZATION OF THE THREE EAS FOR THE EVOLUTION OF THE 31-TAP LOW-PAS<br>FIR filter                                                             | 6-        |

| FIGURE 7.1: COMPARISON OF THE FREQUENCY RESPONSE BETWEEN THE IDEAL AND THE EVOLVED FILTER<br>(FIR1)                                                                  | 1 -       |

| FIGURE 7.2: COMPARISON OF THE FREQUENCY RESPONSE BETWEEN THE IDEAL AND THE EVOLVED FILTER<br>(FIR2) 18                                                               | 2 -       |

| FIGURE 7.3: BLOCK DIAGRAM OF THE DRIVE CONTROL LOOP 18                                                                                                               | 3 -       |

| FIGURE 7.4: RECONFIGURABLE HARDWARE FOR KP AND KI MODULES                                                                                                            |           |

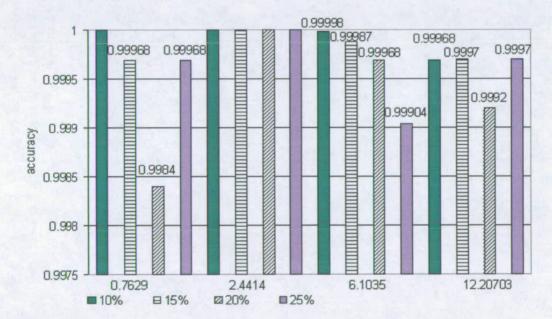

| FIGURE 7.5: SIMULATION RESULTS OF PI CONTROLLER FOR 4 DYNAMICALLY VARYING MUTATION RATES (10%, 15%, 20% AND 25%)                                                     |           |

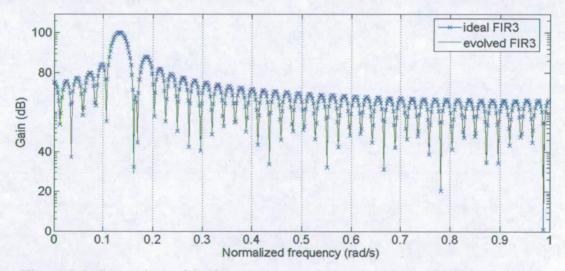

| FIGURE 7.6: COMPARISON OF THE FREQUENCY RESPONSE BETWEEN THE IDEAL AND THE EVOLVED FILTER<br>(FIR3)                                                                  |           |

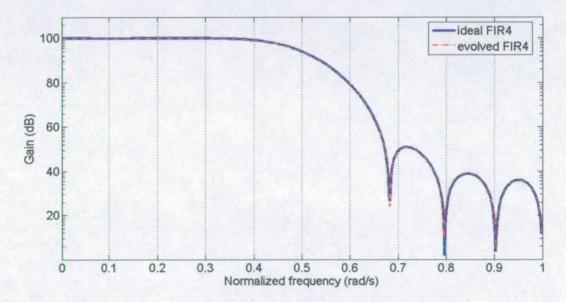

| FIGURE 7.7: COMPARISON OF THE FREQUENCY RESPONSE BETWEEN THE IDEAL AND THE EVOLVED FILTER<br>(FIR4)                                                                  | 6 -       |

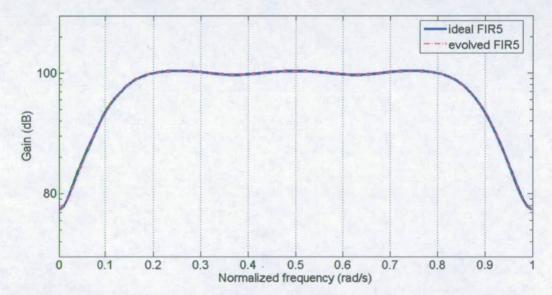

| FIGURE 7.8: COMPARISON OF THE FREQUENCY RESPONSE BETWEEN THE IDEAL AND THE EVOLVED FILTER<br>(FIR5)                                                                  |           |

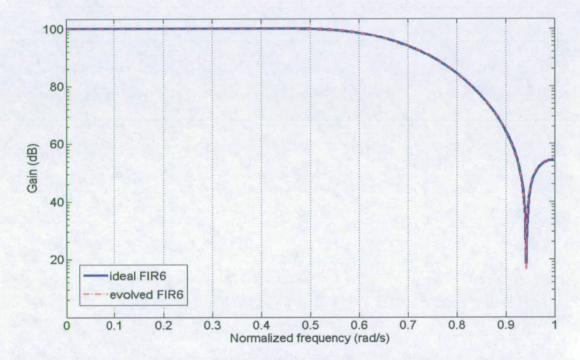

| FIGURE 7.9: COMPARISON OF THE FREQUENCY RESPONSE BETWEEN THE IDEAL AND THE EVOLVED FILTER<br>(FIR6)                                                                  |           |

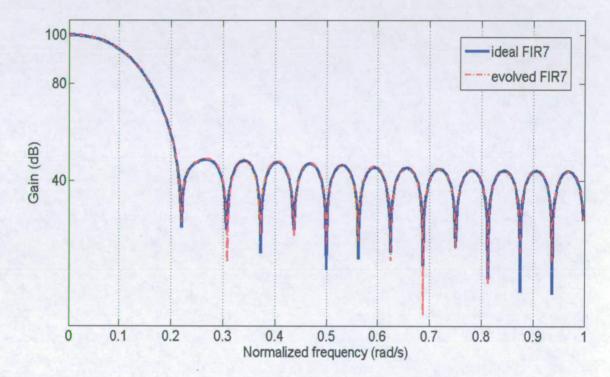

| FIGURE 7.10: COMPARISON OF THE FREQUENCY RESPONSE BETWEEN THE IDEAL AND THE EVOLVED FILTE<br>(FIR7)                                                                  | R         |

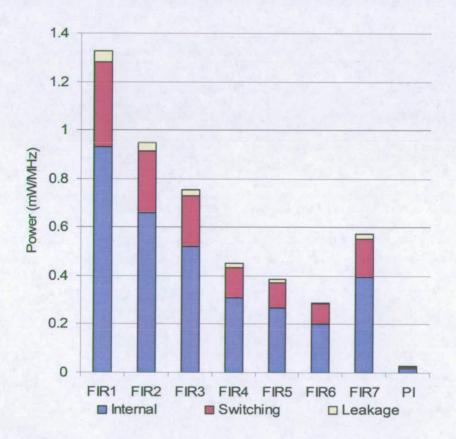

| FIGURE 7.11: POWER ANALYSIS OF THE 7 FIR FILTERS AND THE PI CONTROLLER THAT COMPOSE THE DRIV<br>AND SENSE-REBALANCE LOOP AND THE DEMODULATION STAGE OF THE GYROSCOPE | ve<br>1 - |

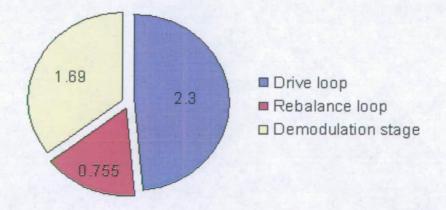

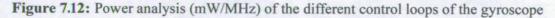

| FIGURE 7.12: POWER ANALYSIS (MW/MHZ) OF THE DIFFERENT CONTROL LOOPS OF THE GYROSCOPE - 19<br>FIGURE 7.13: ON-CHIP SOLUTION OF THE HOUSTIC SYSTEM - 19                |           |

| FIGURE 7.13. UN-UNIP SOLUTION OF THE HOUSTIC SYSTEM                                                                                                                  | 44 -      |

xi

# **List of Tables**

| TABLE 5-1: SYNTHESIS RESULTS OF THE RECONFIGURABLE HARDWARE (13x13 ARRAY)              | 67 -    |

|----------------------------------------------------------------------------------------|---------|

| TABLE 5-2: LOW-PASS FILTER SPECIFICATION                                               |         |

| TABLE 5-3: HIGH-PASS FILTER SPECIFICATION                                              | 76 -    |

| TABLE 5-4: COEFFICIENTS OF THE 8-TAP LOW-PASS FILTER                                   | 80 -    |

| TABLE 5-5: COEFFICIENTS OF THE 12-TAP HIGH-PASS FILTER                                 |         |

| TABLE 5-6: SILICON AREA OF THE RECONFIGURABLE HARDWARE                                 | 82 -    |

| TABLE 5-7: POWER COMPARISON BETWEEN THE RECONFIGURABLE ARCHITECTURE AND SIMILAR FIR    |         |

| IMPLEMENTATIONS WITH ASIC AND FPGA TECHNOLOGIES                                        |         |

| TABLE 5-8: LOW-PASS FILTER SPECIFICATION.                                              |         |

| TABLE 5-9: PASS-BAND FILTER SPECIFICATION                                              |         |

| TABLE 5-10: AREA RESULTS OF RECONFIGURABLE DESIGN (50 VERTICES)                        |         |

| TABLE 5-11: SPECIFICATION OF SYMMETRICAL 17-TAP LOW-PASS FIR FILTER                    |         |

| TABLE 5-12: SPECIFICATION OF SYMMETRICAL 49-TAP PASS-BAND FIR FILTER                   |         |

| TABLE 5-13: SPECIFICATION OF SYMMETRICAL 31-TAP LOW-PASS FIR FILTER                    |         |

| TABLE 5-14: COMPARISON OF RECONFIGURABLE HARDWARE SUBSTRATES                           |         |

| TABLE 6-1: MUTATION RATES PER GENE                                                     |         |

| TABLE 6-2: SPECIFICATION OF IDEAL FILTERS                                              |         |

| TABLE 6-3: EVALUATION OF PROPOSED EVOLUTIONARY TECHNIQUES.                             |         |

| TABLE 7-1: CHARACTERISTICS OF FILTERS' SPECIFICATION AND SIMULATION RESULTS CONCERNING |         |

| HARDWARE UTILIZATION AND CONVERGENCE TIME                                              | - 190 - |

| TABLE 7-2: POWER RESULTS FOR THE FIR FILTERS AND THE PL CONTROLLER                     |         |

# **Acronyms and Abbreviations**

| A/S Unit | Addition/Subtraction Unit               |

|----------|-----------------------------------------|

| ADC      | Analogue-to-Digital Converter           |

| AGC      | Automatic Gain Control                  |

| ASIC     | Application Specific Integrated Circuit |

| CALB .   | Configurable-Arithmetic-Logic-Block     |

| CALU     | Configurable-Arithmetic-Logic-Unit      |

| CPL      | Computational Layer                     |

| CSD      | Canonical-Signed-Digit                  |

| CSE      | Common Sub-expression Elimination       |

| CTL      | Control Layer                           |

| DAC      | Digital-to-Analogue Converter           |

| DFG      | Data Flow Graph                         |

| DSP      | Digital Signal Processing               |

| EA       | Evolutionary Algorithm                  |

| EHW      | Evolvable Hardware                      |

| FFT      | Fast-Fourier-Transform                  |

| FIR      | Finite Impulse Response                 |

| FOG      | Fiber-Optic-Gyroscope                   |

| FPGA     | Field Programmable Gate Array           |

| FSM      | Finite-State-Machine                    |

| GA       | Genetic Algorithm                       |

| GPS      | Global Positioning System               |

| IIR      | Infinite Impulse Response               |

|          |                                         |

| JPL                                                                   | Jet Propulsion Laboratory                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAG                                                                   | Minimum-Adder-Graph                                                                                                                                                                                                                                      |

| МСМ                                                                   | Multiple Constant Multiplication                                                                                                                                                                                                                         |

| MEMS                                                                  | Micro-Electro-Mechanical Systems                                                                                                                                                                                                                         |

| МО                                                                    | Multi-Objective                                                                                                                                                                                                                                          |

| MOEA                                                                  | Multi-Objective Evolutionary Algorithm                                                                                                                                                                                                                   |

| PALU                                                                  | Programmable-Arithmetic-Logic-Unit                                                                                                                                                                                                                       |

| PE                                                                    | Processing Element                                                                                                                                                                                                                                       |

| PGA                                                                   | Parallel Genetic Algorithm                                                                                                                                                                                                                               |

| PID                                                                   | Proportional Integral Derivative                                                                                                                                                                                                                         |

| PLD                                                                   | Programmable Logic Device                                                                                                                                                                                                                                |

| POF                                                                   | Primitive Operation Filtering                                                                                                                                                                                                                            |

| R/L Shifter                                                           | Right/Left Shifter                                                                                                                                                                                                                                       |

|                                                                       | 8                                                                                                                                                                                                                                                        |

| R4SDC                                                                 | Radix-4 Single Delay Commutator                                                                                                                                                                                                                          |

|                                                                       | -                                                                                                                                                                                                                                                        |

| R4SDC                                                                 | Radix-4 Single Delay Commutator                                                                                                                                                                                                                          |

| R4SDC<br>RAG-n                                                        | Radix-4 Single Delay Commutator<br>Reduced-Adder-Graph                                                                                                                                                                                                   |

| R4SDC<br>RAG-n<br>RLG                                                 | Radix-4 Single Delay Commutator<br>Reduced-Adder-Graph<br>Ring-Laser-Gyroscope                                                                                                                                                                           |

| R4SDC<br>RAG-n<br>RLG<br>SCM                                          | Radix-4 Single Delay Commutator<br>Reduced-Adder-Graph<br>Ring-Laser-Gyroscope<br>Single Constant Multiplication                                                                                                                                         |

| R4SDC<br>RAG-n<br>RLG<br>SCM<br>SDF                                   | Radix-4 Single Delay Commutator<br>Reduced-Adder-Graph<br>Ring-Laser-Gyroscope<br>Single Constant Multiplication<br>Standard-Delay-Format                                                                                                                |

| R4SDC<br>RAG-n<br>RLG<br>SCM<br>SDF<br>SEU                            | Radix-4 Single Delay Commutator<br>Reduced-Adder-Graph<br>Ring-Laser-Gyroscope<br>Single Constant Multiplication<br>Standard-Delay-Format<br>Single Event Upset                                                                                          |

| R4SDC<br>RAG-n<br>RLG<br>SCM<br>SDF<br>SEU<br>SHE                     | Radix-4 Single Delay Commutator<br>Reduced-Adder-Graph<br>Ring-Laser-Gyroscope<br>Single Constant Multiplication<br>Standard-Delay-Format<br>Single Event Upset<br>Single Hard Error                                                                     |

| R4SDC<br>RAG-n<br>RLG<br>SCM<br>SDF<br>SEU<br>SHE<br>SoC              | Radix-4 Single Delay Commutator<br>Reduced-Adder-Graph<br>Ring-Laser-Gyroscope<br>Single Constant Multiplication<br>Standard-Delay-Format<br>Single Event Upset<br>Single Hard Error<br>System-on-Chip                                                   |

| R4SDC<br>RAG-n<br>RLG<br>SCM<br>SDF<br>SEU<br>SHE<br>SoC<br>TI        | Radix-4 Single Delay Commutator<br>Reduced-Adder-Graph<br>Ring-Laser-Gyroscope<br>Single Constant Multiplication<br>Standard-Delay-Format<br>Single Event Upset<br>Single Hard Error<br>System-on-Chip<br>Texas Instruments                              |

| R4SDC<br>RAG-n<br>RLG<br>SCM<br>SDF<br>SEU<br>SHE<br>SoC<br>TI<br>TMR | Radix-4 Single Delay Commutator<br>Reduced-Adder-Graph<br>Ring-Laser-Gyroscope<br>Single Constant Multiplication<br>Standard-Delay-Format<br>Single Event Upset<br>Single Hard Error<br>System-on-Chip<br>Texas Instruments<br>Triple Modular Redundancy |

# Nomenclature

| $ F(jw) ^2$         | Amplitude Spectral Density               |

|---------------------|------------------------------------------|

| c(t)                | Actual process variable measurement      |

| Deg/hr              | Degrees per hour                         |

| e(t)                | Error signal                             |

| e <sub>D</sub> [j]  | Digitalized input                        |

| $f_p$               | Pass-band edge frequency                 |

| $F_s$               | Sampling frequency                       |

| $f_s$               | Stop-band edge frequency                 |

| h (k)               | Impulse response                         |

| H (z)               | Transfer Function                        |

| Imag <sub>in</sub>  | Imaginary part of the input data samples |

| Imag <sub>out</sub> | Imaginary part of the system's output    |

| K <sub>d</sub>      | Derivative coefficient                   |

| K <sub>i</sub>      | Integral coefficient                     |

| $K_p$               | Proportional coefficient                 |

| <b>r</b> (t)        | Reference signal of set-point            |

| Real <sub>in</sub>  | Real part of the input data samples      |

| Realout             | Real part of the system's output         |

| $T_c$               | Sampling period                          |

| $T_d$               | Derivative time                          |

| T <sub>i</sub>      | Integral time                            |

| u (n)               | Impulse unit                             |

|                     |                                          |

- x(n) Present values of the input

- X(t) Input data in time domain

- X(z) Input data in frequency domain

- y (n) Current output sample

- Y(t) System's output in frequency domain

- Y(z) System's output in frequency domain

- $\beta$  Elevation Angle

- $\delta_p$  Peak pass-band deviation

- $\delta_s$  Stop-band deviation

- $\varphi$  Azimuth Angle

### Abstract

The advent of System-on-Chip technology and the continuous shrinkage in silicon device feature size are dictating the need for realization of miniaturized integrated robust and autonomous systems. This need is especially evident in systems operating within hostile environments, such as aerospace.

Evolvable Hardware (EHW) is a technology, which shows promise in meeting the needs of systems facing malfunctions due to harsh electronics environments. Key features of EHW are a reconfigurable fabric and an evolutionary strategy. The design of a complete and efficient EHW framework must consider both these features concurrently. This comprehensive approach to the design of EHW based systems is an issue considered by only a few researchers in the literature.

This thesis presents a novel holistic EHW framework that accomplishes all the electronics associated with the JPL/Boeing gyroscope sensor. It includes an efficient fault-tolerant reconfigurable fabric and an integrated on-chip multi-objective evolutionary strategy. The conception and implementation of both parts also consider real-time adaptation and low-power consumption for enabling ultra-long life aerospace missions.

A number of key objectives have been achieved: a) The Verilog implementation of an autonomous reconfigurable fabric that is capable of accomplishing the sensor's electronics with substantial accuracy (>99.7%), b) The implementation of numerous

evolutionary strategies that are able to primarily guide the hardware evolution even in the presence of 30% faults injected in the user and configuration memory of the system, c) This in addition to a reduction from 8.6 to 9.8 times in the number of generations that are needed for the evolution of a 31-tap FIR filter, compared with previous research in this field, d) Furthermore, the circuits evolved consume 3.3 times less power than similar implementations within industrial reconfigurable devices.

xviii

## Chapter 1 Introduction

1

### 1.1 Introduction

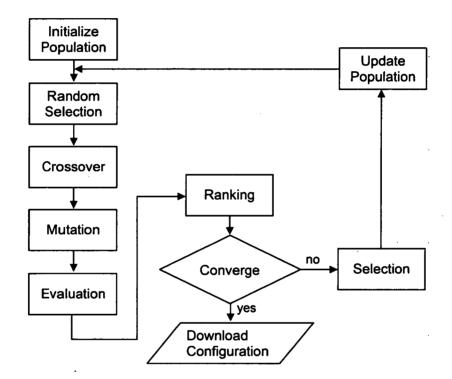

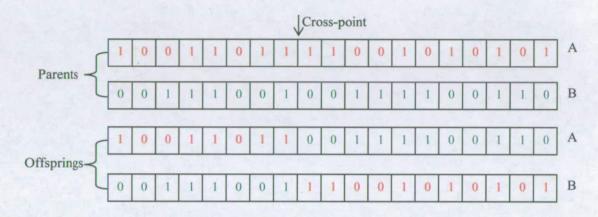

Evolvable Hardware (EHW) is a very promising field at the confluence of *reconfigurable hardware, automatic design, artificial intelligence* and *autonomous systems*. In a narrow sense, EHW is reconfigurable hardware whose on-chip configuration is under the control of an Evolutionary Algorithm (EA) [32], [42]. EAs provide genetic search/optimization algorithms, which work on a population (multiple chromosomes usually expressed with binary strings) of prospective solutions and apply operations motivated by natural selection to provide better solutions to multi-objective problems.

The main objective of EHW is to automate the design of mixed-analog electronic circuits that are capable to adapt/reconfigure their hardware structure [39], [50] over time, so as to achieve an optimal configuration that meets better their functional specifications. Since the emergence of EHW, evolutionary reconfigurable systems have successfully been employed for numerous applications that demand adaptive reconfiguration, such as in fault-recovery systems [92], [100], automated circuit synthesis and design [12], [56], [57], [123], dynamical control of MEMS circuits, evolutionary Global-Positioning-System (GPS) attitude determination of vehicles [119], automated antenna design [66], etc.

The underlying theme of this thesis has been to investigate a number of custom reconfigurable architectures for the autonomous design and reconfiguration of digital high-order FIR filters using the principle of EHW. Each reconfigurable architecture is therefore configured using a Genetic Algorithm (GA) that derives from a class of non-heuristic search and optimization techniques termed EAs, which are inspired by the process of biological evolution.

The outcomes of this research work are evaluated using a real-life application such as the vibratory gyroscope, which has been fabricated by Jet-Propulsion-Laboratory (JPL) and Boeing. Due to the nature of the applications that this sensor targets, the overall design policy of this architecture must be guided by the fact that nowadays ultra-long life space missions require hardware to remain operational within specified performance parameters for decades. Therefore, power consumption is a factor that has a key role in the design of the reconfigurable platforms employed to accommodate the sensor's electronic circuits. Moreover, the reconfigurable hardware fabrics must be able to cope with anticipated faults that occur mainly due to radiation. The goal of this research is very challenging, considering that micro-machined gyroscopes for measuring rotational rates have attracted a lot of attention during the past few years for several applications involving space conquest, military missions, biomedical activities, etc.

This thesis focuses on investigating and implementing a *low-power autonomously reconfigurable EHW architecture* that aims at controlling the core electronics of the JPL/Boeing gyroscope against several unstable factors like aging of electronic devices, fault occurrence and temperature variations.

-2-

The novelty in this research lies on the implementation of an efficient Very-Large-Scale-Integration (VLSI) EHW framework including a *low-power* and *fault-tolerant reconfigurable hardware* substrate and a customized *reconfiguration mechanism* able to efficiently guide the implementation and/or reconfiguration process of the JPL/Boeing gyroscope's electronics, in terms of *accuracy* and *speed of adaptation*. The *reconfigurable hardware* must be able to accomplish and maintain the gyroscope's functionality in the presence of endogenous and exogenous factors, such as anticipated faults and environmental variations. The recovery method should not be based on hardware redundancy because this method is impractical, due to restrictive size and weight requirements imposed on spacecraft. On the contrary, the fault-tolerant method is based on the reconfigurable hardware. This approach differentiates from commercial architectures and presents better performance in terms of silicon occupation, power dissipation and efficiency in adaptation.

### **1.2 Thesis Achievements**

As has been mentioned in the introduction of this thesis the main scope of this research is to invent and implement an EHW framework that is able to accomplish the electronics associated with the JPL/Boeing gyroscope's electronic circuits and satisfy the requirements imposed by the nature of the targeted application. The final achievements of this research work can be summarized below:

-3-

- The development of a low-power and fault-tolerant EHW framework that is able to accommodate the JPL/Boeing gyroscope's electronic circuits and provide to these real-time adaptation/reconfiguration in the presence of endogenous and/or exogenous factors.

- The development of four novel reconfigurable hardware substrates, which target the implementation of the sensor's electronics. The temporal order in the demonstration of these designs within the thesis reveals the problems, which have been emerged, during the implementation of the targeted circuits and the actions, which have been taken in order to work these problems out.

- The development of a fault-tolerant reconfiguration mechanism. It is a novel implementation of a parallel fine-grained GA that aims at providing a faulttolerant solution to applications that require autonomous dynamic reconfiguration mechanisms.

- The development of three novel reconfiguration mechanisms, which in collaboration with a novel reconfigurable hardware substrate target to further improve the implementation of the sensor's electronics in terms of accuracy, power-consumption and real-time adaptation.

### **1.3 Thesis Outline**

This thesis therefore focuses on the implementation of an efficient EHW framework including a low-power and fault-tolerant reconfigurable hardware substrate and a

-4-

customized reconfiguration mechanism able to efficiently guide the implementation and/or reconfiguration process of the JPL/Boeing gyroscope's electronics, in terms of accuracy and speed for adaptation. This thesis is organized as follows:

- Chapter 2 introduces the JPL/Boeing gyroscope and provides an overview of its structure and operation principles. Moreover, it analyses the electronic circuits that implement the control-loops of the gyroscope and presents previous work that has been done concerning the gyroscope itself and possible architectures that could be used to efficiently accomplish the sensor's electronics.

- Chapter 3 introduces the concept of GAs and describes the methodology that these are applied on EHW in general and particularly in this thesis in order to evolve the electronics associated with the JPL/Boeing gyroscope's control-loops.

- Chapter 4 introduces the concept of a stand-alone architecture that consists of a reconfigurable hardware and a reconfiguration mechanism. It mainly presents the implementation of a novel fault-tolerant reconfiguration mechanism. The architecture is based on a parallel fine-grained GA. The overall idea is a System-on-Chip fault-tolerant implementation that would be able to compensate for faults occurring either in the reconfigurable hardware that accommodate the sensor's electronics or the reconfiguration mechanism that guide the evolution of the digital circuits.

- Chapter 5 composes the main part of this thesis and presents the continuous development of several reconfigurable hardware substrates in order to reach the

main objective of this thesis that is to evolve the sensor's electronics under certain requirements.

- Chapter 6 is mainly concentrated on comparing conventional reconfiguration mechanisms with three proposed evolutionary strategies that have not been published before. In this Chapter the best found reconfigurable hardware substrate is employed in order to evaluate the evolutionary strategies.

- Chapter 7 employs the most successful combination of reconfigurable hardware substrate and reconfiguration mechanism to evolve the electronic circuits related with the control-loops of the sensor. Total power calculation is also provided for the majority of the associated electronics.

- Chapter 8 summarizes the conclusions obtained from each of the previous chapters. Furthermore, improvements are suggested concerning the research work that is presented in this thesis in order to further extent the gained knowledge.

#### 1.4 Summary

This research work aims at investigating several architectural solutions for identifying the most appropriate physical mean for the autonomous design of high-order FIR filters. Moreover, these filters must incorporate several techniques such as primitive operations, multi-objective optimization and effective approaches for minimizing the search space of the employed EAs in order to meet the criteria imposed by the electronics associated with the JPL/Boeing vibratory sensor. The following chapters

#### Chapter 1 - Introduction

analyze the nature of the targeted application, the specification of electronics that have to be implemented and presents several EHW architectures that target to successfully achieve the ideal functionality and simultaneously meet the targeted performance in terms of power consumption, speed for adaptation, throughput and fault-robustness when stuck-at faults are injected in the *user* and *configuration* memory of the system.

-7-

## Chapter 2 JPL/Boeing Gyroscope

#### 2.1 Introduction

A gyroscope is a commonly used sensor for measuring angular velocity. Although conventional rotating-wheel, fiber-optic and ring-laser gyroscopes are dominant in many applications, their size, power inefficient mechanism and cost limit their utilization in a wider range of industries such as automobile, satellite, video game and handheld positioning systems. However, with the advent of MEMS machining technologies, micro-machined gyroscopes for measuring rate or angle of rotation have attracted a lot of attention during the past few years, for several applications. They can be used either as a low-cost miniature companion with micro-machined accelerometers to provide heading information for inertial navigation purposes or in other areas including automotive applications for ride stabilization and rollover detection, biomedical applications, in consumer applications (video-camera stabilization, virtual reality, etc.), in robotics and in a wide range of military applications.

JPL/Boeing MEMS gyroscopes aim at providing future Space missions with a low-cost, reduced mass and low-power consumption inertial measurement unit [11]. Typical applications that would benefit from this technology include: inertial spacecraft navigation to complement a star tracker or sun sensor, integration of the device in a planetary rover and detection of angular rotation in all axes of a robotic arm. This sensor presents superiority over conventional designs (spinning-mass) because it is typically orders of magnitude smaller and consumes less power. Moreover, optical gyroscopes such as Fiber-Optic-Gyros (FOGs) [122] and Ring-Laser-Gyros (RLGs) [8], [107] are also large, power consuming and expensive. In addition to this, FOGs suffer from performance degradation when they are left exposed in radiation due to optical fiber darkening [31], while RLGs suffer from laser life issues [63]. Moreover, while there have been several MEMS gyroscopes [13], [14], [54], [121] reported in the literature, the performance of these devices for spaceflight has been inadequate due to large bias stabilities (>1 deg/hr) resulting in non zero-rate drift. On the contrary, the JPL/Boeing gyroscope presents a vastly improved bias stability of 0.1 deg/hr [30], [75].

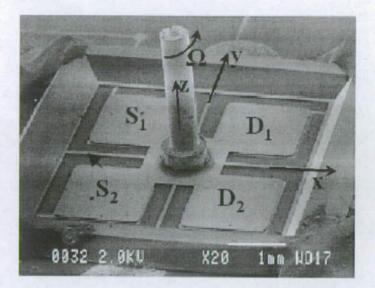

### 2.2 Structure and Operation Overview

The JPL/Boeing gyroscope is a vibratory rate sensor whose operation depends on the Coriolis coupling [80] of one degree of freedom to another degree of freedom within the sensor. Figure 2.1 depicts an electron microscope photograph of the JPL/Boeing gyroscope [20]. There are four paddles labeled  $D_1$ ,  $D_2$ ,  $S_1$  and  $S_2$  that compose the *drive* and *sense* rocking modes, respectively. These paddles are suspended above four electrodes by the thin silicon springs, which are evident in Figure 2.1, between the paddles. Paddles  $D_1$  and  $D_2$  compose the drive axis inputs. Applying a potential between the electrodes beneath  $D_1$  and  $D_2$  causes the paddles to pull closer to the electrodes due to electrostatic forces. Consequently, these forces rock the assembly about the y-axis, shown in Figure 2.1. The large post, in the center, adds inertia to the

rocking modes and aids in coupling the degrees of freedom. Excitation at the drive axis natural frequency is desirable, since a large response is obtained, which boosts the sensitivity of the sensor. Furthermore, angular rotation of the frame about the z-axis induces post-rocking, due to Coriolis Effect, about the x-axis. The x-axis is called the *sense axis* and the rocking velocity about this is measured by capacitive sensors at paddles S<sub>1</sub> and S<sub>2</sub>. These measurements are related to the angular rate of rotation of the frame. In an ideal device, both the *sense* and *drive* rocking modes have equal frequencies and the nodal axes coincide with the x-axis and y-axis in the sensor frame. However, fabrication irregularities may cause a split between the rocking mode frequencies as well as a change in orientation of the nodal axes with respect to the electrodes. Moreover, the *drive* and *sense* axis frequencies are sensitive to temperature variations. Therefore, the JPL/Boeing gyroscope, as any other vibratory sensor, needs the implementation of numerous control-loops to improve its bandwidth, linearity, dynamic range and to maintain performance in the presence of perturbations to the sensor dynamics.

The electronics that compose the control-loops of the gyroscope are presented in the next section, while further details on the design, identification of the sensor's dynamics and operation principles of the sensor can be found in [71], [97], [98], [99], since these are beyond the scope of this research.

- 10 -

Figure 2.1: Electron microscope photograph of the JPL/Boeing gyroscope [20]

### 2.3 Circuits Analysis

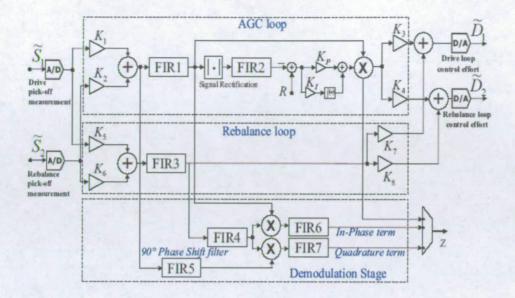

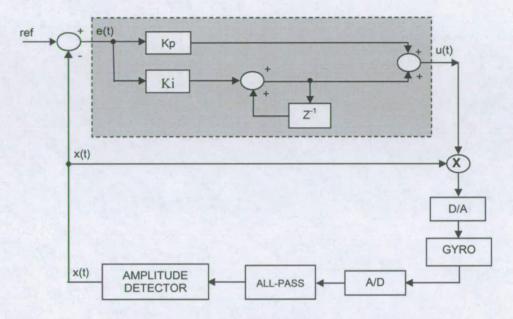

As it was mentioned in Section 2.2, JPL/Boeing gyroscope relies on the coupling of an excited vibration mode into a secondary mode due to Coriolis acceleration. Figure 2.2 depicts a high-level schematic, which presents the functionality of the JPL/Boeing gyroscope [20]. It employs feedback compensation to achieve *harmonic excitation* of selected modes, *disturbance rejection* and *tuning* of the sensor's dynamics. These tasks are employed by two control loops named *drive* and *sense-rebalance* loop. There is also a *demodulation stage* that estimates the angular rotation rate of the gyroscope by demodulating the sense rebalance signal with respect to a measurement of the drive loop response.

Figure 2.2: High-level schematic electronics of the gyroscope's control-loops [20]

Since the Coriolis acceleration is proportional to the velocity of the driven mode, it is desirable to keep the amplitude and the frequency of the *drive* oscillation as large as possible and maintain it constant because small variations can swamp the Coriolis acceleration. This task is accomplished by the *drive-control loop*, which employs for amplitude control, an Automatic-Gain-Control (AGC) loop [72]. According to Figure 2.2, the AGC consists of an all-pass filter (FIR 1), an amplitude detection scheme, a comparator for identifying the amplitude error and a Proportional-Integral (PI) controller that is in charge of providing feedback compensation. According to [20] FIR 1 is an 85-tap filter that achieves attenuation at 2700 Hz. Furthermore, due to the lag that is introduced by the analog-to-digital (ADC) and digital-to-analog (DAC) converters and the anti-aliasing filters, the phase of FIR 1 must be shaped to achieve the target loop phase of 0 degrees at 4428 Hz. Subsequently, the amplitude detection

#### Chapter 2 – JPL/Boeing Gyroscope

scheme consists of a 2's compliment module and a 51-order low-pass filter with 50 Hz cut-off frequency and stop-band attenuation of 40 db. The scope of this module is to produce an estimate of the drive mode response amplitude. Then this amplitude is compared to a programmable level and the error that is generated by the comparator is fed to the PI controller. Finally, the output of the controller modulates the drive mode signal before the signal is fed back to the actuators. The second control loop consists of a linear rebalance loop controller, implemented by FIR3. The primary objective of this loop is to reject the disturbance injected by the Coriolis Effect into the second degree of freedom. A secondary objective is to achieve disturbance rejection in the neighborhood of 2700Hz, which corresponds to damping an elastic mode, whose excitation can lead to degraded sensor performance. Finally, the *demochilation* stage consists of the FIR4 and FIR5 filters, which are typically used to shift signal phases and FIR6 and FIR7, which are low-pass filters, located after the multipliers.

### 2.4 Previous work and new challenges

Significant research work has been done by both JPL and University of California Los Angeles (UCLA) associated with the design, packaging, identification and analysis of the JPL/Boeing gyroscope's dynamics and the implementation of a reprogrammable ASIC solution that incorporates the gyroscope's tasks, introduced in Section 2.3. In [99], JPL has presented up-to-date work on the design, fabrication and packaging of a silicon MEMS gyro design for Space applications. Furthermore, UCLA in [71] discusses the identification of multi input/output models of the JPL/Boeing gyroscope. Subsequently, the authors in [73] show the analysis of a non-linear control system that

#### Chapter 2 - JPL/Boeing Gyroscope

is used to excite and maintain a pre-defined amplitude of a lightly damped degree of freedom in the JPL/Boeing gyroscope. After the completion of the dynamics analysis, further work from UCLA [33] presents on-going achievements on the implementation of the control-loops on a reprogrammable ASIC solution. In addition to this JPL reports in [11] on-going research into a MEMS gyroscope and presents a new fabrication method that improves the gyro's performance. Work analyzing the gyroscope's dependence on temperature variations, is presented in [30], where JPL determines the effect of hysteresis over the range of 35°C to 65°C.

From a hardware perspective, the platform, which accommodates the electronics associated with the gyroscope's control-loops, needs to meet some criteria, such as low-power consumption, adaptability and fault-tolerance that compose significant prerequisites for designs targeting Space applications. UCLA has implemented a low-power reprogrammable ASIC environment, which nevertheless does not provide more flexibility than *custom reconfigurable designs, industrial FPGAs* such as Virtex-II and Virtex-4 devices [118], 2<sup>nd</sup> generation reprogrammable flash devices (ProASIC<sup>PLUS</sup>), provided by Actel [1], AT6000, AT40K and AT40KAL series provided by Atmel [5], *programmable logic devices (PLDs)* [3], [61] and digital signal processing (DSP) platforms, such as the TMS320 provided by Texas Instruments (TI) [105]. On the contrary, these coarse-grained reconfigurable structures are not optimized for a certain application and they target general purpose applications. Therefore, they are quite inefficient in terms of power, while performing evolution on these devices is quite challenging, since their hardware structure is not transparent to the user and the their

configuration string is very long. On the other hand, ASIC designs are not able to compensate for faults that occur in Space, due to the high density of radiation and hence it is very difficult for an organization to invest a huge budget in a Space mission, without securing first high reliability. Therefore, there is a need for new custom reconfigurable architectures that would be able to efficiently accommodate the gyroscope's electronics that mainly consists of seven high-order (up to 128 taps) FIR filters.

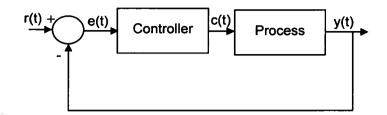

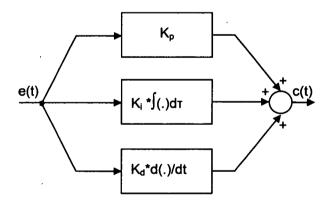

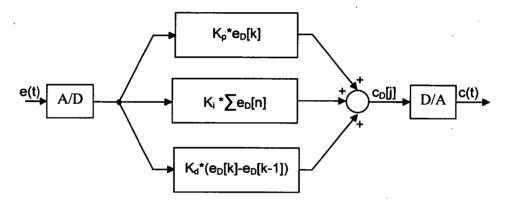

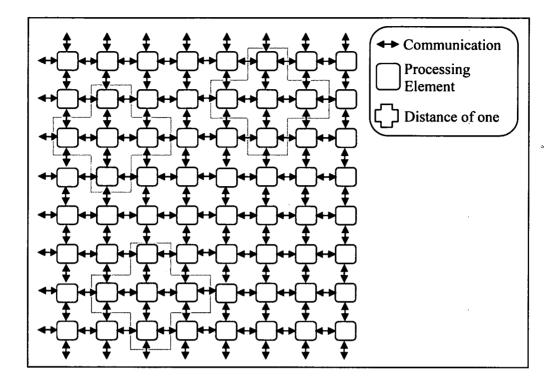

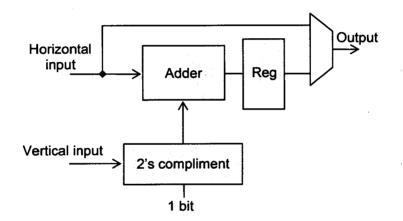

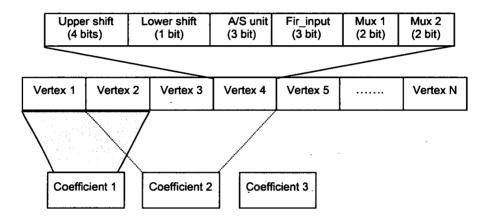

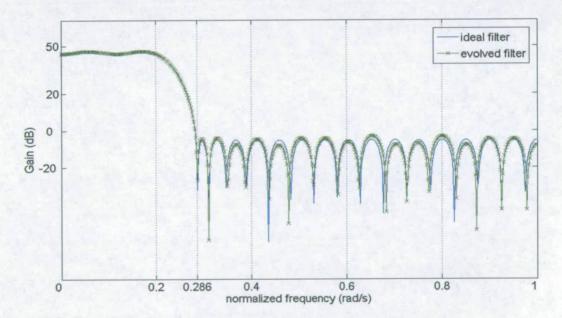

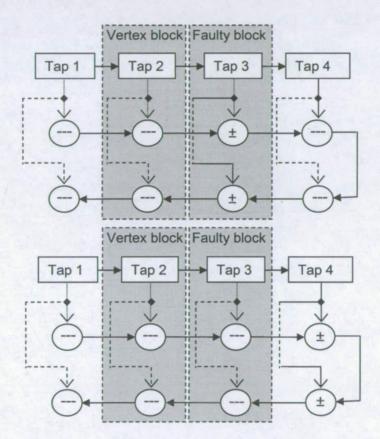

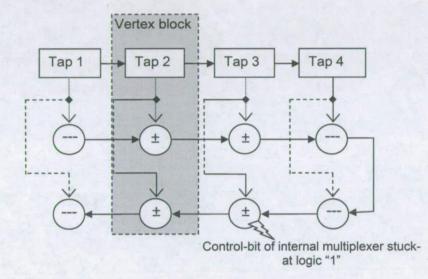

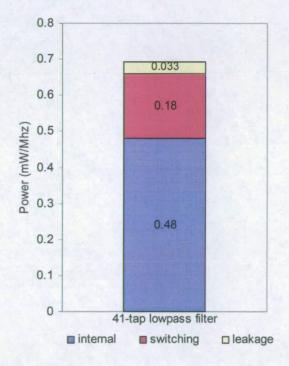

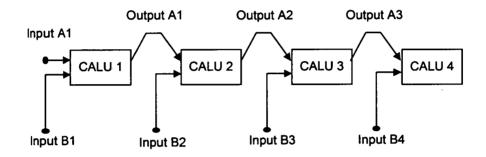

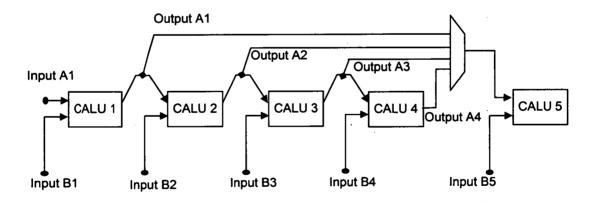

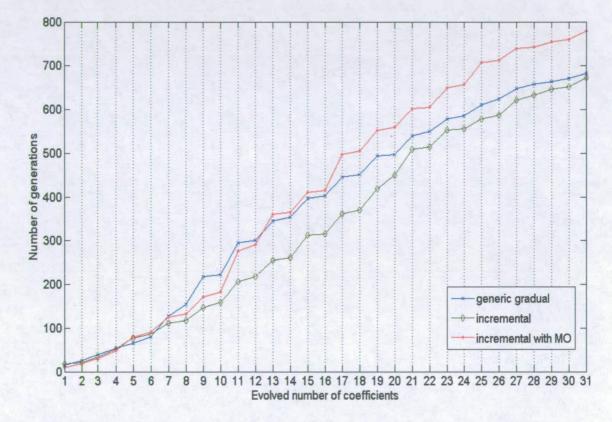

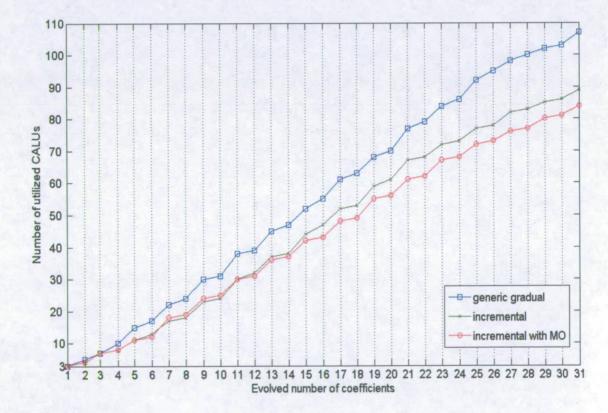

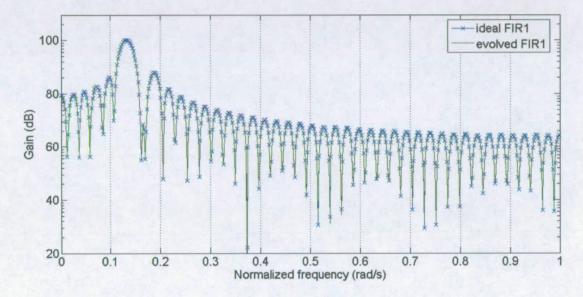

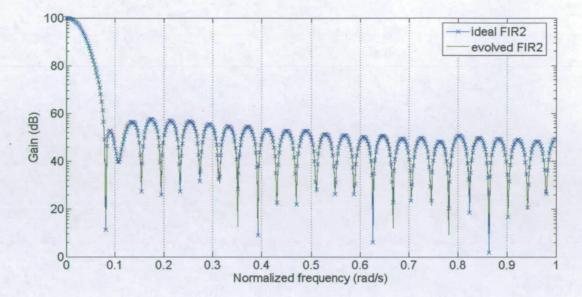

FIR filters are employed in the majority of DSP based electronic systems (image, audio/video processing and coding, sensor filtering etc.) and therefore their efficient implementation within embedded System-on-Chip (SoC) systems is a crucial issue. Specifically, the arithmetic unit and especially the multiplier block in conventional FIR filters, produces several drawbacks that negatively affect the power consumption, the throughput and the fault-tolerance of these filters. Thus, it is imperative for reconfigurable SoC systems that primarily target high robustness, to use a fine-grain design model. According to this model, redundancy can be employed more efficiently because the electronic components that compose the overall architecture are primitive, not complicated operations (such as addition, subtraction and shifting) that do not introduce extensive area overhead, like conventional multipliers do. Hence, the primitive operation filtering technique (POF) [17] is suitable for reconfigurable fabrics that target fault-tolerant applications. Systems that operate in Space must be robust to high density radiation in order to recover from faults without the need of human intervention, which is usually impossible. Particularly, in highly radiated environments,