# The Reconfigurable Instruction Cell Architecture : Reconfiguration and Interconnects

Ioannis Nousias

A thesis submitted for the degree of Doctor of Philosophy.

The University of Edinburgh.

April 2009

#### Abstract

A number of architectural paradigms are available that target different needs, either that is programmability or high performance, ranging from GPPs to ASICs. Since no single architecture can deliver both design traits, the current solutions combine one or more of those paradigms to deliver applications that require post fabrication adaptation and high performance. However, such solutions are faced with the added complexity of a multi-disciplinary task. Reconfigurable computing devices promise to bridge the gap between programmable devices and the sheer performance of ASICs, thus offering a more balanced solution.

This thesis offers a comprehensive set of solutions for the implementation of coarse grained, heterogeneous reconfigurable devices, which led to the development of the Reconfigurable Instruction Cell Array (RICA), an architecture template for reconfigurable computing devices. Based on RISC-like instruction cell, this novel design provides a natural flow for compilers. Unique features introduced in this thesis include, a connection oriented configuration encoding scheme, that takes advantage of the intrinsic characteristics of reconfigurable fabrics, along with the decoding process and the interconnects to accommodate this technique. This innovative code-compression technique offers fast reconfiguration speeds. The work continues by describing a method to improve the routability of the design by deriving a suitable physical placement based on the analysis of a set of input data-paths. It also present a performance improvement by reducing the impact of the configuration latency, by pre-fetching the next configuration context and a method to deal with the variable data-path delays, including memory access operations. Finally, this thesis provides an introduction to a Simultaneous Multi-Threading extension for the RICA core. The above are accompanied by a set of mapping tools, such as routing and allocation, down to bit-stream generation and cycle accurate simulator, as well as a set of architecture generation tools, allowing one to deploy different core setups.

#### Acknowledgements

This thesis would not have been what it is now, without the help of my colleagues and thesis supervisor. More specifically, I would like to thank my colleagues Dr Sami Khawam for his resourcefulness in making the hardware RICA-P1 prototype a reality, Dr Mark J. Milward for his valuable guidance throughout the project, Dr Ying Yi for her work on the compiler and Mr Mark I.R. Muir for his work on the scheduler and software development environment. I would also like to thank Adam Major for his work on porting h264 video decoder on the RICA platform as well as his help in defining the SIMD shuffling operation on RICA-P1. Last but not least, I would like to thank my thesis supervisor Professor Tughrul Arslan for his support and for this unique opportunity to work in an exciting project with important contributions that impact both academia and electronics industry.

### Contents

| 1 | Intr       | Introduction                               |    |  |  |  |  |  |  |  |  |  |  |

|---|------------|--------------------------------------------|----|--|--|--|--|--|--|--|--|--|--|

|   | 1.1        | The RICA project                           | 18 |  |  |  |  |  |  |  |  |  |  |

| 2 | Background |                                            |    |  |  |  |  |  |  |  |  |  |  |

|   | 2.1        | Reconfigurable Computing                   | 24 |  |  |  |  |  |  |  |  |  |  |

|   | 2.2        | Interconnections                           | 25 |  |  |  |  |  |  |  |  |  |  |

|   | 2.3        | Granularity                                | 28 |  |  |  |  |  |  |  |  |  |  |

|   | 2.4        | Coupling                                   | 30 |  |  |  |  |  |  |  |  |  |  |

|   | 2.5        | Programming Model                          |    |  |  |  |  |  |  |  |  |  |  |

|   | 2.6        | Code compression                           | 34 |  |  |  |  |  |  |  |  |  |  |

|   | 2.7        | The role of heuristics in RC architectures | 36 |  |  |  |  |  |  |  |  |  |  |

| 3 | RIC        | RICA overview 3                            |    |  |  |  |  |  |  |  |  |  |  |

|   | 3.1        | Programming Model                          | 43 |  |  |  |  |  |  |  |  |  |  |

|   | 3.2        | Heterogeneous versus Homogeneous           |    |  |  |  |  |  |  |  |  |  |  |

|   | 3.3        | Interconnects                              | 47 |  |  |  |  |  |  |  |  |  |  |

|   | 3.4        | Reconfiguration                            |    |  |  |  |  |  |  |  |  |  |  |

|   | 3.5        | Data memory arbiters                       |    |  |  |  |  |  |  |  |  |  |  |

|   | 3.6        | SIMD instruction cells                     | 50 |  |  |  |  |  |  |  |  |  |  |

|   | 3.7        | Performance figures                        | 51 |  |  |  |  |  |  |  |  |  |  |

| 4 | Inte       | erconnects                                 | 55 |  |  |  |  |  |  |  |  |  |  |

|   | 4.1        | Topologies                                 | 56 |  |  |  |  |  |  |  |  |  |  |

|   | 4.2        | Passive or dynamic interconnects           | 59 |  |  |  |  |  |  |  |  |  |  |

|   | 4.3        |                                            | 60 |  |  |  |  |  |  |  |  |  |  |

| •   |   | •                                                |       |   |

|-----|---|--------------------------------------------------|-------|---|

|     |   | 4.3.1 Virtual Channels with dynamic rate control |       | , |

| ,   |   | 4.3.2 VCDRC performance                          | . 65  |   |

|     | 5 | Path Encoding                                    | 69    |   |

|     |   | 5.1 A connection oriented approach               | . 70  |   |

| ·   |   | 5.2 Path-Encoding Basics                         |       |   |

|     |   | 5.3 Path Encoding displacement format            |       | • |

|     |   | 5.4 Non-monotonic Path-Encoding extension        |       | , |

|     |   | 5.5 Practical example with s-boxes               |       | • |

|     |   | 5.6 Turn-based format and chain encoding         |       |   |

|     |   | 5.7 Splitting paths and fan-outs                 | . 79  |   |

|     |   | 5.8 Implicit port activation                     | . 81  |   |

|     |   | 5.9 Clustered chain                              | . 82  |   |

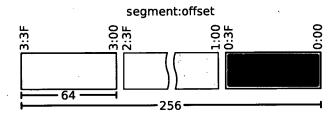

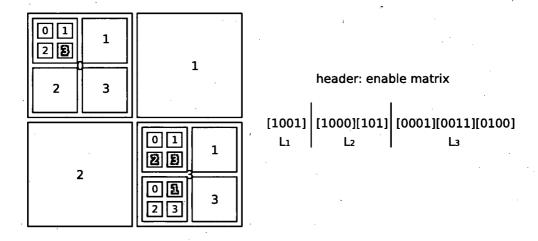

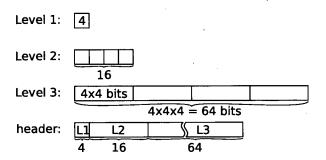

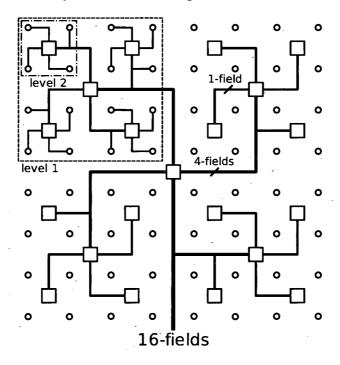

|     |   | 5.10 Hierarchical Enable Matrix                  | . 82  |   |

|     |   | 5.11 Hierarchical clustering for loading         | . 84  |   |

|     |   | 5.12 Irregular/Asymmetric grouping               | . 86  |   |

|     |   | 5.13 Context partitioning. Rows and groups       | . 86  | • |

| ·   |   | 5.14 Compressibility                             | . 89  |   |

|     | 6 | Reconfiguration                                  | 93    |   |

|     |   | 6.1 Configuration distribution                   | . 94  |   |

|     |   | 6.1.1 Off-line routing                           | . 94  |   |

|     |   | 6.1.2 On-line routing                            | . 97  |   |

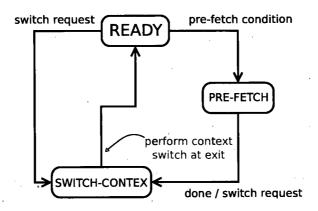

|     | · | 6.2 The Reconfiguration Rate Controller          | . 98  |   |

|     |   | 6.3 Pre-fetching                                 | . 103 |   |

|     |   |                                                  | 4 O E |   |

|     | 7 | Software Toolflow                                | 107   |   |

|     |   | 7.1 Toolflow overview                            |       |   |

|     |   | 7.1.1 Frontend                                   |       |   |

|     |   | 7.1.2 Backend                                    |       |   |

| •   |   | 7.2 Toolflow walk-through example                |       |   |

|     |   | 7.3 RICA Netlist format                          |       |   |

|     |   | 7.4 RICA TLM simulator                           |       |   |

| ,   |   | 7.4.1 Transaction Level Modelling and SystemC    | . 119 |   |

|     |   | 4                                                |       | ı |

|     |   |                                                  |       |   |

| B . |   |                                                  |       |   |

|     |   |                                                  |       |   |

|              | ,          |                                                |            |

|--------------|------------|------------------------------------------------|------------|

| •            |            | •                                              |            |

|              |            |                                                |            |

|              | 7.4.2      | The simulator design                           | 119        |

|              | 7.4.3      | Configurable interconnects in SystemC          | 121        |

|              | 7.4.4      | Features                                       | 122        |

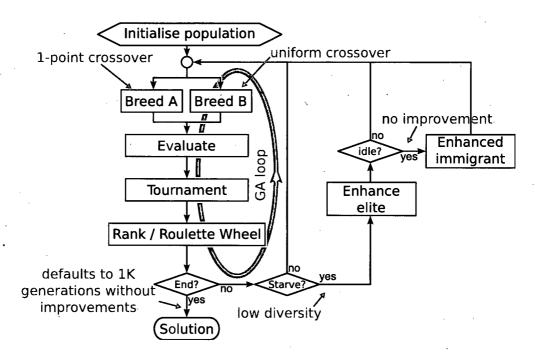

| ,            | 7.5 The M  | Multi-Objective Multi-Threading GA Framework . | <u>124</u> |

|              | 7.5.1      | Enhancement                                    | 127        |

| 1            | 7.6 The R  | RICA EA tools                                  | 128        |

|              | 7.6.1      | Physical Placement for HDRA                    | 129        |

|              | 7.6.2      | Routing and Allocation                         | 141        |

|              | 7.6.3      | Group Optimiser                                | 144        |

|              | 7.6.4      | Chain Generator                                | 145        |

| 8            | SMT on I   | RICA                                           | 147        |

| ;            | 8.1 The S  | MT design paradigm                             | 148        |

|              | 8.2 SMT    | in reconfigurable computing                    | 149        |

| ,            | 8.3 Perfor | mance Improvements                             | 152        |

| 9            | Conclusio  | ${f n}$                                        | <b>153</b> |

|              | 9.1 Contr  | ibution                                        | 154        |

| !            |            | e work                                         |            |

|              | 9.2.1      | Thread partitioning                            | 155        |

|              | 9.2.2      | Multi-Core                                     | 155        |

|              | 9.2.3      | Self-timed                                     | 156        |

|              | 9.2.4      | Dynamic Allocation and Routing                 |            |

| •            | 9.2.5      | Extended vector arithmetic                     | 158        |

|              | 9.2.6      | Source and Target graph matching               | 158        |

| Glo          | ossary     |                                                | 160        |

| Ap           | pendices   |                                                | 173        |

| $\mathbf{A}$ | Path-decc  | oding pseudocode                               | 173        |

| <b>.</b>     |            | tlist Formal Language Syntay                   |            |

| H            | KIL A NA   | FIIST HORMAL LANGUAGO NUNTAV                   | 175        |

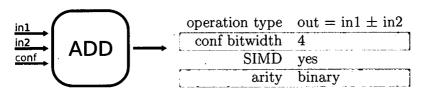

| CA Instruction Set  Adder |                                       | 181       |

|---------------------------|---------------------------------------|-----------|

|                           |                                       | 191       |

| Comparator                |                                       | 101       |

| 2 Comparator              |                                       | 182       |

| 3 Constant                | · · · · · · · · · · · · · · · · · · · | 183       |

| 4 Divider                 |                                       | 184       |

| 5 Jump                    |                                       | 185       |

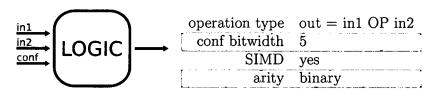

| 6 Logic                   |                                       | 186       |

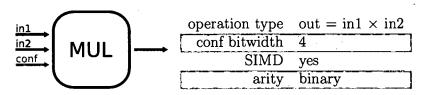

| 7 Multiplier ,            |                                       | 187       |

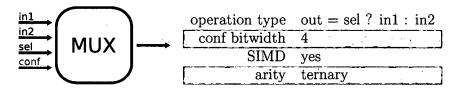

| 8 Multiplexor             |                                       | 188       |

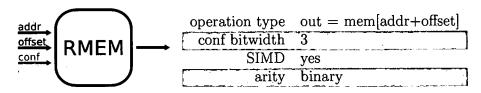

| 9 Read Memory             |                                       | 189       |

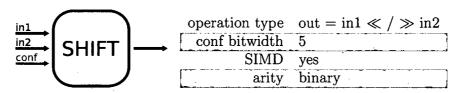

| 10 Shift                  |                                       | 190       |

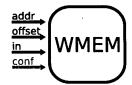

| 11 Write Memory           |                                       | 191       |

| ıblications               | ·                                     | 193       |

| 1                         |                                       |           |

|                           |                                       |           |

| 2 E                       | 4 Divider                             | 4 Divider |

# List of Figures

| Application domain spectrum                                |

|------------------------------------------------------------|

| Design trade-off differences between uP/DSP/VLIW, FPGA     |

| and ASIC                                                   |

| The Reconfigurable Computing promise                       |

| Topologies                                                 |

| Empirical mapping overhead between fine and coarse grained |

| designs                                                    |

| Coupling scenarios                                         |

| Design flow for ASICs and RCs                              |

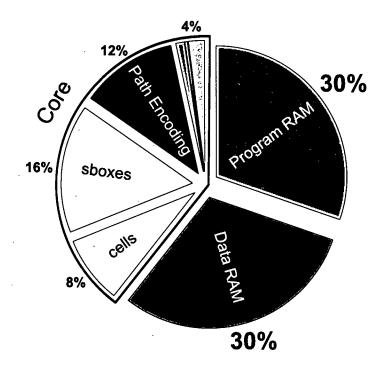

| RICA prototype block diagram                               |

| RICA prototype area breakdown                              |

| RICA prototype chip                                        |

| RICA instruction cells' arity options                      |

| RICA prototype interconnects                               |

| Configuration partitioning                                 |

| Example vector operations                                  |

| ARM vs RICA normalised performance ratios                  |

| Island-based interconnects                                 |

| Cross switch-boxes                                         |

| Logic unit tap points                                      |

| T switch-boxes                                             |

| Simple communication scenario                              |

| Percentage of activity distribution                        |

|                                                            |

|     | 4.7 VCDRC average throughput                         |

|-----|------------------------------------------------------|

|     | 4.8 Average latency in ccs for each flit             |

|     | 4.5 Average facency in ces for each int              |

|     | 5.1 Path formation scenarios                         |

| ·   | 5.2 Y or X monotonic axis                            |

|     | 5.3 Controllable edges' displacements                |

|     | 5.4 Non-monotonic path-encoding extension            |

|     | 5.5 Example intra-connectivity of a 5-way sbox       |

|     | 5.6 Path formation example                           |

|     | 5.7 Turn-based format                                |

|     | 5.8 Chain encoded path                               |

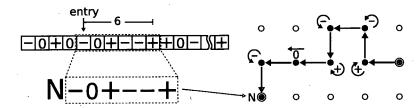

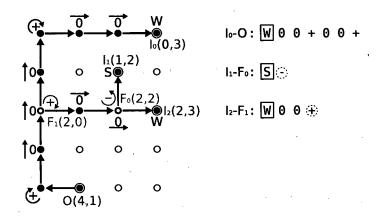

|     | 5.9 Chain encoded path packet                        |

|     | 5.10 Fan-out points                                  |

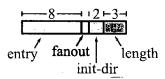

|     | 5.11 Chain encoded path packet with fan-out field 81 |

| *   | 5.12 Clustered chain                                 |

|     | 5.13 Hierarchical Enable Matrix                      |

|     | 5.14 HEM header levels                               |

|     | ·                                                    |

|     | 5.15 Hierarchical symmetric loading network          |

|     | 5.16 Groups                                          |

|     | 5.17 Configuration context rows                      |

|     | 5.18 MP3-libmad compressibility                      |

|     | 5.19 MP3-libmad code transfers                       |

|     | 6.1 Incremental HEM decoding                         |

|     | 6.2 Off-line HEM and path decoder                    |

|     | 6.3 On-line path rendering                           |

|     | 6.4 Pipelined interconnects                          |

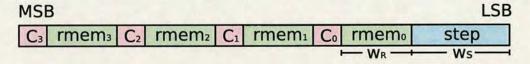

|     | 6.5 RRC fields                                       |

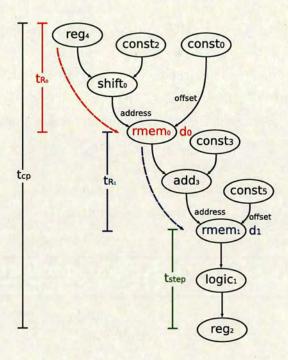

|     | 6.6 RRC read-memory interface start time             |

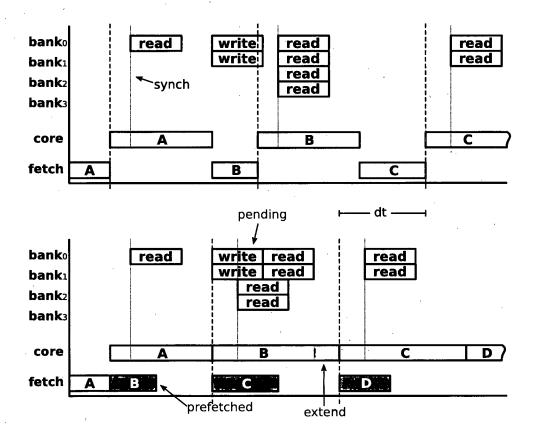

|     | 6.7 Prefetching and dynamic delays                   |

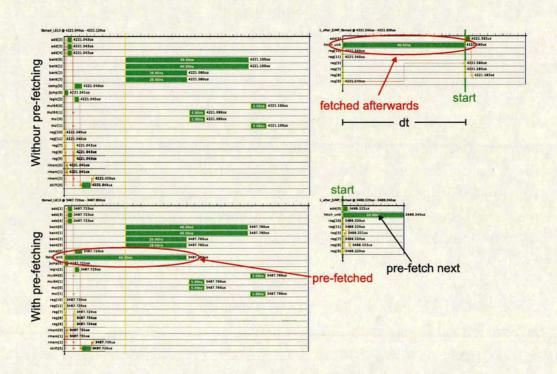

|     | 6.8 Time-charts with and without pre-fetching        |

|     | olo Time charles with and without pre fevering       |

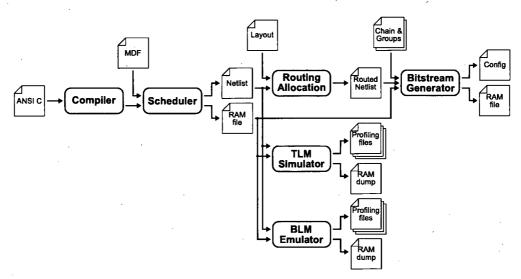

|     | 7.1 Toolflow overview: Frontend                      |

|     | 7.2 Toolflow overview: Backend                       |

|     |                                                      |

|     | 8                                                    |

|     |                                                      |

|     |                                                      |

| · · |                                                      |

|     |                                                      |

|     |                                                      |

|     |                                                      |

| •   |                                                      |

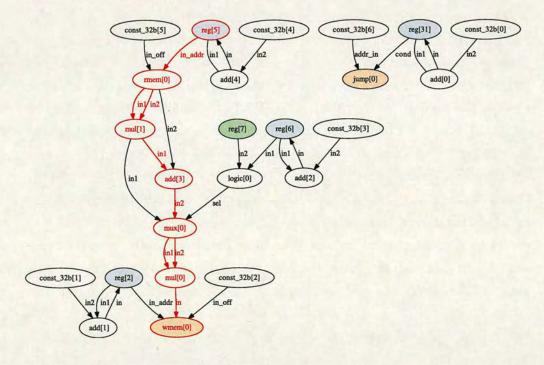

| 7.3  | Example kernel: Data Flow Graph                |

|------|------------------------------------------------|

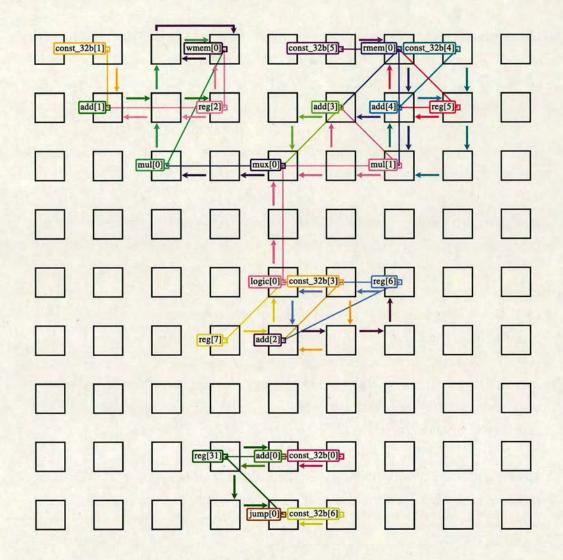

| 7.4  | Example kernel: Routed                         |

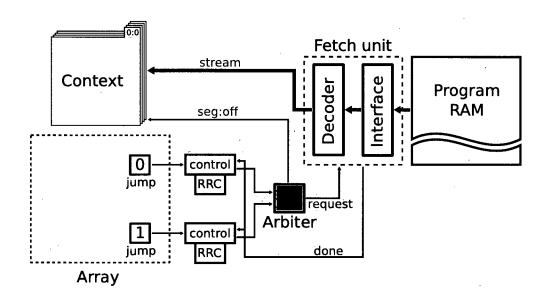

| 7.5  | Simulator overview                             |

| 7.6  | The pre-fetching mechanism                     |

| 7.7  | Core utilisation trace for libmad              |

| 7.8  | Memory utilisation trace for libmad            |

| 7.9  | GA Framework flow chart                        |

| 7.10 | RICA prototype physical placement              |

| 7.11 | Placement tool overview                        |

| 7.12 | 2D toroidal mesh topology                      |

| 7.13 | Chromosome encoding                            |

| 7.14 | Overlapping Routing regions                    |

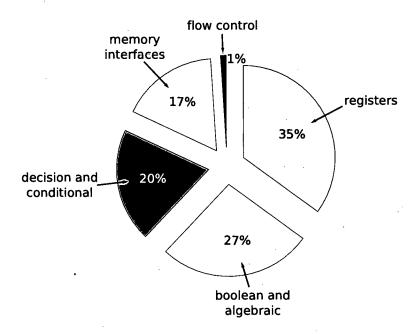

| 7.15 | RICA array operations breakdown                |

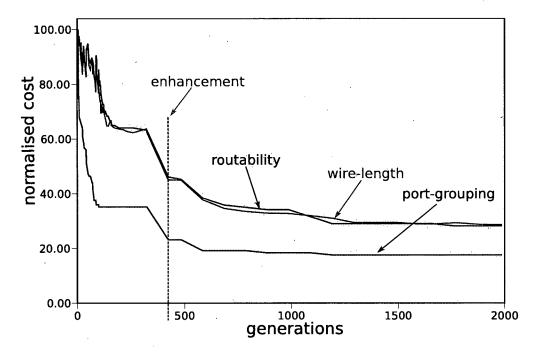

| 7.16 | Normalised cost/generations                    |

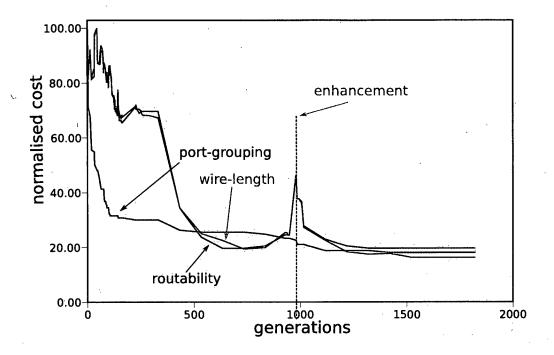

| 7.17 | Normalised cost/generations                    |

| 7.18 | Placement quality                              |

| 7.19 | Average wire-length                            |

| 7.20 | Optimised and uniform placement comparison     |

| 7.21 | Routing chromosome encoding                    |

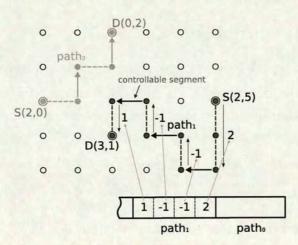

| 7.22 | Example decoding of a -X monotonic path        |

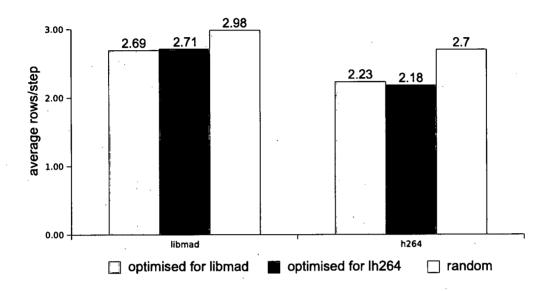

| 7.23 | Average rows/step for MP3(libmad) and h264 145 |

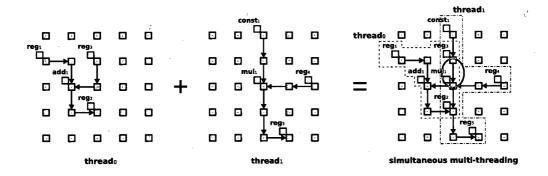

| 8.1  | SMT: Arbitration coupling                      |

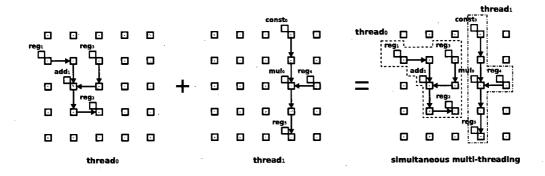

| 8.2  | SMT: Non-Conflicting Threads                   |

| 8.3  | SMT: Conflicting Threads                       |

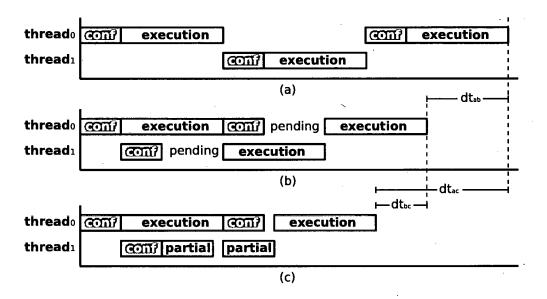

| 8.4  | Example SMT time-charts                        |

### Contents

| 1 | Intr | Introduction                               |            |  |  |  |  |  |  |  |  |

|---|------|--------------------------------------------|------------|--|--|--|--|--|--|--|--|

|   | 1.1  | The RICA project                           | 18         |  |  |  |  |  |  |  |  |

| 2 | Bac  | kground                                    | 23         |  |  |  |  |  |  |  |  |

|   | 2.1  | Reconfigurable Computing                   | 24         |  |  |  |  |  |  |  |  |

|   | 2.2  | Interconnections                           | 25         |  |  |  |  |  |  |  |  |

|   | 2.3  | Granularity                                |            |  |  |  |  |  |  |  |  |

|   | 2.4  | Coupling                                   | 30         |  |  |  |  |  |  |  |  |

|   | 2.5  | Programming Model                          | 32         |  |  |  |  |  |  |  |  |

|   | 2.6  | Code compression                           | 34         |  |  |  |  |  |  |  |  |

|   | 2.7  | The role of heuristics in RC architectures | 36         |  |  |  |  |  |  |  |  |

| 3 | RIC  | CA overview                                | 39         |  |  |  |  |  |  |  |  |

|   | 3.1  | Programming Model                          | 43         |  |  |  |  |  |  |  |  |

|   | 3.2  | Heterogeneous versus Homogeneous           | 46         |  |  |  |  |  |  |  |  |

|   | ,3.3 | Interconnects                              |            |  |  |  |  |  |  |  |  |

|   | 3.4  | Reconfiguration                            | 47         |  |  |  |  |  |  |  |  |

|   | 3.5  | Data memory arbiters                       |            |  |  |  |  |  |  |  |  |

| • | 3.6  | SIMD instruction cells                     | 50         |  |  |  |  |  |  |  |  |

|   | 3.7  | Performance figures                        | 51         |  |  |  |  |  |  |  |  |

| 4 | Inte | erconnects                                 | <b>5</b> 5 |  |  |  |  |  |  |  |  |

|   | 4.1  | Topologies                                 | 56         |  |  |  |  |  |  |  |  |

|   | 4.2  | Passive or dynamic interconnects           | 59         |  |  |  |  |  |  |  |  |

|   | 4.3  |                                            | 60         |  |  |  |  |  |  |  |  |

|   |    |      | 4.3.1  | Virtual Channels with dynamic rate control 61 |

|---|----|------|--------|-----------------------------------------------|

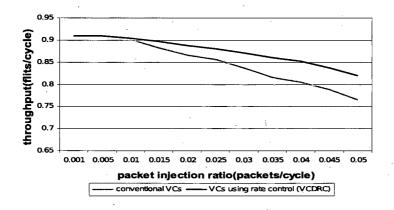

| • |    |      | 4.3.2  | VCDRC performance                             |

|   | 5  | Pat  | h Enc  | oding 69                                      |

|   |    | 5.1  | A con  | nection oriented approach                     |

|   |    | 5.2  | Path-  | Encoding Basics                               |

|   |    | 5.3  | Path   | Encoding displacement format                  |

| ' |    | 5.4  | Non-n  | nonotonic Path-Encoding extension             |

|   |    | 5.5  | Pract  | cal example with s-boxes                      |

|   |    | 5.6  | Turn-  | based format and chain encoding 76            |

|   |    | 5.7  | Splitt | ing paths and fan-outs                        |

|   |    | 5.8  | Implie | cit port activation                           |

|   |    | 5.9  | Cluste | ered chain                                    |

|   |    | 5.10 | Hiera  | chical Enable Matrix                          |

|   |    | 5.11 | Hiera  | chical clustering for loading                 |

|   |    | 5.12 | Irregu | lar/Asymmetric grouping                       |

|   |    | 5.13 | Conte  | xt partitioning. Rows and groups              |

|   |    | 5.14 | Comp   | ressibility                                   |

|   | 6  | Rec  | onfigu | ration 93                                     |

|   |    | 6.1  | Config | guration distribution                         |

|   |    |      | 6.1.1  | Off-line routing                              |

|   |    |      | 6.1.2  | On-line routing                               |

|   |    | 6.2  | The F  | Reconfiguration Rate Controller               |

|   |    | 6.3  | Pre-fe | tching                                        |

|   | 7  | Soft | ware ' | Toolflow 107                                  |

|   |    | 7.1  | Toolfl | ow overview                                   |

|   |    |      | 7.1.1  | Frontend                                      |

|   |    |      | 7.1.2  | Backend                                       |

|   |    | 7.2  |        | ow walk-through example                       |

|   | S. | 7.3  |        | Netlist format                                |

|   |    | 7.4  |        | TLM simulator                                 |

|   |    |      |        | Transaction Level Modelling and SystemC 119   |

|   |       | 7.4.2  | The simulator design                         | . 119 |

|---|-------|--------|----------------------------------------------|-------|

|   |       | 7.4.3  | Configurable interconnects in SystemC        | . 121 |

|   |       | 7.4.4  | Features                                     | . 122 |

|   | 7.5   | The M  | Multi-Objective Multi-Threading GA Framework | . 124 |

|   |       | 7.5.1  | Enhancement                                  | . 127 |

|   | 7.6   | The R  | ICA EA tools                                 | . 128 |

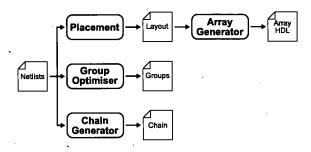

|   |       | 7.6.1  | Physical Placement for HDRA                  | . 129 |

|   |       | 7.6.2  | Routing and Allocation                       | . 141 |

|   |       | 7.6.3  | Group Optimiser                              | . 144 |

|   |       | 7.6.4  | Chain Generator                              | . 145 |

| 8 | SM    | T on F | RICA                                         | 147   |

|   | 8.1   | The S  | MT design paradigm                           | . 148 |

|   | 8.2   |        | in reconfigurable computing                  |       |

|   | 8.3   |        | mance Improvements                           |       |

| 9 | Cor   | clusio | <b>n</b>                                     | 153   |

|   | 9.1   | Contri | ibution                                      | . 154 |

|   | 9.2   | Future | e work                                       | . 155 |

|   |       | 9.2.1  | Thread partitioning                          | . 155 |

|   | ١     | 9.2.2  | Multi-Core                                   | . 155 |

|   |       | 9.2.3  | Self-timed                                   | . 156 |

| ٠ |       | 9.2.4  | Dynamic Allocation and Routing               | . 157 |

|   |       | 9.2.5  | Extended vector arithmetic                   | . 158 |

|   |       | 9.2.6  | Source and Target graph matching             | . 158 |

| G | lossa | ry     |                                              | 160   |

| A | ppen  | dices  |                                              | 173   |

| A | Pat   | h-deco | oding pseudocode                             | 173   |

| В | RIC   | CA Net | tlist Formal Language Syntax                 | 175   |

| *     |              |     |

|-------|--------------|-----|

|       |              |     |

|       |              |     |

|       |              |     |

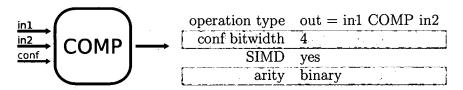

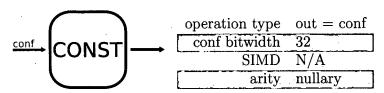

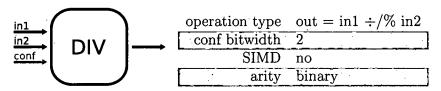

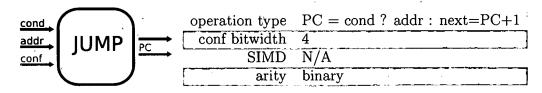

| RIC   |              | 181 |

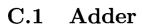

| C.1   | Adder        | 181 |

| C.2   | Comparator   | 182 |

| C.3   | Constant     | 183 |

| C.4   | Divider      | 184 |

| C.5   | Jump         | 185 |

| C.6   | Logic        | 186 |

| C.7   | Multiplier   | 187 |

| C.8   | Multiplexor  | 188 |

| C.9   | Read Memory  | 189 |

| C.10  | Shift        | 190 |

| C.11  | Write Memory | 191 |

| ) Pub | lications    | 193 |

## List of Figures

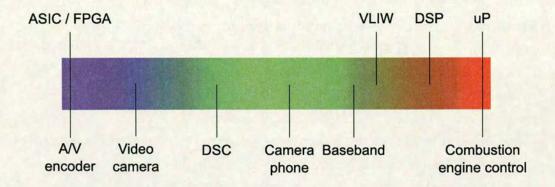

| 1.1 | Application domain spectrum                                | 15 |

|-----|------------------------------------------------------------|----|

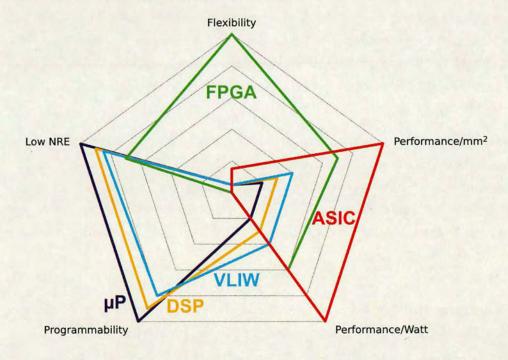

| 1.2 | Design trade-off differences between uP/DSP/VLIW, FPGA     |    |

|     | and ASIC                                                   | 15 |

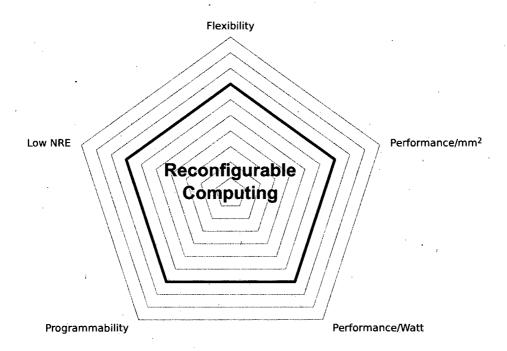

| 1.3 | The Reconfigurable Computing promise                       | 17 |

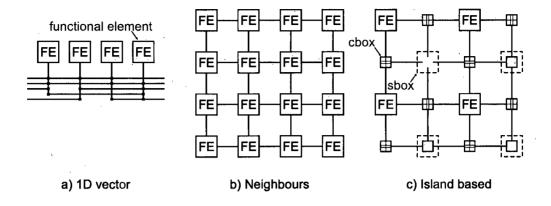

| 2.1 | Topologies                                                 | 26 |

| 2.2 | Empirical mapping overhead between fine and coarse grained |    |

|     | designs                                                    | 29 |

| 2.3 | Coupling scenarios                                         | 31 |

| 2.4 | Design flow for ASICs and RCs                              | 37 |

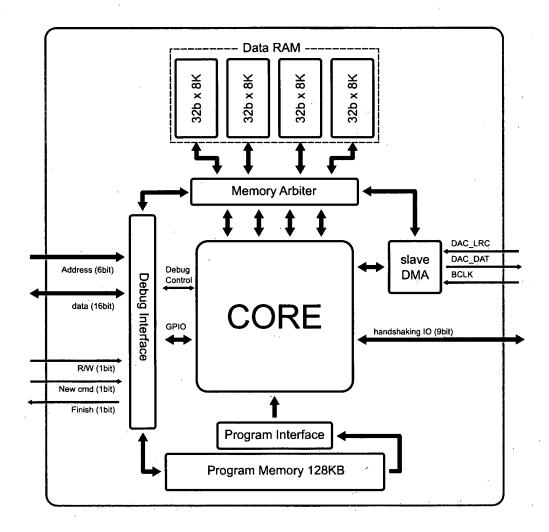

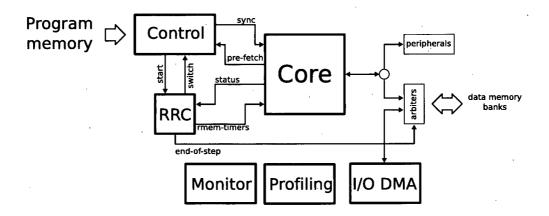

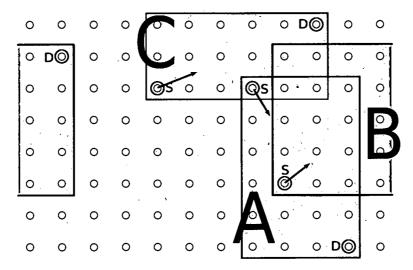

| 3.1 | RICA prototype block diagram                               | 41 |

| 3.2 | RICA prototype area breakdown                              | 42 |

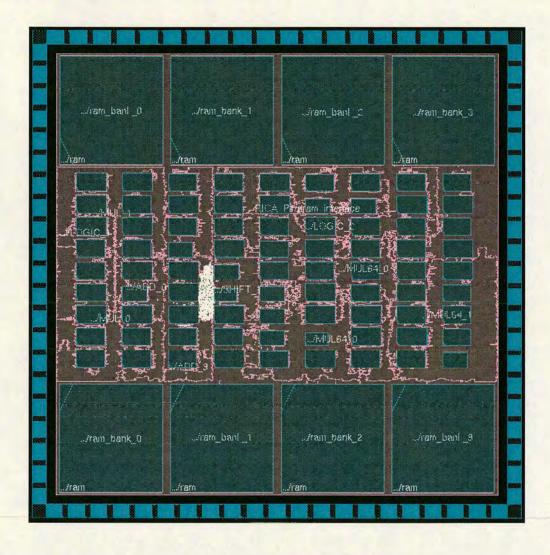

| 3.3 | RICA prototype chip                                        | 43 |

| 3.4 | RICA instruction cells' arity options                      | 44 |

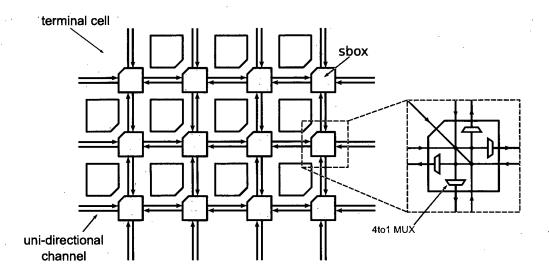

| 3.5 | RICA prototype interconnects                               | 48 |

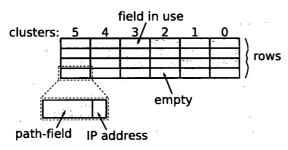

| 3.6 | Configuration partitioning                                 | 49 |

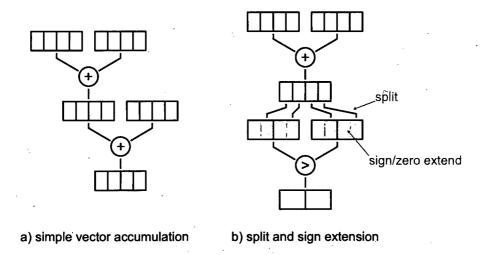

| 3.7 | Example vector operations                                  | 51 |

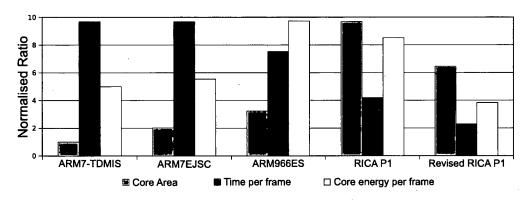

| 3.8 | ARM vs RICA normalised performance ratios                  | 54 |

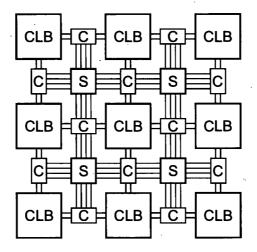

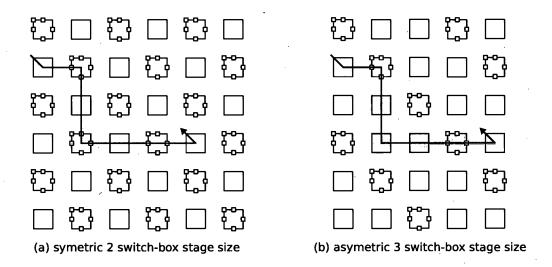

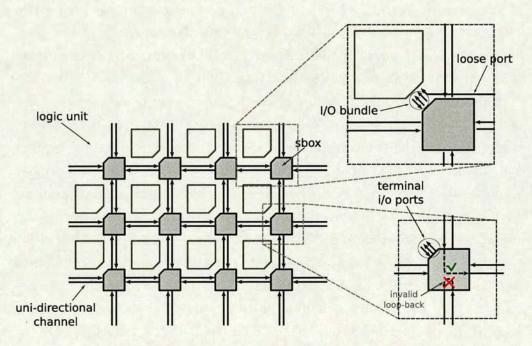

| 4.1 | Island-based interconnects                                 | 57 |

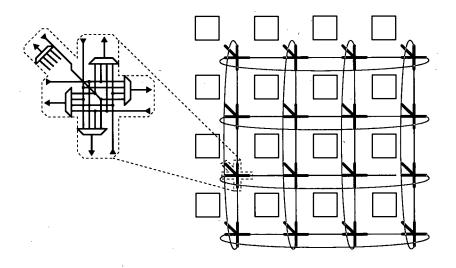

| 4.2 | Cross switch-boxes                                         | 58 |

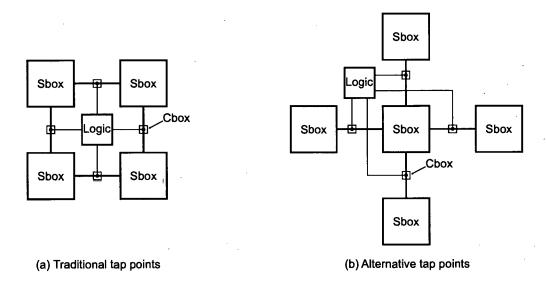

| 4.3 | Logic unit tap points                                      | 58 |

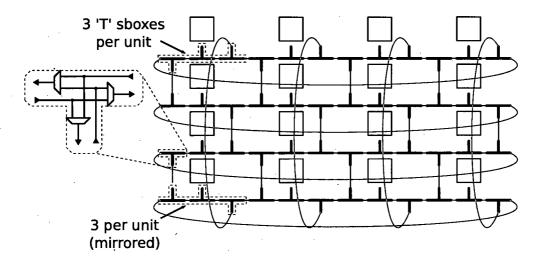

| 4.4 | T switch-boxes                                             | 59 |

| 4.5 | Simple communication scenario                              | 63 |

| 4.6 | Percentage of activity distribution                        | 66 |

|     | 4.7 VCDRC average throughput                         |        |

|-----|------------------------------------------------------|--------|

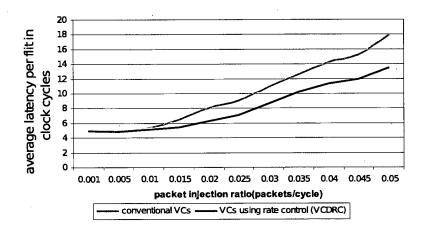

|     | 4.8 Average latency in ccs for each flit             |        |

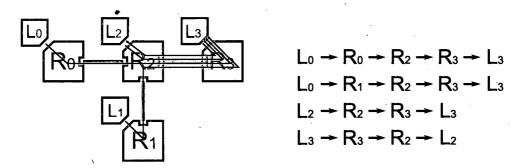

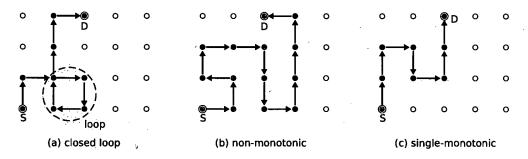

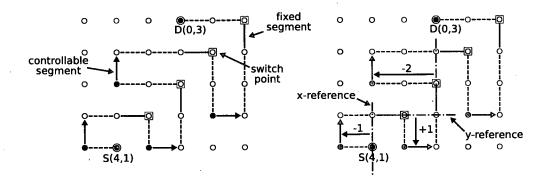

|     | 5.1 Path formation scenarios                         |        |

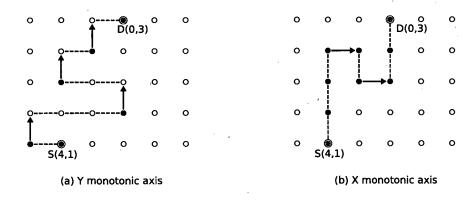

| •   | 5.2 Y or X monotonic axis                            |        |

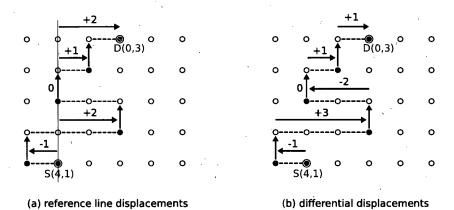

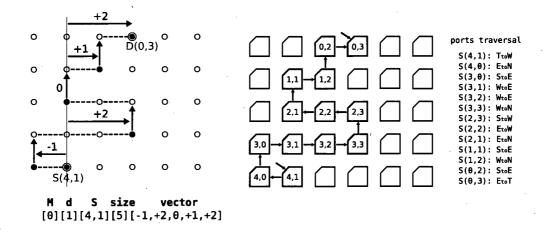

|     | 5.3 Controllable edges' displacements                |        |

|     | 5.4 Non-monotonic path-encoding extension            |        |

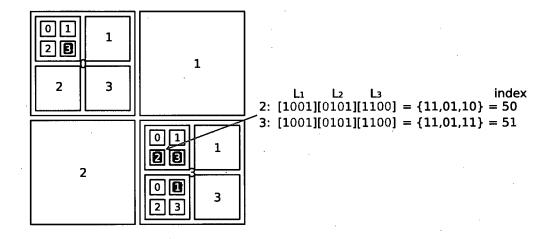

| ·   | 5.5 Example intra-connectivity of a 5-way sbox       |        |

|     | 5.6 Path formation example                           |        |

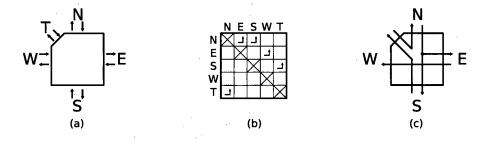

|     | 5.7 Turn-based format                                | •      |

|     | 5.8 Chain encoded path                               |        |

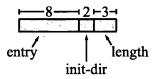

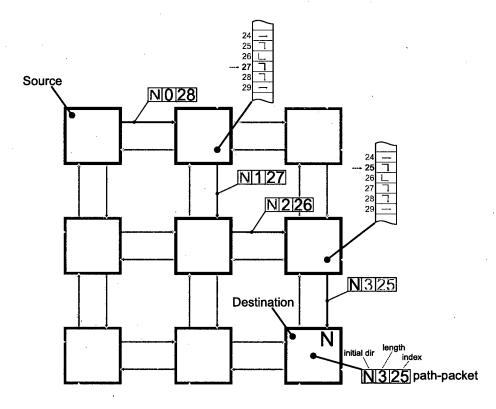

| . ' | 5.9 Chain encoded path packet                        |        |

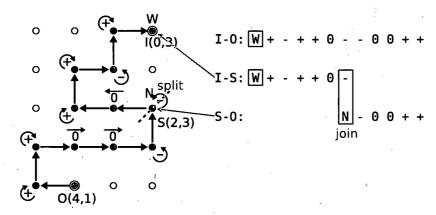

|     | 5.10 Fan-out points                                  |        |

|     | 5.11 Chain encoded path packet with fan-out field 81 |        |

|     | 5.12 Clustered chain                                 |        |

|     | 5.13 Hierarchical Enable Matrix                      |        |

| ,   | 5.14 HEM header levels                               |        |

|     | 5.15 Hierarchical symmetric loading network          |        |

|     | 5.16 Groups                                          |        |

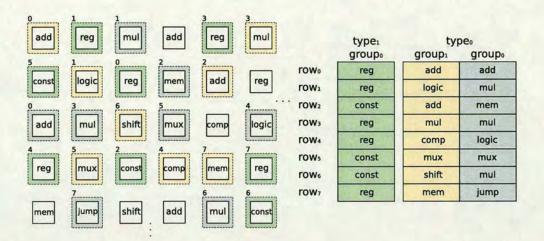

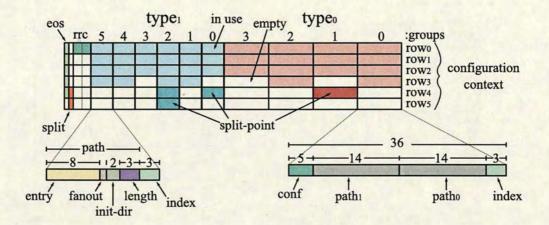

|     | 5.17 Configuration context rows                      |        |

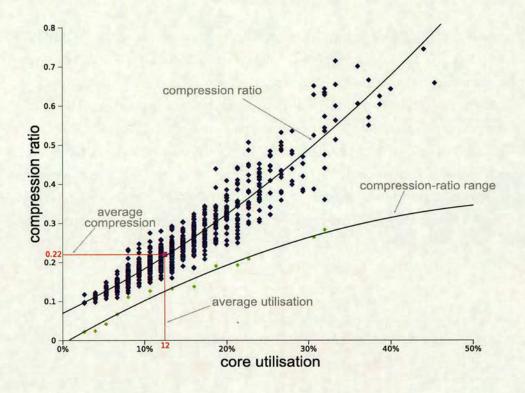

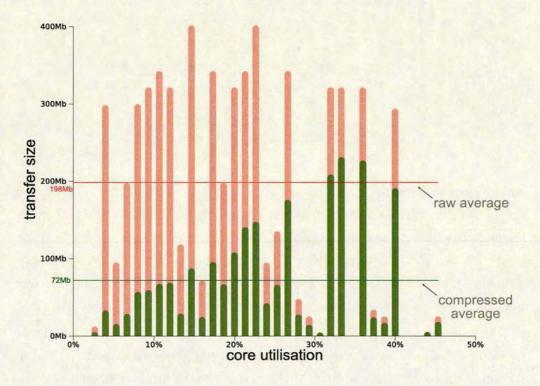

| •   | 5.18 MP3-libmad compressibility                      |        |

|     | 5.19 MP3-libmad code transfers                       |        |

|     | 6.1 Incremental HEM decoding                         |        |

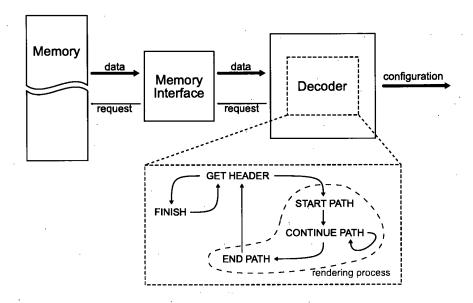

|     | 6.2 Off-line HEM and path decoder                    |        |

|     | 6.3 On-line path rendering                           |        |

| ·   | 6.4 Pipelined interconnects                          |        |

|     | 6.5 RRC fields                                       | •      |

|     | 6.6 RRC read-memory interface start time             |        |

|     | 6.7 Prefetching and dynamic delays                   |        |

|     | 6.8 Time-charts with and without pre-fetching        |        |

|     | 7.1 Toolflow overview: Frontend                      |        |

|     | 7.2 Toolflow overview: Backend                       |        |

|     | 8                                                    |        |

| •   |                                                      |        |

|     |                                                      |        |

|     |                                                      |        |

| ·   |                                                      |        |

|     |                                                      |        |

|     |                                                      | ,<br>, |

| •   |                                                      |        |

|      | ·                                              |

|------|------------------------------------------------|

|      |                                                |

|      |                                                |

| 7.3  | Example kernel: Data Flow Graph                |

| 7.4  | Example kernel: Routed                         |

| 7.5  | Simulator overview                             |

| 7.6  | The pre-fetching mechanism                     |

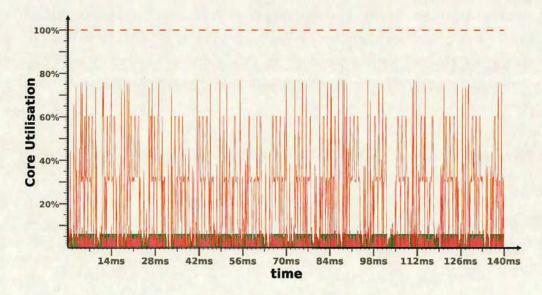

| 7.7  | Core utilisation trace for libmad              |

| 7.8  | Memory utilisation trace for libmad            |

| 7.9  | GA Framework flow chart                        |

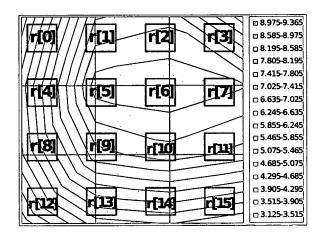

| 7.10 | RICA prototype physical placement              |

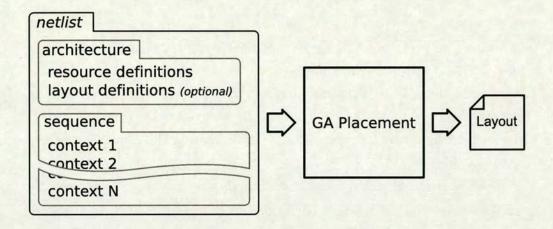

| 7.11 | Placement tool overview                        |

| 7.12 | 2D toroidal mesh topology                      |

| 7.13 | Chromosome encoding                            |

| 7.14 | Overlapping Routing regions                    |

| 7.15 | RICA array operations breakdown                |

| 7.16 | Normalised cost/generations                    |

| 7.17 | Normalised cost/generations                    |

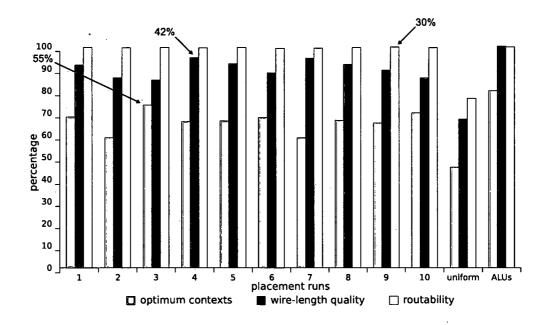

| 7.18 | Placement quality                              |

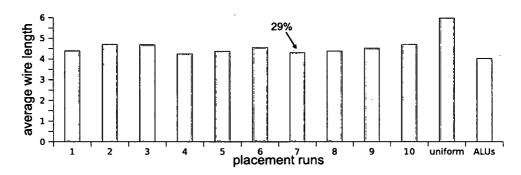

| 7.19 | Average wire-length                            |

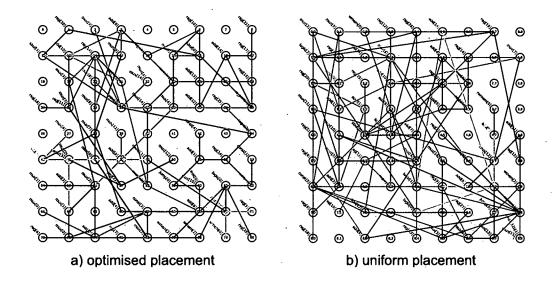

| 7.20 | Optimised and uniform placement comparison     |

| 7.21 | Routing chromosome encoding                    |

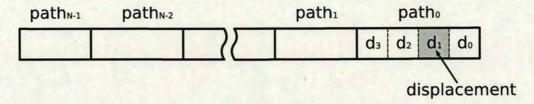

| 7.22 | Example decoding of a -X monotonic path        |

| 7.23 | Average rows/step for MP3(libmad) and h264 145 |

| 8.1  | SMT: Arbitration coupling                      |

| 8.2  | SMT: Non-Conflicting Threads                   |

| 8.3  | SMT: Conflicting Threads                       |

| 8.4  | Example SMT time-charts                        |

## List of Tables

| 3.1 | Heterogeneous versus Homogeneous                |

|-----|-------------------------------------------------|

| 3.2 | RICA cell operation modes                       |

| 3.3 | ARM vs RICA prototype                           |

| 4.1 | Communication pattern in conventional VCs 64    |

| 4.2 | Communication pattern in VCDRC                  |

| 5.1 | Source node addressing methods                  |

| 5.2 | Path-encoding compression examples              |

| 6.1 | Results with and without pre-fetching on libmad |

| 7.1 | Placement quality results                       |

| 7.2 | Wire-length results                             |

| 7.3 | Chain encoding with 255 symbols                 |

### Chapter 1

#### Introduction

In digital electronics, there are several methods one can use to deliver a particular service or functionality. For instance, an algorithm can be realised using General Purpose Processors (GPP), with or without domain specific extensions, or Field Programmable Gate Arrays (FPGA) or Application Specific Integrated Circuits (ASIC), while the result can be a monolithic device or a synergy of several devices. The suitability of each of those implementation choices depends on the application domain one is working on. There are two main superset domains that sit at the two ends of the spectrum of application domains.

Event Driven Respond to signals received from their environment. They are often referred to as 'real-time' application, meaning they are timing critical and latency intolerant. This is a natural domain for  $\mu P$  using interrupt controllers and performing relatively low computational complexity tasks per event.

Streaming Processing a continuous flow of data. They are performance critical, but latency tolerant. A  $\mu P$  does not have the computational capacity to handle the amount of data and the algorithmic complexity often found in such application domains. DSPs include some well suited computational units, such as multiply-accumulate and VLIWs offer extra degrees of parallelism, which all result in performance improvements. However, when data streams are in the range of 10Gbps and above, VLIWs fall short. One needs to turn over to FPGAs, for those designs that require post-synthesis adaptation. Otherwise, the only solution is an ASIC design.

However, most applications are in fact multi-domain. Parts of the system respond to external events and others process large amounts of streaming data. A digital camera is one example that comes to mind. The camera takes a shot as a response to a user's action, controlling the actuators, zoom lens and flash, while the image signal processing pipe works its way through the raw data received from the sensor. Such a mixture of event driven and streaming application is naturally covered by a combination of programmable and fixed hardware devices.

Figure 1.1: Application domain spectrum

Through specialisation, the various architectural paradigms available today position themselves to one or the other side of the spectrum. Unfortunately, that lends itself to various design trade-offs, where no single architecture is able to offer a balanced solution. These are:

Figure 1.2: Design trade-off differences between uP/DSP/VLIW, FPGA and ASIC

Performance/ $mm^2$  The computational density of the device. Programmable devices such as  $\mu$ P, DSP and VLIW have low computational capacity for their size. The arithmetic units account for a small fraction of the overall design, with register files, caches and the execution pipe logic constituting the majority of the silicon area. An ASIC is theoretically the ideal case, where all silicon is contributing to the computational power of the design, be it transistors or metal layers. In reality, many algorithms have multiple modes of operations and thus parts of the design are inactive. Nonetheless, if looking at the individual functionality, an ASIC is the most efficient solution in the performance/area metric. FPGAs have high computational capacity as well, but they also have significant interconnection overheads that limit their maximum speeds and occupy a significant portion of their silicon area.

Performance/Watt The power efficiency of the design. Similarly to the performance/ $mm^2$  metric, the ASICs represent the ideal case. Each evolutionary step of the programmable device delivers some improvement in this area. Although FPGA are not considered low power devices, their performance/Watt is significantly higher than the programmable devices listed here.

Flexibility The ability to be altered to suit a different environment / configuration. This is what FPGAs are designed for. The programmable devices have fixed set of functionality. Some flexibility may exist on the memory setup, although that's rare. In terms of ASIC designs, this appears as modifiable 'parameters' which can alter some aspects of the design, such as memory geometry or algorithm coefficients.

**Programmability** Programmability is the way of expressing an algorithm as a set of commands. In essence, a programmable device follows a written 'script', like an actor performing a play. The entry level is an abstract representation of the algorithm which then gets decomposed to a series of intructions supported by the architecture. The advent of programmable devices allowed rapid development of applications.

Low NRE The amount of effort and time required to implement a new design. Programmable architectures have an advantage here, since developing, testing and deploying a new algorithm is relatively easy. The domain specific instructions in DSP may cause some extra effort to utilise them efficiently. Same applies for the ILP present in VLIWs. Both of these depend on compiler technologies to simplify the process. Since the entry level for FPGAs is HDL, the development cycle resembles that of an ASIC. However, the rapid prototyping and testing reduces NRE significantly.

Figure 1.3: The Reconfigurable Computing promise

The graph in 1.2, which is growing outwards, shows that for every design metric, there is at least one architecture type that scores high. Contrary to popular thought, combining two or more architectural types together does not combine the benefits as well. A good example is NRE that will largely depend on the worst performing architecture in that area and could even increase due to the complexity of working on a multi-disciplinary task. A design that can

approach the power efficiency and computational density of an ASIC, offering comparable programmability and flexibility to GPPs and FPGAs respectively, is sought by the industry and researched by the academia for nearly 50 years.

Reconfigurable computing promises to deliver a high performance and low power solution that maintains a programmable nature, thus occupying a place between ASICs and GPPs. This is normally achieved using a number of functional units and flexible interconnects, coupled with fast reconfiguration times. Such reconfigurable fabrics are able to deploy hardware data-paths, of the target application, thus improve upon GPPs' limited parallelism.

#### 1.1 The RICA project

The focus in reconfigurable computing has been to reduce the area overhead as well as the reconfiguration times, with varying success. The work presented here describes a novel coarse grained heterogeneous reconfigurable computing architecture, a data-flow machine that delivers high performance, with a low area footprint comparable to small GPPs and significant energy savings, while maintaining a high level software design flow similar to DSPs. This is made possible by employing a number of innovative techniques, which are a direct result of the work presented here.

This thesis is part of a joined EPSRC(GR/S24053/01) funded research project, undertaken at the System Level Integration group (SLIg) lab of the Science and Engineering department of the University of Edinburgh, under the name Reconfigurable Instruction Cell Array/Architecture(RICA). The project came to a conclusion at the end of 2007, having manufactured a technology demonstrator RICA chip, referred to here as the RICA-P1 prototype, filed a number of patents covering key aspects of the technology[1, 2, 3] and a number of publications, including the RICA VLSI journal[4]. The following are the people, other than myself, involved in the development of the main aspects of the RICA architecture and their main responsibilities/contributions within the project, under the guidance and supervision of Professor Tughrul Arslan.

**Dr Sami Khawam** Joined the project as a research assistant with previous experience in reconfigurable architectures, working in Domain Specific Arrays[5] at the SLIg lab. He completed his doctorate thesis midway the RICA project, including an initial overview of the architecture in his thesis[6]. Sami has been responsible for the majority of the hardware implementation of the RICA-P1 prototype, including the system level aspects of the design, the DMA controller, memory arbiters, debug interface as well as the backend portion of the ASIC design flow.

**Dr Mark John Milward** Research assistant with a background in parallel data compression techniques. His role included project manager dueties, compiler improvements and sanitising, as well as design verification strategies.

**Dr Ying (Maggie) Yi** Research assistant with a background in FPGA synthesis tools. Maggie has been responsible for the RICA specific optimisation stages added to the GNU GCC compiler framework, the RICA compiler backend as well as the initial RICA scheduler implementation [7].

Mark Muir A PhD candidate working on instruction scheduling for reconfigurable architectures. He took over the RICA scheduler project, helped define the newer RICA netlist format, an evolutionary step of the format described in Appendix B, and shape the RICA software development environment.

Numerous project have spawn based on the RICA architecture, within the SLIg lab, with a wide variety of applications ported to the RICA platform, ranging from communications standards to multimedia applications. Adam Major's work, on porting an h264 video decoder on RICA, is a notable example that has been used in this thesis as a testing case. Adam also helped define the shuffling SIMD operations on RICA-P1's LOGIC cell, listed in Appendix C.6.

The RICA architecture delivers a number of novel techniques that make it an efficient data-flow machine. The following key aspects of the architecture have been defined in collaboration with the other core members of the RICA project.

Autonomous data-flow machine Unlike most known RCs, the presented architecture is a single fabric capable of handling the flow-control operation as well as the computational data-paths. This further simplifies algorithm development, since the core resembles a typical GPP.

Coarse-grained Instruction Cells Takes a different approach to what granularity and interfaces the functional cells have, compared to other known reconfigurable architectures. By using RISC-like single function instruction cells, with a typical of two inputs and one output, the architecture reflects the internals of a typical compiler, such as GCC and thus simplifies the software development flow.

Distributed registers As part of the heterogeneous nature of the core, the storage elements or registers are distributed inside the array. These distributed registers match the parallel nature of the architecture and provide in place storage, while eliminating the serialised and power hungry access of a register file found in conventional GPPs.

Variable length data-paths A synchronous implementation of a reconfiguration rate controller that determines the duration each configuration context should persist, before the core switches to another. This allows the architecture to dynamically adjust its clock cycle based on the critical path delay of each configuration context.

The following are aspects of the architecture I was responsible for, most of which are covered by specific publications.

Setup agnostic tool-flow The various aspects of the target architecture, such as the array composition and size, physical layout description, as well as abstract description of the configuration context, are all defined in a custom language, referred to here as the RICA netlist (see Appendix B). This internal representation is common to all the tools of the RICA tool-flow, making them architecture setup agnostic and allowing varying levels of details in

expressing the configuration contexts, ranging from simple point-to-point description, down to detailed path formations. It is thus easy to deploy diverse array setups, using the same tools, which helps in design explorations.

Refined heterogeneous array A significant portion of the area savings comes from the fact that the architecture is based on heterogeneous single function instruction cells, instead of large ALUs. Using a heterogeneous fabric is a trade-off between area and routability, since allocation is more restricted. This work demonstrates how, with the help of meta-heuristic, a refined placement can be defined that improves routability to levels similar to those of homogeneous counterparts, without requiring extra routing resource.

Parallel data memory access The data memory sub-system of the architecture is partitioned into a number of memory banks, with an arbitration logic that allows parallel access to these banks via the memory interface cells on the core. Simultaneous access to the same bank causes a serialisation with a fixed priority. Due to the parallel nature of the core, the system includes special timer tags per memory interface cell, that aligns the memory access fetches according to the combinatorial delays of the signals feeding the data and address ports of the interfaces. Furthermore, the system provides a suspend and resume mechanism, which dynamically adjusts the reconfiguration rate of the core, taking into account additional memory latencies that can be caused by multiple access to the same bank.

**Prefetching** A dual page configuration context and the associated fetching mechanism that allows the core to pre-fetch a new configuration, while the previous one is still active. This hides the configuration loading latency in most cases, especially for contexts following kernel operations.

Novel code compression A patented connection-oriented code compression technique, that models the point-to-point paths between functional nodes, achieving high compression ratios. Coupled with a distributed dictionary-based compression and a refined configuration context partitioning, the pre-

sented code compression technique offers significant program memory bandwith and latency reductions, which reduce reconfiguration times.

**SMT on RCs** A patented approach for further enhancing the performance of reconfigurable computing architectures, by introducing Simultaneous Multi-Threading capabilities to the fabric, with partial thread execution.

### Chapter 2

### Background

#### 2.1 Reconfigurable Computing

Reconfigurable computing is the field of research that attempts to make use of configurable devices, as efficient general purpose computational machines. It was Gerald Estrin who first described, in 1960, a close coupling between a configurable fabric and a general purpose instruction set processor(GPP) as a way to dynamically map circuits on hardware[8]. There have been several architectures proposed in academia and industry since then, such as Morphosys, Garp, Elixent and Pact XAPP [9, 10, 11, 12] to name a few, which follow that same concept. Nowadays, reconfigurable computing is used mainly in High Performance Computing(HPC) application, which make use of a commercially available FPGAs, such as those from Xilinx, and a loosely coupled GPP or a set of GPPs that control them[13].

It's a thin line that separates a programmable from a configurable device, but one that is required to understand their architectural and execution model differences. A 'computer program' is a set of instructions or commands for a given processor. The processor executes those commands in sequence or as otherwise dictated by the control flow of the program, thus forming 'branches' or 'loops'. The most simple form of a processor, a single-issue machine, would execute one instruction at a time. On the other hand, the 'configuration stream' of a configurable device, forms a static data path that implements the entire functionality of the target algorithm. A traditional FPGA falls in this category. Therefore, we could say that a programmable device is dynamic in nature while a configurable one is static, as far as mapping of an algorithm is concerned. However, a new data path can be formed by mapping a new configuration stream to the FPGA, by means of reconfiguration. This is where the two classes of devices fuse together.

A reconfigurable device bridges the gap between static and dynamic mapping. The algorithm is split into a manageable set of operations which are chained together or placed in parallel or both. Each set forms a configuration context that is mapped for a certain duration of time. In other words, the algorithm is mapped both spatially, like in an FPGA, and temporally, like in a processor, thus combining the best features of both worlds. However, such

combination introduces a number of difficulties, which make reconfigurable computing an interesting and active field of research.

Rapid reconfiguration is an essential requirement and is one of the biggest challenges faced in reconfigurable computing. The speed of reconfiguration depends on the size of the configuration bit-stream as well as the loading mechanism in place. The configuration size depends on the interconnects complexity and flexibility, as well as the computational granularity of the array. The loading mechanism relates to the coupling between the core fabric and the configuration controller. All these factors, which are covered in more detail later in sections 2.2, 2.3, 2.4 and 2.5, form the basis of a general classification system for reconfigurable computing devices.

Aside from the hardware architecture itself, often overlooked is the importance of appropriate software tools that are essential for programming the system and gaining maximum performance. It is vital for reconfigurable devices to be programmed from a high level language, as this enables complex algorithms to be quickly and effectively mapped to the underlying architecture and thus reduce NRE.

#### 2.2 Interconnections

What allows a reconfigurable computing device (RCD) to form arbitrary datapaths, is the intra-communication network between its functional elements (FE). How flexible and scalable the overall design is, is determined by the design of that network. A number of interconnection network are possible:

Shared Bus A common set of wiring is shared between the functional elements. Communication is established by means of arbitration. An arbitration unit resolves conflicts and assigns the bus to one pair of units at a time, the relationship of which is that of master-slave. The bus is often bidirectional, though the same concept can apply to single-drive unidirectional wiring. Such interconnects can offer high speed burst modes, but suffer from high latencies due to the arbitration process. Memory mapping abstraction is offered, via write and read operation with separate or multiplexed address and data buses.

Figure 2.1: Topologies

Standardised interfaces such as AMBA and Wishbone[14] provide easy integration. This type of interconnects does not scale well and the bus becomes a performance bottleneck in high traffic, since all devices share the same routing resources. Extended versions of the typical shared-bus topology include several levels of interconnections, i.e. provide segmentation, in an attempt to localise traffic[15]. This offers some degree of parallelism but with a significant area and complexity overhead. Since most reconfigurable architectures contain tens, hundreds, or million functional elements, as in the case of FPGAs, there is no known practical reconfigurable fabric that makes use of a shared bus topology as part of its intra communication channels. They do make for good system level interconnects where traffic tends to be lower and sporadic. One such example is shown in figure 2.3

One dimensional A set of parallel wires provide a number of 'tap-point' where the functional elements can connect to via connection boxes, as in figure 2.1a. This structure is logically seen as a 1 dimensional vector of units over a set of parallel wires. Both bidirectional and unidirectional wiring can be used. The wiring can be segmented, where some wires extend all the way along the axis, while others may cover only a part of the axis. Each wire segment support one connection at a time and resembles a shared bus. However, unlike shared bus topologies, one dimensional ones often use explicit connec-

tion setup and do not rely on arbitration logic. Compared to shared bus topologies, 1D ones offer higher levels of parallelism and thus scale to a higher number of functional units, which can be up to a few tens of units. Since they do not use an arbitration logic they are also simpler to devise, but they are not autonomous. The RaPiD architecture is one such example reconfigurable fabric with a 1D interconnection structure[16].

Neighbour The functional elements of the device, which are often laid out in a lattice structure, maintain local, dedicated, point-to-point channels between their neighbour units, as in figure 2.1b. These are normally single drive unidirectional channels. Data flows on various direction and each 'hop' performs some operation, which could be chosen to feed-through the data to the next unit. Such structure suffer from scalability issues, since larger data-flow graph tend to have multi-fanout edges. An example architecture using this type of interconnects is Garp, which was developed at the University of California in 1997[10]. Others include the multi-core Ambric[17] architecture and the top-level interconnects of SiliconHive[18].

Sea of interconnects A two dimensional mesh of interconnects with switch boxes at the vertical-horizontal crossing points and connection boxes for allowing the functional units to 'tap' onto available channels, as in figure 2.1c. These are logically and historically seen as the next step after 1D interconnects. Again, both bidirectional and single-drive unidirectional wiring can be used. This type of interconnects is termed as 'sea of interconnects' or island based, because the tiled formation of crossing vertical and horizontal wires leaves empty regions where no wiring is present. This is where the functional units are normally placed. This is particularly useful when considering placing memory blocks in those tiles, which often prevent metal layers passing over them. These kind of interconnects scale well to over thousand of unit. The indirect connection between the functional units, introduces delay overheads. For large designs, the island based topology tends to be large and dominate in silicon area. The most familiar representative use of such structure are FPGAs with their island based topologies. Multi-million gate FPGAs have hierarchi-

cal interconnects build atop a traditional island-based structure. The Elixent architecture is also based on such island based structure[11] as are other more coarse-grained architecture such as picoChip[19]

Crossbar Each unit can connect to every other unit with a point-to-point connection. Crossbars are fast but do not scale well. In fact the size of the interconnects increases exponentially to the number of units used. An example use of crossbar interconnect is found on the top-level interconnects of SiliconHive and QuickSilver.

Hierarchical Otherwise known us 'clustered' interconnects, these define regions of the interconnection network that are grouped together forming a cluster. A cluster can use any of the above topologies as intra-connection structure. The clusters themselves are connected to each other with a separate interconnection network, which again can be any of the above topologies. Examples include modern multi-million gate FPGAs, SiliconHive with crossbar and nearest neighbour interconnects and QuickSilver with a 2D mesh and crossbar.

#### 2.3 Granularity

The culprit for the excessive routing overhead in FPGAs is the fine-grained granularity of the CLBs, which reflects on both the data and configuration interconnection networks, not to mention the local storage for the actual configuration stream. This is where coarse-grained reconfigurable computing devices (RCD) have an advantage, with significantly simplified interconnects and thus smaller configuration streams. The coarse-grained RCDs perform well in terms of speed and effective silicon utilisation when operating at their native level of granularity, but have a large overhead when diverting from that level.

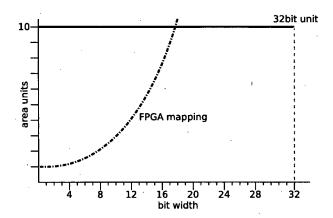

The graph in figure 2.2 gives an empirical comparison between the area usage for a given arithmetic operation, such as an adder, mapped to an FPGA's CLBs and a coarse grain unit of an RCDs, taking into account the routing resources as well. This figure should be used as an indication rather than accurate data. The inefficiency of FPGAs on coarse grain arithmetic has led

Figure 2.2: Empirical mapping overhead between fine and coarse grained designs

to the design of FPGAs with a number of such coarse grain arithmetic units. Similarly, coarse grain RCDs tend to use bit-level manipulation special units or employ SIMD modes to allow finer grain operation, in a packed form.

Bit Performing bit-level operations. Such fine grain granularity offers high degree of flexibility since it allows to construct arbitrary arithmetic logic of varying width down to the bit level. FPGAs are a classic example of bit level configurable devices. The LUT of the CLBs have a number of 1 bit inputs and a 1 bit output. The Garp architecture operates at a 2-bit level, performing logical or arithmetic operations.

Nibble These perform 4-bit level operations. They are still considered fine-grain. Increasing the granularity normally reduces the overhead of the interconnects, with the expense of a reduction in flexibility. One such example architecture is Elixent[11], which is composed of 4bit wide ALUs.

Byte-Word Coarse grain granularity, performing byte or multi-byte arithmetic and logic operations. This level of granularity is suitable for most programming environments assuming byte operations or above.  $\mu P$  have paved the way for such degree of granularity and high level languages like ANSI C

are designed around that assumption. As an example, the Morphosys reconfigurable architectures is composed of 28bit ALUs[9]. Other architecture like SiliconHive[18], combine several VLIWs together to form a fabric of synergetic ALUs. On the end of the spectrum are architectures such as picoChip[19], Ambric[17] and RAW[20], which use a set of small RISC processors connected together via an NoC.

Hybrid Since no given granularity can effectively tackle all domains, combining bit-level with word-level functional units can be a solution. Although beneficial in matching the given granularity of the algorithm natively, the anisotropic nature of such design adds an extra complexity to the interconnects as well as mapping process. Modern FPGAs include wide adders and multipliers, while some also include small RISC cores. Another example is QuickSilver's ACM which mixes bit-level with word-level functional units[21].

## 2.4 Coupling

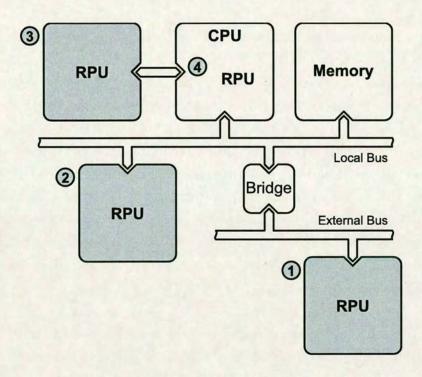

The reconfiguration process involves altering the state of the reconfigurable fabric to accommodate new functionality, which often involves a combination of routing between the functional units as well as modes of operation of those units. There is a range of possible scenarios of what makes the decision to reconfigure, as well as what performs the loading process itself. That responsibility is often assigned to the CPU of the system, while the Reconfigurable Processing Unit(RPU) plays a passive role. But that's only one of many possible 'coupling' setups. In most scenarios, where a well defined CPU exist, this can be a single core or multiple cores in a MP environment. Same applies for the RPU. The various broad coupling scenarios are listed below.

Loosely Coupled The RPU is being controlled by the CPU over a communication channel which is shared between the two and possibly other peripheral devices, as in cases 1 and 2 on figure 2.3. Due to the communication overhead, interaction between the CPU and RPU is kept to a minimum. The RPU is configured to operate on a large chunk of data and notify the CPU when it

Figure 2.3: Coupling scenarios

is done, via an interrupt, message or having the CPU polling status registers. In such loose coupling, the RPU is a stand alone device. Elixent is an example architecture that falls in this category. It combines a RISC processor with a reconfigurable fabric, communicating via an AMBA bus. Other such architecture is Morphosys, while Cray's XD1 system falls in this category as well.

Close Coupled The RPU is seen as a co-processor unit to the central processing unit, like in case 3 on figure 2.3. The two communicate over a dedicated channel and may share the main memory of the system. The closer coupling allows for more frequent exchange of information between the two. Garp combines a MIPS processor with a reconfigurable fabric which share the same memory subsystem. Pact's XAPP reconfigurable array is also seen as a co-processor to some GPP[12], and so are ADRES[22] and Pleiades[23].

Tightly Coupled The RPU is part of the CPU, as in case 4 on figure 2.3. It is seen as an extension to the CPU's instruction set (ISA extension), able to execute complex, specialised, often SIMD instructions. These are also known as reconfigurable Application Specific Instruction Processors (ASIP). As such, the RPU is part of the execution pipeline and shares registers and I/O interfaces with the host CPU. This form of coupling can offer a more unified programming model and is compatible with compiler frameworks. However, the often very dissimilar timing characteristics between the RPU and the rest of the CPUs instructions, makes scheduling a daunting task. A good example of such coupling is the Stretch architecture[24]. In fact, reconfigurable ASIPs are fairly popular, with applications ranging from Software Defined Radio (SDR)[25] to video processing[26].

Fused/Autonomous The data flow and the control flow are handled by the same fabric. There is no clearly defined CPU. The RPU is autonomous, being able to alter its own configuration based on decisions made from the operations it performs and its current state. The sea of processors architectures, such as picoChip[19], Ambric[17], RAW[20] can loosely fall in this category, while Philips' SiliconHive[18] and QuickSilver's ACM[21] are probably better representatives.

## 2.5 Programming Model

Since 1960, when the first reconfigurable device was described by G. Estrin, there have been numerous architectures that followed that same idea. Even though they all claimed a new design paradigm shift to be imminent, to date, no such device has received broad acceptance in industry. The reason is that no reconfigurable device has managed to meet all the design targets of the RC promise, as seen in figure 1.3. Some did not quite meet an acceptable computational density, others failed to meet the target power budget, but where most all fail is in programmability. Either the design entry is not convenient or in order to deliver good performance the designer has to tinker with low level constructs. The following lists a number of programming models.

HDL Hardware Description Languages (HDL), such as VHDL or Verilog, describe a design in terms of interconnected gates or higher functional elements. They offer a varying degree of abstraction, being able to describe an algorithm from a Register-Transfer Level up to behaviourally. However, the 'canvas' is the actual silicon, where the designer has to handle timing and synchronisation between the various elements of the design. The design flow involves a number of stages starting from high level, often behavioural level, design, moving on to a gate-level representation and finally a mask-set in case of ASIC. HDLs are the natural design entry for ASICs and as such describe a static design, with any temporal part described explicitly. Architectures that use this design entry lack in programmability due to the very low level nature of HDL. Traditionally, the design entry for FPGAs is HDL.

Assembly The natural representation for intruction set processors is the assembly language, which describe an algorithm as a sequence of operators and their operands and is specific to that processor architecture. Code written in assembly is not easily portable across varying architectures. Assembly is a very low representation and exposes the inner workings of the underlying hardware. When appropriate high level constructs are not available for a given functionality, assembly can be the only way to expose a feature of the underlying architecture. Developing complex algorithm in assembly is a very difficult task and requires good understanding of the underlying hardware. Because of this and because of the portability issue, NRE tends to be high. Most of the architectures will use assembly as means to achieve higher optimisations than it's possible via high level programming.

Custom HLL Most common high level languages, such as C/C++, have been designed with GPPs in mind, which include coarse-grain granularity and temporal mapping, with no explicit notion of parallelism. The spatial nature of reconfigurable devices is alien to those high level languages, which often fail to provide means to express it. This led to most reconfigurable architectures to provide their own high level languages, which are often extensions to existing ones, such as ANSI C. This form of design entry is a good compromise

between ease of design and mapping efficiency, but cause inevitable portability issues. QuickSilver's ACM SilverC is one such example, which augments ANSI C with temporal and spatial extensions[21]. The RaPiD architecture comes with its own RaPiD-C language, which as the name implies, is also an extension to ANSI-C. Elixent is another example which makes use of Handel-C. However, Handle-C is closer to HDL than C. Ambric has a mixture of ANSI-C, to program the individual DSP cores and a custom language to describe the parallelism between those core.

Generic HLL The use of common high level languages can improve the chance for an architecture to be accepted commercially. The familiarity to such language as well as the large set of algorithms already written in those languages, makes this form of design entry a desirable one. Abstraction from the underlying hardware and portability are some of the obvious benefits. Architectures such as ADRES and Stretch, recognise these advantages and offer ANSI C/C++ as a design entry. However, software partitioning between the host CPU and the coupled RPU is done manually and thus do not offer a complete solution to the problem. Architectures like picoChip, Ambric and RAW provide ANSI C as a design entry for each of their RISC cores, but coordination is done mostly manually. SiliconHive makes use of ANSI C as well which allows quick prototyping and evaluation. Their compiler is able to extract parallelism from the ANSI C code. For higher efficiency the designer needs to restructure the code to conform to a given style for the compiler to identify parallelism in the design. This design entry is comparable to that of DSPs/VLIWs and thus is seen as an acceptable compromise. Other examples include emerging compiler frameworks that promise 'C-to-gates' design flow, allowing FPGAs to be programmed directly from C, with a certain degree of success[27].

## 2.6 Code compression

An aspect that is less explored in reconfigurable computing is code compression. A common practise in single issue cores[28], as well as multiple-issue [29]

architectures, code compression is applied to reduce the program memory bandwidth as well as the memory storage requirements of those devices.

Code compression is a form of lossless compression, specifically designed around the constraints and requirements of the execution engine of programmable devices. These compression techniques trade compression ratio for low latency and are asymmetric, in that the decoder, which is done in hardware, is much simpler than the encoder, which is performed in software at compile time. Furthermore, unlike general lossless data compressions, code compression techniques require random access to the encoded stream, so that the decoder can quickly respond to the execution flow of the running program.

General lossless data compression starts with modeling the source data based on symbol frequency of occurrence. In essence, what modeling does, is extract the 'information' contained in the data source and thus identify potential redundancy in the code. An 'entropy encoding', such as Huffman, arithmetic, Golomb and Rice coding, can then be used to associate variable size code patterns to input source patterns, according to their probability of occurrence, in ascending order [30], or build a 'dictionary' with the most common patterns [31]. Another option is to use 'run length coding' (RLC) that replace a repeating sequence of symbols with a 'run' and that symbol. The choice of coding depends on the characteristics of the source data, which is identified by the modeling performed at the beginning. In many cases, a combination of the above coding techniques is used to complement each other.

Code compression is architecture as well as application domain dependend. While a dictionary based approach is simpler in hardware and potentially faster than entropy coding in single issue cores, it has been shown that, for multi-issue architectures, under dense program codes, entropy coding methods performs better than dictionary based ones [32]. When it comes to reconfigurable architectures, the configuration stream is mostly sparsely populated and it is natural to expect that an entropy encoding does not scale well to a large number of parallel units. A dictionary compression performs well enough, although for very large number of functional units, such as in FPGAs, the dictionaries can be very large [33].

Code compression can be beneficial to reconfigurable computing devices,

due to the high count of functional units such architectures have, which are often underutilised. In many cases, even a simple RLC is enough to remove redundancy in the configuration stream. However, the highly parallel nature of these architecture, which is quite different from that of even VLIWs, makes the design of a fast decoder with low area overhead, as well as the associated program memory interface, a challenging task. Furthermore, the high diversity of reconfigurable computing devices makes it difficult to generalise a code compression technique. The novel technique introduced in chapter 5, represents the first known code-compression technique specifically targeting reconfigurable computing devices, due to its connection-oriented approach, which is an intrinsic characteristic of such designs.

#### 2.7 The role of heuristics in RC architectures

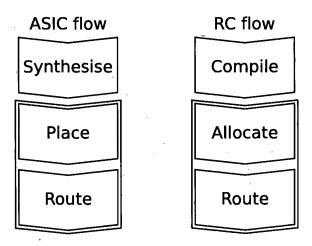

In an ASIC design flow, the high level description of an algorithm, usually expressed in some HDL, is decomposed into primitive operations that correspond to cells from the 'technology library' and are connected with each other so as to form a netlist. This process, which is termed 'synthesis', is followed by a set of physical mapping procedures, with the most notable ones being 'placement' and 'routing'. The placement tries to find optimum relative positions for the cells of the netlist, mainly trying to minimise cross sections and distances, while routing lays metal channels to establish the connections between those cells. Each of those stages are guided by design rules, be it timing constraints, physical spacing, metal layers et cetera. Although the canvas is a plain silicon, both placement and routing operate on some kind of a grid specified by the design rules. There is a lot more to do than that before getting a physical design, some of which are technology process specific, but the above stages form the basis of the ASIC design flow.

The design flow of reconfigurable devices is not very different from that of an ASIC one, at least as far as the above stages are concerned. The application to be mapped is broken down into operations supported by the RC, which are then 'allocated' to the physical instances on the array and finally routed to form the data-paths defined by the target algorithm. The terminology is

slightly different, but the stages perform more or less the same functions, with the exception of the compilation phase that in addition to what a synthesis stage does for spatial mapping, it also deals with the temporal nature of the architecture.

Figure 2.4: Design flow for ASICs and RCs

All these stages are NP-Complete problems, thus the solutions given are approximations. They are usually tackled with some form of heuristic or meta-heuristics algorithm, such as Simulated Annealing(SA), inspired by the process of heating and controlled cooling used in metallurgy to control the crystal structure of metals[34], and Evolutionary Algorithms(EA), inspired by genetics and natural selection process of species evolution[35]. Graph bi-partitioning is also a known technique used in placement algorithms, with Fiduccia-Mattheyses move-based heuristic being a popular one [36].

VPR, which stands for Versatile Place and Route, is an example Place and Route (PnR) tool based on SA[37], delivering quality output and good processing speed. Focusing on FPGAs, it supports homogeneous and heterogeneous FPGAs and means to define the architecture of the interconnects. However, it does make certain assumptions. An island-based topology is assumed for the interconnects and in case of heterogeneous CLBs, they reserve an entire column and can not be freely distributed ac cross the array. Furthermore, there is a strict decoupling of functionality and interconnects.

An example use of GAs for PnR is that used be the Colt/Stallion architecture[38]. The placement here refers to logical placement or allocation. The chromosome encoding used by Colt's PnR uses integers as genes. As it is usually the case in such implementations, the author makes use of special genetic operators to avoid invalid conditions.

This thesis investigates the various aspects of a practical reconfigurable architecture, such as RICA, in an attempt to provide a fairly comprehensive set of solutions in reconfigurable computing. RICA forms a complete platform, that is build on those techniques described here. It all starts by combining the best features of known design, laying down a good foundation. To ensure a flexible a scalable design, the interconnects are build on an island-based approach. The ultimate goal is to have a programmable architecture and typically such architectures are composed of word-sized functional units. The use of coarse-grained intruction cells is compatible to high level programming languages such as C, which generally does not cope well with bit-wise operations. To further simplify the programming model, the reconfigurable fabric can handle both the flow control and computational data-paths, providing an autonomous solution.

More specifically, chapter 3 gives a general overview of the RICA architecture, followed by a more detailed description of the interconnects in chapter 4, an innovative configuration compression technique in chapter 5 and the configuration loading infrastructure in chapter 6. Chapter 7 presents the RICA toolflow, while chapter 8 introduces a Simultaneous Multi-Threading(SMT) extension for the RICA core. Finally, future directions are given in chapter 9.

# Chapter 3

## RICA overview