# Mechanisms to Improve the Efficiency of Hardware Data Prefetchers

Pedro Díaz

Doctor of Philosophy School of Informatics University of Edinburgh 2010

# Abstract

A well known performance bottleneck in computer architecture is the so-called memory wall. This term refers to the huge disparity between on-chip and off-chip access latencies. Historically speaking, the operating frequency of processors has increased at a steady pace, while most past advances in memory technology have been in density, not speed. Nowadays, the trend for ever increasing processor operating frequencies has been replaced by an increasing number of CPU cores per chip. This will continue to exacerbate the memory wall problem, as several cores now have to compete for off-chip data access. As multi-core systems pack more and more cores, it is expected that the access latency as observed by each core will continue to increase. Although the causes of the memory wall have changed, it is, and will continue to be in the near future, a very significant challenge in terms of computer architecture design.

Prefetching has been an important technique to amortize the effect of the memory wall. With prefetching, data or instructions that are expected to be used in the near future are speculatively moved up in the memory hierarchy, were the access latency is smaller. This dissertation focuses on hardware data prefetching at the last cache level before memory (last level cache, LLC). Prefetching at the LLC usually offers the best performance increase, as this is where the disparity between hit and miss latencies is the largest.

Hardware prefetchers operate by examining the miss address stream generated by the cache and identifying patterns and correlations between the misses. Most prefetchers divide the global miss stream in several sub-streams, according to some pre-specified criteria. This process is known as localization. The benefits of localization are well established: it increases the accuracy of the predictions and helps filtering out spurious, non-predictable misses. However localization has one important drawback: since the misses are classified into different sub-streams, important chronological information is lost. A consequence of this is that most localizing prefetchers issue prefetches in an untimely manner, fetching data too far in advance. This behavior promotes data pollution in the cache.

The first part of this thesis proposes a new class of prefetchers based on the novel concept of Stream Chaining. With Stream Chaining, the prefetcher tries to reconstruct the chronological information lost in the process of localization, while at the same time keeping its benefits. We describe two novel Stream Chaining prefetching algorithms based on two state of the art localizing prefetchers: PC/DC and C/DC. We

show how both prefetchers issue prefetches in a more timely manner than their nonchaining counterparts, increasing performance by as much as 55% (10% on average) on a suite of sequential benchmarks, while consuming roughly the same amount of memory bandwidth.

In order to hide the effects of the memory wall, hardware prefetchers are usually configured to aggressively prefetch as much data as possible. However, a highly aggressive prefetcher can have negative effects on performance. Factors such as prefetching accuracy, cache pollution and memory bandwidth consumption have to be taken into account. This is specially important in the context of multi-core systems, where typically each core has its own prefetching engine and there is high competition for accessing memory. Several prefetch throttling and filtering mechanisms have been proposed to maximize the effect of prefetching in multi-core systems. The general strategy behind these heuristics is to promote prefetches that are more likely to be used and cause less interference. Traditionally these methods operate at the *source* level, i.e., directly into the prefetch engine they are assigned to control.

In multi-core systems all prefetches are aggregated in a FIFO-like data structure called the Prefetch Request Queue (PRQ), where they wait to be dispatched to memory. The second part of this thesis shows that a traditional FIFO PRQ does not promote a timely prefetching behavior and usually hinders part of the performance benefits achieved by throttling heuristics. We propose a novel approach to prefetch aggressiveness control in multi-cores that performs throttling at the PRQ (i.e., global) level, using global knowledge of the metrics of all prefetchers and information about the global state of the PRQ. To do this, we introduce the Resizable Prefetching Heap (RPH), a data structure modeled after a binary heap that promotes timely dispatch of prefetches as well as fairness in the distribution of prefetching bandwidth. The RPH is designed as a drop-in replacement of traditional FIFO PRQs. We compare our proposal against a state-of-the-art source-level throttling algorithm (HPAC) in a 8-core system. Unlike previous research, we evaluate both multiprogrammed and multithreaded (parallel) workloads, using a modern prefetching algorithm (C/DC). Our experimental results show that RPH-based throttling increases the throttling performance benefits obtained by HPAC by as much as 148% (53.8% average) in multiprogrammed workloads and as much as 237% (22.5% average) in parallel benchmarks, while consuming roughly the same amount of memory bandwidth. When comparing the speedup over fixed degree prefetching, RPH increased the average speedup of HPAC from 7.1% to 10.9% in multiprogrammed workloads, and from 5.1% to 7.9% in parallel benchmarks.

# Acknowledgements

I would like to thank my supervisor Marcelo Cintra for all the help and guidance he has provided me during these years. I have learned many things from Marcelo but the two most important lessons I have taken from him are how to carry serious research and how to persevere when things do not work out as expected. I value the flexibility and patience that he has shown during my PhD, as well as the freedom he has given me to pursue my research interests. I am also greatly indebted to Marcelo for the opportunity to spend a six month internship at a top research lab such as Intel Labs Germany. Lastly, I am particularly grateful to him for his insightful corrections and constant attention during the writing of this thesis.

I would also like to thank everybody at Institute for Computer Systems Architecture for their support and help. I am thankful to my second supervisor Ariteides Efthymiou and Nigel Topham for being part of my annual thesis review panel. I would also like to thank Mike O'Boyle and Björn Franke for their role in creating a vibrating research group that I have always been pround being part of. My fellow PhD students have made this journey much more enjoyable and interesting. Many thanks to Salman Khan, Hugh Leather, Nikolas Ioannou, Konstantina Mitropoulou, Sofia Pediaditaki, Vasileios Porpodas, Georgios Tournavidis and Polychronis Xekalakis. I am specially grateful to Polychronis for the countless hours of stimulating research conversation by the coffee machine, and generally, for being a constant source of ideas and advice.

On a personal note, I am very grateful to Raniska for her understanding and moral support over these years. Finally, and most importantly, I would like thank my parents Pedro and Cristina for their absolutely unconditional support and encouragement during my PhD.

# **Declaration**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified. Some of the material used in this thesis has been published in the following paper:

• "Stream Chaining: Exploiting Multiple Levels of Correlation in Data Prefetching". Pedro Díaz and Marcelo Cintra. International Symposium on Computer Architecture 2009.

(Pedro Díaz)

# **Table of Contents**

| 1 | Intr | oductio | n                                                         | 1  |

|---|------|---------|-----------------------------------------------------------|----|

|   | 1.1  | Motiva  | ation and Focus of this Dissertation                      | 1  |

|   | 1.2  | Main (  | Contributions                                             | 3  |

|   |      | 1.2.1   | Improving Prefetching Timeliness With Stream Chaining     | 3  |

|   |      | 1.2.2   | Prefetching in Multi-Core Systems with Resizable Prefetch |    |

|   |      |         | Heaps                                                     | 5  |

|   | 1.3  | Thesis  | Structure                                                 | 6  |

| 2 | Bac  | kground | 1                                                         | 8  |

|   | 2.1  | Memor   | ry Hierarchies                                            | 8  |

|   | 2.2  | Prefetc | ching                                                     | 10 |

|   | 2.3  | Basic ( | Operation of a Hardware Data Prefetcher                   | 11 |

|   | 2.4  | Prefetc | ching Metrics                                             | 12 |

|   | 2.5  | Hardw   | are Prefetching Methods                                   | 13 |

|   |      | 2.5.1   | Localization                                              | 13 |

|   |      | 2.5.2   | Correlation                                               | 15 |

|   |      | 2.5.3   | Other Approaches to Data Prefetching                      | 20 |

|   | 2.6  | Hardw   | are Structures for Data Prefetching                       | 21 |

|   |      | 2.6.1   | Miss History hardware data structures                     | 21 |

|   |      | 2.6.2   | The Prefetch Request Queue                                | 23 |

|   | 2.7  | Adapti  | ve Prefetch Throttling and Filtering                      | 24 |

|   |      | 2.7.1   | Prefetch Throttling Techniques                            | 24 |

|   |      | 2.7.2   | Prefetch Filtering Techniques                             | 25 |

|   | 2.8  | Prefetc | ching in Multi-Core Systems                               | 26 |

| 3 | Stre | am Cha  | ining                                                     | 28 |

|   | 3.1  | Introdu | uction                                                    | 28 |

| <ul> <li>3.3 Stream Chaining</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 3.4.1       PC/DC/MG         3.4.2       C/DC/MG         3.4.3       Table-based Alternative Implementations of C/DC/MG         4       Evaluation of Stream Chaining Prefetchers         4.1       Simulation Setup         4.2       Benchmarks         4.3       Benchmark Characterization         4.3.1       L2 Cache Size Sensitivity         4.3.2       Miss Distances         4.4       PC/DC/MG         4.4.1       Performance and Traffic         4.4.2       Coverage and Accuracy         4.4.3       PC Stream Prediction Accuracy         4.4.4       Miss Graph Characterization         4.5.1       Performance and Traffic         4.5.2       Coverage and Accuracy         4.5.3       CZone Transition Prediction Accuracy         4.5.4       CZone Repetition Prediction Accuracy         4.5.5       Miss Graph Characterization         4.5.5       Miss Graph Characterization         4.6       Comparison of PC/DC/MG, C/DC/MG and G/DC         5       Resizable Prefetch Heaps         5.1       Introduction         5.2       Prefetch Heaps         5.1       Introduction         5.2       Prefetch Heaps                              |                 |

| 3.4.2       C/DC/MG         3.4.3       Table-based Alternative Implementations of C/DC/MG         4       Evaluation of Stream Chaining Prefetchers         4.1       Simulation Setup         4.2       Benchmarks         4.3       Benchmark Characterization         4.3.1       L2 Cache Size Sensitivity         4.3.2       Miss Distances         4.4       PC/DC/MG         4.4.1       Performance and Traffic         4.4.2       Coverage and Accuracy         4.4.3       PC Stream Prediction Accuracy         4.4.4       Miss Graph Characterization         4.5       C/DC/MG         4.5.1       Performance and Traffic         4.5.2       Coverage and Accuracy         4.5.3       CZone Transition Prediction Accuracy         4.5.4       CZone Repetition Prediction Accuracy         4.5.5       Miss Graph Characterization         4.5.4       CZone Repetition Prediction Accuracy         4.5.5       Miss Graph Characterization         4.6       Comparison of PC/DC/MG, C/DC/MG and G/DC         5       Resizable Prefetch Heaps         5.1       Introduction         5.2       Prefetch Hreaps         5.3       Case Study: The Hie |                 |

| <ul> <li>3.4.3 Table-based Alternative Implementations of C/DC/MG.</li> <li>4 Evaluation of Stream Chaining Prefetchers <ul> <li>4.1 Simulation Setup</li> <li>4.2 Benchmarks</li> <li>4.3 Benchmark Characterization</li> <li>4.3.1 L2 Cache Size Sensitivity</li> <li>4.3.2 Miss Distances</li> </ul> </li> <li>4.4 PC/DC/MG</li> <li>4.4.1 Performance and Traffic</li> <li>4.4.2 Coverage and Accuracy</li> <li>4.4.3 PC Stream Prediction Accuracy</li> <li>4.4.4 Miss Graph Characterization</li> <li>4.5 C/DC/MG</li> <li>4.5.1 Performance and Traffic</li> <li>4.5.2 Coverage and Accuracy</li> <li>4.5.3 CZone Transition Prediction Accuracy</li> <li>4.5.4 CZone Repetition Prediction Accuracy</li> <li>4.5.5 Miss Graph Characterization</li> <li>4.6 Comparison of PC/DC/MG, C/DC/MG and G/DC</li> </ul> <li>5 Resizable Prefetch Heaps <ul> <li>5.1 Introduction</li> <li>5.2 Prefetch Throttling as Producer-Consumer Problem</li> <li>5.3 Case Study: The Hierarchical Prefetch Aggressiver</li> <li>5.4 Resizable Prefetch Heaps</li> </ul></li>                                                                                                         |                 |

| <ul> <li>C/DC/MG</li> <li>Evaluation of Stream Chaining Prefetchers</li> <li>4.1 Simulation Setup</li> <li>4.2 Benchmarks</li> <li>4.3 Benchmark Characterization</li> <li>4.3 Benchmark Characterization</li> <li>4.3 Benchmark Characterization</li> <li>4.3.1 L2 Cache Size Sensitivity</li> <li>4.3.2 Miss Distances</li> <li>4.4 PC/DC/MG</li> <li>4.4.1 Performance and Traffic</li> <li>4.4.2 Coverage and Accuracy</li> <li>4.4.3 PC Stream Prediction Accuracy</li> <li>4.4.4 Miss Graph Characterization</li> <li>4.5 C/DC/MG</li> <li>4.5.1 Performance and Traffic</li> <li>4.5.2 Coverage and Accuracy</li> <li>4.5.3 CZone Transition Prediction Accuracy</li> <li>4.5.4 CZone Repetition Prediction Accuracy</li> <li>4.5.5 Miss Graph Characterization</li> <li>4.6 Comparison of PC/DC/MG, C/DC/MG and G/DC</li> </ul> 5 Resizable Prefetch Heaps <ul> <li>5.1 Introduction</li> <li>5.2 Prefetch Throttling as Producer-Consumer Problem</li> <li>5.3 Case Study: The Hierarchical Prefetch Aggressiver</li> <li>5.4 Resizable Prefetch Heaps</li> </ul>                                                                                                  | 40              |

| <ul> <li>4 Evaluation of Stream Chaining Prefetchers <ol> <li>Simulation Setup</li> <li>Benchmarks</li> <li>Benchmark Characterization</li> <li>Benchmark Characterization</li> <li>L2 Cache Size Sensitivity</li> <li>A.3.1 L2 Cache Size Sensitivity</li> <li>A.3.2 Miss Distances</li> </ol> </li> <li>4.4 PC/DC/MG</li> <li>A.4.1 Performance and Traffic</li> <li>A.2.2 Coverage and Accuracy</li> <li>A.4.3 PC Stream Prediction Accuracy</li> <li>A.4.4 Miss Graph Characterization</li> <li>C/DC/MG</li> <li>A.5.1 Performance and Traffic</li> <li>A.5.2 Coverage and Accuracy</li> <li>A.5.1 Performance and Traffic</li> <li>A.5.2 Coverage and Accuracy</li> <li>A.5.3 CZone Transition Prediction Accuracy</li> <li>A.5.4 CZone Repetition Prediction Accuracy</li> <li>A.5.5 Miss Graph Characterization</li> <li>A.6 Comparison of PC/DC/MG, C/DC/MG and G/DC</li> </ul> 5 Resizable Prefetch Heaps <ul> <li>5.1 Introduction</li> <li>S.2 Prefetch Throttling as Producer-Consumer Problem</li> <li>S.3 Case Study: The Hierarchical Prefetch Aggressiver</li> <li>S.4 Resizable Prefetch Heaps</li> </ul>                                                  | of PC/DC/MG and |

| <ul> <li>4.1 Simulation Setup</li> <li>4.2 Benchmarks</li> <li>4.3 Benchmark Characterization</li> <li>4.3.1 L2 Cache Size Sensitivity</li> <li>4.3.2 Miss Distances</li> <li>4.4 PC/DC/MG</li> <li>4.4.1 Performance and Traffic</li> <li>4.4.2 Coverage and Accuracy</li> <li>4.4.3 PC Stream Prediction Accuracy</li> <li>4.4.4 Miss Graph Characterization</li> <li>4.5 C/DC/MG</li> <li>4.5.1 Performance and Traffic</li> <li>4.5.2 Coverage and Accuracy</li> <li>4.5.3 CZone Transition Prediction Accuracy</li> <li>4.5.4 CZone Repetition Prediction Accuracy</li> <li>4.5.5 Miss Graph Characterization</li> <li>4.6 Comparison of PC/DC/MG, C/DC/MG and G/DC</li> <li>5 Resizable Prefetch Heaps</li> <li>5.1 Introduction</li> <li>5.2 Prefetch Throttling as Producer-Consumer Problem</li> <li>5.3 Case Study: The Hierarchical Prefetch Aggressiver</li> <li>5.4 Resizable Prefetch Heaps</li> </ul>                                                                                                                                                                                                                                                        |                 |

| <ul> <li>4.2 Benchmarks</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 53              |

| <ul> <li>4.3 Benchmark Characterization</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 53              |

| <ul> <li>4.3.1 L2 Cache Size Sensitivity</li> <li>4.3.2 Miss Distances</li> <li>4.4 PC/DC/MG</li> <li>4.4.1 Performance and Traffic</li> <li>4.4.2 Coverage and Accuracy</li> <li>4.4.3 PC Stream Prediction Accuracy</li> <li>4.4.4 Miss Graph Characterization</li> <li>4.5 C/DC/MG</li> <li>4.5.1 Performance and Traffic</li> <li>4.5.2 Coverage and Accuracy</li> <li>4.5.3 CZone Transition Prediction Accuracy</li> <li>4.5.4 CZone Repetition Prediction Accuracy</li> <li>4.5.5 Miss Graph Characterization</li> <li>4.6 Comparison of PC/DC/MG, C/DC/MG and G/DC</li> </ul> 5 Resizable Prefetch Heaps <ul> <li>5.1 Introduction</li> <li>5.2 Prefetch Throttling as Producer-Consumer Problem</li> <li>5.3 Case Study: The Hierarchical Prefetch Aggressiver</li> <li>5.4 Resizable Prefetch Heaps</li> </ul>                                                                                                                                                                                                                                                                                                                                                    | 54              |

| <ul> <li>4.3.2 Miss Distances</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54              |

| <ul> <li>4.4 PC/DC/MG</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 54              |

| <ul> <li>4.4.1 Performance and Traffic</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |

| <ul> <li>4.4.2 Coverage and Accuracy</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |

| <ul> <li>4.4.3 PC Stream Prediction Accuracy</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |

| <ul> <li>4.4.4 Miss Graph Characterization</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 63              |

| <ul> <li>4.5 C/DC/MG</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 65              |

| <ul> <li>4.5.1 Performance and Traffic</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66              |

| <ul> <li>4.5.2 Coverage and Accuracy</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 70              |

| <ul> <li>4.5.3 CZone Transition Prediction Accuracy</li> <li>4.5.4 CZone Repetition Prediction Accuracy</li> <li>4.5.5 Miss Graph Characterization</li> <li>4.6 Comparison of PC/DC/MG, C/DC/MG and G/DC</li> </ul> 5 Resizable Prefetch Heaps 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70              |

| <ul> <li>4.5.4 CZone Repetition Prediction Accuracy</li> <li>4.5.5 Miss Graph Characterization</li> <li>4.6 Comparison of PC/DC/MG, C/DC/MG and G/DC</li> <li>5 Resizable Prefetch Heaps</li> <li>5.1 Introduction</li> <li>5.2 Prefetch Throttling as Producer-Consumer Problem</li> <li>5.3 Case Study: The Hierarchical Prefetch Aggressiver</li> <li>5.4 Resizable Prefetch Heaps</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 73              |

| <ul> <li>4.5.5 Miss Graph Characterization</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |

| <ul> <li>4.6 Comparison of PC/DC/MG, C/DC/MG and G/DC</li> <li>5 Resizable Prefetch Heaps</li> <li>5.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |

| <ul> <li>5 Resizable Prefetch Heaps</li> <li>5.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |

| <ul> <li>5.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 80              |

| <ul> <li>5.2 Prefetch Throttling as Producer-Consumer Problem</li> <li>5.3 Case Study: The Hierarchical Prefetch Aggressiver</li> <li>5.4 Resizable Prefetch Heaps</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 85              |

| <ul> <li>5.3 Case Study: The Hierarchical Prefetch Aggressive</li> <li>5.4 Resizable Prefetch Heaps</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |

| 5.4 Resizable Prefetch Heaps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | n               |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ness Control 87 |

| 5.4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |

| 5.4.2 Prefetch Throttling with RPHs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |

| 6   | Eval   | uation of Resizable Prefetch Heaps                       | 98  |

|-----|--------|----------------------------------------------------------|-----|

|     | 6.1    | Simulation Setup                                         | 98  |

|     | 6.2    | Benchmarks                                               | 98  |

|     | 6.3    | Prefetch Mechanism and Throttling Strategies             | 99  |

|     | 6.4    | Metrics                                                  | 101 |

|     |        | 6.4.1 Performance                                        | 101 |

|     |        | 6.4.2 Traffic                                            | 101 |

|     |        | 6.4.3 Prefetch Fairness                                  | 101 |

|     | 6.5    | Benchmark Characterization                               | 103 |

|     |        | 6.5.1 L2 Cache-Performance Sensitivity                   | 103 |

|     |        | 6.5.2 L2 Cache Hit Rates and Usage                       | 104 |

|     | 6.6    | Prefetching Performance                                  | 107 |

|     | 6.7    | Bandwidth Usage                                          | 109 |

|     | 6.8    | Prefetch Fairness                                        | 110 |

|     | 6.9    | Influence of Adaptive Resizing                           | 111 |

|     | 6.10   | Characterization RPH Queues                              | 113 |

|     |        | 6.10.1 Average Number of Comparisons per Queue Operation | 113 |

|     |        | 6.10.2 Scaling States Histogram                          | 115 |

| 7   | Sum    | mary of Contributions and Concluding Remarks             | 117 |

|     | 7.1    | Summary of Contributions of this Thesis                  | 117 |

|     |        | 7.1.1 Future Work                                        | 118 |

|     | 7.2    | Concluding Remarks                                       | 119 |

| A   | Benc   | chmark Descriptions                                      | 121 |

|     | A.1    | SPEC CPU2006 benchmarks                                  | 121 |

|     |        | A.1.1 Integer Benchmarks.                                | 121 |

|     |        | A.1.2 Floating Point Benchmarks                          | 123 |

|     | A.2    | BioBench Benchmarks                                      | 124 |

|     | A.3    | Parallel Benchmarks                                      | 125 |

|     |        | A.3.1 PARSEC benchmarks                                  | 126 |

|     |        | A.3.2 ALP Benchmarks                                     | 127 |

|     |        | A.3.3 Standalone programs                                | 128 |

| Bil | bliogr | aphy                                                     | 129 |

# **List of Tables**

| 4.1 | Simulated architectural parameters                                   | 54  |

|-----|----------------------------------------------------------------------|-----|

| 4.2 | PC/DC/MG: miss graphs statistics (a) and GHB hop counts (b)          | 69  |

| 4.3 | C/DC/MG: miss graphs statistics (a) and GHB hop counts (b). $\ldots$ | 79  |

| 5.1 | HPAC decision rules                                                  | 88  |

| 5.2 | Memory utilization scale used to resize the RPH                      | 93  |

| 5.3 | RPH throttling actions.                                              | 96  |

| 6.1 | Architectural parameters: Per core (left) and system-wide (right)    | 99  |

| 6.2 | Multi-programmed workloads                                           | 100 |

| 6.3 | Example Prefetch Fairness calculation                                | 103 |

| 6.4 | Scaling states histogram for multi-programmed workloads (left) and   |     |

|     | parallel benchmarks (right)                                          | 115 |

# **List of Figures**

| 2.1 | Standard memory hierarchy with typical access latencies                      | 9  |

|-----|------------------------------------------------------------------------------|----|

| 2.2 | Execution context, spatial and temporal localization                         | 15 |

| 2.3 | Example of Address Correlation.                                              | 17 |

| 2.4 | Example of Markov Prefetching.                                               | 18 |

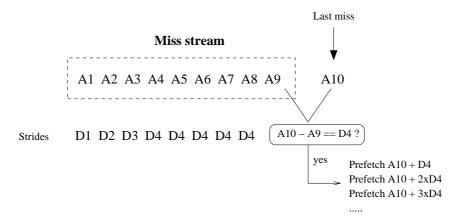

| 2.5 | Example of Constant Stride correlation.                                      | 19 |

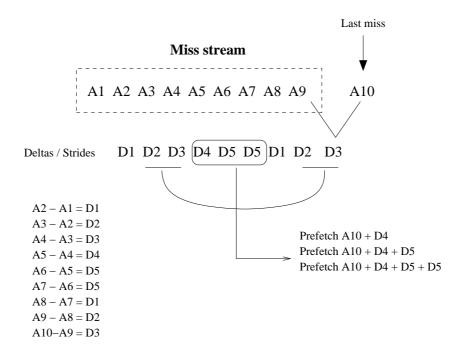

| 2.6 | Example of Delta correlation                                                 | 20 |

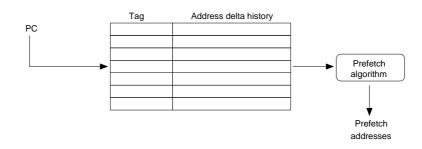

| 2.7 | Table structure for the PC/DC prefetcher                                     | 22 |

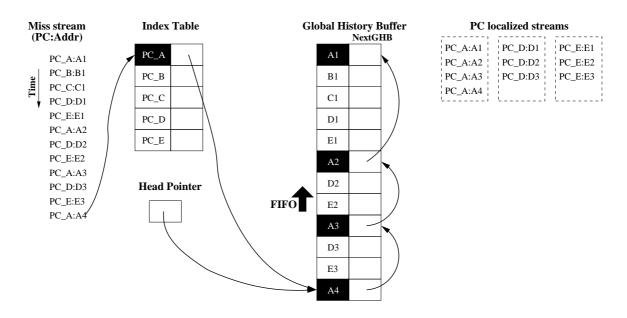

| 2.8 | GHB for the PC/DC prefetcher                                                 | 23 |

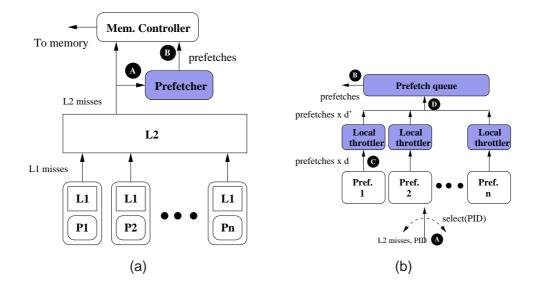

| 2.9 | (a) Overall logical organization of a multi-core architecture; (b) Logi-     |    |

|     | cal organization of L2 prefetchers                                           | 27 |

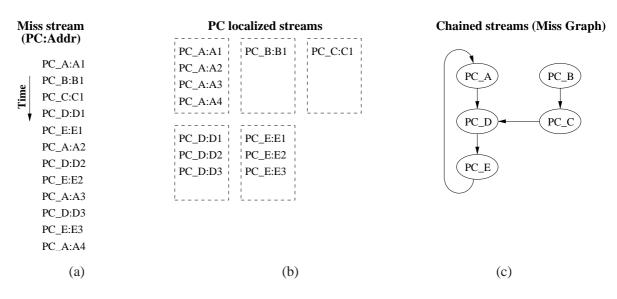

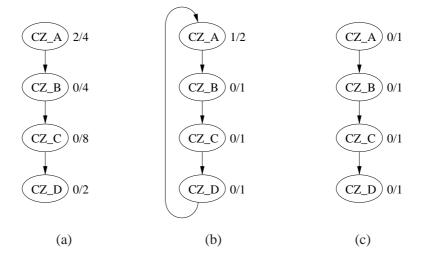

| 3.1 | Example of Stream Chaining applied to PC localization: (a) global            |    |

|     | miss stream, (b) localized streams according to the PC of the missing        |    |

|     | instruction; and (c) one possible chaining of the localized streams          | 31 |

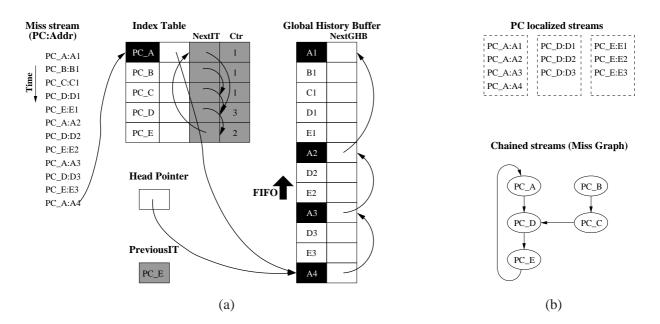

| 3.2 | (a) PC/DC/MG extensions to the GHB. (b) Resulting Miss Graph from            |    |

|     | the example miss stream.                                                     | 35 |

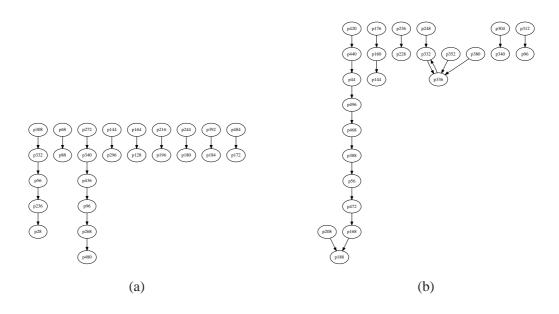

| 3.3 | PC/DC/MG Miss Graph examples from real applications: (a) <i>bzip2</i>        |    |

|     | with 2MB L2. (b) <i>deall1</i> with 256KB L2 (right)                         | 36 |

| 3.4 | PC/DC/MG Miss Graph cases: (a) non-cyclic chain longer than the              |    |

|     | prefetch degree (8); (b) cyclic chain shorter than the prefetch degree;      |    |

|     | and (c) non-cyclic chain shorter than the prefetch degree                    | 37 |

| 3.5 | CZone transitioning problem: (a) global miss stream, PC localization         |    |

|     | and CZone localization; (b) Miss Graphs for PC and CZone localiza-           |    |

|     | tions using the original PC/DC/MG graph construction algorithm. $\therefore$ | 41 |

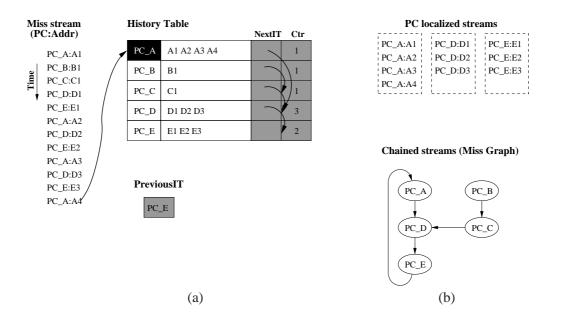

| 3.6 | (a) C/DC/MG extensions to the GHB. (b) Resulting Miss Graph from             |    |

|     | the example miss stream.                                                     | 43 |

| 3.7   | C/DC/MG Miss Graph examples from real applications: (a) <i>bzip2</i> with |          |

|-------|---------------------------------------------------------------------------|----------|

|       | 2MB L2; (b) <i>dealII</i> with 256KB L2                                   | 45       |

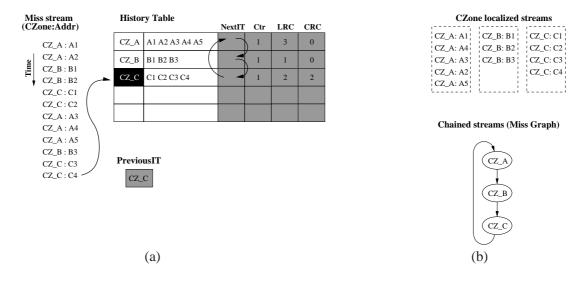

| 3.8   | C/DC/MG Miss Graph cases. The numbers adjacent to each node show          |          |

|       | the CRC/LRC counters. (a) non-cyclic chain with prefetch potential        |          |

|       | bigger than or equal to the prefetch degree (16); (b) cyclic chain with   |          |

|       | lower prefetch potential than the prefetch degree; and (c) non-cyclic     |          |

|       | chain with lower prefetch potential than the prefetch degree              | 45       |

| 3.9   | Design of a table-based PC/DC prefetcher.                                 | 50       |

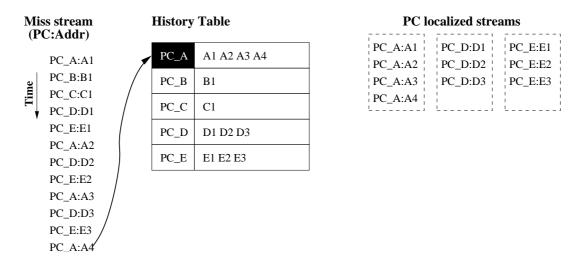

| 3.10  | (a) PC/DC/MG extensions to the history table. (b) Resulting Miss          |          |

|       | Graph from the example miss stream.                                       | 51       |

| 3.11  | (a) C/DC/MG extensions to the history table. (b) Resulting Miss Graph     |          |

|       | from the example miss stream.                                             | 52       |

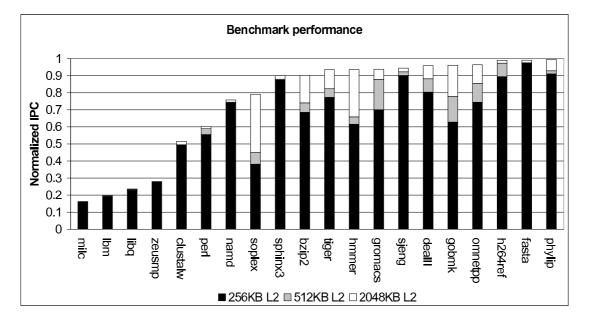

| 4.1   | L2 cache size sensitivity for 256KB, 512KB and 2MB L2 caches              | 55       |

| 4.1   | •                                                                         | 55<br>56 |

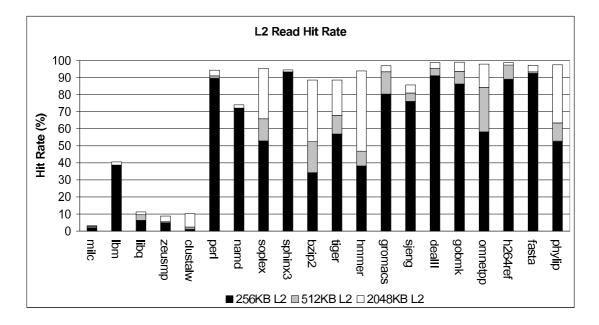

|       | L2 cache Read Hit Rate for 256KB, 512KB and 2MB L2 caches                 | 50<br>57 |

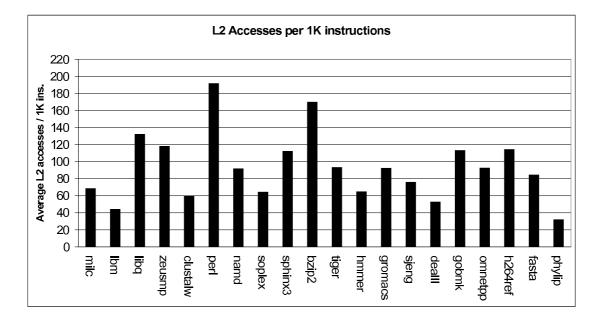

| 4.3   | Number of L2 cache accesses per 1K instructions                           | 57       |

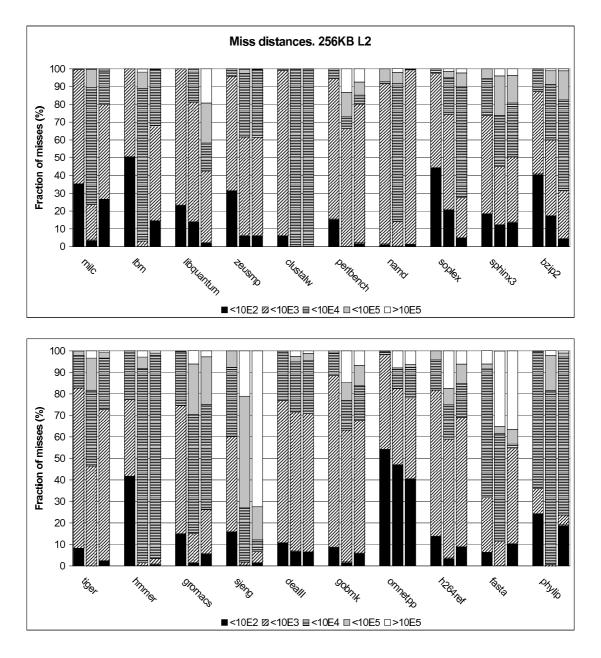

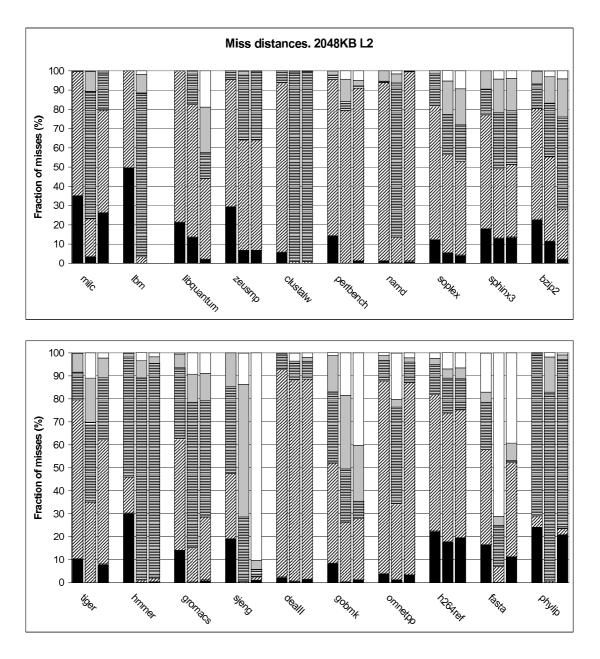

| 4.4   | Miss distances for 256KB L2. Figure shows global (left), per PC (mid-     | 50       |

| 15    | dle) and per CZone (right) miss distances.                                | 59       |

| 4.5   | Miss distances for 2MB L2. Figure shows global (left), per PC (mid-       | 60       |

| 16    | dle) and per CZone (right) miss distances.                                | 60       |

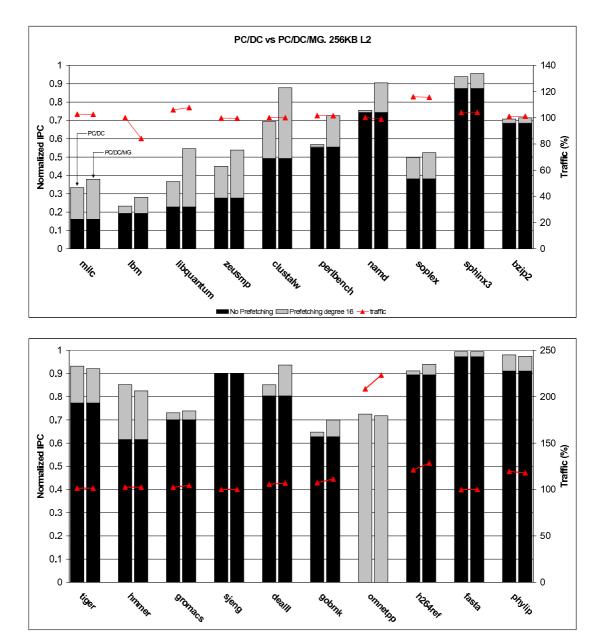

| 4.6   | PC/DC (left bar) and PC/DC/MG (right bar) performance and traffic.        | (1       |

| 4 7   | 256KB L2 cache                                                            | 61       |

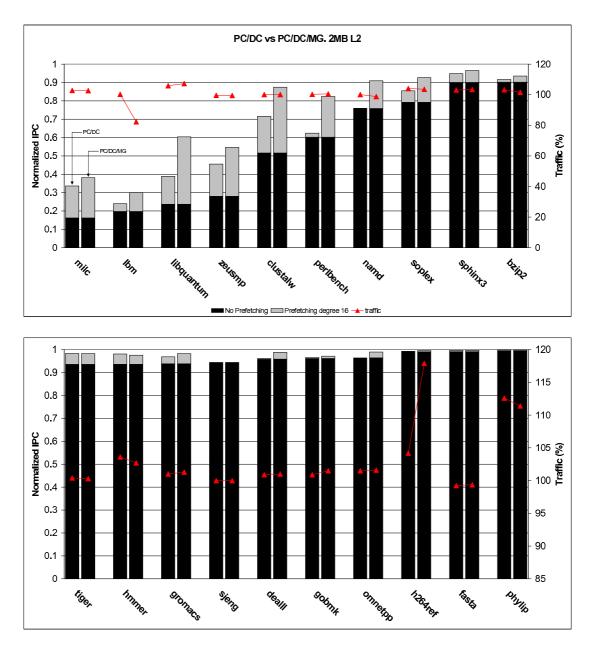

| 4.7   | PC/DC (left bar) and PC/DC/MG (right bar) performance and traffic.        | ()       |

| 4.0   | 2MB L2 cache                                                              | 62       |

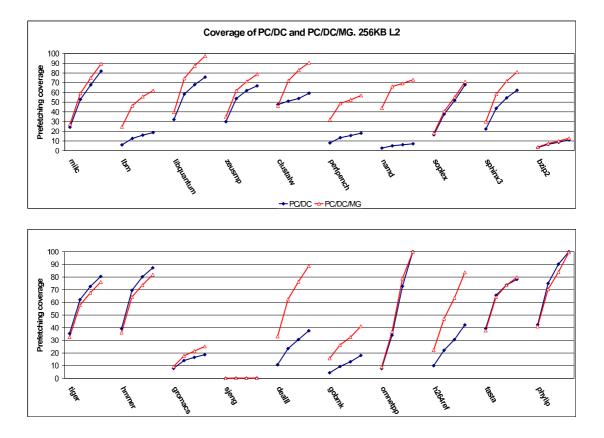

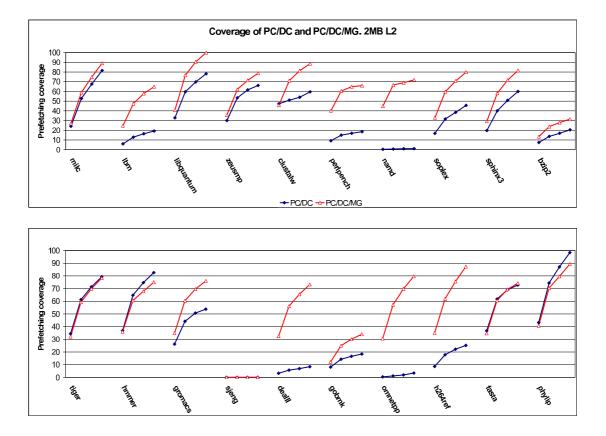

| 4.8   | Prefetching coverage of PC/DC and PC/DC/MG. 256KB L2 cache                | 64       |

| 4.9   | Prefetching coverage of PC/DC and PC/DC/MG. 2MB L2 cache                  | 65       |

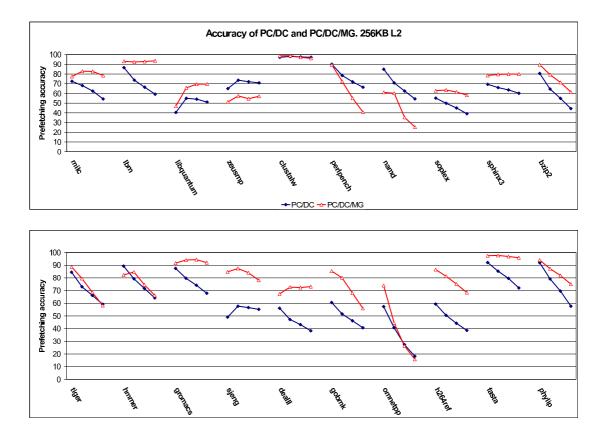

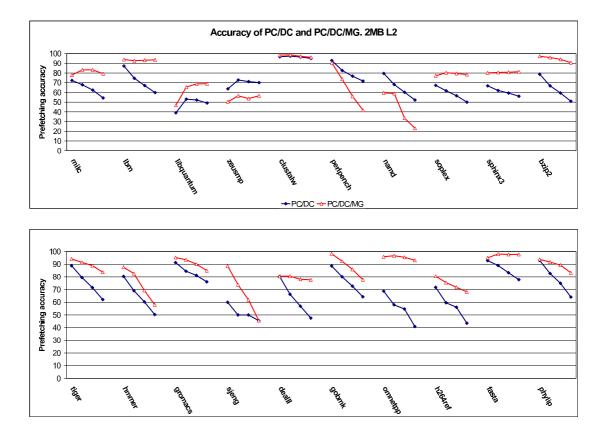

|       | Prefetching accuracy of PC/DC and PC/DC/MG. 256KB L2 cache                | 66       |

|       | Prefetching accuracy of PC/DC and PC/DC/MG. 2MB L2 cache                  | 67       |

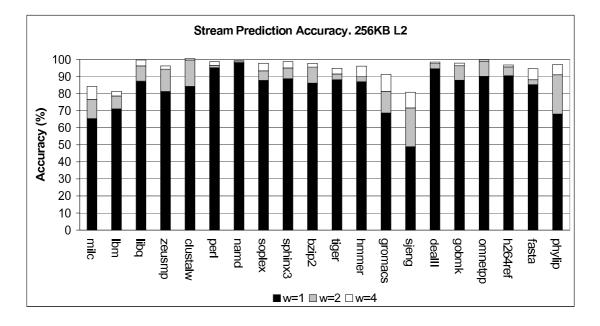

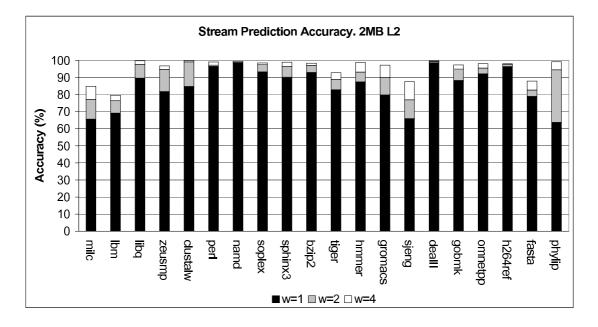

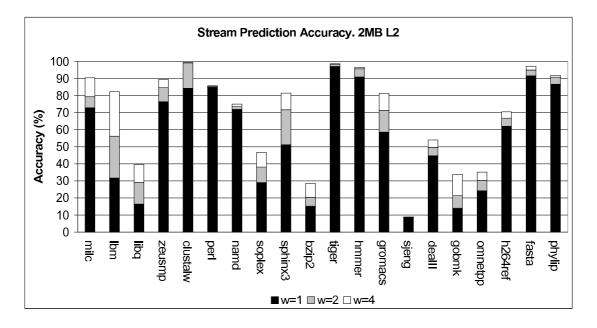

| 4.12  | PC/DC/MG accuracy in predicting the next PC to appear in the next $w$     | 60       |

| 4.4.0 | misses. 256KB L2 Cache.                                                   | 68       |

| 4.13  | PC/DC/MG accuracy in predicting the next PC to appear in the next $w$     | -        |

|       | misses. 2MB L2 Cache.                                                     | 70       |

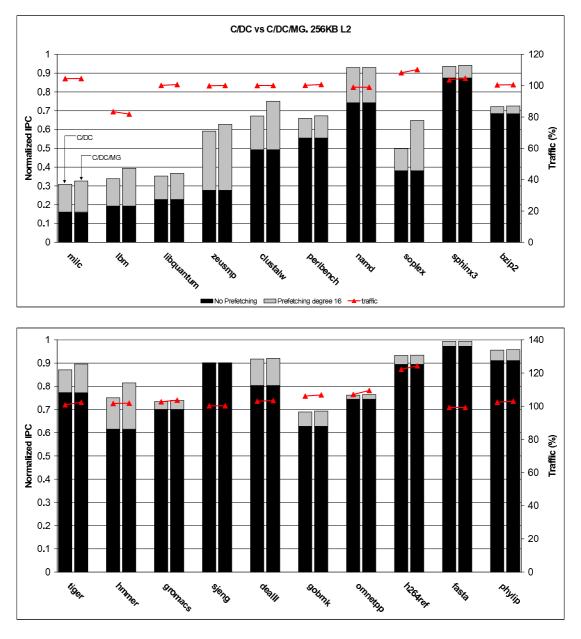

| 4.14  | C/DC (left bar) and C/DC/MG (right bar) performance and traffic.          | _        |

|       | 256KB L2 cache                                                            | 71       |

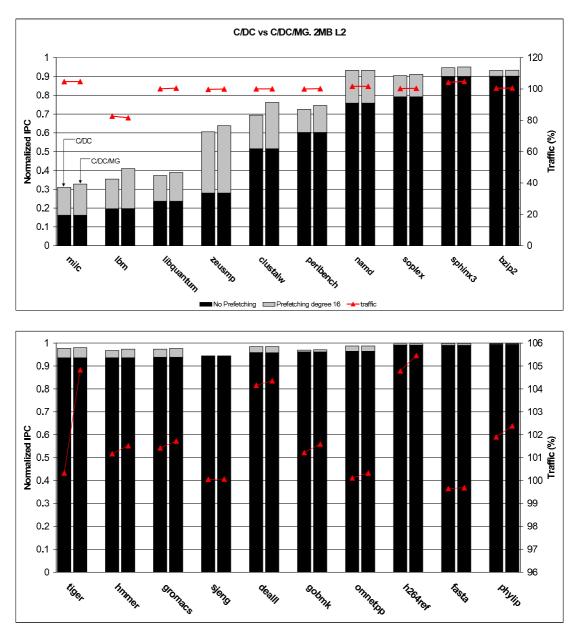

| 4.15       | C/DC (left bar) and C/DC/MG (right bar) performance and traffic.                    |      |

|------------|-------------------------------------------------------------------------------------|------|

|            | 2MB L2 cache                                                                        | 72   |

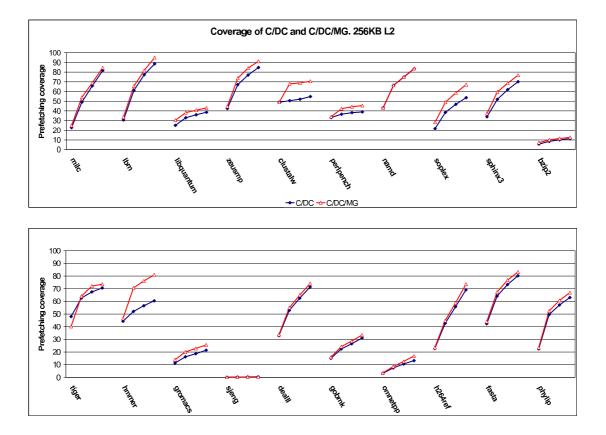

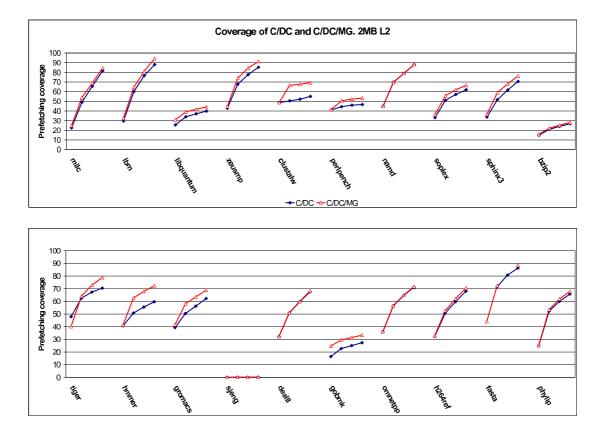

| 4.16       | Prefetching coverage of C/DC and C/DC/MG. 256KB L2 cache                            | 74   |

| 4.17       | Prefetching coverage of C/DC and C/DC/MG. 2MB L2 cache                              | 75   |

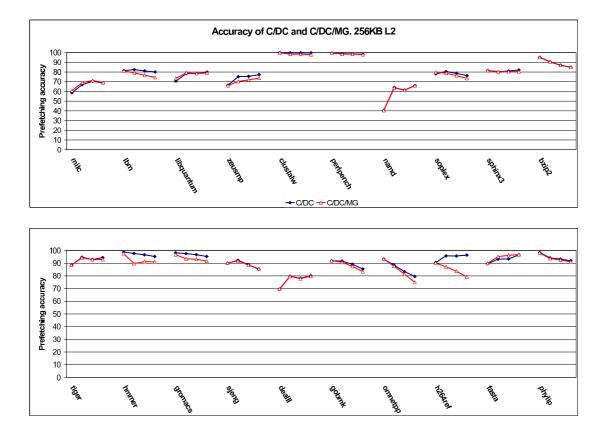

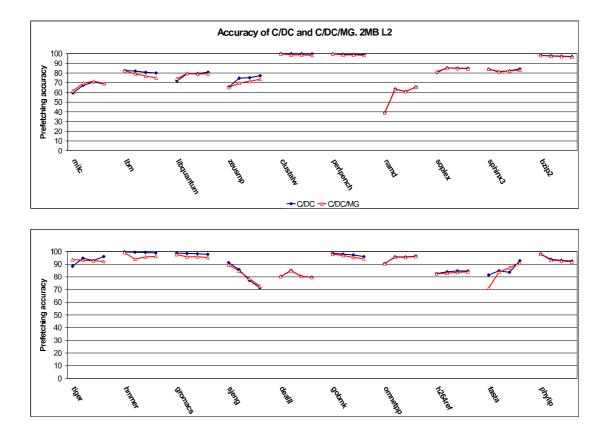

| 4.18       | Prefetching accuracy of C/DC and C/DC/MG. 256KB L2 cache                            | 76   |

| 4.19       | Prefetching accuracy of C/DC and C/DC/MG. 2MB L2 cache                              | 77   |

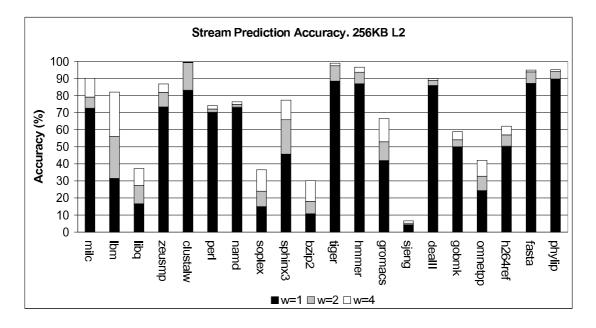

| 4.20       | C/DC/MG accuracy in predicting the next CZone to appear in the next                 |      |

|            | w misses. 256KB L2 Cache.                                                           | 78   |

| 4.21       | C/DC/MG accuracy in predicting the next CZone to appear in the next                 |      |

|            | <i>w</i> misses. 2048KB L2 Cache                                                    | 80   |

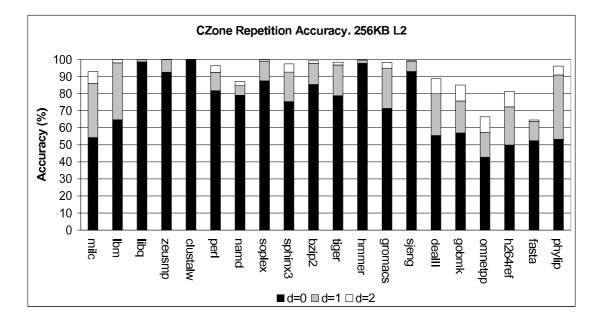

| 4.22       | CZone repetition accuracy. 256KB L2 cache.                                          | 81   |

| 4.23       | CZone repetition accuracy. 2MB L2 cache.                                            | 82   |

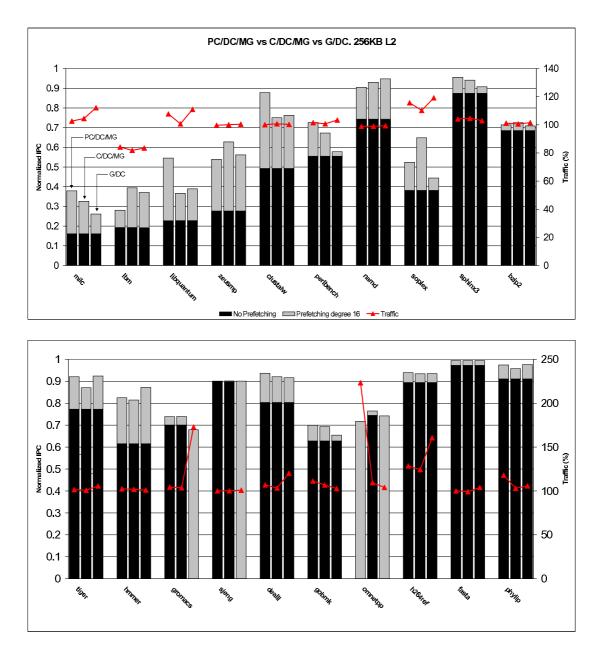

| 4.24       | Comparison of Stream Chaining prefetchers and G/DC. 256KB L2 cache                  | . 83 |

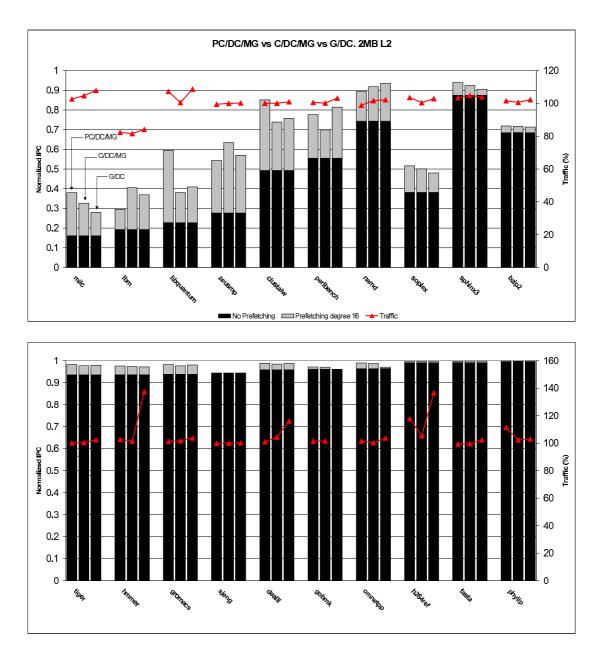

| 4.25       | Comparison of Stream Chaining prefetchers and G/DC. 2MB L2 cache.                   | 84   |

| <b>7</b> 1 |                                                                                     | 00   |

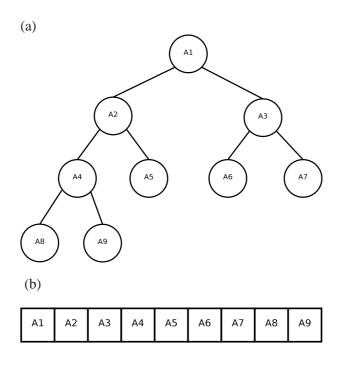

| 5.1        | Logical view of a binary heap: (a) as a tree; and (b) as an array                   | 90   |

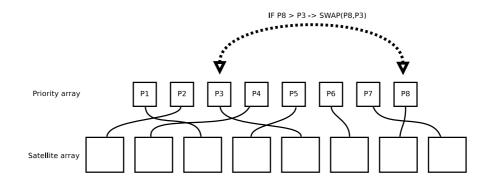

| 5.2        | Heap array split into priority and satellite data arrays.                           | 91   |

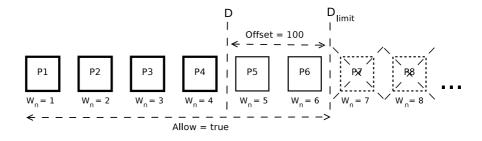

| 5.3        | Role of <i>D</i> and $D_{limit}$ registers. $W_n$ denotes the prefetch request wave | 0.6  |

|            | number                                                                              | 96   |

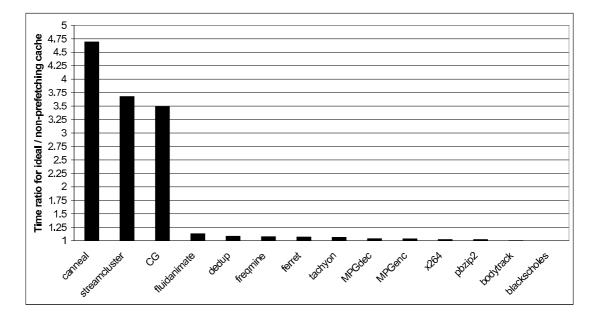

| 6.1        | Cache sensitivity in multi-programmed workloads.                                    | 104  |

| 6.2        | Cache sensitivity in parallel benchmarks                                            | 105  |

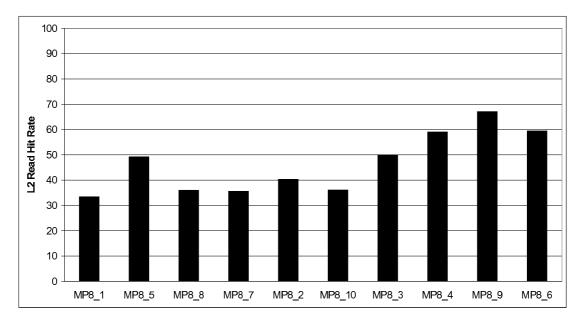

| 6.3        | L2 Read Hit Rate for multi-programmed workloads                                     | 105  |

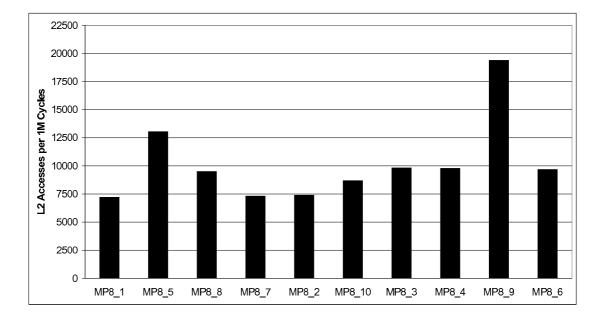

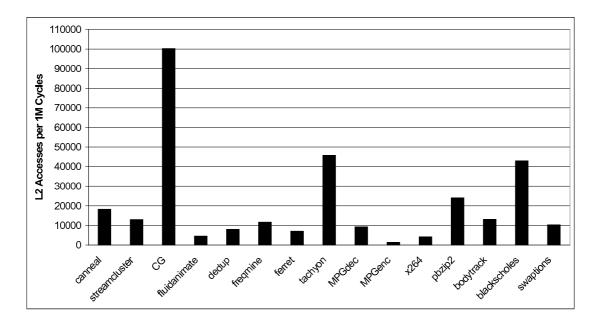

| 6.4        | Number of accesses to the L2 cache per million cycles for multi-programmer          | med  |

|            | workloads                                                                           | 106  |

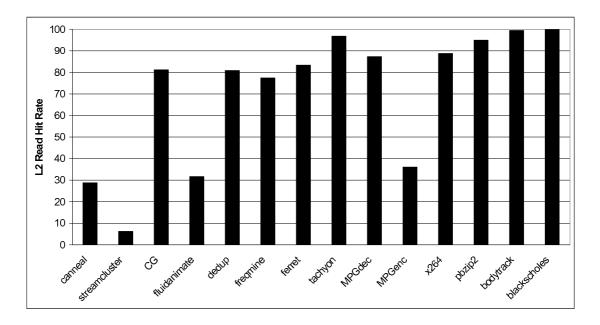

| 6.5        | L2 Read Hit Rate for parallel benchmarks.                                           | 107  |

| 6.6        | Number of accesses to the L2 cache per million cycles for parallel                  |      |

|            | benchmarks                                                                          | 107  |

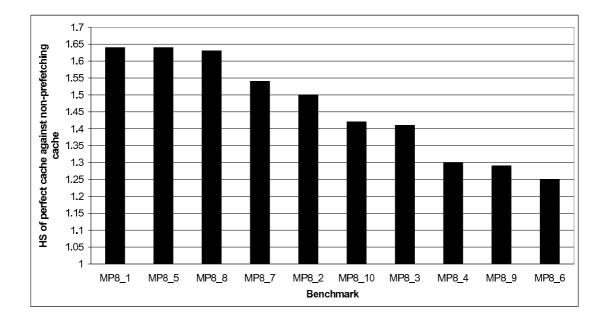

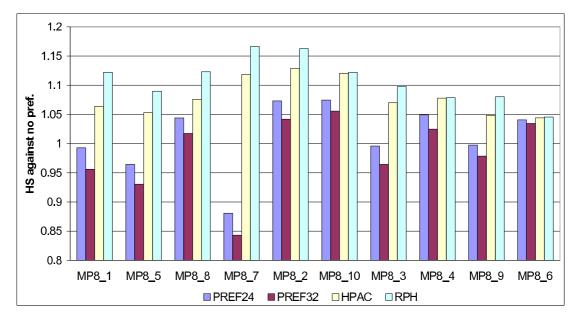

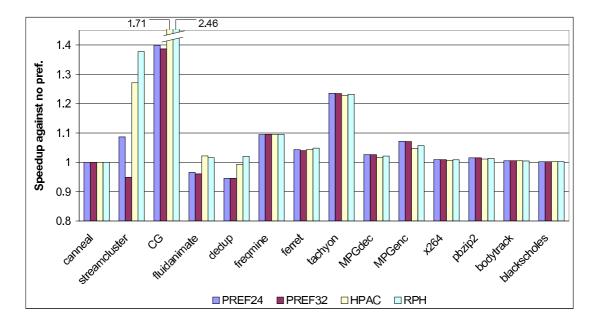

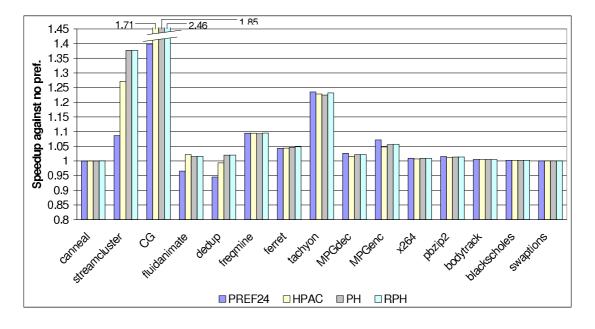

| 6.7        | Prefetching performance of multi-programmed workloads                               | 108  |

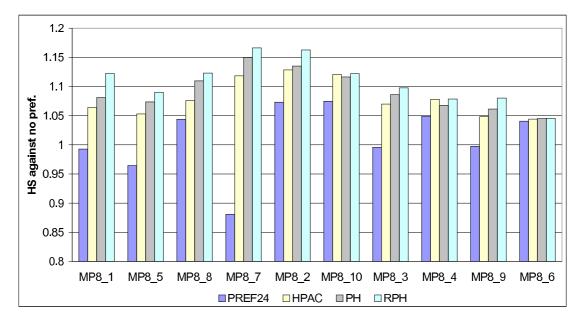

| 6.8        | Prefetching performance of parallel benchmarks                                      | 109  |

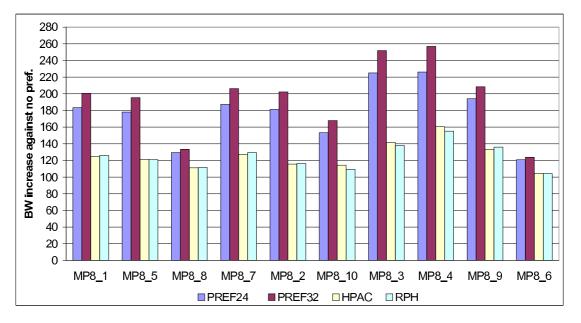

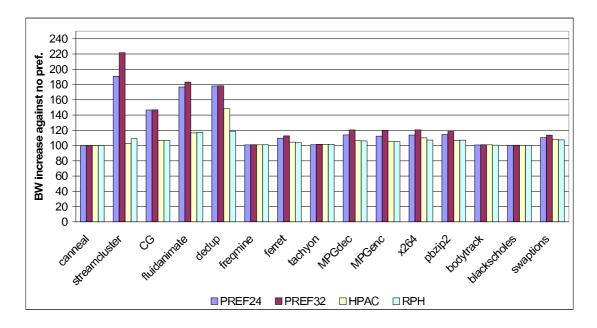

| 6.9        | Prefetching bandwidth increase in multi-programmed workloads                        | 110  |

| 6.10       | Prefetching bandwidth increase in parallel benchmarks                               | 110  |

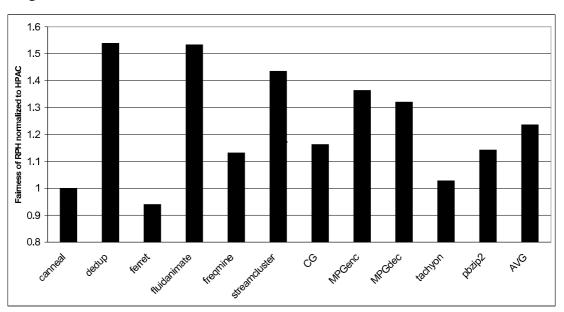

| 6.11       | RPH throttling prefetch fairness normalized to HPAC prefetch fairness.              | 111  |

| 6.12       | Results with and without adaptive resizing in multi-programmed work-                |      |

|            | loads                                                                               | 112  |

| 6.13       | Results with and without adaptive resizing in parallel benchmarks                   | 112  |

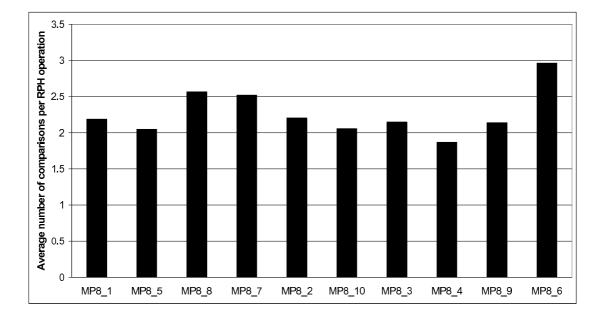

| 6.14 | Average number of comparisons per RPH insertion/extraction opera- |     |

|------|-------------------------------------------------------------------|-----|

|      | tion in multi-programmed workloads.                               | 114 |

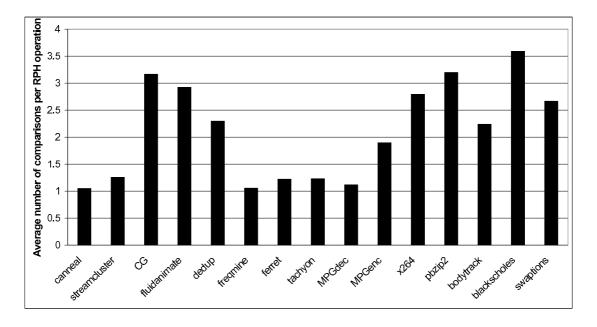

| 6.15 | Average number of comparisons per RPH insertion/extraction opera- |     |

|      | tion in parallel benchmarks                                       | 114 |

# **Chapter 1**

# Introduction

### **1.1 Motivation and Focus of this Dissertation**

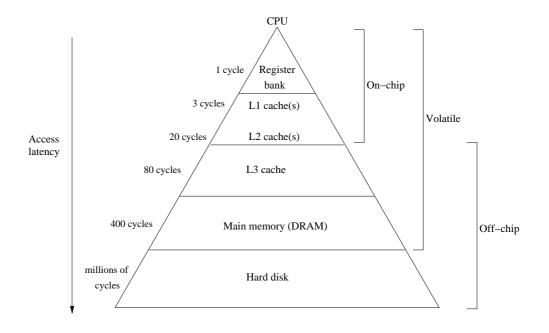

The term Memory Wall [15, 16] refers to the well known performance gap between processor speed and memory access latency. Nowadays off-chip memory requests have a latency of a few hundred processor cycles. Historically, technology has enabled a steady increase in processor operating frequencies while the most significant advances in memory technology have been related to density and not speed, thus creating an ever widening performance gap. At the present time the trend for increasing operating frequency in processors has flattened out. However, this trend has been exchanged for an increasing number of cores per chip. This has the consequence of more concurrent memory accesses and, therefore, an increase in the average off-chip access latency as observed by each core. As a result, even though the difference between processor and memory speed has not been increasing as steeply as in the past, the memory wall is expected to grow bigger.

Several techniques have been proposed to mask the big latencies related to off-chip memory access. Some try to exploit inherent Instruction Level Parallelism (ILP) in order to keep the processor busy with work while the required data arrives. Examples of these techniques include out-of-order execution, register renaming and speculative execution. The level of ILP varies, however, wildly across programs and even between program phases.

Prefetching is another technique historically successful in reducing the observed memory latency. In hardware prefetching, a set of hardware units observe the current memory access patterns. Based on this information, data that is likely to be needed in the future is fetched from memory and placed in one of the cache memory levels. In

#### Chapter 1. Introduction

software prefetching, the compiler uses static program analysis to interleave prefetch instructions throughout the program.

Both hardware and software prefetching have their benefits and drawbacks. In software prefetching there are no timing constraints for the execution of the prefetching algorithm, allowing the application of sophisticated prediction heuristics. However, software prefetching is mostly limited by static program analysis. On the other hand, hardware prefetching algorithms have access to the run-time information of the program, which is very valuable for predicting future accesses. Additionally, hardware prefetching is universally applicable (i.e., it is available to every program being run), whereas software prefetching requires recompilation or at least modification of the program binary. By contrast to software prefetching, hardware prefetching algorithms cannot be arbitrarily complex, and their run time has to fit into the timing constraints imposed to the hardware.

In this dissertation we will focus on hardware data prefetching into the lowest onchip data cache level (typically the L2). This is in accordance to most recent research. There are three reasons for concentrating our study in this cache level:

- The miss latency on higher cache levels is usually quite small and processors can tolerate them without too much degradation in performance.

- The time constraints for implementing prefetching algorithms at the lowest level are much more lenient. This allows us to design more sophisticated algorithms that would be simply unrealistic to implement at a higher cache level

- Finally, the lowest on-chip cache level has the highest miss penalty, since data requests must use the much slower memory interface. Therefore it is on this level were a good, sophisticated prefetching algorithm is expected to provide the greatest returns on investment.

Although hardware prefetching has been shown to improve significantly the performance of the memory subsystem, it is not a technique without problems. An inaccurate prefetcher can generate copious amounts of wasteful memory traffic that will pollute the cache and produce, in the worst case, performance degradation compared to a configuration without prefetching. Simple hardware prefetchers can not capture the complex memory access patterns present in nowadays applications and therefore suffer from low coverage. On the other hand, many of the more complex prefetching algorithms proposed by previous research are too complicated or require too many hardware resources to be implemented in current commercial architectures. While accurate prefetchers with good coverage are desirable, research on prefetching has traditionally focused almost exclusively on these two metrics, sidetracking the equally important aspect of improving prefetch timeliness (i.e., dispatching prefetches at the most optimal moment). Finally, the move to multi-core systems has emphasised the need for good prefetch throttling algorithms that can arbitrate and restrict the traffic coming from a growing number of prefetching units.

### **1.2 Main Contributions**

### 1.2.1 Improving Prefetching Timeliness With Stream Chaining

Virtually all modern prefetching algorithms use past cache miss history information to base their predictions. However, in its original form, the global stream of past miss history contains interleaved misses from several sources (i.e, different streams of memory accesses interleaved by ILP mechanisms within the CPU). This interleaving usually leads to poor predictability of the global miss stream.

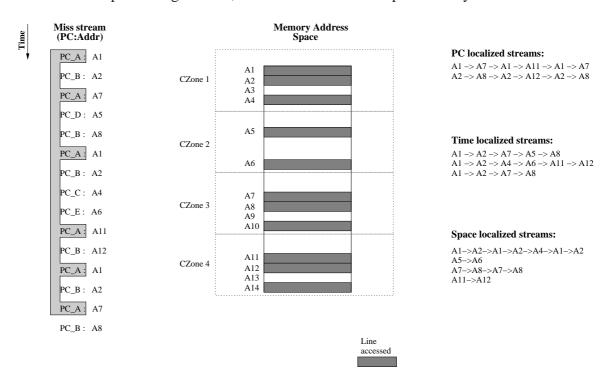

In order to tackle the poor predictability of the global miss stream, modern prefetchers usually resort to a process called *localization*. Localization refers to a clustering process in which misses are classified according to some property. The expectation is that the resulting sub-streams, called *localized streams*, will be more predictable than the global miss stream. When a new miss is registered in a localizing prefetcher, it is first localized (i.e., classified) and added to its corresponding localized stream. The prefetcher then performs its access prediction using only the miss information contained in the localized stream. This way, in a localizing prefetcher, random or noisy (i.e., non-predictable) accesses can be distinguished from regular, predictable memory access streams. Similarly, two predictable streams that appear interleaved in the global miss stream (therefore leading to poor or no predictability) appear now in two separate localized streams. Several criteria can be used to perform localization. Common strategies that have proven to work well across a variety of applications include the address of the missing instruction or the region in memory referred by the miss address.

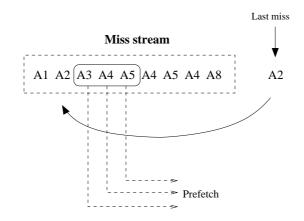

Although localization is an useful mechanism that improves the predictability of the global miss stream, it also carries some negative side effects. In the process of localization, important chronological information about the misses is lost. While localization keeps the time ordering information for misses *within* a single stream, there is no time correlation between misses from different streams. As a consequence, current localizing prefetchers have no way of knowing how many misses from different streams might be interleaved between two misses that are stored consecutively in a given stream. Additionally, current prefetching mechanisms make use of aggressive prefetch degrees in order to hide as much as possible the effects of the memory wall. This, combined with the lack of inter-stream chronological information, leads to two undesirable effects: 1) decreased prefetching accuracy; and 2) decreased prefetch timeliness. Both effects can be attributed to the same root cause: the prefetcher issues too many prefetches for a single stream, too soon in advance. As a prefetcher predicts further into the same stream, the risk of "overrunning" the stream (i.e., predicting accesses past the natural end of the stream) and issuing wrong prefetches increases, therefore lowering the overall accuracy. Furthermore, even if all prefetches issued for a single stream are correct predictions, they might have been issued in an untimely manner (i.e., too soon) and might pollute the cache or be replaced by other misses or prefetch requests.

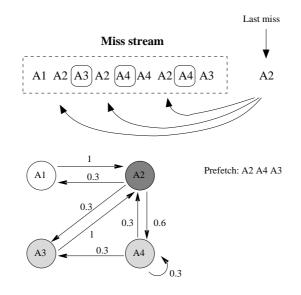

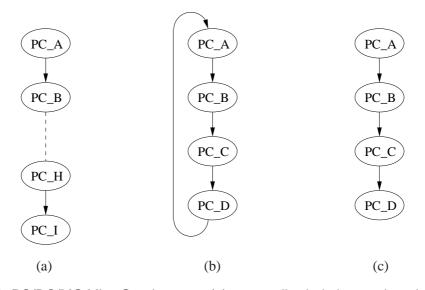

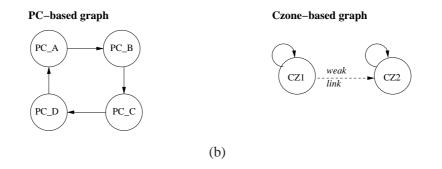

In order to overcome this problem, we introduce the concept of *Stream Chaining*, the first main contribution of this dissertation. The goal of stream chaining is to introduce another layer of correlation that exposes the order of activation of the different miss streams as they are used by a localizing prefetcher. This is done by linking miss streams in such a way that it reflects the core flow of misses of the application. In this context, a link between two streams implies a temporal correlation between the misses of both streams (e.g., if stream *A* is linked to stream *B*, this means that a miss localized in stream *A* is *usually* followed by a stream *B* miss). This way, for each miss, the prefetcher has two sources of information: intra-stream miss history and inter-stream activation information. The latter allows the prefetcher to predict the stream the next miss will belong to. This information can be used by the prefetcher to achieve a more balanced and timely dispatch of prefetches, issuing requests not only from the current miss stream but also from the miss streams that are predicted to be activated next.

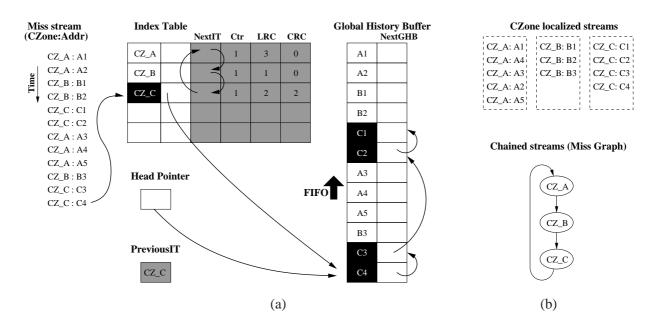

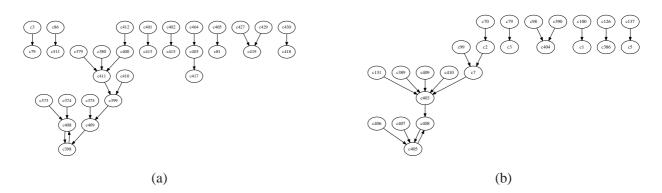

The key to effective stream chaining lies in finding an heuristic that links the streams in such a way that it reflects the common path of misses (or stream activations) caused by the application, while at the same time leaving out spurious misses. In this dissertation we provide a concrete implementation of stream chaining we denote *Miss Graph* (MG) Prefetching. MG prefetching uses past stream activation information to generate a graph of the common stream activation paths for the current program phase.

Furthermore, the graphs generated by MG prefetchers are lightweight and can be stored in hardware with low storage requirements. Therefore, current localizing prefetchers can be adapted with minimal changes to use MG prefetching. We provide details of implementation of MG prefetching for two modern localizing prefetchers: PC/DC and C/DC. We name the resulting MG prefetchers PC/DC/MG and C/DC/MG. In the last part of this contribution we evaluate in detail the performance of these prefetchers against their non-chaining counterparts. We show how stream chaining with miss graphs significantly improves the performance of localizing prefetchers while keeping the complexity of the data structures involved low and well within hardware implementation constraints.

# 1.2.2 Prefetching in Multi-Core Systems with Resizable Prefetch Heaps

In the second part of this dissertation we explore prefetching in multi-core systems. As mentioned in the introduction, in the recent years the trend for increasing processor frequencies has been exchanged for an increased number of cores per processor. In virtually all multi-core architectures prefetching is performed on a per-core basis (i.e., each core has a dedicated prefetcher). This presents a new set of challenges for hardware prefetching, one of the most prominent ones being how to arbitrate access to the memory channel between an increasing number of independent prefetching engines.

Past research has produced a few prefetch throttling and filtering algorithms that regulate the aggressiveness of the prefetcher based on performance metrics and available memory bandwidth. In spite of this, only recently the problem of prefetching interference and arbitration has been researched within the context of multi-core systems. Furthermore, all past research on prefetcher arbitration in multi-core systems has focused on regulating prefetch aggressiveness at the *source* level, that is, directly setting the prefetch degree of each prefetch engine.

We introduce the concept of *Resizable Prefetch Heaps* (RPH), a novel way of arbitrating prefetches in multi-core systems at the Prefetch Request Queue (PRQ) level, with global knowledge of the state and metrics of all prefetching engines in the system. In multi-core systems, the PRQ is the data structure that holds all the prefetch requests issued by the prefetchers that have not yet been issued by the memory controller. Traditionally, this structure is implemented as a FIFO circular queue, where prefetch requests are extracted in the same order they were inserted. The RPH is designed as a drop-in replacement of a traditional FIFO PRQ that, by contrast, works as a priority queue. In the RPH, prefetch requests are assigned a priority based on several metrics, both local to the issuing prefetcher and global to the multi-core system. This priority is used by the RPH to define an order of extraction of prefetch requests. As a result, the RPH is able to prioritize the issue of important prefetch requests over those not deemed as crucial or urgent. Additionally, instead of regulating the prefetch aggressiveness of each prefetch engine locally, we make the decision of whether to insert or drop each prefetch request at the RPH PRQ level.

Another feature of the RPH is its ability to change its size in response to the utilization of the memory bus. At times when the memory channel is saturated by demand requests, the RPH seamlessly shrinks in order to not flood the channel with more prefetching requests. Similarly, when the memory utilization is low, the RPH expands in order to be able to issue as many prefetch requests as possible.

The operation of the RPH is thus defined by two heuristics: how to assign priorities to prefetch requests and how to resize the RPH based on the current memory channel utilization. For assigning priorities, we partially base our heuristic in the principles behind a state-of-the-art throttling algorithm known as HPAC (Hierarchical Prefetcher Aggressiveness Control). We describe in detail how we construct a priority assignment formula backed by some of the operating principles of HPAC. We describe our RPH resizing heuristic, which is based solely on memory channel utilization and can be implemented with minimal hardware modifications. Additionally, we give implementation details and analyze the run-time complexity of the new hardware.

In order to evaluate the performance of the RPH, we use a selection of benchmarks in both multi-programmed and multi-threaded configurations. In contrast to previous research, we use a state-of-the-art, accurate prefetcher (C/DC) that reflects the current development of prefetching algorithms. We compare the performance of the RPH throttling against HPAC, a conventional modern throttling algorithm. We show that throttling prefetches with the RPH improves significantly the performance improvement achieved by throttling in multi-programmed and multi-threaded configurations.

### **1.3 Thesis Structure**

Chapter 2 provides background on the current state-of-the-art in prefetching. In this chapter we introduce the basic concepts behind hardware prefetching and the metrics used to evaluate its performance. We then survey several prefetching methods, from the

#### Chapter 1. Introduction

fundamental and basic algorithms used in the past to the current state-of-the-art. We describe hardware implementation details such as the hardware data structures used to implement prefetching and the architectural organization of prefetching in single and multi-core systems. Additionally, we also provide information on the techniques used to throttle and filter useless prefetches.