# THE MEASUREMENT OF ELECTRICAL PARAMETERS AND TRACE IMPURITY EFFECTS IN MOS CAPACITORS

Thesis submitted by

# IAN GRANT McGILLIVRAY

for the degree of

Doctor of Philosophy

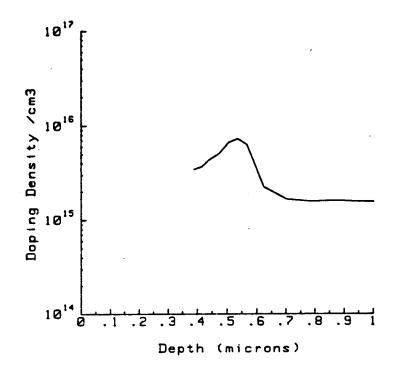

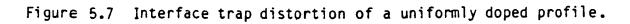

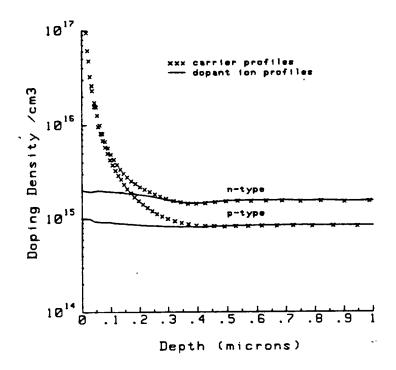

Edinburgh Microfabrication Facility Department of Electrical Engineering University of Edinburgh

1987

# DECLARATION

I declare that all the work done in this thesis is entirely my own except where otherwise indicated.

This thesis is a result of a CASE project with Hughs Microelectronics (Glenrothes) Ltd.

.

:

#### ABSTRACT

A wide ranging review and development of MOS capacitor electrical measurements is presented. Advances are reported in the high frequency CV method, pulsed CV measurements, the determination of interface state densities and calculation of the minority carrier generation lifetime.

A software package called EDUCATES (Edinburgh University Capacitor Test Software) has been written. This provides a comprehensive analysis of the MOS capacitor using accurate measurements implemented in a totally automated manner.

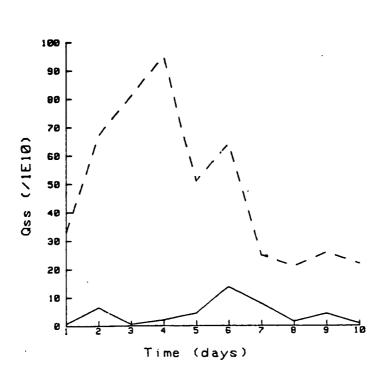

EDUCATES was used to investigate the electrical effects of trace levels of metal ions present hydrofluoric acid which is used for pre-gate oxidation cleaning. It was found that there were no significant effects for concentrations of up to 5 p.p.m. Calcium, Chromium, Cobalt, Lead and Nickel although increases in the fixed and mobile charge densities were observed in iron contaminated oxide.

#### ACKNOWLEDGEMENTS

I would like to thank Professor J.M. Robertson for devising and supervising this CASE PhD project, and I am also indebted to Dr. A.J. Walton for his supervision.

I am grateful to the SERC for providing financial assistance.

I would like to acknowledge the support of Hughes Microelectronics (Glenrothes) Ltd. who collaborated in this project and provided me with additional financial support. I am particularly grateful for the assistance that I have received from Dr A. Hawrilyw my industrial supervisor.

I am grateful to Riedel-de-Hahn (Gmbh.) for the supply of chemicals. I am particularly indebted to Dr. W. Sievert of Riedel.

It would have been impossible to produce devices and test equipment for this project without the help of the staff at the Edinburgh Microfabrication Facility and at Hughes Microelectronics. I am sure the following list is not complete but I am grateful to Messrs A.M. Gundlach, R. Cambell, Z. Chen, M. Fallon, J. Fraser, W. Gammie, G. Gibbs, J. Gow, D. Hope, J. Laurie, J. S. Meek, B. Nielson, A. Ruthven, G. Saunders, J.T.M. Stevenson, G. White, and all the women in Hughes' clean room.

I have greatly appreciated the help in a variety of ways that I have had from my fellow PhD students, namely Messrs A. Buttar, E. Cameron, A. Gribben, G. Maxwell, and J. Serack.

Last, but certainly not least, I would like to acknowledge the assistance of Mrs E. Paterson, Miss J. Blanch and Miss J.M. Anderson in preparing this and other documents.

#### CONTENTS

| CHAPTER ONE: INTRODUCTION                                   | 1  |

|-------------------------------------------------------------|----|

| CHAPTER TWO: INTEGRATED CIRCUIT MANUFACTURING: A REVIEW     |    |

| 2.1 Introduction                                            | 7  |

| 2.2 Integrated Circuits                                     | 8  |

| 2.2.1 The Origin of the Integrated Circuit                  | 8  |

| 2.2.2 NMOS Processing                                       | 8  |

| 2.2.2.1 EMF NMOS Process                                    | 9  |

| 2.2.2.2 Fabrication Technology                              | 11 |

| 2.2.3 VLSI Processing                                       | 13 |

| 2.3 Thermal Oxidation and Cleanliness                       | 15 |

| 2.3.1 Thermal Oxidation of Silicon: Kinetics and Technology | 15 |

| 2.3.2 Wafer and Furnace Cleaning                            | 23 |

| 2.4 Conclusions                                             | 28 |

|                                                             |    |

|                                                             |    |

# CHAPTER THREE: THE METAL OXIDE SEMICONDUCTOR CAPACITOR AND ITS HIGH FREQUENCY CV CHARACTERISTIC

| 3.1 Introduction                                                    | 29 |

|---------------------------------------------------------------------|----|

| 3.2 Definition of Potentials and Bias Regimes of the MOSC           | 29 |

| 3.3 Ideal MOSC CV Characteristic at High Frequencies                | 34 |

| 3.4 Non-Ideal MOSC                                                  | 41 |

| 3.5 Fabrication and Measurement of MOSC Samples                     | 43 |

| 3.5.1 Sample Preparation                                            | 43 |

| 3.5.1.1 Gate Material                                               | 46 |

| 3.5.1.2 Gate Definition                                             | 46 |

| 3.5.1.3 Ohmic Back Contact                                          | 47 |

| 3.5.2 Measuring Equipment                                           | 48 |

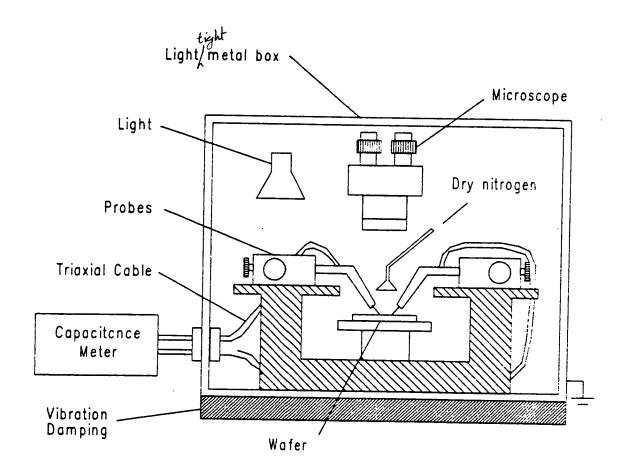

| 3.5.2.1 Probe Needles, Wafer Chuck and Probing Box                  | 48 |

| 3.5.2.2 Capacitance Meters                                          | 49 |

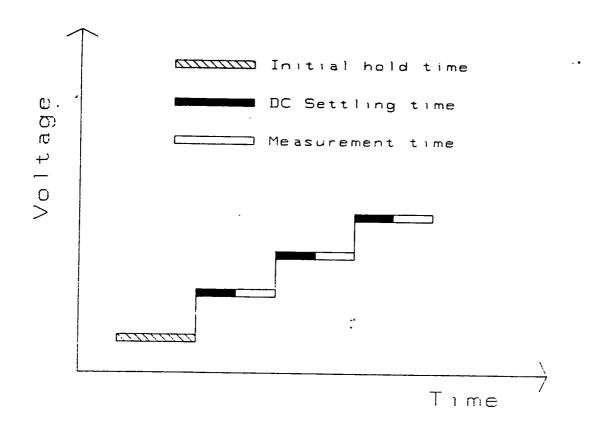

| 3.5.3 Automation of CV Measurements                                 | 50 |

| 3.6 Parameter Extraction from the High Frequency CV Characteristic  | 52 |

| 3.6.1 Calculation of Oxide Thickness                                | 52 |

| 3.6.2 Determination of N <sub>sub</sub>                             | 56 |

| 3.6.3 Flatband Capacitance and Flatband Voltage                     | 62 |

| 3.6.4 Barrier Heights, Work Functions and Work Function Differences | 64 |

| 3.6.5 Oxide Charges                                                 | 67 |

| 3.6.6 Threshold Voltage                                             | 72 |

| 3.7 Analysis of the CV Characteristic of a Non-Uniformly Doped MOSC | 73 |

| 3.8 Control of the MOS Integrated Circuit Fabrication Process       | 74 |

| 3.8.1 Process Control Example                                       | 75 |

| 3.9 Measurement of Mobile Ion Density                               | 79 |

| 3.10 CV Characteristics of MOSCs with Two Capacitive Contacts       | 82 |

| 3.10.1 Comparison of Capacitive Contact Measurements with Theory    | 84 |

| 3.10.2 Conclusions on Capacitive Contacts Measurements              | 86 |

| 3.11 Determination of $C_{min}$ from the High Frequency CV          | 86 |

Characteristic of MOSCs with High Carrier Lifetimes

| 3.11.1 Conventional DC Bias Sweep for High Frequency CV<br>Measurements       | 87 |

|-------------------------------------------------------------------------------|----|

| 3.11.2 Measurement of Equilibrium C <sub>min</sub> for high Lifetime Samples  | 87 |

| 3.11.3 Alternative Methods of Determining $C_{min}$ , $N_{sub}$ and $V_{fb}$  | 92 |

| 3.11.4 Conclusions on the Measurement of Parameters of High<br>Lifetime MOSCs | 93 |

| 3.12 Conclusions                                                              | 94 |

.

# **CHAPTER FOUR: INTERFACE TRAPS**

| 4.1 Introduction                                                                   | 95  |

|------------------------------------------------------------------------------------|-----|

| 4.2 The Effect of Interface Traps on MOSC Characteristics                          | 97  |

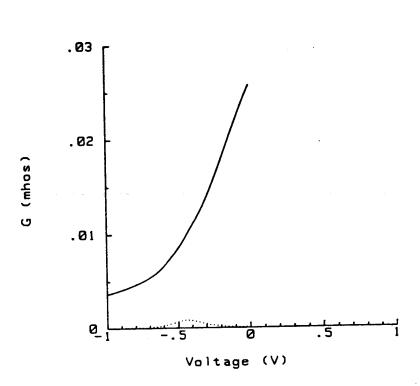

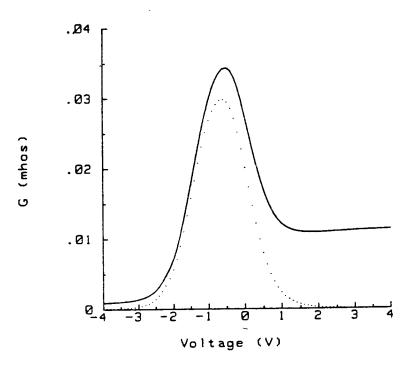

| 4.3 Determination of G <sub>n</sub> from the Measured Conductance                  | 102 |

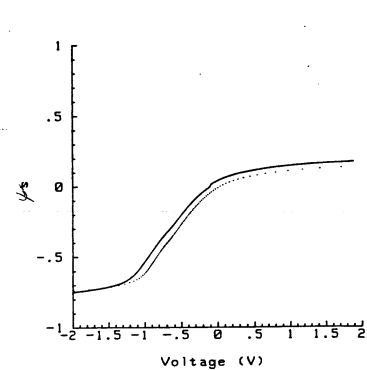

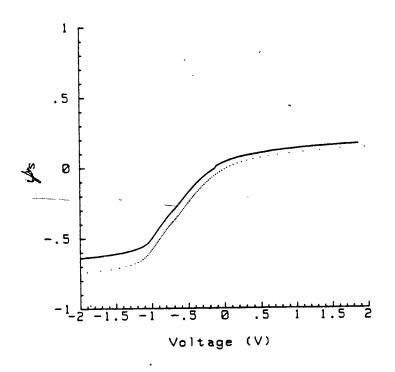

| μ                                                                                  | 104 |

| 4.4 Methods of Determining $D_{it}(E)$ and $\psi$ s-V <sub>G</sub> from Admittance | 104 |

| Measurements                                                                       |     |

| 4.4.1 The Low Frequency CV Method                                                  | 104 |

| 4.4.2 The High Frequency CV Method                                                 | 112 |

| 4.4.3 The Combined High and Low Frequency CV Method                                | 115 |

| 4.4.4 The Conductance Methods                                                      | 117 |

| 4.5 The Accuracy of MOSC Interface Trap Measurements                               | 123 |

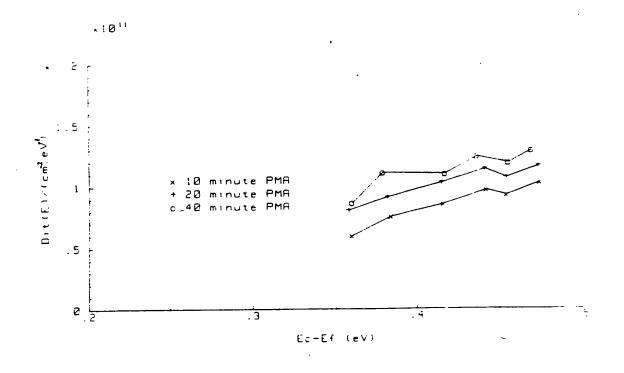

| 4.6 Post Metalisation Annealing of AlSi Gate MOSCS                                 | 128 |

| 4.7 Conclusions                                                                    | 132 |

# CHAPTER FIVE: DOPING PROFILES IN SILICON

.

| 5.1 Introduction                                          | 133 |

|-----------------------------------------------------------|-----|

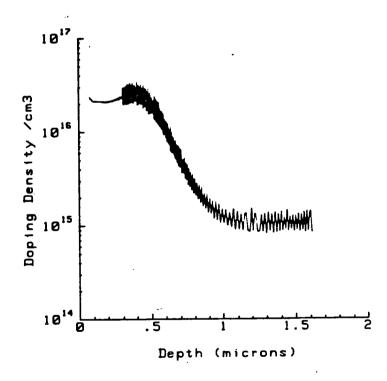

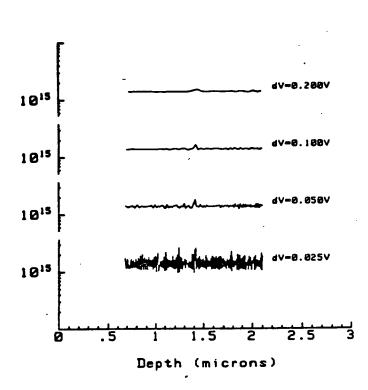

| 5.2 Accurate Measurement of the Complete Doping Profile   | 134 |

| 5.2.1 Data Manipulation                                   | 134 |

| 5.2.2 Quantitative Error Assessment                       | 138 |

| 5.2.3 Other Factors Effecting Doping Profile Measurements | 142 |

| 5.3 Ion Implantation Dose Measurement                     | 149 |

| 5.4 Conclusions                                           | 151 |

### **CHAPTER SIX: MINORITY CARRIER LIFETIMES IN SILICON**

.

| 6.1 Introduction                                                  | 152 |

|-------------------------------------------------------------------|-----|

| 6.2 Leakage Currents in the Deep-Depleted MOSC                    | 153 |

| 6.3 Techniques for Measuring Minority Carrier Generation Lifetime | 155 |

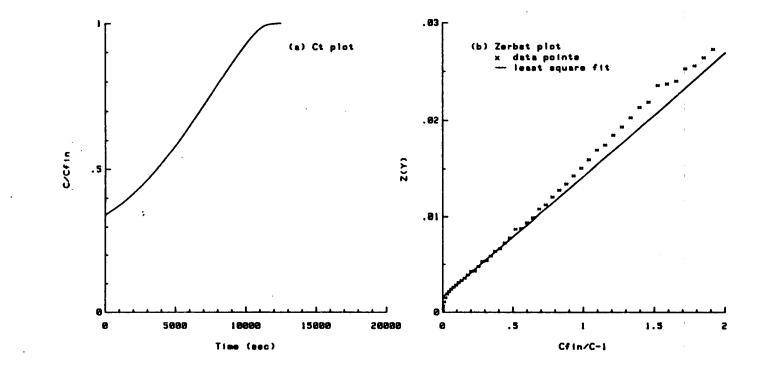

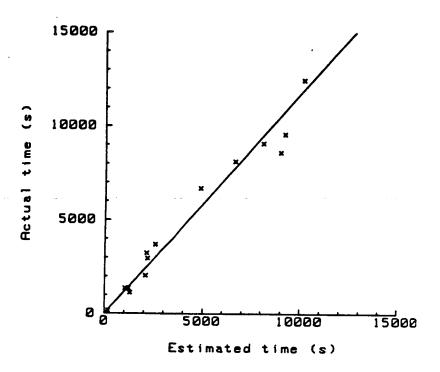

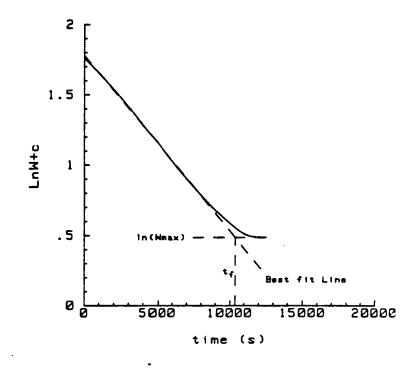

| 6.3.1 Accurate Implementation of the Zerbst Method                | 158 |

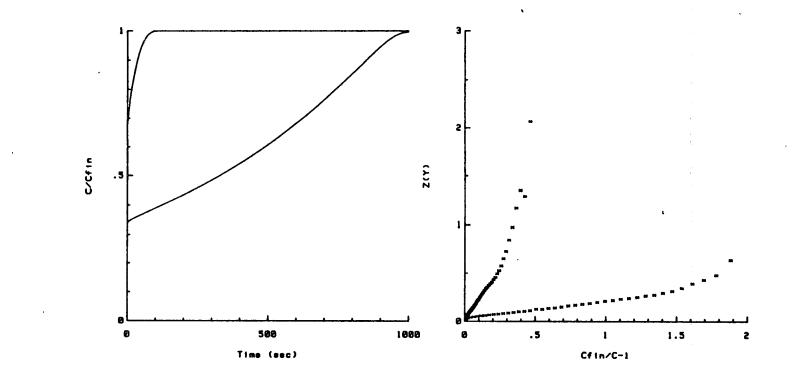

| 6.4 Generation Lifetime in Non-Uniformly Doped Silicon            | 168 |

|                                                                   |     |

# CHAPTER SEVEN: EDUCATES (EDINBURGH UNIVERSITY CAPACITOR TEST SOFTWARE)

| 7.1 Introduction      | 172 |

|-----------------------|-----|

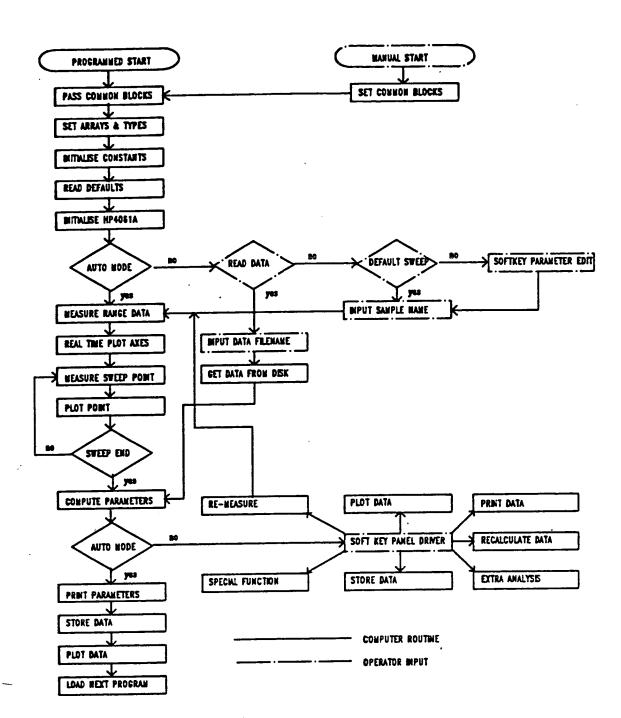

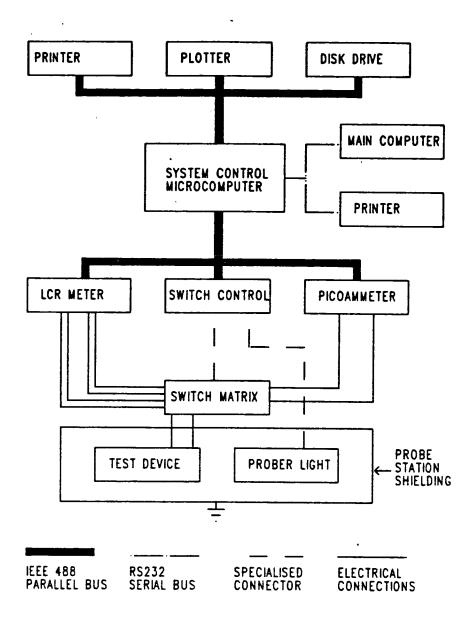

| 7.2 EDUCATES Software | 173 |

| 173 |

|-----|

| 177 |

| 184 |

| 186 |

| 188 |

| 188 |

| 188 |

| 189 |

|     |

# CHAPTER EIGHT: THE ELECTRICAL EFFECTS ON MOS CAPACITORS OF TRACE LEVELS OF DISSOLVED IMPURITIES IN HYDROFLUORIC ACID

| 8.1 Introduction                                 | 190 |

|--------------------------------------------------|-----|

| 8.2 Measuring Impurity Effects                   | 194 |

| 8.3 Preparations for Contamination Experiments   | 195 |

| 8.4 Contamination Experiments                    | 198 |

| 8.4.1 Preparation of Contaminated 5%HF and MOSCs | 198 |

| 8.4.2 Measurements                               | 199 |

| 8.5 Results of Contamination Experiments         | 201 |

| 8.5.1 Calcium                                    | 205 |

| 8.5.2 Iron                                       | 205 |

| 8.5.3 Nickel                                     | 206 |

| 8.5.4 Chromium                                   | 207 |

| 8.5.5 Cobalt                                     | 208 |

| 8.5.6 Lead                                       | 208 |

| 8.6 Discussion                                   | 208 |

| 8.7 Conclusions                                  | 209 |

|                                                  |     |

# **CHAPTER NINE: CONCLUSIONS**

# REFERENCES

215

211

#### CHAPTER ONE

#### INTRODUCTION

Metal Oxide Semiconductor, (MOS), Integrated Circuits, (ICs), are currently the most commercially important and sophisticated microelectronic components[1]. This situation is likely to endure for the forseeable future. The manufacturing technology for producing MOS devices has been extensively improved since Grove, Deal and Snow<sup>2,3</sup> first developed a commercially viable fabrication process in 1963.

Chapter 2 of this thesis reviews the current state-of-the-art in device processing with particular emphasis given to those processes which are of particular relevance to the subject matter of later chapters. Grove et al's first process<sup>2,3</sup> was made possible when it was discovered that trace levels of contamination, (later identified as sodium), were responsible for the instabilities in the MOS Field Effect Transistors (MOSFETS), which were being fabricated at that time. The instabilities were monitored and reduced by measuring the electrical properties of MOS Capacitors, (MOSCS), because they were far simpler to fabricate and analyse than the MOSFET, (which was the active circuit element), whilst they still allowed determination of all the critical factors.

From the early 60's to the present day many new fabrication processes have been developed, and also new devices have been introduced which have additional critical electrical parameters, for example minority carrier lifetime is critical in dynamic memories[4]. New measurements have been developed to measure such parameters, however the basic framework is still the same as that used by Grove et al., i.e. detection of an effect with a MOSC measurement, followed by the elimination or control of

that effect using MOSC experiments.

It was the aim of the work reported here, to investigate certain effects of trace levels of heavy metal ions, and to develop MOSC measurements into a more accurate, reliable and usable form of analysis. It is hoped that the latter effort will help alter the poor reputation that this author has found<sup>†</sup> such measurements have with MOS process and device engineers.

Personal experience<sup>†</sup> has shown that one major reason for this is that MOSC measurements are considerably more difficult to implement in practice, than would appear to be the case, when they are discussed in textbooks or scientific papers. The apparent simplicity leads to a situation where engineers perform experiments which produce patently incorrect results, thereby undermining their confidence in such techniques.

Another problem with MOSC measurements is the bewildering variety of techniques which have been proposed in the literature for measuring certain parameters. For example a recent review of Schroder and Kang<sup>5</sup> on the measurement of minority carrier lifetime found over 20 different methods. In their review and for other measurements which they do not cover the accuracy varies from excellent to so poor as to be useless. Unfortunately when new methods are introduced, special assumptions, samples or selected results make techniques appear more viable than they ever are for general use.

The introduction of automated MOSC measuring systems<sup> $\ddagger$ </sup> in the late 1970's[6,7,8], ought to have brought about a substantial improvement in the

- 2 -

<sup>†</sup> This relates to views expressed by process and device engineers at a number of companies in particular Hughes (my sponsors), Motorola Ltd. of East Kilbride, Analogue Devices of Limerick, and Thorn EMI central research labs. I have also been able to obtain a broad view of affairs from engineers and academics I have met when they were visiting the EMF, and from my own recent visit to the USA.

**<sup>‡</sup>** These are colloquially referred to as "CV systems", i.e. Capacitance Voltage systems, even although the range of their capability is often much greater than this, including measurements as a function of frequency or time, and also measurement of other quantities, such as ac conductance (G), and dc current (I).

unsatisfactory state of affairs, however this didn't happen to any appreciable extent, because they had their own substantial failings. These included a requirement to have a skilled operator initiate and supervise measurements, since important parts were not fully automated, and also the systems produced results even when there  $\zeta^{\omega a S}$  a fundamental error in the measuring technique, such as measuring inversion layer properties in the presence of light. Of course automation does nothing to improve the situation where there is a range of measuring techniques available.

In this thesis a range of established measurements has been developed to a point where they can be incorporated into a fully automated and accurate CV system. This system, which consists of a set of linked computer programs that drive commercially produced hardware<sup>6</sup> is described in chapter 7. In chapters 3-6 the range of measurements which this covers are critically examined and developed.

Since the standard texts of Nicollian and Brews[9], and Sze[10], more than adequately cover most of the device physics underpinning the work in these chapters, only the important results are quoted, because compared to these works this thesis aims to take a radically different perspective. They concentrate on detailed descriptions, (running to approximately 600 pages in the case of Nicollian and Brews), of device physics, largely dealing with concerns and equipment that were of interest in the late 60's and early 70's. In contrast this current work concentrates on the problems and applications of MOSC measurements in the latter half of the 80's, using the best measuring equipment currently available.

In chapter 3 the widely known high frequency MOS capacitor CV analysis is reviewed. The theory and basic shape of ideal MOS capacitor CV curves is described, to provide a basis for the study of curves measured for real capacitors. Following this a wide range of problems with the measurement and analysis of real capacitors is discussed. These problems include choosing the correct equivalent circuit for

- 3 -

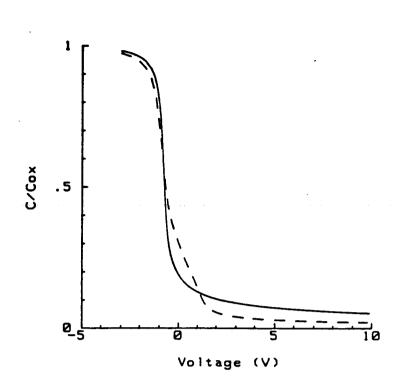

measurements, sample preparation, limitations of work function 'constants', and the measuring environment. After this, examples of the application of high frequency CV measurements to a manufacturing process for the control of both mobile and immobile oxide charges is discussed. These types of examples are serious omissions from many treatments (eg.[9, 10, 11]), of the CV analysis, because the engineer in production is best helped by examples. In the penultimate section the measurement of the high frequency CV characteristic with high minority carrier lifetime is examined, and two methods proposed for parameter determination in a time-efficient manner. Finally it is shown that the dual top contact electrode, (normally formed with two mercury electrodes in a ring dot configuration), is a fundamentally unsound method with which to measure high frequency CV characteristics.

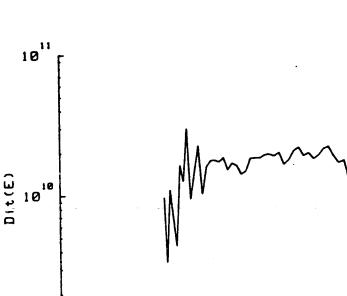

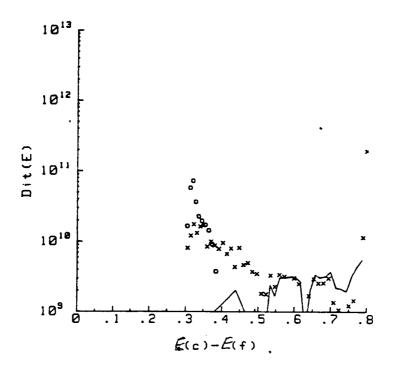

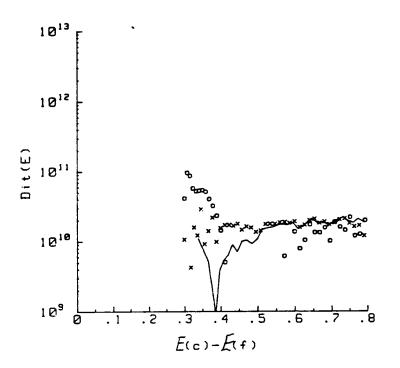

In chapter 4, the basis of capacitance and conductance determinations of interface trap densities is reviewed. The conductance method has been very rarely used in the past because it has been considered too time-consuming[9]. For example when this author visited Bell Laboratories<sup>†</sup> where the conductance method originated and has been developed, it was found that only the low frequency method for most interface trap density evaluations was used there, since there was no system with which to implement an automated conductance analysis. It is shown in the present work that with a simple modification of a method recently proposed by Brews<sup>12</sup> for analysing conductance characteristics, that it is possible to determine densities at seven bandgap energies per sample in less than 20 minutes. This new rapid conductance method is then shown to have superior range and accuracy, compared to all three of the capacitance methods which have traditionally been used for trap density determinations. To end the chapter, the power of the new conductance method is shown, with an investigation of a subtle difference between the annealing of aluminium gate and aluminium-silicon † Bell Laboratories, 600 Mountain Avenue, Murray Hill, New Jersey, U.S.A.

gate MOSCS.

Many MOSC measurements are not as widely used as they might be because they have been incorrectly condemned as inaccurate in the past. An example is statements like,

"this technique (pulsed CV doping profile determination of implant dose) could not be used for process monitoring."

This sounds very authoritative since it originates from IBM central research labs,<sup>‡</sup> however it will be shown in chapter 5 that by using a voltage sweep which allows for the error in modern digital equipment, noise-free profiles can be determined that are suitable for either dose monitoring or for evaluating process simulation.

Of all the MOSC parameters, the most difficult to measure accurately and the one for which there is the greatest variety of measurement techniques is the minority carrier generation lifetime. In chapter 6 it is argued that where accuracy is paramount, a modification[13] of the Zerbst analysis<sup>14</sup> of C-t transients is the best technique to use. The drawbacks attributed to this method in a recent review<sup>[5]</sup>, no longer occur when a fully automated measuring system is used. In this work full automation is achieved by accessing profile information determined using the methods in chapters 3 and 5, and also the equilibrium minimum capacitance using the method described in chapter 3, combined with newly developed methods of implementing the data acquisition in a time-efficient and noise-free manner. This new system is used for measuring lifetimes in chapter 8, and also to measure the carrier lifetime in ion implanted samples. This latter measurement was previously consider too difficult<sup>5</sup> to perform; however this can now be done routinely. This is of importance because in commercially produced  $\frac{1}{1BM}$ , Thomas J. Watson Research Centre, Yorktown Heights, New York, U.S.A.

- 5 -

circuits where lifetime is a critical parameter, ion implantation is always used during device processing.

Chapter 7 describes a new software system which provides a significant improvement in the automation and accuracy of MOSC measurements. This system was originally developed with one specific application in mind, however it has not been customised to this application, and for it only a subset of the systems capabilities is used. The application is the determination of the influence of trace impurities present in MOS grade chemicals on MOSC electrical parameters (chapter 8). The current specifications for chemicals are the tightest of any mass produced chemical. These specifications have arisen due to a fear of all unknown impurity effects rather than being based on experimental evidence. This fear of unknown impurities has its roots work of Grove, Deal and Snow<sup>3</sup> that has already been discussed. in the early 60's Over the intervening period to the present it has been common practice to blame all defects and instabilities which do not have a ready explanation on impurities. The present work presents the first known systematic experimental investigation into chemical specifications and their implications. This is valuable because the trend is currently, (and always has been), for MOS circuit manufacturers to demand evertighter specifications. Meeting this demand will certainly produce increased chemical costs, whilst possibly being a completely unnecessary move. From this experimental investigation, a new basis for assessing current and future specifications has been developed. Extension of the analysis applied here to other elements or other chemicals is straightforward and could be a means by which a team of workers could produce meaningful specifications.

#### **CHAPTER 2**

#### **INTEGRATED CIRCUIT MANUFACTURING: A REVIEW**

#### 2.1. Introduction

The development of measurements, and the experiments in this thesis, are motivated, as they have been for other workers in the past, by a desire to produce as an end product, integrated circuits of greater complexity at a lower cost than has been previously possible. In this chapter a review of integrated circuit manufacturing technology is presented to provide the setting for subsequent chapters. The review begins by describing the origins of integrated modern integrated circuit process and a chronology of the major developments which have taken place. Following this, there is a description of EMF integrated circuit fabrication process. This process is typical of the fabrication used for LSI, (Large Scale Integration) products. It illustrates the magnitude of the complexity of even a 5 µm process, thereby showing the usefulness of techniques described later for evaluating and controlling individual steps, each one of which must be executed to within a specification if any working devices are to be produced. After discussing LSI processing the additional technology requirements for VLSI, (Very Large Scale Integration) devices, which are the current state-of-the-art, are outlined. In section 2.3 those topics which are of particular relevance to later chapters, namely thermal oxidation and cleaning are looked at in greater detail.

#### 2.2. The Integrated Circuit

#### 2.2.1. The Origins of the Integrated Circuit

In March of 1959 at the Institute of Radio Engineers meeting in New York, when he was announcing the recent 'invention' of the Integrated Circuit (IC) by Jack Kily, Mark Shepard of Texas instruments said, "I consider this to be the most significant development ..... since the commercial availability of the transistor"[15]. The period since then has more than justified his bold statement, for it is with the integrated circuit that systems of previously undreamt complexity have been produced in volume, at low cost and having only a minute physical size. In 1958 a team at Fairchild semiconductors led by Jean Hoerni introduced the PLANAR process[16] for producing silicon bipolar transistors using photolithography and silicon dioxide diffusion barriers. This process represents the starting point from which modern integrated circuit technologies have developed. It is a process ideally suited to low cost, high volume production.

#### 2.2.2. NMOS Processing

NMOS[1, 17] is an integrated circuit technology where the basic active circuit element is the MOSFET. After the problems of passivating the MOSFET had been solved in the mid-1960's, MOS based technology quickly moved to become the dominant commercial integrated circuit because it was better suited to digital applications where the demand for parts and the range of new applications was booming. The first commercial MOS technology was p-channel MOS (PMOS) which could be fabricated without any radically different technology from the then established bipolar processes. In Scotland PMOS was first produced by Hughes Microelectronics and Elliot Automation in 1966[18]. Later with the introduction of ion implantation, (at around 1972 in Scotland), NMOS could be manufactured in volume. This new process allowed very small and precise changes to be made in the transistor turn-on (threshold) voltage. The higher mobility of the electrons in the n-channel which results in circuits with higher switching speeds, meant that it quickly overtook PMOS in importance. At the present time, complementary-MOS (CMOS) is becoming of increasing importance because of its lower static power requirement than NMOS. However NMOS still has the largest share of the IC market and will continue to be of importance for the forsee-able future [ see for example Semiconductor International, November, 1985].

#### 2.2.2.1. EMF NMOS Process

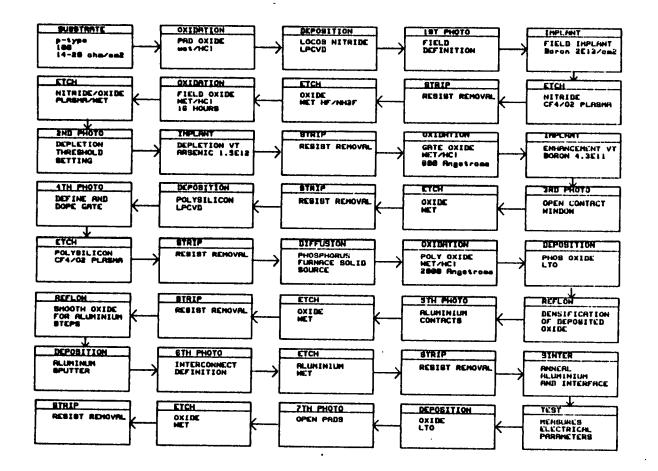

Figure 2.1 is an outline of the major steps involved in the EMF 5-micron NMOS process[1]. (5 microns is the minimum dimension of any horizontal feature). The full process runsheet has many other steps and a wealth of detail on each individual step. As with any integrated circuit fabrication process the sequence achieves three things.

(1) Isolation of each active device from all the other active devices.

- (2) Active circuit element definition.

- (3) Interconnection of active elements to make a circuit.

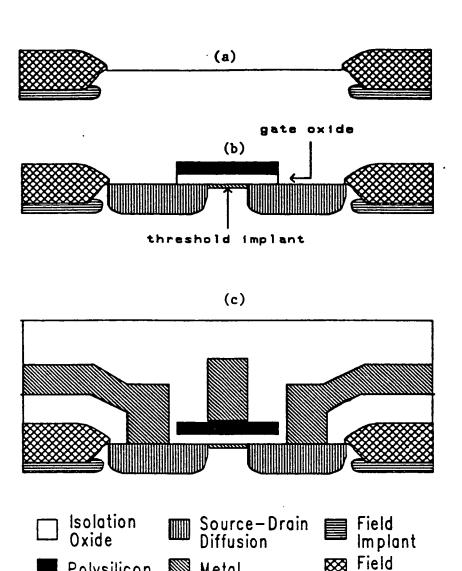

In the NMOS processes, isolation is achieved with regions of thick field oxide on top of heavily boron-doped silicon. The field regions are defined-with the LOCOS process[19] and implantation of boron (figure 2.2(a)).

The active element, (the MOSFET) is fabricated from a thin thermal oxide with heavily phosphorus-doped gate, source and drain regions (figure 2.2(b)). The silicon gate process self-aligns the gate[20,21], source and drain electrodes allowing smaller, faster circuits to be made than is possible with metal gates. Threshold voltages of enhancement (normally off), and depletion (normally on) transistors, are set by low dose boron and arsenic ion implantation respectively.

- 9 -

.

O

÷...

-

Figure 2.1 Simplified sequence of the major steps in the EMF's 5micron NMOS integrated circuit fabrication process.

1

The interconnect which defines the circuit function is placed on top of a thick phosphorus-doped oxide. Contact to the active regions is made via holes etched in this layer and finally the entire circuit is protected by another phosphor $\omega$ -doped oxide (figure 2.2(c)).

#### 2.2.2.2. Fabrication Technology

The fabrication starts with 3" diameter, <100> orientation, p-type Czochralski silicon wafers[22, 23]. In the EMF these are processed in batches of up to 25 at one time. In industry, batch sizes can be up to 200 wafers of diameter between 3 and 6 inches. This batch production with several hundred IC's per wafer is the major reason for the cost effectiveness of the process.

The process schedule basically consists of repeated deposition or doping of layers, followed by photolithographic transfer patterns and then the etching of that design.

The photolithographic process (steps labeled 'photo' and strip in figure 2.1) has been described by McGillis and King[24, 25]. Some of the other important fabrication steps are:

- (1) Thermal Oxidation[9, 26, 27]. Thermal oxidation of silicon in O<sub>2</sub> (dry) or H<sub>2</sub>O (wet) ambients at temperatures in the range 800-1200°C creates a stable, passivated oxide which can be used for both gate dielectric and field isolation. HCl is often added to the oxidising species to give a 'cleaner' oxide[28]. (Section 2.3 discusses oxidation in more detail).

- (2) Deposition[29, 30]. Silicon-dioxide, Silicon-nitride and polysilicon can be deposited in thin uniform layers by Low Pressure Chemical Vapour Deposition (LPCVD). Doped oxides are formed by adding arsine, diborane or phosphene to the reactant gasses. Aluminium is deposited by sputtering an aluminium target with argon ions or by electron beam[31, 32] evaporation. The sputtered

Oxide

Metal

Polysilicon

- 13 -

aluminium deposits in thin uniform layers on wafers in the sputter chamber.

- (3) Implantation/Diffusion[33, 34, 35, 36]. Ion implantation was the major advance in fabrication technology which allowed the commercial fabrication of NMOS circuits. It involves accelerating dopant ions into the silicon crystal at energies in the range 10-200 keV. Ions are typically stopped in the first two microns of the crystal. Implantation allows very small, well controlled adjustments to be made to the doping density near the oxide-semiconductor interface and hence well-defined enhancement and depletion threshold voltages can be set. Diffusion[36] introduces dopant ions into silicon from the gas phase in a furnace at 900-1200°C. The process is not nearly as controllable as implantation and is used only where heavy doping is required.

- (4) Etching[37, 38, 39, 40]. Etching is the selective removal of areas of a thin film to form geometric patterns. Areas left exposed by photoresist can be etched with wet chemicals, plasmas or reactive ions. The choice of etching method can greatly effect the resulting film edge geometry. Wet etching is isotropic, whilst reactive ions etch anisotropically perpendicular to the wafer surface. (Plasma represents etchang a compromise between the two).

- (5) High temperature inert gas treatments are used for a variety of purposes such as annealing implantation damage[33, 41], annealing of the oxide-semiconductor interface[9], or for smoothing(reflowing) and densifying deposited glass.

#### 2.2.3. VLSI Processing

A process such as the standard EMF NMOS process can be scaled without any fundamental changes to have a gate length of 3 microns. If the gate and other dimensions are reduced further, then many new technologies and techniques are required[42]. These are;

- (1) Lithography with contact or projection printing is not adequate and must be replaced by 'wafer stepper' lithography which can produce better resolved lines and more accurate layer to layer alignment[24, 25].

- (2) The standard LOCOS field oxidation process results in a thickening of the gate oxide at the gate edge. This is called the bird's beak effect. A process somewhat similar to LOCOS which uses polysilicon in place of silicon nitride has been shown to give almost beak free field oxide[43]. Other VLSI isolation techniques include SWAMI[44], and trench (moat) isolation[45].

- (3) The gate oxide thickness must be reduced to 200-300 angstroms. This creates problems with gate integrity and thickness uniformity. Lowering the oxidation temperature, and added emphasis on wafer cleaning, computer controlled furnace loading and other measures are all involved in improving gate reliability and quality[46, 47, 48]. Recently interest in thin thermally nitrided gates[49] has boomed because of the improved integrity and higher dielectric constant. The higher dielectric constant helps reduce the short channel effect[49].

- (4) In order to prevent source and drain electrodes from becoming physically connected due to lateral diffusion during high temperature steps, three process changes need to be implemented. Source and drain are implanted rather than diffused for greater dose and depth control, and slower diffusing arsenic is used as the dopant in preference to phosphorus. In addition long high temperature steps can be replaced by rapid thermal processing[41, 50, 51, 52].

- (5) An additional implant is required to raise the punchthrough voltage to well above the operating voltage[53]. This is a medium dose implant placed behind the threshold adjust implant.

(6) The resistance of the gate, source and drain electrodes will limit the speed of a small geometry circuit. This effect can be overcome by using low resistance silicides[54] in place of polysilicon.

Such a process is currently under development in the EMF. The channel length is 1.5 microns, there is a 250 angstrom thermally nitrided gate, source and drain are implanted arsenic, there is a punchthrough suppression implant, lithography is performed with a 10:1 reduction wafer stepper and etching is primarily performed by reactive ion etching. In the near future the addition of rapid thermal annealing and silicides to this process will realise the optimum circuit performance from this process.

#### 2.3. Oxidation and Cleaning

#### 2.3.1. Thermal Oxidation of Silicon: Kinetics and Technology

The development of clean thermally grown  $SiO_2$  films<sup>†</sup> described in chapter 1 was the main thrust for the commercialisation of MOS devices. Since that advance, many other insulator and semiconductor combinations have been assessed for MOS IC applications but none has been found to match the excellent dielectric and interface properties of the Si-SiO<sub>2</sub> system[55].

Thermal oxidation of silicon proceeds by one of two chemical reactions[9, 26, 56, 57],

$$Si_{(solid)} + O_{2(g)} \rightarrow SiO_{2(solid)}$$

(2.1)

$$Si_{(solid)} + H_2O_{(g)} \rightarrow SiO_{2(solid)} + 2H_{2(g)}$$

(2.2)

<sup>†</sup> Hereafter these are referred to as "oxide"

which are known as dry and wet oxidation respectively. In integrated circuit manufacturing the oxidation of silicon is performed in so called diffusion furnaces. (This is because this type of furnace was originally used for diffusion of dopants). Microprocessor control of furnace heating, gas flows and wafer loading, all enable the reproducible growth of high quality oxides[46]. It also allows the safe use of pyrogenic water vapour which is produced by combustion of hydrogen in oxygen in the diffusion furnace. Pyrogenic production of steam is much cleaner than the method which was originally used to produce steam for the oxidation of silicon, which involved the bubbling  $\phi$  oxygen through water at 95°C.

The kinetics of these reactions at temperatures between 700 and  $1300^{\circ}$ C are described by Deal and Grove's well known linear-parabolic relationship[56] for all thicknesses of wet oxide up to 2 microns and for dry oxides of thickness in the range 300 angstroms to 2 microns. The linear-parabolic relationship is,

$$D_{ox} = \frac{A}{2} \left[ \left( 1 + \frac{t + \tau}{A^{2}/4B} \right)^{\frac{\mu}{2}} - 1 \right], \qquad (2.3)$$

where  $D_{OX}$  is the oxide thickness, t is the elapsed time for oxide growth,  $\tau$  is a shift in time to allow for an initial oxide thickness and where A and B are rate-dependent terms. There are two limits of equation 2.3 which are of interest. The first occurs for short oxidation times such that  $(t + \tau) \ll A^2/4B$ . In this case 2.3 reduces to

$$D_{ox} = \frac{B}{A}(t + \tau). \qquad (2.4)$$

This is known as the linear rate law and B/A is the linear rate constant. The other limit occurs at longer times when  $(t + \tau) >> A^2/4B$  for which 2.3 becomes

$$D_{at} = (Bt)^{\frac{t}{2}} \tag{2.5}$$

where B is the parabolic rate constant. The detailed expressions for the linear and parabolic rate constants[56] show that different mechanisms control the reaction rate in these two regimes. In the linear regime there is an abundant supply of oxygen available for reaction to take place and the rate of oxide formation is controlled only by the concentration of silicon available for reaction and the reaction rate constant. Here oxide formation is said to be reaction limited. In the parabolic regime the reaction rate exceeds the supply of fresh oxidant at the reaction interface. In this case the reaction rate is controlled by the diffusion of oxidant to the interface and is said to be diffusion limited.

- 17 -

Plotting  $D_{OX}$  against  $(t + \tau)/D_{ox}$  thickness yields the parabolic rate constant (B) from the slope and -A from the y-axis intercept. For wet oxides  $\tau$  can be taken as zero. For dry oxides an effective initial oxide thickness  $D_{ox}^{i}$  is determined from the intercept at t=0 of the extrapolation of the linear portion of an oxide thickness versus time plot. The linear portion of this plot has a slope, k (=B/A), from which  $\tau$  can be determined using  $\tau = D_{ox}^{i}/k$ .

Many of the details of the chemical reactions which lead to  $SiO_2$  formation are unknown, however the effects of a number of experimental factors on reaction rates are well known and these have provided evidence for modelling certain parts of the oxidation process. The major factors *a*ffecting oxidation rates on non-degenerate silicon are now reviewed. The commercially important topics of oxidation of degenerate silicon and silicon dopant ion segregation during oxidation have been covered by Katz[26], Nicollian and Brews[9] and Plummer[57].

Table 2.1 lists the linear and table 2.2 the parabolic rate constants for wet and dry oxidation as determined by Deal and Grove[56], and they clearly show that

| Temperature<br>( <sup>o</sup> C) | Wet<br>B/A (µ/hour) | Dry<br>B/A (µ/hour) | Wet/Dry |

|----------------------------------|---------------------|---------------------|---------|

| 920                              | 0.406               | 0.0208              | 20      |

| 1000                             | 1.27                | 0.071               | 18      |

| 1100                             | 4.64                | 0.30                | 15      |

| 1200                             | 14.40               | 1.12                | 13      |

- 10

Table 2.1 · Linear rate constants for wet and dry oxidation as determined by Deal and Grove.

| Temperature<br>( <sup>O</sup> C) | Wet<br>B (µ <sup>2</sup> /hour) | Dry<br>B (µ <sup>2</sup> /hour) | Wet/Dry |

|----------------------------------|---------------------------------|---------------------------------|---------|

| 920                              | 0.203                           | 0.0049                          | 41      |

| 1000                             | 0.287                           | 0.0117                          | 25      |

| 1100                             | 0.510                           | 0.027                           | 19      |

| 1200                             | 0.720                           | 0.045                           | 16      |

Table 2.2 Parabolic rate constants for wet and dry oxidation as determined by Deal and Grove.

oxidation in wet ambients is substantially faster in both regimes. This is primarily because the concentration of water vapour in oxide is a factor of 1000 higher than it is for oxygen in oxide. The fact that the diffusivity of water vapour is a factor of 10 less than that of oxygen is of only minor importance compared with the concentration effect in the parabolic (diffusion-limited) regime.

Increased oxidising ambient pressure will increase the concentration of oxidising agent in the oxide and speed its passage to the reaction interface and so both linear and parabolic rate constants are increased at higher pressures[58, 59]. The faster rate of oxide growth may be of commercial importance[60], but only if the problems of temperature uniformity[27], and particles[61] in high pressure furnaces are solved.

The addition of trace quantities of water vapour at concentrations as low as 0.1 ppm can measurably enhance dry oxidation rates and therefore the concentration of water vapour should be either minimised or strictly controlled[62, 63].

A careful consideration of kinetic data by Irene[64] indicates that both atomic and molecular oxygen are involved in dry oxidation, whilst Spitzer and Ligenza[65] showed that the linear pressure dependence of wet oxidation indicated that water vapour adsorbed from the gas phase was transported interstitially to the reaction interface. There is still considerable controversy as to the charge on the diffusing species though current evidence[9, 26] would favour an uncharged oxidant.

The silicon crystal orientation affects the oxidation rate in the linear growth regime. Ligenza[66] successfully modelled the orientation dependence by showing that the rate was dependent upon the density of silicon atoms in the reacting plane. The model predicted, and measurements were in close agreement with, relative rates of 1.00:1.707:1.227 for the orientations <110>,<311> and <111>. (The model predicts a value of 0.707 for the relative rate with <100> orientation). The experimental results of Irene[62] and Deal and Grove[56] showed the orientation effect to be

independent of the reacting species at temperatures in excess of 700°C, so steric effects are not important.

The presence of chlorine-containing species such as HCl[26], trichloroethene (TCE)[26], and trichloroethane (TCA)[67], in the oxidising ambient enhances the linear and parabolic rate constants in dry oxidation[68] but reduces them in wet oxidation[69]. A simple mechanism for the reduced rate for wet oxides[69] suggests that the chlorine containing species simply reduces the water vapour pressure. The mechanism of enhancement for dry oxidation is not understood. It has been proposed[68] that water vapour produced by the reaction of HCl, or TCA and O<sub>2</sub>, by one of the following reactions,

$$4HCl + O_2 - 2H_2O + 2Cl_2 \tag{2.6}$$

$$4C_{2}H_{3}Cl_{3} + 110_{2} - 6H_{2}O + 6Cl_{2} + 8CO_{2}$$

(2.7)

is responsible for the enhancement, however oxidation using pure  $Cl_2[70]$  as the source of chlorine also shows enhancement of the rate constants in which case the pres nce of water vapour can be discounted. Another suggestion which may have limited validity is that the chorine etches the silicon crystal thereby reducing the activation energy for the oxidation of silicon which should be observed as an increased linear rate constant whilst not affecting the parabolic constant. The observation of an orientation dependence of chlorine rate enhancement would support this model. However enhancement of the linear rate constant would only appear to be substantial for HCl additions up to 2% whereas the parabolic rate constant increases monatonically with HCl concentration. No complete model of chlorinated oxidation exists and as a result the kinetics have only been empirically modelled[71] as rate enhancement factors  $\eta$  and  $\epsilon$ , in which case equations 2.4 and 2.5 become,

$$D_{ox} = \eta \frac{B}{A} (t + \tau). \qquad (2.8)$$

$$D_{ox} = (\epsilon B t)^{\frac{1}{2}} \tag{2.9}$$

where the enhancement factors must be determined experimentally as a function of HCl concentration and temperature.

The final factor affecting oxidation rate is the presence of other impurities during oxidation. The only identified culprit to date is sodium[63] which enhances both linear and parabolic rate constants at high concentrations. It has been suggested that high sodium concentration will mean that the presence of Na-Si-O in the oxide will increase the concentration of dissolved oxidant sufficiently for it to affect the reaction rate[63].

McGillivray et al.[72], Matlock[73] and Schwettmann et al.[74] have all reported different aspects of the effect of surface cleanliness prior to thermal oxidation on oxidation rate. All three report growth enhancement due to unidentified species. The effects of cleaning on growth rate are reviewed in more detail in chapter 8.

Thin oxides show an enhanced oxidation growth rate for thicknesses of up to 300 angstroms[9, 56, 75], and this covers the entire growth period of an oxide for a VLSI gate application. The thickness over which the effect occurs is independent of temperature. Massoud et al.[76] have recently made a critical examination of a wide range of physical mechanisms which have been proposed to explain enhanced growth and have concluded that only a rather vaguely defined surface layer model can adequately account for all the experimentally observed behavior[77]. Several attempts have been made to empirically model thin oxide growth kinetics[78, 79, 80, 81]. The following model due to Massoud[78], is most likely to be widely used. It appends two factors to the Deal-Grove model and is now incorporated in the major process model program

SUPREM III[71]. Equation 2.7 becomes

$$D_{ox} = \eta \frac{B}{A} \left( 1 + C_1 \exp(-D_{ox}/L_1) + C_2 \exp(-D_{ox}/L_2) \right) t.$$

(2.10)

$L_1$  and  $L_2$  are characteristic lengths of 10 and 70 angstroms respectively and the constants  $C_1$  and  $C_2$  are constants dependent upon the activation energy for the fast oxidation process. The two pre-exponential terms are of the form[71, 77],

$$C = C_0 \exp(-E_a/kT) \tag{2.11}$$

where  $E_a$  is the activation energy of each of the two enhancements and  $C_0$  is an orientation-dependent constant. Values of  $E_a$ ,  $C_{10}$  and  $C_{20}$  have been determined experimentally for a range of orientations[77]. The first relatively short range superenhanced growth regime can be neglected in the model with a resulting error of approximately 5%[71, 76].

The VLSI gate oxides described in section 2.1 exploit many of those experimental factors described here which reduce oxide growth rate thereby giving improved oxide thickness control.

In addition to controlling oxide thickness, it is important to control the level of oxide charges which remain after growth. Chapter 15 of Nicollian and Brews' book[9] discusses the effects of oxidation ambient, crystal orientation, oxidation temperature, radiation and annealing upon the level of oxide charges. Lai[82] has reviewed some of the electrical properties of oxides grown with oxidation recipes which are typical of modern manufacturing processes. The measurement of oxide charges and a variety of experimental factors affecting their level is the subject of much of the remainder of this thesis.

#### 2.3.2. Wafer and Furnace Cleaning

In 1967 according to Burger and Donovan[83] "attempts to manufacture devices from high quality silicon ..... are beset by perplexing mysteries which provide fertile ground for the rites of the rainmaker, witch doctor and others of that ilk." The exasperation which is comically expressed in this statement reflects the extreme sensitivity of semiconductor devices to trace and even ultra-trace impurities. The DRAM is the most impurity-sensitive MOS circuit, where the basic active element is a storage capacitor which can show unacceptably high levels of leakage with gold concentrations in the silicon surface region of approximately one part in  $10^{11}$ <sup>†</sup> The problems of contamination have been greatly reduced since 1967 with advances in passivation[9], clean room technology[85], impurity gettering[86], and wafer[87] and furnace cleaning[67]. The methods used to clean wafers and furnaces are now reviewed. In chapter 8 the electrical effects of the chemical purity of the cleaning fluids are examined.

Wafer cleaning[87, 88, 89, 90, 91, 92, 93] is used to remove organic films, inorganic ions and inorganic atoms before high temperature furnace processes where the contaminants can diffuse into device regions or interfere with layer growth, thereby causing functional failure of a device. The wafer cleaning sequence should leave the wafer with less particulate contamination than at its start. Monkowski[94] has reviewed the yield limiting effects of particles which have become of increased importance as device geometries have shrunk.

The detrimental effects of only a relatively few impurities are known, and thus cleaning procedures currently in use aim to reduce the level of all surface contamination to as near zero as possible. The vast majority of cleaning experiments which have been publicly reported[87, 88, 95, 96, 97, 98, 99] rely solely upon a chemical assessment  $\dagger$  one part in 10<sup>11</sup>. This figure is calculated from data of Richou et al.[84] who related gold concentration to minority carrier lifetimes and the assumption of a lower limit of 100 microseconds for this DRAM parameter.

of removal, using very gross contaminations of wafers and therefore results may not be directly correlated with any real contamination/cleaning requirement. In chapter 8, trace contamination is assessed with electrical measurements, thereby highlighting only those impurity effects which are electrically active at concentrations which could conceivably occur in a fabrication plant. The proof of the effectiveness of the cleans which are discussed next, relies more on the fact that they are regularly used in the manufacture of working electrical devices, than on any published chemical removal data.

Burkmann[91] has stated that the optimum sequence of cleaning steps is:

- (1) Gross organic film removal (normally photoresist). \*

- (2) Residual organic material removal.

- (3) Native oxide removal. \*

(4) Metal atom and ion removal.

\* = optional

This is the procedure adopted in the widely used "RCA" clean described by Kern[87] in an update of the original cleaning process developed by Kern and Poutinen[88]. Table 2.3 details the steps involved in the RCA method. In IC production oxygen plasma stripping of resist is currently favoured[100] for this step because it is cleaner, cheaper and safer than sulphuric-peroxide mix. A commonly used alternative for photoresist removal is fuming nitric acid. This has the advantages over sulphuric-peroxide, that it can be used when underlying metal is exposed and also that it does not deteriorate nearly as rapidly.

Problems with the complete removal of resist can occur, especially after and ion-implantation, where heating of the wafer by the ion beam causes the resist to bind more tightly to the underlying layer. In the EMF this 'baked-on' resist is removed by

- Remove photoresist or other gross organic film in an oxygen plasma stripper or in Caro's acid.

Caro's acid is a mix of H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub> in the ratio 2:1 volumes. It should be used at 140°C.

- Remove residual resist in NH<sub>4</sub>OH/H<sub>2</sub>O<sub>2</sub>/H<sub>2</sub>O mix in the volume ratio 1:1:5. The wafers should be immersed in the solution at room temperature and then the temperature raised to 80°C and held there for 10 minutes.

- 3. Remove the native oxide film with dilute HF. Concentrations from 2-10% are commonly used. Immerse for 15-60 seconds.

- 4. Remove metallic and ionic contaminants in  $HCL/H_2O_2/H_2O$ mix with a volume ratio (1:1:5). Heat to  $80^{\circ}C$  then add the wafers for 10 minutes.

- 5. Rinse and Spin dry then transfer immediately to furnace loader.

Table 2.3 The RCA wafer cleaning recipe.

#### 25 -

plasma stripping followed by fuming nitric acid immersion. The "RCA" clean uses  $NH_4OH/H_2O_2/H_2O$  for residual organic removal. This is effective but expensive since it has to be used at approximately  $80^{\circ}C$  and at that temperature the solution can only be used once because of rapid decomposition of the peroxide[88].

The HF dip to remove native oxide should be omitted in situations where the acid will attack sensitive areas of devices. This modification of the original RCA method gives improved metal ion removal by directly exposing the native silicon surface[87]. Dilute HF is used for a short time to minimise metal plating. Kern[88] recommends a very brief overflow immersion rinse, (30 seconds), in DI water to prevent reoxidation. This author prefers to use a 5 x 45 second cold spray rinse which should remove more fluoride ions[90], whilst not allowing significant reoxidation of the surface.

The extent of rinsing and the method of rinsing (spray, immersion, scrubbing, or spray/immersion) can have a significant effect on the overall performance of any clean [74, 99 101, 102,]. The mechanisms of rinsing effects are not understood and experimental results show marked inconsistencies.

The final RCA clean is used to remove metal atoms and ions. The only other metal clean commonly in use is hot  $(80^{\circ}C)$  nitric acid, for which experiments performed by this author[103] in an industrial environment showed good results for MOS capacitor electrical parameters. Both of these cleans grow a thin (<20 angstroms) chemical oxide. In some fabrication sequences this is removed with an additional HF dip. This practice is inadvisable since HF causes a higher degree of surface particulate contamination[96] than other cleans and the native silicon surface is more easily recontaminated than the chemically oxidised surface[99].

All cleaning sequences end with a thorough rinse in DI water followed by spin drying in a warm nitrogen ambient.

Throughout the cleaning sequence the quality of DI water[104] and the cleanliness of all utensils[87] is of the utmost importance. Teflon tweezers, unlike metal tweezers, can be cleaned using the same sequence as the wafers and should be used when loading wafers onto a furnace boat after cleaning[87, 105]. In volume production clean batch transfer systems[106] have recently been introduced.

There are three principal methods of implementing cleaning procedures[87]: immersion in baths of liquid, the RCA megasonic system and the FSI spray system. All three methods will give adequate comparable cleaning performance with the major differences between them being cost and safety[87]. In industrial plants the FSI spray system appears to be the dominant method of cleaning in new plants. The specification of commercial cleaning systems would appear rather poor (eg. guaranteeing only a 0.1V mobile ion shift), however this author believes that this is not because the systems are poor, but rather that the cleaning system manufactures do not understand how to assess electrical measurements properly! (They are not alone in this respect).

The work of Pearce and Schmidt[105], Hamsaki[28], and Kriegler[49] implicitly show that wafer cleaning alone is no guarantee that impurities will not find their way into wafers, because the diffusion furnace itself can be the principal source of contamination. Unwanted impurities can enter furnaces in process gasses or by diffusion through the furnace lining whereupon they can enter into wafers by the same mechanism which is used for the deliberate boron, arsenic and phosphoras doping of wafers.

Pearce and Schmidt clearly showed that diffusion through furnace liners is the most serious problem. Several alternative furnace liners to the quartz which is commonly used show better diffusion properties [105, 107]. However they are expensive and do not provide a complete solution. Double walled furnaces work well in inhibiting diffusion [105], but give poorer control over furnace temperature [108]. Since temperature control is of vital importance, particularly for thin oxide growth they are not

- 27 -

widely used. Gassing the furnace with HCl[28, 49, 105] or  $TCA^{\dagger}$  is the most widely applied solution to in-situ furnace contamination because it actively removes impurities from the tube. These gasses can also be used during oxidation cycles where chlorine also becomes incorporated into the growing oxide with beneficial effects.

The cleaning procedure for furnaces[67, 101, 109] normally consists of a dummy oxidation run at a temperature at least 100<sup>o</sup>C higher than the hottest operating temperature of that furnace. The furnace boat and paddle should be in the furnace during cleaning.

#### 2.4. Conclusions

This review of MOS device processing has shown just how complicated their manufacture can be. This helps to explain the requirement for the measurements and analysis presented in later chapters which can be used to assess individual process steps, particularly those which might involve oxidation or contamination, both of which have been looked at in detail in this chapter.

<sup>†</sup> TCE is not used because it is a carcinogen.

#### **CHAPTER THREE**

#### Metal-Oxide-Semiconductor Capacitor (MOSC)

#### 3.1. Introduction

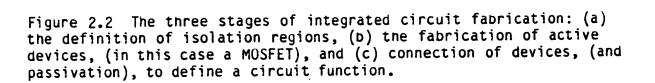

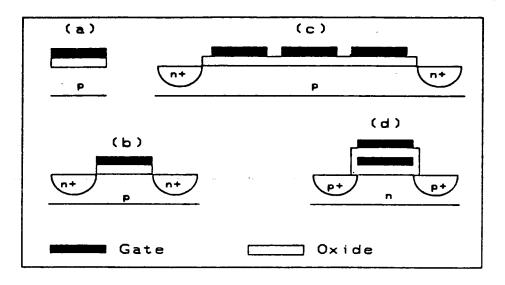

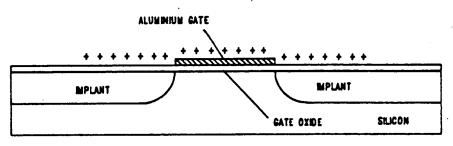

It is widely accepted that the MOS Capacitor is the single most useful device with which to study the basic electrical properties of MOS system[8,9,10,11,110,111,112,113,114]. It can be seen from figure 3.1 that the MOSC forms an important functional part of more complex device structures which are some of the building blocks of monolithic integrated circuits.

The wide utility of the MOSC lies in its simplicity of fabrication and that nearly all the important surface, oxide and silicon parameters can be investigated using relatively simple two terminal measurements.

The useful information which can be derived from this test structure is the subject of this and later chapters. As was explained in chapter 1 the emphasis herein will be on how to measure and interpret the various characteristics with only the most important equations being quoted. The reader should refer to the standard texts for exhaustive proofs or minor detail.

## 3.2. Definition of Potentials and Bias Regimes of the MOSC

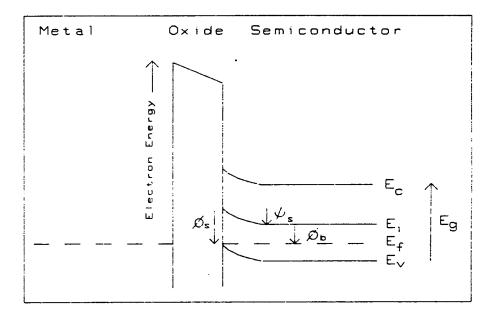

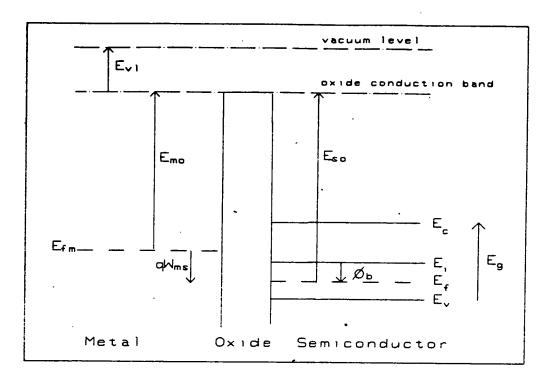

The energy band diagram for the MOS capacitor is shown in figure 3.2. [115]. The diagram is presented here to define the potentials which will be used in later sections.

<sup>\*</sup>The standard texts[9, 10] use slightly different nomenclatures therefore for clarity these quantities are redefined here.

Figure 3.1. The MOS Capacitor (a) and the devices some of which it is a functional component, (b) MOSFET, (c) 3-phase CCD, (d) SAMOS non-volatile memory cell.

i.

Figure 3.2. MUS Capacitor energy bands.

.

The bulk potential  $\phi_B$  is defined first by the equation

$$\mathcal{G}\phi_B = E_f - E_i \tag{3.1}$$

where  $E_f$  is the fermi level and  $E_i$  is the intrinsic level energy deep in the bulk of the semiconductor. When a bias is applied across the capacitor, the bands in the silicon bend in order to restore equilibrium. When the bands are bent, another potential,  $\psi_s$ the surface potential, can be defined such that

$$\psi_s = \phi_s - \phi_B \,. \tag{3.2}$$

The operation of the MOS capacitor can be most easily described by scanning surface potential over a range of negative and positive values. Only equations for a MOSC with a p-type semiconductor will be discussed here since the changes in arguments required for an n-type semiconductor relate only to the type of charge and the signs of potentials and do not involve any differences in fundamental concepts.

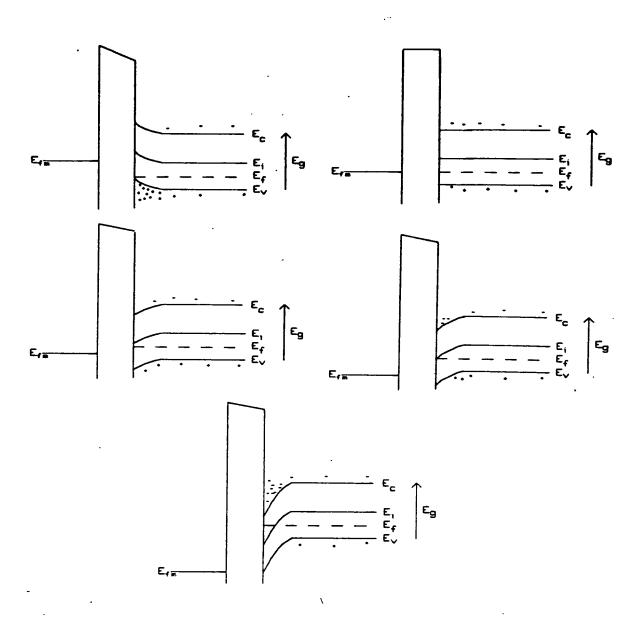

There are five<sup>†</sup> basic surface conditions of the uniformly doped MOSC, accumulation( $\psi_s < 0$ ), flatbands( $\psi_s = 0$ ), depletion ( $0 < \psi_s < \phi_B$ ), weak inversion ( $\phi_B < \psi_s < 2\phi_B$ ) and finally strong inversion where  $\psi_s > 2\phi_B$ . These conditions along with the associated charge distributions in the semiconductor are illustrated in figure 3.3.

Accumulation occurs when the silicon bands bend upward causing the valence band to move closer to the fermi level. The hole density at the surface at any given There is a sixth non-equilibrium state viz. deep depletion. surface potential is given by the equation

$$p_s = N_A \exp(-\beta \psi_s) \tag{3.3}$$

and the number of minority carriers is found from the pn product relationship

$$pn = n_i^2 \tag{3.4}$$

which holds for any value of p at equilibrium therefore

$$n_s = \frac{n_i^2}{(N_A \exp(\beta \psi_s))}$$

(3.5)

Therefore in accumulation( $\psi_s < 0$ ) there is a very large density of holes at the semiconductor surface and a density of electrons so small that it can effectively be ignored. The flatband condition, (hereafter referred to as "flatbands"), occurs when  $\psi_s = 0$ , at this point there is no nett potential across the semiconductor, and hence the nett charge density vanishes throughout. As the name flatbands implies, the energy bands in the silicon are flat all the way from the surface to deep in the bulk.

When the bands begin to bend downward the surface is initially in the depletion,  $(0 < \psi_s < \phi_B)$ , regime where the density of holes in the near-surface region is depleted below the density of holes in the bulk of the semiconductor. The hole density vanishes so rapidly when surface potential exceeds a few eV that effectively the only charges present in the near-surface region are fixed ionised acceptor atoms. As surface

Figure 3.3. The surface conditions of the MOS Capacitor, (a) accumulation, (b) flatbands, (c) depletion, (d) weak inversion, (e) strong inversion.

4

------

potential is increased towards  $\phi_B$ , the width of the depletion region increases in order to balance the charge on the gate.

When the surface potential reaches  $\phi_B$ , a small number of electrons drift to the semiconductor surface creating an inversion layer, i.e. a layer of mobile charges forms near the surface which is of the opposite charge to the carriers for that substrate type. The region where  $\psi_s$  has a value of between  $\phi_B$  and  $2\phi_B$  is called weak inversion because the depletion layer charge exceeds that of the inversion layer.

The final regime is strong inversion  $(\psi_s > 2\phi_B)$ . Here the bands have bent downward sufficiently that the inversion layer charge increases exponentially with increase in  $\psi_s$  so that the inversion layer charge becomes far greater than the depletion layer charge.

# 3.3. MOSC CV Characteristic at high Frequencies<sup>†</sup>

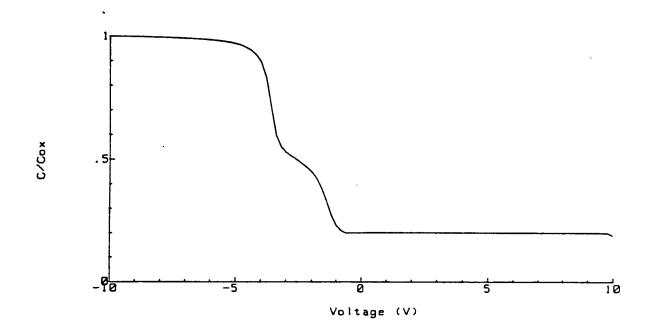

The high frequency CV (HFCV) characteristic of the MOSC is the most important electrical measurement used in process testing of silicon wafers in *all* MOS IC manufacturing plants and is equally important in research and development environments[9, 11, 113].

The MOSC was first proposed and analysed by a number of workers[116, 117, 118, 119] during the years 1959-1962. At the end of this period, Terman[120], applied the measurement of capacitance as a function of voltage and frequency to study surface states. However, the method did not give reproducible results at that time. In 1965 the classic paper of Grove et. al.[3] was the first to describe MOSC CV characteristics in a format similar to that which is used today. (This work represented a true milestone in the development of MOS processes for it included both

<sup>†</sup> Frequency in this context refers to the ac bias applied by a capacitance bridge in order to measure differential capacitance.

the practical application of CV measurements and the fabrication of a large quantity of stable MOS capacitors for the first time). An updated version of the classic description of MOSC CV curves is now presented.

In order to understand the CV characteristic of a real MOSC it is first necessary to consider the ideal MOSC which has the following properties, (1) when a dc bias is applied across the MOSC there is no dc current flow through the oxide i.e. the insulator has infinite resistivity, (2) there are no locally unbalanced charges in the oxide or at the oxide-semiconductor interface at zero bias, (3) The metal semiconductor work function is zero.

When these conditions hold, the structure behaves as a classical parallel plate capacitor whose capacitance is given by

$$C_{ox} = \frac{\epsilon_{ox}}{D_{ox}} . \tag{3.6}$$

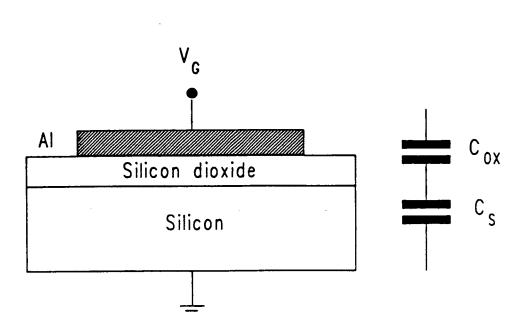

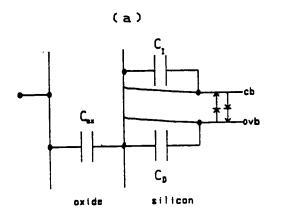

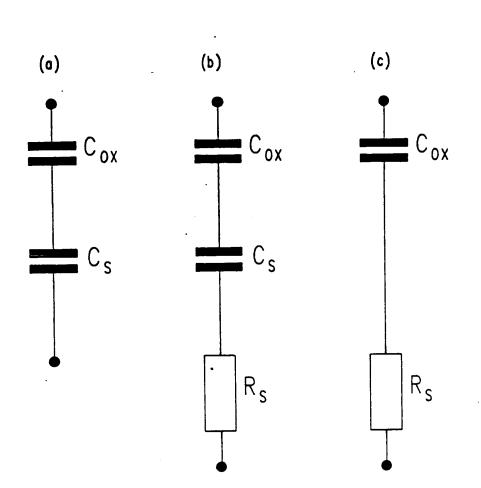

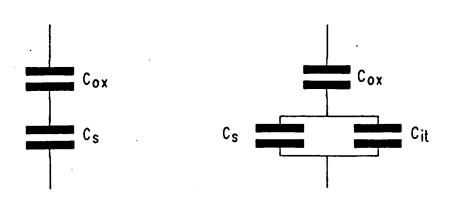

In addition to the oxide capacitance the charge distributions which result from changes in surface potential result in there being a voltage-variable silicon capacitance. The measured MOS capacitance is a series combination of these two capacitors (figure 3.4). To determine the ideal Capacitance-Voltage (CV) characteristics, the silicon capacitance must be evaluated as a function of gate voltage<sup>\*</sup>. It is simpler to determine silicon capacitance as a function of surface potential and then later use Gauss's law to determine the gate voltage for a given value of  $\psi_s$ . The general expression for the silicon capacitance as a function of  $\psi_s$  is [9],

<sup>\*</sup> In order to simplify the discussion only the important results will be quoted.

- 36 -

Figure 3.4. MUS Capacitor structure and equivalent circuit.

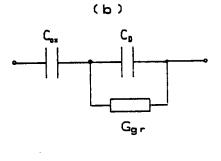

Figure 3.5. (a) Equivalent circuit including generation-recombination centers. (b) Simplification of (a) at nigh frequency.

$$C_{s} = \frac{C_{s/b}}{2^{\frac{u}{2}}} \frac{1 - \exp(-\beta\psi_{s}) + (n_{i}/N_{A})^{2} \exp(\beta\psi_{s}))}{[(\exp(\beta\psi_{s}) - 1) + \exp(-\beta\psi_{s}) + (n_{i}/N_{A})^{2} \exp(-\beta\psi_{s})]^{\frac{u}{2}}}$$

(3.7)

where  $C_{sp}$  is the silicon capacitance at flatbands which is defined by

$$C_{sfb} = \frac{\epsilon_{si}}{\lambda}$$

(3.8)

where  $\lambda$  is the Debye length and is given by

$$\lambda = \left(\frac{\epsilon_{si}kT}{q^2 N_A}\right)^{\frac{1}{2}}.$$

(3.9)

Finally, the measured capacitance  $C_m$  of the MOSC is a series combination of  $C_{ox}$  and  $C_s$  so that

$$\frac{1}{C_m} = \frac{1}{C_{ox}} + \frac{1}{C_s}$$

(3.10)

This however is not the capacitance which is measured over a complete range of  $\psi_s$ , using conventional high frequency capacitance measuring equipment<sup>\*</sup>. To show why this occurs the method by which capacitance is measured and the motion of minority carriers under non-equilibrium conditions are next discussed.

<sup>\*</sup> The characteristic which is generated by equation 3.7 is discussed in chapter 4.

In a capacitance bridge such as the HP4275A LCR, the capacitance is measured by applying a high frequency ac voltage of small amplitude (<50mV) on top of the dc bias across the capacitor. This bridge measures differential capacitance i.e.

$$C_s = \frac{dQ_s}{d\psi_s} \tag{3.11}$$

Since C, is strongly non-linear with respect to  $\psi$ , in certain bias regimes, the amplitude of the ac variation should be kept as small as reasonably possible. In practice a 15mV amplitude suffices for nearly all applications.

The measured silicon capacitance differs from that predicted by equation 3.7 at high ac frequencies because minority carriers cannot redistribute quickly enough to follow the change in ac bias. Silicon capacitance can be measured in depletion and weak inversion because majority carriers respond instantaneously to ac bias frequencies up to at least 10MHz which is the upper frequency limit of practical MOSC measurements[3,9].

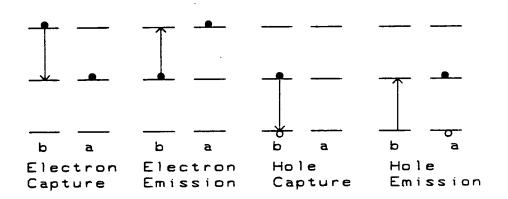

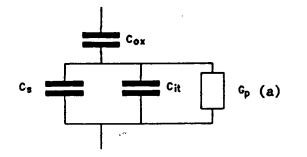

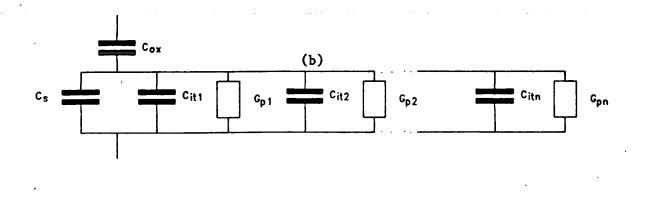

Minority carriers on the other hand must redistribute by generationrecombination (GR) processes, which takes place at room temperature within the depletion layer[9]. They cannot be supplied by the external circuit where the contact which is ohmic for the majority carriers is blocking for minority carriers. Figure 3.5 illustrates the equivalent circuit of the MOSC including generation recombination centres in the depletion layer. These are the states in the silicon bandgap through which charge must pass to change the relative occupancy of the charge carrier energy bands. Figure 3.6 shows the capture and emission processes which are part of generation and recombination[114]. The role of these mechanisms and their effects on CV characteristics will now be described. When an ac signal is suplied to the MOSC in inversion in the positive half of the cycle there will be too few electrons in the inversion layer. The capacitor is no longer in equilibrium and so electrons in the conduction band near the interface diffuse toward the surface. This transfers the disturbance from equilibrium away from the interface to a point at which there is a supply of fresh electrons from the valence band. This occurs at room temperature at a point where the band bending is equal but opposite to the bulk potential because generation-recombination only occurs efficiently with generation-recombination centers near midgap[9]. At this point a hole is emitted followed by an electron being emitted by the trap thus promoting an electron into the conduction band. The emitted hole diffuses toward the back contact. In the negative half of the cycle there are too many electrons in the inversion layer and so the recombination process which is similar to the generation process just described must reduce the inversion layer charge.

The GR processes take a finite time to occur. GR centers are impurity atoms with energies near midgap[9], therefore as will be shown later the purer the semiconductor the slower the GR process is at restoring equilibrium. For moderately pure silicon, GR cannot follow ac signals of more than a few tens of Herz and at typical measurement frequencies of 1MHz, it can be assumed that minority carriers do not follow the ac signal at all. This has the effect of making the measured MOS capacitance different from that predicted by 3.7 when the capacitor is in weak and strong inversion. In depletion and weak inversion, the high frequency silicon capacitance  $(C_{tr}^{HF})$  is[9],

$$C_{s}^{HF} = \frac{C_{sfb}}{2^{4}} \frac{[1 - \exp(-\beta\psi_{s})]}{[\beta\psi_{s} - 1 + \exp(-\beta\psi_{s})]^{4}}$$

(3.12)

This equation is arrived at by neglecting contributions to the capacitance from minority

carriers.

In strong inversion the depletion layer width ceases to widen as it did in depletion and weak inversion. At high frequency this causes the measured MOS capacitance to settle out to a minimum value. The exact expression for the capacitance in strong inversion is rather complex[9]. However, a simple expression first developed by Linder[119], and then improved on by Brews[121], gives inversion layer capacitance to better than 1.5% accuracy which in practice is perfectly adequate. The Linder-Brews method involves estimating the value of band bending at which strong inversion occurs and then simply setting the capacitance at all other values of  $\psi$ , in strong inversion equal to that at the match point where the match point is found from

$$\psi_{sm} = 2.10\phi_B + 1.33\frac{kT}{q} . \tag{3.13}$$

Thus using equation 3.7 in accumulation, equation 3.12 in depletion and weak inversion and equation 3.13 to find the capacitance in strong inversion the high frequency CV characteristic can be calculated over a full range of  $\psi_s$ . The only remaining problem is to relate the surface potential to the applied gate bias.

From Gauss's law, the charge on both the oxide and semiconductor capacitors is equal. Thus if  $Q_s$  can be calculated for each value of  $\psi_s$ , then  $Q_{ox}$  and  $C_{ox}$  are known and using V=Q/C the voltage across the oxide can be calculated. Now  $Q_s$  can be calculated from

$$Q_{s} = Sgn\left(-\beta\psi_{s}\right)\frac{\epsilon_{s}}{\lambda}\left(\frac{kT}{q}\right)F\left(\beta\psi_{s}\right)$$

(3.14)

where F is the electric field and is given by

$$F = \left(\frac{N_A}{n_i}\right)^{\frac{1}{2}} [(\beta\psi_s - 1) + \exp(-\beta\psi_s) + (n_i/N_A)^2 \exp(\beta\psi_s)]^{\frac{1}{2}}.$$

(3.15)

Therefore gate voltage,  $V_g$  is

$$V_g = \frac{-Q_s}{C_{ox}} + \beta \psi_s . \qquad (3.16)$$

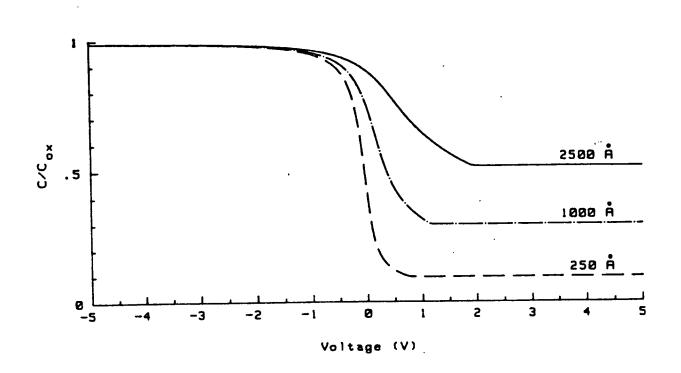

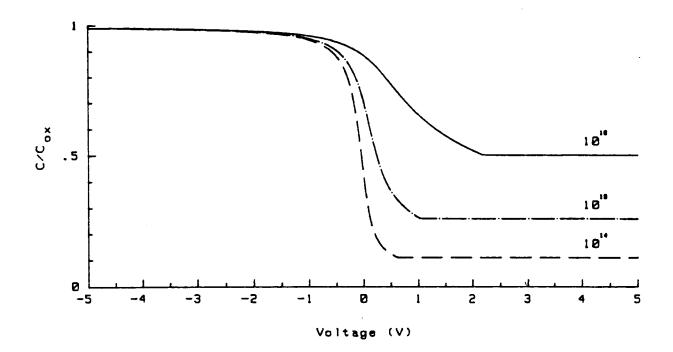

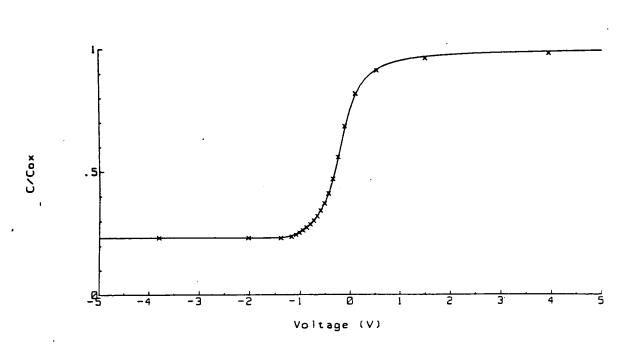

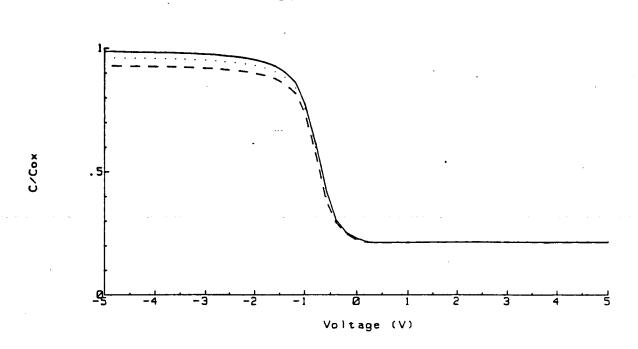

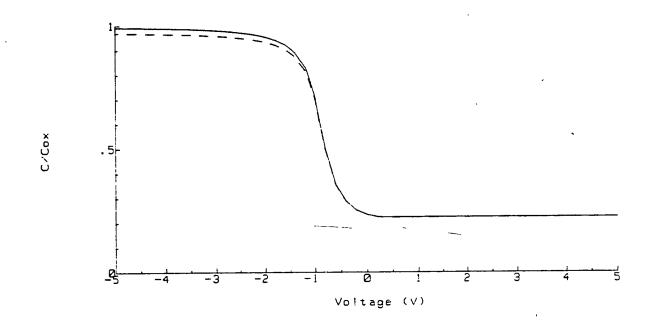

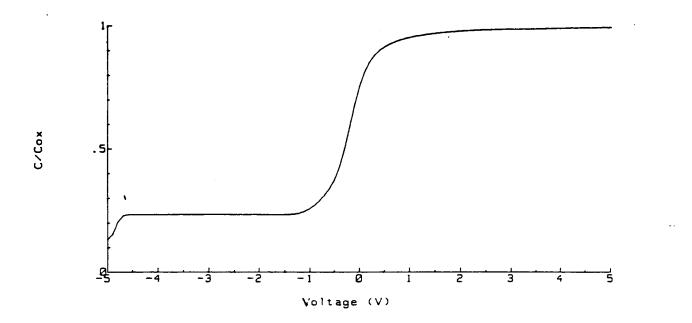

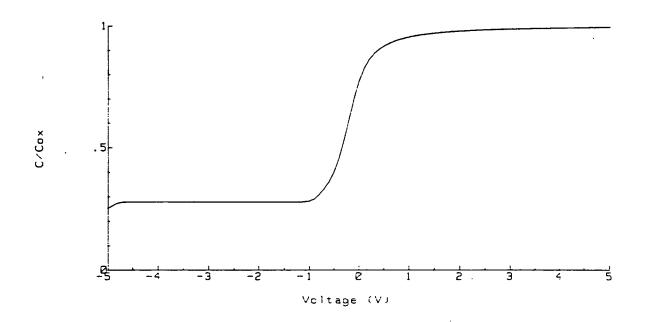

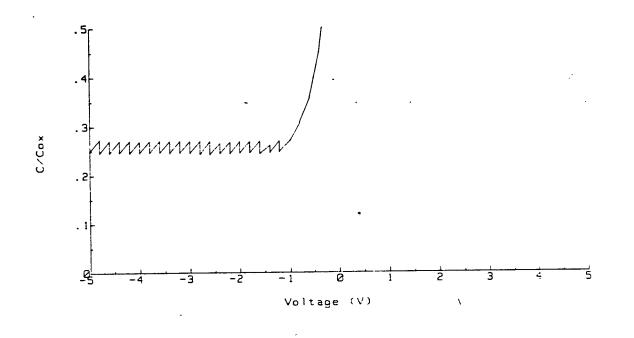

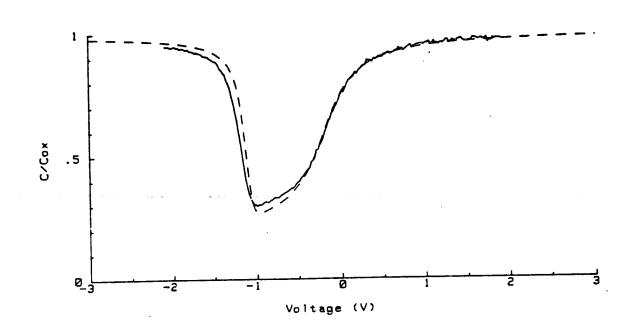

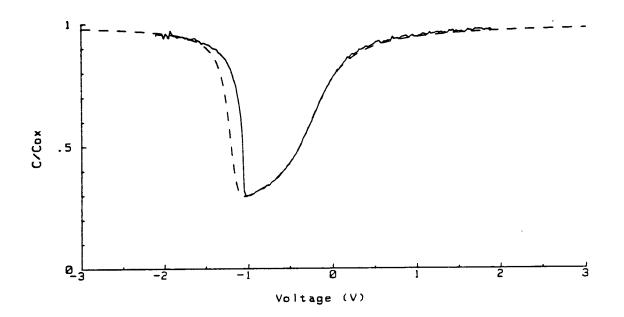

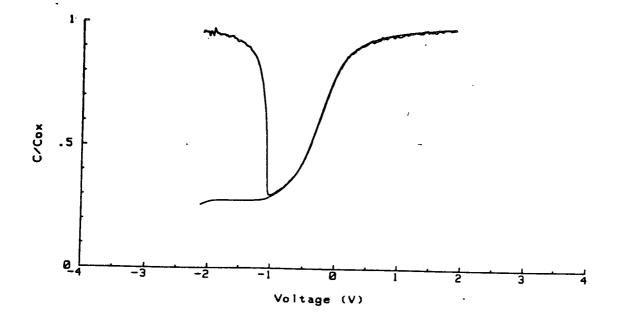

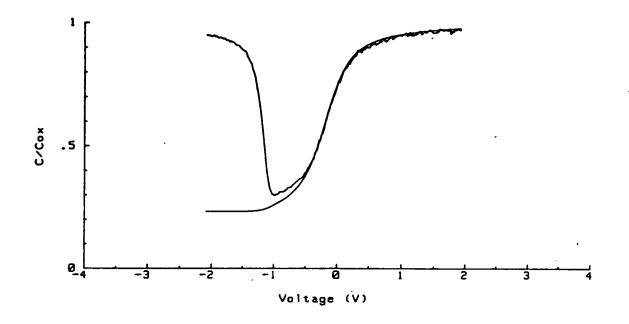

Figure 3.7 shows ideal high frequency CV characteristics for p-type substrates of various uniform doping densities and oxide thicknesses. Real MOS capacitors if carefully fabricated can approach this ideal model. Figure 3.8 shows a a comparison between an ideal curve and an overlayed measured curve.

## 3.4. Non-Ideal MOS Capacitor

Despite the fact that figure 3.8 showed that MOS capacitors with near ideal behavior can be made, this is only achieved with very careful oxide growth and annealing. Real MOS capacitors can support locally unbalanced charges in the oxide. Insulator charge has the effect of either shifting or distorting the high frequency CV characteristic and is of practical importance in IC manufacturing because it effects transistor parameters such as threshold voltage  $(V_T)$  and transconductance  $(g_m)$ .

In 1980 a joint committee of the IEEE and Electrochemical Society[122] under the chairmanship of B. Deal produced an unambiguous oxide charge classification. This set up a working model of the MOS system which is now the common basis for

Figure 3.7 (a) Ideal high frequency CV cnaracteristics for a range of oxide thicknesses.

Figure 3.7 (b) Ideal nigh frequency CV cnaracteristics for a range of substrate doping densities.

÷

discussions of insulator charges. The Deal terminology will be followed in this text.

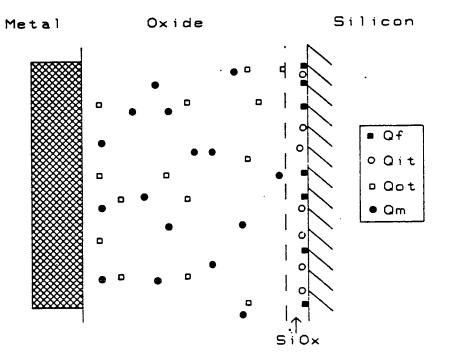

The four types of charges identified by the committee were,

| Q <sub>f</sub>  | Fixed Oxide Charge       |

|-----------------|--------------------------|

| Q <sub>m</sub>  | Mobile Charge            |

| Q <sub>it</sub> | Interface Trapped Charge |

| Q <sub>ot</sub> | Oxide Trapped Charge     |

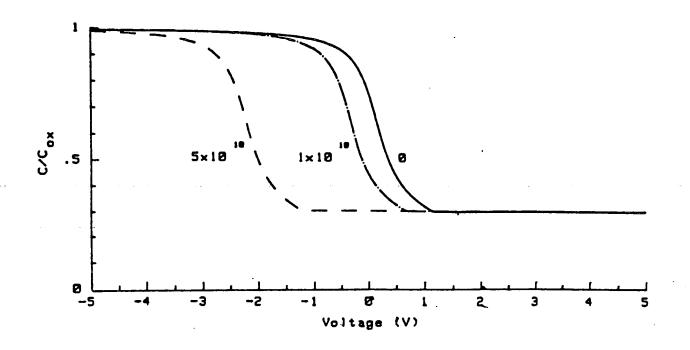

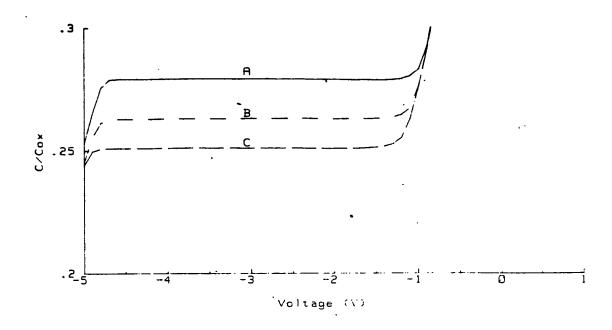

Figure 3.9 shows the spatial location of these charges. In figure 3.10 the effect of a range of fixed oxide charge densities on the CV characteristic are shown. This is an idealised situation because in practice one type of charge seldom occurs on its own. In addition there are other effects which distort CV curves, (1) non- uniform doping pro-files, (2) work functions, (3) measurement errors.

### 3.5. Preparation of MOSC samples and measuring equipment for CV experiments.

Many process engineers in IC fabrication plants are sceptical of the ability of MOSC measurements to provide reliable results. In most cases this is probably because of inadequate sample preparation, measuring equipment, or analysis. In this section the avoidance of the first two problems is discussed.

#### 3.5.1. Fabrication Of MOSC Samples

The following chapters assume that samples are prepared in class 100 cleanrooms[123, 124] or better using modern 'clean' processing equipment using high quality single crystal silicon wafers which have been thermally oxidised at temperatures between 800 and 1200<sup>o</sup>C.

Figure 3.8. A comparison of a measured high frequency CV curve, (solid line), with a corresponding ideal CV cnaracteristic (crosses).

Figure 3.9. Spatial location of oxide charges as classified by Deal.

44 -

Figure 3.10. High frequency CV characteristics shifted by a range of fixed charge densities.

Figure 3.11. Probe station set-up for CV measurements.

### 3.5.1.1. Gate Material

MOS IC manufacturers use aluminium, polysilicon and silicides as gate material[31, 125]. Many other metals such as gold, magnesium and chromium are suitable as gate electrodes but their use is generally restricted to R&D. Different choices of gate material will result in different MOSC behavior[126, 125], therefore it is important to choose the gate metal carefully in order that experiments give meaningful results.

#### 3.5.1.2. Gate Definition

A photolithographic definition, (chapter 2), is the best method for accurate work since this provides a gate with well defined area and uniform thickness. This is the only practical way to define polysilicon or silicide gates.

Shadow masking[127] is a simpler and quicker alternative where a thin flat plate with drilled holes is firmly attached to the front of the wafer. The plate and wafer are then placed in a metal evaporator/sputterer where the plate masks the majority of the wafer from metal. The exposed areas defined by the holes become the capacitor dots. The area definition is not as good as that obtained lithography since the edge definition is poor because metal will be deposited at points near the hole edge where the wafer and mask are not firmly in contact. In addition metal thickness can vary a great deal across a dot.

The final alternative is to use a liquid mercury column[128, 129]. Again the area is not well defined. The contact is generally maintained by placing the wafer face down onto a vacuum chuck and then a column of mercury within the chuck is formed upwards under pressure making contact with the wafer. This author has found the mercury probe difficult to use. Derived results compare very badly with those measured with lithography or shadow masks. Section 3.10 will show that the two top contact mercury probe is not suitable for quantitative analysis.

When the area is not well defined, optical thickness measurements can be used to calibrate area, using equation 3.6. This usually still leaves some error particularly if the oxide is thin.

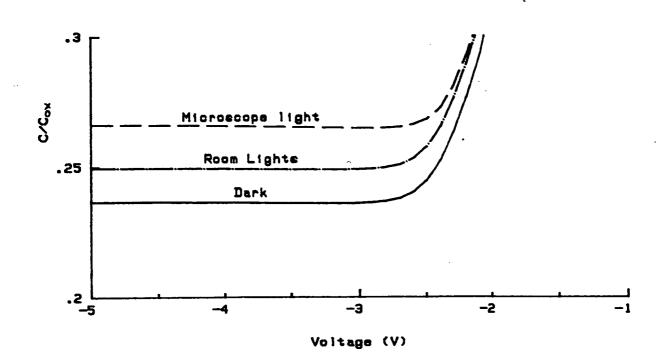

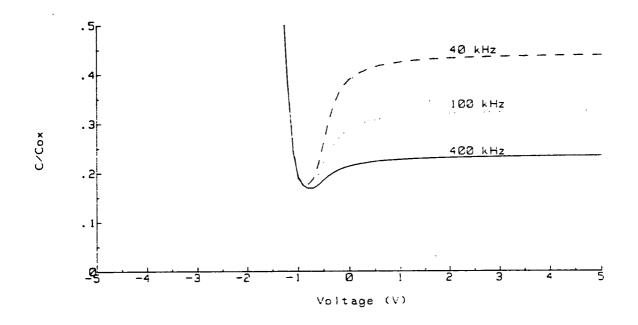

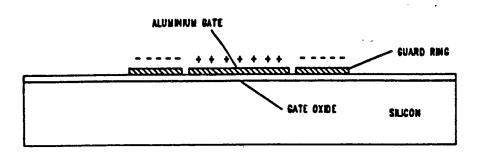

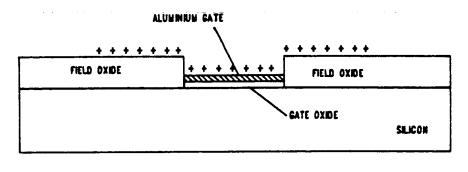

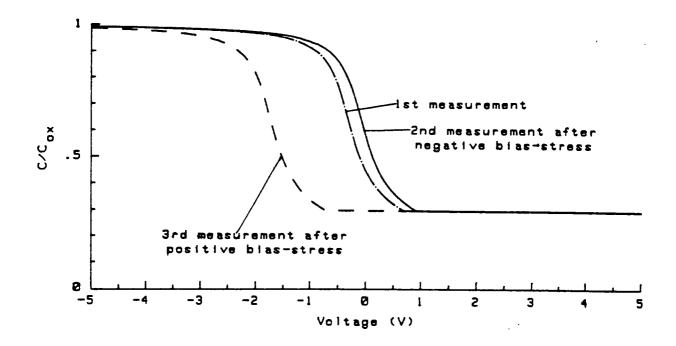

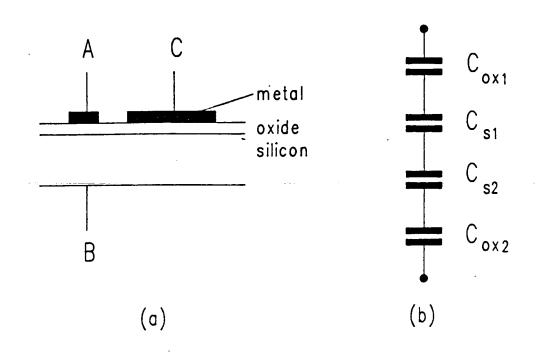

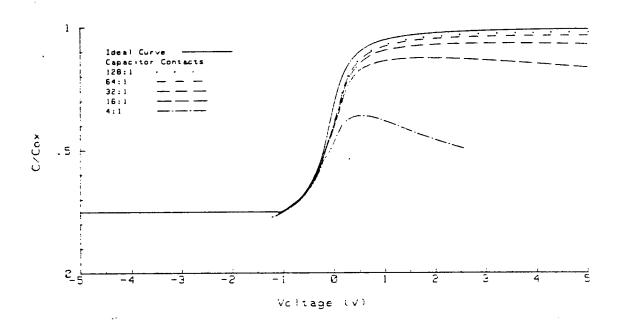

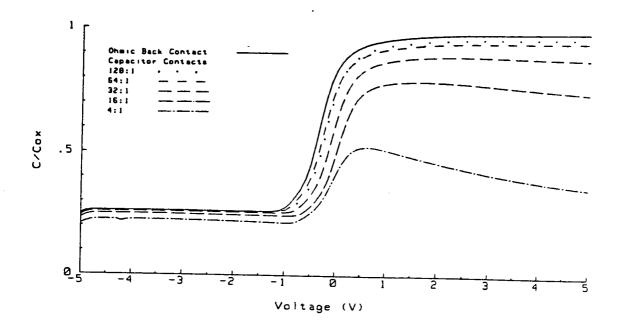

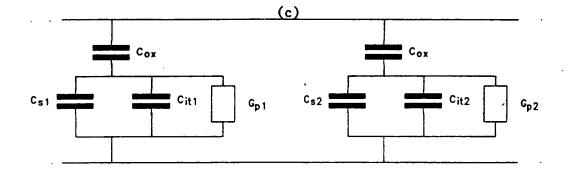

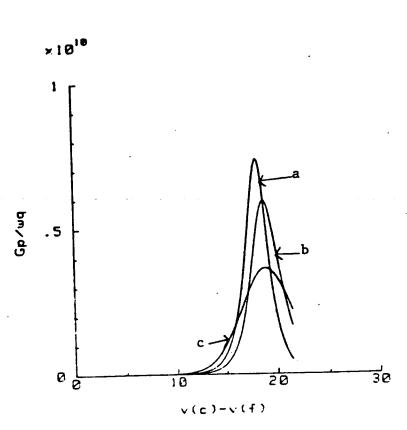

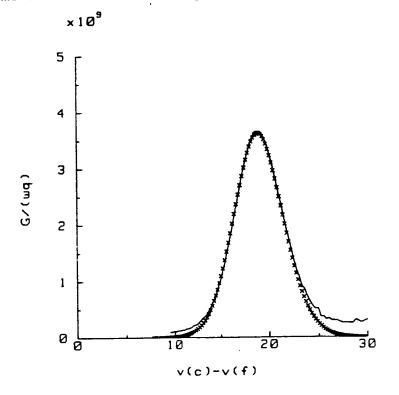

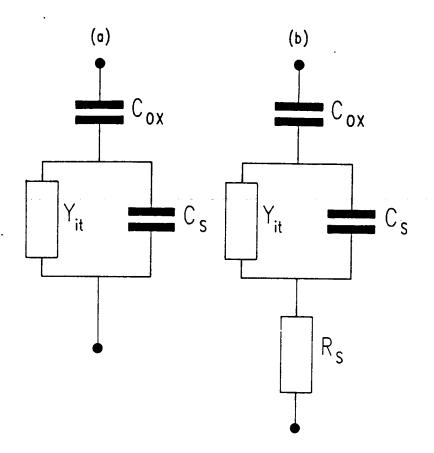

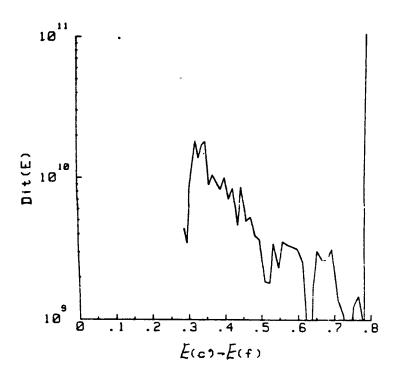

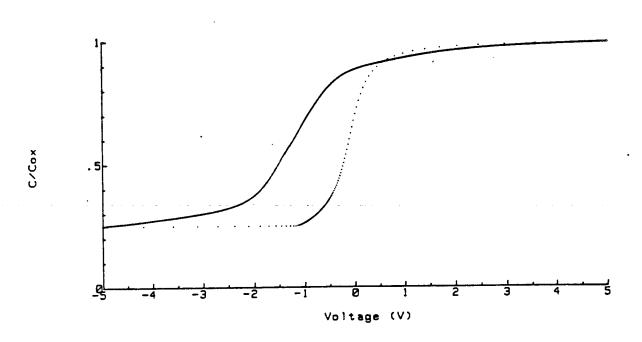

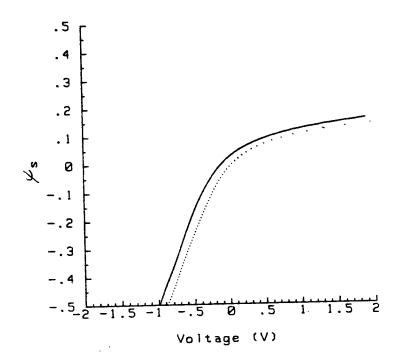

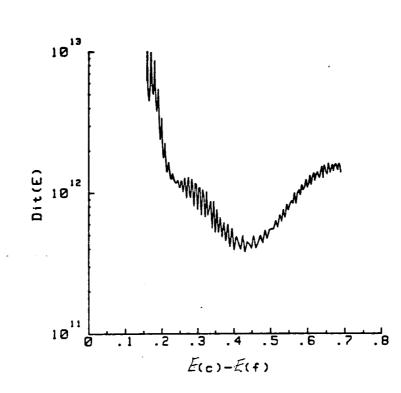

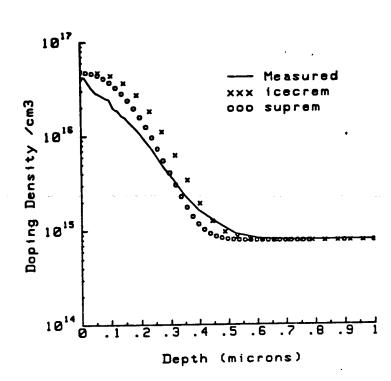

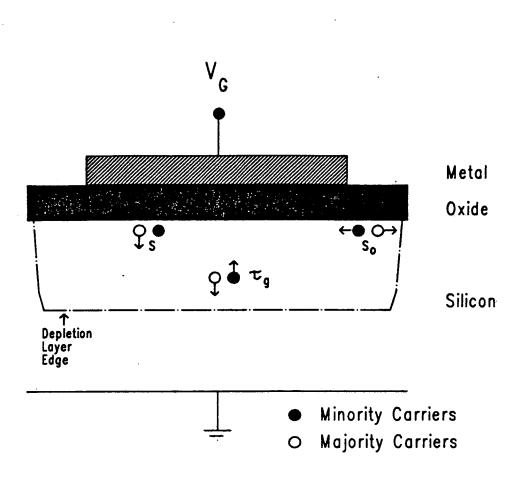

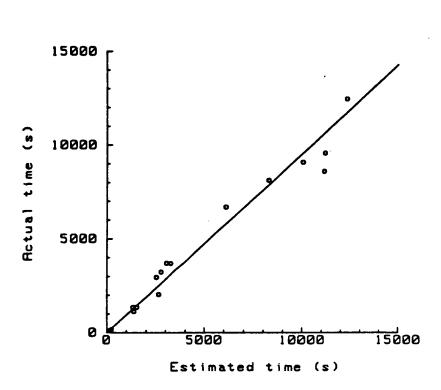

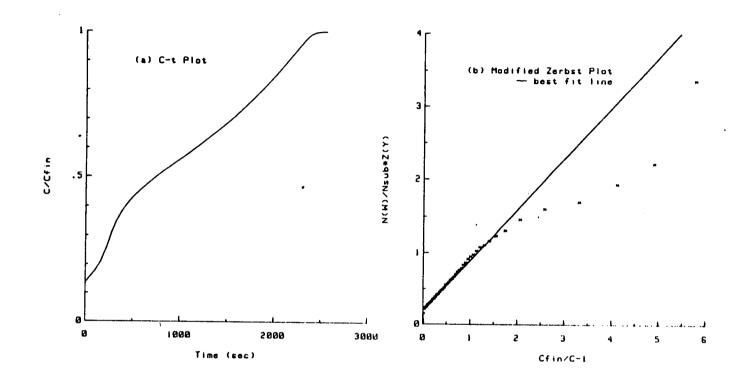

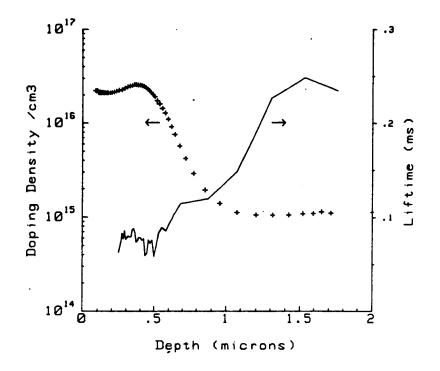

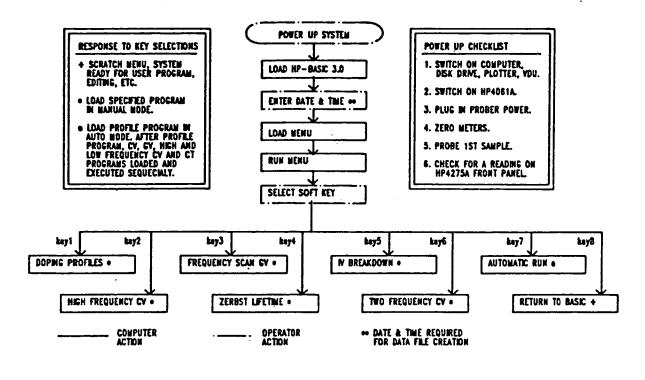

## 3.5.1.3. Ohmic Back Contact