# **VLSI DESIGN METHODOLOGY**

by

Javeed I. Mhar

A thesis submitted to the Faculty of Science,

University of Edinburgh,

for the degree of Doctor of Philosophy

Department of Electrical Engineering

1990 (resubmitted 1991)

#### VLSI DESIGN METHODOLOGY

bу

#### Javeed I. Mhar

#### **Abstract**

The development of FIRST was a significant step in the field of silicon compilation. With FIRST, bit-serial signal processing systems could be rapidly implemented in silicon by high-level designers without requiring layout expertise.

This thesis explores extensions to the compiler, but the methodology and techniques are not specific to FIRST and could be used in the more general VLSI arena. One major theme is the use of process independent layout, allowing the rapid update of a cell library to current state of the art process rules. After surveying other layout strategies, one particular layout style, gate matrix, was evaluated through the manual layout of a bit–serial, two's complement, multiplier utilising novel architectural features. The operation and architectural features of the multiplier are described, as these features were to be incorporated as options in newly generated cell libraries.

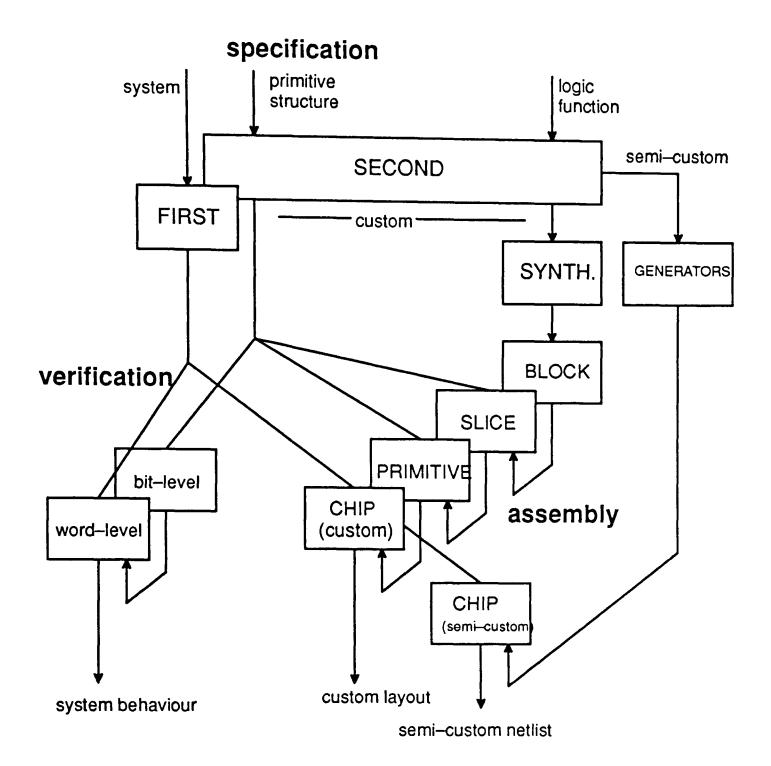

SECOND, a full span silicon compiler, taking the high—level input description of FIRST but synthesizing layout to a process independent form (gate matrix) was developed using ideas gained from the manual assembly procedure. SECOND maintains and extends the hierarchy of FIRST using different assembly strategies for differing levels of hierarchy in the synthesis procedure. The hierarchy is described and the placement, routing and assembly procedures of the new elements of the hierarchy are covered. The automation tools used to generate the gate matrix layout of the lowest hierarchy level of SECOND are covered in a separate chapter.

Using the same concepts of hierarchy, a tool ENGEN which transforms FIRST intermediate code to a gate level network description in HILO is also described as an alternative to SEC-OND in the search for process independence. The thesis ends with a suggestion of a bit-serial/bit-parallel frame for encouraging the acceptability of bit-serial systems.

## **Declaration of Originality**

The material contained within this thesis was researched and developed as part of a group in the Department of Electrical Engineering at the University of Edinburgh, between October 1985 (1 year MSc converted to PhD) and May 1989. This is in accordance with regulation 3.4.7 of the rules governing a university thesis. I have contributed ideas, discussed and developed methodology throughout the work. I have made significant original contributions in the work behind SECOND (chapter 6) and the HILO generation work (chapter 8). I have tried to indicate other members contributions through the references.

Work described in Appendix 1, was done whilst at Thorn EMI, my cooperating industrial partner under the SERC CASE award scheme. This work is original and I have received permission from Thorn EMI for its inclusion within the thesis.

The current chapter 7 was added after comments by the external examiner. It contains extra relevant material obtained after consultation with my project supervisors.

## Acknowledgements

I would first like to thank my supervisor Professor Peter Denyer for his constant support and encouragement, who continued to provide further help and encouragement, after I had left University surroundings, without which this thesis would not have been completed. Thanks are due to all members of the group who contributed to the work on SECOND, the composition of the group had altered during the work, but each has made valuable contributions to the endeavours. This includes Dr Kevin Coplan, Mike Keightley, Mike McGregor, Prof. Kunihiro Asada, and Dr Stewart Smith (who provided much energy, ideas and co-ordination to the SECOND project). I would also like to thank my second supervisor Dr David Renshaw, for encouragement and suggestions, and Dr Lawrence Turner (University of Calgary) who, during his stay at Edinburgh, provided ideas and code which contributed to the work of Chapter 8.

Javeed Iqbal Mhar

# Contents

# Chapter 1

|      | Introduction: Bit-Serial Methodology and Silicon Compilation | 2  |

|------|--------------------------------------------------------------|----|

| 1.1. | Introduction                                                 | 2  |

| 1.2. | Background                                                   | 3  |

|      | Digital Signal Processing                                    | 6  |

|      | Bit-Serial Methodology                                       | 6  |

|      | Bit-Serial Conventions                                       | 9  |

|      | Comparison with Bit-Parallel Systems                         | 10 |

|      | Multiplexing for Hardware Efficiency                         | 11 |

|      | Functional Parallelism                                       | 12 |

|      | Signal Processing in real time                               | 12 |

|      | Hardware Acceleration                                        | 14 |

|      | FIRST                                                        | 14 |

|      | Hierarchical Design                                          | 14 |

|      | Floorplan and Routing                                        | 15 |

|      | Limitations of Silicon Compilers                             | 17 |

|      | Limitations of Cell Libraries                                | 18 |

|      | Statement of Problem this Thesis Addresses                   | 19 |

|      | Circuit Techniques                                           | 19 |

|      | Chapter 2                                                    |    |

|      | Methodologies for the Layout of VLSI systems                 | 20 |

|      | Introduction                                                 | 20 |

|      | Programmable Logic Arrays                                    | 20 |

|      | The Semi-Custom Approach                                     | 22 |

|      | Gate Arrays                                                  | 22 |

|      | Standard Cell Approach                                       | 23 |

| 2.4. | Structured Layout Methodologies                              | 24 |

|      | Tiling Scheme                                                | 26 |

|      | Weinberger Arrays                                            | 28 |

|      | Gate-Matrix                                                  | 28 |

|      | Virtual grid Layout                                          | 29 |

| 2.5. | Knowledge Based Techniques                                   | 31 |

|      | Manual Layout                                                | 33 |

|      | Other Work on Silicon Compilation for Signal Processing      | 34 |

|      | Conclusion                                                   | 35 |

|      | Chapter 3                                                    |    |

|      | Circuit Techniques and Architectures                         | 36 |

| 3.1. | Introduction                                                 | 36 |

|      | Clocking Strategies                                          | 36 |

|      |                                                              |    |

| Synchronous and Asynchronous Operation                       | 37  |

|--------------------------------------------------------------|-----|

| Dynamic Circuits                                             | 37  |

| Clocking Schemes                                             | 39  |

| Pseudo Two-Phase Clocking                                    | 40  |

| Single-Phase Clocking                                        | 43  |

| 3.3. Mixed Tree Logic                                        | 47  |

| 3.4. Twin Pipe Performance Enhancement                       | 49  |

| 3.5. Multiplier Architecture                                 | 52  |

| Multiplication Algorithm                                     | 52  |

| Chapter 4                                                    |     |

| The Generation of Transistor Networks and Gate Matrix Layout | 58  |

| 4.1. Introduction                                            | 58  |

| 4.2. Introduction to the MOS Suite of Programs               | 58  |

| 4.3. Transistor Net Generation – MOSYN                       | 63  |

| Algorithm used for Transistor Net Synthesis                  | 65  |

| Producing Symbolic Layout from the Transistor Net            | 68  |

| 4.4. Producing CIF from Symbolic Layout                      | 68  |

| Chapter 5                                                    |     |

| Layout and Testing of Manually Laid Multiplier               | 71  |

| 5.1. Introduction                                            | 71  |

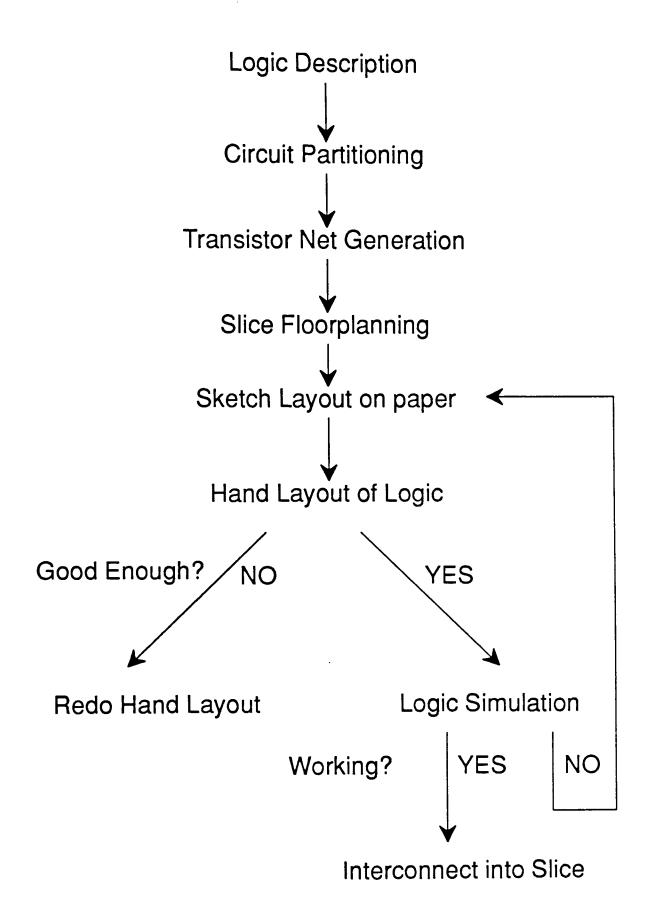

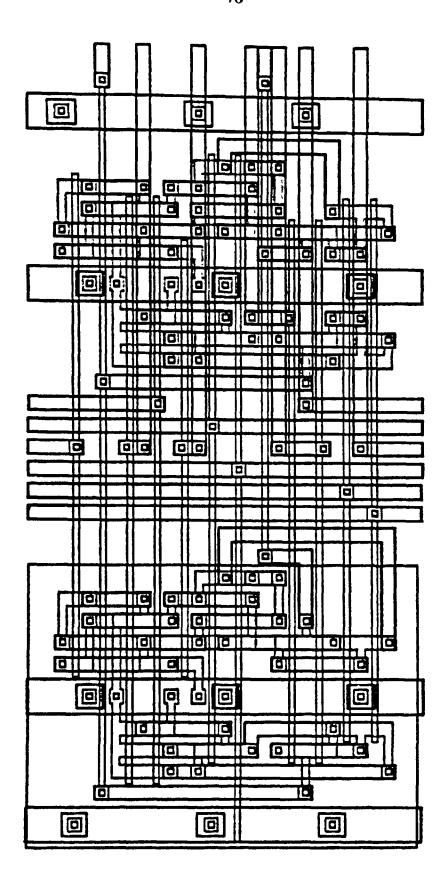

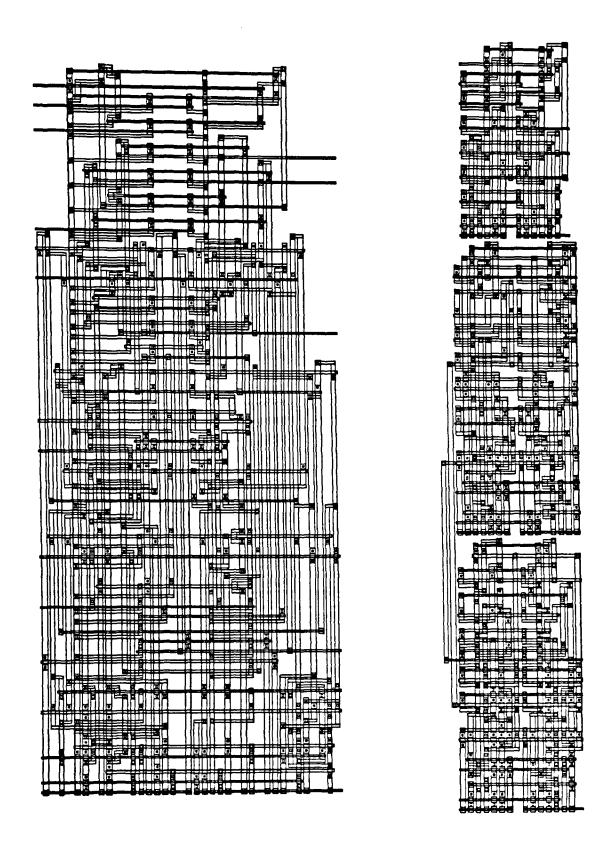

| 5.2. Manual Layout of the Multiplier                         | 71  |

| Deviations from Standard Gate-Matrix                         | 75  |

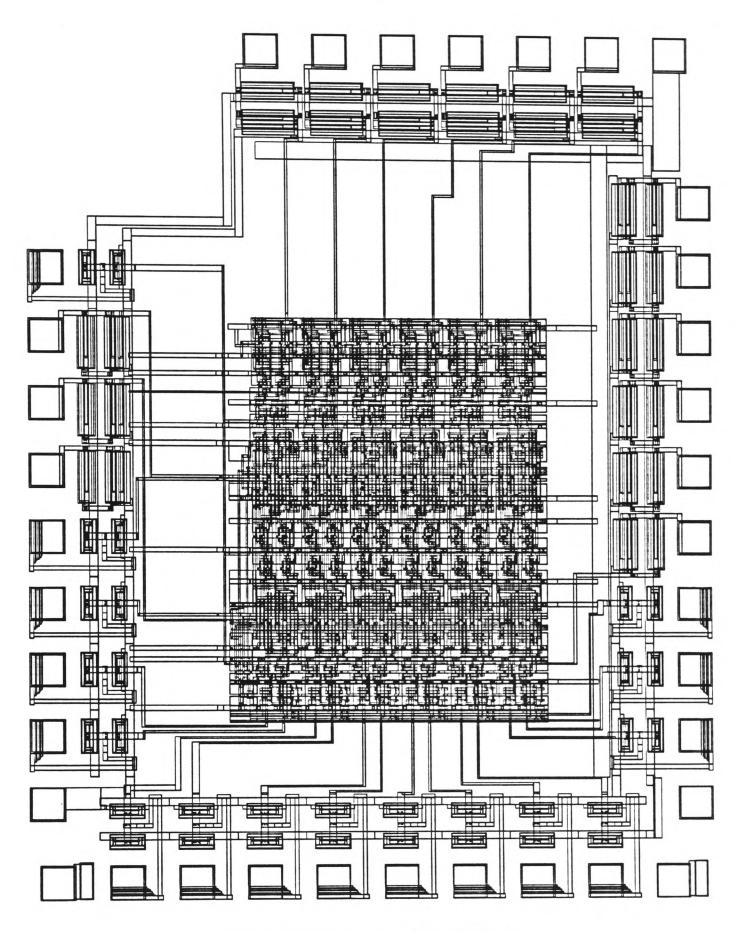

| Connection of the Blocks into a Slice                        | 76  |

| Conclusions from Manual Layout                               | 77  |

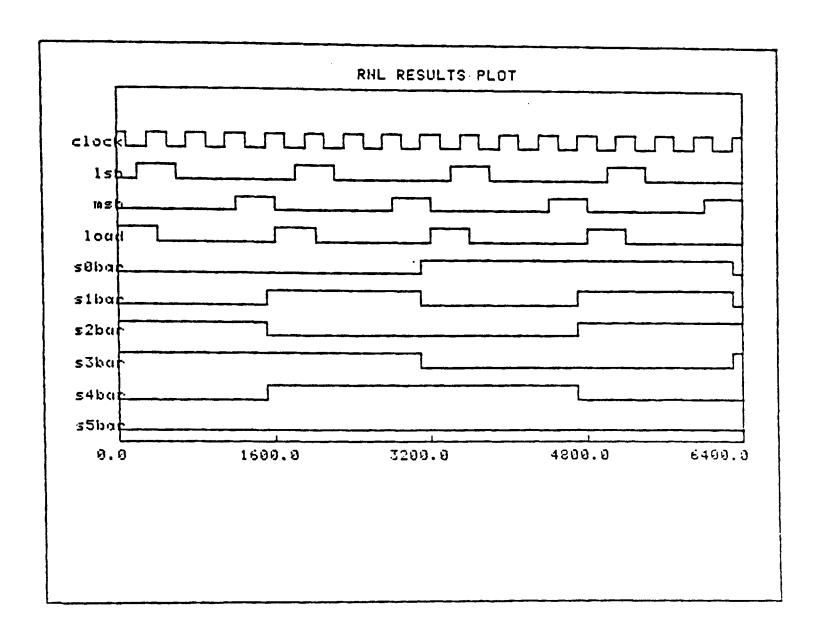

| 5.3. RNL Results                                             | 78  |

| 5.4. Errors in the Layout of the Multiplier                  | 80  |

| 5.5. Electrical Tests                                        | 81  |

| Corrected Versions of Multipliers                            | 83  |

| Chapter 6                                                    |     |

| SECOND                                                       | 88  |

| 6.1. Introduction                                            | 88  |

| 6.2. Goals                                                   | 88  |

| 6.3. Half Span Structural Compilation                        | 89  |

| 6.4. Full Span Structural Compilation: SECOND                | 91  |

| 6.5. Software Structure of SECOND                            | 93  |

| 6.6. Design Capture                                          | 95  |

| 6.7. Logic Partioning                                        | 95  |

| 6.8. SLICE Construction                                      | 96  |

| 6.9. Incorporating the Mixed-Tree Single Phase Scheme        | 100 |

| 6.10. Routing of BLOCKS                                      | 10  |

|                                                              |     |

| 6.11. Transistor Net Synthesis                               | 108<br>112 |

|--------------------------------------------------------------|------------|

| Chanton 7                                                    |            |

| Chapter 7                                                    |            |

| A Comparison of SECOND with Commercial Software              | 113        |

| 7.1. Introduction                                            | 113        |

| 7.2. Area Comparison with Commercial Software                | 113        |

| SECOND Layout Style                                          | 113        |

| SOLO Layout Style – Optimised Arrays                         | 114        |

| Area Comparison of Layout Styles                             | 115        |

| 7.3. Area efficiency in SECOND                               | 116        |

| Area Issues at Hierarchical Levels higher than the SLICE     | 119        |

| Performance Issues in SECOND and SOLO                        | 119        |

| Possible Improvements to SECOND                              | 120        |

| 7.4. Cell Layout Generation vs. Use of Vendor's Cell Library | 120        |

| Conclusion                                                   | 121        |

| Chapter 8                                                    |            |

| Gate Level Expansion                                         | 122        |

| 8.1. Introduction                                            | 122        |

| 8.2. Custom vs Semi–custom                                   | 122        |

| 8.3. Justification for the semi—custom approach              | 123        |

| 8.4. Extending FIRST for gate netlist generation             | 123        |

| 8.5. Overview of HILO                                        | 126        |

| 8.6. Input Format                                            | 127        |

| The structure of the FIRST intermediate file                 | 127        |

| 8.7. ENGEN – Expanded Netlist GENerator                      | 128        |

| Hierarchy in ENGEN                                           | 128        |

| Portability between vendors                                  | 130        |

| Netlist Generation                                           | 131        |

| 8.8. Physical special cases                                  | 134        |

| Latches                                                      | 134        |

| Buffers                                                      | 134        |

| Pads                                                         | 134        |

| 8.9. Example of generated HILO                               | 135        |

| 8.10. Performance of the Resulting Netlist                   | 136        |

| Conclusions                                                  | 137        |

| Chapter 9                                                    |            |

|                                                              | د          |

| Recommendations & Suggestions                                | 141        |

| 9.1. Structural vs. Behavioural Compilation                  | 141        |

| Mixed-Tree Dynamic Logic                                     | 142        |

| 9.2. A Bit–Serial Design Frame                               | 143        |

| Introduction                                                            | 143        |

|-------------------------------------------------------------------------|------------|

| Aims                                                                    | 144        |

| A Frame Implementation                                                  | 146        |

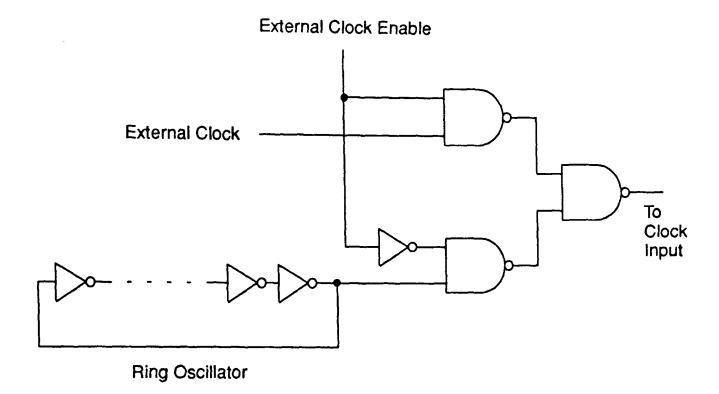

| An Internal Clock Option                                                | 149        |

| Criteria for Frame                                                      | 150        |

| Chapter 10                                                              |            |

| Conclusions                                                             | 152        |

| References                                                              |            |

| •••••                                                                   | 155        |

| Appendix 1                                                              |            |

| CASE Work                                                               | 165        |

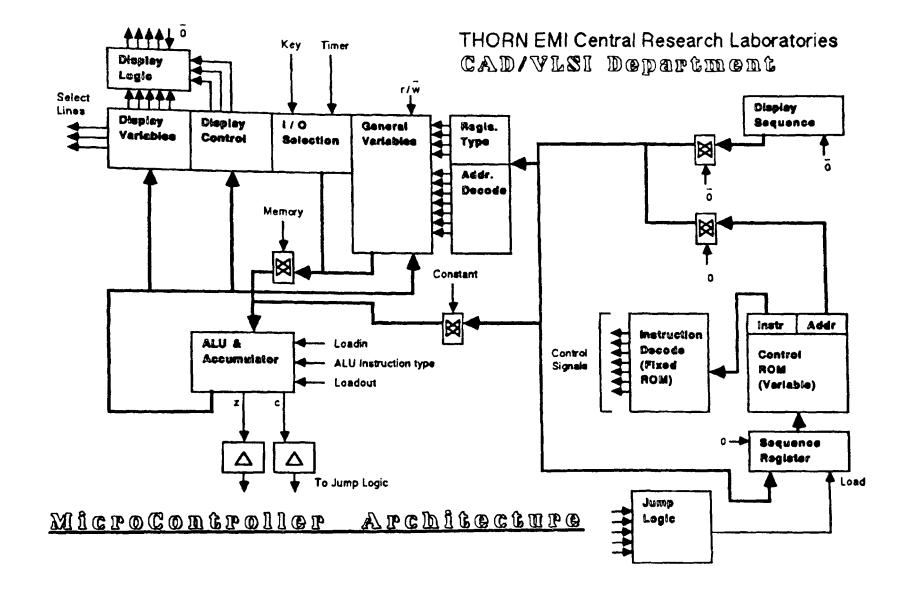

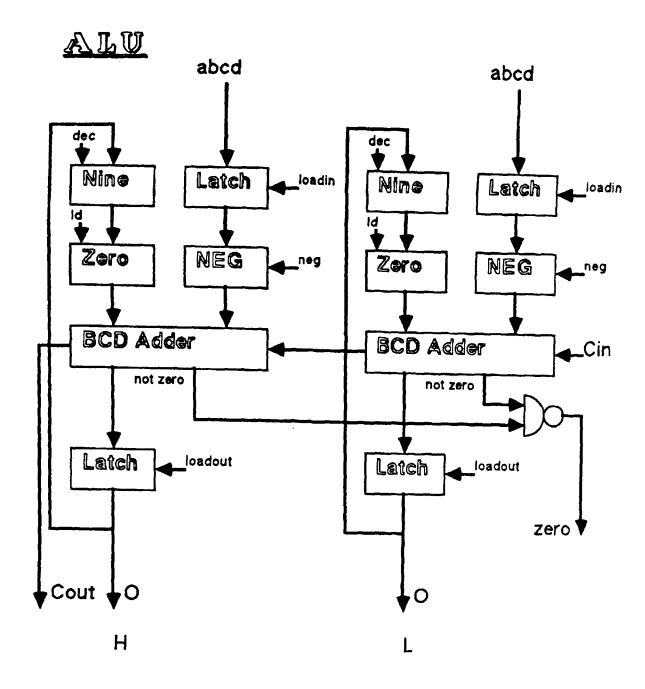

| A1.1. Function to architecture, through the design of a microcontroller | 165        |

| Introduction                                                            | 165        |

| Cell Based approach                                                     | 166        |

| Finite State Machine Approach                                           | 166        |

| Datapath Approach                                                       | 167        |

| A1.2. Requirements of Microcontroller                                   | 167<br>168 |

| A1.3. Description of the HDL Generation                                 | 171        |

| References                                                              | 171        |

| Appendix 2                                                              | 1 / 2      |

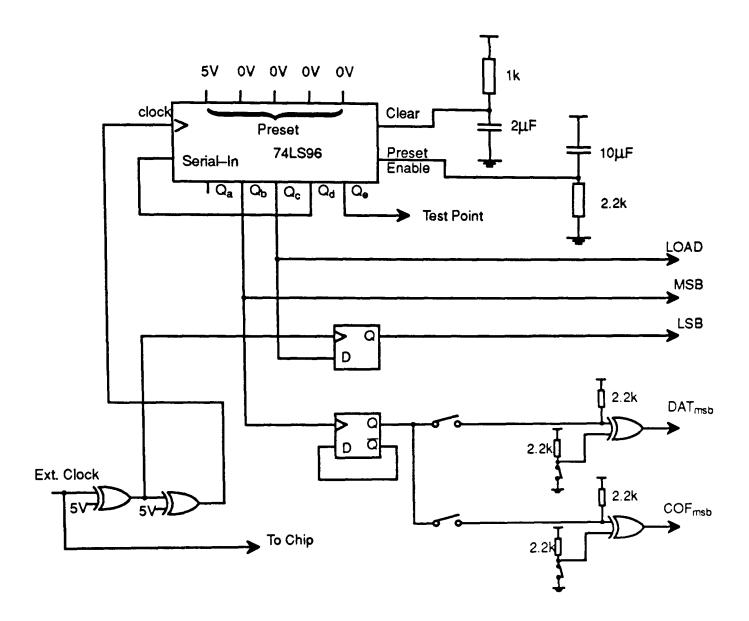

| TTL Test Circuit                                                        | 173        |

|                                                                         | 1,0        |

| Appendix 3                                                              |            |

| Routines used in ENGEN Code                                             | 176        |

| Appendix 4                                                              |            |

| Author's Publications                                                   | 182        |

### Chapter 1

Introduction: Bit-Serial Methodology and Silicon Compilation

#### 1.1. Introduction

Through the rapid advancement of fabrication technology in the field of microelectronics, designers can now produce VLSI integrated circuits of complexities which were impractical earlier. These devices have the capability to perform complex functions in real time. The designer is confronted with the task of the integration of hundreds of thousands of devices onto a single silicon component, greatly increasing the complexity of the design process and also the possibility of mistakes. To make this task more manageable, structured design styles and software tools have been developed.

A software tool which would be of great value to the designer of integrated circuits is the Silicon Compiler. The term Silicon Compiler was used in original work by Johannsen[1], [2] to describe the process of translating a language description of a silicon device to mask information. An ideal silicon compiler would be able to take a high level behavioural description of a system and produce from it the low level mask information for an integrated circuit without any further intervention of the designer, but as the field of silicon compilation is still developing such a compiler is yet to be produced.

It is currently possible to transform high level descriptions (which contain structural descriptions) to low level mask detail if we are prepared to restrict ourselves to a limited domain. Two domains where progress has been made have been with datapaths and with digital signal processing systems. Datapaths have a regular, though flexible architecture which lends itself to automation and their specification can be done through the use of register transfer languages. With digital signal processing systems, their specification can take the form of a flow graph

using small elements such as adders, multipliers and delays, and these can be used to construct the system.

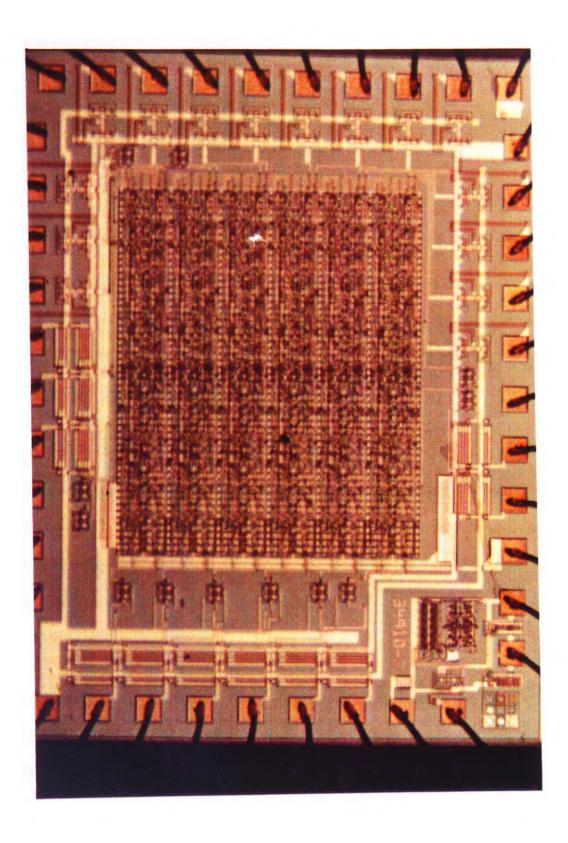

In this thesis, we shall concentrate on developments of the FIRST[3] silicon compiler. FIRST was one of the earliest silicon compilers to be produced and it is targeted at the bit–serial, signal processing domain. FIRST was developed at Edinburgh University and takes as input a structural description of the system for which integrated circuits are required. The structural description describes the interconnection of PRIMITIVEs contained in the library of FIRST. The PRIMITIVE functions have been designed to correspond to those used in digital signal processing algorithms, allowing PRIMITIVE interconnection to correspond directly with the nodes of a signal flow graph. The output from FIRST is the mask information needed for the integrated circuits, for use with a  $5\mu$  NMOS process.

This chapter gives an introduction to the topics of silicon compilation and bit—serial architecture which forms the background for the work described in this thesis.

#### 1.2. Background

The layout of digital integrated circuits can be a tedious and time consuming chore, especially considering that a designer may most productively expend effort on the algorithmic aspects of his/her design. Design Automation has thus become essential in VLSI design environments. CAD tools help manage the complexities of the design process leading to fewer design errors and to a faster turnaround. One tool the *Silicon Compiler* has attracted much attention in the recent past because of its potential to simplify and speed up considerably the most tedious aspect of silicon design, the layout of VLSI designs.

The term Silicon Compiler has been the subject of much controversy and interest, with the suggestion that the term Silicon Assembler be used in its place, as some feel this is a fairer analogy to the compilation of software. Both terms have their merits and certainly there is no dispute that software compilers are in a much more advanced stage than their hardware counterparts, the compilation of a general behavioural description to silicon mask information has yet to be achieved as many complex problems are involved.

The term Silicon Compiler will be used in the remainder of this thesis with the understanding that this is not a tool which is capable of transforming a program written in a high level language such as Pascal, Ada or Fortran into a piece of silicon artwork. What we do claim is that we are able to transform a rigidly defined subset of a language into a piece of working silicon, though it is left up to the designer to ensure that functions performed by the silicon and by his program correspond.

FIRST[3], [4] was one of the earliest silicon compilers to be developed. The aim of FIRST is to get from a formal system specification through to a good working system. The specification is written in the FIRST language, and the working systems are the interconnected chips which are produced after processing at a silicon foundry. In this way a 'naive' user of silicon circuit design methodology could use the tool to produce signal processing systems which he/she has familiarity with, without the inconvenience of having to learn VLSI circuit and layout design techniques.

FIRST is restricted to bit-serial systems, and it is this focus of architecture which makes practical the translation to silicon artwork.

Other early Silicon compilers, for example MacPitts[5] restrain themselves to other types of specific architecture, for example datapaths. Problems of algorithmic complexity are avoided as specific simplified cases of the very complicated general floorplanning and routing problems can be used. The complexity of the these problems in the general case has made the wider spanning silicon compilers impractical.

A further simplification allowing the compiler to be a practical project has been the use of the bit—serial signaling convention. Signals are communicated along single wires instead of multiwire busses in bit—parallel systems, reducing dramatically the number of wires which need to be routed in systems employing this technique. The impetus to use bit—serial systems was supplied by earlier workers constructing architectures for digital filters and more general signal processing systems.

The foundation work on using bit-serial architectures for signal processing systems was presented by Jackson *et al.*[6] in 1968. In their work they identify features which make the serial scheme attractive for use in signal processing:—

- Filters can be constructed from a small set of simple digital circuits.

- The configuration of these circuits is highly modular and well suited to LSI.

- The flexibility to realise a wide range of filter forms is provided by the circuits.

- The filter may easily be multiplexed, either to process multiple data inputs or realise different functions with the same hardware, providing efficient hardware utilisation.

The above being true for systems which can be clocked at rates much higher than the sampling rate, which is the case in audio signal processing. Using bit—serial keeps the size of the digital circuits small, or when implemented as elements on a VLSI chip allows greater numbers to be used.

Powell and Irwin[7] achieved very high performance architectures by advocating the use of Functional parallelism, that is the parallel use of an array of high density, low cost, lower performance devices to achieve a high performance function. They multiplex bit—serial components in large arrays to achieve high throughput rates, even in excess of the bit rate of the bit—serial components.

Lyon[8] proposed a design of a fully serial pipeline multiplier capable of operation on two's complement numbers. This element added another powerful and useful element to the range of bit—serial components. Lyon later proposed an architectural methodology[9] based on the bit—serial technique. This paper established a set of principles on clocking, number format, signaling, etc. which allow bit—serial systems to be constructed. It mentions the type of components required and how multiplexing can be used to achieve a range of performances.

Lyon's methodology was extended by Denyer, Renshaw and Bergmann[10] using it as the basis for FIRST. The useful bit—serial components were included into the compiler as PRIMITIVEs, including extra elements useful for processing. Lyon's principles were incorporated as a rigorous set of conventions [11] which enabled any modules generated with the tool to successfully communicate to each other. The result of strict adherence to these signaling conventions guaranteed correctly functioning circuits, *correct by construction*, aided by a certain amount of overdesign in the underlying PRIMITIVEs.

A designer using the tool need not be aware of these conventions, as they are incorporated in the design of the PRIMITIVEs so allowing him/her to concentrate on the design of complete systems. Any mistakes made by the designer can be spotted easily and corrected quickly because the specification is at a higher and more easily understood level.

### 1.3. Digital Signal Processing

Digital signal processing algorithms implement signal processing functions using digital as against analogue circuitry. Digital signal processing has become deservedly popular and has applications in nearly all branches of electronics from instrumentation to telecommunications. Digital circuits do not suffer from the problems of power supply sensitivity, drift and aging as do their analogue counterparts. Signal processing systems can have a greater range of functionality when composed of digital building blocks, as there are digital elements, to which there are no analogue component equivalents.

The theory behind synthesising digital circuits is well established. The most commonly needed signal processing component is a filter. This is a linear (usually time–invariant i.e. response only dependent on previous sample values) system with memory (i.e. the output is a linear function of some history of the input). Most commonly, the input and output are single scalar signals, though this is not required; complex— and vector—valued signals are easily accommodated in this architecture. In a digital discrete—time architecture, a filter is a computation that operates on a sequence of numbers as input, and produces another sequence of numbers as output. The usual purpose of such computations is to pass some frequencies of signals, while attenuating others. For detailed information on digital filters, Rabiner and Gold[12] is a good reference.

#### **Bit-Serial Methodology**

Bit—serial methodology has some advantages over bit—parallel, especially in size and complexity of the basic blocks. It has shown itself suitable for use in signal processing applications. This section gives an overview of bit serial methodology comparing it with bit parallel and mentioning ways the technique can be extended.

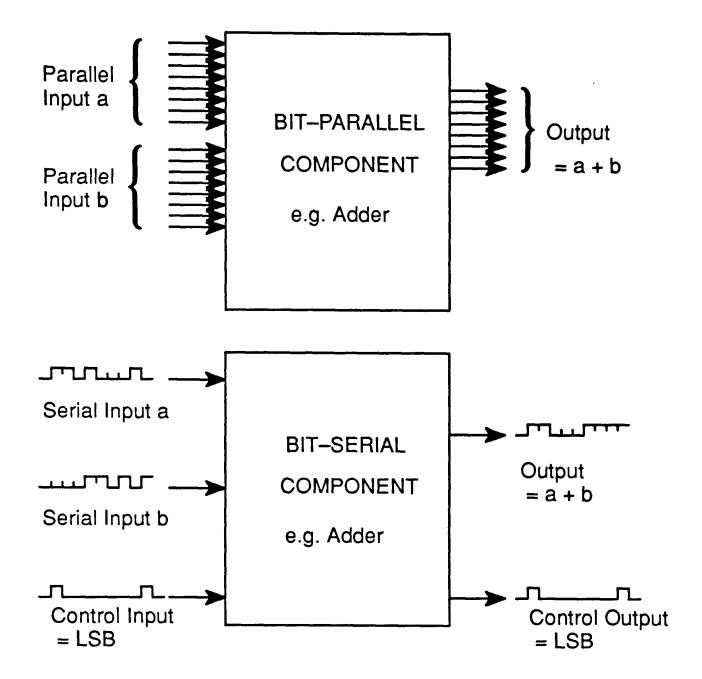

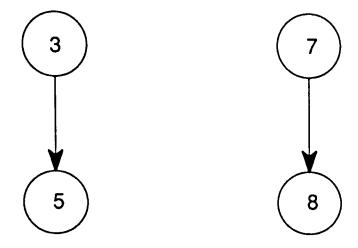

A bit—serial system distinguishes itself from its bit—parallel counterpart by communicating and processing data in a serial—fashion, a single bit from a data—word is processed at a time, rather than processing all the bits of the whole data word as in a parallel system. Communication can take place through a single wire, Figure 1.1, rather than through a parallel bus of width equal to the system wordsize.

The Bit-Serial Component

Figure 1.1

The routing of signals is a complex task and the routing of large numbers of wires can result in very inefficient routing or to a completely unroutable chip. Therefore the use of a single wire to communicate data which results in less signal routing is an important and advantageous feature in the layout generation process.

Complex systems can be produced with serial components as they are small in size allowing a large number of them to be integrated onto a single chip.

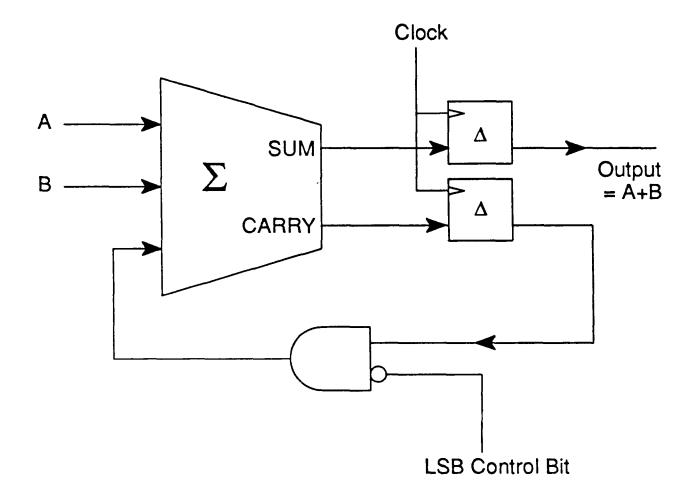

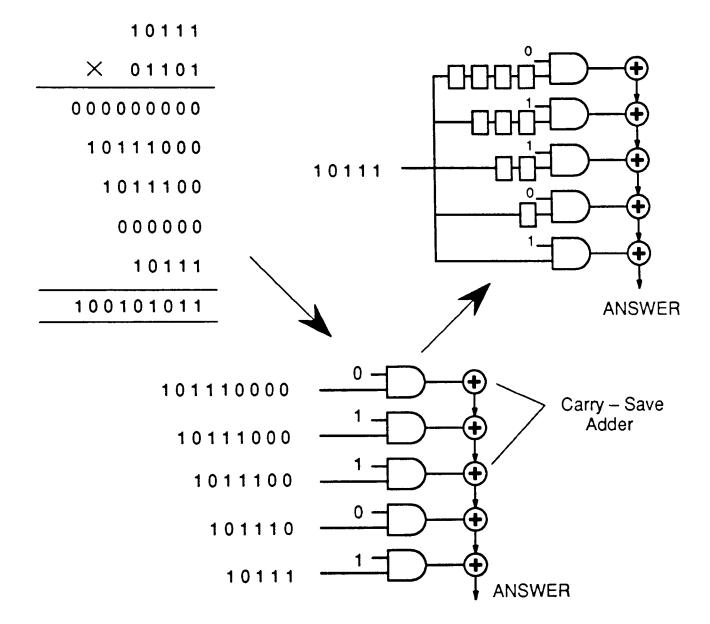

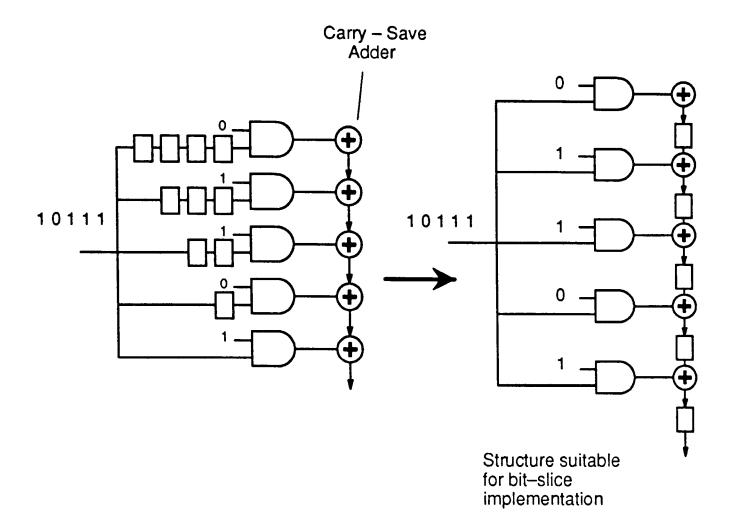

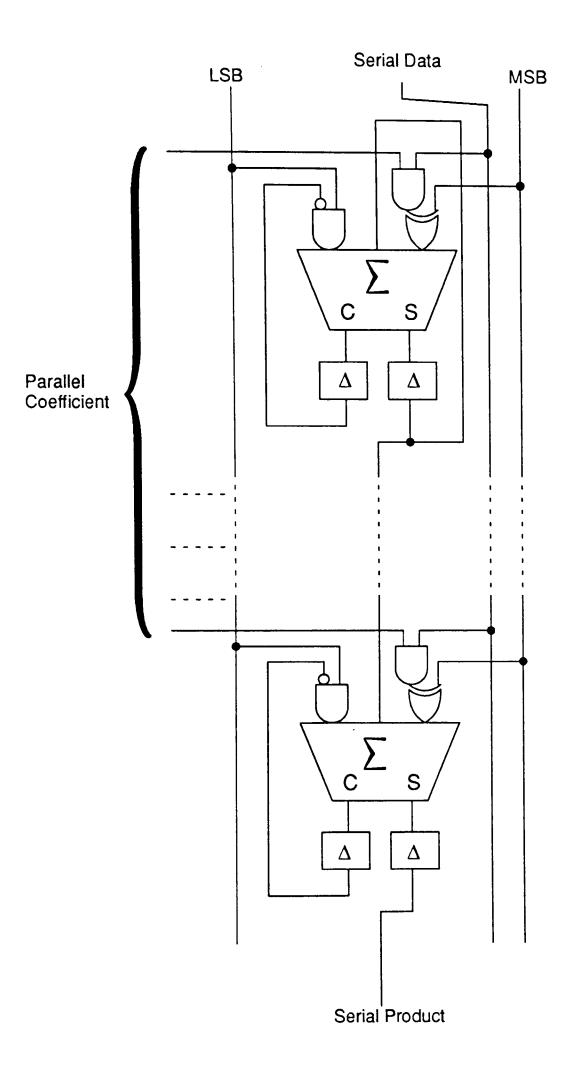

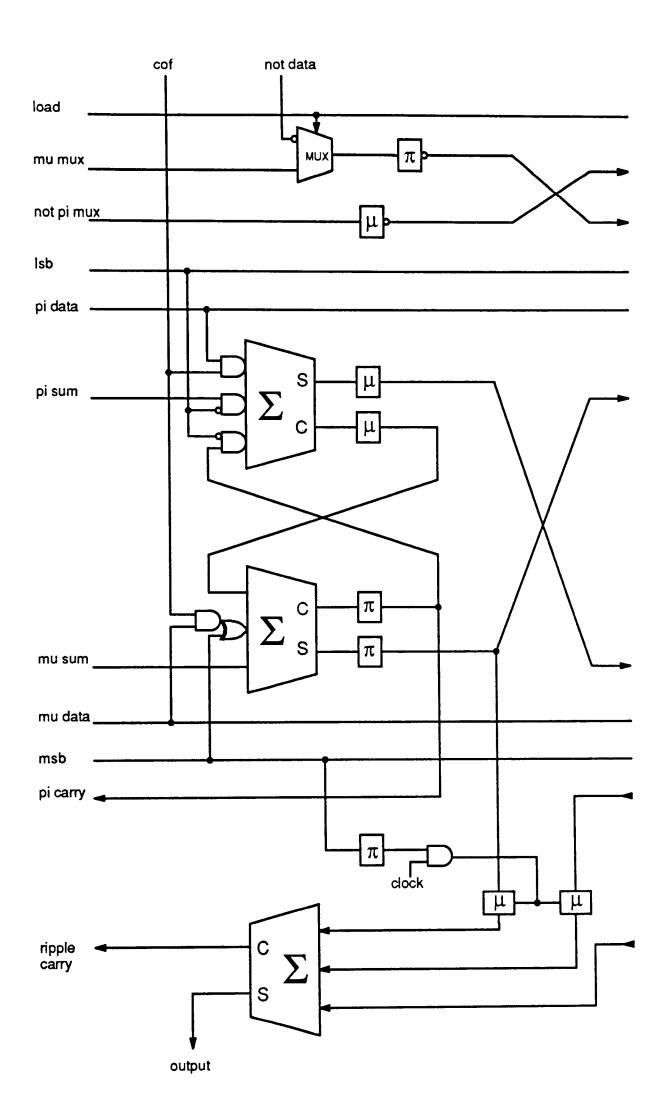

A bit—serial adder is shown in Figure 1.2, it is one of the simplest serial components, which has a size which is independent of the wordlength. More complicated components such as the two's complement multiplier have a regular structure whose size is linear in the wordlength. The structure of this component and similar components has a form amenable to bit—slice implementation. A description of the operation of such a multiplier will be given in chapter 3.

A Bit-Serial Full Adder

Figure 1.2

The order of the bits affects the complexity and size of the components which operates on the bit-serial data stream. In FIRST, the signal convention used is to start with the least significant bit. This is very well suited to adder and multiplier elements but not very well adapted to more advanced signal processing elements such as two input dividers and square-rooters. As very many signal processing systems use only multipliers, adders, subtractors and delay elements

ements, the range of systems which can be implemented with FIRST covers most of the useful signal processing functions.

In summary the main aspects of the bit-serial approach are:-

- Small functional elements

- Regularity of structure; bit-slices are common

- Low communications overhead leading to less routing

#### **Bit-Serial Conventions**

In FIRST[11] a set of conventions is used for bit-serial signaling which allow working systems to be constructed from elements with consistent protocols and interfaces. These conventions are important in hiding the low level problems of signal timing, communication and compatibility. The set of conventions built up from those proposed by Lyon[9] used in FIRST ensure that arbitrary networks constructed from PRIMITIVES perform in a sensible and valid way. By fixing these conventions for each element in the FIRST library, we hide from the user these details and so the user can be assured of successful operation. These conventions are :—

- Communication is bit-serial.

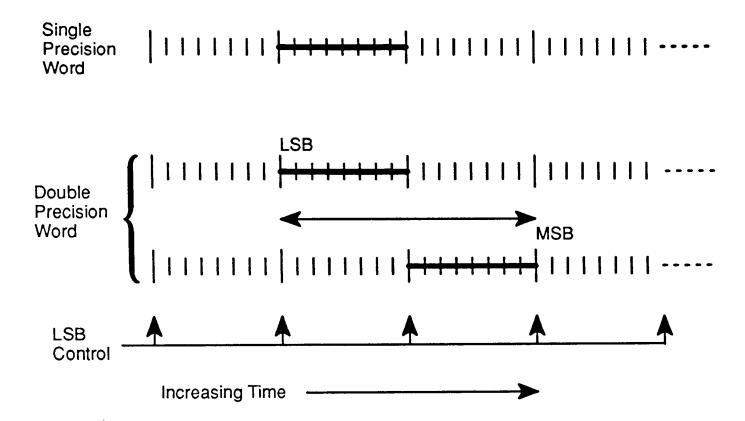

- Bit-serial data bits are in order with the least significant bit first.

- Logical 1 is a high signal & logical 0 is a low signal.

- A valid clocking strategy is used throughout the system, in FIRST this is the two phase non-overlapping clocking strategy as proposed by Mead and Conway[13].

- Numerical format is fixed point, two's complement.

- Data wordlength is fixed and constant in each system.

- Multiple precision signals are produced as in Figure 1.3

- Operators have fixed latency.

- Inputs to Operators are time aligned.

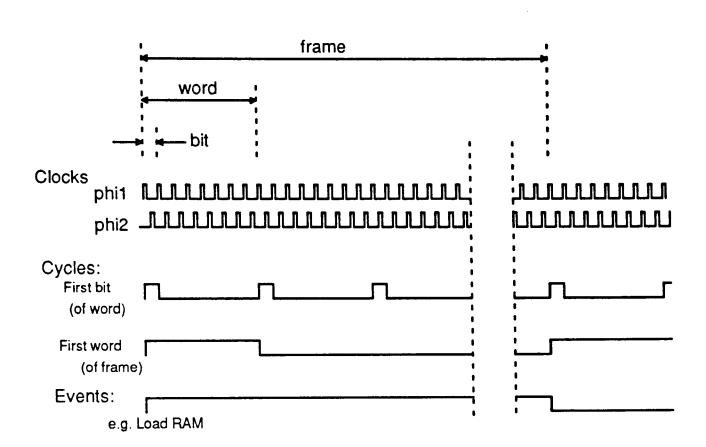

- Control cycles have a format as shown in Figure 1.4

- Each system has one CONTROLGENERATOR to generate the control cycles.

Formatting of multiple-precision words

Figure 1.3

### Comparison with Bit-Parallel Systems

As bit—serial components operate on incoming data a single bit at a time rather than on the whole data word, they tend to be smaller than their bit—parallel counterparts. As bit parallel parts need to replicate logic in order to operate on each bit of the data word, the ratio of the area taken by the bit—parallel part to that taken by the bit—serial part is roughly equal to the wordlength. On the other hand the data rate of the bit—serial system will be slower by a factor equal to the wordlength.

The usual method of implementing a bit-parallel system is through the use of a datapath.

This method has the advantage of being very flexible, but throughput is limited as computa-

tional resources are limited. With an ALU (arithmetic logic unit) all arithmetic operations must take place within this element. The processing algorithm must queue data and wait for the resource to become available.

Format of control cycles in bit-serial machines

Figure 1.4

The bit-serial approach is to use a flow graph model of the computation and elements are provided for each of the computational nodes in the flow graph. This gives the bit-serial system a greater computational throughput as all nodes in the flow graph are exercised, leading to high speed efficient systems. This also limits bit-serial architectures to data independent computations.

# Multiplexing for Hardware Efficiency

With an iterative algorithm, we can multiplex the bit-serial processor to reduce the amount of hardware needed, when the sampling rate is less than the throughput rate. This leads to a more efficient usage of the available processing power.

The multiplexing of the serial processor can be done to various degrees, from an array type architecture with no multiplexing to a von Neumann type architecture with the maximum possible amount of multiplexing, so only requiring a single processor. The degree of multiplexing used needs consideration of both the gain in available silicon area leading to smaller systems and the reduction of bandwidth as processing speeds are reduced through multiplexing.

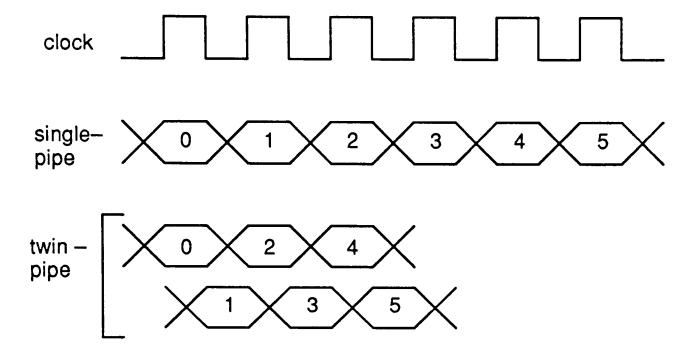

#### **Functional Parallelism**

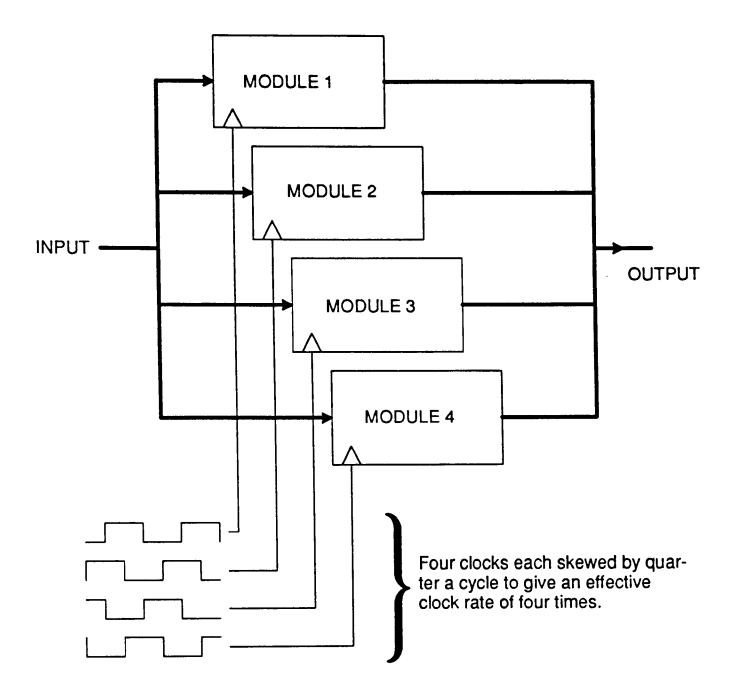

The opposite of multiplexing is to parallel up processors so that greater speeds can be obtained. Here by parallelling up a system and sampling at times which are skewed, we can map regular algorithms into hardware which has a sampling rate greater than word rate of each of the processors in the system. Figure 1.5 shows how the scheme is implemented for algorithms which such a structure.

The scheme has been used by Powell and Irwin[7] to implement the Fast Fourier Transform algorithm using small low cost bit—serial processors. Their hardware attained very high performances with a sampling rate which was faster than the bit rate of each processor.

### Signal Processing in real time

There is a demand for systems capable of processing signals in real—time, this is already possible in the audio frequency range, but in the video, systems for advanced processing are not available. One way of achieving the high processing rates essential for video signal processing is through functional parallelism of small interconnected systems. This is an application where bit—serial systems show an advantage. Their small size combined with their high throughput makes them ideally suited for parallelism and consequently high speed processing.

Functional Parallelism in bit serial systems

Figure 1.5

As the architectural methodology of bit—serial is geared to fixed function, high speed custom processors, there is an application in processing signals in real time, especially in the audio range. Higher speeds are achievable giving a greater range of application than general commodity signal processing components such as the TMS320.

Interconnection of bit—serial processors is straightforward, leading to high—speed, easy to design systems. The only complicating factors are control signals which require some attention on the part of the designer.

#### **Hardware Acceleration**

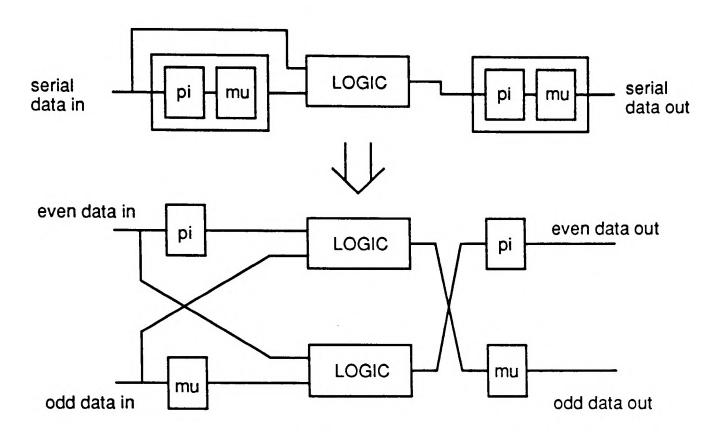

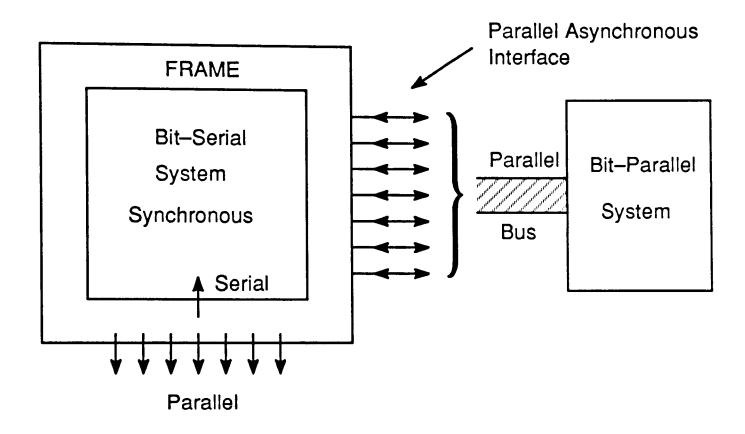

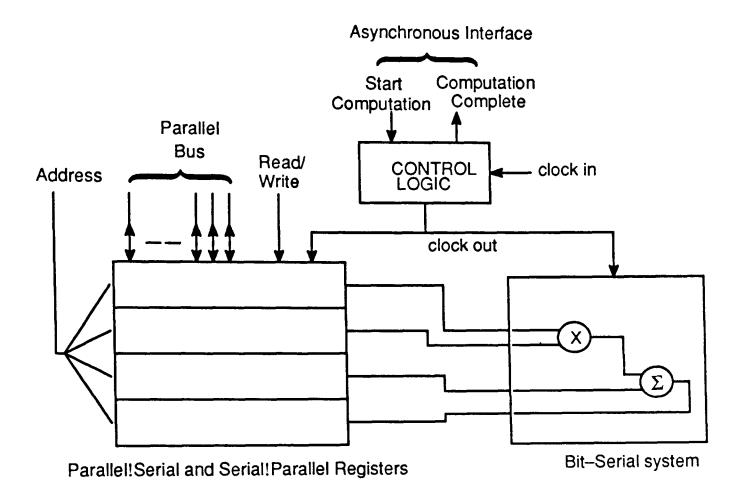

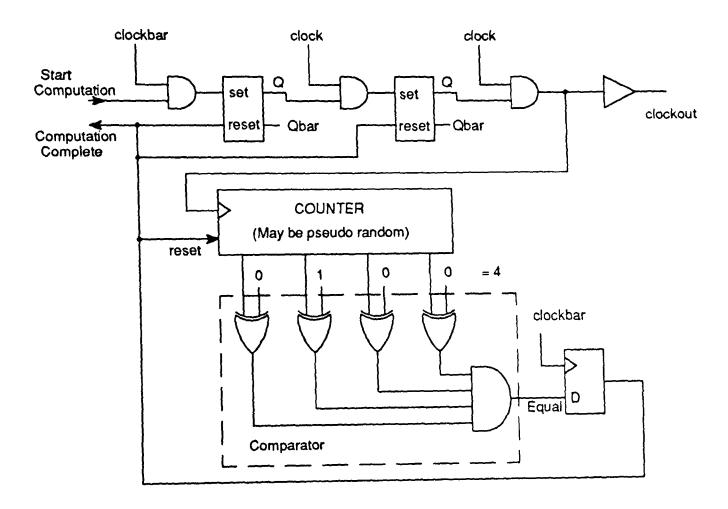

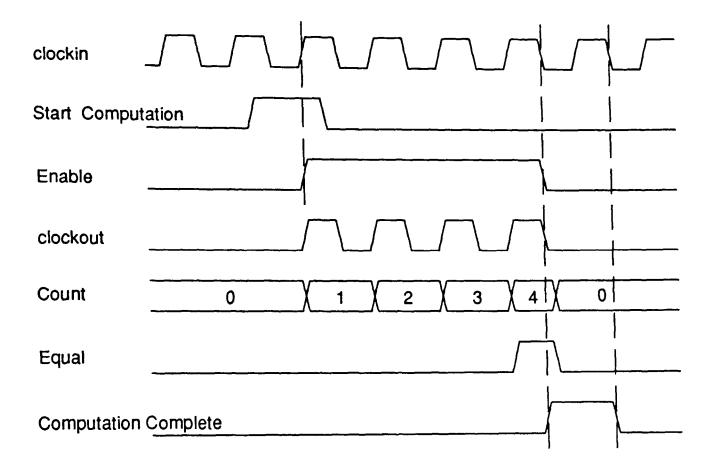

Another application of bit-serial processors is in hardware acceleration. These small asynchronous processors, specific to a particular function could be attached to existing bit-parallel systems and thus retain versatility and familiarity. They can be attached through a bit-serial to bit-parallel interface which can be incorporated into the silicon-compilation schema through the use of a design-frame, described in a later chapter.

A design frame is a consistent piece of hardware which incorporates standard timing and signal conventions, by including the serial—parallel interfaces into this boundary between systems, serial units and parallel units can cooperate without signal contention. This makes the whole exercise of designing a hardware accelerator straightforward and with less likelihood of a mistake.

#### **1.4. FIRST**

This section describes some more details of FIRST, which are built upon later in the thesis in trying to extend the compiler. FIRST lends itself to automation as the scheme is based on a small library of elements built up to make systems hierarchically.

#### Hierarchical Design

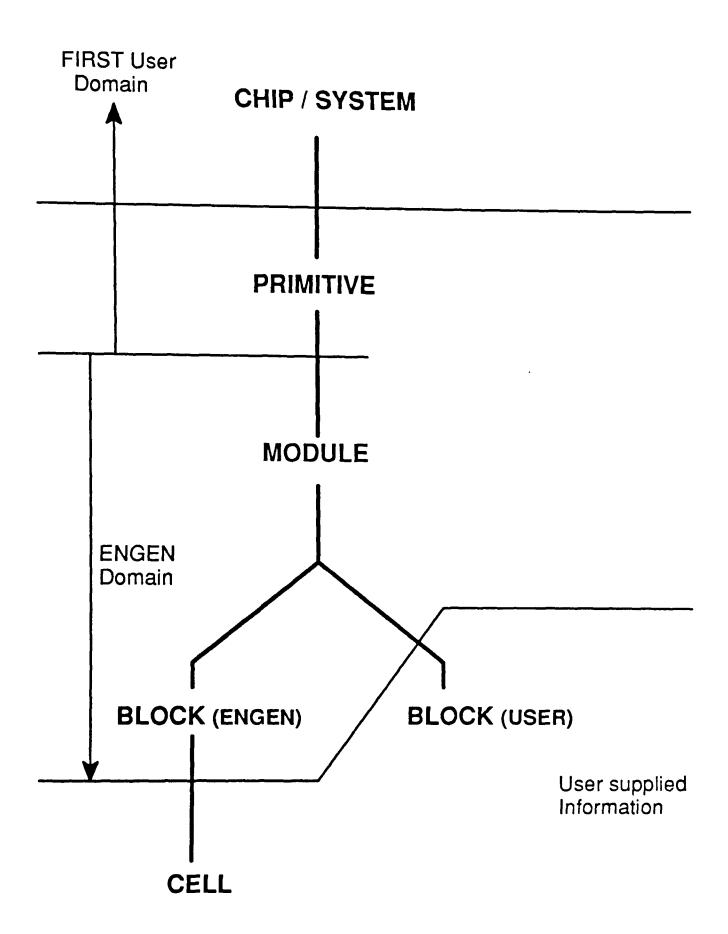

Hierarchical design is the method by which larger system components can be built from smaller system components. It is a very powerful design strategy which simplifies the design of complex systems.

The bit—serial methodology lends itself to a hierarchical design methodology as all operators have similar data and control communication conventions. This means operators built from lower level elements will adhere to the same signaling conventions as those lower level operators.

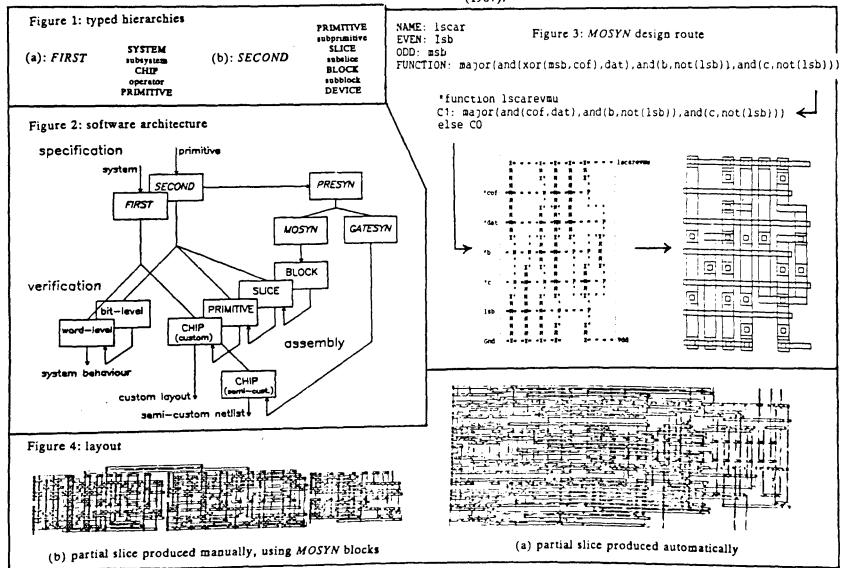

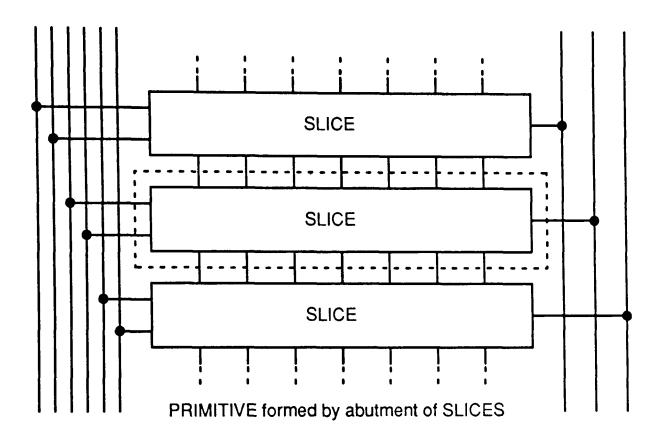

In FIRST, three typed hierarchical levels exist which mark physical boundarys of the level. These are the SYSTEM level, this is a complete system being developed, it is used for

simulation purposes, the CHIP level, this is where partitioning of the system into single chips takes place, it is at this level that floorplanning and routing are needed, and the PRIMITIVE level, this consists of the basic operators of the system, specific layout methods for each primitive are used.

#### Floorplan and Routing

A constrained floorplan is used within FIRST for the layout of primitives in chips. The primitives are pieces of full custom layout, or else are composed of full custom leaf cells through individual software assembly procedures. The leaf cells are dense pieces of layout and connect by abutment to form the PRIMITIVE.

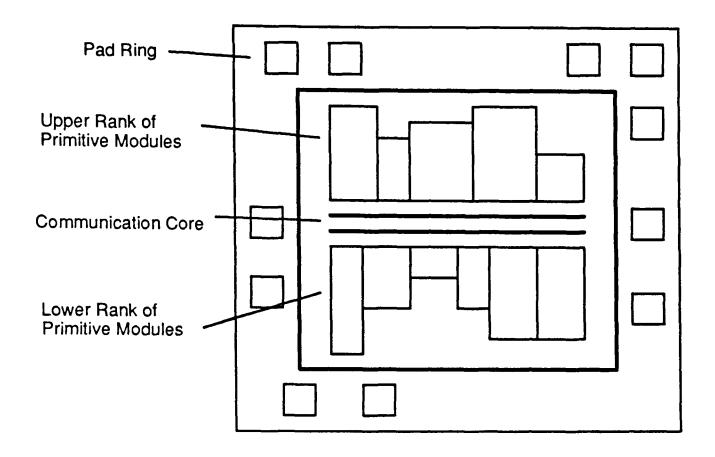

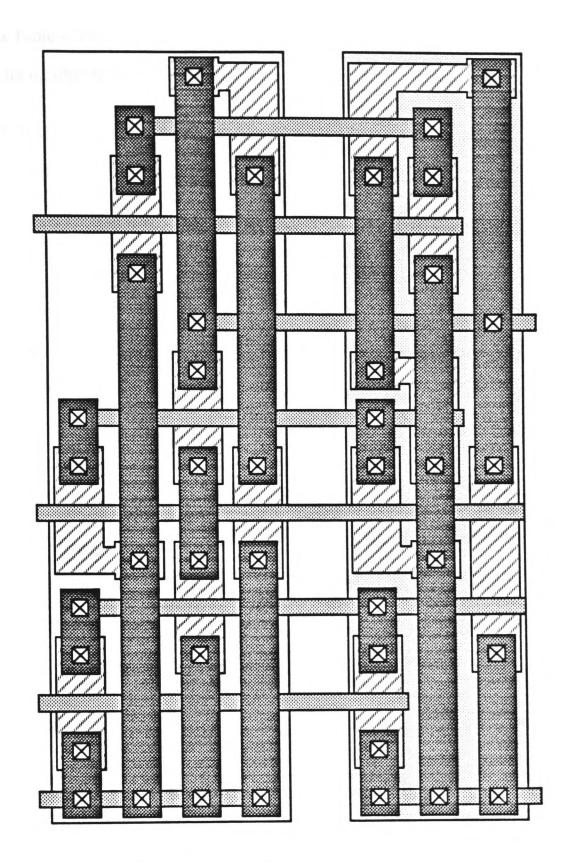

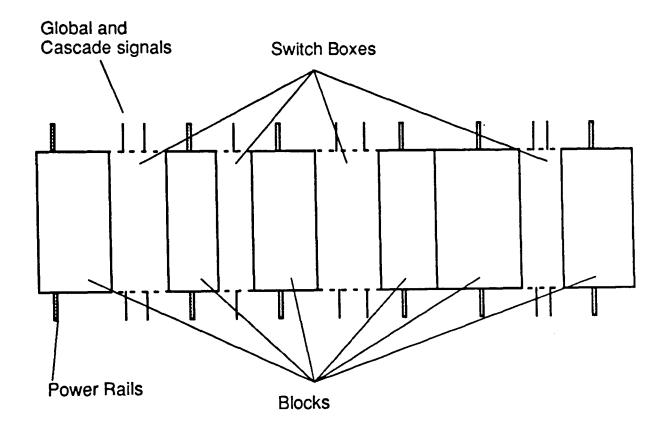

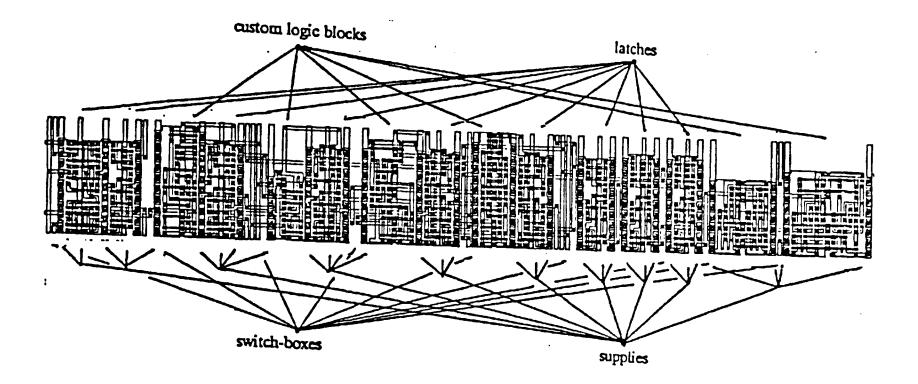

The assembled PRIMITIVEs form rectangular sections of layout, with communication signals on one side of the rectangle, preferably a shorter side, as this is placed next to the communication channel, which determines the length of this resource. An example of the floorplan schema is shown in Figure 1.6, which has been called 'Manhattan Skyline' because of the similarity it bears to a cluster of skyscrapers and their reflections in the water. It comprises a central communications channel, which has two rows of bit—serial primitive modules on either side.

Typical Floorplan in FIRST

Figure 1.6

As the communication between PRIMITIVEs is bit serial, only single wires are required for data communication between the PRIMITIVEs. This leads to a small area communication channel. The two clock phases, power and ground are distributed along either side of the communication channel and around the perimeter of the chip. The buffers to the PRIMITIVEs are allowed to spread beneath these lines in the communication channel.

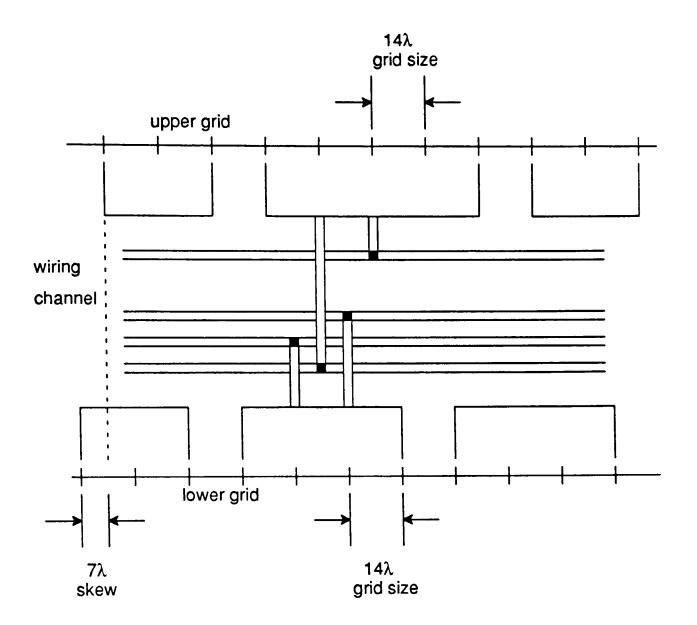

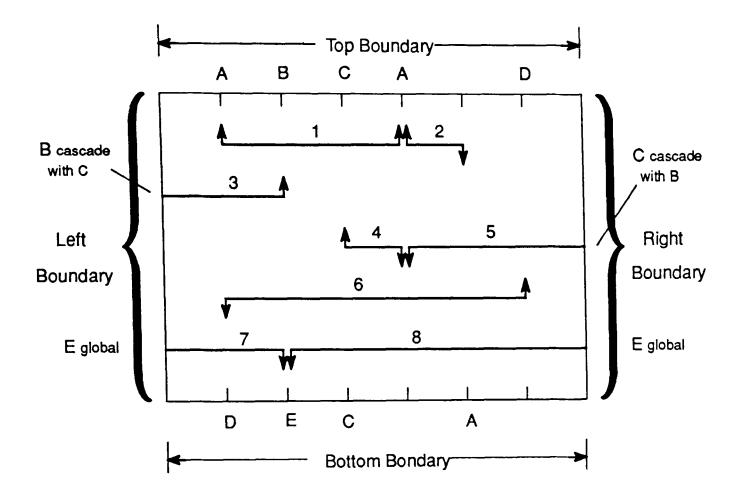

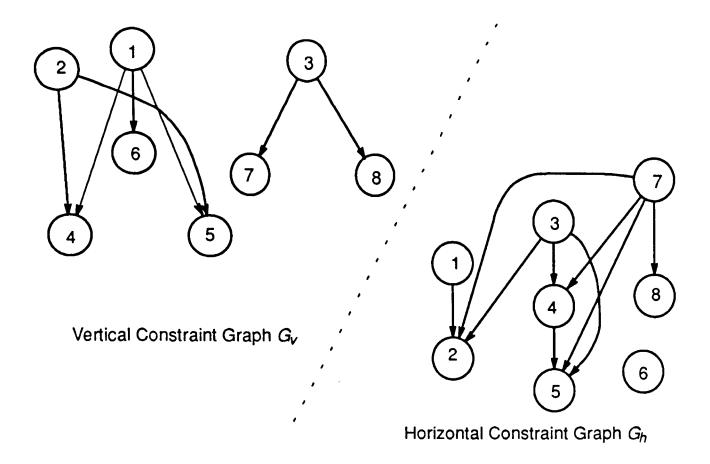

For channel routing, the allowable positions of input and output ports are quantised to be at even multiples of the wire pitch of the vertical wiring layer. In FIRST a standard wire width of 4 lambda is assumed, where lambda is a relative unit of linear dimension, and a wire separation of 3 lambda, giving a total pitch of 7 lambda. Thus input and output ports can be placed at positions separated by twice this value, 14 lambda. The routing scheme is illustrated in Figure 1.7, the 7 lambda skew, between the two sides allows an arbitrary connection of signals to the wiring channel.

Routing in FIRST

Figure 1.7

## 1.5. Limitations of Silicon Compilers

The main problems with a silicon compiler are its limitations. These tend to be of the form:—

- 1. Limited Application restricted only to finite state machines, datapaths, etc.

- 2. Limited Process restricted only to a single process.

- 3. Limited Technology restricted to a single technology, e.g. NMOS.

- 4. Too General the compiler is too general and gives very little advantage over hand layout combined with a structured layout methodology.

# 5. Limited efficiency and performance of generated circuits.

These problems have tended to restrict the use of silicon compilers, where silicon area is an expensive resource, meaning that time spent optimising layout can pay off, especially for integrated circuits produced in mass quantities. A designer may well choose to use a full custom approach to his design, where the compiler is too inefficient or does not exist, for the layout of the work. Many tools such as routers, compacters and floorplanners of full custom modules are useful for this type of work and can be incorporated in manual layout design packages.

On the other hand, many integrated circuits are now application specific, meant to replace boards of discrete components, and may only be produced in hundreds. Here the time for design may well be the overwhelming cost consideration. Silicon compilers offer a rapid turn over allowing impressive design times. The area usage of layout produced by automatic compilation is approaching that of full custom; but, even when minimum silicon area is of prime importance, automatically compiled layout may be favoured, because of the smaller likelihood of a design error.

#### **Limitations of Cell Libraries**

FIRST possesses all the features of a usable design tool, but it has a severe limitation which prevents its wider adoption, that is the total reliance on an underlying cell library. The process library used in the FIRST compiler was a 5 micron NMOS process, which has by now become outdated. Although it is possible to complete a new cell library for new processes, this is a major undertaking involving too high a use of resources in a University environment. The amount of work involved in maintaining such a library is easily seen by examining such a library, for instance that by Newkirk and Mathews[14] which is for a particular NMOS process. Some of the practical aspects for a CMOS cell library are covered in [15].

Each time layout for an updated set of process rules is required, the whole cell library artwork must be redesigned. Each library element is a piece of full—custom layout, on which much time can be spent on optimising to achieve efficient results.

### Statement of Problem this Thesis Addresses

A major limitation of FIRST is the process bound cell library, preventing its use with new processes without the layout of a new cell library. This is the problem which this thesis tackles. It looks into the automatic generation of the cell library using symbolic layout techniques.

Process portability would be achieved since the cell library could be rapidly updated to reflect advances in newer higher density process rules when and as provided by silicon fabricators. Furthermore, flexibility could be added to the compiler, since new primitives could be added to the compiler on demand without the tedium of becoming involved with full-custom layout.

The problem of process portability of the cell library of the FIRST silicon compiler has been identified. New PRIMITIVEs require the layout of new full custom leaf cells deterring users from including their own specific components. This thesis looks at one way in which process portability and flexibility can be added to a compiler such as FIRST through the automatic generation of process portable layout.

#### Circuit Techniques

Circuit techniques which enhance the throughput of bit—serial systems were developed during the layout automation project described in this thesis. We sought to include these techniques in any further library to FIRST to enhance performance of the systems produced.

In most cases these techniques do not affect our layout strategy as they can be incorporated into the boolean description of the constituent logic blocks. However, layout automation proceeded with the inclusion of these techniques in mind and have affected the layout software, so they are described in a later chapter.

The architecture of the multiplier which includes these techniques and was used as a layout evaluation vehicle is also described.

#### Chapter 2

## Methodologies for the Layout of VLSI systems

#### 2.1. Introduction

The first chapter covers the background and applicability of the silicon compiler FIRST. The major problem of this compiler through limitation to a single set of process rules was identified. A means of achieving greater process portability is needed and this chapter surveys some layout methodologies which could form a suitable base for the automatic generation of the cell library in FIRST.

A structured layout methodology is a means by which a system description can be translated to silicon mask information in a rapid manner following a regular design procedure. Characteristics of a good methodology are regularity of structure, portability between different processes or technologies and a consistent algorithm lending itself to automation.

The description of a digital microelectronic system can take many forms, as a truth table or boolean logical expression (low level), as a flow diagram or flow chart or as a high level software description (structural or behavioural). Translating this to layout is an arduous task which takes valuable time and effort to perform. In the competitive world of electronics, there is great pressure in producing working circuits from a designer's description of a system in as short a time as possible and to use the latest processing technologies to gain the benefit of higher performances and greater integration densities. A layout methodology offers savings in time and effort in the layout task and also offers a degree of process independence. Particularly useful is the ability to automate the process, alleviating completely the need for manual layout.

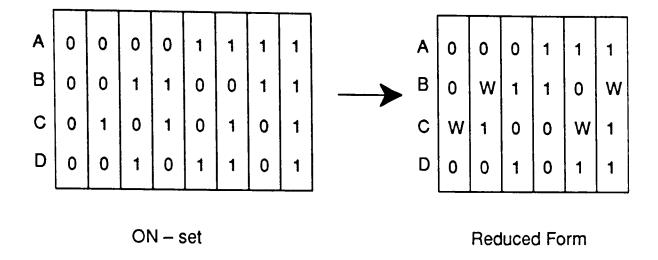

## 2.2. Programmable Logic Arrays

If the digital circuit to be designed can be specified as a small finite state machine, then programmable logic arrays (PLA's) provide a rapid means for a designer to implement such a

system and obtain a working circuit. Much effort has gone into the problems of logic minimisation, [16], [17], [18] and to PLA folding techniques to achieve smaller structures. The layout of a PLA is an easily automatable process and is well understood. The PLA minimisation problem is NP hard, meaning that no algorithm exists which produces an optimal solution in a time proportional to a polynomial function of the size of the PLA. PLA synthesisers thus use heuristic algorithms which give solutions in a practical time using heuristic algorithms, which will settle with a good solution rather than producing the optimal solution.

There are many structures for PLA's to improve performance and increase logic density. With CMOS technologies, where the direct static approach is inefficient on counts of area and performance, various dynamic implementations exist[19].

The PLA structure is highly regular whatever implementation is adopted. PLA's can be built up from a small number of easily changed elements which can be built up to form a complete PLA. Thus a PLA implementation has advantages in designing a maintainable and easily automatable system:—

- Changing to a different process is easily accomplished by changing a base library of the basic elemental blocks.

- -PLA structures can be generated automatically from a logical boolean description.

Despite these advantages, PLA's suffer from a major drawback which prevents their use for a system of any complexity. A PLA will tend to be large and uncompetitive with other forms of layout. A circuit is implemented as two levels of gates which although sufficient to formulate all boolean expressions may not be the most, or even an, efficient method of implementation.

The PLA is still an important component when incorporated into larger silicon systems such as the control sections of a microprocessor, but it would be naive to implement all digital systems as PLA's. In particular in the case of bit—serial components, a PLA implementation is inefficient. A single PLA would be too large and an implementation in terms of multiple PLA is still not as compact as other layout methods and introduces the problem of partioning.

## 2.3. The Semi-Custom Approach

The semi-custom approach[20] allows the designer of a system a greatly simplified route to the layout of an integrated circuit. Gates or cells are pre-formed conceptually, if not physically, and the job of the user is then to specify the interconnection between elements. Software or the vendor of the gate array library will then route these interconnections between gate array elements.

Commercial vendors of silicon processing capability offer traditionally two methods of implementing a semi-custom silicon system, the gate-array and the standard cell library. The vendors usually offer the latest in processing technology, as the uncustomised silicon slices of a gate-array are likely to be one of the first mass produced articles using a new process.

#### **Gate Arrays**

Here the basic uncommitted components are preprocessed onto the silicon slice before customisation takes place, where only a few masks (typically 2–4) are used. The designer has access to the latest technology as the vendor can produce the uncustomised silicon slices with pre–processed gates in large numbers and can easily update these low level components to take advantage of the latest or specialised processing capabilities.

The designer needs only to specify the interconnection of these components by way of a netlist. Software which performs most or all of the routing of the user supplied netlist on the uncustomised array exists and is used in a commercial environment.

A development of the gate array concept is a layout style termed 'sea-of-gates'. With this style high transistor densities are achieved by packing transistor gates as close together as the technology permits, but where not all the transistors can be used, allowing impressive numbers of gates to be fabricated on a chip; over 100K gates is typical. The philosophy of the approach is to fabricate many more transistors than are needed by the designer as not all the transistors are available, since some will need to be sacrificed to allowing routing over them. Developments on this concept, employing a hierarchy in the chip array and design has resulted in the gate forest[21], [22] concept, which has extra unique features. These approaches require state of an

CAD approaches, as the layout of these massive arrays cannot be undertaken manually without a great deal of trouble.

Another variation, core—custom, where the uncustomised gate—array chip incorporates a well known VLSI component such as a commercial microprocessor, leaving a significant portion of chip area for the designer to include their own logic, increase the attractiveness of the approach. A designer can take his board level solution and port it over to the gate—array chip using components and techniques he/she is already familiar with.

#### Standard Cell Approach

Unlike gate arrays, all layers of the mask set are customised and the silicon has to be processed in one go. A vendor of this type of semi—custom process will supply a catalogue of components, which are pieces of full—custom layout, thereby being efficient in terms of area and performance.

Automatic placement and routing software [23], [24] for these cells which does the job wholly or partially are used by vendors to connect user supplied netlists. It is up to the vendor to update their library to new processes as and when they become available.

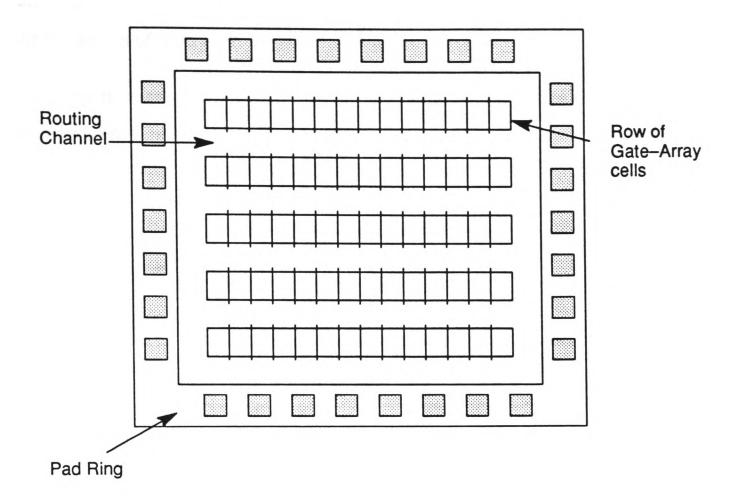

The floorplan of a gate array takes the form of a row of gates separated by routing channels. Two computing problems arise, that of the most efficient placement of the gates and that of routing the channels. Figure 2.1 shows a typical gate array floorplan. Placement algorithms[25], [26] determine where to place the cells for the good routing results, after which routing algorithms[27], [28], [29], [30], [31], [32] route the wires for signals around the chip. Good placement is important as this can affect dramatically the routing results produced with the router. The routing will be bad, even with an efficient routing algorithm if the placement of the gate array cells is poor.

Gate Array – Typical Floorplan

Figure 2.1

Software such as SOLO supplied by ES2, which is an update of the earlier Chipsmith[33], which is mentioned in a later chapter, produces mask information for all the layers of what they call 'optimised' gate arrays. This doesn't have the advantage of requiring only the customisation of the metal layers in a traditional gate array but produces more compact layouts as routing channels can be of an optimum size. The cost of making masks is unimportant in this case as ES2 uses a direct write on the silicon wafer using an electron beam in their fabrication process. The technique allows quick updatability to new process rule sets[34] allowing the software to be used for processes supplied by other fabrication processes.

## 2.4. Structured Layout Methodologies

If the full custom layout route is adopted then full use can be made of all mask layers to produce the most compact and efficient layout possible in practice. The problem with the straightforward use of full custom layout is that it is a difficult and time consuming process re-

quiring skill and patience to do well. It is also non-portable. If a new process becomes available using a new set of process rules, the complete layout has to be repeated.

What is needed is some way to abstract the details of the design rules, leaving the topological and connectivity information supplied by the designer, so that it can be used whatever design rules are given.

This is what is done with a structured layout methodology or symbolic layout system. The two terms will be taken as synonymous throughout this thesis.

# **Tiling Scheme**

This is a layout method that was developed at Edinburgh University. Fourth year electrical engineering students have already used the system with success in their projects, on low cost computers, using CAD software written at the University.

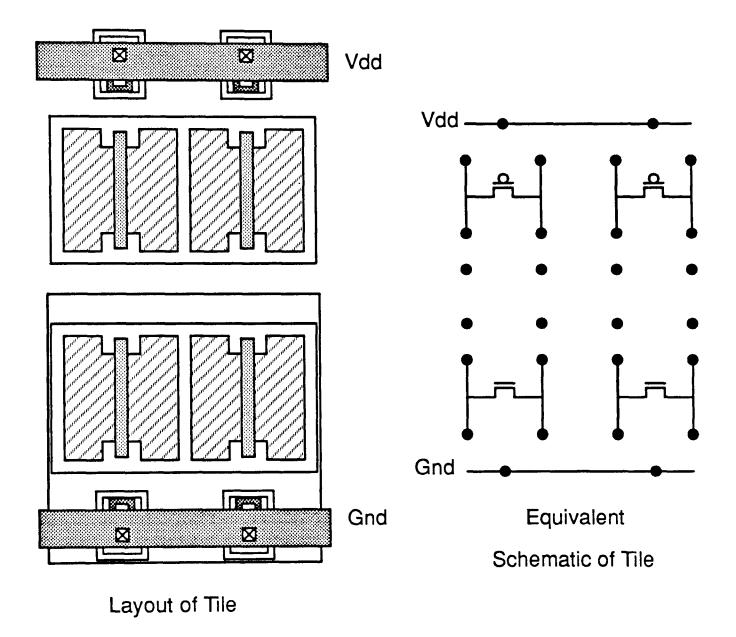

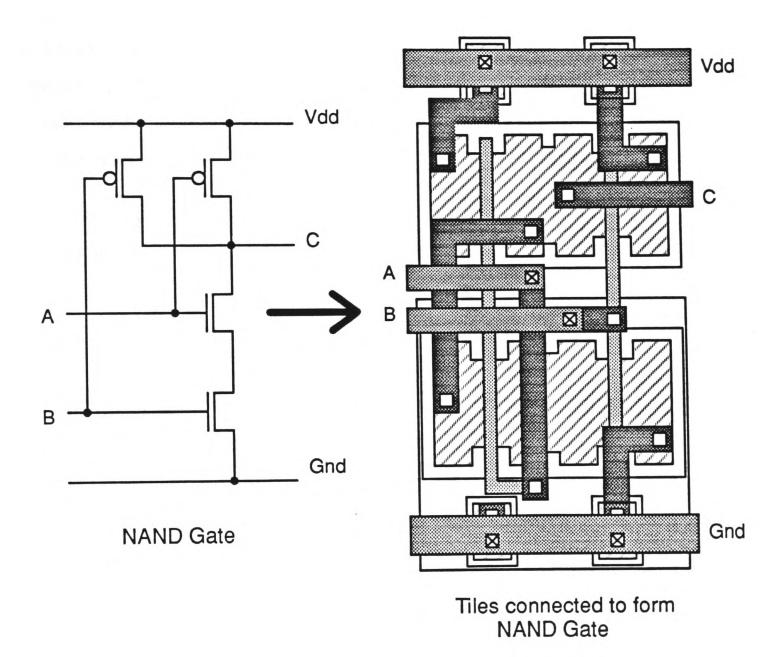

An Uncustomised Tile

Figure 2.2

To reduce the design time of a circuit, standard tiles are used, Figure 2.2 shows an uncustomised blank tile and its equivalent schematic. There are four transistors in a tile; two p-type, near the supply line (Vdd), and two n-type, near ground. Connections are made using all layers to form a completed circuit. Figure 2.3 shows an example of how these tiles may be connected to form a nand gate.

Tiles connected to form a Nand Gate

Figure 2.3

To change to another process only the tiles need be changed, connections between tiles can be stored in a library and reconnected automatically from the library or, without much pain, manually. It is easier to lay out circuits and change process using this tiling scheme rather than trying to perform the lay out completely in a full custom fashion.

## Weinberger Arrays

As long ago as 1967, the benefits of a regular layout style were understood. Weinberger[35] proposed an array of nor-gates to implement sections of digital logic. The array differs from a PLA in that, logic is constructed from multilevel nor logic, whereas only two levels are used in PLA's. Weinberger arrays are thus more general, but more suited for NMOS circuits for which they were originally developed, (NMOS nor-gates can possess large numbers of inputs without a great degradation in performance, unlike CMOS equivalents).

The circuits can quickly be moved to another process because the structures are very regular and hence the redesign of layout can be achieved with ease.

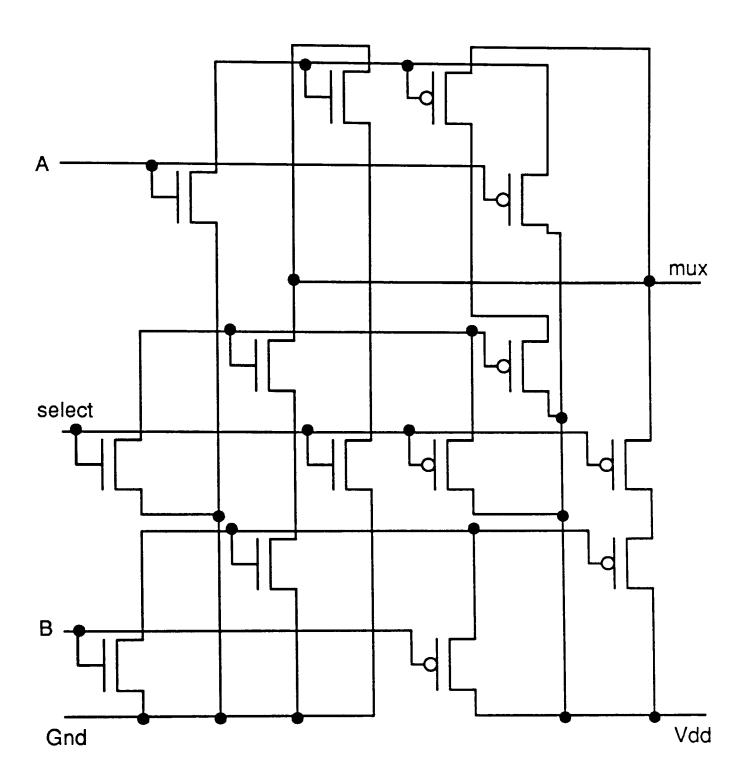

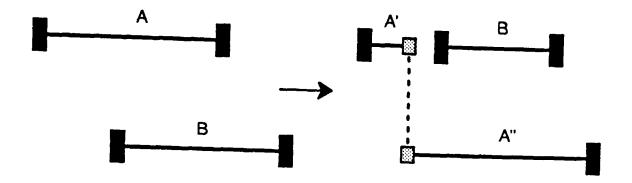

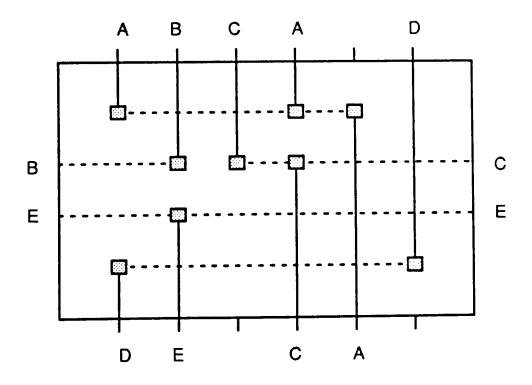

#### Gate-Matrix

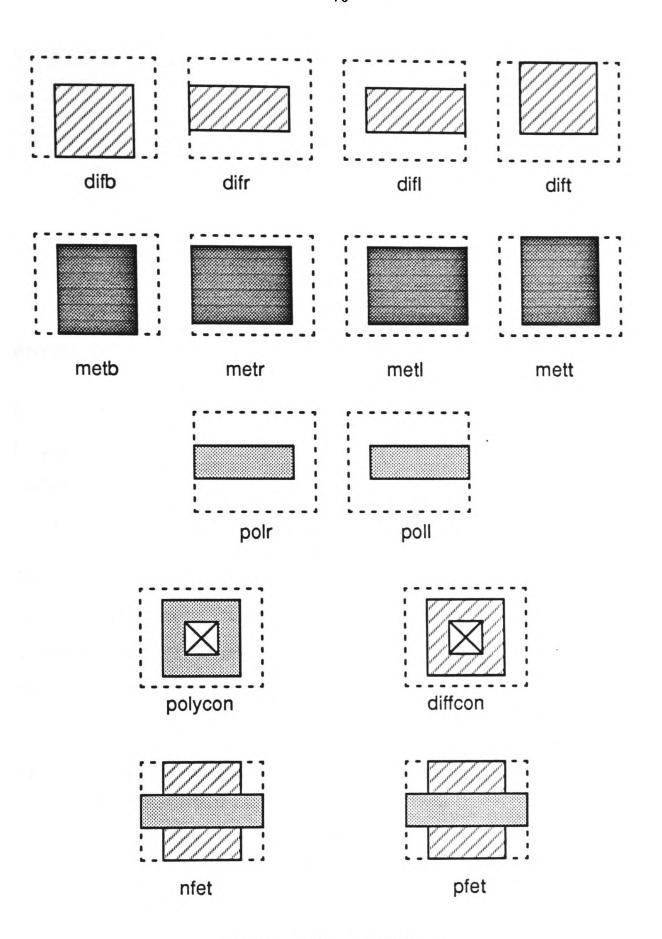

The gate matrix[36] structured design methodology was originally developed at Bell Laboratories[37] and has found the greatest favour for use in the layout automation system described earlier. It can be viewed as a generalisation of the Weinberger array, since it has a similar structure. Unlike the Weinberger array, the types of logical circuits that may be laid out are limited to multilevel nor gate implementations.

The major characteristics applying to gate matrix are:

- Polysilicon runs only in one direction and is constant in pitch.

- Diffusion runners exist between polysilicon columns.

- Metal runs in both directions and is constant in width except for power busses.

- Transistors exist only on the polysilicon columns where diffusion rows intersect it.

These features give the style a regularity which is important from the standpoint of computer automation. Also the layout density is comparable to full custom layout. This may not be so clear when comparing small blocks of layout, but in larger pieces of layout, the advantages of the regularity enable easy interconnection of smaller relatively independent blocks. A major benefit of this style is the ability to update to a new set of process rules quickly and without much effort. Pieces of layout can be stored in the symbolic form, from which actual mask data (incorporating process rule dependencies) can be generated.

The style is well adapted for computer aided design[38] as well as a manual design style [39] on low cost terminals. The style has been used for the layout of a large section of control logic in a 32-bit CPU[40] demonstrating the usefulness and utility of the layout style.

Algorithms for the automated generation of gate matrix layout exist, [41], [42], [43], [44], [45], but as the optimal layout of circuits using the gate matrix style is intractable, the algorithms are heuristic by necessity. It is also possible to extract netlists[46] for simulation with SPICE directly from the gate matrix layout.

The gate matrix methodology is very practical and usable. The style has the following features which we are looking for:—

- A Structured Methodology: allowing the possibility of computer automation and interconnection of independently generated blocks.

- Competitive Layout Densities: the achievable layout density is competitive to that produced by hand.

- Process Updatable: mask information can be generated quickly from a symbolic form which is process rule independent.

- Demonstrated Usefulness: the layout style was developed by AT & T laboratories who have successfully laid out large sections of logic[47] using gate matrix.

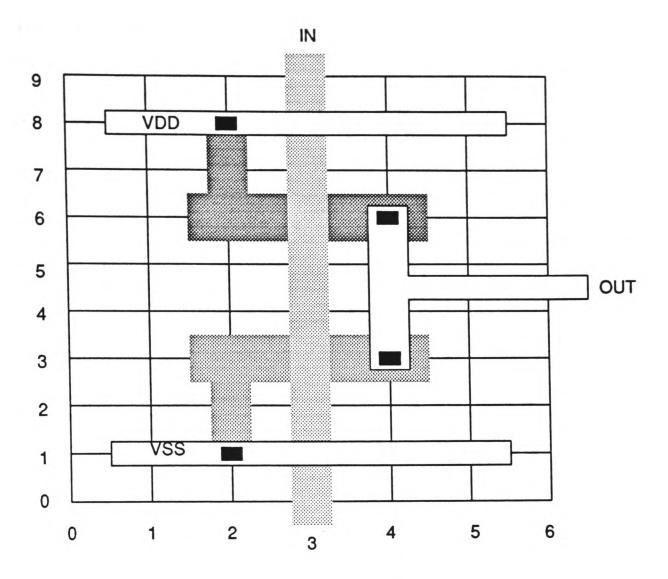

#### Virtual grid Layout

The virtual grid [48] scheme also known as the 'sticks' approach offers another method of achieving design rule independent layout. The method allows the designer to specify the topo-

logical placement of transistors and interconnections. These primitive elements are linked both electrically and topologically through the concept of a *virtual grid*. This relative placement network defines layout topology without specifying the physical distance between elements. Compaction and the production of design rule dependent layout is performed by software on the virtual grid data structure.

A design system using the virtual grid concept is the tool MULGA[49] used for design rule free symbolic layout and verification of MOS integrated circuits.

Figure 2.4, shows a virtual grid representation of an inverter. Absolute positions are unimportant, it is the relative positions of components which is important. The symbolic language used within MULGA contains functional and topological descriptions but no explicit size or spacing information. To translate the symbolic design description into physical mask information requires assignment of physical coordinates to the symbolic grid positions. This is done in two stages. In the first the cell is shrunk to its minimum physical size as determined by process design rules, keeping objects aligned to the grid, in a compaction phase, after which layers can be fleshed. The second stage involves expanding the cell to satisfy global interconnection requirements allowing adjacent cells to abut.

The compaction phase is performed using the technique of *virtual grid* compaction. Elements are constrained to their original grid positions, but the grid is allowed to contract or expand in a non–uniform manner. Compaction proceeds by starting with the X–direction, by comparing grid lines and elements on them for any violations of design rule in that direction ignoring oblique interferences. A minimum spacing between each grid line is used, allowing the grid to vary, which avoids violations. The process then takes place in the perpendicular Y–direction this time taking all oblique violations fully into account.

In this manner mask data can be prepared for many sets of different process rules starting from the same description of the circuit. The designer is left only with the task of specifying the topological layout of his/her design, the inclusion of process dependent data can be left to software.

An Inverter on a Virtual Grid

Figure 2.4

Another design system is STICKS[50], developed at the HIRST Research Centre of GEC. The system consists of a symbolic editor and flesh and compaction software, also using a virtual grid. Extraction of the circuit can be done from the symbolic network and a SPICE file generated.

A similar concept based on the virtual grid symbolic scheme is that of generalised CMOS[51] which includes automatic well generation and is valid in four classes of CMOS technology, P-well, N-well, twin-well and silicon on insulator.

## 2.5. Knowledge Based Techniques

The use of artificial intelligence or knowledge based techniques have become increasingly popular and have been applied to the design and layout of microelectronic systems. They look promising as they can also operate in a process independent way, generating the layout as required. They rely on a set of base rules which specify what can be done to the state of layout at that moment. The activation of a rule can be looked upon as performing a specific optimisation.

Knowledge based systems try to mimic the human designer, and the set of rules are obtained from experts in the field in which the system is meant to operate. It is because of the way they operate that they can be used to solve problems where algorithms for a solution are difficult to produce.

A knowledge based expert system has been described[52] which is able to synthesise the datapaths of CPUs and has successfully done this with the 6502 microprocessor and the IBM SYSTEM/370 with favourable reaction from expert designers.

There have been developments with the automatic generation of VLSI circuit blocks using knowledge—based techniques. TALIB[53] is a program implemented using the general purpose production system language OPS5. It accepts a description of an NMOS circuit in netlist form, which is to be laid out as input and produces the description of mask geometry as output. The technique is not limited to NMOS technologies. Another program is TOPOLOG-IZER[54] which is an experimental expert system for the design of CMOS cells containing fewer than 100 transistors. It uses as input a transistor connection description and a description of the ports required at the boundary of the cell. Its output is a symbolic description using a virtual grid. The tool MULGA[49] can then be used to form the mask information.

# 2.6. Manual Layout

Manual layout despite being the most difficult to do quickly is also the most flexible. In some cases such as the design of analogue circuits, layout automation is still in its infancy and manual layout tools must be used. With digital circuits the densest layout achievable will remain manual full custom, as the layout can be optimised to make full use of the design rules. In many cases it can be justifiable to use a manual editor at the final stage of the layout process in order to optimise certain cells, although without careful use it is not recommended, as functionality of an otherwise correct layout can be destroyed.

Although manual editors allow the most basic operations to be performed on a piece of layout, they are not basic tools. They can possess sophisticated functions within them. Caesar[55] is a basic mask editor, which was used throughout our project for layout purposes, allowing operations on rectangular areas for 'Manhattan' geometry layout. It includes the facility to edit hierarchically and possesses features such as marking points or regions to allow work on large area layouts. It has been updated as magic[56] and uses a better data structure internal to the program allowing algorithms which operate on the layout to be much quicker. Design rule checking is done by a separate program, which means that a user must correct these errors after completion of an area of layout. It has the disadvantage that an error may be difficult to correct when surrounded by remaining layout, but does allow the editor to be used to layout any arbitrary shapes, making it easy to use with any set of design rules.

The Racal—Redac ISIS workstation which is dedicated to the function of integrated circuit layout, on the other hand employs an incremental design rule checker which checks whilst layout is in progress. It stops a user form laying out any piece of logic which would include a design rule error.

These tools make the task of full custom layout far more manageable. They may include useful routines within the editor software, such as a compacter or router, but although giving a designer maximum flexibility suffer in the amount of time and effort needed in using them for any large digital design.

# 2.7. Other Work on Silicon Compilation for Signal Processing

An alternative approach to signal processing hardware has been taken by Pope and Brodersen[57] who use parallel processing elements in their implementations. They assemble systems from macrocells, logical units capable of performing operations at a high level of complexity and not needing many signals for external communication. Typical macrocells which they have identified are:

- 1. Processors, consisting of data memory and a pipelined arithmetic unit.

- 2. Control sequencers, consisting of counters, ROM and PLA.

- 3. Control Modification units, such as address arithmetic units and conditional logic operators.

- 4. Buffer memories and external input/output interfaces.

They have managed to produced an automated layout system [58], [59] using this methodology. By starting with a symbolic description of the system they wish to construct, then using software consisting of a tiler, floorplanner, and a tool for global placement and routing, which is capable of supporting a wide range of technologies, they produce a system consisting of a number of pipelined and microprogrammed signal processors operating in parallel.

The workers on the CATHEDRAL project have produced a sophisticated piece of software capable of generating complex signal processing systems. CATHEDRAL I employed a bit serial cell library [60] of components for use in the system and consisted of software which constituted a complete environment[61] for the design of VLSI signal processing systems. CATHEDRAL II [62], [63] uses bit parallel components and uses multiple processors to achieve performances demanded from the systems designed using the software. CATHEDRAL III allows the use of systolic arrays to achieve very high performance systems. The specification of the system is given in the language SILAGE, data path synthesis tools produce layout from this specification.

A symbolic layout scheme[64] is also used within the system to design a process tolerant cell library. CAMELEON[65] is the name of the symbolic layout software. Cells are specified in

a process rule independent symbolic form and can be edited with a sticks editor (LUDIEC). A compaction program (SPACE) compacts this representation and produces the cells suitable for a specific set of process rules, after consulation with a process rule description file. The tools combine to form a powerful and flexible system.

#### 2.8. Conclusion

Structured design methodologies allow the rapid generation of the layout for cells. Some methods are restrictive in the type of circuit they cater for and are efficient for this type of circuit, for instance PLA's for implementing finite state machines. All the methodologies allow a rapid update when process rules change, making them suitable as a basis for an automatic cell library generation scheme.

The gate matrix approach is a layout methodology which allows rapid update to new process rules and also has considerable flexibility. The layout procedure lends itself to automation through its regular style and is the style preferred for use in our cell library generation scheme. The automatic generation of gate matrix layout and its assembly to form complete components is explored in the remainder of this thesis.

### Chapter 3

## Circuit Techniques and Architectures

#### 3.1. Introduction

Novel circuit techniques have been developed at the University to increase the throughput of bit—serial systems and reduce the size of their implementations. These techniques we wish to include into future cell libraries of FIRST. The techniques alter the generation of the layout to some extent so they are described in this chapter.

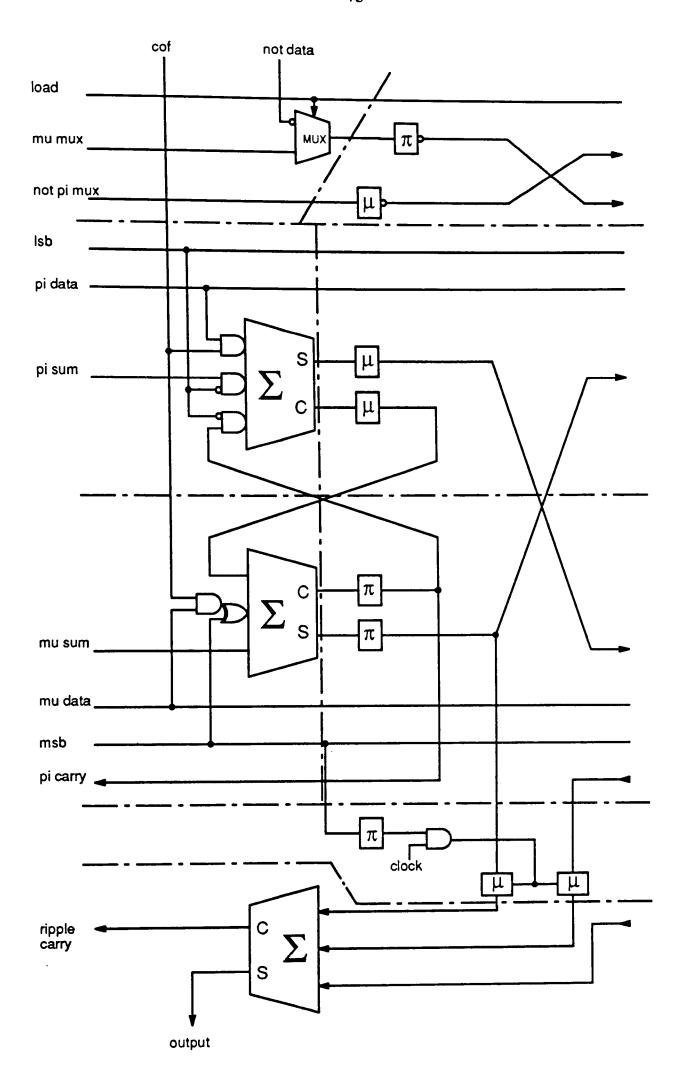

A multiplier using some of these techniques was laid out using a gate matrix style in order to evaluate both the gate matrix layout and the circuit techniques. The layout and results of this exercise are described in a later chapter. The multiplier uses an architecture which doubles its throughput relative to a normal serial—parallel multiplier and this architectural device is also described.

The techniques and architectural devices used to increase throughput and layout efficiency covered are:-

- single phase clocking.

- mixed tree logic.

- twin pipe performance enhancement.

- architecture of the serial/parallel multiplier.

### 3.2. Clocking Strategies

This section looks at various clocking strategies and explains the merits of the single phase clocking strategy developed and used at the University.

# Synchronous and Asynchronous Operation

For any logic circuit, which is not entirely combinatorial, a notion of time is needed. Such logic circuits function as finite state machines which possess at any given moment a definite state, which evolves into another depending on the inputs to the circuit. A form of storage is required to hold the state, in the way of latches or feedback loops.

If this storage is performed by way of feedback, no clock is necessary and the circuit is termed asynchronous. Asynchronous circuits need great care and analysis in their design as they are vulnerable to a large number of complex timing hazards which can prevent them from functioning as intended. They have the advantage of working at their inherently fastest rate and also of being able to work without global signals. These considerations are becoming more important with VLSI circuits where high speed operation and local communication are desirable. Asynchronous circuits with these aspects in mind are gaining increasing popularity as self-timed circuits[66].

Another form of operation is provided by *synchronous* circuits, here clocked latches are used to store the internal state of the circuit. In such circuits, the timing is coordinated throughout by a global clock. Timing considerations are greatly simplified as logic transitions are synchronised with the clock edge. This type of circuit is presently the most popular and universally used in digital circuit design. The clocked latches can either be implemented dynamically or statically.

The design of both types, synchronous and asynchronous, is well established and can be found in many books[67], [68].

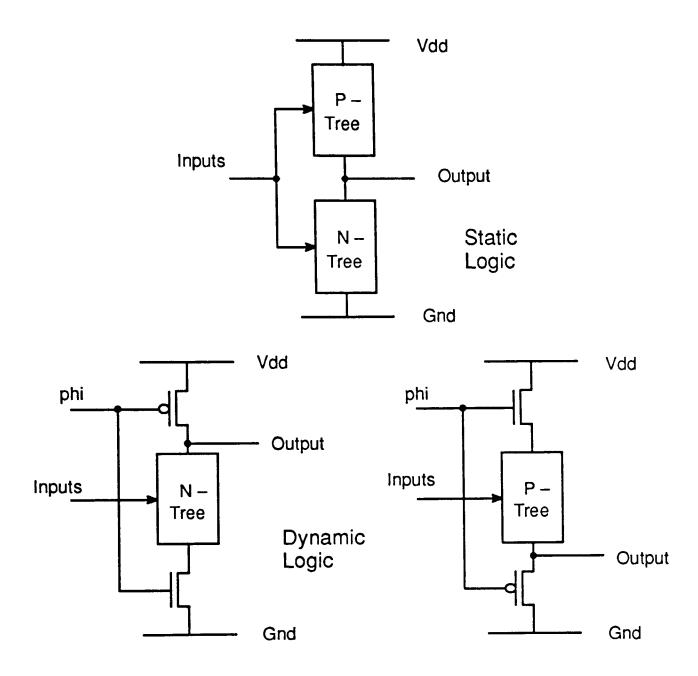

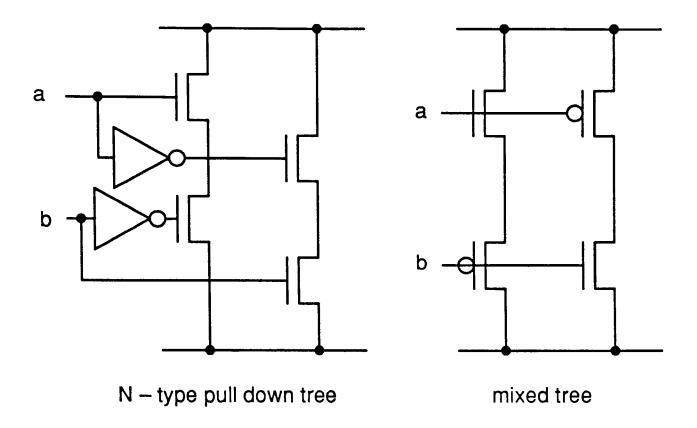

#### **Dynamic Circuits**

With static CMOS circuits, there is a redundancy of circuitry. For the n-type pull down tree, there is a dual p-type pull up tree, with the complete logic function being performed by both trees. This leads to increased area and greater capacitive loading as there are twice as many transistor gates connected to each input of the circuit block.

Dynamic circuit schemes eliminate this redundancy by removing one of the circuit trees.

A pair of clocked transistors replaces this circuit tree, which on each clock cycle charges the

output node. This node is conditionally discharged depending on the inputs to the remaining circuit tree, Figure 3.1.

Static and Dynamic Logic

Figure 3.1

Two transistors are necessary to prevent a conduction path between the supply rails when the circuit is charging the logic node. In cascading such blocks care needs to be taken so that valid logic signals are transmitted between stages and this is taken care of by the clocking scheme used.

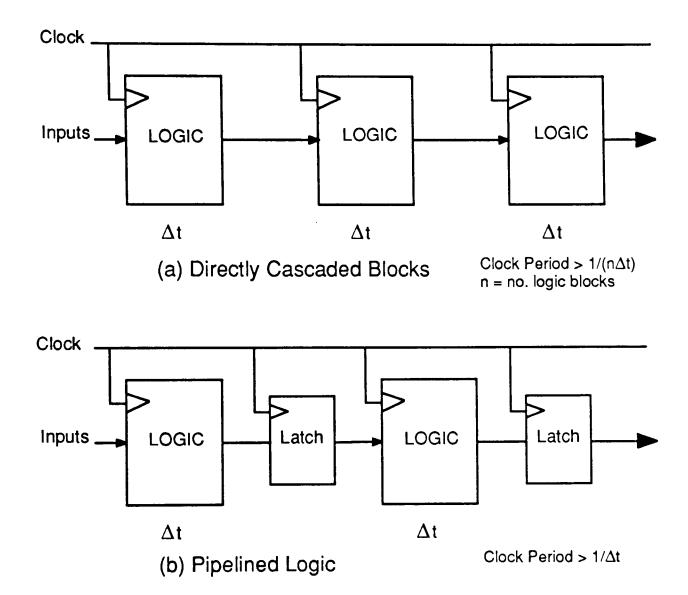

If many stages are cascaded then throughput of the logic circuitry must be reduced as the clock rate has to be long enough for the logic values to propagate through cascaded blocks, Fig-

ure 3.2(a). By inserting latches between logic blocks, we can form a data—pipeline. This allows us to increase the clocking rate, increasing the throughput, as now the longest delay suffered through logic evaluation is only between successive latches, Figure 3.2(b).

Pipelining the Logic

Figure 3.2

## **Clocking Schemes**

We can thus see the following reasons for a clock in digital logic circuits:-

- to coordinate latching in synchronous circuits.

- to provide a pre-charge time in dynamic circuits.

- to provide the clock for latches in pipelined logic.

A number of schemes have been proposed with these functions in mind, Domino Logic[69] and NORA[70] which has been improved so that it now appears similar to the two-phase scheme of NMOS[60], but this chapter will only describe the single-phase scheme used in the multiplier. To understand the scheme and also its advantages it is easiest to describe a simpler scheme first.

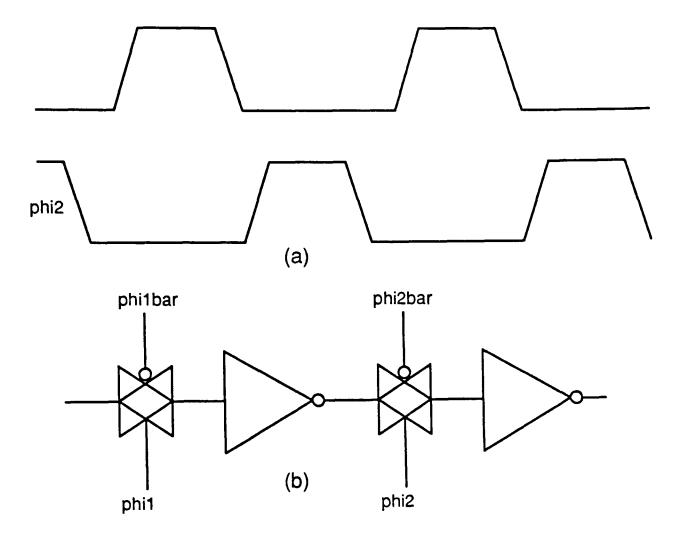

### Pseudo Two-Phase Clocking

In this scheme two non-overlapping clocks, phil and phi2, are used, together with their inverses. This is a CMOS translation of the two-phase non-overlapping NMOS clocking scheme as used in Mead & Conway[13]. This gives four clock phases to route. Clocking waveforms are illustrated in Figure 3.3(a).

A dynamic latch using this scheme is shown in Figure 3.3(b), during the phi1 phase, the first transmission gate conducts allowing the logic value to be stored at the gate of the first inverter, during the phi2 phase, the second transmission gate transfers it, inverted, to the gate of the second inverter. It is held during this phase and reinverted at the output.

Clock skew can prevent this scheme from operating. The clock skew can arise in two ways, by a delay in the clock distribution path causing the clock phases to no longer be non-overlapping or else as a slow rise and slow fall time of the clock edges. Both of these forms of skew can lead to some overlap of clock phases causing both transmission gates to be on simultaneously, allowing the logic state to *race through*, losing the stored state.

To prevent this from happening the period of the clocks must allow for the worst case logic propagation time in combinatorial blocks that are between latches.

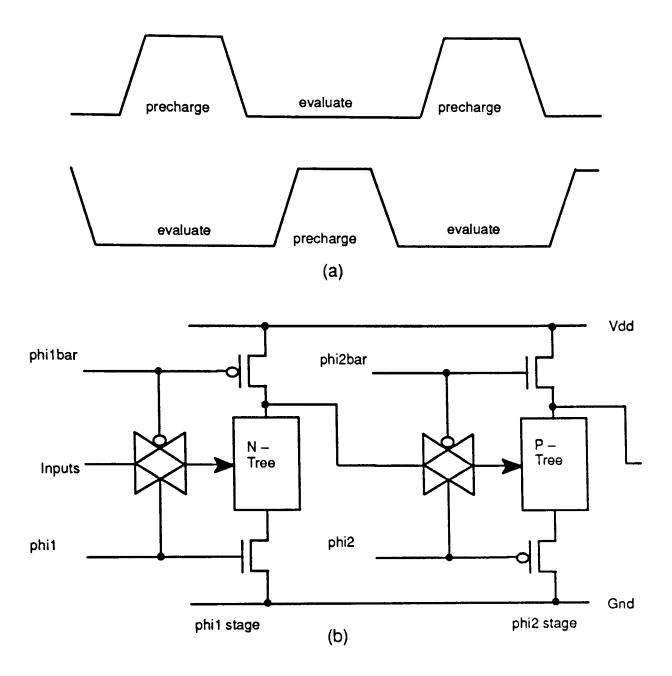

Dynamic logic utilising the pseudo-two phase scheme is illustrated in Figure 3.4(b), with the clock phases in Figure 3.4(a).

Pseudo Two-Phase Clocking

Figure 3.3

During the phi1 clock phase, the output of the phi1 stage is precharged to be evaluated by the logic whilst the phi1 clock is low. Inputs to the logic block are held steady by the closing of the transmission gate at the input. The operation of the phi2 stage is identical but it operates during the phi2 phase.

The scheme allows us a practical way to implement dynamic synchronous logic circuits at the cost of routing four clock lines. The complementary clocks can be generated locally using inverters. The scheme is vulnerable to clock skew between phases which can cause coupling between logic blocks, leading to a race—through condition.

Dynamic Logic using pseudo two-phase clocking

Figure 3.4

Other schemes have been proposed, for instance two phase and four phase schemes (described in Weste and Eshraghian[19]) to either reduce the number of clock lines or of the susceptibility to clock skew.

The NORA scheme[70] reduces the susceptibility to clock skew by making circuit operation tolerant to a degree of clock skew.

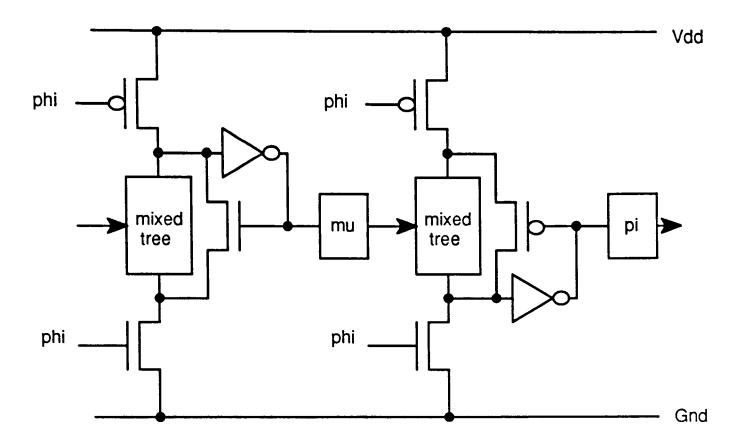

### Single-Phase Clocking

The clocking scheme used in our multiplier uses only a single clock phase [71] which will be described in this section.

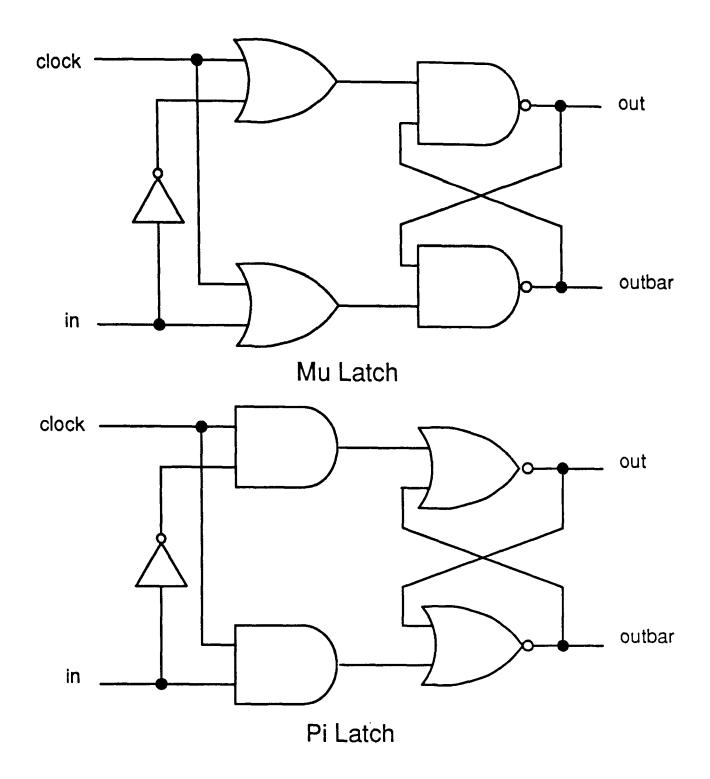

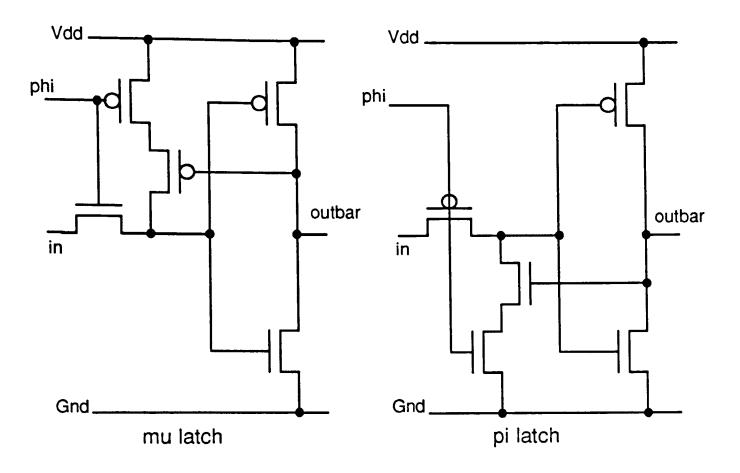

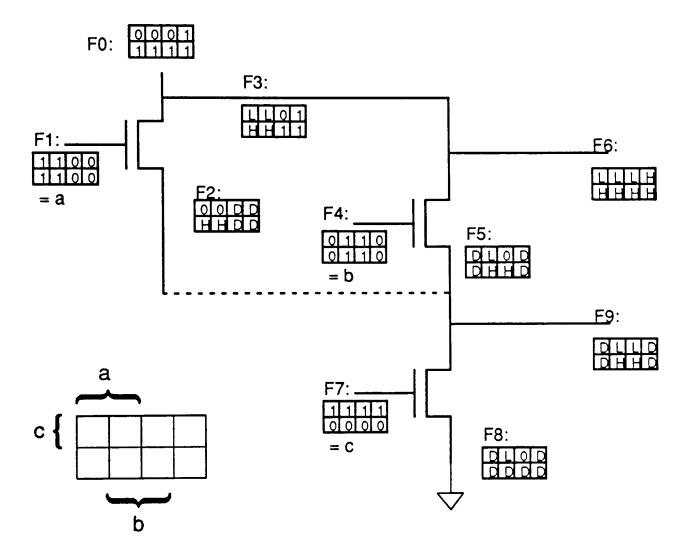

Instead of using multiple clock phases, the scheme uses two types of latch which are designated by the greek letters  $\mu$  (mu) and  $\pi$  (pi), which are mnemonics representing the holding phase of the two latch types. Each latch operates on a different half of the clock cycle. The latches operate as the two transparent D-type latches found in TTL circuits. The mu latch holds its output whilst the clock is low, signified by the lowered joining bar on the  $\mu$  character, and samples whilst the clock is high, the pi latch working in a similar but complementary fashion, i.e. holding whilst the clock is high, signified by the raised joining bar on the  $\pi$  character.

Figure 3.5 show the logic for these two types of latches which can be used to implement static forms for them.

Mu and Pi Latches (Static Forms)

Figure 3.5

Dynamic versions of these latches are shown in Figure 3.6, each latch needing only five transistors. As only a single pass transistor is used in the latch, the transistors of the inverter should be ratioed to overcome the effects of the threshold drop. The logic value is inverted through each latch, though this can be easily compensated for by the logic blocks.

Mu and Pi Latches (Dynamic Forms)

Figure 3.6

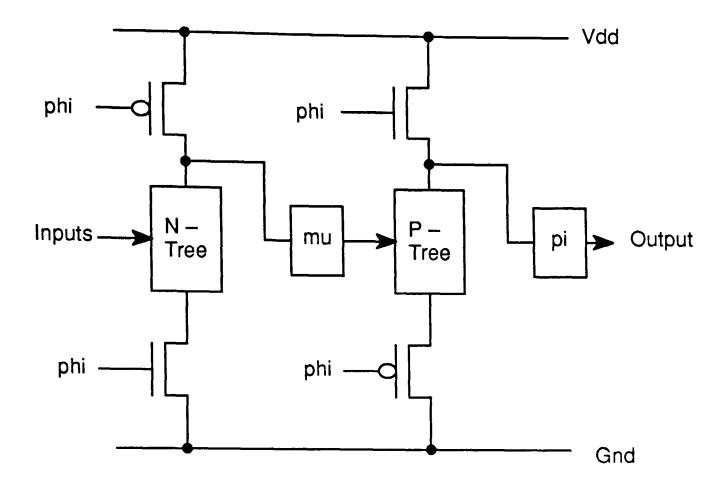

To obtain the benefits of greater integration, dynamic logic is used, this is shown in Figure 3.7. Each stage precharges whilst the next stage is evaluating with the roles reversed in the next half clock cycle. Other schemes such as *Domino* or *Complementary Tree* may also be used[71] with this single phase clocking scheme.

Dynamic Logic with Single-Phase clocking scheme

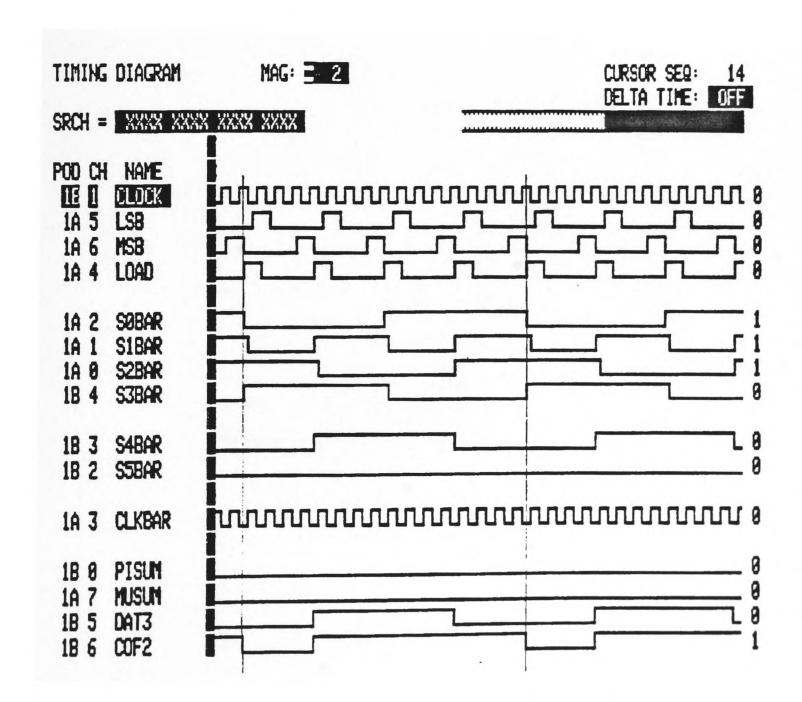

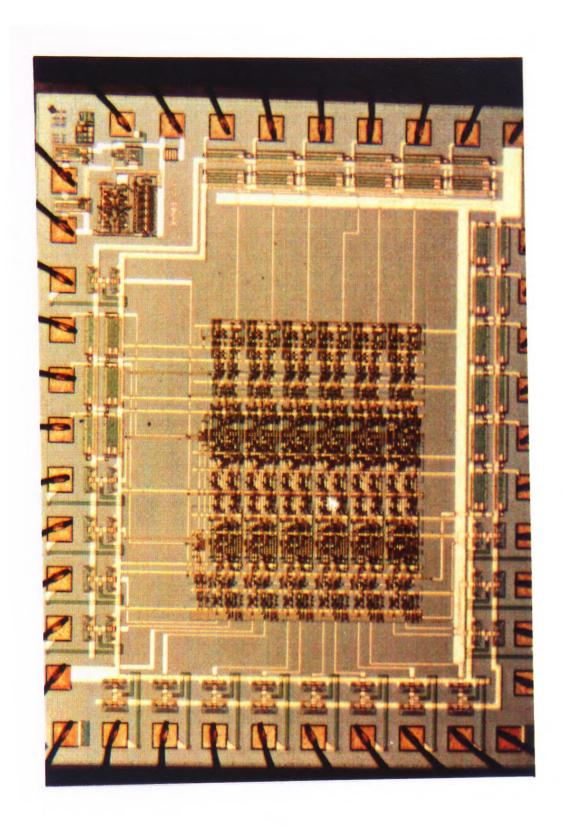

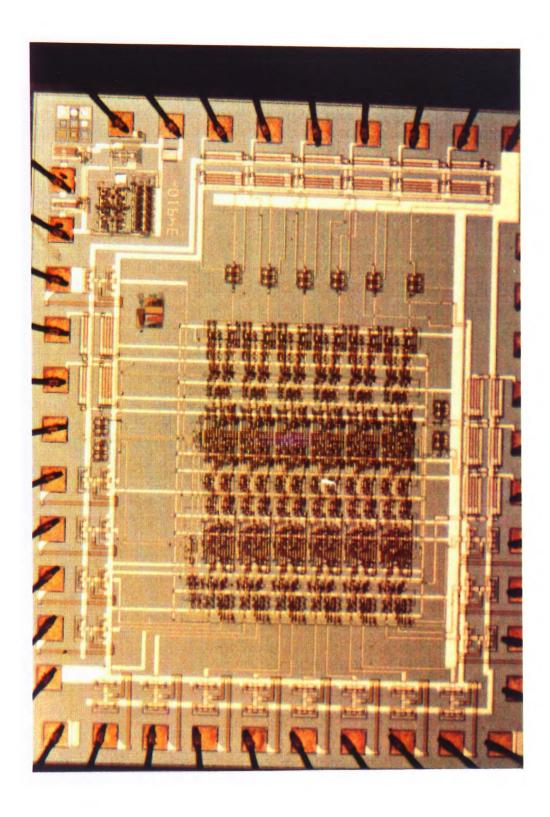

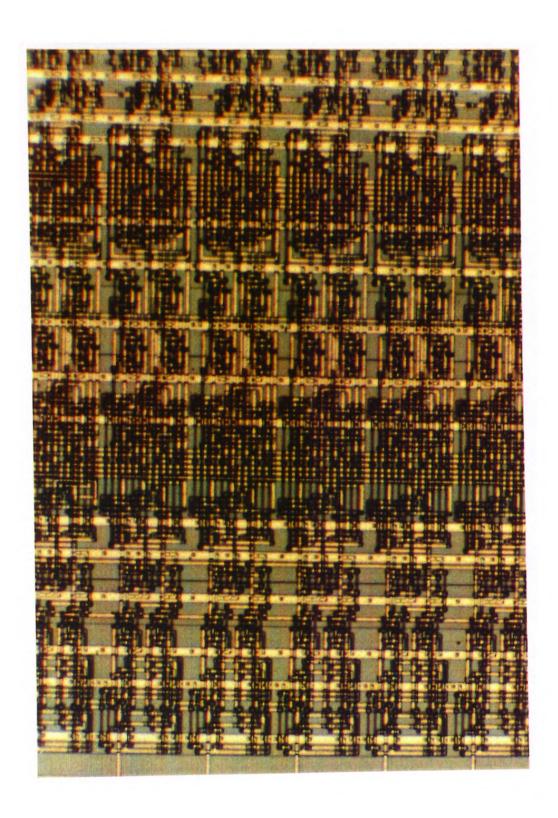

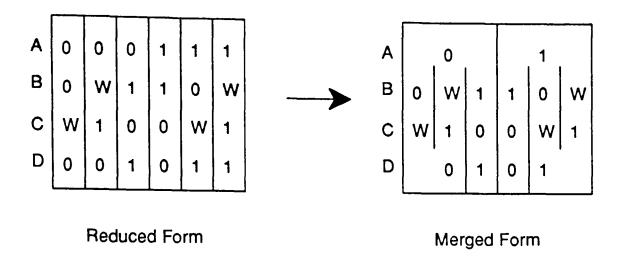

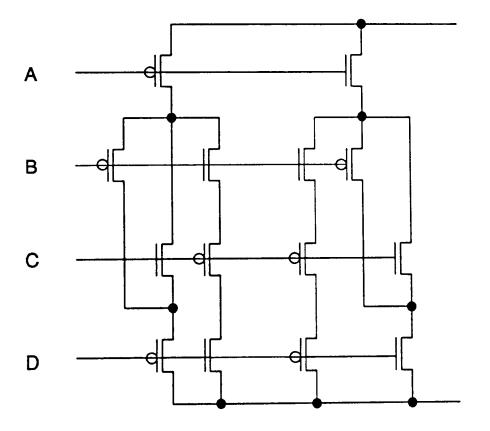

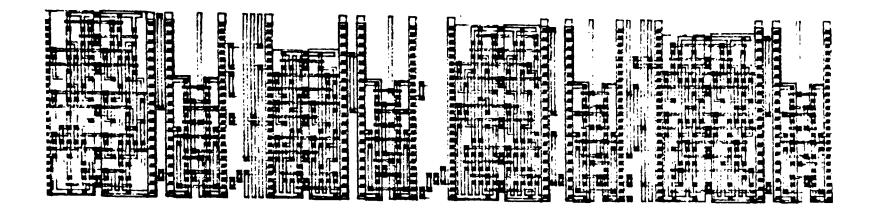

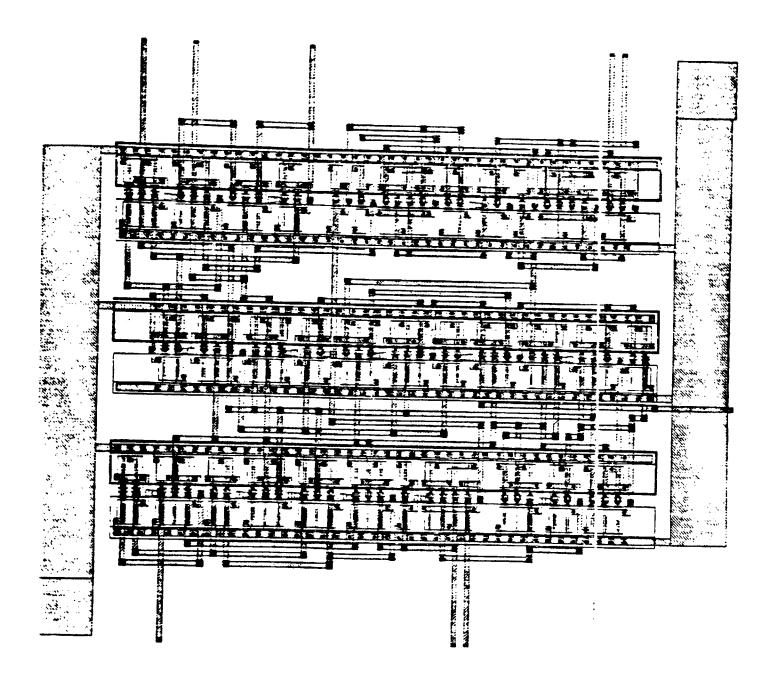

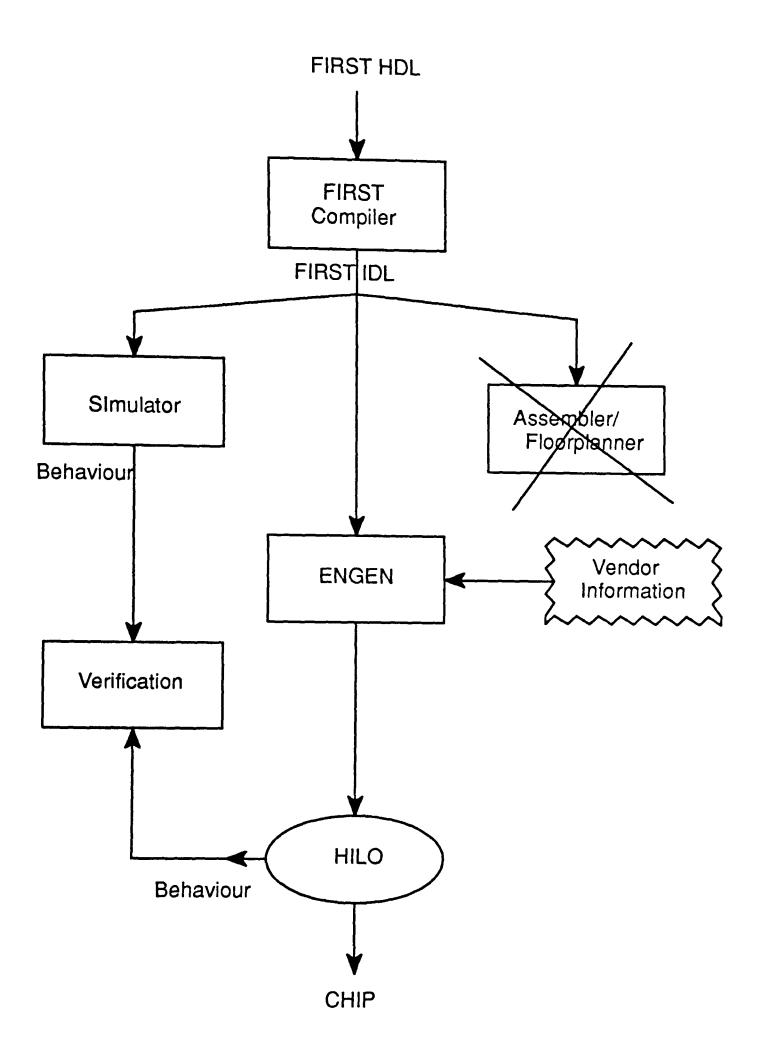

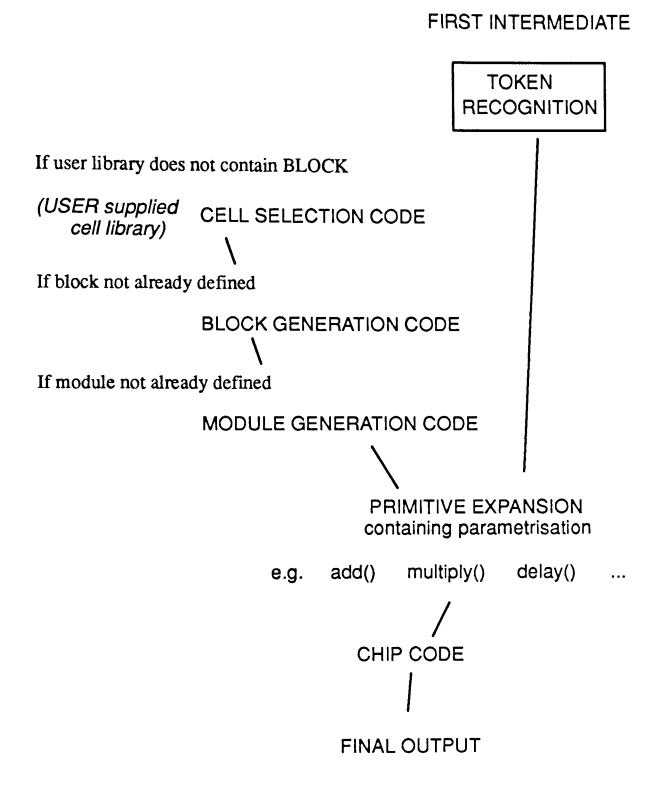

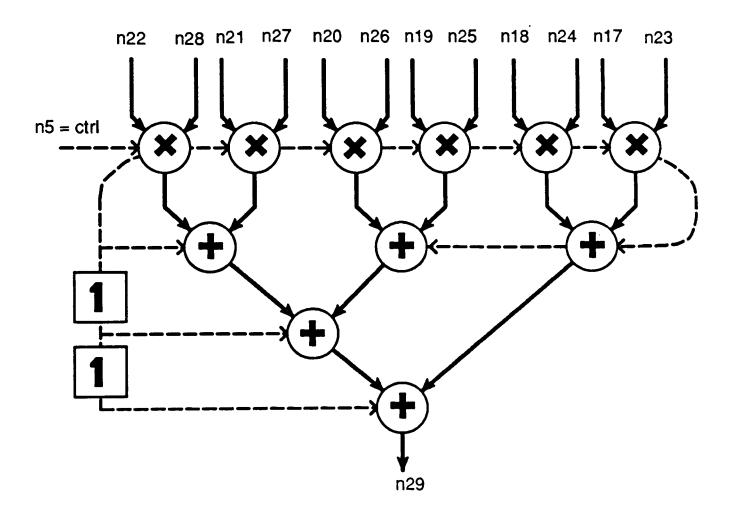

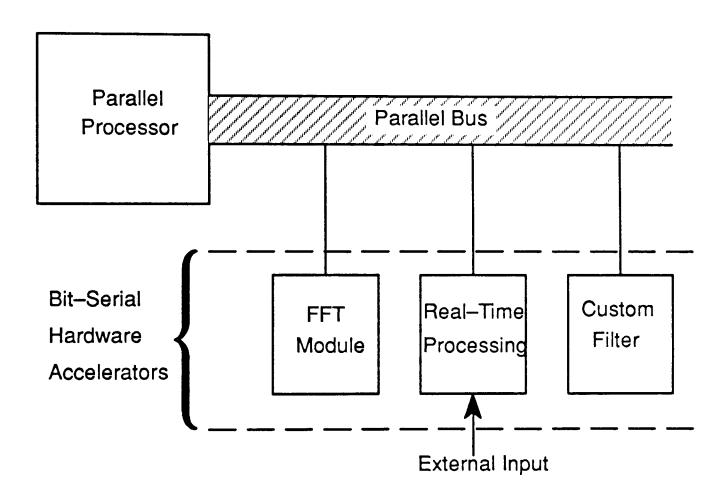

Figure 3.7