# PERFORMANCE MEASUREMENT AND EVALUATION OF TIME-SHARED OPERATING SYSTEMS

John Colin Adams

Ph.D.

University of Edinburgh

1977

## CONTENTS

|                  | Page |

|------------------|------|

| Acknowledgements | į    |

| Abstract         | ii   |

| Chapter 1        | 1    |

| Chapter 2        | 26   |

| Chapter 3        | 66   |

| Chapter 4        | 94   |

| Chapter 5        | 114  |

| Chapter 6        | 140  |

| Chapter 7        | 168  |

| Appendix         | 172  |

| Bibliography     | 175  |

#### Acknowledgements

I would like to acknowledge the contribution made to my understanding of this subject by all the other workers in this field whom I have met and discussed this topic with over the past six years, unfortunately it would be impossible to name them all. However, I would like to give special thanks to Professor H. Whitfield for initially interesting me in this area and to Professor S. Michaelson for his continued encouragement throughout this work. should also like to thank all the people involved with the EMAS project both in the Department of Computer Science and the Edinburgh Regional Computing Centre, especially Dr. G.J. Burns and Dr. A. McKendrick, of the ERCC, whose enlightened approach to system management allowed me to carry out the measurement experiments; G.E. Millard, B.A.C. Gilmore and all the ERCC staff involved in the definition of the interactive benchmark and the construction of the 'stimulator', and P.D. Stephens of the ERCC for all his help in topics concerning the EMAS resident supervisor. Finally I would like to thank my supervisor Dr. D.J. Rees without whose encouragement I should never have completed this thesis, and my wife Judy who not only put up with me, and my odd working hours, throughout this project without complaint, but also made such an excellent job of typing this thesis.

#### Abstract

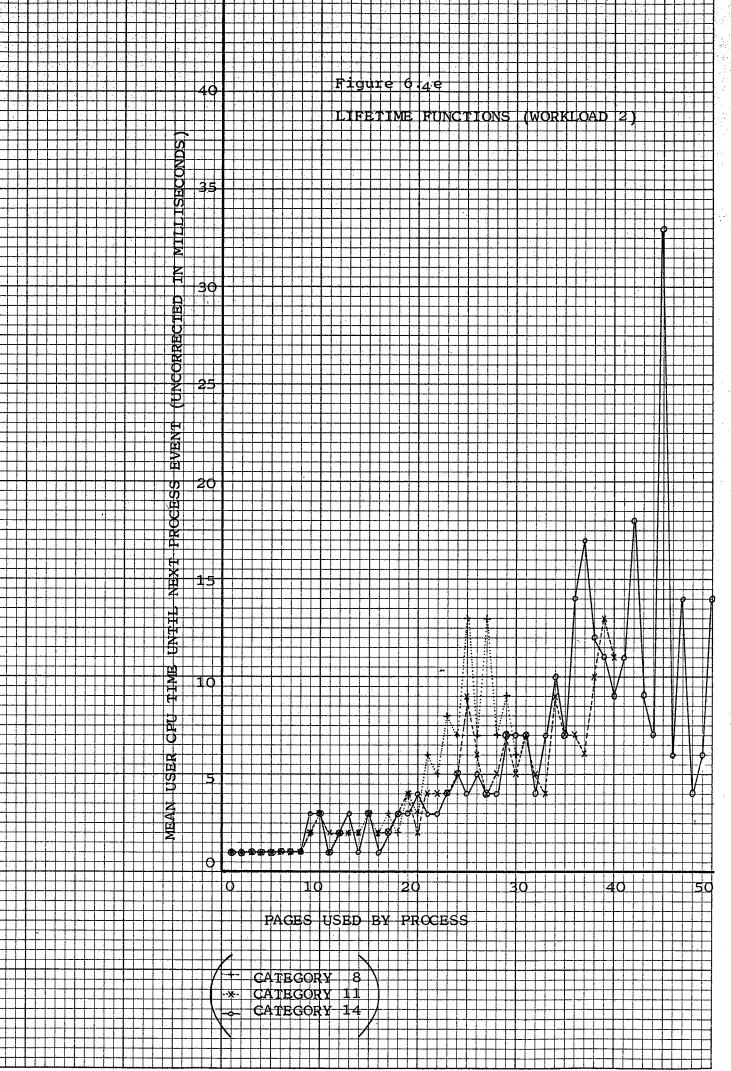

Time-shared, virtual memory systems are very complex and changes in their performance may be caused by many factors - by variations in the workload as well as changes in system configuration. The evaluation of these systems can thus best be carried out by linking results obtained from a planned programme of measurements, taken on the system, to some model of it. Such a programme of measurements is best carried out under conditions in which all the parameters likely to affect the system's performance are reproducible, and under the control of the experimenter. In order that this be possible the workload used must be simulated and presented to the target system through some form of automatic workload driver.

A case study of such a methodology is presented in which the system (in this case the Edinburgh Multi-Access System) is monitored during a controlled experiment (designed and analysed using standard techniques in common use in many other branches of experimental science) and the results so obtained used to calibrate and validate a simple simulation model of the system. This model is then used in further investigation of the effect of certain

system parameters upon the system performance. The factors covered by this exercise include the effect of varying: main memory size, process loading algorithm and secondary memory characteristics.

#### CHAPTER 1

The class of computer systems addressed in this thesis is that of general purpose, time-shared, virtual memory systems. Within these, some form of operating system controls the sharing of a set of centralised computing resources - processors, memories, file storage devices - amongst a large community of users. Users interact with the system, and their programmes running therein, via keyboard like devices, rather than submitting their work on decks of cards, or rolls of paper tape, to some job reception desk whence they will receive their results sometime later (as in a batch form of operation). These systems also provide their users with some form of file system in which programmes and data may be stored, a large address space or virtual memory [Denning 1970] in which these programmes may be run and some mechanism whereby any user's programmes and data may be shared by, or protected from, other users. The range of work the users may carry out on such systems will not be restricted to any one particular language or class of operation as is the case in certain special purpose systems e.g. JOSS [Bryan 1967].

One of the major motivations for introducing such a form of system in the early 1960's

was a desire to make the use of computing more convenient to the programmer. The best way of achieving this would probably be to give each programmer his own processor with a very large main memory, however the cost of computer hardware at the time made this impossible. The solution adopted was to share a powerful mainframe with some form of virtual memory amongst several users, and to divide the available resources (CPU time, memory space, channel bandwidth) in such a way as to give each user the illusion that he had a whole, if less powerful, machine dedicated only to him. Subsequent studies [Gold 1969] have found that interactive use of computers is superior to batch use in problem solving, and with the current trend of dropping hardware costs relative to software costs this more efficient use of programmers ' time will become more and more crucial.

The first time-sharing system, in which each ready to run programme is allocated a small quantum of CPU time in turn, was the Compatible Time Sharing System [Corbato et al. 1962, Crissman 1965] implemented at Massachusetts Institute of Technology on an IBM 7094. This was also the first true general purpose, multi-access system with users communicating with the machine via keyboard terminals attached by means of telegraph lines. A similar type of system -

was developed at Cambridge University on the TITAN computer. These two previous systems did not however provide virtual memory. The concept of virtual memory, in which the address space used by the programmer is split from that used by the hardware of the processor, also appeared in the early 1960's. This splitting of the address spaces allows each programmer to use an address space at least as large as, and often much larger than, the one available in the physical main memory of the machine. The two commonest mechanisms employed in providing virtual memory, either individually or together, are paging (introduced on the ATLAS computer [Kilburn et al. 1962] at Manchester University) and segmentation [Dennis 1965].

Systems which employ both time-sharing and virtual memory include: The Michigan Terminal System - MTS [Alexander 1972] produced at the University of Michigan on an IBM 360/67; the Multiplexed Information and Computing System - MULTICS [Corbato and Vyssotsky 1965, Glazer et al. 1965, Vyssotsky et al. 1965, Daley and Neumann 1965, Ossanna et al. 1965, Organick 1972, Corbato et al. 1972] developed at M.I.T. on a GEC 645; the TENEX system [Bobrow et al. 1972, Murphy 1972] implemented by BBN on a DEC PDP-10; CP/67 [Meyer and Seawright 1970,

IBM 1970] produced for the IBM 360/67 and VM/370 [IBM 1972] produced for the IBM 370 series, both at the IBM Cambridge Scientific Centre.

### The Edinburgh Multi-Access System

The system upon which most of the work reported in this thesis is based is the Edinburgh Multi-Access System - EMAS [Whitfield and Wight 1973, Rees 1975, Millard et al. 1975, Shelness et al. 1974, Wight 1975]. EMAS is amply described in the cited references, but as it plays such a central role in the succeeding work a brief description will be given here.

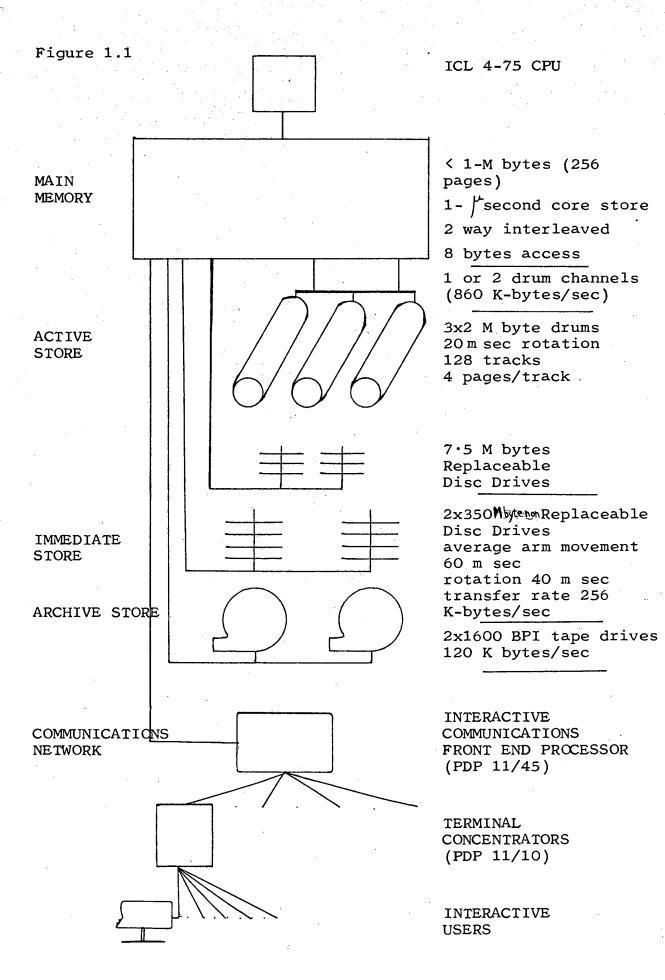

emas is a time-shared, virtual memory operating system implemented at Edinburgh University on an International Computers Ltd. System 4-75. The ICL System 4-75 is a byte addressed, third generation machine similar in structure and order code to the IBM 360/67. It offers virtual memory by means of segmentation and paging, the address space being split so as to present the programmer with 256 segments, each of up to 16 pages, each page of 4096 bytes. Figure 1.1 shows a typical EMAS hardware configuration at the time of the work reported.

TYPICAL EMAS HARDWARE CONFIGURATION

EMAS is written in the high level language IMP [Stephens 1974] and provides a virtual memory of  $2^{24}$  bytes for a number of simultaneous processes (currently up to 63). The system maintains an on-line storage hierarchy of three levels, pages normally being held only at the outermost - immediate level (currently formed by a 700 M-byte disc store) and are moved to the inner levels - active memory (currently formed from one or more two M-byte drum stores) and main store (currently formed by up to one M-byte of core storage) - as required. The user programme has no direct access to any Input/Output hardware, all management of the three tier storage hierarchy being carried out by the system and all unit record I/O being spooled. There is also an automatic archiving system [Wight 1975] which allows currently unused files to be removed from immediate store to archive storage (magnetic tape) and restored therefrom as required. A form of working set policy [Denning 1968] is used in the management of main memory. This is based on usage information obtained from read/write markers associated with each physical core page. Sharing is also supported at all levels of the on-line storage hierarchy.

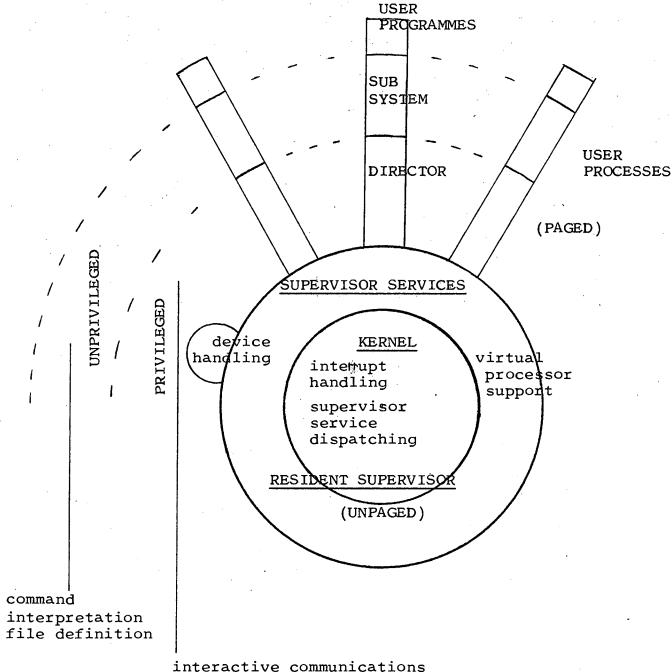

The operating system is itself hierarchically ordered and message based. The logical

structure of the system is shown in Figure 1.2. All communications between processes - both system and user processes - take place via a central message passing area. All supervisor processes (or services) which have a message or request outstanding also have an entry in one central queue - the MAIN-Q. One of the major functions of the innermost level of the system the KERNEL is to remove entries from this queue and call the appropriate service. When there are no outstanding supervisor requests then the KERNEL will load the currently selected user process to the CPU where it will be allowed to remain for a maximum of a time-slice (100 milliseconds at present) at a time. The other major function of the KERNEL is to field interrupts and translate them into messages to the appropriate handling service.

One level out from the KERNEL are the supervisor services themselves. The services take care of two major functions:

## EMAS LOGICAL STRUCTURE

interactive communications file system maintenance

DEVICE HANDLING - The handling of all paged

I/O or interactive

communications hardware

attached to the system,

scheduling transfer requests

and carrying out all

necessary device control.

VIRTUAL PROCESSOR SUPPORT - The allocation

and management of the

available resources

(CPU time, main and active

storage space and channel

bandwidth) between competing

processes and the management

of process virtual memories.

The KERNEL and all supervisor services form the resident supervisor which is always in main memory and runs unpaged - using real addresses.

At the next level out run the user processes. Each user process consists of two levels: the paged supervisor, or DIRECTOR [Rees 1975], and the normal user process. DIRECTOR takes up 31 segments of the 255 segment virtual memory available to each user process (segment 0 is never used because of a

peculiarity of the hardware). It handles all interactive communications messages, maintains the file system and takes care of the allocation of immediate (tertiary) memory space. The resident supervisor knows nothing of files but merely handles page transfers. It is one of the functions of the DIRECTOR to associate virtual memory addresses with files resident in immediate memory when requested to do so by a user (the files are not permanently mapped into the virtual address space as is the case in MULTICS). Most of the DIRECTOR code and data space (interactive communications buffers and file indices) is shared amongst all user processes. The only unshared segment is the master segment which contains all local variables and tables for that process, in particular, one page of this segment - the master page holds various tables and variables used by the resident supervisor and must always be in main memory when the process is on the CPU. Those segments which constitute DIRECTOR may not be accessed by normal user programmes (though the DIRECTOR may access the full virtual memory space) and those entries in the process! segment table are masked out when normal user programmes are running.

Running within the user level of the process is the subsystem [Millard et al. 1975] which

takes care of user command interpretation, file definition, linking and loading and logical I/O mapping. At a level out from this run the users' programmes. All commands on the system are merely external routines which have an entry in one of the user's libraries. A user may add new commands by compiling new external routines and making an entry in an appropriate library, or may call existing commands as routines from within his programme.

Certain 'executive processes' run at the level of user processes and perform such functions as I/O spooling, batch scheduling, archive storage control and the running of engineering test programmes. Though these are essentially user processes they have certain privileges and are scheduled slightly differently by the supervisor.

## Scheduling Within Resident Supervisor

The majority of the work presented later will concentrate upon the workings of the resident supervisor and the scheduling algorithms implemented therein [Shelness et al. 1974]. An overview of these algorithms is now given.

All process scheduling within the system

is table driven from an entity known as the category table. Each process known to the system has assigned to it a category dependent upon the recent past history of that process. Associated with each category are the following attributes:

- 1) A set of resource constraints governing the amount of CPU time, main memory and active memory which each process of that category may consume during a period of main memory residency.

- 2) A priority level.

- 3) A time interval (known as the strobe time) associated with calculation of the working set.

- 4) A set of transitions to other categories dependent upon the actions of the process during its next main memory residency.

During the period covered EMAS had 20 different categories. The values contained in this category table are shown in Table 1.1. All normal user processes start in category 1 and thereafter use categories 5-20. Categories 2-4 are reserved for the

Table 1.1

| EMAS Category Table (EMAS Version 802) |            |                              |                        |                        |      |      |      |            |                            |                              |  |

|----------------------------------------|------------|------------------------------|------------------------|------------------------|------|------|------|------------|----------------------------|------------------------------|--|

| CA                                     | T PRIORITY | CORE<br>ALLOWANCE<br>(PAGES) | A.S.<br>MAX<br>(PAGES) | A.S.<br>MIN<br>(PAGES) | NCY1 | NCY2 | NCY3 | NCY4       | RESIDENCY<br>CPU<br>(SECS) | STROBE<br>INTERVAL<br>(SECS) |  |

|                                        | <i>A</i>   |                              |                        |                        |      |      |      | 1.4        | 1                          | 0.125                        |  |

| 1                                      | 1          | 50                           | 80                     | 50                     | 17   | 15   | 11   | 14         | 1                          | 0.125                        |  |

| 2                                      | 1          | 20                           | 80                     | 50                     | 3 ,  | 2    | 2    | 2          | 0.5                        | 0.5                          |  |

| 3                                      | 1          | 30                           | 80                     | 50                     | 4    | 3    | 2    | 3          | 1                          | 1                            |  |

| 4                                      | 1          | 50                           | 80                     | 50                     | 4    | 4    | 3    | 4          | 2                          | 0.5                          |  |

| 5                                      | 1          | 20                           | 80                     | 50                     | 8    | 6.   | 5    | 5          | 0.5                        | 0.5                          |  |

| 6                                      | 4          | 20                           | 80                     | 50                     | 10   | 7    | 6    | 5          | 4                          | 1                            |  |

| 7                                      | 4          | 20                           | 80                     | 40                     | 10   | 7    | 8    | <u>.</u> 5 | 10                         | 1                            |  |

| 8                                      | 1          | 30                           | 80                     | 50                     | 11   | 9    | 5    | 8          | 1                          | 0.5                          |  |

| 9                                      | 4          | 30                           | 80                     | 50                     | 13   | 10   | 6    | 8 .        | 10                         | 1                            |  |

| 10                                     | 4          | 30                           | 80                     | 45                     | 13   | 10   | 7    | 8          | 6                          | 1                            |  |

| 11                                     | 2          | 40                           | 80                     | 50                     | 14   | 12   | 8    | 11         | 1                          | 1                            |  |

| 12                                     | 4          | 40                           | 80                     | 50                     | 16   | 13   | 9    | 11         | 10                         | 1                            |  |

| CAT | PRIORITY | CORE<br>ALLOWANCE<br>(PAGES) | A.S.<br>MAX<br>(PAGES) | A.S.<br>MIN<br>(PAGES) | NCY1 | NCY2 | NCY3 | NCY4 | RESIDENCY<br>CPU<br>(SECS) | STROBE<br>INTERVAL<br>(SECS) |

|-----|----------|------------------------------|------------------------|------------------------|------|------|------|------|----------------------------|------------------------------|

|     | _        | 4.0                          |                        | <b>50</b>              | 1.6  | 10   | 10   | 44   | 12                         | •                            |

| 13  | 5        | 40                           | 80                     | 50                     | 16   | 13   | 10   | 11   | 12                         |                              |

| 14  | 2        | 50                           | 80                     | 50                     | 17   | 15   | 11   | 14   | 1                          | 1                            |

| 15  | 4        | 50                           | 80                     | 50                     | 19   | 16   | 12   | 14   | 10                         | 1                            |

| 16  | 5        | 50                           | 80                     | 50                     | 19   | 16   | 13   | 14   | 10                         | 1                            |

| 17  | 3        | 60                           | 128                    | 64                     | 20   | 18   | 14   | 17   | 2                          | 0.5                          |

| 18  | 4        | 60                           | 128                    | 64                     | 20   | 19   | 15   | 17   | 7                          | 0.5                          |

| 19  | 5        | 60                           | 128                    | 64                     | 20   | 19   | 16   | 17   | 5                          | 1                            |

| 20  | 3        | 62                           | 128                    | 64                     | 20   | 18   | 15   | 17   | 2                          | 0.25                         |

| A.S. | MAX | Maximum | Active | Store | Allowance |

|------|-----|---------|--------|-------|-----------|

| A.S. | MAX | Maximum | Active | Store | Allowance |

A.S. MIN Minimum Active Store Allowance

NCY1 Next Category if Process runs out of main memory

NCY2 Next Category if Process exceeds CPU time allowance

NCY3 As NCY2 but has used less than the next smallest main memory allowance

NCY4 Next Category if Process goes to sleep

executive processes.

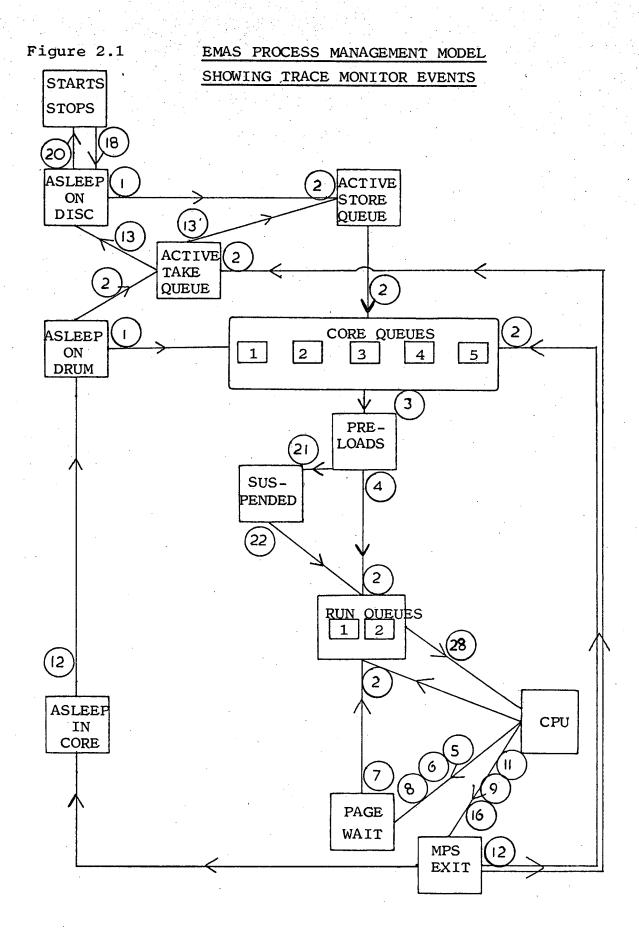

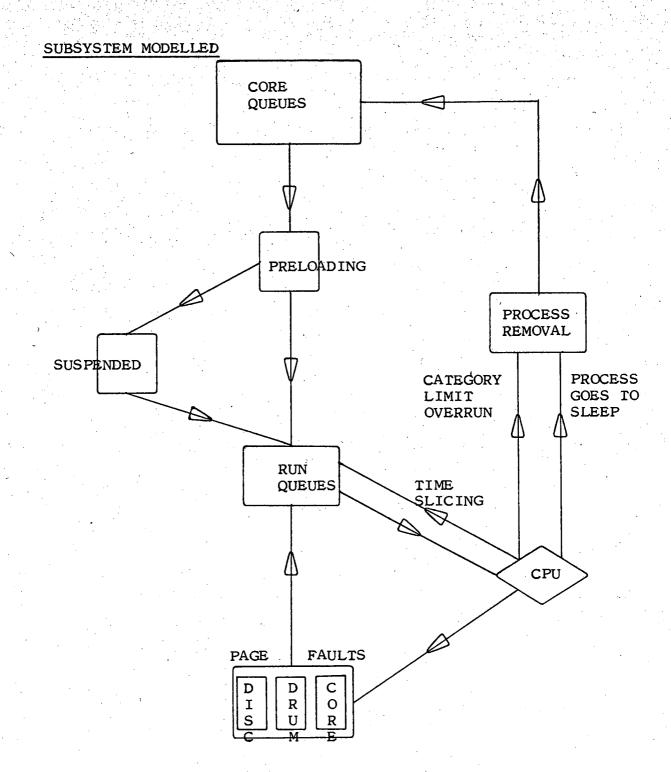

Figure 1.3 shows the major states and supervisor queues involved in the handling of processes on the system. Each process known to the system exists in one of three states:

- a) ASLEEP awaiting user input or the freeing of output buffer space i.e. in terminal wait

- b) AWAKE awaiting allocation of some system resource

- c) PROCESSING on CPU

Each process will also be resident at up to a certain level in the storage hierarchy: immediate, active or central memory. Thus a process which wakes up resident only in immediate memory is first queued in the Active Store Queue to await an allocation of active storage. When an allocation of active store has been given (which at this point involves no identification of the particular physical active store pages to be used) the process will be placed in one of five core queues according to its current category's priority. These core queues are currently serviced

according to a priority scheme which assigns the probability of being selected as 39/64, 17/64, 5/64, 1/32, 1/64 respectively to the five priority levels. Once selected from its core queue the process is then held until it can be given its full allocation of main memory (again defined by its current category). Only when its full allocation of main memory is available may the process enter the multiprogramming set, and the contents of its current working set (which will always consist of at least the master page) will then be transferred (preloaded) into main The system thus carries out a scheme of working set replacement. When all of the process! working set is resident in main memory (and not before) the process is placed on one of two run queues to compete for allocation of the CPU. All processes belonging to categories in the lower three priority levels go onto run queue one, whilst all processes in categories of the top two priority levels are placed on run queue two. The run queues are serviced according to an absolute priority scheme in which run queue one is always serviced first, and if any process from run queue two is holding the CPU when a process arrives for run queue one, then the arriving run queue one process will preempt the CPU process, even if that process has not completed a time-slice. Only processes which are ready to take

the CPU are held in the run queues. Once on the CPU the process may page fault and add a page to its working set from either immediate store, active store or main memory (for shared pages or new pages 'created' in main memory). The process may only hold the CPU for a maximum of a time-slice at a time.

Whenever a process has consumed a full strobe interval of CPU time during any residency, then its working set is recalculated and those pages no longer used are released. A process will remain resident in main memory until it goes to sleep or overruns one of its category allowances. It will then be rescheduled (perhaps into a new category) have its working set recalculated and be removed from main memory before being placed on an appropriate scheduler queue if it is still awake. Whenever a process is to be removed from active to immediate store it is first queued in the active take queue which essentially allocates channel capacity amongst those processes wishing to take this route (which involves pages being transferred first to main memory from active memory, then from main memory to immediate memory). A form of working set algorithm is also applied to the management of a process active storage allocation, the algorithm currently selects pages dependent upon usage over the last four main memory

residencies. There are four algorithms which may be used, the choice being dependent upon the current level of loading on the active store.

There are certain additions and modifications to the basic scheme. Any process which remains asleep for a long period of time (eight minutes) is removed from active store. process which remains awake for a certain interval (two minutes of real time) without interacting with the console is deemed no longer to be an interactive process and is placed in the penalty box. This means that when it comes to the front of a non empty core queue it will be returned to the rear of that queue several times (currently eight) before being removed. Whenever the process interacts with the user its penalty box status is removed. As it is extremely improbable that all the members of the multiprogramming set will be using their full main memory allowance at any given instant, and to take account of sharing, the main memory is over allocated by a certain amount. Another modification concerns preloading. If it is found that the next candidate for entry to the multiprogramming set cannot be given its full main memory allowance (even with the over allocation scheme) but that there is adequate physical space to allow that process working set to be

preloaded (and still leave some free space for use by other members of the MPS) this 'partial' preload is allowed to proceed. If the partial preload has completed and pages still have not been released to make up the process' full allocation, but its current allocation is greater than its working set size and a reasonable number of physical core pages are still free, then this process is allowed to enter the run queues, and acts as a normal MPS process which has a small main memory allocation. However, if this process' allocation is only equal to its working set size, or the number of physical core pages free is less than a safety limit, then it is suspended until adequate pages are released to give it its full There is, of course, a maximum of one allocation. partially preloaded process in the MPS at any instant, and this process has priority for the allocation of any freed central memory space. If a process overruns its current main memory allowance without ever having been strobed (i.e. having its working set recalculated) and, more than half its current pages were brought in by preloading, then there is a chance that the wrong pages were preloaded. To overcome this an EXTRA-STROBE (working set recalculation) is carried out at this point and if sufficient pages are removed, this process is allowed to continue.

space to be used fully, one of the replaceable disc drives is used as though it were a drum i.e. its storage capacity space forms part of the active storage. Allocation of active storage pages is handled so that all the drums are considered as though they formed a linear array of pages with this replaceable disc (known as the pseudo-drum) forming the higher addresses. The lowest free page available is always allocated first, thus the drums which correspond to the lowest active store addresses are kept as fully used as possible.

The main memory management scheme only allows a process to enter the MPS if it is estimated that there is sufficient central memory available for it to run efficiently. All decisions on the management of that process' allocation are then reached with consideration being taken only of that process' behaviour, and any process which is found to have a working set larger than its current main memory allocation is removed. This completely removes the phenomenon of thrashing [Denning 1968] which is due to an overcommitment of main memory. It also provides for the time-sharing of main memory by placing limits on the amount of time any process may remain in main memory. The algorithms are designed to favour highly

interactive processes by time-sharing the main memory and by the priority scheme which gives more residency periods to processes which require smaller amounts of main memory and very little CPU time.

### Quantitative Evaluation Techniques

Performance evaluation is generally carried out for three major reasons [Lucas 1971]:

- The selection of a new system choosing from a set of possible alternatives which system best meets a user's performance/cost specifications.

- 2) The projection of the performance of a new system - estimating the performance of an as yet un-implemented system i.e. as an aid in the system design process.

- The forcasting of the impact of possible changes in an existing system - changing a hardware or software component or the user load applied to the system i.e. system tuning or balancing.

Quantitative evaluation has grown

increasingly more difficult with the evolution of time-shared, virtual memory systems. The systems themselves have grown more complex and the range of programmes executed upon them has become wider and more varied.

In the earliest days of computing a simple figure of merit was considered adequate as a means of judging the performance of any system.

In the case of 'scientific systems' the figure of merit would often be based on the raw power of the central processing unit. This number could be obtained by calculating the execution time of a certain instruction stream, the mix of various classes of instruction included would represent a rough characterisation of the anticipated workload, or be drawn from some generally accepted mix [Gibson 1970]. Meanwhile for more 'commercially orientated' data processing systems the figure of merit would be based upon some measure of I/O throughput capacity.

As early operating systems were introduced their batch type of operation was often judged in terms of the time taken to process a chosen collection of jobs or benchmark. The benchmark would again form a characterisation of the expected workloads in terms of the proportions of the types of jobs it

contained. Other simple one figure measures such as job throughput rate or processor utilisation level were also often used.

However, as the architecture of the systems has become increasingly more complex it has become clear that no single figure of merit, or even any small number of figures of merit, will be adequate to describe a system's performance [Grenader and Tsao 1972], though several continue to be proposed [Merill 1975, Steven 1975].

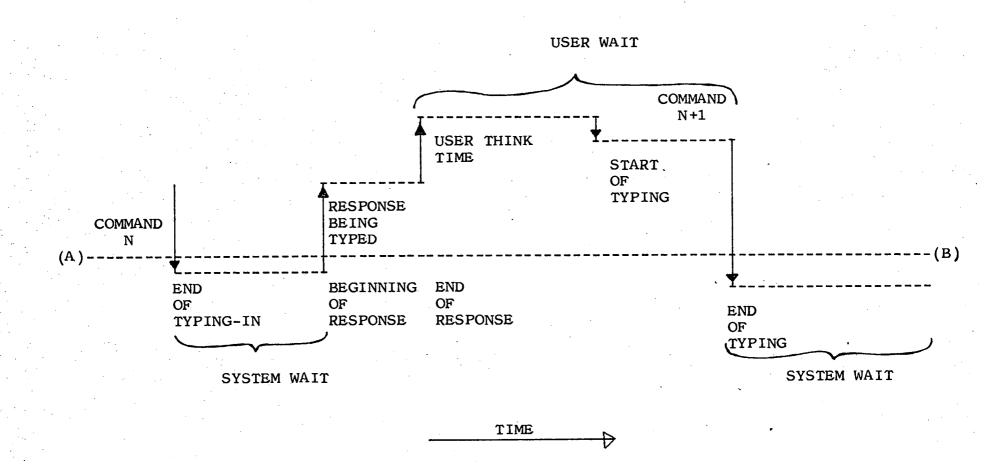

Within an interactive system the only

pure performance metric which every user applies is

that of response time. Response time is loosely

defined as the time a user has to wait, from the

moment he gives a command to the system, until the

moment at which he receives an answer. The distribution

of these responses will be of interest rather than

simply the mean or median response. Studies

[Miller 1968] of human reactions in the

man-computer interaction cycle have shown that if a

response is greater than two seconds then the user

begins to lose concentration, and if a response is

greater than 15 seconds then the use of the computer

ceases to be interactive.

No performance measure upon such systems is meaningful unless accompanied by some measures of the outstanding load upon the system e.g. processor utilisations, memory utilisations, number of simultaneous users, mean working set sizes, mean time between page faults, supervisor overheads. The problem of evaluation is not just to attach some figure of merit to a system or particular system configuration, but to attribute the observed performance to the various contributing factors and identify those factors which are most significant. Performance and load measures will vary from system to system and will depend upon the problem being addressed. Suitable metrics for time-shared virtual memory systems will be introduced later.

The two major aids to evaluation are modelling and measurement.

#### Modelling

Because of the inherent complexity of the systems under consideration the technique of modelling which produces a much simplified, abstract representation of the system has an obvious appeal.

Indeed, no evaluation of a system could proceed without at least the existence of some conceptual

model of how the system functions. Figure 1.3 could be regarded as such a conceptual model of the working of the EMAS process scheduling scheme. The value of a model may not only lie in the quantitative results it produces, but the actual formulation of the model itself, involving as it necessarily does the stripping away of a mass of detail, may reveal the major components of the system and their interrelationships.

Quantitative modelling techniques fall under two headings:

Simulation models

Mathematical models.

Parent 1976] consist of computer programmes, often written in a special purpose simulation language [Dahl and Nygaard 1966], or using a simulation package written in a high level language [Dimsdale and Markowitz 1964]. The representation of the system being modelled is embedded in the simulation programme. Using this technique it is possible to model all the major mechanisms involved in computer systems e.g. parallelism, variance in user programme characteristics, storage capacities, various servicing disciplines and various service time

characteristics. However, simulation is often criticised for being expensive and time consuming in both development and run times. The time and expense involved in certain cases may, in fact, make this approach impractical. However when this is not the case simulation does provide the ability to model whatever phenomenon may be considered significant.

Mathematical modelling mainly centres round probabilistic models and more particularly queueing theory. There has been considerable work in this area. The research has evolved from the study of single queues [McKinney 1968, Chang 1970] to the study of various networks of queues [Jackson 1963, Gordon and Newell 1967, Buzen 1973, Gelenbe 1975, Baskett et al. 1975, Gelenbe 1976]. Following from the classic analysis of CTSS [Scherr 1965] there have been attempts to apply such models to the evaluation of time-shared, virtual memory systems viz MTS [Moore 1971] and MULTICS [Sekino 1972] but it is only recently that such models have been put to practical use with the development and extensive use of a model of IBM's VM/370 system [Bard 1975, Bard 1976, Bard 1977]. Queueing network models still suffer from several limitations: is no direct way to model storage, service disciplines and service time distributions are still limited.

However, they may provide a useful means of studying

the gross performance characteristics of such systems.

#### Measurement

The other major aid to evaluation is that of measurement and experimentation on existing systems i.e. the empirical approach. The only way in which significant system phenomena may be identified in the first instant is through a procedure of empirical evaluation. Measurements from such a process may then be used in the essential step of validating current models and suggesting changes in future models of the system.

Several drawbacks to such an approach do exist. It is often difficult to obtain accurate measurements of particular phenomena, of interest due to inadequate system instrumentation, or due to gross interference caused by the measurement technique. The opposite extreme is also often a problem - the sheer mass of data produced by some measurement tools masking the trends the experimenter is searching for. Measurements taken upon an operational system will depend crucially upon the characteristics of the workload existing at the time

the measurements were taken. These changes in user workload which take place from day to day, or hour to hour and minute to minute, often prevent the acquisition of a consistent set of measurements, from which changes in performance may be attributed to specific system changes. A rigorous approach to system measurement is one of the necessary paths to be followed when attempting to discover just how such systems do function.

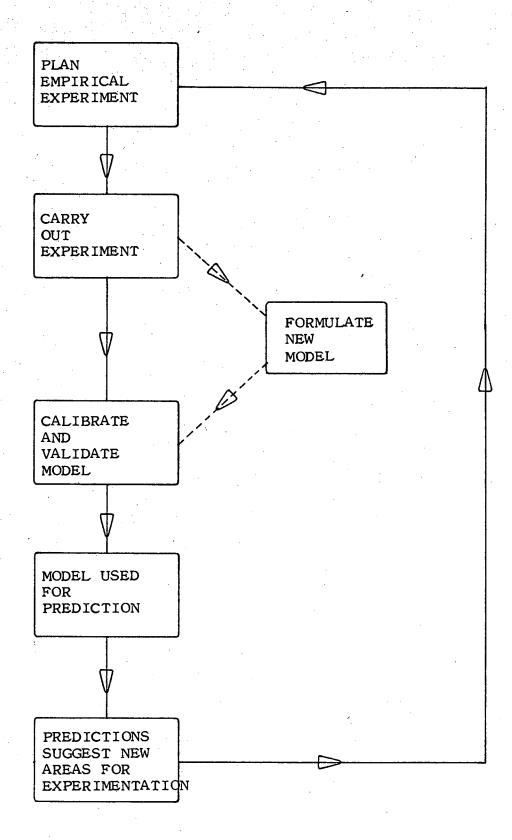

The ideal approach to evaluation is an iterative one with results from a controlled set of experiments being used in a model which, when validated and calibrated by this data, will suggest new areas for experimentation.

The main aim of the work carried out in this thesis is to increase, in some way, the understanding of the mechanisms at work in time-shared, virtual memory systems, and to be able to quantify the impact of any major component upon the overall system performance. This is carried out by the evaluation of the structure (and design) of one particular system (EMAS). The evaluation is thus empirically based and concentrates upon the techniques and aids necessary in such an exercise. The monitoring tools required are discussed first

(Chapter 2). Then the elements necessary to carry out a programme of controlled experimentation on such systems are described and the execution of such an experiment is reported (Chapter 3). The results from this experiment are presented in detail (Chapters 4 and 5) and used in the calibration and validation of a simple simulation model. This model is then used in the further investigation of certain of the parameters affecting system performance (Chapter 6). Considering the three main areas of application of performance evaluation given at the beginning of this section, the techniques used and the approach taken fall under heading 3 - system tuning and balancing. However the results obtained and the techniques applied will also be of use in the other two areas.

## Chapter 2

A comprehensive and effective set of monitoring tools is an essential aid in any empirical investigation of a system's performance. An ideal monitoring aid would be flexible and have the ability to obtain all required data (and only that data required) with absolute accuracy. This ideal monitor would not, of course, interfere with the system in any way either by adding to the supervisor overhead, or changing the behaviour of user processes. Unfortunately, in the case of time-shared, virtual memory (T.S.V.M.) systems such a monitor does not exist. In this chapter available monitoring techniques are reviewed, and those implemented in the EMAS resident supervisor are described.

Before any measure is carried out a clear view must exist of exactly what data is required and what use this data is to be put. Any possible interference caused by the method of measurement must also be known and taken into account. Data may be obtained upon the performance of the system itself or the behaviour of the user processes running thereon, i.e. the workload. The distinction between workload and pure performance measures is often blurred, and

the two are always related. Typical system performance results are often presented on:-

- a) Response time distributions.

- b) Utilisation levels of major system components (e.g. CPU's, memories, channels, supervisor modules).

- c) Distributions of queue lengths or wait times for various system resources.

Typical measures of user process characteristics include:-

- a) Distribution of the time the processes spend in terminal wait state (e.g. think times).

- b) Space requirements of processes at various levels of storage hierarchy.

- (e.g. size distribution and contents of working sets, distribution of times between page faults).

- d) Distribution of resources required by each interaction.

- e) Distribution of interaction classes.

In the following, the terms "target system" or "host system" will be used to mean the system being measured or experimented with.

## Monitoring Techniques

A comprehensive review of current monitoring techniques exists in the literature [Nutt 1975], so only a brief summary of the advantages and disadvantages found in the major classes of monitor is given here.

Three classes of monitor exist:-

- 1) Hardware Monitors

- 2) Software Monitors

- 3) Hybrid Monitors

#### 1) Hardware Monitors

A Hardware Monitor consists of a distinct electrical device (generally with its own clock and storage media) connected to the target system's hardware by a set of one or more probes. Signals received via these probes are interpreted by the device and data is then analysed on line, or logged (usually to magnetic tape) for later off line analysis. The probes used are usually of such a design that they cause no significant perturbations in the circuitry to which they are attached. This gives the hardware monitor its great advantage over all other techniques: it is essentially non-interfering, inducing no supervisor overhead or change of user behaviour in the target system. The accuracy obtained by this method is also usually dependent upon the precision of clock incorporated in the monitor, and not upon the clock facilities in the host mainframe.

The complexity of such devices varies greatly from the extremely simple - monitoring the existence of a single signal (e.g. a trace chart recorder connected to a processor's idle light [Stang 1969]) - to the other end of the spectrum where a fully interactive mini computer is

employed - with special computational as well as interface hardware, capable of simultaneously recording and analysing a very large number of interrelated events [Aschenbrenner et al. 1971].

Such monitors have been found very useful in obtaining summary data such as utilisation levels and degree of overlap on certain hardware components (e.g. CPU's and channels) or execution counts on the instructions in the mainframe's repetoire [Schreiber 1976]. However, it is often impossible to establish relationships between the data obtained and the causes for such levels of performance - user behaviour patterns and software scheduling algorithms. On more complex mainframes the correct placement of probes will become more difficult, and skilled engineering guidance will be required. The mainframe will also probably have to be taken out of service for a time whilst such a device is attached. With the introduction of mainframes using more and more Large Scale Integration (i.e. machines such as the Amdahl 470/V6) the placement of probes will become more and more difficult, and certain data may no longer be available for collection by this method.

The characteristics of hardware

monitors would seem to make them best suited as an aid where the pure performance of the hardware only is of interest e.g. counts of different types of instructions, degree of overlap of certain hardware devices. In the case of T.S.V.M. systems, where the complex characteristics of the user workload must always be taken into account, the use of pure hardware monitors alone is of limited value. have, however, been applied to some time-shared systems such as CDC's Kronos system [Lindsay 1976]. The advantages of hardware monitors seem better suited to special purpose systems where a regular, well understood workload exists [Partridge and Card 1976] in such an environment they may even be used as an aid in programme optimisation [Fryer 1973]. Several types of hardware monitor are now commercially available.

#### 2) Software Monitors

Software monitors provide an extremely flexible and popular method of obtaining performance data. They will, however, always have the great drawback that they necessarily interfere with the target system. They form part of the system, occupy memory space for code and data, consume processor power in execution and often use channel capacity in storing

data. The accuracy of any software monitor will usually be limited by the resolution of the hardware clock available on the mainframe.

A great range of software monitors have been implemented on various systems (indeed nearly every system contains a software monitor in terms of the accounting log). As a broad classification they can be divided according to their recording discipline into:

- a) Sampling Monitors

- b) Continuous-recording or event monitors

and, according to their storage discipline (i.e. the way in which data is disposed of once it has been collected), into:

- c) Accumulating monitors and

- d) Tracing monitors.

#### a) Sampling Monitors

Sampling monitors are perhaps amongst the simplest to implement, and should impose the least

overhead on the target system. As the name indicates, the monitor is only activated at certain times, either at regular intervals using some form of alarm clock interupt, or by the occurrence of some system event, such as the idle process gaining the CPU. The metering routine thus activated will then obtain the required data and save it. This routine is normally distinct from the rest of the target system and so has the advantages of modularity (easy removal or modification). Also, as they are not active all the time they should impose less of an overhead than other monitors. argument against using a sampling technique is that the accuracy will depend upon the number of samples and the randomness of the sample. Very few sampling monitors obtain their samples at truly system independent random intervals, so the result could be affected by periodic or other phenomenas within the This could have a very significant target system. effect upon the accuracy of the results obtained. These monitors have been used in the investigation of code utilisation by sampling the programme counter [Waite 1973], and are often used to obtain approximate distributions of system queue lengths [Jalics 1973, Gonzales 1975].

#### b) Event Monitors

Event monitors are usually formed by a set of software probes scattered throughout the operating system and activated for periods of time by the setting of a group of trigger variables. These probes are necessarily scattered throughout the system, and thus not easily modified. Although data is only gathered when a trigger is set and the flow of control passes a probe, the trigger must be tested every time the probe is encountered, which means there will be a certain overhead even when no data is being collected. Event monitors, however, do not suffer from any suspicions about sampling accuracy, their accuracy only being limited by the resolution of the clock and the speed of the probe.

#### Storage Discipline

Monitors may be further classified according to their actions on obtaining a particular item of data. They may integrate this item into a table in main memory holding a summary of the performance data (accumulating monitors). This involves carrying out a small amount of processing on each item of data when it is collected. The accumulated table is then output (perhaps involving further

processing) regularly after comparatively long periods or on demand. The alternative is to do no on line processing on collection of data, but to output each item immediately, usually with some form of time stamp (tracing monitors). The accumulating method will tend to use more CPU time and code space - though a tracing monitor will use CPU in organising buffers and transfers. The table space used by an accumulating monitor tends to be a constant overhead, whilst tracing monitors may claim buffers from a system wide pool only for the duration of the measurements. Tracing monitors will consume channel capacity, often require exclusive use of a device (e.g. tape drive) and frequently produce great volumes of output. However, the data so produced allows greater flexibility as it may be analysed in several different ways to produce a variety of results.

Software monitoring is certainly the most popular method of measurement. It involves no acquisition of additional hardware, and can usually be implemented easily by the system programmers. They also have the advantage of being able to observe the cause and effect of certain transient events which a hardware monitor cannot. Software monitors are normally highly system dependent, though the principles involved may be transportable between different

operating systems, the monitor itself rarely can.

#### 3) Hybrid Monitors

The logical merging of both hardware and software monitoring techniques results in the most recent monitoring method - that of the hybrid monitor. In this method a complex hardware monitor, usually consisting of a mini computer with associated probes, is however also attached to the host system as a normal device via some form of channel [Rudd 1972, Aschenbrenner et al. 1971, Estrin et al. 1972, Schwemm 1972]. This allows software monitoring aids implemented within the system to communicate with the Thus whilst the majority of the data mini computer. may be obtained in a non interfering fashion by the hardware monitor part, further information, allowing this data to be associated with various phenomenas within the system, may be produced by the software aids communicating via the channel. This method does, of course, suffer from drawbacks of both hardware and software monitors: engineering knowledge is required for the correct placement of the probes; the host system may have to be taken out of service for the attachment of such a device; the software aids will necessarily interfere with the system; much knowledge of the software structure will be necessary for the

gathering of the correct data in the most efficient fashion. However, hybrid monitoring should still reduce overhead, and with many of the large mainframes now being produced, such as the DEC KL 10 and KL20 systems [DEC 1977], containing mini computers with access to most of the important registers and parts of the memory (i.e. a possible built-in hybrid monitor), it would seem to indicate that greater use could be made of hybrid monitors in the future.

One class of system performance measurement devices not covered here is that of the remote terminal emulator. This will be considered in the next chapter.

#### Virtual Memory System Monitors

The majority of instrumentation reported on these systems is carried out in software. Very little use appears to have been made of hardware monitors, almost certainly because of this difficulty in establishing relationships between observed performance and the factors which contribute to it. One reported case of what may be classified as hybrid monitoring does take place on MULTICS [Saltzer and Gintell 1970] with a PDP-8 being used with special access to the host systems tables and some registers.

However, as the data rate between the monitor and the host system is very low (less than 60 words/second) the full potential of this technique has probably not been realised.

As the behaviour of user processes is of such interest an ideal monitor would be one which allows the collection of data on process behaviour as well as the manner in which processes are handled by the scheduling algorithms. An event trace monitor which records an event each time a process moves significantly either within its virtual memory or within the system queues would appear to be one solution. The Data Collection Facility [Alexander 1975, Pinkerton 1969] on MTS is such a Implemented within the code of the resident supervisor the DCF allows the tracing of a set of events of one or more specified processes. The type of events which may be recorded allow data to be obtained on:

- i) The queueing and removal from queues of processes by the supervisor.

- ii) The changing of status of monitored processes.

- iii) All aspects of page movement in and out of physical core, and the migration of pages to the outer levels of the hierarchy.

- iv) The claiming and freeing of pages in virtual memory.

- v) All interpupts generated on the system.

- vi) The opening of files by processes.

- vii) The starting and stopping of user tasks on the system.

A very comprehensive set of possible data items. As MTS is written in machine code some difficulty is involved in adding new events [Alexander 1977]. The vast amounts of data collected during any run are recorded on magnetic tape for off-line analysis. A data reduction programme - the Data Analysis Programme - is also available to aid the investigator in the interpretation of the data. A very sophisticated set of monitoring aids have been built into IBM's VM/370 system [Callaway 1975], allowing both sampling and event trace monitoring at various levels of detail in the system. This also has an associated Statistics Generating Programme to aid analysis.

The VM/370 performance monitor may be bought by customers running VM/370 to assist in tuning and balancing of their system.

MULTICS contains a variety of monitoring facilities to aid in the measurement of process characteristics [Saltzer and Gintell 1970]. Surprisingly, however, no generalised event trace monitor has ever been implemented, although a comment is passed in the Saltzer and Gintell paper that one would have been useful. The monitoring aids which have been implemented include:

- i) A sampling monitor accumulating distributions of the segments used.

- ii) A count which may be kept of all missing pages and segments encountered whilst executing a particular segment.

- iii) A missing-page trace of the last 256 page faults produced by the monitored process (held in a ring buffer).

For the gathering of raw performance statistics on the system (i.e. utilisation levels or queue length distributions) MULTICS makes use of the Graphic Display Monitor which is essentially a PDP-8 with access to certain of the host mainframe's registers and tables. This continuously displays all system queues and arrays, showing execution time profiles for supervisor modules. A count and total CPU time expended in certain supervisor modules is also accumulated.

A very sophisticated event monitor has been implemented on the TENEX system [Gonzales 1975] for the gathering of system performance data. allows the definition of events to be monitored and the switching off and on of data collection to be carried out from a normal user process via a set of special supervisor calls and a password scheme. probes which collect the data and the tables in which the data is initially accumulated are part of the resident supervisor, though the data may be transferred to the user process' file when desired. This contrasts with the considerably more rigid data storage regime of the MTS-DCF which, though obtaining a more general and more accurate range of data (1 millisecond clock in the TENEX scheme to a 13 microsecond clock on MTS), can only be controlled from the operators console, and always outputs to a specified magnetic tape drive. An event monitor which accumulates distributions of various queues and timings has been implemented on the

TOPS-10 system [Jalics 1973]. Both of these event accumulating monitors are used more for obtaining performance statistics on the system than on the behaviour of the user processes.

## Monitoring Aids on EMAS

The purpose of the monitoring aids implemented in EMAS was to give performance data on the system which would be of use in investigations of the architecture and algorithms employed within the system, as well as being of use in tuning the system in practical use. No hardware or hybrid monitoring aids were available, and all monitoring has been carried out by software techniques. The clock used throughout was that provided on the ICL 4-75 mainframe with a precision of 6.5 microseconds. As EMAS was designed as an extensible system on which the user has the capability of writing his own subsystem or even file system, all the performance monitoring aids considered here were implemented within the innermost level, i.e. that of the resident supervisor. Various other monitoring aids have, of course, been implemented at other levels [Adams and Millard 1975]. The entire system is written in the high level language IMP. The advantages accrued from this fact cannot be over-emphasised. Apart from allowing for the easy implementation of

software probes, the modularity of the system allows great flexibility and ease of change, with only the module which has actually been changed needing to be recompiled. The compilation and linking of a modified system, taking in the order of fifteen minutes (real time), is extremely fast for a system of this complexity and size.

#### CPU Time Utilisation

A profile of CPU time utilisation was considered to be vital to such an investigation. The vector of CPU time spent in major states (SUPERVISOR, USER, IDLE) would, of course, be one of many important parameters to be considered. Furthermore, as the supervisor activity within this class of system is inherently higher than that in some other forms of systems, it would be of interest to know in which modules of supervisor code most of the CPU time was being spent.

The message based nature of communication between EMAS supervisor services lends itself well to the monitoring of these variables. A simple change in the kernel where requests are unstacked from the Main-Q allows a count to be kept of the number of calls made on each service, and the total CPU time expended

between calling the service and returning from it. As

the services run uninterruptably this gives a very

precise account of where, within the resident supervisor,

time is being spent.

Whenever the supervisor finds that there is no user process in central memory in a ready to run state and no supervisor requests outstanding which can be fulfilled i.e. that the system is idle, then process ## 0 - the idle process - is loaded onto the CPU, and executes an idle loop until some form of work arrives. This process is essentially handled as a normal user process, and has the CPU time it consumes recorded in its entry in the process list. Thus an accurate measure is obtained of the time the CPU is idle. A further split is made in the idle time between time in which no user processes are active (i.e. no user, process is awake - true idle time) and time in which user processes are active, but for some reason none could proceed - blocked time. CPU time not being used by the supervisor or the idle process within an interval is that consumed by user processes and unaccounted kernel time. analysis this time which is the time spent translating interrupts to requests on appropriate service and on handling the MAIN-Q itself, is attributed to user processes. The time consumed

in this will be further discussed in Chapter 4.

The dumping of the data arrays involved takes place at systems close-down or on the setting of a system test flag from the operators console. First in raw form showing the total number of entries to each service, the total time spent in that service (in seconds) and the average time per call (in microseconds) [Table 2.1]. To minimise the insignificant entries nothing is printed on services which use less than one second during a session. The data is also processed on-line to obtain the CPU breakdown between major states (Supervisor, Idle, User) and the breakdown by function within the supervisor [Table 2.2]. A machine readable form of this data exists in the system main log should further processing be required.

Interference caused by this measurement consists of:

- a) Two arrays of 256 bytes each to hold the data.

- b) A small number of extra instructions in the KERNEL to gather the data.

|                   | METERING               |                      | ION                      | and the second s |

|-------------------|------------------------|----------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2.1         | IDLE TIME<br>NO WORK A | VAILABLE             |                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   | SERVICE<br>3           | COUNT<br>22          | <b>TI</b> ME<br>0        | MUSECS<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   | 6                      | 186<br>54264         | 0<br>133                 | 0<br><b>245</b> 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SAMPLE OF RAW CPU | 7<br>8                 | 1905<br>19145        | 2<br>30                  | 1049<br>1566                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MONITOR DATA      | 9                      | 13556<br>16088       | 12<br>0                  | 885<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                   | 11<br>14               | 1658<br>262          | 0                        | 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

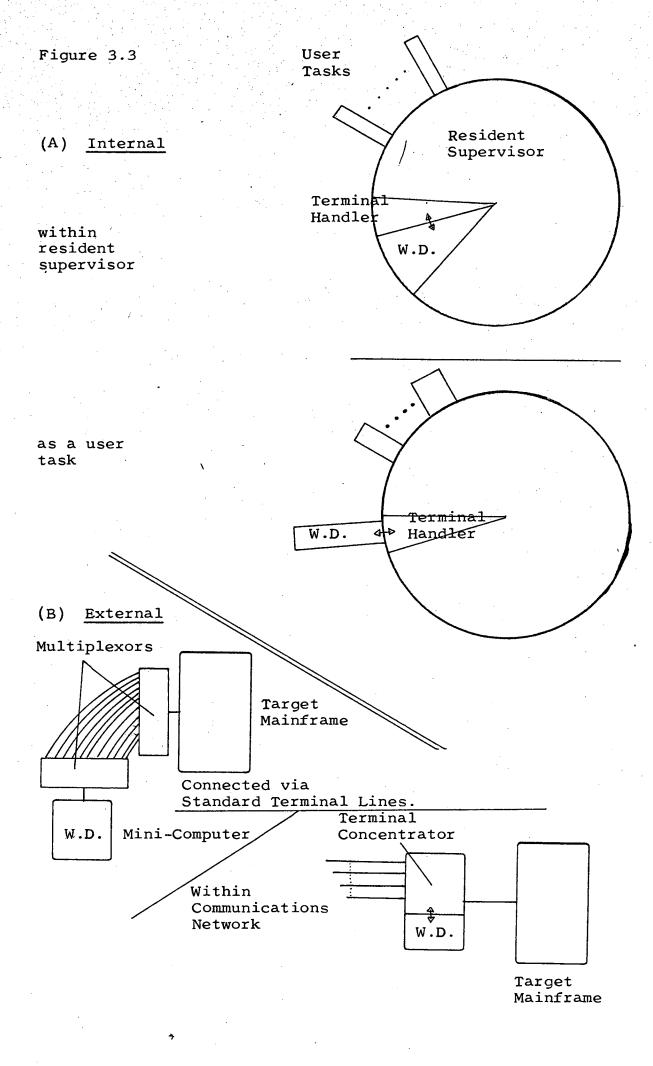

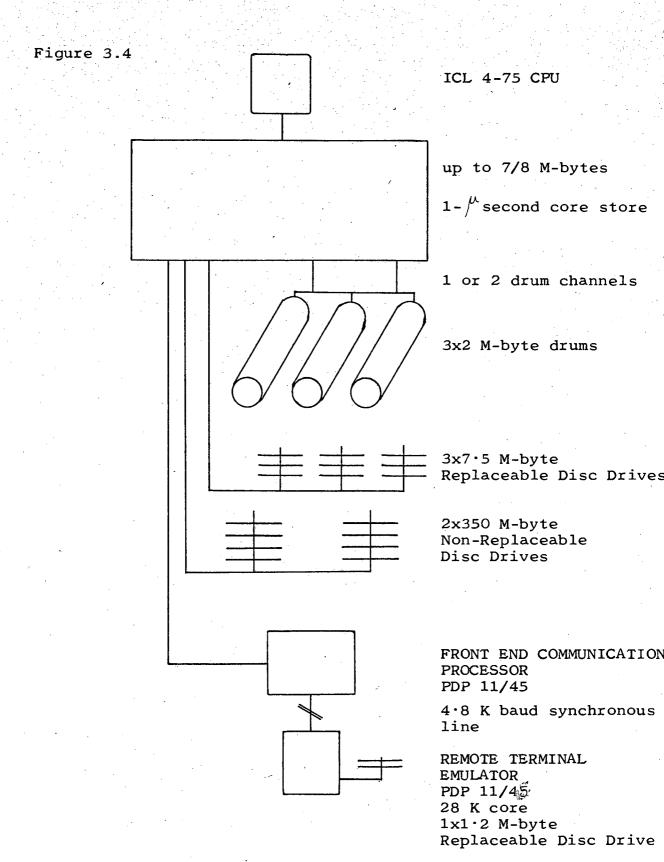

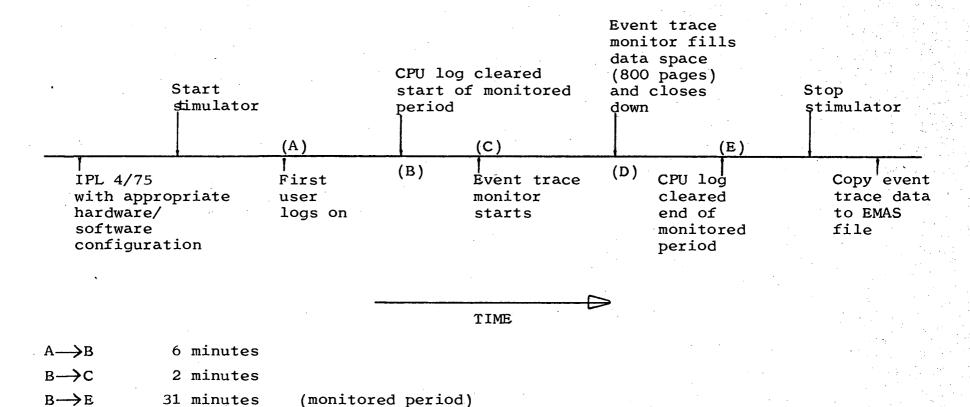

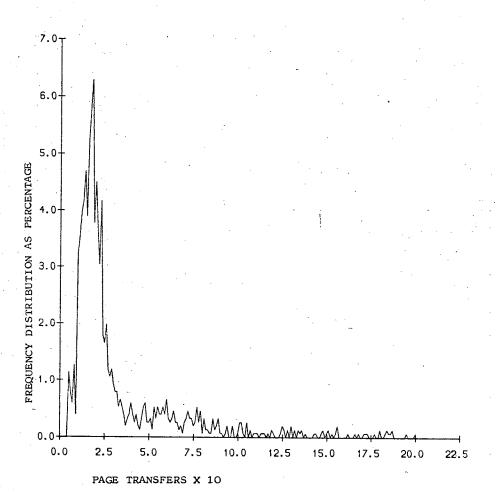

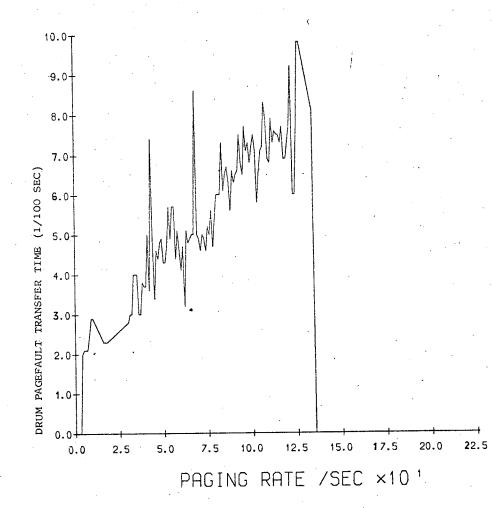

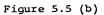

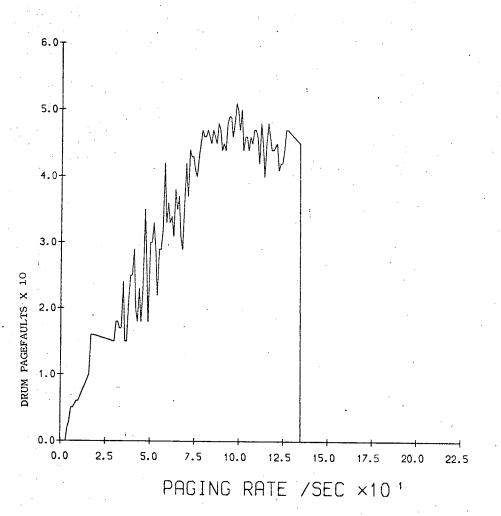

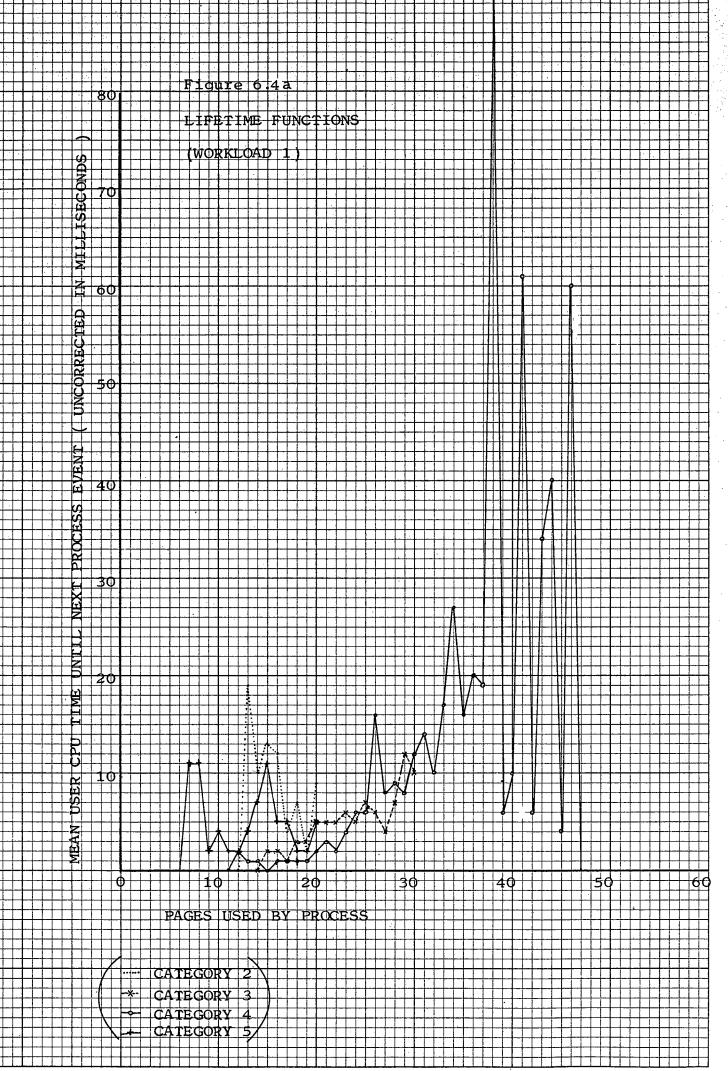

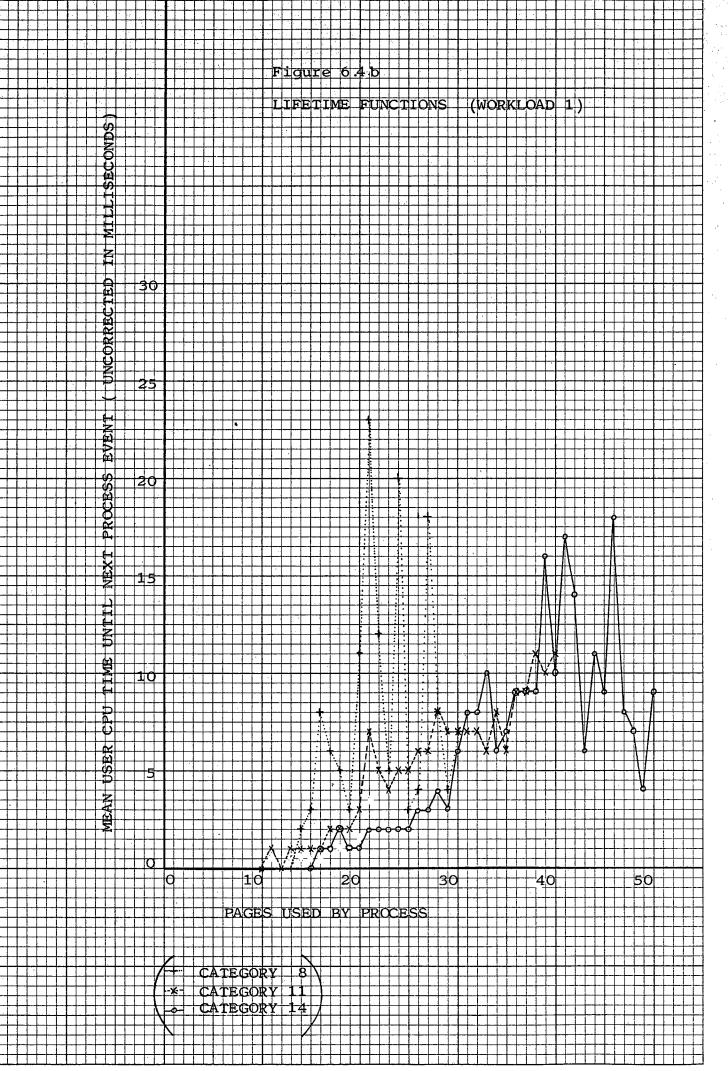

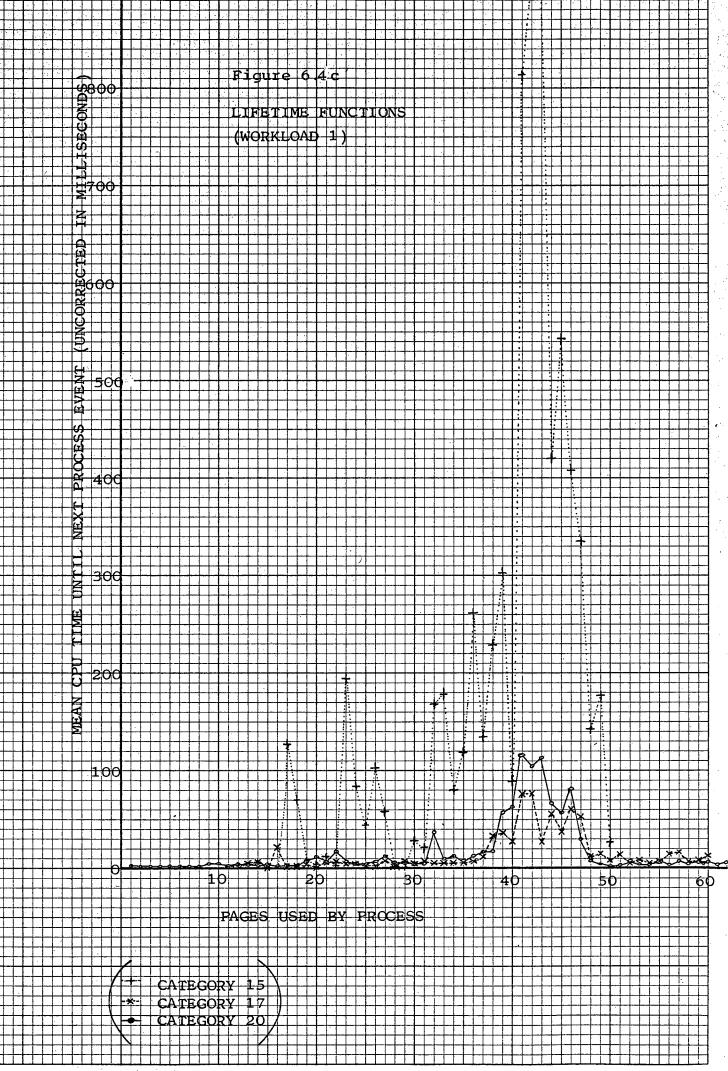

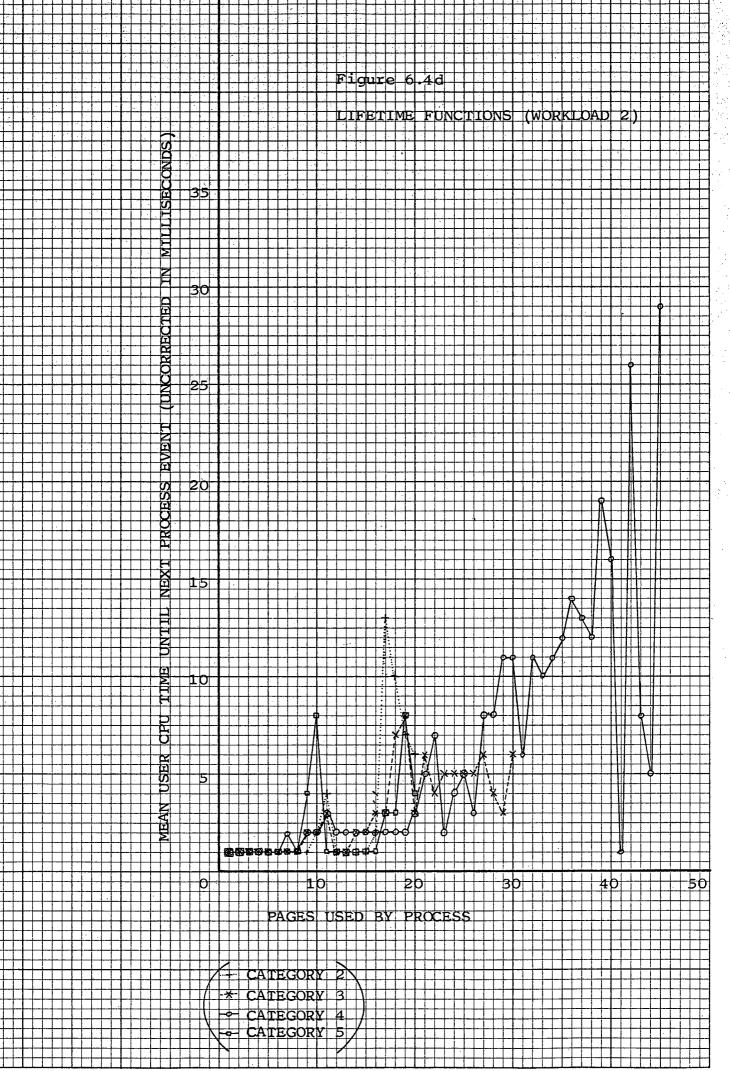

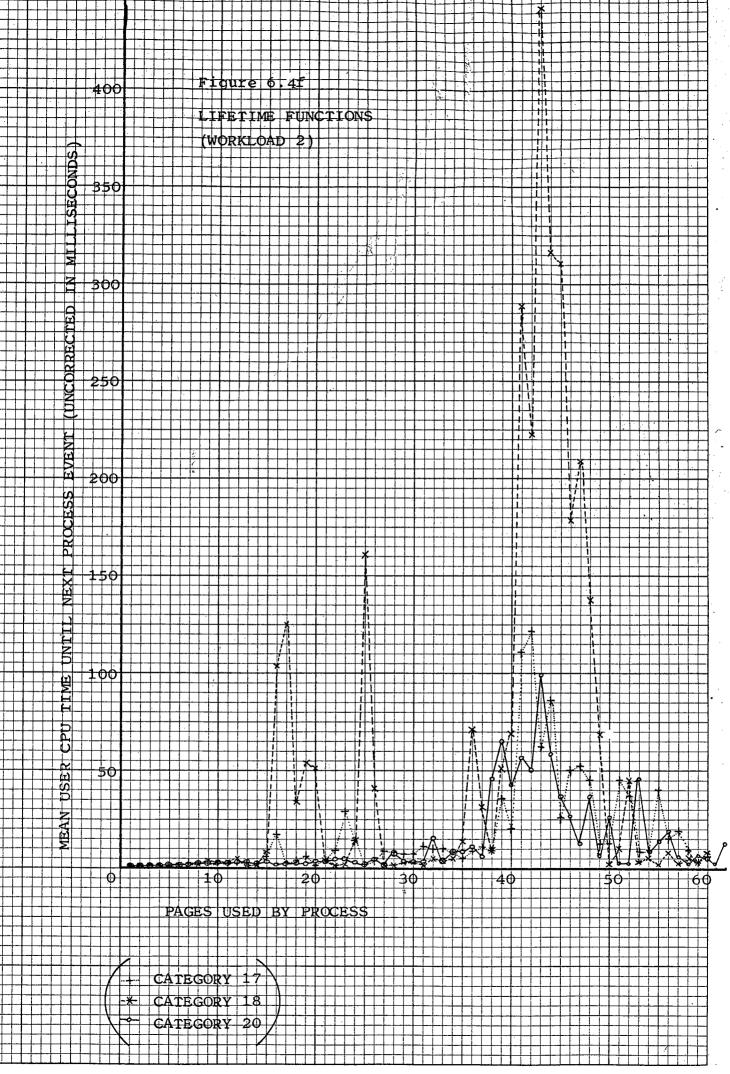

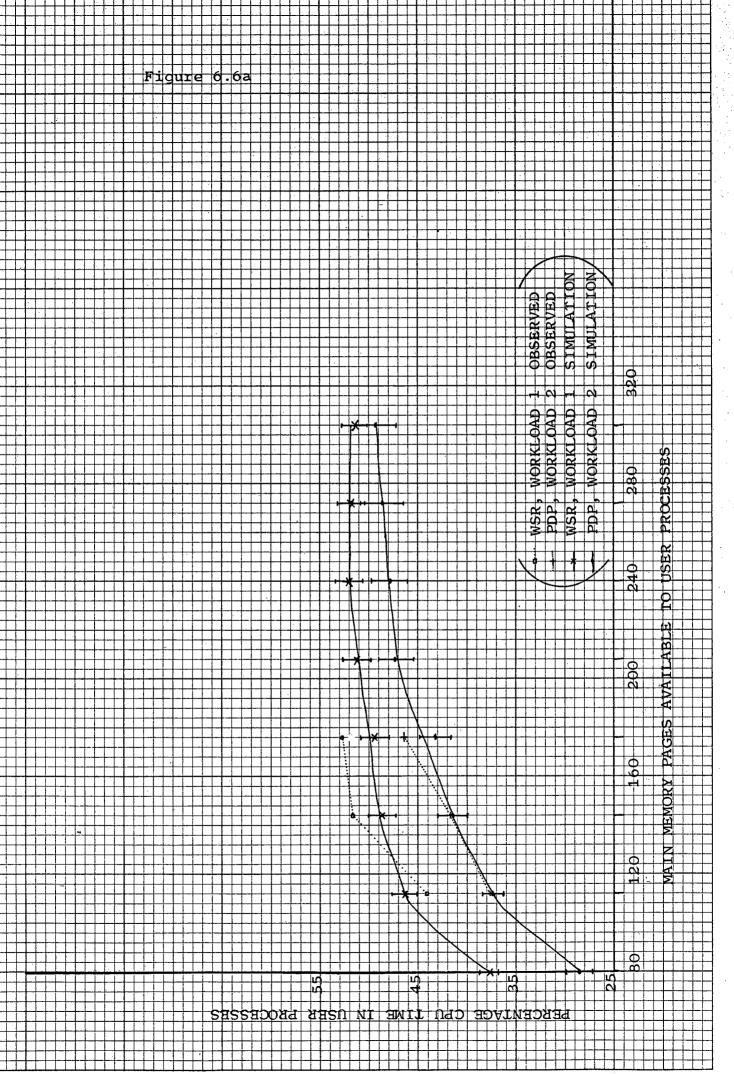

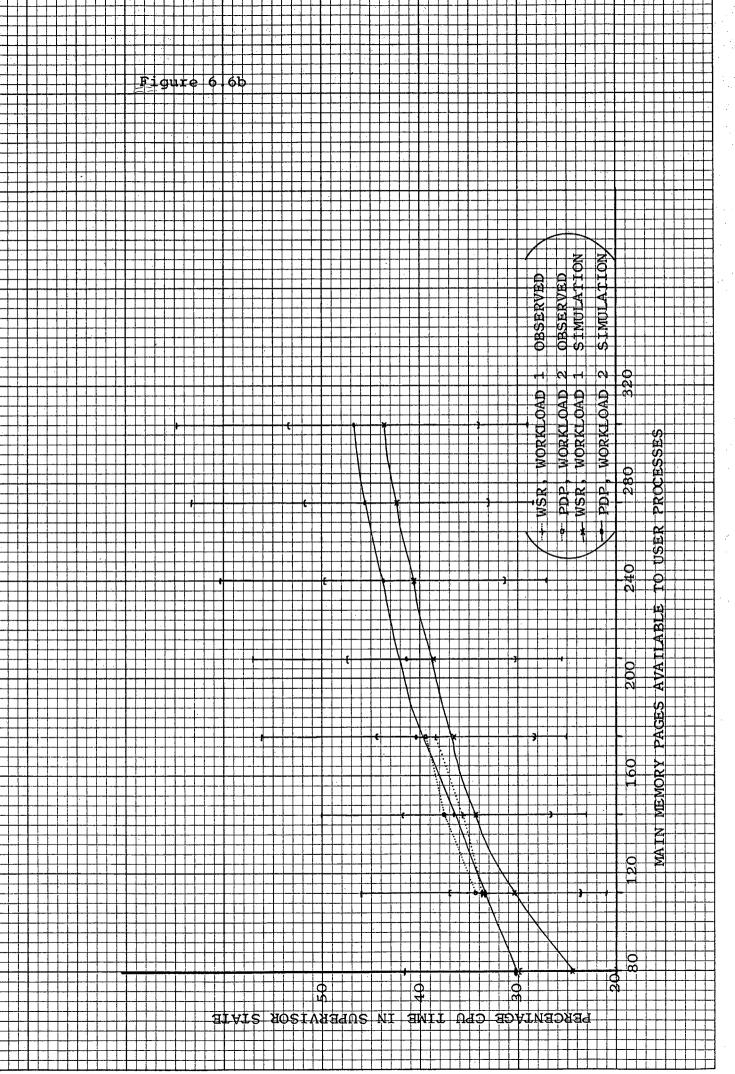

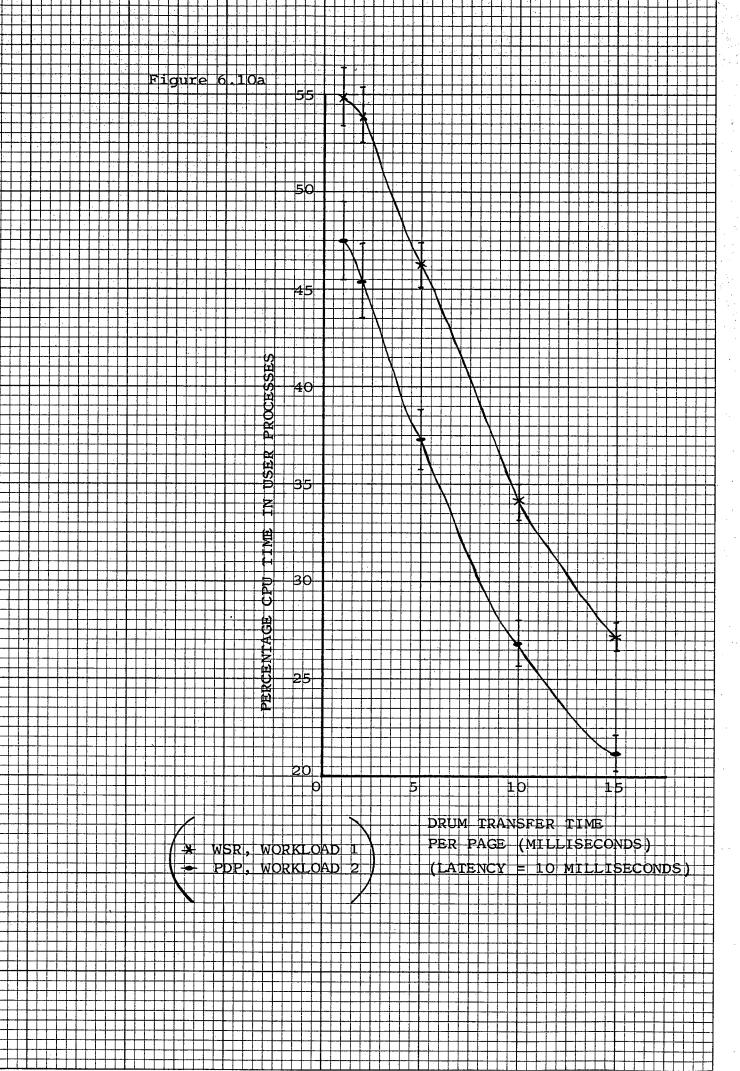

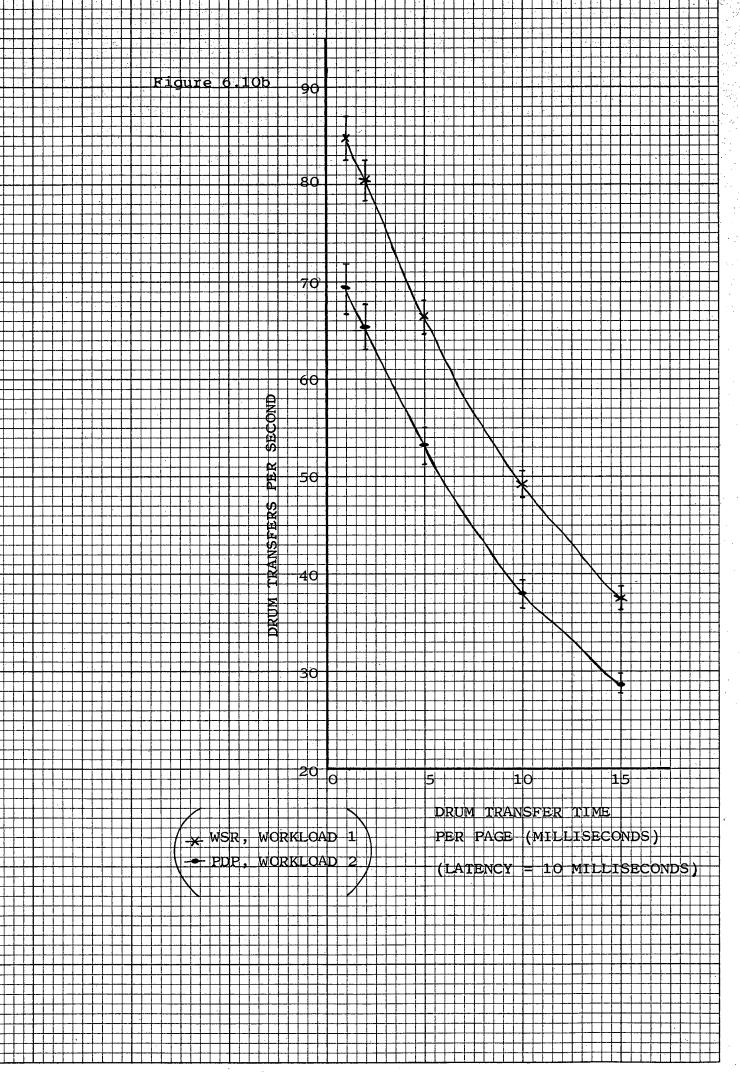

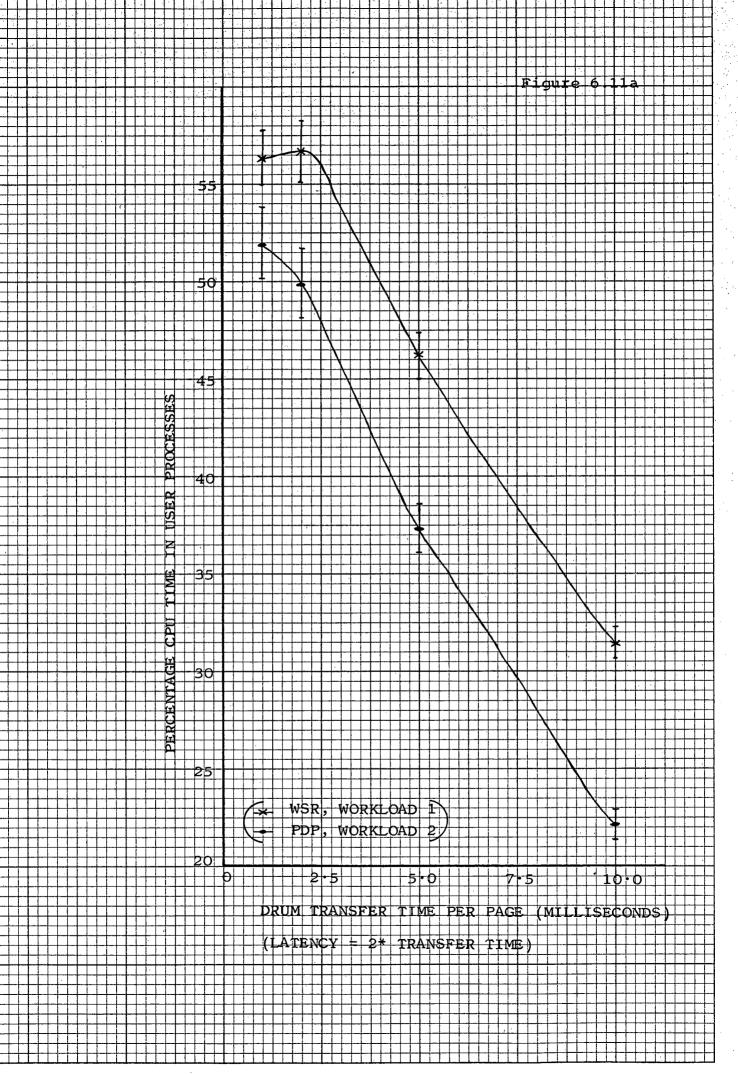

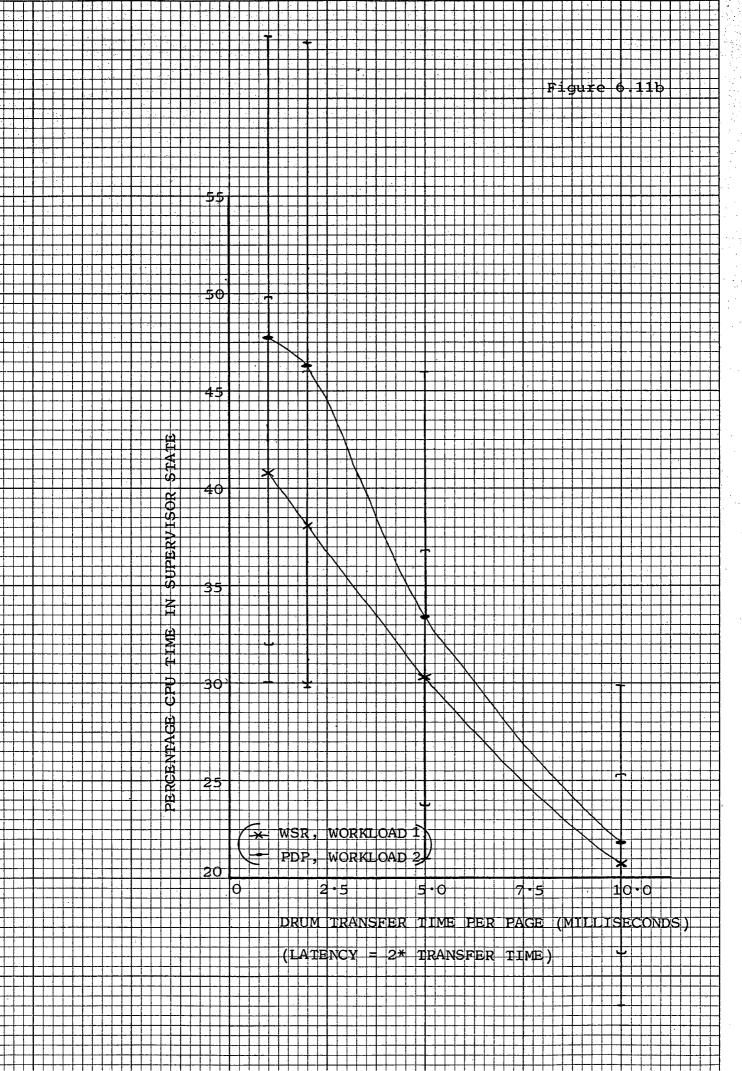

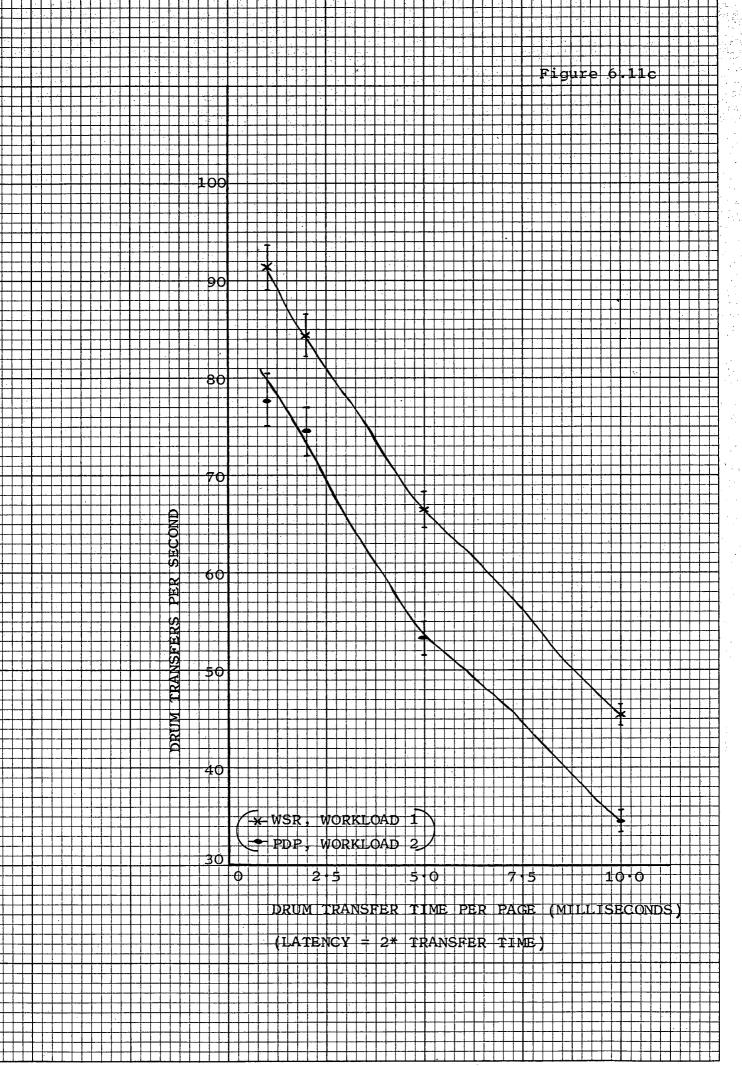

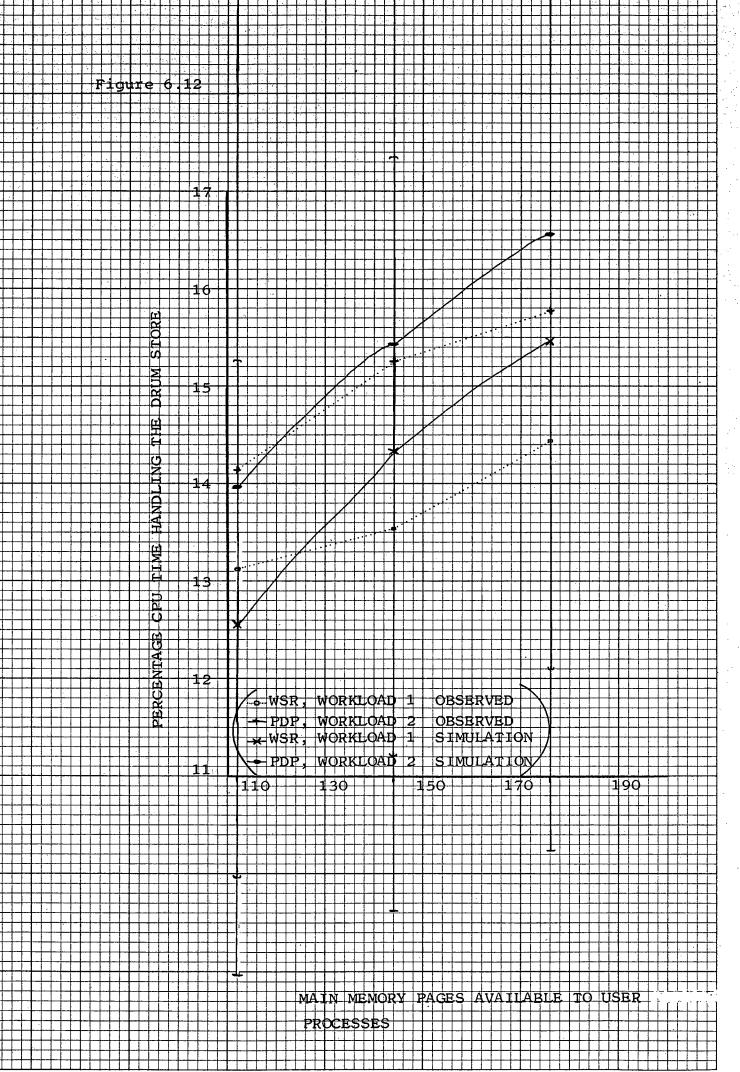

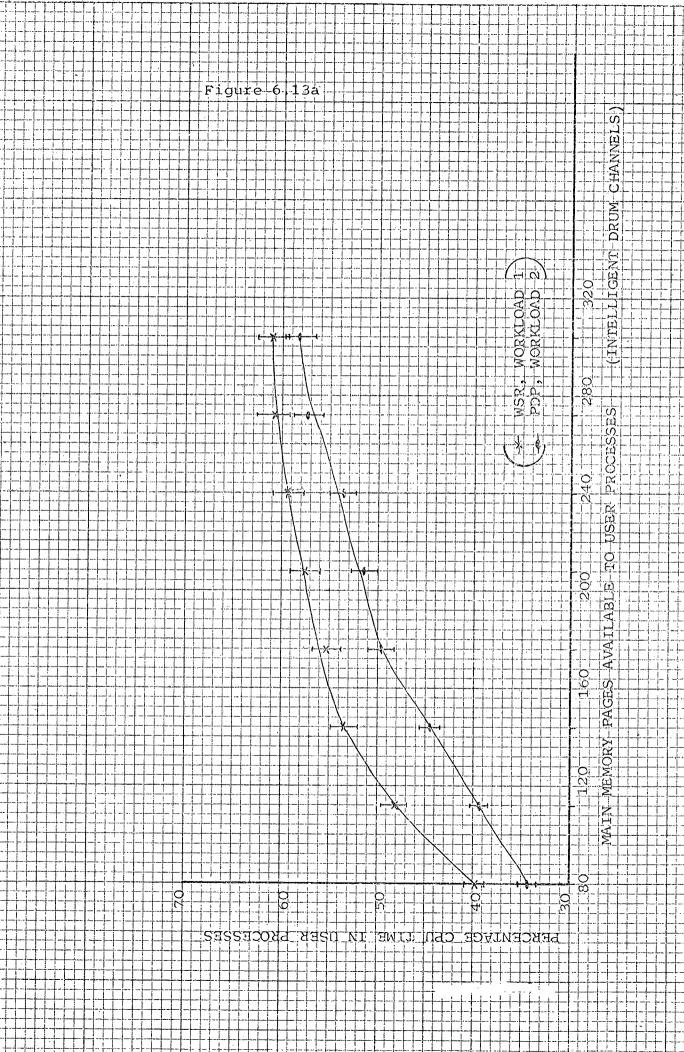

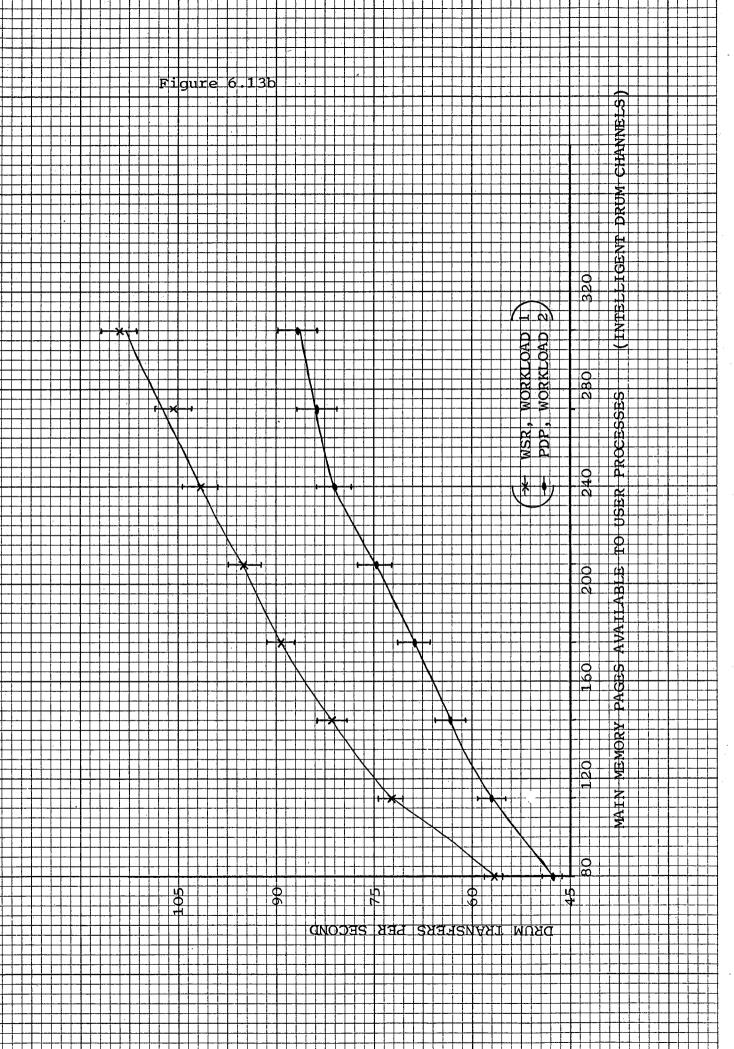

|                   | 26<br>27               | 131<br>131           | 0                        | . 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |