# **High-Level Synthesis Using Structural Input**

Iain William Finlay

Thesis submitted for the degree of Doctor of Philosophy University of Edinburgh March 1992.

# **Abstract**

The task of a high-level behavioural synthesis system is to create a structure to implement a given abstract specification of behaviour. The behaviour is specified at the algorithmic level, typically in the form of a high-level programming language. The synthesized structure is described at the register-transfer level. In such systems the synthesis task is guided only by the behaviour and some physical design constraints such as speed and area. This approach frequently leads to difficulties in synthesizing a suitable architecture.

The synthesis system reported in this thesis tackles this problem by enabling the designer to specify structural input alongside the behaviour. The structural input is described at the register-transfer level and need not define a complete structure. The synthesis tool makes use of this input structure by incorporating it into the design where appropriate or as instructed.

This structurally directed approach is shown to give the designer greater control over structural aspects of the design in addition to enabling greater exploration of possible structural solutions.

# **Declaration of Originality**

This thesis, with the exception of Section 5.2.1, was researched and composed by the author in the Department of Electrical Engineering at the University of Edinburgh between October 1988 and February 1992.

# **Acknowledgements**

I would like to acknowledge the help of my supervisor, Prof. Peter Denyer, and the financial support provided by the Science and Engineering Research Council and British Aerospace. Over the past few years I have received help and advice from my contemporaries: Douglas 'Gooby' Grant, Paul Neil, Jonathan Puddicombe and David Mallon.

Iain William Finlay.

| Abstract                                                      | I  |

|---------------------------------------------------------------|----|

| Declaration of Originality                                    |    |

| Acknowledgements                                              |    |

| Contents                                                      |    |

| Chapter 1<br>Introduction                                     | 1  |

| Design Automation.                                            | 1  |

| High-Level Behavioural Synthesis.                             | 3  |

| Structural Direction.                                         | 5  |

| Thesis Overview.                                              | 7  |

| Chapter 2<br>Behavioural Synthesis Review                     | 8  |

| Historical Overview.                                          | 8  |

| 'One Shot' Systems.                                           | 12 |

| Iterative Systems.                                            | 14 |

| Architecture Specific Systems.                                |    |

| Representations.                                              | 17 |

| Tree Representations.                                         | 19 |

| Semi-data Flow Graphs.                                        | 20 |

| Separate True Data and Control Flow Representations.          | 21 |

| Combined Representations.                                     | 22 |

| Interaction with Allocation.                                  | 23 |

| Scheduling Algorithms.                                        | 25 |

| Data Path Allocation Techniques.                              |    |

| Optimal Register Allocation.                                  |    |

| Graph Theoretical Techniques taking into account Interconnect |    |

| Branch and Bound Technique.                                   | 34 |

# **Contents**

| Iterative Techniques.                                 | 34 |

|-------------------------------------------------------|----|

| Rule-based Schemes.                                   | 35 |

| Chapter 3<br>Models for Behavioural Synthesis         |    |

| Introduction.                                         | 36 |

| Behavioural Model.                                    | 37 |

| Behavioural Elements.                                 |    |

| Data Flow Terminology.                                | 41 |

| Structural Model.                                     | 43 |

| Structural Components.                                | 44 |

| Specifying Structures.                                |    |

| Control Model.                                        | 47 |

| Timing Model.                                         | 47 |

| Binding Model.                                        | 49 |

| Representing Control.                                 | 50 |

| System Overview.                                      | 51 |

| The Mapper.                                           |    |

| The Scheduler.                                        | 53 |

| The Data Path Allocator.                              | 53 |

| Chapter 4<br>Mapping Behaviour to Structure           | 54 |

| Introduction.                                         | 54 |

| Mapping a Data Flow Graph to a Structure.             | 55 |

| The Matchmaking Algorithm.                            | 56 |

| The Dependency Algorithm.                             | 58 |

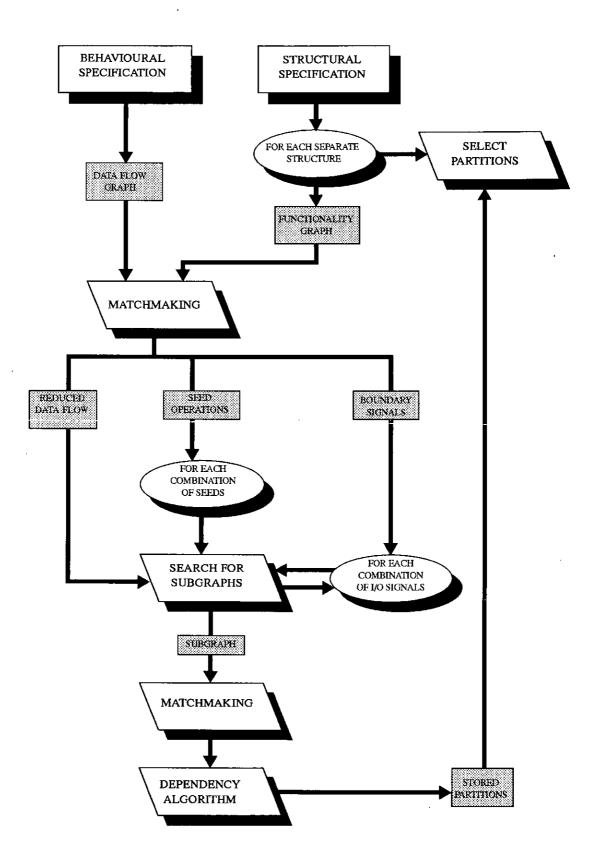

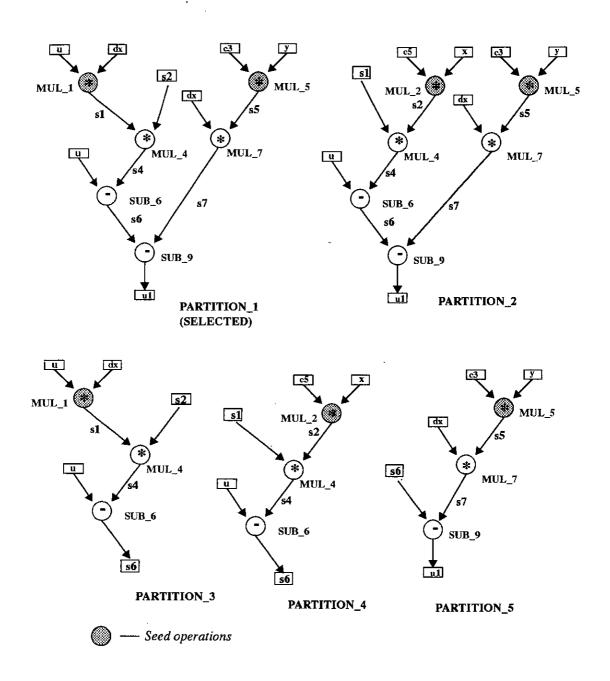

| Mapping Partitions of a Data Flow Graph to Structures | 60 |

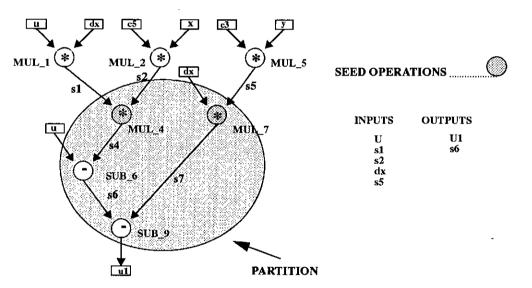

| Identifying Partitions.                               | 60 |

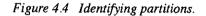

| Partition Selection.                                  | 64 |

| The Integrated Approach.                              | 65 |

|                  | Worked Example                                       |    |

|------------------|------------------------------------------------------|----|

| (                | Concluding Remarks                                   |    |

|                  | Computational Complexity                             |    |

|                  | Memory Considerations                                |    |

| Chapte<br>Schedu | er 5<br>uling and Binding                            | 73 |

| I                | Introduction                                         |    |

| S                | Scheduling                                           |    |

|                  | The Force-Directed Deferral Mechanism75              |    |

| E                | Binding                                              |    |

| ·                | Scheduling and Binding with Interconnected Structure |    |

|                  | Combining with List Scheduling                       |    |

| I                | Integrated Scheduling and Binding                    |    |

|                  | Deferral and Binding for Partitioned Operations      |    |

|                  | Deferral and Binding for Non-partitioned Operations  |    |

| F                | Results91                                            |    |

| C                | Concluding Remarks96                                 |    |

| Chapte<br>Data P | er 6<br>Path Allocation                              | 97 |

| I                | Introduction                                         |    |

| N                | Memory                                               |    |

|                  | Single Location Storage                              |    |

|                  | Multiple Location Storage                            |    |

| I                | nterconnection                                       |    |

|                  | Communications Synthesis                             |    |

|                  | Influence of Scheduling and Binding                  |    |

| S                | Synthesis Algorithms                                 |    |

|                  | Clique Partitioning Method                           |    |

|                  | Synthesising Buses                                   |    |

.

.

| Results115                                    |     |

|-----------------------------------------------|-----|

| The FACET Example                             |     |

| The Differential Equation Example             |     |

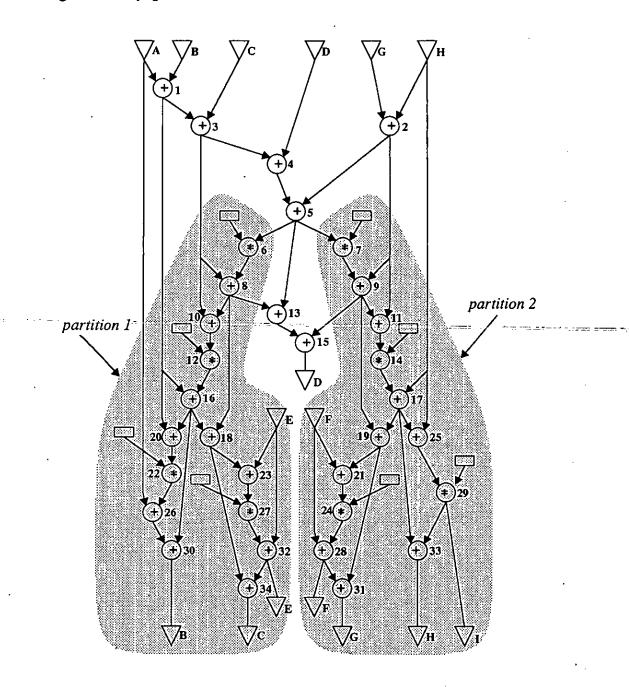

| The Wave Digital Filter Example               |     |

| Concluding Remarks                            |     |

| Chapter 7<br>Worked Examples                  | 126 |

| Introduction                                  |     |

| Reuse of Structure                            |     |

| Iterative Synthesis                           |     |

| Adapting Structure                            |     |

| Influencing the Architecture                  |     |

| Chapter 8<br>Conclusion and Future Directions | 138 |

| Conclusion                                    |     |

| Future Developments with Structural Input     |     |

| Future Directions in High-Level Synthesis     | ٠   |

| References                                    | 142 |

| Appendix A                                    | 147 |

| Clique Partitioning147                        |     |

| Minimum Cost Flow151                          |     |

| Appendix B                                    | 156 |

| Facet Example156                              |     |

| Behaviour                                     |     |

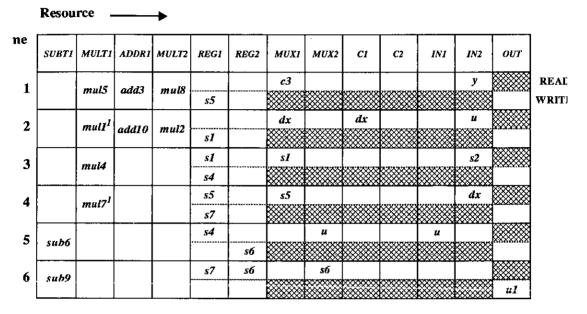

| Resource-time Graph                           |     |

| Differential Equation                         |     |

| Behaviour                                     |     |

| Structures                                    |     |

| Resource-time graphs. |  |

|-----------------------|--|

| Wave Digital Filter.  |  |

| Behaviour.            |  |

| Resource-time graphs. |  |

<del>ч.</del>

,

# Chapter 1 Introduction.

#### **1.1** Design Automation.

The advent of VLSI technology has made it possible to construct integrated circuits consisting of hundreds of thousands of transistors. In achieving this scale of integration advances have been required in design methodology as well as in fabrication process technology. The complexity of circuits has demanded a structured, hierarchical approach to design to enable the efficient use of a team of designers. As complexity has increased there has been a trend towards automating tasks at higher levels in the design hierarchy [1].

A hierarchical approach is used because it makes it possible to partition the design process into smaller, more manageable subtasks. This permits a more efficient use of designers as each can be apportioned a clearly defined subtask. Moreover, it provides the necessary framework for representing the design at different levels of abstraction. As an example, consider a circuit which adds two numbers. At the most abstract level this could be represented by a module with two inputs and one output, which is defined to perform an addition operation. At a lower level, this circuit could be represented as an interconnection of logic gates; lower still it could be represented by an interconnection, the representation becomes less detailed and so more manageable.

The VLSI design process has three domains of design representation: behavioural, structural and physical. The behavioural domain is used to house the description of the function of the circuit. The structural domain is a transitional representation between the behaviour and the physical circuit; it encompasses descriptions of circuit schematics. The physical domain is encountered in the description of the layout of the circuit in silicon. A behaviour can have many correct

structural implementations, just as a structure can have many possible physical implementations [2].

Within each domain a circuit can be represented at various levels of abstraction [3]. A number of commonly defined levels used in VLSI design are presented in Figure 1.1.

| Level                 | Behavioural          | Structural                                      | Physical                     |

|-----------------------|----------------------|-------------------------------------------------|------------------------------|

| Register-<br>transfer | Algorithmic          | Interconnection of processors, ports and memory | IC Floorplan,<br>Macro cells |

| Logic                 | Logic<br>Equations   | Gates,<br>Flip-flops                            | Standard Cell<br>Layout      |

| Circuit               | Network<br>Equations | Transistors,<br>Connections                     | Transistor Layout            |

Figure 1.1 Levels of domain abstraction in VLSI design.

The ideal design of a circuit starts with a behavioural description at a high level of abstraction. From this point synthesis proceeds through the structural domain, descending to lower levels of abstraction until it arrives at the layout description of the circuit's transistors in the physical domain. The constraints of the synthesis process are usually expressed as circuit requirements in the physical domain such as the circuit's minimum speed of operation and maximum silicon area.

The first design tasks to be automated centered around the transition from the structural to the physical domain at low levels of abstraction. These were tasks involving circuit layout such as floor-planning and routing. Automation offers a number of advantages. Most notably both the design time and the risk of errors can be reduced. Accordingly, the greatest benefits from automation are gained when it is applied to large scale tasks. This is why layout received the initial attention. As designs increase still further in terms of complexity and size, there is a greater demand for automating synthesis at higher levels of abstraction. Consequently, automation is beginning to

spread to the behavioural domain.

At present there are a number of commercial systems which automate synthesis from a register-transfer level description of structure. These systems are commonly termed 'silicon compilers' [2]. In addition, a small number of systems perform logic synthesis. These take a behavioural description at the logic-level and create a corresponding structural implementation. Very few systems exist which accept behavioural descriptions at a higher level. This is where much of the current research effort is concentrated: the high-level behavioural synthesis task.

## **1.2** High-Level Behavioural Synthesis.

The task of a high-level synthesis system is to provide a means of generating a low level circuit description from a high level specification. Although often considered synonymous, behavioural synthesis denotes a process which is distinct from high-level synthesis. Behavioural synthesis starts from a description of behaviour defined at any level of abstraction with the aim of producing a structural description. Therefore, highlevel synthesis need not start from the behavioural domain and that behavioural synthesis need not start at a high-level of abstraction [3] [4] [5].

The synthesis task tackled in this thesis can be termed high-level behavioural synthesis. This requires that the input description be a high level specification of behaviour. This specification is usually algorithmic in nature and is typically expressed using a high-level programming language. A high level description of structure is synthesized from the behavioural specification. In a high-level synthesis system, the structural description would then be 'compiled' to a physical layout representation of interconnected transistors, the task of silicon compilation.

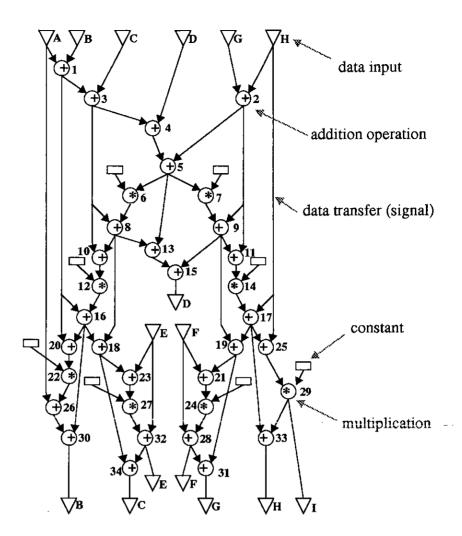

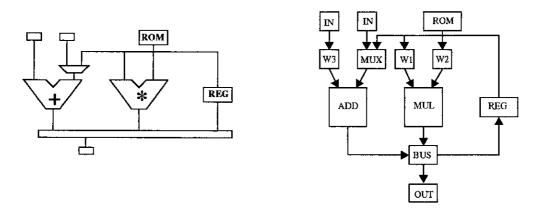

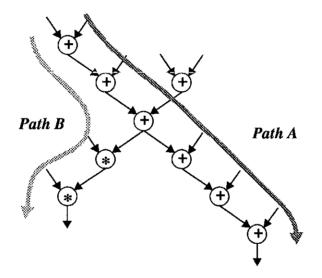

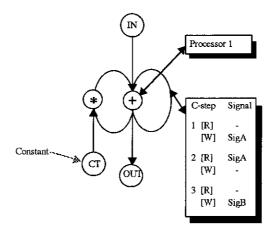

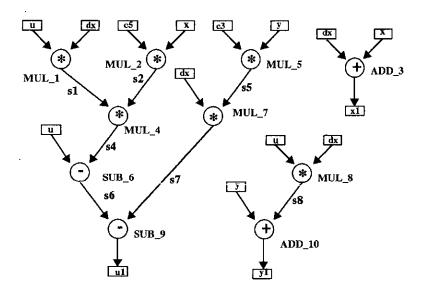

The synthesis task is performed at the register-transfer level. The behavioural description is composed of a set of primitive operations available in hardware at that level. An example in Figure 1.2 defines the behaviour of a wave digital filter at the register-transfer level [6]. The primitive operations are addition and multiplication.

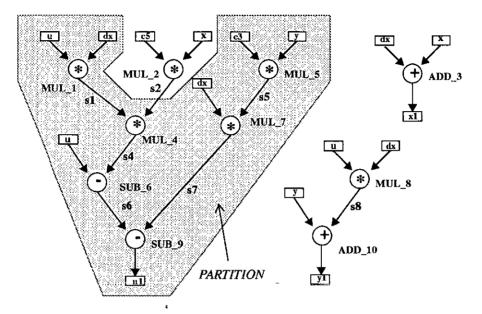

Figure 1.2 Wave digital filter behaviour in a data flow format.

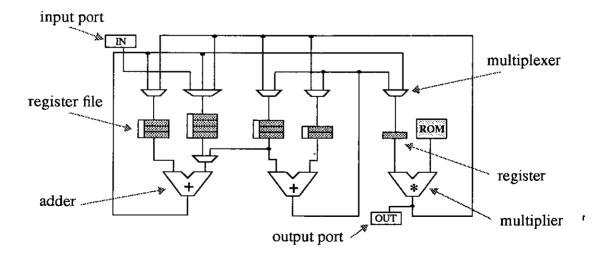

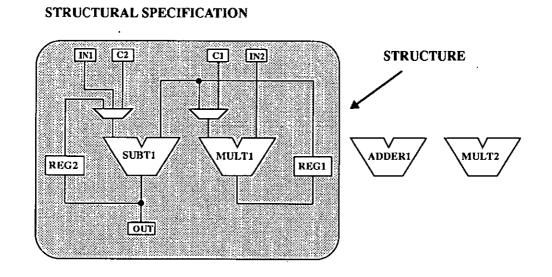

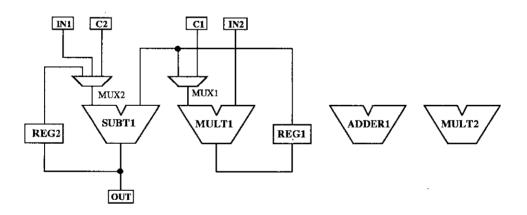

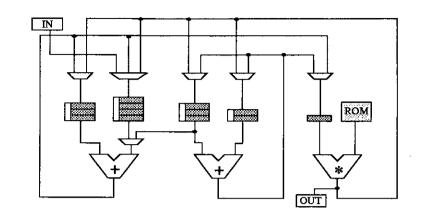

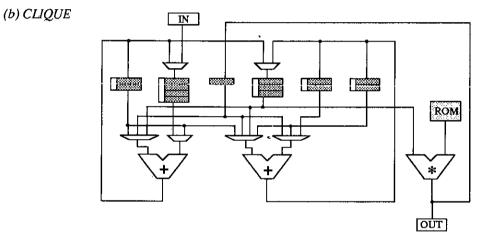

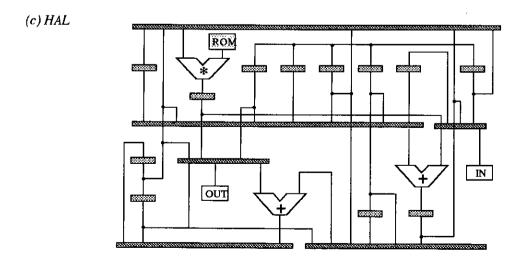

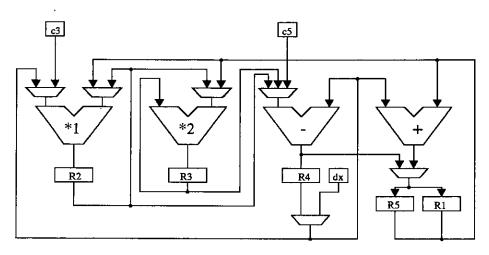

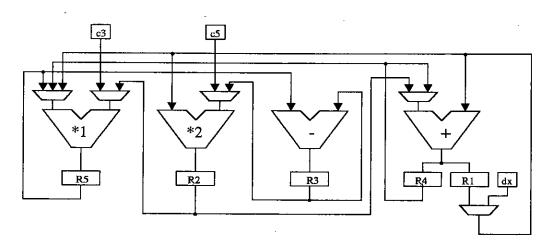

A structure synthesized to implement this behaviour is shown in Figure 1.3.

Figure 1.3 Register-transfer schematic of a wave digital filter data path.

This is a schematic view of the data path with control structure omitted. In addition to implementing the behaviour, the circuit is invariably required to meet physical constraints. The most common constraints involve a limit on the silicon area available in conjunction with a minimum speed of operation. As these constraints are made in the physical domain, it is important that a synthesis system supports a suitable back propagation of these requirements to influence higher level design decisions in the structural and behavioural domains. This is a problem widely recognised in high-level synthesis research.

# **1.3** Structural Direction.

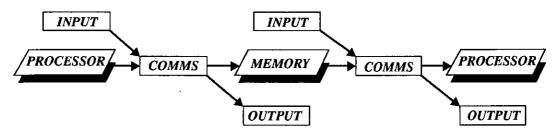

The high-level behavioural synthesis task involves the creation of a registertransfer structure to implement a specified high-level behaviour. Constraints in terms of speed and size will typically be placed on the physical implementation. These constraints will consequently be the sole factors influencing the design architecture. A circuit's architecture is commonly accepted as being the major factor in determining performance. Architecture is a high-level structural attribute defining the style of component interconnection.

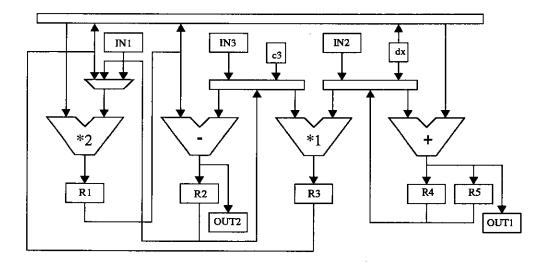

The difficulty encountered in most synthesis systems is in producing an architecture to suit a particular problem when given only a specification of behaviour and some physical requirements. When the designer knows of a suitable architecture, there should be some mechanism for suggesting it to the synthesis tool. In most systems, control over the synthesized register-transfer structure is severely limited. At best only the number of allocated components can be influenced. In only one other system is there a facility for controlling the pattern of interconnection [7].

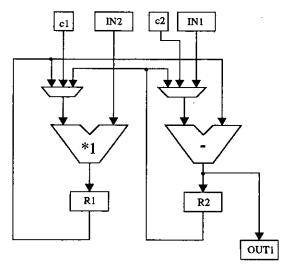

The work presented in this thesis, which takes the form of a prototype high-level behavioural synthesis tool, offers a structurally directed approach to the aforementioned problem. The designer is encouraged to specify partial or complete

structures alongside the behavioural input in an attempt to direct the synthesis process towards a suitable architecture. The synthesis tool makes use of these structures by incorporating them into the design where appropriate or as instructed. The structural input is specified at the register-transfer level, comprising of an interconnection of processing, memory and communications components. As illustrated in Figure 1.4, a partial structure is one where interconnection is left incomplete. It is, therefore, acceptable to leave some or all component ports unconnected.

The use of structural input brings a number of benefits. These stem from the ability to control the synthesized structure. If the designer is dissatisfied with the product of fully automated synthesis, he or she is in the position to alter the architectural style or to modify unacceptable parts of the design by repeating synthesis with structural input. Modifications can be made to the synthesized design and need not be complete or correct before repeating synthesis with the altered design. In this way an effective iterative approach to synthesis is possible. In addition, structures may be reused in future designs. This is particularly useful in the case of 'general purpose' structures which require only modification of control to implement a different behaviour. The synthesis system would then be acting as a 'compiler' for such general purpose data paths.

Figure 1.4 Data path schematic of a partial structure used as input.

# **1.4** Thesis Overview.

In summary, this thesis describes a high-level behavioural synthesis system which accepts a specification of structural input alongside a specification of behaviour. The structural input acts as architectural direction in the synthesis process. This is achieved through the use of specified structures within the synthesized data path. The intention of this approach is primarily to give the designer greater control over the exploration of structural implementations of the behaviour.

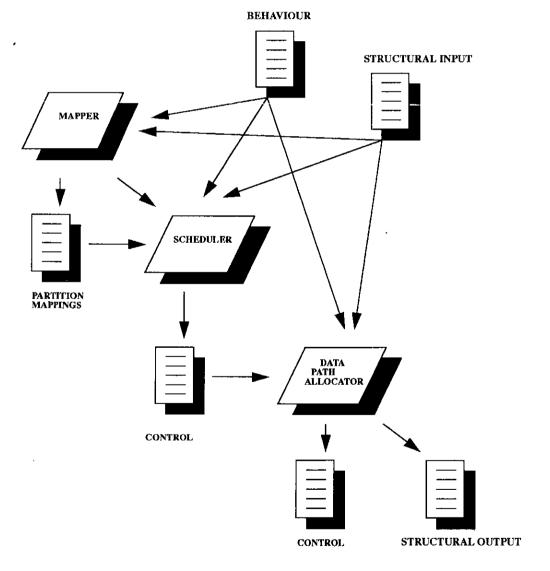

To make use of structural input, the synthesis system must be capable of working out how a behaviour can be implemented by a structure in addition to appreciating the performance of different structures in relation to a particular behaviour. This task is termed *mapping*. In this thesis, synthesis has been broken down into three tasks, each performed by a separate tool. These tasks are *mapping*, *scheduling* and *data path allocation*. They are discussed separately in chapters 4 to 6. Chapter 3 outlines the basic framework designed to represent behaviour and structure and to support the synthesis process.

# Chapter 2 Behavioural Synthesis Review.

# 2.1 Historical Overview.

Research into high-level, or behavioural, synthesis started as long ago as the 1960s. The ALERT system developed at IBM's T.J. Watson Research Center produced a logic level implementation from a register-transfer level, behavioural description [10]. Nevertheless, until the 1980s, work in design automation tended to focus on the lower levels of the design hierarchy such as layout. High-level synthesis research was restricted mainly to universities.

At Carnegie-Mellon University, the EXPL system was developed in the early 1970s. This system was the first to enable exploration of the design space by performing serial-parallel trade-offs in hardware. The structural implementation of designs was made using a set of pre-defined register-transfer modules in order to simplify the synthesis task. The EXPL system was superseded by the CMU-DA (Carnegie-Mellon University Design Automation) System in the late 1970s [11]. This new system addressed a range of behavioural synthesis tasks: behavioural specification and internal representation, scheduling and allocation. In addition, it experimented with a wide range of algorithmic techniques for implementing these tasks, ranging from heuristic methods to expert systems.

In Europe, research started in 1976 at the University of Kiel which led to the MIMOLA system [12]. MIMOLA was capable of synthesising a microprocessor from an input specification of behaviour. Synthesis was performed iteratively under the guidance of a designer until constraints were met. At the University of Karlsruhe development of the CADDY/DSL system [13] started in 1979.

The 1980s have seen a dramatic increase in research into high-level synthesis. Advances in VLSI technology demanded greater design automation and rapid

developments in both computer hardware and software provided greater opportunity. Automation of the lower levels in the design hierarchy, such as layout, routing and logic synthesis, were being accepted in industry. Many research groups sprang up, expanding research to encompass a wider range of architectural styles and applications. At the University of Edinburgh, the FIRST system was developed for bit-serial application [14]. This was followed in 1987 by the SAGE system [15] [16]. This was developed at the Silicon Architectures Research Initiative, a collaborative venture between the University and six companies. It addressed a wider range of bit-parallel applications using the VHDL language to represent both the behavioural specification and structural design. Similarly at IMEC, synthesis work started with a bit-serial system, Cathedral I. Cathedral II moved into the bit-parallel field but was directed at synthesising designs for a small range of DSP applications for which it had a target architecture [17]. Work at Eindhoven University has led to the development of the EASY system [18].

In North America there has been widespread interest in high-level synthesis. In Canada the Universities of Carelton and Waterloo have developed the HAL [20] and SPAID [25] systems respectively with the backing of Bell-Northern Research (BNR). In the United States some of the more prominent research projects are also in universities: the University of Southern California (ADAM) [27], Carnegie-Mellon University (SAM) [34], University of California at Irvine (VSS) [35], University of California at Berkely (HYPER) [36] and the University of Illinois (IBA) [7].

High-level synthesis has been gaining a foothold in industry. The Pyramid and Phideo systems are being developed at Philips Research Labs [37] and the CALLAS system [38] at Siemens. In the United States the YSC [39] and V-compiler [40] are under development at IBM's T.J. Watson Research Center, Bridge [41] and SAM [42] at AT&T Bell Labs and the Parsifal system at General Electric [43]. Work is also being carried out in Japan at NEC [44] and NTT [45].

# 2.2 Synthesis Methodologies.

Within every approach to high-level synthesis can be identified four basic tasks which must be addressed. These tasks are as follows:

• Representation.

A typical synthesis system will accept a specification of behaviour and produce a specification of structure. These specifications are usually made using the constructs of high-level languages and hardware description languages respectively. Some languages such as VHDL incorporate both behavioural and structural constructs [46]. Within the system, behaviour and structure are usually represented in a graphical format to highlight the relationships or connectivity between elements.

• Structural Requirements.

In addition to implementing the desired behaviour, the structure is usually required to meet physical and performance constraints. Typical performance constraints are speed of operation and data throughput. Physical constraints are most likely to be in terms of the silicon area which can be occupied by the design or its power consumption.

The remaining three tasks form what is commonly referred to as data path synthesis.

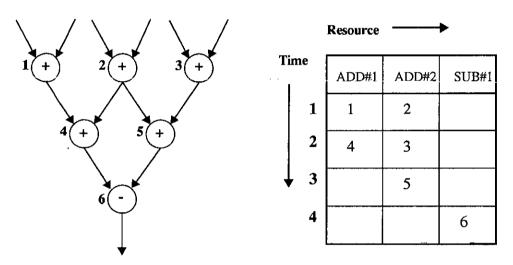

• Scheduling.

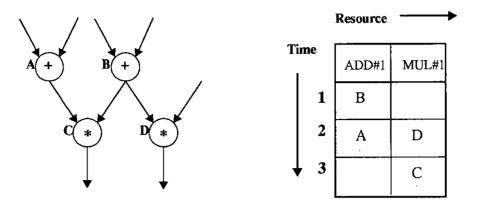

Scheduling dictates the relative timing of behavioural operations. Relative timing is expressed in terms of control steps which represent synchronous states based on clock cycles.

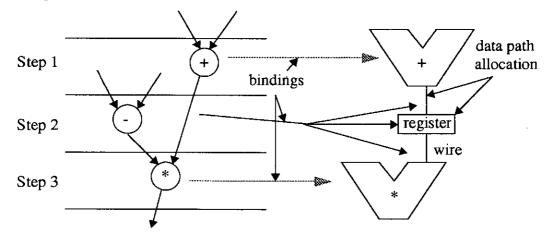

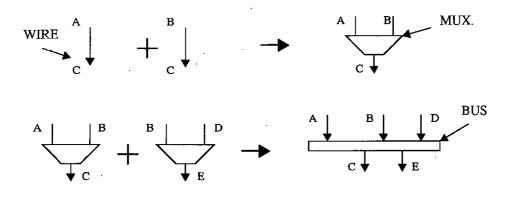

• Allocation.

Allocation governs the use and interconnection of structural components. Different types of component, defined at the register-transfer level, are allocated during different stages in the synthesis process. Processors are usually allocated first and interconnecting components, such as multiplexers, wires and buses, are allocated last.

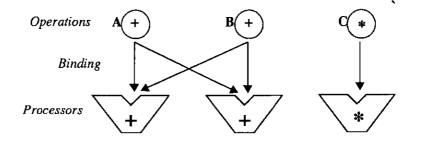

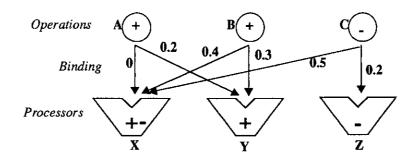

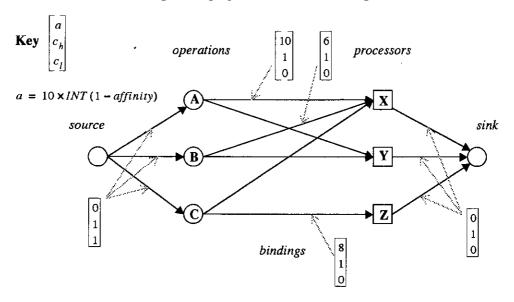

• Binding.

Binding provides the link between behaviour and structure. It is effectively the mapping of behavioural elements to structural components. It is used to determine which processor will implement a particular operation and which memory will store a particular data value.

The synthesis aim is to create a structure which will implement a desired behaviour while satisfying structural requirements. Creating a structure to realise a given behaviour does not present the main problem: it is guiding the synthesis process so that it produces a structure which satisfies realistic requirements which is difficult.

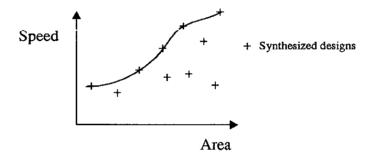

Figure 2.5 Design space bounded by speed and area.

Consider a design where only *speed* and *area* requirements are specified. As shown in Figure 2.5, a simple two-dimensional design space can be constructed using speed and area axes. For many examples, as in Figure 2.5, there is a noticeable tradeoff between speed and area. A high-speed design will exploit parallelism in the behaviour, demanding more processing units and, hence, use more silicon area. On the other hand, a smaller area, low-cost design would opt for a more serial approach to operation execution which required fewer processing units but operated at lower speed. This is a highly idealised view of design space exploration. Only for a design whose behaviour contains sufficient parallelism will there exist an obvious trade-off between speed and area which is dominated by the processor allocation. Other factors such as memory, communications and control can have a dominating effect in certain applications. In image processing, memory is frequently the dominating factor, whereas in microprocessor design control is of greater importance. McFarland [47] has demonstrated the effect of communications, involving the use of multiplexers and buses, on both the speed and area of a number of designs. In the majority of cases, efficient design space exploration requires consideration of the combination of processing, memory and communication as all these factors are required to formulate an architecture suited to a particular application.

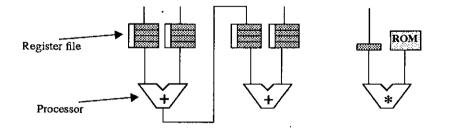

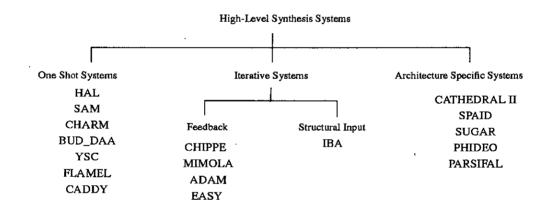

Synthesis systems can be categorised according to the way in which they attempt to satisfy structural requirements. To do this effectively the system must impart a suitable architectural style to the design. Figure 2.6 outlines three categories of synthesis system.

Figure 2.6 Different synthesis methodologies.

#### 2.2.1 'One Shot' Systems.

With 'one shot' systems, designs are discarded if they fail to meet structural requirements. There is no facility to analyse a failed design with a view to modifying it or to directing subsequent synthesis attempts. In other words, the designer has only 'one shot' at synthesising a design to meet a given set of requirements. In some systems it may be possible for the designer to influence certain component allocations or to

manipulate the structural requirements in an attempt to synthesize an adequate design. However, the correlation between these parameters and the final solution is not direct enough to enable an effective search of the design space to be made in the majority of cases.

'One shot' systems tend to employ more complex, global algorithms than those using other approaches. There are several reasons for this. Firstly, the algorithms must locate a satisfactory solution first time without relying on designer guidance. Secondly, there is no time constraint imposed on run time because the designer is not expected to interact with the synthesis process or to use it in an iterative fashion. Finally, the algorithms are expected to cope with a whole range of applications and so cannot be simplified by tailoring them to a specific application using heuristics and designer knowledge.

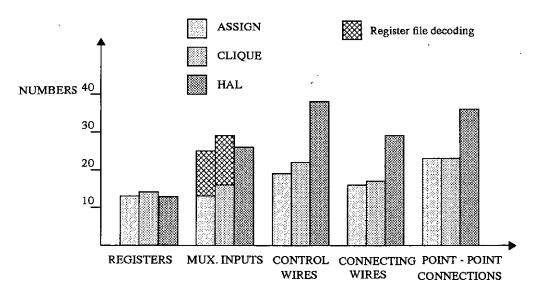

HAL can be classed as a 'one shot' system [20]. The HAL system is dominated by a highly effective scheduling algorithm, called *force-directed* scheduling [21], which has been extended to take into account storage and interconnection factors. Memory and interconnection are synthesized after scheduling using a *weight-directed* clique partitioning method which concentrates on reducing memory costs while taking into account the cost of interconnection. These costs are estimated in terms of the numbers of registers and multiplexer inputs respectively. Both *force-directed* scheduling and *weight-directed* clique partitioning are computationally complex algorithms. Although an attempt has been made to give greater weight to memory and interconnection factors, the allocation of processors and scheduling of operations still dominate the architectural style. This is borne out by the random interconnection topology of synthesized data paths.

The original *force-directed* scheduling algorithm performed processor allocation. The designer could only influence the final design through the specification

of speed and area constraints. To enable better design space exploration, *force-directed* list scheduling (FDLS) was developed. FDLS produces a schedule under resource constraints thus giving the designer control over the number of processors or buses used [23]. The effectiveness of the *force-directed* scheduling approach is highlighted by the number of researchers who have made use of this method [18] [48].

#### 2.2.2 Iterative Systems.

Systems which fall into the iterative category make use of synthesised designs which fail to meet structural requirements. The failed design is analysed in an attempt to discover why it failed. Information from the analysis is then used in one of two ways: either to direct subsequent synthesis attempts or to modify the existing design. The iteration loop need not be completed entirely in software but if analysis is left to the designer then he or she must be allowed sufficient control over the synthesis process so as to be able to direct it.

#### 2.2.2.1 Directing Subsequent Synthesis Attempts.

CHIPPE [49] describes itself as a system for constraint driven behavioural synthesis. It performs iterative synthesis entirely in software. An expert system is used to control the resource allocation and strategies used in the synthesis tasks of scheduling and data path allocation. The expert system is guided in these tasks by an evaluator which assesses the quality of the present, complete or partial, design with respect to the design goals.

CHIPPE effects an iterative or closed-loop design methodology by repeating the synthesis process with constrained resources and refined trade-off knowledge gleaned from previous iterations. As the iterations proceed, estimations become more detailed and greater optimization is permitted with the design tools. This means that the first few iterations can be performed quickly, wasting little time on optimizing designs which will be discarded.

The implementation of CHIPPE is focused on CMOS gate array design which simplifies many of the technological and architectural trade-offs, especially in the analysis of bus delays.

The ADAM system [26] adopts a similar approach but addresses the problem of full-custom design. The iterative design loop must, however, be completed by the designer. The ADAM system is effectively a one shot system with area-prediction tools aimed at assisting the designer in making high-level design decisions. Within an iteration, the synthesis process is modelled as a search tree whose nodes represent design decisions. At any node in this tree, if the area-prediction tools show that no acceptable design can be reached then backtracking to other nodes in the tree is supported. Thus, there is the opportunity for considerable design space exploration within each iteration.

#### 2.2.2.2 Modification of Existing Designs.

When a structure is synthesized to implement a specified behaviour, bindings will be created between behavioural elements, structural components and a timing model. This binding information dictates how the structure implements the behaviour and is essentially a specification of the control task. If the structure fails to meet the necessary requirements, but is to be modified in another attempt to satisfy them, then there are at least two possible iterative methods which could be employed. The first method is based on transformations. Structural transformations which maintain the validity of the bindings can be applied to the structure under the guidance of a structural analysis tool or the designer. The second method permits the structure to be modified without considering the bindings. Synthesis tools would then reconstruct the bindings making additional modifications, if necessary, to implement the behaviour. The second method is more advanced as the tools must have knowledge of how a structure implements behaviour rather than just a set of transform rules.

The IBA system [7] developed at the University of Illinois addresses both approaches. The system is composed of three tools, FASOLT, RLEXT and LE, which interact within the framework of the IMBSL language. It is aimed at designing microprocessor-like instruction-set processors. In the majority of such applications there will not be more than one operator of a particular type and so, as a simplification, scheduling is left entirely to the designer.

The transformational approach to iterative synthesis centres around FASOLT and LE. The layout estimator (LE) drives the choice of optimizing transformations which are housed in FASOLT. There are nine possible transformations, which operate at the level of scheduling and allocation. Typical transformations involve component replacement and interconnection component merging and bypass.

The approach which permits structural modification by the designer involves RLEXT (Register Level Exploration Tool). In IMBSL it is possible to specify a partial structure as a guide to synthesis. RLEXT constructs bindings between behaviour and structure and corrects inconsistencies in the specified structure. In IBA's application area, where the structure may contain only a single processing unit, the problem of constructing a binding between operations and processors is obviously trivial. There is no mention in the current literature of a method for constructing a binding to a structure containing multiple processors.

The system presented in this thesis follows the second approach. It accepts partial or complete structural specifications as input and computes feasible bindings between behaviour and structure which the designer is permitted to modify.

#### 2.2.3 Architecture Specific Systems.

Cathedral II is aimed at synthesising synchronous, multiprocessor ICs for DSP applications [17]. There is a target architecture which is tailored to the behaviour. At the highest level the architecture is composed of concurrently operating processors. Each

processor is tuned to a subtask of the behaviour and consists of a dedicated data path and controller. The data path is assembled from execution units which are interconnected by a restricted number of buses. Each execution unit has memory in the form of register files which are placed on its input side.

Cathedral II operates a 'meet-in-the-middle' methodology between silicon and system design parts. The design of execution units, which includes layout, is performed by the silicon design part and is saved so that it can be used in other designs.

SPAID [25] is also aimed at DSP applications. Its target architecture is aimed at creating a linear communications topology. Registers are stored in files, each of which is connected to a separate bus. Consequently data will only pass through a single register file and bus between processors. This reduces interconnection delays and simplifies the layout task. The synthesis process allows interconnection to be constrained in the allocation phase prior to scheduling. A two-phase bus cycle is imposed on data transfers, separating reads from writes. The control and external communication architectures are also pre-defined.

The SUGAR system is dedicated to the synthesis of microprocessors [52]. The synthesis tools contain embedded knowledge about microprocessor subsystems such as the instruction decode unit and condition code branch logic. They also have knowledge of busing structures found in commercial microprocessors. It should be noted that control issues such as the decoding of instructions and assignment of machine code as well as the choice of busing structure are given precedence over scheduling and register assignment.

# 2.3 Representations.

In the majority of systems, behaviour is the input and structure is the output. It is only in the IBA system [7] and in the system presented in this thesis that a structural specification will be accepted as input.

Behaviour is typically specified in an algorithmic form as a textual description in a high-level language. Most systems have developed their own languages, often based on a subset of an existing procedural language such as ADA, PASCAL or C. More recent approaches make use of hardware description languages, such as VHDL, which can be used to describe both behaviour and structure.

DeMan advocates the use of applicative languages, such as SILAGE and ELLA, over standard procedural ones [53]. A major difference between procedural and applicative is that procedural languages will permit the multiple assignment of variables as shown in Figure 2.7 whereas applicative languages will only allow single assignments. By allowing a variable to appear on both sides of an assignment a serial implementation is suggested. An applicative language is a more direct representation of true data flow. However, multiple assignment can be easily detected and removed during compilation removing the need for a new language. Furthermore, it can be left to the designer to decide whether he or she uses multiple assignment of variables within a procedural language.

Applicative Representation

```

s[0]=0;

for (i=1;i<4;i++)

s[i]=s[i-1]+x[i];

sum=s[4];

```

# Procedural Representation sum=0; for (i=1;i<4;i++) sum=sum+x[i];</pre>

Figure 2.7 Comparison of applicative and procedural representations.

SILAGE offers a number of constructs tailored to data flow representations for DSP applications. These include a built in data stream concept; a delay concept on

streams of bit-true type and decimation and interpolation constructs.

Algorithmic descriptions of behaviour are compiled into an intermediate format. Compilation can be used to perform common software complier tasks such as:

• dead code and common sub-expression elimination;

- constant propagation;

- in-line expansion of procedures;

- loop unrolling.

A number of systems take this opportunity to carry out some hardware-specific transformations.

Internal formats tend to be graphical, consisting of interconnected vertices (nodes) and arcs (edges). Stok has identified three criteria for classifying data and control models of behaviour [18]:

- using a tree or directed graph representation of data flow;

- using a semi-data flow graph or true data flow graph representation;

- representing control flow separate from data flow.

A true data flow graph G(V,E) has vertices (V) which represent only operations and edges (E) which model the data flow between these operations. A semi-data flow graph G(V,W,E), which is usually represented as a bipartite graph, contains two distinct sets of vertices for operations (V) and for variables (W). The edges (E) are used to show the mapping of variables to and from operations.

#### 2.3.1 Tree Representations.

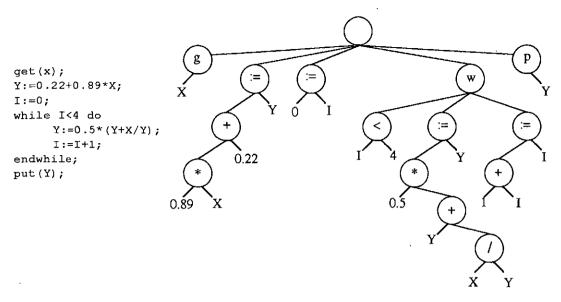

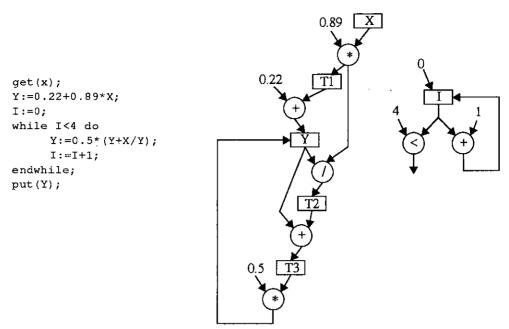

The Cathedral [17] and Mimola [12] systems both represent behaviour using parse trees, a representation taken from software compiler technology. An example of a parse tree representation is shown in Figure 2.8.

Figure 2.8 Parse tree representation.

## 2.3.2 Semi-data Flow Graphs.

DDS is the representation model for the ADAM system [54]. It contains four separate models: data flow, timing and control flow, logical structure and physical structure. The semi-data flow graph is bipartite and acyclic. The behaviour is represented hierarchically. At the top level a single node represents the entire behaviour. This is then recursively subdivided until all nodes represent primitive functions. Control is represented using a directed acyclic graph, in which vertices represent events and arcs denote causal relationships between them.

The system at the University of Karlsruhe (CADDY) uses three graphs which share the same vertex representation of operations. The first graph expresses precedence relations between operations. The second indicates the mapping between operations and variables and the third describes timing constraints between operations. From these graphs a true data flow graph is constructed, introducing temporary variables to cope with multiple assignments as shown in Figure 2.9.

Figure 2.9 Semi-data flow representation.

## 2.3.3 Separate True Data and Control Flow Representations.

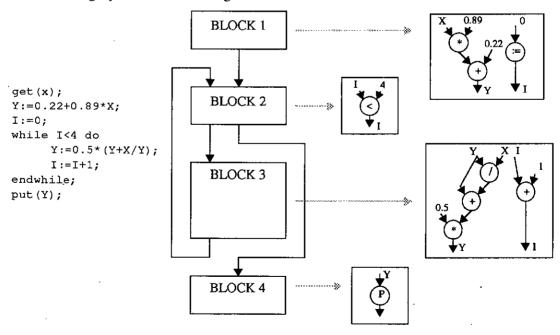

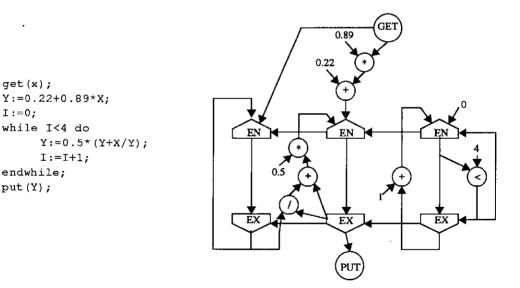

The VHDL Synthesis System (VSS), being developed at the University of California at Irvine, uses separate graphs to represent data and control [35]. Maximal sequences of operations which contain no control flow are defined as basic blocks. These blocks, which represent pure data flow, are then represented by vertices in the control flow graph as shown in Figure 2.10.

Figure 2.10 True data flow representation.

The ASM system of the University of Illinois uses a similar approach [18]. Camposano [39] uses a slightly different representation for VHDL behavioural models. Operation vertices are present in both the data and control flow graphs.

#### 2.3.4 Combined Representations.

SAW [52] and older CMU-DA systems use a combined data and control flow representation called the Value Trace (VT). VT is a directed acyclic graph. As in other representations, operations are denoted by vertices; values, or signals, are denoted by edges. Conditional branching is introduced by separate 'select vertices'. Subroutines are mapped as labelled blocks onto subgraphs which are identified by special 'call vertices' which pass parameters. The EASY system [18] uses a data flow graph representation based on the 'demand' graph shown in Figure 2.11. Conditional statements and looping constructs are modelled using the same set of branch and merge vertices.

Figure 2.11 EASY demand graph representation.

# 2.4 Scheduling Techniques

#### **2.4.1** Interaction with Allocation.

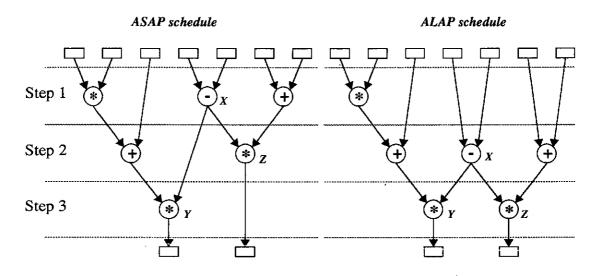

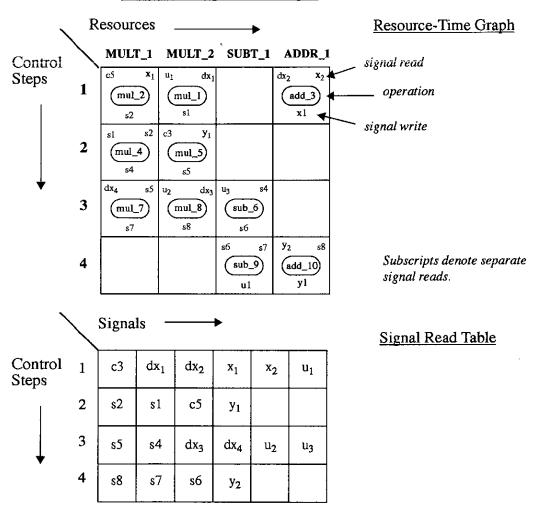

Scheduling and allocation are interdependent synthesis tasks. Before an operation can be scheduled, it must be known if a suitable processor is available. Therefore, some allocation must have been made. However, to decide upon a suitable allocation, scheduling information is required so that a trade-off between resource cost and schedule length can be made within specified constraints. Although this is commonly stated as a vicious circle, it is not an intractable problem. The permutations of processor allocation are small for real examples. It is, therefore, even possible to try all realistic possibilities. Consider the wave digital filter example<sup>1</sup> [6]. The data flow graph is large, containing 34 operations, yet the fastest schedule requires an allocation of two multipliers and three adders while the slowest needs one multiplier and one adder. Consequently the total number of realistic allocations is only six. The upper bound on allocation for the fastest schedule can be obtained by analysing the maximum processor requirements for an ASAP<sup>2</sup> schedule.

## 2.4.1.1 Independent Scheduling and Allocation.

The CMU-DA [11], FLAMEL [70] and DAA [55] systems perform processor allocation before scheduling. The allocation can be set by either the program or the designer. The CHIPPE [49] and MIMOLA [12] systems adopt a similar strategy with the added ability to iteratively re-allocate and re-schedule until a satisfactory result is obtained. MIMOLA uses the designer to control the iterations whereas CHIPPE employs an expert system which governs the data path allocator.

#### 2.4.1.2 Interdependent Scheduling and Allocation.

An alternative approach is to combine processor allocation with scheduling and perform them simultaneously. The *force-directed* scheduling technique of the HAL

<sup>1.</sup> Further details of this example can be found in Appendix B.3 on page 162.

<sup>2.</sup> As Soon As Possible schedule - definition can be found in section 3.2.2 on page 41.

system tries to balance the load of operations on processors in an attempt to meet timing constraints with the minimum allocation [21]. HAL also employs a *force-directed* list scheduling technique which takes a fixed resource allocation. This is a more effective scheduler as it is not burdened by the allocation problem. It is used in conjunction with the *force-directed* scheduler to enable a more effective search of the design space.

The MAHA (ADAM) scheduler [26] uses a list scheduling approach driven by the notion of operation *freedom* rather than force. The system first invokes the Clocking Scheme Synthesis Package (CSSP) [33] which identifies the critical path and divides it into steps, one per clock cycle. MAHA then allocates functional units for the critical path on a first come first served basis. The notion of *freedom* is used to direct the scheduling of nodes outside the critical path. The operation with least *freedom* is chosen for scheduling and allocated a functional unit if necessary.

#### 2.4.1.3 Step-wise Refinement.

The BUD-DAA system [55] uses a step-wise refinement approach to scheduling and allocation. Operations from the behaviour are grouped into clusters according to their potential for sharing processors or interconnect, or for exploiting parallelism. Processors are then assigned to each cluster before scheduling is performed. A number of different clusters are investigated and the selection producing the result most appropriate to the resource-time criteria is selected. BUD uses list scheduling with a similar *a priori* function to that used in SLICER (CHIPPE) [50] and MAHA [26].

In the YSC system [39] scheduling is separated into two stages. Initially each operation is bound to a separate processor and the same control step. Control steps are added to accommodate loop boundaries and memory usage conflicts. In the second stage the hardware is optimized by attempting to share resources as much as possible. Extra control steps are added, if necessary, to reduce the amount of hardware used and the optimization stage is repeated.

#### 2.4.2 Scheduling Algorithms.

Scheduling algorithms can classed in one of three basic categories: transformational, global or constructive.

#### 2.4.2.1 Transformational.

A transformational scheduling algorithm starts with a default schedule. This is usually either maximally parallel or maximally serial. Transforms are then applied in an attempt to obtain a schedule which meets specified requirements. The basic transforms move operations or blocks of operations to either exploit parallelism and reduce the schedule length or exploit serialism and reduce the resource overhead.

The EXPL system uses a exhaustive search approach starting with a maximally serial configuration. YSC uses heuristics to guide the transformations, starting instead with a maximally parallel configuration. Transformations used in the YSC system can be shown to produce the fastest possible schedule, in terms of control steps, for a given specification [3].

#### 2.4.2.2 Global Scheduling.

So-called *global scheduling* algorithms apply an existing optimization technique to the scheduling task. Three such techniques are integer linear programming (ILP), simulated annealing and neural networks.

## (a) Integer Linear Programming.

There have been a number of different approaches to scheduling which use ILP. Papachristou's formulation [56] of the scheduling problem attempts to minimise the cost of processing units. A binary decision variable  $x_{ij}$  is defined to represent an operation *i* being assigned to control step *j*. Another set of variables  $Mt_i$  show the number of permitted processors (modules) of type  $t_i$ . Constraints are added to ensure that:

- no control step contains more than Mt; operations of type, t;;

- operations are scheduled within their execution windows;

- all predecessors of an operation are scheduled before the operation itself.

This formulation performs scheduling under timing constraints. An alternative formulation put forward by Huang [57] allows scheduling to be done under hardware constraints.

The main draw-back of the ILP approach is the time taken to compute results, even for medium-sized data flow graphs. Most methods are aimed at reducing the problem complexity. Huang's method [57] considers only a few control steps at a time in order to reduce the problem size. This, of course, means that it is no longer being applied as a global optimization technique.

Gebotys [58] has put forward an alternative formulation which, it is claimed, can be solved efficiently by drawing on similarities between the node-packing problem and the way in which the scheduling problem is expressed.

#### (b) Neural Networks.

Hemani [59] has put forward a self-organising algorithm based on a neural network model which can schedule a data flow graph under a timing constraint. Operations compete for control steps within their execution intervals. The neural model takes into account the effect of scheduling an operation on its neighbours. The size of the neighbourhood is gradually reduced until only the movement of an individual operation is considered. The effect is a uniform distribution of operations across the schedule space. Again, this sort of approach is computationally intensive and, hence, time consuming. However, it is suited to running on massively parallel machines.

#### (c) Simulated Annealing.

Two approaches using simulated annealing have been identified [60] [61]. In both, the scheduling problem is viewed as one of two-dimensional placement of

operations, where the dimensions are those of resource and time. The aim of the algorithm is to minimise the resource-time area according to a costing function which advises on a suitable rectangular shape as a boundary to the operation placement. The simulated annealing algorithm selects operations at random and perturbs them in resource-time space according to a current value of temperature set by the algorithm. An operation is entitled to move to a position of lower global cost. However, if the temperature is high enough, it is also possible that a move to a position of higher global cost will be accepted. The temperature is controlled by the algorithm to be initially high then cooling off in an exponential manner. This algorithm is often hailed as optimal. It does offer a mechanism for bypassing local cost minima by enabling operations to move to higher cost states initially but there is no guarantee that this will result is an optimal solution. The performance of the algorithm is dependent upon the number of peturbations or iterations and the temperature cooling function. Finding a good solution can, therefore, be time consuming for large examples.

## 2.4.2.1 Constructive Scheduling.

The majority of scheduling algorithms fall into the constructive category. These algorithms are characterised by the fact that operations are scheduled individually, in turn. Within this category, two different schemes can be identified: list scheduling and distribution based scheduling. List schedulers operate on a control step by control step basis starting with the first step. Distribution based schedulers, on the other hand, select operations for scheduling based on criteria relating to the current state of the schedule.

#### (a) List scheduling.

Within the algorithm, a list of operations is constructed for each control step. This is a list of all operations whose data constraints have been satisfied; in other words those operations whose inputs are available at the time of the current control step.

In an ASAP scheduler all operations in this list are scheduled in the current step.

This is effectively scheduling without hardware constraints as sufficient hardware is allocated to accommodate all operations in each step. The CMU-DA system adopted this simple approach to scheduling which produces the fastest possible schedule although often at the expense of excessive hardware cost [11].

In other approaches to list scheduling the allocation of resources is constrained before scheduling begins. Consequently, the situation may arise where there is insufficient hardware available to accommodate all operations in the list. In this case the scheduling of some of the operations must be postponed, or deferred, until a later control step. Deferred operations will automatically then appear in the list constructed for the next control step. List scheduling approaches differ in the way in which operations are selected for deferral.

The ELF system [62] uses an *urgency* weight to determine deferral. The *urgency* of an operation is defined as the length of the shortest path from the operation to a timing constraint. The operations with the greatest *urgency* are scheduled first leaving operations of lower *urgency* to be deferred. The CSTEP (SAW) scheduler uses a similar method [52].

SLICER (CHIPPE) calculates a *mobility* criterion for deferral from initial ASAP and ALAP schedules [50]. The difference between ALAP and ASAP schedule times for an operation is defined as its *mobility*. Operations with a greater *mobility* are more likely to be deferred. Operations with the same *mobility* are sorted according to the number of successors; the operation with the most successors will be scheduled first. The MAHA (ADAM) system uses a *freedom* calculation which is identical to that of *mobility* [26]. Operations on the critical path will automatically have no *mobility* or *freedom*. Therefore, both the MAHA and SLICER approaches can be called critical path scheduling as operations on the critical path will always be given priority. In the ATOMICS scheduler of CATHEDRAL II operations on the critical path are also

scheduled first [17].

The *force-directed* list scheduling approach of the HAL system uses a force calculation to determine deferral [21]. Force measures an operation's attraction to the current control step based on the predicted distribution of operations on resources over time. It is the operation with the lowest force which is deferred. The deferral process is a repeated calculation of forces for operations, followed by the deferral of the operation with the lowest force until all remaining operations can be scheduled in the current step.

All of the list-schedulers outlined so far attempt to calculate the minimum schedule under a resource constraint. A scheduler which minimises resources under a time constraint is described in [57]. In this approach operations are deferred in an attempt to keep the resource overhead as low as possible provided that the time constraint will not be violated.

#### (b) Distribution-based Scheduling.

The main exponent of the distribution-based approach is Paulin's *force-directed* scheduler which is used in the HAL system [21]. The ASAP and ALAP schedules are calculated, as in SLICER, to determine the 'time frames' for each operation. It is assumed that an operation will have an equal probability of being scheduled anywhere in its time frame. This enables distribution graphs to be constructed for each operation type. These graphs show the probable number of operations of a given type which will occur in each control step. A force is then calculated which attempts to balance the load of operations across the control steps. This calculation takes into account the effect of scheduling on an operation's predecessors and successors. The operation selected for scheduling is the one which yields the lowest force. This operation is then scheduled and the process repeated.

The CASCH scheduler in the CADDY system [13] is also distribution-based in that it attempts to average the number of operations of each type across the schedule.

## 2.5 Data Path Allocation Techniques.

The data path allocation task typically encompasses the allocation of memory and communications components and the binding of behavioural elements to structural components. In a number of systems the binding of operations to processing components is done during the scheduling phase. Data path allocation is performed after scheduling and there is seldom interaction between the two phases.

Data path allocation is usually broken down into three tasks which are mutually dependent:

- binding of operations to processors;

- register allocation: allocation of memory and binding of signals to memory;

- allocation of interconnect to enable transfer of data between memory and processors.

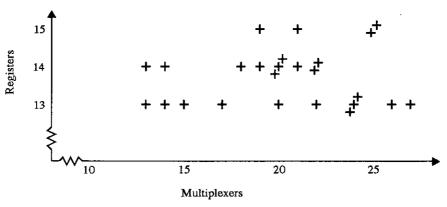

In most systems the data path allocation centres around register allocation. A number of optimal algorithms exist which will solve this problem. The cost of the interconnect allocation is, however, dependent on the register allocation. As McFarland has illustrated, interconnect is an important cost factor in designs [47]. Consequently, there has been considerable effort made to integrate the memory and interconnect allocation tasks.

The greatest problem encountered in data path allocation is assessing the quality of designs. Interconnection cannot be measured directly as a number of components or units. Its impact does not become clear until after layout and routing, by which stage data path allocation decisions will have been obscured by those taken in layout and routing. The majority of systems make do with three simple metrics in assessing data path quality: the number of register, the number of buses and the number of multiplexer inputs. The number of multiplexer inputs is taken to include the number of bus inputs. It is equivalent to the number of two-input multiplexers or tri-state drivers required.

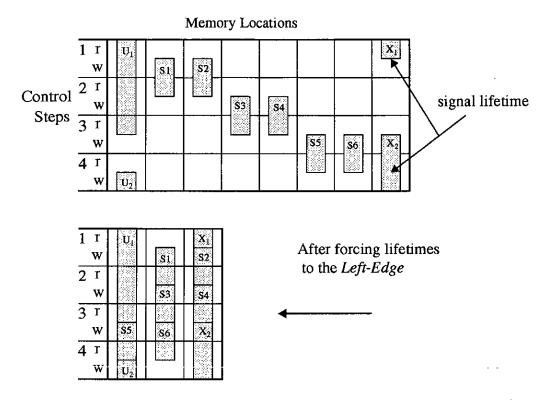

## 2.5.1 Optimal Register Allocation.

Initial work in the area of data path allocation focused around the register allocation problem and ignored interconnection issues. As signals can share the same register if they do not exist at the same time, the register allocation problem is viewed as one of grouping signals with disjoint life-times with the aim minimising the number of groups.

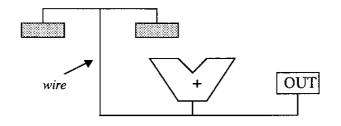

The most effective method is the Left-Edge Algorithm used in REAL [30], part of the ADAM system. The algorithm, taken from channel routing, models signal lifetimes as wires which have to be assigned to a minimum number of tracks, representing registers, without overlap. This is achieved simply by placing signal lifetimes in the left most register which avoids lifetime overlap.

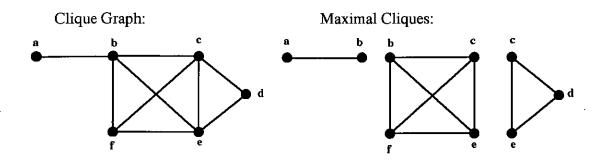

Clique covering is an optimal, although NP-complete, technique used in a large number of data path allocation schemes [63]. An undirected graph G(V,E) is partitioned into cliques. A clique is a subgraph where all vertices connect to all other vertices in the subgraph via a single arc. An example is given in Figure 2.12. Clique partitioning algorithms tend to be constructed to find only maximal cliques, those which are not subsets of any others. In clique covering, the aim is usually to identify the smallest set of cliques which include the most vertices of the graph.

When applied to register allocation, the vertices (V) in the undirected graph, G(V,E), denote signals and the edges, (E), indicate disjoint lifetimes between adjoining signals. G(V,E) is termed a compatibility graph. The aim of the algorithm is therefore to find the minimum clique covering of the graph as each clique represents a register allocation. This approach was used initially by Tseng [64].

Figure 2.12 Clique partitioning.

Edge colouring is another graph theoretical technique used in register allocation. Again, the problem is posed as an undirected graph where the vertices denote signals. The edges, however, represent lifetime clashes. Stok uses an edge colouring formulation to tackle the problem of cyclic register allocation [19]. This looks at an optimal assignment of signals to registers in the presence of loops in the data flow graph. The problem is transformed into a multicommodity network flow problem for which well-known solutions exist.

#### 2.5.2 Graph Theoretical Techniques taking into account Interconnect.

Clique covering and colouring techniques have been extended to take into account the effects of register allocation on the interconnect allocation.

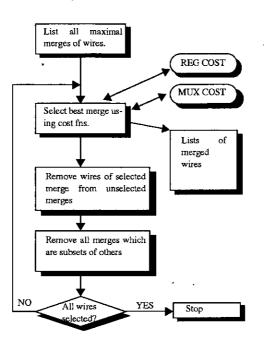

The HAL data path allocation scheme uses a weight-directed clique partitioning method [24]. A standard compatibility graph is constructed. Each arc is then labelled with a weight corresponding to the interconnection cost of combining the two signals into a single register. Four different interconnection patterns are recognised, however, the weight associated with them is an estimate of the interconnection area that would be saved and so it is design dependent rather than simply heuristic. Clique partitioning is performed on the part of the graph which exceeds a given threshold. The vertices of the located cliques are merged and the weights recalculated. The threshold is progressively lowered and partitioning repeated until no more cliques can be found. As clique partitioning is a NP-complete problem, keeping the graph size small by using a threshold enables exhaustive clique searching, even for large problems. Multiplexer merging is performed using a similar technique. Here, the threshold weight is the number of common inputs between multiplexers.

EASY performs data path allocation in three stages [18]. The binding of operations to processors is performed first using a maximal weight clique cover. The cliques with the highest sum of edge weights are selected. Again, a compatibility graph is constructed. The edge weightings are termed *advantages*. *Advantage* is defined as the net cost of binding operations to the same processor taking into account the multiplexing cost. The edge weights are updated as the cliques are merged. Register allocation, the second stage, uses a modified left-edge algorithm. The *advantage* weighting is used again to try to force signals with similar sources and destinations into the same register. This reduces the amount of interconnect required while still yielding the minimum number of registers. The final stage is called register grouping. This is an attempt to reduce the number of buses by grouping registers into register files. The maximal weight clique cover algorithm is again used in this optimization step. The compatibility graph represents registers as vertices and has arcs between registers which are never accessed simultaneously. The edge weighting reflects the number of common sources and destinations of adjoining registers.

The CADDY system uses a weighted graph colouring technique [13]. Two graphs are constructed: a restriction graph and a preference graph. The former is the complement of the compatibility graph. The latter depicts preferred combinations of signals because of shared sources and destinations. The restriction graph is coloured using a general vertex colouring heuristic to establish a minimum number of colours and, hence, the minimum number of registers. Colouring is then repeated, taking into account preferences. If the number of colours required in the second process is close to the minimum then the colouring is accepted and the registers allocated. If it is not accepted then edges with the smallest weight are removed from the preference graph

and the colouring process is repeated. Binding of operations and the construction of buses is performed using a similar colouring approach with both restriction and preference graphs.

#### 2.5.3 Branch and Bound Technique.

SPLICER [50] performs the tasks of register allocation and operation binding while allocating interconnect. Control step by control step, starting with registers containing initial values, the algorithm provides interconnection to processors and then from processors to registers. At each step an attempt is made to use existing hardware. The algorithm is based on a branch and bound search which allows backtracking.

#### 2.5.4 Iterative Techniques.

CHARM [42] claims to have an algorithm which performs register allocation and binding by dynamically exploiting the trade-off between the binding of operations to processors, the binding of signals to registers, the number of processors and the number of registers. The algorithm is based on the iterative merging of compatible operations and their respective data path allocations. Operations are compatible if they can share the same processor and are performed at different times. On each iteration all possible merges of operations and groups of operations are considered. The merge which yields the largest cost gain is selected. Iteration stops when no merge produces a cost saving. The costing function is a combination of four factors: the area costs of processors, registers and multiplexers and the estimated area cost of connecting wires. It is during costing that registers and interconnect are allocated.

In MABAL (ADAM) [28] the main algorithm tries to minimise the total cost by trading off between component cost and interconnect cost for each binding decision. The algorithm allows a limited amount of backtracking. It deals with operations and signals in the order in which they were scheduled. Incremental allocation decisions are taken on the basis of costs calculated for possible allocations with respect to the current

partial design. In this way an operation can be allocated a new processor if the interconnection cost of re-using an existing one is too high.

#### 2.5.5 Rule-based Schemes.

DAA, which is a rule-based expert system, makes allocation decisions on partitions of a design provided by BUD [55]. BUD clusters data flow operations and signals into partitions according to factors including common functionality, degree of interconnection and potential parallelism. Each partition is allocated its own processors, memory and interconnect. Local optimization procedures are then applied to remove or combine components. Finally, optimizations are applied globally to remove unneeded components and allocate bus structures.

In CATHEDRAL II [17], the rule-based 'Jack the Mapper' performs the data path allocation tasks. CATHEDRAL II generates data paths based on a fixed architectural template and this is reflected in the sort of rules used in 'Jack the Mapper'. These rules contain knowledge such as how to construct addressing schemes for array memory, bus structures and loop counters for iterations.

## Chapter 3 Models for Behavioural Synthesis.

## **3.1** Introduction.

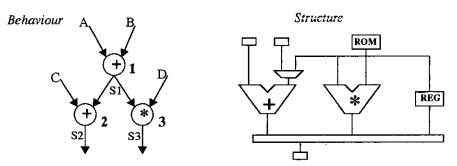

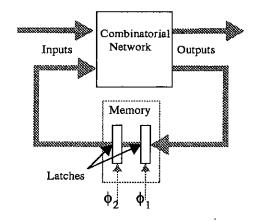

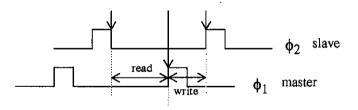

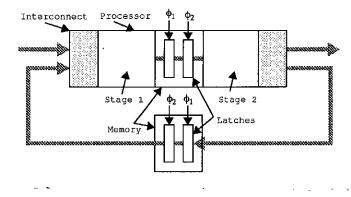

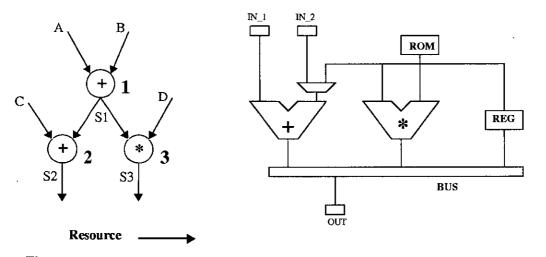

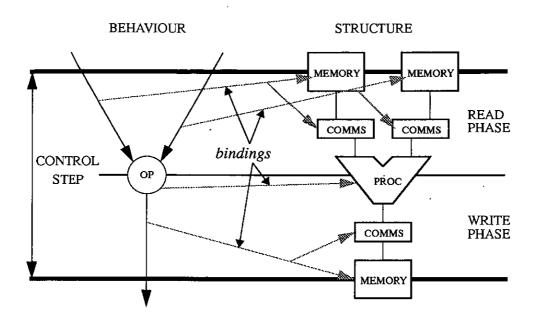

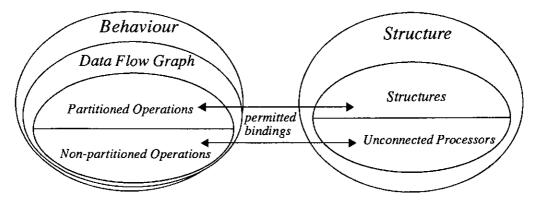

The synthesis system reported here operates on input specifications of behaviour and structure to produce design specifications of structures with associated control information. The control information is necessary to enable the synthesized structure to implement the specified behaviour. The synthesis of structure from behaviour can be performed at different structural levels such as register-transfer, logic gate and device. High-level behavioural synthesis systems typically relate the behaviour to the structure at the register-transfer level as shown in Figure 3.1. In the system presented in this thesis all structures are defined and constructed at the register-transfer level.

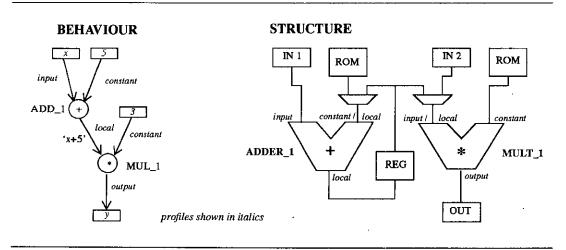

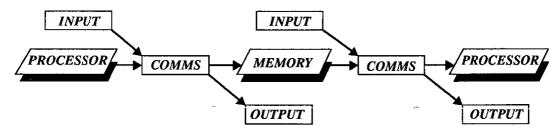

Figure 3.1 A representation of behaviour and structure at the register-transfer level.

The behaviour is related to the structure by a mapping from its behavioural elements to structural components. In order to avoid unnecessary composition or decomposition of behavioural elements, they are defined at a level corresponding to that of the structural components. In other words, a structure consisting of adders, multipliers and registers would relate to a behaviour consisting of additions, multiplications and binary data words.

Behaviour, structure and control form three separate domains of the synthesis system which communicate externally. Each is represented within a separately defined model. The following three sections discuss each model in turn, defining the subset of the domain which is represented and how it is specified. The final section outlines the use of these models within the synthesis system and how the designer can interact with them to direct the synthesis process.

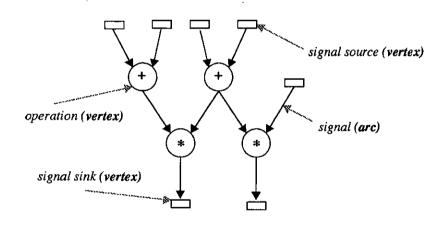

## **3.2** Behavioural Model.

Behaviour is represented within the system by a single data flow graph of the form shown in Figure 3.2. The data flow consists of operations and signals. Within the graph operations are denoted by vertices and signals by directed arcs. Input signals and constants are supplied by signal-source vertices and output signals are removed by signal-sink vertices. The directed arcs within the graph indicate the direction of data flow, the transfer of data with time. Consequently, data flow graphs are acyclic: it is impossible for a loop to exist as this would imply that data could be consumed before it was created.

Figure 3.2 Representing behaviour in a data flow graph.

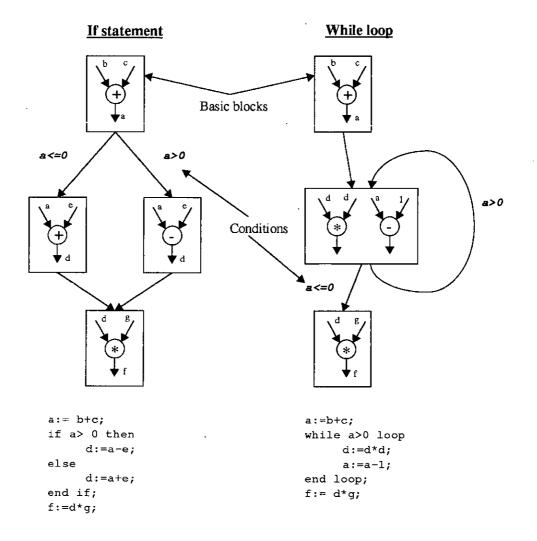

This simple behavioural representation cannot express conditional branching within the data flow. This is when the direction of data flow at some point in the graph depends upon an actual data value. The ability to represent conditional branching is necessary if the behaviour is to express high level programming constructs such as 'while loops' and 'if statements'. The synthesis system presented in this thesis does not tackle conditional branching within the data flow graph. However, it is envisaged that the approach to synthesis reported here can be harnessed within a larger system to tackle behaviours containing conditional branching. Using a representation from compiler technology called 'basic blocks', a behaviour containing such constructs can be modelled [65]. Each 'basic block' is a simple data flow graph representation of behaviour. These blocks form vertices in a control flow graph. The directed arcs in the graph represent conditions based on data flow values and point to the next data flow graph blocks which will be realised if the condition is satisfied. In this way, housing data flow graphs within a control flow graph, data dependent data flow can be represented. A simple example is illustrated in Figure 3.3.

Figure 3.3 Representing conditional constructs with basic blocks.

The synthesis system reported in this thesis can tackle individual basic blocks from the control graph. Assuming no pipelining, the execution of all basic blocks is mutually exclusive: only one block can be active at a given time. Even if pipelining is used basic blocks originating from the same conditional branch will remain mutually exclusive. A reduction in the structural overhead can therefore be made if structures can be synthesized to implement more than one basic block. A synthesis system using structural input can be used to address this problem. A structure synthesized to implement one block can be specified as the structural input in the synthesis of an other basic block in order to make additional use of the structures's components.

### **3.2.1** Behavioural Elements.

The data flow graph behaviour is constructed entirely from operations and signals. Because the structure is defined at the register-transfer level, which consists of a transfer of data between processors and memory, the operations are specified at a level corresponding to the functionality of the processors and the signals at a level corresponding to the data storage format of the memory.

#### 3.2.1.1 Operations.

All operations are dyadic. They are restricted to two inputs and one output. Operations with more inputs must be represented by a combination of two-input operations. The order of inputs is important. For non-commutative operations such as subtraction and division, the order of inputs must be maintained to preserve functional correctness. Each operation is defined as belonging to a type. There is no limitation placed on operation types but if the operation is to be performed then its type must be supported by a processor in the structure. Typical operation types are addition, subtraction and multiplication.

### 3.2.1.2 Signals.

Each directed arc in the data flow graph is a unique signal. There are four classes of signal: input, output, local and constant. The classification denotes a signal's usage within the data flow graph as depicted in Figure 3.4. Signals are assigned names to identify the data which they convey. Signals originating from the same operation convey the same data and so possess the same data name. Similarly, constant signals carrying the same data value will have the same data name.

Figure 3.4 Signal classifications within a data flow graph.

#### 3.2.1.3 Textual Representation.

The behaviour is specified in a textual format from which the data flow graph is constructed. An example is shown in Figure 3.5. The signals and operations are specified separately within the behaviour's text file. The syntax for signals is of the form:

signal <data name> <signal class> end

For operations, which are specified after the signals, the syntax is as follows:

operation <operation name> <operation type> <left data name> <right data name> <output data name> end Textual Representation

Data Flow Graph

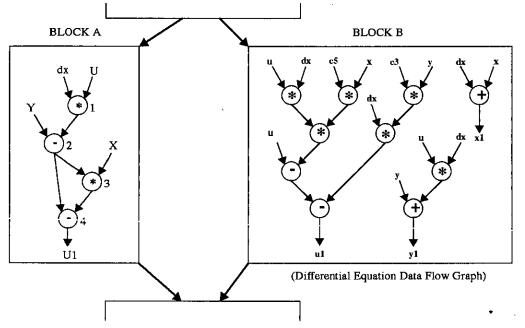

| network DIFF_EQ                                                                                                                                                                                    |                                                             |                                                                    |                                              |                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------|-----------------------------------------|

| signal U input<br>signal X input<br>signal Ul output<br>signal dx constant<br>signal c3 constant<br>signal c5 constant<br>signal s1 local<br>signal s2 local<br>signal s3 local<br>signal s4 local | end<br>end<br>end<br>end<br>end<br>end<br>end<br>end<br>end |                                                                    | U dx c5<br>MUL_2<br>MUL_1 s2<br>s1<br>WUL_53 | x c3 y<br>* MUL_4<br>dx s4<br>3 * MUL_6 |

| signal s5 local<br>signal s6 local                                                                                                                                                                 | end<br>end                                                  |                                                                    | SUB_5                                        | s6                                      |

| operation mul_1 mul<br>operation mul_2 mul<br>operation mul_3 mul<br>operation mul_4 mul<br>operation sub_5 sub<br>operation mul_6 mul<br>operation sub_7 sub                                      | U dx<br>c5 X<br>s1 s2<br>c3 Y<br>U s3<br>dx s4<br>s5 s6     | s1 end<br>s2 end<br>s3 end<br>s4 end<br>s5 end<br>s6 end<br>U1 end | s5<br>SUB                                    |                                         |