# A High Performance Distributed Data Acquisition System for the NA48 Experiment on CP-Violation

Nicholas Ewen Mckay

Submitted for the degree of Doctor of Philosophy The University of Edinburgh 1995

#### Abstract

This thesis describes the data acquisition methods employed by the NA48 experiment at CERN. A brief overview of the physics behind NA48 and a description of the experimental apparatus are given in the introduction. The specification and the implementation of the data acquisition system is then detailed along with a discussion of the design 'philosophy' that influenced the design choices. The section of the data acquisition system on which I have been working, the Data Merger, is discussed in some detail. Next, my main contribution to NA48, the Input Buffer, is described along with its performance in laboratory tests and data taking runs. Alternative solutions to the problems of acquiring data are also discussed along with examples of data taking schemes from similar experiments. Finally, the conclusions that can be drawn from the design and performance of the NA48 data acquisition system are discussed.

#### Declaration

This work represents the efforts of many members of the NA48 collaboration at CERN, the European Center for Particle Physics. I have been an integral part of the small team of five people who have designed and developed the data merger, and have been personally responsible for the Input Buffer. The writing of the thesis has been entirely my own work.

#### Acknowledgements

I would like to acknowledge the Particle Physics and Astronomy Research Council for their financial support during my work at Edinburgh.

My main supervisor, Dr Ken Peach, has been a great source of help and encouragement over the last four years. I would like to thank him, Alan Walker and David Candlin for their help and support.

The help of research Associates Dr. Owen Boyle and Dr. Elizabeth Veitch has been greatly appreciated. I would particularly like to thank Dr. Boyle for his work on the data merger at CERN.

The Input Buffer board, the major product of my research, was laid out by Andrew Main at Edinburgh University. The late Peter McInnes was a great help during the design stages of the board.

The ready wit of the departments postgraduate students, Bruce Hay, Grahame Oakland and Mark Parsons has done much to make my time at Edinburgh enjoyable.

At CERN Dr. Robert Maclaren has arranged for me to have the use of his laboratory and equipment. I would also like to thank Jean-Pol Matheys for his work on the development of software for the data merger and Phillipe Brodier-Yourstone for his work on the optical links.

## Contents

|   | Inti | oduction                      | 1        |

|---|------|-------------------------------|----------|

|   | 1.1  | Overview                      | 1        |

|   | 1.2  | Measurement of $\epsilon'$    | 4        |

|   |      | 1.2.1 The NA48 Beam           | 4        |

|   |      | 1.2.2 The NA48 Detector       | 7        |

|   |      | 1.2.3 The NA48 Trigger System | 12       |

|   | 1.3  | Dataflow Requirements         | 15       |

| 2 | NA   | 48 Dataflow                   | 17       |

|   | 2.1  |                               |          |

|   |      | Overview                      | 17       |

|   | 2.2  |                               | 17<br>21 |

|   | 2.2  | Dataflow hardware             |          |

|   | 2.2  | Dataflow hardware             | 21       |

|   |     | 2.2.4  | The Workstation Farm                  | 27 |

|---|-----|--------|---------------------------------------|----|

|   | 2.3 | Datafl | ow Control Software                   | 29 |

|   |     | 2.3.1  | The Run Control Program               | 29 |

|   |     | 2.3.2  | The Workstation Farm Resource Manager | 30 |

|   |     | 2.3.3  | Slow Control                          | 30 |

| 3 | NA  | 48 Dat | ta Merger                             | 31 |

|   | 3.1 | Gener  | al arrangement of the Data Merger     | 31 |

|   | 3.2 | Imple  | mentation Choices                     | 34 |

|   |     | 3.2.1  | Bus Implementation Choices            | 34 |

|   |     | 3.2.2  | Circuit Board Implementation Choices  | 36 |

|   | 3.3 | Overv  | iew of the Data Transfer Protocol     | 37 |

|   | 3.4 | Input  | Buffer                                | 38 |

|   | 3.5 | R-patl | h backplane                           | 38 |

|   | 3.6 | FIFO   | Output Formatter                      | 40 |

|   |     | 3.6.1  | Overview                              | 40 |

|   |     | 3.6.2  | General Arrangement of the FOF        | 41 |

|   |     | 3.6.3  | R-path and token interface            | 43 |

|   |     | 3.6.4  | Additional data generated by the FOF  | 43 |

|   |     | 3.6.5  | The HIPPI transfer protocol           | 44 |

### 4 Input Buffer Design

|   | 4.1  | Overv   | iew                                  | 47 |

|---|------|---------|--------------------------------------|----|

|   | 4.2  | Desigr  | n Philosophy                         | 48 |

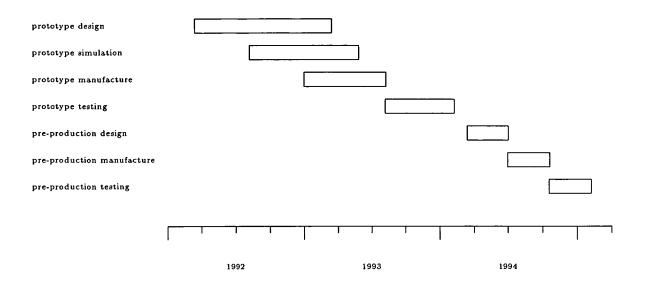

|   | 4.3  | Design  | n Timetable                          | 50 |

|   | 4.4  | Input   | Buffer Logic Circuitry               | 50 |

|   | 4.5  | Xilinx  | Design                               | 52 |

|   |      | 4.5.1   | Xilinx Layout                        | 52 |

|   |      | 4.5.2   | Xilinx Configuration                 | 53 |

|   |      | 4.5.3   | Design Entry                         | 55 |

|   |      | 4.5.4   | Xilinx Fuctionality                  | 55 |

| 5 | Test | : Resu  | lts                                  | 60 |

|   | 5.1  | Input   | Buffer Commissioning                 | 60 |

|   | 5.2  | Input   | Buffer Testing                       | 66 |

|   |      | 5.2.1   | Optical Link Data Transfer           | 67 |

|   |      | 5.2.2   | R-Path Data Transfer                 | 69 |

|   |      | 5.2.3   | Summary                              | 72 |

| 6 | Alte | ernativ | ve Solutions to the Dataflow Problem | 74 |

|   |      |         |                                      |    |

47

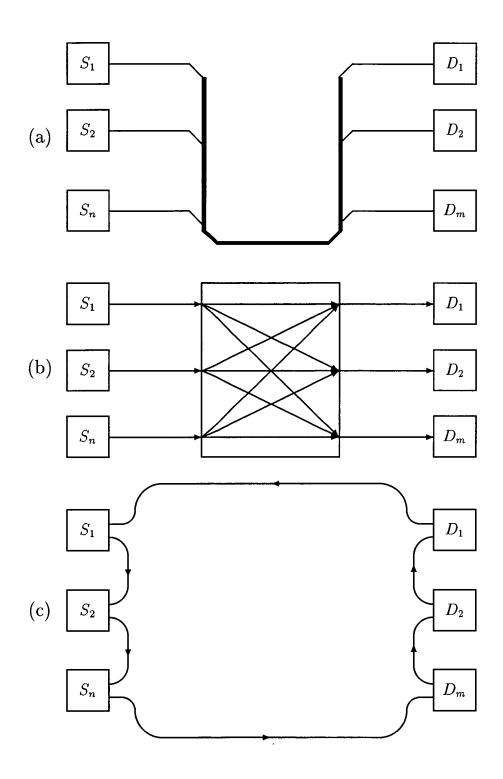

|   |     | 6.1.1   | Bus-based Architectures               | 74  |

|---|-----|---------|---------------------------------------|-----|

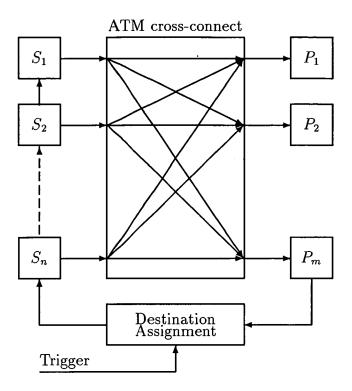

|   |     | 6.1.2   | Switching Network Based Architectures | 76  |

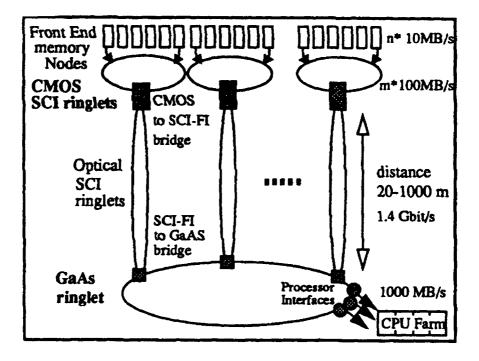

|   |     | 6.1.3   | Ring Based Architectures              | 78  |

|   |     | 6.1.4   | The NA48 Dataflow Architecture        | 79  |

|   | 6.2 | Datafl  | ow Solutions from Other Experiments   | 80  |

|   |     | 6.2.1   | The Atlas DAQ Scheme                  | 80  |

|   |     | 6.2.2   | The DART DAQ Scheme                   | 81  |

| 7 | Cor | clusio  | ns                                    | 84  |

|   | 7.1 | Datafl  | ow                                    | 84  |

|   |     | 7.1.1   | Initial Tests                         | 84  |

|   |     | 7.1.2   | Further Laboratory Tests              | 86  |

|   | 7.2 | Input   | Buffer                                | 86  |

|   | 7.3 | Conclu  | Iding Remarks                         | 87  |

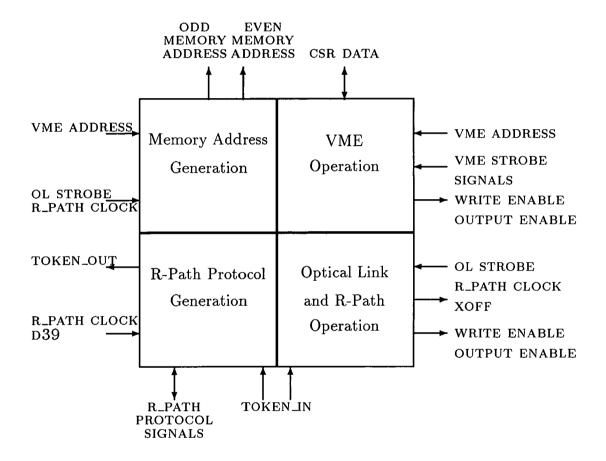

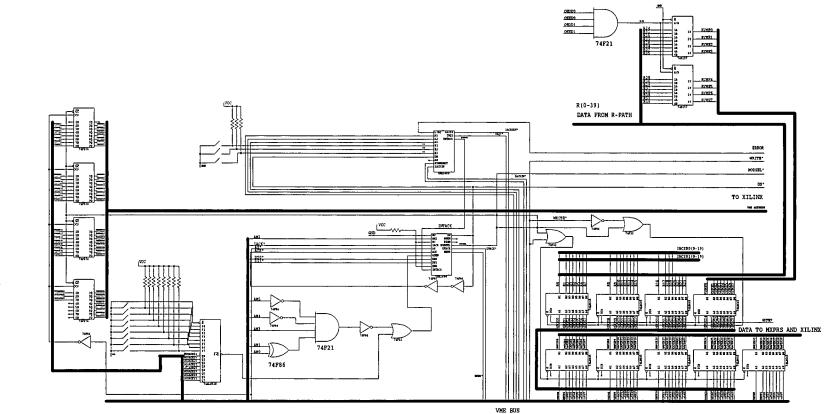

| A | VM  | E Ope   | ration                                | 89  |

| в | Opt | ical Li | nk Interface                          | 93  |

| С | R-P | ath In  | terface                               | 97  |

| D | Tok | en Hai  | ndling                                | 100 |

.

### E Front Panel LEDs

| F            | Xili        | nx Design                              | 104 |

|--------------|-------------|----------------------------------------|-----|

|              | <b>F</b> .1 | VME Interface                          | 104 |

|              | F.2         | Optical Link and R-Path Memory Control | 113 |

| $\mathbf{G}$ | Sim         | ulation Results                        | 120 |

|              | G.1         | Dataflow Simulation                    | 120 |

|              | G.2         | Input Buffer Simulation                | 124 |

102

# List of Figures

| 1.1 | Schematic overview of NA48 experiment                                           | 5  |

|-----|---------------------------------------------------------------------------------|----|

| 1.2 | Read-out Structure of LKr Calorimeter                                           | 10 |

| 1.3 | The triggers in respect to the dataflow scheme                                  | 13 |

| 2.1 | Hardware Components of the Data Acquisition System                              | 18 |

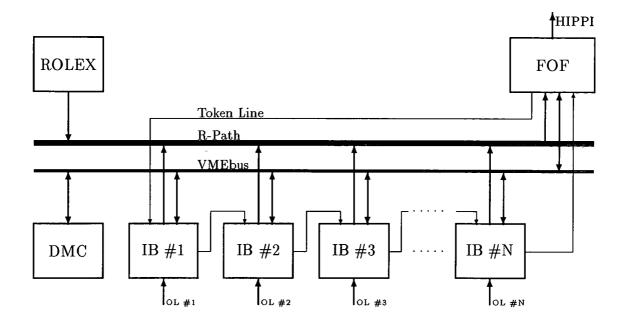

| 2.2 | Layout of Data Merger                                                           | 25 |

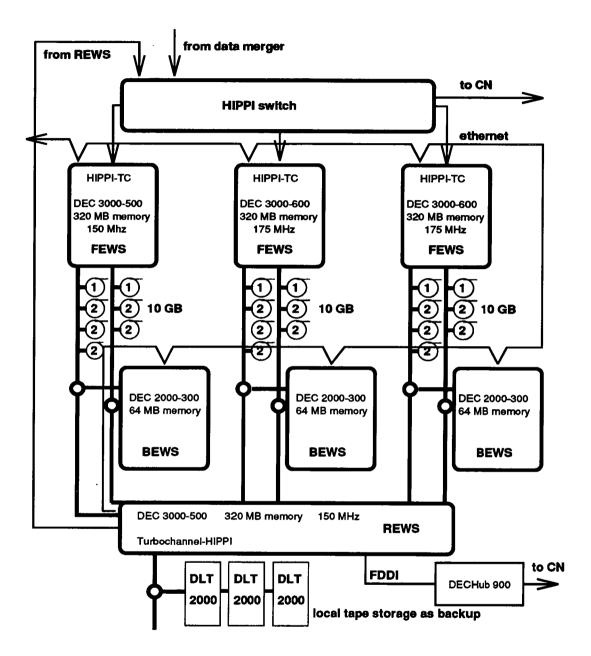

| 2.3 | Level 3 Workstation Farm Architecture                                           | 28 |

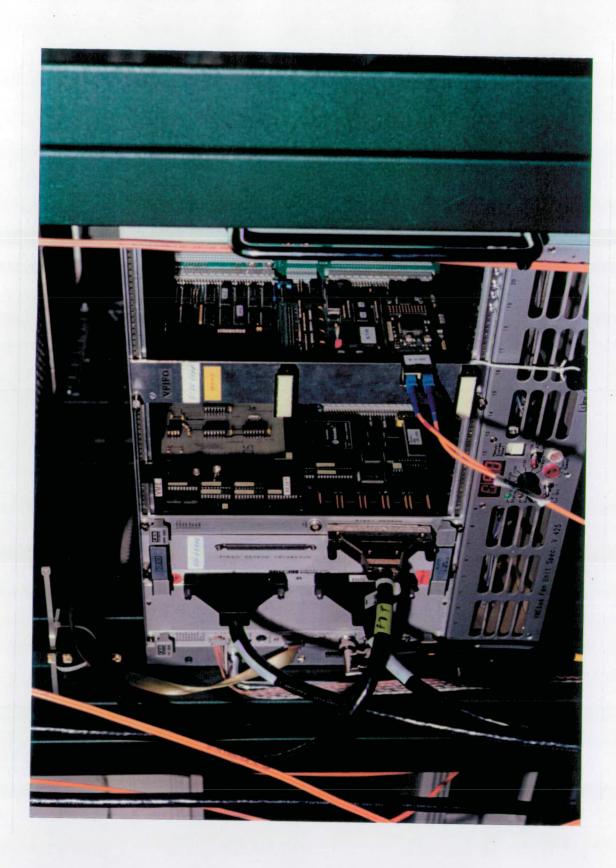

| 3.1 | Photograph of the 6U crate used to house the DMC                                | 32 |

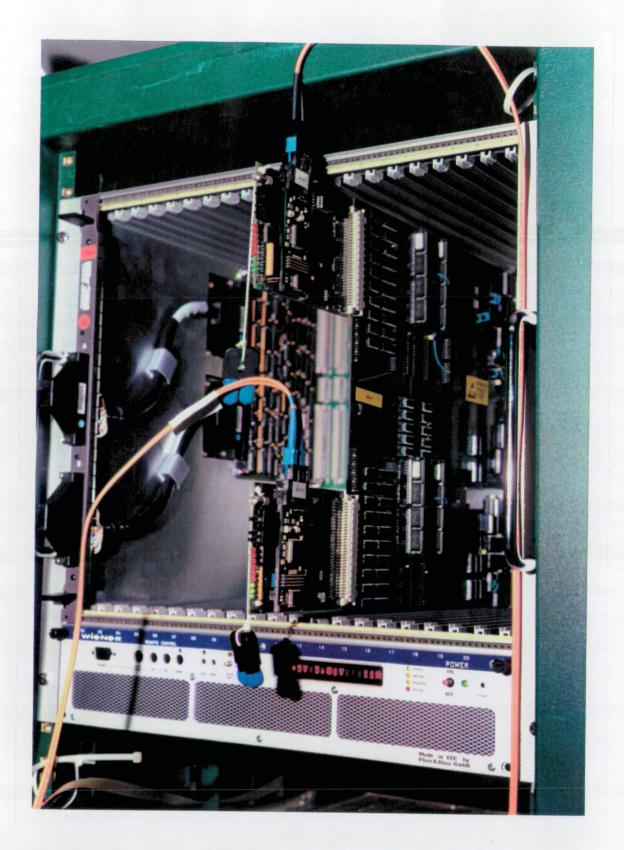

| 3.2 | Photograph of the 9U crate that is used to house the Input Buffers and the FOF. | 33 |

| 3.3 | An example of BTL signals on the CERN backplane                                 | 36 |

| 3.4 | Block diagram of the FOF                                                        | 42 |

| 3.5 | The structure of a FOF HIPPI connection                                         | 45 |

| 3.6 | The structure of an event packet.                                               | 46 |

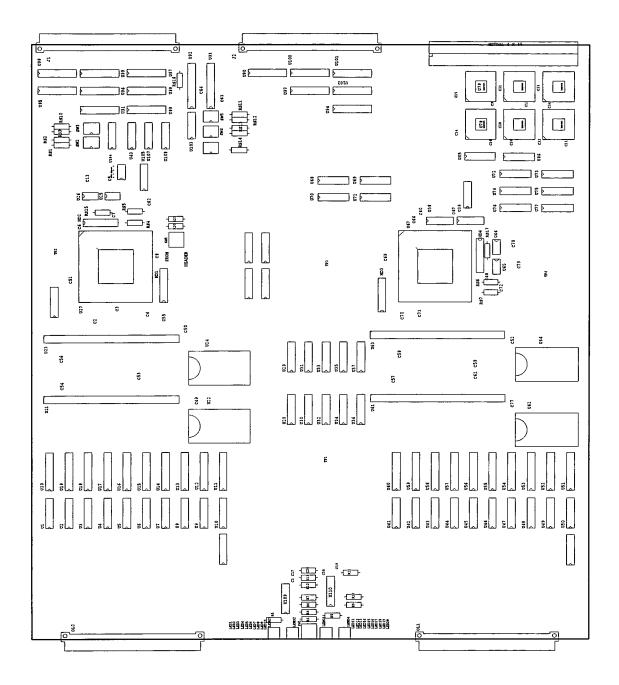

| 4.1 | IB board layout                                                                 | 49 |

| 4.2 | Timescale for Input Buffer Development                                                     | 51 |

|-----|--------------------------------------------------------------------------------------------|----|

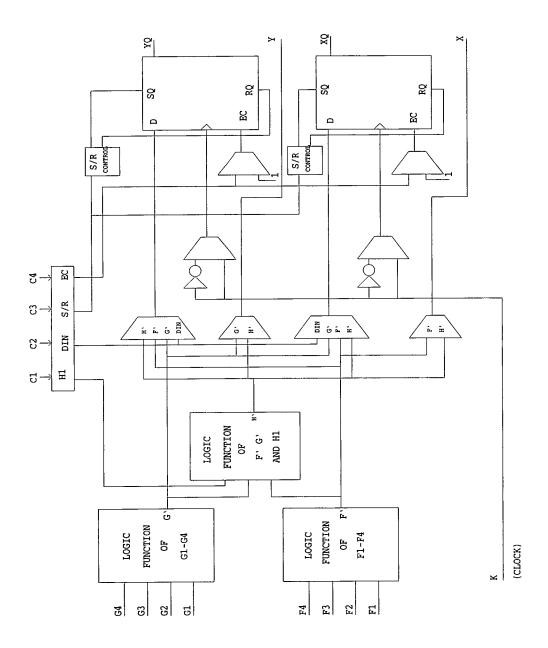

| 4.3 | Block Diagram of XC4000 Configurable Logic Block                                           | 54 |

| 4.4 | Block Diagram of Xilinx                                                                    | 56 |

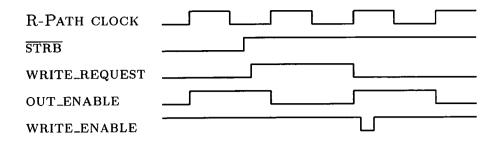

| 4.5 | Generation of Write Enable for even memory                                                 | 58 |

| 5.1 | Initial IB Block Diagram                                                                   | 61 |

| 5.2 | Prototype IB Test Set-up.                                                                  | 62 |

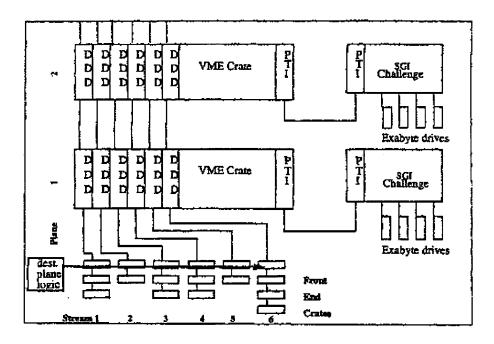

| 5.3 | Dataflow Hardware Setup for the 1994 Test Run                                              | 64 |

| 5.4 | IB Write-in Cycle from Optical Link                                                        | 68 |

| 5.5 | $\overline{\text{XOFF}}$ de-asserted and transfer resumed                                  | 68 |

| 5.6 | Start of transfer of Chequer Board pattern from IB to FOF                                  | 70 |

| 5.7 | End of transfer from IB to FOF                                                             | 70 |

| 5.8 | RP_HAVEDATA and RP_NODATA at the start of a data transfer to an empty IB                   | 72 |

| 6.1 | Data Acquisition Structures (a) Bus (b) Crossbar switch (c) Ring.                          | 75 |

| 6.2 | ATM Switching Architecture                                                                 | 77 |

| 6.3 | A Multi-Ringlet SCI Data Merger                                                            | 78 |

| 6.4 | Block Diagram of the KTeV DA System                                                        | 82 |

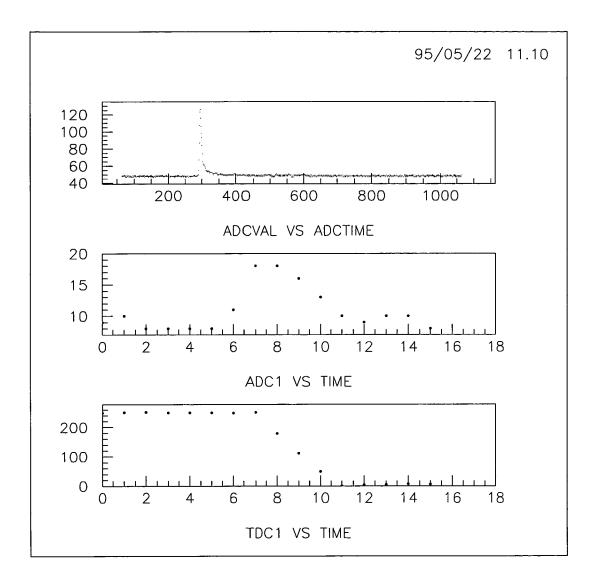

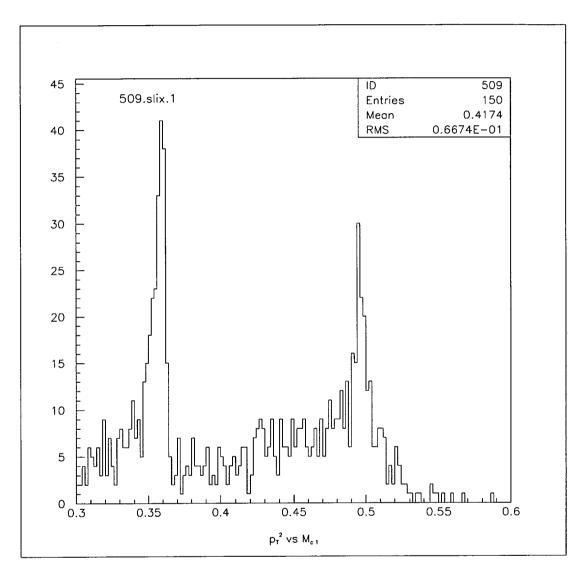

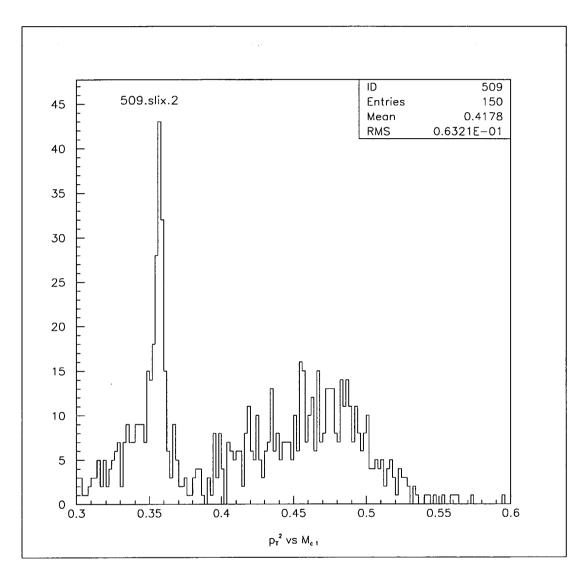

| 7.1 | A plot from the 1994 run showing a hit in the hodoscope together with a hit in the tagger. | 85 |

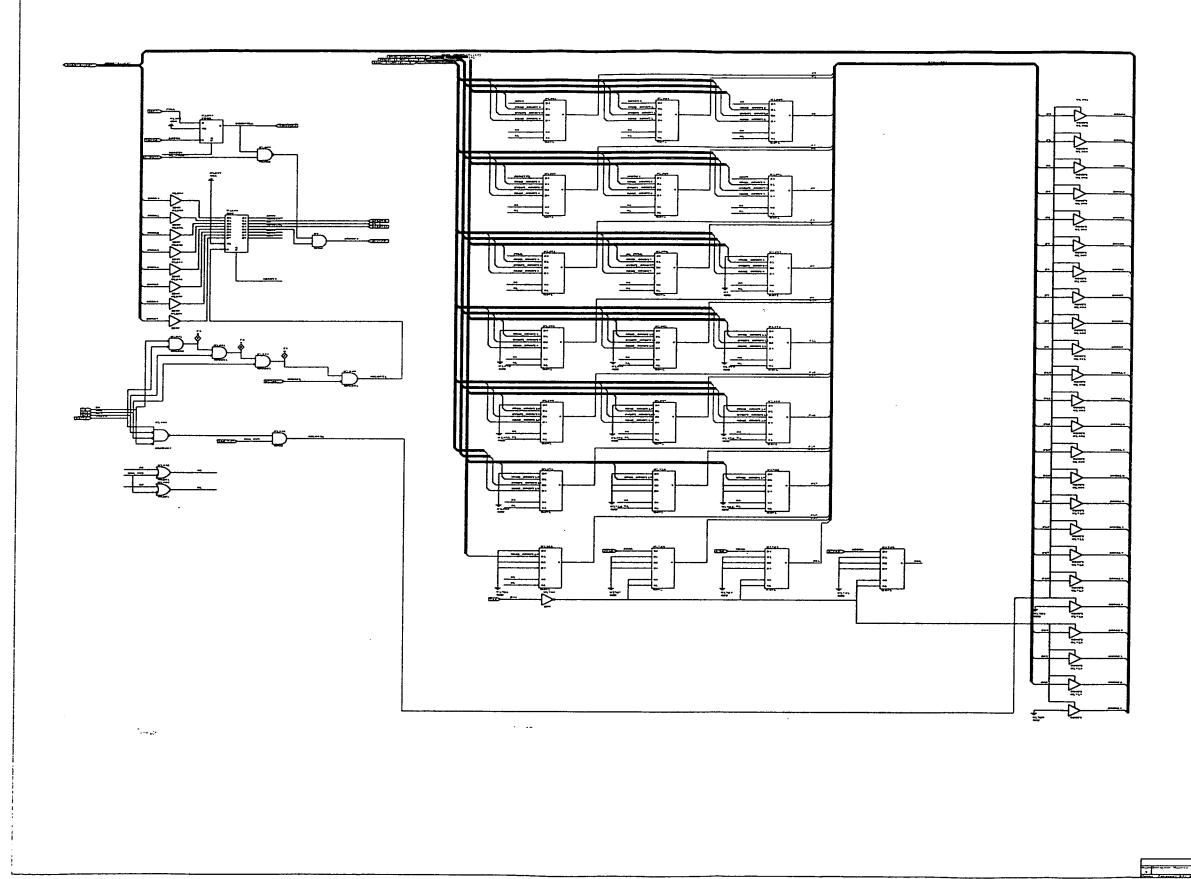

| <b>A</b> .1 | IB VME Interface                                      | 90  |

|-------------|-------------------------------------------------------|-----|

| <b>B</b> .1 | Channel Memory Structure                              | 95  |

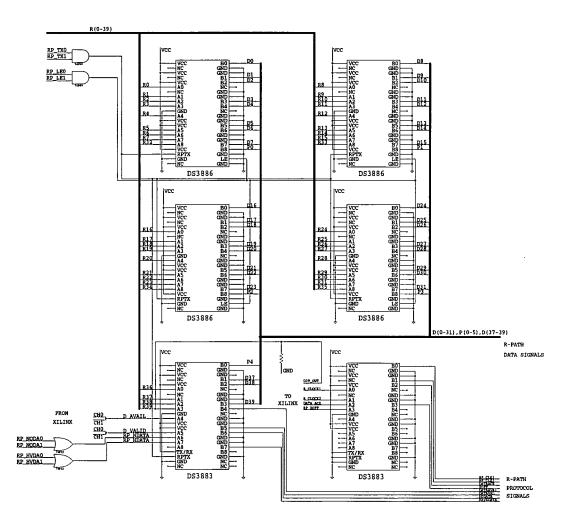

| C.1         | R-Path Interface                                      | 98  |

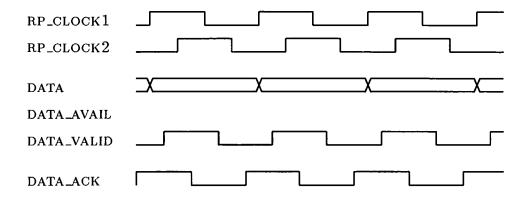

| C.2         | R-Path Data Transfer                                  | 99  |

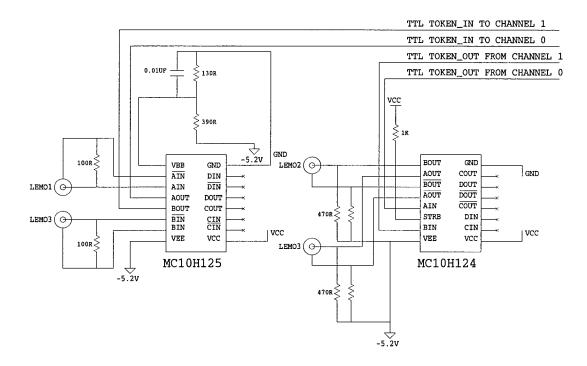

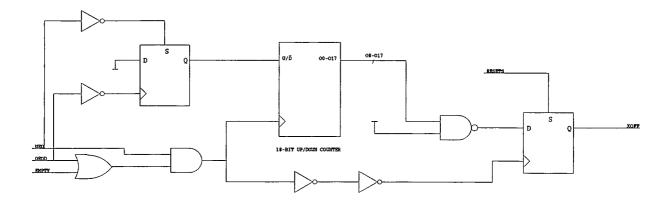

| D.1         | Token Input/Output Circuit                            | 101 |

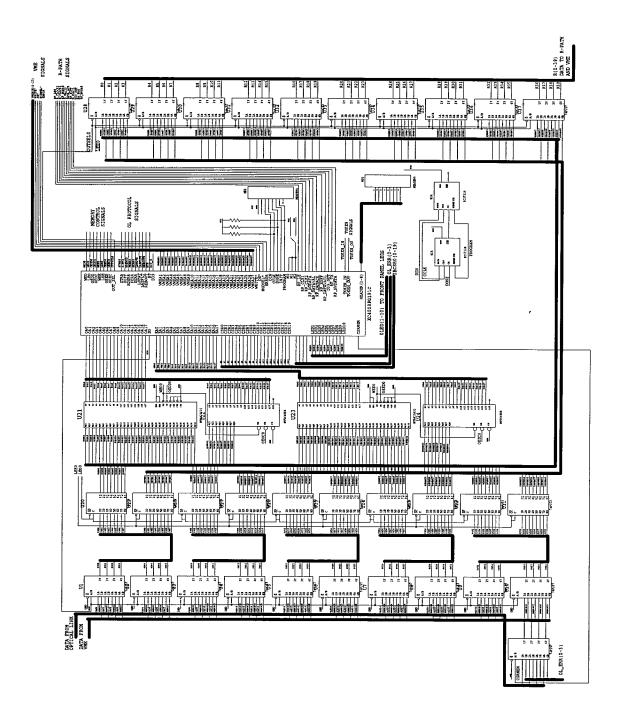

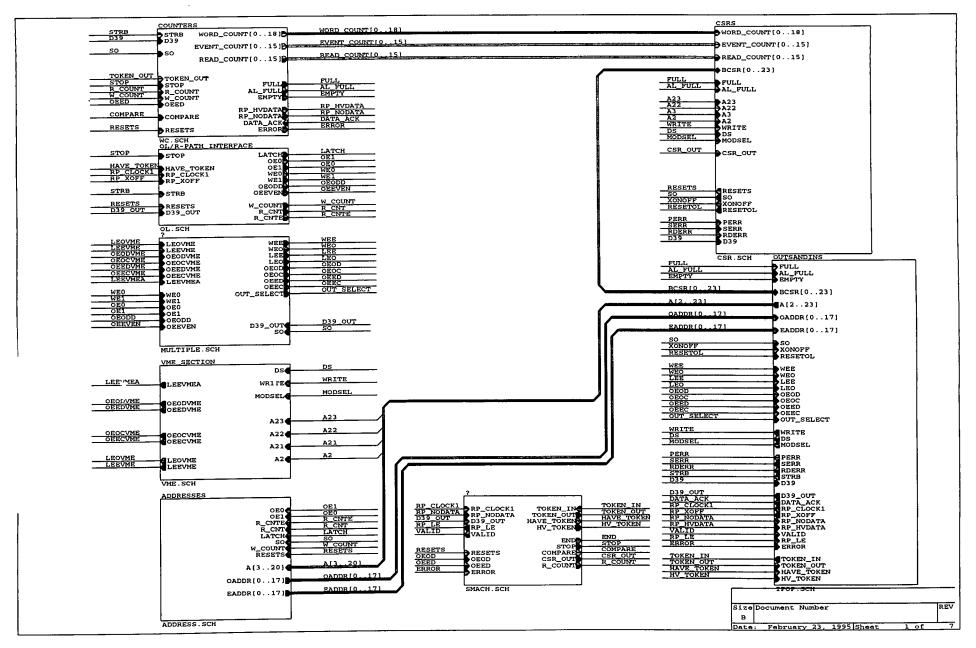

| F.1         | IB Xilinx Top Level Schematic                         | 105 |

| F.2         | Xilinx VME decoding                                   | 106 |

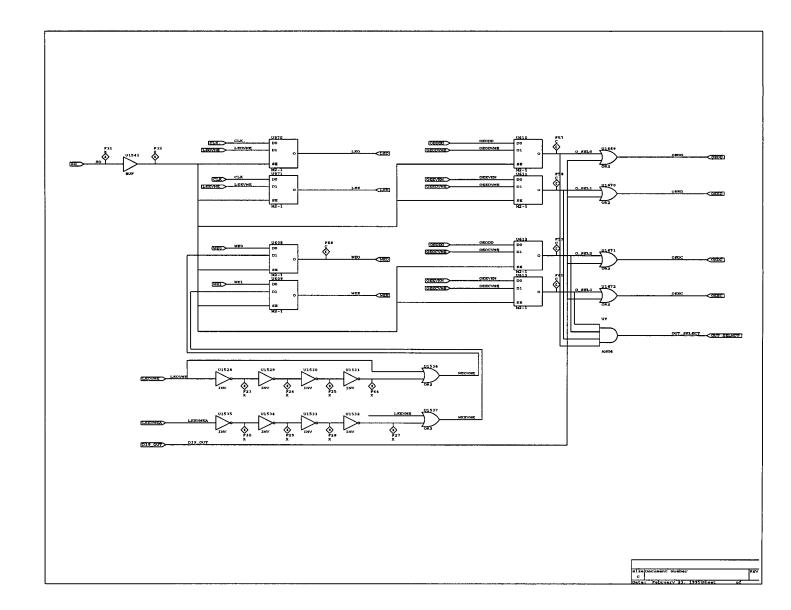

| F.3         | Xilinx Read/Write strobe multiplexer circuit          | 109 |

| F.4         | Xilinx CSR circuit                                    | 110 |

| F.5         | Xilinx Counters and Protocol Circuit                  | 111 |

| F.6         | Xilinx Memory Address Generation                      | 112 |

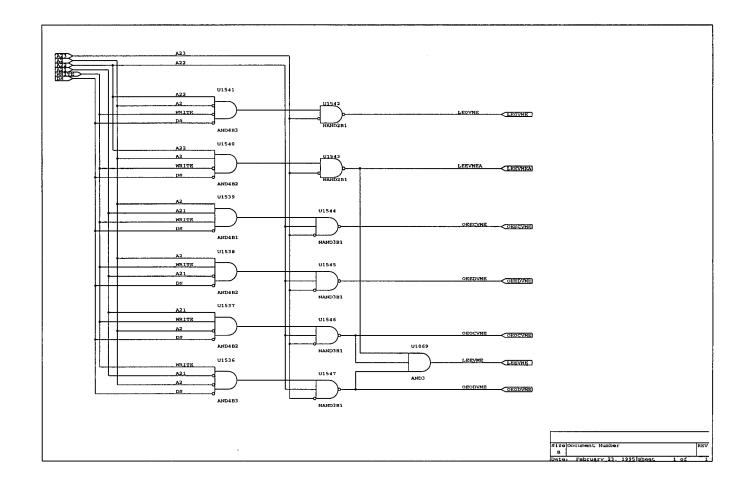

| F.7         | Xilinx Write Enable Circuit                           | 114 |

| F.8         | Generation of Write Enable for even memory            | 115 |

| F.9         | Xilinx token circuit                                  | 116 |

| F.10        | Even Memory Read Signals                              | 118 |

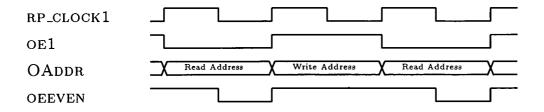

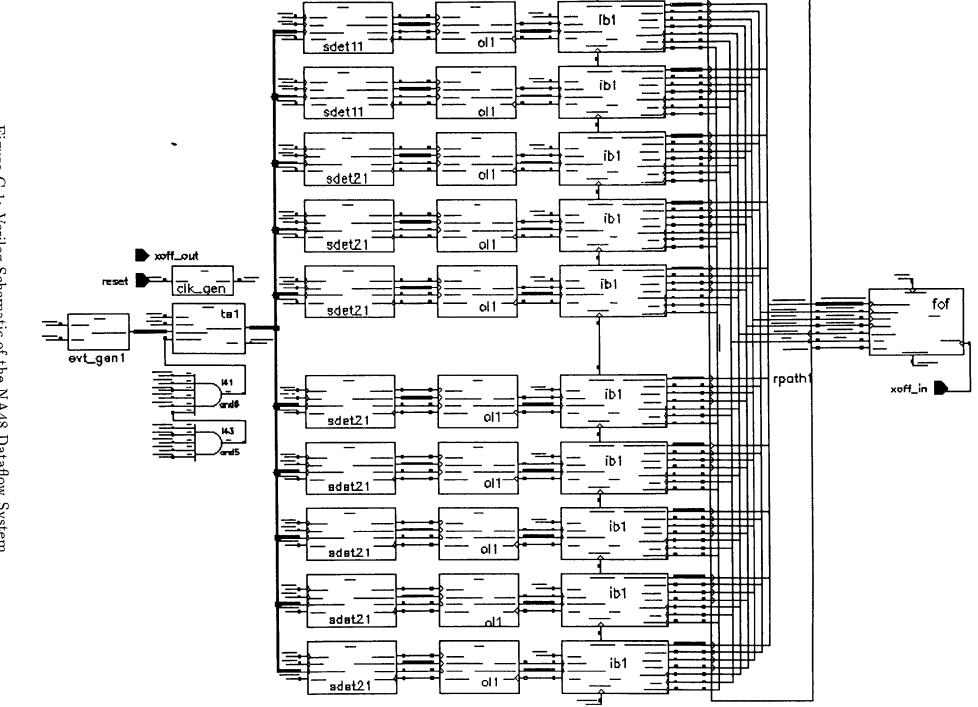

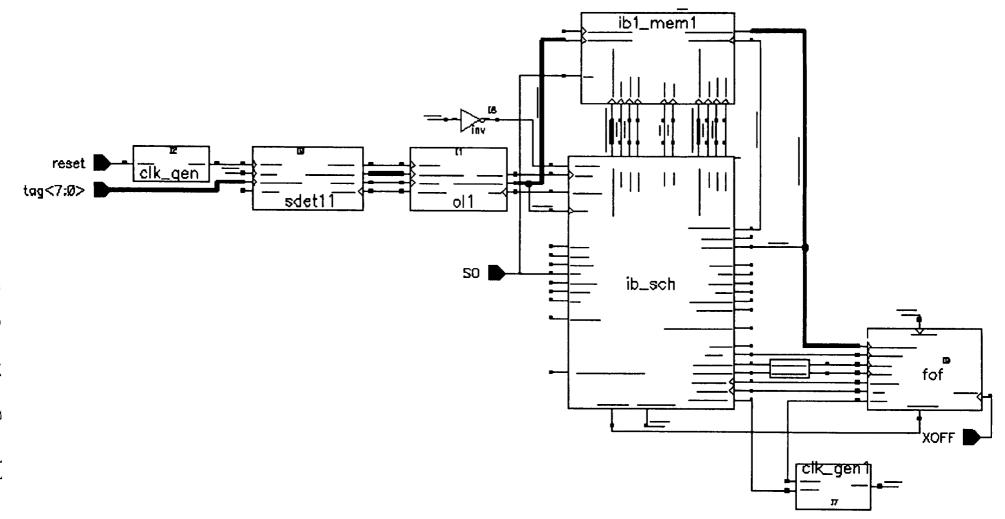

| G.1         | Verilog Schematic of the NA48 Dataflow System         | 121 |

| G.2         | Simulation of the NA48 Dataflow System                | 123 |

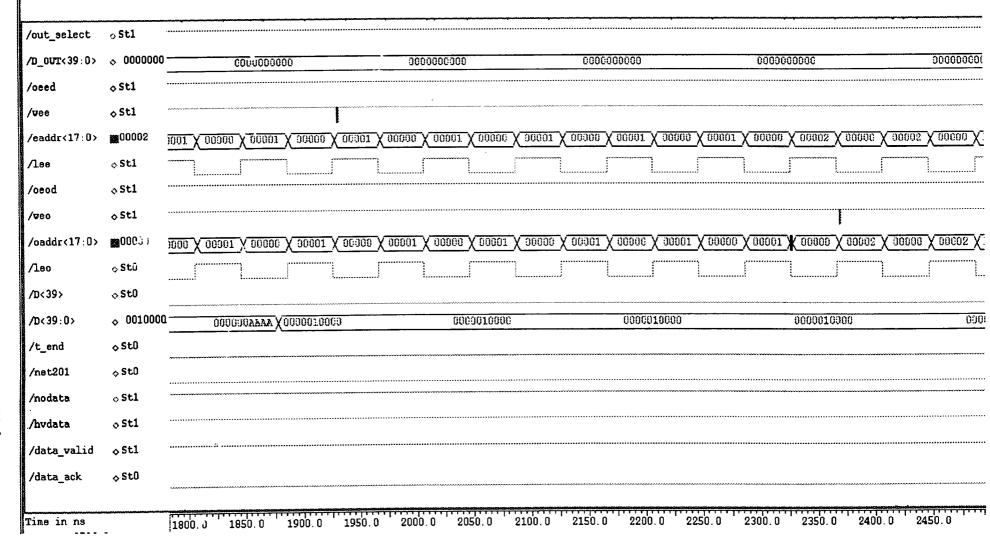

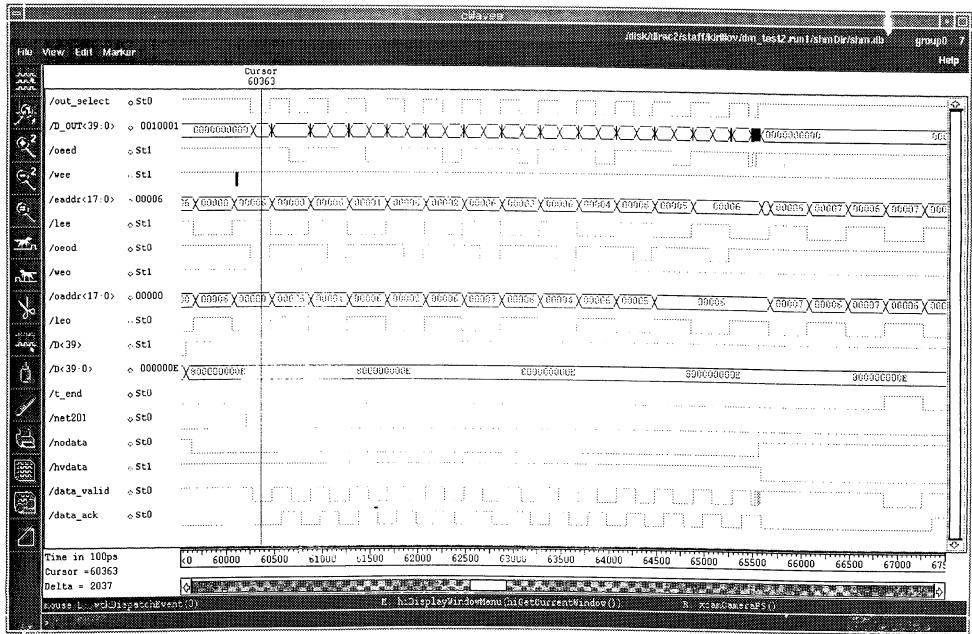

| G.3         | Verilog Schematic of the Dataflow with an Expanded IB | 125 |

•

| G.4 | Input Buffer write-in Cycle from Optical Link | 126 |

|-----|-----------------------------------------------|-----|

| G.5 | Input Buffer read-out Cycle over R-Path       | 127 |

# List of Tables

| 6.1         | Critical ATLAS front end DAQ parameters                 | 80  |

|-------------|---------------------------------------------------------|-----|

| A.1         | VME Addressing Scheme                                   | 91  |

| A.2         | Input Buffer Control and Status Registers               | 91  |

| B.1         | OL protocol signals                                     | 94  |

| E.1         | IB Status LEDs                                          | 103 |

| <b>F</b> .1 | Channel 0 VME Decoding Scheme                           | 107 |

| F.2         | Memory Addressing Scheme Implemented in the Xilinx FPGA | 118 |

| G.1         | Simulation Trigger Rates                                | 122 |

•

.

### Chapter 1

### Introduction

### 1.1 Overview

The NA48<sup>1</sup> experiment at CERN has been designed to measure the magnitude of direct CP violation to an absolute accuracy greater than  $2 \times 10^{-4}$  [1].

Prior to 1964 it was believed that all weak decays were symmetric under CP, where the CP operator is defined to be the combined operations of charge conjugation and parity transformation. However, in 1964 the occurrence of CP violation was observed in the neutral kaon system [2].

Although produced by the strong interaction, kaons decay via the weak interaction. Therefore, the production and decay eigenstates can be different. The strong eigenstates of neutral kaon production are also eigenstates of the strangeness operator  $\hat{S}$ . That is:

$$\hat{S} \left| K^{\mathbf{0}} \right\rangle = \left| K^{\mathbf{0}} \right\rangle \tag{1.1}$$

<sup>&</sup>lt;sup>1</sup>The NA48 collaboration is the 48th experiment to be approved for construction at the North Area of the CERN SPS. The collaboration is made up from physicists and engineers from Cagliari, Cambridge, CERN, Dubna, Edinburgh, Ferrara, Mainz, Orsay, Perugia, Pisa, Saclay, Seigen, Torino and Vienna.

$$\hat{S} \left| \overline{K^0} \right\rangle = - \left| \overline{K^0} \right\rangle \tag{1.2}$$

The CP eigenstates of the neutral kaon decay are different:

$$K_1^0 = \frac{1}{\sqrt{2}} (K^0 + \overline{K^0}) \tag{1.3}$$

$$K_2^0 = \frac{1}{\sqrt{2}} (K^0 - \overline{K^0}) \tag{1.4}$$

Where the convention chosen is that the  $K_0$  transforms to  $\overline{K^0}$  under the CP operator while  $\overline{K^0}$  transforms to  $K_0$ .

$K_1^0$  is CP-even and decays to either  $2\pi^0$  or  $\pi^+\pi^-$  while  $K_2^0$  is CP-odd and predominantly decays to  $3\pi^0$ ,  $\pi^+\pi^-\pi^0$ ,  $\mu\pi\nu$  or  $e\pi\nu$ . All of these reactions obey CP symmetry. However, the  $K_2^0$  may also decay to  $2\pi^0$  and  $\pi^+\pi^-$ . These reactions are CP-violating.

Christenson *et al* [2]. deduced from this that the real weak eigenstates are mixtures of  $K_1^0$  and  $K_2^0$ , (assuming CPT)<sup>2</sup>;

$$K_{S}^{0} = \frac{1}{\sqrt{1 + |\epsilon|^{2}}} (K_{1}^{0} + \epsilon K_{2}^{0})$$

(1.5)

$$K_L^0 = \frac{1}{\sqrt{1 + |\epsilon|^2}} (K_2^0 + \epsilon K_1^0)$$

(1.6)

where the short-lived  $K_S^0$  is mostly CP-even and the long-lived  $K_L^0$  is mostly CPodd. The mixing between  $K_S^0$  and  $K_L^0$  allows the long-lived  $K_L^0$  to oscillate into

<sup>&</sup>lt;sup>2</sup>The CPT Theorem (the combination of CP and Time symmetry) is implicit in quantum field theories such as the standard model of particle interactions. For example the masses and lifetimes of particle – anti-particle pairs are equal. This has been tested in the neutral kaon system to one part in  $10^{18}$ .

$K_S^0$  and then to decay into a CP-even state. This is termed 'Indirect' CP-violation and the constant  $\epsilon$  provides a measure of its magnitude.

The ratio of CP-symmetric to CP-violating decays is described by  $\eta_{+-}$  and  $\eta_{00}$ , where  $\Gamma$  is the partial width of the given decay:

$$|\eta_{+-}|^2 = \frac{\Gamma(K_L \to \pi^+ \pi^-)}{\Gamma(K_S \to \pi^+ \pi^-)}$$

(1.7)

$$\left|\eta_{00}\right|^{2} = \frac{\Gamma(K_{L} \to 2\pi^{0})}{\Gamma(K_{S} \to 2\pi^{0})} \tag{1.8}$$

In the case of indirect CP-violation the  $2\pi$  decays of the  $K_L$  arise from the  $K_1$  component, and therefore  $\eta_{+-} = \eta_{00}$ .

However, it may also be possible for the  $K_2^0$  state to decay directly to a CP-even state. If this were to occur there could be different amounts of CP-violation in the  $2\pi^0$  and  $\pi^+\pi^-$  decay channels. This is termed 'direct' CP-violation and is described by the double ratio of  $\eta_{+-}$  and  $\eta_{00}$ :

$$R = \left|\frac{\eta_{00}}{\eta_{+-}}\right|^2 = \frac{\Gamma(K_L \to 2\pi^0) / \Gamma(K_L \to \pi^+\pi^-)}{\Gamma(K_S \to 2\pi^0) / \Gamma(K_S \to \pi^+\pi^-)} \approx 1 - \frac{1}{6} Re\left(\frac{\epsilon'}{\epsilon}\right)$$

(1.9)

The parameter  $\epsilon'$  is zero if only indirect CP-violation takes place in the neutral kaon system but in general is non-zero if direct CP-violation is present. It is this parameter that NA48 aims to measure. Previous measurements made by NA31 at CERN [3] and E731 at Fermilab [4] have yielded different results. The published result of NA31 of  $Re(\epsilon'/\epsilon) = (2.0 \pm 0.7) \times 10^{-3}$  is three standard deviations away from zero, while the result from E731 ( $Re(\epsilon'/\epsilon) = (0.74\pm0.59) \times 10^{-3}$ ) is consistent with zero. NA48 hopes that by increasing the accuracy of the measurement by a factor of 5 the value of  $\epsilon'$  can be determined.

### **1.2** Measurement of $\epsilon'$

In order to measure the double ratio R given in Equation 1.9, the interesting events must be sorted out from a large background of decays that are unimportant. The decays that are of interest are:

$$K_L \rightarrow 2\pi^0$$

$$K_L \rightarrow \pi^+\pi^-$$

$$K_S \rightarrow 2\pi^0$$

$$K_S \rightarrow \pi^+\pi^-$$

To identify these decay modes we must first be able to differentiate between  $K_S$  and  $K_L$ . In NA48 this is done by generating two beams, one of long-lived kaons  $(K_L)$  and one of short-lived kaons  $(K_S)$ .

#### 1.2.1 The NA48 Beam

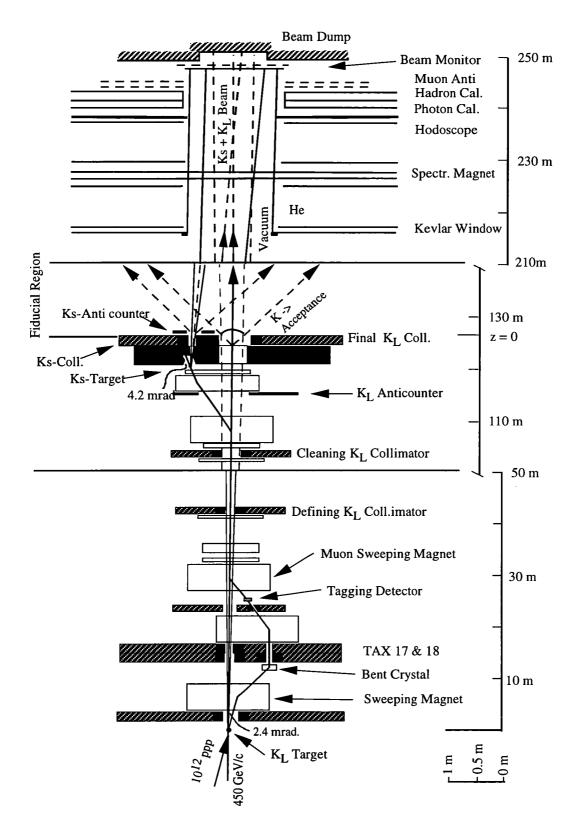

Figure 1.1 shows a schematic overview of the beam line and the detector the major parts of which are detailed below:

The kaon beams are formed by directing a proton beam onto a beryllium target. The charged particles in the resulting shower are swept away from the beamline by magnets so that only neutral particles (kaons, neutrons, photons, neutrinos and lambdas) are present at the output.

The particles move along the beam pipe which passes through the detector. Only the particles which decay while in the beam line are detected. Of the neutral particles only kaons produce decays which are observed by the detector. Neutrons, gammas and neutrinos are all stable in the beam line and so will not be seen. Lambdas will decay into a proton and a charged pion, which decays almost instantly into two photons.

Figure 1.1: Schematic overview of NA48 experiment

#### The $K_L$ Target

The  $K_L$  target is 240 m away from the detector. After the protons hit the beryllium the charged particles at the output are swept away by a magnet and the kaon beam collimated to produce a narrow beam. When the beam reaches the beginning of the decay region some 130 m away it will consist of only  $K_L$  particles as the  $K_S$ decay length in the laboratory frame at 100 GeV is only 5 m. The proton beam for the  $K_S$  is formed by deflecting some of the non-interacting protons away from the main beam and directing them through a bent crystal onto a second target only 120 m away from the detector.

#### The Proton Tagging Counter

To identify an event as being a  $K_S$  the protons from the second beam are tagged upstream from the target. If an event is seen to be accompanied by output from the tagger it is declared a  $K_S$  event, while if the tagger does not fire the event is labelled a  $K_L$ .

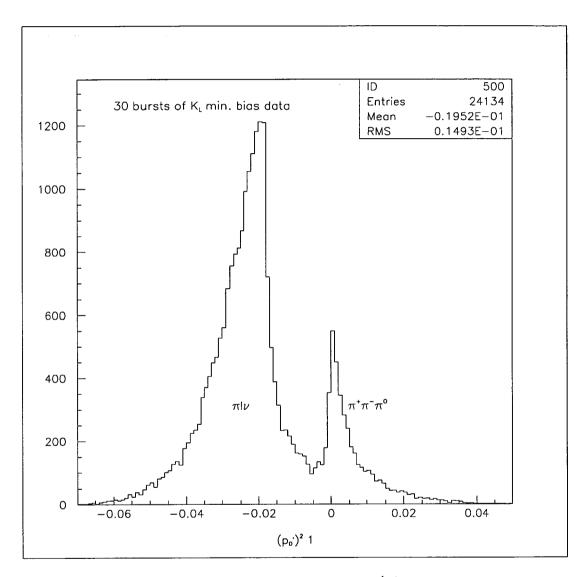

The tagger measures the time of flight between the tagging of a proton and the hodoscope [5]. Events arriving at the hodoscope in coincidence with a hit in the tagger within a certain time window are identified as  $K_S$ . The tagger consists of two sets of twelve staggered scintillation counters arranged alternately in horizontal and vertical orientation. The light from the plastic scintillator is read out through PhotoMultiplier tubes to two trigger counters. A system of Analogue-to-Digital Converters, sampling every 1.1 ns, is used to digitize the analogue pulses from the counters. The system provides a high rate capability (3 × 10<sup>7</sup> protons per 2.7 second spill), a time resolution of under 500ps and a high efficiency. After tagging the protons are deviated back towards the  $K_L$  line and sent to the  $K_S$  target.

#### The $K_S$ Target

The protons are deflected from the  $K_L$  line by a magnet 110 m downstream from the first target and hit the second (the  $K_S$  target) at z=0 m. Before this the proton beam is deflected by 4.2 mrad by a sweeping magnet so that the  $K_S$  beam intersects with the  $K_L$  beam at the subdetectors. This beam will consist of both  $K_S$  and  $K_L$  at the detector but in this short range  $K_L$  decays are unlikely.

#### 1.2.2 The NA48 Detector

The detector has four main functions:

Firstly, to reduce the volume of uninteresting data that is sent to the data acquisition system, the detector must readout only on events of interest. The subdetectors give information to the trigger system (detailed in Section 1.2.3) on what particles they have detected during an event. A trigger is only sent to the readout electronics when a potentially useful decay is observed. The second function of the detector is to alow the reconstruction of the particle parameters, i.e. position, lifetime, energy and momentum. Thirdly the types of particle (i.e. electrons, pions, muons) in the decay must be able to be identified and lastly incomplete tracks and single tracks (single muons for example) must be rejected.

The detector is made up of several subdetectors, the most important of which are:

Liquid Krypton (LKr) Calorimeter Gives information on the energy and position of photons ( $\gamma$ ), positrons ( $e^+$ ) and electrons ( $e^-$ ).

**Hodoscope** Reports on the x, y position of charged particles.

**Hadron Calorimeter** Reports on the energy and position of charged pions  $(\pi^+, \pi^-)$ .

**Muon Veto** Detects muons  $(\mu)$ .

Magnetic Spectrometer Enables the calculation of the momentum of charged particles.

The events that are of interest to us produce 2 pions.  $K_L \to 2\pi^0$  and  $K_S \to 2\pi^0$ generate 4 photons which are detected in the LKr Calorimeter. The  $K_L \to \pi^+\pi^$ and  $K_S \to \pi^+\pi^-$  reactions produce two hits in the Hodoscope.

As well as detecting these reactions we must also identify the other 'un-interesting' decays in order to suppress them:

- $K_L \rightarrow \mu \pi \nu$  The  $\mu$  in this reaction deposits a little energy in the LKr Calorimeter. The  $\mu$  however will also trigger the Muon Veto thus preventing this decay from being taken as a two pion event.

- $K_L \rightarrow e \pi \nu$  This gives two hits in the Hodoscope but also a shower caused by the electron in the LKr Calorimeter.

- $K_L \rightarrow 3\pi^0$  This produces 6 photon showers in the LKr Calorimeter.

- $K_L \to \pi^+ \pi^- \pi^0$  Two hits appear in the Hodoscope but 2 photons are also seen in the LKr Calorimeter

#### The Anticounters

These surround the beamline and detect particles (usually photons) which are outside the acceptance of the magnetic spectrometer and the LKr calorimeter. They each consist of several planes of scintillator, material which produces light when hit by most particles. The light energy from each scintillator is amplified by a photomultiplier tube before being sent to a Flash ADC, where the light is converted to electrical pulses. The output from the FADCs is used by the trigger logic to veto decays which are incomplete due to particles being outside the detector acceptance.

The  $K_S$  anticounter is situated in the  $K_S$  beam and has a photon converter in front of it to veto decays that occur upstream from the anticounter. This is used mainly to set the absolute length and energy scales of the whole detector.

#### The Magnetic Spectrometer

This subdetector consists of a large (2.4 m) dipole magnet and four high precision, high rate drift chambers [6]. The first two drift chambers are in front of the magnet These give the vector of a particle prior to it being subject to the magnetic field (which corresponds to a kick of around 250 MeV/c transverse momentum). The second pair of drift chambers give the vector after the particle has been deflected by the field. Knowing the two vectors and knowledge of the magnetic field strength the momentum of the particle can be deduced. Each drift chamber consists of four gas-filled double planes each with a central hole for the beam pipe. Each of the planes has 256 sense wires spaced on a 1 cm grid. Ionisation of the gas by a particle in the vicinity of these wires produces a voltage drop on the wires which propagates to the read-out wires at each end. From the voltage drop the path of the ionising particle can be deduced. The signals from the sense wires are routed to a TDC system. As only 2 out of 256 wires are hit in a typical  $\pi^+\pi^-$  event this system performs zero suppression on the data before sending it for storage in a time stamp-addressed ring buffer. This buffer is then accessed by the Level 2 Charged Trigger electronics (Section 1.2.3).

#### The Hodoscope

The NA48 hodoscope is a system of scintillation counters which provides the x, y position and, with a high accuracy, the time of arrival at the detector  $(t_0)$  of charged pions resulting from kaon decays in the beam pipe. The subdetector is formed by two planes of counters. The first plane contains 64 horizontal counters while the second plane consists of 64 vertical counters [7]. Each of the planes is divided up into four quadrants of 16 counters. The hodoscope has an accuracy of around 10 cm in the horizontal and vertical directions, transverse to the beam.

Scintillation light from each counter is recorded by a Photomultiplier tube. The Hodoscope trigger system reads the outputs of the PMs and produces a trigger  $(Q_x)$  when it sees an event which appears to correspond to two charged pions (indicating that a  $K_L \rightarrow \pi^+\pi^-$  or a  $K_S \rightarrow \pi^+\pi^-$  decay may have taken place). As a charged pion pair is represented in the Hodoscope as four hits on different counters (two on each plane), four independent time measurements are produced. The resolution of the event time,  $t_0$ , defined as being the average of these four timings, is around 0.5 ns.

#### The Liquid Krypton Calorimeter

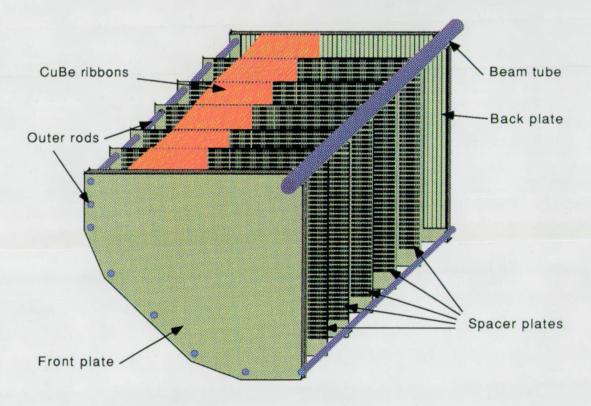

The LKr Calorimeter [8] is designed to give excellent space, energy and time resolution as well as coping with very high particle rates. The read-out structure of a LKr Calorimeter quadrant is shown in Figure 1.2.

The read-out cells are formed on parallel ribbons of Kapton, 75  $\mu$ m thick, clad in

Figure 1.2: Read-out structure of the LKr Calorimeter

copper strips, 19 mm wide and 17  $\mu$ m thick. The strips are 10 mm apart. The cross-section of the read-out towers is 2 cm  $\times$  2 cm. Altogether there will be about 13500 towers. This structure ensures the high rate capability, good space resolution and photon separation that are needed. The use of liquid krypton in a quasi-homogeneous structure (the only other materials present are thin read-out ribbons) minimizes sampling fluctuations. This is required to achieve the very high energy resolution required.

The photons collide with the Liquid Krypton causing electromagnetic showers which produce ionisation. The electrons liberated by this ionisation are subject to a transverse electric field (the anode ribbon is at +5000 V) and cause an induced electric current to flow along the ribbons as they drift. The current is proportional to the size of the charge. It rises quickly and falls away linearly over 3  $\mu$ s as the electrons combine at the anode.

The output from the read-out ribbons is put through a shaper which is sensitive to changes of slope in the current waveform. This produces a 100 ns wide pulse which is sent to the read-out electronics.

#### The Hadron Calorimeter

The hadron calorimeter (HAC) consists of an iron/scintillator sandwich of 1.2 m total iron thickness [9]. It is divided into two sections, each consisting of 24 steel plates, 25 mm thick, of dimensions  $2.7 \times 2.7 m^2$ . Each plane is made up from 44 separate strips of dimensions  $1.3 \text{ m} \times 11.9 \text{ cm} \times 4.5 \text{ mm}$ . Consecutive planes are aligned alternately horizontally and vertically forming a quadrant structure.

The light from the scintillator is fed through photomultiplier tubes and then to a bank of FADCs. There are 176 readout channels. The analogue signals are intergrated and the information on the particles energy is fed to the trigger system. The x, y position and the energy of the particle in the HAC is input to the data acquisition system.

#### The Muon Veto

The Muon Veto [10] consists of three planes of plastic scintillator - the first two

are 1 cm thick and the third is 6 mm thick. The planes are each sited behind 0.8 m of iron which is sufficient to stop most particles except muons from reaching the detector. The first plane consists of eleven horizontal strips, the second of eleven vertical strips. There is a hole in the middle of each plane to enable the beam pipe to pass. These planes output the x,y position of a particle passing through the subdetector. The third plane is used mainly for efficiency calculations. The light from the scintillator is read out to the muon electronics through Photomultiplier tubes attached to each end of the strips.

#### 1.2.3 The NA48 Trigger System

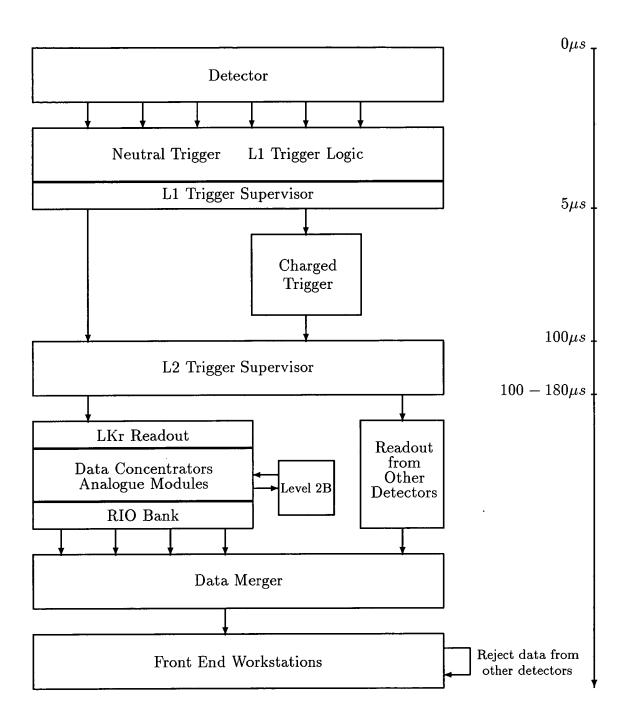

NA48 has three separate levels of triggering. The Level 1 and Level 2 triggers are implemented in hardware. The third level, software filtering of the data, is implemented in the Alpha workstation farm. Figure 1.3 shows the position of the trigger levels in relation to the readout stages [11].

#### The Neutral Trigger

The neutral trigger [12] monitors the signals coming from the LKr Calorimeter and sends a trigger to the trigger supervisor whenever the criteria for a  $2\pi^{\circ}$  event have been satisfied. The calorimeter readout is sampled and a trigger decision sent to the level 1 trigger supervisor every 25 ns. The rates are expected to be around 25  $K_L \rightarrow \pi^{\circ}\pi^{\circ}$ , 1500  $K_L \rightarrow 3\pi^{\circ}$  and 100  $K_S \rightarrow \pi^{\circ}\pi^{\circ}$  per 2.7 second spill.

Four quantities are computed for each 25 ns time bin and these are used to make the trigger decision:

- The number of peaks in the LKr Calorimeter. Good events have 4 or fewer peaks (e.g.  $K_L \to \pi^o \pi^o \to 4\gamma$  produces 4 peaks). The trigger rejects events with more peaks in order to remove  $K_L \to 3\pi^o \to 6\gamma$  background.

- The total energy *E*. This must be above a certain threshold for the event to be considered good.

Figure 1.3: The triggers in respect to the dataflow scheme. The timing in relation to the event time is shown on the right hand side.

- The centre of gravity  $C = \sqrt{(m_{1x}^2 + m_{1y}^2)}/E$  where  $m_{1x} = \sum x_i E_i$  and  $m_{1y} = \sum y_j E_j$ . Where the sum is over *i* (strip number in the x projection) and *j* (strip number in the y projection). C should be close to zero. Single tracks will not pass this cut and therefore will be rejected.

- The proper lifetime of the kaon. This cut is performed to remove the  $K_L \rightarrow \pi \mu \nu$ ,  $K_L \rightarrow \pi e \nu$  and  $K_L \rightarrow \pi^+ \pi^- \pi^o$  decays. The lifetime in these events will usually not be a low enough value to cause a trigger as the neutrino  $(\nu)$  or the charged pions will not be seen by the subdetector.

#### The Charged Trigger

The Level 2 Charged trigger [13] identifies the important charged pion events and the background  $K_L \rightarrow \pi e\nu$  decays. Input to the trigger is provided from the hodoscope and the magnetic spectrometer. The hodoscope readout electronics produce a trigger pulse each time there is activity in opposite quadrants of the subdetector, the  $Q_x$  condition. This indicates that a 2 pion event may have occurred.

For events satisfying the neutral conditions, a fast DSP-based VME processor farm performs a part-reconstruction on the particles detected in the first, second and fourth drift chambers. It then calculates the momenta of all tracks, the vectors for all particle pairs and finally the  $2\pi$  mass. This takes place in the 100  $\mu$ seconds after the decay. The processor farm passes its information on the event to the trigger supervisor.

#### The Trigger Supervisor

The trigger supervisors give decisions for each 25 ns time slice based on the information sent to them from the sub-detectors [14]. They correlate the trigger data received and dispatch a trigger decision to the read out controllers of each subdetector. The information at the sub-detectors is digitized and stored in circular memory buffers where it remains for a minimum of 200  $\mu$ s. When the trigger request arrives at the sub-detector the buffers are accessed and the information for the probable 2 pion time slice is sent to the data acquisition system.

#### The Level 2B Trigger

The Level 2B trigger is included to solve a bottleneck problem at the LKr Calorimeter. This sub-detector provides by far the most data for each event and more rejection power is needed at the Calorimeter in order to prevent the data flow system becoming swamped. The Level 2B trigger works entirely downstream from the rest of the Level 1 and Level 2 triggers. It acts only on triggers issued by the Level 2 trigger supervisor and is highly integrated into the read out of the LKr Calorimeter. When a trigger is received at the Calorimeter data is fetched from a circular memory buffer. As the data is being read out a summary is sent to the Level 2B computer which performs cuts and decides whether an event should be accepted or rejected. If the latter is the case the Calorimeter sends only dummy data to the data acquisition system while the rest of the sub-detectors send full events. The event is finally killed at the Level 3 stage in the workstations.

## **1.3 Dataflow Requirements**

A 'spill' is a stream of protons sent to the experiment by the SPS. Each burst lasts for 2.7 seconds and there is one burst every 14.4 seconds. The amount of data sent from the detector during each burst depends on the trigger rate and the size of the events. The rate of events estimated to be processed after the Level 2 trigger is 1.5 kHz from the  $K_L$  beam and 0.15 kHz from the  $K_S$ . In addition to these there are calibration triggers (0.2 kHz) and 'downscaled' events (1 kHz). The latter are used to monitor the trigger.

The event length is dominated by data from the LKr Calorimeter. This depends on the zero suppression algorithm and the data compression algorithm used in the subdetector readout electronics. The largest amount of data is sent during a  $2\pi^0$ event. With four photon showers contained within a 15 by 15 array of cells, around 900 cells are read out. For each of these 8-10 time samples are recorded to give the amplitude and timing of the pulses caused by the particle showers. With data compression the volume could be reduced by a factor of 2 or 3. The other detectors generate modest amounts of data for each trigger. The Spectrometer gives around 100-200 bytes, the hodoscope, anti-counters, muon veto, tagger, triggers and the hadron calorimeter contribute roughly 2 kbytes in total. Thus the total data volume per event is between 7 kbytes and 20 kbytes.

These figures are estimates, as at the time of the dataflow specification the detector was not yet built or tested, but they give an indication of the event rate and size. Taking the averages of these figures (say a trigger rate of **3** kHz and an event size of **10** kbytes) the data acquisition system has to process 30 MBytes/sec (75 MBytes/burst). However, some overhead must be built in due to the possibility that the trigger is not as efficient as planned or that new trigger categories or low downscaling factors are decided upon.

Therefore it was decided in 1993 to make the specification[15]:

### 100 MBytes/sec and 10 kHz

Which corresponds to 250 MBytes and 25 k events per burst. In the next section the hardware designed to satisfy this specification is discussed.

### Chapter 2

### NA48 Dataflow

### 2.1 Overview

The Dataflow scheme is fed data from the read out controllers of each sub-detector. It merges this data into an event packet which contains all the information needed to decipher the kaon decay that has been triggered upon. The data is then input into a farm of workstations and storage units where detailed analysis and filtering can take place.

The Dataflow scheme consists of several related subsystems as shown in Figure 2.1. The components are usually separate but some tasks can be split between different machines.

The principal stages are:

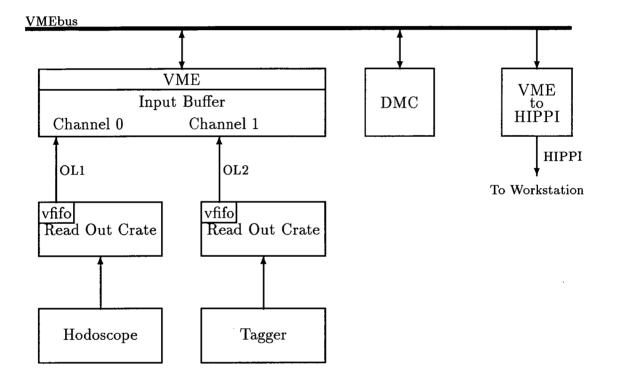

The Front End Electronics Each sub-detector has its own specially commissioned read out electronics. Data collected at most detectors is fed into the dataflow system via a VFIFO module. This takes data from VME and outputs it to an Optical Link Source (OLS) module. Each sub-detector uses the same OLS and VFIFO boards so the rest of the system is the same for each sub-detector.

The Fibre Optic Links These transfer asynchronous data from the subdetector read out crates to the Data Merger across a distance of 200 m.

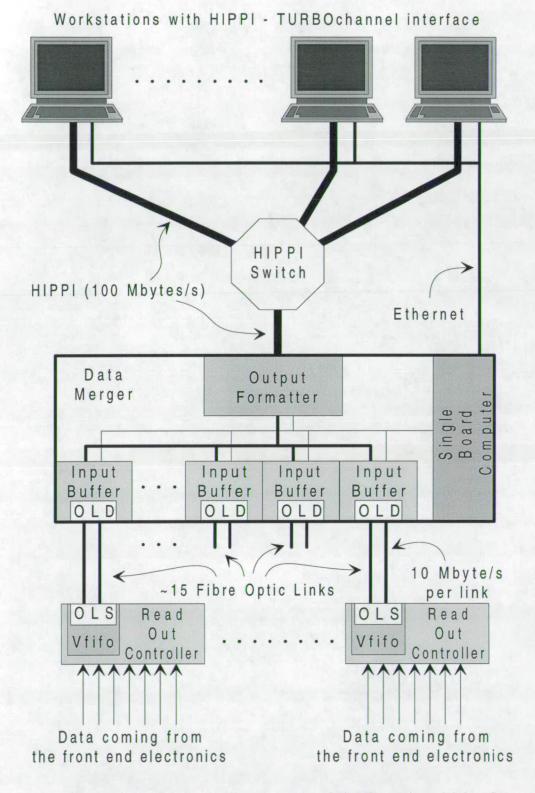

Figure 2.1: Hardware Components of the Data Acquisition System

The Data Merger Each sub-detector outputs a sub-event when a trigger is issued. In the Data Merger the sub-events are buffered and merged together across a backplane to form a full event. The event contains the information from every sub-detector for that trigger. The Data Merger output device formats the event and transmits it to the workstations.

The Data Merger Controller This is a Single Board Computer which sets up and monitors the Data Merger. It also controls the Front End Workstations (FEWS), which receive the data over the HIPPI and Turbochannel links.

The Workstation Farm The workstation farm receives the data from a complete burst. The data is reformatted and then distributed around the farm for Level 3 filtering and eventual recording onto storage media. Various 'special' events containing monitoring and calibration information are sent to special tasks. Software services for the workstation farm are provided by the resource manager.

The Control Program This provides an interface between the dataflow system and the people on shift in the control room. It monitors the condition of the system, reporting errors and responding to requests from the shift crew.

Slow Control This sets and monitors the detector and various components that are not involved directly in the data taking each burst. For example the beam and hall conditions, gas pressures and high and low voltages are set and maintained by the system.

The data acquisition system is also indirectly affected by the following components:

1. The Common Clock

The common clock is distributed to all subdetectors as well as the Control Program. This has a base frequency of 40 MHz.

#### 2. The Trigger Supervisor and the Read Out Controllers

As summarised in Section 1.2.3 The Level 2 Trigger Supervisor is responsible

for accepting an event as interesting, setting off the read out process. It also distributes an event number to the read out controller of each subdetector. This number is checked by software in the Alpha Farm to ensure the event has been merged correctly. The readout controllers collect and buffer the data from each part of the experiment. When all the data is collected from one event they output it to the Optical Links.

#### 3. The Beam Control System and the SPS timing signals

As well as controlling and monitoring the beam, the Beam Control System provides timing signals which split the spill into two stages. One stage is handled by the central data acquisition system and the other is the responsibility of the local data system at the subdetectors.

#### 4. The Local Subdetector Computer

This communicates with the Control Program to provide local requests for actions. For example the shift crew must warn each Local Subdetector Computer of the need to prepare for a new run.

The design of the system makes it possible to provide higher throughput by increasing the parallelism at the stage which is constricting the speed of data transfer. If the workstations are too slow to process the data then another one may be added to quicken the acquisition rate (The HIPPI switch can be configured for up to 8 output devices). Similarly more Optical Link channels can be provided for a subdetector if the volume of data from it is too great to be collected in the required time. Furthermore some resilience is built into the system (i.e. data taking can continue at a reduced rate if a component, a workstation for example, is not available during a run)

The aim of the dataflow design was to produce a scalable data acquisition system which can cope with the high data rates the experiment requires. There are two basic constraints on the system. Firstly the data is driven by the 40 MHz clock at the subdetector level. To buffer data at this rate requires fast and expensive static RAMs. Likewise, when the data is assembled into events the total volume of 100 MBytes every second requires the use of unconventional backplane technol-

ogy. Secondly no elements of the dataflow hardware can be allowed to introduce deadtime into the system. To achieve this the basic architecture consists of consecutive stages in which data is transferred from buffers to FIFO memories over point to point links. There is no horizontal linkage between the transfers from different sources until the Data Merger stage as to do this would necessarily introduce deadtime. Instead each link is controlled by an XOFF, a signal sent from the destination to the source across the link. The source stops sending data when the destination asserts this line. This occurs when the destination has nearly filled its buffer (There must be enough room left to accomodate the data sent while the XOFF is still in transit). It is the responsibility of the trigger supervisor to ensure that the trigger rate does not overload the system. An overload results in the XOFF propagating back to the subdetector which must stop taking data (This is treated as an error condition). No error correction is performed by the system, only error detection takes place. An event in which a bad word is found is rejected by the Level 3 filter. This removes deadtime but also demands that the error rate is kept extremely low.

The buffer-to-FIFO architecture logically isolates each section of the dataflow from the others. The internal on-board logic between each buffer-FIFO connection can be altered without affecting the rest of the system. In particular the development of the system downstream from the Front End Workstations (FEWS) in the workstation farm is completely independent from the development of the parts of the system that lie upstream.

In the next Section the main parts of the Dataflow are described.

### 2.2 Dataflow hardware

#### 2.2.1 Optical Links

The optical links used in the NA48 experiment were designed by Robert McLaren, Leslie McCulloch and Phillipe Brodier-Yourstone of the ECP division at CERN [16]. Each optical link carries two uni-directional channels, a 32-bit data channel and a 32-bit control channel. NA48 only uses one bit of the control channel as an end of event bit (D39).

The task of an optical link is to deliver data from the ReadOut Controller (ROC) of a sub-detector to the Data Merger. In general, each sub-detector has one Optical Link (excepting the LKr calorimeter which requires 8). Each link is a duplex pair which delivers data at 10 Mbytes/sec over a distance of around 200 m and provides electrical isolation. To the hardware that interfaces to the Optical Link it looks like an I/O register where words are clocked in and out one at a time. Although connected to many different sub-detectors, all links are the same; the input to the optical link is defined as the point at which the experiment's data is presented in a common format.

#### **Electrical Specification**

Sub-events to be transferred by the optical link must be formatted as 32-bit wide words. In addition to the user data, an additional bit (called 'D39') is set high on the last word of the sub-event. The user presents data, provides a strobe and then must wait for an acknowledgment strobe back from the optical link source before changing the data.

The Optical link source (OLS) runs a VCO at 265.625 MHz which is phase-locked to the user clock. Incoming 8-bit characters undergo 8-10 bit encoding. The 10-bit characters are then serialised and the bit-stream is transmitted over the optical fibre at this rate. This is a purely serial line with no clock pulse. When the link is first established, the transmitter sends synchronisation characters which lock the phase of the receiver clock to that of the transmitter. One of the reasons for the 8-10 bit encoding scheme is to ensure that all characters transmitted consist of an even mix of 1s and 0s. This avoids transmitting "DC" codes (such as 1111111) and ensures that there are frequent changes of state which keep the clocks synchronised. The Destination (OLD) deserialises the bit-stream and reforms the 10-bit characters which it decodes to recover the original bytes of data. These are then grouped in a 40-bit wide register (the original 4 data bytes plus a control byte consisting of parity bits and D39) and then strobed into the Data Merger. When the source is not transmitting user data it sends a stream of idle characters to the destination. These keep the clocks in synchronisation [17].

On the last word the source sets the top data bit (D39) high. This is termed the  $end_of_event$  bit. It is low for all other transfers.

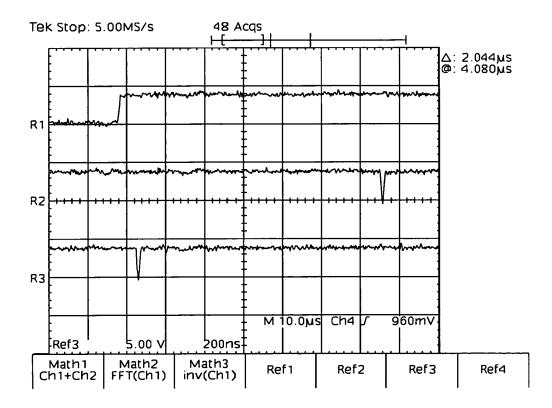

#### Flow control

In the Data Merger an Input Buffer (IB) receives the data from the OLD. The IB contains a 2.5 Mbyte buffer memory. If this begins to fill to capacity, the IB signals to the OLD by asserting the line  $\overline{\text{XOFF}}$ . This can happen asynchronously. When the OLD sees this signal, it sends an  $\overline{\text{XOFF}}$  character back to the OLS using the other fibre of the duplex pair. This causes the OLD to inhibit sending acknowledge strobes to the ROC thus preventing data from being read in to the OLS. When the IB has cleared some space, it de-asserts  $\overline{\text{XOFF}}$  and the destination sends an XON character to the source which releases the inhibit on the acknowledge strobe and the data transfers resume.

The IB asserts  $\overline{\text{XOFF}}$  when it is nearly full, leaving sufficient space to read in any words still in the optical pipeline. Similarly, it de-asserts  $\overline{\text{XOFF}}$  only when it has cleared space well below the nearly full level. This prevents the  $\overline{\text{XOFF}}$  signal from fluttering.

#### **Error Checking**

The optical link monitors itself for errors in several ways. It inputs error information to the IB which stores it for read out at the end of each sub-event.

• Parity Checking The parity of each byte decoded is checked against the parity bit contained in the control byte. If a mis-match occurs, the OLD sets the PERR line to the IB.

- Table Error If a 10-bit character does not correspond to a valid code (of the 1024 possible 10-bit codes only 256 are used) the table error bit is set.

- Running Disparity The 8 to 10-bit encoding system uses two look-up tables to ensure that each bit changes every cycle. If a bit is at the same level for two consecutive words then the OLD sets the RDERR line to the IB. This could mean that the 10-bit character has been corrupted during the transfer.

- Sequence Error D38 is the sequence bit and this must toggle between each word transferred. If two consecutive words have the same value of D38 an error is detected and the SERR line is set in the OLD.

- Hardware Errors The optical link cards are designed to detect an open fibre connection and will set the Link Status line in this eventuality. In addition, if the power available in the laser exceeds a maximum value a Laser Fault line will be set.

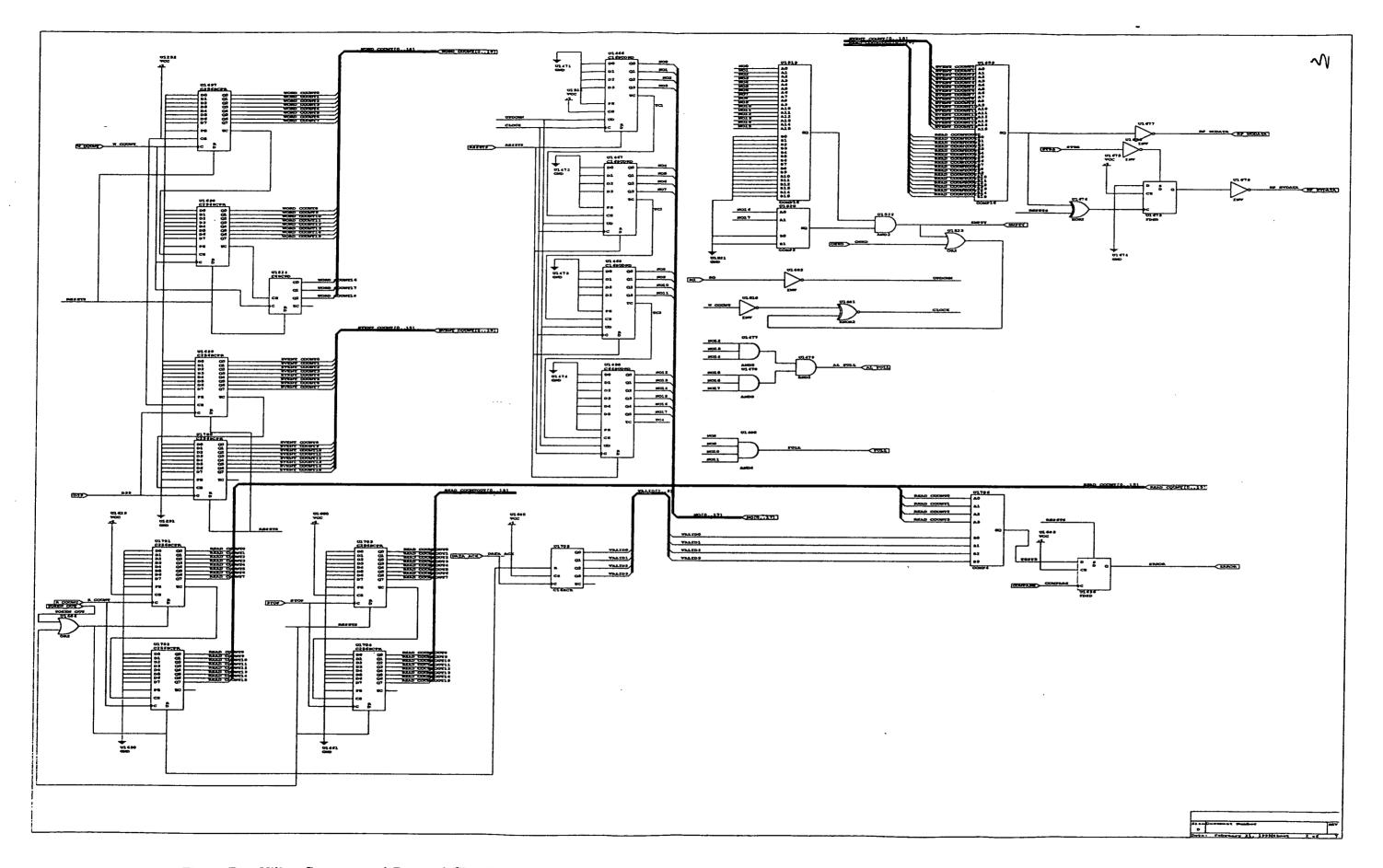

### 2.2.2 Data Merger

The sub-event data generated by the NA48 sub-detector elements arrives at the Data Merger [18] in a bank of IBs. There is one IB serving each sub-detector. The IBs are read out sequentially over the R-path backplane, working at 100 MBytes/sec, to the FIFO Output Formatter (FOF) which concatenates the sub-events and feeds the complete event to the workstation farm via the HIPPI link.

The sub-events are time ordered and each sub-detector produces data for each trigger.

Figure 2.2 shows a schematic of the Data Merger Each IB outputs data onto the R-Path when it receives a token. This is a 40 ns wide logic high ECL pulse which originates in the FOF and is passed to each IB via lemo cable before returning to the FOF. When the IB that holds the token has output a full event the token is passed to the next board in the chain. As the sub-events are time ordered and each sub-detector produces data for each trigger a full event is built up at the FOF from the data from each of the sub-detectors.

Figure 2.2: Layout of Data Merger

The FOF stores the events in a FIFO buffer before reading out to the HIPPI link at the appropriate time. The output can be sent to one of several workstations. The Single Board Computer (DMC) selects the data destination.

The DMC controls the system through VME. The DMC is a single board computer that receives instructions from the central run control program and reports back on the performance of the data merger. Each IB and the FOF are VME slave modules, i.e. they can respond to requests for information from a master module (in this case the DMC) but can not request the bus themselves.

The Data Merger is described in more detail in the next Chapter.

### 2.2.3 HIPPI Link

Point-to-point HIPPI links [15] are used to connect the FOF with the Front End Workstations. The High Performance Parallel Interface (HIPPI) is an ANSI standard describing a simple high-performance point to point communications link. It is designed for transmitting digital data at peak rates of 100 MBytes/sec (32 bit words) or 200 MBytes/sec (64 bit words) using multiple copper twisted-pair cables at distances of up to 25 meters.

The connection from source to destination comprises of one or more 'packets' of unlimited size. Each of these is divided into 'bursts' which can contain from 1 to 256 words. Error detection is based on a parity bit which is sent along with each byte of data and a Length/Longitudinal Redundancy Checkword (LLRC) which is sent at the end of each data burst.

The FOF is linked to a number of FEWS via a HIPPI crossbar switch. HIPPI provides a limited addressing feature that is used by the FOF and the switch to determine the destination of each packet. At the start of each connection the FOF transmits an address (the I-field) which is used by the switch to decide which workstation it will connect.

The workstation farm consists of a number of DEC TURBOchannel machines. An interface from HIPPI to TURBOchannel was developed as a joint project by CERN and DEC [19]. The interface uses a high speed FIFO to take data from the link. It then transfers the data to the workstation memory in a series of DMA transfers. So that the transfers are not hampered by any software intervention the board uses a scatter-gather table to translate logical addresses in HIPPI to physical ones in the workstation memory. Any errors that are detected are logged in a 'history' memory, the contents of which are sent at the end of each event.

Transferring the data block between the source and destination requires the cooperative work of the FOF, the HIPPI to TURBOchannel interface and the HIPPI links and switch. In addition, the Data Merger Controller controls the sending of the data over the HIPPI link by generating the I-field address of the destination workstation. This is sent to the FOF before the connection is made. The data distribution processes running in the workstation must also be able to free enough memory for all the data it receives.

### 2.2.4 The Workstation Farm

The 1995 hardware set-up of the workstation farm is shown in Figure 2.3. The system consists of seven workstations, arranged in front-end (FEWS), back-end (BEWS) and rear-end (REWS) groups. Each FEWS – BEWS pair is connected by two SCSI-2 busses and in turn to the REWS. Five 2 GByte disks are attached to each of the busses.

All of the workstations have equal access to the disks and the filtering and event reconstruction can be performed by any of the CPUs, however each group of workstations also has specific tasks to perform:

The Front-End Workstations highest priority task is to collect the data from the HIPPI to TURBOchannel interface and store it in memory. They also check if the data is intact before writing the data from memory to disk.

The Back-End Workstations concentrate on reading events from the disks to perform monitoring, event reconstruction and Level 3 filtering.

The Rear-End Workstation discards events that have not been triggered, reformats the events into a ZEBRA structure <sup>1</sup>, appends information from the Level 3 trigger to the raw data and transfers bursts of data to tape.

The processed data is sent from the REWS to either the local backup system, consisting of several DLT 2000 tape drives, or the central CERN computing facility. It is here that the data is stored for future analysis.

In the future more workstations may be added to cope with increases in data volume.

<sup>&</sup>lt;sup>1</sup>ZEBRA is a CERN program which allows the creation of structures and dynamic memory allocation in Fortran[20].

Figure 2.3: Level 3 Workstation Farm Architecture

# 2.3 Dataflow Control Software

### 2.3.1 The Run Control Program

The hardware components of the dataflow are set up and monitored by the Run Control Program. This program supervises and coordinates the activities of all the subcomponents in order to allow data to be taken. Its basic task is to start and stop runs, i.e. to configure the dataflow components at the start of data taking and to reset them afterwards. Each Single Board Computer (SBC) in the system runs its own control component (called the 'harness') which interfaces with the central component (called the 'control program').

The harness program running on each SBC monitors the activity of the dataflow electronics with which it interfaces. It performs the following functions:

- The initialization of the dataflow electronics. For example, the Data Merger SBC (the DMC) resets the IBs and the FOF by writing 'reset' to the control registers of the two boards. It also primes the FOF for data taking.

- Monitoring of events. The SBCs can access areas of memory directly to analyse the data at different stages in the dataflow chain.

- Error reporting. Dataflow components can indicate to the SBC that an error has occurred (via a VME interrupt for example). The SBC reports the error to the run control program.

- Calibration and checks of the electronics. These take place out of burst when data is not being processed by the system.

The run control program separates the data taking into 'runs'. A run is defined as a set of contiguous spills taken under identical running conditions. A new run is started whenever the conditions change. At the start of a run the CP sends a 'configure' signal to all the harness running components in the dataflow system and the harness sends back a 'system ready' signal to the CP. The communication takes place over ethernet. During data taking, status checks, burst statistics and error information are transmitted to the CP. When the end of run command is received from the CP the SBC sends back run statistics and performs any clean up that is necessary.

### 2.3.2 The Workstation Farm Resource Manager

The workstation farm resource manager program controls the data flow from the FEWS to the permanent data store by managing the intermediate buffer storage and routing data through filter and reconstruction processes.

### 2.3.3 Slow Control

The slow control program monitors those variables that are not directly connected either to the physics data or to the dataflow hardware path. Examples of these variables are:

- The voltage and current of the power supplies.

- The temperatures of the electronics crates and the sub-detectors.

- The pressure of the gasses in the drift chambers.

- The monitoring and control of the high voltage supplies.

### Chapter 3

# NA48 Data Merger

# 3.1 General arrangement of the Data Merger

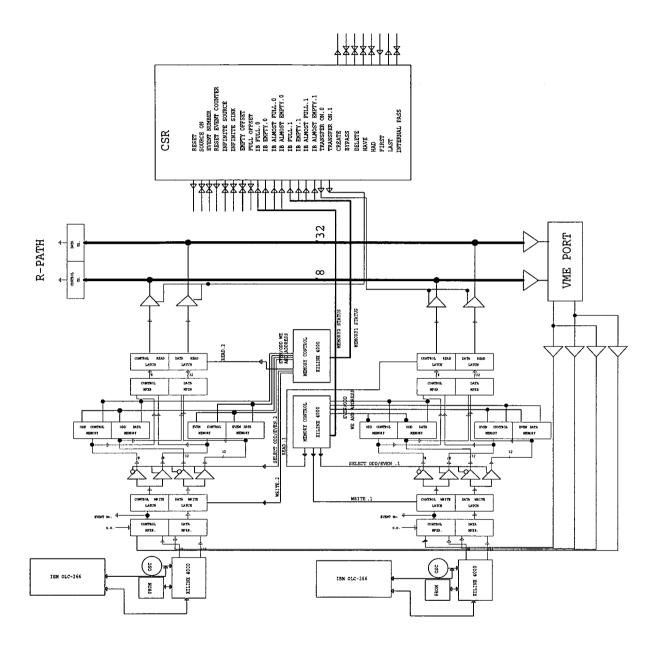

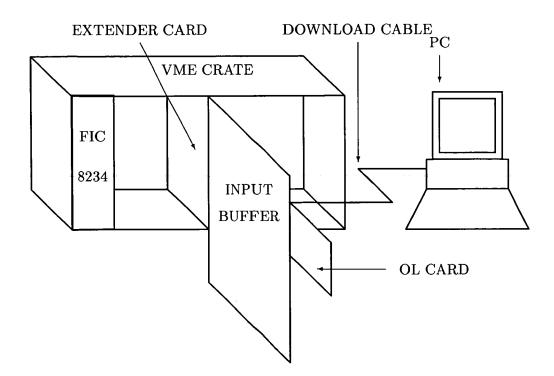

Two photographs of the Data Merger system are given in Figures 3.1 and 3.2. The Data Merger is housed in two 21-slot VME crates. Crate 1 is 6U and contains a FIC 8234 single-board computer which acts as the Data Merger Controller (DMC). This crate also contains a BIT-3 repeater output board which allows the DMC to access Crate 2. These two boards are all that are required in Crate 1 for the Data Merger to function. However, Crate 1 may also contain various VME units for test and diagnostics such as a VFIFO, a VME-HIPPI interface, a SLATE pattern generator or a disk drive for the FIC. None of these units are essential for the operation of the Data Merger.

Crate 2 is 9U by 400 mm and is fitted with a standard VME backplane in J1 and J2. The R-path backplane occupies the J3 position and features 192-pin *Metral* connectors. Slot 1 is occupied by the Read Out Latch Enable Transmitter (ROLEX). This module generates the clock signals which control the data transfer on the R-path bus. The ROLEX has selectable clock speeds and a range of LEDs which indicate the state of the backplane protocol signals. Slot 2 is occupied by the slave board of the BIT-3 repeater. In this way, the DMC can access transparently, over VME, boards in Crate 2. Slots 3 - 20 are available for Input Buffer boards and Slot 21 is occupied by the FOF.

Figure 3.1: Photograph of the 6U crate used to house the DMC.

Figure 3.2: Photograph of the 9U crate that is used to house the Input Buffers and the FOF (the FOF is not present as it had not delivered to CERN at the time the photograph was taken).

# 3.2 Implementation Choices

### 3.2.1 Bus Implementation Choices

The set-up detailed in the previous Section was arrived at after the consideration of other possible systems.

The decision to make the Data Merger cards VME modules was taken at an early stage of the design. VME is a well developed bus standard which is widely used in High Energy Physics experiments at CERN and elsewhere. It has wide commercial support and it is a straightforward task to design circuit board interfaces to the system. However, the VMEbus is not capable of transferring data at the required speed. The maximum bandwidth for 32-bit wide data transfers is 40 MBytes/sec (moving up to 80 MBytes/sec in VME64, a 64-bit version where the data width is doubled by using the address lines as data lines [21]).

A study was carried out to assess whether any commercially available bus systems were capable of data transfers at the required 100 MBytes/sec rate. This showed that there were only two bus systems on the market which could meet the data rate requirement, Fastbus and Futurebus+.

Fastbus was found to have several advantages. It is capable of data transfer at rates in excess of 150 MBytes/sec[22], it is tailored for data acquisition in high energy physics experiments and it is a well defined IEEE standard. However, there is poor industrial support for the system and it is rarely pushed near its bandwidth limit.

Futurebus+ can run at speeds of up to 400 MBytes/sec in 32-bit mode and is designed to be easily integrated into other systems. However at the time of the study it was still a developing standard and was not due to be a full industrial system until 1993[23].

It was concluded that going to a full Fastbus or Futurebus+ implementation for the Data Merger would be expensive and would make integration with the rest of the experiment difficult as the majority of the collaboration had already started designing in VME. Trying to fit a Fastbus or Futurebus+ backplane to the VME modules was also deemed unsuitable as the board and crate sizes are not compatible with each other.

This lead to the conclusion that the only way to implement the Data Merger was to use a 9U VME crate with the R-Path backplane situated in the 'spare' J3 position.

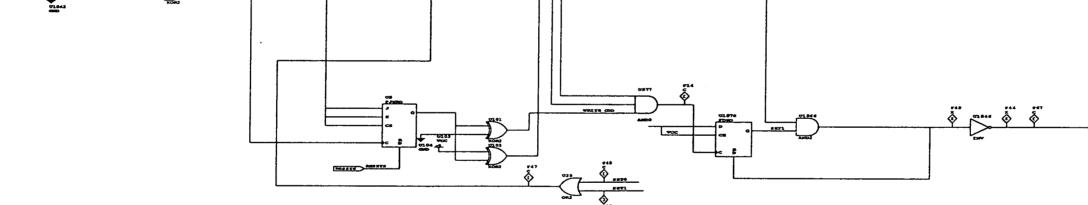

Before the backplane was selected the choice of bus driver chips to be used was made. Although the full Futurebus+ standard was not finalised when the initial decisions were made the bus tranceiver chips for the developing system were already available. The Backplane Tranceiver Logic (BTL) interface circuits are open-collector drivers with a very low capacitance (5 pF). This technology has several advantages over TTL for bus driving applications. Firstly, bus settling time (the time required for crosstalk and reflections to subside before a receiver can reliably sample the bus) is eliminated if the backplane is properly terminated [24]. Secondly, the voltage levels in BTL are 1 V (logic low) and 2.1 V (logic high), these compare with the voltage swing of 3 V for TTL. The lower voltage swing reduces drive current requirements and induced crosstalk between lines.

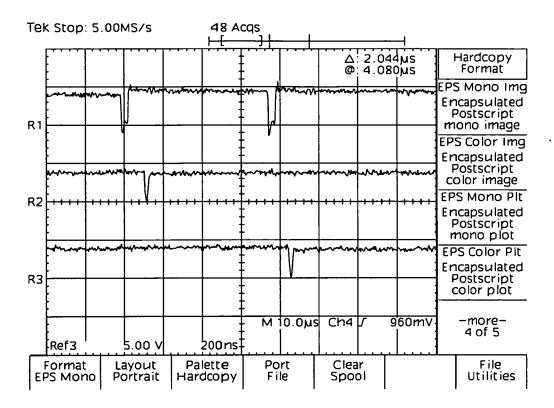

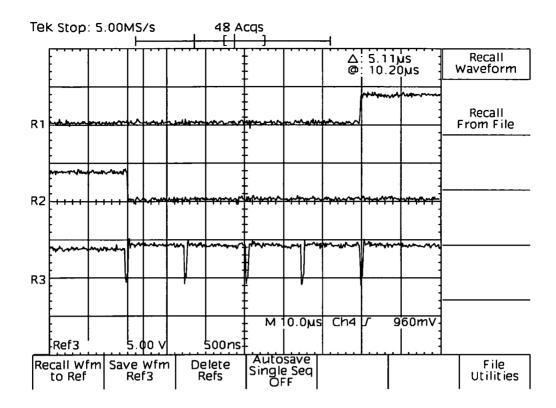

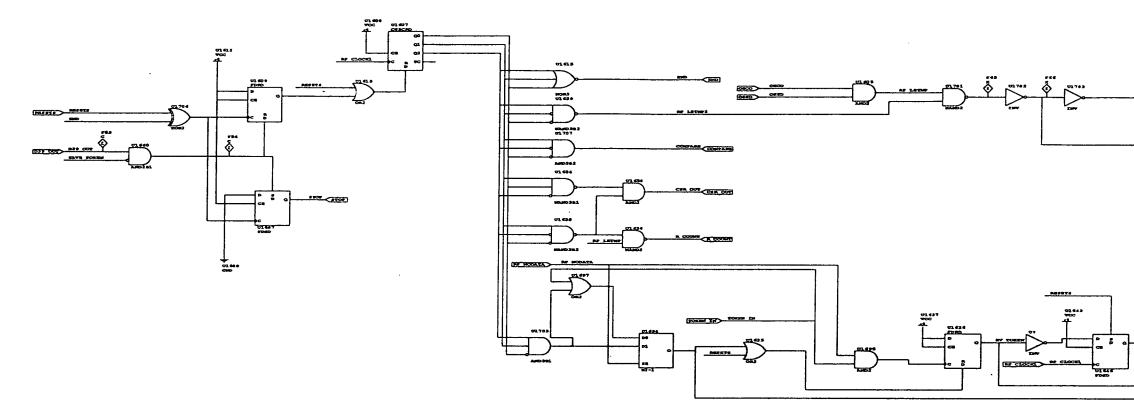

Originally it was decided to use these tranceivers along with a standard CERN backplane. A test set-up was constructed where a driver board transmits a chequer-board pattern along 8 lines of the backplane to multiple receiver boards. An example of 25 MHz operation is shown in Figure 3.3. These tests showed that the backplane was not ideally suited to our needs, increased loading of the backplane degraded the signal quality and cross-talk occurred between adjacent lines. The solution that was arrived at was to manufacture a backplane for the Data Merger.

The R-Path backplane was designed and built by Litton backplanes. It offers good protection from cross-talk and is tuned to the voltage levels that are used by the Futurebus+ tranceivers.

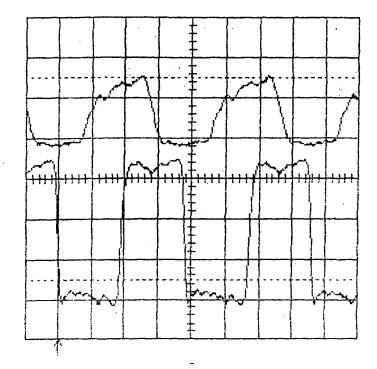

Figure 3.3: An example of BTL signals on the CERN backplane. The top trace shows a 25MHz frequency signal on the backplane, the lower trace shows the output of a receiver chip. T/division = 10 ns and V/division = 1 V.

#### 3.2.2 Circuit Board Implementation Choices

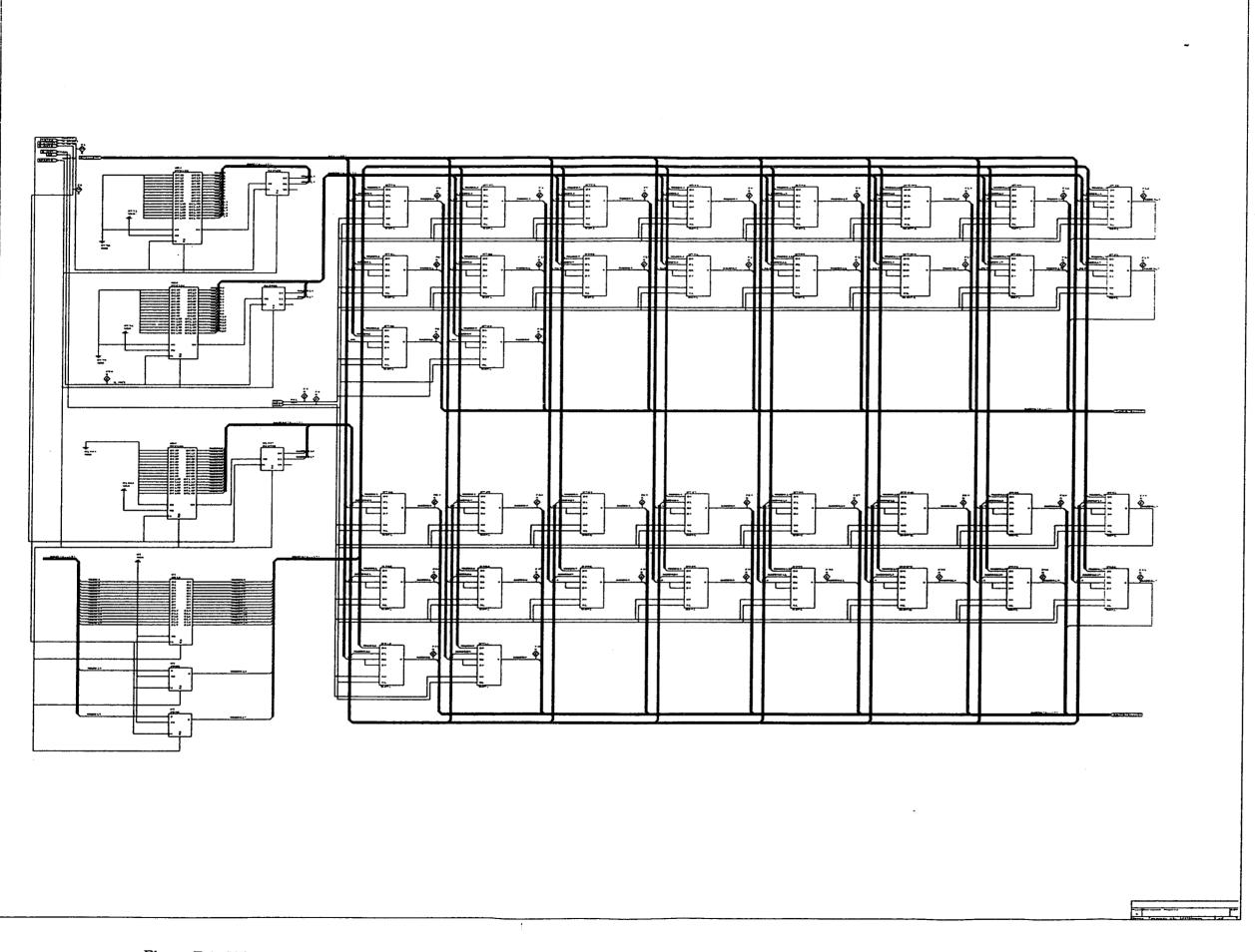

The IB and FOF boards have to be 9U high. This gives a large board area 400 mm x 365 mm) for the logic circuitry.

The majority of the IB control circuitry is implemented in a Xilinx Field Programmable Gate Array (FPGA). The logic circuit (described in Appendix F) is constructed by using the Xilinx range of logic and routing resources. The FPGA provides fast control of the board without occupying a large area. 256k x 32-bit SIMM static RAM modules are used to buffer the data from the Optical Links. These have a small footprint and are easy to address. Differential ECL is used for the token logic. This is less susceptible to noise than TTL and therefore less likely to produce a 'phantom' token if the token line is noisy. The remainder of the IB uses standard fast TTL logic circuits.

Due to the large area available and the space saved through using the FPGAs and SIMMs it was decided to put two IB channels on each board.

# 3.3 Overview of the Data Transfer Protocol

Data transfers are controlled at three levels of hierarchy; by spill, by event and by sub-event.

At spill level, the DMC receives signals on a serial line from the SPS computers. One second before the spill commences, the DMC receives the SPS signal, warning\_of\_warning\_of\_ejection. This is taken as the start\_of\_spill signal. The DMC then 'arms' the FOF over VME. This sets up the Data Merger for the coming spill. When the spill is over, the SPS signal, end\_of\_ejection is received by the FOF. The FOF then finishes reading out the IBs and then sends a data\_cleared signal, via lemo, to the DMC. It then breaks its connection to the HIPPI switch. A spill may contain several thousands events.

An event is the combined output of all the sub-detectors when a trigger is issued. At event level, the data transfer is controlled by the token-ring. The FOF sends out a token when full sets of sub-events are waiting in the IBs. The token is passed along among the IBs and each IB can send its data out onto the R-path only when it is in possession of the token. When the last IB in the ring has been read out, it passes the token back to the FOF thus completing an event read out cycle. An event consists of several sub-events, one from each IB.

A sub-event is the block of data generated by any one sub-detector when a trigger is issued. The data arrives at the IB from the Optical Link as a series of 40-bit wide words. The words consist of 32 bits of user data (D0 - D31) and 8 bits of control data (D32 - D39). The control block is made up of 5 parity bits (one for each byte), 1 end\_of\_event bit and 2 reserved bits. At sub-event level, the words are transmitted unchanged from one IB to the FOF over the R-path backplane. The IBs participate in turn and each transfer follows the same protocol. A sub-event consists of several words of data (up to around 3k bytes).

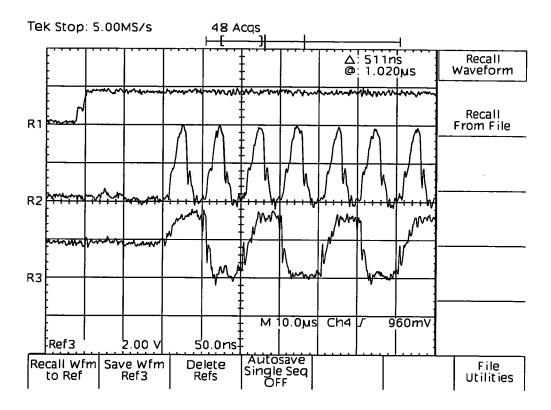

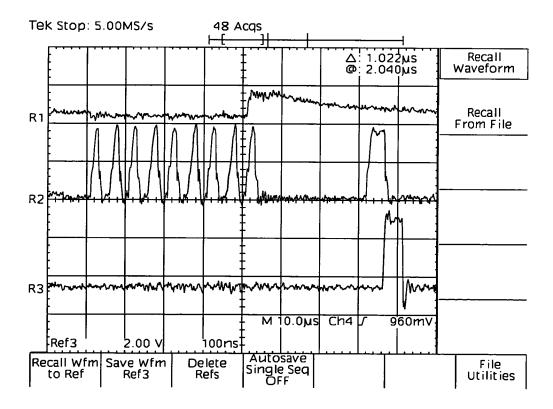

# 3.4 Input Buffer

The Input Buffer is a dual channel 9U by 400mm board which sits in crate 2 (see Figure 3.2). Each channel takes events from one optical link and stores them until it receives a token. When the token arrives the IB sends an event to the FOF across the R-Path. The board also adds a word count and the OL error bits to the data. The word count is added as an extra word and the error bits are placed in the control byte of the last word. The IB memory consists of two banks (ODD and EVEN) of 40 bit-256 kByte static RAM. The control signals to these memories come mainly from a Xilinx FPGA chip. When one bank is being written to by the OL, the other can be read out through the R-Path. This ensures no break in data transmission to the FOF if data arrives over the OL when the module has the token.

The IB has a simple VME slave interface that is used for diagnostic purposes. The control byte is multiplexed down onto the 32-bit data word at the VME interface.

The design and testing of the input buffer has formed the main part of my work during my PhD and a more complete discussion of its function will be given in Chapter 4.

## 3.5 R-path backplane

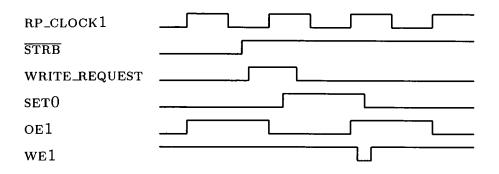

The R-Path carries the 40 bit data words from the IB to the FOF. As well as the 32 bit data word and 8 bit control word the R-Path backplane also carries the following signals:

• **DATA\_VALID** : This is a strobe that is sent by the IB to the FOF along with each data word transferred. The signal goes low on the backplane for 20 ns while the data word is being sent. The FOF uses this to latch the data into its buffers.

- **DATA\_ACK** : The FOF returns an acknowledge signal to the IB for each word that it receives.

- **RP\_NODATA** : The R-Path NoData line on the bus is driven low by an IB when it does not hold a complete sub-event. When the board receives an end of event word from the Optical Link it de-asserts this line. As the bus is wired-or the line does not go high until all the IBs have de-asserted their **RP\_NODATAs**. A high tells the FOF that a complete event has arrived in the Data Merger buffers and hence it can send a token to read out the system.

- **RP\_HAVEDATA**: This signal performs a similar function to the **RP\_NODATA** line. It is asserted (driven low on the backplane) by any IB that has data in its memory. This data does not necessarily need to be full sub-event. A low on the RP\_HAVEDATA line warns the FOF that one or more IBs contain data to be read out even if a full event is not present in the system.

- **RP\_XOFF** : The XOFF line is driven low by the FOF when its buffers are full. This forces the IB to stop sending data.

- +5 V : There are 30 5 V pins on the backplane. These provide extra power to the IB and FOF boards as well as a supply to the ROLEX.

- -5.2 V : 21 pins provide power for the ECL token circuitry.

- +2.1 V : The BTL tranceivers require each line on the backplane to be terminated by a 33  $\Omega$  resistor to 2.1 V and a capacitor to ground. This supply provides the termination voltage.

The start\_of\_spill signal from the SPS causes the DMC to set a bit in a register in the FOF. This action is carried out over VME and is asynchronous with any R-path signals. When this bit is set, the FOF monitors the signal RP\_NODATA (set high when all the IBs have an event in memory). When this happens the FOF sends out a token along the token line. Upon receiving the token each IB sends out one event and passes the token to the next IB in the chain. The IB sends a DATA\_VALID pulse along with every word it transmits and the FOF sends a DATA\_ACK back to the IB for every word that it receives. If there is an error and the number of DATA\_ACK edges does not tally with the number of DATA\_VALID edges then the IB does not send on the token and the data merger stops. Each IB drives RP\_NODATA low when it has cleared its memory.

During the transfer, it may happen that the FOF fills its buffer. If so, like the IB to the OL, it sets  $\overline{\text{XOFF}}$  low. This can happen asynchronously.

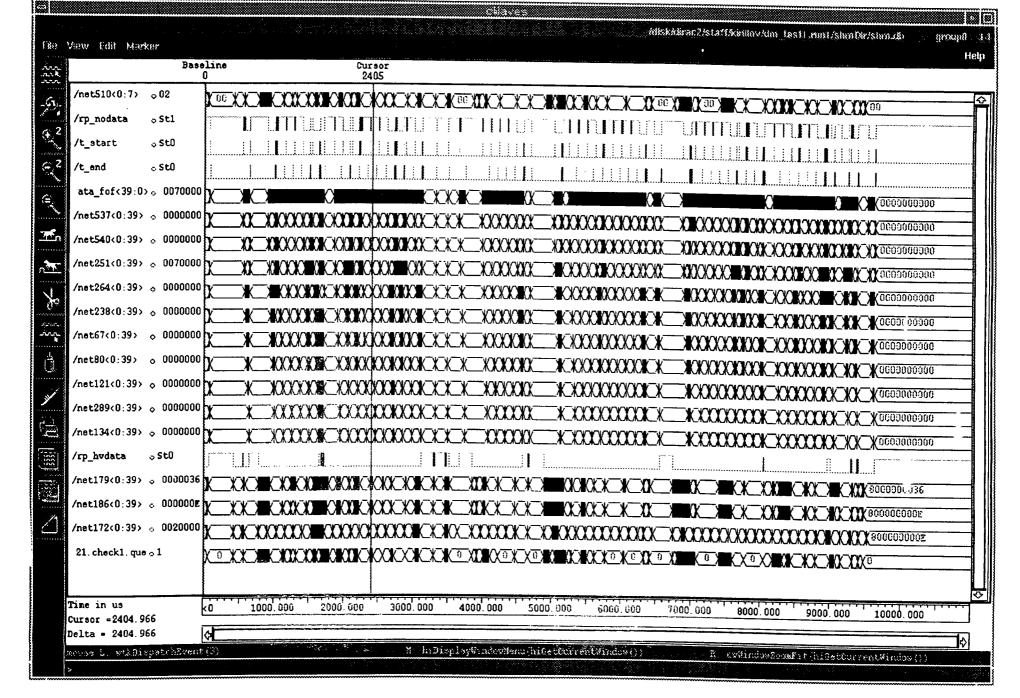

On seeing the  $\overline{\text{XOFF}}$  signal go low, the IB finishes the transfer of the current word. That is, the data remains valid until the next rising edge of the R-Path clock (RP\_CLOCK1), and DATA\_VALID continues to strobe. At that rising edge of RP\_CLOCK1, the address counters in the IB freeze and the data is not changed. DATA\_VALID finishes low. This continues while  $\overline{\text{XOFF}}$  is held low.

When the FOF has cleared sufficient space, it sets  $\overline{\text{XOFF}}$  high (again asynchronously). On the next rising edge of RP\_CLOCK1, a new data word is presented by the IB and DATA\_VALID starts to strobe again.

When the last IB in the chain completes its read out, it passes the token back to the FOF. On receiving the token back, the FOF knows that a complete set of sub-events has been read out.

When the protons from the SPS are directed away from our experiment, an *end\_of\_ejection* signal from the SPS is sent to the FOF. When the FOF receives this signal, it could be in the middle of an event read out cycle. It completes this read out then checks RP\_NODATA. If it is low, it sends off another token and reads out the event and so on until RP\_NODATA goes high. At this point, since the spill is over, no new events can arrive.

# 3.6 FIFO Output Formatter

### 3.6.1 Overview

The FIFO Output Formatter (FOF) was designed and built by Senerath Galagedera and Ben Brierton at the Daresbury Rutherford Appleton Laboratory. The FOF is the output component of the Data Merger. It recognises when a complete set of events is waiting in the IBs and issues a token. It then receives data from the R-path backplane, buffers it in FIFO memories and sends it out again over a HIPPI link to the workstation farm. The FOF also adds event headers, word counts and error information and re-formats the data for HIPPI transmission. The transmission over HIPPI and the reception on the R-path are decoupled and asynchronous and can proceed simultaneously. The FOF can exert flow control by asserting the  $\overline{\text{XOFF}}$  signal in the R-path backplane.

### 3.6.2 General Arrangement of the FOF

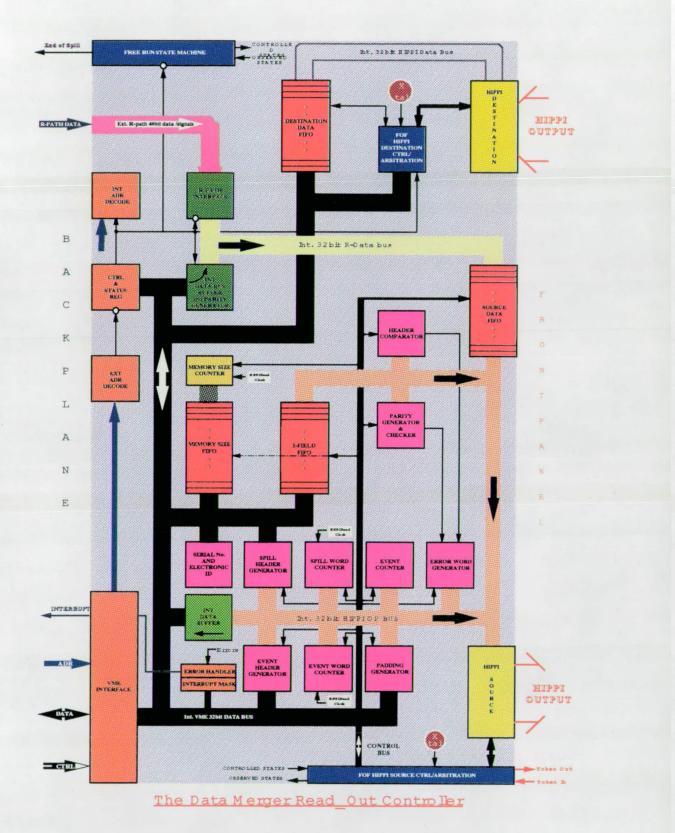

The FOF is a 9U  $\times$  400 mm board which is mounted in the right-most slot of the Data Merger. A block diagram of the FOF is shown in Figure 3.4.

In normal operation, data is received from the R-path backplane via Futurebus+ transceivers and stored in a source data FIFO. At the appropriate moment, the data is shifted out of this FIFO to a HIPPI source chip which transmits the data out of the FOF via a HIPPI cable. The HIPPI source can also receive data from the I-field FIFO, the memory size FIFO and from various data generators. The data generators are contained in a Xilinx FPGA and generate the spill header, the event header, the padding and the error word. There are also an event counter, spill word counter and event word counter in the Xilinx the contents of which can also be sent to the HIPPI source.

The FOF is also equipped with a HIPPI destination chip which can receive HIPPI data and write it to the destination FIFO. By connecting the source to the destination with a cable, the FOF can send data to itself for self-test purposes.

The VME interface allows access to the data generators, the memory size FIFO, the I-field FIFO, the destination data FIFO and to the control and status register via VME.

Figure 3.4: Block Diagram of the FOF

### 3.6.3 R-path and token interface

Data arrives on the R-path backplane synchronously with the strobe DATA\_VALID and the two R-path clocks, RP\_CLOCK1 and RP\_CLOCK2. The latter is used to gate the data through the R-path transceivers and DATA\_VALID is used to latch the data into the source data FIFO. The DATA\_VALID signal is returned by the FOF as DATA\_ACK.

The data transmitted along the R-path is accompanied by parity checking bits which were originally generated by the Optical Link Source (OLS). The FOF generates new parity bits for each data byte which arrives and compares the new bits with those from the backplane. Any time a mis-match occurs, an error counter is incremented. At the end of the event, the contents of the error counter are written to the error word generator.

If the source data FIFO becomes full during the transfer, the FOF drives the  $\overline{\text{XOFF}}$  signal low. This inhibits whichever IB is sending data and thus pauses the dataflow on the backplane. When the source data FIFO has cleared, the FOF removes  $\overline{\text{XOFF}}$  and the dataflow resumes.

The token is generated in the FOF and consists of an active-low pulse in differential ECL of 40 ns duration. This pulse is transmitted from a front panel socket along co-axial lemo cable. The returned token from the last IB is received by a complementary circuit and converted to TTL.

### 3.6.4 Additional data generated by the FOF

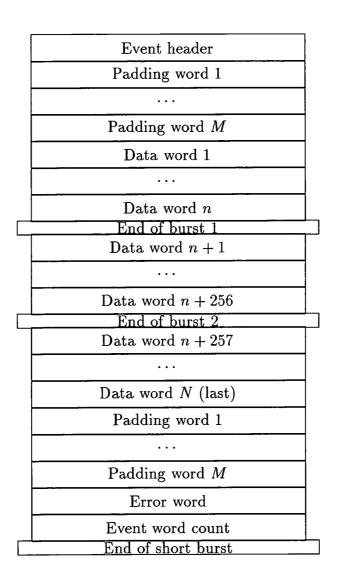

As well as the user data, the FOF generates the following additional blocks of data which are used for book-keeping, debug and analysis:

• The I-field: This is a HIPPI packet which is read by the HIPPI-switch and which tells the switch through which output to route the next HIPPI connection. The I-field is written to the I-field FIFO by the DMC before the spill begins.

- Spill Header: This is a serial number for the spill and is sent at the beginning of the connection.

- Event Header: This contains a serial number for the event.

- Spill Word Count: The total number of words sent during a spill. This includes all protocol and book-keeping words.

- Event Word Count: The total number of words in an event.

- Padding: A string of between 2 and 255 words consisting of an incrementing number sequence (i.e. 00, 01, 02 etc.). The size of the string is determined by the contents of the padding register which is loaded by the DMC.

- Error Word: The number of parity errors detected in the event.

### 3.6.5 The HIPPI transfer protocol

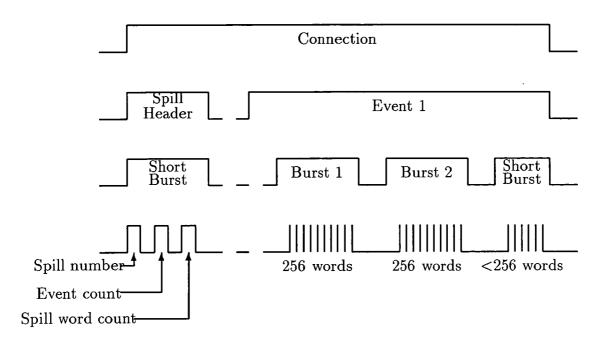

The various blocks of data sent by the FOF are formatted according to the HIPPI protocol. 32-bit parallel HIPPI which consists of differential-ECL signals transmitted over twisted-pair wires is used. HIPPI data is organised at four levels of hierarchy; connection, packet, burst and word.

- Connection: A connection can have an indeterminate duration (several seconds). During a connection many packets are sent.

- Packet: A packet has an indeterminate duration and the delay between packets can be indeterminate. A packet can contain any number of bursts and one short burst.

- Burst: A burst consists of exactly 256 words and is thus of a fixed duration. There can be an indeterminate delay between bursts. A short burst has between 1 and 255 words. There can only be one short burst per packet and this must be either the first or the last burst of the packet.

- Word: A word is the data which is read on the 32 data lines during one clock-cycle. The data is changed at a fixed rate of 25 MHz and so the time between adjacent words is 40 ns.

Figure 3.5: The structure of a FOF HIPPI connection.