# A STUDY OF THE THIN FILM TRIODE

by

Malcolm Alexander Reid, B.Sc. (Glas.)

Thesis presented for the degree of Doctor of Philosophy of the University of Edinburgh in the Faculty of Science.

April, 1968.

#### ACKNOWLEDGEMENTS.

I am indebted to Professor W.E.J. Farvis and to Dr. A.R. Dinnis for their support and guidance throughout the course of this work. I wish to thank Mr. C.P. Sandbank for his encouragement and for the use of the X-ray diffraction facilities at S.T.L., Harlow.

I am also grateful to the S.R.C. for the studentship which made the study possible.

# CONTENTS,

| CHAPTER 1.         | INTRODUCTION.                                          | 1   |

|--------------------|--------------------------------------------------------|-----|

| CHAPTER 2.         | FUNDAMENTALS OF THE THIN FILM FIELD EFFECT TRANSISTOR. | 7   |

| 2.1                | History of field effect.                               | 7   |

| 2.2                | Evolution of TFT.                                      | 11  |

| 2.3                | Physical processes in TFT.                             | 19  |

| 2.4                | Considerations of materials for TFT.                   | 23  |

| 2.4.1              | Substrate materials.                                   | 25  |

| 2.5                | Masking procedure.                                     | 27  |

| 2.6                | Consideration of TFT configuration.                    | 33  |

| CHAPTER 3.         | THEORY OF THE THIN FILM TRANSISTOR.                    | 37  |

| 3.1                | The gradual approximation.                             | 37  |

| 3.2                | The Borkan-Weimer analysis.                            | 4-1 |

| 3.3                | Wright's analysis.                                     | 48  |

| 3.4                | The saturation problem and Geurst's analysis.          | 59  |

| CHAPTER 4.         | THE EVAPORATION OF CADMIUM SULPHID FILMS.              | 69  |

| 2 <sub>1 •</sub> 1 | Properties of cadmium sulphide films.                  | 70  |

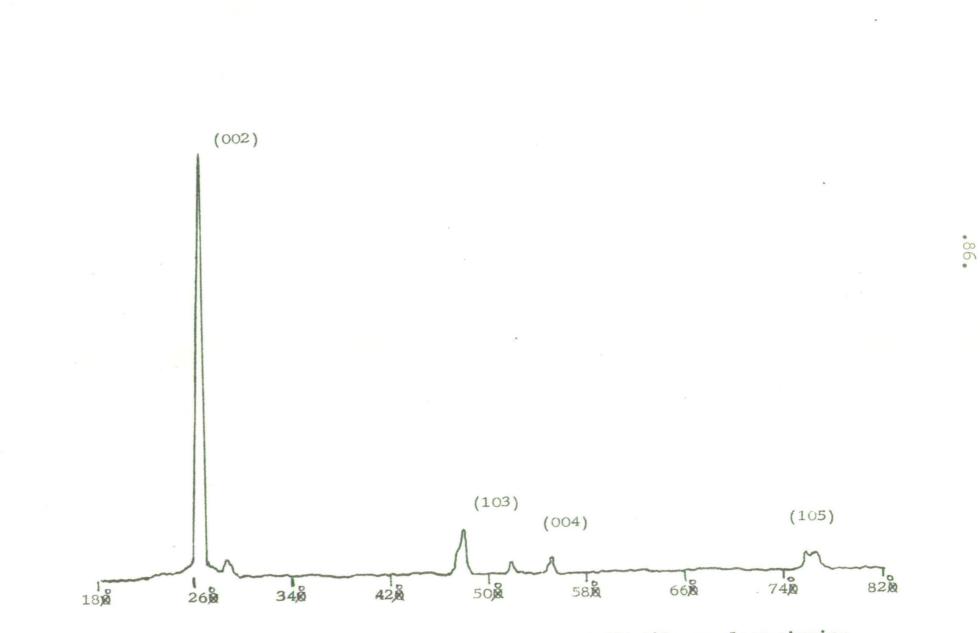

| 4.2                | Techniques for investigation of crystal structure.     | 73  |

| 4.3                | Substrate cleaning procedures.                         | 73  |

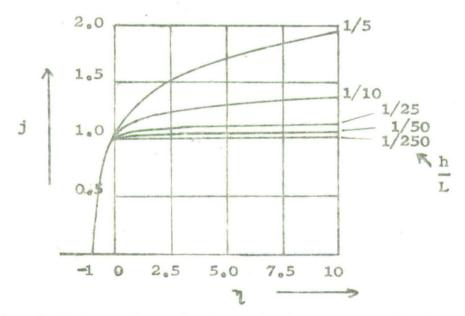

| 44                 | The vacuum system.                                     | 77  |

| 4.5                | Vapour deposition of cadmium sulphide.                 | 77  |

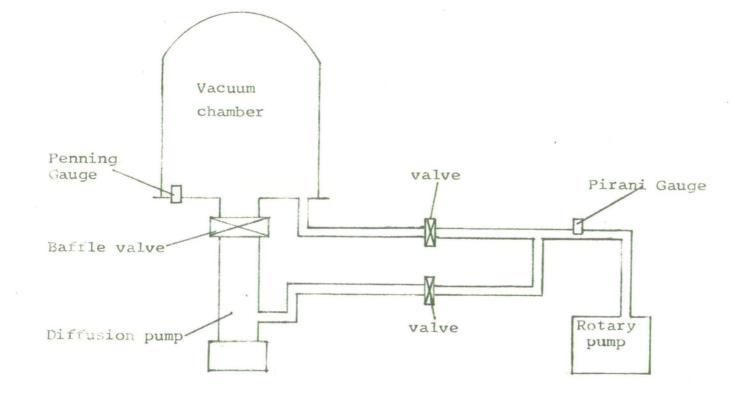

| 4.5.1              | Method 1: Knudsen source.                              | 78  |

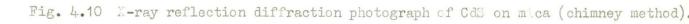

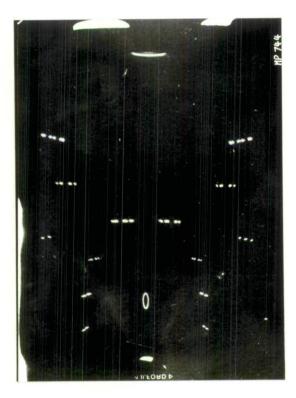

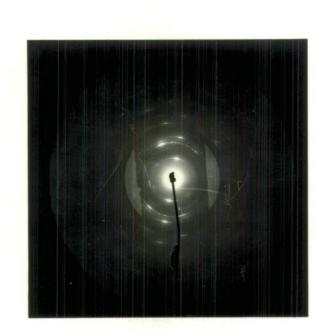

| 4.5.2              | Method 2: "Chimney method".                            | 83  |

| CHAPTER 5.  | THE METAL-SEMICONDUCTOR CONTACT.                   | 96  |

|-------------|----------------------------------------------------|-----|

| 5.1         | Historical notes.                                  | 96  |

| 5.2         | The Schottky barrier.                              | 97  |

| 5.3         | Ohmic contacts to cadmium sulphide.                | 101 |

| 5.4         | Evaporation of source and drain electrodes.        | 104 |

| 5.5         | I-V characteristics using source-drain electrodes. | 110 |

| CHAPTER 6.  | EVAPORATION OF THIN FILM TRANSISTOR.               | 125 |

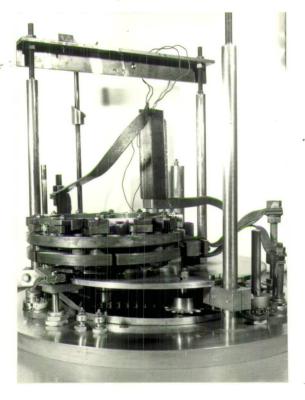

| 6.1         | The mask changer.                                  | 125 |

| 6.2         | Evaporation of silicon monoxide.                   | 125 |

| 6.3         | Discussion of transistor I-V characteristics.      | 130 |

| CHAPTER 7.  | CONCLUSIONS.                                       |     |

| 7.1         | Discussion of results.                             | 141 |

| 7.2         | Conclusion.                                        | 144 |

| REFERENCES. |                                                    | 146 |

#### CHAPTER 1.

#### INTRODUCTION.

Microelectronics now has an accepted place in electronics and is having an impact on the electronics industry rivaling the invention of the transistor. The desire to miniaturize produced a revolution in the design and manufacture of electronic components which involves the mass fabrication and integration of these components together with their interconnections, encapsulations and external contacts, the end product being an integrated circuit. Over the years, different approaches have been taken to the miniaturization of components and circuits and consequently different technologies have evolved, each providing in its own way an integrated form of circuit. Hence, in its widest sense, an integrated circuit may be defined as <sup>[1]</sup>:

> "the physical realization of a number of circuit elements, inseparably associated on or within a continuous body to perform the function of a circuit."

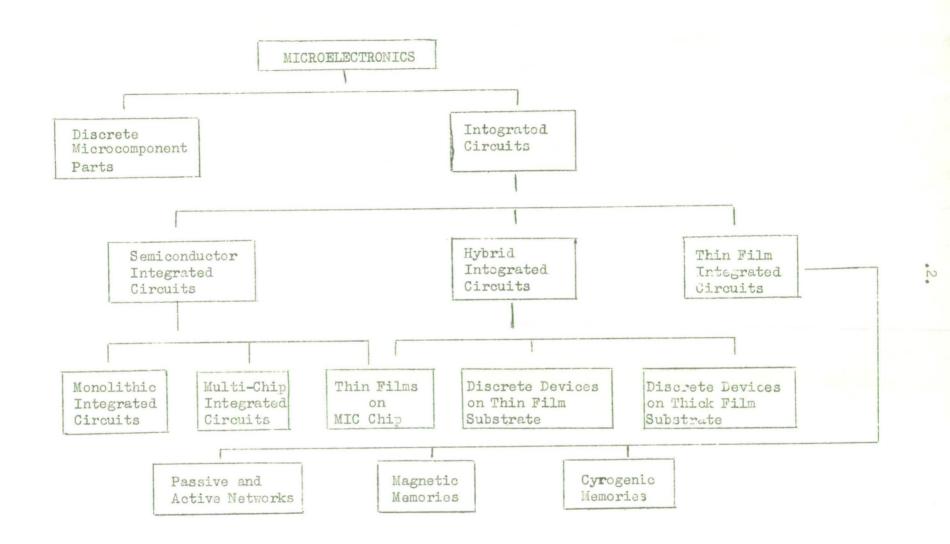

Integrated circuits generally break down into two major categories, one utilizing semiconductor techniques only, the other using film technology to supplement semiconductor contributions. These categories and their position in the microelectronic classification <sup>[1]</sup> are shown in Figure 1.1.

In the first category, all the components of a circuit form an integral part of a piece of bulk semiconductor material. Techniques such as diffusion, epitaxial growth and passivation are used to obtain the particular components

Figure 1.1 Basic Microelectronic Classification.

required within the circuit. Interconnections within the block of material are made by deposition of thin film material. This type of circuit is referred to as a monolithic circuit. They have been used extensively for digital requirements in such forms as RTL, DTL and TTL logic. More recently successful linear circuits have been produced using these techniques. In addition to the monolithic semiconductor integrated circuit, a multi-chip approach to integration has been used. In this case, resistors, capacitors, transistors and diodes are fabircated as individual components which are then connected together to form an integrated circuit. This procedure represented a stepping stone on the way to monolithic integrated circuits.

The second broad category consists of hybrid integration. This is a very general classification which often leads to some misunderstanding owing to the fact that there are hybrid circuits which are a combination of thin film, thick film, metal film and multi-chip circuits. A thin film circuit is usually designated as such if the resistor and dielectric material used in conjunction with the active devices are formed by techniques such as vacuum evaporation. The thickness of these films is measured in terms of Angströms, thus the reference to thin film. Thick films on the other hand incorporate resistor and dielectric materials which have been deposited by silk or metal screening techniques. The material is of the order of 1 micron or more in thickness. Metal film circuits usually refer to a material such as tantalum which is anodised to form resistor material.

Semiconductor integrated circuits find most applications where highly repetitive digital requirements exist, and where relatively few circuit types

.3.

are involved. Under these conditions the volume justifies the high design and tooling costs while the use of batch processing reduces the production costs. On the other hand, thin film hybrid integrated circuits are used for close tolerance analogue applications which require extreme resistor stability and where relatively small total numbers are involved. The economic production of small runs of custom built circuits arises from the low capital cost in the thin film process chosen. The thick film system lends itself to the use of mechanised processing equipment and hence is used for larger runs of any given circuit where the emphasis is on minimum cost.

The classic reasons for using either monolithic or hybrid microelectronics technology are:

- (a) reliability

- (b) cost

- (c) size and weight

Perhaps the most talked about factor is reliability. Integrated circuits in general have fewer connections of dissimilar materials and therefore less connection failures. Historically, electrical connections have been a major problem from a reliability standpoint. Deposited connections are inherently more reliable than discrete soldered connections. There is also control over the formation of the complete circuit. With a circuit of discrete components different components come from different places and so have different reliabilities. However, some of this control is lost in the hybrid forms of integration. In addition, the use of redundancy, brought about by the opportunity to achieve more circuits per unit volume, has contributed to increased overall reliability.

.4.

When integrated circuits were first introduced at the beginning of this decade they were extremely expensive but had the important features of small size and high reliability. The immediate applications that were seen for integrated circuits at that time were mainly confined to military and space systems where small size and high reliability justified the high cost. During the 6 years or so since integrated circuits were first designed into equipment, the manufacturing cost and selling price has decreased faster than anyone could have foretold. Fabrication yields have greatly improved and fabrication cost has become an almost insignificant part of the manufacturing cost. The most significant cost involved in integrated circuits now occurs at the assembling and testing stages of manufacture. Thus individual handling of the devices for bending, sealing and testing contribute greatly to the total manufacturing cost of the devices and it is this that has led to the concept of large scale integration (LSI).

Today, in many types of electronic equipment - military, space and aviation systems, communications, control and laboratory instruments and the consumer electronics industry - integrated circuits have become the basis of design. Although the initial impetus for the development of integrated circuits was the necessity for reducing size and weight, it is now apparent that integrated circuits allow equipment to be made at a lower cost than can be achieved with discrete components and the other advantages which accrue, size and reliability, may be regarded as bonuses.

The basic classification shown in Figure 1.1 points to the possibility of thin film integrated circuits. At present the most satisfactory form of active

.5.

device for incorporation in any form of thin film circuit, thick or thin, is the inverted chip transistor. It is possible to fit such chip transistors by soldering to conducting areas of both thin and thick circuit systems. However, the unity of the thin film process is broken by this technique and there is a requirement for an evaporated thin film active device to permit the formation of thin film integrat**2d** circuits. Weimer <sup>[2]</sup> and his co-workers at the R.C.A. laboratories have produced such a device and experimentation on completely integrated circuits is now being actively carried out.

.6.

The all-thin-film approach to integrated circuits utilizes an inert insulating substrate in place of the single crystal used in semiconductor integrated circuits (MOS and bipolar). Complete electrical isolation of the individual components is readily attained and therefore parasitic coupling effects are avoided. As large area substrates do not present any great problem to vacuum evaporation techniques, thin film integrated circuits are likely to find a specialized application in solid-state image-scanning devices.

This thesis is devoted to a study of the thin film transistor.

### CHAPTER 2.

## FUNDAMENTALS OF THE THIN FILM FIELD EFFECT TRANSISTOR.

#### 2.1 HISTORY OF FIELD EFFECT.

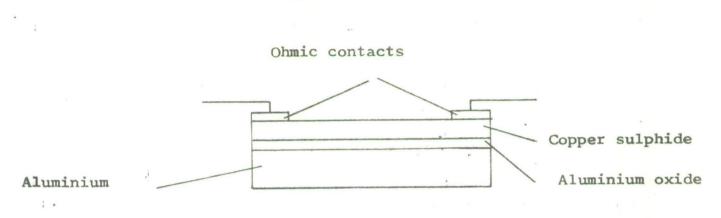

The basic idea of using a transverse electric field to control the longitudinal electric current between two electrodes, or simply the field effect principle, was disclosed by J.E. Lilienfeld <sup>[3]</sup> of New York in a series of patents, the first of which was issued in 1930. Lilienfeld proposed the structure shown in Figure 2.1. In this case, a thin layer of semiconductor, copper sulphide, was separated from a control electrode, aluminium, by a layer of insulation, aluminium oxide. When an electric field is applied across the insulator, the layer of semiconductor charges up, and this increase in charge results in an increase in the number of carriers available for conduction. Thus, it is capable of modulating the conductivity of the current path in the semiconductor.

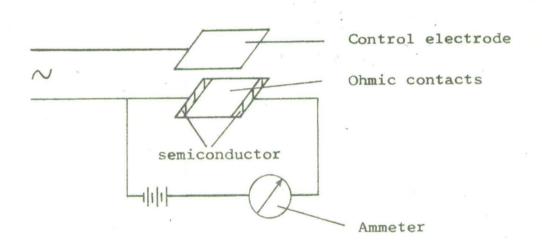

Other early experiments along these lines were undertaken by O. Heil <sup>[4]</sup> in Germany and were recorded in a British patent in 1935. He suggested the use of tellurium, iodine, cuprous oxide or vanadium pentoxide as a semiconductor, this layer being separated from one or more metal plates by either a solid dielectric, a vacuum or an air space. The proposed device is shown in Figure 2.2. These were the first attempts to realize active solid state devices.

The effects to be expected from such arrangements are quite pronounced. The amount of induced charge can be determined from the applied voltage and the capacitance of the system. If the mobility of the charge carriers is known, then the expected change in conductance can be calculated. Consider, for

Fig. 2.1 The metal-oxide-semiconductor transistor proposed by Lilienfeld.

Fig. 2.2 The metal-insulator-semiconductor transistor proposed by Heil.

example, a layer of semiconductor of thickness 1600 Å. Let the resistivity be 10 ohm-cm and the mobility of the electrons be 100  $\text{cm}^2/\text{volt.sec.}$  The electron concentration in the semiconductor may be calculated from the expression,

$$\sigma = \frac{1}{p} = ne\mu$$

Hence,

In a layer of thickness  $t = 1600 \text{ Å} = 6 \times 10^{-5} \text{ cm}$ . there will be  $nt = 1.0 \times 10^{10}$  electrons per sq.cm.

$n = \frac{1}{1.6} \times 10^{15} \text{ ohms/cm}^3$

Consider now the application of a voltage to the control electrode. Owing to the presence of the transverse electromie field a charge will be induced on the surface of the semiconducting layer. A control electrode at a potential of 1.0 volts and separated from the semiconducting layer by a dielectric layer of thickness, 1000 Å, and dielectric constant, would produce a field of  $10^5$  volts/cm. This field in turn will produce a displacement of  $\epsilon_{e_0}$  coulombs. A simple calculation using the above values shows that the number of induced electrons is  $0.9 \times 10^{10}/\text{cm}^2$ . It can be seen that the number of induced electrons is approximately the same as the number normally present. Such a field should thus double the conductivity of the semiconducting layer.

Experiments have been carried out with layers of semiconductors and effects of the kind described on the previous pages have been observed. However, the degree of modulation has been somewhat less than that predicted by calculation. Shockley and Pearson <sup>[5]</sup> in 1948 took measurements on a number of films of p-type germanium. In these experiments, a thin film of germanium with laterally

spaced contacts was evaporated on to one side of a thin mica sheet. The field electrode consisted of an evaporated metal film deposited on the opposite side of the mica substrate. Copper oxide and n-type silicon were also used. In general, the results showed that only about 10 per cent of the induced charges were effective in changing the conductance. Shockley and Pearson used Bardeen's [6 surface states model of a semiconductor to explain this phenomenon. The concept of surface states was introduced by Tamm [7] who showed from fundamental quantum-mechanical considerations that, in contrast to the situation in bulk, localized states can occur at the surface and have energies distributed in the forbidden range between the filled band and the conduction band. Kronig and Penney [8] approximated the potential energy of an electron in a crystal by a periodic array of square wells and were able to show that the electron energy spectrum consisted of allowed bands separated by forbidden zones. Tamm modified the model to include the abrupt termination of the lattice at the surface and treated the crystal as a periodic array of square wells ending with a potential wall, which corresponds to the binding energy of an electron in the crystal. From this model theory predicted the presence at the surface of allowed energy levels, surface states, within the forbidden zone. Further modifications to the model were made by Shockley [9], who showed in a more general treatment that surface states can only occur if there is a separate potential trough at the surface, or if the energy bands arising from separate atomic levels overlap. Bardeen proposed that electrons which move in the bulk of the semiconductor could become tightly bound in surface states on the surface of the semiconductor and thus become immobilized. In this way, a portion of the induced charge becomes ineffective, and makes no contribution to the conductore

.10.

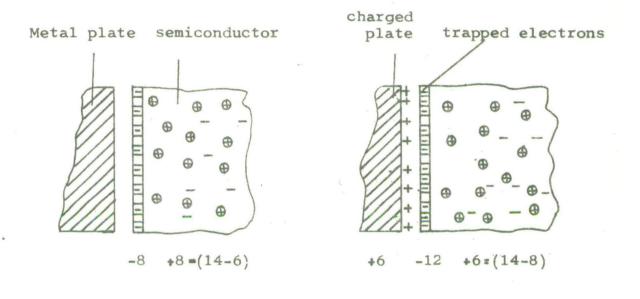

Figure 2.3 represents the surface of an n-type semiconductor and shows, in part (a), eight electrons trapped in the surface states. These electrons repel other electrons in the conduction band and thus produce a layer of depleted conductivity below the surface. The semiconductor surface as a whole is neutral. When the metal capacitor plate is charged positively, an equal negative charge appears on the surface of the semiconductor. In accordance with the results obtained by Shockley and Pearson, 90 per cent of this charge is trapped in surface states. Surface states are believed to be associated with the unsaturated or dangling bonds of the surface atoms. Hence their density should be approximately equal to the number of surface atoms,  $10^{14} - 10^{15}$  per cm<sup>2</sup>.

#### 2.2 EVOLUTION OF TFT.

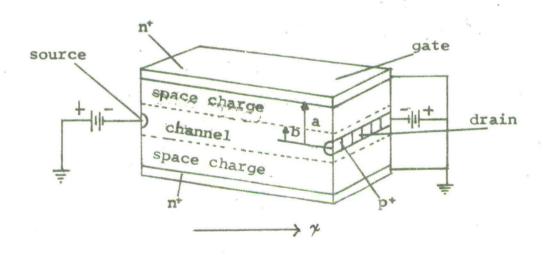

The initial attempts to achieve a solid state amplifier by modulating the **electric** field at the semiconductor surface were not too successful, and this method of conductivity modulation was subsequently used to study the electronic properties of the semiconductor surfaces. However, an alternative approach to an active solid state field-effect device was conceived by Shockley. In order to get round the effects of surface states and other surface problems, Shockley in 1952 <sup>[10]</sup> introduced a completely different field effect configuration which made use of the extension of the depletion region of two reverse biased p-n junctions to control the conductance between two electrodes at the ends of a bar of semiconducting material. The construction is shown in Figure 2.4.

Fig. 2.3 Surface states diagram showing how induced charge may be immobilized (Shockley). (a) neutral semiconductor surface (b) negatively charged surface.

(b) ·

Fig. 2.4 Space charge region and channel in a npn structure

(a)

consequence the current flows in a channel, of p-type material in this case, bounded by space charge regions. In Figure 2.4 the reverse bias is the same at each p<sup>+</sup> terminal and the channel width is uniform over the length of the device. If the reverse bias is made larger at one end, the depletion region increases towards that end, and hence the channel narrows with a consequent change in conductance. A further increase in reverse bias causes the two space charge regions to meet and the current through the channel to saturate. This is known as the "pinch-off" point. With this proposal, then, to move away from the surface with its attendant problems and into the bulk, Shockley suggested a method of modulating the current in a block of semiconducting material. The method bears a closer analogue to the vacuum triode than to conventional bipolar transistors. A signal applied between the control electrode and ground has the effect of altering the width of the channel and hence the current through the device. The current flow is carried by one type of carrier only and the device is said to be "unipolar". This is closely analogous to the action of the grid in a thermionic valve. Shockley also suggested a new electrode terminology for field effect devices. He designated the "source" and "drain" as the electrodes into and out of which current flows and the "gate" as the control electrode. Such transistors were subsequently built and tested by Dacey and Ross in 1955 [11] but had the limitation that rather high voltages were required to pinch off the channel owing to the physical dimensions of the device, thus introducing other adverse effects such as mobility deviation due to high fields and junction leakage problems. The junction gate field effect transistor has since become available commercially.

.13.

The junction gate field effect transistor described above has little in common with thin film transistors and contains no thin film parts, the semiconductor being a single crystal. However, Shockley made a further contribution to the study of field effect transistors by producing a theoretical analysis to explain the current-voltage relationship of the junction gate transistor and some features of the approach have been used by others to explain the operation of the thin film transistor up to the current saturation point. This will be dicussed in Chapter 3.

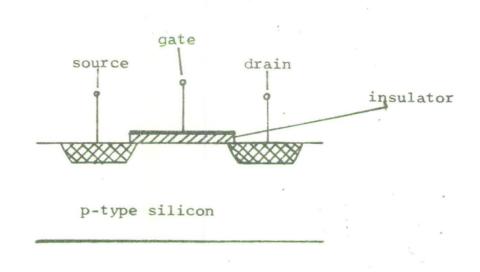

Interest in the original idea of conductivity modulation by an electrode insulated from the surface still persisted. The advent of the conventional bipolar transistor produced a concentration of research work on single crystal germanium and silicon, and the subsequent availability of high purity materials facilitated the study of surface phenomena. The stability of silicon surfaces when they were provided with a chemically bound solid-solid interface was studied by Atalla <u>et.al</u>. <sup>[12]</sup>, and stable surfaces were obtained with the siliconsilicon dioxide system when the oxide was thermally grown. The motal oxide semiconductor field effect transistor (MOST) arose directly from this work. The structure of the device is shown in Figure 2.5. The source and drain electrodes are formed, in this case, by a heavy doping of n-type material. Current is injected at the source by forward biasing the p-n junction and modulated by the gate electrode, usually of aluminium, placed on top of the silicon dioxide insulator.

The thin film version of this transistor did not follow directly from the work of Atalla et.al., but originated more or less simultaneously from a quite

.14.

Fig. 2.5 The metal-oxide-semiconductor transistor

different source, namely the study of space charge limited currents (scl) in wide band gap materials. Transient scl currents in cadmium sulphide crystals were observed by Smith and Rose in 1955 [13]. These currents rapidly decayed to very small values because of carrier trapping and considerable work has since been carried out to understand the influence of carrier trapping on scl currents. The Mott-Gurney square law dependance of current upon voltage was observed by Wright [14] in cadmium sulphide in 1958 and scl dielectric diodes were demonstrated by Conning et.al. in 1959 [15]. At this time, Ruppel and Smith [16] reported the fabrication of an experimental solid state triode which operated under scl conditions. A significant departure from the study of single crystals occurred when Dresner and Shallcross [17], drawing on considerable technological experience with thin films of cadmium sulphide which had been acquired in the fabrication of photoconductive devices <sup>[18]</sup>, reported the observation of scl currents in evaporated polycrystalline cadmium sulphide diodes. They had observed rectification ratios of 10<sup>5</sup> using an underlying gold electrode as the injecting contact and an overlying tellurium electrode as the blocking contact.

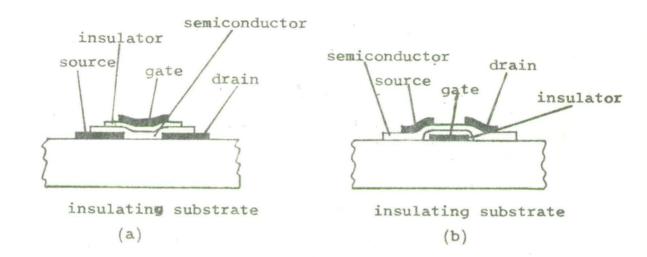

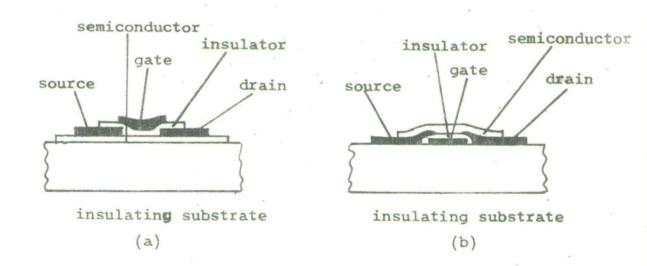

An early attempt at constructing an scl triodo was made by embedding an evaporated grid of tellurium lines in a double layer of evaporated cadmium sulphide <sup>[2]</sup>. Another approach used a single pair of laterally spaced electrodes with an intervening tellurium gate strip in contact with the cadmium sulphide<sup>[16]</sup>. Owing to the large trap density and the low mobility of the films, poor control was obtained in these experiments. Finally Weimer <sup>[2]</sup>, by introducing an insulating layer into the gate structure, produced a successful thin film transistor with the configuration shown in Figure 2.6(a).

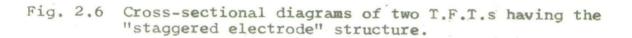

In Weimer's device, all materials, including the metal electrodes, the semiconductor, and the insulator were deposited by evaporation on an insulating glass substrate. The semiconductor has, in most cases, been a polycrystalline layer of cadmium sulphide, although other materials, notably cadmium selenide, (n-type), and tellurium, (p-type), have been used successfully. The source and drain electrodes were formed of metals which made low resistance contacts with the semiconductor and for this structure, gold was initially used. The requirements for the gate electrode are less strigent and either gold or aluminium can be used. The thickness of each film is greatly exaggerated in the cross-sectional drawings. The metal electrodes are several hundred Angstroms in thickness, the insulating layer ranges from 1000 Å to 2000 Å, and the semiconductor from a few hundred Angstroms to one or more microns. The insulating layers are usually of silicon monoxide or calcium fluoride. The spacing between, and the length of the source and drain electrodes are generally of the order of 10 microns and 0.25 cm respectively. Other configurations are possible for the thin film transistor and these are also shown in Figure 2.6(b) and Figure 2.7(a) and (b). As can be seen from these diagrams, there are two main structures for the thin film transistor, depending upon whether all the electrodes are on one side of the semiconductor, referred to as the coplanar electrode structure, or whether electrodes are placed on both sides of the semiconductor, referred to as the staggered electrode structure. Using these materials and similar dimensions, Weimer was able to fabricate devices with transconductances varying between 4000  $\mu$  a/volt and 25,000  $\mu$  a/volt.

.17.

Fig. 2.7 Cross-sectional diagrams of two T.F.T.s having the "co-planar electrode" structure.

#### 2.3 PHYSICAL PROCESSES IN TFT.

The structures used for the classical field effect experiments, in which current modulation was found to be impractical, and the thin film transistor, in which current modulation is possible, have a distinct similarity, the main differences being in the materials and the dimensions used. The very thin evaporated layer of insulation in the thin film transistor allows the control electrode to be anything up to 1000 times closer to the semiconductor than was possible in the early field effect experiments, where an insulating spacer of mica or a vacuum gap of 12 microns was fairly typical. The difference yields correspondingly higher transconductances and a more effective control of the surface potential. Owing to the high capacitance, free carriers can be drawn to the interface at moderate voltages to fill traps and surface states and so inactivate them. The thermally grown oxide on silicon in the MOS transistor also provides a close spacing. The choice of insulating material also determines the surface potential of the semiconductor. For example, with cadmium sulphide, calcium fluoride forms a depletion layer at the surface, whereas silicon oxide can form either a depletion or accumulation layer depending on whether monoxide or a dioxide is used. By mixing calcium fluoride and silicon monoxide in different proportions, it is possible to vary the surface potential between the values obtained for these materials separately. [19]

It is obvious that the semiconductor to insulator interface has some considerable bearing on the operation of a thin film transistor. The formation of a depletion layer at the interface causes no drain current to flow in the transistor when there is zero gate voltage, and it is necessary to apply a positive voltage to the gate in the case of an n-type semiconductor to turn the transistor on. Such a circuit is said to operate in the enhancement mode. A depletion type thin film transistor is one which has a useful current at zero gate bias, and this is provided by the formation of an accumulation layer at the semiconductor to insulator interface. In this case, a negative gate voltage is required to turn the transistor off. Such a unit is capable of operation in either the depletion or enhancement mode.

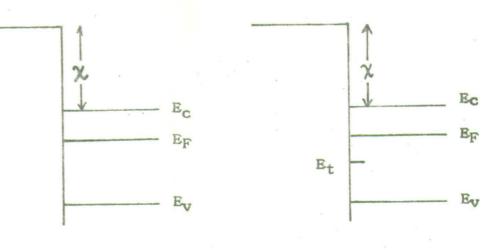

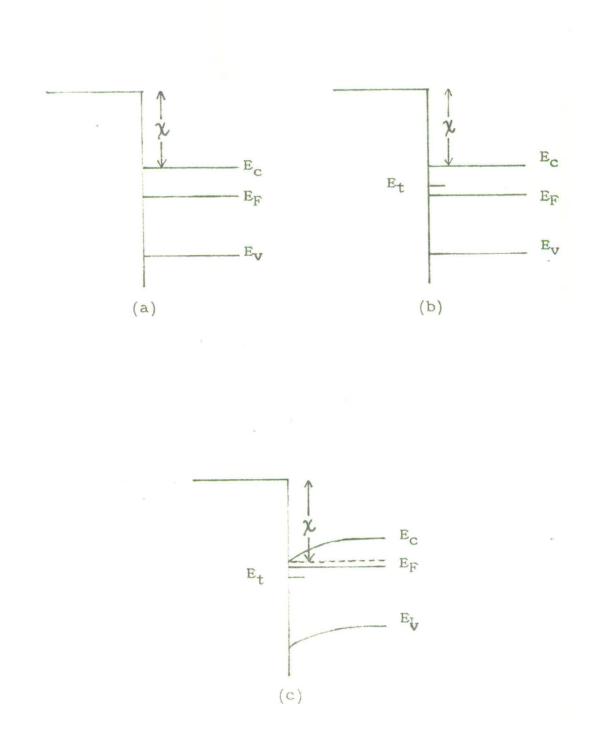

Consider now the effect of surface states on the energy bands of an n-type semiconductor. In the absence of surface states, the energy bands of the semiconductor continue flat up to the surface, provided there is no external field, Figure 2.8(a). When acceptor-like surface states are introduced below the Fermi level, they will not be in equilibrium with the energy bands as long as they remain unoccupied. The situation is illustrated in Figure 2.0(b), where the surface states have been introduced at an energy level Et. Since the states are empty and below the Fermi level, some of the conduction band electrons fall into them In the process the surface becomes negatively charged, and consequently the energy bands at the surface bend upwards with respect to the Fermi level. Since the energy position of the surface states in the forbidden gap is determined by short-range atomic forces and is not affected by the bulk potential, the surface levels rise together with the band edges. The process of charge transfer continues until equilibrium is reached - Figure 2.8(c). Thus the larger the surface state density, the greater the bending of bands near the surface. The situation for donor-like states is analogous and shown in Figure 2.9.

Fig. 2.8 Energy level diagram for an n-type semiconductor (a) no surface states (b) Acceptor-like surface states not at equilibrium (c) at equilibrium.

Fig. 2.9 Energy level diagram for an n-type semiconductor (a) no surface states (b) donor like surface states not at equilibrium (c) at equilibrium.

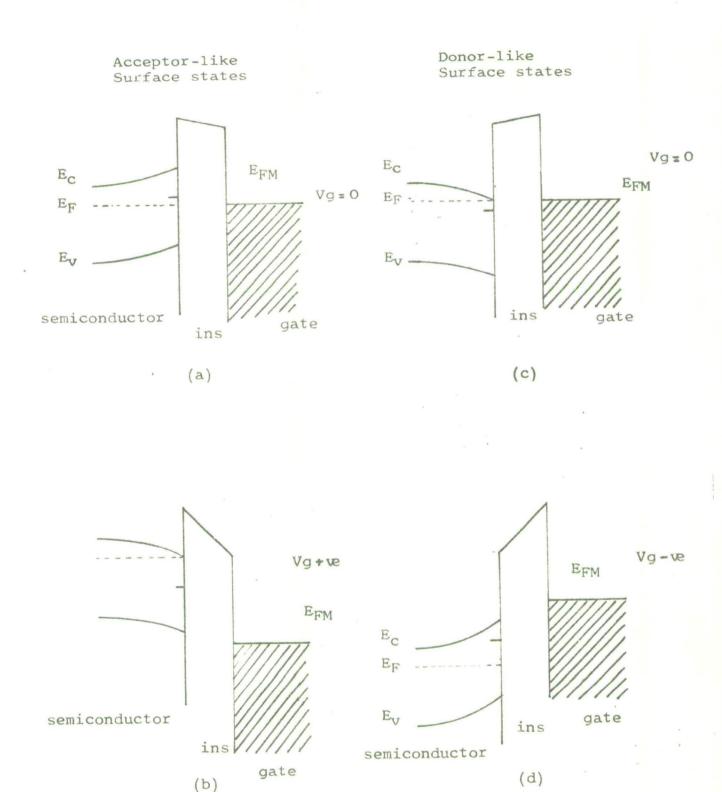

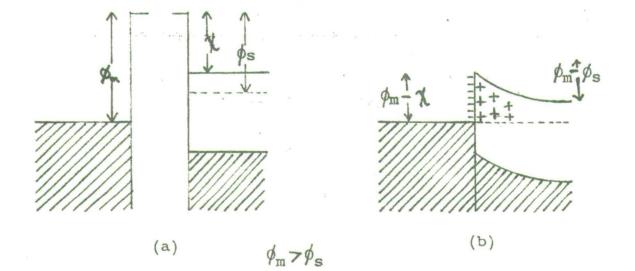

Weimer <sup>[20]</sup> has considered the role that surface states at the semiconductor to insulator interface play in the performance of the thin film transistor and reasons in the following manner. Figure 2.10(a) shows the energy band structure for the gate-insulator-semiconductor system of a thin film transistor. The contact potential difference due to the work function of the metal gate may also play a part. A system with a high density of acceptor-like states or deep traps requires a positive gate bias to convert the depletion layer into an accumulation layer, Figure 2.10(b), and so turn the transistor on. This condition yields an enhancement type transistor. Let N<sub>o</sub> represent the number of unfilled traps or surface states initially present, and let C<sub>g</sub> be the gate capacitance, then the gate bias required for onset of current is given by:

$$V_0 = \frac{N_0 q}{C g}$$

Likewise a high density of donor-like states at the interface provides an accumulation layer at zero bias and yields a depletion type transistor - Figure 2.10(c) and (d). In this case,  $V_0$  is the gate bias required to turn the device off and  $N_0$  represents the number of electrons initially present in the gap region. Weimer has attempted to control the value of  $V_0$  in the fabrication of thin film transistors by processing the semiconductor prior to evaporation of the insulator and also by proper choice of insulator and gate materials.

#### 2.4. CONSIDERATION OF MATERIALS FOR TFT.

Weimer's choice of cadmium sulphide for the semiconducting layer was dictated

Fig. 2.10 The effect of donor-like and acceptor-like surface states upon the energy bands of the semiconductor at the insulator interface.

by the volume of information accumulated over some years of study of its photoconductive behaviour. In previous years in this department, although there was no experience in evaporation techniques to draw on, single crystal platelets of cadmium sulphide had been grown by the vapour phase technique and used to study the fabrication problems and noise properties associated with insulator diodes.<sup>[21, 22]</sup>. The decision to use cadmium sulphide as the semiconductor in a study of the thin film transistor was, in a sense, a natural extension of this work.

Several different materials have been used as insulators in thin film transistors, the commonest being calcium fluoride, and silicon monoxide. It was decided to use silicon monoxide. This material has been ever present over the years in the evaluation of thin film circuits, being mainly used as a dielectric for capacitors. Although it is relatively easy to evaporate, its reaction with oxygen leaves some doubt as to its ultimate composition as an evaporated thin film. However, the fact that it was readily obtainable and a large volume of technical information was available led to its selection.

## 2.4.1 SUBSTRATE MATERIALS.

The substrate does not play an actual role in the electrical performance of a thin film transistor, but its properties are important and capable of having considerable effect on the electrical performance of the device. Ideally a substrate should have the following properties:

.25.

- 1. Chemical inertness.

- 2. Low electrical conductivity.

- 3. A flat, smooth surface.

- 4. High thermal conductivity.

- 5. Compatibility with vacuum processing.

- 6. Be readily available at low cost.

Few materials, if any, which satisfy all these requirements are available at present. One of the main considerations is that since a great deal of processing takes place in vacuum and at elevated temperatures, organic plastic materials cannot be used. Thus the only materials suitable are glass and coramics. The well established use of high quality ceramics for discrete film resistors has led to the use of ceramic substrates for microcircuits both in the United States and in this country. In addition, a number of companies advocate the use of glass substrates.

From the point of view of thin films, a good finish is necessary to provide uniformity and reproducibility of component values. R.J. Settzo <sup>[23]</sup> of the Corning Glass Works has examined materials for their suitability as substrates for thin resistive films of tin oxide and his report suggested that a high aluminad ceramic with its high mechanical strength and high thermal conductivity would be the preferable substrate to use, were it not for the normal surface condition of the material. This disadvantage of ceramics can be overcome if the surface is coated with a suitable glaze. The problem with this approach is that most low temperature glazes have a high alkali content which influences the electrical for ductivity and corrosion resistance and so makes them unsuitable for microcircuits. Considerable advances have been made and several manufacturers have developed a glazed ceramic of sufficient flatness and with a low alkali glass surface. However, the necessary surface finish for thin film components can most readily be obtained on glass. Soda glass, of which ordinary microscope slides are made, cannot be used owing to the alkali content giving rise to conduction by sodium ion migration. To overcome this, slides of borosilicate glass were used. In addition, glass is transparent and this property can be used to advantage if it is necessary to monitor the formation or thickness of the film by optical means. In fact considerable use of this property was made when depositing the thin film of semiconducting cadmium sulphide.

The crystalline structure of the substrate can also be important. The use of amorphous materials such as glass or a ceramic for substrates has little influence on the crystalline growth of the thin evaporated film and, in order to form single crystal films or increase the crystallite size, it is necessary to use a substrate with a crystalline structure similar to that of the film. Mica has a crystalline structure not too dissimilar from that of cadmium sulphide and freshly cleaned slices were also used as substrates in an attempt to encourage an epitaxial growth.

#### 2.5 MASKING PROCEDURE.

In the formation of evaporated thin films of materials it is nearly always necessary to form a repeatable defined profile. Take, for example, the evaporation of a thin film resistor. For a given thickness of film, the aspect ratio determines the value of the resistor. Hence, the accuracy with

.27.

which the aspect ratio can be found determines the tolerance within which a resistor can be deposited. The working of the substrate can be of some importance, particularly when high accuracy is required. Two main methods of masking are used, usually referred to as:

1. In contact masking.

2. Out of contact masking.

In the first method the film is evaporated over the whole substrate, and then covered with a photo-sensitive resist. The resist is exposed through a photograph of the desired pattern to ultra-violet light, which polymerises it. The unexposed resist is then dissolved away to expose the evaporated film underneath, which in turn can be selectively removed by chemical etching, thus leaving the required pattern.

Out of contact masking has the virtue of simplicity but does not lend itself to a very accurate delineation of the pattern. The required film profile is formed on the substrate merely by evaporating the material through a metal foil on which the pattern has previously been cut, usually by the photo-sensitive resist technique. Out of contact masking has been used throughout this work.

It was realized that a combination of both methods could be used in the fabrication of a TFT. In an inverted coplanar structure it would be possible to form a very narrow gate electrode by in contact masking, and add the remaining layers using out of contact masking. Likewise, the source-drain electrodes in a staggered electrode FFT could be formed by selective etching and it is almost certain that the spacing between source and drain attainable by this method would be smaller than by out of contact masking. Thus, the photo-resist process does offer a good method for forming the initial layers of a TFT, provided that the layer is metallic, i.e. either the gate or the source and drain electrodes. However, other factors have to be taken into account, in particular, the problem of keeping the substrate clean. Thin films of some materials stick better to glass than others, and in general, it appears that elements which tend to oxidise readily adhere much more strongly. This high adhesion of oxygen active metals to glass has also been observed in glass to metal seal technology and, as an explanation, bonding of the metal is believed to occur by chemical reaction with an OH layer on the glass. Thin films of the noble elements, such as gold, scarcely adhere at all to glass and can be rubbed off very easily. On the other hand, it is almost impossible to remove a thin film of chromium from a glass substrate. Aliminium,, which readily forms aluminium oxide, also adheres well. However, no thin film will adhere to the substrate unless the substrate is scrupulously clean. The incontact photo-resist masking process demands that the substrate be cleaned prior to the evaporation of the thin film. Selective etching is then carried out by masking in various chemical compounds and the substrate undergoes a fair amount of handling and great care has to be exercised if additional cleaning prior to further evaporations is to be avoided. "Clean room" facilities were not available during the experimental work, and it was thought desirable to reduce the handling and chemical processing of the substrate to a minimum. It was thus decided to use out of contact masking entirely. In addition, this adds a certain uniformity to the process of fabricating a thin film transistor and certainly allows the different layers to be evaporated in any order desired.

.29.

The problem of obtaining a suitable masking material remained. Brass foil was readily available in many thicknesses with a minimum of 1 mil and its easiness to etch chemically made it attractive. The high vapour pressure of the zinc proportion in brass does not recommend it for use in high vacuum systems, particularly if elevated temperatures are required. As the vacuum system available in this laboratory only attained at best  $10^{-6}$  torr and the vapour pressure of zine at  $350^{\circ}$ C is  $10^{-10}$  torr, the use of brass as a masking material was not excluded initially. However, two other properties made its use impossible. Firstly, brass reacts chemically with cadmium sulphide, and secondly, it crinkles very easily, so that close contact with a substrate is not possible. A sharply delineated pattern of the evaporated film cannot then be obtained.

The most suitable material was found to be mild steel feeler strip. This can be readily obtained in a number of thicknesses with a minimum of 1 mil, but unfortunately is only available at a fixed length and breadth of 12 ins. and 0.5 in. respectively. While this length was adequate, the breadth was rather narrow and did not mask completely the 3cm x 2cm borosilicate glass substrate. Apart from a tendency to rust if left exposed to the atmosphere, the feeler strip was very easy to etch, had a smooth surface and did not crinkle.

Ordinary printed circuit techniques were used to make the masks. It is necessary to make a drawing of the pattern to a printed scale, photograph it and reduce it in size to produce a negative of the exact dimensions of the mask. The foil is placed on a platform, witted with a small quantity of

.30.

photo-resist and spun to produce a uniformly thick layer of photo-resist. The required pattern is now produced by first exposing the photo-resist through the negative to ultra-violet light. It is important that the negative and the coated foil should be in intimate contact with one another. This is best ensured by using a vacuum printing frame with a sheet of glass on which the negative and foil are placed. A flexible membrane is placed over the negative and foil, and the air between the plate and membrane is removed by vacuum pumping, causing the membrane to exert a uniform pressure over the glass plate. After developing the exposed resist, the foil can be otched by gentle brushing with ferric chloride or warm dilute nitric acid. Care should be taken to place the emulsion side of the negative next to the resist, otherwise the ultra-violet light is scattered behind the emulsion. This is usually of little consequence when making printed circuit boards, but is certainly detrimental to the formation of masks containing lines a few mils wide.

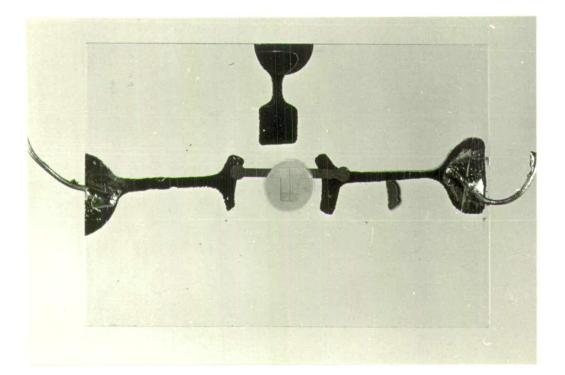

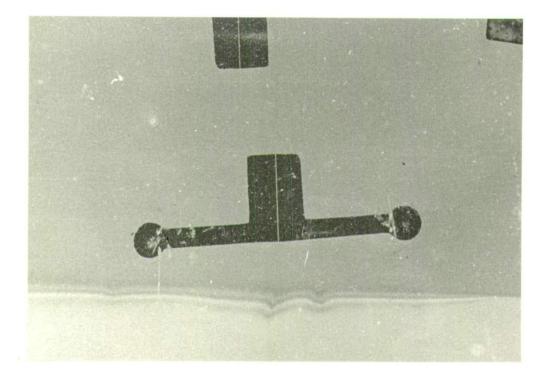

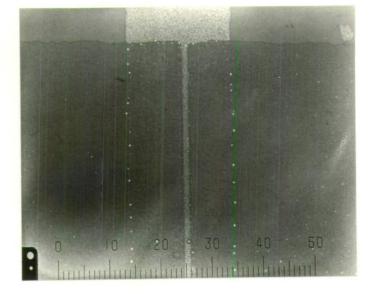

To illustrate the technique, Figure 2.11 shows the negative used to form the masks for the evaporation of a coplanar thin film transistor. During the evaporation, a fine wire was placed in position midway across mask (a) to provide the separation between the source and drain electrodes. In fact, the structure in Figure 2.11 was the one finally chosen for the thin film transistor, with the evaporations being performed in the order listed. This is the coplanar electrode structure. The choice of configuration was dictated to a large extent by the evaporation difficulties associated with the cadmium sulphide film.

.31.

(a) (b) (c)

Figure 2.11 Photographic negative used to form masks (a) source-drain electrodes (b) insulator (c) gate electrode.

35

#### 2.6 CONSIDERATION OF TFT CONFIGURATION.

Cadmium sulphide tends to dissociate readily when heated. The vapour pressures of the constituents differ greatly, and this results in the formation of low resistivity cadmium rich films. It is sufficient at the moment to say that careful evaporation of cadmium sulphide in a separate system is required, and post evaporation heat treatment in an inert atmosphere is generally necessary to improve the stoichiometry of the films. These processes will be described in a later chapter. Furthermore, gold, which normally forms a blocking contact with cadmium sulphide, may be used to inject electrons under certain conditions, viz. when it is deposited beneath the cadmium sulphide. Hence, in some TFT configurations, gold in addition to aluminium is available for an obmic contact. With these facts in mind and with reference to Table 1, consider now in turn the four different configurations as shown in Figure 2.5 and Figure 2.7.

## i. The Staggered Electrode Structure.

As the endmium sulphide has to be deposited in a separate system, the evaporation sequence must be interrupted after evaporating the source and drain contacts on to the substrate. This exposure of the system to the atmosphere followed by a heat treatment process for the cadmium sulphide makes it inadvisable to use aluminium as an injecting contact, owing to its readiness to oxidize. The use of gold also presents a difficulty in that it does not adhere strongly to glass. It is necessary to first deposit an underlay of chromium. To ensure a sharply defined narrow gap between the source

|                  | STAGG                    | FERED TFT STRUCTURE             |                                           |

|------------------|--------------------------|---------------------------------|-------------------------------------------|

| Step             | Semiconductor evaporator | External processing             | Precision mask evapora <mark>t</mark> or  |

| 1<br>2           | Semiconductor deposition |                                 | S - D evaporati <mark>o</mark> n          |

| 3                |                          | Semiconductor<br>heat treatment |                                           |

| 4                |                          |                                 | Insulator deposition                      |

| 5                |                          |                                 | Gate evaporation                          |

|                  | COPI                     | LANAR TFT STRUCTURE             |                                           |

| Step             | Semiconductor evaporator | External processing             | Precision mask evaporator                 |

| 1<br>2<br>3<br>4 | Semiconductor deposition | Semiconductor<br>heat treatment | S - D evaporation<br>Insulator deposition |

| 5                |                          |                                 | Gate evaporation                          |

Table 2.1. Fabrication procedure for making the two main types of thin film transistor.

6

and drain, a double evaporation such as this should be avoided. Having removed the substrate to deposit and heat treat the cadmium sulphide, it is necessary to realign the mask changing system to ensure that the gate electrode is evaporated directly over the source-drain gap. In addition, the surface of the cadmium sulphide can easily be damaged during the realignment.

# ii. The Inverted Staggered Electrode Structure.

This unit has the fabrication difficulties of the staggered electrode structure. Furthermore, the source-drain region is exposed to the atmosphere and would certainly require encapsulation. This would alter the surface potential of the cadmium sulphide within the source-drain region and add another parameter to be considered in any assessment of the performance of the device.

# iii. The Coplanar Electrode Structure.

In this configuration, the cadmium sulphide may be deposited and heat treated without having to consider the effect on the other layers. Also, since the sequence of evaporations is not broken between the formation of the source and drain electrodes and the gate electrode, no critical realignment of the masking system is necessary. Apart from the evaporation of cadmium sulphide, the transistor can be formed during one pump down of the vacuum system. The fabrication process is sample and straightforward.

# iv. The Inverted Coplanar Electrode Structure.

This unit has the advantages in fabrication of the coplanar configuration. However, the fact that the final evaporation is the cadmium layer, does mean that all the previously deposited layers, i.e. the complete transistor, are also subjected to heat treatment.

It is obvious that there is a technological advantage in the use of the coplanar electrode structure, and that it lies in the fact that the cadmium sulphide deposition and processing can be done prior to the laying down of the electrodes. However, the use of a different semiconductor, elemental rather than compound, would require a reappraisal of the fabrication difficulties involved in the various configurations.

## CHAPTER 3.

#### THEORY OF THE THIN FILM TRANSISTOR.

## 3.1 THE GRADUAL APPROXIMATION.

As described by Shockley, the unipolar field effect transistor utilizes the depletion region of a reverse biased p-n junction to control the effective cross-section, and hence the conductance, of a bar of semiconductor material, Figure 2.4. Shockley was able to derive an expression describing the static current voltage characteristic by relating the conductance of the channel to the reverse bias voltage. To do this, he used what has come to be known as the "gradual approximation".

Consider the situation in Figure 2.4 when no current flows. If V represents the potential,  $E_y$  the electric field and y the distance from the centre of the p-layer, then

$$\frac{\mathrm{d}^2 \mathrm{V}}{\mathrm{dy}^2} = -\frac{\rho(\mathrm{y})}{\epsilon_0 \epsilon_1}$$

where  $\rho(y)$  is the charge density. The depletion layer extends to y = b and therefore  $E_y = o$  for y < b. Near y = b the charge density changes from  $\rho = 0$  to  $\rho = \rho_0$

$$\frac{dE_y}{dy} = -\frac{\rho_0}{\epsilon_0\epsilon_1} \quad \text{for } y > b$$

and

$$E_y = -\frac{\rho_0(y-b)}{\epsilon_1 \epsilon_0}$$

Since the n-region is heavily doped, the reverse bias voltage may be considered to occur wholly across the p-region. Thus,

$$V = -\int E_y dy$$

$$= \frac{\rho_0}{\epsilon_0 \epsilon_1} \int (y - b) dy$$

$$= \frac{\rho_0}{2\epsilon_0 \epsilon_1} [(y - b)^2 - (a - b)^2]$$

Where the constant of integration has been chosen to make V = 0 when y = a, corresponding to grounding the n-region. The potential at y = b, the reverse bias, is

$$V(b) = -\frac{\rho_0}{2\epsilon_0\epsilon_1}(a-b)^2$$

Shockley used W, a positive quantity, to represent the reverse bias, giving

$$W = \frac{\rho_0}{2\epsilon_0\epsilon_1}(a-b)^2$$

$$= \frac{\rho_0 a^2}{2\epsilon_0\epsilon_1}\left(1-\frac{b}{a}\right)^2 \qquad (3.1)$$

When b = 0, the depletion region extends completely across the p-region. The magnitude of the reverse bias required for this situation is

$$W_0 = \frac{\rho_0 a^2}{2\epsilon_0 \epsilon_1}$$

Equation 3.1 can be written in the form

$$W = \left(1 - \frac{b}{a}\right)^2 W_0 \qquad (3.1a)$$

$W_0$  is the voltage required to reduce the channel to zero and so planch off the conducting path. Equation 3.1 relates the channel thickness to the reverse bias and the pinch-off voltage.

When the current flows in the x-direction in the channel, an electric field with a component  $E_x$  must be present. The potential changes along the channel and hence the reverse voltage between the channel and the n<sup>t</sup>-region varies As a result, the channel width varies with x. Consequently,

$$E_{x} = -\frac{dV}{dx} \neq 0$$

and in the general case  $\frac{d^2V}{dx^2}$  will not vanish. In such circumstances the reverse bias, W, cannot be expressed as a function of the channel width, b, alone and in calculating the relationship between W and b it is necessary to consider a two-dimensional Poisson's equation, including  $\frac{dE_x}{dx}$ . However, if  $\frac{dE_x}{dx}$  is small compared to  $\frac{\rho_0}{\epsilon_0\epsilon_1}$  an approximation may be made by using the one-dimensional case which was derived for zero current, and considering the electric field in the depletion region to be entirely transverse in direction. The approximation is valid when conditions change gradually along the channel, hence the term "gradual approximation".

For the gradual case, the conductance of the channel can be calculated by making use of Equation 3.1

$$\mathbf{b} = \mathbf{b}(\mathbf{W}) = \{\mathbf{l} - \left(\frac{\mathbf{W}}{\mathbf{W}_{o}}\right)^{\frac{1}{2}}\}\mathbf{a}$$

If  $\sigma$  is the conductivity, the conductance per unit square of a layer 2b thick is

$$g(W) = 2\sigma b(W)$$

or

$$g(W) = 2\sigma \{ 1 - \left(\frac{W}{W_0}\right)^{\frac{1}{2}} \}$$

The current, I, in the device can be calculated from

$$I = g(W)\frac{dW}{dx}$$

If the values of W at the source and drain are  $W_s$  and  $W_d$  and L is their separation

$$I = \frac{1}{L} \int_{W_{S}}^{W_{D}} g(W) dW$$

Shockley has pointed out that this is the basic equation for a field effect device within the terms of the gradual approximation, and can be used to describe structures other than Figure 2.4, provided an appropriate g(W) can be derived.

## 3.2 ANALYSIS DUE TO BORKAN AND WEIMAR.

A similar approximation has been applied in the theoretical analysis of insulated-gate field effect transistors, both MOS and thin film types. In these cases, if the channel **g** ength is several times longer than the thickness of the insulating layer and the drain voltage is of the same order of magnitude as the gate voltage, the electric field in the insulating layer is approximately transverse in direction. The following analysis of the thin film transistor has been suggested by Borkan and Weimer [24] and, as mentioned by those authors, is based on unpublished work of A. Many. In a sense, the analysis follows Shockley's technique and, implicitly, an expression for g(W) is derived and used in the equation

$$I\int dx = \int g(W) dW$$

to obtain the drain characteristics.

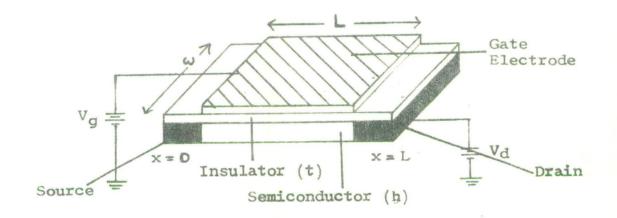

In this analysis, a homogenous layer of semiconductor of thickness, h, as shown in Figure 3.1. is assumed. The gap between the source and drain electrodes provides an active region of length, L, and a width, W. The gate electrode is a narrow metal strip having a width equal to the channel length and is spaced from the semiconductor by an insulating layer of thickness, t. Two simplifying assumptions are made:

- 1. The gate capacitance is a constant independent of the gate voltage.

- 2. The mobility of the carriers throughout the conducting channel is a constant independent of the gate voltage over the useful operating range of the device.

Fig. 3.1 I.F.T. structure use for analysis

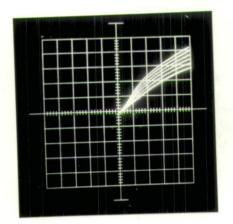

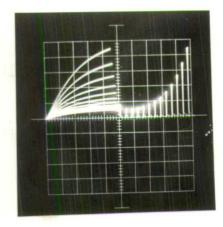

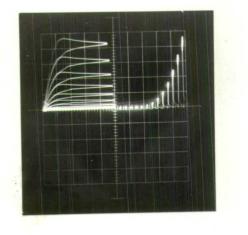

Fig. 3.2 Theoretically predicted T.F.T. drain characteristics.

Let the capacitance across the insulator be  $C_g$ . The potentials applied to the gate and drain electrodes relative to the source electrode are  $V_g$  and  $V_d$  and the potential of the semiconductor at an arbitrary point, x, measured from the source electrode is given by V(x). With  $\Delta N(x)$  charges per unit area impressed on the gate electrode, an equal number of charges of q coulombs per charge is induced in the semiconductor. The charge induced per unit area in the channel region by application of a gate voltage  $V_{\rho}$  is given by

$$q\Delta N(\mathbf{x}) = \frac{C_g}{WL} [V_g - V(\mathbf{x})]$$

(3.2)

Now let  $\mu_d$  = effective drift mobility.

$E_x$  = electric field between source and drain.

$N_0$  = the total number of charges initially present in the gap region of the semiconductor.

$N_o$  is positive for a depletion type unit having an initial excess of donortype states and negative for an enhancement typeunit having an initial excess of unfilled traps or acceptor-type states. The value of  $N_o$  is a function of the volume density of donors and acceptors as well as the thickness of the semiconductor. The drift velocity,  $N_d$ , of an electron is related to the electric field.

$$\mathbf{v}_{d} = \mu_{d} \mathbf{E}$$

Hence the current density, J, can be written as

$$J = nq\mu_d E$$

The drain current may be calculated by summing the contributions from the

initially present charge and the induced charge. Thus the total drain current  $\mathbf{I}_{d}$  may be expressed by

$$I_{d} = \frac{qwN_{o}}{wL} \mu_{d}E_{x} + qw\Delta N(x)\mu_{d}E_{x}$$

$$= w\mu_{d} \left[ \frac{qN_{o}}{wL} + q\Delta N(x) \right] E_{x}$$

(3.3)

Combining equations 3.2 and 3.3

$$I_{d} = w\mu_{d} \left[ \frac{qN_{o}}{wL} + \frac{C_{g}}{wL} (V_{g} - V(x)) \right] E_{\mathbf{x}}$$

$$= \frac{\mu_{d}C_{g}}{L} \left[ \frac{qN_{o}}{C_{g}} + V_{g} - V(x) \right] \frac{dV(x)}{dx}$$

$$I_{d}dx = \frac{\mu_{d}C_{g}}{L} \left[ \frac{qN_{o}}{C_{g}} + V_{g} - V(x) \right] dV(x)$$

$$I_{\tilde{d}} \int^{L} dx = \frac{\mu_{\tilde{d}} C_{g}}{L} \int_{O}^{V_{\tilde{d}}} \left[ \frac{q N_{o}}{C_{g}} + V_{g} - V(x) \right] dV(x)$$

Hence

· • ·

$$I_{dL} = \frac{\mu_{d}C_{g}}{L} \left[ \frac{qN_{o}V(x)}{C_{g}} + V_{g}V(x) - \frac{V(x)^{2}}{2} \right]_{o}^{V_{d}}$$

•••

$$I_d = \frac{\mu_d C_g}{L^2} [(\frac{qN_o}{C_g} + V_g)V_d - \frac{V_d^2}{2}]$$

(3.4)

The term  $\frac{q_N_o}{C_g}$  in Equation 3.4 may be replaced by a voltage  $-V_o$ , where  $V_o$  is the gate voltage required for the onset of drain current. For an n-type semiconductor,  $V_o$  is positive for an enhencement type unit and negative for a depletion type unit. The expression for the drain current becomes

$$I_{d} = \frac{\mu_{d}C_{g}}{L^{2}}[(v_{g} - v_{o})v_{d} - \frac{v_{d}^{2}}{2}]$$

(3.5)

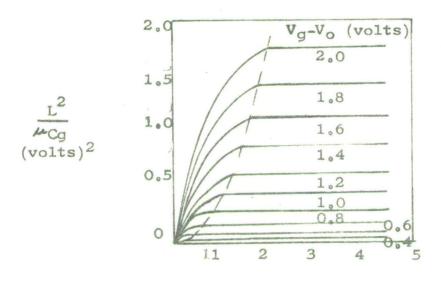

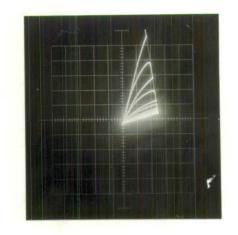

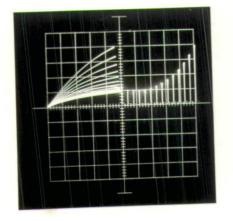

This equation relates the drain current to both the drain and gate voltages. The resulting characteristics calculated from the equation are shown in Figure 3.2. Figure 3.4 is valid for  $\nabla_d < \nabla_g - \nabla_o$  up to the knee of the I<sub>d</sub> versus  $\nabla_d$  characteristic, the point where the slope is zero. Beyond the knee the current is assumed to be substantially constant as predicted by Shockley for the unipolar field effect transistor.

It was suggested by Weimer that the main operating mechanism in the thin film transistor was the formation of a conducting channel by field effect in the semiconductor adjacent to the under-surface of the insulator. To test this proposal, Weimer compared theoretically predicted properties of the drain characteristic with experimentally determined properties. In particular, the maximum drain current at the knee can be determined from Equation 3.5. This occurs when

$$V_d = V_g - V_o$$

and so

$$Id_{(max)} = \frac{\mu C_g}{2L^2} (V_g - V_o)^2$$

Hence there is a square law relationship between the saturated drain current and the effective gate voltage. Good agreement was found for this and other properties, notably the output conductivity and the transconductance below the knee, and thus good evidence was provided for Weimer's proposal that the operation of the TFT is similar to that of the conventional field effect transistor in that the observed characteristics result from modulation of the conductivity of a channel connecting the source and drain electrodes.

In their analysis, Borkan and Weimer have assumed the gate capacitance  $C_g$  to remain constant. Measurements <sup>[25]</sup> have been made on coplanar thin film transistors of the variation of gate capacitance with gate voltage and it has been found that for both source and drain at ground potential the capacitance increases and levels off with gate voltage, but when the drain is positive, as it would be in normal operation, the capacitance reaches a maximum near the value of gate voltage required for the onset of drain current. The gate capacitance thus changes according to the variation of the thickness of the space charge region. At high drain voltages, the major portion of the capacitance appears between the gate and source.

NeuMark <sup>[26]</sup> has considered the case when all the voltage applied to the gate electrode does not fall across the insulating layer but extends into depletion regions. In the theory the capacitances of the insulating layer and the depleted part of the semiconductor are included and the approach given by Borkan and Weimer is followed. The theory is again only valid at most up to the pinchoff point. Furthermore, as there are no depleted regions in the thin film transistor below the pinch-off point, the theory does little to further the description of its operation.

.46.

The second assumption made in the Borkan-Weimer analysis - that the mobility of the carriers in the conducting channel was constant and independent of the gate voltage - has also been investigated. <sup>[2]</sup> Using the expression for drain current, Equation 3.5, the mutual conductance below pinch-off can be obtained by differentiating with respect to  $V_g$ . Thus,

$$g_{\rm m} = \frac{\partial I_{\rm d}}{\partial V_{\rm d}} = \frac{\mu_{\rm d} C_{\rm g} V_{\rm d}}{L^2}$$

(3.6)

If the g<sub>m</sub> and the device dimensions are known, it is possible to derive an effective mobility from Equation 3.6. It is found that the mobilities derived in this way yield values considerably greater than those normally obtained for polycrystalline films, and in fact tend to approach the value for a single crystal. This is remarkable when one considers that no allowance has been made for electron trapping or for the decrease in the surface mobility as the surface channel narrows.

The carrier mobility in the surface channel is thought to alter in several ways in the presence of a transverse field. As impurity or trap states become occupied, their electrical charge changes and hence their scattering cross section changes. The mobility of free carriers decreases when an electricall-neutral trapping site is filled. On the other hand, if the impurity site becomes electrically neutral when filled, then the free carrier mobility will decrease. In addition, the carrier mobility can vary because of changes in the height of the inter-crystalline potential barriers. Weimer has found devices in which both the drift and the Hall mobility are functions of the gate bias  $\begin{bmatrix} 2 \\ 2 \end{bmatrix}$  and Miksie  $\begin{bmatrix} 27 \\ 2 \end{bmatrix}$  has reported cases where the effective mobility is a function of both bias and frequency.

The mobility of carriers in a surface channel has been of interest for some time and Schrieffer <sup>[28]</sup> has calculated the mobility of electrons in surface space charge layers, and has found that the electron mobility in an n-type channel should decrease with increasing surface potential. In fact, experimental work on single crystals of germanium here shown the surface mobility to decrease with surface potential as predicted. The variation of carrier mobility with gate voltage in a thin film transistor appears to be at variance with those results. A single crystal was used in the case of the germanium whereas a polycrystalline film was used to fabricate the transistor. By making use of this fact, Weimer <sup>[29]</sup> was able to explain the mobility variation as a function of surface potential by using the polycrystalline inhomogenous film model <sup>[30]</sup>. This model considers the film to be a matrix of high-and low-resistivity regions between which potential barriers exist. The theory accounts for the increase in the effective mobility by the suppression of intercrystalline potential barriers by the increased surface potential.

It is clear that the single field effect theory proposed by Borkan and Weimer is able to provide (as far as it goes - to the pinch-off point) an insight into the physical processes involved in the operation of the thin film transistor. Wright <sup>[31]</sup>, among others, has taken the theory beyond this point and into the saturation region

# 3.3 WRIGHT'S ANALYSIS OF THE SURFACE CHANNEL DIELECTRIC TRIODE.

In his analysis of his surface channel dielectric triode, which is more commonly known as the Insulated Gate Field Effect Transistor ( IGFET), Wright

.48.

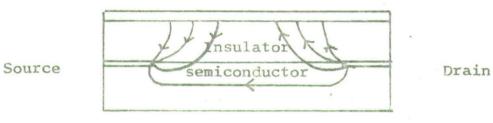

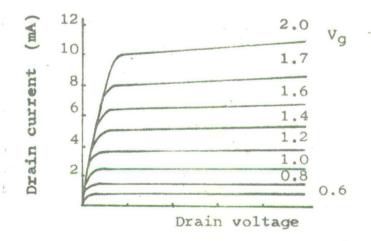

distinguished between a source region where the gradual approximation was valid and a drain region, in which a longitudinally directed electric field existed, and a space charge limited current flowed. Wright's approach and the operating mechanisms of the device can best be understood by referring to Figure 3.3.

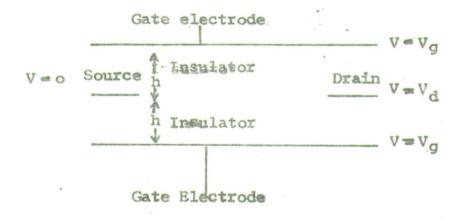

Figure 3.3 is essentially the configuration of the coplanar thin film transistor. The source and drain electrodes are on the surface of the semiconducting layer and separated from the gate by an insulating layer. The electrostatic field pattern in the device is shown for  $V_{\mathbf{D}} > V_{\mathbf{g}}$ , in the absence of space charge. This portrays Wright's idea of a division into source and drain regions. The potential difference across the insulating layer at the source is  $+V_{\mathbf{g}}$  and at the drain  $(V_{\mathbf{g}} - V_{\mathbf{D}})$ . Since  $V_{\mathbf{D}} > V_{\mathbf{g}}$  there is some intermediate point between the source and drain at which the potential across the insulator is zero. Let this be at the point  $\mathbf{x} = \mathbf{d}$ . The region to the left of this point is influenced by the gate potential while that to the right is influenced by the drain potential. This point, then, marks the end of the source region and the beginning of the drain region.

When current flows in the semiconducting layer, lines of force from the gate electrode terminate in the space charge layer which exists between the source and drain. The forces existing in the space charge layer are due to electric fields and to electron concentration gradients. In the y-direction, the electric field  $E_y$  which acts across the insulator produces a drift force which moves electrons towards the interface between the insulator and semiconductor. The electron density increases at the interface until the drift force due to  $E_y$  is balanced by the diffusion forces originating from the concentration

.49.

(a)

V = Vg

| X 888 | 0 | d    | X = D  |

|-------|---|------|--------|

| V =   | 0 | V=Vg | V = VD |

(b)

Fig. 3.3 Wright's Co-planar T.F.T. structure. The electrostatic field configuration in the absence of space charge is shown in (a) for  $V_D \gg V_g$

gradient of the electrons. In the x-direction the electric field  $\mathbb{F}_{x}$  is produced in the source region by the potential difference  $V_{g}$  which emists along this region and in the drain region by the potential difference  $(V_{p}-V_{g})$ which exists along this region. The charge held in the space-charge layer varies from a maximum at the source to smaller values on proceeding towards the drain. However, the current is a constant at all points between these electrodes and so the field  $\mathbb{E}_{x}$  must increase on proceeding towards the drain.

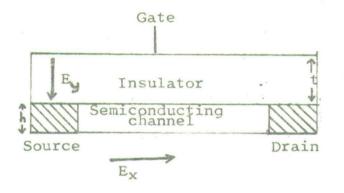

The model used by Wright in his analysis is shown in Figure 3.4 and contains simplifying assumptions. The space-charge layer is assumed to have a uniform charge density in the y-direction and also to be of uniform thickness throughout. The essential features of the device do not appear to be changed by making these simplifications. In terms of this model, Wright divided the space-charge in the conducting channel into two components; one in which the lines of force cmanating from the gate electrode terminate and the other in which the lines of force from the drain electrode terminate.

Let N be the charge density for the former and n be the charge density which produces divergence of the field  $E_x$  in the drain region. At a distance x from the source the potential in the space charge region is V. Then the charge hold in this layer by the electrostatic action of the gate is

$$qNh = \varepsilon_{\varepsilon_1} E_y = \varepsilon_{\varepsilon_1} (V_g - V)/t \qquad (3.6a)$$

where 't' is the thickness of the insulator and 'h' is the thickness of the space-charge layer.

.51.

The divergence of the field  $\mathbb{E}_{\mathbf{x}}$  is given by

$$\frac{dE_x}{dx} = -\frac{qn}{\epsilon_2 \epsilon_0}$$

(3.7)

$\epsilon_{\downarrow}$  and  $\epsilon_{2}$  are the dielectric constants of the insulating and semiconducting layers respectively.

The current is carried by the total space-charge and is given by

$$J = q\mu(N+n)E_{x}$$

(3.8)

$\mu$  is the mobility of the electrons in the semiconductor.

From the Equation 3.6a

$$N = \varepsilon_{\varepsilon_1} (V_g - V) /_{qht}$$

(3.9)

and from Equation 3.7

$$n = -\frac{\varepsilon_{e_2}}{q} \frac{dE_x}{dx} = \frac{\varepsilon_{e_2}}{q} \frac{d^2 V}{dx^2}$$

(3.10)

substitution of Equation 3.9 and Equation 3.10 into Equation 3.8 gives

$$-J = \boldsymbol{\xi} \mu \left[ \frac{\epsilon_1}{ht} (V_g - V) + \epsilon_2 \frac{d^2 V}{dx^2} \right] \frac{dV}{dx}$$

(3.11)

This is the basic equation describing the operation of the device. It can be integrated to yield an expression which describes the longitudinal field in the channel. Thus,

$$\left(\frac{\mathrm{d}\mathbf{V}}{\mathrm{d}\mathbf{x}}\right)^2 - \left(\frac{\mathrm{d}\mathbf{V}}{\mathrm{d}\mathbf{x}}\right)^2_{\mathbf{x}=\mathbf{0}} = -\frac{2\mathrm{J}\mathbf{x}}{\varepsilon_2\mu} - \frac{\varepsilon_1\mathrm{V}}{\varepsilon_2\mathrm{ht}}(2\mathrm{V}_g - \mathrm{V})$$

(3.12)

It is not possible to carry out any further integration of this equation. However, Wright was able to obtain a description of transistor operation from it by applying it in turn to the source and drain regions of the conducting channel, and neglecting the appropriate terms.

Firstly, consider the source region of the transistor. In this region  $\mathbb{E}_x$  is of the order  $\frac{V_g}{d}$  and  $\mathbb{E}_y$  is of the order  $\frac{V_g}{h}$ . The insulating layer is much thinner than the source to drain spacing. Thus  $\mathbb{E}_x << \mathbb{E}_y$  and the terms on the left hand side of Equation 3.12 can be neglected as each is smaller than either term on the right hand side.

Therefore, Equation 3.12 can be written as:

$$\frac{2ix}{\epsilon_{e} \mu w} = \frac{V}{t} (2V_{g} - V)$$

(3.13)

Where i = -Jwh, 'w' is the width of the channel and 'i' is the actual current between source and drain. This equation is valid in the source region where the condition  $E_y >> E_x$  is satisfied. At the end of the source region  $E_y$ decreases to zero, near x = d, and  $E_x$  becomes greater than  $E_y$ . If  $E_x$  is assumed to be constant in the source region, then

$$\frac{(E_y)_{x=0}}{E_x} = \frac{d}{d - d^1}$$

where  $d^1$  is the point at which  $E_y = E_x$ . Then

$$(d - d') = \frac{E_x}{(E_y)_{x=0}} d$$

(3.14)

is the very short distance over which  $E_y < E_x$ . Equation 3.14 is valid up to  $x = d^1$ , where  $(d - d^1) << d$ . In Equation 3.14 itself, the difference between d and  $d^1$  may be neglected and the current given by

$$i = \frac{\xi_{c_1} \mu_W V_g^2}{2td}$$

(3.15)

Wright described the conditions within the source region further by deriving expressions for the potential electric field and the charge density. The potential can be obtained using Equation 3.15 and Equation 3.13.

Hence,

$$V = V_g \left[ 1 - \left[ 1 - \frac{x}{d} \right]^{\frac{1}{2}} \right]$$

(3.16)

The variation of  $E_x$  follows directly from Equation 3.16 by differentiating with respect to x, giving

$$E_{\mathbf{x}} = -\frac{V_{q}}{2\bar{a}}(1-\frac{x}{\bar{a}})^{-\frac{1}{2}}$$

(3.17)

Expressions for the charge densities, N and n, can be obtained from Equation 3.6a and Equation 3.7 respectively. Thus,

$$N = \frac{\boldsymbol{\xi}_{g}\boldsymbol{\epsilon}_{1}}{qht} V_{g} \left(1 - \frac{x}{d}\right)^{\frac{1}{2}}$$

(3.18)

and

$$n = \frac{\varepsilon_{c_2} V_g}{4q d^2} (1 - \frac{x}{d})^{-3/2}$$

(3.19)

The drain region, where  $x \ge d$ , can be treated in a similar manner by making appropriate approximations in Equation 3.12. For  $d \le x \le D$ , where D is the source to drain spacing, N = O, and the last term on the right hand side of the equation can be neglected. In this way Wright obtained the expression

$$E_{x}^{2} - E_{d}^{2} = -\frac{2J}{\epsilon_{2}\mu}(x - d)$$

(3.20)

where  $E_d$  is the electric field at the point x = d in the conducting channel.  $E_d$  cannot be given an exact value because the description of the source region is not valid right up to the pinch-off point. Consequently, it is difficult to link the solutions in the source and drain regions. Wright has accepted the drain region as one of high field in the x-direction and, by neglecting  $E_d$  in Equation 3.20, obtained

$$E_{\mathbf{X}} = \sqrt{\frac{\epsilon_1}{\epsilon_2} \left(\frac{\mathbf{x} - \mathbf{d}}{\mathbf{h} + \mathbf{d}}\right)^2} V_g \qquad (3.21)$$

Equation 3.21 can be used to obtain expressions for the electric potential and charge density. Thus,

$$V - V_g = \left(\frac{\epsilon_1}{\epsilon}\right)^{\frac{1}{2}} \frac{2htd}{3} \left(\frac{x - d}{h + d}\right)^{\frac{3}{2}} V_g \qquad (3.22)$$

and

n =

$$\frac{\varepsilon_{\varepsilon_2} V_g}{2 \text{qhtd}} \left(\frac{\varepsilon_1}{\varepsilon}\right)^{\frac{1}{2}} \left(\frac{x-d}{\text{htd}}\right)^{-\frac{1}{2}}$$

(3.23)

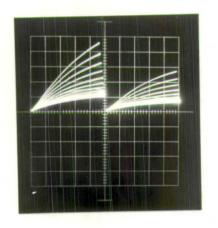

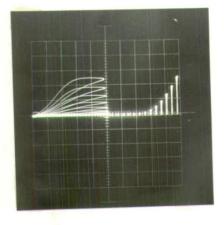

By assigning values which suitably describe a cadmium sulphide TFT to the various parameters - see subscript to Figure 3.5 – and using the relevant expressions which characterise the source and drain regions, Wright deduced the current voltage characteristic for the transistor. Thus if the drain voltage does not exceed the gate voltage, then the source region extends over the complete distance between source and drain, and in this case

$$i = \frac{\varepsilon_1 \mu w}{2tD} (2V_g - V_D) V_D \qquad (3.24)$$

On the other hand, if the drain exceeds the gate voltage

$$i = \frac{\varepsilon_{e_1} \mu w V_g^2}{2td}$$

(3.25)

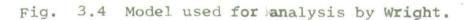

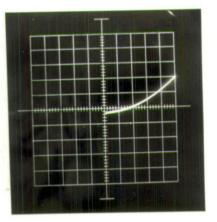

Equation 3.25 is valid in the source region up to the point x = d where  $V = V_g$ . By substituting for  $V_D$  and  $V_g$  in Equation 3.22, Wright obtained a value for d, and hence from Equation 3.25 the current for a given value of  $V_g$  and  $V_D$ . In this way, Wright obtained the characteristic shown in Figure 3.5.

Winslow [32] used the same approach as Wright and likewise obtained the basic

equation

$$J = \boldsymbol{\xi} \mu \, \frac{\mathrm{d} V}{\mathrm{d} x} \left[ \frac{\epsilon_1}{\mathrm{ht}} (V_g - V) + \epsilon_2 \, \frac{\mathrm{d}^2 V}{\mathrm{d} x^2} \right]$$

No attempt was made to solve this equation analytically but a numerical solution  $\omega \omega$  obtained. The dimensionless variables  $\phi = \sqrt[V]{V_D}$  and  $\theta = \frac{x}{D}$  were introduced to give the dimensionless equation

$$\phi^{1}[\phi^{"} + K_{1}(\phi_{g} - \phi)] = K_{2}$$

(3.26)

where

$$\phi_{g} = \frac{\nabla_{g}}{\nabla_{n}}$$

$$K_{1} = \frac{D^{2} \epsilon_{1}}{\epsilon_{2} h t}$$

$$K_{2} = \frac{JD^{3}}{\epsilon_{p} \epsilon_{2} \mu \nabla_{n}^{2}}$$

The boundary conditions which must be satisfied are

(1)  $\phi = 0$  at  $\theta = 0$ (2)  $\phi^{I} = 0$  at  $\theta = 0$ (3)  $\phi = 1$  at  $\theta = 1$

Condition (2) expresses the ohmic quality of the source electiode. Equation 3.26 is a second order differential equation on which three boundary conditions are impressed. Winslow solved the equation by assigning a value to K<sub>1</sub> and

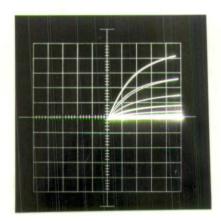

determined K<sub>2</sub> for several values of  $\phi_g$ . The drain characteristics obtained in this way agreed well with Weimer's experimental characteristics.

# 3.4 THE CURRENT SATURATION PROBLEM AND GEURST'S ANALYSIS.

In all types of field effect transistor the transport mechanism in the saturation range is not well understood, and in actual devices, complete current saturation does not occur. In Shockley's theory the channel resistance appears to reach a finite value, at the pinch-off point, and any further increase in drain voltage falls across the pinch-off region. A rough estimate of the length of the high resistance pinch-off region as a function of the drain voltage was made and, consequently, an idea of the channel length was obtained. A slow variation in the channel length with drain voltage occurs and therefore, the I-V characteristics of the transistor show a very small slope beyond pinch-off. In this way the high but finite output resistance was accounted for.

Several other arguments have been put forward to explain the current saturation phenomena. Grosvalet <u>et.al</u>. <sup>[33]</sup> proposed that the saturation current, again in the junction gate type of field effect transistor, was due to the limiting drift velocity at high fields. However, this model is useful only for short channels, the width of which is equal to or is the same order of magnitude as the length. It fails to account for the current saturation effect in long thin channels. The field dependent mobility model was applied to the insulated gate transistor by Root and Vodasz <sup>[34]</sup> but the I-V characteristic varied from the observed. Hofstein and Heinman <sup>[35]</sup> have related the saturation resistance to the capacitance from the drain to the source region of the channel through

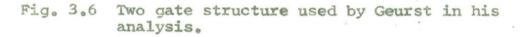

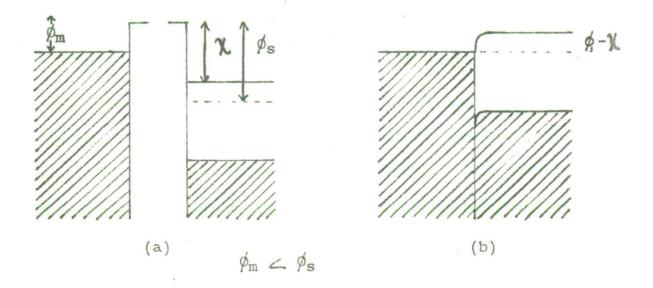

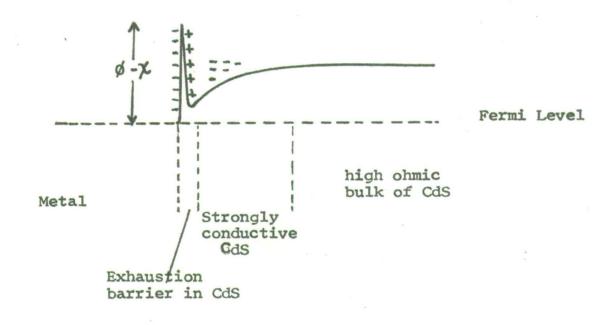

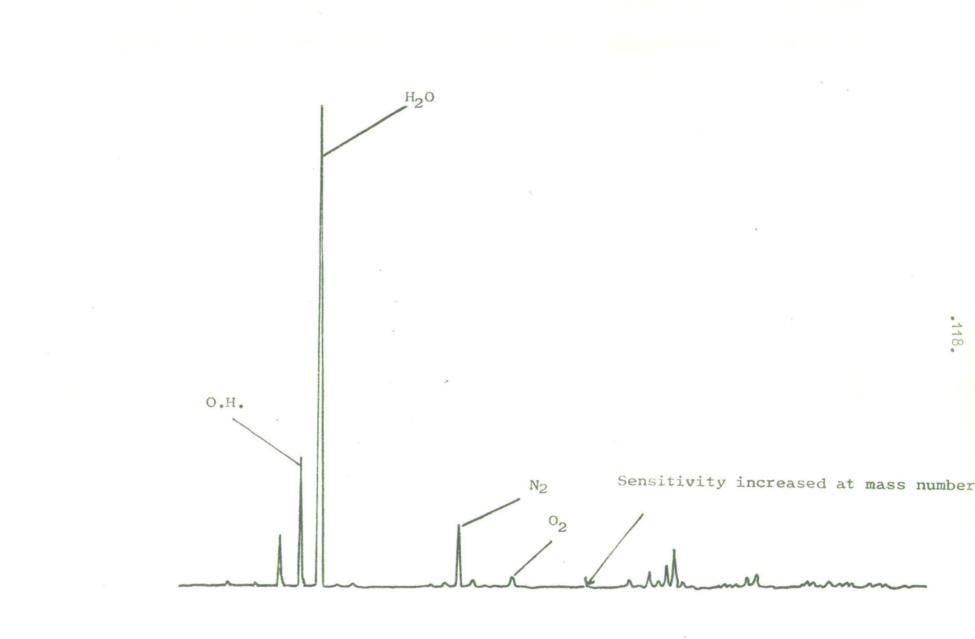

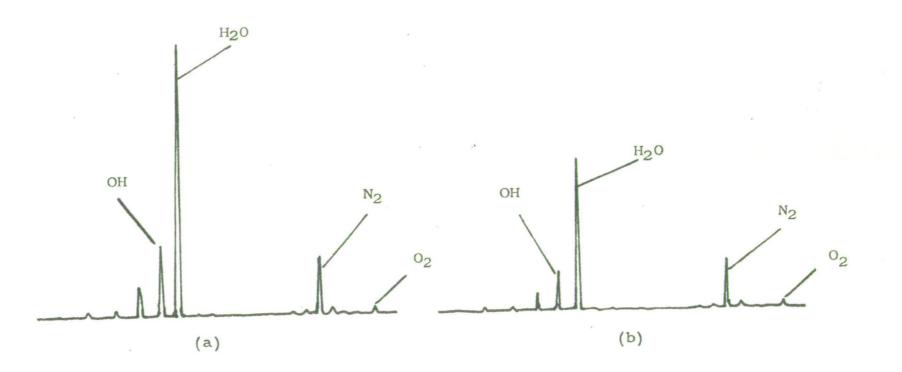

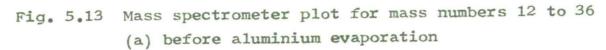

the substrate to channel depletion region. Hence, the output resistance becomes dependent on the induced charge in the channel from the substrate side of the device. Johnson <sup>[36]</sup> approached the problem in an entirely different way. He has shown that a uniform distribution of donors in the semiconductor, which is only partly ionized, can lead to devices which fail to saturate. The saturation region corresponds to the ionization of donors at deeper lying levels. Complete saturation would only occur when all the donors were ionized. This would require large drain voltages, and, in practice, breakdown of the device would occur before complete saturation was attained.